【2020 IEDM】Intel 的技术走向

以下文章来源于半导体百科 ,作者Dick James

半导体集成电路视频与博文分享,共同学习,共同成长。

由于Covid-19,今年IEDM将在12月5日至18日这两周内以在线形式举办。在浏览了“ 2020 IEDM Technical Program”和“tip-sheet”之后,英特尔的两篇篇论文引起了我的注意,其中一篇是关于互补堆叠的纳米片晶体管,另一篇是关于使用反铁电(AFE)电容器的嵌入式DRAM。

NMOS-on-PMOS Nanoribbon Transistors

文章编号20.6, “3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore’s Law Scaling", Cheng-Ying Huang, et al.

一直有人猜测,英特尔的5纳米工艺将是他们采用nanosheet / nanoribbon技术的成果,但是英特尔发表的关于该主题的会议论文很少。

一年前,前英特尔公司的吉姆·凯勒(Jim Keller)发表了有关机器学习的演讲,并介绍了这种器件的发展,这很可能是我们在下一代中可以看到的:

图1 Jim Keller对器件演进的展望

鉴于此,很容易想到7纳米节点将具有24纳米鳍节距,而5纳米将是纳米片(而不是纳米线),论文20.6则展望了堆叠的纳米片阶段:

“我们展示了成功集成垂直堆叠的双源极/漏极和双金属栅极工艺的3-D自对准堆叠NMOS-on-PMOS多个Si-nanoribbon晶体管。NMOS和PMOS均展示了高性能和出色的短沟道控制能力。此外,还演示了具有平衡的电压传输特性的功能性CMOS反相器。这种新颖的晶体管架构有望继续推动摩尔定律的发展。”

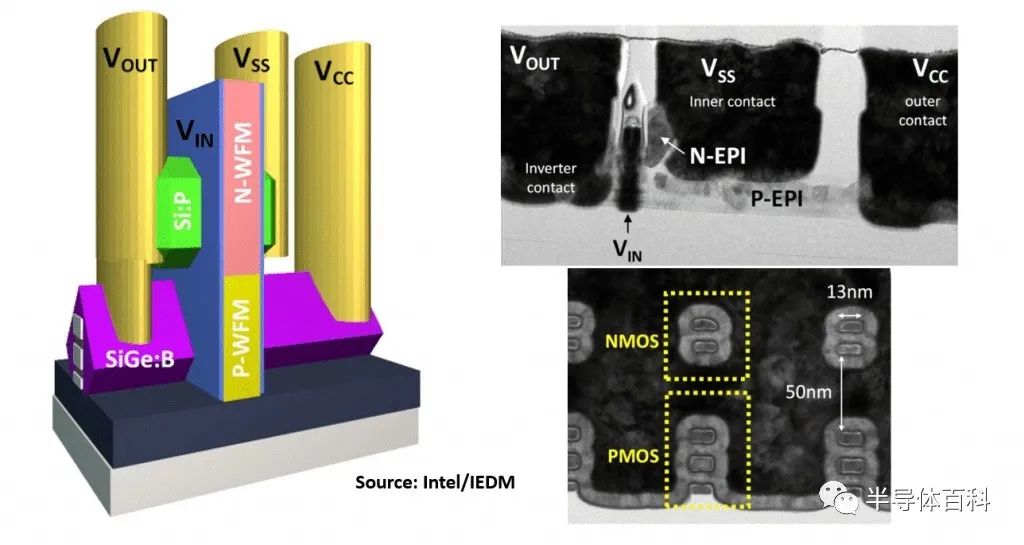

使用垂直堆叠的双源极/漏极外延工艺,以及双金属栅极,可以同时调整P和N纳米管以及Vt。这提供了出色的静电特性–亚阈值摆幅小于75 mV/decade,而DIBL小于30 mV/ V(对于≥30 nm的栅极)。在下图中,左边为反相器的示意图,在右边的右上角是栅极的TEM横截面,下方是P-epi沟道,上面是N-epi的沟道。右下方是垂直沟道方向的截面图,显示了嵌入其中的N和P沟道。栅极长度为40 nm,我们可以看到纳米片宽度为13 nm,我估计约厚度约为5 nm。

图2,反相器示意图(左),栅极截面TEM图像(右上)和纳米片截面TEM图(右下)

下图的左侧展示了工艺流程,右上方是外延顺序的示意图,右下方是双金属栅极工艺流程。

图3,堆叠纳米片工艺流程示意图

请注意,下部的PMOS纳米片保持完整,但顶部的NMOS纳米片被去除(除了栅堆叠之内),然后N-epi在纳米片的根部上生长。使用的双重功函数材(WFM)需要先沉积P-WFM和钨(W),然后将W回蚀刻至N纳米片之下,而W覆盖P纳米片。然后形成N-WFM层,然后进行最终的W沉积和CMP。栅极长度≥ 30nm 时,W栅极填充应该没有问题。

理想情况下,我们希望PMOS沟道为SiGe,以获得更好的迁移率,但这会使初始Epi堆叠工艺和随后的沟道释放工艺变得复杂,因此这里我们采用Si PMOS器件的直接方法。英特尔还有另一篇关于SiGe PMOS纳米片的文章(2.2, “Gate-All-Around Strained Si0.4Ge0.6 Nanosheet PMOS on Strain Relaxed Buffer for High Performance Low Power Logic Application”, Ashish Agrawal, et al.),以及IBM(2.3 ,“Stacked Gate-All-Around Nanosheet pFET with Highly Compressive Strained Si1-xGex Channel”, Shogo Mochizuki, et al.),但它们不会出现在互补堆栈中。

图4,Epi生长图像(上);纳米片的TEM和TEM / EDS图像

上方第一行的SEM图像(b)显示了在底部纳米片上选择性生长的P-epi,然后图(c)显示了在顶部两个纳米片上选择性生长的N-epi。(d)中的正交视图具有SEM和SEM / EDS图像,这些图像显示了堆叠的纳米片晶体管上选择性的N-epi和P-epi生长。

在底行,图(b)是大概在第二次W沉积之前已形成WFM的纳米片的TEM截面图;(c)和(d)是双金属栅极的TEM / EDS图像,(c)在底部纳米片上显示P-WFM,在顶部两个纳米带上显示残留P-WFM,(d)在双金属栅上显示N-WFM在两个纳米片上。

我们将不得不等到会议上才能看到性能特征,但这是一篇有趣的概念验证论文,它说明了在硅技术用尽之前还需要经过一些阶段。

Anti-ferroelectric Capacitor for 3-D Embedded-DRAM

文章编号28.1,“Anti-ferroelectric HfxZr1-xO2 Capacitors for High-density 3-D Embedded-DRAM”, Sou-Chi Chang, et al., Intel Corporation

再次引用文章摘要:

“ 基于3-D反铁电 HfxZr1-xO2电容器的eDRAM展示了:(i)10ns 读/写操作,(ii)低于1.8V的最大工作电压,(iii)数据保持时间长达1ms,(iv) 在80℃达到10E12个循环的耐久性。讨论了疲劳疲劳背后的机制,并提出了一种面向超高密度eDRAM的新颖架构。”

这不是英特尔第一次开发e-DRAM [1、2],它实际上是在2014年与Haswell处理器一起推出的单独的芯片中,它被用作128 MB L4高速缓存,具有芯片大小约79平方毫米,与CPU共同封装。它具有一个COB(cell over bitline)堆叠,在金属电介质堆栈中使用MIM电容器,并在较低金属水平的电介质中形成空腔,并采用英特尔的22纳米工艺制造。

图5,英特尔22纳米,eDRAM堆栈的SEM横截面

MIM cap是由随着金属堆叠的建立而被蚀刻的腔内的TaN/TiN/ZrO/TiN/TiAlN/TaN层形成的。

图6,英特尔22纳米,电容器的TEM横截面

在该IEDM论文中,英特尔的研究人员使用反铁电(AFE)材料铪氧化锆(HfZrO2)形成了3D深沟电容器,作为潜在的嵌入式DRAM存储器单元。他们还尝试 了3D堆栈中的HfZrO2,其中一个字线晶体管并行访问四个AFE电容器。

图7,使用AFE HfZrO 2 电容器的1T-1C存储单元的TEM图像

在上面的TEM图像中,左侧是IEDM文章中的暗场,右侧是我将其反转为明场,标记了晶体管元件,并优化了对比度以尝试阐明我们在看什么。触点上方的垂直条纹是TEM样品制备技术的伪影。电容器本身在晶体管上方,因此尽管它可能是沟槽形的,但它不是常规的沟槽电容器(在基底中,IBM一直使用到14nm节点)。

电容器中心的钨塞很可能已连接到公共极板(common plate)上,尽管此处未显示。栅极的形状表明它是一个FinFET晶体管,但是我看不到任何鳍,所以也许这个样本是在场区拍摄的。这实际也是查看诸如栅极和电容器堆栈之类的结构的有用方法。

在下图显示的1T-4C堆栈中,公共极板似乎已移到电容器的外部,并且我们围绕着各个内部节点板有四个水平放置的极板(PL1-PL4)。该示意图表明,电容器的布局就像DRAM,两个电容器通过一对字线连接到共享位线。电容器已被隔离沟槽分成几行,公共极板通过阶梯结构接触,就像3D NAND堆栈一样。

图8,四个堆叠的垂直电容器的TEM图像(左);1T-4C单元架构的横截面示意图(右)

我们在这里不知道该存储单元的任何尺寸,但是堆叠公共极板的能力必须具有显着的密度优势。如果存储特性良好,并且密度可以超过现有eDRAM的〜1.6 MB / mm2,那么我们可以在不久的将来看到其量产。

就像我们在简介中所说的那样,今年IEDM将以线上形式举办,时间表也大不相同。有关详细信息,请查看IEDM官网。

参考文献:

R. Brain et al., A 22nm High Performance Embedded DRAM SoC Technology Featuring Tri-gate Transistors and MIMCAP COB, Proc VLSI Symp 2013, pp. 16-17

Y. Wang et al., Retention Time Optimization for eDRAM in 22nm Tri-Gate CMOS Technology, Proc IEDM 2013, pp. 240-243.