ASIC 设计中心

# 流程包括

- ❖背景资料

- ❖网表介绍

- ❖元器件描述

- \*简单功能介绍

- ❖高级功能介绍(.measure与.alter)

- ❖实例演示与上机( Lab1-5)

- ❖ Avant! Start-Hspice (现在属于 Synops ys 公司)是 IC 设计中最常使用的电路仿真软件,是目前业界使用最为广泛的 IC 设计工具,甚至可以说是事实上的标准。

- ❖目前,一般书籍都采用 Level 2 的 MOS Model 进行计算和估算,与晶圆厂经常提供的 Level 49 等库不同,而以上 Model 要更加复杂。因此设计者一定要使用电路仿真软件 Hspice、Spectre 等工具进行仿真,以便得到精确的结果。

#### **SPICE Means**

- Simulation Program with Integrated Circuit Emphasis

- 集成电路专用模拟程序

❖ Star-Hspice 有着无与伦比的优势用于快速精确的电路和行为仿真。它使电路级性能分析变得容易,并且生成可利用的 Monte Carlo、最坏情况、参数扫描(sweep),数据表扫描分析,而且还使用了最可靠的自动收敛特性。Star-Hspice 是组成全套 Avant! 工具的基础,并且为那些需要精确的逻辑校验和电路模型库的实际晶体管特性服务。

❖ Star-Hspice 能提供设计规格要求的最大可能的准确度。

❖ Star-HSPICE 的功能包含电路阶层之交、直流及暂态分析,温度特性分析,噪声分析,功耗、各种电路参数等可扩展的性能分析

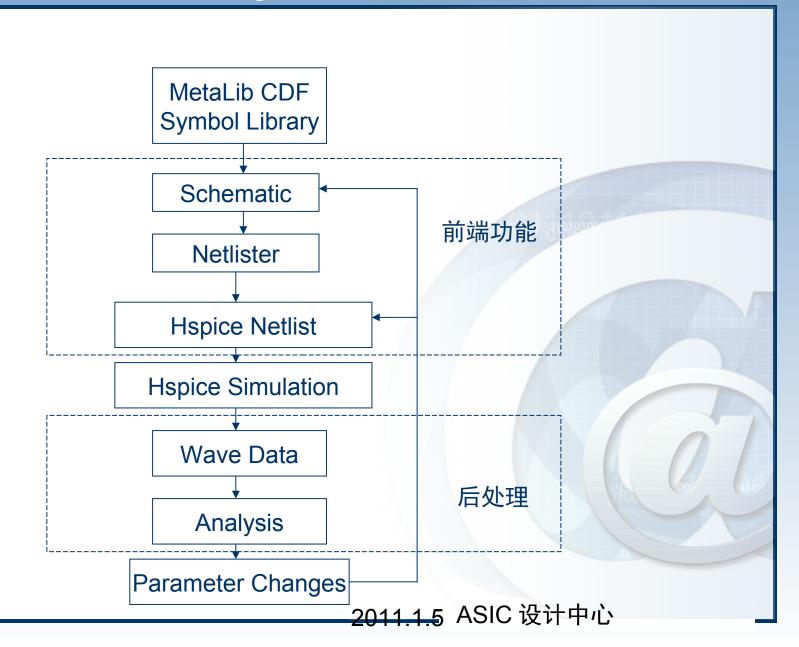

# Hspice 流程

- ❖用 Hspice 分析一个电路,首先要做到以下三点:

- (1) 给定电路的结构(也就是电路连接关系)和元器件参数(指定元器件的参数库);

- (2)确定分析电路特性所需的分析内容和分析类型(也就是加入激励源和设置分析类型);

- (3) 定义电路的输出信息和变量。

# Hspice 流程

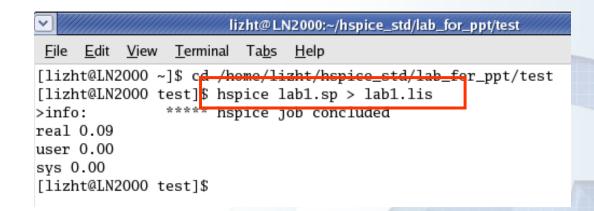

# Hspice 运行

- **❖Hspice** 的运行:

- 使用命令行模式

- 无图形化界面( Windows 下面有)

# <u>@</u>

# Hspice 运行

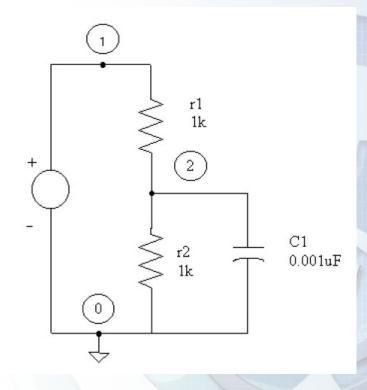

# **❖Hspice** 命令

\$hspice <input\_netlist.sp> > <output\_file.lis>

[lizht@LN2000 test]\$ hspice lab1.sp > lab1.lis

# ❖可使用提示行模式

\$hspice

```

[lizht@LN2000 test]$ hspice

```

```

Enter input file name: lab1.sp

Enter output file name or directory: [lab1.lis] lab1.lis

HSPICE versions are:

1 ==> ./ 2010.03 (2010.03)

Which HSPICE version to run (Enter # [1]):

```

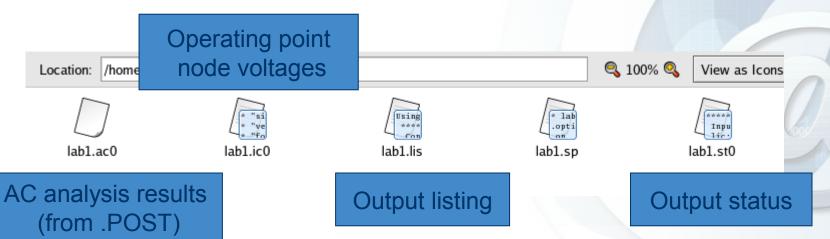

# Hspice 运行

# \*输入输出

- Star-Hspice Input

- Input netlist

- Model /libraries

- Star-Hspice Output

- Run status

- Output listing

- Analysis data, transient

- Analysis data, dc

- Analysis data, ac

- Measure output

.sp

.inc, .lib

- .st0

- .lis

- .tr# (e.g. .tr0)

- .sw# (e.g. .sw0)

- .ac# (e.g. .ac0)

- **.m**\*# (e.g. .mt0)

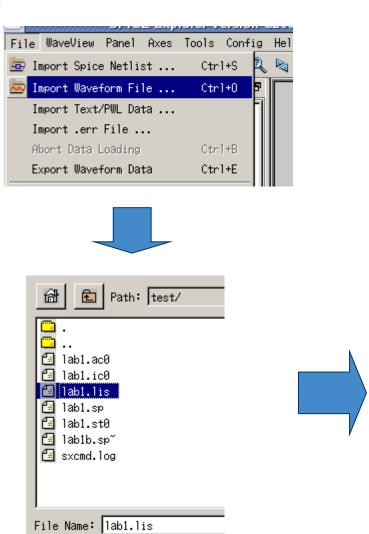

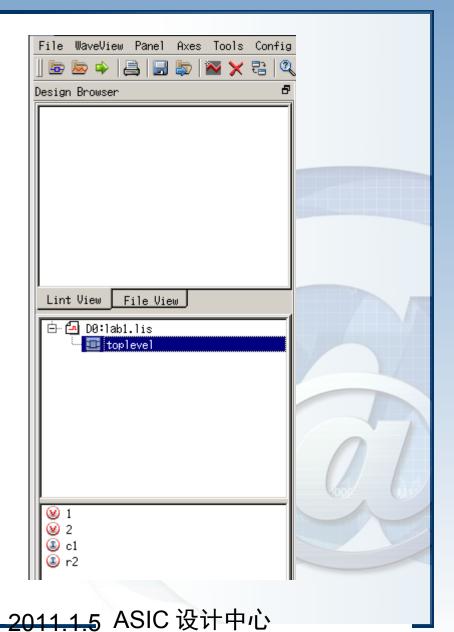

- ❖ AvanWaves Input (Linux 下不支持 AvanWaves )

- All analysis data files

# Hspice 运行

lab1.sp

Input netlist file

2011.1.5 ASIC 设计中心

# 网表介绍

#### ❖ 网表文件结构

TitleFirst line is always the title

Comments **\$\* - comment for a line**

\$ - comment after a command

Options .option post lists nodes and conditions for simulation

Print/Plot/Analysis .print v(d) i(rl)

.plot v(g)

.tran .1n 5n

Initial Conditions .ic v(b) = 0 \$ input state

Sources Vg g0 pulse 0 1 0 0.15 0.15 0.42

**\$example of a voltage source**

Circuit Description MN d g gnd n nmos RL vdd d 1K

Model Libraries .model n nmos level = 49

+ vto = 1 tox = 7n \$ + continuation character

END .end \$ terminates the simulation

标题

输出/分析

注释

操作类型

初始化环境

电路描述

结束提示

输入激励

单元库

2011.1.5 ASIC 设计中心

# ❖无源器件

■ R1 1 2 10k (表示节点 1 与 2 间有电阻 R1, 阻值为 10 k 欧)

C1 1 2 1pf (表示节点 1 与 2 间有电容 C1, 电容值为 1 pf)

L1 1 2 1mh (表示节点 1 与 2 间有电感 L1, 电感值为 1mh)

#### 网表 - 元器件

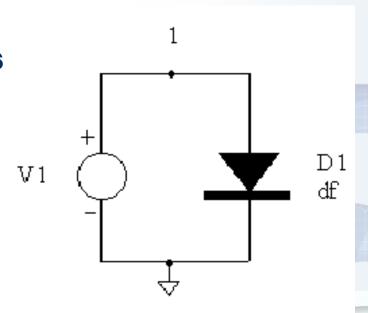

#### \* 有源器件

- 二极管

DXXXX N+ N- MNAME <AREA> <OFF> <IC=VD>D 为元件名称, N+ 和 N- 分别为二极管的正负节点, MNAME 是模型名, 后面为可选项: AREA 是面积因子, OFF 是直流分析所加的初始条件, IC=VD 是瞬态分析的初始条件。

■ 双极型晶体管 QXXXX NC NB NE <NS> MNAME <AREA> <OFF> < IC=VBE,VCE>

Q 为元件名称, NC NB NE <NS> 分别是集电极,基极,发射极和衬底的节点。 缺省时, NS 接地。后面可选项与二极管的意义相同。

- 结型场效应晶体管

JXXXX ND NG NS MNAME <AREA> <OFF> <IC=VD S,VGS>

J 为元件名称, ND NG NS 为漏,栅,源的节点。

- MOS 场效应晶体管 MXXXX ND NG NS NB MNAME <L=VAL> <W=VAL> M 为元件名称, ND,NG,NS,NB 分别是漏,栅,源和 衬底节点。L 沟道长, M 为沟道宽

# 网表 - 元器件

- Instance and Element Names:

- **♦** D

- **⋄** E,F,G,H

- \*

- **⋄** J

- \* K

- L

- **♦** M

- **\*** 0

- R

- \* O,T,U

- \* V

- \* X

- Capacitor

- Diode

- Dependent Sources

- \* Current

- **\* JFET or MESFET**

- Mutual Inductor

- \* Inductor

- MOSFET

- \* BJT

- Resistor

- \* Transmission Line

- Voltage Source

- Sub circuit Call

### 输入激励

- ❖ Hspice 中的激励源分为独立源和受控源两种 ,这里我们仅简单介绍独立源。

- 1. 直流源(DC):

- 电压源 Vxxx n+ n- dcval

- 电流源 Ixxx n+ n- dcval

- 2. 交流源(AC): Vxxx n+ n- AC=acmag,acphase

- 3. 瞬态源(随时间变化):

- 脉冲源: pulse v1 v2 td tr tf pw per

- 线性源: pwl t1 v1 <t2 v2 t3 v3...>

- 正弦源: sin vo va freq td damping phasedelay

# 分析类型

- ※ 1. 直流分析:

- ❖ 对 DC、AC和 TRAN分析将自动进行直流操作点 (DC OP)的计算,但.TRAN UIC将直接设置初始条件,不进行 DC OP的计算。

- .DC var1 start1 stop1 inc1< sweep var2 type np start2 stop2>

#### \* 直流分析包含以下五种语句:

- .DC: 直流扫描分析;

- .OP: 直流操作点分析;

- .PZ: Pole/Zero 分析;

- .SENS: 直流小信号敏感度分析;

- .TF: 直流小信号传输函数分析。

# 分析类型

- \* 2. 交流分析:

- \* 交流分析是指输出变量作为频率的函数。

- AC var1 start1 stop1 inc1 <sweep var2 type np start2 st op2>

- \* 交流分析包括以下四种语句:

- .NOISE: 噪声分析;

- .DISTO: 失真分析;

- .NET: 网络分析;

- .SAMPLE:采样噪声分析。

- \* 3. 瞬态分析:

- ❖ 瞬态分析是指计算的电路结果作为时间的函数。

- \* .TRAN tinc1 tstop1 tinc2 tstop2... START=.. UIC SWEEP...

# .OPTION 语句

- ❖ .options 语句格式: .options opt1 opt2 opt3... opt=x

- \* 一般在每个仿真文件中设置 options 为 .options ac ct list post, 也可以设置为 .options node opts

- ❖ 其中 .option list 表示将器件网表、节点连接方式等输入到列表文件,用于 debug 与电路拓扑结构有关的问题, .option node 表示将输出节点连接表到列表文件,用于 debug 与由于电路拓扑结构引起的不收敛问题, .option acct 表示在列表文件中输出运行时间统计和仿真效率, .option post 表示保存输出波形。

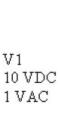

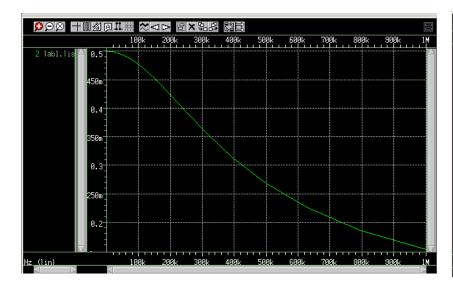

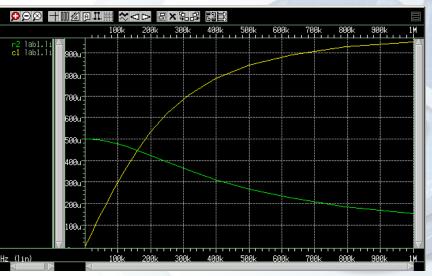

- ❖ Lab1 一个简单例子

- \* \* lab1 an example

- · .options list node pos

- .ac dec 10 1k 1meg

- \* .print ac v(1) v(2) i(r2 V1 10 VDC

- \*v1 1 0 10 ac 1

- \* r1 1 2 1k

- \* r2 2 0 1k

- \*c1 2 0 .001u

- \*.end

```

* lab1 an example

title

Option 控制

.options list node post

直流操作点分析

.op ◀

.ac dec 10 1k 1meg

交流分析

.print ac v(1) v(2) i(r2) i(c1) 输出(类型、节点)

v1 1 0 10 ac 1

r1 1 2 1k

器件与连线

r2 2 0 1k

c1 2 0 .001u

.end

结束

```

2011.1.5 ASIC 设计中心

cap

noise

2011.1.5 ASIC 设计中心

0.

1.000e+00 1.000e+00

0.

\*\*\*\*\*

\*\*\*\*\* ac analysis tnom= 25.000 temp= 25.000 \*\*\*\*\*

| freq      | voltage | voltage   | current   | current   |

|-----------|---------|-----------|-----------|-----------|

|           | 1       | 2         | r2        | c1        |

| 1.00000k  | 1.0000  | 499.9975m | 499.9975u | 3.1416u   |

| 1.25893k  | 1.0000  | 499.9961m | 499.9961u | 3.9550u   |

| 1.58489k  | 1.0000  | 499.9938m | 499.9938u | 4.9790u   |

| 1.99526k  | 1.0000  | 499.9902m | 499.9902u | 6.2682u   |

| 2.51189k  | 1.0000  | 499.9844m | 499.9844u | 7.8911u   |

| 3.16228k  | 1.0000  | 499.9753m | 499.9753u | 9.9341u   |

| 3.98107k  | 1.0000  | 499.9609m | 499.9609u | 12.5059u  |

| 5.01187k  | 1.0000  | 499.9380m | 499.9380u | 15.7433u  |

| 6.30957k  | 1.0000  | 499.9018m | 499.9018u | 19.8182u  |

| 7.94328k  | 1.0000  | 499.8444m | 499.8444u | 24.9468u  |

| 10.00000k | 1.0000  | 499.7534m | 499.7534u | 31.4004u  |

| 12.58925k | 1.0000  | 499.6094m | 499.6094u | 39.5194u  |

| 15.84893k | 1.0000  | 499.3814m | 499.3814u | 49.7293u  |

| 19.95262k | 1.0000  | 499.0206m | 499.0206u | 62.5602u  |

| 25.11886k | 1.0000  | 498.4504m | 498.4504u | 78.6687u  |

| 31.62278k | 1.0000  | 497.5507m | 497.5507u | 98.8592u  |

| 39.81072k | 1.0000  | 496.1347m | 496.1347u | 124.1022u |

| 50.11872k | 1.0000  | 493.9151m | 493.9151u | 155.5364u |

| 63.09573k | 1.0000  | 490.4574m | 490.4574u | 194.4380u |

sys 0.00 [lizht@LN2000 test]\$ sx

<sup>\*</sup> lab1 an example

2011.1.5 ASIC 设计中心

- ❖输出命令包括:

- ◆.PRINT、.PLOT、.GRAPH、.PROBE和.MEASURE。

- .PLOT antype ov1 <ov2...> <plo1,phi1...plo32,phi32>

- .PROBE antype ov1<ov2...ov32>

- .PRINT antype ov1 <ov2...ov32>

- ❖.print: 在输出的 list 文件中打印数字的分析 结果。

- ❖ plot: 在输出的 list 文件中打印低分辨率的曲线(由 ASCII 字符组成)

- ❖ ·graph: 生成高分辨率的曲线

- \*.probe:输出波形(曲线)文件

- ❖.measure: 输出用户定义的分析结果到 mt0 文件

- ❖.op, .tf, .noise, .sens 和 .four 都提供直接 输出功能

#### .model 语句

- ❖.model 模型参数设置

- ❖许多元器件都需用模型语句来定义其参数值。模型语句不同于元器件描述语句,它是以"」" 开头的点语句,由关键字 ■ MODEL,模型名称,模型类型和一组参数组成。 电阻,电容,二极管, MOS 管, 双极管都可设置模型语句。

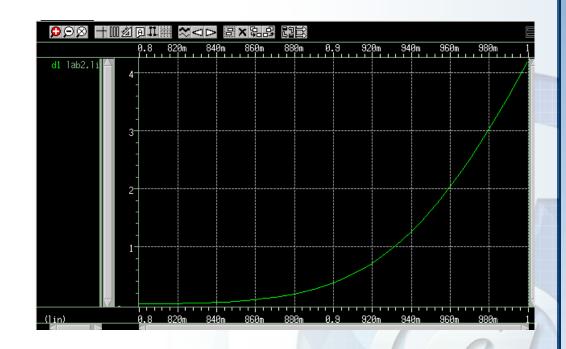

- \* \* lab2 diode sweep

- .options list node pos

- **.**ор

- .dc dv 800m 1 .005

- .print dc v(1) i(d1)

- .model df d

- \* + is = 2.6615e-16

- \* v1 1 0 dv

- **♦ d1 1 0 df**

- \*.end

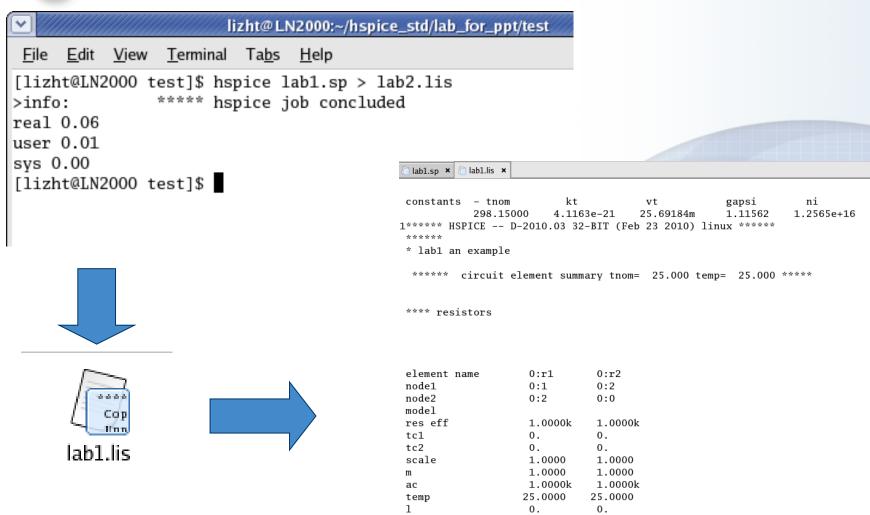

#### .lis 文件中有如下语句

\*\*\*\* diodes

metal cap

ic

name 0:d1

node + 0:1

node - 0:0

model 0:df

res eff 10.0000m

cdsat eff 266.1500a

capd eff 0.

poly cap

#### 二极管电流波形

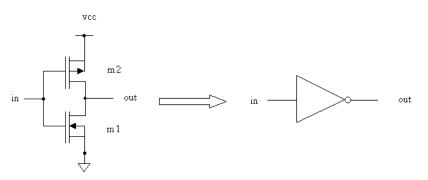

### .GLOBAL 与 .SUBCKT 语句

#### \*全局变量与子电路:

- 1. 采用 .GLOBAL 设置全局节点:

- .GLOBAL node1 node2 node3...

- 2. 子电路语句 .SUBCKT:

- SUBCKT SUBNAM N1

子电路的定义由 .SUBCKT 语句开始。 SUBNAM 是子电路名, N1< N2。。。>是外部节点号

.ENDS(表示结束子电路定义)...

- \* \* lab3 5 stage driver

- .options list node post

- .model pch pmos

- · .model nch nmos

- .tran 1n 10n

- \* .print tran v(1) v(6) i(vc

- \* .global vcc

- vcc vcc 0 5

- vin 1 0 2.5 pulse .2 4.82n 1n 1n 5n 20n

- xinv1 1 2 inv

- xinv2 2 3 inv

- xinv3 3 4 inv

- \* xinv4 4 5 inv

- \* xinv5 5 6 inv

- \* cd1 6 0 1.75f

- .subckt inv in out

- \* m1 out in vcc vcc pch l =1u w=20u

- \* m2 out in 0 0 nch l=1u w=20u

- · .ends inv

- .end

```

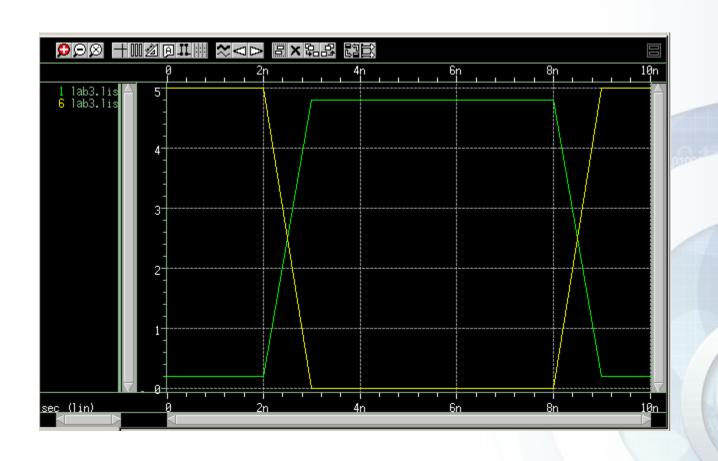

🛅 lab3.sp 🗶

* lab3 – 5 stage driver

.options list node post

.model pch pmos

lab3.pa0

.model nch nmos

.tran 1n 10n

.print tran v(1) v(6) i(vcc)

.global vcc

vcc vcc 0 5

vin 1 0 2.5 pulse .2 4.8 2n 1n 1n 5n 20n

□ lab3.pa0 ×

xinv1 1 2 inv

xinv2 2 3 inv

1 xinv1.

2 xinv2.

xinv3 3 4 inv

3 xinv3.

xinv4 4 5 inv

4 xinv4.

xinv5 5 6 inv

5 xinv5.

cd1 6 0 1.75f

.subckt inv in out

m1 out in vcc vcc pch l=1u w=20u

m2 out in 0 0 nch l=1u w=20u

.ends inv

.end

```

2011.1.5 ASIC 设计中心

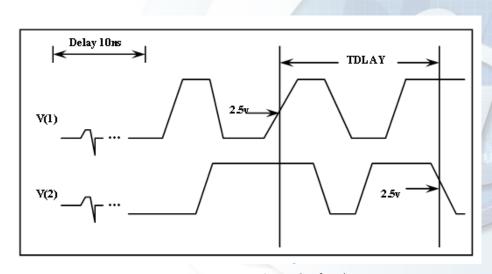

# .MEASURE 语句

### **\*MEASURE**

- Seven fundamental measurement modes:

- ✓ Rise, Fall, Delay 上升沿,下降沿,延时

- ✓ Average, Min, Max, and Peak-to-Peak 平均值, 最大最小值, 峰峰值

- ✓ Find-When 特定条件值

- ✓ Equation Evaluation 方程值

- ✓ Derivative Evaluation 微分值

- ✓ Integral Evaluation 积分值

- ✓ Relative Error 相对误差

# MEASURE: Rise/Fall 语法

#### .MEASURE <DC | TRAN | AC> result TRIG TARG <optimization options>

□ result - name given the measured value in the HSPICE output.

TRIG AT=value

TARG targ\_var VAL=targ\_val <TD=timedelay> <CROSS=#of | LAST><RISE=#of | LAST> <ST>

+ <FALLS=#of | LAST>

#### Example:

- .MEAS TRAN TDELAY TRIG V(1) VAL=2.5 TD=10ns RISE=2

- **+ TARG V(2) VAL=2.5 FALL=2**

2011.1.5 ASIC 设计中心

#### .measure 语句

❖ .measure 是一个后处理的工具,需要在引入分析之后才能够得出结果。

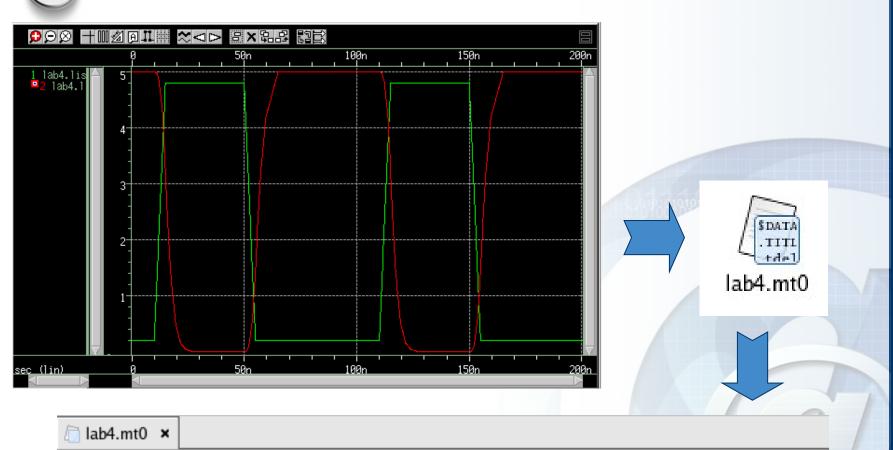

#### ❖ Lab 4 介绍

The circuit to be analyzed is a standard cmos inverter. What the .measure statement will do is measure the propagation delay fro m vin = 2.5 v on the second rising edge, the output at 2.5v on its second falling edge.

- lab4 the measure stat ement

- tran 100p 200n

- .options list node post measout

- .param tdval=5n tstop= 200n

- .meas tran tdelay trig v(1) val=2.5 td=tdval rise=2

- \* +targ v(2) val=2.5 fall=

- .meas tran vmax max v(2) from=tdval to=tstop

- .model pch pmos

- · .model nch nmos

- .print tran v(1) v(2)

- \* vcc vcc 0 5

- vin 1 0 2.5 pulse .2 4.810n 5n 5n 35n 100n

- \* m1 vcc 1 2 vcc pch l=1 u w=20u

- \* m2 2 1 0 0 nch l=1u w= 10u

- · .end

🛅 lab4.sp 🗶

.end

```

lab4 - the measure statement

.tran 100p 200n

.options list node post measout

.param tdval=5n tstop=200n

.meas tran tdelay trig v(1) val=2.5 td=tdval rise=2

+targ v(2) val=2.5 fall=2

.meas tran vmax max v(2) from=tdval to=tstop

.model pch pmos

.model nch nmos

.print tran v(1) v(2)

vcc vcc 0 5

vin 1 0 2.5 pulse .2 4.8 10n 5n 5n 35n 100n

m1 vcc 1 2 vcc pch l=1u w=20u

m2 2 1 0 0 nch l=1u w=10u

c1 2 0 2p

```

2011.1.5 ASIC 设计中心

# <u>@</u>

### Alter 语句

- .ALTER Statement : Description

- Rerun a Simulation Several Times with Different

- Circuit Topology

- Models

- Elements Statement

- Parameter Values

- Options

- Analysis Variables, etc.

- 1st Run: Reads Input Netlist File up to the first .ALTER

- Subsequent: Input Netlists to next .ALTER, etc.

- lab5 the alter control

- .options list node post

- .model snpn npn is=sis bf=sbf

- param sis=1e-16 sbf=1

- .tf v(out) vin

- \* vin in 0 1 1

- q1 vcc 1 2 snpn

- \* q2 3 4 2 snpn

- q3 vcc 3 out snpn

- \* r1 in 1 20k

- \* r2 vcc 3 200k

- r3 out 4 180k

- \* r4 4 0 20k

- \* it 2 0 100u

- \* vcc vcc 0 20

- alter \$ \*\* Change is to 1e-15 / bf to 100

- \* .param sis=1e-15 sbf=1

- alter \$ \*\*\* Change is t

1e-14 / bf to 50

- .param sis=1e-14 sbf=5

0

- alter \$ \*\*\*\* Change is to 1e-13 / bf to 25

- \* .param sis=1e-13 sbf=2

- .end

```

□ lab5.sp ×

lab5 - the alter control

.options list node post

.model snpn npn is=sis bf=sbf

.param sis=1e-16 sbf=150

.tf v(out) vin

vin in 0 1 1

q1 vcc 1 2 snpn

q2 3 4 2 snpn

q3 vcc 3 out snpn

r1 in 1 20k

r2 vcc 3 200k

r3 out 4 180k

r4 4 0 20k

it 2 0 100u

vcc vcc 0 20

.alter $ ** Change is to 1e-15 / bf to 100

.param sis=1e-15 sbf=100

.alter $ *** Change is to 1e-14 / bf to 50

.param sis=1e-14 sbf=50

.alter $ **** Change is to 1e-13 / bf to 25

.param sis=1e-13 sbf=25

.end

```

```

[lizht@LN2000 test]$ hspice lab5.sp > lab5.lis

***** hspice job concluded

>info:

***** hspice job concluded

>info:

>info:

***** hspice job concluded

***** hspice job concluded

>info:

real 0.08

user 0.02

sys 0.02

lab5.ic3

lab5.ic0

lab5.ic1

lab5.ic2

2011.1.5 ASIC 设计中心

```

small-signal transfer characteristics v(out)/vin 9.3879 input resistance at vin = 3.1665xoutput resistance at v(out) = 111.6365 small-signal transfer characteristics v(out)/vin 9.3287 input resistance at vin 2.1175x output resistance at v(out) = 165.5089small-signal transfer characteristics \*\*\*\* v(out)/vin = 9.1528 vin = 1.0689xinput resistance at output resistance at v(out) = 367.7933small-signal transfer characteristics v(out)/vin 8.8118 input resistance at vin = 545.1353k output resistance at v(out) = 936.9004

## 平台与参考资料

- ◆版本: Hspice-D-2010.03

- **❖平台: Linux**

- ❖资料: (不完全清单)

- \*1) User Guide: Simulation and Analysis Version D- Version D-2010.03

- 2 Hspice 3Days Training (2000)

- ◆3) Hspice 的使用 《集成电路课程设计》

(2001.10)

2011.1.5 ASIC 设计中心