# ESD 模型及有关测试

- 1、ESD模型分类

- 2、HBM和MM测试方法标准

- 3、 CDM 模型和测试方法标准

- 4、 EIC 模型和测试方法标准

- 5、 TLP 及其测试方法

- 6、拴锁测试

- 7 、 I-V 测试

- 8、标准介绍

# 1、ESD模型分类

- 因 ESD 产生的原因及其对集成电路放电的方式不同, 经过统计, ESD 放电模型分下列四类:

- (1) 人体放电模式 (Human-Body Model, HBM)

- (2) 机器放电模式 (Machine Model, MM)

- (3) 组件充电模式 (Charged-Device Model, CDM)

- (4) 电场感应模式 (Field-Induced Model, FIM) 另外还有两个测试模型:

- (5) 对于系统级产品测试的 IEC 电子枪空气放电模式

- (6) 对于研究设计用的 TLP 模型

#### 人体放电模式 (Human-Body Model, HBM)

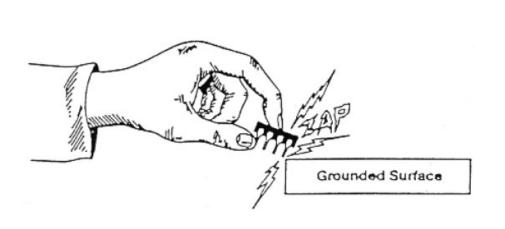

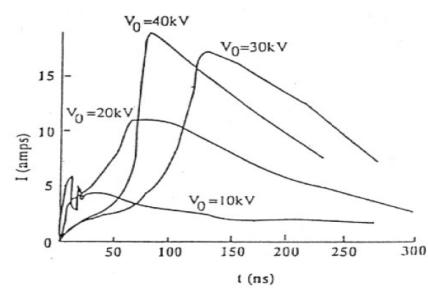

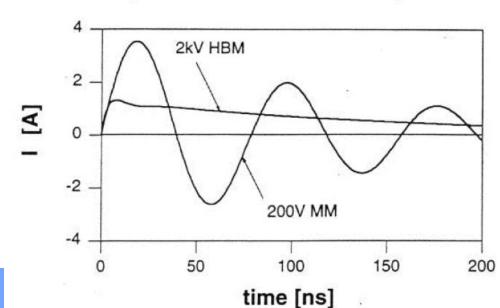

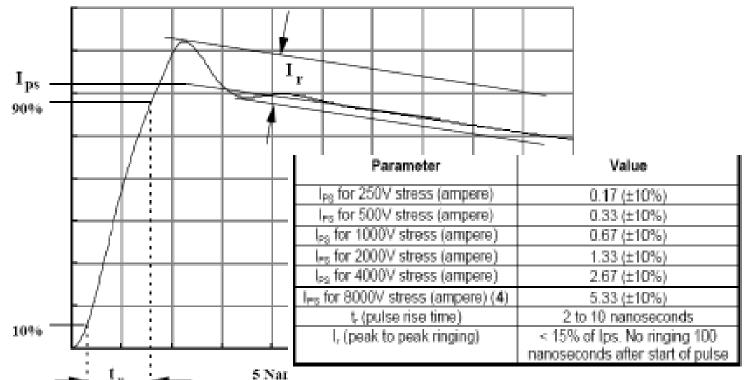

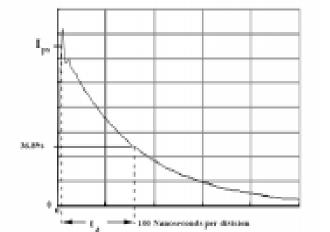

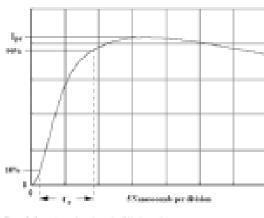

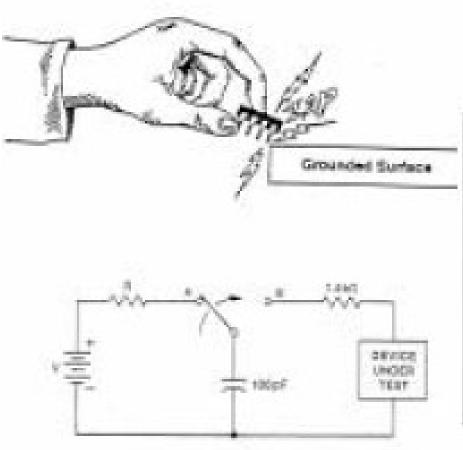

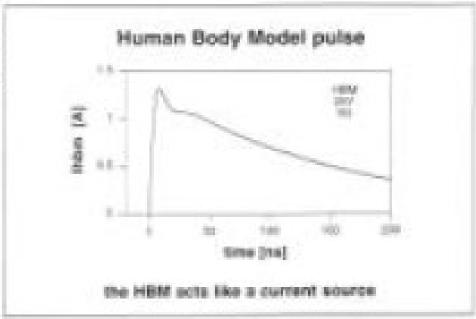

• 人体放电模式 (HBM) 的 ESD 是指因人体在地上走动磨擦或其它因素在人体上已累积了静电,当此人去碰触到 IC 时,人体上的静电便会经由 IC 的脚 (pin) 而进入 IC 内,再经由 IC 放电到地去,如图 2.1-1(a) 所示。此放电的过程会在短到几百毫微秒 (ns) 的时 间内产生数安培的瞬间放电电流,此电流会把 IC 内的组件 给烧毁。 不同 HBM 静电电压相对产生的瞬间放电电流与时间的关系 显示于图 2.1-1(b)。对一般商用 IC 的 2-KV ESD 放电电压而言,其瞬间放电电流的尖峰值大约是 1.33 ESD CURRENTS

#### 人体放电模式 (Human-Body Model, HBM)

- 有关于 HBM 的 ESD 已有工业测试的标准:

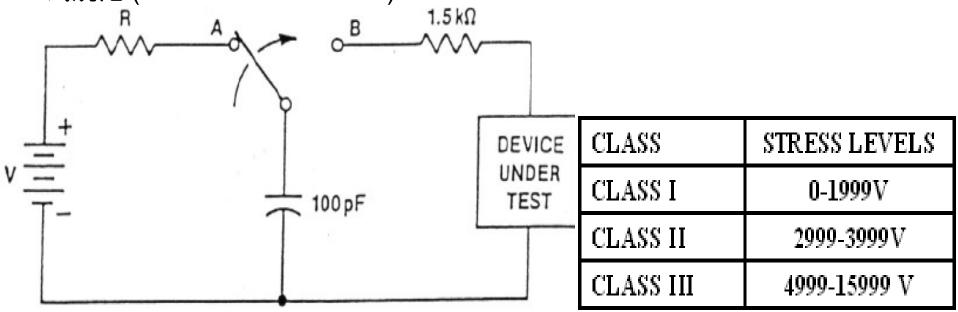

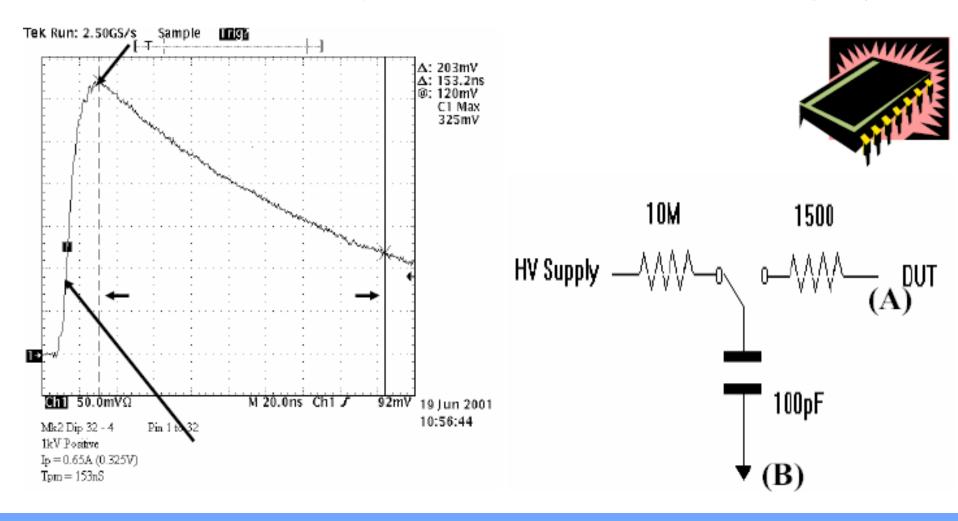

- 图显示工业标准 (MIL-STD-883C method 3015.7) 的等效电路图,其中人体的 等效电容定为 100pF, 人体的等效放电电阻定为  $1.5K\Omega$ 。

- 表是国际电子工业标准 (EIA/JEDEC STANDARD) 对人体放电模式订定测试规范 (EIA/JESD22-A114-A)

#### 机器放电模式 (Machine Model, MM)

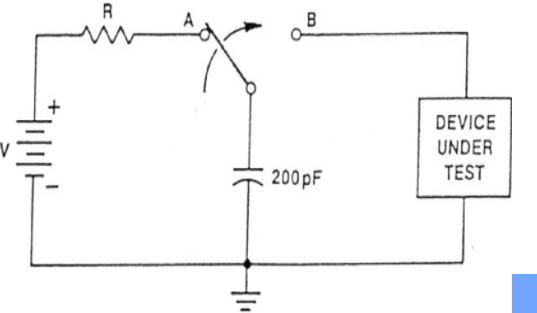

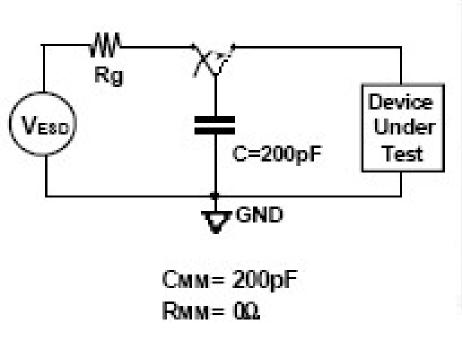

- 机器放电模式的 ESD 是指机器 (例如机械手臂)本身累积了静电,当此机器去碰触到 IC 时,该静电便经由 IC 的 pin 放电。因为机器是金属,其等效电阻为 0Ω,其等效电容为 200pF。由于机器放电模式的等效电阻为 0,故其放电的过程更短,在几毫微秒到几十毫微秒之内会有数安培的瞬间放电电流产生。

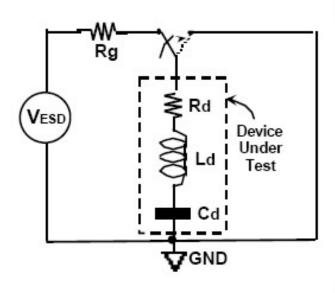

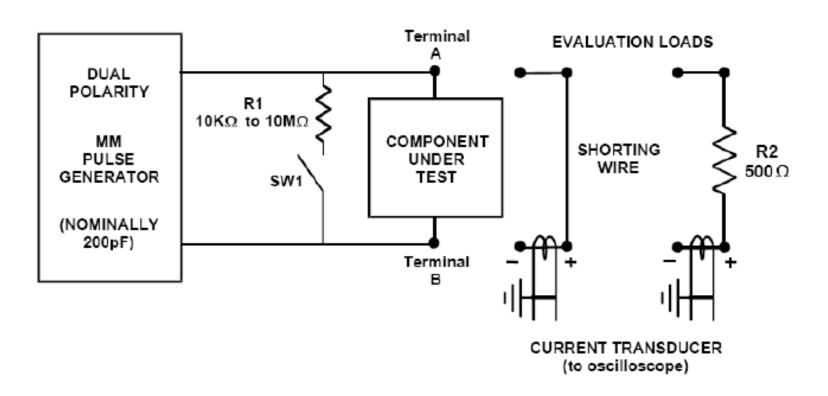

- 此机器放电模式工业测试标准为 EIAJ-IC-121 method20, 其等效电路图和等级如下。

| CLASS | STRESS LEVELS |  |  |  |

|-------|---------------|--|--|--|

| M0    | 0-50V         |  |  |  |

| М     | 50-100V       |  |  |  |

| M2    | 100-200 V     |  |  |  |

| М3    | 200-400 V     |  |  |  |

| M4    | 400-800 V     |  |  |  |

| M5    | >800 V        |  |  |  |

#### 机器放电模式 (Machine Model, MM)

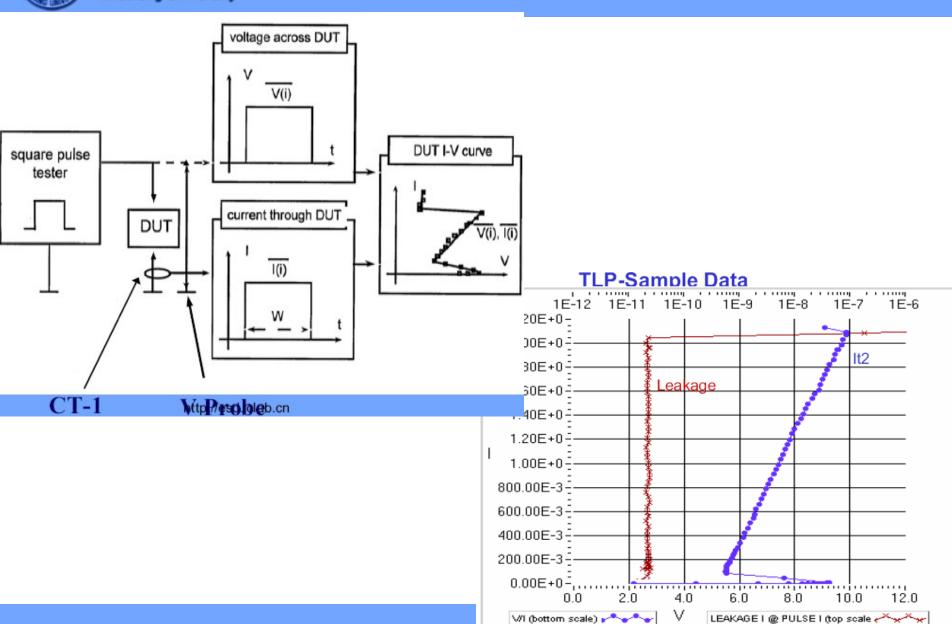

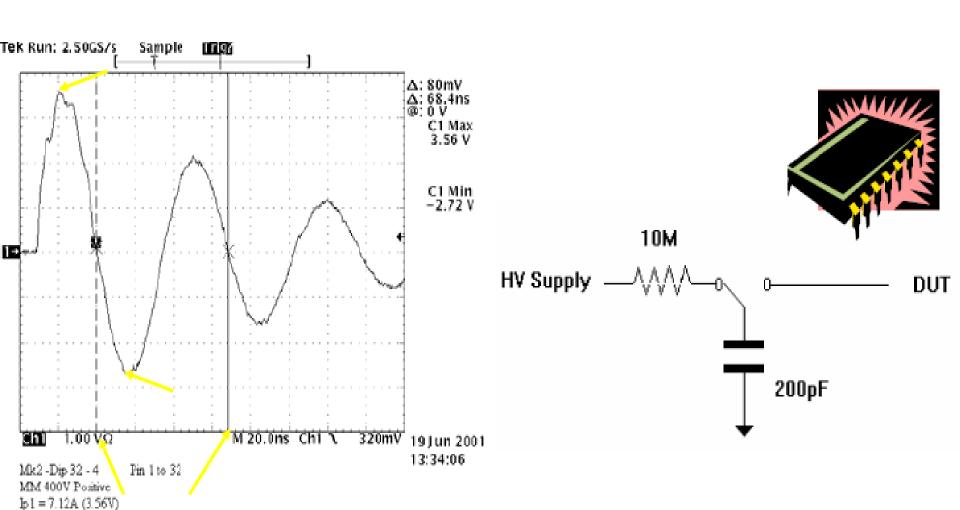

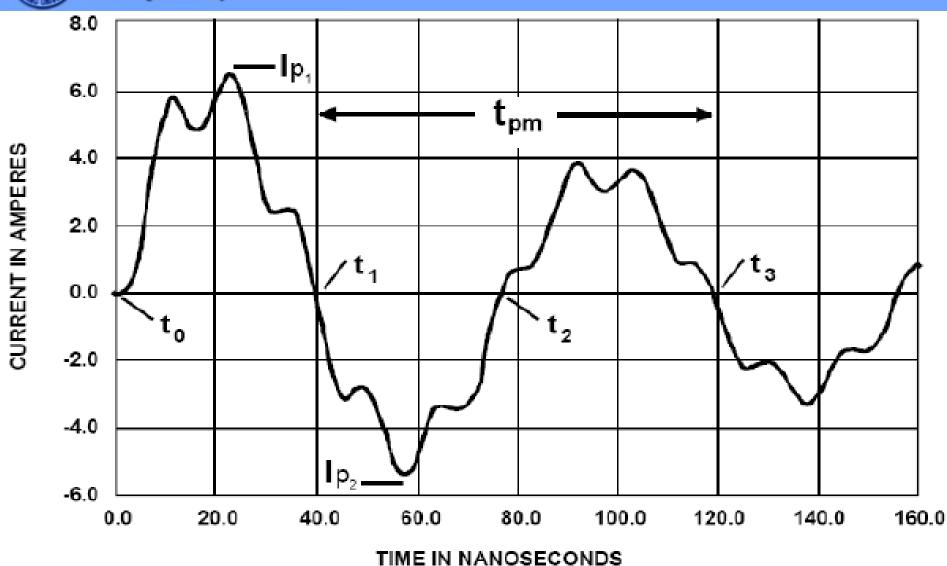

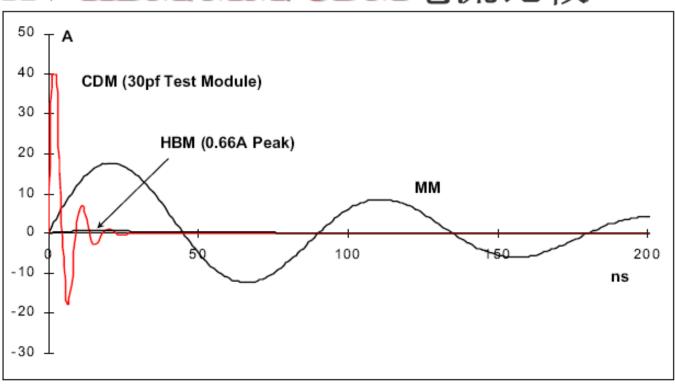

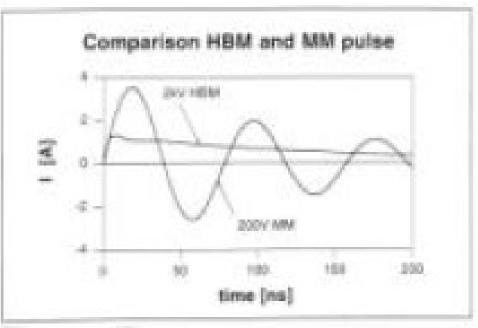

- 2-KV HBM 与 200-V MM 的放电比较如图,虽然 HBM 的电压 2 KV 比 MM 的电压 200V 来得大,但是 200-V MM 的放电电流却比 2-KV HBM 的 放电电流来得大很多,放电电流波形有上下振动 (Ring) 的情形,是因为测试机台导线的杂散等效电感与电容互相耦合而引起的。因此机器放电模式对 IC 的破坏力更大。

- 国际电子工业标准 (EIA/JEDEC STANDARD) 亦对此机器放电模式订定 测试规范 (EIA/JESD22-A115-A) Comparison HBM and MM pulse

## 组件充电模式 (Charged-Device Model, CDM)

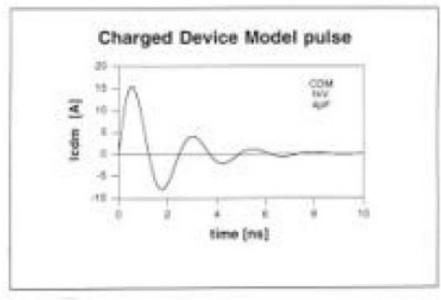

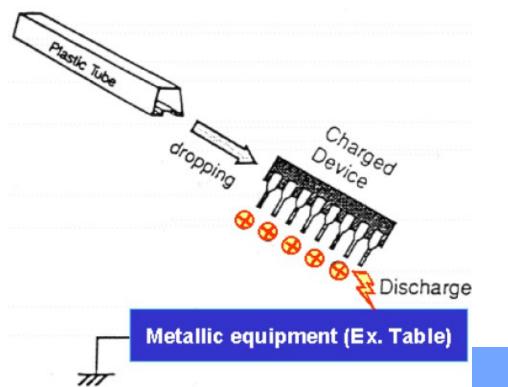

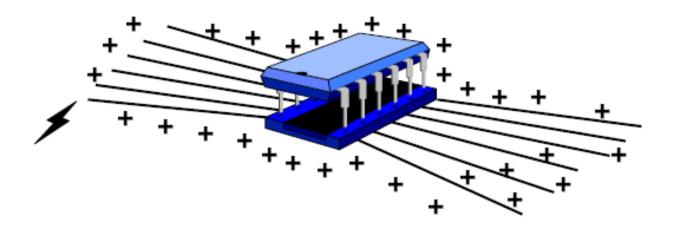

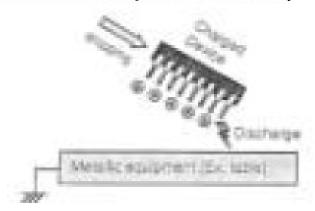

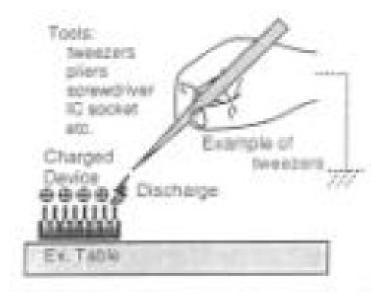

此放电模式是指IC先因磨擦或其它因素而在IC内部累积了静电,但在静电累积的过程中IC并未被损伤。此带有静电的IC在处理过程中,当其 pin 去碰触到接地面时,IC内部的静电便会经由 pin 自IC内部流出来,而造成了放电的现象。 此种模式的放电时间更短,仅约几毫微秒之内,而且放电现象更难以真实的被模拟。

#### 组件充电模式 (Charged-Device Model, CDM)

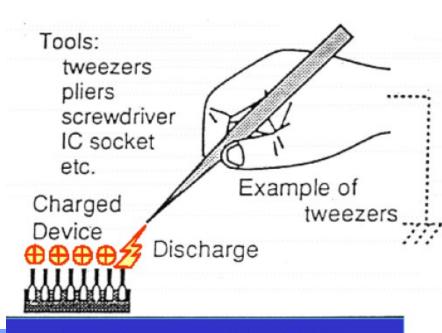

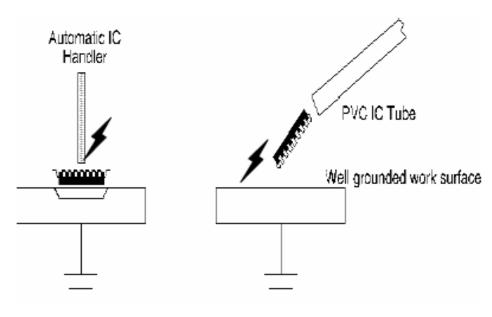

CDM 模式 ESD 可能发生的情形显示:

- (1) IC 自 IC 管中滑出后,带电的 IC 脚接触接到地面而形成放电现象。

- (2) IC 自 IC 管中滑出后, IC 脚朝上, 但经由接地的金属工具 而放电。

(1)

Metallic equipment (Ex. Table)

#### 组件充电模式 (Charged-Device Model, CDM)

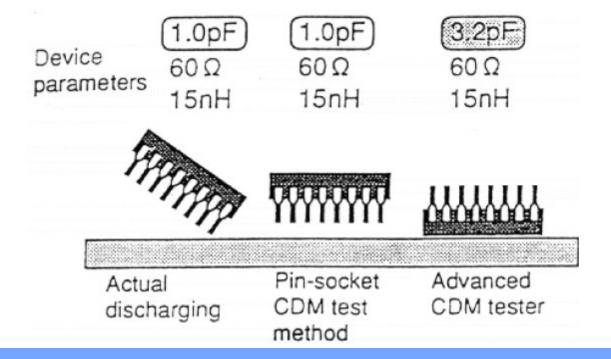

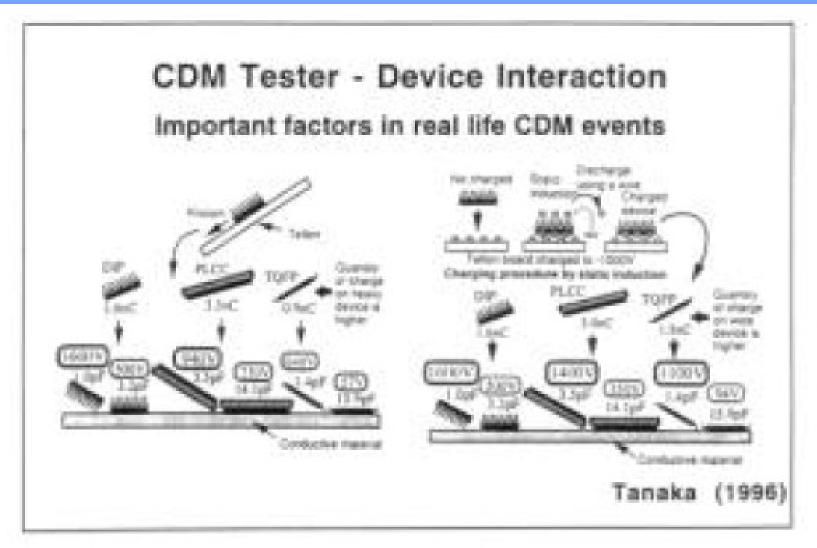

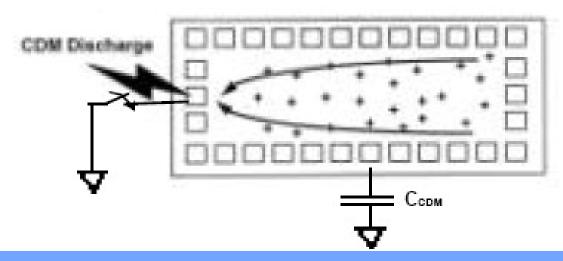

IC 内部累积的静电会因 IC 组件本身对地的等效电容而变, IC 摆放角度与位置以及 IC 所用包装型式都会造成不同的等效电容。此电容值会导致不同的静电电量累积于 IC 内部。

Different dies and packages cause different ESD voltages in the CDM ESD events.

#### 电场感应模式 (Field-Induced Model, FIM)

FIM 模式的静电放电发生是因电场感应而起的。当 IC 因输送带或其它因素而经过一电场时,其相对极性的电荷可能会自一些 IC 脚而排放掉,等 IC 通过电场之后, IC 本身便累积了静电荷,此静电荷会以类似 CDM 的模式放电出来。

有关 FIM 的放电模式早在双载子 (bipolar) 晶体管时代就已被发现,现今已有工业测试标准。

国际电子工业标准 (EIA/JEDEC STANDARD) 中亦有此电场 感应模式订定测试规范 (JESD22-C101) 。

#### IEC 电子枪空气放电模式

主要是接触式放电和非接触式放电

- 8kV air discharge□

- 4kV contact mode for most products

- 6kV contact for medical devices

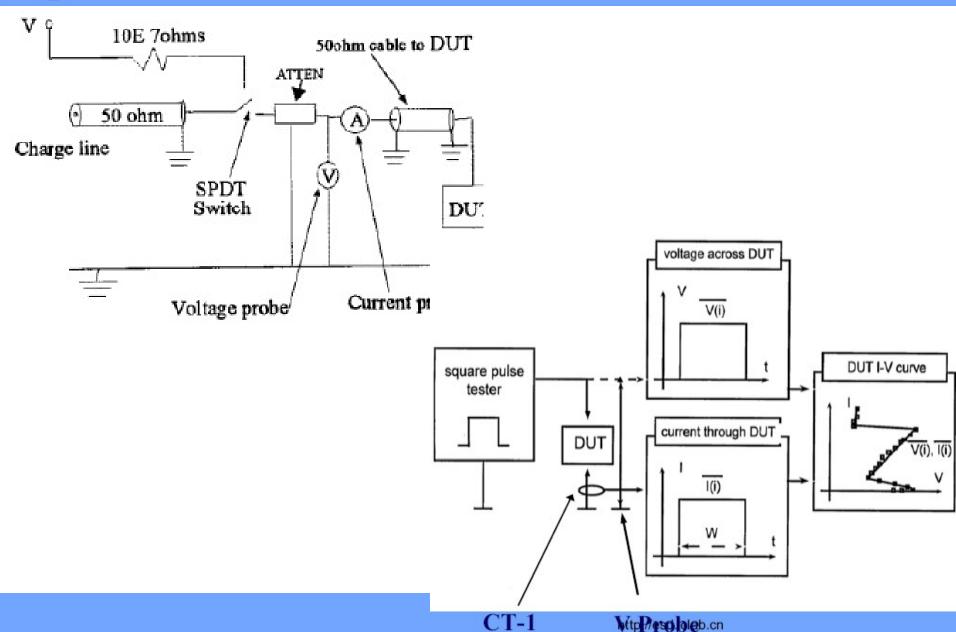

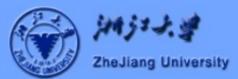

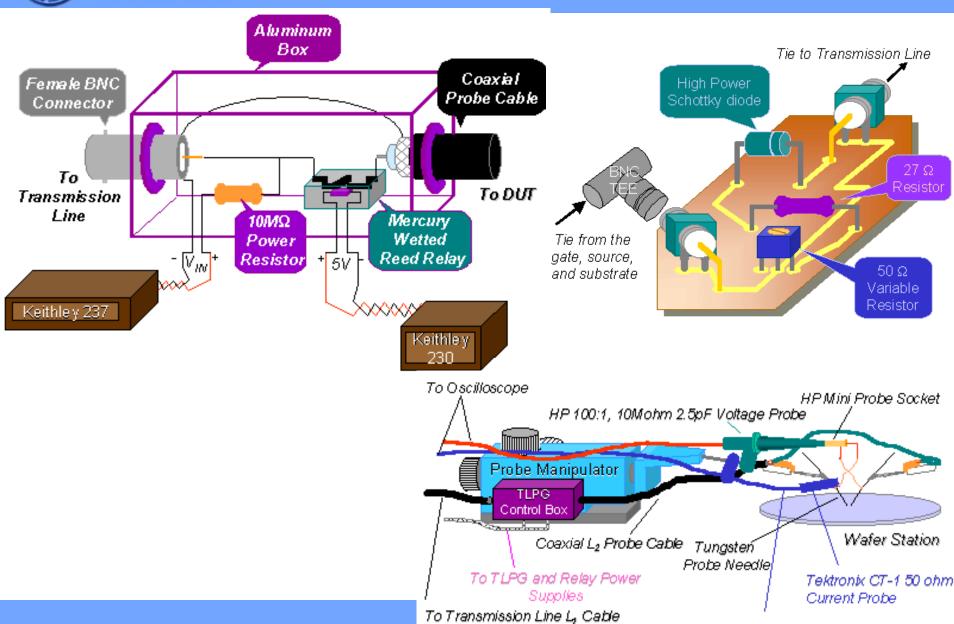

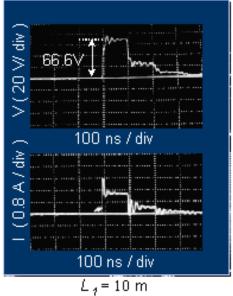

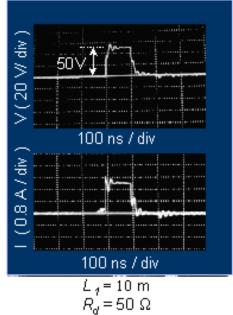

## TLP 模型

- 为了研究 ESD 防护器件的工作特性,了解 ESD 脉冲来的时候,落在 ESD 防护器件上的电压电流,包括开启的电压和 ESD 脉冲持续期间的 ESD 防护器件的每个点的电压电流,也就是触发电压电流、回退电压电流和二次崩溃电压电流等。

- 为了达到上述目的,就要将 ESD 脉冲离散化。这就是用 TLP 的矩形脉冲模拟 HBM 的放电脉冲和放电行为。 TLP 脉冲上升时间和 HBM 一致, TLP 矩形脉冲脉宽西面的能量与 HBM 能量一致。

## HBM, MM与CDM模型参数比较

| Mode | Model Parameters    |                        |              | Parasitic Components |                                             |                | Standard Level |             |              |

|------|---------------------|------------------------|--------------|----------------------|---------------------------------------------|----------------|----------------|-------------|--------------|

| 1    | Time rise<br>(nsec) | Time decay<br>(nsec)   | Vpeak<br>(V) | Cesd<br>(pF)         | $\operatorname{Resd}_{\left(\Omega\right)}$ | Lesd<br>( µ H) | Okey<br>(V)    | Safe<br>(V) | Super<br>(V) |

| HBM  | <10                 | 150±20                 | 2000~15000   | 100                  | 1500                                        | 75             | 2000           | 4000        | 10000        |

| MM   | 6~7.5               | 60-90<br>(ring period) | 100-400      | 200                  | 数十                                          | 1-2            | 200            | 400         | 1000         |

| CDM  | <0.2-0.4            | 0.4-2                  | 250-2000     | 6.8                  | 数十                                          | 1-2            | 1000           | 1500        | 2000         |

| IEC  | 0.7-1               | ~80                    | 2000-15000   | 150                  | 330                                         | -              |                |             |              |

2KV HBM, 200V MM, 与 1KV CDM 的放电电流比较, 其中 1KV CDM 的放电电流在不到 1ns 的时间内, 便已冲到约 15 安培的尖峰值, 但其放电的总时段约在 10ns 的时间内便结束。此种放电现象更易造成集成电路的损伤。

#### Comparison HBM, MM and CDM pulse

#### HBM, MM与CDM比较

|       | 人体放电模式<br>(Human-Body<br>Model) | 机器放电模式<br>(Machine<br>Model) | 组件充电模式<br>(Charged-Device<br>Model) |

|-------|---------------------------------|------------------------------|-------------------------------------|

| Okey  | 2000V                           | 200V                         | 1000V                               |

| Safe  | 4000V                           | 400V                         | 1500V                               |

| Super | 10000V                          | 1000V                        | 2000V                               |

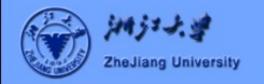

HBM 测试方法及标准

1.ANSI-STM5.1-2001

JESD22-A114D -2005

AEC-Q100-002D -2003

- 2. 该标准用于明确 HBM 模式下的 ESD 电压敏感度 的测试、评价以及分级过程

- 3. 整个测试过程繁琐,尤其对仪器及脉冲波形的校验工作,但非常必要

- 4. ESD 测试中, 器件不在工作状态

## 人体模型HBM电路和短路波形

- 一些比较重要的概念:

- (1) 器件失效 (component failure): 当器件不再符合 合厂商或用户提供的器件动态和静态特性参数

- (2) ESD 敏感度 (sensitivity): 引起器件失效的 ESD 等级 (level)

- (3) ESD 耐受电压 (withstand voltage): 在不引起器件失效前提下的最大 ESD 等级

- (4) 步进耐压增强 (Step stress test hardening): 在步进增加的测试电压下,器件的耐受电压的现象

## HBM短路(0 ohm)和500 ohm负载波形参数

|        |            |             |              | Ir Peak | Tr 500 |               | lpr      |

|--------|------------|-------------|--------------|---------|--------|---------------|----------|

| +/- kV | Trise (ns) | T fall (ns) | I peak (A)   | Ringing | (ns)   | lpr 500       | % of lps |

| 0.1    | 2.0 – 10   | 130 – 170   | 0.060- 0.073 | <15%    |        |               |          |

| 0.25   | 2.0 – 10   | 130 – 170   | 0.15 - 0.19  | <15%    |        |               |          |

| 0.5    | 2.0 – 10   | 130 – 170   | 0.30 - 0.36  | <15%    |        |               |          |

| 1      | 2.0 – 10   | 130 – 170   | 0.60 - 0.73  | <15%    | 5 – 25 | 0.375 - 0.550 | ≥ 63%    |

| 2      | 2.0 – 10   | 130 – 170   | 1.20 - 1.46  | <15%    |        |               |          |

| 4      | 2.0 – 10   | 130 – 170   | 2.40 - 2.94  | <15%    | 5 – 25 | 1.50 – 2.20   | ≥ 63%    |

| 8      | 2.0 – 10   | 130 – 170   | 4.80 - 5.86  | <15%    |        |               |          |

用于验证脉冲电流波形的仪器:示波器、连个电阻 负载和一个电流传感器。具体指标:

- 示波器:分辨率 100mA/1cm 、带宽 350MHz 、1cm/ns 的显示输出速度;

- 负载电阻: Load1: 短路线, Load2: 500ohm

- 电流探针: 带宽 350MHz, 峰值电流 12A, 上 升时间小于 1ns

#### 求是 创新

仪器和脉冲波形检测和校准

- —— 初次使用时检测

- —— 例行检测

- —— 维修后检测

- ——测试版或引脚插槽更换 或移动后检测

记录波形(用于对比和校验)

——新机器

——老机器

测试板的校验程序:

- (1)测试板上所有引脚的电气连贯性

- (2)对于新安装的测试板

找出测试板上离脉冲发生器最近的一个引脚,将其作为参考节点连接到 B 端。其他所有引脚依次连接到 A 端,并且在 AB 间接入短接线。使用正负 1000V 的脉冲电压在 AB 端,观察波形,经过所有引脚对的电流波形必须符合如图波形

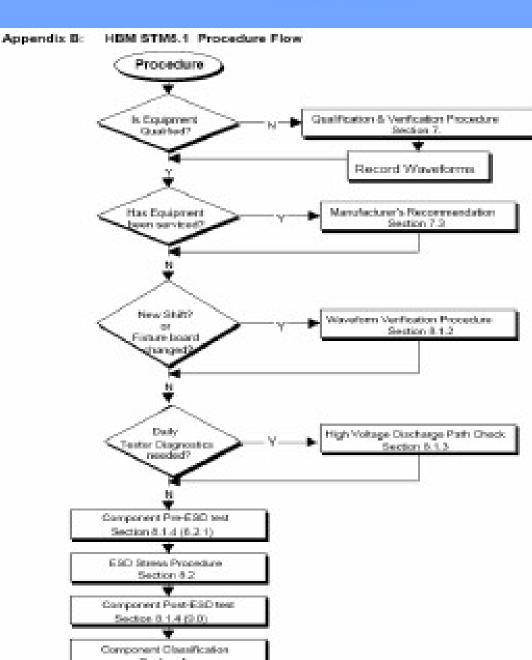

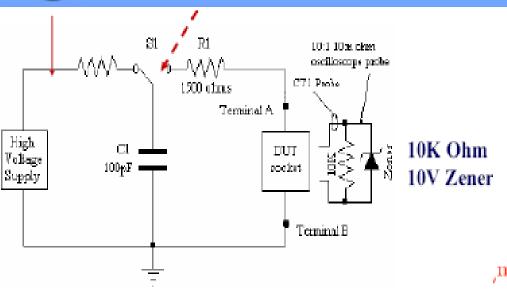

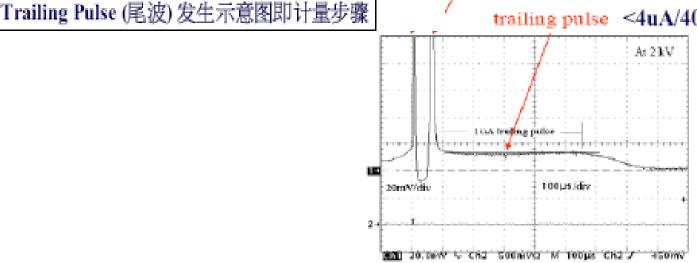

Trailing Pulse (尾波) 示意图 , 0.13um 或更小制程工艺要考虑

Figure 5- Current waveform through a 901 once resistor

HBM 测试方法及标准

1.ANSI-STM5.1-2001

JESD22-A114D -2005

AEC-Q100-002D -2003

- 2. 该标准用于明确 HBM 模式下的 ESD 电压敏感度 的测试、评价以及分级过程

- 3. 整个测试过程繁琐,尤其对仪器及脉冲波形的校验工作,但非常必要

- 4. ESD 测试中,器件不在工作状态

#### 对于非新安装的测试板

- 采用Worst-Case Pair作为AB端,然后在两个AB端接入短路线,电流探针接在离B端最接近的地方,并在AB端分别加1000V,2000V,4000V的5个正脉冲和5个负脉冲,观察波形,必须符合Figure2a的要求

- 将短路线换为500ohm的电阻,分别加1000V和4000V的 正负电压,波形需符合Figure3的要求

- 将示波器的水平时间分度设为1ms/div,接入短路线,加入脉冲观察是否伪脉冲(Spurious Pulse)小于主脉冲(Main Pulse)幅值的15%

#### • 对于尾波校准

main ESD pulse (off scale)

second ESD pulse (off scale)

trailing pulse <4uA/4000V over 1000uS

After HBM ESD

Trailing Pulse (尾波) 示意图 , 0.13um 或更小制程工艺要考虑

#### ESD测试要求和程序

- (1)测试要求

- 对器件进行操作时必须执行ESD防护操作规范

- 对波形进行检测(非常重要步骤!)

- 高压放电路径检测(使用仪器提供商的推荐程序)

- 检测待测器件的特性参数,保证所有器件在ESD测试前都是正常的

- 测试时的引脚组合!

- Maximum # of devices = (# of pin combinations) X (# of voltage steps required) X 3 devices 主要取决于功率引脚数

#### 波形的认证程序

- (1)验证所有测试板引脚的电器连贯性

- (2)在参考引线对之间接入短路线,在短路线尽可能靠近B 端附近放置电流探针

- (3)加上正负1000V和4000V的脉冲电压,如果需要测试高于4000V的电压,还需加8000V的脉冲电压,调整示波器的水平时间分度分别为5ns/div,100ns/div,观察电流波形需符合Figure2a,Figuire2b

- (4)将示波器的水平时间分度设为1ms/div,加上脉冲后伪脉冲幅值小于主脉冲的15%

例如:10 pin device with 2-Vdd, 2-Vss, 2-Vcc, 2-input and 2-output pins

| Sequence # | Pin comb. | Connect to A   | Connect to B           | Float Pins                |

|------------|-----------|----------------|------------------------|---------------------------|

| 1          | 1         | 1st input pin  | 2-Vdd                  | all other 7 pins          |

| 2          | 1         | 2nd input pin  | 2-Vdd                  | all other 7 pins          |

| 3          | 1         | 1st output pin | 2-Vdd                  | all other 7 pins          |

| 4          | 1         | 2nd output pin | 2-Vdd                  | all other 7 pins          |

| 5          | 1         | 1st Vcc pin    | 2-Vdd                  | all other 7 pins          |

| 6          | 1         | 2nd Vcc pin    | 2-Vdd                  | all other 7 pins          |

| 7          | 1         | 1st Vss pin    | 2-Vdd                  | all other 7 pins          |

| 8          | 1         | 2nd Vss pin    | 2-Vdd                  | all other 7 pins          |

| 9          | 2         | Repeat 1-8     | but swap               | Vdd and Vss               |

| 10         | 3         | Repeat 1-8     | but swap               | Vdd and Vcc               |

| 11         | 4         | 1st input pin  | output 1,2 and input 2 | all Vdd, Vss and Vcc pins |

| 12         | 4         | 2nd input pin  | output 1,2 and input 1 | all Vdd, Vss and Vcc pins |

| 13         | 4         | 1st output pin | input 1,2 and output 2 | all Vdd, Vss and Vcc pins |

| 14         | 4         | 2nd output pin | input 1,2 and output 1 | all Vdd, Vss and Vcc pins |

MM测试方法及标准:

- 1. ANSI-STM5.2-1999 JESD22-A115A -1997 AEC-Q100-003E -2003

- 2.该标准用于明确在MM模式下的ESD电压敏感度的测试、评价以及分级过程,与HBM的测试方法基本类似

- 3.与HBM的主要区别是在于是一个低阻抗模型,因而ESD的耐受电压也要低很多

MM模式的测试原理电路图

Figure 1: Typical equivalent MM ESD stress test circuit

MM测试方法及标准:

测试过程中MM于HBM的不同之处

- 仪器的标称电容电阻不同

- 两次脉冲时间间隔最小为1s,使器件中的电荷能够充分释放

Table 3 MM ESD stress levels

- ESD测试电压等级

- 脉冲波形的形状

| Stress Level | Equivalent Charging (±)<br>Voltage<br>Vp (volt) |

|--------------|-------------------------------------------------|

| 1            | 100                                             |

| 2            | 200                                             |

| 3            | 400                                             |

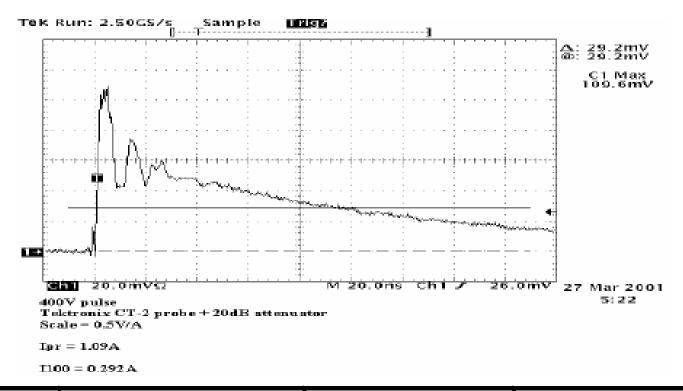

Io2 = 5.44A (2.72V) 76% of Io1

Tpm = 68.4nS

# 机器模型电路和短路波形

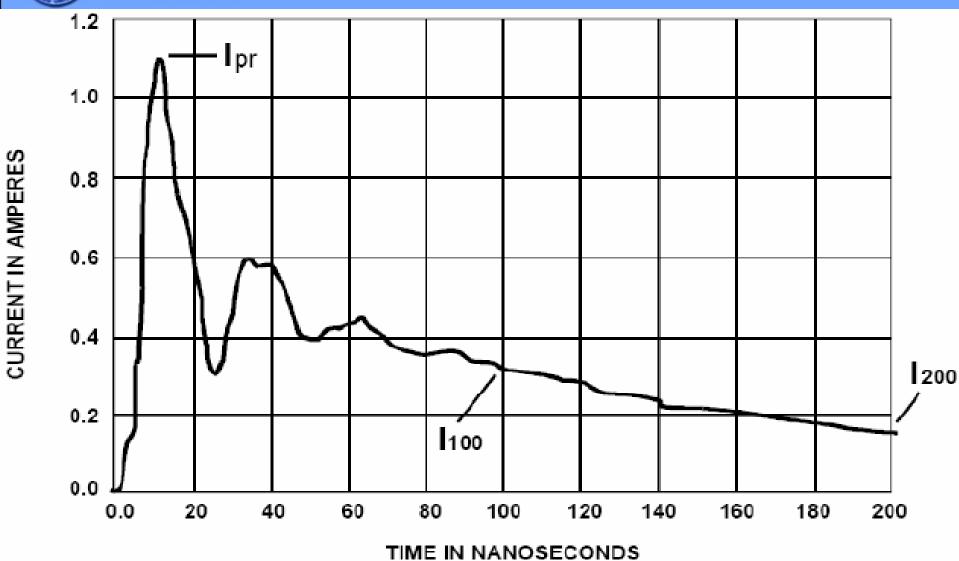

Figure 3: Current waveform through a 500 ohm resistor for a 400 volt discharge

Figure 2: Current waveform through a shorting wire for a 400 volt discharge

### 机器模型(MM)500ohm负载波形

| +/- 400 | lpr            | I100          | I200 as % of I100 |

|---------|----------------|---------------|-------------------|

| Volts   |                |               |                   |

| ESDA    | 0.85 – 1.20    | 0.26 - 0.32   | 35 - 45 %         |

| AEC     | 0.85 – 1.20    | 0.26 - 0.32   |                   |

| JEDEC   | I100 X 4.5 Max | 0.232 - 0.348 |                   |

## HBM 和 MM 测试方法

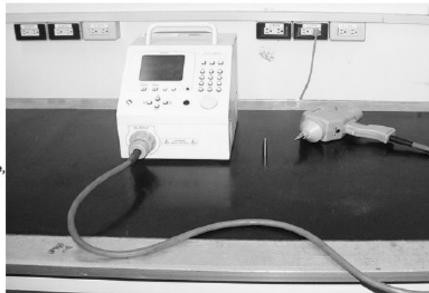

(a) System 700 by Oryx Desktop, HBM, MM & IEC.

(c) System 11000EX by Oryx HBM, MM, TLP & Latch-up.

(b) WaferMaster by KeyTek Wafer level, HBM & MM.

(d) PARAGON by KeyTek HBM, MM & Latch-up.

# HBM/MM 测试内容

所有管脚(一次一根)对(第X组)接地管脚(接地)所有管脚(一次一根)对(第y组)电源管脚(接地)所有 I/O 管脚(一次一根)对所有其他 I/O 管脚(接地)NC 管脚

- —— 依美军标 MIL-883 不测试

- —— 依民标 ESDA/JEDEC/AEC 均要求测试

在每一测试模式下,IC 的该测试脚先被打上 (Zap) 某一 ESD 电压,而且在同一 ESD 电压下,IC 的该测试脚必须要被 Zap 三次,每次 Zap 之间的时间间隔约一秒钟, Zap 三次之后再观看该测试脚是否己被 ESD 所损坏,若 IC 尚未被损坏则调升 ESD 的电压,再 Zap 三次。此 ESD 电压由小而逐渐增大,如此重复下去,直到该 IC 脚己被 ESD 所损坏,此时造成 IC 该测试脚损坏的 ESD 测试电压称为『静电放电故障临界电压 (ESD failure threshold)』。

# HBM/MM 测量方法

如果每次调升的 ESD 测试电压调幅太小,则测试到 IC 脚损坏要经过多次的 ESD 放电,增长测试时间;若每次调升的 ESD 测试电压太大,则难以较精确测出该 IC 脚的 ESD 耐压能力。

#### 规定:

- ■正负极性均要测试

- ■从低压测到高压,起始电压为 70% 的平均 ESD failure threshold (VESD)

- ■步进当小于 1000V 时步进 50V(100V), 大于 1000V 时步进 100V(250V, 500V)

- ■可以是一个管脚步进测量或者所有管脚扫描测量

#### 最短间隔时间和测试次数

|              | HBM      | MM      |  |  |

|--------------|----------|---------|--|--|

| Mil-883      | 1秒,3次    |         |  |  |

| <b>ESDA</b>  | 0.3秒,1次  | 1秒,3次   |  |  |

| <b>JEDEC</b> | 0.1秒, 1次 | 0.5秒,1次 |  |  |

| AEC          | 0.5秒,1次  | 1秒,1次   |  |  |

上述测试的方法在 MM/CDM 中都是相同的

表 3.4-1 某一 IC 的 ESD 测试实际结果 (单位:V)

每一脚都有 ESD failure threshold 。此颗 IC 的 ESD failure threshold 定义为所有 IC 脚中 ESD failure threshold 最小的那个电压值,因此,该颗 IC 的 ESD failure threshold 仅达 500V。

IC 制程特性有时会有 小幅的 (10%) 漂移, 所以在相同批次 IC 中 随机取样至少大于 5 颗

| (单位:V) |                      |       |               |               |  |  |

|--------|----------------------|-------|---------------|---------------|--|--|

| 接地脚测试脚 | 接地脚<br>VDD(+)PD-mode |       | VSS(+)PS-mode | VSS(-)NS-mode |  |  |

| 2      | 2500                 | -1000 | 500           | OK            |  |  |

| 3      | 1750                 | -500  | 500           | OK            |  |  |

| 4      | VDD                  | VDD   | VDD           | VDD           |  |  |

| 5      | 7250                 | OK    | 7000          | OK            |  |  |

| 6      | 7000                 | OK    | 7000          | OK            |  |  |

| 7      | 4250                 | -500  | 4000          | -5750         |  |  |

| 8      | 5000                 | -250  | 4500          | -3000         |  |  |

| 9      | 3000                 | OK    | 4500          | -7000         |  |  |

| 10     | OK                   | OK    | 7500          | OK            |  |  |

| 11     | 7250                 | OK    | 7250          | OK            |  |  |

| 12     | 2000                 | -1000 | 500           | OK            |  |  |

| 13     | 2250                 | -750  | 500           | OK            |  |  |

| 14     | 2250                 | OK    | 750           | OK            |  |  |

| 15     | 6500                 | -750  | 500           | OK            |  |  |

| 16     | 1500                 | OK    | 500           | OK            |  |  |

| 17     | VSS                  | VSS   | VSS           | VSS           |  |  |

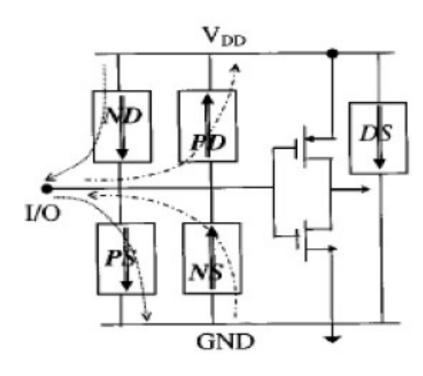

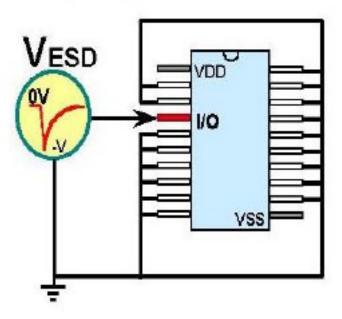

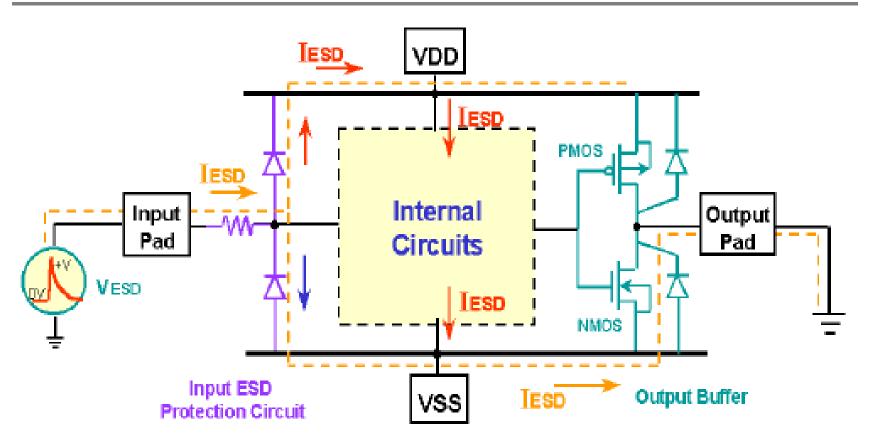

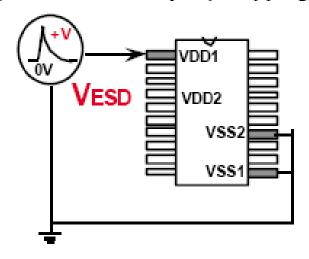

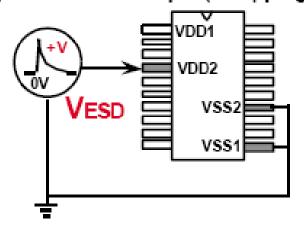

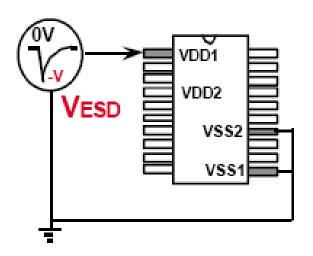

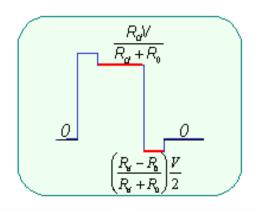

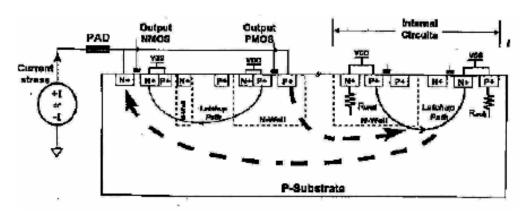

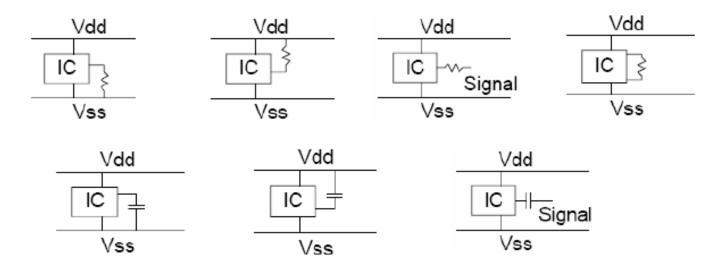

静电的累积可能是正的或负的电荷,因此静电放电测试对同一IC脚而言 是具有正与负两种极性。对每一I/O 而言,HBM与MM静电放电对IC的放 电,有下列四种ESD测试组合,其等效电路示意图如图所示

> ESD stress on the input or output pins with the VDD or VSS pins relatively grounded:

- 1. PS-mode: VSS脚接地,正的ESD电压出现在该I/0 脚对 VSS脚放电,此时VDD与其它脚皆浮接;

- NS-mode: VSS脚接地,负的ESD电压出现在该I/O 脚对 VSS脚放电,此时VDD与其它脚皆浮接;

- 3. PD-mode: VDD脚接地,正的ESD电压出现在该I/0脚对VDD脚放电,此时VSS与其它脚皆浮接;

- 4. ND-mode: VDD脚接地,负的ESD电压出现在该I/0脚对VDD脚放电,此时VDD与其它脚浮接。

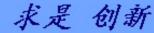

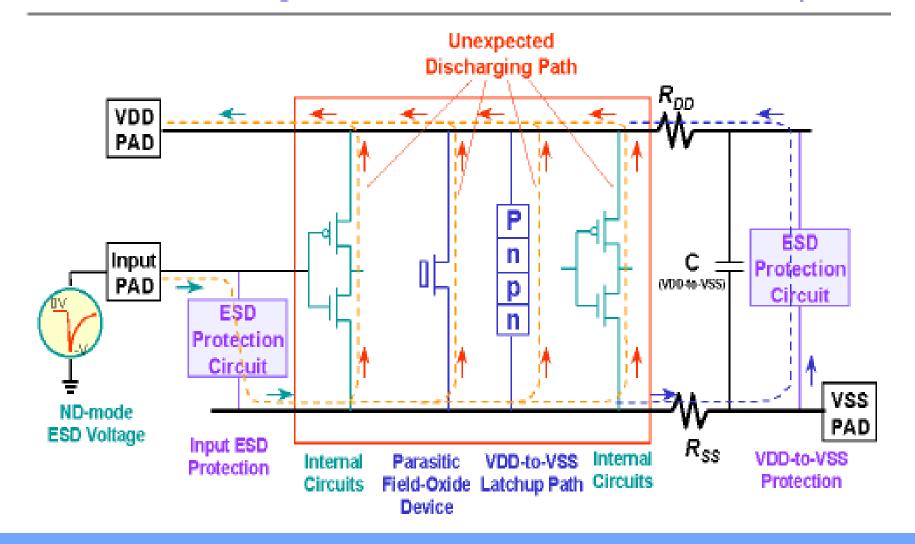

### Internal ESD Damages under ND-mode ESD Stress on Output Pin

#### Internal ESD Damages under ND-mode ESD Stress on Output Pin

#### HBM / MM ESD Failure on the I/O Devices

. Her spec Incotion in markener fallure exponent to the charged harmen body.

Consenty failure showing probable NEAA damage.

Severe damage at compute resulting these MAL. A close-up of a topical pitted contact is observe in Figure 1.

Deep connect pit from MM contrations

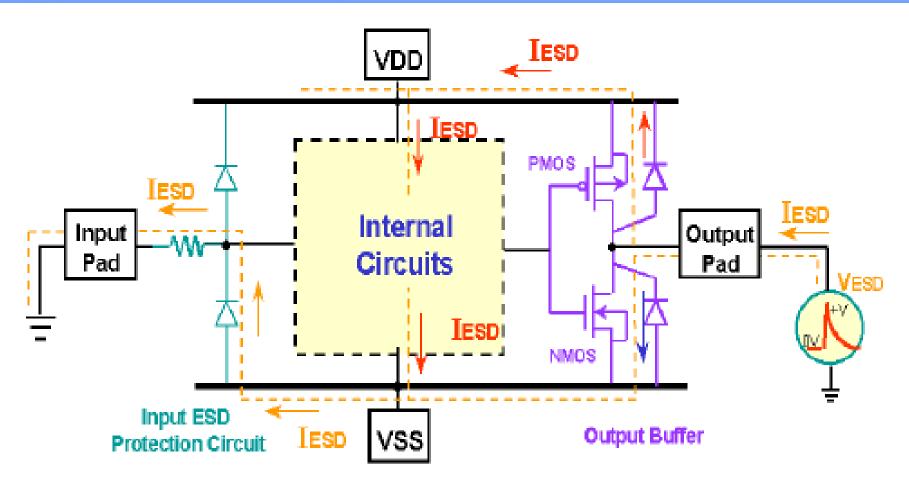

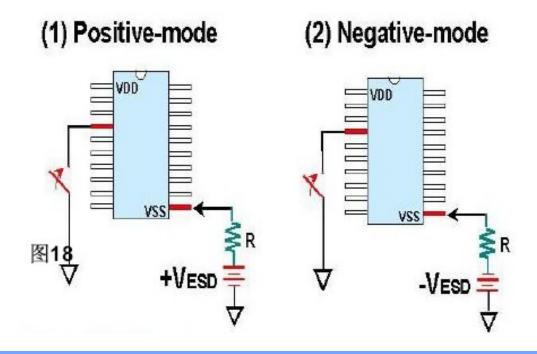

静电放电可能出现在IC的任何两只脚之间,ESD发生在不相干的两支IC脚之间时,静电放电电流会先经由某部份的电路跑到VDD或VSS电源,再由VDD或VSS电源连接线跑到另一支IC脚,再由那支IC脚流出IC之外。测试组合如图。

#### Pin-to-Pin ESD Stress:

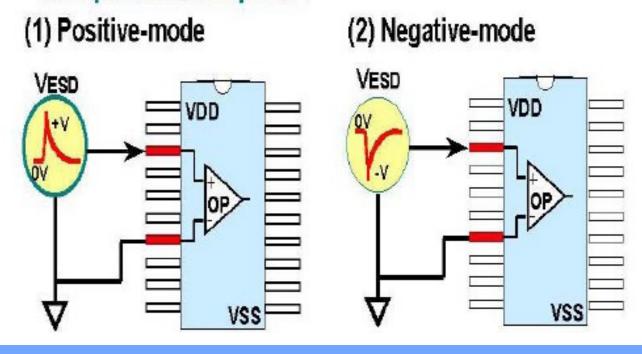

(1) Positive-mode

VESD VDD VSS

(2) Negative-mode

- Positive-mode: 正的ESD电压出现在某一 I/O 脚,此时所有其它I/O 脚皆一起接 地,但所有的VDD脚与VSS脚皆浮接。

- Negative-mode: 负的ESD电压出现在某一 I/O 脚,此时所有其它I/O 脚皆一起接 地,但所有的VDD脚与VSS脚皆浮接。

### Internal ESD Damage Due to Pin-to-Pin ESD Stress

Pin-to-pin ESD stress

ESD voltage across the VDD and VSS power lines.

### Pin-to-pin ESD stress

ESD stress across the VDD and VSS power lines.

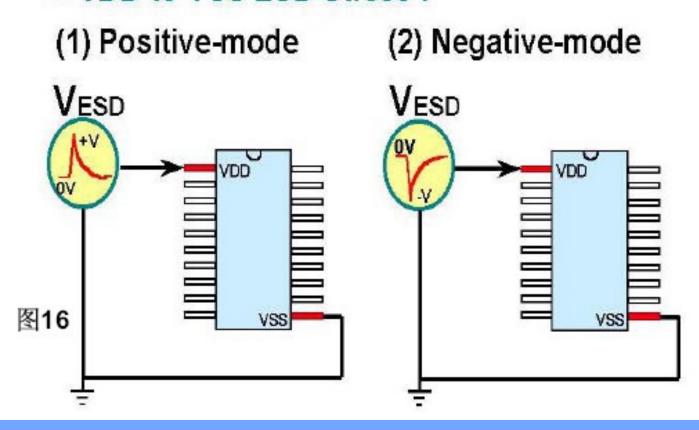

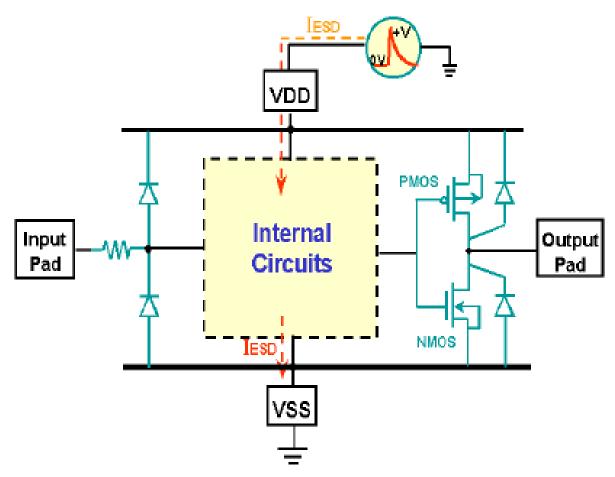

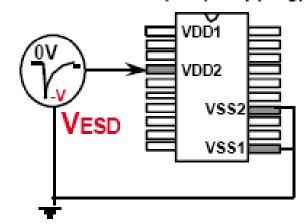

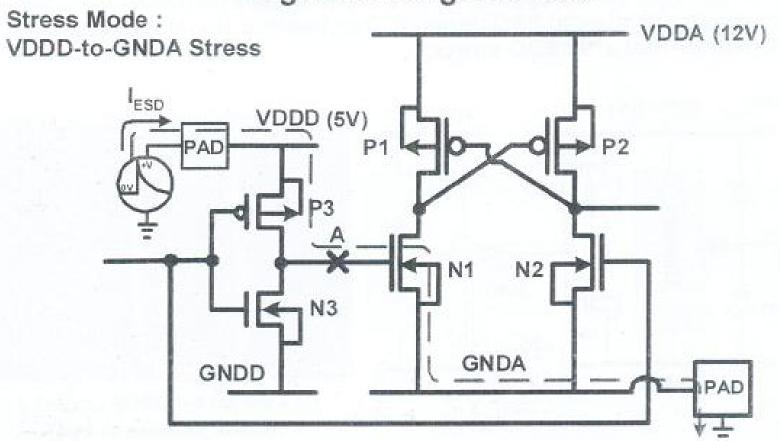

静电放电也可能发生在VDD脚与VSS脚之间,因此对VDD脚与VSS脚有下列的ESD测试组合,其等效电路示意图如图所示。

#### VDD-to-VSS ESD Stress :

- Positive-mode: 正的ESD电压出现在VDD 脚, 此时VSS脚接地,但所有I/O 脚皆浮接;

- Negative-mode: 负的ESD电压出现在VDD

脚,此时VSS脚接地,但所有I/O脚皆浮接。

### Internal ESD Damage Due to VDD-to-VSS ESD Stress

The internal circuits are more vulnerable to ESD damage in this ESD-stress condition.

#### VDD-to-VSS ESD Stress for the IC having multiple power pins :

(1) VDD1 to all VSS pin (+ Zapping)

(2) VDD2 to all VSS pin (+ Zapping)

(3) VDD1 to all VSS pin (- Zapping)

(4) VDD2 to all VSS pin (- Zapping)

An ESD voltage occurs on a digital input pin with an analog input pin grounded, but all the digital and analog power pins are floating.

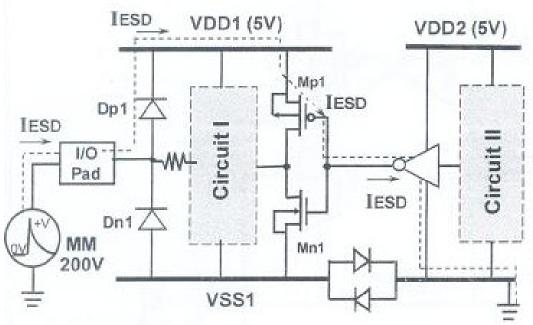

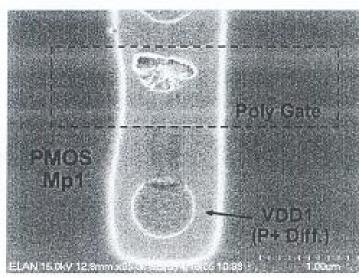

The 200-V MM ESD stress applied to an I/O pin in the Positive-to-VSS (PS) mode to cause the internal ESD damage (that induces the standby failure in the Function Test after ESD stress).

(In a 0.5-µm 5-V CMOS process)

FA picture provided by ELAN.

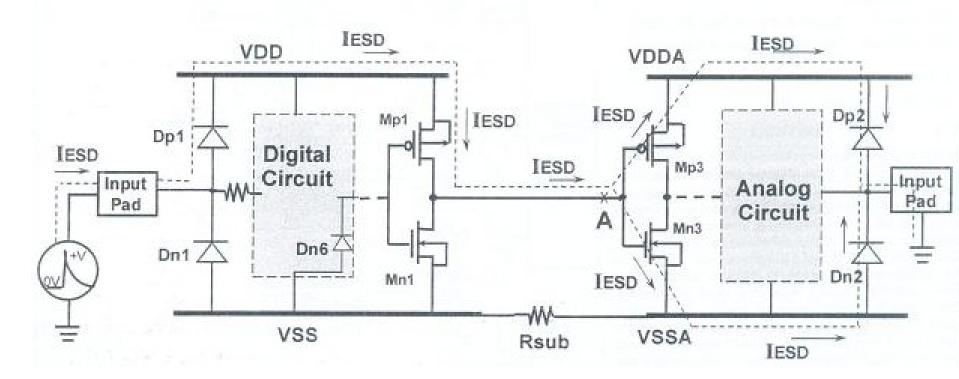

### Digital/Analog Interface

Due to separated GNDD/GNDA lines, the ESD current is forced through the gate of N1 transistor under ESD stress.

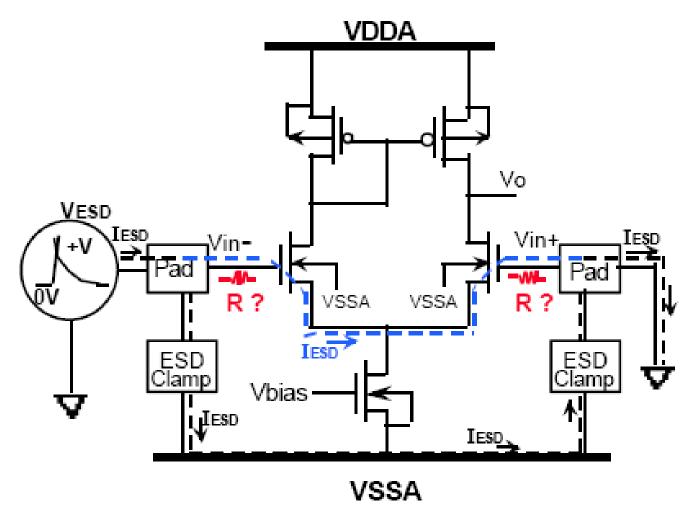

在模拟(Analog) IC内常有差分输入级(Differential Pair),例如运算放大器(OP AMP) 的输入级,如果该差动输入级的正负输入端都连接到IC的Pin时,这两支输入脚要另外单独做R电放电测试,以验证该两支输入脚所连接的差动输入级会不会被静电放电所破坏,其等效电路示意图如图所示。

### ESD stress between the analog input pins of an Operational Amplifier :

- Positive-mode: 正的ESD电压出现在差动 输入级的正输入脚位,此时差动输入级的 负输入脚接地,但其它所有I/0 脚以及 VDD与VSS脚皆浮接;

- Negative-mode: 负的ESD电压出现在差动 输入级的正 输入脚位, 此时差动输入级 的负输入脚接地, 但其它所有I/0 脚以 及VDD与VSS脚皆浮接。

ESD voltage is across the gate oxides of the different-pair input stage of an Operational Amplifier.

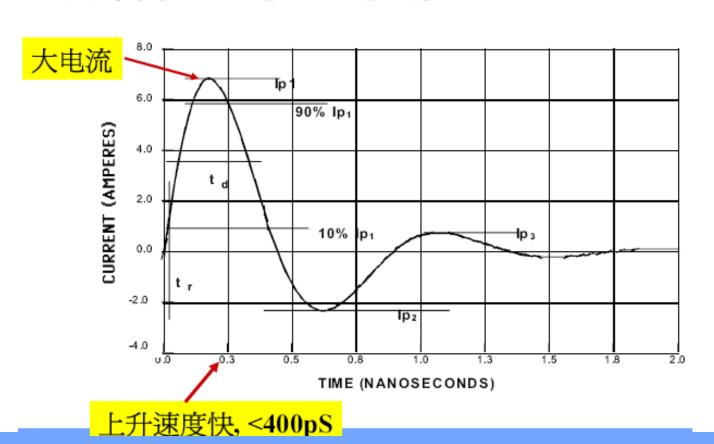

### 3、CDM模型和测试方法标准

## 器件充电模型

- 1.上升时间极短

- <400pS

- 2.电流峰值极大

- 5~20A/500V

- 3.维持时间极短

- 0.5~1.0nS

- 4.一般保护电路来 不及动作

- 1.器件因感应或摩擦带电

- 2.器件上的电荷通过管脚对外放电

## 3、CDM模型和测试方法标准

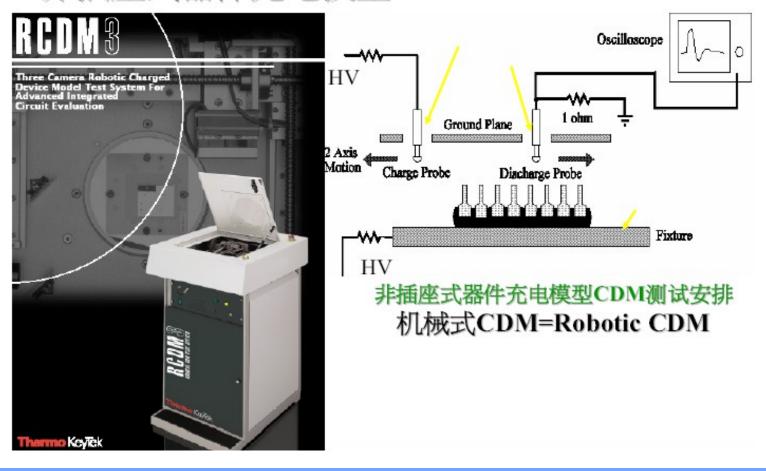

非插座式器件充电模型CDM

### 3 、 CDM 模型和测试方法标准

插座式器件充电模型SCDM测试安排

Zapmaster 选项可以自行SCDM测试

## 3 、 CDM 模型和测试方法标准

## 1KV HBM/MM/CDM电流比較

- The CDM discharge is 100x faster than HBM or MM

- •The neak current can be 40x that of an HRM nulse

## 3、CDM模型和测试方法标准

## 器件充电模型波形

# 3、CDM 模型和测试方法标准 CDM -- JEDEC JESD22-C101-C

Table 3 — CDM waveform characteristics

|                                |    | Test Number   |               |             |              |  |

|--------------------------------|----|---------------|---------------|-------------|--------------|--|

|                                | #1 | #2            | #3            | #4          |              |  |

| Standard test module           |    | Small         | Small         | Large       | Large        |  |

| Test voltage (V)               |    | 500 (± 5%)    | 1000 (± 5%)   | 200 (± 5%)  | 500 (± 5%)   |  |

| Peak current magnitude(A)      | Ip | 5.75 (± 15%)  | 11.5 (± 15%)  | 4.5 (± 15%) | 11.5 (± 15%) |  |

| Rise time (ps)                 | tr | <400          | <400          | -           | -            |  |

| Full width at half height (ns) | Tđ | $1.0 \pm 0.5$ | $1.0 \pm 0.5$ | -           | -            |  |

| Undershoot (A, max.)           | U- | <50% Ip       | <50% Ip       | <50% Ip     | <50% Ip      |  |

| Overshoot                      | U+ | <25% Ip       | <25% Ip       | <25% Ip     | <25% Ip      |  |

## 3、 CDM 模型和测试方法标准

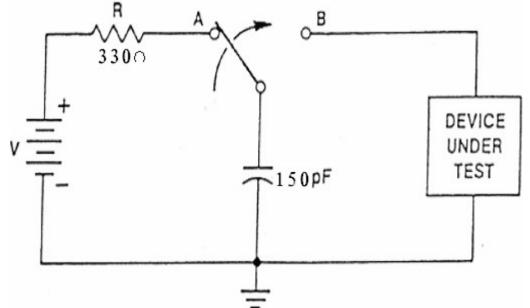

CDM的静电放电测试如图所示。首先,静电电压被充入该集成电路的基体之中,并储存在其基体之中,为避免充电过程造成IC损伤,因此充电电压必须经由一高电阻值( $10M\Omega$ 以上)的限流电阻对IC基体充电。当IC充电之后,IC本身即便带有正极性的或负极性的电压,该IC的其它脚位(包括Input, Output, I/O, 以及VDD脚位)再分别接地放电,以完成CDM的静电放电测试。

## 3、CDM模型和测试方法标准

- Positive-mode:整颗IC处于浮接状态, IC的基体 (Substrate) 先被充电而具有正 极性的电压,然后该 IC的任一脚位以直 接接地的方式放电;

- Negative-mode:整颗IC处于浮接状态, IC的基体(Substrate)先被充电而具有负极性的电压,然后该 IC的任一脚位以直接接地的方式放电。

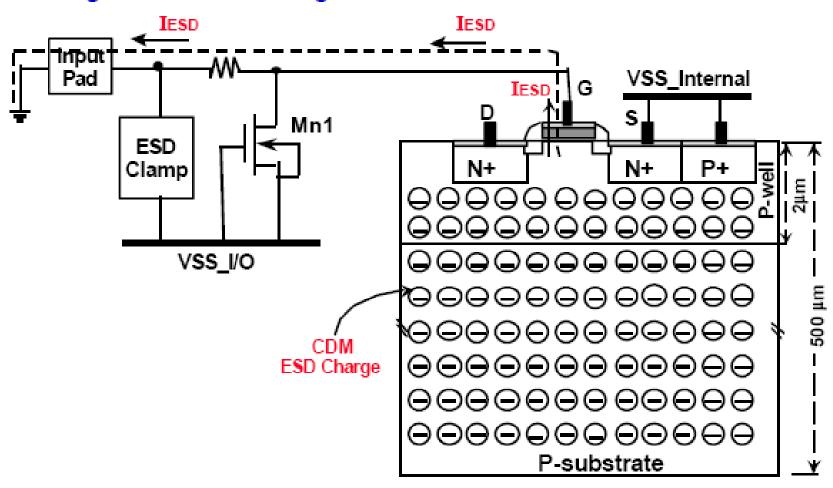

### ESD Damages Due to CDM ESD Events

Negative CDM ESD charges stored in a CMOS IC

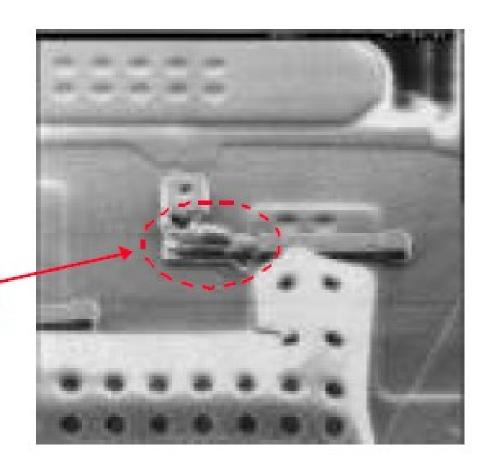

## Picture of the CDM Failure on the First Input Stage

CDM Failure Location

### ESD Damages Due to CDM ESD Events

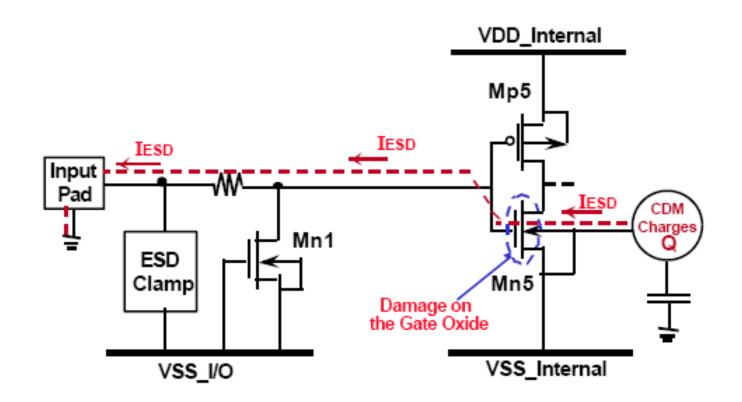

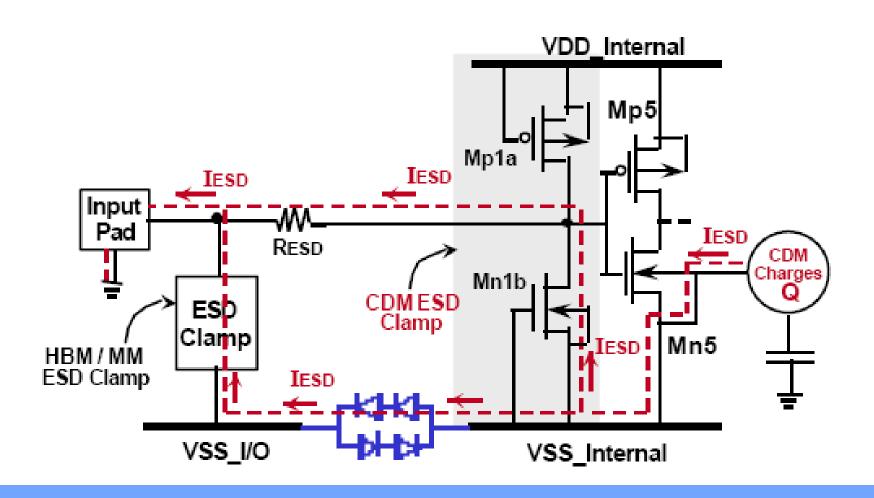

The ESD protection circuit at the input pad can provide effective ESD protection against the HBM and MM ESD events, but it can not provide effective ESD protection against the CDM ESD events.

### ESD Protection for CDM ESD Events

### CDM Failure of IC Product

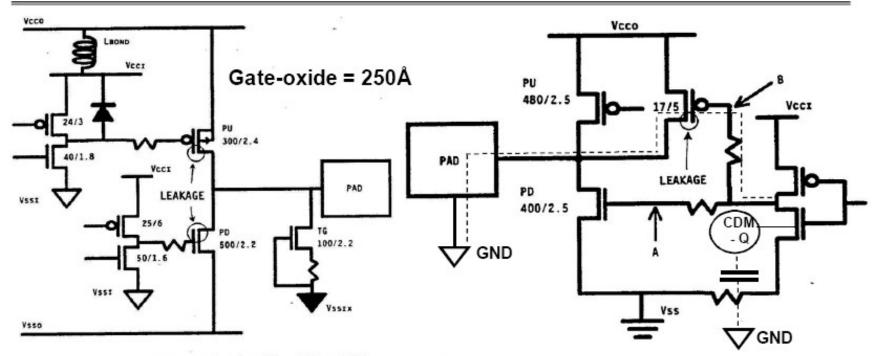

- Fig. 5. N-well CMOS output circuit. PU and PD gates suffer in -CDM test. Vssix is substrate-tapped and is common with Vssi through a long metal connection.

- Fig. 7.

N-well CMOS output circuit with +HBM and -CDM failure in weak PMOS pullup gate-drain due to charge accumulated on the gate common to the NMOS pulldown.

- The output pin fails the –1400V CDM ESD test.

- The output buffer has separated power bus lines, VSSo, VSSI, and VSSix.

Ref.: T. J. Maloney, "Designing MOS inputs and outputs to avoid oxide failure in the charged device model," *Proc. of EOS/ESD Symp.*, 1988, pp. 220-227. (Intel Corp., USA)

- System level(系统级) is also named as on-board level(电路板级)。主要是接触 式放电和非接触式放电

- 8kV air discharge □

- 4kV contact mode for most products

- 6kV contact for medical devices

# IEC (国际电工委员会)

- 静电放电(ESD)抗抗性一一依据IEC801-2: 1984 和1991,对应的新标准是IEC1000-4-2: 1992

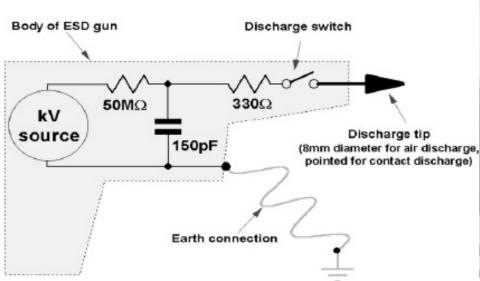

- 其静电放电的指标(150 fU150pf, 8kV)、放电波 形测试系统以及空气放电、测试方法,规定了

- 两种放电位置,并要求设备满足判据B要求。

- 新ESD标准静电放龟要求

- 人体模型由150pf / 150. q, 改变到150pf / 330fl。

- 放电方式由空气放电改变为接触放电,以求更好的重复性。

- 放电电压由8kV降至地V。

中华人民共和国电子行业标准

- 产品制造防静电系统测试方法SJ/T 10694———1998

- GB 2828—87 逐批检查计数抽样程序及抽样表(适用于连续批的检查)

- SJ / T 10533—1994 电子设备制造防静 电技术要求

- SJ / T 10630—1995 电子元器件制造防 静电技术要求

# 欧洲标准: EN50082-I

- EN50082-I中规定了三级性能合格的判据,即:

- 判据A—— 在测试过程和测量完成后,设备都能 连续地按预期方式工作。

- 判据B—— 在测试完成后,设备能继续接预期方式工作,这表明在测试过程中被测设备不必保

- 持其正常功能,但必须能恢复。,

- 判据c——允许暂时失去功能,被测设备可能会停止工作,但应能通过自动重新设置或人工干

- 预后恢复正常运行

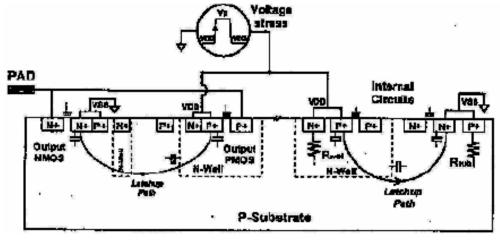

## System-Level ESD Issue

System-Level EMC/ESD Specifications (IEC 61000-4-2):

IEC 61000-4-2: Electromagnetic Compatibility (EMC)

Part 4: Testing and measurement techniques -

Session 2: Electrostatic discharge immunity Test.

EMC → EMI + EMS

| Level | Contact Discharge | Air Discharge |

|-------|-------------------|---------------|

| 1     | +/- 2 kV          | +/- 2 kV      |

| 2     | +/- 4 kV          | +/- 4 kV      |

| 3     | +/- 6 kV          | +/- 8 kV      |

| 4     | +/- 8 kV          | +/- 15 kV     |

On-Board Discrete Components (Magnetic Core, Ferrite Bead, TVS, R, C, ..); Auto-Recovery Methodology (Hardware, Firmware).

### System-Level ESD Gun (IEC/EN 61000-4-2)

Basic circuit of ESD 'gun' for personnel ESD testing to EN 61000-4-2

A. P. 1

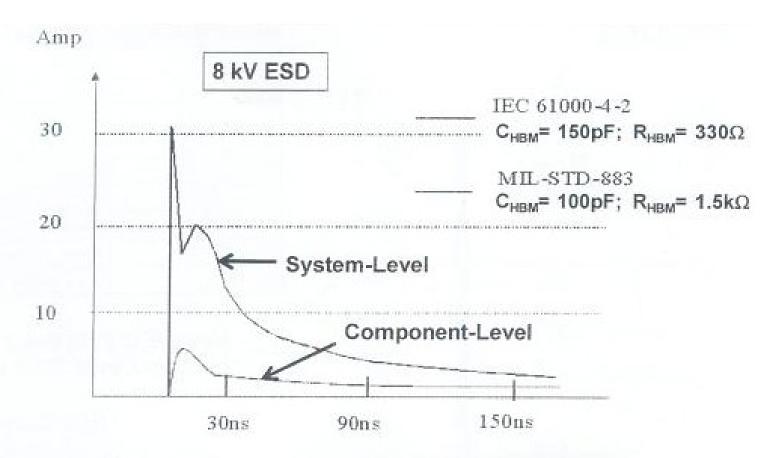

Under 8 kV ESD zapping, the peak current in system-level ESD is about 5 times larger than that in component-level ESD.

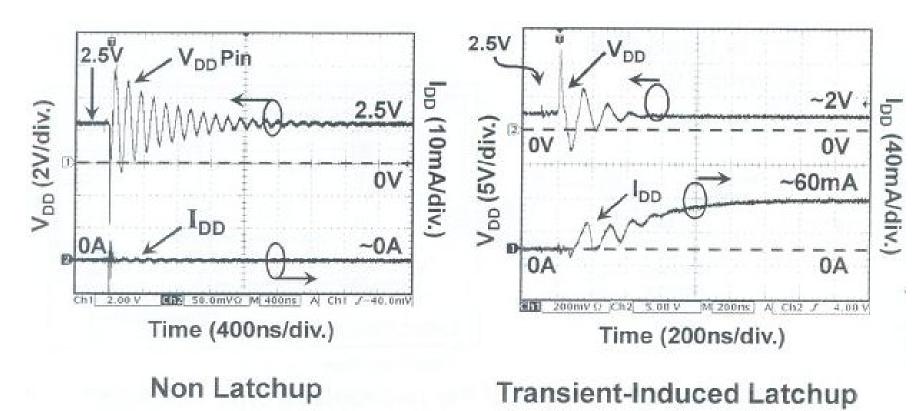

### System level ESD test Cause EMC and latch-up

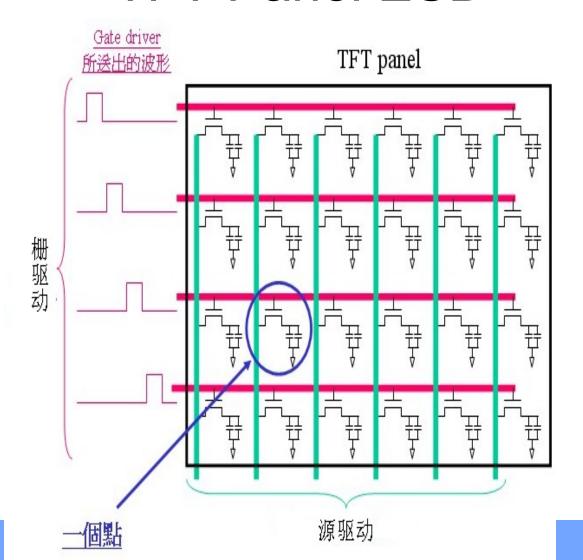

## **TFT Panel ESD**

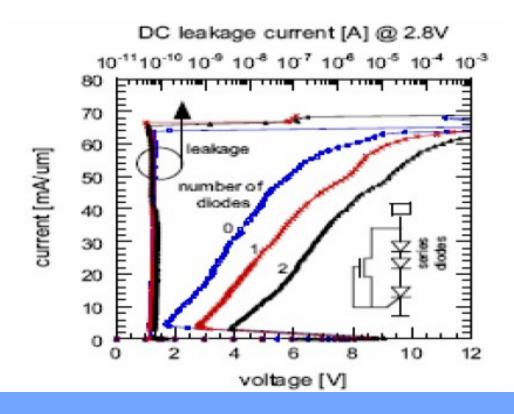

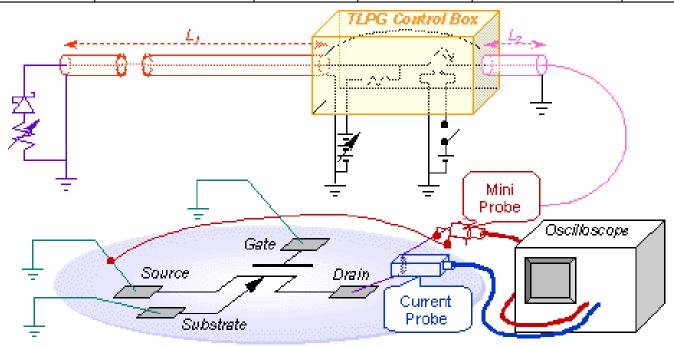

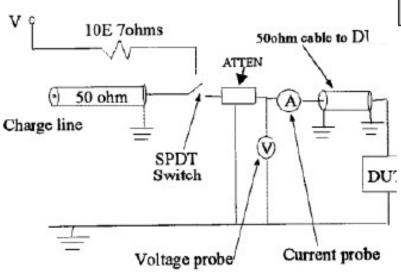

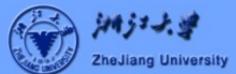

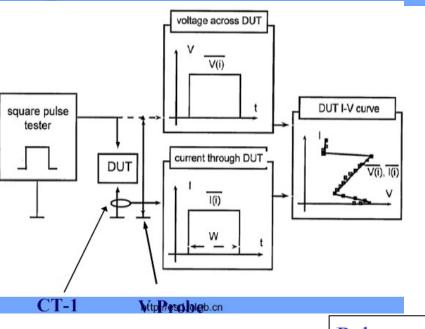

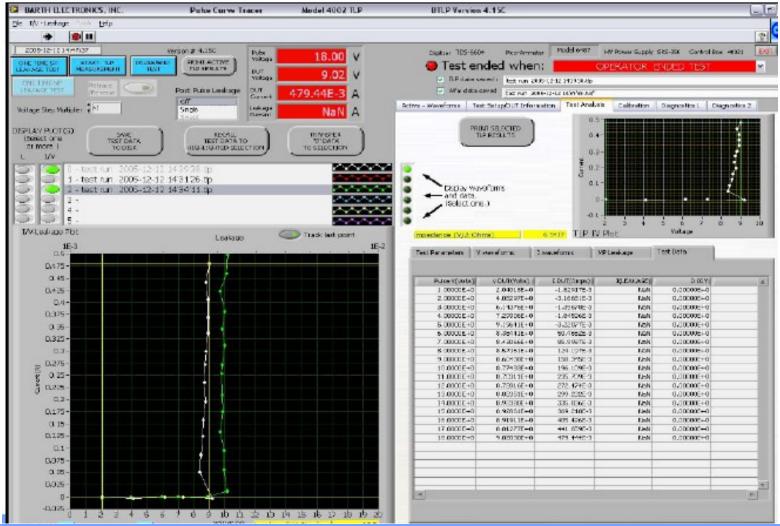

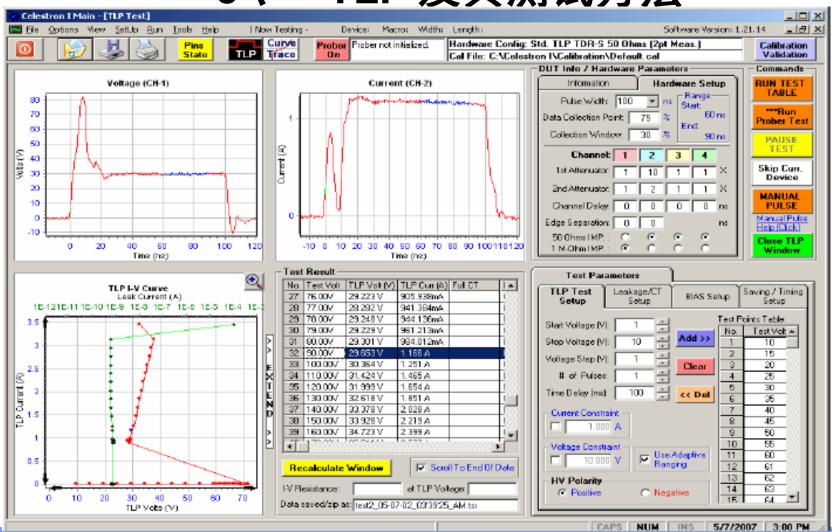

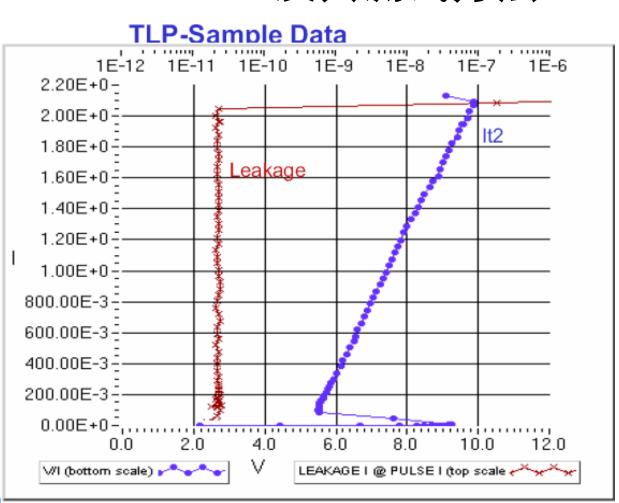

测量器件在不同ESD下的工作特性,主要是在不同ESD电压脉冲下器件的I-V,一般脉冲上升时间10ns持续时间100ns,代表HBM放电曲线的积分能量。可以获得器件的触发、维持和二次崩溃的电压/电流,其中二次崩溃电流(It2)代表了组件到达p-n接面所能承受的最大电流值,而HBM=1500\* It2

| Part           | Polarized<br>Termination     | Transmission Line<br>Region | TLPG<br>Control Box | Power<br>Supplies | DUT Probe                                  | Measurement<br>Equipment |

|----------------|------------------------------|-----------------------------|---------------------|-------------------|--------------------------------------------|--------------------------|

| Core<br>Device | High Power<br>Schottky Diode | Shield Transmission<br>Line | Mercury<br>Relay    | Charge            | Current Probe,<br>Voltage Probe,<br>Socket | Curve Tracer             |

| Function       | Pulse rise time              | Pulse decay time            | INPUT               | Pulse Voltage     | Measurement                                | I-V Curve                |

#### 目前的 TLP 生产厂家有:

美国 Barth 电子公司: Barth 是世界上最早(60年代)从事 TLP 产品的公司, 其产品以经典、稳定、可靠著称,目前其产品占据全球 75%以上市场。主要是 Barth4002TLP 和 Barth4012VF-TLP

美国 Thermo keytek 仪器公司: Thermo keytek 是全球测试仪器的老牌巨头。主要是 HBM/MM tester 的 MK2 和 ZAP MASTER, 以及 CDM tester.

美国 Oryx 公司

日本 Hanwa 公司

价格上从贵到便宜是: Barth — Oryx — Thermo keytek — Hanwa 稳定可靠性从高到低是: Barth — Oryx — Thermo keytek — Hanwa 标称值上从高到低: Thermo keytek — Oryx — Hanwa — Barth 从操作界面说 Hanwa — Oryx — Thermo keytek ~ Barth 从使用的用户调查来看: TSMC、UMC 前前后后都是使用的是 Barth 的 TLP,而 ESD/Lartch-up 基本上使用的是 Keytech 的, SMIC、 HHNEC、 宜硕以及广州五所使用的是 Barth 4002 和 Keytech 的 ESD/Lartch-up。 , GRACE 宏利使用的是 Oryx。

### 目前业界认可的数据: Barth 4002B TLP

对于更快脉波测试使用 : Keytech 4012B TLP

### 求是 创新

Tektronix P6041 BNC Probe Cable

## TLP 测试标准

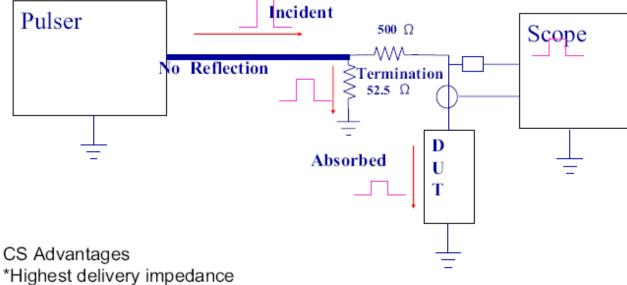

测试标准: ESD SP5.5.1-2004(Standard Practice)

Electrostatic Discharge Sensitivity Testing Transmission Line Pulse (TLP) Component Level

- \*CS Current Source

- \*TDR -Time Domain Reflection

- \*TDT Time Domain Transmission

- \*TDRT Time Domain Reflection & Transmission

<sup>\*</sup>There are no reflections back to the pulser to attenuate or clamp

(a) Snapback Region

(b) Secondary Breakdown Point

Secondary Breakdown Region

# 各种测试的校准和比对性

• 实际上使用 TLP/HBM 等的结果很多情况下是不一致的,即使一样的设备和测试方法有时候重复性也不是很好。 ESDA: 硬盘驱动 IC、音频 IC、数据通信接口 IC、汽车电子 IC, 0.9、1.2、1.5 工艺

#### 一般:

- ➤ TLP 的 IT2×1500 = HBM

- $\rightarrow$  MM×(9-10) = HBM

- $\triangleright$  IEC (1300-2000) = HBM

- ▶ 栅氧 ESD 击穿电压= 1.2× 栅氧静态击穿电压

- \* 栅氧击穿场强 × 栅氧厚度=静态击穿电压

1.5A TLP: D-

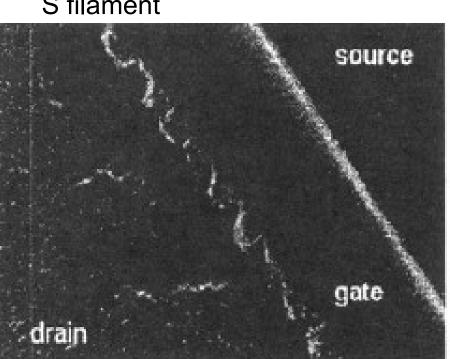

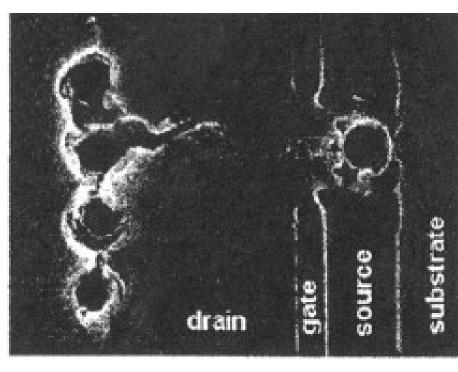

## • TLP 和 HBM 也会产生不同的失效机理

1.3A HBM: drain 区多晶硅 filament 和 Si 熔化 S filament

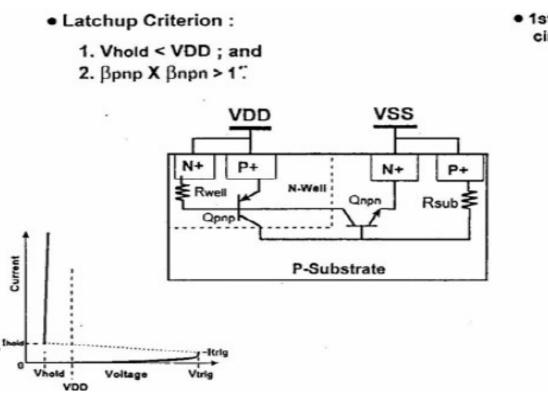

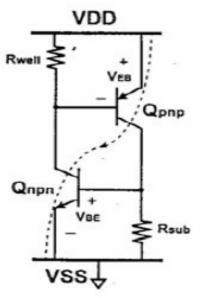

#### SCR的拴锁原理:

1st-order lumped equivalent circuit of latchup :

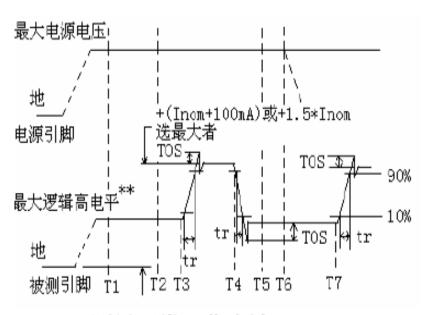

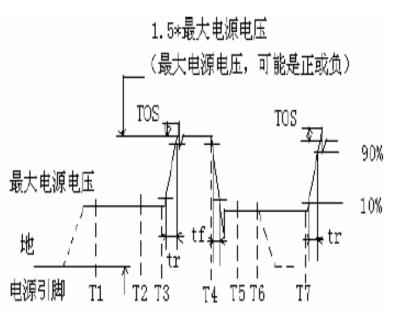

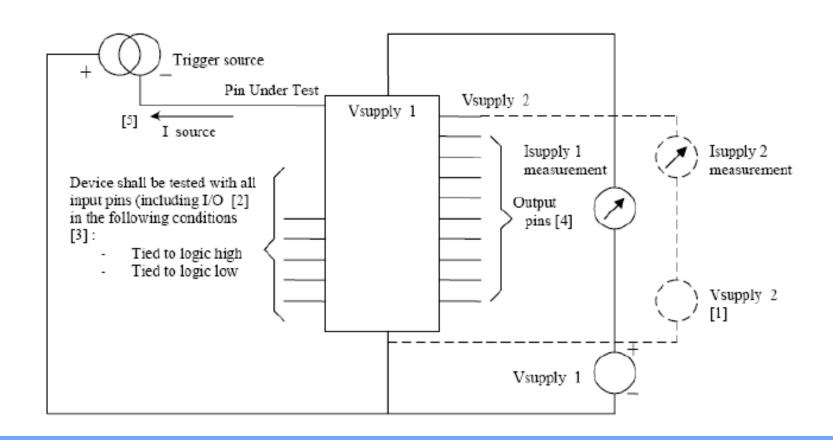

### Latch-Up拴锁测试方法:

- 1. T2测量正常工作电流

- 2. T3~T4 加入干扰信号(I/O管脚加电流、电源管脚加电压)

- 3. T5干扰信号结束后再次测量工作电流

- 4. 比较T5和T2的电流差异,判断是否有拴锁发生

- 5. 正电流只使用最大逻辑高电平,负电力只使用最小逻辑低电平

Standard JEDEC1996:将正或负脉冲加到VDD/VSS/I/O,测试SCR触发与否:

Trigger Current/Voltage(触发电流/电压)

1. I/O: (一般管脚)

正電流: Inorm+100mA or 1.5xInorm

負電流: -100mA or -0.5xInorm

JESD 78A: +100mA or -100mA

2. Power Pin (电源管脚): 1.5xVmax.

以上为JEDEC规定

AEC对于I/O管脚可加至1.5xVmax

沒轮到测试的output管脚浮接(floating),沒轮到测试的input管脚需接至最脆弱的电位;时钟管脚或其他特殊管脚或需特別处理

电路須特別考量测试条件:

需考虑到最高工作温度影响:常温或85℃

未达到+/-100mA的器件或管脚须标识最大容许电流值

## 使用 curve tracter 测试拴锁

测试结构:

Latch-Up判据:

Inorm+10mA or 1.4xInorm

取其中较大值为判断标准:

Inorm<25mA,取Inorm+10mA为判断标准

Inorm>25mA,取1.4xInorm为判断标准

# JESD78A附表A摘录

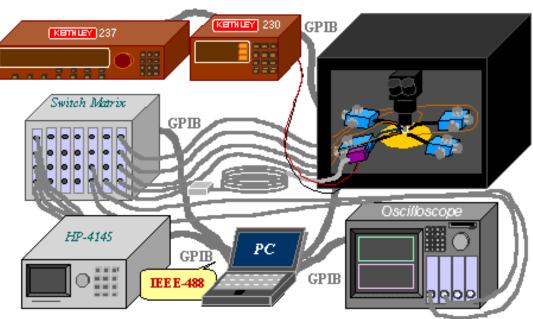

## 7、 I-V 测试

- 使用 HP4155/4156C

- 使用 KIELITHY4200B

• 测试方法略

# 8、ESD测试标准和分类

#### 根据 ESD 模式分类

- HBM 测试标准

- · MM 测试标准

- · CDM测试标准

#### 根据提出标准的组织分类

- JESD22 系列, JEDEC Solid State Technology Association (Joint Electron Device Engineering Council) 提出

- ANSI-ESDSTM5.X 系列, ESDA 协会提出

- AEC-Q100 系列, 汽车电子委员会 Automotive Electronics Council 提出

- MIL-STD-883E 系列,美国军方国防部提出 HBM

#### 测试特点

- · HBM 测试标准基本上是依据美国军方测试标准 MIL-STD-883E 改进而成

- HBM 和 MM 测试方法差不多□□□□□□□□□

- · CDM 测试方法和测试仪器与前两者差别大

#### (1). Human Body Model (HBM)

#### Standards:

- MIL-STD-833C Method 3015.7

- EIA/JESD22-A114-A (JEDEC, 1997)

- ESD STM 5.1 (EOS/ESD, 1998)

CHBM= 100 DF: RHBM=  $1.5 \text{k}\Omega$

#### (2). Machine Model (MM)

#### Standards:

- 1. EIAJ-IC-121 Method 20

- EIA/JESD22-A115-A (JEDEC, 1997)

- ESD STM 5.2 (EOS/ESD, 1999)

#### (3). Charged Device Model (CDM)

#### Standards:

- 1. JESD22-C101 (JEDEC, 1997)

- 2. ESD DS5.3.1 (EOS/ESD, 1996)

### 国内企业常用标准(电子产品静电冲击防护标准)

|     | Standard                                                                                                                                                                                                   | PKG<br>/Wafer | Model                    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|

| нвм | *美国军标883: MIL-STD-883F Method 3015.7 notice 8 *美国静电协ESDA: STM5.1-1998 *电子工业协会: 2006年: JEDEC EIA/JESD22-A114- <b>D</b> *汽车电子协会: AEC-Q100-002-REV-C                                                          | PKG           | Thermo<br>Keytek/<br>MK2 |

| ММ  | *美国静电协会: ESDA STM5.2-1999<br>*电子工业协会: JEDEC EIA/JESD22-A115(即将被冻结)<br>*汽车电子协会: AEC-Q100-003-REV-E                                                                                                          | PKG           | ThermoKey<br>tek<br>MK2  |

| CDM | 1. 插座式器件充电模型 SCDM (Socketed CDM)<br>美国静电协会: *ESDA SP5.3.2 (草案)<br>2. 非插座式器件充电模型 CDM (Non-Socketed CDM)<br>美国静电协会: *ESDA STM5.3.1<br>*电子工业协会: JEDEC EIA/JESD22-C101-C (更受重視)<br>*汽车电子协会: AEC-Q100-011-REV-A |               |                          |

| FIM | JESD22-C101                                                                                                                                                                                                |               |                          |

# 新的系列标准:

- JESD22系列

- 1. HBM标准: JESD22-A114D -2005

- 2. MM标准: JESD22-A115A 1997

- 3. CDM标准: JESD22-C101C -2004

- 美国标ANSI-ESDSTM 5系列

- 1. HBM标准: ANS I-ESD STM5. 1-2001

- 2. MM标准: ANSI-ESD STM5. 2-1999

- 3. CDM标准: ANSI-ESD STM5. 3. 1-1999

- 汽车协会AEC-Q100系列

- 1. HBM标准: AEC-Q100-002D -2003

- 2. MM标准: AEC-Q100-003E -2003

- 3. CDM标准: AEC-Q100-011B -2003

### 国内企业常用标准(电子产品静电冲击防护标准)

|                    | Standard                                                      | PKG/Wafe | Model                                    |

|--------------------|---------------------------------------------------------------|----------|------------------------------------------|

|                    |                                                               | r        |                                          |

| TLP                | 美国静电协会:<br>ESDA Standard Practice                             | Wafer    | Barth 4002                               |

| Latch-up           | 电子工业协会: JEDEC<br>EIA/JESD78;<br>汽车电子协会:<br>AEC-Q100-004-REV-C | PKG      | Thermo Keytek<br>MK2                     |

| System Level (IEC) | 国际电工委员会: IEC<br>61000-4-2<br>美国标: ANSI C63.16<br>中国机标: GB7816 | PKG      | Schaffner NSG435  GB7816 (100pf+1500ohm) |

```

HBM MM CDM

```

可以 2kV 200V 1kV

安全 4kV 400V 1.5kv

超强 10kV 1kV 2kV

ESD的一般要求

\*HBM: >=2kV (美军标>2kV国标>500V)

\*MM: >=200V

\*CDM: >=700V~1000V (可选)

汽车电子ESD要求

\*HBM: >=4kV

\*MM: >=400V

\*CDM: >=2KV (可选)

更高(工业控制)

\*HBM: >=4kV (军标亦要求>2kV)

\*MM: >=400V

\*CDM: >=2KV (可选)