# Integrated Circuits for Analog Signal Processing

Esteban Tlelo-Cuautle Editor

# Integrated Circuits for Analog Signal Processing

Editor

Esteban Tlelo-Cuautle

INAOE

Luis Enrique Erro No. 1.

Tonantzintla

Mexico

ISBN 978-1-4614-1382-0 ISBN 978-1-4614-1383-7 (eBook) DOI 10.1007/978-1-4614-1383-7 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2012938259

#### © Springer Science+Business Media New York 2013

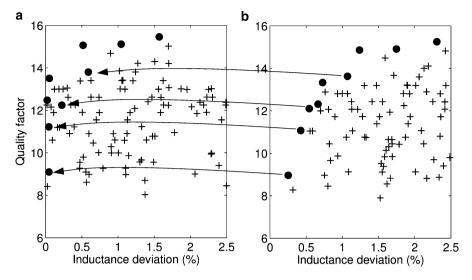

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### **Preface**

Analog integrated circuits encounter applications in signal amplification, filtering, data acquisition systems, sensor conditioning, biomedical implants, actuator conditioning, oscillators, mixers, and so on. Those applications are possible, thanks to the availability of a huge plethora of active devices/elements, and thanks to the appropriate exploitation of their electrical characteristics. For instance, active devices can be classified according to the kind of signal (voltage/current) and port characteristics. Some examples are: voltage operational amplifier, current operational amplifier, operational transconductance amplifier, operational transresistance amplifier, current conveyor, current differencing transconductance amplifier, and so on. In this manner, this book collects recent theories and design methods and applications of active devices/elements (working in voltage-, current-, and/or mixed-mode) and summarizes challenges imposed by the nanometer technology.

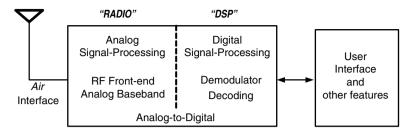

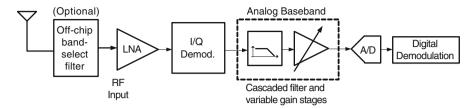

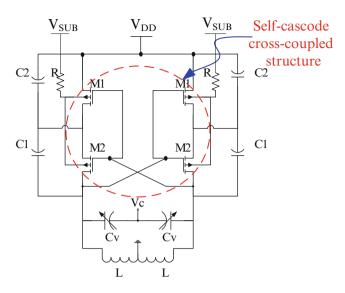

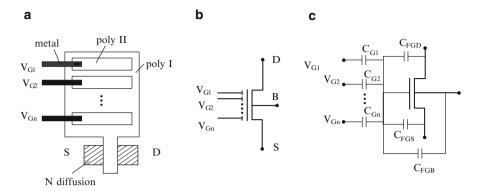

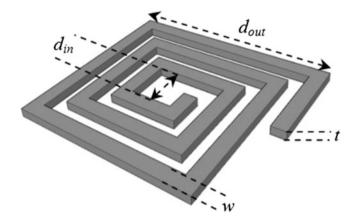

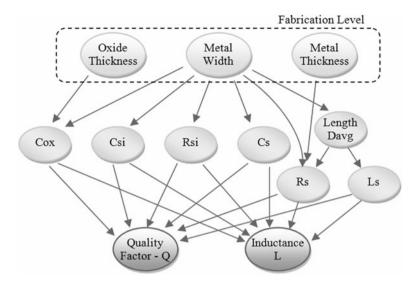

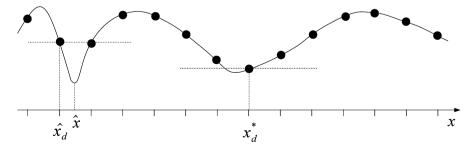

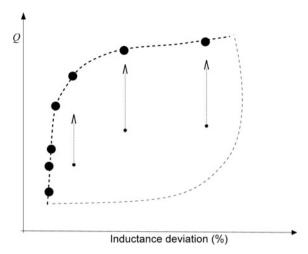

The book consists of 13 chapters focused on: analysis, design, and optimization of active devices; nullors, their bipolar and CMOS implementations and applications in analog circuit synthesis and design; current feedback op-amps, their variants, integratable implementations and applications in analog signal processing; generation of grounded capacitors minimumcomponent oscillators; active filter design using a two-graph based transformation technique; analog baseband filter design considerations for wireless receivers; flexible nanometer CMOS low-noise amplifiers for the next-generation software-defined-radio, mobile systems; clocked nanometer CMOS comparators; low-power electronics for biomedical sensors; sensor conditioning circuits; steady-state simulation of mixed analog/digital circuits; variability-aware optimization of RF integrated inductors in nanometer-scale technologies; and a survey on the static and dynamic translinear paradigm.

The topics covered in this book are intended for people in academy and industry, as well as a key guidance for students and practitioners in the very wide field of analog integrated circuits.

# **Contents**

| 1 | I. Guerra-Gómez, E. Tlelo-Cuautle, M.A. Duarte-Villaseñor, and C. Sánchez-López                                                                                              | J   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Nullors, Their Bipolar and CMOS Implementations<br>and Applications in Analog Circuit Synthesis and Design                                                                   | 31  |

| 3 | Current-Feedback Op-Amps, Their Applications, Bipolar/CMOS Implementations and Their Variants R. Senani, D.R. Bhaskar, S.S. Gupta, and V.K. Singh                            | 61  |

| 4 | Generation of Grounded Capacitors Minimum Component Oscillators                                                                                                              | 85  |

| 5 | Active Filter Design Using a Two-Graph Based Transformation Technique  Mourad Fakhfakh and Marian Pierzchała                                                                 | 107 |

| 6 | Analog Baseband Filter Design Considerations for Wireless Receivers  Jose Silva-Martinez and Raghavendra Kulkarni                                                            | 121 |

| 7 | Flexible Nanometer CMOS Low-Noise Amplifiers for the Next-Generation Software-Defined-Radio Mobile Systems Edwin C. Becerra-Alvarez, F. Sandoval-Ibarra, and J.M. de la Rosa | 145 |

| 8 | Clocked Nanometer CMOS Comparators                                                                                                                                           | 171 |

viii Contents

| 9   | Low-Power Electronics for Biomedical Sensors                                              | 193 |

|-----|-------------------------------------------------------------------------------------------|-----|

| 10  | Sensor Conditioning Circuits                                                              | 223 |

| 11  | Steady State Simulation of Mixed Analog/Digital Circuits                                  | 243 |

| 12  | Variability-Aware Optimization of RF Integrated Inductors in Nanometer-Scale Technologies | 271 |

| 13  | A Survey on the Static and Dynamic Translinear Paradigm                                   | 289 |

| Ind | ex                                                                                        | 307 |

### **Contributors**

**Edwin C. Becerra-Alvarez** CUCEI, University of Guadalajara, Guadalajara, México

**D. R. Bhaskar** Department of Electronics and Communication Engineering, Jamia Millia Islamia, New Delhi, India

**Federico Bizzarri** Dipartimento di Elettronica e Informazione, Politecnico di Milano, pza. Leonardo da Vinci, Milano, Italy

**Angelo Brambilla** Dipartimento di Elettronica e Informazione, Politecnico di Milano, pza. Leonardo da Vinci, Milano, Italy

**Fernando Coito** DEE, Faculdade de Ciências e Tecnologia, UNL, Caparica, Portugal

**Carlos A. De La Cruz Blas** Departamento de Ingeniería Eléctrica y Electrónica, Universidad Pública de Navarra, España, CP, Spain

José M. de la Rosa IMSE-CNM, CSIC/University of Seville, Seville, Spain

Miguel Aurelio Duarte Villaseñor INAOE, Tonantzintla, Puebla, México

Mourad Fakhfakh University of Sfax, Sfax, Tunisia

Helena Fino DEE, Faculdade de Ciências e Tecnologia, UNL, Caparica, Portugal

**Giancarlo Storti Gajani** Dipartimento di Elettronica e Informazione, Politecnico di Milano, pza. Leonardo da Vinci, Milano, Italy

**Bernhard Goll** Vienna University of Technology, EMCE, Vienna, Austria

**Giambattista Gruosso** Dipartimento di Elettronica e Informazione, Politecnico di Milano, pza. Leonardo da Vinci, Milano, Italy

Ivick Guerra-Gómez INAOE, Tonantzintla, Puebla, Mexico

**S. S. Gupta** Department of Industrial policy and promotion, Ministry of Commerce and Industry, New Delhi, Government of India

x Contributors

Julia Hsin-Lin Lu Purdue University, West Lafayette, IN, USA

Byunghoo Jung Purdue University, West Lafayette, IN, USA

Syed Kamrul Islam The University of Tennessee, Knoxville, TN, USA

Raghavendra Kulkarni Texas A&M University, College Station, TX, USA

**Pragati Kumar** Department of Electrical Engineering, Delhi Technological University, New Delhi, India

Pedro Pereira DEE, Faculdade de Ciências e Tecnologia, UNL, Caparica, Portugal

Marian Pierzchala Wrocław University of Technology, Wrocław, Poland

Melika Roknsharifi The University of Tennessee, Knoxville, TN, USA

Carlos Sánchez-López Universidad Autónoma de Tlaxcala, Tlaxcala, México

Federico Sandoval-Ibarra Cinvestav-Unidad Guadalajara, Guadalajara, México

**Raj Senani** Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology, New Delhi, India

Fahmida Shaheen Tulip The University of Tennessee, Knoxville, TN, USA

**R. K. Sharma** Department of Electronics and Communication Engineering, Ambedakar Institute of Technology, New Delhi, India

Jose Silva-Martinez Texas A&M University, College Station, TX, USA

**A. K. Singh** Department of Electronics and Communication Engineering, ITS Engineering College, Greater Noida, India

**V. K. Singh** Department of Electronics Engineering, Institute of Engineering & Technology, Lucknow, UP, India

**A.M. Soliman** Department of Electronics and Communication Engineering, Cairo University, Giza, Egypt

Esteban Tlelo-Cuautle INAOE, Tonantzintla, Puebla, México

**Rafael Vargas-Bernal** Departamento de Ingeniería en Materiales, Instituto Tecnológico Superior de Irapuato, Guanajuato, México

Kai Zhu The University of Tennessee, Knoxville, TN, USA

Horst Zimmermann Vienna University of Technology, EMCE, Vienna, Austria

## Chapter 1 Analysis, Design and Optimization of Active Devices

I. Guerra-Gómez, E. Tlelo-Cuautle, M.A. Duarte-Villaseñor, and C. Sánchez-López

#### 1.1 Introduction

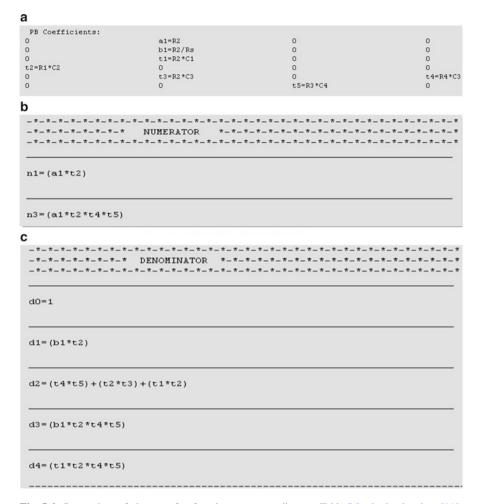

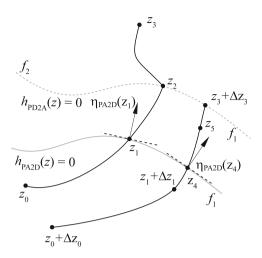

This chapter describes three computational techniques for the design automation of analog integrated circuits (ICs): Symbolic nodal analysis using the nullor concept and pathological elements, systematic design of active devices from a binary genetic encoding approach, and circuit biasing and sizing by applying evolutionary algorithms.

Symbolic analysis techniques are very useful in generating analytical expressions of analog ICs. Their main characteristics can be identified by the kind of models they use. For instance, in the case of symbolic nodal analysis techniques, the use of active devices models based on pathological elements has demonstrated advantages in the formulation of small and sparse matrices [1]. In fact, using the pathological elements accompanied of passive circuit elements, e.g. resistances, one can model the behavior of almost all active devices, as already shown in [1–3]. It is also possible to include parasitic circuit elements into the models [4], and performances characteristics such as input and output impedances and gain [5].

In performing symbolic analysis one is interested in generating exact or approximated symbolic expressions [6]. However, using detailed models of active devices, the generated expressions can be too large, while by using compact models the expression may be very compact or reduced. In both cases, the generated symbolic expression approximates the exact response with some error tolerance [7, 8]. To generate compact expressions, a big circuit can be partitioned so that some blocks

1

I. Guerra-Gómez  $(\boxtimes)$  • E. Tlelo-Cuautle • M.A. Duarte-Villaseñor

INAOE, Tonantzintla, México

e-mail: ivickguerra@gmail.com; etlelo@inaoep.mx; miauduvi@gmail.com

C. Sánchez-López

Universidad Autónoma de Tlaxcala, Tlaxcala, México,

e-mail: carlsanmx@yahoo.com.mx

E. Tlelo-Cuautle (ed.), *Integrated Circuits for Analog Signal Processing*, DOI 10.1007/978-1-4614-1383-7\_1, © Springer Science+Business Media New York 2013

can be replaced by their dominant characteristics, and the symbolic analysis is accelerated by applying determinant decision diagrams (DDD) [9], and parallel DDD-based analysis [10]. For instance, in [5] is presented the symbolic nodal analysis of ICs containing current mirrors (CMs). The nullor-equivalent of the CM is very useful in formulating a reduced system of equations, as shown in the following section by performing symbolic nodal analysis of an all-pole third-order low-pass filter implemented with dual-output CMs [11]. Symbolic nodal analysis can also be applied in the synthesis of analog ICs through deriving performance-analytical-expressions of the active devices [6].

Recently, a binary genetic encoding (BGE) representation for the automatic synthesis of mixed-mode circuit topologies was introduced in [12]. The chromosomal representation of the four unity-gain cells was generated from nullator/norator descriptions, and the binary strings are represented by hexadecimal numbers in order to have a unique meaning when they are decoded to create transistor-based circuits. In Sect. 1.3, a summary on the synthesis of the voltage and current followers, and voltage and current mirros, is presented. The synthesis of more complex active devices is also described by combining and/or superimposing unity-gain cells. This kind of synthesis methodology is part of evolutionary electronics, because this research area involves applications of evolutionary computation in the domain of electronics. On this direction, analog design is much amenable for evolutionary techniques, because contrasting with the digital design, there is no solid set of design rules or procedures to automate circuit synthesis. For instance, analog synthesis begins by selecting a specific topology and its design is performed by finding parameter values (e.g. transistor lengths and widths). Furthermore, to have an idea among all the currently available design methodologies, a classification of design strategies developed by researchers in recent history over more than 20 years is presented in [13]. That way, yet there is a founded interest in the development of automatic techniques capable to find new circuit topologies and optimum component values.

In general, the design of analog ICs requires the use of different kinds of active devices, as the ones summarized in [1,4,14]. Moreover, to improve the performances of those analog ICs, optimized active devices are required. In this manner, Sect. 1.4 summarizes the application of three evolutionary algorithms to compute the biases and sizes of analog ICs. That way, several active devices are optimized taking into account design constraints, and linking HSPICE<sup>TM</sup> like circuit simulator to evaluate electrical characteristics.

## 1.2 Symbolic Nodal Analysis

This section summarizes several models of active devices using the nullor concept and pathological elements [1, 4, 5]. Those models are used to derive symbolic expressions of analog ICs.

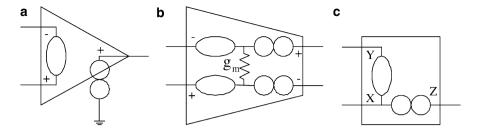

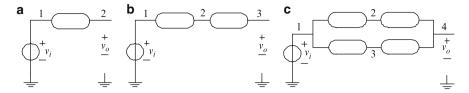

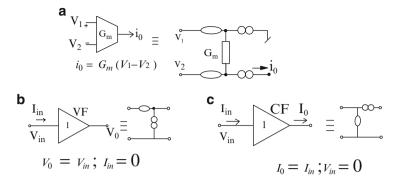

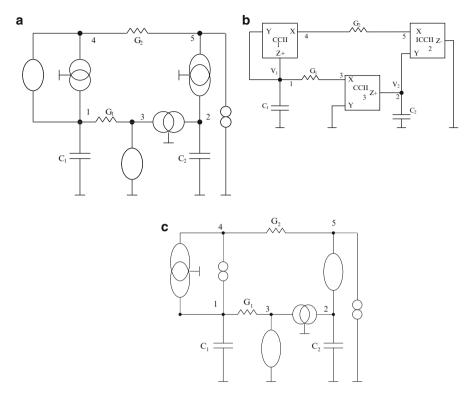

Fig. 1.1 (a) Operational amplifier, (b) operational transconductance amplifier, and (c) negative-type second generation current conveyor modeled by using nullors

# 1.2.1 Modeling Active Devices Using Nullors and Pathological Elements

The symbolic behavioral model generation of analog ICs can be found in [1, 4–6], where it is demonstrated that when using nullors and/or pathological elements, one not only can describe the dominant behavior of analog ICs, but also one can add or remove parasitic elements to generate models at different abstraction levels. The transfer relationships of the models are expressed by two kinds of signals: voltage and current. When the signals are voltages, the circuit works in voltage-mode, when they are currents, it works in current-mode, and when they are both voltage and current signals, it works in mixed-mode. Therefore, in general four transfer relationships are obtained.

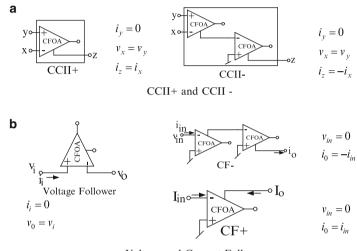

One mixed-mode active device was introduced in 1968 [15], it was named first-generation current conveyor (CCI). Nowadays, the current conveyor has evolved into three generations [4], basically composed of unity-gain cells [12], to drive voltages and currents. The models of several active devices by using controlled-sources are given in [14]. Those models have the drawback of generating systems of equations bigger than by using nullors or pathological elements [1]. For instance, Fig. 1.1 shows the ideal models of the operational amplifier (opamp), operational transconductance amplifier (OTA) and negative-type second generation current conveyor (CCII—[4]). These nullor equivalents are quite useful to derive simplified symbolic expressions.

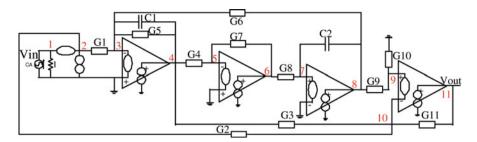

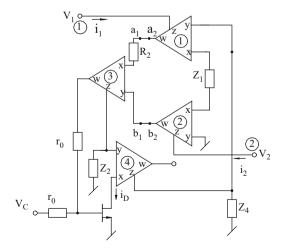

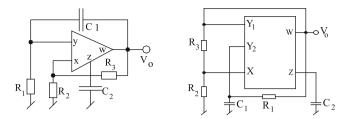

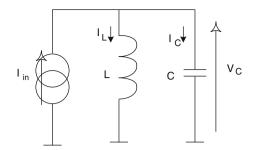

Lets us consider the active RC filter shown by Fig. 1.2. The modified nodal analysis (MNA) [6], generates one equation for each node plus one equation for each opamp, leading to a system of order 15. On the other hand, the symbolic nodal analysis using nullors generates a system equal to the number of nodes minus the number of nullors, leading to a system of order 6, as shown by (1.1). The symbolic transfer function is obtained by applying the symbolic technique presented in [1], and it is given by (1.2) [6].

Fig. 1.2 RC filter

Fig. 1.3 OTA-C filter

$$\begin{bmatrix} v_{in} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ -G1 - G5 - sC1 & 0 & -G6 & 0 & 0 \\ 0 & -G4 & -G7 & 0 & 0 & 0 \\ 0 & 0 & -G8 - sC2 & 0 & 0 \\ 0 & 0 & 0 & -G9 & G9 + G10 & 0 \\ -G2 & -G3 & 0 & 0 & G2 + G3 + G11 - G11 \end{bmatrix} \begin{bmatrix} v_{1,2} \\ v_4 \\ v_6 \\ v_8 \\ v_{9,10} \\ v_{11} \end{bmatrix}$$

(1.1)

$$\frac{v_{\text{out}}}{v_{\text{in}}} = \frac{-(G9 + G10)C1G2C2G7s^2 + ((G1G3 - G2G5)(G9 + G10))}{G2G7s - G4G8(G9G1(G2 + G3 + G11) + G2G6(G9 + G10))}{G11(G9 + G10)(G6G8G4 + sC2G7G5 + s^2C2G7C1)}.$$

(1.2)

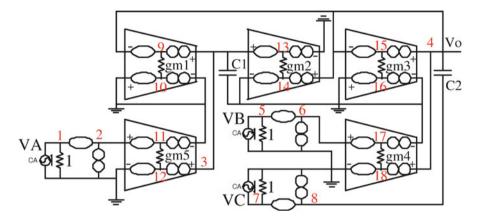

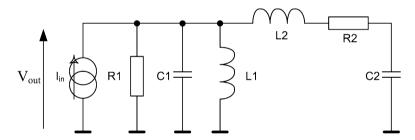

The OTA-C filters [16], can also be modeled using nullors. Lets us consider the one shown by Fig. 1.3, the system is given in [6], and the expression by (1.3).

$$v_4 = \frac{s^2 C1C2v_C + sC1gm4v_B + gm2gm5v_A}{s^2 C1C2 + sC1gm3 + gm2gm1}.$$

(1.3)

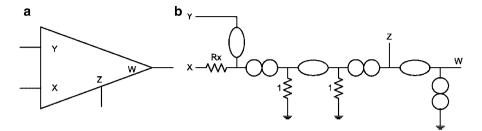

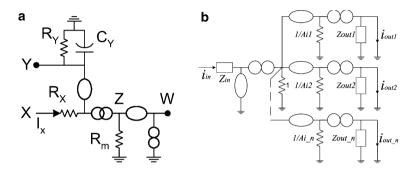

Fig. 1.4 (a) CFOA description, and its (b) nullor-equivalent including  $R_x$  [4]

Fig. 1.5 (a) Pathological-equivalent of the CFOA including dominant parasitics [1], and (b) Nullor-equivalent of the multiple-outputs current mirror including input impedance and independent gain and output impedances [5]

The current-feedback opamp (CFOA) is another active device quite useful in linear and nonlinear applications [17–20]. It has four ports as shown in Fig. 1.4a, and basically, it can be designed by cascading a positive-type second generation current conveyor (CCII+) with a voltage follower (VF) [12]. That way, its nullor-equivalent is shown in Fig. 1.4b [4]. Besides, by using the pathological CM element [21], a compact model can be derived, as shown in Fig. 1.5a [1], where the dominant parasitics are included.

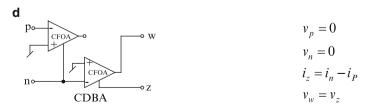

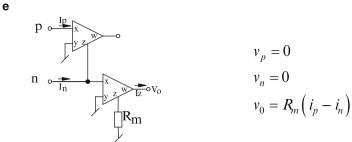

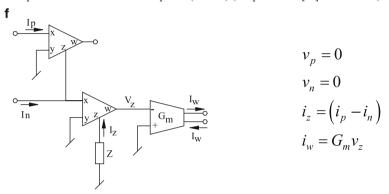

In a similar manner, other kinds of active devices, such as the current differencing buffered amplifier (CDBA) [22], operational transresistance amplifier (OTRA) [23], current operational amplifier (COA) [24], and the ones summarized in [14], can be modeled by using nullors and pathological elements, as already shown in [1,4].

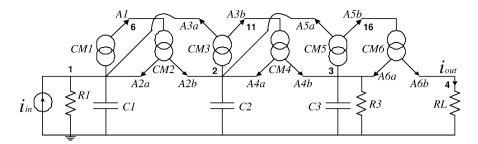

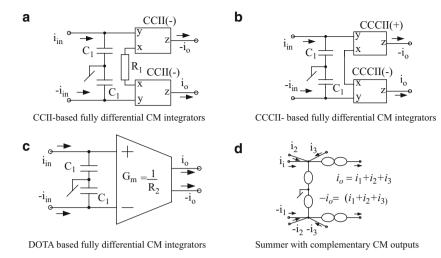

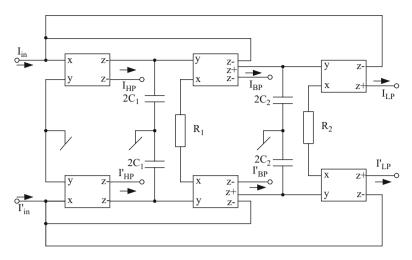

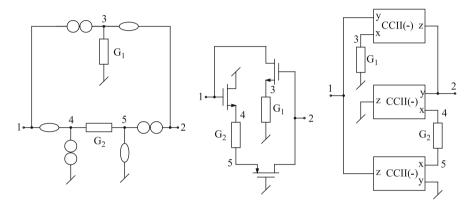

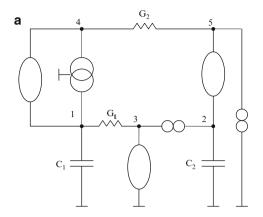

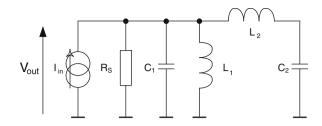

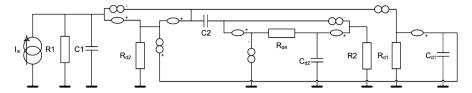

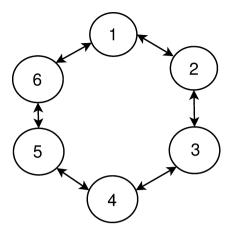

#### 1.2.2 Current-Mode Filter Based on Current Mirror Arrays

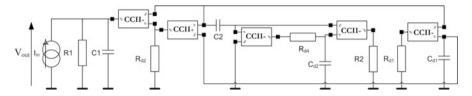

The CM can be modeled as shown in Fig. 1.5b, including multiple-outputs, input impedance and independent gain and output impedance at each output current-path. To highlight its usefulness, lets us consider the active filter shown in Fig. 1.6.

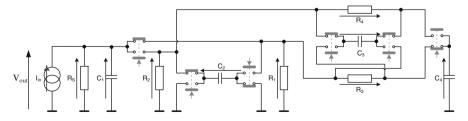

Fig. 1.6 All-pole low-pass filter implemented with dual-output CMs [11]

This filter can easily be simulated using hardware description languages [25], but it is necessary to generate the symbolic behavioral model including the gains of each CM (CM1-CM6). By applying symbolic nodal analysis [1], the admittance matrix is computed by (1.4).

When the output impedances of the CMs are ideal and the gains unitary, the symbolic expression becomes,

$$\frac{i_{\text{out}}}{i_{\text{in}}} = \frac{g_i^6}{\left(C_2 g_i^3 C_3 g_1 + C_2 g_i^3 g_3 C_1\right) s^2 + \left(g_i^5 C_3 + g_i^5 C_1 + C_2 g_i^3 g_3 g_1\right) s}.$$

$$+g_i^5 g_1 + g_i^5 g_3 + C_2 g_i^3 C_3 C_1 s^3.$$

(1.5)

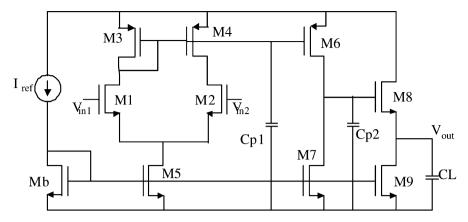

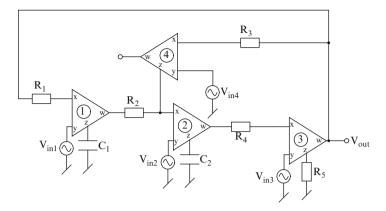

Fig. 1.7 Three stages uncompensated low voltage amplifier

Fig. 1.8 Nullor equivalent of Fig. 1.7

# 1.2.3 Symbolic Behavioral Modeling of Amplifiers and Oscillators

Lets us consider the three stages uncompensated low-voltage amplifier shown in Fig. 1.7. Its nullor equivalent is given in Fig. 1.8. The nodal admittance matrix has an order  $7 \times 7$  [7]. The exact symbolic transfer function is given in [26], which is too large, so that a further step should be performed to simplify large symbolic expressions [6].

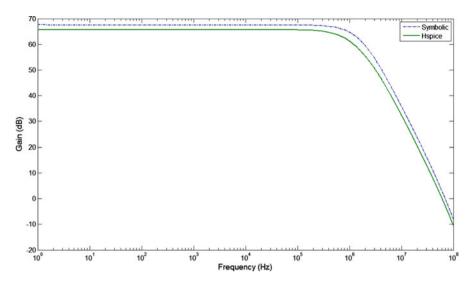

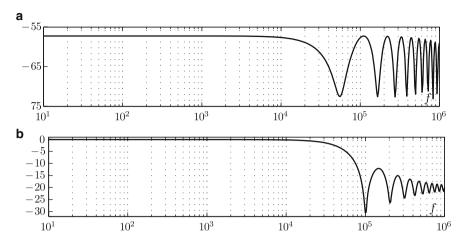

If the low voltage amplifier is designed with standard CMOS IC technology, its gain performance comparison with respect to its behavioral model is shown in Fig. 1.9. The noise analysis of CMOS amplifiers using nullor-equivalents and DDDs is presented in [8].

Fig. 1.9 Comparison between HSPICE and the derived symbolic expression [7]

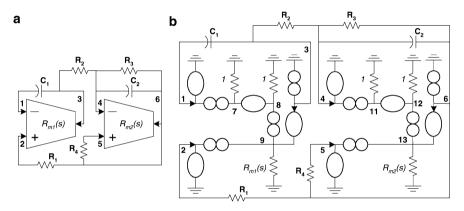

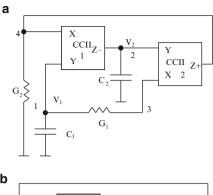

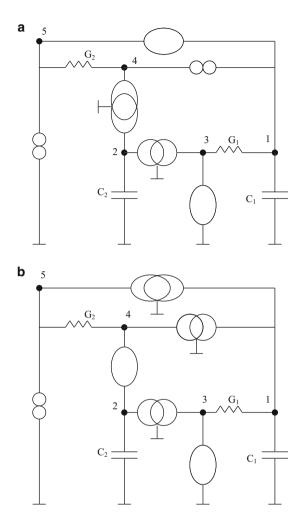

Fig. 1.10 (a) OTRAs-based oscillator, and (b) its nullor-equivalent [23]

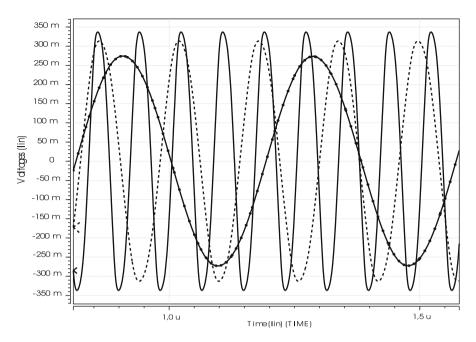

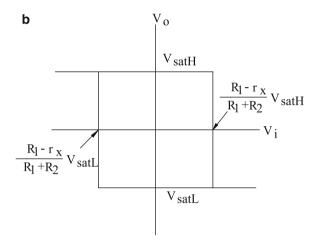

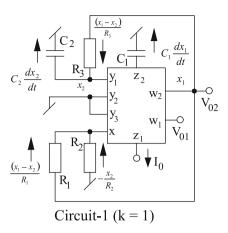

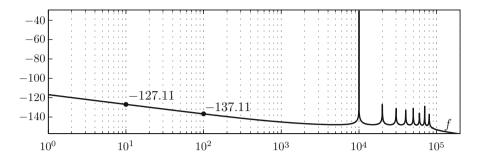

The symbolic behavioral modeling of sinusoidal oscillators is quite useful for design purposes. Lets us consider the oscillator composed of OTRAs, as shown in Fig. 1.10. The system of equations by applying symbolic nodal analysis is derived in [23], where the characteristic equation is approached by (1.6), and the condition and frequency of oscillation are given by (1.7). By choosing  $R_1 = R_2 = 2 \,\mathrm{k}\Omega$ ,  $R_3 = R_4 = 10 \,\mathrm{k}\Omega$ , the value of the frequencies of oscillation are shown in Fig. 1.11 as:  $f_1 = 2.65 \,\mathrm{MHz}$  (Dashed-line) with  $C_1 = C_2 = 24 \,\mathrm{pF}$ ,  $f_2 = 6.29 \,\mathrm{MHz}$  with  $C_1 = C_2 = 6.46 \,\mathrm{pF}$  (Dotted-line), and  $f_3 = 12 \,\mathrm{MHz}$  (Solid line) with  $C_1 = C_2 = 0.1 \,\mathrm{pF}$ .

Fig. 1.11 Time responses of the OTRA-based sinusoidal oscillator

The parasitic capacitances are approximated to  $C_{m1} = C_{m2} = 6.46$  pF. From Fig. 1.11 one can observe that the maximum frequency of oscillation ( $f_3 = 12$  MHz) is limited by  $C_{m1,2} = C_{Z2}$ .

$$s^{2} + \frac{1}{C_{2} + C_{m2}} \left( \frac{1}{R_{s}} - \frac{1}{R_{4}} \right) s + \frac{1}{R_{1}R_{2}(C_{1} + C_{m1})(C_{2} + C_{m2})}.$$

(1.6)

$$C.O.: R_3 = R_4, \quad \omega_o = \frac{1}{\sqrt{R_1 R_2 (C_1 + C_{m1})(C_2 + C_{m2})}}.$$

(1.7)

## 1.3 Systematic Design of Active Devices

In the field of analog CAD, recent developments on the computational synthesis of analog ICs are given in [13]. Another recent technique is given in [12], where the VF is evolved to a voltage mirror (VM), and the dual topology of the VF leads us to design a current follower (CF). These are three unity-gain cells, and the fourth one is the CM.

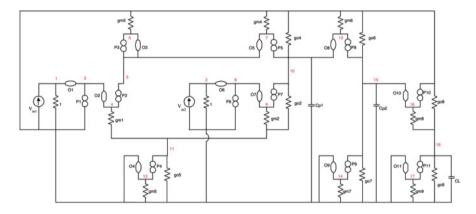

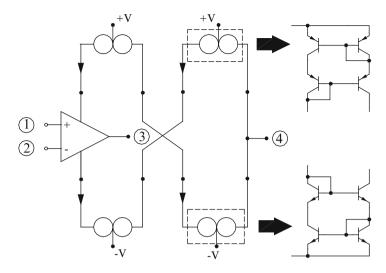

In summary, the computational synthesis of the VF includes [27]: generation of the small-signal circuitry, addition of the bias circuitry, replacement of nullator-norator pairs by transistors, and replacement of current biases by CMs. That is, since

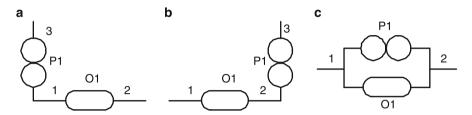

Fig. 1.12 Nullator-equivalent circuits to describe a VF

Fig. 1.13 Addition of a norator  $P_1$  at: (a) node 1, (b) node 2, and (c) between nodes 1 and 2 of the nullator  $O_1$

the voltage across a nullator is zero [1], the VF is modeled as shown by Fig. 1.12. A norator is joined to each nullator to form nullator-norator joined-pairs, as shown by Fig. 1.13. The combinations for the descriptions in Fig. 1.12 are given in [12].

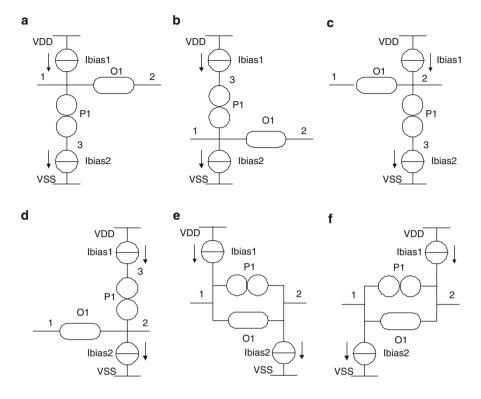

The bias circuitry is generated by addition of DC voltage and current bias levels to each nullator-norator joined-pair. That way, global DC voltage sources (VDD and VSS) are added, and ideal DC current sources are added to each norator  $P_i$ , as shown by Fig. 1.14. Besides, several bias sources can be eliminated as shown in [12, 27].

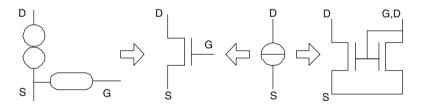

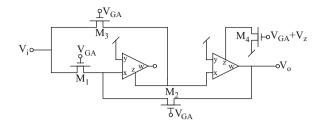

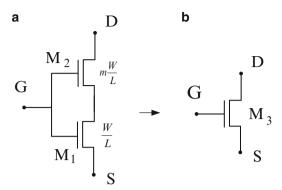

Each nullator-norator joined-pair ( $O_i$ - $P_i$ ) is replaced by a MOSFET, where the joined terminals are associated to the source, and the other terminals of the nullator and norator, are associated to the gate and drain, as shown by Fig. 1.15. The kind of MOSFET, i.e. channel N or P, is determined by the direction of the current biases from VDD to VSS. In the same manner, an ideal current source is replaced by either a CMOS current mirror or a single MOSFET, as shown by Fig. 1.15. For instance, the biased circuits shown by Fig. 1.14c, d, are synthesized in Fig. 1.16 [27]. One can note that the VF topology in Fig. 1.16e is the flipped VF [28].

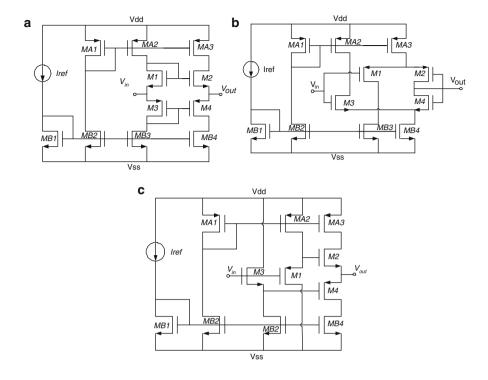

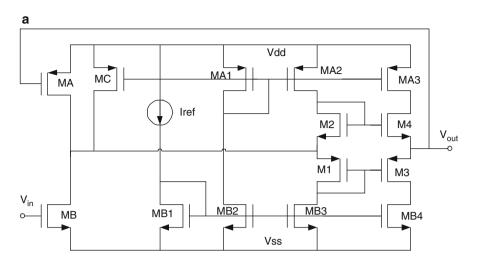

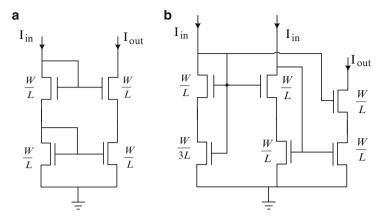

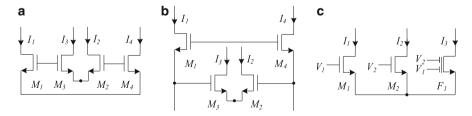

Figure 1.17 shows three well-known CMOS VFs. They can be evolved to design VMs, as the ones shown in Fig. 1.18, where the VF topologies for Fig. 1.17a, b are embedded into topologies Fig. 1.18a, b, respectively [12].

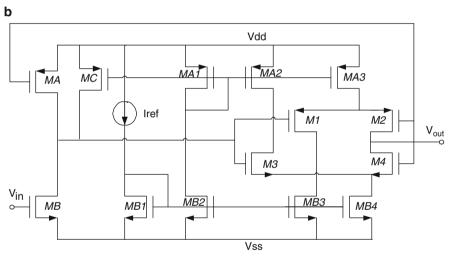

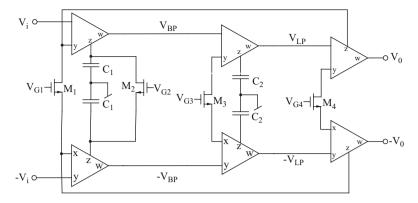

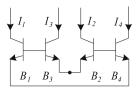

## 1.3.1 Computational Synthesis of CMs

The synthesis of a CM begins by using four nullators (O) and four norators (P), as shown by Fig. 1.19a. Each gate (G1, G2, G3, G4) in Fig. 1.19a can be connected

Fig. 1.14 Addition of current biases to Fig. 1.13

Fig. 1.15 Synthesis of the nullor by a MOSFET, and of a current source by a CM

to nodes: A, B, C, D,  $V_{\rm BIAS}$ , Vdd or to an extra node (NG1, NG2, NG3, NG4) who is also used to add level shifters. The chromosomal representation consists of three genes [12]: genBias, genIO, and genLS. Lets us consider the chromosome 611669. Its BGE is shown in Fig. 1.19d. Figure 1.19e shows its generic description. Six synthesized CMs are shown in Table 1.1.

Fig. 1.16 Synthesis of the VFs from Fig. 1.14c, d

## 1.3.2 Computational Synthesis of Mixed-Mode Active Devices

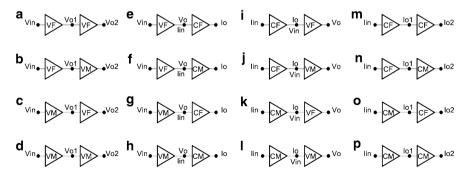

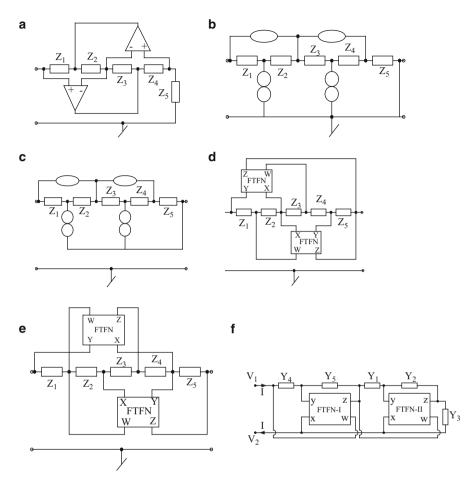

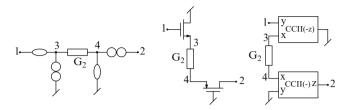

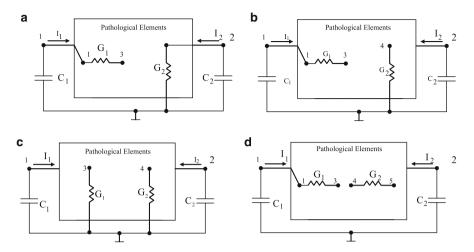

The four unity-gain cells find applications in filter and oscillator design [29–31]. Furthermore, the interconnection or superimposing of two or more of them [12], leads us to create known or new active devices. For instance, several combinations among two unity-gain cells are shown in Fig. 1.20.

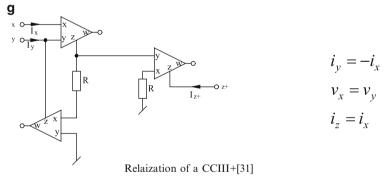

From Fig. 1.20, the negative and positive types second generation current conveyors (CCII-/+) [4], are generated by Figs. 1.20e, f, and their inverting realizations (ICCII-/+) by Fig. 1.20g, h. Other topologies like the OTRA, CBDA and inverting current conveyors can be synthesized by augmenting the interconnection strategies from [12]. For example, the superimposing of Fig. 1.20f, k generates the CFOA, i.e., it is the connection of three blocks VF-CM-VF, or equivalently, the CCII+ in cascade connection with a VF [4].

Fig. 1.17 Three VFs already synthesized in [27]

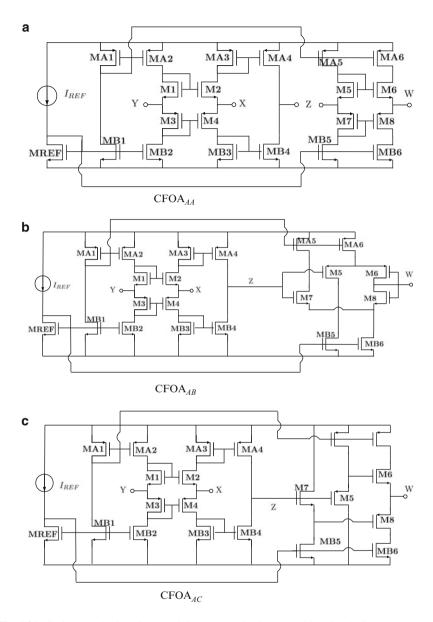

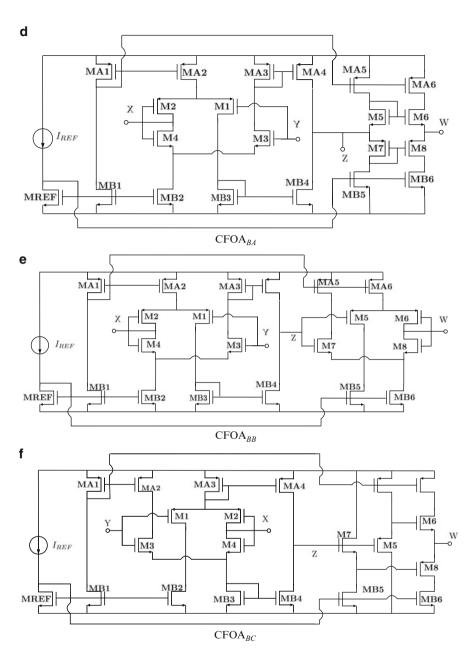

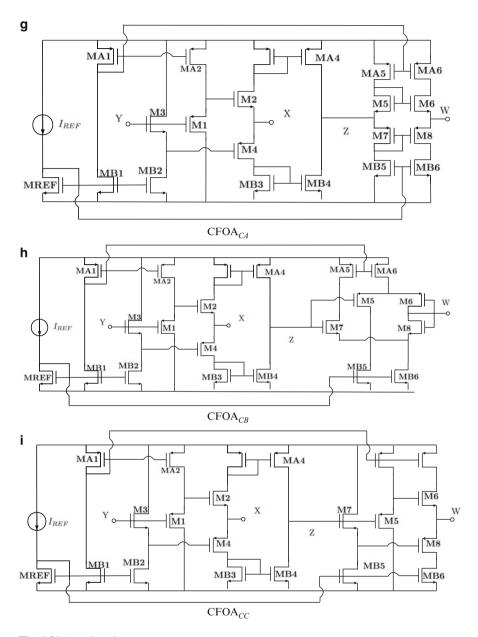

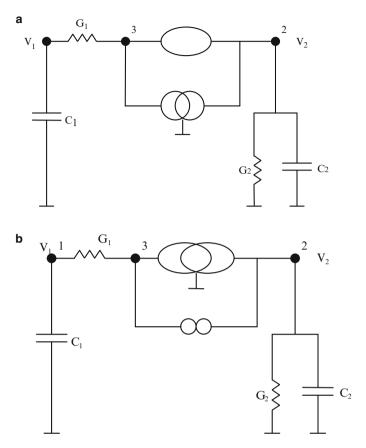

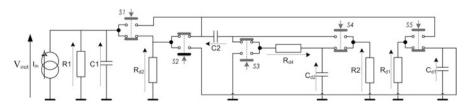

By combining the three VFs depicted in Fig. 1.17 with a simple CM, nine CFOAs arise. The VFs are labeled with capital letters A, B and C.

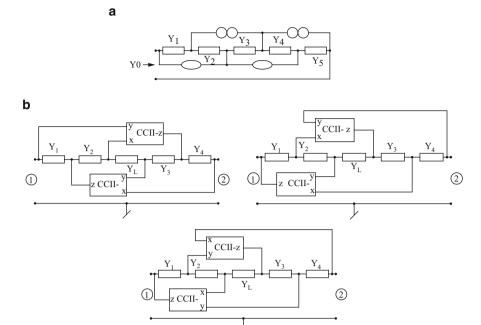

#### 1.4 Circuit Optimization

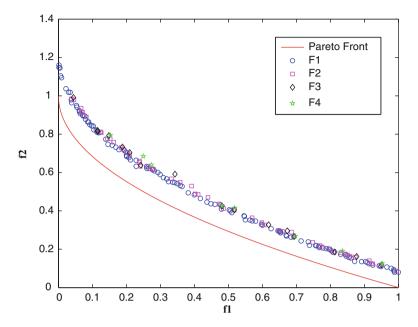

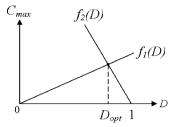

The biasing and sizing of analog ICs is a challenge in the development of electronic design automation tools [26]. Multi-objective evolutionary algorithms have demonstrated their usefulness in generating suitable/feasible solutions [32–34]. In this manner, we summarize three evolutionary algorithms for the multi-objective optimization of the nine CFOA-topologies synthesized in Fig. 1.21.

A multi-objective optimization problem (MOP) can formally be defined as the problem of finding the vector:

$\mathbf{x} = [x_1, x_2, \dots, x_n]^{\mathrm{T}}$ , satisfying k inequality constraints:

$$g_i(\mathbf{x}) < 0$$

; for  $i = 1, 2, ..., k$

Fig. 1.18 Two VMs synthesized from the VFs in Fig. 1.17

the p equality constraints

$$h_j(\mathbf{x}) = 0$$

; for  $j = 1, 2, \dots p$

and minimizing the vector function

$$\mathbf{f}: \mathbb{R}^n \to \mathbb{R}^m$$

$\mathbf{f}(\mathbf{x}) = [f_1(\mathbf{x}), f_2(\mathbf{x}), \dots, f_m(\mathbf{x})]^{\mathrm{T}}.$

**Fig. 1.19** (a) Modeling a CM; (b) and (c) extra circuits for  $I_{OUT}$ ; (d) codification of chromosome: 611669; (e) generic model of the CM 611669 [12]

The goal is focused on determining from the set S, all vectors (points) satisfying the constraints that yield the optimum values for all the m objective functions simultaneously. The constraints define the feasible region S, and any point  $\mathbf{x}$  in the feasible region is called a feasible point.

Pareto dominance: A vector  $\mathbf{u} \in \mathbb{R}^m$  is said to dominate a vector  $\mathbf{v} \in \mathbb{R}^m$ ,  $\mathbf{u} \prec \mathbf{v}$ , if and only if  $\mathbf{u}$  is partially less than  $\mathbf{v}$ , i.e.,  $\forall i \in \{1, \dots m\}$ ,  $u_i \leq v_i \land \exists i \in \{1, \dots m\}$ :  $u_i < v_i$ , (assuming minimization). One solution dominates another one when it is strictly better in at least one objective, and not worse in any of them.

Formal definition of Pareto optimality: A solution  $\mathbf{x}_u \in S$  (where S is the feasible region) is said to be Pareto optimal if and only if there is no  $x_v \in S$  for which  $\mathbf{v} = \mathbf{f}(\mathbf{x}_v) \in \mathbb{R}^m$  dominates  $\mathbf{u} = \mathbf{f}(\mathbf{x}_u) \in \mathbb{R}^m$ , where m is the number of objectives.

This definition says that  $\mathbf{x}_u$  is Pareto optimal if there exists no feasible vector  $\mathbf{x}_v$  which would decrease some objective without causing a simultaneous increase in at least one another objective (assuming minimization). This definition does

Table 1.1 Six synthesized CMs

Fig. 1.20 Combinations among two unity-gain cells [12]

Fig. 1.21 CFOAs synthesized by combining the VFs in Fig. 1.17 with a simple CM

not provide us a single solution (in decision variable space), but a set of solutions which form the so-called Pareto Optimal Set or Pareto Front. All the vectors that correspond to the solutions included in the Pareto Front are non-dominated.

Fig. 1.21 (continued)

Fig. 1.21 (continued)

#### Algorithm 1 NSGA-II Algorithm

```

1: P_0 = \text{random}, Q_0 = \text{random}

2: t = 0

3: P_{t+1} = \emptyset and i = 1

4: repeat

5:

R_t = P_t \cup O_t

6:

F = \text{fast-non-dominated-sort}(R_t)

7:

crowding-distance-assignment(F_i)

8:

9:

P_{t+1} = P_{t+1} \cup F_i

10:

i = i + 1

11:

until |P_{t+1}| + |F_i| \le N

12:

Sort(F_i, \prec_n)

13:

P_{t+1} = P_{t+1} \cup F_i[1:(N-|P_{t+1}|)]

14:

Q_{t+1} = \text{make-new-pop}(P_{t+1})

15: until stop criteria

```

#### 1.4.1 Non-Dominated Sorting Genetic Algorithm II (NSGAII)

This is an improved version of the (NSGA) by including elitism and was named as NSGA-II [35]. The NSGA-II procedure is summarized in Algorithm 1, and it approximates the Pareto Front of a MOP by sorting and ranking all solutions in order to choose the better solutions to make a new offspring. This means, by ranking all the population in different Pareto subfronts that it will be possible to know which solutions show better performance. In this algorithm is contemplated a way to choose the best solution between two solutions in the same subfront preserving diversity, in this form it is possible to select the best part of a population without losing diversity.

NSGA-II is based on two main procedures: Fast Nondominated Sort and Crowding Distance Assignment. These two procedures ensure elitism and it is possible to add constraints to ensure that the solutions are feasible [34, 35].

At the begining it is necessary to randomly initialize the parameters and start by generating two populations ( $P_o$  and  $Q_o$ ) each one of size N, from random values into a feasible region. The NSGA-II procedure in each generation consists of rebuilding the current population ( $R_t$ ) from the two original populations ( $P_t$  and  $Q_t$ ) then the new size of current population will be 2N. Now, through a nondominated sorting all solutions in  $R_t$  are ranked, and classified in a family of subfronts, as shows Fig. 1.22. In the next step is necessary to create from the current population  $R_t$  (previously ranked and ordered by subfront number) a new offspring ( $P_{t+1}$ ), the objective will be to choose from a population of size 2N, the N solutions which belong to the first subfronts. In this manner, the last subfront could be greater than is necessary, then it is used a measure ( $i_{distance}$ ) that allows to identify the better solutions and preserving elitism by selecting the solutions that are far the rest, this is possible simply by modifying a little bit the concept of Pareto dominance by including constraints in the dominance concept.

Fig. 1.22 Fast Non-dominated sorting

# 1.4.2 Multi-Objective Evolutionary Algorithm Based on Decomposition

The basic idea of MOEA/D is the decomposition of a multiobjective problem in scalar optimization subproblems by a *weights vector* [36]. This vector associates a weight  $(\lambda)$  for each subproblem which is considered as a single individual in the population which is going to try to improve by itself and to its nearby (*neighbors*).

After the initialization of the parameters the first step in MOEA/D is related to define the N spread weights vector over the objectives space (to each individual corresponds one  $\lambda_i$ ). One way can be by using a parameter H in a sequence as described by (1.8):

$$\left\{\frac{0}{H}, \frac{1}{H}, \dots, \frac{H}{H}\right\}. \tag{1.8}$$

Therefore, for m = 2, N = H + 1, with m > 2 the number of such vectors is defined by the combination in (1.9):

$$N = C_{H+m-1}^{m-1} (1.9)$$

In Algorithms 2 and 3 are the pseudocode to generate these vectors, for three and m objectives, respectively. It is necessary to chose a value for H, so that the population size depends on this number.

#### Algorithm 2 Build spread of N weight vectors (m = 3)

```

1: i = 1, set H

2: for \mu_1 = 0 to 1, step \frac{1}{H} do

3: for \mu_2 = 0 to 1, step \frac{1}{H} do

4: if 1 - (\mu_1 + \mu_2) \ge 0 then

5: \lambda_i = \{\mu_1 \ \mu_2 \dots \left(1 - (\mu_1 + \mu_2)\right)\}

6: i = i + 1

7: end if

8: end for

9: end for

```

#### **Algorithm 3** Build spread of N weight vectors for *m* objectives

```

2: for \mu_1 = 0 to 1, step \frac{1}{H} do

3:

for \mu_2 = 0 to 1, step \frac{1}{\mu} do

4:

5:

for \mu_{m-1} = 0 to 1, step \frac{1}{H} do

6:

if 1 - (\mu_1 + \mu_2 + \dots + \mu_{m-1}) \ge 0 then

7:

\lambda_{\mathbf{i}} = \{ \mu_1 \ \mu_2 \dots (1 - (\mu_1 + \mu_2 + \dots \mu_{m-1})) \}

8:

i = i + 1

9:

end if

10:

end for

11:

12:

end for

13: end for

```

#### Algorithm 4 MOEA/D Algorithm

```

1: build an uniform spread of N weight vectors (\lambda)

2: B(i) = \{i_1, i_2, \dots, i_T\}

3: t = 1, POP=random(), set E = \emptyset, T

4: repeat

5:

for i = 1, 2, ..., N do

6:

randomly select parents from B(i)

7:

generate new individual v

8:

for each \ell \in B(i) do

9:

if g(\mathbf{y} \mid \lambda_{\ell}, \mathbf{Z}^*) \leq g(\mathbf{x}_{\ell} \mid \lambda_{\ell}, \mathbf{Z}^*) then

10:

x_{\ell} = y

F_{\ell} = F(\mathbf{y})

11:

12:

end if

end for

13:

14:

end for

remove from EP all vectors dominated by F(\mathbf{y})

15:

16: until stop criteria

```

A number (T) of neighborhoods is defined for each  $\lambda_i$ . The Euclidean distance between each  $\lambda_i$  is calculated. Finally, for each  $\lambda_i$  there are (T) neighborhoods nearby, saved in B. Algorithm 4 shows the steps performed by MOEA/D [36].

In each generation there is a population of N points  $\mathbf{x}_1, \mathbf{x}_2, \dots, \mathbf{x}_N \in X$  where  $\mathbf{x}_i = (x_i^1, x_i^2, \dots, x_i^n)$  is the current solution to the  $i_{th}$  subproblem and there are  $F_1, F_2, \dots, F_N$ , where  $F_i = F(\mathbf{x}_i) : \mathbb{R}^n \to \mathbb{R}$ .

#### Algorithm 5 Pseudocode for MO-PSO

```

1: Initialize NoLoops, bound limits, population (N) and velocities

```

- 2: Evaluate population

- 3: Update Pbest

- 4: Select non-dominated particles

- 5: Select Gbest randomly among non-dominated particles

- 6: for i= 1 to NoLoops do

- 7: **for** j=1 to N **do**

- 8: Update particle velocity

- 9: Update particle position

- 10: Ensuring new position is into bound limits

- 11: end for

- 12: Evaluate population

- 13: Update Pbest

- 14: Select non-dominated particles and save them in REP

- 15: Select Gbest randomly among non-dominated particles

- 16: **end for**

In the procedure, a new individual  $\mathbf{y}$  is generated and compared with all its neighborhood by applying a decomposition approach  $(g[\mathbf{x}_i \mid \lambda_i, \mathbf{Z}^*])$ , e.g. the *Tchebycheff Approach*, and each neighbor worse than this new individual will be replaced by it in an external population (EP), which is used to store non-dominated solutions.

In the Tchebycheff Approach, the scalar optimization problem is described by (1.10), where  $\mathbf{Z}^* = \{z_1^*, z_2^*, \dots, z_m^*\}^T$  are the best current objective functions found.

$$g(\mathbf{x}_i \mid \lambda_i, \mathbf{Z}^*) = \max\{\lambda_i | f_j(\mathbf{x}_i) - z_j^* | \}_{\substack{1 \le i \le N \\ 1 \le j \le m}}.$$

(1.10)

#### 1.4.3 Multi-Objective Particle Swarm Optimization

In the Multi-Objective Particle Swarm Optimization Algorithm (MO-PSO) [32], there are N particles denoted by  $\mathbf{x}_i$ , where  $i=1,2,\ldots,N$ , and are represented by their positions in the search space. Each particle  $\mathbf{x}_i = (x_i^1, x_i^2, \ldots, x_i^n)$  represents a position in the space and depends on its previous local best position  $(P_{\text{best}})$  and global best position  $(G_{\text{best}})$ . Equation (1.11) is used to compute the speed of each particle, where  $V_i$  is the current velocity of the particle ith,  $k_w$  is the inertia weight which takes typical values lower than 1;  $P_{\text{best}i}$  is the best position of particle ith,  $P_i$  is the position of the current particle and  $G_{\text{best}}$  is a global best selected among the global best solutions. The new position of each particle is computed by (1.12).

$$V_i = k_w V_i + R_1 (P_{\text{besti}} - P_i) + R_2 (G_{\text{best}} - P_i). \tag{1.11}$$

$$P_i = P_i + V_i. (1.12)$$

In Algorithm 5 our proposed MO-PSO is described. It takes care of the new position to avoid going beyond the bound limits. Step 1 is the initialization

procedure to set the bound limits, and the particles are initialized randomly within those bound limits. The velocities are initialized with zero values. In step 2, the population is evaluated to update the best position ( $P_{best}$ ) at step 3, for each particle. Afterwards, the non-dominated particles are gathered to select randomly a global best ( $G_{best}$ ) into that repository (steps 4 and 5). Then, the velocity and position of each particle is updated, and avoiding going beyond the bound limits (steps 7–11). Once all the particles are updated, an evaluation process updates the best position for each particle, the non-dominated particles are selected and saved in a repository (REP). Among the solutions contained in REP, one of them is selected randomly to be the global best for the next loop (steps 12–15). This process continues until a determined number of loops.

# 1.4.4 Optimization of Active Devices by Evolutionary Algorithms

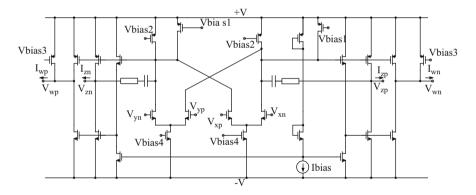

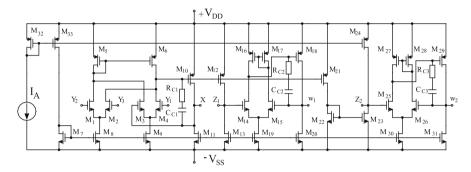

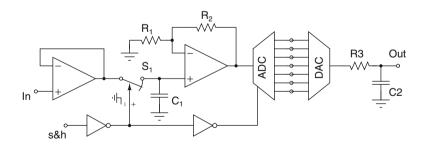

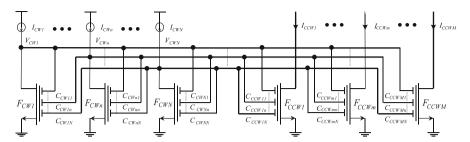

This section shows the application of NSGA-II, MOEA/D and MO-PSO, in the optimization of the nine CFOAs shown in Fig. 1.21. Those algorithms were programmed with a PERL script, and the circuit simulations are made with HSPICE. The goal is to find the optimal width ( $W_i$ ) and length (L) of each MOSFET. The simulation results are collected by using the HSPICE .MEASURE instruction, that is capable to save electronic measurements in the output listing. The CFOAs are biased with VDD=1.5 V and VSS=-1.5 V. The electrical measurements were executed with a load capacitor of 1 pF and the HSPICE simulations were performed with a LEVEL 49 standard CMOS Technology of 0.18  $\mu$ m.

As already shown in [32-34], the optimization problem is expressed as:

minimize

$$\mathbf{f}(\mathbf{x}) = [f_1(\mathbf{x}), f_2(\mathbf{x}), \dots, f_{11}(\mathbf{x})]^{\mathrm{T}}$$

subject to  $h_k(\mathbf{x}) \ge 0$ ,  $k = 1 \dots p$ , (1.13)

where  $\mathbf{x} \in X$ .

$\mathbf{f}(\mathbf{x})$  is the vector formed by eleven objectives:

- $f_1(\mathbf{x}) = \text{Power consumption}$

- $f_2(\mathbf{x}) = |1$  Voltage gain from Y port to X port (GAIN<sub>X</sub>)

- $f_3(\mathbf{x}) = -1*$  Voltage band width from Y port to X port (BW<sub>X</sub>)

- $f_4(\mathbf{x}) = -1*$  Input resistance on Y port  $(\mathbf{Z}_Y)$

- $f_5(\mathbf{x}) = \text{Output resistance on X port } (\mathbf{Z}_X)$

- $f_6(\mathbf{x}) = |1$  Current gain from X port to Z port (GAIN<sub>Z</sub>)

- $f_7(\mathbf{x}) = -1*$  Current band width from X port to Z port (BW<sub>Z</sub>)

- $f_8(\mathbf{x}) = -1 * \text{Output resistance on Z port } (\mathbf{Z}_Z)$

- $f_9(\mathbf{x}) = |1$  Voltage gain from Z port to W port | (GAIN<sub>W</sub>)

- $f_{10}(\mathbf{x}) = -1$  \* Voltage band width from Z port to W port (BW<sub>W</sub>)

- $f_{11}(\mathbf{x}) = \text{Output resistance on W port } (\mathbf{Z}_W)$

Table 1.2

CFOAAA ENCODING

| gene                  | Design variable | Encoding              | Decision space                                       |

|-----------------------|-----------------|-----------------------|------------------------------------------------------|

| $\overline{x_1}$      | L               | All transistors       | $0.18 \mu \text{m} \le L \le 0.9 \mu \text{m}$       |

| $x_2$                 | $W_1$           | MREF, MB1-MB4, M1, M2 | $0.18  \mu \text{m} \leq W_1 \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>3</sub> | $W_2$           | MA1-MA4, M3, M4       | $0.18  \mu \text{m} \leq W_2 \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>4</sub> | $W_3$           | MB5, MB6, M5, M6      | $0.18  \mu \text{m} \leq W_3 \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>5</sub> | $W_4$           | MA5, MA6, M7, M8      | $0.18  \mu \text{m} \leq W_4 \leq 200  \mu \text{m}$ |

| $x_6$                 | I               | $I_{ m BIAS}$         | $10\mu A \leq I \leq 400\mu A$                       |

Table 1.3 CFOA<sub>BC</sub> ENCODING

| gene                   | Design variable | Encoding                      | Decision space                                          |

|------------------------|-----------------|-------------------------------|---------------------------------------------------------|

| $\overline{x_1}$       | $L_1$           | MREF, MA1-MA4, MB1-MB4, M1-M4 | $0.18  \mu \text{m} \leq L_1 \leq 0.9  \mu \text{m}$    |

| $x_2$                  | $L_2$           | MA5, MA6, MB5, MB6, M6-M8     | $0.18  \mu \text{m} \leq L_2 \leq 0.9  \mu m$           |

| <i>x</i> <sub>3</sub>  | $W_1$           | MREF, MB1, MB2, M3, M4        | $0.18  \mu \text{m} \leq W_1 \leq 200  \mu \text{m}$    |

| <i>X</i> 4             | $W_2$           | MA1, MA2, M1, M2              | $0.18  \mu \text{m} \leq W_2 \leq 200  \mu \text{m}$    |

| $x_5$                  | $W_3$           | MB3, MB4                      | $0.18  \mu \text{m} \leq W_3 \leq 200  \mu \text{m}$    |

| $x_6$                  | $W_4$           | MA3, MA4                      | $0.18  \mu \text{m} \leq W_4 \leq 200  \mu \text{m}$    |

| $x_7$                  | $W_5$           | MB5, MB6                      | $0.18  \mu \text{m} \leq W_5 \leq 200  \mu \text{m}$    |

| <i>x</i> <sub>8</sub>  | $W_6$           | MA5, MA6                      | $0.18  \mu \text{m} \leq W_6 \leq 200  \mu \text{m}$    |

| <i>X</i> 9             | $W_7$           | M5                            | $0.18  \mu \text{m} \leq W_7 \leq 200  \mu \text{m}$    |

| $x_{10}$               | $W_8$           | M6                            | $0.18  \mu \text{m} \leq W_8 \leq 200  \mu \text{m}$    |

| $x_{11}$               | $W_9$           | M7                            | $0.18  \mu \text{m} \leq W_9 \leq 200  \mu \text{m}$    |

| $x_{12}$               | $W_{10}$        | M8                            | $0.18  \mu \text{m} \leq W_{10} \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>13</sub> | I               | $I_{ m BIAS}$                 | $10\mu A \leq I \leq 400\mu A$                          |

**Table 1.4** CFOA<sub>CC</sub> encoding

| gene                   | Design variable | Encoding                      | Decision space                                          |

|------------------------|-----------------|-------------------------------|---------------------------------------------------------|

| $\overline{x_1}$       | $L_1$           | MREF, MA1-MA4, MB1-MB4, M1-M4 | $0.18  \mu \text{m} \leq L_1 \leq 0.9  \mu \text{m}$    |

| $x_2$                  | $L_2$           | MA5, MA6, MB5, MB6, M6-M8     | $0.18  \mu \text{m} \leq L_2 \leq 0.9  \mu \text{m}$    |

| $x_3$                  | $W_1$           | MREF, MB1-MB4                 | $0.18  \mu \text{m} \leq W_1 \leq 200  \mu \text{m}$    |

| $\chi_4$               | $W_2$           | MA1-MA4                       | $0.18  \mu \text{m} \leq W_2 \leq 200  \mu \text{m}$    |

| <i>x</i> <sub>5</sub>  | $W_3$           | M3                            | $0.18  \mu \text{m} \leq W_3 \leq 200  \mu \text{m}$    |

| $x_6$                  | $W_4$           | M1                            | $0.18  \mu \text{m} \leq W_4 \leq 200  \mu \text{m}$    |

| <i>X</i> 7             | $W_5$           | M2                            | $0.18  \mu \text{m} \leq W_5 \leq 200  \mu \text{m}$    |

| $x_8$                  | $W_6$           | M4                            | $0.18  \mu \text{m} \leq W_6 \leq 200  \mu \text{m}$    |

| <i>X</i> 9             | $W_7$           | MB5, MB6                      | $0.18  \mu \text{m} \leq W_7 \leq 200  \mu \text{m}$    |

| $x_{10}$               | $W_8$           | MA5, MA6                      | $0.18  \mu \text{m} \leq W_8 \leq 200  \mu \text{m}$    |

| $x_{11}$               | $W_9$           | M6                            | $0.18  \mu \text{m} \leq W_9 \leq 200  \mu \text{m}$    |

| $x_{12}$               | $W_{10}$        | M5                            | $0.18  \mu \text{m} \leq W_{10} \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>13</sub> | $W_{11}$        | M7                            | $0.18  \mu \text{m} \leq W_{11} \leq 200  \mu \text{m}$ |

| $x_{14}$               | $W_{12}$        | M8                            | $0.18  \mu \text{m} \leq W_{12} \leq 200  \mu \text{m}$ |

| <i>x</i> <sub>15</sub> | I               | $I_{ m BIAS}$                 | $10\mu A \leq I \leq 400\mu A$                          |

| ; |            | 1              |

|---|------------|----------------|

| ÷ | _          | į              |

| į | Ė          | į              |

|   | =          | Ξ              |

| - | Character  | S SILO WIL     |

| 4 | 1          | 1              |

|   | Ĭ          | 7              |

| - | 2          | 2              |

| ٠ | 2          | 101            |

| ٠ | Ė          | perioritations |

|   | 797 I WILL | 2711112        |

| ( |            | )              |

| , | •          | 3              |

|   | 0          | Table          |

|   |            |                |

| Table 1.3            | Opumzeu p | periorinances for une | s ioi uic c     | L'OAS SIIU       | WII III II W   | 15.1.5                         |        |          |                     |              |          |

|----------------------|-----------|-----------------------|-----------------|------------------|----------------|--------------------------------|--------|----------|---------------------|--------------|----------|

| Objective            | POWER     | $GAIN_X$              | $\mathrm{BW}_X$ | $\mathbf{Z}_{Y}$ | $\mathbf{Z}_X$ | $GAIN_Z$                       | $BW_Z$ | $Z_Z$    | $GAIN_W$            | ${\bf BW}_W$ | $Z_W$    |

| Units                | Watts     | $ \frac{V_X}{V_Y} $   | Hz              | $\Omega$         | $\Omega$       | $\left \frac{V_Z}{V_X}\right $ | Hz     | $\Omega$ | $ \frac{V_X}{V_Y} $ | Hz           | $\Omega$ |

| $CFOA_{AA}$          |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 1.61E-4   | 0.9883                | 5.54E7          | 20612            | 1737           | 0.9825                         | 5.26E7 | 391360   | 0.9849              | 1.82E6       | 83091    |

| MOEA/D               | 1.58E-4   | 0.9881                | 6.48E7          | 32139            | 1976           | 0.9711                         | 9.29E7 | 442150   | 0.9811              | 1.30E6       | 120800   |

| MOPSO                | 3.77E-4   | 0.9883                | 8.79E7          | 7227             | 905.6          | 0.9864                         | 6.28E7 | 11138    | 0.9881              | 4.77E7       | 2853     |

| $\mathrm{CFOA}_{AB}$ |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 3.32E-4   | 0.9851                | 1.34E8          | 16870            | 904.8          | 0.9943                         | 1.93E8 | 173730   | 0.9779              | 1.42E6       | 100800   |

| MOEA/D               | 1.59E-4   | 0.9881                | 6.30E7          | 33626            | 1921           | 9026.0                         | 8.42E7 | 466010   | 0.9783              | 7.85E5       | 185980   |

| MOPSO                | 3.91E-4   | 0.9869                | 1.02E8          | 10257            | 922.3          | 0.9823                         | 9.42E7 | 15928    | 0.9749              | 2.53E7       | 6699     |

| ${ m CFOA}_{AC}$     |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 2.70E-4   | 0.9871                | 6.54E7          | 7357             | 2042           | 0.9942                         | 6.84E7 | 134620   | 0.9778              | 4.39E7       | 3968     |

| MOEA/D               | 3.13E-4   | 0.9882                | 6.26E7          | 88956            | 1835           | 0.9801                         | 6.92E7 | 132850   | 0.9754              | 4.39E7       | 2456     |

| MOPSO                | 1.13E-3   | 0.9835                | 1.40E8          | 45082            | 738.7          | 0.9752                         | 6.98E7 | 2344     | 0.9878              | 1.25E8       | 645.2    |

| ${ m CFOA}_{BA}$     |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 3.35E-4   | 0.987                 | 2.69E7          | 106960           | 4071           | 0.9907                         | 5.68E7 | 5700     | 0.9848              | 7.60E7       | 2173     |

| MOEA/D               | 4.73E-4   | 0.9873                | 2.70E7          | 142350           | 4350           | 0.9829                         | 6.01E7 | 4444     | 0.9871              | 1.17E8       | 643.2    |

| MOPSO                | 1.50E-3   | 0.9865                | 7.01E7          | 20337            | 1259           | 0.9912                         | 8.25E7 | 975      | 0.9856              | 1.94E8       | 275.9    |

| ${ m CFOA}_{BB}$     |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 6.84E-3   | 0.9734                | 7.51E7          | 269280           | 1994           | 0.9735                         | 2.27E8 | 1007     | 0.9457              | 7.89E8       | 176.6    |

| MOEA/D               | 4.85E-4   | 0.9851                | 2.46E7          | 756260           | 6110           | 0.9829                         | 5.73E7 | 60735    | 0.974               | 1.98E7       | 9002     |

| MOPSO                | 6.75E-3   | 0.9821                | 1.53E8          | 27306            | 821.4          | 0.9912                         | 1.29E8 | 709.3    | 0.9403              | 3.65E8       | 337.5    |

| ${ m CFOA}_{BC}$     |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| NSGA-II              | 8.76E-4   | 0.986                 | 1.70E7          | 382410           | 7816           | 0.9948                         | 4.08E7 | 2470     | 0.9807              | 1.95E8       | 313.9    |

| MOEA/D               | 1.43E-3   | 0.9857                | 9.01E7          | 55392            | 1471           | 0.975                          | 7.24E7 | 100230   | 0.9839              | 3.32E7       | 3423     |

| MOPSO                | 6.89E-3   | 0.9828                | 1.13E8          | 51479            | 1054           | 0.9801                         | 1.32E8 | 1431     | 0.9786              | 4.62E8       | 148.6    |

|                      |           |                       |                 |                  |                |                                |        |          |                     |              |          |

| $\mathrm{CFOA}_{CA}$ |         |        |        |         |       |        |        |        |        |        |        |

|----------------------|---------|--------|--------|---------|-------|--------|--------|--------|--------|--------|--------|

| NSGA-II              | 3.34E-4 | 0.9823 | 6.59E7 | 172600  | 1953  | 0.9898 | 6.35E7 | 298510 | 0.9859 | 9.25E5 | 162920 |

| MOEA/D               | 2.84E-4 | 0.9825 | 2.72E7 | 1012100 | 5376  | 0.9924 | 2.97E7 | 558540 | 0.9833 | 3.52E6 | 42719  |

| MOPSO                | 1.13E-3 | 0.9835 | 1.40E8 | 45082   | 738.7 | 0.9752 | 6.98E7 | 2344   | 0.9878 | 1.25E8 | 645.2  |

| $\mathrm{CFOA}_{CB}$ |         |        |        |         |       |        |        |        |        |        |        |

| NSGA-II              | 6.93E-4 | 0.9838 | 1.25E8 | 92861   | 736.9 | 0.9789 | 8.85E7 | 141830 | 0.9747 | 4.87E6 | 32926  |

| <b>MOEA/D</b>        | 4.53E-4 | 0.9847 | 5.55E7 | 277830  | 2480  | 0.9801 | 7.00E7 | 422190 | 0.9774 | 2.08E6 | 68170  |

| MOPSO                | 1.77E-3 | 0.9829 | 1.85E8 | 35788   | 545.5 | 0.9837 | 1.10E8 | 2723   | 0.9769 | 7.75E7 | 1360   |

| $\mathrm{CFOA}_{CC}$ |         |        |        |         |       |        |        |        |        |        |        |

| NSGA-II              | 7.45E-4 | 0.9835 | 1.20E8 | 119030  | 844.4 | 0.9885 | 1.08E8 | 129250 | 0.9844 | 2.34E7 | 9885   |

| <b>MOEA/D</b>        | 7.26E-4 | 0.9858 | 7.88E7 | 81182   | 1552  | 0.9911 | 6.97E7 | 305020 | 0.9773 | 3.72E7 | 5151   |

| MOPSO                | 2.00E-3 | 0.9843 | 1.54E8 | 21114   | 698.3 | 0.9822 | 7.14E7 | 28261  | 0.9763 | 1.12E8 | 1463   |

28 I. Guerra-Gómez et al.

where  $X : \mathbb{R}^n \mid 0.18 \ \mu\text{m} \le L_i \le 0.9 \ \mu\text{m}, \ 0.18 \ \mu\text{m} \le W_j \le 200 \ \mu\text{m}, \ 10 \ \mu\text{m} \le I_{\text{BIAS}} \le 400 \ \mu\text{A}$ , is the decision space for the *n* variables. Finally,  $h_k(\mathbf{x}), \ k = 1 \dots p$  are performance constraints, in our experiments we include the saturation condition in all transistors as constraints.

All CFOAs are encoded with  $L_i$  and  $W_i$ , where i represents a specific transistor or transistors sharing the same L or W. All L and W values are rounded to multiples of the minimum allowed by the technology process. The variables encoding for some CFOAs from Fig. 1.21 are listed in Tables 1.2–1.4. Table 1.5 shows the optimization results of the nine CFOAs. The three evolutionary algorithms are listed along with the best feasible solutions for the 11 objective functions. From this table, one can select the desired topology accomplishing target specifications [37].

#### 1.5 Conclusions

This chapter summarized recent developments on the analysis and design of active devices by using the nullor concept and pathological elements. Those active devices find applications in the area of analog signal processing, as shown in the following chapters. The optimization of active devices was discussed by presenting the application of three evolutionary algorithms, which provide similar results, but their computational capabilities still being for future research.

Acknowledgment This work is supported by CONACyT/MEXICO under project 131839-Y.

#### References

- Sánchez-López C, Fernández FV, Tlelo-Cuautle E, Tan SX-D (2011) Pathological elementbased active device models and their application to symbolic analysis. IEEE Trans Circuits Syst I Regul pap 58(6):1382–1395

- Wang HY, Huang WC, Chiang NH (2010) Symbolic nodal analysis of circuits using pathological elements. IEEE Trans Circuits Syst II Express Briefs 57(11):874

–877

- Saad RA, Soliman AM (2008) Use of mirror elements in the active device synthesis by admittance matrix expansion. IEEE Trans Circuits Syst I Fundam Theory Appl 55(9):2726–2735

- Tlelo-Cuautle E, Sánchez-López C, Moro-Frias D (2010) Symbolic analysis of (MO)(I)CCI(II)(III)-based analog circuits. Int J Circuit Theory Appl 38(6):649–659

- Tlelo-Cuautle E, Sánchez-López C, Martinez-Romero E, Tan SX-D (2010) Symbolic analysis

of analog circuits containing voltage mirrors and current mirrors. Analog Integr Circuits Signal

Process 65(1):89–95

- Fakhfakh M, Tlelo-Cuautle E, Fernández FV (2012) Design of Analog Circuits through Symbolic Analysis. Bentham Sciences Publishers Ltd., United Arab Emirates

- Tlelo-Cuautle E, Martinez-Romero E, Sánchez-López C, Tan SX-D (2010) Symbolic behavioral modeling of low voltage amplifiers. IEEE international conference on electrical engineering, computing science and automatic control (CCE), México, pp 510–514

- Rodriguez-Chavez S, Tlelo-Cuautle E, Palma-Rodriguez AA, Tan SX-D (2012) Symbolic DDD-based tool for the computation of noise in CMOS analog circuits. International Caribbean Conference on Devices, Circuits and Systems (ICCDCS), Playa del Carmen, Mexico

- Shi G (2011) A survey on binary decision diagram approaches to symbolic analysis of analog integrated circuits. Analog Integr Circuits Signal Process. doi: 10.1007/s10470-011-9773-8

- Tan SX-D, Liu X-X, Molinar E, Tlelo-Cuautle E (2012) Parallel symbolic analysis of large analog circuits on GPU platforms. In: VLSI Design, InTech Publisher. Available via InTech— Open Science

- Souliotis G, Haritantis I (2008) Current-mode filters based on current mirror arrays. Int J Circuit Theory Appl 36:173–183

- 12. Duarte-Villaseñor MA, Tlelo-Cuautle E, Gerardo de la Fraga L (2011) Binary genetic encoding for the synthesis of mixed-mode circuit topologies. Circuits Syst Signal Process. doi:10.1007/s00034-011-9353-2

- Martens E, Gielen G (2008) Classification of analog synthesis tools based on their architecture selection mechanisms. Integr VLSI J 41:238–252

- 14. Biolek D, Senani R, Biolkova V, Kolka Z (2008) Active elements for analog signal processing: classification, review, and new proposals. Radioengineering 17(4):15–32

- 15. Sedra A, Smith KC (1968) The current conveyor: a new circuit building block. Proc IEEE 56:1368–1369

- Mobarak M, Onabajo M, Silva-Martinez J, et al (2010) Attenuation-predistortion linearization of CMOS OTAs with digital correction of process variations in OTA-C filter applications. IEEE J Solid State Circuits 45(2):351–367

- Abhirup L, Maneesha G (2011) Realizations of grounded negative capacitance using CFOAs. Circuits Syst Signal Process 30(1):143–155

- Gupta SS, Bhaskar DR, Senani R, et al (2011) Synthesis of linear VCOs: the state-variable approach. J Circuits Syst Comput 20(4):587–606

- Soliman AM (2011) Generation of CFOA, CCII and DVCC based oscillators from passive RLC filter. J Circuits Syst Comput 20(4):621–639

- Trejo-Guerra R, Tlelo-Cuautle E, Sánchez-López C, Muñoz-Pacheco JM, Cruz-Hernández C (2010) Realization of multiscroll chaotic attractors by using current-feedback operational amplifiers. Revista Mexicana de Fisica 56(4):268–274

- 21. Saad RA, Soliman AM (2010) A new approach for using the pathological mirror elements in the ideal representation of active devices. Int J Circuit Theory Appl 38(2):148–178

- 22. Biolek D, Bajer J, Biolkova V, et al (2011) Z copy-controlled gain-current differencing buffered amplifier and its applications. Int J Circuit Theory Appl 39(3):257–274

- 23. Sánchez-López C, Martinez-Romero E, Tlelo-Cuautle E (2011) symbolic analysis of OTRAs-Based circuits. J Appl Res Technol 9(1):69–80

- 24. Sánchez-López C, Fernández FV, Tlelo-Cuautle E (2010) Generalized admittance matrix models of OTRAs and COAs. Microelectronics J 41(8):502–505

- Tlelo-Cuautle E, Duarte-Villaseñor MA, Garcia-Ortega JM, Sánchez-López C (2007) Designing SRCOs by combining SPICE and Verilog-A. Int J Electronics 94(4):373–379

- 26. Tlelo-Cuautle E (2011) Advances in analog circuits. InTech Publisher. Online Available http://www.intechweb.org/books/show/title/advances-in-analog-circuits

- Tlelo-Cuautle E, Torres-Muñoz D, Torres-Papaqui L (2005) On the computational synthesis of CMOS voltage followers. IEICE Trans Fundam Electronics Commun Comput Sci E88-A(12):3479–3484

- Carvajal RG, Ramirez-Angulo J, López-Martin A, Torralba A, Galán J, Carlosena A, Muñoz F (2005) The flipped voltage follower: a useful cell for low-voltage low-power circuit design. IEEE Trans Circuits Syst II 52(7):1276-1291

- 29. Gupta SS, Senani R (2006) New voltage-model/current-mode universal biquad filter using unity-gain cells. Int J Electronics 93(11):769–775

- 30. Sánchez-López C, Castro-Hernandez A, Perez-Trejo A (2008) Experimental verification of the Chua's circuit designed with UGCs. IEICE Electron Express 5(17):657–661

30 I. Guerra-Gómez et al.

Trejo-Guerra R, Tlelo-Cuautle E, Jiménez-Fuentes JM, Muñoz-Pacheco JM, Sánchez-López C (2011) Multiscroll floating gate based integrated chaotic oscillator. Int J Circuit Theory Appl. doi:10.1002/cta.821

- 32. Tlelo-Cuautle E, Guerra-Gómez I, Reyes-Garcia CA, Duarte-Villaseñor MA (2010) Synthesis of analog circuits by genetic algorithms and their optimization by particle swarm optimization. In: Chiong R (ed) Intelligent systems for automated learning and adaptation: emerging trends and applications. Information Science Reference: IGI Global, pp 173–192

- 33. Tlelo-Cuautle E, Guerra-Gómez I, Duarte-Villaseñor MA, de la Fraga LG, Flores-Becerra G, Reyes-Salgado G, Reyes-Garcia CA, Rodriguez-Gómez G (2010) Applications of evolutionary algorithms in the design automation of analog integrated circuits. J Appl Sci 10(17):1859–1872

- 34. Tlelo-Cuautle E, Guerra-Gómez I, de la Fraga LG, Flores-Becerra G, Polanco-Martagón S, Fakhfakh M, Reyes-Garcia CA, Rodriguez-Gómez G, Reyes-Salgado G (2011) Evolutionary algorithms in the optimal sizing of analog circuits. In: Koeppen M, Schaefer G, Abraham A (eds.) Intelligent computational optimization in engineering: techniques & applications, vol 366. Springer, Hershey, PA, pp 109–138

- 35. Deb K, Pratap A, Agarwal S, Meyarivan T (2002) A fast and elitist multiobjective genetic algorithm: NSGA-II. IEEE Trans Evol Comput 6(2):182–197

- 36. Zhang QF, Li H (2007) MOEA/D: a multiobjective evolutionary algorithm based on decomposition. IEEE Trans Evol Comput 11(6):712–731

- 37. Polanco-Martagón S, Reyes-Salgado G, Flores-Becerra G, Guerra-Gómez I, Tlelo-Cuautle E, de la Fraga LG, Duarte-Villaseñor MA (2012) Selection of MOSFET sizes by fuzzy sets intersection in the feasible solutions space. J Appl Res Technol 10(2) In press

## Chapter 2 Nullors, Their Bipolar and CMOS Implementations and Applications in Analog Circuit Synthesis and Design

Raj Senani, A.K. Singh, Pragati Kumar, and R.K. Sharma

#### 2.1 Introduction

Analog circuits using the traditional voltage mode (VM) op-amps suffer from the well-known drawbacks resulting from the limited slew rate, gain-bandwidth conflict and requirements of passive component-matching in the realization of several functions (such as controlled current sources, non-inverting integrators/differentiators and variable gain differential/instrumentation amplifiers, to name a few). The requirement of component-matching quite often leads to increased sensitivities and may even cause instability in several cases.

During the past four decades, a number of research groups around the world have toiled with the idea of searching for a universal analog building block overcoming the aforementioned limitations. Of various building blocks proposed so far, nullors have been regarded to be universal building blocks since the four controlled sources and all existing analog circuit building blocks can be represented using only nullors

R. Senani (⊠)

Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology,

New Delhi, India

e-mail: senani@nsit.ac.in

A.K. Singh

Department of Electronics and Communication Engineering, ITS Engineering College,

Greater Noida, India

e-mail: abdheshks@yahoo.com

P. Kumar

Department of Electrical Engineering, Delhi Technological University, New Delhi, India

e-mail: pragati\_1964@yahoo.co.in

R.K. Sharma

Department of Electronics and Communication Engineering, Ambedakar Institute of Technology, New Delhi, India

e-mail: 21ravindra@gmail.com

E. Tlelo-Cuautle (ed.), *Integrated Circuits for Analog Signal Processing*, DOI 10.1007/978-1-4614-1383-7\_2,

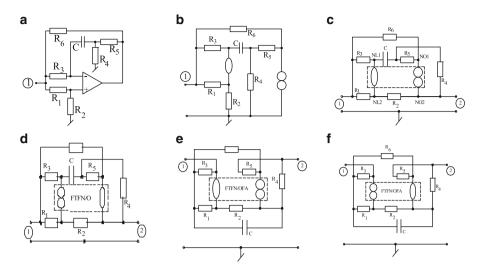

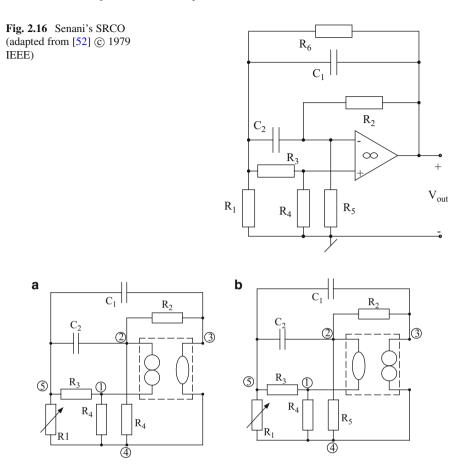

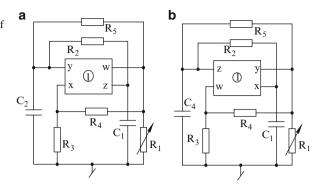

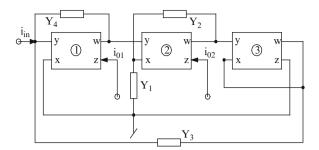

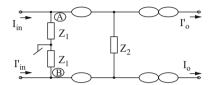

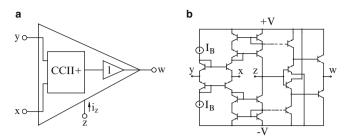

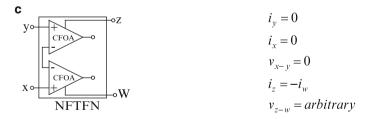

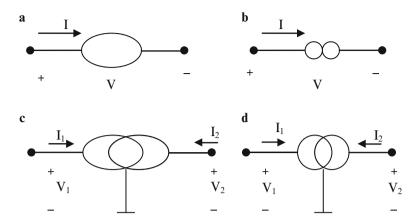

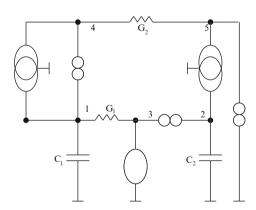

Fig. 2.1 Symbols and definitions of nullator, norator and nullor

and resistors. The floating nullor is a special form of nullor in which ground is external to the four terminals forming the two-port (with nullator comprising the input port and norator comprising the output port).

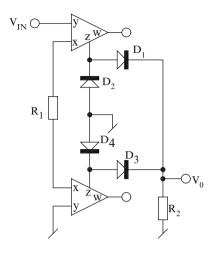

Although the origin of the concept of nullor itself was advanced as early as 1961–1964, by Carlin and Youla [1, 2] till about 1984 or so, theses elements were largely regarded as theoretical concepts useful only in generating equivalent networks of BJT and Op-Amp based circuits such as gyrators and impedance converters/inverters. However, over the years, nullors have attracted a lot of attention in literature and there have been a large number of publications dealing with applications and implementations of nullors, for instance, see [3] and the references cited therein. It was shown by a number of researchers (such as Nordholt [4], Stevenson [5], Huijsing [6] and Senani [7] (who coined the term "four-terminal floating-nullor" (FTFN) to represent a fully floating nullor) that fully floating versions of Op-Amps [termed as operational floating amplifier (OFA)] and FTFNs are more versatile and flexible building blocks than the traditional op-amps in several applications. Thus, the "OFA" and "FTFN" got going and soon attracted the attention of circuit designers as attractive building blocks for a number of voltagemode and current-mode signal processing applications. In most of the investigations, the FTFNs have been realized by a composite connection of two CCIIs as suggested by Senani in [7]. The current feedback op-amp AD844 from Analog Devices, which embodies a CCII+ followed by an on-chip buffer, became a preferred choice for implementing FTFNs using the quoted formulation (shown explicitly in Fig. 2.7d in this chapter). However, it is the CMOS implementability of the concept of FTFN which has brought it to the forefront of analog design in more recent years. A number of CMOS implementations of the FTFNs are now known, for instance, see [8–11] and references cited therein.

In this chapter, we deal with the nullors, particularly the floating ones namely, the FTFNs or OFAs, their hardware implementations and applications in circuit synthesis and design.

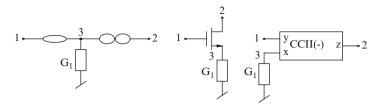

The symbolic notation and characterizing equations for nullator, norator and nullor have been depicted in Fig. 2.1.

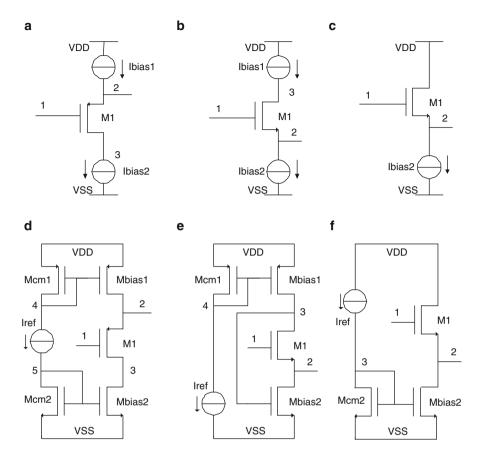

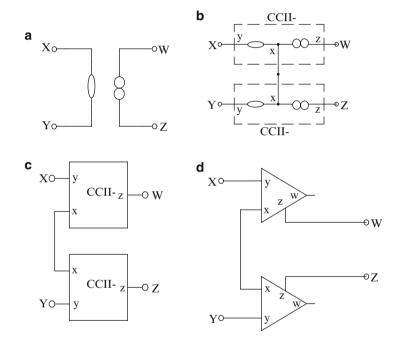

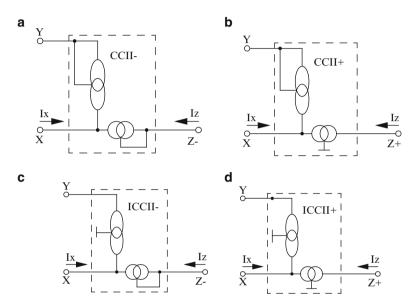

## 2.2 Nullor Representation of Various Analog Circuit Building Blocks

Since the evolution of nullors, the utility of nullor representation of ideal transistors (both BJT, FET) and the ideal Op-Amps was soon understood [12]. Subsequently, nullors have also been used to model other active building blocks which came into existence later on. Thus, it is well known that an ideal BJT as well as an ideal FET/MOSFET is a three-terminal nullor (see Fig. 2.2a); an ideal op-amp is also a three-terminal nullor with its input terminals representing a nullator and the output terminal with respect to the ground representing the norator; see Fig. 2.2b. A CCII—is equivalent to a three-terminal nullor (Fig. 2.3). This equivalence and the basic properties of nullators and norators and different ways of combining these have been used by Senani [13] and Higashimura and Fukui [14, 15] to synthesize a number of interesting CCII—based inductance simulation circuits.

In principle, since all the four controlled sources (namely, the voltage-controlled/current-controlled voltage/current sources) can be represented by nullators, norators and resistors, a CCII+ can also be represented by nullors but requires two resistors in addition (see Fig. 2.4).

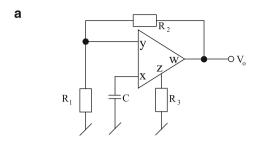

A nullor representation of an operational transconductance amplifier (OTA), voltage follower (VF) and current follower (CF) are shown in Fig. 2.5.

Fig. 2.2 Nullor models of active devices: (a) Ideal transistor (BJT). (b) Ideal op-amp

Fig. 2.3 Nullor model of CCII-

$$\mathbf{i}_{y} = 0, \mathbf{v}_{x} = \mathbf{v}_{y}, \quad \mathbf{i}_{z} = -\mathbf{i}_{x}$$

Fig. 2.4 Nullor model of CCII+

$$\mathbf{i}_{y} = 0, \quad \mathbf{v}_{x} = \mathbf{v}_{y}, \quad \mathbf{i}_{z} = \mathbf{i}_{x}$$

Fig. 2.5 Nullor model of other active building blocks. (a) Nullor model of an OTA. (b) Nullor model of a VF. (c) Nullor model of a CF

Since nullors can be used to represent a variety of active elements, they provide a unified framework not only for analysis, synthesis and design of active networks but also for inter-relating the realizations using different active elements. This fact will be unfolded in subsequent sections of this chapter. However, before proceeding further, we briefly look into the advent of OFAs and FTFNs.

#### 2.3 The Advent of OFA and FTFN

Nordholt in 1982 [4], presented a method of extending op-amp capabilities using current source power supplies. This "extended op-amp" represented a four-port active element which was loosely equivalent to a floating nullor.

Another op-amp-based floating nullor was employed by Stevenson in 1984 in realizing two-way circuits with inverse transmission properties in [5]. This floating nullor circuit was derived from a three-terminal nullor realized with two op-amps, proposed earlier by Cox, Su and Woodland in 1971 [16].

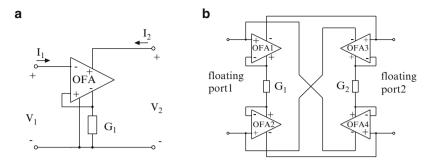

Huijsing in [6, 17], introduced the concept of an OFA which is same as a floating nullor (Fig. 2.6). It was demonstrated that an OFA is particularly useful in realizing current amplifiers, gyrators and instrumentation amplifier with a minimum possible number of external passive components in contrast to conventional op-amp-based circuits for the same functions and hence, an OFA can be regarded to be a versatile building block.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>For a differential difference version of an OFA, see [18].

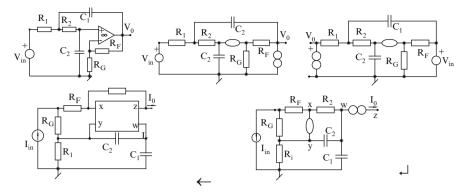

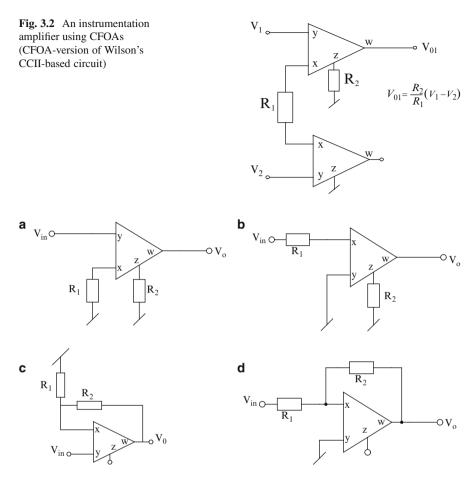

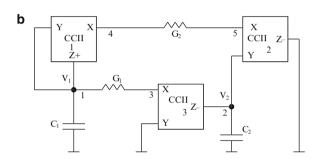

Fig. 2.6 OFA-based circuits (adapted from [17]  $\odot$  1993 Springer). (a) V to I converter  $I_1 = G_1 V_1$ . (b) Floating gyrator ( $I_1 = G_2 V_2$ ,  $I_2 = -G_1 V_1$ )

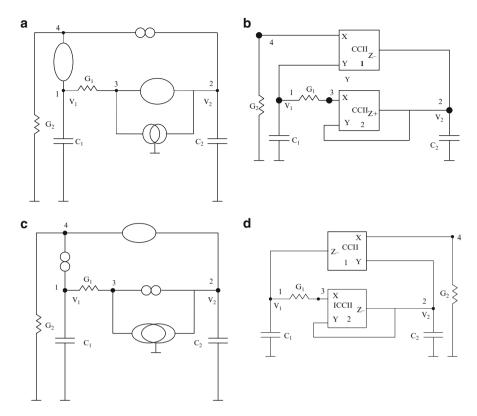

**Fig. 2.7** A FTFN implementation using CCIIΘ. (a) FTFN. (b) A FTFN using two three-terminal nullors. (c) FTFN using two CCIIΘ. (d) FTFN using two CFOAs

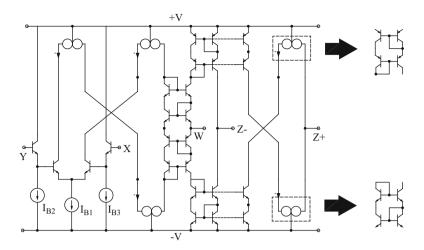

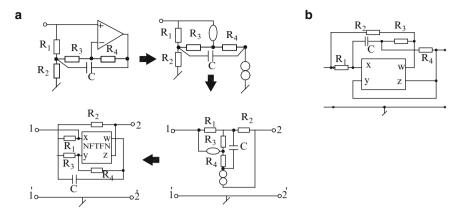

It was shown by Senani in [7, 13] that FTFNs provide a novel solution to the problem of RC active synthesis of floating impedances. A discrete implementation of the FTFN using only an op-amp, OTA and a resistance was proposed in [7]. It was also suggested in [7] that a composite connection of two CCII— can be used to realize an FTFN (see Fig. 2.7a—c of this chapter). This follows from the fact that the representation of FTFN of Fig. 2.7a is equivalent to the combination of two 3-terminal nullors as shown in Fig. 2.7b where each 3-terminal nullor is equivalent to a

Fig. 2.8 An OMAΘ-based FTFN realization (adapted from [22] © 1994 IEEE)

CCII—, thus, finally, leading to the implementation of Fig. 2.7c. In fact, two CCII+ or two current feedback op-amps (CFOA) such as AD844, which contains a CCII+ and a VF, can also be used to realize an FTFN using the same configuration. In the recent years, the CFOA-based implementation of Fig. 2.7d has been quite frequently used by various circuit designers to implement an FTFN.<sup>2</sup>

Another implementation, which has also been employed in several instances, is the one based upon the concept of an operational mirrored amplifier (OMA) [20, 21], and is shown here in Fig. 2.8 which employs an OFA configuration particularly referred as OMA $\Theta$ . The outputs (3) and (4) are, however, dissimilar, the former being a voltage output (with ideally zero output impedance) and the later being a current output having ideally infinite output impedance).

### 2.4 CMOS and Bipolar Implementations of FTFN

Though a bipolar three-terminal nullor in integratable form was presented as early as in 1977 by Huijsing and Dekorte in [23], the renewed interest in the applications of nullors grew after workable discrete implementations of the floating nullor (FTFN) using the off-the-shelf components as detailed in the previous section started becoming available. Subsequently, during the late nineties, a number of researchers

<sup>&</sup>lt;sup>2</sup>It was suggested in [19] that the OTA Max 435 could also be used as an FTFN although to the best knowledge of the authors the same does not appear to have been employed as an FTFN experimentally anywhere in the open literature so far.

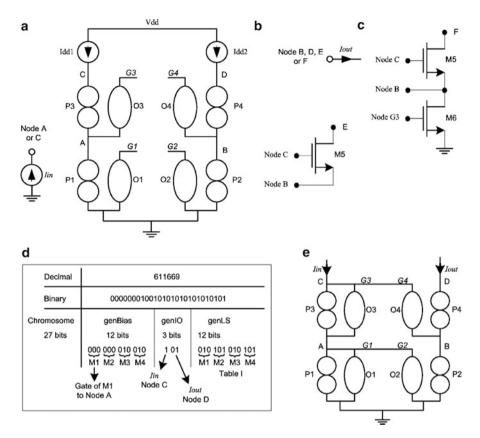

Fig. 2.9 CMOS FTFN proposed by Cam and Kuntman (adapted from [10] © 2000, Taylor and Francis)

worked out a number of CMOS implementations of the FTFN. Because of space limitations, it is difficult to describe all bipolar/CMOS OFAs/FTFNs reported so far, the discussion would be limited to a few representative implementations only.

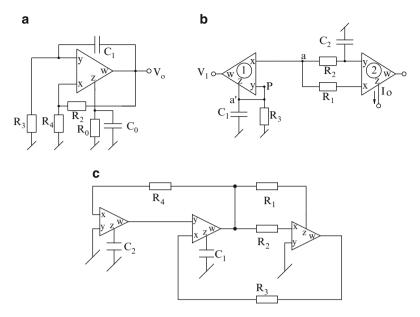

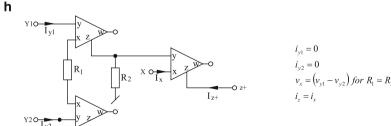

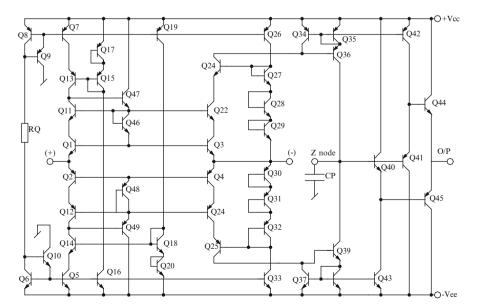

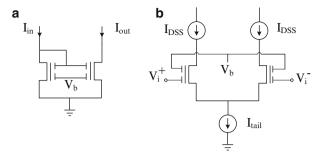

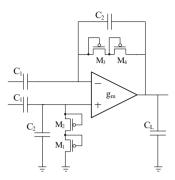

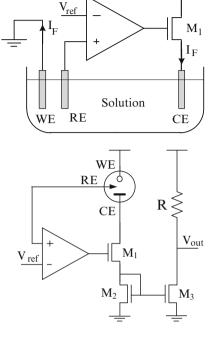

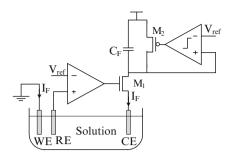

In 1999, Cam and Kuntman presented a CMOS implementation of two circuits that realize FTFNs [8]. Both these implementations were based on CMOS CCII—architecture. In yet another proposition in 2000, Cam, Toker and Kuntman [9] presented a CMOS implementation of FTFN based on translinear cells. Though not mentioned there explicitly, this implementation is in fact, an interconnection of two translinear CCII+- conforming to the scheme of Fig. 2.7b.

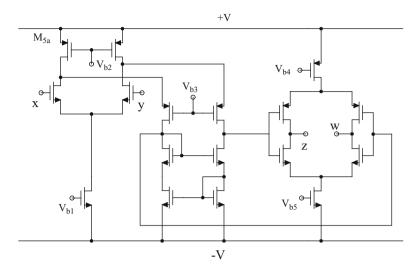

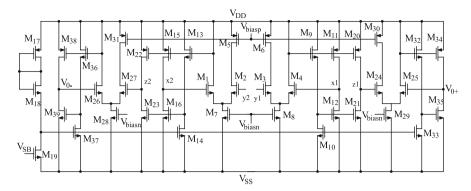

Cam and Kuntman in [10] proposed another CMOS realization of the FTFN which combines the advantages of a cascade of common-source and common-gate amplifiers and a floating current source. This circuit was shown to exhibit wideband operation (unity gain bandwidth in excess of 250 MHz) with a wide dynamic range. Fig. 2.9 shows the circuit proposed in [10].

Tansritat, Unhavanich, Dumawipata and Surakompontorn [24] presented a bipolar implementation of an FTFN with variable current gain which they termed as a tunable FTFN. This implementation is a modification of the basic supply current sensing method for the realization of FTFN. Jiraseri-amornkun, Chipipop and Surakompontorn [25] presented another bipolar implementation of an FTFN with multiple complementary outputs. This implementation is based on a transconductor and an improved translinear cell wherein a number of CMs have been used to replicate the output currents (see Fig. 2.10).

Fig. 2.10 Bipolar implementation of the multiple output floating nullor (adapted from [25] © 2001, IEEE)

Fig. 2.11 CMOS fully-balanced FTFN (adapted from [11] © 2002, IEEE)

In 2002, Al-Zaher and Ismail in [11] presented the notion of a fully-balanced FTFN and its CMOS implementation. They modified the design of the Op-Amp used in supply current sensing mode, by providing two input differential stages. Provision of two balanced outputs was made instead of a single output from the op-amp. These outputs are finally mirrored to the output port of the FTFN. This circuit is shown in Fig. 2.11 and is characterized by the following equations:  $I_{xp} = I_{xn} = I_{yp} = I_{yn} = 0$ ;  $V_{dx} = V_{xp} - V_{xn} = V_{dy} = V_{yp} - V_{yn}$ ;  $I_{dz} = I_{zp} - I_{zn} = -I_{dw} = -(I_{wp} - I_{wn})$ .

<sup>&</sup>lt;sup>3</sup>For another extension of FTFN or OFA termed as "Differential difference operational floating amplifier", the reader is referred to [18].

From survey of literature and the exemplary implementations outlined here, the opinion of the authors is that any "perfect" bipolar/CMOS implementation of the FTFN has yet not been achieved.

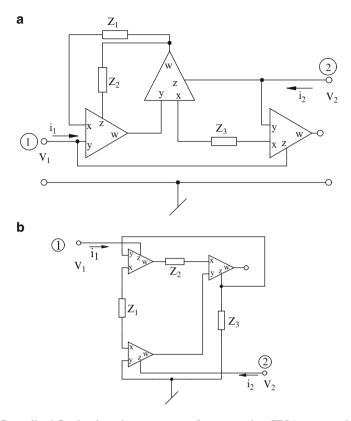

In the subsequent sections, we will show important applications of nullors/FTFNs in the areas of floating impedance simulation, generation of equivalent oscillators and universal biquad filter realization which may serve as a motivation for developing a fully integrable bipolar/CMOS FTFN as an off-the-shelf IC.

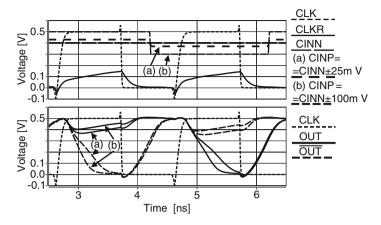

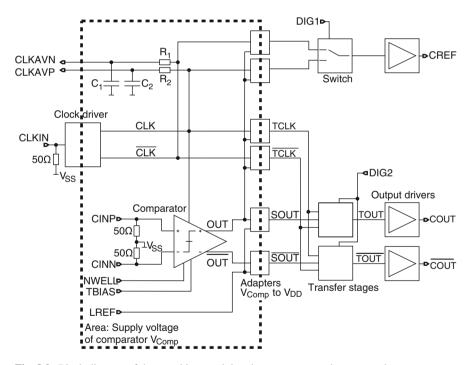

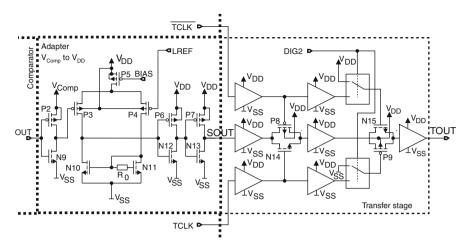

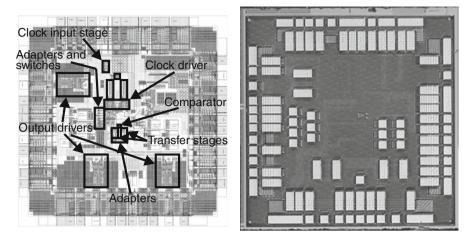

#### 2.5 Novel Applications of FTFN in Impedance Synthesis