# High-Performance D/A-Converters

The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists.

Series Editors:

Dr. Kiyoo Itoh Hitachi Ltd., Central Research Laboratory, 1-280 Higashi-Koigakubo Kokubunji-shi, Tokyo 185-8601, Japan

Professor Thomas H. Lee Department of Electrical Engineering, Stanford University, 420 Via Palou Mall, CIS-205 Stanford, CA 94305-4070, USA

Professor Takayasu Sakurai Center for Collaborative Research, University of Tokyo, 7-22-1 Roppongi Minato-ku, Tokyo 106-8558, Japan

Professor Willy Sansen ESAT-MICAS, Katholieke Universiteit Leuven, Kasteelpark Arenberg 10 3001 Leuven, Belgium

Professor Doris Schmitt-Landsiedel Lehrstuhl für Technische Elektronik, Technische Universität München Theresienstrasse 90, Gebäude N3, 80290 München, Germany

For further volumes: http://www.springer.com/series/4076

# Martin Clara

# High-Performance D/A-Converters

Application to Digital Transceivers

Martin Clara LANTIQ-A GmbH Villach Austria

ISSN 1437-0387 ISBN 978-3-642-31228-1 ISBN 978-3-642-31229-8 (eBook) DOI 10.1007/978-3-642-31229-8 Springer Heidelberg New York Dordrecht London

Library of Congress Control Number: 2012954677

#### © Springer-Verlag Berlin Heidelberg 2013

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Preface**

D/A-converters synthesize analog signals at the very heart of digital transceivers, thus linking the world of digital signal processing to the analog signal domain. The integration of the digital signal processor (DSP) together with data converters and analog signal processing functions in advanced CMOS technologies finally enables the realization of complete transceivers on a single silicon chip. This so-called system-on-chip (SoC) integration drastically reduces the cost and the form factor of the overall system, a highly desirable situation in cost-driven hardware development.

The topic of this work is the modeling and the implementation of high-performance current-steering D/A-converters for digital transceivers in nanometer CMOS technology. To comply with the target of SoC integration, the designed converter modules are fully embeddable in a mixed-signal system. They use only core devices, operate from a single supply voltage, and are optimized for small silicon area and low-power dissipation.

In the first part of this book the fundamental performance limitations of current-steering DACs are investigated. Based on simplified models, closed-form expressions for a number of basic nonideal effects are derived and tested. A special focus is put on the signal-dependent noise performance in multitone systems, showing that the traditional full-scale single-tone criteria are not adequate and may lead to substantial overdesign of biasing and/or clocking circuits. The knowledge of the basic performance limits allows to optimize the converter and system architecture already in an early design phase, essentially trading off circuit complexity, silicon area, and power dissipation for static and dynamic performance.

The second part of this book describes the design and experimental verification of four different current-steering DAC testchips, implemented in standard 130 nm CMOS. The converters use a single 1.5 V supply and have a resolution in the range of 12–14 bits for an analog bandwidth between 2.2 MHz and 50 MHz. Sampling rates between 100 MHz and 350 MHz are used. Dynamic element matching (DEM) and advanced dynamic current calibration techniques are employed to minimize the required silicon area. High-resolution converters with an active output stage to maximize the analog output signal swing, traditionally only used for low-frequency

vi Preface

applications, are demonstrated to reach signal bandwidths of 30–50 MHz, while maintaining a dynamic linearity larger than 70 dB over the whole bandwidth.

This book is organized into seven chapters:

- Chapter 1 provides an overview of D/A-converter fundamentals, especially focusing on the current-steering architecture and segmentation strategies.

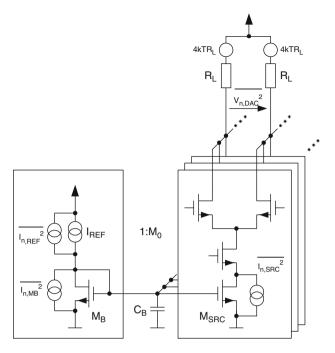

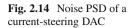

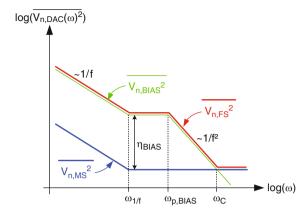

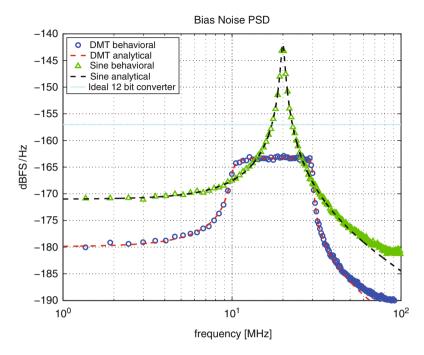

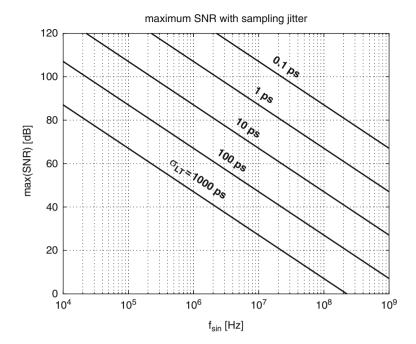

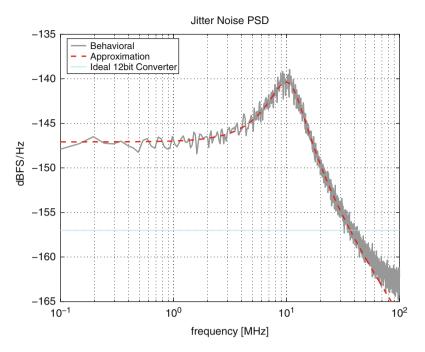

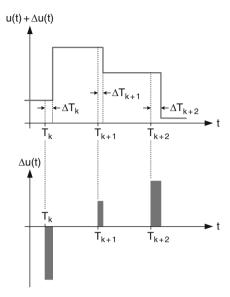

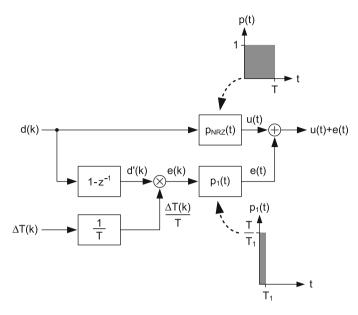

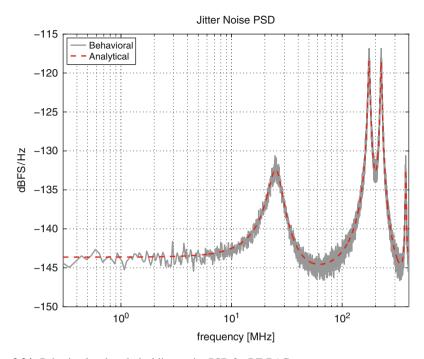

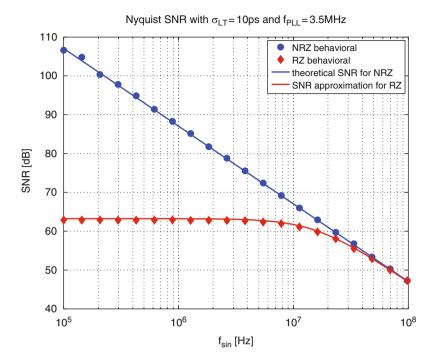

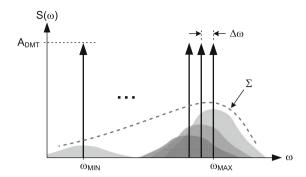

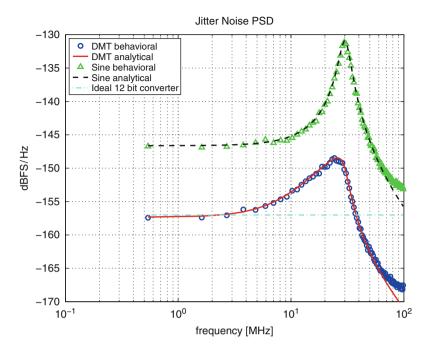

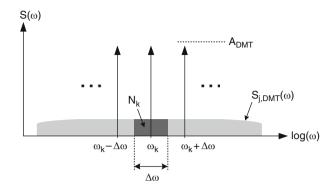

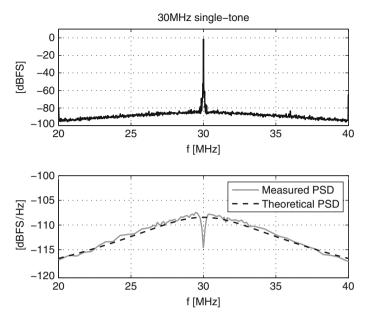

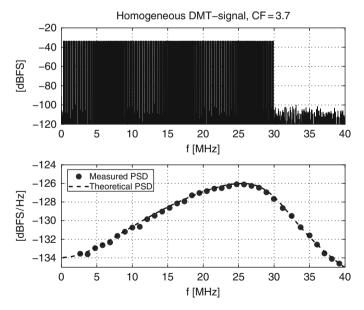

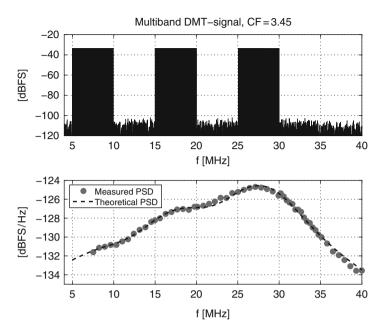

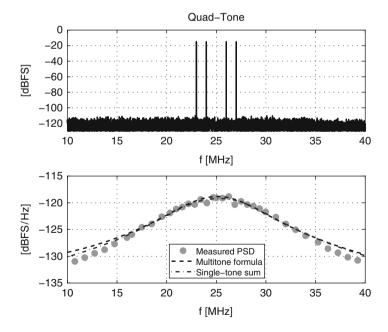

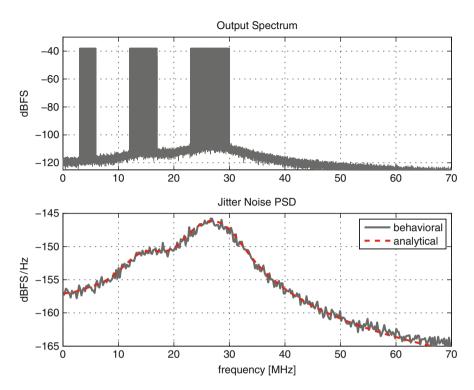

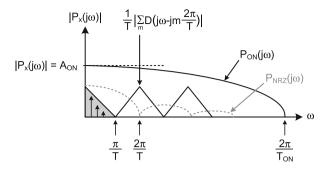

- In Chap. 2 the generally accepted performance figures used to characterize D/A-converters are reviewed. The impact of correlated bias noise and sampling jitter on the noise performance of a current-steering DAC is analyzed, and, based on simplified models, exact descriptions of the noise spectra for single-tone and multitone signals are derived. The jitter noise expressions obtained for multitone signals in an NRZ-DAC are also verified experimentally.

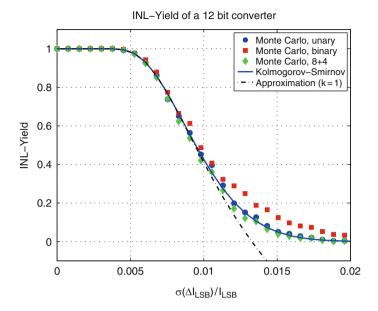

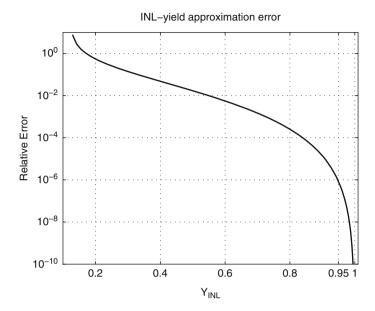

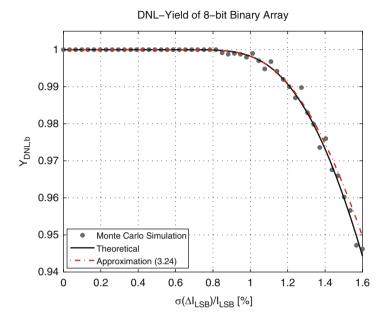

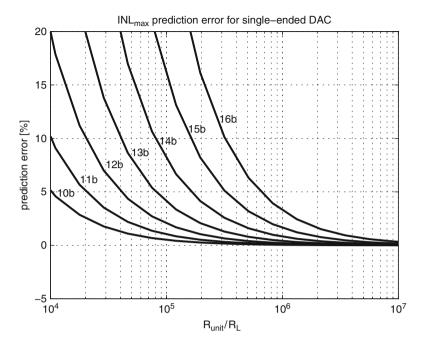

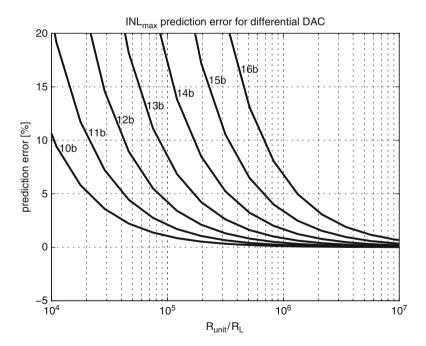

- In Chap. 3 the static linearity limited by random mismatch of the current sources is explored. Based on a statistical description of the fabrication yield, expressions for the required minimum current-source area fulfilling a given yield specification are derived. The code-dependent output resistance of the current-source array is identified as a further limiting factor for the static linearity. Expressions for the INL of the single-ended and the fully differential converter as a function of the finite output resistance of the unit current cell are given. The second part of Chap. 3 gives a general overview of two known methods to improve the static linearity: DEM and current calibration.

- Chapter 4 analyzes the three basic effects that limit the dynamic linearity of a current-steering D/A-converter. Under the idealizing assumption of perfectly matched current cells, which are also not influenced by any other large-scale imperfections, it is possible to derive closed-form expressions for the nonlinear distortion of a synthesized sine wave. The first effect is given by switching asymmetries that result in unsymmetrical current pulses. These are shown to generate even-order harmonic distortion in fully differential converters. The second effect is caused by the finite feed-through of the output voltage to the parasitic capacitance connected at the common tail node of the current switch pair. The resulting code-dependent error charge packets injected into the output generate odd-order harmonic distortion. The third effect that limits the dynamic linearity of a current-steering D/A-converter is the frequency-dependent distortion due to the code-dependent output impedance of the current-source array. It is shown that in a fully differential converter with standard current-cell architecture this effect is at least within the boundaries of practical sampling frequencies, not likely to become dominant compared to the switching errors. Nevertheless, it is a fundamental limitation to the achievable dynamic linearity, since it cannot be compensated straightforwardly, e.g., by applying a special switching algorithm. The second part of Chap. 4 describes various known circuit techniques to improve the dynamic linearity of current-steering D/A-converters.

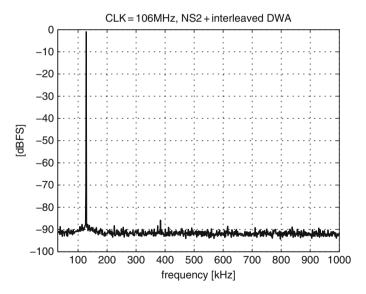

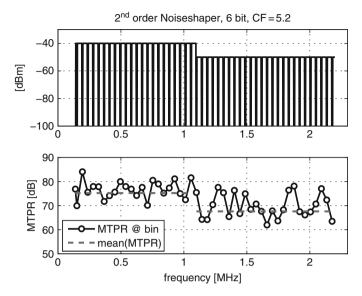

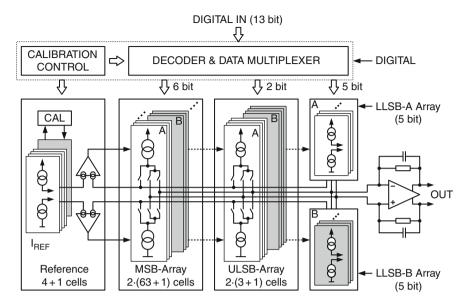

- Chapter 5 describes the implementation of two ΣΔ D/A-converter testchips targeted at wireline communication applications. The first design is a 14-bit DAC targeted at the ADSL2+ downstream bandwidth of 2.2 MHz. It uses a second-order noiseshaper together with a very simple barrel-shift algorithm and

Preface vii

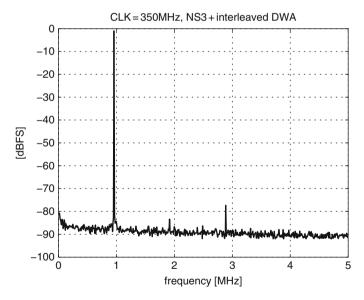

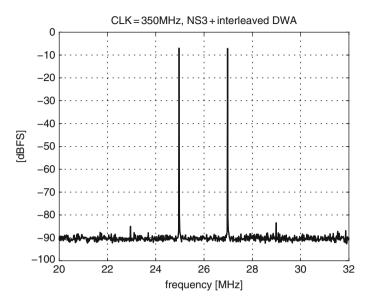

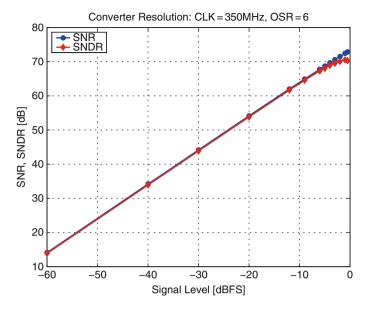

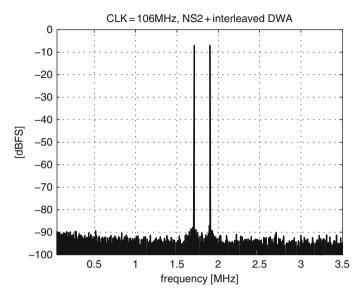

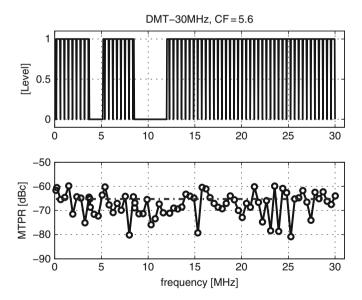

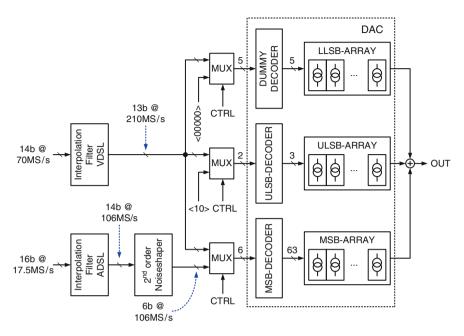

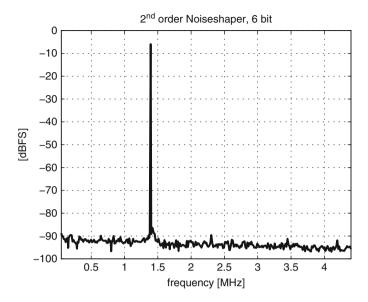

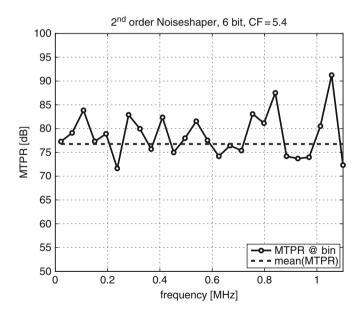

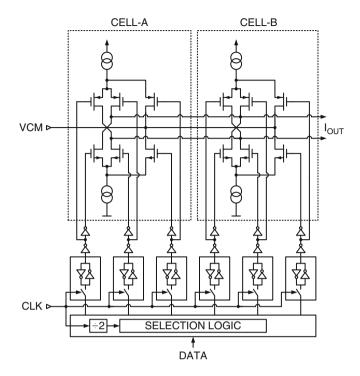

is optimized for low-power dissipation. The second design is a multi-mode  $\Sigma\Delta$ -converter for ADSL and VDSL. An interleaved current-cell architecture implements an effective return-to-zero (RZ) for the single current cell and also allows to use a modified data weighted averaging (DWA) algorithm. With a sampling rate of 350 MHz and an oversampling ratio of only 6, a dynamic range of 12 bits in a bandwidth very close to 30 MHz is demonstrated. Due to the effective RZ, the dynamic linearity around 30 MHz remains above 75 dB. The converter module is readily scalable—by register programming—to lower signal bandwidths, with not only drastically reduced power consumption but also increased resolution.

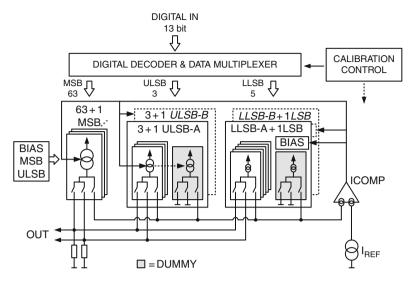

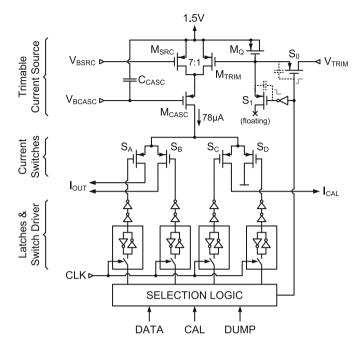

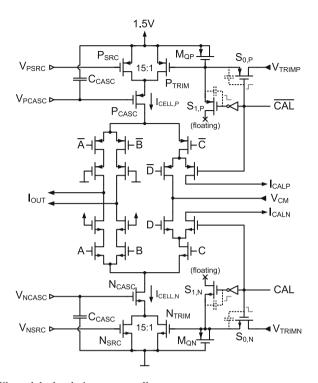

- In Chap. 6 two Nyquist-rate D/A-converter testchips using dynamic current calibration in the background are described. Both designs implement a segmented 13-bit converter core. The first module is a classical, resistively terminated single-polarity DAC, while the second converter uses a dual-polarity core with active transimpedance output stage to maximize the available voltage swing. In conjunction with an interleaved current-cell architecture this DAC achieves a signal bandwidth of 50 MHz with a dynamic linearity exceeding 70 dB over the full signal bandwidth. The periodicity of the background calibration, normally a source of low-frequency tonal disturbances, is destroyed by the introduction of a randomized calibration slot length. Thereby the calibration refresh tones are spectrally shaped and merged with the noise floor. This randomization also helps to suppress the image tone due to dynamic calibration effects in an interleaved architecture. Two novel strategies to trim the elements in converter segments with different weights are employed. The first design tries to match the segment boundaries by appropriately summing together uncalibrated and previously calibrated DAC elements for comparison with a unique reference element. The second design performs direct calibration of single DAC elements in differently weighted segments. In order to generate the required scaled reference currents with an accurate ratio, a reference cell array is introduced, which calibrates its constituting elements in a separate calibration loop, also running fully in the background.

- Finally, Chap. 7 summarizes the main results of this work, while trying to draw general conclusions. Also, it provides an outlook on future developments that are expected to happen in the area of CMOS current-steering D/A-converters targeted at digital communication systems.

Villach, Austria Martin Clara

# Contents

| 1 | Intro | oductio | n                                               | 1  |

|---|-------|---------|-------------------------------------------------|----|

|   | 1.1   | Integra | ated D/A-Converters                             | 1  |

|   | 1.2   | DACs    | for Highly Integrated Transceivers              | 7  |

|   | 1.3   | The Id  | deal D/A-Converter                              | 11 |

|   |       | 1.3.1   | The Non Return-to-Zero DAC                      | 12 |

|   |       | 1.3.2   | The Return-to-Zero DAC                          | 14 |

|   | 1.4   | The C   | urrent-Steering DAC                             | 16 |

|   |       | 1.4.1   | General Description                             | 16 |

|   |       | 1.4.2   | Single-Polarity and Dual-Polarity Current Cells | 18 |

|   |       | 1.4.3   | Passive and Active Output Stage                 | 18 |

|   | 1.5   | Array   | Coding                                          | 20 |

|   |       | 1.5.1   | Unary Array                                     | 20 |

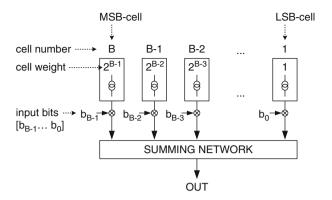

|   |       | 1.5.2   | Binary Array                                    | 21 |

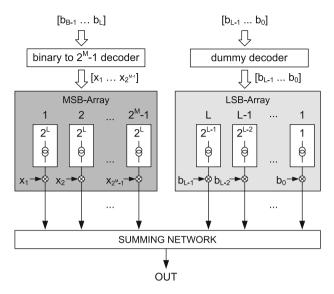

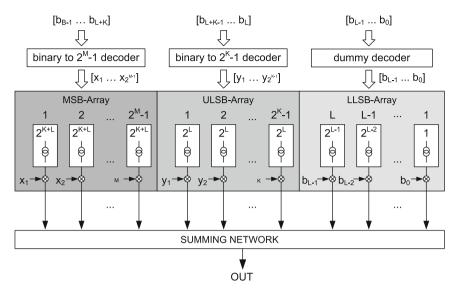

|   |       | 1.5.3   | Segmented Array                                 | 22 |

| 2 | Perf  | ormanc  | ce Figures of D/A-Converters                    | 25 |

| _ | 2.1   |         | Accuracy                                        | 25 |

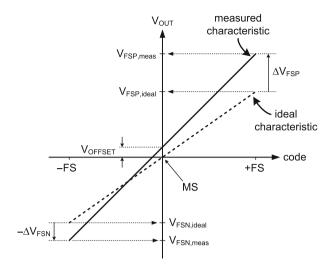

|   |       | 2.1.1   | Gain and Offset Error                           | 25 |

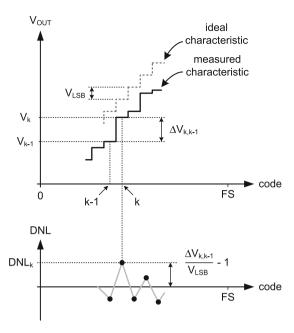

|   |       | 2.1.2   | Differential Nonlinearity                       | 26 |

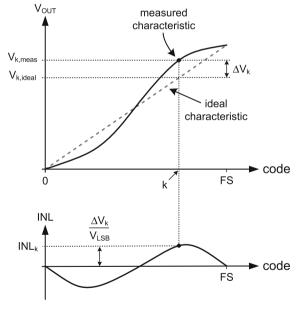

|   |       | 2.1.3   | Integral Nonlinearity                           | 27 |

|   | 2.2   | Dynar   | mic Performance                                 | 28 |

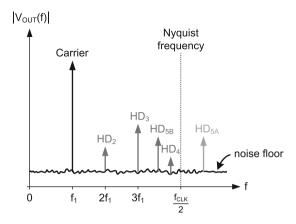

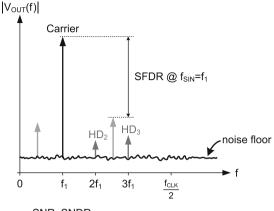

|   |       | 2.2.1   | Harmonic Distortion                             | 28 |

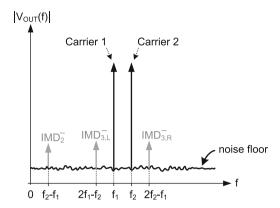

|   |       | 2.2.2   | Intermodulation Distortion                      | 29 |

|   |       | 2.2.3   | Spurious Free Dynamic Range                     | 30 |

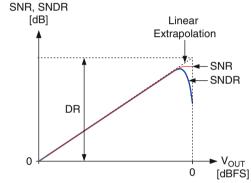

|   |       | 2.2.4   | Dynamic Range                                   | 31 |

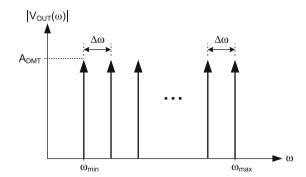

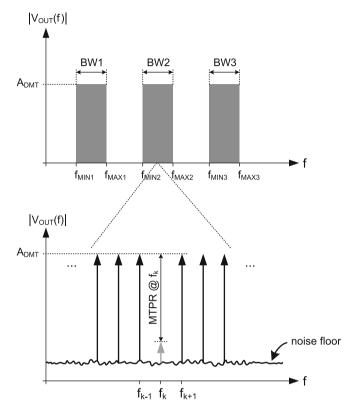

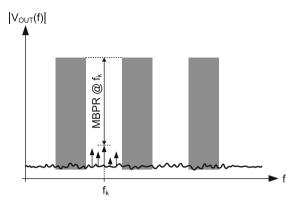

|   |       | 2.2.5   | Multitone Linearity                             | 32 |

|   | 2.3   | Noise   | Performance                                     | 35 |

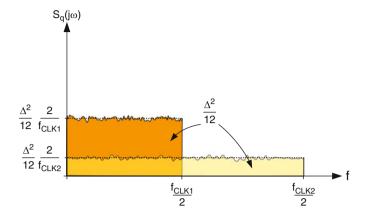

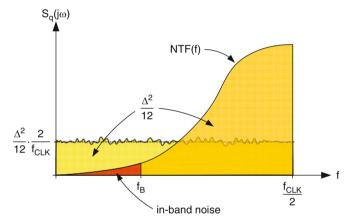

|   |       | 2.3.1   | Quantization "Noise"                            | 35 |

|   |       | 2.3.2   | Circuit Noise                                   | 38 |

|   |       | 2.3.3   | Jitter Noise                                    | 46 |

x Contents

| 3 | Stati | ic Linea | rity                                           | 63    |

|---|-------|----------|------------------------------------------------|-------|

|   | 3.1   | Limita   | ations for the Static Linearity                | 63    |

|   |       | 3.1.1    | Matching of Current Sources                    | 64    |

|   |       | 3.1.2    | Statistical Description of the INL             | 65    |

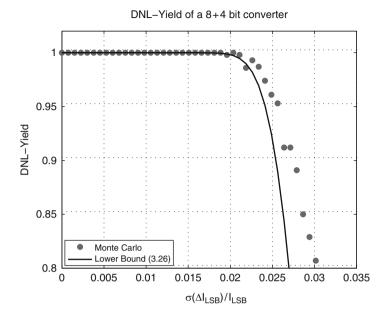

|   |       | 3.1.3    | Statistical Description of the DNL             | 66    |

|   |       | 3.1.4    | Minimum Area Requirements                      | 68    |

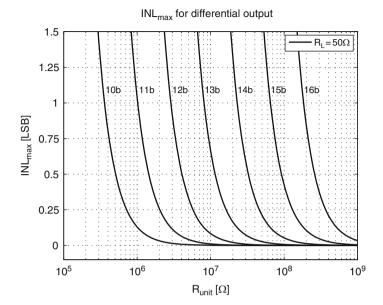

|   |       | 3.1.5    | Code-Dependent Output Impedance                | 74    |

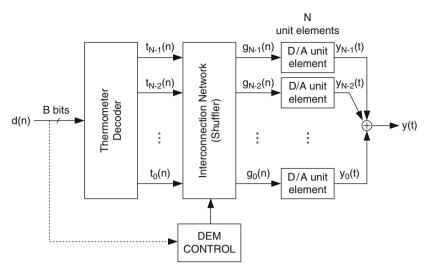

|   | 3.2   | Dynar    | nic Element Matching Techniques                | 78    |

|   |       | 3.2.1    | Clocked Level Averaging                        | 80    |

|   |       | 3.2.2    | Data-Weighted Averaging                        | 81    |

|   |       | 3.2.3    | Other DEM Techniques                           | 82    |

|   | 3.3   | Currer   | nt Source Calibration                          | 84    |

|   |       | 3.3.1    | Factory Trimming                               | 85    |

|   |       | 3.3.2    | Self-calibration                               | 86    |

|   |       | 3.3.3    | Local Calibration DAC                          | 88    |

|   |       | 3.3.4    | Global Calibration DAC                         | 89    |

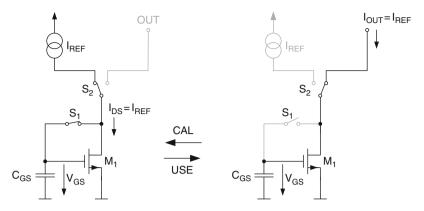

|   |       | 3.3.5    | Trimmable Floating Current Source              | 90    |

|   |       | 3.3.6    | Dynamic Current Calibration                    | 91    |

|   |       |          | •                                              |       |

| 4 | •     |          | nearity                                        | 97    |

|   | 4.1   |          | ations for the Dynamic Linearity               | 97    |

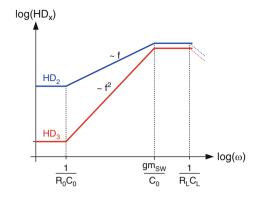

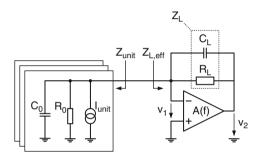

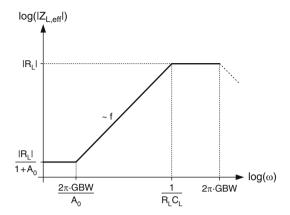

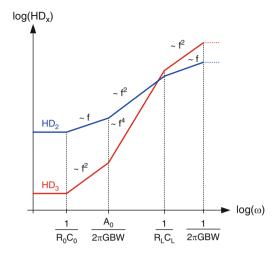

|   |       | 4.1.1    | Frequency-Dependent Output Impedance           | 97    |

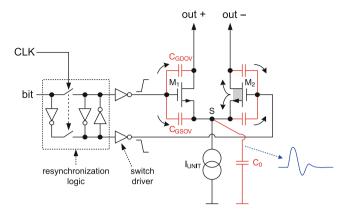

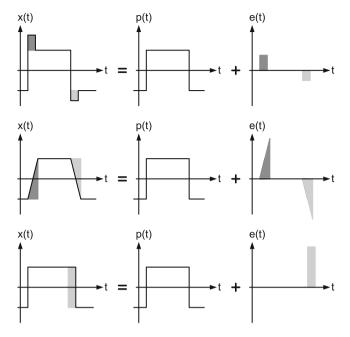

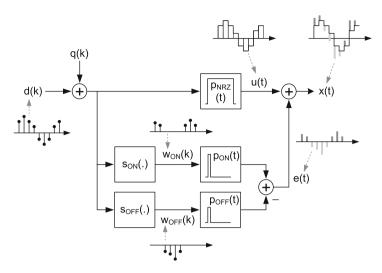

|   |       | 4.1.2    | A Generalized Switching Error Model            | 102   |

|   |       | 4.1.3    | Switching Transition Mismatch                  | 107   |

|   |       | 4.1.4    | Charge Sharing at the Switching Node           | 111   |

|   |       | 4.1.5    | A SPICE-Simulation Example                     | 116   |

|   |       | 4.1.6    | Other Nonlinear Effects                        | 118   |

|   | 4.2   |          | ds to Improve the Dynamic Performance          | 118   |

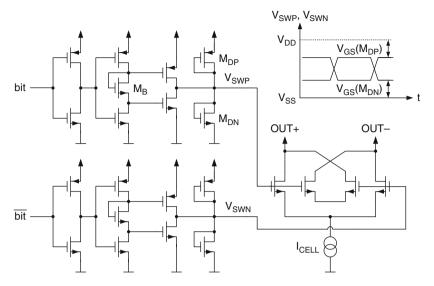

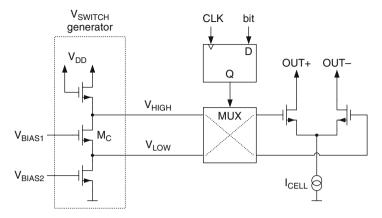

|   |       | 4.2.1    | Current Switch with Reduced Gate Voltage Swing | 119   |

|   |       | 4.2.2    | Source Node Bootstrapping                      | 122   |

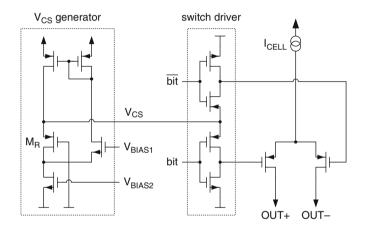

|   |       | 4.2.3    | Source Node Isolation                          | 123   |

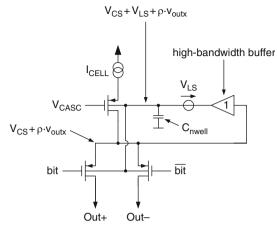

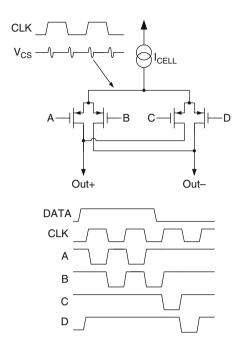

|   |       | 4.2.4    | Differential Quad Switching                    | 124   |

|   |       | 4.2.5    | Constant Digital Activity                      | 125   |

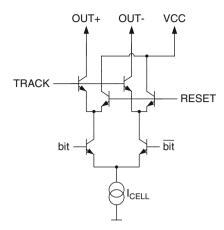

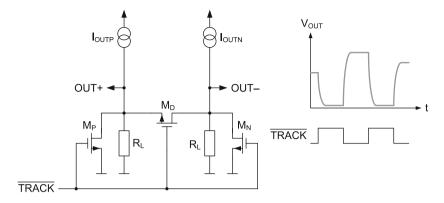

|   |       | 4.2.6    | Return-to-Zero and Track/Attenuate             | 126   |

|   |       | 4.2.7    | Double Return-to-Zero                          | 128   |

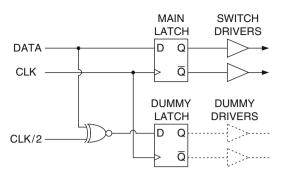

|   |       | 4.2.8    | Full-Clock Interleaved Current Cells           | 129   |

| 5 | Nois  | eshane   | d D/A-Converters                               | 133   |

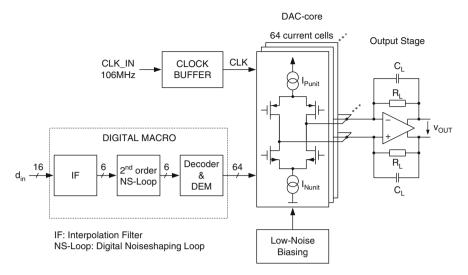

|   |       |          | oit Low-Power D/A-Converter                    | 133   |

|   | 0.1   | 5.1.1    | Converter Architecture                         | 134   |

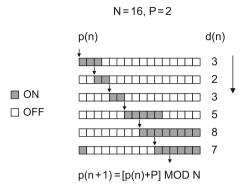

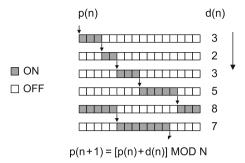

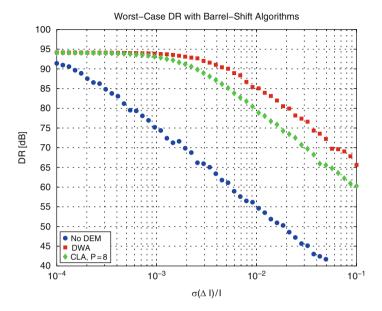

|   |       | 5.1.2    | DEM Selection                                  | 135   |

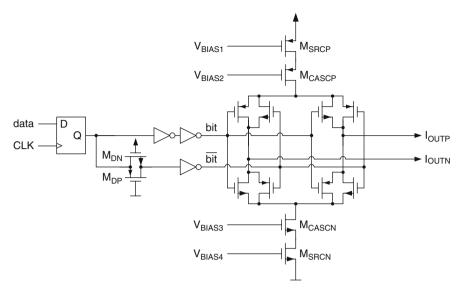

|   |       | 5.1.3    | Unit Current Cell                              | 136   |

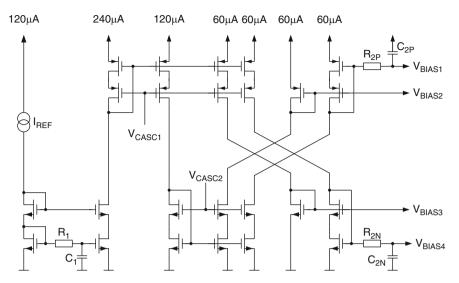

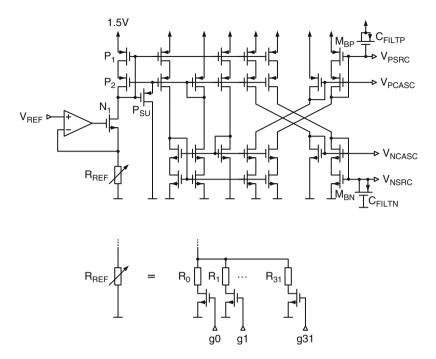

|   |       | 5.1.4    | Low-Noise Biasing                              | 138   |

|   |       | 5.1.5    | Output Stage                                   | 138   |

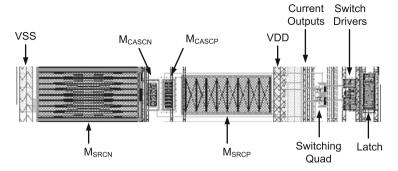

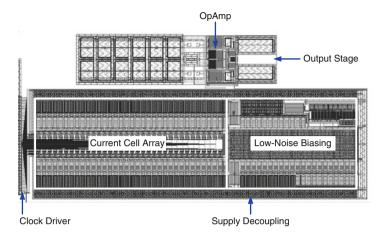

|   |       | 5.1.6    | Layout                                         | 139   |

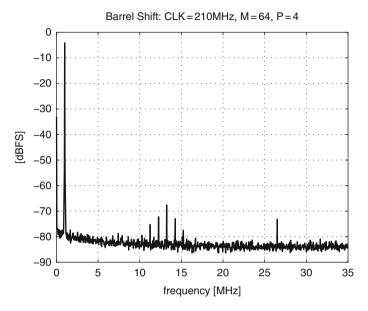

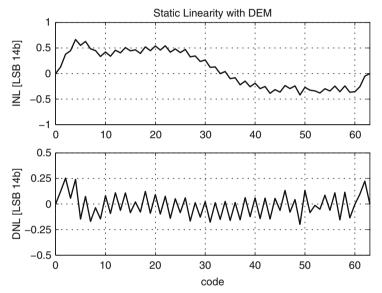

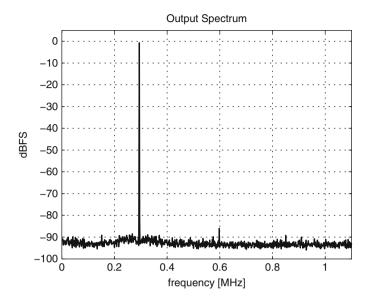

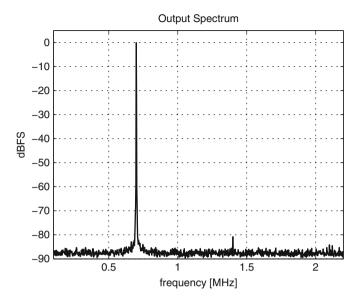

|   |       | 5.1.7    | Experimental Results                           | 141   |

|   |       | J.1.1    |                                                | - 1 I |

Contents xi

|   | 5.2   | A 12-1  | Bit/14-Bit Multistandard DAC                   | 144 |

|---|-------|---------|------------------------------------------------|-----|

|   |       | 5.2.1   | Low-OSR Noiseshaper                            | 145 |

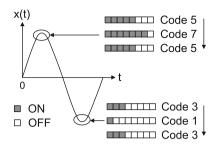

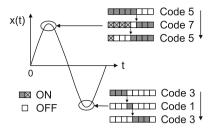

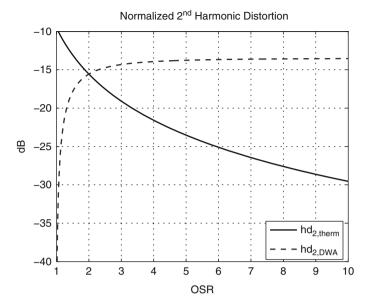

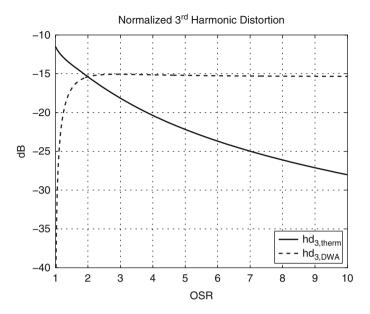

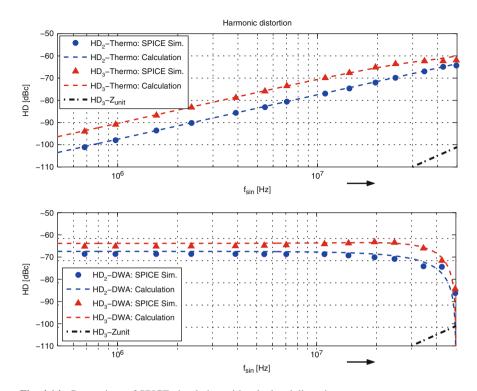

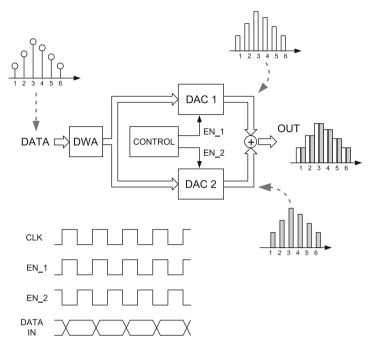

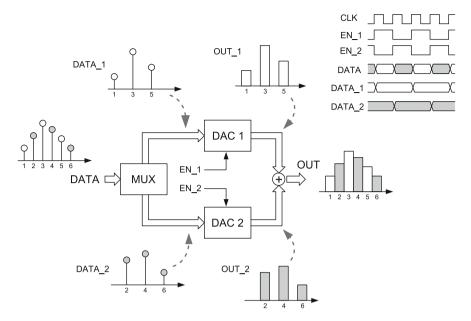

|   |       | 5.2.2   | Interleaved Data Weighted Averaging            | 147 |

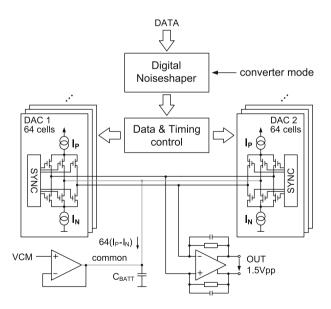

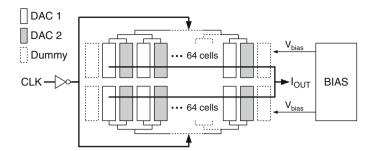

|   |       | 5.2.3   | Converter Architecture                         | 150 |

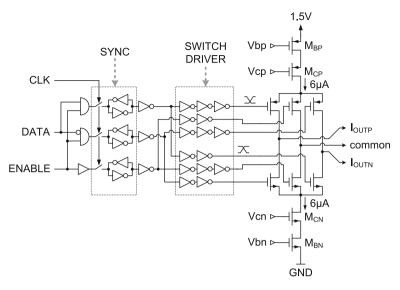

|   |       | 5.2.4   | Current-Cell Design                            | 152 |

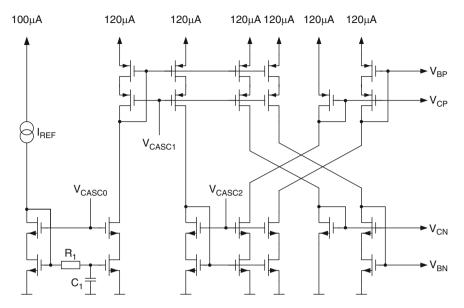

|   |       | 5.2.5   | Low-Noise Biasing                              | 153 |

|   |       | 5.2.6   | Output Stage Design                            | 155 |

|   |       | 5.2.7   | Layout                                         | 157 |

|   |       | 5.2.8   | Experimental Results                           | 159 |

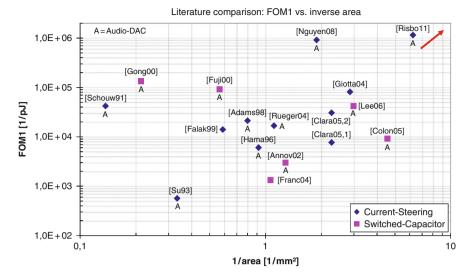

|   | 5.3   | Literat | ture Comparison of Noiseshaped DACs            | 163 |

| 6 | Adva  | anced C | Current Calibration                            | 167 |

|   | 6.1   | A Self  | E-calibrated 13-Bit 100–200 MS/s D/A-Converter | 168 |

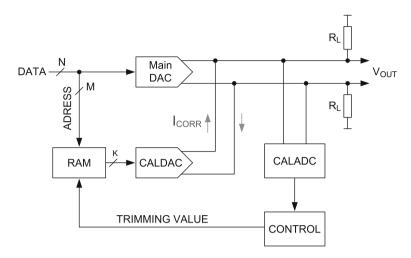

|   |       | 6.1.1   | Converter Architecture                         | 168 |

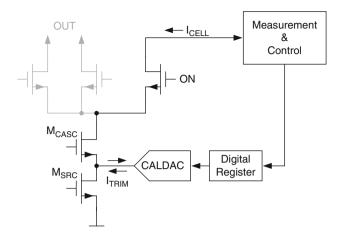

|   |       | 6.1.2   | Trimmable PMOS Current Cell                    | 169 |

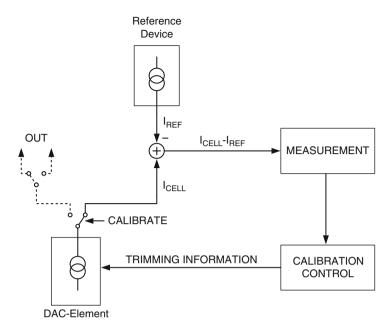

|   |       | 6.1.3   | Segmented Background Calibration               | 172 |

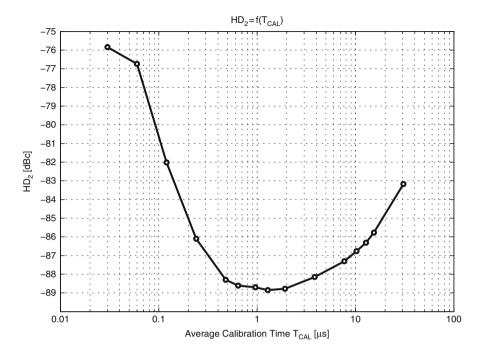

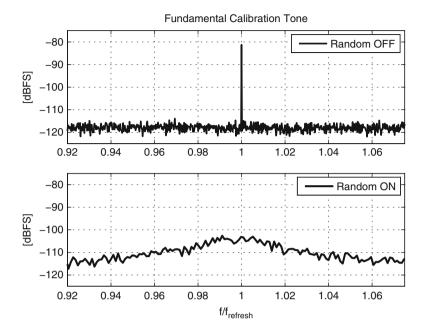

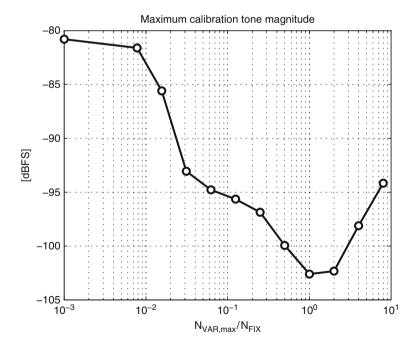

|   |       | 6.1.4   | Randomized Calibration Cycle                   | 176 |

|   |       | 6.1.5   | Layout                                         | 180 |

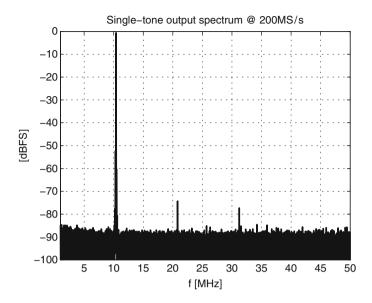

|   |       | 6.1.6   | Experimental Results                           | 181 |

|   | 6.2   | A 13-1  | Bit 130–300 MS/s DAC with Active Output Stage  | 190 |

|   |       | 6.2.1   | Converter Architecture                         | 191 |

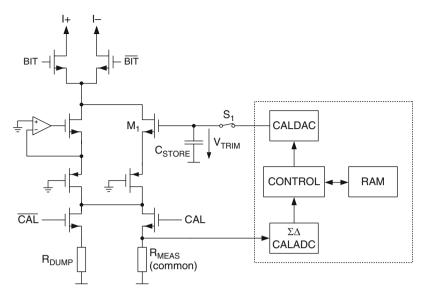

|   |       | 6.2.2   | The Current Cells                              | 192 |

|   |       | 6.2.3   | Direct Segment Calibration                     | 194 |

|   |       | 6.2.4   | Programmable Biasing                           | 198 |

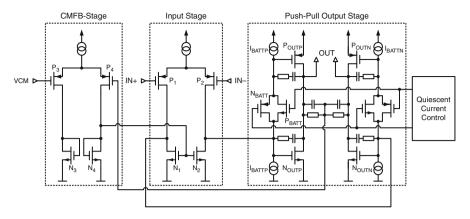

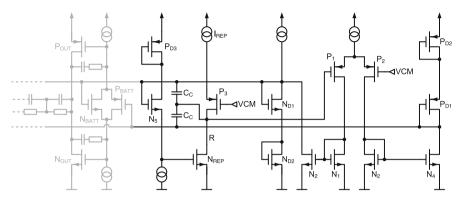

|   |       | 6.2.5   | Push-Pull Operational Amplifier                | 199 |

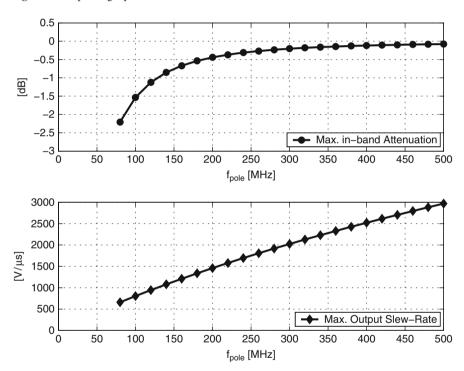

|   |       | 6.2.6   | Output Stage Optimization                      | 200 |

|   |       | 6.2.7   | Layout                                         | 202 |

|   |       | 6.2.8   | Experimental Results                           | 203 |

|   | 6.3   | A Figu  | ure-of-Merit for Nyquist D/A-Converters        | 211 |

| 7 | Con   | clusion | and Outlook                                    | 217 |

|   | 7.1   | Concl   | usions                                         | 217 |

|   | 7.2   | Outloo  | ok                                             | 219 |

| A | DAC   | Bias N  | Joise Model                                    | 223 |

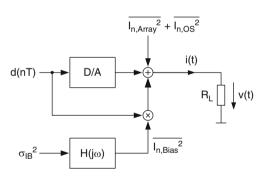

|   | A.1   |         | Noise Model Without 1/f-Noise                  | 223 |

|   | A.2   |         | Synthesis with Correlated 1/f-Noise            | 225 |

|   | A.3   |         | num SNR Limited by Correlated Bias Noise       | 228 |

| В | Jitte | r Noise |                                                | 231 |

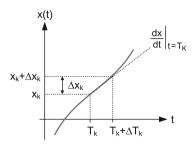

| _ | B.1   |         | ling Jitter Model                              | 231 |

|   | B.2   |         | Return-to-Zero DAC                             | 233 |

|   | B.3   |         | n-to-Zero DAC                                  | 235 |

|   | B.3   |         | n Multitone Systems                            | 238 |

xii Contents

| $\mathbf{C}$ | Code   | e-Dependent Output Resistance                              | 243 |

|--------------|--------|------------------------------------------------------------|-----|

|              | C.1    | Single-Ended Converter                                     |     |

|              | C.2    | Fully Differential Converter                               |     |

| D            | Swit   | ching errors                                               | 249 |

|              | D.1    | Generalized Switching Error Model                          | 249 |

|              | D.2    | Switching Transition Mismatch with Thermometer Coding      | 251 |

|              | D.3    | Switching Transition Mismatch with Data Weighted Averaging | 253 |

|              | D.4    | Charge Sharing with Thermometer Coding                     | 255 |

|              | D.5    | Charge Sharing with Data Weighted Averaging                | 256 |

|              | D.6    | Output Voltage Feedthrough Factor                          | 257 |

|              |        | D.6.1 Single-Polarity DAC with Passive Termination         | 258 |

|              |        | D.6.2 Dual-Polarity DAC with Active Termination            | 260 |

|              | D.7    | Third-Order Two-Tone Nonlinearity                          | 261 |

| Al           | out tl | he Author                                                  | 267 |

| Re           | feren  | ces                                                        | 269 |

| In           | dex    |                                                            | 279 |

# **Acronyms and Abbreviations**

ADC Analog-to-digital converter

ADSL Asymmetric digital subscriber line

AFE Analog front-end CF Crest factor

CLA Clocked level averaging CML Current mode logic

CO Central office

CPE Customer premises equipment

CRFB Cascade of resonators with distributed feed-back

DAC Digital-to-analog converter dBFS dB relative to full-scale DEM Dynamic element matching

DMT Discrete multi-tone

DNL Differential nonlinearity

DPD Digital pre-distortion

DR Dynamic range

DSL Digital subscriber line

DSP Digital signal processor

DWA Data weighted averaging

FDM Frequency division muliplexing

FOM Figure-of-merit FS Full-scale FSR Full-scale range GBW Gain-bandwidth

IF Intermediate frequency

ILA Individual level averaging

INL Integral nonlinearity

LHP Left-half-plane

LFSR Linear feedback shift register

LSB Least significant bit LMS Least mean square

MBPR Missing band power ratio MIM Metal-insulator-metal MMS Modified mismatch shaping

MSB Most significant bit

MTPR Missing tone power ratio NRZ Non return-to-zero NTF Noise transfer function

OFDM Orthogonal frequency division multiplexing

OSR Oversampling ratio PAR Peak-to-average ratio

PGA Programmable gain amplifier PLC Power line communication

PRDEM Partial randomization dynamic element matching

PSD Power spectral density

QCC Quiescent current control

RAM Random access memory

RX Receiver

RZ Return-to-zero

SAR Successive approximation register SFDR Spurious free dynamic range SNDR Signal-to-noise and distortion ratio SQNR Signal-to-quantization noise ratio

SNR Signal-to-noise ratio SoC System-on-chip TX Transmitter

VDSL Very high-speed digital subscriber line

WLAN Wireless local-area network

ZOH Zero-order-hold

# **List of Symbols**

#### **Mathematical Symbols**

```

Symbol

Description

Convolution

Transformation symbol: f(t) \longrightarrow F(s), F(j\omega)

L

Laplace transform operator: F(s) = \mathcal{L}(f(t))

\mathcal{L}^{-1}

Inverse Laplace transform operator: f(t) = \mathcal{L}^{-1}(F(s))

Ľ

Z-transform operator: F(z) = \mathcal{Z}(f(n))

\overline{x}

Average value of x

Variance of x

arctan(x)

Arctangent

\delta(t)

Continuous-time Dirac function

\delta(k), \delta_k

Discrete-time Dirac function

Expectation operator

E(.)

e^x

Exponential function

erf(x)

Error function

f^{-1}(x)

Inverse of function f: f^{-1}(f(x)) = x

Greatest common divisor of integer numbers a, b

gcd(a, b)

Imaginary unit, j = \sqrt{-1}

j

lim

Limit operator

ln(x)

Natural logarithm

\log_{10}(x)

Decadic logarithm

max(x)

Maximum operator

Minimum operator

min(x)

mod

Modulus operator

P[.]

Probability operator

П

Series of products

Ratio of circle's circumference to diameter, \pi = 3.141592...

Rectangular function: rect(x) = 1 for |x| \le \frac{1}{2}, 0 otherwise

rect(x)

Sinc-function: sinc(x) = \frac{sin(x)}{x}

sinc(x)

Discrete sum

\Sigma

Standard deviation of x

\sigma(x), \sigma_x

```

xvi List of Symbols

## **Physical Symbols**

| Symbol | Description                                           | Unit       |

|--------|-------------------------------------------------------|------------|

| C      | Capacitance                                           | [F]        |

| f      | Frequency                                             | [Hz]       |

| k      | Boltzmann's constant, $k \approx 1.38 \cdot 10^{-23}$ | [J/K]      |

| ω      | Radian frequency                                      | [rad/s]    |

| q      | Elementary charge, $q = 1.602 \cdot 10^{-19}$         | [As]       |

| T      | Absolute temperature                                  | [K]        |

| t      | Time                                                  | [s]        |

| I      | Current                                               | [A]        |

| R      | Resistance                                            | $[\Omega]$ |

| V      | Voltage                                               | [V]        |

| Y      | Complex admittance                                    | [A/V]      |

| Z      | Complex impedance                                     | $[\Omega]$ |

## **Special dB-Units**

| Symbol | Description |

|--------|-------------|

|        |             |

dBc dB relative to carrier dBFS dB relative to Full-Scale

dBm dB relative to 1 mW signal power

List of Symbols xvii

## **MOS-Transistor Parameters**

| Symbol              | Description                                             | Unit              |

|---------------------|---------------------------------------------------------|-------------------|

| $A_{eta}$           | Current-factor mismatch constant                        | [%·µm]            |

| $A_{ m VT}$         | Threshold voltage mismatch constant                     | $[mV\cdot \mu m]$ |

| $C_{ m GD}$         | Gate-drain capacitance                                  | [F]               |

| $C_{ m GDov}$       | Gate-drain overlap capacitance                          | [F]               |

| $C'_{ m GDov}$      | Gate-drain overlap capacitance per unit gate width      | [F/m]             |

| $C_{ m GS}$         | Gate-source capacitance                                 | [F]               |

| $C_{\mathrm{GSov}}$ | Gate-source overlap capacitance                         | [F]               |

| $C_{ m ox}$         | Oxide capacitance per unit area                         | $[F/m^2]$         |

| Γ                   | Combined current matching constant                      | $[\mu m^2]$       |

| gm                  | Transconductance                                        | [A/V]             |

| $gm_{ m MB}$        | Transconductance of bias transistor $M_B$               | [A/V]             |

| $gm_{\mathrm{SRC}}$ | Transconductance of current-source transistor $M_{SRC}$ | [A/V]             |

| $gm_{\rm SW}$       | Transconductance of current switch                      | [A/V]             |

| gds                 | Drain conductance                                       | [A/V]             |

| $gds_{\mathrm{SW}}$ | Drain conductance of current switch                     | [A/V]             |

| $I_{ m DS}$         | Drain current of MOS-transistor                         | [A]               |

| $KF_F$              | Flicker noise voltage coefficient                       | $[A^2s^2/m^2]$    |

| $K_F$               | Flicker noise current coefficient                       | $[F \cdot A]$     |

| L                   | Channel length of MOS-transistor                        | [m]               |

| $\mu$               | Carrier mobility in the channel                         | $[m^2/(Vs)]$      |

| n                   | subthreshold slope factor                               |                   |

| $\omega_T$          | Transit frequency                                       | [rad/s]           |

| $V_{ m GS}$         | Gate-source voltage of MOS-transistor                   | [V]               |

| $V_T$               | Threshold voltage of MOS-transistor                     | [V]               |

| W                   | Channel width of MOS-transistor                         | [m]               |

xviii List of Symbols

# **Data Converter Theory**

| Symbol                        | Description                                                | Unit  |

|-------------------------------|------------------------------------------------------------|-------|

| $A(j\omega)$                  | Open-loop gain of operational amplifier                    |       |

| $A_0$                         | Open-loop gain of operational amplifier at DC              |       |

| $A_1$                         | Amplitude of fundamental                                   |       |

| $A_k$                         | Amplitude of <i>k</i> th order harmonic product            |       |

|                               | DMT: intermodulation distortion at bin $k$                 |       |

| $A_{\rm CAL}$                 | Open-loop gain of calibration circuit at DC                |       |

| $A_{\rm CLK}$                 | Clock signal peak amplitude                                |       |

| $A_{\mathrm{DMT}}$            | Multitone peak amplitude                                   |       |

| $A_{\mathrm{OFF}}$            | Area of switch-off error                                   | [Vs]  |

| $A_{\rm ON}$                  | Area of switch-on error                                    | [Vs]  |

| $A_{\rm peak}, A_{\rm sin}$   | Single-tone peak amplitude                                 |       |

| $a_{\rm LSB}(t)$              | LSB-current step response                                  | [V/s] |

| α                             | Ratio of full-scale voltage to gate overdrive              |       |

| B                             | Converter resolution in bits                               |       |

| $B_{j}(\omega)$               | Jitter noise frequency shaping function for DMT            |       |

| $B_n(\omega)$                 | Bias noise frequency shaping function for DMT              |       |

| $C_B$                         | Filter capacitor in DAC-biasing                            | [F]   |

| $C_C$                         | Compensation capacitor of calibration loop                 | [F]   |

| CF                            | Crest factor                                               |       |

| D                             | Duty factor of RZ-DAC, $D = T_S/T$                         |       |

| DNL(k)                        | Differential nonlinearity at code k                        |       |

| $DNL_{max}$                   | Worst-case DNL: $DNL_{max} = max( DNL(k) )$                |       |

| DR                            | Dynamic range                                              | [dB]  |

| $d_k, d(k)$                   | Discrete-time converter input                              |       |

| d(t)                          | Hypothetical continuous-time converter input               |       |

| Δ                             | LSB-size, unit DAC-element size                            |       |

| $\delta_1$                    | Deviation of calibrated cell current relative to $I_{LSB}$ |       |

| $e_k$                         | Error signal in sample $k$                                 |       |

| e(t)                          | Ideally reconstructed continuous-time error signal         |       |

| $E\left(e^{j\omega T}\right)$ | Spectrum of sampled continuous-time error signal           |       |

| $\eta_{ m BIAS}$              | Noise excess factor of DAC-biasing                         |       |

| f                             | Frequency variable                                         | [Hz]  |

| $f_B$                         | Signal bandwidth                                           | [Hz]  |

| $f_{\rm CLK}$                 | Clock frequency                                            | [Hz]  |

| $f_{ m PLL}$                  | PLL-bandwidth                                              | [Hz]  |

| $f_{ m refresh}$              | Calibration refresh frequency                              | [Hz]  |

| $f_{\sin}$                    | Single-tone frequency                                      | [Hz]  |

| $\varphi(t)$                  | Instantaneous phase                                        | [rad] |

| GBW                           | Unity gain-bandwidth product                               | [Hz]  |

| $GBW_{CAL}$                   | Unity gain-bandwidth of calibration loop                   | [Hz]  |

| GE                            | Gain-error                                                 |       |

| $HD_k$                        | Harmonic distortion product of order k                     |       |

| $I_{\mathrm{cell}}$           | Current of DAC-element                                     | [A]   |

|                               |                                                            |       |

List of Symbols xix

| $I_{\mathrm{FS}}$                                                           | Full-scale output current                                                | [A]        |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|------------|

| $I_{ m LEAK}$                                                               | Leakage current                                                          | [A]        |

| $I_{\mathrm{LSB}}$                                                          | LSB-current                                                              | [A]        |

| $I_{ m OUTP}$                                                               | Positive output current                                                  | [A]        |

| $I_{ m OUTN}$                                                               | Negative output current                                                  | [A]        |

| $\frac{I_{001N}}{I_{n,\text{array}}^2(f)}$                                  | Squared noise current density of DAC-array                               | $[A^2/Hz]$ |

|                                                                             |                                                                          |            |

| $\frac{I_{n,\operatorname{array}N}^2(f)}{I_{n,\operatorname{array}N}^2(f)}$ | Squared noise current density of NMOS-array                              | $[A^2/Hz]$ |

| $\frac{I_{n,\operatorname{array}P}^2(f)}{2}$                                | Squared noise current density of PMOS-array                              | $[A^2/Hz]$ |

| $\underline{I_{n,\mathrm{Bias}}^2(f)}$                                      | Squared noise current density of DAC-bias                                | $[A^2/Hz]$ |

| $\underline{I_{n,\mathrm{MB}}^2(f)}$                                        | Squared noise current density of bias diode                              | $[A^2/Hz]$ |

| $I_{n,\text{MBN}}^2(f)$                                                     | Squared noise current density of NMOS bias diode                         | $[A^2/Hz]$ |

| $I_{n,\text{MBP}}^2(f)$                                                     | Squared noise current density of PMOS bias diode                         | $[A^2/Hz]$ |

| $\frac{I_{n,\text{MBP}}^2(f)}{I_{n,\text{OS}}^2(f)}$                        | Squared noise current density of output stage                            | $[A^2/Hz]$ |

| $\overline{I_{n,\text{REF}}^2(f)}$                                          | Squared noise current density of reference current                       | $[A^2/Hz]$ |

| $\overline{I_{n,SRC}^2(f)}$                                                 | Squared noise current density of $M_{SRC}$                               | $[A^2/Hz]$ |

| $I_O$                                                                       | Quiescent current in output stage                                        | [A]        |

| $I_{ m REF}$                                                                | Reference current for calibration or biasing                             | [A]        |

| $I_{ m ULSB}$                                                               | Cell current in ULSB-current                                             | [A]        |

| $I_{ m unit}$                                                               | Unit cell current                                                        | [A]        |

| INL(k)                                                                      | Integral nonlinearity at code k                                          |            |

| INL <sub>max</sub>                                                          | Worst-case INL: $INL_{max} = max( INL(k) )$                              |            |

| INL <sub>max,s</sub>                                                        | Worst-case INL for single-ended converter                                |            |

| $INL_{max,d}$                                                               | Worst-case INL for differential converter                                |            |

| $\Delta I_{ m MSB,0}$                                                       | Uncalibrated current error of MSB-cell                                   | [A]        |

| $\Delta I_{ m MSB,cal}$                                                     | Calibrated current error of MSB-cell                                     | [A]        |

| K                                                                           | Number of bits in intermediate converter segment                         |            |

| K                                                                           | Reference current noise scaling factor                                   |            |

| $K_{	au}$                                                                   | Dynamic constant for active output stage model                           |            |

| κ                                                                           | Area overhead factor in DAC-bias                                         |            |

| L                                                                           | Noiseshaper order                                                        |            |

| L                                                                           | Number of bands in multi-band DMT signal                                 |            |

| L                                                                           | Number of bits in (L)LSB converter segment                               |            |

| M                                                                           | Number of bits in MSB converter segment                                  |            |

| $M(j\omega)$                                                                | Mirror factor of DAC-biasing                                             |            |

| $M_0$                                                                       | Mirror factor of DAC-biasing at DC                                       |            |

| $MBPR(f_k)$                                                                 | Missing band power ratio at frequency $f_k$                              | [dB]       |

| $MTPR(f_k)$                                                                 | Missing tone power ratio at frequency $f_k$                              | [dB]       |

| N                                                                           | Number of equal DAC-elements (in unary array)                            |            |

| $N_C$                                                                       | Number of carriers in multitone signal                                   |            |

| $N_x$                                                                       | Integrated noise power of variable x                                     | [W]        |

| $N_{ m eq}$                                                                 | Excess quantization noise power                                          | [W]        |

| $N_{j,\mathrm{NRZ}}$                                                        | Noise power due to sampling jitter                                       | [W]        |

| $N_{j,RZ}$                                                                  | Sampling jitter noise power for RZ-DAC                                   | [W]        |

| $N_{j,\mathrm{RZ},0}$                                                       | Sampling jitter noise power for RZ-DAC for $\omega_{\sin} \rightarrow 0$ | [W]        |

| $N_k$                                                                       | Total sampling jitter noise power for carrier $k$                        | [W]        |

| $N_{ m FIX}$                                                                | Minimum calibration slot length in number of clocks                      |            |

| $N_{\mathrm{VAR}}(k)$                                                       | Output of random number generator in slot $k$                            |            |

|                                                                             |                                                                          |            |

xx List of Symbols

| $N_{ m VAR,max}$                  | Maximum output of random number generator               |             |

|-----------------------------------|---------------------------------------------------------|-------------|

| NTF(f)                            | Noise transfer function                                 |             |

| OSR                               | Oversampling ratio                                      |             |

| $\omega_0, \omega_{\mathrm{CLK}}$ | Sampling clock radian frequency                         | [rad/s]     |

| $\omega_C$                        | Corner frequency of correlated bias noise               | [rad/s]     |

| $\omega_L$                        | Lower intercept frequency for charge-sharing effect     | [rad/s]     |

| $\omega_{ m min}$                 | Lower band edge of multitone signal                     | [rad/s]     |

| $\omega_{ m max}$                 | Upper band edge of multitone signal                     | [rad/s]     |

| $\omega_{\mathrm{PLL}}$           | PLL-bandwidth                                           | [rad/s]     |

| $\omega_{p1}$                     | Closed-loop bandwidth of calibration loop               | [rad/s]     |

| $\omega_{p1,\mathrm{min}}$        | Minimum bandwidth of calibration loop                   | [rad/s]     |

| $\omega_{p,\mathrm{BIAS}}$        | Pole frequency of first-order bias noise model          | [rad/s]     |

| $\omega_{\rm sin}$                | Single-tone radian frequency                            | [rad/s]     |

| $\omega_{\rm RZ,3dB}$             | Lowpass frequency for jitter-limited SNR in RZ-DAC      | [rad/s]     |

| $\omega_{KZ,3dB}$ $\omega_U$      | Upper intercept frequency for charge-sharing effect     | [rad/s]     |

| $\Delta\omega$                    | Carrier spacing of multitone signal                     | [rad/s]     |

| P                                 | Array pointer increment of barrel shifter algorithm     | [radio]     |

| $P_{\text{carrier}}$              | Signal power of carrier in homogeneous DMT-signal       | [W]         |

| $P_{S,RZ}$                        | Signal power of sine wave in baseband for RZ-DAC        | [W]         |

| $P_{\sin}$                        | Signal power of sine wave in baseband                   | [W]         |

| $P_{\rm ON}(j\omega)$             | Transformed impulse-response of switch-on error         | [ ,, ]      |

| $P_{\text{OFF}}(j\omega)$         | Transformed impulse-response of switch-off error        |             |

| p(k)                              | Array pointer in sample $k$                             |             |

| p(k) $p(t)$                       | DAC impulse response                                    |             |

| $p(t)$ $p_{ON}(t)$                | Impulse-response of switch-on error                     |             |

| *                                 | Impulse-response of switch-off error                    |             |

| $p_{\text{OFF}}(t)$               |                                                         |             |

| $p_{\text{NRZ}}(t)$               | Impulse-response of NRZ-DAC Impulse-response of RZ-DAC  |             |

| $p_{\rm RZ}(t)$                   |                                                         |             |

| $p_q(x)$                          | Probability density function of quantization noise      | F A a I     |

| $Q_{\mathrm{C}0,n}$               | Charge stored on tail capacitance, negative output      | [As]        |

| $Q_{\text{C0},p}$                 | Charge stored on tail capacitance, positive output      | [As]        |

| $Q_{\rm err}(k)$                  | Charge error injected into differential output          | [As]        |

| $Q_{\text{ov}}$                   | Charge injected via $C_{\text{GDov}}$ of current switch | [As]        |

| $Q_{\text{unit}}$                 | Charge of unit current pulse                            |             |

| q(t)                              | Quantization error signal                               |             |

| q(k)                              | Discrete-time quantization error                        | FA -1       |

| $\Delta q_0$                      | Charge error at end of calibration period               | [As]        |

| $R_B$                             | Open-loop resistance of calibration circuit             | [Ω]         |

| $R_L$                             | Load resistor, feedback resistor                        | $[\Omega]$  |

| $R_{\mathrm{TRIM}}$               | Relative trimming range of current cell: $\pm R_{TRIM}$ | 101         |

| $R_{\rm unit}$                    | Output resistance of unit current cell                  | $[\Omega]$  |

| $\rho(\omega)$                    | Output voltage feedthrough factor                       |             |

| $S_x(\omega)$                     | Power spectral density of x                             | FXX / / T 1 |

| $S_B(\omega)$                     | PSD of correlated bias noise                            | [W/Hz]      |

| $S_{\rm eq}(\omega)$              | Excess quantization noise PSD                           | [W/Hz]      |

| $S_i(\omega)$                     | Circuit noise PSD                                       | [W/Hz]      |

| $S_{i,\mathrm{DMT}}(\omega)$      | Circuit noise PSD for DMT                               | [W/Hz]      |

| $S_{i,\mathrm{SIN}}(\omega)$      | Circuit noise PSD for sine-wave                         | [W/Hz]      |

|                                   |                                                         |             |

List of Symbols xxi

| $S_{j,\mathrm{DMT}}(\omega)$                       | Jitter noise PSD for DMT                           | [W/Hz]     |

|----------------------------------------------------|----------------------------------------------------|------------|

| $S_{j,NRZ}(\omega)$                                | Jitter noise PSD for NRZ-DAC                       | [W/Hz]     |

| $S_{j,RZ}(\omega)$                                 | Jitter noise PSD for RZ-DAC                        | [W/Hz]     |

| $S_T(\omega)$                                      | PSD of jitter sequence $\Delta T_k$                | $[s^2/Hz]$ |

| SNR                                                | Signal-to-noise-ratio                              | [dB]       |

| SNR <sub>jitter</sub>                              | Signal-to-noise-ratio due to sampling jitter       | [dB]       |

| $SNR_{j,RZ}$                                       | Signal-to-noise-ratio of RZ-DAC due to jitter      | [dB]       |

| $SNR_k$                                            | Signal-to-noise-ratio for carrier <i>k</i>         | [dB]       |

| $SR_{LSB}(t)$                                      | LSB-step Slew-Rate as function of time             | [V/s]      |

| S S S S S S S S S S S S S S S S S S S              | Laplace-domain complex frequency variable          | [,,,,]     |

| $\sigma_F$                                         | Bias noise constant for 1/f-noise model            | [A]        |

| $\sigma_{ m IB}$                                   | Integrated rms bias noise current                  | [A]        |

| $\sigma_{tj}$                                      | Absolute rms jitter                                | [s]        |

| $\sigma_{ m LT}$                                   | Long-term rms jitter                               | [s]        |

| T                                                  | Sampling period                                    | [s]        |

| $T_{\text{CAL}}(k)$                                | Calibration slot length for DAC-element <i>k</i>   | [s]        |

| $\frac{T_{\text{CAL}}(N)}{T_{\text{CAL}}}$         | Average calibration slot length                    | [s]        |

| $T_{\rm CAL,max}$                                  | Maximum calibration slot length                    | [s]        |

| $T_{\rm CAL,min}$                                  | Minimum calibration slot length                    | [s]        |

| $T_{ m fall}$                                      | Unit current pulse fall-time                       | [s]        |

| $T_{ m OFF}$                                       | Duration of switch-off error impulse response      | [s]        |

| $T_{ m ON}$                                        | Duration of switch-on error impulse response       | [s]        |

| $T_{ m refresh}$                                   | Refresh period                                     | [s]        |

| $T_{\rm refresh,max}$                              | Maximum acceptable refresh period                  | [s]        |

| $T_{\rm rise}$                                     | Unit current pulse rise-time                       | [s]        |

| $T_{\rm S}$                                        | Active period of RZ-DAC                            | [9]        |

| $T(s), T(j\omega)$                                 | Transimpedance transfer function                   | [V/A]      |

| $t_0$                                              | Absolute time at end of calibration period         | [s]        |

| $t_1$                                              | Absolute time during normal operation period       | [s]        |

| $\Delta T_k$                                       | Timing uncertainty of sampling clock in sample $k$ | [s]        |

| $	au_{\mathrm{CAL}}$                               | Closed-loop time constant of calibration loop      | [s]        |

| u(t)                                               | Time-domain converter output signal                | [-]        |

| $u_{\rm NRZ}(t)$                                   | Time-domain output signal of NRZ-DAC               |            |

| $u_{\rm RZ}(t)$                                    | Time-domain output signal of RZ-DAC                |            |

| $V_0$                                              | Clock sine-wave peak voltage                       | [V]        |

| $V_{ m FS}$                                        | Full-scale output voltage range                    | [V]        |

| $V_k$                                              | Converter output voltage at code $k$               | [V]        |

| $V_{k,\mathrm{ideal}}$                             | Ideal converter output voltage at code k           | [V]        |

| $V_{k,\mathrm{meas}}$                              | Measured converter output voltage at code k        | [V]        |

| $V_{ m LSB}$                                       | LSB-voltage                                        | [V]        |

| $\overline{V_{n,\mathrm{DAC}}^2(f)}$               | Squared noise voltage density at DAC-output        | $[V^2/Hz]$ |

| $\frac{V_{n,\text{DAC}}(f)}{V_{n,\text{FS}}^2(f)}$ | Squared noise voltage density at full-scale        | $[V^2/Hz]$ |

| $\frac{r_{n,FS}(J)}{V^2}$                          |                                                    | $[V^2/Hz]$ |

| $\overline{V_{n,\text{MS}}^2(f)}$                  | Squared noise voltage density at midscale          |            |

| $V_{\text{OFFSET}}$ $V_{}(t)$                      | Zero-code or midscale offset voltage               | [V]        |

| $V_{\text{OUT}}(t)$                                | Converter output voltage                           | [V]        |

| $V_{\text{OUT,ideal}}(t)$                          | Ideal converter output voltage                     | [V]        |

| $V_{\text{OUT},N}(t)$                              | Voltage at negative converter output               | [V]        |

| $V_{\mathrm{OUT},P}(t)$                            | Voltage at positive converter output               | [V]        |

xxii List of Symbols

| $V_S(t)$                     | Voltage at switching node                            | [V]        |

|------------------------------|------------------------------------------------------|------------|

|                              | Clock signal waveform                                |            |

| v(t)                         | E .                                                  | [V]        |

| $\Delta V_{ m FSN}$          | Negative full-scale voltage error                    | [V]        |

| $\Delta V_{	ext{FSP}}$       | Positive full-scale voltage error                    | [V]        |

| $\Delta V_G$                 | Gate voltage difference in switch pair               | [V]        |

| $\Delta V_{G, \mathrm{min}}$ | Minimum gate voltage difference in switch pair       | [V]        |

| $\Delta V_k$                 | Deviation of converter output voltage at code k      | [V]        |

| $\Delta V_{ m max}$          | Maximum deviation of converter output voltage        | [V]        |

| $w_{\text{OFF}}(k)$          | Discrete-time switch-off sequence                    |            |

| $w_{\text{OFF}}(t)$          | Equivalent continuous-time switch-off signal         |            |

| $W_{ m OFF}(j\omega)$        | Spectrum oft continuous-time switch-off signal       |            |

| $w_{\rm ON}(k)$              | Discrete-time switch-on sequence                     |            |

| $w_{\rm ON}(t)$              | Equivalent continuous-time switch-on signal          |            |

| $W_{ m ON}(j\omega)$         | Spectrum of continuous-time switch-on signal         |            |

| $Y_X$                        | Fabrication yield with respect to parameter <i>X</i> |            |

| $Y_{ m INL}$                 | Fabrication yield with respect to worst-case INL     |            |

| $Y_{ m DNL}$                 | Fabrication yield with respect to worst-case DNL     |            |

| $Y_L$                        | Load admittance                                      | [A/V]      |

| $Y_{\mathrm{OUT},N}$         | Admittance seen into negative converter output       | [A/V]      |

| $Y_{\mathrm{OUT},P}$         | Admittance seen into positive converter output       | [A/V]      |

| $Y_{ m unit}$                | Output admittance of unit current cell               | [A/V]      |

| z                            | z-domain complex frequency variable                  |            |

| $Z_{ m unit}$                | Output impedance of unit current cell                | $[\Omega]$ |

| $Z_L$                        | Load impedance, feedback impedance                   | $[\Omega]$ |

| $Z_{L,{ m eff}}$             | Effective load impedance                             | $[\Omega]$ |

# Chapter 1 Introduction

#### 1.1 Integrated D/A-Converters

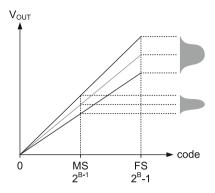

A digital-to-analog converter (DAC) is designed to perform an accurate summation of a given number of electrical unit quantities. This number is specified by the digital input code applied to the converter. The result of the summation appears as an analog electrical signal at the converter output. Thus, the output signal of the DAC represents, with more or less accuracy, the digital input code in the analog domain and can be further processed by subsequent analog circuitry, e.g., filters, amplifiers, mixers, or transducer interfaces. Fundamentally, it is the summing operation of appropriate electrical unit quantities that marks the actual transition from the digital into the analog domain. This data conversion process is also subject to a number of error sources that introduce distortion, as well as additional noise, into the analog output signal. Since these nonideal effects tend to limit the performance of practical converters, they should be adequately considered already during the design phase. The modeling of conversion inaccuracies is believed to be of central importance for close-to-optimum, system-specific DAC design. Indeed, a large part of this work is dedicated to providing theoretical insight into fundamental nonidealities of integrated D/A-converters with a focus on the current-steering architecture and, wherever appropriate, linking it to the system-level perspective.

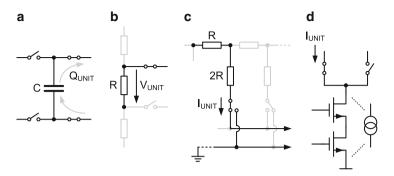

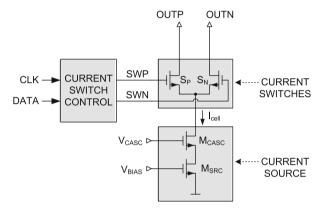

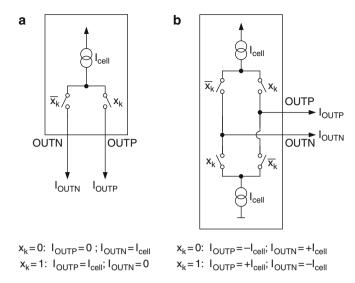

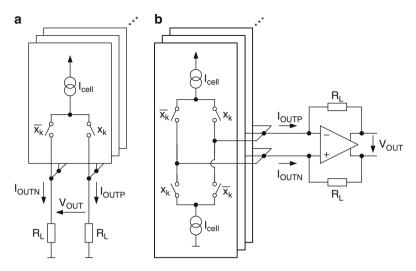

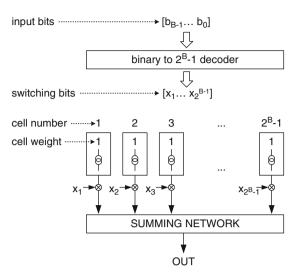

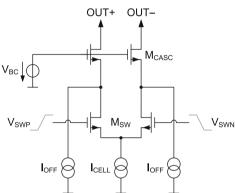

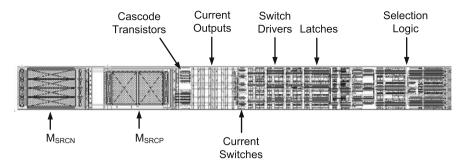

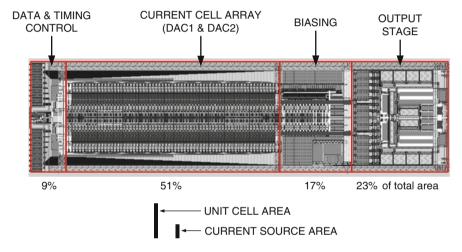

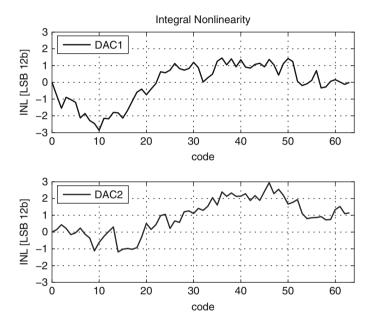

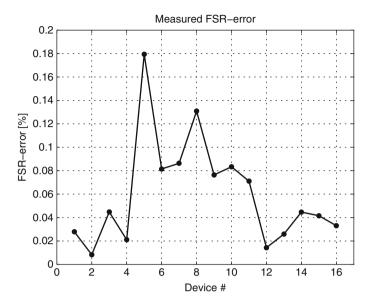

The DAC unit cell comprises one or more primary circuit elements that generate the summable electrical unit quantity in the first place, as well as a couple of analog switches that allow to connect the unit cell to common circuit nodes within the converter. Primary circuit elements in integrated converters are capacitors, resistors, or transistors. Important types of DAC unit cells used in integrated converters are shown in Fig. 1.1. The complete D/A-converter is eventually constructed using a suitable number of such unit cells, together with a couple of auxiliary circuits required for proper operation of the DAC. Auxiliary circuits include, e.g., biasing and clocking circuits, an output stage interfacing the converter to subsequent analog processing blocks, decoders and control circuitry, as well as digital interfaces.

Fig. 1.1 DAC unit cell types: (a) charge, (b) voltage, (c) current, and (d) current

In general, a D/A-converter can have a voltage or a current output, depending on the type of input the circuitry connected to the converter provides. In high dynamic range AFEs the preferred method for analog signal interfacing is usually voltage mode, which in turn requires the D/A-converter to perform an accurate conversion from the previously summed up primary electrical quantity into the corresponding output voltage. In other circumstances, the electrical unit quantity is already available as a voltage, but a direct connection to the load would destroy the accuracy. In such cases, the data converter must include a sufficiently low-noise and linear voltage buffer.

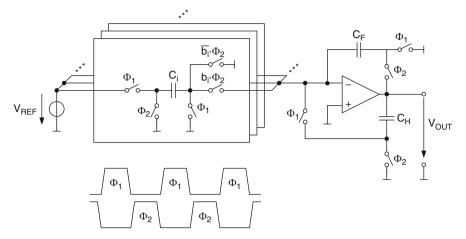

Charge-based D/A-conversion is performed by storing electrical unit charges O<sub>UNIT</sub> on an array of integrated capacitors (Fig. 1.1a) and appropriately redistributing them onto a summation capacitor. Such converters are called Switched-Capacitor DACs and are especially popular as subsystems in more complex integrated MOS A/D-converters [1]. The main reason is that MOS technologies offer high-quality and easy-to-drive switches. Equally important, many integrated capacitor types are very linear and can be laid out to exhibit good matching behavior [2]. Switched-capacitor DACs are also found as stand-alone building blocks, especially for high-resolution, low-frequency applications, e.g., in audio front ends [3, 4]. Figure 1.2 shows the principle of a multibit Switched-Capacitor DAC [5]. The charge stored on the unit capacitors  $C_i$  in phase  $\Phi_1$  is transferred to capacitor  $C_F$  during phase  $\Phi_2$ , provided that the corresponding input bits are set, i.e.,  $b_i = 1$ . The charges of those capacitors  $C_i$ , for which  $b_i = 0$ , are instead dumped to ground in phase  $\Phi_2$  and do not contribute to the output signal. The low-impedance node required for complete charge transfer from  $C_i$  to  $C_F$  is provided by the virtual ground node of the operational amplifier. The output voltage at the end of phase  $\Phi_2$  is additionally stored on the holding capacitor  $C_H$ , which is then put in the feedback of the operational amplifier during the subsequent phase  $\Phi_1$ .

<sup>&</sup>lt;sup>1</sup>An exception are diffusion- and MOS-based capacitors, which display a relatively strong voltage dependency. High-precision converters therefore tend to use poly-poly, poly-metal and metal-metal structures to form integrated capacitors.

Fig. 1.2 Multibit parallel switched-capacitor DAC

Fig. 1.3 Multibit pipelined switched-capacitor DAC

This clock phase is also used to precharge the unit capacitors  $C_i$  to  $V_{\rm REF}$  and discharge the summing capacitor  $C_F$ , in effect preparing the converter for the next conversion cycle, while the actual output voltage is held on  $C_H$ .

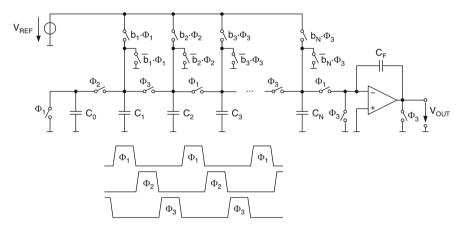

Another approach is the pipelined switched-capacitor DAC [6] shown in Fig. 1.3. Using only N+1 identical capacitors  $C_0$ - $C_N$ , an N-bit converter can be constructed, which is very area efficient. The operating principle is in some sense similar to a charge-coupled device (CCD), but with additional input-code-dependent precharging of the single capacitors. Using three clock phases and appropriately delayed input bits, the binary-weighted output charge corresponding to the digital input word is building up by successive charge redistribution along the capacitor pipeline. The reconstructed "analog" charge on the last capacitor  $C_N$  can finally be transferred to the output via a SC-amplifier. Drawbacks of this DAC architecture

Fig. 1.4 Basic resistor-DAC types: (a) R-string and (b) R-2R multiplying DAC

are the latency of N+2 clock cycles and, possibly, a certain limit on the achievable resolution due to error progression along the capacitor pipeline. Nevertheless, due to the pipelining of the conversion process, it allows operation at respectably high sampling rates, as demonstrated for example in [7].

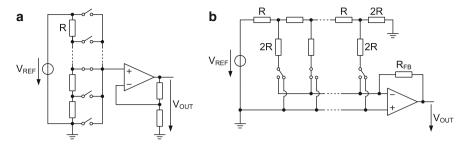

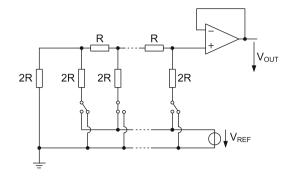

Integrated matched resistors can be arranged either as a programmable voltage divider (Fig. 1.1b), also called resistor string, or as a programmable current divider in the form of an R-2R ladder (Fig. 1.1c). In the voltage divider case, the output node must display a sufficiently high impedance compared to the total resistance of the string. Since the output impedance of a tapped resistor string depends on the actual position of the tap, the voltage distribution within the resistor stack is (code-dependently) disturbed, in case a significant current is flowing into the output. In the current divider case, on the other hand, the output node must be of very low impedance, otherwise the current distribution within the R-2R ladder will depend on the actual setting of the switches, i.e. on the digital input code. In practical implementations, both types of resistor-based D/A-converters require not only a precise voltage reference driving the resistor array but also a highquality operational amplifier as output stage.<sup>2</sup> This amplifier either serves as a high-impedance voltage amplifier/buffer in the string-type converter, or it provides the low-impedance current-summing node for the current divider, along with the implicit current to voltage conversion using resistive feedback.

Figure 1.4 shows the two basic resistor-type DACs in greater circuit-level detail. Figure 1.4a shows the resistor string DAC or string-DAC [8]. The converter in Fig. 1.4b with accessible reference voltage  $V_{\rm REF}$  is called R-2R multiplying DAC [9], owing to the fact that the output voltage is the product of the reference voltage and the digital input code [10], both applied externally. With the amplifier configured as a voltage buffer, the R-2R ladder can also be tapped in voltage mode, as shown in Fig. 1.5. In this case, the ladder behaves like a programmable voltage divider. Such an arrangement is called voltage-mode R-2R ladder DAC [10], sometimes also R-2R back-DAC [11].

<sup>&</sup>lt;sup>2</sup>This is certainly true for general purpose instrumentation applications. However, for on-chip control applications with known suitable loading a dedicated op-amp is often not necessary.

**Fig. 1.5** Voltage-mode R-2R DAC (R-2R back-DAC)

**Fig. 1.6** Transistor-based current sources: (a) BJT and (b) MOS

As stand-alone converters, resistor-based DACs are heavily used not only in instrumentation and control applications but also in high-end digital audio products [12–14]. In conjunction with resistor (and reference) trimming, these converters can achieve exceptional accuracy, linearity, and long-term stability at very low power dissipation [15,16]. The signal bandwidth covered by resistor-based D/A-converters is normally quite small, nevertheless sufficient for the usual target applications. A notable exception that covers video bandwidths, albeit displaying also considerably less resolution, can be found in [17].

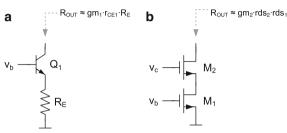

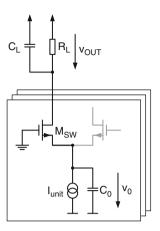

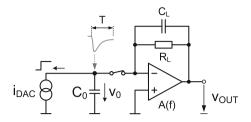

Integrated current sources based on active elements require at least one transistor operated in the active region (Fig. 1.1d). In most cases, either resistive degeneration or cascoding is employed to further boost the output resistance to sufficiently high values. Traditionally, bipolar designs tend to use resistive emitter degeneration, while MOS current sources are normally in favor of cascoding. Both techniques are shown in Fig. 1.6. Extensive treatments of integrated current sources can be found in reference texts on integrated analog circuit design; see, e.g., [5, 18–20]. D/A-converters built with active current sources are called current-steering DACs because the unit cell currents must not be turned on and off. Instead, they have to be *steered*, rather cautiously, to the appropriate summing node(s) in order not to disturb the potentially delicate biasing required for these circuits. Current-steering DACs implemented in CMOS-technologies are the main subject of this book and described in more detail starting from Sect. 1.4.

In general, every unit cell contains at least one high-accuracy switch. This switch connects the unit cell, when triggered by the digital input code, to an appropriate common node within the converter circuitry, where, e.g., the summation of the electrical unit quantities occurs. Differential architectures (see below) have two

Fig. 1.7 Single-ended (a) and differential output (b) DAC

output nodes, obviously requiring at least two high-accuracy switches within each unit cell. Additional switches may be needed to establish a proper behavior of the unit circuit element during subsequent conversion cycles. For example, in charge-based converters, as described above, the unit capacitors must be correctly precharged prior to each summation operation.

In a D/A-converter, the unit cells need not necessarily be all of the same type. Nevertheless, true hybrid D/A-converters are not very common, an example using voltage division plus charge redistribution is reported in [21]. On the other hand, resistor-based current division of transistor current sources appears to be quite popular in bipolar designs [22–24], because it allows the construction of a true binary-weighted current-cell array, while employing only equal-sized current source transistors. This architecture has already been used<sup>3</sup> in the feedback DAC of EPSCO's 1954 11-bit 50 kS/s SAR-ADC (the "DATRAC"), an all-valve 500 W (!) A/D-converter system [10, 25].

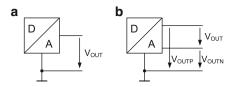

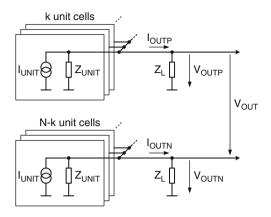

On a more architectural level, we can distinguish between single-ended output and differential output D/A-converters; see Fig. 1.7. Single-ended output DACs are mostly found in low-frequency instrumentation and control applications, whenever the output node is single-ended by definition. Differential output DACs, on the other hand, are nowadays the primary choice for dynamic signal synthesis, whenever the spectral purity, i.e., the signal quality with respect to noise and distortion, is of primary importance. According to common understanding, this has to do with the doubled signal swing of differential architectures, leading to 3 dB better signal to noise performance. Additionally, defining the output signal as being the difference of two single-ended, opposite polarity signals<sup>4</sup> has the tendency to suppress even-order harmonic distortion, as well as providing a certain immunity against disturbance and noise present on common circuit nodes, e.g. the supply rails. Note, also, that any differential output DAC can be converted into a single-ended DAC by using only one of its two output nodes and discarding the other. Of course, by doing so, any previously present common-mode rejection is given up on as well.

On system level we can distinguish between Nyquist-rate and noiseshaped D/A-converters. Nyquist-rate converters exhibit a flat quantization noise spectrum (see Sect. 2.3.1), and, in principle, allow to exploit the full converter bandwidth for signal synthesis. Since virtually all communication systems require a certain

<sup>&</sup>lt;sup>3</sup>According to [10] for the first time in data converter history.

<sup>&</sup>lt;sup>4</sup>The two single-ended signals in a differential configuration are opposite in polarity relative to a fixed common-mode level above on-chip ground. Ideally, the differential output appears floating with respect to any fixed ground-referenced potential.

amount of oversampling, e.g., to facilitate the necessary analog filtering, in practical applications, only a certain fraction of the full Nyquist bandwidth, as defined by half the sampling rate, is actually used.

Noiseshaped D/A-converters, on the other hand, try to concentrate the major part of the quantization noise outside of the signal bandwidth of interest, thereby greatly improving the in-band resolution. As a consequence, they can only be used for signal synthesis within a relatively small fraction of the Nyquist bandwidth. Noiseshaped D/A-converters are also called  $\Sigma\Delta$ -DACs.

The MOS-transistor based, current-steering, and differential output converter topology (see Sect. 1.4) has become the most prominent DAC architecture for signal synthesis in communication systems, because it offers high-speed and high-accuracy capability at moderate power consumption. Whether oversampling, or even noiseshaping is employed, largely depends on the overall system specification, because these decisions usually have a rather big influence on the overall AFE architecture. In any case, current-steering D/A-converters can be realized quite straightforwardly, even in standard digital CMOS processes, and are easily combined with a fair amount of digital circuitry, e.g., to control DAC-element shuffling or calibration algorithms. This "digital assistance" is used extensively in the hardware examples in later chapters of this book, with the goal to improve the converter performance, while keeping the required silicon area small.

#### 1.2 DACs for Highly Integrated Transceivers

Digital communication systems have become an integral part of the infrastructure in our modern information society. Although the bulk of the signal processing is already done in the digital domain, still the transmission medium, or channel, across which the connection of the so-called data link is finally established, is analog by nature [26]. Therefore, the digital data must be converted into an appropriate analog signal by the transmitter and back into digital data samples by the receiver.

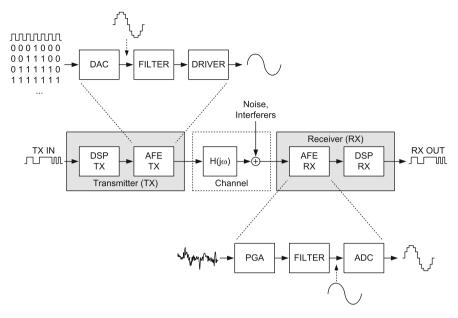

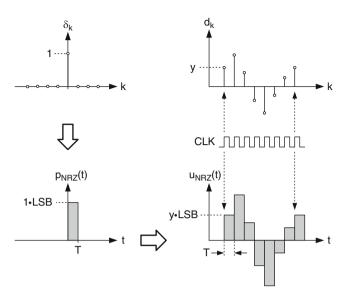

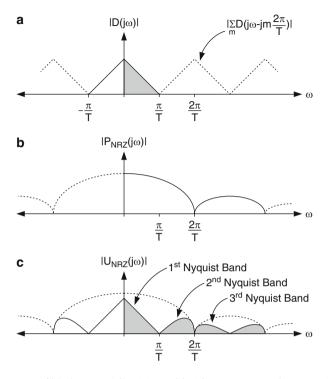

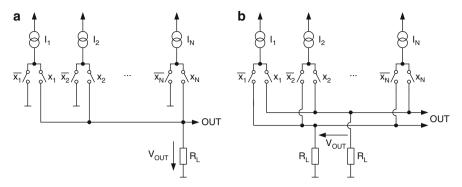

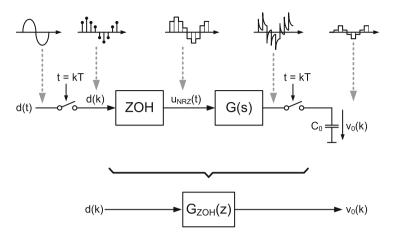

Figure 1.8 shows a generic (unidirectional) digital communication link. In the transmitter (TX) a digital signal processor (DSP) performs the necessary coding and modulation of the input bit stream. In the AFE the encoded digital data is then converted into an analog signal by a DAC. After suitable filtering and power amplification, the analog transmit signal is finally applied to the channel.

The input signal of the receiver (RX) consists of the attenuated and spectrally distorted wanted signal together with noise and interferers. This composite signal is first amplified by a programmable gain amplifier (PGA), then filtered, and subsequently converted back into a digital signal by an analog-to-digital converter (ADC). Only then can the DSP in the receiver recover the original bit stream sent by the transmitter down through the channel. For bidirectional (duplex) operation a complete receiver and transmitter module must be implemented at both data terminals. This combination of *trans*mitter and receiver is often called *transceiver*. If transmitter and receiver are active at the same time, i.e.,

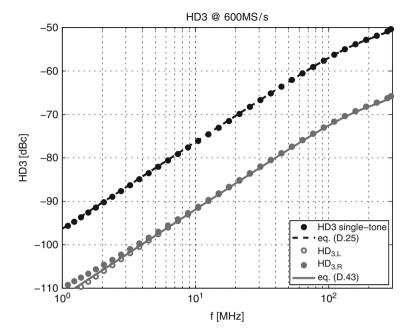

Fig. 1.8 Digital communication link

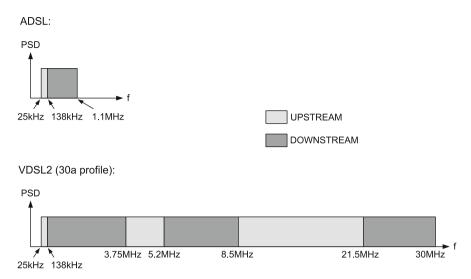

a bidirectional data link is established simultaneously, we speak of full-duplex operation, whereas in so-called half-duplex systems transmitter and receiver are active and transmitting/receiving only alternately. A typical example for full-duplex systems is the current xDSL-families using DMT modulation, while today's WLAN-standards and most PLC-systems operate in half-duplex.

In wireless systems we additionally find an analog mixer in the transmitter for spectral upconversion of the signal to the desired center frequency. In the corresponding receiver there is at least one analog mixer for downconversion of the antenna signal, either directly to the baseband frequency, or first to some intermediate frequency for further amplification and filtering, before the signal is downconverted to the baseband and digitized by the ADC [27]. In case the A/D-converter is able to sample the signal at an intermediate frequency (IF), the final downconversion can also be performed in the digital domain [28].

In any case, the two inverse data conversion operations in the analog front-end (AFE), D/A in the transmitter and A/D in the receiver, constitute very central signal processing functions that can be found in every digital communication system. The fidelity with which the data conversion can be accomplished on either side of the analog channel has an immediate impact on the quality of the data link. Therefore, considerable effort is spent in optimizing the performance of the data converters in the context of a limited power budget and silicon area constraints. These boundary conditions tend to become especially stringent in multi-channel integration, where multiple transmit and receive channels must be integrated together on the same silicon die.

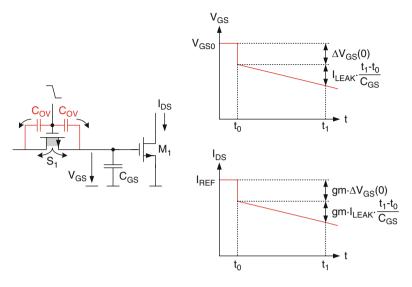

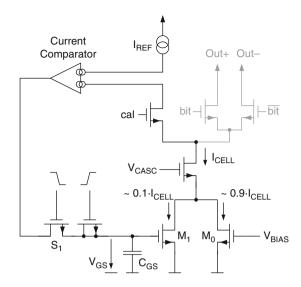

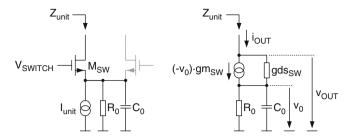

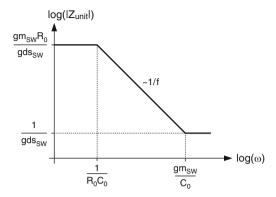

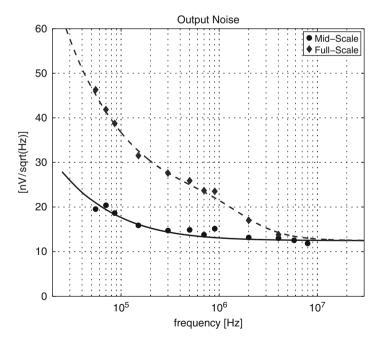

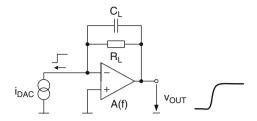

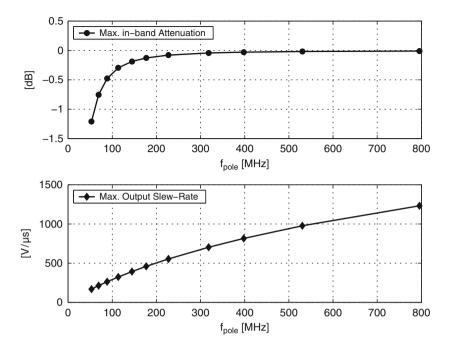

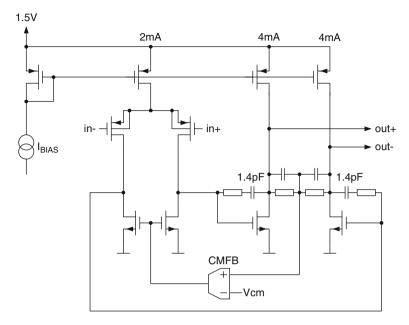

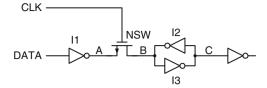

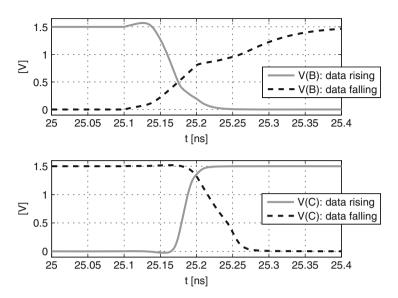

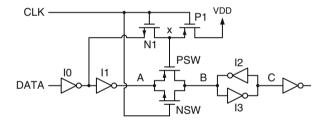

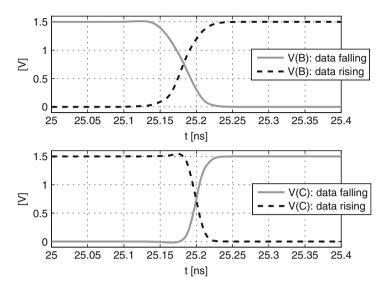

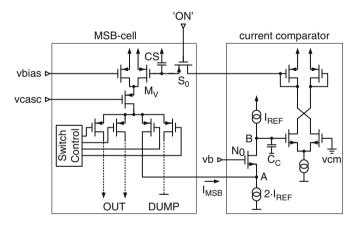

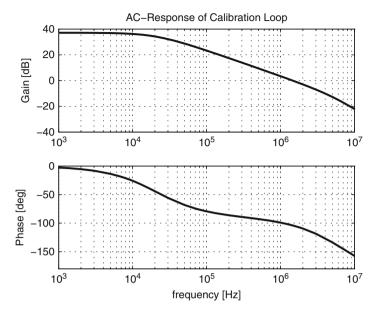

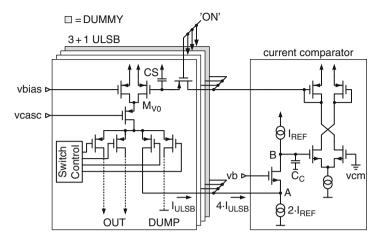

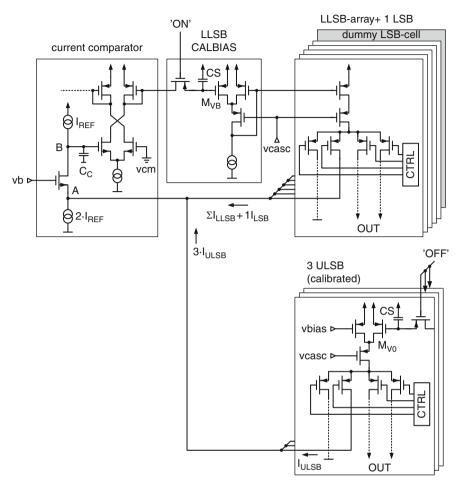

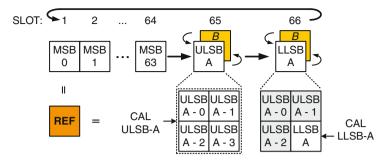

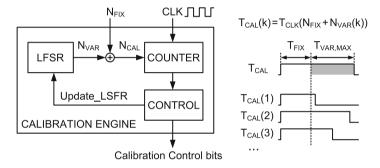

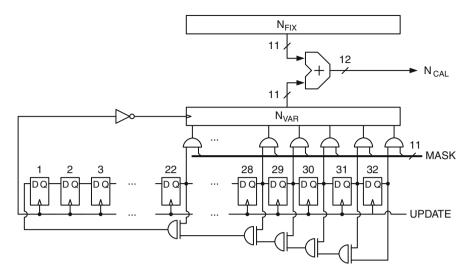

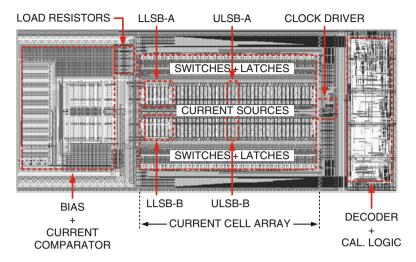

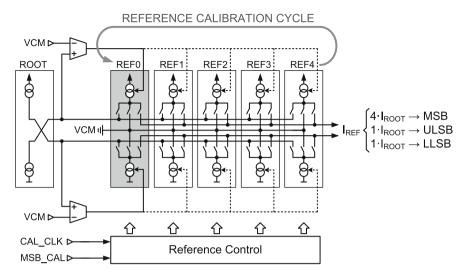

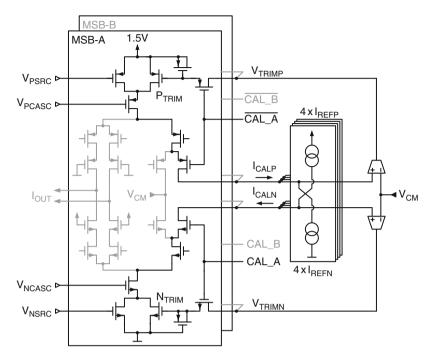

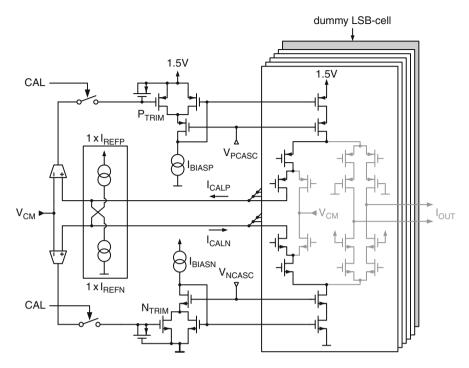

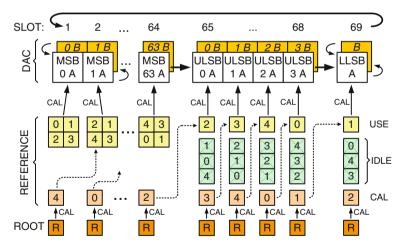

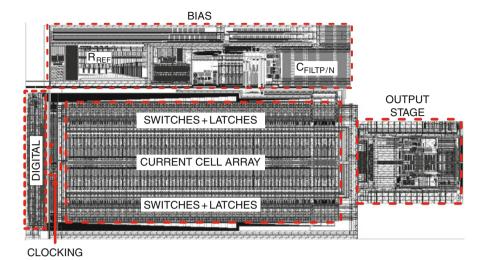

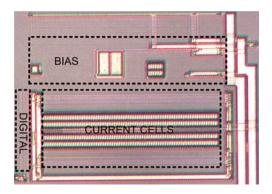

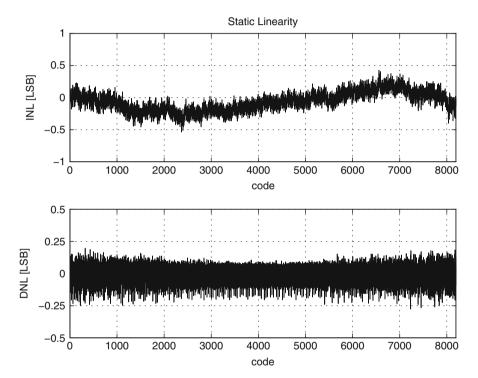

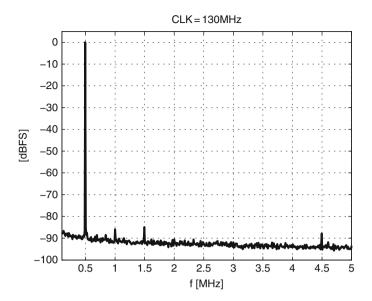

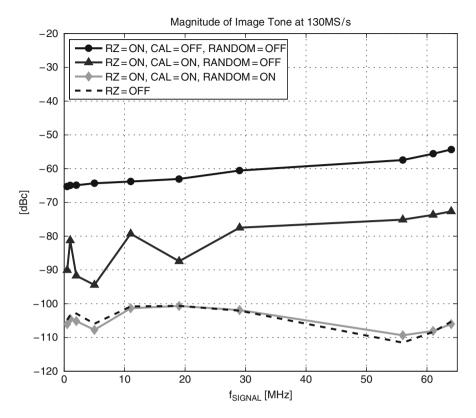

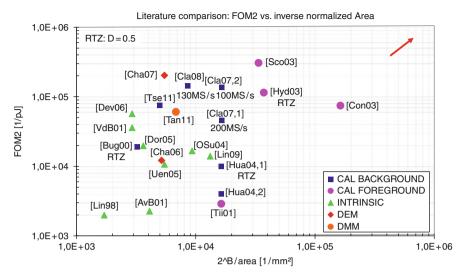

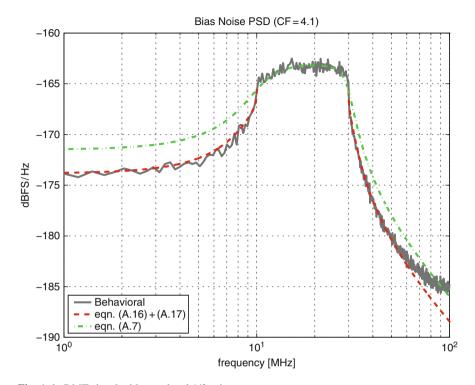

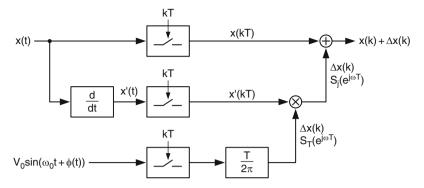

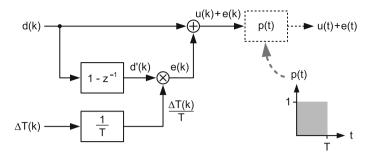

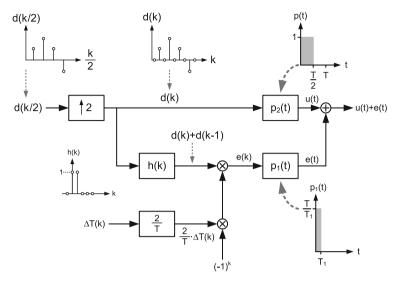

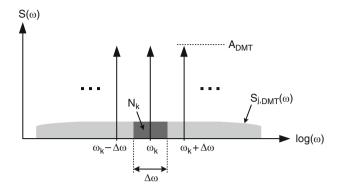

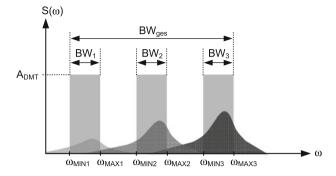

Fig. 1.9 DSL frequency-band plan examples