# A 1.5V Multirate Multibit Sigma Delta Modulator for GSM/WCDMA in a 90nm Digital CMOS Process

A Dissertation

Presented to

The Academic Faculty

by

#### Oguz Altun

In Partial Fulfillment

of the Requirements for the Degree of

Doctor of Philosophy in Electrical and Computer Engineering

Georgia Institute of Technology April 2005

Copyright © 2005 by Oguz Altun

UMI Number: 3183182

Copyright 2005 by Altun, Oguz

All rights reserved.

#### UMI Microform 3183182

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# ${\bf A~1.5V~Multirate~Multibit} \\ {\bf Sigma~Delta~Modulator~for~GSM/WCDMA} \\ {\bf in~a~90nm~Digital~CMOS~Process} \\ \\$

| ${f Approved}:$            |

|----------------------------|

|                            |

| Phillip E. Allen, Chairman |

| T T 1                      |

| Joy Laskar                 |

| Farrold Arosi              |

| Farrokh Ayazi              |

|                            |

| Date approved by Chairman  |

To my wife Didem

### Acknowledgements

It has been a real privilege to be a graduate student in the ECE department at the Georgia Institute of Technology. My experience here has been full of opportunities to learn from a faculty and student body with a wide and deep expertise in engineering. I would like to directly thank those people in the department who were particularly instrumental in contributing to my experience at Georgia Tech.

I would like to thank my advisor, Professor Phillip E. Allen, for his invaluable guidance throughout my long journey as a graduate student. His many years of circuit design experience have allowed him to focus in on the critical and interesting issues of any problem. It has been a unique privilege to be in his group.

I would like to thank the members of my thesis committee - Dr. Marshall Leach, Dr. Joy Laskar, Dr. Faroukh Ayazi and Dr. Thomas Morley - for their valuable feedback and the time they spent reading my thesis.

I spent quite a while at Wireless Analog Technology Center of Texas Instruments Inc. as a design engineer when at the same time I was working on my PhD work. This has been a tremendous opportunity as I had the chance to work with a very experienced group of industry veterans in the field of IC design. A number of colleagues deserve special credit. I would like to thank Baher Haroun, whose quick insightful analysis of complex problems always amazed me. Also, I would like to thank Gabriel J. Gomez, who -as my section manager- continuously encouraged me in going forward with my PhD. I would like to thank Jinseok Koh, Rahmi Hezar, Srinath Ramaswamy and Vijay Rentala for the fruitful technical discussions we had thoughout the years. I want to thank Yunfei Tuan for sharing his layout expertise with me and Charles Kim for helping me in testing the experimental prototype.

I would like to thank Texas Instruments Inc., for especially two things. First of

all, for being elected as their Analog Fellow when I was a student at Georgia Tech and for providing me access to a test chip using their 90nm node which was one of the cutting edge technologies they possessed at the time this prototype was submitted.

Finally, I would like to thank my family, for being supportive and patient throughout the years. My wife Didem Altun, whose support has been the most critical, has waited so long including all the weekends and after hours during the week. I would like to thank my parents, Fatma and Kenan Altun, to my brother, Ediz Altun, for believing me every time I said I was graduating next year.

# Contents

| A  | ckno             | wledgements                                                   | iv  |

|----|------------------|---------------------------------------------------------------|-----|

| Li | st of            | Tables                                                        | x   |

| Li | st of            | Figures                                                       | хi  |

| Sı | ımm              | ary                                                           | xiv |

| 1  | INT              | TRODUCTION                                                    | 1   |

|    | 1.1              | INTRODUCTION                                                  | 1   |

|    | 1.2              | RESEARCH TARGETS                                              | 2   |

|    | 1.3              | THESIS ORGANIZATION                                           | 3   |

| 2  | <b>FU</b>        | NDAMENTALS OF SIGMA-DELTA ( $\Sigma\Delta$ ) Oversampling A/D | )   |

|    | CO               | NVERTERS                                                      | 4   |

|    | 2.1              | INTRODUCTION                                                  | 4   |

|    | 2.2              | PERFORMANCE METRICS                                           | 4   |

|    | 2.3              | PEAK SNR/SNDR AND DYNAMIC RANGE                               | 5   |

|    | 2.4              | NYQUIST RATE                                                  | 6   |

|    | 2.5              | DYNAMIC RANGE FORMULA                                         | 6   |

|    | 2.6              | FUNDAMENTAL LIMITS OF POWER DISSIPATION                       | 9   |

|    |                  | 2.6.1 Dynamic Power Dissipation                               |     |

|    |                  | 2.6.2 Static Power Dissipation                                | 12  |

| 3  | TE               | CHNIQUES FOR IMPROVING RESOLUTION OF HIGH-SPE                 | ED  |

|    | $(\Sigma \Delta$ | A) OVERSAMPLING A/D CONVERTERS                                | 15  |

|    | 3.1              | INTRODUCTION                                                  | 15  |

|   | 3.2 | INCR  | EASING THE OVERSAMPLING RATIO                           | 15         |

|---|-----|-------|---------------------------------------------------------|------------|

|   |     | 3.2.1 | Sampling Jitter                                         | 16         |

|   |     | 3.2.2 | Dependence of Power Dissipation to Clock Frequency      | 17         |

|   | 3.3 | INCR  | EASING THE ORDER OF THE MODULATOR                       | 18         |

|   |     | 3.3.1 | Single-Loop Modulators                                  | 19         |

|   |     | 3.3.2 | Cascade Modulators                                      | 20         |

|   | 3.4 | MULI  | TIBIT QUANTIZATION                                      | 21         |

| 4 | MU  | LTIR  | ATE $\Sigma\Delta$ MODULATORS                           | <b>2</b> 4 |

|   | 4.1 | INTR  | ODUCTION                                                | 24         |

|   | 4.2 | ΜΜ-Σ  | ΣΔ MODULATOR                                            | 26         |

|   |     | 4.2.1 | Analysis of the MM- $\Sigma\Delta$ Modulator            | 27         |

|   |     | 4.2.2 | Relative Performances of MM- $\Sigma\Delta$ Modulators  | 30         |

| 5 | MO  | DULA  | ATOR DESIGN                                             | 32         |

|   | 5.1 | CONV  | VENTIONAL SECOND ORDER 5 LEVEL $\Sigma\Delta$ MODULATOR | 33         |

|   | 5.2 | IDEA  | L SECOND ORDER MM- $\Sigma\Delta$ MODULATOR             | 34         |

|   |     | 5.2.1 | Practical limitations of a MM-SD modulator              | 36         |

|   | 5.3 | PROF  | POSED ARCHITECTURE AND CLOCKING SCHEME                  | 38         |

|   | 5.4 | FIR F | ILTER                                                   | 41         |

|   | 5.5 | ADVA  | ANTAGES OF THE PROPOSED MODULATOR                       | 43         |

|   | 5.6 | SYST  | EM LEVEL SIMULATIONS                                    | 43         |

| 6 | CIF | CUIT  | DESIGN OF THE EXPERIMENTAL PROTOTYPE                    | 48         |

|   | 6.1 | INTR  | ODUCTION                                                | 48         |

|   | 6.2 | INTE  | GRATOR DESIGN                                           | 49         |

|   |     | 6.2.1 | Switch Design                                           | 51         |

|   |     | 6.2.2 | Level Shifter                                           | 54         |

|   |     | 6.2.3 | Sampling and Integrating Capacitors                     | 56         |

|   |     | 6.2.4 | Operational Transconductance Amplifier                  | 58         |

|              |                         |        | 6.2.4.1        | DC Gain                                         | 58 |

|--------------|-------------------------|--------|----------------|-------------------------------------------------|----|

|              |                         |        | 6.2.4.2        | Linear Settling and Slew Rate                   | 59 |

|              |                         |        | 6.2.4.3        | Output Swing                                    | 60 |

|              |                         |        | 6.2.4.4        | OTA Topology selection and design               | 61 |

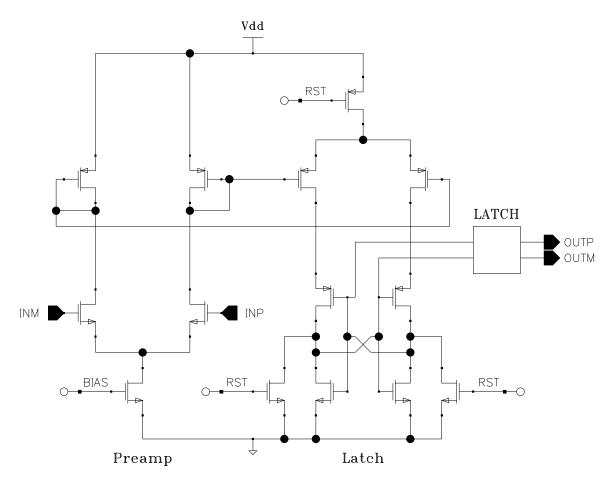

|              |                         | 6.2.5  | Compar         | ator                                            | 64 |

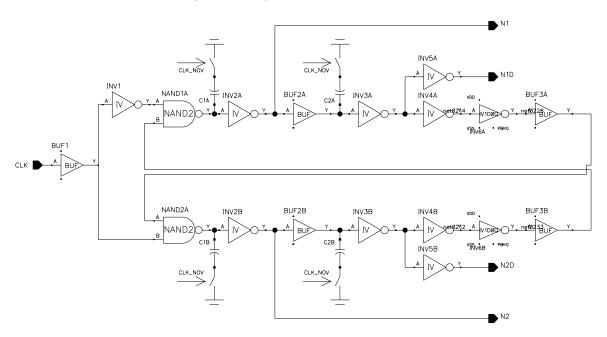

|              |                         | 6.2.6  | Clock ge       | enerator                                        | 65 |

|              |                         | 6.2.7  | Design a       | and Implementation of the FIR filter            | 67 |

|              |                         | 6.2.8  | Individu       | al Level Averaging for Dynamic Element Matching | 68 |

|              |                         | 6.2.9  | Bias gen       | nerator                                         | 69 |

|              |                         | 6.2.10 | Layout         | Considerations                                  | 70 |

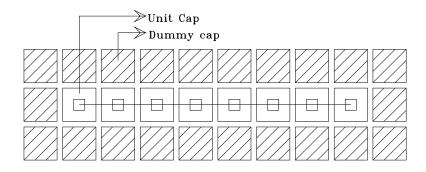

|              |                         |        | 6.2.10.1       | Sampling and Integrating Capacitor Layout       | 71 |

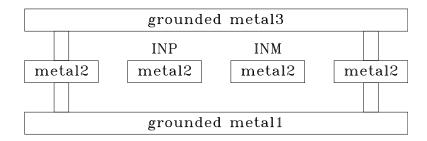

|              |                         |        | 6.2.10.2       | Interconnect Layout and Shielding               | 71 |

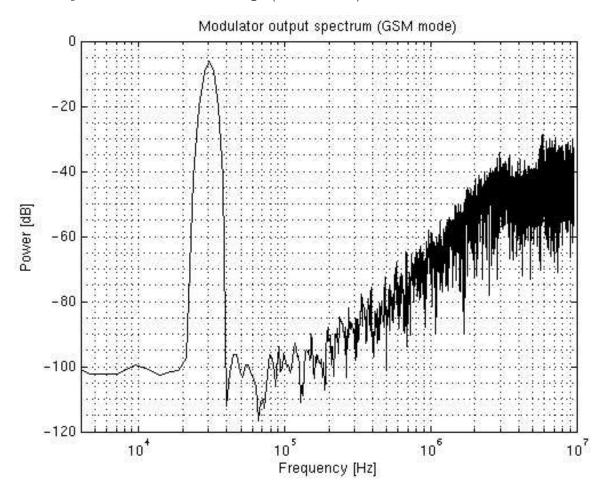

|              | 6.3                     | TOP I  | LEVEL S        | IMULATION RESULTS AND DISCUSSION                | 74 |

|              | 6.4                     | SUMM   | MARY .         |                                                 | 76 |

| 7            | EX                      | PERIN  | <b>IENTA</b> I | L RESULTS                                       | 77 |

|              | 7.1                     | INTRO  | ODUCTI         | ON                                              | 77 |

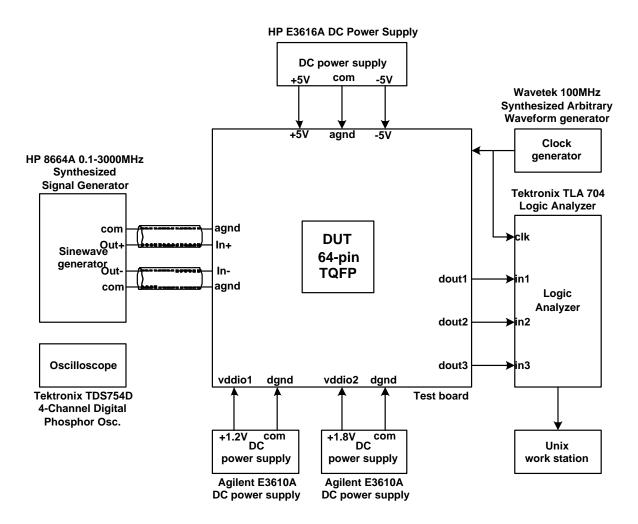

|              | 7.2                     | MEAS   | SUREME         | NT SETUP                                        | 77 |

|              | 7.3                     | RESU   | LTS            |                                                 | 80 |

|              | 7.4                     | COMF   | PARISON        | OF $\Sigma\Delta$ ARCHITECTURES                 | 86 |

| 8            | CO                      | NCLU   | SIONS          |                                                 | 87 |

|              | 8.1                     | INTRO  | ODUCTI         | ON                                              | 87 |

|              | 8.2                     | KEY I  | RESEAR         | CH CONTRIBUTIONS AND RESULTS                    | 87 |

|              | 8.3                     | RECO   | MMEND          | DED FUTURE WORK                                 | 88 |

|              | 8.4                     | RELA   | TED PU         | BLICATIONS                                      | 89 |

| $\mathbf{A}$ | $\mathbf{E}\mathbf{X}'$ | TEND   | ING TH         | E PROPOSED IDEA TO IMPLEMENT HIGHEI             | R  |

|              | PE                      | RFORI  | MANCE          | $\Sigma \Delta MODULATORS$                      | 90 |

|              | Δ 1                     | INTRO  | ЭПИСТЬ         | $\cap$ N                                        | QΩ |

|      | A.1.1 | Option 1 | 90  |

|------|-------|----------|-----|

|      | A.1.2 | Option 2 | 91  |

|      | A.1.3 | Option 3 | 91  |

|      | A.1.4 | Option 4 | 91  |

|      | A.1.5 | Option 5 | 92  |

|      | A.1.6 | Option 6 | 92  |

|      | A.1.7 | Summary  | 92  |

| Vita |       |          | 101 |

# List of Tables

| 3.1 | Theoretical dynamic range of modulators having different loop orders              |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | (OSR=32 and single-bit feedback quantization is assumed)                          | 18 |

| 3.2 | Improvement in SNR of modulators having different loop orders due                 |    |

|     | to the optimum placement of NTF zeros                                             | 20 |

| 6.1 | First integrator OTA specifications determined from behavioral simu-              |    |

|     | lations using MATLAB-Simulink                                                     | 63 |

| 6.2 | Truth table for the Individual Level Averaging<br>(ILA) Block                     | 69 |

| 7.1 | Comparison of three different $\Sigma\Delta$ architectures including the work re- |    |

|     | ported in this thesis.                                                            | 86 |

# List of Figures

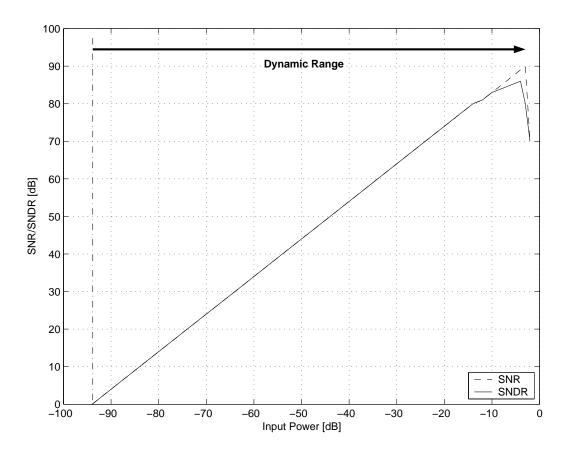

| 2.1 | SNR and SNDR curves for a $\Sigma\Delta$ modulator                                      | 6  |

|-----|-----------------------------------------------------------------------------------------|----|

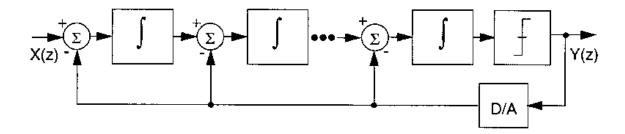

| 2.2 | $\Sigma\Delta$ modulator block diagram                                                  | 7  |

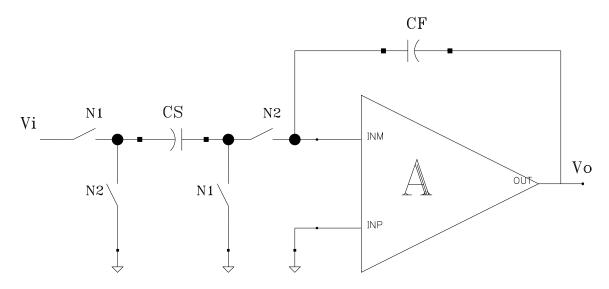

| 2.3 | Switched-Capacitor integrator                                                           | 10 |

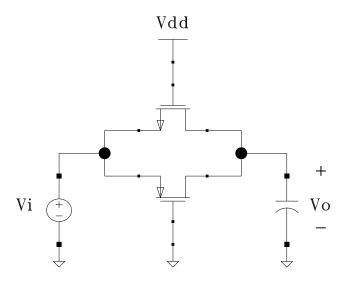

| 2.4 | CMOS sample and hold circuit                                                            | 11 |

| 2.5 | Single transistor op amp model of a switched-capacitor integrator                       | 13 |

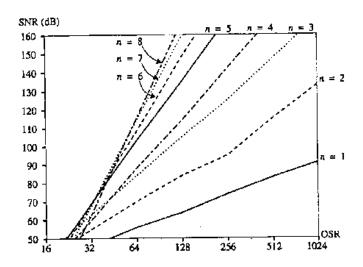

| 3.1 | Maximum SNR achievable by modulators of order $n$ with coincident                       |    |

|     | zeros, as a function of the oversampling ratio.                                         | 20 |

| 3.2 | Cascaded modulator architecture                                                         | 21 |

| 3.3 | Signal-to-quantization noise of a second-order multibit modulator as a                  |    |

|     | function of the number of feedback bits $m$                                             | 22 |

| 4.1 | Architecture of second-order $\Sigma\Delta$ modulators (a) MM- $\Sigma\Delta$ modulator |    |

|     | (b) Conventional single-bit architecture (c) Conventional multibit ar-                  |    |

|     | chitecture                                                                              | 26 |

| 4.2 | Block diagram equivalent to the MM- $\Sigma\Delta$ modulator of Fig 4.1 (a).            | 28 |

| 4.3 | Ratio between the inband power of the quantization noise and the                        |    |

|     | contribution of the aliasing terms, in a MM- $\Sigma\Delta$ modulator with $N=4,$       |    |

|     | for three different values of the low oversampling ratio $M_1$                          | 30 |

| 5.1 | Conventional implementation of a Second Order 5-Level $\Sigma\Delta$ modulator          | 33 |

| 5.2 | Layout floorplan of the $2^{nd}$ Order 5-Level $\Sigma\Delta$ modulator given in Fig    |    |

|     | 5.1                                                                                     | 35 |

| 5.3 | Second Order MM- $\Sigma\Delta$ modulator                                               | 36 |

| 5.4 | Sampling and integration half cycles for the Second Order 5-Level MM-                   |    |

|     | $\Sigma\Delta$ modulator                                                                | 37 |

| 5.5 | Sampling and integration half cycles for the Proposed MM- $\Sigma\Delta$ modulator      | 38 |

| 5.6 | Top level implementation of the proposed architecture                                   | 39 |

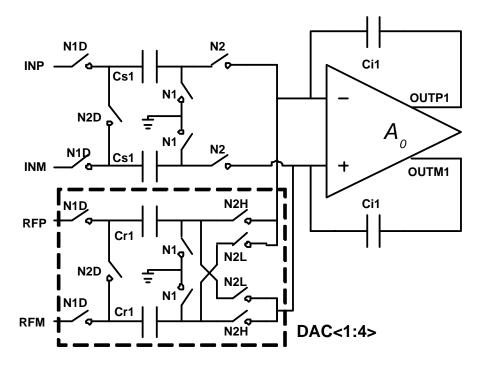

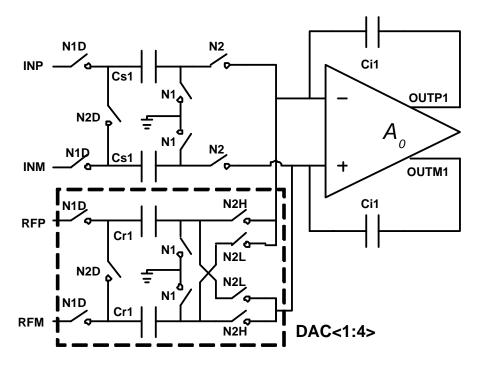

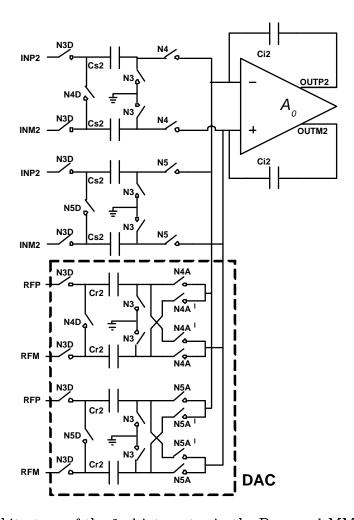

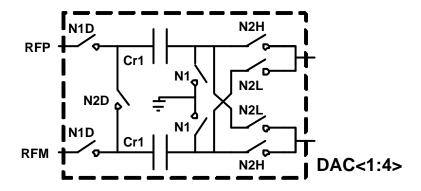

| 5.7  | Architecture of the 1st integrator in the Proposed MM- $\Sigma\Delta$ modulator.  |    |

|------|-----------------------------------------------------------------------------------|----|

|      | The structure in dashed rectangle is repeated 4 times and connected               |    |

|      | in parallel, hence the notation $DAC < 1: 4 > \dots \dots$                        | 40 |

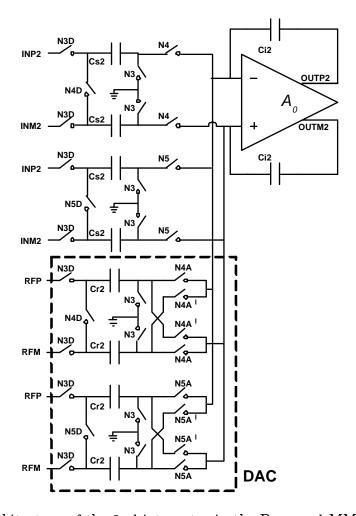

| 5.8  | Architecture of the 2nd integrator in the Proposed MM- $\Sigma\Delta$ modulator   | 41 |

| 5.9  | Clocking scheme for the Proposed MM- $\Sigma\Delta$ modulator                     | 42 |

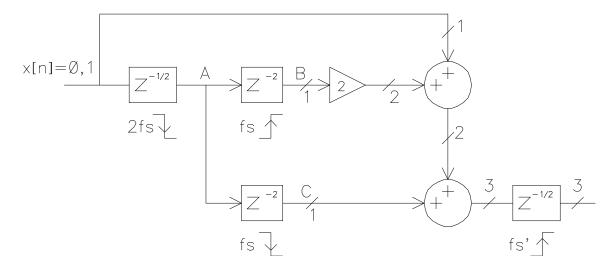

| 5.10 | Block diagram of the FIR filter structure used in the proposed system             | 42 |

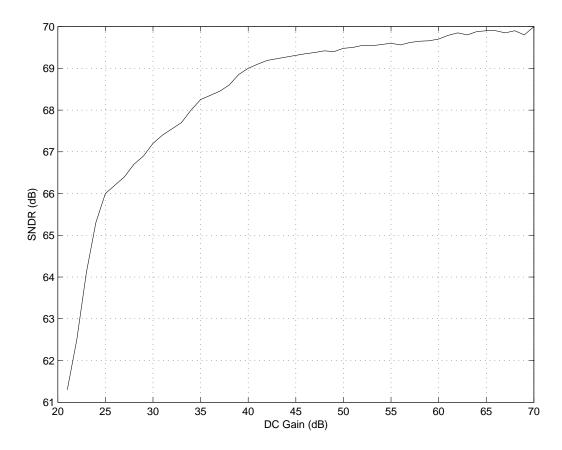

| 5.11 | SNDR vs. first amplifier DC gain                                                  | 45 |

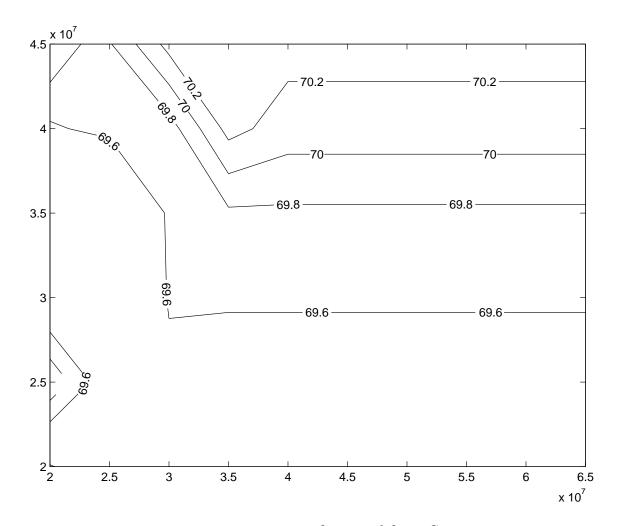

| 5.12 | SNDR vs. first amplifier DC gain                                                  | 46 |

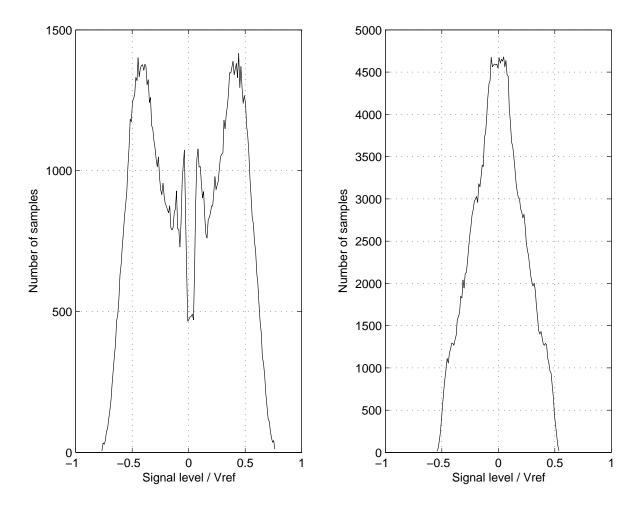

| 5.13 | Histogram of integrator outputs                                                   | 47 |

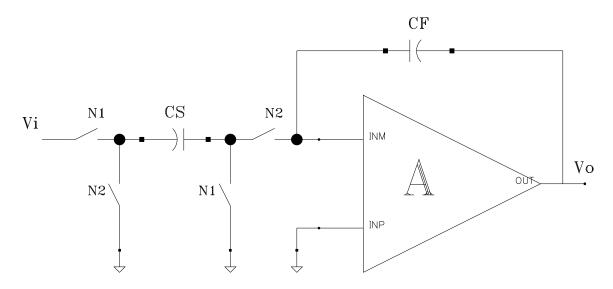

| 6.1  | Architecture of the first integrator in the proposed MM- $\Sigma\Delta$ modulator | 50 |

| 6.2  | Architecture of the 2nd integrator in the Proposed MM- $\Sigma\Delta$ modulator   | 51 |

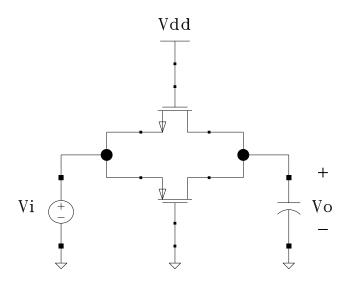

| 6.3  | CMOS switch used in sampling networks                                             | 52 |

| 6.4  | On resistance (Ron) versus Input voltage (Vin) in a CMOS switch                   | 53 |

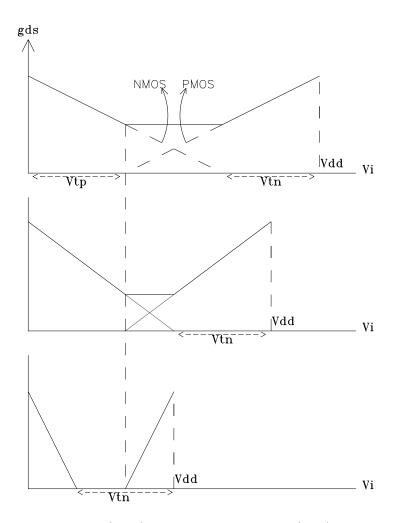

| 6.5  | A fast cross-coupled level shifter for clock signals                              | 55 |

| 6.6  | Switched-Capacitor integrator with finite amplifier dc gain                       | 59 |

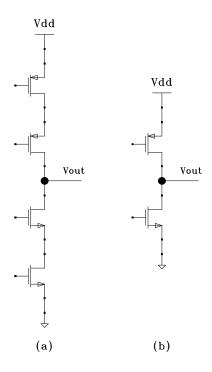

| 6.7  | Operational amplifier output configurations (a)cascoded and (b)common             |    |

|      | source                                                                            | 61 |

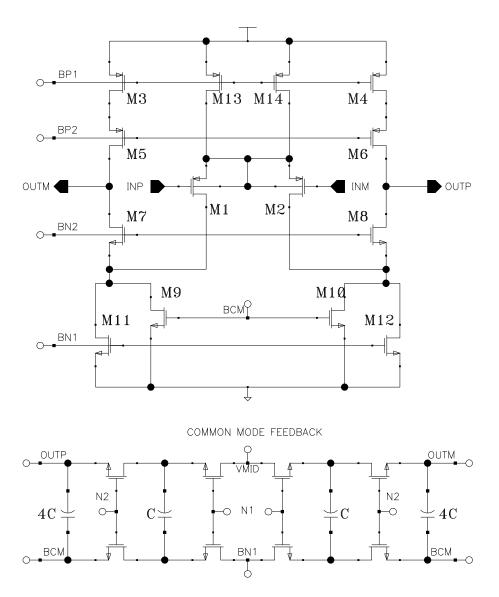

| 6.8  | Operational amplifier with switched-capacitor common mode feedback                | 62 |

| 6.9  | Comparator schematic                                                              | 65 |

| 6.10 | Two-phase nonoverlapping clock generator                                          | 66 |

| 6.11 | Modified diagram of the FIR filter to write RTL level VHDL code $$                | 67 |

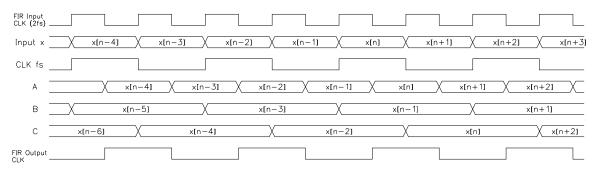

| 6.12 | The clocking of the FIR filter and other timing information                       | 67 |

| 6.13 | DAC element used in the first integrator (Fig 5.7)                                | 68 |

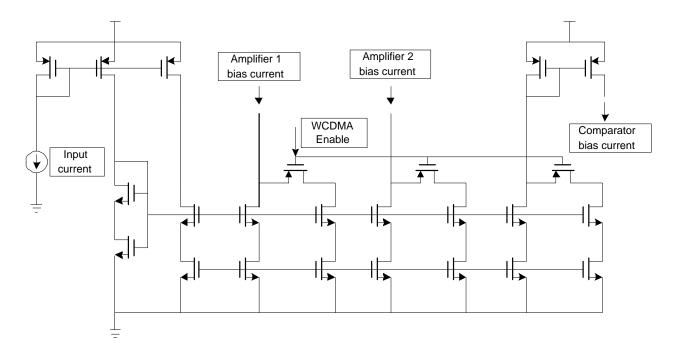

| 6.14 | The bias generator circuit                                                        | 70 |

| 6.15 | Sampling Capacitor Array in the layout                                            | 71 |

| 6.16 | Cross sectional view of the shielded interconnect line                            | 72 |

| 6.17 | Modulator output spectrum in GSM mode                                             | 74 |

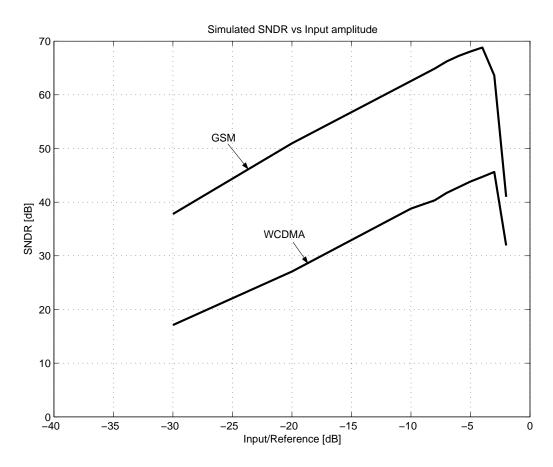

| 6.18 | Simulated SNDR versus input signal level in GSM and WCDMA modes                   | 75 |

| 7 1  | Test setup                                                                        | 70 |

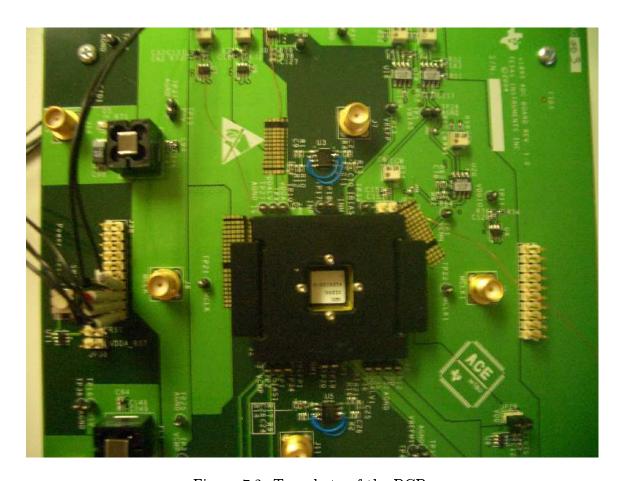

| 7.2 | Top photo of the PCB                                              | 80 |

|-----|-------------------------------------------------------------------|----|

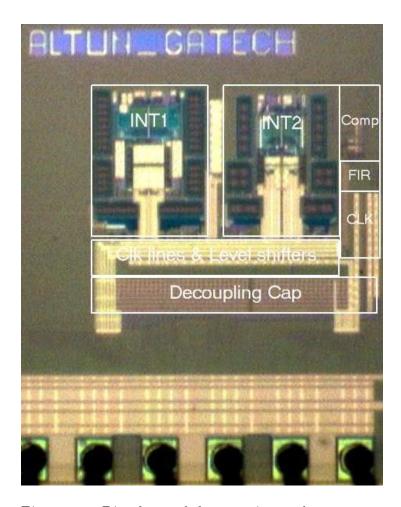

| 7.3 | Die photo of the experimental prototype                           | 81 |

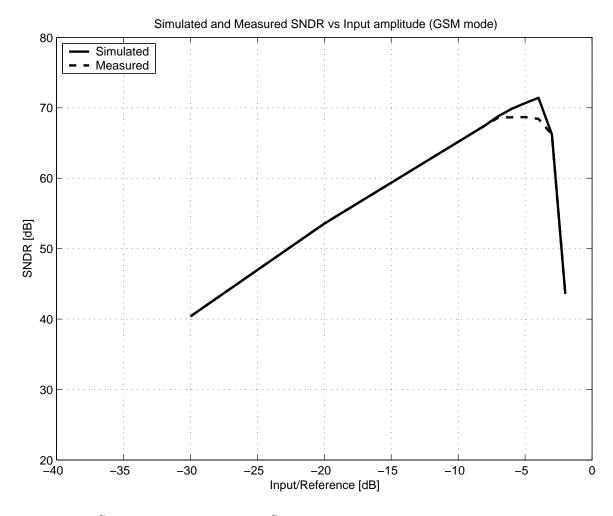

| 7.4 | Simulated and measured SNDR versus input power across 200kHz sig- |    |

|     | nal band (GSM mode)                                               | 82 |

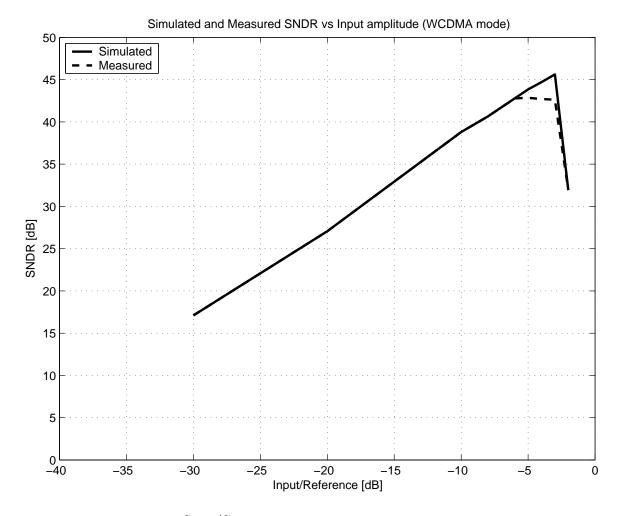

| 7.5 | Measured SNR/SNDR versus input power across 2MHz signal band      |    |

|     | (WCDMA mode)                                                      | 83 |

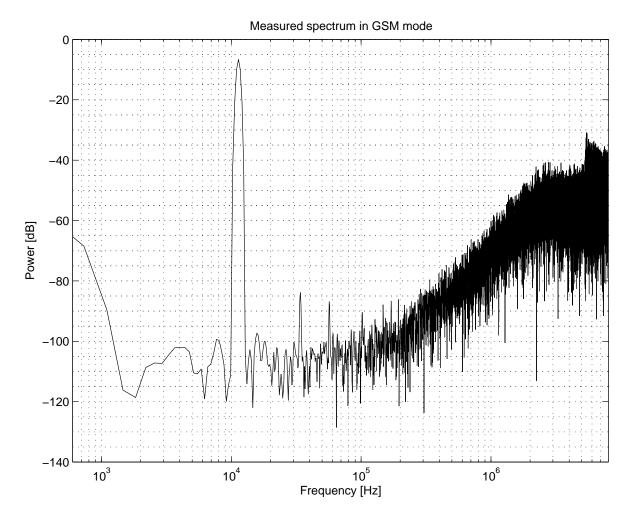

| 7.6 | FFT for -6dB signal in GSM mode                                   | 84 |

### Summary

The development of low-voltage and low-power mixed signal CMOS integrated circuits has been one of the key objectives in the last decade. Thus, a significant amount of effort has been devoted for this purpose. There are two main reasons that fuel this need. First reason is the increasing demand for portable battery operated systems. The second one is the ongoing transistor scaling. Analog to digital converters based on  $\Sigma\Delta$  modulators are widely used in the analog front ends of various mixed signal integrated circuit. Hence they have to operate from low supply voltages as well as with minimum power dissipation.

This dissertation investigates the use of digital techniques to replace some of the functionalities that were traditionally performed by analog circuits. By doing so, the aim is to increase the share of digital blocks in the  $\Sigma\Delta$  system and decrease area and power consumption of the modulator. This dissertation also investigates the design techniques of low-voltage, power efficient analog building blocks which are then used in the design of a  $\Sigma\Delta$  modulator for wireless applications (i.e., 200kHz and 1.94MHz for GSM and Wideband CDMA, respectively).

In order to demonstrate the techniques presented here, a prototype  $\Sigma\Delta$  modulator is designed and fabricated in a 90nm five metal single poly n-well CMOS process. The presented  $\Sigma\Delta$  modulator operates from two different supplies: 1.5V for analog side and 1.3V for digital side. The modulator is realized with fully-differential stray insensitive switched capacitor integrators. Both integrator stages use a fully differential folded cascode operational transconductance amplifier with switched capacitor common mode feedback to set the common mode voltages of the output nodes. Both amplifiers have PMOS input pairs. Simple level shifters are used to increase the voltage level of the clock signals so that the switches that are driven by these clock signals

can be minimized. A careful capacitor scaling is performed in the second integrator stage in order to take advantage of the noise shaping that is due to the first integrator stage. The presented  $\Sigma\Delta$  modulator achieves 68.6/42.8dB peak SNDR and dissipates 1.1/1.9mA of current (mostly from 1.5V analog supply) in GSM and WCDMA modes, respectively.

#### Chapter 1

#### INTRODUCTION

#### 1.1 INTRODUCTION

The market for mobile radio frequency personal communication devices is rapidly expanding with the development of new services and applications. The variety of applications and devices has led to a proliferation of communications standards with different modulation schemes, channel bandwidths, dynamic range requirements and so forth. In addition, consumers are demanding low-cost, low-power, and small form factor devices to satisfy these communication requirements. As a result, recent efforts in the design of integrated circuits for personal communication transceivers have focussed on increased integration in a low cost technology (e.g. CMOS) as well as adaptability to multiple RF communication standards. This requires research into new architectures and circuit techniques that enable both integration and programmability in RF transceivers [1, 2].

As more and more sophisticated digital signal processing (DSP) functions are implemented on a single IC, the emphasis on the interface circuitry used to convert signals between analog and digital domains increases.  $\Sigma\Delta$  A/D converters combine oversampling and feedback to shape the noise and then use a digital lowpass filter to attenuate the noise that has been pushed out-of-band. This way, it is possible to achieve a dynamic range as high as 16 bits or more at relatively modest oversampling ratios [11].

A very significant feature of  $\Sigma\Delta$  A/D converters is the transfer of much of the

signal processing into the digital domain where power consumption can be dramatically reduced simply by scaling the technology and reducing the supply voltage [16]. In addition to this, digital systems are easier to implement when moving to a newer technology node since they are generally synthesized by commercial CAD tools. This generally means reduced design cycle and time to market.

This research focuses on bringing more of the digital functionality into the  $\Sigma\Delta$  modulator architectures due to the benefits mentioned above. A new idea is explored and it is verified by both behavioral simulation tools and Spice. An experimental prototype design is fabricated using a 90nm digital CMOS process.

#### 1.2 RESEARCH TARGETS

This research seeks to address issues of integration and programmability in RF receivers by investigating the use of multi-rate multi-bit design techniques in the design of a high-speed  $\Sigma\Delta$  modulator. A more general goal of this research, which is critical for the RF application, is to develop techniques at both the architecture and circuit design levels to minimize power dissipation in high-speed  $\Sigma\Delta$  modulators. In the context of these goals, some key research results are as follows:

- Demonstrated that a multi-rate multi-bit ΣΔ modulator(MMSD) can meet the

baseband processing requirements for RF receivers at a reasonable power dissipation. An experimental prototype implemented in a 90nm single-poly, 5

metal CMOS process achieved 68.6dB of Signal-to-Noise and Distortion ratio

(SNDR) and required 1.1mA of current across 200kHz signal band. This dual

mode modulator also achieved 42.8dB of SNDR across 2MHz signal band and

required 1.9mA.

- Showed that scaling integrator sampling capacitors to the minimum value required by kT/C noise at each stage is an effective technique for reducing power dissipation.

- The issues with the ideal multi-rate multi-bit  $\Sigma\Delta$  modulators are addressed with a new integrator architecture and a novel clocking scheme. This made the practical implementation of such systems possible.

- Bulky flash A/D converter inside the feedback loop of the ΣΔ modulator is replaced with a single comparator, a very simple digital FIR filter and an upsampling in the second integrator stage of the modulator. This resulted in significant area and power savings.

#### 1.3 THESIS ORGANIZATION

Chapter 2 provides a brief overview of the fundamentals of  $\Sigma\Delta$  modulators. Techniques for improving resolution of high-speed  $\Sigma\Delta$  A/D converters are discussed in Chapter 3. In Chapter 4, the specifics of multirate modulators are explained. Chapter 5 describes the system level design of the modulator. The circuit design aspects of the modulator are presented in Chapter 6. An experimental prototype and test results are discussed in Chapter 7. Chapter 8 contains concluding remarks.

## Chapter 2

# FUNDAMENTALS OF SIGMA-DELTA $(\Sigma \Delta)$ Oversampling A/D CONVERTERS

#### 2.1 INTRODUCTION

This chapter reviews some of the fundamental issues in the design of  $\Sigma\Delta$  modulators. The discussion begins with a variety metrics used to evaluate modulator performance with emphasis on those which are important for RF applications. Then, the basic concept of how a  $\Sigma\Delta$  modulator works is described, and the basic linearized models are reviewed and related to performance issues. Finally, the fundamental power limits for  $\Sigma\Delta$  modulators implemented using switched-capacitor circuits are derived. Following this basic introduction, tradeoffs among a variety of sigma-delta architectures suitable for high-speed applications are explored in the next chapter.

#### 2.2 PERFORMANCE METRICS

This section defines the metrics used to evaluate  $\Sigma\Delta$  modulator performance. For RF applications, the key requirements for a  $\Sigma\Delta$  modulator are dynamic range, Nyquist rate and power dissipation. In addition,  $\Sigma\Delta$  designers usually specify peak SNR (signal-to-noise ratio) and peak SNDR (signal-to-noise-and-distortion ratio), which measure the degradation of the signal due to noise alone, and due to a combination of noise and distortion, respectively.

#### 2.3 PEAK SNR/SNDR AND DYNAMIC RANGE

Peak SNR, SNDR and dynamic range are related specifications and will be defined together. Dynamic range is the ratio in power between the maximum input signal level that the modulator can handle and the minimum detectable input signal. SNR is the ratio of the signal power at the output of the modulator to the noise power. SNR includes all noise sources in the modulator, both thermal and quantization. SNDR is the ratio of the signal power at the output of the modulator to the sum of the noise and harmonic distortion powers. Peak SNDR is a useful metric for evaluating the capability of a  $\Sigma\Delta$  modulator for handing large in band signals at acceptable linearity and is especially important for applications such as digital audio. Note that peak SNDR is frequency dependent and can be used to measure the degradation of modulator performance as the input signal increases in frequency. Peak SNR, SNDR and dynamic range are typically reported using the type of plot shown in Fig. 2.1. The plot shows SNR and SNDR as a function of input signal power in dB relative to the full scale of the modulator. For small signal levels, distortion is not important implying that the SNR and SNDR are approximately equal. As the signal level increases, distortion degrades the modulator performance, and the SNDR will be less than the SNR. Dynamic range on the plot is the difference between the input level where the SNDR drops 3 dB beyond the peak and the x-intercept of the SNDR curve.

A closely related specification to dynamic range is the resolution of the modulator expressed in bits. The resolution in bits (N) is defined in equation 2.1 where DR is the dynamic range of the modulator expressed in dB. The correspondence is such that each bit of resolution is equivalent to 6 dB of dynamic range.

$$N = \frac{DR - 2}{6} \tag{2.1}$$

Figure 2.1: SNR and SNDR curves for a  $\Sigma\Delta$  modulator.

#### 2.4 NYQUIST RATE

The Nyquist rate is a measure of the speed of a  $\Sigma\Delta$  modulator. The Nyquist sampling theorem states that to avoid aliasing, a lowpass signal must be sampled at a rate that is twice its bandwidth. As a result, specifying the Nyquist rate is equivalent to specifying the modulator input bandwidth.

#### 2.5 DYNAMIC RANGE FORMULA

The forward path of a  $\Sigma\Delta$  modulator consists of a series of integrators, and a quantizer. Fig. 2.2 illustrates an example modulator. The effect of the feedback loop is to bring the average value at the first integrator input to zero. This implies that the output of the D/A converter is on average equal to the input signal X(z). Since the

Figure 2.2:  $\Sigma\Delta$  modulator block diagram.

output of the D/A converter is merely an analog representation of the digital output Y(z) of the quantizer, it follows that Y(z) on average equals to X(z). If the modulator samples the input signal at a higher rate than required by the Nyquist sampling criterion and multiple samples are averaged to produce a digital output Y(z), the  $\Sigma\Delta$  modulator can then be used as an oversampled A/D converter.

Assume that each integrator has the transfer function given by:

$$I(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2.2}$$

If we further assume that the quantizer and D/A converter can be modeled as additive error sources, then a linearized transfer function of an Lth order  $\Sigma\Delta$  modulator neglecting delays can be expressed as

$$Y(z) = X(z) + (1 - z^{-1})^{L} E(z) - E_{DAC}(z)$$

(2.3)

Equation (2.3) indicates that errors in the D/A converter add directly at the input of the  $\Sigma\Delta$  loop. This implies that the D/A converter must be linear to the full resolution of the  $\Sigma\Delta$  modulator to avoid degrading the overall modulator performance. One way to ensure that this linearity constraint is met is to use a single-bit quantizer and two-level D/A converter. A two-level D/A converter is inherently linear (it can only result in a dc offset at the input of the modulator [8]). Multi-bit D/A converters need some kind of calibration to meet this linearity constraint [11].

The overall quantization noise power in the baseband  $(-f_B, f_B)$  can be found by

integrating the quantization error term in (2.3) evaluated on the unit circle [8].

$$S_q \approx \sigma_e^2 \int_{-f_B}^{f_B} |(1 - e^{j2\pi f/f_S})^L|^2 df$$

$\approx \sigma_e^2 \frac{\pi^{2L}}{2L+1} \frac{1}{M^{2L+1}}$  (2.4)

$\sigma_e^2$  in (2.4) is the variance of the quantization error. If the quantizer has a linear input range  $\left(-\frac{\Delta}{2}, \frac{\Delta}{2}\right)$  and B bits of resolution, it follows that the one least significant bit (LSB) will have a value

$$\delta = \frac{\Delta}{2^B - 1} \tag{2.5}$$

Assuming that the quantization error can be modeled as white and is uniformly distributed between  $(-\frac{\delta}{2}, \frac{\delta}{2})$ , then from a statistical analysis the quantization noise power can be expressed as

$$\sigma_e^2 = \frac{\delta^2}{12} = \frac{\Delta^2}{12(2^B - 1)^2} \tag{2.6}$$

Combining the results of (2.4),(2.5) and (2.6), the dynamic range of a  $\Sigma\Delta$  modulator is calculated as [9]

$$DR = \frac{3}{2} \frac{2L+1}{\pi^{2L}} M^{2L+1} (2^B - 1)^2$$

(2.7)

Equation (2.7) indicates that the dynamic range of a  $\Sigma\Delta$  modulator is a strong function of the oversampling ratio and the order of the modulator loop. It is important to note that, especially for single-bit quantizers and two-level DACs, the white noise assumption is not a good one. Furthermore, the stability of  $\Sigma\Delta$  modulators is an important concern and in general the practical dynamic range figures significantly deviate from the ideal formula. Thus, (2.7) should be viewed as an upper bound on the dynamic range.

# 2.6 FUNDAMENTAL LIMITS OF POWER DIS-SIPATION

In order to design a low-power low-voltage modulator, it is first necessary to understand where the power is going in sigma-delta modulators and what are the fundamental power limits.

The key circuit building block in a sigma-delta modulator is the integrator. Typically implemented using switched-capacitor techniques, the integrators will dominate the power dissipation of the modulator. The minimum achievable power dissipation is set by the need to charge and discharge capacitors of a given size at a given speed. This will be referred to as the dynamic power limit. In practice, switched-capacitor circuits are implemented using amplifiers which have static bias currents and burn significantly more power than the dynamic limit. In this section, both the dynamic and static power limits for switched-capacitor integrators employed in an oversampled system will be investigated.

#### 2.6.1 Dynamic Power Dissipation

The dynamic power dissipation limit assumes that the only power dissipated in a SC integrator is that which is required to charge and discharge the sampling capacitor. This is the absolute lower bound on the achievable power dissipation in an SC circuit. Suppose the amplifier in Fig. 2.3 delivers just the required charge for the sampling capacitor, dissipates no static power and introduces no additional noise into the circuit. Let the system Nyquist rate be  $f_N$  and oversampling ratio be M. The maximum voltage swing will be limited by the power supply Vdd. Then, it follows that the integrator power will obey the relationship in 2.8.

$$P \propto C_S V_{dd}^2 f_N M \tag{2.8}$$

Now consider the noise introduced by the sampling process. The circuit in Fig.

Figure 2.3: Switched-Capacitor integrator

2.4 is a switched-capacitor MOS sample and hold circuit. When the switch is on, the voltage across the capacitor tracks the input voltage. At the instant the switch opens, a sample of both the input signal and the noise due to the switch is held on the capacitor. Since the switch is in the triode region, the single-sided power spectral density of the noise given in 2.9 models the switch by its effective on resistance Ron [46]. The quantity of interest is not the power spectral density but the total inband noise power which can be found by integrating the power spectral density accounting for the bandwidth of the switch and capacitor as in 2.10. Note that  $P_{N,TOT}$  represents the

$$\overline{v}^2 = 4kTR_{on}\Delta f \tag{2.9}$$

$$P_{N,TOT} = \int_0^\infty \frac{\overline{v}^2}{\Delta f} \frac{df}{|1 - j2\pi R_{on} C_S f|^2} = \int_0^\infty \frac{4kT R_{on}}{1 + (2\pi R_{on} C_S f)^2} df = \frac{kT}{C}$$

(2.10)

total sampled noise in the interval  $(\frac{-f_s}{2}, \frac{f_s}{2})$  where  $f_s$  is the sampling frequency. Since the sampling process causes uncorrelated noise from higher frequencies to alias into this frequency region, the noise may be modeled as white with the two-sided

Figure 2.4: CMOS sample and hold circuit

power spectral density in 2.11. Since this is an oversampled system, only noise in the region  $(-f_b, f_b)$  corrupts the desired signal.

$$S_N = \frac{kT}{f_s C_S} \tag{2.11}$$

The noise power in the region of interest  $(P_N)$  is simply the integral of the power spectral density over the bandwidth in 2.12.

$$P_{N} = \int_{-f_{b}}^{f_{b}} \frac{kT}{f_{s}C_{S}} df = \frac{2f_{b}kT}{f_{s}C_{S}} = \frac{kT}{MC_{S}}$$

(2.12)

Note that the overall noise is independent of the switch resistance and inversely proportional to the sampling capacitance. In addition, the noise is inversely proportional to the oversampling ratio which implies that oversampling ratio and capacitor size trade off for a fixed noise specification.

We also need to relate the thermal noise to the dynamic range requirement for a switched-capacitor integrator. Assume that the maximum signal power is limited by the power supply voltage Vdd. Then, it follows that the dynamic range obeys the relationship in 2.13. Note that the dynamic range is proportional to the capacitor

size, the oversampling ratio and the square of the power supply voltage. This dynamic range expression does not include quantization noise, but for this analysis it is assumed that the modulator is thermal noise limited.

$$DR \propto \frac{MC_S V_{dd}^2}{kT} \tag{2.13}$$

We can now relate power dissipation to dynamic range by combining equations 2.8 and 2.13. This is given in 2.14.

$$P \propto kT(DR)f_N \tag{2.14}$$

As seen in 2.14, the dynamic power limit for an oversampled switched-capacitor circuit is independent of the oversampling ratio and the power supply voltage. Power and speed trade off since power is directly proportional to the Nyquist rate  $f_N$ . In addition, power and noise trade off since power is directly proportional to dynamic range.

#### 2.6.2 Static Power Dissipation

In SC integrators, significant static power is dissipated in the operational amplifiers. Fig. 2.5 illustrates the simplest model of an operational amplifier driving a series of capacitors [4]. The amplifier is biased at a current (I) and therefore dissipates static power given by 2.15.

$$P = V_{dd}I (2.15)$$

With a series of simplifying assumptions, it is possible to relate the static power to fundamental parameters of the system:

• Assume the device is biased at fixed  $V_{GS} - V_T$  which implies that the device transconductance  $(g_m)$  is directly proportional to the bias current (I).

Figure 2.5: Single transistor op amp model of a switched-capacitor integrator

• Assume that the feedback factor (f) given by 2.16 is fixed. This is equivalent to assuming that the gate capacitance  $C_{GS}$  of the transistor is small compared to the sampling capacitance.

$$f = \frac{C_F}{C_F + C_S + C_{GS}} \sim \frac{C_F}{C_F + C_S}$$

(2.16)

• Assume that the total capacitive  $(C_{L,TOT})$  loading on the operational amplifier given by 2.17 is dominated by the sampling network. Note that the device parasitics and any external load capacitance has been lumped into  $C_L$ .

$$C_{L,TOT} = \frac{C_F(C_S + C_{GS})}{C_F + C_S + C_{GS}} \sim \frac{C_F C_S}{C_F + C_S}$$

(2.17)

A single transistor amplifier has a single pole settling characteristic with time constant given by 2.18. At a given sampling rate and for a given dynamic range the amplifier must settle to a certain accuracy which can be defined by a number of single pole time constants. This implies that the time constant can be related to the sampling frequency though the proportionality in 2.19.

$$\tau = \frac{C_{L,TOT}}{fg_m} = \frac{C_S}{g_m} \tag{2.18}$$

$$\tau \propto \frac{1}{Mf_N} \tag{2.19}$$

Using the first assumption above and substituting with the result from 2.18, 2.15 can be rewritten as the proportionality in 2.20.

$$P \propto V_{dd}g_m = \frac{V_{dd}C_S}{\tau} \tag{2.20}$$

Substituting the results from 2.13 and 2.19 into 2.20 yields the static power limit in 2.21.

$$P \propto \frac{(DR)kTf_N}{V_{dd}} \tag{2.21}$$

Like the dynamic power dissipation limit, the static power limit is independent of oversampling ratio. In addition, dynamic range and power trade off as do speed and power. However, the static limit is inversely proportional to the power supply voltage which suggests that the trend toward lower supplies favored by digital circuits and required by deep submicron CMOS processes will have an adverse effect on power dissipation.

### Chapter 3

# TECHNIQUES FOR IMPROVING RESOLUTION OF HIGH-SPEED $(\Sigma \Delta)$ OVERSAMPLING A/D CONVERTERS

#### 3.1 INTRODUCTION

In this chapter, a brief summary of possible approaches to improve the resolution of High-Speed Oversampling  $\Sigma\Delta$  ADCs will be presented. A simple observation of the DR equation, (2.7), reveals that there are 3 main ways of achieving higher resolution in a  $\Sigma\Delta$  ADC. These are: increasing the oversampling ratio, using a higher order loop filter and increasing the number of bits for the quantizer that is used inside the feedback loop.

# 3.2 INCREASING THE OVERSAMPLING RA-TIO

The first look at (2.7) reveals that DR is strongly dependent on the oversampling ratio (M). The expression

$$\Delta(SNR) = 3(2L+1)dB \tag{3.1}$$

in which L is the order of the  $\Sigma\Delta$  modulator, describes the increase of the SNR for every doubling of the sampling rate [11]. This translates directly in terms of the resolution as

$$\Delta(Resolution) = (L + 0.5)bits \tag{3.2}$$

In the specific case of a second-order loop (L=2), this improvement is 15 dB or 2.5 bits [12]. Because of this strong dependence, increasing the oversampling ratio is the most attractive method for improving the resolution of  $\Sigma\Delta$  modulators.

Although using high oversampling ratios is desirable in a  $\Sigma\Delta$  modulator design, it is not always practically possible to increase the clock frequency because the analog circuits may not be able to meet the performance requirements of a very high clock rate. In switched-capacitor (SC) implementations, two non-overlapping clock waveforms are needed. In the first half of the clock period, sampling, the input signal and the signal fed back from the output of the feedback quantizer are sampled onto the sampling capacitors. In the second half, integration, this voltage is integrated. Thus, only 50% of one clock cycle is available for settling to the desired accuracy. As the clock rate is increased, performance of the operational amplifier has to be increased. Specifically, the slew rate (SR) and the gain-bandwidth product (GBWP) of the operational amplifier must be increased in accordance with the clock rate.

Other than the increased performance required from the operational amplifiers, there are two main concerns related with using a high oversampling ratio in a  $\Sigma\Delta$  modulator: the sampling jitter and excessive power consumption.

#### 3.2.1 Sampling Jitter

The sampling theorem states that a sampled signal can be perfectly reconstructed provided that the sampling frequency is at least twice the signal bandwidth and that the sampling occurs at uniformly distributed instances in time. An anti-aliasing filter preceding the sampler ensures that the first of these requirements is fulfilled. Sampling clock jitter results in non-uniform sampling and increases the total error power in the quantizer output. An upper limit for the tolerable clock jitter is derived in [13].

$$\Delta t \le \frac{1}{2\pi B \cdot 2^b} \sqrt{\frac{2M}{3}} \tag{3.3}$$

The error caused by clock jitter is inversely proportional to the oversampling ratio M and adds directly to the total error power  $S_N$  at the output of the A/D converter. The amount of clock jitter that can be tolerated decreases for an increase in oversampling ratio [13].

As an example, if the baseband error power induced by clock jitter to be no larger than the quantization noise resulting from an ideal second-order modulator with 1-bit quantization, then it is necessary that  $\Delta t \leq 874ps$  for a 20 kHz bandwidth.

#### 3.2.2 Dependence of Power Dissipation to Clock Frequency

A typical operational-transconductance amplifier (OTA) has a gain-bandwidth product (GBWP) given by

$$GBWP = \frac{g_M}{C} \tag{3.4}$$

where  $g_M$  is the transconductance of the input stage and C is the total equivalent loading capacitance in its integrator functionality. When this OTA is implemented in a CMOS technology, the transconductance of the input stage according to a simplified second-order model [14] is given by

$$g_M = \sqrt{2K\frac{W}{L}I_{DS}} \tag{3.5}$$

where K is the gain constant of the transistor,  $\frac{W}{L}$  is the aspect ratio, and  $I_{DS}$  is the bias current. For most typical SC integrators, if the value of the sampling capacitors is kept constant, doubling the clock frequency requires doubling the GBWP of the op amp. Thus the combined effects of (3.4) and (3.5) show that the bias current has to be quadrupled, or alternatively doubled in combination with the doubling of the transistor ratios [12].

Table 3.1: Theoretical dynamic range of modulators having different loop orders (OSR=32 and single-bit feedback quantization is assumed).

| L | SNR (dB) | Resolution (bits) |

|---|----------|-------------------|

| 2 | 64.1     | 10                |

| 3 | 85.7     | 14                |

| 4 | 107      | 17                |

# 3.3 INCREASING THE ORDER OF THE MOD-ULATOR

The DR equation, (2.7), implies that the quantization noise power can be lowered below a desired level by simply inserting more integrators into the forward path of the modulator given in Fig. 2.2. Table 3.1 illustrates the dynamic range predicted by (2.7) for different loop orders (an oversampling ratio of 32 and single-bit quantization in the feedback is assumed in preparing this table).

At first look, increasing the order of noise shaping is a very attractive way of improving the resolution of a  $\Sigma\Delta$  modulator. Especially in high-speed applications, where the increase in the oversampling ratio is practically restricted to values of 32 or less, utilizing a more aggressive noise transfer function becomes even more important. But high-order modulators have some practical limitations and because of these limitations, dynamic figures only well below predicted by equation (2.7) can be achieved.

In fact, there are two different ways of implementing an Lth order  $\Sigma\Delta$  modulator: single-loop and cascade architectures. Although they are both intended to realize an Lth order noise shaping, they have some advantages and disadvantages with respect to each other. So, a separate treatment of both architectures will be appropriate.

#### 3.3.1 Single-Loop Modulators

A single-loop  $\Sigma\Delta$  modulator is the one shown in Fig. 2.2. It is a cascade of integrators and each integrator accepts the output of the previous integrator and the output of the D/A converter in the feedback as its inputs.

In Chapter 2, the  $\Sigma\Delta$  modulator is considered as a linear system. However, in reality, a  $\Sigma\Delta$  modulator is a highly nonlinear circuit. When more than two integrators are cascaded in the loop filter as shown in Fig. 2.2, the modulator may become unstable [20]. When third or higher-order modulators are excited by a large input signal, the two-level quantizer overloads implying increased quantization noise. In the forward path of the modulator, this large quantization noise is then amplified, resulting in large, uncontrollable, low-frequency oscillations [3]. Even if the modulator is not driven by an input signal, instability may occur depending on the initial conditions of integrators [39]. Clearly, stability is an absolute necessity if a  $\Sigma\Delta$  modulator is to be usable [19].

Because of these complicating factors, a designer sorts to simulations for the verification of the stability and the achievable SNR figure out of a  $\Sigma\Delta$  modulator architecture. Fig. 3.1 is a result of such simulations for different modulator orders and oversampling ratios.

In addition to single-loop modulators having a noise transfer function (NTF) with all of its zeros at dc, it is also possible to spread the zeros of NTF across the band of interest [10]. By spreading the zeros across the band of interest, the in-band noise power can be reduced.

A detailed derivation of the location of optimum zeros for a modulator order up to 8 can be found in [19]. As a result of this optimum zero placement, significant SNR improvements are achieved when compared to modulators using NTF's with coincident zeros (all zeros at dc). Table 3.2 shows this SNR improvement for modulator orders up to 4. As this table shows, optimized zero placement can yield an improvement amounting to several bits in high-order modulators.

Figure 3.1: Maximum SNR achievable by modulators of order n with coincident zeros, as a function of the oversampling ratio.

Table 3.2: Improvement in SNR of modulators having different loop orders due to the optimum placement of NTF zeros.

| L | $\Delta$ SNR (dB) |

|---|-------------------|

| 2 | 3.5               |

| 3 | 8                 |

| 4 | 13                |

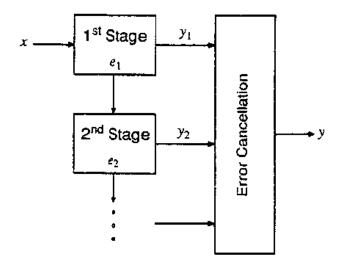

#### 3.3.2 Cascade Modulators

A second way of realizing Lth order noise shaping is by cascading lower order modulators. In a cascaded architecture, each of the multiple stages is itself a single-stage  $\Sigma\Delta$  modulator. As depicted in Fig. 3.2, the quantizer error in each stage serves as the input to the following stage. The output of that following stage is then an approximation of the quantizer error. By subtracting the approximate error from the previous stage's output, most of the quantization error can be canceled, and the performance of a cascaded architecture is approximately equivalent to that of a single-stage architecture having the same total number of integrators. The important thing is that, unlike the single-loop modulators, the instability is avoided because each individual stage is a self-contained first- or second-order  $\Sigma\Delta$  modulator with only one or two

Figure 3.2: Cascaded modulator architecture.

integrators in its forward path.

Because the instability concern is removed, cascade modulators give better performance and their DR figures are much closer to the upper bound defined by (2.7) as compared to single-loop architectures. But there is another problem associated with the design of cascade modulators: the component mismatch problem. The operation of cascade modulators and the importance of component mismatch problem is investigated in detail in [8] on a third-order cascade modulator (implemented by cascading a second-order first stage with a first-order second stage).

# 3.4 MULTIBIT QUANTIZATION

Multibit quantization can be identified as a third way in order to improve the dynamic range of a given modulator.

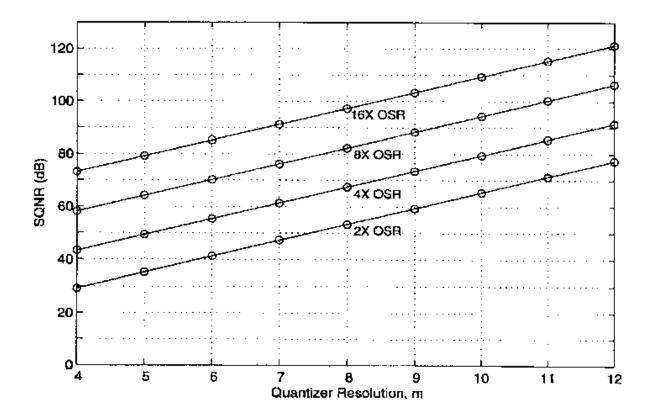

The dynamic range equation, (2.7), obtained through the simple linear analysis suggests a 6-dB per bit SNR improvement in a  $\Sigma\Delta$  modulator. Especially in high-speed applications, where the oversampling ratio should be kept small, this is pretty important. Fig 3.3 shows the SNR as a function of resolution m, for an m-bit second-order modulator loop [21]. According to this figure, even with a second-order loop

Figure 3.3: Signal-to-quantization noise of a second-order multibit modulator as a function of the number of feedback bits m.

and a low oversampling ratio such as 16, it is possible to achieve more than 80-90 dB of SNR with the use of multi-bit quantizers inside the feedback loop. An additional benefit of multibit quantization is that it enhances system stability. This makes it possible to more closely approach the theoretical SNR through better pole placement [22, 23].

The main problem associated with the use of multi-bit quantization is the non-linearity of the D/A converter, which is used to convert the digital output of the  $\Sigma\Delta$  modulator into analog in order to be able to feed that signal back into the first integrator. DACs having only two levels of quantization do not suffer from nonlinearity problems. In fact, it is this property that has been primarily responsible for the popularity of  $\Sigma\Delta$  modulation and it is the reason that many  $\Sigma\Delta$  modulators employ two-level quantizers. When more than two levels of quantization are used, any

real DAC will have mismatches in the spacing between the levels. Any mismatches in the output level spacing of the internal DAC translate directly to input referred distortion and increased noise [26], which significantly reduces the SNR at the output of the modulator.

As a consequence of this nonlinearity problem, multibit quantization brings less performance improvement than theoretically expected 6-dB per bit improvement. Thus, in order to fully benefit from this technique, it is necessary to alleviate the nonlinearity problem. In order to correct DAC nonlinearity in  $\Sigma\Delta$  ADCs, digital self-calibration [27] and dynamic element matching (DEM) [28, 25, 24] have been used. A drawback of digital self-calibration is the added complexity to the system design. The DEM techniques are easier to implement but they are prone to aliasing [24]. Nevertheless, the DEM approach is more popular in the literature. Different DEM techniques have been proposed in the literature. These are: randomization [25], clocked averaging [28], individual level averaging [28], and data-weighted averaging [24].

# Chapter 4

# MULTIRATE $\Sigma\Delta$ MODULATORS

### 4.1 INTRODUCTION

All the techniques mentioned in chapter 3 are conventional methods of achieving high performance from  $\Sigma\Delta$  modulators. However, as the signal band of interest increases, new methods have to be devised for an efficient design of A/D converters employing such modulators. For example for xDSL and wireless applications, new high performance CMOS A/D converters with high accuracy are required. For these application several modulators have been recently proposed with different topologies [21, 29, 30, 31, 32, 33]. Usually they are high-order cascaded structures of single bit first- or second-order stages, with a multibit quantizer at the last stage of the cascade, showing that selecting the optimal modulator is a compromise between modulator order, oversampling ratio and resolution of internal quantizers.

Conventional first-order analysis shows that, for a given dynamic range (DR), power consumption of  $\Sigma\Delta$  modulators does not depend on the oversampling ratio M. For switched capacitor implementations, this analysis assumes that the DR is limited by the kT/C noise of the first integrator. Increasing M has a twofold consequence on the first integrator opamp. On the one hand, the capacitor load can be decreased, as the kT/C noise is inversely proportional to M. On the other hand, the opamp has to settle faster. Both effects counteract so that power consumption does not change. Similar first-order analysis can be done for continuous-time and switched-current implementations [17].

Nevertheless, this simple analysis assumes a one-pole model of the opamp, which

is only valid for low sampling frequencies. Therefore, it does not apply for new high-speed modulators, where opamps are operated near their maximum bandwidth. In that case, power consumption dramatically increases with sampling frequency because 1) parasitic capacitances become a significant fraction of the total capacitance, and 2) clock nonoverlap, and rise and fall times become a significant fraction of the clock cycle. This issue was addressed in [18], where an analysis of three different opamp topologies including first order parasitics, showed a significant increase of the power consumption in the first integrator of a  $\Sigma\Delta$  modulator for a high sampling frequency. A recent example can be seen in [30] and [32], where two modulators with similar performances were built in the same technology. The implementation in [30] used M=24, while the implementation in [32] used M=16, achieving more than a 70% of power saving.

In these approaches the oversampling ratio was unique for all the integrators. However, the use of different oversampling ratios along the structure of a  $\Sigma\Delta$  modulator can alleviate some of the major problems faced in its design. As the integrators have a considerable amount of gain at frequencies in the baseband, baseband noise and distortion occurring in the integrators succeeding the first one are greatly attenuated when referred back to the modulator input. Therefore, the noise and distortion performance of a  $\Sigma\Delta$  modulator is primarily determined by the first integrator, which, in turn, determines the power consumption of the full converter. A reduction in the oversampling ratio of the first integrator(s) of a  $\Sigma\Delta$  modulator can be compensated by an increase in the oversampling ratio of the last integrators, whose contribution to power consumption is not so significant. In this sense, the proper selection of the oversampling ratio in each integrator of a single-loop or a cascaded-  $\Sigma\Delta$  modulator is another architectural decision to be considered in the design of high-resolution, low-power, high-speed  $\Sigma\Delta$  modulators.

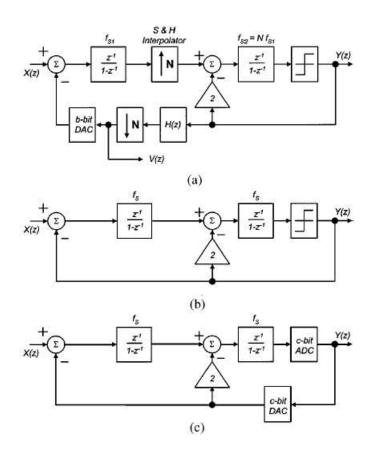

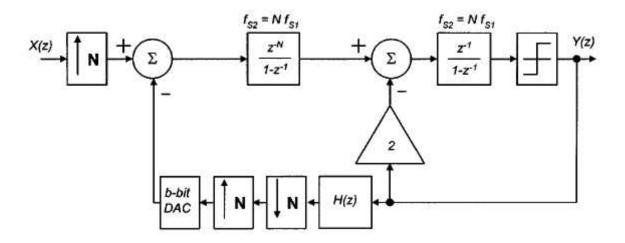

In single-loop multirate  $\Sigma\Delta$  modulators, the first integrator works at a lower oversampling ratio than the rest of the integrators [34]. The second order version is shown in Fig 4.1. As the modulator output in Fig 4.1 (a) has a high sampling

rate, it has to be down-sampled before being fed back to the first integrator. In order to avoid aliasing a digital filter H(z) and one DAC have to be included in the feedback path. This architecture can be also considered to be a multibit modulator where the multibit quantizer in the forward path has been replaced by a single bit one, operating at a higher frequency, by the increase in the sampling rate of the last integrator; therefore, it is called a Multibit-Multirate (MM- $\Sigma\Delta$ ) Modulator.

Figure 4.1: Architecture of second-order  $\Sigma\Delta$  modulators (a) MM- $\Sigma\Delta$  modulator (b) Conventional single-bit architecture (c) Conventional multibit architecture.

### 4.2 MM- $\Sigma\Delta$ MODULATOR

Fig 4.1 (b) shows the architecture of a conventional second-order  $\Sigma\Delta$  modulator. Let  $f_S$  be the sampling rate and let  $f_N$  be the input signal Nyquist frequency. The oversampling ratio is defined as  $M = f_S/f_N$ . Unlike the conventional  $\Sigma\Delta$  modulator of Fig 4.1 (b), in the MM- $\Sigma\Delta$  modulator of Fig 4.1 (a), the first and second integrators are operated at different sampling frequencies. Therefore, this modulator has two different oversampling ratios,  $M_1 = f_{S1}/f_N$  and  $M_2 = f_{S2}/f_N = N * M_1$ , where N is the oversampling ratio increment of the second integrator.

In the MM- $\Sigma\Delta$  modulator, the output y has to be downsampled at rate  $f_{S1}$  before being fed back to the first integrator. To avoid aliasing, y is filtered by means of the digital filter H(z), before being decimated. For this purpose, simple comb-type digital filters can be used [11]. In a practical implementation, the modulator output would be taken from v, rather than from y, to benefit from the decimation process done in the feedback path. After decimation, signal v is  $(b = 2log_2N)$ -bit wide, and a b-bit DAC is required to convert it back to the analog world.

The MM- $\Sigma\Delta$  modulator can be also considered to be a multibit  $\Sigma\Delta$  modulator, where the multibit quantizer in the forward path [Fig 4.1 (c)] has been replaced by a single bit one, operating at a higher frequency, by the increase in the clock rate of the second integrator. In the following sections, a relation between the word lengths in the feedback path of a MM- $\Sigma\Delta$  modulator and of a multibit  $\Sigma\Delta$  modulator with similar performances will be given.

In a MM- $\Sigma\Delta$  modulator with order higher than 2, every integrator is operated at the high frequency rate  $f_{S2}$ , except the first one which is operated at the low frequency rate  $f_{S1}$ . Note that other intermediate solutions could be considered, extending the low oversampling ratio to integrators other than the first one.

### 4.2.1 Analysis of the MM- $\Sigma\Delta$ Modulator

The circuit in Fig 4.1 (a) can be shown to be equivalent to the circuit in Fig 4.2. The first integrator of Fig 4.1 (a), working at the rate  $f_{S1}$ , and the sample and hold interpolator have been replaced in Fig 4.2 by an integrator working at the rate  $f_{S2}$  and a N-delay.

Using a linear model for the quantizer in Fig 4.2, the expression in (4.1) can be

Figure 4.2: Block diagram equivalent to the MM- $\Sigma\Delta$  modulator of Fig 4.1 (a).

obtained where X(z) is the z-transform of the subsampled input sequence and E(z) is the quantization noise.

$$Y(z) = STF(z)X(z^{N}) + NTF(z)E(z) + W(z)$$

$$(4.1)$$

The second member of expression (4.1) is the summation of three terms: the input signal filtered by the signal transfer function (STF), the shaped quantization noise, and an error term, W(z), due to aliasing in the decimation process. The STF(z) and the noise transfer function NTF(z) are given by [35]

$$STF(z) = \frac{z^{-(N+1)}}{F(z)}$$

(4.2)

$$NTF(z) = \frac{(1-z^{-1})^2}{F(z)}$$

(4.3)

The common denominator F(z) in (4.2) and (4.3) is given in (4.4).

$$F(z) = 1 - z^{-2} + \frac{1}{N} z^{-(N+1)} H(z)$$

(4.4)

The error term W(z) is given by

$$W(z) = -\frac{1}{N} STF(z) \sum_{k=1}^{N-1} [H(ze^{-j\frac{2\pi k}{N}})Y(ze^{-j\frac{2\pi k}{N}})]$$

(4.5)

When H(z) is a second-order comb-type filter given by (4.6), it can be shown that for commong values of N, the spectral components of W(z) folded into the signal band  $[0, f_N]$  are negligible.

$$H(z) = \frac{1}{N^2} \left(\frac{1 - z^{-N}}{1 - z^{-1}}\right)^2 \tag{4.6}$$

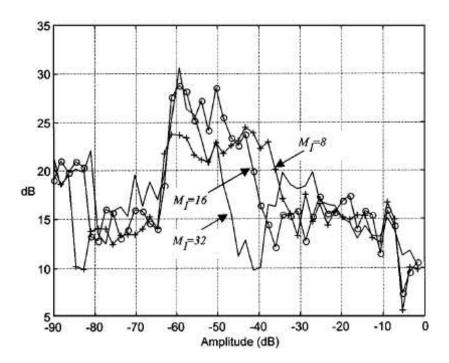

Fig 4.3 shows the ratio between the inband power of the shaped quantization noise and the contribution of the aliasing term, for different input signal amplitudes, in a MM- $\Sigma\Delta$  modulator with N=4 and H(z) given by (4.6). Fig 4.3 has been obtained by simulation using the model of Fig 4.2.

Based on the results shown in Fig 4.3, the term W(z) can be ignored in the baseband. Besides, as  $F(e^{j0} = 1/N)$ , and dF/dz(ej0) = 0, in a first order approach, the denominator F(z) can be replaced by 1/N. Then, we can write Y(z) as:

$$Y(z) \approx N[z^{-(N+1)}X(z^N) + (1-z^{-1})^2 E(z)]$$

(4.7)

In (4.7), the N factor which multiplies  $X(z^N)$  in (4.7) cancels the attenuation introduced by the input interpolator (see Fig 4.2). Proceeding as in [11], the inband quantization noise power (QNP) is given by [35]

$$QNP(\Delta, M_1, N, 2) \approx \frac{\pi^4}{60} \frac{\Delta^2}{M_1^5 N^3}$$

(4.8)

where  $QNP(\Delta, M_1, N, L)$  is the inband QNP of a Lth-order  $\Sigma\Delta$  modulator with quantization step  $\Delta$ , oversampling ratio  $M_1$  in the first integrator, and  $M_2 = NM_1$  in the rest of the stages.

Figure 4.3: Ratio between the inband power of the quantization noise and the contribution of the aliasing terms, in a MM- $\Sigma\Delta$  modulator with N=4, for three different values of the low oversampling ratio  $M_1$ .

Following a similar procedure, the inband QNP of high-order MM- $\Sigma\Delta$  modulators can be obtained

$$QNP(\Delta, M_1, N, L) \approx \frac{\pi^{2L}}{12(2L+1)} \frac{\Delta^2}{M_1^{2L+1} N^{2L-1}}$$

(4.9)

#### 4.2.2 Relative Performances of MM- $\Sigma\Delta$ Modulators

To evaluate the performances of MM- $\Sigma\Delta$  modulators, the ratio between the inband QNP of a *L*th-order MM- $\Sigma\Delta$  modulator with oversampling ratios  $M_1$  and  $M_2 = NM_1$ , and the inband QNP of a conventional *c*-bit *L*th-order  $\Sigma\Delta$  modulator with oversampling ratio M is presented in (4.10) [35].

$$\frac{QNP(\Delta, M_1, N, L)}{QNP(\Delta/(2^c - 1), M, 1, L)} \approx \left(\frac{M}{M_1}\right)^{2L+1} \frac{(2^c - 1)^2}{N^{2L-1}}$$

(4.10)

From (4.10), we shall consider three cases:

- 1-bit Lth-order conventional  $\Sigma\Delta$  modulator operating at the low oversampling ratio  $M_1$  (i.e.,  $c=1, M=M_1$ ). In this case, the ratio between the inband QNP's falls by 3(2L-1)dB, for every doubling of the oversampling ratio increment N.

- 1-bit Lth-order conventional ΣΔ modulator with oversampling ratio M (i.e., c = 1), and a MM-ΣΔ modulator with M<sub>1</sub> = M/2 and M<sub>2</sub> = 2M (i.e., N = 4). According to expression (4.10), the inband QNP of the MM-ΣΔ modulator is 3(2L 3)dB smaller than the inband QNP of the conventional ΣΔ modulator. This result shows that a lower oversampling in the first integrator can be favorably compensated by an increase in the oversampling ratio of the rest of integrators.

- c-bit Lth-order conventional  $\Sigma\Delta$  modulator operating at the low oversampling ratio  $M_1$  (i.e.,  $M=M_1$ ). According to (4.10), the MM- $\Sigma\Delta$  modulator and the c-bit conventional  $\Sigma\Delta$  modulator have the same inband QNP when

$$c = log_2(N^{(L-0.5)} + 1) (4.11)$$

As expected, this result clearly shows that, compared to a multibit structure, the gain in resolution for MM- $\Sigma\Delta$  modulators comes from replacing the multibit quantizer in the forward path by a single bit one, operating at a higher frequency, by the increase in the oversampling ratio of last integrators.

# Chapter 5

# MODULATOR DESIGN

The objective of this research is to investigate the use of the Multirate Multibit  $\Sigma\Delta$  modulator (MM- $\Sigma\Delta$ ) structure in the design of very low power ADC design. One of the end goals of this research is to design and implement a  $\Sigma\Delta$  modulator that is tailored for wireless communications applications. Although the design will be optimized for a GSM receiver, it will be programmable and have a second mode for a wider bandwidth application like wideband CDMA (WCDMA). The modulator will be fabricated in a 90nm digital CMOS technology provided by Texas Instruments Inc.

The sections in this chapter are arranged as follows: First, the conventional implementation of a 2nd order  $\Sigma\Delta$  modulator with 5 levels of quantization in its feedback path is described for comparison purposes. Then, the ideal 2nd order MM- $\Sigma\Delta$  structure and its ideal clocking scheme will be given. The practical limitations of this ideal MM- $\Sigma\Delta$  structure will be the topic of the section following this. In section 4, the proposed architecture and the clocking scheme will be explained in detail. Then, a comparison of the proposed modulator system and the modulator designed by using the conventional approach will be given. An extension of this idea into different  $\Sigma\Delta$  modulator architectures will be discussed in the appendix with the sole idea of designing higher performance  $\Sigma\Delta$  A/D converters in mind.

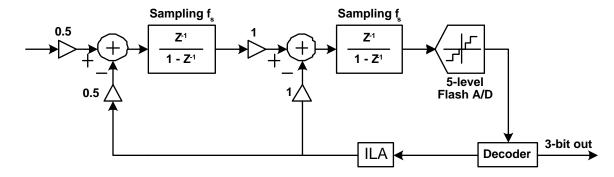

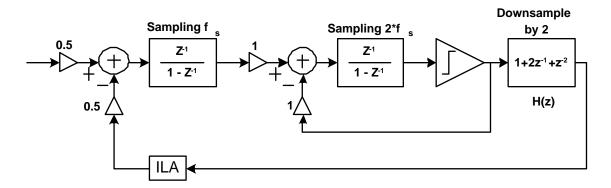

Figure 5.1: Conventional implementation of a Second Order 5-Level  $\Sigma\Delta$  modulator

# 5.1 CONVENTIONAL SECOND ORDER 5 LEVEL $\Sigma\Delta$ MODULATOR

Fig. 5.1 illustrates a conventional implementation of a Second order  $\Sigma\Delta$  modulator with 5 levels of quantization in the feedback path [36]. In this structure, both integrators run at the same sampling rate with a frequency of fs. In general, the Switched-Capacitor (SC) implementations of this structure employs two non-overlapping clock phases for the sampling and integration operations performed by the sample-and-hold network and the integrator. Therefore, if the period of the sampling clock is T=1/fs, sampling and integration operations each have T/2 time allocated for them. This means that the voltages at the output of the sampling network and the integrator output must converge to their final values within an acceptable error in T/2 time.

The quantization in the feedback path is usually implemented by employing a flash A/D converter. The main reason for this is stability. The modulator feedback loop is very sensitive to delays in the loop. Other types of A/D converters like pipeline or successive approximations A/D converters provide more accuracy than the flash converters but they also need a delay of a number of clock cycles. Such a delay causes instability. On the other hand, flash converters gives out the output to a certain input almost instantenously and so they found popular use in such modulator structures so far. However, the use of a flash A/D converter is also not without problems. In order to increase the Signal-to-Noise ratio (SNR) of a flash converter by 6dB, we need to

double the number of comparators employed. This means doubling the area and the power dissipation of the flash converter, both of which are very undesirable. Hence, the practical implementations of a flash A/D converter that will be used in such a  $\Sigma\Delta$  modulator is limited to a certain number of bits. In the past, 5-bit (or 32 level) flash was sort of the limit for the designers and very few designers actually used such a 5-bit flash A/D converter in their systems [15].

Fig. 5.2 shows the floorplan of the system given in Fig. 5.1. This floorplan shows an accurate partitioning of the area to different sub-blocks. From this floorplan, we observe that the integrators and the 5 level flash A/D converter are almost the same size. Hence, the flash A/D converter consumes one third of the total area of the  $\Sigma\Delta$  modulator. This is why it is not practical to use a flash A/D converter which has many levels. Furthermore, that is also why the technique described in this work is important. Because, by means of this technique, we may replace the flash with a much simpler system and save both area and power.

# 5.2 IDEAL SECOND ORDER MM- $\Sigma\Delta$ MODU-LATOR

Consider an L-th order MM- $\Sigma\Delta$  modulator with first integrator OSR of  $M_1$  and upsampling of N in the remaining stages. Also, consider a conventional c-bit L-th order  $\Sigma\Delta$  modulator with an OSR of M= $M_1$ . These two modulators have the same inband quantization noise power (QNP) provided [35]:

$$c = log_2(N^{(L-0.5)} + 1) (5.1)$$

Equation 5.1 shows the relation between the quantizer resolution in a conventional modulator and the upsampling ratio in a MM- $\Sigma\Delta$  modulator for an L-th order system.

From the theory of conventional  $\Sigma\Delta$  modulators, we determine that a  $2^{nd}$  order loop with a quantizer resolution of 2 bits is needed to achieve our design specifications.

Figure 5.2: Layout floorplan of the  $2^{nd}$  Order 5-Level  $\Sigma\Delta$  modulator given in Fig 5.1

The required OSR is 36 and 9 for GSM and WCDMA, respectively. From equation 5.1, with L=2 and c=2, we find the upsampling ratio N of the corresponding MM- $\Sigma\Delta$  modulator is 2. Thus, the modulator in Fig 5.3 is designed for optimum power and area as well as good performance.

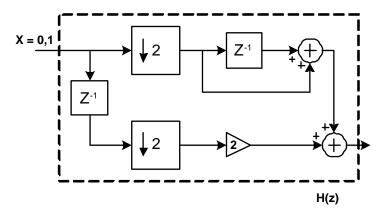

In this structure, the quantizer is only a single-bit comparator. Since the second integrator and comparator is running twice as fast as the first integrator, the output needs to be downsampled before it is fed back to the first integrator. A second-order digital FIR filter is used as a low pass filter to avoid aliasing. After this filter, the data is downsampled. Single-bit comparator and the FIR filter along with an upsampling in the second integrator replaces a bulky flash A/D converter if we were to design a second order modulator with conventional multibit quantization. In order to remedy the DAC non-linearity problem, a dynamic element-matching (DEM) block using the

Figure 5.3: Second Order MM- $\Sigma\Delta$  modulator

individual level averaging (ILA) algorithm is included in the feedback.

The transfer function of the comb filter is:

$$H(z) = 1 + 2z^{-1} + z^{-2} (5.2)$$

The comparator preceding the comb filter can generate only two different outputs 0 and 1. Hence, at the output of the comb filter, we can observe 5 different output values 0,1,2,3,4.

The actual strength of the MM- $\Sigma\Delta$  systems comes from the fact that the flash A/D conveter, which is bulky and consumes significant static power, is replaced by a comparator and a simple FIR filter along with an increase in the sampling rate of the second integrator. Significant area and power savings can be achieved through the use of these systems.

#### 5.2.1 Practical limitations of a MM- $\Sigma\Delta$ modulator

The MM- $\Sigma\Delta$  modulator that is explained in the last section is an idealized system and so it does not take into account the settling limitations of the amplifiers used inside the integrators. In the ideal system, we assume that settling at the output of the integrators happen instantenously. The fundamental problem of MM- $\Sigma\Delta$  modulators shows itself in the practical implementation. Every amplifier is designed with a certain bandwidth and so the amplifier outputs settle to their final values within an acceptable error in a certain time. In order to increase this bandwidth and improve the settling

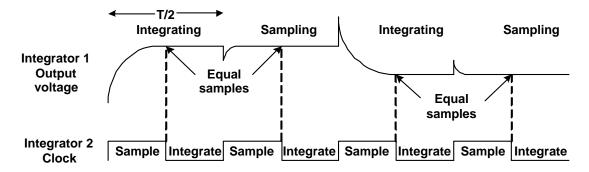

Figure 5.4: Sampling and integration half cycles for the Second Order 5-Level MM- $\Sigma\Delta$  modulator

characteristics, one needs to increase power dissipation of the amplifier. Thus, if amplifiers settle much faster than needed, then they consume more current than is really needed. It is a good practice in terms of saving power to design the amplifier such that it utilizes the whole half period with some margin for slewing and settling of the amplifier output.

Therefore, in the modulator depicted in Fig 5.3, there is an important problem that needs to be addressed for the circuit implementation of this architecture. The second integrator samples the output of the first integrator twice in one clock period T=1/fs. If the first integrator uses the whole half clock cycle T/2 to slew and settle to its final value, then one of the samples that the second integrator is receiving from the first integrator output will not be a valid sample. So, for correct operation, the settling behavior should be such that the first integrator output settles to its final value in about T/4 time. This case is depicted in Fig 5.4. However, then we will have to design an amplifier for the first integrator that is able to run with a 2\*fs clock, which means extra current consumption.

Consequently, in its current form, an MM- $\Sigma\Delta$  implementation is not useful. A technique should be devised to get the benefits of an MM- $\Sigma\Delta$  without requiring the first integrator to be as fast as the practical implementations impose.

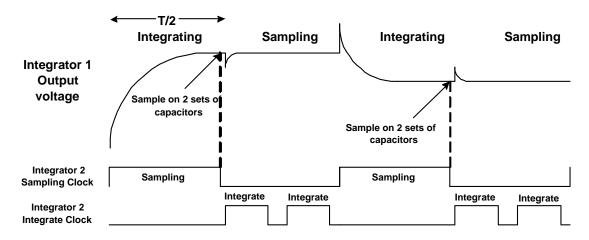

Figure 5.5: Sampling and integration half cycles for the Proposed MM- $\Sigma\Delta$  modulator

# 5.3 PROPOSED ARCHITECTURE AND CLOCK-ING SCHEME

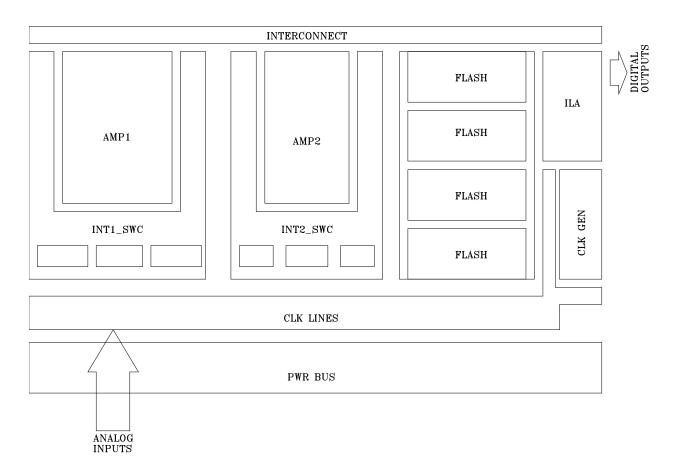

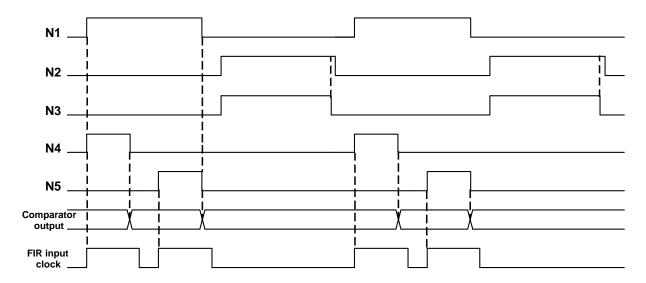

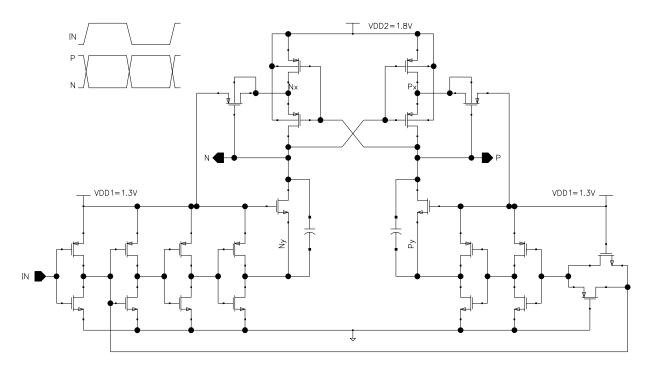

A power efficient method is proposed in Fig 5.5 to implement the sampling and integration operations. First note that in the case depicted by Fig 5.4, the two samples received by the second integrator from the output of the first integrator in the same clock period are exactly the same provided the first integrator is designed to settle fast enough. In Fig 5.5, we let the first integrator use the full half clock period for integration (during N2 is high in Fig 5.9). At the same time, the sampling switches of the second integrator are also ON and the sampling capacitors of the second integrator are charging. The second integrator has two sampling capacitors instead of only one. After the first integrator output settles to its final value, we take a sample of the first stage output on to these two sampling capacitors (falling edge of N3 in Fig 5.9).

After the data is stored on the sampling capacitors, we integrate the charge stored on one of these capacitors immediately (during N4 is high in Fig 5.9). After integration, the comparator following the second integrator makes a comparison and determines the new feedback bit. This new feedback bit is used to determine the direction of charge flow when we integrate the charge stored on the second sampling

Figure 5.6: Top level implementation of the proposed architecture

capacitor (during when N5 is high in Fig 5.9).

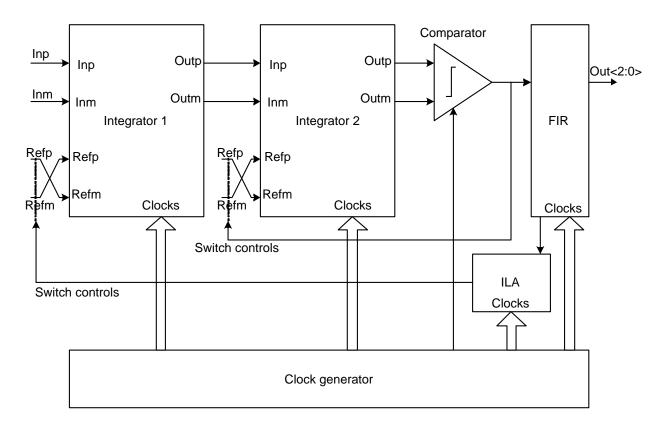

Fig. 5.6 shows the top level implementation of the proposed architecture. In Fig. 5.7 and 5.8 the implementation of the first and the second integrators are given. On these figures, the name of the clock signal that controls a switch is given next to it. N1D is a delayed version of the clock N1 by a few hundred picoseconds. Then in Fig. 5.9, the clocking scheme that is devised and used in this implementation is provided. This clocking is an essential part of the proposed technique for the implementation of a power efficient system. In the next section, the details about the implementation of the digital filter will be given.