# **Schematic/Symbol Editor**

## **User Guide**

**Zeni EDA System**

**CEC Huada Electronic Design Co., Ltd.**

**Copyright © 2002-2008, HED. All rights reserved.**

**Trademarks:** Zeni is the trademark of HED. All other trademarks are the property of their respective holders.

**Print Permission:** This document contains information that is proprietary to HED. Unauthorized reproduction of the materials contained here in, in whole or in part, is prohibited without the written consent of HED.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of HED.

CEC Huada Electronic Design Co., Ltd.

1# Gaojiayuan, Chaoyang District, Beijing, 100015, P.R.China

Phone:+86(10)64365577

FAX: +86(10)64360985

Email: [zenisupport@hed.com.cn](mailto:zenisupport@hed.com.cn)

Website: <http://www.zeni-eda.com>

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>1 SCHEMATIC EDITOR COMMAND .....</b>          | <b>1</b>  |

| <b>1.1 Design Menu.....</b>                      | <b>1</b>  |

| 1.1.1 Design->Check and Save.....                | 1         |

| 1.1.2 Design->Save.....                          | 1         |

| 1.1.3 Design->Save As .....                      | 1         |

| 1.1.4 Design->Save All.....                      | 2         |

| 1.1.5 Design->Design Property .....              | 2         |

| 1.1.6 Design->Component Property .....           | 3         |

| 1.1.7 Design->Pin Order.....                     | 4         |

| 1.1.8 Design->Make Read Only/Make Editable ..... | 5         |

| 1.1.9 Design->Discard Edits.....                 | 5         |

| 1.1.10 Design->Reload.....                       | 6         |

| 1.1.11 Design->Print .....                       | 6         |

| 1.1.12 Design->Close .....                       | 7         |

| <b>1.2 Add menu.....</b>                         | <b>7</b>  |

| 1.2.1 Add->Instance.....                         | 7         |

| 1.2.2 Add->Wire .....                            | 10        |

| 1.2.3 Add->Wide Wire.....                        | 12        |

| 1.2.4 Add->Wire Name .....                       | 12        |

| 1.2.5 Add->Pin .....                             | 15        |

| 1.2.6 Add->Block .....                           | 17        |

| 1.2.7 Add->Solder Dot .....                      | 18        |

| 1.2.8 Add->Property Label .....                  | 19        |

| 1.2.9 Add->Patchcord.....                        | 20        |

| 1.2.10 Add->NoERC .....                          | 21        |

| 1.2.11 Add->Note Text .....                      | 22        |

| 1.2.12 Add->Note Shape .....                     | 23        |

| <b>1.3 Edit menu.....</b>                        | <b>24</b> |

| 1.3.1 Edit->Undo .....                           | 24        |

| 1.3.2 Edit->Redo.....                            | 24        |

| 1.3.3 Edit->Stretch.....                         | 25        |

| 1.3.4 Edit->Move.....                            | 27        |

| 1.3.5 Edit->Copy .....                           | 28        |

| 1.3.6 Edit->Delete.....                          | 30        |

| 1.3.7 Edit->Rotate.....                          | 30        |

| 1.3.8 Edit->Align .....                          | 31        |

| 1.3.9 Edit->Find.....                            | 32        |

| 1.3.10 Edit->Replace .....                       | 33        |

| 1.3.11 Edit->Alternate View.....                 | 34        |

| 1.3.12 Edit->Renumber Instance .....             | 34        |

|            |                                        |           |

|------------|----------------------------------------|-----------|

| 1.3.13     | Edit->Reattach Wire Name.....          | 35        |

| 1.3.14     | Edit->Hide Label .....                 | 35        |

| 1.3.15     | Reset Invisible Label .....            | 36        |

| 1.3.16     | Edit->Show/Hide Property .....         | 36        |

| 1.3.17     | Edit->Route Flight.....                | 36        |

| 1.3.18     | Edit->Property .....                   | 37        |

| 1.3.19     | Edit->Property Notepad.....            | 39        |

| <b>1.4</b> | <b>Window menu.....</b>                | <b>40</b> |

| 1.4.1      | Window->Redraw.....                    | 40        |

| 1.4.2      | Window->Fit.....                       | 40        |

| 1.4.3      | Window->Fit Object .....               | 40        |

| 1.4.4      | Window->Fit Selection .....            | 41        |

| 1.4.5      | Window->Zoom In .....                  | 41        |

| 1.4.6      | Window->Zoom In By 2.....              | 41        |

| 1.4.7      | Window->Zoom Out.....                  | 41        |

| 1.4.8      | Window->Zoom Out By 2 .....            | 41        |

| 1.4.9      | Window->Center .....                   | 41        |

| 1.4.10     | Window->Last View.....                 | 42        |

| 1.4.11     | Window->Mark View .....                | 42        |

| 1.4.12     | Window->Jump View .....                | 42        |

| 1.4.13     | Window->Birds-eye View .....           | 42        |

| 1.4.14     | Window->Copy Window .....              | 43        |

| 1.4.15     | Window->Raise Design Manager.....      | 43        |

| <b>1.5</b> | <b>Select Menu .....</b>               | <b>43</b> |

| 1.5.1      | Select->Area Select .....              | 43        |

| 1.5.2      | Select->Line Select .....              | 44        |

| 1.5.3      | Select->Select All .....               | 45        |

| 1.5.4      | Select->Select By Property .....       | 45        |

| 1.5.5      | Select->Select Wires .....             | 46        |

| 1.5.6      | Select->Filter .....                   | 46        |

| 1.5.7      | Select->Trace Net .....                | 46        |

| 1.5.8      | Select->Remove Trace .....             | 47        |

| 1.5.9      | Select->Remove All Traces .....        | 48        |

| 1.5.10     | Select->Trace Explain .....            | 48        |

| <b>1.6</b> | <b>Hierarchy-&gt;Descend Edit.....</b> | <b>48</b> |

| 1.6.1      | Hierarchy->Descend Read .....          | 48        |

| 1.6.2      | Hierarchy->Return .....                | 49        |

| 1.6.3      | Hierarchy->Return To Top .....         | 49        |

| 1.6.4      | Hierarchy->Show Scope .....            | 49        |

| 1.6.5      | Hierarchy->Show Tree.....              | 49        |

| <b>1.7</b> | <b>Cellview menu .....</b>             | <b>50</b> |

|             |                                      |           |

|-------------|--------------------------------------|-----------|

| 1.7.1       | Cellview->Create From Cellview ..... | 50        |

| 1.7.2       | Cellview->Create From Instance ..... | 51        |

| <b>1.8</b>  | <b>Page menu.....</b>                | <b>52</b> |

| 1.8.1       | Page->Add Sheet .....                | 52        |

| 1.8.2       | Page->Edit Title .....               | 52        |

| 1.8.3       | Page->Make Multi-Pages .....         | 53        |

| 1.8.4       | Page->New Page.....                  | 57        |

| 1.8.5       | Page->Delete Page.....               | 58        |

| 1.8.6       | Page->Renumber .....                 | 59        |

| 1.8.7       | Page->Resequence.....                | 59        |

| <b>1.9</b>  | <b>Check menu .....</b>              | <b>60</b> |

| 1.9.1       | Check->Current Cellview .....        | 60        |

| 1.9.2       | Check->Hierarchy.....                | 60        |

| 1.9.3       | Check->Find Marker .....             | 61        |

| 1.9.4       | Check->Delete Marker .....           | 62        |

| 1.9.5       | Check->Delete All Markers .....      | 62        |

| 1.9.6       | Check->Show Label Attachment .....   | 62        |

| 1.9.7       | Check->Summary .....                 | 62        |

| <b>1.10</b> | <b>Tools menu.....</b>               | <b>63</b> |

| 1.10.1      | Tools->Export Netlist .....          | 63        |

| 1.10.2      | Tools->Export EDIF.....              | 65        |

| 1.10.3      | Tools->SPICE Deck .....              | 65        |

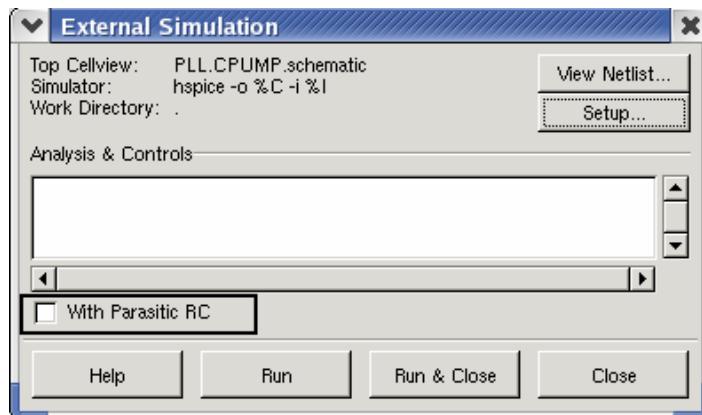

| 1.10.4      | Tools->External Simulation.....      | 65        |

| 1.10.5      | Tools->Run Script.....               | 65        |

| 1.10.6      | Tools->Export Tcl Script .....       | 66        |

| 1.10.7      | Tools->Clear Back Annotation .....   | 66        |

| 1.10.8      | Navigator .....                      | 67        |

| <b>1.11</b> | <b>Options menu .....</b>            | <b>68</b> |

| 1.11.1      | Options->Editor.....                 | 68        |

| 1.11.2      | Options->Display .....               | 71        |

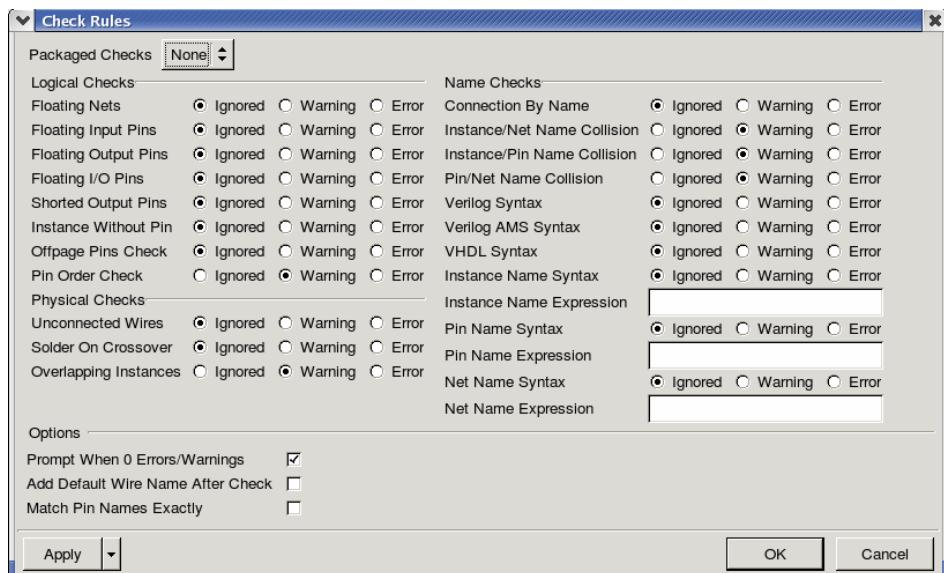

| 1.11.3      | Options->Check Rules.....            | 72        |

| 1.11.4      | Options->Export Format.....          | 78        |

| 1.11.5      | Options->Tools .....                 | 81        |

| 1.11.6      | Options->Load Options .....          | 82        |

| 1.11.7      | Options->Save Options.....           | 82        |

| 1.11.8      | Options->Color.....                  | 82        |

| 1.11.9      | Options->Key Mapping.....            | 83        |

| 1.11.10     | Options->Toolbox.....                | 83        |

| <b>2</b>    | <b>SYMBOL EDITOR COMMAND .....</b>   | <b>84</b> |

|            |                                                            |            |

|------------|------------------------------------------------------------|------------|

| <b>2.1</b> | <b>Design-&gt;Design Property.....</b>                     | <b>84</b>  |

| <b>2.2</b> | <b>Add menu.....</b>                                       | <b>85</b>  |

| 2.2.1      | Add->Rectangle.....                                        | 85         |

| 2.2.2      | Add->Line .....                                            | 85         |

| 2.2.3      | Add->Polygon.....                                          | 86         |

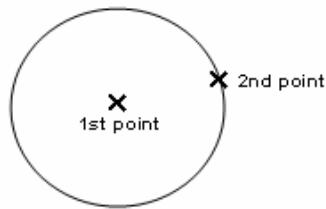

| 2.2.4      | Add->Circle .....                                          | 87         |

| 2.2.5      | Add->Ellipse.....                                          | 87         |

| 2.2.6      | Add->Arc .....                                             | 88         |

| 2.2.7      | Add->Pin .....                                             | 89         |

| 2.2.8      | Add->Lable.....                                            | 91         |

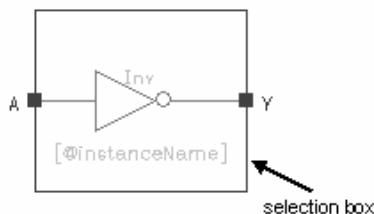

| 2.2.9      | Add->Selection Box .....                                   | 91         |

| 2.2.10     | Add->Note Text .....                                       | 92         |

| 2.2.11     | Add->Note Shape .....                                      | 93         |

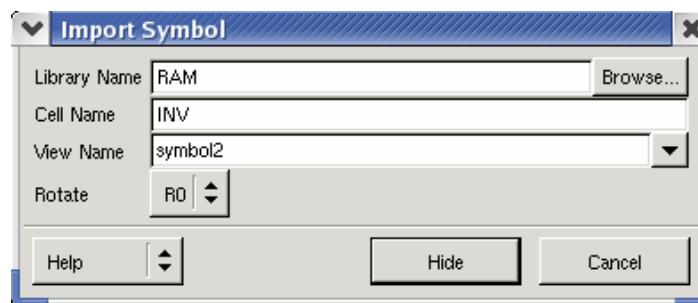

| 2.2.12     | Add->Import Symbol .....                                   | 94         |

| <b>3</b>   | <b>WHAT IS AEL.....</b>                                    | <b>95</b>  |

| <b>4</b>   | <b>WHAT IS PPAR(), IPAR().....</b>                         | <b>97</b>  |

| <b>5</b>   | <b>HOW TO IMPORT CADENCE EDIF FILE.....</b>                | <b>99</b>  |

| <b>6</b>   | <b>HOW TO IMPORT CDL NETLIST AND VERILOG NETLIST .....</b> | <b>99</b>  |

| <b>7</b>   | <b>HOW TO PRE-DEFINE PARASITIC PARAMETERS .....</b>        | <b>103</b> |

| 7.1        | Parasitic Loads Symbols.....                               | 103        |

| 7.2        | Add Parasitic On Wires.....                                | 104        |

| 7.3        | Export SPICE Netlist With Parasitic Loads .....            | 105        |

| 7.4        | Simulation With Parasitic Loads .....                      | 105        |

| <b>8</b>   | <b>HOW TO DO CIRCUIT SIMULATION .....</b>                  | <b>106</b> |

| 8.1        | Using External Simulator.....                              | 106        |

| 8.2        | Using SPICE Deck Simulation Environment .....              | 106        |

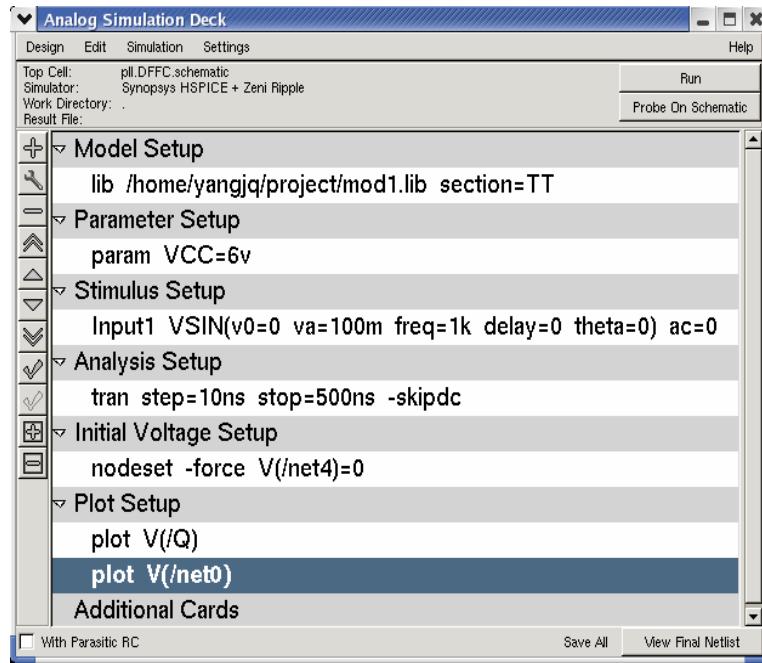

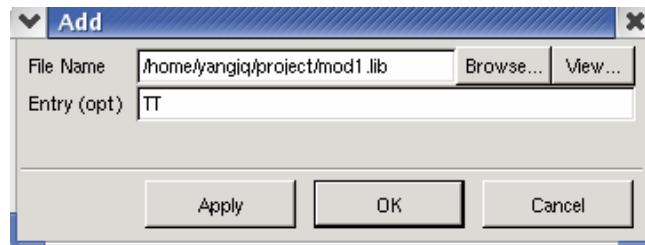

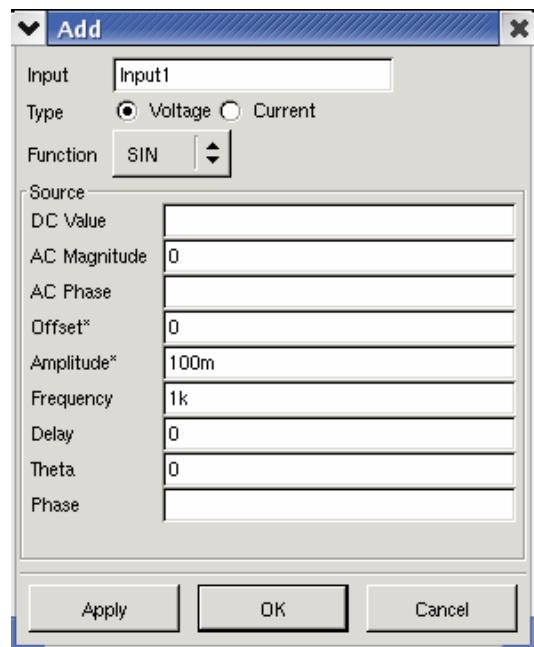

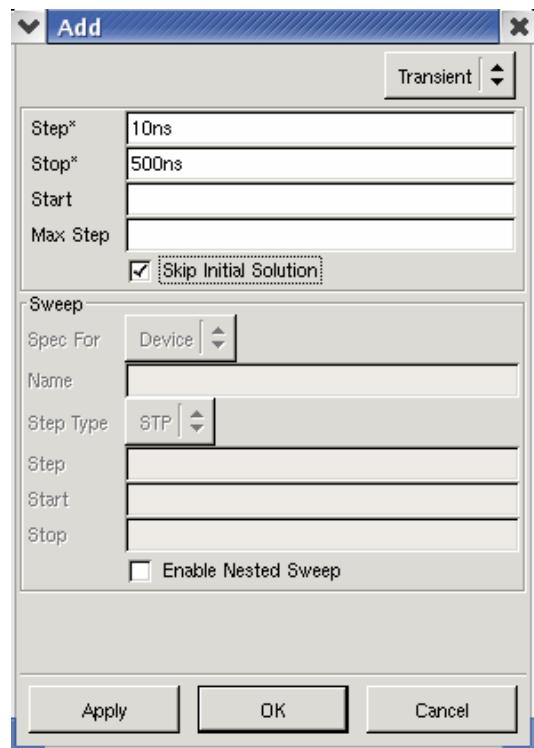

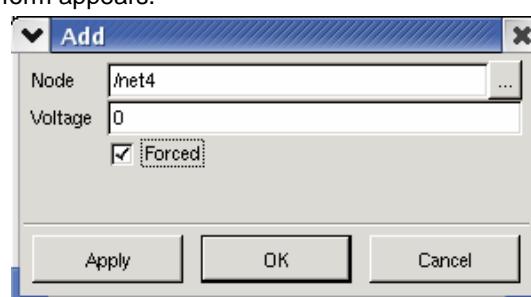

| 8.2.1      | Setting Up Simulation Statement .....                      | 108        |

| 8.2.2      | Copy From Another Deck.....                                | 113        |

| 8.2.3      | Setting Up Simulator .....                                 | 113        |

| 8.2.4      | Run Simulation .....                                       | 114        |

| 8.2.5      | View Log File .....                                        | 115        |

| 8.2.6      | View Final Netlist File .....                              | 115        |

|        |                                                      |     |

|--------|------------------------------------------------------|-----|

| 8.2.7  | Probe Waveform .....                                 | 115 |

| 8.2.8  | Load Waveform File .....                             | 115 |

| 8.2.9  | Directly Probing.....                                | 115 |

| 8.2.10 | Automatically Plot Waveforms During Simulation ..... | 117 |

| 8.2.11 | Plot Waveform In The Plot Section .....              | 117 |

| 8.2.12 | New Waveform Window .....                            | 117 |

| 8.2.13 | Back-annotate DC Values .....                        | 117 |

# 1 Schematic Editor Command

## 1.1 Design Menu

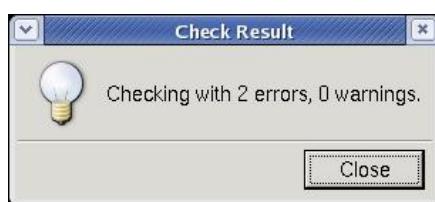

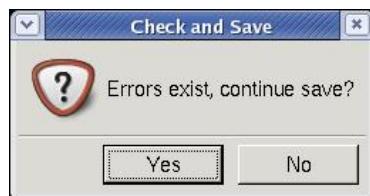

### 1.1.1 Design->Check and Save

Check current view and save it.

Select this command or click icon , SE checks current view and shows the results in pop-up form.

If this design is error, SE will pop up a form after you click Close button and inquire you save it or not with the errors.

Click Yes button to save the view with errors. Otherwise, you need modify the design before saving.

### 1.1.2 Design->Save

Save current view.

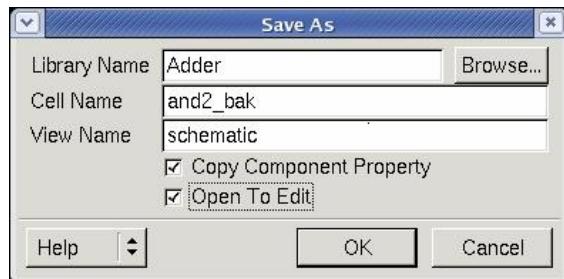

### 1.1.3 Design->Save As

Save current view with another name.

Select this command, "Save As" form is shown as figure below.

**Library Name** specifies the destination library name.

**Cell Name** specifies the destination cell name.

**View Name** specifies the destination view name.

**Copy Component Property** controls whether to copy the component property to new view.

**Open To Edit** controls whether SE opens the new view automatically after saving.

#### 1.1.4 Design->Save All

Save all of opened views.

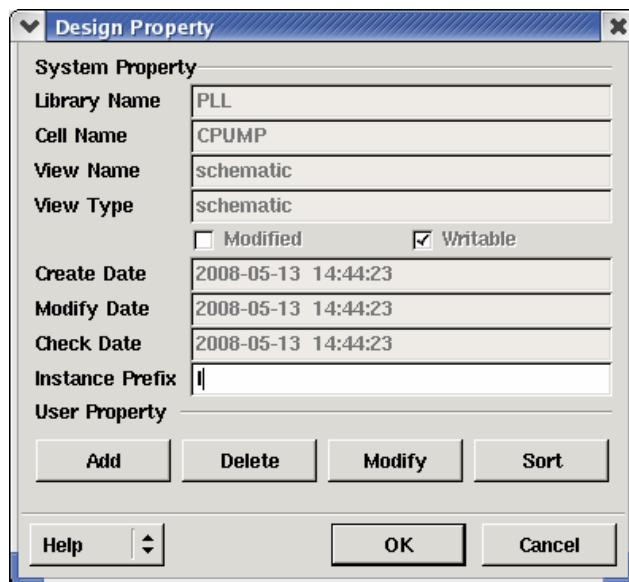

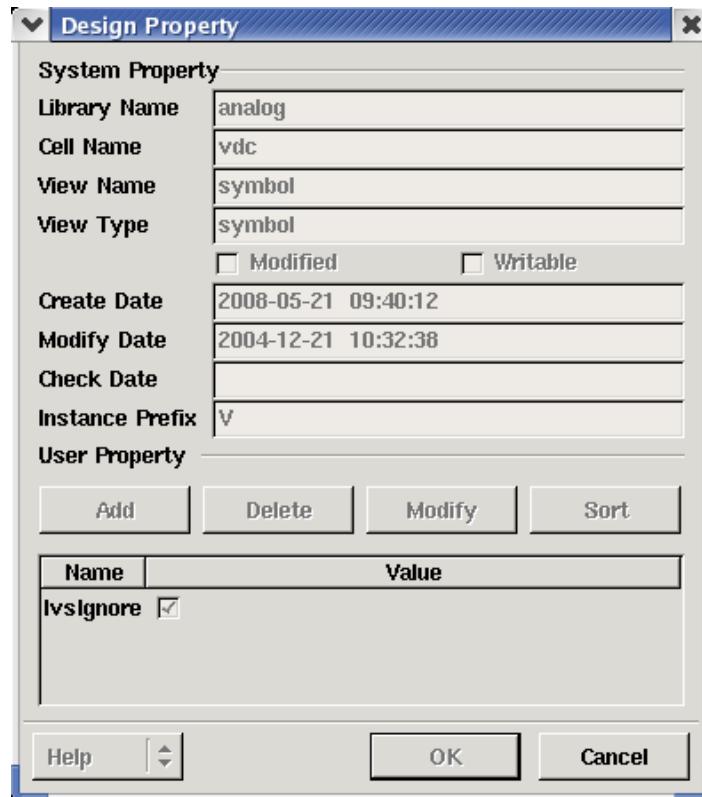

#### 1.1.5 Design->Design Property

Display or edit property of the current cellview.

**Instance Prefix** specifies the prefix when current view is invoked by another view (Please refer to *Add->Instance* for details). The valid value is from 'A' to 'Z'.

User property lets you add some properties for this cellview. Please refer to symbol editor: *design->property*.

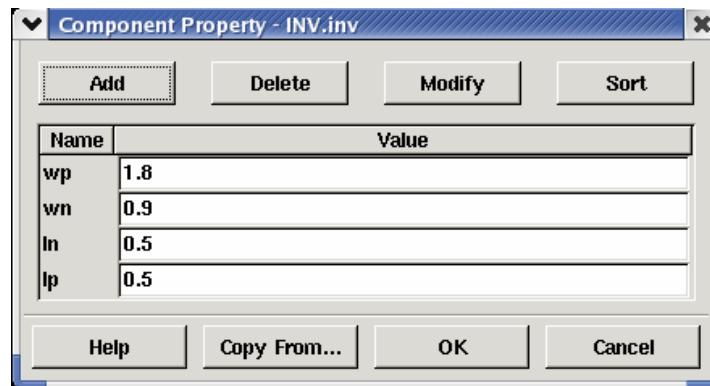

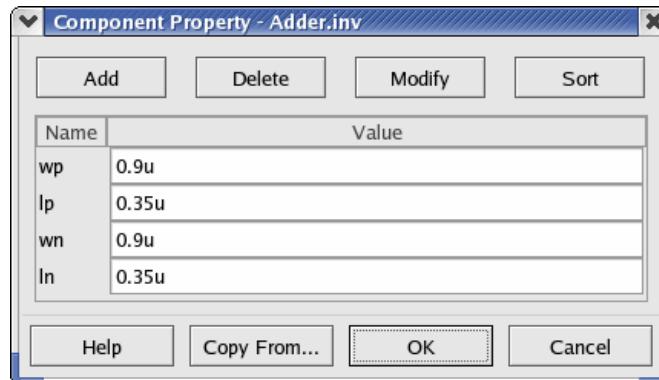

### 1.1.6 Design->Component Property

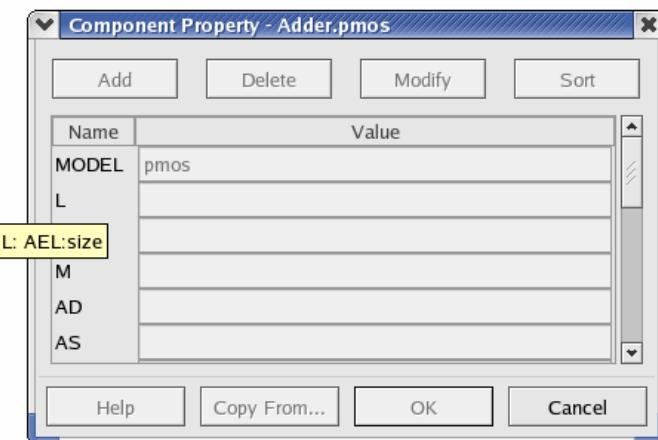

This command lets you add parameters to this cell as component parameters. When this cell is invoked by another cell, you can modify these parameters value according to different instantiation. A cell should have and only have a set of component parameters. So these parameters will be inherited by another schematic cellviews and symbol cellviews of this cell.

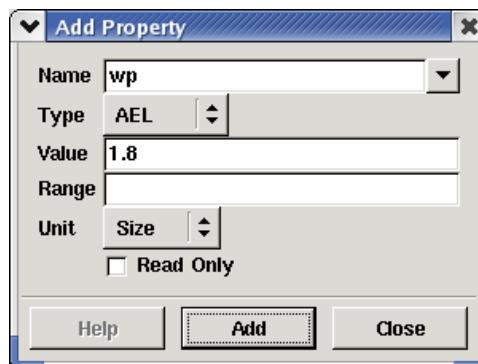

**Add** button lets you add a new property.

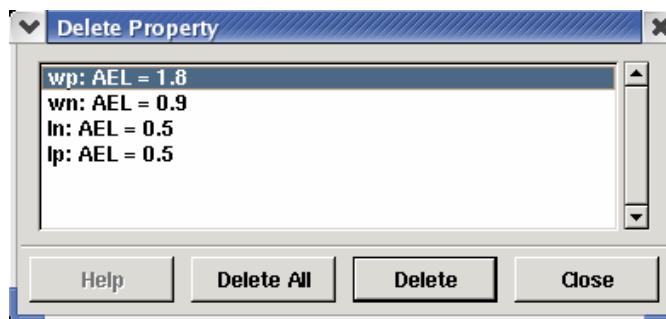

**Delete** button lets you delete property items

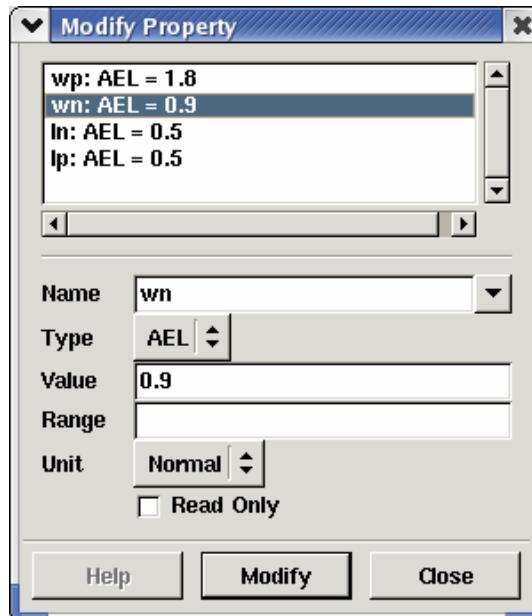

**Modify** button lets you modify this property value

After modifying, click *Modify* to update the property.

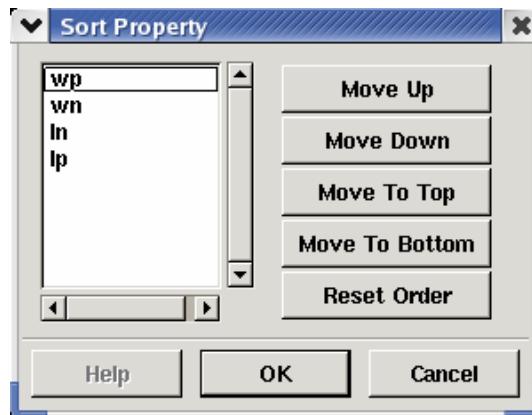

**Sort** button lets you sort these properties.

Select an item and move its order by clicking *Move up*, *Move Down*, *Move To Top*, etc.

Click *OK* button to get the newly order and update *Design Property* form.

### 1.1.7 Design->Pin Order

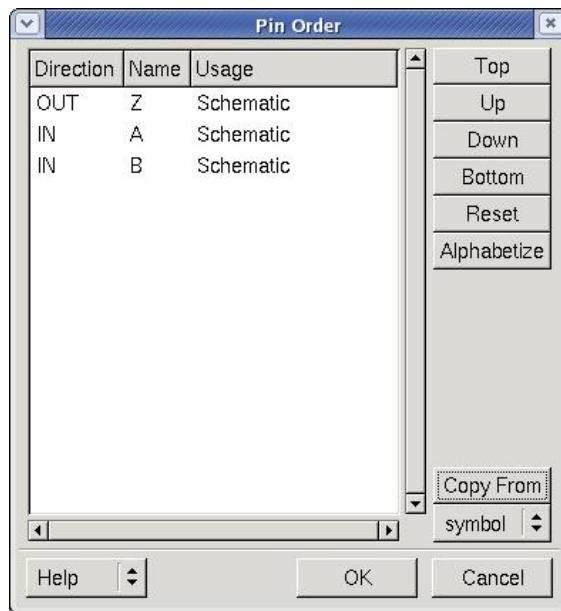

This command lists the order of pin. The order depends on the sequence of pin creation. You can modify the order by *Top*, *Up*, *Down*, *Bottom*, etc. Pin order in both Schematic Editor and Symbol Editor should be consistent.

**Top** moves the selected pin to the top of list.

**Up** moves selected pin to up level in list.

**Down** moves selected pin to down level in list.

**Bottom** moves selected pin to the bottom of list.

**Reset** restores default order.

**Alphabetize** sorts pins by alphabetize.

**Copy From** lets you copy the pins order from another view. Select a view name from *Copy From* dropdown list, and click *Copy From* button.

## 1.1.8 Design->Make Read Only/Make Editable

Make current view editable or read only.

Select *Design-> Make Editable* to make this view editable. At this time, you can find the command menu changes to *Make Read Only*.

Select *Design-> Make Read Only* to make this view read only. At this time, you can find the command menu changes to *Make Editable*.

## 1.1.9 Design->Discard Edits

To discard any modification since the design was saved last time. After doing this command, the commands Undo and Redo do not work.

## 1.1.10 Design->Reload

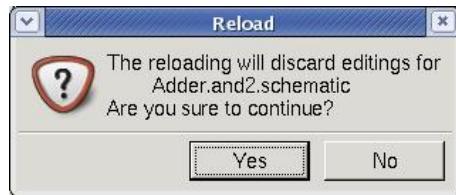

Reload the design data from disk and refresh current view. It is useful for a project team to synchronize the design data.

If current view has already been modified, SE will pop up a form to inquire you want to continue discard modification or not before reloading.

## 1.1.11 Design->Print

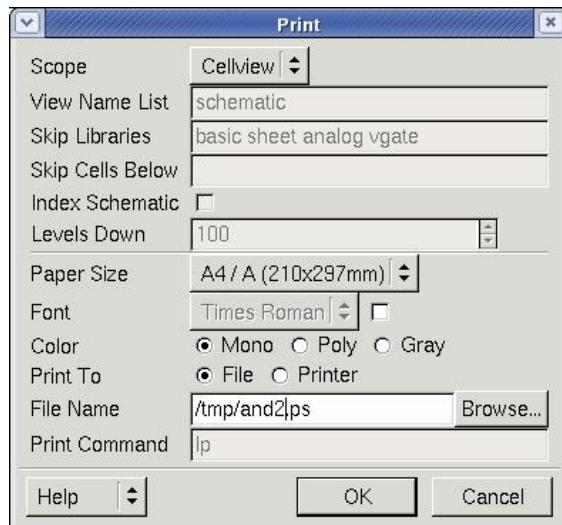

Print current view to a printer or a postscript (.ps) file.

**Scope** specifies print scope.

**Cellview** prints current view in fit window view.

**Hierarchy** prints current view and its sub-cells.

**Library** prints all cellviews listed in *View Name List* in this library.

**Window** prints current view in current view state.

**View Name List** specifies the views you want to print. It is activated when you select *Library* from *Scope* drop-down list.

**Skip Libraries** specifies library list. View in this library will not be printed. It is activated when you select *Hierarchy* from *Scope* dropdown menu.

**Skip Cells Below** specifies to print subcells till this one specified here. It is activated when you select *Hierarchy* from *Scope* dropdown menu.

**Index Schematic** specifies whether to print Index Schematic or not.

**Levels Down** specifies how many levels in the design hierarchy to be printed. It is activated when you select *Hierarchy* from Scope dropdown menu.

**Paper Size** specifies the paper size, for example, A0-A5, B0-B5.

**Font** specifies output text font.

**Color** specifies printing color.

**Mono** -- monochrome

**Poly** -- colorful

**Gray** -- gray

**Print To** specifies printing to a ps file or to printer.

**File** specifies to print to a ps file, Type file name in *File Name* field.

**Printer** specifies print to printer. Type the print command in *Print Command* field.

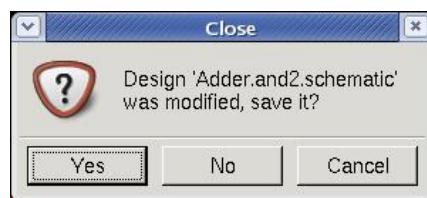

### 1.1.12 Design->Close

Close the current cellview and exit the layout editor.

If the current cellview has been modified and not been saved, a dialog appears and enquire you whether to save it or not.

Click *Yes* to save it and exit SE. Otherwise, click *No* to exist SE without saving.

## 1.2 Add menu

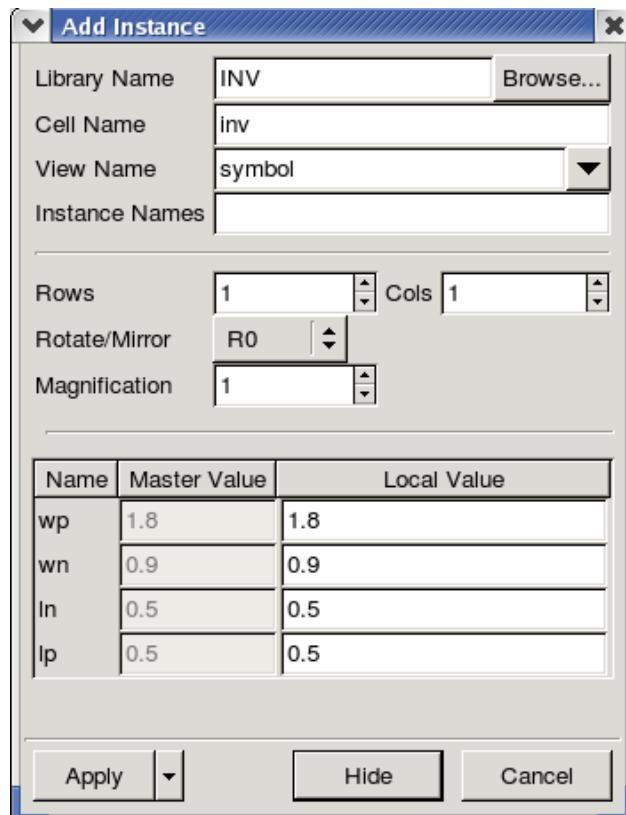

### 1.2.1 Add->Instance

Place instance in your design.

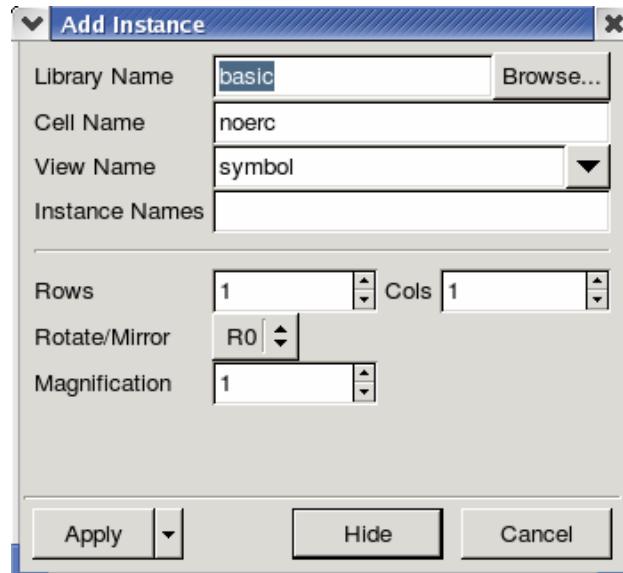

Select *Add->Instance* or click icon  , Add Instance form appears.

In **LibraryName**, **CellName**, and **ViewName** fields, specify the cellview of the instance.

You can also click at *Browse* button to assist you in finding the cellview you want to add.

If you do not add instance names in the **Instance Names** field, the system generates default instance names prefixed with the letter I.

**Rotate/Mirror** make the instance rotate.

R0/R90/R180/R270 - Rotate 0/90/180/270 degrees.

MX - Flip by X-axis.

MY - Flip by Y-axis.

MXR90 - Flip by X-axis and rotate 90 degrees.

MYR90 - Flip by Y-axis and rotate 90 degrees.

**Magnification** specifies enlarge instance by some times. The default value is 1.

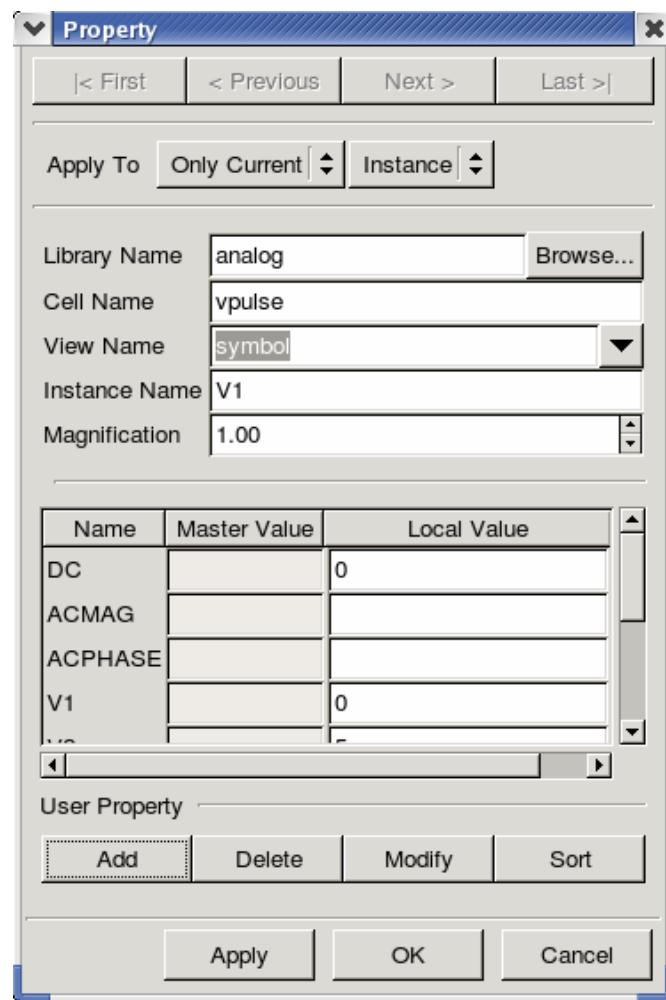

**Name**, **Master Value**, **Local Value** are parameters related to the instance. You can give a set of new parameters in *Local Value* field to fit your design. If not, the instance's parameters will be the same as Master Value.

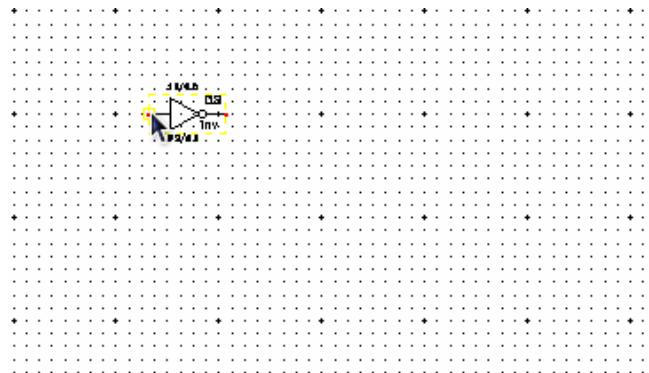

Methods of Adding Instances to Your Design:

*One by one*

This method lets you place multiple copies of a single instance in a schematic, based on a single lib/cell/view name.

1. Choose Add – Instance;

2. In the Library, Cell, and View fields, specify the cellview of the instance;

3. Move the pointer into your cellview. The instance appears attached to the pointer.

Click in your cellview to place the instance.

**Note:**

*Add – Instance* command is repeatable (if repeat mode is turned on), and continues to prompt you to add another instance. Please refer to *Options->Editor Command* field. To stop generating instances, press the Esc key, or choose another command.

*By rows and columns (an array)*

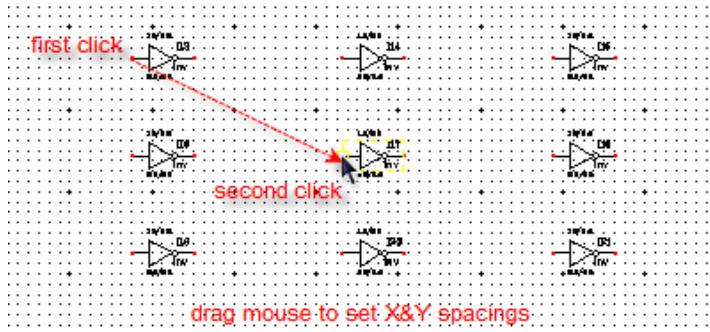

Add an array of instance using rows and columns, do the following:

1. Choose Add – Instance.

2. In the Library, Cell, and View fields, specify the cellview of the instance. Fill in the Rows and Columns fields.

3. Move the pointer into your cellview. The first instance appears, attached to the pointer. Place the first instance by clicking the mouse.

4. Drag the mouse vertically and horizontally, and then click on a location to set the X and Y spacing for the array. The rest of the instances follow the cursor.

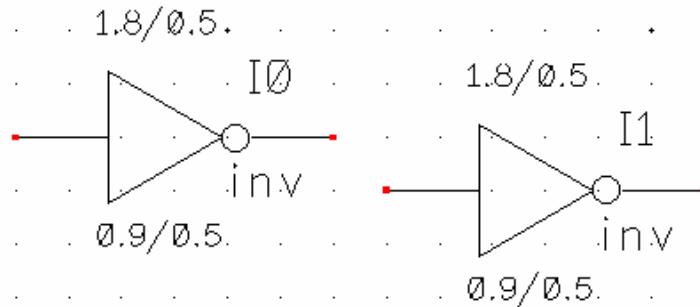

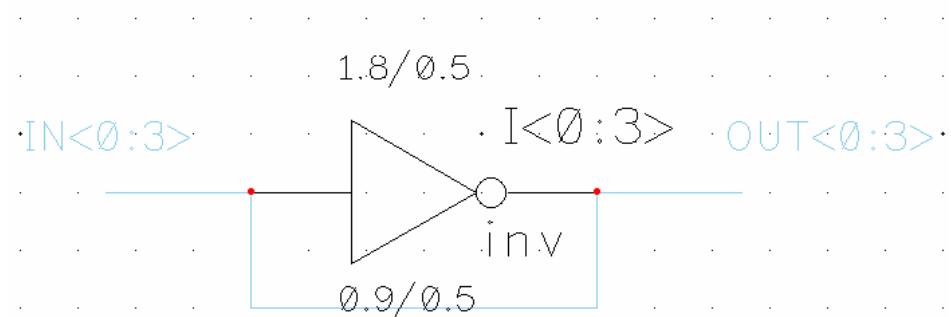

#### By using iterative expressions

Instance iteration is a compact way of displaying repeated instances of a symbol in your schematic. It is particularly useful in bus-type or data-flow architectures that have identical structures to handle each bit on the bus.

To save space in your design window when you need to add several instances of the same type, you can express multiple unique names with an iterative expression. For example,  $I<0:3>$  generates one graphic representing four instances:  $I0$ ,  $I1$ ,  $I2$ , and  $I3$ . Add instances using an iterative expression, do the following:

1. Choose Add – Instance.

2. Fill the form. In *Instance Names* field, type a name using iterative expression format such as  $I<0:3>$ .

3. Move the pointer into your cellview. The instance appears attached to the pointer. Click in your cellview to place the instance.

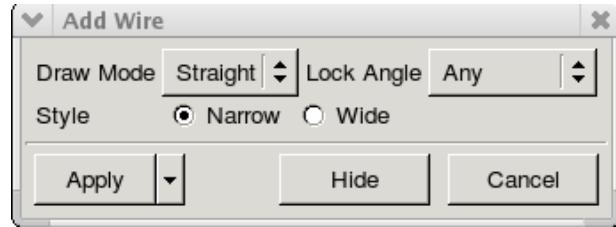

## 1.2.2 Add->Wire

Add a wire in the current cellview.

Select *Add->Wire* or click icon to add a wire. If you selected *Always* option in *Option->Popup Option Form*, or press "F3" key, the Add Wire form appears.

Set the form above, and then begin to draw wire in your schematic as the following steps:

1. Click on a point to start drawing wire;

2. Drag mouse to the destination point and left click or double click anywhere to finish drawing wire.

If *option->Editor->Wire Snapping* is checked, the closest pin to mouse will be marked by a small diamond shape while drawing. Holding Shift or Ctrl and click LMB, the wire will connect to this closest pin automatically.

The snap marker appears when drawing

Holding Shift or Ctrl and clicking LMB, automatically connect to the closest pin

f

**Draw Mode** specifies the wire entry method.

**Straight** (/): draw a straight line between two points on the following **Lock Angle** mode:

**Any**: any angle.

**Orthogonal**: 90 degrees angle.

**Diagonal**: 45 degrees angle.

**XY** (\_J): draw line along X-axis first, then along Y-axis.

**YX** (\_L): draws line along Y-axis first, then along X-axis.

**L45** (\_J): draw line along X-axis or Y-axis first, then along 45 degrees direction.

**45L** (\_L): draw line along 45 degrees direction, then along X-axis or Y-axis.

**Route**: route between 2 points by the following **Route Method**:

**Full**: draw line between two points at 90 degrees angle.

**Direct**: draws a straight line between two points at any angle.

**Flight**: draws a dotted line between two points at any angle.

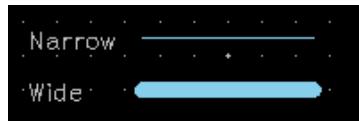

**Style** specifies the wire width as below. If you select Wide option, Add Wire is the same as command Add Wide Wire.

### 1.2.3 Add->Wide Wire

Add a wide wire in the current cellview. It is the same as *Add->Wire*.

1. In *Options->Editor* menu, turn on "Always" in "Popup option form" option, Add Wire form will pop up all the time, without pressing "F3" key.

2. In *Options->Editor* menu, turn off "Wire Snapping" option, the small yellow diamond will not appear.

3. While creating a wire, you can right-click mouse to change the wire mode. If the "Add Wire" form still exists, the value of Draw Mode will be changed with each right-click mouse.

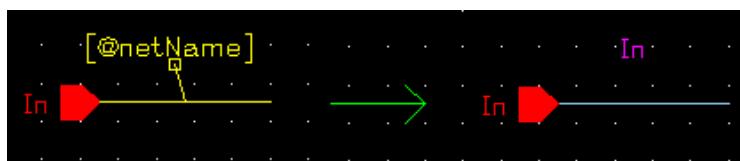

### 1.2.4 Add->Wire Name

Assign a name to a wire.

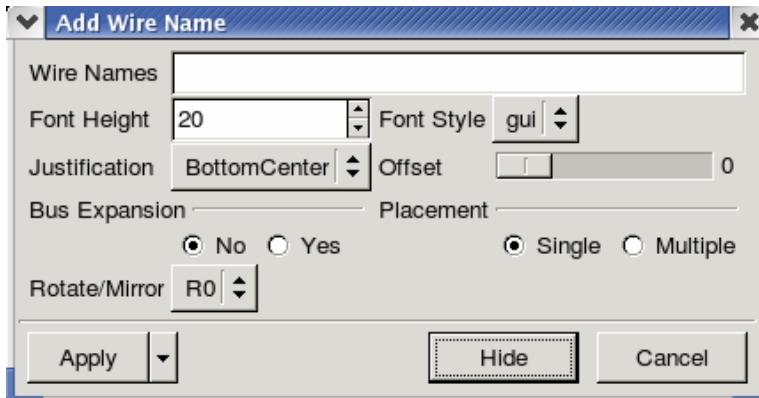

Select *Add->Wire Name* or click icon , the *Add Wire Name* form appears.

**Wire Names** specifies one or more names will be assigned to wires. You can specify multiple names, and separating each name by a space. You can also use a bus expression to name an array of wire names.

**Font Height** specifies the size of your wire name text as a floating-point value, in user units. The default is 0.625.

**Font Style** specifies the typeface that system uses to display the wire name.

**Justification** specifies the position of the cursor with respect to the wire name.

**Offset** specifies the distance between the text *Justification* and the anchor (cursor).

Notice that when you select "Center Left", "Center Center" or "Center Right" in

*Justification, Offset is invalid.*

**Bus Expansion** specifies how the system interprets bus names.

*No* (default) interprets the bus name as a single name and generates a single name that includes all the bits in the bus range. For example, for the name  $A<0:1>$ , the system generates only the name  $A<0:1>$ .

*Yes* interprets the bus name as multiple names and generates a name for each bit of a bus range that you specify in the Names field. For example, for the name  $A<0:1>$ , the system generates names  $A<0>$  and  $A<1>$ .

**Placement** controls whether you can place multiple wire names automatically once.

*Single* (default) requires you to point and click to identify each wire name location.

*Multiple* lets you drag your mouse between two points to designate the wires that you want to name automatically.

**Rotate/Mirror** specify how to rotate the wire name.

*R0/R90/R180/R270*: rotate wire name by 0/90/180/270 degrees

*MX*: flip wire name by X-axis

*MY*: flip wire name by Y-axis

*MXR90*: flip wire name by X-axis and rotate 90 degrees

*MYR90*: flip wire name by Y-axis and rotate 90 degrees

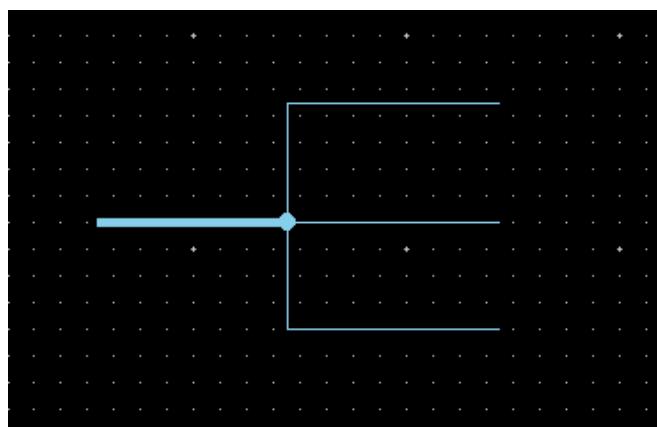

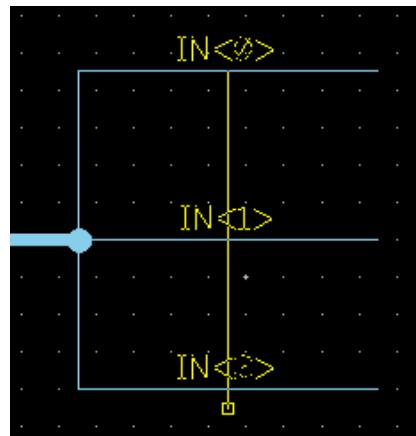

Add wire names one by one for the following figure:

1. Click icon , fill out the Add Wire Name form with the following information.

Wire Names:  $IN<0:2>$

Bus Expansion: No

Placement: Single

2. Directly move your cursor into the wire segment as the figure below. Click left mouse button to add the wire name to this wire segment.

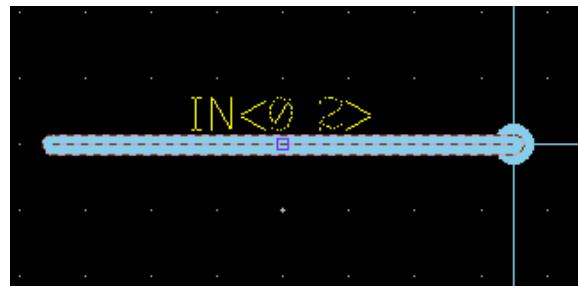

3. Choose Add->Wire Name

带格式的: 项目符号和编号

4. Move your cursor into "Add Wire Name" form, fill out name, like "IN<0:2>" in Wire Names field and set the option Bus Expansion to "Yes".

5. Directly move your cursor into Schematic Editor window. Click left mouse button to add the wire name to these tree wire segment one by one.

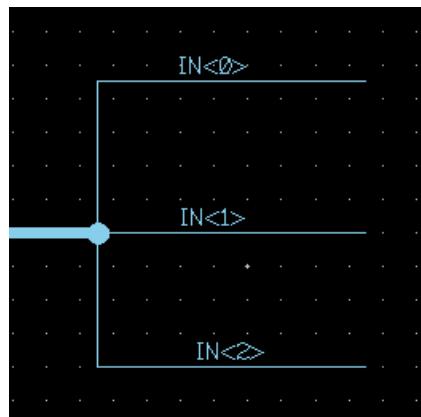

Add names for bus:

1. Click icon  again, fill out the Add Wire Name form with the following information.

Wire Names: IN<0:2>

Bus Expansion: Yes

Placement: Multiple

2. Hide the "Add Wire Name" form, move mouse to the first wire segment and click left mouse button to fix it.

3. Drag and move the cursor cross the other two wire segments. You can find the other names IN<1> and IN<2> appear in the cross point automatically as shown in the figure below.

4. Click left mouse button to fix them.

5. Save and close this schematic view.

Note:

To do this operation successfully, you must make sure that “Repeat” option is turned on in Command field of menu command Options->Editor.

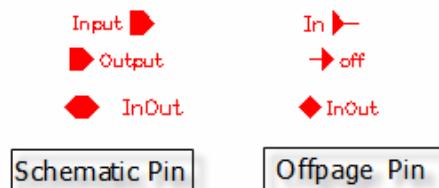

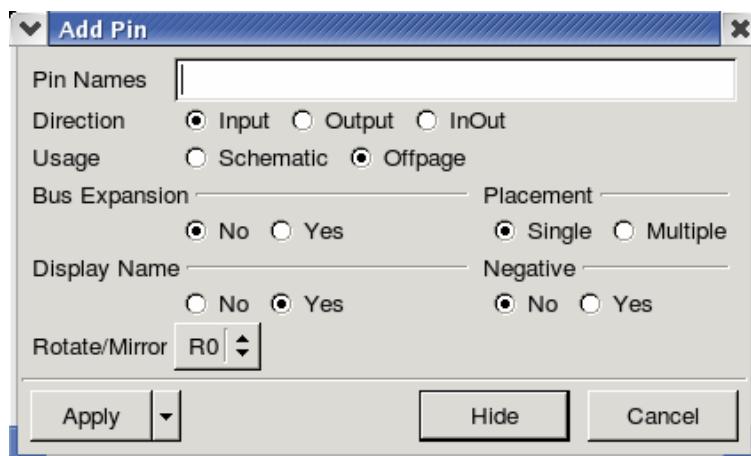

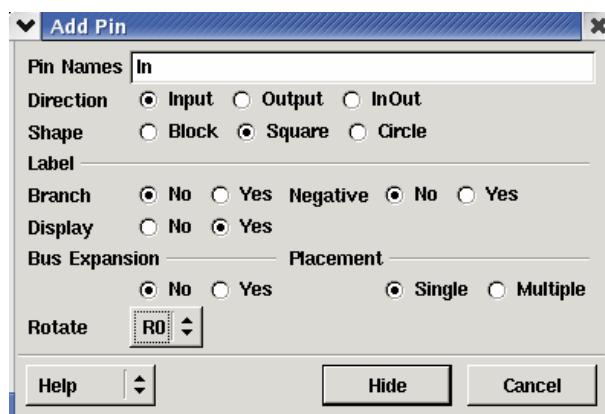

### 1.2.5 Add->Pin

Create schematic pin or Offpage pin.

Schematic pin is an interface of input or output data in cellview. Offpage pin is as a connector connects pages. Please refer to Page menu.

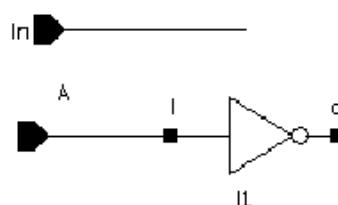

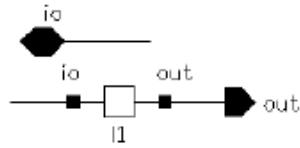

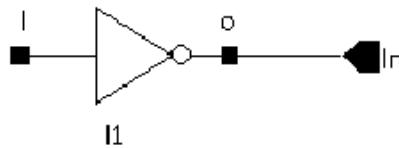

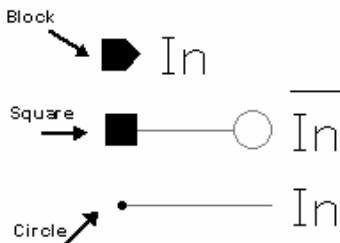

The shape of schematic pin and Offpage pin are shown as below.

Select *Add->Pin* or click icon , the Add Pin form appears.

**Pin Names** specifies the pin name. It can be single pin and multiple pins. For multiple pin names, use "space" to separate names or use bus expression (for example: A<0:x>, x is digit).

**Direction** specifies pin type: Input, Output or InOut.

**Usage** specifies this pin is used for schematic pin or page connector in multi-page schematic.

**Bus Expansion** specifies how the system interprets bus names.

**No** (default) causes the system to interpret a bus name as a single name and generate a single pin that includes all the bits in the bus range. For example, for the name A<0:1>, the system generates only the pin A<0:1>.

**Yes** causes the system to interpret a bus name as multiple names and generate a pin for each bit of a bus range that you specify in the Pin Names field. For example, for the pin A<0:1>, the system generates pins A<0> and A<1>.

**Placement** controls whether you can place multiple pins automatically in one operation.

**Single** (default) requires you to point and click to identify the location for each pin.

**Multiple** prompts you to point and click to specify the first and second pin locations.

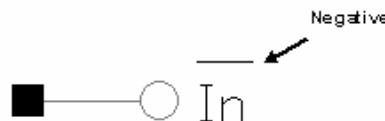

**Negative** specifies pin logic. If you select Yes, an bar is on the top of pin name.

Negative: No

Negative: Yes

**Display Name** specifies whether pin name is visible or invisible.

**Rotate/Mirror** is to rotate the pin name.

**R0/R90/R180/R270**: rotate pin name by R0/R90/R180/R270 degrees.

**MX**: flip pin name by X-axis

**MY**: flip pin name by Y-axis

**MXR90**: flip pin name by X-axis and rotate 90 degrees

**MYR90**: flip pin name by Y-axis and rotate 90 degrees

#### Note:

You can right-click mouse to rotate pin before you place the pin.

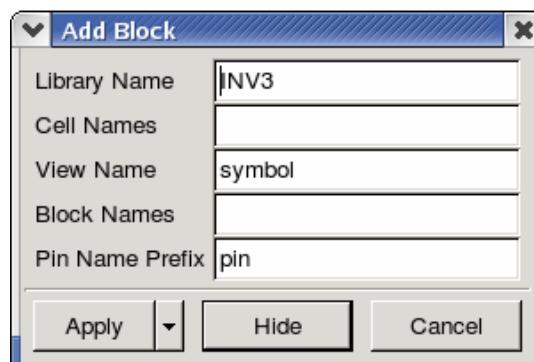

### 1.2.6 Add->Block

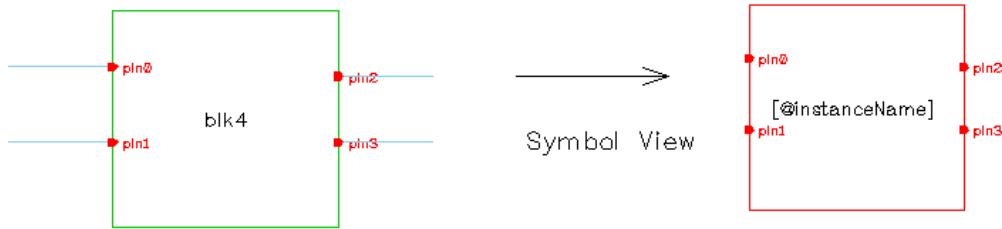

Create a block. This method is used for design method of Top-Down.

Select *Add->Block* or click icon , the Add Block form appears.

Enter library/cell/view names in *Library Name*, *Cell Name* and *View Name* fields. In fact, SE will create a symbol view after you click *Apply* button.

**Block Names** specifies the block name, which is instance name. If not giving any name, "I" is as the default.

**Pin Name Prefix** specifies the prefix of pin name when wire connects to block editor creates a pin automatically. The default prefix is "pin".

After filling up all fields and clicking *Apply* button, you can start to create this block.

The steps are as below:

1. Move the cursor in editor window

2. Click the first point to locate the top-left corner of the rectangle

3. Drag the mouse and click the second point to locate the bottom-right corner of the rectangle.

Create Block Pin Automatically

After creating a block, you can add pin to block automatically. The steps are as below:

1. Activate *Add Wire* or *Add Wide Wire* command first.

2. Draw a wire to or from block edge.

3. Click on a point to end the wire.

The created entire block and its symbol view are as following.

**Note:**

The library that you type in Library Name field must be existed.

The symbol view that you type in View Name field must not be existed.

Block pin's direction is controlled by Option->Editor->Block Pin Order .

If you checked Freezed Pin Add in Design->Property, in block symbol view, you will not add pin automatically.

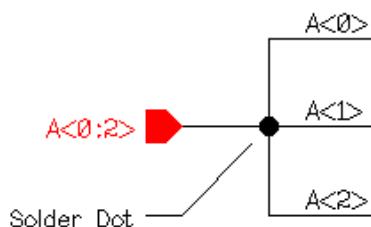

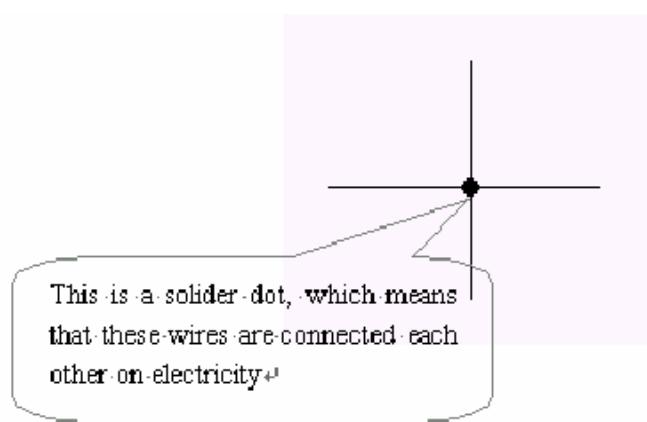

## 1.2.7 Add->Solder Dot

When two wires cross like "+" shape, you need to manually add a solder dot at the intersection in order to connect two crossing wires.

Select *Add->Solder Dot* or click icon , and click at cross point.

To delete a solder dot, select Edit->Delete or click icon , click at the solder dot you want to delete.

**Note:**

When two wires cross like "T" shape, the editor adds a solder dot at the intersection point automatically.

To remove anyone wire in "T" structure, the solder dot is deleted by editor.

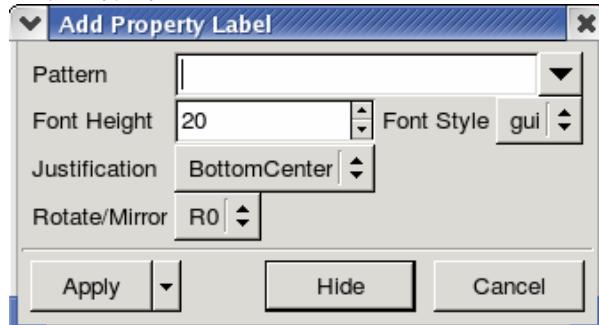

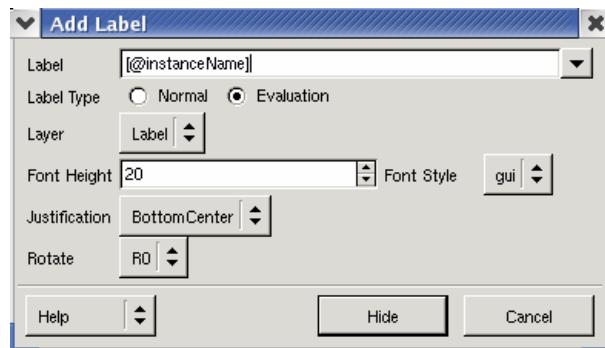

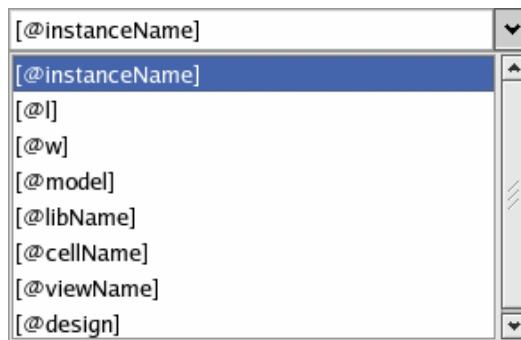

## 1.2.8 Add->Property Label

Create a property label for an object.

Select *Add->Property Label* first, the Add Property Label form appears. Click to choose an object (wire, pin, instance, etc.) on layout, then the *Pattern* field is valid according to the object type you choose.

**Pattern** specifies the label pattern or a user given name. According to difference object, the label is different in pull-down menu list. For example, if you select a wire, the candidate label is "[@NetName]", "[@NetName]" specifies the current selected wire's name. If the name of this wire is changed, the label will be changed as well after *check* operation.

**Font Height** specifies the size of the label. Default is 20.

**Font Style** specifies the style of label.

**Justification** specifies the anchor of text.

**Rotate** to rotate the label.

*R0/R90/R180/R270*: rotate label by 0/90/180/270 degrees.

*MX*: flip label by X- axis.

*MY*: flip label by Y-axis.

*MXR90*: flip label by X-axis and rotate 90 degrees.

*MYR90*: flip label by Y-axis and rotate 90 degrees.

After setting the label, move cursor to editor window, the selected object highlights and a line attached label start from the selected object. Click a point to place the label at the desired location.

**Note:**

Do check operation before doing this command.

## 1.2.9 Add->Patchcord

Patchcord is a connection symbol used to establish aliases between the signals of two different nets.

You can use the patchcord to map bits from one net to different bits of another net.

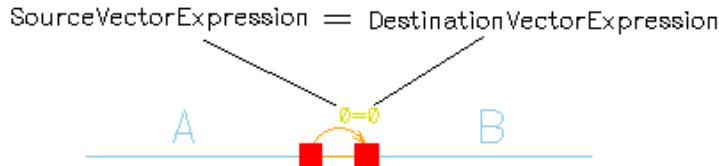

The patchcord connects wires in format: Source Vector Expression = Destination Vector Expression

The vector expression syntax is:

single bit: for example: "0=0" "2=2" "3=4"

multiple bits: for example: "0:2=2:4" "0,1,3= 2,3,4"

The number of bits in SourceVectorExpression must equal to the number of bits in DestinationVectorExpression

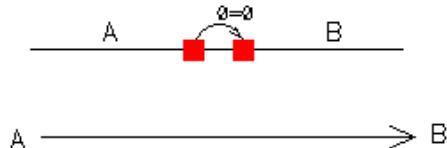

In the following example, net "A" and net "B" are aliased together.

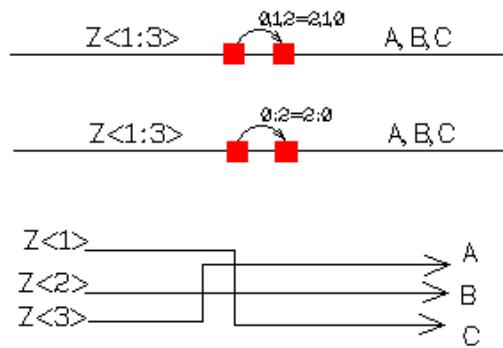

In the following example, no matter the expression is "0,1,2=2,1,0" or "0:2=2:0", the results are same, that is, signal "Z<1>" is aliased to signal "C", signal "Z<2>" is aliased to signal "B", signal Z<3> is aliased to signal "A".

Add a patchcord in your design as below:

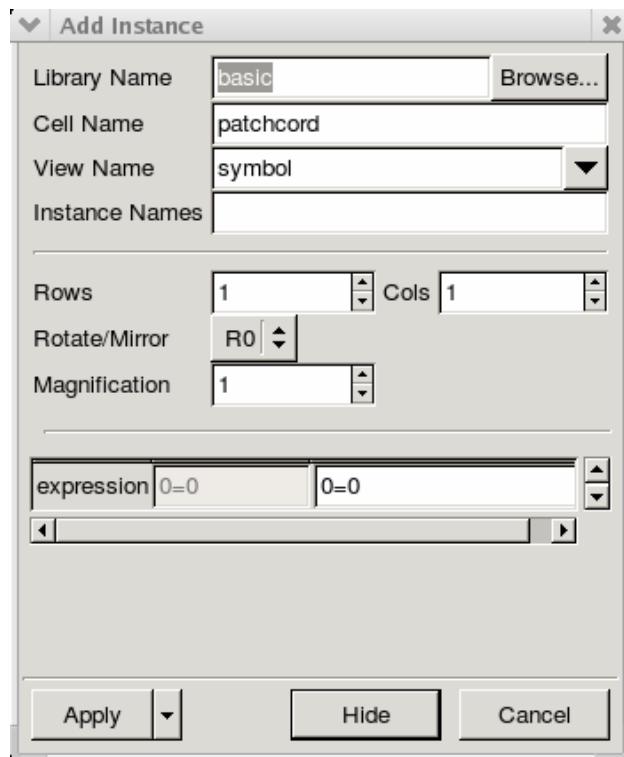

Select Add->Patchcord or click icon , the Add Instance form appears.

Enter vector expression in *expression*, for example: "0=1", "1=0" or "0:3=0:3", etc. The system puts 0=0 in the *expression* field, which indicates that the nets are equal to or greater than 1 bit wide. If the nets are more than 1 bit wide, you can update the expression value on the Add Instance form.

Move the cursor to editor window, the patchcord symbol attached to the cursor, click to place the patchcord at the desired location.

### 1.2.10 Add->NoERC

Used for floating nets and floating pins are not be checked by ERC.

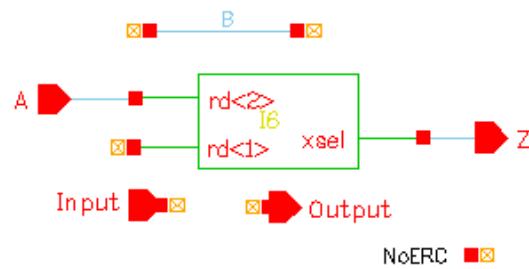

Select *Add->NoERC*, the Add Instance form appears.

The NoERC form is filled automatically. Move the cursor to editor window, the NoERC symbol attached to the cursor, click to place NoERC at the desire location.

In the following example, the net "B", instance pin "rd<1>", pins "Input", "Output" will not be regard as floating while do ERC check.

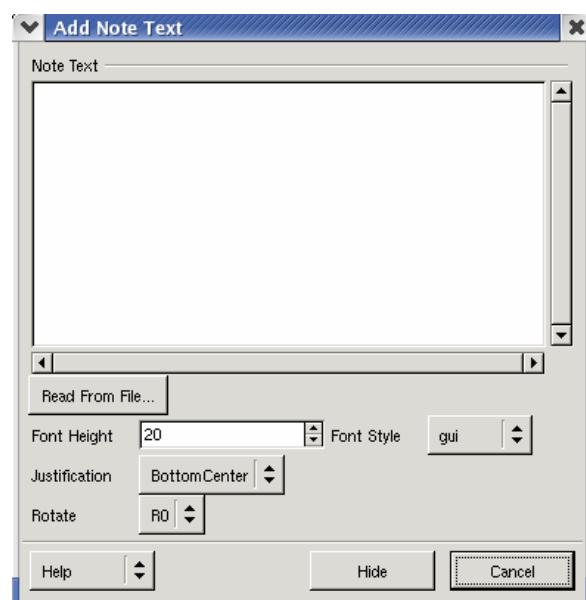

### 1.2.11 Add->Note Text

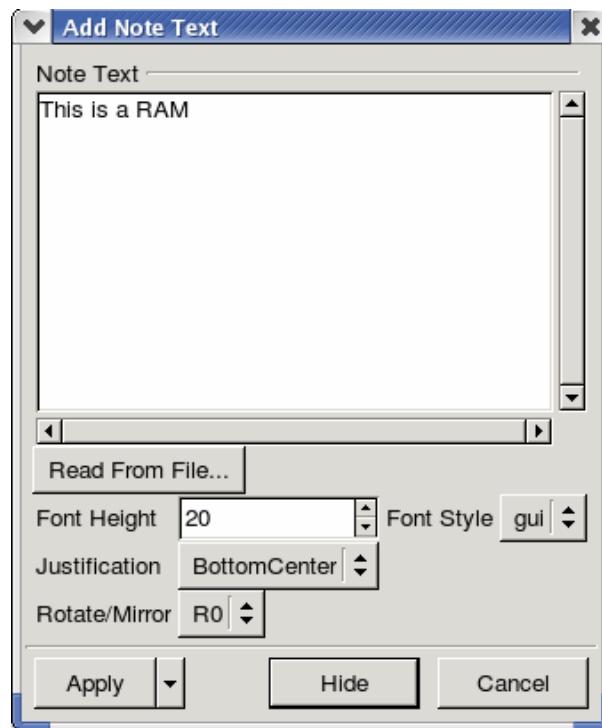

Add comments for an object or for entire schematic/symbol view.

Select *Add->Note Text*, the Add Note Text form appears.

**Note Text** field is used to edit the text you want to add. You still can load a note text in some file by Read From File button.

**Font Height** specifies the size of note text. Default is 20.

**Font Style** specifies the font style.

**Justification** specifies the anchor of note text.

**Rotate/Mirror** to rotate the text.

*R0/R90/R180/R270*: rotate text by 0/90/180/270 degrees.

*MX*: flip text by X-axis.

*MY*: flip text by Y-axis.

*MXR90*: flip text by X-axis and rotate 90 degrees.

*MYR90*: flip text by Y-axis and rotate 90 degrees.

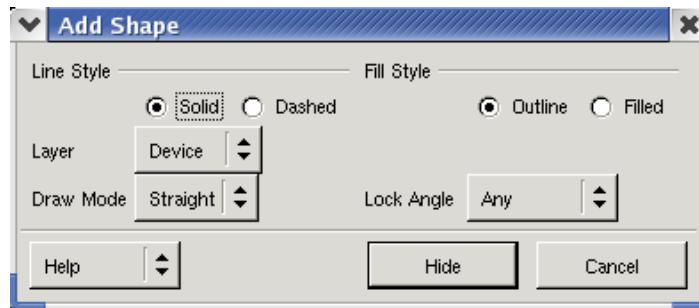

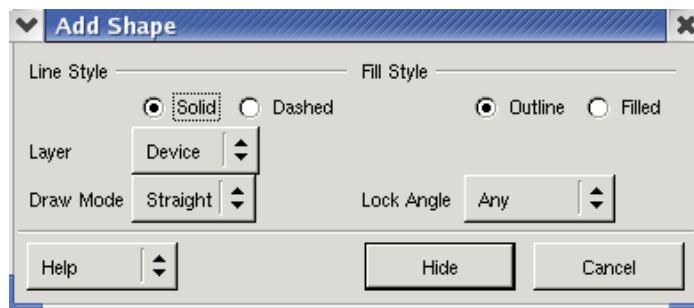

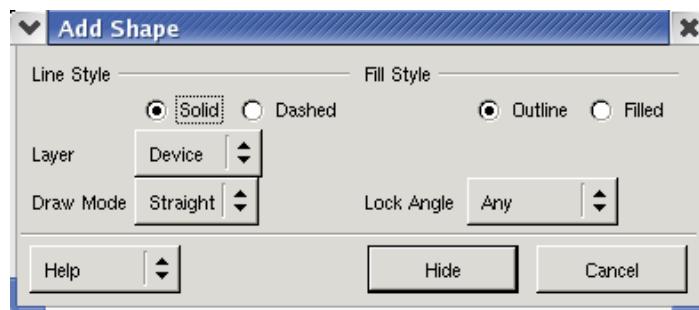

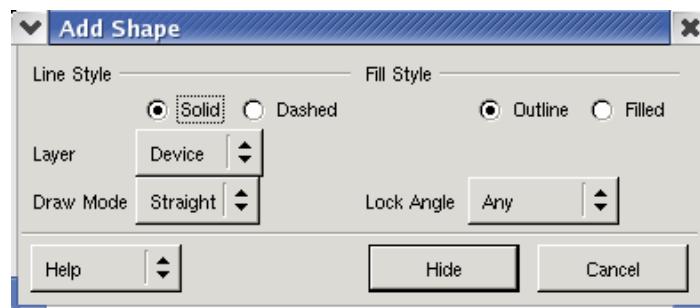

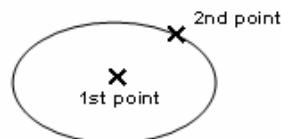

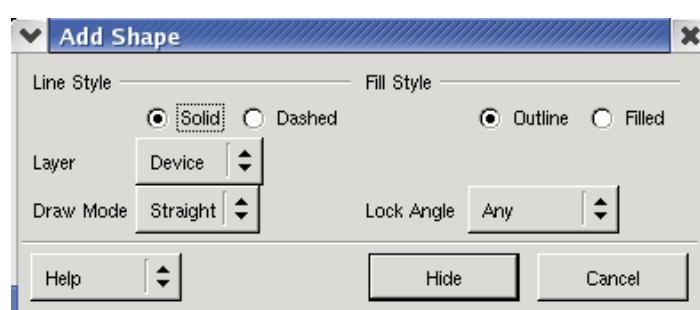

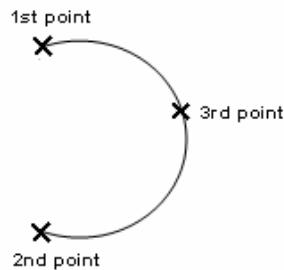

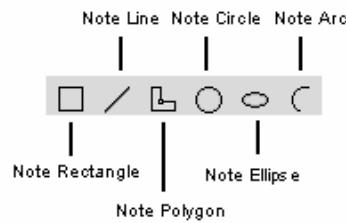

### 1.2.12 Add->Note Shape

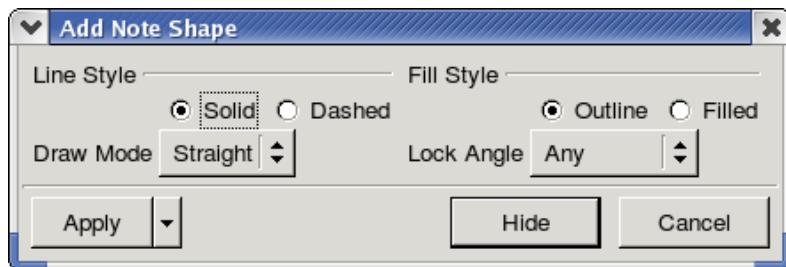

Add graphical notes to the schematic.

There are 6 note shapes that you can choose: Rectangle, Line, Polygon, Circle, Ellipse and Arc.

Select one of shapes from submenu of command *Add->Note Shape*, the Add Note Shape form appear according to the shape you choose.

**Line Style** section, you can choose the shape of outline is Solid line or dashed line.

**Fill Style** section, you can decide whether to fill the shape.

**Draw Mode** specifies the drawing mode:

*Straight()*: draw a straight between two points

*XY(\_)*: draw along X-axis first, then along Y-axis

*YX(\_)*: draw along Y-axis, then along X-axis

*L45(\_)*: draw along X-axis or Y-axis first, then at 45 degrees to the axis

*45L(\_)*: draw at 45 degrees to axis first, then along X-axis or Y-axis

**Lock Angle** specifies the angle while drawing line.

*Any* (Default): at any angle

*Diagonal*: at 90-degrees angle to the axes

*Orthogonal*: at 45-degree angle to the axes

## 1.3 Edit menu

### 1.3.1 Edit->Undo

Reverse the action of the previous edit command. You can set the undo limit from 0 to 100 in Option->Editor->Undo Limit.

Select *Edit->Undo* or click icon  to do it.

Note:

After you doing Check and Save, Save, Check or Discard Edits commands, this command does not work.

### 1.3.2 Edit->Redo

To cancel the previous undo commands. Select *Edit->Redo* or click icon  to do it.

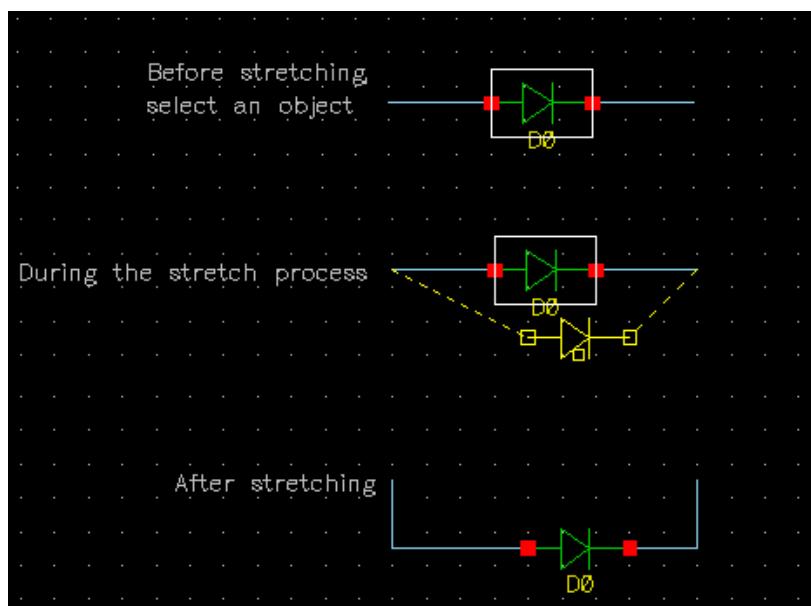

### 1.3.3 Edit->Stretch

Move the selected object to another location without losing connectivity between wires and pins.

To stretch an object, do the following:

1. Select an object first.

2. Choose Edit->Stretch or click icon .

3. Click the selected object and hold LMB.

4. Drag the LMB and release it at the desired location to complete the stretch.

The editor reroutes wires to maintain connectivity.

The following figure shows the stretch process.

To stretch multiple objects, you need to press Shift key while selecting objects. After activating Stretch command, you just select one object only to stretch, and then the remains are stretched at the meanwhile.

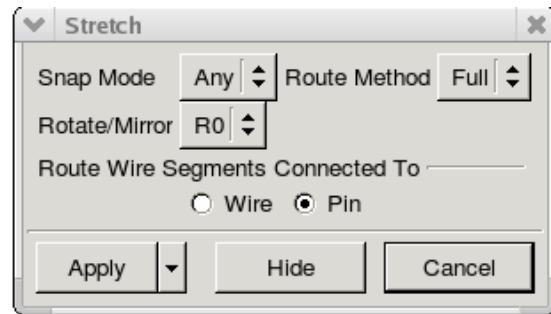

About the Stretch form:

When you activate stretch command, the Stretch form appears.

**Snap Mode** specifies the angles along which you can move stretched objects.

*Any* (default) - move stretched objects along any angle.

*Diagonal* - move stretched objects along 45-degree, 90-degree, and 180-degree angles from the current location.

*Orthogonal* - move stretched objects along the X and Y axes from current location.

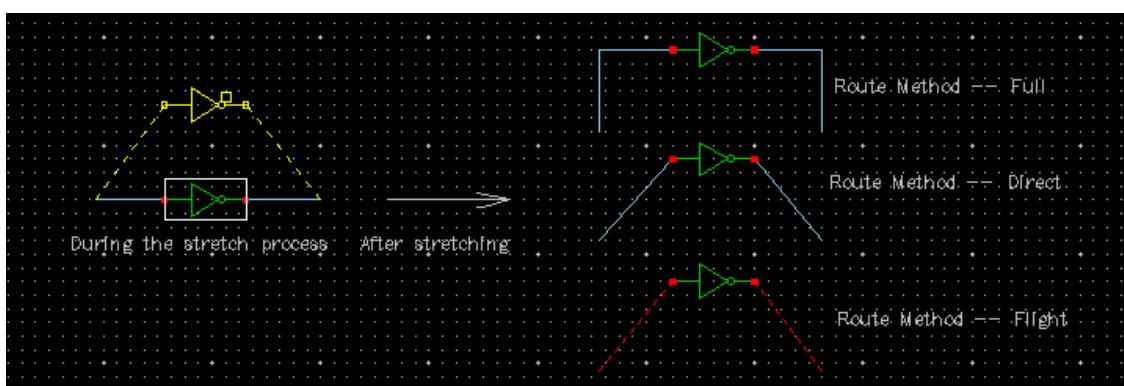

**Route Method** specifies how the editor routes wire.

*Full* - automatically routing by editor.

*Direct* -- draw a straight line between two points.

*Flight* -- draw a dashed line between two points.

**Rotate/Mirror** to rotate the stretched objects during the stretch process.

*R0/R90/R180/R270* - rotate objects 0/90/180/270 degrees.

*MX* - flip objects by X-axis.

*MY* - flip objects by Y-axis.

*MXR90* - flip objects by X-axis and rotate 90 degrees.

*MYR90* - flip objects by Y-axis and rotate 90 degrees.

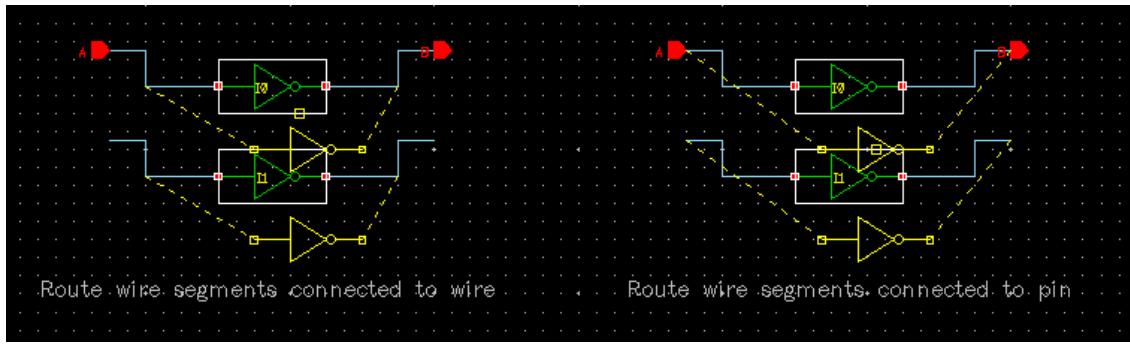

**Route Wire Segments Connected To** specifies the point that rubberband line begin from.

*Wire* - the rubberband line begin from the last segment of the wires

*Pin* - the rubberband line begin from a pin, a solder dot, or a wire ending.

Note:

The stretch command does not stretch objects from one cellview to another.

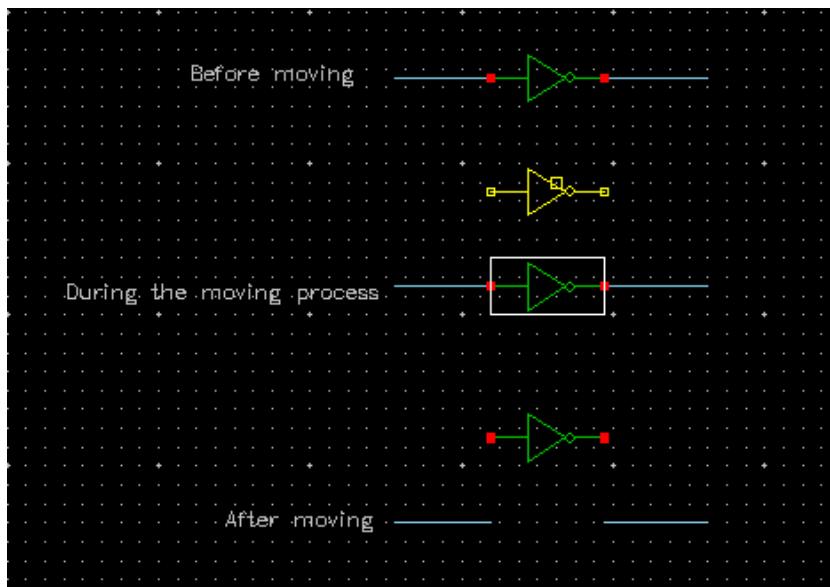

### 1.3.4 Edit->Move

Move the selected objects to another location or cellview without keeping the connectivity between wires and pins.

To move an object, do as the following steps:

1. Select an object first.

2. Choose Edit->Move or click icon

3. Click the selected object and hold LMB.

4. Drag the LMB and release it at the desired location to complete the move.

The following figure shows the moving process.

To move multiple objects, you need to press Shift key while selecting objects. After

activating Move command, you just select one of the objects only and move, the remains are moved at the meanwhile.

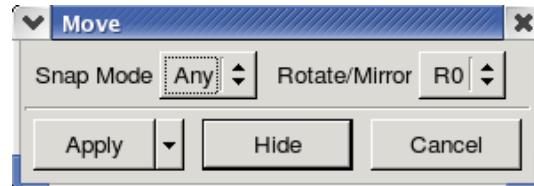

About the Move form:

When you activate move command, the Move form appears.

**Snap Mode** specifies the angles along which you can move objects.

*Any* (default) - move objects along any angle.

*Diagonal* - move objects along 45-degree, 90-degree, and 180-degree angles from the current location.

*Orthogonal* - move objects along the X and Y axes from current location.

**Rotate/Mirror** to rotate the moved objects during moving process.

*R0/R90/R180/R270* - rotate objects 0/90/180/270 degrees.

*MX* - flip objects by X-axis.

*MY* - flip objects by Y-axis.

*MXR90* - flip objects by X-axis and rotate 90 degrees.

*MYR90* - flip objects by Y-axis and rotate 90 degrees.

**Note:**

1. Move command can move objects from one cellview to another.

2. You can right-click mouse to rotate object before you place it.

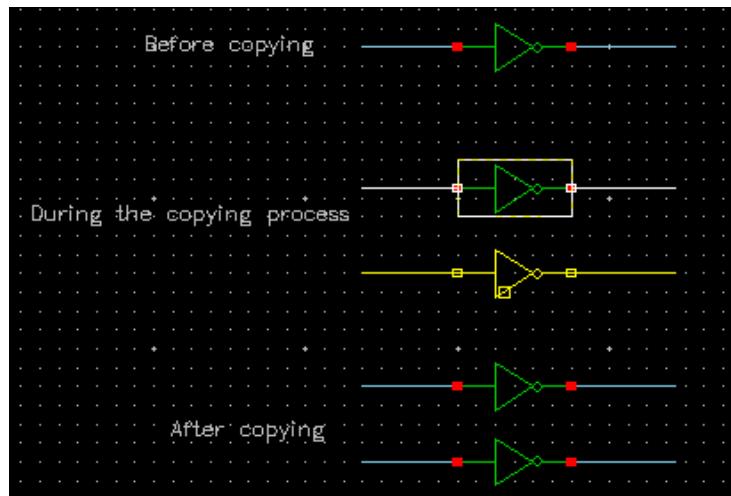

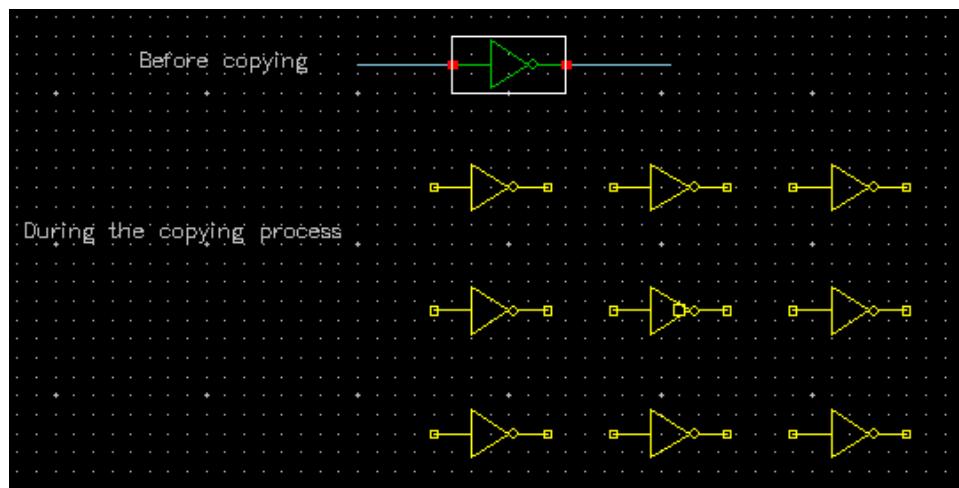

### 1.3.5 Edit->Copy

Copy objects in current cellview or to another cellview.

Copy an object, do the following steps:

1. Select an object first.

2. Choose Edit->Copy or click icon

3. Click the selected object and hold LMB.

4. Drag the LMB and release it at the desired location to complete the copy.

The following figure shows the copy process.

Copy multiple objects, you need to press Shift key while selecting objects, or draw a box to select objects you want to copy. After activating Copy command, you just select one of the objects to copy; the remains are copied at the meanwhile.

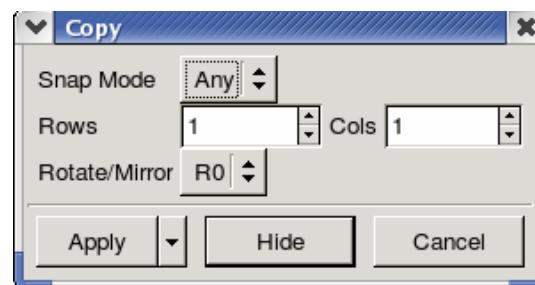

Copy one object to an array.

When you activate Copy command, the Copy form appears.

Rows and Cols let you copy object to make an array. For example, the following figure shows copying an instance to make a 3x3 array objects.

Make an array of objects, do as the following steps:

1. Select objects you want to copy.

2. Choose Edit->Copy or click icon

3. Click to place the first copied objects

4. Click again to place all the other copied objects.

The editor uses the distance between the first click and the second click to determine the distance between objects.

Note:

Copy command can copy objects from one cellview to another.

### 1.3.6 Edit->Delete

Delete objects.

Select Edit->Delete, or press Del key, or click icon  to delete.

**Usage1:** Select Objects First (Pre-Selection)

You can select objects before you activate the Delete command. The Delete command ends after the selected objects are deleted.

**Usage2:** Select Command First (Post-Selection)

You can activate Delete command first before you delete objects. The Delete command can delete more objects by clicking at the objects. Press ESC key to end the Delete command.

Note:

Delete Sheet Border, you should select Page->Add Sheet, and then choose NONE from pull-down menu of *Sheet Name*.

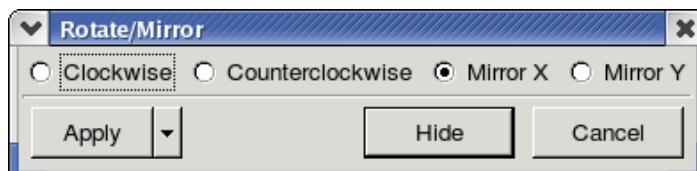

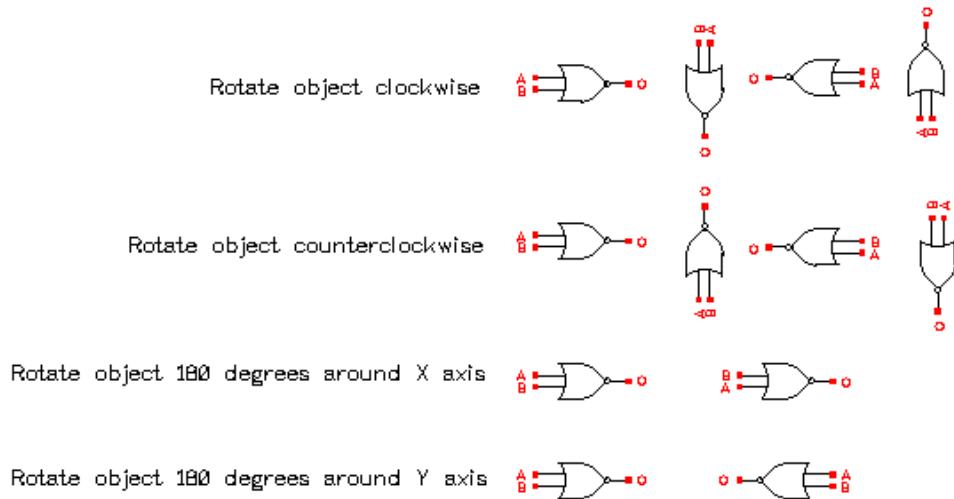

### 1.3.7 Edit->Rotate

Rotate object clockwise, counterclockwise, sideways, and upside down.

You can activate command Edit->Rotate first, or select objects first. Click at the object you want to rotate, the editor rotates the object counterclockwise. Press F3 key to modify the rotate mode.

**Clockwise** rotate object by 90 degrees increments clockwise.

**Counterclockwise** rotate object by 90 degrees increments counterclockwise.

**Mirror X** rotate objects 180 degrees around X axis.

**Mirror Y** rotate objects 180 degrees around Y axis.

To rotate pre-selected objects, do the following steps:

1. Select objects first.

2. Click Edit->Rotate.

3. Point at a reference point around the objects.

4. Left-click mouse time by time to rotate objects.

5. Press "Esc" key to terminate the command.

To rotate post-selected objects, do the following steps:

1. Click Edit->Rotate.

2. Select objects.

3. Point at a reference point around the object.

4. Left-click mouse time by time to rotate objects.

5. Press "Esc" key to terminate the command.

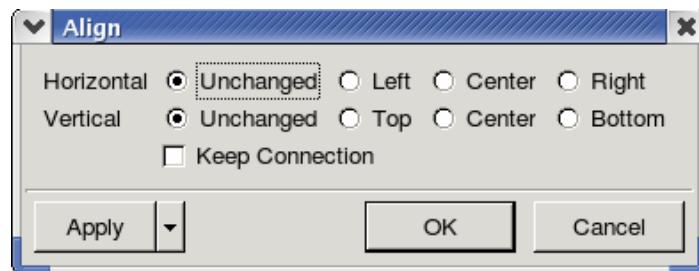

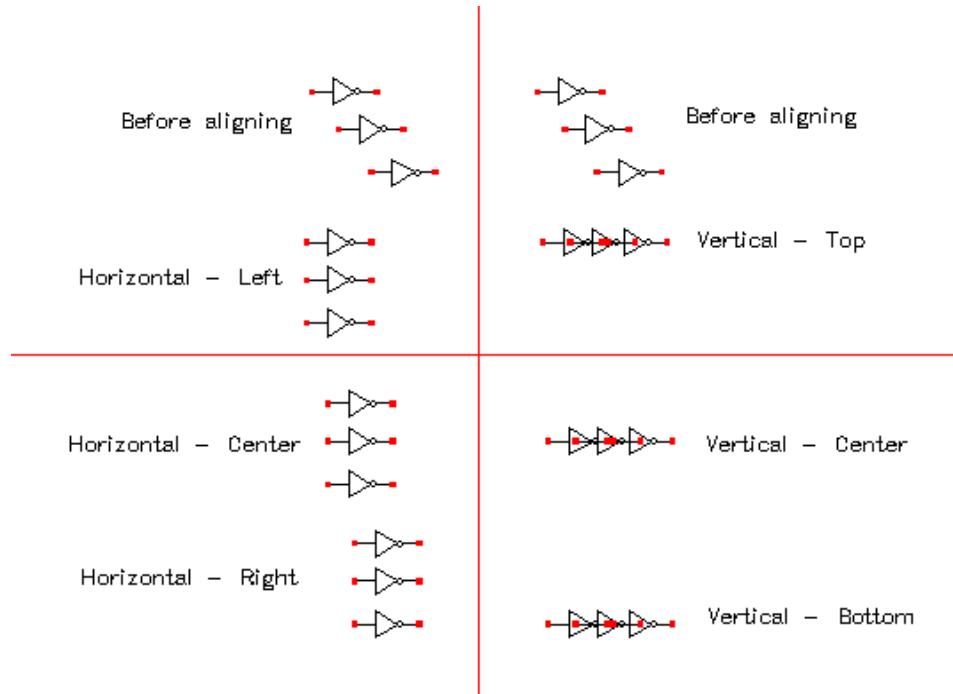

### 1.3.8 Edit->Align

Align objects in horizontal or (and) vertical direction.

Select the objects you want to align first, choose Edit->Align, the Align form appears.

You can select align mode in *Horizontal* and *Vertical* direction, and select Keep Connection if you want to align with keeping connectivity.

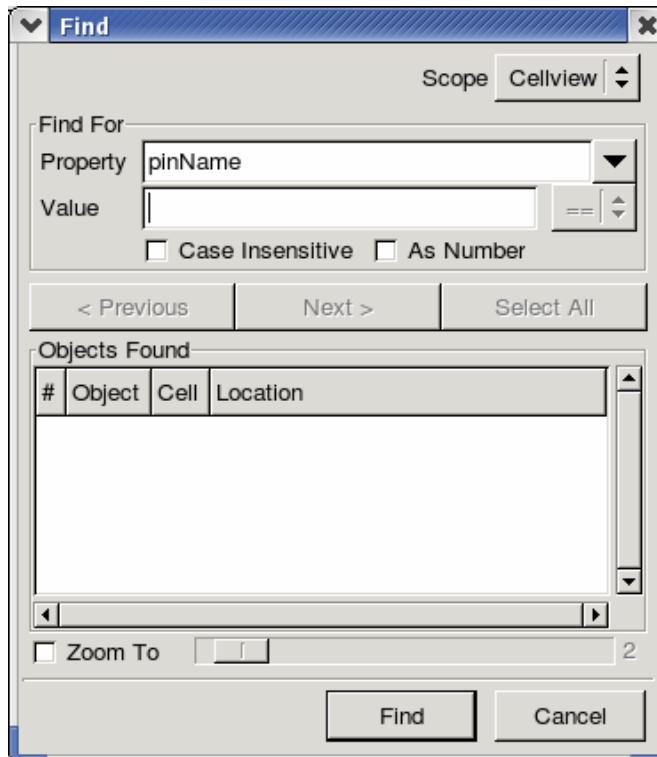

### 1.3.9 Edit->Find

Search objects with a specific property.

Select *Edit->Find*, the Find form appears.

**Scope** specifies searching scope. There are 3 options that you can choose: *Cellview*, *Hierarchy* and *Library*.

If you choose *Cellview*, the editor searches objects in the current cellview.

If you choose *Hierarchy*, the editor searches objects from all cellviews specified in the design hierarchy.

If you choose *Library*, the editor searches objects from all cellviews in the library.

**Property** specifies the object property you want to search. There are 7 object's property : instanceName, netName, pinName, wireName, libraryName, cellName and Orient.

**Value** specifies the value of the property. If you leave it blank or key in asterisk ( \* ), the editor will search all objects that match the property.

**Objects Found** shows the result of all objects that been found. You can use *Previous*, *Next*, and *Select All* to select any item.

Double click at a selected item, the object will be shown on the cellview. If the object belongs to another cellview, the editor will open that cellview and show the object in it.

If you select *Zoom To*, the object will be magnified and shown on the center of the cellview.

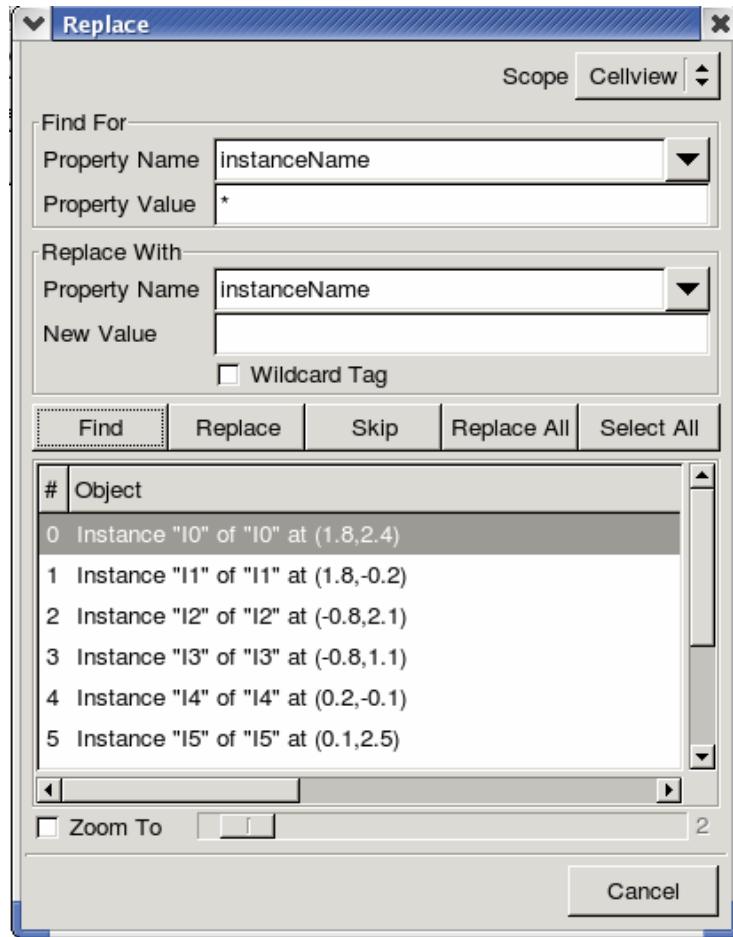

### 1.3.10 Edit->Replace

Replace objects or replace property of an object.

Select *Edit->Replace*, the Replace form appears.

**Find For** field specifies *Property Name* and *Property Value* that you want to replace.

**Replace With** field specifies *Property Name* and a *New Value* that you use to replace.

**Object** field lists the objects that have been found by *Find* button, and then will be replaced by *Replace* or *Replace All* button.

### 1.3.11 Edit->Alternate View

A schematic view could have more than one symbol views, for example Symbol1, Symbol2 ... When Symbol1 view is referenced, and you can use this command to change the Symbol1 view to Symbol2 view if you need.

Select Edit->Alternate View first, or select an instance first, the difference symbol view is shown when you click at the instance continuously.

### 1.3.12 Edit->Renumber Instance

Assign new numbers to all of the instances in the current cellview.

Select Edit->Renumber Instance to reset all of the instance names automatically.

**Note:**

If the prefix name of an instance is different from the prefix defined in Design->Design Property->Instance Prefix field, system doesn't renumber it.

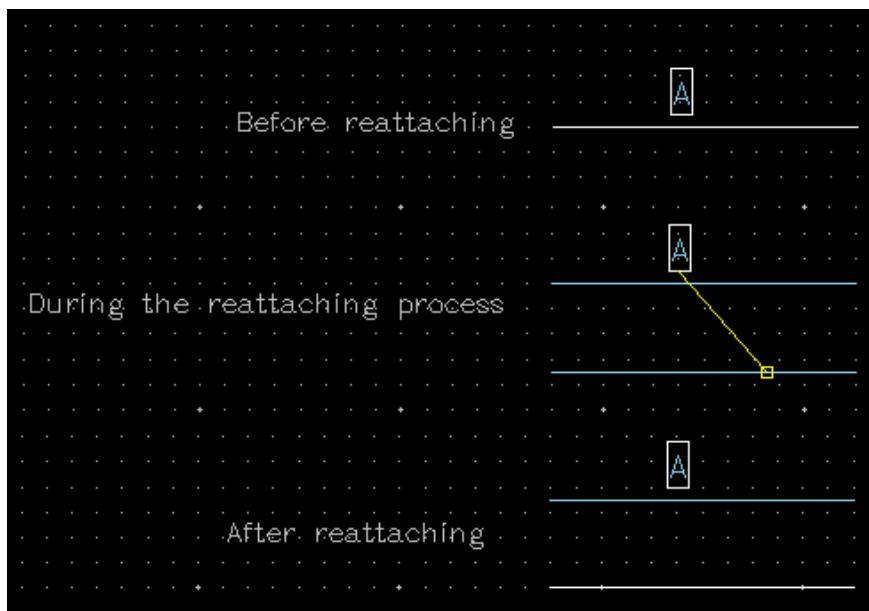

### 1.3.13 Edit->Reattach Wire Name

Re-assign a wire name to another wire.

If you select Edit->Reattach Wire Name first, and then you select a wire name, a cartoon line from the wire name appears and attach to the cursor.

If you select a wire name first, and then you activate command Edit->Reattach Wire Name, a cartoon line from wire name appears and attach to the cursor.

Click at another wire, the net name is reattached to that wire.

**Note:**

Double click at a wire; the corresponding wire name is highlighted.

Double click at a wire name, the corresponding wire is highlighted.

### 1.3.14 Edit->Hide Label

Make label invisible.

Select Edit->Hide Label first, click at the label you want to hide, the label is invisible immediately. You can click at the labels to hide one by one until you press Esc key.

Set the label visible by Reset-> Invisible Label.

### 1.3.15 Reset Invisible Label

Make the hidden labels visible.

Select Edit->Reset Invisible Label first, all hidden labels will flash in the cellview. Click at a flashed label you want to be visible, the label will be displayed in the cellview immediately. You can click at labels one by one until you press Esc key.

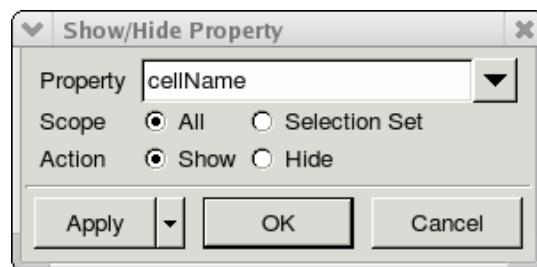

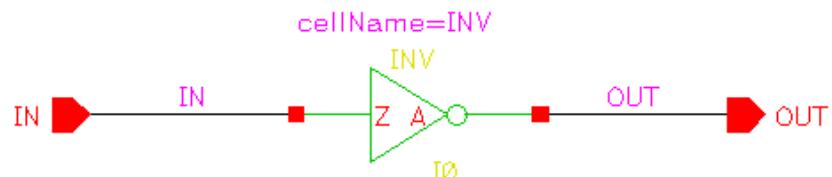

### 1.3.16 Edit->Show/Hide Property

Show or hide object property.

Select Edit->Show/Hide Property, the Show/Hide Property form appears.

Fill property name in *Property* field, or select a property from drop down list.

You can show or hide properties either all of objects or one of objects you selected.

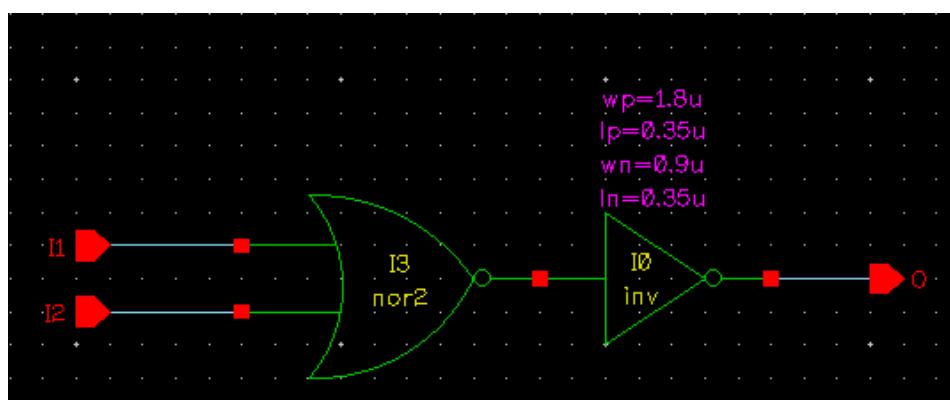

For example, in the below figure, the magenta text is property value.

Note:

Please do check option after Show/Hide Property to show net name.

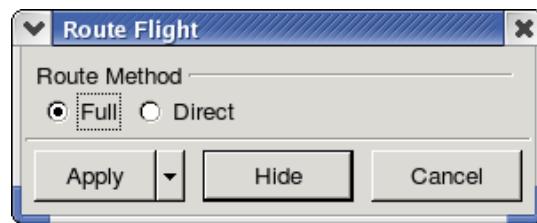

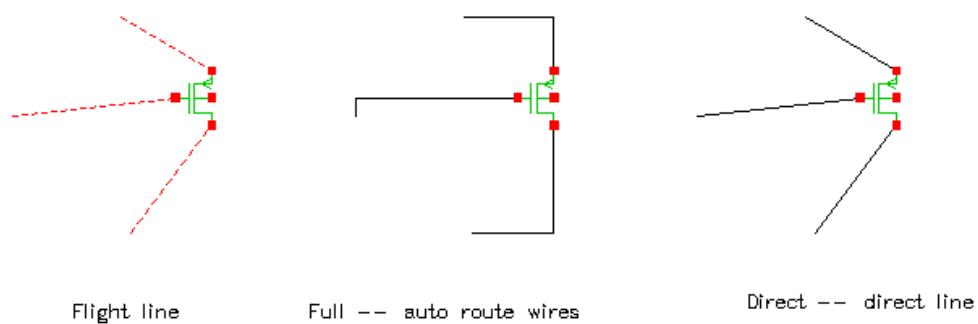

### 1.3.17 Edit->Route Flight

Route wires between two given points.

Select Edit->Route Flight first, click at a flight line to route wires.

You can press F3 key to change *Route Method* in the Route Flight form.

#### Route Method

*Full* Automatically route wires by editor. Sometime, the editor cannot route wires successfully, the dashed line remains there.

*Direct* Draw a direct line between two given points.

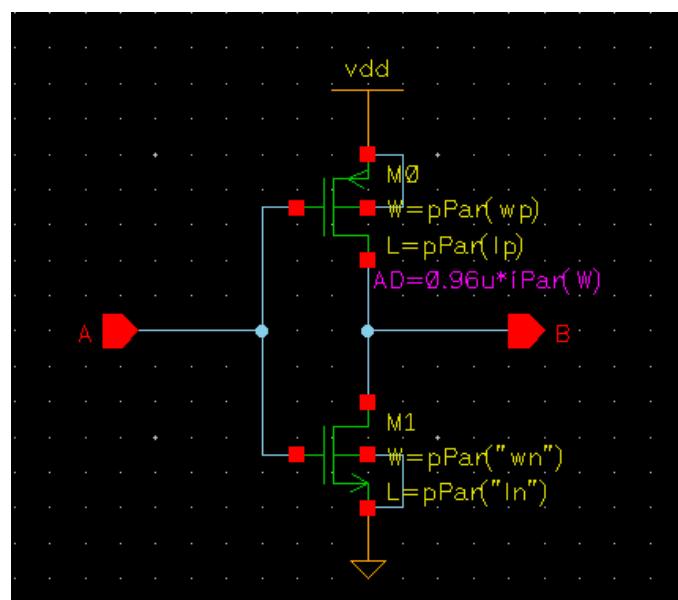

### 1.3.18 Edit->Property

Display and modify object's property.

Select Edit->Property or click icon , the object-related Property form appears. You can Add/modify/Delete some properties on it.

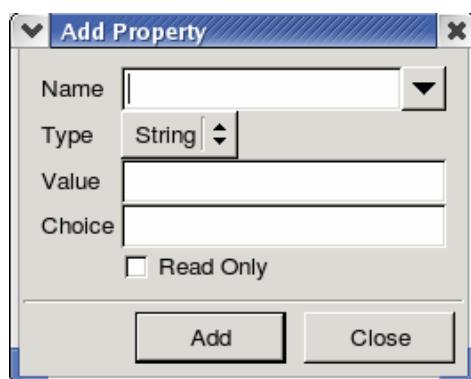

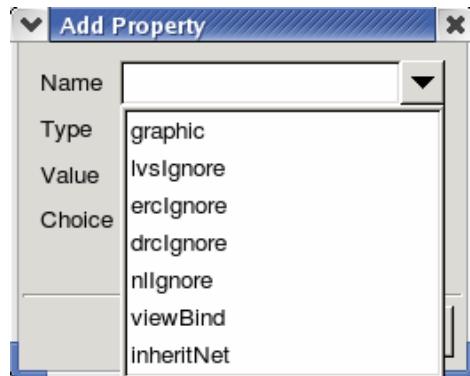

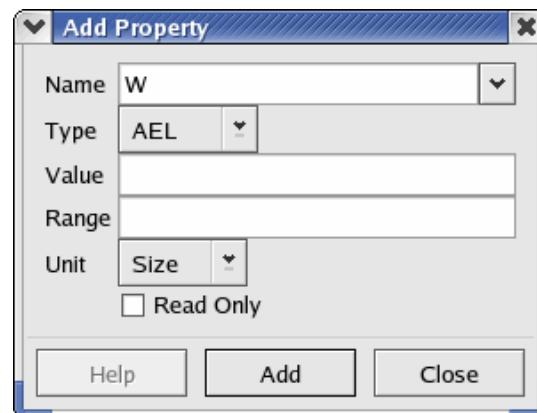

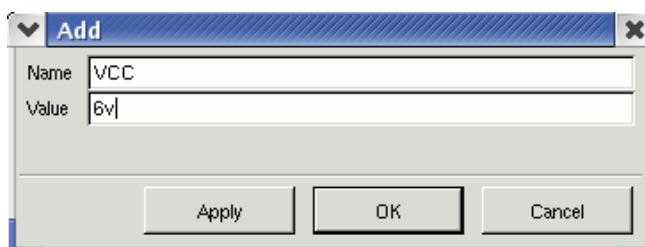

**User Property** field is for you to Add/Delete/Modify/Sort user-defined properties. Click Add button to add a new property, “Add Property” form pop-up as below, you can fill the form to add a property you want:

Zeni also provides you some properties on *Name* drop-down list. You can get more detail about these properties on the table below.

|            |                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| graphic    | Instance with graphic property should have no pin, and it will not be regarded as device and will not be exported to netlist file. Mainly used for Title Box.                                                                                                                                                                                                                                                  |

| ercIgnore  | Instance without any pin will not be checked as error if it has ercIgnore property. Mainly used for symbols come from Sheet library and Spice library.                                                                                                                                                                                                                                                         |

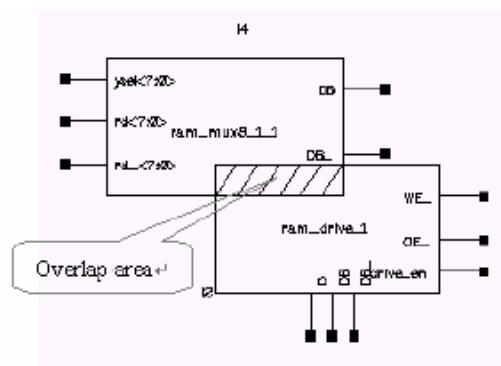

| drcIgnore  | System will not do overlap checking on instances with drcIgnore property.                                                                                                                                                                                                                                                                                                                                      |

| lvSIgnore  | Instance with lvSIgnore property will not be exported to CDL netlist file; while export Spice netlist, sub-circuits in this instance will be ignored.                                                                                                                                                                                                                                                          |

| nIIgnore   | Instance with nIIgnore property will be skipped while you export any kind of netlist.                                                                                                                                                                                                                                                                                                                          |

| viewBind   | Bind a specified view to this instance. It takes precedence of settings on ViewNameList.                                                                                                                                                                                                                                                                                                                       |

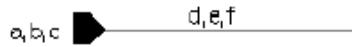

| inheritNet | <p>inheritNet is an extension to the connectivity model that allows you to create special global signals and override their names for selected branches of the design hierarchy. This flexibility allows you to use</p> <ul style="list-style-type: none"> <li>● Multiple power supplies in a design</li> <li>● Overridable substrate connections</li> <li>● Parameterized power and ground symbols</li> </ul> |

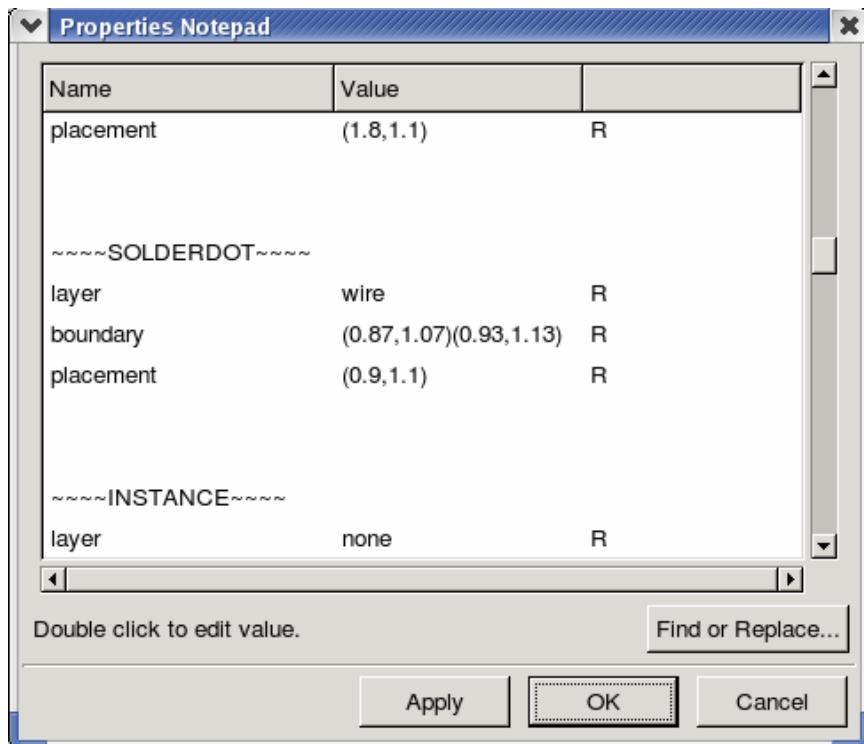

### 1.3.19 Edit->Property Notepad

Show and edit objects' properties in a pad text.

Select some objects, then choose *Edit->Property Notepad*, all the properties of selected objects will be shown.

## 1.4 Window menu

### 1.4.1 Window->Redraw

Refresh the entire layout window.

Select this command or click icon  to do it.

### 1.4.2 Window->Fit

Resize the display area and show the entire view in full window.

Select this command or click icon  to do it.

### 1.4.3 Window->Fit Object

Show all the objects in the current view in full window. Those objects exclude cell in "Sheet".

#### **1.4.4 Window->Fit Selection**

Only show the selected objects in full window.

#### **1.4.5 Window->Zoom In**

Display objects within a rectangle area in full window.

To do it, you should,

Select this command, or click icon  first.

Draw a rectangle area to enclose the objects you want to display in full window.

#### **1.4.6 Window->Zoom In By 2**

Magnify two times to display objects.

Select this command or click icon  to do it.

#### **1.4.7 Window->Zoom Out**

Reduce displaying all objects in a rectangle area.

To do it, you should,

Select this command or click icon  first.

Draw a rectangle area to enclose the objects you want to display in full window.

#### **1.4.8 Window->Zoom Out By 2**

Reduce two times to display objects.

Select this command or click icon  to do it.

#### **1.4.9 Window->Center**

Make a point appear in the center of the editor window.

Select this command and click on a point that you want to display in the center of the editor window. The image moves and places the reference point in the center of editor window.

## 1.4.10 Window->Last View

Discard current view and show the last view.

## 1.4.11 Window->Mark View

Record the current view status. You can jump to this marked view by *Jump View* command.

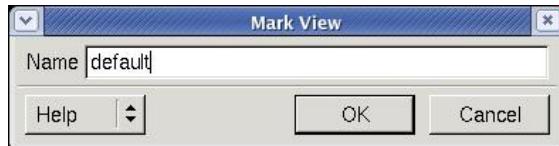

Select this command, "Mark View" form appears shown as below.

Type the maker name in *Name* field and click *OK* button. You can find this name will appear in *Jump View* form when you activate *Jump View* command.

## 1.4.12 Window->Jump View

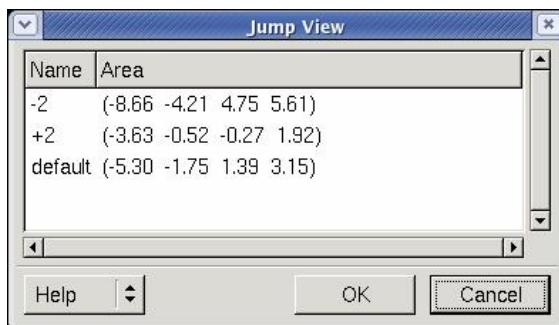

Jump to a previously marked view.

Select this command, "Jump View" appears shown as below.

The view names marked by *Mark View* are listed in this window. You can double click on a view name item or select a view name item and click *OK*, the view will be shown in editor window.

## 1.4.13 Window->Birds-eye View

Show the current view's panorama in a mini window. We call this mini view "Birds-eye View".

Select this command to show or hide the Birds-eye View.

In Birds-eye view window, the highlighted yellow rectangle presents an outline of a full opened cell. There are two ways to choose the area in the Birds-eye View.

One is moving the mouse cursor and click LMB at a dot, this dot is regarded as a center of the highlighted yellow rectangle, when you move the dot, the highlighted yellow rectangle will be changed. Another way is dragging the RMB to specify an area on the Birds-eye View.

The location of mini window can be set at Top Left, Top Right, Bottom Left and Bottom Right by Options->Display->Birds-eye View At.

The size of mini window can be set also by *Options->Display->Birds-eye View Size*.

## 1.4.14 Window->Copy Window

Duplicate current cellview window and open the new one.

## 1.4.15 Window->Raise Design Manager

This command raises Design Manager window to the top of the screen. It's very convenient for you to return to Design Manager window directly from schematic editor window.

## 1.5 Select Menu

### 1.5.1 Select->Area Select

Select objects within a specified area. All objects inside this area will be selected.

To do it, you should

1. Choose this command.

2. Click the first corner of the selection area with LMB.

3. Hold and drag LMB to select the area, click to confirm the second corner.

### 1.5.2 Select->Line Select

Select objects by trail of cursor. All objects cross this line will be selected.

To do it, you should

1. Choose this command.

2. Click the first point with LMB.

3. Hold and drag LMB to the second point, release LMB.

For example, below table shows the process of line selection.

| Action                                                                   | Illustration |

|--------------------------------------------------------------------------|--------------|

| Drag left mouse button to cross objects you want to select.              |              |

| Release left mouse button, objects in this trail of cursor are selected. |              |

#### Note:

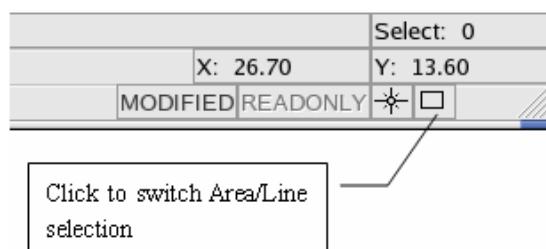

You can click a icon at the right bottom of Schematic Editor window to switch area selection or line selection.

Comparing with menu command method, this method is different. Using menu

command Select->Area/Line, select only works on the current operation. When the command is finished, the default selection mode still depends on the icon command located at the right bottom of the Schematic Editor window.

### 1.5.3 Select->Select All

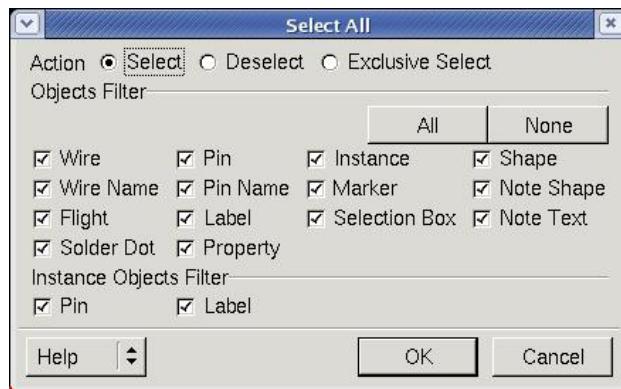

Select, deselect or exclusive select objects in current cellview.

**Action** controls which type operation does you want in this session.

**Objects Filter** and **Instance Objects Filter** sections let you select the object types that will be selected/deselected/exclusive selected in current cellview.

### 1.5.4 Select->Select By Property

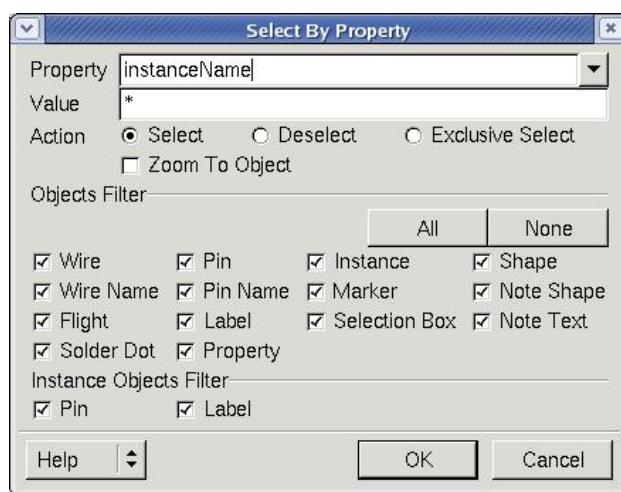

Select objects by some specified properties.

Select this command or click icon . “Select By Property” form is shown as figure below.

**Property** lets you type object's property or select a candidate property from drop-down list. The candidate properties are *instanceName*, *netName*, *pinName*, *wireName*, *libraryName*, *cellName* and *viewName*.

**Value** lets you type the value of the property. Use asterisk (\*) for wildcard.

**Action** specifies the action of selecting.

**Zoom To Object** controls whether to magnify the selected object at the center of the editor window.

### 1.5.5 Select->Select Wires

Click a segment of one wire to select entire wire.

**Note:** You can double click a segment of a wire to select entire wire.

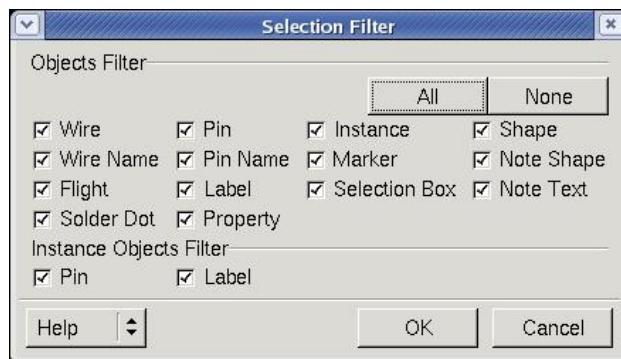

### 1.5.6 Select->Filter

Specify which type objects will be selectable.

Turning on an object option means the type of object is selectable. Click *All* button to turn on all type of objects. Click *None* button to turn off all type of objects.

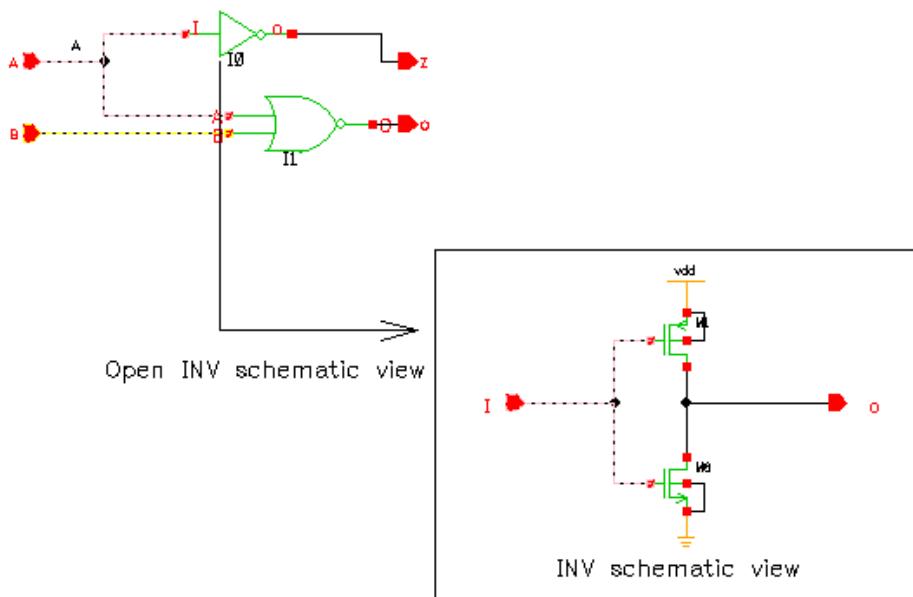

### 1.5.7 Select->Trace Net

Highlight an electrical connectivity net.

Select this command; click a segment of a net, the editor highlights the whole net in color. The editor can pass the net connectivity into its sub-cell that connected with this net.

To trace a net, do as follow:

1. select Check->Hierarchy to check full hierarchy first

2. Choose "Select->Trace Net"

3. Click on any segment of a net or a hierarchy pin

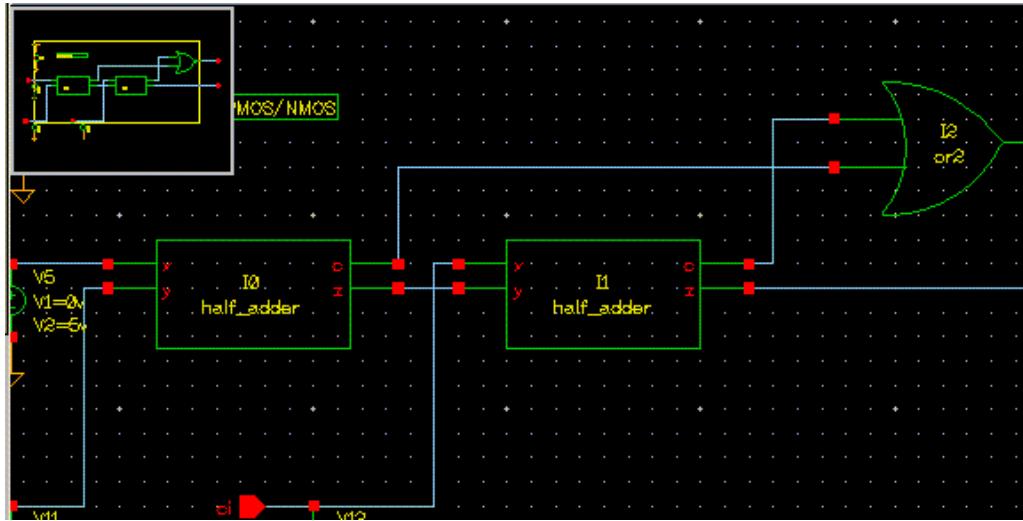

For example, the following figure shows the electrical connectivity net "A" in pink. The

net "A" connects two instances "INV" and "NOR2". The editor passes the connectivity into internal of instance via instance pin. Try to open "INV" schematic view, you can find the editor highlights the net "I" in pink as well.

You can trace net one by one until you press *Esc* key. The editor allows you to specify 6 colors for tracing, when you trace the 7th net; the color is the same as the first one. As the above figure, the second tracing net "B" is in yellow.

#### Note:

1. Before tracing net, you must check hierarchy cell.

2. You can trace more nets one by one until pressing "Esc" key.

3. Using Select->Remove Trace or Select->Remove All Traces to remove the highlight.

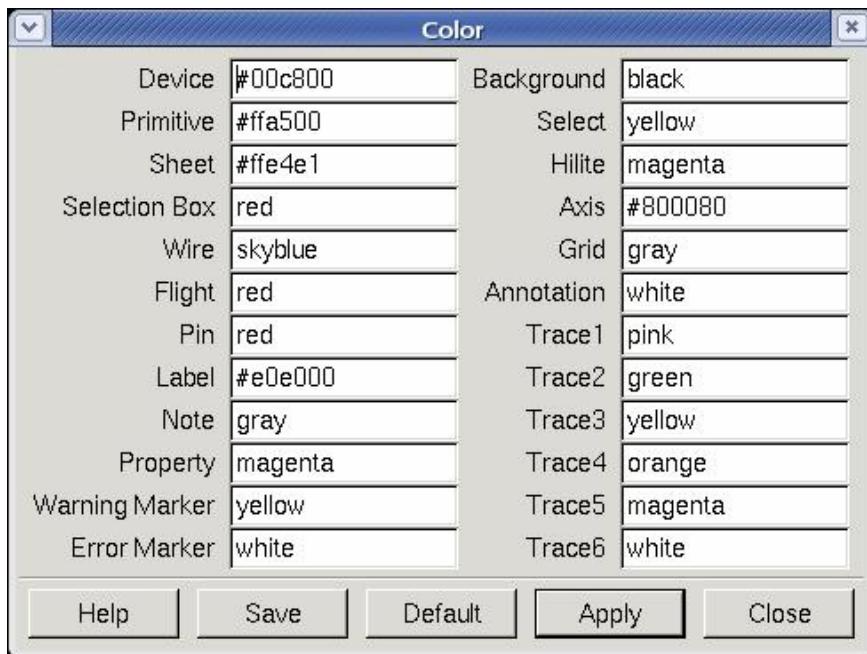

4. The color of highlighted dashed is specified in Option->Color.

### 1.5.8 Select->Remove Trace

Change the highlighted net to normal. This net is highlighted by command *Trace Net* before.

Choose this command; click on a highlighted net, the net will be cancelled highlight.

You can remove highlighted net one by one until you press *Esc* key.

## 1.5.9 Select->Remove All Traces

Change all highlighted nets to normal. These nets are highlighted by command *Trace Net* before.

Choose this command; all highlighted net will be cancelled highlight.

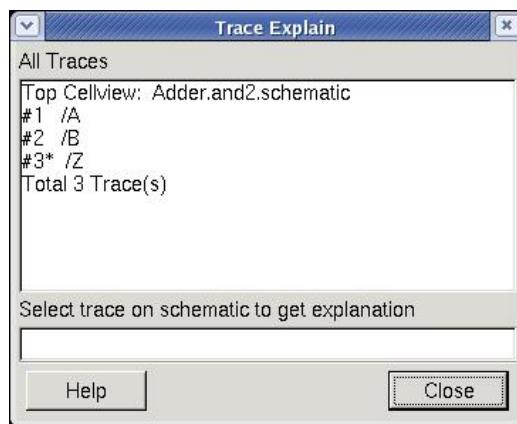

## 1.5.10 Select->Trace Explain

Display information of electrical connectivity net.

After doing *Trace Net* command, select this command, information of all electrical connectivity nets is shown in "Trace Explain" form.

This form displays the top cellview name and the number of traced net. '\*' represents this net is in the current cellview. Select one of nets in the current cellview editor, associated information with this net will display in *Explain Selection* field.

## 1.6 Hierarchy->Descend Edit

This command allows you to edit a sub-cell in current window directly, which avoids opening this sub-cell by Design Manager.

Select this command or click icon  , click on an instance, editor will display all the views of the cell in a pop up menu. Select one of view, the editor will open the associated editor for editing in current window.

## 1.6.1 Hierarchy->Descend Read

This command allows you to open a sub-cell in current window for read.

Select this command; click on an instance, editor will display all the views of the cell in

a pop up menu. Select one of view, the editor will open the associated editor for read only in current window.

## 1.6.2 Hierarchy->Return

This command returns to an upper level cell.

Select this command or click icon  to return to an upper level cell.

**Note:** The current view must be opened by command Descend Edit or command Descend Read, otherwise, this command is invalid. For example, if the current view is opened by Design Manager directly, this command does not work.

## 1.6.3 Hierarchy->Return To Top

Return to the top cell directly.

**Note:** The current view must be opened by command Descend Edit or command Descend Read, otherwise, this command is invalid. For example, if the current view is opened by Design Manager directly, this command does not work.

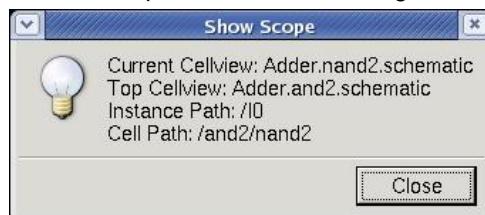

## 1.6.4 Hierarchy->Show Scope

Display information of current cellview.

Select this command, "Show Scope" form is shown as figure below.

This form displays the current cellview name. If the current cell does not a top cell, it also displays the top cell name, the instance path and cell path.

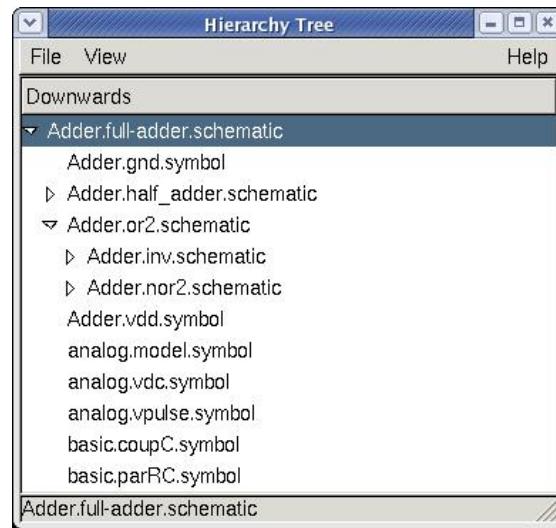

## 1.6.5 Hierarchy->Show Tree

This command displays all sub-cells of current view.

Select this command, "Show Tree" form is shown as figure below.

## 1.7 Cellview menu

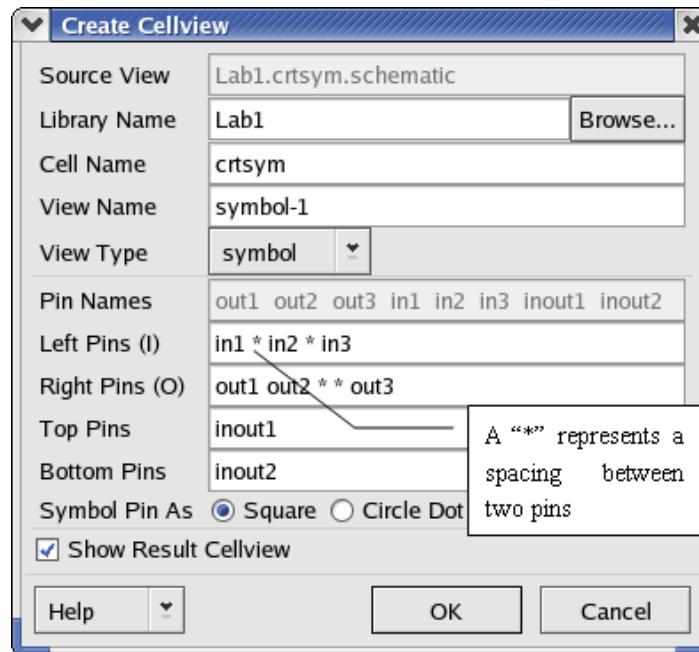

### 1.7.1 Cellview->Create From Cellview

This command automatically creates a new cellview according to current view.

Select this command or click icon , "Create Cellview" form is shown as figure below.

**Source View** specifies the current view.

**Library Name** specifies library name you want to create.

**Cell Name** specifies cell name you want to create.

**View Name** specifies view name you want to create.

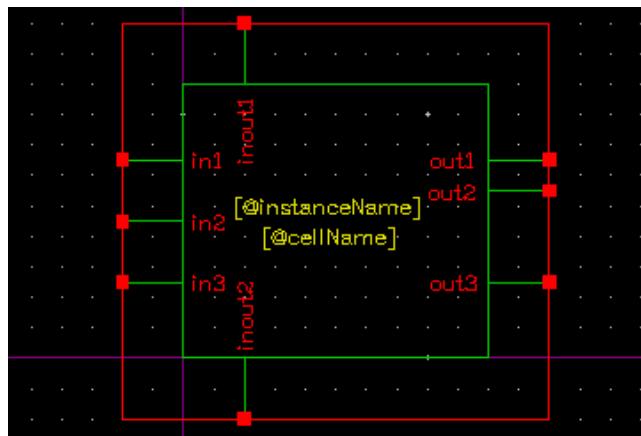

**View Type** lets you choose a view type you want. If you choose "symbol" from the drop-down list, the editor will create a symbol view. This symbol view includes a rectangle and some pins, these pins are around the rectangle.

**Pin Names** lists all of pins in current view. The order of list follows the definition of command *Pin Order*. You cannot modify it. These pins will be created in symbol view,. You can also specify the location of these pins in following fields.

**Left Pins** specifies pins are on the left side of rectangle in symbol view.

**Right Pins** specifies pins are on the right side of rectangle in symbol view.

**Top Pins** specifies pins are on the top of rectangle in symbol view.

**Bottom Pins** specifies pins are on the bottom of rectangle in symbol view.

#### Note:

1. If you don't type any pin name in these fields, the system puts all of input pins or inout pins on the left of rectangle and puts all of output pins on the right of rectangle.

2. In these fields, you can use one or multiple "\*" to control the distance of two pins. For example, setting all the pins as the Create Cellview form above, then the symbol will be as figure below:

**Symbol Pin As** specifies the shape of the pin is either *Square* or *Circle Dot* in symbol view.

**Show Result Cellview** opens the new view in a new window.

## 1.7.2 Cellview->Create From Instance

This command automatically creates a new cellview according to an instance you selected.

The form and usage are similar to command *Create From Cellview*, please refer to 1.4.1 *Cellview->Create From Cellview*.

## 1.8 Page menu

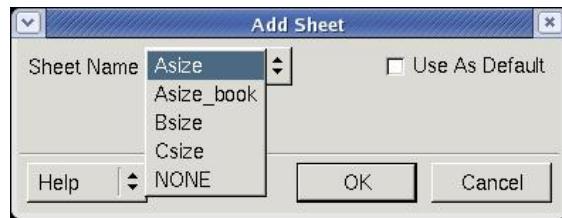

### 1.8.1 Page->Add Sheet

Add a sheet frame around the schematic cellview.

You can use default sheets in the system library “sheet” or create your own sheets and add them to “sheet” library.

Select this command or click icon , “Add Sheet” form is shown as figure below.

**Sheet Name** lets you select a sheet from dropdown list. "NONE" specifies to remove sheet from current cellview.

**Use As Default** lets you automatically add this sheet when creating a new schematic view.

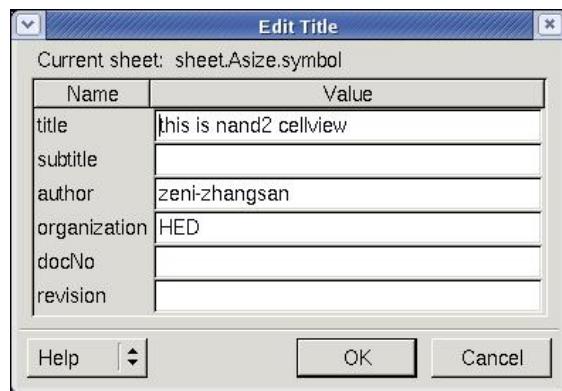

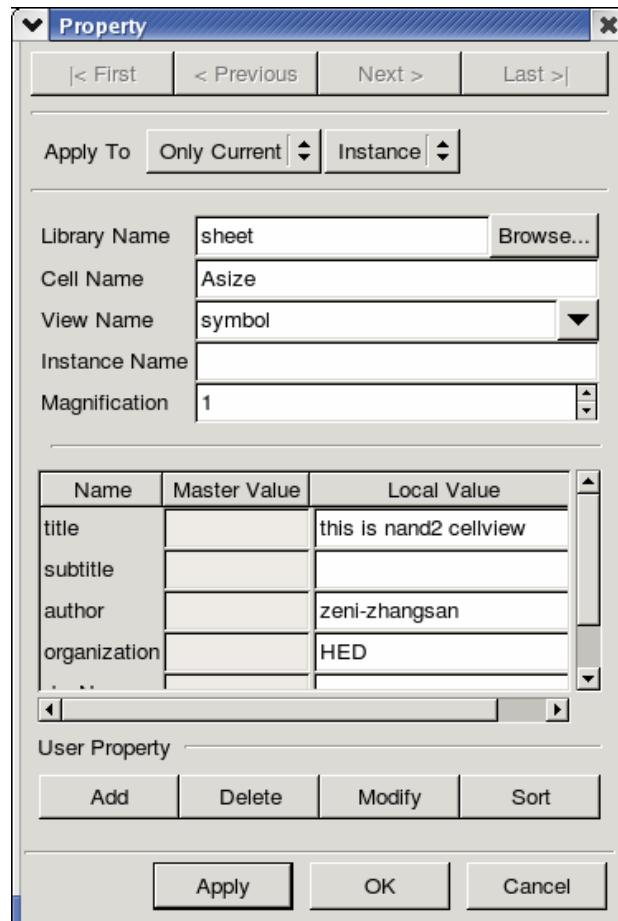

### 1.8.2 Page->Edit Title

Edit the sheet information, such as title, author, organization, etc.

Select this command, “Edit Title” form is shown as figure below.

Type the valid information in this form, click *Apply* or *OK* button, the information will be display in sheet shown as below.

|                                 |                               |                   |

|---------------------------------|-------------------------------|-------------------|

| Title<br>this is nand2 cellview |                               | DocNo<br>Revision |

| Design<br>Adder.nand2.schematic | Update<br>2008-04-22 10:45:38 |                   |

| Author<br>zeni-zhangsan         | Organization<br>HED           |                   |

Some information, such as *Design* and *Update* are updated automatically.

You can also modify the information in sheet property form. Please refer to figure below.

### 1.8.3 Page->Make Multi-Pages

Partition multi-pages schematic views to your design in several pages.

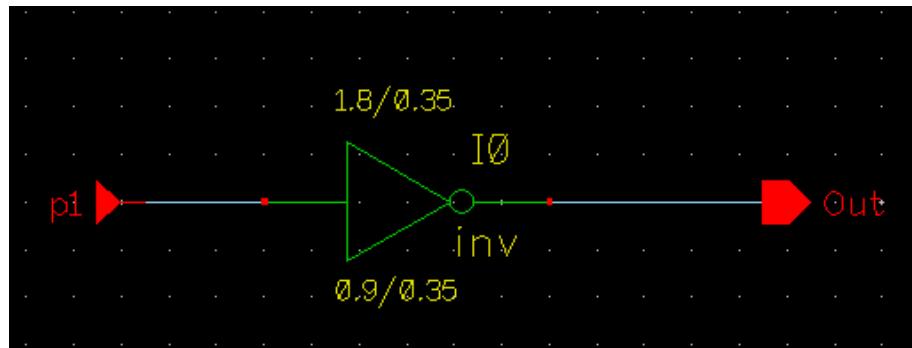

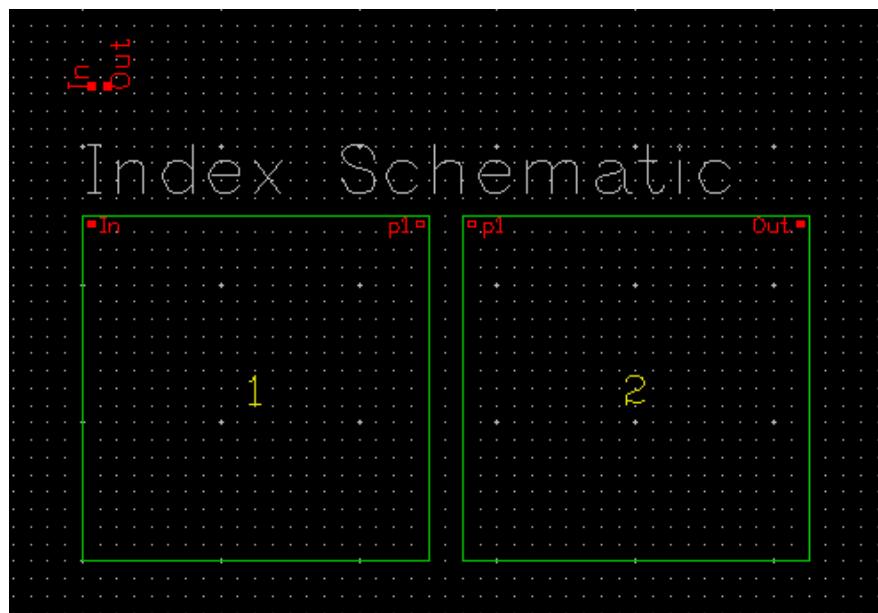

Select *Page->Make Multi-Pages*, the editor renames the current cell name to "cellname@1", which means this design is the first page design. In the meanwhile, the editor creates an index schematic named "cellname" to organize the pages; each page design is as an instance in Index schematic. To add more pages, select *Page->New Page* from the Index Schematic.

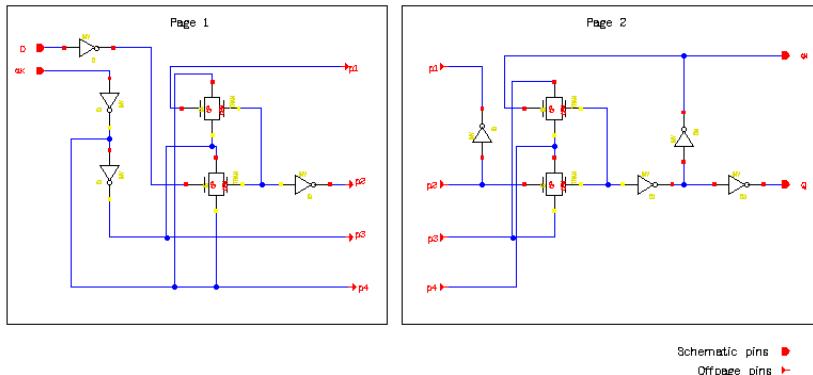

The following is an example of a design that consists of 2 pages. Offpage pins p1, p2, p3, p4 connect two pages. These offpage pins must be used twice. In page 1, offpage pin direction is output. In page 2, offpage pin direction is input.

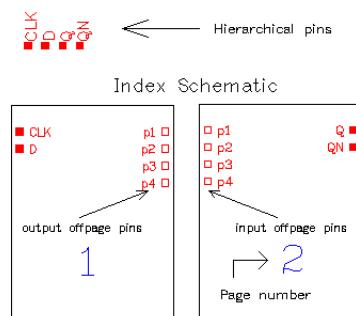

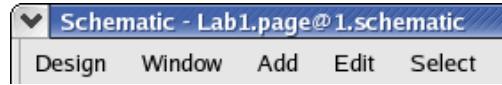

In the top level, the index schematic is as below.

It displays all of hierarchical pins (schematic pins) and all of page symbols. In each page symbol, the input pins (schematic pins or offpage pins) are placed on the left side, the output pins (schematic pins or offpage pins) are placed on the right side.

The ■ represents this pin is a hierarchical pin.

The  represents this pin is an offpage pin.

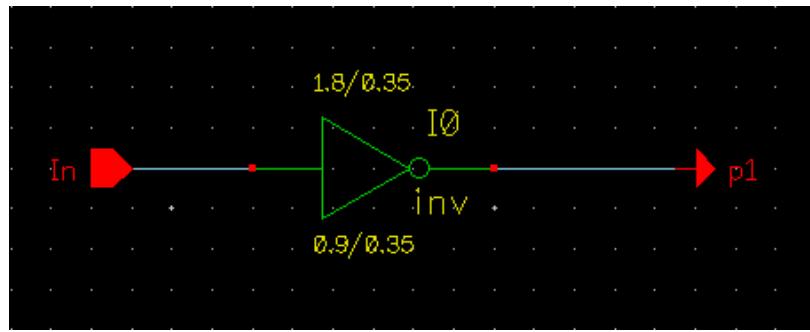

Here is an example to show how to make Multi-Pages:

1. Create a new cellview "Lab1.page.schematic"

2. In Schematic Editor window, create following objects:

- schematic input pin "In"

- instance of cell "INVtest.inv.schematic"

- offpage output pin "p1".

3. Save the cellview.

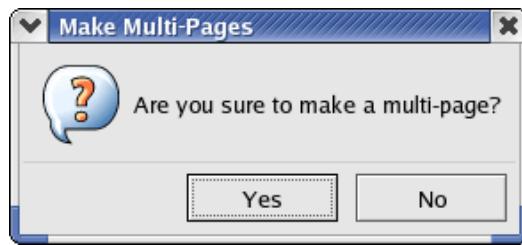

4. Select page->Make Multiples page. A question form appears as below.

5. Yes the form.

6. The title of current Schematic Editor window becomes to "Lab1.page@1.schematic". "@1" represents the first page.

7. Close the current Schematic Editor window.

8. Open the cellview "Lab1.page.schematic", this cellview looks as the figure below.

9. This cellview includes an instance of cell "page@1", and extracts the schematic pin of cell "page@1" as schematic pin of itself.

10. In instance of cell "page@1",

- represents the schematic pin

- represents the offpage pin.

Input pin is in the left, output pin is on the right

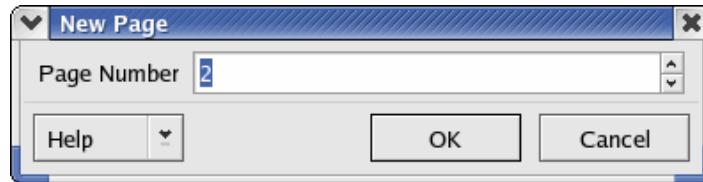

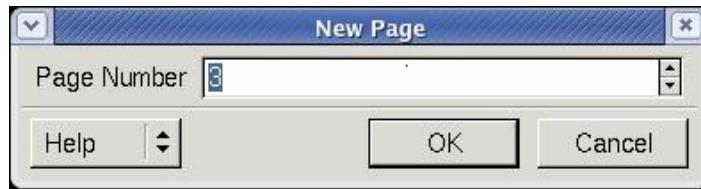

11. In this cellview window, select Page->New Page. A New Page form appears.

12. System automatically fills out '2' in Page Number to represent the next page is the second one.

13. Ok the form. The cell "page@2" is created in Design Manager window, and the Schematic Editor pops up.

14. In Schematic Editor window, create following objects:

- offpage input pin p1.

- instance of cell "INVtest.inv.schematic"

- schematic output pin out

15. Save the current cellview.

16. Open the cellview “Lab1.page.schematic” again. There are two instances as below.

17. Save and close the cellview.

**Note:**

Offpage pin must appear twice with reverse direction between two pages.

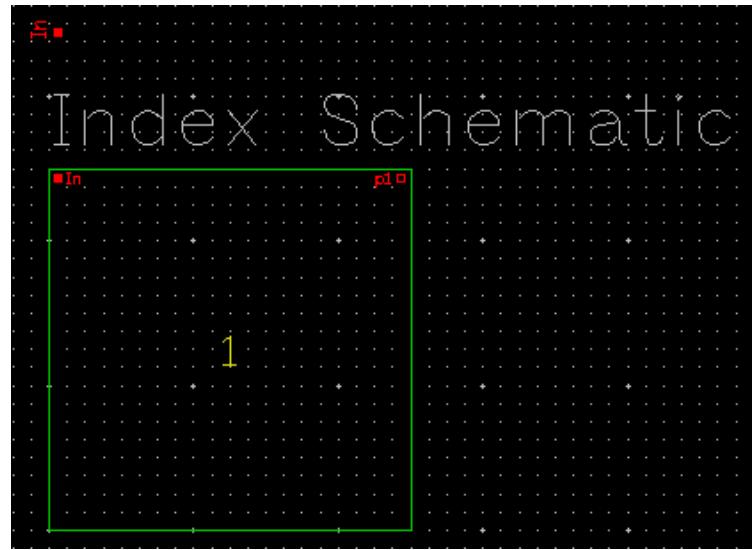

#### 1.8.4 Page->New Page

Create a new page.

In index schematic view, select this command, the “New Page” form is shown as

figure below.

The editor automatically fills the page number in *Page Number* field. This page number is the current maximum page number plus 1. You can modify this number as you want.

Click *Apply* or *OK* button, Design Manager will create a new cell named "cellname@3", here cellname is the cell name. Meanwhile, system will open the schematic editor in the current window.

You can use , or *Hierarchy->Return*, or *Hierarchy->Return To Top* to return to the index schematic.

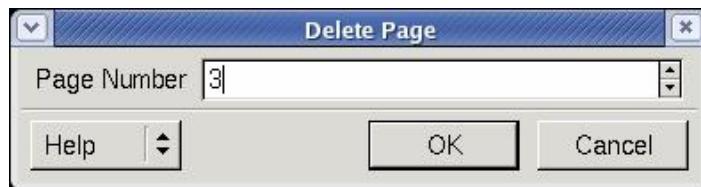

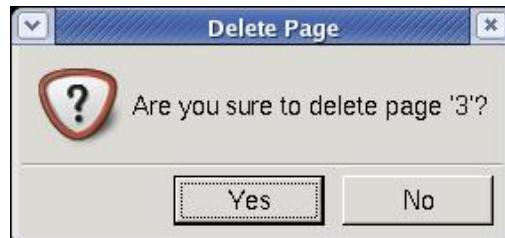

### 1.8.5 Page->Delete Page

Delete a page design.

In index schematic view, select this command, the "Delete Page" form is shown as figure below.

Type the page number you want to delete in *Page Number* field. Click *Apply* or *OK* button, a question dialog box pops up to enquire whether you are sure to delete this page.

Click *Yes* to delete this page design. In the meantime, the associated cell "cellname@3" is deleted.

**Note:** If you delete the page symbol with *Del* key or *Edit->Delete* in index schematic, the associated cell will not be deleted. This operation cannot be undone.

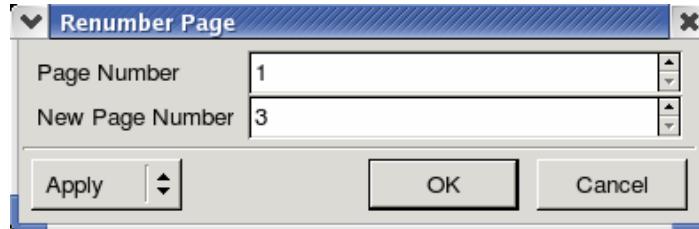

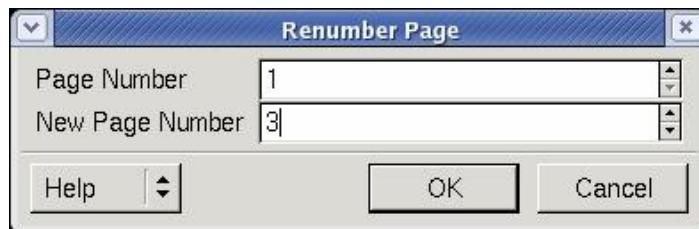

## 1.8.6 Page->Renumber

Reset the page number.

In index schematic view, select this command, the "Renumber Page" form is shown as figure below.

Specify the page number you want to reset in Page Number field.

Specify the new page number in New Page Number field.

If the new page number already exists, the editor will give you a question dialog box to enquire whether you continue to renumber this page.

Click Yes to renumber the page 1 to page 3, the associated cell name "cellname@1" is renamed to "cellname@3". Original page 3 will be forced renamed to page 4, the associated cell name "cellname@3" is renamed to "cellname@4".

**Note:** This operation cannot be undone.

## 1.8.7 Page->Resequence

To reset sequence number of all page views.

In index schematic view, select this command, the editor rennumbers all pages sequentially beginning with page 1.

For example, if there are page 2, page 3 and page 5, this command reorders the pages in sequence page 1, page 2 and page 3.

## 1.9 Check menu

### 1.9.1 Check->Current Cellview

Check circuit in current cellview.

Select this command, editor will pop up a mini window and show the number of errors after checking. The detailed error information will be displayed in Design Manager.

If you turn off Prompt When 0 Errors/Warnings option in *Options->Check Rules*, editor does not pop up the mini window if no errors and warnings.

When circuit is error, the error marker and warning marker are placed in the corresponding position. You can modify the colors of error marker and warning marker by *Options->Color*. You can also remove these markers by *Check->Delete Marker* or *Check->Delete All Markers*.

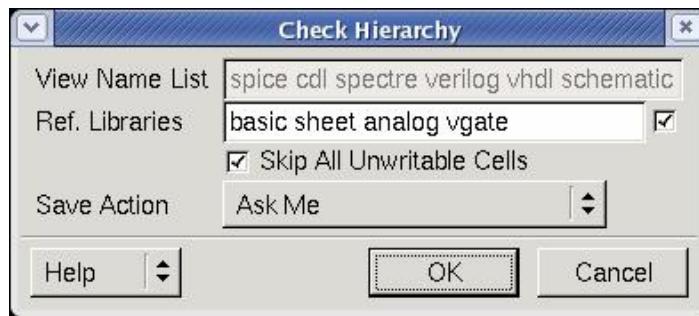

### 1.9.2 Check->Hierarchy

To check all of related schematic views in the hierarchy design.

Select this command, the "Check Hierarchy" form is shown as figure below.

**View Name List** shows which view you will be checked. This list is defined in *Options->Editor* form, you have no write access here. From the heading of this list, editor will search view name one by one for related cells, and check the first founded view. This list is defined in *Options->Editor*

**Ref. Libraries** list some referenced libraries which will not be checked.

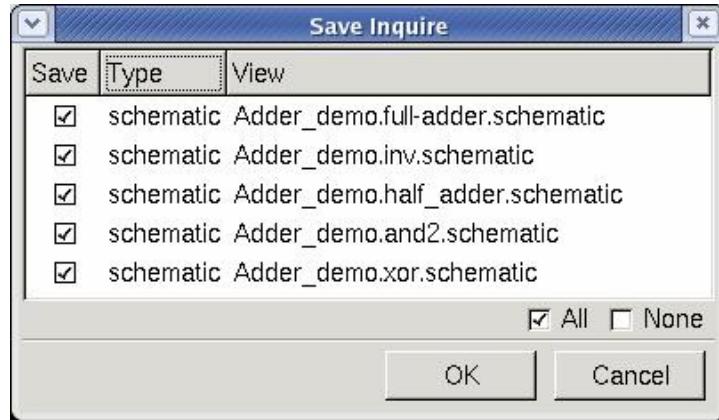

**Save Action** specifies whether editor saves checked cellviews after checking.

**Auto.Save** -- automatically save all of checked cellviews.

**No Need Save** -- don't save all of checked cellviews.

**Ask Me** -- pop up a dialog box to inquire you which cellview need to be saved.

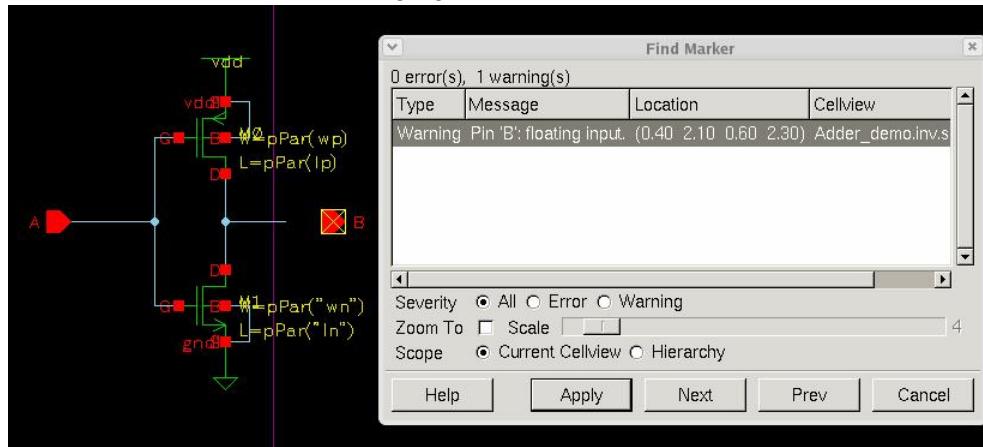

### 1.9.3 Check->Find Marker

Find the error in cellview recorded by marker.

Select *Check->Find Marker*, the editor pops up a dialog box which displays all of the error and the warning messages generated by check. Click on an error or warning item in the list, and the editor will highlight the associated marker in the window.

**Severity** determines displaying what kinds of markers, *Error/Warning/All*.

**All** display both errors and warnings.

**Error** only displays all of errors.

**Warning** only displays all of warnings.

**Zoom To** lets you magnify the error object and show it in the center of window. **Scale** specifies the ratio of magnification.

**Scope** specifies displaying errors either in the current cellview or in all of the cellviews within the hierarchy.

## 1.9.4 Check->Delete Marker

Delete marker by your cursor.

Select *Check->Delete Marker* first; move your cursor to marker, no matter either error marker or warning marker, click on this marker, the marker will be removed.

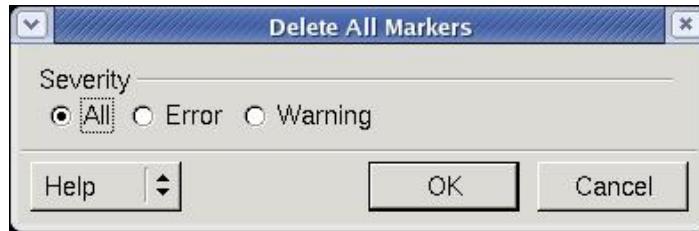

## 1.9.5 Check->Delete All Markers

Delete all markers.

Select *Check->Delete All Markers*, the “Delete All Markers” form is shown as figure below.

Select an option in above form,

**All** delete all markers.

**Error** only deletes error markers.

**Warning** only deletes warning markers.

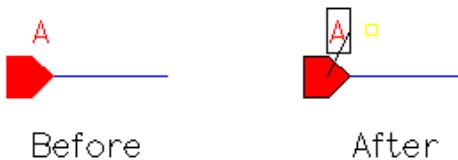

## 1.9.6 Check->Show Label Attachment

Highlight the association between a label and its owner (pin, wire or instance).

Select *Check->Show Label Attachment*, you click either an object (pin, wire or instance) or a label, system will draw a highlighted line between them, and highlight it. The following figure shows the result of showing label attachment.

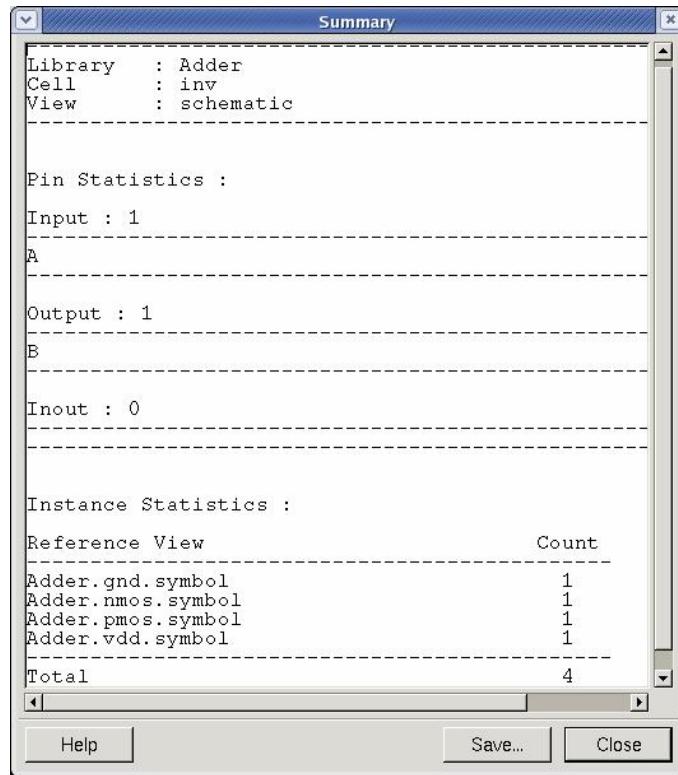

## 1.9.7 Check->Summary

To display detailed information about how many pins and instances are in the current cellview.

Select *Check->Summary*, the “Summary” form is shown as figure below.

## 1.10 Tools menu

### 1.10.1 Tools->Export Netlist

This command generates 7 kinds of netlists, there are *SPICE*, *CDL*, *Verilog*, *Verilog-A*, *VHDL*, *Spectre* and *Mixed-Mode*.

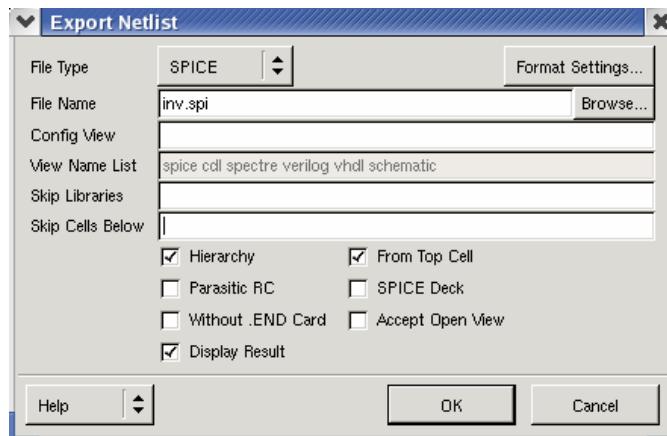

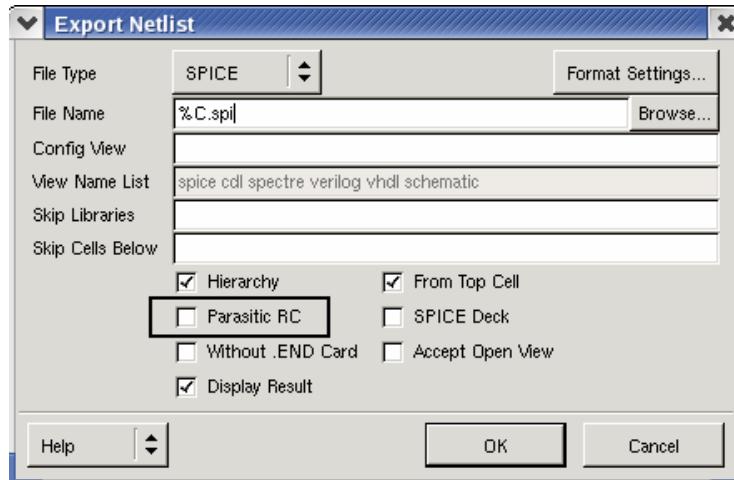

Select *Tools->Export Netlist* or click icon , the “Export Netlist” form is shown as figure below.

**File Type** specifies to generate which type of netlist format. Click on the *Format Settings* button to specify the netlist format.

**File Name** lets you type the netlist file name. You can also fill out this field with "%C".

For example, File Name   . Here, %C

stands for the current cellview name. Suppose that the current cellview name is "inv". The netlist file name will be "/tmp/inv/inv.spi".

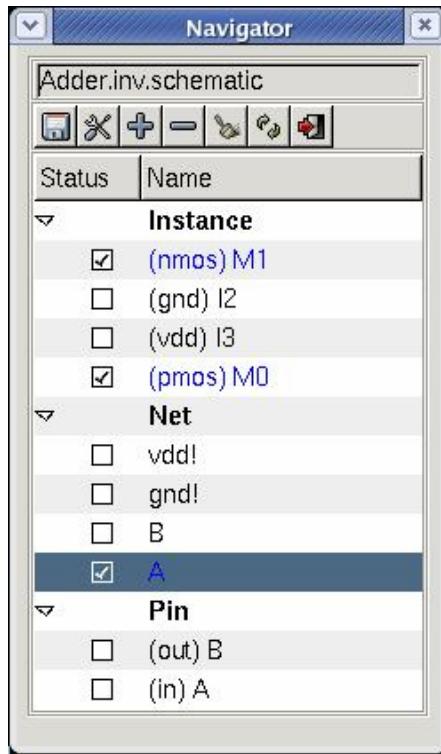

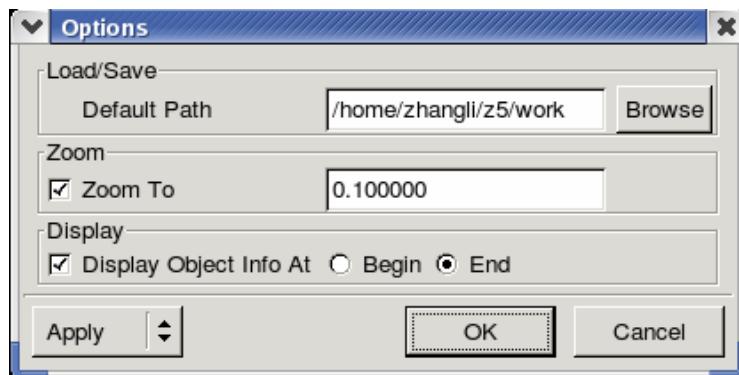

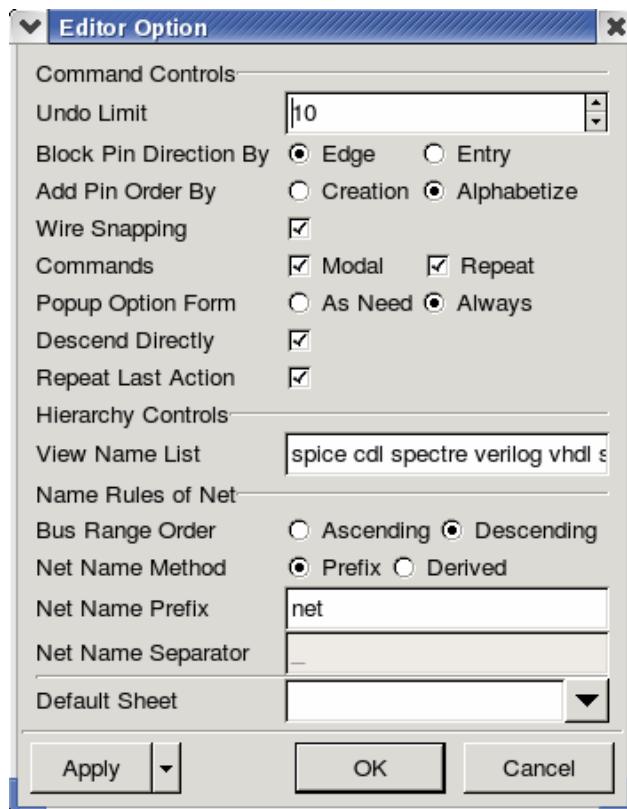

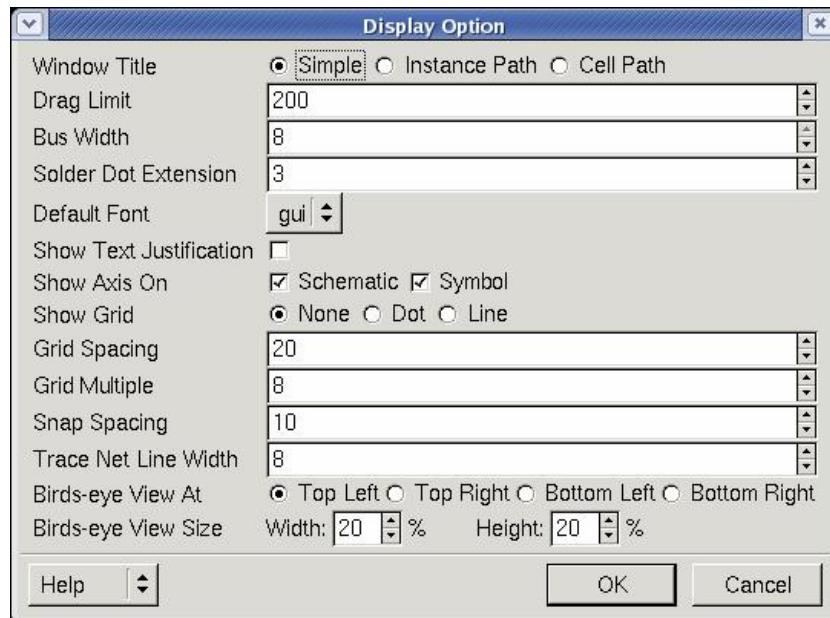

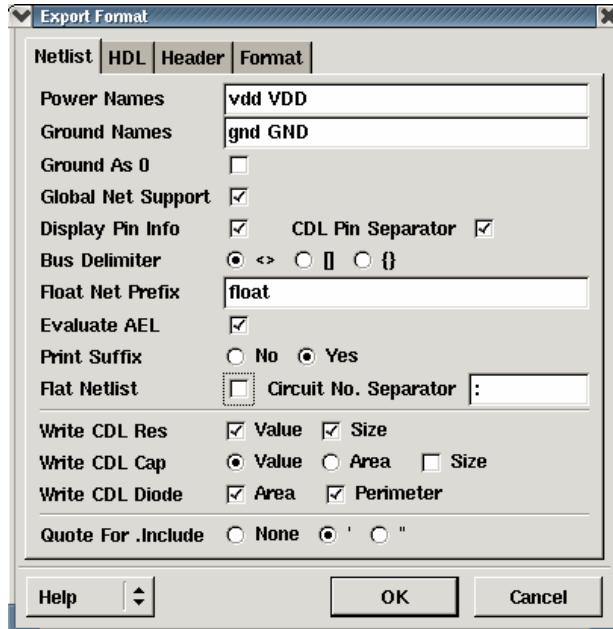

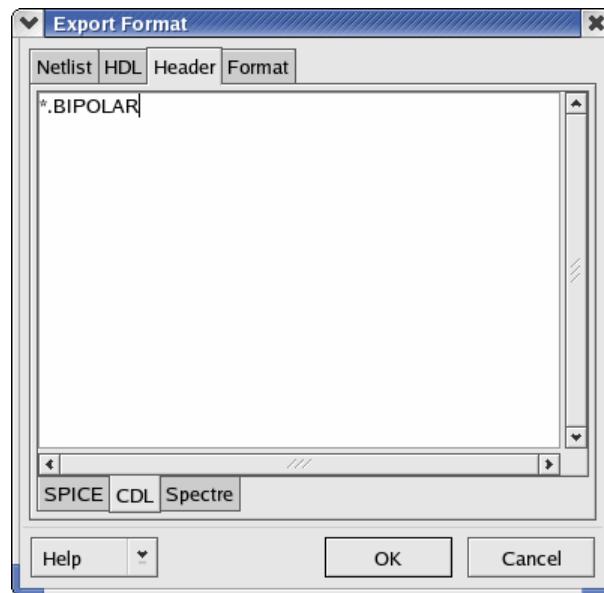

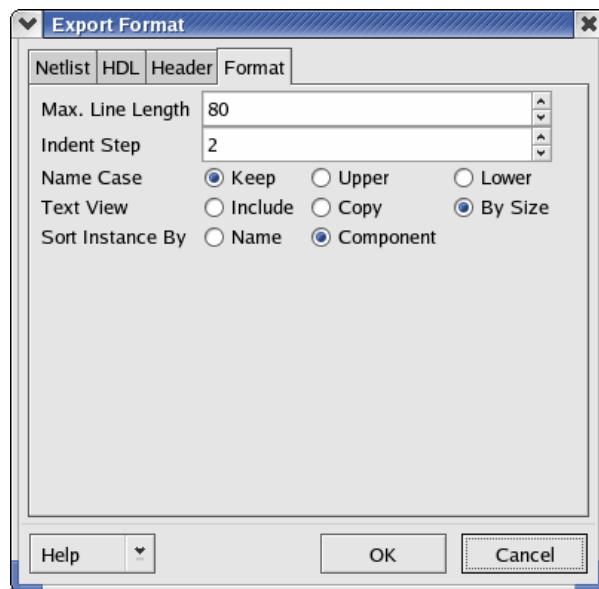

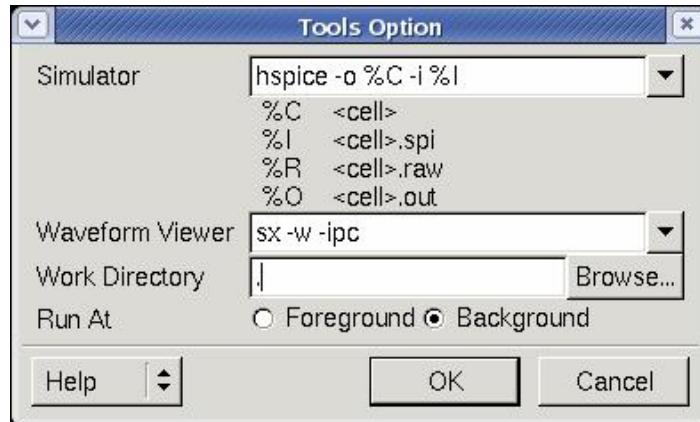

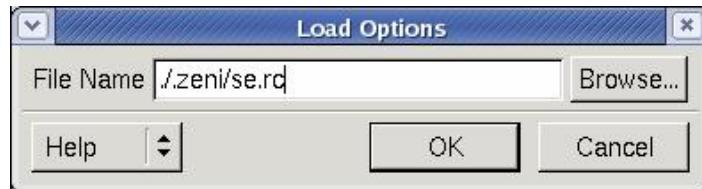

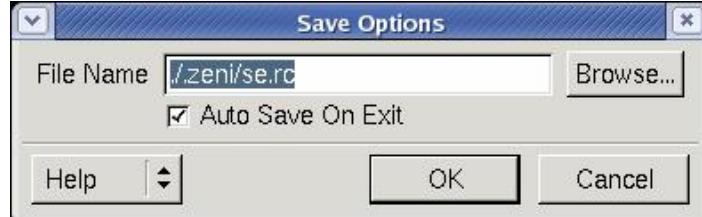

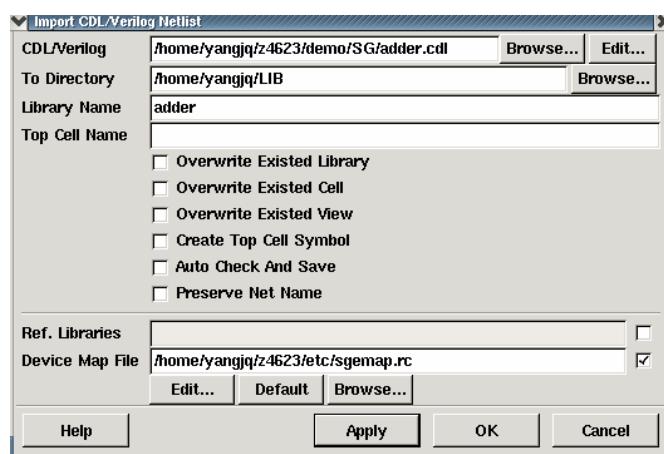

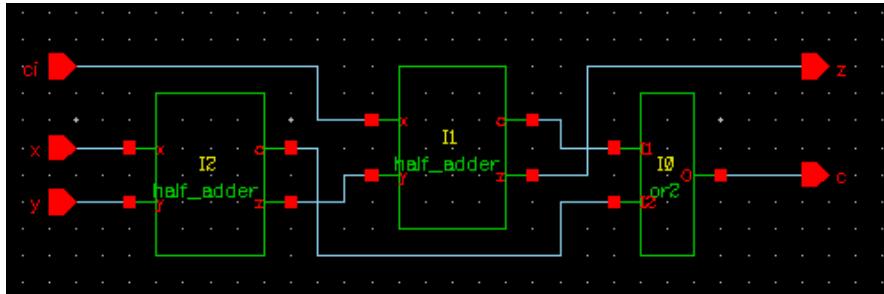

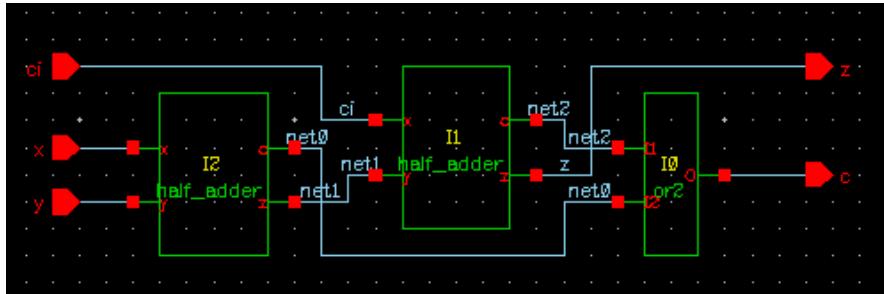

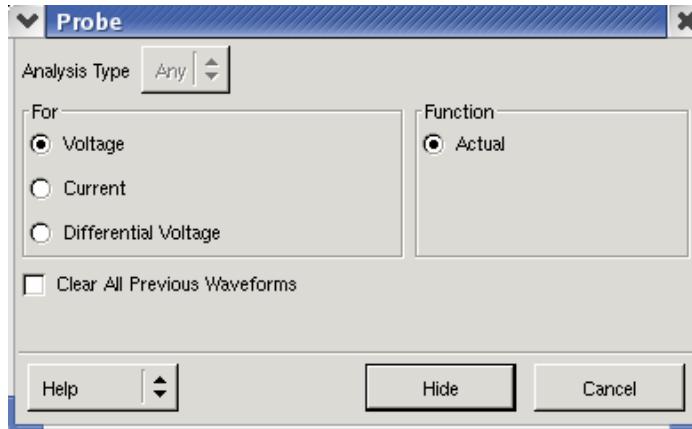

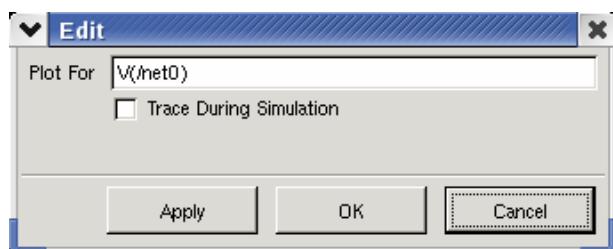

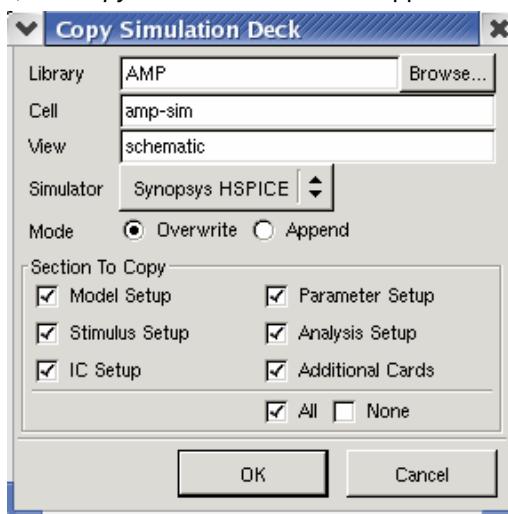

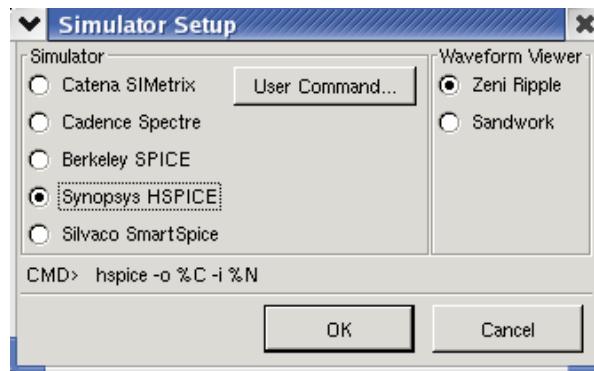

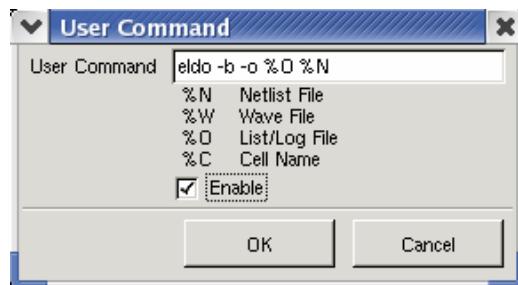

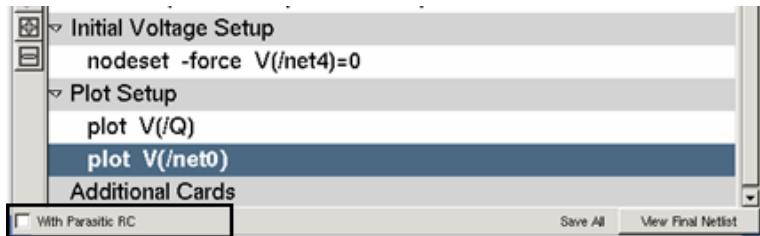

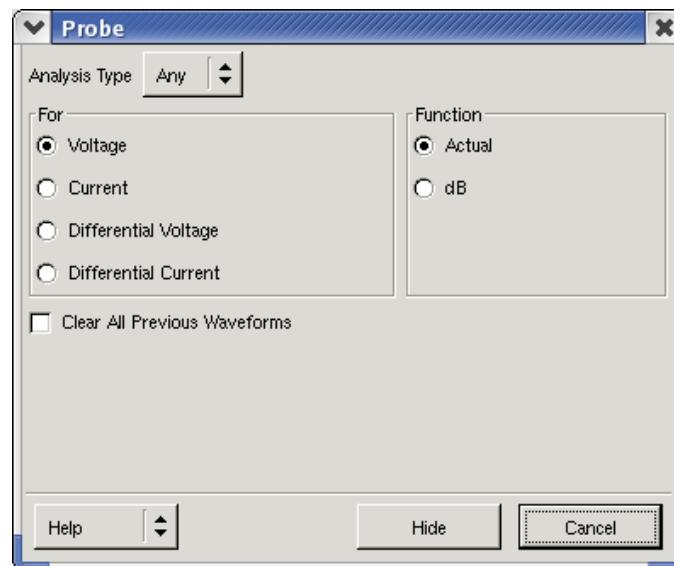

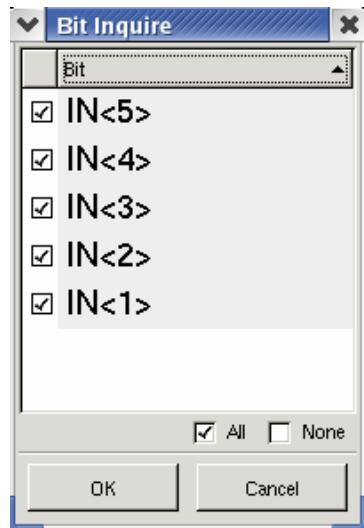

**Config View** lets you type a configuration cellview name. This cellview is used for exporting a *Mixed Mode* netlist.