# **Phase-Locked Loops**

Ching-Yuan Yang

National Chung-Hsing University

Department of Electrical Engineering

#### Overview

- Main Readings

- B. Razavi, Chapter 15 of Design of Analog CMOS Integrated Circuit, 2002.

- □ Cicero S. Vaucher, Chapter 2 of Architectures for RF Frequency Synthesizers, 2002

- □ Dean Banerjee, PLL Performance, Simulation, and Design.

- Outline

- Simple Phase-Locked Loops

- Charge-Pump Phase-Locked Loops

- Nonideal Effects in PLLs

- Jitter/Noise in PLLs

- Applications of PLLs

- Behavior Simulation

# Simple Phase-Locked Loops

1-2

PLL ICs

Ching-Yuan Yang / EE, NCHU

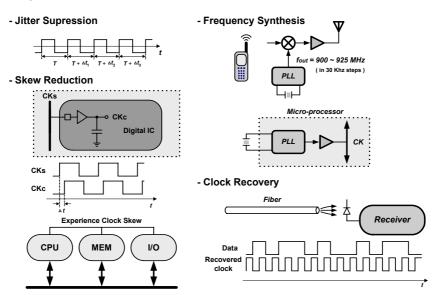

# Why phase-lock?

#### What is PLL?

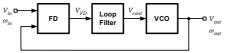

- Operates on excess phase of x(t) and y(t).

- Feedback system with PD as an error amplifier.

- "Locked" when phase difference between input and output is constant with time.

PLL ICs

1-4

Ching-Yuan Yang / EE, NCHU

## **History of PLL**

- First PLL: 1932 by de Bellesize, Coherent communication

- First PLL IC: 1965, purely analog (Linear PLL)

- First Digital PLL: around 1970 (using Digital Phase Detector)

- All Digital PLL: Digital Filters, NCO (Numerically Controlled Oscillator), ...

- Software PLL: Using DSP

- 1990s: Most of the PLL is Charge Pump PLL

#### **Terminology**

Locking

When VCO output is in phase as well as in frequency with the reference input signal

Lock Range

Input frequency range over which the loop can maintain locking

Capture Range

Input frequency range onto which the loop can lock

Free Running Frequency

VCO running frequency when no input applied

Acquisition Time: Pull-in time + Settling time

Time required for the PLL to lock itself on to the reference clock

Phase Offset or Phase Error (Steady State)

When PLL is locked, the phase difference between input and output

PLL ICs

1-6

Ching-Yuan Yang / EE, NCHU

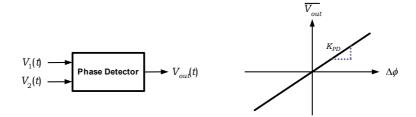

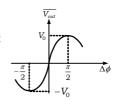

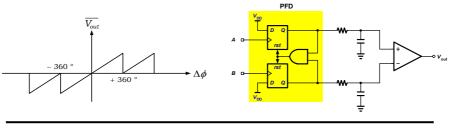

#### Phase detector

- A phase detector is a circuit whose average output,  $\overline{V_{out}}$ , is linearly proportional to the phase difference,  $\Delta\phi$ , between its two inputs.

- In the ideal case, the relationship between  $\overline{V_{out}}$  and  $\Delta \phi$  is linear, crossing the origin for  $\Delta \phi = 0$ .

- The operation of phase detectors is similar to that of differential amplifiers in that both sense the difference between the two inputs, generating a proportional output.

- Gain  $K_{PD}$ : the slope of the line, is expressed in V/rad.

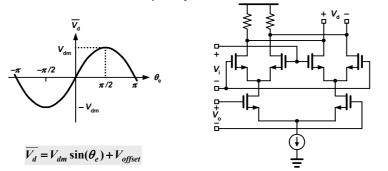

### Phase detector: Multiplier

- Phase Detector using Analog Multiplier

- Gilbert multiplier

- □ Output voltage dependent on the input signal amplitudes

- □ Narrow linear range (Narrow lock range)

- ☐ Cannot discriminate frequency difference

PLL ICs

1-8

Ching-Yuan Yang / EE, NCHU

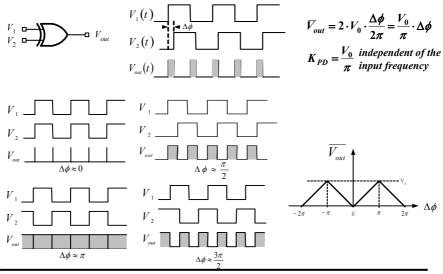

## Phase detector: XOR

#### Phase detector: XOR (cont'd)

- When locked, the phase difference is 90 degree

- Output voltage independent on the input signal amplitudes

- Output voltage dependent on the input duty cycles

- Narrow linear range (Narrow lock range)  $\Rightarrow \pm \pi/2$

- Cannot discriminate frequency difference

- Use for Data/Clock Recovery PLL: input noise dominant

- Hybrid PLL (Analog PLL + Digital PLL)

- No Dead Zone

PLL ICs

1-10

Ching-Yuan Yang / EE, NCHU

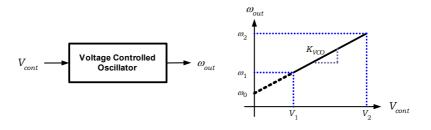

## **Voltage-controlled oscillators (VCOs)**

An ideal VCO is a circuit whose output frequency is a linear function of its control voltage:

$$\omega_{out} = \omega_0 + K_{VCO} V_{cont}$$

- $\omega_0$  represents the intercept corresponding to  $V_{cont} = 0$ .

- $K_{VCO}$  denotes the *gain* or *sensitivity* of the circuit (expressed in rad/s/V).

- The achievable range,  $\omega_2 \omega_1$ , is called the *tuning range*.

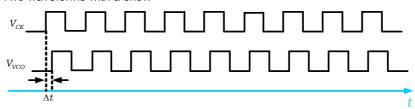

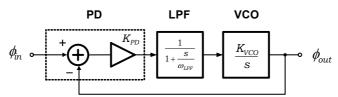

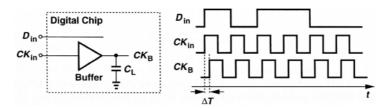

## **Basic PLL topology**

Two waveforms with a skew

Change of VCO frequency to eliminate the skew

PLL ICs

1-12

Ching-Yuan Yang / EE, NCHU

#### Discussion

- To vary the phase, we *must* vary the frequency and allow the integration  $\phi = \int (\omega_0 + K_{VCO}V_{cont})dt$  to take place.

- ⇒ Phase alignment can be achieved only by a (temporary) frequency change.

- $\hfill \Box$  The output phase of a VCO can be aligned with the phase of a reference if

- the frequency of the VCO is changed momentarily,

- a phase detector is used to determine when the VCO and reference signals are aligned.

- Phase locking is a task of aligning the output phase of the VCO with the phase of the reference.

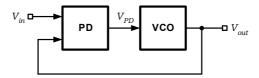

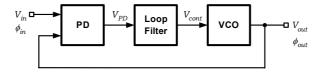

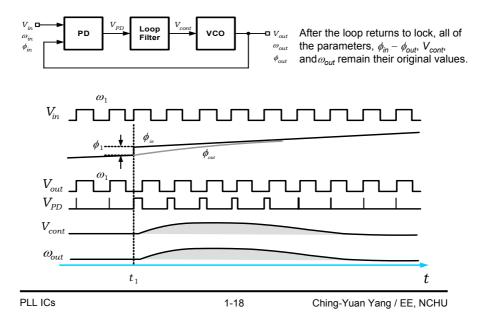

### Basic PLL topology (cont'd)

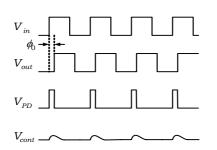

Feedback loop comparing input and output phases

- □ The PD compares the phases of  $V_{out}$  and  $V_{in}$ , generating an error that varies the VCO frequency until the phases are aligned, i.e., the loop is locked.

- ☐ The topology must be modified because

- the PD output, V<sub>PD</sub>, consists of a dc component (desirable) and high frequency components (undesirable),

- the control voltage of the oscillator must remain quiet in the steady state, i.e., the PD output must be filtered.

PLL ICs

1-14

Ching-Yuan Yang / EE, NCHU

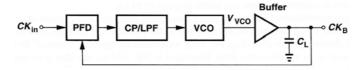

#### Simple PLL

- A low-pass filter is interposed between the PD and the VCO, suppressing the high-frequency components of the PD output and presenting the dc level to the oscillator.

- □ The feedback loop compares the phases of the input and output. If the loop gain is large enough, the difference between the input phase,  $\phi_{in}$ , and the output phase,  $\phi_{out}$ , falls to a small value in the steady state, providing phase alignment

- lacktriangle Phase lock condition:  $\phi_{out} \phi_{in}$  is constant and preferably small.

$$\frac{d\phi_{out}}{dt} - \frac{d\phi_{in}}{dt} = 0 \qquad \Rightarrow \quad \omega_{out} = \omega_{in}$$

When locked, a PLL produces an output that has a small phase error with respect to the input but exactly the same frequency.

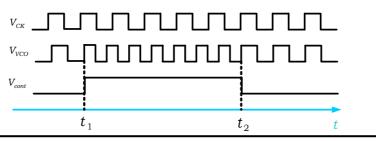

#### PLL waveforms in locked condition

• If the input and output frequencies are equal to  $\omega_1$ , then the required oscillator control voltage is unique  $V_1$ . Since  $\omega_{out} = \omega_0 + K_{VCO}V_{cont}$  and , we can write

$$V_1 = \frac{\omega_1 - \omega_0}{K_{VCO}} \quad \text{and} \quad \phi_0 = \frac{V_1}{K_{PD}} = \frac{\omega_1 - \omega_0}{K_{PD}K_{VCO}}$$

- It reveals two important points:

- ☐ as the input frequency of the PLL varies, so does the phase error,

- $\Box$  to minimize the phase error,  $K_{PD}K_{VCO}$  must be maximized.

PLL ICs

1-16

Ching-Yuan Yang / EE, NCHU

## PLL waveforms in locked condition (cont'd)

Nonlinear PD

If the frequency is high enough (=  $\omega_x$ ) to mandate  $V_{cont}$  =  $V_0$ , then the PD must operate at the peak of its characteristic. However, the PD gain drops to zero here and feedback loop fails. Thus, the circuit cannot lock if  $\omega_{in}$  =  $\omega_x$ .

Drift of data with respect to clock in the presence of small frequency error

Frequency-locked loop

The frequency detector (FD) would suffer from a finite difference between  $\omega_{in}$  and  $\omega_{out}$  due to various mismatches and other nonidealities.

## Response of a PLL to a phase step

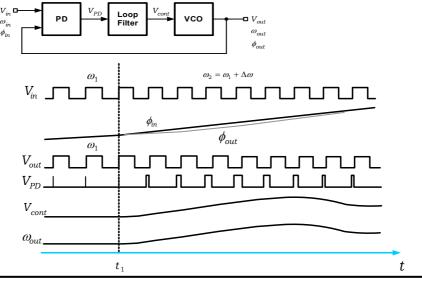

# Response of a PLL to a frequency step

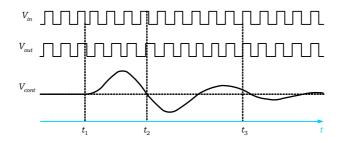

#### **Example of phase step response**

- The control voltage of the oscillator can serve as a suitable test point in analysis of PLLs.

While it is difficult to measure the time variations of phase and frequency, V<sub>cont</sub> (= V<sub>LPF</sub>) can be readily monitored in simulations and measurements.

- The state of the loop:

- □ At t = t₂, the output frequency is equal to its final value but the loop continues the transient because the phase error deviates from the required value.

- $\square$  At  $t = t_3$ , the phase error is equal to its final value but the output frequency is not. For the loop to settle, both the phase and the frequency must settle to proper values.

PLL ICs

1-20

Ching-Yuan Yang / EE, NCHU

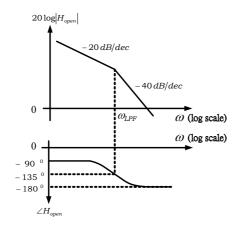

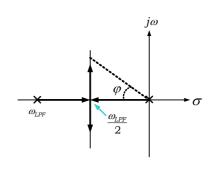

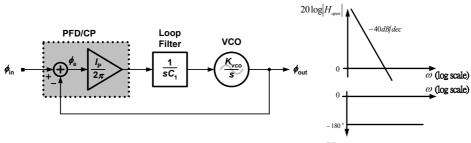

## Linear model of type I PLL

• The open-loop transfer function is given by

$$H(s)|_{\text{open}} = \frac{\phi_{out}}{\phi_{in}}(s)|_{\text{open}} = K_{PD} \cdot \frac{1}{1 + \frac{s}{\omega_{tors}}} \cdot \frac{K_{VCO}}{s}$$

revealing the poles at  $s=-\omega_{LPF}$  and s=0. Since the loop gain contains a pole at the origin, the system is called "type I."

Owing to the pole at the origin, the loop gain goes

to infinity as s approaches to zero. Thus, the PLL

ensures that the change in φ<sub>out</sub> is exactly equal

the change in φ<sub>n</sub> as s goes to zero

• The closed-loop transfer function can be written as

$$|H(s)|_{\text{close}} = \frac{\phi_{out}}{\phi_{in}}(s)\Big|_{\text{close}} = \frac{K_{PD}K_{VCO}}{\frac{s^2}{\omega_{LPF}} + s + K_{PD}K_{VCO}} = \frac{\omega_{out}}{\omega_{in}}(s)$$

If  $s\to 0$ ,  $H(s)\to 1$  because the infinite loop gain. Since the loop gain contains a pole at the origin, the system is called "type I."

ullet Since a change in  $\omega_{ ext{out}}$  must be accompanied by a

change in  $V_{cont}$ , we have  $H(s) = K_{VCO} \cdot \frac{V_{cont}}{\omega_{in}}(s)$

The response of  $V_{cont}$  to variations in  $\omega_{in}$  indeed yields the response of the close-loop system.

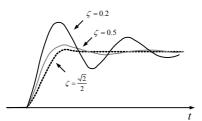

## Linear model of type I PLL (cont'd)

• 2<sup>nd</sup> order transfer function:  $H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

where natural frequency  $\omega_n = \sqrt{\omega_{LPF} K_{PD} K_{VCO}}$  and damping ratio  $\zeta$ :

$$\zeta = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K_{PD} K_{VCO}}}$$

• The two poles of the closed-loop system are given by

$$s_{1,2} = -\zeta \omega_n \pm \sqrt{(\zeta^2 - 1)\omega_n^2} = (-\zeta \pm \sqrt{\zeta^2 - 1})\omega_n$$

- $\triangleright$  If  $\zeta > 1$ , the system is overdamped.

- $\triangleright$  If  $\zeta$  < 1, the pole are complex, the system is underdamped and the response to an input frequency step  $\omega_{in} = \Delta \omega u(t)$  is equal to

$$\omega_{out} = \left[1 - \frac{1}{\sqrt{1 - \zeta^2}} e^{-\zeta \omega_n t} \sin\left(\omega_n \sqrt{1 - \zeta^2} t + \theta\right)\right] \Delta \omega u(t)$$

where  $\omega_{out}$  denotes the change in the output frequency and  $\theta = \sin^{-1} \sqrt{1 - \zeta^2}$

The step response contains a sinusoidal component with a frequency  $\sqrt{1-\zeta^2}$  that decays with a time constant  $(\zeta \omega_n)^{-1}$ .

PLL ICs

1-22

Ching-Yuan Yang / EE, NCHU

## Linear model of type I PLL (cont'd)

- Settling speed of PLLs: The exponential decay determines how fast the output approaches its final value, implying that  $\zeta \omega_n$  must be maximized. For the type I PLL, we have  $\zeta \omega_n = \frac{1}{2} \omega_{LPF}$

- ☐ It reveals a critical trade-off between the settling speed and the ripple on the VCO control line: the lower  $\omega_{LPF}$  the greater the suppression of the high-frequency components produced by the PD but the longer the settling time constant.

- Underdamped response:

□ 900 MHz PLL:

$$\omega_{LPF} = 2\pi \cdot (20\text{KHz}),$$

$f_{out} = 901\text{MHz} \rightarrow 901.2\text{MHz},$

how long does the PLL output frequency take to settle within 100Hz of its final value?

In the worst case, we have

$$e^{-\zeta \omega_n t_s} \approx \frac{100 \text{ Hz}}{200 \text{ KHz}} \implies t_s = 0.12 \text{ms}$$

# Linear model of type I PLL (cont'd)

### Bode plots

#### Root locus

PLL ICs

1-24

Ching-Yuan Yang / EE, NCHU

# **Charge-Pump Phase-Locked Loops**

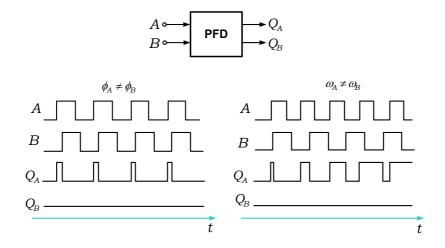

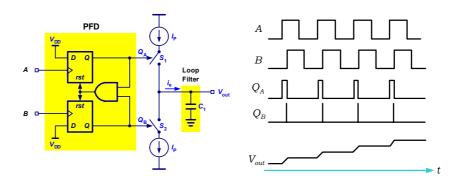

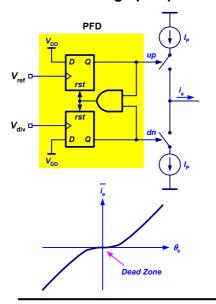

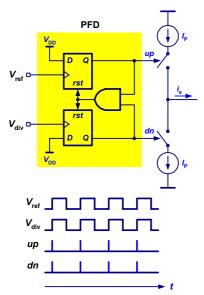

# Conceptual operation of a phase-frequency detector (PFD)

PLL ICs

1-26

Ching-Yuan Yang / EE, NCHU

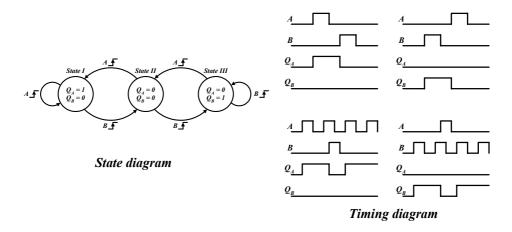

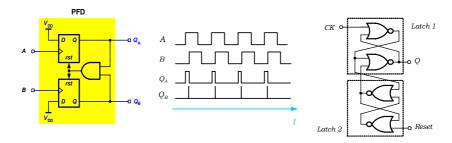

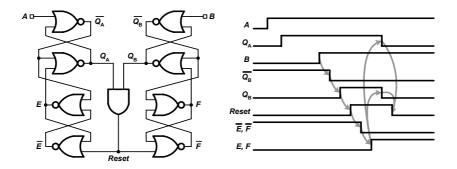

### Phase detector: PFD - three-state PD

## - Implementation of PFD

Input-output characteristic:

PFD followed by low-pass filters:

PLL ICs

1-28

Ching-Yuan Yang / EE, NCHU

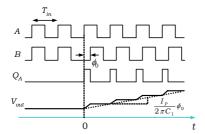

#### - Phase detector: PFD

- When locked, the phase difference is 0 degree

- Output voltage independent on the input signal amplitudes

- Output voltage independent on the input duty cycles

- Wide linear range (Wide lock range)  $\Rightarrow \pm 2\pi$

- Discriminate frequency difference

- Use carefully for Data/Clock Recovery PLL

- Hybrid PLL (Analog PLL + Digital PLL)

- Dead Zone problem

- □ Due to finite gate delay

- ☐ Introduce large jitter or poor phase noise

# - The width of the narrow reset pulses

PLL ICs

1-30

Ching-Yuan Yang / EE, NCHU

# - Dynamic CMOS PFD

Kim, JSSC, May 1997

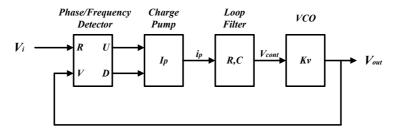

#### **Charge-pump PLL**

#### Why charge pump PLL?

- Advantages

- □ No active component for zero steady state phase error

- □ Large frequency and phase capture range

- □ Digital output (full CMOS swing)

- ☐ Simple and robust design

- ☐ Discrete time analysis

- Disadvantages

- □ Slow comparing with analog PLL

- ☐ May create dead zone problem

- Noisy

PLL ICs

1-32

Ching-Yuan Yang / EE, NCHU

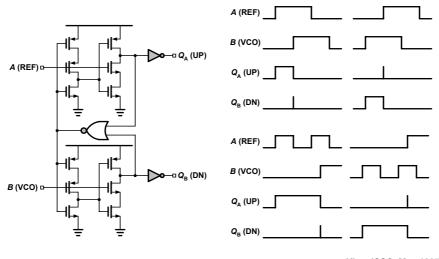

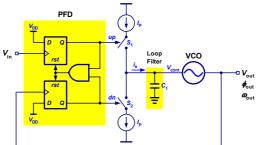

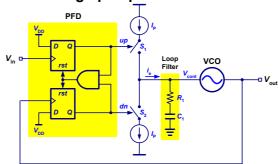

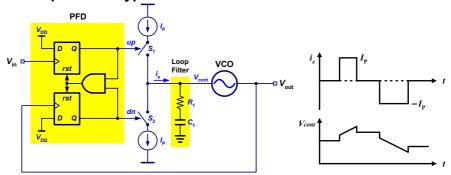

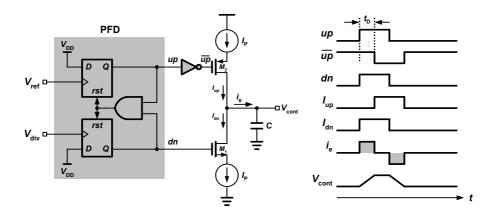

## PFD with charge pump

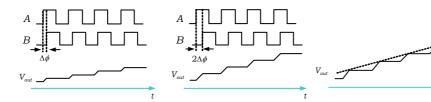

### Simple charge-pump PLL (Type II PLL)

Operation

- When the loop is turned on,  $\omega_{out}$  may be far from  $\omega_{in}$ , and the PFD and the charge pump vary the control voltage such that  $\omega_{out}$  approaches to  $\omega_{in}$ .

- When ω<sub>out</sub> and ω<sub>in</sub> are sufficiently close, the PFD operates as a phase detector, performing phase lock.

- The loop locks when the phase difference drops to zero and the charge pump remains relatively idle.

- $\square$  If  $V_{cont}$  remains constant for a long time, the VCO frequency and phase begin to drift. The PFD then detects the phase difference, producing a corrective pulse on up and dn that adjusts the VCO frequency through the charge pump and the filter.

- □ Since phase comparison is performed in every cycle, the VCO phase and frequency cannot drift substantially.

- In locked condition, the gain of the PFD/CP combination is infinite, i.e., a nonzero (deterministic) difference between  $\phi_n$  and  $\phi_{out}$  leads to indefinite charge buildup on  $C_1$ . Therefore, the input phase error must be exactly zero.

PLL ICs

1-34

Ching-Yuan Yang / EE, NCHU

## Linearity of PFD/CP/LPF combination

Step response:

- The system is not linear in the strict sense.

We approximate a discrete-time system by a continuous-time model.

- Approximated by a ramp,  $\Delta \phi = \phi_0 u(t)$

$$V_{out}(t) = \frac{I_P}{2\pi C_1} t \cdot \phi_0 u(t)$$

- $\Rightarrow \text{ transfer function } \frac{V_{out}}{\Delta \phi}(s) = \frac{I_P}{2\pi C_1} \cdot \frac{1}{s}$

- It contains a pole at the origin.

#### Linear model of simple charge-pump PLL

• Open-loop transfer function  $\frac{\phi_{out}}{\phi_{in}}(s) = \frac{I_P}{2\pi C_1} \frac{K_{VCO}}{s^2}$

Since the loop gain has two poles at the origin, this topology is called a "type II" PLL.

It contains two imaginary poles at  $s_{1,2}=\pm j\sqrt{I_PK_{VCO}/(2\pi C_1)}$  and is unstable. LICs 1-36 Ching-Yuan Yang / EE

PLL ICs

Ching-Yuan Yang / EE, NCHU

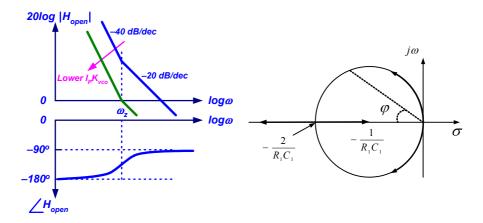

## Addition of zero to charge-pump PLL

- $\bullet \text{ Open-loop transfer function } \left. \frac{\phi_{out}}{\phi_{in}}(s) \right|_{\text{open}} = \frac{I_P}{2\pi} \left( R_1 + \frac{1}{C_1 s} \right) \frac{K_{VCO}}{s} \quad \Rightarrow \text{a zero at } s_z = -1/(R_1 C_1).$

- Closed-loop transfer function  $H(s) = \frac{\frac{I_P K_{VCO}}{2\pi C_1} (R_1 C_1 s + 1)}{s^2 + \frac{I_P}{2\pi} K_{VCO} R_1 s + \frac{I_P}{2\pi C_1} K_{VCO}}$

$$\Rightarrow \quad \omega_n = \sqrt{\frac{I_P K_{VCO}}{2\pi C_1}} \quad , \quad \zeta = \frac{R_1}{2} \sqrt{\frac{I_P C_1 K_{VCO}}{2\pi}} \quad \text{and decay time constant} \quad \frac{1}{\zeta \omega_n} = \frac{4\pi}{R_1 I_1 K_{VCO}}$$

### Stability degradation of charge-pump PLL

PLL ICs

1-38

Ching-Yuan Yang / EE, NCHU

## Stability limit and overload limit

In fact, the elegant way to determine the stability limit in the charge pump PLL is to linearize a set of difference equations, to transform it into the z-domain, and to apply the stability criterion on it.

- Normalize PLL parameters:

- the normalized loop gain  $K_N = I_P R_1 K_{vco} T / 2\pi$

- **2** the normalized loop filter  $\tau_{1N} = R_1 C_1 / T$

- **3** the normalized natural frequency  $F_N = f_n / f_i = f_n T$

$$\Rightarrow \qquad F_N = \frac{1}{2\pi} \sqrt{\frac{K_N}{\tau_{1N}}} \qquad \zeta = \frac{\sqrt{K_N \tau_{1N}}}{2}$$

Stability limit condition:

$$K_N < \frac{2}{1 + \frac{1}{2\tau_{1N}}} \qquad \Rightarrow \qquad F_N < \frac{\sqrt{1 + \zeta^2} - \zeta}{\pi}$$

Overload Limit

$$V_{CON} = \frac{f_i}{K_{WCO}} - I_P R_1 > 0 \quad \Rightarrow \quad K_N < 1 \quad \Rightarrow \quad F_N < \frac{1}{4\pi\zeta}$$

Gardner, IEEE Trans. on Comm., Nov. 1980. Paemel, IEEE Trans. on Comm., Jul. 1994

0.2 0.4 0.6 0.8

#### Compensated type II PLL

#### Critical drawback:

- ince the charge pump drives the series combination of R<sub>P</sub> and C<sub>P</sub>, each time a

current is injected into the loop filter, the control voltage experiences a large jump.

- In lock condition, the mismatches between I<sub>1</sub> and I<sub>2</sub> and charge injection and clock feedthrough of S<sub>1</sub> and S<sub>2</sub> introduce voltage jumps in V<sub>cont</sub>.

- ⇒ The resulting ripple severely disturbs the VCO, corrupting the output phase.

PLL ICs

1-40

Ching-Yuan Yang / EE, NCHU

# Design flow of 2<sup>nd</sup>-order PLLs

- Determine  $K_{VCO}$ .

- **2** Choose the natural frequency  $\omega_n$  to be about or less then one-tenth of the input frequency.

- Select  $I_p$ , to meet the reasonable trade-off between the value the filter components (i.e., chip area) and the pump current.

- **9** Set the damping factor  $\zeta$  to be 0.707.

- $\odot$  Calculate  $R_p$  and  $C_p$ .

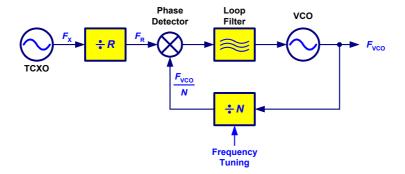

#### PLL frequency synthesizer using dividers

**TCXO: Temperature Compensated Crystal Oscillator**

**VCO: Voltage Controlled Oscillator**

In the locked state:

$$F_{\text{VCO}} = N \times F_{\text{R}}, N \in N$$

$F_{VCO} / N = F_X / R = F_R$

PLL ICs

1-42

Ching-Yuan Yang / EE, NCHU

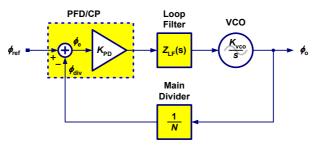

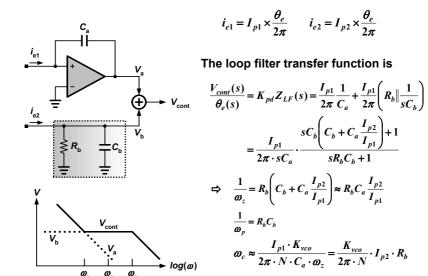

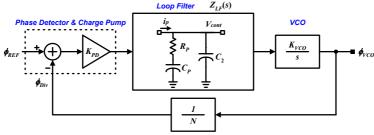

# Linear model of 3<sup>rd</sup>-order PLLs with 2<sup>nd</sup>-order loop filter

#### PLL phase transfer functions:

Forward-loop gain

$$G(s) = \frac{\theta_o}{\theta_e} = \frac{K_{PD}Z_{LF}(s)K_{vco}}{s}$$

Reverse-loop gain

$$\beta(s) = \frac{\theta_{div}}{\theta_o} = \frac{1}{N}$$

Open-loop gain

$$\beta(s)G(s) = \frac{\theta_{div}}{\theta} = \frac{K_{PD}Z_{LF}(s)K_{vco}}{N_{S}}$$

Open-loop gain

$$\beta(s)G(s) = \frac{\theta_{div}}{\theta_e} = \frac{K_{PD}Z_{LF}(s)K_{vco}}{Ns}$$

Closed-loop gain

$$\frac{\theta_o}{\theta_{ref}} = \frac{G(s)}{1 + \beta(s)G(s)}$$

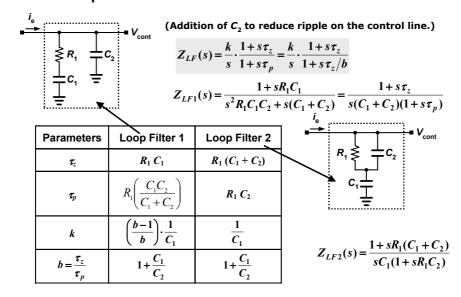

### - 2<sup>nd</sup>-order passive filter

PLL ICs

1-44

Ching-Yuan Yang / EE, NCHU

## - Open-loop bandwidth $\omega_{\rm c}$ and phase margin $\phi_{\rm m}$

Open-loop gain

$$\beta(s)G(s) = \frac{\theta_{div}}{\theta_e} = \frac{K_{PD}Z_{LF}(s)K_{vco}}{Ns} = \frac{I_P \cdot K_{vco} \cdot k}{2\pi \cdot N \cdot s^2} \cdot \frac{1 + s\tau_z}{1 + s\tau_p}$$

$$\Rightarrow \beta(s)G(s)\Big|_{s=j\omega} = -\frac{I_P \cdot K_{vco} \cdot k}{2\pi \cdot N \cdot \omega^2} \cdot \frac{1 + j\omega\tau_z}{1 + j\omega\tau_p}$$

$$\phi(\omega) = \tan^{-1}(\omega \cdot \tau_z) - \tan^{-1}(\omega \cdot \tau_p) + 180^{\circ}$$

Gain

$$\phi_{m,max} : \frac{d\phi}{d\omega} = \frac{\tau_z}{1 + (\omega \cdot \tau_z)^2} - \frac{\tau_p}{1 + (\omega \cdot \tau_p)^2} = 0$$

$$\Rightarrow \omega_c = \frac{1}{\sqrt{\tau_z \cdot \tau_p}}$$

and

$$\phi_{m,max} = \tan^{-1}\left(\frac{\tau_z - \tau_p}{2\sqrt{\tau_z \cdot \tau_p}}\right) = \tan^{-1}\left(\frac{b - 1}{2\sqrt{b}}\right)$$

Bode plot of open loop response

ullet If the loop bandwidth  $\omega_{

m c}$  and the phase margin  $\phi_{

m m}$  are specified, we have

$$b = \frac{1}{\left(-\tan\phi_m + \frac{1}{\cos\phi_m}\right)^2} \quad \text{and} \quad \tau_z = \frac{\sqrt{b}}{\omega_c} \quad \tau_p = \frac{1}{\sqrt{b} \cdot \omega_c}$$

For loop filter 1:

| $\phi_m$ | b      | sqrt(b) |

|----------|--------|---------|

| 20°      | 2.04   | 1.42    |

| 30°      | 3.00   | 1.73    |

| 40°      | 4.59   | 2.14    |

| 45°      | 5.82   | 2.41    |

| 50°      | 7.55   | 2.74    |

| 55°      | 10.06  | 3.17    |

| 60°      | 13.93  | 3.73    |

| 70°      | 32.16  | 5.67    |

| 80°      | 130.64 | 11.43   |

and

$$au_z = rac{\sqrt{b}}{\omega_c}$$

$au_p = rac{1}{\sqrt{b} \cdot \omega_c}$

$$\omega_c = \frac{I_P K_{vco}}{2\pi \cdot N} R_1 \frac{b-1}{b} = \frac{I_P K_{vco}}{2\pi \cdot N} R_1 \frac{C_1}{C_1 + C_2}$$

$$R_1 = \frac{2\pi \cdot N \cdot \omega_c}{I_P \cdot K_{vco}} \frac{b}{b-1}$$

$$C_1 = \frac{\tau_z}{R_1} \quad \text{and} \quad C_2 = \frac{1}{R_1} \cdot \frac{\tau_z \tau_p}{\tau_z - \tau_p}$$

For loop filter 2:

$$\omega_c = \frac{I_P K_{vco}}{2\pi \cdot N} R_1 \frac{b}{b-1} = \frac{I_P K_{vco}}{2\pi \cdot N} R_1 \frac{C_1 + C_2}{C_1}$$

$$R_1 = \frac{2\pi \cdot N \cdot \omega_c}{I_P \cdot K_{vco}} \frac{b-1}{b}$$

$$C_1 = \frac{\tau_z - \tau_p}{R_1} \quad \text{and} \quad C_2 = \frac{\tau_p}{R_1}$$

1-46 Ching-Yuan Yang / EE, NCHU

PLL ICs

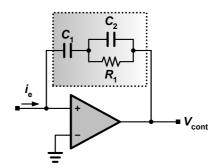

## **Active loop filter implementation**

The active loop filter is often used when the charge-pump output can not directly provide the required voltage range for tuning of the VCO. Such voltages are incompatible with charge-pumps built in standard IC technologies, so that a (partly external) active loop filter is then used to isolate the charge-pump output from the VCO tuning input, and to generate the high tuning voltages.

### Multi-path charge-pump filter

PLL ICs

1-48

J. Craninckx, IEEE JSSC, Dec. 1998 Ching-Yuan Yang / EE, NCHU

#### **Nonideal Effects in PLLs**

### PFD and charge-pump filter

Owing to the finite risetime and falltime resulting from the capacitance seen at the nodes, the pulse may not find enough time to reach a logical high level, failing to turn on the charge pump switches.

- For  $|\Delta \phi| < \phi_0$ , the charge pump injects no current.

- The loop gain drops to zero and the output phase is not locked.

- The PFD/CP suffers from a dead zone equal to  $\pm \phi_0$  around  $\Delta \phi = 0$ .

- ⇒ Jitter resulting from the dead zone

PLL ICs

1-50

Ching-Yuan Yang / EE, NCHU

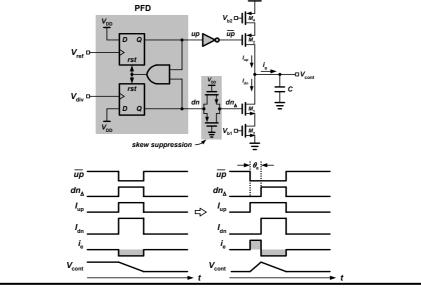

## Reference spurs

Periodic disturbance of VCO control line due to charge pump activity:

$$i_{e}(t) = I_{p}\delta_{cp} + 2I_{p}\delta_{cp}\sum_{n=1}^{\infty}\cos(2\pi n f_{ref}t)$$

$$\frac{1}{DC}$$

Spectral components

- Main effects which generate reference spurious breakthrough:

- leakage current in the loop filter,

- skew between *up* and *down* (*dn*) signals,

- mismatch in the charge *up* and *down* current sources,

- □ Charge sharing.

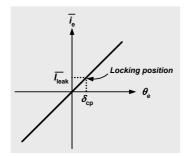

### - Effect of leakage current

- Sources of leakage currents:

- the capacitor of loop filter,

- the input of VCO,

- the charge-pump output,

- the input biasing current of the op-amp, when active loop filter configuration is used.

- The duty cycle of the charge-pump output is

$$\overline{i_e} = I_p \delta_{cp} = I_{leak} \quad \Rightarrow \quad \delta_{cp} = \frac{I_{leak}}{I_p}$$

The amplitude of charge-pump output:

$$i_e(t) = I_{leak} + 2I_{leak} \sum_{n=1}^{\infty} \cos(2\pi n f_{ref} t)$$

- The spectral component are twice the value of  $I_{leak}$ .

- **2** Not dependent on the nominal charge-pump current  $I_P$ .

PLL ICs

1-52

Ching-Yuan Yang / EE, NCHU

Link the leakage current to the magnitude of the spurious components at the output of the VCO:

$$V_{rinnle}(n \cdot f_{ref}) = 2I_{leak} | Z_{LF}(j2\pi n f_{ref}) |$$

Phase deviation

$$\theta_{P}(n \cdot f_{ref}) = \frac{\Delta f(n \cdot f_{ref})}{n \cdot f_{ref}} = \frac{V_{ripple}(n \cdot f_{ref}) K_{vco}}{n \cdot f_{ref}} = \frac{2I_{leak} |Z_{LF}(j2\pi n f_{ref})| K_{vco}}{n \cdot f_{ref}}$$

- Each of baseband modulation frequencies  $n \cdot f_{\text{ref}}$  generates two RF spurious signals at offset frequencies  $\pm n \cdot f_{\text{ref}}$  from the carrier  $f_{\text{LO}}$ .

- 2 The amplitude of each spurious signal

$$A_{SP}(f_{LO} \pm n \cdot f_{ref}) = A_{LO} \frac{\theta_P(n \cdot f_{ref})}{2} = A_{LO} \frac{I_{leak} \left| Z_{LF}(j2\pi n f_{ref}) \right| K_{vco}}{n \cdot f_{ref}}$$

$$\Rightarrow \frac{A_{SP}(f_{LO} \pm n \cdot f_{ref})}{A_{LO}} = \frac{I_{leak} |Z_{LF}(j2\pi n f_{ref})| K_{vco}}{n \cdot f_{ref}}$$

$$\Rightarrow \left[\frac{A_{SP}}{A_{LO}}\right]_{dBc} = 20\log\frac{\theta(n \cdot f_{ref})}{2} = 20\log\frac{I_{leak} \left|Z_{LF}(j2\pi n f_{ref})\right| K_{vco}}{n \cdot f_{ref}} \text{ [dBc]}$$

The relative amplitude of the spurious signal is *not* dependent on the value of loop bandwidth or on the nominal charge-pump current  $I_P$ .

Theoretically, if  $I_{leak} = 0$  there are *no* reference spurs in the output.

# - Effect of skew between up and down signals

PLL ICs

1-54

Ching-Yuan Yang / EE, NCHU

# - Effect of mismatch in the charge-pump current sources

#### - Effect of mismatch in the charge-pump current sources

- For the loop to remain locked, the average value of V<sub>cont</sub> must remain constant.

The PLL therefore creates a phase error between the input and the output such that the net current injected by the charge pump in every cycle is zero.

- ⇒ The control voltage still experiences a periodic ripple.

- ⇒ Owing to the low output impedance of short-channel MOSFETs, the current mismatch *varies* with the output voltage.

- $\Rightarrow$  The clock feedthrough and charge injection mismatch between  $M_1$  and  $M_2$  further increases both the phase error and the ripple.

- The magnitude of the spectral components of the ripple voltage due to currentsource mismatch can be found

$$\begin{aligned} V_{mismatch}(n \cdot f_{ref}) &= I_{out}(n \cdot f_{ref}) \cdot \left| Z_{LF}(j2\pi n f_{ref}) \right| \\ \Rightarrow & \left[ \frac{A_{sp}(n \cdot f_{ref})}{A_{LO}} \right]_{dBc} = 20 \log \frac{I_{out}(n \cdot f_{ref}) \left| Z_{LF}(j2\pi n f_{ref}) \right| K_{vco}}{2 \cdot n \cdot f_{ref}} \end{aligned}$$

PLL ICs

1-56

Ching-Yuan Yang / EE, NCHU

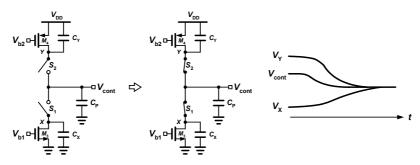

### - Effect of charge sharing

- Charge sharing between  $C_P$  and capacitances at X and Y:

- $\square$   $S_1$  and  $S_2$  are off, allowing  $M_3$  to discharge X to ground and  $M_4$  to charge Y to  $V_{DD}$ .

- □ At the next phase comparison instant, both  $S_1$  and  $S_2$  turn on,  $V_X$  rises,  $V_Y$  falls, and  $V_X \approx V_Y \approx V_{cont}$ .

- If the phase error is zero and  $I_{D3} = |I_{D3}|$ , does  $V_{cont}$  remain constant after the switches turn on? Even if  $C_X = C_Y$ , the change in  $V_X$  is not equal to that in  $V_Y$ .

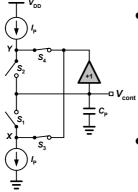

### - Effect of charge sharing

- Bootstrapping *X* and *Y* to minimize charge sharing:

- When  $S_1$  and  $S_2$  turn off,  $S_3$  and  $S_4$  turn on, allowing the unity-gain amplifier to hold nodes X and Y at a potential equal to  $V_{cont}$ .

- At the next phase comparison instant,  $S_1$  and  $S_2$  turn on,  $S_3$  and  $S_4$  turn off, and  $V_X$  and  $V_Y$  begin with a value equal to  $V_{cont}$ .

- The ideal is to "pin" V<sub>X</sub> and V<sub>Y</sub> to V<sub>cont</sub> after phase comparison is finished. Thus, no charge sharing occurs between C<sub>P</sub> and the capacitances at X and Y.

PLL ICs

1-58

Ching-Yuan Yang / EE, NCHU

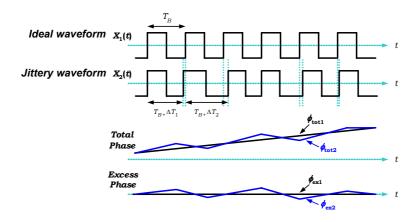

### Jitter/Noise in PLLs

#### **Jitter in PLLs**

PLL ICs

1-60

$y_1(t)$

y2(t

Excess

Ching-Yuan Yang / EE, NCHU

## Jitter in PLLs (cont'd)

Slow-jitter waveform

#### Fast-jitter waveform

• Effect of input jitter

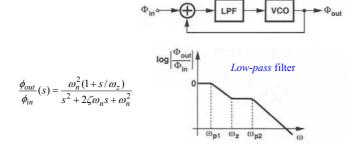

$$\frac{\phi_{out}}{\phi_{in}}(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

$$\frac{\phi_{out}}{\phi_{in}}(s) = \frac{\omega_n^2 (1 + s\tau_z)}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

$\Rightarrow$  Low-pass characteristic. Slow jitter at the  $_\Phi$  input propagates to the output unattenuated but fast jitter does not.

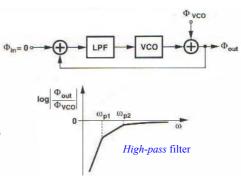

Effect of VCO jitter

$$\frac{\phi_{out}}{\phi_{in}}(s) = \frac{s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

⇒ *High-pass* characteristic. Slow jitter components generated by the VCO are suppressed but fast jitter components are not.

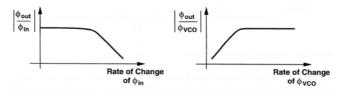

### Jitter in PLLs (cont'd)

Transfer functions of jitter from input and VCO to the output

- Effect of VCO jitter:

- □ If  $\phi_{VCO}$  changes slowly (e.g., the oscillation period drifts with temperature), then the comparison with  $\phi_{in}$  = 0 (i.e., a perfectly periodic signal) generates a slowly varying error that propagates through the LPF and adjusts the VCO frequency, thereby counteracting the change in  $\phi_{VCO}$ .

- □ If  $\phi_{VCO}$  varies rapidly, (e.g., high-frequency noise modulates the oscillation period), then the error produced by the phase detector is heavily attenuated by the poles in the loop, failing to correct for the change.

- In summary, depending on the application and environment, one or both sources may be significant, requiring an optimum choice of the loop bandwidth.

PLL ICs

1-62

Ching-Yuan Yang / EE, NCHU

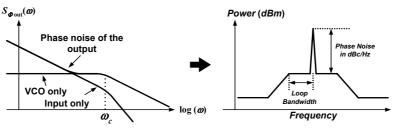

#### **Noise in PLLs**

- Phase noise  $\phi_n(t) \Rightarrow x(t) = A \cos(\omega_c t + \phi_n(t))$ If the input signal or the building blocks of a PLL exhibit noise, then the output signal will also suffer from noise.

- Phase noise at input

### Noise in PLLs (cont'd)

Phase noise of VCO

$$\frac{\phi_{out}}{\phi_{VCO}}(s) = \frac{s^2}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

The VCO phase noise experiences a high-pass transfer function as it appears at the output of a PLL. Thus, increasing the bandwidth of the PLL can lower the contribution of the VCO phase noise.

PLL ICs

1-64

Ching-Yuan Yang / EE, NCHU

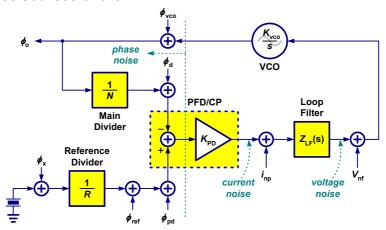

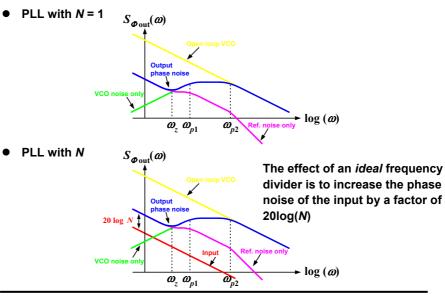

#### Noise sources of the PLL

The rms phase noise power density of the loop's output signal is denoted  $\phi_0(f_m)$ .

The output phase noise power density:

$\phi_o^2(f_m) = \phi_{oLP}^2(f_m) + \phi_{oHP}^2(f_m)$

Low-pass transfer function

High-pass transfer function

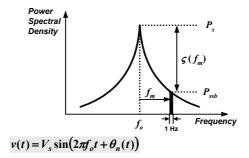

#### - Phase noise

The phase noise  $\varsigma(f_m)$ , usually in dBc, is the ratio of the single-sideband (SSB) power in a 1-Hz band width  $f_m$  Hz away from the carrier to the total signal power, i.e.,

$\varsigma(f_m) \equiv \frac{P_s}{P_{rel}}$

Let  $S_{\theta n}(f)$  be the power spectral density of  $\theta_n(t)$  in frequency domain, it can be

shown that  $S_{\theta_n}(f_m) \approx 2\varsigma(f_m)$  and  $\overline{\theta_n^2} = \int_0^\infty S_{\theta_n}(f) df$

PLL ICs

#### - Phase noise originated from dividers, PFD/CP and crystal reference sources

•

$$\phi_{\rm d}(f_{\rm m}), \ \phi_{\rm ref}(f_{\rm m}) \ {\rm and} \ \phi_{\rm pd}(f_{\rm m}) \ {\rm to} \ \phi_{\rm o}(f_{\rm m})$$

:  $H_{LP}(s) = N \frac{G(s)}{1 + G(s)} = N \cdot H(s)$  (Low pass)

with open-loop transfer function

$$G(s) = \frac{\theta_{Div}(s)}{\theta_{ref}(s)} = K_{pd} Z_{LF}(s) \frac{K_{vco}}{s} \frac{1}{N}$$

and closed-loop transfer function

$$H(s) = \frac{\phi_{Div}(s)}{\phi_{ref}(s)} = \frac{G(s)}{1 + G(s)} = \frac{K_{pd} Z_{LF}(s) K_{vco} / N}{s + K_{pd} Z_{LF}(s) K_{vco} / N}$$

$$\Rightarrow \phi_{oLP}^{2}(f_{m}) = N^{2} |H(j2\pi f_{m})|^{2} \left(\phi_{d}^{2}(f_{m}) + \phi_{ref}^{2}(f_{m}) + \phi_{pd}^{2}(f_{m}) + \frac{i_{np}^{2}(f_{m})}{K_{pd}^{2}} + \frac{\phi_{x}^{2}(f_{m})}{R^{2}}\right)$$

where

$$\phi_{eq}^{2}(f_{m}) \equiv \phi_{d}^{2}(f_{m}) + \phi_{ref}^{2}(f_{m}) + \phi_{pd}^{2}(f_{m}) + \frac{i_{np}^{2}(f_{m})}{K_{pd}^{2}} + \frac{\phi_{x}^{2}(f_{m})}{R^{2}}$$

$$\phi_{eq}^{2}(f_{m}) \equiv \phi_{d}^{2}(f_{m}) + \phi_{ref}^{2}(f_{m}) + \phi_{pd}^{2}(f_{m}) + \frac{i_{np}^{2}(f_{m})}{K_{pd}^{2}} + \frac{\phi_{x}^{2}(f_{m})}{R^{2}}$$

⇒ The equivalent synthesizer phase noise floor at the input of the phase detector.

$$\Rightarrow \phi_{oLP}^2(f_m) = N^2 |H(j2\pi f_m)|^2 \phi_{eq}^2(f_m)$$

#### - Phase noise due to loop filter and free-running VCO phase noise

• Oscillator:

$$\phi_{vco}^2(f_m) \approx \frac{Fk_BT}{P_{rf}} \left[ 1 + \left( \frac{f_{vco}}{2Q_l f_m} \right)^2 \right] \left( 1 + \frac{f_k}{f_m} \right) \text{ rad}^2 / Hz$$

where F is a noise factor,  $k_B = 1.37 \times 10^{-23}$  J/K (Boltzmann constant),

T is the absolute temperature,  $P_{rf}$  is the power of the oscillator signal,

$f_{vco}$  is the output frequency of the oscillator,

$Q_I$  is the loaded quality factor of the tuning circuit,

$f_m$  is the offset frequency from the frequency fvco, and

$f_k$  is the offset frequency which delimits the 9dB/octave dependency of the phase noise power density on the offset frequency ( $\Rightarrow \phi_{vco}^2 \propto 1/f_m^3$ ).

Assume

$$f_k \approx 0$$

and  $f_m$  is small,  $\phi_{vco}^2(f_m) \approx \frac{Fk_BT}{4P_{rf}} \frac{1}{Q_l^2} \frac{f_{vco}^2}{f_m^2} \text{ rad}^2/Hz$

$\Rightarrow$  -6dB/oct dependency on  $f_m$

$\Rightarrow \phi_{\text{VCO}}^{2}(f_{m})$  as a function of the phase noise power density at an offset

frequency  $f_r$ :

VCO noise floor power density

$\phi_{vco}^{2}(f_{m}) = \phi_{vco}^{2}(f_{r}) \frac{f_{r}^{2}}{f_{m}^{2}}$   $\Rightarrow \text{Exact function:}$  VCO noise floor power  $\phi_{vco}^{2}(f_{r}) = \phi_{vco}^{2}(f_{r}) \frac{f_{r}^{2}}{f_{m}^{2}} \left(1 + \frac{f_{k}}{f_{m}}\right) + \phi_{vco,nf}^{2}$

PLL ICs

Ching-Yuan Yang / EE, NCHU

#### - Phase noise due to loop filter and free-running VCO phase noise

Loop filter: Thermal noise voltage originated in the loop filter resistor causes unintended phase modulation of the VCO.

$$\phi_{lf}^{2}(f_{m}) = v_{nf}^{2}(f_{m}) \frac{K_{vco}^{2}}{f_{m}^{2}} \operatorname{rad}^{2}/Hz$$

• Influence of the loop: The influence of the feedback loop on the free-running VCO phase noise power density  $\phi_{\text{VCO}}^{2}(f_{m})$  and on the open-loop phase noise power density generated by the loop filter elements  $\phi_{lf}^{2}(f_{m})$  is expressed with the transfer function  $T_{HP}(s)$ ,

$$T_{HP}(s) = \frac{1}{1 + G(s)} \quad (High pass) \qquad |T_{HP}(j2\pi f_m/f_c)|^2$$

$$\Rightarrow \quad \phi_{oHP}^2(f_m) = |T_{HP}(j2\pi f_m)|^2 \left(\phi_{vco}^2(f_m) + \phi_{lf}^2(f_m)\right)$$

$- f_m/f_c$

### - Total phase noise at the output of the PLL

• Total phase noise noise power spectral density:

$$\phi_{o}^{2}(f_{m}) = N^{2}\phi_{eq}^{2}(f_{m}) \cdot \frac{\left|H(j2\pi f_{m})\right|^{2} + \left(\phi_{vco}^{2}(f_{m}) + \phi_{lf}^{2}(f_{m})\right) \cdot \left|T_{HP}(j2\pi f_{m})\right|^{2}}{(\text{High pass})} \quad \text{rad}^{2} / H_{2}$$

Typical phase noise spectral plot for PLL:

PLL ICs

1-70

Ching-Yuan Yang / EE, NCHU

### - General bandwidth requirements

- Low PLL System Jitter

- ⇒ Wide Loop Bandwidth

- Large Input Jitter Reduction

- ⇒ Narrow Loop Bandwidth

- Fast Locking

- ⇒ Wide Loop Bandwidth

- Phase Fluctuation Tracking

- ⇒ Adaptive Loop Bandwidth Control

- There are Trade-offs: No single good solution for All

### Spectral purity & design of PLL loop filter

- Consideration:

- $\square$  Decrease  $I_P$  to acceptable level in order to decrease the power dissipation and to simplify the design of the charge-pump circuitry.

- ☐ The impedance level of the loop filter should be maximized, for the chiparea of fully integrated loop filters to be minimized.

Note: high impedance level  $\Rightarrow$  small  $C_1$  and  $C_2$ , large  $R_1$ , and small  $I_P$ .  $\Rightarrow$  a higher noise contribution from the filter.

- Spurious reference breakthrough:

$$(f_c << f_{ref}) \ \left| Z_{LF}(j2\pi f_{ref}) \right| \approx \frac{1}{2\pi f_{ref} C_2} \qquad \Rightarrow \qquad C_{2,\min} = \frac{I_{leak} \cdot K_{vco}}{2\pi \cdot n \cdot f_{ref}^2} 10^{\frac{Max.spurious}{20}}$$

**2** Effect of charge-pump current mismatch  $C_{2,\text{min}} = \frac{I_{out}(f_{ref}) \cdot K_{vco}}{4\pi \cdot n \cdot f_{ref}^2} 10^{\frac{-Max.spurious}{20}}$

PLL ICs

1-72

Ching-Yuan Yang / EE, NCHU

Phase noise contribution from the loop filter resistor

$$\begin{aligned} v_{nf}^{2}(f_{m}) &= \left(\frac{b-1}{b}\right)^{2} \cdot \frac{4k_{B}TR_{1}}{\left|1 + j2\pi f_{m}\tau_{p}\right|^{2}} \\ & \Rightarrow \phi_{lf}^{2}(f_{m}) = v_{nf}^{2}(f_{m}) \frac{K_{vco}^{2}}{f_{m}^{2}} = \left(\frac{b-1}{b}\right)^{2} \cdot \frac{4k_{B}TR_{1}}{\left|1 + j2\pi f_{m}\tau_{p}\right|^{2}} \frac{K_{vco}^{2}}{f_{m}^{2}} \end{aligned}$$

Define

$$\alpha_{lf}(f_m) = \frac{\phi_{lf}^2(f_m)}{\phi_{veo}^2(f_m)} = \left(\frac{b-1}{b}\right)^2 \cdot \frac{4k_B T R_1 K_{veo}^2}{\phi_{veo}^2(f_r) f_r^2} \cdot \frac{1}{\left|1 + j2\pi f_m \tau_p\right|^2} \quad \text{where } \phi_{veo}^2(f_m) = \phi_{veo}^2(f_r) \frac{f_r^2}{f_m^2}$$

$$\Rightarrow \alpha_{lf}(f_m) = \alpha_{lf,dc} \cdot \frac{1}{\left|1 + j2\pi f_m \tau_p\right|^2} \quad \text{with} \quad \alpha_{lf,dc} = \left(\frac{b-1}{b}\right)^2 \cdot \frac{4k_B T R_1 K_{vco}^2}{\phi_{vco}^2(f_r) f_r^2}$$

Maximum value of  $R_1$ :  $R_{1,\max} = \alpha_{lf,dc} \left(\frac{b}{b-1}\right)^2 \cdot \frac{\phi_{vco}^2(f_r)f_r^2}{4k_B T K_{vco}^2}$

A smaller value than  $R_{1,max}$  for the loop filter resistor obviously leads to a smaller  $\alpha_{lf,dc}$ , which is always an acceptable situation from the point of view of phase noise performance.

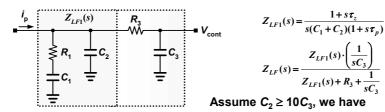

#### More attenuation of unwanted spurs with the 3th-order filter

$$Z_{LF1}(s) = \frac{1}{s(C_1 + C_2)(1 + s\tau_p)}$$

$$Z_{LF}(s) = \frac{Z_{LF1}(s) \cdot \left(\frac{1}{sC_3}\right)}{Z_{LF1}(s) + R_3 + \frac{1}{sC_3}}$$

Assume  $C_2 \ge 10C_3$ , we have

The added attenuation from the low-pass filter:

$$ATTEN = 20\log[(2\pi f_{ref}\tau_{p3})^2 + 1]$$

where

$$\tau_{p3} = R_3 C_3$$

$$\Rightarrow \qquad \tau_{p3} = \frac{\sqrt{10^{\frac{ATTEN}{20}} - 1}}{2\pi f_{ref}}$$

$$\tau_{p3} = R_3 C_3$$

$$(low-pass pole)$$

$$\Rightarrow C_2 = \frac{\tau_p}{\tau_z} \cdot \frac{K_{pd} \cdot K_{vco}}{\omega_c^2 \cdot N} \cdot \left( \frac{(1 + \omega_c^2 \cdot \tau_z^2)}{(1 + \omega_c^2 \cdot \tau_p^2)(1 + \omega_c^2 \cdot \tau_{p3}^2)} \right)^{\frac{1}{2}}$$

$$\tau_{p3} = \frac{\sqrt{10^{\frac{ATTEN}{20}} - 1}}{2\pi f_{ref}}$$

$$\Rightarrow C_1 = C_2 \cdot \left( \frac{\tau_z}{\tau_p} - 1 \right) \quad \text{and} \quad R_1 = \frac{\tau_z}{C_1}$$

$$(similar to the 2^{nd-order filter})$$

PLL ICs

Ching-Yuan Yang / EE, NCHU

- Derivation of  $\omega_c$

- **Derivation of**

$$\omega_{\mathbf{C}}$$

The impedance of the loop filter:  $Z_{LF}(s) = \frac{Z_{LF1}(s) \cdot \left(\frac{1}{sC_3}\right)}{Z_{LF1}(s) + R_3 + \frac{1}{sC_3}}$  and  $Z_{LF1}(s) = \frac{1 + s\tau_z}{s(C_1 + C_2)(1 + s\tau_p)}$

Knowing that  $C_2 \ge 10 C_3$  and  $\tau_{p3} = R_3 C_3$

Open-loop gain:

$$\beta(\mathbf{s})G(\mathbf{s})\big|_{\mathbf{s}=j\omega} = -\frac{K_{PD}\cdot K_{vco}}{\omega^2\cdot C_1\cdot N}\cdot \frac{1+j\omega\tau_z}{1+j\omega\tau_p}\cdot \frac{\tau_p}{\tau_z}\cdot \frac{1}{1+j\omega\tau_{p3}}$$

$$\phi(\omega) = \tan^{-1}(\omega\cdot\tau_z) - \tan^{-1}(\omega\cdot\tau_p) - \tan^{-1}(\omega\cdot\tau_{p3}) + 180^\circ \quad \dots \text{ (A)}$$

Assume  $\omega_z < \omega < \omega_p < \omega_{p3}$ , we have

$$\phi_{\text{m,max}} : \frac{d\phi}{d\omega} = \frac{\tau_z}{1 + (\omega \cdot \tau_z)^2} - \frac{\tau_p}{1 + (\omega \cdot \tau_p)^2} - \frac{\tau_{p3}}{1 + (\omega \cdot \tau_{p3})^2} = 0$$

$$\Rightarrow \frac{\tau_z}{(\omega \cdot \tau_z)^2} - \tau_p - \tau_{p3} \approx 0 \qquad \Rightarrow \qquad \frac{\tau_z}{\tau_z} = \frac{1}{\omega^2 (\tau_p + \tau_{p3})} \qquad \cdots \text{ (B)}$$

Substituting (B) into (A) gives

$$\tan \phi = \frac{-\omega \cdot (\tau_p + \tau_{p3}) - \frac{\omega \cdot \tau_p \tau_{p3}}{\tau_p + \tau_{p3}} + \frac{1}{\omega \cdot (\tau_p + \tau_{p3})}}{2 - \omega^2 \cdot \tau_p \tau_{p3}}$$

$$\Rightarrow \qquad \omega^2 + \omega \frac{2 \tan \phi}{(\tau_p + \tau_{p3})^2 + \tau_p \tau_{p3}} - \frac{1}{(\tau_p + \tau_{p3})^2 + \tau_p \tau_{p3}} = 0$$

$$\Rightarrow \omega^2 + \omega \frac{2\tan\phi}{(\tau_p + \tau_{p3})^2 + \tau_p \tau_{p3}} - \frac{1}{(\tau_p + \tau_{p3})^2 + \tau_p \tau_{p3}} = 0$$

Taking the negative root

$$\Rightarrow \qquad \omega_{c} = \frac{\tan\phi_{m}\cdot(\tau_{p}+\tau_{p3})}{(\tau_{p}+\tau_{p3})^{2}+\tau_{p}\tau_{p3}} \cdot \left(\sqrt{1+\frac{(\tau_{p}+\tau_{p3})^{2}+\tau_{p}\tau_{p3}}{(\tan\phi_{m}\cdot(\tau_{p}+\tau_{p3}))^{2}}}-1\right)$$

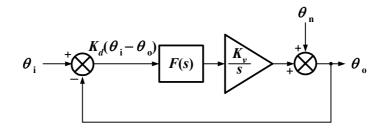

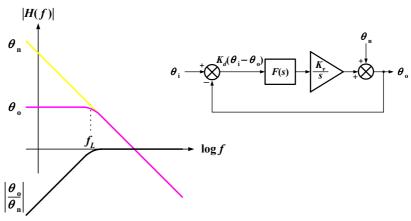

### PLL block diagram

Noise transfer function:

$$\frac{\theta_{\rm o}}{\theta_{\rm n}} = \frac{s}{s + 2\pi f_L}$$

where the loop bandwidth  $f_i$  is determined by  $K_d$ ,  $K_v$  and F(s).

•  $\theta_n$  can be represented by integrated white noise giving a 1 /  $f^2$  power spectral density (psd).

PLL ICs

1-76

Ching-Yuan Yang / EE, NCHU

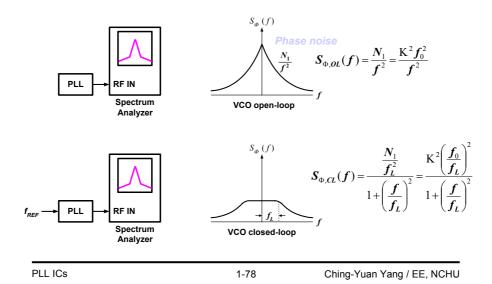

### PLL output phase noise psd

- $\theta_n$ : open-loop phase noise psd (integrated white noise)

- $\theta_{\rm o}$  : closed-loop phase noise psd (lowpass due to shaping by loop)

### Measured phase noise: frequency domain

## Measured phase noise: time domain

### Design example

- A VCO with center frequency of  $f_0$  = 622 MHz and phase noise –106 dBc at a 1-MHz offset is to be used in a PLL. Assuming the VCO is the dominant source of jitter, what is the required loop bandwidth  $f_L$  to realize a jitter of  $\sigma_x$  = 10 ps rms?

- $\boxtimes$  Determine  $N_1$ :

Phase noise @

$$f_{os}$$

= 10 log  $(N_1/f_{os}^2)$

- 106 dBc = 10 log  $(N_1/(1\text{MHz})^2)$   $\Rightarrow$   $N_1$  = 25.1 Hz

$\boxtimes$  Find  $f_i$ :

$$\text{Jitter } \sigma_{\scriptscriptstyle X} = \frac{1}{f_0} \sqrt{\frac{N_1}{4\pi f_L}}$$

$$\Rightarrow f_L = 51.6 \text{ kHz}$$

PLL ICs

1-80

Ching-Yuan Yang / EE, NCHU

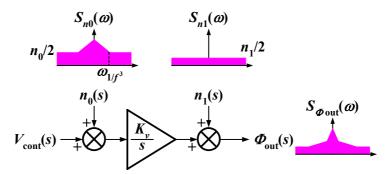

# Equivalent model for the phase noise of a VCO

- VCO acts as an ideal integrator.

- The input source,  $n_0(s)$ , has white and 1/f noise portions that will generate the  $1/f^2$  and  $1/f^3$  regions in the output spectrum. The output source,  $n_1(s)$ , models the noise floor.

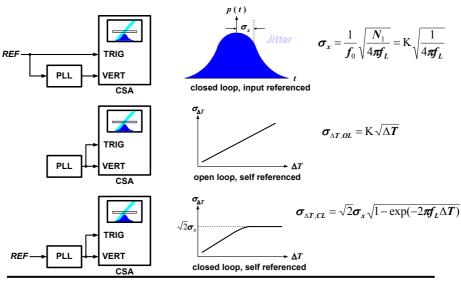

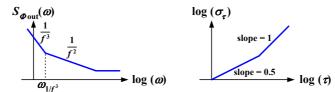

### Typical phase noise and timing jitter of a free running VCO

Output power spectrum

$$\boldsymbol{S}_{\Phi_{out}}(\boldsymbol{\omega}) = \left|\frac{\boldsymbol{K}_{V}}{\boldsymbol{j}\boldsymbol{\omega}}\right|^{2} \boldsymbol{S}_{n}(\boldsymbol{\omega}) + \frac{\boldsymbol{N}_{1}}{2} = \frac{\boldsymbol{K}_{V}^{2} \boldsymbol{N}_{0}}{2\boldsymbol{\omega}^{2}} \left(1 + \frac{\boldsymbol{\omega}_{1/f^{3}}}{\boldsymbol{\omega}}\right) + \frac{\boldsymbol{N}_{1}}{2}$$

where  $N_{0,1}/2$  are the double-sideband power spectral densities of the input and output white noise sources,  $n_{0,1}(s)$ , and  $\omega_1/f^3$  is the 1/f noise corner of the input behavior noise source,  $n_0(s)$ , that is equal to the  $1/f^3$  noise corner of the VCO.

- In the time domain, the uncertainties in the transition times accumulate continuously, increasing the timing jitter of the oscillator.

- riangleq Uncorrelated part:  $\sigma_{ au} = \kappa \sqrt{ au}$  where  $\sigma_{ au}$  is the rms jitter au seconds after the reference, and  $\kappa$  is the proportionality constant.

- Correlated part: the magnitudes add directly resulting in an additional region with a slope of one.

PLL ICs

1-82

Ching-Yuan Yang / EE, NCHU

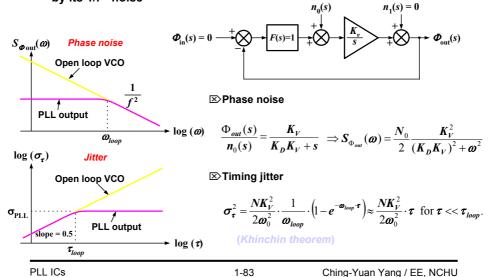

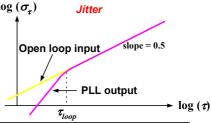

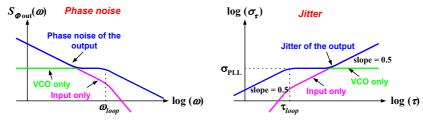

### Phase noise and jitter in 1st order loops

Assuming a noiseless input and assuming the VCO noise is dominated by its 1/f<sup>2</sup> noise

### Phase noise and jitter in 1st order loops

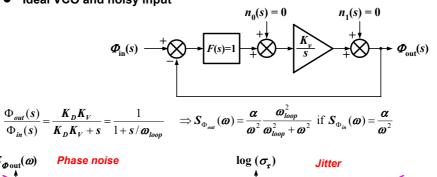

Ideal VCO and noisy input

PLL ICs

1-84

Ching-Yuan Yang / EE, NCHU

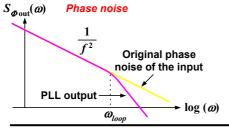

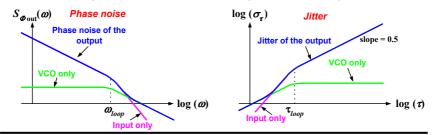

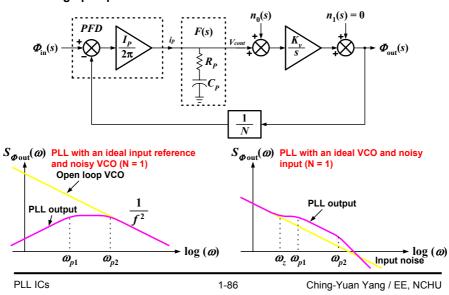

### Phase noise and jitter in 1st order loops

• PLL with large VCO noise (e.g. clock generators, frequency synthesizers)

• PLL with large input reference noise (e.g. clock recovery)

### Phase noise in higher-order loops

• Charge-pump PLL

## Phase noise in higher-order loops

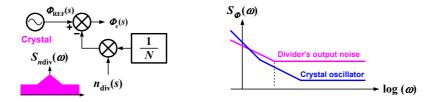

### Noise contribution of the frequency divider

• Equivalent model for frequency divider noise

- The divider's noise usually appears as directly at the input of the PD and experiences the same transfer function as the noise on the input terminal.

- Digital dividers usually have a large white noise floor at their output. If the divider is implemented using active devices with large 1/f noise, it may even swamp the noise of the reference completely.

- Due to the resonant nature, analog regenerative and injection-locked dividers are generally less noisy than the digital synchronous and asynchronous counterparts.

PLL ICs

1-88

Ching-Yuan Yang / EE, NCHU

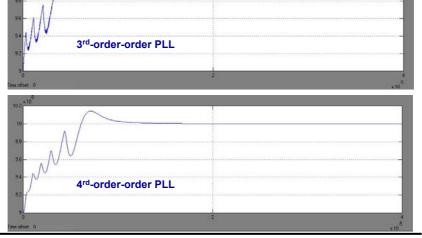

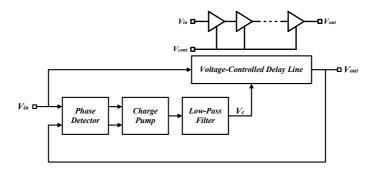

# **Applications of PLLs**

#### **Delay-locked loops**

- Delay line much less noisy than VCOs.

- First-order system (for first-order LPF), thus very stable.

- But input and output frequencies must be equal.

PLL ICs

1-90

Ching-Yuan Yang / EE, NCHU

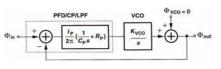

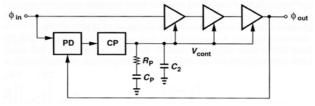

#### **Transfer function of DLL**

Transfer function of PD/CP/LPF

$$\frac{V_{cont}}{\Delta \phi}(s) = \frac{I_P}{2\pi} \left[ \left( R_P + \frac{1}{C_P s} \right) \middle| \frac{1}{C_2 s} \right] = \frac{I_P}{2\pi} \frac{R_P C_P s + 1}{(R_P C_P C_2 s + C_P + C_2) s}$$

Close-loop transfer function

$$\frac{\phi_{out}}{\phi_{in}}(s)\bigg|_{closed} = \frac{\frac{I_p K_{VCDL}}{2\pi} (R_p C_p s + 1)}{R_p C_p C_2 s^2 + \left\lceil C_p + C_2 + \frac{I_p K_{VCDL} R_p C_p}{2\pi} \right\rceil s + \frac{I_p K_{VCDL}}{2\pi}}$$

#### Discussion

- The closed-loop transfer can be used to determine how  $\phi_{out}$  settles if  $\phi_{in}$  experiences a change.  $\Rightarrow \omega_n$ ,  $\zeta$

- In practice R<sub>P</sub> may not be need because the loop contains only one pole at the origin.

#### Skew reduction

Skew between data and buffered clock

Use of a PLL to eliminate skew

PLL ICs

1-92

Ching-Yuan Yang / EE, NCHU

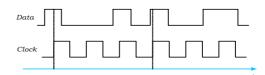

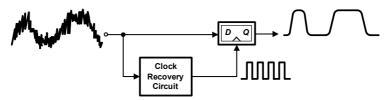

### **Data Recovery (Jitter reduction)**

Retiming data with D flipflop driven by a low-noise clock

- Random binary signals experience jitter because

- crosstalk on the chip and in the package,

- package parasitics,

- additive electronic noise of devices, etc.

- ☐ The idea is to resample the midpoint of each bit by a D flipflop that is driven by a low-noise clock.

- □ Clock recovery circuit (CRC): The CRC produces the clock from the data. Employing phase locking with a relatively narrow loop bandwidth, the CRC minimizes the effect of the input jitter on the recovered clock.

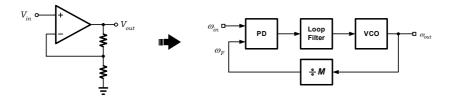

## Frequency multiplication

- When the loop is locked,  $\omega_F = \omega_{in}$ , and hence  $\omega_{out} = M \cdot \omega_{in}$ . The divide ratio of M is called the "modulus."

- ullet Frequency multiplication also amplifies the input phase noise. For example, the magnitude of phase noise components within the  $-3 \, \mathrm{dB}$  bandwidth of the PLL is multiplied by a factor of approximately M.

PLL ICs

1-94

Ching-Yuan Yang / EE, NCHU

**Phase-Locked Loops**

**Behavior Simulation**

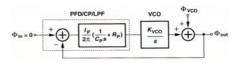

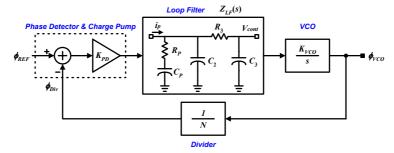

### Linear model of 3rd-order PLLs

**Loop filter:**  $Z_{LF}(s) = \frac{1 + s\tau_z}{s(C_P + C_2)(1 + s\tau_p)}$  with  $\tau_z = R_P \cdot C_P$  and  $\tau_p = R_P \cdot (C_P^{-1} + C_2^{-1})^{-1}$ .

Open-loop transfer function:  $GH(s) = \frac{I_P \cdot K_{VCO}}{2\pi \cdot N} \cdot \frac{1 + s \tau_Z}{s^2 (C_P + C_2) \cdot (1 + s \tau_P)}$

**Phase margin**  $\phi(\omega) = 180^{\circ} + \tan^{-1}(\omega \tau_Z) - \tan^{-1}(\omega \tau_P)$

PLL ICs

Ching-Yuan Yang / EE, NCHU

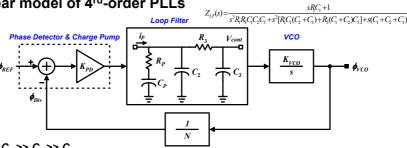

#### Linear model of 4rd-order PLLs

Assume  $C_p >> C_2 >> C_3$ ,

Loop filter:  $Z_{LF}(s) \approx \frac{1 + s\tau_Z}{sC_P(1 + s\tau_{P1}) \cdot (1 + s\tau_{P2})}$  with  $\tau_z = R_P \cdot C_P$ ,  $\tau_{P1} = R_1 C_2$  and  $\tau_{P2} = R_3 C_3$ .

Open-loop transfer function:  $GH(s) \approx \frac{I_P \cdot K_{VCO}}{2\pi \cdot N} \cdot \frac{1 + s\tau_Z}{s^2 C_P \cdot (1 + s\tau_{Pl}) \cdot (1 + s\tau_{Pl})}$

$\Rightarrow$  Crossover frequency  $\omega_C \approx \frac{I_P \cdot R_P \cdot K_{VCO}}{2\pi \cdot N}$

$GH(s)\Big|_{s=j\omega} \approx -\frac{I_p K_{VCO}}{2\pi \cdot N} \cdot \frac{(1+j\omega\tau_Z)}{\omega^2 C_D \cdot (1+j\omega\tau_{D1}) \cdot (1+j\omega\tau_{D2})}$ Gain margin

Phase margin  $\phi(\omega) \approx 180^{\circ} + \tan^{-1}(\omega \tau_Z) - \tan^{-1}(\omega \tau_{P1}) - \tan^{-1}(\omega \tau_{P2})$

## Linear model of 4<sup>rd</sup>-order PLLs

Design the extra pole  $\omega_{p2}$  on the top of  $\omega_{p1}$  by taking  $\tau_{p2} = \tau_{p1}$ .

- $\Rightarrow \quad \tau_{p2} = R_3 \cdot C_3 = (\lambda R_3) \cdot (C_3 / \lambda) \text{ with } \lambda > 10.$

- $\Rightarrow$  Crossover frequency  $\omega_{C} \approx \frac{I_{P} \cdot R_{P} \cdot K_{VCO}}{2\pi \cdot N}$

$\text{Gain margin} \qquad \qquad GH(s) \Big|_{s=j\omega} \approx -\frac{I_{p}K_{VCO}}{2\pi \cdot N} \cdot \frac{(1+j\omega\tau_{Z})}{\omega^{2}C_{p} \cdot (1+j\omega\tau_{Pl})^{2}}$

Phase margin  $\phi(\omega) \approx 180^{\circ} + \tan^{-1}(\omega \tau_Z) - 2 \tan^{-1}(\omega \tau_{P1})$

PLL ICs

1-98

Ching-Yuan Yang / EE, NCHU

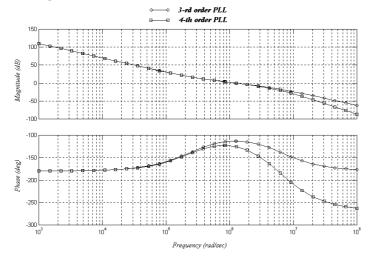

# Bode diagram of 3<sup>rd</sup>-order and 4<sup>rd</sup>-order PLLs

Choose  $\omega_C$  =  $2\pi \times 200$  Krad/s and  $\gamma$  = 5

$\Rightarrow$  N = 50,  $K_{v}$  = 50 MHz/V,  $I_{P}$  = 100  $\mu$ A,  $R_{1}$  = 13.4 K $\Omega$ ,  $C_{1}$  = 237 pF,  $C_{2}$  = 16 pF, and  $\lambda$  = 12.

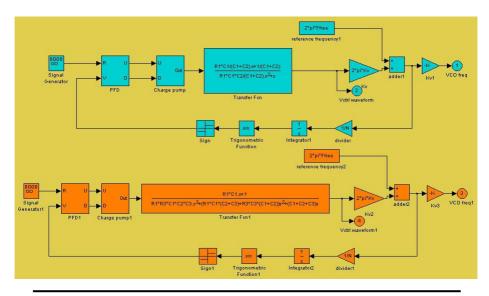

# Simulink behavior simulation of 3<sup>rd</sup>-order and 4<sup>rd</sup>-order PLLs

PLL ICs

1-100

Ching-Yuan Yang / EE, NCHU