# A 16-bit 16-MS/s SAR ADC With On-Chip Calibration in 55-nm CMOS

Junhua Shen<sup>®</sup>, *Member, IEEE*, Akira Shikata, Lalinda D. Fernando, Ned Guthrie, Baozhen Chen<sup>®</sup>, Mark Maddox, Nikhil Mascarenhas, Ron Kapusta, *Senior Member, IEEE*, and Michael C. W. Coln, *Member, IEEE*

Abstract—This paper presents a successive approximation register (SAR) analog-to-digital converter (ADC) that is much smaller and faster than other recently reported precision (16-bit and beyond) SAR ADCs. In addition, it features low input capacitance and an efficient on-chip foreground calibration algorithm to fix bit weight errors. Several other enabling techniques are also used, including signal independent reference using reservoir capacitors to improve speed and reduce area, plus LSB repeats and statistical residue measurement to improve efficiency. The prototype achieves 97.5-dB spurious-free dynamic range at 100-kHz input while operating at 16 MS/s and consumes 16.3 mW. It was fabricated in a 55-nm CMOS process and occupies 0.55 mm².

Index Terms—Analog-to-digital converter (ADC), calibration, optimal LSB repeats, precision, reservoir capacitor, statistical residue measurement (SRM), successive approximation register (SAR).

#### I. INTRODUCTION

Successive approximation register (SAR) analog-to-digital converters (ADCs) have gained considerable research interest over the past decade or so [1]–[9]. The relatively simple architecture due to hardware reuse without requiring operational amplifiers (opamps) makes it more power efficient and easier to port between processes. Furthermore, the supply voltage scaling in advanced CMOS processes has less of a toll on SAR ADCs because the comparator only requires a small output swing to distinguish decisions from noise. This is unlike the opamps in pipelined ADCs or sigmadelta ADCs, where reduced supply voltage translates to much lower opamp output swing due to fixed circuit overhead voltage drop, which leads to much decreased ADC signal to noise ratio (SNR).

One of the performance spaces that SAR ADCs excel at is high resolution at relatively low speed. They find many applications ranging from medical imaging, instrumentation, to industrial process control, etc. Compared to sigma-delta ADCs, which are also well suited in the low-speed space, SAR ADCs distinguish themselves with the capability of converting one sample at a time, among others. Furthermore, SAR ADCs better handle multiplexed inputs compared to incremental sigma-delta ADCs especially when only lower oversampling

Manuscript received August 7, 2017; revised October 18, 2017 and November 27, 2017; accepted December 4, 2017. Date of publication January 5, 2018; date of current version March 23, 2018. This paper was approved by Guest Editor Ken Chang. (Corresponding author: Junhua Shen.)

The authors are with Analog Devices, Inc., Wilmington, MA 01887 USA (e-mail: junhua.shen@analog.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2017.2784761

ratio is allowed, and SAR ADCs do not require much signal post-processing.

Typically, precision SAR ADCs [3], [4], which are generally defined at 16 bits and greater, sample at below a few MS/s. A few works [1], [2] have pushed the speed further. They use 2-bit/trial and the pipelined SAR architecture [7], [10] to speed up the operation, at the cost of added design complexity and a high-accuracy amplifier. In addition, these ADCs typically have a sampling capacitance larger than 20 pF to achieve more than 90-dB SNR, which may require more power in the ADC driver than the ADC itself [11], [12]. Last, they employ off-chip linearity calibration [1]–[4] which takes significant test time and entails extra cost.

As system-on-a-chip (SoC) solutions are gaining more popularity in an effort to reduce overall system cost, as well as to improve system performance, the precision SAR ADCs aforementioned cannot meet the needs due to their large footprint, difficulty to drive, and high cost of testing. Furthermore, most of them are in older processes like 0.18  $\mu$ m, which is not ideal for SoC chips due to their significant digital content. This paper describes a precision SAR ADC in 55-nm CMOS that addresses these issues, which was first reported in [13]. It is fast in the precision ADC category to enable more ADC output averaging where needed, which in turn allows one to have noisier individual conversions and thus dramatically smaller sampling capacitance. As an example, the user may average this ADC output 16 times to hit the 90-dB SNR target. This paper also features a much smaller footprint as well as on-chip calibration which makes it well suited for embedded applications.

This paper is organized as follows. In Section II, the architectural and block level designs are described. Circuit design techniques that help enable this ADC are presented in Section III, including optimal LSB repeats, one reservoir-capacitor per bit-capacitor digital-to-analog converter (DAC), calibration with existing LSB capacitors, and statistical residue measurement (SRM). Experimental results are shown in Section IV followed by the conclusion in Section V.

# II. ARCHITECTURAL AND BLOCK-LEVEL DESIGN

# A. ADC Top Level

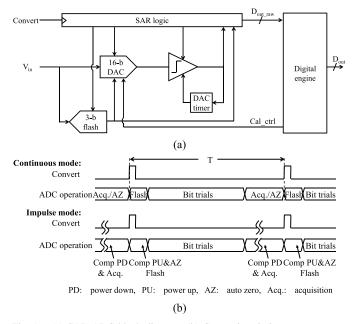

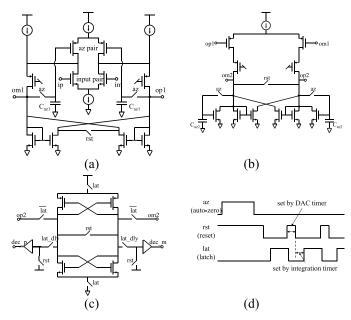

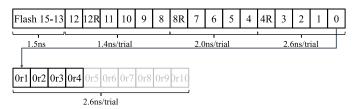

Fig. 1(a) shows the proposed ADC top-level block diagram. It is a fully self-timed 16-bit asynchronous SAR ADC [14]–[17] with three MSBs resolved by the flash sub-ADC. The flash speeds up the conversion and attenuates the DAC output significantly to ease reliability concerns [17]–[19].

Fig. 1. (a) SAR ADC block diagram. (b) Conversion timings.

The ADC sampling network, which includes the 16-bit DAC and the 3-bit flash blocks other than the flash comparators, operates at 3.3 V to accommodate traditional precision applications, the rest of the circuits all operate under 1.2-V supply. The digital engine includes bit weight calibration and data reconstruction. The ADC operates in two modes, illustrated in Fig. 1(b). The default continuous mode has a periodic input convert clock. When the convert signal comes, the flash makes the MSB decisions and the result is fed to the DAC to start the bit trials. After the last bit trial finishes, the ADC enters the acquisition phase, when auto-zero is also performed on the comparator. This process is repeated when the next convert signal comes, at a known conversion rate. The other mode is the impulse mode, where the ADC converts on demand and goes to an inactive state afterward while passively tracking the input signal. In this mode, after the convert signal goes active, the comparator is powered up and auto-zero is performed. The flash powers up the reference ladder and decides in parallel with the comparator auto-zero. It shuts down after the flash decisions are fed to the DAC. When all the subsequent bit trials finish, the ADC turns off and enters the passive acquisition phase until the next convert signal is detected. This impulse mode lets power scale with throughput when the input signal is sparse and the application does not require full speed conversion, such as many environmental or patient monitoring sensors. Though input bootstrapping circuit needs to be avoided in the impulse mode as the passive acquisition phase could last long and the bootstrapping capacitor may not hold its charge.

To take advantage of the 55-nm deep-sub-micron CMOS process, we designed the ADC to convert up to 16 MS/s, which is very fast in the precision ADC category but not so fast as to compromise the SAR ADC efficiency. The high-speed operation gives the user an option to average the ADC output data further to lower noise. This in turn allows much noisier individual conversions and thus a much smaller

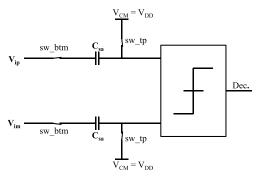

Fig. 2. VDD referenced sampling.

sampling capacitance to dramatically reduce area. Compared to traditional precision ADCs that run slower and rely on accurate individual conversion, this ADC trades noise for speed to maintain the same efficiency but results in a much smaller footprint.

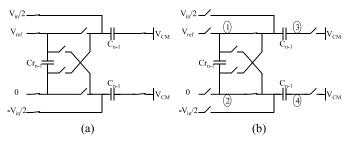

#### B. VDD Referenced Sampling

The impulse mode mentioned earlier requires passive acquisition, so that the ADC is not consuming any active power while it is tracking the input signal and waiting for the next convert signal to come. VDD referenced sampling technique is introduced to enable that. Fig. 2 shows the sampling circuit in acquisition phase while the comparator is turned off. In order to not consume any active power, we cannot use active circuitry to generate the common mode (CM) voltage  $V_{\rm CM}$ shown in Fig. 2. A conventional approach to solve this is to split each sampling capacitor  $C_{sa}$  into two halves, connect the top plate of one half to VDD and the other half to GND. After the acquisition, the top plates of the two halves are shorted together to realize the VDD/2 CM voltage. The downside of this approach is added layout routing complexity and the resulting parasitics. In addition, it also requires an extra clock phase to short the two top plates. In this design, we take advantage of the fact that the DAC output or comparator input swing is only 1/8th of ADC V<sub>ref</sub> thanks to the flash sub-ADC that resolves the three MSBs. Assuming  $V_{\rm ref}$  is 3.3 V and some reasonable amount of DAC output attenuation due to loading capacitors, we only have roughly ±150 mV max swing at each of the comparator inputs. This enables the use of the VDD supply, which is typically well regulated, to replace  $V_{\rm CM}$  at the top plate of the sampling DAC, thus avoiding an extra CM generator that would consume power. The upward of 150-mV transient at the comparator input may cause brief leakage through the top plate acquisition switch. To eliminate most of this potential leakage we may either use a high threshold core pMOS switch controlled by core supply, or use an IO nMOS switch controlled by IO supply. The latter has been implemented in this design. The slightly higher swing does not cause reliability concern to the input pair of the comparator, as will be covered in the comparator sub-section.

# C. Flash Sub-ADC

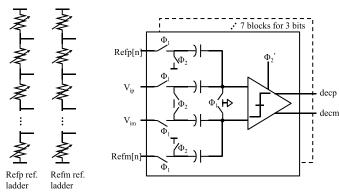

The flash sub-ADC resolves three MSBs mainly as a tradeoff between added complexity and the amount of DAC output attenuation. In this design, shown in Fig. 3, a resistor ladder is

Fig. 3. Flash sub-ADC block diagram.

Fig. 4. SAR comparator block diagram.

used to generate the flash references, and the reference levels are dithered to match the SAR DAC dither, which is up to the equivalent of b12 weight. Dither is used here to improve ADC linearity [20]. The seven flash comparators sample the ADC input (up to 6.6  $V_{pp,diff}$  with  $V_{ref} = 3.3$  V) and reference during acquisition phase  $\Phi_1$ , and the comparison is done immediately afterward in  $\Phi_2$ ,  $\Phi_2$ ' is a slightly delayed version of  $\Phi_2$ . After the comparison is done in roughly 1.5 ns and the decisions are fed to the DAC, the comparator and resistor ladder is shutdown to preserve power. Since the SAR DAC has a built-in redundancy, the flash comparator offset and noise are not critical as long as the resulting decision errors are covered by the DAC redundancy. We allocate 1/4 of the redundancy to tolerate the flash decision error. As such, the flash comparator is designed for speed and power to maximize its efficiency and minimize the overhead.

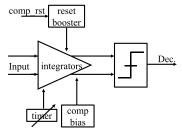

# D. SAR Comparator

The comparator is a critical block in terms of power, noise, speed, and reconfigurability. Fig. 4 shows the block diagram of the comparator. The integrators before the latch are controlled by the programmable timer to trade integration speed with noise. The comparator reset signal comp\_rst is boosted to ensure there is negligible memory effect in between two comparisons, even when the comparator input has a big step change. Fig. 5 shows the two integrator stage schematics and the latch stage. Cross-coupled positive feedback is used for both integrator loads to maximize dc gain and to eliminate the need for a CM feedback circuit. Both stages are auto-zeroed to minimize offset and 1/f noise for precision applications. The auto-zero phase shown in Fig. 5(d) overlaps with the ADC acquisition phase, both integrator stages store the offset information on the auto-zero capacitors  $C_{\rm az}$  during this phase,

Fig. 5. SAR comparator schematic and operation timing. (a) First integrator stage. (b) Second integrator stage. (c) Latch. (d) Operation timing.

while the input to the integrators are differentially shorted. Two stages are used, instead of one, to achieve a wider range of integration gain versus time. The first integrator stage incorporates a folded cascode structure to enable the use of VDD as its input CM. Simulation shows that the input pair can handle up to VDD +400-mV transient input without stressing the transistor, as the source node of the input pair largely tracks the comparator input.

Comparator noise is the dominant source for the ADC conversion noise. We designed the steady-state gain of the two integrator stages to be sufficiently high so that they operate in integration mode instead of linear settling mode to achieve better noise performance [21]. The gain of each integrator is given in the following equation:

$$Av = \frac{gm}{C}t\tag{1}$$

where gm is dominated by the input pair, C is the loading parasitic capacitors (not drawn) at op/om nodes in Fig. 5(a) and (b). The input referred noise power is inversely proportional to the gm of the input pair and integration time t, shown in (2). The  $\gamma$  factor accounts for the excessive noise from transistors other than the input pair

$$V_{n_{-\text{rti}}}^{2} = \frac{\frac{4\gamma k T g m}{C^{2}} t^{2} \times \frac{1}{2t}}{A v^{2}} = \frac{2\gamma k T}{g m \times t}.$$

(2)

Note that the auto-zero operation contributes to overall kT/C sampling noise, which is also accounted for in the design. The implemented comparator has an estimated noise of around  $180~\mu V_{rms}$ .

# E. DAC

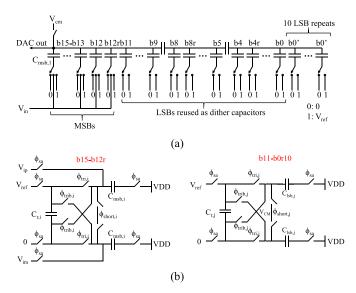

The charge redistribution DAC with three capacitor array segments is shown in Fig. 6(a). Three segments are used to reduce the capacitance spread in each segment and to enable

Fig. 6. (a) DAC structure. (b) Simplified bit-capacitor operation.

Fig. 7. Bit trials with optimized trial groups.

an 8-fF unit capacitor. The DAC sampling capacitance is only 1 pF from b15 to b12 and b12r, which greatly eases the input driver and reference buffer requirements. Three redundant capacitors (b12r, b8r, and b4r) are included to tolerate decision errors [22], [23] from the flash sub-ADC and earlier bit trials. During the track phase, capacitors b11-b0 do not sample the input, but instead sample a random dither value to improve linearity. Up to 10 LSB repeats are included to improve noise performance, covered in more detail in Section III-A. Fig. 6(b) illustrates the operations of both sampling and non-sampling capacitors. One reservoir-capacitor per bit-capacitor DAC cell structure is employed to speed up operation and achieve signal independent bit weight errors. It is explained in depth in Section III-B.

For an SAR ADC, the earlier bit trials are less critical given that the comparator input is typically much larger than the conversion noise level. Harpe *et al.* [24] and Kim *et al.* [25] take advantage of this by changing the comparator preamp loading capacitance to reduce power consumption for the earlier trials, without sacrificing the overall noise performance. In this design, we may optimize the bit trials further, with an example setting illustrated in Fig. 7. Given the redundancy employed at b8r and b4r, we divide the bit trials into several groups shown in Fig. 7 and set both smaller bit-capacitor settling time and comparator integration time for earlier groups. The resulting settling error and higher comparator noise are tolerated by the redundant bits.

Fig. 8. LSB repeats in the presence of noise.

Fig. 9. Simulated ADC noise versus number of repeats with different weights.

#### III. CIRCUIT DESIGN TECHNIQUES

#### A. Optimal LSB Repeats

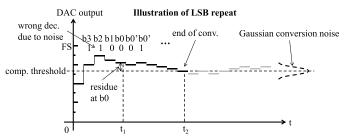

The ADC noise comes from both the acquisition phase and the conversion phase, which is roughly 130 and 250  $\mu V_{rms}$ , respectively, in this design. The acquisition phase noise is mainly kT/C sampling noise, which is a tradeoff between noise level and area, as well as the power associated with driving the capacitance. Once the noise is sampled, it generally cannot be removed. Here, we introduce a technique that focuses on reducing effective noise from the conversion phase only. The conversion noise affects the SAR comparator decision and it mainly originates from the comparator, the reference, and the series switch  $R_{ON}$  and routing resistance at the comparator inputs. From (2) or [26], we know that it takes 4× power to reduce the comparator noise by 2x, assuming current efficiency gm/I remains the same. In [9], [27], and [28], comparator decision majority voting is used for critical bit trials where input to the comparator is very small to reduce conversion noise. This technique requires a detection circuit to identify the critical bit trials, which tends to be sensitive to process, voltage, and temperature variations. In [29], an adaptive-averaging technique was presented, where b0 is repeated 8 times. It treats the first few LSB repeat bit trials as redundant trials to correct earlier DAC settling errors, and averages the rest of the repeat decisions after detecting a 01 or 10 transition during the LSB repeats. The effectiveness of this detection was limited due to the presence of conversion noise.

In this paper, an optimal LSB repeat technique is proposed to reduce noise. The b0 decision can be repeated up to 10 times, depending on conversion rate and noise requirements. Unlike that in [29], we report that reconstructing the ADC output with the LSB repeat bits considered equivalent to the other bits yields better noise performance, i.e., the final ADC output is weighted sum of all the bits trialed, including the repeat bits. Fig. 8 illustrates the proposed LSB repeat technique using a 4-bit example. In the presence of conversion

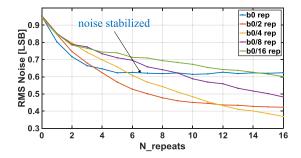

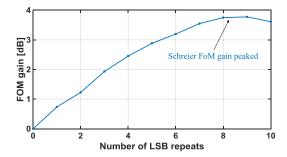

Fig. 10. FoM gain versus number of repeats.

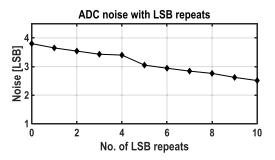

Fig. 11. Measured noise of the proposed optimal LSB repeats and adaptive averaging [29]; the ADC conversion noise is configured to dominate the sampling noise.

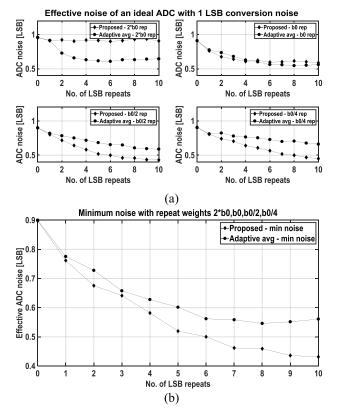

noise, b2 makes a wrong decision and the DAC output contains a residual error larger than one LSB after the regular b0 trial. With subsequent LSB repeats, the residual error will be pulled down because the mean conversion noise is zero. After a number of LSB repeats, the DAC output will start to move around the comparator threshold. Furthermore, LSB repeats will not improve conversion noise, and the optimal number of LSB repeats can be determined given conversion noise level and the repeat bit weight. Fig. 9 shows simulation results of effective ADC noise versus number of repeats, at five different repeat bit weight settings. The ADC is ideal other than one LSB nominal conversion noise. We observe that depending on the conversion time available and thus the number of LSB repeats allowed, there exists an optimal repeat bit weight to get the minimal effective ADC noise. For example, if we have time to do four LSB repeats, choosing repeat bit weight b0/2 will yield better result than a b0 weight repeat. Also, as described earlier, for a given repeat bit weight, the effective ADC noise would stabilize after a number of repeats. In Fig. 9, the noise stabilizes at around five repeats for repeat bit weight b0. The smaller the repeat bit weight, the more repeats it takes for the effective ADC conversion noise to stabilize. As mentioned earlier, this design uses b0 repeat as it is found to be the most effective repeat bit weight given the designed noise level and speed.

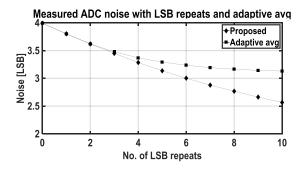

The proposed LSB repeat technique essentially trades speed for noise, but the noise reduction more than makes up for the speed penalty in terms of efficiency or figure of merit (FoM). Fig. 10 shows the calculated FoM improvement of this design versus the number of repeats available, without accounting for the acquisition noise. Fig. 11 also compares measured results of this technique versus the adaptive-averaging algorithm

Fig. 12. Simulated noise of (a) ideal ADC with different repeat bit weights using optimal LSB repeats and adaptive averaging [29] and (b) minimum noise achievable with optimal LSB repeats and adaptive averaging [29].

in [29]. The proposed approach improves noise further by up to 20%. In a more generic case, simulation results are given in Fig. 12 to compare the two LSB repeat algorithms. In this simulation, the ideal ADC has 1 LSB of conversion noise. Fig. 12(a) shows the effective ADC noise versus the number of LSB repeats, with four different repeat bit weights at  $2 \times 60$ , b0, b0/2, and b0/4, respectively. Fig. 12(b) then aggregates the results from Fig. 12(a) and picks the lowest noise out of those four repeat bit weights. For example, with five LSB repeats available for both techniques, minimum noise from adaptive-averaging is 0.6 LSB with b0 weight repeats, and minimum noise from the proposed is 0.52 LSB with b0/2 weight repeats. Fig. 12(b) demonstrates that the proposed optimal LSB repeat is again more effective by up to around 20%.

In addition, as no averaging is applied to the proposed optimal LSB repeats, the DAC output residue after the repeats could be processed to further reduce noise and quantization error. This will be covered in Section III-D.

#### B. One Reservoir-Capacitor Per Bit-Capacitor DAC

DAC settling or reference settling during each bit trial is often a bottleneck for precision SAR ADC speed, especially when the reference is provided off-chip through chip bondwires [30]. Another approach is to use an on-chip high-speed reference buffer which comes at a cost of excessive power consumption. In [15] and [17], on chip reservoir capacitors are used as "references" to significantly improve DAC settling

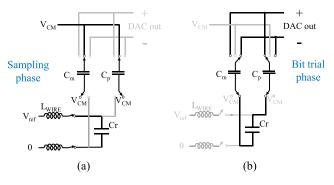

Fig. 13. Reservoir capacitor as reference to speed up bit settling [17]. (a) Sampling phase. (b) Bit trial phase.

speed. Fig. 13 illustrates how using a reservoir capacitor improves DAC settling speed dramatically. During the sampling phase, the reservoir-capacitor Cr is charged up to the reference level. During the bit trial phase, the bit capacitors Cp and Cm absorbs the reference charge from Cr instead of an off-chip reference through the bond-wires. This makes the DAC settling much faster as the settling speed is only limited by the switch Ron and the bit capacitance. However, in both [15] and [17], the reservoir capacitors would need to be sufficiently big so that the reference inaccuracy due to charge sharing is minimized. To avoid this, in [17], DAC capacitors are separated from sampling capacitors to ensure charge drawn from the reservoir capacitor is signal independent. This leads to larger area and, more significantly, degrades noise performance. Reported in [3] and [13], we propose one reservoir-capacitor per bit-capacitor technique. This is in contrast to [15] where multiple reservoir capacitors are switched to one sampling capacitor; and [17] where one reservoir capacitor is shared with multiple bit capacitors. In this design, some of the bit capacitors (b15-b12, b12r) are also used as sampling capacitors. And unlike those in [15] and [17], each and every bit capacitor is driven to a reference during its bit trial by a unique pre-charged reservoir capacitor [see Fig. 6(b)] that is sized 10× that of the corresponding bit capacitors. It will be shown shortly that this DAC structure results in inputsignal independent bit weights, enabling more straightforward calibration. As a result, relatively small reservoir capacitors are used, reducing area and easing pre-charging while maintaining the full speed benefit.

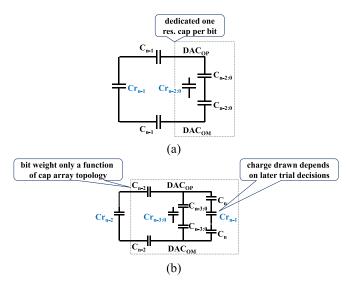

Fig. 14 illustrates at a conceptual level how this DAC structure achieves signal independent bit weights. Fig. 14(a) shows the simplified capacitor array during the first bit trial, where  $C_{n-1}$  is the MSB capacitor and  $Cr_{n-1}$  is the corresponding reservoir capacitor,  $C_{n-2:0}$  are the rest of the bit capacitors in the DAC. Assuming the bit capacitor  $C_{n-1}$  was either differentially shorted to  $V_{\rm CM}$  (an option for sampling bit capacitors) or reset to CM  $V_{\rm CM}$  (for non-sampling bit capacitors) right before the bit trial, when the pre-charged reservoir-capacitor  $C_{n-1}$  connects to bit capacitor  $C_{n-1}$ , it is going to produce a DAC output step DAC<sub>OP</sub>-DAC<sub>OM</sub> independent of the input signal or the bit decision. The output step size is only a function of the capacitor ratios as the initial value on  $Cr_{n-1}$  and the left-hand side of  $C_{n-1}$  are signal

Fig. 14. One reservoir capacitor per bit capacitor. (a) First bit trial illustration. (b) Second bit trial illustration.

Fig. 15. Operation of a sampling capacitor. (a) MSB capacitor during acquisition phase. (b) MSB capacitor during conversion phase.

independent. Fig. 14(b) further illustrates the second bit trial, where the reservoir capacitor  $Cr_{n-1}$  from the first bit trial is now part of the loading capacitors. This does not change the fact that  $DAC_{OP}$ - $DAC_{OM}$  is still deterministic for the second bit trial, only the step size changes due to different loading capacitor values. The signal independent DAC output step size at each bit trial essentially represents the corresponding bit weight, so this one reservoir-capacitor per bit-capacitor DAC structure leads to signal independent bit weight errors from the charge sharing. An interesting observation is that even though the bit weight is signal independent, the charge drawn from each reservoir capacitor, illustrated in Fig. 14(b), is decision or signal dependent.

The conceptual explanation above assumes that the bit capacitor is shorted to a CM right before the bit trial. In a more general case, the sampling bit capacitors may not have their bottom plates shorted before the bit trials, if there is a separate sub-ranging ADC that decides the first few MSBs. In this case, the bottom plates of the sampling capacitors could have initial value of  $V_{\rm in}$  instead of a fixed  $V_{\rm CM}$  right before the bit decision(s) are applied to the bit capacitor(s). We will prove mathematically that this still results in signal independent bit weights. Fig. 15(a) shows the MSB capacitor during the acquisition phase, Fig. 15(b) shows the MSB during its bit trial. DAC output loading capacitance is not shown in Fig. 15. For simplicity, we start by assuming only the MSB acquires the reference from a reservoir capacitor, which may

cause reference droop due to charge sharing. All of the lower bits have ideal references. Applying the charge conservation rule on node 1 and 2 right before the end of the acquisition phase and at the end of the conversion phase (where node 3 and 4 converge to  $V_{\rm CM}$  as well), we can arrive at the following:

$$Vr_{n-1} = \frac{2Cr_{n-1}Vref + b_{n-1}C_{n-1}V_{in}}{2Cr_{n-1} + C_{n-1}}$$

(3)

where  $Vr_{n-1}$  is the reference voltage drop on the reservoircapacitor  $Cr_{n-1}$  after the charge sharing,  $V_{ref}$  is the ideal reference voltage, and  $b_{n-1}$  is the bit decision +1 or -1. We see that  $Vr_{n-1}$  is proportional to input voltage  $V_{in}$ . The MSB weight at the end of the conversion is thus proportional to  $Vr_{n-1}$  and thus  $V_{in}$

$$w'_{n-1} = \frac{Vr_{n-1}}{Vref} w_{n-1,id}$$

(4)

where  $w_{n-1,id}$  is the ideal weight defined just by the MSB capacitor value. The aggregate ADC output  $D_{out}$  is defined by

$$D_{\text{out}} = \sum_{i=0}^{n-1} (b_i w_i)$$

(5)

where  $b_i$  is bit decision  $\pm 1$ ,  $w_i$  is the corresponding half bit weight. Then, we have  $D_{\text{out}}$  shown in the following equation assuming that all bit weights are ideal other than the MSB:

$$D_{\text{out}} = b_{n-1}w'_{n-1} + \sum_{i=0}^{n-2} (b_i w_{i,\text{id}}).$$

(6)

Plugging (3) and (4) into (6), we get

$$D_{\text{out}} = b_{n-1} \frac{2\text{Cr}_{n-1} V_{\text{ref}} + b_{n-1} C_{n-1} V_{\text{in}}}{(2\text{Cr}_{n-1} + C_{n-1}) V_{\text{ref}}} w_{n-1, \text{id}} + \sum_{i=0}^{n-2} (b_i w_{i, id}).$$

(7)

We can further define  $\alpha_i$  and  $\beta_i$  as

$$a_i = \frac{2Cr_i}{2Cr_i + C_i}$$

where  $i \in \{0, 1, \dots n - 1\}$  (8)

$$\beta_i = \frac{C_i}{2\text{Cr}_i + C_i} \text{ where } i \in \{0, 1, \dots n - 1\}.$$

(9)

So we have

$$D_{\text{out}} = b_{n-1} \alpha_{n-1} w_{n-1, \text{id}} + \beta_{n-1} w_{n-1, \text{id}} \frac{V_{\text{in}}}{V_{\text{ref}}} + \sum_{i=0}^{n-2} (b_i w_{i, \text{id}}).$$

(10)

And by definition

$$\frac{D_{\text{out}}}{\sum_{i=0}^{n-1} w_{i,\text{id}}} = \frac{V \text{in}}{V \text{ref}}.$$

(11)

Solving (10) and (11), we arrive at

$$D_{\text{out}} = \frac{b_{n-1}\alpha_{n-1}w_{n-1,id} + \sum_{i=0}^{n-2} (b_i w_{i,id})}{1 - \beta_{n-1}w_{n-1,id} / \sum_{i=0}^{n-1} w_{i,id}}.$$

(12)

We see that  $D_{\text{out}}$  is effectively signal independent even though the MSB has signal-dependent reference voltage droop shown in (3). And the effective MSB bit weight is not dependent on  $V_{\text{in}}$ , unlike  $w_{n-1}$ ' in (4). To generalize from the derivation above, let us now assume each bit capacitor has its corresponding reservoir capacitor in the SAR DAC, we will arrive at the following general formula:

$$D_{\text{out}} = \frac{\sum_{i=0}^{n-1} (b_i \alpha_i w_{i,\text{id}})}{1 - \sum_{i=0}^{n-1} (\beta_i w_{i,\text{id}}) / \sum_{i=0}^{n-1} w_{i,\text{id}}}.$$

(13)

Effectively, the charge sharing from each reservoir-capacitor contributes to the following constant and  $D_{\text{out}}$  can also be rewritten as:

$$\gamma_i = \frac{\alpha_i}{1 - \sum_{i=0}^{n-1} (\beta_i w_{i,id}) / \sum_{i=0}^{n-1} w_{i,id}}$$

(14)

$$D_{\text{out}} = \sum_{i=0}^{n-1} (b_i \gamma_i w_{i,\text{id}}).$$

(15)

The ideal bit weight defined by the capacitor value is scaled by a constant from reservoir capacitor charge sharing. And the effective half bit weight ( $w_{i,id}$  is defined as half bit weight) is shown in the following equation:

$$w_i = \gamma_i w_{i,id}. \tag{16}$$

It is interesting to note that the bit weight  $w_i$  no longer corresponds to the DAC output step size at the bit trial. For example, DAC output step size for the MSB bit trial is linearly proportional to  $V_{\rm in}$  as the bit capacitor has  $V_{\rm in}$  as its initial value. Equations (10) and (11) indicate that  $V_{\rm in}$ dependent DAC output step would be further resolved by the lower bits, leading to (12) and (13) where the effective bit weights are signal independent. One caveat of this technique is, since the reference is not driven with an active circuitry during the bit trials, the input signal-dependent nonlinear parasitic capacitance in the DAC will affect the charge sharing between the reservoir capacitor and the corresponding bit capacitor. This in practice limits the application of this technique to 18-bit ADC and below, assuming we are not using very large reservoir capacitors to save area. On the other hand, any fixed parasitic capacitors in the DAC capacitor array will not affect the signal independence of the bit weights, as they only modify the charge-sharing ratios between the reservoir capacitors and the corresponding bit capacitors, resulting in slightly different but still signal independent bit weights.

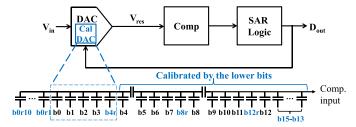

#### C. Calibration With LSB Capacitors

To correct bit weight errors due to mismatches, parasitics, and reservoir-capacitor charge-sharing errors, calibration is performed to help achieve 16-bit level linearity. A number of SAR ADC calibration approaches have been proposed in the literature. In [31] and [32], equalization-based digital engines are used to find the ADC bit weights. They require different ADC decision paths for the same input to make it work. In [33], the pipelined SAR ADC uses the back stage to calibrate the bit weights in the first stage, while in [34] an extra DAC is introduced to measure the bit weight errors in the main SAR DAC. Most recently, a calibration method using an extra trial is introduced [35], though it only works with analog bit weight compensation.

Fig. 16. SAR ADC calibration with existing LSB capacitor array.

The on-chip foreground calibration with minimal overhead proposed here is similar in concept to [17] and [36]. However, we make it possible to calibrate the lower bits as well, which is essential for precision ADCs. The ADC measures the bit weights during calibration and compensates the errors in digital domain during normal operation. Instead of using the back stage or introducing an extra reference DAC to measure the bit weights, some of the LSBs in the ADC (b4r-b0 in this design) are used to calibrate the more significant bits (b4 and above), illustrated in Fig. 16. b4 is measured first with b4r-b0 using the existing SAR ADC feedback loop, while the ADC input is grounded and all the bits above b4 are not trialed. Specifically, we force b4 to 0 and get the ADC output codes which correspond to the b4 weight at force 0, plus the ADC offset, and then we force b4 to 1 to get another set of output codes; the generalized formulas are shown in the following equations:

$$w_{i,\text{force0}} = -\sum_{j=0}^{i-1} (b_{j,\text{force0}} w_j) + \text{os}$$

(17)

$$w_{i,\text{force1}} = -\sum_{j=0}^{i-1} (b_{j,\text{force1}} w_j) + \text{os.}$$

(18)

To remove the offset, we subtract the two to get

$$w_i = (w_{i,\text{force1}} - w_{i,\text{force0}})/2 \tag{19}$$

$$w_i = \left(\sum_{j=0}^{i-1} (b_{j,\text{force}0} w_j) - \sum_{j=0}^{i-1} (b_{j,\text{force}1} w_j)\right) / 2.$$

(20)

After b4 is calibrated, then b5 is measured with b4-b0, and so on, as generalized in the following equation:

$$w_{i+1} = \left(\sum_{j=0}^{i} (b_{j,\text{force}0} w_j) - \sum_{j=0}^{i} (b_{j,\text{force}1} w_j)\right) / 2. \quad (21)$$

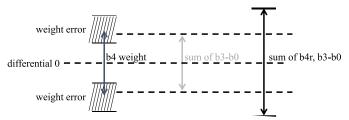

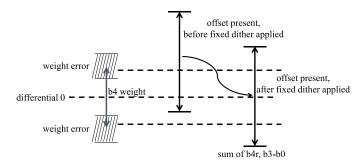

Multiple measurements are taken for each bit weight to average out the effects of noise. This calibration is made possible as redundancy (e.g., b4r) is available to increase the available range for measuring bit weight errors, shown in Fig. 17, otherwise the LSBs would not be able to measure the bit weight if it is larger than nominal weight. Also, as pointed out in [36] and illustrated in Fig. 18, ADC offset eats into the LSB measurement range. To achieve 16-bit level linearity, lower bits like b4 also need to be calibrated. Offsets in the system can be greater than the calibration range for these lower bits. To solve this issue, we introduce offset cancellation with fixed dither during the calibration. Fig. 6(a) illustrated

Fig. 17. Capacitor measurement with redundancy.

Fig. 18. Capacitor measurement with offset compensation by applying a fixed dither amount.

Fig. 19. SRM for SAR conversion residue. (a) Block diagram. (b) CDF to derive residue value based on decision probability P.

that we have b11-b0 reused as dither capacitors. During the foreground calibration, we measure the ADC offset and cancel it by apply the appropriate amount of offset using the dither capacitors. Thus, the ADC appears offset free during the bit weight calibration, enabling us to calibrate much smaller bit weights than those in [17] and [36], which is essential for achieving precision ADC performance.

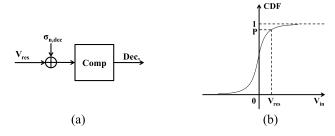

#### D. Statistical Residue Measurement

As previously mentioned, after LSB repeats, the DAC output or comparator input still contains a small residual error  $V_{\rm res}$ . The finite  $V_{\rm res}$  is due to the conversion noise as well as the quantization error. As reported in [37]–[39], we may take advantage of the noisy comparator to measure the value of  $V_{\rm res}$  and thus improve overall ADC accuracy. Fig. 19 illustrates how  $V_{\rm res}$  measurement works. Assume the comparator has Gaussian noise, whose cumulative distribution function (CDF) is defined as

$$P = \frac{1}{2} \left[ 1 + \operatorname{erf}\left(\frac{x - u}{\sqrt{2}\sigma}\right) \right] \tag{22}$$

Fig. 20. Chip micrograph.

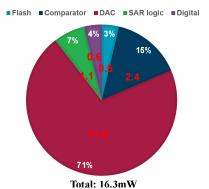

Fig. 21. ADC power breakdown.

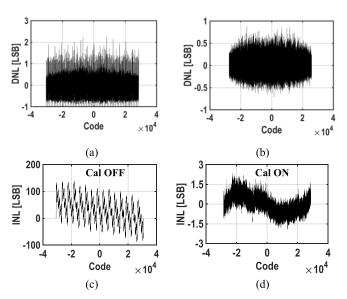

Fig. 22. Typical dc linearity plots. (a) DNL before calibration. (b) DNL after calibration. (c) INL before calibration. (d) INL after calibration.

where we denote

$$V_{\text{res}} = x - u \tag{23}$$

$$\sigma_{n,\text{dec}} = \sigma.$$

(24)

We can derive  $V_{\text{res}}$  as

$$V_{\text{res}} = \sqrt{2}\sigma_{n,\text{dec}} \operatorname{erfinv}(2P - 1).$$

(25)

At the end of the regular trials or LSB repeats, the comparator makes a number of sequential decisions with its input unchanged. Based upon the probability of decision one, the small comparator input can be estimated with (25) given knowledge of the comparator noise level. A small lookup table in the digital engine can be used to approximate the

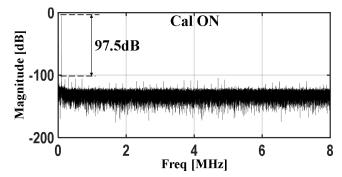

Fig. 23. Typical ac spectrum after calibration with 100-kHz input.

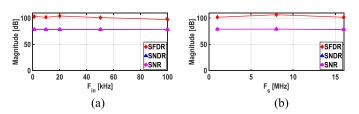

Fig. 24. AC performance. (a) SFDR/SNDR/SNR versus  $F_{\rm in}$  with  $F_{\rm S}=16$  MS/s. (b) SFDR/SNDR/SNR versus  $F_{\rm S}$  with  $F_{\rm in}=100$  kHz.

Fig. 25. Measured ADC noise with number of LSB repeats.

Fig. 26. Measured ADC noise with number of SRM decisions.

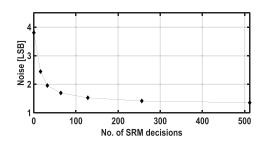

solution to this nonlinear (25) and the ADC digital output is compensated accordingly. Compared to those in [38] and [39], the number of comparator decisions in this paper can be varied in silicon to demonstrate effectiveness and examine trade-offs with measured data. This technique is only enabled when the ADC is running slower than 16 MS/s so that we have time left in the conversion phase after all the bit trials, allowing for the comparator to fire a number of times afterward to estimate its input voltage, i.e., the DAC output residual voltage.

#### IV. EXPERIMENTAL RESULTS

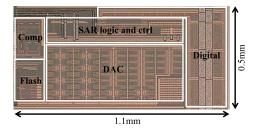

The chip is fabricated in a 55-nm CMOS process. Die micrograph is shown in Fig. 20 and it measures 1.1 mm by

Fig. 27. SFDR comparison with Nyquist ADCs from ISSCC and VLSI in the past 10 years with SFDR > 85 dB or SNDR > 80 dB.

TABLE I

COMPARISON WITH RECENT MEDIUM-SPEED

AND HIGH-RESOLUTION SAR ADCS

|                         | This work | Hurrell [1] | Bannon [2] | Maddox [3] | Kramer [12] | Miki [29] |

|-------------------------|-----------|-------------|------------|------------|-------------|-----------|

| Туре                    | SAR       | Pipe SAR    | Pipe SAR   | SAR        | SAR         | SAR       |

| Resolution<br>[bit]     | 16        | 18          | 18         | 16         | 14          | 13        |

| Speed [MS/s]            | 16        | 12.5        | 5          | 1          | 35          | 50        |

| Power [mW]              | 16.3      | 105         | 30.5       | 6.95       | 54.5        | 4.2       |

| SFDR/<br>SNDR [dB]      | 98/78     | 82/80       | 100/99     | 100/81     | 99/75       | 85/71     |

| INL [LSB]               | -1.9/2.3  | -2.5/2.5    | -2/2       | -0.8/0.8   | -0.9/0.7    | -1.3/2    |

| Cin [pF]                | 1.14      | 25          | NA         | 25.6       | 0.2         | 2         |

| VDD [V]                 | 3.3/1.2   | 5/2.5       | 5/1.8      | 1.2        | 2.5/1.2     | 1.2       |

| Area [mm <sup>2</sup> ] | 0.55      | 4.5         | 5.74       | 4.1        | 0.24        | 0.097     |

| Calibration             | On        | Off         | Off        | Off        | Off         | On        |

|                         | chip      | chip        | chip       | chip       | chip        | chip      |

| FoM_S [dB]              | 165       | 157.7       | 177.7      | 159.6      | 159.5       | 166.8     |

| Process                 | 55nm      | 250nm       | 180nm      | 55nm       | 40nm        | 90nm      |

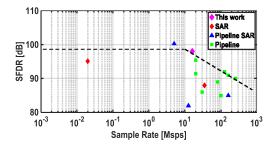

0.5 mm. The digital engine which also includes calibration is small thanks to the dense logic. The ADC input interface operates at 3.3 V while all other circuits use 1.2 V. By default, optimal LSB repeats is turned on and SRM is turned off to operate at 16 Msps. Fig. 21 shows the power breakdown where the DAC consumes 11.6 mW, which also includes the estimated 2.8 mW from the level shifters. With the dramatically reduced sampling capacitance at 1.14 pF (including flash sampling capacitance) for precision ADCs, particular attention was paid to coupling through sub-fF level parasitics to maintain 16-bit linearity performance. Fig. 22 shows the dc linearity performance both with calibration OFF and ON. Before calibration, we see large INL error up to roughly 250 LSBpp mainly due to the charge-sharing error from the reservoir capacitors. After calibration, the INL is -1.9/2.3 LSB. It is limited by sampling distortion because input bootstrapping was avoided to support passive sampling in impulse mode. Fig. 23 shows the spectrum with 100-kHz input signal, and the ac performance is summarized in Fig. 24, where spurious-free dynamic range (SFDR)/SNDR/SNR versus  $F_{in}$  and  $F_s$  are shown, respectively. For most precision applications, input-signal bandwidth is below 100 kHz, where over 97.5-dB SFDR is maintained. The SNR is over 78 dB and the equivalent ADC noise is about 3 LSB, meeting our design target. In Fig. 25, the measured ADC noise versus number of LSB repeats is shown to demonstrate its effectiveness. When operating at a lower frequency, SRM could be enabled to further improve accuracy. Fig. 26 shows the ADC noise versus number of SRM decisions. We observe that the ADC noise does approach the sampling noise level as number of SRM decisions increases. Note that for both noise plots, the conversion noise is configured higher to dominate the sampling noise to better observe the effect. The plot in Fig. 27 compares the linearity performance of this ADC with recent Nyquist ADCs from ISSCC and VLSI in the past 10 years with SFDR > 85 dB or SNDR > 80 dB [40]. Comparison with recently published medium speed and high-resolution SAR ADCs is given in Table I. Hurrell *et al.* [1] and Bannon *et al.* [2] use a pipelined SAR architecture and are roughly  $10 \times$  larger area with  $20 \times$  larger input capacitance. In addition, all the other precision ADCs (16-bit+) rely on off-chip calibration and thus have much increased test cost.

### V. CONCLUSION

A precision 16-bit SAR ADC that achieves 16 MS/s operation in 55-nm CMOS is presented in this paper. It supports both continuous mode and impulse mode operations. The fast conversion and small area is enabled by the small capacitor array and the signal independent, one reservoir-capacitor per bit-capacitor DAC structure. The minimal overhead on-chip calibration that calibrates down to lower bits helps ensure the ADC achieves 16-bit precision. Optimal LSB repeats and SRM further improves the ADC accuracy and efficiency. Compared to traditional precision SAR ADCs, this ADC has  $10\times$  smaller area,  $20\times$  smaller sampling capacitance, and on-chip calibration to make it well suited for precision SoC applications. To our knowledge, this work is also the first fast-precision SAR ADC in a deep sub-micron CMOS node.

#### ACKNOWLEDGMENT

The authors would like to thank A. Meenakshisubramanian, A. Bandyopadhyay, H. Ngo, D. McCartney, K. Nakamura, and the entire layout, evaluation and support team.

# REFERENCES

- [1] C. P. Hurrell, C. Lyden, D. Laing, D. Hummerston, and M. Vickery, "An 18 b 12.5 MS/s ADC with 93 dB SNR," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2647–2654, Dec. 2010.

- [2] A. Bannon, C. P. Hurrell, D. Hummerston, and C. Lyden, "An 18 b 5 MS/s SAR ADC with 100.2 dB dynamic range," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2014, pp. 33–34.

- [3] M. Maddox, B. Chen, M. Coln, R. Kapusta, J. Shen, and L. Fernando, "A 16 bit linear passive-charge-sharing SAR ADC in 55 nm CMOS," in *IEEE Asian Solid-State Circuits Conf. (A-SSCC) Tech. Papers*, Nov. 2016, pp. 153–156.

- [4] D. Hummerston and P. Hurrell, "An 18-bit 2MS/s pipelined SAR ADC utilizing a sampling distortion cancellation circuit with -107 dB THD at 100 kHz," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2017, pp. 280–281.

- [5] B. P. Ginsburg and A. P. Chandrakasan, "500-MS/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 739–747, Apr. 2007.

- [6] N. Verma and A. P. Chandrakasan, "An ultra low energy 12-bit rateresolution scalable SAR ADC for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 42, no. 6, pp. 1196–1205, Jun. 2007.

- [7] S. M. Louwsma, A. J. M. van Tuijl, M. Vertregt, and B. Nauta, "A 1.35 GS/s, 10 b, 175 mW time-interleaved AD converter in 0.13 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 778–786, Apr. 2008.

- [8] A. Shikata, R. Sekimoto, T. Kuroda, and H. Ishikuro, "A 0.5 V 1.1 MS/sec 6.3 fJ/conversion-step SAR-ADC with tri-level comparator in 40 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 1022–1030, Apr. 2012.

- [9] P. Harpe, E. Cantatore, and A. van Roermund, "A 10b/12b 40 kS/s SAR ADC with data-driven noise reduction achieving up to 10.1b ENOB at 2.2 fJ/conversion-step," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3011–3018, Dec. 2013.

- [10] C. C. Lee and M. P. Flynn, "A SAR-assisted two-stage pipeline ADC," IEEE J. Solid-State Circuits, vol. 46, no. 4, pp. 859–869, Apr. 2011.

- [11] R. K. Palani and R. Harjani, "High linearity PVT tolerant 100 MS/s rail-to-rail ADC driver with built-in sampler in 65nm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2014, pp. 1–4.

- [12] M. Kramer, E. Janssen, K. Doris, and B. Murmann, "A 14 b 35 MS/s SAR ADC achieving 75 dB SNDR and 99 dB SFDR with loopembedded input buffer in 40 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 2891–2900, Dec. 2015.

- [13] J. Shen et al., "A 16-bit 16 MS/s SAR ADC with on-chip calibration in 55 nm CMOS," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2017, pp. 282–283.

- [14] S.-W. M. Chen and R. Brodersen, "A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2669–2680, Dec. 2006.

- [15] J. Craninckx and G. van der Plas, "A 65fJ/conversion-step 0-to-50MS/s 0-to-0.7 mW 9b charge-sharing SAR ADC in 90 nm digital CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2007, pp. 246–247.

- [16] P. J. A. Harpe et al., "A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1585–1595, Jul. 2011.

- [17] R. Kapusta, J. Shen, S. Decker, H. Li, E. Ibaragi, and H. Zhu, "A 14b 80 MS/s SAR ADC with 73.6 dB SNDR in 65 nm CMOS," *IEEE J. Solid State Circuits*, vol. 48, no. 12, pp. 3059–3066, Dec. 2013.

- [18] Y.-Z. Lin, C.-C. Liu, G.-Y. Huang, Y.-T. Shyu, and S.-J. Chang, "A 9-bit 150-MS/s 1.53-mW subranged SAR ADC in 90-nm CMOS," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2010, pp. 243–244.

- [19] S. Lee, A. P. Chandrakasan, and H. S. Lee, "A 1 GS/s 10b 18.9 mW time-interleaved SAR ADC with background timing skew calibration," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2846–2856, Dec. 2014.

- [20] M. Wagdy and M. Goff, "Linearizing average transfer characteristics of ideal ADC's via analog and digital dither," *IEEE Trans. Instrum. Meas.*, vol. 43, no. 2, pp. 146–150, Apr. 1994.

- [21] J. K. Fiorenza, T. Sepke, P. Holloway, C. G. Sodini, and H.-S. Lee, "Comparator-based switched-capacitor circuits for scaled CMOS technologies," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2658–2668, Dec. 2006

- [22] F. Kuttner, "A 1.2V 10b 20MSample/s non-binary successive approximation ADC in 0.13 μm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2002, pp. 176–177.

- [23] C.-C. Liu et al., "A 10b 100 MS/s 1.13 mW SAR ADC with binary-scaled error compensation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2010, pp. 386–387.

- [24] P. Harpe, Y. Zhang, G. Dolmans, K. Philips, and H. De Groot, "A 7-to-10b 0-to-4MS/s flexible SAR ADC with 6.5-to-16fJ/conversionstep," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 472–473.

- [25] W. Kim et al., "A 0.6 V 12 b 10 MS/s low-noise asynchronous SAR-assisted time-interleaved SAR (SATI-SAR) ADC," IEEE J. Solid-State Circuits, vol. 51, no. 8, pp. 1826–1839, Aug. 2016.

- [26] P. Nuzzo, F. De Bernardinis, P. Terreni, and G. Van der Plas, "Noise analysis of regenerative comparators for reconfigurable ADC architectures," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 6, pp. 1441–1454, Jul. 2008.

- [27] M. Ahmadi and W. Namgoong, "A 3.3fJ/conversion-step 250 kS/s 10b SAR ADC using optimized vote allocation," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2013, pp. 1–4.

- [28] P. Harpe, E. Cantatore, and A. van Roermund, "An oversampled 12/14b SAR ADC with noise reduction and linearity enhancements achieving up to 79.1dB SNDR," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 194–195.

- [29] T. Miki et al., "A 4.2 mW 50 MS/s 13 bit CMOS SAR ADC with SNR and SFDR enhancement techniques," *IEEE J. Solid-State Circuits*, vol. 50, no. 6, pp. 1372–1381, Jun. 2015.

- [30] G. Miller, M. Timko, H.-S. Lee, E. Nestler, M. Mueck, and P. Ferguson, "An 18 b 10 μs self-calibrating ADC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 1990, pp. 168–169.

- [31] J. A. McNeill, K. Y. Chan, M. C. W. Coln, C. L. David, and C. Brenneman, "All-digital background calibration of a successive approximation ADC using the 'Split ADC' architecture," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 10, pp. 2355–2365, Oct. 2011.

- [32] W. Liu, P. Huang, and Y. Chiu, "A 12-bit, 45-MS/s, 3-mW redundant successive-approximation-register analog-to-digital converter with digital calibration," *IEEE J. Solid-State Circuits*, vol. 46, no. 11, pp. 2661–2672, Nov. 2011.

- [33] B. Verbruggen, K. Deguchi, B. Malki, and J. Craninckx, "A 70 dB SNDR 200 MS/s 2.3 mW dynamic pipelined SAR ADC in 28 nm digital CMOS," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2014, pp. 1–2.

- [34] H.-S. Lee, D. A. Hodges, and P. R. Gray, "A self-calibrating 15 bit CMOS A/D converter," *IEEE J. Solid-State Circuits*, vol. 19, no. 6, pp. 813–819, Dec. 1984.

- [35] M. Ding, P. Harpe, Y.-H. Liu, B. Busze, K. Philips, and H. de Groot, "A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration," *IEEE J. Solid-State Circuits*, vol. 52, no. 2, pp. 423–432, Feb. 2017.

- [36] C. C. Lee, C.-Y. Lu, R. Narayanaswamy, and J. B. Rizk, "A 12b 70 MS/s SAR ADC with digital startup calibration in 14nm CMOS," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2015, pp. 62–63.

- [37] J. Shen and R. A. Kapusta, "Accuracy enhancement techniques for ADCs," U.S. Patent 9 071 261, Jun. 30, 2015.

- [38] B. Verbruggen, J. Tsouhlarakis, T. Yamamoto, M. Iriguchi, E. Martens, and J. Craninckx, "A 60 dB SNDR 35 MS/s SAR ADC with comparator-noise-based stochastic residue estimation," *IEEE J. Solid-State Circuits*, vol. 50, no. 9, pp. 2002–2011, Sep. 2015.

- [39] L. Chen, X. Tang, A. Sanyal, Y. Yoon, J. Cong, and N. Sun, "A 0.7-V 0.6-μW 100-kS/s low-power SAR ADC with statistical estimation-based noise reduction," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1388–1398, May 2017.

- [40] B. Murmann. ADC Performance Survey 1997–2016. Accessed: Jul. 1, 2017. [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html

**Junhua Shen** (M<sup>\*</sup>10) received the B.Eng. degree in information science and electronic engineering from Zhejiang University, Hangzhou, China, in 2002, and the M.Phil. degree in electronic engineering from The Chinese University of Hong Kong, Hong Kong in 2004. He received the Ph.D. degree in electrical engineering from Columbia University, New York, NY, USA, in 2010.

Since 2010, he has been with Analog Devices, Wilmington, MA, USA, as a Design Engineer and Technical Lead. His current research interests

include high-performance ADCs and ultra-low-power mixed-signal circuits. He holds nine issued U.S. patents.

Dr. Shen was a co-recipient of the 2013 JSSC Best Paper Award.

Akira Shikata received the B.S., M.S., and Ph.D. degrees in electronics and electrical engineering from Keio University, Yokohama, Japan, in 2008, 2010, 2013, respectively.

From 2013 to 2015, he was a Design Engineer with Analog Devices Japan Design Center, Tokyo, Japan. Since 2015, he has been with Analog Devices, Wilmington, MA, USA, where he is involved in the design of low power and precision data converters.

Lalinda D. Fernando received the B.Eng. degree in electrical engineering from the University of Edinburgh, Scotland, U.K., and the M.Eng. degree in electrical engineering from the University of Limerick, Limerick, Ireland, in 2000 and 2004, respectively.

In 2000, he joined Analog Devices, Inc. Ireland, and thereafter Analog Devices, Inc. Wilmington, MA, USA, and has since been involved in the design of monolithic high-resolution Nyquist converters and precision signal chain ASICs for medical imaging

products used in electroanatomical mapping. He has authored or co-authored several technical papers in the domain of integrated circuit design and has received several U.S. patents.

Ned Guthrie was born in New York in 1978. He received the B.A. and B.E. degrees in electrical engineering from Dartmouth College, Hanover, NH, USA, in 2001.

In 2001, he joined Analog Devices, Wilmington, MA, USA, where he is currently a Digital Design Engineer. His current research interests include digitally assisted analog and low-power digital design.

signal verification.

Nikhil Mascarenhas was born in Mumbai, India, in 1989. He received the B.E. degree in electronic engineering from the University of Mumbai, India, in 2011, and the M.S. degree in computer engineering from Arizona State University, Tempe, AZ, USA, in 2014. He served as the Chairperson for the IEEE Student Chapter at Fr. Conceicao Rodrigues College of Engineering, Mumbai, from 2010 to 2011

He is currently an IC Design Engineer with Analog Devices, Norwood, MA, USA. His current research interests include digital signal processing, logic design for ADCs and mixed

Baozhen Chen received the B.S. degree from the University of Science and Technology of China, Hefei, China, in 2005, and the M.S. degree and Ph.D. degree in electrical engineering from Iowa State University, Ames, IA, USA, in 2010.

In 2009, he joined BCD Semiconductor (now part of Diodes, Inc), Shanghai, China, as an Intern. From 2010 to 2013, he was a Design Engineer with Maxim Integrated, Raleigh, NC, USA, and San Jose, CA, USA, with audio group. In 2013, he joined Analog Devices, Inc., Wilmington, MA, USA, in Precision

ADC Group and Healthcare Group.

He has authored seven articles and has received or has pending seven U.S. patents. His current research interests include data converters, CMOS biosensors, and healthcare electronics.

Mark Maddox received the B.S. degree in electrical engineering from the University of Toledo, Toledo, OH, USA, in 1985, and the M.S. degree in electrical engineering from Cleveland State University. Cleveland, OH, USA, in 1994.

From 1988 to 1996, he was a Design Engineer with the Analog I/O group at Allen-Bradley now Rockwell International. Since 1996, he has been with Analog Devices, Wilmington, MA, USA, focusing on the design of precision analog-to-digital converters. He has authored two articles and has

received or has pending five U.S. patents. His current research interests include data converters and high-accuracy analog circuits.

Ron Kapusta (SM'13) received the B.S. and M.Eng. degrees from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 2002.

He joined Analog Devices, designing data converters and sensor interface circuits for multiple channel data acquisition systems. He has been with the Autonomous Transportation Group, focusing on sensor systems to enable automated driving. He has served on the technical program committees for CICC and VLSI Circuits.

Michael C. W. Coln (M'80) received the B.S. degree from the California Institute of Technology, Pasadena, CA, USA, in 1976, and the M.S. and Ph.D. degrees in electrical engineering from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1979 and 1985, respectively.

He was with Hewlett-Packard Laboratories, Palo Alto, CA, USA, from 1985 to 1988 as a Member of Technical Staff in the area of highperformance converters. Since 1988, he has been with Analog Devices, Wilmington, MA, and he is

currently a Designer with the Precision Converter Group. His current research interests include monolithic high-resolution Nyquist converters, high-accuracy analog integrated circuit design, and low-noise architectures for instrumentation. He has developed innovative monolithic architectures for extended signal chains, such as precision data acquisition ASICs for computedtomography (CT) or digital X-ray medical imaging. More recently, he has been exploring approaches for high-resolution ADCs in nanometer technologies, including digital-intensive calibration and non-traditional architectures. He has authored or co-authored several technical papers in the area of integrated circuit design, and has received over three dozen U.S. patents.

Dr. Coln was recognized as an Analog Devices Fellow in 2005. He was a co-recipient of the Lewis Winner Award for Outstanding Conference Paper at ISSCC 2005, and the Jan van Vessem Best European Paper Award at ISSCC