## **NOTE TO USERS**

This reproduction is the best copy available.

# High-Performance Pipeline A/D Converter Design in Deep-Submicron CMOS

by

#### Yun Chiu

B.S. (University of Science and Technology of China) 1993M.S. (University of California, Los Angeles) 1997

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences in the

**GRADUATE DIVISION**

of the

UNIVERSITY of CALIFORNIA, BERKELEY

Committee in charge:

Professor Paul R. Gray, Chair Professor Bernhard E. Boser Professor Paul K. Wright

Fall 2004

UMI Number: 3165324

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

#### UMI Microform 3165324

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# High-Performance Pipeline A/D Converter Design in Deep-Submicron CMOS

Copyright © 2004

by

Yun Chiu

#### Abstract

# High-Performance Pipeline A/D Converter Design in Deep-Submicron CMOS

by Yun Chiu

Doctor of Philosophy in Engineering

University of California, Berkeley

Professor Paul R. Gray, Chair

Analog-to-digital converters (ADCs) are key design blocks in modern microelectronic digital communication systems. With the fast advancement of CMOS fabrication technology, more and more signal-processing functions are implemented in the digital domain for a lower cost, lower power consumption, higher yield, and higher re-configurability. This has recently generated a great demand for low-power, low-voltage ADCs that can be realized in a mainstream deep-submicron CMOS technology.

Intended for embedded communication applications, specifications of these converters emphasize high dynamic range and low spurious spectral performance. For example, the worst-case blocking specs of some wireless standards, such as GSM, dictate a conversion linearity of 14-16 bits to avoid losing a weak received signal due to distortion artifacts. It is nontrivial to achieve this level of linearity in

a monolithic environment where post-fabrication component trimming or calibration is cumbersome to implement for certain applications or/and for cost and manufacturability reasons.

Another hurdle to achieve full system integration stems from the power efficiency of the A/D interface circuits supplied by a low voltage dictated by the gate-oxide reliability of the deeply scaled digital CMOS devices. It has been observed recently that these interface analog/mixed-signal circuits are gobbling a larger chunk of the chip area as well as total power consumption; hence it becomes essential to accomplish an optimized design from both the architecture and the circuit standpoints. To achieve high linearity, high dynamic range, and high sampling speed simultaneously under low supply voltages in deep-submicron CMOS technology with low power consumption has thus far been conceived of as extremely challenging.

This thesis addresses these challenges using the pipeline ADC as a demonstration platform. Specific new design techniques/algorithms include (1) a power-efficient, capacitor ratio-independent conversion scheme, (2) a pipeline stage-scaling algorithm, (3) a nested CMOS gain-boosting technique, (4) a  $\Delta\Sigma$  common-mode voltage regulation circuit, (5) an amplifier and comparator sharing technique, and the use of minimum channel-length, thin oxide transistors with clock bootstrapping and in-line switch techniques. The prototype design of a 14-

3

bit pipeline ADC fabricated in a 0.18- $\mu$ m CMOS technology that achieves an over 100-dB spurious-free dynamic range (SFDR) demonstrates the effectiveness of these techniques.

Professor Paul R. Gray, Chair

### **Table of Contents**

| List of Figures                                  | vi |

|--------------------------------------------------|----|

| List of Tables                                   | ix |

| Chapter 1 Introduction                           | 1  |

| 1.1 Wireless Communication                       | 1  |

| 1.2 Challenges of Broadband Radio                | 3  |

| 1.3 CMOS Technology Scaling                      | 5  |

| 1.4 A/D Interface                                | 8  |

| 1.5 Research Contribution                        | 10 |

| 1.6 Thesis Organization                          | 11 |

| Chapter 2 Pipeline Architecture Power Efficiency | 14 |

| 2.1 Pipeline ADC Architecture                    | 14 |

| 2.2 Power Efficiency under Low Supply Voltage    | 17 |

| 2.2.1 kT/C Noise                                 | 17 |

| 2.2.2 Power Consumption of Pipeline ADC          | 18 |

| 2.3 Stage-Scaling Analysis of Pipeline ADC       | 20 |

| 2.3.1 Cline-Gray Model                           | 21 |

| 2.3.2 Parasitic-Loaded Amplifier Model           | 22 |

| 2.3.3 Stage-Scaling Analysis Revisited           | 25 |

| 2.3.4 Summary                                    | 28 |

| 2.3.4.1 Speed Factor                             | 29 |

| 2.3.4.2 Taper Factor                             | 30 |

| Chapter 3 Capacitor Error-Averaging              | 35 |

| 3.1 Pipeline ADC Error Mechanism                 | 36 |

| 3.2 Canacitor Matching Accuracy                  | 38 |

| 3.3 Precision Conversion Techniques                  |

|------------------------------------------------------|

| 3.3.1 Active Capacitor Error-Averaging               |

| 3.3.2 Passive Capacitor Error-Averaging - Part I 44  |

| 3.3.3 Passive Capacitor Error-Averaging - Part II 47 |

| 3.3.4 Power Efficiency                               |

| 3.3.5 Monte Carlo Simulation                         |

| Appendix                                             |

| A3.1 MDAC Capacitor Matching 52                      |

| A3.2 Active CEA                                      |

| A3.3 Passive CEA (I)                                 |

| A3.4 Passive CEA (II)                                |

| Chapter 4 Prototype Design                           |

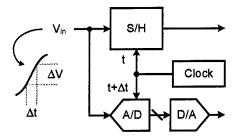

| 4.1 Sampling Clock Skew 62                           |

| 4.2 Amplifier and Sub-ADC Sharing64                  |

| 4.3 Nested CMOS Gain Boosting 68                     |

| 4.4 Discrete-Time Common-Mode Regulation69           |

| 4.5 Dynamic Comparator                               |

| 4.6 Sampling Switch74                                |

| Appendix                                             |

| A4.1 Discrete-Time Common-Mode Regulation 75         |

| Chapter 5 Experimental Results                       |

| 5.1 Static Linearity                                 |

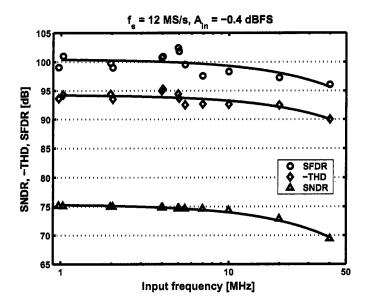

| 5.2 Dynamic Linearity82                              |

| 5.2.1 SNDR, THD, and SFDR82                          |

| 5.2.2 ADC Performance Sensitivity 84                 |

| Chapter 6 Conclusion                                 |

## **List of Figures**

| Figure 1.1 | Ericsson single-chip $0.18$ - $\mu$ m CMOS Bluetooth radio               |

|------------|--------------------------------------------------------------------------|

|            | (2001)                                                                   |

| Figure 1.2 | Scaling trend of silicon CMOS according to the 2003                      |

|            | edition international technology roadmap of                              |

|            | semiconductor (ITRS). <sup>3</sup>                                       |

| Figure 1.3 | (a) Simplified block diagram of a direct-conversion RF                   |

|            | receiver. Shaded blocks are off-chip components. (b)                     |

|            | Simplified block diagram of a double-conversion                          |

|            | receiver. (c) Signal spectrum at point A (after antenna)                 |

|            | and B (before ADC).                                                      |

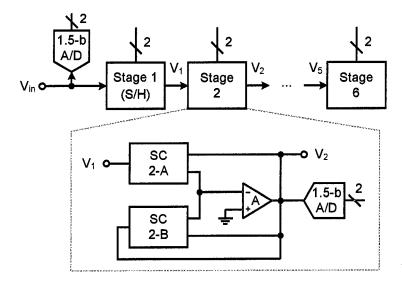

| Figure 2.1 | Block diagram of a pipeline A/D converter15                              |

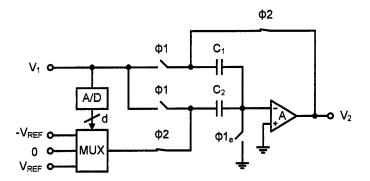

| Figure 2.2 | Circuit diagram of the 1.5-b/s MDAC16                                    |

| Figure 2.3 | Noise model of MDAC including parasitic loading                          |

|            | effects                                                                  |

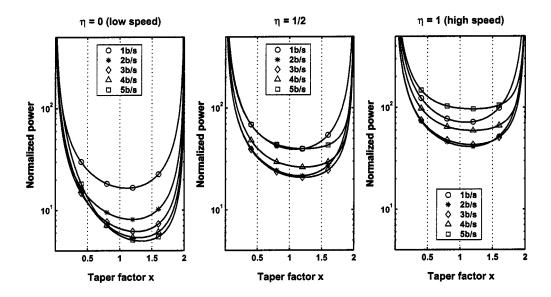

| Figure 2.4 | Evaluation of $g(n, \gamma, \eta)$ versus the scaling factor $\gamma$ 29 |

| Figure 2.5 | Evaluation of $g(n, \gamma, \eta)$ versus the speed factor $\eta$ 30     |

| Figure 2.6 | Evaluation of $g(n, \gamma, \eta)$ versus the taper factor x31           |

| Figure 2.7 | Evaluation of $\gamma_{opt}$ versus the stage resolution $n$             |

| Figure 3.1 | Voltage transfer characteristic of a 1.5-b/s residue gain                |

|            | stage. The solid curve shows the ideal transfer function                 |

|            | and the dashed one exhibits static nonlinearity due to                   |

|            | analog circuit non-idealities                                            |

| Figure 3.2 | Circuit diagram of an n-b/s pipeline ADC and its                         |

|            | residue transfer characteristic. (a) Sampling mode. (b)                  |

|            | Amplification mode38                                           |

|------------|----------------------------------------------------------------|

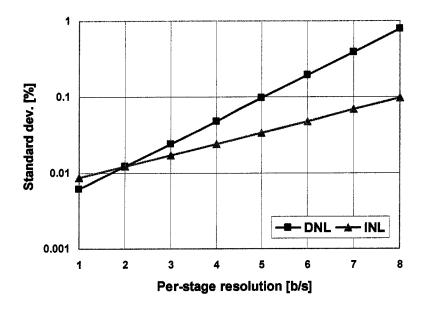

| Figure 3.3 | Capacitor matching accuracy versus stage resolution            |

|            | for a 14-bit pipeline ADC. A half LSB maximum DNL              |

|            | and INL error is assumed40                                     |

| Figure 3.4 | Circuit diagram of the active CEA technique. The stage         |

|            | operates on a three-phase clock. $\phi 1$ is the sampling      |

|            | phase (not shown). $\phi 2$ and $\phi 3$ are the amplification |

|            | phases shown in (a) and (b), respectively43                    |

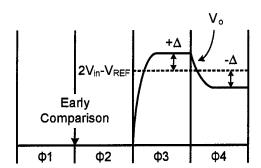

| Figure 3.5 | Voltage waveforms of the active CEA gain stage of              |

|            | Figure 3.444                                                   |

| Figure 3.6 | Circuit diagram of the passive CEA technique (I). $C_1$        |

|            | and $C_2$ are the sampling capacitors of the current           |

|            | pipeline stage, while $C_3$ and $C_4$ are from the trailing    |

|            | stage45                                                        |

| Figure 3.7 | Voltage waveforms of the passive CEA gain stages of            |

|            | Figure 3.6 and Figure 3.846                                    |

| Figure 3.8 | Circuit diagram of the passive CEA technique (II).             |

|            | Here $C_3$ and $C_4$ are also the sampling capacitors from     |

|            | the trailing stage47                                           |

| Figure 3.9 | Results of the Monte Carlo yield simulation. 14-bit            |

|            | INL and DNL are achieved with a 6-bit capacitor                |

|            | matching accuracy (3 $\sigma$ ). Amplifier gain is assumed to  |

|            | be large (100 dB)51                                            |

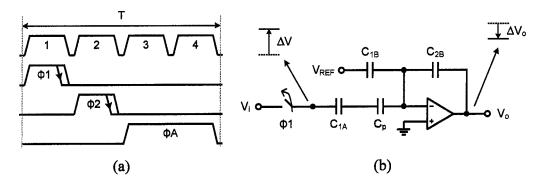

| Figure 4.1 | Sampling clock skew in the front-end pipeline stage62          |

| Figure 4.2 | Block diagram of the 14-b pipeline ADC64                       |

| Figure 4.3 | Potential summing node crosstalk through the parasitic         |

|            | capacitance of off switches65                                  |

| Figure 4.4 | (a) Timing diagram. (b) Summing node crosstalk path                                          |     |

|------------|----------------------------------------------------------------------------------------------|-----|

|            | during the falling edge of $\phi 1$                                                          | 65  |

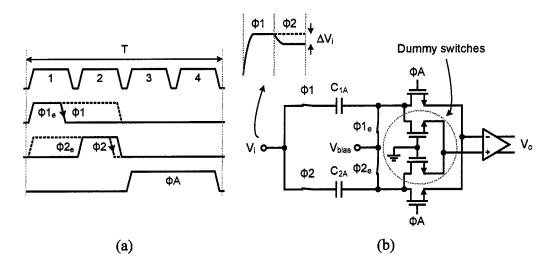

| Figure 4.5 | (a) Modified timing diagram. (b) Dummy switches                                              | 66  |

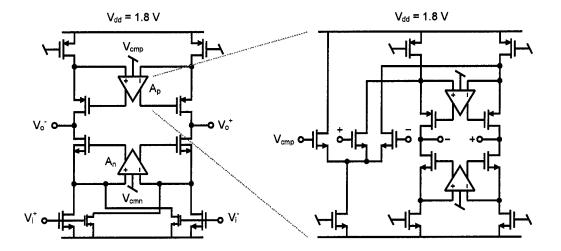

| Figure 4.6 | Nested CMOS gain-boosted amplifier                                                           | 68  |

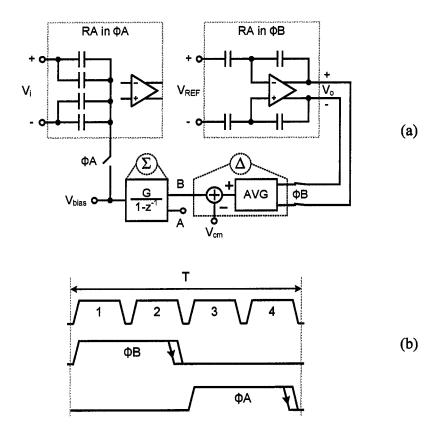

| Figure 4.7 | (a) $\Delta\Sigma$ common-mode regulation circuit. (b) Timing                                |     |

|            | diagram                                                                                      | 70  |

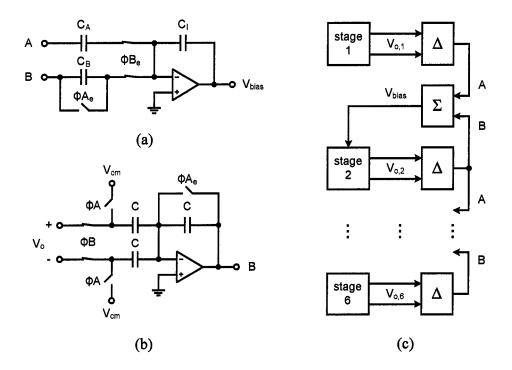

| Figure 4.8 | (a) Discrete-time integrator with look-ahead capacitor                                       |     |

|            | $C_A$ . (b) Averaging and differencing amplifier. (c)                                        |     |

|            | Common-mode feedback and feedforward connections                                             |     |

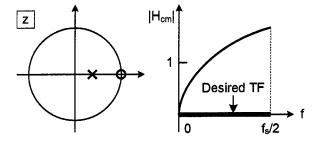

|            | of the six pipeline stages                                                                   | 71  |

| Figure 4.9 | Pole-zero and frequency response plots of the CMFB                                           |     |

|            | loop                                                                                         | 73  |

| Figure 4.1 | 0 (a) Dynamic comparator. (b) Timing diagram                                                 | 74  |

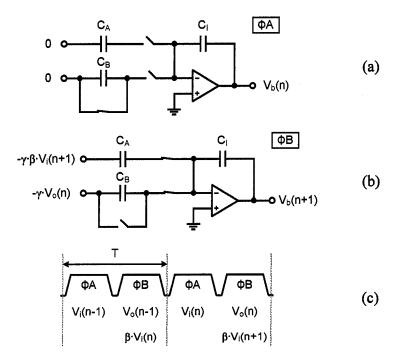

| Figure 4.1 | <b>1</b> (a) Integrator in $\phi A$ (sampling). (b) Integrator in $\phi B$                   |     |

|            | (integration). (c) Timing diagram.                                                           | 75  |

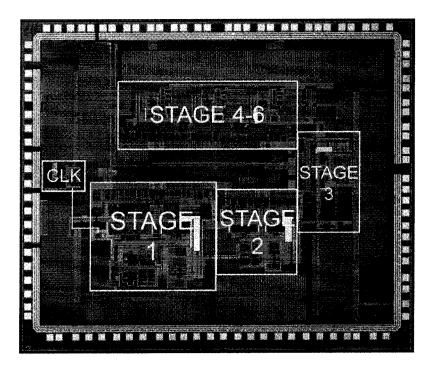

| Figure 5.1 | Die photo of the prototype 14-b pipeline ADC                                                 | 79  |

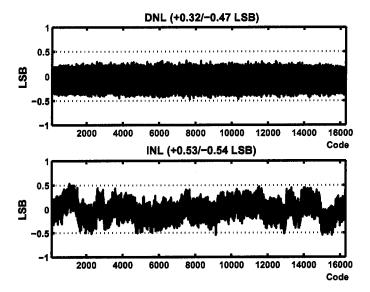

| Figure 5.2 | Measured DNL and INL ( $f_s = 12 \text{ MS/s}$ , $f_{in} = 1 \text{ MHz}$ )                  | .80 |

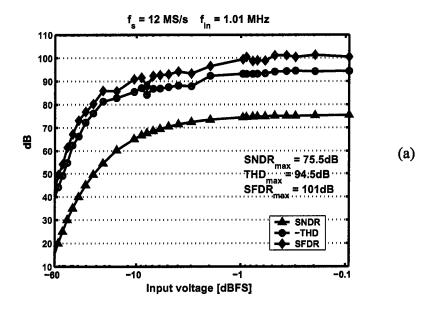

| Figure 5.3 | Measured ADC performance versus input signal level.                                          |     |

|            | (a) $f_s = 12 \text{ MS/s}, f_{in} = 1.01 \text{ MHz}$ . (b) $f_s = 12 \text{ MS/s}, f_{in}$ |     |

|            | = 5.47 MHz                                                                                   | .81 |

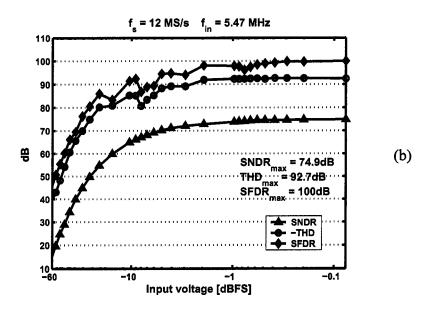

| Figure 5.4 | FFT spectrum at $f_{in}$ = (a) 1 MHz, (b) 5 MHz, and (c) 40                                  |     |

|            | MHz.                                                                                         | .83 |

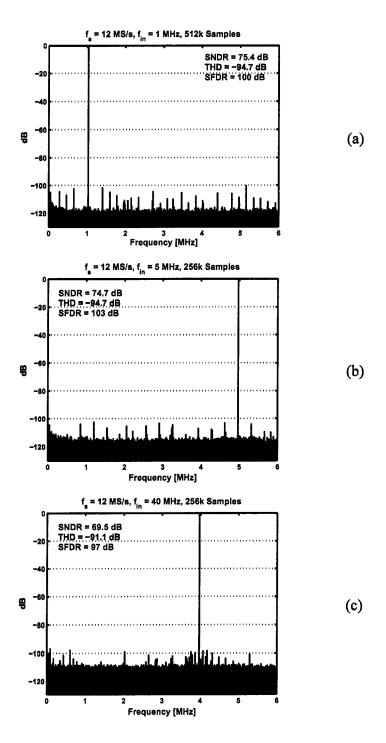

| Figure 5.5 | Measured dynamic performance.                                                                | .84 |

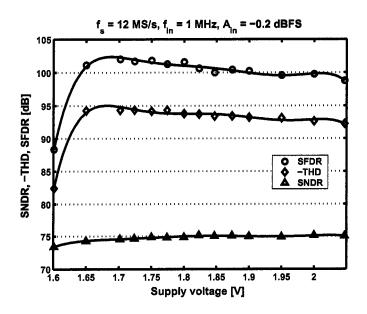

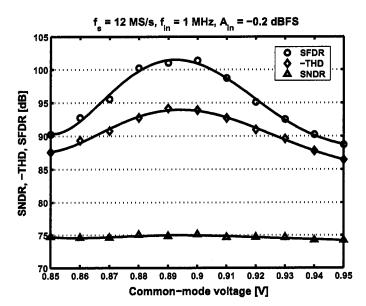

| Figure 5.6 | Measured performance versus $V_{dd}$ .                                                       | .84 |

| Figure 5.7 | Measured performance versus $V_{cm}$                                                         | .85 |

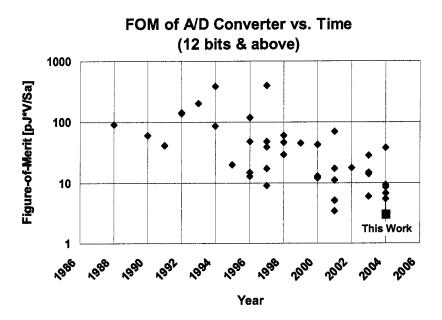

| Figure 6.1 | Comparison of this design (square) and previously                                            |     |

|            | published high-resolution ADCs (diamonds)                                                    | .88 |

### **List of Tables**

| Table 1.1 Overview of broadband wireless technologies           | 2  |

|-----------------------------------------------------------------|----|

| Table 1.2 Impact of technology scaling on analog circuit design | 7  |

| Table 3.1 Averaging effects of CEA techniques                   | 48 |

| Table 3.2 ADC architecture power efficiency                     | 49 |

| Table 3.3 Monte Carlo simulation results of a 14-b pipeline ADC | 50 |

| Table 3.4 Circuit parameters used in Monte Carlo simulation     | 50 |

| Table 5.1 Measured ADC Performance (1.8 V, 25 °C)               | 86 |

### INTRODUCTION

#### 1.1 WIRELESS COMMUNICATION

The rapid evolution of the silicon integrated circuits (IC) during the last two decades has enabled the miniaturization of narrow-band mobile phones that can operate on batteries for reasonable lifetimes. The aggregation of the research results of the radio-frequency (RF) microelectronics — carried out in both universities and industry — has spurred an exponential growth in the market of personal wireless communications, especially when the CMOS technology was demonstrated to be a good contender to achieve an integrated RF, intermediate-

Figure 1.1 Ericsson single-chip  $0.18-\mu m$  CMOS Bluetooth radio (2001).

frequency (IF), and baseband analog/mixed signal front-end in conjunction with the back-end digital signal-processing (DSP) circuits. The economics has thus far been the major driving force to accomplish a higher level of integration with potential requital of lower power dissipation, smaller form factor, and ultimately lower cost. One example of this genre is the all-CMOS Bluetooth transceiver from Ericsson that has achieved the RF-analog-digital integrated wireless system on a chip (SoC). A die photo of this chip is shown in Figure 1.1.

With the proliferation of wireless communication products and standards, broadband radios are rapidly emerging as the dominant technology to provide users with high data-rate connections in limited geographical areas where a traditional wired infrastructure may incur high installation and maintenance costs. Among these endeavors, the wireless local area network (LAN) standards – the

Table 1.1 Overview of broadband wireless technologies

| Technology          | Data Rate<br>(Mb/s) | Range (m) | Multi-Access<br>Technique | Bandwidth<br>(MHz) | Carrier Frequency           |

|---------------------|---------------------|-----------|---------------------------|--------------------|-----------------------------|

| Bluetooth           | 1                   | 10        | FHSS                      | 1                  | 2.4-GHz ISM                 |

| IEEE 802.11a        | 54                  | 20        | OFDM                      | 20                 | 5-GHz UNII                  |

| <i>IEEE</i> 802.11b | 11                  | 50        | DSSS                      | 22                 | 2.4-GHz ISM                 |

| <i>IEEE</i> 802.11g | 54                  | 50        | DSSS, OFDM                | 22                 |                             |

| DVB-T               | 5-32                | 80,000    | OFDM                      | 8                  | 130-160 MHz,<br>430-862 MHz |

| UWB                 | 100-500             | 10        | DSSS, OFDM                | ≥ 500              | 3.1-10.6 GHz                |

IEEE 802.11a/b/g — are the most noteworthy. Commercial products in this category can now be purchased in retail electronic stores worldwide. The Bluetooth radio, intended for short-range applications such as computer peripherals, PDAs, consumer electronics, and smart home appliances, is also gaining a wider deployment. Most recently, the ultra-wideband (UWB) radio and the cognitive radio are directing the spotlight of wireless communications industry. The UWB radio envisions a transmission rate of 100-500 Mb/s for short-range applications with a nearly undetectable transmission power level that seamlessly hides its operation in the background noise. The cognitive radio is promoting a concept similar to that of the software-defined radio (SDR) where the ability to adapt to the environment is the prominent feature as well as the major technical challenge. Table 1.1 provides an overview of these wireless technologies.

#### 1.2 CHALLENGES OF BROADBAND RADIO

The exponentially growing demand of wireless data-rate coupled with the increasingly crowded usage of the incumbent RF spectrum directs the radio research on the physical layer communications engineering. Although the data-rate and the bandwidth required for transmission are not identical, they are closely related by the law of information theory, known as the Shannon limit

$$C = W \cdot \log_2(1 + \frac{P_{av}}{W \cdot N_0}), \tag{1.1}$$

where, C is the channel capacity in bits/s, W is the channel bandwidth in hertz,  $P_{av}$  is the average signal power in watts, and  $N_0$  is the power spectral density (PSD) of the additive white Gaussian noise (AWGN) in watts/Hz.<sup>2</sup>

It is deduced from (1.1) that a higher transmission data-rate can be achieved by increasing either the channel bandwidth or the signal-to-noise ratio (SNR). Although this observation is drawn from the simple hypothesis of an AWGN channel, the underlying principle is ubiquitous even when sophisticated wireless channel models are assumed, be it a multi-path propagation or with advanced time-frequency-space coding. The implication is that a broadband radio is technically more challenging than its narrowband counterparts in that the information to be processed by the transceiver potentially occupies more bandwidth, exhibits a higher sensitivity to noise, or both.

In addition to the principal hurdles, the cost and mobility of a broadband radio are also adversely affected by the following factors that have been challenging the wireless communications system engineers all along:

Fading. The non-stationary nature of the mobiles or the environment dictates the wireless channel to be time-varying. The channel response may be quite different from the start of transmission to the end. Ideally, a flat frequency response is desired but often very difficult to come across for broadband channels. Narrowband channels are benign in the sense that the channel response hardly

exhibits variations for a very narrow RF bandwidth – a phenomenon termed "flat fading".

Multi-User. The users of the wireless medium are geographically separated and often uncoordinated. To achieve spectral efficiency in a cellular multipoint-to-point or point-to-multipoint communication is significantly more challenging than in a single-user environment, particularly when the data-rate requirements are heterogeneous. The transmission of one user may also be completely "blocked" when his/her desired signal is overwhelmed by a strong nearby interference signal, often unintentionally exerted by another user.

**Power Limitation**. Since the majority of mobile users are battery operated, power efficiency, in addition to spectral efficiency, is crucial. This applies not only to the transmitted power but also to the circuit-dissipated power. Sophisticated designs required to approach the capacity limit, e.g., certain coding algorithms, may not be advisable for a battery-operated terminal.

#### 1.3 CMOS TECHNOLOGY SCALING

Propelling the great venture and unprecedented success of digital techniques, the CMOS technology has emerged and dominated the mainstream silicon IC industry in the last few decades. As the lithography technology improved, the MOS device has kept shrinking its minimum feature size over the last forty years and greatly impacted the performance of digital integrated circuits – the

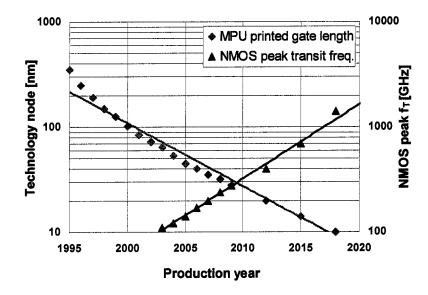

Figure 1.2 Scaling trend of silicon CMOS according to the 2003 edition international technology roadmap of semiconductor (ITRS).<sup>3</sup>

computing power that can be packed into a single chip has been constantly doubled every 18-24 months, known as the Moore's law (Figure 1.2).

During the course of pursuing a higher level of system integration and lower cost, the economics has driven technology to seek solutions to integrate analog and digital functionalities on a single die using the same or compatible fabrication processes. With the inexorable scaling of the MOS transistors, the raw device speed takes great leaps over time, measured by the exponential increase of the transit frequency  $f_T$  – the frequency where a transistor still yields a current gain of unity (Figure 1.2). The advancement of technology culminated in a dramatic performance improvement of CMOS analog circuits, opening an avenue to

Table 1.2 Impact of technology scaling on analog circuit design

|                 | Design Constraints                       |       |                               |                       |      |

|-----------------|------------------------------------------|-------|-------------------------------|-----------------------|------|

| CMOS Technol    | Channel length                           | Oxide | $V_{\scriptscriptstyle DSAT}$ | Circuit<br>Complexity |      |

| Intrinsic Speed | $f_{\scriptscriptstyle T}$ $\uparrow$    | Short | Thin                          | Large                 | Low  |

| Power Supply    | $V_{\scriptscriptstyle DD}$ $\downarrow$ | /     | /                             | Small                 | Low  |

| Thermal Noise   | $4kT(\gamma \cdot g_m)\uparrow$          | Long  | Thick                         | /                     | Low  |

| Intrinsic Gain  | $g_m \cdot r_{out} \downarrow$           | Long  | Thick                         | Small                 | High |

| Device Matching | $W,L\downarrow$                          | Long  | /                             | /                     | Low  |

| Device Modeling | SCE                                      | Long  | Thick                         | /                     | /    |

achieve system integration using a pure CMOS technology. Process enhancements, such as the triple-well option, even helped to reduce the noise crosstalk problem – one of the major practical limitations of sharing the substrate of precision analog circuits with noisy digital logic gates.

As CMOS integrated circuits are moving into unprecedented operating frequencies and accomplishing unprecedented integration levels, potential problems associated with device scaling – the short-channel effects (SCE) – are also looming large as technology strides into the deep-submicron regime. Besides that it is costly to add sophisticated process options to control these side effects, the compact device modeling of short-channel transistors has become a major challenge for device physicists. In addition, the loss of certain device characteristics, such as the square-law I-V relationship, adversely affects the

portability of the circuits designed in an older generation of technology. Smaller transistors also exhibit relatively larger statistical variations of many device parameters (i.e., doping density, oxide thickness, threshold voltage and etc.). The resultant large spread of the device characteristics also causes severe yield problems for both analog and digital circuits.

Table 1.2 summarizes the offerings of technology scaling alongside with the desired features from an analog design standpoint. In general, a short channel length gives rise to a short carrier transit time, hence a high  $f_T$ . However, the accompanying reduction of the supply voltage due to the reliability issue of thin oxide and the degradation of some fundamental device characteristics – e.g., intrinsic gain  $g_m r_{out}$  – substantially limit the choice of analog circuit architectures and the achievable power efficiency. The conflicting design constraints shown in the right half of Table 1.2 also indicate that no unique set of process options can meet all the expectations for a specific analog/mixed-signal design. In other words, to achieve the optimal trade-offs given a set of design constraints seems to be a sensible target for good analog/mixed-signal designs.

#### 1.4 A/D INTERFACE

One critical functional block in highly integrated CMOS wireless transceivers that exhibits keen sensitivity to technology scaling is the analog-to-digital interface circuit. Influenced by the advancement of the fabrication technology, the

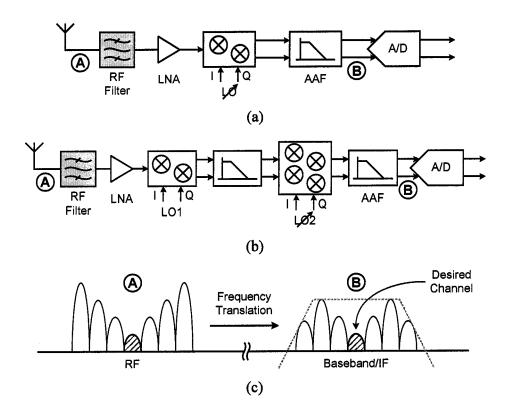

Figure 1.3 (a) Simplified block diagram of a direct-conversion RF receiver. Shaded blocks are off-chip components. (b) Simplified block diagram of a double-conversion receiver. (c) Signal spectrum at point A (after antenna) and B (before ADC).

boundary between analog and digital functionalities in these transceivers is constantly redefined. The trend toward more digital signal-processing for multi-standard agility in receiver designs has recently created a great demand for low-power, low-voltage analog-to-digital converters (ADCs) that can be realized in a mainstream deep-submicron CMOS technology.

Intended for embedded applications, the specifications of such converters

emphasize high dynamic range and low spurious spectral performance. In a CMOS radio SoC, regardless of whether frequency translation is accomplished with a single conversion, e.g., the direct-conversion (Figure 1.3a) and low-IF architecture, or a wideband-IF double conversion (Figure 1.3b), the lack of high-O on-chip IF channel-select filters inevitably leads to a large dynamic range imposed on the baseband circuits in the presence of in-band blockers (strong adjacent channel interference signals as shown in Figure 1.3c). For example, the worst-case blocking specs of some wireless standards, such as GSM, dictate a conversion linearity of 14-16 bits to avoid losing a weak received signal due to distortion artifacts. 4, 5, 6 Recent works also underline the trend toward the IFdigitizing architecture to enhance programmability and to achieve a more "digital" receiver. 7, 8, 9 However, advancing the digitizing interface toward the antenna exacerbates the existing dynamic range problem, as it also requires a high oversampling ratio. To achieve high linearity, high dynamic range, and high sampling speed simultaneously under low supply voltages in deep-submicron CMOS technology with low power consumption has thus far been conceived of as extremely challenging.

#### 1.5 RESEARCH CONTRIBUTION

Among various ADC architectures, the pipeline converter is widely used in Nyquist sampling applications that require a combination of high resolution and high throughput. This dissertation describes the prototype design of a 14-bit pipeline ADC fabricated in a 0.18- $\mu$ m digital CMOS technology. Specific research contributions of this work include:

- A power-efficient passive capacitor error-averaging technique, which achieves a ratio-independent A/D conversion scheme;

- Identifying a precise breakdown of the circuit noise contribution in a switched-capacitor pipeline converter. A pipeline stage-scaling algorithm that addresses the capacitor taper factor and the per-stage resolution simultaneously is introduced;

- A nested CMOS gain-boosting technique that achieves a minimum of 130dB DC-gain with 0.2-μm thin oxide transistors;

- A  $\Delta\Sigma$  common-mode voltage regulation circuit is introduced to facilitate the control of the common-mode levels in pseudo-differential amplifiers;

- An amplifier and comparator sharing technique that reduces the total number of the amplifiers and comparators by half. A 14-b pipeline ADC is realized with six amplifiers and seven sub-ADCs.

#### 1.6 THESIS ORGANIZATION

Chapter 2 of this thesis reviews the pipeline ADC architecture and discusses the design challenges for switched-capacitor circuits in deep-submicron CMOS

technology. To alleviate the prominent issue of power efficiency under low supply voltages, a pipeline ADC stage-scaling analysis is then introduced that determines the optimum stage resolution and scaling factor simultaneously. Following this, Chapter 3 highlights the key linearity technique of this design – the passive capacitor error-averaging technique. In Chapter 4, the details of the circuit implementation issues are presented. The experimental results of the prototype chip are summarized in Chapter 5 with the conclusion and future works following in Chapter 6.

#### REFERENCES

- P. T. M. van Zeijl, J. W. Eikenbroek, P. P. Vervoort, S. Setty, J. Tangenberg, G. Shipton, E. Kooistra, I. Keekstra, and D. Belot, "A Bluetooth radio in 0.18-μm CMOS," *IEEE International Solid-State Circuits Conference*, vol. 1, pp. 86-448, 2002.

- 2. J. G. Proakis, *Digital communications*, 4<sup>th</sup> ed. McGraw-Hill, New York, 2001, Ch. 7.

- 3. Semiconductor Industry Association (2003). International Technology Roadmap for Semiconductors. Available @ http://www.sematech.org/.

- T. L. Brooks, D. H. Robertson, D. F. Kelly, A. Del Muro, and S. W. Harston,

"A cascaded sigma-delta pipeline A/D converter with 1.25-MHz signal

bandwidth and 89-dB SNR," *IEEE Journal of Solid-State Circuits*, vol. 32,

pp. 1896-1906, Dec. 1997.

- 5. R. Feldman, B. E. Boser, and P. R. Gray, "A 13-bit, 1.4-MS/s sigma-delta

- modulator for RF baseband channel applications," *IEEE Journal of Solid-State Circuits*, vol. 33, pp. 1462-1469, Oct. 1998.

- 6. J. C. Rudell, J. A. Weldon, J. J. Ou, L. Lin, and P. R. Gray, *An Integrated GSM/DECT Receiver: Design Specifications*, UC Berkeley Electronics Research Laboratory Memorandum, Memo #: UCB/ERL M97/82.

- 7. T. Gratzek, B. Brannon, J. Camp, and F. Murden, "A new paradigm for base station receivers: high IF sampling + digital filtering," *IEEE Radio Frequency Integrated Circuits (RFIC) Symposium*, pp. 143-146, June 1997.

- 8. R. Schreier, J. Lloyd, L. Singer, D. Paterson, M. Timko, M. Hensley, G. Patterson, K. Behel, and J. Zhou, "A 10-300-MHz IF-digitizing IC with 90-105-dB dynamic range and 15-333-kHz bandwidth," *IEEE Journal of Solid-State Circuits*, vol. 37, pp. 1636-1644, Dec. 2002.

- 9. W. H. W. Tuttlebee, "Advances in software-defined radio," *Electronics Systems and Software*, vol. 1, pp. 26-31, 2003.

| Chapter 2 | <b>,</b> |  |

|-----------|----------|--|

|           |          |  |

## PIPELINE ARCHITECTURE POWER EFFICIENCY

#### 2.1 PIPELINE ADC ARCHITECTURE

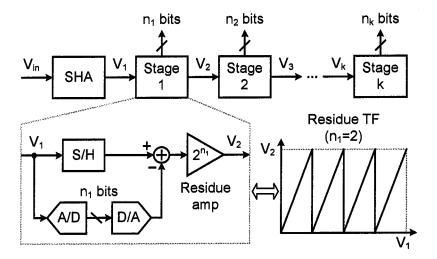

A pipeline A/D converter is inherently a multi-step amplitude quantizer in which the digitization is performed by a cascade of many topologically similar or identical stages of low-resolution analog-to-digital encoders. Pipelining enables high conversion throughput by inserting analog registers, i.e., sample-and-hold amplifiers (SHAs), in between stages that allow a concurrent operation of all stages. This is done at the cost of an increased latency. The block diagram of a pipeline ADC is shown in Figure 2.1.

A pipeline stage takes two actions when an input signal arrives (signaled by a master clock) – a snapshot of the input by the sample-and-hold (S/H) and a coarse quantization by the sub-ADC. These two operations are often performed simultaneously or in tandem. The resolution of a typical pipeline stage is usually

Figure 2.1 Block diagram of a pipeline A/D converter.

no more than four bits. The resolution of the conversion is enhanced by passing a residue signal – the unconverted part of the input signal – to the later stages where it is further quantized (Figure 2.1). The conversion residue is created by a digital-to-analog converter (DAC) and a subtraction circuit. The maximum swing of this residue signal is often brought back to the full-scale reference level with a precision amplifier – the residue amplifier in Figure 2.1. This keeps the signal level constant and allows the sharing of an identical reference throughout the pipeline stages.

Breaking a high-resolution conversion into multiple steps greatly reduces the total number of comparators required in contrast to a flash converter. In the limiting case, a 1-bit/stage (b/s) pipeline ADC only needs N comparators to resolve an N-bit code as opposed to  $2^N$  comparators required by a flash converter.

**Figure 2.2** Circuit diagram of the 1.5-b/s MDAC.

The large accumulative inter-stage gain also relaxes the impact of circuit non-idealities, such as noise, nonlinearity, and offset, of later stages on the overall conversion accuracy. For medium- to high-resolution Nyquist applications, pipeline ADCs have been demonstrated to achieve the lowest power consumption at relatively high conversion rates.<sup>1-10</sup>

In CMOS circuit technology, a typical pipeline ADC stage usually consists of a coarse comparator and a compact switched-capacitor circuit termed the multiplier DAC (MDAC), which integrates the sample-and-hold, the DAC, the subtraction, and the residue-gain functions.<sup>3</sup> The circuit diagram of a single-ended 1.5-b/s MDAC is shown in Figure 2.2. This architecture is also known to tolerate large comparator offsets due to the built-in decision level overlaps between successive stages, usually referred to as digital redundancy or digital error-correction (DEC).<sup>3</sup> The conversion accuracy thus solely relies on the precision of the residue signals; the conversion speed, on the other hand, is largely determined by the settling speed of the residue amplifier.

#### 2.2 POWER EFFICIENCY UNDER LOW SUPPLY VOLTAGE

As mentioned in Chapter 1, while the scaling of CMOS technology offers a potential for improvement on the operating speed of mixed-signal circuits, the accompanying reduction in the supply voltage and various short-channel effects create both fundamental and practical limitations on the achievable gain, signal swing, and noise level of these circuits, particularly under a low power constraint.

## 2.2.1 $\frac{kT}{C}$ Noise

For noise-limited analog designs, the circuit fidelity relies on the relative contrast of the signal strength to that of the noise, measured by the signal-to-noise ratio (SNR) in decibels. Although the final calculation should have all man-made noise sources included, the scope of discussion in this chapter will be limited to those that are fundamental – the thermal noise, the Flicker noise, and etc.

For discrete-time analog signal-processing circuits, especially those using the switched-capacitor technology, analog signals are usually acquired and processed in a batched fashion where a snapshot of the signal is taken periodically controlled by a clock signal – a process termed sampling. As the sampling circuit cannot differentiate the noise from the signal, part of that snapshot corresponds to the instantaneous value of the noise at the moment the sampling takes place. In the context of switched-capacitor circuits where the sample is stored as charge on

a capacitor, the root-mean-square (rms) total integrated thermal noise voltage is

$$\sqrt{\overline{V_N^2}} = \sqrt{\int_0^\infty \frac{4kTR}{1 + (2\pi f \cdot RC)^2} df} = \sqrt{\frac{kT}{C}},$$

(2.1)

where kT is the thermal energy, R is the switch resistance, C is the sampling capacitance. This is often referred to as the  $\frac{kT}{C}$  noise.

Note that (2.1) indicates that the integrated noise is independent of the switch resistance R (cancelled after integration). This is not surprising as when R is increased, hence higher noise floor, the bandwidth of the circuit is reduced and the total integrated noise stays constant.

#### 2.2.2 POWER CONSUMPTION OF PIPELINE ADC

For noise-limited designs, it can be derived that the power consumption of a switched-capacitor circuit is inversely proportional to the supply voltage for a fixed dynamic range (DR),

$$P \propto kT \cdot DR \cdot \left(\frac{V_{gs} - V_{th}}{V_{dd}}\right) \cdot f_s,$$

(2.2)

where kT is the thermal energy,  $f_s$  is the sampling rate,  $V_{gs} - V_{th}$  is the overdrive voltage of the amplifier input transistors, and  $V_{dd}$  is the supply voltage.<sup>12</sup>

In pipeline ADCs, the sampling process inherent in switched-capacitor circuits

introduces the  $\frac{kT}{C}$  noise at each pipeline stage when a residue voltage is captured.

This noise usually comprises two major contributions – the channel noise of the switches and the amplifier noise. Since no direct current is conducted by the switch right before a sampling takes place (the bandwidth of the switch-capacitor network is assumed large and the circuit is assumed settled), the 1/f noise is not of concern here; only the thermal noise contributes, which is a function of the channel resistance that is weakly affected by the technology scaling. On the other hand, the amplifier output noise is in most cases dominated by the channel noise of the input transistors, where the thermal noise and the 1/f noise both contribute.

Because the input transistors of the amplifier are usually biased in saturation region to derive large transconductance  $(g_m)$ , impact ionization and hot carrier effect tend to enhance their thermal noise level; <sup>14, 15</sup> the 1/f noise increases as well due to the reduced gate capacitance resulted from finer lithography and therefore shorter minimum gate length. It follows that, as CMOS technology scaling continues, amplifier increasingly becomes the dominant noise source for switched-capacitor circuits. An accurate consideration of the intrinsic noise sources in such a circuit should have the thermal noise of switches, all amplifier noises readily included.

Interestingly, the total integrated output noise (the input-referred noise as well)

still takes the form of  $\frac{kT}{C}$  with some correction factor, as those will be shown in the next section. Thus a fundamental technique to reduce the noise level, or to increase the signal-to-noise ratio of a switched-capacitor circuit, is to increase the size of the sampling capacitors. The penalty associated with this technique is the increased power consumption as larger capacitors demand larger charging/discharging current to keep up the sampling speed.

#### 2.3 STAGE-SCALING ANALYSIS OF PIPELINE ADC

Exploiting the fact that later stages contribute a diminishing input-referred noise because of the accumulative inter-stage gain, one architectural approach to maximize the signal-to-noise ratio with a given power budget is to determine an optimum way of distributing the biasing current to each pipeline stage. The optimization involves choosing an optimum per-stage resolution and reducing the sampling capacitor sizes along the pipeline.

Both of the techniques are commonly encountered in the literature.<sup>4, 11</sup> Although it increases the design and layout time dramatically, tapering capacitor sizes can often greatly reduce the overall power consumption of a high-resolution pipeline ADC. But to choose the right per-stage resolution is not as straightforward – it often involves other architectural considerations such as the component matching accuracy in the front-end stages. The following discussion

will assume that to maximize the SNR is the sole constraint of the design.

Intuitively, a too low per-stage resolution (hence more stages) increases the number of residue resampling events. Coupled with a low inter-stage gain, this leads to larger capacitors and more biasing current. Conversely, although a high per-stage resolution (hence fewer stages) minimizes the number of resampling events and allows a rapid tapering of the capacitor size, the per-stage power increases exponentially due to the reduction of the feedback factor of residue amplifiers. This is clearly not power efficient as well. It follows that the optimum stage resolution has to be somewhere in between, but the exact answer depends on the conversion speed, the technology used, the circuit topology, and a specific layout. Due to the complexity of this problem, simple hand analyses, albeit lacking in numerical accuracy, are commonly used to reveal qualitative parametric trade-offs and to offer insight to circuit designers.

#### 2.3.1 CLINE-GRAY MODEL

The first such analysis was introduced by Cline and Gray. Analytical results were shown attempting to optimize both the per-stage resolution and the taper factor of the sampling capacitors. The noise model readily confirms the existence of an optimum taper factor, which is determined to be approximately the interstage voltage gain. A prototype 13-b, 5-MS/s pipeline ADC that achieved an SNDR of 80.1 dB was demonstrated dissipating only 166 mW on a 5-V supply.

As the analytical model predicted a monotonic decrease of the overall conversion power when the per-stage resolution is increased, a 2.5-b/s architecture was chosen based on inspection.<sup>11</sup>

It was pointed out that the analysis leading to the counterintuitive observation neglected the loading effect of parasitic capacitances on the amplifier, the interconnect capacitances, and the capacitive loading of the comparators on the output. In the next section, the parasitic-loading effects are considered as the analytical model is revisited. We will prove that for high-speed conversions, a 2-3-b/s architecture is indeed optimum from a power standpoint.

#### 2.3.2 PARASITIC-LOADED AMPLIFIER MODEL

It was mentioned before that amplifier is increasingly becoming the dominant noise source in switched-capacitor circuits implemented in deep-submicron CMOS technology. It is therefore essential for a noise model intended to optimize

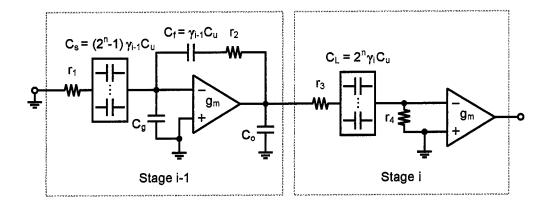

Figure 2.3 Noise model of MDAC including parasitic loading effects.

the SNR of a pipeline ADC to accurately account for all noise sources that ultimately contribute to the  $\frac{kT}{C}$  noise. In addition, the noise transfer functions must be individually sorted as they originate from different components at different parts of the circuit.

Figure 2.3 shows the single-ended circuit diagram of two consecutive multiplier DAC stages of a typical switched-capacitor pipeline ADC, with all noise sources included – the  $g_m$  blocks that model the amplifier and  $r_1$  through  $r_4$  that model the switch on-resistance. Here, stage i-1 is assumed in phase  $\phi$ 2 (amplifying mode) and stage i is assumed in phase  $\phi$ 1 (sampling mode).

To begin the calculation, we assume that the per-stage resolution n is constant. The unit sampling capacitor for stage i is  $\gamma_i C_u$ , where  $C_u$  is the first stage unit sampling capacitor and the capacitor scaling factor for stage i is  $\gamma_i$ . The prominent feature of this model is the inclusion of the loading from the amplifier, the comparators, the switches, and the wiring, modeled by two capacitors  $-C_o$  at the output node and  $C_g$  at the summing node of the residue amplifier, respectively (Figure 2.3). An accurate account of the parasitics requires a post-layout extraction that is design specific.

At the architectural level, two observations are noteworthy in modeling these parasitics. First, to keep up the conversion speed, the transconductance of the

amplifier (hence its size and biasing current) must increase exponentially as a function of the stage resolution due to the exponential decrease of the feedback factor. Meanwhile the number of comparators and sampling switches, the wiring complexity of layout exhibit the same dependence. Second, the parasitic-loading effects worsen as the conversion rate increases. In a high-speed converter, the parasitic capacitance can be comparable to the total sampling capacitance. The model  $C_o \approx C_g \approx \eta \left(2^n \gamma_i C_u\right)$  captures these dependences, where a technology independent "speed factor"  $\eta$  is introduced to model the loading effects as a function of the conversion speed. The value of this "speed factor" varies between 0 and 1 in this analysis by observing the following facts:

- When conversion speed is low, the loading due to parasitics is insignificant and the residue amplifier is mainly loaded by the sampling capacitors. This indicates a small "speed factor", hence η is set to 0 for this scenario;

- When conversion speed is high, the parasitic-loading effect is severe. If a specific technology is given, an exact relationship between  $\eta$  and the sampling rate can be derived. To make this analysis more general and technology independent, the maximum parasitic capacitance is set to equal

<sup>†</sup> This "speed factor" essentially stands for the ratio of the total parasitic capacitance to the total sampling capacitance ( $2^n \gamma_i C_u$ ) of a certain pipeline stage.

the total sampling capacitance, i.e.,  $C_o \approx C_g \approx 2^n \gamma_i C_u$  or  $\eta = 1$ .

Note that we assumed  $C_o \approx C_g$  in this analysis, which is approximate to make the algebra simpler. A full-length treatment would of course introduce two speed factors, one for  $C_o$  and one for  $C_g$ .

#### 2.3.3 STAGE-SCALING ANALYSIS REVISITED

In Figure 2.3, a feedforward factor can be defined as

$$\alpha = \frac{C_s}{C_s + C_f + C_g} = \frac{1}{1 + \eta} \left( 1 - \frac{1}{2^n} \right), \tag{2.3}$$

and a feedback factor as

$$\beta = \frac{C_f}{C_s + C_f + C_g} = \frac{1}{1 + \eta} \cdot \frac{1}{2^n}.$$

(2.4)

Assuming a first-order frequency response, the  $g_m$  noise floor at the output of

the stage i-1 is  $\left(\frac{1}{\beta}\right)^2 4kT \frac{N_{op}}{g_m}$ , where  $N_{op}$  is the "noise factor" of the amplifier.

In a single-ended amplifier, if the input transistor is the only noise contributor, then  $N_{op} = 2/3$  holds for long-channel devices. However, for short-channel devices, the "noise factor" can be substantially greater than 2/3. Furthermore, other devices in a complicated amplifier also contribute noise. E.g., in a one-stage folded-cascode amplifier, the current sources generate noise at the output equally

as the input devices do; the cascode devices' noise, albeit suppressed at low frequencies, contribute substantially at high frequencies. In a two-stage amplifier, the input devices of the second stage also produce noise at the output. In this analysis, we assume  $N_{op}=3$  for single-ended amplifiers.

The noise transfer functions of the switches  $r_1$  through  $r_4$  can be calculated individually. As the switch noises are band-limited by the amplifier, their contribution is reduced compared to the scenario where the circuit bandwidth is only determined by the lowpass filter formed by the switch and the sampling capacitors. The exact solution, taking into account the effect of the switch resistance on the frequency response, is quite involved. Instead of an accurate account of these second-order effects, the total noise floor at the output of the stage i-1 is approximated as

$$N_{i}(f) = 4kT \cdot \left[ \left( \frac{1}{\beta} \right)^{2} \frac{N_{op}}{g_{m}} + \left( \frac{\alpha}{\beta} \right)^{2} r_{1} + r_{2} + (r_{3} + r_{4}) \right], \qquad (2.5)$$

where the first term stems from the amplifier noise and the rest from the switches. The frequency response is assumed first-order, band-limited by the closed-loop bandwidth ( $\omega_{-3dB}$ ) of the residue amplifier. In addition, the switches are sized such that they will not limit the settling speed of the amplifier. For this reason, assume

$$r_1 C_s, r_2 C_f, (r_3 + r_4) C_L \le \frac{1}{5} \frac{1}{\omega_{-3dB}} = \frac{1}{5} \frac{C_T}{\beta \cdot g_m},$$

(2.6)

where  $C_T$  is the total output load capacitance of the residue amplifier given by

$$C_{T} = \left[1 - \frac{1}{(1+\eta) \cdot 2^{n}} + \eta \cdot 2^{n}\right] \gamma_{i-1} C_{u} + 2^{n} \gamma_{i} C_{u}. \tag{2.7}$$

Combining (2.5) and (2.6), we have

$$N_{i}(f) = \frac{4kT}{5g_{m}} \cdot \left[ \frac{5N_{op}}{\beta^{2}} + \left( \frac{\alpha}{\beta} \right)^{2} \frac{C_{T}}{\beta C_{s}} + \frac{C_{T}}{\beta C_{f}} + \frac{C_{T}}{\beta C_{L}} \right]. \tag{2.8}$$

The input-referred integrated noise sampled by the stage i is

$$N_{i} = \frac{1}{\left(4^{n}\right)^{i-1}} \left[ \frac{\pi}{2} N_{i}(f) BW \right] = \frac{1}{\left(4^{n}\right)^{i-1}} \frac{kT}{5C_{u}} \cdot \left[ \frac{(1+\eta)2^{n}5N_{op}}{C_{T}/C_{u}} + \frac{2^{n}}{\gamma_{i-1}} + \frac{1}{2^{n}\gamma_{i}} \right]. \quad (2.9)$$

If a uniform scaling is assumed, i.e.,  $\gamma_i = \gamma^{i-1}$  for  $i = 1, \dots, \infty$ ,  $\sum_i N_i$  is summable for  $\gamma > 1/4^n$  and is given by

$$\sum_{i=1}^{\infty} N_{i} = \frac{kT}{2^{n} C_{u}} + \frac{kT}{5C_{u}} \left( \frac{1}{4^{n} \gamma - 1} \right) \left[ \frac{(1+\eta) \cdot 2^{n} \gamma \cdot 5N_{op}}{1 - \frac{1}{(1+\eta) \cdot 2^{n}} + \eta \cdot 2^{n} + 2^{n} \gamma} + 2^{n} \gamma + \frac{1}{2^{n}} \right], \quad (2.10)$$

where the first term  $\frac{kT}{2^nC_u}$  represents the noise of the front-end S/H circuit as no SHA is assumed.

In addition, if slewing is ignored, the settling speed is determined by the small-signal closed-loop bandwidth ( $\omega_{-3dB}$ ) of the residue amplifier. The total conversion power can be derived as

$$P \propto SNR \cdot kT \cdot f_s \cdot \left(\frac{V_{gs} - V_{th}}{V_{dd}}\right) \cdot g(n, \gamma, \eta),$$

(2.11)

where  $f_s$  is the sampling rate,  $V_{gs} - V_{th}$  is the overdrive voltage of the amplifier input transistor, and  $V_{dd}$  is the supply voltage. Function g(.) is given by

$$g(n,\gamma,\eta) = \left(\frac{1+\eta}{1-\gamma}\right) \left(2^{n} - \frac{1}{1+\eta} + \eta \cdot 4^{n} + 4^{n}\gamma\right) \cdot \left\{\frac{1}{2^{n}} + \frac{1/5}{4^{n}\gamma - 1} \left[\frac{(1+\eta) \cdot 4^{n}\gamma \cdot 5N_{op}}{2^{n} - \frac{1}{1+\eta} + \eta \cdot 4^{n} + 4^{n}\gamma} + 2^{n}\gamma + \frac{1}{2^{n}}\right]\right\}.$$

(2.12)

#### 2.3.4 SUMMARY

Equation (2.11) supports the widely known result of (2.2) with an addition of the new  $g(n,\gamma,\eta)$  function, which captures the dependence of the overall power consumption of a pipeline ADC on the per-stage resolution n, the scaling factor  $\gamma$ , and the speed factor  $\eta$ . For a given speed factor, minimizing this function yields the optimum stage resolution and scaling factor at the same time.

#### 2.3.4.1 SPEED FACTOR

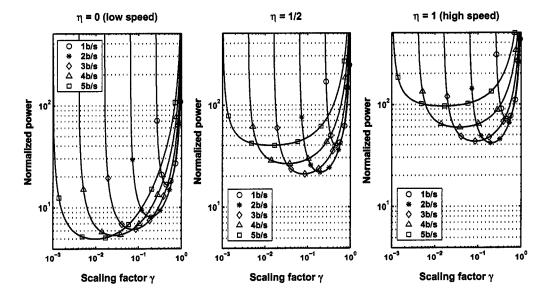

In Figure 2.4, the function g(.) is plotted against the scaling factor  $\gamma$  for a perstage resolution n=1 5 and a speed factor  $\eta=0$ , 0.5, and 1. The plot indicates a significant impact of the speed factor on the optimum stage resolution and the minimum power consumption.

For a small  $\eta$ , or a low conversion speed, the model predicts the same dependency between the stage resolution and the power consumption as the Cline-Gray model does – a higher per-stage resolution always results in a lower total power consumption for a fixed resolution (the leftmost plot of Figure 2.4).

When  $\eta$  approaches one, i.e., for high conversion speeds, the amplifier is

**Figure 2.4** Evaluation of  $g(n, \gamma, \eta)$  versus the scaling factor  $\gamma$ .

Figure 2.5 Evaluation of  $g(n, \gamma, \eta)$  versus the speed factor  $\eta$ .

increasingly loaded by parasitics. The total power consumption rises collectively regardless of the stage resolution as expected. However, high per-stage resolution architectures exhibit a higher sensitivity to the speed factor in that their minimum power rises much faster when n exceeds 3-b/s (the middle and the right plots of Figure 2.4). The optimum resolution is 2- or 3-b/s for a pipeline converter operating at these speeds. This is the typical scenario encountered in a practical design.

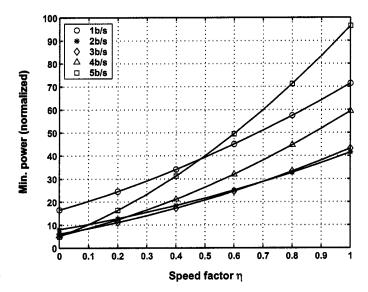

The above conclusion is better observed in Figure 2.5, where the minimum power consumption is plotted against the speed factor for n = 1 5.

#### 2.3.4.2 TAPER FACTOR

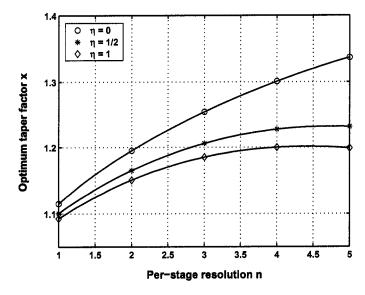

A "taper factor" x was defined in the Cline-Gray model, which relates to the

**Figure 2.6** Evaluation of  $g(n, \gamma, \eta)$  versus the taper factor x.

scaling factor by the equation  $\gamma = \frac{1}{2^{nx}}$ . One important observation drawn by the Cline-Gray model was that the optimum scaling factor  $\gamma_{opt}$  is approximately equal to the inter-stage voltage gain of the pipeline. In other words, the optimum taper factor  $x_{opt}$  is approximately one.

This observation is confirmed by Figure 2.6, where the power is plotted against the taper factor x. The optimum taper factor for any per-stage resolution is slightly greater than one regardless of the speed factor (varying from 0 to 1). To better observe this,  $x_{opt}$  is plotted against the stage-resolution for different speed factors in Figure 2.7.

**Figure 2.7** Evaluation of  $\gamma_{opt}$  versus the stage resolution n.

The optimum taper factor is a weak function of the stage resolution, and this statement is increasingly accurate for higher conversion speeds (indicated by the flat right half of the curves in Figure 2.7. The plot also points out that the optimum taper factor is neither a strong function of the speed factor. These observations are probably justified by the fact that the speed factor influences all stages uniformly and the inter-stage gain remains constant for a given n.

The summary serves as guideline for pipeline ADC designs when the trade-off between SNR and power consumption is critical. Note that the derivation does not include the SHA noise if one is used. The uniform scaling factor throughout the pipeline may not be practical due to an increased layout effort. In addition, scaling of the last few pipeline stages may be difficult when they become too small. Lastly, although a uniform per-stage resolution helps to keep a design modular,

increasing the resolution of the backend stages (a non-uniform scaling essentially) may result in more power savings.

## REFERENCES

- 1. S. Sutardja and P. R. Gray, "A pipelined 13-bit 250-ks/s 5-V analog-to-digital converter," *IEEE Journal of Solid-State Circuits*, vol. 23, no. 6, pp. 1316-1323, Dec. 1988.

- Y.-M. Lin, B. Kim, and P. R. Gray, "A 13-b 2.5-MHz self-calibrated pipelined A/D converter in 3-μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 26, no. 4, pp. 628-636, Apr. 1991.

- 3. S. H. Lewis, H. S. Fetterman, G. F. Gross, Jr., R. Ramachandran, and T. R. Viswanathan, "A 10-b 20-Msample/s analog-to-digital converter," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 3, pp. 351-358, Mar. 1992.

- 4. T. Cho and P. R. Gray, "A 10-b, 20-Msample/s, 35-mW pipeline A/D converter," *IEEE Journal of Solid-State Circuits*, vol. 30, no. 3, pp. 166-172, Mar. 1995.

- 5. S.-U. Kwak, B.-S. Song, and K. Bacrania, "A 15-b, 5-Msample/s low-spurious CMOS ADC," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 1866-1875, Dec. 1997.

- 6. Y.-I. Park, S. Karthikeyan, F. Tsay, and E. Bartolome, "A 10-b 100-MSample/s CMOS pipelined ADC with 1.8-V power supply," *IEEE International Solid-State Circuits Conference*, pp. 130-131, Feb. 2001.

- W. Yang, D. Kelly, L. Mehr, M. T. Sayuk, and L. Singer, "A 3-V 340-mW 14-b 75-Msample/s CMOS ADC with 85-dB SFDR at Nyquist input," *IEEE Journal of Solid-State Circuits*, vol. 36, pp. 1931-1936, Dec. 2001.

- 8. D. Miyazaki, M. Furuta, and S. Kawahito, "A 16-mW 30-MSample/s 10-b pipelined A/D converter using a pseudo-differential architecture," *IEEE International Solid-State Circuits Conference*, pp. 174-175, Feb. 2002.

- B.-M. Min, P. Kim, F. W. Bowman, D. M. Boisvert, and A. J. Aude, "A 69-mW 10-bit 80-MSample/s pipelined CMOS ADC," *IEEE Journal of Solid-State Circuits*, vol. 38, pp. 2031-2039, Dec. 2003.

- Y. Chiu, P. R. Gray, and B. Nikolic, "A 1.8-V, 14-b, 10-MS/s Pipelined ADC in 0.18-μm CMOS with 99-dB SFDR," *IEEE International Solid-State Circuits Conference*, vol. 47, pp. 458-459, Feb. 2004.

- 11. D. W. Cline and P. R. Gray, "A power optimized 13-b 5-Msamples/s pipelined analog-to-digital converter in 1.2-μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 3, pp. 294-303, Mar. 1996.

- 12. A. M. Abo and P. R. Gray, "A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter," *IEEE Journal of Solid-State Circuits*, vol. 34, pp. 599-606, May 1999.

- 13. J. M. Rabaey, A. Chandrakasan, and B. Nikolic, *Digital integrated circuits: a design perspective*, 2<sup>nd</sup> Ed. Prentice Hall, New Jersey, 2003.

- A. A. Abidi, "High-frequency noise measurements on FETs with small dimensions," *IEEE Transactions on Electron Devices*, vol. ED-33, pp. 1801-1805, Nov. 1986.

- 15. C. Enz and Y. Cheng, "MOS transistor modeling for RF IC design," *IEEE Journal of Solid-State Circuits*, vol. 35, pp. 186-201, Feb. 2000.

| Chapter 3 |

|-----------|

|-----------|

# CAPACITOR ERROR-AVERAGING

In Chapter 2, we discussed the fundamental trade-off between the achievable  $\frac{kT}{C}$  noise level and the power consumption of a pipeline ADC. A revised pipeline stage-scaling algorithm was introduced that optimizes the conversion power given the target SNR specification.

In practice, however, the performance of a high-speed, high-accuracy pipeline ADC is also limited by other device or circuit non-idealities that degrade the fidelity of the digitization process — often manifested as nonlinearities and memory effects. Depending on application, the distortion artifact can sometimes be more harmful than an additive white noise.

In this chapter, a discussion of the pipeline ADC error mechanism is presented, followed by a brief review of the previous precision conversion techniques. Upon analyzing the pros and cons of these prior arts, the discussion gradually develops

a focus on the capacitor error-averaging technique – an inherently linear pipeline A/D conversion scheme. The shortcomings of an earlier averaging approach are discussed in details, and then a new technique – the passive capacitor error-averaging – is introduced. Quantitative comparisons using both analytical methods and a Monte Carlo computer simulation are included toward the end of the chapter.

#### 3.1 PIPELINE ADC ERROR MECHANISM

Although a pipeline ADC makes use of considerable amount of digital logic, most of its signal-processing functions are executed in the analog domain. The conversion process therefore is susceptible to analog circuit and device impairments. As pointed out in Chapter 2, as the quantization takes a divide-and-conquer approach, the requirements on the comparators are greatly relaxed compared to that of a flash-type converter. The conversion accuracy is solely determined by the residue transfer accuracy.

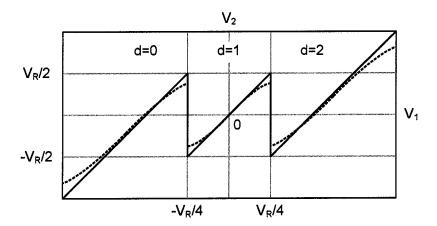

Static non-idealities that affect the residue accuracy include the sampling capacitor mismatch, finite amplifier gain, and switch-induced charge injection errors. The capacitor mismatch and finite amplifier gain effect can be readily evaluated by inspecting the voltage transfer characteristic obtained for the circuit shown in Figure 2.2 of a 1.5-b/s pipeline ADC:

**Figure 3.1** Voltage transfer characteristic of a 1.5-b/s residue gain stage. The solid curve shows the ideal transfer function and the dashed one exhibits static nonlinearity due to analog circuit non-idealities.

$$V_{2} = \frac{V_{1}(C_{1} + C_{2}) - (d - 1) \cdot V_{REF}C_{2} + V_{os}(C_{1} + C_{2})}{C_{1} + \frac{C_{1} + C_{2}}{A(V_{2})}},$$

(3.1)

where  $V_{os}$  is the offset voltage of the amplifier. These errors effect a nonlinear residue transfer function as indicated in Figure 3.1.

In addition to static errors, finite circuit bandwidth limits the tracking speed hence the accuracy of the front-end track-and-hold (T/H) circuit. The same issue exists for the residue amplifier as well. On the other hand, the dynamic errors of the comparators include hysteresis and metastability, although neither affects the conversion accuracy of a pipeline converter as harmfully as they do to a flash converter.<sup>1,2</sup>

Figure 3.2 Circuit diagram of an *n*-b/s pipeline ADC and its residue transfer characteristic. (a) Sampling mode. (b) Amplification mode.

#### 3.2 CAPACITOR MATCHING ACCURACY

Among the static conversion nonlinearities, the capacitor mismatch — a random error due to the imperfection of the manufacture process — is the one mostly discussed in the literature. In a fully optimized pipeline ADC, random capacitor mismatch is often the most important error source of nonlinearity. In the absence of a post-fabrication component trimming or calibration, the conversion accuracy is usually limited to approximately 10-12 bits.

To understand how exactly the capacitor mismatch affects the conversion linearity, specifically DNL and INL, we consider the *n*-b/s, *N*-bit pipeline ADC

shown in Figure 3.2. A single-ended circuit diagram is shown for simplicity.

The circuit operates on a two-phase clock. In  $\phi 1$ , all k (=2<sup>n</sup>) capacitors are connected together to the input; in  $\phi 2$ ,  $C_1$  is switched to the feedback path and the rest of the capacitors act as an n-bit DAC by switching the top plates to either ground or  $V_{REF}$  according to the comparison outcome. The transfer characteristic of the stage consists of k segments spanning between 0 and  $V_{REF}$ . Ideally, the end points of each segment should precisely land at 0 and  $V_{REF}$  if all circuit elements are ideal and all segmental transitions ( $\Delta$ 's in Figure 3.2) should be exactly  $V_{REF}$ .

Now let's study the capacitor mismatch effect alone by setting the amplifier gain to infinite and nullifying all offset errors. In the Appendix, the matching accuracy required to achieve *N*-bit linearity is calculated. The important conclusions are as follows:

- DNL is a direct result of the mismatch error between adjacent capacitors in the MDAC. This error is not carried over from segment to segment;

- INL is the result of the cumulative mismatch error of all sampling capacitors, albeit the first *i* capacitors have a more severe impact on the linearity for the *i*<sup>th</sup> segment. Therefore the INL is more susceptible to the mismatch errors among the capacitors.

In Figure 3.3, the MDAC capacitor matching accuracy as a function of the stage resolution of a 14-b pipeline ADC is plotted as an example. Indeed, the

Figure 3.3 Capacitor matching accuracy versus stage resolution for a 14-bit pipeline ADC. A half LSB maximum DNL and INL error is assumed.

matching accuracy is gradually relaxed by placing more bits in the front-end stage. Quite a few works in the literature exploit this fact.<sup>3-8</sup> As studied in Chapter 2, the penalty of this approach, however, is a much degraded power efficiency when the stage resolution is pushed over 3-4-b/s. In the next section, conversion techniques that do not require matched capacitors will be discussed.

## 3.3 Precision Conversion Techniques

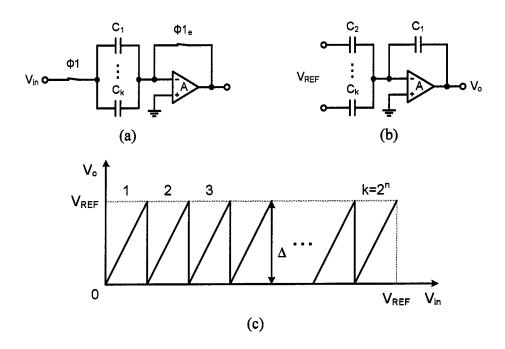

To combat the mismatch error, ratio-independent voltage multiplication techniques were invented in the 80 s and 90 s. Although most of these techniques are discussed in the context of an algorithmic (also called cyclic) A/D converter,

they often can be applied to the pipeline architecture with little modification. 9-12

Most of the ratio-independent techniques rely on sampling an input or residue voltage on the same capacitor multiple times to achieve an accurate multiply-by-n function that is immune to capacitor matching errors. The techniques often involve a second capacitor acting as the temporary storage of the intermediate charge. The penalty associated with this is the extra time required to process the signal, which inevitably impacts the conversion speed.

A few techniques that reduce this timing overhead deserve to be mentioned here. The first implements an exact multiplication by four with two clock cycles in a 1.5-b/cycle algorithmic ADC. <sup>11</sup> The scheme takes advantage of the fact that an algorithmic ADC makes use of the same circuit cyclically. By alternating the roles of two capacitors as the sampling and feedback capacitors, the residue gain error is inverted every other iteration, which results in a complete error cancellation for every two consecutive bits. However, this two-cycle error cancellation is only possible with an algorithmic ADC, where the gain error is constant each time the residue voltage circulates around the loop. The second is a capacitor error-averaging (CEA) technique that is well suited for a pipelined implementation. <sup>13, 14, 15</sup> This scheme exhibits inherent linearity even in the presence of large capacitor mismatch errors, and will be discussed in more details in the following sections. The third technique implements a mismatch-

independent DNL architecture, which in essence is a decision code-weighted capacitor ratio selection algorithm. However, the INL of this architecture still relies on the capacitor matching accuracy. <sup>16, 17, 18</sup>

In the late 80 s and 90 s, the pipeline ADCs using a power-on or background digital capacitor trimming or calibration technique have become increasingly popular. Since the conversion linearity is not inherent, the performance sensitivity to temperature and supply voltage drift, component aging has been problematic for these types of converters. The power consumption and silicon area of the logic circuitry have been important metrics in evaluating the performance and complexity of the digital techniques until recently, when the advancement of the CMOS technology scaling made the digital transistors abundantly available to circuit designers in a cost-effective way. Many sophisticated digital signal-processing algorithms now can be assembled in a small silicon area in these deep-submicron processes with relatively small power overhead. This is especially advantageous in a system-on-a-chip (SoC) design, where large amount of digital circuits share the same die with the front-end analog circuits.

#### 3.3.1 ACTIVE CAPACITOR ERROR-AVERAGING

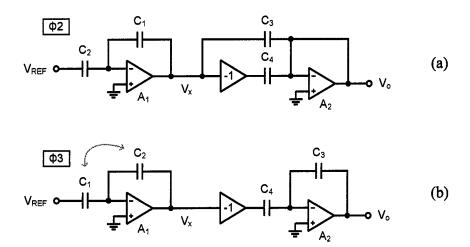

As mentioned in the last section, one approach to treat mismatch error is the capacitor error-averaging. For a 1-b/s pipeline architecture, the error correction is performed by interchanging the roles of two sampling capacitors during the

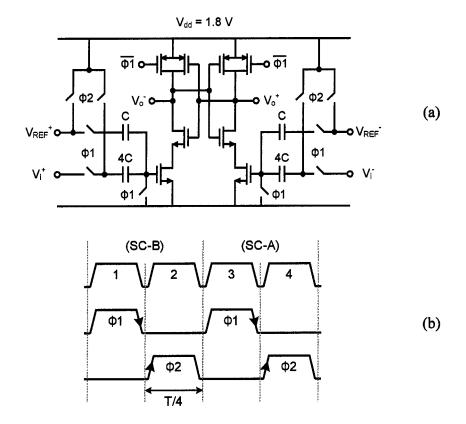

**Figure 3.4** Circuit diagram of the active CEA technique. The stage operates on a three-phase clock.  $\phi 1$  is the sampling phase (not shown).  $\phi 2$  and  $\phi 3$  are the amplification phases shown in (a) and (b), respectively.

amplification phases (Figure 3.4). Two residue voltages that contain complementary errors are generated consecutively. A second amplifier and two extra capacitors are used to obtain the average of the residue voltage pair (hence the name "active"). The gain-of-minus one block is implemented by simply cross-connecting the differential signals. It has been shown that the first order gain error resulted from capacitor mismatch is removed by averaging. <sup>13, 15</sup>

The active CEA technique is capable of realizing an excellent linearity with poorly matched capacitors. However, this is achieved at the cost of an added circuit complexity and more power consumption due to the residue resampling process. Assuming the averaging amplifier generates an equal amount of noise while draining the same current as the residue amplifier, the approach leads to a

**Figure 3.5** Voltage waveforms of the active CEA gain stage of Figure 3.4.

four times power and area increase for the same SNR compared to the conventional architecture. Moreover, the averaging amplifier and the residue resampling process impose additional nonlinearities on the signal path, compromising the overall linearity of the converter.

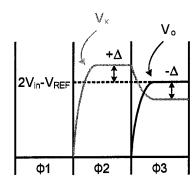

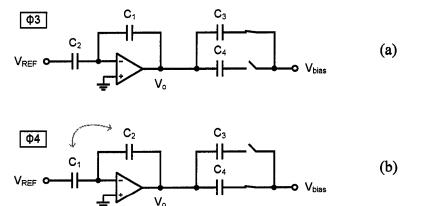

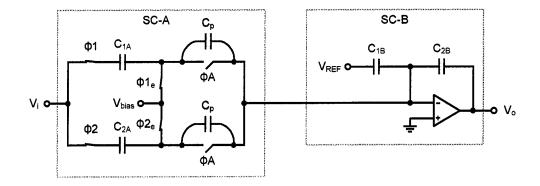

# 3.3.2 Passive Capacitor Error-Averaging - Part I

The essence of the CEA technique is to generate a residue voltage pair that contain complementary gain errors, and then average them to obtain an accurate multiply-by-two function. However, the averaging operation using an additional amplifier is extravagant. The pipeline nature of the conversion renders the opportunity to exploit the sampling capacitors from the trailing stages to realize the averaging function without the resampling of the residue voltages.<sup>14</sup> This section describes the first realization of this technique.

The new approach is illustrated in Figure 3.6. The sampling capacitors  $C_1$  and  $C_2$  are split in half into  $C_1$  and  $C_1$ ,  $C_2$  and  $C_2$ . The stage operates on a four-phase clock.  $\phi 1$  and  $\phi 2$  are the sampling phases (not shown in the figure).  $\phi 3$  and  $\phi 4$  are

**Figure 3.6** Circuit diagram of the passive CEA technique (I).  $C_1$  and  $C_2$  are the sampling capacitors of the current pipeline stage, while  $C_3$  and  $C_4$  are from the trailing stage.

the amplification phases.

Assuming that the previous pipeline stage produces a residue voltage pair  $V_{in}$  and  $V_{in}$ ,  $C_1$  and  $C_2$  are used to sample the first residue voltage  $(V_{in})$  in  $\phi 1$ , and then  $C_1$  are used to sample the second one  $(V_{in})$  in  $\phi 2$ . The two samples acquired in tandem are then merged by the two split capacitors in the following amplification phases  $(\phi 3$  and  $\phi 4)$ . The charge sharing between the half capacitors therefore performs the error-averaging function on the fly while the output residue is produced. No extra amplifier is required to explicitly produce an averaged

**Figure 3.7** Voltage waveforms of the passive CEA gain stages of Figure 3.6 and Figure 3.8.

output voltage as compared to the active CEA approach – hence the name "passive" CEA. The operation of double sampling and double amplification is repeated by each stage of the pipeline ADC. The double sampling of the input voltage is not required in the first stage.

Assuming that the input residues are complementary, the output residues produced in  $\phi 3$  and  $\phi 4$  are calculated in the Appendix. Equation (3.24) shows that all of the first-order gain error terms in the output residue expression stem from the current stage; the mismatch errors from the previous stage are reduced to the second order after averaging. Interestingly, the first-order gain error terms remain complementary.

One side advantage of producing two residue voltages instead one is that it allows more comparator settling time if an early comparison approach is used. <sup>14, 15</sup> This is indicated in Figure 3.7 by the arrow in between  $\phi 1$  and  $\phi 2$ , where the first residue is compared against the reference thresholds. With this approach, the comparator settling time is as long as one quarter of the clock period as opposed

to just the non-overlapping time between the two phases ( $\phi$ 1 and  $\phi$ 2) for the conventional architecture.

#### 3.3.3 Passive Capacitor Error-Averaging – Part II

Another circuit architecture that equally performs the passive averaging technique is shown in Figure 3.8. Each residue gain stage consists of one amplifier and two capacitors similar to that of a conventional 1.5-b/s architecture. The timing diagram of this approach is shown in Figure 3.7. The circuit operates as follows. In  $\phi$ 1 and  $\phi$ 2, the complementary input voltage pair ( $V_{in}$  and  $V_{in}$ ) produced by the previous stage is sampled by  $C_1$  and  $C_2$ , respectively. During  $\phi$ 3 and  $\phi$ 4, two output residue voltages ( $V_o$  and  $V_o$ ) are generated by swapping the positions of  $C_1$  and  $C_2$ , followed by the sampling by  $C_3$  and  $C_4$  from the trailing stage, respectively. The charge averaging is performed on the fly in this circuit, which

**Figure 3.8** Circuit diagram of the passive CEA technique (II). Here  $C_3$  and  $C_4$  are also the sampling capacitors from the trailing stage.

Architecture **Passive** Passive Conventional **Active CEA** CEA (II) CEA (I) (1.5-b/s) $\sigma^2$  $0.5\sigma^2$  $\sigma^2$ 0  $E(\varepsilon)$  $3\sigma^4$  $\sigma^2$  $\sigma^4$  $3.75\sigma^{4}$  $Var(\varepsilon)$

Table 3.1 Averaging effects of CEA techniques

is identical to the first approach. Again, no explicitly averaged residue voltage is produced and no averaging amplifier and capacitors are required.

The comparison between the averaging effects of the passive and active CEA techniques are calculated in the Appendix and summarized in Table 3.1.

#### 3.3.4 POWER EFFICIENCY

Both of the passive CEA techniques discussed in the previous two sections are more power-efficient averaging approaches compared to the active one. Avoiding the residue resampling process reduces the total conversion power by a factor of four. In addition, the uncorrelated noise in two separately acquired residue samples further increases the SNR by three decibels. Furthermore, the loading of the residue amplifier is reduced because only half of the sampling capacitance switches on during either one of the sampling phases.

A limitation of the passive CEA technique is that it takes four clock phases to complete the sampling-comparison-amplification process, in contrast to two for a conventional implementation with no averaging, or three for the active CEA.

Table 3.2 ADC architecture power efficiency

| Architecture (1.5-b/s) | Conventional | Active CEA | Passive CEA |

|------------------------|--------------|------------|-------------|

| Averaging              | No           | Yes        | Yes         |

| Power                  | 1            | 4          | 1/2         |

| Speed                  | 1            | 2/3        | 1/2         |

| Power/speed            | 1            | 6          | 1           |

Table 3.2 summarizes the power-saving results of the new approaches. For the same target SNR, the power efficiency is defined by normalizing the total conversion power to the sampling rate. It follows that the passive CEA approach is as efficient as the conventional technique, and six times more efficient than the active approach.

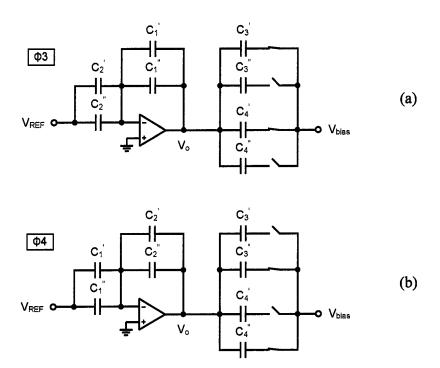

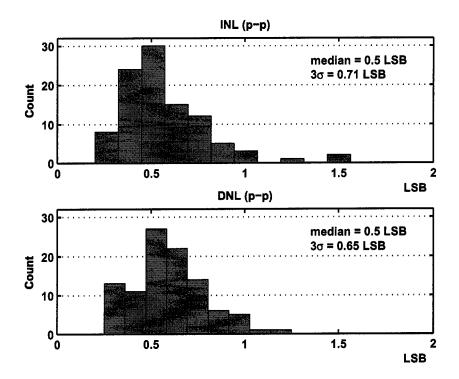

# 3.3.5 MONTE CARLO SIMULATION

A MATLAB behavioral model of the new averaging technique was constructed. A 1.5-b/s, 14-b pipeline ADC using the passive CEA (II) approach was evaluated. Various circuit non-idealities –sampling capacitor mismatch, amplifier finite gain effect, comparator and amplifier offset – were considered in the simulation. As the averaging reduces the matching requirement quadratically, it is expected that an *n*-bit capacitor matching accuracy is adequate to achieve a 2*n*-bit INL.

The results of the Monte Carlo yield simulation are summarized in Table 3.3.

A Gaussian distribution is assumed for all circuit parameters except the amplifier

Table 3.3 Monte Carlo simulation results of a 14-b pipeline ADC

| Simulation results | INL <sub>p-p</sub> (median) | DNL <sub>p-p</sub> (median) | ENOB<br>(median) | Yield ( INL  ≤0.5LSB) |

|--------------------|-----------------------------|-----------------------------|------------------|-----------------------|