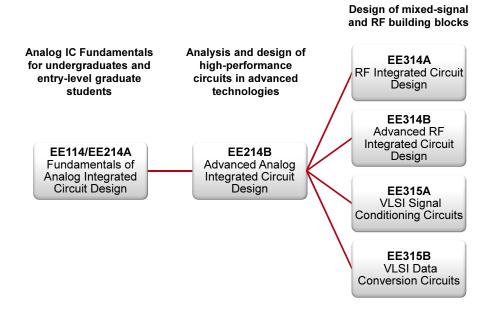

## EE315A VLSI Signal Conditioning Circuits

- Spring 2013 -

Boris Murmann Stanford University murmann@stanford.edu

#### **Table of Contents**

| Chapter 1 | Introduction                                  |

|-----------|-----------------------------------------------|

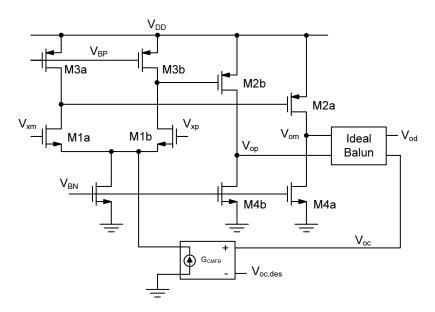

| Chapter 2 | Biquad Filter Realization                     |

| Chapter 3 | Ladder Filter Realization                     |

| Chapter 4 | Integrator Realization & Nonidealities        |

| Chapter 5 | Switched Capacitor Filters                    |

| Chapter 6 | Operational Transconductance Amplifier Design |

| Chapter 7 | Precision Analog Circuit Techniques           |

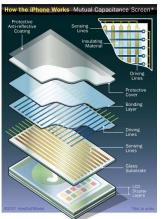

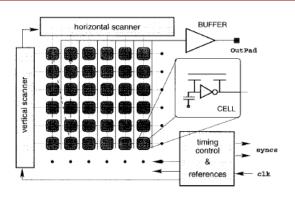

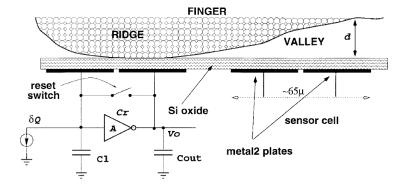

| Chapter 8 | Sensor Interfaces                             |

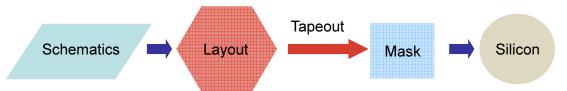

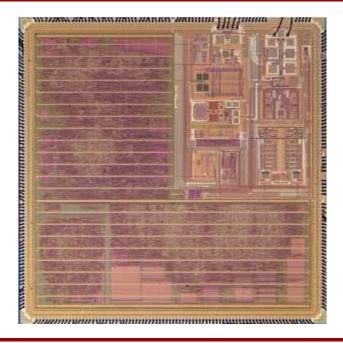

| Chapter 9 | Physical Layout                               |

#### Introduction

#### Boris Murmann Stanford University murmann@stanford.edu

Copyright © 2013 by Boris Murmann

B. Murmann EE315A - Chapter 1 1

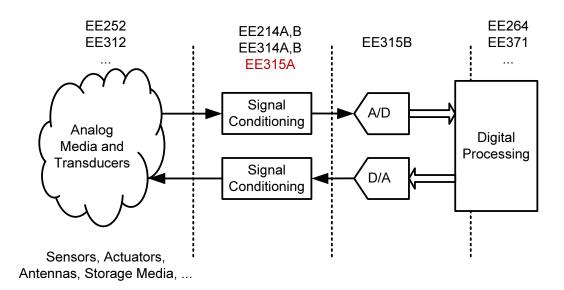

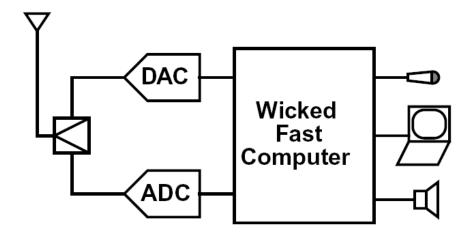

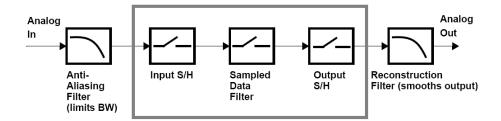

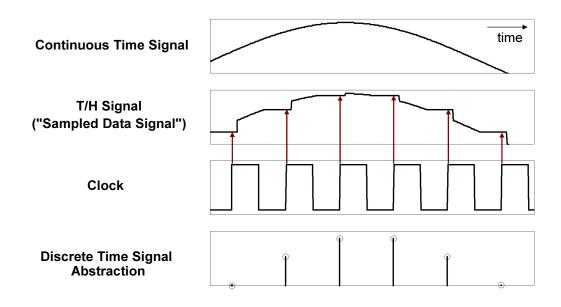

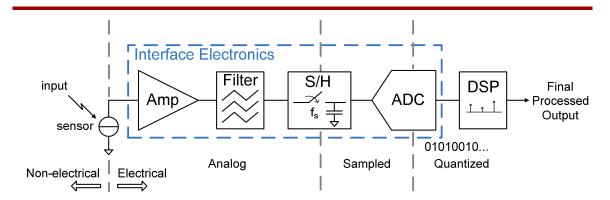

## **Mixed Signal System**

#### **Signal Conditioning**

('sig·nəl kən'dish·ən·iŋ) (communications) Processing the form or mode of a signal so as to make it intelligible to or compatible with a given device, such as a data transmission line, including such manipulation as pulse shaping, pulse clipping, digitizing, and linearizing.

#### [www.answers.com]

In electronics, signal conditioning means manipulating an analogue signal in such a way that it meets the requirements of the next stage for further processing.

Signal conditioning can include amplification, filtering, converting, range matching, isolation and any other processes required to make sensor output suitable for processing after conditioning.

[http://en.wikipedia.org]

B. Murmann EE315A - Chapter 1 3

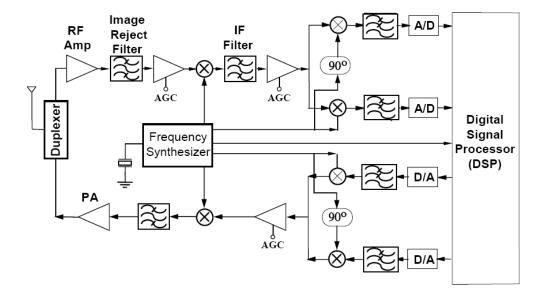

## **Example: Cellular Phone**

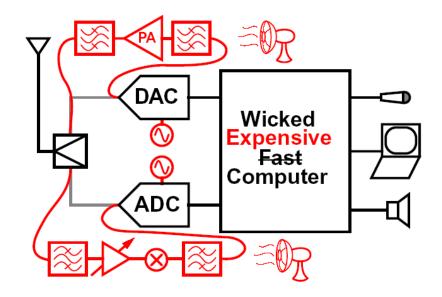

## The Vision - "Software Radio"

[Schreier, "ADCs and DACs: Marching Towards the Antenna," GIRAFE workshop, ISSCC 2003]

B. Murmann EE315A - Chapter 1 5

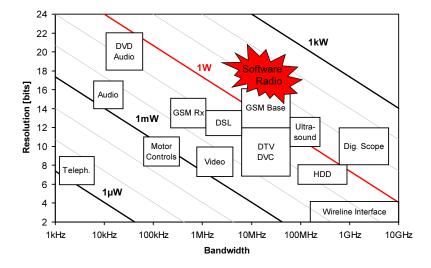

## **ADC for Software Radio**

Ouch!

## Reality

[Schreier, "ADCs and DACs: Marching Towards the Antenna," GIRAFE workshop, ISSCC 2003]

B. Murmann EE315A - Chapter 1 7

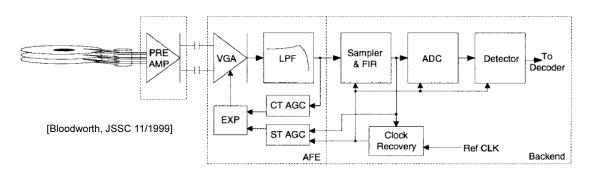

## **Example: Hard Disk Drive**

| AGC Specifications                 |                                                     | LPF Specifications                                               |                                              |

|------------------------------------|-----------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|

| Input Signal Range                 | $45 \text{ mVppd} < V_{IN} < 500 \text{ mVppd}$     | LPF Bandwidth                                                    | $20 \text{ MHz} \le f_c \le 120 \text{ MHz}$ |

| Output Target                      | 1.400 Vppd                                          | Cutoff Variation                                                 | < ± 2.5 %                                    |

| PGA Gain Settings                  | -3 dB, 3 dB, 9 dB                                   | Group Delay Variation<br>(0.30f <sub>c</sub> to f <sub>c</sub> ) | < 5 %                                        |

| VGA Gain Range<br>w/Extended Range | $-24 dB \le A_V \le 0 dB$ $-30 dB \le A_V \le 6 dB$ | Group Delay Variation (f <sub>c</sub> to 1.75f <sub>c</sub> )    | < 8 %                                        |

| AFE THD                            | < 1.0 %                                             | Group Delay Adjustment                                           | ± 30 %                                       |

| AFE SNR                            | > 35 dB                                             | Boost                                                            | 0 dB to 15 dB at $f_c$                       |

| AFE Output Offset                  | < 5.0 mV                                            | CT Acquisition Time                                              | < 10 bytes                                   |

|                                    |                                                     | Power Dissipation                                                | < 250 mW                                     |

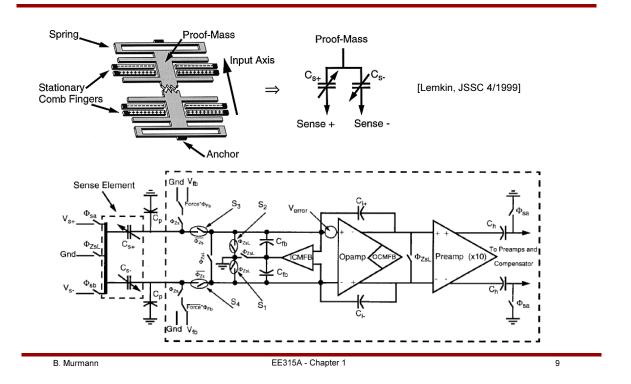

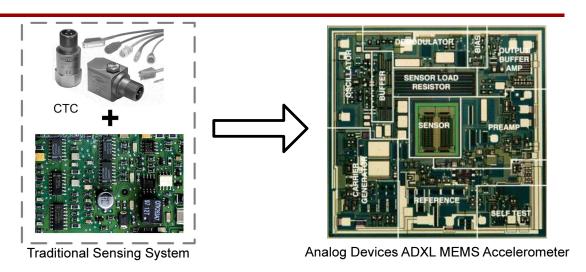

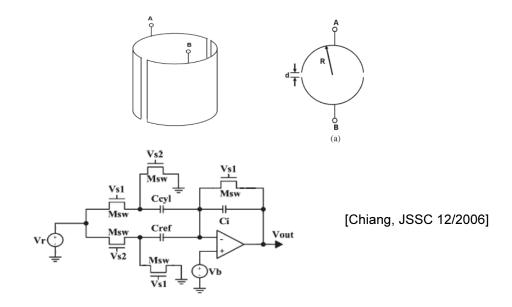

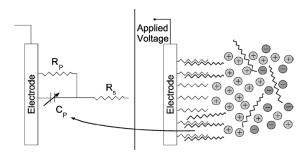

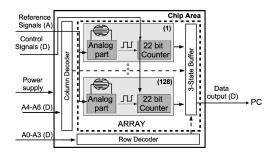

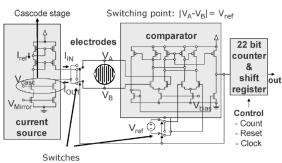

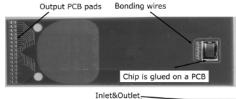

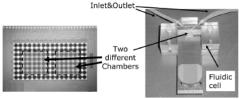

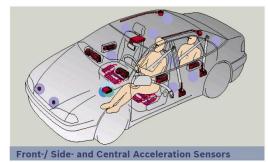

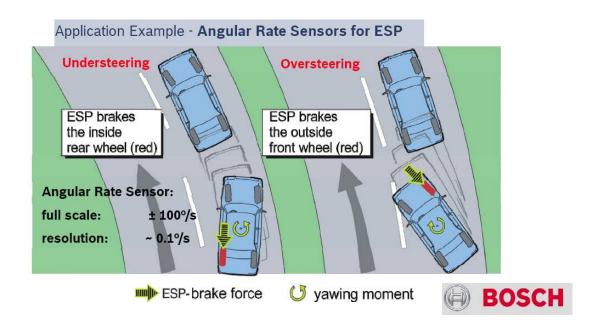

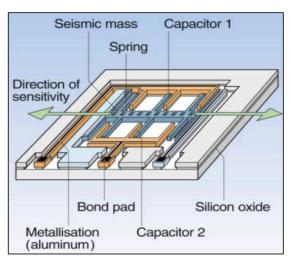

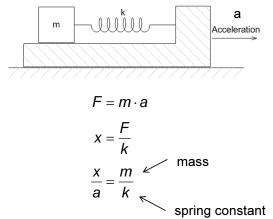

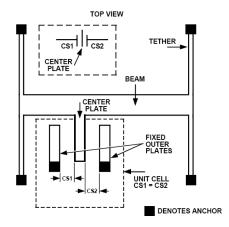

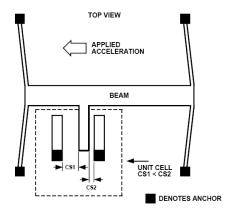

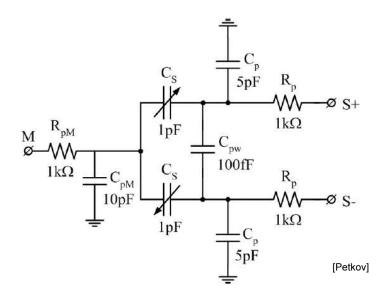

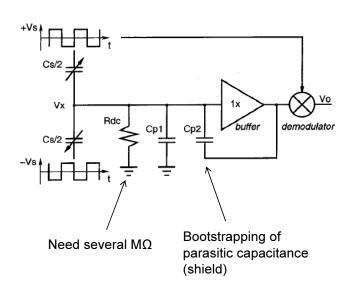

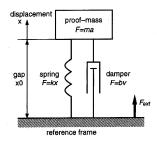

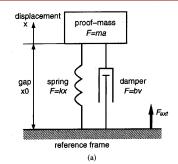

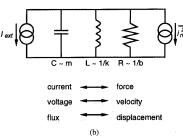

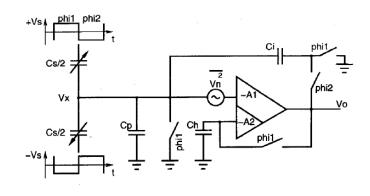

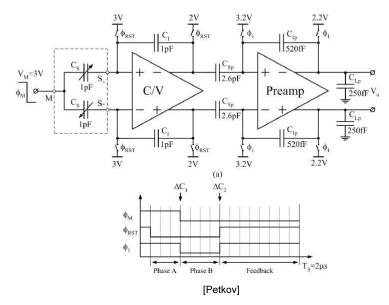

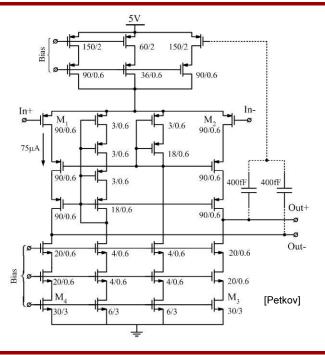

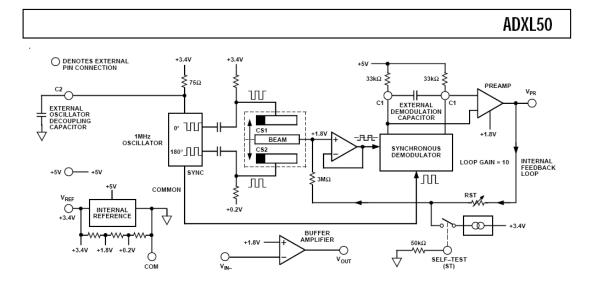

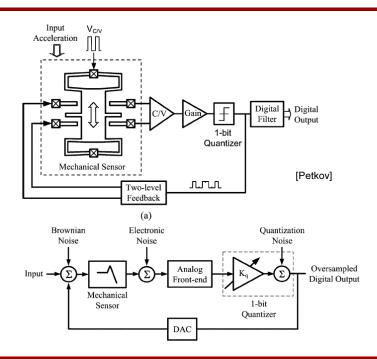

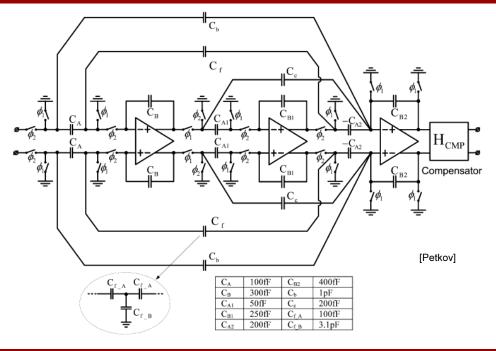

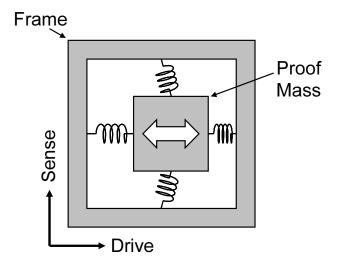

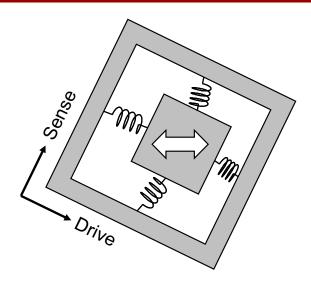

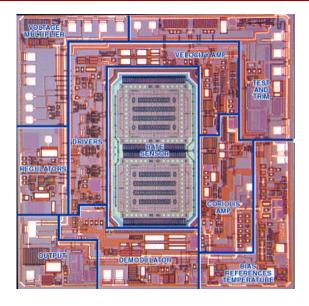

## **Example: MEMS Accelerometer**

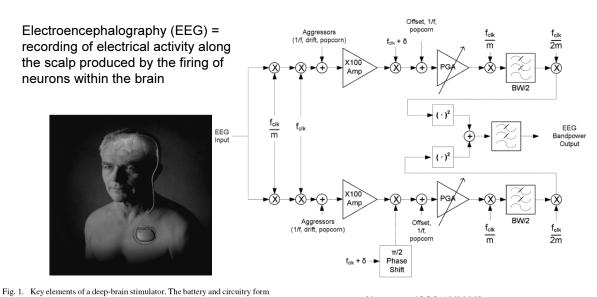

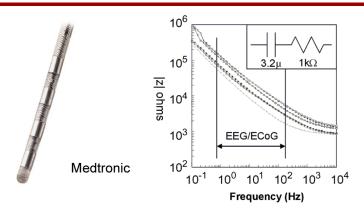

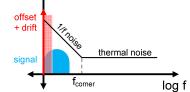

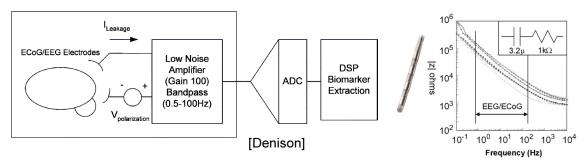

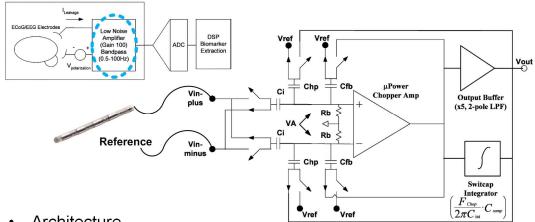

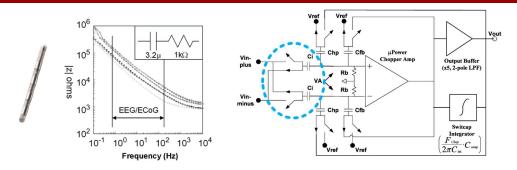

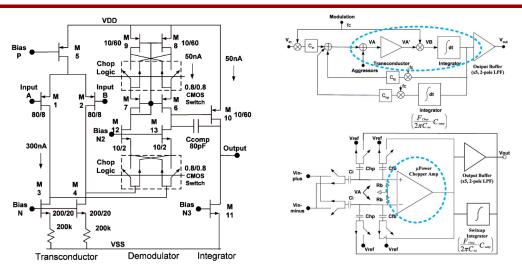

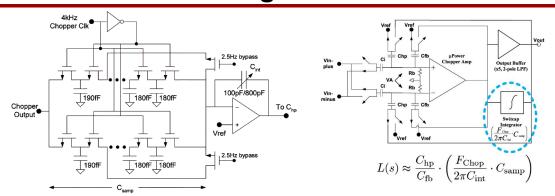

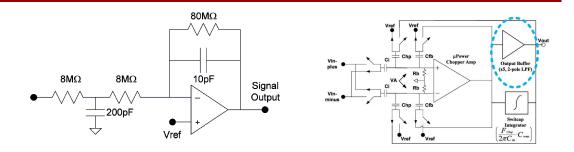

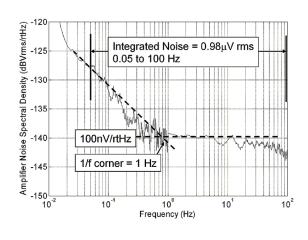

## **Example: Neural Field Potential Amplifier**

the IPG, which is implanted in the chest. The electrodes are placed into a specific neural circuit within the brain. Connections are made between the IPG and electrodes via a lead system placed in the neck.

[Avestruz, JSSC 12/2008]

#### **Course Objective**

- Acquire a thorough understanding of the basic principles, challenges and limitations in signal conditioning circuit design

- Focus on concepts that are unlikely to expire

- Preparation for further study of state-of-the-art "fine-tuned" realizations

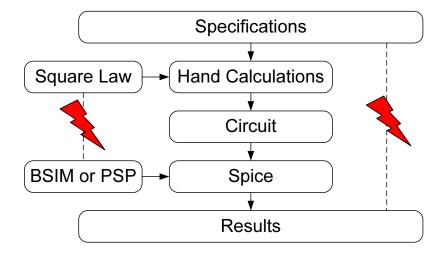

- Strategy

- Acquire basic intuition by studying a selection of commonly used circuit and design techniques

- Acquire depth through a design project that entails design, optimization and thorough characterization of a filter circuit in modern technology

B. Murmann EE315A - Chapter 1 11

#### Staff and Website

- Teaching assistants

- TBD

- · Administrative support

- Ann Guerra, Allen 207

- Lecture videos are provided on the web, but please come to class to keep the discussion intercative

- Web page: <a href="http://ccnet.stanford.edu/ee315a">http://ccnet.stanford.edu/ee315a</a>

- Check regularly, especially the "bulletin board" section

- Only enrolled students can register for conet access

- We synchronize the ccnet database with axess.stanford.edu manually, ~ once per day during first week of instruction

#### **Preparation**

- Course prerequisites

- EE214B or equivalent

- · Device physics and models

- · Transistor level analog circuits, elementary gain stages

- · Frequency response, feedback, noise

- Prior exposure to Spice, Matlab

- Basic signals and systems

- · Laplace and z-transforms

- Please talk to me if you are not sure if you have the required background

B. Murmann EE315A - Chapter 1 13

## **Analog Circuit Sequence**

#### **Assignments**

- Homework: (30%)

- Handed out on Thu, due following Thu after lecture (1 pm)

- Lowest HW score is dropped in final grade calculation

- Project: (30%)

- Design of a high performance filter circuit

- Architecture design using idealized components

- Implementation of a critical sub-block at the transistor level

- Project report in the format of an IEEE journal paper

- Final Exam (40%)

B. Murmann EE315A - Chapter 1 15

#### **Honor Code**

- Please remember you are bound by the honor code

- I will trust you not to cheat

- I will try not to tempt you

- But if you are found cheating it is very serious

- There is a formal hearing

- You can be thrown out of Stanford

- Save yourself and me a huge hassle and be honest

- For more info

- http://www.stanford.edu/dept/vpsa/judicialaffairs/guiding/pdf/ honorcode.pdf

#### **Tools and Technology**

- Primary tools

- Cadence Virtuoso Schematic Editor

- Cadence Virtuoso Analog Design Environment

- Cadence SpectreRF simulator

- You can use your own tools/setups "at own risk"

- · Getting started

- Read "remote connection" tutorial

- Read "virtuoso tutorial"

- All tool related documents are in the "CAD" section of the website

- EE315A Technology

- 0.18-μm CMOS

- BSIM3v3 models provided under /usr/class/ee315a/models

- Same models are used in EE214B

B. Murmann EE315A - Chapter 1 17

#### **Reference Books**

- Schauman, Xiao and Van Valkenburg, Design of Analog Filters, 2<sup>nd</sup> Edition, Oxford University Press, 2009

- Chan Carusone, Johns, Martin, Analog Integrated Circuit Design, 2<sup>nd</sup> Edition, Wiley, 2011

- Deliyannis, Sun, and Fidler, Continuous-Time Active Filter Design, CRC Press 1998, <a href="http://www.crcnetbase.com/isbn/9780849325731">http://www.crcnetbase.com/isbn/9780849325731</a>

- Gray, Hurst, Lewis and Meyer, Analysis and Design of Analog Integrated Circuits, 5th Edition, Wiley, 2008 (Chapter 12)

- Laker and Sansen, Design of Analog Integrated Circuits and Systems, McGraw-Hill, 1994

- Gregorian and Temes, Analog MOS Integrated Circuits for Signal Processing, Wiley, 1986

- Williams and Taylor, Electronic Filter Design Handbook, 3rd edition, McGraw-Hill, 1995

- Zverev, Handbook of Filter Synthesis, Wiley, 1967

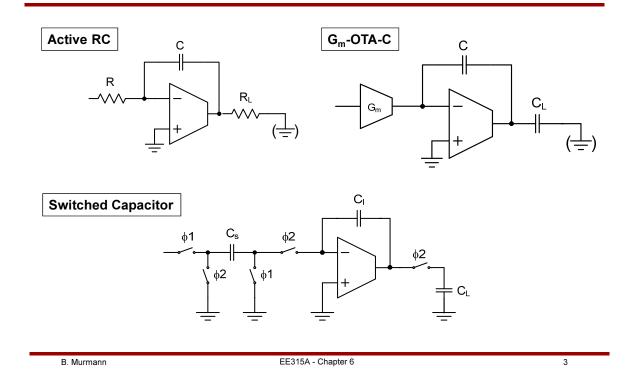

#### **Course Topics**

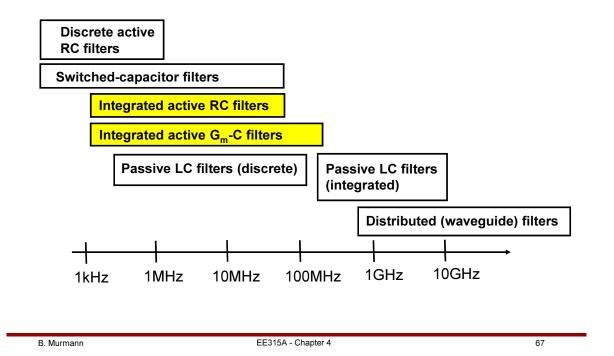

- Continuous time filters

- Biquad and ladder-based designs

- Active-RC and G<sub>m</sub>-C filters

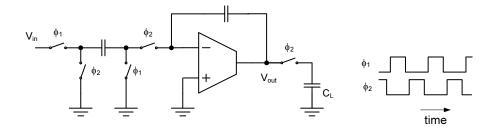

- · Switched capacitor filters

- Approximation errors

- Circuit simulation (periodic ac and noise analysis)

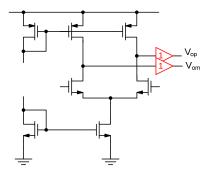

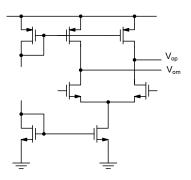

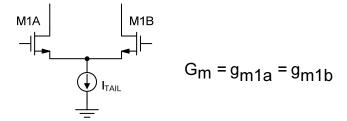

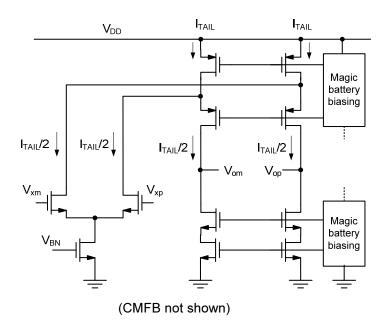

- Design of Operational Transconductance Ampilfiers (OTAs)

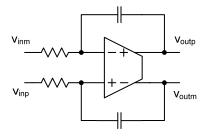

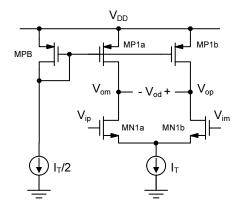

- Analysis and design of fully differential implementations

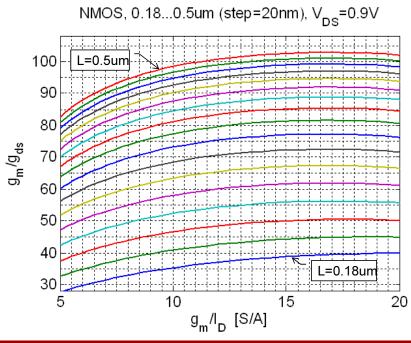

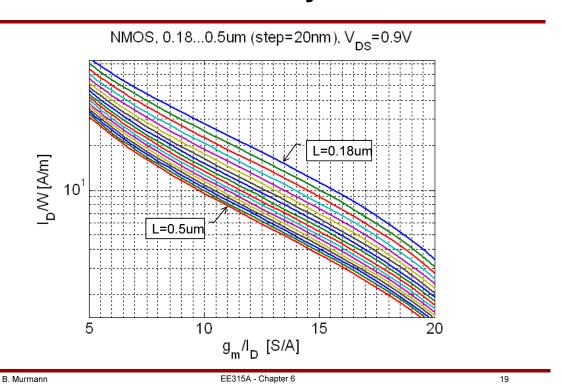

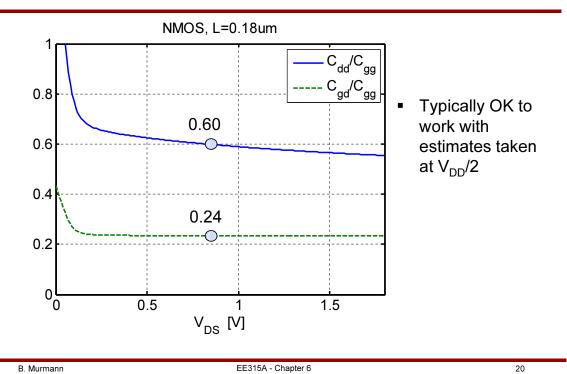

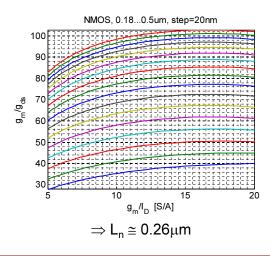

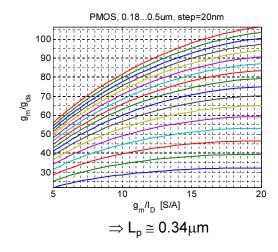

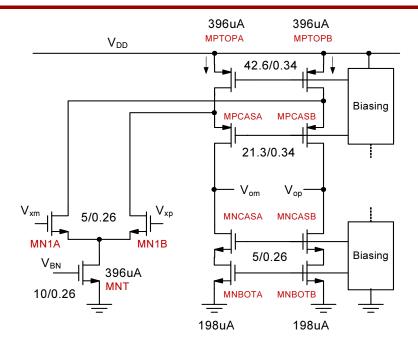

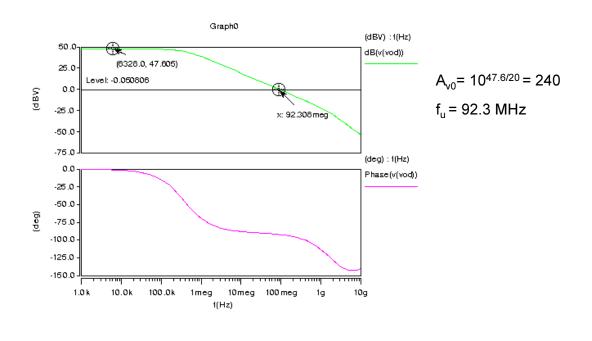

- G<sub>m</sub>/I<sub>D</sub>-based optimization (BW noise power dissipation)

- · Precision Analog Circuit Techniques

- Sensor interface examples

- Layout techniques

B. Murmann EE315A - Chapter 1 19

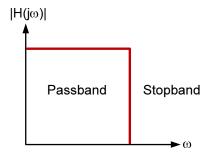

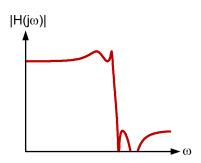

## The Filter Approximation Problem

- Ideal Filter

- Brick-wall characteristic

- Flat magnitude response in the passband

- Infinite attenuation in the stopband

- Practical filter

- Ripple in either or both the passband and stopband

- Limited attenuation in the stopband

#### Filter Design

- Ideal filters are non-causal or otherwise impractical

- No global optimization techniques known

- · In practice, chose from several known solutions

- Butterworth, Elliptic, Bessel, ...

- The overall goal of filter design is to approximate the ideal response by one that implements a reasonable compromise between filter complexity (number of poles and zeros) and approximation error

- Filter design, in general, requires a compromise between magnitude response, phase response, step response, complexity, etc.

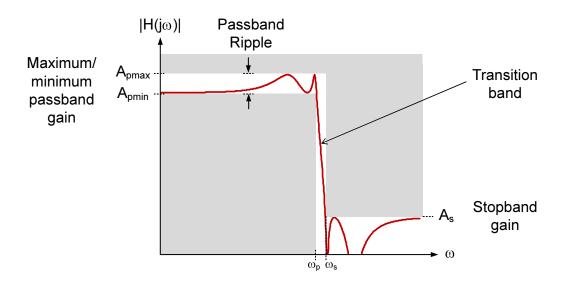

## **Lowpass Filter Template**

• Magnitude response is fully specified by  $A_{pmin},\,A_{pmax},\,A_{s},\,\omega_{p},\,\omega_{s}$

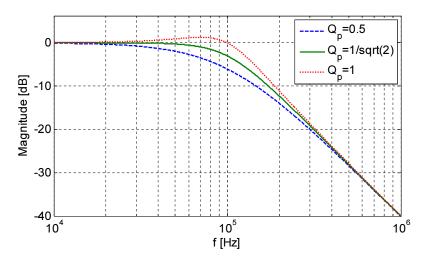

## **Second Order Lowpass Filter**

$$H(s) = \frac{1}{1 + \frac{s}{\omega_P Q_P} + \frac{s^2}{\omega_P^2}}$$

Magnitude response is "maximally flat" (no peaking) for Q<sub>P</sub> = 1/sqrt(2)

B. Murmann EE315A - Chapter 1 23

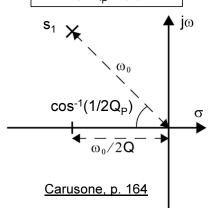

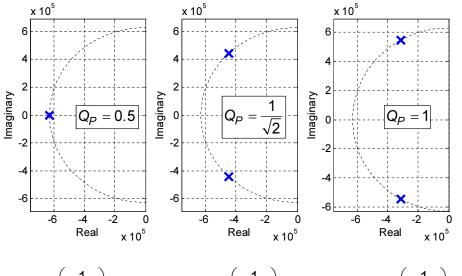

#### **Pole Positions**

· The poles are the roots of the denominator polynomial

$$1 + \frac{s}{\omega_0 Q_P} + \frac{s^2}{\omega_0^2} = 0$$

Location in the s-plane for

$$Q_p > 0.5$$

for

$$Q_P > 0.5$$

$s_{1,2} = -\frac{\omega_0}{2Q_P} \left( 1 \pm j \sqrt{4Q_P^2 - 1} \right)$

→ Complex Conjugate Poles

for

$$Q_P \le 0.5$$

$s_{1,2} = -\frac{\omega_0}{2Q} \left( 1 \pm \sqrt{1 - 4Q_P^2} \right)$

→ Real Poles

s<sub>o</sub> X

#### **Pole Positions**

$$\psi = cos^{-1} \Biggl(\frac{1}{2Q_P}\Biggr) = 0^\circ \qquad \quad \psi = cos^{-1} \Biggl(\frac{1}{2Q_P}\Biggr) = 45^\circ \qquad \psi = cos^{-1} \Biggl(\frac{1}{2Q_P}\Biggr) = 60^\circ$$

B. Murmann EE315A - Chapter 1 25

## **Improvements**

- A maximally flat response is great, but how can we make the roll-off steeper?

- Let's look at

- Imaginary zeros

- Increasing the filter order

- High-Q poles

- High-Q poles and imaginary zeros

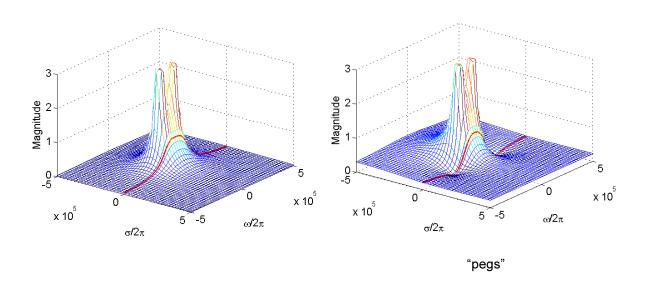

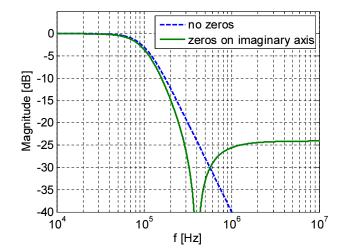

## **Adding Zeros on the Imaginary Axis**

#### **Bode Plot**

$$H(s) = \frac{1 + \left(\frac{s}{\omega_z}\right)^2}{1 + \frac{s}{\omega_p Q_p} + \left(\frac{s}{\omega_p}\right)^2}$$

$$\left| H(j\omega) \right|_{\omega \to \infty} = \left( \frac{\omega_P}{\omega_Z} \right)^2$$

• Steeper roll-off at the expense of reduced stopband rejection

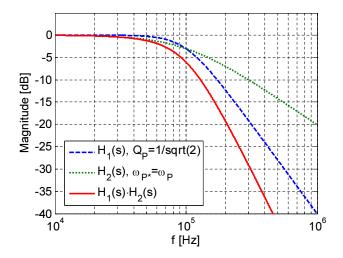

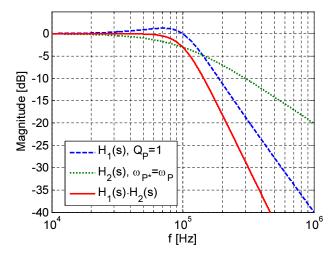

## **Adding Another Pole**

$$H(s) = H_1(s) \cdot H_2(s)$$

$$H_1(s) = \frac{1}{1 + \frac{s}{\omega_P Q_P} + \left(\frac{s}{\omega_P}\right)^2}$$

$$H_2(s) = \frac{1}{1 + \left(\frac{s}{\omega_{P^*}}\right)}$$

- · As expected, steeper roll-off, but transition is not all that sharp

- Can fix this issue by increasing Q<sub>P</sub> of H<sub>1</sub>(s)!

B. Murmann EE315A - Chapter 1 29

# Utilizing Peaking in H<sub>1</sub>(s)

$$\begin{aligned} H(s) &= H_1(s) \cdot H_2(s) \\ H_1(s) &= \frac{1}{1 + \frac{s}{\omega_P Q_P} + \left(\frac{s}{\omega_P}\right)^2} \\ H_2(s) &= \frac{1}{1 + \left(\frac{s}{\omega_{P^*}}\right)} \end{aligned}$$

- Win-win improvement

- Passband flat, roll-off steeper

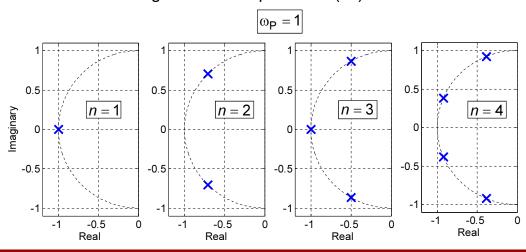

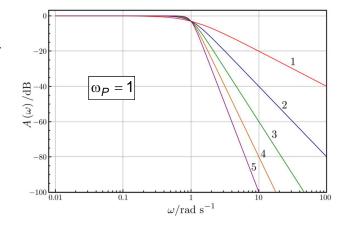

#### nth Order Generalization

Stephen Butterworth showed in 1930 that the magnitude response of an n<sup>th</sup> order maximally flat lowpass filter is given by

$$\left|H(j\omega)\right| = \frac{1}{\sqrt{1 + \left(\frac{\omega}{\omega_P}\right)^{2n}}}$$

This magnitude response is monotonically decreasing and satisfies

$$\left. \frac{d^k \left| H(j\omega) \right|}{d\omega^k} \right|_{\omega=0} = 0 \quad \text{ for } \quad 1 \le k \le 2n-1$$

· The corresponding pole locations can be determined using

$$\left|H(s)\right|^2 = H(s) \cdot H(-s) = \frac{1}{1 + \left(\frac{-s^2}{\omega_P^2}\right)^n} \qquad \frac{-s^2}{\omega_P^2} = \left(-1\right)^{1/n} = e^{\frac{j(2k-1)\pi}{n}} \qquad k = 1, 2, 3 ..., n$$

B. Murmann EE315A - Chapter 1 31

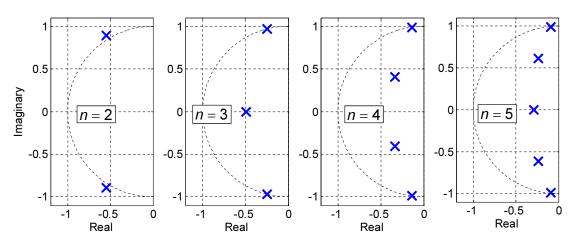

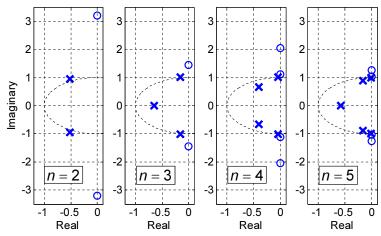

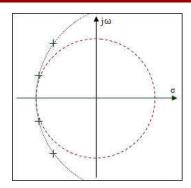

#### **Pole Locations**

- The poles lie equally spaced (in angle) on a circle in the s-plane centered at the origin with radius  $\omega_P$

- The LHP roots are taken to be the poles of H(s), while those in the RHP are regarded as the poles of H(-s)

## **Magnitude Response and Coefficients**

http://en.wikipedia.org/wiki/Butterworth filter

#### **Denominator Polynomial**

- 2  $s^2 + 1.4142s + 1$

- 3  $(s+1)(s^2+s+1)$

- 4  $(s^2 + 0.7654s + 1)(s^2 + 1.8478s + 1)$

- $(s + 1)(s^2 + 0.6180s + 1)(s^2 + 1.6180s + 1)$

- $(s^2 + 0.5176s + 1)(s^2 + 1.4142s + 1)(s^2 + 1.9319s + 1)$

- $(s + 1)(s^2 + 0.4450s + 1)(s^2 + 1.2470s + 1)(s^2 + 1.8019s + 1)$

- $(s^2 + 0.3902s + 1)(s^2 + 1.1111s + 1)(s^2 + 1.6629s + 1)(s^2 + 1.9616s + 1)$

B. Murmann EE315A - Chapter 1

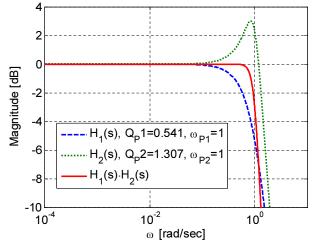

#### A Closer Look at n=4

$$H_{1}(s) = \frac{1}{1 + \frac{s}{\omega_{P1}Q_{P1}} + \left(\frac{s}{\omega_{P1}}\right)^{2}}$$

$$H_{2}(s) = \frac{1}{1 + \frac{s}{\omega_{P1}Q_{P1}} + \frac{s}{\omega_{P1}Q_{P1}}}$$

$H(s) = H_1(s) \cdot H_2(s)$

$$H_2(s) = \frac{1}{1 + \frac{s}{\omega_{P2}Q_{P2}} + \left(\frac{s}{\omega_{P2}}\right)^2}$$

$$\psi = cos^{-1} \left( \frac{1}{2Q_P} \right) \qquad Q_{P1} = \frac{1}{2 cos \left( 22.5^{\circ} \right)} = 0.541 \qquad Q_{P2} = \frac{1}{2 cos \left( 67.5^{\circ} \right)} = 1.307$$

$$Q_{P2} = \frac{1}{2\cos(67.5^{\circ})} = 1.307$$

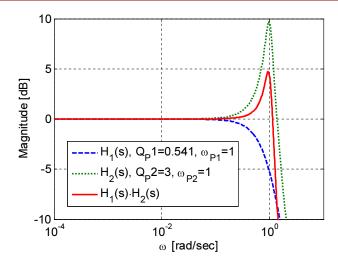

## Increasing Q<sub>P2</sub>

- Helps make the roll-off steeper, but introduces peaking

- We can try to alleviate this problem this by reducing  $\omega_{\text{P1}}$

B. Murmann EE315A - Chapter 1 35

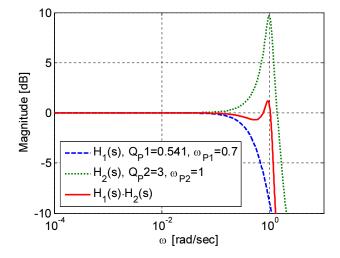

## Increased $Q_{P2}$ , Reduced $\omega_{P1}$

· This may not a bad choice of we can tolerate some peaking or ripple

B. Murmann

EE315A - Chapter 1

36

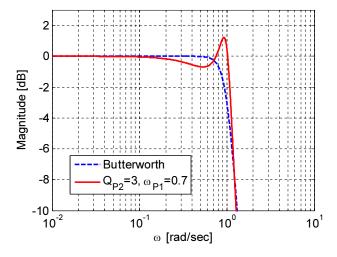

#### **Comparison with Original Butterworth**

How can we optimize this situation, i.e. minimize the transition band for a given tolerable peaking (or "ripple") in the passband?

B. Murmann EE315A - Chapter 1 37

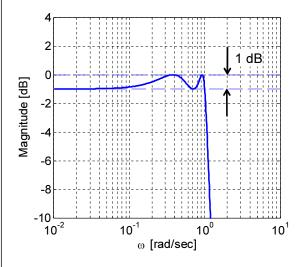

## **Chebyshev1 Filter Approximation**

- Fortunately someone has already figure this out

- The "Chebyshev1" filter approximation minimizes the error between the idealized response and the actual filter, with the passband ripple as a parameter (1dB for examples below)

#### **Matlab Code**

```

1; % Edge of passband

% Passband ripple in dB

p, k] = cheby1(4, R, wp, 's');

= zpk(z, p, k);

w = logspace(-2, 1, 1000);

[mag, phase] = bode(sys, w);

db = 20*log10(reshape(mag, 1, length(w)));

figure(1)

semilogx(w, db, 'linewidth', 2); hold on;

plot([w(1) w(end)], [0 0], '--');

plot([w(1) w(end)], [-1 -1], '--');

set(gca, 'fontsize', 14);

xlabel('\omega [rad/sec]')

ylabel('Magnitude [dB]');

axis([min(w) max(w) -10 4])

grid;

```

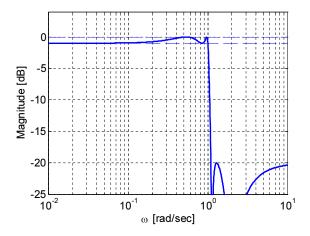

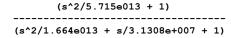

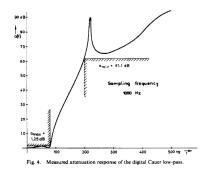

## **Elliptic (Cauer) Filter Approximation**

- The Elliptic filter approximation combines our previous ideas and adds imaginary zeros to sharpen the transition band

- This approximation has the passband ripple and stopband attenuation as a parameter (1dB and 20dB, respectively, for example below)

## **Matlab Code**

```

wp = 1; % Edge of passband

Rp = 1; % Passband ripple in dB

Rs = 20; % Stopband attenuation

[z, p, k] = ellip(4, Rp, Rs, wp, 's');

```

B. Murmann EE315A - Chapter 1 41

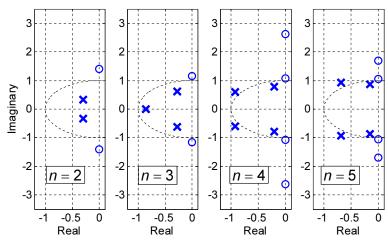

## **Chebyshev2 Filter Approximation**

- No ripple in the passband, but finite stopband attenuation and ripple due to imaginary zeros

- This approximation takes the stopband attenuation as a parameter (20 dB in the example below)

B. Murmann

EE315A - Chapter 1

42

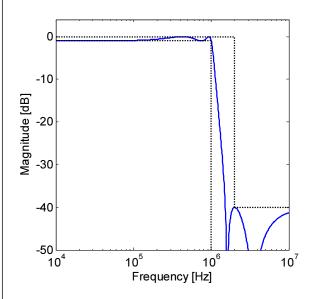

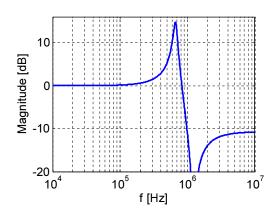

## **Design Example**

```

wp=2*pi*1e6; % Passband edge

ws=2*pi*2e6; % Stopband edge

Rp=1; % Passband ripple

Rs=40; % Stopband attenuation

% Determine required order and synthesize

[N, wp] = ellipord(wp, ws, Rp, Rs, 's');

[z, p, k] = ellip(N, Rp, Rs, wp, 's');

sys = zpk(z, p, k);

f = logspace(4, 7, 1000);

[mag, phase] = bode(sys, 2*pi*f);

db = 20*log10(reshape(mag, 1, length(f)));

figure(1)

semilogx(f, db, 'linewidth', 2);

```

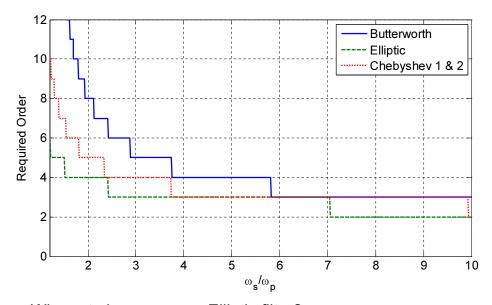

# Filter Order for $R_p=1dB$ , $R_s=40dB$

Why not always use an Elliptic filter?

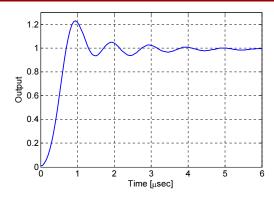

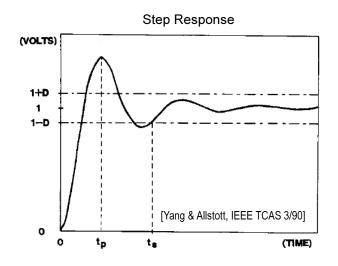

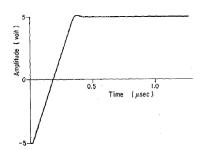

## **Step Response of Design Example**

- Overshoot and other forms of pulse deformation can be problematic in some systems

- Consider e.g. oscilloscopes, pulse-based data links, etc.

- The pulse deformation is mostly due to the fact that different frequency components pass the filter with different time delays

- This is called phase distortion

B. Murmann EE315A - Chapter 1 45

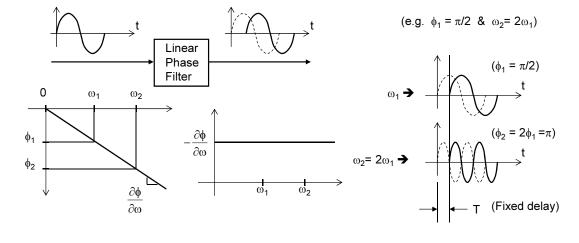

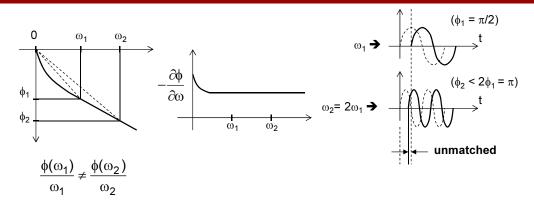

## **Phase Distortion (1)**

· Consider a filter with transfer function

$$H(j\omega) = |H(j\omega)| e^{j\phi(\omega)}$$

Apply two sine waves at different frequencies

$$v_{in}(t) = A_1 \sin(\omega_1 t) + A_2 \sin(\omega_2 t)$$

## **Phase Distortion (2)**

• Assuming that the difference between  $|H(j\omega_1)|$  and  $|H(j\omega_2)|$  is small, the "shape" of the time-domain output signal will be preserved as long as

$$\frac{\phi(\omega_1)}{\omega_1} - \frac{\phi(\omega_2)}{\omega_2} = 0$$

· This condition is satisfied for

$$\phi(\omega) = T \cdot \omega \qquad T = constant$$

A filter with this characteristic is called "linear phase"

B. Murmann EE315A - Chapter 1 47

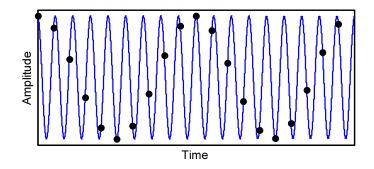

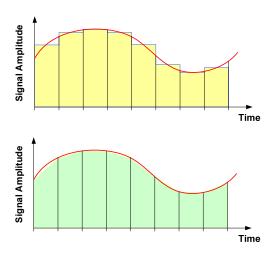

## **Delay with Linear Phase**

[U. Moon]

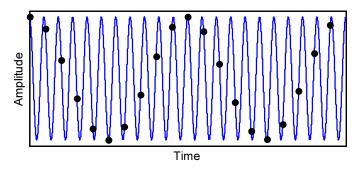

## **Delay with Nonlinear Phase**

- Phase distortion occurs whenever the phase is nonlinear, i.e. the derivative of the phase is not constant

- The (negative) derivative of the phase is also called "group delay" or  $\tau_{\alpha}$

- Note that for a linear phase filter, we have  $\tau_{\rm g}$  =  $\tau_{\rm d}$  = const.

B. Murmann EE315A - Chapter 1 49

## **Group Delay**

- The name group delay (or envelope delay) comes from the fact that it specifies the delay experienced by a narrow-band "group" of sinusoidal components within some Δω around a carrier w<sub>c</sub>

- The width of Δω is limited to a range over which dφ/dω is approximately constant

- For example, for an AM modulated signal, the carrier experiences a delay of  $\tau_p$  (phase delay) and the envelope sees a delay of  $\tau_q$  (group delay)

- For a proof, see e.g.

- http://ccrma-www.stanford.edu/~jos/fp2/Derivation\_Group\_Delay\_Modulation.html

- In this course, we are using the term group delay merely to refer

-dφ/dω (and not to argue about group delay per se)

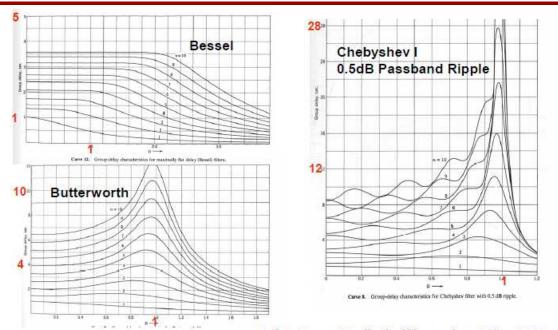

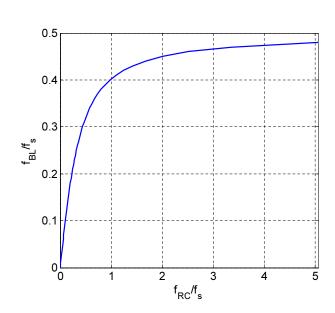

## **Bessel Filter Approximation**

- · All poles

- · Poles are relatively low Q

- Maximally flat group delay

- Poor stopband attenuation

| Order (N) | Re Part (-σ) | Im Part (±jω) |

|-----------|--------------|---------------|

| 1         | 1.0000       |               |

| 2         | 1.1030       | 0.6368        |

| 3         | 1.0509       | 1.0025        |

| 3         | 1.3270       | 1.0025        |

| 4         | 1.3596       | 0.4071        |

| 4         | 0.9877       | 1.2476        |

|           | 1.3851       | 0.7201        |

| 5         | 0.9606       | 1.4756        |

|           | 1.5069       | 1.4/00        |

http://www.rfcafe.com/references/electrical/bessel-poles.htm

B. Murmann EE315A - Chapter 1 51

## **Group Delay Comparison**

Ref: A. Zverev, Handbook of filter synthesis, Wiley, 1967.

B. Murmann

EE315A - Chapter 1

52

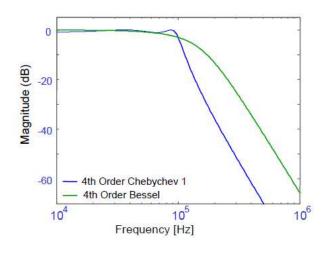

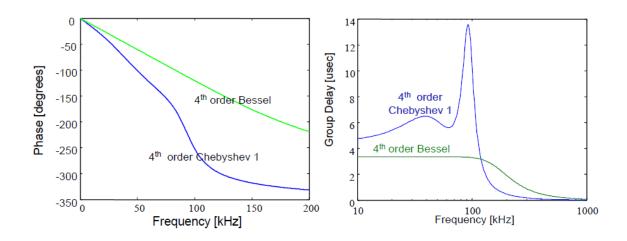

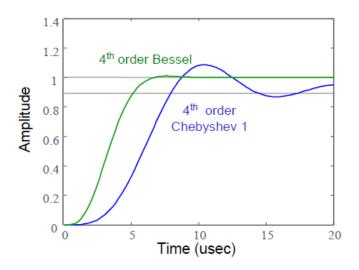

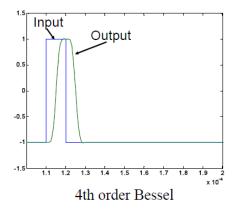

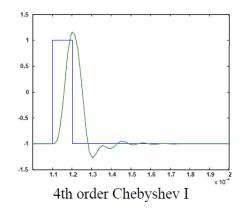

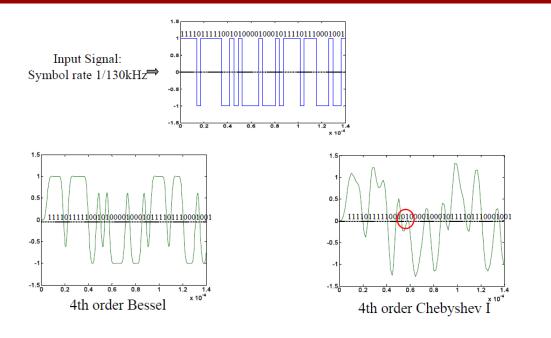

## Comparison: Bessel vs. Chebyshev1

- Lowpass filters with 100 kHz passband

- Both filters are 4th order with the same -3 dB frequency

- Passband ripple of 1dB for Chebyshev I

[H. Khorramabadi]

B. Murmann EE315A - Chapter 1 53

## **Phase and Group Delay**

B. Murmann

EE315A - Chapter 1

5

## **Step Response**

B. Murmann EE315A - Chapter 1 55

## **Pulse Response**

## **Intersymbol Interference**

B. Murmann

EE315A - Chapter 1

57

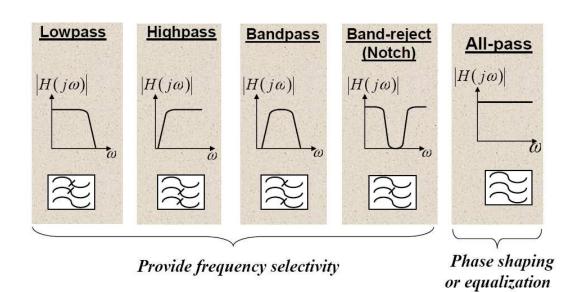

# **Beyond Lowpass Filtering**

[H. Khorramabadi]

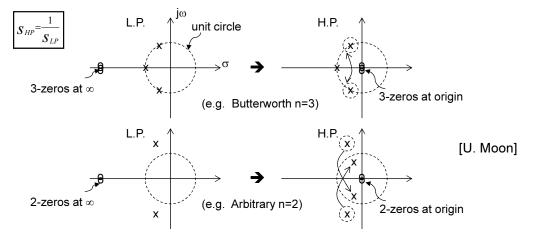

#### **Lowpass to Highpass Transformation**

The s-domain poles and zeros simply become inverted. As shown by the examples, zeros at infinity move to the origin, and finite-valued poles become |1/pole<sub>LP</sub>| in magnitude and become conjugates (flips between quadrant II & III). The mapping boundary is the *unit circle*.

B. Murmann

EE315A - Chapter 1

59

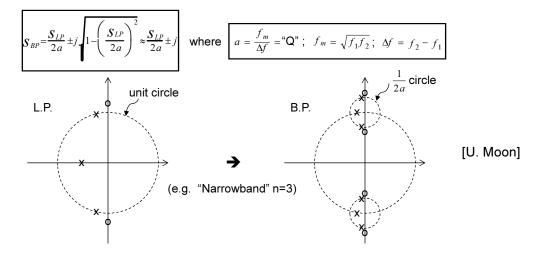

## **Lowpass to Bandpass Transformation**

For a "narrowband" approximation, the s-domain poles and zeros simply become replicated at  $\pm j\omega$  with a smaller unit circle of radius 1/2a. To realize a wideband filter, use a cascade of highpass and lowpass filters.

#### **Biquad Filter Realization**

#### Boris Murmann Stanford University murmann@stanford.edu

Copyright © 2013 by Boris Murmann

B. Murmann EE315A - Chapter 2

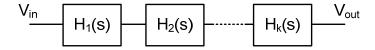

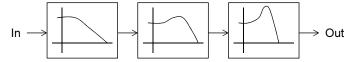

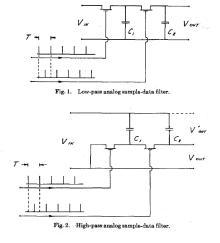

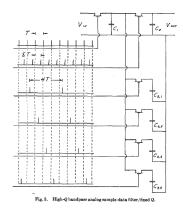

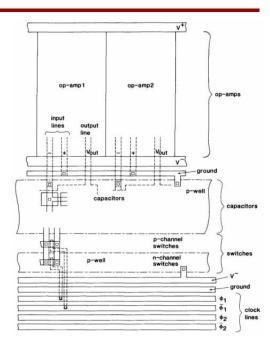

## **Architectural Options for High-Order Filters**

Cascades of (active) first and second-order sections

Ladder filters (passive or emulated using active components)

- · Specialized architectures, typically emphasizing low complexity

- Watch out for sensitivity issues (more later)

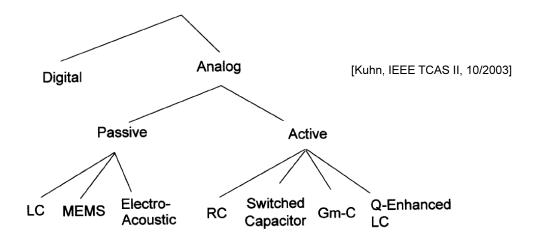

## **Building Block Options**

B. Murmann EE315A - Chapter 2

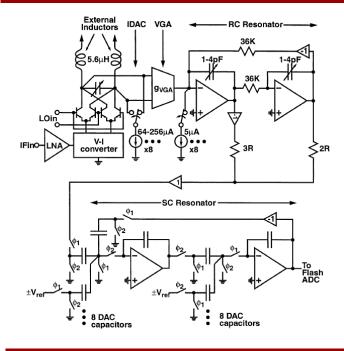

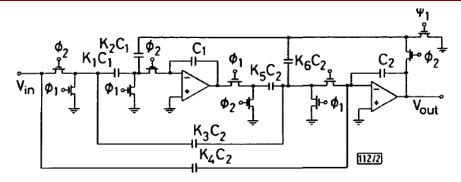

## **Example**

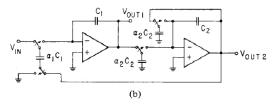

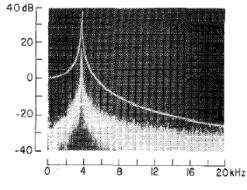

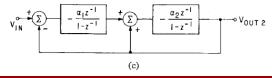

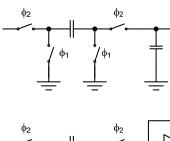

- An interesting filter that combines three different approaches

- Passive LC

- Active RC

- Switched capacitor

[Schreier, JSSC 12/2002]

#### The Challenge

- · Way too many options available

- Deciding on which implementation is "best" may only be possible once several options have been thoroughly compared

- In terms of both first-order properties and second-order nonidealities, which aren't always easy to understand

- The following discussion starts from the most basic ideas, and derives some of the most popular solutions used in practice

- For now, we will focus on the realization of second order sections, and cover ladder-based implementations in chapter 3

- The treatment of second order sections will help us understand why we may ultimately want to go for a ladder implementation

B. Murmann EE315A - Chapter 2

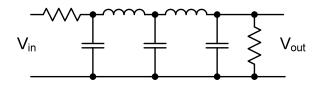

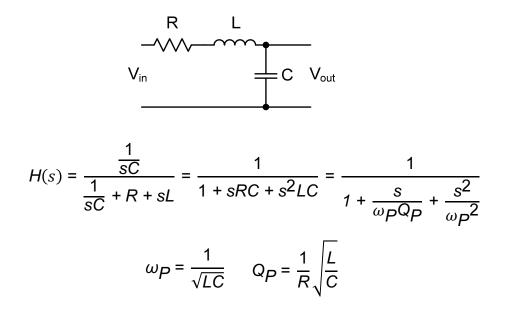

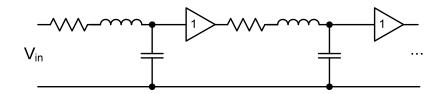

## **Passive LC Lowpass Filter**

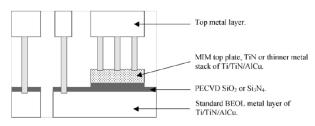

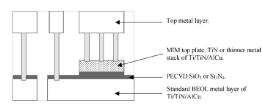

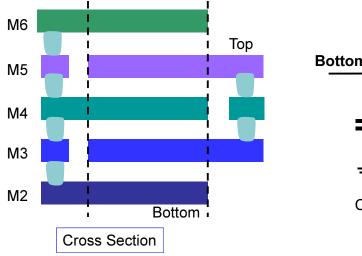

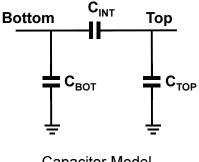

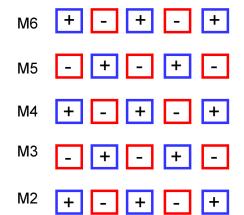

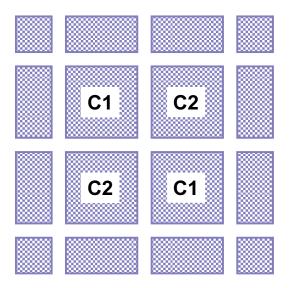

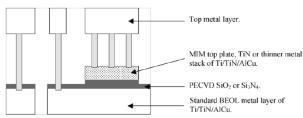

#### **On-Chip Capacitors**

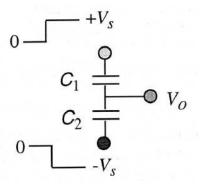

#### Metal-Insulator-Metal (MIM)

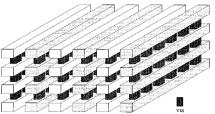

# **Vertical Parallel Plate (VPP)**

[Ng, Trans. Electron Dev., 7/2005]

[Aparicio, JSSC 3/2002]

- Typically 1-2 fF/μm<sup>2</sup> (10-20 fF/μm<sup>2</sup> for advanced structures)

- For 1 fF/μm<sup>2</sup>, a 10 pF capacitor occupies ~100μm x 100μm

- Both MIM and VPP capacitors have good electrical properties

- Mostly worry about parasitic caps

- Series and parallel resistances are often not a concern

B. Murmann

EE315A - Chapter 2

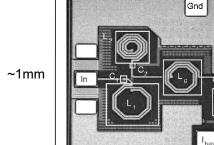

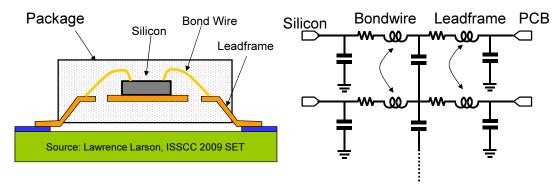

## **On-chip Inductors**

[Bevilacqua, ISSCC 2004]

- Many nonidealities, hard to model, low "Q"

- Area inefficient, typically achieve L < 10nH

- Sometimes bondwires are used as an alternative, L ~ 1nH/mm

EE315A - Chapter 2 B. Murmann 8

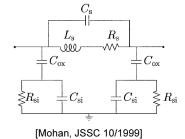

### **Inductor Quality Factor**

In general

$$Y = \frac{1}{R + iX(\omega)}$$

$\Rightarrow$   $Q = \frac{X(\omega)}{R}$

$$Y = \frac{1}{R_s + j\omega L}$$

$\Rightarrow$   $Q_L = \frac{\omega L}{R_s}$

On-chip inductors typically achieve Q<sub>L</sub> < 5-10 at our frequencies of interest (EE315A)

B. Murmann

EE315A - Chapter 2

٥

### **LC Lowpass Example**

• Assuming that we (very generously) use C=100pF, L=10nH

$$\omega_P = \frac{1}{\sqrt{LC}} = 2\pi \cdot 160MHz$$

- Integrated passive LC filters become practical for f > 200-500MHz

- For our LC lowpass, if we assume R=Rs (i.e. we only use the parasitic resistor of the inductor, no explicitly added resistance)

$$Q_{L} = \frac{\omega L}{R_{s}} \qquad Q_{P} = \frac{1}{R} \sqrt{\frac{L}{C}} = \frac{Q_{L}}{\omega L} \sqrt{\frac{L}{C}} = Q_{L} \frac{\omega_{P}}{\omega}$$

• This means that at  $\omega$ = $\omega_P$ , the magnitude peaking that we can get is limited to the Q<sub>L</sub> of the inductor (~5-10); not all that great

#### **Summary**

- On-chip capacitors are great, even though they're usually not as large as we would like them to be

- On-chip inductors tend to be avoided whenever possible, and are typically not useful in a filter with poles at frequencies below < 200-500 MHz</li>

- The solution to this problem is to "simulate" the inductors using active components

B. Murmann EE315A - Chapter 2 11

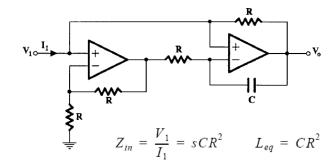

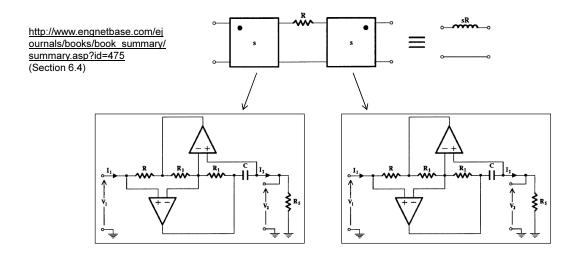

### **Gyrators**

Gyrators are "active inductors"

T. L. Deliyannis, J. K. Fidler and Y. Sun, Continuous-Time Active Filter Design

http://www.engnetbase.com/ej ournals/books/book summary/ summary.asp?id=475 (Section 3.5)

- The above circuit is not all that useful for our lowpass filter; we need a "floating" inductor

- Don't want the inductance to be ground referenced

### **Floating Gyrator**

- Floating gyrators are pretty complex (and sensitive to parasitics)

- There must be a better way to solve this problem...

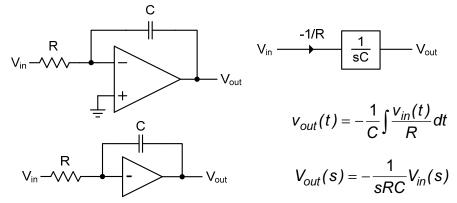

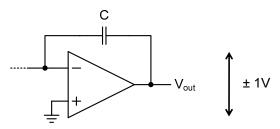

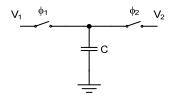

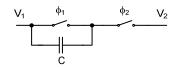

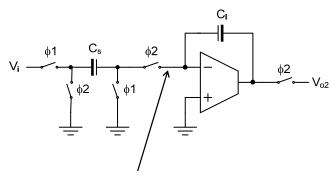

### Integrators

- A circuit that we can build without much sweat is an active integrator, e.g. using an op-amp

- Many more options exist (more later)

- Assuming the availability of an ideal op-amp, we have

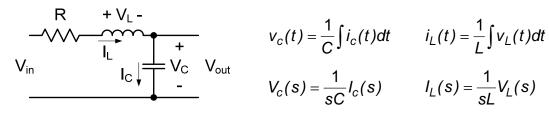

#### **State-Space Realization**

#### State variables

(integrator outputs)

$$v_c(t) = \frac{1}{C} \int i_c(t) dt$$

$$i_L(t) = \frac{1}{L} \int v_L(t) dt$$

$$V_c(s) = \frac{1}{sC}I_c(s)$$

$$I_L(s) = \frac{1}{sL}V_L(s)$$

$$V_C = \frac{1}{sC}I_C = \frac{1}{sC}I_L = V_{out}$$

$$I_L = \frac{1}{sL}V_L = \frac{1}{sL}(V_{in} - I_LR - V_{out})$$

B. Murmann

EE315A - Chapter 2

15

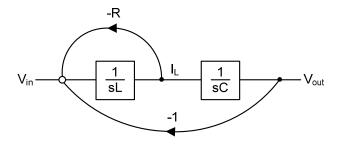

### **Block Diagram**

- Looks promising, but the problem with this realization is that the first integrator takes a voltage at the input and produces a current at the output

- We need the opposite if we want to realize the circuit with an RC integrator

EE315A - Chapter 2 B. Murmann

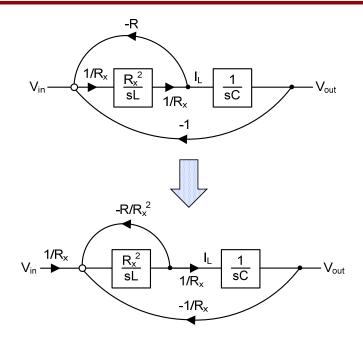

### **Modified (Equivalent) Block Diagrams**

B. Murmann EE315A - Chapter 2 17

### **Implementation**

- · One remaining issue is that the transfer function is inverted

- We could fix that (if needed) using a fourth op-amp

- Or by pushing A2 toward the input, and utilizing both its inverting and non-inverting input

- The latter trick is used in the so-called KHN biquad

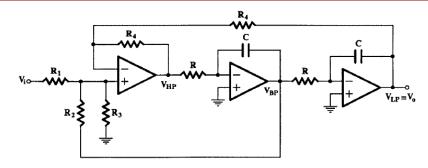

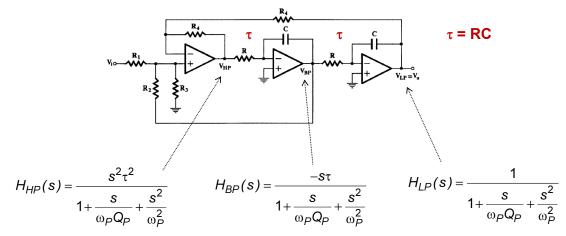

#### **KHN Biquad**

W.J. Kerwin, L.P. Huelsman, R.W Newcomb, "State-Variable Synthesis for Insensitive Integrated Circuit Transfer Functions," *IEEE JSSC*, vol.2, no.3, pp. 87-92, Sep. 1967.

http://www.engnetbase.com/ejournals/books/book\_summary/summary.asp?id=475 (Section 4.9)

$$\frac{V_O}{V_i} = \frac{V_{LP}}{V_i} = \frac{K'}{1 + \frac{s}{\omega_O Q} + \frac{s^2}{\omega_O 2}}$$

$$\omega_O = \frac{1}{RC}$$

$$Q = \frac{R_1 R_2 + R_1 R_3 + R_2 R_3}{2R_1 R_3}$$

$$K' = \frac{2R_2 R_3}{R_1 R_2 + R_1 R_3 + R_2 R_3} = \frac{R_2}{R_1} \cdot \frac{1}{Q}$$

### **Highpass and Bandpass Output**

An interesting feature of some biquads (including the HKN) is that they provide additional highpass and bandpass outputs for "free"

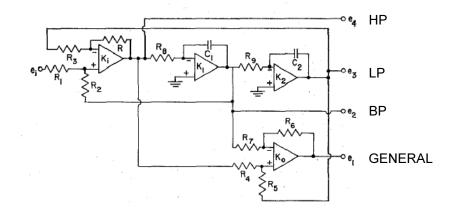

### The General KHN Biquad

$$H_{GENERAL}(s) = \frac{b_2 s^2 + b_1 s + b_0}{1 + \frac{s}{\omega_P Q_P} + \frac{s^2}{\omega_P^2}}$$

Implements arbitrary poles and zeros

B. Murmann EE315A - Chapter 2 2

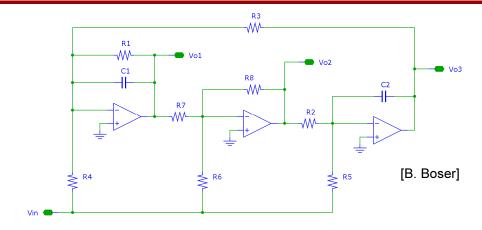

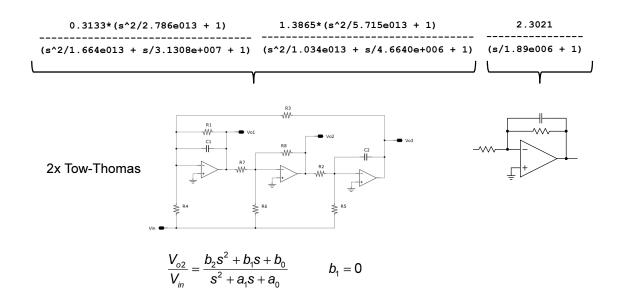

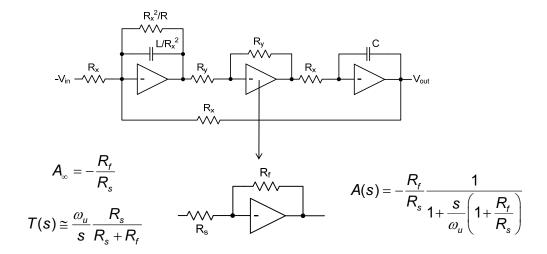

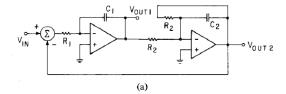

# **Tow-Thomas Biquad**

P. E. Fleischer and J. Tow, "Design Formulas for biquad active filters using three operational amplifiers," Proc. IEEE, vol. 61, pp. 662-3, May 1973.

General biquad using only three op-amps

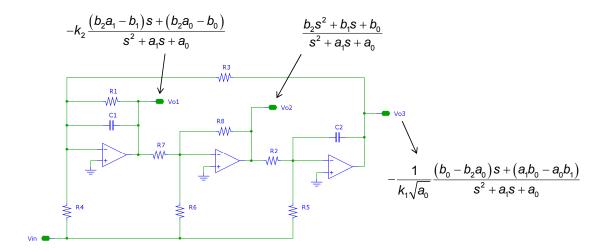

#### **Tow-Thomas Transfer Functions**

$$\frac{V_{o1}}{V_{in}} = -k_2 \frac{\left(b_2 a_1 - b_1\right) s + \left(b_2 a_0 - b_0\right)}{s^2 + a_1 s + a_0}$$

$$\frac{V_{o2}}{V_{in}} = \frac{b_2 s^2 + b_1 s + b_0}{s^2 + a_1 s + a_0}$$

$$\frac{V_{o3}}{V_{in}} = -\frac{1}{k_1 \sqrt{a_0}} \frac{\left(b_0 - b_2 a_0\right) s + \left(a_1 b_0 - a_0 b_1\right)}{s^2 + a_1 s + a_0}$$

- V<sub>o2</sub>/V<sub>in</sub> implements a general biquad section with arbitrary poles and zeros

- V<sub>o1</sub>/V<sub>in</sub> and V<sub>o3</sub>/V<sub>in</sub> realize the same poles but are limited to at most one finite zero

B. Murmann EE315A - Chapter 2 23

### **Tow-Thomas Design Equations**

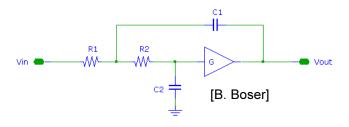

### Sallen-Key LPF

R.P. Sallen and E. L. Key "A Practical Method of Designing RC Active Filters." *IRE Trans. Circuit Theory*, Vol. CT-2, pp. 74-85, 1955

- Single gain element

– typically 1 ≤ G ≤ 10

- · Poles only, no zeros

- Sensitive to parasitic capacitances

- Versions exist for HP, BP, ...

- http://en.wikipedia.org/wiki/Sallen\_Key\_filter

$$H(s) = \frac{G}{1 + \frac{s}{\omega_p Q_p} + \frac{s^2}{\omega_p ^2}}$$

$$\omega_{p} = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}}$$

$$Q_p = \frac{\omega_p}{\frac{1}{R_1 C_1} + \frac{1}{R_2 C_1} + \frac{1 - G}{R_2 C_2}}$$

B. Murmann EE315A - Chapter 2 25

## **Tow-Thomas or Sallen-Key?**

- Suppose we now wanted to realize a biquad that has poles only

- · Should we use a Tow-Thomas or Sallen-Key realization?

- Clearly, from the perspective of complexity, we would probably want to go for Sallen-Key

- Unfortunately, the Sallen-Key realization comes with disadvantages in terms of sensitivity to component variations

- Let's take a closer look...

#### **Sensitivity**

The sensitivity of any variable y to any parameter x is defined as (See e.g. Gray & Meyer, Section 4.2)

$$S_{x}^{y} = \lim_{\Delta x \to 0} \left( \frac{\Delta y / y}{\Delta x / x} \right) = \frac{x}{y} \lim_{\Delta x \to 0} \frac{\Delta y}{\Delta x} = \frac{x}{y} \frac{\partial y}{\partial x}$$

In order to relate fractional changes in y to fractional changes in x we can then write

$$\frac{\Delta y}{y} \cong S_x^y \frac{\Delta x}{x}$$

Example

$$S_x^y = 10$$

$\frac{\Delta x}{x} = 2\%$   $\Rightarrow \frac{\Delta y}{y} \cong 20\%$

Common sense: sensitivity is a first order approximation, accurate only for "small" errors

B. Murmann EE315A - Chapter 2 2

## **Parameter Variations (1)**

Discrete resistors and capacitors

- · Come in many different shapes and sizes and accuracies

- E.g. metal film resistors, ~0.1% accurate, 5ppm/°C

- E.g. C0G dielectric capacitors, 2% accurate, very small temperature dependence

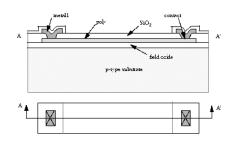

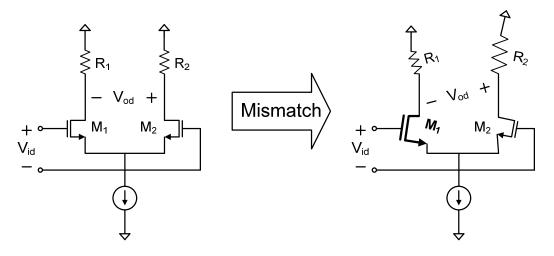

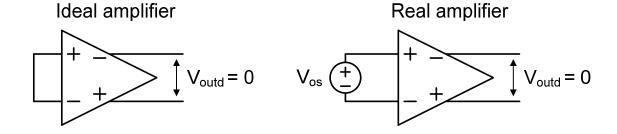

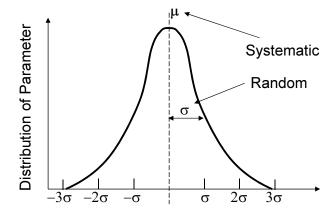

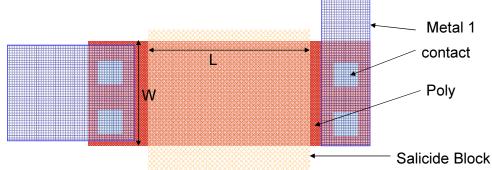

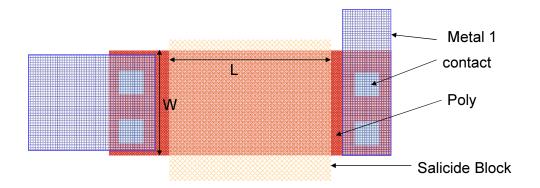

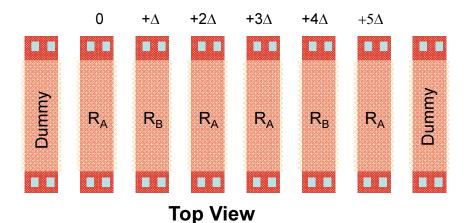

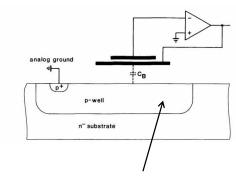

### **Parameter Variations (2)**

Integrated resistors and capacitors

Poly resistor

MIM Capacitor

- Important to distinguish between

- Global process variations → On the order of +/- 20%!

- Device-to-device mismatch → On the order of 1% or less

B. Murmann

EE315A - Chapter 2

29

### **Sensitivity to Global Variations**

#### **Tow-Thomas**

$$\omega_P = \sqrt{\frac{R_8}{R_2 R_3 R_7 C_1 C_2}} \propto \frac{1}{RC}$$

$$\omega_P = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}} \propto \frac{1}{RC}$$

$$Q_P=\omega_P R_1 C_1 \propto 1$$

$$Q_{P} = \frac{\omega_{P}}{\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{1}} + \frac{1-G}{R_{2}C_{2}}} \propto 1$$

- Q<sub>P</sub> is independent of global variations in both realizations

- Assuming all R and C use the same device structure, respectively

- ω<sub>P</sub> varies with the RC product of the components

### Sensitivity to Mismatch (Sallen-Key)

$$\begin{split} \omega_{P} &= \frac{1}{\sqrt{R_{1}C_{1}R_{2}C_{2}}} \\ \omega_{P} &= \frac{1}{\sqrt{R_{1}C_{1}R_{2}C_{2}}} \\ Q_{P} &= \frac{\omega_{P}}{\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{1}} + \frac{1-G}{R_{2}C_{2}}} \\ S_{G}^{Q_{P}} &= -S_{C_{2}}^{Q_{P}} = -\frac{1}{2} + Q_{P}\sqrt{\frac{R_{2}C_{2}}{R_{1}C_{1}}} \\ S_{C_{1}}^{Q_{P}} &= -S_{C_{2}}^{Q_{P}} = -\frac{1}{2} + Q_{P}\left(\sqrt{\frac{R_{1}C_{2}}{R_{2}C_{1}}} + \sqrt{\frac{R_{2}C_{2}}{R_{1}C_{1}}}\right) \\ S_{G}^{Q_{P}} &= Q_{P}G\sqrt{\frac{R_{1}C_{1}}{R_{2}C_{2}}} \end{split}$$

Sensitivity depends on Q<sub>P</sub> and "component spread" i.e. the ratios of the resistors and capacitors, respectively

B. Murmann EE315A - Chapter 2 31

### Example (1)

- Want to design a Sallen-Key filter with Q<sub>P</sub>=10

- Choice 1: All R and C are the same  $\Rightarrow$  G = 3 -(1/Q<sub>P</sub>) = 2.9

- Very nice from the perspective of component spread, but bad for sensitivity, e.g.

$$S_{R_1}^{Q_P} = -S_{R_2}^{Q_P} = -\frac{1}{2} + Q_P = 9.5$$

- · Choice 2: Reduce sensitivity by accepting large component spread

- Can show that G=1 is a good choice

- See e.g. <a href="http://www.maxim-ic.com/appnotes.cfm/an\_pk/738">http://www.maxim-ic.com/appnotes.cfm/an\_pk/738</a>

- Note: The expression for  $S_{\rm K}^0$  is incorrect this application note (R<sub>3</sub> and R<sub>1</sub> should be interchanged in this expression to match the result from slide 36)

### Example (2)

• For G=1, we have

$$Q_{P} = \frac{\omega_{P}}{\frac{1}{R_{1}C_{1}} + \frac{1}{R_{2}C_{1}}}$$

and it follows that

$$S_{R_1}^{Q_P} = -S_{R_2}^{Q_P} = -\frac{1}{2} + \frac{R_2}{R_1 + R_2} = 0$$

for  $R_1 = R_2$

· Unfortunately, in this case

$$\frac{C_1}{C_2} = 4Q_P^2 = 400$$

for  $Q_P = 10$

Bottom line: The Sallen-Key realization suffers from a strong tradeoff between sensitivity and component spread

B. Murmann EE315A - Chapter 2 33

#### **Case Studies**

MAXIM APPLICATION NOTE 738

Minimizing Component-Variation Sensitivity in Single Op Amp Filters http://www.maxim-ic.com/appnotes.cfm/an\_pk/738/

### **Sensitivity to Mismatch (Tow-Thomas)**

$$\omega_{P} = \sqrt{\frac{R_{8}}{R_{2}R_{3}R_{7}C_{1}C_{2}}} \qquad S_{R2}^{\omega_{P}} = S_{R3}^{\omega_{P}} = S_{R3}^{\omega_{P}} = S_{R3}^{\omega_{P}} = S_{C1}^{\omega_{P}} = S_{C2}^{\omega_{P}} = -\frac{1}{2}$$

$$S_{R_{1}}^{Q_{P}} = 1$$

$$Q_{P} = \omega_{P}R_{1}C_{1} = R_{1}\sqrt{\frac{R_{8}C_{1}}{R_{2}R_{3}R_{7}C_{2}}} \qquad S_{R_{2}}^{Q_{P}} = S_{R_{3}}^{Q_{P}} = S_{R_{7}}^{Q_{P}} = -S_{R_{8}}^{Q_{P}} = -S_{C_{1}}^{Q_{P}} = S_{C_{2}}^{Q_{P}} = -\frac{1}{2}$$

- · Constant sensitivities, independent of Q and component spread

- Much nicer!

B. Murmann EE315A - Chapter 2 35

#### **Conclusions**

- Biquads can be realized in numerous different ways

- Implementation and component sizing have a big impact on sensitivity to variations

- Of course, we must avoid high-sensitivity circuits in practice

- No theory for finding a low-sensitivity architecture

- Use proven circuits & check!

- Tow-Thomas biquad

- Arbitrary poles and zeros, three amplifiers

- Well-behaved sensitivities

- · Sallen-Key biquad

- Only poles, one amplifier

- Sensitivities trade off with component spread

- Typically use G=1 and use this circuit only for "low Q" poles

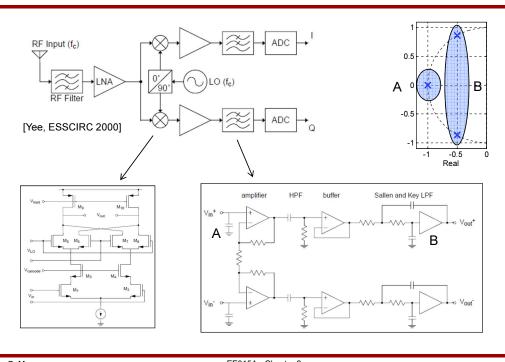

### **Example1: WCDMA Receiver**

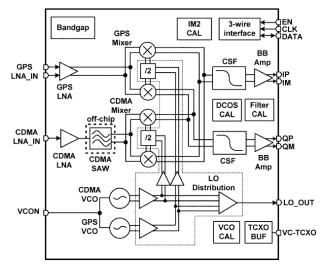

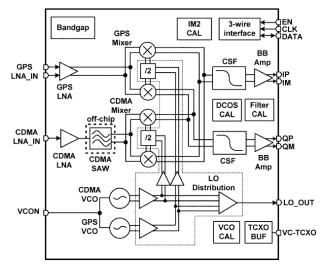

## **Example 2: CDMA/GPS Receiver**

Lim et al., "A Fully Integrated Direct-Conversion Receiver for CDMA and GPS Applications," IEEE JSSC, Nov. 2006

- Channel select filters (CSF)

- 640 kHz passband, lowpass

- 0.5 dB passband ripple

- > 40 dB stopband attenuation at 900 kHz

- 5<sup>th</sup> order elliptical filter

- Phase distortion can be tolerated in this application

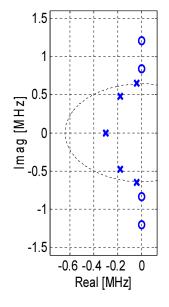

# **Matlab Synthesis Result**

### **Pole and Zero Locations**

|                  |                       | $\omega_{P}$ | $Q_P$  |

|------------------|-----------------------|--------------|--------|

| p <sub>1,2</sub> | -42.30 ± j6.4783 kHz  | 649.21 kHz   | 7.6748 |

| p <sub>3,4</sub> | -176.45 ± j4.8030 kHz | 511.68 kHz   | 1.4499 |

| p <sub>5</sub>   | -300.80 kHz           |              |        |

|                  |                       |              |        |

| Z <sub>1,2</sub> | ± j1203.2 kHz |

|------------------|---------------|

| Z <sub>3,4</sub> | ± j840.1 kHz  |

# Pairing Options for $p_{1,2}$ (High-Q)

- Pairing with nearby zero

- · Pairing with remote zero

B. Murmann

EE315A - Chapter 2

41

### **Pole-Zero Pairing**

- Pairing high-Q poles with nearby zeros is desirable from a dynamic range perspective

- $-\,$  Say that the amplifier at the output of the biquad can handle a maximum signal of 1  $V_{\text{peak}}$

- If the biquad response peaks 20 dB above unity, this means that we can only process inputs with 100 mV amplitude near the frequency of the peak (which lies in the passband)

- The signal is therefore reduced relative to the thermal noise of the circuit, which is highly undesirable

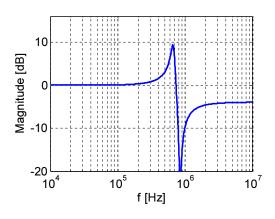

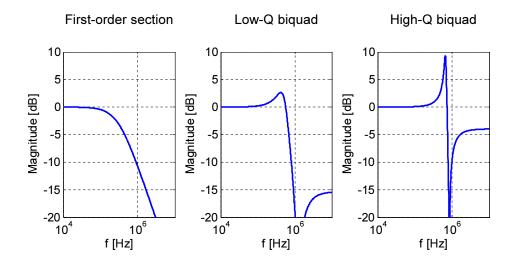

#### **Response of the Individual Sections**

In which order should we cascade these sections?

B. Murmann EE315A - Chapter 2 43

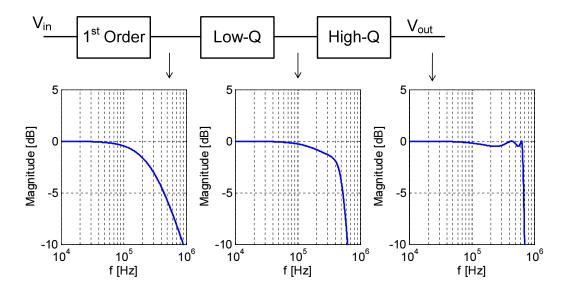

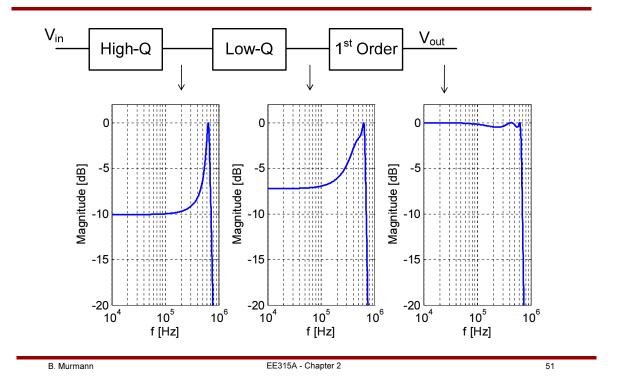

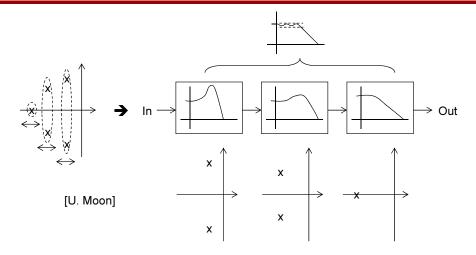

### **Biquad Ordering**

Ordering the Biquads from low-Q to high-Q generally yields "smooth" transfer functions from the input to the intermediate nodes, and often helps minimize harmonic distortion, but the output will have significant noise peaking near the corner frequency due to the last stage with high-Q.

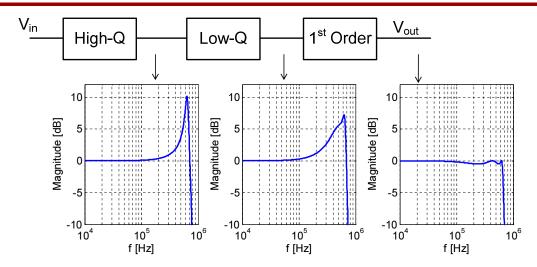

Reversing the ordering will allow the later stages to filter out the noise peaking near corner frequency. May also filter out harmonics (but not intermodulation).

In practical filter design, it would be worthwhile giving some thoughts to the options that you may have for the ordering of the biquads. In a non-lowpass filter application, inherent accoupling may also be used to your advantage to suppress offset accumulation.

(Some good system-level discussions in Schaumann/Ghausi/Laker.)

[U. Moon]

### Intermediate Outputs for Low-Q → High-Q

This ordering is most frequently used in practice

B. Murmann EE315A - Chapter 2 45

### Intermediate Outputs for High-Q → Low-Q

- At first glance this looks bad, but the noise from the high-Q biquad is filtered before it reaches the output

- We will revisit this situation in the context of noise analysis

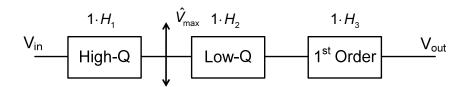

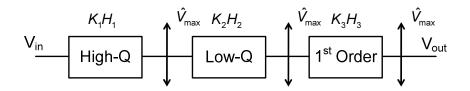

#### **Dynamic Range Scaling**

- Suppose we decided that the second ordering is what we want to use for our design

- In this case, we need to think about a proper gain distribution that avoids "clipping" in the individual amplifiers

- For this purpose, we introduce gain scale factors for each section, while keeping the overall gain constant (K<sub>1</sub>K<sub>2</sub>K<sub>3</sub> = 1 in this example)

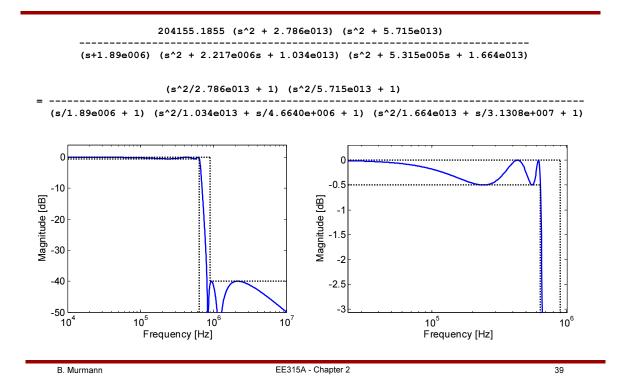

```

(s^2/2.786e013 + 1) (s^2/5.715e013 + 1) 1

(s^2/1.664e013 + s/3.1308e+007 + 1) (s^2/1.034e013 + s/4.6640e+006 + 1) (s/1.89e006 + 1)

K1*(s^2/2.786e013 + 1) K2*(s^2/5.715e013 + 1) K3

(s^2/1.664e013 + s/3.1308e+007 + 1) (s^2/1.034e013 + s/4.6640e+006 + 1) (s/1.89e006 + 1)

```

### Analysis (1)

- Suppose we chose K<sub>1</sub>=K<sub>2</sub>=K<sub>3</sub>=1 and assume that we will apply single sine waves with arbitrary frequencies to the input

- Since  $H_1$  has significant peaking ( $|H1|_{max} \cong 3.19 \cong 10$  dB), we can guarantee proper operation only for input amplitudes up to

$$\frac{\hat{V}_{\text{max}}}{|H_1|_{\text{max}}}$$

e.g.  $\frac{1V}{3.19} = 314mV$

Since the overall gain is unity (with no peaking above 1), this means V<sub>out</sub> swings only 314mV, meaning that we are "wasting" available signal range

### Analysis (2)

- A more desirable outcome may be to scale K<sub>1</sub>, K<sub>2</sub>, K<sub>3</sub> such that all stages utilize the maximum available swing as the input tone is swept across all frequencies

- Note that in general, the maximum output swings for each stage may not occur at the same frequency

### Analysis (3)

This is achieved for

$$K_1 |H_1|_{\text{max}} = K_1 K_2 K_3 |H_1 H_2 H_3|_{\text{max}}$$

$K_1 K_2 |H_1 H_2|_{\text{max}} = K_1 K_2 K_3 |H_1 H_2 H_3|_{\text{max}}$

In our example

$$K_1K_2K_3 = 1$$

$|H_1|_{max} = 3.19$   $|H_1H_2|_{max} = 2.3$   $|H_1H_2H_3|_{max} = 1$

and therefore

$$K_1 = \frac{1}{|H_1|_{\text{max}}} = \frac{1}{3.19}$$

$K_2 = \frac{1}{K_1|H_1H_2|_{\text{max}}} = \frac{3.19}{2.3}$   $K_3 = \frac{1}{K_1K_2} = \frac{3.19 \cdot 2.3}{3.19}$

#### **Intermediate Outputs After DR Scaling**

#### **Arguments Against "Sinusoidal" DR Scaling**

- If the input signal is wide-band (as in many telecommunication systems), the node with peaking may not saturate due to limited signal power in that frequency region

- May want to optimize the gain distribution based on a power spectral density "template" of the incoming signal

- Aligning the peaks for each output perfectly will require noninteger component ratios

- But we may want to use integer ratios to improve matching

- For a discussion on why sinusoidal dynamic range scaling may not always the best choice, see Behbahani, JSSC 4/2000

#### **Expressions for Implementation**

B. Murmann EE315A - Chapter 2 53

### **Tow-Thomas Component Values (b₁=0)**

$$R_{1} = \frac{1}{a_{1}C_{1}} \qquad R_{2} = \frac{k_{1}}{\sqrt{a_{0}C_{2}}} \qquad R_{3} = \frac{1}{k_{1}k_{2}} \frac{1}{\sqrt{a_{0}C_{1}}}$$

$$R_{4} = \frac{1}{k_{2}} \frac{1}{a_{1}b_{2}} \frac{1}{C_{1}} \qquad R_{5} = \frac{k_{1}\sqrt{a_{0}}}{b_{0}C_{2}} \qquad R_{6} = \frac{R_{8}}{b_{2}} \qquad R_{7} = k_{2}R_{8}$$

$$\omega_{Z} = \sqrt{\frac{R_{6}}{R_{3}R_{5}R_{7}C_{1}C_{2}}} \qquad \omega_{P} = \sqrt{\frac{R_{8}}{R_{2}R_{3}R_{7}C_{1}C_{2}}} \qquad Q_{P} = \omega_{P}R_{1}C_{1}$$

- $a_0$ ,  $a_1$ ,  $b_0$ ,  $b_1$ ,  $b_2$  are known; can pick  $k_1$ ,  $k_2$ ,  $C_1$ ,  $C_2$  and R8

- Reasonable starting values

- $k_1 = k_2 = 1$

- Set C<sub>1</sub> = C<sub>2</sub> to a reasonable value that is easily implemented, e.g. 1pF

- Set R<sub>8</sub> to a reasonable value that is easily implemented and represents an integer multiple or fraction of R<sub>2</sub>, R<sub>3</sub> or R<sub>7</sub>

#### **Example Design Flow**

- First cut component calculation using reasonable starting values for k<sub>1</sub>, k<sub>2</sub>, C<sub>1</sub>, C<sub>2</sub> and R<sub>8</sub>

- Dynamic range scaling of internal amplifier outputs by adjusting k<sub>1</sub> and k<sub>2</sub>

- · Thermal noise scaling using ideal amplifiers

- Increase all capacitors and reduce all resistors until noise specification is met

- Design amplifiers

- · Repeat thermal noise scaling to accommodate amplifier noise

- Analyze sensitivity to component variations and devise tuning mechanism (if needed)

B. Murmann EE315A - Chapter 2 55

#### **Dynamic Range Scaling of Internal Nodes**

Scale k<sub>1</sub> and k<sub>2</sub> such that peak magnitude at V<sub>o1</sub> and V<sub>o2</sub> corresponds to maximum available amplifier swing

#### **Sensitivity Analysis**

- Ideally, we would like to have an analytical expression that relates "interesting points" of the response to variations in all components

- E.g. calculate variations in the passband ripple as a function of the percent error in R<sub>2</sub>

- This is almost impossible or at least impractical to do in practice

B. Murmann EE315A - Chapter 2 57

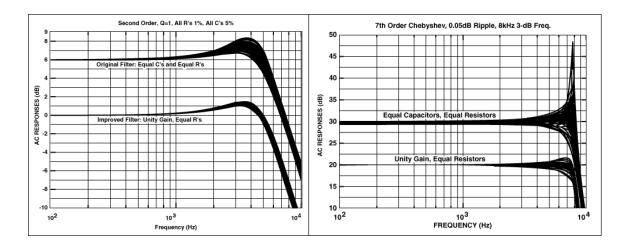

### **Sensitivity Analysis – Monte Carlo**

- Monte Carlo Analysis

- Have a statistical model for all components

- Run a large number of simulations (Matlab or Spectre) to capture many statistical outcomes and create overlay plot from all runs

MAXIM APPLICATION NOTE 738: Minimizing Component-Variation Sensitivity in Single Op Amp Filters http://www.maxim-ic.com/appnotes.cfm/an\_pk/738/

Such an analysis is very useful for validation, but perhaps too much work for intuition building and/or design guidance

#### **Basic Sensitivity Analysis**

- · Say we just want to get a basic feel for the sensitivities

- Look at impact of

- Global process variations

- Component mismatch

- · For global process variations, we have already seen that

$$\omega_{Z} = \sqrt{\frac{R_{6}}{R_{3}R_{5}R_{7}C_{1}C_{2}}} \propto \frac{1}{RC} \qquad \omega_{P} = \sqrt{\frac{R_{8}}{R_{2}R_{3}R_{7}C_{1}C_{2}}} \propto \frac{1}{RC} \qquad Q_{P} = \omega_{P}R_{1}C_{1} \propto 1$$

- If all R and C vary by the same percentage, the filter "shape" is preserved and shifted back and forth along the frequency axis

- If this is a problem for the application, we can "tune" either R or C to bring the filter response back to the desired location

B. Murmann EE315A - Chapter 2 59

### **Mismatch Analysis**

$$\omega_{Z} = \sqrt{\frac{R_{6}}{R_{3}R_{5}R_{7}C_{1}C_{2}}}$$

$\omega_{P} = \sqrt{\frac{R_{8}}{R_{2}R_{3}R_{7}C_{1}C_{2}}}$

$Q_{P} = \omega_{P}R_{1}C_{1}$

- Suppose we had resistors and capacitors that deviate from their nominal component value (which is subject to global variations) by a standard deviation of 1%

- Since

$$S_{R2}^{\omega_P} = S_{R3}^{\omega_P} = S_{R3}^{\omega_P} = -S_{R8}^{\omega_P} = S_{C1}^{\omega_P} = S_{C2}^{\omega_P} = -\frac{1}{2}$$

this means

$$\sigma_{\Delta\omega_P/\omega_P} = \frac{1}{2}\sqrt{6} \cdot 1\% = 1.22\%$$

$$3\sigma_{\Delta\omega_P/\omega_P} = 3.67\% \cong 4\%$$

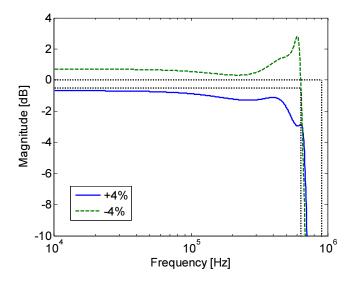

## Passband with Pole Errors (1)

•  $\pm$  4% change in  $\omega_{\text{P}}$  of first order section

B. Murmann EE315A - Chapter 2 6

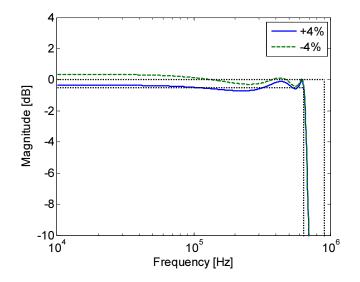

# Passband with Pole Errors (2)

•  $\pm$  4% change in  $\omega_{\text{P}}$  of low-Q section

Worse.

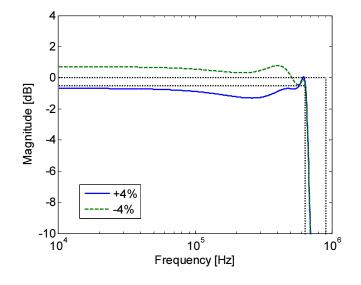

# Passband with Pole Errors (3)

+  $\pm$  4% change in  $\omega_{\text{P}}$  of high-Q section

Bad!

#### **Ladder Filter Realization**

#### Boris Murmann Stanford University murmann@stanford.edu

Copyright © 2013 by Boris Murmann

B. Murmann EE315A - Chapter 3

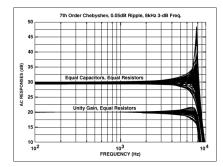

#### **Sensitivity Problem with Cascaded Biquads**

- · Passband response is sensitive to shifts in the pole positions

- Especially for high Q

- Typically, integrated continuous time filters use biquads to realize filters only up to ~5<sup>th</sup> order

B. Murmann

EE315A - Chapter 3

2

#### **Conceptual View of a Biquad Cascade**

- Individual sections are actively decoupled

- Variations in individual components affect only one pair of poles (and/or zeros)

- Ideally, we would like all the poles (and zeros) to "move together"

- This would at least preserve the "shape" of the filter response

B. Murmann EE315A - Chapter 3

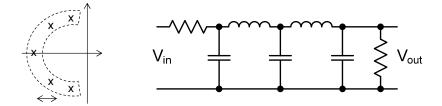

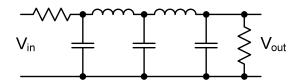

### **Doubly Terminated LC Ladder Filters**

- The <u>passband</u> response of ladder filters is much less sensitive to component variations when compared to a biquad cascade

- Poles "tend" to move together

- For a sensitivity analysis, see e.g.

- G. C. Temes and H. J. Orchard, "First order sensitivity and worst-case analysis of doubly terminated reactance two-ports," IEEE Trans. Circuit Theory, 20 (5), pp. 567–571, 1973.

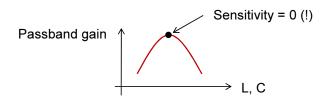

#### **Basic Intuition**

- In the passband, the gain from  $V_{\text{in}}$  to  $V_{\text{out}}$  is maximum (0.5)

- · Any detuning of L and C can only reduce the passband gain

- Therefore, the passband gain is convex in L and C, and the sensitivity is zero around the nominal design point!

B. Murmann EE315A - Chapter 3

### **Analysis Example (1)**

$$i_{4} = V_{out}Y_{4} = i_{3}$$

$$V_{2} = i_{3}Z_{3} + V_{out}$$

$$i_{2} = V_{2}Y_{2}$$

$$V_{in} = i_{1}Z_{1} + V_{2}$$

$$= (V_{2}Y_{2} + V_{out}Y_{4})Z_{1} + V_{2}$$

$$= ([Y_{4}Z_{3}V_{out} + V_{out}]Y_{2} + V_{out}Y_{4})Z_{1} + V_{out}Y_{4}Z_{3} + V_{out}$$

$$\frac{V_{out}}{V_{in}} = \frac{1}{([Y_{4}Z_{3} + 1]Y_{2} + Y_{4})Z_{1} + Y_{4}Z_{3} + 1}$$

$$= \frac{1}{Y_{4}Z_{3}Y_{2}Z_{1} + Y_{4}Z_{3} + Y_{4}Z_{1} + Y_{2}Z_{1} + 1}$$

#### **Analysis Example (2)**

E.g. for

$$Z_1 = R_1 \qquad Z_3 = sL_3$$

$$Y_2 = sC_2 \qquad Y_4 = sC_4$$

it follows that

$$\frac{V_{out}}{V_{in}} = \frac{1}{s^3 C_4 L_3 C_2 R_1 + s^2 C_4 L_3 + s (C_4 R_1 + C_2 R_1) + 1}$$

- A third order lowpass filter

- Zeros can be realized by utilizing parallel and series combinations of inductors and capacitors

- Analysis is doable

- But very tedious!

B. Murmann EE315A - Chapter 3

### **LC Ladder Synthesis**

- Filter tables

- A. Zwerev, Handbook of filter synthesis, Wiley, 1967

- R. Saal, Handbook of filter synthesis, AEG-Telefunken, 1979

- A. B. Williams and F. J. Taylor, *Electronic filter design*, 3<sup>rd</sup> edition, McGraw-Hill, 1995

- CAD tools

- http://www.circuitsage.com/filter.html

- · Comprehensive list of available tools

- http://tonnesoftware.com/elsie.html

- Free version of Elsie supports ladder synthesis up to 7<sup>th</sup> order

- http://www.nuhertz.com/download.html

- FilterFree up to 3<sup>rd</sup> order

- FilterSolutions \$\$\$

- Agilent ADS

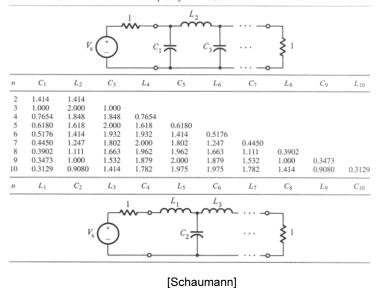

#### **Butterworth Filter Table**

**TABLE 13.1** Table of Element Values for Doubly Terminated Butterworth Filters for n=2 to n=10 Normalized to Half-Power Frequency of 1 rad/s

Denormalization

$$L_{i,den} = L_i \frac{R}{\omega_{-3dB}}$$

$$C_{i,den} = C_i \frac{1}{\omega_{-3dB} \cdot R}$$

R is the desired value of the source and termination resistor

B. Murmann EE315A - Chapter 3

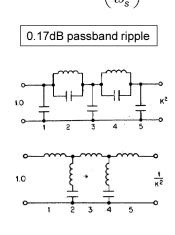

# 5<sup>th</sup> Order Elliptic Filter Table (1)

[Williams & Taylor] Table 11-56

|      |         |                | K <sup>2</sup> | = 1.0   |         |         |         |

|------|---------|----------------|----------------|---------|---------|---------|---------|

| θ    | С,      | C <sub>2</sub> | L <sub>2</sub> | C.      | C.      | L.      | Ck      |

| С    | 1.302   | 0.0000         | 1.346          | 2.129   | 0.0000  | 1.346   | 1.302   |

| 1.0  | 1.80183 | 0.00008        | 1.34548        | 2.12835 | 0.00020 | 1.34532 | 1.30170 |

| 2.0  | 1.30163 |                | 1.34523        | 2.12770 | 0.00082 | 1.34459 | 1.30112 |

| 3.0  | 1.50150 | 0.00070        | 1.34483        | 2.12660 |         | 1.34339 | 1.30016 |

| 4.0  | 1.30084 | 0.00125        | 1.84426        | 2.12507 | 0.00328 | 1.34170 | 1.29881 |

| 5.0  | 1.30024 | 0.00196        | 1.34353        | 2.12311 | 0.00513 | 1.33954 | 1.29708 |

| 6.0  | 1.29951 | 0.00282        | 1.34264        | 2.12070 | 0.00740 | 1.33689 | 1.29496 |

| 7.0  | 1.29865 | 0.00384        | 1.34159        |         | 0.01008 | 1.33376 | 1.29246 |

| 8.0  | 1.29766 |                |                | 2.11459 | 0.01318 | 1,33015 | 1.28957 |

| 9.0  | 1.29653 | 0.00637        | 1.53899        | 2.11088 | 0.01671 | 1.32607 | 1.28630 |

| 10.0 | 1.29527 | 0.00787        | 1.33744        | 2.10675 | 0.02067 | 1.32150 | 1.28264 |

| 11.0 | 1.29387 | 0.00953        | 1.53573        | 2.10217 | 0.02506 | 1.31646 | 1.27859 |

| 12.0 | 1.29234 | 0.01136        | 1.53386        | 2.09717 | 0.02989 | 1.31094 | 1.27417 |

| 13.0 | 1.29067 | 0.01335        | 1.53182        | 2.09172 | 0.03516 | 1.30495 | 1.26936 |

| 14.0 | 1.28887 | 0.01551        | 1.32961        | 2.08588 | 0.04089 | 1.29848 | 1.26416 |

| 15.0 | 1.28693 | 0.01783        | 1.52724        | 2.07959 | 0.04707 | 1.29154 | 1.25858 |

| 16.0 | 1.28485 | 0.02033        | 1.32470        | 2.07288 | 0.05371 | 1.28413 | 1.25261 |

| 17.0 | 1.28263 | 0.02300        | 1.52199        | 2.06574 | 0.06084 | 1.27625 | 1.24627 |

| 18.0 | 1.28027 | 0.02584        | 1.81911        | 2.05819 | 0.06844 | 1.26790 | 1.23953 |

| 19.0 | 1.27778 | 0.02885        | 1.31607        | 2.05021 | 0.07655 | 1.25909 | 1.23241 |

| 20.0 | 1.27514 | 0.03205        | 1.31285        | 2.04182 | 0.08515 | 1.24981 | 1.22491 |

| 21.0 | 1.27236 | 0.03542        | 1.30945        | 2.03301 | 0.09428 | 1.24007 | 1.21703 |

| 22.0 | 1.26943 |                | 1.30589        | 2.02379 | 0.10393 | 1.22987 | 1.20876 |

| 23.0 | 1.26636 |                | 1.30215        | 2.01416 |         | 1.21921 | 1.20010 |

| 24.0 | 1.26314 | 0.04666        | 1.29823        |         |         | 1.20809 | 1.19107 |

| 25.0 | 1.25978 | 0.05079        | 1.29413        |         |         | 1.19652 | 1.18164 |

| 26.0 | 1.25262 | 0.05511        | 1.28985        |         | 0.14819 | 1.18450 | 1.17183 |

| 27.0 | 1.25259 | 0.05963        | 1.28540        |         |         | 1.17203 | 1.16164 |

| 28.0 | 1.24877 | 0.06436        | 1.28075        |         | 0.17396 |         | 1.15106 |

| 29.0 | 1.22480 | 0.06930        | 1.27592        |         |         | 1.14576 | 1.14010 |

| 30.0 | 1.24067 | 0.07446        | 1.27091        | 1.93550 | 0.20239 | 1.13196 | 1.12874 |

## 5<sup>th</sup> Order Elliptic Filter Table (2)

| -    | $K^2 = 1.0$             |                |                |                |         |                |                |

|------|-------------------------|----------------|----------------|----------------|---------|----------------|----------------|

| 0    | C <sub>1</sub>          | C <sub>2</sub> | L <sub>2</sub> | С,             | C.      | L <sub>4</sub> | C <sub>5</sub> |

| 31.0 | 1.23638                 | 0.07983        | 1.26570        | 1.92270        | 0.21768 | 1.11772        | 1.11700        |

| 32.0 | 1.23192                 | 0.08543        | 1.26030        | 1.90952        | 0.23371 | 1.10305        | 1.10487        |

| 33.0 | 1.22731                 | 0.09126        | 1.25470        | 1.89596        | 0.25054 | 1.08795        | 1.09235        |

| 34.0 | 1.22252                 | 0.09732        |                | 1.88203        | 0.26819 | 1.07242        |                |

| 35.0 | 1.21757                 | 0.10363        | 1.24290        | 1.86773        | 0.28671 | 1.05648        | 1.06614        |

| 36.0 | 1.21244                 | 0.11019        | 1.23669        | 1.85307        |         | 1.04011        | 1.05244        |

| 37.0 | 1.20714                 | 0.11701        | 1.23028        |                |         | 1.02332        | 1.03835        |

| 38.0 | 1.20166                 | 0.12410        | 1.22364        |                | 0.34795 |                | 1.02386        |

| 39.0 | 1.19600                 | 0.13146        | 1.21679        |                | 0.37044 |                |                |

| 40.0 | 1.19015                 | 0.13911        | 1.20971        | 1.79093        | 0.39408 | 0.97053        | 0.99368        |

| 41.0 | 1.18411                 | 0.14706        | 1.20241        | 1.77455        | 0.41894 |                |                |

| 42.0 | 1.17787                 | 0.15532        | 1.19486        | 1.75784        | 0.44510 | 0.93335        | 0.96187        |

| 43.0 | 1.17144                 | 0.16389        | 1.18708        | 1.74081        | 0.47265 | 0.91417        | 0.94535        |

| 44.0 | 1.16480                 | 0.17280        | 1.17904        | 1.72347        | 0.50170 | 0.89462        | 0.92841        |

| 45.0 | 1.15794                 | 0.18206        | 1.17075        | 1.70583        | 0.53236 | 0.87470        | 0.91105        |

| 46.0 | 1.15088                 | 0.19169        | 1.16219        |                |         |                | 0.89326        |

| 47.0 | 1.14359                 | 0.20169        |                | 1.66967        | 0.59903 |                |                |

| 48.0 | 1.13607                 | 0.21210        | 1.14425        | 1.65117        | 0.63534 | 0.81276        |                |

| 49.0 | 1.12831                 | 0.22293        | 1.13484        | 1.63241        | 0.67386 | 0.79141        | 0.83727        |

| 50.0 | 1.12031                 | 0.23421        | 1.12513        | 1.61339        | 0.71481 | 0.76973        | 0.81771        |

| 51.0 | 1.11206                 | 0.24596        | 1.11509        | 1.59413        | 0.75841 | 0.74773        | 0.79768        |

| 52.0 | 1.10354                 | 0.25821        | 1.10473        |                | 0.80492 |                | 0.77717        |

| 55.0 | 1.09476                 | 0.27099        | 1.09401        | 1.55494        | 0.85465 | 0 70278        | 0.75619        |

| 54.0 | 1.08569                 | 0.28433        | 1.08293        | 1.53504        | 0.90794 | 0.67986        | 0.73470        |

| 55.0 | 1.07633                 | 0.29828        | 1.07147        | 1.51496        | 0.96518 | 0.65667        | 0.71270        |

| 56.0 | 1.06666                 | 0.31288        | 1.05960        | 1.49471        |         |                | 0.69016        |

| 57.0 | 1.05668                 | 0.32817        | 1.04731        | 1.47431        | 1.09344 |                | 0.66709        |

| 58.0 | 1.04636                 | 0.34422        | 1.03456        | 1.45379        |         |                | 0.64344        |

| 59.0 | 1.03570                 | 0.36109        | 1.02134        | 1.43317        |         |                | 0.61920        |

| 60.0 | 1.02467                 | 0.37885        | 1.00760        | 1.41247        | 1.32969 | 0.53702        | 0.59435        |

| θ    | <i>l</i> . <sub>1</sub> | Lı             | C <sub>2</sub> | L <sub>3</sub> | L,      | C4             | Ls             |

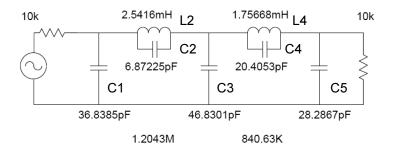

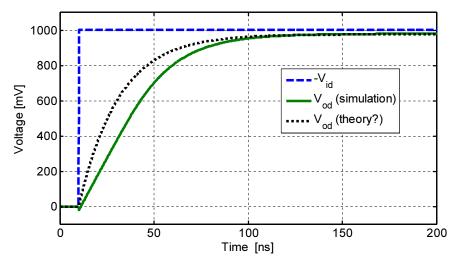

### **Back to Our Design Example**

Lim et al., "A Fully Integrated Direct-Conversion Receiver for CDMA and GPS Applications," IEEE JSSC, Nov. 2006

- Channel select filters (CSF)

- 640 kHz passband, lowpass

- 0.5 dB passband ripple

- > 40 dB stopband attenuation at 900 kHz

- 5<sup>th</sup> order elliptical filter

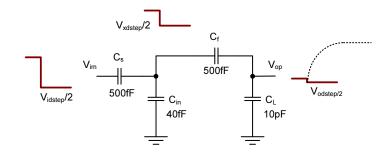

### **Synthesis Result (Using Elsie)**

Bandwidth: 640K Family: Cauer Passband ripple: 0.49426 Stopband freq: 815K Stopband depth: 40

4/11/2009 5:56:58 PM - Elsie 2.29 - www.tonnesoftware.com

Termination resistors arbitrarily set to 10kΩ

B. Murmann EE315A - Chapter 3 13

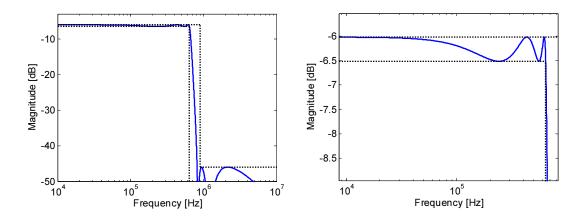

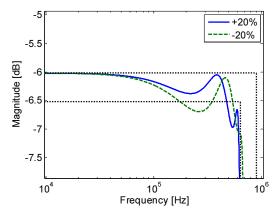

### **Spice Simulation Result**

- 6 dB passband attenuation due to resistive termination

- Easy to change to 0dB in an active realization

#### 20% Variation in L2

- Only a very small change in the passband response; moderate degradation in the stopband

- Smaller (i.e. more realistic) variations than 20% can be easily handled through overdesign

B. Murmann EE315A - Chapter 3 15

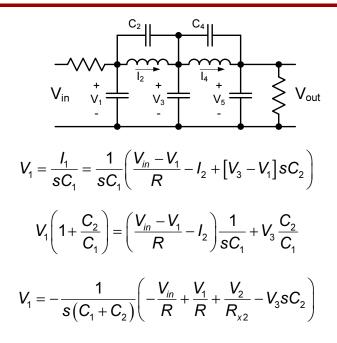

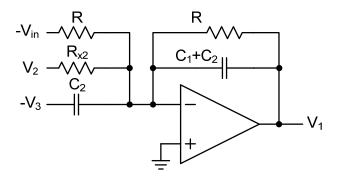

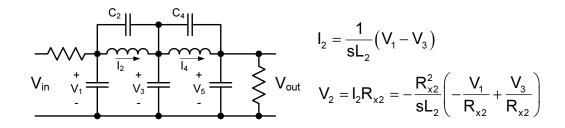

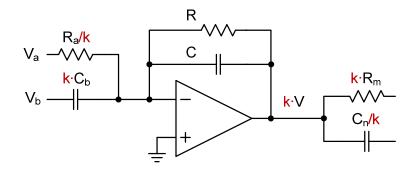

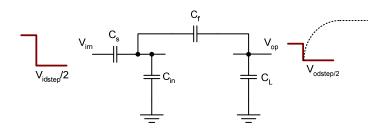

## State-Space Description for C<sub>1</sub>

## Implementation of C<sub>1</sub> Integrator

$$V_{1} = -\frac{1}{s(C_{1} + C_{2})} \left( -\frac{V_{in}}{R} + \frac{V_{1}}{R} + \frac{V_{2}}{R_{x2}} - V_{3}sC_{2} \right)$$

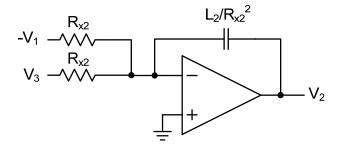

# Implementation of L<sub>2</sub> Integrator

## **Remaining Integrators**

$$V_{3} = -\frac{1}{s(C_{2} + C_{3} + C_{4})} \left( -\frac{V_{2}}{R_{x4}} + \frac{V_{4}}{R_{x4}} - V_{1}sC_{2} - V_{5}sC_{4} \right)$$

$$V_{4} = I_{4}R_{x4} = -\frac{R_{x4}^{2}}{sL_{4}} \left( -\frac{V_{3}}{R_{x4}} + \frac{V_{5}}{R_{x4}} \right)$$

$$V_{out} = V_{5} = -\frac{1}{s(C_{4} + C_{5})} \left( \frac{V_{5}}{R} - \frac{V_{4}}{R_{x4}} - V_{3}sC_{4} \right)$$

B. Murmann EE315A - Chapter 3 19

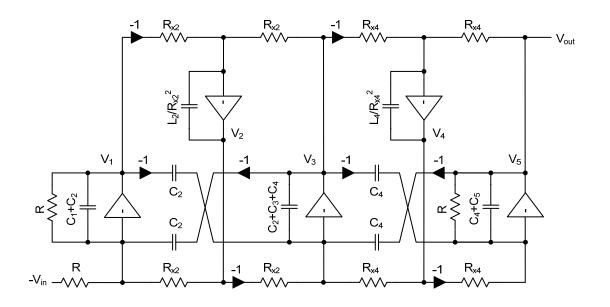

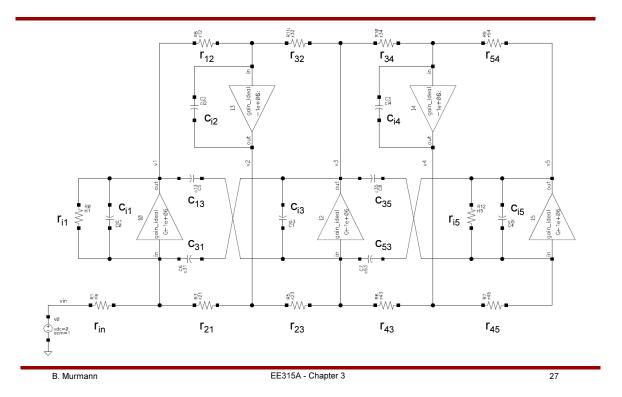

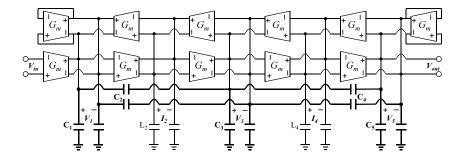

## **Complete Realization**

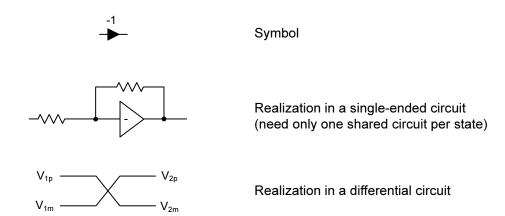

### **Signal Inversion**

In a first-cut (single-ended) simulation, signal inversion can also be achieved using negative resistors and capacitors

B. Murmann EE315A - Chapter 3 21

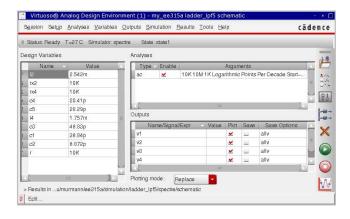

#### **Simulation Setup**

- AC analysis with 1V applied at the input

- Amplifiers are ideal, with an open loop gain of 10<sup>6</sup>

- Set  $R_{x2}$ = $R_{x4}$ =R= $10k\Omega$

- Somewhat arbitrary at this point

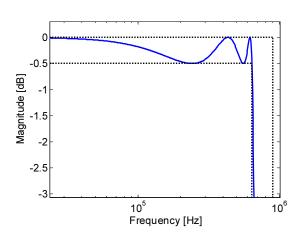

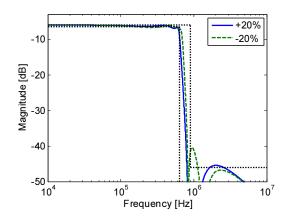

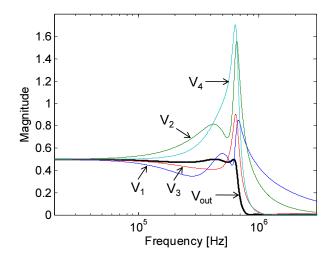

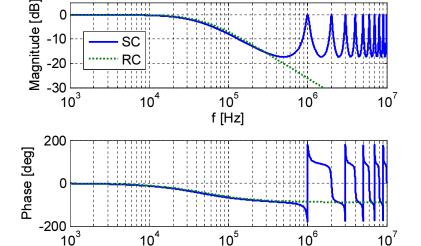

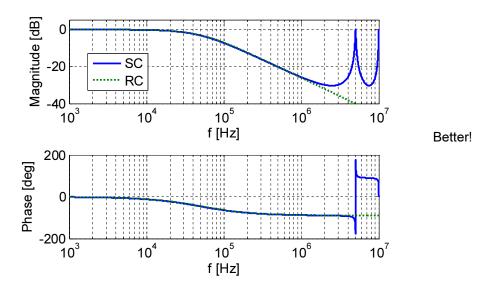

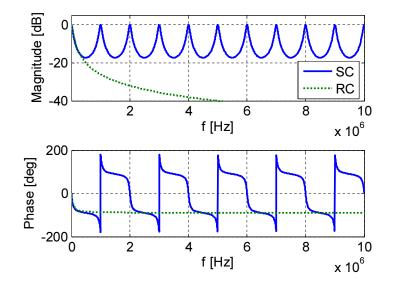

#### **Frequency Response**

```

|V_1|_{max} = 0.8505 \text{ V}

|V_2|_{max} = 1.5585 \text{ V}

|V_3|_{max} = 0.9039 \text{ V}

|V_4|_{max} = 1.7072 \text{ V}

|V_{out}|_{max} = 0.5000 \text{ V}

```

B. Murmann

EE315A - Chapter 3

23

#### **Node Voltage Scaling**

- To scale the peak output voltage of an integrator by a factor of k, scale all resistors and capacitors connected to the input and output node as shown below

- Feedback R and C remain unchanged

- Will be scaled together with all other components to adjust the thermal noise (more later)

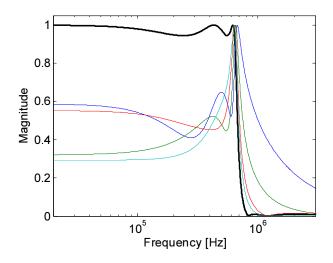

#### Frequency Response After 0dB Scaling

B. Murmann EE315A - Chapter 3 25

## **Component Values After 0dB Scaling**

ci1 = 4.3711e-011 ri1 = 10000 ci2 = 2.5416e-011ci3 = 7.4108e-011ci4 = 1.7567e-011ci5 = 4.8692e-011 ri5 = 10000% coupling R  $[\Omega]$ rin = -8.5052e + 003r12 = -1.8324e+004 r21 = 5.4573e+003 r23 = -5.7997e + 003r32 = 1.7242e+004 r34 = -1.8888e+004 r43 = 5.2944e + 003r45 = -2.9287e+003 r54 = 3.4145e+004 % zero C [F]

c13 = -6.4665e-012 c31 = -7.3035e-012

c35 = -3.6888e-011 c53 = -1.1287e-011

% feedback R [ $\Omega$ ] and C [F]

- Resistors

- $-R_{min} = 2.93 \text{ k}\Omega$

- $-R_{max} = 34.1 \text{ k}\Omega$

- Capacitors

- $C_{min} = 6.47 pF$

- $C_{max} = 48.7 pF$

- Component spread ~10

- Manageable in practice

- May be able to reduce spread by scaling integration capacitors, subject to noise constraints

- A very complex optimization problem!

#### **Schematic**

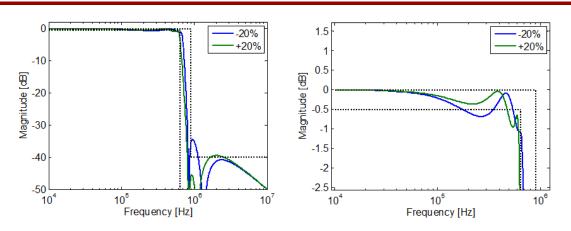

## 20% Variation in C<sub>i2</sub>

- · Only small passband variations despite large component variation

- · Active realization of ladder retains low sensitivity of passive prototype

- More analysis is needed to determine the actual precision requirements for all components

28

E.g. through a Monte Carlo simulation

## **Summary**

- Higher-order filter realization

- Cascade of biquads

- High sensitivity often problematic for order ≥ 5

- Ladder filters

- Based on LC prototypes

- Low sensitivity

- · Active RC simulation retains low sensitivity

#### **Integrator Realization & Nonidealities**

#### Boris Murmann Stanford University murmann@stanford.edu

Copyright © 2013 by Boris Murmann

B. Murmann EE315A - Chapter 4

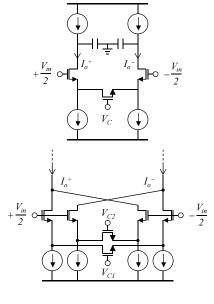

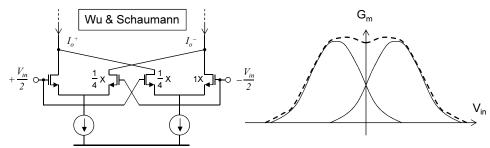

#### **Outline**

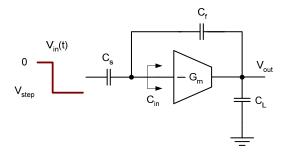

- Impact of finite amplifier bandwidth and gain in active RC integrators

- Thermal noise

- Passive filters

- Active RC filters

- Alternative integrator realizations

- Parameter tuning

B. Murmann

EE315A - Chapter 4

2

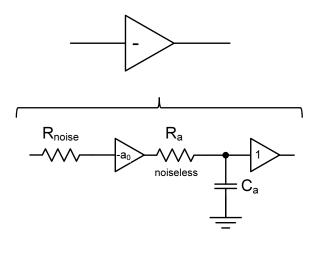

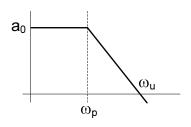

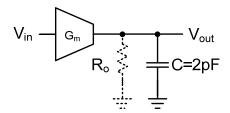

#### **Amplifier Model with First Order Nonidealities**

$$\omega_p = \frac{1}{R_a C_a} \qquad \omega_u \cong a_0 \cdot \omega_p$$

$$a(s) = -\frac{a_0}{1 + \frac{s}{\omega_p}} \cong -\frac{a_0 \omega_p}{s} \cong -\frac{\omega_u}{s}$$

for  $\omega >> \omega_p$

B. Murmann EE315A - Chapter 4

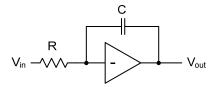

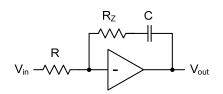

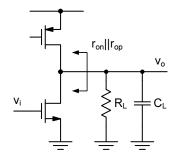

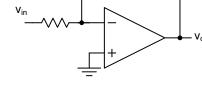

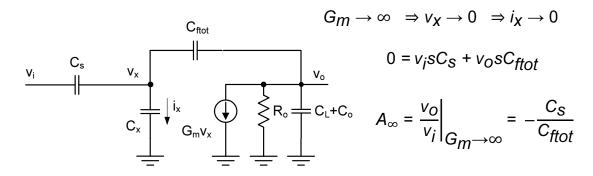

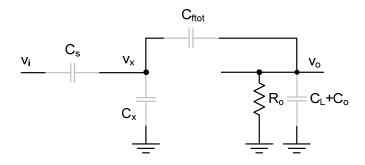

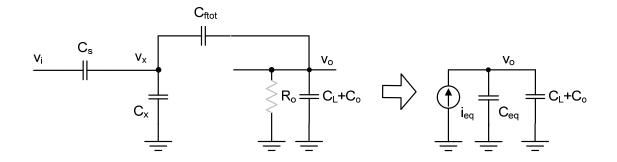

## **RC Integrator with Nonideal Amplifier**

Using return ratio analysis, we can write

$$A_{\infty} = -\frac{1}{sRC} = -\frac{\omega_0}{s} \qquad A(s) = \frac{V_{out}(s)}{V_{in}(s)} = A_{\infty} \frac{T(s)}{1 + T(s)}$$

$$T(s) = -a(s) \frac{R}{R + \frac{1}{sC}} = \frac{a_0}{1 + \frac{s}{\omega_0}} \frac{\frac{s}{\omega_0}}{1 + \frac{s}{\omega_0}} \qquad \omega_p \cong \frac{\omega_u}{a_0}$$

As long as T(s) is large, the transfer function A(s) is close to the desired ideal transfer function (A<sub>∞</sub>)

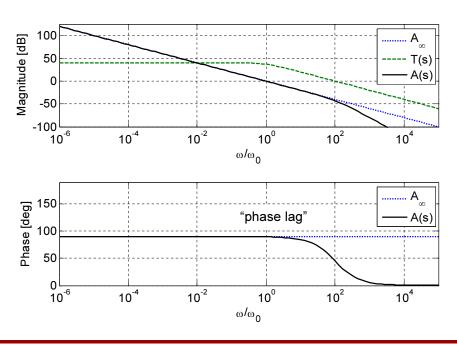

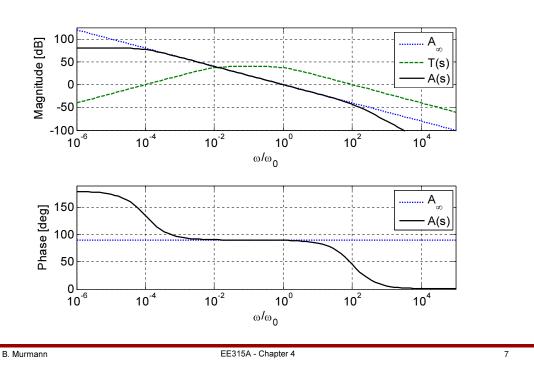

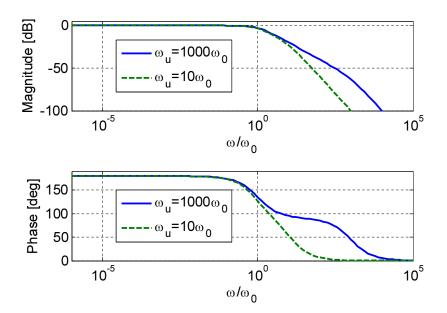

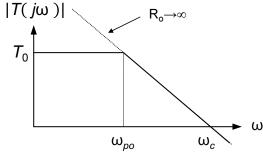

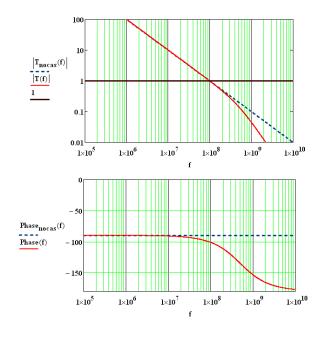

# $a_0 \rightarrow \infty$ , $\omega_u = 100\omega_0$

B. Murmann EE315A - Chapter 4 5

# $a_0$ =10,000, $\omega_u \rightarrow \infty$

## $a_0$ =10,000, $\omega_u$ =100 $\omega_0$

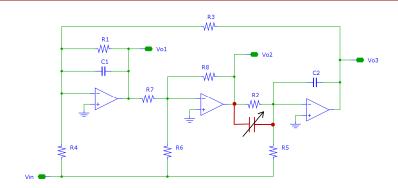

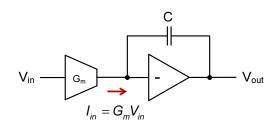

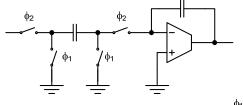

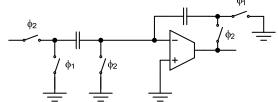

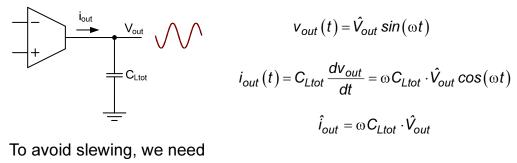

## RC Integrator with Finite $\omega_u$

· Ignoring finite DC gain for the time being, i.e. using

$$a(s) = -\frac{\omega_u}{s}$$

· The equations from slide 4 yield for this case

$$A_{actual}(s) = -\frac{\omega_o}{\frac{s}{A_{ideal}}} \frac{1}{1 + \frac{\omega_0}{\omega_u}} \frac{1}{1 + \frac{s}{\omega_o + \omega_u}}$$

Magnitude error

Undesired pole (Magnitude and phase error)

• The first error term modifies only the magnitude, and effectively alters the integration time constant (RC =  $1/\omega_0$ )

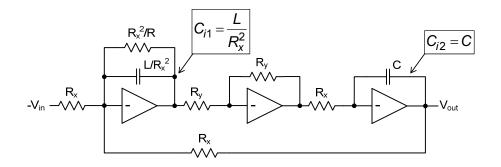

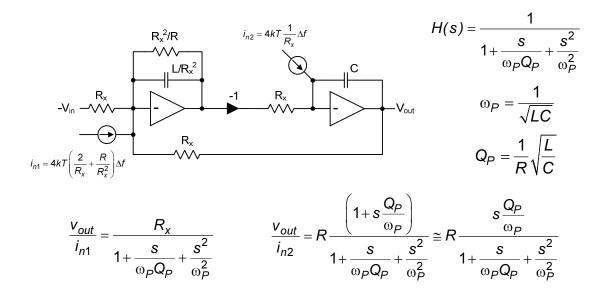

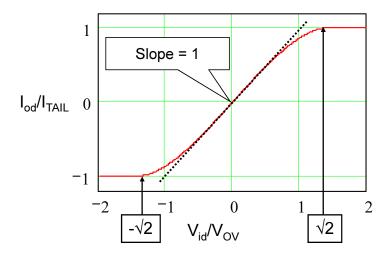

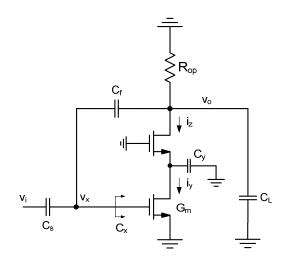

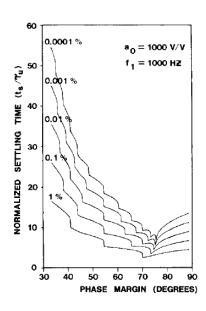

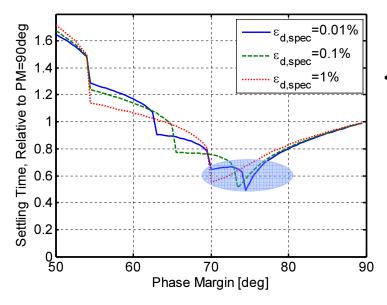

### Significance of $\omega_0$ (Biquad Example)

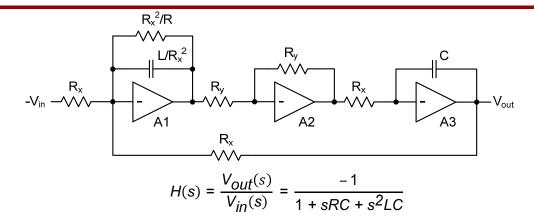

$$H(s) = -\frac{1}{1 + sRC + s^2LC} = -\frac{1}{1 + \frac{s}{\omega_P Q_P} + \frac{s^2}{\omega_P^2}} \qquad \qquad \omega_P = \frac{1}{\sqrt{LC}} = \frac{1}{\sqrt{R_x C_{i1} R_x C_{i2}}} = \sqrt{\omega_{01} \cdot \omega_{02}}$$

• Integrator  $\omega_0$  typically not too far off from pole frequency  $\omega_P$

B. Murmann EE315A - Chapter 4

## Baseline Requirement for $\omega_u$

$$A_{actual}(s) = \underbrace{-\frac{\omega_o}{s}}_{A_{ideal}} \underbrace{\frac{1}{1 + \frac{\omega_o}{\omega_u}}}_{Magnitude \ error} \underbrace{\frac{1}{1 + \frac{s}{\omega_o + \omega_u}}}_{Undesired \ pole}$$

(Magnitude and phase error)

- High-Q filters will be sensitive to variations and uncertainty in the "effective" value of  $\omega_0$

- In a practical design, we therefore require  $\omega_u >> \omega_0$ , typically  $\omega_u = 10...50 \cdot \omega_0$

- Assuming that we comply with this guideline, we are left with

$$A_{actual}(s) \cong -\frac{\omega_o}{s} \frac{1}{1 + \frac{s}{\omega_u}}$$

#### **Effect on Filter Response**

· For a filter that uses ideal integrators, we know that

$$H_{\text{filter}}(s)|_{s=p_{\text{ideal}}} \to \infty$$

For the case with finite ω<sub>u</sub>

$$H_{\text{filter}}\left(s\left(1+\frac{s}{\omega_u}\right)\right)\Big|_{s=0,\dots,n}\to\infty$$

and therefore

$$p_{ ext{ideal}} = p_{ ext{actual}} \left( 1 + rac{p_{ ext{actual}}}{\omega_u}

ight)$$

$p_{ ext{ideal}} = lpha_i \pm jeta_i$   $p_{ ext{actual}} = lpha_a \pm jeta_a$

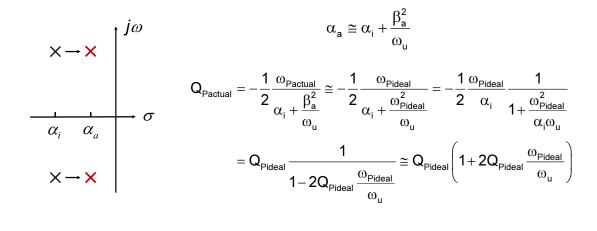

# Solving for p<sub>actual</sub> (1)

$$\alpha_{_{i}}+j\beta_{_{i}}=\left(\alpha_{_{a}}+j\beta_{_{a}}\right)\!\!\left(1\!+\!\frac{\alpha_{_{a}}+j\beta_{_{a}}}{\omega_{_{u}}}\right)$$

Equating real and imaginary parts, we find

$$\alpha_{i} = \alpha_{a} \left( 1 + \frac{\alpha_{a}}{\omega_{u}} \right) - \frac{\beta_{a}^{2}}{\omega_{u}} \qquad \beta_{i} = \beta_{a} \left( 1 + 2 \frac{\alpha_{a}}{\omega_{u}} \right)$$

To proceed, it makes sense to customize the analysis for high-Q poles, which should represent the most critical case

$$\begin{split} Q_{\text{Pideal}} &= -\frac{1}{2}\frac{\omega_{\text{Pideal}}}{\alpha_i} >> 1 & \qquad \omega_{\text{Pideal}} &= \sqrt{\alpha_i^2 + \beta_i^2} \cong \beta_i \\ Q_{\text{Pactual}} &= -\frac{1}{2}\frac{\omega_{\text{Pactual}}}{\alpha_a} >> 1 & \qquad \omega_{\text{Pactual}} &= \sqrt{\alpha_a^2 + \beta_a^2} \cong \beta_a \end{split}$$

# Solving for p<sub>actual</sub> (2)

$$\alpha_{i} = \alpha_{a} \Biggl( 1 + \frac{\alpha_{a}}{\omega_{u}} \Biggr) - \frac{\beta_{a}^{2}}{\omega_{u}} \qquad \qquad \beta_{i} = \beta_{a} \Biggl( 1 + 2 \frac{\alpha_{a}}{\omega_{u}} \Biggr)$$

We can now simplify using

$$\alpha_a << \omega_{Pactual} \cong \omega_0 << \omega_u$$

to obtain

$$\alpha_{i} \cong \alpha_{a} - \frac{\beta_{a}^{2}}{\omega_{u}}$$

$$\beta_{i} \cong \beta_{a}$$

$$\alpha_{a} \cong \alpha_{i} + \frac{\beta_{a}^{2}}{\omega_{u}}$$

$$\beta_{a} \cong \beta_{i}$$

• Negligible change in the pole's imaginary part; real part affected by finite  $\omega_{\rm u}$

B. Murmann EE315A - Chapter 4 13

#### **Effect on Pole Locations**

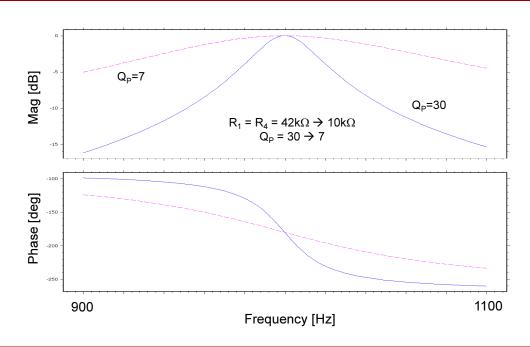

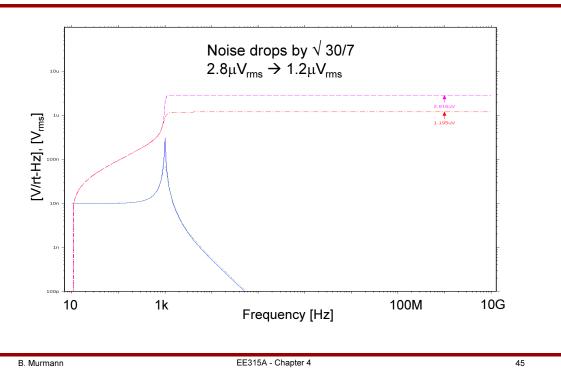

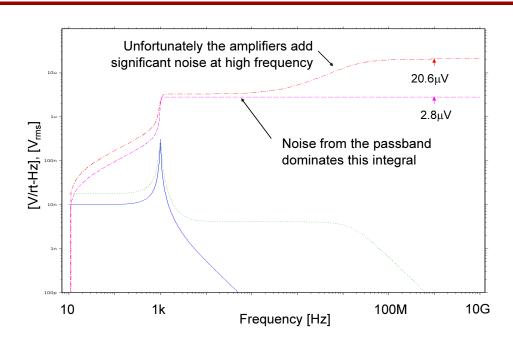

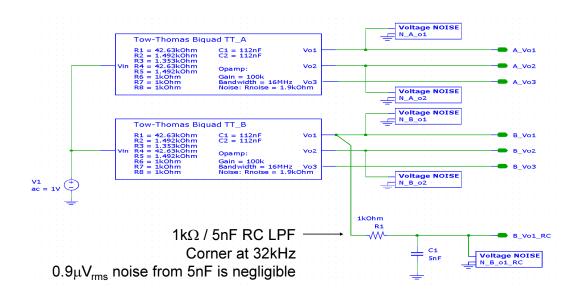

Example for Q<sub>Pideal</sub> = 30, <2% (0.17dB) increase in Q<sub>Pactual</sub>

$$2 \cdot 30 \cdot \frac{\omega_{\text{Pideal}}}{\omega_{\text{u}}} < 2\% \qquad \qquad \frac{\omega_{\text{u}}}{\omega_{\text{Pideal}}} > 3000 \quad (!)$$

#### **Corresponding Phase Error**

$$\omega_u = 3000 \omega_{Pideal}$$

and

$$\omega_{Pideal} \cong \omega_0$$

we can estimate the phase error of the integrator at  $\omega_0$  using

$$\phi_{err} = \measuredangle \left(\frac{1}{1+j\frac{\omega_0}{\omega_u}}\right) \cong \measuredangle \left(1-j\frac{\omega_{P_{ideal}}}{\omega_u}\right) = \tan^{-1}\left(-\frac{\omega_{P_{ideal}}}{\omega_u}\right) \cong -\frac{1}{3000} = -\frac{1}{3000} \cdot \frac{180^\circ}{\pi} = -0.02^\circ$$

B. Murmann

EE315A - Chapter 4

15

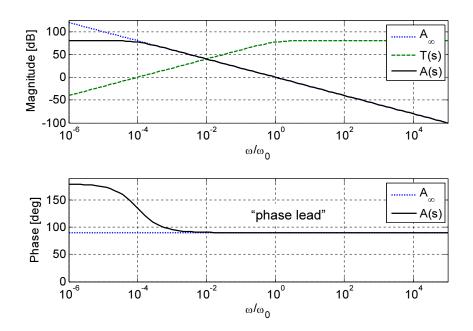

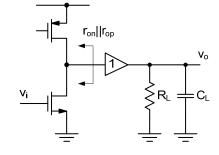

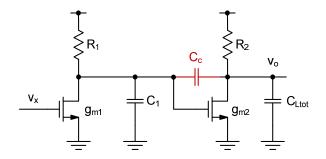

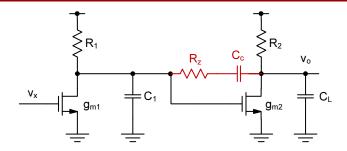

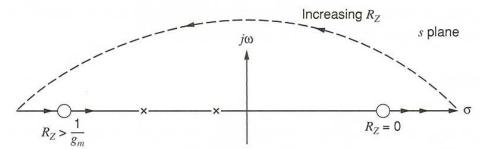

#### **Pole-Zero Cancellation (1)**

$$H(s) = -\frac{1 + sR_zC}{sRC\left(1 + \frac{s}{\omega_u}\right) + \frac{s}{\omega_u}(1 + sR_zC)}$$

$$= -\frac{1}{\frac{sRC}{sRC}} \frac{1 + \frac{s}{\omega_u} + \frac{1}{\omega_uRC}(1 + sR_zC)}{1 + \frac{s}{\omega_u} + \frac{1}{\omega_uRC}(1 + sR_zC)}$$

$$= -\frac{\omega_o}{s} \frac{1 + sR_zC}{1 + \frac{\omega_o}{\omega_u} + \frac{s}{\omega_u}\left(1 + \frac{R_z}{R}\right)}$$

$$= -\frac{\omega_o}{s} \frac{1}{1 + \frac{\omega_o}{\omega_u}} \frac{1 + sR_zC}{1 + \frac{R_z}{R}}$$

$$= -\frac{\omega_o}{s} \frac{1}{1 + \frac{\omega_o}{\omega_u}} \frac{1 + sR_zC}{1 + \frac{R_z}{R}}$$

$$= -\frac{\omega_o}{s} \frac{1}{1 + \frac{\omega_o}{\omega_u}} \frac{1 + sR_zC}{1 + \frac{R_z}{R}}$$

#### **Pole-Zero Cancellation (2)**

- We can achieve "ideal" operation by letting  $\frac{\left(1 + \frac{R_z}{R}\right)}{\omega_u \left(1 + \frac{\omega_o}{\omega_u}\right)} = R_z C$

- Assuming  $\omega_u >> \omega_0$ , this is accomplished for  $R_z \cong \frac{1}{\omega_u C}$

- In high-speed filters, this trick typically helps reduce the amplifier bandwidth requirements by more than an order of magnitude

- Note that the requirements do not drop to "zero" because we still need to maintain  $\omega_u >> \omega_0$

- Practicality issue: How to ensure that  $R_Z$  tracks variations in  $\omega_u$  and C, for both global variations and random mismatch errors

B. Murmann EE315A - Chapter 4 17

## **Auxiliary Amplifiers**

- · No (good) way to cancel error from inverting or summing amplifiers

- But these amplifiers also contribute to the overall phase shift

#### "Tweaking" a Tow-Thomas Biquad

L. C. Thomas, "The Biquad: Part I -Some Practical Design Considerations," IEEE Trans. Ckt. Theory, Vol. CT-I, No. 3, May 1971.

- May be able to cancel the phase error from all stages by introducing a "strategically" tuned zero

- Practicality questionable

B. Murmann EE315A - Chapter 4 19

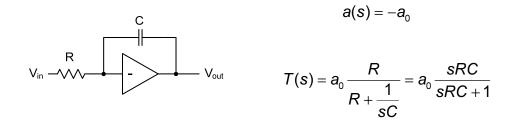

#### **RC Integrator with Finite Gain**

$$A_{actual}(s) = -\frac{1}{sRC} \frac{1}{1 + \frac{1}{T(s)}} = -\frac{1}{sRC} \frac{1}{1 + \frac{1 + sRC}{a_0 sRC}} = -\omega_0 \frac{1}{s \left(1 + \frac{1}{a_0}\right) + \frac{\omega_0}{a_0}}$$

#### **Effect on Filter Response**

· For the case of finite gain, we can therefore write

$$p_{\text{ideal}} = p_{\text{actual}} \left( 1 + \frac{1}{a_0} \right) + \frac{\omega_0}{a_0}$$

· For the case of high-Q poles, it can then be shown that

$$Q_{ ext{Pactual}} \cong Q_{ ext{Pideal}} rac{1}{1 + 2 rac{Q_{ ext{Pideal}}}{a_0}} \cong Q_{ ext{Pideal}} \left(1 - 2 rac{Q_{ ext{Pideal}}}{a_0}

ight)$$

• Example for  $Q_{pideal} = 30$ , <2% (0.17dB) decrease in  $Q_{Pactual}$

$$2 \cdot \frac{30}{a_0} < 2\%$$

$a_0 > 3000$

B. Murmann EE315A - Chapter 4 21

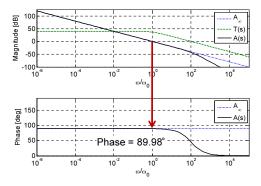

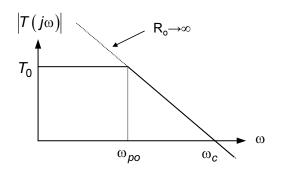

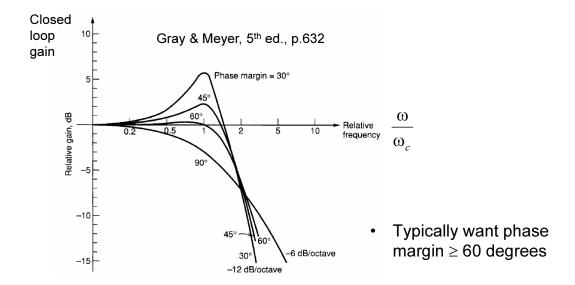

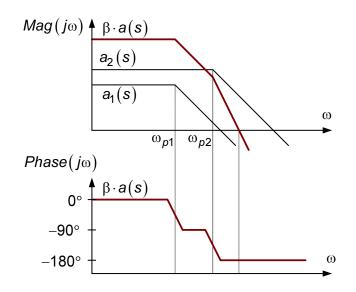

#### **Summary**

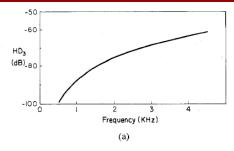

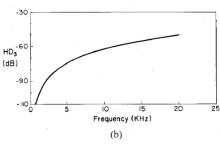

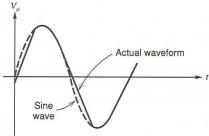

- Finite amplifier bandwidth leads to Q<sub>P</sub> enhancement

- Typically seen as excess peaking in the filter's magnitude response

- Finite amplifier gain leads to Q<sub>P</sub> degradation

- Typically seen as droop in the filter's magnitude response

- Wait!

- Can't we cancel the Q<sub>P</sub> enhancement against the Q<sub>P</sub> degradation?

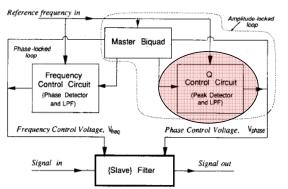

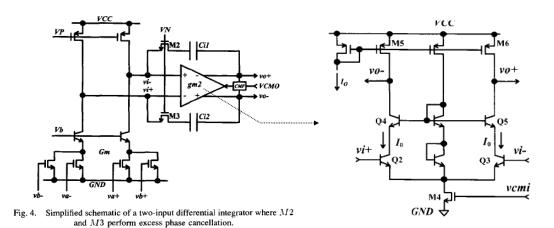

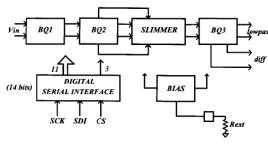

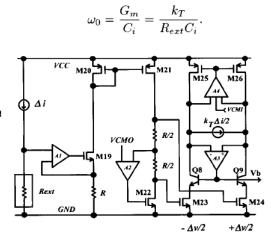

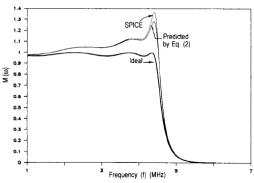

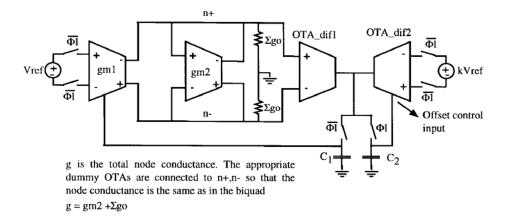

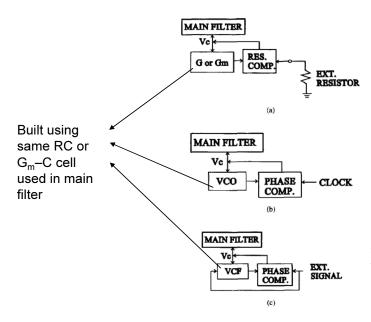

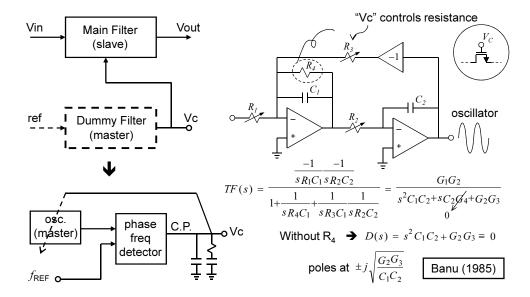

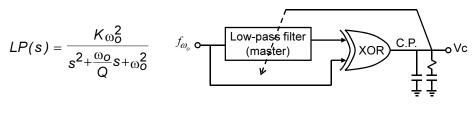

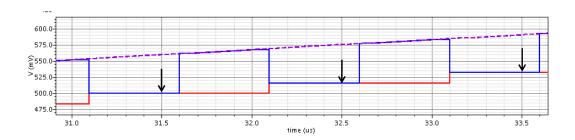

## **Q-Tuning**

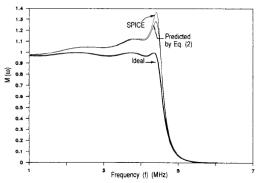

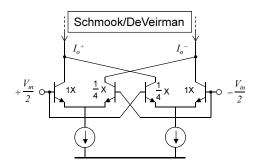

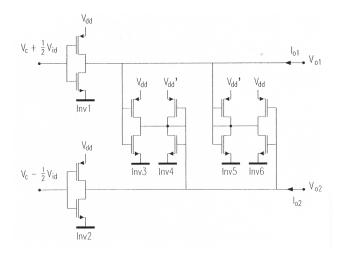

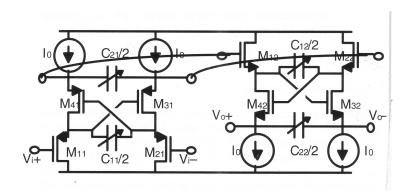

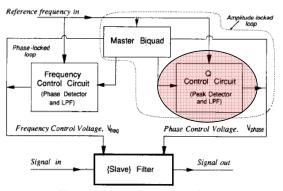

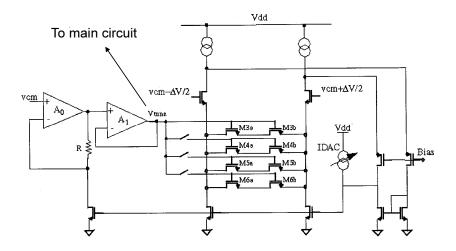

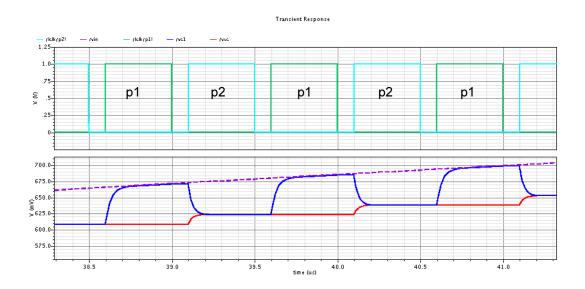

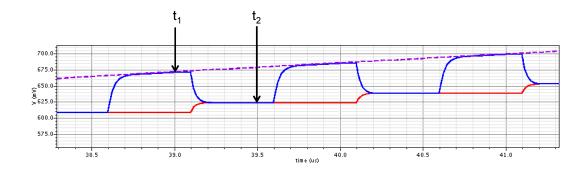

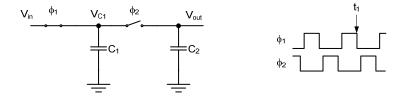

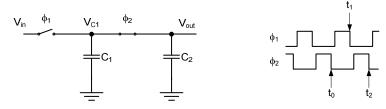

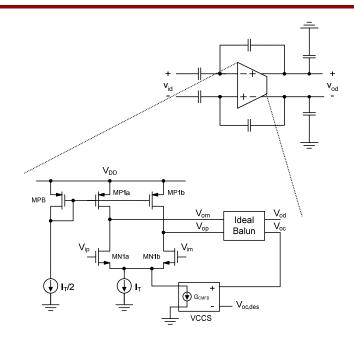

Fig. 1. Master-slave tuning scheme.

Fig. 2. Prediction of filter response with integrator nonidealities.

V. Gopinathan et al., "Design Considerations for High-Frequency Continuous-Time Filters and Implementation of an Anti-aliasing Filter for Digital Video," IEEE JSSC, Vol. 25, No. 6, Dec. 1990.

B. Murmann EE315A - Chapter 4 23

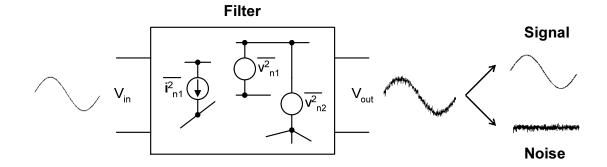

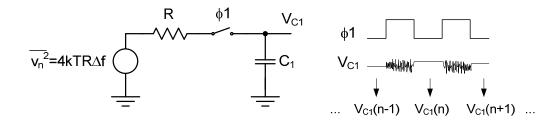

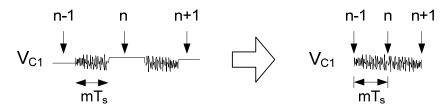

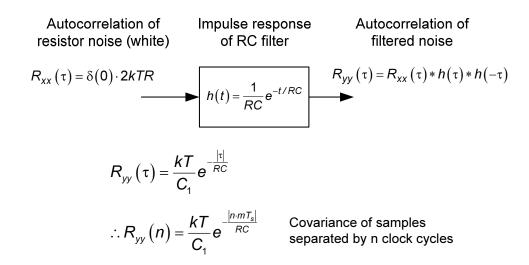

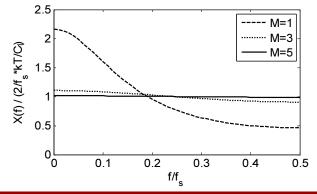

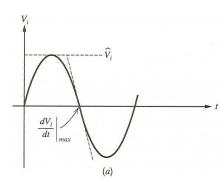

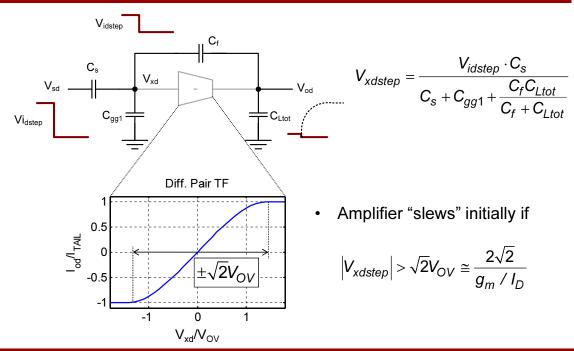

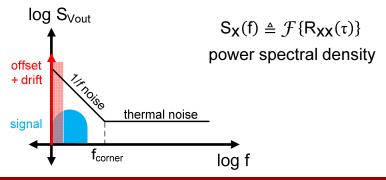

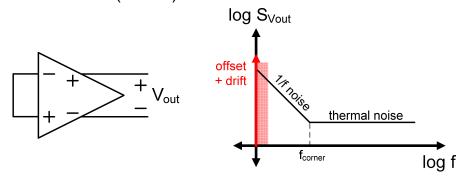

#### **Noise**

$$SNR = \frac{P_{signal}}{P_{noise}} = \frac{\frac{1}{2}\hat{V}_{out}^2}{\int_{f_1}^{f_2} \frac{V_{out}^2}{\Delta f} \cdot df}$$

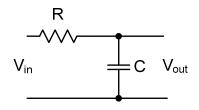

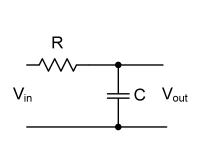

#### **RC Lowpass Filter**

$$\overline{v_{out}^{2}} = \int_{f_{1}}^{f_{2}} 4kTR \cdot \left| \frac{1}{1 + j2\pi f \cdot RC} \right|^{2} df$$

$$= 4kTR \int_{f_{1}}^{f_{2}} \frac{df}{1 + (2\pi fRC)^{2}}; \qquad \int \frac{du}{1 + u^{2}} = tan^{-1}u$$

EE315A - Chapter 4 B. Murmann

## **Total Integrated Noise**

$$\frac{\nabla^{2}_{out,tot}}{\nabla^{2}_{out,tot}} = \int_{0}^{\infty} 4kTR \cdot \left| \frac{1}{1+j2\pi f \cdot RC} \right|^{2} df$$

$$= 4kTR \int_{0}^{\infty} \frac{df}{1+(2\pi fRC)^{2}}; \quad \int \frac{du}{1+u^{2}} = tan^{-1}u$$

$$= 4kTR \cdot \frac{1}{4RC}$$

$$= \frac{kT}{C}$$

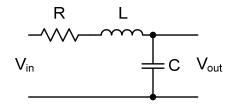

#### **LC Lowpass Filter**

$$\overline{v_{out,tot}^2} = \int_0^\infty 4kTR \cdot \left| \frac{1}{1 + \frac{s}{\omega_P Q_P} + \frac{s^2}{\omega_P^2}} \right|^2 df$$

$$Q_P = \frac{1}{\sqrt{LC}}$$

$$\omega_P = \frac{1}{\sqrt{LC}}$$

$$Q_P = \frac{1}{R} \sqrt{\frac{L}{C}}$$

B. Murmann EE315A - Chapter 4

#### **Useful Integrals**

$$\begin{split} \int_0^\infty \left| \frac{1}{1+\frac{s}{\omega_0}} \right|^2 df &= \frac{\omega_0}{4} \\ \int_0^\infty \left| \frac{1}{1+\frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2}} \right|^2 df &= \frac{\omega_0 Q}{4} \\ \int_0^\infty \left| \frac{\frac{s}{\omega_0}}{1+\frac{s}{\omega_0 Q} + \frac{s^2}{\omega_0^2}} \right|^2 df &= \frac{\omega_0 Q}{4} \end{split}$$

$$\int_0^\infty \left| \frac{n_2 s^2 + n_1 s + n_0}{d_3 s^3 + d_2 s^2 + d_1 s + d_0} \right|_{s=j\omega}^2 df = 1/4 \frac{n_2^2 d_1 d_0 + n_1^2 d_3 d_0 + n_0^2 d_3 d_2 - 2 n_2 n_0 d_3 d_0}{d_3 \left( d_2 d_1 - d_3 d_0 \right) d_0}$$

A. Dastgheib and B. Murmann, "Calculation of total integrated noise in analog circuits," IEEE Trans. on Circuits and Systems I, Vol. 55, pp. 2988-2993, Nov. 2008.

#### **Total Integrated Noise of LC Filter**

$$\overline{V_{out,tot}^{2}} = \int_{0}^{\infty} 4kTR \cdot \left| \frac{1}{1 + \frac{s}{\omega_{P}Q_{P}} + \frac{s^{2}}{\omega_{P}^{2}}} \right|^{2} df \qquad \qquad \omega_{P} = \frac{1}{\sqrt{LC}}$$

$$= 4kTR \frac{\omega_{P}Q_{P}}{4} \qquad \qquad Q_{P} = \frac{1}{R} \sqrt{\frac{L}{C}}$$

$$= \frac{kT}{C} \qquad \qquad \omega_{P}Q_{P} = \frac{1}{RC}$$

B. Murmann EE315A - Chapter 4 29

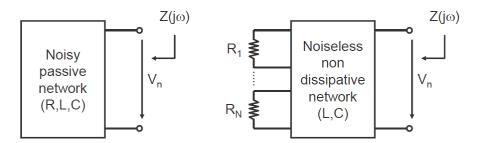

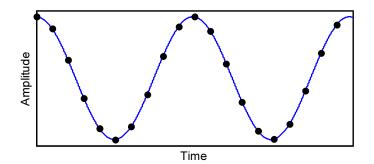

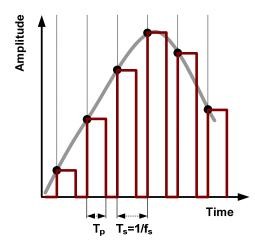

#### The Nyquist Theorem

Christian C. Enz and Eric A. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design, Wiley, 2006 (p. 106)

$$\frac{\overline{v_n^2}}{\Delta f} = 4kT \cdot Re\{Z(j2\pi f)\}$$

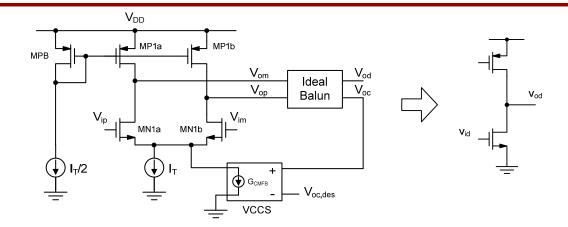

PSD

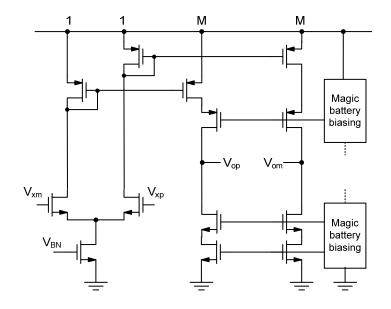

$$\overline{v_n^2} = 4kT \cdot \int_0^\infty Re\{Z(j2\pi f)\}$$

Variance

#### The Bode Theorem

Christian C. Enz and Eric A. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Model for Low-Power and RF IC Design, Wiley, 2006 (p. 107)

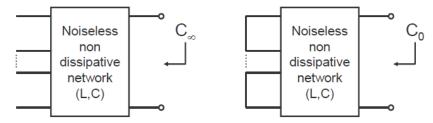

$$\frac{1}{C_{\infty}} = \lim_{s \to \infty} [s \cdot Z(s)] \qquad \qquad \frac{1}{C_0} = \lim_{s \to \infty} [s \cdot Z(s)]$$

$$\boxed{\overline{v_n^2} = kT \cdot \left[\frac{1}{C_{\infty}} - \frac{1}{C_0}\right]}$$

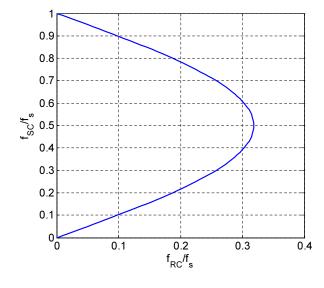

Let's you calculate the total integrated noise of passive networks without sweating through integrals!

B. Murmann EE315A - Chapter 4 31

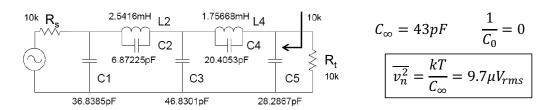

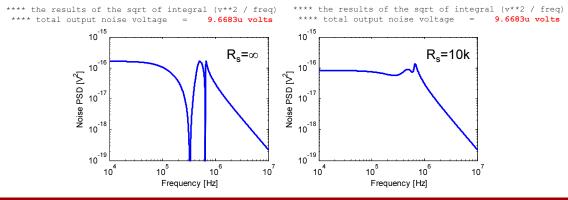

# **Example: LC Ladder**

Simulation with and without  $R_s$  (makes no difference!)

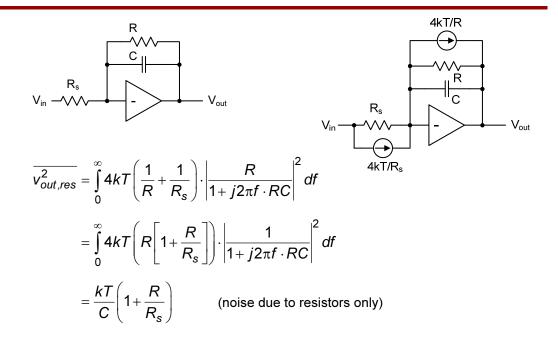

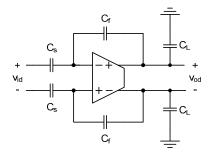

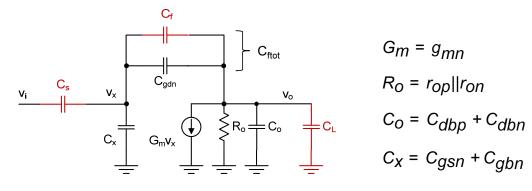

#### **Active RC Lowpass**

B. Murmann EE315A - Chapter 4 33

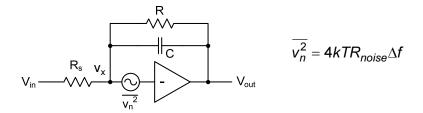

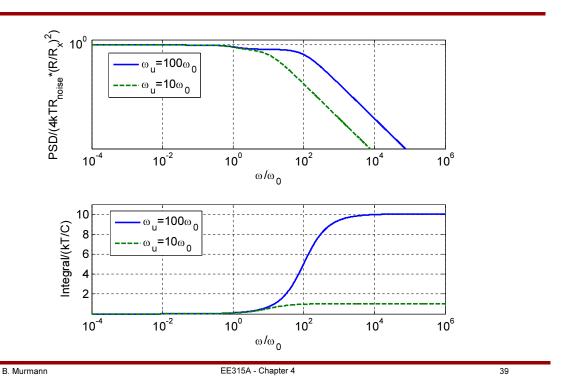

## **Amplifier Noise Analysis (1)**

$$v_{out} = -\frac{\omega_u}{s} (v_x + v_n) \qquad \frac{v_x}{v_{out}} = \frac{R_s}{R_s + \frac{1}{\frac{1}{R} + sC}} = \frac{1}{1 + \frac{R}{R_s}} \frac{1 + \frac{s}{\omega_0}}{1 + \frac{s}{\omega_x}}$$

$$\omega_0 = \frac{1}{RC} \qquad \omega_x = \frac{1}{R_x C} \qquad R_x = R \| R_s$$

#### **Amplifier Noise Analysis (2)**

Solving for  $v_{out}/v_n$  yields

$$\frac{V_{out}}{V_n} = -\frac{R}{R_x} \frac{1 + \frac{s}{\omega_x}}{1 + s\left(\frac{1}{\omega_u} \frac{R}{R_x} + \frac{1}{\omega_0}\right) + \frac{s^2}{\omega_u \omega_0}}$$

$$\frac{V_{out,amp}}{V_{out,amp}^2} = \int_0^\infty 4kTR_{noise} \cdot \left(\frac{R}{R_x}\right)^2 \frac{1 + \frac{s}{\omega_x}}{1 + s\left(\frac{1}{\omega_u} \frac{R}{R_x} + \frac{1}{\omega_0}\right) + \frac{s^2}{\omega_u \omega_0}} df$$

$$\frac{1 + \frac{s}{z}}{1 + \frac{s}{z}} \frac{1}{\omega_u \omega_0} df = \frac{\omega_n Q}{1 + \frac{\omega_n^2}{2}} \frac{1 + \frac{\omega_n^2}{2}}{1 + \frac{\omega_n^2}{2}} \frac{\omega_n Q}{1 + \frac{\omega_n^2}{2}} \frac{1 + \frac{s}{\omega_n^2}}{1 + \frac{s}{\omega_n^2}} \frac{1 + \frac{s}{\omega_n^2}}{1 + \frac{s}{\omega_$$

$$\int_{0}^{\infty} \left| \frac{1 + \frac{s}{z}}{1 + \frac{s}{\omega_{n}Q} + \frac{s^{2}}{\omega_{n}^{2}}} \right|^{2} df = \frac{\omega_{n}Q}{4} \left( 1 + \frac{\omega_{n}^{2}}{|z|^{2}} \right) \qquad \qquad \omega_{n}Q = \left( \frac{1}{\omega_{u}} \frac{R}{R_{x}} + \frac{1}{\omega_{0}} \right)^{-1}$$

$$\omega_{n}^{2} = \omega_{u}\omega_{0} \qquad z = -\omega_{x}$$

B. Murmann EE315A - Chapter 4

#### **Amplifier Noise Analysis (3)**

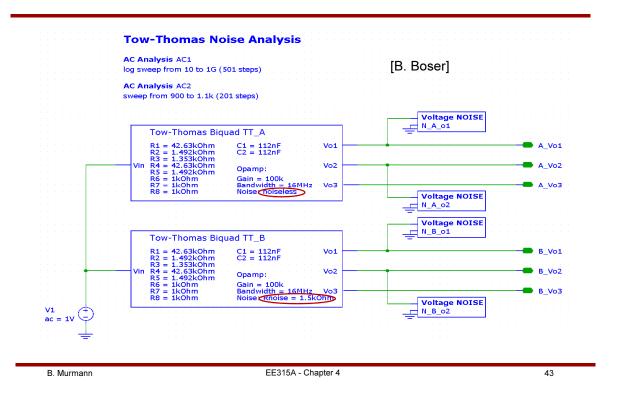

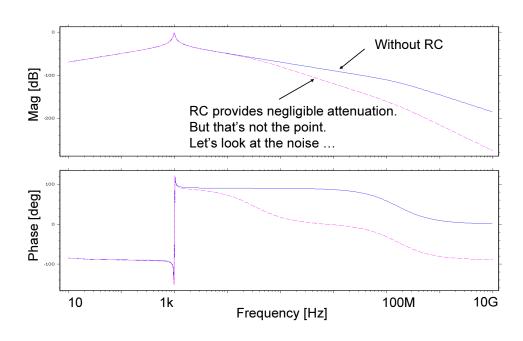

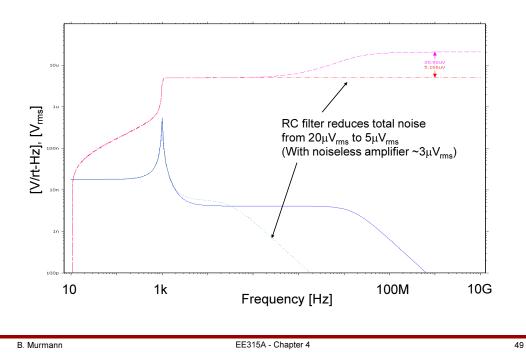

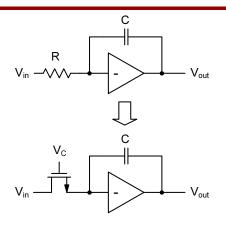

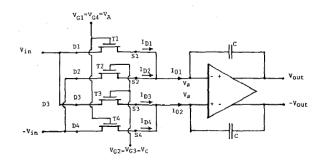

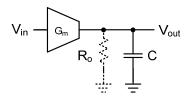

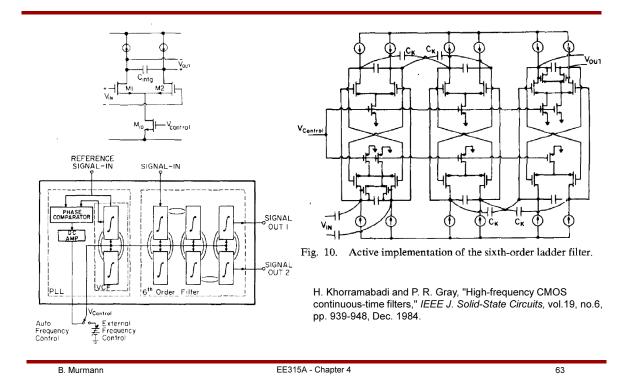

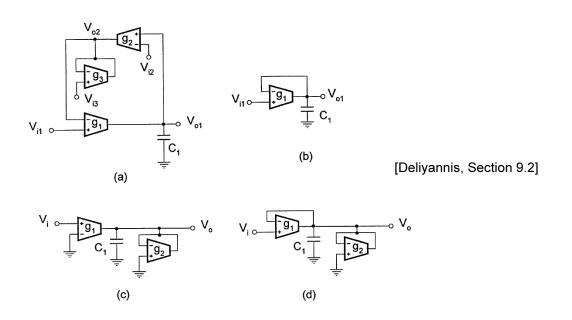

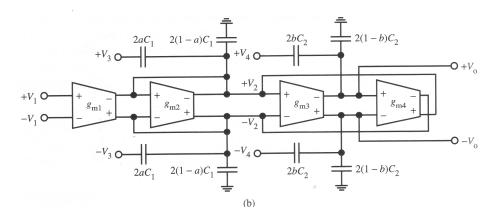

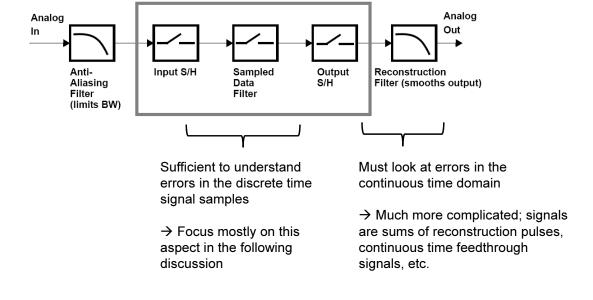

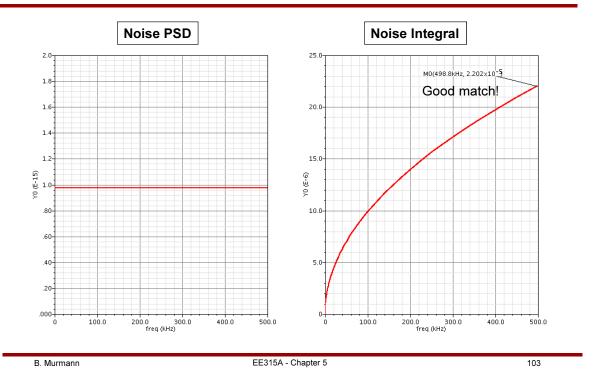

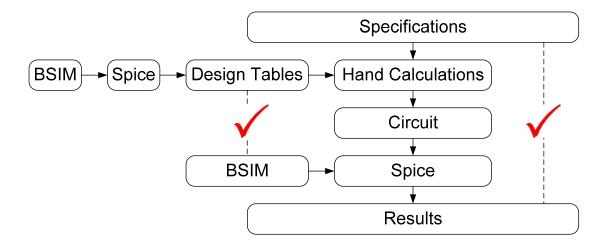

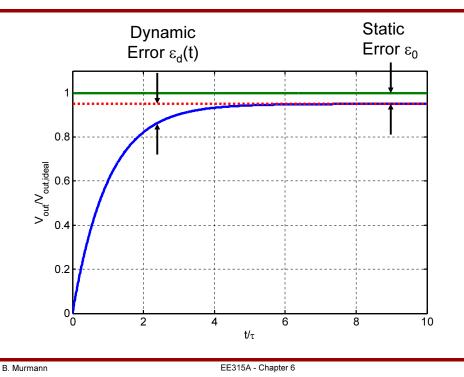

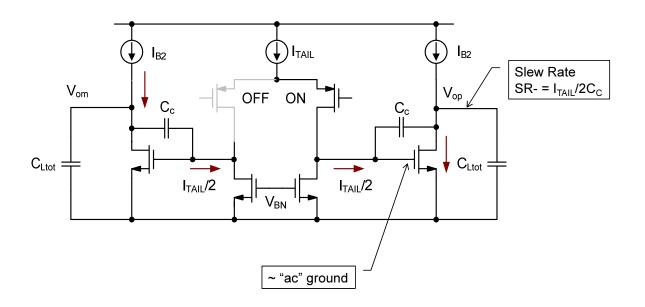

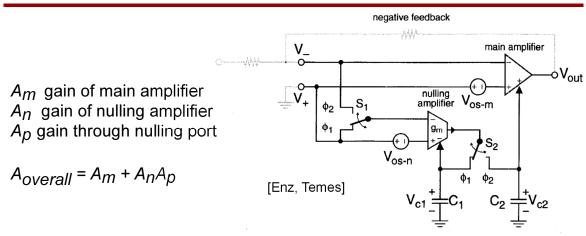

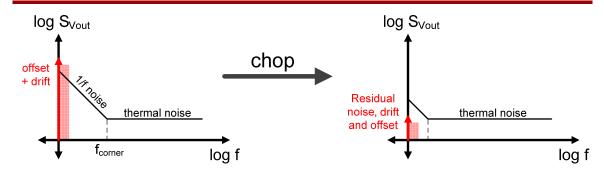

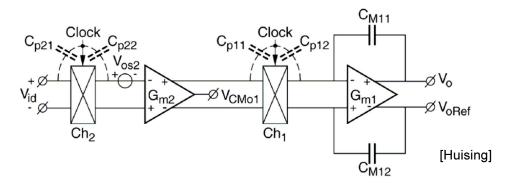

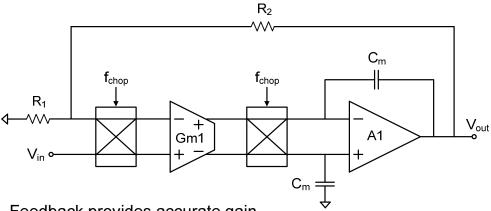

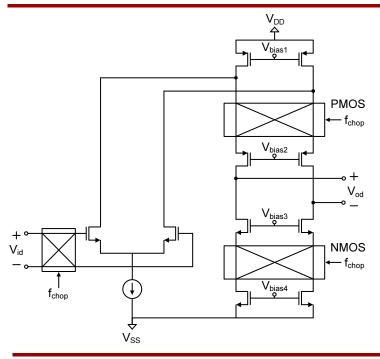

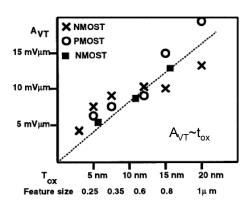

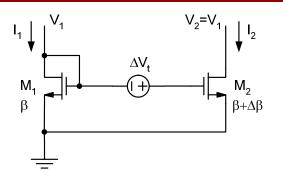

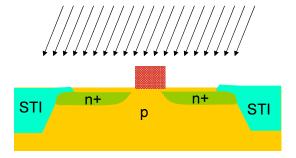

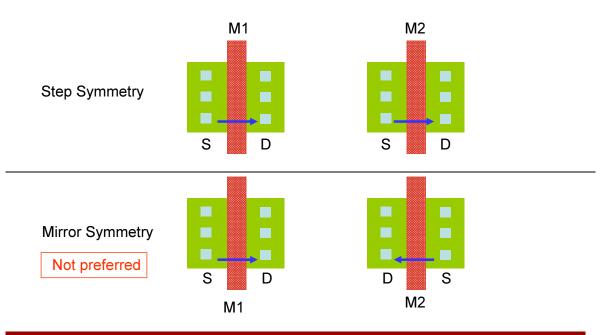

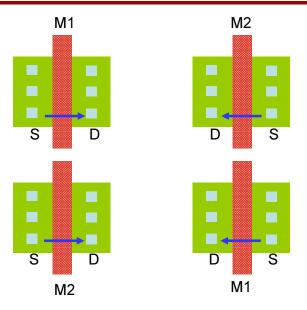

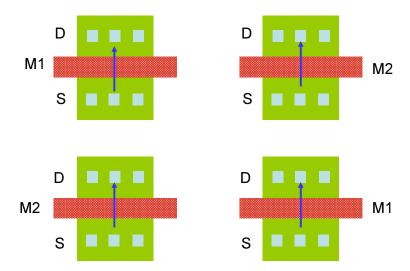

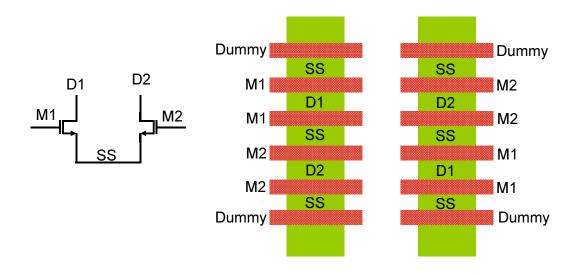

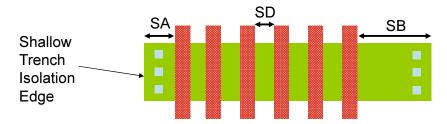

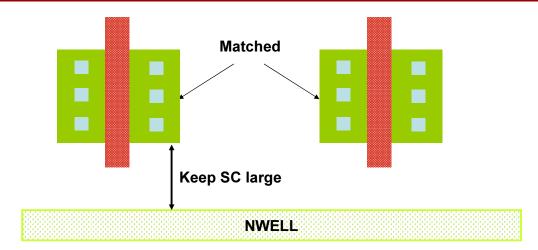

$$\overline{v_{out,amp}^2} = 4kTR_{noise} \left(\frac{R}{R_x}\right)^2 \frac{\omega_n Q}{4} \left(1 + \frac{\omega_n^2}{|z|^2}\right) = kTR_{noise} \left(\frac{R}{R_x}\right)^2 \left(\frac{1}{\frac{1}{\omega_u}} \frac{R}{R_x} + \frac{1}{\omega_0}\right) \left(1 + \frac{\omega_u \omega_0}{\omega_x^2}\right)$$