# MOSFET MODELING & BSIM3 USER'S GUIDE

Yuhua Cheng Chenming Hu

## MOSFET MODELING & BSIM3 USER'S GUIDE

This page intentionally left blank.

## MOSFET MODELING & BSIM3 USER'S GUIDE

by

#### Yuhua Cheng Conexant Systems, Inc.

and

**Chenming Hu** University of California, Berkeley

#### **KLUWER ACADEMIC PUBLISHERS**

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN 0-306-47050-0 Print ISBN 0-792-38575-6

©2002 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: and Kluwer's eBookstore at: http://www.kluweronline.com http://www.ebooks.kluweronline.com

### Contents

| Contents v |                                                 |      |

|------------|-------------------------------------------------|------|

| Prefa      | ce                                              | xiii |

| Chapt      | er 1 Introduction                               | 1    |

| 1.1        | Compact MOSFET Modeling for Circuit Simulation  | 1    |

| 1.2        | The Trends of Compact MOSFET Modeling           | 5    |

|            | 1.2.1 Modeling new physical effects             | 5    |

|            | 1.2.2 High frequency (HF) analog compact models | 6    |

|            | 1.2.3 Simulation robustness and efficiency      | 7    |

|            | 1.2.4 Model standardization                     | 8    |

|            | References                                      | 8    |

#### Chapter 2 Significant Physical Effects In Modern MOSFETs...13

| 2.1 | MOSFET Classification and Operation                          | 13 |

|-----|--------------------------------------------------------------|----|

|     | 2.1.1 Strong inversion region (Vgs>Vth)                      | 17 |

|     | 2.1.2 Weak and moderate inversion or the subthreshold region |    |

| 2.2 | Effects Impacting the Threshold Voltage                      | 18 |

|     | 2.2.1 Non-uniform doping effects                             | 19 |

|     | 2.2.2 Normal short channel effects                           |    |

|      | 2.2.3 Reverse short channel effects           | . 23 |

|------|-----------------------------------------------|------|

|      | 2.2.4 Normal narrow-width effects             | . 25 |

|      | 2.2.5 Reverse narrow-width effects            |      |

|      | 2.2.6 Body bias effect and bulk charge effect | ·28  |

| 2.3  | Channel Charge Theory                         | . 30 |

|      | 2.3.1 Accumulation                            | . 33 |

|      | 2.3.2 Depletion                               | . 33 |

|      | 2.3.3 Inversion                               | . 34 |

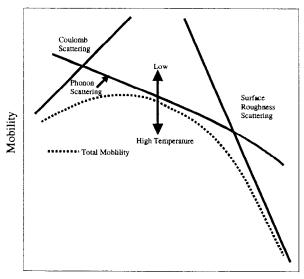

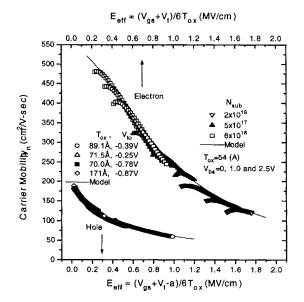

| 2.4  | Carrier Mobility                              | . 37 |

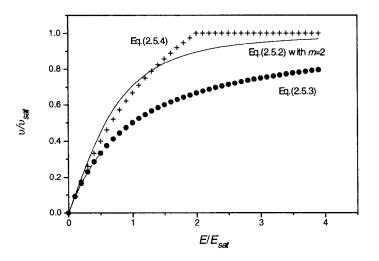

| 2.5  | Velocity Saturation                           | . 39 |

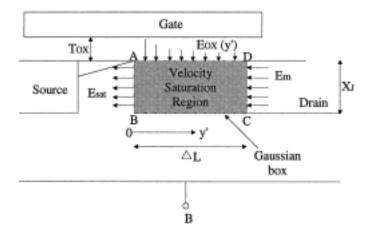

| 2.6  | Channel Length Modulation                     | . 41 |

| 2.7  | Substrate Current Due to Impact Ionization    | .44  |

| 2.8  | Polysilicon Gate Depletion                    | .48  |

| 2.9  | Velocity Overshoot Effects                    | . 51 |

| 2.10 | Self-heating Effect                           | . 53 |

| 2.11 | Inversion Layer Quantization Effects          | . 55 |

|      | References                                    | . 57 |

|      |                                               |      |

| Chapt | ter 3 Threshold Voltage Model                                                    | 65  |

|-------|----------------------------------------------------------------------------------|-----|

| 3.1   | Threshold Voltage Model for Long Channel Devices                                 | 65  |

| 3.2   | Threshold Voltage Model with Short Channel Effects                               |     |

|       | 3.2.1 Charge sharing model                                                       |     |

|       | 3.2.2 Quasi 2-D models for drain induced barrier lowering effect                 |     |

| 3.3   | Narrow Width Effect Model                                                        |     |

| 3.4   | Threshold Voltage Model in BSIM3v3                                               | 80  |

|       | 3.4.1 Modeling of the vertical non-uniform doping effects                        |     |

|       | 3.4.2 Modeling of the RSCE due to lateral non-uniform channel doping             |     |

|       | 3.4.3 Modeling of the short channel effect due to drain induced barrier lowering |     |

|       | 3.4.4 Modeling of the narrow width effects                                       | 88  |

|       | 3.4.5 Complete Vth model in BSIM3v3                                              | 90  |

| 3.5   | Helpful Hints                                                                    | 92  |

|       | References                                                                       | 101 |

| Chapt | ter 4 I-V Model                                                                  | 105 |

4.1 Essential Equations Describing the I-V Characteristics ......105

| 4.2 | Channel Charge Density Model                                 |     |

|-----|--------------------------------------------------------------|-----|

|     | 4.2.1 Channel charge model in the strong inversion region    |     |

|     | 4.2.2 Channel charge model in the subthreshold region        |     |

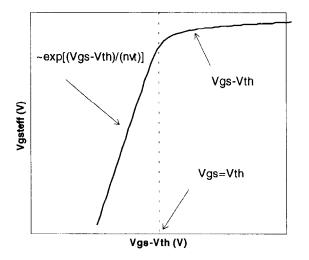

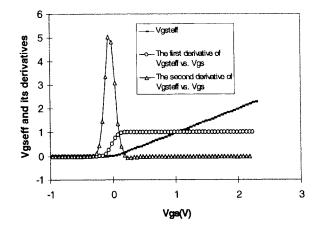

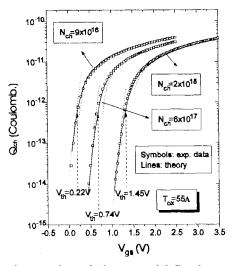

|     | 4.2.3 Continuous channel charge model of BSIM3v3             |     |

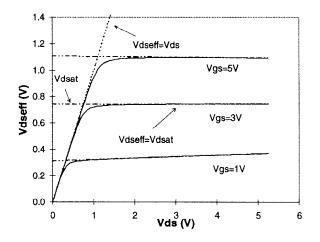

|     | 4.2.4 Continuous channel charge model with the effect of Vds |     |

| 4.3 | Mobility Model                                               | 114 |

|     | 4.3.1 Piece-wise mobility models                             | 114 |

|     | 4.3.2 Mobility models in BSIM3v3                             | 116 |

| 4.4 | I-V Model in the Strong Inversion Region                     | 117 |

|     | 4.4.1 I-V model in the linear (triode) region                | 117 |

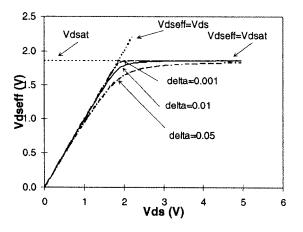

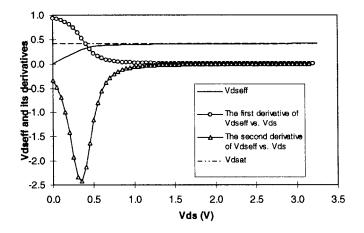

|     | 4.4.2 Drain voltage at current saturation, Vdsat             | 118 |

|     | 4.4.3 Current and output resistance in the saturation region |     |

| 4.5 | Subthreshold I-V Model                                       | 124 |

| 4.6 | Single Equation I-V model of BSIM3v3                         |     |

| 4.7 | Polysilicon Gate Depletion Effect                            | 129 |

| 4.8 | Helpful Hints                                                | 130 |

|     | References                                                   | 140 |

|     |                                                              |     |

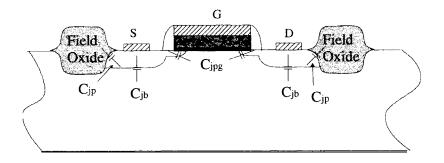

| Chapte | er 5 Capacitance Model                                                    | 143   |

|--------|---------------------------------------------------------------------------|-------|

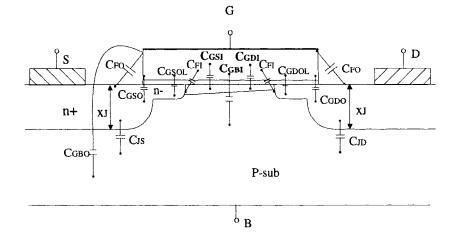

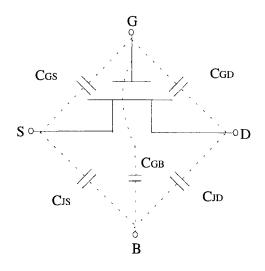

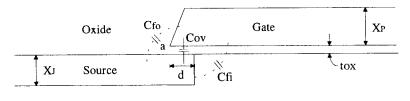

| 5.1    | Capacitance Components in a MOSFET                                        | . 144 |

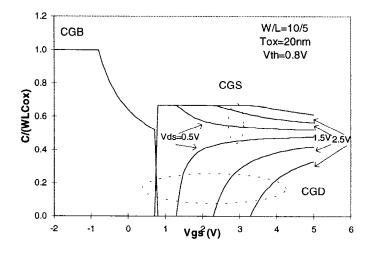

| 5.2    | Intrinsic Capacitance Model                                               | .145  |

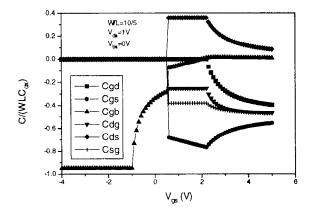

|        | 5.2.1 Meyer model                                                         | . 145 |

|        | 5.2.2 Shortcomings of the Meyer model                                     | . 151 |

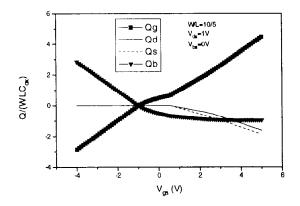

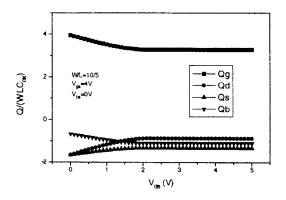

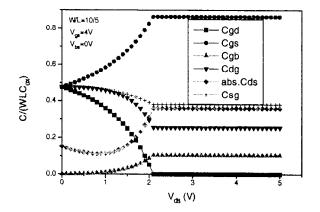

|        | 5.2.3 Charge-based capacitance model                                      | .154  |

| 5.3    | Extrinsic Capacitance Model                                               | .161  |

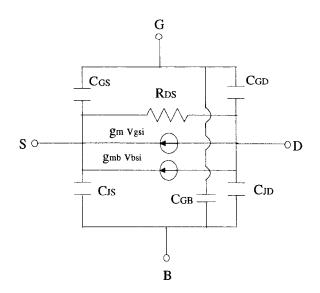

| 5.4    | Capacitance Model of BSIM3v3                                              | .163  |

|        | 5.4.1 Long channel capacitance model (capMod=0)                           | . 164 |

|        | 5.4.2 Short channel capacitance (capMod=1)                                | . 170 |

|        | 5.4.3 Single-equation short channel capacitance model (capMod=2)          | .178  |

|        | 5.4.4 Short channel capacitance model with quantization effect (capMod=3) | . 186 |

| 5.5    | Channel Length/Width in Capacitance Model                                 | .197  |

| 5.6    | Helpful Hints                                                             | . 198 |

|        | References                                                                | .207  |

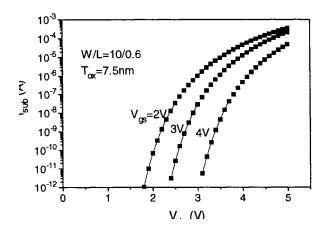

| Chapter | 6 Substrate Current Model   |     |

|---------|-----------------------------|-----|

| 6.1 Si  | ubstrate Current Generation | 211 |

| 6.2 | Substrate Current Model in BSIM3v3 | 212 |

|-----|------------------------------------|-----|

|     | Helpful Hints                      |     |

|     | References                         |     |

\_\_\_\_\_

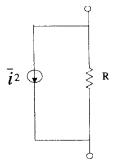

#### Chapter 7 Noise Model ......219

| 7.1 | The Physical Mechanisms of Flicker (1/f) Noise       |     |

|-----|------------------------------------------------------|-----|

| 7.2 | The Physical Mechanism of Thermal Noise              |     |

| 7.3 | Flicker Noise Models in BSIM3v3                      |     |

|     | 7.3.1 SPICE2 flicker noise model (noiMod=1)          |     |

|     | 7.3.2 Unified flicker noise model (noiMod=2)         | 222 |

| 7.4 | Thermal Noise Models in BSIM3v3                      |     |

|     | 7.4.1 Modified SPICE2 thermal noise model (noiMod=1) | 230 |

|     | 7.4.2 BSIM3 thermal noise model (noiMod=2)           |     |

| 7.5 | Helpful Hints                                        |     |

|     | References                                           |     |

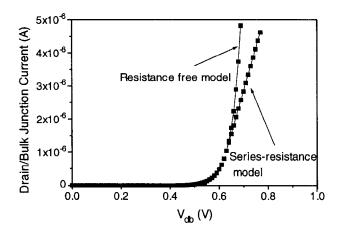

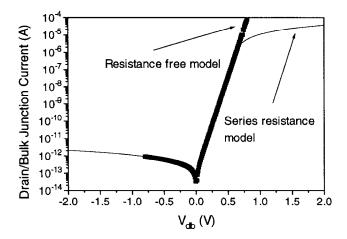

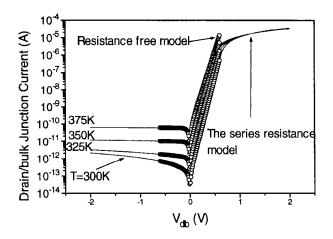

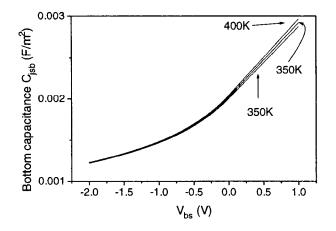

| Chapt | er 8 Source/Drain Parasitics Model                               |  |

|-------|------------------------------------------------------------------|--|

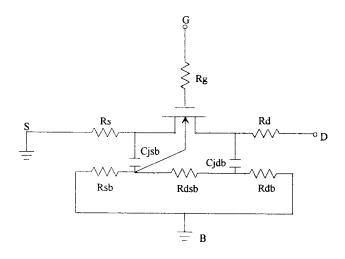

| 8.1   | Parasitic Components in a MOSFET                                 |  |

| 8.2   | Models of Parasitic Components in BSIM3v3                        |  |

|       | 8.2.1 Source and drain series resistances                        |  |

|       | 8.2.2 DC model of the source/drain diodes                        |  |

|       | 8.2.3 Capacitance model of the source/bulk and drain/bulk diodes |  |

| 8.3   | Helpful Hints                                                    |  |

|       | References                                                       |  |

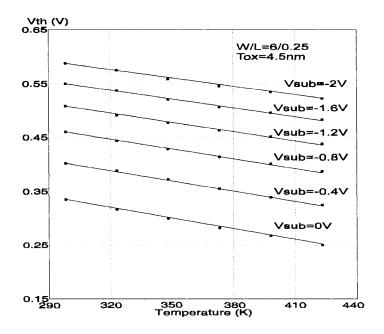

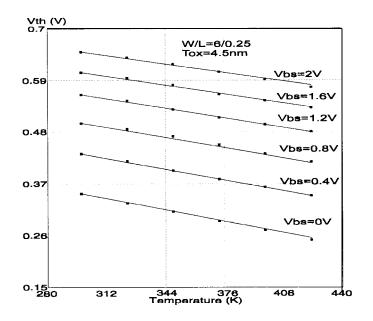

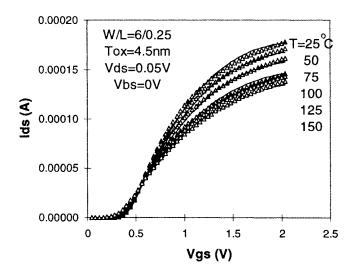

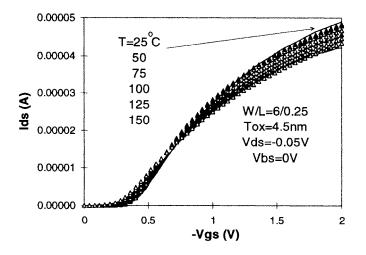

| Cha | pter 9  | Temperature Dependence Model                                |     |

|-----|---------|-------------------------------------------------------------|-----|

| 9.  | l Temp  | erature Effects in a MOSFET                                 | 263 |

| 9.  | 2 Temp  | erature Dependence Models in BSIM3v3                        | 265 |

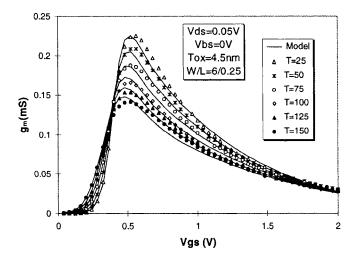

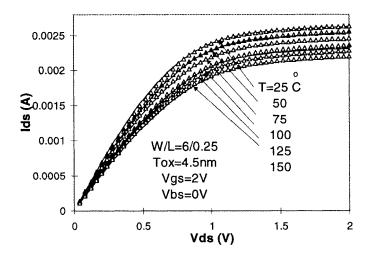

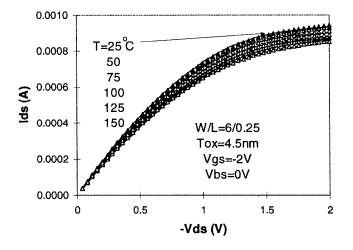

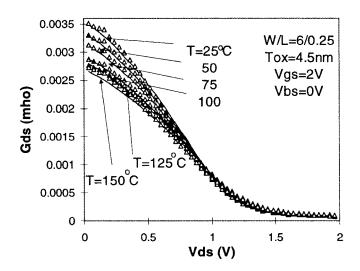

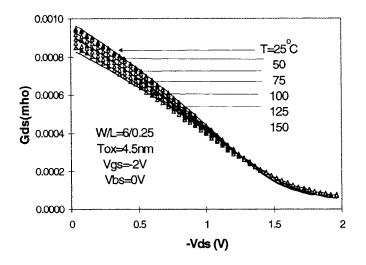

| 9.  | 3 Com   | parison of the Temperature-Effect Models with Measured Data | 270 |

| 9.  | 4 Helpf | ul Hints                                                    | 276 |

|     | Refer   | ences                                                       | 279 |

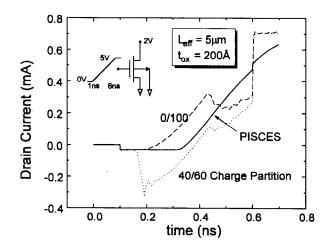

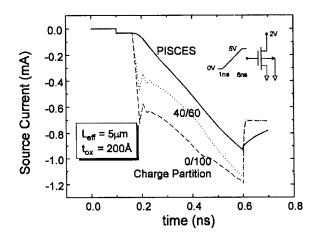

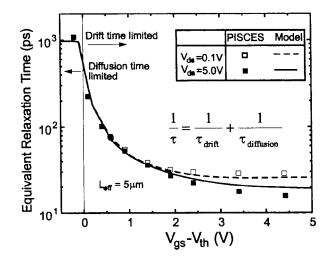

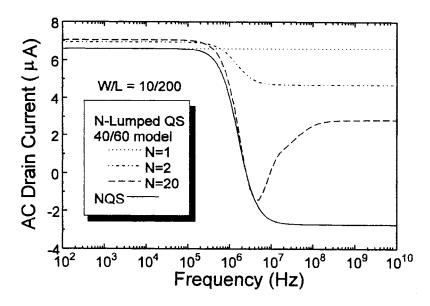

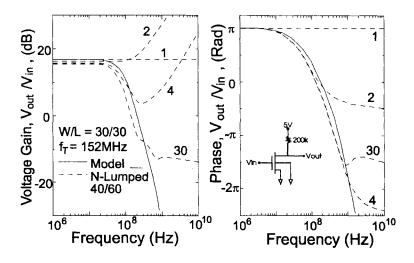

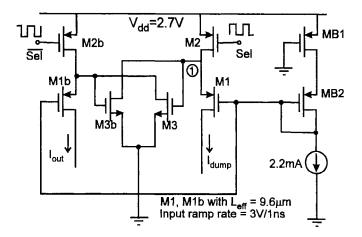

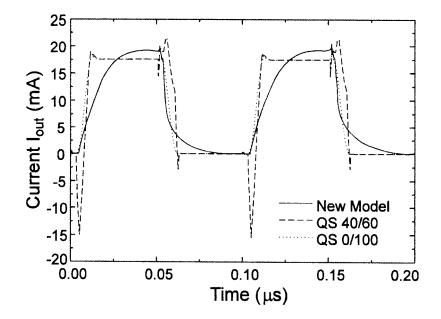

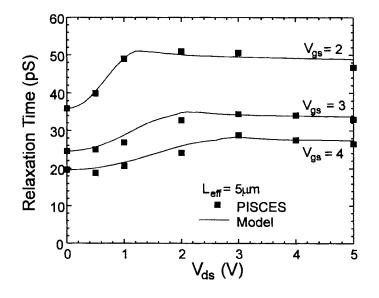

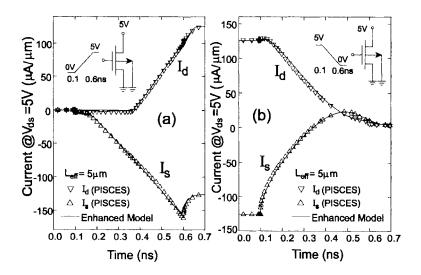

| Chapter 10  | Non-quasi Static (NQS) Model.   |  |

|-------------|---------------------------------|--|

| 10.1 The Ne | cessity of Modeling NQS Effects |  |

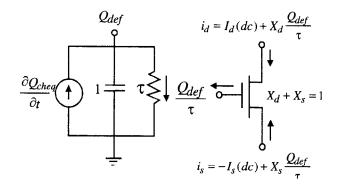

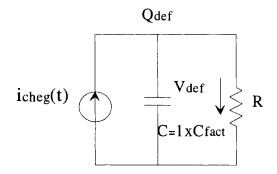

| 10.2 The NQS Model in BSIM3v3             |  |

|-------------------------------------------|--|

| 10.2.1 Physics basis and model derivation |  |

| 10.2.2 The BSIM3 NQS model                |  |

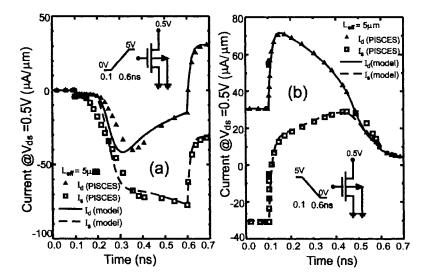

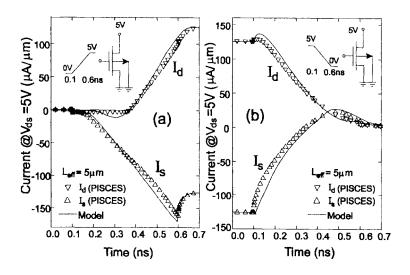

| 10.3 Test Results of the NQS Model        |  |

| 10.4 Helpful Hints                        |  |

| References                                |  |

####

| 11.1 | General Structure of BSIM3v3 Model Implementation         | 303 |

|------|-----------------------------------------------------------|-----|

| 11.2 | Robustness Consideration in the Implementation of BSIM3v3 | 306 |

| 11.3 | Testing of Model Implementation                           | 315 |

| 11.4 | Model Selectors of BSIM3v3                                | 317 |

| 11.5 | Helpful Hints                                             | 319 |

|      | References                                                | 324 |

| Chapte | er 12 Model Testing                                   | 327 |

|--------|-------------------------------------------------------|-----|

| -      | Requirements for a MOSFET Model in Circuit Simulation |     |

| 12.2   | Benchmark Tests                                       | 329 |

| 12.3   | Benchmark Test Results                                | 333 |

| 12.4   | Helpful Hints                                         | 350 |

|        | References                                            | 351 |

###

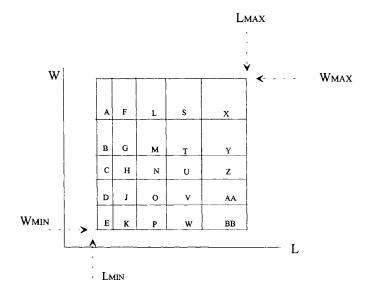

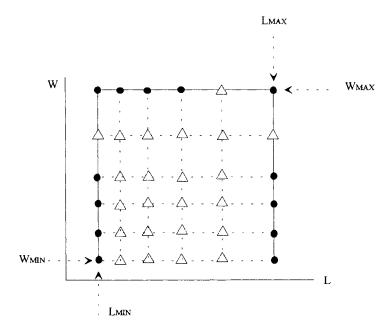

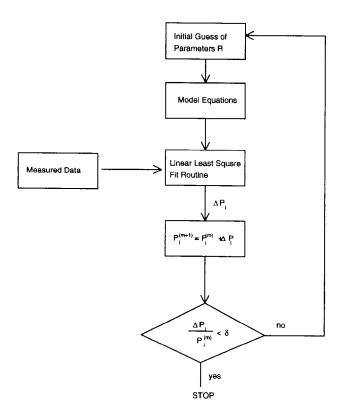

| 13.1 | Overview of Model Parameter Extraction          | 353 |

|------|-------------------------------------------------|-----|

| 13.2 | Parameter Extraction for BSIM3v3                | 355 |

|      | 13.2.1 Optimization and extraction strategy     | 355 |

|      | 13.2.2 Extraction routines                      | 355 |

| 13.3 | Binning Methodology                             | 367 |

| 13.4 | Recommended Value Range of the Model Parameters | 368 |

| 13.5 | Automated Parameter Extraction Tool             | 372 |

|      | References                                      | 373 |

|      |                                                 |     |

####

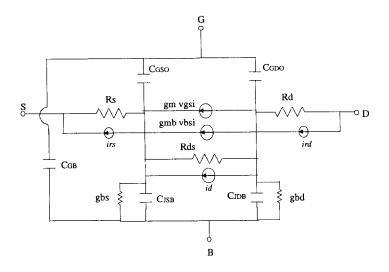

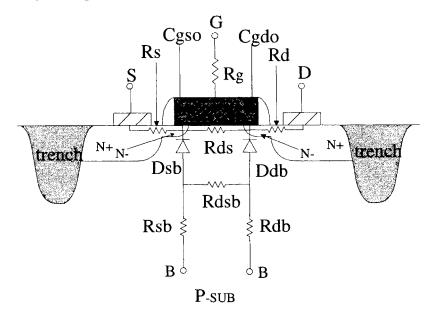

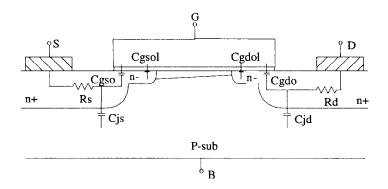

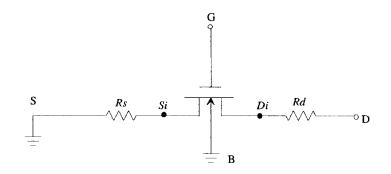

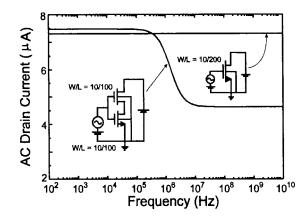

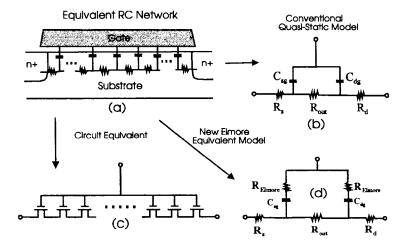

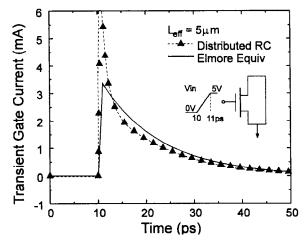

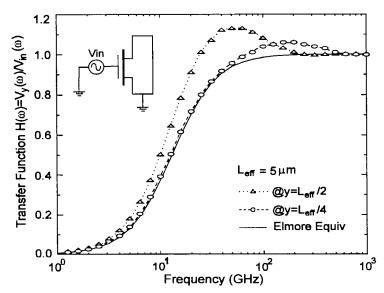

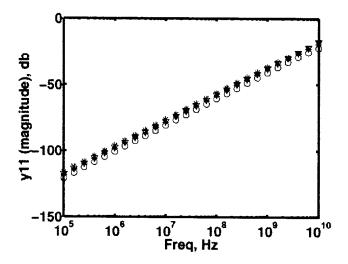

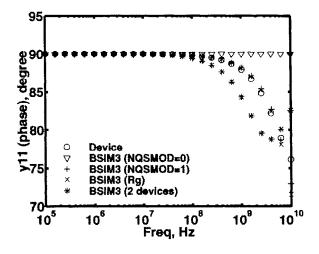

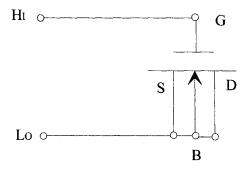

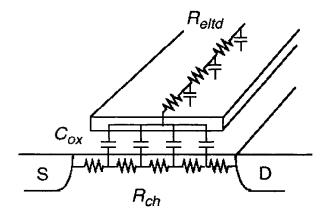

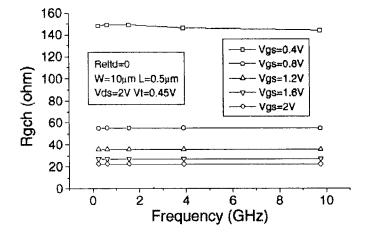

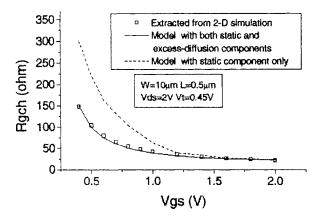

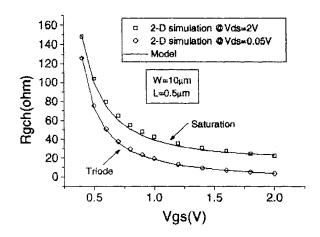

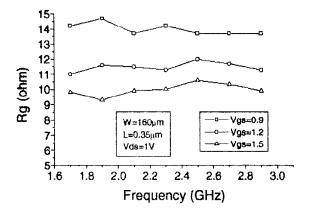

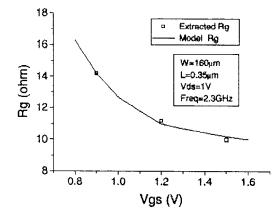

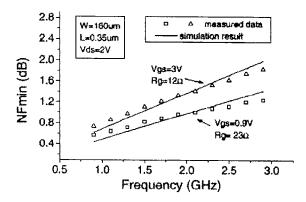

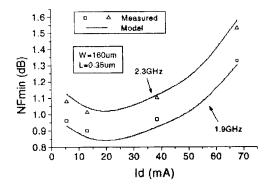

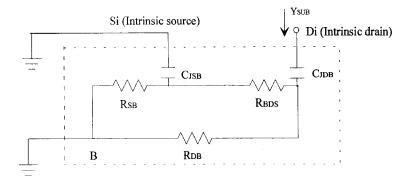

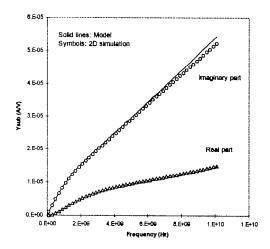

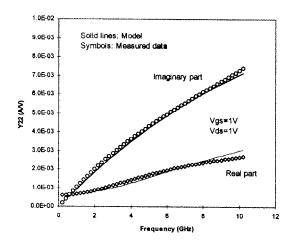

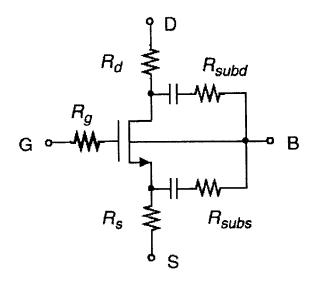

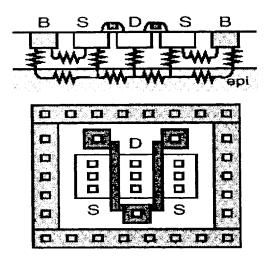

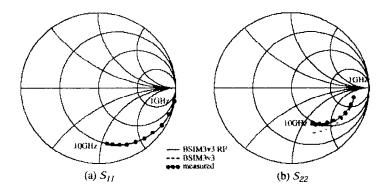

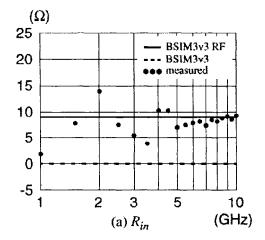

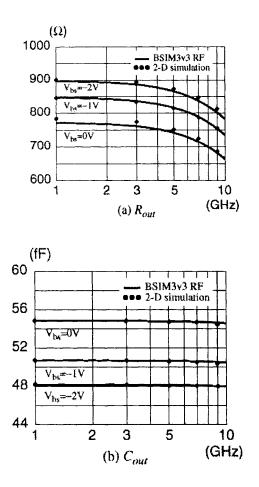

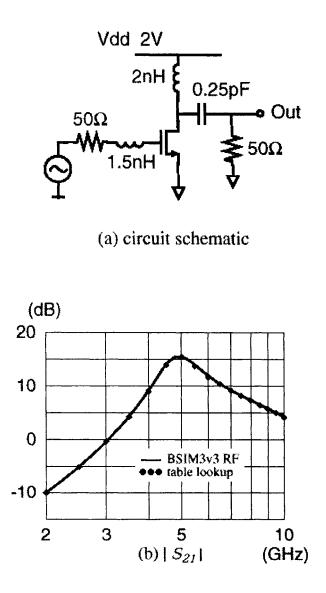

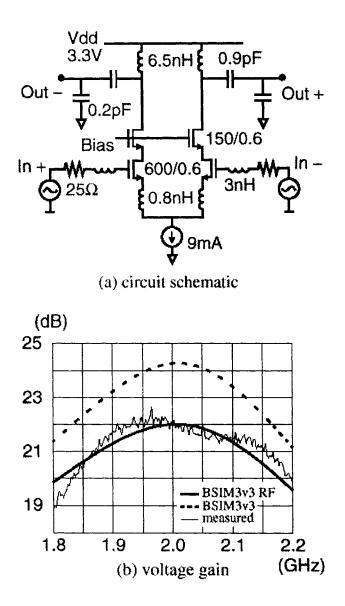

| 14.1 | RF Modeling                                                          | 375   |

|------|----------------------------------------------------------------------|-------|

|      | 14.1.1 Modeling of the gate resistance                               |       |

|      | 14.1.2 Modeling the substrate network                                | . 383 |

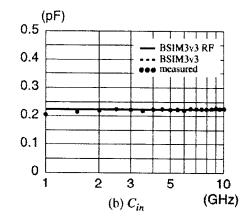

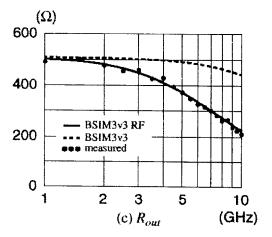

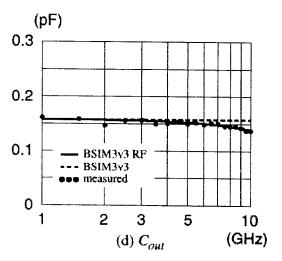

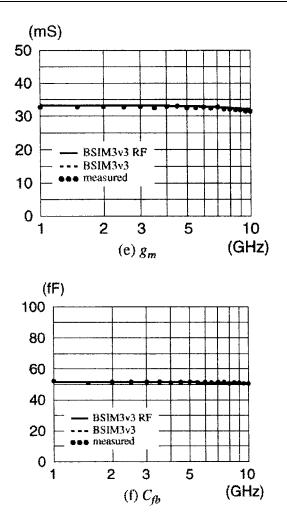

|      | 14.1.3 A RF MOSFET model based on BSIM3v3 for GHz communication IC's | .385  |

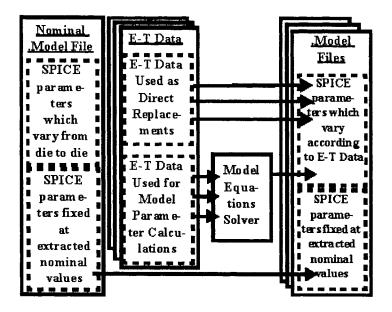

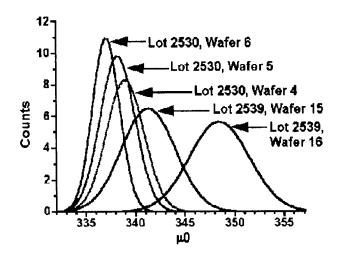

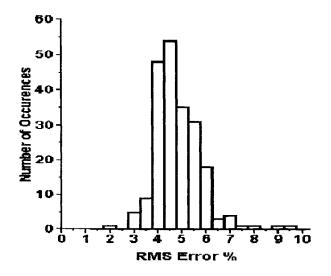

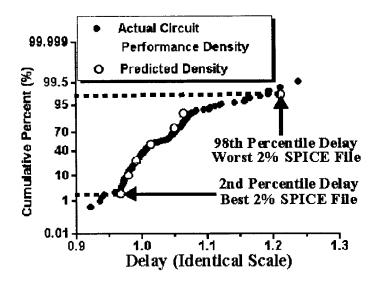

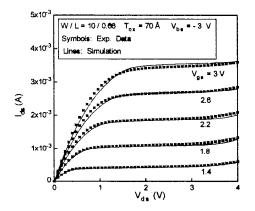

| 14.2 | Statistical Modeling                                                 | 393   |

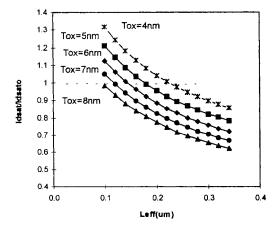

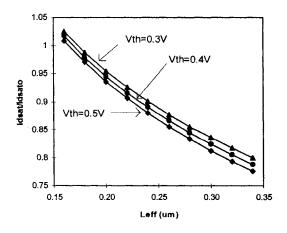

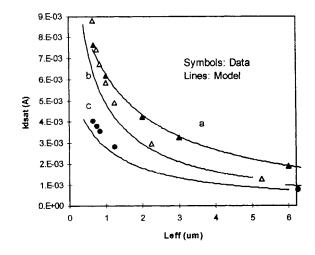

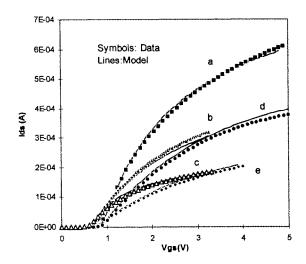

| 14.3 | Technology Extrapolation and Prediction Using BSIM3 Model            | .399  |

|      | References                                                           | .406  |

####

| A.1   | Model control parameters                                   |     |

|-------|------------------------------------------------------------|-----|

| A.2   | Process parameters                                         |     |

| A.3   | Parameters for Vth model                                   |     |

| A.4   | Parameters for I-V model                                   |     |

| A.5   | Parameters for capacitance model                           |     |

| A. 6  | Parameters for effective channel length/width in I-V model |     |

| A. 7  | Parameters for effective channel length/width in C-V model |     |

| A.8   | Parameters for substrate current model                     |     |

| A.9   | Parameters for noise models                                | 417 |

| A. 10 | Parameters for models of parasitic components              | 418 |

| A.11  | Parameters for models of temperature effects               | 419 |

| A.12  | Parameters for NQS model                                   |     |

####

| B.1        | Vth equations                       |     |

|------------|-------------------------------------|-----|

| <i>B.2</i> | Effective Vgs-Vth                   |     |

| B.3        | Mobility                            |     |

| <i>B.4</i> | Drain saturation voltage            |     |

| B.5        | Effective Vds                       |     |

| B.6        | Drain current expression            |     |

| B.7        | Substrate current                   |     |

| B.8        | Polysilicon depletion effect        |     |

| B.9        | Effective channel length and width  |     |

| B.10       | Drain/Source resistance             | 426 |

| B.11       | Capacitance model equations         |     |

|            | Noise model equations               |     |

|            | DC model of the source/drain diodes |     |

| B.14 | Capacitance model of the source/bulk and drain/bulk diodes | 444 |

|------|------------------------------------------------------------|-----|

| B.15 | Temperature effects                                        | 445 |

| B.16 | NQS model equations                                        | 447 |

| B.17 | A note on the poly-gate depletion effect                   | 448 |

| Appendix C | Enhancements and Changes in BSIM3v3.1 versus |

|------------|----------------------------------------------|

| BSIM3v3.0  | 449                                          |

|            |                                              |

| <i>C. I</i> | Enhancements     | 449 |

|-------------|------------------|-----|

| <i>C.2</i>  | Detailed changes | 449 |

| Appendix<br>BSIM3v3.1 | D Enhancements and Changes in BSIM3v3.2 versus<br>1 | 5<br>5 |

|-----------------------|-----------------------------------------------------|--------|

| D.1                   | Enhancements                                        | 55     |

| D.2                   | Detailed changes                                    | 6      |

|                       |                                                     |        |

| Index |

|-------|

|-------|

This page intentionally left blank.

### Preface

At the dawn of its fifth decade, the semiconductor industry continues to grow at an amazing pace. High-speed and low-power integrated circuits (IC) are used in an ever expanding plethora of applications, permeating every aspect of human life. A critical part of this technology is high-quality circuit design.

Circuit simulation is an essential tool in designing integrated circuits. The accuracy of circuit simulation depends on the accuracy of the model of the transistors. Reduction in transistor size continually complicates the device physics and makes device modeling more challenging and sophisticated. Recently, BSIM3v3 (BSIM for Berkeley Short-channel IGFET Model) was selected as the first MOSFET model for standardization by the Compact Model Council, consisting of many leading companies in the semiconductor industry such as Advanced Micro Devices, Analog Devices, Avant!, BTA Technology, Cadence design Systems, Compaq, Conexant Systems (formerly Rockwell Semicondutor Systems), Hewlett Packard, Hitachi, IBM, Intel, Lucent Technologies, Mentor Graphics, Motorola, NEC, Philips, Siemens, Texas Instruments, and TSMC. This is a historic milestone in device modeling for circuit design.

As two of the principal developers of BSIM3v3, the authors have received hundreds of comments and questions from device engineers and circuit designers. They revealed to us the areas and the points that require explana-

tions and clarifications. We realized the need for a reference book on BSIM3 that takes the readers from device physics through model equations to applications in circuit design.

This book explains the important physical effects in MOSFETs, and presents the derivations of the model expressions. The purpose is to help the model users understand the concepts and physical meanings of the model equations and parameters. The book emphasizes the BSIM3 compact model for use in digital, analog and RF circuit design. It covers the complete set of models, i.e., I-V model, capacitance model, noise model, parasitic diode model, substrate current model, temperature effect model and non-quasi-static model. The book also addresses model implementation and new applications such as technology prediction using BSIM3. As a special feature of this book, many helpful hints based on our personal knowledge and experience are presented at the end of chapters 3 through 12 to help readers understand and use the models correctly and effectively.

This book is a summary of the contributions from many former and current colleagues and students. One of us (CH) had the distinct pleasure of collaborating with Prof. Ping K. Ko, Hong Kong University of Science and Technology (formerly with University of California, Berkeley) on the development of BSIM1, BSIM2, and BSIM3, and MOSFET physics research over a period of 15 years. His contributions to BSIM3 are countless. Dr. Jianhui Huang is one of the principal developers of the first version of BSIM3. It is a pleasure to acknowledge the following contributors to the development of BSIM3v3: Mansun Chan, Zhihong Liu, Minchie Jeng, Kelvin Hui, Weidong Liu, Xiaodong Jin, Jeff Ou, Kai Chen, James Chen, Ya-chin King, and Michael Orshansky.

We would like to acknowledge many colleagues in the Compact Model Council, Britt Brooks, Bhaskar Gadepally, Keith Green, Tom Vrotsos, Colin McAndrew, David Newmark, Marc McSwain, Pratheep Balasingam, Bob Daniel, Mishel Matloubian, Sally Liu, Shiuh-Wuu Lee, Chris Lyons, Joseph Watts and many more for their valuable inputs and comments that have been incorporated in BSIM3 and, indirectly, into this book.

We thank Prof. Michael Shur of Rensselaer Polytechnic Institute, Prof. Tor A. Fjeldly of Norwegian University of Science and Technology, and Dr. Mishel Matloubian of Conexant Systems, for reviewing the manuscript and giving helpful comments. We also thank Dennis Sylvester for technical editing, Jeff

Ou, Weidong Liu, Xiaodong Jin, Sandeep D'souza, Michael Orshansky, Mark Cao, and Pin Su for reading and commenting on individual chapters. Finally we would like to give our thanks to our families for their patience, support and help that made this book possible.

Yuhua Cheng Conexant Systems, Inc. Newport Beach, CA

Chenming Hu University of California Berkeley, CA This page intentionally left blank.

**CHAPTER 1**

Introduction

This chapter presents a brief review of the history and recent developments of MOSFET compact modeling for circuit simulation. We first survey the scene of open MOSFET compact models. Then we discuss the trends of compact model development.

## 1.1 Compact MOSFET Modeling for Circuit Simulation

During the 1970's, MOS technology emerged as the major driving force for VLSI [1.1]. At the same time, circuit simulators, principally SPICE, appeared as tools for circuit design. The development of SPICE started at the University of California at Berkeley in the late 1960s, and continued into the 90's [1.2].Today, commercial SPICE simulators such as HSPICE (Avant!), SPEC-TRE (Cadence), ELDO (Mentor Graphics), SSPICE (Silvaco), PSPICE (MicroSim) are widely used for circuit simulation. In addition, many semiconductor companies use their proprietary circuit simulators. There is also a class of fast circuit simulators such as Starsim (Avant!) and Timemill (Synopsis) that can achieve much faster simulation speeds than SPICE. In order to use these simulators, device models are needed to describe the device behaviors in the circuits. In other words, device models are the link between the physical world (technology, manufacturing, ...) and the design world (device

level simulation, timing simulator model, macro model, synthesis, ...) of the semiconductor industry. In the development of modern MOS technology, many new processing techniques have been introduced into IC fabrication, and the channel length of MOSFETs has been scaled down to the  $0.1\mu m$  range. The increasing level of complexity of the device structure and the appearance of new physical mechanisms that govern the characteristics of advanced devices have increased the difficulty of device modeling.

Today, circuit simulators are employed to optimize circuit performance, and verify timing and functionality of circuits. The accuracy of SPICE simulation is mainly determined by the accuracy of the device models since the simulation algorithms and convergence techniques in circuit simulators have become mature [1.3, 1.4]. As a result, there is a strong need for accurate device models to predict circuit performance. In addition to accuracy, it is desirable for a compact model to have some predictive capability. For example, a device model should ideally predict the effect of device size fluctuations and technology modifications so that it can be used by the circuit designers to study the statistical behavior of the circuits, and to explore circuit design for a modified or more advanced technology.

There are three categories of device models, (1) numerical models, (2) table lookup models, and (3) analytical (or compact) models.

Two or three dimensional numerical models use device geometry, doping profiles, and carrier transport equations, which are solved numerically, to get the device electrical characteristics [1.5, 1.6, 1.7]. Since these numerical models are computationally intensive they are not used for simulation of large circuits. Instead, numerical models may be used, for example, to explore the effects of a new transistor structure on the speed of a small ring oscillator. Table look-up models present the measured device current and capacitance as functions of bias voltages and device sizes in a tabular form for access by the circuit simulators [1.8]. There are many advantages to generate the data tables from analytical models rather than directly from the measured data. Table look-up models are used in the fast circuit simulators. Numerical models and pure table look-up models are far less popular for circuit simulation than the compact model and are not the subject of this book.

Analytical or compact models are based on device physics. However, some analytical models have such a poor grounding in device physics that they are not much more than empirical curve fitting equations. This type of empirical model [1.9] is no longer popular. The compact model equations are necessarily long and complex in order to describe the device characteristics accurately in all the operation regimes [1.10-1.25]. Fitting parameters are introduced to improve the accuracy of the model. Most of the models used in today's simulators are examples of such physical compact models.

Very sophisticated models such as the Pao-Sah model have been available to explain the device characteristics for a long time [1.26, 1.27]. These models were too complicated, i.e. too time consuming for circuit simulation and they require iteration or integration and are only semi-analytical models. These models played an important role in describing the physics of MOSFETs but were not intended nor suitable for use in circuit simulators. Simpler models have also been developed to clarify the device physics [1.28]. The explicit development of MOSFET compact models for circuit simulation started with the appearance of circuit simulators in the 1970's. Since then, more than 100 MOSFET models, including, MOS 1 [1.10], MOS 2 [1.11], MOS 3 [1.12], MOS9 [1.20], PCIM [1.18], EKV [1.21], Level 28 [1.29], ISIM [1.19], BSIM1 [1.13], BSIM2 [1.14], and BSIM3 [1.15, 1.16, 1.17] have been reported. Many of these models have been implemented in various circuit simulators but only a small number are used widely [1.29, 1.30, 1.31]. Some of these are closed (meaning the model equations are known only to the owner of the model) and proprietary (meaning the access to the model is controlled) models, such as Level 28 in HSPICE [1.29]. Implemented in nearly all circuit simulators, MOS 1, MOS 2, MOS 3, BSIM1, BSIM2, and BSIM3 are examples of open MOSFET models in the sense that the model equations are public knowledge and free licenses of the source code are provided to all users [1.10-1.17]. Some of these models can be downloaded from worldwide-web sites freely, such as BSIM3v3 [1.32]. We now give a brief review of some of these public compact models.

MOS 1 is a very simple MOSFET model based on device physics appropriate for long-channel and uniform-doping devices used two decades ago [1.10]. Because the model equations are simple and easy for circuit designers to understand, MOS 1 is still used occasionally for hand calculation and preliminary circuit simulation.

MOS 2 includes more device physics than MOS 1 [1.11]. However, it is still not accurate for devices with submicron geometries.

MOS 3 introduced many empirical parameters to model short channel effects [1.12]. However, the accuracy and scalability (the ability to model devices over a wide range of channel length and width using one set of model param-

eters) of the model is not entirely satisfactory to the circuit designers. The short channel and narrow width effects are not modeled accurately in the MOS 1, 2, and 3 models and high field effects are not considered properly because of the limited understanding of the physics of short channel devices at the time these models were developed.

BSIM1 (Berkeley Short Channel IGFET Model 1) was developed for 1 $\mu$ m MOSFET technology [1.13]. It incorporated some improved understanding of the short channel effects, and worked well for devices with channel length of 1  $\mu$ m and above. However, it also introduced several fitting parameters for each model parameter just to enhance the model scalability. Even then, the model scalability was not totally satisfactory. Also, circuit designers did not like the use of the many fitting parameters which did not have any physical meaning.

BSIM2 improved upon the BSIM1 model in several aspects such as model continuity, output conductance, and subthreshold current [1.14]. However, the model still cannot use one set of parameters for a wide range of device sizes. Users typically need to generate a few or many sets of model parameters (process files), each covering a limited range of device geometries in order to obtain good accuracy over the full range of device sizes. This makes the parameter extraction difficult. Also it is difficult to use these parameters to perform statistical modeling or extrapolation of the model parameters from the present technology to a future one.

To address these issues, BSIM3 was developed from a coherent quasi-twodimensional analysis of the MOSFET. The device theory has been developed over a number of years [1.15, 1.17]. The model explicitly takes into account the effects of many device size and process variables for good model scalability and predictability. The short channel and narrow width effects as well as high-field effects are well modeled.

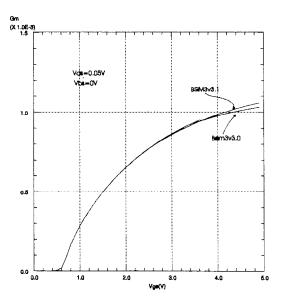

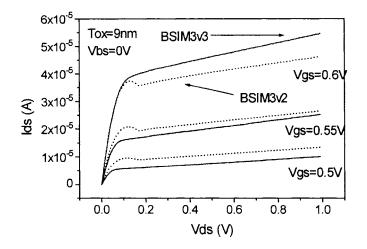

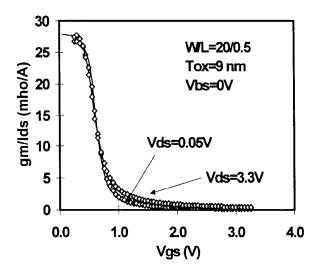

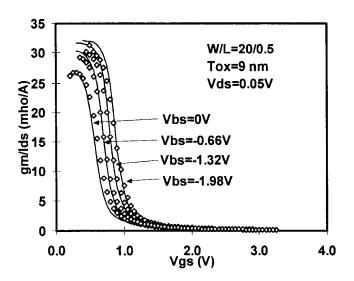

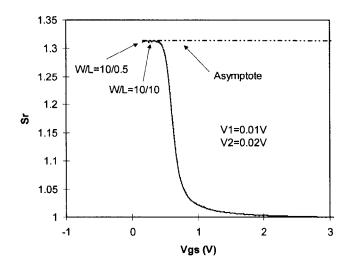

The first version of BSIM3 was released in 1994 [1.15]. BSIM3v2 (BSIM3 version 2) has been implemented in many circuit simulators [1.29, 1.30, 1.31]. BSIM3v2 has better model accuracy and scalability than the previous BSIM models but still suffers from discontinuity problems such as negative conductance and glitches in the  $g_m/I_d$  vs.  $V_g$  plot at the boundary between weak inversion and strong inversion. In the mean time, the need for a good open MOSFET model had been widely recognized by the semiconductor companies.

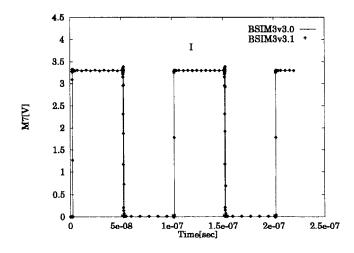

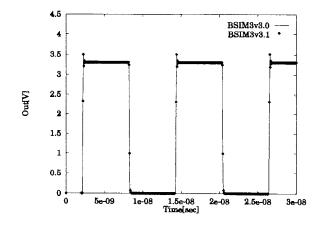

To eliminate all the kinks and glitches in BSIM3v2, BSIM3v3 (BSIM3 version 3) uses a single-equation approach with enhanced modeling of small size and other physical effects [1.16, 1.33]. The first version, BSIM3v3.0, was released in Oct. 1995 [1.32]. The model is scalable and may even be considered predictive, and can be used for statistical analysis [1.34, 1.35, 1.36]. It has been verified extensively by both model developers and model users from many different companies [1.37, 1.38], and has been selected as the first compact MOSFET model for industry standardization [1.39]. The next version, BSIM3v3.1, was released in Dec. 1996 with improvements in the robustness of model implementation, modification of source/drain diode models, parameter checking etc. [1.40]. The convergence performance of BSIM3v3.1 was enhanced in comparison with BSIM3v3.0, according to tests on many benchmark circuits. It is now used widely in the semiconductor industry. The latest version, BSIM3v3.2, was released in June 1998. It introduces a new charge/ capacitance model that accounts for the quantization effect, and improves the threshold voltage model, the substrate current model, the Non-quasi-static (NQS) model, etc. [1.41]. The research of compact MOSFET modeling is continuing with efforts from both academia and industry. Table 1.1 gives a performance comparison of the models discussed above.

| Model   | Mini-<br>mum L<br>(um) | Mini-<br>mum<br>Tox (nm) | Model<br>Continu-<br>ity | Id Accuracy<br>in Strong<br>Inversion | Id Accuracy<br>in Subthresh-<br>old | Small sig-<br>nal parame-<br>ter | Scalability |

|---------|------------------------|--------------------------|--------------------------|---------------------------------------|-------------------------------------|----------------------------------|-------------|

| MOS1    | 5                      | 50                       | POOR                     | POOR                                  | NOT MOD-<br>ELED                    | POOR                             | POOR        |

| MOS2    | 2                      | 25                       | POOR                     | POOR                                  | POOR                                | POOR                             | FAIR        |

| MOS3    | 1                      | 20                       | POOR                     | FAIR                                  | POOR                                | POOR                             | POOR        |

| BSIM1   | 0.8                    | 15                       | FAIR                     | GOOD                                  | FAIR                                | POOR                             | FAIR        |

| BSIM2   | 0.35                   | 7.5                      | FAIR                     | GOOD                                  | GOOD                                | FAIR                             | FAIR        |

| BSIM3v2 | 0.25                   | 5                        | FAIR                     | GOOD                                  | GOOD                                | GOOD                             | GOOD        |

| BSIM3v3 | 0.15                   | 4                        | GOOD                     | GOOD                                  | GOOD                                | GOOD                             | GOOD        |

**Table 1.1 Performance Comparison of Models**

#### 1.2 The Trends of Compact MOSFET Modeling

#### 1.2.1 Modeling new physical effects

For more than 20 years, continuous scaling of CMOS devices to smaller dimensions has resulted in higher device density, faster circuit speed, and lower power dissipation. Currently, 0.25µm CMOS technologies are widely used in the manufacturing of ICs [1.42, 1.43]. Meanwhile, 0.1µm CMOS

devices have been developed and the technology will be transferred to production in the first decade of the next millennium [1.44].

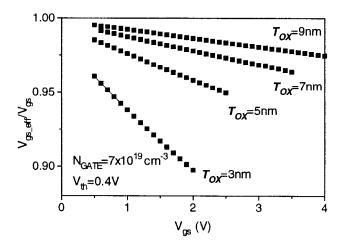

Many new physical effects become significant as the device size shrinks. Examples are the normal and reverse short-channel and narrow-width effects [1.45, 1.46, 1.47, 1.48], channel length modulation (CLM) [1.49], drain induced barrier lowering (DIBL) [1.50], velocity saturation [1.51], mobility degradation due to the vertical electric field [1.52], impact ionization [1.53], band-to-band tunneling [1.54], velocity overshoot [1.55], self-heating [1.56], channel quantization [1.57], polysilicon depletion [1.58], and so on. Some of these have been modeled well in compact models, such as the short channel effect, and velocity saturation. Some of these have been studied extensively but have not vet been widely implemented in compact models for circuit simulation, such as velocity overshoot and band-to-band tunneling. The study of new physical effects in MOS devices will continue as devices become smaller. The quantization effect and radio frequency (RF) behaviors are the new frontiers at the present. Established models for some well-known physical effects such as DIBL and CLM may need to be reinvestigated for devices with channel length of 0.1µm or less. We will discuss the important physical effects in modern MOS devices in Chapter 2. It is likely that future compact MOSFET models will include more and more physical effects.

#### 1.2.2 High frequency (HF) analog compact models

With the fast growth of the RF wireless communications market, the demand for high performance and low cost RF solutions is high. Because small MOS-FETs fabricated on silicon offer ultra-large-scale integration capability and a high cut-off frequency, RF designers have already done a lot of work to explore the use of CMOS in RF circuits [1.59]. To design and optimize circuits operating at radio frequency, accurate high frequency MOSFET models are required. Compared with the modeling of MOSFETs for both digital and analog application at lower frequencies, compact RF models are more difficult to develop and do not presently exist in commercial circuit simulators. A common modeling approach for RF applications is to build sub-circuits based on "low-frequency" MOSFET models. The accuracy of such a model depends on having the right topology for the sub-circuits, and having a methodology for extracting the parameters for the elements of the sub-circuit. Recently, work has been reported for modeling the RF performance of submicron MOS devices [1.60-1.64]. However, further study is still needed to bring HF compact modeling to the level of maturity comparable to the modeling for digital and analog circuit design at the low and intermediate frequency ranges.

Besides the well known requirements for a compact MOSFET model in lower frequency applications, such as accuracy and scalability of the DC model [1.65, 1.66], there are additional requirements unique to the RF model. They include [1.67]:

(1) the model should accurately predict the bias dependence of small signal parameters at high frequency.

(2) the model should correctly describe the nonlinear behavior of the devices in order to permit accurate simulation of intermodulation distortion and highspeed large-signal operation.

(3) the model should accurately predict HF noise.

(4) the components in the sub-circuit, if the subcircuit approach is adopted, should be physics-based and scalable.

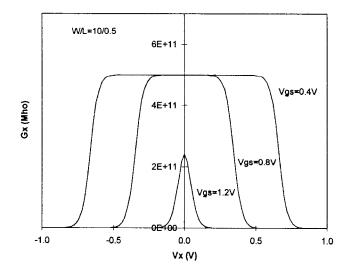

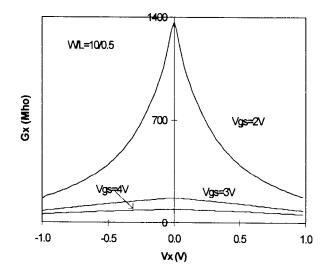

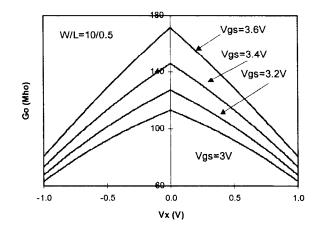

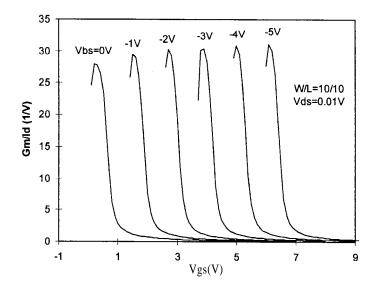

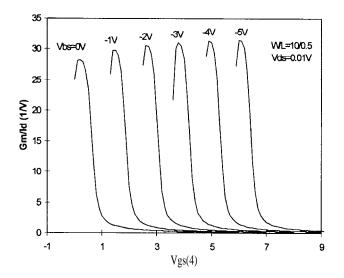

#### 1.2.3 Simulation robustness and efficiency

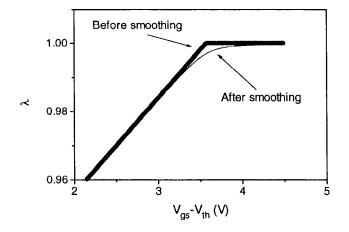

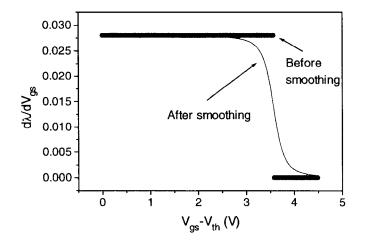

It is a common understanding of circuit designers and model developers that models should have good mathematical continuity for the circuit simulators to obtain robust simulation results with fast convergence [1.66, 1.68]. It is known that the discontinuity of model equations can result in non-convergence in circuit simulation [1.68]. Many model developers have been working on the improvement of the model equation's continuity [1.16-1.25]. In the past two decades, most of the MOSFET models implemented in circuit simulators used piece-wise equations based on the regional approach, in which different equations are used for different operation regions, such as subthreshold and strong inversion regions as well as the linear and saturation regions. Such models can describe the device characteristics quite accurately in each region, but cannot guarantee the higher order continuities of the model at the transition point from one region to another. Even if the equations and their first derivatives are continuous at the boundary of the two regions, the model can still introduce non-physical peaks and valleys or small negative values in transconductance  $(g_m)$  and conductance  $(g_{ds})$  [1.69]. Some notorious examples are  $g_m/l_d$  glitches at the boundary of the subthreshold and the strong inversion regions and the sharp bend in  $g_{ds}$  at the boundary between the linear and saturation regions [1.70]. It is suspected that such behavior not only influences the simulation accuracy, but also results in numerical convergence problems during the iteration process in circuit simulation [1.66,1.68]. The robustness of model implementation also needs to be investigated to ensure

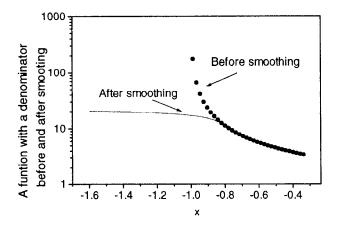

efficient simulation performance of the model. Good model implementation must avoid numerical problems such as divide-by-zero and overflow/under-flow as well as any inadvertent discontinuities in the model equations caused by implementation [1.70].

#### 1.2.4 Model standardization

As mentioned above, over a hundred MOSFET models have been developed [1.12-1.31]. Realizing the difficulty and waste in supporting a large number of compact models, model developers and users have recently made a joint effort to establish a standard compact MOSFET model with good robustness, accuracy, scalability and computational efficiency to meet the needs of digital, analog and mixed analog/digital designs [1.69-1.73]. It is clear that a standard model common to all or most semiconductor manufacturers and circuit simulators is desirable to facilitate inter-company collaborations [1.39].

Since 1996, an independent Compact Model Council, consisting of many leading companies in the semiconductor industry, has spearheaded the model standardization process [1.39, 1.69-1.73]. The Compact Model Council is affiliated with the Semiconductor Industry Alliance [1.74], and consists of Advanced Micro Devices, Analog Devices, Avant!, BTA Technology, Cadence Design Systems, Conexant Systems (formerly Rockwell), Hewlett Packard, Hitachi, IBM, Intel, Lucent Technologies, Motorola, NEC, Philips, Siemens, Texas Instruments, and TSMC. The standard model will simplify the interactions between foundry/client, technology partners, and even groups within large companies.

#### References

- [1.1] J. Y. Chen, "CMOS The Emerging Technology," *IEEE Circuit and Devices Magazine*, March 1986, p. 16.

- [1.2] A. Vladimirescu, *The SPICE Book*, John Wiley & Sons, Inc., New York, 1994.

- [1.3] K. Lee, M. Shur, T. A. Fjeldly, and T. Ytterdal, Semiconductor Device Modeling for VLSI, Prentice Hall, Englewood Cliffs, New York, 1993.

- [1.4] N. Arora, MOSFET Models for VLSI Circuit Simulation, Springer-Verlag, Wien New York, 1994.

- [1.5] S. Selberherr, Analysis and Simulation of Semiconductor Devices, Spring-Verlag, Wien, New York, 1984.

- [1.6] R. Dutton, "Modeling silicon integrated circuits", *IEEE Trans. Electron Devices*, ED-30, p.935 1983.

- [1.7] T. Toyabe et al., "Three dimensional device simulator CADDETH with highly convergent matrix solution algorithm," *IEEE Trans. Computer-Aided Design*, CAD-4, pp. 482-488, 1985.

- [1.8] T. Shima, H. Yamada, and R L. M. Dang, "Table look-up MOSFET modeling system using 2-D device simulator and monotonic piecewise cubic interpolation," *IEEE Trans. Computer-Aided Design*, CAD-2 pp. 121-126, 1983.

- [1.9] R. F Vogel, "Analytical MOSFET model with easily extraction parameters," *IEEE Trans. Computer-Aided Design*, CAD-4, pp. 127-134, 1985.

- [1.10] H. Shichman and D. A. Hodges, "Modeling and simulation of insulatedgate field-effect transistor switching circuits," *IEEE Journal of Solid-state Circuits*, vol. SC-3, pp. 285-289, 1968.

- [1.11] A. Vladimirescu, and S. Liu, *The simulation of MOS Integrated Circuits Using SPICE2*, ERL Memorandum No. UCB/ERL M80/7, University of California, Berkeley, Feb. 1980 (Rev. Oct. 1980).

- [1.12] S. Liu, A unified CAD model for MOSFETs, ERL Memorandum No. UCB/ ERL M8I/31, University of California, Berkeley, May 1981.

- [1.13] B. J. Sheu, D. L. Scharfetter, P. K. KO, and M. C. Jeng, "BSIM: Berkeley short -channel IGFET model for MOS transistors," *IEEE J. solid-state Circuits*, vol. SC-22, pp.558-565, 1987.

- [1.14] M. C. Jeng, *Design and modeling of deep-submicrometer MOSFETs*, ERL memorandum ERL M90/90, University of California, Berkeley, 1990.

- [1.15] J. H. Huang et al., *BSIM3 Manual (Version 2.0)*, University of California, Berkeley, March 1994.

- [1.16] Y. Cheng et al., *BSIM3 version 3.0 User's Manual*, University of California, Berkeley, 1995.

- [1.17] Y. Cheng et al., BSIM3 version 3.1 User's Manual, University of California, Berkeley, Memorandum No. UCB/ERL M97/2, 1997.

- [1.18] N. D. Arora, R. Rios, C. L. Huang and K. Raol, "PCIM: a physically based continuous short-channel IGFET model for circuit simulation," *IEEE Trans. Electron Devices*, vol.41, pp. 988-997, 1994.

- [1.19] D. H. Cho and S. M. Kang, "A new deep submicrometer compact physical model for analog circuits," in *IEEE Custom Integrated Circuits Conf.*, pp.41-44, 1994.

- [1.20] R. M. D. A. Velghe, D. B. M. Klassen, and F. M. Klassen, "Compact MOS modeling for analog circuit simulation", In *IEEE IEDM 93, Tech. Dig.*, pp.485-488, Dec. 1993.

- [1.21] C. C. Enz, F. Krummenacher and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low voltage and low-current applications", *J. Analog Integrated Circuit and Signal Processing*, Vol. 8, pp.83-114, 1995.

- [1.22] J. A. Power and W. A. Lane, "An enhanced SPICE MOSFET model suitable for analog applications", *IEEE Trans. Computer-Aided Design*, vol.CAD-11 pp.1418-1425, 1992.

- [1.23] A. R. Boothroyd, S. W. Tarasewicz and C. Slaby, "MISNAN-A physically based continuous MOSFET model for CAD applications", *IEEE Transactions on CAD*, vol. 10, pp.1512-1529, 1991.

- [1.24] M. Miura-Mattausch, "Analytical MOSFET model for quarter micron technologies", *IEEE Trans. Computer-aided Design of Integrated Circuits* and Systems, Vol. 13, (5), p. 564, 1994.

- [1.25] M. Shur, T. A. Fjeldly, T. Ytterdal, and K. Lee, "A unified MOSFET model," *Solid-State Electronics*, 35, pp. 1795-1802, 1992.

- [1.26] H. C. Pao and C. T. Sah, "Effects of diffusion current on characteristics of metal-oxide(insulator)-semiconductor transistors," *Solid-State Electron*. Vol. 9, p927, 1966.

- [1.27] J. R. Brews, "A charge-sheet model of the MOSFET", *Solid-state Electronics*, Vol.21, pp345-355, 1978.

- [1.28] G. Baccarani et al., "Analytical i.g.f.e.t. model including drift and diffusion currents," *IEE Journal on Solid-State and Electron Devices*, vol.2, p.62, 1978.

- [1.29] Star-Hspice user's manual, Avanti Corporation, 1997.

- [1.30] *Cadence Spectre User's manual,* Cadence Design Systems, 1996.

- [1.31] *Eldo user's manual*, Mentor Graphics, 1996.

- [1.32] http://www-device.eecs.berkeley.edu/~bsim3.

- [1.33] Y. Cheng, T. Sugii, K. Chen, and C. Hu, "Modeling of small size mosfets with reverse short channel and narrow width effects for circuit simulation", *Solid State Electronics*, vol. 41, (9), pp. 1227-1231, 1997.

- [1.34] Y. Cheng et al., "An investigation on the robustness, accuracy and simulation performance of a physics-based deep-submicrometer BSIM model for analog/digital circuit simulation", *CICC'96*, pp. 321-324, May 1996.

- [1.35] J. Chen, C. Hu, C. Wan, P. Bendix, and A. Kapoor, "E-T based statistical modeling and compact statistical circuit simulation methodology," *IEDM Tech. Dig.*, pp. 635-639, 1996.

- [1.36] Y. Cheng et al., "A Study of deep-submicon MOSFET technology prediction and scaling with BSIM3", *Techcon*'97, 1996.

- [1.37] A. Dognis and C. Lyons, *Compact Models Workshop*, Washington D. C, Dec., 1995.

- [1.38] M. Jeng and Z. Liu, Compact Models Workshop, Washington D. C., Dec., 1995.

- [1.39] Compact Model Workshop, Washington D. C., Dec, 1995.

- [1.40] C. Hu et al., BSIM3v3.1 *release note*, http://www-device. eecs.berkeley.edu/~bsim3.

- [1.41] C. Hu et al., BSIM3v3.2 *release note*, http://www-device. eecs.berkeley.edu/~bsim3.

- [1.42] T. Yuan et al., "CMOS scaling into the manometer regime", *Proceedings of the IEEE*, Vo1.85, pp. 486-504, 1997.

- [1.43] M. Bohr et al., "A high performance 0.25um logic technology optimized for 1.8V operation," *IEDM Tech. Dig.*, pp. 847-850, 1996.

- [1.44] A. Shijiro, and W. Yasuo, "Technology challenges for integration near and below 0.1um", *Proceedings of the IEEE*, Vo1.85, pp. 505-520, 1997.

- [1.45] C. Duvvury, "A guide to short channel effects in MOSFETS," *IEEE Circuit and Systems Magazine*, p.6, 1986.

- [1.46] C. Y. Lu and J. M. Sung, "Reverse short channel effects on threshold voltage in submicron salicide devices", *IEEE Electron Device letters*, EDL-10, p. 446, 1989.

- [1.47] E. H. Li et al., "The narrow channel effect in MOSFET with semi-recessed oxide structures," *IEEE Trans. Electron Devices*, ED-37, p. 692, March 1990.

- [1.48] L. A. Akers, "The inverse narrow width effect," *IEEE Electron Device Letters*, EDL-7 (7), p. 419, July 1986.

- [1.49] W. Fichtner and H. W. Potzl, "MOS modeling by analytical approximations -subthreshold current and subthreshold voltage," Int. J. Electronics, Vol. 46, p33. 1979.

- [1.50] R. R. Troutman, "VLSI limitations from drain-induced barrier lowering," *IEEE Trans. Electron Devices*, Vol ED-26, p.461, 1979.

- [1.51] C. G. Sodini, P. K. Ko, and J. L. Moll, "The effects of high fields on MOS device and circuit performance," *IEEE Trans. Electron Devices*, ED-31, p1386, 1984.

- [1.52] M. S. Liang et al., "Inversion layer capacitance and mobility of very thin gate oxide MOSFETs," *IEEE Trans. Electron Devices*, ED-33, p409, 1986.

- [1.53] C. Hu, "Hot Carrier Effects," Chpt.3 in Advanced MOS Device and Physics, N. G. Einspruch and G. Gildenblat, EDS., Vol. 18,s VLSI Electronics Microstructure Science, Academic Press, San Diego, CA, p. 119-160, 1989.

- [1.54] I. C. Chen et al., "Interface-trap enhanced gate-induced leakage current in MOSFET," *IEEE Electron Letters*, EDL-10, p216, 1989.

- [1.55] F. Assderaghi et al., "Observation of velocity overshoot in silicon inversion layers", *IEEE Electron Device letters*, Vol. 14, p. 484, 1993.

- [1.56] Y. Cheng and T. A. Fjeldly, "Unified physical I-V model including selfheating effect for fully depleted SOI/MOSFET's," *IEEE Trans. Electron Devices*, vol. 43, pp. 1291-1296, 1996.

- [1.57] Y. King, H. Fujioka, S. Kamohara, W. C. Lee, and C. Hu, "AC charge centroid model for quantization of inversion layer in NMOSFET," *Int. Symp. VLSI Technology, Systems and Applications, Proc. of Tech. Papers,* Taipei, Taiwan, pp. 245-249, June 1997.

- [1.58] K. Chen et al., "Polysilicon gate depletion effect on IC performance", Solid-State Electronics, pp. 1975-1977, Vol. 38, No. 11, November 1995.

- [1.59] A. A. Abidi, "Low power RF-ICs in wireless transceivers", 1994 IEEE Symposium on low power electronics, pp. 18-21, 1994.

- [1.60] W. Liu et al., "RF MOSFET modeling accounting for distributed substrate and channel resistances with emphasis on the BSIM3v3 SPICE model", *IEDM Tech. Dig.*, pp. 309-312, 1997.

- [1.61] D. Pehlke et al., "High frequency application of MOS compact models and their development for scalable RF model libraries," *CICC*'98, pp. 219-222, 1998.

- [1.62] J. Ou et al., "CMOS RF modeling for GHz communication IC's," Digest of Technical Papers, 1998 Symposium on VLSI Technology, June 1998.

- [1.63] C. Enz and Y. Cheng, "MOS transistor modeling issues for RF IC design", Workshop of Advances in Analog Circuit Design, France, March 1999.

- [1.64] S. H. Jen et al., "Accurate modeling and parameter extraction for MOS transistor valid up to 10GHz", *ESDERC'98*, Sept. 1998.

- [1.65] C. McAndrew and M. McSwain, Compact Model Workshop, Sunnyvale, CA, Aug., 1995.

- [1.66] Y. Tsividis and G. Masetti, "Problems in precision modeling of the MOS transistor in analogue applications", *IEEE Trans. CAD*, vol.-3, pp. 72-79, 1984.

- [1.67] Y. Cheng et al., "RF modeling issues of deep-submicron MOSFETs for circuit design," 1998 International Conference of Solid-state and Integrated Circuit Technology, pp.416-419, 1998.

- [ 1.68] A. Vladimirescu, and J. J. Charlot, "MOS analogue circuit simulation with SPICE", *IEE Proc. Circuits Device Systems*, Vol 141, No.4 pp. 265-274, 1994.

- [1.69] Compact Model Workshop, Dallas, TX, March, 1995.

- [1.70] Compact Model Workshop, Austin, TX, June, 1995.

- [1.71] *Compact Model Workshop*, Sunnyvale, CA, Aug., 1995.

- [1.72] Compact Model Workshop, Austin, Taxis, Mar, 1996.

- [1.73] Compact Model Workshop, Burlington, Vermont, Aug, 1996.

- [1.74] http://www.eia.org/eig/CMC.

#### **CHAPTER 2**

## Significant Physical Effects In Modern MOSFETs

This chapter will describe the important physical phenomena that ought to be accounted for in a compact model of a modern MOSFET. They are: (1) Nonuniform doping effect; (2) Charge sharing and *DIBL*; (3) Reverse short channel effect; (4) Normal narrow width effect; (5) Reverse narrow width effect; (6) Body effect; (7) Subthreshold conduction; (8) Field dependent mobility; (9) Velocity saturation; (10) Channel length modulation; (11) Substrate current due to impact ionization; (12) Gate-induced drain leakage; (13) Polysilicon gate depletion; (14) Inversion layer quantization effect; (15) Velocity overshoot; (16) Self-heating effect.

#### 2.1 MOSFET Classification and Operation

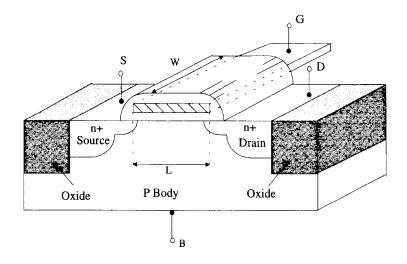

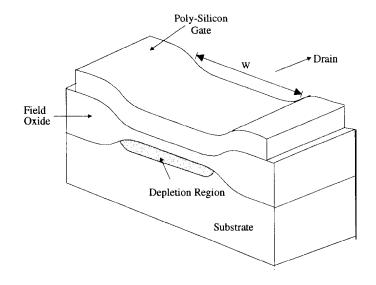

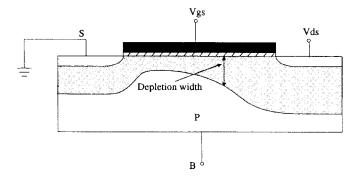

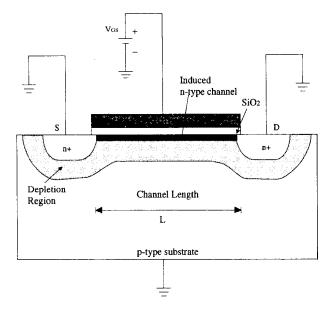

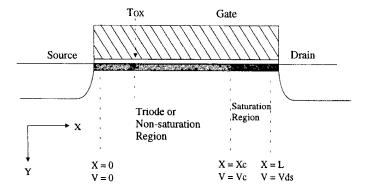

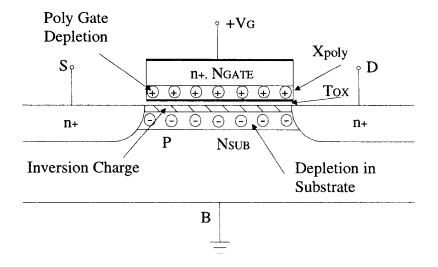

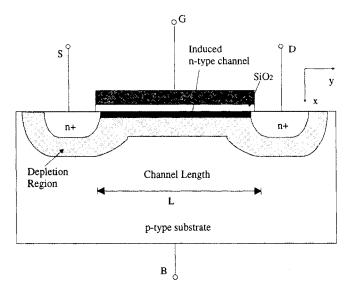

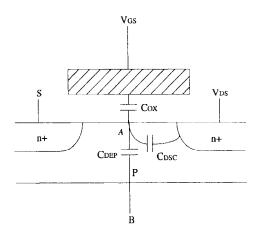

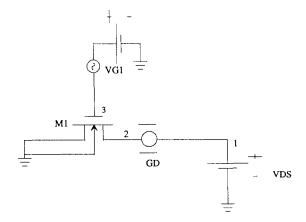

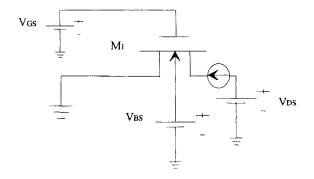

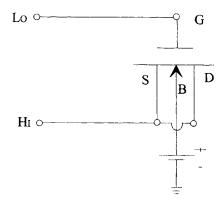

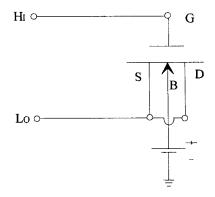

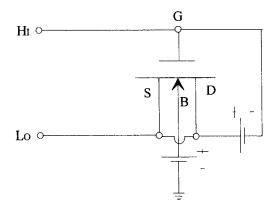

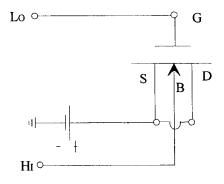

A Metal-Oxide-Semiconductor transistor is shown in Fig. 2.1.1, where an nchannel device is illustrated as an example. The MOS transistor is a four terminal device, and the four terminals are called drain (D), gate (G), source (S), and body (B). The source and drain junctions are connected to the inversion layer in the channel region. The length of the channel between the source and drain is called the channel length (L). The width of the channel, in the direction normal to the channel length, is called the channel width (W). Usually, the MOS transistor is symmetric, meaning there is no difference between the source and drain in the design and fabrication, and they are assigned as the drain or source according to their functions in the circuit and the applied bias conditions. MOSFETs with asymmetric source and drain have also been reported in some special applications.

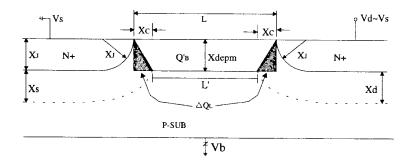

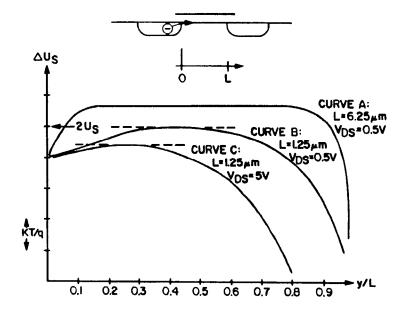

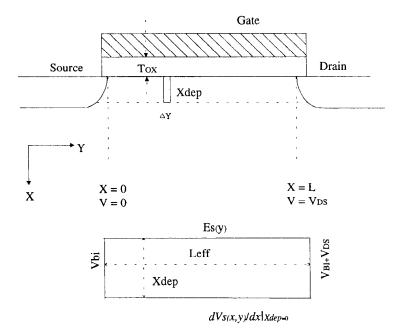

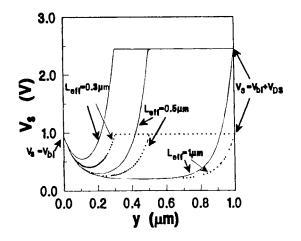

Fig. 2.1.1 A MOSFET structure.

When an appropriate voltage  $V_g$  is applied to the gate terminal, an inversion layer is formed between the drain and source to conduct current. The current depends on the applied gate and drain voltages when the source is biased at a fixed voltage (e.g. grounded for an nMOSFET). In fact, the gate and drain voltages and the electric fields (both vertical and lateral directions) produced by these voltages in the channel of the device control the device operation in all bias regimes which we will discuss next. That is the reason why it is called a MOS Field-Effect-Transistor (MOSFET). Because the gate is electrically isolated from the other parts of the device a MOSFET is also known as an Insulated-Gate Field-Effect Transistor (IGFET) [2.1]. We may note that BSIM stands for <u>Berkeley Short-channel IGFET Model</u>.

The critical gate voltage, at which an inversion layer is formed, is called the threshold voltage  $(V_{th})$ When the voltage between the gate and source,  $V_{gs}$ , is larger than  $V_{th}$  by several times the thermal voltage  $v_t$  ( $K_BT/q$ ), the device is said to be in the strong inversion regime. When  $V_{gs} = V_{dd}$  (the power supply voltage), the device is in the "on" state. When  $V_{gs}$  is less than  $V_{th}$ , the device is in the subthreshold (or weak inversion) regime. When  $V_{gs} = 0$ , the device is in the "off" state. When  $V_{gs}$  is biased near  $V_{th}$ , the device operates in the moderate inversion regime, which is an important operation region in low power analog applications.

Depending on the type of charge carriers conducting the current in the channel, MOSFETs can be either n-channel or p-channel devices. For an n-channel MOSFET, electrons are the charge carriers and the source and drain regions, which are heavily doped with n-type impurities, are formed on a p-type substrate. In a p-channel MOSFET, the source and drain regions are doped heavily with p-type impurities in an n-type substrate. In circuit applications, a combination of n-channel and p-channel MOSFETs are used. This technology is called complementary MOS (CMOS) technology. Compared with NMOS or PMOS technologies, CMOS technology has a huge advantage in its low power consumption, and has been the workhorse of VLSI since the early 1980's [2.2].

MOSFETs can be either surface channel devices or buried channel devices [2.3]. It is commonly believed that the names refer to the location of the conduction channel in the devices. A MOSFET is a surface channel device if its conduction channel is at the SiO<sub>2</sub>-Si interface. In a buried channel device the current flows along the path in the bulk of the device. In reality, the names only refer to the net doping type of the surface layer of the substrate. For example, the surface channel PMOSFET has an n-type doped substrate, while the buried channel PMOSFET has a p-type doped but depleted surface layer in the n-type substrate. However, the current in a buried channel device is still conducted by a surface charge layer when the device is in the on state.

A MOSFET is called an enhancement-mode device if it does not conduct significant current when the gate voltage  $V_g$  is zero [2.4]. It is a normally-off device, and a minimum gate voltage, the threshold voltage, is needed to induce an inversion layer in the channel to conduct the current. If a MOSFET is normally-on, i.e. a conducting channel is present in the device even when  $V_g$  =0V, it is called a depletion-mode device because a gate bias is needed to deplete the channel to turn the device off [2.5]. Depletion mode devices are rarely used in CMOS circuits.

Next, we will give a qualitative description of the operation of a long channel enhancement n-channel MOSFET to illustrate the device characteristics in the various operating regimes, and to introduce some important terms used in compact modeling.

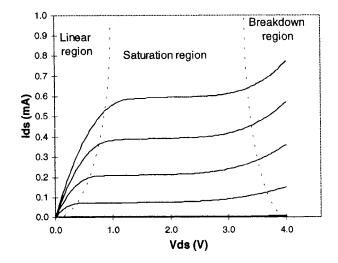

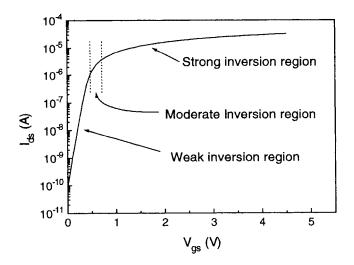

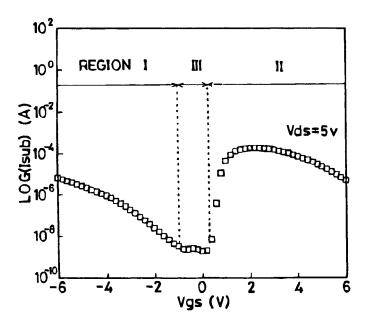

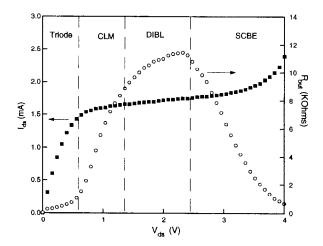

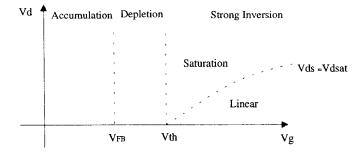

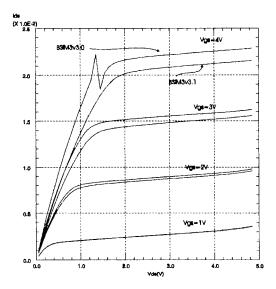

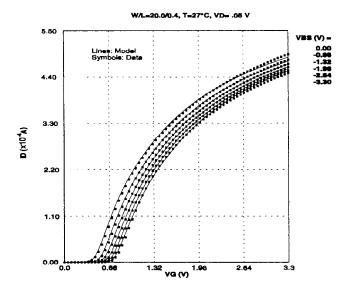

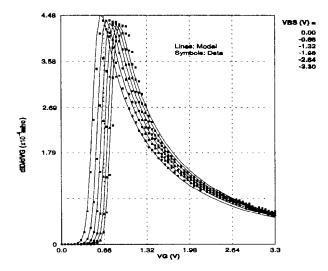

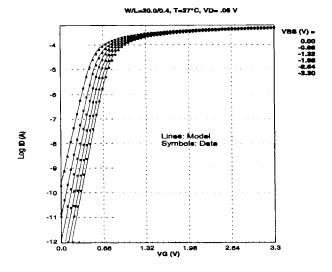

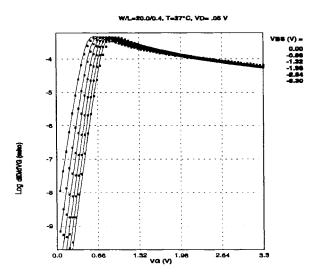

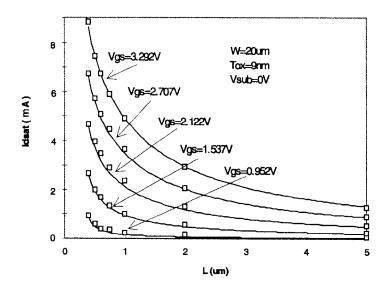

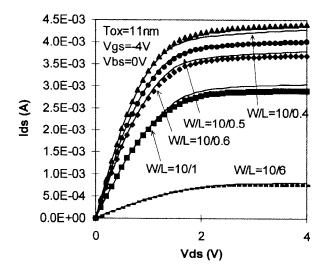

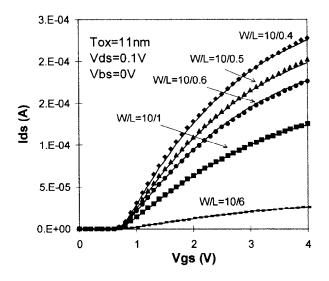

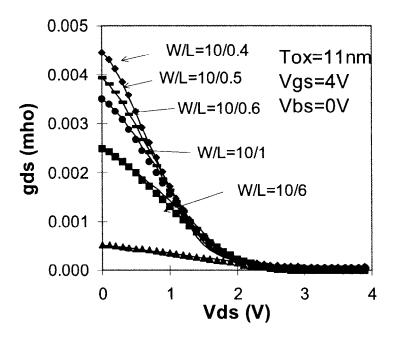

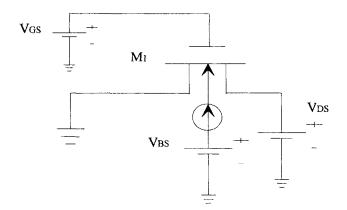

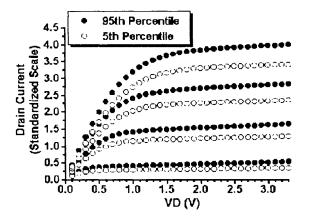

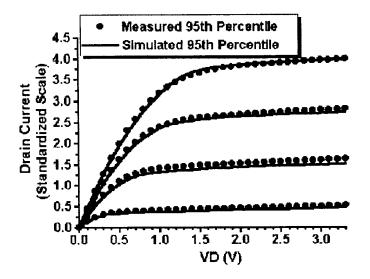

Depending on the bias voltages applied to the drain for fixed gate, source and body biases, a MOSFET may operate in the linear, saturation, or breakdown regions as shown in Fig. 2.1.2. Likewise, depending on the bias voltages applied to the gate for fixed drain, source, and body biases, a MOSFET may operate in the weak inversion, moderate inversion, or strong inversion regions as shown in Fig. 2.1.3. Next, we will discuss the device characteristics in the strong inversion region. Then we will discuss the device characteristics in the weak inversion and moderate inversion regions.

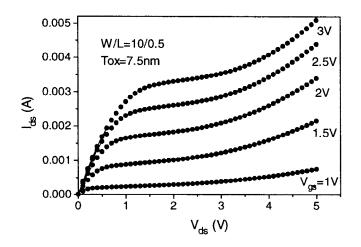

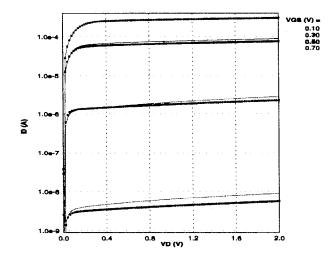

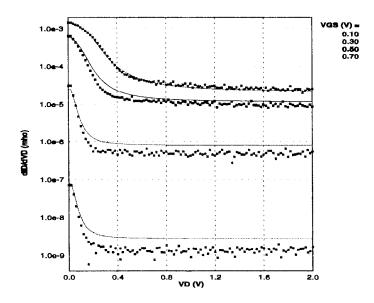

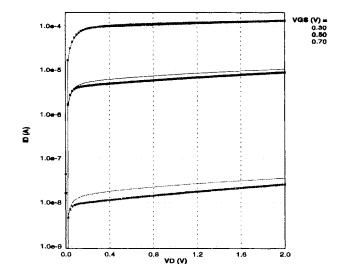

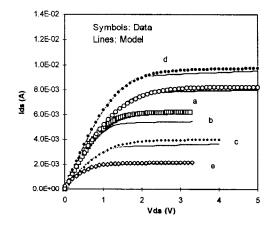

Fig. 2.1.2  $I_{ds}$  - $V_{ds}$  characteristics of an n-channel MOSFET.

Fig. 2.1.3  $Log(I_{ds})$ - $V_{gs}$  characteristics of an n-channel MOSFET.

#### 2.1.1 Strong inversion region (V<sub>gs</sub> >V<sub>th</sub>)

When the bias applied to the gate terminal of an n-channel MOSFET is larger than  $V_{th}$ , an inversion layer is induced at the Si/SiO<sub>2</sub> interface. Current can flow through the channel from the source to the drain if a positive drain voltage is applied (the source is normally used as the voltage reference). Depending on the magnitude of the drain voltage, the device may be in the linear, saturation, or breakdown regions of operation.

a. Linear region  $(0 < V_{ds} < V_{dsat})$

As shown in Fig. 2.1.2, when  $V_{ds}$  is small (i.e.,  $V_{ds} << V_{gs} - V_{th}$ ), the inversion channel behaves like a simple resistor. The drain current  $I_{ds}$  increases linearly as the drain voltage  $V_{ds}$  increases. However, when  $V_{ds}$  is larger it will cause an increase of the voltage in the inversion layer at all points along the channel (except for the singular point at the source edge). This reduces the voltage across the gate capacitor and the inversion charge density is reduced. The smaller amount of mobile inversion charges results in a decrease in channel conductance, which leads to a smaller slope in the  $I_{ds}$ - $V_{ds}$  characteristics as  $V_{ds}$  increases. Eventually,  $V_{ds}$  reaches the saturation voltage  $V_{dsat}$ , at which point the mobile carriers at the drain side disappear in this first order model, and the channel is "pinched off" at the drain side [2.4, 2.6]. The condition of no mobile carriers at the pinch-off point has traditionally been used to obtain the analytical saturation voltage expressions for long channel compact models [2.7].

b. Saturation region ( $V_{dsat} \leq V_{ds} < V_{bk}$ )

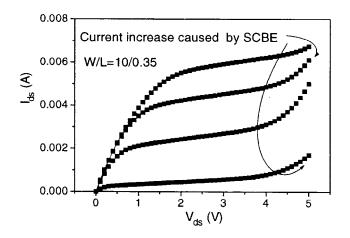

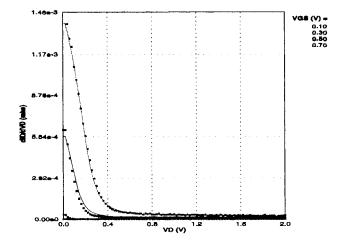

When  $V_{ds} > V_{dsat}$ , the pinched-off region of the channel increases and extends towards the source. The excess drain voltage beyond  $V_{dsat}$  will drop across this pinched-off region and the drain current remains approximately constant as shown in Fig. 2.1.2. However, we need to point out that the constant saturation current behavior is only an approximation. The small but non-zero slope of the  $I_{ds}$  - $V_{ds}$  characteristics in the saturation region is very important to analog circuit performance and must be accurately modeled by a compact model. In addition to the finite length of the pinch-off region (channel length modulation), drain induced barrier lowering and substrate current induced body effect must be accounted for in modeling the current in the saturation region [2.8]. They will be described in sections 2.6 and 2.7.

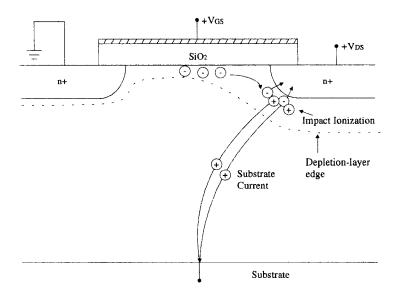

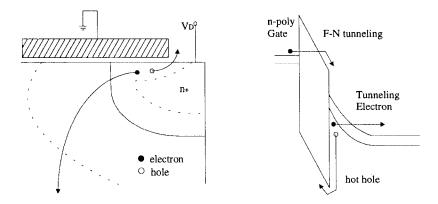

c. Breakdown region  $(V_{ds} \ge V_{bk})$

When  $V_{ds}$  is much larger than  $V_{dsat}$ , the device may enter the breakdown region [2.9]. When  $V_{ds}$  is larger than the "breakdown voltage",  $V_{bk}$ , as shown in Fig. 2.1.2, the current increases dramatically as  $V_{ds}$  increases. The definition of  $V_{bk}$  in compact modeling is often vague and arbitrary for practical reasons. It should be noted that the breakdown mechanism may be different between long channel devices and short channel devices. Breakdown in a long channel device is caused by the breakdown of the drain-body p-n junction [2.10]. Breakdown of a short channel device may be caused by the breakdown of the parasitic bipolar transistor. The latter is triggered by the substrate current produced by impact ionization [2.11]. We will give further analysis of this in section 2.7.

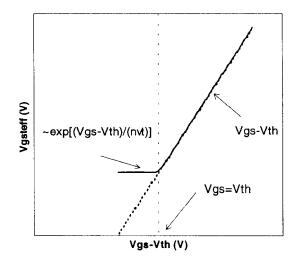

#### 2.1.2 Weak and moderate inversion or the subthreshold region

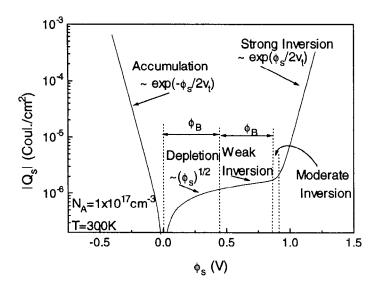

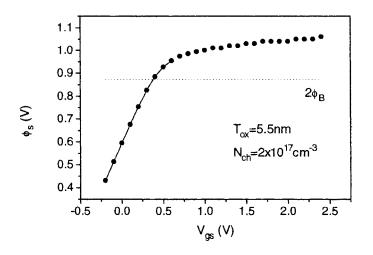

The characteristics discussed above are all related to the strong inversion operation, where the gate bias is much larger than  $V_{th}$  and surface potential is larger than  $2\phi_B$  (here  $\phi_B$  is a doping parameter relating the potential of an electron at the Fermi level to the doping concentration) [2.4, 2.6]. When the gate bias is less than  $V_{th}$ , the mobile charge density is very small but nonzero. In this case, a depletion layer exists and the surface potential is smaller than  $2\phi_B$ . This device operation region is called the weak inversion or the sub-threshold regime. Unlike the strong inversion region where drift current dominates, subthreshold conduction is dominated by diffusion current.

The current increases exponentially as the gate bias increases in the weak inversion region ( $V_{gs} << V_{th}$ ) [2.12], as shown in 2.1.3. However, this exponential relationship between the source-drain current and the gate bias breaks down as the gate bias approaches  $V_{th}$ . Another operation region called "moderate inversion" exists between the weak inversion and strong inversion regions [2.13, 2.14]. Usually, this region is defined as several  $v_t$  around  $V_{th}$  [2.13]. In moderate inversion, both the drift and diffusion currents are significant, making compact modeling very difficult.

#### 2.2 Effects Impacting the Threshold Voltage

In this section we discuss the physical effects impacting the threshold voltage of a MOSFET. Unless we point out otherwise, we will base our discussion on an enhancement mode n-channel MOSFET. For a device with a long and wide channel geometry and uniformly doped substrate,  $V_{th}$  can be derived easily by solving the one dimensional Poisson equation in the vertical direction [2.4, 2.14]:

$$V_{th} = V_{th0} + \gamma (\sqrt{\phi_s - V_{bs}} - \sqrt{\phi_s})$$

(2.2.1)

$$V_{th0} = V_{FB} + \phi_s + \gamma \sqrt{\phi_s} \tag{2.2.2}$$

where  $\phi_s$  is the surface potential at threshold,  $V_{FB}$  is the flat band voltage,  $V_{th0}$  is the threshold voltage of a long channel device at zero body bias, and  $\gamma$  is the coefficient of the body bias effect which is given by

$$\gamma = \frac{\sqrt{2\varepsilon_{si}qNa}}{C_{ox}}$$

(2.2.3)

where  $N_a$  is the substrate doping concentration.  $C_{ox}$  is the gate oxide capacitance. The surface potential  $\phi_s$  at  $V_{gs} = V_{th}$  is given by [2.4, 2.14]

$$\phi_s = 2v_t \ln(\frac{N_a}{n_i}) \equiv 2\phi_B \tag{2.2.4}$$

where  $v_t$  is the thermal voltage, and  $n_i$  is the intrinsic carrier density. This model is valid only when the substrate doping concentration is constant and the channel length is long. Under these conditions, the potential is uniform along the channel. But in reality, these two conditions are not always satisfied in today's MOSFET because of the small device size and the complex doping profile employed to improve device performance.

#### 2.2.1 Non-uniform doping effects

In making a VLSI MOSFET, many ion implantation doping process steps are used to adjust the threshold voltage value and suppress the punch-through and hot carrier effects [2.15, 2.16, 2.17]. A non-uniform doping density in both the vertical and lateral directions is typical. In that case, the threshold voltage characteristics cannot be described by the classic  $V_{th}$  model given above. The influence of the non-uniform doping effect on  $V_{th}$  should be carefully considered.

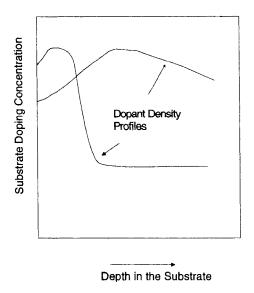

#### 1. Vertical non-uniform doping effects

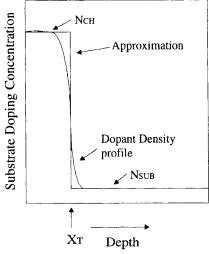

To adjust the threshold voltage and suppress punchthrough, multiple implantation steps are often used in VLSI fabrication. A shallow implantation of channel dopants of the same type as that of the substrate is designed to achieve a suitable  $V_{th}$  value, and another deep implantation of the same type of dopant is used to suppress punchthrough and *DIBL* [2.18]. Two doping profiles produced by implantation are given in Fig. 2.2.1. The doping concentration in one case is higher near the silicon and silicon dioxide interface than deep in the substrate. In the other case, the doping concentration is lower at the surface and higher in the bulk. This is called the retrograde doping profile [2.19]. One extreme example is the delta doped device [2.20].

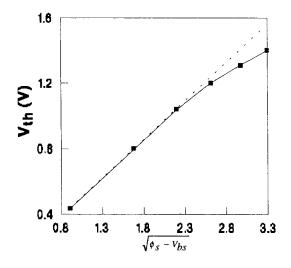

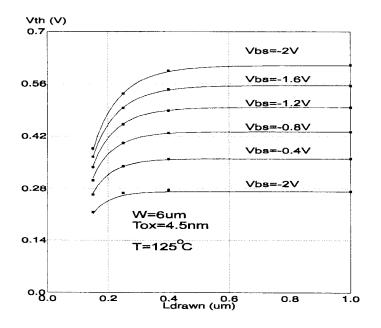

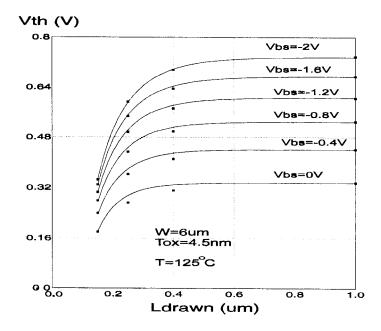

It is well known that the threshold voltage of a MOSFET with a uniformly doped substrate is proportional to  $\sqrt{\phi_s - V_{bs}}$ , with the proportionality constant equal to  $\gamma$  as given in Eq. (2.2.1). However, the experimental data shown in Fig. 2.2.2 displays a non-linear dependence. The slope  $\gamma$  becomes smaller as the body bias  $V_{bs}$  becomes more negative (for NMOS). This non-linearity comes from non-uniform substrate doping in the vertical direction. This non-uniformity makes  $\gamma$  in Eq. (2.2.3) a function of the substrate bias.

Fig. 2.2.1 Two examples of the vertical doping profiles in MOSFETs.

Fig. 2.2.2 The threshold voltage versus  $\sqrt{\phi_s - v_{bs}}$ . After Huang et al. [2.8].

Detailed considerations are needed to derive an expression of the threshold voltage for a device with a non-uniformly doped substrate. Strictly speaking, an integration of bulk charge density distribution along the vertical direction is needed to obtain the total bulk charge as given in the following:

$$V_{th} = V_{FB} + \phi_s + \frac{q}{C_{ox}} \int_0^{x_{di}} n(x) dx \qquad (2.2.5)$$

where n(x) is the doping profile along the vertical direction, and  $X_{di}$  is the width of the depletion layer at  $V_{gs} = V_{th}$ .

Eq. (2.2.5) states that the threshold voltage in a non-uniformly doped device is dependent on the integral of the doping profile rather than the doping profile function itself. In other words, the threshold voltage is determined by the total amount of bulk charge, which may be obtained with some approximation for the charge density function, without using the real doping profile in the device! This approach has been used in compact modeling to get simple analytic expressions for  $V_{th}$  in the device with non-uniformly doped substrate, and will be discussed in Chapter 3.

In addition to the third term in Eq. (2.2.5), the parameters  $V_{FB}$  and  $\phi_s$ , which have clear definitions for uniformly doped substrates, also need to be examined for devices with vertical non-uniform doping.

**a. Flat band voltage**  $V_{FB}$ : The definition of the flat band voltage is simple for a uniformly doped substrate. It is the gate voltage at which the surface potential is zero, the surface electric field is zero, and the entire substrate is charge neutral. For a non-uniformly doped device, no gate voltage can cause the substrate to be charge neutral at all depths.  $V_{FB}$  in a non-uniformly doped MOSFET may be taken as the gate voltage at which the sum of all the charge in the substrate is zero. At  $V_{FB}$ , the surface potential may be nonzero, but the surface electric field is zero. The  $V_{FB}$  parameter is important in compact modeling. It is often considered a model parameter that is to be extracted from the device characteristics of a given technology to reflect the real process and device details.

**b. Strong inversion condition:** For a uniformly doped device, the strong inversion condition is the well known  $\phi_s = 2\phi_B$  criteria [2.4,2.13]. For non-uniformly doped MOSFET it is appropriate to use

$$\phi_s = 2vt \ln(\frac{N_{ch}}{n_i}) \tag{2.2.6}$$

where Nch is an average doping concentration in the channel.

### 2. Lateral non-uniform doping effects

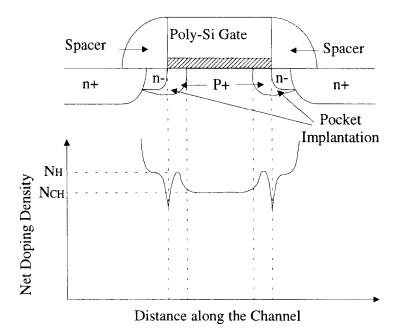

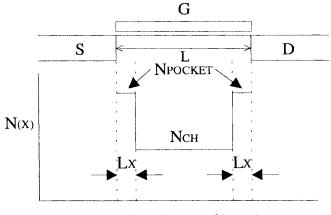

To reduce the short channel effects, local high doping concentration regions near the source/drain junction edges have been employed recently. This may be called lateral channel engineering, or more specifically halo [2.21] or pocket implantation [2.22]. Significant suppression of the short channel effects has been demonstrated in  $0.1\mu$  m n-channel and buried p-channel MOSFETs with Large-Angle-Tilt-Implanted (*LATI*) pocket technology [2.22, 2.23]. The pocket implant technology is a promising new option to tailor the short channel performance of deep submicron MOSFETs.

With the introduction of lateral doping engineering, the doping concentration in the channel along the channel length becomes non-uniform as shown in Fig. 2.2.3. The non-uniform doping with higher doping concentration near the source/drain regions will result in an increase in the average doping concentration in the channel and hence cause an increase in the threshold voltage. As the device channel length becomes shorter, this non-uniform lateral doping profile may cause a significant increase in the threshold voltage. This is know as the Reverse Short Channel Effect (*RSCE*) as will be discussed later in this section [2.24].

Fig. 2.2.3. Doping profile along the channel of a MOSFET with pocket implantation.

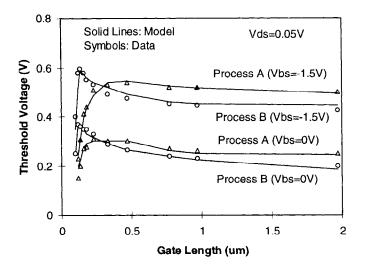

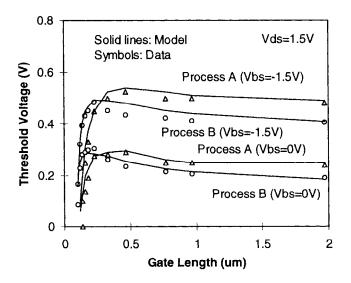

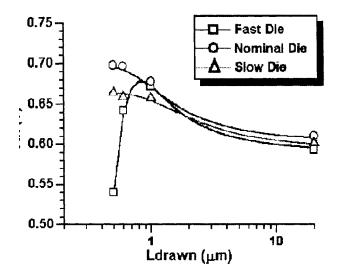

### 2.2.2 Normal short channel effects

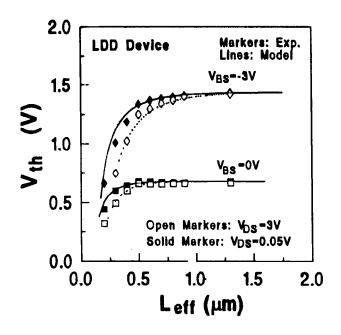

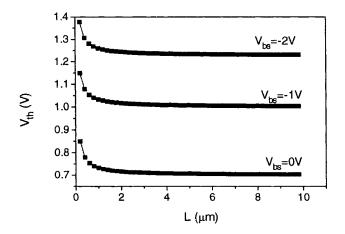

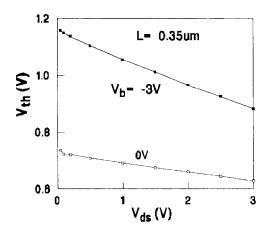

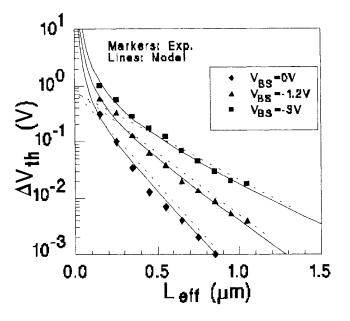

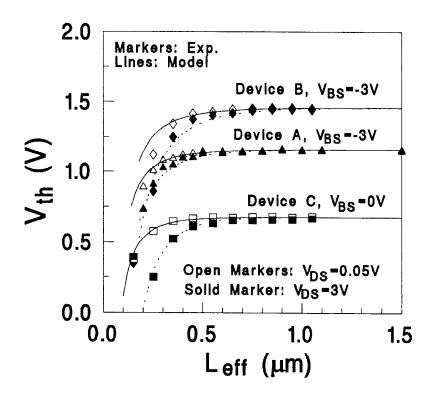

The threshold voltage of a long channel device is independent of the channel length *L* and the drain voltage  $V_d$ . However, experimentally it is observed that  $V_{th}$  decreases as *L* decreases or  $V_d$  increases, as shown in Fig. 2.2.4. This effect is called the short channel effect [2.25] (in this section, we will discuss only the so called normal short channel effect, that is,  $V_{th}$  decreases monotonically as the channel length *L* decreases [2.26, 2.29-2.40].) It is also known as  $V_{th}$  roll-off. The dependence of  $V_{th}$  on *L* and  $V_{ds}$  in short-channel devices cannot be ignored. MOSFETs are normally designed with a  $V_{th}$  around 0.5V. If the value of  $V_{th}$  drops greatly as the channel length and  $V_{ds}$  vary, the device may exhibit excessive drain leakage current even when  $V_{gs} = 0V$  [2.27, 2.28]. The modeling of  $V_{th}$  roll-off will be discussed in Chapter 3.

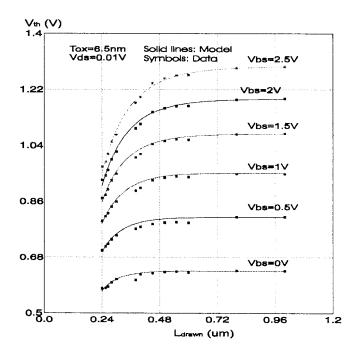

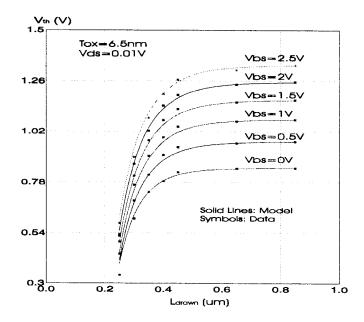

### 2.2.3 Reverse short channel effects

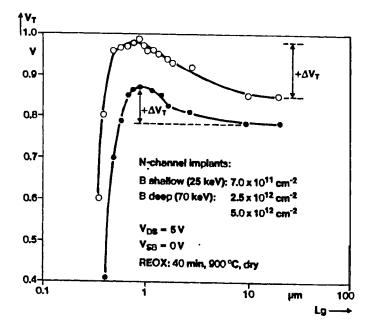

In the pervious section we discussed the so-called normal short channel effect. That is, the  $V_{th}$  of a MOSFET decreases monotonically as device channel length decreases. However, in devices using halo or pocket implantation, it

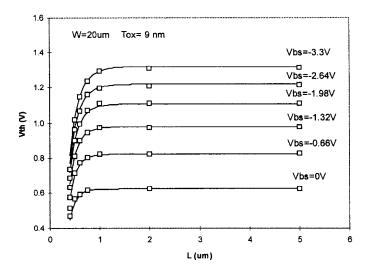

has been found that, as shown in Fig 2.2.5,  $V_{th}$  initially increases with decreasing channel length. This is called the reverse short channel effect (*RSCE*), or  $V_{th}$  roll-up [2.41]-[2.44].  $V_{th}$  reaches a maximum value at a certain channel length, and as *L* decreases further,  $V_{th}$  starts to decrease. The latter is the  $V_{th}$  roll-off [2.45]. The combined *RSCE* and  $V_{th}$  roll-off effects result in a 'hump' in the characteristics of  $V_{th}$  vs. *L*, *as* shown in Fig. 2.2.5 [2.46]. The cause of *RSCE* is the non-uniform lateral doping [2.47, 2.48, 2.49]. As discussed in section 2.2.2, for some technologies such as pocket implantation, the channel doping concentration near the source and drain is higher than in the middle of the channel. The increased doping concentration in these regions can result in an increase in  $V_{th}$  if the channel length becomes small.

Fig. 2.2.4 Decrease of  $V_{th}$  caused by the short channel effect as device channel length decreases. After Liu et al. [2.36].

Even without an intentional pocket implant, channel doping concentration may still be higher near S and D, leading to *RSCE* [2.50, 2.51]. The cause is the transient-enhanced-diffusion (*TED*) of dopants near the source and drain from the deep buried peak to the surface due to the implant-induced intersti-

tial defects produced by S and D implantation [2.43, 2.51]. Compact modeling of *RSCE* will be discussed in Chapter 3.

Fig. 2.2.5 A hump can be seen in the  $V_{th}$ -L characteristics of a device with RSCE. After Orlowski et al. [2.42].

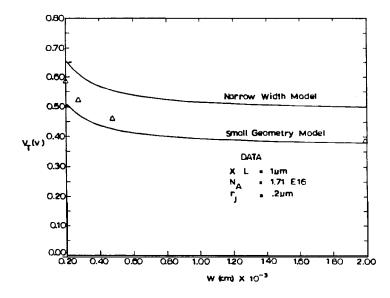

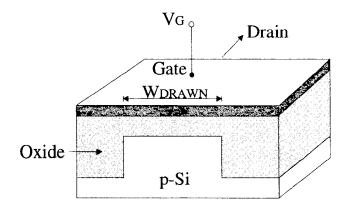

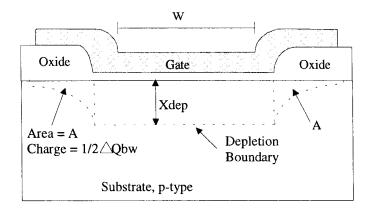

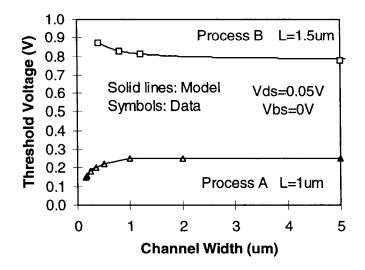

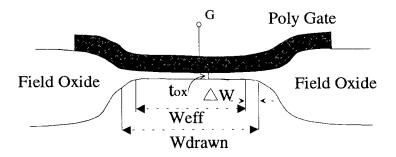

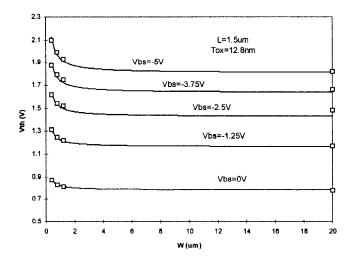

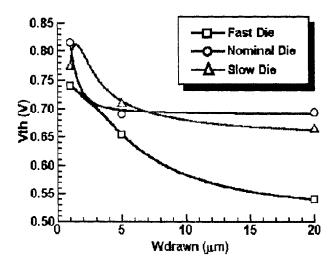

## 2.2.4 Normal narrow-width effects

Device width has been found to have a significant effect on the device characteristics. Fig. 2.2.6 shows a cross-sectional view of a Localized-oxidation-ofsilicon (*LOCOS*) isolated MOSFET along the width direction. It can be seen that the polysilicon gate overlaps the thick oxide on both sides of the thin gate oxide or channel region. The thick oxide on both sides, which is tapered and recessed, is called the field oxide. Under the field oxide, a field implantation may be performed to prevent surface inversion by the gate electrode. For the devices fabricated with the widely used *LOCOS* isolation process, it has been found that  $V_{th}$  increases as the channel width decreases, as shown in Fig. 2.2.7. This is considered the "normal" narrow width effect and is explained by the contribution of charges in the depletion layer region or in the edge of the field implant region. As the width of the device decreases, the contribution of these charges to the total depletion region charge becomes greater, leading to an increased  $V_{th}$  [2.52, 2.53]. Many different approaches have been proposed to model  $V_{th}$  changes caused by the narrow width effect [2.54, 2.55]. They will be discussed in Chapter 3.

Fig. 2.2.6 A cross section of a LOCOS isolated MOSFET along the width direction.

Fig. 2.2.7 Increase of  $V_{th}$  caused by the narrow width effect as device channel width decreases. After Akers [2.55].

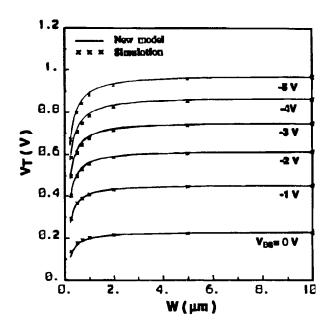

## 2.2.5 Reverse narrow-width effects

The effect discussed above is called the normal narrow width effect, in which  $V_{th}$  increases as the channel width decreases. Another narrow width effect, in which  $V_{th}$  decreases as the channel width decreases as shown in Fig. 2.2.8 [2.56], has been observed in devices with certain new isolation technologies such as fully recessed or trench isolation technologies shown in Fig. 2.2.9. For a device with trench isolation, the field oxide is buried in the substrate and the field lines from the gate electrode are focused by the sharp geometry of the channel edge. Thus, at the edges of the channel an inversion layer is formed at a lower voltage than at the center. As a result,  $V_{th}$  is lower in devices with smaller W's. This behavior is called the reverse narrow-width effect, in deference to the "normal" narrow width effect discussed in section 2.2.4.

The reverse narrow width effect is sensitive to several process and device factors such as the doping concentration in the sidewalls of the silicon, the trench isolation spacing, and the shape of the corner region at the edge of the gate.

Fig. 2.2.8  $V_{th}$  may decrease as channel width decreases. After Chung and Li [2.57].

Fig. 2.2.9 A MOSFET device with trench isolation.

## 2.2.6 Body bias effect and bulk charge effect

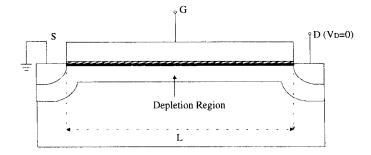

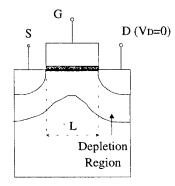

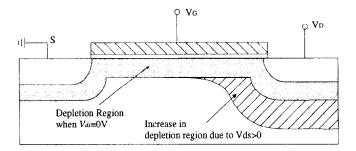

In circuit applications, MOSFETs are biased at the drain, gate, and body (often with the source as the reference). In that case, the voltage between the body and the source  $(V_{bs})$  and the voltage between the drain and the source  $(V_{ds})$  are not zero. The body effect refers to the influence of  $V_{bs}$  on  $V_{th}$ . The body effect results in an increase in the threshold voltage of a MOSFET (with reference to the source) when a reverse bias  $V_{bs}$  is applied. The bulk charge effect is closely related to the body bias effect and refers to the changing threshold voltage along the channel when  $V_{ds}>0$ .  $V_{th}$  is not constant along the channel because the width of the depletion region along the channel is not uniform in the presence of a nonzero  $V_{ds}$ . In that case,  $V_{th}$  will be a function of the position, that is, a function of V(y) along the channel. V(y) is the channel potential voltage.

### **1.** Body effect due to $V_{bs}$

We begin by assuming that the surface potential at the onset of inversion in a MOSFET is  $2\phi_B$  when  $V_{bs}=0$ . With a reverse bias  $V_{bs}$ , the surface potential at the onset of the strong inversion becomes [2.58]

$$\phi_S(inv) = 2\phi_B - V_{bs} \tag{2.2.7}$$

The channel depletion layer becomes wider due to the  $V_{bs}$  bias, and can be expressed approximately as:

$$X_{dep} = \sqrt{\frac{2\varepsilon_{si}(2\phi_B - V_{bs})}{qN_{ch}}}$$

(2.2.8)

The depletion layer charge (per unit area) is

$$Qb \max = -qNchXdep \tag{2.2.9}$$

The inversion charge (per unit area)  $Q_{inv}$  in strong inversion in terms of  $V_{gb}$  and  $V_{bs}$  is:

$$Q_{inv} = -C_{ox}(V_{gb} - V_{FB} - 2\phi_B + V_{bs} - \gamma\sqrt{2\phi_B - V_{bs}})$$

$$(2.2.10)$$

Assuming again that  $Q_{inv}$  is zero at the onset of inversion, and also noting that  $V_{gs} = V_{gb} + V_{bs}$ , we can find the threshold voltage when  $V_{bs} \neq 0$  from Eq. (2.2.10),

$$V_{th} = V_{FB} + 2\phi_B + \gamma \sqrt{2\phi_B - V_{bs}}$$

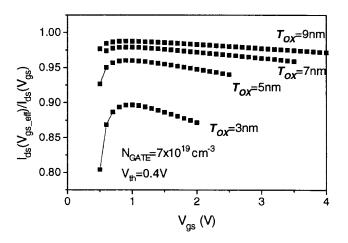

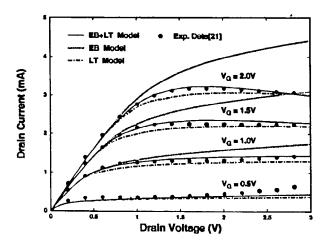

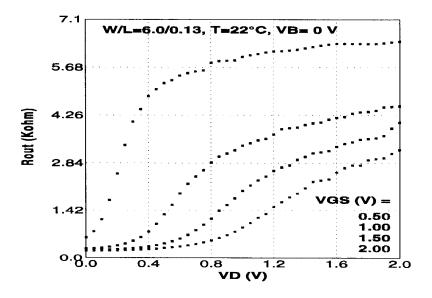

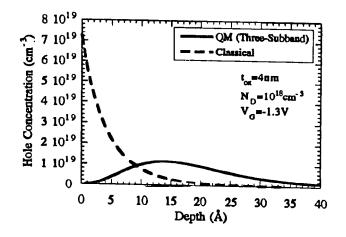

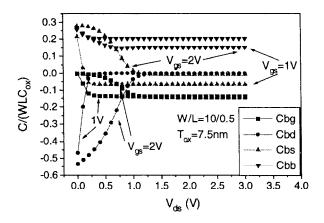

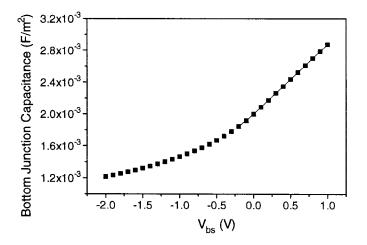

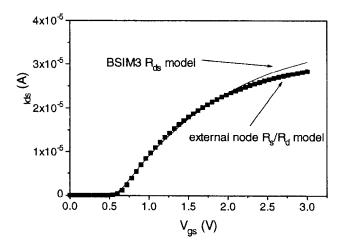

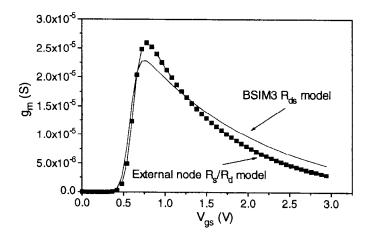

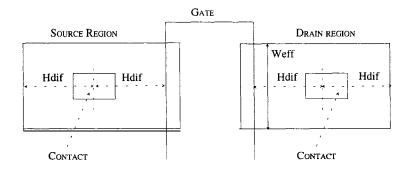

(2.2.11)