# CHAPTER 10 – DIGITAL-ANALOG AND ANALOG-DIGITAL CONVERTERS

- Section 10.0 Introduction

- Section 10.1 Characterization of Digital-Analog Converters

- Section 10.2 Parallel Digital-Analog Converters

- Section 10.3 Extending the Resolution of Parallel Digital-Analog Converters

- Section 10.4 Serial Digital-Analog Converters

- Section 10.5 Characterization of Analog-Digital Converters

- Section 10.6 Serial Analog-Digital Converters

- Section 10.7 Medium Speed Analog-Digital Converters

- Section 10.8 High Speed Analog-Digital Converters

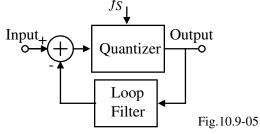

- Section 10.9 Oversampling Converters

- Section 10.10 Summary

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Introduction (2/25/03)

Page 10.0-1

### 10.0 - INTRODUCTION

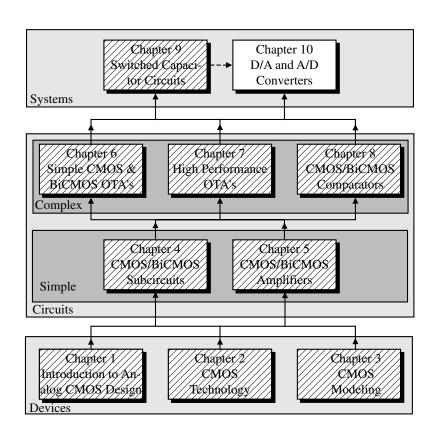

# **Organization**

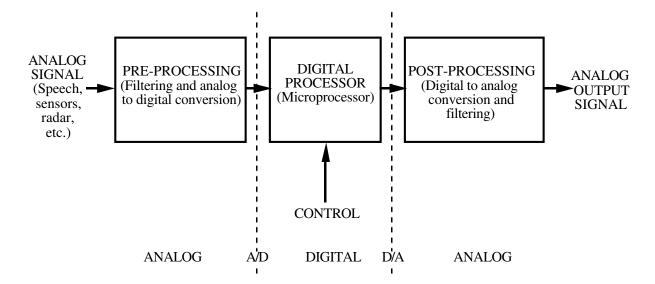

# **Importance of Data Converters in Signal Processing**

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Introduction (2/25/03)

Page 10.0-3

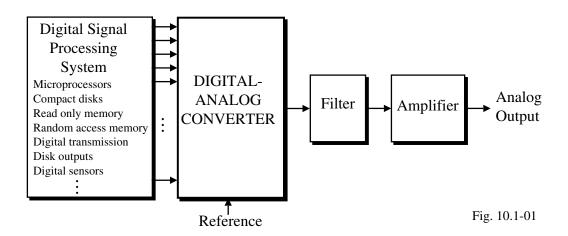

# **Digital-Analog Converters in Signal Processing Applications**

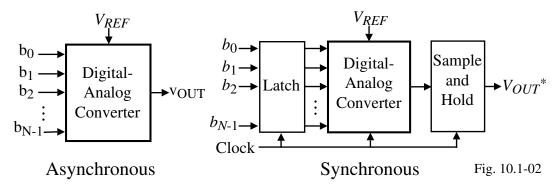

# **Asynchronous Versus Synchronous Digital-Analog Converters**

(Asterisk represents a sample and held signal.)

CMOS Analog Circuit Design

Chapter 10 – Introduction (2/25/03)

Page 10.0-5

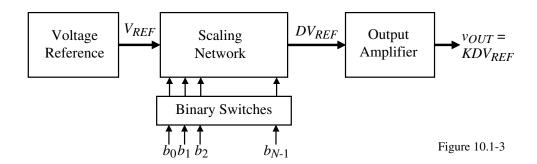

# **Block Diagram of a Digital-Analog Converter**

$b_0$  is the most significant bit (MSB)

The MSB is the bit that has the most (largest) influence on the analog output

$b_{N-1}$  is the least significant bit (LSB)

The LSB is the bit that has the least (smallest) influence on the analog output

# SECTION 10.1 - CHARACTERIZATION OF DIGITAL-ANALOG CONVERTERS STATIC CHARACTERISTICS

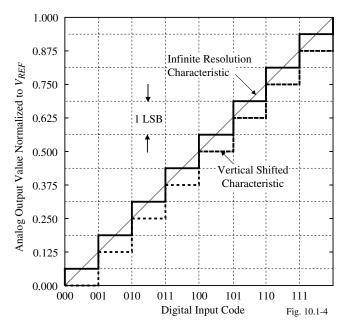

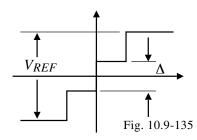

# **Output-Input Characteristics**

Ideal input-output characteristics of a 3-bit DAC

CMOS Analog Circuit Design

Chapter 10 – Section 1 (2/25/03)

Page 10.1-2

### **Definitions**

- Resolution of the DAC is equal to the number of bits in the applied digital input word.

- *The full scale* (FS):

FS = Analog output when all bits are 1 - Analog output all bits are 0

FS =

$$(V_{REF} - \frac{V_{REF}}{2N}) - 0 = V_{REF} \left(1 - \frac{1}{2N}\right)$$

• Full scale range (FSR) is defined as

$$FSR = \underset{N \to \infty}{\lim} FS = V_{REF}$$

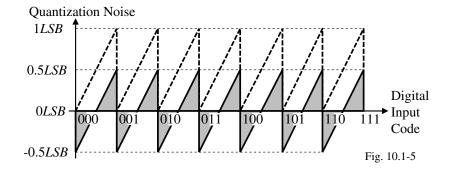

• Quantization Noise is the inherent uncertainty in digitizing an analog value with a finite resolution converter.

### **More Definitions**

• *Dynamic Range (DR)* of a DAC is the ratio of the *FSR* to the smallest difference that can be resolved (i.e. an *LSB*)

$$DR = \frac{FSR}{LSB \text{ change}} = \frac{FSR}{(FSR/2N)} = 2^N$$

or in terms of decibels

$$DR(dB) = 6.02N(dB)$$

• *Signal-to-noise ratio* (*SNR*) for the DAC is the ratio of the full scale value to the *rms* value of the quantization noise.

$$rms(\text{quantization noise}) = \sqrt{\frac{1}{T} \int_{0}^{T} LSB^{2} \left(\frac{t}{T} - 0.5\right)^{2} dt} = \frac{LSB}{\sqrt{12}} = \frac{FSR}{2^{N} \sqrt{12}}$$

$$\therefore SNR = \frac{v_{OUT}(rms)}{(FSR/\sqrt{12} \ 2^N)}$$

• Maximum SNR (SNR<sub>max</sub>) for a sinusoid is defined as

$$SNR_{max} = \frac{v_{OUT_{max}}(rms)}{(FSR/\sqrt{12} \ 2^N)} = \frac{FSR/(2\sqrt{2})}{FSR/(\sqrt{12} \ 2^N)} = \frac{\sqrt{6} \ 2^N}{2}$$

or in terms of decibels

$$SNR_{max}(dB) = 20log_{10}\left(\frac{\sqrt{62^N}}{2}\right) = 10 log_{10}(6) + 20 log_{10}(2^N) - 20 log_{10}(2) = 1.76 + 6.02N dB$$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 1 (2/25/03)

Page 10.1-4

#### **Even More Definitions**

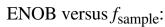

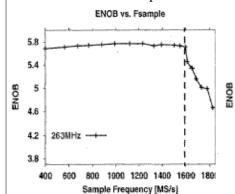

• Effective number of bits (ENOB) can be defined from the above as

$$ENOB = \frac{SNR_{Actual} - 1.76}{6.02}$$

where *SNR*<sub>Actual</sub> is the actual *SNR* of the converter.

#### Comment:

The DR is the amplitude range necessary to resolve N bits regardless of the amplitude of the output voltage.

However, when referenced to a given output analog signal amplitude, the *DR* required must include 1.76 dB more to acount for the presence of quantization noise.

Thus, for a 10-bit DAC, the *DR* is 60.2 dB and for a full-scale, *rms* output voltage, the signal must be approximately 62 dB above whatever noise floor is present in the output of the DAC.

# Accuracy Requirements of the i-th Bit

Weighting factor of the *i-th* bit =

$$\frac{V_{REF}}{2^{i+1}} \left(\frac{2^n}{2^n}\right) = 2^{n-i-1} LSBs$$

Accuracy of the *i-th* bit =

$$\frac{\pm 0.5 \ LSB}{2^{n-i-1} \ LSB} = \frac{1}{2^{n-i}} = \frac{100}{2^{n-i}} \%$$

Result: The highest accuracy requirements is always the MSB (i = 1).

The LSB bit only needs ±50% accuracy.

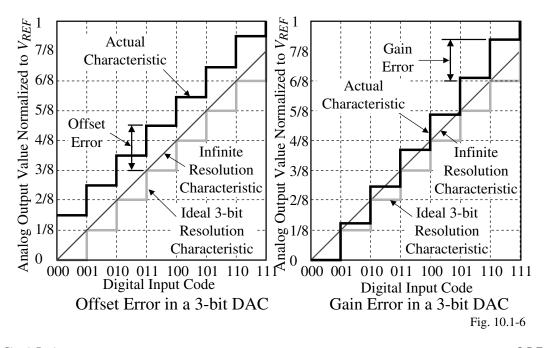

### **Offset and Gain Errors**

An *offset error* is a constant difference between the actual finite resolution characteristic and the ideal finite resolution characteristic measured at any vertical jump.

A *gain error* is the difference between the slope of the actual finite resolution and the ideal finite resolution characteristic measured at the right-most vertical jump.

CMOS Analog Circuit Design

Chapter 10 – Section 1 (2/25/03)

Page 10.1-6

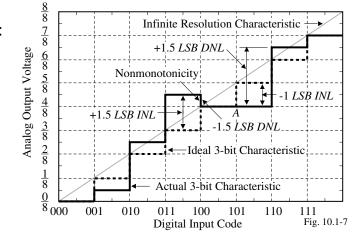

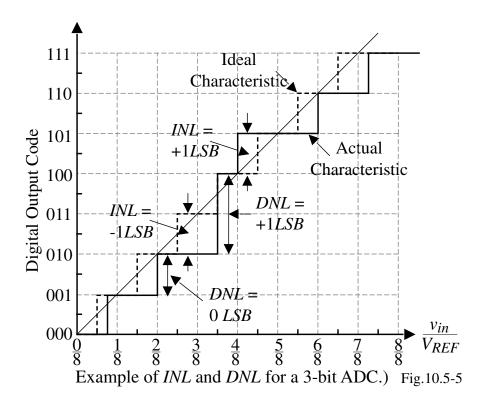

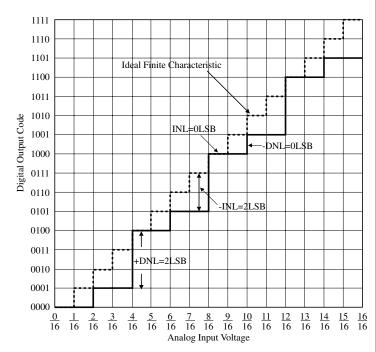

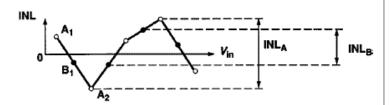

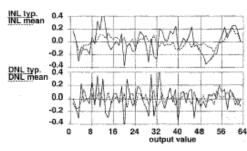

# **Integral and Differential Nonlinearity**

- *Integral Nonlinearity (INL)* is the maximum difference between the actual finite resolution characteristic and the ideal finite resolution characteristic measured vertically (% or *LSB*).

- *Differential Nonlinearity (DNL)* is a measure of the separation between adjacent levels measured at each vertical jump (% or *LSB*).

$$DNL = V_{CX} - V_{S} = \left(\frac{V_{CX} - V_{S}}{V_{S}}\right) V_{S} = \left(\frac{V_{CX}}{V_{S}} - 1\right) LSBS$$

where  $V_{CX}$  is the actual voltage change on a bit-to-bit basis and  $V_s$  is the ideal LSB

change of  $(V_{FSR}/2^N)$

Example of a 3-bit DAC:

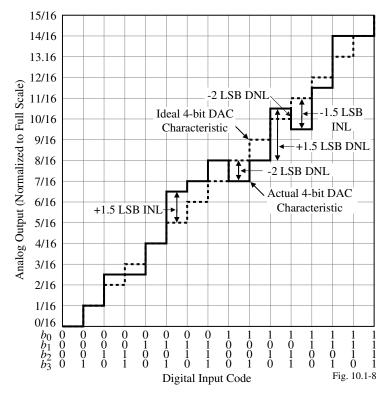

# **Example of INL and DNL of a Nonideal 4-Bit Dac**

Find the  $\pm INL$  and  $\pm DNL$  for the 4-bit DAC shown.

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 1 (2/25/03)

Page 10.1-8

### DYNAMIC CHARACTERISTICS OF DIGITAL-ANALOG CONVERTERS

Dynamic characteristics include the influence of time.

### **Definitions**

• *Conversion speed* is the time it takes for the DAC to provide an analog output when the digital input word is changed.

Factor that influence the conversion speed:

Parasitic capacitors (would like all nodes to be low impedance)

Op amp gainbandwidth

Op amp slew rate

• Gain error of an op amp is the difference between the desired and actual output voltage of the op amp (can have both a static and dynamic influence)

Actual Gain = Ideal Gain

$$x \left( \frac{\text{Loop Gain}}{1 + \text{Loop Gain}} \right)$$

Gain error = Ideal Output-Actual Output =

$$\frac{\text{Ideal Gain-Actual Gain}}{\text{Ideal Gain}} = \frac{1}{1 + \text{Loop Gain}}$$

# **Example of Influence of Op Amp Gain Error on DAC Performance**

Assume that a DAC using an op amp in the inverting configuration with  $C_1 = C_2$  and  $A_{vd}(0) = 1000$ . Find the largest resolution of the DAC if  $V_{REF}$  is 1V and assuming worst case conditions.

### Solution

The loop gain of the inverting configuration is  $LG = \frac{C_2}{C_1 + C_2} A_{vd}(0) = 0.5 \cdot 1000 = 500$ . The gain error is therefore  $1/501 \approx 0.002$ . The gain error should be less than the quantization noise of  $\pm 0.5 LSB$  which is expressed as

$$Gain\ error = \frac{1}{501} \approx 0.002 \le \frac{V_{REF}}{2^{N+1}}$$

Therefore the largest value of N that satisfies this equation is N = 7.

CMOS Analog Circuit Design

© P.E. Allen - 2003

Chapter 10 - Section 1 (2/25/03)

Page 10.1-10

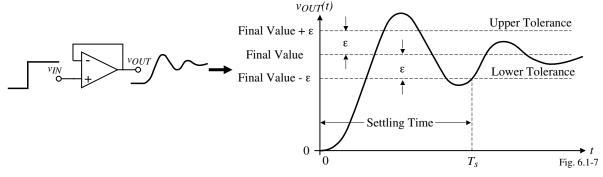

# **Influence of the Op Amp Gainbandwidth**

Single-pole response:

$$v_{out}(t) = A_{CL}[1 - e^{-\omega_H t}]v_{in}(t)$$

where

$A_{CL}$  = closed-loop gain

$$\omega_H = GB\left(\frac{R_1}{R_1 + R_2}\right) \text{ or } GB\left(\frac{C_2}{C_1 + C_2}\right)$$

To avoid errors in DACs (and ADCs),  $v_{out}(t)$  must be within  $\pm 0.5LSB$  of the final value by the end of the conversion time.

Multiple-pole response:

Typically the response is underdamped like the following (see Appendix C of text).

CMOS Analog Circuit Design

© P.E. Allen - 2003

### Example of the Influence of GB and Settling Time on DAC Performance

Assume that a DAC uses a switched capacitor noninverting amplifier with  $C_1 = C_2$  and GB = 1 MHz. Find the conversion time of an 8-bit DAC if  $V_{REF}$  is 1V.

### Solution

From the analysis in Secs. 9.2 and 9.3, we know that

$$\omega_H = \left(\frac{C_2}{C_1 + C_2}\right) GB = (2\pi)(0.5)(10^6) = 3.141 \times 10^6$$

and  $A_{CL} = 1$ . Assume that the ideal output is equal to  $V_{REF}$ . Therefore the value of the output voltage which is 0.5LSB of  $V_{REF}$  is

$$1 - \frac{1}{2N+1} = 1 - e^{-\omega_H} T$$

or

$$2N+1 = e\omega_H T$$

Solving for *T* gives

$$T = \left(\frac{N+1}{\omega_H}\right) \ln(2) = 0.693 \left(\frac{N+1}{\omega_H}\right) = \left(\frac{9}{3.141}\right) 0.693 = 1.986 \mu s$$

CMOS Analog Circuit Design

Chapter 10 – Section 1 (2/25/03)

Page 10.1-12

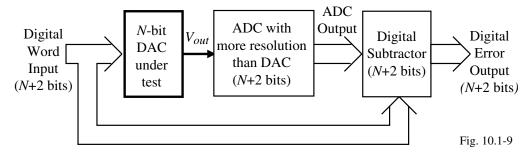

### **TESTING OF DACs**

# **Input-Output Test**

Test setup:

#### Comments:

Sweep the digital input word from 000...0 to 111...1.

The ADC should have more resolution by at least 2 bits and be more accurate than the errors of the DAC

INL will show up in the output as the presence of 1's in any bit.

If there is a 1 in the Nth bit, the *INL* is greater than  $\pm 0.5 LSB$

DNL will show up as a change between each successive digital error output.

The bits which are greater than N in the digital error output can be used to resolve the errors to less than  $\pm 0.5 LSB$

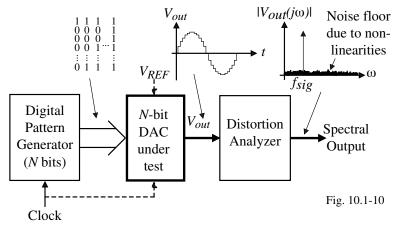

### **Spectral Test**

Test setup:

### Comments:

Digital input pattern is selected to have a fundamental frequency which has a magnitude of at least 6*N* dB above its harmonics.

Length of the digital sequence determines the spectral purity of the fundamental frequency.

All nonlinearities of the DAC (i.e. *INL* and *DNL*) will cause harmonics of the fundamental frequency

The THD can be used to determine the SNR dB range between the magnitude of the fundamental and the THD. This SNR should be at least 6N dB to have an INL of less than  $\pm 0.5LSB$  for an ENOB of N-bits.

Note that the noise contribution of  $V_{REF}$  must be less than the noise floor due to nonlinearities.

If the period of the digital pattern is increased, the frequency dependence of *INL* can be measured.

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 2 (2/25/03)

Page 10.2-1

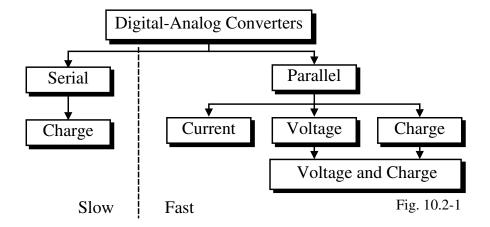

### SECTION 10.2 - PARALLEL DIGITAL-ANALOG CONVERTERS

# **Classification of Digital-Analog Converters**

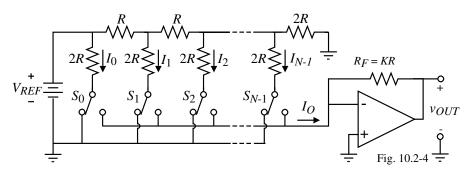

# CURRENT SCALING DIGITAL-ANALOG CONVERTERS General Current Scaling DACs

The output voltage can be expressed as

$$V_{OUT} = -R_F(I_0 + I_1 + I_2 + \dots + I_{N-1})$$

where the currents  $I_0$ ,  $I_1$ ,  $I_2$ , ... are binary weighted currents.

CMOS Analog Circuit Design

© P.E. Allen - 2003

Chapter 10 – Section 2 (2/25/03)

Page 10.2-3

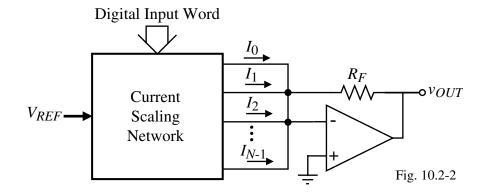

# **Binary-Weighted Resistor DAC**

Circuit:

#### Comments:

1.)  $R_F$  can be used to scale the gain of the DAC. If  $R_F = KR/2$ , then

$$v_{OUT} = -R_F I_O = \frac{-KR}{2} \left( \frac{b_0}{R} + \frac{b_1}{2R} + \frac{b_2}{4R} + \dots + \frac{b_{N-1}}{2^{N-1}R} \right) V_{REF} \Rightarrow v_{OUT} = -K \left( \frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \dots + \frac{b_{N-1}}{2^N} \right) V_{REF}$$

where  $b_i$  is 1 if switch  $S_i$  is connected to  $V_{REF}$  or 0 if switch  $S_i$  is connected to ground.

- 2.) Component spread value =  $\frac{R_{MSB}}{R_{LSB}} = \frac{R}{2^{N-1}R} = \frac{1}{2^{N-1}}$

- 3.) Attributes:

Insensitive to parasitics  $\Rightarrow$  fast Trimming required for large values of N Large component spread value Nonmonotonic

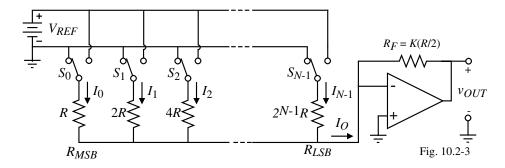

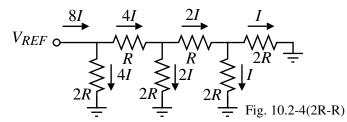

# R-2R Ladder Implementation of the Binary Weighted Resistor DAC

Use of the R-2R concept to avoid large element spreads:

How does the R-2R ladder work?

"The resistance seen to the right of any of the vertical 2R resistors is 2R."

### Attributes:

- Not sensitive to parasitics (currents through the resistors never change as  $S_i$  is varied)

- Small element spread. Resistors made from same unit (2*R* consist of two in series or *R* consists of two in parallel)

- Not monotonic

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 - Section 2 (2/25/03)

Page 10.2-5

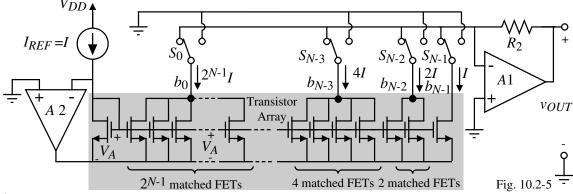

# **Current Scaling Using Binary Weighted MOSFET Current Sinks**

Circuit:

Operation:

$$v_{OUT} = R_2(b_{N-1} \cdot I + b_{N-2} \cdot 2I + b_{N-3} \cdot 4I + \dots + b_0 \cdot 2^{N-1} \cdot I)$$

If  $I = I_{REF} = \frac{V_{REF}}{2^N R_2}$ ,

then

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \dots + \frac{b_{N-3}}{2^{N-2}} + \frac{b_{N-2}}{2^{N-1}} + \frac{b_{N-1}}{2^N}\right) V_{REF}$$

### Attributes:

Fast (no floating nodes) and not monotonic

Accuracy of MSB greater than LSBs

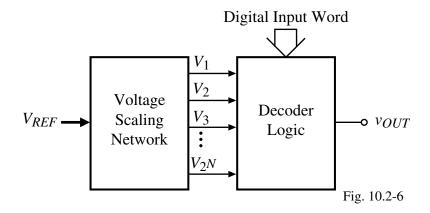

# **VOLTAGE SCALING DIGITAL-ANALOG CONVERTERS**

# **General Voltage Scaling Digital Analog Converter**

# Operation:

Creates all possible values of the analog output then uses a decoding network to determine which voltage to select based on the digital input word.

CMOS Analog Circuit Design

Chapter 10 - Section 2 (2/25/03)

Page 10.2-7

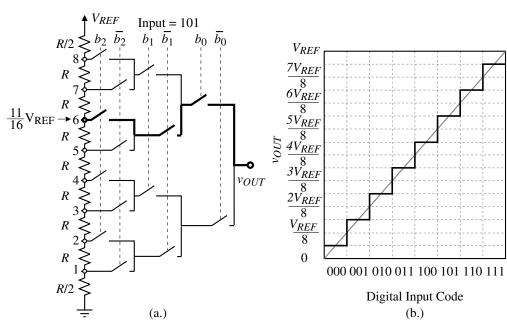

# 3-Bit Voltage Scaling Digital-Analog Converter

The voltage at any tap can be expressed as:  $v_{OUT} = \frac{V_{REF}}{8}(n - 0.5) = \frac{V_{REF}}{16}(2n - 1)$

### Attributes:

- Guaranteed monotonic

- Compatible with CMOS technology

- Large area if *N* is large

- Sensitive to parasitics

- Requires a buffer

- Large current can flow through the resistor string.

Figure 10.2-7 - (a.) Implementation of a 3-bit voltage scaling DAC. (b.) Input-output characteristics of Fig. 10.2-7(a.)

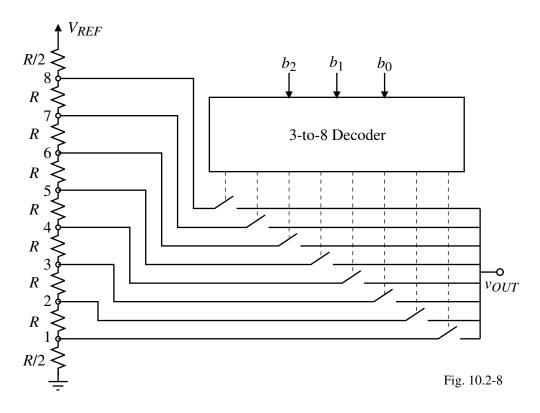

# **Alternate Realization of the 3-Bit Voltage Scaling DAC**

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 2 (2/25/03)

Page 10.2-9

# INL and DNL of the Voltage Scaling DAC

Find an expression for the INL and DNL of the voltage scaling DAC using a worst-case approach. For an n-bit DAC, assume there are  $2^n$  resistors between  $V_{REF}$  and ground and that the resistors are numbered from 1 to  $2^n$  beginning with the resistor connected to  $V_{REF}$  and ending with the resistor connected to ground.

# **Integral Nonlinearity**

The voltage at the *i*-th resistor from the top is,  $v_i = \frac{(2^{n}-i)R}{(2^{n}-i)R + iR} V_{REF}$

where there are *i* resistors above  $v_i$  and  $2^{n}$ -i below. For worst case, assume that  $i = 2^{n-1}$  (midpoint). Define  $R_{max} = R + \Delta R$  and  $R_{min} = R - \Delta R$ .

The worst case INL is

$$INL = v_{2n-1}(\text{actual}) - v_{2n-1}(\text{ideal})$$

Therefore,

$$INL = \frac{2^{n-1}(R + \Delta R)V_{REF}}{2^{n-1}(R + \Delta R) + 2^{n-1}(R - \Delta R)} - \frac{V_{REF}}{2} = \frac{\Delta R}{2R} V_{REF}$$

$$INL = \frac{2^{n}}{2^{n}} \left( \frac{\Delta R}{2R} \right) V_{REF} = 2^{n-1} \left( \frac{\Delta R}{R} \right) \left( \frac{V_{REF}}{2^{n}} \right) = 2^{n-1} \left( \frac{\Delta R}{R} \right) LSBs$$

# **Differential Nonlinearity**

The worst case *DNL* can be found as

$$DNL = v_{step}(\text{actual}) - v_{step}(\text{ideal})$$

Substituting the actual and ideal steps gives,

$$= \frac{(R \pm \Delta R)V_{REF}}{2^{n}R} - \frac{R V_{REF}}{2^{n}R}$$

$$= \left(\frac{R \pm \Delta R}{R} - \frac{R}{R}\right) \frac{V_{REF}}{2^{n}} = \frac{\pm \Delta R}{R} \frac{V_{REF}}{2^{n}}$$

Therefore,

$$DNL = \frac{\pm \Delta R}{R} LSBs$$

# **Example 10.2-1 - Accuracy Requirements of a Voltage-Scaling digital-analog Converter**

If the resistor string of a voltage scaling digital-analog converter is a 5  $\mu$ m wide polysilicon strip having a relative accuracy of  $\pm 1\%$ , what is the largest number of bits that can be resolved and keep the worst case *INL* within  $\pm 0.5$  LSB? For this number of bits, what is the worst case *DNL*?

### Solution

From the previous page, we can write that

$$2^{n-1} \left( \frac{\Delta R}{R} \right) = 2^{n-1} \left( \frac{1}{100} \right) \le \frac{1}{2}$$

This inequality can be simplified

$$2^n \le 100$$

which has a solution of n = 6.

The value of the *DNL* for n = 6 is found from the previous page as

$$DNL = \frac{\pm 1}{100} LSBs = \pm 0.01 LSBs$$

(This is the reason the resistor string is monotonic.)

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 2 (2/25/03)

Page 10.2-11

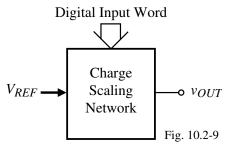

# CHARGE SCALING DIGITAL-ANALOG CONVERTERS

# **General Charge Scaling Digital-Analog Converter**

General principle is to capacitively attenuate the reference voltage. Capacitive attenuation is simply:

$V_{REF} = \begin{array}{c} C_1 \\ \\ \hline \\ C_2 \end{array} \quad V_{out}$ Fig. 10.2-9

Calculate as if the capacitors were resistors. For example,

$$V_{out} = \frac{\frac{1}{C_2}}{\frac{1}{C_1} + \frac{1}{C_2}} V_{REF} = \frac{C_1}{C_1 + C_2} V_{REF}$$

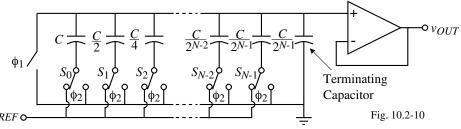

# Binary-Weighted, Charge Scaling DAC

Circuit:

Operation:

1.) All switches connected to ground during  $\phi_1$ .

2.) Switch  $S_i$  closes to  $V_{REF}$  if  $b_i = 1$  or to ground if  $b_i = 0$ .

Equating the charge in the capacitors gives,

$$V_{REF}C_{eq} = V_{REF}\left(b_0C + \frac{b_1C}{2} + \frac{b_2C}{2^2} + \dots + \frac{b_{N-1}C}{2^{N-1}}\right) = C_{tot} \, v_{OUT} = 2C \, v_{OUT}$$

which gives

$$v_{\text{OUT}} = [b_0 2^{-1} + b_1 2^{-2} + b_2 2^{-3} + \dots + b_{N-1} 2^{-N}] V_{\text{REF}}$$

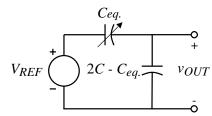

Equivalent circuit of the binary-weighted, charge scaling DAC is:

Attributes:

- Accurate

- Sensitive to parasitics

- Not monotonic

- Charge feedthrough occurs at turn on of switches

Fig. 10.2-11

CMOS Analog Circuit Design

Chapter 10 - Section 2 (2/25/03)

Page 10.2-13

# **Integral Nonlinearity of the Charge Scaling DAC**

Again, we use a worst case approach. Assume an *n*-bit charge scaling DAC with the *MSB* capacitor of *C* and the *LSB* capacitor of  $C/2^{n-1}$  and the capacitors have a tolerance of  $\Delta C/C$ .

The ideal output when the *i*-th capacitor only is connected to  $V_{REF}$  is

$$v_{OUT}$$

(ideal) =  $\frac{C/2^{i-1}}{2C} V_{REF} = \frac{V_{REF}}{2^i} \left(\frac{2^n}{2^n}\right) = \frac{2^n}{2^i} LSBs$

The maximum and minimum capacitance is  $C_{max} = C + \Delta C$  and  $C_{min} = C - \Delta C$ . Therefore, the actual worst case output for the *i*-th capacitor is

$$v_{OUT}(\text{actual}) = \frac{(C \pm \Delta C)/2^{i-1}}{2C} V_{REF} = \frac{V_{REF}}{2^i} \pm \frac{\Delta C \cdot V_{REF}}{2^i C} = \frac{2^n}{2^i} \pm \frac{2^n \Delta C}{2^i C} LSBs$$

Now, the INL for the i-th bit is given as

$$INL(i) = v_{OUT}(\text{actual}) - v_{OUT}(\text{ideal}) = \frac{\pm 2^n \Delta C}{2^i C} = \frac{2^{n-i} \Delta C}{C} LSBs$$

Typically, the worst case value of i occurs for i = 1. Therefore, the worst case INL is

$$INL = \pm 2^{n-1} \frac{\Delta C}{C} LSBs$$

### **Differential Nonlinearity of the Charge Scaling DAC**

The worst case *DNL* for the binary weighted capacitor array is found when the *MSB* changes. The output voltage of the binary weighted capacitor array can be written as

$$v_{OUT} = \frac{C_{eq.}}{(2C - C_{eq.}) + C_{eq.}} V_{REF}$$

where  $C_{eq}$  are capacitors whose bits are 1 and  $(2C - C_{eq})$  are capacitors whose bits are 0.

The worst case DNL can be expressed as

$$DNL = \frac{v_{\text{step}}(\text{worst case})}{v_{\text{step}}(\text{ideal})} - 1 = \frac{v_{OUT}(1000...) - v_{OUT}(0111...)}{LSB} - 1 LSBs$$

The worst case choice for the capacitors is to choose  $C_1$  larger by  $\Delta C$  and the remaining capacitors smaller by  $\Delta C$  giving,

$$C_1 = C + \Delta C$$

,  $C_2 = \frac{1}{2}(C - \Delta C)$ ,..., $C_{n-1} = \frac{1}{2^{n-2}}(C - \Delta C)$ ,  $C_n = \frac{1}{2^{n-1}}(C - \Delta C)$ , and  $C_{term} = \frac{1}{2^{n-1}}(C - \Delta C)$

Note that

$$\sum_{i=2}^{n} C_i + C_{term} = C_2 + C_3 + \dots + C_{n-1} + C_n + C_{term} = C - \Delta C$$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 - Section 2 (2/25/03)

Page 10.2-15

# **Differential Nonlinearity of the Charge Scaling DAC - Continued**

$$\therefore v_{OUT}(1000...) = \left(\frac{C + \Delta C}{(C + \Delta C) + (C - \Delta C)}\right) V_{REF} = \left(\frac{C + \Delta C}{2C}\right) V_{REF}$$

and

$$v_{OUT}(0111...) = \left(\frac{(C-\Delta C) - C_{term}}{(C+\Delta C) + (C-\Delta C)}\right) V_{REF} = \frac{(C-\Delta C) - \frac{1}{2n-1}(C-\Delta C)}{(C+\Delta C) + (C-\Delta C)} V_{REF}$$

$$= \left(\frac{C-\Delta C}{2C}\right) \left(1 - \frac{2}{2^n}\right) V_{REF}$$

$$\therefore \frac{v_{OUT}(1000...) - v_{OUT}(0111...)}{LSB} - 1 \ LSBs = 2n \left(\frac{C + \Delta C}{2C}\right) - 2n \left(\frac{C - \Delta C}{2C}\right) \left(1 - \frac{2}{2n}\right) - 1 = (2^{n} - 1)\frac{\Delta C}{C} \ LSBs$$

Therefore,

$$DNL = (2^n - 1) \frac{\Delta C}{C} LSBs$$

# Example 10.2-2 - DNL and INL of a Binary Weighted Capacitor Array DAC

If the tolerance of the capacitors in an 8-bit, binary weighted, charge scaling DAC are  $\pm 0.5\%$ , find the worst case *INL* and *DNL*.

### Solution

For the worst case INL, we get from above that

$$INL = (2^7)(\pm 0.005) = \pm 0.64 LSBs$$

For the worst case *DNL*, we can write that

$$DNL = (28-1)(\pm 0.005) = \pm 1.275 LSBs$$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 2 (2/25/03)

Page 10.2-17

# **Example 10.2-3 - Influence of Capacitor Ratio Accuracy on Number of Bits**

Use the data of Fig. 2.4-2 to estimate the number of bits possible for a charge scaling DAC assuming a worst case approach for *INL* and that the worst conditions occur at the midscale (1 *MSB*).

#### Solution

Assuming an INL of  $\pm 0.5$  LSB, we can write that

$$INL = \pm 2^{N-1} \frac{\Delta C}{C} \le \pm \frac{1}{2}$$

$\rightarrow \left[ \frac{\Delta C}{C} \right] = \frac{1}{2^N}$ .

From the data presented in Chapter 2, it is reasonable to assume that the relative accuracy of the capacitor ratios will decrease with the number of bits. Let us assume a unit capacitor of 50  $\mu$ m by 50  $\mu$ m and a relative accuracy of approximately  $\pm 0.1\%$ . Solving for N in the above equation gives approximately 10 bits. However, the  $\pm 0.1\%$  figure corresponds to ratios of 16:1 or 4 bits. In order to get a solution, we estimate the relative accuracy of capacitor ratios as

$$\frac{\Delta C}{C} \approx 0.001 + 0.0001N$$

Using this approximate relationship, a 9-bit digital-analog converter should be realizable.

Page 10.2-19

# **Binary Weighted, Charge Amplifier DAC**

### Attributes:

Chapter 10 - Section 2 (2/25/03)

- No floating nodes which implies insensitive to parasitics and fast

- No terminating capacitor required

- With the above configuration, charge feedthrough will be  $\Delta V_{error} \approx -(C_{OL}/2C^{N})\Delta V$

- Can totally eliminate parasitics with parasitic-insensitive switched capacitor circuitry but not the charge feedthrough

CMOS Analog Circuit Design © P.E. Allen - 2003

# **Summary of the Parallel DAC Performance**

| DAC Type           | Advantage                              | Disadvantage                                   |

|--------------------|----------------------------------------|------------------------------------------------|

| Current<br>Scaling | Fast, insensitive to switch parasitics | Large element spread, nonmonotonic             |

| Voltage<br>Scaling | Monotonic, equal resistors             | Large area, sensitive to parasitic capacitance |

| Charge<br>Scaling  | Fast, good accuracy                    | Large element spread, nonmonotonic             |

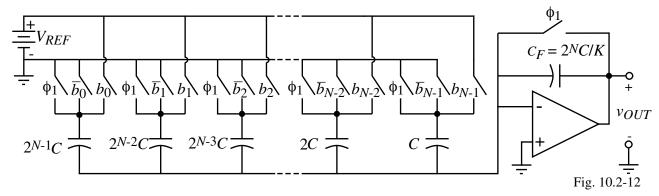

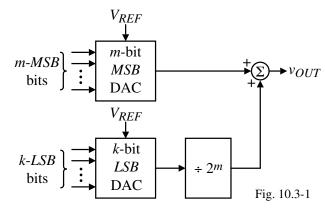

# SECTION 10.3 - EXTENDING THE RESOLUTION OF PARALLEL DIGITAL-ANALOG CONVERTERS

### **Background**

Technique:

Divide the total resolution N into k smaller sub-DACs each with a resolution of  $\frac{N}{k}$ .

Result:

Smaller total area.

More resolution because of reduced largest to smallest component spread.

# Approaches:

• Combination of similarly scaled subDACs

Divider approach (scale the analog output of the subDACs)

Subranging approach (scale the reference voltage of the subDACs)

• Combination of differently scaled subDACs

CMOS Analog Circuit Design

© P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-2

### COMBINATION OF SIMILARLY SCALED SUBDACS

# **Analog Scaling - Divider Approach**

Example of combining a *m*-bit and *k*-bit subDAC to form a *m*+*k*-bit DAC.

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \dots + \frac{b_{m-1}}{2^m}\right) V_{REF} + \left(\frac{1}{2^m}\right) \left(\frac{b_m}{2} + \frac{b_{m+1}}{4} + \dots + \frac{b_{m+k-1}}{2^k}\right) V_{REF}$$

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \dots + \frac{b_{m-1}}{2^m} + \frac{b_m}{2^{m+1}} + \frac{b_{m+1}}{2^{m+2}} + \dots + \frac{b_{m+k-1}}{2^{m+k}}\right) V_{REF}$$

Accuracy?

Weighting factor of the *i-th* bit =  $\frac{V_{REF}}{2^{i+1}} \left(\frac{2^n}{2^n}\right) = 2^{n-i-1} LSBs$

Accuracy of the *i-th* bit =

$$\frac{\pm 0.5 LSB}{2^{n-i-1} LSB} = \frac{1}{2^{n-i}} = \frac{100}{2^{n-i}} \%$$

# **Example 10.3-1 - Illustration of the Influence of the Scaling Factor**

Assume that m = 2 and k = 2 in Fig. 10.3-1 and find the transfer characteristic of this DAC if the scaling factor for the *LSB* DAC is 3/8 instead of 1/4. Assume that  $V_{REF} = 1$ V. What is the  $\pm INL$  and  $\pm DNL$  for this DAC? Is this DAC monotonic or not?

### Solution

The ideal DAC output is given as

$$v_{OUT} = \frac{b_0}{2} + \frac{b_1}{4} + \frac{1}{4} \left( \frac{b_2}{2} + \frac{b_3}{4} \right) = \frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \frac{b_3}{16}.$$

The actual DAC output can be written as

$$v_{OUT}(\text{act.}) = \frac{b_0}{2} + \frac{b_1}{4} + \frac{3b_2}{16} + \frac{3b_3}{32} = \frac{16b_0}{32} + \frac{8b_1}{32} + \frac{6b_2}{32} + \frac{3b_3}{32}$$

The results are tabulated in Table 10.3-1 for this example.

CMOS Analog Circuit Design

© P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-4

# **Example 10.3-1 - Continued**

Table 10.3-1

Ideal and Actual Analog Output for the DAC in Ex. 10.3-1,

| Input   | $v_{OUT}(act.)$ | $v_{OUT}$ | $v_{OUT}(act.)$    | Change in                |

|---------|-----------------|-----------|--------------------|--------------------------|

| Digital |                 |           | - v <sub>OUT</sub> | v <sub>OUT</sub> (act) - |

| Word    |                 |           | 001                | 2/32                     |

| 0000    | 0/32            | 0/32      | 0/32               | -                        |

| 0001    | 3/32            | 2/32      | 1/32               | 1/32                     |

| 0010    | 6/32            | 4/32      | 2/32               | 1/32                     |

| 0011    | 9/32            | 6/32      | 3/32               | 1/32                     |

| 0100    | 8/32            | 8/32      | 0/32               | -3/32                    |

| 0101    | 11/32           | 10/32     | 1/32               | 1/32                     |

| 0110    | 14/32           | 12/32     | 2/32               | 1/32                     |

| 0111    | 17/32           | 14/32     | 3/32               | 1/32                     |

| 1000    | 16/32           | 16/32     | 0/32               | -3/32                    |

| 1001    | 19/32           | 18/32     | 1/32               | 1/32                     |

| 1010    | 22/32           | 20/32     | 2/32               | 1/32                     |

| 1011    | 25/32           | 22/32     | 3/32               | 1/32                     |

| 1100    | 24/32           | 24/32     | 0/32               | -3/32                    |

| 1101    | 27/32           | 26/32     | 1/32               | 1/32                     |

| 1110    | 30/32           | 28/32     | 2/32               | 1/32                     |

| 1111    | 33/32           | 30/32     | 3/32               | 1/32                     |

Table 10.3-1 contains all the information we are seeking. An LSB for this example is 1/16 or 2/32. The fourth column gives the +*INL* as 1.5*LSB* and the -*INL* as 0*LSB*. The fifth column gives the +*DNL* as -0.5*LSB* and the -*DNL* as -1.5*LSB*. Because the -*DNL* is greater than -1*LSB*, this DAC is not monotonic.

# **Example 10.3-2 - Tolerance of the Scaling Factor to Prevent Conversion Errors**

Find the worst case tolerance of the scaling factor  $(x = 1/2^m = 1/4)$  in the above example that will not cause a conversion error in the DAC.

### Solution

Because the scaling factor only affects the LSB DAC, we need only consider the two LSB bits. The worst case requirement for the ideal scaling factor of 1/4 is given as

$$\frac{b_2}{2}(x \pm \Delta x) + \frac{b_3}{4}(x \pm \Delta x) \le \frac{xb_2}{2} + \frac{xb_3}{4} \pm \frac{1}{32}$$

or

$$\Delta x \left(\frac{b_2}{2}\right) + \Delta x \left(\frac{b_3}{4}\right) = \Delta x \left(\frac{b_2}{2} + \frac{b_3}{4}\right) \le \frac{1}{32} \ .$$

The worst case value of  $\Delta x$  occurs when both  $b_2$  and  $b_3$  are 1. Therefore, we get

$$\Delta x \left( \frac{3}{4} \right) \leq \frac{1}{32} \ \to \ \Delta x \leq \frac{1}{24} \, .$$

The scaling factor, x, can be expressed as

$$x \pm \Delta x = \frac{1}{4} \pm \frac{1}{24} = \frac{6}{24} \pm \frac{1}{24}$$

Therefore, the tolerance required for the scaling factor x is 5/24 to 7/24. This corresponds to an accuracy of  $\pm 16.7\%$  which is less than the  $\pm 25\%$  ( $\pm 100\%/2^k$ ) because of the influence of the *LSB* bits. It can be shown that the *INL* will be equal to  $\pm 0.5LSB$  or less (see Problem 10.3-6 of text).

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-6

# **Reference Scaling - Subranging Approach**

Example of combining a *m*-bit and *k*-bit subDAC to form a *m*+*k*-bit DAC.

$$v_{NEF}$$

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \dots + \frac{b_{m-1}}{2m}\right)V_{REF} + \left(\frac{b_m}{2} + \frac{b_{m+1}}{4} + \dots + \frac{b_{m+k-1}}{2k}\right)\left(\frac{V_{REF}}{2m}\right)$$

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \dots + \frac{b_{m-1}}{2m}\right)V_{REF} + \left(\frac{b_m}{2} + \frac{b_{m+1}}{4} + \dots + \frac{b_{m+k-1}}{2k}\right)\left(\frac{V_{REF}}{2m}\right)$$

Accuracy considerations of this method are similar to the analog scaling approach.

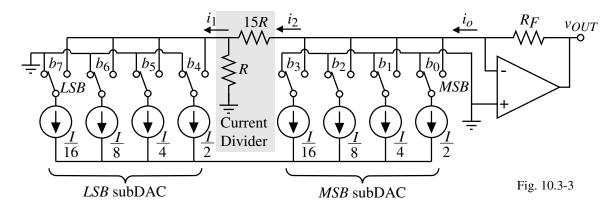

# **Current Scaling Dac Using Two SubDACs**

Implementation:

$$v_{OUT} = R_F I \left[ \left( \frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \frac{b_3}{16} \right) + \frac{1}{16} \left( \frac{b_4}{2} + \frac{b_5}{4} + \frac{b_6}{8} + \frac{b_7}{16} \right) \right]$$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03) Page 10.3-8

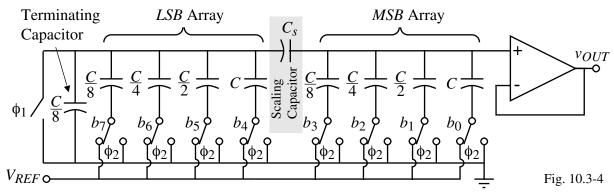

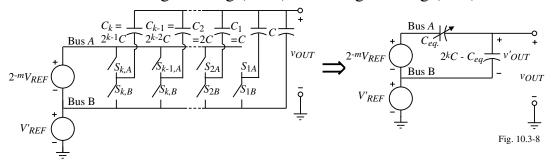

# **Charge Scaling DAC Using Two SubDACs**

Implementation:

Design of the scaling capacitor,  $C_s$ :

The series combination of  $C_s$  and the *LSB* array must terminate the *MSB* array or equal C/8. Therefore, we can write

$$\frac{C}{8} = \frac{1}{\frac{1}{C_s} + \frac{1}{2C}}$$

or  $\frac{1}{C_s} = \frac{8}{C} - \frac{1}{2C} = \frac{16}{2C} - \frac{1}{2C} = \frac{15}{2C}$ .

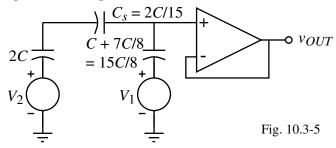

# **Equivalent Circuit of the Charge Scaling Dac Using Two SubDACs**

Simplified equivalent circuit:

where the Thevenin equivalent voltage of the MSB array is

$$V_1 = \left[ \left( \frac{1}{15/8} \right) b_0 + \left( \frac{1/2}{15/8} \right) b_1 + \left( \frac{1/4}{15/8} \right) b_2 + \left( \frac{1/8}{15/8} \right) b_3 \right] V_{REF} = \frac{16}{15} \left( \frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \frac{b_3}{16} \right) V_{REF}$$

and the Thevenin equivalent voltage of the *LSB* array is

$$V_2 = \left[ \left( \frac{1/1}{2} \right) b_4 + \left( \frac{1/2}{2} \right) b_5 + \left( \frac{1/4}{2} \right) b_6 + \left( \frac{1/8}{2} \right) b_7 \right] V_{REF} = \left( \frac{b_4}{2} + \frac{b_5}{4} + \frac{b_6}{8} + \frac{b_8}{16} \right) V_{REF}$$

Combining the elements of the simplified equivalent circuit above gives

$$v_{OUT} = \left(\frac{\frac{1}{2} + \frac{15}{2}}{\frac{1}{2} + \frac{15}{2} + \frac{8}{15}}\right) V_1 + \left(\frac{\frac{8}{15}}{\frac{1}{2} + \frac{15}{2} + \frac{8}{15}}\right) V_2 = \left(\frac{15 + 15 \cdot 15}{15 + 15 \cdot 15 + 16}\right) V_1 + \left(\frac{16}{15 + 15 \cdot 15 + 16}\right) V_2 = \frac{15}{16} V_1 + \frac{1}{16} V_2$$

$$v_{OUT} = \left(\frac{b_0}{2} + \frac{b_1}{4} + \frac{b_2}{8} + \frac{b_3}{16} + \frac{b_4}{32} + \frac{b_5}{64} + \frac{b_6}{128} + \frac{b_7}{256}\right) V_{REF} = \sum_{i=0}^{7} \frac{b_i V_{REF}}{2^{i+1}}$$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-10

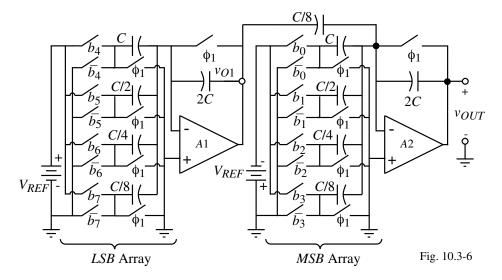

# Charge Amplifier DAC Using Two Binary Weighted Charge Amplifier SubDACs Implementation:

Attributes:

- *MSB* subDAC is not dependent upon the accuracy of the scaling factor for the *LSB* subDAC.

- Insensitive to parasitics, fast

- Limited to op amp dynamics

- No ICMR problems with the op amp

### COMBINATION OF DIFFERENTLY SCALED SUBDACS

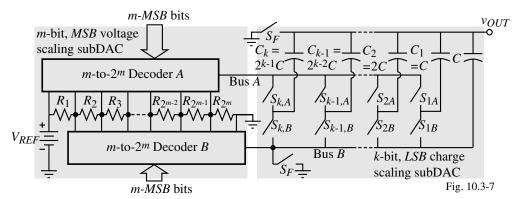

# **Voltage Scaling MSB SubDAC And Charge Scaling LSB SubDAC**

Implementation:

### Operation:

- 1.) Switches  $S_F$  and  $S_{1B}$  through  $S_{k,B}$  discharge all capacitors.

- 2.) Decoders A and B connect Bus A and Bus B to the top and bottom, respectively, of the appropriate resistor as determined by the *m*-bits.

- 3.) The charge scaling subDAC divides the voltage across this resistor by capacitive division determined by the k-bits.

#### Attributes:

- MSB's are monotonic but the accuracy is poor Accuracy of LSBs is good

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-12

# **Voltage Scaling MSB SubDAC And Charge Scaling LSB SubDAC - Continued**

Equivalent circuit of the voltage scaling (MSB) and charge scaling (LSB) DAC:

where,

$$V'_{REF} = V_{REF} \left( \frac{b_0}{2^1} + \frac{b_1}{2^2} + \dots + \frac{b_{m-2}}{2^{m-1}} + \frac{b_{m-1}}{2^m} \right)$$

and

$$v'_{OUT} = \frac{V_{REF}}{2^m} \left( \frac{b_m}{2} + \frac{b_{m+1}}{2^2} + \dots + \frac{b_{m+k}}{2^{k-1}} + \frac{b_{m+k-1}}{2^k} \right) = V_{REF} \left( \frac{b_m}{2^{m+1}} + \frac{b_{m+1}}{2^{m+2}} + \dots + \frac{b_{m+k}}{2^{m+k-1}} + \frac{b_{m+k-1}}{2^{m+k}} \right)$$

Adding  $V'_{REF}$  and  $v'_{OUT}$  gives the DAC output voltage as

$$v_{OUT} = V'_{REF} + v'_{OUT} = V_{REF} \left( \frac{b_0}{2^1} + \frac{b_1}{2^2} + \dots + \frac{b_{m-2}}{2^{m-1}} + \frac{b_{m-1}}{2^m} + \frac{b_m}{2^{m+1}} + \frac{b_{m+1}}{2^{m+2}} + \dots + \frac{b_{m+k}}{2^{m+k-1}} + \frac{b_{m+k-1}}{2^{m+k}} \right)$$

which is equivalent to an  $m+k$  bit DAC.

© P.E. Allen - 2003 CMOS Analog Circuit Design

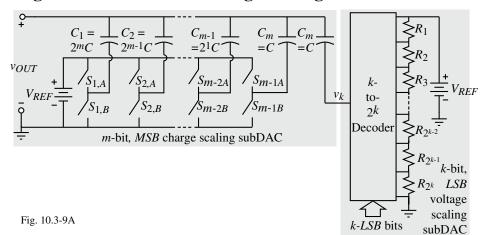

# Charge Scaling MSB SubDAC and Voltage Scaling LSB SubDAC

$$v_{OUT} = \left(\frac{b_0}{2^1} + \frac{b_1}{2^2} + \dots + \frac{b_{m-2}}{2^{m-1}} + \frac{b_{m-1}}{2^m}\right) V_{REF} + \frac{v_k}{2^m} \quad \text{where} \quad v_k = \left(\frac{b_m}{2^1} + \frac{b_{m+1}}{2^2} + \dots + \frac{b_{m+k}}{2^{k-1}} + \frac{b_{m+k-1}}{2^k}\right) V_{REF}$$

$$\therefore \quad v_{OUT} = \left(\frac{b_0}{2^1} + \frac{b_1}{2^2} + \dots + \frac{b_{m-2}}{2^{m-1}} + \frac{b_{m-1}}{2^m} + \frac{b_m}{2^{m+1}} + \frac{b_{m+1}}{2^{m+2}} + \dots + \frac{b_{m+k}}{2^{m+k-1}} + \frac{b_{m+k-1}}{2^{m+k}}\right) V_{REF}$$

### Attributes:

- MSBs have good accuracy

- LSBs are monotonic, have poor accuracy require trimming for good accuracy

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-14

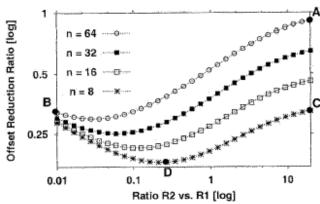

# **Tradeoffs in SubDAC Selection to Enhance Linearity Performance**

Assume a *m*-bit *MSB* subDAC and a *k*-bit *LSB* subDAC.

<u>MSB Voltage Scaling SubDAC and LSB Charge Scaling SubDAC (n = m+k)</u>

*INL* and *DNL* of the *m*-bit *MSB* voltage-scaling subDAC:

$$INL(R) = 2^{m-1} \left(\frac{2^n}{2^m}\right) \frac{\Delta R}{R} = 2^{n-1} \frac{\Delta R}{R} LSBs$$

and  $DNL(R) = \frac{\pm \Delta R}{R} \left(\frac{2^n}{2^m}\right) = 2^k \frac{\pm \Delta R}{R} LSBs$

*INL* and *DNL* of the *k*-bit *LSB* charge-scaling subDAC:

$$INL(C) = 2^{k-1} \frac{\Delta C}{C} LSBs$$

and  $DNL(C) = (2^{k}-1) \frac{\Delta C}{C} LSBs$

Combining these relationships:

$$INL = INL(R) + INL(C) = \left(2^{n-1} \frac{\Delta R}{R} + 2^{k-1} \frac{\Delta C}{C}\right) LSBs$$

and

$$DNL = DNL(R) + DNL(C) = \left(2^{k} \frac{\Delta R}{R} + (2^{k-1}) \frac{\Delta C}{C}\right) LSBs$$

MSB Charge Scaling SubDAC and LSB Voltage Scaling SubDAC

$$INL = INL(R) + INL(C) = \left(2^{k-1} \frac{\Delta R}{R} + 2^{n-1} \frac{\Delta C}{C}\right) LSBs$$

and

$$DNL = DNL(R) + DNL(C) = \left(\frac{\Delta R}{R} + (2^{n-1})\frac{\Delta C}{C}\right) LSBs$$

# Example 10.3-3 - Design of a DAC using Voltage Scaling for MBSs and Charge Scaling for LSBs

Consider a 12-bit DAC that uses voltage scaling for the *MSBs* charge scaling for the *LSBs*. To minimize the capacitor element spread and the number of resistors, choose m = 5 and k = 7. Find the tolerances necessary for the resistors and capacitors to give an *INL* and *DNL* equal to or less than 2 *LSB* and 1 *LSB*, respectively.

### Solution

Substituting n = 12 and k = 7 into the previous equations gives

$$2 = 2^{11} \frac{\Delta R}{R} + 2^6 \frac{\Delta C}{C} \quad \text{and} \quad 1 = 2^7 \frac{\Delta R}{R} + (2^7 - 1) \frac{\Delta C}{C}$$

Solving these two equations simultaneously gives

$$\frac{\Delta C}{C} = \frac{2^{5}-2}{2^{11}-2^{6}-2^{5}} = 0.0154 \implies \frac{\Delta C}{C} = 1.54\%$$

and

$$\frac{\Delta R}{R} = \frac{2 - 26(0.0154)}{211} = 0.0005 \rightarrow \frac{\Delta R}{R} = 0.05\%$$

We see that the capacitor tolerance will be easy to meet but that the resistor tolerance will require resistor trimming to meet the 0.05% requirement. Because of the  $2^{n-1}$  multiplying  $\Delta R/R$  in the relationship, it will not do any good to try different values of m and k. This realization will consist of 32 equal value resistors and 7 binary-weighted capacitors with an element spread of 64.

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 3 (2/25/03)

Page 10.3-16

# Example 10.3-4 - Design of a DAC using Charge Scaling for MBSs and Voltage Scaling for LSBs

Consider a 12-bit DAC that uses charge scaling for the MSBs voltage scaling for the LSBs. To minimize the capacitor element spread and the number of resistors, choose m = 7 and k = 5. Find the tolerances necessary for the resistors and capacitors to give an INL and DNL equal to or less than 2 LSB and 1 LSB, respectively.

#### Solution

Substituting the values of this example into the relationships developed on a previous slide, we get

$$2 = 2^4 \frac{\Delta R}{R} + 2^{11} \frac{\Delta C}{C} \quad \text{and} \quad 1 = \frac{\Delta R}{R} + (2^{12} - 1) \frac{\Delta C}{C}$$

Solving these two equations simultaneously gives

$$\frac{\Delta C}{C} = \frac{2^{4}-2}{2^{16}-2^{11}-2^{4}} = 0.000221 \rightarrow \frac{\Delta C}{C} = 0.0221\%$$

and  $\frac{\Delta R}{R} \approx \frac{3}{2^{5}-1} = 0.0968 \rightarrow \frac{\Delta R}{R} = 9.68\%$

For this example, the resistor tolerance is easy to meet but the capacitor tolerance will be difficult. To achieve accurate capacitor tolerances, we should decrease the value of m and increase the value of k to achieve a smaller capacitor value spread and thereby enhance the tolerance of the capacitors. If we choose m = 5 and k = 7, the capacitor tolerance remains about the same but the resistor tolerance becomes 2.36% which is still reasonable. The largest to smallest capacitor ratio is 16 rather than 64 which will help to meet the capacitor tolerance requirements.

### **Summary of Extended Resolution Dacs**

- DAC resolution can be achieved by combining several subDACs with smaller resolution

- Methods of combining include scaling the output or the reference of the non-MSB subDACs

- SubDACs can use similar or different scaling methods

- Tradeoffs in the number of bits per subDAC and the type of subDAC allow minimization of the *INL* and *DNL*

CMOS Analog Circuit Design

Chapter 10 – Section 4 (2/25/03)

Page 10.4-1

# SECTION 10.4 - SERIAL DIGITAL-ANALOG CONVERTERS

### **Serial DACs**

- Typically require one clock pulse to convert one bit

- Types considered here are:

Charge-redistribution

Algorithmic

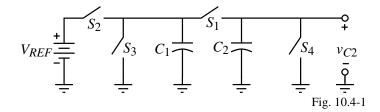

# **Charge Redistribution DAC**

Implementation:

# Operation:

Switch  $S_1$  is the redistribution switch that parallels  $C_1$  and  $C_2$  sharing their charge

Switch  $S_2$  precharges  $C_1$  to  $V_{REF}$  if the *i*th bit,  $b_i$ , is a 1

Switch  $S_3$  discharges  $C_1$  to zero if the *i*th bit,  $b_i$ , is a 0

Switch  $S_4$  is used at the beginning of the conversion process to initially discharge  $C_2$  Conversion always begins with the *LSB* bit and goes to the *MSB* bit.

# Example 10.4-1 - Operation of the Serial, Charge Redistribution Digital-Analog Converter

Assume that  $C_1 = C_2$  and that the digital word to be converted is given as  $b_0 = 1$ ,  $b_1 = 1$ ,  $b_2 = 0$ , and  $b_3 = 1$ . Follow through the sequence of events that result in the conversion of this digital input word.

### Solution

- 1.)  $S_4$  closes setting  $v_{C2} = 0$ .

- 2.)  $b_3 = 1$ , closes switch  $S_2$  causing  $v_{C1} = V_{REF}$ .

- 3.) Switch  $S_1$  is closed causing  $v_{C1} = v_{C2} = 0.5V_{REF}$ .

- 4.)  $b_2 = 0$ , closes switch  $S_3$ , causing  $v_{C1} = 0$ V.

- 5.)  $S_1$  closes, the voltage across both  $C_1$  and  $C_2$  is  $0.25V_{REF}$ .

- 6.)  $b_1 = 1$ , closes switch  $S_2$  causing  $v_{C1} = V_{REF}$ .

- 7.)  $S_1$  closes, the voltage across both  $C_1$  and  $C_2$  is  $(1+0.25)/2V_{REF} = 0.625V_{REF}$ .

- 8.)  $b_0 = 1$ , closes switch  $S_2$  causing  $v_{C1} = V_{REF}$ .

- 9.)  $S_1$  closes, the voltage across both  $C_1$  and  $C_2$  is  $(0.625 + 1)/2V_{REF} = 0.8125V_{REF} = (13/16)V_{REF}$ .

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 4 (2/25/03)

Page 10.4-3

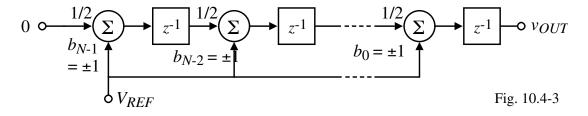

# **Pipeline DAC**

Implementation:

$$V_{out}(\mathbf{z}) = [b_0 z^{-1} + 2^{-1} b_1 z^{-2} + \cdots + 2^{-(N-2)} b_{N-2} z^{-(N-1)} + b_{N-1} z^{-N}] V_{REF}$$

where  $b_i$  is either  $\pm 1$  if the *i*th bit is high or low.

### Attributes:

- Takes N+1 clock cycles to convert the digital input to an analog output

- However, a new analog output is converted every clock after the initial N+1 clocks

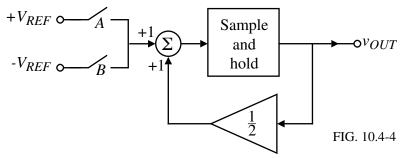

# **Algorithmic (Iterative) DAC**

Implementation:

Closed form of the previous series expression is,

$$V_{out}(z) = \frac{b_i z^{-1} V_{REF}}{1 - 0.5 z^{-1}}$$

### Operation:

Switch *A* is closed when the *i*th bit is 1 and switch *B* is closed when the *i*th bit is 0. Start with the *LSB* and work to the *MSB*.

CMOS Analog Circuit Design

Chapter 10 – Section 4 (2/25/03)

Page 10.4-5

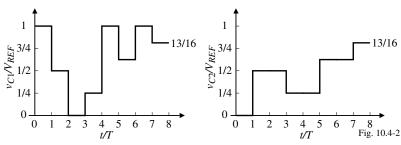

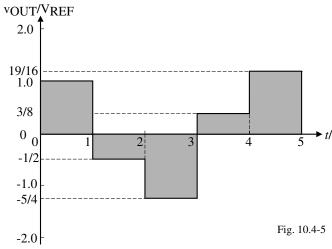

# **Example 10.4-2 - Digital-Analog Conversion Using the Algorithmic Method**

Assume that the digital word to be converted is 11001 in the order of MSB to LSB. Find the converted output voltage and sketch a plot of  $v_{OUT}/V_{REF}$  as a function of t/T, where T is the period for one conversion.

#### Solution

- 1.) The conversion starts by zeroing the output (not shown on Fig. 10.4-4).

- 2.) The LSB = 1, switch A is closed and  $V_{REF}$  is summed with zero to give an output of  $+V_{REF}$ .

- 3.) The next LSB = 0, switch B is closed and  $v_{OUT} = -V_{REF} + 0.5V_{REF} = -0.5V_{REF}$ .

- 4.) The next LSB = 0, switch B is closed and  $v_{OUT} = -V_{REF} + 0.5(-0.5V_{REF}) = -1.25V_{REF}$ .

- 5.) The next LSB = 1, switch A is closed and  $v_{OUT} = V_{REF} + 0.5(-1.25V_{REF}) = 0.375V_{REF}$ .

- 6.) The MSB = 1, switch A is closed and  $v_{OUT} = V_{REF} + 0.5(0.375V_{REF}) = 1.1875V_{REF} = (19/16)V_{REF}$ . (Note that because the actual  $V_{REF}$  of this example if  $\pm V_{REF}$  or  $2V_{REF}$ , the analog value of the digital word 11001 is 19/32 times  $2V_{REF}$  or (19/16) $V_{REF}$ .)

# **Summary of Serial DACS**

Table 10.4-1 - Summary of the Performance of Serial DACs

| Serial DAC                       | Figure | Advantage               | Disadvantage                                                        |

|----------------------------------|--------|-------------------------|---------------------------------------------------------------------|

| Serial, Charge<br>Redistribution | 10.4-1 | Simple,<br>minimum area | Slow, requires complex external circuitry, precise capacitor ratios |

| Serial,<br>algorithmic           | 10.4-3 | Simple,<br>minimum area | Slow, requires complex external circuitry, precise capacitor ratios |

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 4 (2/25/03) Page 10.4-7

# SUMMARY OF THE PERFORMANCE OF DIGITAL-ANALOG CONVERTERS

| DAC                                            | Figure  | Primary Advantage                                                    | Primary Disadvantage                                                                   |

|------------------------------------------------|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Current-scaling, binary weighted resistors     | 10.2-3  | Fast, insensitive to parasitic capacitance                           | Large element spread, nonmonotonic                                                     |

| Current-scaling, R-2R ladder                   | 10.2-4  | Small element spread, increased accuracy                             | Nonmonotonic, limited to resistor accuracy                                             |

| Current-scaling, active devices                | 10.2-5  | Fast, insensitive to switch parasitics                               | Large element spread, large area                                                       |

| Voltage-scaling                                | 10.2-7  | Monotonic, equal resistors                                           | Large area, sensitive to parasitic capacitance                                         |

| Charge-scaling, binary weighted capacitors     | 10.2-10 | Best accuracy                                                        | Large area, sensitive to parasitic capacitance                                         |

| Binary weighted, charge amplifier              | 10.2-12 | Best accuracy, fast                                                  | Large element spread, large area                                                       |

| Current-scaling subDACs using current division | 10.3-3  | Minimizes area, reduces element spread which enhances accuracy       | Sensitive to parasitic capacitance, divider must have –0.5 <i>LSB</i> accuracy         |

| Charge-scaling subDACs using charge division   | 10.3-4  | Minimizes area, reduces element spread which enhances accuracy       | Sensitive to parasitic capacitance, slower, divider must have –0.5 <i>LSB</i> accuracy |

| Binary weighted charge amplifier subDACs       | 10.3-6  | Fast, minimizes area, reduces element spread which enhances accuracy | Requires more op amps, divider must have –0.5 <i>LSB</i> accuracy                      |

| Voltage-scaling (MSBs), charge-scaling (LSBs)  | 10.3-7  | Monotonic in <i>MSBs</i> , minimum area, reduced element spread      | Must trim or calibrate resistors for absolute accuracy                                 |

| Charge-scaling (MSBs), voltage-scaling (LSBs)  | 10.3-8  | Monotonic in <i>LSBs</i> , minimum area, reduced element spread      | Must trim or calibrate resistors for absolute accuracy                                 |

| Serial, charge redistribution                  | 10.4-1  | Simple, minimum area                                                 | Slow, requires complex external circuits                                               |

| Pipeline, algorithmic                          | 10.4-3  | Repeated blocks, output at each clock after <i>N</i> clocks          | Large area for large number of bits                                                    |

| Serial, iterative algorithmic                  | 10.4-4  | Simple, one precise set of components                                | Slow, requires additional logic circuitry                                              |

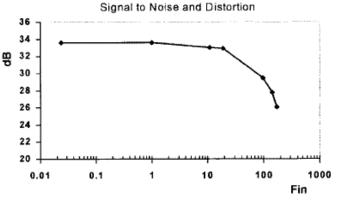

# 10.5 - CHARACTERIZATION OF ANALOG-DIGITAL CONVERTERS ALL YOU EVER WANTED TO KNOW ABOUT A/D CONVERTERS<sup>†</sup>

<sup>†</sup> From *The Institute*, September 1989, page 5 *CMOS Analog Circuit Design*

© P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-2

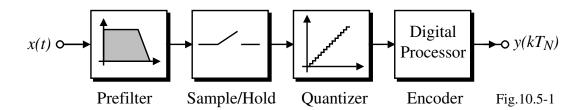

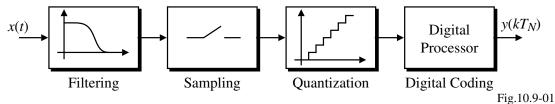

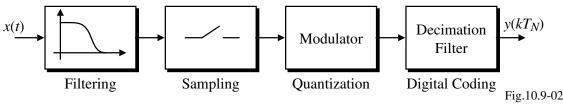

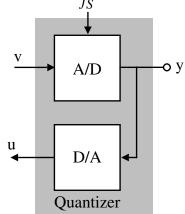

# **General Block Diagram of an Analog-Digital Converter**

- Prefilter Avoids the aliasing of high frequency signals back into the baseband of the ADC

- Sample-and-hold Maintains the input analog signal constant during conversion

- Quantizer Finds the subrange that corresponds to the sampled analog input

- Encoder Encoding of the digital bits corresponding to the subrange

Fig. 10.5-2

Page 10.5-4

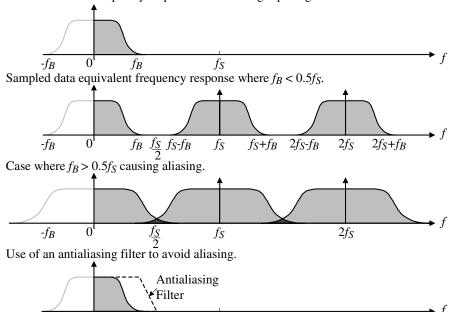

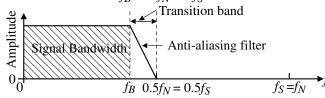

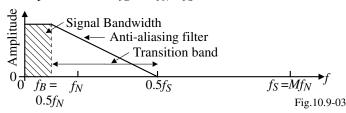

# **Nyquist Frequency Analog-Digital Converters**

The sampled nature of the ADC places a practical limit on the bandwidth of the input signal. If the sampling frequency is  $f_S$ , and  $f_B$  is the bandwidth of the input signal, then

$$f_B < 0.5 f_S$$

which is simply the *Nyquist* relationship which states that to avoid aliasing, the sampling frequency must be greater than twice the highest signal frequency.

Continuous time frequency response of the analog input signal.

$f_{S}$

CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

# **Classification of Analog-Digital Converters**

Analog-digital converters can be classified by the relationship of  $f_B$  and  $0.5f_S$  and by their conversion rate.

- Nyquist ADCs ADCs that have  $f_B$  as close to 0.5 $f_S$  as possible.

- Oversampling ADCs ADCs that have  $f_B$  much less than  $0.5f_S$ .

Table 10.5-1 - Classification of Analog-to-Digital Converter Architectures

| Conversion<br>Rate | Nyquist ADCs                                                | Oversampled ADCs              |

|--------------------|-------------------------------------------------------------|-------------------------------|

| Slow               | Integrating (Serial)                                        | Very high resolution >14 bits |

| Medium             | Successive Approximation1-bit Pipeline Algorithmic          | Moderate resolution >10 bits  |

| Fast               | Flash Multiple-bit<br>Pipeline Folding and<br>interpolating | Low resolution > 6 bits       |

# STATIC CHARACTERIZATION OF ANALOG-TO-DIGITAL CONVERTERS Digital Output Codes

Table 10.5-2 - Digital Output Codes used for ADCs

| Decimal | Binary | Thermometer | Gray | Two's      |

|---------|--------|-------------|------|------------|

|         |        |             |      | Complement |

| 0       | 000    | 0000000     | 000  | 000        |

| 1       | 001    | 0000001     | 001  | 111        |

| 2       | 010    | 0000011     | 011  | 110        |

| 3       | 011    | 0000111     | 010  | 101        |

| 4       | 100    | 0001111     | 110  | 100        |

| 5       | 101    | 0011111     | 111  | 011        |

| 6       | 110    | 0111111     | 101  | 010        |

| 7       | 111    | 1111111     | 100  | 001        |

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-6

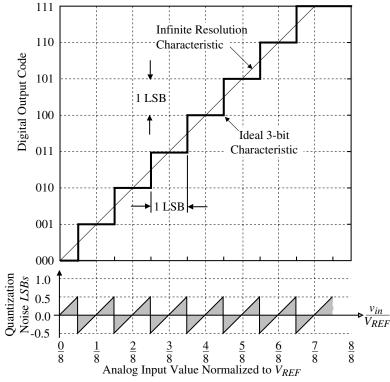

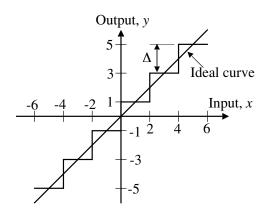

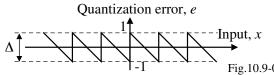

# **Input-Output Characteristics**

Ideal input-output characteristics of a 3-bit ADC

Figure 10.5-3 Ideal input-output characteristics of a 3-bit ADC.

#### **Definitions**

- The *dynamic range*, *signal-to-noise ratio* (*SNR*), and the *effective number of bits* (*ENOB*) of the ADC are the same as for the DAC

- Resolution of the ADC is the smallest analog change that distinguishable by an ADC.

- Quantization Noise is the  $\pm 0.5LSB$  uncertainty between the infinite resolution characteristic and the actual characteristic.

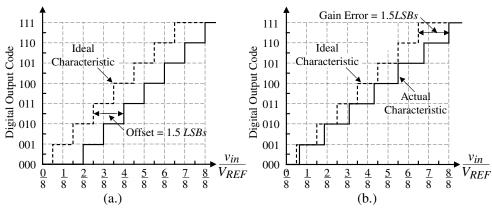

- Offset Error is the difference between the ideal finite resolution characteristic and actual finite resolution characteristic

- Gain Error is the difference between the ideal finite resolution characteristic and actual finite resolution characteristic measured at full-scale input. This difference is proportional to the analog input voltage.

Figure 10.5-4 - (a.) Example of offset error for a 3-bit ADC. (b.) Example of gain error for a 3-bit ADC.

CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

Page 10.5-8

# **Integral and Differential Nonlinearity**

The integral and differential nonlinearity of the ADC are referenced to the vertical (digital) axis of the transfer characteristic.

- *Integral Nonlinearity (INL)* is the maximum difference between the actual finite resolution characteristic and the ideal finite resolution characteristic measured vertically (% or *LSB*)

- *Differential Nonlinearity (DNL)* is a measure of the separation between adjacent levels measured at each vertical step (% or *LSB*).

$$DNL = (D_{cx} - 1) LSBs$$

where  $D_{cx}$  is the size of the actual vertical step in LSBs.

Note that *INL* and *DNL* of an analog-digital converter will be in terms of integers in contrast to the *INL* and *DNL* of the digital-analog converter. As the resolution of the ADC increases, this restriction becomes insignificant.

# Example of INL and DNL

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-10

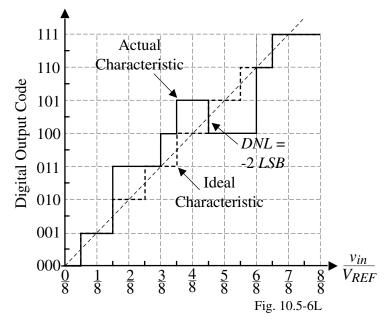

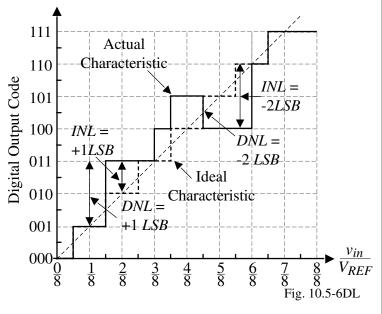

# **Monotonicity**

A *monotonic* ADC has all vertical jumps positive. Note that monotonicity can only be detected by *DNL*.

Example of a nonmonotonic ADC:

If a vertical jump is 2LSB or greater, missing output codes may result. If a vertical jump is -1LSB or less, the ADC is not monotonic.

## Example 10.5-2 - *INL* and *DNL* of a 3-bit ADC

Find the *INL* and *DNL* for the 3-bit ADC shown on the previous slide.

### Solution

With respect to the digital axis:

- 1.) The largest value of *INL* for this 3-bit ADC occurs between 3/16 to 5/16 or 7/16 to 9/16 and is 1*LSB*.

- 2.) The smallest value of *INL* occurs between 11/16 to 12/16 and is -2*LSB*.

- 3.) The largest value of DNL occurs at 3/16 or 6/8 and is +1LSB.

- 4.) The smallest value of *DNL* occurs at 9/16 and is -2*LSB* which is where the converter becomes nonmonotonic.

CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

Page 10.5-12

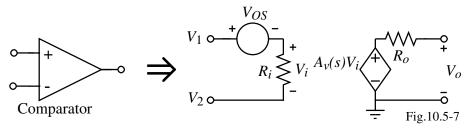

## DYNAMIC CHARACTERISTICS

The dynamic characteristics of ADCs are influenced by:

- Comparators

- Sample-hold circuits

- Circuit parasitics

- Logic propagation delay

## **Comparator**

The comparator is the quantizing unit of ADCs.

Open-loop model:

Nonideal aspects:

- Input offset voltage,  $V_{OS}$  (a static characteristic)

- Propagation time delay

- Bandwidth (linear)

$$A_{\nu}(s) = \frac{A_{\nu}(0)}{\frac{s}{\omega_{c}} + 1} = \frac{A_{\nu}(0)}{s\tau_{c} + 1}$$

- Slew rate (nonlinear)

$$\Delta T = \frac{C \cdot \Delta V}{I}$$

(*I* is constant)

© P.E. Allen - 2003 CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

Page 10.5-14

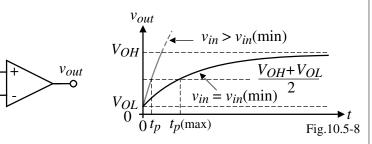

# **Linear Propagation Time Delay (Small input changes)**

If  $V_{OH}$  and  $V_{OL}$  are the maximum and minimum output voltages of the comparator, then minimum input to the comparator (resolution) is

$$v_{in}(\min) = \frac{V_{OH} - V_{OL}}{A_{v}(0)}$$

If the propagation time delay,  $t_p$ , is the time required to go from  $V_{OH}$  or from  $V_{OL}$  to  $\frac{V_{OH}+V_{OL}}{2}$ , then if  $v_{in}$ (min) is applied to the comparator, the  $t_p$  is,

$$\frac{V_{OH} - V_{OL}}{2} = A_{\nu}(0) \left[ 1 - e^{-t_p/\tau_c} \right] v_{in}(\min) = A_{\nu}(0) \left[ 1 - e^{-t_p/\tau_c} \right] \left( \frac{V_{OH} - V_{OL}}{A_{\nu}(0)} \right)$$

Therefore,  $t_p$  is

$$t_p(\text{max}) = \tau_c \ln(2) = 0.693\tau_c$$

If  $v_{in}$  is greater than  $v_{in}(\min)$ , i.e.  $v_{in} = kv_{in}(\min)$ , then

$$t_p = \tau_c \ln \left( \frac{2k}{2k-1} \right)$$

Illustration of these results:

CMOS Analog Circuit Design

© P.E. Allen - 2003

## **Nonlinear Propagation Time Delay (Large input changes)**

The output rises or falls with a constant rate as determined by the slew rate, SR.

$$\therefore t_p = \Delta T = \frac{\Delta V}{SR} = \frac{V_{OH} - V_{OL}}{2 \cdot SR}$$

(If the rate of the output voltage of the comparator never exceeds SR, then the propagation time delay is determined by the previous expression.)

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-16

## **Example 10.5-2 - Propagation Delay Time of a Comparator (Large input changes)**

Find the propagation delay time of an open loop comparator that has a dominant pole at  $10^3$  radians/sec, a dc gain of  $10^4$ , a slew rate of  $1V/\mu s$ , and a binary output voltage swing of 1V. Assume the applied input voltage is 10 mV.

### Solution

The input resolution for this comparator is  $1V/10^4$  or 0.1mV. Therefore, the 10mV input is 100 times larger than  $v_{in}(\text{min})$  giving a k of 100. From the previous work,

$$t_p = \frac{1}{10^3} ln \left( \frac{2 \cdot 100}{2 \cdot 100 - 1} \right) = 10^{-3} ln \left( \frac{200}{199} \right) = 5.01 \mu s$$

If the output is slew-rate limited, then

$$t_p = \frac{1}{2.1 \times 10^6} = 0.5 \mu s$$

Therefore, the propagation delay time for this case is the larger or 5.01µs.

Note that the maximum slope of the linear response is

$$\operatorname{Max}\left(\frac{dv_{out}}{dt}\right) = \frac{d}{dt}(A_{v}(0)[1 - e^{-t/\tau_{c}}](0.01V)) = \frac{A_{v}(0)}{\tau_{c}}e^{-t/\tau_{c}}(0.01V) = \frac{A_{v}(0)}{100\tau_{c}} = \frac{104 \cdot 103}{100} = 0.1V/\mu s$$

Since the maximum rate of the linear response is less than the slew rate, the response is linear and the propagation time delay is  $5.01\mu s$ .

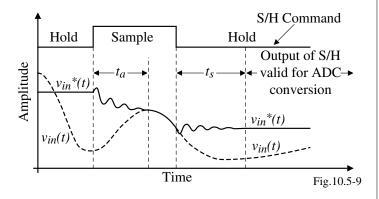

## Sample-and-Hold Circuit

Waveforms of a sample-and-hold circuit:

### **Definitions:**

- Acquisition time  $(t_a)$  = time required to acquire the analog voltage

- *Settling time*  $(t_s)$  = time required to settle to the final held voltage to within an accuracy tolerance

$$T_{sample} = t_a + t_s -$$

Maximum sample rate =  $f_{sample}(max) = \frac{1}{T_{sample}}$

#### Other considerations:

- *Aperture time*= the time required for the sampling switch to open after the S/H command is initiated

- *Aperture jitter* = variation in the aperture time due to clock variations and noise Types of S/H circuits:

- No feedback faster, less accurate

- Feedback slower, more accurate

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-18

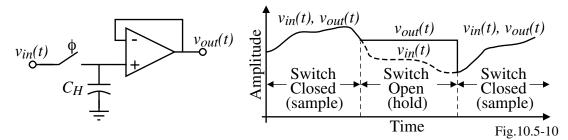

# Open-Loop, Buffered S/H Circuit

#### Circuit:

#### Attributes:

- Fast, open-loop

- Requires current from the input to charge  $C_H$

- DC voltage offset of the op amp and the charge feedthrough of the switch will create dc errors

## **Settling Time**

Assume the op amp has a dominant pole at  $-\omega_a$  and a second pole at -GB.

The unity-gain response can be approximated as,  $A(s) \approx \frac{GB^2}{s^2 + GB \cdot s + GB^2}$

The resulting step response is,  $v_{out}(t) = 1 - \left(\sqrt{\frac{4}{3}}e^{-0.5GB \cdot t}\right) \sin\left(\sqrt{\frac{3}{4}}GB \cdot t + \phi\right)$

Defining the error as the difference between the final normalized value and  $v_{out}(t)$ , gives,

Error(t) =

$$\varepsilon = 1 - v_{out}(t) = \sqrt{\frac{4}{3}} e^{-0.5GB \cdot t}$$

In most ADCs, the error is equal to  $\pm 0.5 LSB$ . Since the voltage is normalized,

$$\frac{1}{2^{N+1}} = \sqrt{\frac{4}{3}} e^{-0.5GB \cdot t_s} \longrightarrow e^{0.5GB \cdot t_s} = \frac{4}{\sqrt{3}} 2^N$$

Solving for the time,  $t_s$ , required to settle with  $\pm 0.5 LSB$  from the above equation gives

$$t_s = \frac{2}{GB} ln \left( \frac{4}{\sqrt{3}} 2^{N} \right) = \frac{1}{GB} [1.3863N + 1.6740]$$

Thus as the resolution of the ADC increases, the settling time for any unity-gain buffer amplifiers will increase. For example, if we are using the open-loop, buffered S/H circuit in a 10 bit ADC, the amount of time required for the unity-gain buffer with a *GB* of 1MHz to settle to within 10 bit accuracy is 2.473µs.

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-20

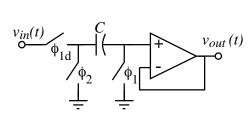

# Open-Loop, Switched-Capacitor S/H Circuit

Circuit:

Switched capacitor S/H circuit.

Differential switched-capacitor S/H Fig.10.5-11

- Delayed clock used to remove input dependent feedthrough.

- Differential version has lower *PSRR*, cancellation of even harmonics, and reduction of charge injection and clock feedthrough

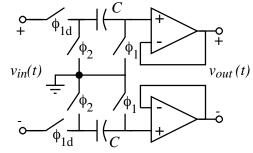

## Open-Loop, Diode Bridge S/H Circuit

## Circuit:

Attributes:

Diode bridge S/H circuit.

Practical implementation of the diode bridge S/H.

Fig.10.5-12

- Fast

- Clock feedthrough is signal independent

- Sample uncertainty caused by the finite slope of the clocks is minimized

- During the hold phase the feedthrough from input to hold node is minimized because of D5 and D6

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-22

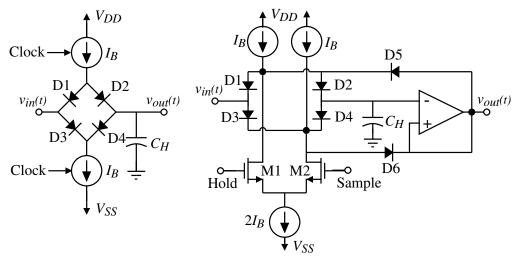

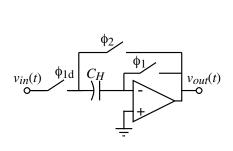

## **Closed-Loop S/H Circuit**

#### Circuit:

Closed-loop S/H circuit.  $\phi_1$  is the sample phase and  $\phi_2$  is the hold phase.

An improved version.

Fig.10.5-13

#### Attributes:

- Accurate

- First circuit has signal-dependent feedthrough

- Slower because of the op amp feedback loop

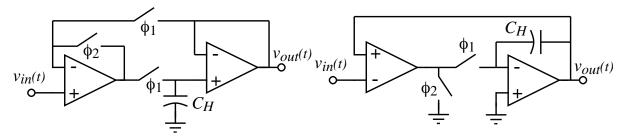

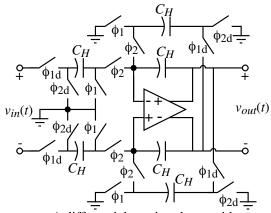

## **Closed-Loop, Switched Capacitor S/H Circuits**

## Circuit:

Switched capacitor S/H circuit which autozeroes the op amp input offset voltage.

A differential version that avoids large changes at the op amp output

Fig.10.5-14

#### Attributes:

- Accurate

- Signal-dependent feedthrough eliminated by a delayed clock

- Differential circuit keeps the output of the op amps constant during the  $\phi_1$  phase avoiding slew rate limits

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-24

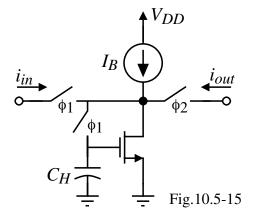

## **Current-Mode S/H Circuit**

## Circuit:

## Attributes:

- Fast

- Requires current in and out

- Good for low voltage implementations

© P.E. Allen - 2003 CMOS Analog Circuit Design

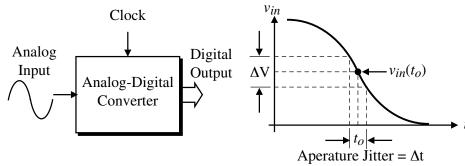

## **Aperature Jitter in S/H Circuits**

Illustration:

If we assume that  $v_{in}(t) = V_p sin\omega t$ , then the maximum slope is equal to  $\omega V_p$ .

Therefore, the value of  $\Delta V$  is given as

Figure 10.5-14 - Illustration of aperature jitter in an ADC.

$$\Delta V = \left| \frac{dv_{in}}{dt} \right| \Delta t = \omega V_p \Delta t .$$

The rms value of this noise is given as

$$\Delta V(\text{rms}) = \left| \frac{dv_{in}}{dt} \right| \Delta t = \frac{\omega V_p \Delta t}{\sqrt{2}}.$$

The aperature jitter can lead to a limitation in the desired dynamic range of an ADC. For example, if the aperature jitter of the clock is 100ps, and the input signal is a full scale peak-to-peak sinusoid at 1MHz, the rms value of noise due to this aperature jitter is  $111\mu V(\text{rms})$  if the value of  $V_{REF} = 1V$ .

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-26

# **TESTING OF ADCs**

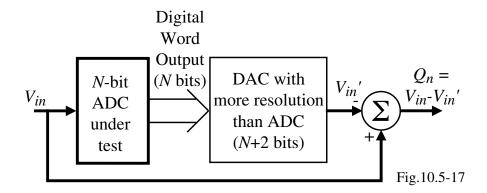

# **Input-Output Test for an ADC**

Test Setup:

The ideal value of  $Q_n$  should be within  $\pm 0.5LSB$

Can measure:

- Offset error = constant shift above or below the 0 *LSB* line

- Gain error = contant increase or decrease of the sawtooth plot as  $V_{in}$  is increased

- *INL* and *DNL* (see following page)

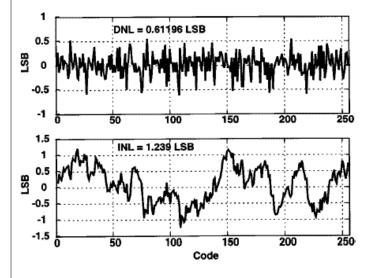

## **Illustration of the Input-Output Test for a 4-Bit ADC**

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 5 (2/25/03)

Page 10.5-28

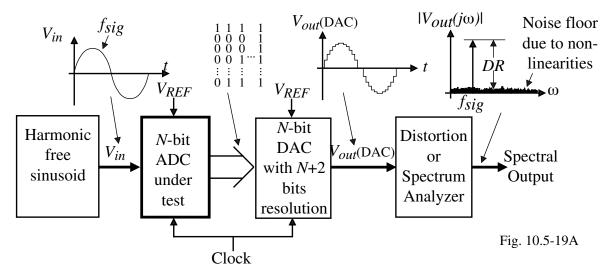

# Measurement of Nonlinearity Using a Pure Sinusoid

This test applies a pure sinusoid to the input of the ADC. Any nonlinearity will appear as harmonics of the sinusoid. Nonlinear errors will occur when the dynamic range (DR) is less than 6N dB where N = number of bits.

#### Comments:

- Input sinusoid must have less distortion that the required dynamic range

- DAC must have more accuracy than the ADC

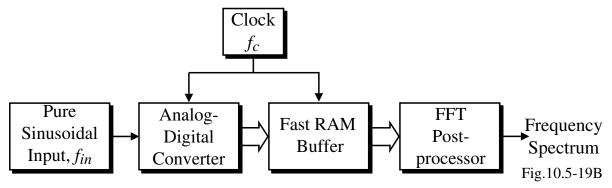

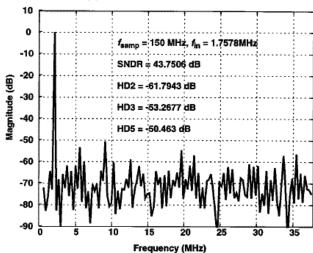

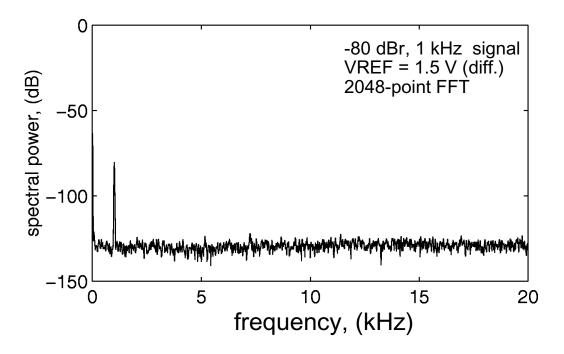

## FFT Test for an ADC

Test setup:

### Comments:

- Stores the digital output codes of the ADC in a RAM buffer

- After the measurement, a postprocessor uses the FFT to analyze the quantization noise and distortion components

- Need to use a window to eliminate measurement errors (Raised Cosine or 4-term Blackmann-Harris are often used)

- Requires a spectrally pure sinusoid

CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

Page 10.5-30

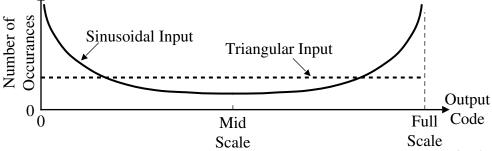

# **Histogram Test for an ADC**

The number of occurances of each digital output code is plotted as a function of the digital output code.

Illustration:

Comments:

Fig.10.5-20

• Emphasizes the time spent at a given level and can show *DNL* and missing codes

• DNL

$$DNL(i) = \frac{\text{Width of the bin as a fraction of full scale}}{\text{Ratio of the bin width to the ideal bin width}} - 1 = \frac{H(i)/N_t}{P(i)} - 1$$

where

H(i) = number of counts in the *i*th bin

$N_t$  = total number of samples

P(i) = ratio of the bin width to the ideal bin width

• *INL* is found from the cumulative bin widths

## **Comparison of the Tests for Analog-Digital Converters**

## Other Tests

- Sinewave curve fitting (good for *ENOB*)

- Beat frequency test (good for a qualitative measure of dynamic performance)

## Comparison

| Test →                | Histogram                                      |                                 | Sinewave | Beat                            |

|-----------------------|------------------------------------------------|---------------------------------|----------|---------------------------------|

| Error                 | or                                             | FFT Test                        | Curve    | Frequency                       |

| $\downarrow$          | Code Test                                      |                                 | Fit Test | Test                            |

| DNL                   | Yes (spikes)                                   | Yes (Elevated noise floor)      | Yes      | Yes                             |

| Missing Codes         | Yes (Bin counts with zero counts)              | Yes (Elevated noise floor)      | Yes      | Yes                             |

| INL                   | Yes (Triangle input gives <i>INL</i> directly) | Yes (Harmonics in the baseband) | Yes      | Yes                             |

| Aperature Uncertainty | No                                             | Yes (Elevated noise floor)      | Yes      | No                              |

| Noise                 | No                                             | Yes (Elevated noise floor)      | Yes      | No                              |

| Bandwidth<br>Errors   | No                                             | No                              | No       | Yes (Measures analog bandwidth) |

| Gain Errors           | Yes (Peaks in distribution)                    | No                              | No       | No                              |

| Offset Errors         | Yes (Offset of distribution average)           | No                              | No       | No                              |

CMOS Analog Circuit Design

Chapter 10 – Section 5 (2/25/03)

Page 10.5-32

## **Bibliography on ADC Testing**

- 1.) D. H. Sheingold, *Analog-Digital Conversion Handbook*, Analog Devices, Inc., Norwood, MA 02062, 1972.

- 2.) S.A. Tretter, *Introduction to Discrete-Time Signal Processing*, John Wiley & Sons, New York, 1976.

- 3.) J. Doernberg, H.S. Lee, and D.A. Hodges, "Full-Speed Testing of A/D Converters," *IEEE J. of Solid-State Circuits*, Vol. SC-19, No. 6, December 1984, pp. 820-827.

- 4.) "Dynamic performance testing of A to D converters," *Hewlett Packard Product Note* 5180A-2.

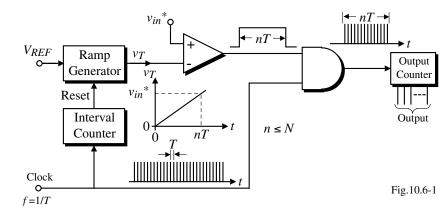

## SECTION 10.6 - SERIAL ANALOG-DIGITAL CONVERTERS

## Introduction

Serial ADCs typically require  $2^{N}T$  for conversion where T = period of the clock Types:

- Single-slope

- Dual-slope

## **Single-Slope ADC**

Block diagram:

Attributes:

- Simplicity of operation

- Subject to error in the ramp generator

- Long conversion time  $\leq 2^{N}T$

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 6 (2/25/03)

Page 10.6-2

## **Dual-Slope ADC**

Block diagram:

Positive  $v_{int}$   $V_{REFO}$ Digital  $C_{Output}$ Carry  $C_{Output}$ Output

Output

Fig.10.6-2

Operation: 1.) Initially  $v_{int} = 0$  and  $v_{in}$  is sampled and held  $(v_{IN}^* > 0)$ .

- 2.) Reset the positive integrator by integrating a positive voltage until  $v_{int}(0) = V_{th}$ .

- 3.) Integrate  $v_{in}^*$  for  $N_{REF}$  clock cycles to get,

$$v_{int}(t_1) = K \int_0^{N_{REF}T} v_{in}^* dt + v_{int}(0) = KN_{REF}Tv_{in}^* + V_{th}$$

4.) After  $N_{REF}$  counts, the carry output of the counter closes switch 2 and  $V_{REF}$  is applied to the positive integrator. The output of the integrator at  $t = t_1 + t_2$  is,

$$v_{int}(t_1+t_2) = v_{int}(t_1) + K \int_{t_1}^{N_{out}T} (-V_{REF}) dt = V_{th} \rightarrow KN_{REF}Tv_{in}^* + V_{th} - KN_{out}TV_{REF} = V_{th}$$

5.) Solving for  $N_{out}$  gives,  $N_{out} = N_{REF} (v_{in}*/V_{REF})$

Comments: Conversion time  $\leq 2(2^N)T$  and the operation is independent of  $V_{th}$  and K.

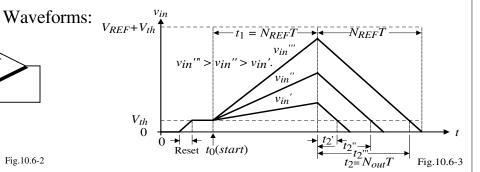

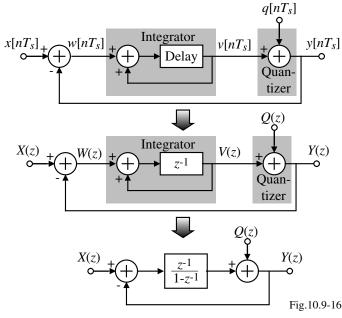

## SECTION 10.7 - MEDIUM SPEED ANALOG-DIGITAL CONVERTERS

## **Introduction**

Successive Approximation Algorithm:

- 1.) Start with the MSB bit and work toward the LSB bit.

- 2.) Guess the *MSB* bit as 1.

- 3.) Apply the digital word 10000.... to a DAC.

- 4.) Compare the DAC output with the sampled analog input voltage.

- 5.) If the DAC output is greater, keep the guess of 1. If the DAC output is less, change the guess to 0.

- 6.) Repeat for the next MSB.

If the number of bits is N, the time for conversion will be NT where T is the clock period.

#### Illustration:

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 7 (2/25/03)

Page 10.7-2

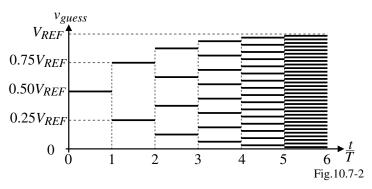

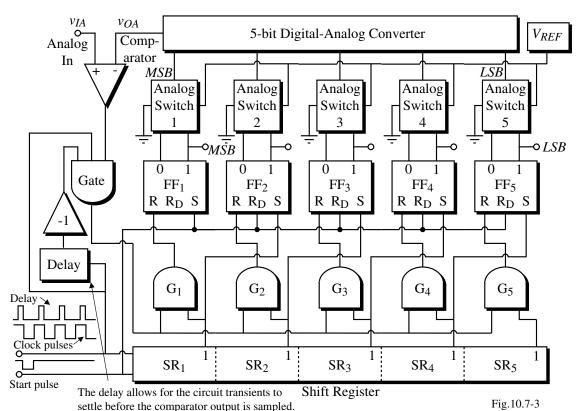

# Block Diagram of a Successive Approximation ADC†

<sup>&</sup>lt;sup>†</sup> R. Hnatek, *A User's Handbook of D/A and A/D Converters*, JohnWiley and Sons, Inc., New York, NY, 1976. *CMOS Analog Circuit Design*

# **5-Bit Successive Approximation ADC**

CMOS Analog Circuit Design

Chapter 10 – Section 7 (2/25/03)

Page 10.7-4

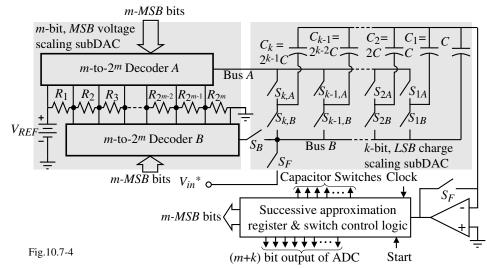

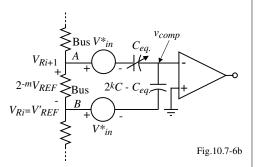

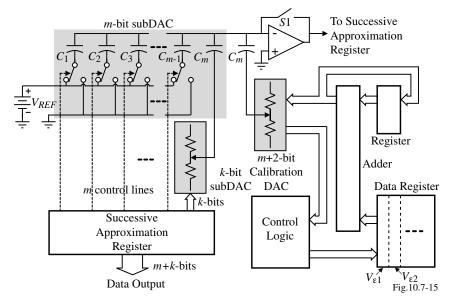

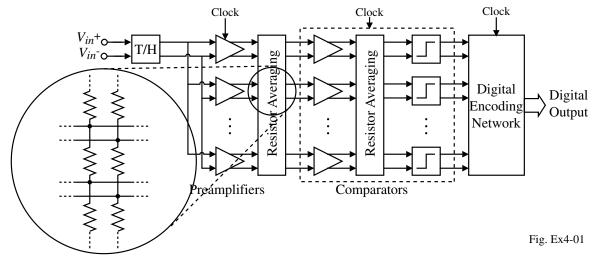

# m-Bit Voltage-Scaling, k-Bit Charge-Scaling Successive Approximation ADC

Implementation:

Operation:

- 1.) With the two  $S_F$  switches closed, all capacitors are paralleled and connected to  $V_{in}^*$  which autozeros the comparator offset voltage.

- 2.) With all capacitors still in parallel, a successive approximation search is performed to find the resistor segment in which the analog signal lies.

3.) Finally, a successive approximation search is performed on charge scaling subDAC to establish the analog output voltage.

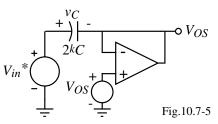

# **Voltage-Scaling, Charge-Scaling Successive Approximation ADC - Continued**

Autozero Step

Removes the influence of the offset voltage of the comparator.

The voltage across the capacitor is given as,

$$v_C = V_{in}^* - V_{OS}$$

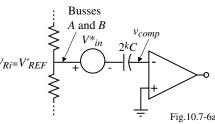

Successive Approximation Search on the Resistor String

The voltage at the comparator input is

$$v_{comp} = V_{Ri} - V_{in}^*$$

If  $v_{comp} > 0$ , then  $V_{Ri} > V_{in}^*$ , if  $v_{comp} < 0$ , then  $V_{Ri} < V_{in}^*$   $V_{Ri} = V_{REF}$  Successive Approx. Search on the Capacitor SubDAC

The input to the comparator is written as,

$$v_{comp} = (V_{Ri+1} - V_{in}^*) \frac{C_{eq}}{2^k C} + (V_{Ri} - V_{in}^*) \frac{2^k C - C_{eq}}{2^k C}$$

However,  $V_{Ri+1} = V_{Ri} + 2^{-m}V_{REF}$

Combining gives,

$$v_{comp} = (V_{Ri} + 2^{-m}V_{REF} - V_{IN}^{*}) \frac{C_{eq}}{2^{k}C} + (V_{Ri} - V_{IN}^{*}) \frac{2^{k}C - C_{eq}}{2^{k}C}$$

$$= V_{Ri} - V_{IN}^{*} + 2^{-m}V_{REF} \frac{C_{eq}}{2^{k}C}$$

© P.E. Allen - 2003

CMOS Analog Circuit Design

Chapter 10 – Section 7 (2/25/03)

Page 10.7-6

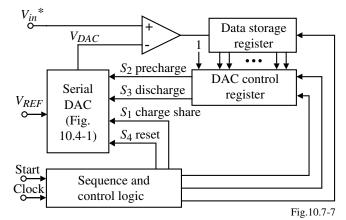

## A Successive Approximation ADC Using a Serial DAC

Implementation:

Conversion Sequence:

Digital-Number Digital-analog Input Word Comparat analog of Conversion Charging Number  $d_1$ Output Steps  $d_{N-1}$   $d_N$ 1 2  $a_N$ 2 4  $a_{N-1}$  $a_{N-2}$ 2N

Total number of charging steps = N(N+1)

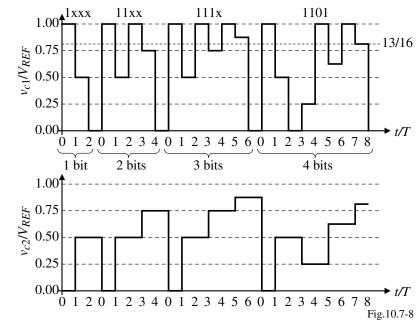

## A Successive Approximation ADC Using a Serial DAC - Continued

Example:

Analog input is 13/16.

Digital word out is  $b_0 = 1$ ,  $b_1 = 1$ ,  $b_2 = 0$ , and  $b_3 = 1$ .

CMOS Analog Circuit Design

Chapter 10 – Section 7 (2/25/03) Page 10.7-8

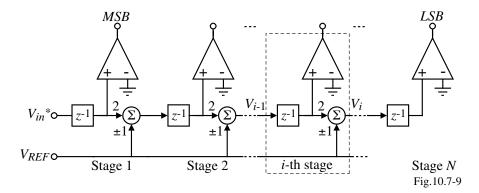

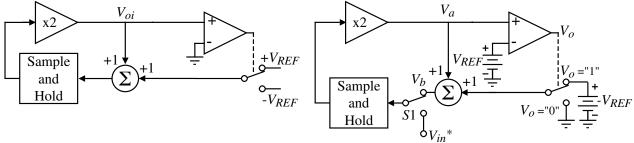

# Pipeline Analog-Digital Algorithmic Converter

Implementation:

Operation:

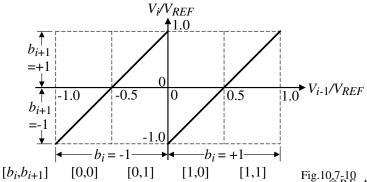

- Each stage muliplies its input by 2 and adds or subtracts  $V_{REF}$  depending upon the sign of the input.

- *i*-th stage,

$$V_i = 2V_{i-1} - b_i V_{REF}$$

where  $b_i$  is given as

$$b_i = \begin{cases} +1 & \text{if } V_{i-1} > 0 \\ -1 & \text{if } V_{i-1} < 0 \end{cases}$$

Fig.10.7-10 © P.E. Allen - 2003

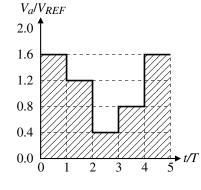

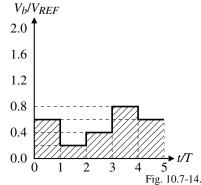

# **Example 10.7-1 - Illustration of the Operation of the Pipeline Algorithmic ADC**

Assume that the sampled analog input to a 4-bit pipeline algorithmic analog-digital converter is 2.00 V. If  $V_{\text{REF}}$  is equal to 5 V, find the digital output word and the analog equivalent voltage.

**Solution**

| Stage No. | Input to the <i>i</i> th stage, $V_{i-1}$ | $V_{i-1} > 0$ ? | Bit <i>i</i> |

|-----------|-------------------------------------------|-----------------|--------------|

| 1         | 2V                                        | Yes             | 1            |

| 2         | $(2V \cdot 2) - 5 = -1V$                  | No              | 0            |

| 3         | $(-1V\cdot 2) + 5 = 3V$                   | Yes             | 1            |

| 4         | $(3V \cdot 2) - 5 = 1V$                   | Yes             | 1            |

Illustration:

$$V_{\text{analog}} = 5\left(\frac{1}{2} - \frac{1}{4} + \frac{1}{8} + \frac{1}{16}\right)$$

$$= 5(0.4375) = 2.1875$$

where  $b_i = +1$  if the *i*th-bit is 1 and  $b_i = -1$  if the *i*th bit is 0

CMOS Analog Circuit Design

© P.E. Allen - 2003

Chapter 10 - Section 7 (2/25/03)

Page 10.7-10

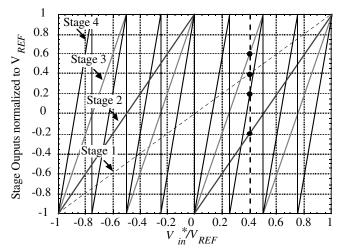

## Achieving the High Speed Potential of the Pipeline Algorithmic ADC

If shift registers are used to store the output bits and align them in time, the pipeline ADC can output a digital word at every clock cycle with a latency of *NT*.

Illustration:

# **Errors in the Pipeline Algorithmic ADC**

The output voltage for the N-th stage can be written as,

$$V_{N} = \prod_{N=1}^{i=1} A_{i} V_{in} - \left[ \sum_{i=1}^{N-1} \left( \prod_{j=i+1}^{N} A_{j} \right) b_{i-1} + b_{N-1} \right] V_{REF}$$

where  $A_i(A_i)$  is the actual gain of 2 for the *i*-th (*j*-th) stage.

Errors include:

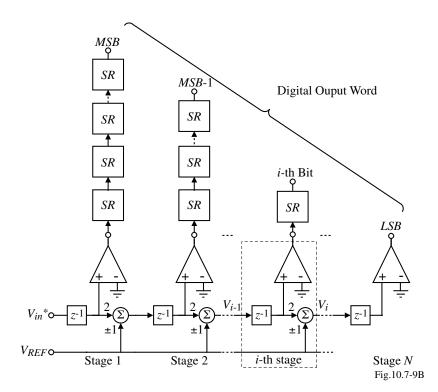

- 1.) Gain errors x2 amplifier or summing junctions

- 2.) Offset errors comparator or summing junctions *i*-th stage including errors,

$$V_{i} = A_{i}V_{i-1} + V_{OSi} - b_{i}A_{si}V_{REF}$$

$$b_{i} = \begin{cases} = +1 \text{ if } V_{i-1} > V_{OCi} \\ = -1 \text{ if } V_{i-1} < V_{OCi} \end{cases}$$

where

$A_i$  is the gain of "2" amplifier for the *i*-th stage

$V_{OSi}$  is the system offset errors of the *i*-th stage

$A_{si}$  is the gain of "1" summer for the *i*-th stage

$V_{OCi}$  is the comparator offset voltage of the *i*-th stage

CMOS Analog Circuit Design © P.E. Allen - 2003

Chapter 10 – Section 7 (2/25/03)

Page 10.7-12

# **Errors in the Pipeline Algorithmic ADC - Continued**

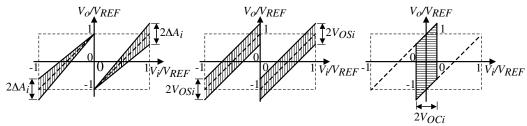

<u>Illustration of</u> the errors

Gain error,  $A_i$ .

System offset error,  $V_{OSi}$ .

Comparator offset error,  $V_{OCi}$ .

Fig.10.7-12

## Example of an error analysis for a 4-bit pipeline algorithmic ADC

The output of the 4th stage can be written as,

$$V_4 = 2^4 \cdot V_{in} - (2^3 \cdot b_0 + 2^2 \cdot b_1 + 2^4 \cdot b_2 + 2^4 \cdot b_3) V_{REF}$$

The difference between the actual,  $V_4$ , and the ideal,  $V_4$ , can be written as,

$$|V_4' - V_4| = 2^3 \cdot \Delta A_1 V_{in}$$

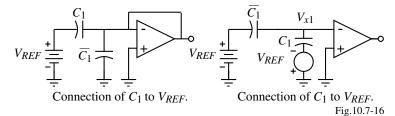

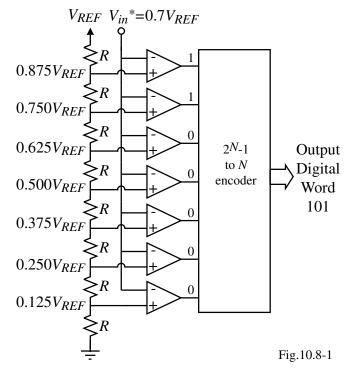

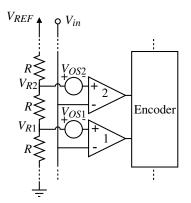

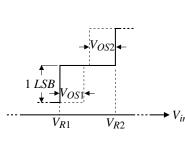

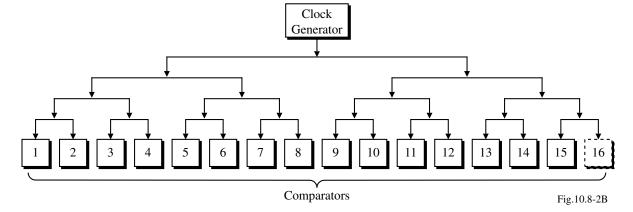

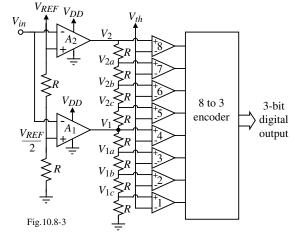

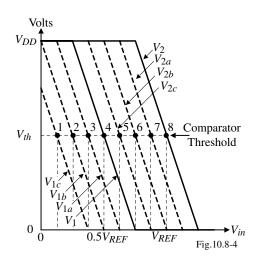

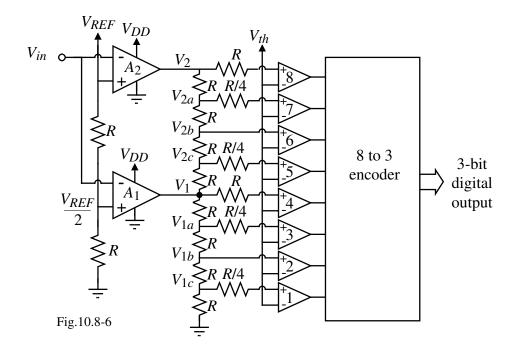

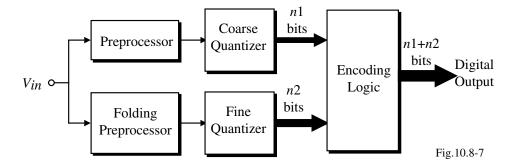

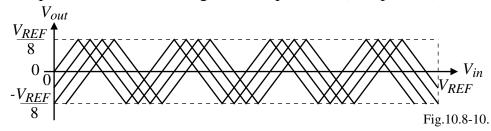

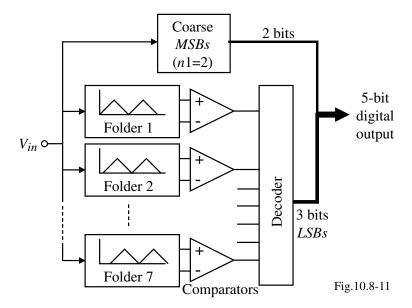

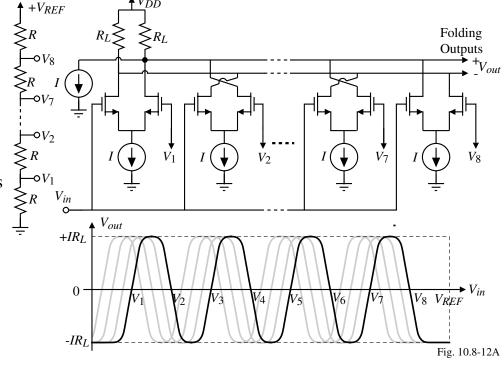

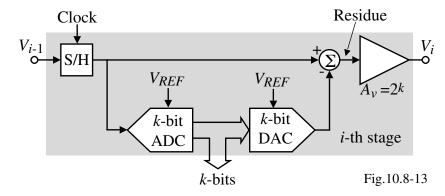

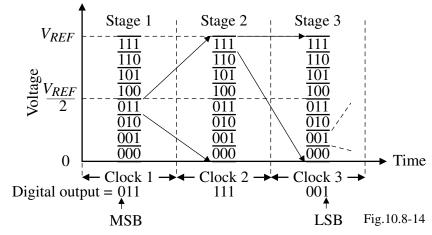

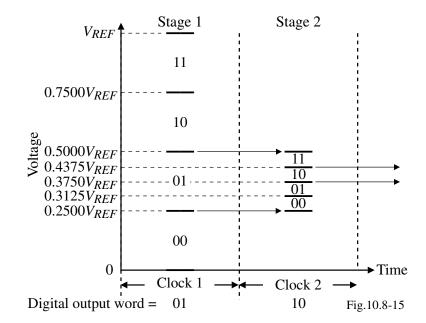

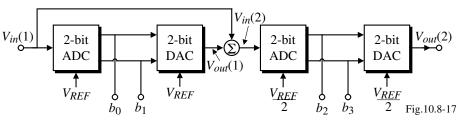

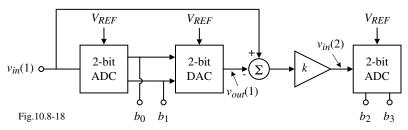

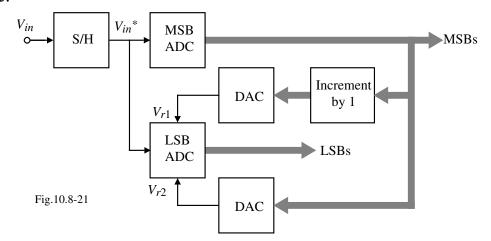

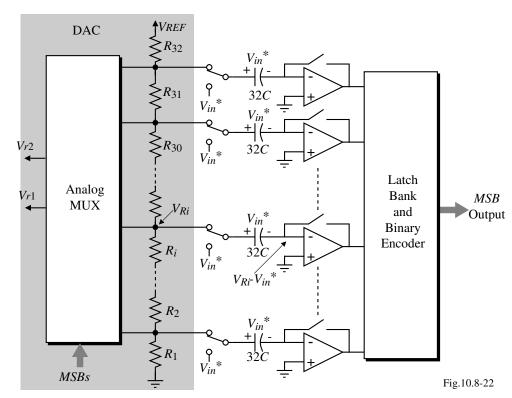

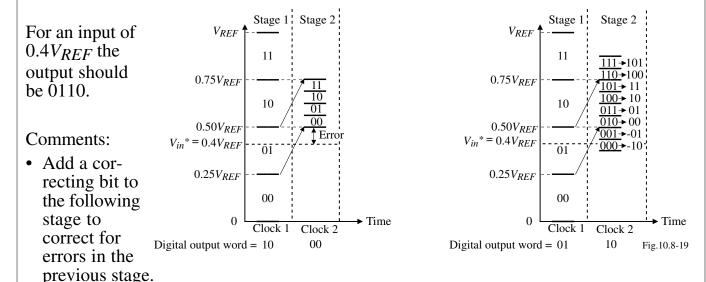

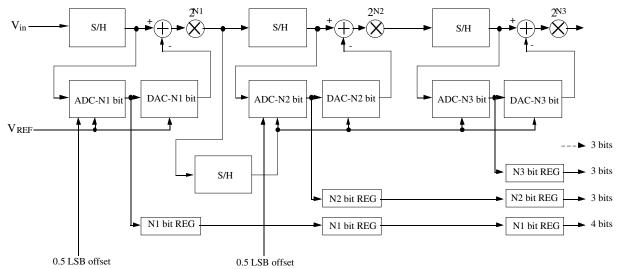

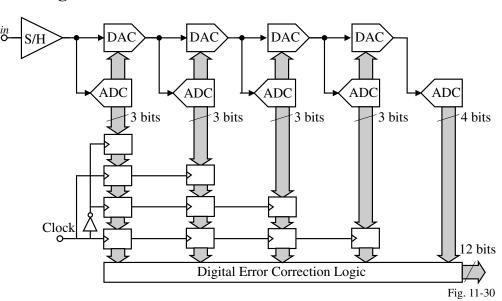

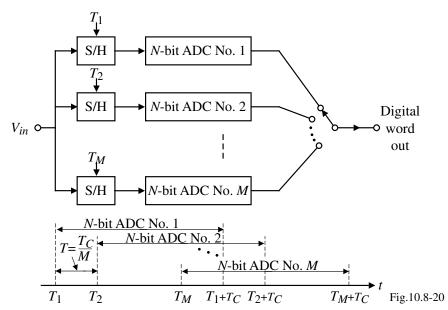

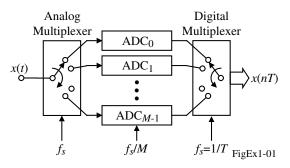

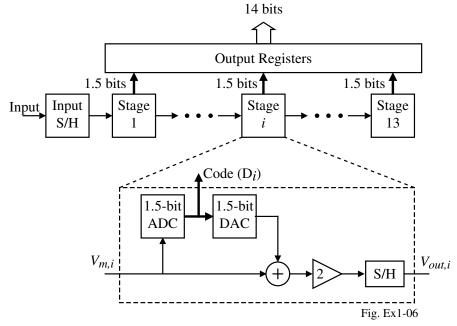

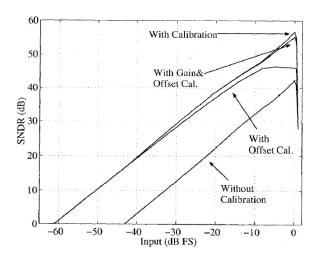

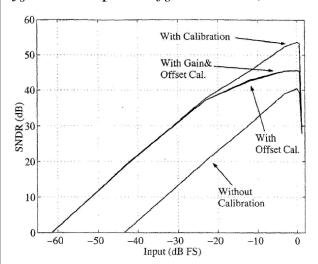

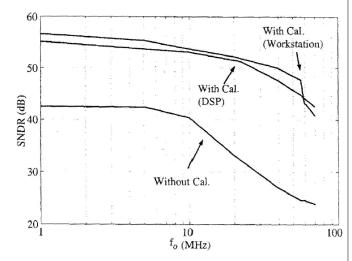

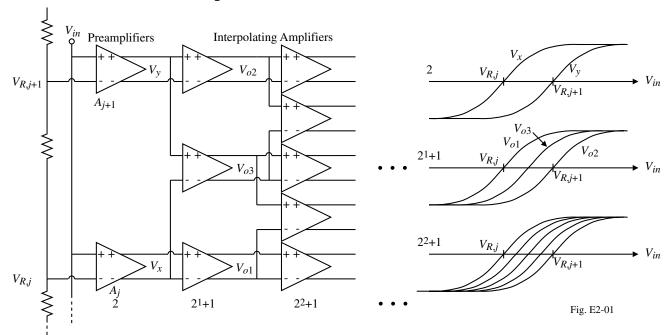

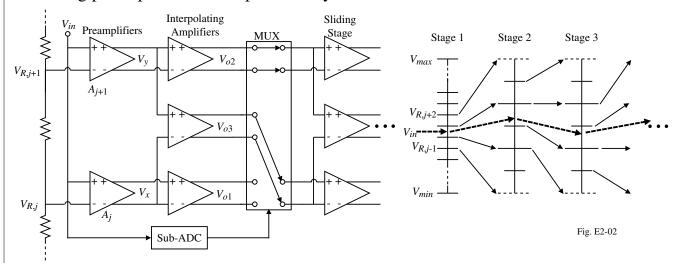

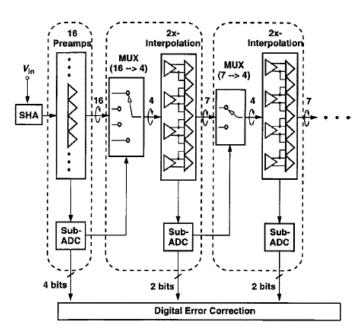

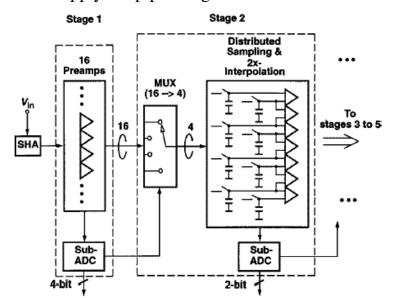

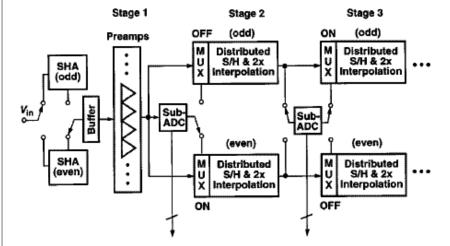

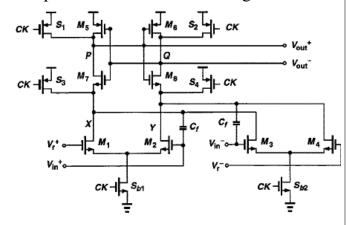

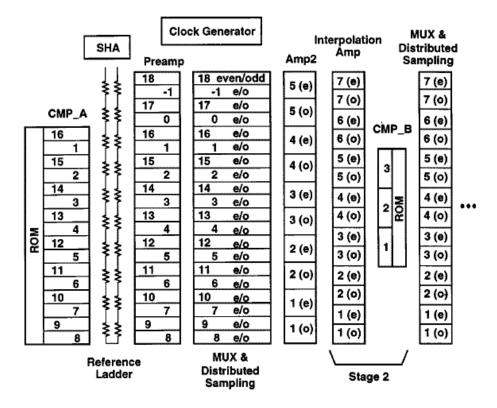

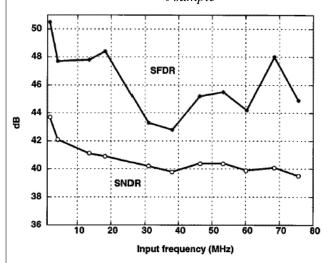

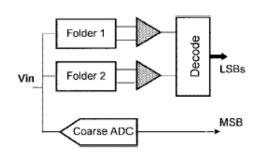

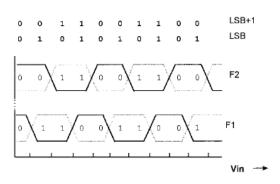

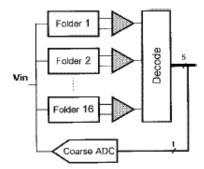

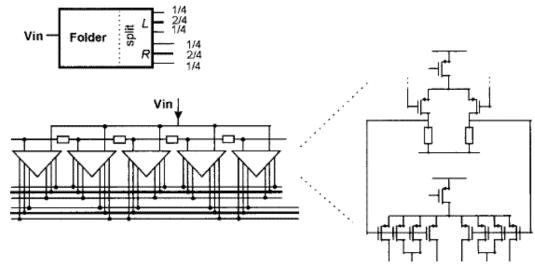

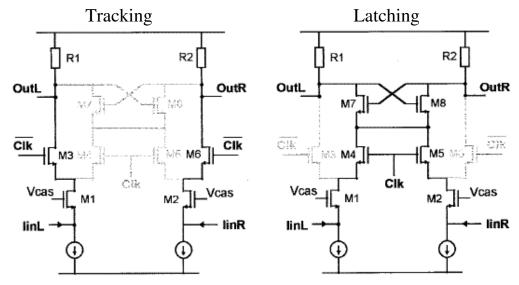

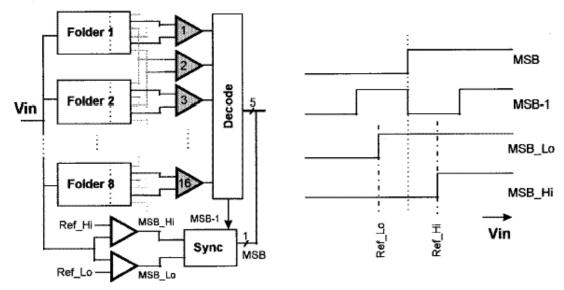

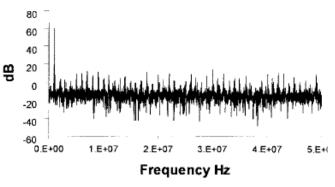

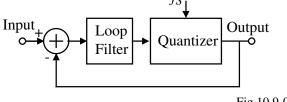

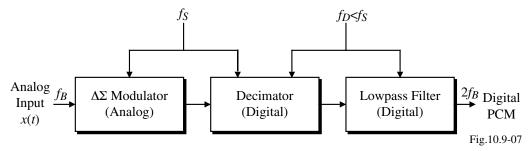

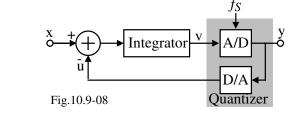

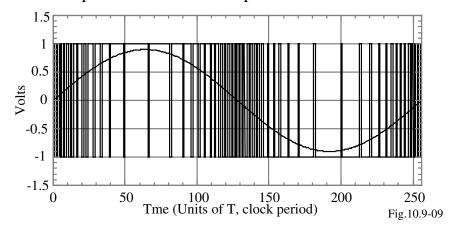

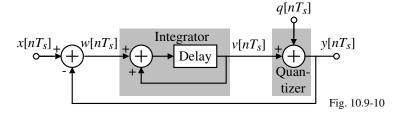

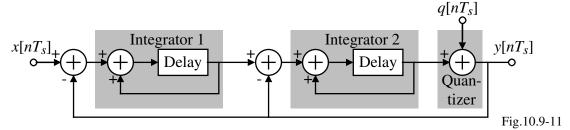

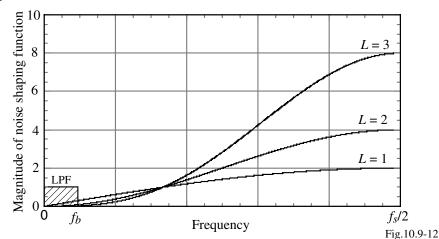

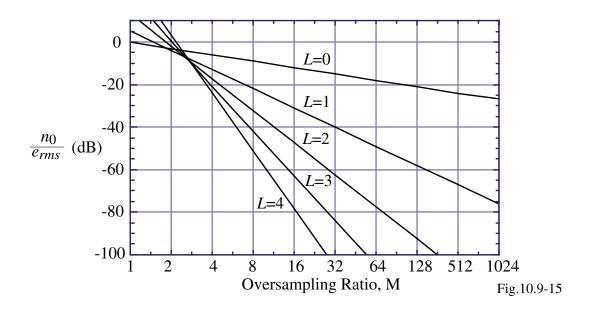

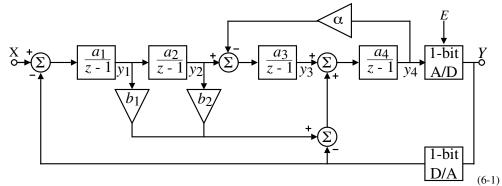

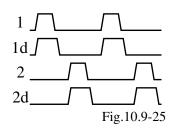

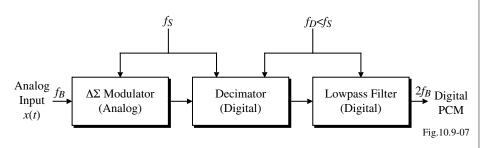

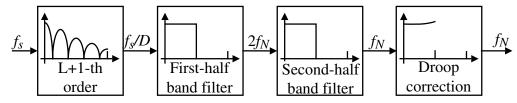

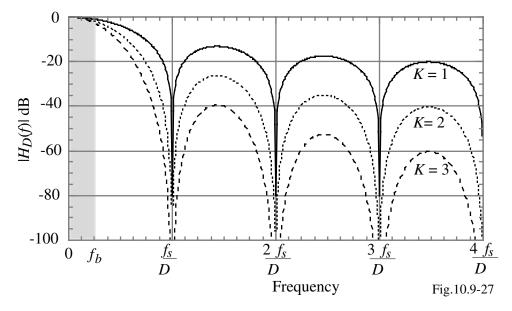

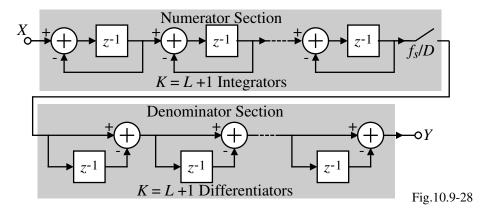

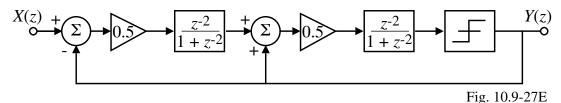

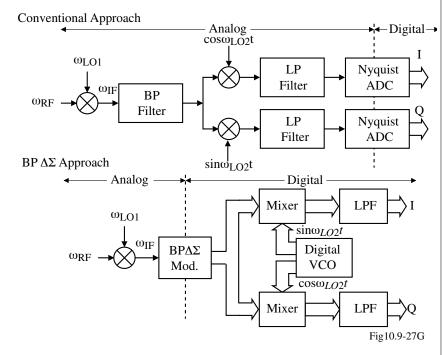

An error will occur in the output of stage 4 if  $|V_4'-V_4| > V_{REF}$ .