# Modern DRAM (DDR2/DDR3) Architecture

This presentation is copyrighted material and is intended solely for the use of students who have attended this MindShare course. Any other distribution is not allowed.

Please do not copy or distribute our material without permission.

[training@mindshare.com](mailto:training@mindshare.com)

1-800-633-1440

## MindShare Classroom

In-House Training

Public Training

### **Classroom Training**

Invite MindShare to train you in-house, or sign-up to attend one of our many public classes held throughout the year and around the world. No more boring classes, the 'MindShare Experience' is sure to keep you engaged.

## MindShare Virtual Classroom

Virtual In-House Training

Virtual Public Training

### **Virtual Classroom Training**

The majority of our courses live over the web in an interactive environment with WebEx and a phone bridge. We deliver training cost-effectively across multiple sites and time zones. Imagine being trained in your cubicle or home office and avoiding the hassle of travel. Contact us to attend one of our public virtual classes.

## MindShare eLearning

Intro eLearning Modules

Comprehensive eLearning Modules

### **eLearning Module Training**

MindShare is also an eLearning company. Our growing list of interactive eLearning modules include:

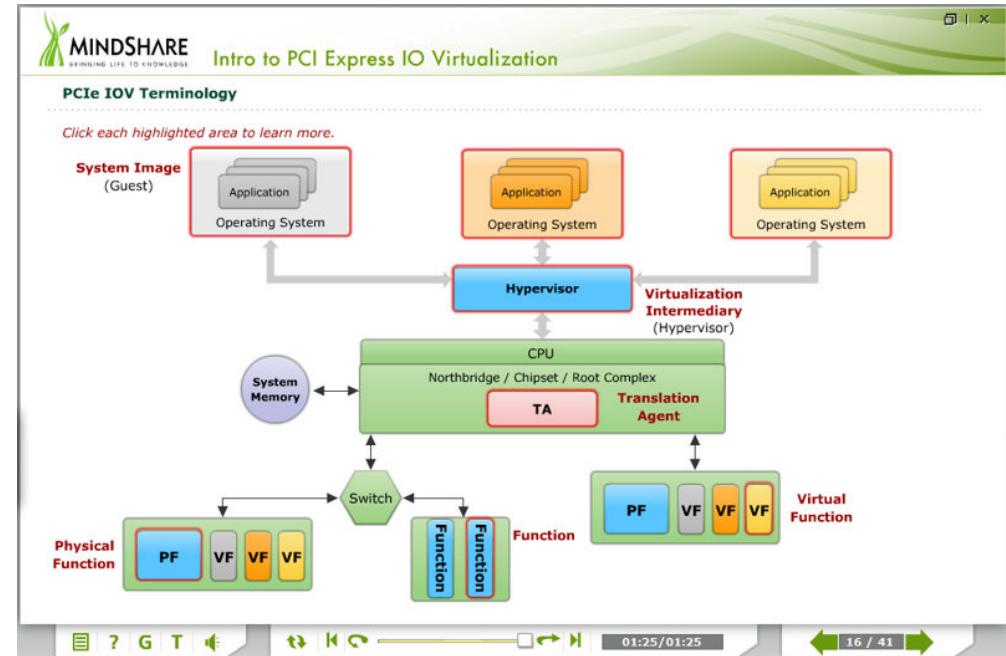

- **Intro to Virtualization Technology**

- **Intro to IO Virtualization**

- **Intro to PCI Express 2.0 Updates**

- **PCI Express 2.0**

- **USB 2.0**

- **AMD Opteron Processor Architecture**

- **Virtualization Technology**

- ...and more

## MindShare Press

Books

eBooks

### **MindShare Press**

Purchase our books and eBooks or publish your own content through us. MindShare has authored over 25 books and the list is growing. Let us help make your book project a successful one.

## Intel Architecture

- Intel Core 2 Processor (Penryn)

- Intel Core Processor (Nehalem)

- Intel QuickPath Interconnect (QPI)

- Intel 64 and IA-32 Architecture

- Intel PC and Chipset Architecture

- Intel Core 2 Processor and Chipset Combo

## AMD Architecture

- AMD Opteron Processor (Barcelona)

- AMD64 Architecture

## x86 Programming

- Assembly Language Programming

- System Programming for the x86 Architecture

## IO Buses

- PCI Express 2.0

- USB 3.0

- Embedded USB 2.0 & Workshop

- PCI / PCI-X

## Memory Technology

- Modern DRAM Architecture (DDR2/DDR3)

## Virtualization Technology

- PC Virtualization

- IO Virtualization (IOV)

## Storage Technology

- SAS Architecture

- Serial ATA Architecture

➤ In-House classroom

➤ Virtual classroom

➤ eLearning Courses

➤ Check our website for Public course offerings

➤ PCI Express 2.0

➤ USB 3.0

➤ Embedded USB 2.0 & Workshop

➤ Protected / Long Mode Programming

➤ Modern DRAM Technology

➤ High-Speed Design

➤ We can customize any of our classes to meet your budget and content needs

- Some of our eLearning courses include:

- Comprehensive PCI Express

- Intro to PCI Express Changes

- Intro to PCI Express IO Virtualization

- Intro to Virtualization Technology

- and more .....

- Visit [www.mindshare.com](http://www.mindshare.com) for a full list of our eLearning courses.

**MINDSHARE**

BRINGING LIFE TO KNOWLEDGE

CART CONTACT US MY ACCOUNT

Search MindShare

LEARN a subject with the experts SHOP for a learning experience CONNECT with the standard in training ENGAGE with content creation with MindShare

Shop > SATA Storage Technology

**Books + eBooks**

EMAIL TO A FRIEND HOW eBooks WORK eBooks FAQ

All Available Titles

- HyperTransport 3.1 Interconnect Technology

- SATA Storage Technology**

- SAS Storage Architecture

- PCI Express System Architecture

- The Unabridged Pentium 4

- PCI System Architecture (4th Edition)

- PCI-X System Architecture

- InfiniBand Network Architecture

- Universal Serial Bus System Architecture

- HyperTransport System Architecture

- FireWire System Architecture (2nd Edition)

Most Popular Titles

- PCI Express System Architecture

- HyperTransport 3.1 Interconnect Technology

- Universal Serial Bus System Architecture

Most Popular eBooks

- The Unabridged Pentium 4

- PCI Express System Architecture

- SATA Storage Technology

**SATA Storage Technology**

Author(s) Don Anderson

Publisher MindShare Press

Pages 496

Retail Price \$59.99

**ADD BOOK TO CART** Book Price \$55.99

**ADD eBook TO CART** eBook Price \$32.00

**ADD TO CART** Book + eBook Price \$71.99

**PEEK INSIDE**

**"This SATA Storage Technology book from MindShare is the ultimate tutorial on the SATA specification and its implementation. Any SATA based product developer will find the clear and concise explanations of the various features found in this protocol to be invaluable. Particular emphasis is placed on the sections of the spec that enable SATA to be such an important interface for enterprise storage systems."**

- Mark Adams, Product Marketing Manager of the LeCroy Corporation

MindShare's **SATA Storage Technology** book provides ATA background information necessary to understand the Serial ATA implementation. This book provides detailed information regarding the serial protocol, commands, and electrical interface. A tutorial approach is taken to facilitate thorough understanding, using numerous illustrations, tables and examples. The text is also designed to provide easy to access valuable reference information.

The SATA (Serial ATA) interface is intended to expand and eventually replace the parallel ATA interface that has been the standard connection for hard drives and CD-ROM/DVD drives in Personal Computers for nearly twenty years. SATA, a high-speed serial version of ATA, is designed to maintain compatibility with software written for the standard ATA implementation, thus easing the transition to SATA. New advances in SATA provide new capabilities such as

**PCI EXPRESS SYSTEM ARCHITECTURE**

**UNIVERSAL SERIAL BUS SYSTEM ARCHITECTURE**

**SECOND EDITION**

**SAS Storage Architecture**

**HyperTransport 3.1 Interconnect Technology**

# Register on MindShare's Website

8

- Receive our quarterly newsletter

- Download course presentations and eBooks

- Shop for eLearning modules and Books/eBooks

- Register for Public courses

The screenshot displays the homepage of the MindShare website. At the top, there are navigation links for 'LEARN', 'SHOP', 'CONNECT', and 'ENGAGE'. The main header reads 'MINDSHARE' and 'THE MINDSHARE QUARTERLY NEWSLETTER'. Below this, the 'sept 08 technologybrief' is shown. The page is divided into several sections:

- ALUMNI MODULES:** Intro to PCI Express® 2.0 Changes, Public Courses, Memory, SATA, USB, PCI, and more.

- IN THIS ISSUE:** PCI Express 2.0 Changes, Public Courses, Memory, SATA, USB, PCI, and more.

- UPCOMING PUBLIC ENROLLMENT COURSES:** Q3, 2008, including PCI Express 2.0 Architecture, Embedded USB 2.0 Architecture, Embedded USB 2.0 Workshop, PCI Express 2.0 Architecture, and PCI Express 2.0 Compliance.

- ALUMNI MODULES:** Intro to PCI Express® 2.0 Changes, Purchase Module, Learn More.

- BOOKS + eBOOKS:** HyperTransport 3.1 Interconnect Technology, Authors: Brian Holden, Dan Anderson, Publisher: Mindshare Press, Price: \$95.99, Purchase Book/eBook, Learn More.

- MINDSHARE COURSE LIST:** World-Class Technical Training, including PCI Express 2.0, Intel® Core™ Processor Architecture, AMD Opteron Processor Architecture, Intel® 64 & IA-32 Software Architecture, Intel® PC and Chipset Architecture, PCI Virtualization, USB 2.0, and Wireless USB. Courses Coming Soon: Intel® QuickPath Interconnect, Intel® Core™ ( Nehalem ) Processor, and USB 3.0.

- TECHNICAL WHITE PAPERS:** PCI Express® Compliance Using a Predictable Metrics Based Verification Closure Methodology, by Mike Berlin and Johnathan ClearSpeed Technology Pte. This article from ClearSpeed Technology and Cedex describes the methodology, tools used, and implementation guidelines employed in designing a PCI Express based SOC. The paper also highlights technical and business benefits of using this approach.

- NEWSROOM:** Press Release - 8/15/2008, Intel® and Mindshare to develop courses and train customers on the new Intel® QuickPath Interconnect (QPI) Technology and Intel® Core™ ( Nehalem ) Processor. Press Release - 8/16/2008, Mindshare's partner, Agilent Technologies, introduces Active State Power Management support in their PCI Express testing tools.

- MINDSHARE BROCHURE:** Now Available MindShare's Service Brochure, Download Now.

System Architecture

DRAM Feature Summary

Intro to DRAM

Historical Background

Why DRAM?

DRAM Cell Architecture

DRAM Chip Architecture

DRAM Modules

Commands and Waveforms

DDR Initialization

SMBus Overview

Electrical Specifications

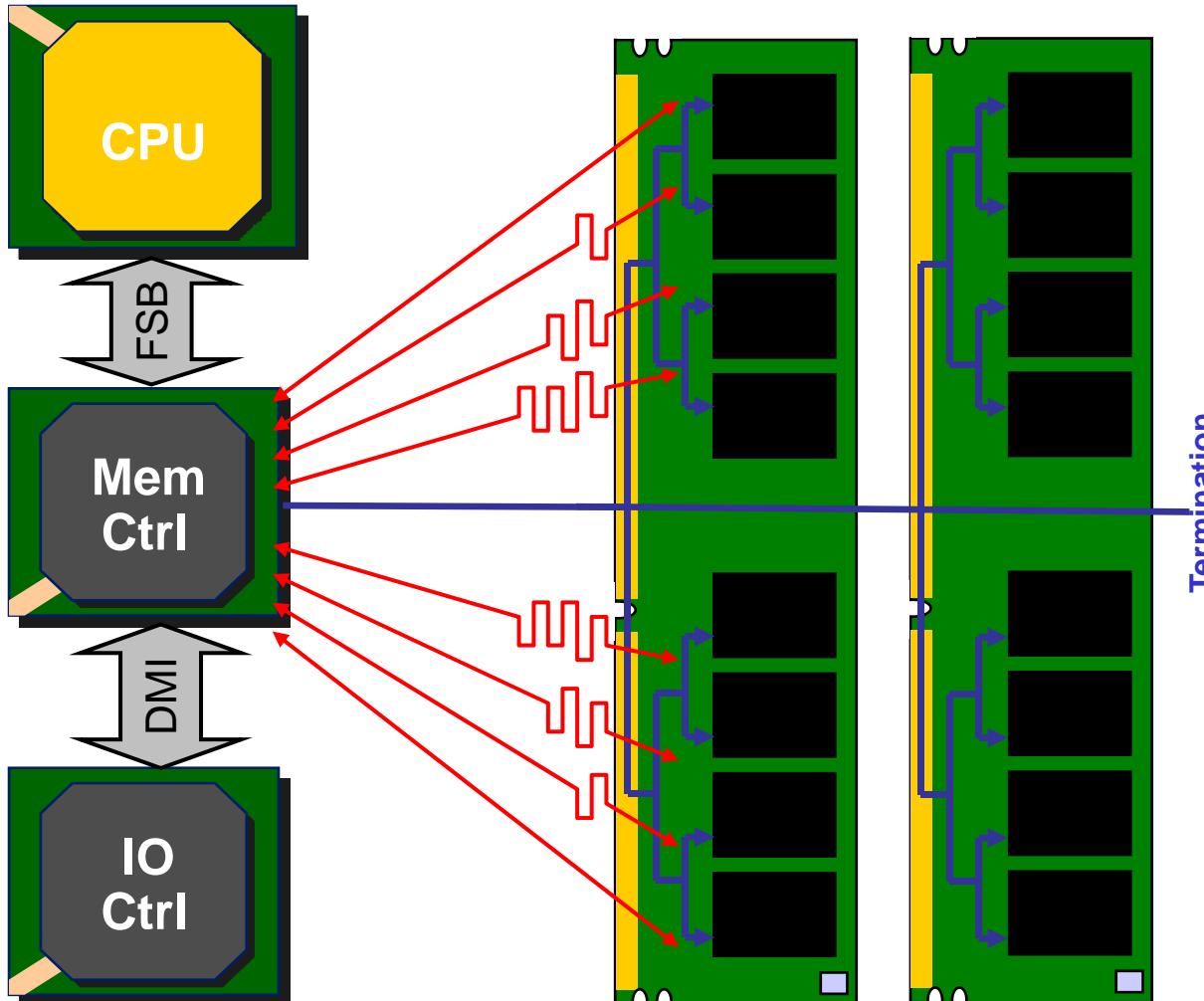

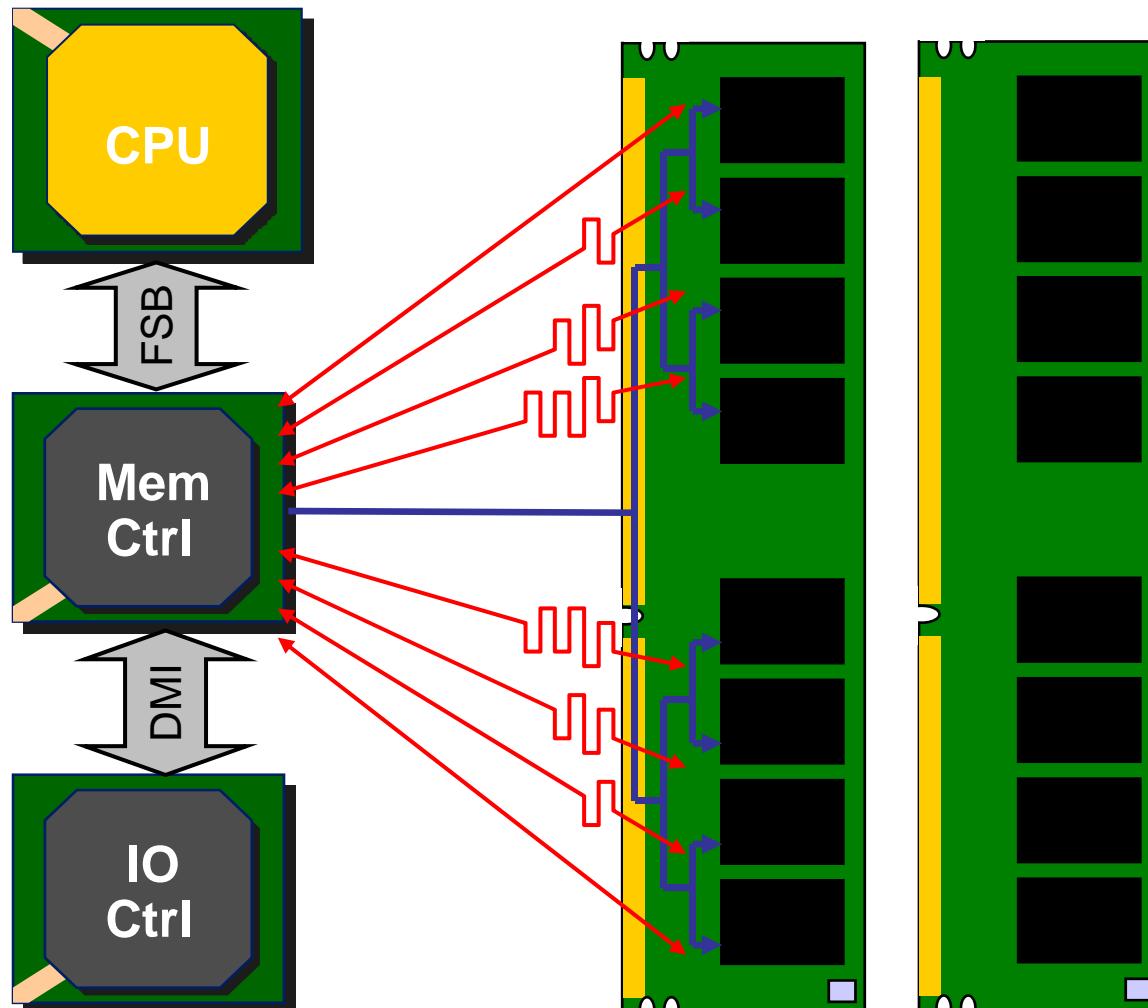

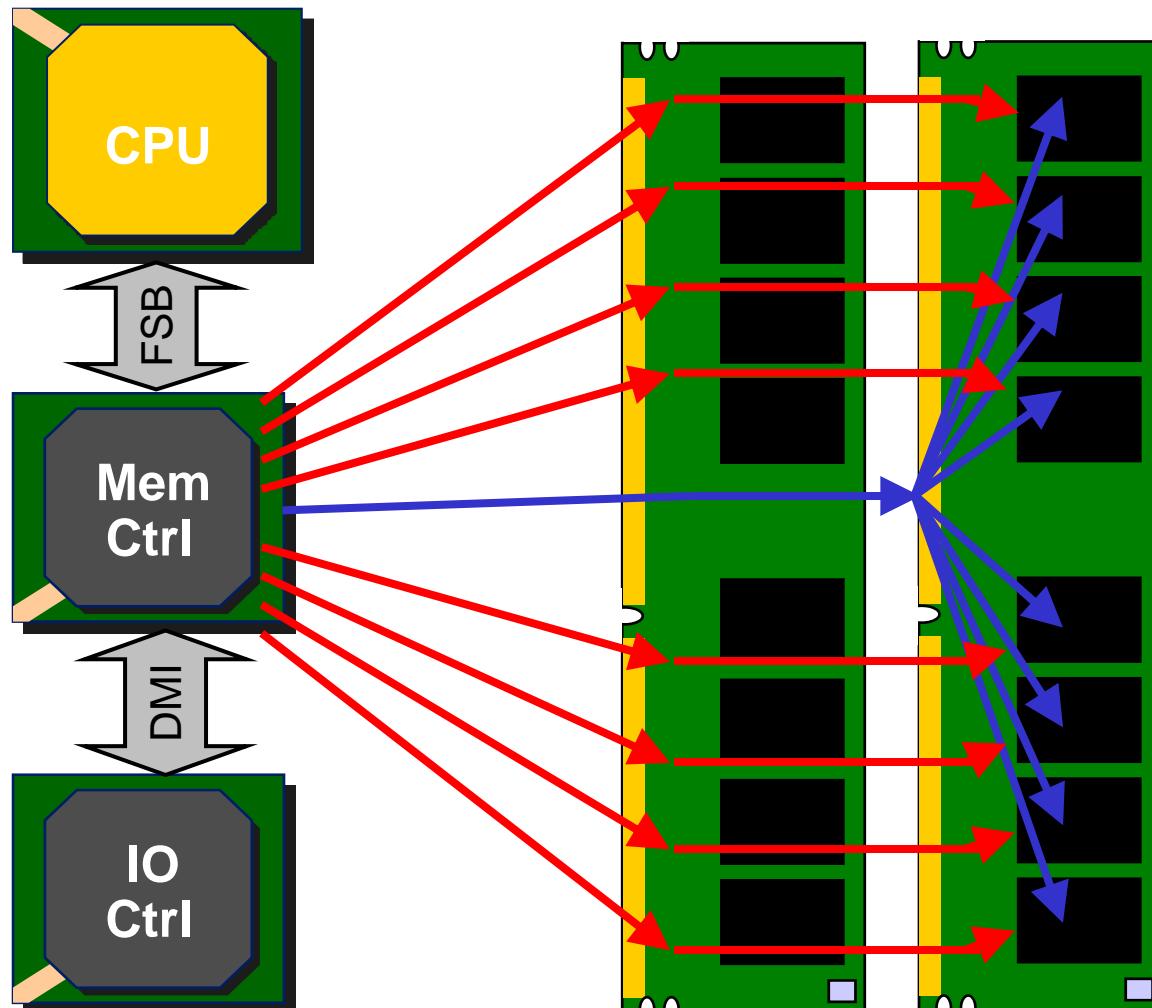

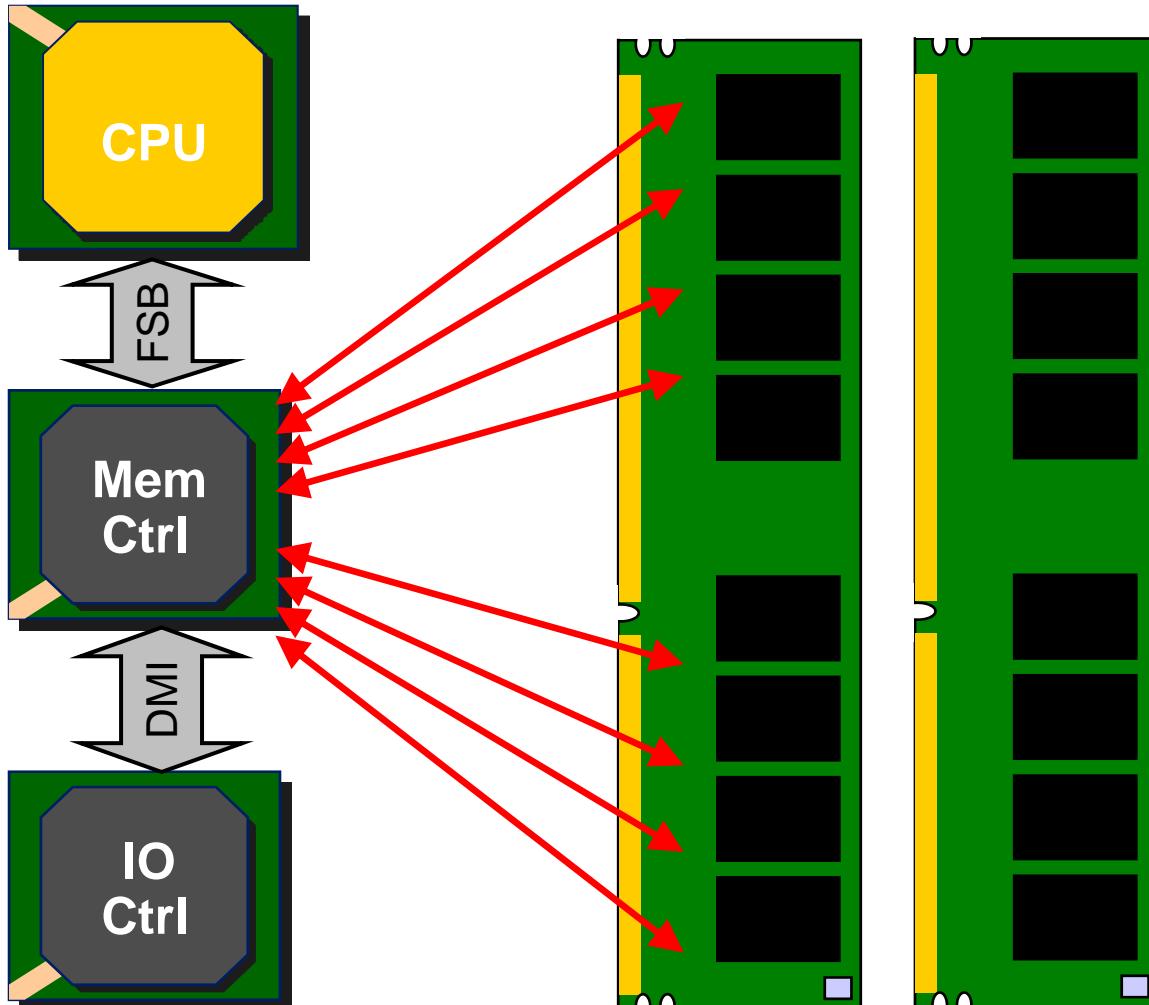

DDR1 and DDR2 Routing

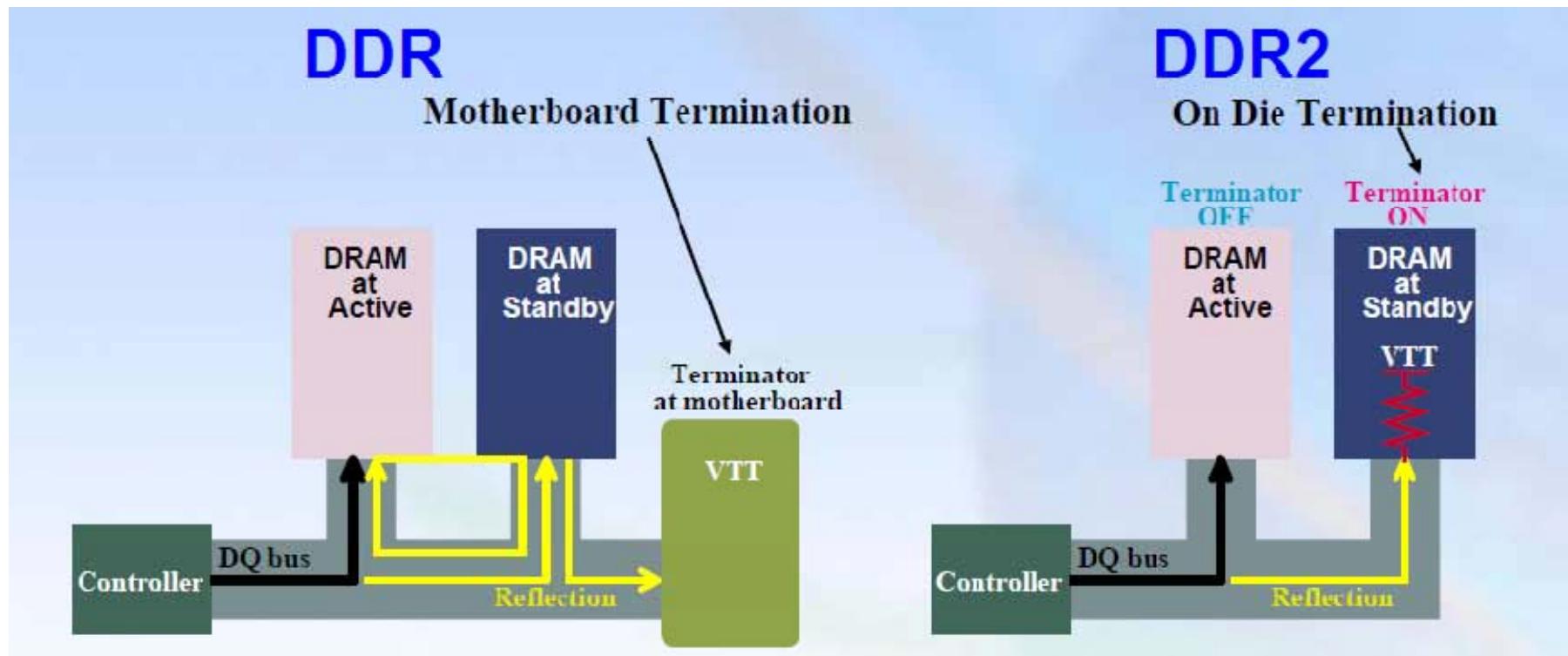

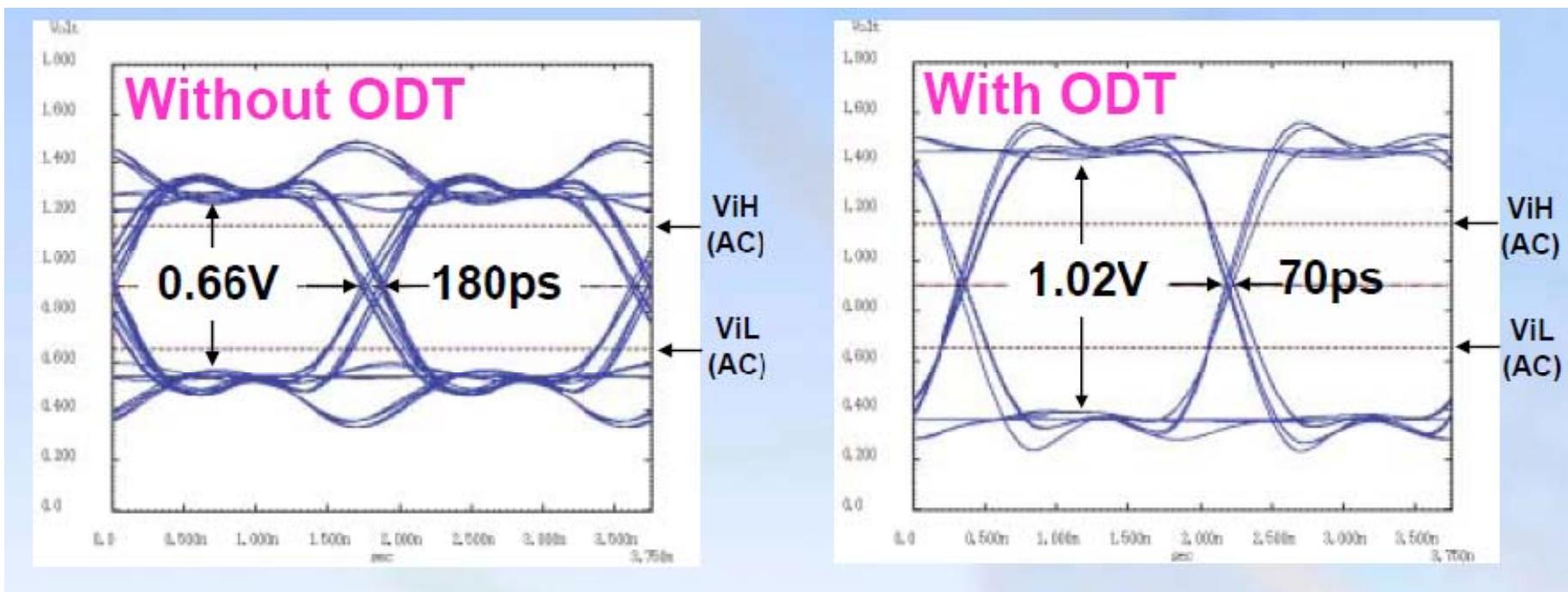

On-Die Termination

Errors

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

Additional DDR3 Topics

Timing and Electrical Differences

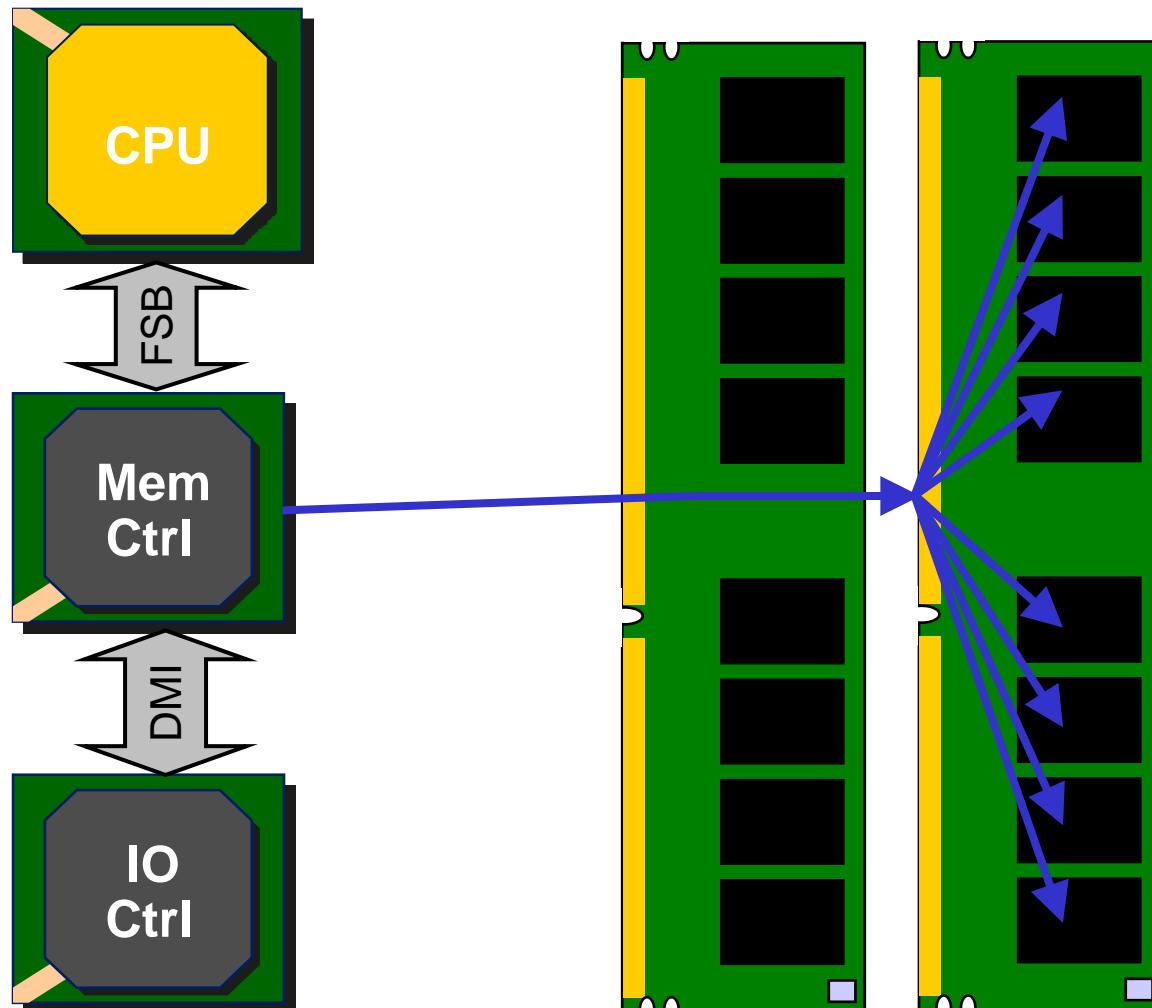

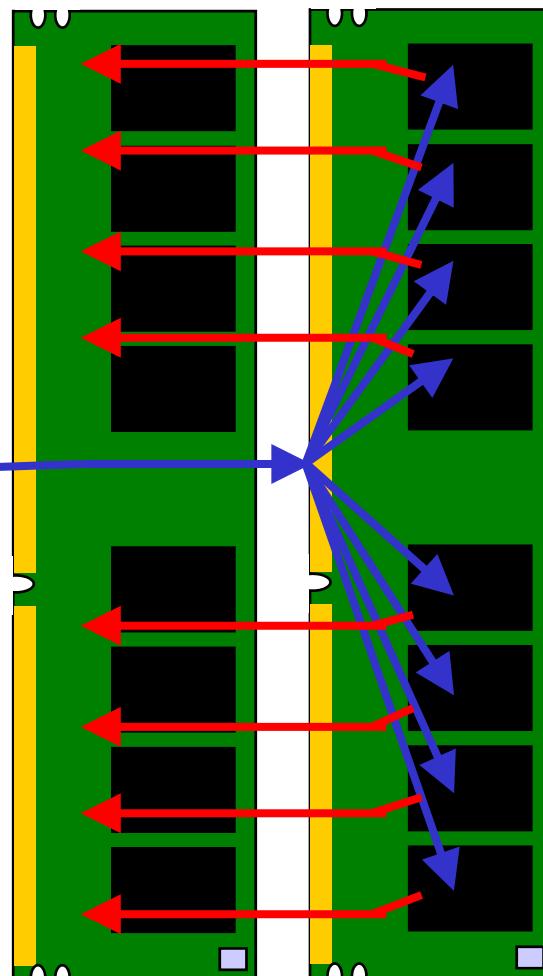

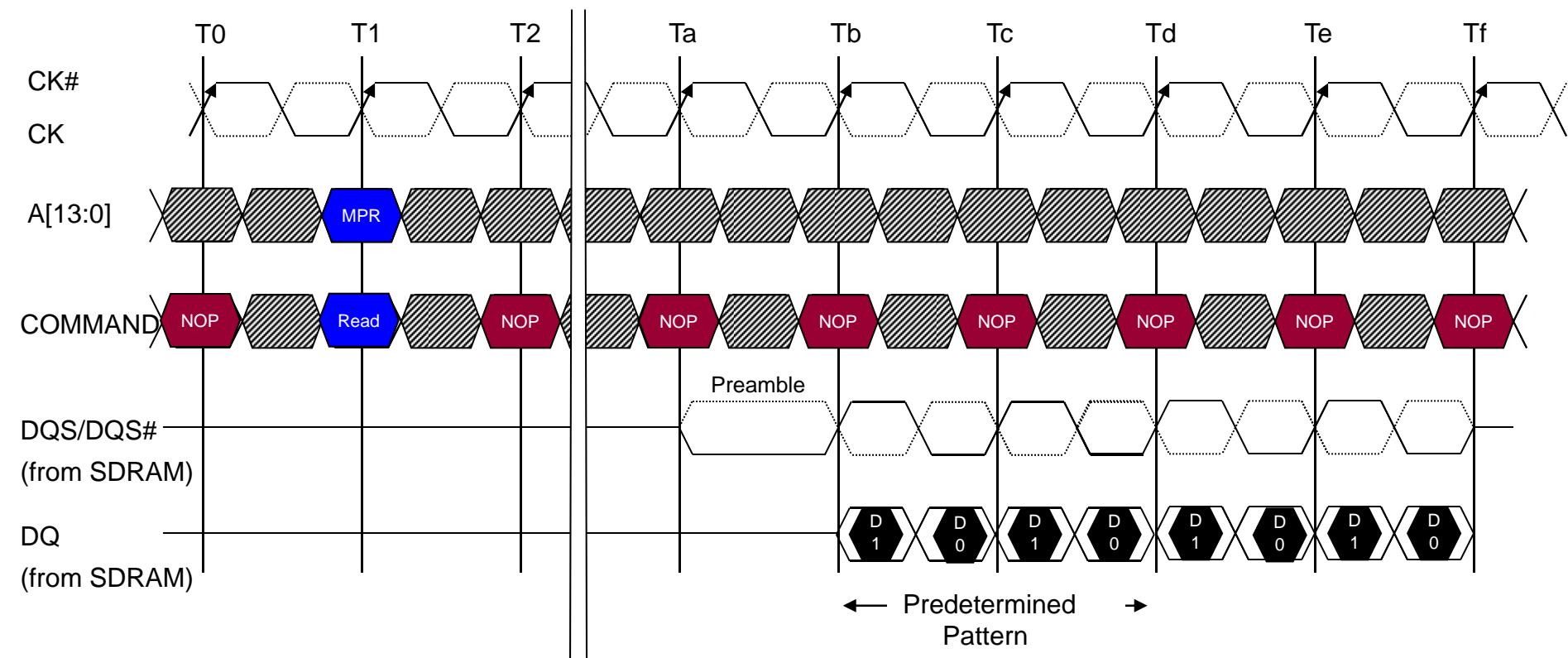

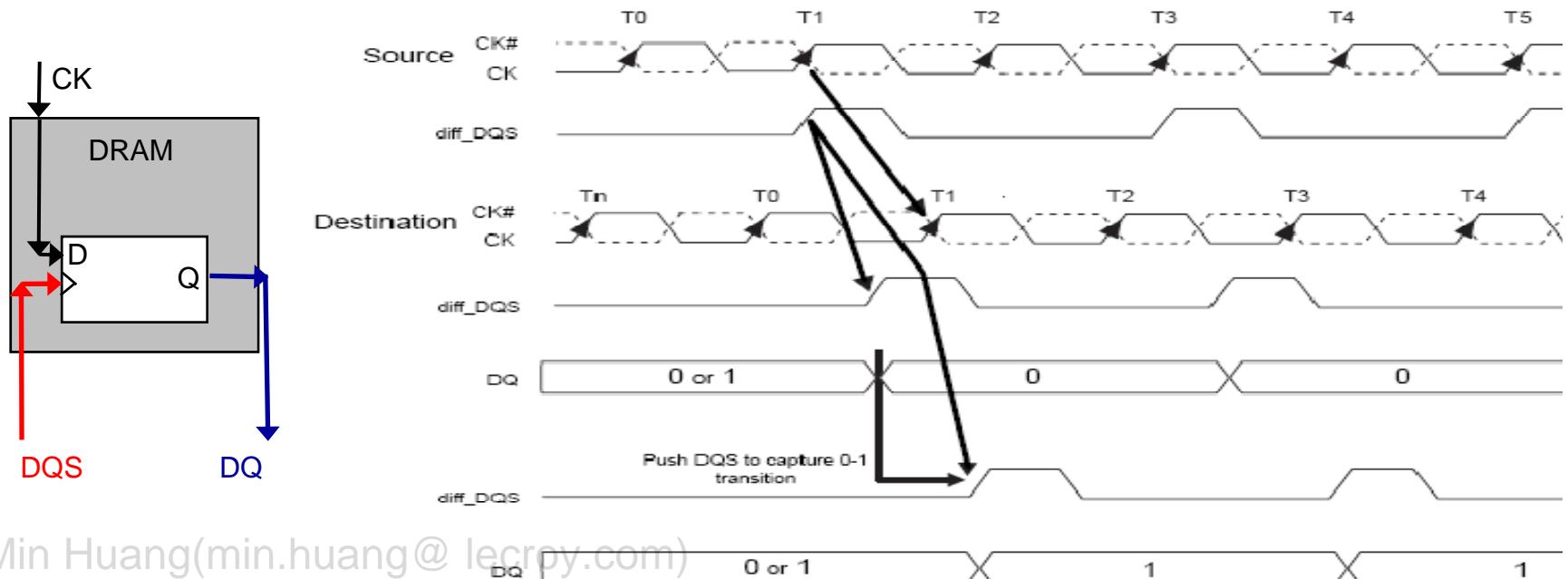

Fly-by Routing Read Example

Read Calibration

Fly-by Routing Write Example

Write Leveling

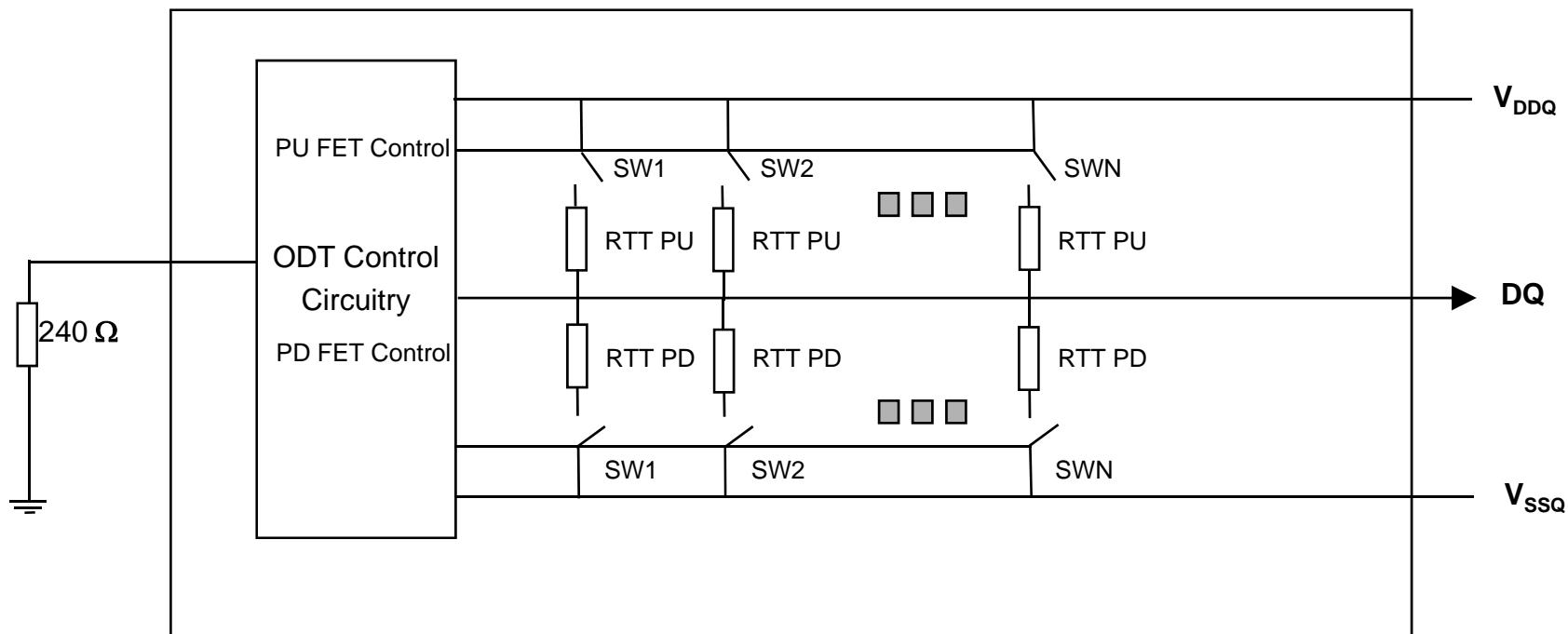

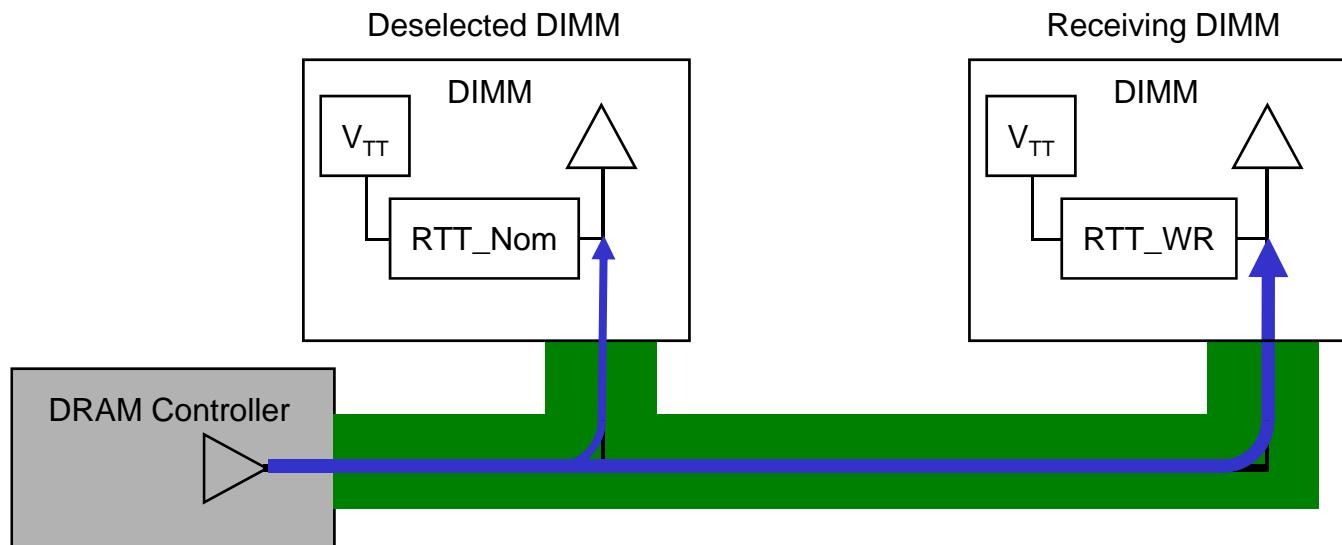

DDR3 On-Die Termination

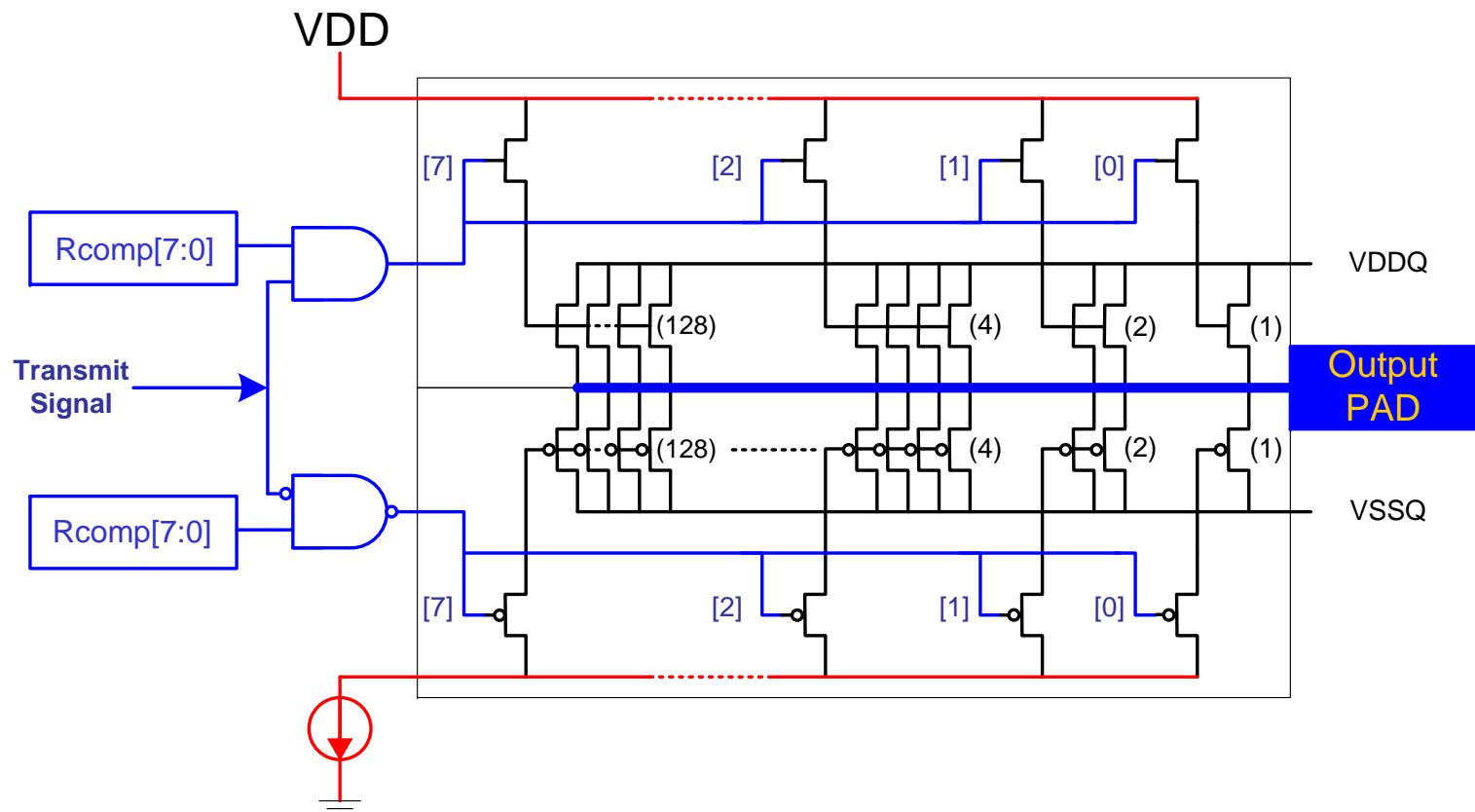

ZQ Calibration

Reset

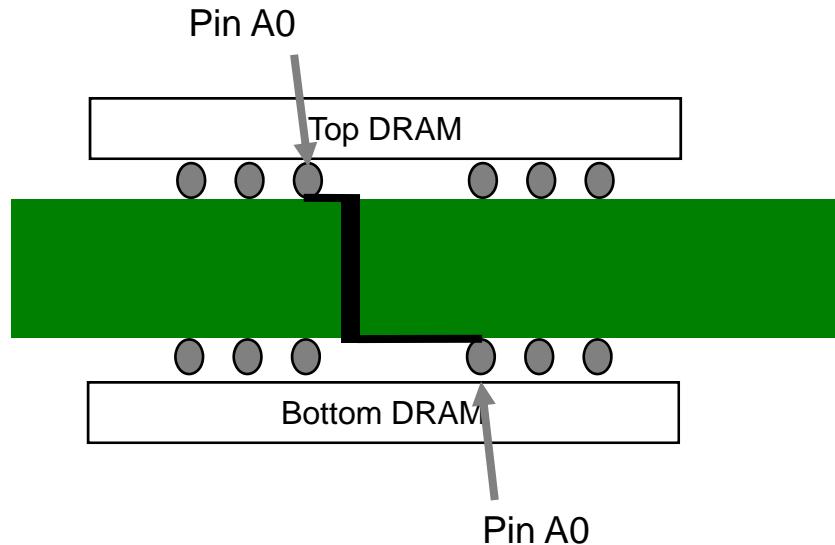

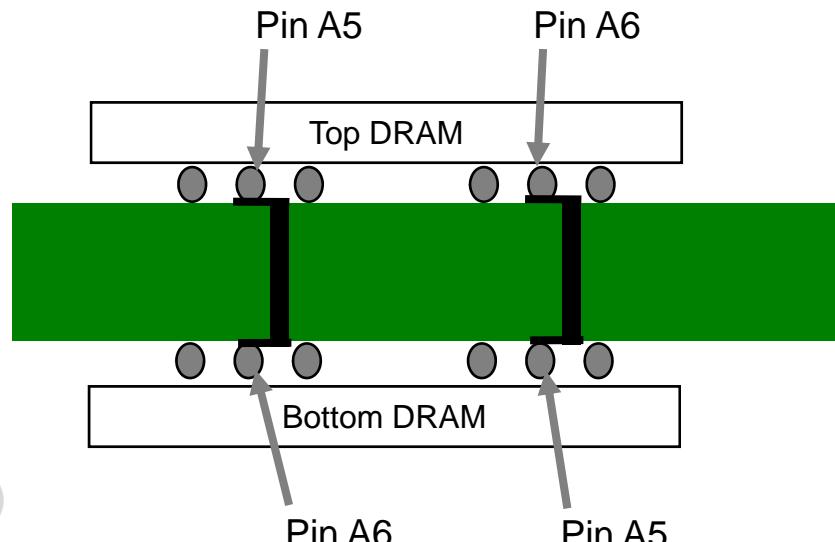

On-DIMM Address Mirroring

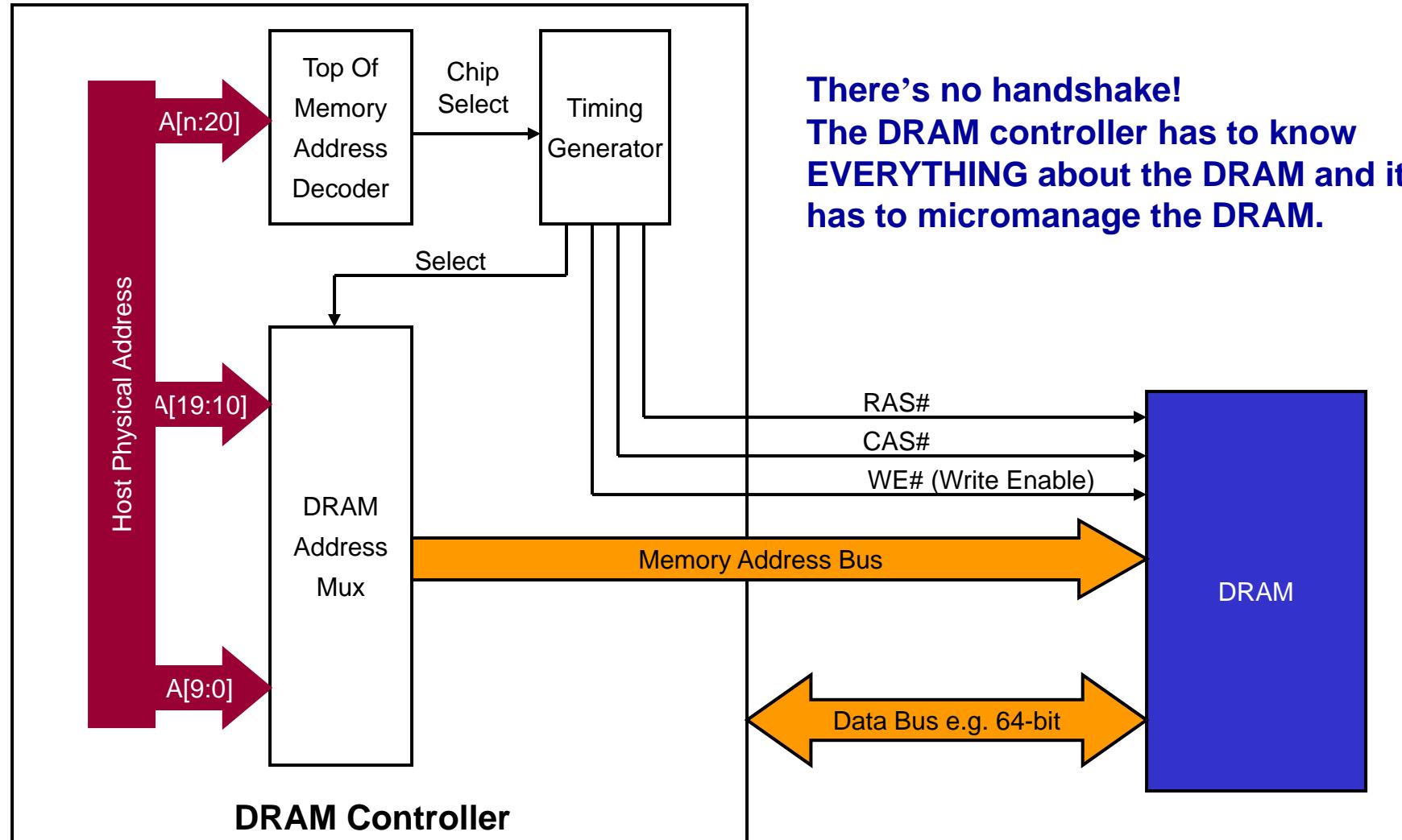

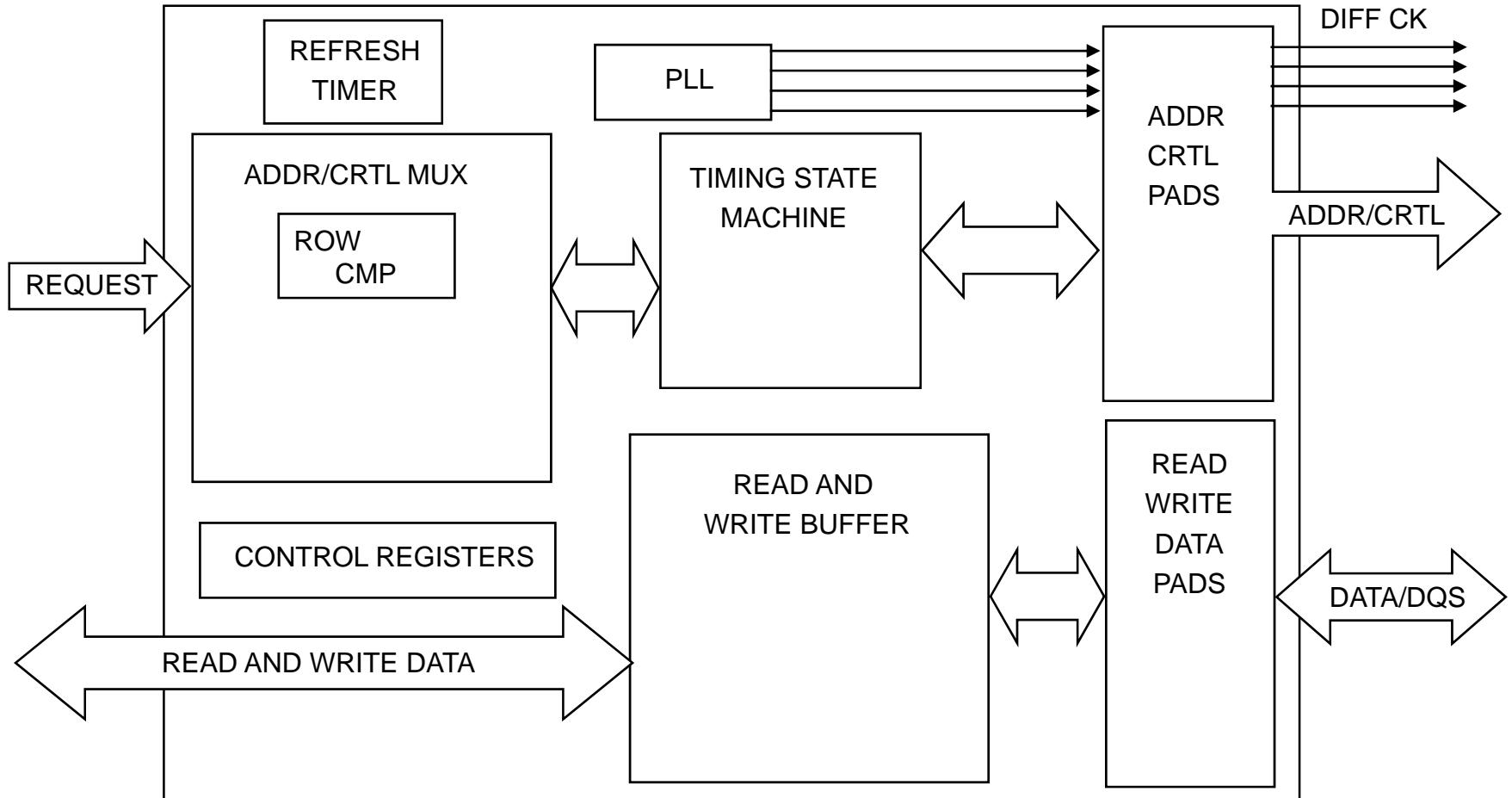

DRAM Controller Basics

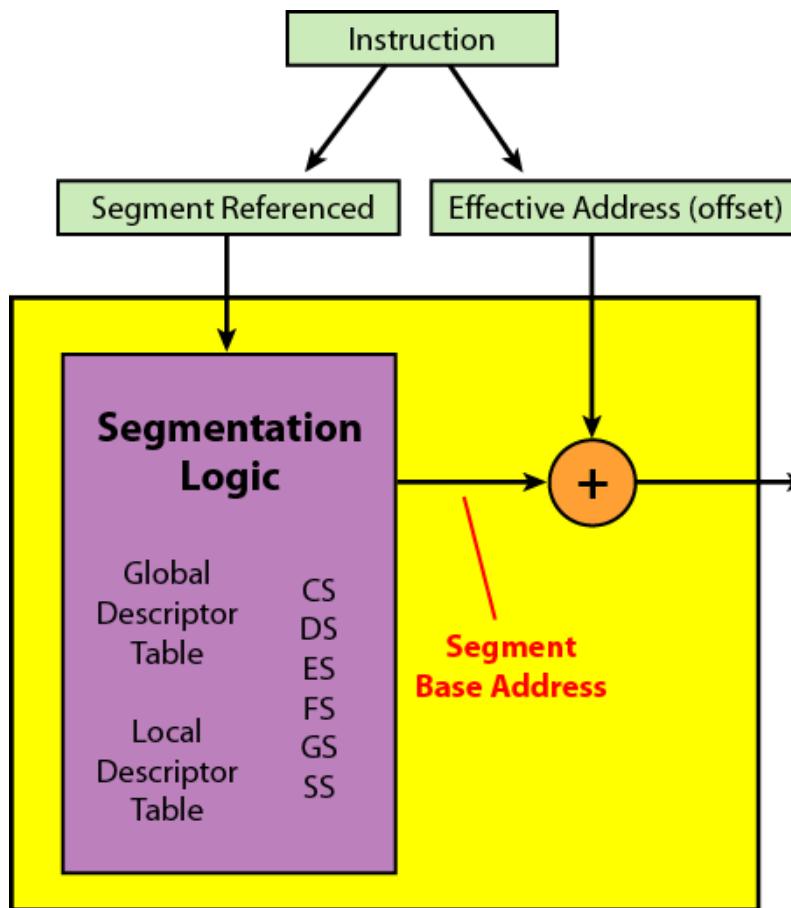

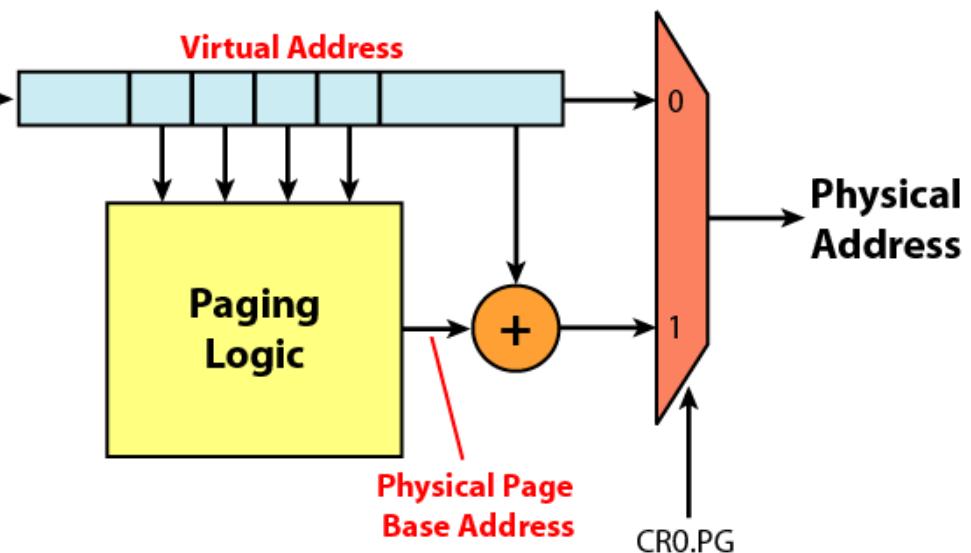

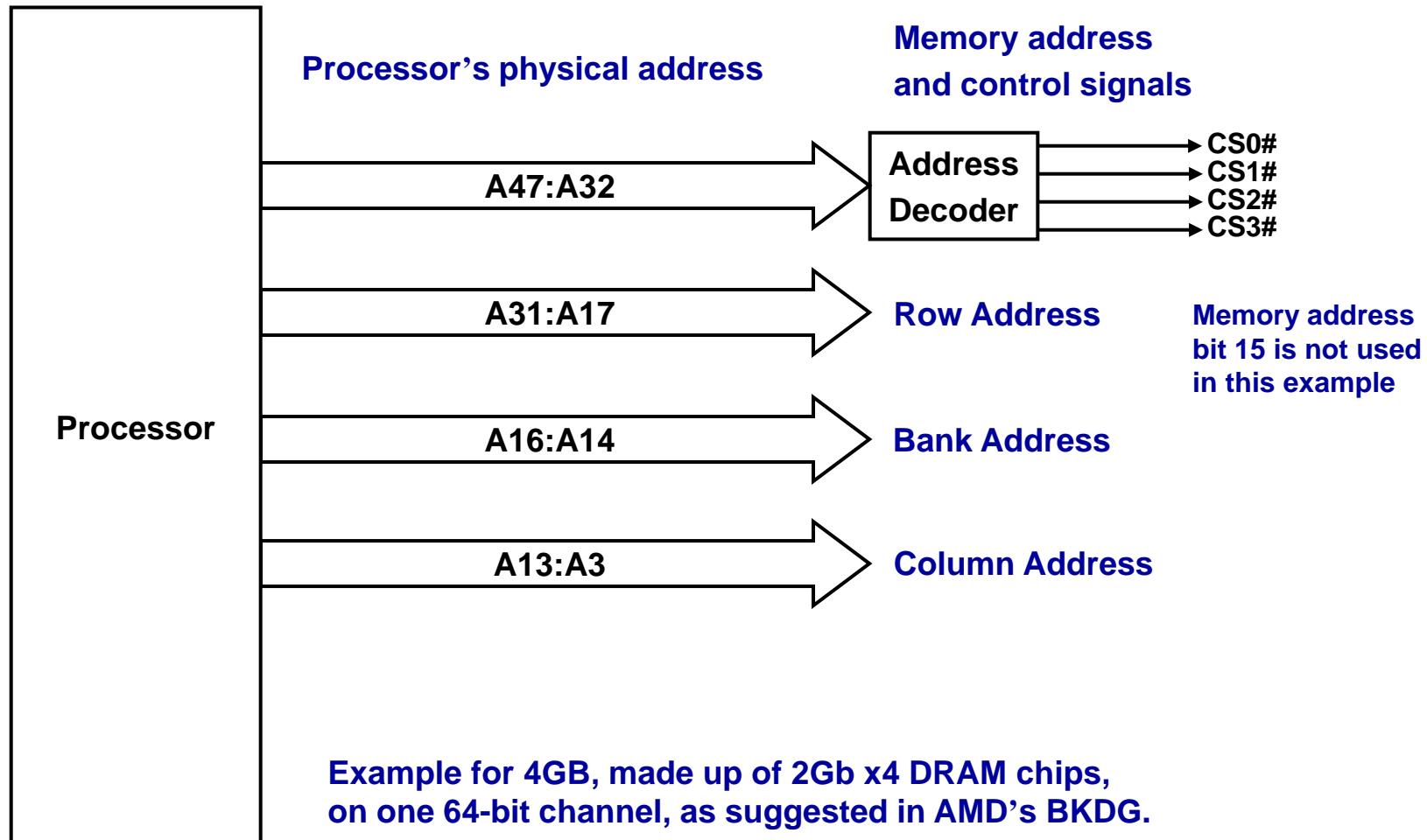

Addresses

Alternative DRAM Solutions

Upon completion, the student should:

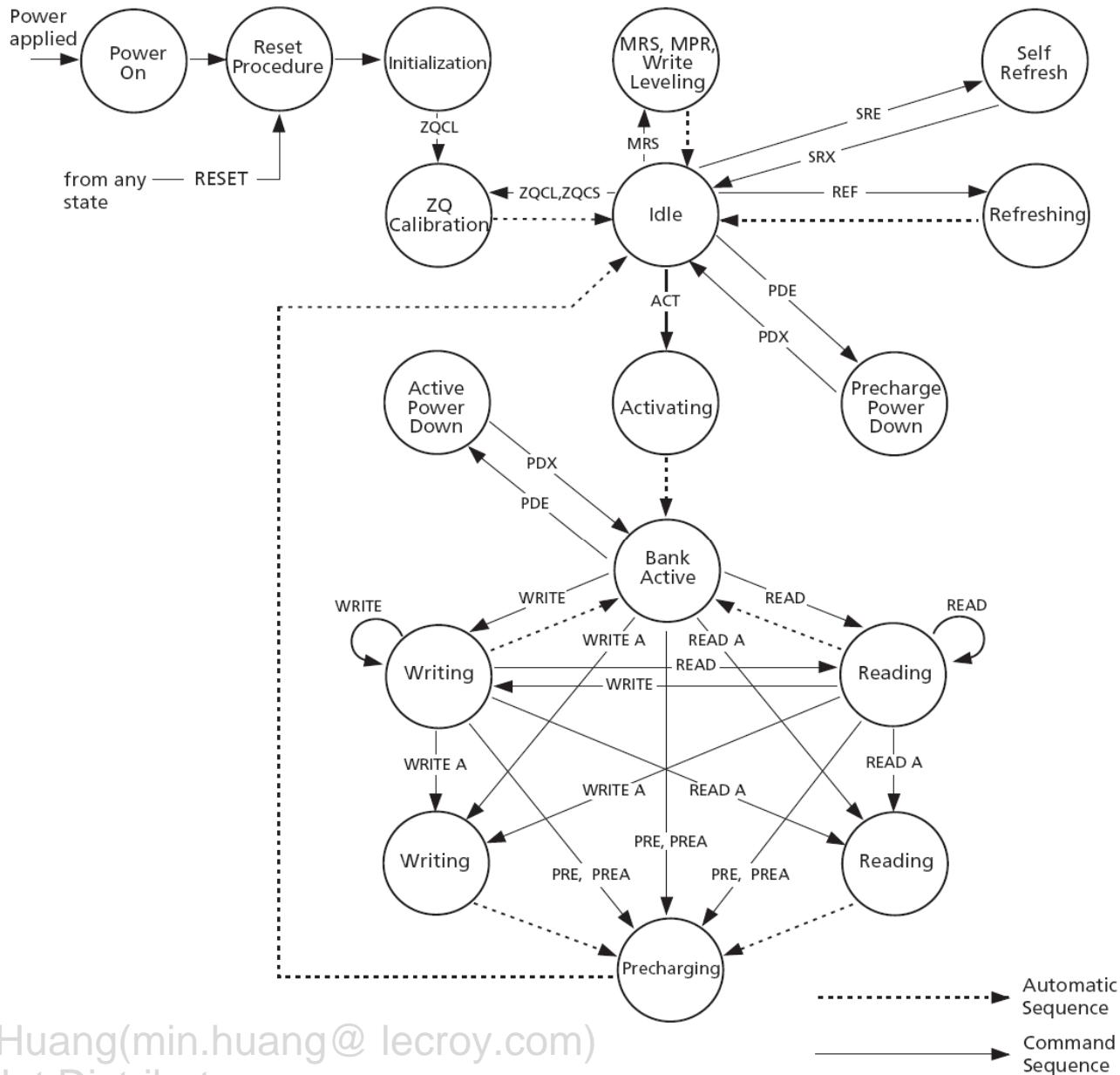

- Understand the DRAM bank state diagram

- Understand the JEDEC initialization procedure

- Understand the timing waveforms

- Know why the DRAM controller has to do so much of the work

- Know what motivates the move to DDR3 and the associated problems

- Know what elements of the system determine the address of a DRAM cell

- Know these terms and their concepts:

**Prefetch width**

**Refresh vs. auto refresh vs. self refresh vs. auto self refresh**

**Activate**

**Precharge vs. auto precharge vs. precharge all**

**Additive latency**

**Bank vs. rank**

**SSTL**

**ODT, dynamic ODT**

**ZQ calibration**

**Fly-by routing, read calibration, and write leveling**

**SPD and Mode Registers**

**On-the-fly burst chop (the Austin Powers mode)**

**Unbuffered vs. registered vs. fully-buffered**

**1T vs. 2T timing**

Remember the

quick reference

handout

# Where's the Money?

| DRAM Maker   | 2007 Revenue \$ billions |

|--------------|--------------------------|

| Samsung      | 8.7                      |

| Hynix        | 6.7                      |

| Qimonda      | 4.0                      |

| Elpida       | 3.8                      |

| Micron       | 3.2                      |

| Nanya        | 1.6                      |

| Powerchip    | 1.4                      |

| ProMos       | 1.1                      |

| Etron        | 0.4                      |

| Elite        | 0.2                      |

| Others       | 0.4                      |

| <b>Total</b> | <b>31.5</b>              |

| Logic Maker | 2007 Revenue \$ billions |

|-------------|--------------------------|

| Intel       | 39.2                     |

| AMD         | 6.3                      |

So who has the greatest responsibility

for new features such as fly-by?

Follow the money.

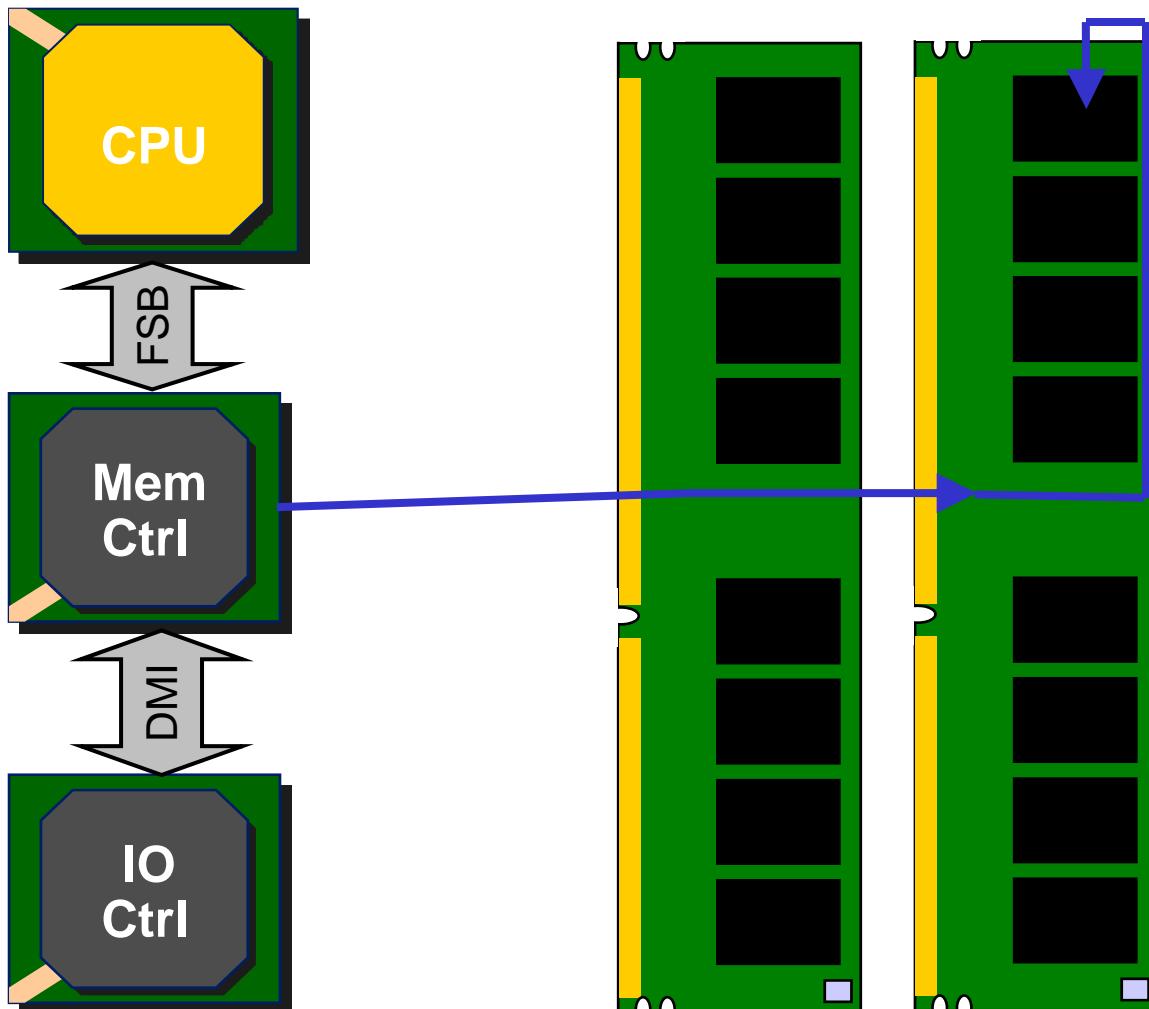

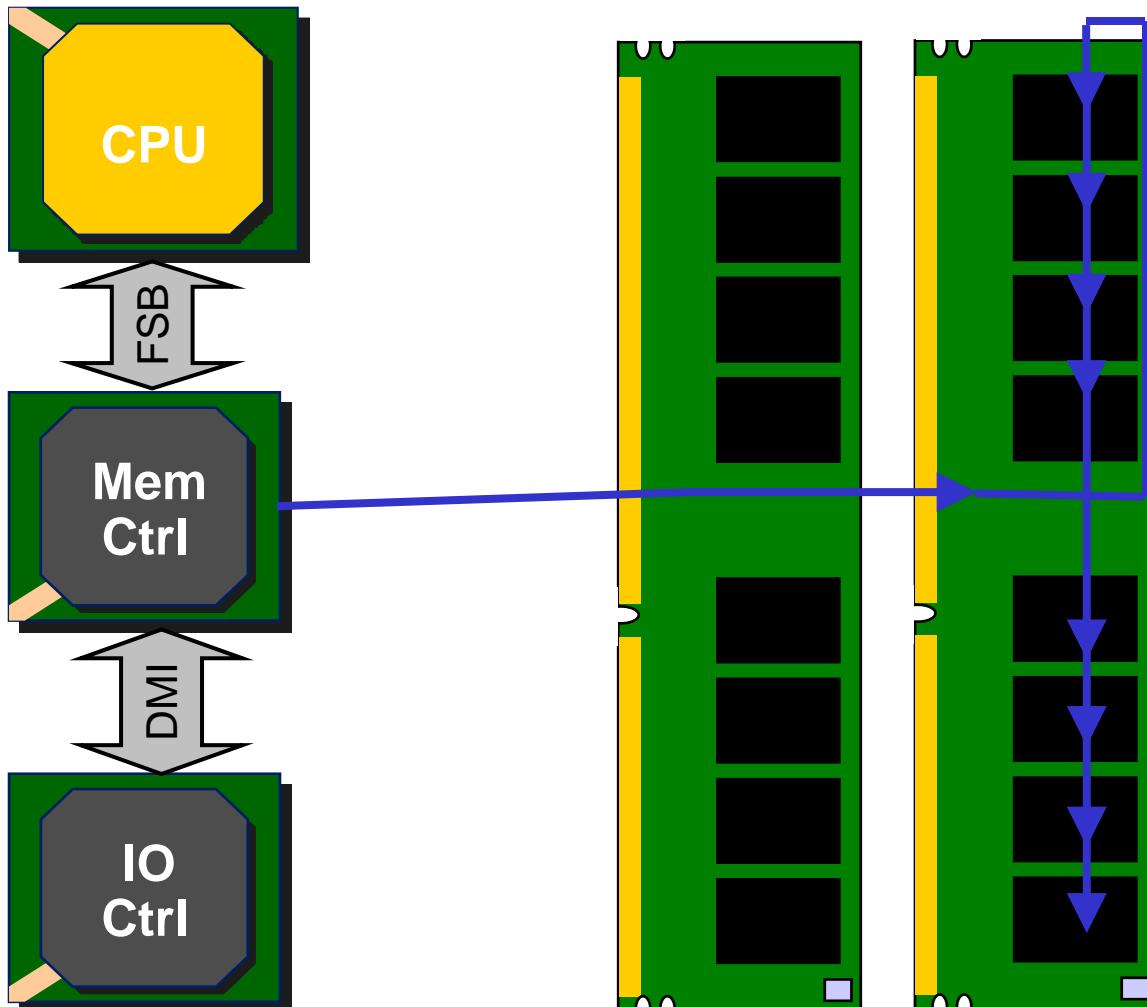

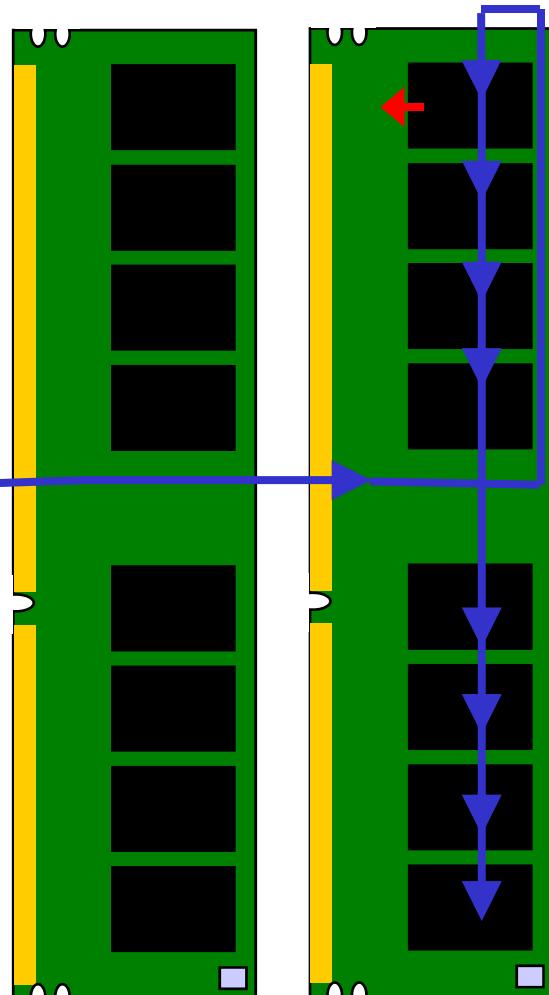

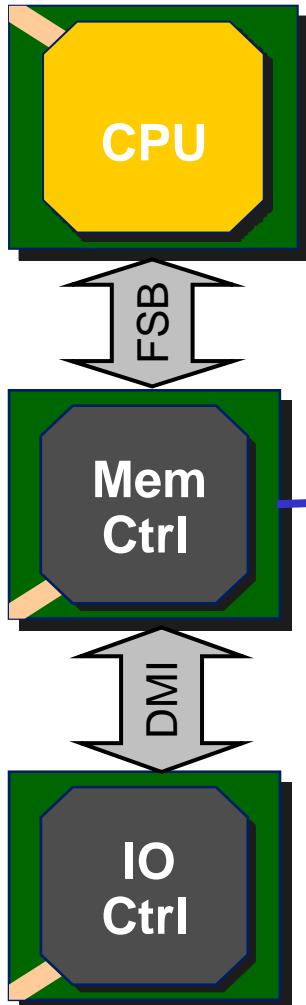

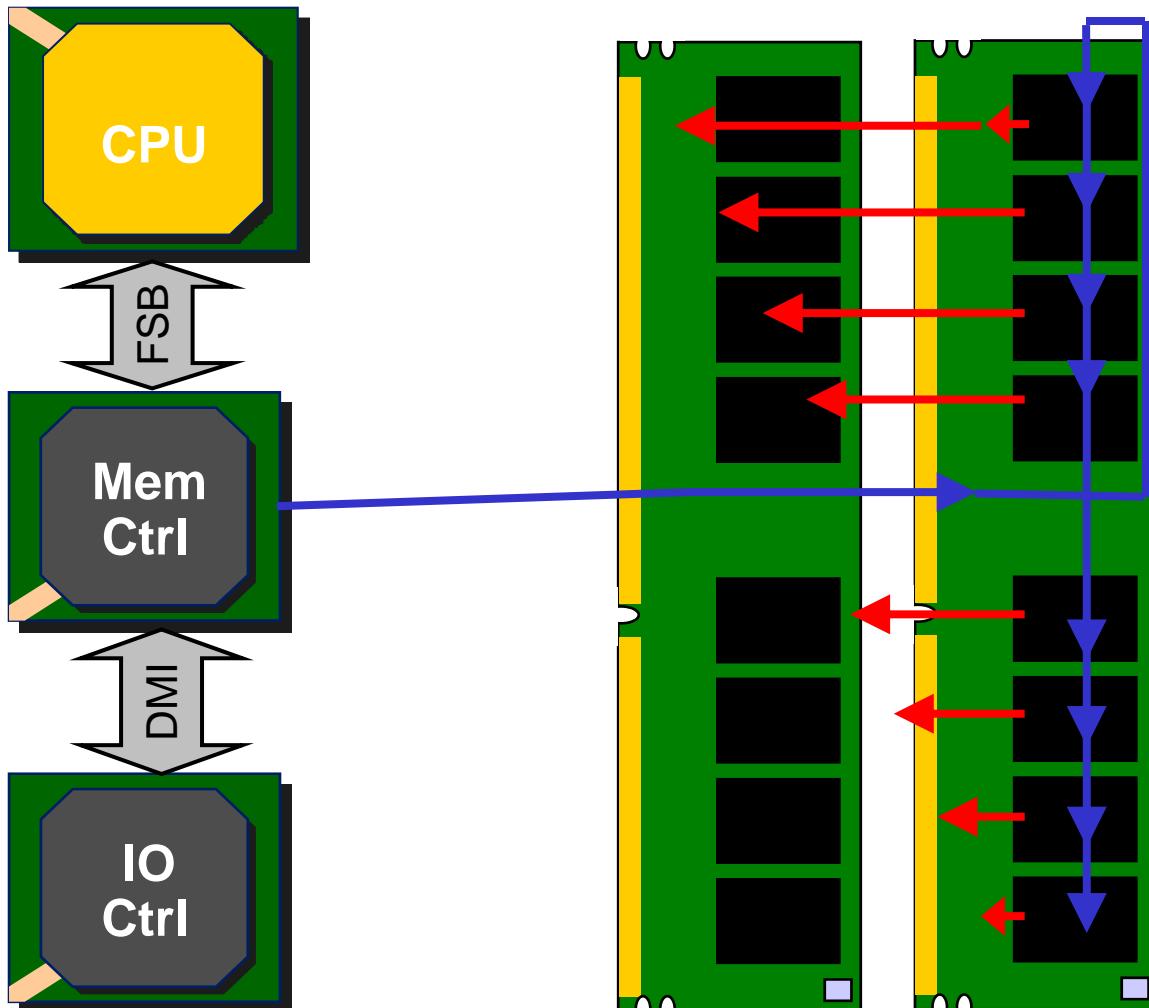

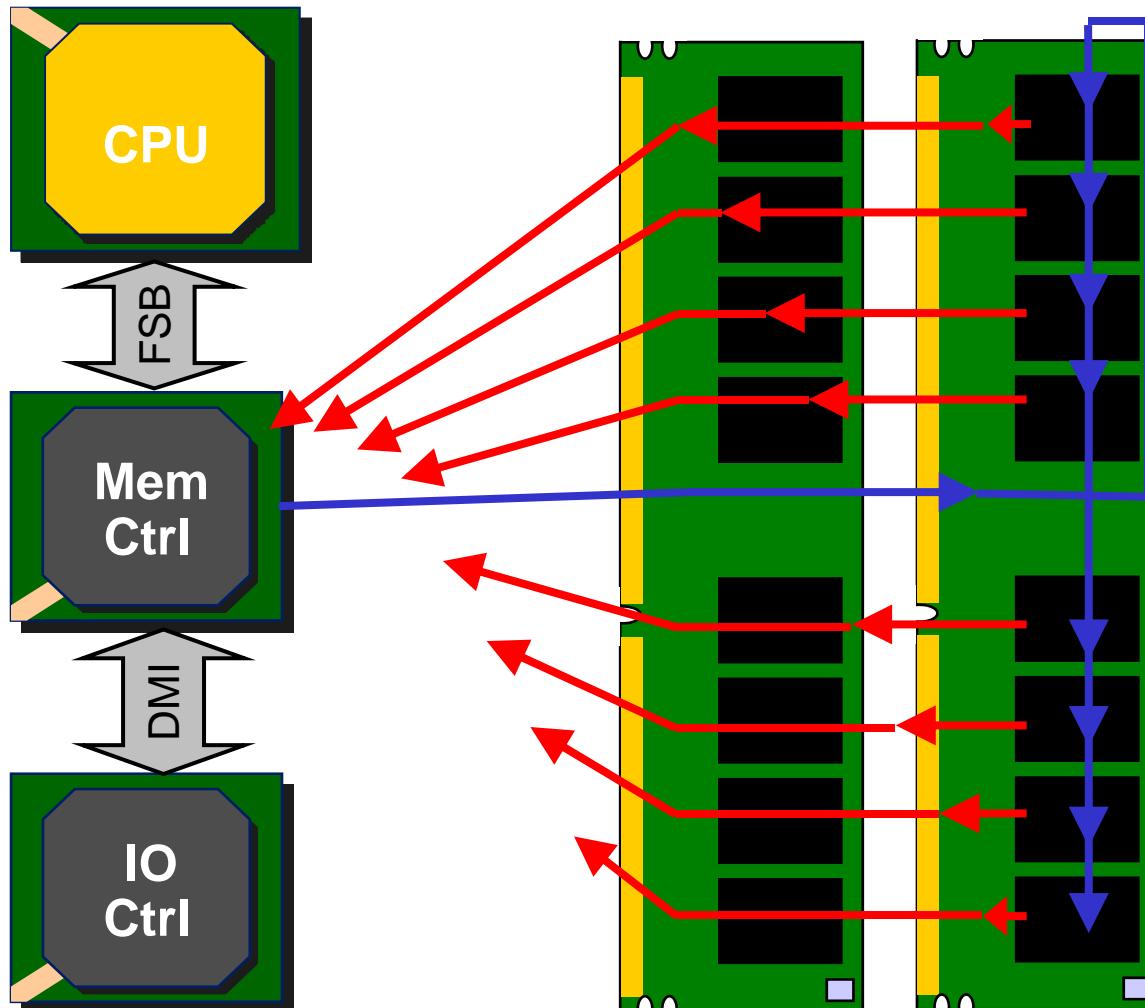

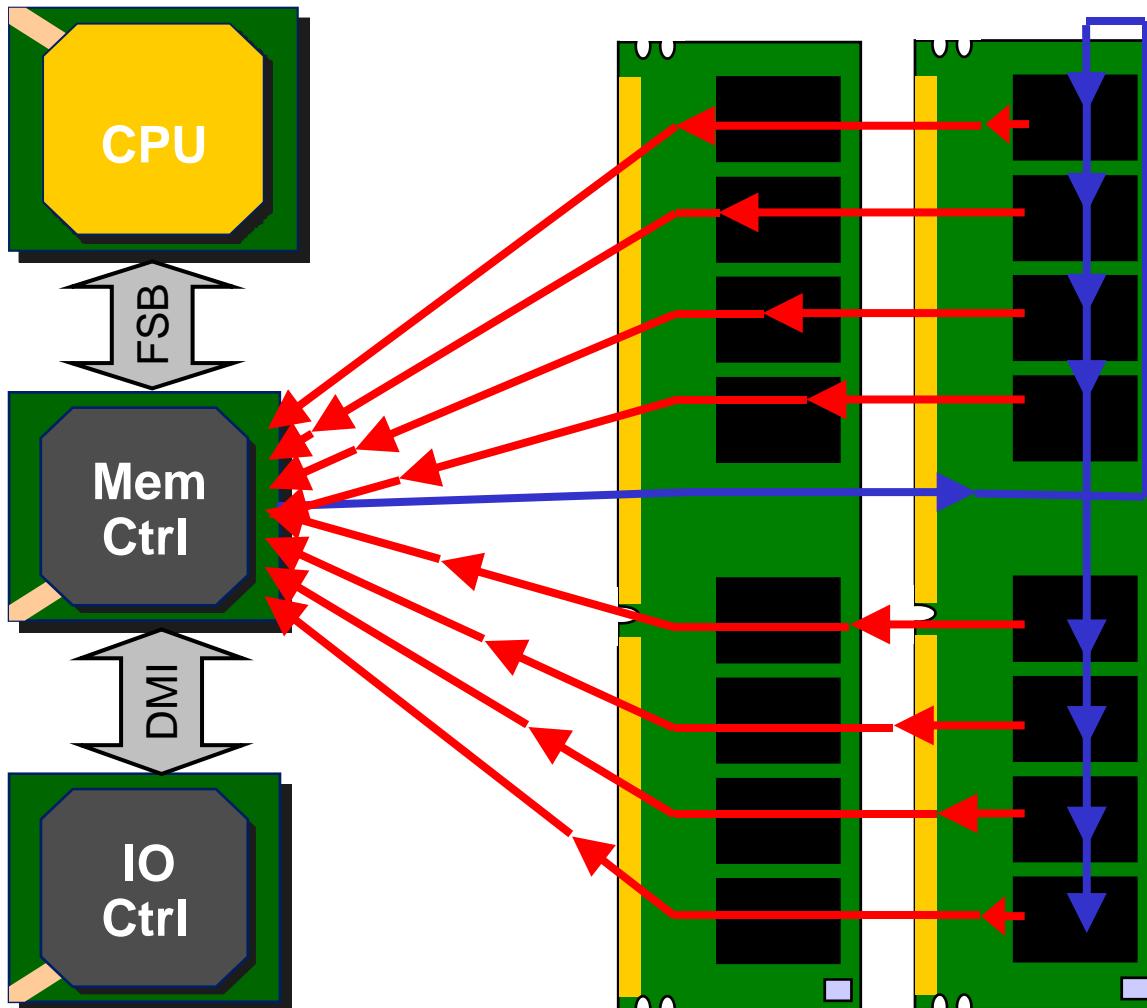

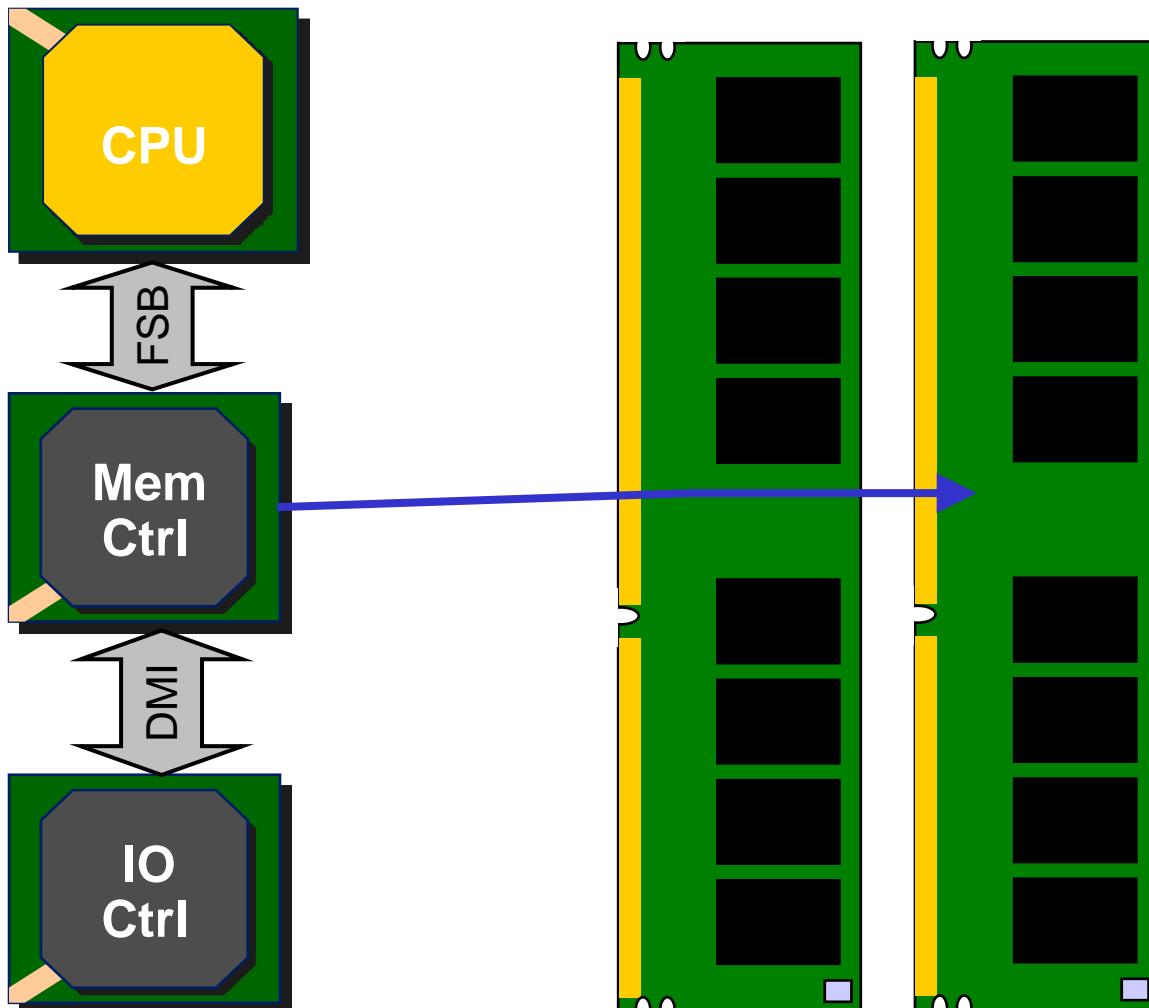

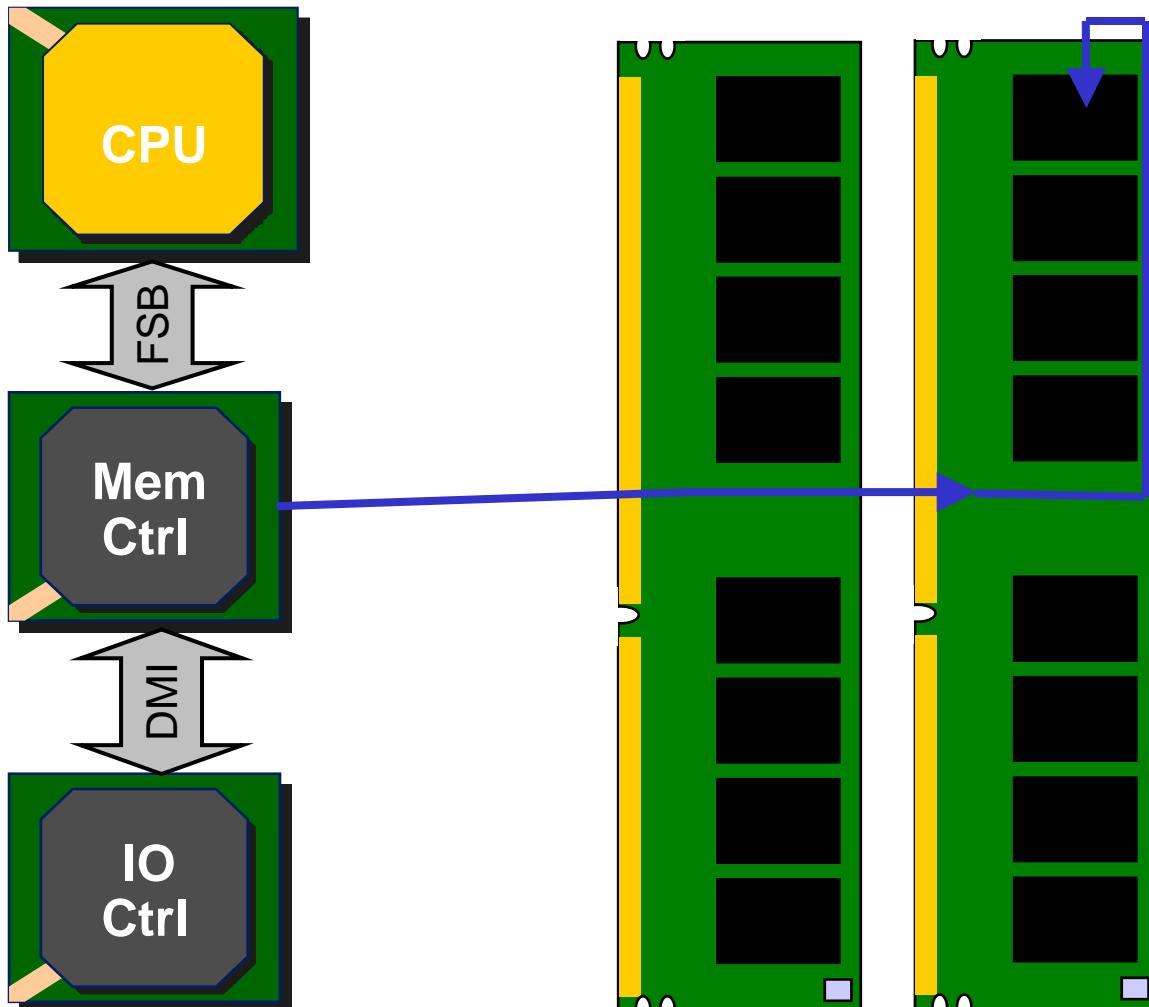

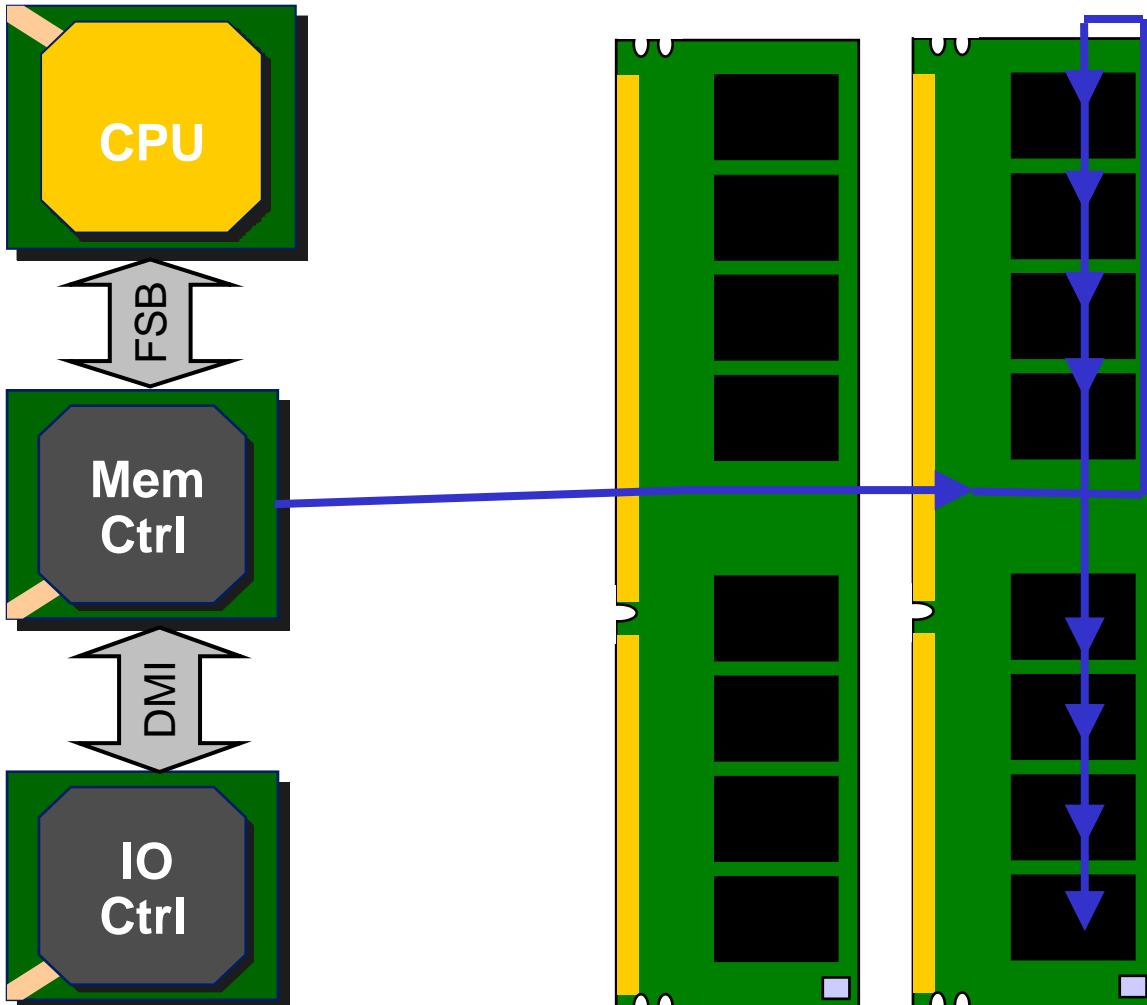

# System Architecture

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

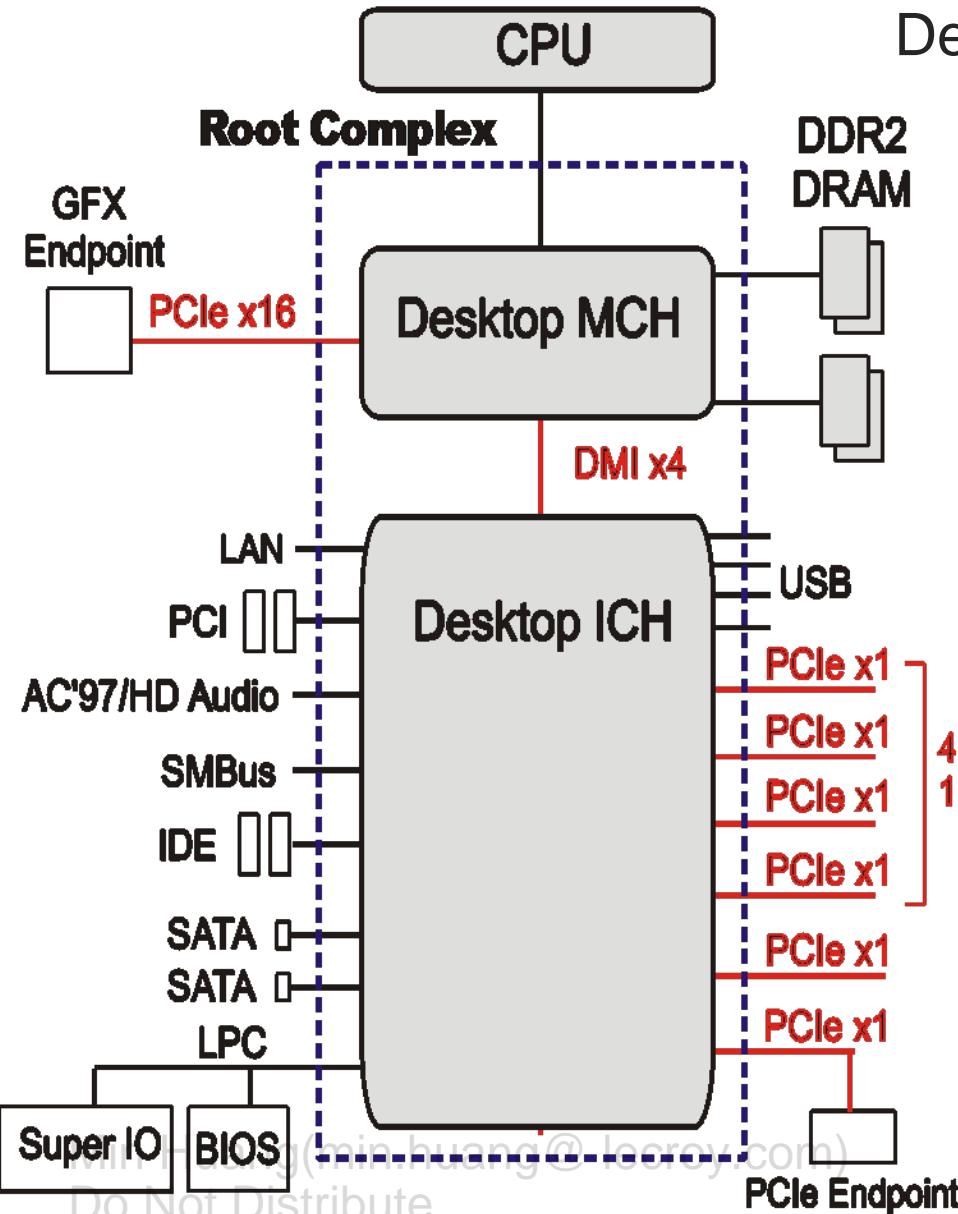

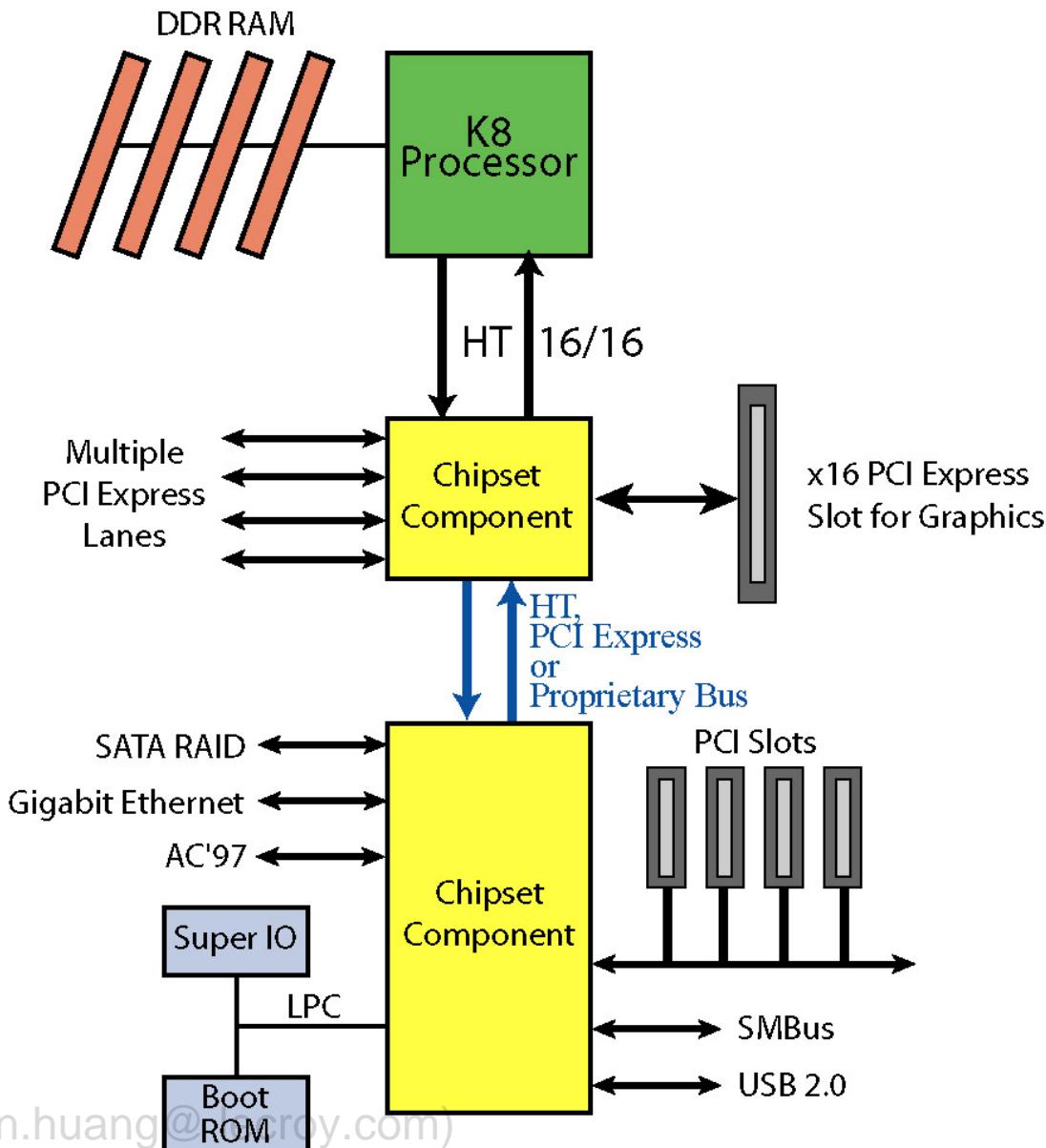

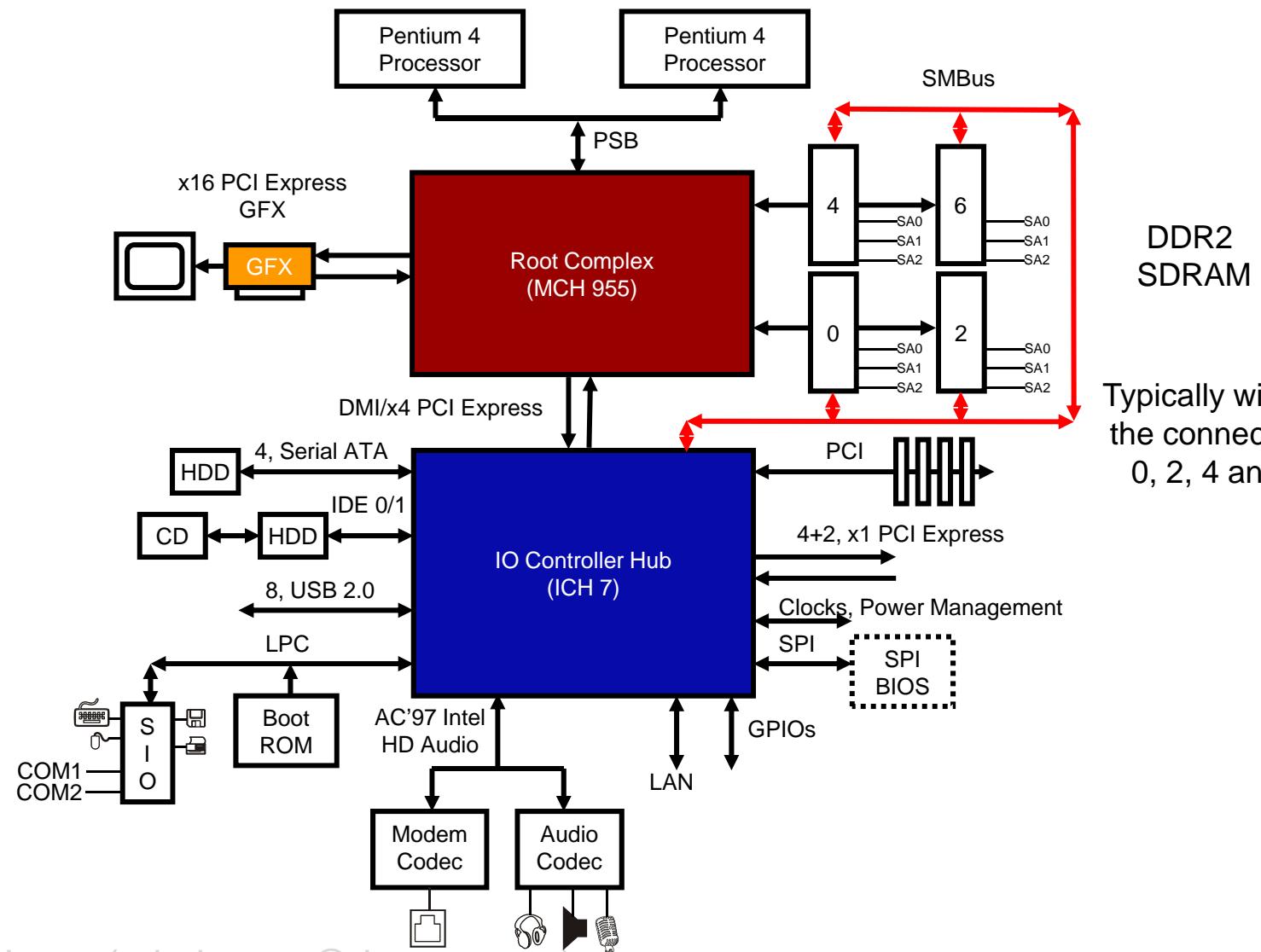

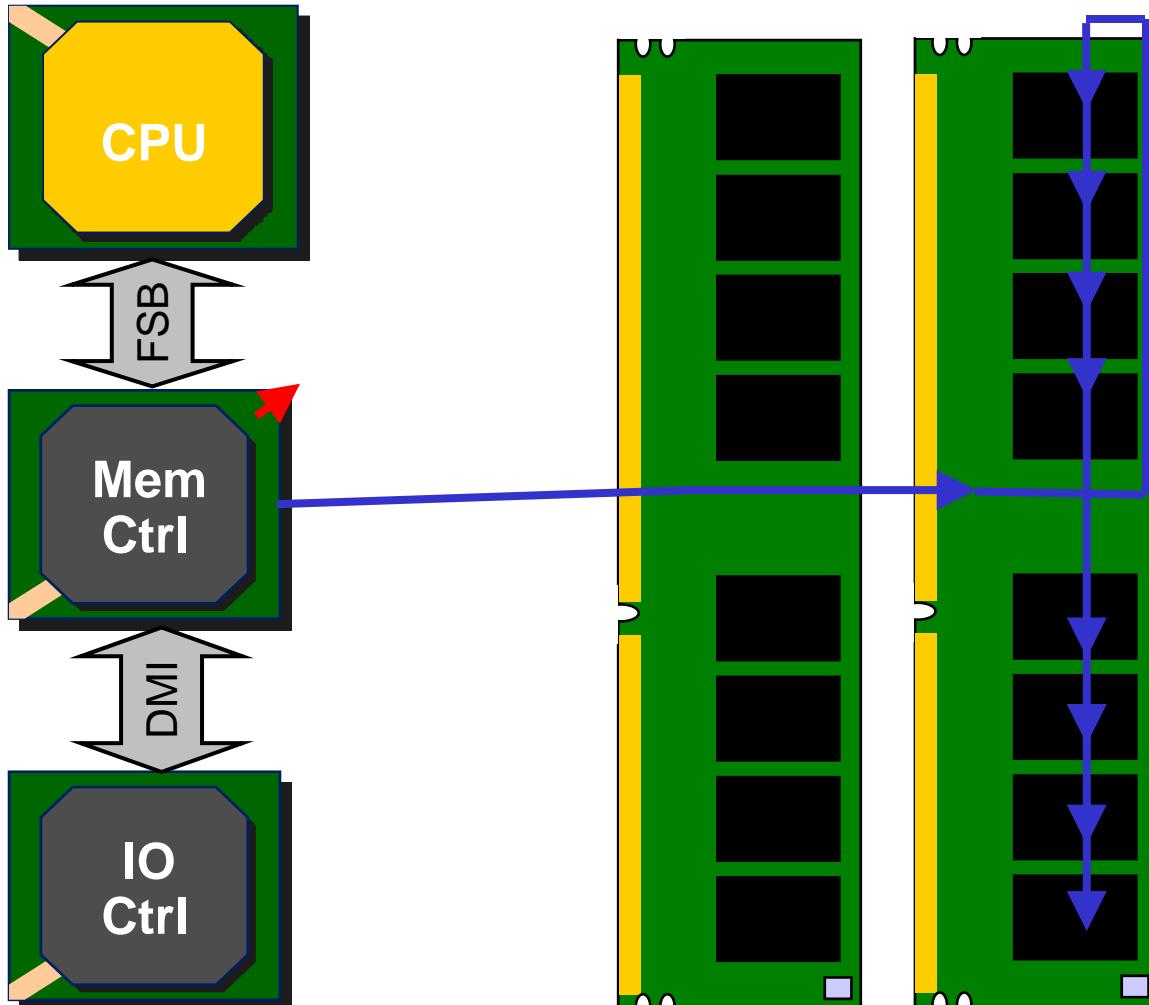

## Desktop Chipset PCIe Support

- MCH hosts a 16-bit PCIe Link interface for high-performance graphics.

- DMI (Direct Media Interface) is an Intel-specific version of x4 PCIe.

- ICH (IO Controller Hub) supports multiple x1 PCIe Links, four of which may operate as x1 Links or ganged together as a single x4 Link.

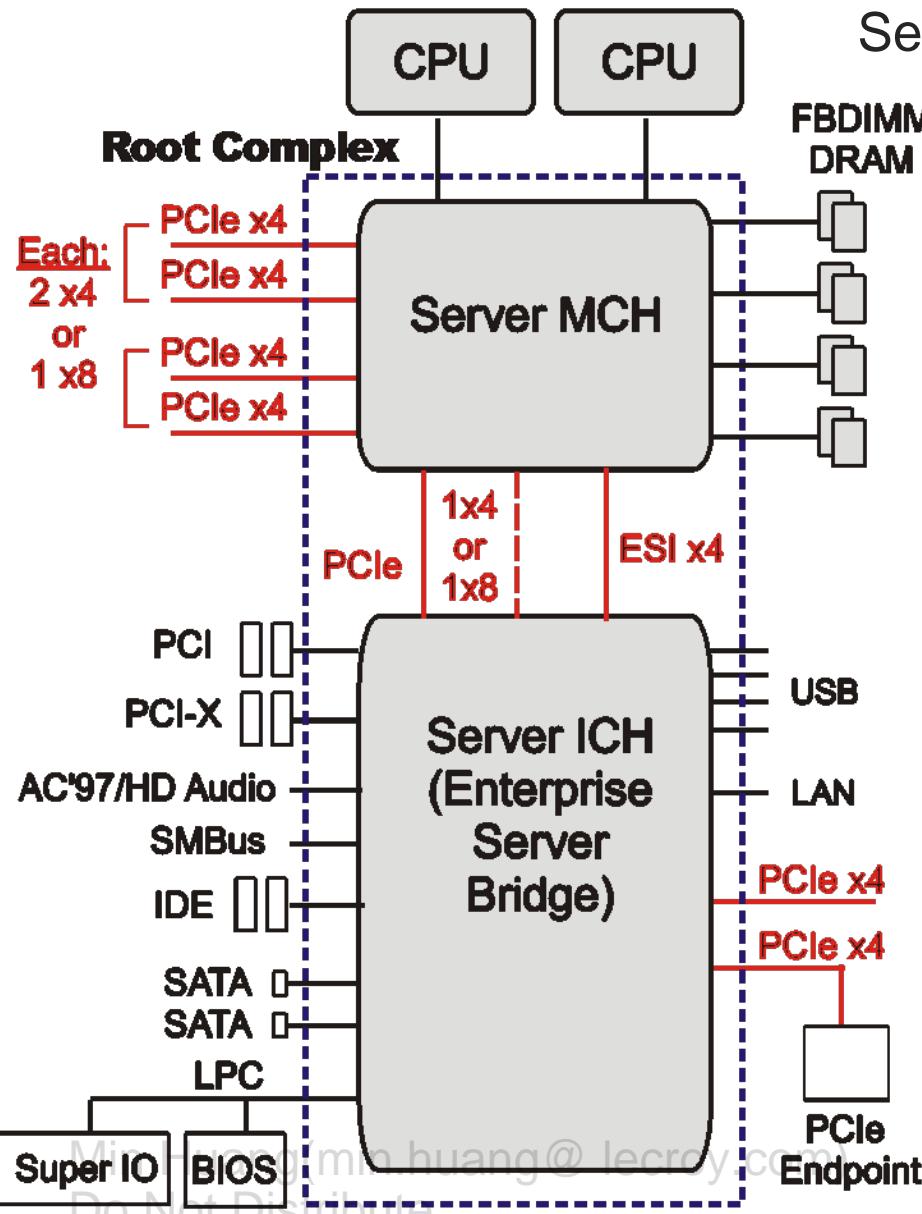

## Server Chipset PCIe Support

- MCH hosts 16 PCIe Lanes, organized as 2x8, 4x4, etc.

- ESI (Enterprise Server Interface) is a variant of x4 PCIe used for general chipset traffic.

- An additional x4 or x8 Link can connect the MCH and ICH for improved DMA performance.

- The Enterprise Server Bridge ICH supports two additional PCIe x4 Links.

- Note presence of both PCI and PCI-X slots.

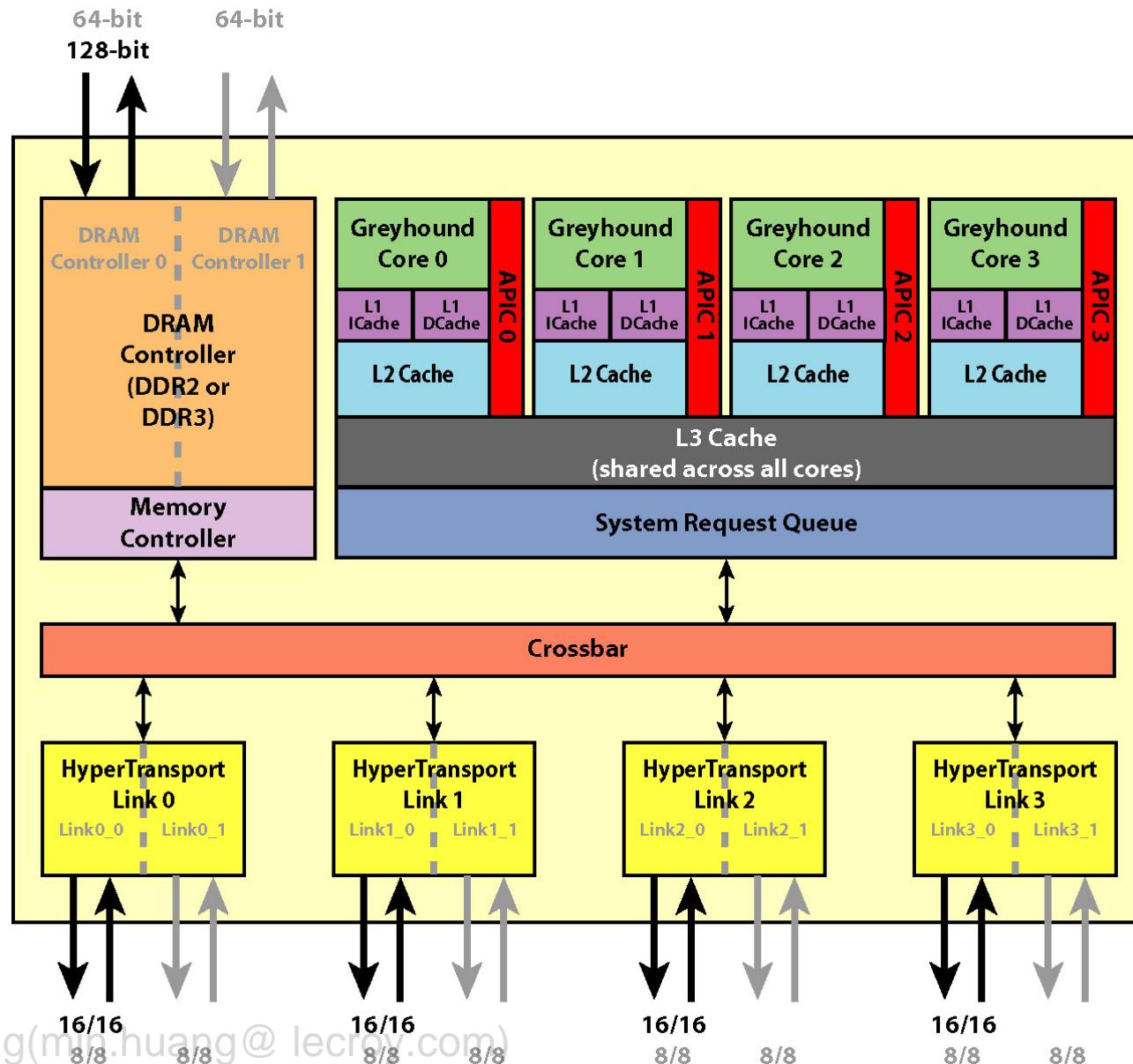

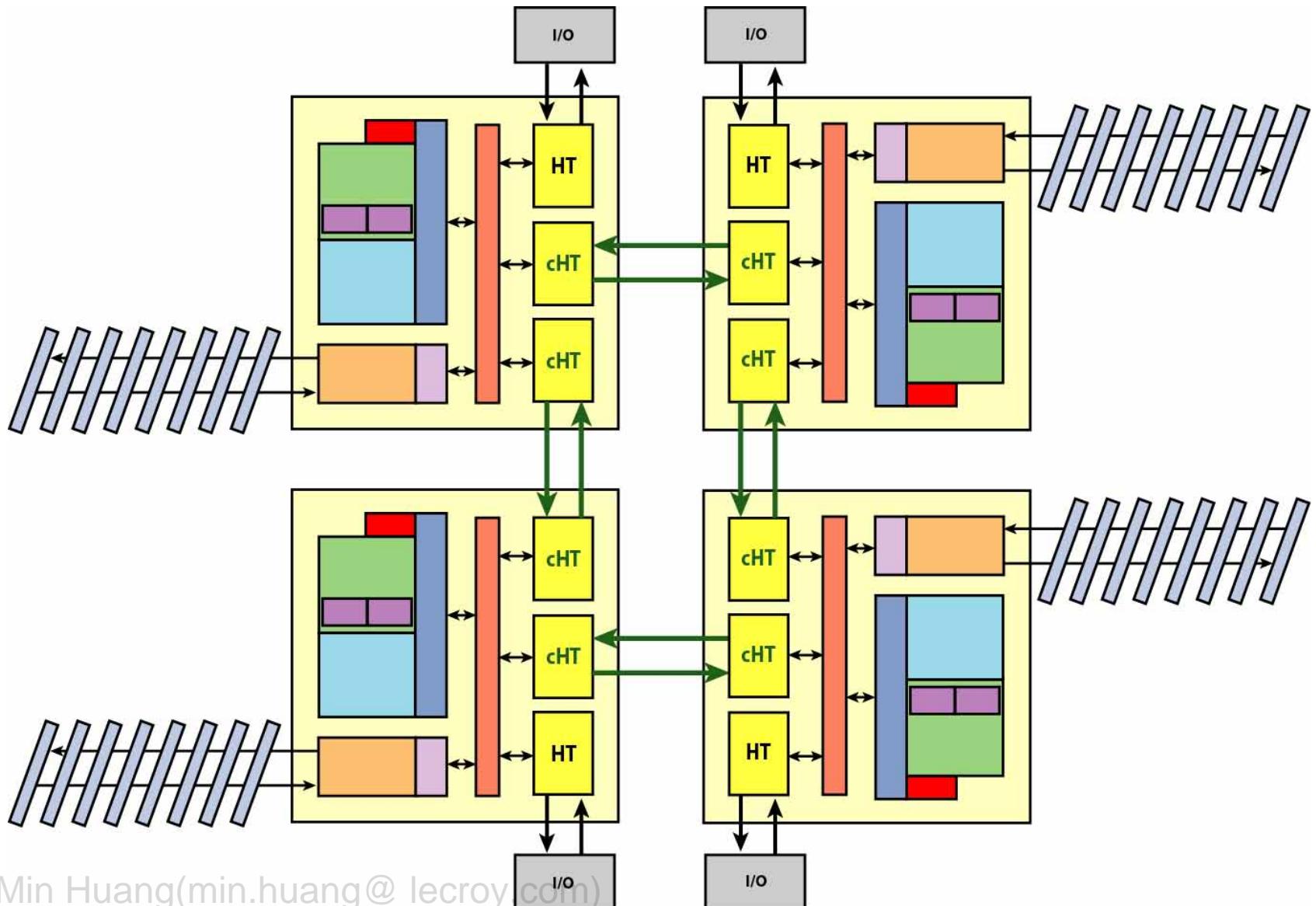

# AMD Quad Core Greyhound Processor

16

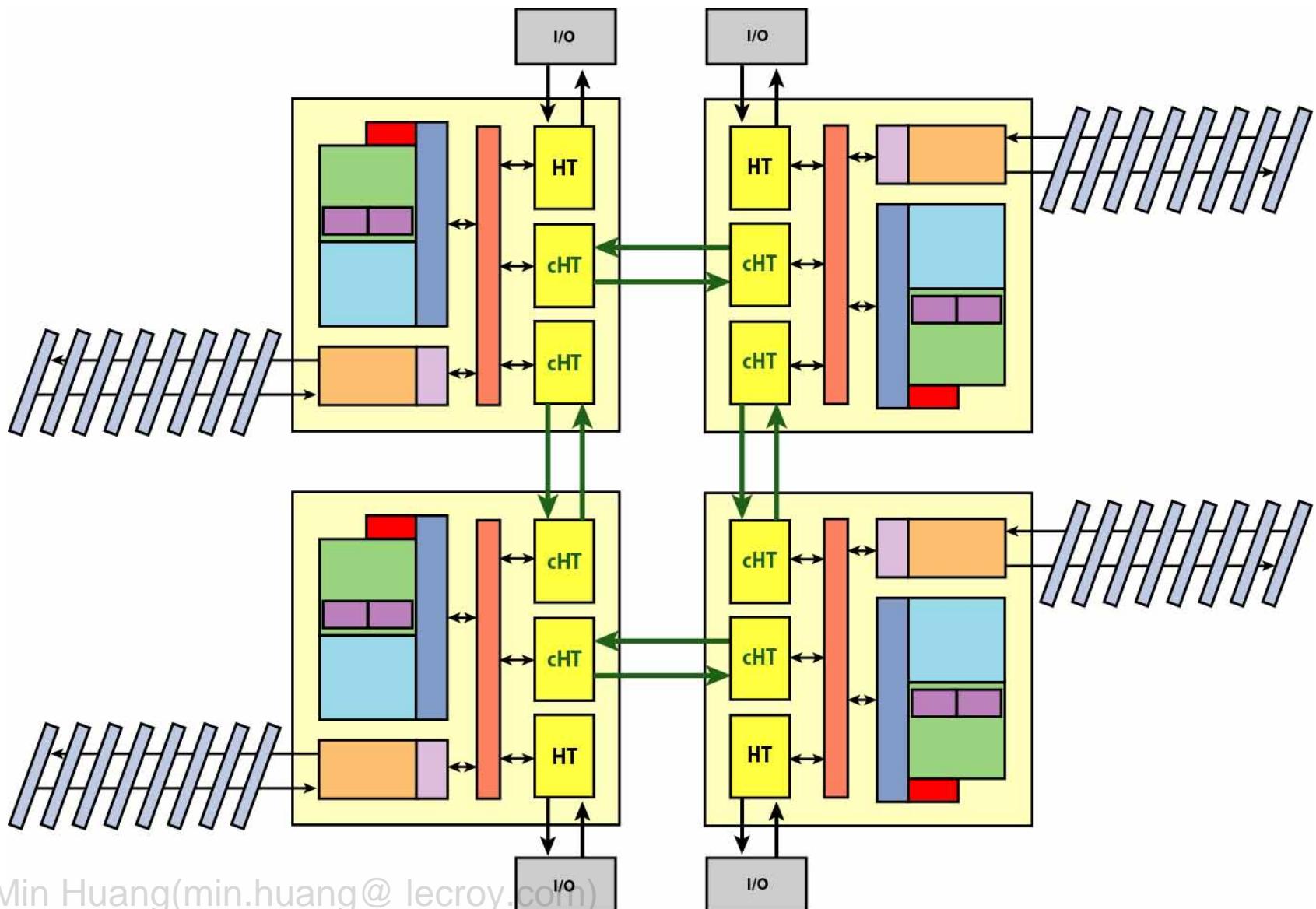

# Example 4-Way System

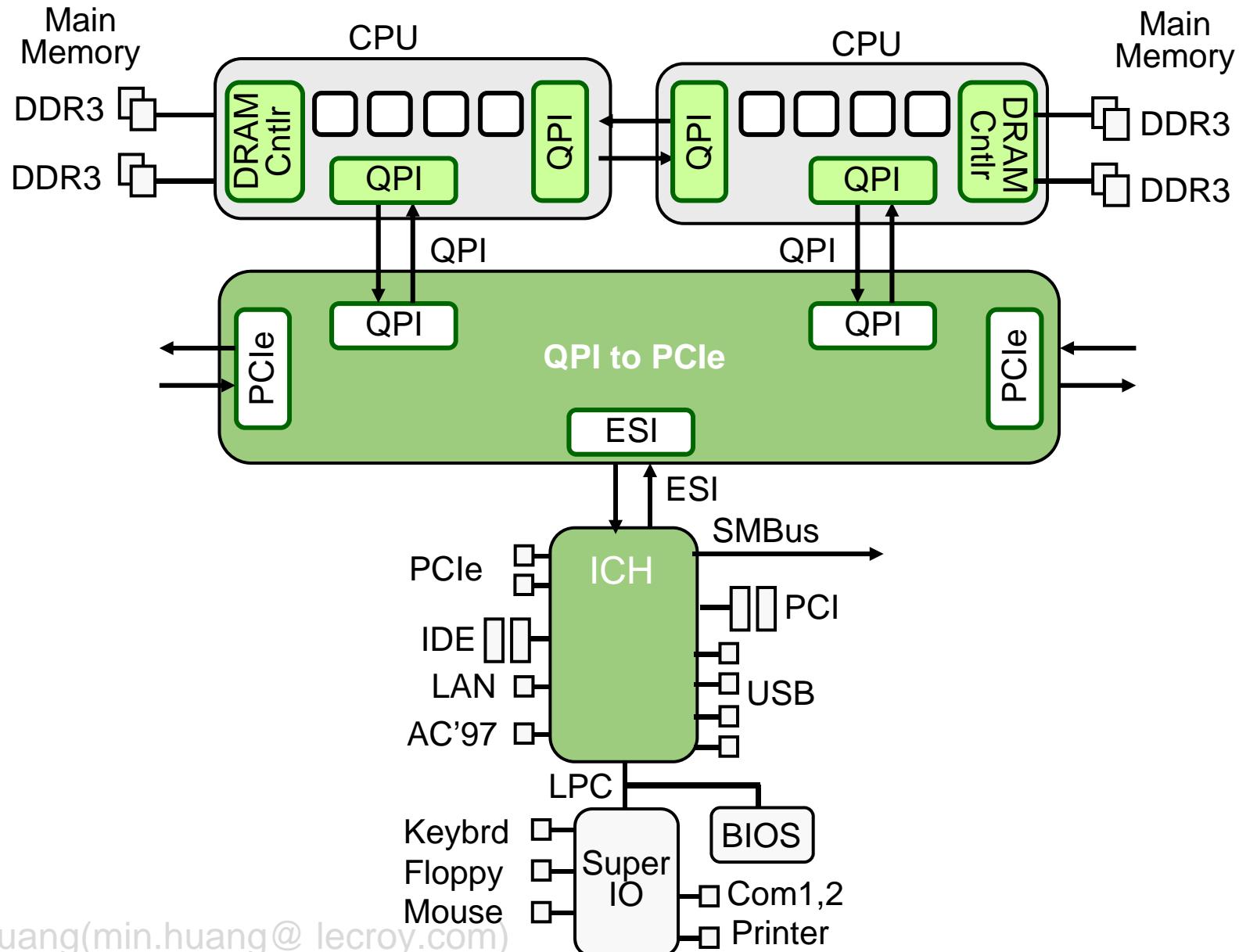

# Possible Intel Nehalem Topology

# DRAM Feature Summary

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

| Device Architecture                                      | Explanation                                | Clock Frequency (MHz) | Data Bus Rate (MT/s) | Bandwidth per 64-bit channel (MB/s) |

|----------------------------------------------------------|--------------------------------------------|-----------------------|----------------------|-------------------------------------|

| FPM DRAM                                                 | <u>Fast Page Mode DRAM</u>                 | NA                    | -                    | -                                   |

| EDO DRAM                                                 | <u>Extended Data Out DRAM</u>              | NA                    | -                    | -                                   |

| SDR SDRAM<br>PC66 – PC133                                | <u>Single Data Rate Synchronous DRAM</u>   | 66 – 133              | 66 – 133             | 533 – 1066                          |

| DDR SDRAM<br>DDR200 – DDR400<br>PC-1600 – PC-3200        | <u>Double Data Rate Synchronous DRAM</u>   | 100 – 200             | 200 – 400            | 1600 – 3200                         |

| DDR2 SDRAM<br>DDR2-400 – DDR2-800<br>PC-3200 – PC-6400   | <u>Double Data Rate 2 Synchronous DRAM</u> | 200 – 400             | 400 – 800            | 3200 – 6400                         |

| DDR3 SDRAM<br>DDR3-800 – DDR3-1600<br>PC-6400 – PC-12800 | <u>Double Data Rate 3 Synchronous DRAM</u> | 400 – 800             | 800 – 1600           | 6400 – 12800                        |

|                           | SDRAM                   | DDR1                     | DDR2                                         | DDR3                            |

|---------------------------|-------------------------|--------------------------|----------------------------------------------|---------------------------------|

| <b>Performance</b>        | <b>66-133MT/s</b>       | <b>200-400MT/s</b>       | <b>400-800MT/s</b>                           | <b>800-1600MT/s</b>             |

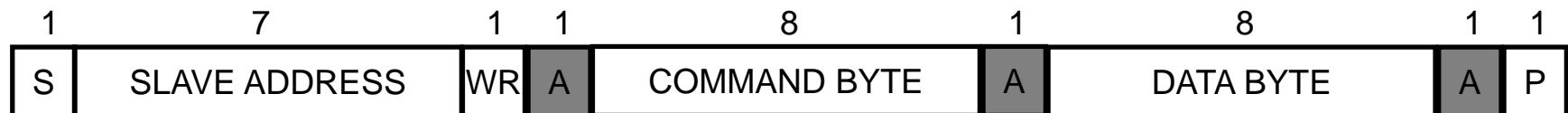

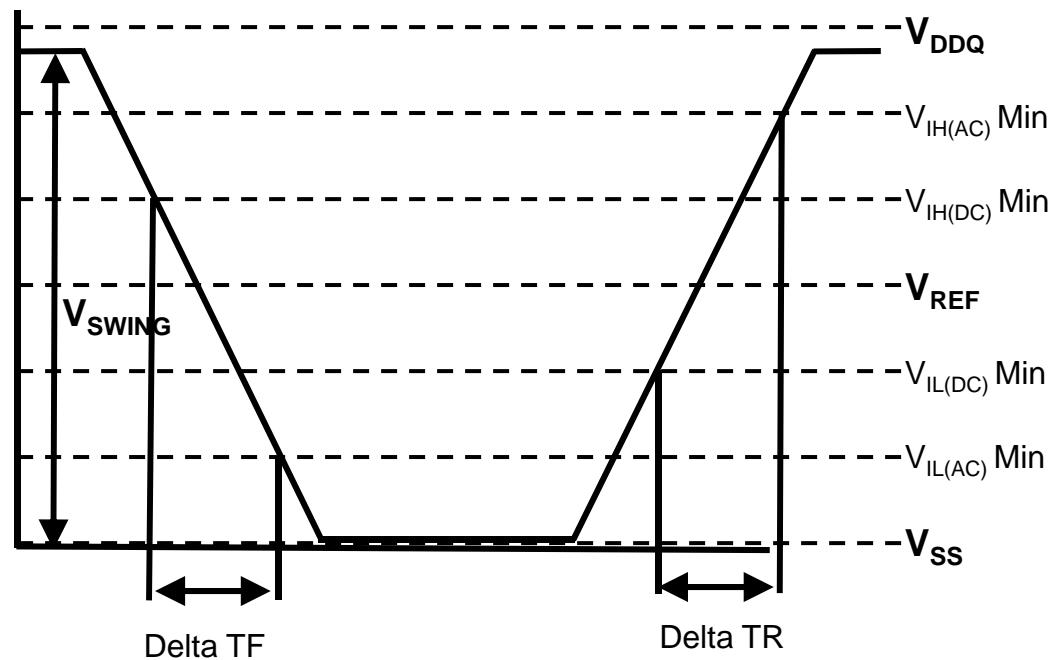

| $V_{DDQ}$                 | 3.3 Volts               | 2.5 Volts                | 1.8 Volts                                    | 1.5 Volts                       |

| $V_{TT}$                  | NA                      | $\frac{1}{2} V_{DDQ}$    | $\frac{1}{2} V_{DDQ}$                        | $\frac{1}{2} V_{DDQ}$           |

| <b>IO Interface Logic</b> | <b>LVTTL</b>            | <b>SSTL_2</b>            | <b>SSTL_18</b>                               | <b>SSTL_15</b>                  |

| <b>Organization</b>       | <b>x4, x8, x16</b>      | <b>x4, x8, x16</b>       | <b>x4, x8, x16</b>                           | <b>x4, x8, x16</b>              |

| <b>Density</b>            | <b>16Mb-512Mb</b>       | <b>64Mb-2Gb</b>          | <b>256Mb-4Gb</b>                             | <b>512Mb-8Gb</b>                |

| <b>Number of Banks</b>    | <b>4</b>                | <b>4</b>                 | <b>4 (256Mb-512Mb)</b><br><b>8 (1Gb-4Gb)</b> | <b>8</b>                        |

| <b>Package</b>            | <b>TSOP</b>             | <b>TSOP2/BGA</b>         | <b>BGA</b>                                   | <b>BGA (mirrored option)</b>    |

| <b>Prefetch</b>           | <b>1</b>                | <b>2</b>                 | <b>4</b>                                     | <b>8</b>                        |

| <b>Burst Length</b>       | <b>1, 2, 4, 8, Page</b> | <b>2, 4, 8</b>           | <b>4, 8</b>                                  | <b>8 (chop 4)</b>               |

| <b>Clock</b>              | <b>Single Ended</b>     | <b>Differential</b>      | <b>Differential</b>                          | <b>Differential</b>             |

| <b>Strobes</b>            | <b>NA</b>               | <b>Single-Ended (SE)</b> | <b>SE or Differential</b>                    | <b>Differential</b>             |

| <b>DQ Driver Strength</b> | <b>Wide Envelope</b>    | <b>Narrow Envelope</b>   | <b>18 Ohm OCD</b>                            | <b>ZQ cal</b>                   |

| <b>Termination</b>        | <b>NA</b>               | <b>Mother Board</b>      | <b>Mo Bo, Dyn ODT</b>                        | <b>DIMM, Dyn ODT</b>            |

| <b>Read Latency</b>       | <b>CL=1,2,3</b>         | <b>CL=1.5, 2, 2.5, 3</b> | <b>CL=2, 3, 4, 5, 6</b>                      | <b>CL=5, 6, 7, 8, 9, 10, 11</b> |

| <b>Additive Latency</b>   | <b>NA</b>               | <b>NA</b>                | <b>AL=0, 1, 2, 3, 4</b>                      | <b>AL=0, CL-2, CL-1</b>         |

| <b>Burst Interrupts</b>   | <b>Yes</b>              | <b>Yes</b>               | <b>R-R, W-W 4n only</b>                      | <b>Burst Chop</b>               |

Since the mid 1990s, JEDEC (was the Joint Electron Device Engineering Council, now the Solid State Technology Association) has controlled the DRAM standards. Specs can be found at:

<http://www.jedec.org>

- DDR1 spec is JESD79E

- DDR2 spec is JESD79-2C

- DDR3 spec is JESD79-3C

- Package specs are MO-207 (for example)

- DIMM and SPD specs are JESD21C

# Intro to DRAM

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

# Historical Background

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

|                                      | 1950                                                              | 1960                                                  | 1970                                         | 1980                                                           |

|--------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------|

|                                      | 1949 Pulse Transfer core invented                                 | Ferrite core memory moves into high-volume production | Intel announces the 1103 1K device           | Page Mode introduced                                           |

| Tubes primary source of early memory | Coincident current core invented by Forester for flight simulator |                                                       | First silicon memory devices invented by IBM | Core memory used in the first space shuttle for its robustness |

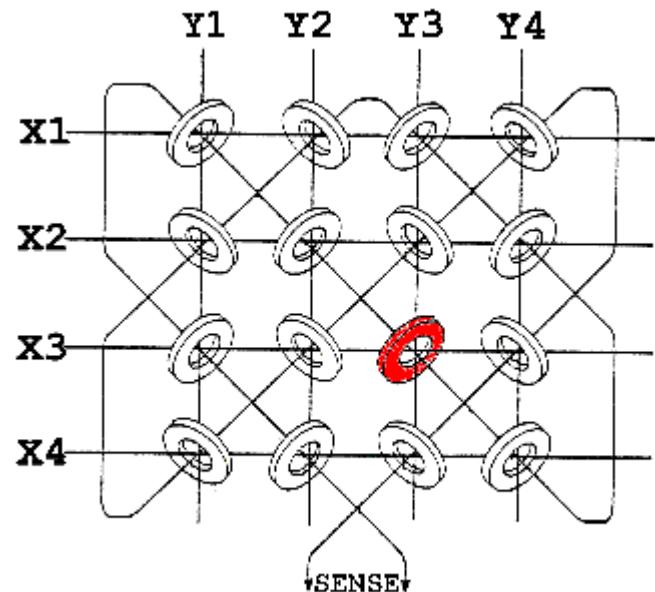

- Vacuum tubes were the first electronic devices used for memory. Tubes were plagued with problems like excessive heat, size, and voltage as well as being unreliable and temperamental. This set the stage for a magnetic “core memory”.

- Magnetic core memories dominated the market for more than two decades.

- The basic concept is changing the magnetic properties of a ferrite ring using current.

- It takes 3 wires through each ring to read, write, and erase a bit.

| 1980                                         | 1990                                                                            | 2000                              | 2010                      |

|----------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|---------------------------|

| <b>Fast Page Mode introduced at 28.5 MHz</b> | <b>EDO memory becomes available</b>                                             | <b>DDR introduced at 200MT/s</b>  | <b>DDR3 spec released</b> |

| <b>Intel exits DRAM business</b>             | <b>SDRAM introduced</b><br><b>JEDEC holds memory standards from here on out</b> | <b>DDR2 introduced at 400MT/s</b> |                           |

|                                              |                                                                                 |                                   |                           |

- With the invention of the PC in 1981, silicon-based memory demand skyrocketed. Other countries like Japan begin to manufacture low cost DRAMs. By 1985, Japan has nearly dominated the market. US lawmakers team up with silicon manufacturers to equalize the playing field. New laws against price gouging are instituted.

# Why DRAM?

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

- What is RAM?

- Random Access Memory.

- Why is it called Random access memory?

- Previously there were other kinds of memory that were sequentially accessed. These other kinds of memory were usually in the form of magnetic tape or drum. To my knowledge the term SAM was never coined.

- What are the 2 types of RAM?

- Static RAM and Dynamic RAM.

- Which is better?

- Well it depends on the application.

| Type of RAM | Cost per cell | Size of each cell | Power Dissipated | Speed |

|-------------|---------------|-------------------|------------------|-------|

| Dynamic RAM | Low           | Very small        | High             | Slow  |

| Static RAM  | High          | Large             | Low              | High  |

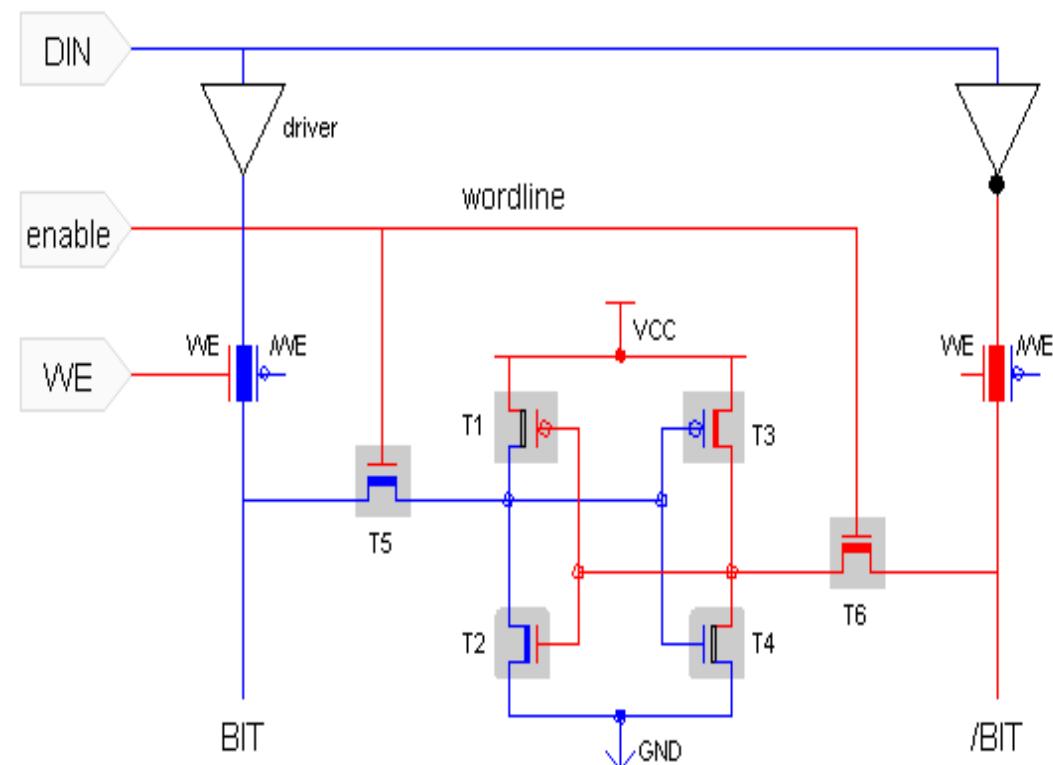

## ➤ SRAM Cell

- A SRAM cell is composed of many transistors.

- The cell consists of two cross-coupled CMOS inverters that store one bit of information, and two N-type transistors that connect the cell to the bitlines.

- To read the information, the word line is activated while the external bit line drivers are switched off. Therefore, the inverters inside the SRAM cell drive the bitlines, whose value can be read-out by external logic.

- To write new data into the cell, the big (external) tristate drivers are activated to drive the bitlines. Next, the word line transistors are enabled. Because the external drivers are much bigger than the small transistors used in the 6T SRAM cell they easily override the previous state of the cross-coupled inverters.

CMOS: 6T-SRAM Zelle

# DRAM Cell Architecture

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

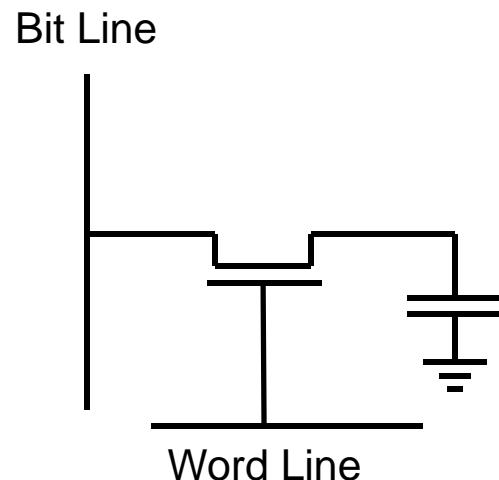

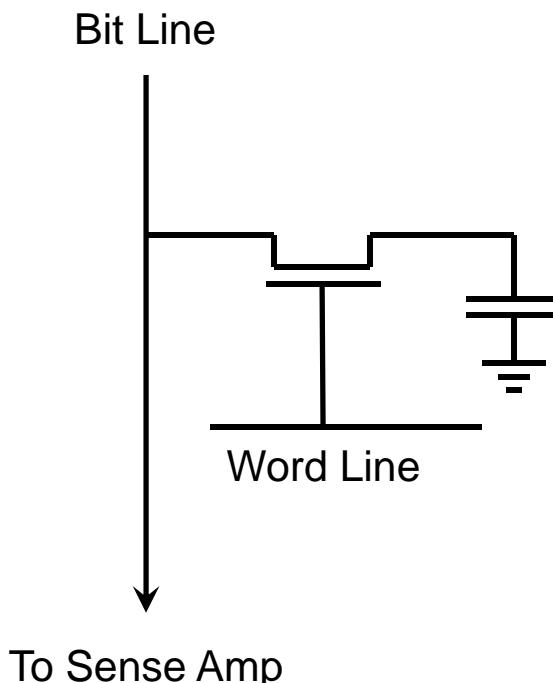

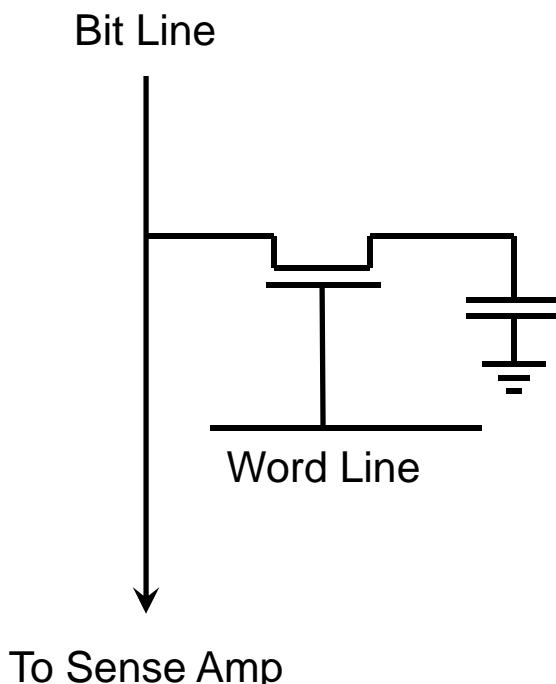

- DRAM Cell (conceptual)

- A DRAM cell is composed of a capacitor and a transistor.

- The data is stored in the capacitor.

- Capacitors lose charge over time due to leakage (dissipation), so it is necessary to recharge them periodically. This is called Refresh and is controlled by the chipset.

- The act of reading the capacitor is destructive because the charge in the cap is so small (<30fF). The data in the cap is always read out to a Sense Amp and then written back at a later time (Precharge).

## ➤ DRAM Cell Read

1. Bit line is precharged to Sense Amp threshold voltage ( $V_{DD} / 2$ ).

2. Word line turns on transistor to allow charge to flow from capacitor to bit line. (Read from Cell)

3. Sense Amp latches electrical high or low.

## ➤ DRAM Cell Write or Precharge

1. Charge or discharge the bit line to core voltage or GND as needed to store 0 or 1. DRAM manufacturer decides what state (1 or 0) is represented by a charged cell.

2. Word line turns on transistor to allow charge to flow from bit line to capacitor.

3. During writes the word line may need to be forced above  $V_{DD}$  to take care of voltage drop.

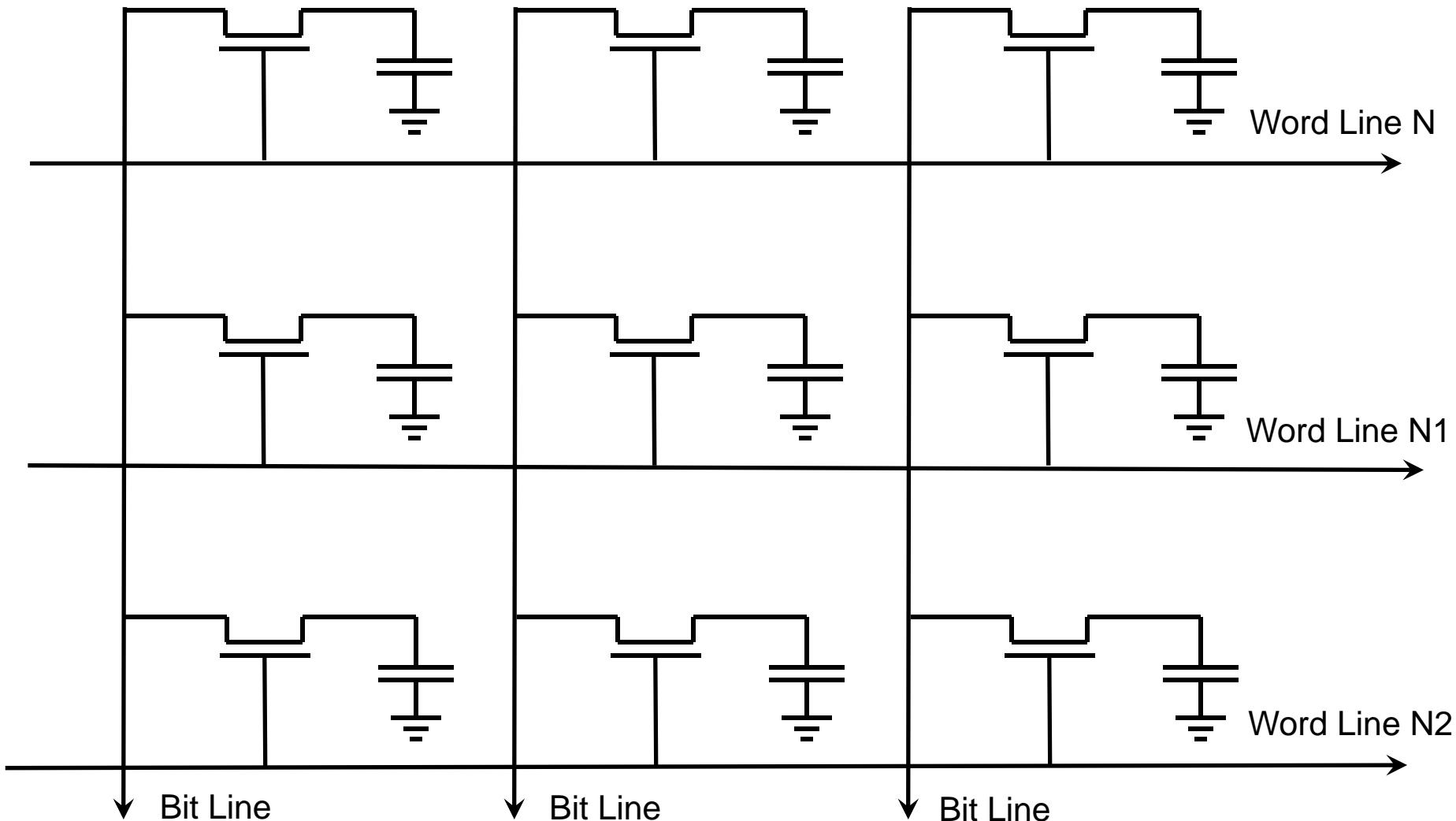

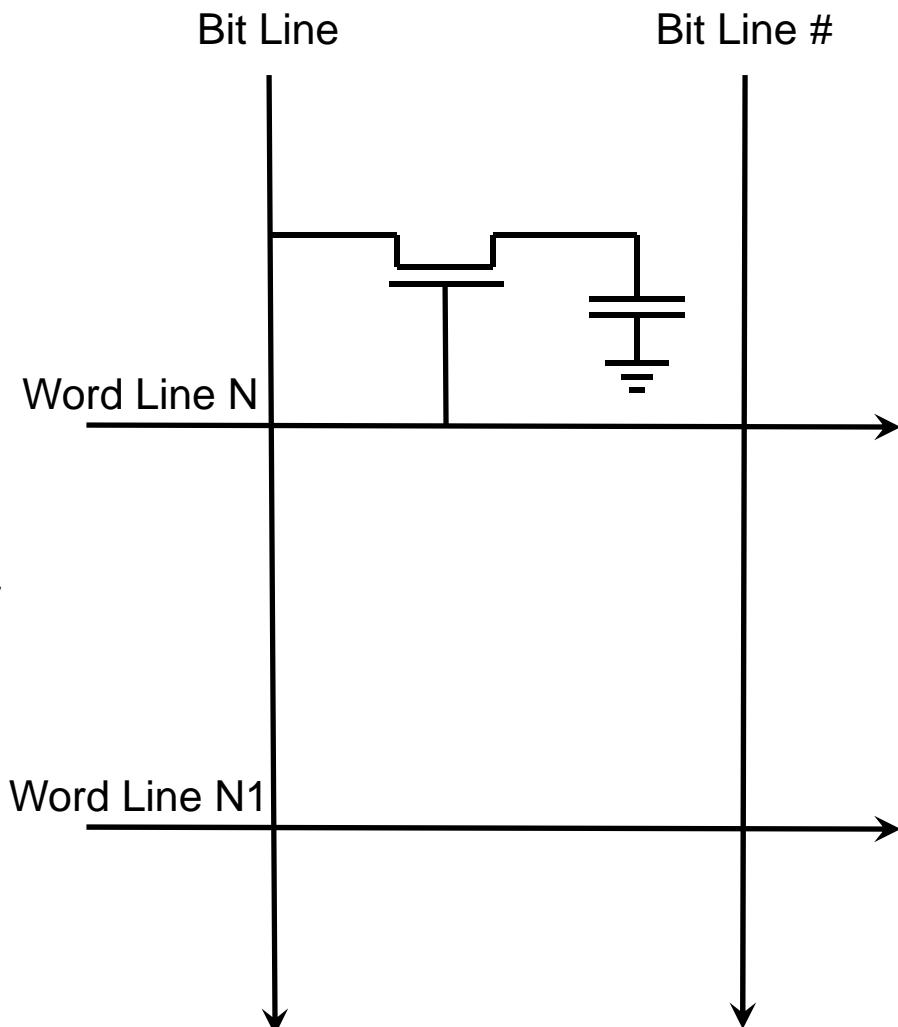

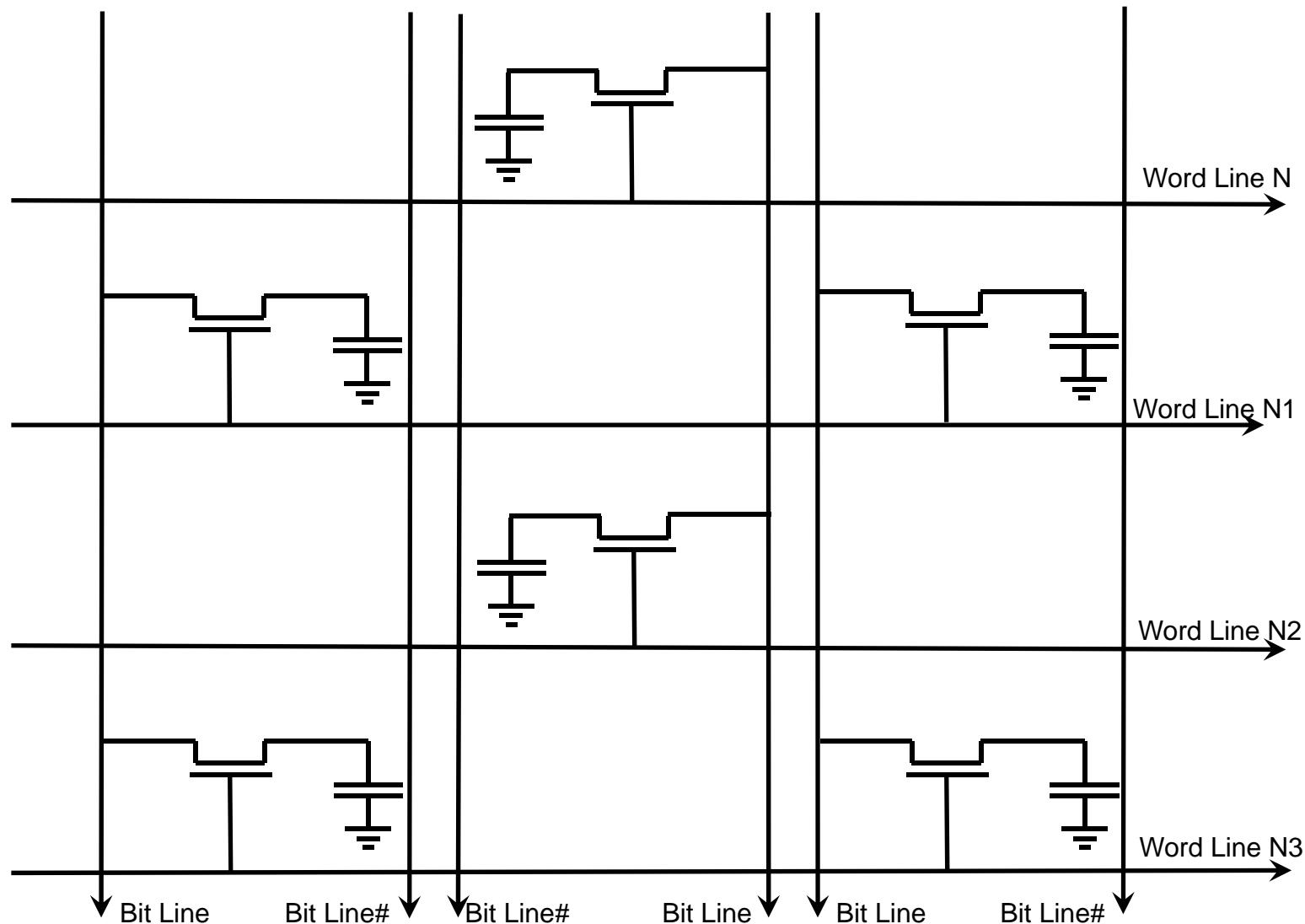

# Open Cell Array Architecture

- Folded DRAM Cell (conceptual)

- Adjacent bit lines are organized as differential inputs to the sense amplifier.

- During a read operation one bit line acts as the reference input to the sense amp.

- Folded bit lines have better noise immunity due to equal coupling of noise on the neighboring reference bit line.

# Folded Cell Array Architecture

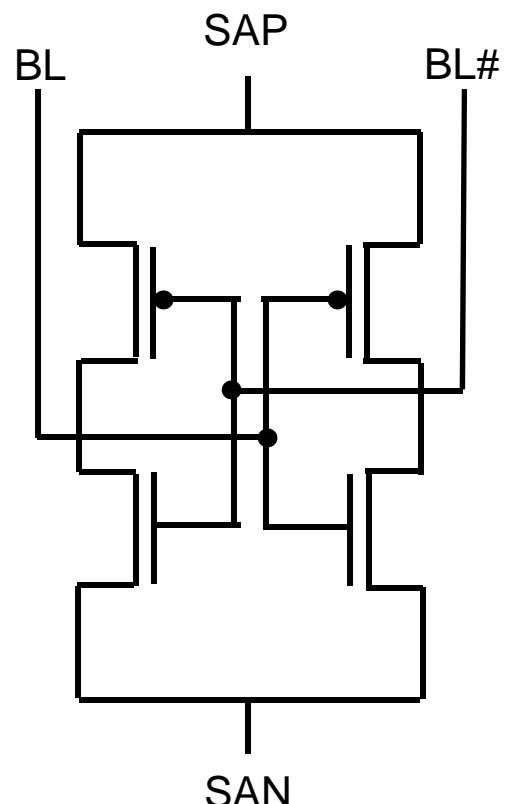

- Sense Amplifier (conceptual)

- The sense amplifier is a differential latch.

- Example of reading a “0”

- Bit lines are charged to  $V_{DD}/2$ , SAN (Sense Amp Negative) =  $V_{DD}/2$ , SAP (Sense Amp Positive) = 0. The latch is off.

- When word line is asserted, one of the bit lines changes by delta V while the other bit line remains unchanged.

- SAN is discharged to 0

- As SAN falls below the higher of the bit lines, the corresponding NMOS transistor turns on and starts pulling the lower bit line to 0.

- After a small delay, SAP is pulled high. The cross coupled PMOS transistor pulls the higher bit line voltage up to  $V_{DD}$

- Isolation and equalization circuits not shown

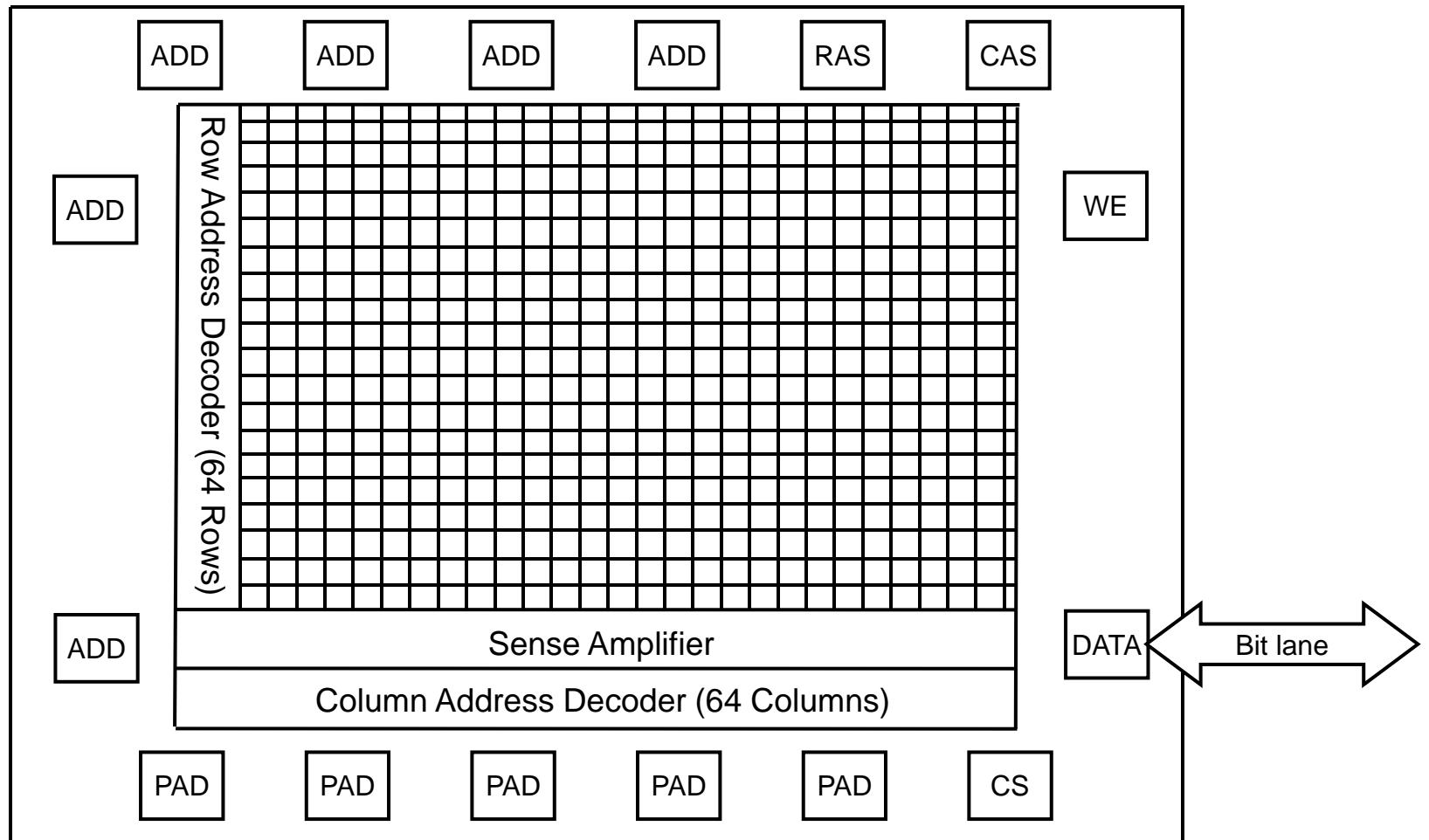

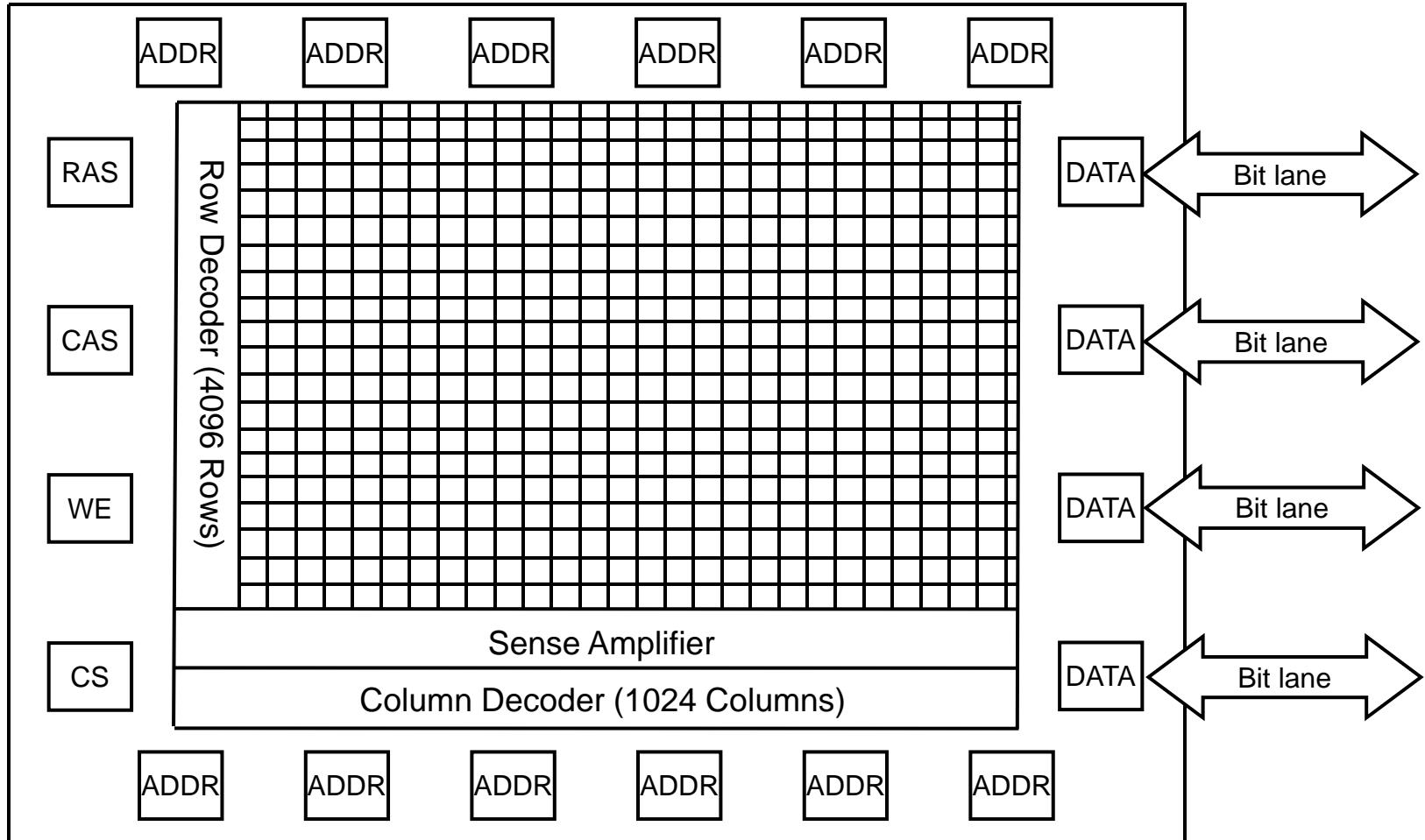

# DRAM Chip Architecture

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

- The first LSI (Large Scale Integration) DRAMs were manufactured by Intel in 1970 starting with the 1103 chip.

- The 1103 had a 1,024-bit array with one data line. The following examples show the evolution of the DRAM.

- The core of the chip is the Array block.

- The total size of the chips is determined by multiplying the number of Rows by the number of Columns by the number of Banks.

- There may be more than one bit at each individual column address.

- This total size is referred to as the Chip Technology and is always stated in bits not bytes.

- 4096 bit Array X1 example ( $2^{12}$  Bits)

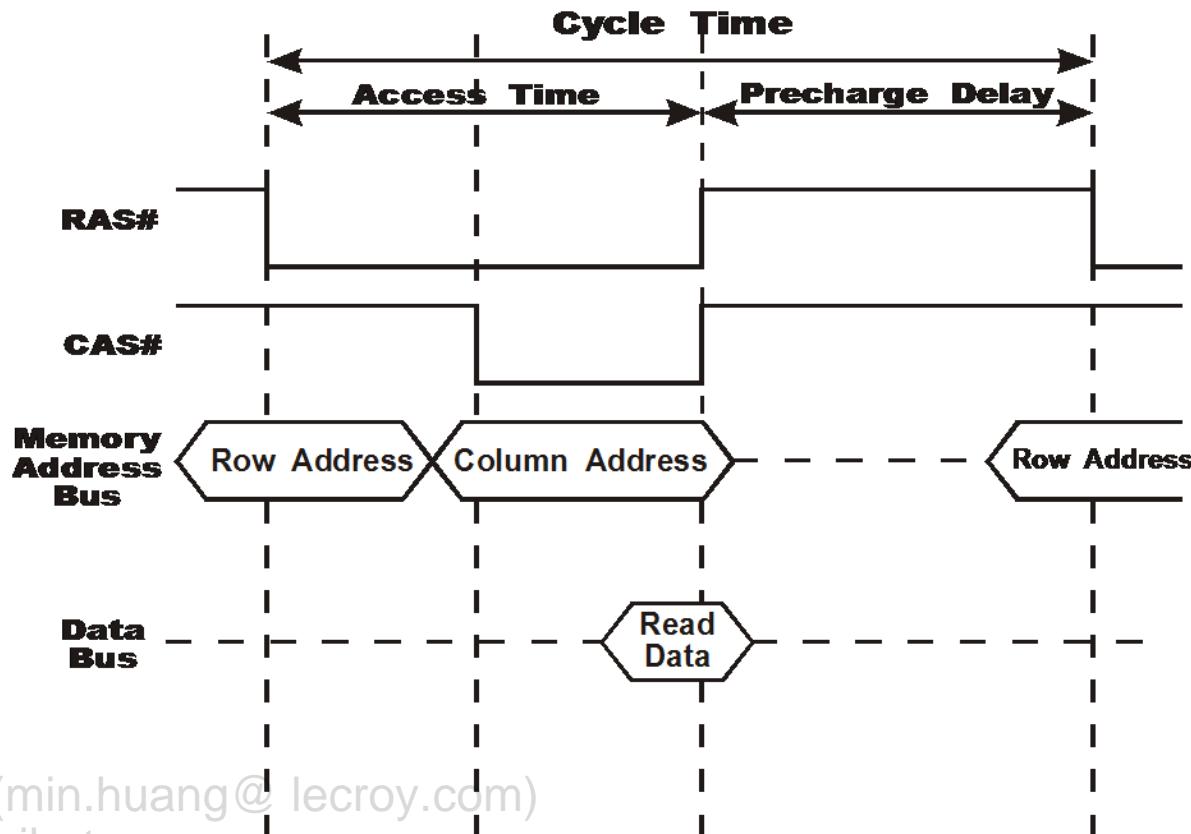

Each time a DRAM location is read, the capacitor associated with that cell is discharged. Before the device is read again, DRAM logic must recharge these locations, which takes some time—called the precharge delay.

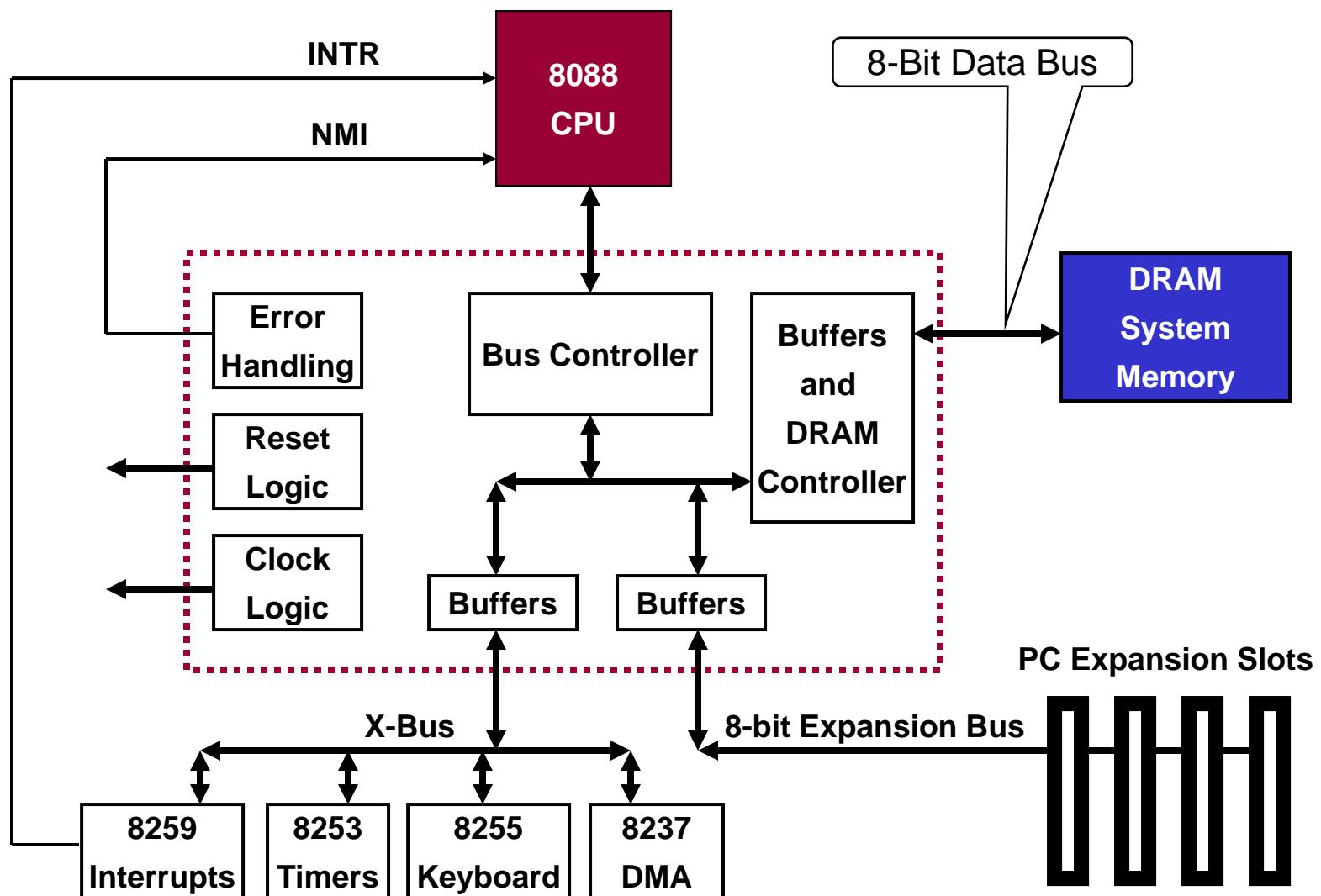

# Simple Async DRAM Controller Design

- The 8088 memory bus was 8 bits wide.

- By using 8 chips with 1 data line (X1) and a single chip select to all 8 chips, the chips would perform in unison to drive the 8-bit bus.

- As technology evolved, the DRAM controllers demanded wider buses to increase speed.

- In response, the DRAM manufacturers made the arrays bigger and added more data lines to the chips.

16M bit Array example; 4M X 4

Sometimes shown as density X data width X #banks (4M X 4 X 1)

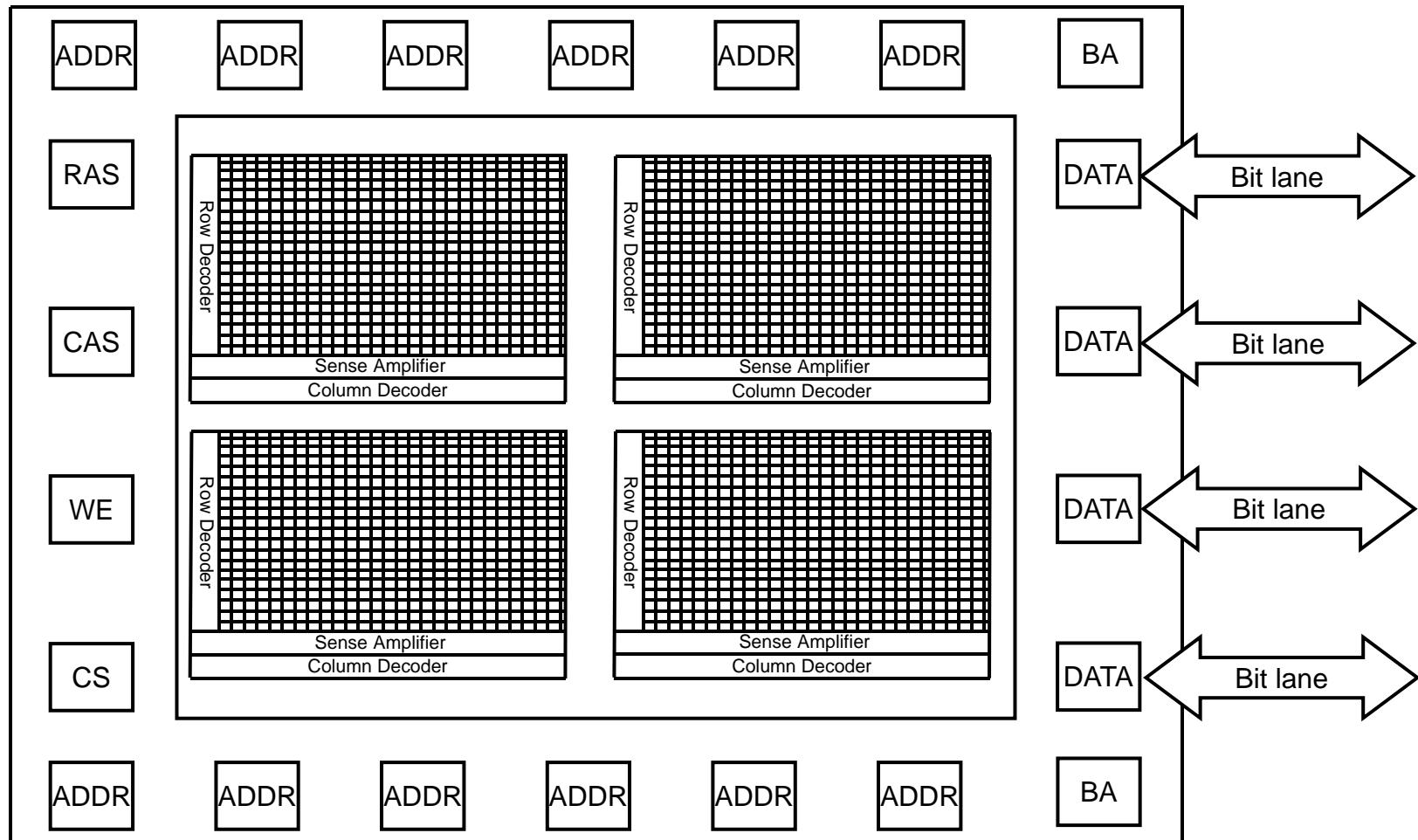

- One of the first changes in architecture to increase the speed of modern chips was to split the array into multiple banks.

- This allows more than one bank to be active at the same time.

- This can effectively “hide” precharge/activate and other timings related to single bank implementations.

- Refresh timing is not affected since all the banks are refreshed at the same time.

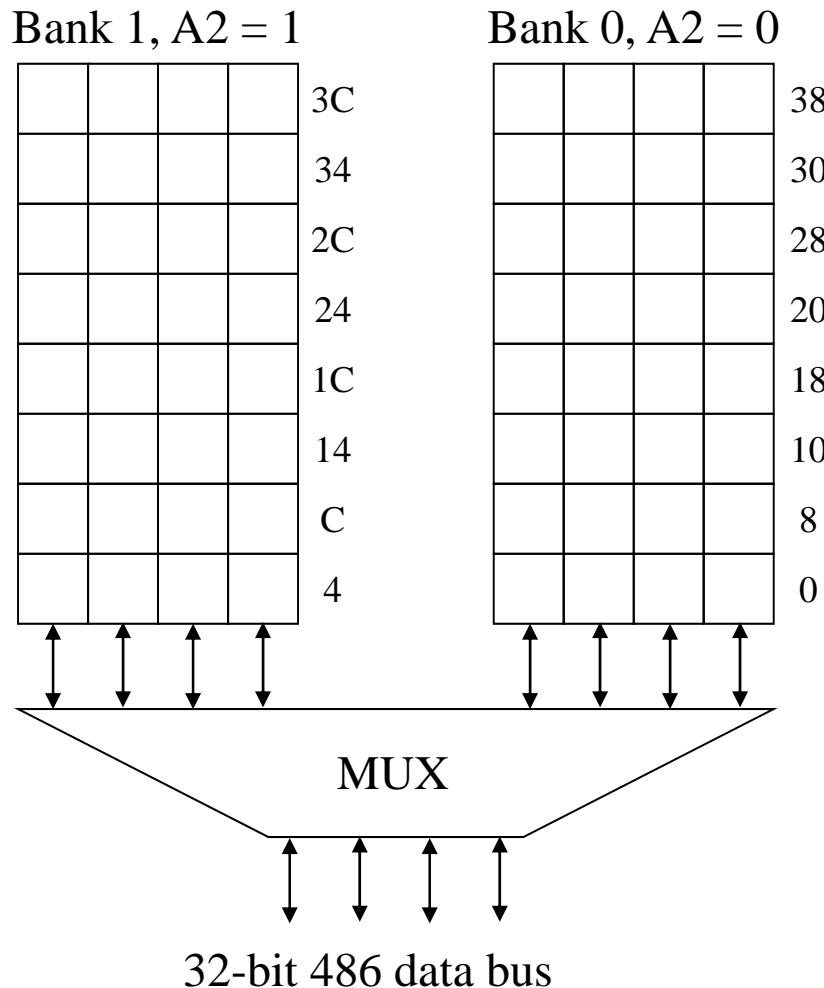

# Banks and Toggle-Mode Addressing

Intel 80486 has a 32-bit data bus and 16-byte cache lines.

Intel's toggle-mode burst line fill address sequence optimized DRAM performance regardless of whether DRAM was single-bank 32-bit memory (single SIMM channel), dual-bank 32-bit memory, or 64-bit memory. The sequence is shown in the Commands and Waveforms section of this slide show.

# Multiple Banks

16M bit Array example;  $1M \times 4 \times 4$

Shown as density X data width X #banks

- Chips can be organized into data bus widths of 4, 8, 16, and 32.

- This was shown in the previous example as number of bits X (by) number of data lines X (by) number of banks. The number of bits is referred to as the density.

- Here is an exercise of how the same technology can yield different chip organizations.

For this example,

use a 512 Mb

technology chip.

| Density | Data Lines | Banks |

|---------|------------|-------|

| 32M     | 4          | 4     |

| 16M     | 8          | 4     |

| 8M      | 16         | 4     |

| 4M      | 32         | 4     |

## Features of an SDRAM Chip

- PC 100, PC 133

- Fully Synchronous

- Internally pipelined column address can be changed every clock. (1T timing)

- Multiple internal banks for hiding row access/precharge timing. Single bank precharge or all bank precharge.

- Programmable burst length 1, 2, 4, 8, or full page (Row)

- Self refresh and low power states

- LVTTL 3.3 volt operation

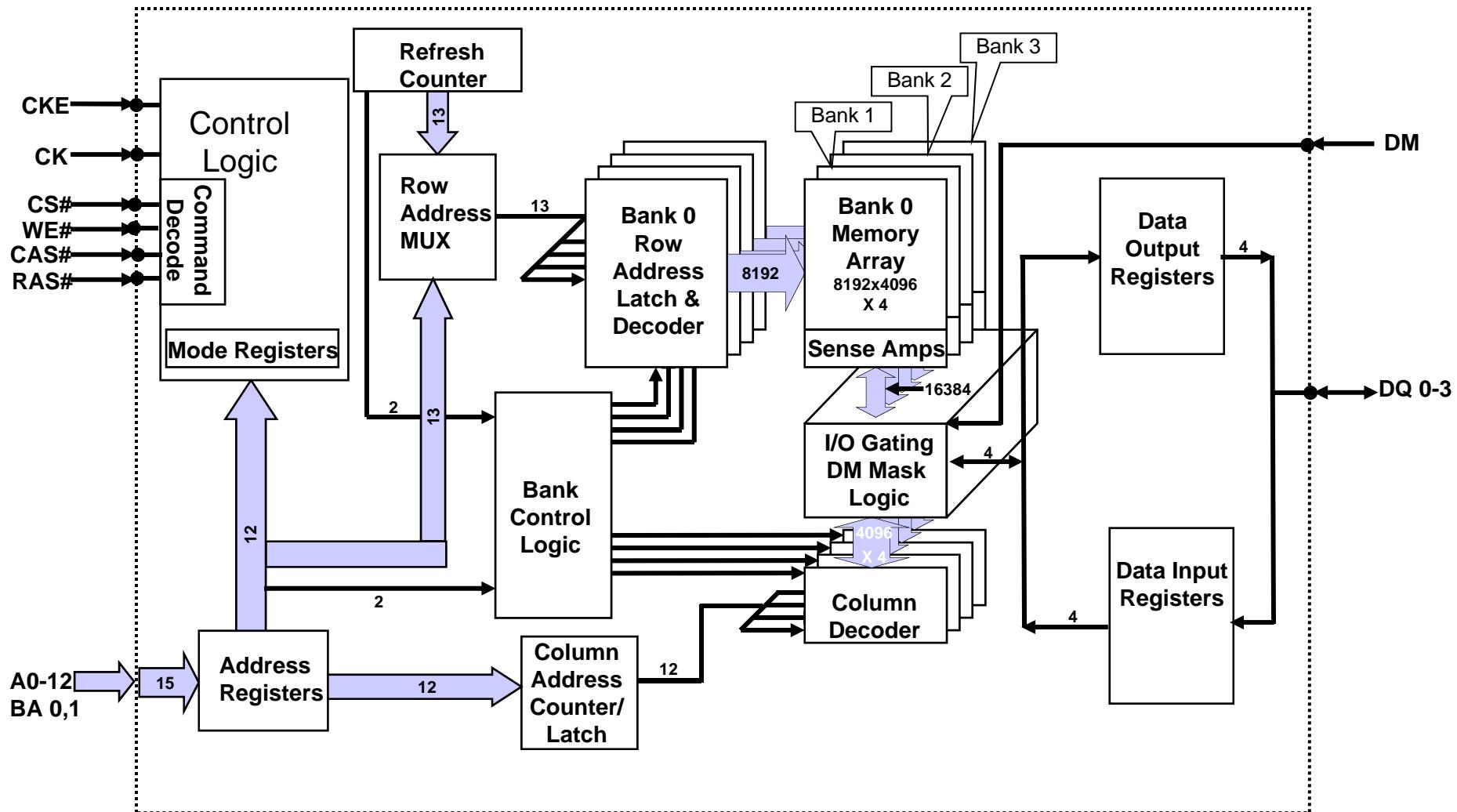

## Architecture of a 512 Mb SDRAM chip organized as 32M X 4 X 4

## Features of a DDR1 Chip

- DDR 200, 266, 333, and 400

- Bidirectional Data Strobes for source synchronous capture (x16 has 2)

- DDR architecture two data accesses per clock

- 2n prefetch architecture

- Multiple internal banks for hiding row access/precharge timing.

- Differential clock inputs (CK and CK#)

- Commands active on rising edge of clock.

- DQS edge aligned for data reads and center aligned for writes.

- Addition of DLL (Delay Lock Loop) to align DQS and Data

- Programmable burst length of 2, 4, and 8

- Auto refresh and Self refresh modes

- “Auto refresh” is called “Refresh” for DDR3.

- 2.5 volt operation for I/O (SSTL\_2 compatible) 2.4 volts for 400MT/s DRAMs

# DDR1 SDRAM Architecture

56

Architecture of a 512 Mb DDR1 chip organized as 32M X 4 X 4

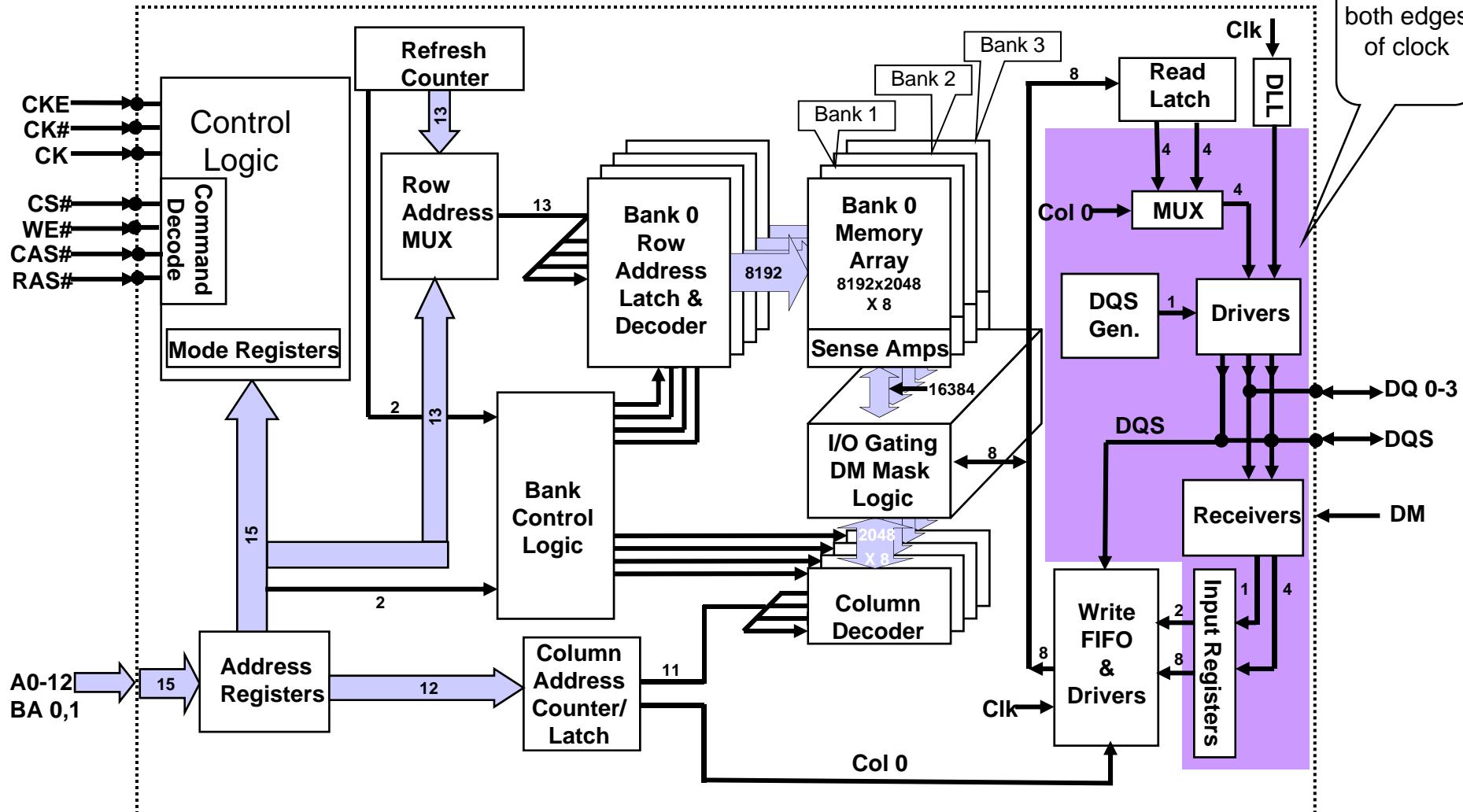

## Features of a DDR2 Chip

- DDR 400, 533, 667 and 800

- Bidirectional Differential Data Strobes (DQS, DQS#) for source synchronous capture (x16 has 2 pairs)

- Duplicate output strobes (RDQS) for x8 devices

- 4n prefetch architecture

- 4 Banks for concurrent operation 1Gb devices have 8 Banks

- Differential clock inputs (CK and CK#)

- Programmable CAS latency

- Posted CAS additive latency

- On Die Termination (ODT)

- Programmable burst length of 4 or 8

- Auto refresh and Self refresh modes

“Auto refresh” is called “Refresh” for DDR3.

- 1.8 volt operation for I/O (SSTL\_18 compatible)

# DDR2 SDRAM Architecture

Architecture of a 512 Mb DDR2 chip organized as 32M X 4 X 4

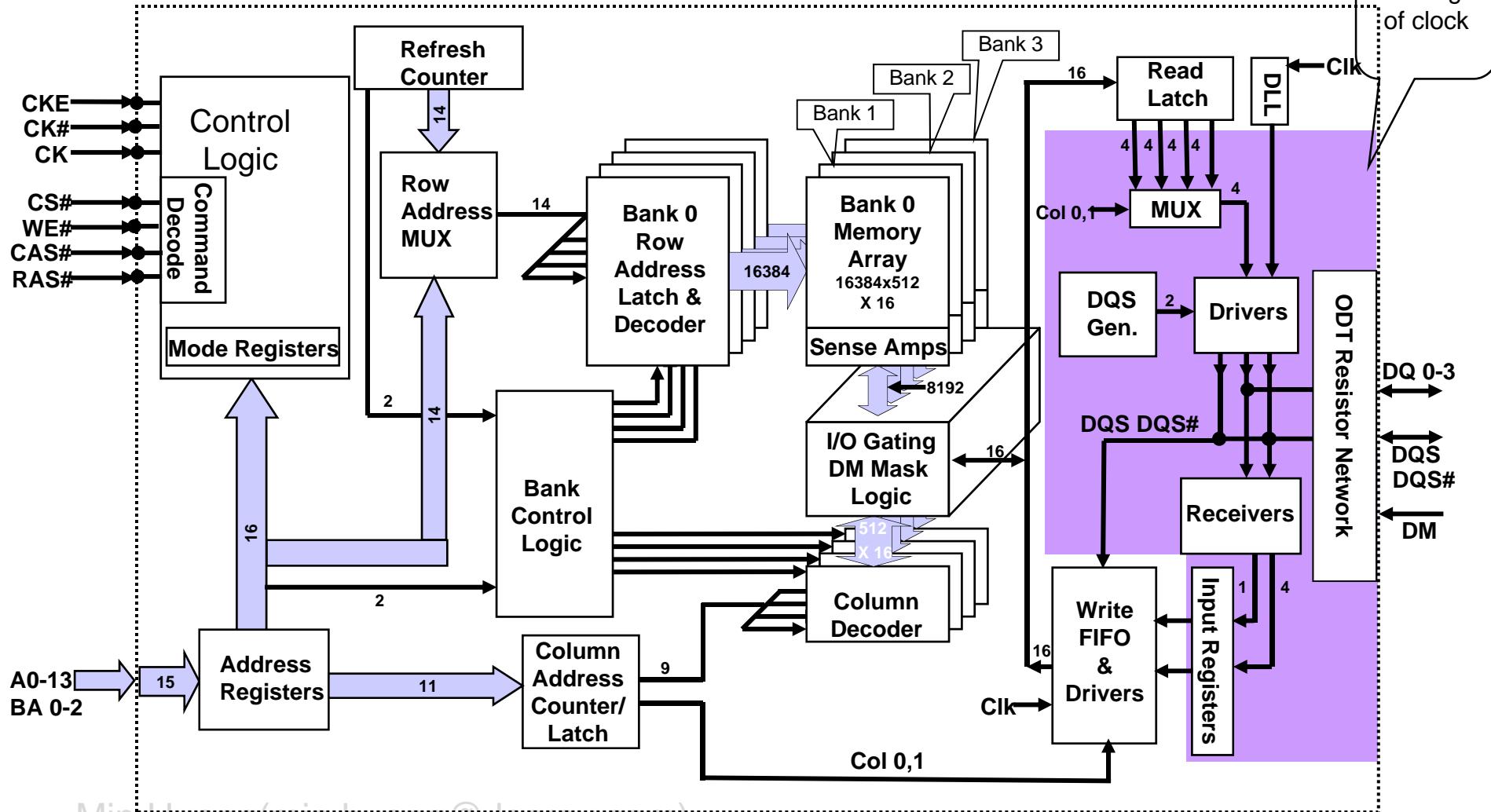

## Features of a DDR3 Chip

- 8n prefetch architecture

- Fly-by routing which requires read delay calibration and write leveling.

- On-die termination (ODT) improvements

- ZQ calibration (OCD) redefined

- Speeds up to 1600MT/s (800 MHz)

- Burst Chopping

- MRS definition changed

- $V_{DDQ}$  goes to 1.5 volts and  $V_{REF}$  and  $V_{TT}$  are  $\frac{1}{2} V_{DDQ}$

- Addition of asynchronous reset pin

- Package changes to accommodate pin mirroring and support balls

# Core Speed vs. I/O Speed

| Memory Technology | Input Clock | Prefetch Width | Bus Speed | DRAM Core Speed |

|-------------------|-------------|----------------|-----------|-----------------|

| SDRAM-100         | 100MHz      | 1              | 100MT/s   | 100MHz          |

| DDR-200           | 100MHz      | 2              | 200MT/s   | 100MHz          |

| DDR-400           | 200MHz      | 2              | 400MT/s   | 200MHz          |

| DDR2-400          | 200MHz      | 4              | 400MT/s   | 100MHz          |

| DDR2-800          | 400MHz      | 4              | 800MT/s   | 200MHz          |

| DDR3-800          | 400MHz      | 8              | 800MT/s   | 100MHz          |

| DDR3-1600         | 800MHz      | 8              | 1600MT/s  | 200MHz          |

- Many fabrication processes have evolved over the last 35 years for DRAMs.

- One of the biggest challenges are creating the capacitors. Some of these basic concepts are:

- Planar

- Deep Trench

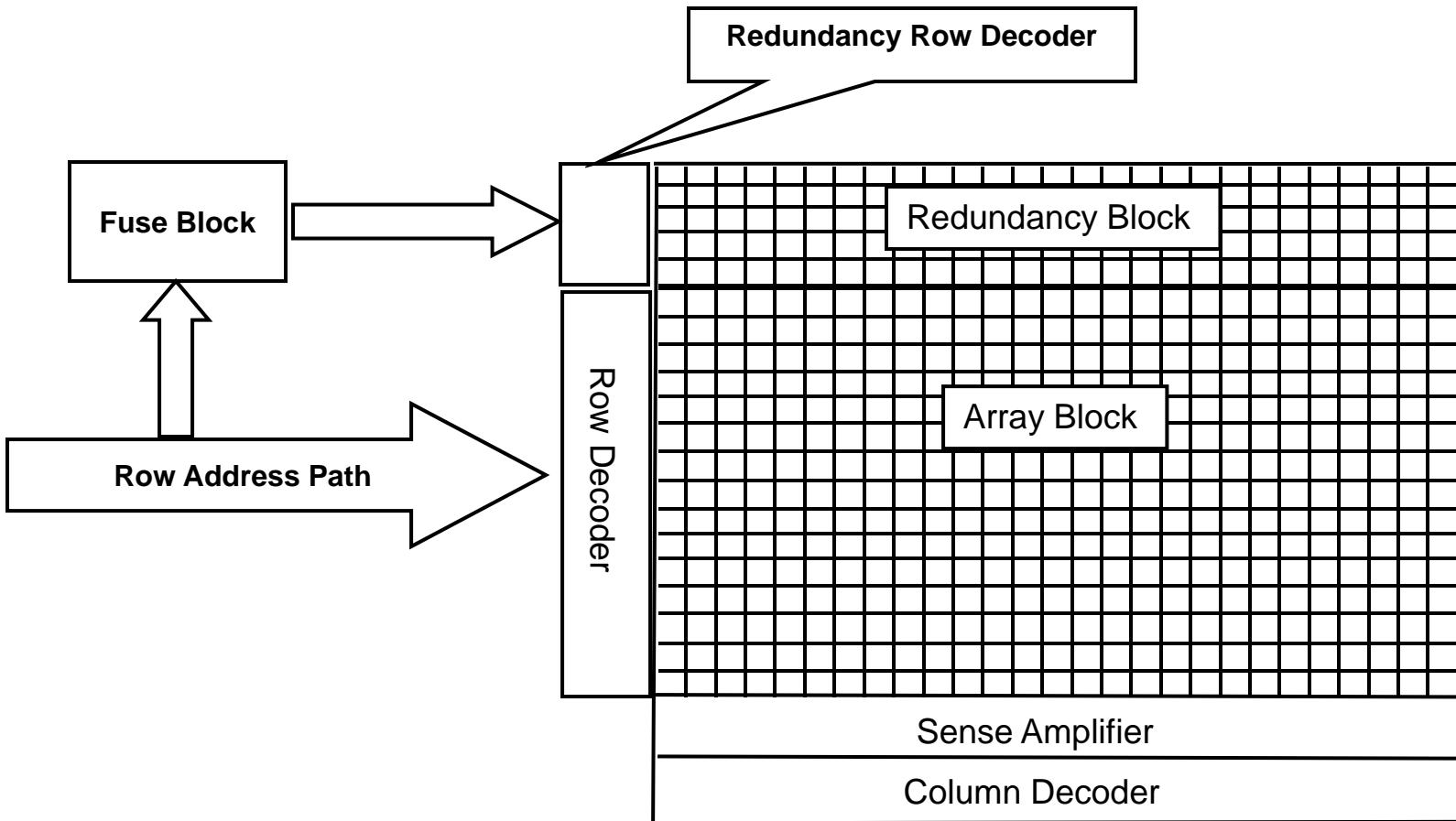

- As with all silicon products flaws occur during the manufacturing process.

- To keep costs low DRAM manufacturers build redundant Rows into the array to increase yields.

- When the Sort/Test process is done “bad” Rows are identified and a new row is assigned in the redundant region of the array.

# Redundancy

- After silicon manufacturing the die are ready for packaging.

- Package type is going to affect electrical performance of the chip. TSOPs (Thin Small Outline Package) have been used up until the higher speed DDR required a change to BGA (Ball Grid Array)

# TSOPs Still in Production

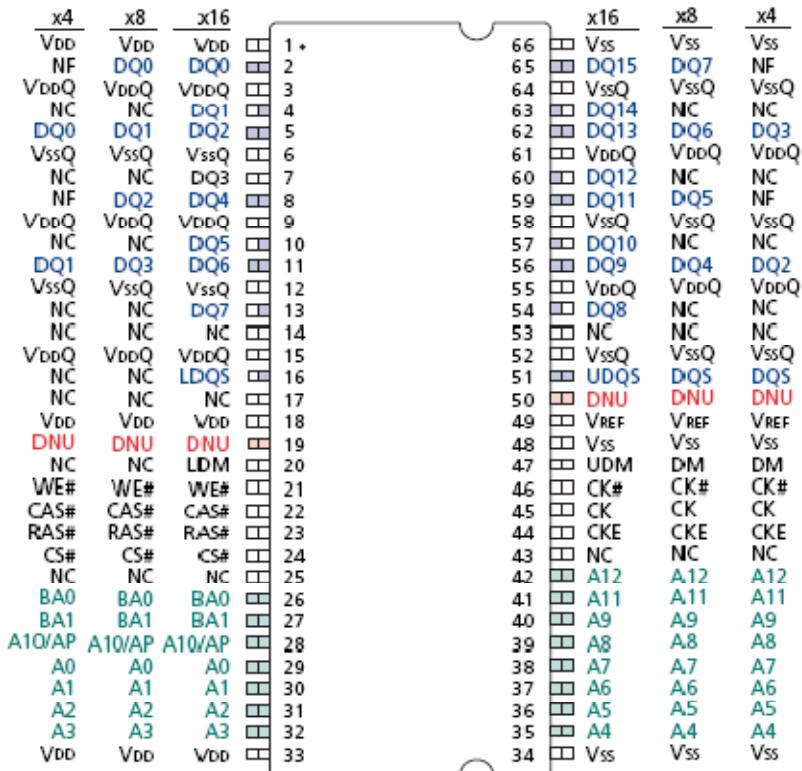

- This 66-pin TSOP is used in DDR1 for x4, x8, and x16.

- With DDR1, it was not necessary to go to a BGA package for electrical performance issues.

- Many manufacturers did use BGA packages for DDR1 in order to build high density modules.

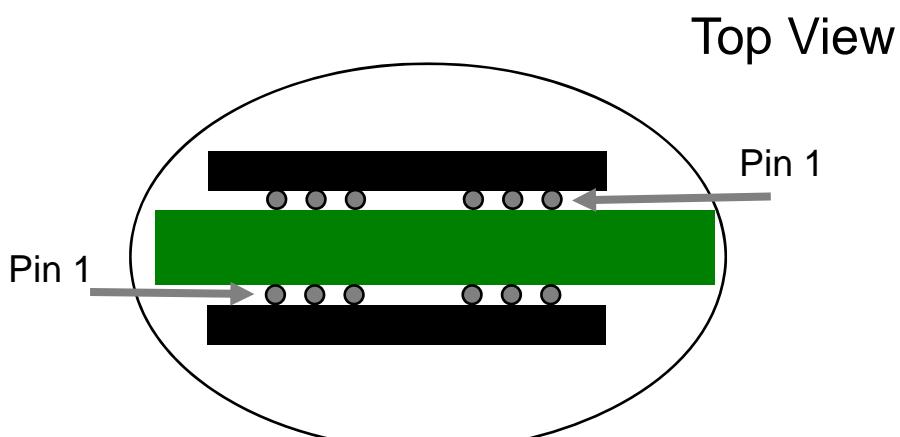

Top View

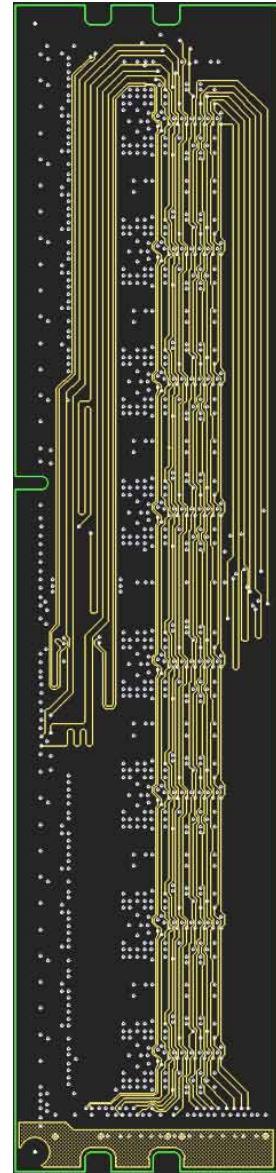

- This is a 60-pin package used for x4 and x8 DDR2.

- JEDEC wrote in the DDR2 spec that TSOP packages were not to be used.

- This package is JEDEC standard and is referred to as MO-207.

- Ball-out depends on die organization.

Looking through the package

# BGA Packages in Production

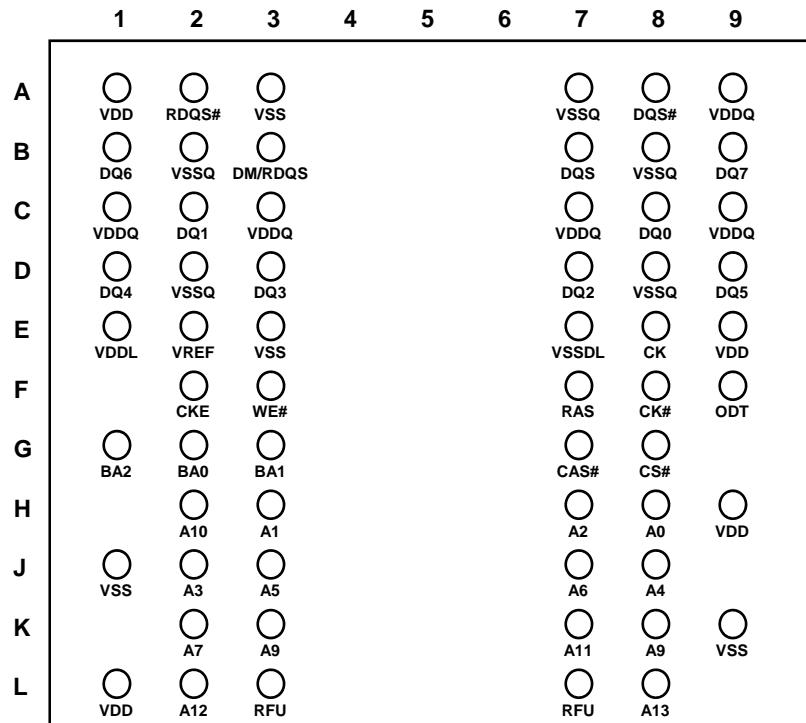

- This is the 84-pin version of the MO-207 package used for x16 DDR2 devices.

- A DDR3 BGA package is shown in the On-DIMM Mirroring section of this presentation.

|   | 1         | 2         | 3         | 4 | 5 | 6 | 7          | 8          | 9         |

|---|-----------|-----------|-----------|---|---|---|------------|------------|-----------|

| A | ○<br>VDD  | ○<br>NC   | ○<br>VSS  |   |   |   | ○<br>VSSQ  | ○<br>UDSQ# | ○<br>VDDQ |

| B | ○<br>DQ14 | ○<br>VSSQ | ○<br>UDM  |   |   |   | ○<br>UDQS  | ○<br>VSSQ  | ○<br>DQ15 |

| C | ○<br>VDDQ | ○<br>DQ9  | ○<br>VDDQ |   |   |   | ○<br>VDDQ  | ○<br>DQ8   | ○<br>VDDQ |

| D | ○<br>DQ12 | ○<br>VSSQ | ○<br>DQ11 |   |   |   | ○<br>DQ10  | ○<br>VSSQ  | ○<br>DQ13 |

| E | ○<br>VDD  | ○<br>NC   | ○<br>VSS  |   |   |   | ○<br>VSSQ  | ○<br>LDQS# | ○<br>VDDQ |

| F | ○<br>DQ6  | ○<br>VSSQ | ○<br>LDM  |   |   |   | ○<br>LDQS  | ○<br>VSSQ  | ○<br>DQ7  |

| G | ○<br>VDDQ | ○<br>DQ1  | ○<br>VDDQ |   |   |   | ○<br>VDDQ  | ○<br>DQ0   | ○<br>VDDQ |

| H | ○<br>DQ4  | ○<br>VSSQ | ○<br>DQ3  |   |   |   | ○<br>DQ2   | ○<br>VSSQ  | ○<br>DQ5  |

| J | ○<br>VDDL | ○<br>VREF | ○<br>VSS  |   |   |   | ○<br>VSSDL | ○<br>CK    | ○<br>VDD  |

| K |           | ○<br>CKE  | ○<br>WE#  |   |   |   | ○<br>RAS   | ○<br>CK#   | ○<br>ODT  |

| L | ○<br>BA2  | ○<br>BA0  | ○<br>BA1  |   |   |   | ○<br>CAS#  | ○<br>CS#   |           |

| M |           | ○<br>A10  | ○<br>A1   |   |   |   | ○<br>A2    | ○<br>A0    | ○<br>VDD  |

| N | ○<br>VSS  | ○<br>A3   | ○<br>A5   |   |   |   | ○<br>A6    | ○<br>A4    |           |

| P |           | ○<br>A7   | ○<br>A9   |   |   |   | ○<br>A11   | ○<br>A9    | ○<br>VSS  |

| R | ○<br>VDD  | ○<br>A12  | ○<br>RFU  |   |   |   | ○<br>RFU   | ○<br>A13   |           |

Looking Through from Top

# DRAM Modules

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

- In the 486 and earlier processors, as the memory data bus width grew, the need to integrate monolithic DRAMs onto a module grew with it.

- This started with the SIMM or Single Inline Memory Module.

- SIMMs only have gold finger connections on one side of the module as well as all of the necessary Command/Address and PWR/GND.

- The module matched up with the 386 and 486 32-bit processor buses.

- To speed the Pentium and K5 to market, the same 32-bit SIMMs were used.

- Due to the Pentium and K5's 64-bit memory data bus two SIMMs were used.

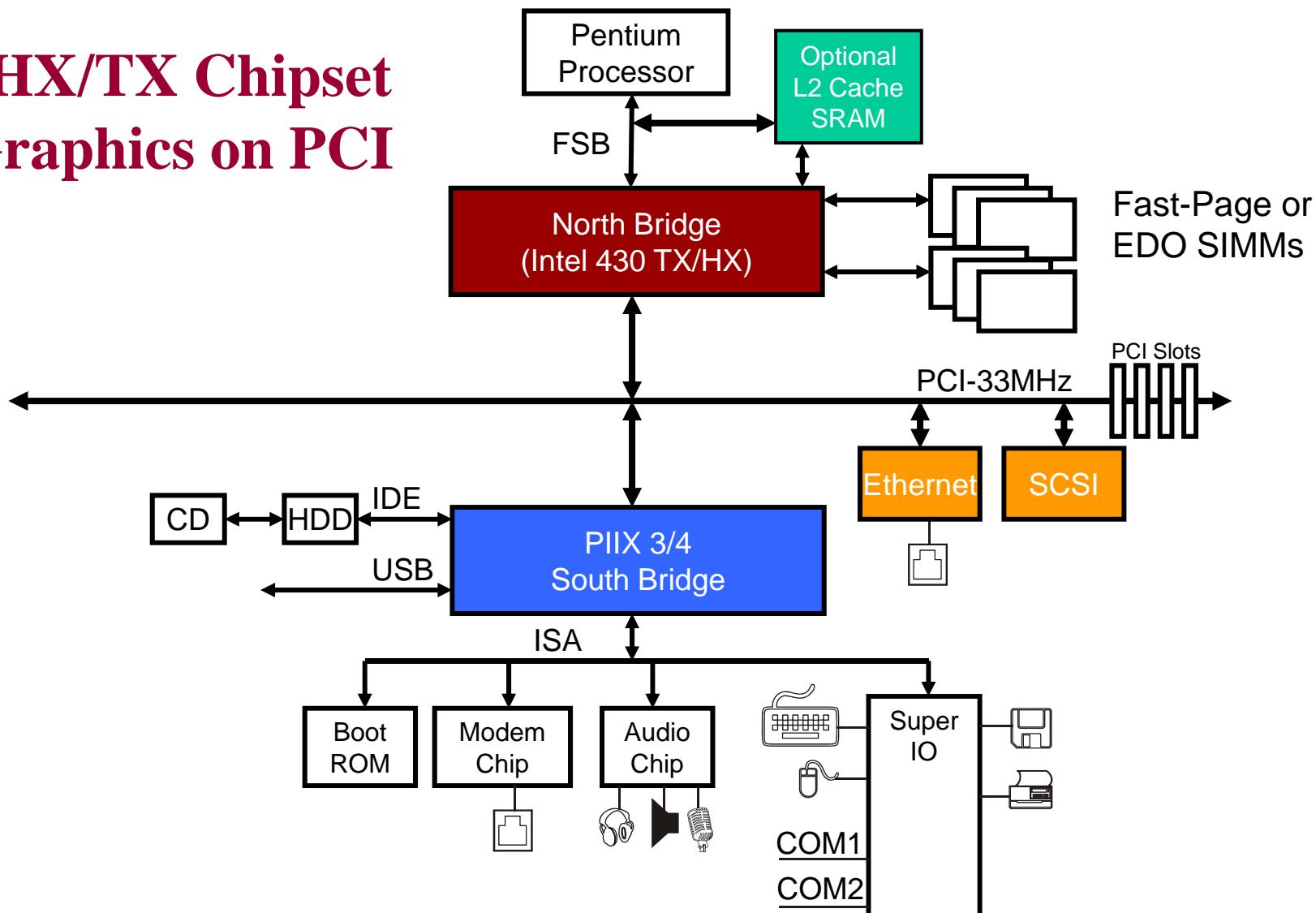

## 430 HX/TX Chipset w/ Graphics on PCI

- Gold fingers on both sides accommodating a full 64-bit-wide data bus and 8 bits of ECC as well as all of the necessary Command, Address, power and ground pins.

- 168-pin DIMMs, used for SDRAM

- 184-pin DIMMs, used for DDR SDRAM

- 240-pin DIMMs, used for DDR2 SDRAM

- 240-pin DIMMs, used for DDR3 SDRAM

- Key is different than DDR2 DIMMs

- Beware that pins are numbered differently (such as location of pin 2) for SO-DIMMs than for UDIMMs.

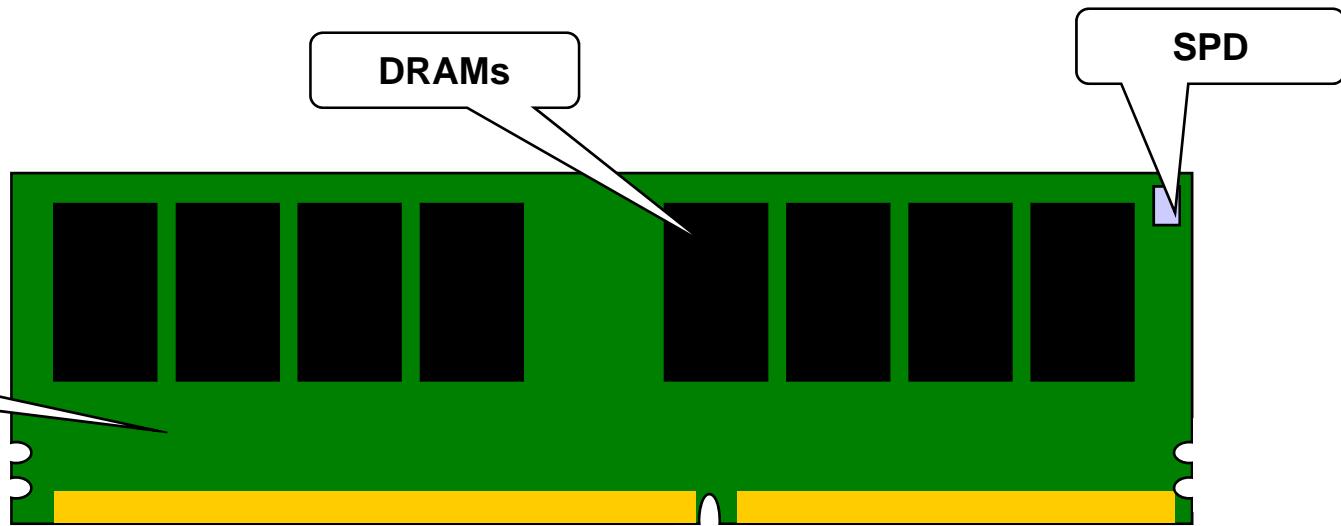

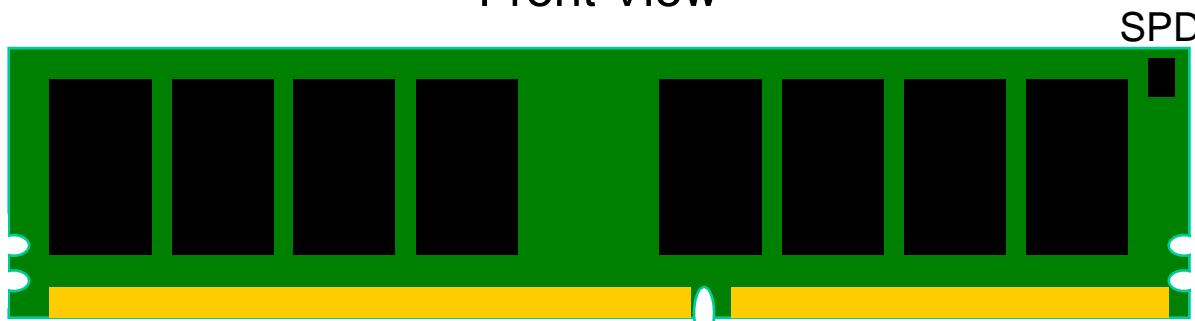

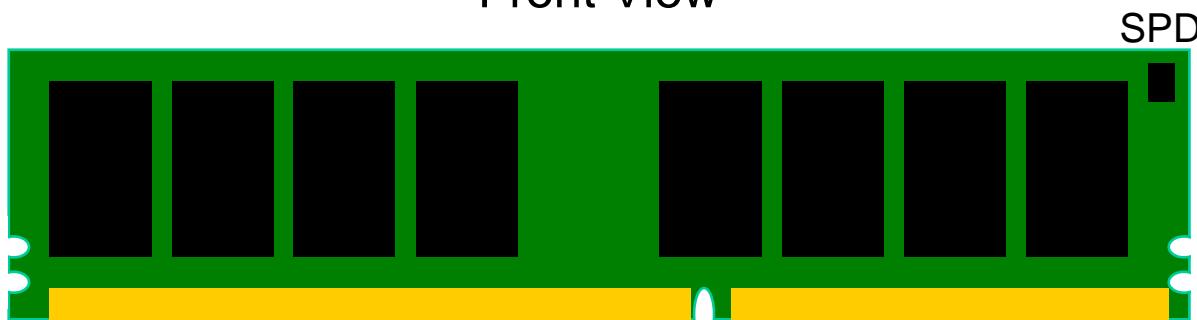

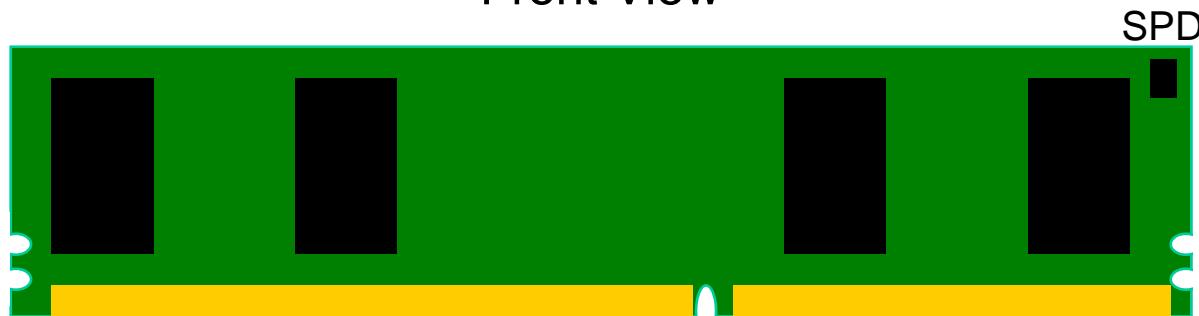

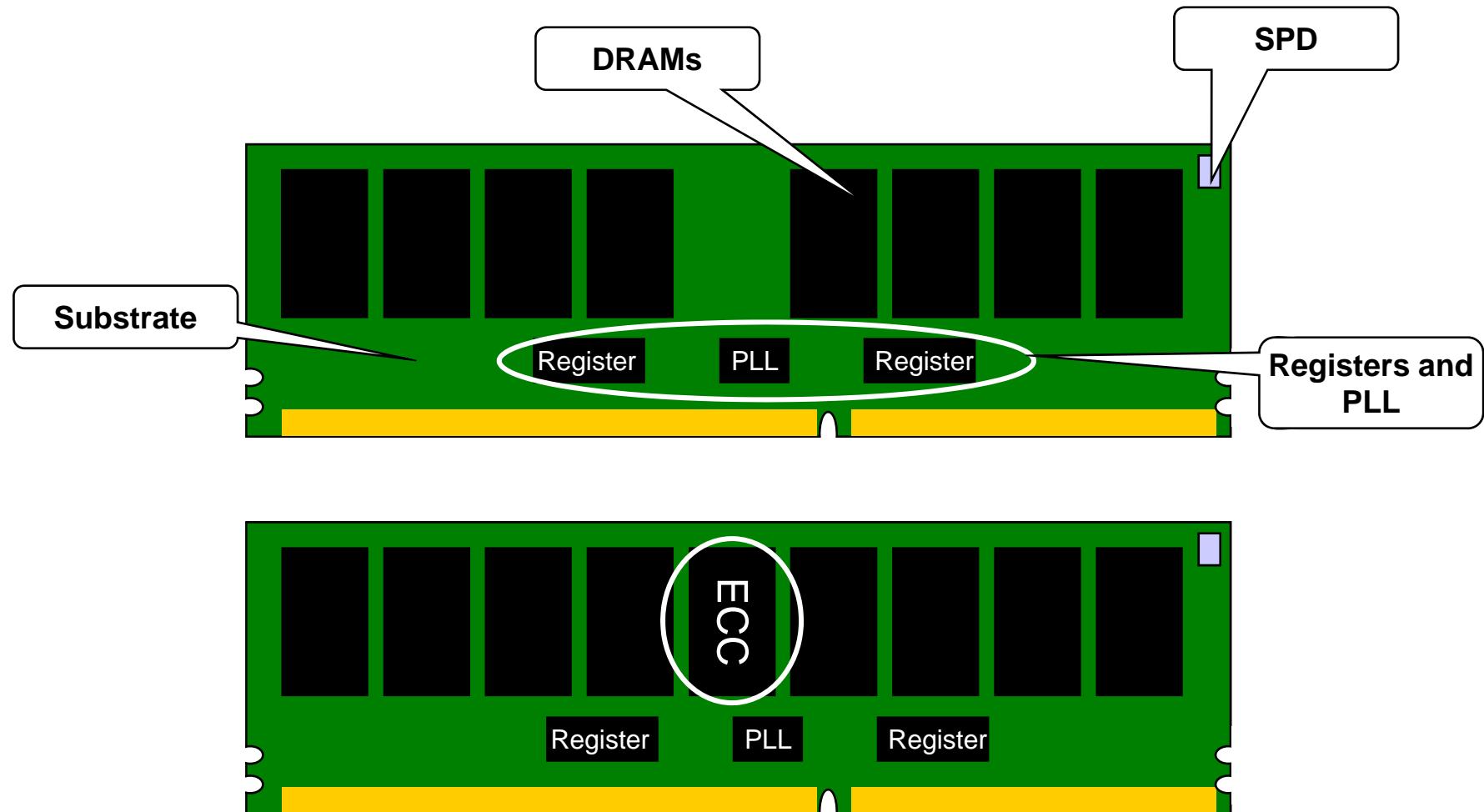

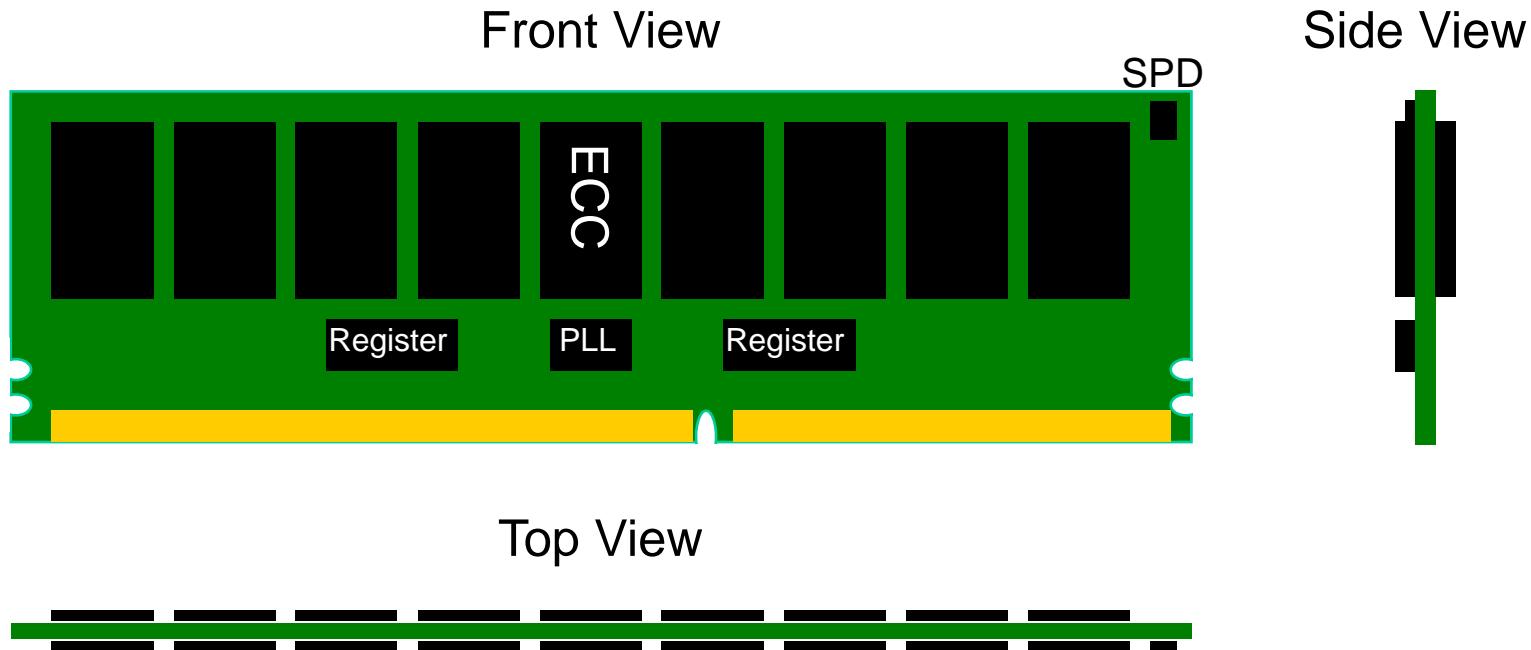

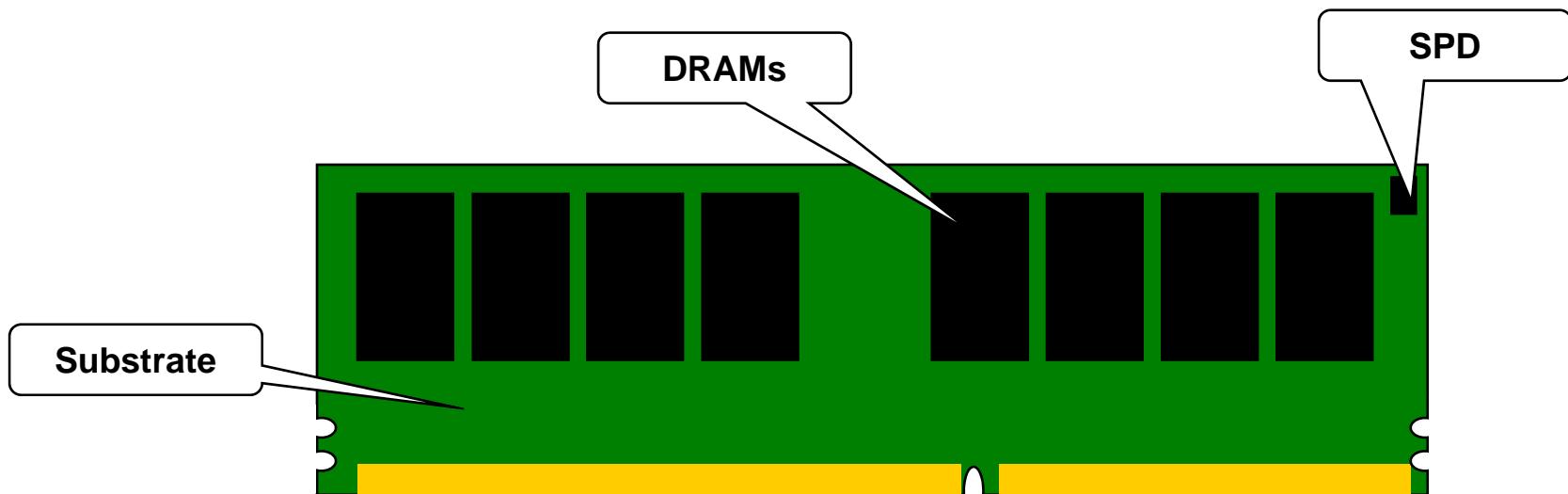

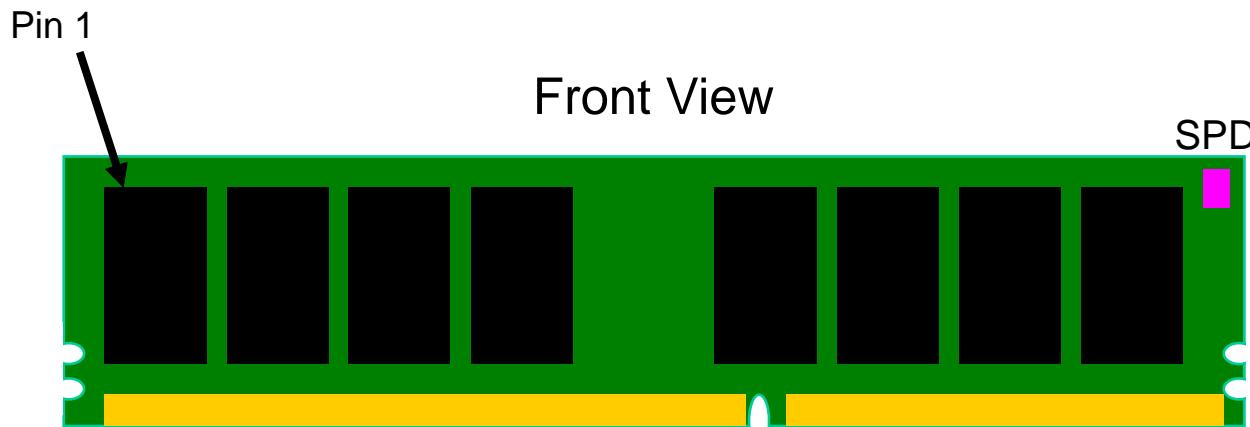

- The most common DIMMs are Unbuffered.

- These DIMMs have 3 basic components:

- The PCB substrate

- The DRAMs

- The SPD (Serial Presence Detect)

- These are mostly for the Desktop and Mobile markets.

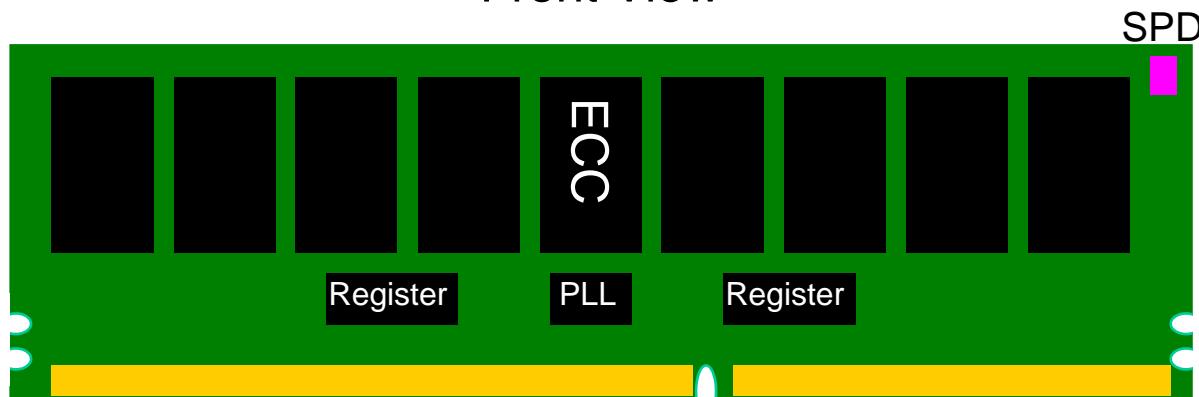

- The other very common type of DIMM used in server and workstation PCs is the Registered DIMM. Unlike an Unbuffered DIMM where all of the signals are routed directly to the DRAMs, the Registered DIMM uses registers and a PLL for the command, address, and clocks.

- The PCB substrate

- The DRAMs

- The SPD (Serial Presence Detect)

- Registers

- PLL

- The registers and PLL reduce electrical loading on the most heavily loaded signals.

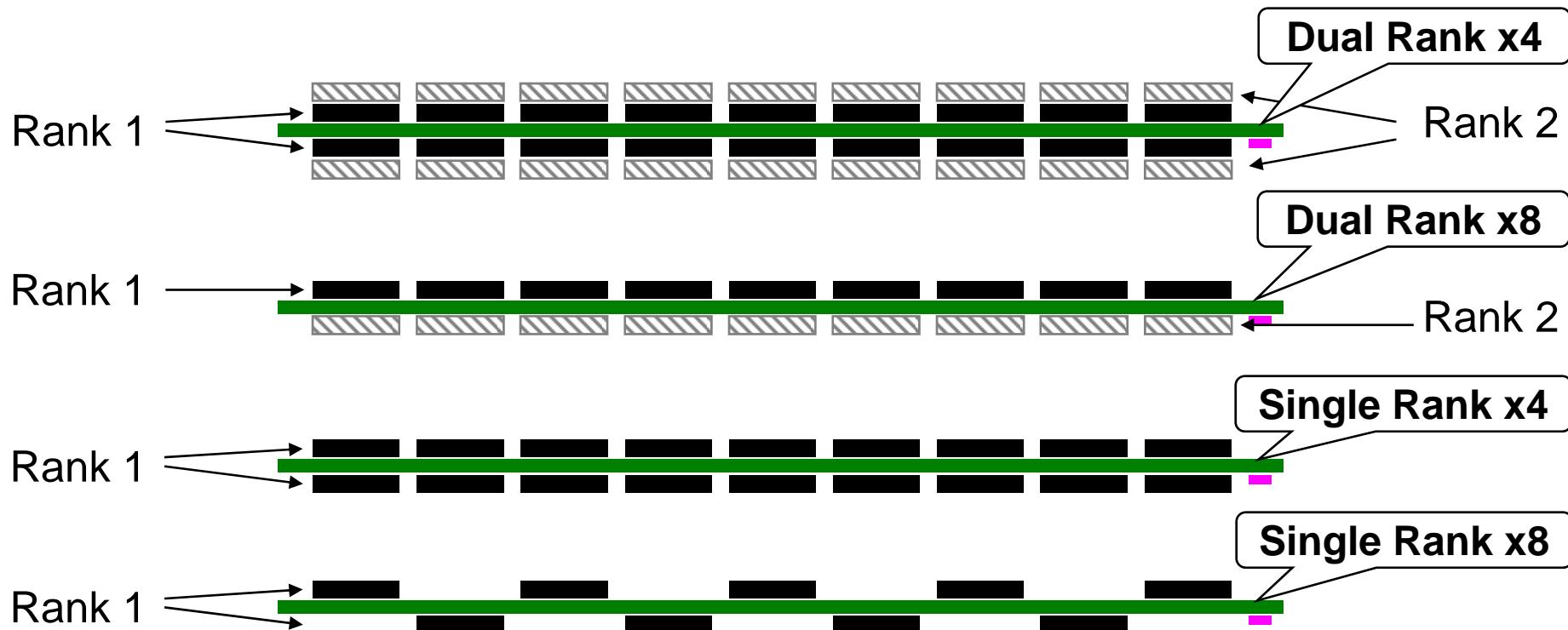

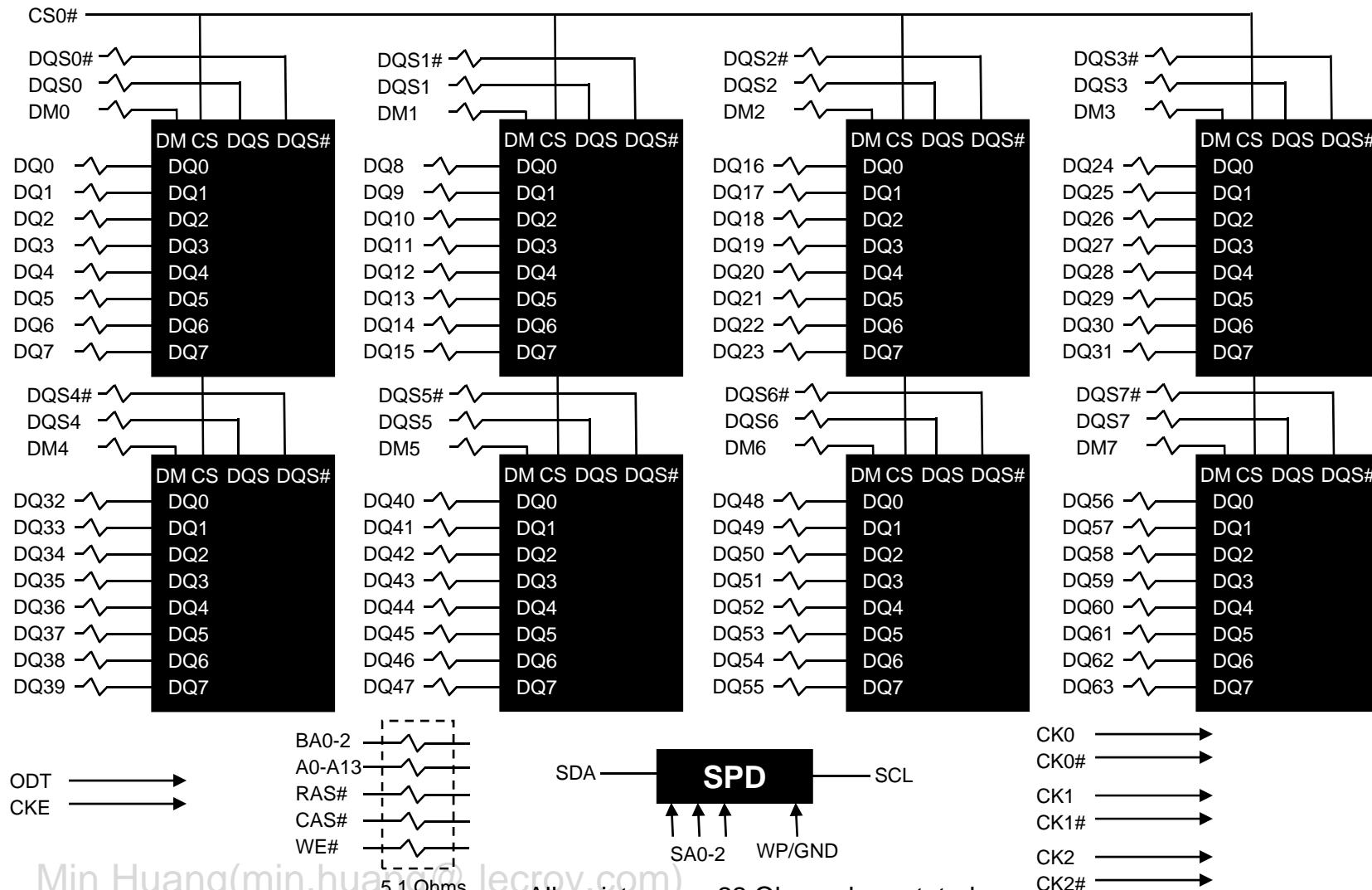

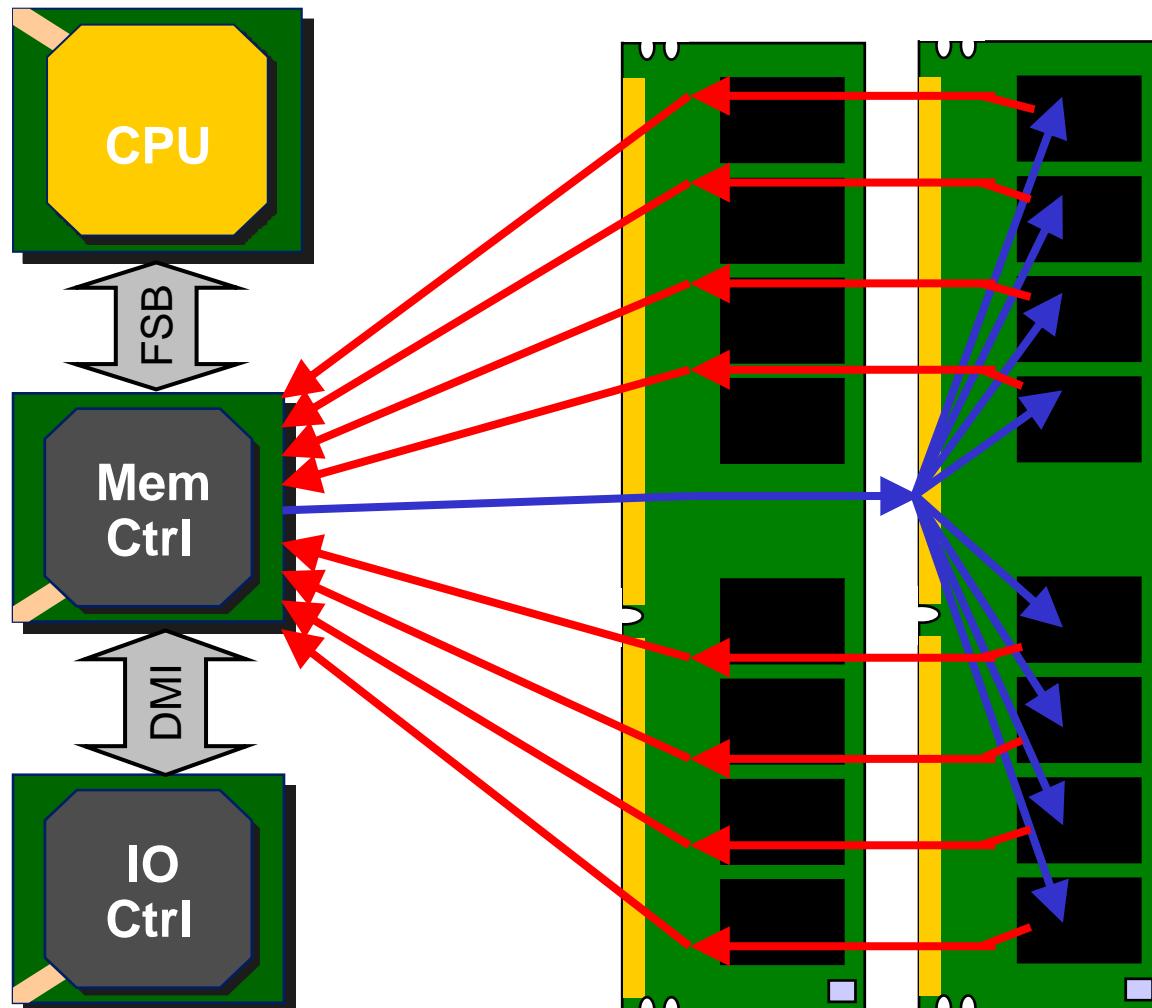

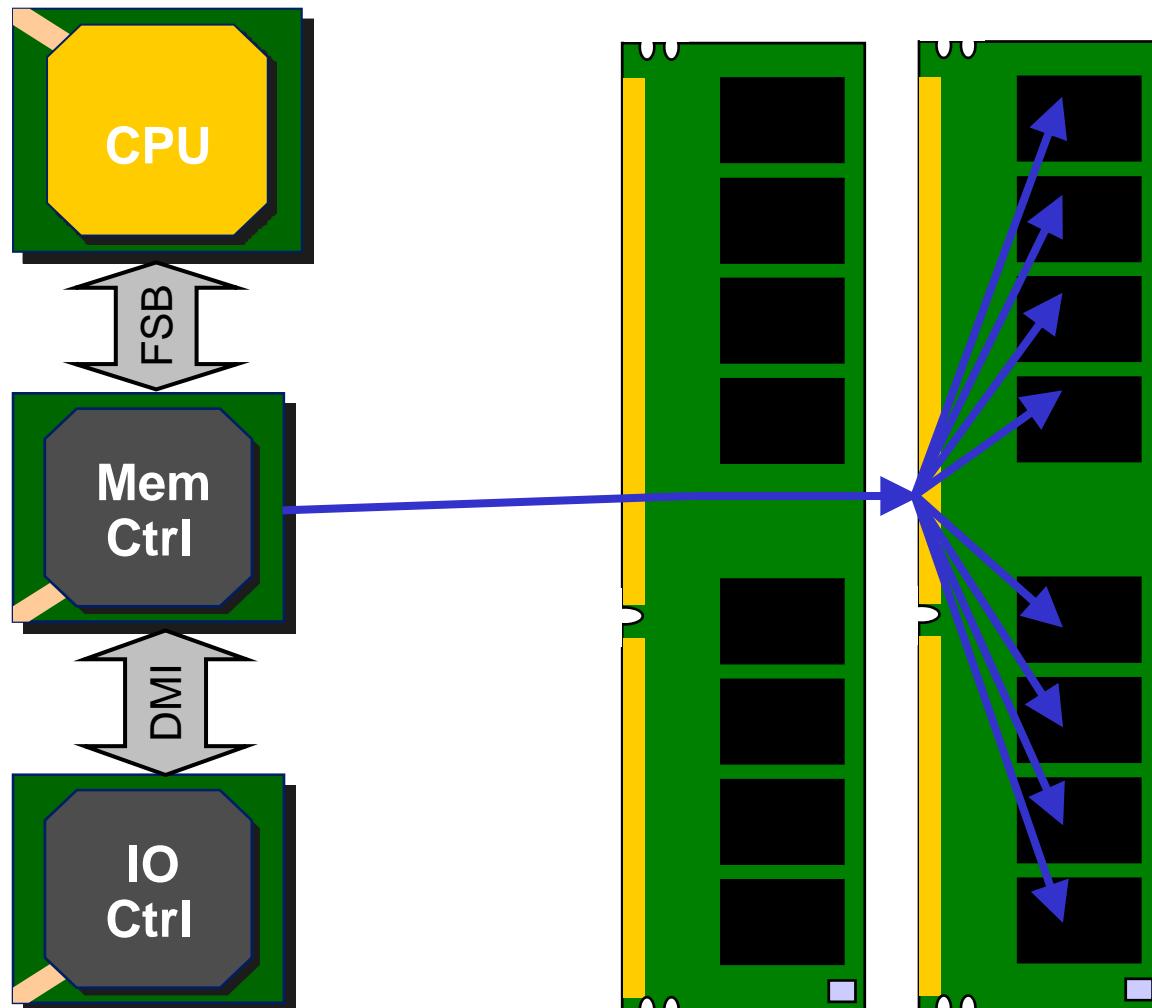

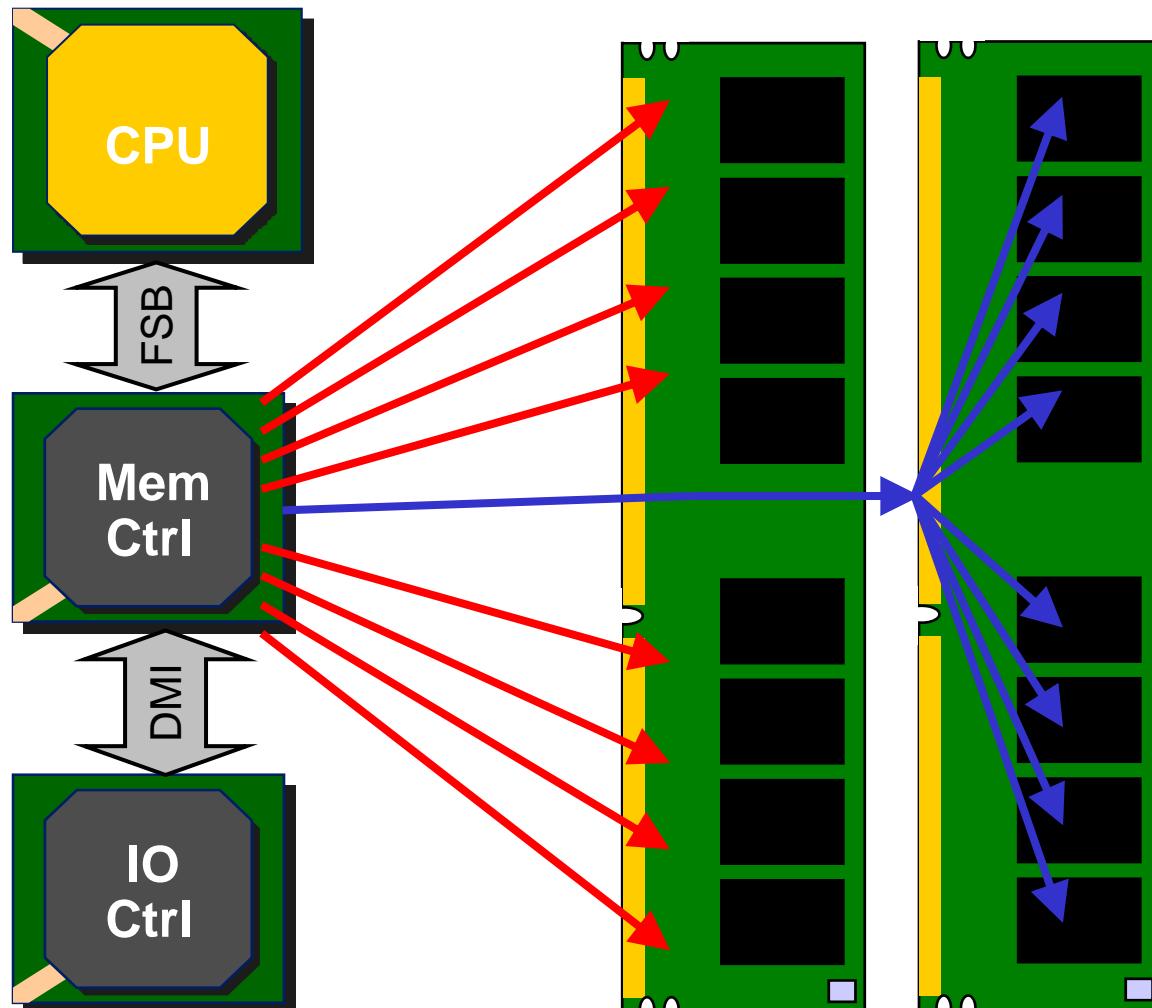

- The DRAMs on DIMMs are ordered into Ranks.

- A Rank consists of enough DRAMs to drive the full width of the system data bus. In most systems this is 64 bits wide or 72 bits with ECC.

- A quadword is 64 bits (eight bytes) using the Intel Architecture definition that one word is 16 bits.

- This concept used to be referred to as single sided and double sided.

- Examples of Rank Configurations:

- Shown with ECC

# Module Types Unbuffered

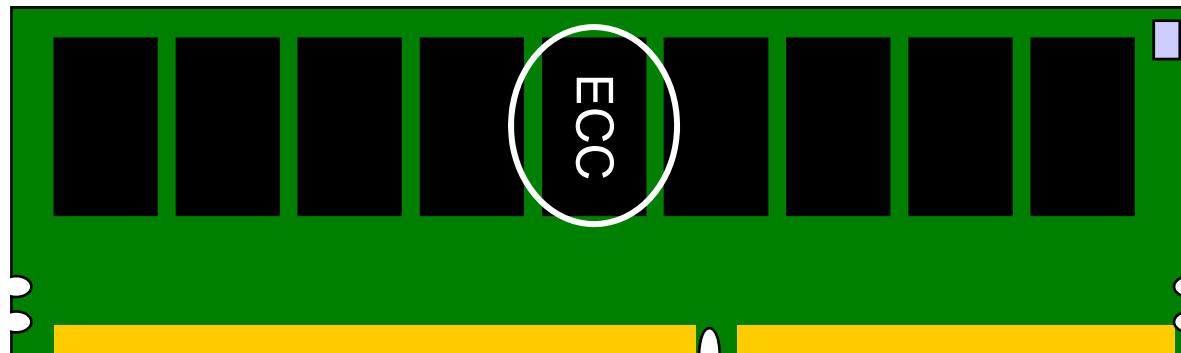

**Shown with optional ECC chip. Typically unbuffered DIMMs do not have ECC support.**

# Unbuffered Logical Example

- This example assumes 512Mb DRAMs on the DIMMs.

- Total size = number of chips X size of chip / 8

|                                     | Configuration | # of chips | Ranks  | Total Size |

|-------------------------------------|---------------|------------|--------|------------|

| Unbuffered<br>Mobile Desktop        | x16           | 4          | Single | 256MB      |

|                                     | x16           | 8          | Dual   | 512MB      |

|                                     | x8            | 8          | Single | 512MB      |

| Registered<br>Server<br>Workstation | x8            | 16         | Dual   | 1GB        |

|                                     | x4            | 16         | Single | 1GB        |

|                                     | x4            | 32         | Dual   | 2GB        |

x8 Single Rank, 8 components

Front View

Side View

Top View

x8 Dual Rank, 16 components

Front View

Side View

Top View

x16 Single Rank, 4 components

Front View

Side View

Top View

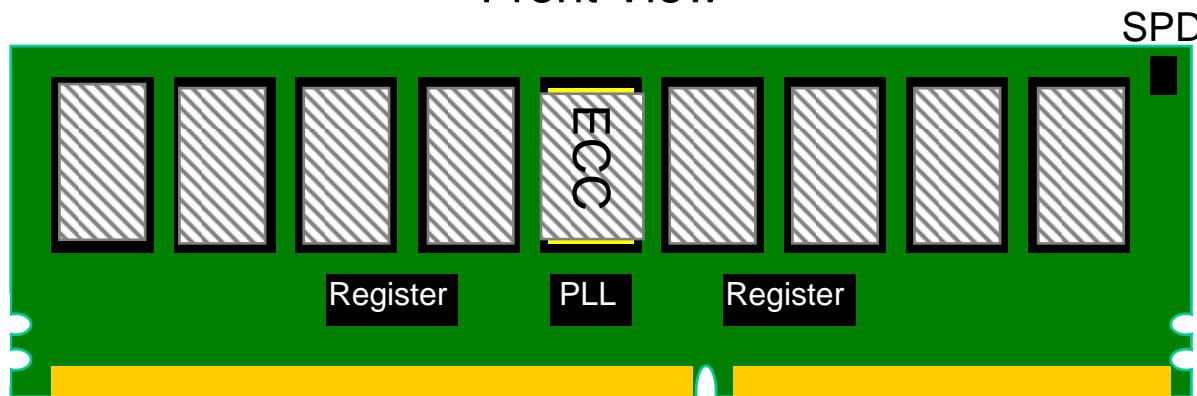

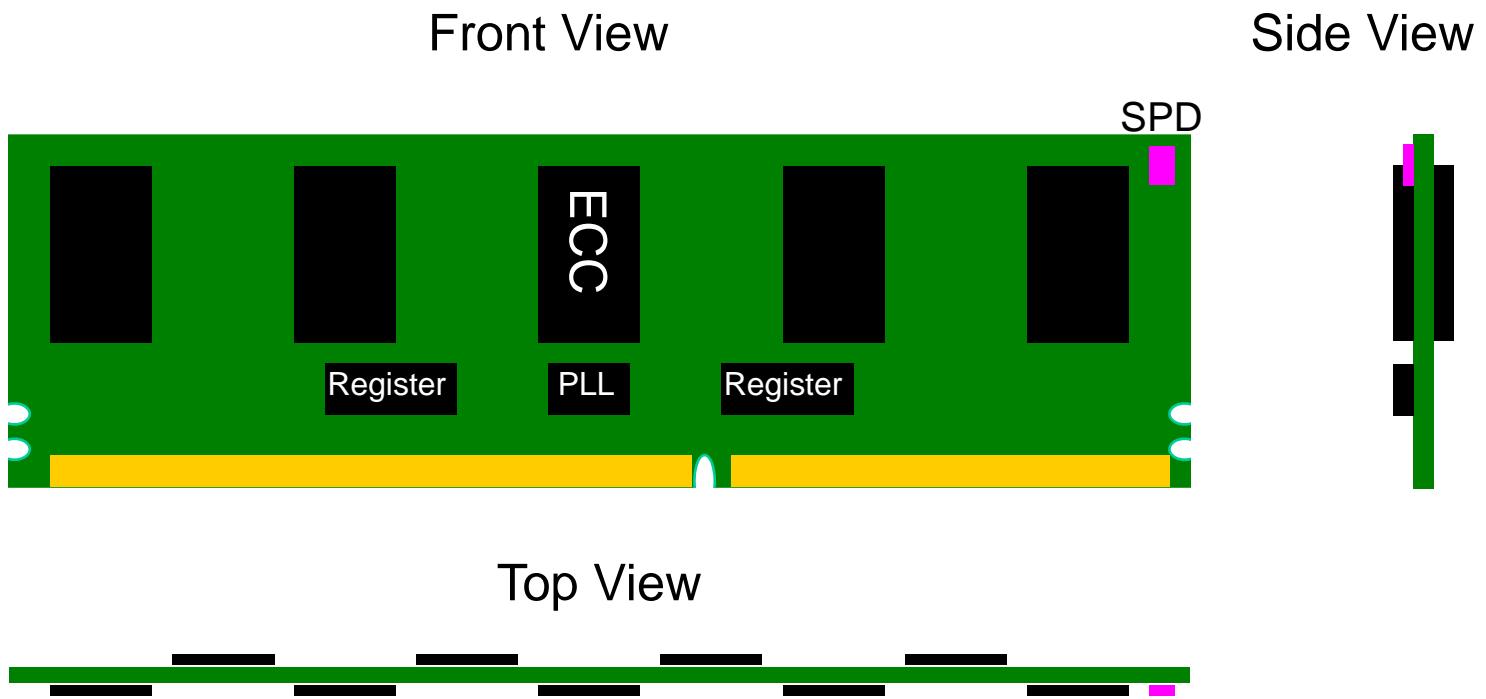

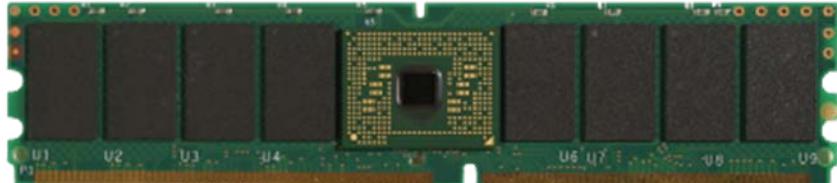

# Module Types Registered

x4 Single Rank, 18 components (with ECC)

x4 Dual Rank, 36 components (with ECC)

Front View

Side View

Top View

- x8 Single Rank, 8 components (with ECC)

- x8 Dual Rank, 18 components (with ECC)

Front View

Side View

Top View

# Module Types

**UDIMM:** Unbuffered Desktop standard

**RDIMM:** Registered Server standard

**SODIMM:** Notebook standard

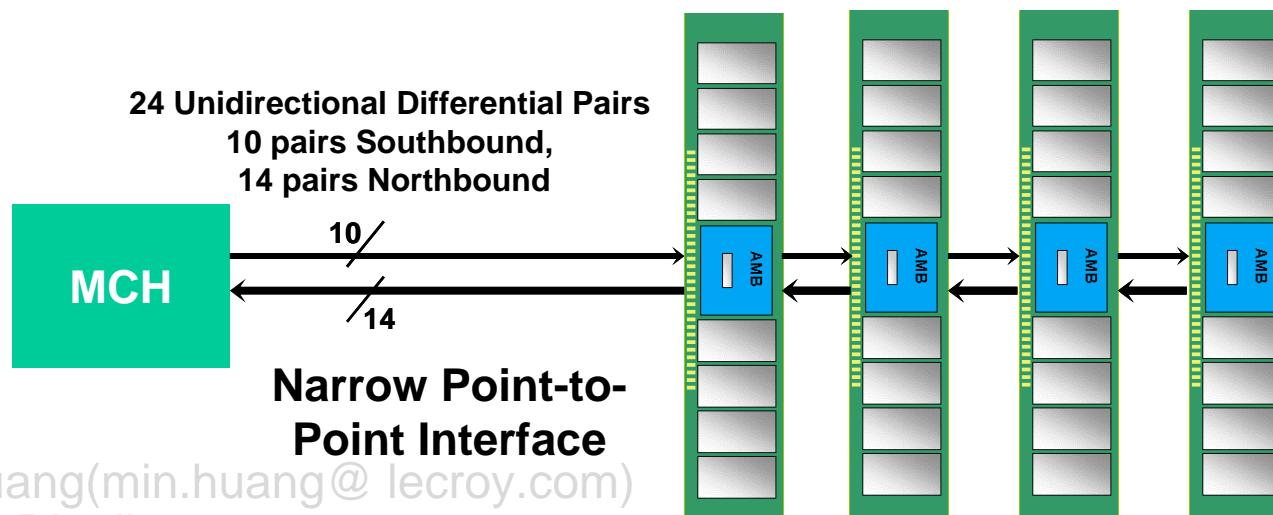

**FBDIMM:** Fully Buffered Server

**VLP RDIMM:** Very Low Profile Computing and Networking

**MiniDIMM:**

Computing and Networking

**VLP MiniDIMM:**

Computing and Networking

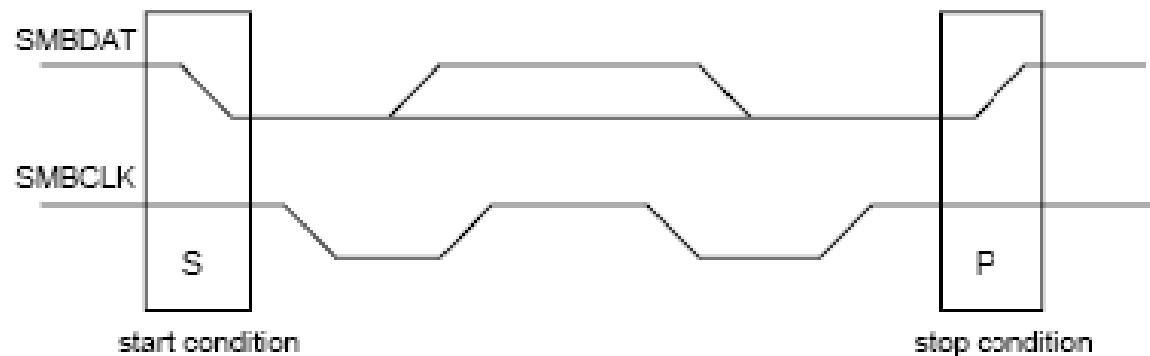

## Clock (CK, CK#)

- Input Differential For DDR2 single ended for DDR1

- Address & control signals sampled on the crossing of the positive edge of CK & the negative edge of CK#

- Output (read) data is referenced to the crossing of CK and CK# (both directions)

- One pair to each DIMM in Registered DIMM and 3 pairs for Unbuffered. For SODIMMs one of the clocks can be shut off

## Clock Enable (CKE)

- Input High

- HIGH activates, LOW deactivates internal CK signals, input buffers and output drivers.

- Must remain high throughout read/write accesses. Primarily used for self refresh and sleep states like active power down.

- Each Rank has its own CKE

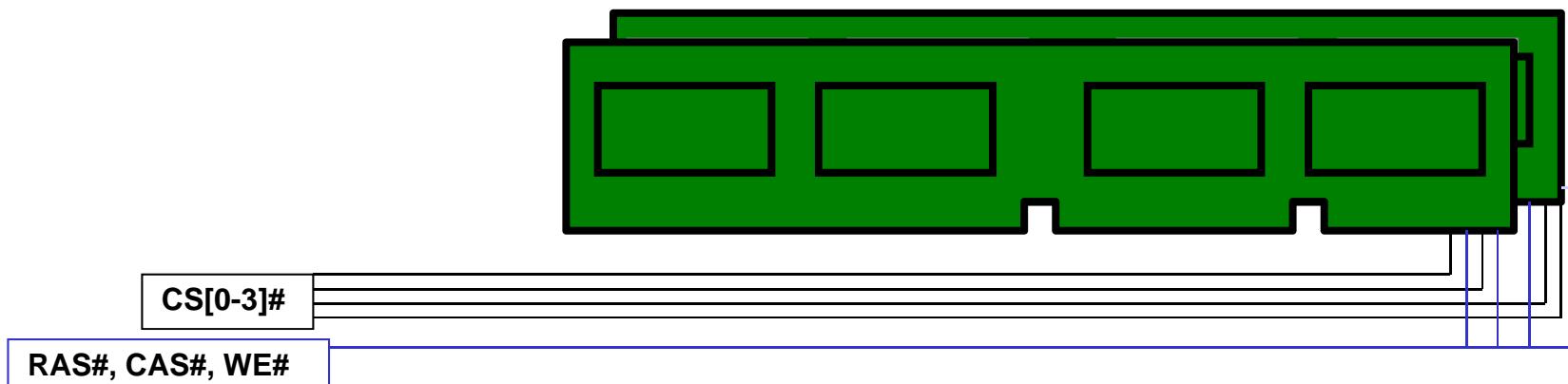

## Chip Select (CS0#-CS3#)

- Input Low

- All commands are ignored when CS# is inactive (considered part of each command)

- Each rank has its own chip select.

- Which CS# is asserted for a given physical address is based on the programming of the memory controller (DRB's – DRAM Rank Boundary Registers)

- How many ranks can be supported on a single DIMM.

## ODT

- Input High

- On Die Termination enables internal termination resistors to the following signals: DQ, DQS, DQS#, CB and Data Mask.

- Every Rank has its own ODT signal.

- ODT will be discussed more later

Row Address Strobe (RAS#), Column Address Strobe (CAS#), Write Enable (WE#)

- Input Low

- Define (along with CS#) the command being entered.

- Command truth table defined in JEDEC spec

- RAS#, CAS#, and WE# are broadcast to each chip.

## Bank Address (BA 0-2)

- Input High

- Define to which bank an Active, Read, Write or Precharge command is being applied.

- Determines if the mode register or extended mode register is being accessed during an MRS or EMRS cycle.

## Address (A 0-15)

- Input High

- Defines the Row Address for Active commands

- Defines the Column Address and auto precharge bit for read/write commands.

- A10 is Row Address during an Active (Activate) command.

- A10 is sampled during a Precharge command.

- A10 Low = Precharge one bank

- A10 High = Precharge all banks

- A10 is Auto Precharge (AP) during a Read or Write command.

- A10 Low = No Precharge

- A10 High = Auto Precharge when command is complete.

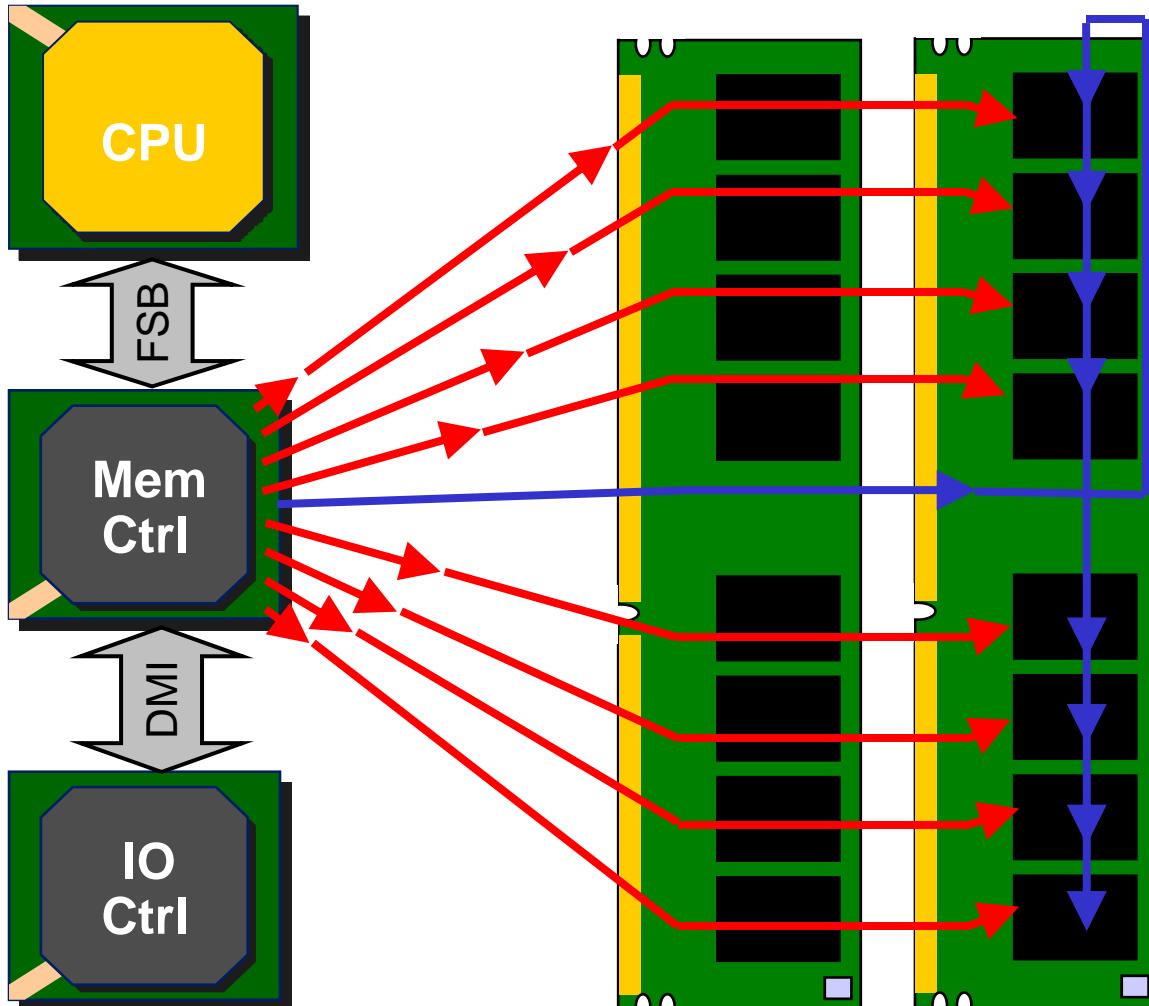

## Data Input/Output (DQ 0-63)

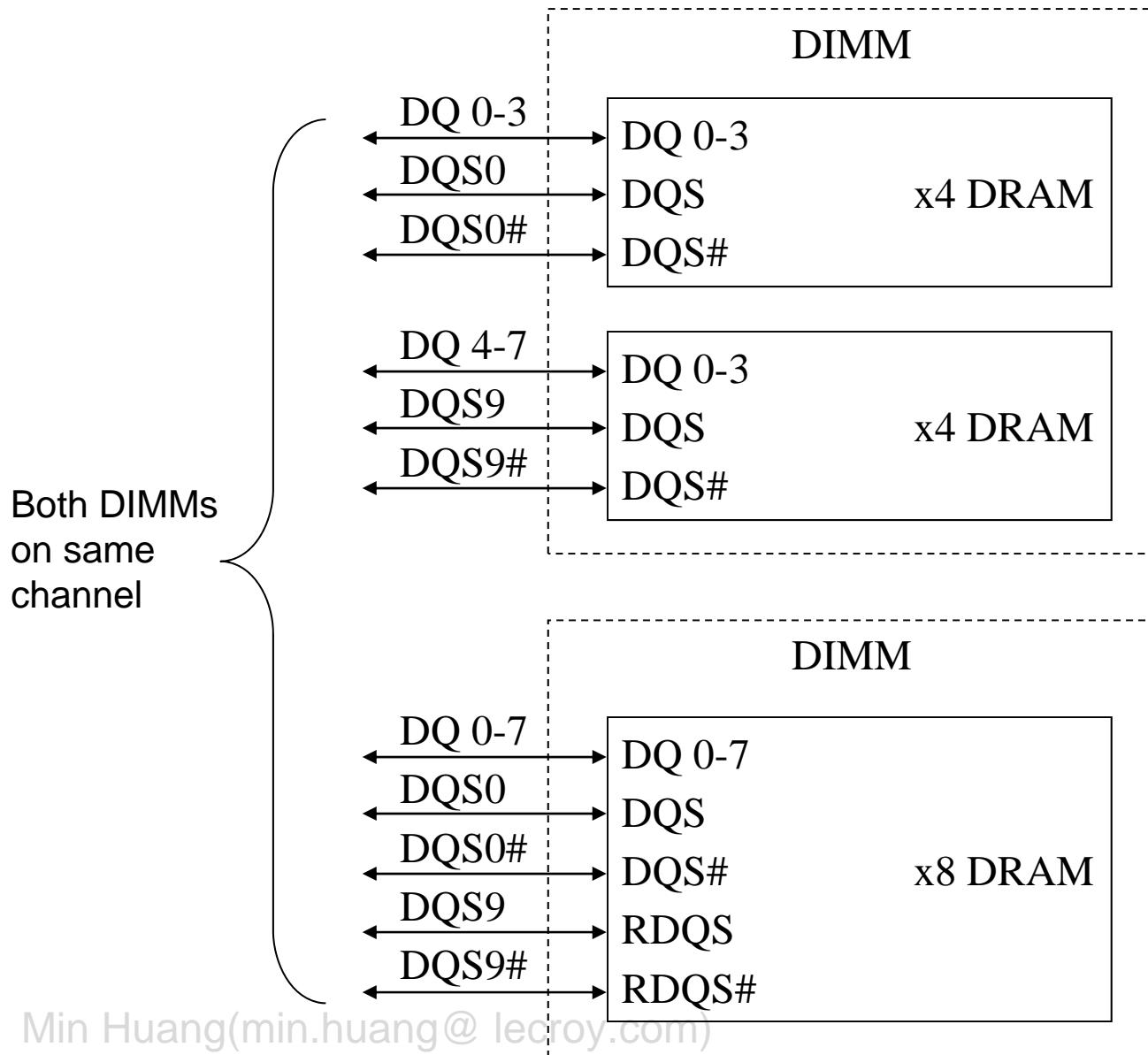

- Bi-directional data bus.

- DQ is a bused signal so every rank is seen as a load on the bus.

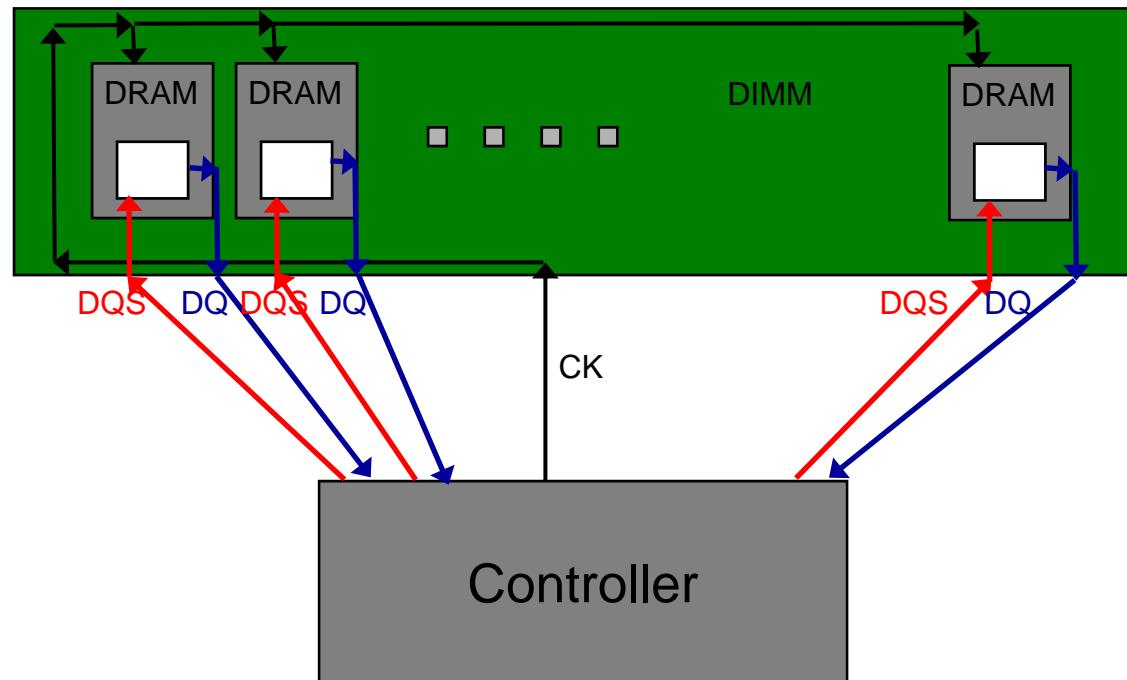

## Data Strobes (DQS, DQS#, UDQS, UDQS#, LDQS, LDQS#, RDQS, RDQS#) 0-17, 0-17#

- Bi-directional Differential in some cases (EMRS Programming)

- Used to latch data signals at the receiver.

- Edge-aligned with data (DQ) during reads (DRAM driving)

- Center-aligned with data (DQ) on writes (Chipset driving)

- For x4 devices, 16 or 18 pairs are used, one pair per chip (DQS, DQS#)

- For x8 devices, 8 or 9 pairs are used, one pair per chip (DQS, DQS#), except that in RDQS mode, 16 or 18 pairs are used (DQS, DQS#, RDQS, RDQS#)

- For x16 devices, 8 or 9 pairs are used, 2 pairs per chip (LDQS, LDQS#, UDQS, UDQS#). For x16, the ECC chip is x16, not x8.

- DQS is bused, so every rank is seen as a load on the bus.

## Data Mask (DM 0-7, UDM, LDM)

- Input High

- Input mask signal for write data. When DM is high, write DQS is ignored. When DM is low, DQS is valid.

- Same pins as DQS 9-17 on DIMMs.

- Pins are DM for DIMMs using x8 and x16 devices

- Pins are DQS for DIMMs using x4 devices. DM of x4 devices are tied low on DIMMs.

- For x16 devices, these signals are named UDM and LDM. On DIMMs with x16 devices, there is an unconnected set of DM pins, which are the pins that would have been the DQS of the x4 devices.

- DM is bused, so every rank is seen as a load on the bus.

## Check Bits (CB 0-7)

- Bi-directional data bus.

- Check bits used for ECC.

- CB 0-7 are strobed with DQS 8 on x8 devices, and with DQS 8 and 17 on x4 devices.

## Par\_In

- Parity for the address and control bus. Not used on most Intel controllers. Implemented in the chipset and register.

## Err\_Out#, QERR#

- Indicates parity error found on the address or control bus.

- QERR# is register pin. Err\_Out# is DIMM pin.

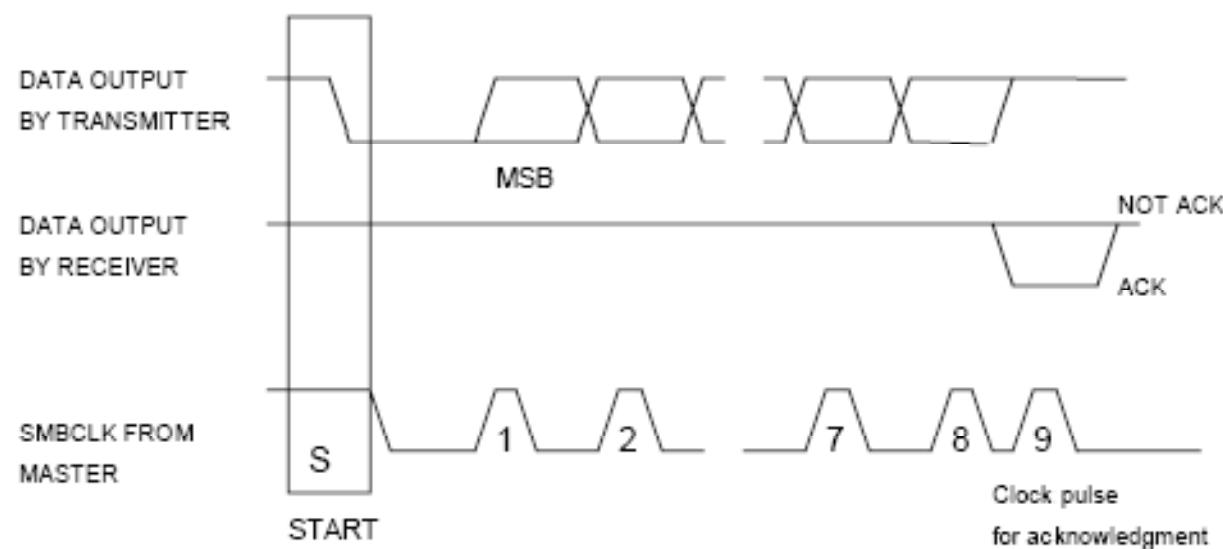

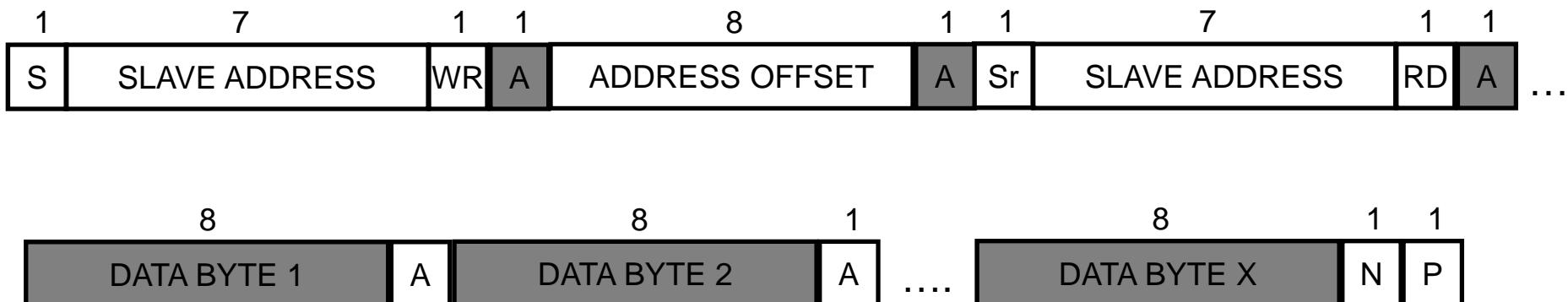

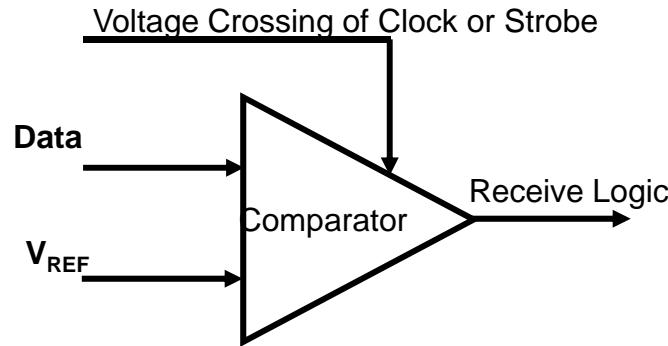

## Serial Presence Detect (SPD) Clock Input (SCL)

- Serial clock used to synchronize the SPD logic.

## SPD Data (SDA)

- Bidirectional pin to transmit address and data in and out of the SPD.

## SPD Address (SA 0-2)

- Must be hardwired to different addresses for each module.

RESET# - Active when low

- CKE must be pulled low first.

- When RESET# is deasserted, CKE may be deasserted 500uS later. During this time internal initialization is started.

- RESET# forces DRAM into a defined state.

- RESET# can be asserted asynchronously during any operation.

- Data in DRAM may be lost and DRAM must be re-initialized, which includes (but not limited to) load mode registers and DLL reset.

A12/BC# Burst Chop - Active when low

- BC# during Read and Write commands.

- A12 during Active (Activate) command.

TDQS/TDQS# - Termination Data strobe

- Only applicable to x8 DRAMs (replaces RDQS/RDQS#).

$V_{REFDQ}$ ,  $V_{REFCA}$  – Separate  $V_{REF}$  for DQ and CMD/ADDR

- This decoupling reduces noise on the reference planes.

ZQ – Reference pin for ZQ calibration

CK,CK# - Unbuffered DDR3 DIMMs only have 2 pairs instead of 3.

# Commands and Waveforms

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

# DDR3 Bank States

# DDR2 Commands

| Command                   | CKE            |               | CS# | RAS# | CAS# | WE# | BA2<br>BA1<br>BA0 | A13<br>A12<br>A11 | A10<br>AP | A9-0     |

|---------------------------|----------------|---------------|-----|------|------|-----|-------------------|-------------------|-----------|----------|

|                           | Previous Cycle | Current Cycle |     |      |      |     |                   |                   |           |          |

| Mode Register Set         | H              | H             | L   | L    | L    | L   | MRn               | Op Code           |           |          |

| Refresh                   | H              | H             | L   | L    | L    | H   | X                 | X                 | X         | X        |

| Self Refresh Entry        | H              | L             | L   | L    | L    | H   | X                 | X                 | X         | X        |

| Self Refresh Exit         | L              | H             | L   | H    | H    | H   | X                 | X                 | X         | X        |

| Single Bank Precharge     | H              | H             | L   | L    | H    | L   | BA                | X                 | L         | X        |

| All Banks Precharge       | H              | H             | L   | L    | H    | L   | X                 | X                 | H         | X        |

| Bank Activate             | H              | H             | L   | L    | H    | H   | BA                | Row Address       |           |          |

| Write                     | H              | H             | L   | H    | L    | L   | BA                | Col Addr          | L         | Col Addr |

| Write with Auto Precharge | H              | H             | L   | H    | L    | L   | BA                | Col Addr          | H         | Col Addr |

| Read                      | H              | H             | L   | H    | L    | H   | BA                | Col Addr          | L         | Col Addr |

| Read with Auto Precharge  | H              | H             | L   | H    | L    | H   | BA                | Col Addr          | H         | Col Addr |

| No Operation              | H              | X             | L   | H    | H    | H   | X                 | X                 | X         | X        |

| Device Deselect           | H              | X             | H   | X    | X    | X   | X                 | X                 | X         | X        |

| Power Down Entry          | H              | L             | L   | H    | H    | H   | X                 | X                 | X         | X        |

| Power Down Exit           | H              | L             | H   | H    | H    | H   | X                 | X                 | X         | X        |

# DDR3 Command Additions

| Command                        | CKE               |                  | CS# | RAS# | CAS# | WE# | BA0-<br>BA3 | A13<br>A14<br>A15 | A12<br>BC# | A10<br>AP | A0-9,<br>A11 |

|--------------------------------|-------------------|------------------|-----|------|------|-----|-------------|-------------------|------------|-----------|--------------|

|                                | Previous<br>Cycle | Current<br>Cycle |     |      |      |     |             |                   |            |           |              |

| Write BL= 4 (Burst Chop)       | H                 | H                | L   | H    | L    | L   | BA          | CA                | L          | L         | CA           |

| Write BL= 8                    | H                 | H                | L   | H    | L    | L   | BA          | CA                | H          | L         | CA           |

| Write with Auto Precharge BL=4 | H                 | H                | L   | H    | L    | L   | BA          | CA                | L          | H         | CA           |

| Write with Auto Precharge BL=8 | H                 | H                | L   | H    | L    | L   | BA          | CA                | H          | H         | CA           |

| Read BL= 4 (Burst Chop)        | H                 | H                | L   | H    | L    | H   | BA          | CA                | L          | L         | CA           |

| Read BL= 8                     | H                 | H                | L   | H    | L    | H   | BA          | CA                | H          | L         | CA           |

| Read with Auto Precharge BL=4  | H                 | H                | L   | H    | L    | H   | BA          | CA                | L          | H         | CA           |

| Read with Auto Precharge BL=8  | H                 | H                | L   | H    | L    | H   | BA          | CA                | H          | H         | CA           |

| ZQ Calibration Long            | H                 | H                | L   | H    | H    | L   | X           | X                 | X          | H         | X            |

| ZQ Calibration Short           | H                 | H                | L   | H    | H    | L   | X           | X                 | X          | L         | X            |

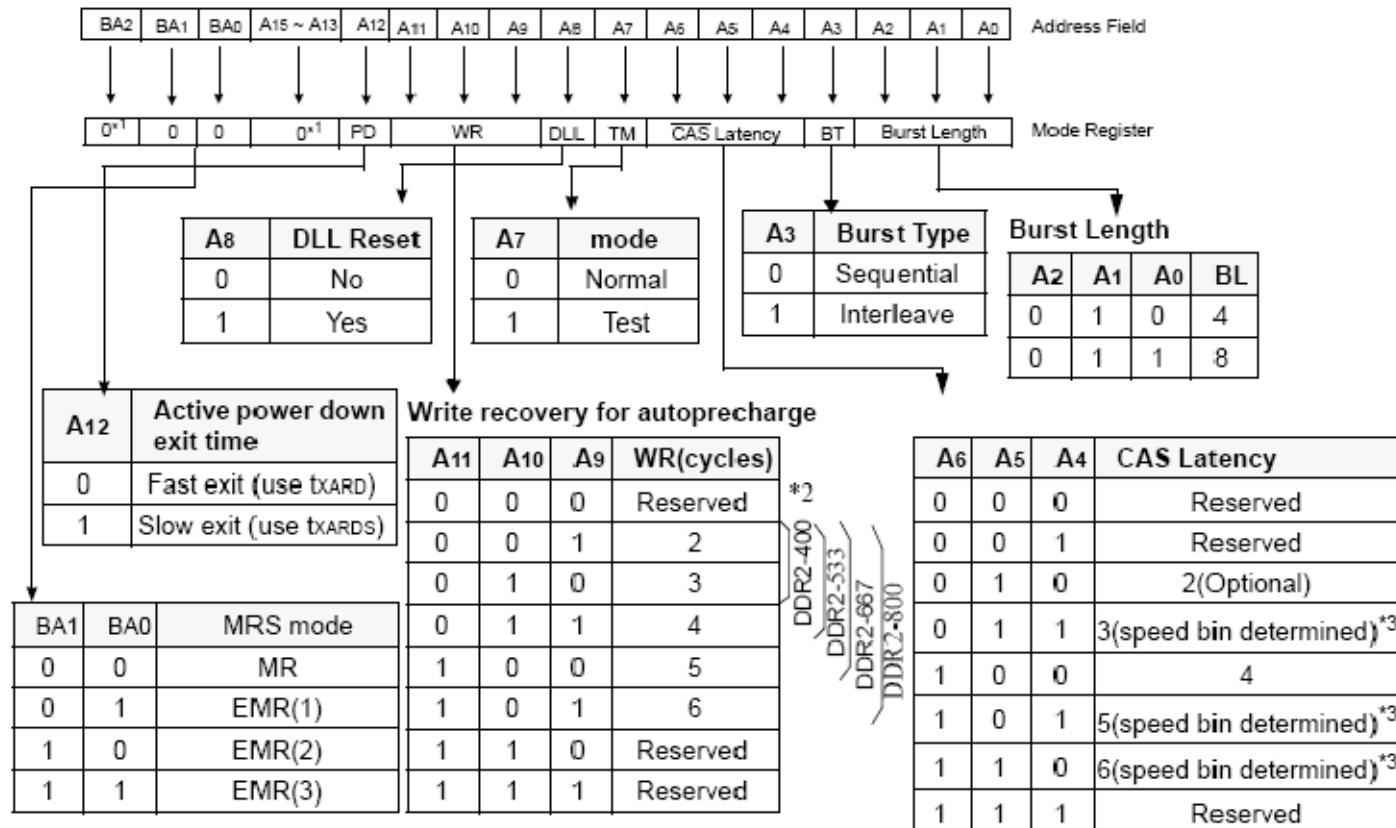

- Mode Register Set – Sometimes referred to as Load Mode Register.

- Mode Register Set issued to load the MRS and EMRS values via the Bank Address and Address lines.

- The MRS command can only be used when all banks are idle. No command can be issued after MRS command until  $t_{MRD}$  is met.

# Mode Register Set Waveforms

\*MRS = Mode Register Set Command used to initialize SDRAM registers

4 SDRAM registers to initialize consist of: MR (Mode Register), EMR (Extended-MR), EMR(2) and EMR(3)

OCD = Off-Chip Driver Impedance Calibration.

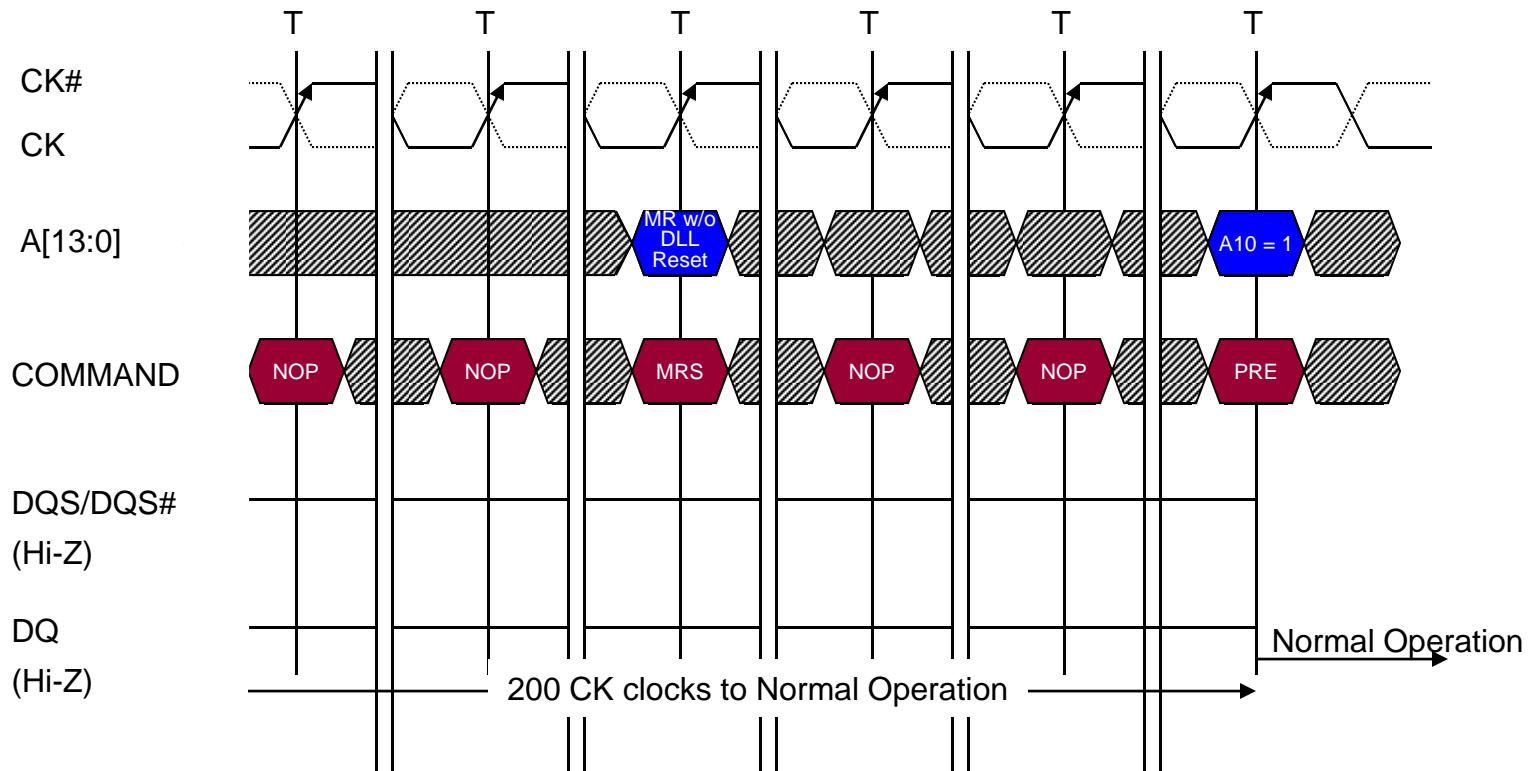

- The Activate command is used to open (activate) a row in a particular bank for a subsequent access.

- The values of BA0 through BA2 select the bank to be activated.

- The row remains active for accesses until a Precharge (or Read or Write with Autoprecharge) is issued to that bank.

- Only one row per bank can be open at a time.

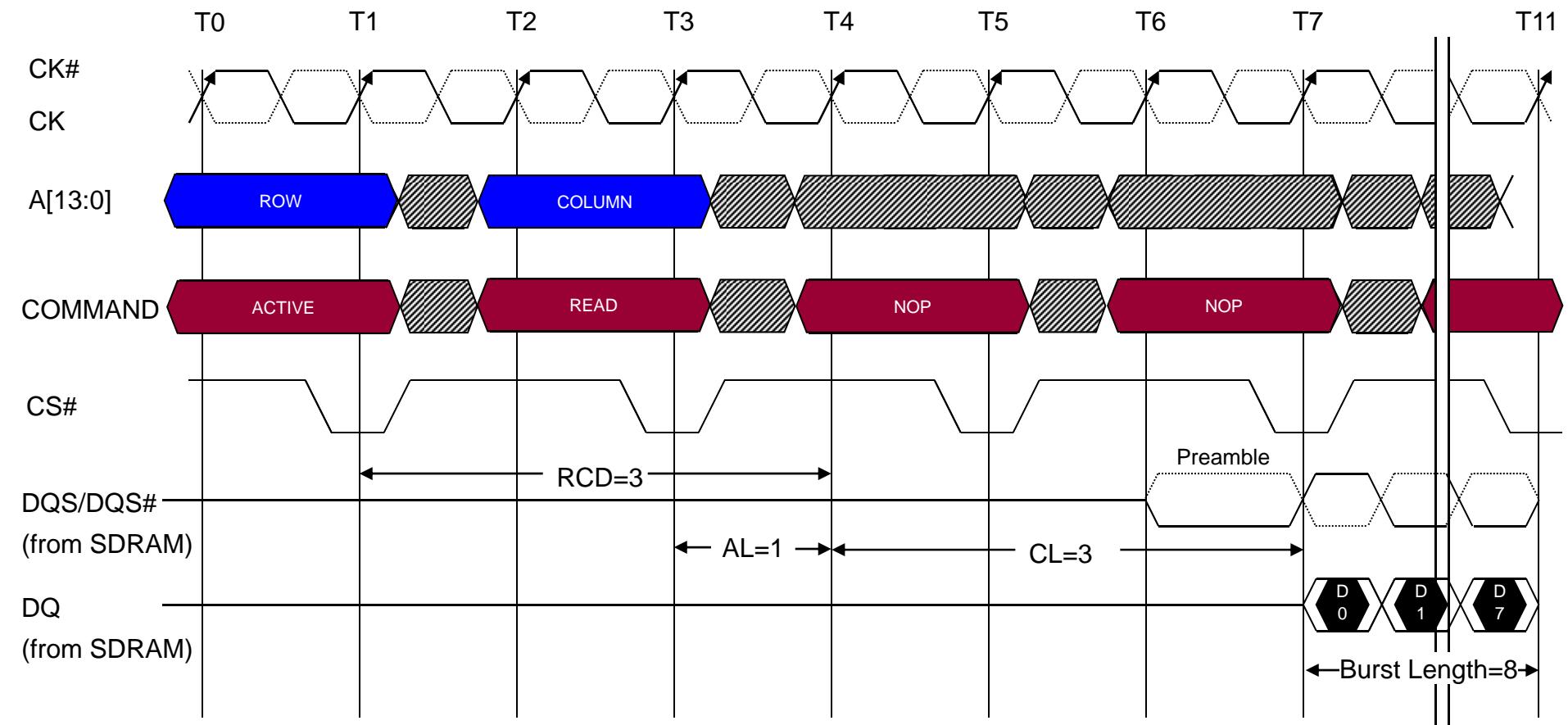

- There are typically 3 timings that are referred to for DIMM speed besides the frequency

- CL - Column Address Strobe Latency is the amount of time in base clocks from when CAS is asserted until data should be valid.

- DDR2 requires the clock interval to be in whole clocks.

- CAS latency is a function of the DRAMs internal speed. The faster the DRAM the lower the CAS Latency.

- RCD – RAS-to-CAS Delay is the time in base clocks required from an Activate to a Read or Write.

- RP – Time in base clocks required to precharge or write back a row.

- Example: DIMM might say on it 4 – 4 – 4

CL – RCD – RP

# Activate Waveform

107

$t_{RRD}$  is the Minimum time interval from one Bank Activate to another Bank (RAS to RAS delay)

$t_{RCD}$  is the Minimum time from activate to a read or write command (RAS to CAS delay)

**DDR2 400 3 - 3 - 3**

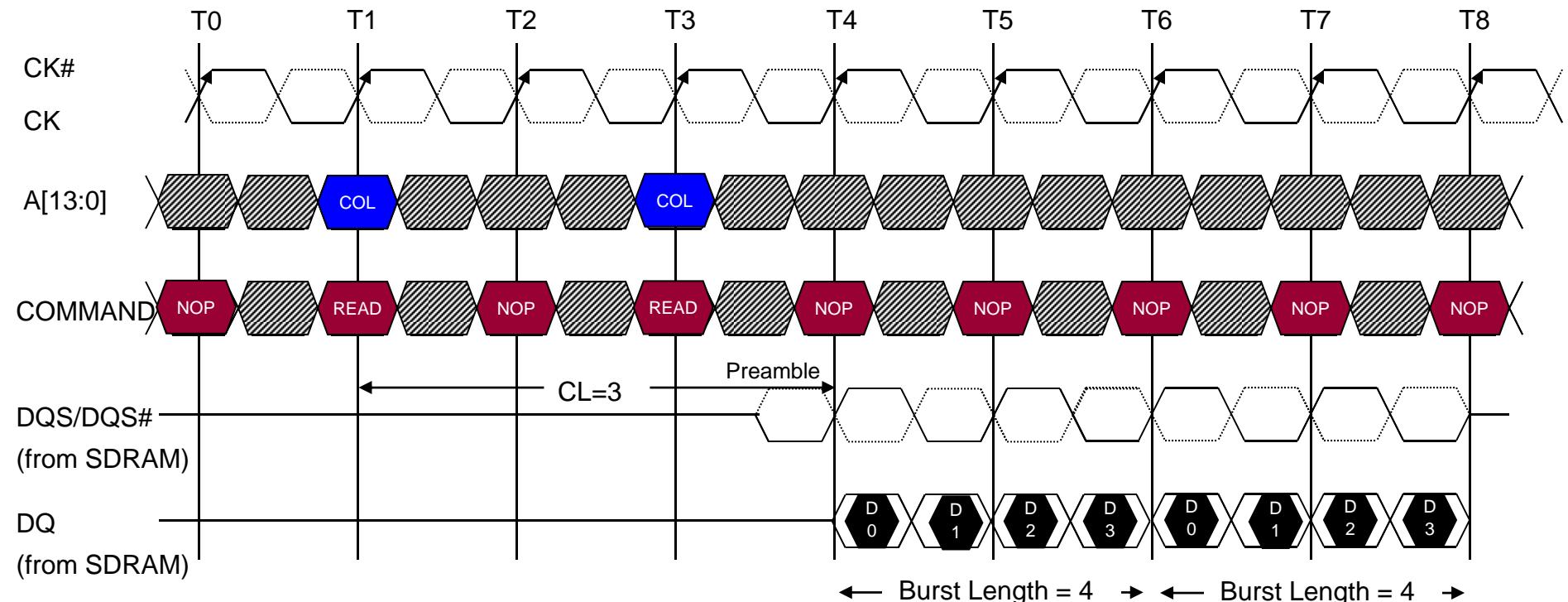

- The Read command is used to issue a burst read access to an active row. The value of BA0 through BA2 will determine the bank to be accessed.

- A0-Ax provide the column address.

- The value on A10 during the Read command determines whether or not to use Auto Precharge.

- If Auto Precharge is selected, the row currently active will be precharged at the end of the burst.

- All DDR SDRAM (DDR1, DDR2, DDR3) are burst oriented.

- Accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

- Two parameters define burst operation:

- Burst Type: Interleaved or Sequential

- Burst Length: 2, 4, or 8

- DDR1 supports burst of 2, 4, or 8.

- DDR2 supports burst of 4 or 8 only.

- DDR3 supports burst of 8 with option to chop to 4.

- When issuing back-to-back bursts of 4, CAS# can be asserted every other clock. In back-to-back bursts of 8, CAS# can be asserted every 4<sup>th</sup> clock.

- Programmed during initialization

- Burst type is programmed to be sequential or interleaved by bit A3 in the Mode Register (MR0).

- Interleaved is used on the FSB of all Intel chipsets and is also referred to as toggle mode.

- Sequential mode is used in all other PC-based designs, i.e., AMD.

- Burst length is programmed by A0-A2 in MR0 and determines the maximum number of column locations that can be accessed for a Read or Write command.

- All accesses for a burst take place within a block. The burst wraps within the block if a boundary is reached.

- The least significant address bit(s) is (are) used to select the starting location within the block.

- BL/2 is the minimum number of clocks to wait until the next CAS command

# DDR2 Burst Order

| Burst Length | Starting Column Address (A2,A1,A0) | Order of Access within a Burst        |                                         |

|--------------|------------------------------------|---------------------------------------|-----------------------------------------|

|              |                                    | Burst Type = Sequential (Linear wrap) | Burst Type = Interleaved (Toggle Intel) |

| 4            | 000                                | 0,1,2,3                               | 0,1,2,3                                 |

|              | 001                                | 1,2,3,0                               | 1,0,3,2                                 |

|              | 010                                | 2,3,0,1                               | 2,3,0,1                                 |

|              | 011                                | 3,0,1,2                               | 3,2,1,0                                 |

| 8            | 000                                | 0,1,2,3,4,5,6,7                       | 0,1,2,3,4,5,6,7                         |

|              | 001                                | 1,2,3,0,5,6,7,4                       | 1,0,3,2,5,4,7,6                         |

|              | 010                                | 2,3,0,1,6,7,4,5                       | 2,3,0,1,6,7,4,5                         |

|              | 011                                | 3,0,1,2,7,4,5,6                       | 3,2,1,0,7,6,5,4                         |

|              | 100                                | 4,5,6,7,0,1,2,3                       | 4,5,6,7,0,1,2,3                         |

|              | 101                                | 5,6,7,4,1,2,3,0                       | 5,4,7,6,1,0,3,2                         |

|              | 110                                | 6,7,4,5,2,3,0,1                       | 6,7,4,5,2,3,0,1                         |

|              | 111                                | 7,4,5,6,3,0,1,2                       | 7,6,5,4,3,2,1,0                         |

# DDR3 Burst Order

| Burst Length | Read/ Write | Starting Column Address (A2,A1,A0) | Order of Access within a Burst        |                                   |

|--------------|-------------|------------------------------------|---------------------------------------|-----------------------------------|

|              |             |                                    | Burst Type = Sequential (Linear wrap) | Burst Type = Interleaved (Toggle) |

| 4 Chop       | Read        | 000                                | 0,1,2,3,Z,Z,Z,Z                       | 0,1,2,3,Z,Z,Z,Z                   |

|              |             | 001                                | 1,2,3,0,Z,Z,Z,Z                       | 1,0,3,2,Z,Z,Z,Z                   |

|              |             | 010                                | 2,3,0,1,Z,Z,Z,Z                       | 2,3,0,1,Z,Z,Z,Z                   |

|              |             | 011                                | 3,0,1,2,Z,Z,Z,Z                       | 3,2,1,0,Z,Z,Z,Z                   |

|              |             | 100                                | 4,5,6,7,Z,Z,Z,Z                       | 4,5,6,7,Z,Z,Z,Z                   |

|              |             | 101                                | 5,6,7,4,Z,Z,Z,Z                       | 5,4,7,6,Z,Z,Z,Z                   |

|              |             | 110                                | 6,7,4,5,Z,Z,Z,Z                       | 6,7,4,5,Z,Z,Z,Z                   |

|              |             | 111                                | 7,4,5,6,Z,Z,Z,Z                       | 7,6,5,4,Z,Z,Z,Z                   |

|              | Write       | 0VV                                | 0,1,2,3,X,X,X,X                       | 0,1,2,3,X,X,X,X                   |

|              |             | 1VV                                | 4,5,6,7,X,X,X,X                       | 4,5,6,7,X,X,X,X                   |

| 8            | Read        | 000                                | 0,1,2,3,4,5,6,7                       | 0,1,2,3,4,5,6,7                   |

|              |             | 001                                | 1,2,3,0,5,6,7,4                       | 1,0,3,2,5,4,7,6                   |

|              |             | 010                                | 2,3,0,1,6,7,4,5                       | 2,3,0,1,6,7,4,5                   |

|              |             | 011                                | 3,0,1,2,7,4,5,6                       | 3,2,1,0,7,6,5,4                   |

|              |             | 100                                | 4,5,6,7,0,1,2,3                       | 4,5,6,7,0,1,2,3                   |

|              |             | 101                                | 5,6,7,4,1,2,3,0                       | 5,4,7,6,1,0,3,2                   |

|              |             | 110                                | 6,7,4,5,2,3,0,1                       | 6,7,4,5,2,3,0,1                   |

|              |             | 111                                | 7,4,5,6,3,0,1,2                       | 7,6,5,4,3,2,1,0                   |

|              | Write       | VVV                                | 0,1,2,3,4,5,6,7                       | 0,1,2,3,4,5,6,7                   |

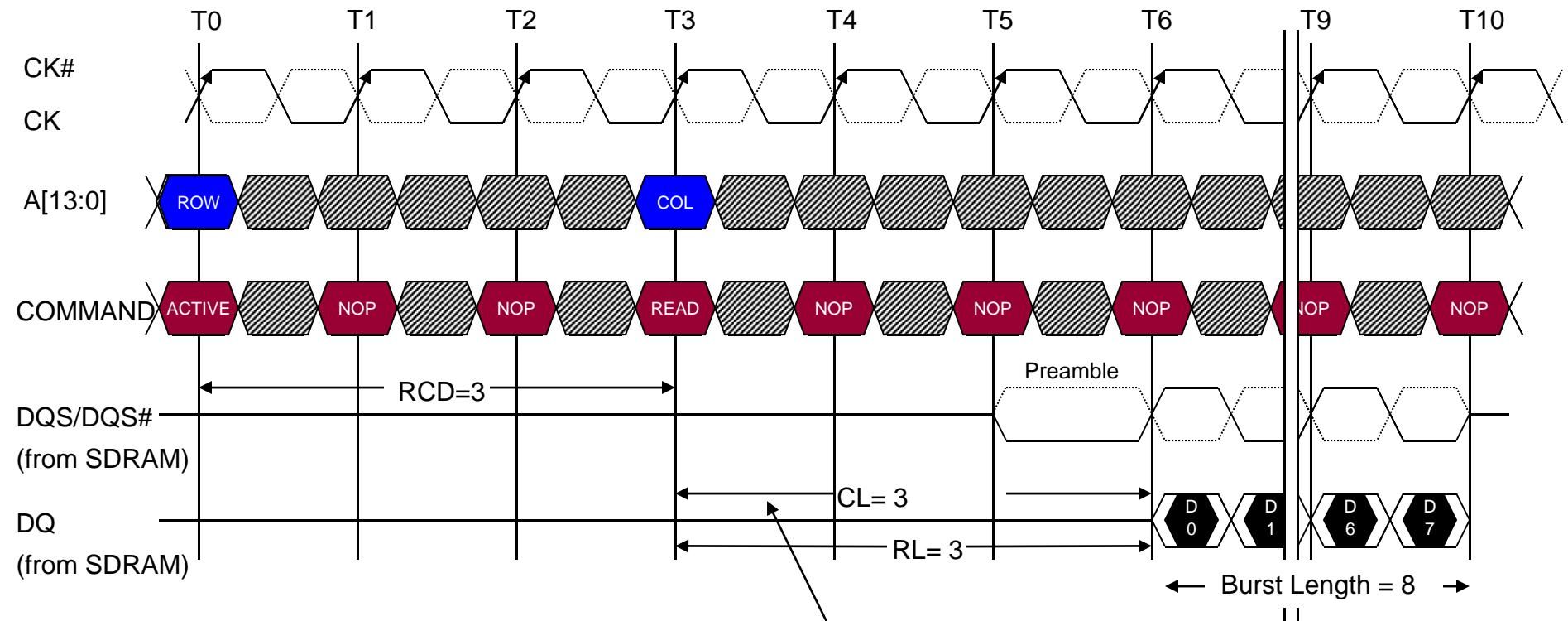

# Read Burst without Additive Latency

113

CL = CAS# Latency

AL = Additive Latency

RCD = RAS#-to-CAS# delay

RL = Read Latency

Burst Length = 8

**DDR2 400** 3 - 3 - 3

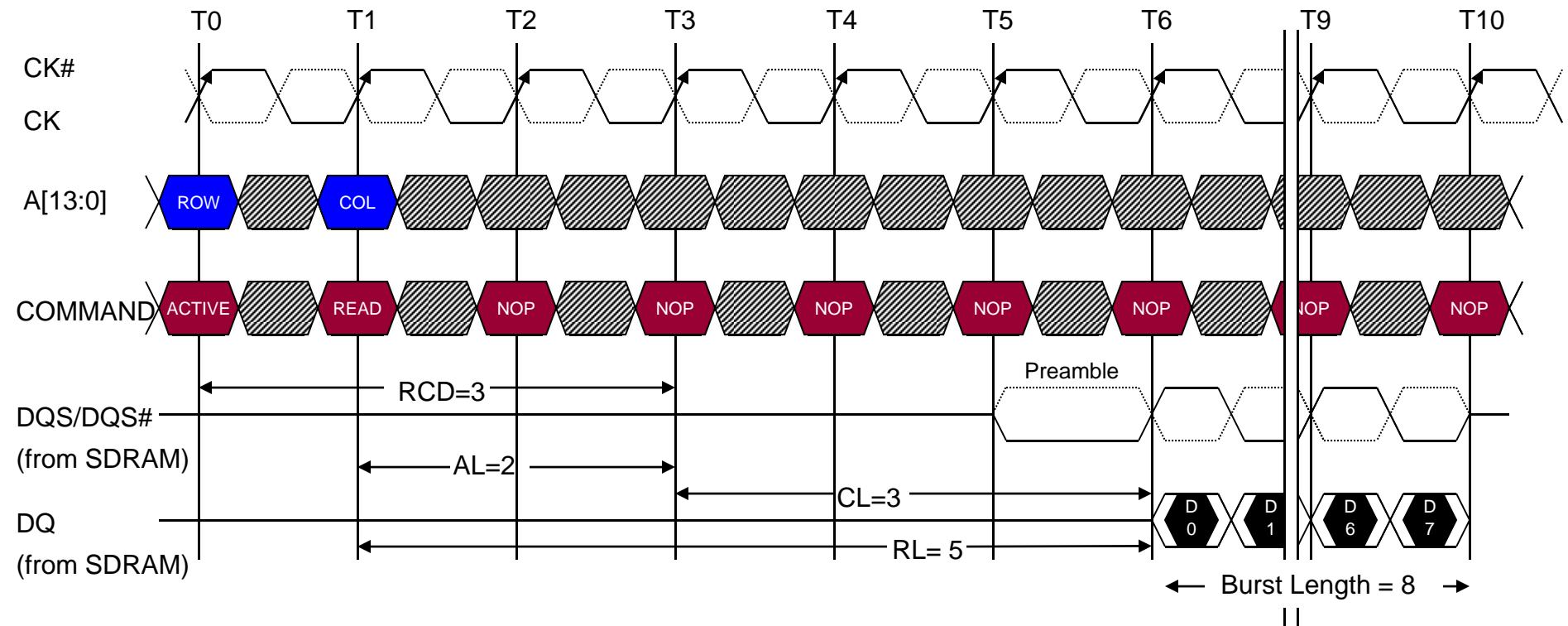

# Read Burst with Additive Latency

114

CL = CAS# Latency

AL = Additive Latency

RCD = RAS#-to-CAS# delay

RL = Read Latency

Burst Length = 8

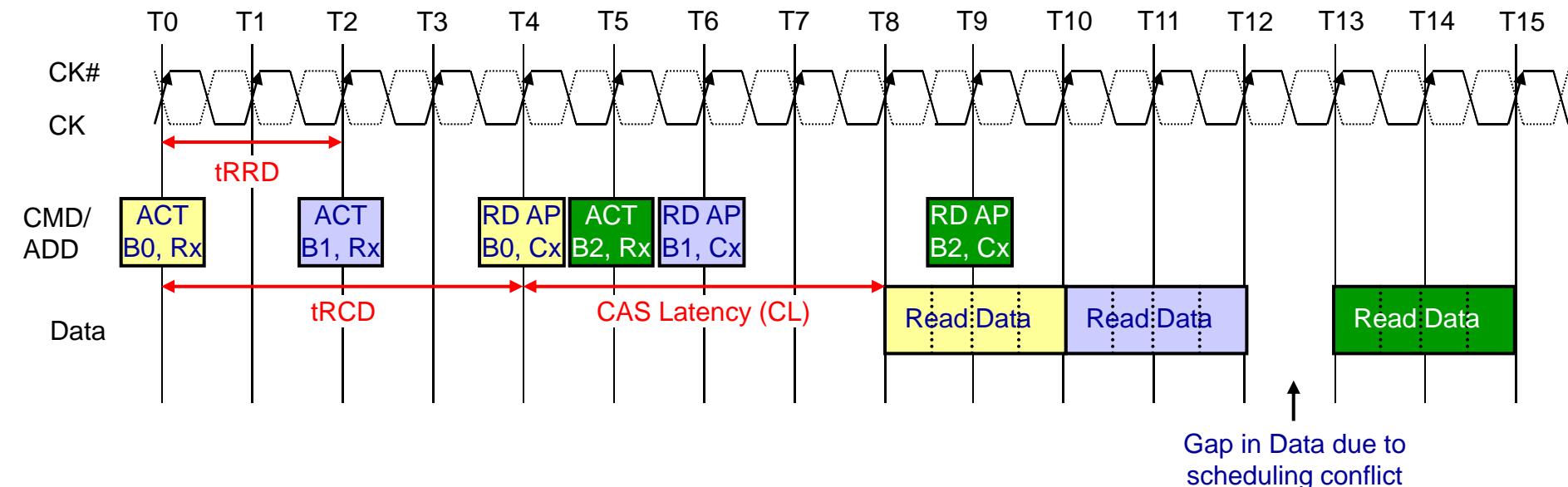

# Why Have Additive Latency?

## DDR2 with AL=0, CL=4

- The Read Command for Bank0 was sent during cycle T4.

- The memory controller would have liked to send the Activate Bank2 command on cycle T4 instead of T5.

- Due to this delay in activating Bank2, it results in a gap in the data stream being returned by the SDRAM because of this scheduling conflict.

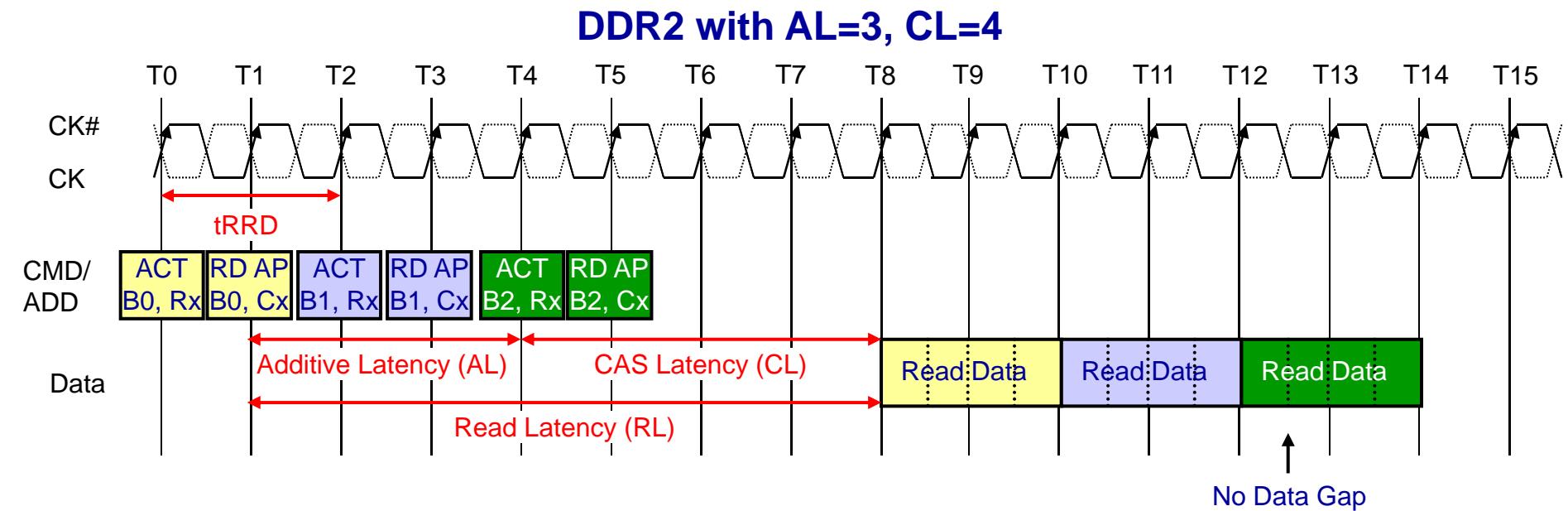

# Why Have Additive Latency?

- DDR2 SDRAM can queue commands and schedule them at the appropriate time based on the programmed value of Additive Latency (AL).

- The memory controller no longer has a scheduling conflict because the commands can be sent to SDRAM back-to-back and the SDRAM will schedule them at the appropriate time.

- The data gap seen in the previous example no longer exists.

# Read Burst Consecutive

CL = CAS# Latency

AL = Additive Latency

RCD = RAS#-to-CAS# delay

Burst Length = 4

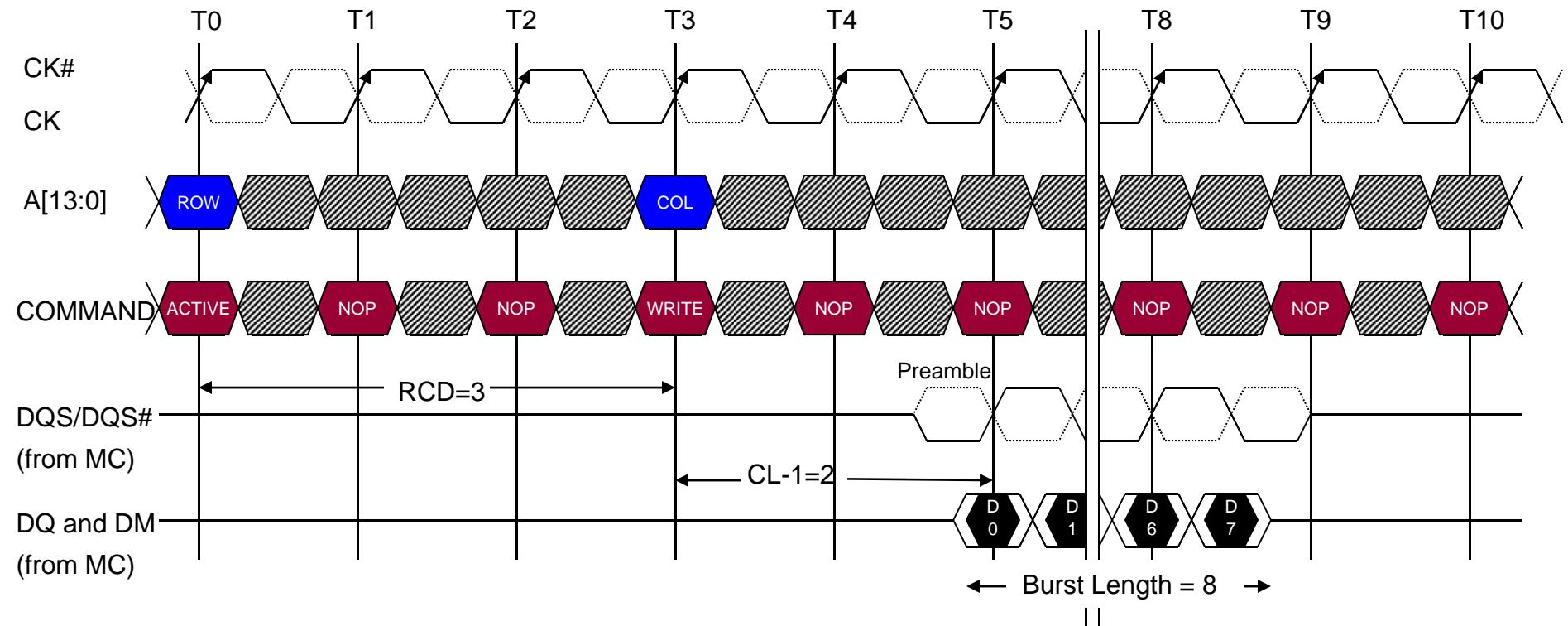

- The Write command is used to issue a burst write to an active row.

- The value of BA0 through BA2 will determine the bank to be accessed. A0-Ax provide the column address.

- The value on A10 determines whether or not Auto Precharge is to be used. If Auto Precharge is selected the row currently accessed will be precharged at the end of the burst.

- Write data appearing on the DQ pins are written to the memory array if DM is registered low. If DM is registered high the data is ignored.

# Write Waveform

CL = CAS# Latency

AL = Additive Latency

RCD = RAS#-to-CAS# delay

WL = Write Latency

Burst Length = 8

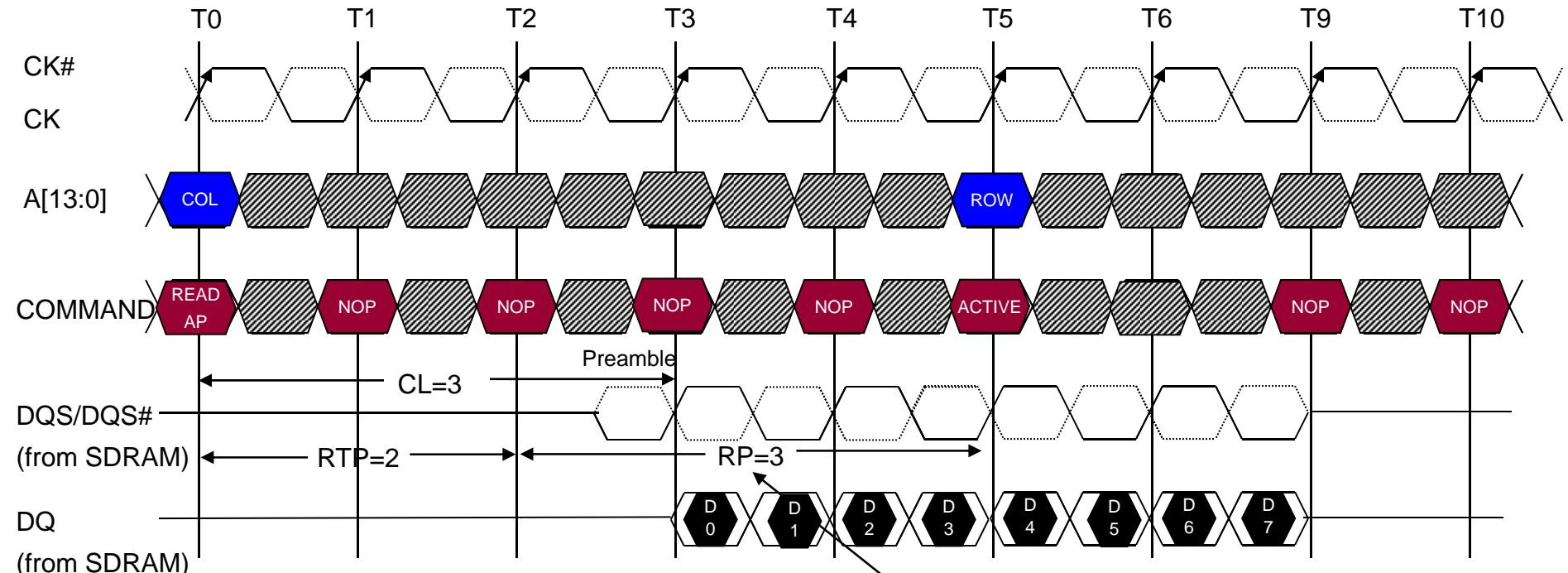

- The Precharge command deactivates the open (active) row in a particular bank, or in all banks.

- The bank(s) will be ready for an Activate command after  $t_{RP}$  is met. A10 determines whether all or one bank is to be precharged.

- In the case where only one bank is to be precharged, BA0-BA2 will select the bank. Once a bank is precharged it is in the idle state.

- If no bank is active a Precharge is seen as a NOP.

- The same effect as with a separate Precharge command, but doesn't require a separate command.

- Indicated by asserting A10 during a Read or Write command.

- Auto Precharge ensures that the Precharge is going to happen at the earliest possible time after the Read or Write command completes.

# Read with Auto Precharge

$t_{RP}$  is the time required to internally precharge an active Row until the next command

Min Huang (min.huang@leecy.com)

Do Not Distribute

## Refresh

Controller told async DRAM chips which row to refresh.

## Auto Refresh

SDRAM feature. CAS-before-RAS refresh.

Row counters are inside the SDRAM chips.

Controller only tells chips when to refresh, not which row.

Simply called “refresh” now.

## Self Refresh

System powered off; DRAM fully powered.

Refresh interval timer inside SDRAM chips.

Interval is fixed before starting self refresh.

## Auto Self Refresh

Self refresh where DDR3 chips automatically choose their refresh interval based on their temperature.

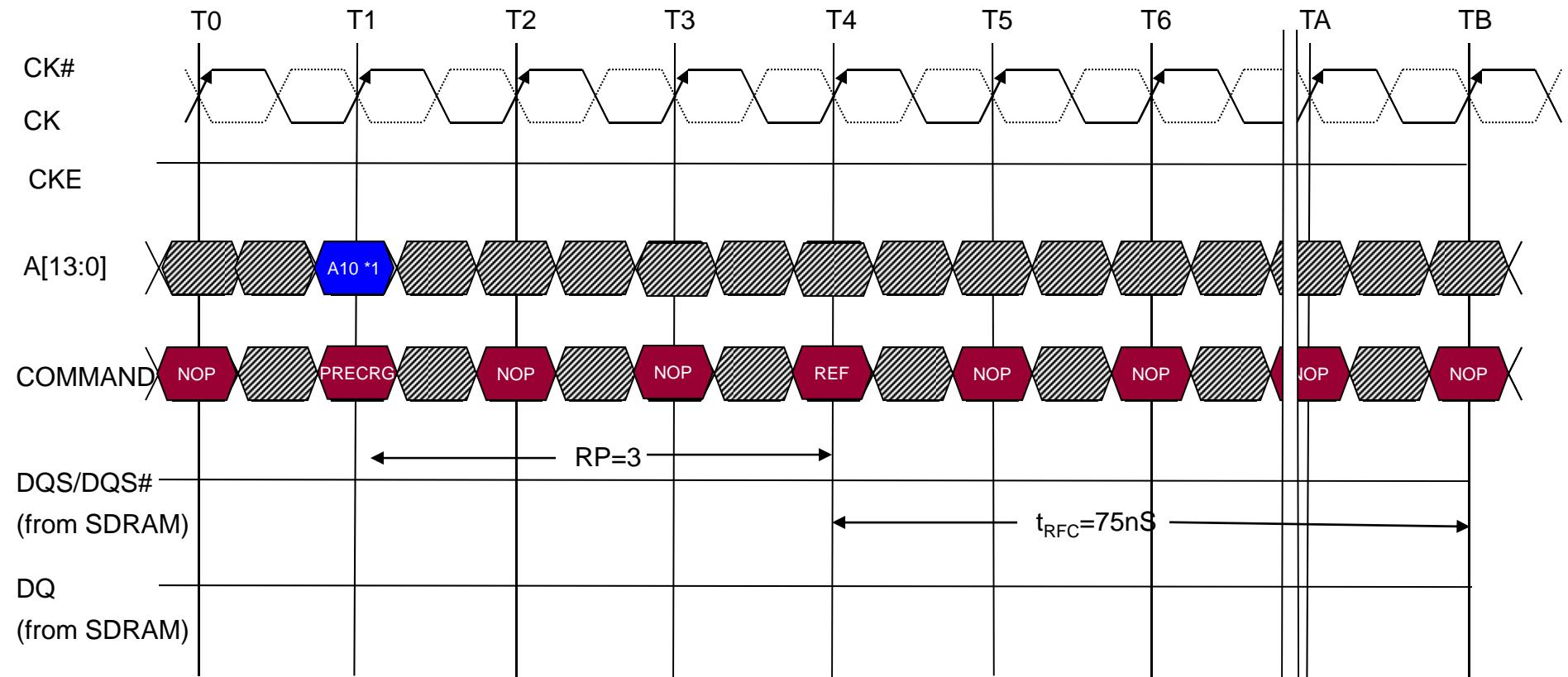

- Refresh is used in normal operation and is the same as CAS-before-RAS (CBR) refresh in older DRAM.

- This command is non-persistent and must be issued every time a refresh is required. No address is required.

- The address is internally generated.

- Refresh can be posted up to 8 times. This means the max time can be as much as  $9 \times t_{REFI}$ . That is the Refresh Interval ( $t_{REFI}$ )  $\times$  8 plus the current Refresh command (giving 9).

- No more than 16 Refresh commands may be issued within  $2 \times t_{REFI}$ .

- The minimum time between Refresh commands is Refresh Cycle Time ( $t_{RFC}$ ).

- The refresh period is 64ms (32ms for high temp) which equals one refresh every 7.8us ( $t_{REFI}$ ) for a device with 8192 rows.

- A single refresh command may refresh one or more Rows. For example here are the refresh requirements for different densities.

- $t_{RFC}$  Refresh Cycle Time is how long it takes for the DRAM to finish the refresh command.

| Density | DDR2 $t_{RFC}$ | Estimated number of Rows Refreshed, depending on organization |

|---------|----------------|---------------------------------------------------------------|

| 256Mb   | 75ns           | 1 (8192 Rows)                                                 |

| 512Mb   | 75-105ns       | 1-2 (8192,16384 Rows)                                         |

| 1Gb     | 105-127.5ns    | 1-2 (8192,16384 Rows)                                         |

| 2Gb     | 127.5-197.5ns  | 2-4 (16384, 32768 Rows)                                       |

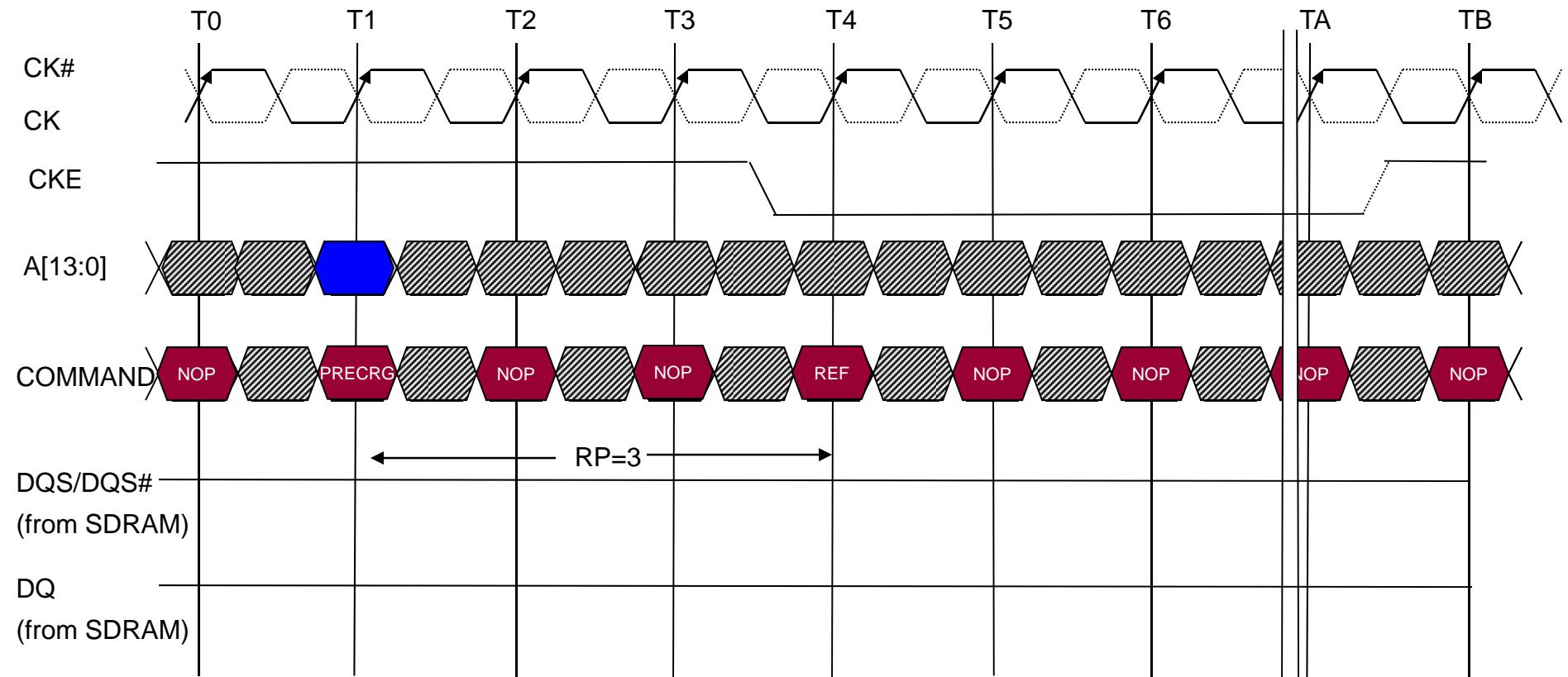

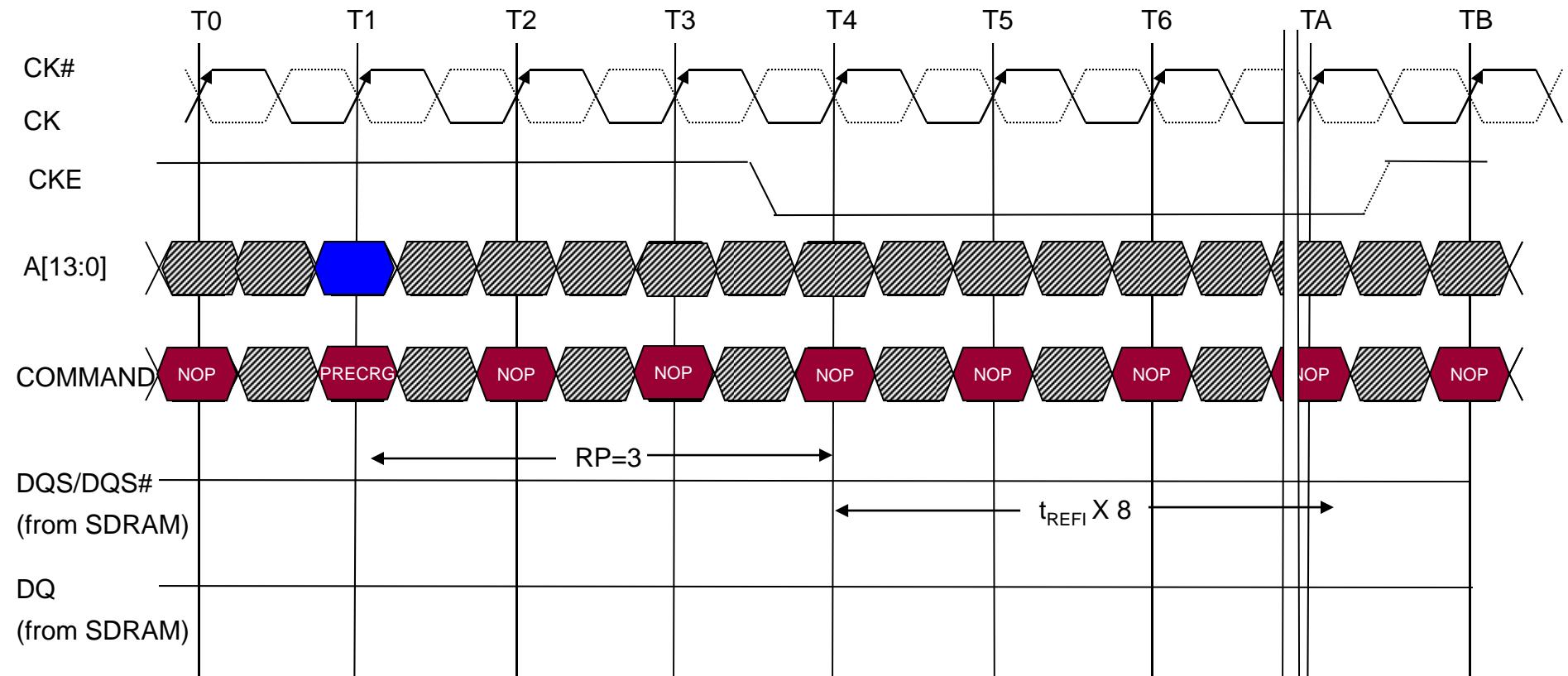

\*1 A10 must be high for more than 1 bank to get Precharged. Precharge all must be done before entering the Refresh mode.

$t_{RFC}$  is the refresh cycle time

- Self Refresh is the same command as Refresh except CKE is low. This command is used to keep data integrity while the rest of the system is powered down. The DLL is automatically disabled going into self refresh and automatically enabled coming out of a Self Refresh state. CKE must stay low during Self Refresh.

- Here is the procedure for coming out of Self Refresh:

- CK and CK# must be stable before CKE goes high.

- CKE goes high

- NOP command issued for tXSNR (Exit Self Refresh to a Non Read Command) because time is required for internal refreshes to complete

- Refresh command is recommended

- No DLL reset is required

# Self Refresh Waveform

128

All banks must be precharged before entering the Self Refresh mode.

Refresh with CKE low will cause the DRAM to go into a Self Refresh state.

$t_{RP}$  is the time required to internally precharge an active Row until the next command

- No Operation - NOP command is used to perform a NOP to the selected DRAM (DRAM whose CS# = low). Operations in progress are not affected.

- Deselect - Deselect (CS# = high) prevents new commands from being executed. DRAM is effectively disabled.

- Prevents unwanted commands from being registered in an idle state.

- Power Down – Also called CKE power down. CKE is brought low synchronously with CS and the other commands high. This low power state can only be held for  $8 \times t_{REFI}$  of the device because no refreshes can happen in this state. The  $8 \times t_{REFI}$  is due to the fact that refresh can be posted up to 8 times.

- Clock must be active in this state.

- Fast exit refers to leaving the DLL on and Slow Exit turns the DLL off. If Slow exit is used the DLL must relock.

Precharge Power Down shown. If any banks are left open, this becomes Active Power Down.

$t_{REFI}$  is Refresh interval time times the 8 posted refreshes until exit of Power Down is required.

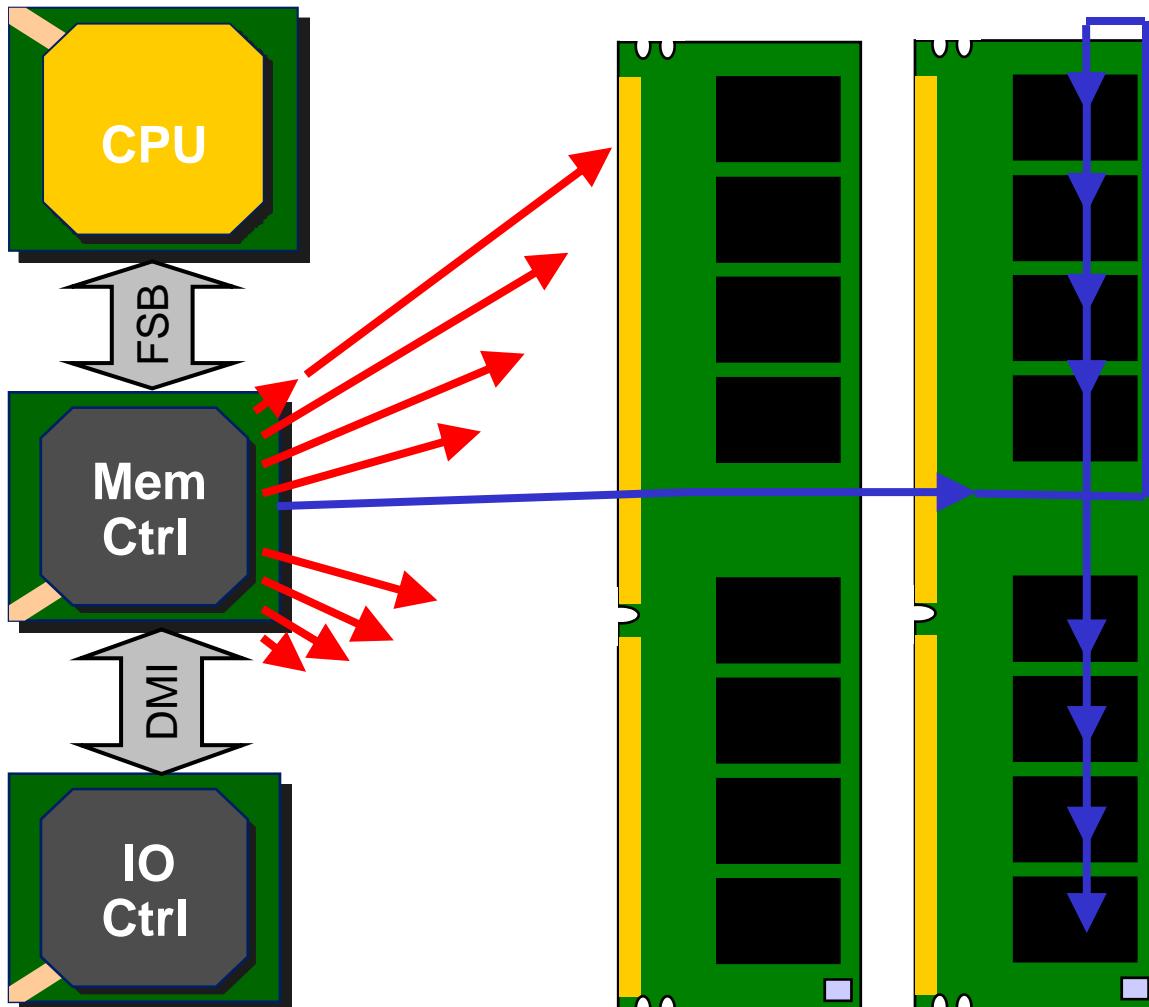

- 1T and 2T timings

- Depending on how many DIMMs the system needs to support, the DRAM controller may use one of 2 different address and command timing schemes.

- 1T: The address and command signals are held active by the controller for 1 clock. This allows for faster turnaround times.

- 2T: The address and command signals are held active by the controller for 2 clocks. For systems with more loads, this allows for longer setup and hold times. Control signals (CS#, CKE, ODT) must still obey 1T timing.

# 2T Timing Example

# DDR Initialization

Min Huang(min.huang@ lecroy.com)

Do Not Distribute

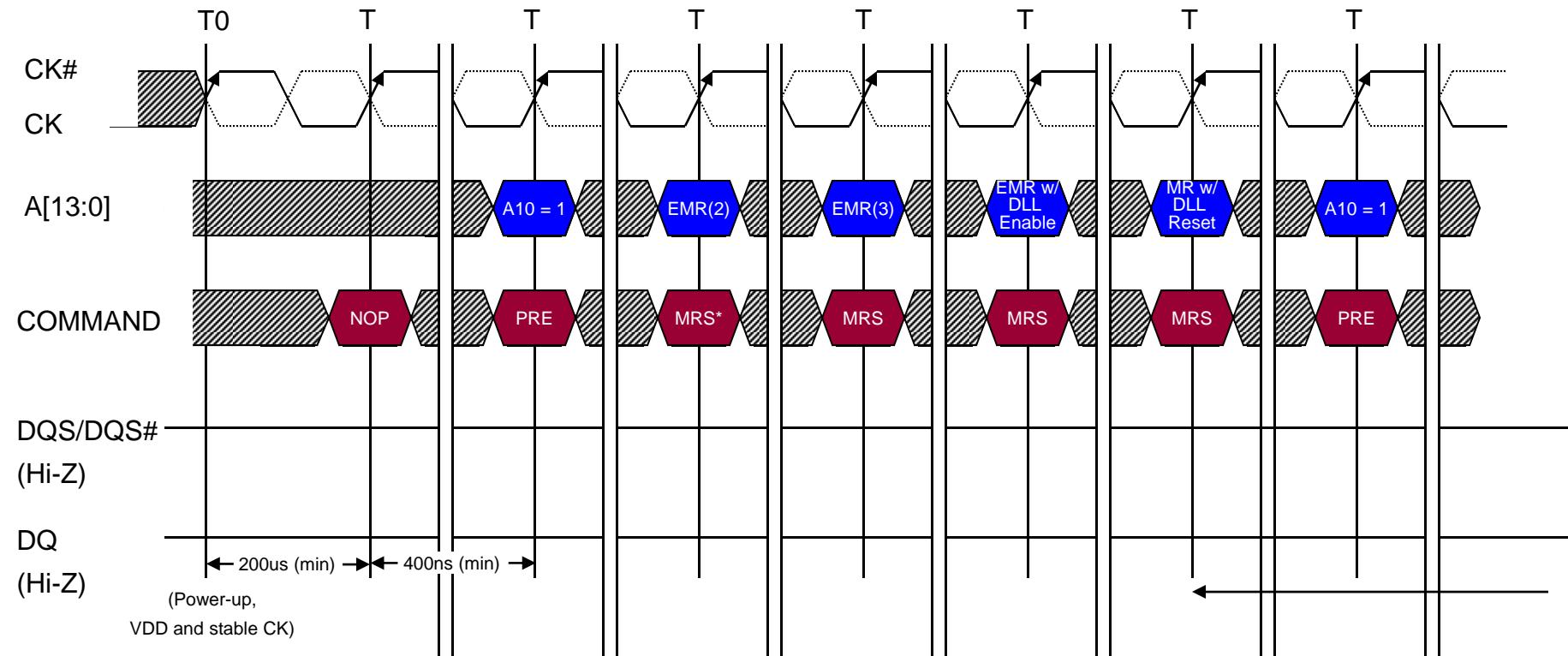

- DDR SDRAMs must be powered up and initialized in a very specific sequence to ensure stable working parts.

- Every time power is lost the procedure must be repeated.

- The initialization code is typically held in firmware and is often referred to as JEDEC initialization.

## ➤ Step 1

- Apply power. Keep CKE below  $0.2 \times \text{VDDQ}$  and ODT LOW. All other inputs may be undefined.

- Refer to the JESD79-2C standard for details about the allowable voltage ramp times.

## ➤ Step 2

- Start clock and maintain stable condition with CKE held low.

## ➤ Step 3

- For the minimum of 200 us after stable power and stable clock (CK, CK#), then apply NOP or Deselect & take CKE HIGH.

## ➤ Step 4

- Wait minimum of 400 ns then issue precharge all command. NOP or Deselect applied during 400 ns period.

- Step 5

- Issue MRS command to EMR2.

- Step 6

- Issue MRS command to EMR3.

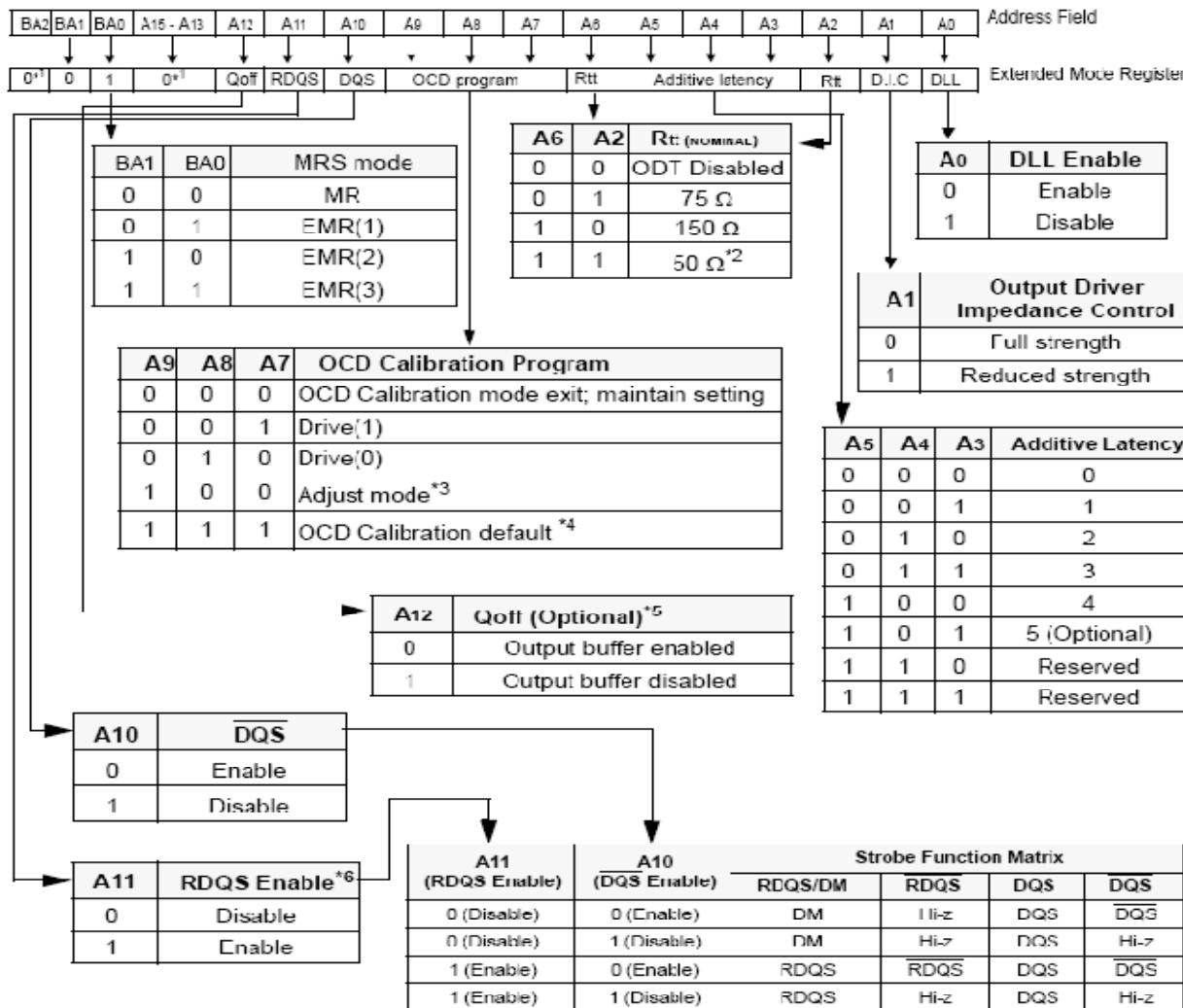

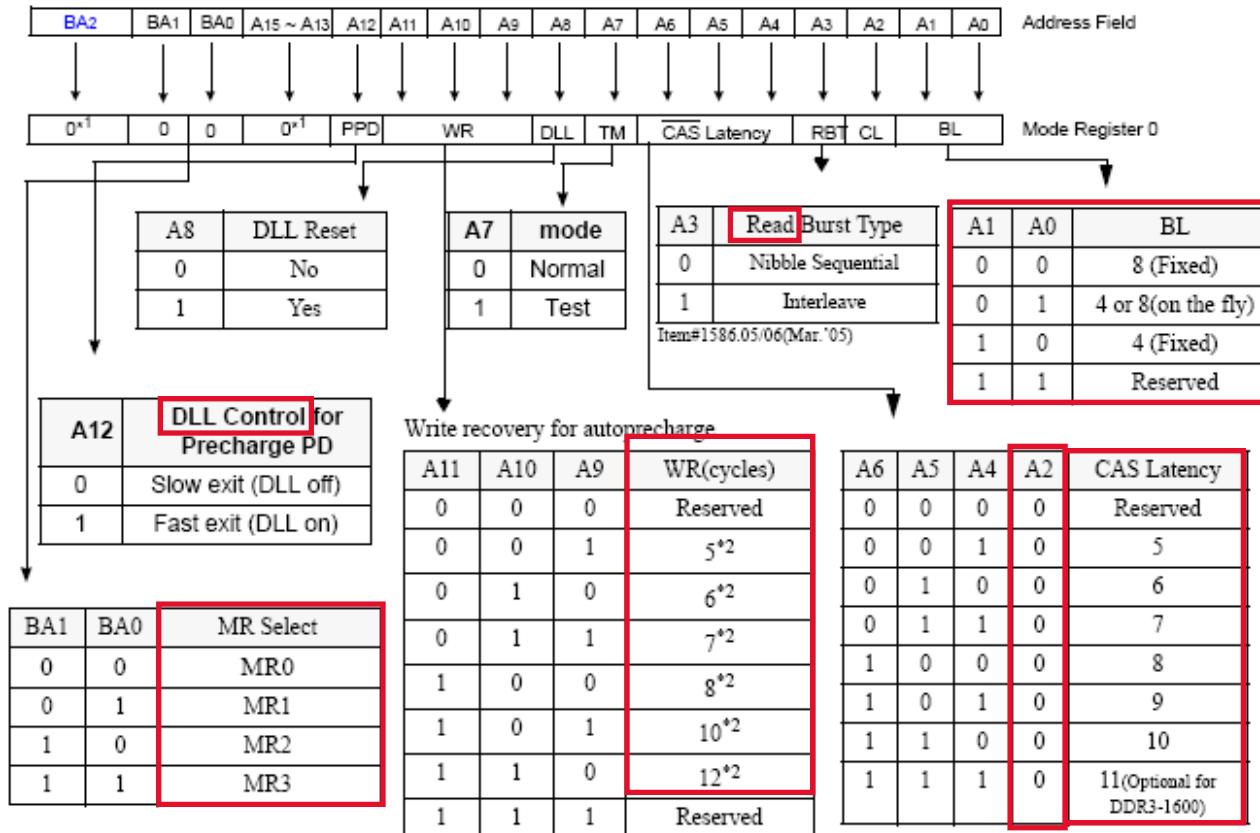

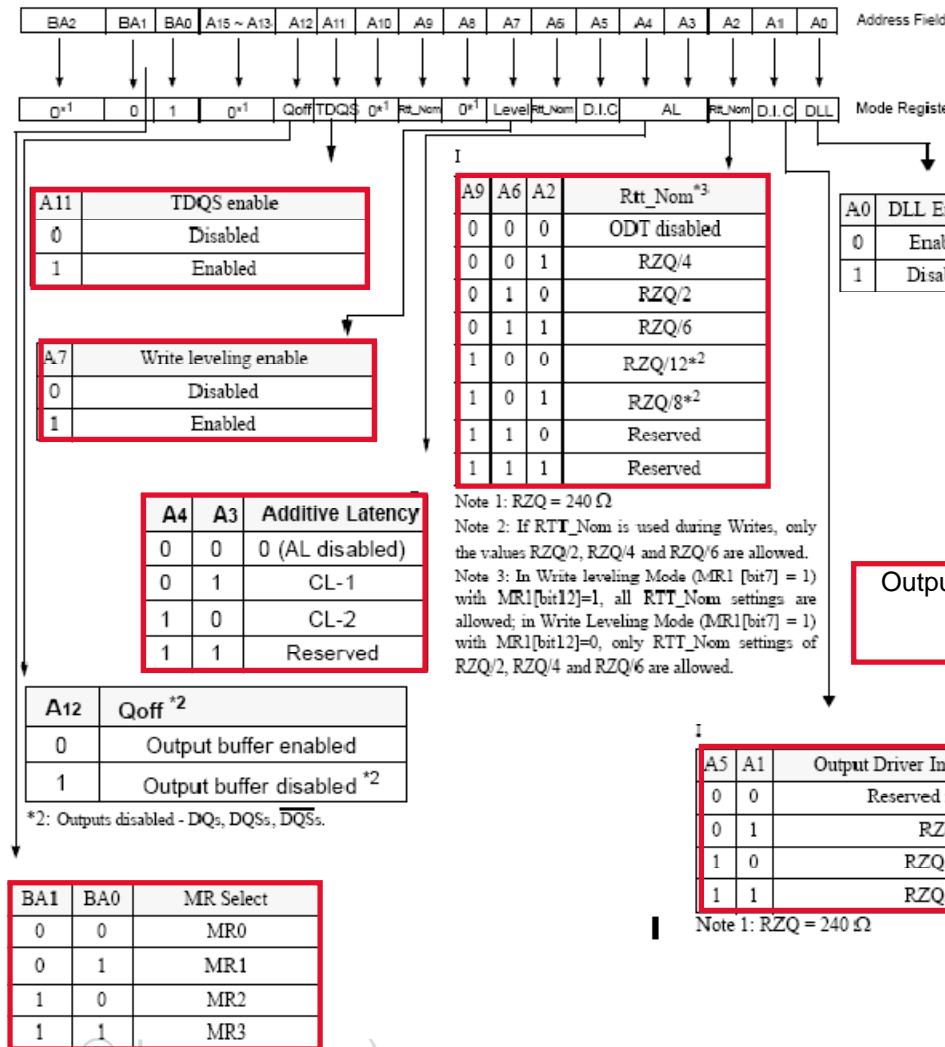

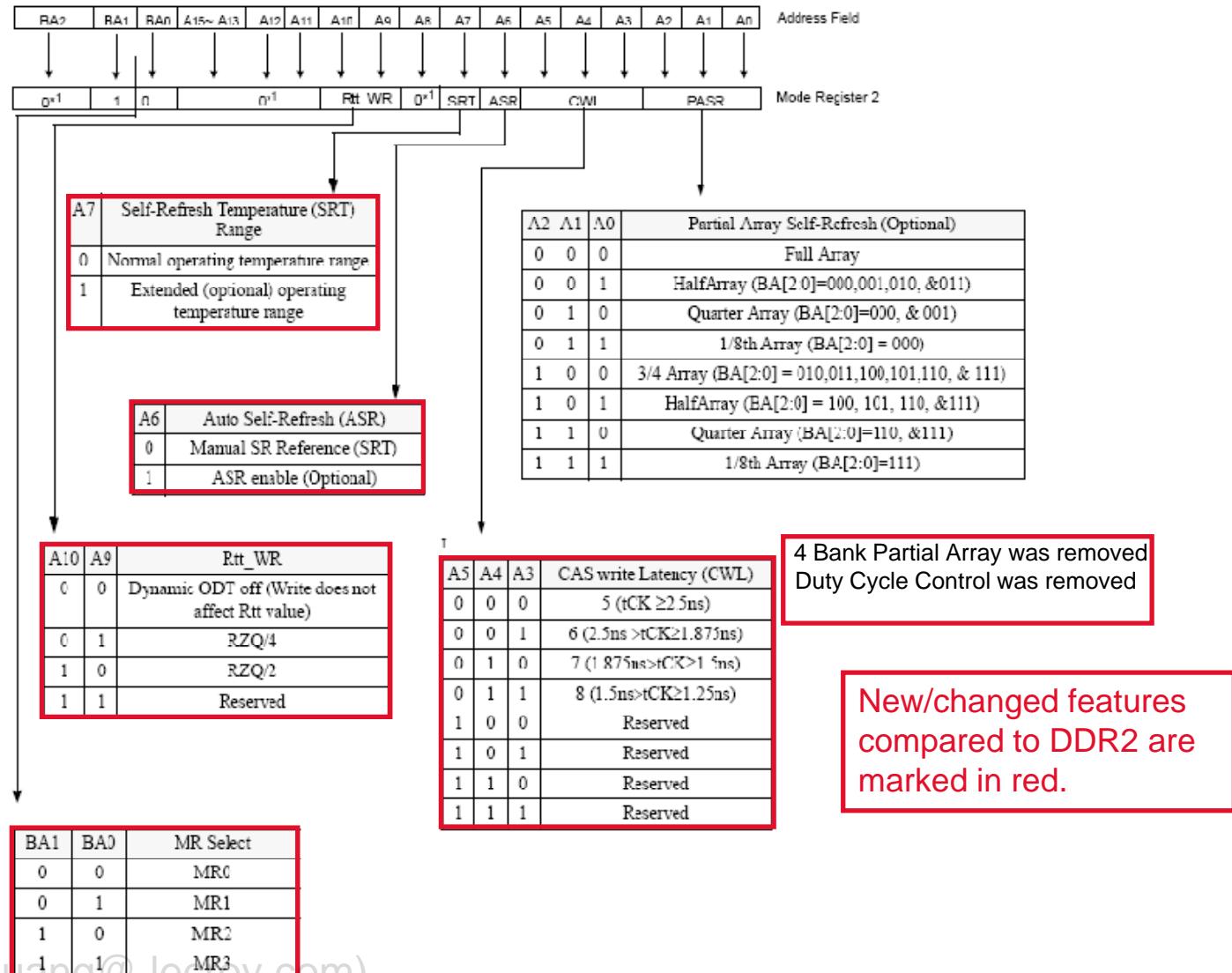

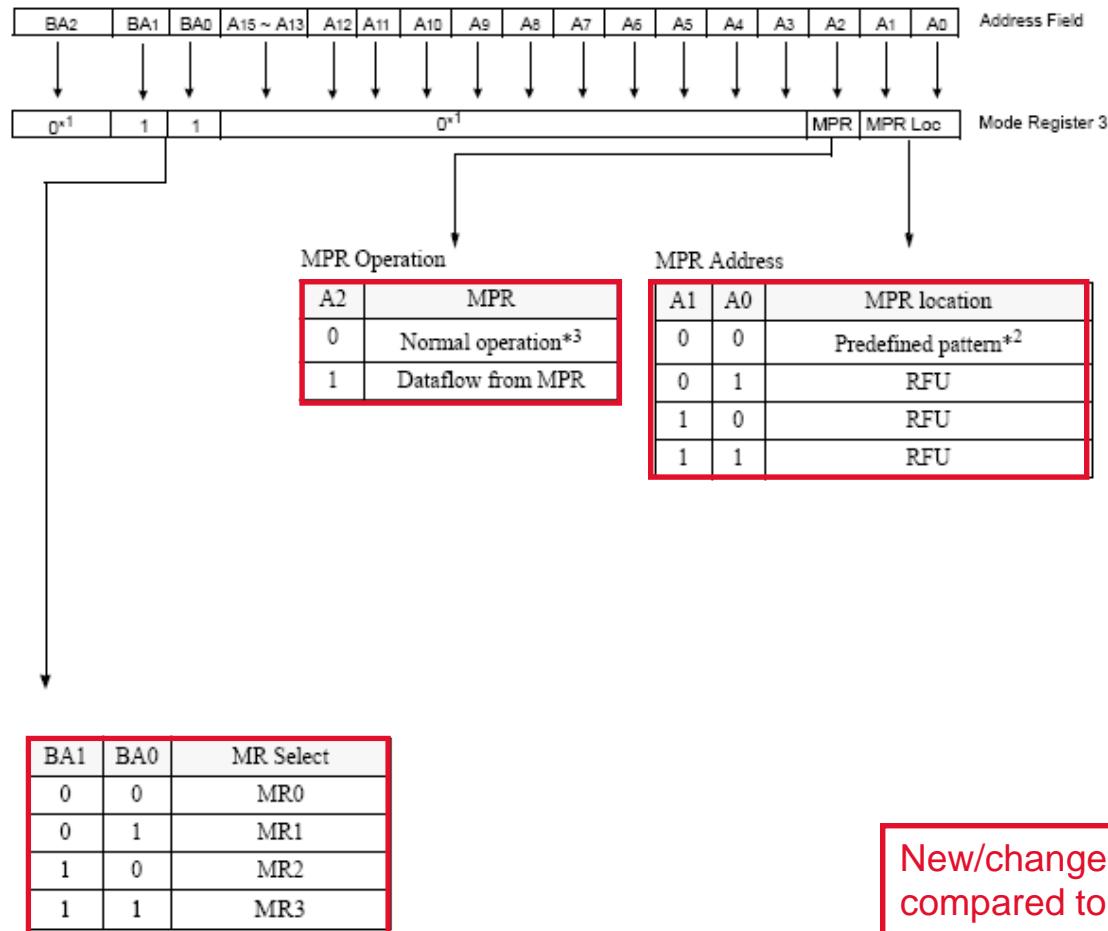

- Let's see what's in the mode registers and also see how we learn what values to program into the mode registers.

- Mode Register (MR) & Extended Mode Register (EMR)

- The mode registers are used to define the specific mode of operation of the SDRAM

- The default value for these registers is not defined.

- Mode registers will retain all information until rewritten or power is removed from the device except bit A8 (DLL reset) which is self clearing

- Reprogramming the mode registers during operation will not alter the information held in the DRAM

- The Bank Address bits are used to determine which mode register is being written to.

- The Address bus is used to write to each of the registers.

- Why is the Address bus used to program Mode Registers??

# Step by Step DDR2 Initialization MR0

NOTE 1 BA2 and A13-A15 are reserved for future use and must be set to 0 when programming the MR.

NOTE 2 For DDR2-400/533, WR (write recovery for autorecharge) min is determined by tCK max and WR max is determined by tCK min. WR in clock cycles is calculated by dividing tWR (in ns) by tCK (in ns) and rounding up to the next integer ( $WR[\text{cycles}] = RU\{ tWR[\text{ns}] / tCK[\text{ns}] \}$ , where RU stands for round up). For DDR2-667/800, WR min is determined by tCK(avg) max and WR max is determined by tCK(avg) min. WR[cycles] = RU { tWR[ns] / tCK(avg)[ns] }, where RU stands for round up. The mode register must be programmed to this value. This is also used with tRP to determine tDAL.

NOTE 3 Speed bin determined. Not required on all speed bins.

# Step by Step DDR2 Initialization EMR1

NOTE 1 BA2 and A13-A15 are reserved for future use and must be set to 0 when programming the EMR(1).

NOTE 2 Optional for DDR2-400/533/667, mandatory for DDR2-800.

NOTE 3 When Adjust mode is issued, AL from previously set value must be applied.

NOTE 4 After setting to default, OCD calibration mode needs to be exited by setting A9-A7 to 000. Refer to section 2.4.3 for detailed information.

NOTE 5 Output disabled - DQs, DQ9s, DQ3s, RDQS, RDQS. This feature is used in conjunction with DIMM IDD measurements when IDDQ is not desired to be included.

NOTE 6 If RDQS is enabled, the DM function is disabled. RDQS is active for reads and don't care for writes.

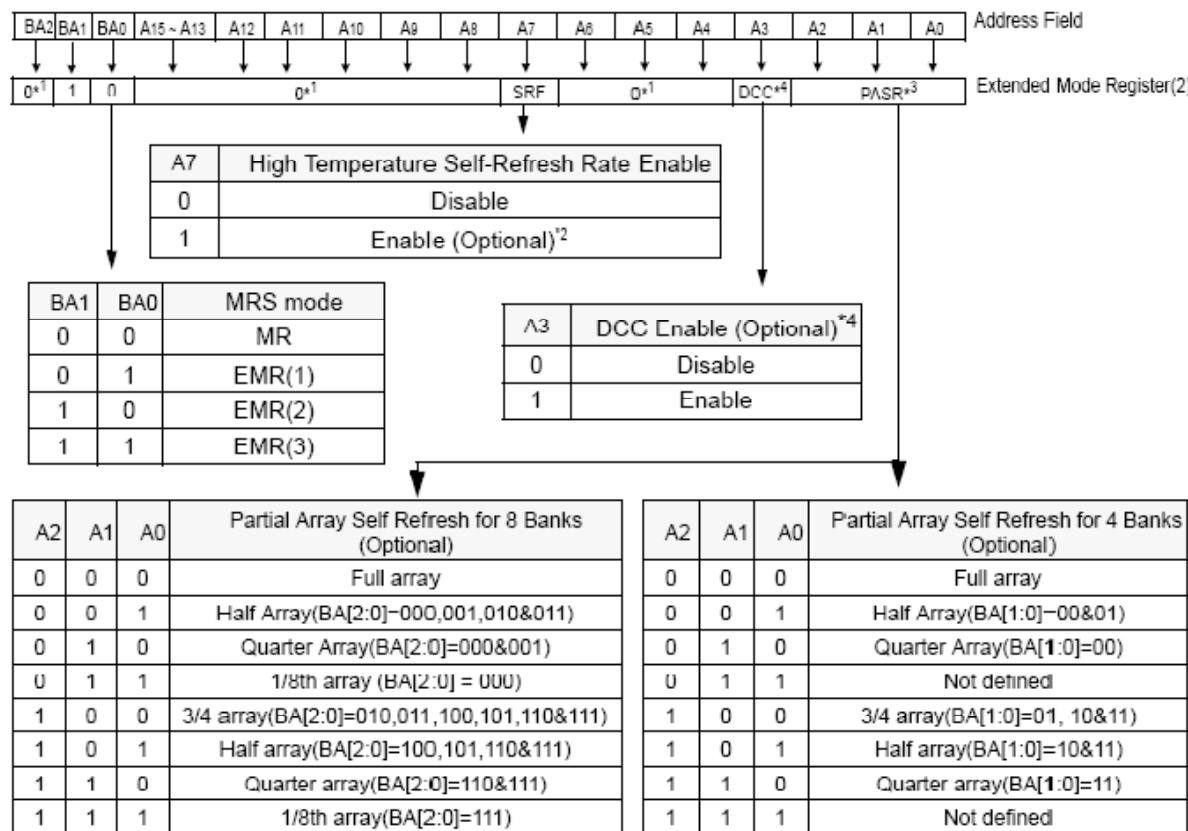

# Step by Step DDR2 Initialization EMR2

NOTE 1 BA2 and A4-A6, A8-A15 are reserved for future use and must be set to 0 when programming the EMR(2).

NOTE 2 As industry adoption of high temperature parts proceeds, users need to determine if a DRAM supports High Temperature Self-Refresh Rate Enable mode before attempting to use it in that mode. JEDEC standard DDR2 SDRAM Module user can look at DDR2 SDRAM Module SPD field Byte 49 bit [0]. If the high temperature self-refresh mode is supported then controller can set the EMR(2)[A7] bit to enable the self-refresh rate in case of higher than 85 °C temperature self-refresh operation. For the loose part user, please refer to DRAM Manufacturer's part number and data sheet to check the high temperature self-refresh rate availability.

NOTE 3 Optional in DDR2 SDRAM. If PASR (Partial Array Self Refresh) is enabled, data located in areas of the array beyond the specified address range will be lost if self refresh is entered. Data integrity will be maintained if tRFF conditions are met and no Self Refresh command is issued. If the PASR feature is not supported, EMR(2)[A0-A2] must be set to 000 when programming EMR(2).

NOTE 4 Optional in DDR2 SDRAM. JEDEC standard DDR2 SDRAM may or may not have DCC (Duty Cycle Corrector) implemented, and in some of the DRAMs implementing DCC, user may be given the controllability of DCC thru EMR(2)[A3] bit. JEDEC standard DDR2 SDRAM users can look at manufacturer's data sheet to check if the DRAM part supports DCC controllability. If optional DCC Controllability is supported, user may enable or disable the DCC by programming EMR(2)[A3] accordingly. If the controllability feature is not supported, EMR(2)[A3] must be set to 0 when programming EMR(2).

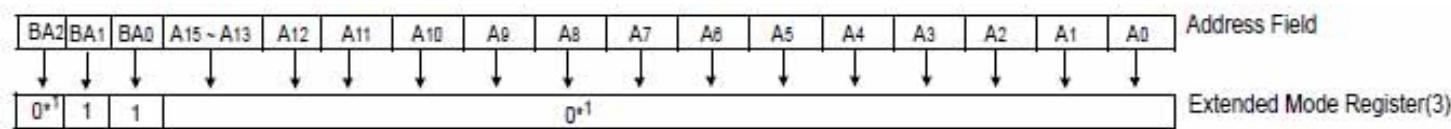

# Step by Step DDR2 Initialization EMR3

144

The information required from each DIMM is held in the SPD.

- Prior to JEDEC initialization, the BIOS/Firmware has read all data from SPD and worst-case timings have been calculated. Example:

- If two DIMMs are installed where one has a CAS latency of 2 and one with a CAS latency of 2.5, then CAS latency 2.5 will be used for both DIMMs.

- A DLL reset will be performed during this step. Anytime DLL reset occurs 200uS must be provided for it to relock before issuing a read command.

This is an example of the data stored in the SPD.

- The first 128 bytes are defined by the memory manufacturer.

- The last 128 bytes can be used by the customer.

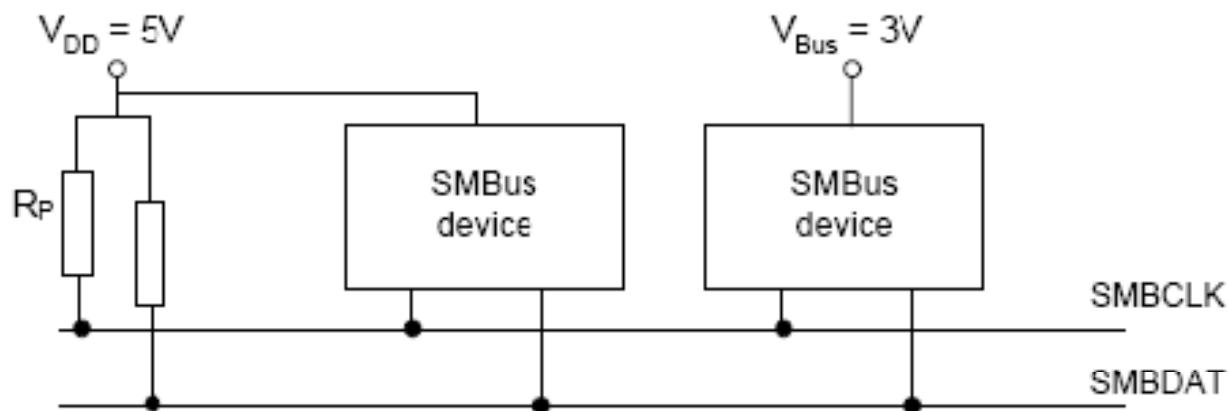

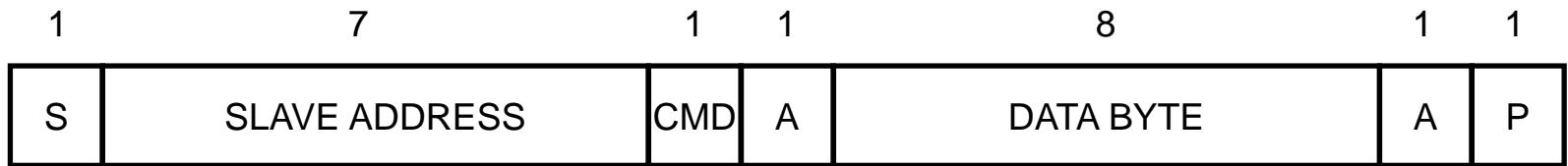

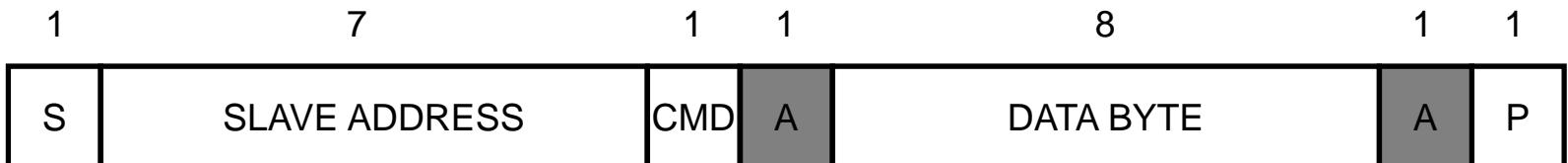

- Each SPD has a unique SMBus address hardwired on the motherboard typically on the lower 3 address bits of the SMBus.

- The SMBus can attach to the MCH or the ICH.

| BYTE | TITLE                                               | VALUE |

|------|-----------------------------------------------------|-------|

| 0    | NUMBER OF BYTES USED BY MICRON                      | 80    |

| 1    | TOTAL NUMBER OF SPD MEMORY BYTES                    | 08    |

| 2    | MEMORY TYPE                                         | 07    |

| 3    | NUMBER OF ROW ADDRESSES                             | 0D    |

| 4    | NUMBER OF COLUMN ADDRESSES                          | 0C    |

| 5    | NUMBER OF MODULE RANKS                              | 02    |

| 6    | MODULE DATA WIDTH                                   | 48    |

| 7    | MODULE DATA WIDTH (CONTINUED)                       | 00    |

| 8    | MODULE VOLTAGE INTERFACE LEVELS                     | 04    |

| 9    | DDR SDRAM CYCLE TIME (CAS LATENCY = 2.5)            | 75    |

| 10   | DDR SDRAM ACCESS FROM CLOCK (CAS LATENCY = 2.5)     | 75    |

| 11   | MODULE ERROR CORRECTION CONFIGURATION TYPE          | 02    |

| 12   | MODULE REFRESH RATE AND TYPE                        | 82    |

| 13   | SDRAM DEVICE WIDTH                                  | 04    |

| 14   | ERROR CHECKING WIDTH                                | 04    |

| 15   | MIN CLOCK DELAY FOR BACK-TO-BACK RANDOM COLUMN ADDR | 01    |

| 16   | BURST LENGTHS SUPPORTED                             | 0E    |

| 17   | NUMBER OF BANKS INTERNAL TO DISCRETE SDRAM DEVICES  | 04    |

| 18   | CAS LATENCIES SUPPORTED                             | 0C    |

| 19   | CS LATENCY                                          | 01    |

| 20   | WE LATENCY                                          | 02    |

| 21   | SDRAM MODULE ATTRIBUTES                             | 26    |

| 22   | SDRAM DEVICE ATTRIBUTE: GENERAL                     | C0    |

| 23   | DDR SDRAM CYCLE TIME (TCK) AT CL = 2                | A0    |

| 24   | DDR SDRAM ACCESS FROM CLOCK (TAC) AT CL = 2         | 75    |

| 25   | DDS SDRAM CYCLE TIME (TCK) AT CL = 1                | 00    |

| 26   | DDR SDRAM ACCESS TIME FROM CLOCK (TAC) AT CL = 1    | 00    |

| 27   | SDRAM: MINIMUM ROW PRECHARGE TIME (TRP)             | 50    |

| 28   | MINIMUM ROW ACTIVE TO ROW ACTIVE                    | 3C    |

| 29   | MINIMUM RAS TO CAS DELAY                            | 50    |

| BYTE    | TITLE                                               | VALUE             |

|---------|-----------------------------------------------------|-------------------|

| 30      | MINIMUM RAS PULSE WIDTH                             | 2D                |

| 31      | MODULE RANK DENSITY                                 | 01                |

| 32      | COMMAND/ADDRESS SETUP                               | A0                |

| 33      | COMMAND/ADDRESS HOLD                                | A0                |

| 34      | DATA SIGNAL INPUT SETUP                             | 50                |

| 35      | DATA SIGNAL INPUT HOLD                              | 50                |

| 36-40   | RESERVED 5                                          | 0000000000        |

| 41      | DEVICE MINIMUM ACTIVE/AUTO-REFRESH TIME (TRC)       | 41                |

| 42      | DEVICE MINIMUM AUTO-REFRESH TO ACTIVE/AUTO-REFRESH  | 4B                |

| 43      | DEVICE MAXIMUM DEVICE CYCLE TIME (TCK MAX)          | 34                |

| 44      | DEVICE DQS-DQ SKEW FOR DQS AND ASSOCIATED DQ SIGNAL | 32                |

| 45      | DEVICE READ DATA HOLD SKEW FACTOR (TQHS)            | 75                |

| 46      | RESERVED (BYTE 46)                                  | 00                |

| 47      | DIMM HEIGHT                                         | 01                |

| 48-61   | RESERVED BYTES 48-61                                | 0000...00         |

| 62      | SPD REVISION                                        | 10                |

| 63      | CHECKSUM FOR BYTES 0 THRU 62                        | EB                |

| 64      | MANUFACTURER'S JEDEC ID CODE                        | 2C                |

| 65-71   | MANUFACTURER'S JEDEC ID CODE (CONTINUED)            | FFFFFFFFFFFF      |

| 72      | MANUFACTURING LOCATION                              | 00                |

| 73-90   | MODULE PART NUMBER                                  | 36VDDF25672G265C2 |

| 91      | PCB IDENTIFICATION CODE                             | 02                |

| 92      | PCB IDENTIFICATION CODE (CONTINUED)                 | 00                |

| 93      | YEAR OF MANUFACTURE                                 | 00                |

| 94      | YEAR OF MANUFACTURE                                 | 00                |

| 95-98   | MODULE SERIAL NUMBER                                | 00000000          |

| 99-127  | MANUFACTURER SPECIFIC DATA (RSVD) 99-127            | 0000...00         |

| 128-191 | UNUSED                                              | FFFF...FF         |

| 192-255 | UNUSED2                                             | FFFF...FF         |

- Step 7

- Issue MRS command to EMR1 to enable DLL.

- Step 8

- Issue MRS command to MR0 to reset DLL.

- Step 9

- Issue a Precharge All command.

- Step 10

- Issue 2 or more Refresh commands.

- Step 11

- Issue a MRS command to MR0 with LOW to A8 to program the desired device operation without resetting the DLL.

## ➤ Step 12

➤ At least 200 clocks after resetting the DLL, execute OCD Calibration (Off Chip Driver impedance adjustment). If OCD calibration is not used, issue a MRS command to EMR1 to set OCD Calibration Default followed by issuing a MRS command to EMR1 to exit OCD Calibration Mode while also setting other operating parameters of EMR1.

## ➤ Done!

➤ The standard says the DRAM is now ready for normal operation, but the controller still needs to train the timing.

## ➤ Step 1