# A Low Power Inductorless LNA With Double $\rm G_m$ Enhancement in 130 nm CMOS

François Belmas, Frédéric Hameau, and Jean-Michel Fournier

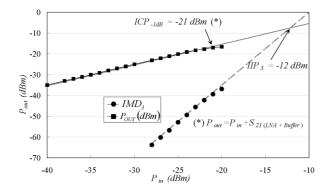

Abstract—This paper presents the design of a low power differential Low Noise Amplifier (LNA) in 130 nm CMOS technology for 2.45 GHz ISM band applications. The circuit benefits from several  $g_m$ -enhancements. These techniques provide a high gain and reduced Noise Figure (NF) in spite of the low intrinsic  $g_m$  of the MOS transistors. Moreover, the circuit is fully inductorless. Main design points are described and the performance tradeoffs of the circuit are discussed. A prototype has been implemented and it exhibits a 20 dB gain with a 4 dB NF while dissipating 1.32 mW. The IIP<sub>3</sub> is -12 dBm for an input compression point of -21 dBm.

*Index Terms*—Inductorless, ISM band, LNA, low power, 245 GHz.

#### I. INTRODUCTION

7 IRELESS Sensor Network (WSN) standards like IEEE 802.15.4 require drastically low active mode power consumption  $(P_{DC})$  for remote applications with long battery lifetime. The particular case of WSN apin the 2.45 GHz ISM band usually leads to RF Integrated Circuits (RFICs) using LNAs circuit with multiple inductors. These bulky inductors result in expensive RFIC [1]. Removing them is definitely a cost effective approach. Conversely, low P<sub>DC</sub> inductorless LNAs cannot offer the narrowband and low Noise Figure (NF) of their inductor-based counterparts. Designing such low cost circuits is then very challenging. To be relevant for a WSN application, inductorless LNAs should provide a large voltage gain (given the low  $g_m$  values available) as well as drastically reduced silicon area. Additionally, RFIC SoC architectures must handle the increased NF and the inherent wideband nature of such inductorless LNA. This work proposes an inductorless LNA suitable for 2.45 GHz ISM band WSN applications with a milliwatt range  $P_{DC}$ . We focus on LNA design with  $g_m$ -boost techniques [2], [3]. These techniques have been widely used in common gate LNAs where  $P_{DC}$  is a key point as in [4]. More recently, some papers investigated the benefit of "active" gm-boost techniques applied to LNAs [5], [6]. We push further the investigation in order to reach the highest possible voltage gain with a NF as low as possible. For that, a new doubly  $g_m$ -boosted differential LNA is presented [7]. The combination of gain, noise and bandwidth improvement techniques

F. Belmas and F. Hameau are with CEA LETI, F-38054 Grenoble, France (e-mail:francois.belmas@csr.com; rederic.hameau@cea.fr).

J.-M. Fournier is with IMEP-LHAC, F-38016 Grenoble, France (e-mail: fournier@minatec.inpg.fr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2012.2185533

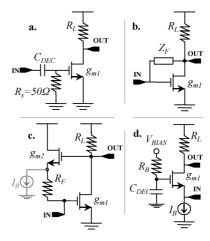

Fig. 1. Inductorless LNAs : a. Resistive matched LNA, b. Impedance-based SFB LNA, c. Source-follower-based SFB LNA, d. Basic CG LNA.

offers a good global performance tradeoff. While keeping a very low  $P_{\rm DC}$ , the circuit is fully differential for an easier SoC integration. This paper is organized as follow: Section II details the known design techniques of inductorless LNAs. The proposed circuit is presented in Section III. In addition to [7], we detail more deeply the input matching as well as gain, bandwidth, linearity, noise, and stability. Finally, part IV presents experimental results.

# II. BACKGROUND IN INDUCTORLESS LNA DESIGN

Inductorless LNA design is mainly based on circuit techniques for low input impedance while maintaining good gain and noise performance. The difficulty lies on the generation of mainly real impedance while a MOS transistor exhibits generally capacitive high input impedance. A straightforward solution could be a discrete matching using a 50  $\Omega$  input shunt resistance Fig. 1(a) bounding the NF to 3 dB in conflict with low noise goals. A more acute approach points to circuits either based on shunt feedback (SFB) amplifiers or common gate (CG) topology. Schematics of these structures are given in (Fig. 1) and their performance metrics are summarized in Table I.

# A. Shunt Feedback Technique

The impedance-based SFB amplifier (Fig. 1(b)) provides real input matching using feedback impedance. It generally consists of either a pure resistance  $Z_F = R_F$  [8] or a parallel tank  $Z_F = R_F //C_F$  [9]. In any case, the input matching is obtained thanks to the LNA voltage gain G<sub>V</sub>. The degraded output impedance ( $Z_F //R_L$ ) is a major drawback of impedance based SFB amplifiers. Indeed, this limitation enforces larger g<sub>m</sub> value when higher gain is targeted and thus P<sub>DC</sub> increases.

Manuscript received September 01, 2011; revised November 18, 2011; accepted December 18, 2011. Date of publication February 15, 2012; date of current version April 25, 2012. This work is supported in part by FP7 ICT-IP project SENSEI 215923. This paper was approved by Guest Editor Georg Boeck.

| LNA Circuit                                                     | Impedance based SFB [8]                                                                                                                                    | Source Follower based SFB [11]                                                                                                  | CG [10]                                                                                |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Voltage Gain                                                    | $G_V = -\frac{g_{m1} - g_F}{g_L + g_F}$                                                                                                                    | $G_V = -g_{ml}RL$                                                                                                               | $G_V = +g_{ml}RL$                                                                      |

| Input<br>Admittance<br>Y <sub>IN</sub> =1/Z <sub>IN</sub>       | $Y_{IN} = g_{F'} \left( 1 - A_{V'} \right)$                                                                                                                | $Y_{IN} = \underbrace{\frac{g_{m2}}{1 + g_{m2}R_F}}_{g_{m2Eq}} (1 - A_V)$                                                       | $Y_{IN} = g_{m1}$                                                                      |

| Matching<br>Condition (M.C)                                     | $R_F = (g_{m1}R_L + 1)R_S - R_L$                                                                                                                           | $g_{m2Eq} = R_S^{-1} (1 - A_V)^{-1}$                                                                                            | $g_{m1} = R_S^{-1}$                                                                    |

| $F_{um} \stackrel{(^{*})}{\approx} $ (Noise Factor without M.C) | $1 + \frac{NEF_1}{g_{m1}R_S} + \frac{4R_S}{R_F} \left(\frac{(1 + g_{m1}R_S)R_L}{(1 + g_{m1}R_S)R_L + R_F + R_S}\right)^2 + \frac{1}{R_S R_L g_{m1}^2}$     | $1 + \frac{NEF_1}{g_{m1}R_S} (R_S^{-1} + g_{m2Eq})^2 + g_{m2Eq}^2 R_F R_S + \frac{1}{R_S R_L g_{m1}^2} (R_S^{-1} + g_{m2Eq})^2$ | $1 + \frac{NEF_1}{g_{m1}R_S} + \frac{R_S}{R_L} \left(1 + \frac{1}{g_{m1}R_S}\right)^2$ |

| $F_m^{(*)} \approx $ (Noise Factor with M.C)                    | $1 + \frac{NEF_1}{g_{m1}R_S} + \frac{\left(1 + \left(g_{m1}R_S\right)^{-1}\right)^2}{\left(g_{m1}R_L + 1\right) - R_L / R_S} + \frac{1}{R_S R_L g_{m1}^2}$ | $1 + \frac{NEF_1}{g_{m1}R_S} + \frac{R_F}{R_S(1 + A_V)^2} + \frac{1}{R_S R_L g_{m1}^2}$                                         | $1 + NEF_1 + \frac{4R_S}{R_L}$                                                         |

TABLE I

BASIC EQUATIONS OF KNOWN INDCUTORLESS LNA CIRCUITS OF FIG. 1

(\*) It assumes a MOS drain current noise PSD expressed as 4kT.NEF<sub>1</sub>.g<sub>m</sub>.  $\Delta f$ , with NEF<sub>1</sub> the Noise Excess Factor as it is defined in [15].

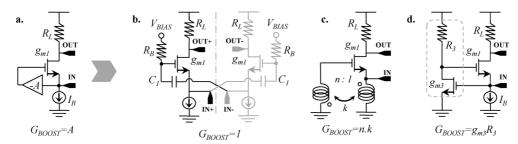

Fig. 2. Gm-boosted LNA a. generic gm-boost CG, b. Differential CCC LNA, c. Transformer based gm-boost, d. CS based gm-boost circuit.

For that, [11] proposed a feedback circuit with a degenerated source follower (Fig. 1(c)). Although extra  $P_{DC}$  is required for the feedback, it efficiently decouples the output from the input impedance. Authors in [11] detail the underlying linearity-gain tradeoff inherent to such source-follower-based SFB circuits. As in [11] and [12], it is commonly known that the SFB amplifiers, whatever the feedback type, exhibit poor NF and poor linearity performance when  $g_m$  values are very low (i.e., few mS). Note that some more elaborate feedbacks based on multi-stage [13] or current-reuse [14] can slightly improve the linearity-gain tradeoff while keeping the same basic approach.

## B. Common Gate (CG) Technique

The main alternative to SFB amplifiers is the CG topology (Fig. 1(d)). The basic CG circuit benefits from the  $1/g_{\rm m}$  source terminal impedance. It follows that the amplifying  $g_m$  simultaneously sets the gain and the input impedance. The input matching condition  $g_{m1}R_S = 1$  results in a matched noise factor limited to  $1 + NEF_1$  where  $NEF_1$  is the noise excess factor of the MOS transconductance  $g_{m1}$  [15]. For this reason, CG circuits are considered noisy regarding SFB amplifiers where  $g_{m1}R_S$  can be much larger than unity (Table I). CG circuits still have some advantages. First, they have a better linearity as they exhibit a low input voltage gain. Another difference between CG and SFB circuits concerns the available accessibility of the gate terminal. In fact, this node does not need to be a pure DC node for correct operation. This statement leads to a class of circuits called  $g_m$ -boost CG circuits [2], [4] which are usually dedicated to low power operation.

# C. G<sub>m</sub>-Boost Technique

The basics of  $g_m$ -boost techniques consist of applying simultaneously the signal on both gate and source pins to increase the  $v_{GS}$  swing on the MOS transistor (Fig. 2).

The technique requires an auxiliary voltage gain ( $G_{BOOST}$ ) aside from the CG circuit (Fig. 2(a)). Assuming an ideal boosting amplifier, the obtained LNA metrics are reported in (Table II). This technique enables a reduction of the noise factor (F) while simultaneously offering a favorable  $P_{DC}$ -matching tradeoff. This approach is very popular in differential LNA design [4], [10]. Indeed, a gm-boosting effect is simply enabled through a Capacitive Cross Coupling (CCC - Fig. 2(b)) of the inputs at no  $P_{DC}$  costs. However, the improvement of the P<sub>DC</sub>-matching tradeoff is somewhat limited: since the CCC is based on a passive amplification, it limits G<sub>BOOST</sub> to values lower than 1. One could address that point through the use an inductive transformer (Fig. 2(c)) [3] but a large extra silicon area will be required. The last solution involves an auxiliary active amplifier, a CS stage for instance, with a dedicated  $P_{DC}$  budget [5] (Fig. 2(d)). To improve performance in such actively-boosted CG LNA, both main and auxiliary amplifiers must be power-optimized. The gm-boosting amplifier in previous works ([5], [6] & [16]) always shows high input impedance. A design of this amplifier with a finite input impedance would relax even more the P<sub>DC</sub>-matching tradeoff. Indeed, the boosting amplifier will then reduce the input impedance not only through its own gain (GBOOST) but also through its finite input impedance. Furthermore, nothing forbids the use of gm-boosting techniques inside the auxiliary

TABLE II GENERIC METRICS IMPROVEMENT IN  $\rm g_m$  -Boosted CG LNA

| LNA Metrics                        | G <sub>m</sub> -boosted LNA –Single Ended Case with G <sub>BOOST</sub> =A           |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------|--|--|--|--|

| Gain                               | $G_V = -g_{ml}RL(1+A)$                                                              |  |  |  |  |

| Y <sub>IN</sub> =1/Z <sub>IN</sub> | $Y_{IN} = g_{m1} (1 + A)$                                                           |  |  |  |  |

| Matching condition                 | $g_{m1}R_S(1+A) = 1$                                                                |  |  |  |  |

| $(F_{um}, F_m) \approx$            | $F_{nm} = 1 + \frac{NEF_1}{(1+A)^2 g_{m1}R_S} \qquad F_m = 1 + \frac{NEF_1}{(1+A)}$ |  |  |  |  |

| IIP <sub>3</sub>                   | ≈IIP <sub>3 (CG No Boost)</sub> /(1+A)                                              |  |  |  |  |

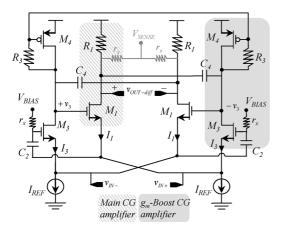

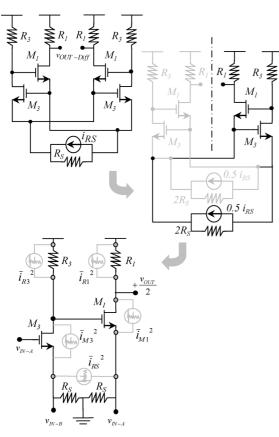

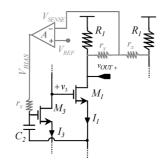

Fig. 3. Schematic of the proposed differential CGAB LNA circuit.

amplifier circuit in order to reduce its  $P_{DC}$  budget. In the following section we propose a  $g_m$ -boosted LNA that consider these two remarks.

#### III. PROPOSED COMMON GATE ACTIVE BOOST LNA

# A. Basic Idea

The proposed circuit is depicted in Fig. 3 and includes a CG circuit being  $g_m$ -boosted through another CG circuit rather than a CS. The "main CG amplifier", made with  $M_1$  and  $R_1$ , is enhanced by the " $g_m$ -boost amplifier" made with  $M_3$  and  $R_3$ . A CCC technique is added to the boosting amplifier (C<sub>2</sub> MOM capacitor). It further enhances its gain and reduces its noise. The boosting gain is therefore doubled without extra  $P_{DC}$  and becomes  $G_{BOOST} \approx 2g_{m3}R_3$ .

The obtained Common Gate Active Boost LNA (CGAB) is thus a double-gm-enhanced LNA. Moreover, the finite input impedance at the source terminal of M<sub>3</sub> is a novel degree of freedom to define the LNA input impedance. Using a CG circuit, known to be more linear than a CS circuit [2], helps to improve the linearity of the whole LNA at low  $\mathrm{P}_{\mathrm{DC}}$  where low bias current usually degrades linearity. The proposed circuit also involves a capacitive coupling of both CG circuit's outputs through  $C_4$  capacitance for bandwidth enhancement. The active load made by M4 avoids large DC voltage drop through  $R_3$ . Both  $M_4$  gates are connected together to form a dynamic ground. This connection disables the parasitic active inductor at node  $v_3$  which is mainly created by  $M_4$  gate capacitor. Since this inductance is usually large, it results in an unwanted low frequency gain resonance. The DC current of both amplifiers is shared in a common input current source and  $I_{REF} = I_1 + I_3$  in order to avoid extra input current mirror. The  $I_1/I_3$  ratio is set by

$V_{BIAS}$  through a large value resistor  $r_x (20 \text{ k}\Omega)$  which isolates the biasing parts from the RF parts. It has to be noticed that the  $M_1$  gate is DC coupled and it doesn't require any extra RC-bias tee. The high-pass cut-off of the  $r_xC_2$  network ( $f_{rx} = 16 \text{ MHz}$ ) is neglected hereafter. Finally, it is assumed that the LNA is loaded with a capacitor  $C_L = 50$  fF at each output in the following analysis to model the input capacitance of a succeeding mixer. The circuit is scaled to operate at milliwatt range  $P_{DC}$ (< 2 mW). All active transistors are of minimum gate length (0.13  $\mu$ m) and they operate with positive overdrives above saturation limits. Next sections detail the metrics of the LNA of Fig. 3. The various tradeoffs related to the low  $P_{DC}$  and the inductorless aspects are discussed.

# B. Input Matching

The differential input admittance  $Y_{IN-D}$  is calculated with the MOS small-signal equivalent circuit:  $g_m$ ,  $g_{DS}$ ,  $c_{gs}$ ,  $c_{gd}$ . The low-frequency approximation of  $Y_{IN-D}$  is given in (1) where the two first terms define the low input impedance. The last terms in (1) involving the finite MOS conductances ( $g_{DS1}$  &  $g_{DS3}$ ) are the positive feedbacks proportional to the LNA gain  $G_V$  and the boosting gain  $G_{BOOST}$ . These terms tend to moderately increase the input impedance. They are neglected in the next simplified theory, but they must be considered during circuit design. We neglect  $M_1$  and  $M_3$  transition frequencies  $f_T$ , which are very high compared to the operating frequency

$$Y_{\rm IN-D} = \frac{g_{\rm m1}}{2} \left( 1 + G_{Boost} \right) + g_{\rm m3} + g_{DS1} \left( 1 - G_V \right) + g_{DS3} \left( 1 - G_{Boost} \right) \Rightarrow Y_{\rm IN-D} \approx \frac{g_{\rm m1}}{2} \left( 1 + 2g_{\rm m3}R_3 \right) + g_{\rm m3}$$

(1)

$$Y_{\rm IN-MATCH} = R_S^{-1} \to g_{\rm m1} \cong \frac{2(1 - g_{\rm m3}R_S)}{R_S(1 + 2g_{\rm m3}R_3)} \quad (2)$$

$$Y_{\text{IN}-DIFF-FIG.2d} = R_S^{-1} \to g_{\text{m1}} \cong \frac{2}{R_S(1+g_{\text{m3}}R_3)}.$$

(3)

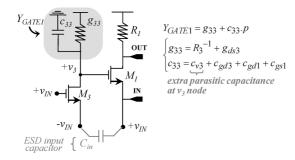

A simplified matching condition can be defined and applied to  $g_{m1}$  leading to (2). We compare this with the matching condition (3) obtained for the differential active-boost LNA in Fig. 2(d) ([5], [6]). It results in an improved  $P_{DC}$ -matching tradeoff. The improvement is mainly related to the CCC technique that doubles the boosting gain. We focus now on the input impedance second order effects related to the back-to-back connection of  $M_1$  and  $M_3$ . This topology defines an impedance gyrator which leads to a finite imaginary part in  $Y_{IN-D}$  [17]. A more detailed expression than (1) is obtained from the schematic of Fig. 4 and results in (4) (with  $p = j\omega$ , the Laplace variable)

$$Y_{\rm IN-D} \approx g_{\rm m3} + \frac{g_{\rm m1}}{2} \left( 1 + \frac{2g_{\rm m3}}{g_{33}} \cdot \left( \frac{1}{1 + \frac{(c_{33} + c_{\rm gs1})}{g_{33}} p} \right) \right).$$

(4)

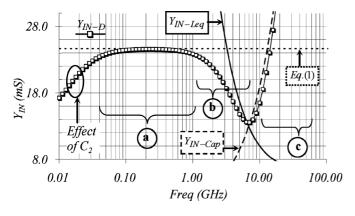

In Fig. 4, a simplified load ( $Y_{GATE1}$ ) resulting from  $g_{33}$  in parallel with the equivalent capacitor  $c_{33}$  is used at  $g_m$ -boost amplifier output to simplify the analysis. The evolution of  $Y_{IN-D}$  (4) versus frequency is detailed in Fig. 5 and in Table III, through 3 separate frequency domains (namely **a**, **b** & **c**). At low frequency (**a**)  $Y_{IN-D}$  follows the relation (1), the expected boosted admittance. In (**b**), as  $\omega$  increases close to  $\omega_{LEQ} = g_{33}/(c_{33} + c_{gs1})$ ,

Fig. 4. Schematic used to calculate the input impedance. The  $c_{v3}$  capacitor models extra parasitic capacitance at node  $v_3$ .

Fig. 5. Input admittance of circuit from Fig. 4 versus frequency. Frequency ranges a, b & c are schematically delimited and they are detailled hereafter in Table III.

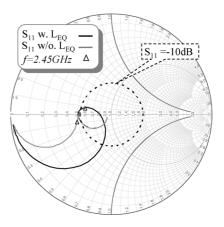

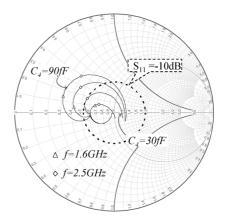

the boosting amplifier load decreases, and consequently, the boosting effect disappears. Aside from that, an active inductor  $L_{EQ} = (c_{33} + c_{gs1})/g_{m3}g_{m1}$  appears in parallel of the  $Y_{IN-D}$  real part admittance. Finally, at high frequency (c), the input capacitor  $C_{in}$  tends to dominate  $Y_{IN-D}$  behavior and degrades the input matching. Fig. 6 illustrates the simulated  $S_{11}$  with and without active inductor  $L_{EQ}$ . In our case where the CGAB LNA is close to the mismatch limit ( $S_{11} = -10$  dB), it appears that the active inductor helps to maintain the matching at high frequency inside the -10 dB  $S_{11}$  circle. That shows how this imaginary part can be advantageously used to fine tune the input matching. For instance, the inductive part can resonate with  $C_{in}$ , an input capacitor related to the necessary input ESD protection circuit. We consider in our simulation a  $C_{in}$  value of 0.3 pF for each single-ended input.

#### C. Gain and Bandwidth

LNA design at low  $P_{DC}$  implies low DC current and hence small transistor  $g_m$  values. To maintain acceptable gain and noise, output impedance has to be high enough. With this high impedance requirement, it becomes difficult to maintain a large gain-bandwidth product. In the proposed circuit, the  $g_m$ -boost gain-bandwidth – and consequently the whole LNA gain-bandwidth – is greatly limited. For that,  $C_4$  is added for bandwidth extension purposes [18]. The transfer function of the whole LNA gain ( $G_V(p)$ ) and the boosting gain ( $G_{BOOST}(p)$ ) are detailed hereafter (5)–(8)

Fig. 6. Simulated  $\rm S_{11}$  of the model of Fig. 4 with and without including the active inductor  $\rm L_{EQ}$ . (from 100 MHz to 20 GHz).

TABLE III  $Y_{IN-D}$  Behavior Versus Frequency for A,B,C Domains.

| ω. range                                            | $Y_{IN-D} \approx$                                                                  |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| <b>a.</b> $\omega_{rx} \ll \omega \ll \omega_{LEQ}$ | $g_{m3} + \frac{g_{m1}}{2}(1 + 2g_{m3}R_3)$                                         |  |  |

| <b>b.</b> <i>ωLEQ</i> << <i>ω</i> << <i>ωCap</i>    | $g_{m3} + \frac{g_{m1}}{2} + \frac{g_{m3}g_{m1}}{(c_{33} + c_{gs1})p} = Y_{IN-Leq}$ |  |  |

| <b>с.</b><br><i>@<sub>Сар</sub> &lt;&lt; 0</i>      | $C_{in} \cdot p = Y_{IN-Cap}$                                                       |  |  |

$$G_{V}(p) = \frac{v_{OUT}}{v_{IN}} = G_{V-DC} \cdot \frac{1 + a_{1}p + a_{2}p^{2}}{1 + \frac{2\xi}{\omega_{0}}p + \left(\frac{p}{\omega_{0}}\right)^{2}}$$

(5)

$$G_{BOOST}(p) = \frac{v_{3}}{v_{IN}} = G_{BOOST-DC} \cdot \frac{1 + b_{1}p + b_{2}p^{2}}{1 + \frac{2\xi}{\omega_{0}}p + \left(\frac{p}{\omega_{0}}\right)^{2}}$$

(6)

$$G_{V-DC} = \frac{g_{m1}R_{1}}{1 + R_{1}g_{DS1}} \left(1 + \frac{g_{DS1}}{g_{m1}} + G_{BOOST-DC}\right)$$

(7)

$$G_{\rm BOOST-DC} = \frac{(2g_{\rm m3} + g_{DS3}) R_3}{1 + R_3 g_{DS3}}.$$

(8)

Both gains share an identical 2nd-order pole systems with a common un-damped angular frequency  $(\omega_0)$  and a damping factor ( $\xi$ ) given in (9) and (10). The terms  $g_{33}$  and  $c_{33}$  are defined in Fig. 4 while  $g_{11} = R_1^{-1} + g_{DS1}$  and  $c_{11} = C_L + c_{gd1}$ . High-frequencies zeros ( $a_1$ ,  $a_2$ ) in (5) are neglected while the effect of ( $b_1$ ,  $b_2$ ) in (6) result in bandwidth extension, as explained hereafter

$$\omega_{0} = \sqrt{\frac{g_{11} \cdot g_{33}}{c_{11} \cdot c_{33} - c_{\text{gd}1}^{2} + C_{4}(c_{11} + c_{33} + 2c_{\text{gd}1})}} = \sqrt{\frac{g_{11} \cdot g_{33}}{C_{\alpha}^{2}}}$$

(9)

$$\xi = \frac{c_{33}g_{11} + c_{11}g_{33} + C_4(g_{11} + g_{33} - g_{m1})}{2\sqrt{g_{11}g_{33} \cdot C_\alpha^2}}.$$

(10)

$$\overline{i_{Mi}}^2 = 4kT \left( NEF_i \right) g_{mi} \Delta f \tag{13}$$

$$\overline{i_{Ri}}^2 = \left(\frac{4kT}{R_i}\right)\Delta f.$$

(14)

Then, each noise transfer function (TFn) associated with a given noise source is computed to obtain the noise factor with the definition in (15). The contributions of each noise source are then separated between  $F_{M3}$ ,  $F_{R3}$ ,  $F_{M1}$ ,  $F_{R1}$  terms forming the complete noise factor F of the LNA (16)

$$F = 1 + \frac{\overline{i_{Ri}}^2 \cdot (TFn_{Ri})^2 + \overline{i_{Mi}}^2 \cdot (TFn_{Mi})^2}{4kT \cdot \left(\frac{1}{2R_s}\right) \cdot (TFn_{RS})^2} \quad (15)$$

$$F = 1 + F_{\rm M3} + F_{\rm R3} + F_{\rm M1} + F_{\rm R1}.$$

(16)

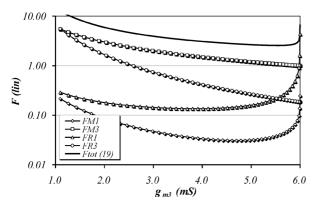

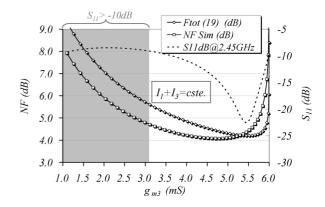

Assuming  $G_{BOOST} = 2g_{m3}R_3$ ,  $2R_3 \gg R_S$ ,  $2g_{m3}R_3 \gg 1$ , and  $g_{m1,3}R_S \ll 1$ , a simplified noise factor expression  $F_{TOT}$ is derived (17). It highlights the benefits of using the capacitive cross-coupling technique in the boosting amplifier since it both reduces its noise contribution and doubles the boosting gain. This also improves noise reduction of the main amplifier. The relative contribution of each noise source to  $F_{TOT}$  versus the chosen  $g_{m3}$  transconductance is detailed in Fig. 9

$$F_{\text{TOT}} \approx 1 + \frac{NEF_3}{2g_{\text{m}3}R_S} + \frac{1}{2g_{\text{m}3}^2R_3R_S} + \frac{2.NEF_1}{g_{\text{m}1}R_S(1+G_{boost})^2} + \frac{2(1+g_{\text{m}1}R_S\left(1+\frac{G_{boost}}{2}\right))^2}{g_{\text{m}1}^2R_1R_S(1+G_{boost})^2}.$$

(17)

A constant  $P_{DC}$  is assumed (i.e., a constant  $I_{REF} = I_1 + I_3$ ) and therefore when  $g_{m3}$  increases,  $g_{m1}$  decreases. It highlights  $F_{M3}$  and  $F_{R3}$  as the main noise contributors. To emphasize the advantage of this technique compared to another actively-boosted LNA design, we derive the noise factor of a differential LNA based on the circuit of Fig. 2(d). ([5], [6]). Using again the simplification process of Fig. 8 we obtain (18). Although  $P_{DC}$ -matching tradeoffs are different, (17) and (18) can be compared while assuming an identical  $P_{DC}$ . It follows that the proposed circuit limits more the noise degradation related to the boosting amplifier. The key improvement is related to the extra CCC added into the circuit

$$F_{FIG2D-diff} \approx 1 + \frac{2NEF_3}{g_{m3}R_S} + \frac{2}{g_{m3}^2R_3R_S} + \frac{2NEF_1}{g_{m1}R_S(1+g_{m3}R_3)^2} + \frac{(2+g_{m1}R_S(1+g_{m3}R_3))^2}{2g_{m1}^2R_1R_S(1+g_{m3}R_3)^2}.$$

(18)

Inspecting Fig. 9 highlights an optimal design point reached when both  $g_{m3}$  and  $g_{m1}$  are bigger than 3 mS. Finally our model (17) is compared to NF simulation of the LNA using the BSIM v3.3 MOS transistor model (Fig. 10). It appears that (17) predicts correctly the simulation result. Moreover, the optimal noise is obtained for an acceptable power matching

Fig. 7. Simulated  $G_V$  and  $G_{BOOST}$  for different  $C_4$  values.

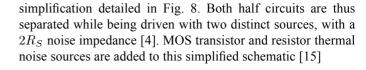

The boosting gain impacts the whole LNA gain since we have roughly  $(v_{gs} - M1/v_{in})(p) \cong G_{BOOST}(p)$ . The purpose of C<sub>4</sub> in such circuits is to act as a neutralizing capacitor which creates a peaking effect by means of positive feedback and extends the bandwidth. C<sub>4</sub> reduces the value of  $\xi$  and also creates an extra zero in  $G_{BOOST}(p)$  which causes an overshoot effect in the  $G_{BOOST}(p)$  before the main pole at  $\omega_0$ . Given the tight coupling between both gains the peaking effect helps to increase the whole LNA bandwidth. The maximum gain (G<sub>V-MAX</sub>) (11) occurs at a resonance frequency (noted  $\omega_R$ ) defined by (12)

$$G_{V-MAX} = G_{V DC} \left( 2\xi \sqrt{1 - \xi^2} \right)^{-1}$$

(11)

$$\omega_{\rm R} = \omega_0 \sqrt{1 - 2\xi^2}.$$

(12)

Moreover, inspecting (9) to (12), it follows that increasing  $C_4$  increases the overshoot (by decreasing  $\xi$ ) but also decreases  $\omega_0$ . Since we have always  $\omega_R < \omega_0$ , this positive feedback technique is limited and high  $C_4$  values result in early overshoot frequency. The obtained  $G_V$  and  $G_{BOOST}$  are depicted in Fig. 7. Consequently, the  $C_4$  value must be carefully chosen to extend sufficiently the bandwidth while avoiding the early peaking effect and to limit the in-band gain peaking. The effect of  $C_4$  value on  $\xi$  and ripple is detailed in Fig. 7. With  $C_4 = 30$  fF, the system is critically damped. We choose to implement this value.

The obtained gain peaking is kept small with this capacitance value. The physical implementation of C4 must not introduce extra parasitic capacitance.

A MOM capacitor without the first metal level is used in this design to obtain the critically damped case of Fig. 7. The layout of  $C_4$  results in enough small parasitic capacitance on node  $v_3$  to be neglected versus the neutralizing effect. Without this bandwidth extension technique we would be forced to reduce output impedance resulting in lower gains and higher noises.

## D. Noise

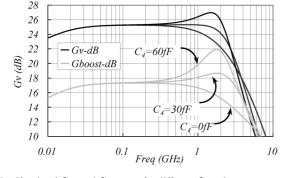

The noise factor equation from Table II does not include the contribution from the boosting amplifier. This extra noise will impact the noise-power tradeoff in the circuit. In order to calculate the noise factor, some simplifications are performed to obtain a more insightful equation. First, it is stated that both half-circuit noise sources are correlated. It then implies a fully differential noise voltage at the output with the pessimistic assumption that no common mode cancellation occurs between both half circuits. This statement enables the circuit

Fig. 8. Circuit simplification to compute the noise figure assuming correlated noise sources of each half-circuit.

Fig. 9. Noise contributor to  $F_{\rm TOT}$  versus  $g_{\rm m3}$  at constant power consumption.

$(S_{11} < -10 \text{ dB})$ . The proposed circuit shows an acceptable NF for WSN applications. The noise- $P_{DC}$  tradeoff is kept good, even at low  $g_m$  values.

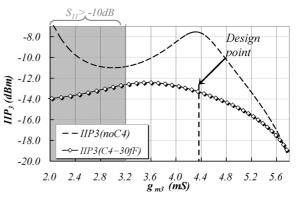

# E. Linearity

The g<sub>m</sub>-boosting block increases the  $v_{\rm gs}$  swing on M<sub>1</sub> enabling the noise reduction highlighted above. On the other hand, the increased voltage swing increases the g<sub>m</sub> related distortion by M<sub>1</sub>. It is worth mentioning that the boosting amplifier also introduces its own extra distortion. Authors in [5] proposed an estimation of the g<sub>m</sub>-boosted LNA IIP<sub>3</sub> using IIP<sub>3</sub> and IIP<sub>2</sub> of both main and g<sub>m</sub>-boosting amplifiers (19). If we assume that both IIP<sub>2-CG</sub> and IIP<sub>2-BOOST</sub> are very high given the differential implementation, and that G<sub>BOOST</sub>/(1 + G<sub>BOOST</sub>)  $\approx$  1,

Fig. 10. Equation (17) and simulated NF versus  $g_{m3}$  value.

Fig. 11. Simulated IIP3 at 2.45 GHz of the LNA versus  $g_{m3}$  at constant PDC.

it follows that the IIP<sub>3</sub> is lower than the non-boosted IIP<sub>3</sub> of the main CG circuit (IIP<sub>3-CG</sub>) divided by a factor  $(1 + G_{BOOST})$

$$\frac{1}{IIP_{3}^{2}} = \frac{(1+G_{\rm BOOST})^{2}}{IIP_{3-\rm CG}^{2}} + \frac{G_{\rm BOOST}}{(1+G_{\rm BOOST})IIP_{3-\rm BOOST}^{2}} + \frac{3}{2} \cdot \frac{G_{\rm BOOST}}{IIP_{2-\rm CG} \cdot IIP_{2-\rm BOOST}}.$$

(19)

The performance scaling of CGAB LNA thus includes a noiselinearity tradeoff since a high boosting gain is necessary for low NF but leads to a degraded linearity performance.

Fig. 11 depicts the evolution of IIP<sub>3</sub> versus  $g_{m3}$  with and without the neutralizing capacitor  $C_4$ . As the bandwidth extension technique results in a 3–4 dB higher boosting gain (Fig. 7) it logically degrades the LNA IIP<sub>3</sub> by almost the same factor. The use of  $C_4$  is still necessary since otherwise the LNA does not meet > 2 GHz bandwidth. Ideally, a design point is chosen to simultaneously minimize the noise at an acceptable IIP<sub>3</sub> value having an S<sub>11</sub> lower than -10 dB. Because of the differential operation the simulated IIP<sub>2</sub> is found to be as high as +13.7 dBm.

## F. Stability

Given the multiple cross-connections and feedbacks in the circuit (crossing of the sources, CCC on M3 gate, C4 neutralizing capacitors) the stability must be investigated. Two different points are addressed in this section. The first one is related to the DC biasing scheme which requires a close-loop control for good reliability. The second one concerns the effect of C4 on high-frequency stability.

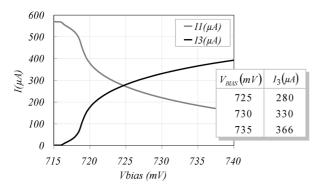

Fig. 12. Evolution of I1 & I3 bias current versus  $V_{\rm BIAS}$  on  $M_3$  gate.

Fig. 13. DC loop feedback,  $V_{REF} = R_1$ .  $I_{1-REF}$ .

1) DC Feedback Stability: The DC coupling between  $M_1$  gate and  $M_3$  drain makes the  $I_1/I_3$  ratio shown in Fig. 12 very sensitive to the biasing voltage on  $M_3$  gate ( $V_{BIAS}$ ). To control precisely the biasing for optimal noise and linearity operation, a DC feedback is necessary. The DC common mode at LNA output is sensed to generate  $V_{BIAS}$  with a DC comparator (Fig. 13). The comparator draws 5  $\mu$ A from the power supply, the phase margin of the total loop gain is 60°. The bandwidth of the comparator is kept very low and thus it does not introduce any loop instability.

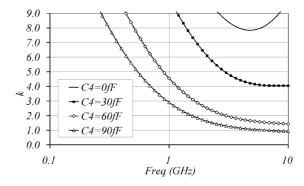

2) High Frequency Stability: At high frequency the stability robustness is investigated by means of k-factor (20) [19], which indicates unconditional stability when k > 1.

$$k = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11}S_{22} - S_{12}S_{21}|^2}{2|S_{12}S_{21}|}.$$

(20)

$C_4$  is the most likely parameter to cause instability since the positive feedback it induces can strongly lower k-factor. In Fig. 14,  $C_4$  is swept till k-factor falls under unity for at least one frequency between 100 MHz to 10 GHz. The corresponding  $S_{11}$ curves are plotted in Fig. 15. It follows that the LNA is matched and unconditionally stable for  $C_4 < 30$  fF. Between 30 fF and 90 fF the LNA is no longer matched since  $S_{11} > -10$  dB but it still shows an unconditional stability. At 90 fF, the stability is no longer guaranteed at high frequency.

Finally  $C_4$  capacitor is set to 30 fF in order to reach a critical damped behavior. Even with strong technological variations on  $C_4$  the LNA will not exhibit stability problem.

#### G. Circuit Implementation and Statistical Behavior

The geometry and biasing of the designed LNA is summarized in Table V. The output loads are somewhat high given the

Fig. 14. K-factor between 0.1 GHz and 10 GHz for  $C_4 = 0$  fF, 30 fF, 60 fF, 90 fF.

Fig. 15. Simulated input reflection coefficient  $\rm S_{11}$  for  $\rm C_4=0~fF,$  30 fF, 60 fF and 90 fF.

TABLE IV EFFECT OF C4 ON BANDWIDTH AND GAIN PEAKING.

| C <sub>4</sub> (fF) | ٤     | BW-3dB-SIM (GHz) | Gain Peaking(dB) |

|---------------------|-------|------------------|------------------|

| 10                  | 0.98  | 1.99             | Under-damped     |

| 30                  | 0.710 | 2.63             | +0.2             |

| 60                  | 0.49  | 2.66             | +1.01            |

desired voltage gain of ~ 20 dB. The power consumption is reduced to 1.32 mW (biasing excluded) for the whole circuit. The obtained NF is 4 dB. The robustness of the design from Table V versus technological variation is investigated through Monte Carlo analysis. Over 500 runs, both technological process deviations and in-wafer device mismatches are considered. PVT variations are simulated on all LNA components, including C<sub>4</sub> capacitor. Mean ( $\mu$ ) and standard deviation ( $\sigma$ ) of the LNA metrics are given in Table VI.

Because of the high gain and the low power consumption, the linearity is the most likely metric to vary. The rest of the metrics appear reliable versus technological variations.

## **IV. EXPERIMENTAL RESULTS**

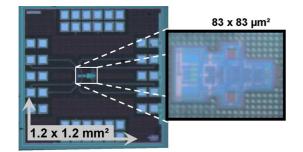

The proposed LNA has been implemented in ST-Microelectronics CMOS 0.13  $\mu$ m-GP process. The implemented design is described in Table V and the differential LNA draws 1.1 mA from a 1.2 V power supply. The active area is 83 × 83  $\mu$ m<sup>2</sup> (~ 0.007 mm<sup>2</sup>) of a 1.44 mm<sup>2</sup> pad-limited test-chip (Fig. 16) dedicated for on-wafer-probe measurement. No RF-specific process

TABLE V IMPLEMENTED DESIGN OF THE CGAB LNA.

|                | Main CG amp.                      |                                                                                                                         |  | G <sub>m</sub> -boosting CG amp.                              |                                                                                                                                                                                           |                        |  |

|----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| Size &<br>Bias | Vov                               | $(L)_{1} = (18/0, 13) \mu m R_{1} = 700$<br>$V_{OV} \approx 40 m V I_{1} = 220 \mu A$<br>$C_{L} = 50 f F (25 f F diff)$ |  |                                                               | $\begin{array}{l} (W/L)_{3} = (18/0,13) \mu m \\ (W/L)_{4} = (10/0,13) \mu m \ R_{3} = 1500 \\ V_{OV} \approx 55 m V \ I_{3} = 330 \mu A \\ C_{2} = 500 f F \ C_{4} = 32 f F \end{array}$ |                        |  |

| Small          | $g_{m1}=3.5mS$ $g_{ds1}=214\mu S$ |                                                                                                                         |  | $g_{m3}$ =4.6ms $g_{ds3}$ =345 $\mu$ S $g_{ds4}$ =230 $\mu$ S |                                                                                                                                                                                           |                        |  |

| Signal.        | $c_{gs1}=13 fF$ $c_{gd1}=9 fF$    |                                                                                                                         |  | $c_{gs3}=13 fF$ $c_{gd3}=9 fF$ $c_{v3}\approx 20 fF$          |                                                                                                                                                                                           |                        |  |

| Gv (dB)        |                                   | NF <sub>SIM</sub> (dB)                                                                                                  |  | S <sub>11</sub> (dB)                                          |                                                                                                                                                                                           | IIP <sub>3</sub> (dBm) |  |

| 23.0           |                                   | 4.5                                                                                                                     |  |                                                               | -10.9                                                                                                                                                                                     | -14.3                  |  |

TABLE VI

500 Runs Monte Carlo Statistical Distributions.

| I <sub>LNA</sub> (μA) | Gv* (dB) | NF <sub>SIM</sub> (dB) | S <sub>11</sub> (dB) | IIP <sub>3</sub> (dBm) |

|-----------------------|----------|------------------------|----------------------|------------------------|

| μ=551                 | μ=23.4   | μ=4.5                  | μ=-10.9              | μ=-14.3                |

| σ=10                  | σ=0.4    | σ=0.56                 | σ=0.47               | σ=1.05                 |

| -                     |          |                        |                      |                        |

\* : The voltage gain Gv value is extracted at 2,45GHz for each run result

Fig. 16. Micrograph of the measured LNA and area of the core circuit.

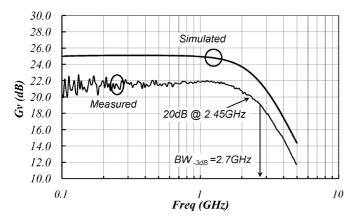

Fig. 17. Measured gain of the proposed CGAB LNA.

options like MIM capacitor or extra thick metals were used. For test purposes, the LNA is loaded with an output buffer, which consumes 5.5 mA using a dedicated power supply. It isolates the LNA output from the testing apparatus. The designed buffer shows an input parasitic capacitor which is close to the 50 fF  $C_L$ capacitor assumed before. A stand-alone version of this testing buffer is added next to the LNA for gain de-embedding purposes. The buffer IIP<sub>3</sub> (+10 dBm) and its NF (7 dB) do not affect the measurements of the LNA IIP<sub>3</sub> and NF. The gain and input matching measurement of the differential circuit are performed on a 4-port VNA providing true differential-mode S-parameters.

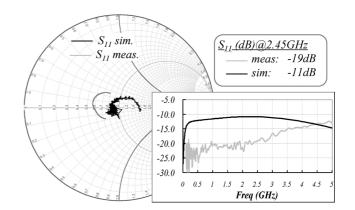

Fig. 18. Measured and simulated  $S_{11}$  of the CGAB LNA.

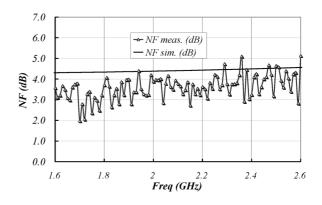

Fig. 19. Measured NF of proposed CGAB LNA.

Other measurements like NF and IIP<sub>3</sub> require extra off-chip 180° couplers for single-to-diff conversions. The bandwidth of these couplers is limited from 1.5 GHz to 3 GHz. Measurements are compared to post-layout simulations with layout parasites of the core LNA circuit. The measured gain is depicted in Fig. 17. It shows a significant drop of almost 3 dB which has been identified to be caused by long-length RF input lines that exhibit a parasitic series inductance. The reduced boosting gain logically improves the measured  $S_{11}$  as shown in Fig. 18. The NF can be only measured in the working bandwidth of the hybrid couplers. Couplers with reduced bandwidth are preferred since they offer lower insertion losses. NF measurement is presented in Fig. 19. A significant fluctuation is observed in the NF plot because of the low gain of the chain. Indeed, the buffer losses reduce the accuracy of the measurement. However, Fig. 19 exhibits an average value around 4 dB. The measured  $ICP_{-1 \text{ dB}}$  and the  $IIP_3$  at 2.45 GHz are shown in Fig. 20. They are performed with a two-tone test at 2.45 GHz with 5 MHz tone spacing. Because of the gain drop, the LNA exhibits an improved  $IIP_3$  of 2 dB compared to simulation. The compression point is not surprisingly quite low given the low bias current of the LNA.

Table VII presents recently published low power LNAs. A Figure of Merit (FoM) defined in (21) is introduced for comparison purposes. The circuit area (A[mm<sup>2</sup>]) has been added in (21) to provide a fair comparison with non- inductorless LNAs ([1]–[3]). In Table VII, among the circuits that exhibit a FoM close to 100 dB, our circuit is the less consuming. We moreover

| Ref.            | BW       | Gv or                      | NF            | IIP <sub>3</sub> | P <sub>DC</sub> | Area       | FOM    |

|-----------------|----------|----------------------------|---------------|------------------|-----------------|------------|--------|

| Tech.           | (GHz)    | S <sub>21</sub> (dB)       | ( <b>dB</b> ) | (dBm)            | (mW)            | (mm²)      | (dB)   |

| [1]<br>0.13 µm  | 2.45     | 14.6<br>(S <sub>21</sub> ) | 3.8           | -12              | 0.12†<br>(0.6V) | 0.63 *     | 77.90  |

| [2]<br>0.18 µm  | 0.3-0.92 | 21                         | 2-4           | -3.2             | 3.6             | 0.33<br>** | 68.79  |

| [3]<br>0.18 µm  | 5.8      | 9.4 (S <sub>21</sub> )     | 2.5           | +7,6             | 3.42 †          | 0.610<br>* | 95.66  |

| [4]<br>0.13 μm  | 0.1-0.9  | 13 (S <sub>21</sub> )      | 4             | -10.2            | 0.72            | 0.268      | 62.39  |

| [5]<br>0.18 µm  | 9.6      | 24 (S <sub>21</sub> )      | 4             | -11.3            | 18              | 0.115<br>* | 71.14  |

| [6]<br>0.13 µm  | 3.8      | 19                         | 3.4           | -4.2             | 5.7 †           | 0.0252     | 97.56  |

| [8]<br>90 nm    | 7        | 22                         | 2.9           | -8.5             | 12†             | 0.012      | 99.18  |

| [10]<br>0.18 µm | 0.4-0.9  | 20.7                       | 2.95          | -16‡             | 0.385<br>(0.5V) | 0.07<br>** | 79.42  |

| [11]<br>90 nm   | 6        | 16.5                       | 2.5           | -10              | 9.2 †           | 0.0017     | 109.90 |

| [20]<br>0.13 µm | 0.01-1.4 | 22                         | 7             | -17              | 0.9 †           | 0.03       | 70.23  |

| [21]<br>90 nm   | 0.1-1.66 | 10.5<br>(S <sub>21</sub> ) | 5.9           | -4.5             | 0.425†          | Sim.       | -      |

| [22]<br>0.13 µm | 0.2-3.8  | 11.2                       | 2.85          | -2.7             | 1.9             | Sim.       | -      |

| Т.W<br>0.13µm   | 0.1-2.7  | 20                         | 4.0           | -12              | 1.32            | 0.007      | 101.72 |

TABLE VII

COMPARISON WITH PUBLISHED LOW POWER LNA.

<sup>†</sup> Single ended input LNA. \* Use on-chip inductor \*\*Use off-chip inductor ‡Obtained from authors of [10]

Fig. 20. Measured IIP3 and ICP-1 dB of proposed CGAB LNA.

offer a high-IIP<sub>2</sub> fully- differential circuit robust to common mode noise

$$FoM = 20\log_{10} \left( \frac{BW \,[\text{GHz}] \cdot G_V \,[\text{lin.}] \cdot IIP_3 \,[\text{mW}]}{P_{\text{DC}} \,[\text{mW}] \cdot (F-1) \cdot A \,[\text{mm}^2]} \right).$$

(21)

# V. CONCLUSION

A doubly- $g_m$ -boosted CG LNA circuit is presented. It achieves a power consumption of 1.32 mW for fully differential operation. The LNA design makes use of both active and passive  $g_m$ -boosting effects in order to reach a 4 dB NF and a large voltage gain at milliwatt range  $P_{DC}$ . Tradeoff between noise and linearity has been discussed. The LNA shows good stability as well as good robustness versus technological variations. The measured circuit shows good performances compared to other low  $P_{\rm DC}$  LNAs. Inductorless implementation result in a silicon area of 0.007 mm<sup>2</sup>.

#### REFERENCES

- T. Taris, A. Mabrouki, H. Kraimia, Y. Deval, and J.-B. Begueret, "Reconfigurable ultra low power LNA for 2.4 GHz wireless sensor networks," in *Proc. IEEE ICECS*, Dec. 2010, pp. 74–77.

- [2] S. Woo and W. Kimal, "A 3.6 mW differential common gate CMOS LNA with positive-negative feedback," in *Proc. IEEE ISSCC*, Feb. 2009, pp. 218–219.

- [3] X. Li, S. Shekhar, and D. J. Allstot, "G<sub>m</sub>-boosted common-gate LNA and differential colpitts VCO/QVCO in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2609–2619, Dec. 2005.

- [4] S. B. T. Wang, A. M. Niknejad, and R. W. Brodersen, "Design of a sub-mW 960-MHz UWB CMOS LNA," *IEEE J. Solid-State Circuits*, vol. 41, no. 11, pp. 2449–2456, Nov. 2006.

- [5] I. R. Chamas and S. Raman, "Analysis, design, and X-band implementation of a self-biased active feedback g<sub>m</sub>-boosted common-gate CMOS LNA," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 3, pp. 542–551, Mar. 2009.

- [6] H. Wang, L. Zhang, and Z. Yu, "A wideband inductorless LNA with local feedback and noise cancelling for low-power low-voltage applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 8, pp. 1993–2005, Aug. 2010.

- [7] F. Belmas, F. Hameau, and J.-M. Fournier, "A 1.3 mW 20 dB gain low power inductorless LNA with 4 dB noise figure for 2.45 GHz ISM band," in *Proc. IEEE Int. Symp. RFIC*, Jun. 5–7, 2011, pp. 1–4.

- [8] B. G. Perumana, J.-H. C. Zhan, S. S. Taylor, B. R. Carlton, and J. Laskar, "Resistive-feedback CMOS low-noise amplifiers for multiband applications," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 5, pp. 1218–1225, May 2008.

- [9] J.-H. C. Zhan and S. S. Taylor, "A 5 GHz resistive-feedback CMOS LNA for low-cost multi-standard applications," in *Proc. IEEE Solid-State Circuits Conf. (ISSCC)*, Feb. 6–9, 2006, pp. 721–730.

- [10] J. Liu, H. Liao, and R. Huang, "0.5 V ultra-low power wideband LNA with forward body bias technique," *Electron. Lett.*, vol. 45, no. 6, pp. 289–290, Mar. 2009.

- [11] J. Borremans, P. Wambac, C. Soens, Y. Rolain, and M. Kuijk, Low-area active-feedback low-noise amplifier design in scaled digital CMOS," IEEE J. Solid-State Circuits, vol. 43, no. 11, pp. 2422-2433, Nov. 2008.

- [12] A. Ismail and A. A. Abidi, "A 3-10-GHz low-noise amplifier with wideband LC-ladder matching network," IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2269-2277, Dec. 2004.

- [13] A. Bevilacqua, M. Camponeschi, M. Tiebout, A. Gerosa, and A. Neviani, "Design of broadband inductorless LNAs in ultra-scaled CMOS technologies," in Proc. ISCAS, May 18-21, 2008, pp. 1300-1303.

- [14] R. Ramzan, S. Andersson, J. Dabrowski, and C. Svensson, "A 1.4 V 25 mW inductorless wideband LNA in 0.13 µm CMOS," in Proc. ISSCC, Feb. 11-15, 2007, pp. 424-613.

- [15] Y. Cui et al., "On the excess noise factors and noise parameter equations for RF CMOS," in Proc. 2007 IEEE Topical Meeting Silicon Monolithic Integr. Circuits RF Syst. Dig. Papers, Jan. 10-12, 2007, pp. 40-43.

- [16] P.-I. Mak and R. Martins, "A 0.46 mm<sup>2</sup> 4 dB-NF unified receiver front-end for fullband mobile TV in 65 nm CMOS," in Proc. ISSCC, Feb. 20-24, 2011, pp. 172-174.

- [17] C.-C. Hsiao, C.-W. Kuo, C.-C. Ho, and Y.-J. Chan, "Improved qualityfactor of 0.18-µm CMOS active inductor by a feedback resistance design," IEEE Microw. Wireless Components Lett., vol. 12, no. 12, pp. 467-469, Dec. 2002.

- [18] S.-S. Song, D.-G. Im, H.-T. Kim, and K. Lee, "A highly linear wideband CMOS low-noise amplifier based on current amplification for digital TV tuner applications," IEEE Microw. Wireless Components Lett., vol. 18, no. 2, pp. 118-120, Feb. 2008.

- [19] B. Razavi, RF Microelectronics. Englewood Cliffs, NJ: Prentice Hall, 1997

- [20] T.-T. Liu and C.-K. Wang, "A 0.9 mW 0.01-1.4 GHz wideband CMOS low noise amplifier for low-band UWB application," in Proc. IEEE ASSCC, Nov. 2005, pp. 345-348.

- [21] K. Allidina and M. N. El-Gamal, "A 1 V CMOS LNA for low power ultra-wideband systems," in Proc. ICECS, Aug.-Sep. 31-3, 2008, pp. 165 - 168

- [22] A. Amer, E. Hegazi, and H. Ragai, "A low-power wideband CMOS LNA for WiMAX," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no. 1, pp. 4-8, Jan. 2007.

François Belmas received the M.S. degree in electrical engineering from the National Institute of Applied Science- INSA, Lyon, France, in 2008. He received the Ph.D. degree at the Institut National Polytechnique de Grenoble (INPG) at RF laboratory/CEA-LETI, Grenoble, France, where he worked on CMOS RF design.

He was with NXP semiconductor from 2007 to 2008 where he worked on DTV SiP design. His main interest was inductorless design for low power RFICs. He is now with Cambridge Silicon Radio (CSR), Sophia Antipolis, France, as an RF Designer.

Frédéric Hameau received the M.S. degree in microelectronics from Ecole Nationale Supérieure d'Electronique, d'Informatique et de Radiocommunications de Bordeaux, France, in 2001.

He did a 6 month period as RF designer in the STmicroelectronics R&D Center, Crolles, France, where he designed a power amplifier for bluetooth applications in 0.12  $\mu$ m SOI technology. He joined CEA-LETI laboratory as RF designer in 2001, where he designed RF frontend blocs using SOI and CMOS

technology. He is now in charge of System On Chip integration in the wireless sensor network field. His work includes ultra-wide band applications as well as ultra-low power applications.

Jean-Michel Fournier graduated in electronic engineering from the National Engineer School (EN-SEEIHT), Toulouse, France, in 1974. He received the M.S. and Ph.D. degrees from the Department of Solid-State Physic, University Claude Bernard, Lyon, France, in 1975 and 1979, respectively.

In 1979, he joined the R&D in Microelectronic Department of France Telecom, Grenoble, where he worked on analog MOS ASIC development (High speed video amplifiers, Gmc filters, device modeling). Between 1992 and 1996, he was in charge of

the analog design group, and he focused his interest on BiCMOS process for RF applications. From 1996, he is a Professor at PHELMA (School Electronic and Physic of INPG). At IMEP-LAHC laboratory, his main research interest is the design of analog RF and millimeter-wave integrated circuits in CMOS technology.