# DESIGN OF FREQUENCY SYNTHESIZERS FOR SHORT RANGE WIRELESS TRANSCEIVERS

A Dissertation

by

ARI YAKOV VALERO LOPEZ

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2004

Major Subject: Electrical Engineering

UMI Number: 3132138

## UMI Microform 3132138

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

\_\_\_\_\_

ProQuest Information and Learning Company 300 North Zeeb Road PO Box 1346 Ann Arbor, MI 48106-1346

# DESIGN OF FREQUENCY SYNTHESIZERS FOR SHORT RANGE WIRELESS TRANSCEIVERS

A Dissertation

by

ARI YAKOV VALERO LOPEZ

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| oved as to style and content by:            |                                 |

|---------------------------------------------|---------------------------------|

| Edgar Sánchez-Sinencio (Chair of Committee) | José Silva-Martínez<br>(Member) |

| Kai Chang<br>(Member)                       | Eva Sevick-Muraca (Member)      |

| Chanan Singh (Head of Department)           |                                 |

May 2004

Major Subject: Electrical Engineering

## **ABSTRACT**

Design of Frequency Synthesizers for Short RangeWireless Transceivers.

(May 2004)

Ari Yakov Valero Lopez, B.S., University of Guanajuato, Mexico;

M.S., National Institute for Astrophysics, Optics and Electronics, Mexico

Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

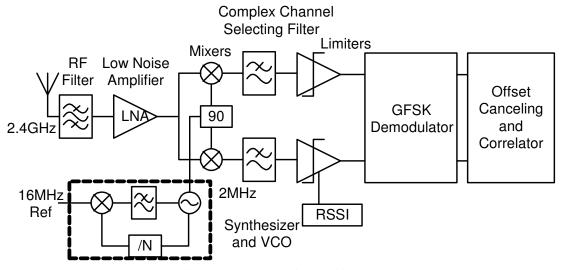

The rapid growth of the market for short-range wireless devices, with standards such as Bluetooth and Wireless LAN (IEEE 802.11) being the most important, has created a need for highly integrated transceivers that target drastic power and area reduction while providing a high level of integration. The radio section of the devices designed to establish communications using these standards is the limiting factor for the power reduction efforts. A key building block in a transceiver is the frequency synthesizer, since it operates at the highest frequency of the system and consumes a very large portion of the total power in the radio. This dissertation presents the basic theory and a design methodology of frequency synthesizers targeted for short-range wireless applications. Three different examples of synthesizers are presented. First a frequency synthesizer integrated in a Bluetooth receiver fabricated in 0.35µm CMOS technology. The receiver uses a low-IF architecture to downconvert the incoming Bluetooth signal to 2MHz.

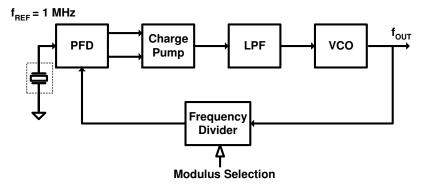

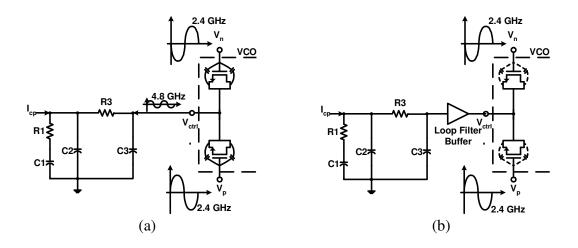

The second synthesizer is integrated within a dual-mode receiver capable of processing signals of the Bluetooth and Wireless LAN (IEEE 802.11b) standards. It is

implemented in BiCMOS technology and operates the voltage controlled oscillator at twice the required frequency to generate quadrature signals through a divide-by-two circuit. A phase switching prescaler is featured in the synthesizer. A large capacitance is integrated on-chip using a capacitance multiplier circuit that provides a drastic area reduction while adding a negligible phase noise contribution.

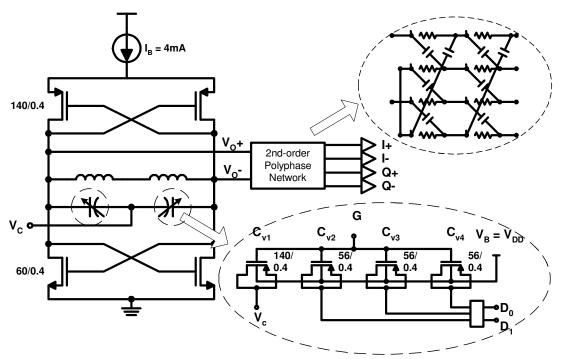

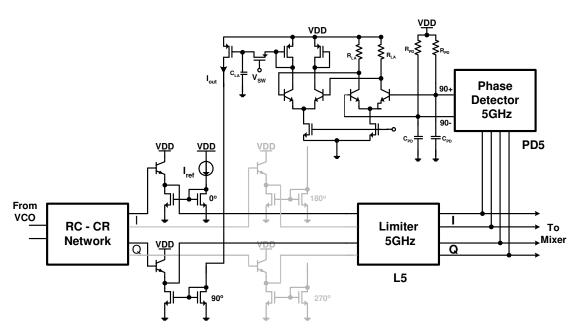

The third synthesizer is an extension of the second example. The operation range of the VCO is extended to cover a frequency band from 4.8GHz to 5.85GHz. By doing this, the synthesizer is capable of generating LO signals for Bluetooth and IEEE 802.11a, b and g standards. The quadrature output of the 5-6 GHz signal is generated through a first order RC – CR network with an automatic calibration loop. The loop uses a high frequency phase detector to measure the deviation from the 90° separation between the I and Q branches and implements an algorithm to minimize the phase errors between the I and Q branches and their differential counterparts.

## **DEDICATION**

To my beloved wife Marcia Gisela and daughter Aimee Carolina,

my father Mario Alberto, my brother Alberto,

and to the memory of my mother Elizabeth.

For all their love and unconditional support.

## **ACKNOWLEDGMENTS**

The road of knowledge is long and full of obstacles, but it is exactly going over those obstacles what ultimately enlightens the individual and strengthens his spirit. I have been very fortunate to walk through the road of knowledge, not alone, but accompanied by the brightest and warm hearted individuals I have ever met. I will always treasure the memories of the years we have shared.

First of all, I want to express my most sincere thanks to my advisor, Dr. Edgar Sánchez-Sinencio with my deepest gratitude. He has been an inspiration to me since I first met him. His energetic style and never ending flow of ideas has been a model in my academic and personal life. I also want to thank him for trusting in me and encouraging me to pursue this adventure, his moral support during the five years of my program has been fundamental to the conclusion of this lifelong dream. His guidance during the development of my research has been invaluable.

I would also like to express special thanks to Dr. Jose Silva-Martínez, who has given me and my family the honor of his friendship. His technical insight and willingness to help have played a very important role in the course of development of this research. In particular at times when there seems to be no solution to a problem, Dr. Silva always came with the simple and "obvious" solution. I want to thank him for giving me the opportunity to experience Texas A&M University during my master's studies and giving me the last push to come into this group.

I want to thank Dr. Eva Sevick-Muraca for serving on my committee and allowing me to work in her group. Her enthusiasm and hard working style is so contagious it motivated me to keep going on.

I thank Dr. Kai Chang for serving on my committee and giving suggestions to my dissertation.

Special thanks go to the secretary of the AMSC, Ms. Ella Gallagher. Her prompt help and joyful character are a valuable treasure for the group.

I was very fortunate to work with a group of very enthusiastic and bright students in two major projects, the Bluetooth and Chameleon receivers. Alberto Valdes, Sung Tae Moon, Ahmed Emira, Bo Xia, Ahmed Mohieldin, Chunyu Xin and Wenjun Sheng. Their enormous effort and enthusiasm were key to the successful completion of the projects. The personal and technical experience I obtained through the collaboration with all of them is a very valuable part of my educational experience.

I want to thank all my friends for the support and encouragement during all the years I spent in Texas A&M. I want to thank my friend and officemate Alberto Valdes for all his support, advice and for lifting up my spirit when I needed it the most, and Artur Lewinski for being always there. I had the opportunity to work with Sung Tae Moon in three different projects, his optimism and easy going nature were always very important to keep my nerves in control. I also want to thank my friends Antonio, Adriana, Artur, Isabel, David, Benoit, Fikret, Feyza, Fan, Joseph, Erkan, Luis Ignacio, Sony, Gerardo, Joel, Vero, Adan, Regina, Alfonso, Yadhira, Jose Carlos, Lupita, Jose

Miguel, Tere, Felipe, Chinmaya and Arun for their friendship. Thanks to Keliu, Faramarz for their help in technical discussions.

I would like to express my gratitude to Mayo for her invaluable help during these years.

The deepest gratitude goes to my beloved wife Marcia Gisela who has always been my inspiration. Her unconditional support, sacrifice and encouragement have been the driving force that keeps me going. I do not have words to thank her for sacrificing her own doctorate to give me the opportunity to go ahead with mine. I am a very fortunate man to have such an intelligent and wonderful woman by my side. I would like, also, to thank my daughter, Aimee Carolina, for making me so happy with all the love she emanates. Her innocence and joyful character provided me with the much needed energy and peace to keep going. Both of the women in my life are the most valuable treasure I have.

I want to thank my father, Mario Alberto, and my brother, Alberto, for providing me with love and support through these years. To my late mother, Elizabeth, I want to thank for teaching me that there are no boundaries to our dreams when we are willing to take the risk and put the required effort. She always wanted me to obtain an advanced degree, and now I have the opportunity to show her that her dream has been fulfilled.

# TABLE OF CONTENTS

|                                                                                                                                                                                                                                               | Page                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                      | iii                                    |

| DEDICATION                                                                                                                                                                                                                                    | v                                      |

| ACKNOWLEDGMENTS                                                                                                                                                                                                                               | vi                                     |

| TABLE OF CONTENTS                                                                                                                                                                                                                             | ix                                     |

| LIST OF FIGURES                                                                                                                                                                                                                               | xii                                    |

| LIST OF TABLES                                                                                                                                                                                                                                | xviii                                  |

| CHAPTER                                                                                                                                                                                                                                       |                                        |

| I INTRODUCTION                                                                                                                                                                                                                                | 1                                      |

| 1.1. Background and Motivation  1.2. Short-Range Wireless Communications  1.2.1. Bluetooth  1.2.2. Wireless LAN IEEE 802.11  1.2.3. Ultra-Wideband (UWB)  1.3. Role of a Frequency Synthesizer in RF Transceivers  1.4. Dissertation Overview | 5<br>10<br>12                          |

| II FREQUENCY SYNTHESIZERS FOR WIRELESS APPLICATIONS  2.1. Definition                                                                                                                                                                          | 21<br>24<br>36<br>37<br>42<br>44<br>47 |

| 2.4 Non ideal Parameters Effects                                                                                                                                                                                                              |                                        |

| CHAF | TER                                                              | Page       |

|------|------------------------------------------------------------------|------------|

|      | 2.4.1 Phase Engagement Detector                                  | <i>C</i> 1 |

|      | 2.4.1. Phase – Frequency Detector                                |            |

|      | 2.4.2. Charge Pump                                               |            |

|      | 2.4.2. Frequency Dividers                                        |            |

|      | 2.5. Mapping Standards into Frequency Synthesizer Specifications |            |

|      | 2.5.1. Bluetooth                                                 |            |

|      | 2.5.2. Wireless LAN 802.11b                                      |            |

|      | 2.6 Frequency Synthesizers State-of-the-Art Survey               |            |

|      | 2.6.1. Architectures                                             |            |

|      | 2.6.2. Linearization Techniques                                  |            |

|      | 2.6.3. Digital Phase-Locked Loop                                 |            |

|      | 2.6.4. Fast Settling Techniques                                  |            |

|      | 2.6.5. Building Blocks                                           |            |

|      | 2.6.6. Low Voltage Low Power                                     | 89         |

| III  | FREQUENCY SYNTHESIZER FOR BLUETOOTH RECEIVER                     | 91         |

|      | 3.1. Low-IF Bluetooth Receiver                                   | 91         |

|      | 3.1.1. Frequency Synthesizer Specifications                      |            |

|      | 3.2. Frequency Synthesizer Architecture                          |            |

|      | 3.2.1. Phase Frequency Detector                                  |            |

|      | 3.2.2. Charge Pump                                               |            |

|      | 3.2.3. Voltage Controlled Oscillator (VCO)                       |            |

|      | 3.2.4. Lowpass Filter Buffer                                     | 98         |

|      | 3.2.5. Programmable Divider                                      |            |

|      | 3.3. Layout and Measurement Results                              | 108        |

| IV   | FREQUENCY SYNTHESIZER FOR DUAL MODE RECEIVER                     | 113        |

|      | 4.1. Dual Mode Receiver                                          |            |

|      | 4.1.1. Frequency Synthesizer Specifications                      |            |

|      | 4.2. Frequency Synthesizer Architecture                          |            |

|      | 4.2.1. Phase-Frequency Detector                                  |            |

|      | 4.2.2. Charge Pump                                               |            |

|      | 4.2.3. Loop Filter and Capacitance Multiplier                    |            |

|      | 4.2.4. Voltage Controlled Oscillator (VCO)                       |            |

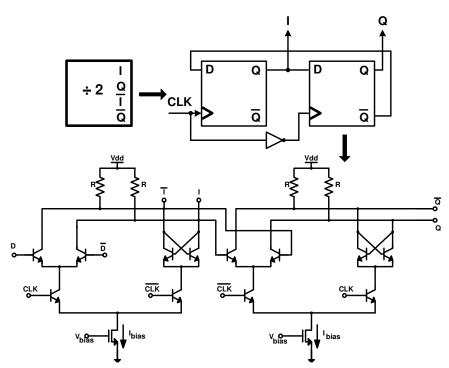

|      | 4.2.5. Frequency Divider                                         |            |

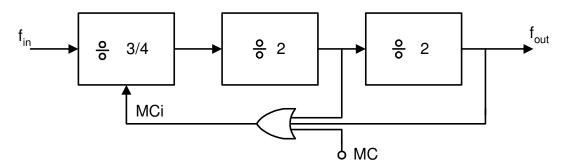

|      | 4.2.5.1 Phase Switching Prescaler                                |            |

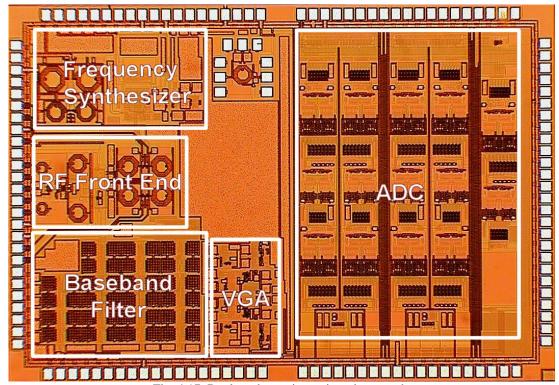

|      | 4.3. Layout                                                      |            |

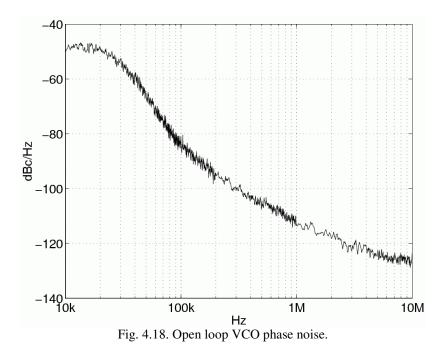

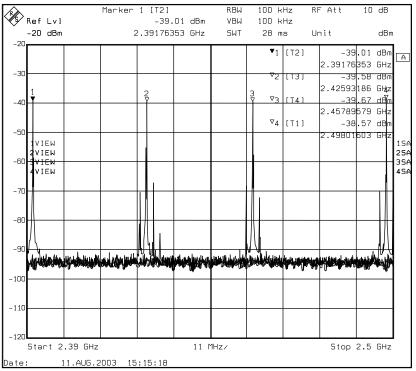

|      | 4.4 Measurements Results                                         | 140        |

| CHAPTER                                                  | Page |

|----------------------------------------------------------|------|

| V FREQUENCY SYNTHESIZER FOR BUILT-IN TESTING             | 149  |

| 5.1. Built-in Testing                                    | 149  |

| 5.2. Phase Frequency Detector                            |      |

| 5.3. Differential Charge Pump with CMFB, Loop Filter     |      |

| 5.4. Differential Oscillator                             |      |

| 5.5. Design Considerations                               | 163  |

| 5.6. Layout                                              |      |

| 5.7. Measurements Results                                |      |

| VI SELF CALIBRATED QUADRATURE GENERATOR FOR              |      |

| MULTISTANDARD FREQUENCY SYNTHESIZER                      | 171  |

| 6.1. Quadrature Generation for Communication Receivers   | 171  |

| 6.2. Quadrature Generation Techniques: A Review          |      |

| 6.2.1. Polyphase Networks                                |      |

| 6.2.2. Divide-by-Two Master-Slave Flip-Flop              |      |

| 6.2.3. Cross Coupled VCO                                 |      |

| 6.3. Self-Calibration Techniques: Background             |      |

| 6.3.1. Level-Locked Loop                                 |      |

| 6.3.2. Adjustable Divide-by-Two Stage                    | 181  |

| 6.3.3. Self-Calibrated Generator                         |      |

| 6.4. Proposed Self-Calibration Technique                 | 184  |

| 6.4.1. Passive Phase Shift Network with Active Phase Shi |      |

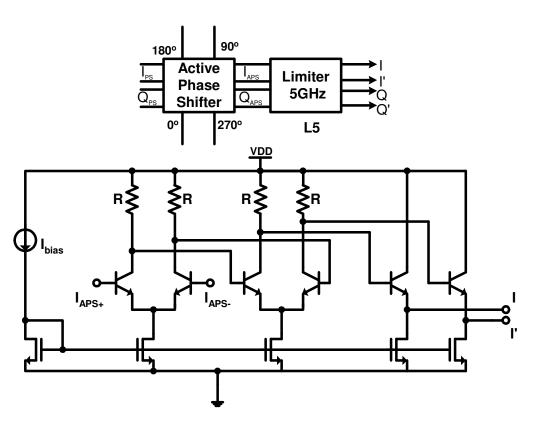

| 6.4.2. Limiting Amplifier                                | 195  |

| 6.4.3. Phase Detector and Correction Amplifier           |      |

| 6.4.4. Phase Correction Algorithm                        |      |

| 6.4.5. Stability Considerations                          |      |

| 6.5 Layout                                               | 209  |

| 6.6 Testing Setup                                        |      |

| 6.7 Summary of Design Results                            |      |

| VII CONCLUSIONS                                          | 213  |

| REFERENCES                                               | 215  |

| APPENDIX A                                               | 228  |

| APPENDIX B                                               | 233  |

| VITA                                                     | 235  |

# LIST OF FIGURES

|                                                                                      | Page |

|--------------------------------------------------------------------------------------|------|

| Fig. 1.1. Bandwidth comparison of different types of wireless systems                | 15   |

| Fig. 1.2. Typical communications transceiver block diagram.                          | 18   |

| Fig. 2.1. PLL block diagram.                                                         | 21   |

| Fig. 2.2. PLL for obtaining the ML estimate of the phase of an unmodulated carrier   | 24   |

| Fig. 2.3. Linear model of PLL.                                                       | 26   |

| Fig. 2.4. Passive loop filter.                                                       | 28   |

| Fig. 2.5. Closed loop transfer function of the PLL type-I for different loop filters | 29   |

| Fig. 2.6. Charge pump PLL block diagram.                                             | 30   |

| Fig. 2.7. Phase frequency detector combined with charge-pump.                        | 32   |

| Fig. 2.8. Magnitude of loop filter transimpedance.                                   | 33   |

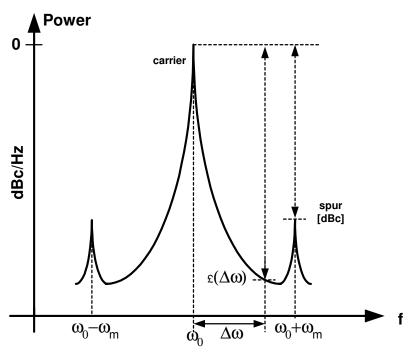

| Fig. 2.9. Phase noise and spurs in oscillator                                        | 38   |

| Fig. 2.10. Effect of phase noise in a receiver.                                      | 42   |

| Fig. 2.11. PLL linear phase noise model.                                             | 43   |

| Fig. 2.12. Implementation of G(s) for settling time analysis.                        | 55   |

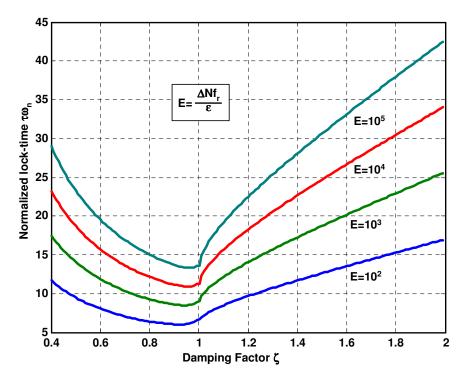

| Fig. 2.13. Normalized locking time as a function of damping factor                   | 59   |

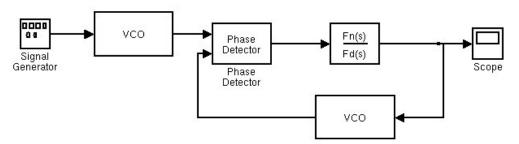

| Fig. 2.14. PLL simulink block diagram.                                               | 60   |

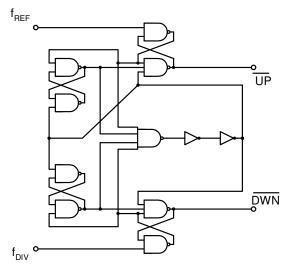

| Fig. 2.15. Phase – frequency detector block diagram.                                 | 61   |

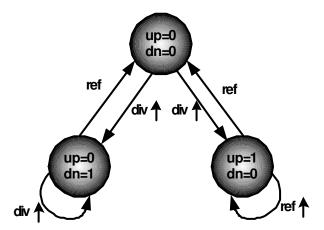

| Fig. 2.16. State diagram of phase-frequency detector                                 | 62   |

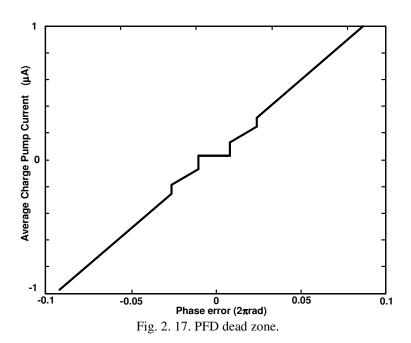

| Fig. 2. 17 PFD dead zone                                                             | 63   |

|                                                                                                        | Page |

|--------------------------------------------------------------------------------------------------------|------|

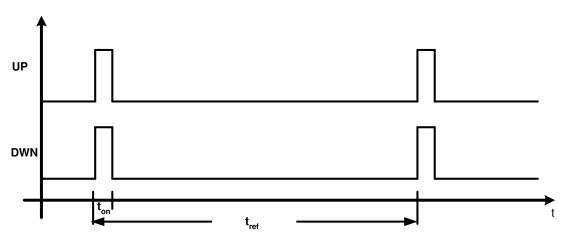

| Fig. 2.18. Up/Dwn pulses for dead zone removal.                                                        | 64   |

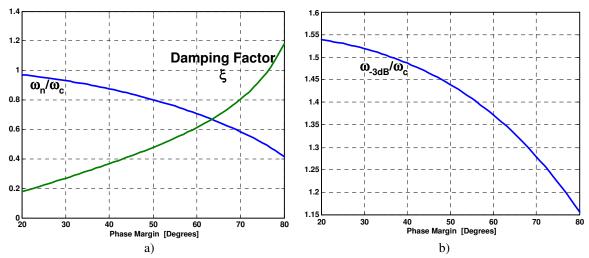

| Fig. 2.19. Phase margin dependence of damping factor, $\omega_n/\omega_c$ and $\omega_{-3dB}/\omega_c$ | 69   |

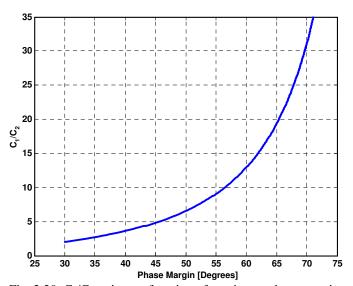

| Fig. 2.20. C <sub>1</sub> /C <sub>2</sub> ratio as a function of maximum phase margin                  | 70   |

| Fig. 2.21.Third order loop filter.                                                                     | 74   |

| Fig. 2.22. Dual-loop architecture block diagram.                                                       | 83   |

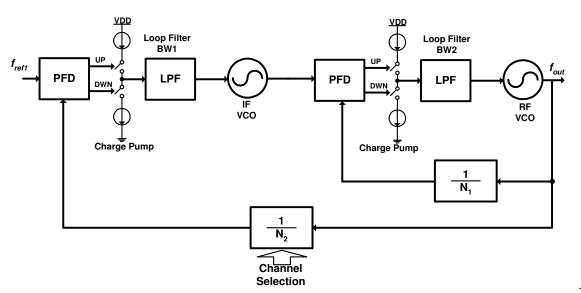

| Fig. 2.23. Nested-loop phase-locked loop architecture                                                  | 84   |

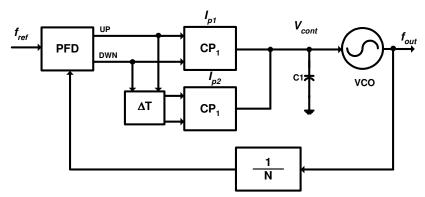

| Fig. 2.24. PLL architecture with delayed charge pump circuit.                                          | 85   |

| Fig. 3.1. Low-IF receiver architecture.                                                                | 92   |

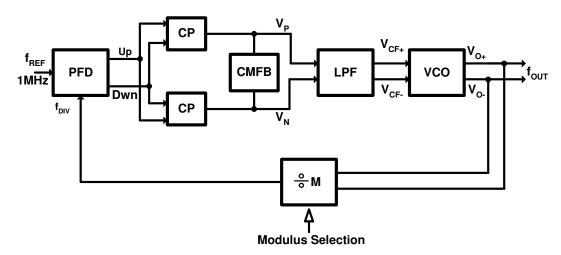

| Fig. 3.2. Frequency synthesizer block diagram.                                                         | 94   |

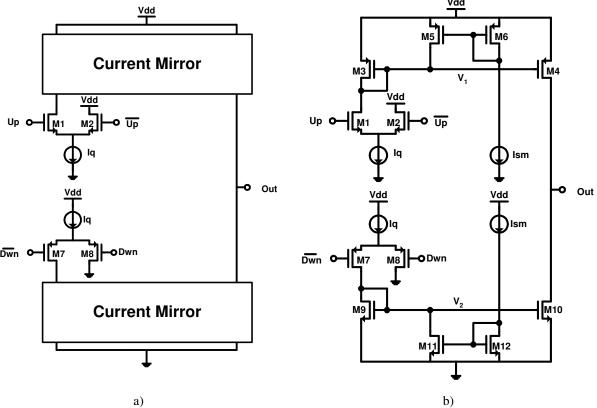

| Fig. 3.3. Charge pump.                                                                                 | 96   |

| Fig. 3.4. VCO with varactor array                                                                      | 98   |

| Fig. 3.5. Effect of VCO on the loop filter                                                             | 99   |

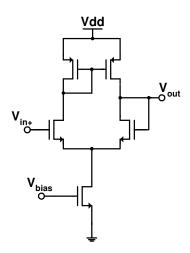

| Fig. 3.6. LPF buffer amplifier.                                                                        | 100  |

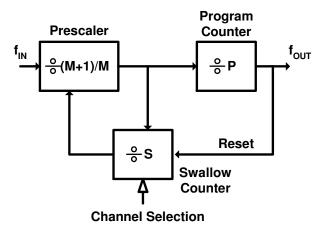

| Fig. 3.7. Pulse swallow frequency divider.                                                             | 102  |

| Fig. 3.8. Prescaler block diagram.                                                                     | 102  |

| Fig. 3.9. 15/16 Prescaler detailed block diagram.                                                      | 103  |

| Fig. 3.10. Current steering NOR D flip-flop.                                                           | 105  |

| Fig. 3.11. Reference voltage generator                                                                 | 107  |

| Fig. 3.12. High speed NOR logic gate.                                                                  | 108  |

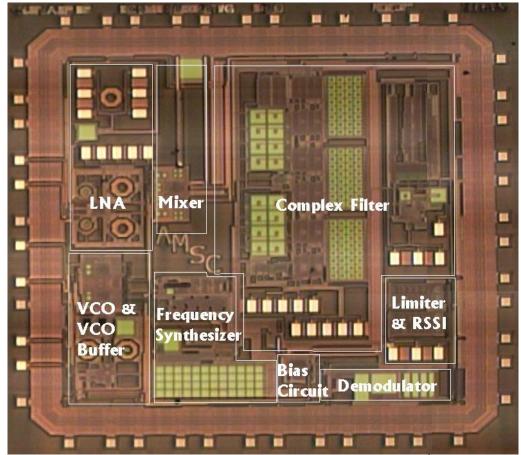

| Fig. 3.13. Die microphotograph of Bluetooth receiver (6.25 mm <sup>2</sup> )                           | 109  |

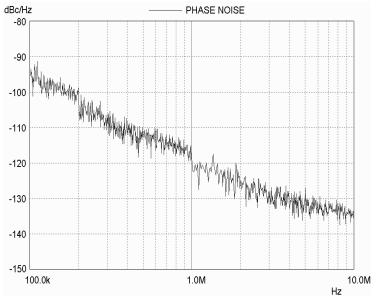

| Fig. 3.14. Measured phase noise of the VCO                                                             | 110  |

|                                                                                        | Page |

|----------------------------------------------------------------------------------------|------|

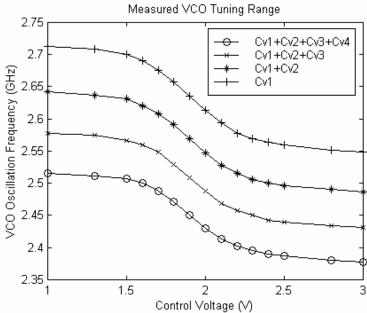

| Fig. 3.15. VCO tuning range testing result.                                            | 110  |

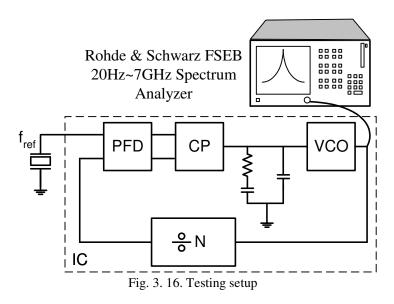

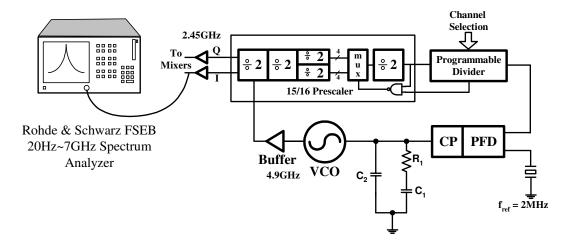

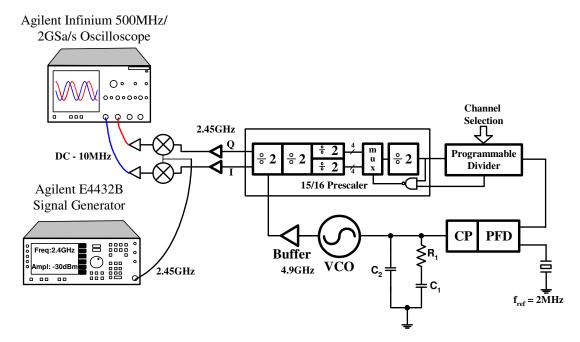

| Fig. 3. 16. Testing setup                                                              | 111  |

| Fig. 3.17. Testing board.                                                              | 112  |

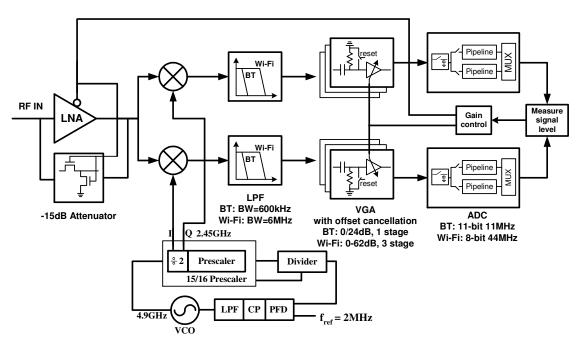

| Fig. 4.1. Dual mode receiver block diagram.                                            | 114  |

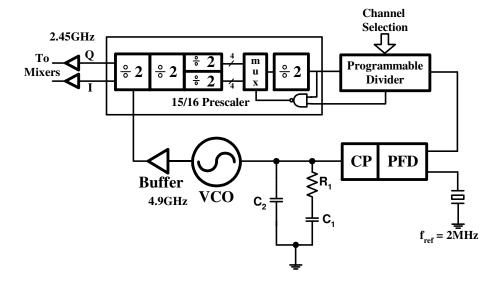

| Fig. 4.2. Frequency synthesizer block diagram                                          | 117  |

| Fig. 4.3. Phase-frequency detector with capacitive delay                               | 118  |

| Fig. 4.4. Charge pump with cascode output.                                             | 119  |

| Fig. 4.5. Capacitance multiplier schematic diagram.                                    | 121  |

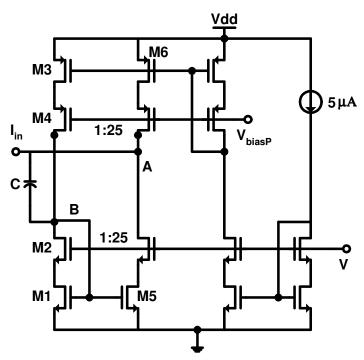

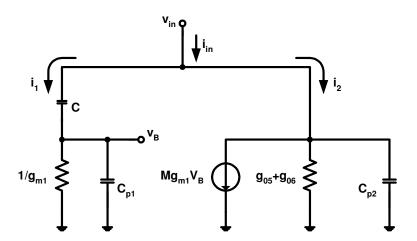

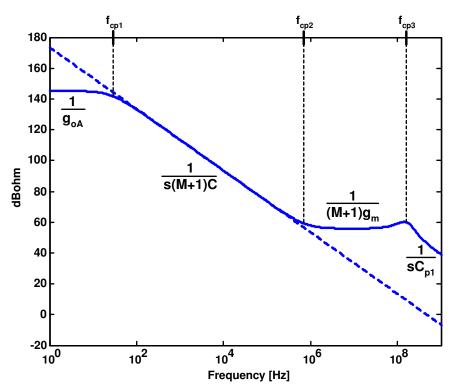

| Fig. 4. 6. Capacitance multiplier small signal equivalent.                             | 122  |

| Fig. 4.7. Magnitude response comparison of ideal capacitor and capacitance multiplier. | 124  |

| Fig. 4.8. VCO schematic diagram.                                                       | 128  |

| Fig. 4.9. Original phase switching prescaler.                                          | 129  |

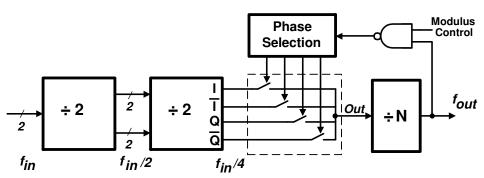

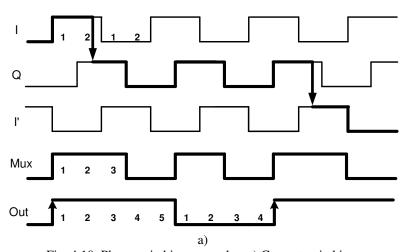

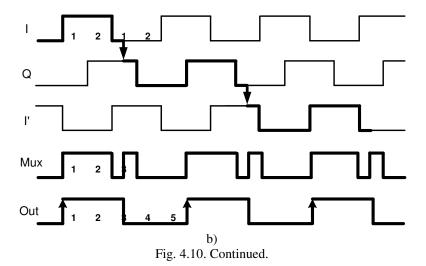

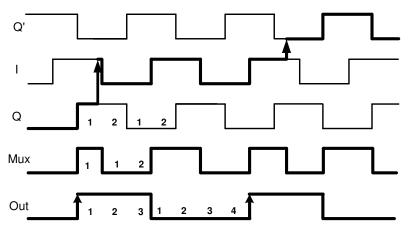

| Fig. 4.10. Phase switching examples                                                    | 130  |

| Fig. 4.11. Enhanced phase switching timing example.                                    | 132  |

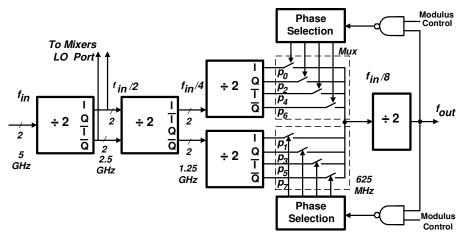

| Fig. 4.12. 15/16 Dual modulus phase switching prescaler.                               | 133  |

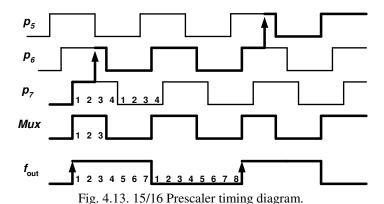

| Fig. 4.13. 15/16 Prescaler timing diagram.                                             | 134  |

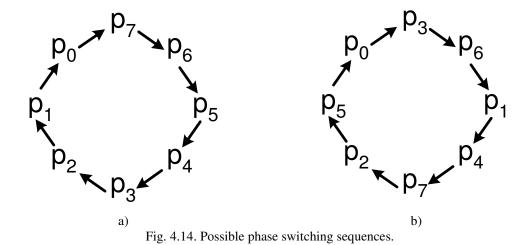

| Fig. 4.14. Possible phase switching sequences.                                         | 135  |

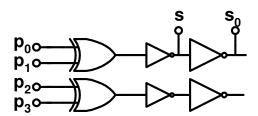

| Fig. 4. 15. XOR for relative phase detection.                                          | 135  |

| Fig. 4.16. High speed D flip-flop. Representation and implementation                   | 137  |

| Fig. 4.17. Dual mode receiver microphotograph.                                         | 140  |

| Page                                                                            |

|---------------------------------------------------------------------------------|

| Fig. 4.18. Open loop VCO phase noise.                                           |

| Fig. 4.19. Synthesized VCO output covering the ISM band                         |

| Fig. 4.20. Testing setup for phase noise and VCO tuning range measurement       |

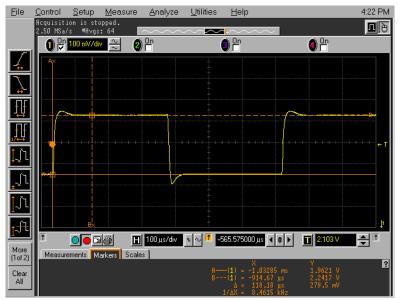

| Fig. 4.21. VCO control signal showing switching of the synthesizer144           |

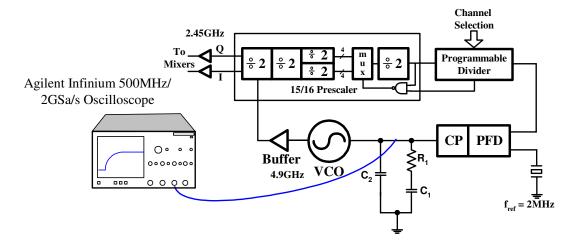

| Fig. 4. 22. Testing setup for settling time measurement                         |

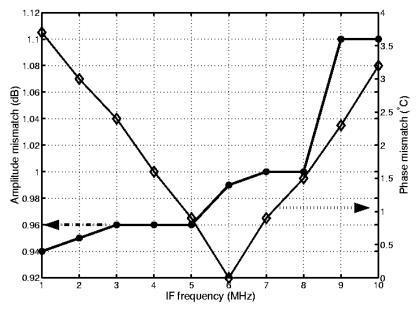

| Fig. 4.23. Phase and amplitude mismatch of RF front-end                         |

| Fig. 4. 24. Testing setup for quadrature mismatch measurement                   |

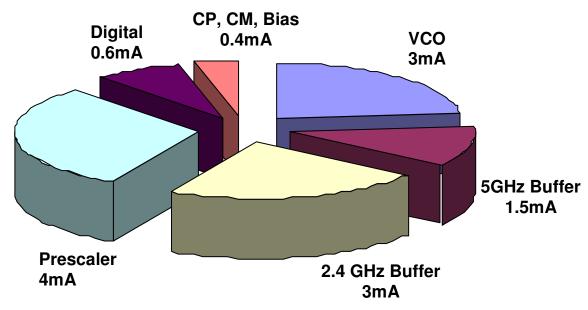

| Fig. 4.25. Power consumption distribution in dual mode frequency synthesizer148 |

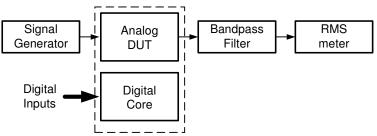

| Fig. 5.1. A setup for testing a mixed-signal device                             |

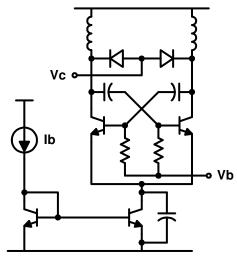

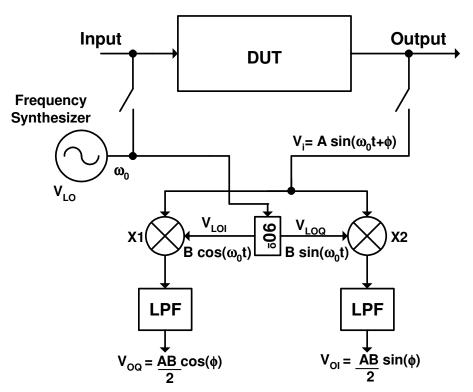

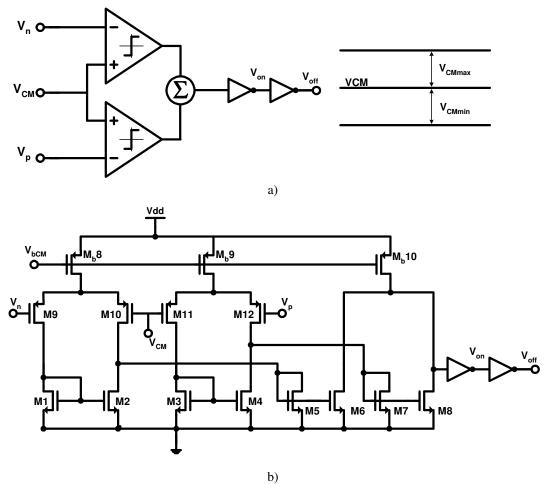

| Fig. 5.2. Amplitude and phase detector                                          |

| Fig. 5.3. Frequency synthesizer block diagram                                   |

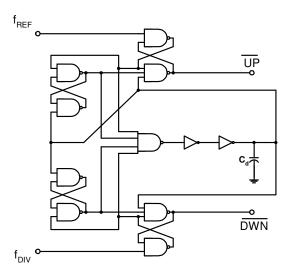

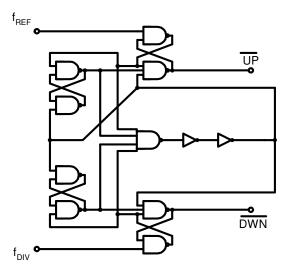

| Fig. 5.4. Phase-frequency detector gate level diagram                           |

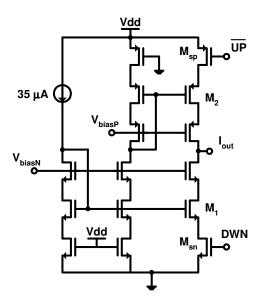

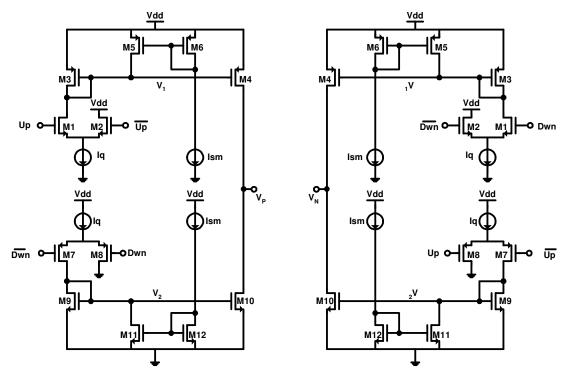

| Fig. 5. 5. Differential charge pump schematic diagram                           |

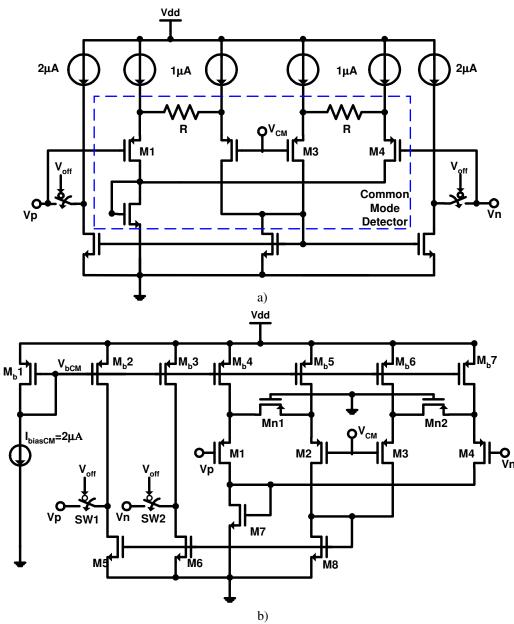

| Fig. 5.6. Charge pump common mode feedback schematic                            |

| Fig. 5.7. Common mode feedback control circuit                                  |

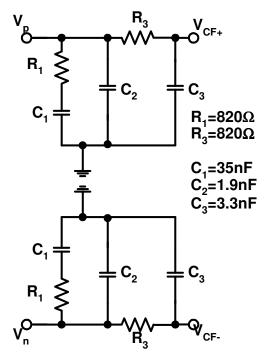

| Fig. 5. 8. Differential third order loop filter.                                |

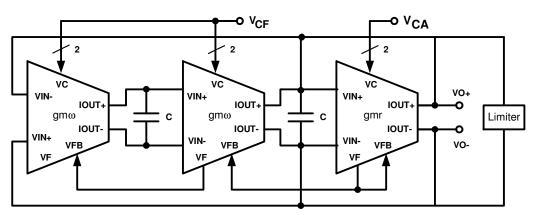

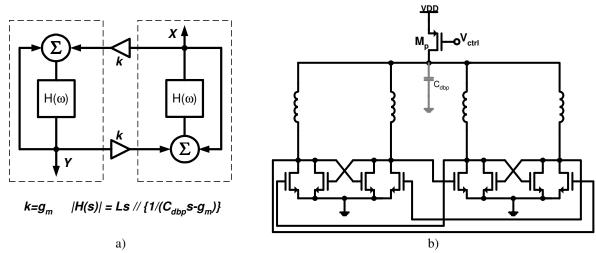

| Fig. 5.9. OTA-C VCO block diagram                                               |

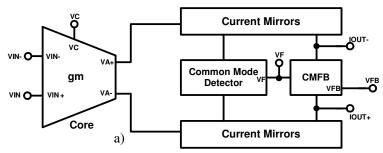

| Fig. 5.10. Voltage controlled transconductor.                                   |

| Fig. 5. 11. Frequency synthesizer microphotograph                               |

| Fig. 5.12. Testing setup.                                                       |

| Fig. 5.13. Output spectrum.                                                     |

|                                                                            | Page |

|----------------------------------------------------------------------------|------|

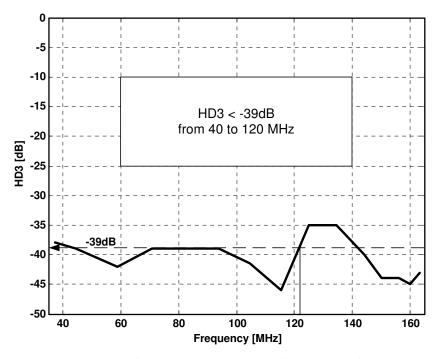

| Fig. 5.14. Variation of the third order harmonic distortion with frequency | 167  |

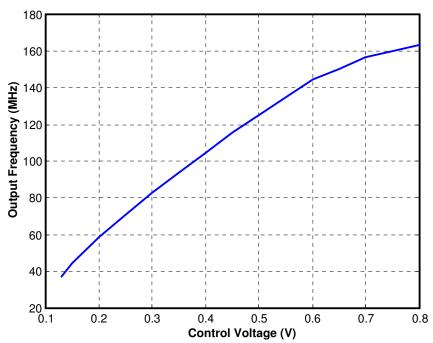

| Fig. 5.15. Measured VCO transfer characteristic.                           | 168  |

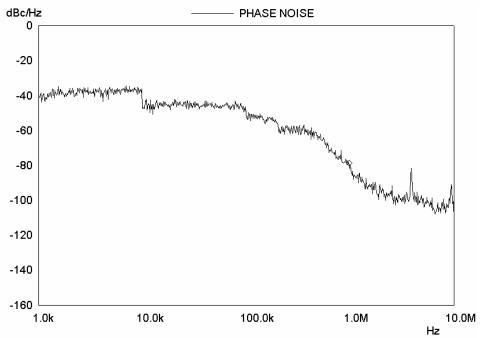

| Fig. 5.16. Measured VCO phase noise.                                       | 169  |

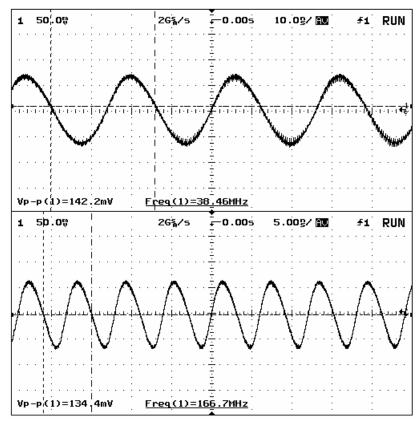

| Fig. 5. 17. Transient output of quadrature oscillator                      | 170  |

| Fig. 6.1. Quadrature signals                                               | 172  |

| Fig. 6.2. SNR degradation in Wireless LAN due to phase imbalance           | 174  |

| Fig. 6.3. Quadrature generation with divide-by-two circuit                 | 176  |

| Fig. 6.4. Master – slave flip-flop timing diagram.                         | 177  |

| Fig. 6.5. Quadrature LC oscillator.                                        | 178  |

| Fig. 6.6. Level-locked loop.                                               | 179  |

| Fig. 6.7. Phase detector block diagram.                                    | 180  |

| Fig. 6.8. Level locked-loop block diagram.                                 | 182  |

| Fig. 6.9. Self-calibrated quadrature generator.                            | 183  |

| Fig. 6.10. Relative phase comparator block diagram.                        | 184  |

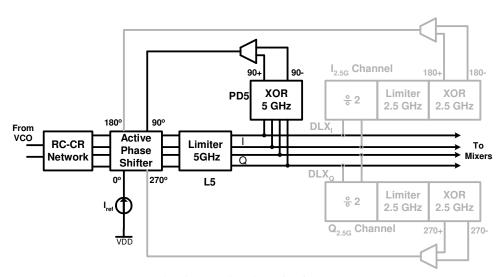

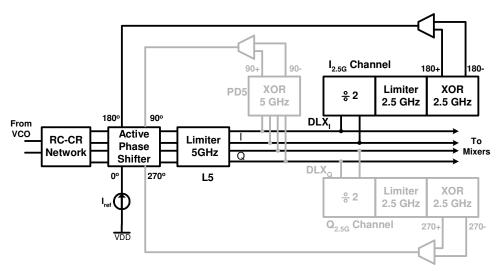

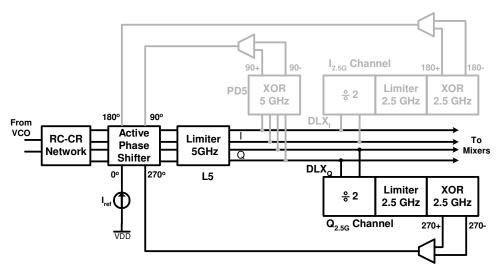

| Fig. 6.11. Multistandard frequency synthesizer.                            | 186  |

| Fig. 6.12. Proposed self-calibration quadrature scheme.                    | 187  |

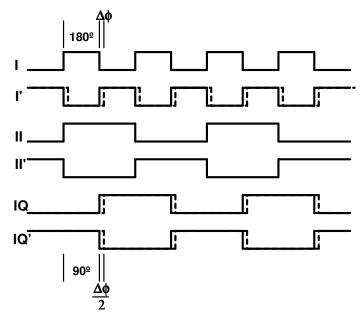

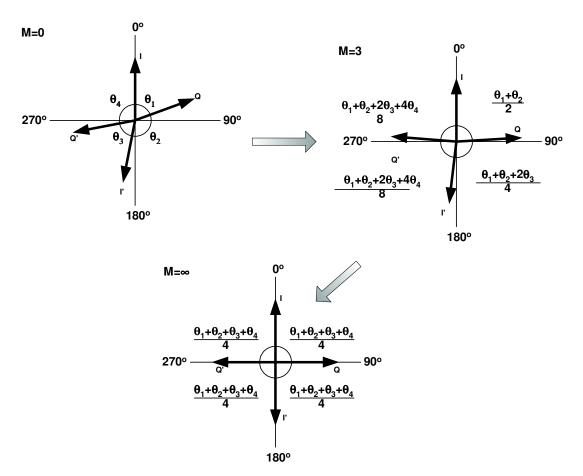

| Fig. 6.13. Mapping 180° difference into 90° at half the LO frequency       | 189  |

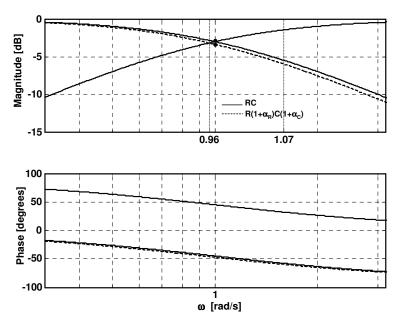

| Fig. 6.14. Magnitude and phase response of the RC – CR network             | 192  |

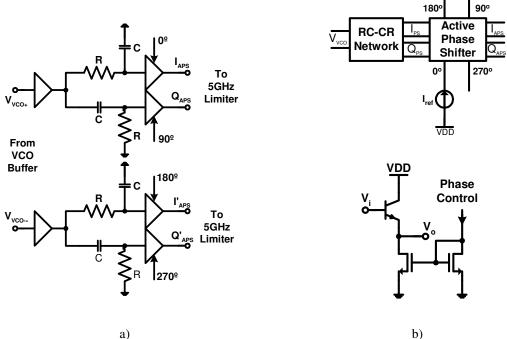

| Fig. 6.15. Passive and active phase shifter.                               | 194  |

| Fig. 6.16. Limiting amplifier with buffer.                                 | 195  |

| Fig. 6.17. Phase detector schematic diagram.                               | 198  |

|                                                                          | Page |

|--------------------------------------------------------------------------|------|

| Fig. 6.18. Phase detector operation.                                     | 199  |

| Fig. 6. 19. Phase response plot.                                         | 200  |

| Fig. 6.20. Error amplifier (EA) schematic diagram.                       | 201  |

| Fig. 6.21. Calibration of 90° branch.                                    | 203  |

| Fig. 6.22. Calibration of 180° branch.                                   | 204  |

| Fig. 6.23. Calibration of 270° branch.                                   | 204  |

| Fig. 6.24. Phase calibration process.                                    | 205  |

| Fig. 6.25. Schematic diagram of complete calibration loop                | 207  |

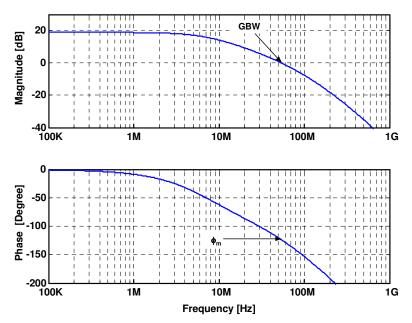

| Fig. 6.26. Open loop response of calibration DLL                         | 209  |

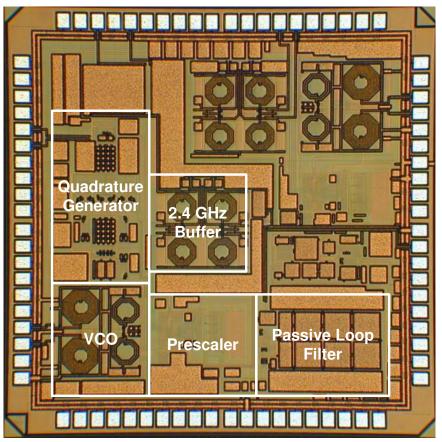

| Fig. 6.27. Frequency synthesizer micrograph.                             | 210  |

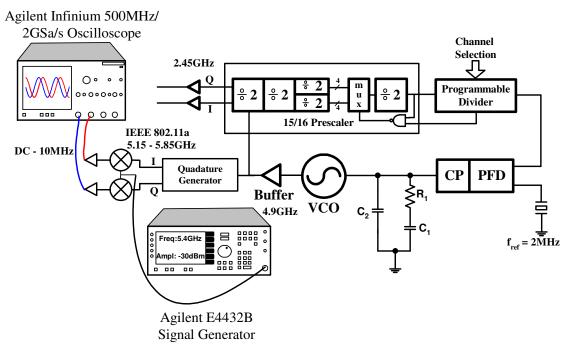

| Fig. 6.28. Quadrature generator testing setup.                           | 211  |

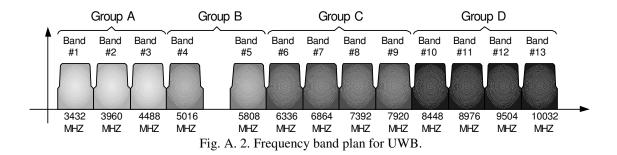

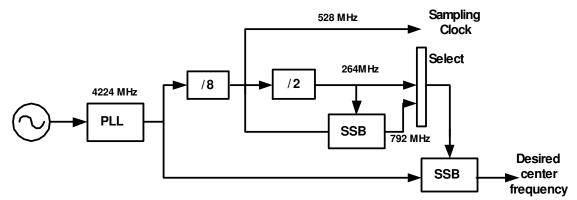

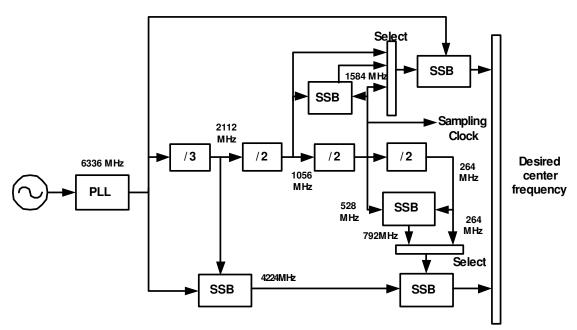

| Fig. A.1. Receiver architecture for UWB                                  | 229  |

| Fig. A. 2. Frequency band plan for UWB.                                  | 229  |

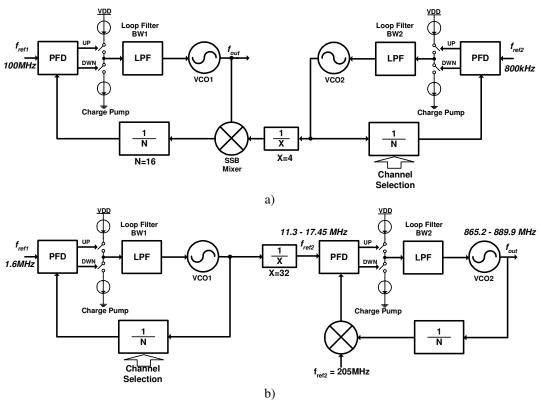

| Fig. A. 3. Frequency synthesizer architecture for Mode 1 UWB transceiver | 231  |

| Fig. A. 4. Frequency synthesizer architecture for Mode 1 UWB transceiver | 232  |

# LIST OF TABLES

| TABLE                                                                         | Page |

|-------------------------------------------------------------------------------|------|

| Table 1.1 Short range wireless standards comparison                           | 17   |

| Table 2.1. Frequency resolution and accuracy for different wireless standards | 37   |

| Table 2.2. Summary of frequency synthesizer specifications                    | 75   |

| Table 2.3. Parameters of frequency synthesizer for Bluetooth                  | 78   |

| Table 2.4. Specification comparison for Bluetooth / Wireless LAN              | 79   |

| Table 2.5. Parameters of frequency synthesizer for Bluetooth / Wireless LAN   | 82   |

| Table 3.1. Summary of frequency synthesizer specifications                    | 93   |

| Table 4.1. Specification comparison for Bluetooth / Wireless LAN              | 116  |

| Table 4.2. D flip-flops component values                                      | 138  |

| Table 5.1. Summary of building block specifications                           | 164  |

| Table 5.2. Summary of experimental results                                    | 170  |

| Table 6.1. Comparison of quadrature generation techniques                     | 184  |

| Table 6.2. Summary of relevant design parameters                              | 212  |

## **CHAPTER I**

#### INTRODUCTION

As we enter the 21st century, information technology (IT) and communications are leading a revolution in the way we live. The number of cellular telephone subscribers and people accessing the Internet, the growth of electronic business, and the abundance of companies on the Web are leading the evolution of information technologies. Access to information has become a necessity. The information available on the Internet and the easy access to this information allows professionals of many different fields to use tools that would have been otherwise unavailable without this communication facility. Competitive, up-to-date companies are offering their services and products on the Web. Members of the research community are presenting their ideas and results via the Web. The Internet has become an indispensable consultation tool as well as an open window in which people can showcase their information to the world. In the information technology (IT) field, there are two types of companies: the long established, wellknown firms and the young start-ups. Those in the first category, such as Cisco Systems, Hewlett-Packard, and Lucent, are devoted to the development and commercialization of existing products. On the other hand, the start-ups provide innovative ideas, some of which succeed and some that fail. It is interesting to note that the research effort in wireless LAN (WLAN) systems that started some 20 years ago has allowed for the development of new ideas that have yielded applications and systems [1].

This dissertation follows the style and format of IEEE Journal of Solid-State Circuits.

With so many new wireless systems and applications from so many suppliers in so many countries, the need for standardization is essential. As a result, cooperation between wireless manufacturers and user interest groups has given rise to the creation of open associations to develop standards.

One of the main standardization groups, the Infrared Data Association (IrDA), focuses on the development of infrared (IR) wireless systems, IEEE 802.11, in high-performance radio LAN (HIPERLAN), and Bluetooth in home radio frequency (RF) for the evolution of different applications of RF wireless systems.

The development of wireless systems is subject to several technical limitations, such as transfer capacity, quality, and range. The environments in which wireless and mobile systems can be used are classified into five categories, depending on the range of coverage [2]:

Home-cell environments for in-house applications

Picocell environments for in-building systems and applications

Microcell environments for applications covering urban areas

Macrocell environments for applications covering suburban areas

The global environment for applications using satellite-based systems

Systems and applications for the home-cell and picocell environments have evolved over the last decade, and today there are standards and commercial equipment that allow for the installation of wireless systems using RF and IR technologies.

There are two main standards that assure the compatibility of wireless communication systems for indoor applications. They are IEEE 802.11, and Bluetooth. IEEE 802.11 is a standard that covers RF and IR technologies for WLAN applications. Meanwhile, Bluetooth deals with elimination of cables through RF links. They are used for local applications either for the expansion of existing wired networks, the installation of new wireless networks, or special applications different from the standard LAN (voice transmission between a cellular phone and a headset, for example). Wireless indoor systems are the ideal complement to buildings that have been designed with a structured cabled infrastructure, because they allow users to expand the cabled network, reallocate terminal equipment, add new segments, and install temporary working groups in an easy, cheap, and fast way.

## 1.1. Background and Motivation

When designing future short-range wireless systems one needs to take into account the increasingly omnipresent nature of communications and computing based on the vision that wireless systems beyond the third generation (3G) will enable connectivity for "everybody and everything at any place and any time." This ambitious view assumes that the new *wireless world* will be the result of a comprehensive integration of existing and future wireless systems, including wide area networks (WANs), wireless local area networks (WLANs), wireless personal area and body area networks (WPANs and WBANs), as well as ad hoc and home area networks that link devices as diverse as portable and fixed appliances, personal computers, and

entertainment equipment. However, the realization of this vision requires the creation of new wireless technologies and system concepts offering easy-to use interfaces with the user at the center. In the scenarios envisaged for future smart environments the user needs to manage electronic information easily by having complete access to time-sensitive data, regardless of physical location.

Short-range wireless technology will play a key role in scenarios where "everybody and everything" is connected by different types of communication links: human to human, human to machine, machine to human, and machine to machine. While the majority of human-to-human information exchanges are still by voice, a rapid increase in data transfers is observed in other types of links as manifested by the rising need for location-aware applications and video transfer capability within the home and office environments. In the future, we expect the need for even higher data rates to develop jointly with a flourishing increase in large numbers of low-rate wireless devices embedded in common appliances, sensors, beacons, as well as identification tags, spontaneously interacting in ambient intelligence networks [3].

In order for the communications to keep up with the increasing user demand for high speed data transfer and mobility, the industry is continuously looking for cheaper and more efficient mobile devices. It is well known that the design of the RF transceiver is usually the key element that determines the cost, size, and useful battery life of the equipment, as well as how the equipment is used.

A critical building block in a radio transceiver is the frequency synthesizer, which is in charge of generating a reference signal at high frequency used to

downconvert the incoming signal into a lower frequency where it can be processed to extract the information it is carrying. The same reference signal can be used to upconvert a desired message to an RF frequency, such that it can be transmitter over the air. There is a large set of requirements imposed into the generation and characteristics of the reference signal. As the advance of the technology allows for faster and smaller transistors, the trade-offs in the design of frequency synthesizers needs to be studied and exploited in the never ending search for a compact and low power transceiver implementation. The main goal of this dissertation is to present a general study of the design of frequency synthesizers intended for short range wireless applications such as Bluetooth and Wireless LAN IEEE 802.11. A design methodology that includes the nonidealities of the building blocks is presented. This methodology allows the designer to map the specifications from the standard into a set of requirements for the building blocks. The stringent requirements for the radio in a wireless system mandate a proper design methodology that targets a drastic reduction of silicon area and power consumption in the proposed circuit solutions.

## 1.2. Short-Range Wireless Communications

Radio-based short-range wireless (SRW) communication is an alternative class of emerging technologies designed primarily for indoor use over very short distances. It is intended to provide fast (tens or hundreds of megabits per second) and low cost, cable free connections to the internet and between portable devices. SRW features transmission powers of several microwatts up to miliwatts, yielding a communication

range between 10 and 100 meters. SRW provides connectivity to portable devices such as laptops, PDAs, cell phones and others.

Short-range communications standards fall into two broad but overlapping categories: personal area networks (PAN) and local area networks (LAN). Wireless PAN technologies emphasize low cost and low power consumption, usually at the expense of range and peak speed. In a typical wireless PAN application, a short wireless link, typically under 10 meters, replaces a computer serial cable or USB cable. Standards, such as Bluetooth and HomeRF, have been created to regulate short-range wireless communications. Bluetooth has appeared recently in many mobile devices. Bluetooth can transmit data through solid nonmetal objects and supports a nominal link range of 10cm-10m at a moderate baud rate up to 720kb/s (raw data rate is 1Mb/s) [4]. An optional high power mode in the current specifications allows for ranges up to 100m. Because of the nature of radio, Bluetooth is a point to multipoint communication system, which supports connections of two devices as well as ad hoc networking between several devices. In order to prevent unauthorized access, Bluetooth requires sophisticated authentication and encryption mechanisms, which hamper fast connection establishment. Therefore, Bluetooth is best for applications that require stable point-to-point or point-to multipoint connections for data exchange at moderate speeds, where mobility is a key requirement. Ultra-wideband (UWB) is an emerging new technology that shows great potential for SRW applications. Unlike conventional wireless communications systems that are carrier-based, UWB-based communication is baseband. It uses a series of short pulses that spread the energy of the signal from near DC to a few GHz.

Wireless LAN technologies, on the other hand, emphasize a higher peak speed and longer range at the expense of cost and power consumption. Typically, wireless LANs provide wireless links from portable laptops to a wired LAN access point. To date, 802.11b has gained acceptance rapidly as a wireless LAN standard. It has a nominal open-space range of 100m and a peak over-the-air speed of 11Mb/s. Users can expect maximum available speeds of about 5.5Mb/s. Other communication standards offer even higher data rates, like 802.11a and 802.11g.

#### 1.2.1. Bluetooth

In 1994, Ericsson Mobile Communications, the global telecommunications company based in Sweden, initiated a study to investigate the feasibility of a low-power, low-cost radio interface between mobile phones and their accessories. The aim of the study was to find a way to eliminate cables between mobile phones and PC cards, headsets, desktops, and other devices. The study was part of a larger project investigating how different communications devices could be connected to the cellular network via mobile phones. The company determined that the last link in such a connection should be a short-range radio link. As the project progressed, it became clear that the applications for a short-range radio link were virtually unlimited [5].

The Bluetooth specification comprises a system solution consisting of hardware, software and interoperability requirements. The set of Bluetooth specifications developed by Ericsson and other companies answers the need for short-range wireless

connectivity for ad hoc networking. The Bluetooth baseband protocol is a combination of circuit and packet switching, making it suitable for both voice and data.

Bluetooth wireless technology is implemented in tiny, inexpensive, short-range transceivers in the mobile devices that are available today, either embedded directly into existing component boards or added into an adapter device such as a PC card inserted into a notebook computer. Potentially, this will make devices using the Bluetooth specification the least expensive wireless technology to implement.

Bluetooth wireless technology uses the globally available unlicensed ISM radio band of 2.4 GHz. The ISM (industrial, scientific, and medical) bands include the frequency ranges at 902—928 MHz and 2.4—2.484 GHz, which do not require an operator's license from the Federal Communications Commission (FCC) or any international regulatory authority. The use of a common frequency band means that devices using the Bluetooth specification can be used virtually anywhere in the world and they will be able to link up with other such devices, regardless of what country they are being operated in.

When it comes to ad hoc networking for data, a device equipped with a radio using the Bluetooth specification establishes instant connectivity with one or more other similarly equipped radios as soon they come into range. Each device has a unique 48-bit Medium Access Control (MAC) address, as specified in the IEEE 802 standards for LANs. For voice, when a mobile phone using Bluetooth wireless technology comes within range of another mobile phone with built-in Bluetooth wireless technology

conversations occur over a localized point-to-point radio link. Since the connection does not involve a telecommunications service provider, there is no per-minute usage charge.

The radio link itself is very robust, using frequency-hopping spread-spectrum technology to mitigate the effects of interference and fading. As noted, spread spectrum is a digital coding technique in which the signal is taken apart or "spread" so that it sounds more like noise to the casual listener. The coding operation increases the number of bits transmitted and expands the bandwidth used.

Using the same spreading code as the transmitter, the receiver correlates and collapses the spread signal back down to its original form. With the signal power spread over a larger band of frequencies, the result is a robust signal that is less susceptible to impairment from electromechanical noise and other sources of interference. It also makes voice and data communications more secure. With the addition of frequency hopping—having the signals hop from one frequency to another—wireless transmissions are made even more secure against eavesdropping.

The objective of the Bluetooth standard is to enable seamless communications of data and voice over short-range wireless links between both mobile and stationary devices. The standard specifies how mobile phones, wireless information devices (WIDs), handheld computers, and personal digital assistants (PDAs) using Bluetooth wireless components can interconnect with each other, with desktop computers, and with office or home phones. With its use of spread-spectrum technology, the first generation of the Bluetooth specification permits the secure exchange of data up to a rate of about 1 Mbps—even in areas with significant electromagnetic activity. With its use of

continuously variable slope delta modulation (CVSD) for voice encoding, the Bluetooth specification allows speech to be carried over short distances with minimal disruption.

#### **1.2.2. Wireless LAN IEEE 802.11**

The IEEE 802.11 wireless LAN standard is sponsored by the 802 Local and Metropolitan Area Networks Standards Committee (LMSC) of the IEEE Computer Society. The standard allows multiple vendors to develop interoperable LAN products for the globally available 2.4 GHz industrial, scientific, and medical (ISM) band. The IEEE 802.11 standard specifies wireless connectivity for fixed, portable, and moving nodes in a geographically limited area. Specifically, it defines an interface between a wireless client and an access point, as well as among wireless clients. As in any IEEE 802.x standard such as 802.3 (CSMA/CD) and 802.5 (token ring), the 802.11 standard defines both the physical (PHY) and medium access control (MAC) layers. However, the 802.11 MAC layer also performs functions that are usually associated with higher layer protocols (e.g., fragmentation, error recovery, mobility management, and power conservation). These additional functions allow the 802.11 MAC layer to conceal the unique characteristics of the wireless PHY layer from higher layers.

802.11b, also known as Wi-Fi (for Wireless Fidelity), emerged in 1999 and is the most popular wireless networking standard. Operating in the 2.4GHz radio band, 802.11b is also the current mainstay of the 802.11 family of wireless networking standards established by the IEEE (Institute of Electrical and Electronics Engineers).

802.11a was proposed before 802.11b, hence the designation in 802.11a. 802.11b, however, came to the market first.

802.11a/b uses the unlicensed spectrum for transmission and thus it must use spread spectrum techniques. This process increases the communication channels interference immunity or the processing gain, decreases interference between multiple users and increases the ability to re-use the spectrum. 802.11b uses the 2.400 GHz to 2.483 GHz spectrum. An Access Point (AP) is the center of the Basic Service Set (BSS) which may overlap partially, completely or not at all with each other without fear of interfering with functionality. Mobile users can roam from AP to AP and these APs are connected together with other APs using the same ESS\_ID which forms an Extended Service Set (ESS). Each AP has its own MAC and IP addresses and they are fault tolerant when setup with multiple failure points. Addition of capacity to the network can be as simple as adding APs to a new Ethernet port which uses the same ESS\_ID. 802.11b uses DSSS (Direct Sequence Spread Spectrum) to disperse the data frame signal over a relatively wide (30 MHz) portion of the 2.4 GHz band. This results in greater immunity to radio frequency interference as compared to narrowband signaling. Because of the relatively wide DSSS signal, you must set the 802.11b AP to specific channels to avoid channel overlap which might cause a reduction in performance. In order to actually spread the signal, the transmitter combines the Physical Layer Convergence Procedure protocol data unit PLCP (PPDU) with a spreading sequence through the use of a binary adder. PLCP is a frame modification technique used by 802.11b which is out of the scope of discussion in this paper. For higher data rates (5Mbps, 11Mbps) 802.11b

uses Complementary Code Keying (CCK) to provide spreading sequences. Detailed 802.11b standard specifications can be found in [6, 7].

The IEEE 802.11 extension for the 5-GHz band, 802.11a, claims primacy in selecting OFDM for packet based networks. It uses a 16-QAM with a coding rate of 1/2. The bit rate can be as high as 55 Mbps. At the MAC level there are more important differences. The MAC in the IEEE 802.11a is an extension of the CSMA/CD protocol employed in wired LANs.

Last year, a combination of 802.11a and 802.11b was presented as a proposal for an extension of the standard. It is called 802.11g and incorporates the same modulation scheme and MAC as 802.11a, but it operates in the 2.4GHz band. The main reason for the introduction of this modification to the previous versions of the standard is the increased data rate, provided over the same frequency band as 802.11b. This technology, instead of competing against the legacy versions of the standard, complements them and provides a high speed solution. Current trends are moving toward the design of multistandard transceivers capable of dual band operation and complying with the three versions of the standard. 802.11a/b/g.

#### 1.2.3. Ultra-Wideband (UWB)

In the short-range application space, ultra-wideband radio technology (UWB-RT) can drive the potential solutions for many of today's problems identified in the areas of spectrum management and radio systems engineering. The novel and unconventional approach underlying the use of UWB-RT is based on optimally sharing the existing

radio spectrum resources rather than looking for still available but possibly unsuitable new bands. This disruptive idea has recently received legal adoption by the regulatory authorities in the United States [8], and efforts to achieve this status have started in both Europe [9] and Asia, particularly Japan and Singapore. It is widely anticipated that UWB-RT will have a sizable impact on the multimedia- driven home networking and entertainment market, and will allow implementation of intelligent networks and devices enabling a truly pervasive and user-centric wireless world.

A generic definition used within the FCC's *First Report and Order* [8] and widely accepted by the industry defines a UWB device as any device emitting signals with a fractional bandwidth greater than 0.2 or a bandwidth of at least 500 MHz at all times of transmission. The fractional bandwidth is defined by the expression  $2(f_H - f_L)/(f_H + f_L)$ , where  $f_H$  is the upper frequency and  $f_L$  the lower frequency at the -10 dB emission point. The center frequency of the signal spectrum emitted by such a system is defined as the average of the upper and lower -10 dB points (i.e.,  $f_C = (f_H + f_L)/2$ ). At the PHY level, UWB communication systems operate by spreading rather small amounts of average effective isotropic radiated power (EIRP) — always less than 0.56 mW (according to FCC masks) — across a very wide band of frequencies relative to its center frequency. This quantity is easily calculated from the imposed power spectral density limit of 75 nW/MHz (-41.3 dBm/MHz) between 3.1 GHz and 10.6 GHz, as per FCC (and draft ETSI) spectral masks. Inherent in this UWB definition is a high temporal resolution that not only allows the design of radios with much lower fading margins than

classical narrowband systems, but also enables precision ranging capabilities combined with data transmissions.

The potential classes of UWB devices are many, ranging from imaging systems (groundpenetrating radar, wall-imaging systems, medical systems, and surveillance systems) to vehicular radar systems, and communications and measurement systems. They all have high spectrum efficiency potential in common, as stated in [8]: "With appropriate technical standards, UWB devices can operate using spectrum occupied by existing radio services without causing interference, thereby permitting scarce spectrum resources to be used more efficiently." Further spectrum efficiency can be achieved by applying ad hoc networking concepts between the nodes of a WBAN/WPAN network. As an example, using multihop routing, UWB transmitters could reduce their power emissions and thus also their covering area; this in turn would allow a larger number of transmitters to operate simultaneously in the same given area, yielding increased spectral reuse and resulting in higher capacity per area. Building dynamic ad hoc networks on demand could be particularly effective in combination with the use of spectrum overlay and reuse techniques (Fig. 1.1) Frequency reuse naturally leads to increased spectral efficiencies when measured in terms of spatial capacity (ratio of a cell's aggregate data rate and the coverage area [(b/s)/m<sub>2</sub>]). Because a system's maximum transmission range scales inversely with data rate, the cost of "continuous and every where at all times" coverage increases sharply with data rate. Thus, short-range radio systems covering relatively small areas (micro/picocells), particularly those based on UWB-RT, will be important enablers of future high-spatial-capacity networks. Besides the ability to potentially operate worldwide across bands occupied by existing narrowband systems, UWB radio systems offer additional flexibility in that they can maintain a cell's spatial capacity by adapting to either a large number of low-rate nodes or a smaller number of high-rate nodes, depending on the requirements of the application.

Fig. 1.1. Bandwidth comparison of different types of wireless systems.

A number of practical usage scenarios well suited to UWB have been identified. In these scenarios system implementations based on UWB-RT could be beneficial and potentially welcome by industry and service providers alike:

High-data-rate wireless personal area network (HDR-WPAN)

Wireless Ethernet interface link (WEIL)

Intelligent wireless area network (IWAN)

Outdoor peer-to-peer network (OPPN)

Sensor, positioning, and identification network (SPIN)

The first three scenarios assume a network of UWB devices deployed in a residential or office environment, mainly to enable wireless video/audio distribution for entertainment, control signals, or high-rate data transfers. The fourth scenario presents a deployment in outdoor peer-to-peer situations, while the fifth takes industry and commercial environments into account [3].

Table 1.1 shows a comparison of the main radio parameters of the leading short-range wireless standards. In this table it can be observed that there is a large range or data rates and maximum distance in the standards, yielding a very broad range of applications suitable for each standard.

Table 1.1 Short range wireless standards comparison

| Characteristic<br>Max. data | Bluetooth<br>1 Mb/s | <b>IEEE 802.11b</b><br>11 Mb/s | <b>IEEE 802.11g</b> 54 Mb/s | <b>IEEE 802.11a</b> 24 Mb/s | <b>UWB+ HDR</b><br>110 Mb/s            |

|-----------------------------|---------------------|--------------------------------|-----------------------------|-----------------------------|----------------------------------------|

| rate                        |                     |                                |                             | mandatory, 54               | (10m)                                  |

|                             |                     |                                |                             | Mb/s optional               | 200 Mb/s (4m)                          |

|                             |                     |                                |                             |                             | (mandatory)                            |

| Max. distance               | 10 m                | 100 m                          | 100 m                       | 50 m                        | 10 m                                   |

| Frequency                   | 2.4 GHz (ISM)       | 2.4 GHz (ISM)                  | 2.4 GHz (ISM)               | 5 GHz UNII                  | 3.1-10.6 GHz                           |

| allocation                  |                     |                                |                             | (5.15-5.35 +                |                                        |

|                             |                     |                                |                             | 5.725-5.825)                |                                        |

| ~-                          | 43.677              | 25.157                         | 25.157                      | GHz                         | ) // / / / / / / / / / / / / / / / / / |

| Channel                     | 1 MHz               | 25 MHz                         | 25 MHz                      | 20 MHz                      | Min. 500 MHz                           |

| bandwidth                   |                     |                                |                             |                             | Max. 7.5 GHz                           |

| Modulation                  | GFSK                | 11 Mbaud                       | OFDM 64+                    | COFDM                       | BPSK, QPSK                             |

| type                        |                     | QPSK (CCK                      | CCK (legacy)                | BPSK, 16                    |                                        |

|                             |                     | coding)                        |                             | QAM                         |                                        |

| Spreading                   | DS-FH               | CCK                            | OFDM                        | OFDM                        | Multiband                              |

| Maximum                     | 0 dBm               | 30 dBm                         | 30 dBm                      | 50 mW; 250                  | -41.3                                  |

| allowed RF                  | 20 dBm              |                                |                             | mW; 1 watt                  | dBm/MHz                                |

| power                       |                     |                                |                             |                             |                                        |

| Required                    | -70 dBm BER         | -76 dBm BER                    | From -76 dBm                | From -82 dBm                |                                        |

| receiver                    | < 10 <sup>-3</sup>  | <10 <sup>-5</sup>              | to -74 dBm                  | to -65 dBm                  |                                        |

| sensitivity                 |                     | $FER < 8 \times 10^{-2}$       | $FER < 8 \times 10^{-2}$    | FER <10 <sup>-5</sup>       |                                        |

## 1.3. Role of a Frequency Synthesizer in RF Transceivers

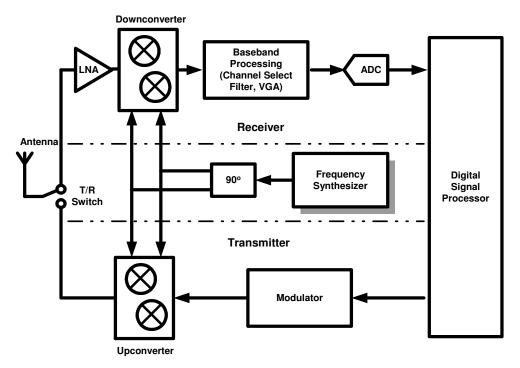

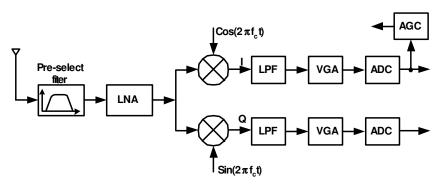

Before starting a discussion on the characteristics and implementation of frequency synthesizers, it is important to stop and describe the systems where the synthesizer will be used. As stated in the introduction to the dissertation, the main focus of the designs presented will be oriented towards the integration of a receiver for wireless communications. The block diagram of a typical wireless receiver is illustrated in Fig. 1.2. In most of the transceiver architectures, the frequency synthesizer is shared between the receiver and transmitter paths. In the receiver path, the RF signal is detected by the antenna and fed into a low-noise amplifier (LNA), which provides a limited amplification to the signal and contributes a very small amount of noise into it. This

incoming signal contains all the channels allowed in the operating frequency band of the receiver. The amplified signal is then applied into a downconverter, along with the reference signal from the frequency synthesizer, usually denoted as local oscillator (LO). In the downconverter both signals, the incoming RF signal and the LO, are mixed and a frequency translation is performed. The frequency of the signal coming out of the downconverter is the difference between the frequency of the RF signal and the frequency of the LO signal, and is usually known as IF.

The output of the downconverter is amplified and filtered to isolate the desired channel from the adjacent channels. Finally, the signal is converted into the digital domain by and analog-to-digital converter (ADC) for demodulation.

Fig. 1.2. Typical communications transceiver block diagram.

As can be noted from the previous discussion, the role of the frequency synthesizer is providing a reference signal with a proper frequency, such that the modulated information carried in the RF signal is downconverted to a lower frequency (IF) such that the frequency of the desired channel lies in the operating frequency of the channel select filter.

On the transmitter path, the role of the frequency synthesizer is similar to the one on the receiver path. The message coming from the digital signal processor is modulated and fed into an upconverter along with the reference signal from the frequency synthesizer (LO). The output of the upconverter contains the output of the modulator but shifted in frequency to the desired RF frequency.

#### 1.4. Dissertation Overview

Chapter II begins with a detailed description and analysis of the phase-locked loop (PLL). The analysis starts from the linear model and goes through the transfer function of the PLL and the noise transfer functions from different nodes of the PLL. The effects of phase noise and spurious tones on a communication system are analyzed and quantified. Non linear effects of the building blocks of the frequency synthesizer are studied to help in the design of the synthesizer to estimate the effect they will have in the overall performance. Finally, a design procedure that maps the specifications into the loop filter and sets the limits of the non-idealities is presented. As examples of the use of the proposed procedure the parameters of a synthesizer for Bluetooth and a dual mode synthesizer for Bluetooth and IEEE 802.11b are calculated. The implementation of a

frequency synthesizer that is integrated within a Bluetooth receiver is presented in Chapter III. Chapter IV describes the design and implementation of frequency synthesizer suitable for integration in a dual mode Bluetooth / Wireless LAN receiver. The synthesizer incorporates a capacitance multiplier that reduces the area required to implement a very large capacitor of the loop filter and a phase switching prescaler. In Chapter V, a built-in testing technique that makes use a frequency synthesizer is shown. The frequency synthesizer uses a differential charge pump and common mode feedback (CMFB) circuitry. The voltage controlled oscillator (VCO) is based on a very linear transconductor.

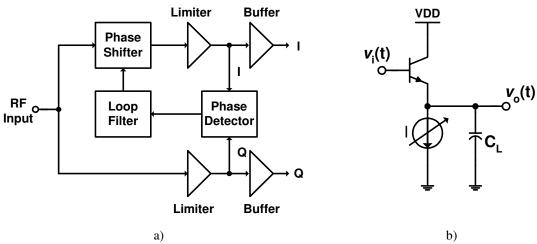

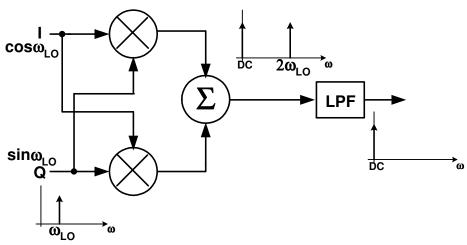

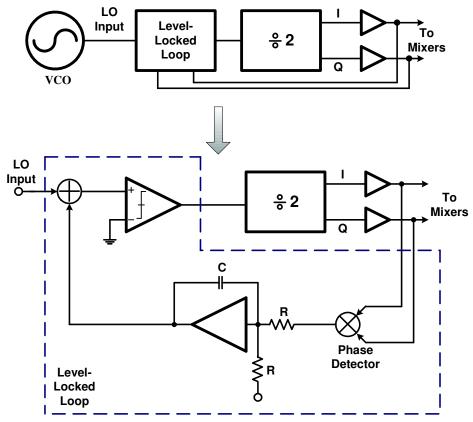

Chapter VI contains a frequency synthesizer which is an extension of the one presented in chapter IV, but with an additional quadrature calibration scheme. This calibration scheme is used in the 5GHz output to ensure the quadrature of the signals used as a local oscillator (LO) for the IEEE 802.11a standard. The calibration technique employs a simple phase shifter whose output phase can be electronically controlled. Finally, Chapter VII summarizes the contributions presented in this dissertation.

### **CHAPTER II**

# FREQUENCY SYNTHESIZERS FOR WIRELESS APPLICATIONS

#### 2.1. Definition

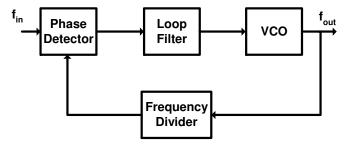

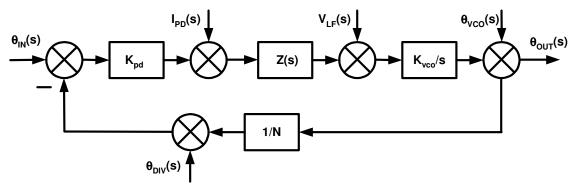

A frequency synthesizer is a device capable of generating a signal of a given output frequency  $f_{out}$  from a reference signal of frequency  $f_{in}$ . The signal generated at the output of the frequency synthesizer is commonly known as local oscillator (LO) since it is used in communication systems as the reference oscillator for frequency translation. The most popular technique of frequency synthesis in wireless communications systems is based on the use of a phase-locked loop (PLL). In the PLL, the output of a voltage controlled oscillator (VCO) is divided and phase-locked to a very stable reference signal. The loop is synchronized or *locked* when the phase of the input signal and the phase of the output from the frequency divider are aligned. Fig. 2.1 shows the block diagram of a basic phase-locked loop.

Fig. 2.1. PLL block diagram.

The phase-locked loop (PLL) consists of three basic blocks: a phase detector, a loop filter and a voltage controlled oscillator. Additionally, an optional frequency divider can be added to extend the functionality of the loop to frequency synthesis.

If the divider ratio is integer, the PLL is called an *integer-N frequency* synthesizer. The relation between the input and output frequency of the frequency synthesizer is given by:

$$f_{out} = N \cdot f_{in}$$

2.1

where N is the divide ratio of the frequency divider. The frequency step at the output of the PLL is equal to  $f_{in}$ , which is generally referred as  $f_{ref}$ , of reference frequency. If the frequency step at the output of the synthesizer needs to be smaller than the frequency reference,  $f_{ref}$ , then the divide ratio is non-integer and the synthesizer is called *fractional-N frequency synthesizer*. The use of a fractional-N frequency synthesizer is very common when a small frequency resolution is required and the use of a small reference frequency is impractical. The choice of a particular type of frequency synthesizer depends on the design needs. Complexity, power consumption and frequency resolution are some of the factors that are considered in deciding the type of synthesizer.

#### 2.2. PLL Basics

In order to understand the operation and trade-offs present in the frequency synthesizer, a study of the basic principles of operation of the phase-locked loop is

required. From a communications point of view, a phase-locked loop is an optimum phase estimator. Let us use an unmodulated carrier  $A\cos 2\pi f_c t$ . The receiver signal corresponds to the same carrier plus and unknown phase  $\phi$ :

$$r(t) = A\cos(2\pi f_c t + \phi)$$

2.2

It is required to find the value of  $\phi$ , say  $\hat{\phi}_{ML}$ , that maximizes the likelihood function  $\Lambda_{\rm L}(t)$ :

$$\Lambda_{L}(\phi) = \frac{2}{N_{0}} \int_{T_{0}} r(t)s(t:\phi)dt = \frac{2A}{N_{0}} \int_{T_{0}} r(t)\cos(2\pi f_{c}t + \phi)dt$$

2.3

where  $N_0$  is related to the variance of the phase as  $N_0=2\sigma^2$ ,  $T_0$  is the period of integration and  $s(t:\phi)$  is the signal whose phase  $\phi$  is unknown. A necessary condition for a maximum is that:

$$\frac{d\Lambda_L(\phi)}{d\phi} = 0$$

This condition yields;

$$\int_{T_0} r(t) \sin(2\pi f_c t + \hat{\phi}_{ML}) dt = 0$$

2.5

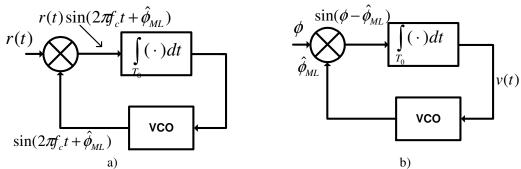

The optimality condition given in Equ. 2.5 implies the use of a loop to extract the estimate of the phase as illustrated in Fig. 2.2a. The loop filter is an integrator whose bandwidth is proportional to the reciprocal of the integration period  $T_0$  [10]. Fig. 2.2b shows a phase representation of the operation of the loop, v(t) represents the voltage that controls the VCO output frequency.

Fig. 2.2. PLL for obtaining the ML estimate of the phase of an unmodulated carrier.

a) Time domain, b) Phase domain.

# 2.2.1. Linear Model

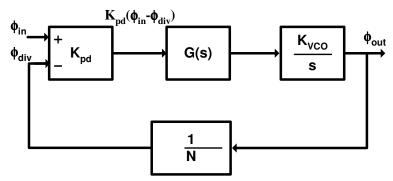

The linear model of the PLL is shown in Fig. 2.3. This model assumes the loop is in lock and that the phase detector is linear in the region of operation. Three main blocks are present in the PLL model: phase detector, loop filter and VCO. The phase detector is characterized by:

$$V_{PFD} = K_{PD} \Delta \phi 2.6$$

where the phase difference  $\Delta \phi$  is given by:

$$\Delta \phi = \phi_{in} - \phi_{div} \tag{2.7}$$

where  $K_{PD}$  is the phase detector gain. G(s) is the transfer function of the loop filter. The VCO is modeled as an integrator. It can be demonstrated as follows. The transfer characteristic of a VCO can be written as:

$$f_{VCO}(t) = K_{VCO}V_{ctrl}(t)$$

2.8

where  $V_{ctrl}$  is the input control voltage of the VCO and  $K_{VCO}$  is the VCO gain. This equation states the linear relation of the output frequency of the VCO and the control voltage applied at the input. Integrating Equ. 2.8 on both sides, we obtain:

$$\phi_{VCO}(t) = K_{VCO} \int_0^t V_{ctrl}(t) dt$$

2.9

which can be represented in the s-domain as:

$$G_{VCO}(s) = \frac{\Phi_{VCO}(s)}{V_{ctrl}(s)} = \frac{K_{VCO}}{s}$$

2.10

Fig. 2.3. Linear model of PLL.

Using the linear model presented in Fig. 2.3, the closed-loop transfer function can be derived as in Equ. 2.11.

$$H_{out}(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = N \frac{K_{PD} K_{VCO} G(s)}{Ns + K_{PD} K_{VCO} G(s)}$$

2.11

The transfer function from the output of the phase detector is:

$$H_{\Delta\phi}(s) = \frac{\Phi_{out}(s)}{\Phi_{\Delta\phi}(s)} = N \frac{K_{VCO}G(s)}{Ns + K_{PD}K_{VCO}G(s)}$$

2.12

The order of a PLL is defined by the number of poles in the open and closed loop transfer functions and the type of a PLL indicates the number of perfect (lossless) integrators in the loop.

First, type-I PLL will be described. If the loop filter is omitted; that is G(s) = 1, the loop transfer function  $H_{out1}(s)$  becomes:

$$H_{out1}(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = N \frac{K_{PD} K_{VCO}}{Ns + K_{PD} K_{VCO}}$$

2.13

The loop gain ( $K_{PD}K_{VCO}$ ) is the only design parameter available. If the loop has a large gain (for good tracking), then the bandwidth must be also large. Thus, narrow bandwidth and good tracking are opposing parameters in the design of the loop.

A second case deals with the addition of a pole in the loop filter to increase the flexibility on the design. The loop filter transfer function then becomes:

$$G(s) = G_2(s) = \frac{1}{s\tau + 1}$$

2.14

and the loop transfer function  $H_{out2}(s)$  is therefore:

$$H_{out2}(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = N \frac{K_{PD} K_{VCO} G_2(s)}{Ns + K_{PD} K_{VCO} G_2(s)}$$

$$H_{out2}(s) = \frac{K_{PD} K_{VCO} / \tau}{s^2 + s / \tau + K_{PD} K_{VCO} / N\tau}$$

2.15

The natural frequency  $\omega_n$  and the damping factor  $\xi$  are:

$$\omega_n = \sqrt{\frac{K_{PD} K_{VCO}}{N \tau}}$$

$$\xi = \frac{1}{2} \sqrt{\frac{N}{\tau K_{PD} K_{VCO}}}$$

2.16

Although this loop is unconditionally stable, there are still a larger number of specifications than equations. The circuit parameters available:  $\tau$  and  $K_{PD}K_{VCO}$  are not enough to set independently the loop parameters  $\omega_n$ ,  $\xi$  and  $K_{PD}K_{VCO}$ .

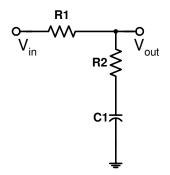

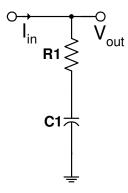

A third case considers the use of a more practical passive loop filter, as shown in Fig. 2.4, which has a transfer function:

$$G(s) = G_3(s) = \frac{s\tau_2 + 1}{s(\tau_1 + \tau_2) + 1}$$

2.17

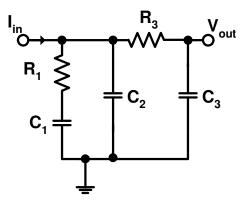

Fig. 2.4. Passive loop filter.

For the previous loop filter  $\tau_1$ =R1C1 and  $\tau_2$ =R2C1 and the loop transfer function is:

$$H_{out3}(s) = \frac{2\xi\omega_{n}s + \omega_{n}^{2}}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

2.18

where the damping factor  $\xi$  and natural frequency  $\omega_n$  are given by:

$$\omega_{n} = \sqrt{\frac{K_{PD}K_{VCO}}{N(\tau_{1} + \tau_{2})}}$$

$$\xi = \frac{1}{2}\sqrt{\frac{K_{PD}K_{VCO}}{N(\tau_{1} + \tau_{2})}} + \left(\tau_{2} + \frac{N}{K_{PD}K_{VCO}}\right)$$

2.19

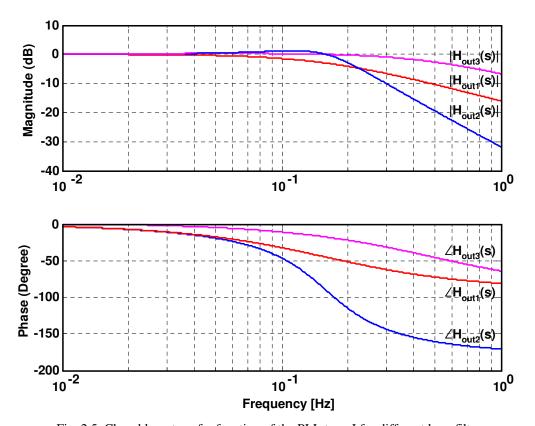

A comparison of the closed loop transfer function of the PLL for the three previous loop filters is presented in Fig. 2.5.

Fig. 2.5. Closed loop transfer function of the PLL type-I for different loop filters.

A drawback of type-I phase-locked loops is that it is not possible to set independently the loop bandwidth  $\omega_n$ , the damping factor  $\xi$  and the loop gain  $K_{PD}K_{VCO}$

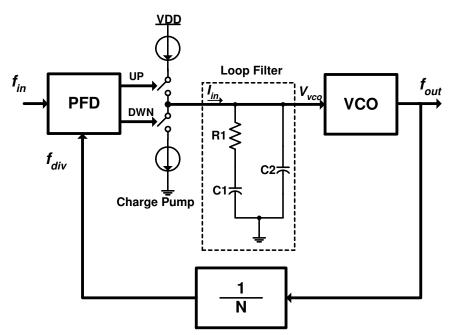

A type-II PLL is the most commonly used for frequency synthesizer applications, it is also known as charge-pump PLL, Fig. 2.6 illustrates a typical implementation. The charge-pump PLL has several advantages over other types of PLLs. Among them can be listed: an increased locking range and speed up in the capture process. The combination of a phase-frequency detector (PFD) and charge pump along with the loop filter create an extra pole at zero frequency<sup>1</sup>. This extra pole provides infinite gain in DC, which results in zero phase error for an ideal locked case.

Fig. 2.6. Charge pump PLL block diagram.

In the phase-locked state, the PFD and charge-pump are used as a phase detector.

When the phase error is very small, small pulses are generated either in the UP or

<sup>1</sup> Note that the type-II PLL has two lossless integrators; one provided by the VCO and the other by the charge pump – loop filter combination.

\_

DOWN output of the PFD to compensate the phase error through a small change in the voltage of the VCO. Assuming this condition, the gain of the of the phase detector,  $K_{PD}$ , can be determined. If the period of the input frequency of the PLL is T, and the phase difference between the input,  $f_{in}$ , and the divided signal,  $f_{div}$ , is  $\Delta \phi$ , the on-time for the UP/DWN switch is:

$$t_{up} = \frac{\Delta\phi \cdot T}{2\pi}$$

2.20

The average current in an input frequency period T is:

$$\bar{I}_{pd} = I_{cp} \frac{t_{up}}{T} = \frac{I_{cp}}{2\pi} \Delta \phi$$

2.21

and the phase detector gain is given by:

$$K_{pd} = \frac{I_{cp}}{2\pi}$$

2.22

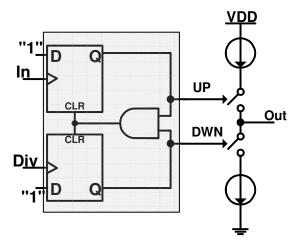

A common implementation of the phase-frequency detector includes two D Flip-Flops and an AND gate used for reset purpose. The charge pump is formed by a current source and a current sink, controlled by the UP/DWN outputs of the phase-frequency detector, as illustrated in Fig. 2.7. A detailed implementations and design issues of the phase-frequency detector and charge-pump are presented in Section 2.4.1 and 2.4.2 respectively.

Fig. 2.7. Phase frequency detector combined with charge-pump.

The current coming out of the charge-pump is injected into the loop filter and converted into a voltage that controls the VCO. In general, a second or third order loop filter is used for typical applications. The loop filter depicted in Fig. 2.6 is a second order filter. Capacitor  $C_I$  is the main integrating capacitor; it generates the pole at zero frequency. Resistor  $R_I$  introduces a stabilizing zero. Capacitor  $C_2$  is added to the loop filter to reduce the glitches on the VCO control voltage that occur due to small current pulses coming from the charge-pump every reference cycle.

The transimpedance of the second order loop filter<sup>2</sup> is:

$$Z(s) = \frac{V_{VCO}}{I_{in}} = R_1 \frac{1 + sR_1C_1}{s[R_1C_1R_1C_2s + R_1(C_1 + C_2)]}$$

2.23

where  $Z(0) = \infty$  and  $Z(\infty) = 0$ .

-

$<sup>^2</sup>$  G(s) in a type-I PLL is a V/V transfer function; whereas Z(s) in a type-II PLL is a V/I transfer function.

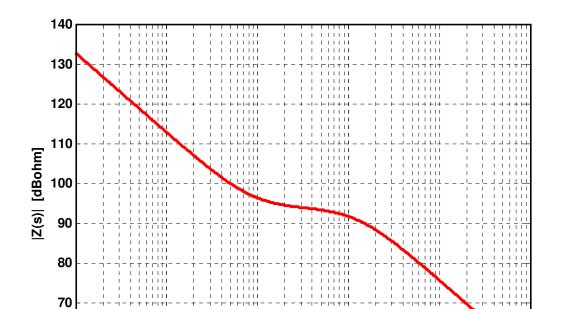

Fig. 2.8 depicts the typical transimpedance of the loop filter.

Fig. 2.8. Magnitude of loop filter transimpedance.

Frequency [Hz]

The zero of the loop filter is given by:

10<sup>3</sup>

$$\omega_z = \frac{1}{R_1 C_1}$$

2.24

10<sup>6</sup>

and the second pole is:

60

$$\omega_{p2} = \frac{1}{R_1 \frac{C_1 C_2}{C_1 + C_2}} \approx \frac{1}{R_1 C_2}$$

2.25

The open loop transfer function of the third order PLL is:

$$H_{ol}(s) = \frac{\phi_{div}}{\phi_{in}} = \frac{K_{PD}K_{VCO}Z(s)}{N} = \frac{K_{VCO}I_{cp}}{2\pi N}R_1 \frac{1 + sR_1C_1}{s[R_1C_1R_1C_2s + R_1(C_1 + C_2)]}$$

2.26

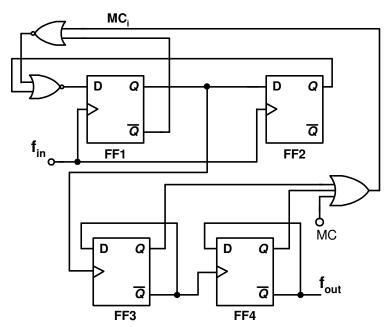

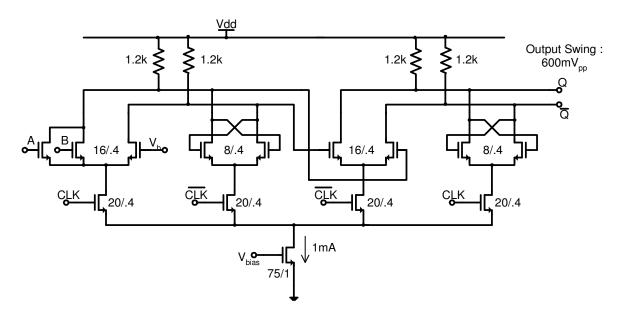

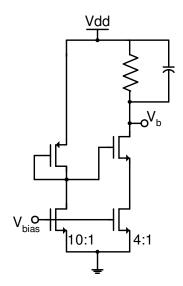

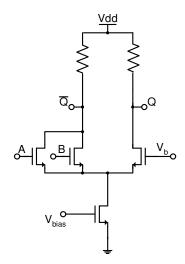

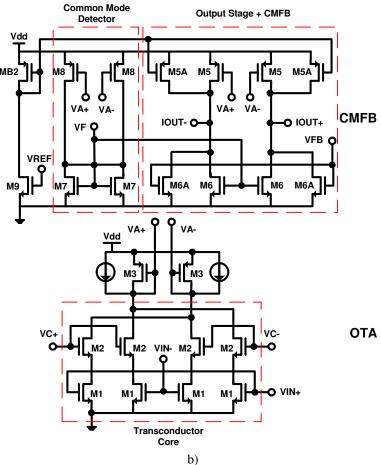

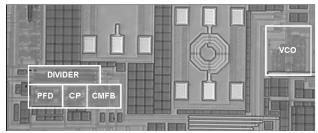

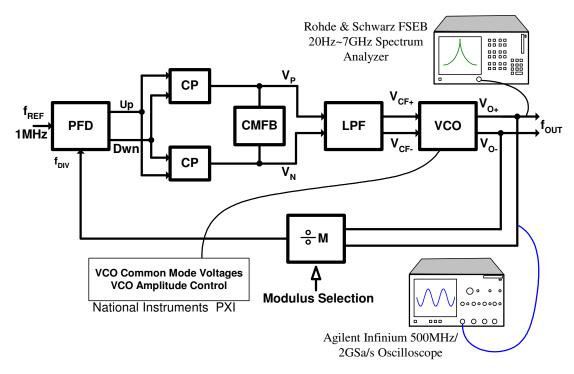

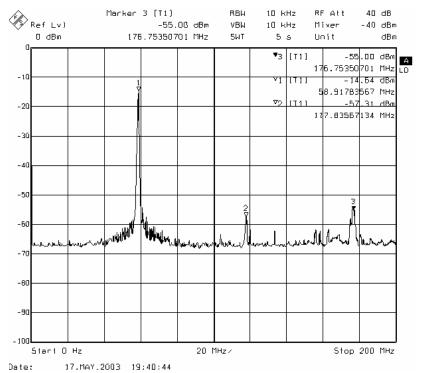

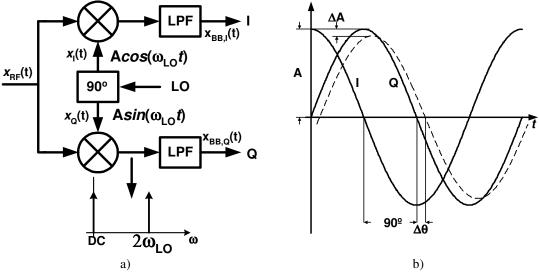

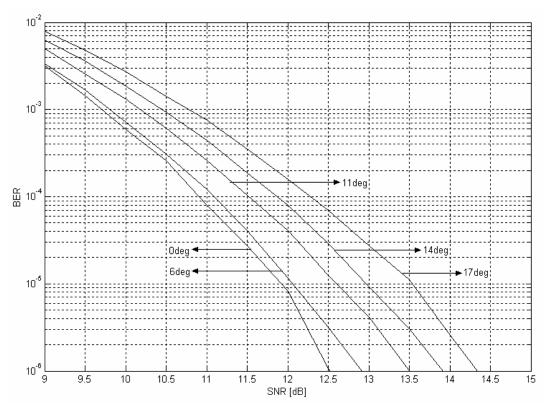

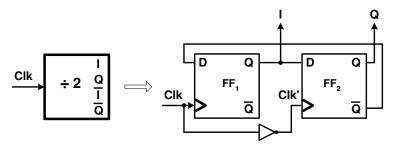

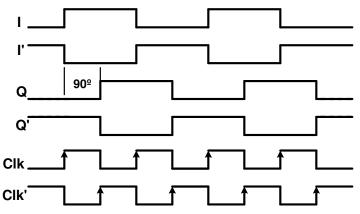

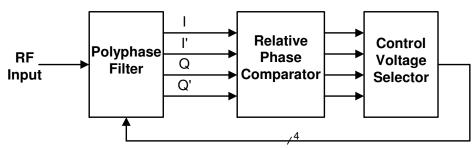

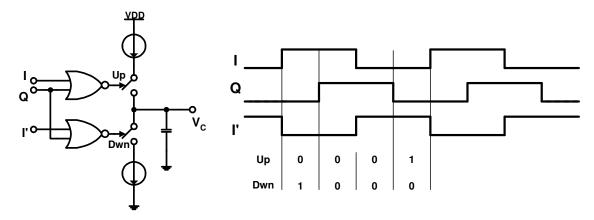

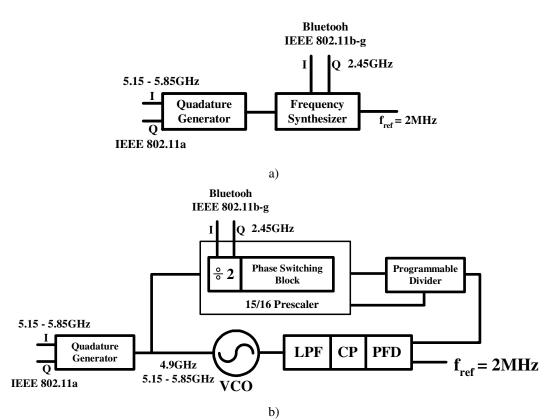

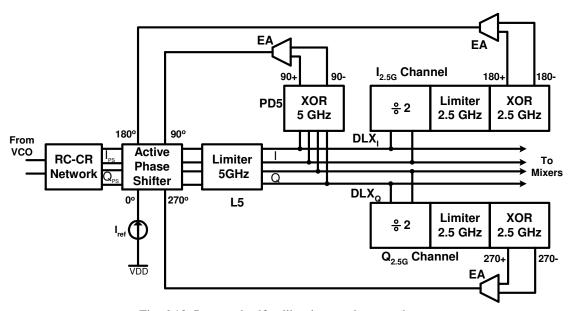

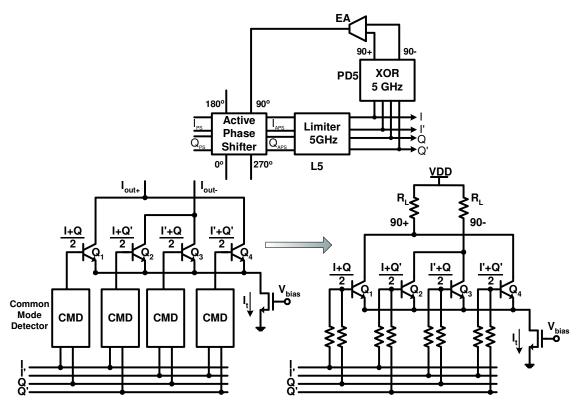

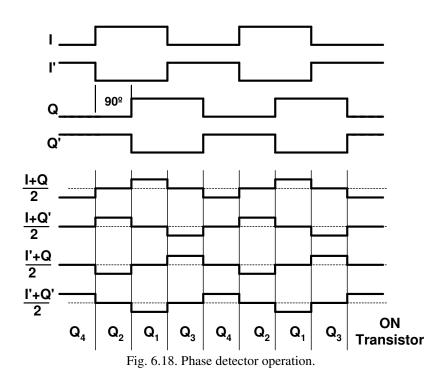

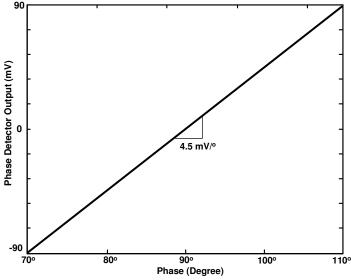

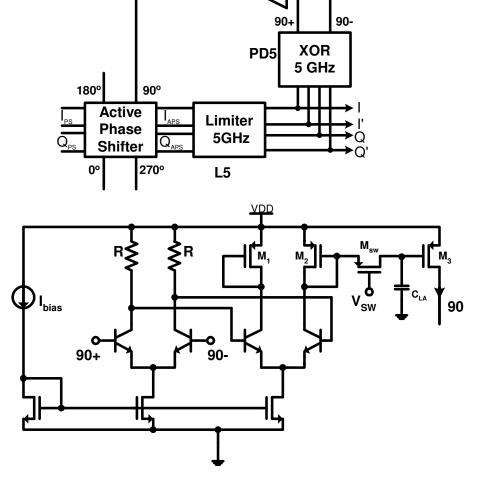

The phase margin of the loop is: