國立成功大學電機工程學系項士論文

# 具自我頻率校正功能的鎖相迴路 A PLL Circuit with Self-Frequency-Calibration

研究生:王俊元 Student:Jun-Yuan Wang

指導教授:黃尊禧 Advisor:Tzuen-Hsi Huang

Department of Electrical Engineering

National Cheng Kung University

Tainan, Taiwan, R.O.C.

Thesis for Master of Science

July, 2006

中華民國九十五年七月

# 國立成功大學電機學系 碩士論文

具自我頻率校正功能的鎖相迴路

研究生: 王俊元

本論文業經審查及口試合格特此證明

碩士學位論文考試委員

黄薄穗

楊子慰

溺赦文

為春紅

孝建治山

指導教授:

系主任:

尊 複

1 一日

中華民國 九十五 年 七 月 二十一 日

# A PLL Circuit with Self-Frequency-Calibration

by

Jun-Yuan Wang

A thesis submitted to the graduate division in partial fulfillment of the requirement for the degree of Master of Science

at

National Cheng Kung University Tainan, Taiwan, Republic of China July 2006

Approved by:

Truen-laksi lakuang Chun Ling Yang, Tru-yi Chien Hung Tsas Ching-Wen Toung

Advisor:

Chairman:

# 具自我頻率校正功能的鎖相迴路

王俊元† 黄尊禧‡ 國立成功大學電機工程學系研究所

#### <u>摘</u>要

本論文可分為三大主要部份:第一部份我們設計一個常見的鎖相迴路,其中包含相位檢測器、電流幫浦、二階低通濾波器、可切換式共振器的壓控振盪器與整數型 N 除頻器。第二部份中,我們設計一個自我頻率校正電路來校正因振盪器的製程變異而造成的頻率偏移,當鎖相迴路第一次啟動時,此校正迴路進行一次校正,此校正迴路利用偵測頻率偏移的變異,然後相對應地設定共振器的開關來補償此頻率偏移。在第三部份中,我們使用 Simulink 軟體來預測鎖相迴路中振盪器的頻率跳躍、除頻器的除數值、迴路頻寬與鎖定時間之間的關係,從觀察彼此之間的關係,我們可以找到一個新的方式來應用在超寬頻系統的射頻頻率合成器中。

我們試著整合第一部份與第二部份來建構一個符合 GSM/WLAN 共存系統的射頻頻率合成器,此頻率合成器不僅提供在 GSM 與 ISM 的頻帶中可鎖定所要的頻率,更擁有校正功能來補償因製程變異而造成的頻率偏移;另一方面,也將鎖相迴路的鎖定行為做為一個主題做來研究,藉著將切換式電感整合到壓控振盪器中,利用切換開關來使振盪器的輸出頻率快速跳頻,穩定的迴路由於跳頻的影響而需要一段額外的時間來鎖定振盪頻率,在理想的狀況下,我們發現當迴路頻寬夠大並且除頻器的除數值可同時作調整下,則當頻率跳躍時將不需要額外的時間來鎖定,因此鎖定時間將可小於 9.5 ns,使新式的超寬頻射頻頻率合成器將可能被實現。

而此論文的創意貢獻在於:第一,提出並驗證了一個符合 GSM/WLAN 共存系統的射頻頻率合成器;第二,提出一個新的訊號產生方案來設計超寬頻射頻頻率合成器。

<sup>\*</sup> 作者

<sup>‡</sup> 指導教授

## A PLL Circuit with

# Self-Frequency-Calibration

Jun-Yuan Wang † Tzuen-Hsi Huang ‡

Department of Electrical Engineering, National Cheng Kung

University, Tainan, Taiwan, Republic of China

#### **Abstract**

This thesis can be divided into three major parts: In the first part we concern about the design of a general phase lock loop (PLL) including a phase-frequency detector (PFD), a charge pump (CP), a second-order low pass filter (LPF), a voltage controlled oscillator (VCO) with switched resonator, and an integer-N type of frequency divider. In the second part, we design a self-frequency-calibration circuit to correct the frequency shift caused by the process variation in a VCO circuit. The calibration loop would function once when the PLL circuit starts at the first time. The calibration loop detects the variation of frequency shift and correspondingly sets on the switches of the resonator to compensate such frequency shift. In the third part, we use the Simulink software to predict the relation among the frequency jump of VCO, the division number of the frequency divider, the loop bandwidth, and the settling time in a locked PLL. From the observation of such relation, we find a new way of application in an ultra-wide-band (UWB) RF synthesizer.

We try to integrate the results of the first and the second parts to construct an RF synthesizer for the GSM/WLAN co-existence system. Such synthesizer can provide not only the locked local signals for the GSM and the ISM bands as desired but also the calibration function to compensate the frequency shift due to the process variation. On the other hand, a special topic on the locking behavior of a PLL circuit is studied. By integrating a switched inductor into a VCO circuit, the output oscillation frequency can jump quickly by turning the switch on and off. The locked loop is disturbed by this frequency jump and need an extra time to settle on a final oscillation frequency. In an ideal case, we find that there does not need an extra settling time after frequency jumping if the

loop bandwidth is wide enough and the division number of the frequency divider can be adjustable simultaneously. This observation make a new design methodology of an UWB RF synthesizer possible because that the switching time can be less than 9.5 ns.

The innovatory contributions of this thesis are: The first, an RF synthesizer is proposed and demonstrated for the GSM/WLAN co-existence system use. The second, a new scheme of signal generation is proposed for the design of an UWB RF synthesizer.

\_\_\_\_\_

- † The author

- ‡ The advisor

#### 誌謝

在射頻積體電路電腦輔助設計實驗室的這兩年中,由於本實驗室為新成立,因此一切必須由基礎打起,然而這兩年來最主要要感謝指導教授黃尊禧博士的細心教導,老師一步步的帶領我們的進入此領域中,並且不厭其煩的解答我們的疑惑,使我們由懵懂無知到現今的略有心得;此外對於口試委員昆山科技大學盧春林老師、中正大學湯敬文老師、工研院晶片中心的楊子毅副組長及成功大學蔡建泓老師對於本論文所提出的珍貴意見,在此致上最誠心的謝意。

感謝嘉綸、訓豪及益良在這兩年來不論在生活上、研究上互相的幫忙與勉勵,郭老師實驗室的家宏、蔚邦、榮文及倚彰為這兩年的生活更添了許多色彩,還有學弟予中、文賢、本立、益宏及傑仁的盡力幫忙,在此也祝福你們可以順利畢業,感謝許多曾經幫助過我與一路上互相勉勵的好朋友們;最後也最重要的要感謝我們家人,在我求學的路程上對我不斷的支持與鼓勵,並無限的付出與關愛,此外更感謝二姐與姊夫,兩年來的寄住與打擾,並且細心打理生活上的點滴,還有可愛的小姪子,讓我在這兩年中添加了許多歡笑。謹以此論文獻給我最親愛的家人與朋友們。

# 目錄

| 摘  |    | 要.          |                     | I       |

|----|----|-------------|---------------------|---------|

| Ab | st | rac         | t                   | II      |

|    |    |             |                     |         |

| 第  |    | •           | 序論                  |         |

|    |    | 1.1         | 研究動機                | . 1     |

|    |    | 1.2         | GSM 與 WLAN 系統簡介     | . 2     |

|    |    |             | 超寬頻系統簡介             |         |

|    |    | 1.4         | 論文組織架構              | . 6     |

| -  | _  | ٠.          | Alb L Amark # 1 mm  | _       |

| 第  |    |             | 鎖相迴路基本原理            |         |

|    |    | 2.1         |                     |         |

|    |    | 2.2         | 2.1.1 鎖相迴路基本架構      |         |

|    |    | 2.2         | 回路系統分析              |         |

|    |    |             | 2.2.1 鎖相迴路線性模型      |         |

|    |    |             | 2.2.2 穩定度分析         |         |

|    |    |             | 2.2.3 穩定相位誤差        |         |

|    |    |             | 2.2.4 暫態分析          |         |

|    |    | 2.3         | 電流幫浦與相位/頻率檢測器       |         |

|    |    |             | 2.3.1 演進與原理         |         |

|    |    |             | 2.3.2 相位/頻率檢測器      |         |

|    |    |             | 2.3.3 電流幫浦          |         |

|    |    |             | 2.3.4 非理想效應         |         |

|    |    | 2.4         | 低通濾波器               |         |

|    |    |             | 2.4.1 二階低通濾波器設計     |         |

|    |    |             | 2.4.2 迴路頻寬與低通濾波器的設定 | 23      |

|    |    | 2.5         | 除頻器                 | 24      |

|    |    | 2.6         | 壓控振盪器               | 26      |

|    |    | 2.7         | 相位雜訊                | 27      |

|    |    |             | 2.7.1 相位雜訊的定義       | 27      |

|    |    |             | 2.7.2 鎖相迴路的相位雜訊     | 29      |

|    |    | 2.8         | 自我校正電路              | 32      |

| -  | •  | *           |                     | <b></b> |

| 第  |    |             | 電路架構的實現             |         |

|    |    |             | 簡介                  |         |

|    |    | <b>3.</b> 2 | 鎖相迴路                |         |

|    |    |             | 3.2.1 相位檢測器         |         |

|    |    |             | 3.2.2 電流幫浦          |         |

|    |    |             | 3.2.3 低通濾波器         |         |

|    |    |             | 3.2.4 壓控振盪器與切換式電感   |         |

|    |    |             | 3.2.5 降頻 哭          | 46      |

|     | 3.3 | 自我步   | <b>頻率校正電路</b>      | 51  |

|-----|-----|-------|--------------------|-----|

|     |     | 3.3.1 | 簡介                 | 51  |

|     |     | 3.3.2 | 自我頻率校正迴路           | 53  |

|     |     | 3.3.3 | 校正迴路的電流幫浦與充放電電容    | 57  |

|     |     | 3.3.4 | 比較器與邏輯電路           | 58  |

|     |     | 3.3.5 | 控制訊號               | 59  |

|     |     | 3.3.6 | 校正迴路的操作流程          | 63  |

| 第   | 4章  | 模擬絲   | 5果                 | 65  |

| - [ | •   |       |                    |     |

|     |     | . •   | 回路                 |     |

|     |     |       | 相位檢測器              |     |

|     |     |       | 電流幫浦與低通濾波器         |     |

|     |     |       | 壓控振盪器              |     |

|     |     |       | 除頻器                |     |

|     |     | 4.2.5 | 迴路模擬               | 80  |

|     | 4.3 | 自我步   | 頃率校正迴路             | 82  |

|     |     |       | 校正迴路的電流幫浦與充放電電容    |     |

|     |     |       | 比較器                |     |

|     |     |       | 邏輯電路與控制訊號          |     |

|     |     | 4.3.4 | 具自我頻率校正的鎖相迴路模擬     | 90  |

| 第   | 5章  | 鎖相距   | <b>旦路於超寬頻系統的應用</b> | 93  |

|     |     |       | 頃頻率合成器             |     |

|     | 5.2 | UWB   | 的鎖相迴路與 Simulink 模擬 | 96  |

| 第   | 6章  | 結論與   | 早未來工作              | 105 |

| 杂   | 老文  | 擂     |                    | 106 |

# 表目錄

| 表 1.1 | WLAN 802.11a/b/g 比較                               | 4   |

|-------|---------------------------------------------------|-----|

| 表 2.1 | 各型鎖相迴路系統對於不同輸入訊號的相位誤差穩態響應                         | 12  |

| 表 3.1 | 迴路頻寬與二階低通濾波器的參數關係                                 | 42  |

| 表 4.1 | 鎖相迴路模擬特性總表                                        | 82  |

| 表 4.2 | (a) $V_{min}$ 比較器的電阻變異影響 (b) $V_{max}$ 比較器的電阻變異影響 | 86  |

| 表 4.3 | 具自我頻率校正的鎖相迴路模擬特性總表                                | 92  |

| 表 5.1 | 新式頻率規劃                                            | 95  |

| 表 5.2 | 不同的頻率偏移量所需的鎖定時間                                   | 99  |

| 表 5.3 | 不同的迴路頻寬所需要的鎖定時間                                   | 100 |

| 表 5.4 | 整數型與分數型頻率合成器在不同頻率偏移所需的鎖定時間                        | 102 |

| 表 5.5 | 參考頻率為 1056 MHz 時不同迴路頻寬的鎖定時間                       | 103 |

# 圖目錄

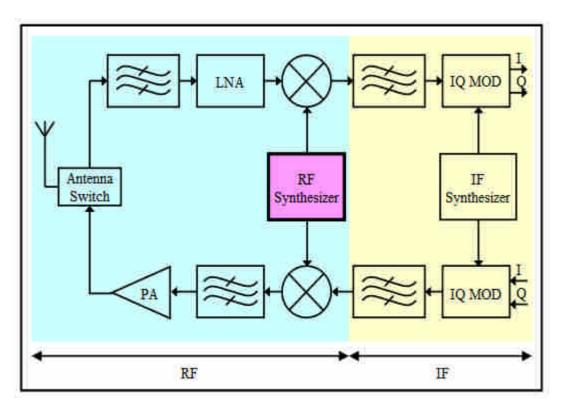

| 啚 | 1.1  | 射頻收發機方塊圖                                  | 1   |

|---|------|-------------------------------------------|-----|

| 置 | 1.2  | DS-UWB 與 MB-OFDM UWB 的頻譜圖                 | 5   |

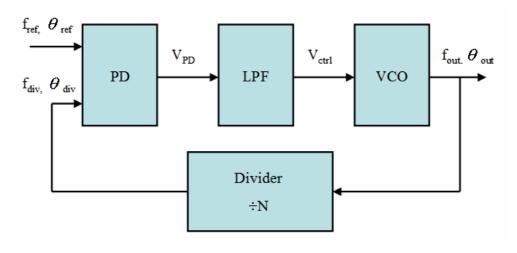

| 圖 | 2.1  | 基本的鎖相迴路架構                                 | 8   |

| 圖 | 2.2  | 鎖相迴路線性模型                                  | 8   |

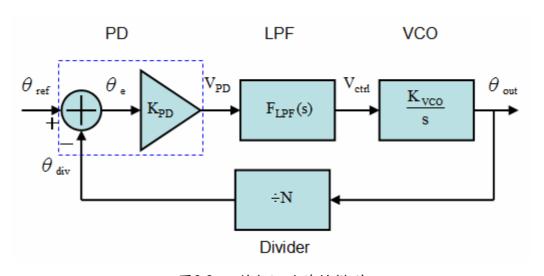

| 置 | 2.3  | 三類常見低通濾波器                                 | 9   |

| 置 | 2.4  | Type-Ⅱ的暫態響應                               | 14  |

| 圖 | 2.5  | 增加頻率檢測器部分來增加擷取範圍                          | 15  |

| 圖 | 2.6  | (a) 基本電流幫浦方塊圖;(b) 時序圖                     | 16  |

| 啚 | 2.7  | (a) 基本相位檢測器;(b) 相位差與輸出平均電壓關係              | 17  |

| 啚 | 2.8  | 相位檢測器狀態機                                  | 17  |

| 置 | 2.9  | 零相位差時 PFD 輸出脈波                            | 19  |

| 置 | 2.10 | (a) 零相位差時輸出無脈波產生;(b) 相位差極小                | 20  |

| 置 | 2.11 | Dead zone: (a) 有死區與無死區的轉移曲線; (b) 電流幫浦輸出電流 | 20  |

| 置 | 2.12 | 充放電電流不匹配效應                                | 21  |

| 圖 | 2.13 | 一階低通濾波器輸入電流與輸出電壓關係                        | 22  |

| 置 | 2.14 | 二階低通濾波器                                   | 22  |

| 圖 | 2.15 | 迴路頻寬設計時各頻率的關係圖                            | 23  |

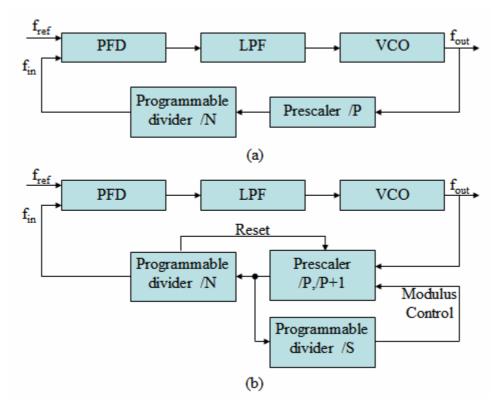

| 圖 | 2.16 | 整數型頻率合成器:(a) 單模數;(b) 雙模數                  | 25  |

| 圖 | 2.17 | (a) 單一頻帶方式; (b) 多子頻帶相互重疊組成                | 27  |

| 圖 | 2.18 | (a) 理想振盪器輸出功率頻譜;(b) 真實振盪器輸出功率頻譜           | 27  |

| 圖 | 2.19 | 振盪器的輸出頻譜                                  | 29  |

| 置 | 2.20 | 鎖相迴路的相位雜訊模型                               | _30 |

| 啚 | 2.21 | (a) 參考頻率、相位檢測器、電流幫浦與除頻器雜訊的轉移函數;(b) 壓      |     |

|   |      | 控振盪器與低通濾波器雜訊的轉移函數                         | _32 |

| 啚 | 2.22 | 鎖相迴路的迴路頻寬選取                               | 32  |

| 昌 | 2.23 | (a) 因製程偏移造成的頻帶漂移;(b) 具校正電容陣列的壓控振盪器        | 33  |

| 圖 3.1  | 具有自我頻率校正功能的鎖相迴路                    | 35 |

|--------|------------------------------------|----|

| 圖 3.2  | 傳統相位檢測器的電路架構                       | 36 |

| 圖 3.3  | 預充型相位檢測器                           | 37 |

| 圖 3.4  | 傳統的電流幫浦電路                          | 38 |

| 圖 3.5  | 改良後的電流幫浦電路                         | 39 |

| 圖 3.6  | 二階低通濾波器                            | 40 |

| 圖 3.7  | 多標準系統下的低通濾波器設定                     | 43 |

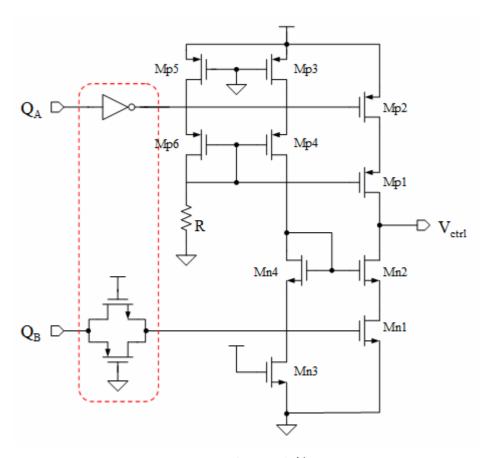

| 圖 3.8  | (a) 振盪器回授架構;(b) 電晶體交互耦合對           | 43 |

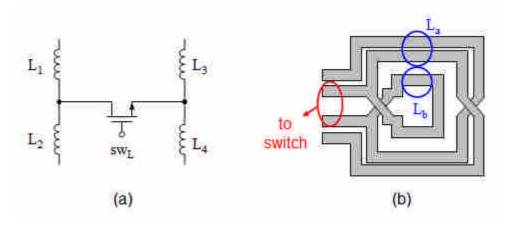

| 圖 3.9  | (a) 傳統切換式電感;(b) 新式切換式電感架構          | 45 |

| 圖 3.10 | 壓控振盪器架構                            | 46 |

| 圖 3.11 | 前置緩衝放大器                            | 46 |

| 圖 3.12 | 整數型除頻器架構區塊圖                        | 47 |

| 圖 3.13 | 雙模數預除器-2/3                         | 48 |

| 圖 3.14 | 雙模數預除器-2/3 時序圖                     | 48 |

| 圖 3.15 | 雙模數預除器-8/9                         | 49 |

| 圖 3.16 | 真單相時脈 D 型正反器                       | 49 |

| 圖 3.17 | 5-bits 的可程式計數器                     | 50 |

| 圖 3.18 | 閉迴路的自我頻率校正                         | 51 |

| 圖 3.19 | 開迴路的自我頻率校正                         | 52 |

| 圖 3.20 | 自我頻率校正電路方塊圖                        | 53 |

| 圖 3.21 | 校正因製程引起的頻帶偏移                       | 54 |

| 圖 3.22 | 校正頻率時的頻帶跳躍方式                       | 55 |

| 圖 3.23 | (a) 連續校正;(b) 一次校正後隨即重置,確保同相位       | 56 |

| 圖 3.24 | 校正迴路的電流幫浦與電容 C <sub>C</sub>        | 57 |

| 圖 3.25 | V <sub>max</sub> 比較器               | 58 |

| 圖 3.26 | 邏輯電路                               | 59 |

| 圖 3.27 | V <sub>pre_</sub> on_off 控制訊號的電路架構 | 60 |

| 圖 3.28 | comp_to_logic 控制訊號的電路架構            | 61 |

| 周 3 29 | logic to SWC 控制訊號的雷路架構             | 61 |

| 圖 3.30 | divider_reset 控制訊號的電路架構                   | 62 |

|--------|-------------------------------------------|----|

| 圖 3.31 | Calib_off 控制訊號的電路架構                       | 62 |

| 圖 3.32 | 自我頻率校正操作流程                                | 63 |

| 圖 4.1  | 參考訊號相位領先除頻器輸出                             | 66 |

| 圖 4.2  | 參考訊號相位落後除頻器輸出                             | 66 |

| 圖 4.3  | 參考訊號頻率比除頻器輸出慢                             | 67 |

| 圖 4.4  | 參考訊號頻率比除頻器輸出快                             | 67 |

| 圖 4.5  | 相位檢測器內部的延遲時間 T <sub>D</sub>               | 68 |

| 圖 4.6  | 相位檢測器輸出充電至下級電路的輸入臨界電壓所需要的時間 t             | 69 |

| 圖 4.7  | 無相位差時的輸出脈波                                | 69 |

| 圖 4.8  | 低通濾波器的波德圖                                 | 70 |

| 圖 4.9  | 無相位差時電流幫浦的充放電電流                           | 70 |

| 圖 4.10 | 參考訊號端相位領先電流幫浦對低通濾波器充電                     | 71 |

| 圖 4.11 | 參考訊號端相位落後電流幫浦對低通濾波器放電                     | 71 |

| 圖 4.12 | GSM 系統下的可調頻寬                              | 72 |

| 圖 4.13 | GSM 系統下的相位雜訊                              | 73 |

| 圖 4.14 | WLAN 系統下的可調頻寬                             | 73 |

| 圖 4.15 | WLAN 系統下的相位雜訊                             | 74 |

| 圖 4.16 | 真單相時脈 D 型正反器的除二電路                         | 75 |

| 圖 4.17 | 模數控制訊號為 0,預除器輸出除 9                        | 75 |

| 圖 4.18 | 模數控制訊號為1,預除器輸出除8                          | 76 |

| 圖 4.19 | 可程式計數器                                    | 76 |

| 圖 4.20 | 模數控制訊號:(a) $S < 2^5/2$ ;(b) $S > 2^5/2$   | 77 |

| 圖 4.21 | 產生模數控制訊號的電路                               | 78 |

| 圖 4.22 | 模數控制訊號的模擬結果                               | 78 |

| 圖 4.23 | N <sub>total</sub> =244,輸出結果為鎖定在 2.45 GHz | 79 |

| 圖 4.24 | 總除數為 175 的除頻器輸出結果                         | 80 |

| 圖 4.25 | 1.88 GHz 時鎖相迴路模擬                          | 81 |

| 周 4 26 | 前署緩衝器                                     | 81 |

| 圖 4.27 | 7 V_SWL=0 V, (SW <sub>Ccalib2</sub> ,SW <sub>Ccalib1</sub> )=(0,1)的可調頻率範圍 | 83  |

|--------|---------------------------------------------------------------------------|-----|

| 圖 4.28 | 8 校正迴路電流幫浦與充放電電容設計(V <sub>C</sub> =V <sub>max</sub> )                     | 84  |

| 圖 4.29 | 9 校正迴路電流幫浦與充放電電容設計(V <sub>C</sub> =V <sub>min</sub> )                     | 84  |

| 圖 4.30 | 0 V <sub>max</sub> 比較器的轉移特性曲線                                             | 85  |

| 圖 4.3  | l V <sub>min</sub> 比較器的轉移特性曲線                                             | 85  |

| 圖 4.32 | 2 差動對輸出端的電阻 R                                                             | 86  |

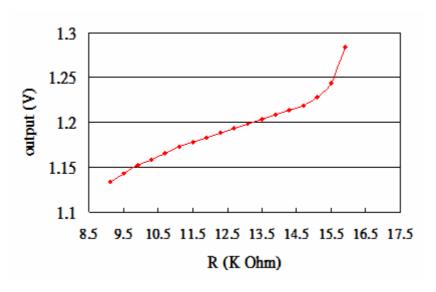

| 圖 4.33 | 3 V <sub>min</sub> 比較器的差動對輸出端電阻值的輸出電壓曲線                                   | 87  |

| 圖 4.34 | 4 V <sub>max</sub> 比較器的差動對輸出端電阻值的輸出電壓曲線                                   | 87  |

| 圖 4.35 | 5 自我頻率校正製程變異往低頻偏移時各個訊號的模擬結果                                               | 89  |

| 圖 4.36 | 6 自我頻率校正時 $N_{C}$ =182,鎖相迴路時 $N_{total}$ =180                             | 90  |

| 圖 4.37 | 7 鎖相迴路 N <sub>total</sub> =180 的輸出頻率                                      | 91  |

| 圖 5.1  | UWB 頻率合成器架構[31]                                                           | 93  |

| 圖 5.2  | 經頻率規劃後的頻率合成器架構[31]                                                        | 94  |

| 圖 5.3  | 輸出 4224 MHz 的振盪器搭配除二電路                                                    | 95  |

| 圖 5.4  | 用 Simulink 模擬切換電感 QVCO 的 PLL 架構                                           | 97  |

| 圖 5.5  | 理論上切換頻率 settling-time 為 0 ns                                              | 98  |

| 圖 5.6  | 不同的頻率偏移量對鎖定時間的關係曲線圖                                                       | 99  |

| 圖 5.7  | 當迴路頻寬為 70 MHz 與 80 MHz 時,系統將無法穩定                                          | 101 |

| 圖 5.8  | 迴路頻寬與鎖定時間的關係曲線圖                                                           | 101 |

## 第1章 序論

# 1.1 研究動機

在這無線通訊的時代,隨著市場的需求驅動了無線通訊技術的提昇,而高頻通訊技術可提供高速率的傳輸通道,並且有效的將訊號發射與接收,因此高頻的多通道無線接收器的整合性要求逐漸被提高。然而在現今各種無線通訊發展中,如GSM/CDMA通訊系統、無線區域網路(Wireless LAN)、個人無線網路(Personal Area Network; PAN)、全球定位系統(GPRS)、射頻辨識系統(RFID)及藍牙無線傳輸(Bluetooth)等相關應用,都將直接或是間接應用到高頻通訊的技術,圖 1.1 為一射頻收發器(RF transceiver)的方塊圖:

圖1.1 射頻收發機方塊圖

在上圖中的頻率合成器(Frequency Synthesizer)用來產生一個穩定的本地振盪訊號(LO signal)給混頻器將資料作頻率上的平移,內部除了需要一個振盪器產生頻率訊號,還需要鎖相迴路(Phase Locked Loop; PLL)來穩定振盪器的輸出頻率,因此鎖相迴路被廣泛的應用在收發機上。然而,鎖相迴路早在1932年首先使用於無線電信號的同步檢波上。1947年時應用於電視接收機與太空探測方面。近幾年來,由於超大型積體電路(VLSI System)的蓬勃發展,大大提昇了電路的效能,同時也加速了操作時脈,因此鎖相迴路顯得更為重要。

隨著產品方便性與輕巧性的要求逐漸提昇,往往需要將符合多種標準系統的電路整合在一個產品當中[1]~[7],然而傳統方式則利用多顆振盪器來產生不同的中心頻率以符合多標準系統的規格,但將消耗大量的面積與功率,因此,若能將不同中心頻率的系統以一個多標準多頻段(multi-standards, multi-bands)的壓控振盪器的鎖相迴路來實現,將可以減少振盪器的個數並降低IC的成本。目前商品最普遍使用的GSM與WLAN兩種標準中,GSM擁有較大的涵蓋範圍,而WLAN有較高的傳輸速率,因此,若將兩種標準整合後,在戶外時可以利用GSM來傳輸資料訊息,在室內則可切換至WLAN來得到較高的傳輸速率。故在本論文中,將研究一個能滿足GSM(1.8 GHz)及WLAN(2.4 GHz)的多標準多頻段的壓控振盪器的鎖相迴路。

有鑑於現今的積體電路因製程技術的不斷創新與突破,使電路面積越做越小,因此在同樣的IC面積下可以放入更龐大的電晶體個數,而擁有更強大的電路功能,致使產品的成本大幅降低,並且商品也越來越輕薄,對生活帶來更多的便利。但是,當製程逐漸縮小時,製程變異的問題也越來越需要被重視,以壓控振盪器來說,倘若製程的偏移量太大,將會導致輸出頻率偏移而不在預設的操作頻率範圍內,使電路無法正確的操作。故在此論文中,除了基本的鎖相迴路,更加上了自我頻率校正電路(Self-Frequency-Calibration circuit),利用此校正迴路在電路開機時對製程的偏移作適當的修正,以確保鎖相迴路可操作在正確的頻率範圍下。

#### 1.2 GSM 與 WLAN 系統簡介

泛歐數位式行動電話系統 GSM (Global System for Mobile Communications),它的

名字是來自於一個 Group Speciale Mobile 的團體。GSM 的主要目的在提供泛歐洲的漫遊(roaming),讓用戶能在歐洲的任何地方使用他們的設備,而不需要經由地區經營者做特殊的安排。而目前國內採用的 GSM 規格有 GSM 900(890~960 MHz)與 GSM 1800(1850~1990 MHz),而 GSM 系統採蜂巢式細胞概念來建構[10],所謂的蜂巢式細胞概念即以多個小功率發射機的基地台,取代一個高功率發射機的基地台(base statio)。並且 GSM 系統則採用分時多工(Time Division Multiple Access; TDMA)的存取方式。

GSM 900 的最大發射功率為 2 W,GSM 1800 的最大發射功率為 1 W,由於頻率越高的電磁波在空氣中的衰減量越大,因此 GSM 1800 系統的蜂巢半徑(4 公里)比 GSM 900 系統的蜂巢半徑(35 公里)小,所以 GSM 1800 系統在相同的涵蓋範圍需要架設較多的基地台;在頻道數目方面,GSM 1800 系統擁有 374 個使用頻率,而 GSM 900 只有 124 個使用頻率,因此 GSM 1800 可以容許較大的話務量;此外,GSM 900 的電波容易受地形干擾,穿透力也比較弱,而 GSM 1800 的電波穿透力較好,可以輕易的達到不易通訊的死角範圍,但傳輸距離較短;眾觀各種優缺點,GSM 900 系統適合用於使用率較少但涵蓋範圍較廣的偏遠地區,而 GSM 1800 系統則適合應用於使用率較高的人口密集處,亦可以藉由兩者的互補而得到最佳的通話品質[9][10]。在此論文僅設計 GSM 1800 系統的頻率範圍,而將 GSM 1800 的涵蓋頻率延伸至 1920 MHz 後再除二即可得到 GSM 900 系統的需求。

而 WLAN(Wireless Local Area Network)是指傳輸範圍在一百公尺左右的無線區域網路,WLAN指基於 IEEE (電子電機工程師協會) 訂製的 802.11 系列的無線傳輸標準,最常見的便是傳輸頻寬包括 802.11a、802.11b、802.11g,或安全標準 802.11i等,其中 802.11a、802.11b和 802.11g,802.11g是最近才出現的標準,而 802.11b則是目前廣泛被使用的標準,而 802.11a的優點是頻寬較大,比 802.11b晚被推出,但相對的傳輸距離較短,如在 2 樓使用 802.11a的 WLAN,可能就無法在 3 樓連接得上 WLAN,而 802.11g是最近推出的規格,它採用的頻段和 802.11b相同(2.4 GHz),但因改良過的封包格式及通訊協定,所以其傳輸速度較 802.11b要快上許多。表 1.1為三種規格的比較[11][12]。

表1.1 WLAN 802.11a/b/g 比較

|             | IEEE 標準         |                |                 |  |

|-------------|-----------------|----------------|-----------------|--|

|             | 802.11a         | 802.11b        | 802.11g         |  |

| 傳輸頻寬(理論/實際) | 54 Mbps/22 Mbps | 11 Mbps/5 Mbps | 54 Mbps/22 Mbps |  |

| 傳輸距離        | 約 30 公尺         | 約 40~50 公尺     | 約 40~50 公尺      |  |

| 使用頻帶        | 5 GHz           | 2.4 GHz        | 2.4 GHz         |  |

| 使用頻寬        | 300 MHz         | 83.5 MHz       | 83.5 MHz        |  |

| 調變技術        | OFDM            | DSSS           | OFDM            |  |

| 普及度         | 少               | <b>多</b>       | 中               |  |

因此在本論文中,將整合涵蓋範圍大的 GSM 1800 與傳輸數率高的 WLAN 兩個系統。當使用者在戶外時,可使用 GSM 系統以得到可隨時隨地傳輸資料的便利性,而在戶內時,則可切換至 WLAN 利用其高傳輸數率的優點使資料傳輸更有效率。

#### 1.3 超寬頻系統簡介

早在 1989 年美國國防部 DARPA(Defense Advanced Research Projects Agency)就提出超寬頻一詞,並在 1990 年正式成立超寬頻發展計畫,主要是針對軍事上雷達、定位系統與通訊技術進行開發。根據美國聯邦通訊委員會對超寬頻技術的定義,當中心頻率大於 2.5 GHz 的超寬頻系統至少需要 500 MHz、-10 dB 的頻寬,而中心頻率在 2.5 GHz 以下的超寬頻系統則需要至少 20%的頻寬比(fractional bandwidth)。UWB(Ultra wide band)是目前 IEEE 802.15.3a 正在制定的技術,此技術適用於個人無線區域網路(WPAN),並且被定位在短距離(2~10 公尺)與高速率(53.3~480 Mbps)的使用環境下。此外,還具有保密性高、抗干擾、精準定位功能、低成本術、低耗電量等優點。

目前市場上的UWB系統分為兩大標準:分別為Freescale/Motorola 所支持的直接序列超寬頻(DS-UWB),與MultiBand OFDM Alliance(MBOA)集團提出的多頻帶正交分頻多工(MultiBand OFDM; MB-OFDM)。兩種標準都屬於多頻帶系統,由於UWB使用的頻段從3.1到10.6 GHz,而多頻帶的方式是把整個7.5 GHz的頻寬分成好幾個子頻段(每段至少500 MHz以上)來操作,這個方法的好處是當系統偵測到某頻段有干擾或被佔用時,它可以藉著關閉頻段來彈性地避開干擾。另一方面,不同國家對於應該開放多少頻寬或該開放哪個頻帶將可能會有不同意見,因此採用多頻帶方案,較容易因應各國不同的法規限制,同時也較能兼顧與現有系統的相容性。

OFDM 技術發展至今已有 40 年歷史,並在很多系統上獲得採用,如 IEEE 802.11a/g/n、ADSL、WiMax、DAB 與 DVB 等,其優點包括頻譜效益較高、能有效收集多路徑能量,並且對於窄頻干擾有較高的免疫力。MB-OFDM 系統將 3.1~10.6 GHz 的頻寬劃分成 14 個 528 MHz 的子頻段[13],如圖 1.2 所示。並且使用頻寬較小的子頻段可減低接收機設計的複雜度,同時減少射頻端的功率消耗,進而降低系統成本,且能使頻譜運用更具彈性。

圖1.2 DS-UWB 與 MB-OFDM UWB 的頻譜圖

在本論文的第五章節,將針對 UWB 規格下,是否能利用切換式電感四相位振盪

器的電感切換方式來達到迴路穩定時間小於 9.5 ns , 將利用 Matlab 下的 Simulink 軟體來進行鎖相迴路模擬。

### 1.4 論文組織架構

本論文架構分為六個章節,第一章說明研究動機與目前通訊系統發展的背景。第二章敘述鎖相迴路與自我頻率校正的基本原理。第三章則描述鎖相迴路與自我頻率校正電路中各個子電路的實現方式。第四章為電路模擬結果。第五章將以 Simulink 來模擬在 UWB 系統下,鎖相迴路的鎖定時間與迴路頻寬的關係。第六章為對此篇論文的總結與未來的工作期許。

## 第2章 鎖相迴路基本原理

## 2.1 簡介

在無線通訊中,為了避免訊號失真,因此需要一個穩定輸出的壓控振盪器(Voltage Controlled Oscillator),但是振盪器輸出訊號容易受到環境因素的影響而產生偏移,故需要一個鎖相迴路(Phase Locked Loop)的回授系統將輸出頻率穩定,而自我頻率校正電路(Self-Frequency-Calibration circuit)主要是用來修正製程上的變異。

#### 2.1.1 鎖相迴路基本架構

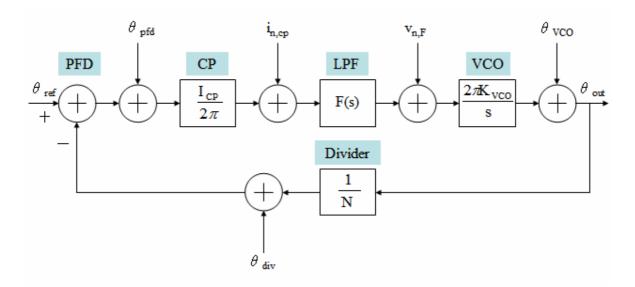

鎖相迴路是一個閉迴路系統,傳統的鎖相迴路基本架構如下圖 2.1 所示,由四個區塊構成,分別為相位檢測器(Phase Detector)、低通濾波器(Low Pass Filter)、壓控振盪器(Voltage Controlled Oscillator)及除頻器(Divider)。壓控振盪器輸出頻率為  $f_{out}$  其相位為  $\theta_{out}$ ,經由除頻之後的頻率與相位分別為  $f_{div}$  與  $\theta_{div}$ ,參考頻率  $f_{ref}$  的訊號來自於外加的低雜訊石英振盪器(Crystal Oscillator),藉由相位檢測器比較參考頻率與除頻器輸出端兩者的相位差( $\theta_{ref}-\theta_{div}$ ),可得到一輸出電壓  $V_{PD}$ 與相位差成正比, $V_{PD}$ 經過低通濾波器後濾掉高頻部份產生一電壓控制訊號  $V_{ctrl}$ ,利用電壓控制訊號  $V_{ctrl}$ 來改變壓控振盪器裡的可變電容值,使壓控振盪器對應到不同的  $V_{ctrl}$ 有不同的輸出頻率。故鎖相迴路的基本原理即藉由比較除頻器輸出端與參考頻率端兩者的相位差來調整壓控振盪器輸出至所需要的頻率。

圖2.1 基本的鎖相迴路架構

### 2.2 迴路系統分析

#### 2.2.1 鎖相迴路線性模型

一般而言鎖相迴路是一個非線性系統,但非線性系統並不容易分析比較,然而在 系統穩定的狀態下,鎖相迴路是可由線性模型來近似[14]。

圖2.2 鎖相迴路線性模型

上圖 2.2 為鎖相迴路的線性模型,其中  $\theta_{div}$  的相位等於  $\theta_{out}$ -N,  $K_{PD}$  為相位檢測器

的增益大小其單位為 V/rad,而相位檢測器的輸出  $V_{PD}$ 與  $\theta_{ref}$ 、 $\theta_{out}$ 的兩個相位之間的關係為:

$$V_{PD}(t) = K_{PD}\left(\theta_{ref}(t) - \frac{\theta_{out}(t)}{N}\right) = K_{PD}\left(\theta_{ref}(t) - \theta_{div}(t)\right) = K_{PD}\theta_{e}(t)$$

(2.1)

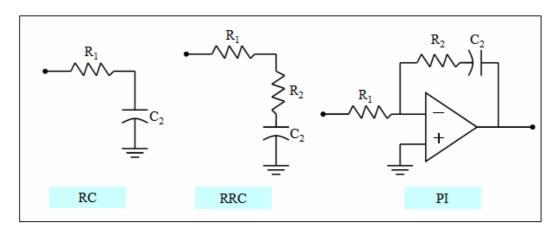

低通濾波器一般可分為三類[15],分別為 RC、RRC 與 PI,電路架構如下圖 2.3 所示:

圖2.3 三類常見低通濾波器

#### 轉移函數分別為:

RC型

$$F(s) = K_h \frac{\omega_1}{s + \omega_1}; \quad \sharp r K_h = 1; \ \omega_1 = \frac{1}{R_1 C_2}$$

RRC型

F(s) =

$$K_h \frac{s + \omega_2}{s + \omega_1}$$

;  $\sharp r = \frac{R_2}{R_1 + R_2}$ ;  $\omega_1 = \frac{1}{(R_1 + R_2)C_2}$ ;  $\omega_2 = \frac{1}{R_2C_2}$

PI型

$$F(s) = K_h \frac{s + \omega_2}{s}; \quad \sharp r K_h = \frac{-R_2}{R_1}; \quad \omega_2 = \frac{1}{R_2 C_2}$$

壓控振盪器的增益為  $K_{VCO}$ =  $(2\pi\Delta f_{out})/\Delta V_{ctrl}$ , 單位為 rad/s/V, 而輸出角頻率的變動量

$$\theta_{\text{out}}(t) = \int \Delta \omega(t) dt = K_{\text{VCO}} \times \int \Delta V_{\text{ctrl}}(t) dt$$

(2.2)

對上式作 Laplace 轉換可得:

$$\theta_{\text{out}}(s) = \frac{K_{\text{VCO}} \times \Delta V_{\text{ctrl}}(s)}{s}$$

(2.3)

故可得壓控振盪器的轉移函數為:

$$\frac{\theta_{\text{out}}(s)}{\Delta V_{\text{ctrl}}} = \frac{K_{\text{VCO}}}{s}$$

(2.4)

因此可得知此回授系統的前向增益為  $A=K_{PD}\times F_{LPF}(s)\times K_{VCO}/s$ ,而回授部份僅有除頻器,故回授增益可表示為  $\beta=1/N$ ,則系統的開迴路增益函數(2.5 式)與閉迴路增益函數(2.6 式)分別如下所示:

$$A\beta = K_{PD} \times F_{LPF}(s) \times \frac{K_{VCO}}{s} \times \frac{1}{N}$$

(2.5)

$$H(s)\big|_{closed} = \frac{\theta_{out}(s)}{\theta_{ref}(s)} = \frac{A}{1 + A\beta} = \frac{K_{PD} \times F_{LPF}(s) \times \frac{K_{VCO}}{s}}{1 + K_{PD} \times F_{LPF}(s) \times \frac{K_{VCO}}{s} \times \frac{1}{N}}$$

(2.6)

#### 2.2.2 穩定度分析

欲判斷一個回授系統的穩定性時,可利用開迴路增益函數(2.5 式)以柏德圖(Bode plot)方式繪出,依據相位邊緣(Phase Margin)與增益邊緣(Gain Margin)的大小來判斷迴路是否穩定,而相位邊緣指的是放大器前向增益 A 與回授增益 β 之乘積等於 1,且相

位未到達—180 度時,此時相位與—180 度的相位差。相位差越大則相位邊緣越大穩定度越高。而在開回路增益函數中,於複數座標原點上的極點有 N 個時,定義為Type-N 的鎖相迴路[16],故可知 RC 型與 RRC 型低通濾波器的鎖相迴路系統皆屬於Type-II,而 PI 型的低通濾波器的鎖相迴路則是為 Type-II。在 Type-I 中 RRC 型比RC 型在原點上的極點之後又多了一個零點,因此採用 RRC 型低通濾波器鎖相迴路的相位邊緣將比 RC 型大,且系統較穩定。而 Type-II 中,由於在原點有兩個極點存在,因此開迴路增益函數的相位在原點為—180 度,因此需在兩極點之後加入零點來提高相位邊緣。

#### 2.2.3 穩定相位誤差

接下來討論當鎖相迴路系統於穩定的狀態下,相位檢測器的輸入端產生一個步階相位差或步階頻率差甚至是線性的頻率變化時,對於系統輸出端的輸出相位誤差響應的影響。相位檢測器檢測出來的相位誤差為  $\theta_e = \theta_{ref} - (\theta_{out}/N)$ ,因此:

$$\theta_{e} = \theta_{ref} \left[ 1 - \left( \frac{\theta_{out}}{\theta_{ref}} \div \mathbf{N} \right) \right] = \theta_{ref} \left[ 1 - \left( \frac{\mathbf{H}(\mathbf{s})}{\mathbf{N}} \right) \right] = \frac{\theta_{ref}}{1 + \mathbf{K}_{PD} \times \mathbf{F}_{LPF}(\mathbf{s}) \times \frac{\mathbf{K}_{VCO}}{\mathbf{s}} \times \frac{1}{\mathbf{N}}}$$

(2.7)

由終值理論可得穩態值為:

$$\lim_{t \to \infty} \theta_{e}(t) = \lim_{s \to 0} s \cdot \theta_{e}(s) = \lim_{s \to 0} \frac{s^{2} \times \theta_{ref} \times N}{K_{PD} \times K_{VCO} \times F_{LPF}(s)}$$

(2.8)

當相位檢測器的輸入產生步階相位差、步階頻率與線性頻率變化三種情況時,分別帶入(2.8)式中計算,即可求得在不同的非理想輸入訊號下相位檢測器的穩態相位誤差結果,整理如下表 2.1 所示[15]:

| Type-N<br>輸入訊號                                      | Type- I | Туре- [[ | Туре-Ш |

|-----------------------------------------------------|---------|----------|--------|

| 步階相位 $	heta_{ m ref} = rac{\Delta \phi}{ m s}$     | 0       | 0        | 0      |

| 步階頻率 $\theta_{ref} = \frac{\Delta \omega_{o}}{s^2}$ | 常數      | 0        | 0      |

| 線性頻率變化 $\theta_{ref} = \frac{a}{s^3}$               | 隨時間增加   | 常數       | 0      |

表2.1 各型鎖相迴路系統對於不同輸入訊號的相位誤差穩態響應

由上表 2.1 可知,假設參考訊號有步階頻率產生時,而欲使穩態相位誤差為零, 則鎖相迴路系統至少必須選擇 Type-Ⅱ以上。然而鎖相迴路皆是利用改變除頻器的除 數值來切換頻率,因此在相位檢測器的輸入端等效上為產生步階的頻率變化,因此鎖 相迴路至少必須選擇 Type-Ⅲ以上的架構。若考慮輸入訊號端有線性的頻率變化時, 欲使穩態相位誤差為零,則必須選擇 Type-Ⅲ以上的鎖相迴路。

#### 2.2.4 暫態分析

由以上穩定相位誤差的分析可知鎖相迴路至少選擇 Type-II 以上的架構,因此接下來將針對 PI 型的低通濾波器作暫態響應的探討。將(2.6)式閉迴路增益函數中的  $K_{PD}$ 、 $K_{VCO}$ 、N 與低通濾波器 F(s)中常數  $K_h$  四者的乘積用 K 來表示,則  $K=K_{PD}\times K_{VCO}\times K_h/N$ ,且當  $K\geq 4\omega_2$  時,閉迴路的頻寬可近似於 K,即迴路頻寬 (Loop-Bandwidth)約等於開迴路的直流增益[15],再將 PI 型的低通濾波器的轉移函數  $F(s)=K_h\times (s+\omega_2)/s$  代入閉迴路增益函數中,則(2.6)式可重新寫成:

$$H(s)\big|_{closed} = \frac{N \times K \times \frac{s + \omega_2}{s} \times \frac{1}{s}}{1 + K \times \frac{s + \omega_2}{s} \times \frac{1}{s}} = \frac{N \times K(s + \omega_2)}{s^2 + Ks + K\omega_2}$$

(2.9)

將此 Type-Ⅱ的閉迴路增益函數的分母以控制系統的方式來表示:

$$s^{2} + Ks + K\omega_{2} = s^{2} + 2\zeta\omega_{n}s + \omega_{n}^{2}$$

(2.10)

其中  $\omega_n$  為自然頻率(Natural frequency),  $\zeta$  為阻尼常數(Damping constant), 而閉迴路中兩個極點的解為:

$$s_{1,2} = -\zeta \omega_n \pm \sqrt{(\zeta^2 - 1)\omega_n^2} = \left(-\zeta \pm \sqrt{\zeta^2 - 1}\right) \times \omega_n$$

(2.11)

其中 $\zeta$ 小於 1 為欠阻尼(under damping),兩個極點解為複數; $\zeta$ 大於 1 為過阻尼(over damping),兩個極點皆為實數; $\zeta$ 等於 1 為臨界阻尼(critical damping),兩個極點解相等為 $-\omega_n$ 。將(2.10)式等號兩端參數比較,可得自然頻率為:

$$\omega_{\rm n} = \sqrt{K \times \omega_2} \tag{2.12}$$

阻尼常數為:

$$\zeta = \frac{K}{2 \times \omega_{n}} = \frac{1}{2} \times \sqrt{\frac{K}{\omega_{2}}}$$

(2.13)

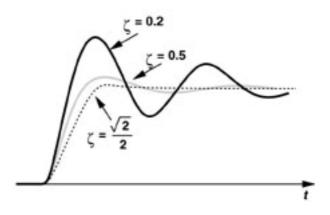

一般將零點  $\omega_2$ 取為迴路頻寬 K 的二分之一時, $\zeta$  等於 0.707 時可得最平坦的頻率響應,如下圖 2.4 為 Type- $\Pi$  的暫態響應,當阻尼常數  $\zeta$  越小時,曲線上升的速度越快,但也抖動的越厲害,需要較長的時間才可達到穩定,反之阻尼常數  $\zeta$  越大,上升速度雖慢,但可較快達到穩定。由(2.13)式知可藉由增加零點  $\omega_2$  的值來增加阻尼常數  $\zeta$ ,使加快迴路的穩定時間,但是當零點  $\omega_2$  值變大時將縮小相位邊緣(Phase Margin) 而使系統處於較不穩定的狀態,因此阻尼常數  $\zeta$  與穩定度之間需做取捨(trade-off)。

圖2.4 Type-Ⅱ的暫態響應

#### 2.3 電流幫浦與相位/頻率檢測器

#### 2.3.1 演進與原理

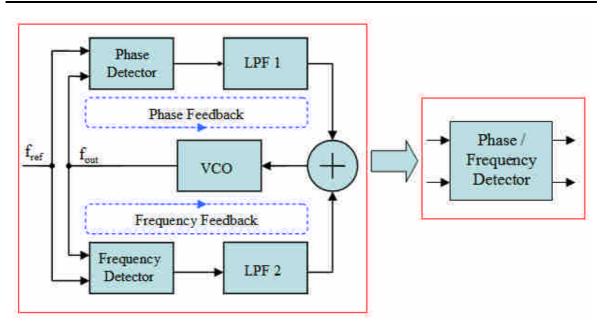

當鎖相迴路啟動時,振盪器的輸出可能會操作在與預定頻率相差很大的頻率上,當迴路由未鎖定至鎖定的狀態過程是一個非線性的現象,由於相位檢測器(PD)將會檢測到不同的頻率,因此當頻率相差甚大時可能會造能相位檢測器無法正常運作。故利用另一個含有頻率檢測器(Frequency Detector; FD)的迴路來比較參考頻率與除頻器輸出的頻率訊號,當兩者頻率相差太大時,先利用頻率檢測器比較而產生一個與相位差成正比的直流電壓給壓控振盪器,先將振盪器輸出頻率鎖至一定範圍內之後,再交由相位檢測器(PD)來做比較[16],如圖 2.5 所示。而將兩個檢測器合併在一起即為相位/頻率檢測器(Phase/Frequency Detector)(在接下來文中以相位檢測器簡稱之)。

圖2.5 增加頻率檢測器部分來增加擷取範圍

由先前分析知 PI 型低通濾波器(Type-II)比 RC 型與 RRC 型更適合應用於鎖相迴路中,但 PI 型低通濾波器中需要一個運算放大器,相當佔面積且耗成本,故將尋找另一電路架構來取代 PI 低通濾波器的功用。

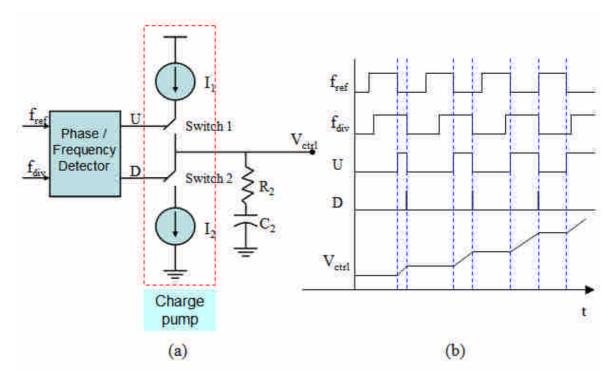

首先由圖 2.3 來分析,運算放大器的兩輸入端視為虛接地,故相位檢測器的輸出電壓  $V_{PD}$ 完全降在電阻  $R_1$  兩端上,然而運算放大器的輸入阻抗視為無窮大,因此流經電阻  $R_1$  的電流將完全流向電阻  $R_2$  與電容  $C_2$ ,在運算放大器的輸出端產生一電壓降給壓控振盪器,整體來說即是利用相位檢測器的輸出產生電流源  $V_{PD}/R_1$  對一階低通滤波  $R_2C_2$  進行充放電來產生電壓控制訊號  $V_{ctrl}$ ,故 PI 型低通滤波器可以等效如圖 2.6(a)所示,偵測得相位檢測器的輸出後,用電流幫浦(Charge pump)產生電流  $V_{PD}/R_1$ ,對一階的低通滤波器  $R_2C_2$  充放電得到電壓控制訊號  $V_{ctrl}$ 。

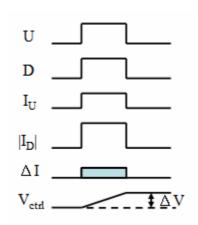

圖2.6 (a) 基本電流幫浦方塊圖;(b) 時序圖

#### 2.3.2 相位/頻率檢測器

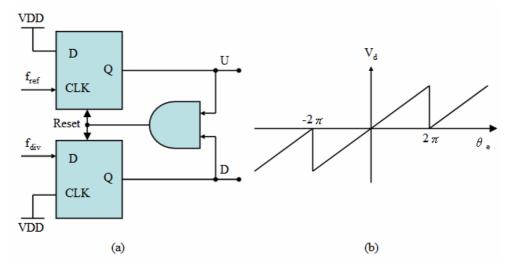

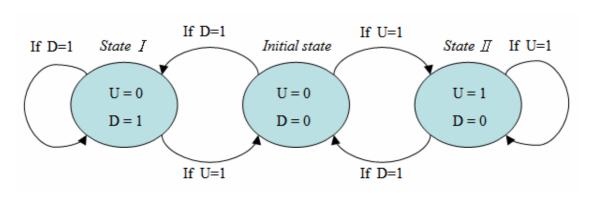

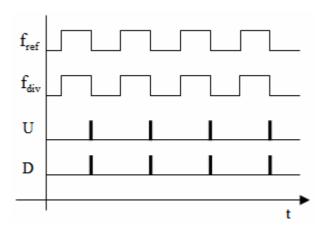

基本的相位/頻率檢測器可利用兩個 D 型正反器(D-flipflop)與一個及閘(And gate) 組成,如圖 2.7(a)所示。其中 D 型正反器的輸入端 D 皆給高準位(Vdd)電壓,參考頻率與除頻器輸出訊號由 D 型正反器的時脈觸發端(clock)輸入,且兩個 D 型正反器的輸出端 Q 接至及閘,當 U 與 D 輸出同時為高準位時,藉由及閘輸出為 1 將兩個 D 型正反器的重置(Reset)訊號拉起,使 U 與 D 訊號再重新降回低準位,其時序圖可參考圖 2.6(b);圖 2.7(b)為輸入相位差與輸出平均電壓的關係圖,其中  $V_d$ 表示 U 與 D 兩端的電壓差,由圖可看出此相位檢測器可以檢測的相位差範圍為 $-2\pi\sim2\pi$ ;圖 2.8 為相位檢測器的狀態機圖,例如當參考訊號領先時,訊號 U 會先拉起為高準位,由 Initial state 跳至 State  $\Pi$  並維持,直到訊號 D 也拉起時才會脫離 State  $\Pi$ ,並同時將訊號 U 與 D 重置為 0 回到 Initial state。

圖2.7 (a) 基本相位檢測器;(b) 相位差與輸出平均電壓關係

圖2.8 相位檢測器狀態機

#### 2.3.3 電流幫浦

在此將推導圖 2.6(a)中電流幫浦加上一階低通濾波器與 PI 型低通濾波器兩者架構有相同的轉移函數,證明可利用圖 2.6(a)來取代較高成本的 PI 低通濾波器。由於電流幫浦進行充放電動作時系統為離散式(discrete-time system),假設比較脈衝的頻率遠大於迴路頻寬,且每次充放電後平均值改變量很小,因此對平均電流的改變而言可視為連續系統(continuous-time system)。並假設充放電的電流相等均為  $I_P$ ,由圖 2.6(b)的 U 訊號波形可知在一個週期內總充電荷量為  $I_P \times \theta_e \times T/2\pi$ ,其中  $\theta_e$  為參考頻率與除頻器輸出訊號的相位差,因此平均電流為  $I_{avg} = I_P \times \theta_e/2\pi$ ,而一階濾波器  $R_2C_2$  的阻抗為:

$$Z(s) = R_2 + \frac{1}{sC_2}$$

(2.14)

電壓控制訊號 Vctrl 可表示成:

$$V_{ctrl} = I_{avg} \times Z(s) = \frac{I_p \theta_e}{2\pi} \times R_2 \left( \frac{s + \frac{1}{R_2 C_2}}{s} \right)$$

(2.15)

因此輸出相位  $\theta_{\text{out}} = V_{\text{ctrl}} \times K_{\text{VCO}} / s$ ,可用相位誤差來表示成:

$$\theta_{\text{out}} = \frac{K_{\text{VCO}}}{s} \times \frac{I_{\text{P}}}{2\pi} \times R_2 \times \left(\frac{s + \frac{1}{R_2 C_2}}{s}\right) \times \theta_{\text{e}}$$

(2.16)

而 PI 型低通濾波器的輸出相位與相位誤差的關係可由圖 2.2 得知:

$$\theta_{\text{out}} = \frac{K_{\text{VCO}}}{s} \times K_{\text{PD}} \times K_{\text{h}} \times \left(\frac{s + \frac{1}{R_2 C_2}}{s}\right) \times \theta_{\text{e}}$$

(2.17)

比較(2.16)式與(2.17)式可得知相位檢測器的常數  $K_{PD} = I_P/2\pi$ ,低通濾波器的常數  $K_h = R_2$ ,故電流幫浦加上一階的  $R_2C_2$  低通濾波器與 PI 型低通濾波器具有相同的轉移函數形式,因此圖 2.6 的架構可等效 Type-II。

#### 2.3.4 非理想效應

#### (a) 死區

當參考頻率與除頻器輸出訊號的波形同頻率同相位之時,U與D訊號會同時拉起,再經由及閘來作重置,使U與D訊號隨即又回歸低準位,因此U與D訊號會有脈波波形產生如圖 2.9 所示:

圖2.9 零相位差時 PFD 輸出脈波

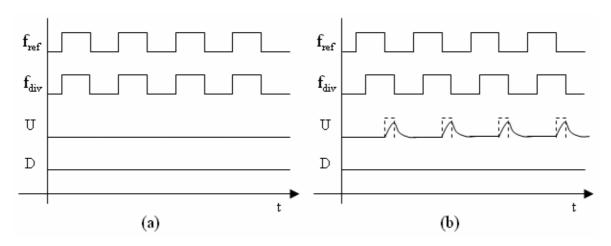

接下來將探討此脈波訊號是否應該存在。假設當零相位差時,U 與 D 訊號並不會產生脈波訊號而一直維持在低準位,如圖 2.10(a)所示,在實際電路中由於相位檢測器受到負載影響,當輸入相位誤差很小時,如圖 2.10(b),導致輸出訊號來不及上升到下級電路輸入的臨界電壓就被及閘訊號重置,隨即又下降回低準位,因此輸出將無法正常反應而呈現一平坦狀,這無法正常判斷的相位誤差區間即稱為死區(Dead Zone)。圖 2.11(a)為有死區時,轉移曲線在相位誤差 $-\phi_0\sim+\phi_0$ 之間無法正確反應。圖 2.11(b),在死區範圍間,由於相位檢測器本身無法確實反應出相位誤差,導致電流幫浦在死區無輸出電流。

圖2.10 (a) 零相位差時輸出無脈波產生;(b) 相位差極小的情形

圖2.11 Dead zone: (a) 有死區與無死區的轉移曲線; (b) 電流幫浦輸出電流

因此在零相位誤差之時,圖 2.9 中相位檢測器的輸出脈波訊號是必須存在,因為可利用此脈衝訊號來做預先充電的動作,使誤差相位極小時仍可觸發臨界電壓來驅動下一級電路。然而脈波寬度大小與相位檢測器中的延遲時間有關,此段延遲時間即由及閘的輸入端開始,然後做重置動作直到相位檢測器的輸出改變。此延遲時間不可太小,太小則死區仍然存在;但亦不可太大,因輸出脈波時電流幫浦的充放電開關皆為ON的狀態,若延遲太大將因電流幫浦的充放電流不匹配效應而造成輸出相位誤差。

#### (b) 充放電流不匹配

在實際電路中,電流幫浦是由 pMOS 與 nMOS 來實現的,因此充放電流很難做

到完全相等,故在理論上相位誤差為零時,充放電流相等,在脈波訊號時充電量與放電量將會相互抵消,使電壓控制訊號  $V_{ctrl}$  維持不變。但由於充放電流的不匹配效應,導致零相位誤差時  $V_{ctrl}$  仍會有些許變化,而使輸出存在相位誤差,如圖 2.12 所示:

圖2.12 充放電電流不匹配效應

此外充放電流不匹配,亦會造成在鎖定過程中,往高頻鎖定與往低頻鎖定的鎖定時間(settling time)不同。因此可利用電流鏡(current mirror)電路來平衡充放電電流,使降低充放電電流的不匹配效應。

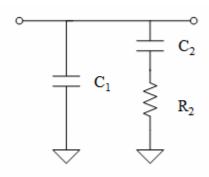

## 2.4 低通滤波器

# 2.4.1 二階低通濾波器設計

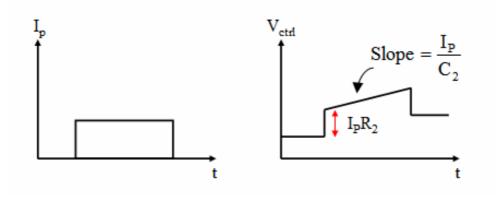

先前討論過圖 2.6 電流幫浦加上一階低通濾波器架構的轉移函數,但此架構容易受到比較脈衝的干擾,因為以時域的觀點上來看如圖 2.13,當電流幫浦端產生一個正電流的脈衝訊號,則在低通濾波器端電壓控制訊號  $V_{ctrl}$  會瞬間上升  $I_{px}R_2$  的壓降,而這個瞬間改變的壓降會對壓控振盪器的輸出頻率產生干擾,瞬間改變了壓降是因為訊號含有較高頻的成份,因此為了減少對振盪器輸出的干擾將再並聯一個電容  $C_1$  形成二階的低通濾波器,即利用較高階的濾波器來濾除高頻部份,電路如圖 2.14 所示。

圖2.13 一階低通濾波器輸入電流與輸出電壓關係

圖2.14 二階低通濾波器

而二階低通濾波器的轉移函數為:

$$Z(s) = \frac{1}{sC1} \left\| \left( R_2 + \frac{1}{sC_2} \right) \right\| = \frac{C_2 R_2 \left( s + \frac{1}{C_2 R_2} \right)}{\left( C_1 + C_2 \right) s \left( \frac{s}{C_1 C_2 R_2} \right)} = K_h \times \frac{s + \omega_2}{s \left( \frac{s}{\omega_3} + 1 \right)}$$

(2.18)

其中零點 ω2 與極點 ω3 分別為:

$$\omega_2 = \frac{1}{R_2 C_2} \tag{2.19}$$

$$\omega_3 = \frac{C_1 + C_2}{C_1 C_2 R_2} = \omega_2 \left( 1 + \frac{C_2}{C_1} \right)$$

(2.20)

在一般實際應用中,極點頻率約取為零點頻率的16倍,因此C2約為C1的15倍大[16]。

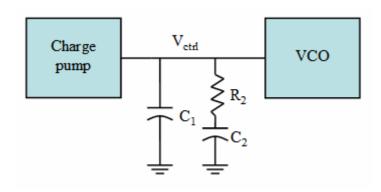

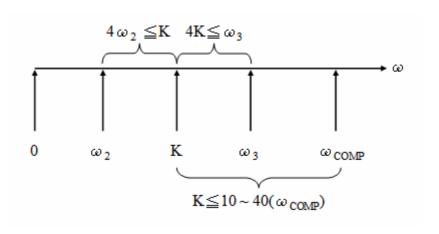

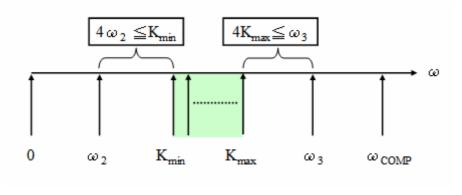

#### 2.4.2 迴路頻寬與低通濾波器的設定

接下來對迴路頻寬(Loop-Bandwidth)與低通濾波器的極、零點設定考量做討論, 迴路頻寬主要影響到鎖定時間(settling time)和雜訊(noise)的抑制。在此將對三階的鎖 相迴路系統進行討論,亦即使用二階的低通濾波器如圖 2.14。設計迴路頻寬時,首先 必須了解在迴路中的幾個重要頻率之間的關係,其中包含:比較頻率  $\omega_{COMP}$ 、迴路頻 寬 K、低通濾波器的零點頻率  $\omega_2$  與極點頻率  $\omega_3$ 。比較頻率為相位檢測器的真正操作 頻率,也就是參考訊號的頻率,是上列幾項中頻率最高的,以整數型頻率合成器 (Integer-N Synthesizer)來說,比較頻率即為頻道的解析度,因此解析度要高,則需使 用較小的比較頻率,但如此一來也將導致迴路的鎖定時間變長;反之,若欲使鎖定時 間短,則須提高比較頻率,但頻道的解析度將會變大。

首先探討上面所提到的四個頻率間的關係,如下圖 2.15 所示:

圖2.15 迴路頻寬設計時各頻率的關係圖

比較頻率  $\omega_{COMP}$ : 即為參考頻率大小,相位檢測器的參考端是由外接的低雜訊石 英振盪器(Crystal Oscillator)提供參考頻率,比較頻率  $\omega_{COMP}$  的值在整數型 頻率合成器即由系統的頻道解析度決定,在分數型頻率合成器(Fractional-N Synthesizer)除了系統的頻道解析度還須配合所使用的除頻器(Divider)來決定出比較頻率的值。

- 迴路頻寬 K:一般迴路頻寬為比較頻率的十分之一至四十分之一之間,太小則迴路的反應時間長,太大則靠近比較頻率使得極點頻率ω3不易加入來濾除比較脈衝訊號。

- 零點  $\omega_2$ : (2.13)式為阻尼常數,故零點  $\omega_2$ 通常會取在 K/4 以下,使得阻尼常數  $\zeta$  值大於 1,雖然暫態上升的速度比較緩慢,但是 overshoot 較小能夠較快達 到穩態;反之,若零點太靠近迴路頻寬 K,則  $\zeta$  值很小 overshoot 太大抖動的太厲害,需要較長的時間才能穩定。

- 極點  $\omega_3$ :相位檢測器輸出的相位差訊號經由電流幫浦(Charge Pump)、低通濾波器後將電壓送至壓控振盪器,因此須靠低通濾波器中的極點來將相位比較所產生的比較脈衝抑制,避免在輸出頻譜兩旁產生突波(spurious),而在此我們所探討的是二階低通濾波器,故在頻寬外的抑制能力為一40dB/dec,因此若欲提高衰減量則須將迴路頻寬與比較頻率的距離拉大,即提高比較頻率,迴路頻寬也將隨之提高而兩者間的距離拉大,但此方法將會犧牲掉頻道的解析度;另一個提高衰減量的方法即為增加低通濾波器的階數,再加入極點增加衰減量,但此時需注意極點的所在,一般不可小於四倍的迴路頻寬 K,否則 overshoot 會太大,也不能太靠近比較頻率,不然將會失去抑制比較脈衝的作用。

因此驗證了在 2.4.1 章節中提及的在一般實際應用,極點頻率約取為零點頻率的 16 倍,電容  $C_2$  約為  $C_1$  的 15 倍大。

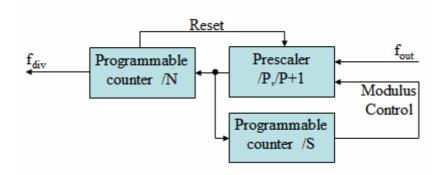

# 2.5 除頻器

在鎖相迴路架構中,除頻器(Divider)的輸入直接來自於壓控振盪器的輸出,是整個迴路中頻率最高的部份之一,操作頻率為 GHz 級,而一般的可程式除頻器 (Programmable Divider)只能操作在 MHz 級,因此為了能在高頻中操作,將在一般的

除頻器之前先使用一個預除器(Prescaler)將振盪器輸出除到較低的頻率範圍,再交給一般的可程式除頻器運作。這種除頻器組合稱為單模數(single modulus),如圖 2.16(a) 所示,其振盪器輸出頻率可表示為:

$$f_{out} = N \times P \times f_{in}$$

(2.21)

圖2.16 整數型頻率合成器:(a) 單模數;(b) 雙模數

由於預除器的除數是一個固定值,因此能只能靠可程式除頻器來調整除數值,故單模數除頻器的解析度即為  $P imes f_{in}$ 。為了得到較高的解析度,將單模數改良為雙模數 (two modulus),架構如圖 2.16(b)所示。運作流程為:首先將預除器除數值設定在 (P+1),且預除器輸出同時送給可程式除頻器 /N 與可程式除頻器 /S,其中 N 必須大於 S,當可程式除頻器 /S 數完時,送出一個模數控制訊號(Modulus Control)將預除器的除數值切換為 P,直到可程式除頻器 /N 將剩下的(N-S)數完後,拉起重置訊號 (Reset)進行重置,並將預除器切回(P+1),如此完成一個週期。則輸出頻率為:

$$f_{out} = [S \times (P+1) + (N-S) \times P] \times f_{in}$$

$$= (N \times P + S) \times f_{in}$$

(2.22)

此雙模數除頻器組合的解析度大小等於可程式除頻器 /S 的一個單位變化量。

此外,可程式除頻器 /N 與 /S 亦可用可程式化計數器(Programmable Counter)來取代,由外加控制訊號來決定計數器的值,可更加提高解析度。

# 2.6 壓控振盪器

壓控振盪器(Voltage Controlled Oscillator)即藉由輸入電壓控制訊號 V<sub>ctrl</sub> 的變化來 改變輸出頻率。因此振盪器的輸出訊號可表示為:

$$\omega_{\text{out}} = \omega_0 + K_{\text{VCO}} \times V_{\text{ctrl}}$$

(2.23)

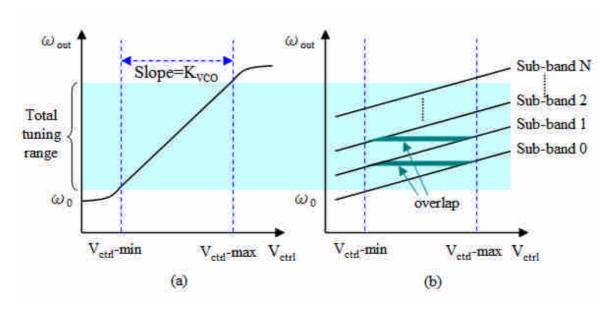

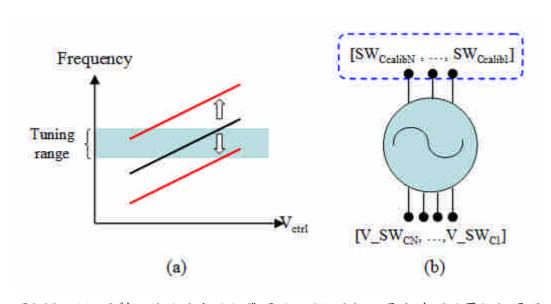

其中  $\omega_0$ 為自然振盪頻率(free-running frequency),為電壓控制訊號為 0 V 時,振盪器的輸出頻率; $V_{ctrl}$ 為電壓控制訊號,來自於電流幫浦對低通濾波器進行充放電得到的壓降; $K_{VCO}$ 為壓控振盪器的增益,單位為 rad/s/V。電壓控制訊號是送給壓控振盪器裡的可變電容(Varactor),由於可變電容會因不同的電壓降而產生不同的電容值,藉此特性來改變壓控振盪器內部 LC 諧振槽的電容值,使輸出頻率可藉由  $V_{ctrl}$  電壓變化而改變。圖 2.17(a)為使用單一頻帶式壓控振盪器的轉移特性曲線,而電壓控制範圍應設計在線性區域為佳,並且線性區域的斜率即為振盪器的增益  $K_{VCO}$  (rad/s/V)。但是,當可調頻率範圍(tuning range)很大時,壓控振盪器的增益值必須夠大才能完全覆蓋可調頻率範圍,然而壓控振盪器的增益值越大,將使鎖相迴路的輸出相位雜訊也隨之被放大,因此為了能有較大的可調頻率範圍,又要小的壓控振盪器增益值減少輸出雜訊,需如圖 2.17(b)所示,利用多個較小  $K_{VCO}$ 的子頻帶來共同完成[17],而每個相鄰的子頻帶之間必須有一段互相重疊(overlap)的區域,才能連續且完整的涵蓋所有頻率。

圖2.17 (a) 單一頻帶方式;(b) 多子頻帶相互重疊組成方式

# 2.7 相位雜訊

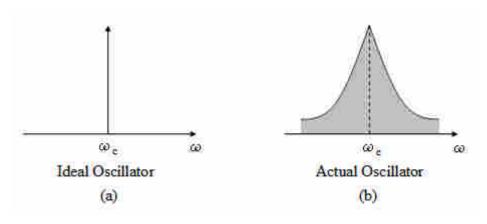

## 2.7.1 相位雜訊的定義

在類比電路中雜訊(Noise)是個很重要的議題。雜訊將會引起訊號的相位、振幅變化,在頻域中稱為相位雜訊(Phase Noise),在時域中則稱為相位閃動(Jitter)。一個理想的壓控振盪器輸出頻譜應如圖 2.18(a)所示,訊號為  $A_ccos(\omega_ct)$ ,其中  $A_c$ 為輸出振幅, $\omega_c$ 為中心角頻率。

圖2.18 (a) 理想振盪器輸出功率頻譜;(b) 真實振盪器輸出功率頻譜

當有雜訊源干擾時,輸出訊號將會受到振幅雜訊與相位雜訊的影響,首先探討載波訊號受到振幅雜訊干擾時,其輸出訊號為:

$$S(t) = A_c (1 + m \cdot \cos \omega_m t) \cos \omega_c t$$

(2.24)

其中 m 為振幅雜訊的最大值, ωm 為調變頻率。(2.24)式可展開表示成:

$$S(t) = A_{c} \left[ \cos \omega_{c} t + \frac{m}{2} \cos(\omega_{c} + \omega_{m}) t + \frac{m}{2} \cos(\omega_{c} - \omega_{m}) t \right]$$

(2.25)

但是,一般來說振盪器的振幅雜訊影響通常較小,即 m 值較小,並且會在極短時間 內趨於穩定,因此振幅雜訊可視為一個常數量。

假設相位雜訊會隨著時間而變化  $\theta(t) = \theta_m sin(\omega_m t)$ ,其中  $\theta_m$ 為最大的偏移角度, $\omega_m$ 為調變頻率,因此輸出訊號為:

$$S(t) = A_c \cos[\omega_c t + \theta_m \sin(\omega_m t)]$$

$$= A_c \{\cos(\omega_c t) \times \cos[\theta_m \sin(\omega_m t)] - \sin(\omega_c t) \times \sin[\theta_m \sin(\omega_m t)] \}$$

(2.26)

當 $\theta_{m}$ <<1時,(2.26)式可近似成:

$$S(t) \cong A_{c} \left[ \cos(\omega_{c} t) - \frac{\theta_{m}}{2} \cos(\omega_{c} + \omega_{m}) t + \frac{\theta_{m}}{2} \cos(\omega_{c} - \omega_{m}) t \right]$$

(2.27)

其中  $A_c\cos(\omega_c t)$ 項為不含任何雜訊的載波(carrier),後兩項即為相位雜訊,可看出相位雜訊以載波頻率  $\omega_c$  為中心,距離載波兩旁  $\omega_m$  的位置呈現大小相等相位相反的兩個旁波,以頻譜來觀察可發現在載波中心頻率的周圍會形成"裙帶(skirts)"狀,如圖 2.18(b) 所示。

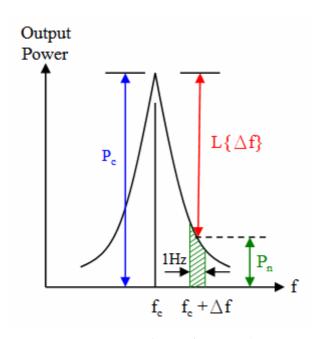

而基本的相位雜訊定義為:振盪器輸出頻譜中,距離中心載波 $(f_c)$ 某一個特定頻率偏移量 $(\Delta f)$ 之下,1 Hz 頻寬的總雜訊相對應於中心載波的功率比:

$$L\{\Delta f\} = \frac{在頻偏爲\Delta f 的雜音功率/1Hz}{中心點信號功率} = \frac{P_n}{P_c}$$

(2.28)

#### 圖 2.19 為(2.28)式相位雜訊定義的示意圖:

圖2.19 振盪器的輸出頻譜

### 2.7.2 鎖相迴路的相位雜訊

整體鎖相迴路的輸出相位雜訊是由迴路內不同的雜訊源共同貢獻,雜訊源有參考頻率端的  $\theta_{ref}$ 、相位檢測器  $\theta_{pfd}$ 、電流幫浦  $i_{n,cp}$ 、低通濾波器  $v_{n,F}$ 、壓控振盪器  $\theta_{vco}$  及除頻器的  $\theta_{div}$ ,如圖 2.20 所示[17]:

圖2.20 鎖相迴路的相位雜訊模型

而每個雜訊源在鎖相迴路中有不同的頻率響應,下列為每個雜訊源對鎖相迴路輸出端的轉移函數:

參考頻率端:

$$H_{ref}(s) = \frac{\theta_{out}(s)}{\theta_{ref}(s)} = \frac{\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}}{1 + \left[\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}\right] \times \left[\frac{1}{N}\right]} = \frac{A(s)}{1 + A(s)\beta(s)}$$

(2.29)

相位檢測器:

$$H_{pfd}(s) = \frac{\theta_{out}(s)}{\theta_{pfd}(s)} = \frac{\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}}{1 + \left[\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}\right] \times \left[\frac{1}{N}\right]} = \frac{A(s)}{1 + A(s)\beta(s)}$$

(2.30)

電流幫浦:

$$H_{i_{n,cp}}(s) = \frac{\theta_{out}(s)}{i_{n,cp}(s)} = \frac{F(s) \times \frac{2\pi K_{VCO}}{s}}{1 + \left[F(s) \times \frac{2\pi K_{VCO}}{s}\right] \times \left[\frac{1}{N} \times \frac{I_{cp}}{2\pi}\right]} = \frac{2\pi}{I_{cp}} \times \frac{A(s)}{1 + A(s)\beta(s)}$$

(2.31)

低通濾波器:

$$H_{v_{n,F}}(s) = \frac{\theta_{out}(s)}{v_{n,F}(s)} = \frac{\frac{2\pi K_{VCO}}{s}}{1 + \left[\frac{2\pi K_{VCO}}{s}\right] \times \left[\frac{1}{N} \times \frac{I_{cp}}{2\pi} \times F(s)\right]} = \frac{2\pi K_{VCO}}{s} \times \frac{A(s)}{1 + A(s)\beta(s)} (2.32)$$

壓控振盪器:

$$H_{\text{VCO}}(s) = \frac{\theta_{\text{out}}(s)}{\theta_{\text{VCO}}(s)} = \frac{1}{1 + 1 \times \left[\frac{I_{\text{cp}}}{2\pi} \times F(s) \times \frac{2\pi K_{\text{VCO}}}{s}\right]} = \frac{1}{1 + A(s)\beta(s)}$$

(2.33)

除頻器:

$$H_{div}(s) = \frac{\theta_{out}(s)}{\theta_{div}(s)} = \frac{\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}}{1 + \left[\frac{I_{cp}}{2\pi} \times F(s) \times \frac{2\pi K_{VCO}}{s}\right] \times \left[\frac{1}{N}\right]} = \frac{A(s)}{1 + A(s)\beta(s)}$$

(2.34)

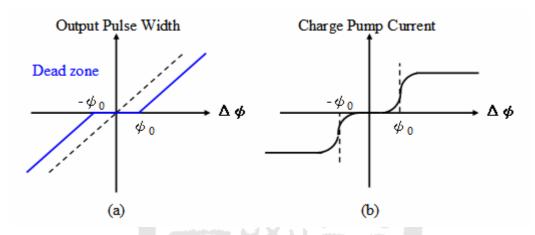

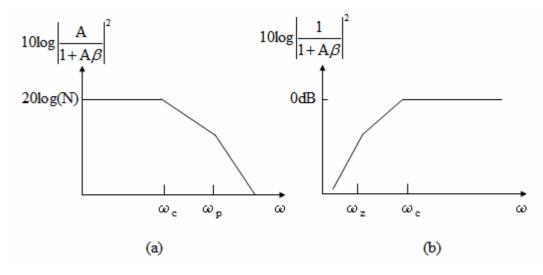

其中參考頻率、相位檢測器、電流幫浦與除頻器雜訊源的轉移函數皆為低通特性,在頻寬外的高頻雜訊可以被抑制,因此對這四個雜訊源來說,迴路頻寬越小雜訊抑制能力越好,因此在迴路頻寬內的相位雜訊是由這四個雜訊源所主宰,並且轉移函數的常數項皆含有除數 N,代表這些雜訊源的貢獻會因為閉迴路而放大 N 倍到鎖相迴路的輸出端,因此劣化因素為 20×log(N),如圖 2.21(a)所示。而低通濾波器與壓控振盪器雜訊源的轉移函數為高通特性,如圖 2.21(b),在迴路頻寬內的低頻雜訊可以被有效的抑制,因此對這兩個雜訊源來說迴路頻寬越大對雜訊的抑制能力越好,故迴路頻寬外的相位雜訊是由這兩個雜訊源所主宰,尤其是壓控振盪器。

圖2.21 (a) 參考頻率、相位檢測器、電流幫浦與除頻器雜訊的轉移函數;(b) 壓控振 盪器與低通濾波器雜訊的轉移函數

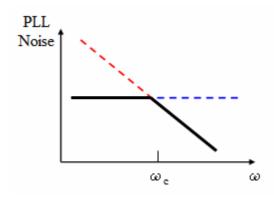

因此迴路頻寬的選擇將會直接影響到鎖相迴路的輸出相位雜訊大小,要擁有最佳的輸出相位雜訊則迴路頻寬選擇須如圖 2.22 所示,斜直線是由壓控振盪器提供的相位雜訊,水平線是由參考頻率、相位檢測器、電流幫浦與除頻器提供的相位雜訊,迴路頻寬應選擇在兩條線的交點處可得最小的輸出相位雜訊。

圖2.22 鎖相迴路的迴路頻寬選取

# 2.8 自我校正電路

在實際電路中,壓控振盪器將會受到製程(process)、供應電壓(supply voltage)與 溫度(temperature)的變異影響(PVT),因此可能會造成原本可覆蓋住的可調頻率範圍 (tuning range),因為這些變異因素而使頻帶偏移,如圖 2.23(a)所示,頻帶將因變異因素而往高頻或往低頻處偏移,而無法再覆蓋可調頻率範圍。然而上列三種變異因素中,供應電壓(supply voltage)與溫度(temperature)的變異影響較小,影響最大的則是製程(process)的變異[17],因此,將利用自我頻率校正電路(Self-Frequency-Calibration circuit)來修正製程變異造成的偏移。

自我頻率校正電路即是除了原本用來增加可調頻率範圍的電容陣列之外,在壓控振盪器內部又增加一組電容陣列給校正電路使用。首先利用自我頻率校正電路判斷頻帶是否偏移,然後輸出一組數位控制訊號[SW<sub>CcalibN</sub>...,SW<sub>Ccalib2</sub>, SW<sub>Ccalib1</sub>]給壓控振盪器中校正用的電容陣列開闢,若判斷出頻帶往高頻部份偏移,則切換電容開闢,增加LC 諧振電路的電容值,以降低壓控振盪器的輸出頻率,若往低頻部份偏移時,則減少LC 諧振電路的電容值,以提高壓控振盪器的輸出頻率,藉由改變LC 諧振槽中的電容值將製程變異造成的偏移量修正回來。而圖 2.23(b)中[V\_SW<sub>CN</sub>,...,V\_SW<sub>CI</sub>]訊號是給用來增加可調頻率範圍的電容陣列的開闢使用,對多頻帶壓控振盪器的頻帶作選擇,如所示。

圖2.23 (a) 因製程偏移造成的頻帶漂移;(b) 具校正電容陣列的壓控振盪器

# 第3章 電路架構的實現

# 3.1 簡介

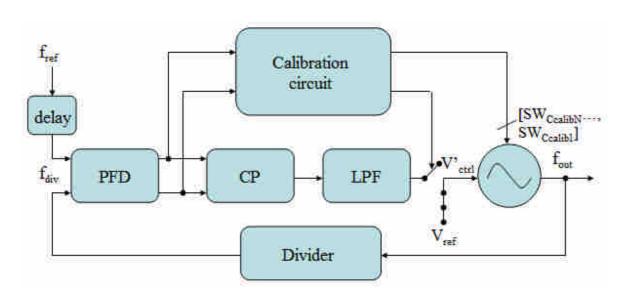

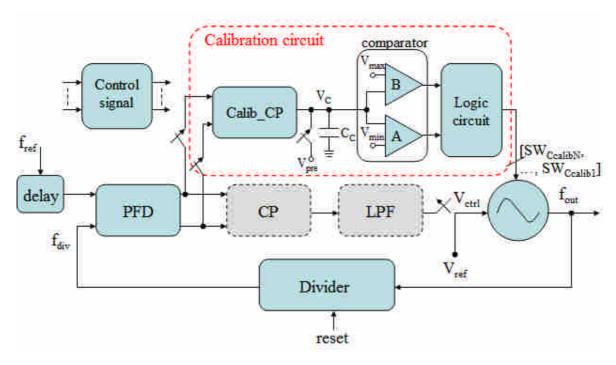

在此章節將介紹具有自我頻率校正功能的鎖相迴路中各個電路方塊的電路實現方式,圖 3.1 為方塊圖。將分兩個部份來說明:首先為鎖相迴路部分,其中包含相位檢測器(PFD)、電流幫浦(CP)、低通濾波器(LPF)、壓控振盪器(VCO)及除頻器(Divider);另一部份為自我頻率校正電路(Self-Frequency-Calibration circuit)。

圖3.1 具有自我頻率校正功能的鎖相迴路

當電路剛開始啟動時,首先進入自我頻率校正階段,此時鎖相迴路部份則在電壓控制訊號端(Vctrl)由自我頻率校正電路中的控制訊號來關閉,使鎖相迴路成為開迴路狀態,由自我頻率校正電路來對製程變異的偏移作修正,校正結束後將最終得到的 [SW<sub>CcalibN</sub>...,SW<sub>Ccalib2</sub>, SW<sub>Ccalib1</sub>]控制訊號給壓控振盪器中校正用電容陣列的開關並維持訊號,然後將自我頻率校正電路部份關閉,使鎖相迴路回到閉迴路狀態,並開始進行鎖相功能。

# 3.2 鎖相迴路

#### 3.2.1 相位檢測器

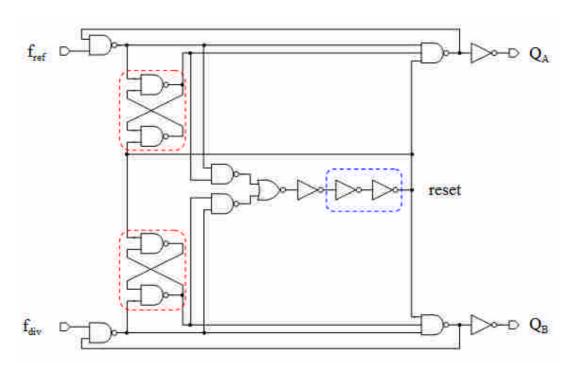

圖 3.2 是一個傳統的相位檢測器(Phase Frequency Detector),使用 RS 型的正反器 (RS-type flip-flops)電路,當輸入訊號拉昇為高準位時,經邊緣觸發後輸出訊號跟著拉為高準位,且維持輸出直到兩輸出端  $Q_A$  與  $Q_B$  同時皆為高準位的瞬間,才會將重置訊號(reset)觸發,使兩個輸出訊號被重置回低準位,而重置訊號也隨即回到低準位狀態,一個周期檢測完成。如先前 2.3.4 章節中提到相位檢測器的死區(Dead zone)問題,將導致無法正確判斷出較小的相位誤差,使鎖相迴路的輸出端產生閃動(Jitter),因此為了克服死區問題必須使相位檢測器的內部延遲時間夠大,在兩個輸入端訊號無相位差的狀態下,利用此延遲時間讓相位檢測器的輸出端可做預充(pre-charge)動作,將輸出端的壓降預先充電至下一級電路輸入端的臨界電壓,如此一來,即使相位檢測器的兩個輸入端相位誤差極小,仍可驅動電流幫浦正確的對低通濾波器進行充放電,故在圖 3.2 的架構中重置訊號端多串聯了兩個反閘(inverter)來增加延遲時間[19]。

圖3.2 傳統相位檢測器的電路架構

因此,當鎖相迴路處在穩定狀態時,相位檢測器兩輸入端無相位差,兩輸出端仍會產生脈波訊號使死區問題解決,但此脈波訊號卻也將電流幫浦的充電與放電開關同時開啟,又考慮電流幫浦充放電流的不匹配效應,此時將在電壓控制訊號端 $V_{ctrl}$ 產生干擾,使鎖相迴路的輸出端產生閃動(Jitter),並降低了相位檢測器的線性度(linearity) [20]。

圖 3.3 為預充型相位檢測器(Precharge Type PFD),其中 M14、M15、M16 與 M24、M25、M26 為門栓(Latch)電路的功能,而反及閘(NAND gate)是用來對門栓(Latch)電路重置。相較於傳統的相位檢測器,修正的預充型相位檢測器只需要 16 個電晶體,與圖 3.2 電路相較下,在重置路徑所需經過的電晶體個數較少故延遲時間也較短,可提高操作頻率,此外在功率消耗及面積也都比傳統式來的要小。並且當兩輸入端的相位誤差為零時,此修正的預充型相位檢測器產生的脈波寬度比傳統相位檢測器的小,因此縮短了脈波下電流幫浦充電與放電電流同時開啟的時間,故可改善鎖相迴路的輸出閃動(Jitter)與相位檢測器的線性度(linearity)。

圖3.3 預充型相位檢測器

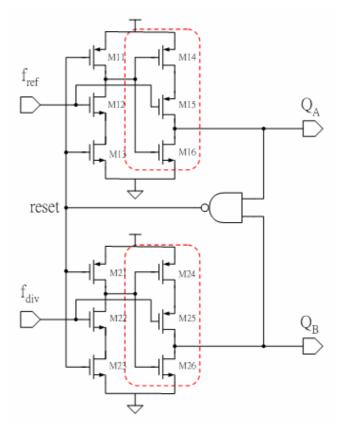

### 3.2.2 電流幫浦

圖 3.4 為傳統型的電流幫浦電路架構,由於從相位檢測器來的 QA與 QB 訊號為高準位時表示要將充電或放電的開關打開,低準位時表示要將開關關閉,而在電流幫浦中充電方向卻是利用 pMOS 來當作開關,因此須在相位檢測器輸出後接上一個反閘 (inverter gate),如圖 3.4 所示:

圖3.4 傳統的電流幫浦電路

此時  $Q_A$  訊號路徑多了一個反閘電路的延遲時間,因此  $Q_A$  與  $Q_B$  訊號並非同時到達電流幫浦,而產生了一相位誤差,導致電流幫浦在電壓控制訊號( $V_{ctrl}$ )上產生擾動,增加了鎖相迴路的相位雜訊。此外,當  $Q_A$  與  $Q_B$  訊號同為低準位時,開關 Mp1 與 Mn1 皆為關閉(OFF)狀態,電壓控制訊號( $V_{ctrl}$ )為浮接且電壓須維持不變,此時,開關 Mp1 的源極(source)電壓被拉升至 Vdd,而開關 Mn1 的源極電壓被降到 Gnd,導致在下一周期  $Q_A$  與  $Q_B$  訊號為高準位時,開關 Mp1 與 Mn1 一切換到開的狀態(ON)時,電壓控制訊號( $V_{ctrl}$ )會有跳躍現象而使電壓產生不連續,此不連續將在鎖相迴路變成雜訊,且使壓控振盪器的輸出頻率不穩定[16]。

圖 3.5 為改良後的電流幫浦電路架構[24],其中為了避免 QA 與 QB 訊號無法同時

到達電流幫浦輸入端的情況,在  $Q_B$  訊號進入電流幫浦之前加入一個傳輸閘,使傳輸閘的延遲時間與反閘的延遲時間相近,來縮短兩端訊號的時間差異;在此電路中電流幫浦的開關為 Mn2、Mp2 而不是 Mn1、Mp1,如此可以減少電壓控制訊號( $V_{ctrl}$ )產生跳躍的現象;而電流源部份則是利用電流鏡方式來完成,藉由電流鏡電路的特性來匹配充電電流與放電電流。

圖3.5 改良後的電流幫浦電路

# 3.2.3 低通濾波器

在此鎖相迴路中我們所使用的是二階低通濾波器,如圖 3.6 所示。由第二章的討論,在此先假設符合下面三個條件:

- (1.) 閉迴路增益函數的常數(  $K=K_{PD}\times K_{VCO}\times K_h/N$  )大於等於四倍的零點頻率  $\omega_2$  時,迴路頻寬(Loop Bandwidth)近似於開迴路的直流增益 K。

- (2.) 取迴路頻寬大小為參考頻率的十分之一。

#### (3.) 零點頻率 ω2 為迴路頻寬的四分之一,極點頻率 ω3 為迴路頻寬的四倍。

圖3.6 二階低通濾波器

在以上條件下,來計算二階低通濾波器的參數值,根據第一個條件:

$$K = \frac{K_{pd} \times K_{VCO} \times K_{h}}{N} = \frac{I_{pd}}{2\pi} \times \frac{K_{VCO} \times K_{h}}{N}$$

(3.1)

其中  $I_{pd}$ 、 $K_{VCO}$ 、N 皆為已知,K 符合第二個條件,故可得低通濾波器的常數為:

$$K_{h} = \frac{2\pi}{I_{pd}} \times \frac{K \times N}{K_{VCO}}$$

(3.2)

而可從二階低通濾波器的轉移函數中推導得常數項為:

$$K_{h} = \frac{C_{2}R_{2}}{C_{1} + C_{2}} \tag{3.3}$$

且零點 ω2 與極點 ω3 的關係為:

$$\omega_3 = \frac{C_1 + C_2}{C_1 C_2 R_2} = \omega_2 \left( 1 + \frac{C_2}{C_1} \right)$$

(3.4)

再根據上述的第三個條件可知  $C_2$  需為  $C_1$  的 15 倍, 帶入(3.3)式後再與(3.2)式做整理,

可推得電阻 R<sub>2</sub>為:

$$K_h = \frac{15C_1R_2}{16C_1} = \frac{2\pi}{I_{pd}} \times \frac{K \times N}{K_{VCO}}$$

$$R_2 = \frac{16}{15} \times \frac{2\pi}{I_{pd}} \times \frac{K \times N}{K_{VCO}}$$

(3.5)

求得電阻  $R_2$ 後,再利用第三個條件即可將電容  $C_2$ 與  $C_1$  求得:

$$\omega_2 = \frac{1}{R_2 C_2} \tag{3.6}$$

$$C_{2} = \frac{1}{\omega_{2}} \times \frac{1}{R_{2}} = \frac{4}{K} \times \left( \frac{15}{16} \times \frac{I_{pd}}{2\pi} \times \frac{K_{VCO}}{K \times N} \right) = \frac{15}{4} \times \frac{I_{pd}}{2\pi} \times \frac{K_{VCO}}{K^{2} \times N}$$

(3.7)

$$C_{1} = \frac{C_{2}}{15} = \frac{1}{4} \times \frac{I_{pd}}{2\pi} \times \frac{K_{VCO}}{K^{2} \times N}$$

(3.8)

迴路頻寬與二階低通濾波各個參數間的關係整理如表 3.1 所示。

| 參考頻率 f <sub>ref</sub> | 10×K                                                                          |

|-----------------------|-------------------------------------------------------------------------------|

| 迴路頻寬 K                | K                                                                             |

| 零點 ω2                 | $\frac{1}{R_2C_2}$                                                            |

| 極點 ω3                 | $\frac{C_1 + C_2}{C_1 C_2 R_2} = \omega_2 (1 + \frac{C_2}{C_1}) = 16\omega_2$ |

| 電容 C <sub>l</sub>     | $\frac{1}{4} \times \frac{I_{pd}}{2\pi} \times \frac{K_{VCO}}{K^2 \times N}$  |

| 電容 C <sub>2</sub>     | $\frac{15}{4} \times \frac{I_{pd}}{2\pi} \times \frac{K_{VCO}}{K^2 \times N}$ |

| 電阻 R <sub>2</sub>     | $\frac{16}{15} \times \frac{2\pi}{I_{pd}} \times \frac{K \times N}{K_{VCO}}$  |

表3.1 迴路頻寬與二階低通濾波器的參數關係

但是,在此所使用的壓控振盪器必須同時符合 GSM 與 WLAN 雙標準系統,因此也必須讓每個 sub-band 上的迴路頻寬與極、零點的關係能符合 2.4.2 章節圖 2.15 所述的規則。而低通濾波器的 R、C 值一旦被選定即無法改變,並且每個 sub-band 的  $K_{VCO}$  值並不相同,因此在選定 R、C 值時則必須考量全部 sub-band 的狀況,即必須使所有 sub-band 的迴路頻寬大於四倍的零點頻率,且小於四分之一倍的極點頻率。然而,由 2.2.4 章節可知,當  $K \geq 4\omega_2$  時迴路頻寬可近似於  $K = K_{PD} \times K_{VCO} \times K_h/N$ ,假設低通濾波器的 R、C 值已選定,此時迴路頻寬將只會受到不同 sub-band 不同的  $K_{VCO}$  或是不同除數 N 的改變而影響,首先利用壓控振盪器找出 $(K_{VCO} \div N)$   $\mid$  min 與 $(K_{VCO} \div N)$   $\mid$  max,即分別對應到低通濾波器固定後迴路頻寬的  $K_{min}$ 與 $K_{max}$ ,然後將零點頻率選擇小於四分之一倍的  $K_{min}$ ,極點頻率選擇大於四倍的  $K_{max}$ ,如圖 3.7 所示,以確保所有狀況下迴路頻寬都符合  $4\omega_2 \leq K \leq \omega_3/4$ 。

圖3.7 多標準系統下的低通濾波器設定

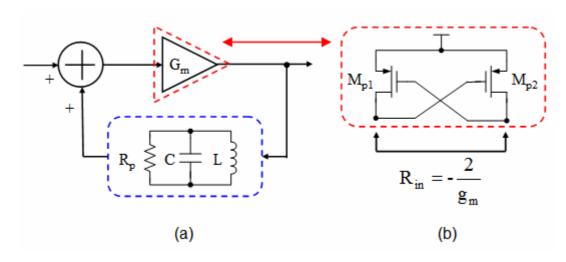

### 3.2.4 壓控振盪器與切換式電感

一般常見的振盪器分為兩類:環形振盪器(ring oscillator)與 LC 諧振(LC-tank)振盪器。環形振盪器的優點是可調頻率範圍(tuning range)較廣,並且本身可產生多相位的輸出,但是卻有較高的相位雜訊,尤其應用在射頻通訊時相位雜訊更是嚴重;LC 諧振振盪器的優點則是較低的相位雜訊,尤其對共模雜訊有很好的抑制能力,並且適合應用在射頻頻率範圍內,缺點是可調的頻率範圍較小,並且被動元件的製程偏移較嚴重。在此將採用 LC 諧振振盪器並進行探討。

圖3.8 (a) 振盪器回授架構;(b) 電晶體交互耦合對

LC 諧振振盪器的基本架構如圖 3.8(a)所示,為一個正回授系統,增益放大器本

身產生 360 度的相位移,而 LC 諧振槽則提供頻率選擇功能,並在達到諧振時如同開路,由外部只看到寄生電阻  $R_p$ ,故為了使迴路可以起振或是持續振盪,增益放大器等效上須為一個負電阻,以抵消並聯諧振電路的電阻性損耗。增益放大器可利用電晶體交互耦合對(cross-coupled pair)來實現,如圖 3.8(b),其中電晶體的汲極(drain)與閘極(gate)的相位差為 180 度,經過交叉耦合之後,在  $M_{p1}$ 與  $M_{p2}$ 電晶體的汲極端的相位差即為 360 度,而此交互耦合對的輸入阻抗為:

$$R_{in} = -\frac{2}{g_{m}} \tag{3.9}$$

其中 gm 為電晶體的轉導增益,當此負電阻 Rin 與諧振的寄生電阻 Rp 並聯:

$$R_{\text{total}} = \frac{R_{\text{in}} \times R_{\text{p}}}{R_{\text{in}} + R_{\text{p}}}$$

(3.10)

因此  $R_{in}$  的絕對值必須小於  $R_p$  以確保整體電阻值為負,使電路持續振盪。 而振盪器的輸出頻率為:

$$f_{\text{out}} = \frac{1}{2\pi\sqrt{LC}} \tag{3.11}$$

由共振槽中的 L 與 C 決定,因此通常會使用切換電容陣列(switched capacitor array)與切換式電感(switched inductor)來增加振盪器的可調頻率範圍,傳統的切換式電感如圖 3.9 所示,由  $L_1$ 、 $L_2$ 、 $L_3$ 、與  $L_4$ 四個電感與一個開關組成,當開關 ON 時,LC 諧振槽中的電感值為  $L=L_1+L_2+L_3+L_4$ ,開關 OFF 時,電感值為  $L=L_1+L_3$ ,故藉由開關的切換可達到不同的輸出頻率。在此我們利用一個新式可切換式差動式電感架構,如圖 3.9(b),只需要一個電感面積再加上 MOS 開關即可達到切換電感的目的,當開關 OFF 時,可得到電感值  $L=L_a+L_b$ ,而當開關 ON 時,內圈的電感  $L_b$ 沒有貢獻,因此電感值  $L=L_a$ ,因此經由適當的設計  $L_a$ 與  $L_b$ 值,此新式電感架構可達到與傳統切換式電感一樣的功能。而此新式電感架構與傳統式切換電感相較下可以節省 50%以上的

面積[25]。

圖3.9 (a) 傳統切換式電感;(b) 新式切換式電感架構

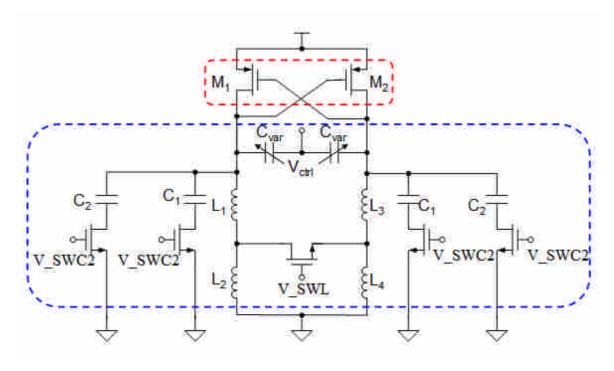

圖 3.10 為壓控振盪器的架構,上半部  $M_1$ 、 $M_2$  電晶體為交互耦合對,即負電阻產生器,下半部為 LC 諧振槽,其中有三個種方法可改變輸出頻率:(1)切換切換式電感的開關。(2)切換切換式電容陣列的開關,有兩種電容值  $C_1$  與  $C_2$ ,因此可產生四種組合。(3)由低通濾波器送來的電壓控制訊號  $V_{ctrl}$  控制可變電容(Varactor)  $C_{var}$ 。其中第一種與第二種方式是對頻率作粗調(coarse tuning),切換式電感可作較大的頻率改變,而切換式電容陣列則可用來選擇頻帶,而第三種是作微調(fine tuning)動作,使輸出最終穩定在所要的頻率上。然而振盪器輸出波形的 DC 準位通常不會在 Vdd/2,並且輸出振幅很小,為了避免讓下級電路無法正確判斷波形,因此在振盪器的輸出端會加上一級前置緩衝放大器(pre-Amplifier)來修正輸出直流準位並放大振幅,架構如圖 3.11 所示,其中利用電阻 R 的米勒效應(Miller effect)來增加放大倍率。

圖3.10 壓控振盪器架構

圖3.11 前置緩衝放大器

# 3.2.5 除頻器

整數型除頻器的架構如圖 3.12 所示,其中需要一個雙模數預除器(two modulus

prescaler)與兩個可程式計數器(programmable counter),因此可得到除頻器的總除數值 為  $N_{total}$ = $P \times N + S$ ,而頻道解析度即為參考頻率大小。

圖3.12 整數型除頻器架構區塊圖

因此輸出頻率為  $f_{out}=(P\times N+S)\times f_{in}=N_{total}\times f_{in}$ ,其中 N 需大於 S,在此應用的頻率範圍有  $1.71\sim1.88$  GHz 與  $2.40\sim2.48$  GHz,其中參考頻率為 10 MHz,因此整體除數值  $(P\times N+S)$ 至少需涵蓋  $171\sim188$  與  $240\sim248$ ,而  $P\cdot N$  與 S 的決定步驟為: (1) 首先大約選取一個 P 值,在此使用 P=8。 (2) 利用  $N_{total}$  的最小值來決定出 S 的最大上限,在此  $N_{total}$  的最小值為 171,故可得到  $P=8\cdot N=21\cdot S=3$ ,因此 21 也是為 N 的最小值,又由於 N 比需大於 S 的先決條件,所以 S 的最大值必須小於等於 21。 (3) 檢查所有除數間是否有縫隙,而為了確保無縫隙存在,S 的最大值必須大於等於 (P-1)。如此可決定出  $P\cdot N$  與 S 的值。

#### (a) 雙模數預除器

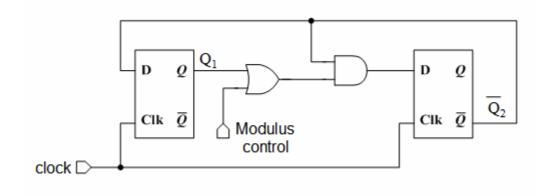

雙模數預除器中必須有一個模數控制訊號,才能控制在除數 P 與(P+1)間切換, 圖 3.13 為一個 P=2 的雙模數預除器,當模數控制訊號為低準位時,預除器執行除三 的動作,當模數控制訊號為高準位時,或閘(OR gate)如同開路,及閘(AND gate)如同 短路,此時為除二的功能,圖 3.14 為其時序圖。

圖3.13 雙模數預除器-2/3

圖3.14 雙模數預除器-2/3 時序圖

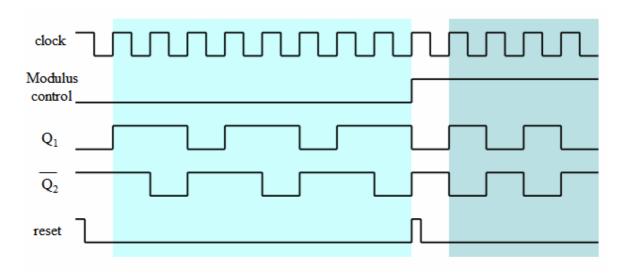

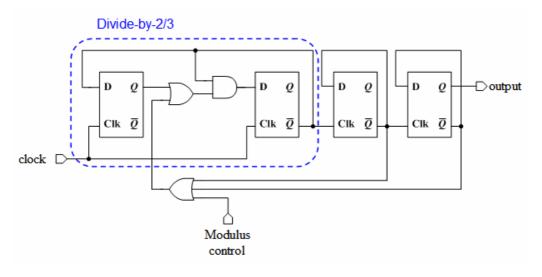

時序圖的前半部模數控制訊號在低準位,將輸入訊號除三,後半部則模數控制訊 號為高準位,將輸入訊號除二。當在雙模數預除器 2/3 的後面再串接一個除二電路時, P值變成 4,為雙模數預除器 4/5;而在雙模數預除器 2/3 的後面再串接兩個除二電路 時,P值變成 8,為雙模數預除器 8/9,電路架構如圖 3.15 所示:

圖3.15 雙模數預除器-8/9

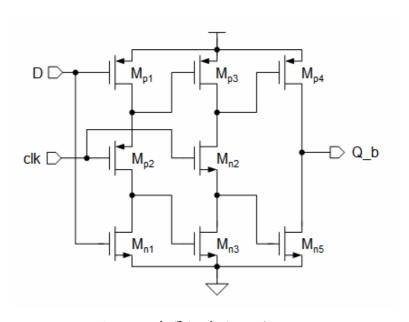

然而,預除器為除頻器中的第一級電路,直接接收來自於壓控振盪器的 GHz 級的輸出訊號,因此在設計預除器的挑戰在於內部的正反器,必須使用能夠操作在高頻的電路架構,因此利用如圖 3.16 真單相時脈(true single-phase clock, TSPC)電路,clk 訊號輸入到電晶體  $M_{p2}$  與  $M_{n2}$ ,用此兩個電晶體來控制訊號 D 是否被送至輸出端,只有當 clk 由低準位上升至高準位的瞬間,輸入訊號 D 才會被輸出,並且被保持直到下一個 clk 訊號觸發,因此可以視為一個正緣觸發(positive-edge trigger)的 D 型正反器,並且只需要 8 個電晶體即可完成。

圖3.16 真單相時脈 D型正反器

然而在校正時為了使除頻器能具有重置(reset)功能,因此在雙模數預除器 2/3 之後的兩級正反器使用靜態邏輯的正反器來實現,在此應用的最高頻率經除 2/3 後,靜態邏輯正反器已可正常運作。

#### (b) 可程式計數器

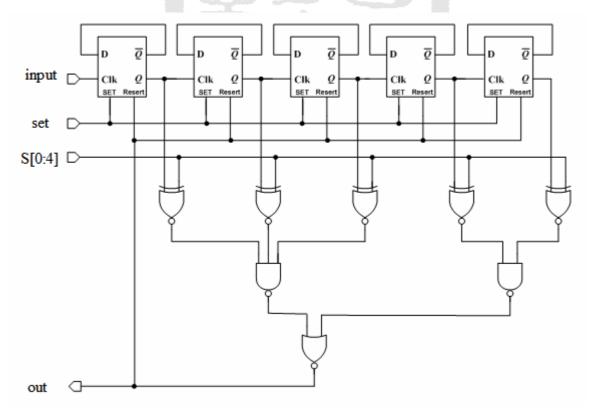

由上敘述可知,可程式計數器 /S 的最大值為 21,而  $N_{total}$  的最大值為 248,因此可程式計數器 /N 的最大值為 31,故這兩個可程式計數器至少都需要 5 個 bits 以上,如圖 3.17。可程式計數器的輸入端來自於預除器的輸出,而壓控振盪器的輸出訊號經過預除器之後,已經從 GHz 級降到 MHz 級,因此可程式計數器中的 D 型正反器可使用傳統靜態邏輯(staric logic)的正反器架構即可完成。而可程式計數器是利用外部輸入控制訊號 S[0:4]來決定計數器的值,輸入訊號經過一連串的除二電路,當每個 bit 訊號皆與控制訊號 S[0:4]相同時,拉起輸出訊號並且對 D 型正反器重置(reset)。

圖3.17 5-bits 的可程式計數器

將兩個可程式計數器與預除器如圖 3.12 組合在一起,再利用門閂(latch)電路與一些邏輯閘來產生預除器的模數控制訊號(modulus control signal),即可完成除頻器架構,由改變兩個可程式計數器的控制訊號來得到所要的除數值。

# 3.3 自我頻率校正電路

### 3.3.1 簡介

為了避免製程變異的偏移而縮小可調頻率範圍,因此需要一個自我頻率校正電路 (Self-Frequency-Calibration circuit)將頻帶作修正。而一般的自我校正電路可分為開迴路與閉迴路兩類。

#### (a) 閉迴路自我頻率校正迴路

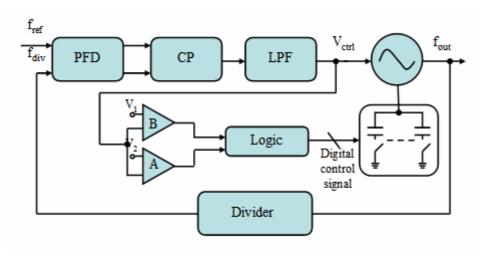

圖3.18 閉迴路的自我頻率校正架構

如圖 3.18 所示,在此電路架構中,當進行校正時鎖相迴路系統仍維持閉迴路狀態 [28],此架構是先讓鎖相迴路進行頻率鎖定,當達到穩態後可以得到一個穩定的電壓控制訊號  $V_{ctrl}$ ,將此電壓送至校正迴路中的比較器,與預設的參考電壓  $V_1$  與  $V_2$  比較,如果此時的  $V_{ctrl}$  值不在預設的  $V_1$  與  $V_2$  範圍內,即代表因製程變異使原本預設的

頻帶偏移,振盪器的輸出不在預定的操作頻率上,並且偏移超過特定的頻率範圍,而觸發了比較器的輸出,因此再利用邏輯電路(Logic)將比較結果產生數位控制訊號來切換振盪器中校正用的電容陣列開關,使振盪器選擇至另一個新的操作頻帶上,然後由鎖相迴路再進行一次頻率鎖定,將重新鎖定後得到的電壓控制訊號  $V_{\text{ctrl}}$  送至比較器作比較,直到  $V_{\text{ctrl}}$  的值介於參考電壓  $V_{1}$  與  $V_{2}$  的範圍內,此時邏輯電路(Logic)產生的數位控制訊號為最終需要為修正製程偏移而改變的電容值,自我頻率校正完成。然而,每當  $V_{\text{ctrl}}$  不在預定的範圍內,則需在改變電容陣列開關後,等待鎖相迴路將頻率鎖定後得到新的  $V_{\text{ctrl}}$  值才能進行下一次比較,因此閉迴路的自我頻率校正方式將會花費很長的校正時間。

#### (b) 開迴路自我頻率校正迴路

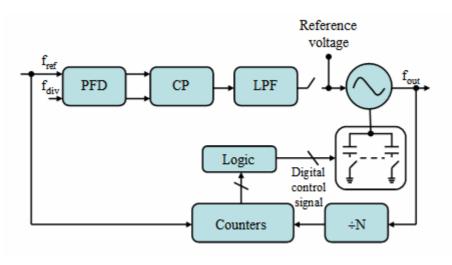

圖3.19 開迴路的自我頻率校正架構

圖 3.19 為一般常見的開迴路式自我頻率校正方式[29],當進行校正時鎖相迴路由低通濾波器(LPF)被斷開成開迴路狀態,並且壓控振盪器的輸入端被接至一個參考電壓(reference voltage),一般為 Vdd/2,此架構將參考頻率 fref 與振盪器輸出除 N 後的頻率 fout/N 送至一個計數器(counter)中,直到其中一個訊號先溢位(overflow)時,表示此訊號頻率較高,周期較短,比較快計數結束,因此再利用邏輯電路(Logic)輸出數位控制訊號,適當的調整電容陣列開關來修正操作頻帶,如此重複校正直到兩頻率間的誤差小於一定範圍內,自我頻率校正完成。然而,兩頻率的起始相位無法確定是否同相,

為了避免可能因此而產生的錯誤,故計數器的計數周期要設計的夠多,所以此開迴路方式的校正時間亦無法做到很短。

### 3.3.2 自我頻率校正迴路

圖3.20 自我頻率校正電路方塊圖

圖 3.20 為我們所設計的自我頻率校正電路架構,也是屬於開迴路式的校正迴路,當進行校正動作時,鎖相迴路由低通濾波器(LPF)的輸出端斷開為開迴路,並且壓控振盪器的電壓控制訊號端接至一個參考電壓( $V_{ref}$ ),同時將相位檢測器(PFD)的輸出端切換至自我頻率校正迴路,校正迴路中的電容  $C_C$  在相位檢測器尚未有輸出之前先預充至電壓  $V_{pre}$ ,而除頻器的除數設在預定值  $N_C$ ,並且除頻器設計有重置(reset)訊號來控制除頻器的輸出,參考頻率  $f_{ref}$  部份則有一個延遲電路,將此延遲時間長短設計與除頻器內部的延遲時間相同,如此利用除頻器的重置訊號與控制訊號的配合下,使相位檢測器兩端的輸入起始相位相同,因此藉由同相位的兩輸入頻率在相位檢測器得到的相位誤差結果,使校正迴路中電流幫浦( $Calib\_CP$ )對電容  $C_C$  進行充放電,若製程變異造成偏移夠大時,相位檢測器得到的相位誤差將會使電容  $C_C$  上的壓降  $V_C$  可以充電

或放電至觸發比較器(comparator),再由比較結果經邏輯電路(Logic circuit)而產生數位控制訊號[ $SW_{CcalibN}$ ..., $SW_{Ccalib2}$ ,  $SW_{Ccalib1}$ ]給電容陣列開關,適當的調整 LC 諧振槽中的電容值來修正操作頻帶,如此重複比較直到  $V_{C}$  電壓落在兩比較器的參考電壓範圍內,表示已選擇到適合的電容陣值,將操作頻帶修正回預定頻率範圍上,故自我頻率校正完成。

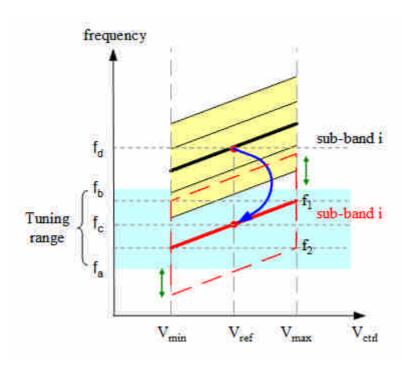

圖3.21 校正因製程引起的頻帶偏移

利用輸出頻率對電壓控制訊號曲線(frequency- $V_{ctrl}$ )來說明,如圖 3.21 所示, $f_a$  到  $f_b$  為操作頻率範圍,紅色虛線的區域為不考慮製程變異影響時振盪器的輸出範圍,粗紅色線條為其中的 sub-band i ,並且在 sub-band i 上,當除頻器的除數值設為  $N_C$  時,可得到鎖相迴路穩定時的電壓控制訊號為  $V_{ref}$ ,且振盪器的輸出頻率為  $f_c$ ,此外,當電壓控制訊號為  $V_{max}$  對應的輸出頻率為  $f_1$ ,電壓為  $V_{min}$  時對應的輸出頻率為  $f_2$ 。在 sub-band i 上,若經由適當的設計校正迴路的電流幫浦(Calib\_CP)與電容  $C_C$ ,當振盪器輸出頻率為  $f_1$  且除數為  $N_C$  時,相位檢測器的輸出誤差量可以使  $V_C$  電壓由  $V_{pre}$  放電至  $V_{min}$ ,並剛好觸發比較器 A;反之,在振盪器輸出頻率為  $f_2$  且除數為  $N_C$  時,相位檢測器的輸出誤差量可以使  $V_C$  電壓由  $V_{pre}$  充電至  $V_{max}$ ,並剛好觸發比較器  $P_{max}$  。而當觸發比較器  $P_{max}$  時,代表目前振盪器的輸出頻率太快,需要放電來緩慢輸出頻率,

因此要往低頻帶作切換;當觸發比較器 B 時,代表目前振盪器的輸出頻率太慢,需要充電來加快輸出頻率,因此要往高頻帶作切換。

現在來考慮製程變異的影響,假設振盪器的輸出頻率因製程變異而往高頻處偏移,如圖 3.21 中的米黃色區域,此時 sub-band i 偏移至粗黑色線條上,此偏移量造成振盪器輸出不能完全覆蓋操作頻率  $f_a \sim f_b$ ,因此必須藉由自我頻率校正電路來增加 LC 諧振槽中的電容值使振盪器的輸出頻率往低頻處修正。當電路進入自我校正頻率階段時,將利用先前不考慮製程偏移時得到的  $V_{ref}$  直接輸入給壓控振盪器,且固定在 sub-band i 上,除頻器的除數值設為  $N_C$ ,當無製程偏移或是偏移量很小時,相位檢測器輸出的相位差不大,電壓  $V_C$  將不會觸發比較器 A 或 B ,因此不需要做修正;當偏移量很大如米黃色區域,輸入  $V_{ref}$  對應到的輸出頻率為  $f_d$ ,而頻率  $f_d$  遠大於  $f_1$ ,因此  $V_C$  電壓將會被大量放電而觸發比較器 B ,並得到一組新的  $[SW_{CalibN}...,SW_{Calib2}$ , $SW_{Calib1}]$ 控制訊號,使 LC 諧振槽中的電容值變大,降低振盪器的輸出頻率,如此持續校正直到電壓  $V_C$  不會觸發比較器 A 與 B ,然後維持最終的  $[SW_{CalibN}...,SW_{Calib2}$ , $SW_{Calib1}]$ 數位控制訊號,並利用迴路中控制訊號將鎖相迴路切回閉迴路狀態,自我頻率校正完成並關閉。

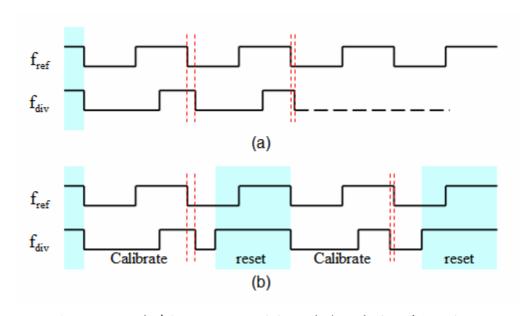

圖3.22 校正頻率時的頻帶跳躍方式

因此,若經過適當的設計,完成一次頻率校正動作的時間約略大於參考頻率的一個周期,若振盪器設計有 N 個 bits 來做校正動作,則校正用的電容陣列可產生  $2^N$  個 sub-band,若設定起始值從第  $2^{N-1}$  個 sub-band 開始往上或往下校正,則最多只需要校正  $2^{N-1}$  次即可修正回操作頻帶範圍,如圖 3.22 所示,因此只需要 $(2^{N-1})$  × $T_{ref}$  的校正時間即可完成,但實際上,在第二次的校正周期時,除頻器輸出的訊號並沒有與參考訊號同相位產生,因此比較出來的相位誤差是錯誤的,如圖 3.23(a),若沒做重置動作使相位相同,則在第二個周期時,除頻器的輸出周期原本應該變短,但仍出現參考訊號的負緣領先除頻器輸出的負緣的情況,使原本應是對電容  $C_C$  放電,卻誤判而持續充電。因此,將設計當每做完一次校正周期之後,隨即將除頻器端的輸出訊號重置,並等待一個參考訊號週期,在第三個參考訊號周期時同相位輸出給相位檢測器,如圖 3.23(b)所示,因此執行一次校正動作包含了一個校正周期與一個重置周期,如此才能確實的對電容  $C_C$  執行充放電動作,故自我頻率校正最多則是需要花費 $[(2^{N-1})+1]$  ×  $(2\times T_{ref})$  的時間,其中 $(2\times T_{ref})$ 的2 是因為一個周期拿來做重置使用,而加 1 則是利用多一次校正來確保  $V_C$  已不會觸發比較器 A 與 B ,校正到操作頻率的範圍內。

圖3.23 (a) 連續校正; (b) 一次校正後隨即重置,確保同相位

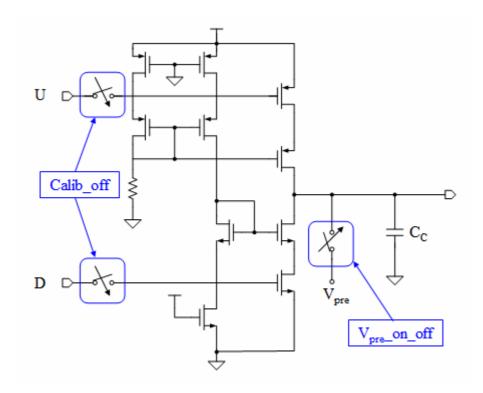

### 3.3.3 校正迴路的電流幫浦與充放電電容

圖 3.24 為自我頻率校正電路中的電流幫浦(Calib\_CP)電路架構與充放電電容  $C_C$ ,而電流幫浦的架構與鎖相迴路中的相同,只是分別在反閘與傳輸閘的輸出接上一個開關,以便在校正結束後關閉校正迴路,以減少功率損耗。此外,在相位檢測器有相位誤差輸出之前,電容  $C_C$  必須先預充至電壓  $V_{pre}$ ,因此在  $V_{pre}$  電壓源處也需要一個開關來控制預充的時刻,只要再經過適當的調整電流幫浦的電晶體大小與  $C_C$  電容值的選擇,在除數值設為  $N_C$  時,當振盪器輸出頻率在  $f_1$ (圖 3.21),相位檢測器檢測出來的相位誤差可使此電流幫浦的充放電電流將電容  $C_C$  上的電壓放電至  $V_{min}$ ;反之,振盪器輸出頻率為  $f_2$  時,相位檢測器檢測出來的相位誤差可使電流幫浦將電容  $C_C$ 上的電壓充電至  $V_{max}$ ,再將此電壓送給比較器作比較。

圖3.24 校正迴路的電流幫浦與電容 Cc

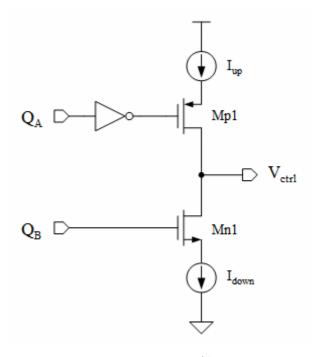

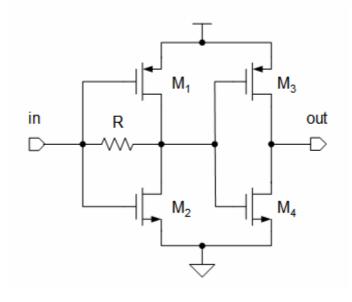

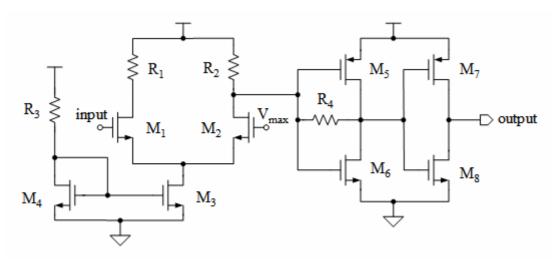

#### 3.3.4 比較器與邏輯電路

參考電壓為  $V_{max}$  的比較器架構是採用如圖 3.25 方式來實現,其中電晶體  $M_1$ 、  $M_2$  與電阻  $R_1$ 、  $R_2$  形成差動對,電晶體  $M_3$ 、  $M_4$  與電阻  $R_3$  為電流鏡, $M_3$  作為差動對的電流源,並將差動對電晶體  $M_2$  的汲極(drain)端拉為比較輸出,隨後接上一個前置放大器(pre-Amplifier)將輸出直流準位調至 Vdd/2 並且放大輸出振幅。而參考電壓為 $V_{min}$  的比較器架構,由於  $V_{min}$  電壓值通常較小,若使用 nMOS 的電流鏡架構,可能造成差動對的電晶體  $M_1$ 、  $M_2$  無法正常操作在飽和區,因此需將圖 3.25 的 nMOS 電流鏡部分改用 pMOS 的電流鏡,即可完成  $V_{min}$  的比較器電路。並設計當輸入電壓比參考電壓  $V_{max}$  或  $V_{min}$  大時,輸出結果為高準位;比參考電壓  $V_{max}$  或  $V_{min}$  小時,輸出為低準位。

圖3.25 V<sub>max</sub> 比較器

假設  $V_{max}$  比較器的輸出為  $S_1$ , $V_{min}$  比較器的輸出為  $S_0$ ,當比較器的輸出結果為  $(S_1,S_0)=(0,1)$ 時,則表示電容  $C_C$  上的電壓  $V_C$  介於  $V_{max}$  與  $V_{min}$  之間;若輸出結果為  $(S_1,S_0)=(0,0)$ 時,則表示電壓  $V_C$  小於  $V_{min}$ ,也代表目前振盪器的輸出頻率往高頻偏移,因此必須往較低頻的頻帶修正;若輸出結果為 $(S_1,S_0)=(1,1)$ 時,則表示電壓  $V_C$  大於  $V_{max}$ ,也代表目前振盪器的輸出頻率往低頻偏移,因此必須往較高頻的頻帶修正;而輸出結果不會有 $(S_1,S_0)=(1,0)$ 的狀況產生。

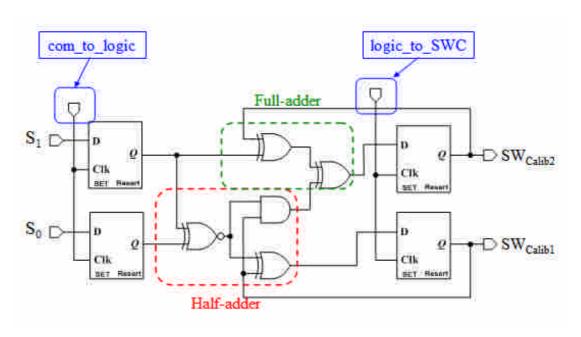

假設壓控振盪器有 N-bits 的電容陣列來給校正製程變異使用,電容值由大至小為  $C_{CalibN}$ ,... $C_{Calib2}$ , $C_{Calib1}$ , 此電容陣列的控制訊號為 $[SW_{CalibN}...,SW_{Calib2}]$ , 即  $C_{CalibN}$  的控制訊號  $SW_{CalibN}$  為 MSB, $C_{Calib1}$  的控制訊號  $SW_{Calib1}$  為 LSB,因此當比較器判斷出要往上或往下切換一個 sub-band 時,只要將陣列開關的控制訊號減 1或加 1 即可,因此圖 3.20 中的邏輯電路(Logic circuit)即利用全加器與半加器的組合與簡單的邏輯閘即可完成。如果振盪器有 2-bits 的電容陣列是來做製程變異的修正,其中  $C_1$  的電容值大於  $C_0$ ,則邏輯電路可如圖 3.26 所示,其中 4 個正反器是用來控制比較器輸出訊號進入的時間與邏輯電路輸出的時間,並且可以利用輸出端的兩個正反器來設定 $[SW_{CalibN}...,SW_{Calib2},SW_{Calib1}]$ 訊號進入自我頻率校正時的初始值,即設定校正之前預設的初始值頻帶。

圖3.26 邏輯電路

#### 3.3.5 控制訊號

在此電路架構中很多地方需要控制訊號,使訊號可以在適當的時候輸入與輸出, 其中有5個比較重要的控制訊號分別為:

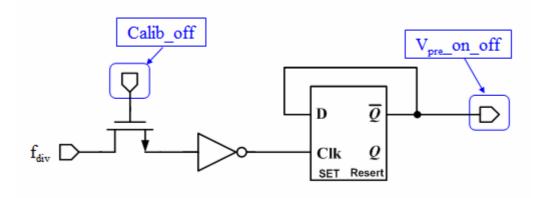

$V_{pre\_on\_off}$ :控制校正迴路中 $V_{pre}$ 的預充電時間。在校正周期的一開始與重置周

期對電容  $C_C$  預充至電壓  $V_{pre}$ , 並在比較誤差結果出來之前,將預充電壓關閉,交由校正迴路的電流幫浦依相位誤差大小對電容  $C_C$  進行充放電,電路架構如圖 3.27 所示,利用除頻器的輸出訊號反向後除二得到,並在自我頻率校正結束後關閉。

圖3.27 V<sub>pre\_on\_off</sub> 控制訊號的電路架構

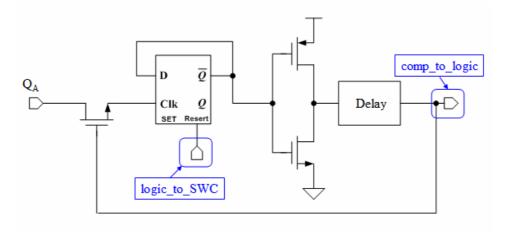

comp\_to\_logic:在相位誤差一結束後,對此時的比較器輸出結果取樣給邏輯電路(logic circuit)。故此訊號應比相檢測器輸出訊號的負緣還要晚一個延遲時間,而此延遲時間即為由校正迴路到比較器輸出的時間,且兩個周期作一次取樣(校正周期+重置周期),因此電路架構如圖 3.28 所示,其中由於延遲電路(delay)我們是利用一個電容器使訊號達到延遲效果,為了對此電容進行充放電,因此延遲電路的訊號是來自於反閘而不是正反器的Q輸出端,利用反閘對電容進行充放電。將 comp\_to\_logic 訊號輸入給圖 3.26中前面兩個正反器的 clk 作觸發,使比較結果輸入給邏輯電路。

圖3.28 comp\_to\_logic 控制訊號的電路架構

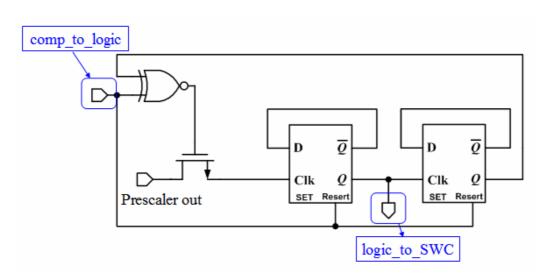

logic\_to\_SWC:控制[SW<sub>CcalibN</sub>...,SW<sub>Ccalib2</sub>, SW<sub>Ccalib1</sub>]訊號輸出給電容陣列開關的時間。利用 logic\_to\_SWC 訊號輸入給圖 3.26 中輸出端的兩個正反器的 clk 作觸發來控制,並在自我頻率校正結束後,此訊號不會再有輸出,因此即可利用圖 3.26 中的正反器在校正結束後無 clk 觸發而維持校正結果,使[SW<sub>CcalibN</sub>...,SW<sub>Ccalib2</sub>, SW<sub>Ccalib1</sub>]訊號不會因為邏輯電路內部或電容 C<sub>C</sub>上的漏電而改變,電路如圖 3.29 所示,在比較器輸入給邏輯電路後,利用計數器數預除器輸出周期數個之後將訊號拉起。

圖3.29 logic\_to\_SWC 控制訊號的電路架構

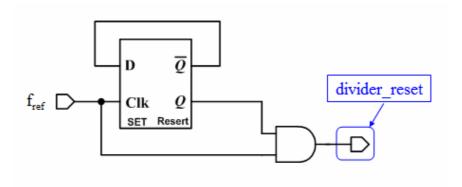

divider\_reset:在執行一次校正後,為了能使參考訊號與除頻器輸出訊號同相位

輸入給相位檢測器,則需在重置周期時將除頻器作重置(reset)動作,首先 將未經過延遲電路的參考訊號輸入給圖 3.30 的架構,產生 divider\_reset 訊號對除頻器做重置,而相位檢測器輸入端的參考訊號則是經由延遲電 路後的輸出如圖 3.20,因此可使參考訊號經延遲時間後與除頻器輸出同 相位產生。而此控制訊號的電路架構如圖 3.30 所示,即是取參考訊號端 的偶數周期出來給除頻器做重置使用。

圖3.30 divider reset 控制訊號的電路架構

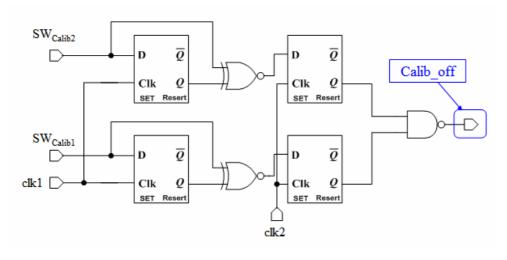

$Calib\_off$ : 此控制訊號使自我頻率校正結束後將電路切換回鎖相迴路系統。電路架構如圖 3.31,利用正反器與 clk1 來判斷在每次校正周期後電容陣列開關的控訊號是否有變動,如果有改變則繼續執行下一個校正周期,若訊號相同沒有改變,則表示  $V_C$  電壓未觸發比較器的  $V_{max}$  與  $V_{min}$ ,已經修正回操作頻率範圍內,故此時可將校正迴路關閉,並開啟鎖相迴路。

圖3.31 Calib\_off 控制訊號的電路架構

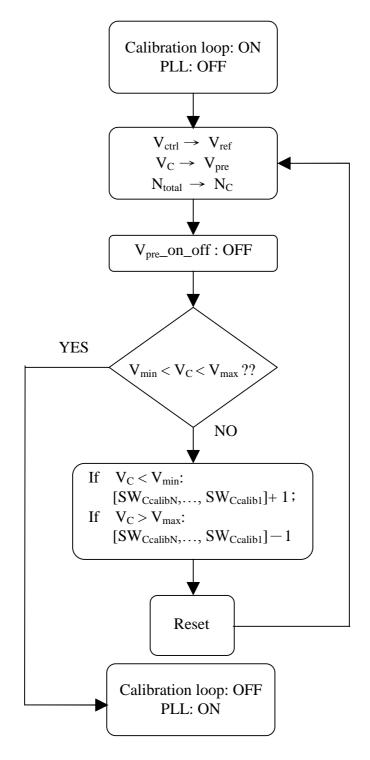

### 3.3.6 校正迴路的操作流程

圖 3.32 為我們設計的自我頻率校正電路的操作流程圖:

圖3.32 自我頻率校正操作流程

## 第4章 模擬結果

# 4.1 簡介

為了驗證前述的電路架構,在此我們利用 SpectreRF 的軟體來進行模擬,而模擬結果主要分為兩大部份:第一部份為鎖相迴路部份,首先個別模擬每個子電路,然後將所有子電路組合成鎖相迴路進行模擬,並評估其效能;而第二部份則著重在自我頻率校正電路上,也是先個別驗證每個子電路的功能,然後針對校正狀態下進行模擬,最終再與鎖相迴路組合起來一起模擬,並評估整體電路的效能與校正迴路加入後對鎖相迴路系統的影響。

#### 4.2 鎖相迴路

#### 4.2.1 相位檢測器

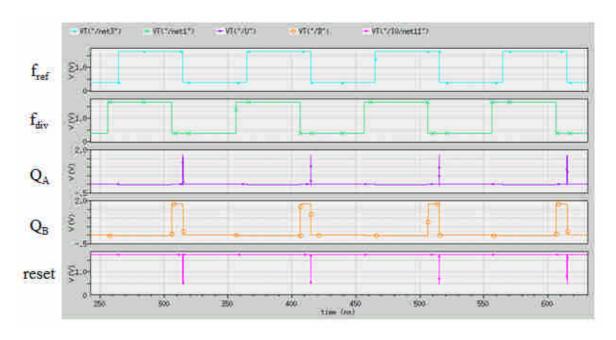

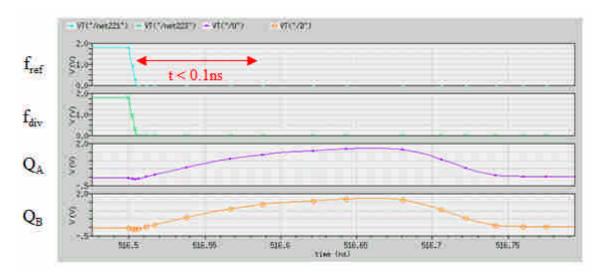

電路架構如圖 3.3 所示,此電路是一個負緣觸發的預充型相位檢測器(Precharge Type PFD),因此在訊號由高準位降至低準位之前,輸出訊號  $Q_A$ 與  $Q_B$  皆不會被觸發而維持在低準位狀態,圖 4.1 為參考訊號端的相位領先除頻器輸出端,因此將會先遇到參考訊號端訊號的負緣,此時  $Q_A$  拉起為高準位,而  $Q_B$  仍處在低準位,直到除頻器輸出訊號也由高準位降至低準位, $Q_B$  訊號才會拉起,而  $Q_B$  訊號拉起瞬間,由於  $Q_A$ 與  $Q_B$  皆在高準位狀態,因此觸發了反及閘(NAND gate),使原本一直處在高準位的重置訊號(reset)隨之降至低準位,並將輸出  $Q_A$ 與  $Q_B$ 降回低準位,而  $Q_A$ 與  $Q_B$ 處在高準位的時間差與參考訊號、除頻器輸出訊號的相位誤差成正比。而圖 4.2 為參考訊號端的相位落後除頻器的輸出端。

圖4.1 參考訊號相位領先除頻器輸出

圖4.2 參考訊號相位落後除頻器輸出

而相位檢測器除了能檢測出兩輸入相位誤差之外,在 2.3.1 章節中提到,當參考 訊號與除頻器輸出兩者頻率相差很大時,則必須要產生一個與相位差成正比的直流電 壓給壓控振盪器。如圖 4.3 與圖 4.4 所示,當兩輸入的頻率相差甚大時,相位檢測器 的其中一端輸出會長時間拉起,使電流幫浦進行大量的充放電動作,將電壓控制訊號  $V_{ctrl}$  充放電至一直流電壓,直到兩者頻率相近時才進行相位比較。

圖4.3 參考訊號頻率比除頻器輸出慢

圖4.4 参考訊號頻率比除頻器輸出快

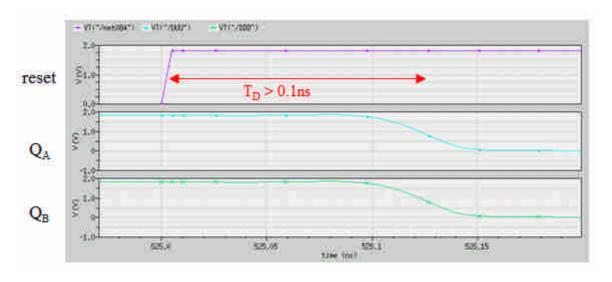

接下來討論非理想狀況,在2.3.4章節中曾探討過的死區(Dead zone)問題,簡單

來說,假設從相位檢測器的兩輸出端同時拉起後,經反及閘(NAND gate)重置相位檢測器直到輸出被拉回低準位的延遲時間為  $T_D$ ,而相位檢測器的輸出端要拉起為高準位時,輸出端充電至可驅動下級電路的輸入臨界電壓所需的時間為 t,若要消除死區問題,則必須使  $T_D > t$ ,使同相位輸入時,輸出的脈波夠寬,可以使輸出端的電壓拉昇至下級的臨界電壓。而圖 4.5 為相位檢測器內部的延遲時間  $T_D$ 模擬,由波形可看出延遲時間  $T_D$ 大於 0.1 ns,而圖 4.6 為模擬相位檢測器的輸出拉昇至下級電路的輸入臨界電壓所需要的時間,由波形得知充電時間 t 小於 0.1 ns,因此此相位檢測器在輸入為同相位時,輸出的脈波寬度夠寬,使輸出電壓有足夠的時間作預充的動作,因此死區問題可以被消除。圖 4.7,當兩輸入端無相位差時,輸出  $Q_A$ 與  $Q_B$ 仍會拉起但隨即降回低準位,而此時的輸出電壓已被充電超過下級輸入的臨界電壓值。

圖4.5 相位檢測器內部的延遲時間 T<sub>D</sub>

圖4.6 相位檢測器輸出充電至下級電路的輸入臨界電壓所需要的時間 t

圖4.7 無相位差時的輸出脈波

## 4.2.2 電流幫浦與低通濾波器

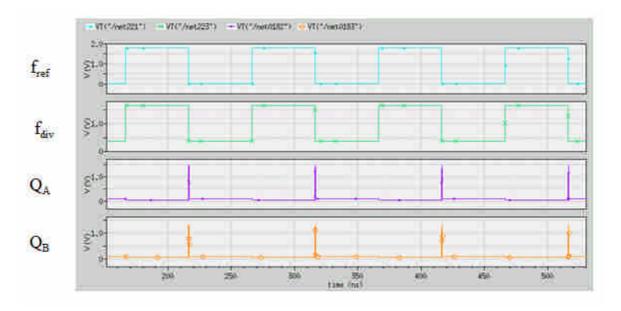

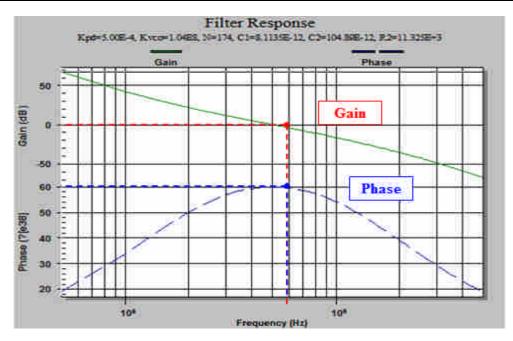

參照圖 3.5 與圖 3.6 為電流幫浦與二階低通濾波器的架構。設計電流幫浦的充放電電流皆為 0.5 mA,迴路頻寬為 500 KHz,並以 3.2.3 章節中提到的方式來設計,則可得到二階低通濾波器的波德圖(Bode diagram)如圖 4.8 所示:

圖4.8 低通濾波器的波德圖

波德圖中上面的曲線為增益曲線,下面則為相位曲線,增益曲線在頻率為 500 KHz 時交於 0 dB 的橫軸上,此時的相位邊緣(Phase Margin)為 60 度。

圖4.9 無相位差時電流幫浦的充放電電流

為了減少電流幫浦產生的相位雜訊,則必須盡量使充放電電流匹配,以避免當輸

入訊號同相位時,因充放電電流的不相等而產生電壓控制訊號  $V_{ctrl}$  的偏移,造成振盪器輸出端的相位雜訊。圖 4.9 為輸入訊號同相位時的充電電流  $i_{up}$  與放電電流  $i_{down}$  模擬,由於兩電流值相近約為 0.5 mA,因此,當無相位差時對電壓控制訊號  $V_{ctrl}$  影響較小。圖 4.10 為參考訊號相位領先時,電流幫浦對低通濾波器充電,來提昇壓控振盪器的輸出頻率,圖 4.11 為參考訊號相位落後時,電流幫浦對低通濾波器放電,來降低壓控振盪器的輸出頻率。

圖4.10 參考訊號端相位領先電流幫浦對低通濾波器充電

圖4.11 參考訊號端相位落後電流幫浦對低通濾波器放電

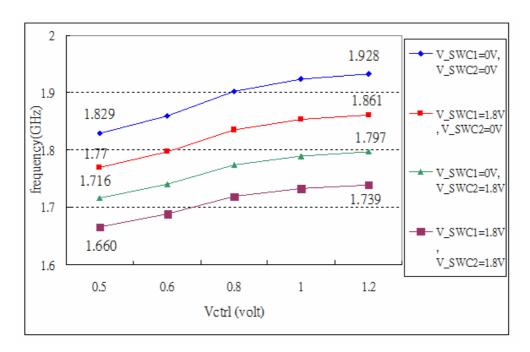

### 4.2.3 壓控振盪器

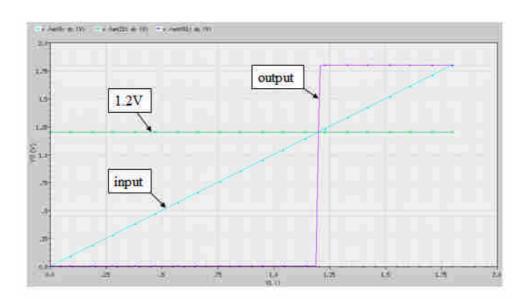

圖 4.12 為切換式電感壓控振盪器在 GSM 系統時的可調頻寬(tuning range),當電壓控制訊號  $V_{ctrl}$  的範圍由 0.5 V 到 1.2 V,輸出頻率可由 1.66 GHz 到 1.982 GHz,可調頻寬為 322 MHz。

圖4.12 GSM 系統下的可調頻寬

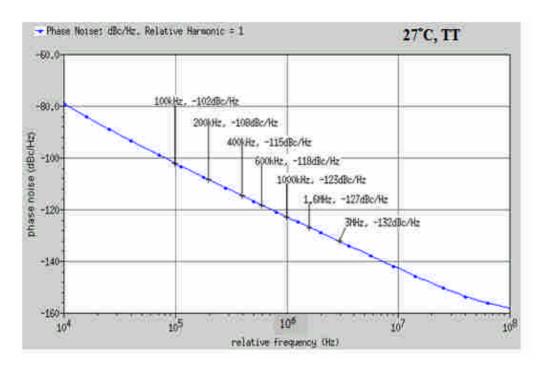

在 GSM 系統下壓控振盪器的相位雜訊如圖 4.13 所示,偏移中心頻率 1 MHz 的相位雜為-123 dBc/Hz。

圖4.13 GSM 系統下的相位雜訊

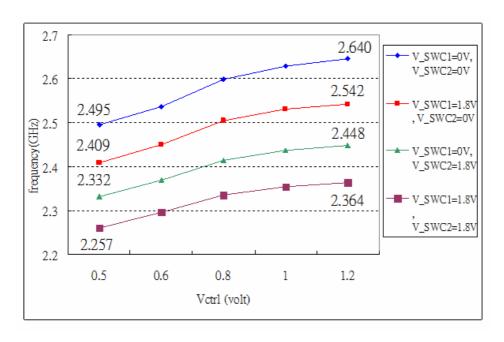

圖 4.14 為切換式電感壓控振盪器在 WLAN 系統時的可調頻寬,電壓控制訊號由 0.5 V 到 1.2 V,輸出頻率可由 2.257 GHz 到 2.640 GHz,可調頻寬為 383 MHz。

圖4.14 WLAN系統下的可調頻寬

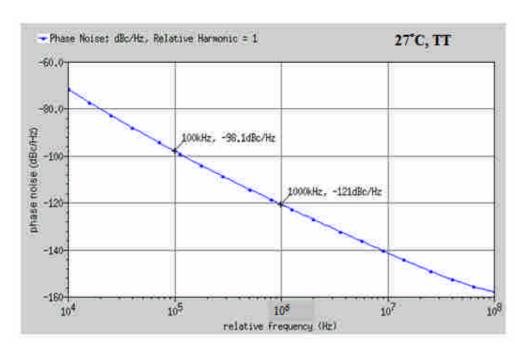

在 WLAN 系統下壓控振盪器的相位雜訊如圖 4.15 所示,偏移中心頻率 1 MHz 的相位雜為-121 dBc/Hz。

圖4.15 WLAN系統下的相位雜訊

### 4.2.4 除頻器

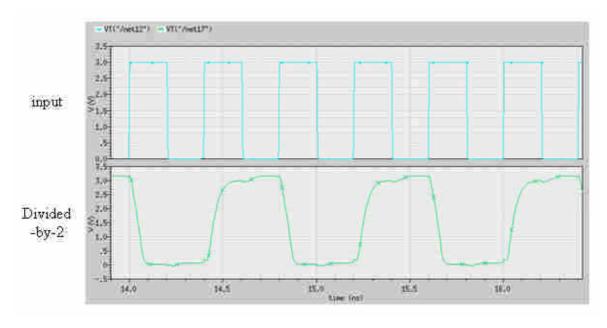

為了能承受振盪器的高頻輸出訊號,需使用雙模數(dual-modulus)除 8/9 預除器 (prescaler)先將頻率除至較低的頻率上,再交給可程式計數器(programmable counter) 來作除數的選擇,因此預除器中的正反器則必須使用能操作在 GHz 級的真單相時脈 (TSPC) D型正反器如圖 3.16。而圖 4.16 是將 TSPC 正反器接成除二電路的輸入與輸出波形,而此時的輸入頻率為 2.5 GHz,由輸出波形可得知 TSPC 正反器能正確的將高頻訊號除二。

圖4.16 真單相時脈 D 型正反器的除二電路

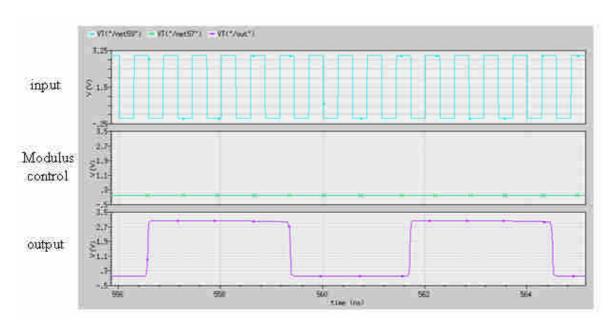

因此利用 TSPC D 型正反器來組合成雙模數除 8/9 的預除器架構,可得波形如圖 4.17,而為了在高頻操作預除器使用 3 V 的直流供應電壓源。當模數控制訊號(modulus control signal)在低準位時,三輸入反或閘(NOR gate)的輸出則由另外兩個訊號決定,因此內部的雙模數除 2/3 電路將依此輸出訊號而在除 2 與除 3 之間切換,因此最終在 雙模數除 8/9 的預除器可得到除 9 的輸出訊號。

圖4.17 模數控制訊號為 0,預除器輸出除 9

圖 4.18 為模數控制訊號在高準位時,內部的雙模數除 2/3 電路則維持在除 2 功能,再加上後面兩個除 2 電路,此時雙模數除 8/9 預除器可得到除 8 輸出訊號。

圖4.18 模數控制訊號為1,預除器輸出除8

圖4.19 可程式計數器

振盪器的輸出經由預除器後輸出訊號已從 GHz 級降至 MHz 級,因此在預除器之後的可程式計數器可利用傳統靜態邏輯(staric logic)的正反器架構即可操作,在此需要

的兩組 5-bits 的可程式計數器,例如當控制訊號輸入為  $(S_3,S_2,S_1,S_0)=(1,0,1,0,1)$  時,表示計數器數到 21 之後應拉起輸出訊號並對 D 型正反器作重置(reset),如圖 4.19 所示,然後繼續數 21 個周期再拉起輸出訊號,如此週而復始,直到控制訊號被改變才會變更除數值。

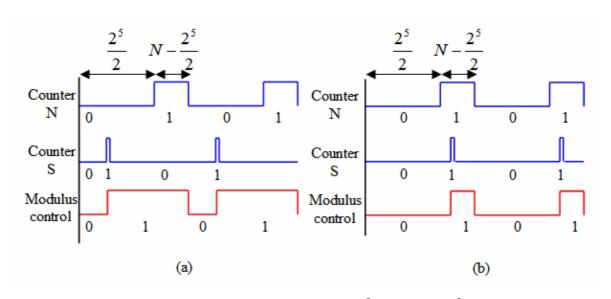

除頻器是由雙模數除 8/9 預除器、可程式計數器 /S 與可程式計數器 /N 組成,整體的除數為  $N_{total}=N\times 8+S$ ,即周期的一開始預除器設定在除 9,然後分別輸出給兩個計數器,由於 N 必須大於 S,故等到 S 數完後輸出訊號拉起,並且同時將預除器的模數控制訊號切換至除 8,而可程式計數器 /N 仍繼續執行直到數完剩下的(N-S)個輸入周期,拉起輸出並重置。然而可程式計數器 /N 為 5-bits,因此當數到第 16 個周期時,輸出訊號會由低準位拉升為高準位,故控制模數訊號的設計可能會遇到  $S>2^5/2$  或  $S<2^5/2$  兩種情況,如圖 4.20 所示:

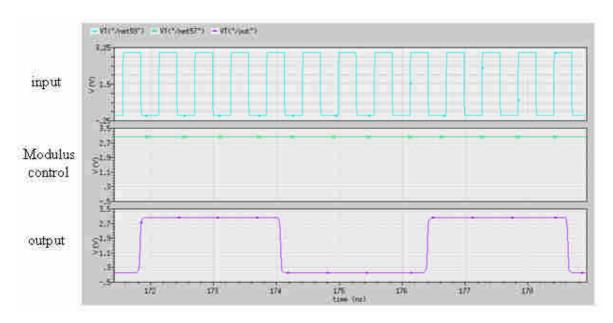

圖4.20 模數控制訊號: (a)  $S < 2^{5}/2$ ; (b)  $S > 2^{5}/2$

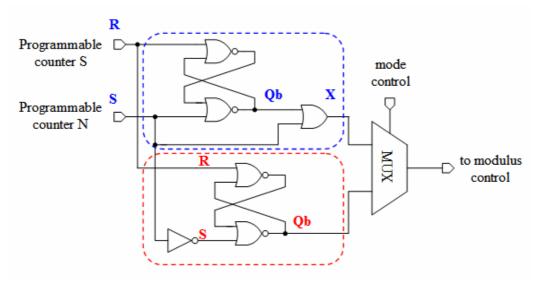

而想要得到模數控制訊號(modulus control signal)可利用門閂(latch)電路來完成,使用門門電路與簡單的邏輯閘即可由兩個可程式計數器的輸出訊號得到上列兩種情狀的模數控制訊號,電路如圖 4.21 所示:

圖4.21 產生模數控制訊號的電路

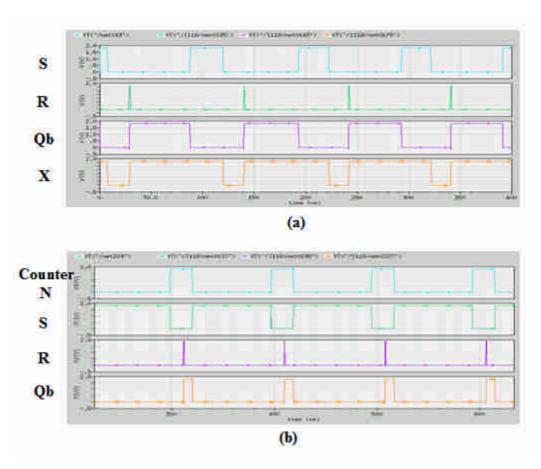

圖4.22 模數控制訊號的模擬結果:(a)  $S < 2^5/2$ ;(b)  $S > 2^5/2$

圖 4.22 為模數控制訊號電路的模擬結果,圖 4.22(a)為  $S < 2^5/2$  的狀況,其中訊號

X 為輸出;圖 4.22(b)為  $S>2^5/2$  的狀況,其中輸出訊號為 Qb。並且模數控制訊號亦可給可程式計數器 /S 中的正反器作重置(reset)訊號使用。利用上述電路在大部分的頻率都可以正確的鎖定,但是模擬 2.44 GHz 時,卻出現鎖定在 2.45 GHz,由模擬結果來看如圖 4.23 所示,預除器的輸出訊號原本應該數四個周期後由除 9 變為除 8,但由於門閂電路與多工器路徑的延遲效應,而此延遲效應在 GSM 下並沒有影響結果,但由於 WLAN 的操作頻率較高,使模數控制訊號在第四個周期出現之後才將預除器的除數值改變為除 8,使除 9 周期數了 5 個而除 8 周期數了 25 個,故除數值變為  $9\times5+8\times25=245$ ,因此為了改善此狀況,可將圖 4.21 的  $S>2^5/2$  的電路與多工器去掉,只剩下  $S<2^5/2$  的電路架構,如此經過模擬可正確得到 2.44 GHz 的輸出頻率,故此時 S 必須小於  $2^5/2$ ,而在  $S>2^5/2$  的狀況可藉由增加 N 值來解決。

圖4.23 N<sub>total</sub>=244, 輸出結果為鎖定在 2.45 GHz

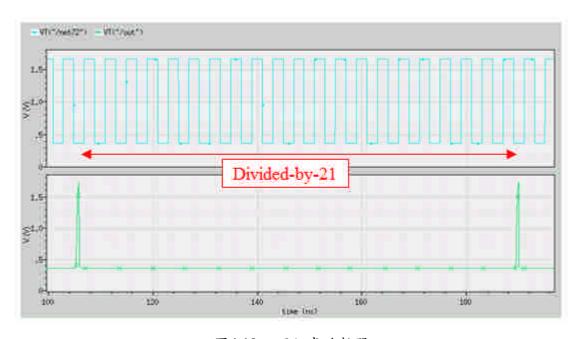

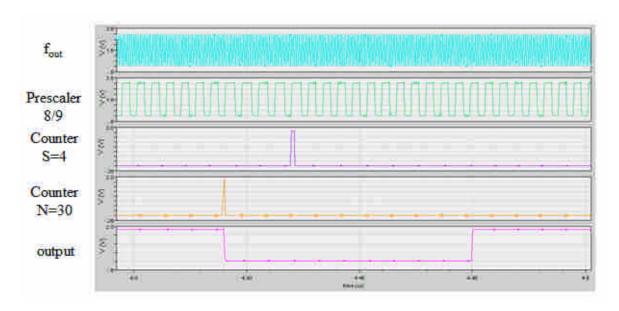

圖 4.24 為整體除頻器的模擬結果,其中  $N=21 \cdot S=7 \cdot P=8$  時,因此可得  $N_{total}=21 \times 8$  +7=175 的除數值,波形如圖 4.24 所示:

圖4.24 總除數為 175 的除頻器輸出結果

#### 4.2.5 迴路模擬

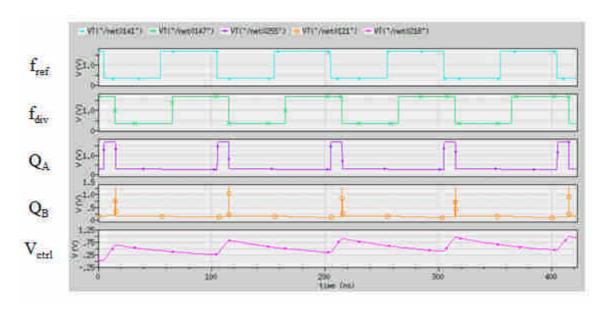

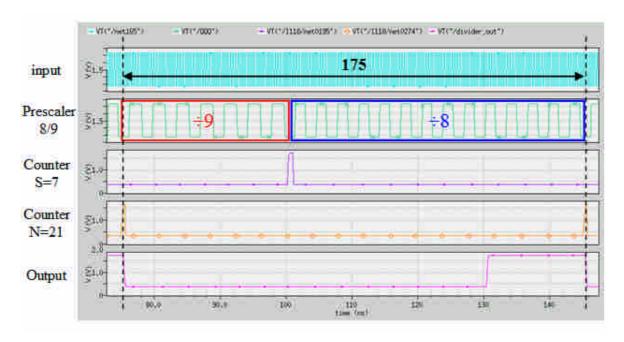

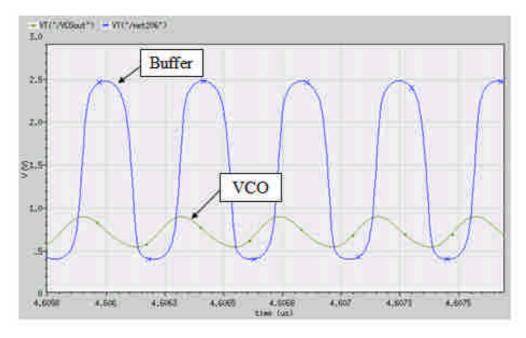

當參考頻率  $f_{ref}$ =10 MHz,且(V\_SWL,V\_SWC1,V\_SWC2) = (0,0,0),可程式計數器為 S=4、N=23,預除器 P=8,因此總除數  $N_{total}$ =23×8+4=188。圖 4.25 是此設定下鎖相迴路的模擬結果,由圖可看出充放電電流皆約為 500 mA,鎖定時間小於 4us,且鎖定後電壓控制訊號  $V_{ctrl}$  為 650 mV,由於使用整數型頻率合成器的架構,因此頻道解析度等於參考頻率為 10 MHz。圖 4.26 為前置放大器(pre-Amplifier)的輸出結果,修正了振盪器輸出訊號的振幅大小與 DC 準位,由於前置放大器的下級電路為預除器,因此前置放大器的直流供應電壓源也是使用 3 V。

圖4.25 1.88 GHz 時鎖相迴路模擬

圖4.26 前置緩衝器

而表 4.1 為此鎖相迴路系統的特性總表:

表4.1 鎖相迴路模擬特性總表

| Supply Voltage             | 1.8V / 3V       |                 |  |  |

|----------------------------|-----------------|-----------------|--|--|

| Frequency Range            | 1.660~1.928 GHz | 2.257~2.640 GHz |  |  |

| Phase Noise (@1MHz offset) | -123dBc         | -121dBc         |  |  |

| PLL Locking Time           | < 4 us          |                 |  |  |

| Power consumption          |                 |                 |  |  |

| VCO                        | 17.423 mW       |                 |  |  |

| PFD                        | 0.177 mW        |                 |  |  |

| СР                         | 1.158 mW        |                 |  |  |

| Divider                    | 22.966 mW       |                 |  |  |

| Total                      | 64.923 mW       |                 |  |  |

## 4.3 自我頻率校正迴路

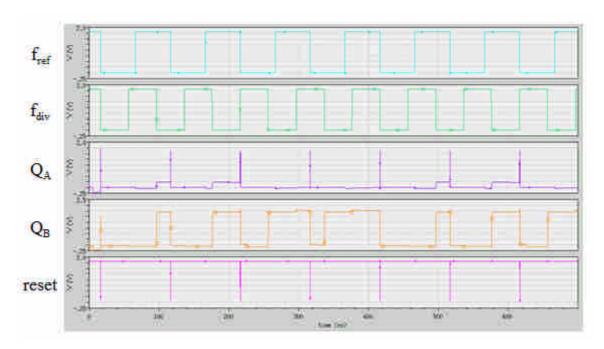

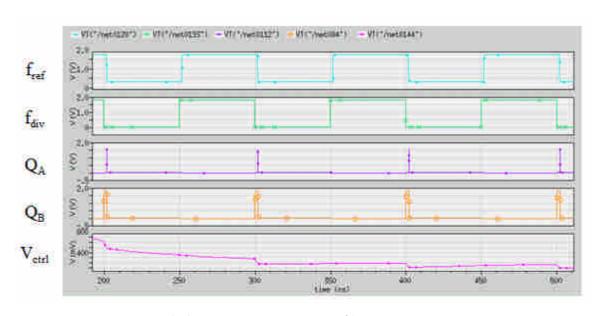

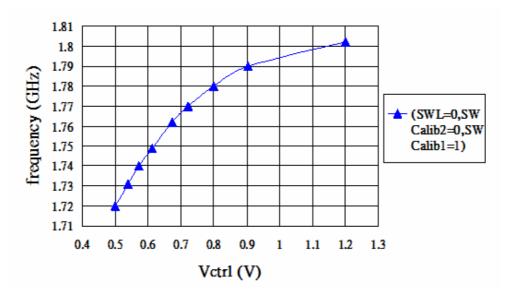

當執行自我頻率校正時,鎖相迴路在低通濾波器部份由開關控制為開迴路。在 4.2章節中的使用的壓控振盪器有 2-bits 的電容陣列,因此有 4 個 sub-band 可提供可調頻率範圍,然而這些 sub-band 在先前鎖相迴路中是用來增加可調頻率範圍使用,而在此章節這 2-bits 的電容陣列將當成校正製程偏移的電容陣列使用,所以接下來將  $V_SWCN$  換以  $SW_{CcalibN}$  表示。以 GSM  $V_SWL=0V$  時來作討論,如 3.3.2 章節所述,取  $(SW_{Ccalib2},SW_{Ccalib1})=(0,1)$  時為預設的操作頻帶,而此 sub-band 的頻率範圍由 1.77 GHz 到 1.861 GHz,為了方便校正電路的電流幫浦設計,除數值  $N_C$  取中心頻率 1.82 GHz,由於此 sub-band 並非在可變電容的線性區,如圖 4.27,因此利用鎖相迴路將除數值設在  $N_{total}=182$  時,可得到鎖定時的電壓控制訊號  $V_{ctrl}=670$  mV,此電壓即為校正時壓控振盪器的輸入參考電壓  $V_{ref}$ 。

圖4.27 V\_SWL=0 V, (SW<sub>Ccalib2</sub>,SW<sub>Ccalib1</sub>)=(0,1)的可調頻率範圍

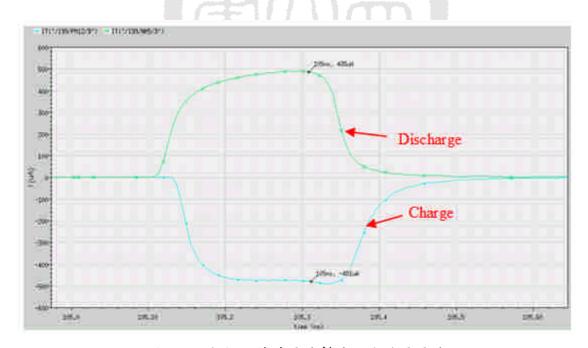

#### 4.3.1 校正迴路的電流幫浦與充放電電容

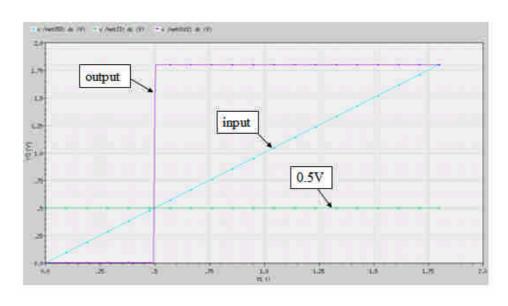

$N_C$ 與 $V_{ref}$ 值都確定了之後,接下來要調整校正迴路電流幫浦(Calib\_CP)的電晶體大小與充放電電容 $C_C$ 的電容值,而電容 $C_C$ 的預充電壓 $V_{pre}$ 選擇為( $V_{max}+V_{min}$ )/2。為了使( $SW_{Ccalib2}$ , $SW_{Ccalib1}$ )=(0,1)這 sub-band 上的  $V_{max}$ (1.2 V)對應到的輸出頻率恰可將電容 $C_C$ 放電至 $V_{min}$ ,故先將壓控振盪器的輸入電壓設為 1.2V, $N_C$ 仍為 188,此時在相位檢測器檢測出來的相位誤差則是這 sub-band 上參考訊號相位落後最大的時候,模擬波形如圖 4.28 所示,圖中虛線之前電容 $C_C$ 由預充電壓 $V_{pre}$ 作預充動作,而微調電容 $C_C$ 與校正迴路電流幫浦的充放電電流後,使 $V_C$ 電壓恰可觸發 $V_{min}$ 比較器。

反之,為了使( $SW_{Ccalib2}$ , $SW_{Ccalib1}$ )=(0,1)這 sub-band 上的  $V_{min}$ (0.5 V)對應到的輸出頻率恰可將電容  $C_C$  充電至  $V_{max}$ ,故先將壓控振盪器的輸入電壓設為 0.5 V, $N_C$  仍為 188,此時在相位檢測器檢測出來的相位誤差則是這 sub-band 上參考訊號相位領先最大的時候,模擬波形如圖 4.29 所示,圖中虛線之前電容  $C_C$  由預充電壓  $V_{pre}$  作預充動作,而微調電容  $C_C$  與校正迴路電流幫浦的充放電電流後,使  $V_C$  電壓恰可觸發  $V_{max}$  比較器。

圖4.28 校正迴路電流幫浦與充放電電容設計(V<sub>C</sub>=V<sub>max</sub>)

圖4.29 校正迴路電流幫浦與充放電電容設計( $V_C=V_{min}$ )

## 4.3.2 比較器

比較器的架構如圖 3.25 所示,適當的設計差動的電晶體大小與電阻值,使差動對輸出端的 DC 偏壓與前置放大器輸入 DC 偏壓相同。如圖 4.30 與圖 4.31 分別為  $V_{max}$  與  $V_{min}$  比較器的轉移特性曲線,輸出曲線在輸入電壓與參考電壓(1.2V 與 0.5V)交點之前為低準位,直到輸入電壓大於參考電壓之後,輸出拉為高準位狀態。

圖4.30 V<sub>max</sub> 比較器的轉移特性曲線

圖4.31 V<sub>min</sub>比較器的轉移特性曲線

圖4.32 差動對輸出端的電阻 R

表4.2 (a) V<sub>min</sub> 比較器的電阻變異影響 (b) V<sub>max</sub> 比較器的電阻變異影響

| R (K Ohm) | output (V) |  |  |

|-----------|------------|--|--|

| 9.8       |            |  |  |

| 9.4       | fail       |  |  |

| 9.0       | 0.338645   |  |  |

| 8.6       | 0.446212   |  |  |

| 8.2       | 0.469075   |  |  |

| 7.8       | 0.481332   |  |  |

| 7.4       | 0.486351   |  |  |

| 7.0       | 0.491365   |  |  |

| 6.6       | 0.496379   |  |  |

| 6.2       | 0.501393   |  |  |

| 5.8       | 0.501393   |  |  |

| 5.4       | 0.506407   |  |  |

| 5.0       | 0.511421   |  |  |

| 4.6       | 0.511421   |  |  |

| 4.2       | 0.516435   |  |  |

| 3.8       | 0.516435   |  |  |

| 3.4       | 0.521448   |  |  |

| 3.0       | 0.521458   |  |  |

| 2.6       | 0.526462   |  |  |

| 2.2       | 0.531476   |  |  |

| (a)       |            |  |  |

| R (K Ohm) | output (V) |  |  |

|-----------|------------|--|--|

| 16.7      |            |  |  |

| 16.3      | fail       |  |  |

| 15.9      | 1.28425    |  |  |

| 15.5      | 1.24353    |  |  |

| 15.1      | 1.22874    |  |  |

| 14.7      | 1.21929    |  |  |

| 14.3      | 1.21381    |  |  |

| 13.9      | 1.20872    |  |  |

| 13.5      | 12.037     |  |  |

| 13.1      | 1.19869    |  |  |

| 12.7      | 1.19368    |  |  |

| 12.3      | 1.18864    |  |  |

| 11.9      | 1.18355    |  |  |

| 11.5      | 1.17843    |  |  |

| 11.1      | 1.17323    |  |  |

| 10.7      | 1.16562    |  |  |

| 10.3      | 1.15851    |  |  |

| 9.9       | 1.15244    |  |  |

| 9.5       | 1.14329    |  |  |

| 9.1       | 1.13336    |  |  |

| (h)       |            |  |  |

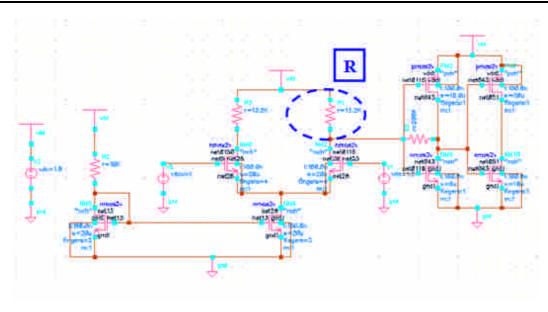

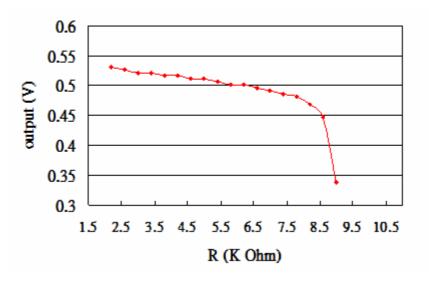

然而比較器中差動對的兩個電阻亦會受到製程變異的影響,若架構對電阻的變異容忍度不夠大時,那麼很容易就受到製程變異影響而無法正確比較。因此,接下來將 針對差動對中輸出端的電阻做製程變異的討論,圖 4.32 虛線圈中的電阻。 表 4.2(a)與(b)分別為 V<sub>min</sub> 比較器與 V<sub>max</sub> 比較器考慮差動對輸出端電阻製程變異影響,表中標示部份為原本設計的電阻值,考慮電阻變大或變小時轉移特性曲線中輸入與輸出曲線的交點電壓,而圖 4.33 與圖 4.34 分為其曲線圖。

圖4.33 V<sub>min</sub> 比較器的差動對輸出端電阻值的輸出電壓曲線

圖4.34 Vmax 比較器的差動對輸出端電阻值的輸出電壓曲線

因此,若考慮電阻有 $\pm 20\%$ 的製程變異,則  $V_{min}$  比較器輸入與輸出的轉移曲線交點電壓範圍約 0.486  $V\sim 0.511$  V,而  $V_{max}$  比較器輸入與輸出的轉移曲線交點電壓範圍約 1.16  $V\sim 1.25$  V;若此校正電路設計在比較器判斷電壓時,可容許有 $\pm 2.5\%$ 的誤差,

則差動對輸出端電阻的變異量在  $V_{min}$  比較器中 4.6 KOhm $\sim$  7.4 KOhm, 在  $V_{max}$  比較器中 11.1 KOhm $\sim$  15.1 KOhm, 約可容忍  $15\%\sim$  25% 的製程變異量。

#### 4.3.3 邏輯電路與控制訊號

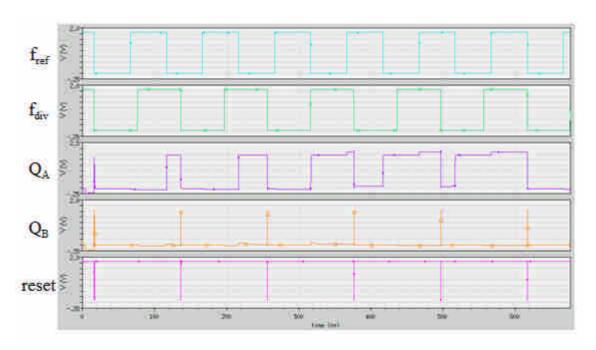

當進行校正迴路時,除了 3.3.5 章節中提到的五個主要的控制訊號,尚有其他的控制訊號需要去設計產生。在此為了要模擬校正製程變異的偏移,原本預設的 sub-band 應為 $(SW_{Ccalib2},SW_{Ccalib1})=(0,1)$ ,假設因製程偏移而偏移至 $(SW_{Ccalib2},SW_{Ccalib1})=(1,1)$  sub-band 上,因此利用邏輯電路 $(Logic\ circuit)$ 輸出端的 D 型正反器將  $(SW_{Ccalib2},SW_{Ccalib1})$ 的初始值設在(1,1)上,然後進行自我頻率校正,藉由校正迴路最終應要把 $(SW_{Ccalib2},SW_{Ccalib1})$ 修正回(0,1)的 sub-band 上。

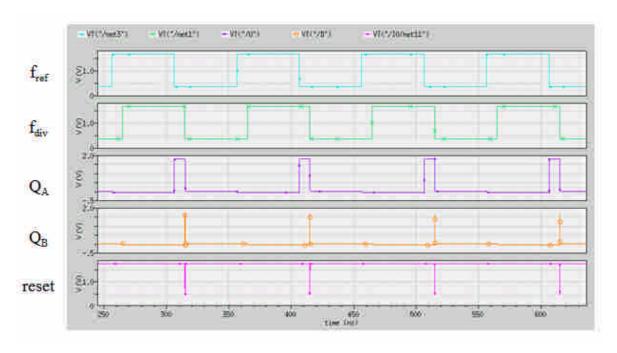

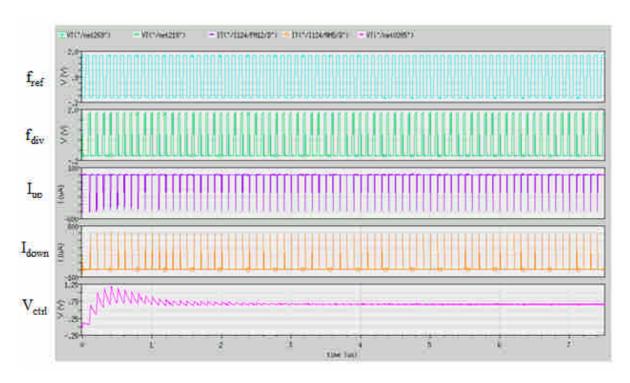

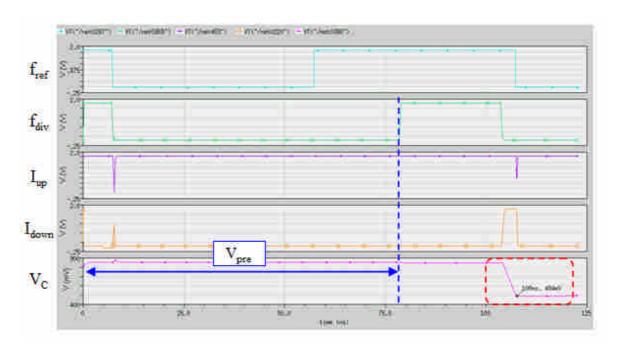

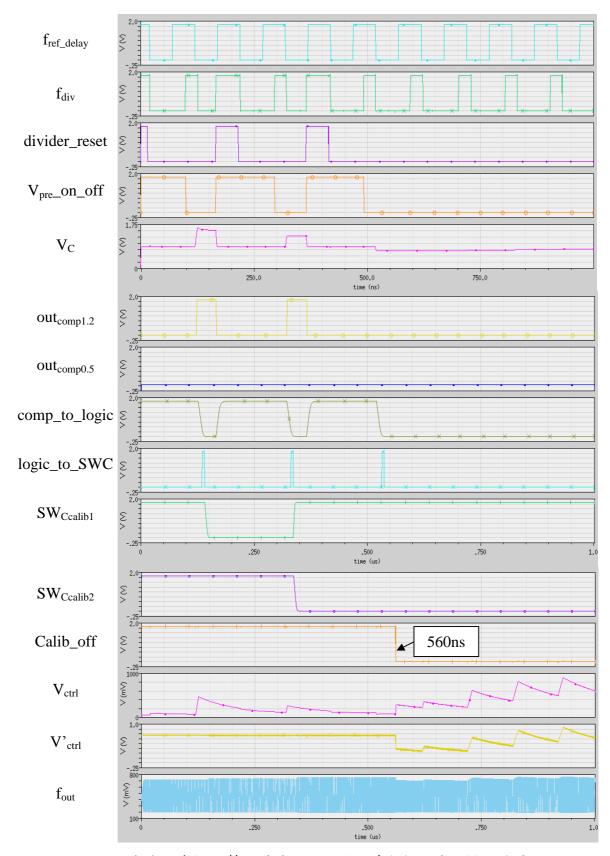

圖 4.35 為自我頻率校正製程變異往低頻偏移時,迴路中的邏輯電路的輸入輸出訊號與各個控制訊號波形,其中  $V_{ctrl}$  為低通濾波器上開關之前的電壓, $V'_{ctrl}$  則是開關之後振盪器輸入端的電壓,兩電壓間由一 MOS 開關控制;而藉由 divider\_reset 控制訊號使經過延遲之後的  $f_{ref\_delay}$  與除頻器輸出  $f_{div}$  可以同相位輸入給相位檢測器; $V_{pre\_on\_off}$  控制訊號則在校正迴路的電流幫浦(Calib\_CP)對電容  $C_C$  充電之前先對電容  $C_C$  預先充電至  $V_{pre}$ ;  $V_C$  電壓在第一與第二校正周期都比  $V_{max}$  電壓還大,因此促使頻帶往低頻帶修正,如( $SW_{Ccalib2}$ , $SW_{Ccalib1}$ )訊號所示,第一個校正周期由(1,1)切換至(1,0),第二校正周期由(1,0)切換成(0,1),而在第三個校正周期  $V_C$  電壓在  $V_{max}$  與  $V_{min}$  範圍之間,因此( $SW_{Ccalib2}$ , $SW_{Ccalib1}$ )訊號並沒有變動,而  $V_C$  電壓在  $V_{max}$  與  $V_{min}$  能圍之間,因此( $V_C$ 0, 以對率校正完成,因此  $V_C$ 1, 以對應數量之間,因此( $V_C$ 1, 以對應數量之( $V_C$ 1, 以對數量之( $V_C$ 1, 以對數量之( $V_C$ 1, 以對數量之( $V_C$ 1, 以對數量之( $V_C$ 1, 以對數學之( $V_C$ 1, 以對數學

圖4.35 自我頻率校正製程變異往低頻偏移時各個訊號的模擬結果

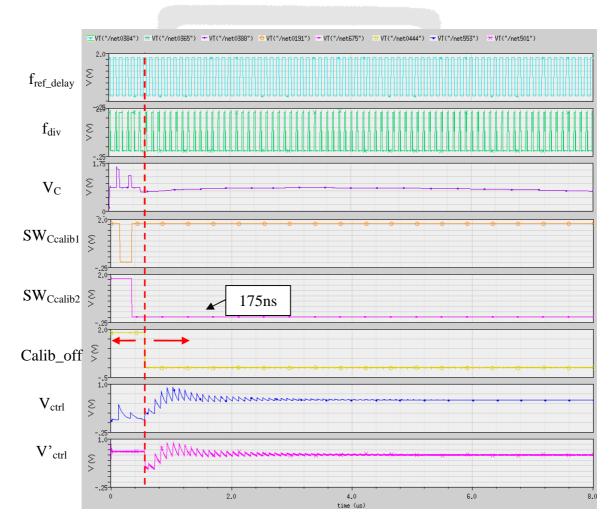

### 4.3.4具自我頻率校正的鎖相迴路模擬

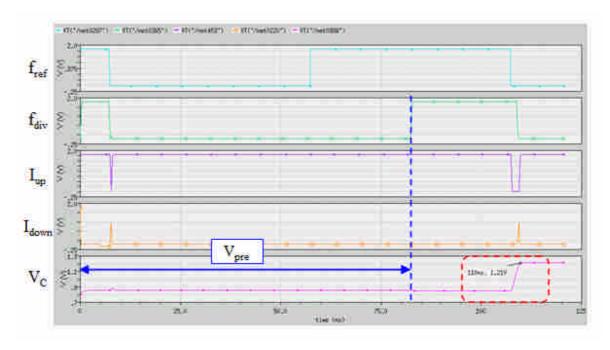

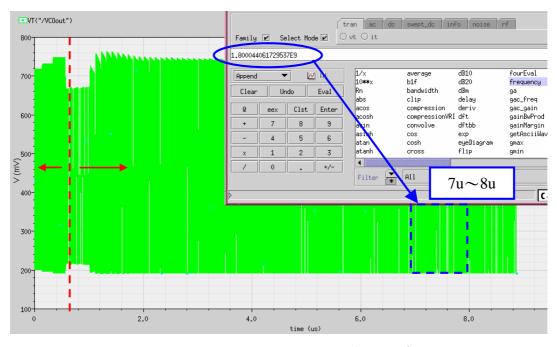

由於目前我們只有一顆 2-bits 電容陣列的壓控振盪器,因此首先在一開機時,將 迴路切換至自我頻率校正電路,當校正完成後,在修正後的 sub-band 上再利用鎖相 迴路來鎖在特定的頻率上。如圖 4.36 所示,在紅色虛線之前進行自我頻率校正,而校正時除頻器的除數值為  $N_C$ =182,並假設一開始因製成偏移而使頻帶往低頻處偏移;而當校正結束之後,即紅色虛線之後,將自我校正電路部份關閉,鎖相迴路切回 閉迴路系統,並將除頻器的除數值設在  $N_{total}$ =180,因此當迴路鎖定之後,如圖 4.37 振盪器的輸出頻率確實鎖定在 1.80 GHz 上。

圖4.36 自我頻率校正時  $N_C=182$ , 鎖相迴路時  $N_{total}=180$

圖4.37 鎖相迴路 Ntotal=180 的輸出頻率

在圖 4.36 中, $V'_{ctrl}$  則是開關之後振盪器輸入端的電壓,而開關在此是利用一顆 nMOS 電晶體來完成,因此在  $V'_{ctrl}$  端比  $V_{ctrl}$  端有更多的雜訊引入,迴路穩定時  $V'_{ctrl}$  上電壓有較大的抖動,因此  $V'_{ctrl}$  電壓輸入給壓控振盪器,將會造成鎖相迴路的輸出端產生額外的相位雜訊。表 4.3 為 2-bits 校正電容陣列的自我頻率校正鎖相迴路的模擬特性總表,利用 GSM 系統的 sub-band 來做校正,模擬結果整體的輸出直流功率消耗約 82~mW,校正時間小於 600~ns,鎖相迴路鎖定時間約 4~us。

表4.3 具自我頻率校正的鎖相迴路模擬特性總表

| Supply Voltage            | 1.8V / 3V       |                 |  |

|---------------------------|-----------------|-----------------|--|

| Frequency Range           | 1.660~1.928 GHz | 2.257~2.640 GHz |  |

| PLL Locking Time          | < 4 us          |                 |  |

| Calibration Time (2-bits) | < 600 ns        |                 |  |

| Power consumption         |                 |                 |  |

| VCO                       | 17.423 mW       |                 |  |

| PFD                       | 0.177 mW        |                 |  |

| СР                        | 1.158 mW        |                 |  |

| Divider                   | 22.966 mW       |                 |  |

| Calib_CP                  | 1.946 mW        |                 |  |

| Comparator                | 20.363 mW       |                 |  |

| Logic circuit             | 0.002 mW        |                 |  |

| Control signal            | 0.0015 mW       |                 |  |

| Total                     | 82.088 mW       |                 |  |

## 第5章 鎖相迴路於超寬頻系統的應用

### 5.1 超寬頻頻率合成器

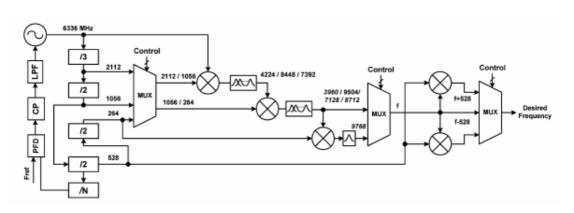

在 UWB 的系統中,頻率涵蓋 3.1 GHz 到 10.6 GHz 的範圍,可分為 5 個 Band Groups,如 1.3 章節中圖 1.2 所示,其中又可細分為 14 個子頻帶,因此 UWB 的頻率合成器只要可以產生這 14 個子頻帶的中心頻率,再搭配 528 MHz 的頻率即可達到 UWB 規格標準的需求,因此頻率合成器的架構取決於頻率的規劃方式。一般常見的 UWB Synthesizer 實現方式為利用一組鎖相迴路產生 6336 MHz 的頻率,然後再搭配除 2、除 3 電路以及混頻器(Mixer)來產生主要的 5 個 Band Groups 的 Main tones,接著由多工器(Multiplexer)來選擇所需要的 Main tone,最後再搭配 528 MHz 的頻率即可涵蓋 14 Band 的頻帶範圍,架構如圖 5.1 所示[31]。圖 5.2 是經由重新頻率規劃 (Frequency Planning)後得到的頻率合成器的架構,與圖 5.1 無頻率規劃的架構相較下,經頻率規劃後的架構少了一個多工器電路,因此在複雜度與成本上都有改善。

圖5.1 UWB 頻率合成器架構[31]

圖5.2 經頻率規劃後的頻率合成器架構[31]

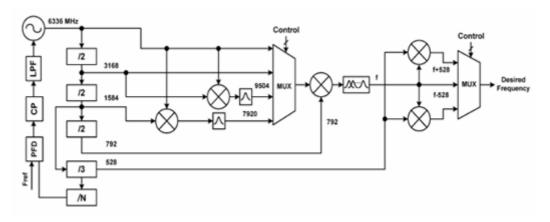

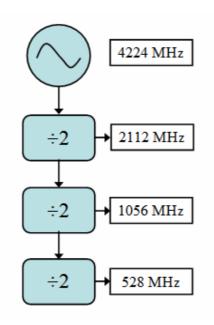

在此我們提出了一個新的頻率規劃[32],由本實驗室所提出的專利,目前尚在審核當中,如表 5.1 所示。而此新的頻率規劃只需一顆可切換式電感的射頻四相位振盪器,利用切換電感的方式使輸出頻率在 6072 MHz 與 6600 MHz 間切換,搭配如圖 5.3 所示經鎖相迴路而鎖定頻率在 4224 MHz 之壓控振盪器,再搭配三個除 2 電路以及兩個 SSB 混頻器(Mixer)來產生主要的 5 個 Main tone,接著利用多工器(Multiplexer)來選擇所需要的 Main tone,最後再搭配 528 MHz 的頻率來完成涵蓋 14 Bands 的中心頻率。相較於圖 5.2 所示之頻率合成器的架構,雖然我們多使用了一組四相位振盪器,但是我們卻可省去兩組 Mixer 電路,因此在 UWB Synthesizer 的架構上我們不但可以更進一步的降低晶片的成本,而且也減少了混頻的次數,因此在性能上也可大大的提升,並且電路實現上也較容易許多。

表5.1 新式頻率規劃

| 14 Bands(MHz) | QVCO(6072 MHz) |  |  |  |  |

|---------------|----------------|--|--|--|--|

|               |                |  |  |  |  |

| 3432          | 3960-528       |  |  |  |  |

| 3960          | 6072-2112      |  |  |  |  |

| 4488          | 3960+528       |  |  |  |  |

| 5016          | 6072-1056      |  |  |  |  |

| 5544          | 6072-528       |  |  |  |  |

| 6072          | 6072           |  |  |  |  |

| 6600          | 6072+528       |  |  |  |  |

| 7128          | 6072+1056      |  |  |  |  |

| 7656          | 7128+528       |  |  |  |  |

| 8184          | 8712-528       |  |  |  |  |

| 8712          | 6600+2112      |  |  |  |  |

| 9240          | 8712+528       |  |  |  |  |

| 9768          | 10296-528      |  |  |  |  |

| 10296         | 6072+4224      |  |  |  |  |

圖5.3 輸出 4224 MHz 的振盪器搭配除二電路

而此頻率規劃的創意在於:

- (a) 利用新的 Frequency plan 以完成 MB-OFDM UWB 所需的 14 個子頻帶的振盪中心頻率。

- (b) 利用自行開發的可切換式差動電感來實現 6072 MHz/6600 MHz 的四相位壓 控振盪器。

- (c) 適當地設計鎖相迴路的低通濾波器,我們可以得到極小的鎖定穩定時間 (settling time < 9.5 ns,理論值為 0 ns),所以當切換 6072 MHz 與 6600 MHz 的振盪頻率時,可在極小的時間(< 9.5 ns)內完成。

- (d) 電路主體僅需要兩個振盪器與兩個混頻器與四個除2電路來實現。

- (e) 一般電路需要除3電路,此專題僅需用到熟知的高速除2電路方塊即可。

#### 5.2 UWB 的鎖相迴路與 Simulink 模擬

由表 5.1 可知,在此新式的 UWB 頻率規劃中,頻率合成器的架構將需要一個固定產生 4224 MHz 的振盪器,與一個利用可切換式差動電感的四相位壓控振盪器來產生 6072 MHz /6600 MHz,利用這兩個振盪器的輸出頻率組合即可產生 14 個子頻帶的中心頻率。然而依 UWB 的系統標準,切換頻率的時間不可大於 9.5 ns,因此接下來將以 Matlab 下的 Simulink 軟體來模擬,並探討此四相位振盪器的頻率切換所需的時間,當切換電感而使產生輸出頻率在 6072 MHz 與 6600 MHz 之間跳躍時,鎖相迴路的迴路頻寬大小與鎖定時間的關係,並且尋求能達到小於 9.5 ns 要求的迴路頻寬值。

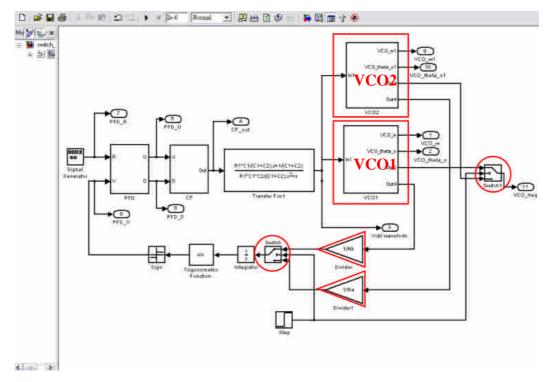

然而,要在 Simulink 中模擬切換電感來改變輸出頻率的方式,可利用兩組 VCO、兩組除頻器並且配合開關的切換來達到與四相位振盪器切換頻率的等效輸出。因此電路架構如圖 5.4 所示:

圖5.4 用 Simulink 模擬切換電感 QVCO 的 PLL 架構

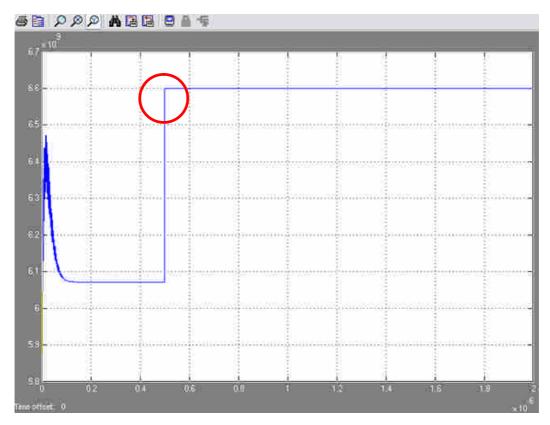

首先假設參考頻率為 264 MHz,此參考頻率可由 4224 MHz 的振盪器搭配除二電路得到,而欲產生 6072 MHz 與 6600 MHz 的輸出頻率,故除數值需設為 23 與 25,若迴路頻寬設計如先前 2.4.2 章節所述取比較頻率的四十分之一,則迴路頻寬應為 7 MHz,此外假設電感切換前後子頻帶的 Kvco 值皆相同為 230 MHz/V,並且四相位振盪器可以設計為在輸出 6072 MHz 與 6600 MHz 時,Vctrl 穩定電壓值皆為 0.85 V,模擬時利用開關使切換頻率的同時也切換除頻器的除數值。首先假設整個鎖相迴路皆為理想電路時,由圖 5.5 Simulink 的模擬桔果可看出當振盪器輸出頻率由 6072 MHz 切換至 6600 MHz 時,其鎖定時間(settling time)為 0 ns,這結果表示只要切換電感開關同時改變除數值,則迴路中其他電路 PFD、CP與 LPF的狀態並不受影響,相位檢測器的輸出相位誤差維持不變。然而此架構實際上只需要一顆四相位振盪器即可完成,Simulink 電路圖中的兩個振盪器只是為模擬切換式電感的等效電路,因此,理想上若可以在切換電感時,使四相位振盪器的輸出頻率正確的產生 528 MHz 頻率變化,那麼此新式頻率規劃的頻率成器架構不僅只需要一顆四相位振盪器,並且鎖相迴路鎖定時間理想上為 0 ns。

圖5.5 理論上切換頻率 settling-time 為 0 ns

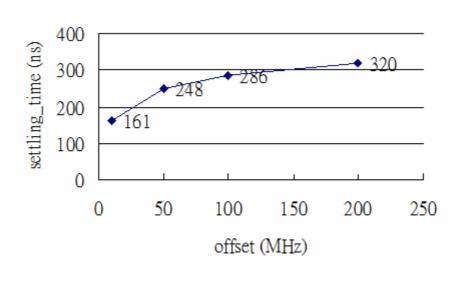

但實際上,電路的的設計會受到製程與環境的影響,而導致四相位振盪器內部 LC 諧振槽中共振頻率的偏移,尤其以製程變異的影響最為嚴重,此些變異因素將導致切換電感時輸出頻率無法正正確產生 528 MHz 的頻率偏移,使相位檢測器的輸出端將有相位誤差,此時必定需要一段鎖定時間直到鎖相迴路穩定。故接下來將探討製程與環境造成的偏移對鎖定時間的影響,是否還能達到 UWB 系統標準的規格內。同樣利用 Simulink 軟體模擬,當輸出頻率由 6072 MHz 切換至 6600 MHz後,在 6600 MHz上的頻率偏移分別為 200 MHz、100 MHz、50 MHz 和 10 MHz,模擬此時利用鎖相迴路將頻率鎖回 6600 MHz 所需要的鎖定時間,其結果整理如表 5.2 所示,而圖 5.6 為其關係曲線圖。

| Frequency (MHz)            | Settling time (ns) | V <sub>ctrl</sub> (V)   |

|----------------------------|--------------------|-------------------------|

| 6400→6600 (offset 200 MHz) | 320                | $0.85 \rightarrow 1.72$ |

| 6500→6600 (offset 100 MHz) | 286                | $0.85 \to 1.28$         |

| 6550→6600 (offset 50 MHz)  | 248                | $0.85 \to 1.065$        |

| 6590→6600 (offset 10 MHz)  | 161                | $0.85 \to 0.89$         |

表5.2 不同的頻率偏移量所需的鎖定時間

圖5.6 不同的頻率偏移量對鎖定時間的關係曲線圖

由曲線圖可看出頻率偏移量與所需要的鎖定時間成正比,並且當頻率偏移量小於 50~MHz 時所需要的鎖定時間明顯降低,而以偏移 200~MHz 的情況來看,系統穩定時 振盪器的壓電壓控制訊號  $V_{ctrl}$  必須上升到 1.72~V,但是實際的電路中由於電流幫浦輸 出端的電晶體  $V_{DS}$  會消耗壓降,導致  $V_{ctrl}$  在並無法上升至這麼高的電壓( $V_{dd}$  使用  $1.8~V_{de}$ ),因此在實際電路中,頻率偏移 200~MHz 的狀況可能會有無法鎖定的情形。

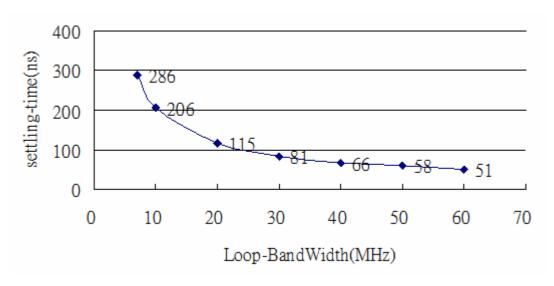

然而迴路的鎖定時間主要與迴路頻寬的大小有關,當迴路頻寬越大,系統反應速度越快,鎖定的時間越短,因此接下來探討鎖相迴路中迴路頻寬與鎖定時間的關係。

其中假設振盪器輸出頻率由  $6072~\mathrm{MHz}$  切換到  $6600~\mathrm{MHz}$  時,在  $6600~\mathrm{MHz}$  的頻帶上振盪器有著  $100~\mathrm{MHz}$  的頻率偏移量,即切換電感開關後當  $V_{ctrl}$  尚未改變仍在 0.85

V 時,輸出頻率是由 6072 MHz 切換到 6500 MHz,模擬此時鎖相迴路將頻率從 6500 MHz 鎖回 6600 MHz 時所需要的鎖定時間,設參考頻率為 264 MHz,欲產生 6072 MHz 與 6600 MHz,故除數值為 23 與 25,且假設切換前後的  $K_{VCO}$  值相同皆為 230 MHz/V,並令振盪器可以設計在產生 6072 MHz 時  $V_{ctrl}$  為 0.85 V,而當切換電感開關後  $V_{ctrl}$  0.85 V 則是對應到 6500 MHz。探討分別對於迴路頻寬為 7 MHz、10 MHz、20 MHz、30 MHz、40 MHz、50 MHz、60 MHz、70 MHz、80 MHz、90 MHz 與 100 MHz 時,以 Simulink 來模擬鎖定時間,可得結果如下表 5.3 所示:

表5.3 不同的迴路頻寬所需要的鎖定時間

| Loop-Bandwidth | Settling time |  |

|----------------|---------------|--|

| 7 MHz          | 286 ns        |  |

| 10 MHz         | 206 ns        |  |

| 20 MHz         | 115 ns        |  |

| 30 MHz         | 81 ns         |  |

| 40 MHz         | 66 ns         |  |

| 50 MHz         | 58 ns         |  |

| 60 MHz         | 51 ns         |  |

| 70 MHz         | 6.072GHz Fail |  |

| 80 MHz         | Fail          |  |

| 100 MHz        | Fail          |  |

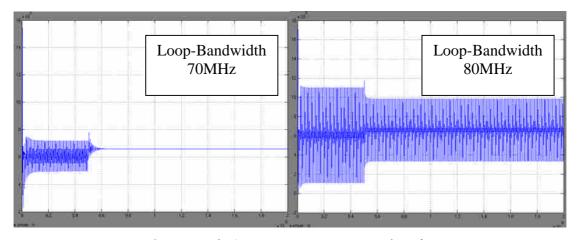

上列表格為迴路頻寬分別所對應到的鎖定時間大小,可觀察得迴路頻寬大約比參考頻率(264 MHz)的四分之一(66 MHz)還要大時,因系統的阻尼常數ζ將太大而導至迴路無法穩定,如圖 5.7 所示,波形將持續振盪而無法收斂:

圖5.7 當迴路頻寬為 70 MHz 與 80 MHz 時,系統將無法穩定

而下圖 5.8 為迴路頻寬與鎖定時間的關係曲線圖,當迴路頻寬比參考頻率的十分之一(約 26 MHz)大的時候,改變迴路頻寬的大小對於鎖定時間的影響逐漸降低了,因此,迴路頻寬建議取在參考頻率的十分之一至四十分之一之間,如此也不會因迴路頻寬太大而導致低通濾波器的極點頻率 ω3 不易加入,而無法抑制比較脈衝雜訊。

圖5.8 迴路頻寬與鎖定時間的關係曲線圖

由以上結果得知,此時增加迴路頻寬已無法有效的縮短鎖定時間來達到 UWB 標準的要求,因此若想要再將鎖定時間縮短則需將參考頻率提高,如此一來所對應到的十分之一參考訊號頻率也隨之提高,而可以選擇更大的迴路頻寬來加速系統的反應時間。故接下來嘗試把參考頻率提高一倍為 528 MHz,而此頻率亦可由 4224 MHz 的振

盪器搭配除二電路得到,但此時在此四相位振盪器要產生 6072 MHz 與 6600 MHz 時,除頻器的除數值則必須為 11.5 與 12.5,此除數已無法用整數型頻率合成器得到,故鎖相迴路需改為分數型頻率合成器(Fractional-N Synthesizer)的架構。在此仍將分數型頻率合成器的迴路頻寬取為參考頻率的四十分之一(約 14 MHz),再做頻率偏移量與鎖定時間的模擬,最後與表 5.3 的整數型頻率合成器(Integer-N Synthesizer)迴路頻寬為 7 MHz 的結果做比較,如表 5.4。