# 國立交通大學

# 電子工程學系 電子研究所碩士班

## 碩士論文

一個包含等化器及時脈與資料回復電路之 高速序列傳輸接收機設計

Clock and Data Recovery Circuit and Equalizer for High-Speed Serial-Link Receiver

研究生: 黃文杰 (Wen-Chieh Huang)

指導教授: 陳巍仁 教授 (Prof. Wei-Zen Chen)

中華民國一〇〇年十一月

## 一個包含等化器及時脈與資料回復電路之

### 高速序列傳輸接收機設計

# Clock and Data Recovery Circuit and Equalizer for High-Speed Serial-Link Receiver

研 究 生:黄文杰 Student : Wen-Chieh Huang

指導教授:陳巍仁 Advisor : Wei-Zen Chen

國立交通大學

電子工程學系 電子研究所

碩士論文

#### **A Thesis**

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering

National Chiao-Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Electronics Engineering

November 2011

Hsin-Chu, Taiwan, Republic of China

中華民國一○○年十一月

## 一個包含等化器及時脈與資料回復電路的

### 高速序列傳輸接收機設計

研究生: 黃文杰 指導教授: 陳巍仁教授

國立交通大學

電子工程學系電子研究所碩士班

### 摘要

隨著資訊科技的進步,高速傳輸的需求與日俱增。但有限的通道 頻寬將造成資料在傳送時遇到符際干擾(Inter-symbol interference, ISI) 的現象,符際干擾可能造成資料判決上的錯誤。因此能補償通道損失 的等化器在高速傳輸中扮演著重要的角色。

本論文提出了一個操作在 8Gbps 的高速序列傳輸接收機。其中包含了類比等化器、決策回授等化器以及時脈與資料回復電路。類比等化器部份採用在回授路徑加入額外極點的方式以提供高頻增益峰化。決策回授等化器將運用 sign-sign LMS 演算法,因此將可適應性調整係數以解決通道頻寬不足所造成的後指標符際干擾問題。此外決策回授等化器將採用軟決策的架構以進一步使電路操作在更高的速度之上。接收端採用的時脈與資料回復電路能利用相位內插器來調整相位輸出,相位偵測器利用偵測資料斜率的機制可使相位鎖定在適當的地方。最後,我們也加入了展頻時脈追蹤的功能。

İ

此電路採用 UMC 55 nm 互補式金氧半導體製程技術實現,總面 積為  $1.0\,\mathrm{X}\,1.85\,\mathrm{mm}^2$ ,在  $1.0\mathrm{V}$  的操作電壓下,整體功率消耗為  $65.9\mathrm{mW}$  。

# Clock and Data Recovery Circuit and Equalizer for High-Speed Serial-Link Receiver

Student: Wen-Chieh Huang Advisor: Wei-Zen Chen

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

### Abstract

With the advances in information technology, the demand of high speed transmission increase with each passing day. But the limitation bandwidth of the channel will causes the inter-symbol interference (ISI) when the data passes through the channel. ISI may cause wrong symbol detection. Therefore, the equalizer, which can be used to compensate for the channel loss, play an important role in high speed transmission.

In this thesis, we propose a high speed serial link receiver that operates at 8 Gbps. The receiver includes an analog equalizer, a decision feedback equalizer(DFE) and a clock and data recovery circuit (CDR). The analog equalizer provides gain peaking at high frequency by putting an additional pole in the feedback path. The decision feedback equalizer

iii

will adjust the coefficient adaptively by sign-sign LMS algorithm to cancel the post-cursor ISI. Using soft-decision architecture will enhance the operation speed of the decision feedback equalizer. The clock and data recovery circuit can adjust the phase of the clock signal by using a phase interpolator. The phase detector of the CDR will let the clock phase lock at proper position by detecting the slope of the data. Finally, we also add an SSCG clock tracking function in the receiver.

Implemented in a 55nm CMOS technology, the area is 1.0x1.85 mm<sup>2</sup> including PAD, the chip consumes 65.9mW from 1V supply.

#### 致謝

歷經三年多的時間,從一開始對電路實做一點經驗都沒有,到這本論文的完成,實在很感謝我的指導教授,陳巍仁老師的帶領。在此過程,無論是在專業領域以及待人處世,都讓我受益匪淺。

在這段漫長的研究生涯,特別感謝本實驗室-台祐學長、世豪學長的幫助,唯有你們的幫助,才有本論文的誕生。也感謝塔哥、歐陽、彥緯、小賴、順天、凱悌、邱神、昕爺、敬程等學長們的指導,還有本實驗室的同學及學弟妹們書瑾、旻毅、健軒、川逸、豔婷、建宏、逸弘、仲廷、曜嘉、佩妤、政豪和弘凱,以及新進的新血欣彥、凱婷、欣蓓…等。由於你們的陪伴以及幫忙,帶給我許多的方便以及快樂的回憶,祝福你們未來在工作或學業上都能夠一路順風,而還沒畢業的學弟妹能早日畢業。

最後要特別感謝在背後默默支持我的家人,在這段期間對與我的 關懷和付出,讓我可以無後顧之憂完成碩士學位。

黄文杰 Nov., 2011

# 目錄

| 摘要       |                                        | i    |

|----------|----------------------------------------|------|

| Abstract |                                        | iii  |

| 致謝       |                                        | v    |

| 目錄       |                                        | vi   |

| 圖目錄      |                                        | viii |

| 表目錄      |                                        | xii  |

| 第1章      | 簡介                                     | 1    |

| 1.1      | 相關背景與動機                                | 1    |

| 1.2      | 相關背景與動機<br>論文概要                        | 2    |

| 第2章      | 高速有線傳輸基本觀念簡介                           | 3    |

| 2.1      | 有線傳輸系統基本架構                             | 3    |

| 2.2      | 符際干擾(Inter -Symbol Interference , ISI) | 4    |

| 2.3      | 通道模型                                   | 7    |

| 2.4      | 等化器簡介                                  | 9    |

| 第3章      | 等化器之設計與實現                              | 13   |

| 3.1      | 接收機架構                                  | 13   |

| 3.2      | 類比等化器架構與電路設計                           | 14   |

|          | 3.2.1 類比等化器架構                          | 14   |

|          | 3.2.2 極點主動回授式濾波器                       | 15   |

|          | 3.2.3 可變增益放大器                          | 19   |

| 3.3      | 最小均方演算法(Least Mean Square Algorithms)  | 21   |

|   | 3.4 | 決策    | 回授等化器架構               | 28 |

|---|-----|-------|-----------------------|----|

|   | 3.5 | 決策    | 回授等化器電路設計             | 34 |

|   |     | 3.5.1 | 加法器                   | 34 |

|   |     | 3.5.2 | 電流模式邏輯閂鎖器             | 36 |

|   |     | 3.5.3 | 減法器                   | 38 |

|   |     | 3.5.4 | 多工器與乘法器               | 38 |

|   |     | 3.5.5 | 積分器                   | 40 |

|   |     | 3.5.6 | 决策回授等化器模擬結果           | 41 |

| 第 | 4章  | 時脈,   | 與資料回復電路之設計與實現         | 43 |

|   | 4.1 | 時脈    | 與資料回復電路架構             | 43 |

|   | 4.2 | 時脈,   | 與資料回復電路設計             | 44 |

|   |     |       | 相位偵測器                 |    |

|   |     | 4.2.2 | 迴路濾波器                 | 46 |

|   |     | 4.2.3 | 相位內插器                 | 50 |

|   |     | 4.2.4 | 時脈與資料回復電路模擬結果         | 60 |

|   | 4.3 | 接收    | 機模擬結果                 | 63 |

| 第 | 5章  | 佈局:   | 與量測結果                 | 66 |

|   | 5.1 | 晶片    | 佈局(Chip Layout)       | 66 |

|   | 5.2 | 量測    | 環境(Measurement Setup) | 67 |

| 第 | 6章  | 結論    |                       | 68 |

| 4 | 女士虎 | Ŀ     |                       | 60 |

### 圖目錄

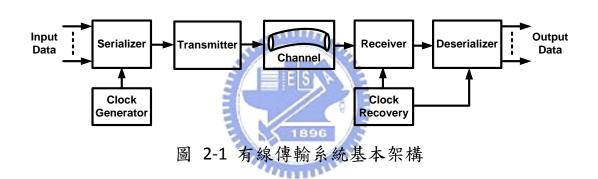

| 圖 | 2-1 有線傳輸系統基本架構                  | 3  |

|---|---------------------------------|----|

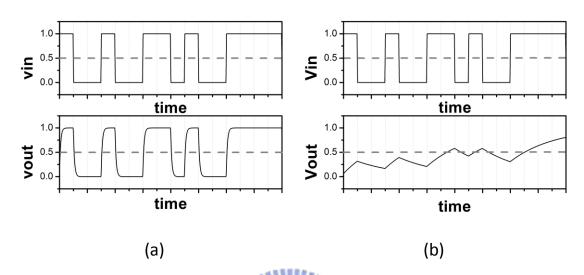

| 邑 | 2-2 (a) 通道頻寬足夠時之波形 (b) 通道頻寬不足時之 | -  |

|   | 波形                              | 5  |

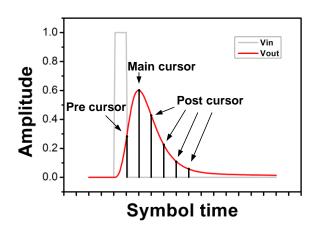

| 圖 | 2-3 通道頻寬不足下輸入脈衝響應的輸出波形圖         | 6  |

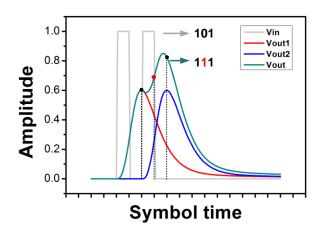

| 圖 | 2-4 輸入信號連續改變情形下的輸出波形圖           | 6  |

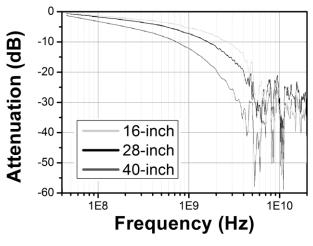

| 圖 | 2-5 不同通道長度下的頻率響應                | 7  |

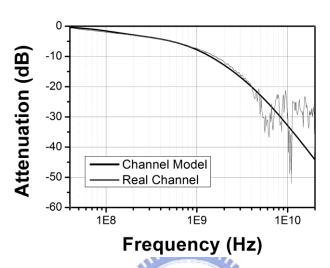

| 圖 | 2-6 28-inch 長的通道模型與量測的通道比較      | 8  |

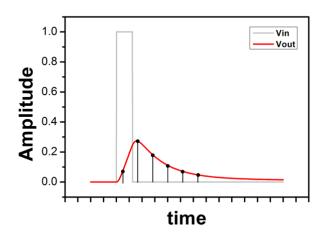

| 邑 | 2-7 28-inch 通道模型下輸入脈衝響應的輸出波形圖   | 8  |

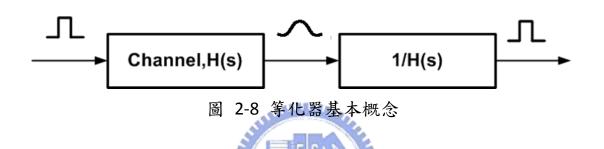

| 圖 | 2-8 等化器基本概念                     | 9  |

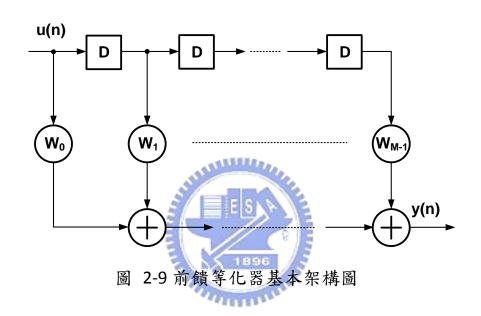

| 圖 | 2-9 前饋等化器基本架構圖                  | 11 |

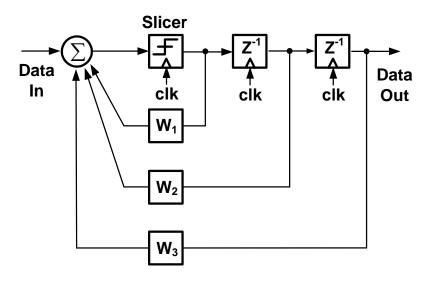

| 圖 | 2-10 決策回授等化器基本架構圖               | 12 |

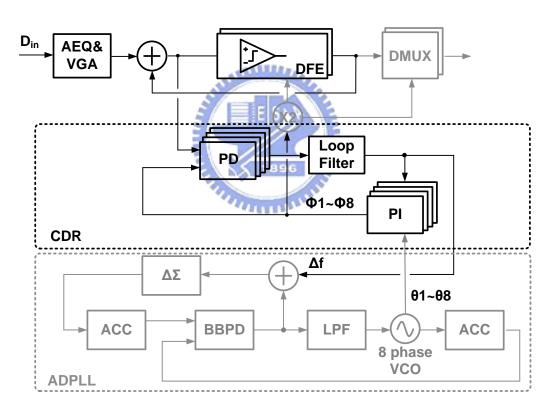

| 圖 | 3-1 接收機基本架構圖                    | 13 |

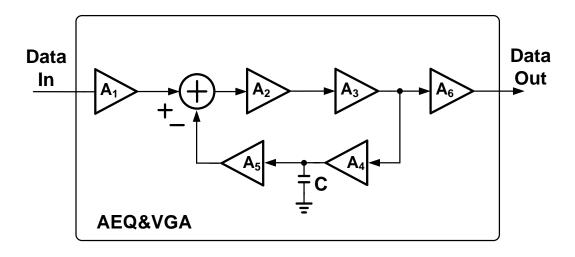

| 圖 | 3-2 類比等化器架構圖                    | 15 |

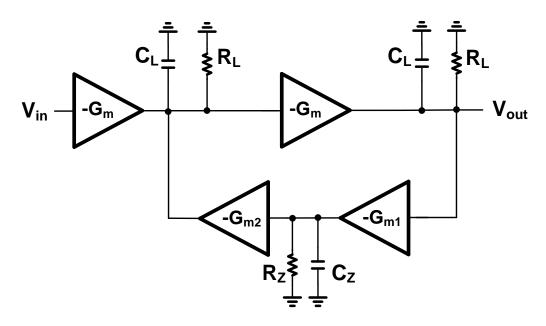

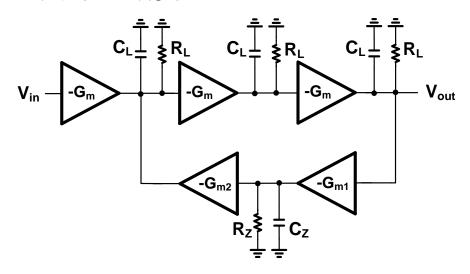

| 圖 | 3-3 二級式極點主動回授式濾波器電路圖            | 16 |

| 圖 | 3-4 三級式極點主動回授式濾波器電路圖            | 17 |

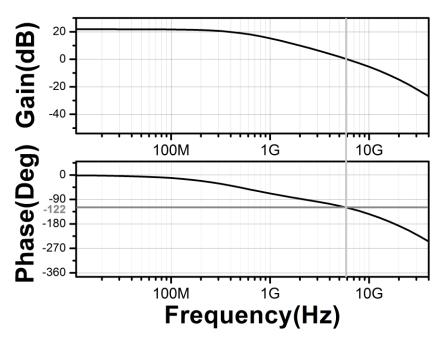

| 圖 | 3-5 穩定度模擬結果                     | 18 |

| 圖 | 3-6 極點主動回授式濾波器模擬結果              | 18 |

| 圖 | 3-7 可變增益放大器電路圖                  | 19 |

| 昌 | 3-8 類比等化器模擬結果                   | 20 |

| 圖 | 3-9 最佳化問題範例                     | 21 |

| 圖 | 3-10 有限脈衝響應濾波器                  | 21 |

| 昌 | 3-11 梯度下降法             | 23 |

|---|------------------------|----|

| 圖 | 3-12 梯度下降法與隨機梯度下降法比較   | 26 |

| 圖 | 3-13 M 階係數可調之有限脈衝響應濾波器 | 27 |

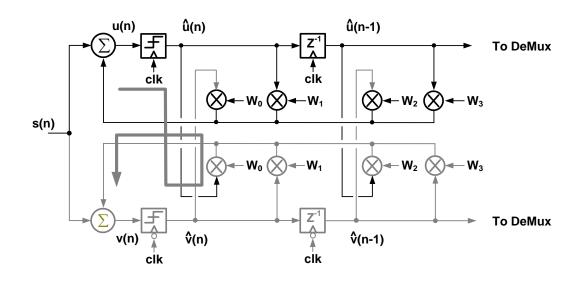

| 圖 | 3-14 基本決策回授等化器架構圖      | 28 |

| 圖 | 3-15 誤差量化器架構圖          | 30 |

| 圖 | 3-16 輸入對輸出的關係圖         | 31 |

| 圖 | 3-17 全速率決策回授等化器架構圖     | 31 |

| 圖 | 3-18 迴圈展開全速率決策回授等化器架構圖 | 32 |

| 圖 | 3-19 半速率決策回授等化器架構圖     | 33 |

| 圖 | 3-20 採用的決策回授等化器架構圖     |    |

| 圖 | 3-21 加法器電路圖            | 35 |

| 圖 | 3-22 傳統電流模式邏輯閂鎖器電路圖    | 36 |

| 圖 | 3-23 電流模式閂鎖器電路圖        | 37 |

| 圖 | 3-24 減法器電路圖            | 38 |

| 圖 | 3-25 多工器電路圖            | 39 |

| 圖 | 3-26 乘法器電路圖            | 40 |

| 圖 | 3-27 積分器電路圖            | 41 |

| 圖 | 3-28 眼圖模擬結果            | 42 |

| 圖 | 3-29 係數收斂結果            | 42 |

| 圖 | 4-1 時脈與資料回復電路架構圖       | 43 |

| 圖 | 4-2 相位偵測器架構圖           | 44 |

| 圖 | 4-3 相位偵測器架構圖           | 45 |

| 圖 | 4-4 斜率偵測電路圖            | 46 |

| 圖 | 4-5 迴路濾波器架構圖           | 47 |

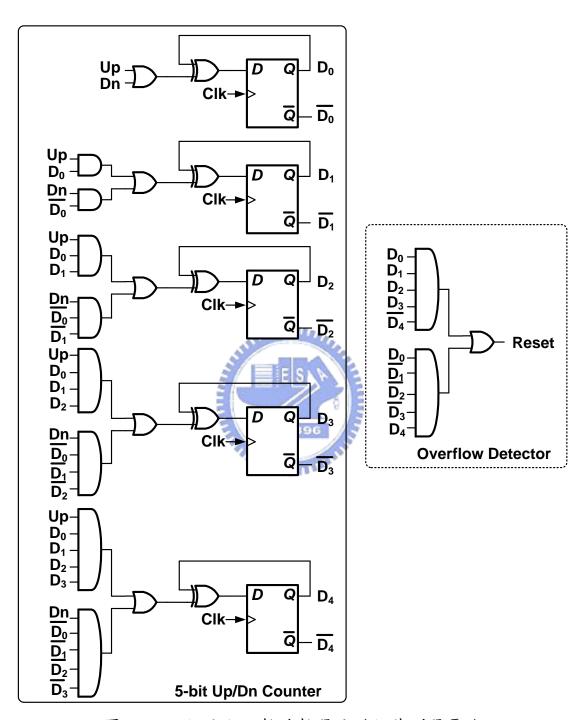

| 圖 | 4-6 五                 | .位元上下數計數器及溢位偵測器電路48    |

|---|-----------------------|------------------------|

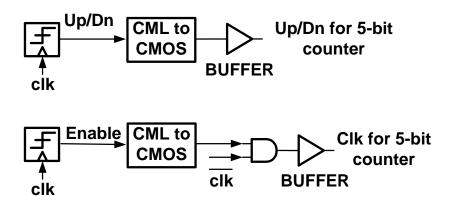

| 昌 | 4-7 五                 | 位元計數器的上下數信號與觸發時脈來源49   |

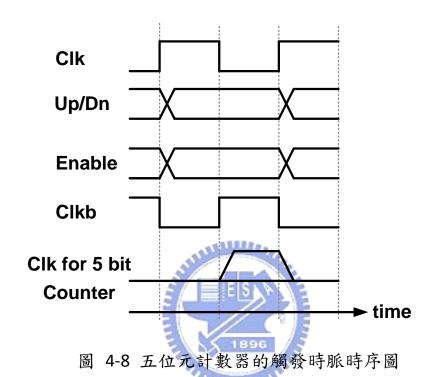

| 昌 | 4-8 五                 | 位元計數器的觸發時脈時序圖50        |

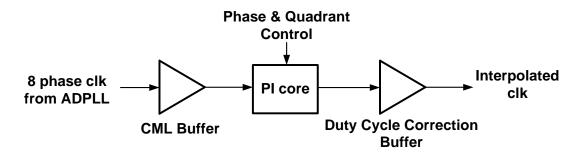

| 昌 | 4-9 相                 | 位內插器架構圖51              |

| 昌 | 4-10                  | 簡化的相位內插器核心電路51         |

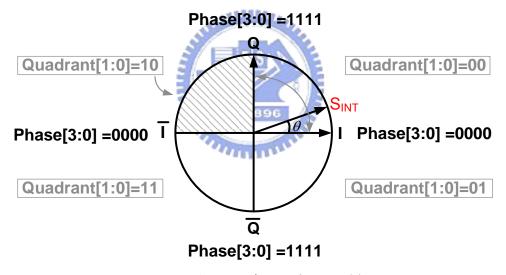

| 昌 | <b>4-11 </b>          | 極座標圖52                 |

| 圖 | 4-12                  | 電流式數位類比轉換器電路54         |

| 圖 | 4-13                  | 相位內插器核心電路54            |

| 昌 | 4-14                  | 相位內插器電路控制碼55           |

| 圖 | <b>4-15 </b>          | 输入級緩衝器電路56             |

| 圖 | <b>4-16 </b>          | 输入級緩衝器電路模擬圖56          |

| 圖 | <b>4-17 </b>          | 输出級緩衝器電路57             |

| 圖 | 4-18                  | 相位內插器經緩衝器輸出模擬圖58       |

| 昌 | <b>4-19</b> $\dagger$ | 相位內插器內插出的 16 相位模擬圖58   |

| 昌 | 4-20                  | 输入控制碼對輸出相位59           |

| 昌 | 4-21 F                | 內插相位 INL59             |

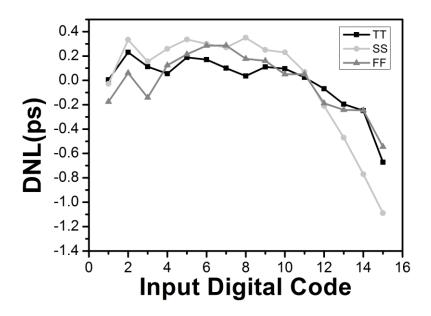

| 昌 | 4-22 J                | 內插相位 DNL60             |

| 昌 | 4-23 E                | <b>痔脈與資料回復電路模擬方法60</b> |

| 昌 | <b>4-24</b> B         | 痔脈與資料回復電路鎖定結果61        |

| 昌 | 4-25                  | 展頻時脈追蹤模擬結果(1)62        |

| 昌 | 4-26                  | 展頻時脈追蹤模擬結果(2)62        |

| 昌 | 4-27 ‡                | 接收機模擬眼圖63              |

| 圖 | 4-28                  | 输出時脈之眼圖64              |

| 圖 | 4-29 1                | <b>係數收斂情形64</b>        |

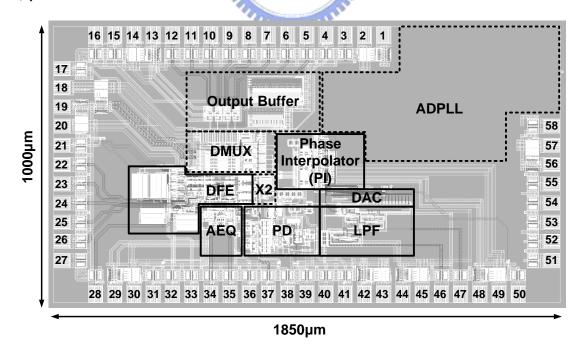

| 置 | 5-1 | 晶片佈局圖 | 66 |

|---|-----|-------|----|

| 圖 | 5-2 | 量測環境  | 67 |

# 表目錄

| 表 | 1-1 | 目前常見的有線傳輸規格 | 1  |

|---|-----|-------------|----|

| 表 | 4-1 | 相位偵測器真值表    | 45 |

| 表 | 4-2 | 總體功率消耗表     | 65 |

| 表 | 4-3 | 效能摘要表       | 65 |

#### 1.1 相關背景與動機

在現今高速發展的資訊時代下,對高速傳輸的需求與日俱增,但由於通道的頻寬有限,因此當傳輸速度持續上升時,通道頻寬的不足勢必是要面臨的問題。表 1-1 為目前常見的高速有線傳輸規格。如表所示,操作速度皆在 5Gb/s 以上。而在此操作速度之下,經過通道所造成的衰減非常嚴重,因此將會產生嚴重的符際干擾(Inter-Symbol Interference, ISI)問題,使得前後位元互相影響導致眼圖張不開,進而導致誤碼率(Bit Error Rate, BER)上升。

| 傳輸規格     | 傳輸速率  |

|----------|-------|

| SATA 3.0 | 6Gbps |

| PCIE 3.0 | 8Gbps |

| USB 3.0  | 5Gbps |

表 1-1 目前常見的有線傳輸規格

為了適當的補償由通道所造成的符際干擾效應,使接收到的訊號錯誤率降低,等化器成為高速傳輸中必要的電路,無論是在傳送端 [1]-[3]或接收端[4]-[6],甚至結合兩者[7][8]之各種不同的等化器技術已被提出。而由於通道的特性會隨環境而變,等化器必須要有隨環境改變自我調整等化係數的功能,因此適應性等化器在現今被廣泛的使 用。

由於本論文的目標為可應用在傳輸速率 8Gbps 的 PCIE3.0 傳輸規格。此規格下為了解決電磁干擾 (Electromagnetic Interference, EMI) 效應,將加入展頻時脈(Spread-Spectrum Clocking)的技術。其原理是將原本時脈的中心頻率加以展頻使得能量能夠平均分散在附近的頻率上,因此中心頻率的能量將往下降低,同時高頻諧波項也將因此而分散能量,以達到抑制電磁干擾的效果[9]。

本論文將提出一個採用 sign-sign LMS 演算法為基礎以適應性消除符際干擾問題之完整接收器架構,同時包含了追蹤展頻時脈的功能。 展頻時脈之目標規格為由中心頻率向下展頻 5000ppm,而改變頻率為 33KHz。

#### 1.2 論文概要

本論文主要分六個章節,第一章,說明相關背景和動機;第二章,介紹高速序列傳輸的基本架構及遇到的問題,此外會對使用在接收端的等化器類型做基本的介紹;第三章,介紹完整的接收機架構,並對其中等化器的架構和設計考量做一說明,適應性等化器所使用的最佳化演算法也會在這章中一併做簡介;第四章,對時脈與資料回復電路的架構和設計考量做一介紹;第五章,實驗結果和量測;第六章,結論。

### 第2章 高速有線傳輸基本觀念簡介

#### 2.1 有線傳輸系統基本架構

一個基本的有線傳輸系統架構如下圖 2-1 所示,可分為平行序列轉換器(Serializer)、時脈產生器(Clock Generator)、傳送器(Transmitter)、通道(Channel)、接收器(Receiver)、時脈回復電路(Clock Recovery)以及序列平行轉換器(Deserializer)等部分。

由於高速平行資料傳輸會遇到資料間互相干擾以及傳輸線佔面積等問題,因此現行的高速有線傳輸系統均採用序列的方式進行傳輸。多個低速且平行的全擺幅資料將會經由平行序列轉換器轉換成單筆高速且擺幅較小的序列資料,而此平行序列轉換器的時脈將由時脈產生器提供。擺幅較小的訊號能比全擺幅訊號有更快的傳送速度且能降低功率的損耗。此較小擺幅的高速序列資料將會經由傳送器處理過後傳入通道,傳送器通常為一驅動器,目的在於加強訊號的推動能力。此外部分系統中的傳送器可能還會加上預加強(pre-emphasis)的功能,以預先彌補通道的高頻衰減。通道的部分通常是光纖、同軸電纜線以

及印刷電路板等材質。經過通道的訊號將由接收器加以接收,而接收器主要的作用在於判決出接收到的資料,但前提是必須要有時脈回復電路提供正確的時脈訊息,此外在高速傳輸時通常會加入等化器(Equalizer)的功能,將訊號通過通道造成的衰減補償回來。時脈回復電路的目的在於設法從接收到的資料中擷取出時脈的訊息,以提供給接收器將資料正確的判斷出來。最後判決出的資料會經由序列平行轉換器,轉換為慢速的平行資料以供後端使用。

#### 2.2 符際千擾(Inter-Symbol Interference, ISI)

如上節所述,有線傳輸必須經過通道。但隨著傳輸頻率的上升, 集膚效應(skin effect)與電介質損失(dielectric loss)將會越加嚴重,此將 導致通道之頻率響應隨頻率上升有更加嚴重的衰減。其中集膚效應為 當頻率很高的電子在導體中傳導時,並不會平均分佈於整個導體的截 面積中,而是只聚集於導體表層。由於此情形等效於導體的截面積減 小,因此結果將導致導體的等效電阻增加。至於電介質損失則是由於 介質中的原子受到了電磁波的擾動而消耗掉了電磁波的能量。頻率越 高,上述兩效應將會越嚴重,導致了前面所述之越高頻,頻率衰減越 嚴重的情形。

通道頻寬的不足,將會導致資料充放電的速度變慢。如下圖 2-2 所示,其中圖 2-2(a)為通道頻寬足夠時的圖形,而圖 2-2(b)為頻寬不足時的圖形。明顯的,當頻寬不足時,訊號無法在一個位元時間內完成充放電到目標電壓的動作。此將導致每一位元都會受到前後位元未完成充放電動作的影響,此影響即稱之為符際干擾(Inter-Symbol

Interference, ISI)。由圖可知,最終將導致在判斷資料時產生誤判。因此在高速有線傳輸中符際干擾成為所面臨的最重要課題。

圖 2-2 (a) 通道頻寬足夠時之波形 (b) 通道頻寬不足時之波形

接著進一步說明符際干擾的成因,試著在通道頻寬不足的情形下輸入一個寬度為傳輸資料一位元時間的脈衝響應,如圖 2-3 所示,觀察其輸出結果可發現,由於訊號的高頻成分在通過通道時受到了衰減,因此輸出的充放電速度減緩了許多。在此例子中,需花兩位元的時間才能充電到最高峰,而放電更需花四位元以上的時間才能完成。由於我們可將實際傳輸的資料視為多次脈衝響應的疊加,因此未完成的充放電行為將會嚴重的影響到前後的位元。

圖 2-3 中輸出波形最高的部分定義為主指標(Main-cursor),而在 主指標之前一個位元時間的部分,代表著對前面位元的干擾,因此定 義為前指標(pre-cursor),至於在主指標之後 N 個位元時間的部分代表 著對後面位元的干擾,將定義為後指標(post-cursor)

圖 2-3 通道頻寬不足下輸入脈衝響應的輸出波形圖

圖 2-4 為輸入信號 101 時的輸出波形,由於我們可將輸入訊號拆解成兩個脈衝響應,因此輸出也可視為兩個脈衝響應經通道後輸出的疊加,由圖 2-4 可以很明顯的發現,當通道頻寬不足時,脈衝響應經過道的輸出將會互相的影響。因此雖然輸入為 101,因此中間的BIT 為 0,但輸出會受到前後 BIT 充放電速度過慢的影響,而造成誤判成 1 的情形。由此例子可知,符際干擾對資料傳輸的判斷有很大的影響,因此如何適當的消去符際干擾即為本論文欲達成之目標。

圖 2-4 輸入信號連續改變情形下的輸出波形圖

#### 2.3 通道模型

在要對符際干擾做處理之前,首先必須知道欲處理目標其符際干擾之情形,因此必須先建立出通道的模型,以利於之後的處理。如 2.1 節所述,高速有線傳輸所使用的通道有許多種材質。而由於本論文的架構是針對 PCIE3.0 的規格設計,因此接下來將針對 PCIE3.0 所使用的背板傳輸通道建立出通道模型。

圖 2-5 為不同通道長度之下量測出的頻率響應,如圖所示頻率響應也會隨著通道長度的增加而衰減。可以發現 28-inch 的通道在目標傳輸速率的一半頻率(4GHz)上約有 20dB 的衰減,接著將先針對 28-inch 的通道長度建立模型。

圖 2-5 不同通道長度下的頻率響應

根據 28-inch 通道量測到的結果,我們可以以極零點分析來模擬通道,如式(2-1)所示,使用了一個零點與四個極點,來模擬通道的頻率響應。圖 2-6 為通道模型與量測到的頻率響應結果比較,可看出在4GHz內,頻率響應有非常高的符合度,誤差小於 1dB。

$$H(s) = \frac{\left(1 + \frac{s}{\omega_{z1}}\right)}{\left(1 + \frac{s}{\omega_{p1}}\right)\left(1 + \frac{s}{\omega_{p2}}\right)\left(1 + \frac{s}{\omega_{p3}}\right)\left(1 + \frac{s}{\omega_{p4}}\right)}$$

(2-1)

圖 2-6 28-inch 長的通道模型與量測的通道比較

接著輸入脈衝響應至此通道模型,由圖 2-7 所示,可看出建立的通道模型之符際干擾會有一個前指標及四個後指標需要消除。

圖 2-7 28-inch 通道模型下輸入脈衝響應的輸出波形圖

#### 2.4 等化器簡介

等化器的基本概念如圖 2-8 所示,如果已知通道的頻率響應為 H(s),只要能設法產生出頻率響應為 1/H(s)的濾波器,即可有效的補 償掉通道的頻率響應,使經過通道以及濾波器之後的輸出波形與未經 過通道前完全一樣。

但要能夠準確的將通道的頻率響應找出,並設法製造頻率響應為 其反函數的濾波器是極為困難的。除此之外,通道本身的頻率響應也 有可能會隨著時間而改變,因此濾波器的轉移函數也需要能夠隨著通 道的變化一起跟著變化,此即為適應性等化的基本概念。

現今在接收端所使用的等化器主要可被分為兩種形式,分別是類比等化器以及離散時間等化器。其中類比等化器為線性結構的等化器,其概念為直接對通道的頻率響應做等化,由於通道有越高頻衰減越多的特性,因此這類的等化器通常直接提供高頻增益以補償通道。其主要優點為由於是直接針對通道的頻域進行補償,因此能夠同時消除前指標與後指標的符際干擾,而且不需要時脈即可運作。但其主要缺點為在提供高頻增益的同時,也會同時對高頻的雜訊進行放大進而降低了雜訊邊限(Noise Margin),除此之外受限於自身電路的頻寬影響,

能提供的高頻增益將是有限的,此兩缺點將會導致當面臨到通道衰減 很嚴重的情形時,光靠類比等化器無法非常有效的補償通道。

此外,若想將類比等化器加入適應性等化的機制[10][11],通常是使用比較頻譜分佈的技術,此種方式由於需要利用到濾波器將訊號先做高低通的處理,因此需要準確的定義出濾波器的轉角頻率。但設計出之轉角頻率若隨著製程的漂移而改變,將會嚴重的影響到等化的效果,因此對設計上的考量非常嚴苛。

離散時間等化器有別於類比等化器針對頻域進行補償,而是直接針對時域進行補償,根據等化器能補償的符際干擾類型還能進一步的區分為前饋等化器(Feed Forward Equalizer)及決策回授等化器(Decision Feedback Equalizer)。其中前饋等化器將能同時消除前指標與後指標的符際干擾,而決策回授等化器只有能力處理後指標的符際干擾。此外,由於離散時間等化器是在資料的取樣時間點上做等化,因此較容易使用一些演算法做最佳化的運算以達到適應性等化的效果。

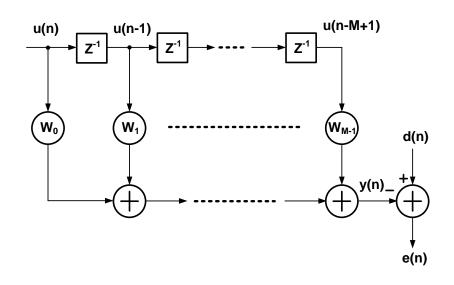

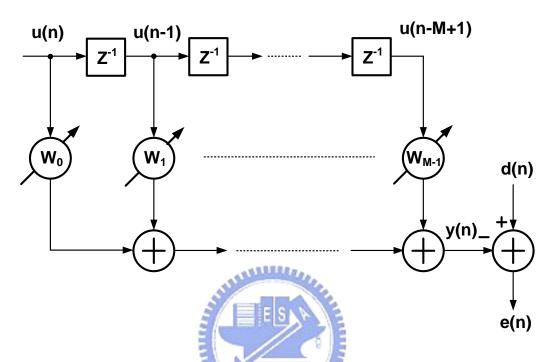

前饋等化器基本架構如圖 2-9 所示,為一個可控制係數的有限脈衝響應濾波器。輸入信號 u(n)經過延遲單元(D)的延遲後乘上係數(W<sub>n</sub>)之結果相加後輸出,適當的調整係數將能有效的消去包含前指標與後指標之符際干擾,是個非常有效的等化器架構。其根據延遲單元的實現方式不同又可分為數位延遲單元與類比延遲單元[12][13]兩種實現的架構。

由於數位延遲單元實現,需先將輸入訊號由類比訊號轉為數位的形式,之後才能使用數位的區塊做延遲。因此在輸入端需要一個非常高速且高解析度的類比數位轉換器,隨著傳輸資料速度的上升,此架

構的實現將會越加困難。而類比實現的延遲單元雖然不需要類比數位轉換器,但由於延遲的資料為高速的類比訊號,故在當速度更高時,要將延遲單元之延遲時間設計的非常準確是很大的挑戰。因此前饋等化器,雖然有著能同時消去前指標與後指標的優點,但在高速電路的實現上,有嚴重的課題需要面對。

決策回授等化器基本架構如圖 2-10 所示,相較於前饋等化器, 決策回饋等化器是一有回授路徑的系統架構。其操作方式為先將資料 經由一切片機(Slicer)量化為一位元資料,再經延遲單元延遲後乘上係 數值,輸入的訊號將會減去此回授回來的乘積值。如果能適當的調整 係數,則此回授回來的乘積值將會有消去後指標的效果。與前饋等化 器相比,由於此架構不需高速的類比數位轉換器而是以一位元高速切 片機取代,因此在實現上的困難度將會大大的降低,不過無法消去前 指標的符際干擾是此架構的最大缺點。

圖 2-10 決策回授等化器基本架構圖

### 第3章 等化器之設計與實現

#### 3.1 接收機架構

本論文的系統架構將如圖 3-1 所示(圖中黑線的部分將是本論文 所包含的部份),主要包含了類比等化器(AEQ)、決策回授等化器(DFE) 以及時脈與資料回復電路(CDR)三個部分。

圖 3-1接收機基本架構圖

綜合 2.4 節的討論,本架構採用了類比等化器串接決策回授等化器的形式,由類比等化器(AEQ)提供部分的頻率補償,在此將設計能提供 10dB 的增益峰化(gain peaking)值在輸入訊號的一半頻率上,以

同時消去前指標與部分的後指標符際干擾,此外由於決策回授等化器之演算法收斂需要一定的輸入範圍,因此類比等化器還結合了一個可變增益放大器(VGA),以調整輸出振幅到下一級可接受的範圍。接著訊號再由決策回授等化器(DFE)將剩餘的後指標符際干擾消除。其中決策回授等化器將使用 sign-sign LMS 演算法的機制達到適應性等化的效果。而由於決策回授等化器需要提供適當的時脈才能正確的運作,因此我們也結合了一個時脈與資料回復電路(CDR),以提供時脈給決策回授等化器使用。此時脈與資料回復電路同時包含了追蹤展頻時脈的功能。接著在 3.2 節將介紹類比等化器,3.4 及 3.5 節中則會說明決策回授等化器的架構與設計,最後在第 4 章中介紹時脈與資料回復電路的設計。

### 3.2 類比等化器架構與電路設計

#### 3.2.1 類比等化器架構

由於本論文的目標是針對 PCIE3.0 的傳輸規格設計,因此輸入訊號的速率將為 8Gbps。而由 2.4 節所述,類比等化器提供高頻增益的同時由於會一起放大高頻雜訊,因此我們並不希望提供太大的增益峰化值。在此我們將補償的目標設定在當頻率為輸入資料頻率一半,意即 4GHz 時有最高的增益峰化值 10dB。使用的類比等化架構如圖 3-2 所示,其中  $A_1$ ~ $A_5$  皆為增益固定的基本放大器,而  $A_6$ 為一可變增益放大器(Variable Gain Amplifier,VGA)。

圖 3-2 類比等化器架構圖

整個架構之操作基本原理為在回授路徑中將會加入一電容(C)以產生可控制的極點,此極點將會成為閉迴路中的零點而達到產生增益峰化的功能。至於 A<sub>6</sub> 為可變增益放大器的目的在於後級串接的決策回授等化器必須要有一定的輸入範圍,其使用的演算法才能夠收斂。我們將可變增益的範圍目標值設定在±3dB,並要求有 8GHz 的頻寬。在此將 A<sub>1</sub>~A<sub>5</sub>稱之為極點主動回授式濾波器,而 A<sub>6</sub>為可變增益放大器,在下面的章節將會對電路分上述兩部分做更進一步的分析。

#### 3.2.2 極點主動回授式濾波器

極點主動回授式濾波器架構如圖 3-3 所示。如同之前所述,設計目標為在 4GHz 時能提供最高的增益峰化值 10dB。圖 3-3 中之-Gm區塊皆為基本的源級耦合差動對電路,Cz 為外加的電容及那點原本的輸出負載電容之總和。推導之轉移方程式如式(3-1)所示:

圖 3-3 二級式極點主動回授式濾波器電路圖

$$A(s) = \frac{-G_{m}R_{L}}{(1 + sR_{L}C_{L})}$$

$$\beta(s) = \frac{G_{m1}R_{z}G_{m2}R_{L}}{(1 + sR_{z}C_{z}) \times (1 + sR_{L}C_{L})}$$

$$T(s) = A(s) \times \frac{A(s)}{1 + \beta(s)A(s)}$$

$$= \frac{\left[\frac{G_{m}R_{L}}{(1 + sR_{L}C_{L})}\right]^{2}}{1 + \frac{G_{m1}R_{z}G_{m2}R_{L}}{(1 + sR_{L}C_{L})} \times \frac{G_{m}R_{L}}{(1 + sR_{L}C_{L})}}$$

$$= \frac{(1 + sR_{z}C_{z})(G_{m}R_{L})^{2}}{(1 + sR_{L}C_{L})^{2}(1 + sR_{z}C_{z}) + (G_{m1}R_{z}G_{m2}R_{L}G_{m}R_{L})}$$

$$= \frac{(G_{m}R_{L})^{2}(1 + sR_{z}C_{z})}{\left[(1 + G_{m1}R_{z}G_{m2}R_{L}G_{m}R_{L}) + s \times (2R_{L}C_{L} + R_{z}C_{z})\right]}$$

$$= \frac{(G_{m}R_{L})^{2}}{(1 + G_{m1}R_{z}G_{m2}R_{L}G_{m}R_{L})} \times \frac{(1 + \frac{s}{\omega_{z}})}{(1 + \frac{s}{\omega_{m1}})(1 + \frac{s}{\omega_{m2}})(1 + \frac{s}{\omega_{m3}})}$$

由式(3-1)的推導結果可以得知回授路徑上的極點 $(1/R_zC_z)$ 直接等同於閉迴路上之零點,因此可得知預設計的零點位置 $\omega_z=1/R_zC_z$ ,此外 $\omega_{p1}$ 與 $\omega_{p2}$ 為一組位置受主動回授濾波器本身架構頻寬所影響的高頻共軛根而 $\omega_{p3}$ 為一個更高頻的實數根。

由於目標為在 4GHz 提供 10dB 增益峰化,因此我們可計算出閉迴路的零點頻率並由此決定外掛電容大小。因設計之極點離主動回授濾波器自身的高頻寬極點遙遠,而迴路增益又不高的情形下,此架構並不會有穩定性的問題。故即使將主動回授濾波器電路變成三級式以提高迴路增益(Loop gain),藉此增加回授系統整體增益響應的線性度仍不會造成穩定性不足的問題。三級式主動回授濾波器架構如圖 3-4 所示。圖 3-5 則為三級式電路的穩定度模擬結果,如同之前所述,由於設計的極點離電路自身的頻寬遙遠,且迴路增益不高,因此有足夠的相位邊限(phase margin)。模擬結果所得的相位邊限為 58 度,因此我們可以確保閉迴路的穩定性。

圖 3-4 三級式極點主動回授式濾波器電路圖

圖 3-5 穩定度模擬結果

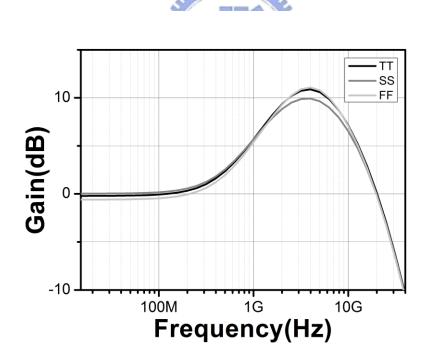

圖 3-6 極點主動回授式濾波器模擬結果

圖 3-6 則為電路模擬結果,可看出確實如設計目標,在 4GHz 時, 有大約 10dB 的增益峰化。

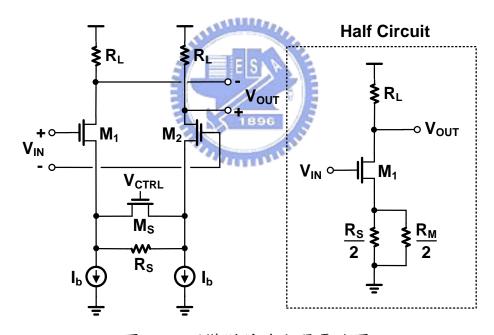

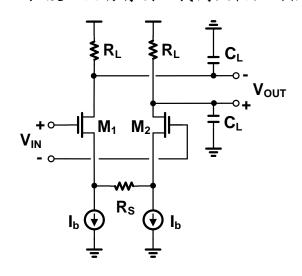

#### 3.2.3 可變增益放大器

可變增益放大器電路如圖 3-7 所示,為一在源極端加上源極退化電阻(R<sub>S</sub>)並聯一個可控制閘極電壓之電晶體(M<sub>S</sub>)的差動對電路。其等效之半電路如圖 3-7 右邊所示,其中 R<sub>M</sub> 為電晶體(M<sub>S</sub>)之等效電阻,藉由此半電路,可寫出電路的轉移方程式(3-2)如下:

$$A_{v}(s) = \frac{g_{m}R_{L}}{1 + g_{m}\left(\frac{R_{s}}{2}||\frac{R_{M}}{2}\right)} \times \frac{1}{1 + s/\omega_{p}}$$

(3-2)

其中 $\omega_p = 1/R_L C_L$ , $C_L$ 為此電路的輸出負載電容。

圖 3-7 可變增益放大器電路圖

由於可變增益放大器不希望影響到前級類比等化器的輸出結果, 因此首先需確保此電路有足夠的操作頻寬。類比等化器的目的為在 4 GHz 的頻率上提供 10dB 的增益峰化值,而在不希望影響到增益峰化值大小的條件下,需將可變增益放大器的頻寬設計的比 4 GHz 還大, 最後將此電路頻寬設計為 8 GHz。而由式子(3-2)可知,頻寬是由輸出 負載電容(CL)以及負載電阻(RL)決定,故我們可以調整負載電阻以改變 頻寬達到要求。此電路之低頻增益可以表示為式子(3-3)如下:

$$A_{v}(0) = \frac{g_{m}R_{L}}{1 + g_{m}\left(\frac{R_{S}}{2}||\frac{R_{M}}{2}\right)} \approx \frac{2R_{L}}{R_{S}||R_{M}}$$

(3-3)

由式子(3-3)可知,透過調整電晶體(M<sub>S</sub>)的等效電阻值(R<sub>M</sub>),將可達到調整放大器低頻增益的目的。而當電晶體的源極電壓與汲極電壓非常接近時,此電晶體將操作在三極體區,此時電晶體的等效電阻公式(3-4)如下:

$$R_M = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{gs} - V_t)}$$

(3-4)

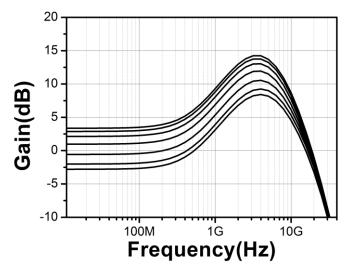

明顯的,可藉由調整電晶體(M<sub>s</sub>)的閘極電壓(V<sub>gs</sub>)大小達到改變其 等效電阻進而達到調整整個放大器增益的目的。最後,圖 3-8 為整個 類比等化器模擬結果,包含在 4GHz 有約 10dB 的增益峰化,以及±3dB 的增益可調範圍。

圖 3-8 類比等化器模擬結果

### 3.3 最小均方演算法(Least Mean Square Algorithms)

在這節,將會稍微介紹一下本論文使用的最小均方演算法之演進 [14],以及如何應用在本論文的系統之上。

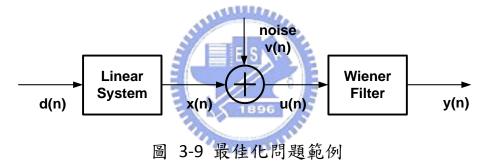

首先考慮一最佳化問題,如圖 3-9 所示,假設有一輸入信號 d(n),經過一個線性系統後成為 x(n), x(n)與雜訊 v(n)相加後成為 u(n),此 u(n)將會經過一個有限脈衝響應濾波器(如圖 3-10)成為 y(n)。希望經過濾波器處理後的訊號 y(n)能與輸入信號 d(n)相同,亦即使定義之誤差 e(n)=d(n)-y(n)能夠為零。因此目標為設法找出最適當的濾波器係數以達到上述要求。

圖 3-10 有限脈衝響應濾波器

為了達成上述目標首先我們先定義均方差(mean square error)  $J=E[e^{2}(n)] ,接著由於使用的是有限脈衝響應濾波器,因此我們可將$ 其係數(3-5)與輸入信號(3-6)以矩陣表示如下:

$$\mathbf{W} = [W_0 \quad W_1 \quad \dots \quad W_{M-1}]^T \tag{3-5}$$

$$\mathbf{u}(n) = [u(n) \quad u(n-1) \quad \dots \quad u(n-M+1)]^T$$

(3-6)

因此濾波器的輸出 y(n)即可用內積表示如下式:

$$y(n) = \mathbf{W}^T \mathbf{u}(n) \tag{3-7}$$

代入式(3-7)我們可以改寫均方差(3-8)如下式:

$$J = E[e^{2}(n)] = E\{[d(n) - y(n)]^{2}\}$$

$$= E\{[d(n) - W^{T}u(n)]^{2}\}$$

(3-8)

接著我們將均方差對濾波器係數做偏微分的動作, 可推出式子 (3-9)如下:

$$\frac{\partial J}{\partial \mathbf{W}} = \frac{\partial E\{[d(n) - \mathbf{W}^T \mathbf{u}(n)]^2\}}{\partial \mathbf{W}}$$

$$= -E\{\mathbf{u}(n)[d(n) - \mathbf{W}^T \mathbf{u}(n)]\}$$

$$= R\mathbf{W} - \mathbf{P}$$

(3-9)

其中 R、P 如下雨式(3-10)、(3-11)所示:

$$\mathbf{R} = E\{\mathbf{u}(n)\mathbf{u}^{T}(n)\}\tag{3-10}$$

$$\mathbf{P} = E\{\mathbf{u}(n)d(n)\}\tag{3-11}$$

由於微分結果為零代表此時有極值,因此直接令上述偏微分結果為零,即是在求當濾波器係數為何時,均方差能有最小值。故我們可將此時求得的濾波器係數定義為  $W_{opt}$ ,表示如下:

$$RW_{opt} = P \rightarrow W_{opt} = R^{-1}P \tag{3-12}$$

此結果稱為 Wiener Solution,藉由此方法,將可得到最佳的濾波器係數  $W_{opt}$  使定義的均方差最小化。

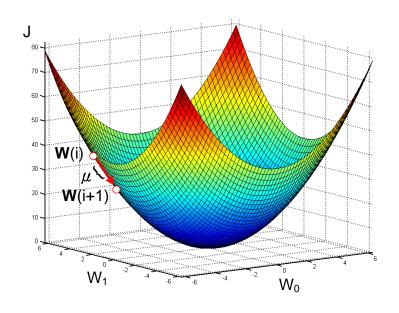

由於 Wiener Solution 是一次就算出最佳化係數,且方程式(3-12)中包含著反矩陣的運算,因此需要相當龐大的運算量。若能設法以遞迴的方式得到答案,慢慢地將係數更新至目標值,則將可大幅降低運算量。一個常見的方法為梯度下降法(Gradient Descent,GD),如圖3-11 所示,目標設在均方差最小的底部,此方法並不馬上找出底部所在的位置,而是藉由找出目前所在位置的梯度方向,接著遞迴前進,如此將可快速的到達目標位置。

圖 3-11 梯度下降法

實際演算流程如下:首先隨意猜測一個位置,其座標為 W=W(0),接著找出此點梯度方向,其找法即為將均方差對濾波器係數做偏微分如式(3-13)所示,其中i代表做第i次的遞迴運算,最後由找出的梯度方向遞迴更新位置,如(3-14)所示。其中 µ代表一次更新量的大小,其將會決定到達底部速度之快慢。如此遞迴運算下去,最終可得到最佳的濾波器係數 W 使均方差最小化。

$$\nabla\{J[W(i)]\} = \frac{\partial E\{[d(n) - W^{T}(i)u(n)]^{2}\}}{\partial W(i)}$$

$$= -2E\{u(n)e(n)\}$$

$$= -2E\{u(n)[d(n) - u^{T}(n)W(i)]\}$$

$$= -2P + 2RW(i)$$

$$= -2P + 2RW(i)$$

$$= W(i) - \frac{1}{2}\mu\nabla\{J[W(i)]\}$$

$$= W(i) + \mu[P - RW(i)]$$

(3-14)

注意到與之前 Weiner Solution 不同之處在於運算過程中雖然一樣 取偏微分卻不令偏微分結果為零,如此運算式中將不會有反矩陣的存 在,因此大大的降低了運算量。

梯度下降法與 Weiner Solution 相比雖然減少了運算量,但由於仍需計算出 P 以及 R,此為期望值之計算,此外式(3-14)中的 RW(i)為矩陣運算,因此仍需要不少的運算量。因此更進一步的我們可將期望值:亦即多次事件的平均,改為一個事件長時間的平均。如此可將計算梯度的方式近似如下式(3-15)所示:

$$\nabla \{J[\mathbf{W}(i)]\} = -2E\{\mathbf{u}(n)e(n)\} \approx (-2)\frac{1}{L}\sum_{n}\mathbf{u}(n)e(n)$$

(3-15)

其中L代表著多長時間取一筆平均,L越小,代表取較少筆資料做平均,因此計算出的梯度將會較為不準,但由於資料較少,因此能較快的更新資料以調整梯度方向。反之L越大,雖然估算出的梯度較為準確,不過卻要很久才能調整一次方向,因此各有優劣。將式(3-15)代入(3-14)可得新的遞迴公式(3-16),如下:

$$W(i+1) = W(i) - \frac{1}{2} \mu \nabla \{J[W(i)]\}$$

$$= W(i) + \mu E\{u(n)e(n)\}$$

$$\approx W(i) + \mu \frac{1}{L} \sum_{n} u(n)e(n)$$

(3-16)

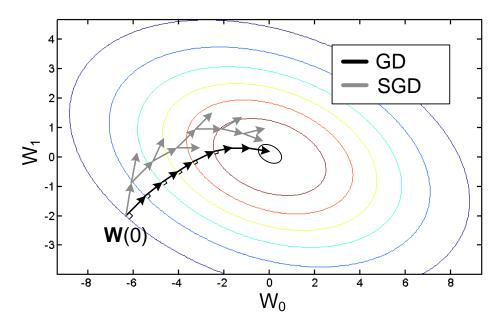

注意到以此近似法所計算出的梯度、將不是真正的梯度方向,因此稱之為隨機梯度下降法(Stochastic Gradient Descent,SGD),雖然近似出的梯度並不是真正的梯度,但若將真正的梯度與近似的梯度兩者皆取期望值後可發現,真正的梯度(亦即多次事件平均)再取期望值與近似出的梯度(亦即一次事件長時間的平均)再取期望值將會相同。如圖3-12 所示,令最小圓的圓心為最小均方差的位置。原本的梯度下降法,因為垂直的方向即為梯度方向,因此將會每次都往垂直的方向前進,而隨機梯度下降法卻是往隨機的方向前進。但由於之前所說,兩者再取期望值後結果相同,因此可得知,雖然方向隨機前進,但最後的目的地將會相同,一樣會朝能達到最小均方差的位置前進。

圖 3-12 梯度下降法與隨機梯度下降法比較

接著更進一步的,我們將長時間的平均,改為每筆資料皆取一次平均,亦即令 L=1,此法即稱之為最小均方演算法(Least Mean Square Algorithms)。由於每筆資料均取平均輸出,因此遞迴運算的次數 i 將會與資料的時間 n 相同。因此可將隨機梯度下降法的遞迴運算更新如式(3-17)所示:

$$W(n+1) = W(n) + \mu E\{u(n)e(n)\}$$

$$= W(n) + \mu u(n)e(n)$$

(3-17)

注意到現在的運算並不包含了期望值以及矩陣的運算,因此再次 大量的降低了運算量。最後將最小均方演算法需實現的運算整理如下, 主要需實現三個方程式,首先必須要有一個 M 階可調整係數的有限 頻率響應濾波器,如圖 3-13 所示,濾波器輸出 y(n)將可表示如下式 (3-18)所示:

$$y(n) = \mathbf{W}^T \mathbf{u}(n) = \sum_{i=0}^{M-1} W_i(n) \cdot u(n-i)$$

(3-18)

圖 3-13 M 階係數可調之有限脈衝響應濾波器

接著運算出其誤差值 e(n),其中 d(n)為目標值,如下式(3-19)所示:

$$e(n) = d(n) - y(n)$$

(3-19)

最後將此運算出的誤差與輸入資料做運算處理後,更新有限脈衝響應濾波器的係數,如式(3-20)所示,即可遞迴的算出最佳係數以得到最小的均方差,注意到 µ 將決定收斂速度的快慢,以及收斂後的誤差值。

$$\boldsymbol{W}(n+1) = \boldsymbol{W}(n) + \mu \boldsymbol{u}(n)e(n) \tag{3-20}$$

值得注意的是使用遞迴的運算求出係數,還擁有一個極大的優點 在於由於最小均方演算法的運算資料將隨環境改變而變,因此濾波器 係數也能隨著環境改變而自我調整,達到適應性等化的效果。

最後為了便於電路方面的實現,將上述的誤差項 e(n)以及資料項 u(n)皆取極值,亦即將上述兩資料判決為一位元的輸出,稱為 sign-sign LMS 演算法。因此遞迴方程式能將之改寫為式(3-21)所示:

$$W(n+1) = W(n) + \mu \cdot sign[u(n)] \cdot sign[e(n)]$$

(3-21)

此演算法相較於傳統最小均方法,缺點為收斂較慢及誤差相對較 大,但由於大幅降低了硬體的複雜度,因此是現今最流行的作法。

### 3.4 決策回授等化器架構

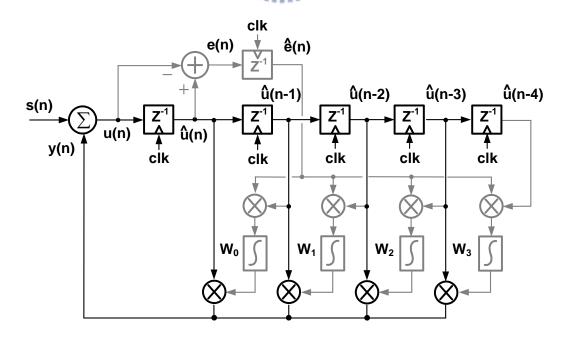

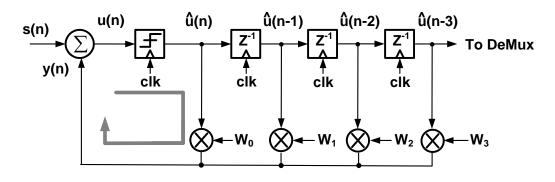

由前一節演算法之說明,可得知為了實現,架構上需包含一個有限脈衝響應濾波器,一個誤差產生器,以及一個能遞迴運算並調整有限脈衝響應濾波器係數的區塊。最後架構將如圖 3-14 所示[15]。

圖 3-14 基本決策回授等化器架構圖

此為一個混合式訊號電路架構,黑線部分為四階的有限脈衝響應 濾波器加上處理回授信號的加法器。來自類比等化器輸出的類比訊號 S(n),與回授回來的訊號 y(n)相加後獲得訊號 u(n),此訊號將經由切 片器量化為一位元訊號,並經過延遲後,乘上濾波器係數輸出至加法 器。注意到由於之前通道的脈衝響應模擬結果,有四個後指標需要消 除,因此我們採用了四階的濾波器架構。

圖 3-14 中灰線的部分為 sign-sign LMS 演算法的實現電路,包含了一個減法器以計算出誤差值,一個切片器將誤差值量化為一位元訊號,及四組乘法器與積分器組成的係數遞迴運算電路以實現式(3-22),由此部分架構可看出使用 sign-sign LMS 演算法的最大優點,即是將乘法器簡化為一位元的運算,因此大大的降低了電路複雜度。而由於積分器我們將以一個充電泵(charge pump)對電容充放電的方式實現,因此式(3-22)中的 W 將會是存在四個積分器電容上的電壓值,在每個位元時間內對此電容做充放電的動作即可完成係數更新,此外 µ 將由積分器中的電容大小決定。

$$W(n+1) = W(n) + \mu \cdot sign[u(n)] \cdot sign[e(n)]$$

(3-22)

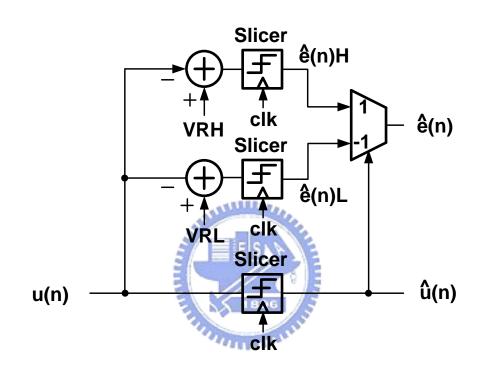

接著考慮較細部的架構,由於誤差之量化資訊  $\hat{e}(n)$ 需等輸入訊號的量化資訊  $\hat{u}(n)$ 出現並算出誤差值 e(n)後才可執行量化,因此  $\hat{e}(n)$ 將會晚  $\hat{u}(n)$ 一個位元時間才出現,如此將與演算法中係數更新的方程式不同,因此將這部分架構稍做修改如圖 3-15 所示,方式為先將理想的高位準(VRH)和理想的低位準(VRL)分別和輸入訊號 u(n)做相減。經由比較器量化後,可分別得到兩筆誤差量化訊號 $\hat{e}(n)$ H和 $\hat{e}(n)$ L。此結果會經由輸入訊號的量化資訊  $\hat{u}(n)$ 做選擇來決定誤差值之量化

資訊 ê(n)。此方法可確保誤差量化資訊與輸入訊號量化資訊出來的時間並不會差到一個位元時間,而是僅差一個多工器(mux)的延遲時間。這段延遲時間並不會影響到方程式的結果,因此電路可以良好的執行係數遞迴運算之方程式。

圖 3-15 誤差量化器架構圖

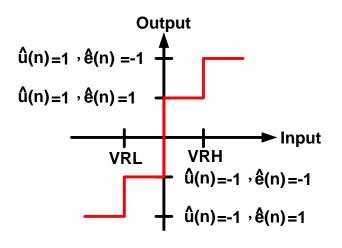

圖 3-16 為輸入訊號與輸出訊號的關係圖,當輸入的訊號量化為 1(高準位邏輯)時,選擇輸入訊號與理想高位準相減的結果做量化為輸出,ê(n) = ê(n)H,反之當輸入的訊號量化為 0(低準位邏輯)時, ê(n) = ê(n)L。值得注意的是,若理想的高位準與理想的低位準設計不好,將影響演算法收斂,因此我們才在類比等化器中加入可變增益 放大器,用以將輸入訊號大小調整至設定的理想位準值範圍內。

圖 3-16 輸入對輸出的關係圖

接著考慮決策回授等化器中主要迴路即有限脈衝響應濾波器的部分。如圖 3-17 所示,當欲加快整個架構的操作速度,使其能處理更快速的資料時,所面臨的最大問題為需在一位元的時間內完成一個加法器,一個切片器及一個乘法器的動作,如圖中灰線所示。若無法在一位元的時間內完成,電路即無法操作在此速度之下,因此如何加快此路徑操作速度,將是面臨的最大課題。

圖 3-17 全速率決策回授等化器架構圖

圖 3-18 的電路架構改進了上述的問題,稱之為迴圈展開

(loop-unrolled)決策回授等化器[5],其想法為將第一階的係數預先在加法器中做好運算,由於輸入訊號量化的結果不是1就是-1,因此第一階係數經過乘法器回授給加法器之值不是 Wo 就是-Wo,因此可先將  $\pm$  Wo 兩者都先運算,之後輸入值的量化結果 $\hat{u}(n)$  只需將已預先算出的結果經多工器選擇出正確的值即可,如此第一階的回授路徑,如灰色實線所示,將修改成為一個切片器與一個多工器,此將比前一個架構快上許多。但此架構的缺點為只適用於在只有一階回授的系統中,因為第二階回授路徑,如圖 3-18 灰色虛線所示,仍需經過一個切片器一個乘法器及一個加法器,並無加速的效果。若將迴圈展開的概念延伸到多階,則預先相加的係數選擇,將成二的次方上升,此將造成硬

圖 3-18 迴圈展開全速率決策回授等化器架構圖

圖 3-19 為一個半速率操作的架構,分為黑色與灰色上下兩路徑 交互判決出結果。明顯的,雖然切片器與延遲單元操作在原本的一半 速率上,但由於上路的切片器輸出,乘上係數送給下路的加法器仍需 在原本的一位元時間內完成,下路才趕得及輸出。因此並沒有達到加 快回授路徑操作速度或降低回授路徑速度要求的功能。

圖 3-19 半速率決策回授等化器架構圖

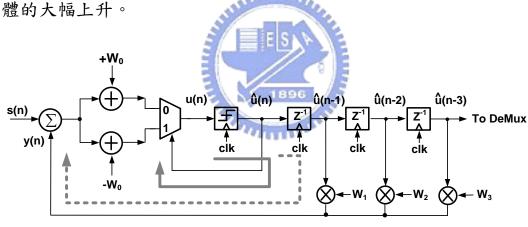

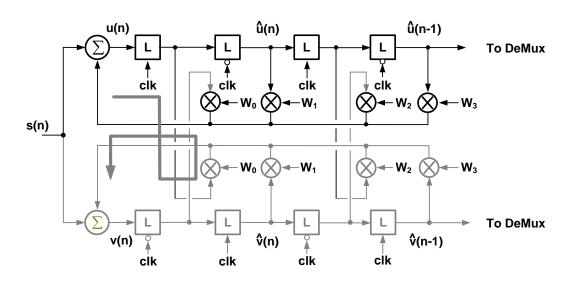

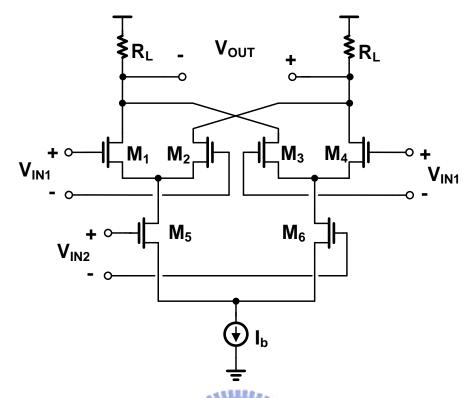

雖然半速率操作的決策回授等化器並無特別好處,但可基於此架構做變化[16],如圖 3-20 所示,此架構稱之為軟決策式決策回授等化器。由於我們將以 D 型正反器實現之前架構上的切片器以及延遲單元,因此可將 D 型正反器拆成兩個門鎖器,第一個門鎖器的輸出將預先回授給另一路徑的加法器使用,如此回授路徑將成為一個加法器一個門鎖器及一個乘法器,與先前相比少了一個門鎖器。此架構的優點在於能使用在多階的架構,如圖 3-20 所示第一階回授需在一個位元時間內完成,我們已將其速度加快。而第二階回授由於是操作在半速率的電路,因此只要在兩個位元的時間內完成即可,依此類推,第三階回授須在一個位元完成但已加快,第四階回授在兩位元時間內完成。隨著階數的上升,並不需要增加硬體上的需求。由於我們使用的是四階的脈衝響應濾波器,因此我們的決策回授等化器將使用此架構實現。

實際上電路的實現方式我們將在 3.5 節中做詳細的說明。

圖 3-20 採用的決策回授等化器架構圖

# 3.5 決策回授等化器電路設計

本節將對上述決策回授等化器的內部電路設計分區塊做分析,整個電路皆使用全差動的方式設計,因此可有效的改善共模雜訊的影響,此外電路也將採用電流模式邏輯(current-mode logic,CML)的架構,使其有較高之操作速度及雜訊免疫能力。

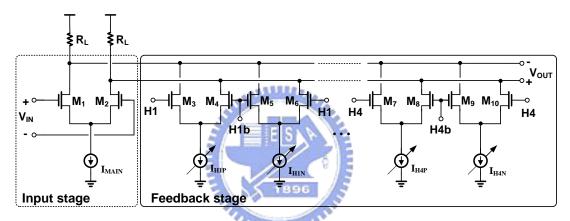

#### 3.5.1 加法器

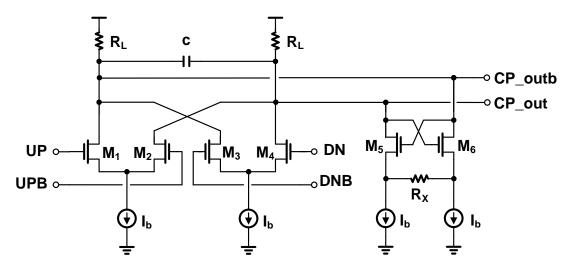

加法器在決策回授等化器架構中的工作為將輸入信號與回授回來的信號做相減以消去後指標符際干擾。在電路實現上,會將架構中的加法器與輸入訊號給加法器之乘法器做結合,以達到節省功率消耗與面積的目的。實際電路如圖 3-21 所示,M<sub>1</sub>、M<sub>2</sub> 為輸入級,輸入信

號經過此級處理後輸出。M<sub>3</sub>~M<sub>10</sub>皆為回授級,H1與H1b為迴路中第一級閂鎖器的輸出,依此類推H4與H4b則為第四級閂鎖器的輸出。 閂鎖器的輸出,如同之前說明已量化為一位元訊號,因此其目的為決定尾電流流向。注意到回授級每一組皆做成雙差動的形式,是為了無論後指標符際干擾值為正或負皆能加以補償。回授級下面的尾電流大小差(I<sub>Hip</sub>-I<sub>HiN</sub>)將可視為濾波器係數W,因此W將能涵蓋正值與負值。 最後此電路將經由演算法適應性的調整電流大小,以達到消去後指標符際干擾的功能。

圖 3-21 加法器電路圖

此電路最重要的設計考量在於因其位於影響操作速度最重要的回授路徑中,因此此電路能操作的越快速越好。此電路操作速度將由負載電阻 R<sub>L</sub>及輸出負載電容 C<sub>L</sub>決定,為了增加電路的操作速度,最簡單的作法為降低負載電阻 R<sub>L</sub>,但將會付出增加功率損耗的代價。因此適當的選取負載電阻大小將是非常重要的。在我們的設計中,可由模擬得知負載電容大小約為 40fF,因此我們將電阻值取在 400 歐姆,以符合迴路速度要求。

### 3.5.2 電流模式邏輯鬥鎖器

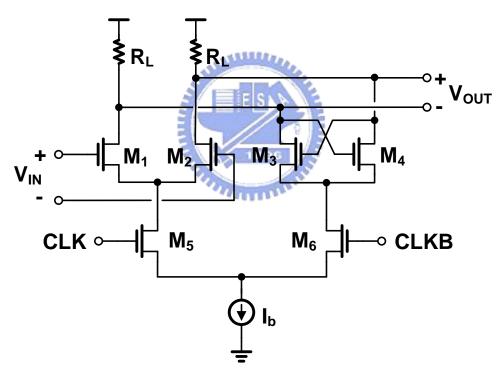

決策回授等化器架構中的切片器與閂鎖器將使用電流模式邏輯來實現,使用電流模式邏輯的目的在於相較於靜態邏輯,其訊號擺幅較小,因此可以操作在更快的速度,閂鎖器電路如圖 3-22 所示,可分為  $M_1$ 、 $M_2$  組成的源級耦合差動對及  $M_3$ 、 $M_4$  組成的交叉耦合差動對,而  $M_5$ 、 $M_6$  將決定電路操作模式。串接兩個電流模式閂鎖器,並將時脈反接即可成為一個電流模式 D 型正反器,可將之當作切片器使用。

圖 3-22 傳統電流模式邏輯閂鎖器電路圖

此電路操作模式如下所述,當時脈訊號為高準位時,尾電流將全 部流向源級耦合差動對,此時進入取樣模式,輸出信號將追蹤輸入信 號的改變。而當時脈訊號為低準位時,尾電流將全部流向交叉耦合差 動對,進入保持模式,輸出信號將由交叉耦合差動對拉開並維持其邏 輯準位不變直到下次取樣模式。

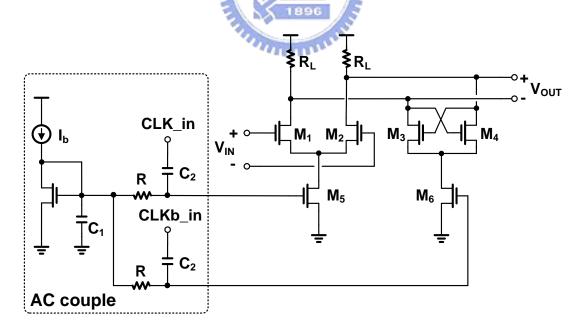

由於我們所使用的製程將只有 1V 的操作電壓,而傳統的閂鎖器電路必須要疊接三層電晶體,因此輸出的擺幅範圍將會受到壓縮,可將電路修改為如圖 3-23 所示[17],採用交流耦合的方式輸入時脈訊號給 M<sub>5</sub>、M<sub>6</sub>,藉由調整 I<sub>b</sub>的大小將可調整 M<sub>5</sub>、M<sub>6</sub>之直流偏壓點,以控制操作電流。此電路由於移除掉了尾電流源,因此電壓空間 (headroom)將獲得改善,可提供更大的輸出擺幅。此外同時 M<sub>5</sub>、M<sub>6</sub>之尺寸將可設計得更小,因此對提供時脈的緩衝器而言看到的電容負載將更低,可降低緩衝器的功率損耗。最後,如同電流模式加法器,此電路也在最重要的回授路徑中,因此負載值(R<sub>L</sub>)與消耗功率的取捨 同樣是重要的課題,在此我們同樣將阻值取在 400 歐姆。

圖 3-23 電流模式閂鎖器電路圖

### 3.5.3 減法器

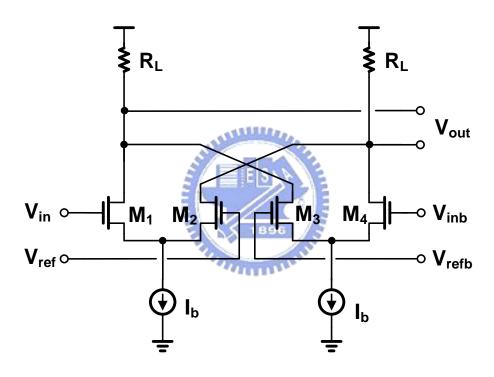

將加法器輸出訊號與理想目標值相減的減法器電路如圖 3-24 所示,採用正端輸入與正參考電壓相比,而負端輸入與負參考電壓相比的方式,此電路優點在於輸入電壓範圍要求較小,只要包含在輸入共模電壓與參考共模電壓的壓差範圍即可。

圖 3-24 減法器電路圖

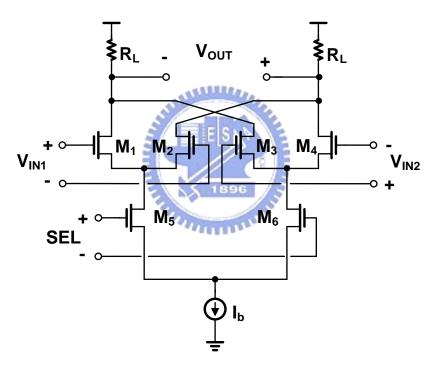

## 3.5.4 多工器與乘法器

多工器電路如圖 3-25 所示,同樣採用電流模式邏輯的架構,由於其輸入訊號  $V_{IN1}$ 、 $V_{IN2}$  及 SEL 皆為電流模式邏輯訊號,因此可以很簡單的述說其操作行為。當 SEL 訊號為邏輯 1 時,電流將會全流向

$M_5$ ,此時由  $V_{IN1}$  訊號決定輸出,反之則由  $V_{IN2}$  訊號決定。 $I_bR_L$  將決定輸出直流準位與輸出擺幅, $R_L$  同時決定了電路操作速度。由於我們使用了 sign-sign LMS 來做遞迴運算,因此資料與誤差相乘動作的電路也將簡化為邏輯運算,故可用與多工器相同的電路來實現,值得注意的是此電路架構下  $V_{IN1}$  與  $V_{IN2}$  所需推動的電容負載大小是不同的,由於架構中誤差訊號的量化值要同時推動四個乘法器,因此我們會將誤差訊號的量化值接在  $V_{IN2}$ ,而將資料的判決訊號接在  $V_{IN1}$ ,如此可避免誤差訊號的量化值推動太大的電容負載。

圖 3-25 多工器電路圖

圖 3-26 乘法器電路圖

## 3.5.5 積分器

積分器電路圖如圖 3-27 所示,使用充電泵(charge pump)對電容(C) 充放電以將電荷累積在電容上,由於當電容兩端壓差增加之後,電荷可能會透過  $R_L$  放電,而使得壓差減少,因此我們將利用  $M_5$ 、 $M_6$ 和  $R_X$  形成等效負阻與  $R_L$  並聯,其單端看入阻值大小如式(3-23)所示,若將負阻值設計的與  $R_L$  接近,並聯後將可使電容兩端等效上看到一極大電阻,以降低漏電流效應。注意到如之前所述,容值大小的選取將會影響到演算法之收斂速度,經過模擬之後,我們將容值大小取為 10pF。

圖 3-27 積分器電路圖

$$Z_i \approx -\left(\frac{1}{gm5,6} + \frac{R_X}{2}\right) \tag{3-23}$$

# 3.5.6 决策回授等化器模擬結果

1896

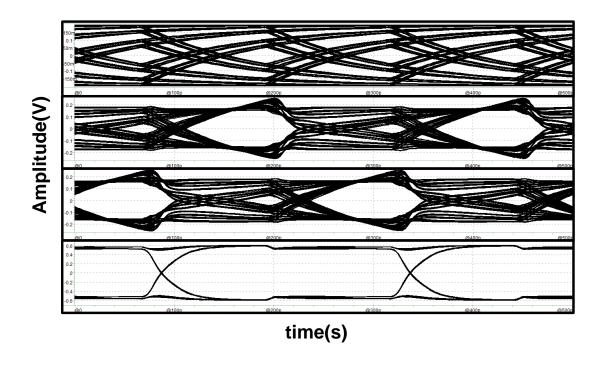

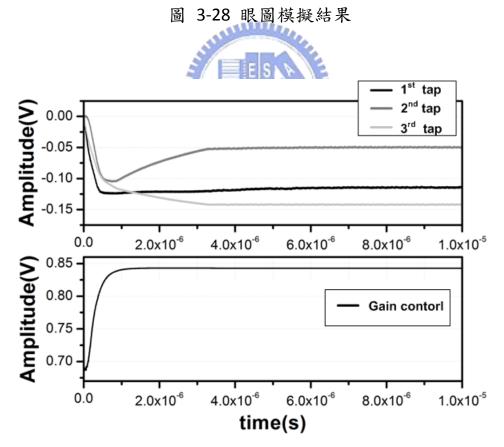

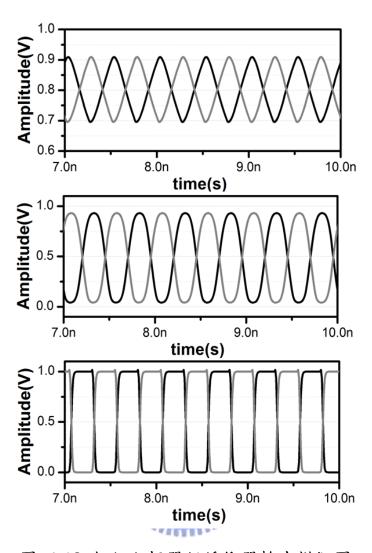

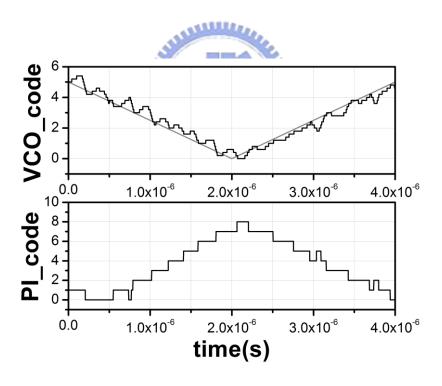

圖 3-28 為決策回授等化器之模擬結果,由於之前所述,決策回授等化器只能消除後指標的符際干擾,因此在此先建立一階 RC 濾波器當作通道,如此將只會有後指標符際干擾產生。在給定時脈下,最上圖為 2<sup>7</sup>-1之 PRBS 訊號經過了一階 RC 濾波器通道後的眼圖,而下兩張則為決策回授等化器的加法器輸出,由於採用半速率軟決策的架構,因此有兩個加法器輸出,且眼圖將會是一大一小的型式。由圖形可看出決策回授等化器確實有消除後指標符際干擾以增加眼圖垂直大小的功能,而最下面為切片器的輸出結果。圖 3-29 則為係數收斂結果,上圖為決策回授等化器三個不同階的收斂情形,而最下圖為增益的收斂情形,可看出大約需要 4µs 的時間收斂。

圖 3-29 係數收斂結果

# 第4章 時脈與資料回復電路之設計與實現

### 4.1 時脈與資料回復電路架構

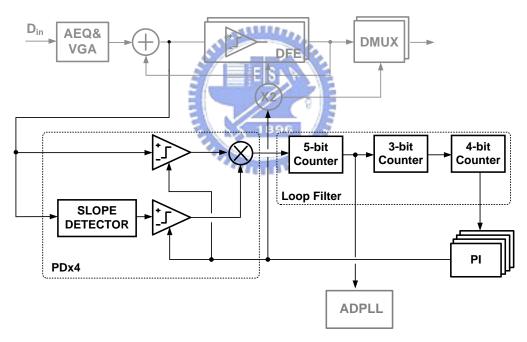

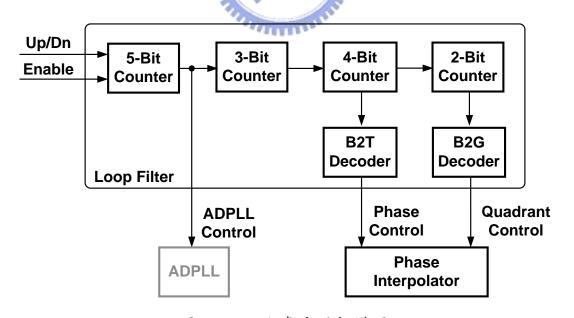

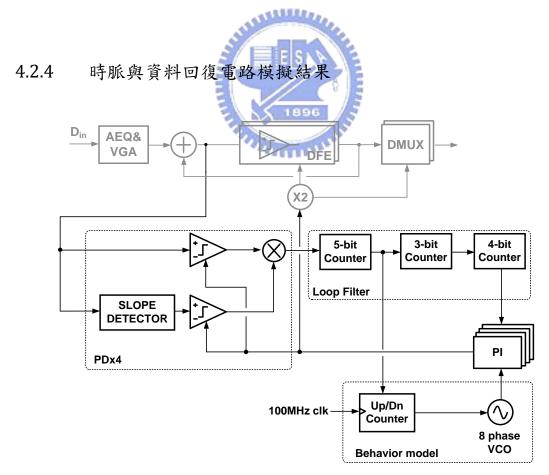

在時脈與資料回復電路的架構上,使用了時脈速率為輸入資料速率的四分之一倍的方式,相較於全速率方式能降低功率的損耗以及設計上的困難度。架構如圖 4-1 所示,可簡單分為三大區塊,分別是相位偵測電路(Phase Detector, PD)、迴路濾波器(Loop Filter)以及相位內插器(Phase Interpolator, PI)。

圖 4-1 時脈與資料回復電路架構圖

此架構的操作流程如下:決策回授等化器內之加法器的輸出訊號 將提供給相位偵測器,由於操作在 1/4 的資料傳輸速率下,因此我們 必須使用四組相位偵測器來偵測相位誤差。偵測到的相位誤差資訊將 會輸出給迴路濾波器,而迴路濾波器則將經過計數器累加溢位後的訊 號輸出給相位內插器。相位內插器將接收到的信號用以調整輸出時脈的相位,使最終能提供適當的時脈訊號給各個區塊使用。此外由於本架構包含了追蹤展頻時脈(Spread Spectrum Clock)的功能,因此在迴路濾波器的中間還另外拉出一路訊號提供給全數位式鎖相迴路(ADPLL),使其能調整除數以更改提供給相位內插器的時脈頻率。下一節將對各個區塊的功能分別做詳細的介紹。

### 4.2 時脈與資料回復電路設計

#### 4.2.1 相位偵測器

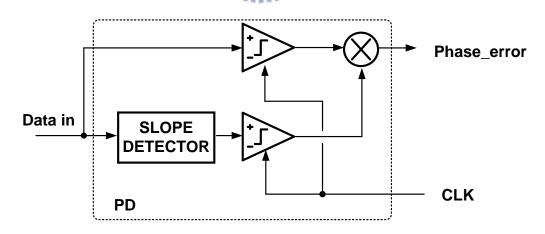

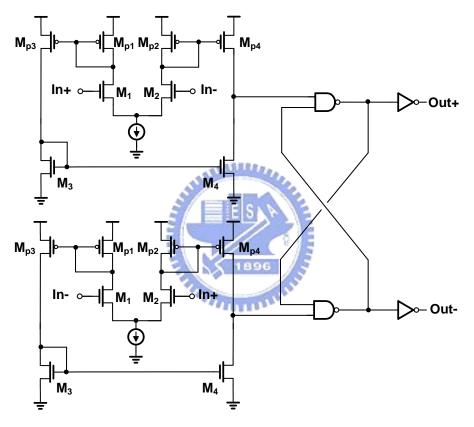

圖 4-2為使用的相位偵測器架構圖,注意到其主要可分為兩路徑, 一路經由斜率偵測器(Slope Detector)達到偵測資料斜率正負的目的, 另一路則是判決資料,決定資料的正負值。將此兩值相乘之後成為一 位元的相位誤差信號,可提供給相位內插器以決定相位改變的方向。

圖 4-2 相位偵測器架構圖

使用上述的作法,將可使相位最後鎖定在斜率大小較小之處,亦即眼圖中較平坦的部份。因此預期將可偵測並鎖定在資料的眼圖垂直

方向大小最大之處,而達到降低錯誤率的目的。一個簡單的範例如圖 4-3 所示,相位偵測器操作行為則如表 4-1 所示,假設輸入信號為一 弦波,此時的時脈信號為黑虛線,則將判決出資料為正,且斜率也為 正,查表可得知輸出相位領先理想取樣點,此時將會送出訊號給相位 內插器,將其相位往後調整。依照此原則,時脈信號最終將會停在黑 色實線之處,此即為最適當的相位所在。

| 斜率 | 資料 | 輸出相位 |

|----|----|------|

| 正  | 正  | 領先   |

| 正  | 負  | 落後   |

| 負  | 正  | 落後   |

| 負  | 負  | 領先   |

表 4-1 相位偵測器真值表

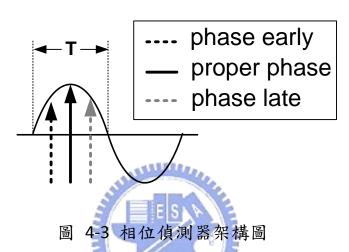

圖 4-4 為斜率偵測電路,其操作的目標在於希望當訊號斜率較大時,能有大的輸出信號,給切片器正確判決出資料。注意到輸入同一組差動對的信號將是 INP 與 INP 的延遲訊號,及 INN 與 INN 的延遲訊

號。當訊號有較大斜率時代表此訊號正在切換,故 INP 與 INP 的延遲訊號在同時間電壓上將會有一差距。而當訊號斜率較小時,代表訊號處在較為平坦的位置,此時 INP 的延遲訊號在電壓上由於已經有足夠時間追上 INP,所以同時間電壓上將不會有差距。而此電路要做的即是將差距放大,由上面的說明可得知,訊號切換的瞬間有較大的差距,這時間將不會持續很久,因此等效上為高頻的訊號,因此我們可以使用一提供高頻增益峰化的電路,增加高頻訊號的放大量,即可達到偵測斜率的功能。注意到電路可分為兩部分,分別為在源極端接上電容的  $M_1 \times M_2$  差動對以提供高頻增益及一組基本的  $M_3 \times M_4$  差動對提供直流增益。

圖 4-4 斜率偵測電路圖

### 4.2.2 迴路濾波器

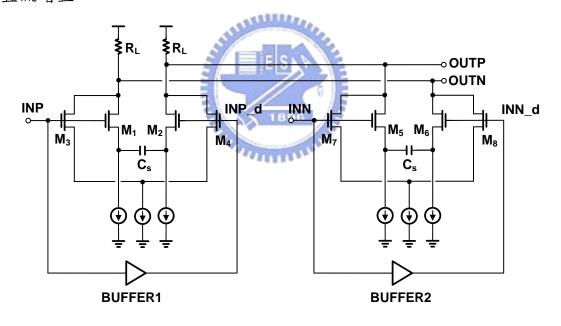

圖 4-5 為使用的迴路濾波器架構圖,由相位偵測器送來的相位領 先、落後信號,將控制五位元上下計數器上數或下數,當五位元計數 器溢位之後將會重設計數器,並將溢位的方向信號同時傳遞給三位元 上下計數器及全數位式鎖相迴路(ADPLL)。三位元計數器將繼續執行累加的動作直到溢位後送出資料給四位元計數器,並同樣會重設計數器。而剛剛送給全數位式鎖相迴路的訊號將會更改鎖相迴路之除數倍數,進而達到改變振盪器輸出頻率而使迴路能達到追蹤頻率變化的目的。四位元計數器的輸出將經過一個二進位碼對溫度計碼轉換器(B2T Decoder)控制相位內插器內插的相位,另外當四位元計數器溢位時,將輸出信號給二位元計數器,並經過二進位碼對格雷碼轉換器(B2G Decoder)後同樣送給相位內插器做改變象限使用。

值得注意的是,第一個計數器取五位元的原因在於考量展頻時脈的變換頻率為 33KHz 改變 5000ppm,而計數器的輸出一次能更改振盪器輸出頻率的大小為 50KHz,且全數位式鎖相迴路的參考頻率為100MHz,綜合考量下,取五位元能夠有效追蹤展頻時脈的變化,接著將對細部電路設計做進一步介紹。

圖 4-5 迴路濾波器架構圖

圖 4-6 為架構中使用到的上下數計數器電路[18],由於不同位元

圖 4-6 五位元上下數計數器及溢位偵測器電路

其中  $D_0$  為最低有效位元(LSB), 而  $D_4$  為最高有效位元(MSB)。起初電路將會重置於 00000 的地方, 而此輸出狀態將會暫存於 D 型正反器

中,當時脈信號進來時,電路才根據前面邏輯電路運算出的值改變輸出狀態,當輸出狀態為 01111 或 10001 時,此時溢位偵測電路將會偵測到溢位產生,進而送出重置訊號給 D 型正反器,將暫存的輸出狀態全部重置為 00000。

可以注意到此上下數計數器邏輯電路的規律性如下式所示:

$$D_m(new) = D_m \oplus [UpD_0 \cdots D_{m-1} + DnD_0 \cdots D_{m-1}] \tag{4-1}$$

第 m 個位元更新的值將是上數(Up)信號與前 m-1 個位元做 AND 後的結果與下數(Dn)信號與前 m-1 個位元做 AND 後的結果一起做 OR, 其結果再與第 m 個位元之舊的值做互斥或(XOR)即可完成更新。

注意到圖 4-6 中 D 型正反器的時脈輸入信號,希望由圖 4-5 架構中的 Enable 信號控制是否要執行上數下數的動作。由於要使用此 Enable 信號當作 D 型正反器的時脈,必須要先將 Enable 與真正的時脈做 AND 的動作。

圖 4-7 五位元計數器的上下數信號與觸發時脈來源

但由圖 4-7 所示,由於 Enable 信號與上下數信號是同一個時間改

變的,但上下數信號需要一段時間運算邏輯才能準備好給 D型正反器取樣,因此我們會將 Enable 信號與當初觸發他的時脈之反向訊號做 AND,如此將多出一半的位元時間給運算邏輯準備,其時序圖如圖 4-8 所示。

### 4.2.3 相位內插器

圖 4-9 為使用的相位內插器架構圖,首先全數位鎖相迴路中的振 盪器將提供八相位的時脈信號經過緩衝器後給予相位內插器核心使 用,相位內插器核心如上小節所述,將受到兩個信號分別控制內插的 輸出相位及象限。本架構使用四位元之相位內插器,因此在 90 度間 將可內插出 16 個相位,最後將經由責任週期修正電路輸出並提供內 插後的時脈信號給決策回授等化器以及時脈與資料回復電路使用,下 面將對內部電路做詳細的介紹。

圖 4-9 相位內插器架構圖

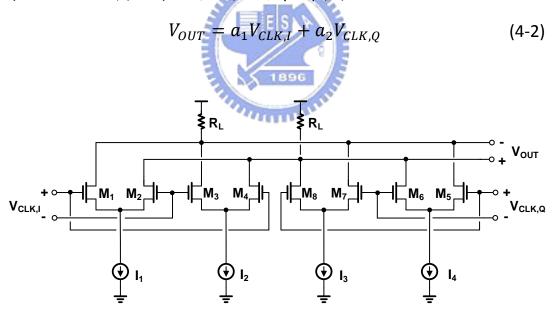

相位內插器的基本工作原理為輸入兩個彼此相差 90 度相位的時脈,利用權重的方式在這 90 度的區間中做內插,內插出來的合成相位將介於輸入的兩個相位之間。圖 4-10 是相位內插器的核心電路[19],其中  $V_{CLK,I}$  與  $V_{CLK,Q}$  為相差 90 度的時脈訊號, $V_{OUT}$  為經過內插輸出的時脈,它可用輸入時脈的加權總和(4-2)來表示:

圖 4-10 簡化的相位內插器核心電路

其中 a1 與 a2 代表著內插的權重,將可藉由調整四條電流大小來控制。接著為了將內插輸出的範圍擴展到能涵蓋 0 到 360 度,代表著 a1 與 a2 係數必須能同時涵蓋正與負的範圍,在此電路架構上這將是

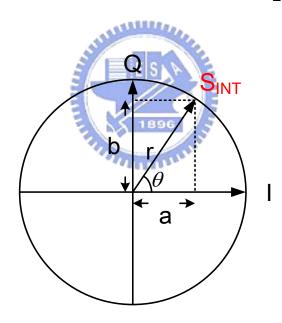

很容易實現的,只要藉由調整電流流向即可達到控制輸出象限的目的。例如欲內插出第一象限的訊號,只要使 |<sub>1</sub> 與 |<sub>3</sub> 有電流而 |<sub>2</sub>、 |<sub>4</sub> 無電流即可。接著探討電流權重對內插相位的關係,此電路是要把輸入差90 度的 |、Q 時脈做加權總和,因此可將權重對內插相位之關係式(4-3)表示如下[20]:

$$S_{INT} = rsin(\omega t + \theta)$$

$$= rcos\theta \times sin(\omega t) + rsin\theta \times cos(\omega t)$$

$$= rcos\theta \times sin(\omega t) + rsin\theta \times sin\left(\omega t + \frac{\pi}{2}\right)$$

$$= a \times sin(\omega t) + b \times sin\left(\omega t + \frac{\pi}{2}\right)$$

(4-3)

圖 4-11 極座標圖

以極座標表示將如圖 4-11 所示,其中  $S_{INT}$  為內插出的相位,而  $sin(\omega t)$ 與  $sin(\omega t+\pi/2)$ 為相差 90 度之輸入 I、Q 時脈訊號,因此  $r\cos\theta$  為 I 時脈的權重,而  $r\sin\theta$  為 Q 時脈的權重。假設以內插第一象限為 例,如同之前所述,只有流  $I_1$ 、 $I_3$  電流,在圖 4-11 中可以看到當  $S_{INT}$

內插於第一象限,內插角度為 $\theta$ 時,時脈 I 的權重是  $r\cos\theta=a$ ,而時脈 Q 的權重是  $r\sin\theta=b$ ,且兩權重比例為  $r\sin\theta/r\cos\theta=\tan\theta$ 。由於 I、Q 時脈所占權重,在電路中將由電流比重決定,因此  $r\cos\theta$ 、 $r\sin\theta$ 分別與  $I_1$ 、 $I_3$  電流大小成正比關係,所以電流源大小在設計時將要求符合  $I_3/I_1=\tan\theta$  這樣的關係。

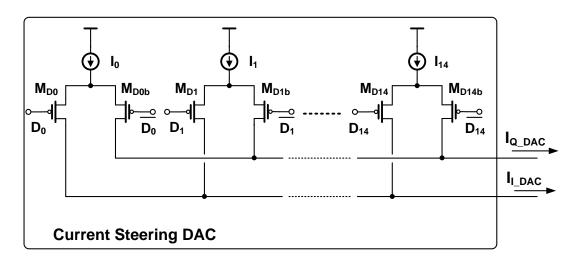

有了上述關係式,即可以開始設計電流源,我們將使用電流式數位類比轉換器(Current Steering DAC),來調整相位內插器電流源大小以控制內插出的相位。此電流式數位類比轉換器將採用溫度計碼(thermometer code)的架構來設計,理由在於若採用二位元加權(Binary Weighted)的方式,在中間碼切換時,可能會有瞬間改變多個位元發生,此將造成電流瞬間的跳動(Current Glitch),由於相位內插器將提供整個電路的時脈所需,因此我們不希望有瞬間大電流跳動的情形發生。而使用溫度計碼,同時間最多只切換一個電流源,將可降低電流切換瞬間所造成的電流的跳動,且由於溫度計碼每個單位電流源大小接近,因此也能保證一定會單調遞增(Monotonic Increasing)。

電流式數位類比轉換器電路如圖 4-12 所示,由於使用的相位內插器有四個位元以在 90 度相位間內插出 16 個相位,故我們採用 15 個電流源(I<sub>0</sub>~I<sub>14</sub>)實現。首先當要內插出相位為零度時,使 D<sub>0</sub>~D<sub>14</sub> 為低準位,則左邊開關全開而右邊開關全關,將使電流將全流向 I<sub>1\_DAC</sub>,接著隨著欲內插出的相位增加,左邊開關將依序關閉,而右邊開關將依序打開,採用一開一關的方式,因此 I<sub>1\_DAC</sub> 將逐漸下降而 I<sub>Q\_DAC</sub> 將逐漸上升,直到最後左邊開關全關,而右邊開關全開,將使電流全流向 I<sub>Q\_DAC</sub> 而內插出 90 度的相位。注意到由於採一開一關的方式,故總電

流量是不變的,此方式也有當象限改變時相位依然均勻的優點。

圖 4-12 電流式數位類比轉換器電路

圖 4-13 相位內插器核心電路

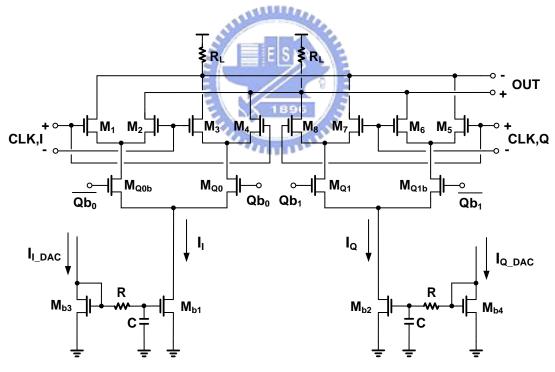

有了調整電流大小的電路之後,最後我們將象限選擇加入相位內插器核心電路如圖 4-13 所示,加入  $M_{Q0}$ 、 $M_{Q1}$ , $M_{Q0b}$ 、 $M_{Q1b}$ 選擇電流

流向,即可不用使用四個電流源,就達到選擇象限的功能。注意到此處在電流源的部分,還加入了一組 RC 電路,其功用是做為整個相位內插器系統的迴路濾波器使用,其頻寬約取在 10MHz 的地方。加入此濾波器的目的在於希望電流源切換時相位能慢慢的反應出變化,使最後穩定時疊出來的眼圖抖動量(jitter)能較小。

實際上電路操作時的控制碼如圖 4-14所示,操作在第一象限時,隨著內插的角度上升,相位控制碼會跟著上升。但需特別注意的是為了輸出時脈訊號在象限改變時的連續性,當象限改變時,相位控制碼需先保持不變,而只改變象限控制碼,如此在象限切換時,才能確保內插出來的相位不變。

圖 4-14 相位內插器電路控制碼

接著考量架構中的輸入級緩衝器,由於從振盪器提供的時脈訊號為全擺幅的方波訊號,此將不利於我們做內插的動作。輸入時脈訊號越接近弦波,內插出的相位才能越接近我們的要求。採用的電路如圖4-15 所示,為一個有源級退化電阻的差動對,分析如同 3.2.3 節,不同的地方在於此電路中我們將會故意增加 CL 值造成電路頻寬不足的

情形,而達到降低充放電速度的效果,由於充放電速度不足,輸出的波形將會較近似於弦波,此將有利於我們做相位內插的動作。

圖 4-15 輸入級緩衝器電路

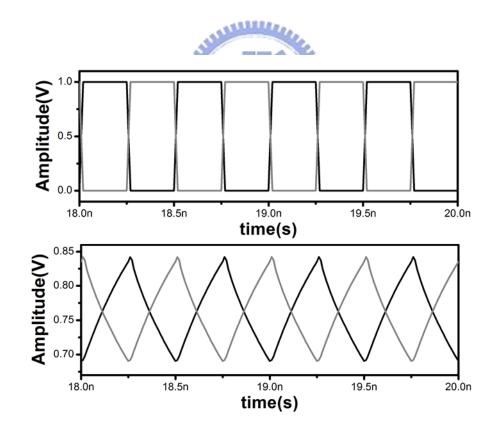

圖 4-16 輸入級緩衝器電路模擬圖

圖 4-16 為輸入級緩衝器電路模擬結果,圖上半為全擺幅的輸入

時脈,下半部則為輸入級緩衝器的輸出。

輸出級緩衝器電路如圖 4-17 所示,負責將內插出的時脈訊號轉成全擺幅的方波給其他電路使用。將會分為三個部分,內插出的時脈信號將先經由一個簡單的兩級放大器將電流模式雙端信號轉為單端數位訊號,接著後面的 SR 閂鎖器電路將會修正輸出的責任週期,最後再經由反向器組成的緩衝器將訊號輸出。

圖 4-17 輸出級緩衝器電路

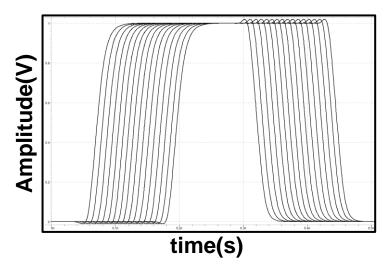

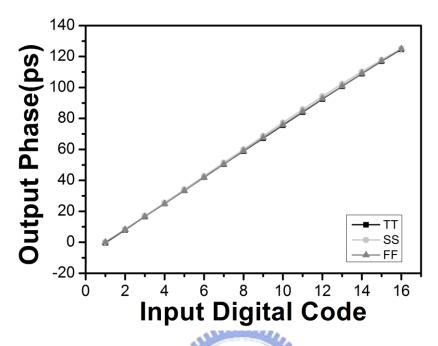

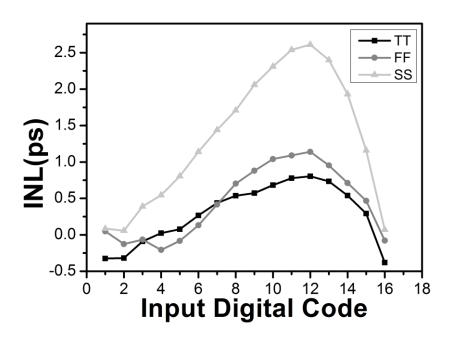

相位內插器最後經緩衝器輸出結果模擬如圖 4-18 所示,由上而下依序為相位內插器的輸出、雙端轉單端電路輸出以及最後的緩衝器輸出。圖 4-19 為內插出的 16 個相位的輸出圖。圖 4-20 至圖 4-22 則為考量製程偏移下內插出的相位與理想相位之間差距的統計結果。由圖可得知,最大相位誤差約偏離了理想相位 2.5ps。

圖 4-18 相位內插器經緩衝器輸出模擬圖

圖 4-19 相位內插器內插出的 16 相位模擬圖

圖 4-20 輸入控制碼對輸出相位

圖 4-21 內插相位 INL

圖 4-22 內插相位 DNL

圖 4-23 時脈與資料回復電路模擬方法

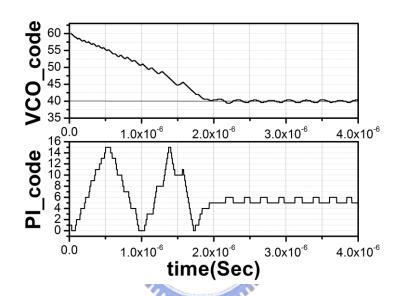

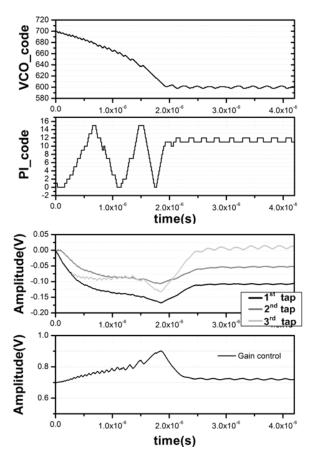

如圖 4-23 我們將使用行為階層的模型來取代全數位式鎖相迴路 以進行模擬。將全數位式鎖相迴路置換為一數位控制振盪器,且定義 振盪器之最小變動量為 50kHz。圖 4-24 為時脈與資料回復電路鎖定 過程模擬結果,圖中的一個 VCO\_code 代表改變 250KHz,而 PI\_code 代表調動一個相位,目標頻率為當 VCO\_code 為 40 時。

圖 4-24 時脈與資料回復電路鎖定結果

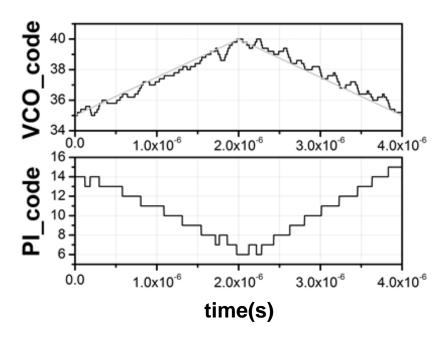

接著進行展頻時脈的模擬,圖 4-25 為目標頻率往上增加直到頻率最大值之後改變方向往下減少的模擬圖,圖中灰線為欲追蹤的頻率。 而圖 4-26 為目標頻率起初向下減少直到頻率最小值後改變方向向上增加的模擬圖,可發現輸出的時脈頻率皆有追隨著目標頻率改變而改變。

圖 4-25 展頻時脈追蹤模擬結果(1)

圖 4-26 展頻時脈追蹤模擬結果(2)

#### 4.3 接收機模擬結果

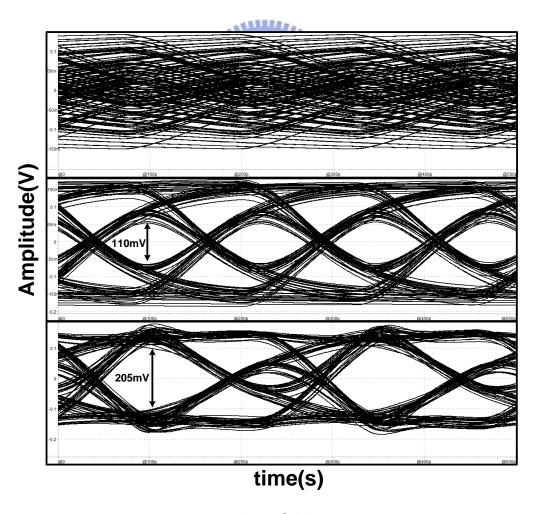

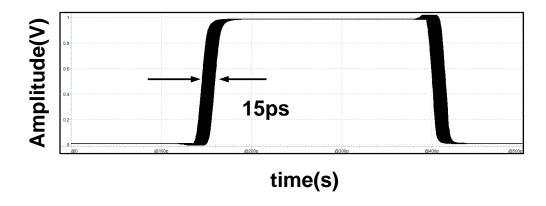

最後整個接收機模擬結果如下圖 4-27 所示,最上方為經過通道 後的輸出波形,第二張為經過類比等化器之輸出波形,可看出眼圖已 初步睜開,最下面為決策回授等化器的兩個加法器其中之一輸出波形, 可看出垂直方向被進一步拉開,如同圖 3-28 結果,由於採用半速率 軟決策架構,因此眼圖將會呈現一大一小。而圖 4-28 為鎖定後輸出 時脈的眼圖,抖動大約為 15ps。圖 4-29 則為整個接收機的係數收斂 情形,由上而下分別為頻率、相位、三個不同階係數以及增益。

圖 4-27 接收機模擬眼圖

圖 4-28 輸出時脈之眼圖

圖 4-29 係數收斂情形

# 總體功率消耗如表 4-2 所示

|           | 功率消耗    | 百分比    |

|-----------|---------|--------|

| 類比等化器     | 6 mW    | 9.1 %  |

| 決策回授等化器   | 29.8 mW | 45.2 % |

| 時脈與資料回復電路 | 30.1 mW | 45.7 % |

| 總和        | 65.9 mW | 100 %  |

表 4-2 總體功率消耗表

## 最後所提出的接收機效能摘要如表 4-3 所示

|              | This work               |  |

|--------------|-------------------------|--|

| Technology   | 55nm CMOS               |  |

| Power supply | 1V                      |  |

| Data rate    | 8Gbps                   |  |

| Architecture | AEQ + soft decision DFE |  |

| Clock Rate   | Half-rate for DFE       |  |

|              | Quarter-rate for CDR    |  |

| Channel Loss | 20dB@4GHz               |  |

| Adaption     | Yes                     |  |

| CDR          | Yes                     |  |

| Area         | 1000μmX1850μm           |  |

| Power        | 65.9mW                  |  |

表 4-3 效能摘要表

### 5.1 晶片佈局(Chip Layout)

如圖 5-1 所示為晶片佈局圖,此晶片採用 UMC 55nm CMOS 製程實現,包括 Bounding Pads 和 I/O 的面積約為 1.85mm²,本論文包含的電路為黑色實線部分,訊號將由下方差動輸入,依序經過類比等化器(AEQ)、決策回授等化器(DFE)、解多工器(DMUX)後由緩衝器(buffer)從上方輸出。決策回授等化器的輸入端向右傳送資料給相位偵測器(PD),之後經過迴路濾波器(LPF)傳送相位誤差訊號給相位內插器(PI),最後內插出時脈提供給晶片內的電路使用。圖右上角的部分為全數位式鎖相迴路,主要目的為提供目標頻率時脈給予相位內插器做內插使用。

圖 5-1 晶片佈局圖

### 5.2 量測環境(Measurement Setup)

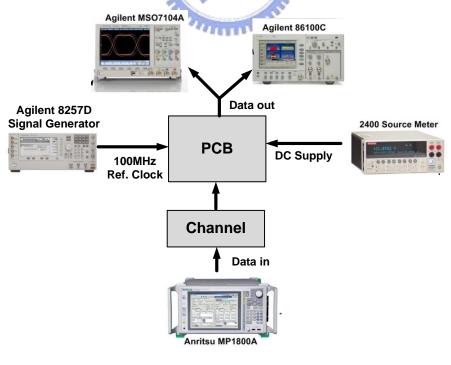

我們將使用兩個印刷電路板來量測接收機電路,分為 AC 印刷電路板以及 DC 印刷電路板。晶片將直接經過 Bond Wire 和 AC 印刷電路板做連接,以減少封裝的負載效應。DC 印刷電路板則經過排針與 AC 印刷電路板相連以提供直流的供應和偏壓,如此在更換測試晶片時,將只需更動 AC 印刷電路板,而 DC 印刷電路板可重復使用。

量測環境的設置如圖 5-2 所示,將由 2400 Source Meter 提供所需的直流電壓。安立 MP1800A 可產生序列資料經 FR4 建立的通道後輸入晶片,輸出則採用 3.5mm SMA 外接 cable 線至儀器,安捷倫MSO7104A 及 86100C 可觀察暫態的輸出和抖動的表現,並利用安立MP1800A 模組去量測 BER。全數位鎖相迴路所使用的參考訊號100MHz 則由 Agilent 8257D 訊號產生器送入。

圖 5-2 量測環境

## 第6章 結論

本論文提出了一個操作在 8Gbps 的接收機架構,其中包含了等化器以及時脈與資料回復電路,等化器採用了類比等化器串接決策回授等化器的架構。類比等化器將採用回授架構以提供 10dB 的增益峰化在輸入資料速度一半的頻率之上以消去部分的符際干擾。決策回授等化器則使用 sign-sign LMS 演算法達到適應性等化的功能,其將可自我調整係數以將剩餘的後指標符際干擾消除。時脈與資料回復電路採用了一個以斜率偵測為基礎的相位偵測器架構,將提供相位誤差資訊給四位元之相位內插器以內插出正確的相位供給整個電路使用,除此之外,時脈與資料回復電路也加入了追蹤展頻時脈的功能。經由模擬驗證了此架構能補償 28-inch 長度的通道造成的通道損失。整體電路功耗約為 65.9mW ,其中等化器佔了 35.8mW ,晶片面積為1000μmX1850μm。

## 参考文獻

- [1] J. H. R. Schrader, et al., "Pulse-Width Modulation Pre-Emphasis Applied in a Wireline Transmitter, Achieving 33 dB Loss Compensation at 5-Gb/s in 0.13-µm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 41, no.4, pp. 990–999, Apr. 2006.

- [2] J. Buckwalter, et al., "Phase and amplitude pre-emphasis techniques for low-power serial links," *IEEE Journal of Solid-State Circuits*, pp. 1391–1399, Jun. 2006.

- [3] M. Bichan and A. Carusone, "A 6.5Gb/s Backplane Transmitter with 6-tap FIR Equalizer and Variable Tap Spacing," *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 611-5614, Sep. 2008.

- [4] S. Gondi, et al., "A 10 Gb/s CMOS adaptive equalizer for backplane applications," *IEEE ISSCC Digest of Technical Papers*, pp. 328–329, Feb. 2005.

- [5] R. S. Kajley, et al., "A mixed-signal decision-feedback equalizer that uses a look-ahead architecture," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 3, pp. 450–459, Mar. 1997.

- [6] A. Kiaei, et al., "A 10Gb/s Equalizer with Decision Feedback for High Speed Serial Links," *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 285-288, May. 2007.

- [7] T. Beukema, et al, "A 6.4-Gb/s CMOS SerDes core with feedforward and decision-feedback equalization", *IEEE Journal of Solid-State*

- Circuits, vol. 40, pp. 2633–2645, Dec. 2005.

- [8] V. Balan, et al., "A 4.8-6.4-Gb/s Serial Link for Backplane Applications Using Decision Feedback Equalization," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 9, pp. 1957-1967, Sep. 2005.

- [9] H. S. Li, et al., "Dual-loop spread-spectrum clock generator," *IEEE ISSCC Digest of Technical Papers*, pp. 184-185, Feb. 1999.

- [10] J.-S. Choi, et al., "A 0.18-μm CMOS 3.5-Gb/s Continuous-Time Adaptive Cable Equalizer Using Enhanced Low-Frequency Gain Control Method," *IEEE Journal of Solid-State Circuits*, vol. 39, pp. 419–425, Mar. 2004.

- [11] J. Lee, "A 20 Gb/s adaptive equalizer in 0.13 μm CMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 9, pp. 2058–2066, Sep. 2006.

- [12] H. Wu, et al., "Differential 4-tap and 7-tap Transverse Filters in SiGe for 10Gb/s Multimode Fiber Optic Link Equalization," *IEEE ISSCC Digest of Technical Papers*, pp.180-181, Feb. 2003.

- [13] S. Reynolds, et al., "A 7-tap transverse analog-FIR filter in a 0.13 μm CMOS for Equalization of 10 Gb/s Fiber-Optic Data Systems," *IEEE ISSCC Digest of Technical Papers*, pp. 330–331, Feb. 2005

- [14] S. Haykin, *Adaptive Filter Theory*, 4<sup>th</sup> ed., Prentice Hall, 2008.

- [15] M. Q. Le, et al., "An Analog DFE for Disk Drives Using a Mixed-Signal Integrator," *IEEE Journal of Solid-State Circuits*, vol. 34, pp.592-598, May. 1999.

- [16] K. L. Wong, et al., "A 5-mW 6-Gb/s Quarter-Rate Sampling Receiver With a 2-Tap DFE Using Soft Decisions," *IEEE Journal of Solid-State Circuits*, vol. 42, pp. 881-888, Apr. 2007.

- [17] J. Lee and B. Razavi, "A 40 Gb/s clock and data recovery circuit in 0.18-µm CMOS technology," *IEEE Journal of Solid-State Circuits*, vol. 38, no.12, pp. 2181–2190, Dec. 2003

- [18] C. H. Roth, Jr. and L. Kinney, *Fundamentals of Logic Design*, 6<sup>th</sup> edition, Cengage, 2010.

- [19] R. Kreienkamp, et al., "A 10Gb/s CMOS clock and data recovery circuit with an analog phase interpolator," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 3, pp. 736–743, Mar. 2005.

- [20] Christian Kromer, et al., "A 25-Gb/s CDR in 90-nm CMOS for High-Density Interconnects," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 12, pp. 2921–2929, Dec.2006.