# Architectures for RF Frequency Synthesizers

# Cicero S. Vaucher

# ARCHITECTURES FOR RF FREQUENCY SYNTHESIZERS

# THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

#### ANALOG CIRCUITS AND SIGNAL PROCESSING

Consulting Editor: Mohammed Ismail. Ohio State University

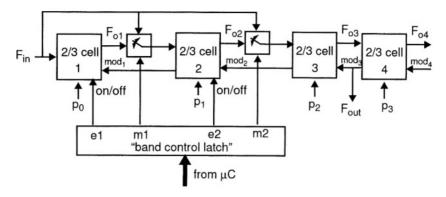

Related Titles:

#### DATA CONVERTERS FOR WIRELESS STANDARDS

C. Shi and M. Ismail ISBN: 0-7923-7623-4

#### AUTOMATIC CALIBRATION OF MODULATED FREQUENCY SYNTHESIZERS

D. McMahill

ISBN: 0-7923-7589-0

#### MODEL ENGINEERING IN MIXED-SIGNAL CIRCUIT DESIGN

S. Huss

ISBN: 0-7923-7598-X

#### CONTINUOUS-TIME SIGMA-DELTA MODULATION FOR A/D CONVERSION IN RADIO

**RECEIVERS** L. Breems, J.H. Huijsing ISBN: 0-7923-7492-4

#### DIRECT DIGITAL SYNTHESIZERS: THEORY, DESIGN AND APPLICATIONS

J. Vankka, K. Halonen ISBN: 0-7923 7366-9

#### SYSTEMATIC DESIGN FOR OPTIMISATION OF PIPELINED ADCs

J. Goes, J.C. Vital, J. Franca ISBN: 0-7923-7291-3

#### **OPERATIONAL AMPLIFIERS: Theory and Design**

J. Huijsing

ISBN: 0-7923-7284-0

#### HIGH-PERFORMANCE HARMONIC OSCILLATORS AND BANDGAP REFERENCES

A. van Staveren, C.J.M. Verhoeven, A.H.M. van Roermund ISBN: 0-7923-7283-2

HIGH SPEED A/D CONVERTERS: Understanding Data Converters Through SPICE

A. Moscovici

ISBN: 0-7923-7276-X

# ANALOG TEST SIGNAL GENERATION USING PERIODIC $\Sigma A$ -ENCODED DATA STREAMS

B. Dufort, G.W. Roberts ISBN: 0-7923-7211-5

#### HIGH-ACCURACY CMOS SMART TEMPERATURE SENSORS

A. Bakker, J. Huijsing ISBN: 0-7923-7217-4

## DESIGN, SIMULATION AND APPLICATIONS OF INDUCTORS AND TRANSFORMERS

FOR Si RF ICs

A.M. Niknejad, R.G. Meyer ISBN: 0-7923-7986-1

#### SWITCHED-CURRENT SIGNAL PROCESSING AND A/D CONVERSION CIRCUITS:

#### DESIGN AND IMPLEMENTATION

B.E. Jonsson

ISBN: 0-7923-7871-7

# RESEARCH PERSPECTIVES ON DYNAMIC TRANSLINEAR AND LOG-DOMAIN CIRCUITS

W.A. Serdijn, J. Mulder ISBN: 0-7923-7811-3

#### CMOS DATA CONVERTERS FOR COMMUNICATIONS

M. Gustavsson, J. Wikner, N. Tan

ISBN: 0-7923-7780-X

#### DESIGN AND ANALYSIS OF INTEGRATOR-BASED LOG -DOMAIN FILTER CIRCUITS

G.W. Roberts, V. W. Leung

ISBN: 0-7923-8699-X

### VISION CHIPS

A. Moini

ISBN: 0-7923-8664-7

# ARCHITECTURES FOR RF FREQUENCY SYNTHESIZERS

by

### Cicero S. Vaucher

Philips Research Laboratories Eindhoven

with a Foreword by

**Bram Nauta**

### KLUWER ACADEMIC PUBLISHERS

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN: 0-306-47955-9 Print ISBN: 1-4020-7120-5

©2003 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2002 Kluwer Academic Publishers Dordrecht

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://kluweronline.com

and Kluwer's eBookstore at: http://ebooks.kluweronline.com

# **Foreword**

The progress in the semiconductor industry has brought us advanced electronic systems available for large groups of people. By putting more and more functionality on an integrated circuit (IC) these systems could become cheap in mass production. This is the reason why scientists and engineers put constant effort in integrating more functions into ICs.

Many of these electronic systems need internal signals with a tunable, stable and accurate frequency. An example of this is a radio-frequency receiver, where a signal with a stable frequency is used to tune to a radio-station of interest. In the past this frequency was generated with the help of bulky passive mechanically tunable components. But if one wishes to integrate such a receiver on a chip, other components are needed to generate the tunable frequency. In this case, one needs to integrate a so-called frequency synthesizer, which relies on a clean fixed reference frequency, usually derived from a crystal, to create a variety of other frequencies.

A frequency synthesizer is usually realized with a phase-locked loop (PLL) which in turn can be implemented with on-chip components like transistors, resistors and capacitors. Such a synthesizer is far more complex than the old-days mechanically tuned resonators and can contain thousands of components. But still they are cheaper, more reliable, and easier in use: everybody wants a "digitally tunable" radio.

The application of synthesizers has gone through an enormous growth in the past years. Today they are widely used in wireless telecommunication systems like mobile phones but also in optical communication systems and cable modems. PLL circuits are also widely used as clock generators for microprocessors. PLL frequency synthesizers, and in particular radio-frequency (RF)

#### viii Foreword

synthesizers, are therefore important components of modern electronic systems.

A PLL frequency synthesizer may be cheap in mass production, but it is certainly not a simple circuit to design. Phase-locked loops are non-linear systems with very complex behaviour. Furthermore, PLLs are hard to simulate because time-constants are involved which may differ by many orders of magnitude. The output of a synthesizer has inaccuracies which are characterised as jitter and phase noise. These effects are very difficult to understand and to simulate. Finally, PLL design requires deep insight in system level design as well as transistor level design. So it is no surprise that there is a large need for design know-how on frequency synthesizers.

This book deals with the design of RF frequency synthesizers. It contains basic information for the beginner as well as in-depth knowledge for the experienced designer. Since frequency synthesizers are used in many different applications, different performance aspects are important in every case. Sometimes settling-time is important, sometimes residual phase deviation is important and sometimes residual frequency deviation is important. In all cases the design must be optimized in a completely different way. This book describes a conceptual framework for the different optimisations. It is, furthermore, widely illustrated with practical design examples used in industrial products.

The book was originally the Ph.D. thesis of Cicero Vaucher, who wrote it after 10 years of experience in RF frequency synthesizers at Philips Research Laboratories. I really enjoyed working with Cicero during the preparation of his thesis and now I feel very happy that it has been published as a book. Cicero has a natural talent in clear writing and therefore I believe this book is really worth reading for a broad group of scientists and engineers.

BRAM NAUTA

Professor IC Design

University of Twente, The Netherlands

# Preface

Frequency synthesizers are an essential building block of RF communication products. Digital tuning has become commonplace in traditional market segments, such as TVs and AM/FM radios, and is fundamental to the operation of personal cellular communication systems, in which the RF channels are dynamically allocated as the users move within the network, and the mobile hand-sets have to automatically and transparently re-tune to different RF carrier frequencies.

The design of high-performance frequency synthesizers involves familiarity with system optimization techniques and knowledge of state-of-the-art system and building block architectures. Common technical requirements which need to be considered during the design phase include high spectral purity, fast settling time and low power dissipation. These are the main aspects treated in this book.

The main body of the text presents a theoretical analysis of different PLL properties, followed by descriptions of innovative architectures, circuit implementations and measurement results. The analysis of the PLL properties is performed with the use of the open-loop bandwidth and phase margin concepts, to enable the influence of higher-order poles to be taken into account from the beginning of the design process. The common concepts of undamped natural frequency and damping factor, originated in the analysis of second-order systems, are therefore not used in the text.

Chapters 1, 2 and 3 are of a tutorial nature. Chapters 1 and 2 review basic communication techniques and the main specification points of frequency synthesizers for tuning system applications. Chapter 3 focuses on single-loop architectures, with a discussion of the properties of PLL building blocks on the

system level and a review of single-loop architectures in which the minimum step size is not equal to the reference frequency.

When organising this book I had the option to place the system-level analysis of different performance aspects in different chapters, that is, separated from more practical considerations such as the description of the application requirements and the implementation of the building blocks. Instead, I have chosen to "frame" the theoretical analysis within a few chapters which also describe the requirements of the intended applications. In this way, I hope that the reader will have a better understanding of the background and of the need for the theoretical system analysis being presented. Chapter 4, for example, focuses on tuning systems for phase-modulation communication systems, having as a practical application an L-band tuner for digital satellite reception. Here, a crucial specification point is the residual phase deviation of the oscillator signal; as such, Chapter 4 includes an in-depth analysis of the residual phase deviation of PLL frequency synthesizers.

Chapter 5 is the result of a frequency-modulation receiver project for carradio applications, where the challenge was the combination of fast settling time with low residual frequency deviation. An analysis of the settling time performance as a function of the open-loop bandwidth and phase margin is presented, followed by an analysis of the residual frequency deviation performance. This analysis led to the perception that the design procedure which optimises the residual phase deviation performance, described in Chapter 4, must be avoided in frequency-modulation applications, as it always results in a suboptimal residual frequency deviation performance. In other words, it is necessary to consider, during the optimization of the PLL frequency synthesizer parameters, whether it will be used in a phase-modulation or in a frequency-modulation communication system.

Chapter 6 focuses on programmable frequency dividers, having as practical application a low-power paging receiver. Among others, a truly-modular and an adaptive-power architecture for low-power multi-band applications are presented. Chapter 7 presents a summary of conclusions. Appendix A looks at the stability limits of PLLs using a PFD/CP combination, and Appendix B links the design of clock-conversion PLLs for optical networks to the wide-band loop design techniques developed in Chapter 4.

The circuit design of VCOs and crystal oscillators is not treated in this work. However, extensive reference lists to literature on VCO design have been included at the end of Chapters 1 and 3.

### **Acknowledgements**

Many persons contributed to the development of this book. I would especially like to thank Dieter Kasperkovitz for his support and motivation during the execution of the projects described in the text. Dieter is also acknowledged for his valuable inputs to the circuits and architectures presented in Chapters 4, 5 and 6. I would also like to thank Prof. Bram Nauta for his continuous assistance and constructive remarks during the preparation of the manuscript. The circuits described in the text were realised in close cooperation with many colleagues, mainly from Philips Semiconductors. In particular, I want to acknowledge the following persons: Jon Stanley, Onno Kuijken, Philippe Gorisse, Alain Vigne, Pascal Walbrou and Johan van der Tang for contributions to the work described in Chapter 4. For contributions to Chapter 5, I would like to thank Kave Kianush, Huub Vereijken, Bert Egelmeers, Jan Meeuwis and Gerrit van Werven. I am also grateful to Zhenhua Wang and Gerrit van Veenendaal for contributions to Chapter 6. Pieter Hooijmans is gratefully acknowledged for the support provided for this work. Finally, I would like to thank everyone who proposed improvements to earlier versions of the text.

CICERO S. VAUCHER

Eindhoven, The Netherlands

April 2002

# **Contents**

| rewo    | rd                                                                                                                                          | vii                                                                                                                                                                                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eface   | •                                                                                                                                           | ix                                                                                                                                                                                                                                                                                                                        |

| st of A | Acronyms                                                                                                                                    | xix                                                                                                                                                                                                                                                                                                                       |

| st of S | Symbols                                                                                                                                     | xxi                                                                                                                                                                                                                                                                                                                       |

| Intro   | oduction                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                         |

| 1.1     | Overview of the Book                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                         |

| Refe    | rences                                                                                                                                      | 7                                                                                                                                                                                                                                                                                                                         |

| Tuni    | ng System Specifications                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                        |

| 2.1     | Tuning Range                                                                                                                                | 11                                                                                                                                                                                                                                                                                                                        |

| 2.2     | Minimum Step Size                                                                                                                           | 12                                                                                                                                                                                                                                                                                                                        |

| 2.3     | Settling Time                                                                                                                               | 13                                                                                                                                                                                                                                                                                                                        |

| 2.4     | Spurious Signals                                                                                                                            | 14                                                                                                                                                                                                                                                                                                                        |

| 2.5     | Phase Noise Sidebands                                                                                                                       | 18                                                                                                                                                                                                                                                                                                                        |

| 2.6     | Power Dissipation                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                        |

| 2.7     | Integration Level                                                                                                                           | 24                                                                                                                                                                                                                                                                                                                        |

| 2.8     | Interference Generation                                                                                                                     | 24                                                                                                                                                                                                                                                                                                                        |

| Refe    | rences                                                                                                                                      | 25                                                                                                                                                                                                                                                                                                                        |

| Sing    | le-Loop Architectures                                                                                                                       | 27                                                                                                                                                                                                                                                                                                                        |

| 3.1     | Introduction                                                                                                                                | 27                                                                                                                                                                                                                                                                                                                        |

| 3.2     | Integer-N PLL Architecture                                                                                                                  | 28                                                                                                                                                                                                                                                                                                                        |

| 3.3     | PLL Building Blocks                                                                                                                         | 28                                                                                                                                                                                                                                                                                                                        |

|         | eface<br>st of A<br>st of S<br>Intro<br>1.1<br>Refer<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>Refer<br>Sing<br>3.1<br>3.2 | References  Tuning System Specifications  2.1 Tuning Range  2.2 Minimum Step Size  2.3 Settling Time  2.4 Spurious Signals  2.5 Phase Noise Sidebands  2.6 Power Dissipation  2.7 Integration Level  2.8 Interference Generation  References  Single-Loop Architectures  3.1 Introduction  3.2 Integer-N PLL Architecture |

### xiv Contents

4

|      | 3.3.1    | Voltage-Controlled Oscillators                               | 28  |

|------|----------|--------------------------------------------------------------|-----|

|      | 3.3.2    | Frequency Dividers                                           | 30  |

|      | 3.3.3    | Phase Detectors                                              | 31  |

|      | 3.3.4    | The Phase-Frequency Detector/Charge-Pump Combi-              |     |

|      |          | nation                                                       | 33  |

|      | 3.3.5    | Loop Filter                                                  | 38  |

| 3.4  | Dimen    | sioning of the PLL Parameters                                | 42  |

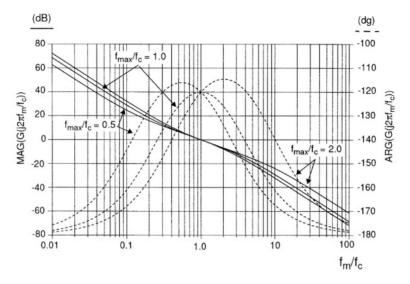

|      | 3.4.1    | Open- and Closed-loop Transfer Functions                     | 42  |

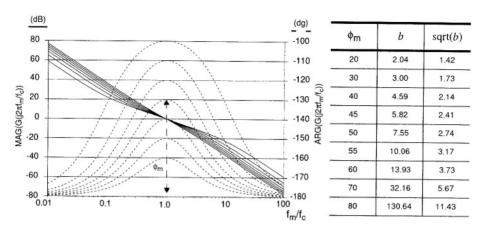

|      | 3.4.2    | Open-loop Bandwidth $f_c$ and Phase Margin $\phi_m$          | 43  |

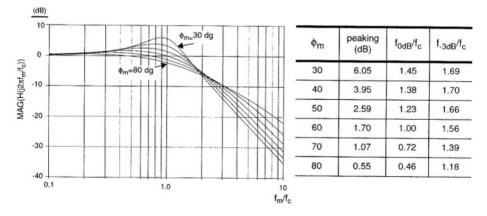

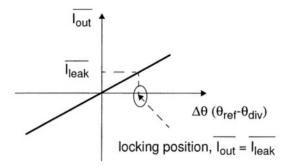

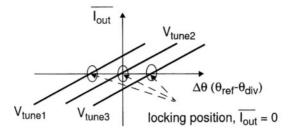

| 3.5  | Spectr   | al Purity Performance                                        | 49  |

|      | 3.5.1    | Spurious Reference Breakthrough                              | 49  |

|      | 3.5.2    | Phase Noise Performance                                      | 53  |

| 3.6  | Design   | of the Loop Filter                                           | 62  |

|      | 3.6.1    | Spurious Reference Breakthrough                              | 63  |

|      | 3.6.2    | Phase Noise Contribution from the Loop Filter Resistor       | 64  |

|      | 3.6.3    | Dimensioning of Time Constant $\tau_2$ and Capacitance $C_1$ | 66  |

| 3.7  | The Cl   | hoice of the Reference Frequency                             | 70  |

| 3.8  | Single   | loop PLL with Divided Oscillator Output                      | 70  |

| 3.9  | Fractio  | onal-N PLL Techniques                                        | 75  |

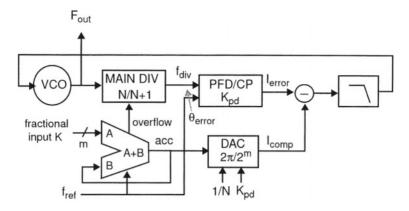

|      | 3.9.1    | Phase Error Compensation                                     | 77  |

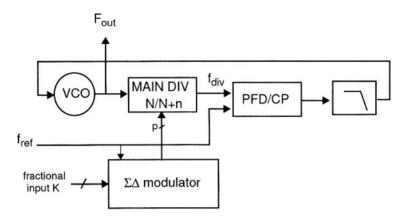

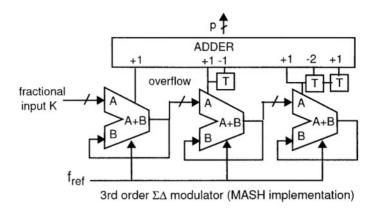

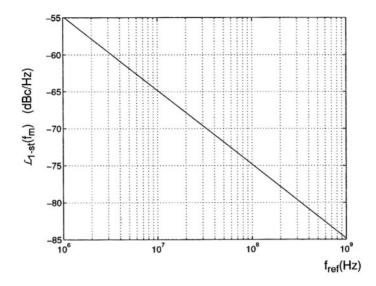

|      | 3.9.2    | $\Sigma\Delta$ Modulation Techniques                         | 80  |

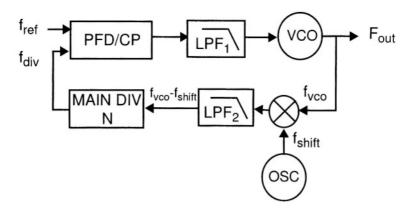

| 3.10 | Transl   | ation Loops                                                  | 85  |

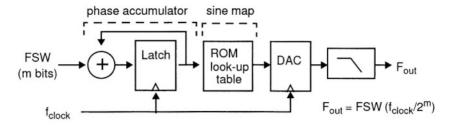

| 3.11 | Direct   | Digital Frequency Synthesizers                               | 87  |

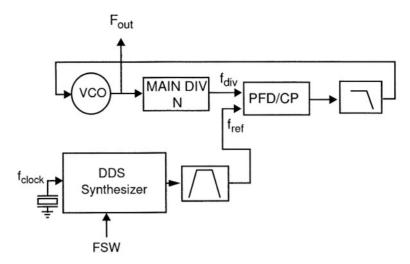

| 3.12 | Archit   | ectures Combining PLL and DDS Synthesizers                   | 89  |

| 3.13 | Summ     | ary of Conclusions on Single-Loop Architectures              | 90  |

| Refe | rences . |                                                              | 91  |

| Wide | e-Band   | Architectures                                                | 99  |

| 4.1  | Introdu  | action                                                       | 99  |

| 4.2  | Receiv   | rer Architectures                                            | 99  |

| 4.3  | Residu   | al Phase Deviation                                           | 102 |

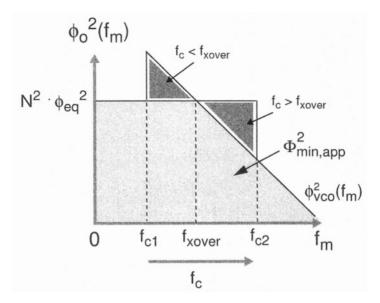

|      | 4.3.1    | The Residual Phase Deviation Power $\Phi_{res}^2$            | 102 |

|      | 4.3.2    | The Open-Loop Bandwidth for Optimum Phase Noise              |     |

|      |          | Performance                                                  | 104 |

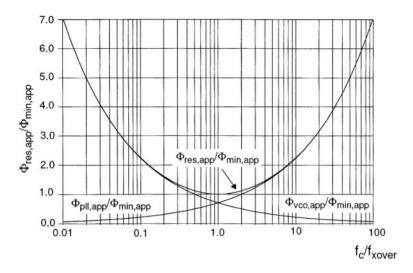

|      | 4.3.3    | Minimum Approximated Residual Phase Deviation                | 107 |

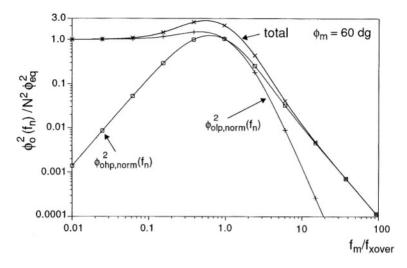

|      | 4.3.4    | Influence of the Phase Margin on the Residual Phase          |     |

|      |          | Deviation                                                    | 109 |

|   |      | 4.3.5    | The Influence of the Open-Loop Bandwidth $f_c$ on the |

|---|------|----------|-------------------------------------------------------|

|   |      |          | Residual Phase Deviation $\Phi_{res}$                 |

|   |      | 4.3.6    | The Condition for the Implementation of the Optimum   |

|   |      |          | Loop Bandwidth $f_c = f_{xover} \dots 115$            |

|   | 4.4  | Single-  | -Loop Design                                          |

|   |      | 4.4.1    | Specification of the PLL Building Blocks 117          |

|   |      | 4.4.2    | Single-Loop Architectures                             |

|   |      | 4.4.3    | Wide-Band Loop Design                                 |

|   | 4.5  | Multi-   | Loop Design                                           |

|   |      | 4.5.1    | Phase Noise Performance                               |

|   |      | 4.5.2    | Specification of the Different Loops                  |

|   |      | 4.5.3    | The Limiting Values for the Reference Frequency 130   |

|   | 4.6  | Satelli  | te Tuning System                                      |

|   |      | 4.6.1    | Double-loop Tuning System Architecture 133            |

|   |      | 4.6.2    | Phase Noise Performance                               |

|   | 4.7  | Divide   | rs in Bipolar Technology                              |

|   |      | 4.7.1    | Architecture                                          |

|   |      | 4.7.2    | Logic Implementation of the Divider Cells 138         |

|   |      | 4.7.3    | Circuit Implementation                                |

|   |      | 4.7.4    | Power Dissipation Optimization and Sensitivity Mea-   |

|   |      |          | surements                                             |

|   | 4.8  | VHF I    | PFD/CP Architectures                                  |

|   |      | 4.8.1    | Architecture                                          |

|   |      | 4.8.2    | Circuit Implementation                                |

|   |      | 4.8.3    | Measurement Results                                   |

|   | 4.9  | Conclu   | sions                                                 |

|   | Refe | rences . |                                                       |

| 5 | Δda  | ntive Pl | L Architecture 157                                    |

| • | 5.1  | •        | action                                                |

|   | 5.2  |          | Car-Radio Application                                 |

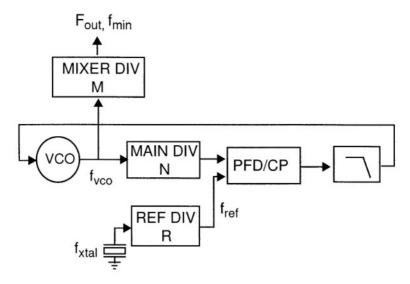

|   | 5.3  | Multi-l  | Band Tuner Architecture                               |

|   | 5.4  |          | g Time                                                |

|   | ۶.٦  | 5.4.1    | Settling Behaviour                                    |

|   |      | 5.4.2    | Open-Loop Bandwidth, Phase Margin and Settling        |

|   |      | <u>.</u> | Time Specifications                                   |

|   | 5.5  | Settlin  | g Time Requirements                                   |

|   |      |          | 1 20,                                                 |

### xvi Contents

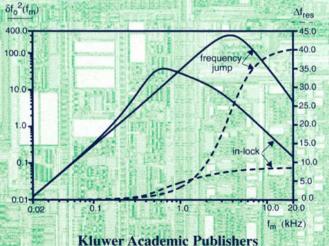

|   | 5.6  | Residu   | al Frequency Deviation                                  | )  |

|---|------|----------|---------------------------------------------------------|----|

|   |      | 5.6.1    | Introduction                                            | Ś  |

|   |      | 5.6.2    | Basic Concepts                                          | 58 |

|   |      | 5.6.3    | Simplified Treatment of the Residual Frequency Devi-    |    |

|   |      |          | ation of a PLL                                          | 7( |

|   |      | 5.6.4    | Numerical Results with Analytic Transfer Functions . 17 | 72 |

|   |      | 5.6.5    | Conclusions                                             | 18 |

|   | 5.7  | Terresti | rial FM Broadcasting                                    | 3( |

|   | 5.8  | Referen  | nce Spurious Signals and Loop Filter Attenuation 18     | 32 |

|   | 5.9  | Limitat  | ions of Existing PLL Architectures                      | 33 |

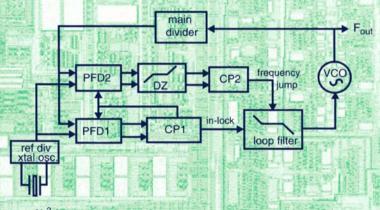

|   | 5.10 | Adaptiv  | ve PLL Architecture                                     | 33 |

|   |      | _        | Basic Architecture                                      | 34 |

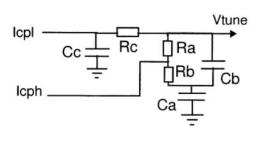

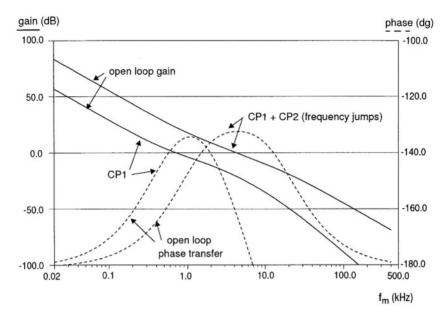

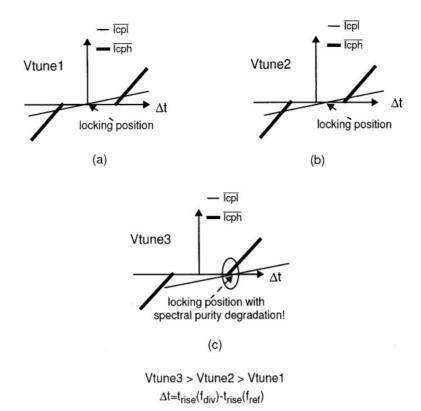

|   |      | 5.10.2   | Loop Filter Implementation                              | 35 |

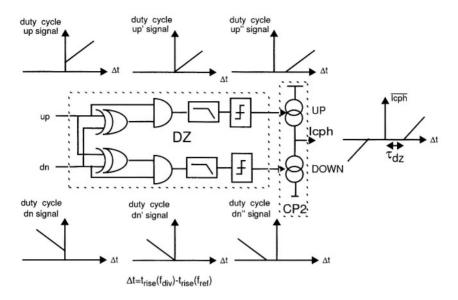

|   |      | 5.10.3   | Dead-Zone Implementation                                | ;7 |

|   | 5.11 |          | Implementation                                          | 1  |

|   |      | 5.11.1   |                                                         | 1  |

|   |      | 5.11.2   | Oscillators                                             | 2  |

|   |      |          | Charge-Pumps                                            | )2 |

|   | 5.12 |          | rements                                                 | 13 |

|   | 5.13 | Conclu   | sions                                                   | 6  |

|   |      |          |                                                         | 8  |

| 6 | Prog | rammal   | ble Dividers 20                                         | 1  |

|   | 6.1  |          | ction                                                   | 1  |

|   | 6.2  |          | Architectures                                           |    |

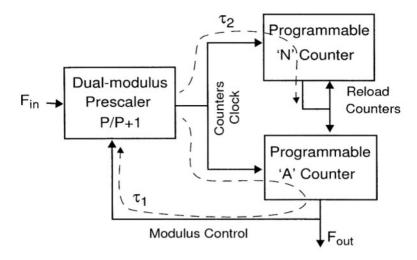

|   |      | 6.2.1    | Architecture Based on a Dual-Modulus Prescaler 20       |    |

|   |      | 6.2.2    | Presettable Programmable Counters 20                    | 5  |

|   |      | 6.2.3    | Basic Programmable Prescaler 20                         | 5  |

|   |      | 6.2.4    | Adaptive Power Prescaler Architecture for Multi-Band    |    |

|   |      |          | Applications                                            | 7  |

|   |      | 6.2.5    | Prescaler with Extended Programmability 20              | 9  |

|   | 6.3  | Divider  | s in CMOS Technology                                    |    |

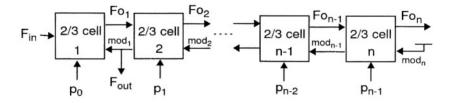

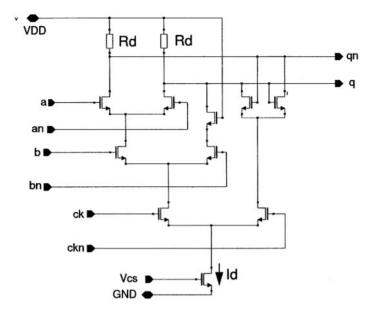

|   |      | 6.3.1    | Logic Implementation of the Divider Cells 21            |    |

|   |      | 6.3.2    | Circuit Implementation of the Divider Cells 21          |    |

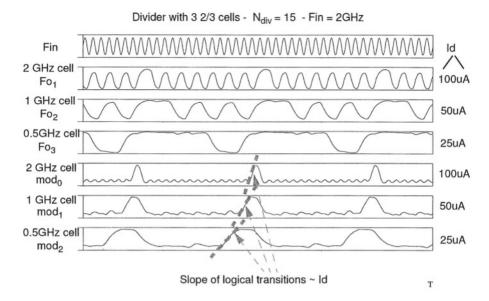

|   |      | 6.3.3    | Power Dissipation Optimization                          |    |

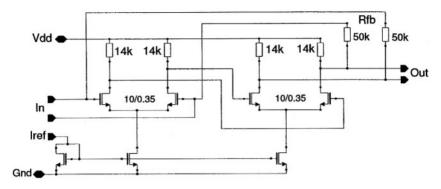

|   |      | 6.3.4    | Input Amplifier                                         | 6  |

|   |      |          |                                                         |    |

| _      |          | •••     |

|--------|----------|---------|

| 1.0    | ntents   | XVII    |

| $\sim$ | HILCHILS | ~ V I I |

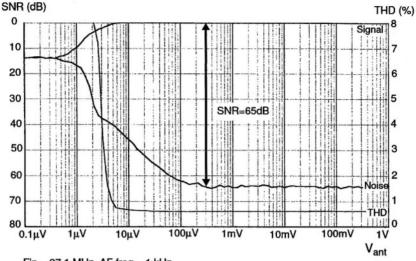

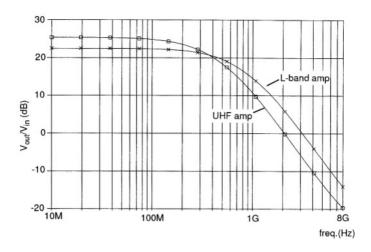

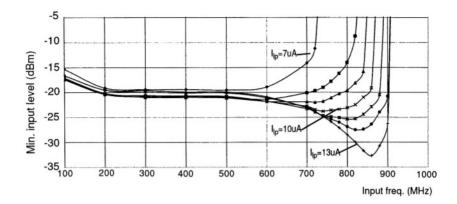

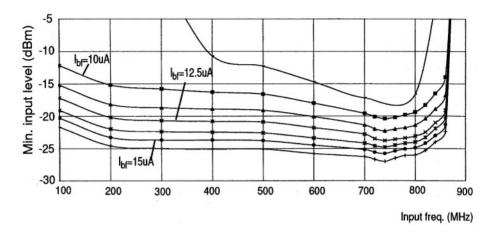

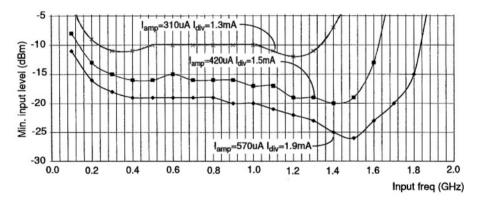

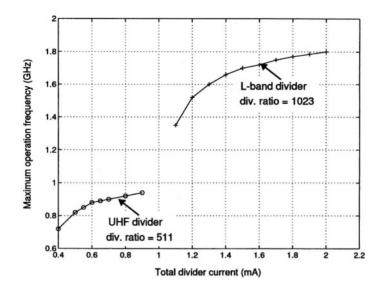

|     |        | 6.3.5     | Input Sensitivity Measurements and Maximum Oper-   |     |

|-----|--------|-----------|----------------------------------------------------|-----|

|     |        |           | ation Frequencies                                  | 217 |

|     |        | 6.3.6     | Phase Noise Measurements                           | 222 |

|     | 6.4    | Conclu    | sions                                              | 225 |

|     | Refe   | rences .  |                                                    | 225 |

| 7   | Con    | clusions  | 3                                                  | 229 |

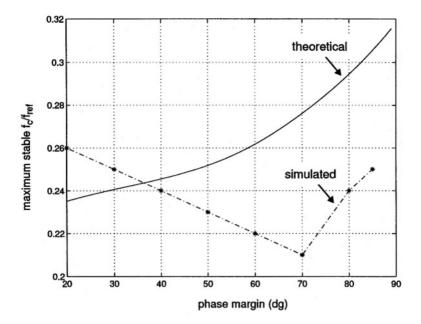

| Α   | PLL    | Stability | y Limits Due to the Discrete-Time PFD/CP Operation | 237 |

|     | A.1    | Stabilit  | y Limits                                           | 237 |

|     | Refe   | rences .  |                                                    | 240 |

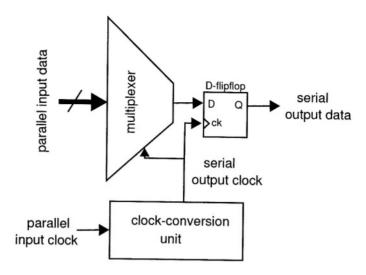

| В   | Cloc   | k-Conv    | ersion PLLs for Optical Transmitters               | 241 |

|     | Refe   | rences .  |                                                    | 243 |

| Ab  | out tl | he Auth   | or                                                 | 245 |

| Inc | lex    |           |                                                    | 247 |

# List of Acronyms

ADC Analog-to-Digital Converter AFC Automatic Frequency Control

AM Amplitude Modulation

BER Bit Error Rate CP Charge-Pump

DAC Digital-to-Analog Converter dBc dB with respect to the Carrier DDS Direct Digital Synthesizer

D-FF D-type Flip-flop

dg Degree

DSB Double Sideband

EMC Electromagnetic Compatibility

EXOR Exclusive-OR

FM Frequency Modulation FSW Frequency Setting Word

GFSK Gaussian Frequency Shift Keying

GMSK Gaussian Minimum Shift Keying

IF Intermediate Frequency

J Joule K Kelvin

LO Local Oscillator LPF Low-Pass Filter

MASH Multi-Stage Noise Shaping Modulator

PC Personal Computer

PFD Phase-Frequency Detector

PLL Phase-Locked Loop

### xx List of Acronyms

PM Phase Modulation

QPSK Quadrature Phase Shift Keying

RDS Radio Data System

RF Radio Frequency

rms Root-Mean-Square

ROM Read Only Memory

S-H Sample-and-Hold

SNR Signal-to-Noise Ratio

SSB Single Sideband

VCO Voltage-Controlled Oscillator

VHF Very High Frequency

VLSI Very Large Scale Integration

# List of Symbols

| Symbol       | Meaning                                                                         | Page |

|--------------|---------------------------------------------------------------------------------|------|

| acc          | Output of a digital accumulator                                                 | 79   |

| $A_{LO}$     | Amplitude of the carrier signal (V)                                             | 15   |

| $A_{sp}$     | Amplitude of a spurious signal (V)                                              | 16   |

| $a_{sp}$     | Relative amplitude of a spurious signal with respect to the carrier (dBc)       | 16   |

| b            | Ratio of the time constants of the loop filter $\tau_2/\tau_3$                  | 39   |

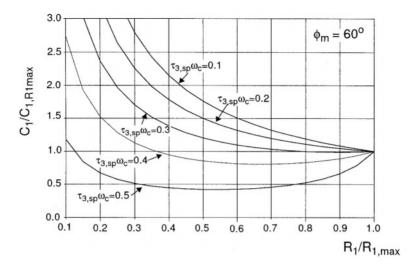

| $C_1, C_2$   | Capacitances of the loop filter (F)                                             | 40   |

| F            | Fractional (decimal) part of division ratio                                     | 75   |

| $F_{out}$    | Output frequency of a PLL (Hz)                                                  | 28   |

| $f_c$        | Open-loop bandwidth, 0 dB cross-over frequency (Hz)                             | 44   |

| $f_{center}$ | Output frequency of a VCO when $V_{tune} = 0 \text{ V (Hz)}$                    | 28   |

| $f_{c,min}$  | Minimum value of the open-loop bandwidth (Hz)                                   | 124  |

| $f_{clock}$  | Clock frequency of a DDS synthesizer (Hz)                                       | 88   |

| $f_{div}$    | Frequency of the signal at the output of a frequency divider (Hz)               | 28   |

| $f_{eq,r}$   | Reference frequency at which the equivalent phase noise floor is specified (Hz) | 58   |

| $f_{error}$  | Maximum frequency error with respect to $f_{lock}$ (Hz)                         | 13   |

| $f_h$        | Higher offset frequency for integration of noise power density (Hz)             | 103  |

| $f_{in}$     | Input frequency to a frequency divider or PFD/CP (Hz)                           | 30   |

# xxii List of Symbols

| $f_{LO}$         | Output frequency of the tuning system (Hz)         | 4   |

|------------------|----------------------------------------------------|-----|

| $f_l$            | Lower offset frequency for integration of noise    | 103 |

|                  | power density (Hz)                                 |     |

| $f_{lock}$       | Target frequency after a frequency step (Hz)       | 13  |

| $f_m$            | Fourier frequency (offset, modulation or baseband  | 15  |

|                  | frequency) (Hz)                                    |     |

| $f_{max}$        | Frequency of maximum phase advance of the open-    | 45  |

| <i>y</i> max     | loop transfer function (Hz)                        |     |

| $f_{min}$        | Minimum step size of the tuning system (Hz)        | 12  |

| $f_r$            | Offset frequency at which the free-running VCO     | 104 |

|                  | phase noise power density is specified (Hz)        |     |

| $f_{ref}$        | Operation frequency of the PFD (Hz)                | 28  |

| $f_{ref,max}$    | Maximum PFD operation frequency at which fre-      | 36  |

| y reg ,max       | quency discrimination can be realized (Hz)         |     |

| $f_{ref,min}$    | Minimum value of the reference frequency in a      | 131 |

| 5 / 6/3,111.11   | wide-band loop (Hz)                                |     |

| $f_{S}$          | Symbol rate in a digital communication system (Hz) | 103 |

| $f_{shift}$      | Mixing frequency in a translation loop (Hz)        | 86  |

| $f_{start}$      | Operation frequency before a frequency step (Hz)   | 13  |

| $f_{step}$       | Magnitude of a frequency step (Hz)                 | 162 |

| $f_{xtal}$       | Frequency of crystal oscillator (Hz)               | 28  |

| $f_{xover}$      | Phase noise cross-over frequency (Hz)              | 106 |

| G(s)             | Open-loop transfer function of a PLL               | 43  |

| H(s)             | Closed-loop transfer function of a PLL             | 43  |

| $H_d(j2\pi f_m)$ | Low-pass transfer function (de-emphasis network)   | 169 |

| $I_{cp}$         | Amplitude of the output current of a charge pump   | 33  |

| - ( <i>p</i>     | (A)                                                |     |

| $I_{leak}$       | Leakage current in the tuning line of the VCO (A)  | 50  |

| Iout             | Instantaneous output current of a charge pump (A)  | 34  |

| i                | An integer                                         |     |

| $i_{np}(f_m)$    | rms current noise density originated in the charge | 54  |

| np (3 m)         | pump $(A/\sqrt{Hz})$                               |     |

| K                | Binary input to a digital accumulator              | 75  |

| $K_{pd}$         | Gain of PFD/CP combination (A/rad)                 | 35  |

| $K_{vco}$        | VCO gain factor (Hz/V)                             | 28  |

| k                | Gain factor which depends on the configuration of  | 39  |

|                  | the loop filter                                    |     |

|                                   | List of Symbols                                          | xxiii |

|-----------------------------------|----------------------------------------------------------|-------|

| $k_B$                             | Boltzmann constant; $1.37 \times 10^{-23}$ J/K           | 59    |

| $\mathcal{L}(f_m)$                | SSB phase noise power density in a 1 Hz band-            | 20    |

| (3 1117                           | width to total signal power, at offset frequency $f_m$   |       |

|                                   | (dBc/Hz)                                                 |       |

| $\mathcal{L}_{eq}$                | SSB equivalent synthesizer phase noise floor at the      | 58    |

| -4                                | input of the phase detector (dBc/Hz)                     |       |

| $\mathcal{L}_{\Sigma\Delta}(f_m)$ | SSB phase noise power density due to quantization        | 83    |

| (),,,,                            | noise from a $\Sigma\Delta$ modulator (dBc/Hz)           |       |

| $\mathcal{L}_{vco}(f_m)$          | SSB free-running phase noise power density of the        | 109   |

| 0.0 ( <b>)</b> ,                  | VCO (dBc/Hz)                                             |       |

| l                                 | An integer                                               |       |

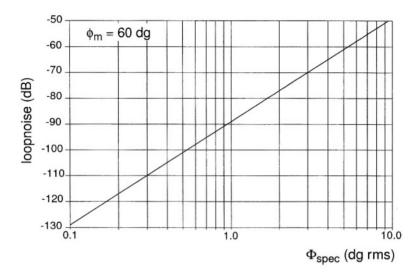

| loopnoise                         | Upper limit to the sum of the noise specification of     | 118   |

|                                   | the building blocks (dB)                                 |       |

| M                                 | Integer denoting frequency division                      | 71    |

| m                                 | Number of bits, word-width of a digital accumulator      | 75    |

| maxspurious                       | Maximum (specified) magnitude of spurious signals        | 63    |

|                                   | (dBc)                                                    |       |

| N                                 | Main divider division ratio, integer                     | 28    |

| $N_{max}$                         | Maximum value of $N$ which leads to compliance to        | 123   |

|                                   | $\Phi_{spec,wb}$                                         |       |

| n                                 | An integer                                               |       |

| n'                                | Effective length of a programmable divider chain         | 209   |

| $P_{comp}$                        | Proportionality factor                                   | 79    |

| p                                 | Order of a $\Sigma\Delta$ modulator                      | 81    |

| $p_i$                             | Binary number                                            | 138   |

| R                                 | Reference divider division ratio, integer                | 28    |

| $R_1$                             | Resistor used in the loop filter ( $\Omega$ )            | 40    |

| $R_p$                             | Ratio of the limiting values of the residual frequency   | 173   |

|                                   | deviation                                                |       |

| $s = \sigma + j\omega$            | Laplace transform complex variable                       |       |

| T                                 | Absolute temperature (K)                                 | 64    |

| $T_{hp}(s)$                       | High-pass transfer function                              | 60    |

| $T_{in}$                          | Period of the input signal to a frequency divider (s)    | 206   |

| $T_{out}$                         | Period of the output signal of a frequency divider (s)   | 206   |

| $T_{ref}$                         | Period of the input signal to the PFD, = $1/f_{ref}$ (s) |       |

| t                                 | Time (s)                                                 |       |

| $t_{lock}$                        | Locking time after a frequency step (s)                  | 13    |

# xxiv List of Symbols

| $V_{mismatch}$        | Magnitude of the ripple voltage due to mismatch in                                                               | 53  |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-----|

|                       | the CP current sources (V)                                                                                       |     |

| $V_{ripple}$          | Magnitude of the ripple voltage at the VCO tuning line (V)                                                       | 51  |

| $V_{tune}$            | Voltage at the tuning input of a VCO (V)                                                                         | 28  |

| $v_{nf}(f_m)$         | rms voltage noise density originated in the loop filter $(V/\sqrt{Hz})$                                          | 54  |

| $Z_f(s)$              | Transimpedance of the loop filter $(\Omega)$                                                                     | 39  |

| x                     | A positive number, expresses the dependency of the equivalent phase noise floor on the reference frequency       | 58  |

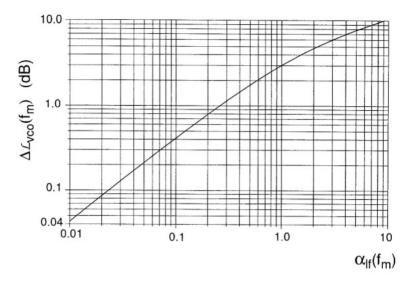

| $\alpha_{lf}(f_m)$    | Relative magnitude of the phase noise due to loop filter elements                                                | 64  |

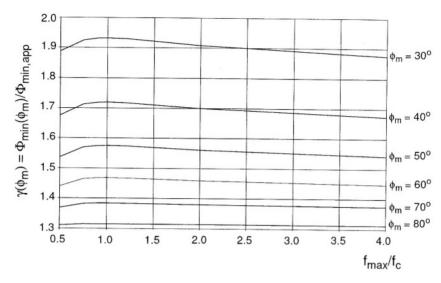

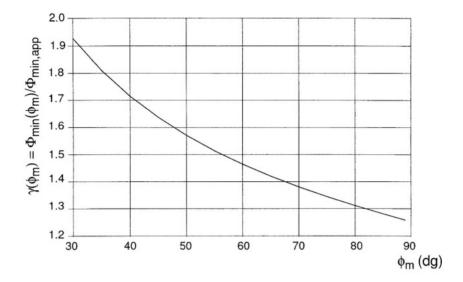

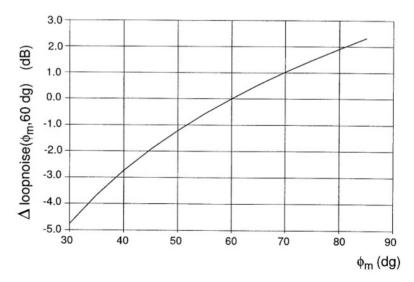

| $\gamma(\phi_m)$      | Excess noise factor                                                                                              | 109 |

| $\Delta f_e(t)$       | Remaining frequency error with respect to final value (Hz)                                                       | 162 |

| $\Delta f$            | Peak frequency deviation (Hz)                                                                                    | 51  |

| $\Delta f_{res}^2$    | Residual frequency deviation power (Hz <sup>2</sup> )                                                            | 169 |

| $\Delta f_{vco,fr}^2$ | VCO free-running frequency deviation power (Hz <sup>2</sup> )                                                    | 172 |

| $\Delta loopnoise$    | Expresses the influence of the phase margin on <i>loop-noise</i> (dB)                                            | 120 |

| $\Delta R$            | Reset time of the D-FFs when the loop is phase-locked (s)                                                        | 36  |

| $\Delta 	heta$        | Phase difference at the input of a phase frequency detector (rad)                                                | 35  |

| $\Delta 	heta_{hf}$   | Maximum phase difference that can be detected be-<br>fore PFD/CP switches polarity of the output pulses<br>(rad) | 37  |

| $\delta_{cp}$         | Duty-cycle of the output pulse of a charge-pump                                                                  | 38  |

| $\delta f_o^2(f_m)$   | Frequency deviation power spectral density (Hz <sup>2</sup> /Hz)                                                 | 169 |

| $\delta f_{vco,fr}^2$ | Free-running VCO frequency deviation power density (Hz²/Hz)                                                      | 174 |

| $\zeta_e$             | Effective damping coefficient                                                                                    | 164 |

| $\theta(t)$           | Excess phase of a sinusoidal signal (rad)                                                                        | 15  |

| $	heta_{div}$         | Phase of the output signal of a frequency divider (rad)                                                          | 30  |

# xxiv List of Symbols

| $V_{mismatch}$        | Magnitude of the ripple voltage due to mismatch in                                                               | 53  |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-----|

|                       | the CP current sources (V)                                                                                       |     |

| $V_{ripple}$          | Magnitude of the ripple voltage at the VCO tuning line (V)                                                       | 51  |

| $V_{tune}$            | Voltage at the tuning input of a VCO (V)                                                                         | 28  |

| $v_{nf}(f_m)$         | rms voltage noise density originated in the loop filter $(V/\sqrt{Hz})$                                          | 54  |

| $Z_f(s)$              | Transimpedance of the loop filter $(\Omega)$                                                                     | 39  |

| x                     | A positive number, expresses the dependency of the equivalent phase noise floor on the reference frequency       | 58  |

| $\alpha_{lf}(f_m)$    | Relative magnitude of the phase noise due to loop filter elements                                                | 64  |

| $\gamma(\phi_m)$      | Excess noise factor                                                                                              | 109 |

| $\Delta f_e(t)$       | Remaining frequency error with respect to final value (Hz)                                                       | 162 |

| $\Delta f$            | Peak frequency deviation (Hz)                                                                                    | 51  |

| $\Delta f_{res}^2$    | Residual frequency deviation power (Hz <sup>2</sup> )                                                            | 169 |

| $\Delta f_{vco,fr}^2$ | VCO free-running frequency deviation power (Hz <sup>2</sup> )                                                    | 172 |

| $\Delta loopnoise$    | Expresses the influence of the phase margin on <i>loop-noise</i> (dB)                                            | 120 |

| $\Delta R$            | Reset time of the D-FFs when the loop is phase-locked (s)                                                        | 36  |

| $\Delta 	heta$        | Phase difference at the input of a phase frequency detector (rad)                                                | 35  |

| $\Delta 	heta_{hf}$   | Maximum phase difference that can be detected be-<br>fore PFD/CP switches polarity of the output pulses<br>(rad) | 37  |

| $\delta_{cp}$         | Duty-cycle of the output pulse of a charge-pump                                                                  | 38  |

| $\delta f_o^2(f_m)$   | Frequency deviation power spectral density (Hz <sup>2</sup> /Hz)                                                 | 169 |

| $\delta f_{vco,fr}^2$ | Free-running VCO frequency deviation power density (Hz²/Hz)                                                      | 174 |

| $\zeta_e$             | Effective damping coefficient                                                                                    | 164 |

| $\theta(t)$           | Excess phase of a sinusoidal signal (rad)                                                                        | 15  |

| $	heta_{div}$         | Phase of the output signal of a frequency divider (rad)                                                          | 30  |

# xxiv List of Symbols

| $V_{mismatch}$        | Magnitude of the ripple voltage due to mismatch in                                                               | 53  |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-----|

|                       | the CP current sources (V)                                                                                       |     |

| $V_{ripple}$          | Magnitude of the ripple voltage at the VCO tuning line (V)                                                       | 51  |

| $V_{tune}$            | Voltage at the tuning input of a VCO (V)                                                                         | 28  |

| $v_{nf}(f_m)$         | rms voltage noise density originated in the loop filter $(V/\sqrt{Hz})$                                          | 54  |

| $Z_f(s)$              | Transimpedance of the loop filter $(\Omega)$                                                                     | 39  |

| x                     | A positive number, expresses the dependency of the equivalent phase noise floor on the reference frequency       | 58  |

| $\alpha_{lf}(f_m)$    | Relative magnitude of the phase noise due to loop filter elements                                                | 64  |

| $\gamma(\phi_m)$      | Excess noise factor                                                                                              | 109 |

| $\Delta f_e(t)$       | Remaining frequency error with respect to final value (Hz)                                                       | 162 |

| $\Delta f$            | Peak frequency deviation (Hz)                                                                                    | 51  |

| $\Delta f_{res}^2$    | Residual frequency deviation power (Hz <sup>2</sup> )                                                            | 169 |

| $\Delta f_{vco,fr}^2$ | VCO free-running frequency deviation power (Hz <sup>2</sup> )                                                    | 172 |

| $\Delta loopnoise$    | Expresses the influence of the phase margin on <i>loop-noise</i> (dB)                                            | 120 |

| $\Delta R$            | Reset time of the D-FFs when the loop is phase-locked (s)                                                        | 36  |

| $\Delta 	heta$        | Phase difference at the input of a phase frequency detector (rad)                                                | 35  |

| $\Delta 	heta_{hf}$   | Maximum phase difference that can be detected be-<br>fore PFD/CP switches polarity of the output pulses<br>(rad) | 37  |

| $\delta_{cp}$         | Duty-cycle of the output pulse of a charge-pump                                                                  | 38  |

| $\delta f_o^2(f_m)$   | Frequency deviation power spectral density (Hz <sup>2</sup> /Hz)                                                 | 169 |

| $\delta f_{vco,fr}^2$ | Free-running VCO frequency deviation power density (Hz²/Hz)                                                      | 174 |

| $\zeta_e$             | Effective damping coefficient                                                                                    | 164 |

| $\theta(t)$           | Excess phase of a sinusoidal signal (rad)                                                                        | 15  |

| $	heta_{div}$         | Phase of the output signal of a frequency divider (rad)                                                          | 30  |

# List of Symbols xxv

| $\theta_{error}$                  | Phase error at the input of PFD/CP (rad)                                                       | 78  |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------|-----|--|--|--|

| $\theta_{in}$                     | Phase of the input signal to a frequency divider (rad)                                         |     |  |  |  |

| $\theta_{max}$                    | Maximum value of $\theta_{error}$ during a settling transient (rad)                            | 166 |  |  |  |

| $\theta_p$                        | Peak phase deviation of phase modulation (rad)                                                 | 15  |  |  |  |

| $	heta_{ref}$                     | Phase of the output signal of the reference divider (rad)                                      | 35  |  |  |  |

| $\theta_{rms,i}$                  | rms phase deviation associated with a pair of PM spurious signals (rad)                        | 17  |  |  |  |

| $\theta_{rms,total}$              | rms phase deviation due to several pairs of PM spurious signals (rad)                          |     |  |  |  |

| $\theta_{rms,single}$             | rms phase deviation associated with a single spurious signal (rad)                             | 18  |  |  |  |

| τ                                 | Active time of the charge pump output signal (s)                                               | 38  |  |  |  |

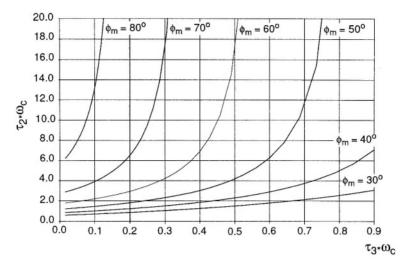

| $\tau_2$ , $\tau_3$               | Time constants of the loop filter (s)                                                          | 39  |  |  |  |

| $\tau_{3,sp}$                     | Time constant determined from spectral purity considerations (s)                               | 68  |  |  |  |

| $	au_{dz}$                        | Single-sided magnitude of the dead-zone (s)                                                    | 187 |  |  |  |

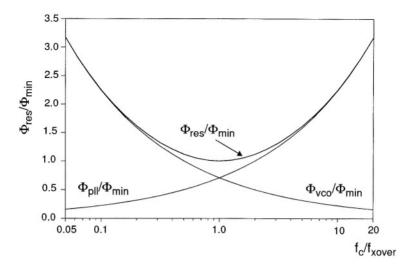

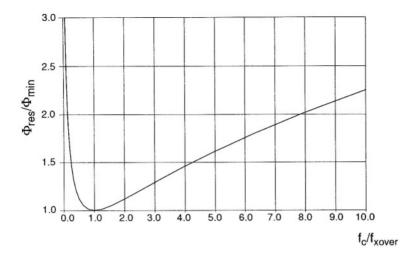

| $\Phi_{min}^2$                    | Minimum residual phase deviation power (rad <sup>2</sup> )                                     | 109 |  |  |  |

| $\Phi^2_{min,app}$                | Minimum approximated residual phase deviation power (rad <sup>2</sup> )                        | 108 |  |  |  |

| $\Phi^2_{res}$ $\Phi^2_{res,app}$ | Residual phase deviation power (rad <sup>2</sup> )                                             | 103 |  |  |  |

| $\Phi^2_{res,app}$                | Approximated residual phase deviation power (rad <sup>2</sup> )                                | 105 |  |  |  |

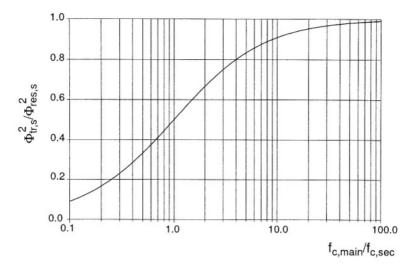

| $\Phi^2_{res,ml}$                 | Residual phase deviation power of a multi-loop tuning system (rad <sup>2</sup> )               | 125 |  |  |  |

| $\Phi_{spec,max}$                 | Specification for the maximum residual phase deviation of the LO (rad rms)                     | 116 |  |  |  |

| $\Phi_{spec}$                     | Specification for the residual phase deviation due to stochastic phase noise sources (rad rms) | 116 |  |  |  |

| $\Phi_{spec,spur}$                | Specification for the residual phase deviation due to spurious signals (rad rms)               | 116 |  |  |  |

| $\Phi_{spec,wb}$                  | Residual phase deviation specification for a wide-<br>band loop (rad rms)                      | 122 |  |  |  |

| $\Phi^2_{tr,i}$                   | Residual phase deviation power transferred to the output of a multi-loop tuning system (rad²)  | 125 |  |  |  |

| $\phi_d(f_m)$                     | rms phase noise power density of main divider $(rad/\sqrt{Hz})$                                | 54  |  |  |  |

# CHAPTER ONE

# Introduction

The last three decades of the 20th century were marked by significant advances in integrated circuit technologies [1,2]. The technological advances made monolithic integration of complex electronic functions at ever lower cost prices possible. Eventually, this trend enabled the breakthrough of "digital" tuning functions into the consumer market. This was a most important step in the advance of Consumer Electronics: digital tuning increased the comfort and satisfaction level of "ancient" consumer goods, such as televisions and AM/FM radios, and enabled a whole new range of personal communication products—from which cellular mobile phones are a striking example.

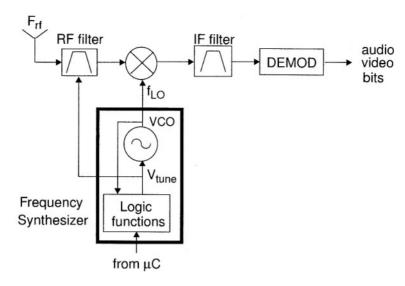

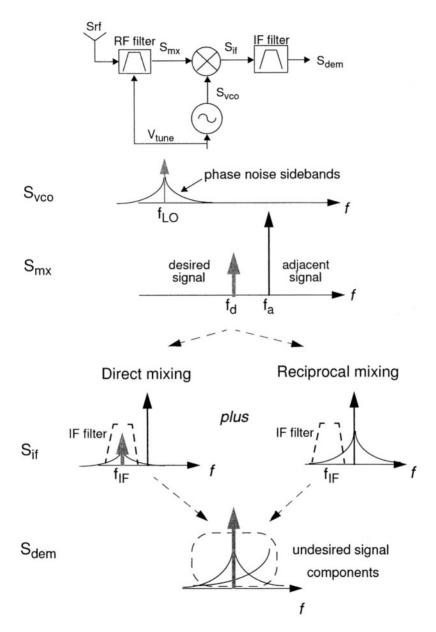

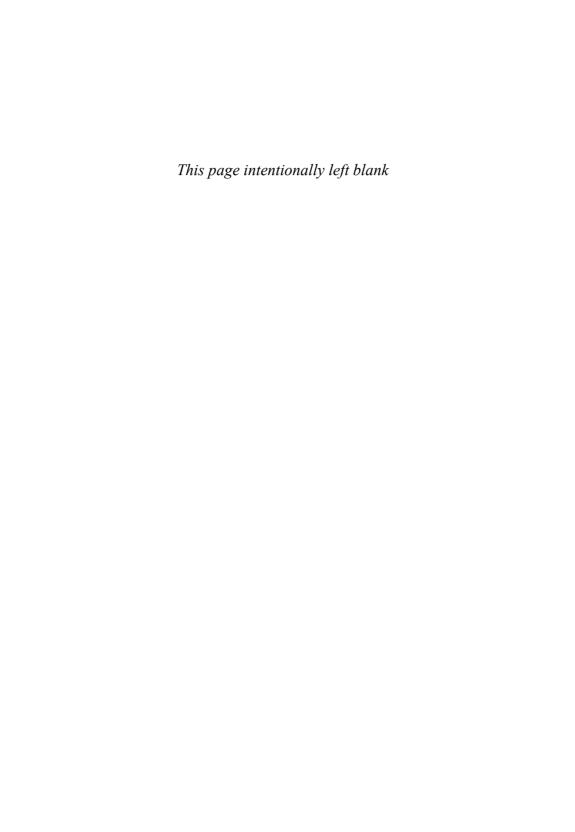

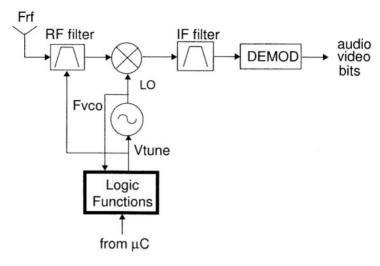

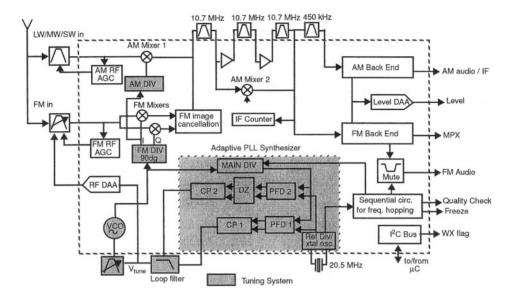

Digital tuning in modern communication systems almost always rely on a particular implementation of a phase-locked loop frequency synthesizer [3, 4]. The PLL frequency synthesizer, once it became available at affordable prices, was readily coupled to the super-heterodyne receiver architecture [5–7] as depicted in Figure 1-1. In this way, the frequency synthesizer complemented the receiver functionality without compromising the performance of the signal processing blocks.

The cost and the performance level of the frequency synthesizer have a direct impact on the price and on the functionality of the product in which it will be applied. This fact justifies the world-wide research efforts to improve the performance, to decrease the cost and to achieve frequency synthesizer implementations which are optimally tailored for each intended application. These aspects form the background of this work. Before going in more details into the

#### 2 Introduction

**Figure 1-1** A super-heterodyne receiver architecture: signal path and tuning system (frequency synthesizer).

subjects treated in the text, a brief review of basic communication techniques will be given.

# **Principles of Receiver Operation**

Frequency multiplexing plays a key role in RF communication systems. With this technique the information from different users are translated to different portions of the electromagnetic frequency spectrum before being transmitted. A receiver, in turn, recovers the information from a desired RF channel by performing frequency translation and filtering operations on the signals originally present at its input.

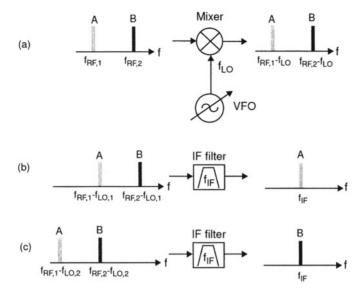

Figure 1-2 schematically depicts the basic building blocks of a superheterodyne receiver architecture: a mixer, a variable-frequency oscillator (VFO) and an intermediate frequency (IF) filter. In Figure 1-2(a) the input signals to the receiver lie at RF frequencies  $f_{RF,1}$  and  $f_{RF,2}$ . We will refer to the signal at  $f_{RF,1}$  as "signal A" and to the signal at  $f_{RF,2}$  as "signal B." The oscillator generates a *local oscillator* (LO) signal  $f_{LO}$  which is multiplied ("mixed") with the RF input signals in the mixer. The mixing operation shifts the signals originally at frequencies  $f_{RF,1}$  and  $f_{RF,2}$  to  $f_{RF,1} - f_{LO}$  and  $f_{RF,2} - f_{LO}$  re-

Figure 1-2 Basic receiver building-blocks, frequency translation and filtering operations.

spectively. 1 This operation is referred to as the "down-conversion" of the RF signals. So, a mixer provides a convenient and efficient way to transfer information from one portion of the frequency spectrum to another. The next step is to filter out undesired signals and to retain only the signal which is carrying the desired information. This operation is normally done by means of an IF filter as depicted in Figure 1-2(b) and (c). The IF filter in this example is a band-pass filter centered at frequency  $f_{LF}$ . The output of the IF filter contains (ideally) only the signal located at its pass-band, as signals outside the pass-band are attenuated. The RF frequency  $f_{RF}$  of the input signal which appears at the output of the IF filter after frequency translation is related to the frequency of the LO signal  $f_{LO}$  and to the center frequency of the IF filter  $f_{IF}$  as

$$f_{RF} = f_{LO} + f_{IF}.$$

<sup>&</sup>lt;sup>1</sup>In this example the LO frequency is assumed to be lower than the frequency of the input signals, and the signals appearing at the sum frequencies  $f_{RF,1} + f_{LO}$  and  $f_{RF,2} + f_{LO}$  are ignored, for the sake of simplicity.

#### 4 Introduction

It readily follows that for reception of a RF signal at frequency  $f_{RF,i}$  the LO frequency must be set to

$$f_{LO,i} = f_{RF,i} - f_{IF}.$$

In the case of Figure 1-2(b) the remaining signal at the output of IF filter is "signal A" which was originally located at RF frequency  $f_{RF,1}$ . For this situation the LO frequency is

$$f_{LO,1} = f_{RF,1} - f_{IF}$$

.

For reception of "signal B" as depicted in Figure 1-2(c) the local oscillator must be *tuned* to oscillate at frequency

$$f_{LO.2} = f_{RF,2} - f_{IF}.$$

In "old times" the tuning operation was made by hand, normally by turning a round knob. The knob was coupled to a variable capacitor or inductor whose value determined the oscillation frequency of the local oscillator [8]. Nowadays, the variable-frequency oscillator almost always consists of a voltage-controlled oscillator (VCO) which is incorporated in a feedback control loop, often in a phase-locked loop (PLL) configuration. In Figure 1-1, the frequency of the local oscillator signal  $f_{LO}$  can be set to a desired value by means of a digital control word generated by, for example, a micro-controller ( $\mu$ C). If another RF channel must be received a different control word is sent to the frequency synthesizer, which then adjusts the frequency of the VCO to the new value. The receiver of Figure 1-1 also comprises a demodulator, placed at the output of the IF filter, which delivers the original base-band information for subsequent processing by base-band circuits. These could be audio-amplifiers in an AM-FM system or a digital decoder in a GSM handset. The band-pass RF filter placed before the mixer is used to attenuate the RF image frequency.

The spectral purity of the LO signal  $f_{LO}$  influences the quality of the recovered base-band signal and several performance aspects of the receiver depicted in Figure 1-1.<sup>2</sup> The mixing process, which is used for down-conversion of the RF signals, superposes the phase noise of the LO signal on the modulation of the RF signal. Hence, the signal-to-noise ratio at the output of the demodulator is a function of LO's phase noise level [9]. Furthermore, reciprocal mixing of

<sup>&</sup>lt;sup>2</sup>As discussed in more detail in Section 2.5.

adjacent channels decrease the receiver's selectivity and disturbs the reception of weak signals [7]. Therefore, spectrum purity is a main topic of concern in frequency synthesizers for receiver applications. The phase noise of the LO signal  $f_{LO}$  is determined by the "free-running" phase noise level of the VCO, by the quality of the "digital functions" within the PLL, by the PLL architecture, and by the choice of system parameters within each specific application.

The subject of low-noise VCO design has received extensive attention in the literature [10–24], and it is not treated here. Instead, we will concentrate on PLL architectures, on system analysis and on circuit implementation of PLL building blocks. A more in-depth description of the work is presented in the next section.

#### 1.1 OVERVIEW OF THE BOOK

This work focuses on

- 1. innovative system and building block architectures for RF PLL frequency synthesizers,

- 2. in-depth analysis of the different performance aspects of PLL frequency synthesizers,

- 3. circuit implementations of PLL building blocks in different process technologies.

A general outline of this book, describing the main subjects of the different chapters, is presented in Table 1-1.

Chapter 2 describes the main specification points of a tuning system in the context of transceiver applications.

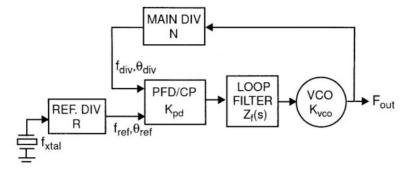

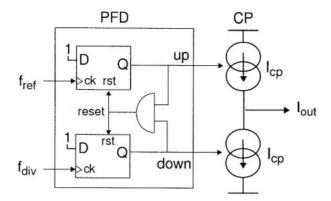

Chapter 3 provides an overview and analysis of single-loop PLL architectures. The properties of the PLL building blocks on the system level are reviewed and the concepts of open-loop bandwidth and phase margin, which enable evaluation of the influence of a second pole in the loop filter on the different performance aspects of the PLL, are introduced. Chapter 3 proceeds with an analysis of the spectral purity of a single-loop PLL, namely spurious reference breakthrough and phase noise performance, followed by a section on the dimensioning of the loop filter components when taking spectral purity specifications into account. After that, a review of single-loop PLL architectures in which the reference frequency is not equal to the minimum step size is

|           | Architectures            |                            | System analysis                    |                               | Circuit |

|-----------|--------------------------|----------------------------|------------------------------------|-------------------------------|---------|

|           | System                   | Building<br>blocks         | Spectral purity                    | Settling<br>time              | design  |

| Chapter 3 | single-loop              |                            | spurious<br>break-<br>through      |                               |         |

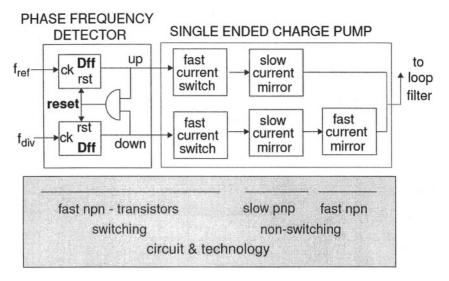

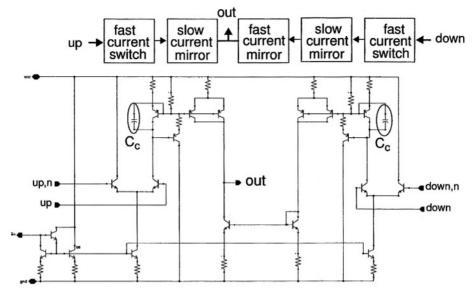

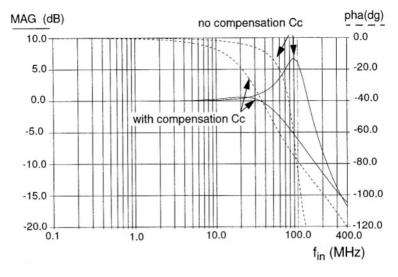

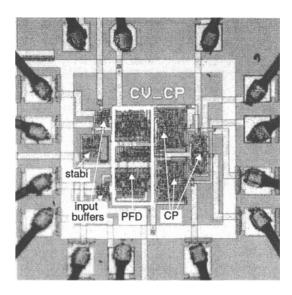

| Chapter 4 | wide-band,<br>multi-loop | dividers,<br>PFD/CP        | residual<br>phase<br>deviation     |                               | bipolar |

| Chapter 5 | adaptive-<br>loop        | dead-<br>zone,<br>dividers | residual<br>frequency<br>deviation | type-2<br>third-order<br>loop | bipolar |

| Chapter 6 |                          | dividers                   |                                    |                               | CMOS    |

**Table 1-1** Main contents of the different chapters, arranged by topic.

presented: the single-loop PLL with divided output is discussed, followed by fractional-*N* frequency synthesizers, translation loops and DDS techniques.

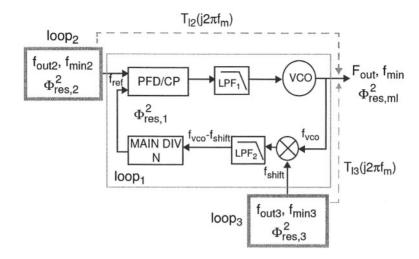

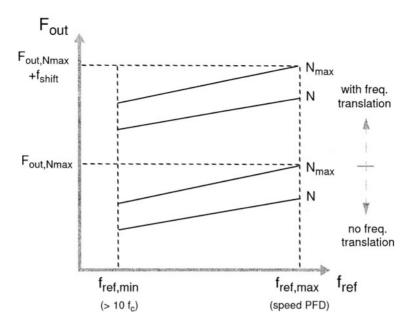

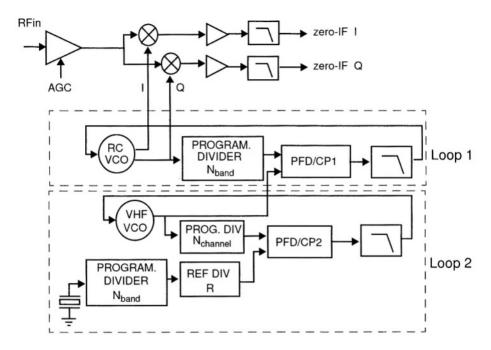

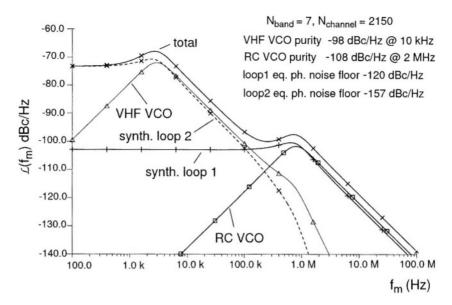

Chapter 4 focuses on tuning systems for phase-modulation communication systems. It starts with an analysis of the residual phase deviation of PLL frequency synthesizers, followed by the implementation of a design methodology for single-loop and multi-loop PLLs. Then, a double-loop PLL architecture, used for the reception of QPSK satellite signals, is described [25,26]. The remaining of Chapter 4 describes the architecture and circuit implementation of bipolar building blocks for wide-band PLLs.

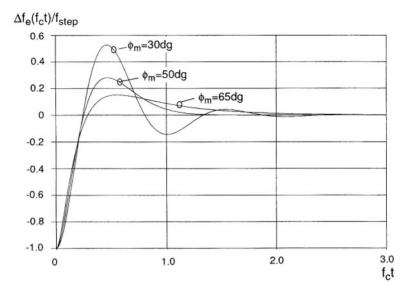

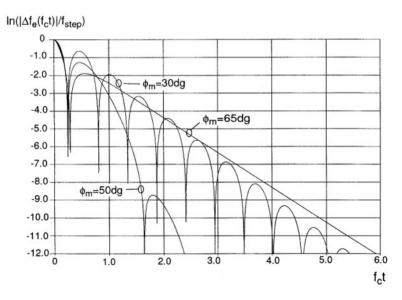

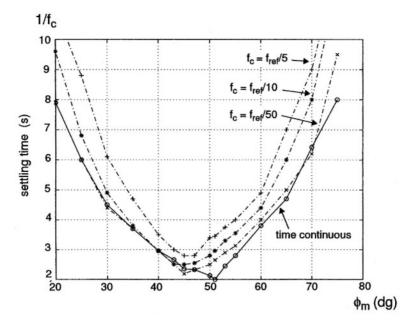

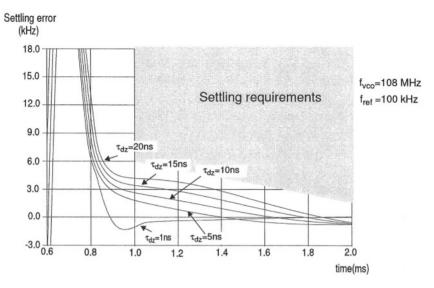

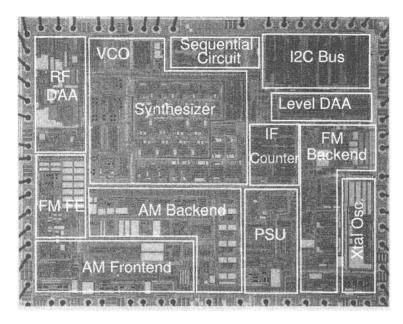

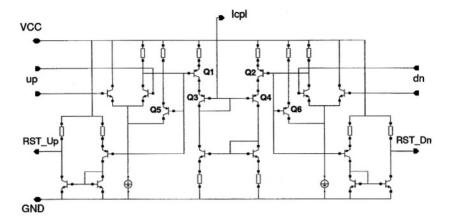

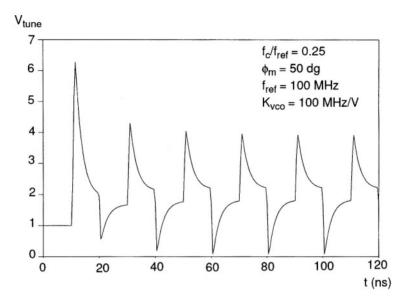

Chapter 5 concentrates on tuning systems for frequency-modulation communication systems. First, the settling performance of a type-2 third-order PLL as a function of the open-loop bandwidth and of the phase margin is investigated. Then, the optimization of the residual frequency deviation performance is addressed. Next, a practical situation is presented where the loop bandwidth requirement, derived from the settling time specification, leads to an unacceptable residual frequency deviation performance. This situation forms the background for the remaining of Chapter 5, where an adaptive PLL architecture, designed to be used in a global car-radio tuner IC, is presented and implemented [27, 28]. With this architecture adaptation of the loop bandwidth occurs smoothly as a function of the phase error in the loop, without the necessity of switching circuit elements in the loop filter.

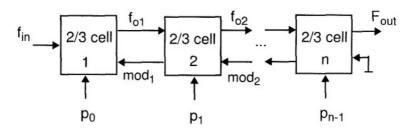

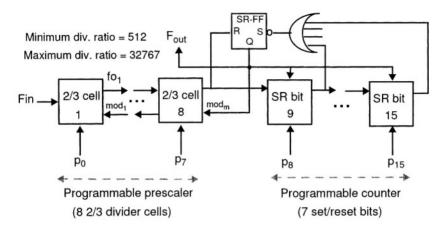

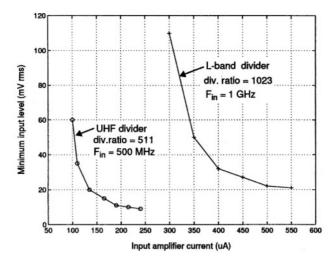

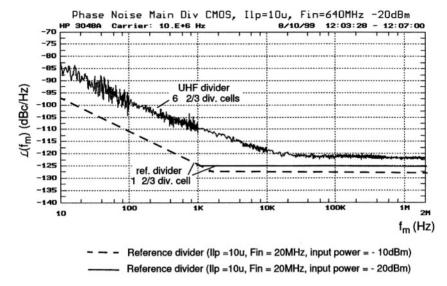

Chapter 6 presents a truly-modular architecture for low-power programmable frequency dividers. The architecture provides building blocks with low power dissipation, high design flexibility and high reusability. A property of the modular divider architecture, the scaling-down of the input frequency for each cell, was exploited in an adaptive-power frequency divider architecture for wireless multi-band applications. Chapter 6 proceeds with the description of a family of low-power fully programmable divider circuits in a standard 0.35  $\mu$ m bulk CMOS technology [29, 30]. The implementation of the divider cells and the power optimization procedure are described, and design aspects of the input amplifiers are discussed. The chapter is concluded with a presentation of measured results.

Chapter 7 is a summary of the main conclusions established in the text. Appendix A considers the stability limits of PLLs using a PFD/CP combination, and Appendix B briefly treats the design of clock-conversion PLLs for optical networks.

#### **REFERENCES**

- [1] W.F. Brinkman, D.E. Haggan and W.W. Troutman, "A History of the Invention of the Transistor and Where It Will Lead Us," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 12, pp. 1858–1865, Dec. 1997.

- [2] L.E. Larson, "Integrated Circuit Technology Options for RF IC's—Present Status and Future Directions," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 3, pp. 387–399, Mar. 1998.

- [3] F.M. Gardner, *Phase-lock Techniques*, Wiley, New York, 2nd. edition, 1979.

- [4] U.L. Rohde, *RF and Microwave Digital Frequency Synthesizers*, Wiley, New York, 1997.

- [5] J.L. Hogan Jr., "The Heterodyne Receiving System, and Notes on the Recent Arlington-Salem Tests," *Proceedings of the IRE*, vol. 1, pp. 75– 102, July 1913, Reprinted in Proceedings of the IEEE, Vol. 87, no. 11, Nov. 1999.

- [6] E. Armstrong, "The super-heterodyne its origin, development, and some recent improvements," *Proceedings of the IRE*, vol. 12, pp. 539–552, Oct. 1924.

- [7] B. Razavi, RF Microelectronics, Prentice Hall, New York, 1998.

#### 8 Introduction

- [8] K.R. Thrower, "History of Tuning," in *International Conference on 100 Years of Radio*, 1995, pp. 107–113.

- [9] W.P. Robins, *Phase Noise in Signal Sources*, 9. IEE Telecomm., London, 2nd edition, 1996.

- [10] D.B. Leeson, "A Simple Model of Feedback Oscillator Noise Spectrum," *Proceedings of the IEEE*, vol. 53, no. 2, pp. 329–330, Feb. 1966.

- [11] A.A. Abidi and R.G. Meyer, "Noise in Relaxation Oscillators," *IEEE Journal of Solid-State Circuits*, vol. SC-18, no. 12, pp. 794–802, Dec. 1983.

- [12] C.J.M. Verhoeven, "A High-Frequency Electronically Tunable Quadrature Oscillator," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 7, pp. 1097–1100, July 1992.

- [13] M.J. Underbill, "Fundamentals of Oscillator Performance," *Electronics and Communication Engineering Journal*, vol. 4, no. 4, pp. 185–193, Aug. 1992.

- [14] T.C. Weigandt, B. Kim and P.R. Gray, "Analysis of Timing Jitter in CMOS Ring Oscillators," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, 1994, vol. 4, pp. 27–30.

- [15] M. Soyuer *et al.*, "A 2.4-GHz Silicon Bipolar Oscillator with Integrated Resonator," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 2, pp. 268–270, Feb. 1996.

- [16] A. Rofougoran *et al.*, "A 900 MHz CMOS LC Oscillator with Quadrature Outputs," in *IEEE International Solid-State Circuits Conf. (ISSCC)*, 1996, pp. 316–317.

- [17] B. Razavi, "A Study of Phase Noise in CMOS Oscillators," *IEEE Journal of Solid-State Circuits*, vol. 31, no. 3, pp. 331–343, Mar. 1996.

- [18] J. Craninckx and M. Steyaert, "A 1.8-GHz Low Phase Noise CMOS VCO using Optimized Hollow Inductors," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 5, pp. 736–744, May 1997.

- [19] J.A. McNeill, "Jitter in Ring Oscillators," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 6, pp. 870–879, June 1997.

- [20] A. Hajimiri and T. Lee, "A General Theory of Phase Noise in Electrical Oscillators," IEEE Journal of Sol id-State Circuits, vol. 33, no. 2, pp. 179-194, Feb 1998.

- [21] C. Samori et al., "Spectrum Folding and Phase Noise in LC Tuned Oscillators," IEEE Transactions on Circuits and Systems II, vol. 45, no. 7, pp. 781–790, July 1998

- [22] O. Huang. "Phase-Noise-to-Carrier Ratio in LC Oscillators." *IEEE* Transactions on Circuits and Systems-I: Fund. Theory and Appl., vol. 47, no. 7, pp. 965–980, July 2000.

- [23] J.D. van der Tang and D. Kasperkovitz, "A Low-Phase-Noise Reference Oscillator with Integrated pMOS Varactors for Digital Satellite Receivers," IEEE Journal of Solid-State Circuits, vol. 35, no. 8, pp. 1238– 1243, Aug. 2000.

- [24] P.W.J. van de Ven et al., "An Optimally Coupled 5 GHz Quadrature Oscillator," in IEEE Symposium on VLSI Circuits, 2001, pp. 115–118.

- [25] C.S. Vaucher and D. Kasperkovitz, "A wide band Tuning System for Fully Integrated Satellite Receivers," in Proc. of the 23rd European Solid-State Circuits Conference (ESSCIRC), 1997, vol. 23, pp. 56-59.

- [26] C.S. Vaucher and D. Kasperkovitz, "A Wide-Band Tuning System for Fully Integrated Satellite receivers," IEEE Journal of Solid-State Circuits, vol. 33, no. 7, pp. 987–997, July 1998.

- [27] K. Kianush and C.S. Vaucher, "A Global Car Radio IC with Inaudible Signal Quality Checks," in *IEEE International Solid-State Circuits Conf.* (ISSCC), 1998, pp. 130–131.

- [28] C.S. Vaucher, "An Adaptive PLL Tuning System Architecture Combining High Spectral Purity and Fast Settling Time," IEEE Journal of Solid-State Circuits, vol. 35, no. 4, pp. 490–502, Apr. 2000.

- [29] C.S. Vaucher and Z. Wang, "A Low-power Truly-modular 1.8GHz Programmable Divider in Standard CMOS Technology," in *Proc. of the 25th* European Solid-State Circuits Conference (ESSCIRC), 1999, vol. 25, pp. 406-409.

# 10 Introduction

[30] C.S. Vaucher *et al.*, "A Family of low power truly-modular Programmable Dividers in Standard 0.35μm CMOS Technology," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 7, pp. 1039–1045, July 2000.

# Tuning System Specifications

This chapter describes the main specification points of tuning systems used within modern receiver and transceiver products. The specification points determine important parameters of the frequency synthesizer implementation. Furthermore, the concept of base-band phase noise power spectral density is introduced in Section 2.5. This concept is used extensively in this book to quantify the noise performance of several synthesizer architectures.

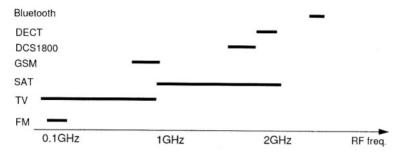

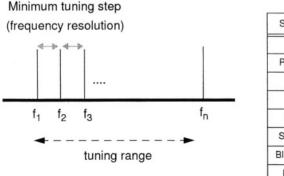

#### 2.1 TUNING RANGE

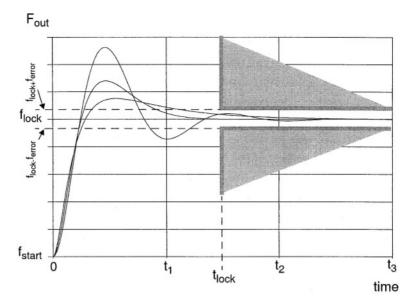

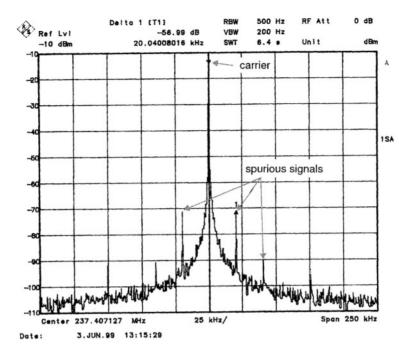

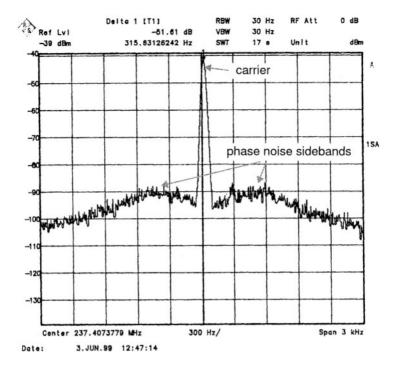

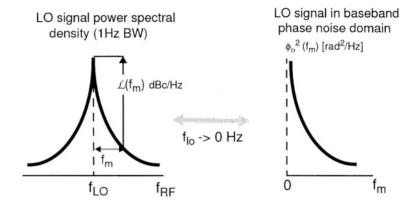

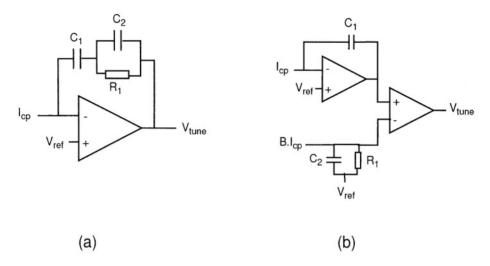

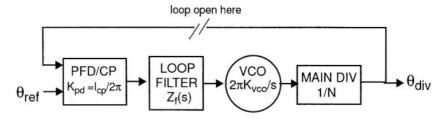

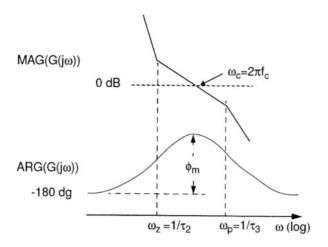

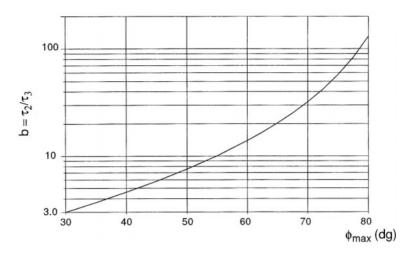

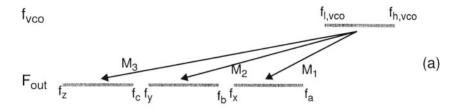

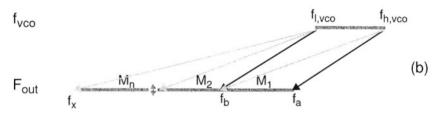

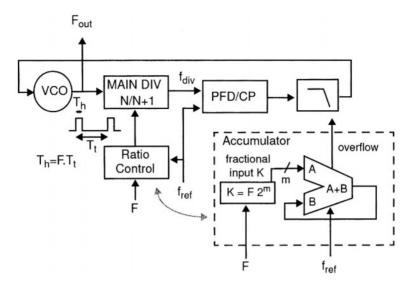

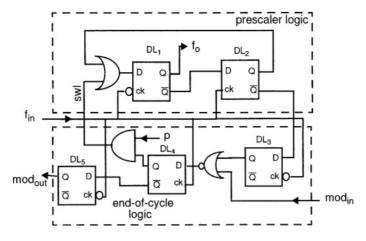

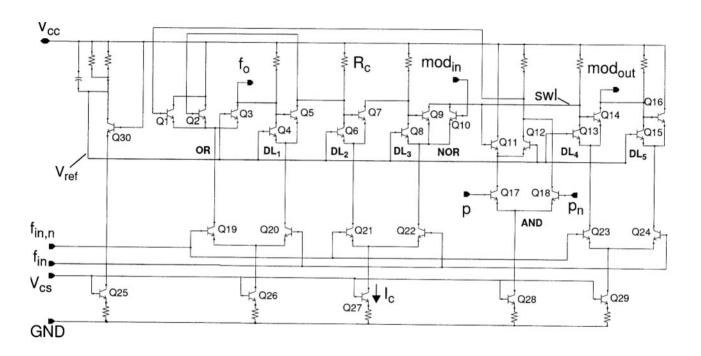

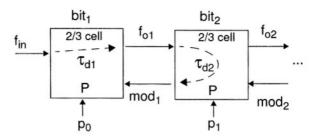

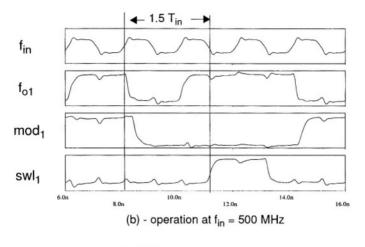

The tuning range denotes the range of frequencies to be generated by the synthesizer, see Figure 2-1. The tuning range is a function of the RF input frequency range in receiver applications, and of the input and output frequency ranges in transceiver systems.