## **Objectives**

- Build SDC files for constraining PLD designs

- Verify timing on simple & complex designs using TimeQuest TA

# **Timing Analysis Agenda**

- TimeQuest basics

- Timing constraints

- Example

**♦ Console** (History /

For Help, press F1

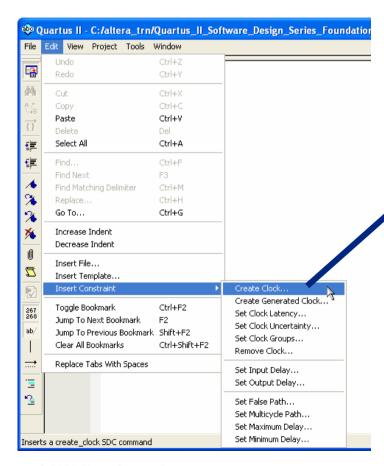

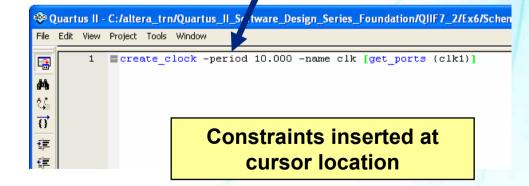

#### **SDC File Editor = Quartus II Text Editor**

- Use Quartus II editor to create and/or edit SDC

- SDC editing unique features (for .sdc files)

- Access to GUI dialog boxes for constraint entry (Edit ⇒ Insert Constraint)

- Syntax coloring

- Tooltip syntax help

TimeQuest File menu ⇒ New/Open SDC File Quartus II File menu ⇒ New ⇒ Other Files

```

Edit View Project Tools Window

35

36

38

39

40

41

create Tclock -name (clk1) -period 6.000 -waveform ( 0.000 3.000 ) [get ports (clk1)] -add

42

create_clock[-add][-name <clock_name>]-period <value>[-waveform <edge_list>][<targets>]]

43

-add: Adds clock to a node with an existing clock

-name <clock_name>; Clock name of the created clock

-period <value>: Speed of the clock in terms of clock period

-waveform <edge list>: List of edge values

# * * * * * <targets >: List or collection of targets

set_input_delay -add_delay -nax -clock [get_clocks {clk1}] 3.250 [get_ports {dataa[1]}]

set_input_delay -add_delay -nin -clock [get_clocks {clk1}]

1.750 [get ports (dataa[1])]

set input delay -add delay -max -clock [get clocks (clk1)] 3.250 [get ports (dataa[3])]

51

set input delay -add delay -nin -clock [get clocks (clk1)] 1.750 [get ports (dataa[3])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wraddress[0])]

set input delay -add delay -min -clock [get clocks (clk1)] 1.000 [get ports (wraddress[0])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wraddress[1])]

set input delay -add delay -min -clock [get clocks (clk1)] 1.000 [get ports (wraddress[1])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wraddress[2])]

set input delay -add delay |min -clock [get clocks (clk1)] 1.000 [get ports (wraddress[2])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wraddress[3])]

59

set input delay -add delay -min -clock [get clocks (clk1)] 1.000 [get ports (wraddress[3])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wren)]

set input delay -add delay -min -clock [get clocks (clk1)] 1.000 [get_ports (wren)]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (rdaddress[4])]

set input delay -add delay -min -clock [get clocks (clk1)] 1.000 [get ports (rdaddress[4])]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (wraddress[4])]

set input delay -add delay -min -clock [get clocks {clk1}] 1.000 [get ports {wraddress[4]}]

set input delay -add delay -max -clock [get clocks (clk1)] 2.500 [get ports (rdaddress[0])]

set input delay -add delay -min -clock [get clocks (clk1)]

1.000 [get ports {rdaddress[0]}]

or Help, press F1

Ln 41. Col 9

```

Place cursor over command to see tooltip

#### **SDC File Editor (cont.)**

Construct an SDC file using TimeQuest graphical constraint creation tools

© 2009 Altera Corporation

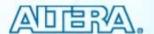

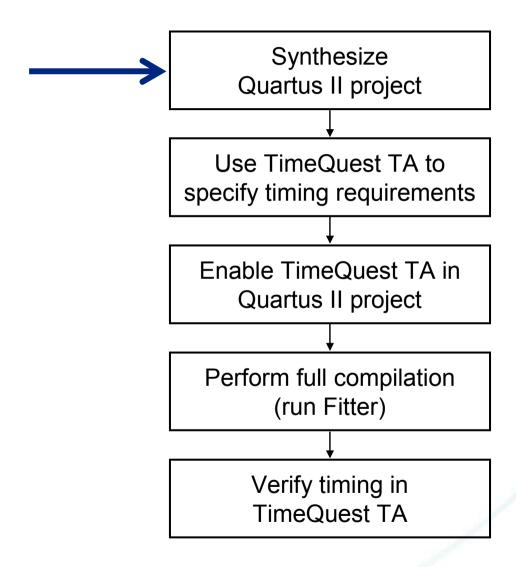

# **Basic Steps to Using TimeQuest TA**

- Generate timing netlist

- Enter SDC constraints

- Create and/or read in SDC file (recommended method)

or

- Constrain design directly in console

- Update timing netlist 3.

- Generate timing reports

- Save timing constraints (optional)

#### **Using TimeQuest TA in Quartus II Flow**

# **Timing Analysis Agenda**

- TimeQuest basics

- Timing constraints

- Example

## Importance of Constraining

- Timing analysis tells how a circuit WILL behave

- Providing timing constraints tells tools how you WANT the design to behave

- Constraints paint picture of how design should operate

- Based on design specs & specs from other devices on PCB

- Provide goals for fitter to target during compilation

- Provide values to which to compare timing results

- TimeQuest TA performs limited analysis without timing constraints

# Timing Requirements: Enter Constraints

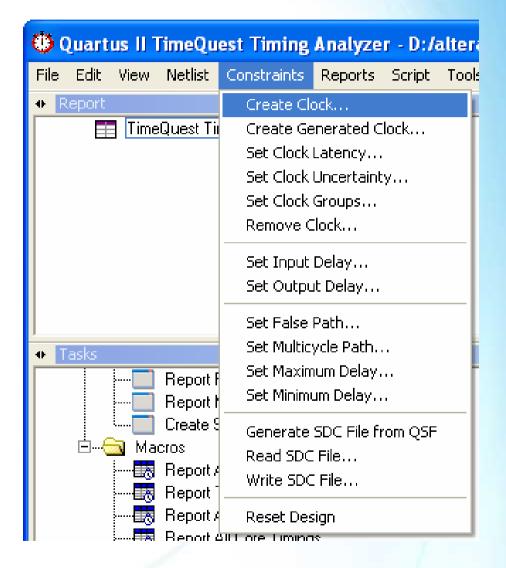

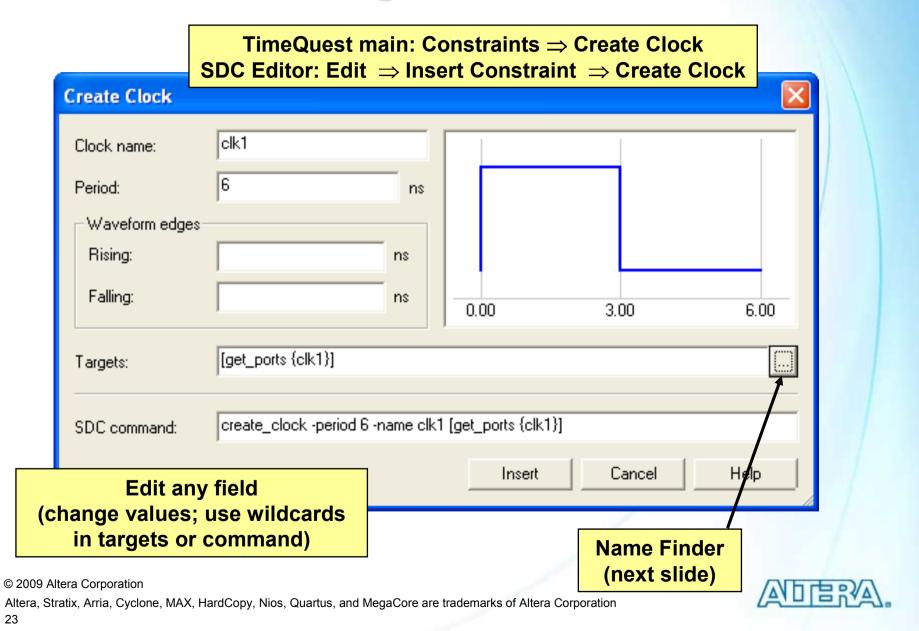

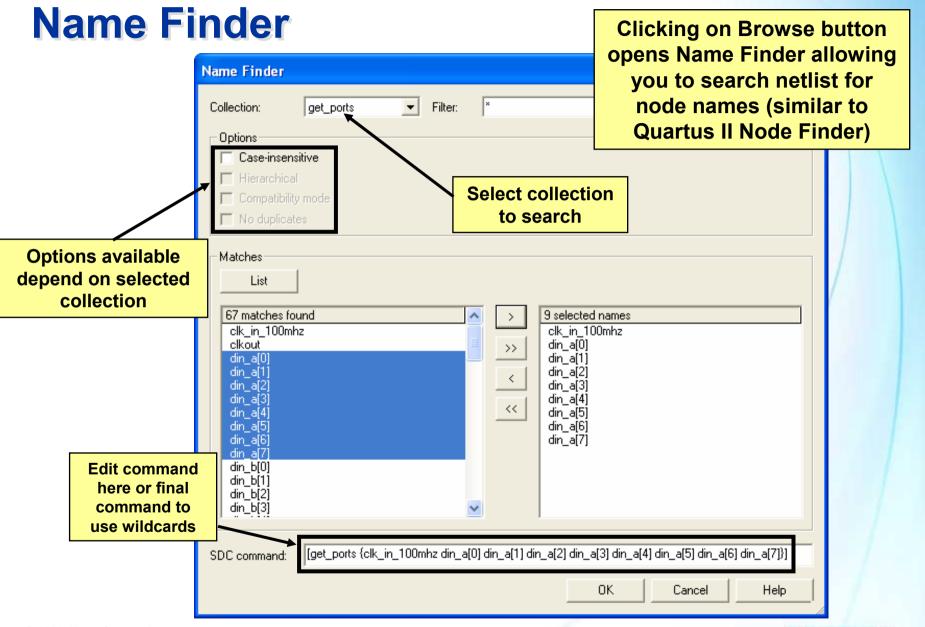

- All constraints discussed can be easily accessed in TimeQuest GUI

- Constraints menu of **TimeQuest**

- Edit ⇒ Insert Constraint menu of SDC File Editor

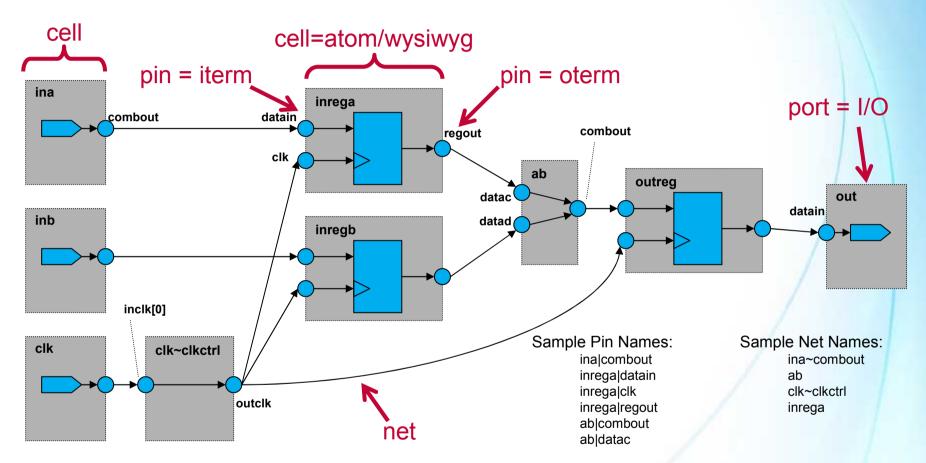

# **SDC Netlist Terminology**

| Term | Definition                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------|

| Cell | Device building blocks (e.g. look-up tables, registers, embedded multipliers, memory blocks, I/O elements, PLLs, etc.) |

| Pin  | Input or outputs of cells                                                                                              |

| Net  | Connections between pins                                                                                               |

| Port | Top-level inputs and outputs (e.g. device pins)                                                                        |

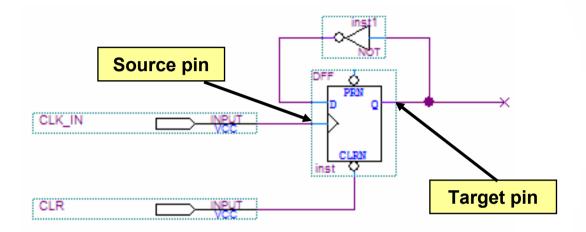

## **SDC Netlist Example**

Paths defined in constraints by targeted endpoints (pins or ports)

#### **Collections**

- Searches and returns from the design netlist with a list of names meeting criteria

- Used in SDC commands

- Some collections searched automatically during a command's usage and may not need to be specified

#### Examples

- get ports

- get pins

- get clocks

- all clocks

- all\_registers

- all inputs

- all outputs

See "TimeQuest Timing Analyzer" chapter of the Quartus II Software Handbook (Volume 3) for a complete list & description of each

# **SDC Timing Constraints**

- Clocks

- I/O

- False paths

- Multicycle paths

#### What are clocks in SDC?

- Defined, repeating signal characteristics applied to a point anywhere in the design

- Internal: applied to a specific node being used as a clock in design (port or pin)

- "Virtual": No real source in, or direct interaction with design

- Example: Clocks on external devices that feed or are fed by the FPGA design, required for I/O analysis

- Name clocks after node to which they are applied or something more meaningful

- Similar to clock settings in older Quartus II timing engine (Classic timing analyzer)

# Clocks in SDC (cont.)

- Two types

- Clock

- Absolute or base clock

- Generated clock

- Timing derived from another clock in design

- Must have defined relation with source clock

- Apply to output of logic function that modifies clock input

- PLLs, clock dividers, output clocks, ripple clocks, etc.

- Clock inversions automatically detected unless derived from more complex logic structure

- All clocks are related by default

- Cross-domain transfers analyzed

#### **Clock Constraints**

- Create clock

- Create generated clock

- PLL clocks

- Automatic clock detection & creation

- Default constraints

- Clock latency

- Clock uncertainty

- Common clock path pessimism removal

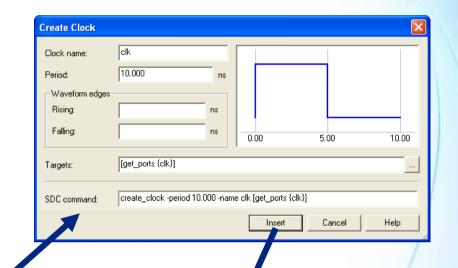

# **Creating a Clock**

- Command: create clock

- Options

```

[-name <clock_name>]

-period <time>

[-waveform {<rise_time> <fall_time>}]

[<targets>]

[-add]

```

[] = optional

Note: In general, the more options added to a constraint command, the more specific the constraint is. When options are not specified, the constraint is more generalized and pertains to more of the target.

## create\_clock Notes

- name: Assigns name to the clock to be used in other commands & reports when referring to clock

- Optional; defaults to target name if not specified

- -waveform: Indicates clock offset or non-50% duty cycle clocks

- 50% duty cycle is assumed unless otherwise indicated

- -add: Adds clock to node with existing clock

- Without -add, warning given and subsequent clock constraints ignored

- <targets>: Target ports or pins for clock setting

- Virtual clock created if no target specified

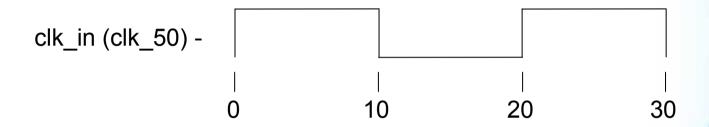

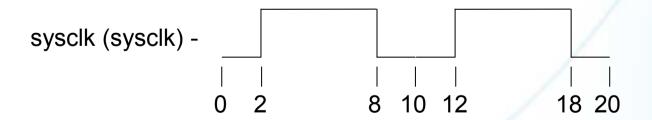

## create\_clock Examples

create clock -period 20.0 -name clk 50 [get ports clk in]

create\_clock -period 10.0 -waveform {2.0 8.0} [get\_ports sysclk]

# **Create Clock using GUI**

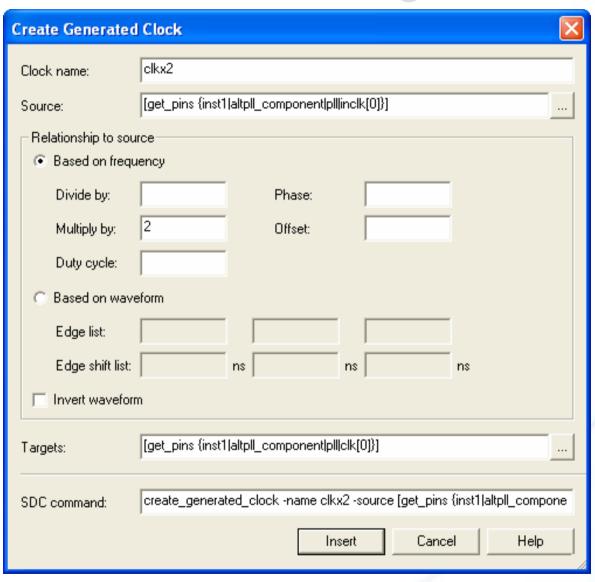

## **Creating a Generated Clock**

- Command: create generated clock

- Options

```

[-name <clock_name>]

-source <master_pin>

[-master_clock <clock_name>]

[-divide_by <factor>]

[-multiply_by <factor>]

[-multiply_by <factor>]

[-duty_cycle <percent>]

[-invert]

[-phase <degrees>]

[-edges <edge_list>]

[-edge_shift <shift_list>]

[<targets>]

[-add]

```

#### create generated clock Notes

- -source: Species the node in design from which generated clock is derived

- Ex. Placing source before vs. after an inverter would yield different results

- -master clock: Used if multiple clocks exist at source due to -add option

- -edges: Relates rising/falling edges of generated clock to rising/falling edges of source based on numbered edges

- -edge shift: Relates edges based on amount of time shifted (requires -edges)

#### **Create Generated Clock using GUI**

## **Generated Clock Example 1**

```

create_clock -period 10 [get_ports clk_in]

create_generated_clock -name clk_div \

-source [get_pins inst|clk] \

-divide_by 2 \

[get_pins inst|regout]

```

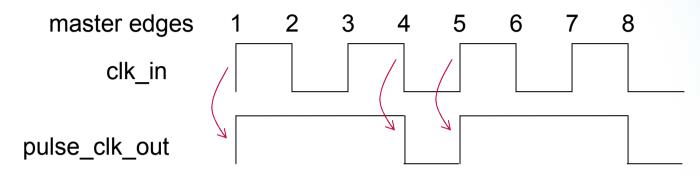

## **Generated Clock Example 2**

```

create clock -period 10 [get ports clk in]

```

```

create generated clock -name pulse clk out -source clk in \

-edges {1 4 5}

[get pins pulse logic|out]

```

```

# Master edges are numbered 1..<n>. In the edge list, the first

#

number corresponds to the first rising edge of the generated

clock. The second number is the first falling edge. The third

number is the second rising edge. Thus, a clock is created that

is half the period of the source with a 75% duty cycle.

```

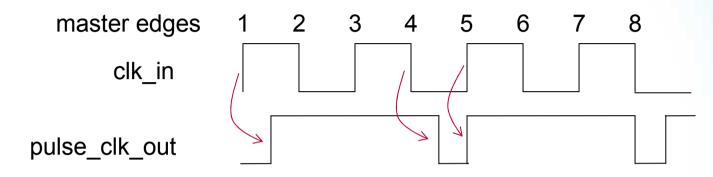

## **Generated Clock Example 3**

```

create_clock -period 10 [get_ports clk_in]

```

```

create_generated_clock -name pulse_clk_out -source clk_in \

-edges {1 4 5} -edge_shift {2.5 2.5 0}

[get pins pulse logic|out]

```

```

# Same as example 2 except -edge_shift shifts each edge indicated

# amount of time

```

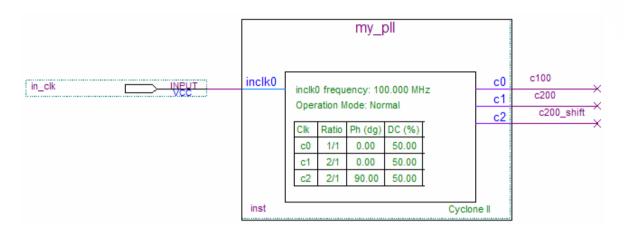

## PLL Clocks (Altera SDC Extension)

- Command: derive pll clocks

- [-use\_tan\_name]: names clock after design net name from Classic timing analyzer settings instead of the default PLL output SDC pin name

- [-create\_base\_clocks]: generates create\_clock constraint(s) for PLL

input clocks

- Create generated clocks on all PLL outputs

- Based on input clock & PLL settings

- Requires defining PLL input as clock unless -create\_base\_clocks is used

- Automatically updates generated clocks on PLL outputs as changes made to PLL design

- write\_sdc -expand expands constraint into standard

create clock and create generated clock commands

- Not in GUI; must be entered in SDC manually

# derive\_pll\_clocks Example

#### **Using generated clock commands**

```

create_clock -period 10.0 [get_ports in_clk]

create_generated_clock -name c100 \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-divide_by 1 \

[get_pins {inst|altpll_component|pll|clk[0]}]

create_generated_clock -name c200 \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-multiply_by 2 \

[get_pins {inst|altpll_component|pll|clk[1]}]

create_generated_clock -name c200_shift \

-source [get_pins {inst|altpll_component|pll|inclk[0]}] \

-multiply_by 2 \

-phase 90 \

[get_pins {inst|altpll_component|pll|clk[2]}]

```

#### **Using derive pll command**

```

create_clock -period 10.0 \

[get_ports in_clk]

derive_pll_clocks

# or simply:

derive_pll_clocks \

-create_base_clocks

# Note the clock names for

# the generated clocks

# will be the names of

# the PLL output pins

```

© 2009 Altera Corporation

#### **Automatic Clock Detection & Creation**

- Command: derive clocks

- [-period]: same use as with create clock

- [-waveform]: same use as with create clock

- No target required

- Automatically create clocks on clock pins in design that don't already have clocks defined

- Does not work with PLL outputs (use derive pll clocks)

- SDC extension expanded with write sdc -expand

- Not in GUI

- Not recommended for final timing sign-off

#### **Default Clock Constraints**

- Remember, all clocks must be constrained to analyze design with timing analysis

- If no clock constraints exist, default constraints created through two commands

```

derive_clocks -period 1.0 derive_pll_clocks

```

- Default constraints not applied if at least one clock constraint exists

- Not in GUI

- Not recommended for final timing sign-off

#### **Non-Ideal Clock Constraints**

- So far, all clocks have been ideal

- Nice square waves

- No accounting for delays outside of FPGA

- Add extra constraints to define realistic, non-ideal clocks

- Three special constraints

- set\_clock\_latency

- set clock uncertainty

- derive\_clock\_uncertainty

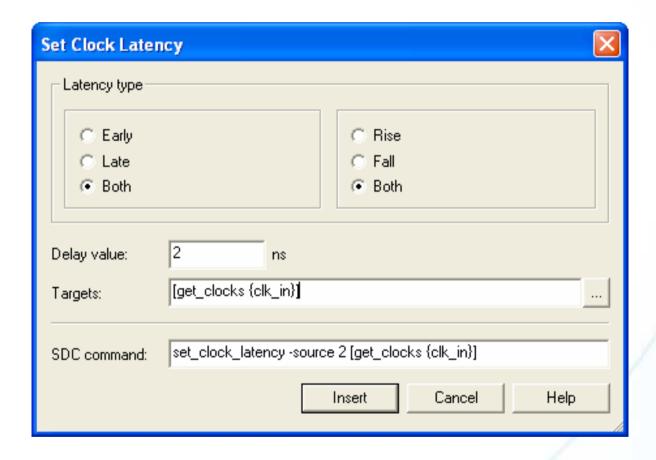

## **Clock Latency**

- Two types of latency

- Source: From clock source to input port (board latency)

- Network: From input port to destination register clock pin

- Network latency handled and understood by timing analysis automatically

- Need to model source latency

- TimeQuest TA knows nothing about delays external to device

- Provide a more realistic picture of external clock behavior

- Example

- External feedback clock: need to specify delay from clock output I/O to clock input I/O

- Clocks created with create\_clock have default source latency of 0

# **Clock Latency (cont.)**

- Command: set\_clock\_latency

- Specify source latency on external path(s) to device

#### Options

```

- -source

```

```

- [-clock <clock list>]

```

```

- [-early | -late]

```

- <delay>

- <targets>

## set\_clock\_latency Notes

- -source: required argument for constraint (no options)

- -fall | -rise: latency applied on only falling or rising edge of clock

- -early | -late: latency on shortest/longest

external path

- Used by timing analyzer as part of definition of data/clock arrival paths for setup/hold analyses

# **Clock Latency (GUI)**

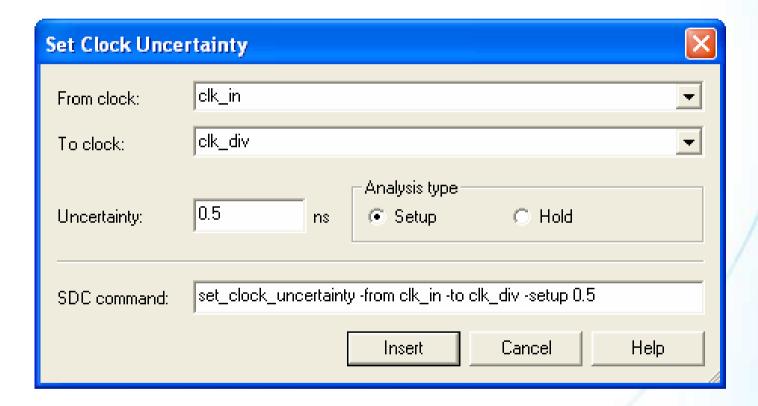

## **Clock Uncertainty**

- Command: set\_clock\_uncertainty

- Use to model jitter, guard band, or skew

- Allows generation of clocks that are non-ideal

#### Options

- [-setup | -hold]

- [-fall from <fall from clock>]

- [-fall to <fall to clock>]

- [-from <from\_clock>]

- [-rise from <rise from clock>]

- [-rise\_to <rise\_to\_clock>]

- [-to <to\_clock>]

- <value>

#### **Clock Uncertainty**

- Setup uncertainty decreases setup required time

- Hold uncertainty increases hold required time

Ex. To add a 0.5-ns guardband around clock, use 250 ps of setup uncertainty and 250 ps of hold uncertainty.

# **Clock Uncertainty (GUI)**

## **Automatically Derive Uncertainty**

- Command: derive clock uncertainty

- Automatically derive clock uncertainties in supported devices

- Cyclone III, Stratix II, HardCopy® II, Stratix III, and new devices

- Uncertainties created manually with set clock uncertainty have higher precedence

- Options

- [-overwrite]: overwrites any existing uncertainty constraints

- [-add]: adds derived uncertainties to existing constraints

- SDC extension expanded with write sdc -expand

- Not in GUI

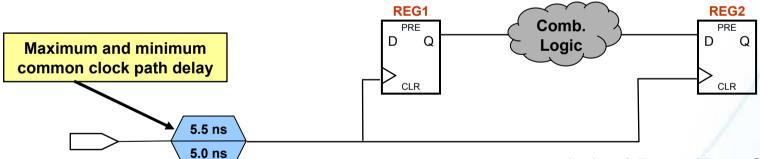

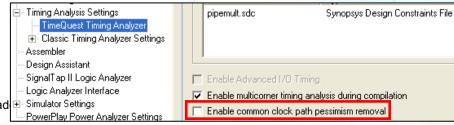

#### **Common Clock Path Pessimism Removal**

- Remove clock delay pessimism to account for min/max delays on common clock paths (Cyclone III, Stratix III and newer devices)

- Ex: Max delay for data arrival time; min delay for data required time

- Also used to improve minimum required clock pulse widths

- Enable for fitter and for timing analysis

- TimeQuest Timing Analyzer settings in Quartus II software

- enable ccpp removal in TimeQuest script or console

CCPP = 5.5 - 5.0 = 0.5 ns

setup slack = 0.7 ns *without* CCPP removal setup slack = 1.2 ns *with* CCPP removal

© 2009 Altera Corporation

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trad Simulator Settings 47

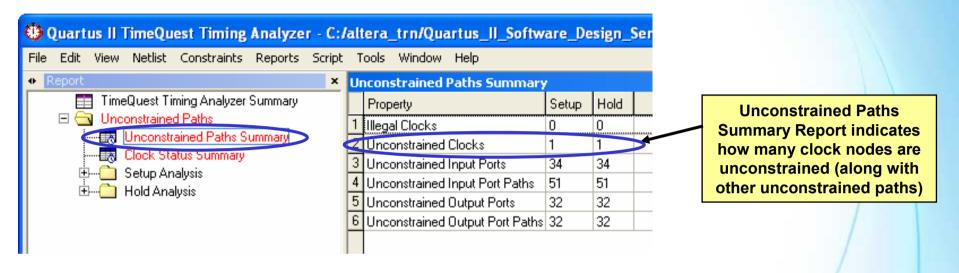

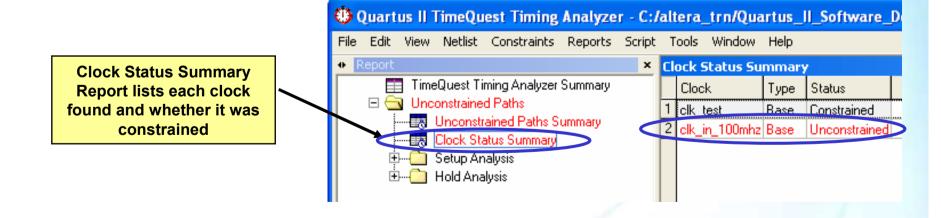

#### **Checking Clock Constraints**

- Nodes used as clocks but not defined with SDC clock constraint considered unconstrained

- Solution

- Use Unconstrained Paths Report to find unconstrained clocks

- Quartus II Compilation Report timing summary

- Run report ucp command

- Choose Report Unconstrained Paths (Tasks Pane or Reports menu)

- Use Clock Report to verify clocks are constrained correctly

## **Unconstrained Path Report**

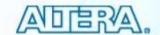

## Report Clocks (report\_clocks)

List details about the properties of constrained clocks

## **SDC Timing Constraints**

- Clocks

- I/O

- False paths

- Multicycle paths

#### **I/O Constraints**

- Combinatorial I/O interface

- Synchronous I/O interface

- Source synchronous interface

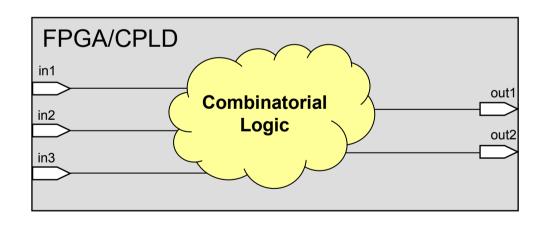

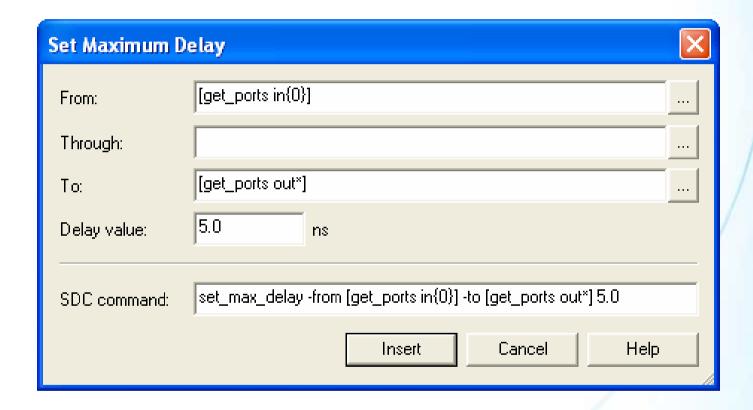

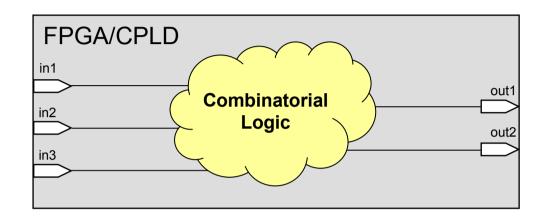

#### **Combinatorial Interface**

- All paths from IN to OUT need to be constrained

- Use set max delay & set min delay commands

- Specify an absolute maximum & minimum delay between points

#### **Options**

```

[-from <names>]

[-to <names>]

[-fall from <clocks>]

[-rise from <clocks>]

[-fall to <clocks>]

[-rise to <clocks>]

[-through]

<delay>

```

#### set\_max\_delay & set\_min\_delay Notes

- -from & -to: Use to indicate source & destination nodes for constraints

- -through: Use to indicate the constraint should only be applied to path(s) going through a particular node name

#### set max delay & set min delay (GUI)

#### **Combinatorial Interface Example**

```

set_max_delay -from [get_ports in1] -to [get_ports out*] 5.0

set_max_delay -from [get_ports in2] -to [get_ports out*] 7.5

set_max_delay -from [get_ports in3] -to [get_ports out*] 9.0

set_min_delay -from [get_ports in1] -to [get_ports out*] 1.0

set_min_delay -from [get_ports in2] -to [get_ports out*] 2.0

set_min_delay -from [get_ports in3] -to [get_ports out*] 3.0

```

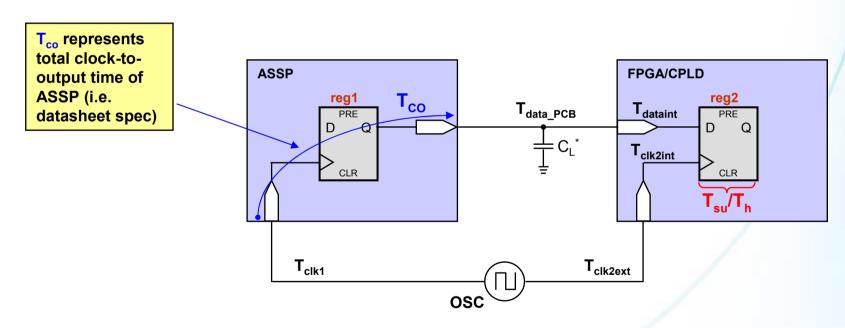

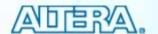

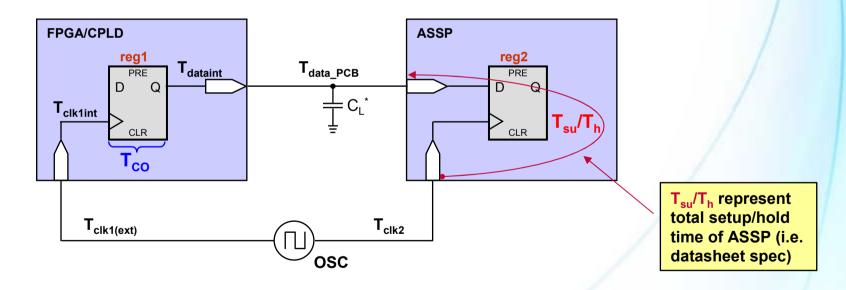

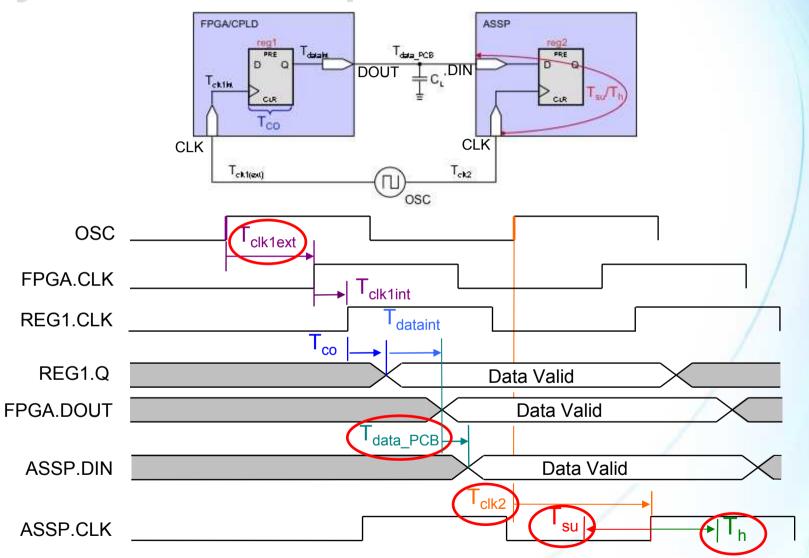

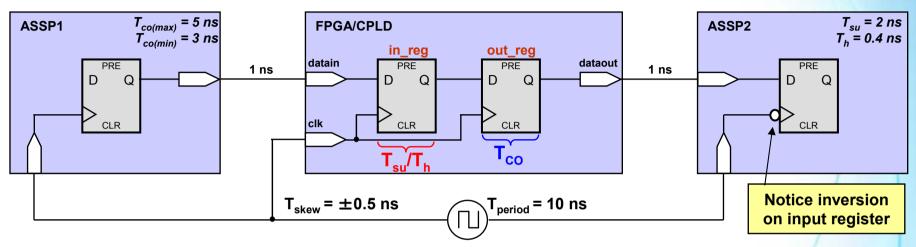

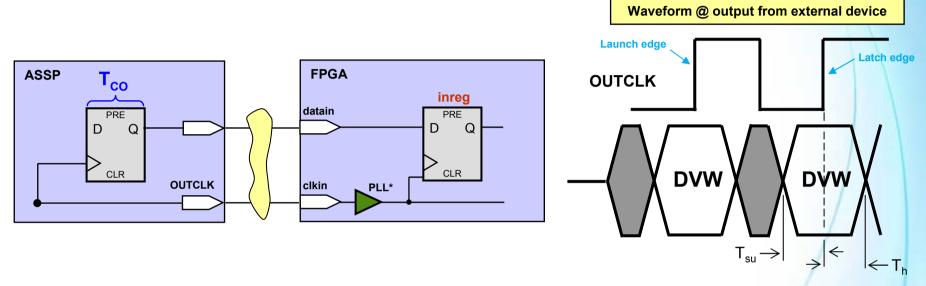

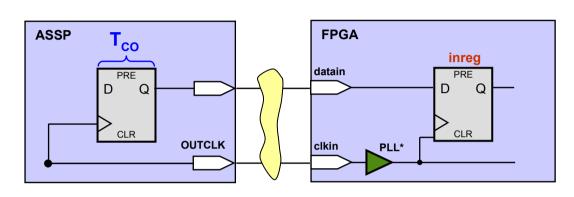

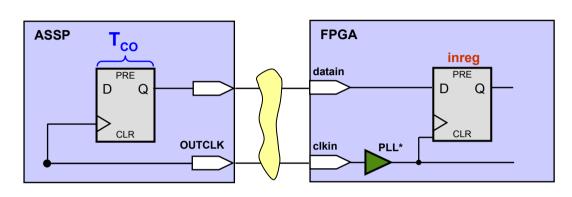

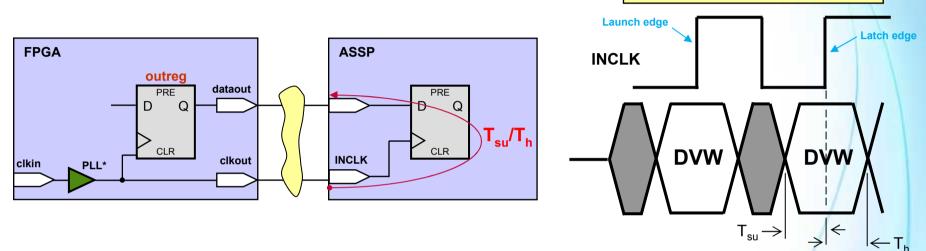

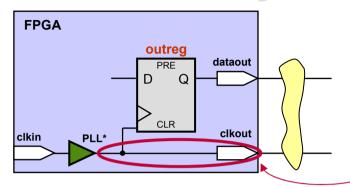

## **Synchronous Inputs**

Need to specify timing relationship from ASSP to FPGA/CPLD to guarantee setup/hold in FPGA/CPLD

<sup>\*</sup> Represents delay due to capacitive loading

## **Synchronous Inputs**

#### **Constraining Synchronous Inputs**

- Use set input delay (-max option) command to constrain input setup time (maximum time to arrive and still meet T<sub>su</sub>)

- Calculated input delay value represents all delays external to device

```

= Board Delay (max) - Board clock skew (min) + T<sub>co(max)</sub>

input delay max

= (T_{data PCB(max)} + T_{CL}) - (T_{clk2ext(min)} - T_{clk1(max)}) + T_{co(max)}

= launch edge + input delay max + T<sub>dataint</sub>

data arrival time

data required time

= latch edge + T<sub>clk2int</sub> - T<sub>su</sub>

= required time - data arrival time

slack

```

- Use set input delay (-min option) command to constrain input hold time (minimum time to stay active and still meet  $T_h$ )

- Calculated input delay value represents all delays external to device

```

= Board Delay (min) - Board clock skew (max) + T<sub>co(min)</sub>

input delay min

= (T_{data\_PCB(min)} + T_{CL}) - (T_{clk2ext(max)} - T_{clk1(min)}) + T_{co(min)}

data arrival time

= launch edge + input delay min + T<sub>dataint</sub>

= latch edge + T_{clk2int} + T_h

required time

slack

= data arrival time - data required time

```

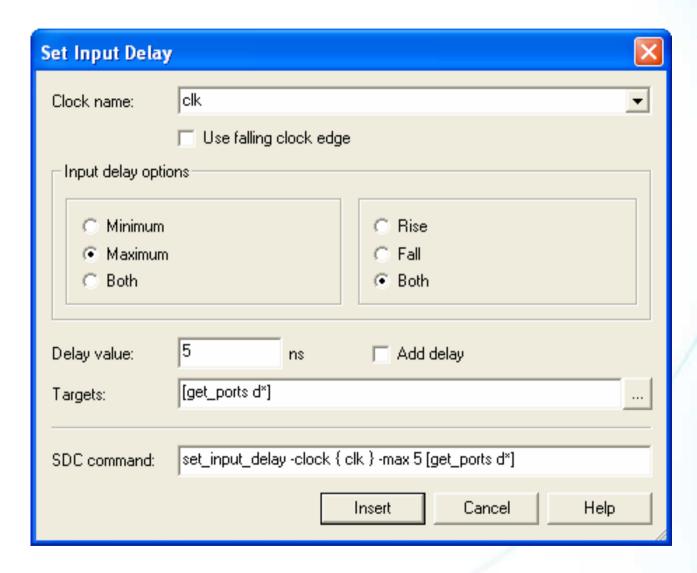

## set\_input\_delay Command

- Constrains input pins by specifying external device timing parameters

- Options

```

-clock <clock_name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-reference_pin <target>]

[-source_latency_included]

<delay value>

<targets>

```

## set input delay Notes

- -clock: Specifies the clock driving the source (external) register

- Used to determine launch edge vs. latch edge relationship

- -clock fall: Use to specify input signal was launched by a falling edge clock transition

- -rise | -fall: Use to indicate whether input delay value is for a rising or falling edge transaction

- -add delay: Use to specify multiple constraints on single input

- Only one set of max/min & rise/fall constraints allowed on an input pin

- Ex. Constraining one input port driving two registers in different clock domains would require the -add delay option

## set\_input\_delay Notes

- -reference\_pin: Use to specify that delays are with respect to some other port or pin in the design

- Example: Feedback clock: Input delay is relative to an output port being fed by a clock

- -source\_latency\_included: input delay value specified includes clock source latency normally added automatically

- Tells TimeQuest to ignore any clock latency constraints applied to source clock

- To fully constrain, must specify both -max & -min

- Each will default to the value of the other setting if only one assigned (same with rise/fall)

- Warning message if one or the other not specified

## **Synchronous Outputs**

Need to specify timing relationship from FPGA/CPLD to ASSP to guarantee clock-tooutput times in FPGA/CPLD

<sup>\*</sup> Represents delay due to capacitive loading

#### **Synchronous Outputs**

#### **Constraining Synchronous Outputs**

- Use set output delay (-max option) command to constrain maximum clock-to-output (maximum time to arrive and still meet ASSP's T<sub>su</sub>)

- Calculated output delay value represents all delays external to device

```

output delay max

= Board Delay (max) - Board clock skew (min) + T<sub>su</sub>

= (T_{data\_PCB(max)} + T_{CL}) - (T_{clk2(min)} - T_{clk1ext(max)}) + T_{su}

= launch edge + T_{clk1int} + T_{co(max)} + T_{dataint}

data arrival time

data required time

= latch edge - output delay max

slack

= data required time - data arrival time

```

- Use set output delay (-min option) command to constrain minimum clock-to-output (minimum time to stay active and still meet ASSP's T<sub>h</sub>)

- Calculated output delay value represents all delays external to device

```

= Board Delay (min) - Board clock skew (max) - T<sub>h</sub>

output delay min

= (T_{\text{data PCB(min)}} + T_{\text{CL}}) - (T_{\text{clk2(max)}} - T_{\text{clk1ext(min)}}) - T_{\text{h}}

= launch edge + T_{clk1int} + T_{co(min)} + T_{dataint}

data arrival time

data required time

= latch edge - output delay min

slack

= data arrival time - data required time

```

## set\_output\_delay Command

- Constrains output pins by specifying external device timing parameters

- Options

```

-clock <clock_name>

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-reference_pin <target>]

<delay value>

<targets>

```

## set\_output\_delay Notes

Same notes as set\_input\_delay command

## Input/Output Delays (GUI)

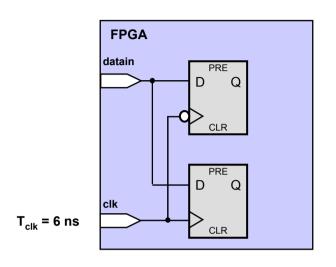

## Synchronous I/O Example

create\_clock -period 10 -name clk [get\_ports clk]

```

set_input_delay -clock clk -max [expr 1 - (-0.5) + 5] [get_ports datain]

set_input_delay -clock clk -min [expr 1 - 0.5 + 3] [get_ports datain]

```

-clock\_fall [get\_ports dataout]

Note: expr in these constraints is used to simply calculate the value of the equation broken down into the 3 parts defined by the input/output delay equations

© 2009 Altera Corporation

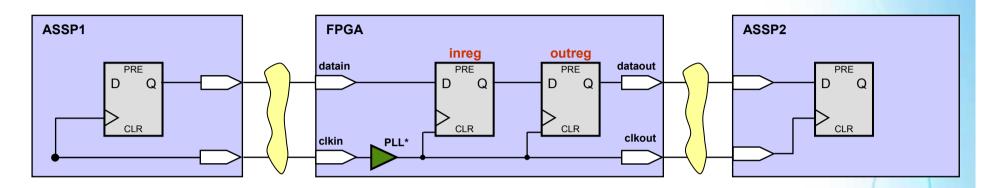

#### Source-Synchronous Interfaces

- Both data & clock transmitted by host device with designated phase relationship (e.g. edge or center-aligned)

- No clock tree skew included in calculation

- Target device uses transmitted clock to sample incoming data

- Data & clock routed identically to maintain phase relationship at destination device

- Board delay not included in external delay calculations

- Clock trace delay (data required time) & Data trace delay (data arrival time) are equal and offset

- Enables higher interface speeds (compared to using system clock)

<sup>\*</sup> The PLL in this example, represented by a single symbol, is actually generating multiple outputs clocks

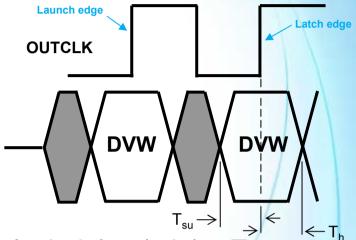

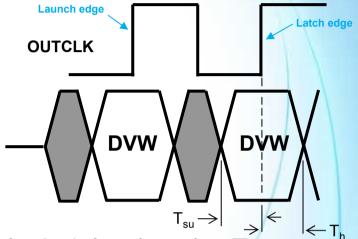

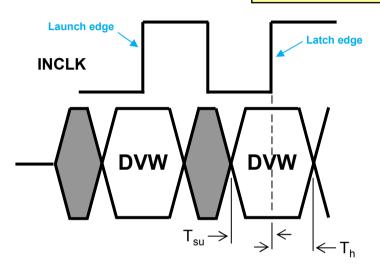

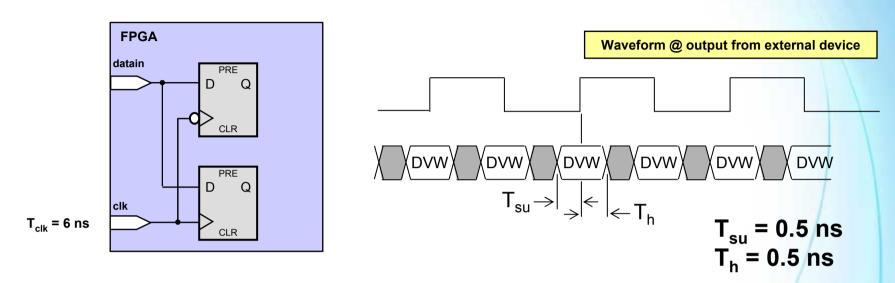

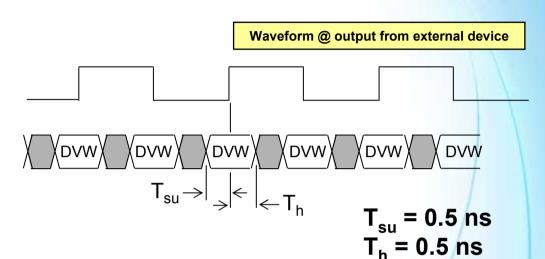

#### SDR Source-Synchronous Input (Center-Aligned)

- Total setup/hold relationship of FPGA to clock (clkin) already defined by output waveform of external device

- T<sub>su</sub> is start of DVW

- T<sub>h</sub> is end of DVW

- Must derive set input delay values from T<sub>su</sub> & T<sub>h</sub>

<sup>\*</sup> The PLL in this example is used to maintain the input clock to data relationship

#### SDR Source-Synchronous Input (Center-Aligned)

Waveform @ output from external device

input delay max = board delay (max) - clock delay (min) + T<sub>co(max)</sub>

$= T_{co(max)}$

setup slack = data required time - data arrival time

If setup slack = 0 (start of DVW):

data arrival time = data required time

latch edge -  $T_{su}$  = launch edge + input delay max

SO

input delay max = (latch edge - launch edge)\* - T<sub>su</sub> \*Typically 1 clock period for SDR

Note: In reality for high-speed designs, there would be some max/min board & clock delay that would need to be figured into the analysis.

Altera, Stratix, Arria, Cyclone, MAX, HardCopy, Nios, Quartus, and MegaCore are trademarks of Altera Corporation

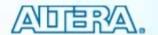

#### SDR Source-Synchronous Input (Center-Aligned)

Waveform @ output from external device

input delay min = board delay (min) - clock delay (max) + T<sub>co(min</sub>

$= T_{co(min)}$

hold slack = data arrival time - data required time

If hold slack = 0 (end of DVW):

data required time = data arrival time

latch edge +  $T_h$  = launch edge + input delay min

For hold analysis, latch and launch edges cancel out, so

input delay min  $= T_h$

Note: In reality for high-speed designs, there would be some max/min board & clock delay that would need to be figured into the analysis.

#### **Using SDC with Source-Sync Input**

- Create clock on clock input port

- Use set input delay command with reference to clock input

- Same as with synchronous input

- Do not include board delay parameters in value

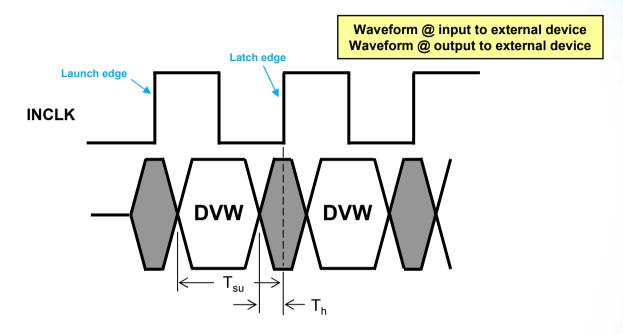

#### SDR Source-Synchronous Output (Center-Aligned)

\* The PLL in this example is used to shift output clock to establish an output clock to data relationship

#### Notes:

- 1) In reality for high-speed designs, there would be some max/min board & clock delay that would need to be figured into the analysis.

- 2) The PLL in this example is used to shift output clock to establish an output clock to data relationship © 2009 Altera Corporation

Waveform @ input to external device

## **Using SDC with Source-Synch Output**

This path must be analyzed when calculating data required time

- Must tell TimeQuest to analyze path from clock source to output clock port during analysis

- Use set\_output\_delay command on dataout with reference to generated clock on output port

- Create generated clock on output clock port (source is PLL output pin)

- Use -clock argument in output delay assignment to associate output clock to output data bus

- Path from PLL output pin to output port still considered unconstrained (clock path viewed as a data path by timing analyzer)

- Constrain path from PLL pin to output port with false path (described later), set min/max delay, or set output delay

### **Constraining Source-Sync Output Example**

```

create clock 5 -name clkin \

[get ports clkin]

create generated clock -name pllclk divide by 1 \

-source [get ports clkin]

[get pins inst|altpll component|pll|clk[0]]

# Place clock on external clock output

create generated clock -name clkout \

-source [get pins inst|altpll component|pll|clk[0]] \

-divide by 1 \

[get ports clkout]

# Constrain dataout with an external tsu of 0.5 ns

# and th of 0.5 ns using clkout as clock

set output delay -clock [get clocks clkout]

-max 0.500 \

[get ports dataout]

set output delay -clock [get clocks clkout]

-min -0.500 \

[get ports dataout]

```

### **Source Synchronous Summary (Center-Aligned)**

Waveform @ input to external device Waveform @ output to external device

|                           | Maximum                                      | Minimum         |

|---------------------------|----------------------------------------------|-----------------|

| Input delay setting (ns)  | (latch edge – launch edge) - T <sub>su</sub> | T <sub>h</sub>  |

| Output delay setting (ns) | T <sub>su</sub>                              | -T <sub>h</sub> |

### **Source Synchronous (Edge-Aligned)**

|                           | Maximum                                      | Minimum         |

|---------------------------|----------------------------------------------|-----------------|

| Input delay setting (ns)  | (latch edge – launch edge) - T <sub>su</sub> | -T <sub>h</sub> |

| Output delay setting (ns) | T <sub>su</sub>                              | T <sub>h</sub>  |

### **Checking I/O Constraints**

- Helpful TimeQuest reports to run to verify constraints

- Report SDC

- Report Unconstrained Paths (again)

- Report Ignored Constraints

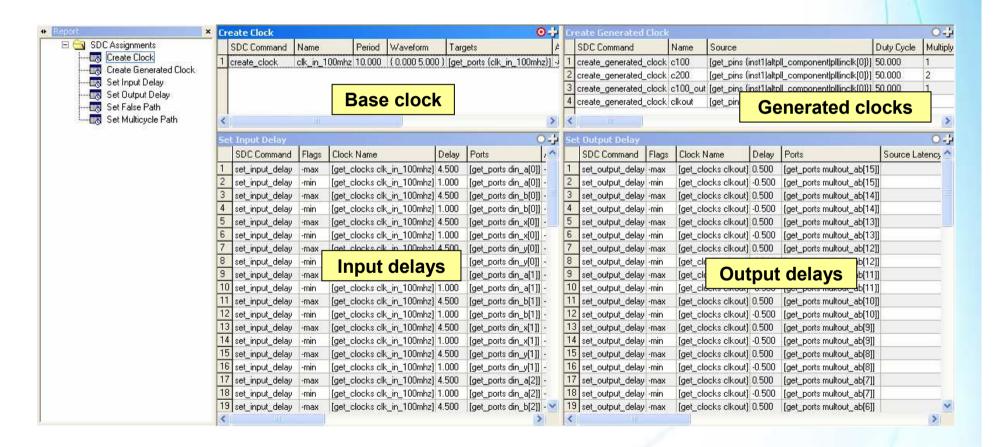

# Report SDC (report\_sdc)

List SDC constraints applied to netlist

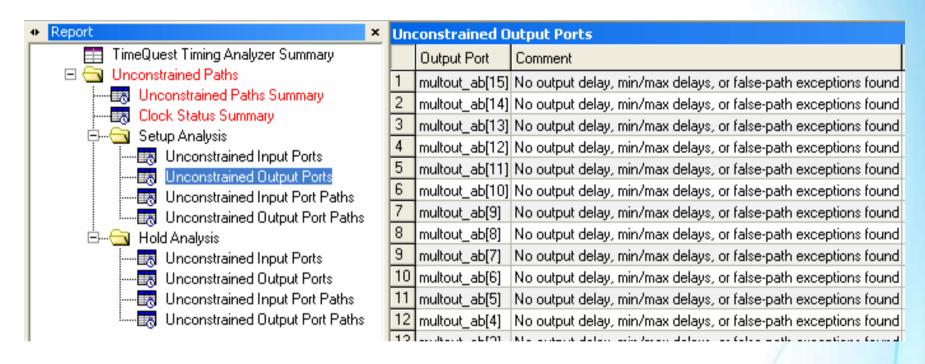

### Report Unconstrained Paths (report\_ucp)

- Same report as before used for unconstrained clocks (Clock Status Summary report)

- Setup and Hold Analysis folders list unconstrained I/O ports and paths

### **Verifying Clocks & I/O Timing**

Use Setup & Hold Summary reports to check worst slack for each clock

#### "Did I make it or did I not make it?"

- Positive slack displayed in black, negative in red

- Obtaining summary reports

- Use create\_timing\_summary Tcl command

- TimeQuest folder of Compilation Report

- Run Report Setup Summary & Report Hold Summary reports from Tasks pane or Reports menu

- For detailed slack/path analysis

- Run Report Timing from Tasks pane or Constraints menu

- Use report\_timing command

# **SDC Timing Constraints**

- Clocks

- I/O

- False paths

- Multicycle paths

### **Timing Exceptions: False Paths**

- Logic-based

- Paths not relevant during normal circuit operation

- e.g. Test logic, static or quasi-static registers

- Timing-based

- Paths intentionally not analyzed by designer

- e.g. Bridging asynchronous clock domains using synchronizer circuits

- Must be marked by constraint to tell TimeQuest to ignore them

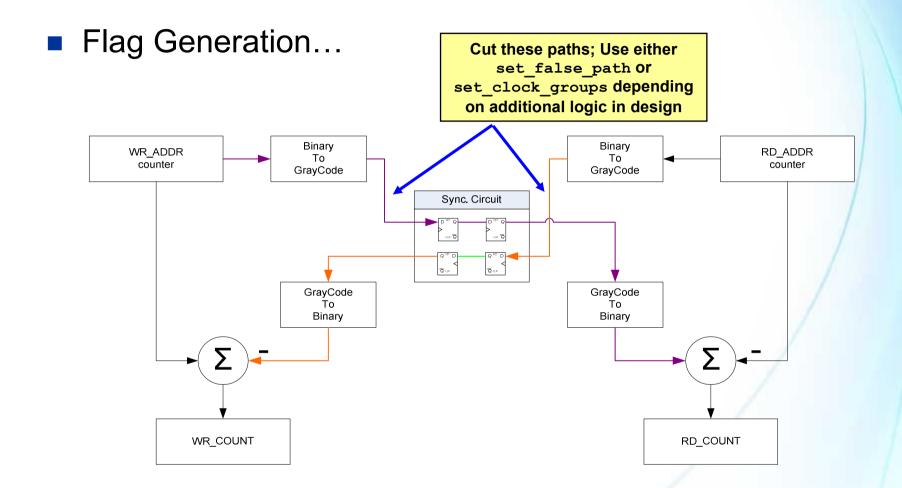

#### **Two Methods to Create False Paths**

- set\_false\_path command

- Use when particular nodes are involved

- Examples

- All paths from an input pin to a set of registers

- All paths from a register to another clock domain

- set\_clock\_groups command

- Use when just clock domains are involved

### set\_false\_path Command

- Indicates paths that should be ignored during fitting and timing analysis

- Options

```

[-fall_from <clocks>]

[-rise_from <clocks>]

[-from <names>]

[-through <names>]

[-to <names>]

[-fall_to <clocks>]

[-rise_to <clocks>]

[-setup]

[-hold]

<targets>

```

### set false path Notes

- -from & -to: Use to specify source & target nodes

- Target nodes can be clocks, registers, ports, pins or cells

- For registers, -from should be source register clock pin

- Specify a clock name to constrain all paths going into or out of its domain

- Constrains both rising and falling edge clock transitions

- More efficient than specifying individual nodes

- -rise from & -fall from: Use to indicate clocks for the source node & whether constraint is for a rising or falling edge clock transition; not in GUI

- -rise to & -fall to: Use to indicate clocks for destination node & direction of transition; not in GUI

- -setup & -hold: Use to apply false paths to only setup/recovery or hold/removal analysis; not in GUI

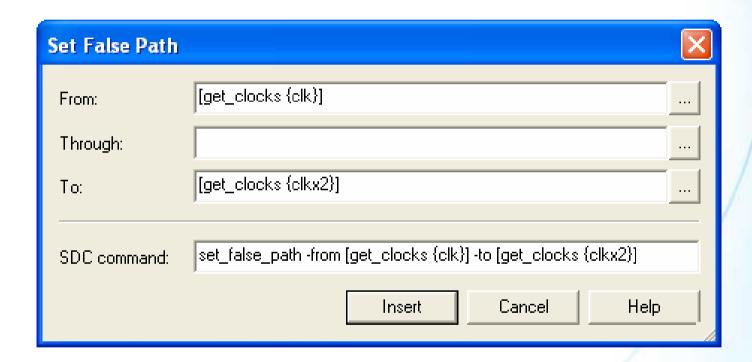

### **Set False Path (GUI)**

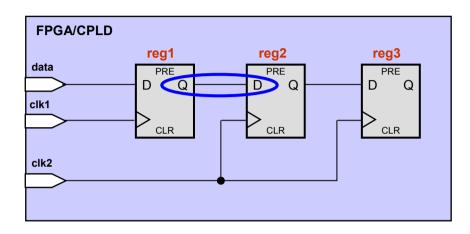

### False Path Example 1

Simple synchronizer circuit between two asynchronous clock domains

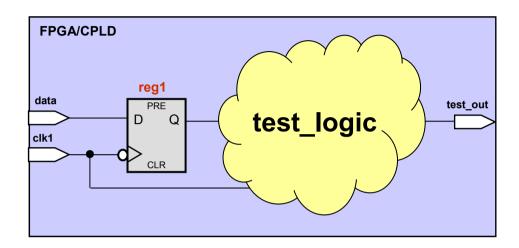

### False Path Example 2

Cutting analysis of inserted test logic

# set\_clock\_groups Command

- Tells fitter and timing analyzer to ignore ALL paths between specified clock domains

- Great for clock muxes

- Equivalent to setting false paths (-from & -to) on all paths between domains

#### Options

```

[-asynchronous | -exclusive]

-group <clock name>

-group <clock_name>

[-group <clock name>]...

```

### set\_clock\_groups Notes

-group: each group of clock names is asynchronous to other clock groups

- -asynchronous: no phase relationship, but clocks active at the same time

- -exclusive: clocks not active at the same time

- Example: clock muxes

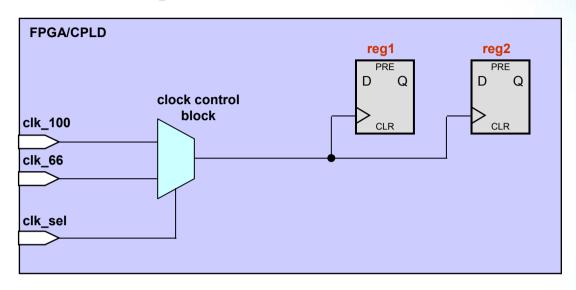

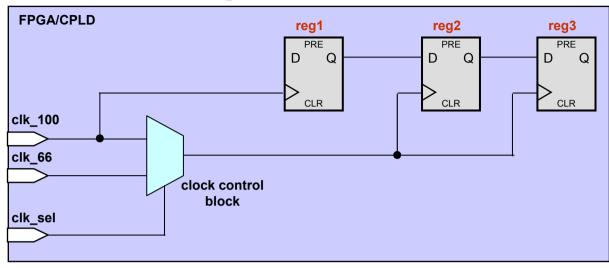

### **Clock Mux Example 1**

```

create_clock -period 10.0 [get_ports clk_100]

create_clock -period 15.0 [get_ports clk_66]

set_clock_groups -exclusive -group {clk_100} -group {clk_66}

# Since clocks are muxed, TimeQuest should not analyze

# cross-domain paths as only one clock will be driving the

# registers at any one time.

```

### **Clock Mux Example 1 (Alternative)**

```

create clock -period 10.0 [get ports clk 100]

create clock -period 15.0 [get ports clk 66]

```

```

set false paths -from [get clocks clk 100] -to [get clocks clk 66]

set false paths -from [get clocks clk 66] -to [get clocks clk 100]

```

For an equivalent constraint using false paths, you must consider paths going both directions

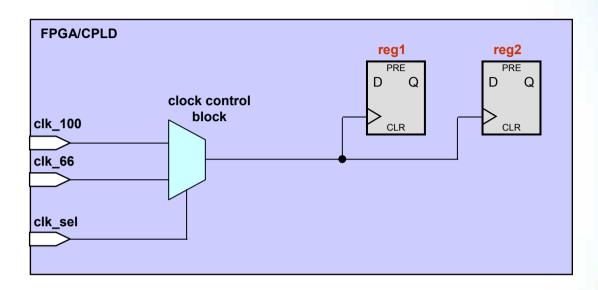

### **Clock Mux Example 2**

**Applying two clock** settings to same input port

```

create clock -name clk 100 -period 10.0 [get ports clk]

create clock -name clk 66 -period 15.0 [get ports clk] -add

create_clock -period 5.0 [get ports clk 200]

```

```

set clock groups -exclusive -group {clk 100} \

-group {clk 66} -group {clk 200}

```

```

# As before, never will more that one clock be driving all

registers

```

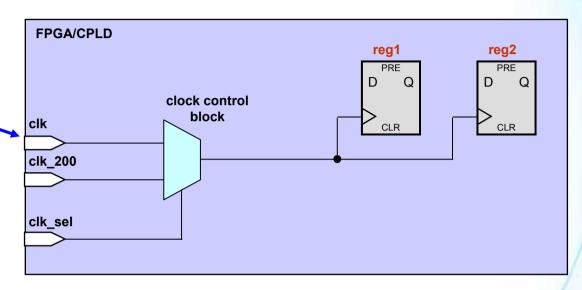

### **Clock Mux Example 3**

```

create clock -period 10.0 [get ports clk 100]

create clock -period 15.0 [get ports clk 66]

create generated clock -name clkmux 100 -source clk 100 \

[get pins clkmux|clkout]

create generated clock -name clkmux 66 -source clk 66 \

[get pins clkmux|clkout] -add

set clock groups -exclusive -group {clkmux 100} -group {clkmux 66}

# Since clk 100 is also feeding into the core, now you need to make generated

clocks on the mux outputs and use them for the clock groups

```

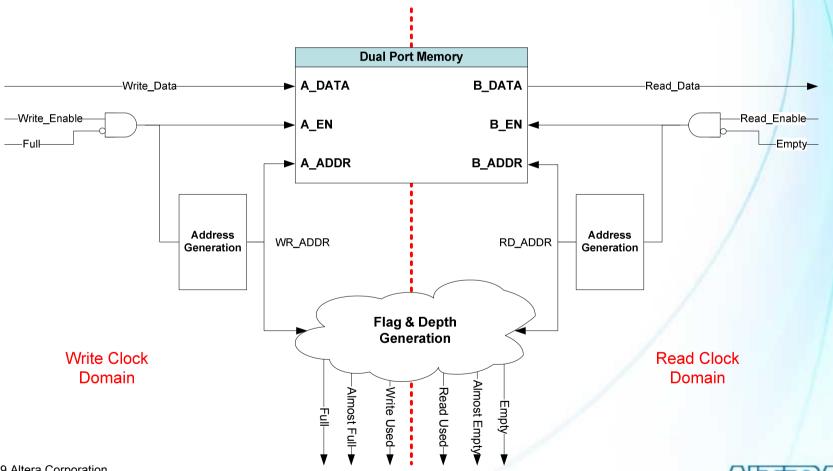

### Real World Example: Memory FIFO

FIFO bridging two clock domains; Flags indicate status of FIFO

© 2009 Altera Corporation

ALTERIA.

#### **False Paths on FIFO**

### **Verifying False Paths & Groups**

#### False paths

- Perform report timing on specified paths to ensure no results are returned

- Create false paths report

- report\_timing -false\_path

- Tasks pane or Reports menu: Report False Path

#### Clock groups

- Check clock transfers to ensure no paths are returned

- report\_clk\_transfers

- Tasks pane or Reports menu: Report Clock Transfers

# **SDC Timing Constraints**

- Clocks

- I/O

- False paths

- Multicycle paths

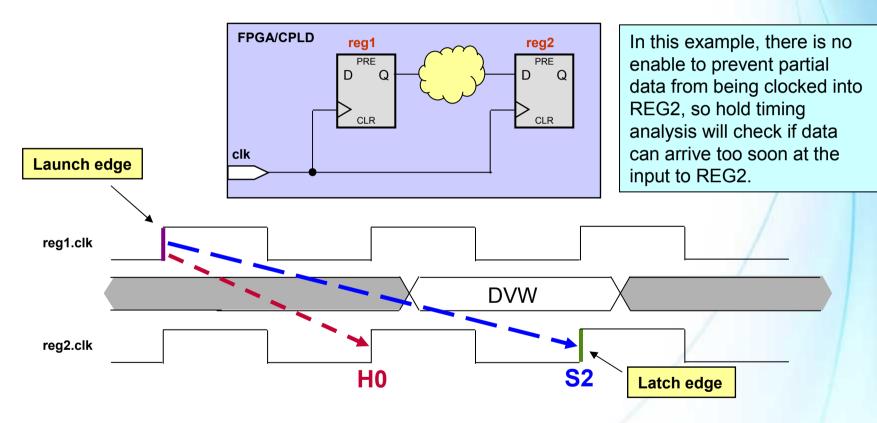

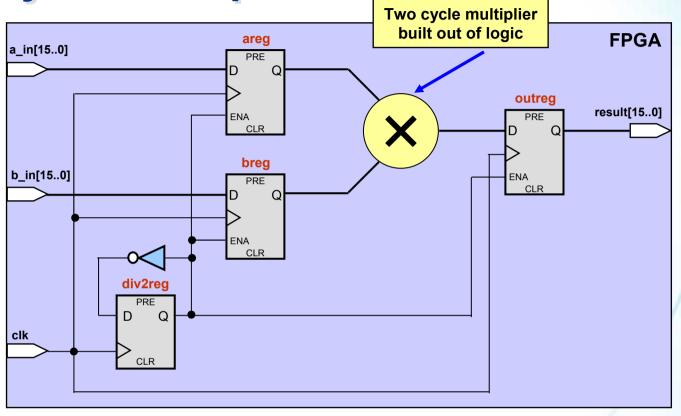

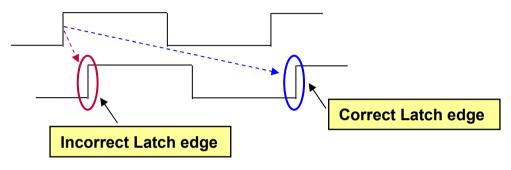

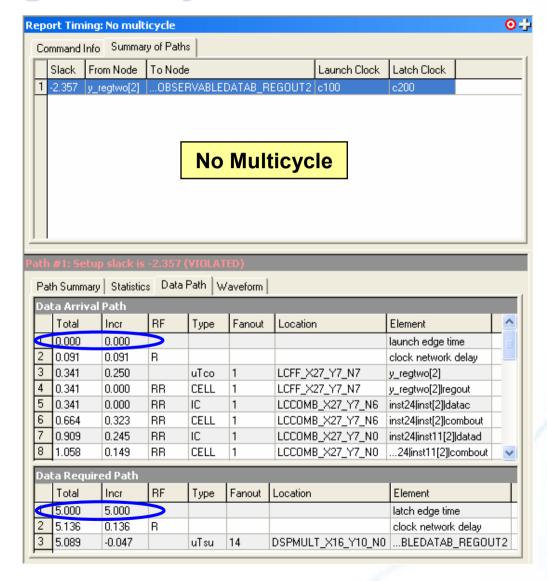

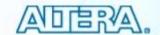

### **Timing Exceptions: Multicycle Paths**

- Paths requiring more than one cycle for data to propagate

- Causes timing analyzer to select another latch or launch edge

- Designer specifies number of cycles to move edge

- Logic must be designed to work this way

- Constraint informs timing analysis how logic is supposed to function

### Other Instances to Use Multicycle Paths

- Design does not require single cycle to transfer data (non-critical paths)

- Otherwise needlessly over-constrain paths

- Clocks are integer multiples of each other with or without offset

- Demonstrated in Exercise 4

- Clock enables ensuring register(s) not sampling data every clock edge

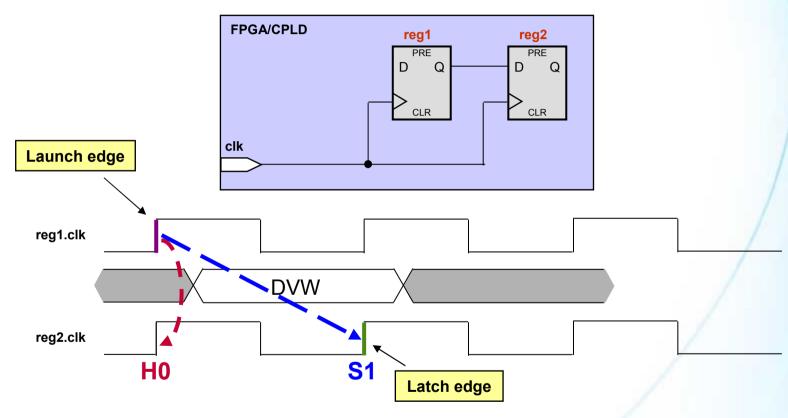

# **Multicycle Types (1)**

#### Destination

- Constraint based on destination clock edges

- Moves latch edge backward (later in time) to relax required setup/hold time

- Used in most multicycle situations

#### Source

- Constraint based on source clock edges

- Moves launch edge forward (earlier in time) to relax required setup/hold time

- Useful when source clock is at higher frequency than destination

# **Multicycle Types (2)**

#### Setup

- Increases the number of cycles for setup analysis

- Default is 1

#### Hold

- Increases the number of cycles for hold analysis

- Default is 0

#### \*Notes:

- 1) Subtract 1 from the Classic Timing Analyzer hold multicycle value to convert to SDC

- 2) TimeQuest TA also supports negative multicycles

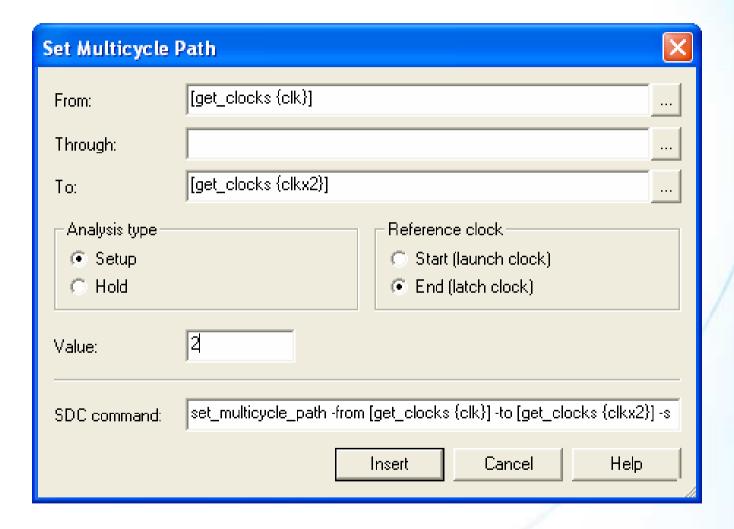

### set\_multicycle\_path Command

- Indicates by how many cycles the required time (setup or hold) should be extended from defaults

- Options

```

[-start | -end]

[-setup | -hold]

[-fall_from <clocks>]

[-rise_from <clocks>]

[-from <names>]

[-through <names>]

[-to <names>]

[-fall_to <clocks>]

[-rise_to <clocks>]

<targets>

<value>

```

# set\_multicycle\_path Notes

- -start: Use to select a source multicycle

- -end: Use to select a destination multicycle (default)

- -setup | -hold: Specifies if the multicycle value is applied to the setup or hold calculation

- <value>: Cycle multiplier Number of edges by which to extend analysis

- All other options behave similar to set\_false\_path options

### **Set Multicycle Path (GUI)**

### **Understanding Multicycle (1)**

Standard single-cycle register transfer

- · Multicycle Setup = 1 (Default)

- — • Multicycle Hold = 0 (Default)\*

\*Default hold edge is one edge before/after setup edge

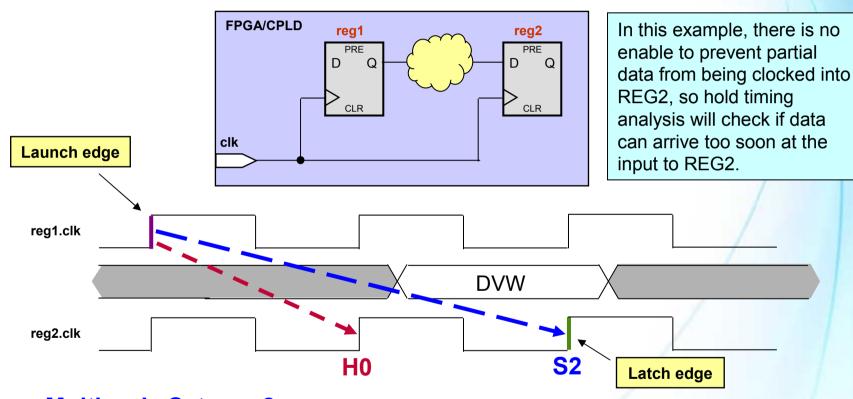

# **Understanding Multicycle (2)**

Change to a two cycle setup; single cycle hold transfer

- · Multicycle Setup = 2

- — - Multicycle Hold = 0 (Default)

\*Default hold edge is one edge before/after setup edge; hold edge moves with setup edge

### **Understanding Multicycle (2) (cont.)**

Change to a two cycle setup; single cycle hold transfer

set multicycle path -from [get pins reg1|clk] -to [get pins reg2|datain] \ -end -setup 2

\*Default hold edge is one edge before/after setup edge; hold edge moves with setup edge

**Multicycle Example**

ALTERIA.

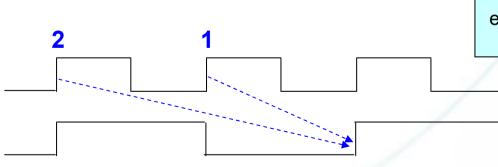

# **Other Multicycle Cases**

Positive clock phase shift or offset

- Source clock at higher frequency

- Use -start option

Note using the -start option moves the latch edge forward one edge (to relax constraint)

### **Reporting Multicycles**

### Reporting Multicycles

© 2009 Altera Corporation

# **Timing Analysis Agenda**

- TimeQuest basics

- Timing constraints

## **DDR Input Example**

- What constraints do you need?

- Clock

- Input delay maximum & minimum

- Use source-synchronous methodology

### **DDR Input Example**

- What's different about this circuit than prior examples?

- Rising & falling edge input registers from same input port

- Registers have ½ clock period for required time

### **DDR Input Example**

# Rising edge clock constraint

create clock -period 6 [get ports clk]

## **DDR Reporting**

- Use report timing Command

- Must check all rising & falling edge transitions

- Two data valid windows to check

- One from a rising edge source clock

- One from a falling edge source clock

- Use rise\_from, rise\_to, fall\_from, fall\_to

## **Timing Analysis Summary**

- Timing constraints are very important in FPGA/CPLD design

- Use timing constraints to tell fitter & timing analyzer how logic is designed to function

- SDC provides an easy-to-use, standard interface for constraining design

- See the Quartus II Handbook: Volume 3, Section II, for more information about timing analysis

### **Reference Documents**

Quartus II Handbook, Volume 3, Chapter 7 The Quartus II TimeQuest Timing Analyzer

http://www.altera.com/literature/hb/qts/qts\_qii53018.pdf

Quick Start Tutorial

http://www.altera.com/literature/hb/qts/ug\_tq\_tutorial.pdf

- Cookbook

- http://www.altera.com/literature/manual/mnl\_timequest\_ cookbook.pdf

### **Reference Documents**

- SDC and TimeQuest API Reference Manual

- http://www.altera.com/literature/manual/mnl\_sdctmq.p

df

- AN 481: Applying Multicycle Exceptions in the TimeQuest Timing Analyzer

- http://www.altera.com/literature/an/an481.pdf

- AN 433: Constraining and Analyzing Source-Synchronous Interfaces

- http://www.altera.com/literature/an/an433.pdf

### **Learn More Through Technical Training**

#### **Instructor-Led Training**

With Altera's instructor-led training courses, you can:

- Listen to a lecture from an Altera technical training engineer (instructor)

- Complete hands-on exercises with guidance from an Altera instructor

- >Ask questions & receive real-time answers from an Altera instructor

- Each instructor-led class is one or two days in length (8 working hours per day).

### **Online Training**

With Altera's online training courses, you can:

- Take a course at any time that is convenient for you

- Take a course from the comfort of your home or office (no need to travel as with instructor-led courses)

Each online course will take approximate one to three hours to complete.

http://www.altera.com/training

View training class schedule & register for a class

### Other Quartus II Design Series courses

#### Quartus II Software Design Series: Foundation

- Project creation and management

- Design entry methods and tools

- Compilation and compilation results analysis

- Creating and editing settings and assignments

- I/O planning and management

- Introduction to timing analysis with TimeQuest

#### Quartus II Software Design Series: Verification

- Basic design simulation with ModelSim-Altera

- Power analysis

- Debugging solutions

#### Quartus II Software Design Series: Optimization

- Incremental compilation

- Quartus II optimization features & techniques

### **Altera Technical Support**

- Reference Quartus II software on-line help

- Quartus II Handbook

- Consult Altera applications (factory applications engineers)

- MySupport: <a href="http://www.altera.com/mysupport">http://www.altera.com/mysupport</a>

- Hotline: (800) 800-EPLD (7:00 a.m. 5:00 p.m. PST)

- Field applications engineers: contact your local Altera sales office

- Receive literature by mail: (888) 3-ALTERA

- FTP: ftp.altera.com

- World-wide web: <a href="http://www.altera.com">http://www.altera.com</a>

- Use solutions to search for answers to technical problems

- View design examples