# Registered Copy - Do Not Distribute **XILINX Synopsys**

### ABOUT YOUR PERSONALIZED EBOOK EDITION OF THE FPMM

This copy of the electronic edition of the *FPGA-Based Prototyping Methodology Manual* (FPMM) version 110202 is provided to you for your use only and is <u>electronically</u> <u>marked with your identification</u>. You may not distribute this copy to others; instead, please refer them to download their own copy at: <u>www.synopsys.com/fpmm</u> or <u>www.xilinx.com/fpmm</u>.

Unauthorized reproduction or distribution is strictly prohibited. You are authorized to reproduce sections up to 10 pages for your company's use; such limited reproductions are considered reasonable use. Other reproductions may not be shared or transmitted in any form or by any means, electronic or mechanical, without the express written consent of Synopsys.

You may purchase the print edition of the FPMM through Amazon.com.

For more information about the FPMM as well as any addenda or errata published subsequent to this edition, please refer to the FPMM website: www.synopsys.com/fpmm.

# FPGA-Based Prototyping Methodology Manual

Best practices in Design-for-Prototyping

Doug Amos Austin Lesea René Richter

#### FPGA-Based Prototyping Methodology Manual

Doug Amos, Austin Lesea and René Richter

"ARM has developed its own FPGA boards for prototyping for over a decade and uses these alongside simulation and emulation for validation of early operating system ports and for improving quality and confidence. The FPMM is recommended reading to anybody considering FPGA prototyping as part of their validation methodology, especially for proving their IP and for early software development."

Spencer Saunders, Engineering Manager – Platforms ARM

"The modular nature of the Synopsys HAPS systems coupled with our Design-for-Prototyping approach has allowed LSI Corporation to do pre-silicon development on multiple SoC projects so far. If you are looking to benefit from FPGA-Based Prototyping then the FPMM is a great place to start, for management and engineers alike. Even experienced prototypers will find the FPMM a source of inspiration and guidance. I wish we'd had this when we started!"

Brian Nowak, Senior Integration Engineer LSI Corporation

"At NVIDIA we have benefited from FPGA-Based Prototyping for over a decade. In all cases we have been able to validate functionality and exercise software months in advance of the first silicon being available. The FPMM book and accompanying online community will educate our industry in the methodology of prototyping and share the latest techniques in implementation and leading edge technologies. I recommend the FPMM to anybody considering prototyping as a validation vehicle for developing silicon products."

Fernando Martinez, Engineer, Mobile R&D NVIDIA Corporation

eBook Edition Not for resale

## FPGA-Based Prototyping Methodology Manual

Best Practices in Design-for-Prototyping

Doug Amos Synopsys, Inc.

Austin Lesea Xilinx, Inc.

René Richter Synopsys, Inc.

### SYNOPSYS® EXILINX.

Doug Amos Synopsys, Inc. Reading United Kingdom

René Richter Synopsys, Inc. Erfurt Germany Austin Lesea Xilinx, Inc. San Jose, CA USA

Library of Congress Control Number: 2011920198 Hardcover ISBN 978-1-61730-003-5 Paperback ISBN 978-1-61730-004-2 eBook ISBN 978-1-61730-005-9

Copyright © 2011 Synopsys, Inc. All rights reserved. Portions Copyright© 2009-2011 Xilinx, Inc. Used by permission. Portions Copyright© 2011 ARM Limited. Used by permission.

This work may not be translated or copied in whole or in part without the written permission of Synopsys, Inc. (700 E. Middlefield Road, Mountain View, CA 94117 USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Published by Synopsys, Inc., Mountain View, CA, USA http://www.synopsys.com/synopsys\_press

Publishing services provided by Happy About® http://www.happyabout.com

Printed in the United States of America February 2011

#### TRADEMARKS

Synopsys, the Synopsys logo, ARC, Certify, Design Compiler, DesignWare, HAPS, HapsTrak, Identify, Synplicity, Synplify, Synplify Pro, and VCS are registered trademarks or trademarks of Synopsys, Inc.

LSI is a trademark of LSI Corporation. The LSI logo is a registered trademark of LSI Corporation.

NVIDIA and the NVIDIA logo are registered trademarks of NVIDIA Corporation in the United States and other countries.

Xilinx, Inc., XILINX, the Xilinx logo, ChipScope, CORE Generator, ISE, MicroBlaze, Spartan, System ACE, and Virtex, are trademarks of Xilinx in the United States and other countries.

ARM, the ARM logo, and AMBA are registered trademarks of ARM Limited. AHB, APB, AXI, Cortex, and Mali are trademarks of ARM Limited. "ARM" is used to represent ARM Holdings plc; its operating company ARM Limited; and its regional subsidiaries. ARM, the ARM logo, and AMBA are registered trademarks of ARM Limited.

All other brands or product names are the property of their respective holders.

#### DISCLAIMER

All content included in this FPGA-Based Prototyping Methodology Manual is the result of the combined efforts of Synopsys, Inc., Xilinx, Inc., and other named contributors. Because of the possibility of human or mechanical error, neither the authors, contributors, Synopsys, Inc., Xilinx Inc, nor any of their affiliates guarantees the accuracy, adequacy or completeness of any information contained herein and is not responsible for any errors or omissions, or for the results obtained from the use of such information. THERE ARE NO EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE relating to the FPGA-Based Prototyping Methodology Manual. In no event shall the authors, contributors, Synopsys, Inc., Xilinx, Inc., or their affiliates be liable for any indirect, special or consequential damages in connection with the information provided herein.

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY CAN WHICH BE VIEWED AT http://www.xilinx.com/warranty.htm. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### Foreword

We are grateful to Helena Krupnova of STMicroelectronics for sharing her insight and experience of FPGA-based prototyping in this foreword.

Grenoble - December 2010

In this book are introduced the "Three Laws of Prototyping."

For the last ten years here at STMicroelectronics in Grenoble, France, I'm working within a hardware-based verification team providing FPGA-based prototyping solutions for the use of software development teams worldwide and we have learnt that there are many steps and obstacles for the unwary prototyper. This book covers most of them, but they all distil down to these three "laws":

- SoCs are larger than FPGAs

- SoCs are faster than FPGAs

- SoC designs are FPGA-hostile

And yet, FPGAs provide a platform for SoC development and verification unlike any other and their greatest value is in their unique ability to provide a fast and accurate model of the SoC in order to allow pre-silicon validation of the embedded software.

Like all leading-edge developers, we at STMicroelectronics use a wide range of different tools and platforms during SoC design and verification. There is a prototyping community within ST, including several teams belonging to different divisions and addressing different design environments with a variety of prototyping approaches – real-time prototyping, commercial solutions, and custom machines. We use FPGA-based prototypes because they are often more than ten-times faster than emulators and this allows us to respond to the needs for a fast platform for interactive testing of new SoC software by a large number of developers on different sites.

Embedded software has become the dominant part of the effort in modern SoC design. We need to start earlier in our project just to allow enough time for the completion of the software and this means running it on the SoC "pre-silicon." It is very clear to me that the main benefit from FPGA-based prototyping is precisely for the software teams. Prototyping is the hardware team's answer to the software team's problems.

It is simply the only type of technology that offers realism to pre-silicon software developers by, for example, giving instantaneous response from JTAG debuggers, allowing operating system booting in near real-time and allowing real-time

interfaces to the system peripherals. I could go on but you can read for yourselves the benefits that others have obtained from using FPGA-based prototyping in the introductory chapters of this book.

This book discusses different possible board and system architectures and I believe that learning from previously available architectures is mandatory for everybody building high-speed prototypes. The make versus buy decision criteria, both technical and commercial, are also to be found in this book reinforcing in my mind my belief that the only reason to build a custom platform in-house is when a high number of replicated platforms need to be built. How many is a "high number?" There is help in these pages for the reader to work this out for themselves, but in general only dozens of copies of the board will allow users to get the return on the engineering cost invested for the board's development. Certainly, for any single usage, buying a commercial solution is much more economical!

The obstacles to FPGA-based prototyping that I mentioned in my opening make it daunting for some. However, there are also a number of steps in overcoming those three laws of prototyping that can be taken by us all. These are outlined in this comprehensive book and if you read this before embarking on your project, especially the Design-for-Prototyping guidelines, then you are more likely to succeed.

The book ends with a discussion of linking prototypes to simulation tools via transaction-level interfaces and leads into a glimpse of future directions. I believe that we will see more integration of FPGA-based prototyping with ESL modeling to create transaction-based platforms which will extend the benefit to software developers from before RTL right through FPGA-based prototyping to first silicon.

This book, and its companion web-based forum, will attract managers' attention to the importance of prototyping and I expect it will be a great support to the prototyping community!

Helena Krupnova

Prototyping Team Leader ST Microelectronics Grenoble, France

#### The aim of this book

This book is a seed.

It is a seed around which the sum knowledge of FPGA-based prototyping can crystallize.

We have gathered input from far and wide in order to present a snapshot of best practices in the field of FPGA-based prototyping. We hope that there is something in this manual for everyone but undoubtedly, owing to time and space constraints, there is probably something missing for everyone too.

The book in your hand (or the eBook on your screen) represents a first edition of the FPMM. From an early stage, we have been planning that this book will have a parallel on-line component, in which we can add or correct information, provide download pdf copies and build upon each reader's experience to build further editions as required. In this way, the FPMM will thrive on feedback and in turn can provide even more in-depth education for prototypers around the world. Using new media we can help to unite otherwise isolated and outnumbered prototyping experts into a respected forum of real value. This value will not just benefit the prototypers but also the SoC teams of which they will be an increasingly important part, promoting FPGA-based prototyping into its rightful place as a serious verification and validation methodology.

We hope you like the book and we look forward to seeing you on the FPMM on-line community soon (go to www.synopsys.com/fpmm).

Austin, Doug and René January, 2010

#### A note from the publisher

Thank you for your interest in this technical series book from Synopsys and our partners. We at Synopsys Press are excited to introduce the FPGA-Based Prototyping Methodology Manual (FPMM), which, like our previous successful Methodology Manuals (e.g., *Verification Methodology Manual for Low Power* (VMM-LP), aims not only to educate practitioners but also inform leaders.

We are particularly pleased that so many experts were involved in the creation of the contents and for the extensive peer review. At the end of each chapter we acknowledge to those who made a significant contribution to its content.

To learn more about this Synopsys Press book and the others in both the technical and business series, please visit www.synopsys.com/synopsys\_press.

We hope you enjoy the book,

Phil Dworsky

Publisher, Synopsys Press, February, 2011

#### The book's organization

The book is organized into chapters which are roughly in the same order as the tasks and decisions which are performed during an FPGA-based prototyping project.

Readers will be approaching this book from a number of directions. Some will be experienced with many of the tasks involved in FPGA-based prototyping but are looking for new insights and ideas; others will be relatively new to the subject but experienced in other verification methodologies; still others may be project leaders who need to understand if the benefits of FPGA-based prototyping apply to their next SoC project. So, depending on your starting point you may need to start reading the book in a different place. In anticipation of this, we have tried to make each subject chapter relatively standalone, or where necessary, make numerous forward and backward references between subjects, and provide recaps of certain key subjects

**Chapters 1&2**: We start by analyzing the complexity of the problem of validating an SoC and the software embedded within it. We introduce a number of different prototyping methods, not just FPGA. We then go on to describe the benefits of FPGA-based prototyping in general terms and give some real-life examples of successful projects from some leading prototypers in the industry.

**Chapter 3**: This is a primer on FPGA technology and the tools involved, giving a new perspective on both in the context of FPGA-based prototyping. Experienced FPGA users may feel that they can skip this chapter but it is still recommended as a way to look at FPGAs from possibly a new viewpoint.

**Chapter 4**: Every journey begins with a single step. After hopefully whetting the reader's appetite for FPGA-based prototyping, this chapter brings together sufficient information to get us started, allowing us to gauge the effort, tools and time needed to create a prototype.

**Chapters 5 and 6:** The hardware component of a prototype should be chosen early in the project. These chapters give guidance on how to best create a platform in house, or how to choose between the many commercial platforms and how to make an informed comparison between them (see also Appendix B)

**Chapter 7, 8, 9 and 10:** Key information on manipulating a design to make it ready for implementation in FPGA hardware, with special focus on RTL changes, partitioning and IP handling. There is also guidance on how a Design-for-Prototype SoC design style can be adopted to make designs more suitable for FPGA-based prototyping team.

**Chapters 11&12**: The board is ready; the design is ready; what happens when the two are put together? These chapters cover how to bring up the prototype in the lab and then go on to debug the RTL and software on the system and make fast

iterations of the design. There is also a discussion of the deployment of the prototype outside the lab.

**Chapter 13**: We have a working FPGA-based prototype; what else can be done with such a useful platform? This chapter shows the benefit of tailoring the prototype to be used within wider verification environments including RTL simulators and SystemC<sup>TM</sup>-based virtual models.

**Chapter 14**: Here we perform some future-gazing on FPGA-based prototyping and beyond into a hybrid prototyping, taking concepts from chapter 13 and other places to some new conclusions.

**Chapter 15:** This then leads into some conclusions and re-iteration of key rules and suggestions made throughout the manual.

**Appendix A**: Here is an instructive worked example of a recent FPGA-based prototype project performed at Texas Instruments giving details of the various steps taken and challenges overcome.

**Appendix B:** There is also an economic and business comparison between making prototype hardware in-house 'v' obtaining them commercially.

NOTE: the majority of the FPMM contents are intended to be generic and universally applicable, however, where examples are given, we hope that readers will forgive us for using tool and platforms best known to us at Synopsys<sup>®</sup> and Xilinx<sup>®</sup> (i.e., our own).

### Table of Contents

| 2.1.5. Example prototype usage for software validation               | 30 |

|----------------------------------------------------------------------|----|

| 2.2. Interfacing benefit: test real-world data effects               | 33 |

| 2.2.1. Example: prototype immersion in real-world data               | 34 |

| 2.3. Benefits for feasibility lab experiments                        | 35 |

| 2.4. Prototype usage out of the lab                                  | 36 |

| 2.4.1. Example: A prototype in the real world                        | 36 |

| 2.5. What can't FPGA-based prototyping do for us?                    | 38 |

| 2.5.1. An FPGA-based prototype is not a simulator                    | 38 |

| 2.5.2. An FPGA-based prototype is not ESL                            | 39 |

| 2.5.3. Continuity is the key                                         | 39 |

| 2.6. Summary: So why use FPGA-based prototyping?                     | 40 |

| CHAPTER 3 FPGA technology today: chips and tools                     | 41 |

| 3.1. FPGA device technology today                                    | 41 |

| 3.1.1. The Virtex <sup>®</sup> -6 family: an example of latest FPGAs |    |

| 3.1.2. FPGA logic blocks                                             | 43 |

| 3.1.3. FPGA memory: LUT memory and block memory                      | 46 |

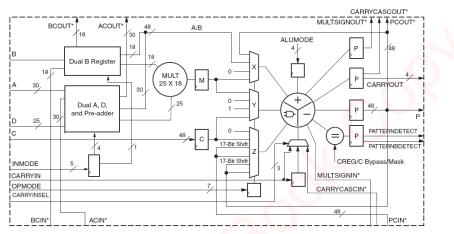

| 3.1.4. FPGA DSP resources                                            | 47 |

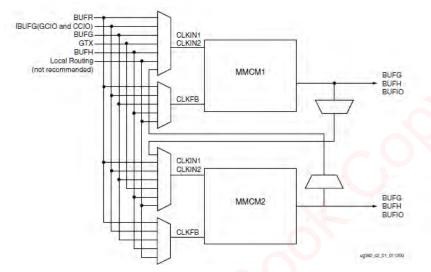

| 3.1.5. FPGA clocking resources                                       | 49 |

| 3.1.6. FPGA input and output                                         | 51 |

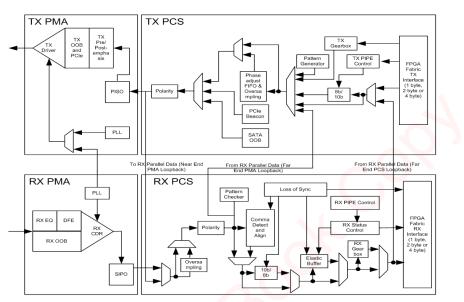

| 3.1.7. Gigabit transceivers                                          | 53 |

| 3.1.8. Built-in IP (Ethernet, PCI Express <sup>®</sup> , CPU etc.)   | 54 |

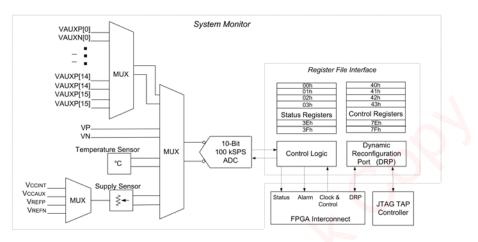

| 3.1.9. System monitor                                                | 55 |

| 3.1.10. Summary of all FPGA resource types                           | 56 |

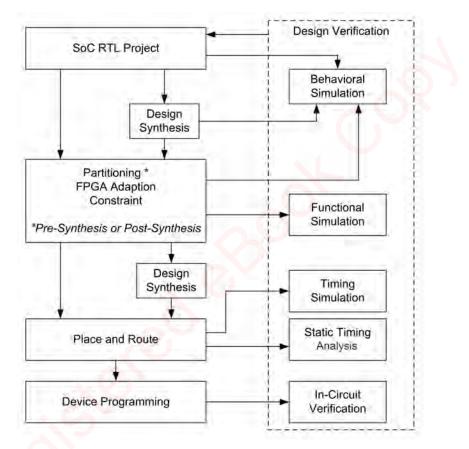

| 3.2. FPGA-based Prototyping process overview                         | 57 |

| 3.3. Implementation tools needed during prototyping                  |    |

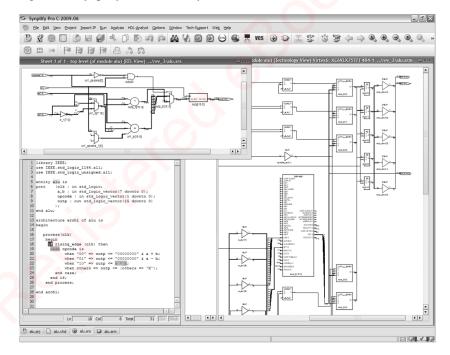

| 3.3.1. Synthesis tools                                               | 60 |

| 3.3.2. Mapping SoC design elements into FPGA                         | 61 |

| 3.3.3. Synthesis and the three "laws" of prototyping                 | 63 |

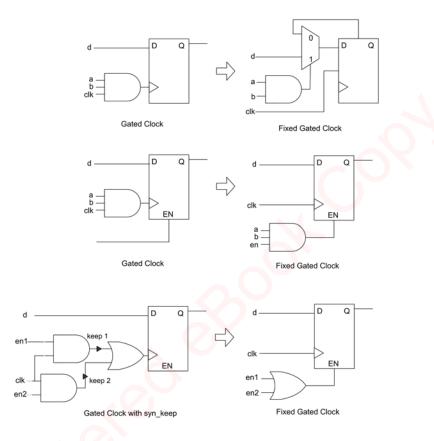

| 3.3.4. Gated clock mapping                                           | 65 |

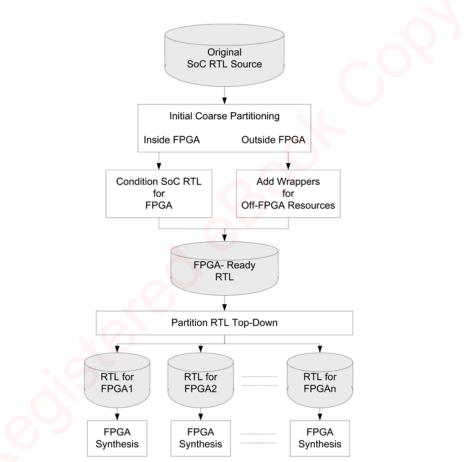

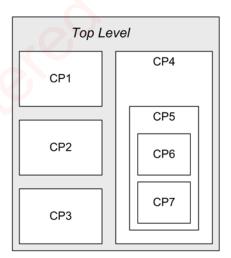

| 3.4. Design partitioning flows                                       | 66 |

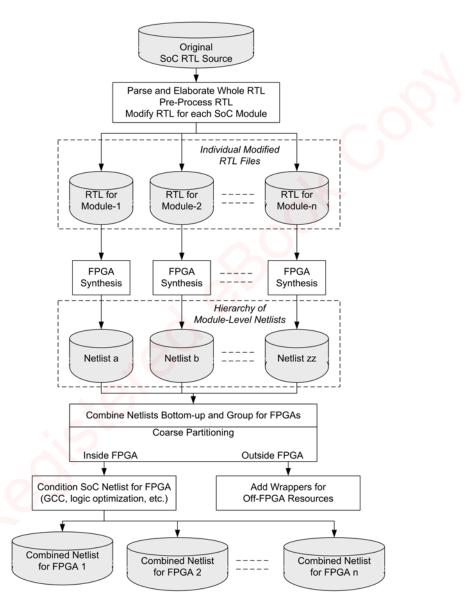

| 3.4.1. Pre-synthesis partitioning flow                               | 67 |

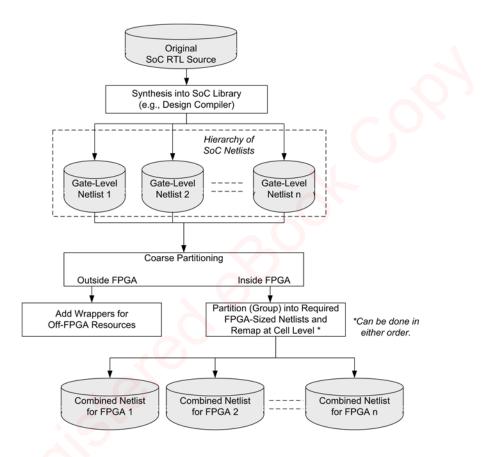

| 3.4.2. Post-synthesis partitioning flow                              | 68 |

| 3.4.3. Alternative netlist-based partitioning flow                   | 70 |

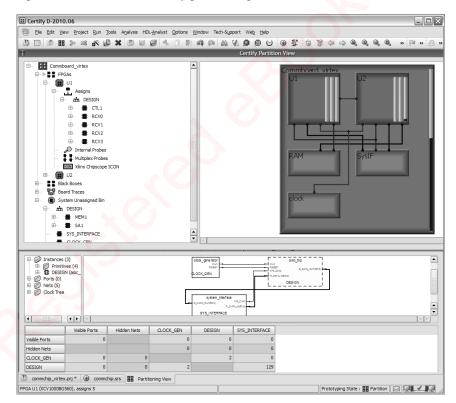

| 3.4.4. Partitioning tool example: Certify®                           | 72 |

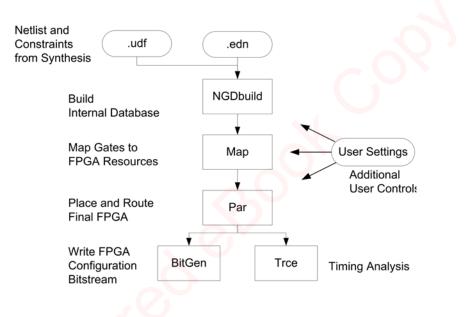

| 3.5. FPGA back-end (place & route) flow                              | 73 |

|           | 3.5.1. Controlling the back-end                             | . 75      |

|-----------|-------------------------------------------------------------|-----------|

|           | 3.5.2. Additional back-end tools                            | . 77      |

| 3.6. Debu | gging tools                                                 | . 77      |

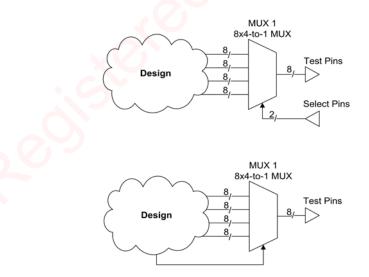

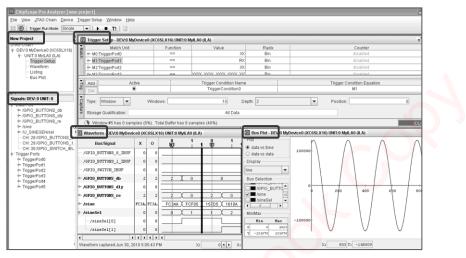

|           | 3.6.1. Design instrumentation for probing and tracing       | . 78      |

|           | 3.6.2. Real-time signal probing: test points                | . 78      |

|           | 3.6.3. Real-time signal probing: non-embedded               | . 80      |

|           | 3.6.4. Non real-time signal tracing                         | . 81      |

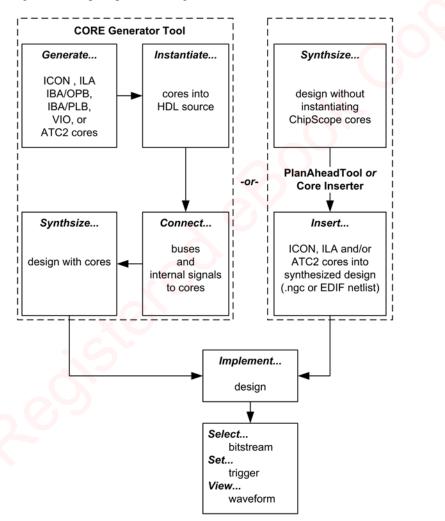

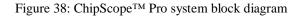

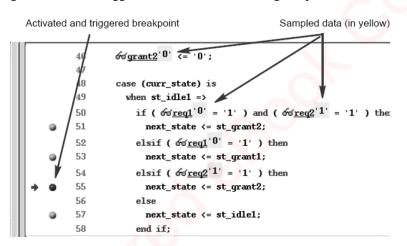

|           | 3.6.5. Signal tracing at netlist level                      | . 82      |

|           | 3.6.6. Signal tracing at RTL                                | . 85      |

|           | 3.6.7. Summarizing debugging tool options                   | . 89      |

| 3.7. Summ | nary                                                        | . 90      |

| CHAPTER 4 | Getting started                                             | <b>Q1</b> |

|           | ting-started checklist                                      |           |

| U         | ating the required resources: FPGAs                         |           |

|           | 4.2.1. How mature does the SoC design need to be?           |           |

|           | 4.2.2. How much of the design should be included?           |           |

|           | 4.2.3. Design blocks that map outside of the FPGA           |           |

|           | 4.2.4. How big is an FPGA?                                  |           |

|           | 4.2.5. How big is the whole SoC design in FPGA terms?       |           |

|           | 4.2.6. FPGA resource estimation                             |           |

|           | 4.2.7. How fast will the prototype run?                     |           |

|           | many FPGAs can be used in one prototype?                    |           |

|           | ating required resources                                    |           |

|           | long will it take to process the design?                    |           |

|           | 4.5.1. Really, how long will it take to process the design? |           |

|           | 4.5.2. A note on partitioning runtime                       |           |

|           | much work will it be?                                       |           |

|           | 4.6.1. Initial implementation effort                        | 110       |

|           | 4.6.2. Subsequent implementation effort                     | 111       |

|           | 4.6.3. A note on engineering resources                      | 111       |

| 4.7. FPGA | A platform                                                  | 112       |

| 4.8. Sumn | nary                                                        | 113       |

| CHAPTER 5 | Which platform? (1) build-your-own                          | 115       |

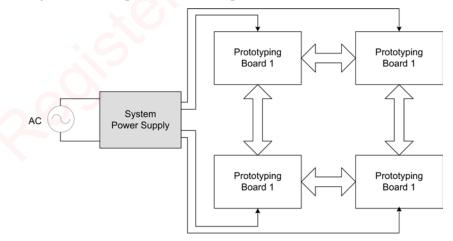

|           | is the best shape for the platform?                         |           |

|           | 5.1.1. Size and form factor                                 |           |

|           |                                                             |           |

|     | 5.1.2. Modularity117                                     |

|-----|----------------------------------------------------------|

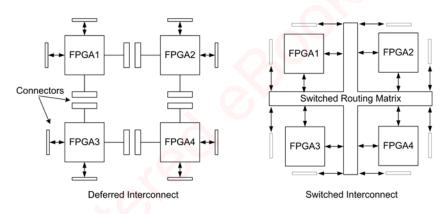

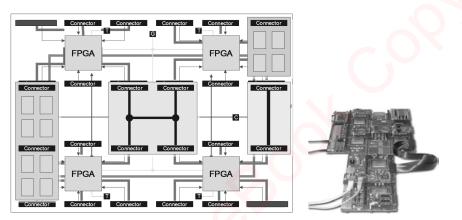

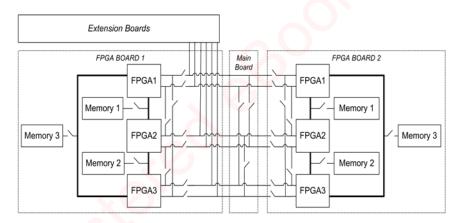

|     | 5.1.3. Interconnect                                      |

|     | 5.1.4. Flexibility 121                                   |

|     | 5.2. Testability                                         |

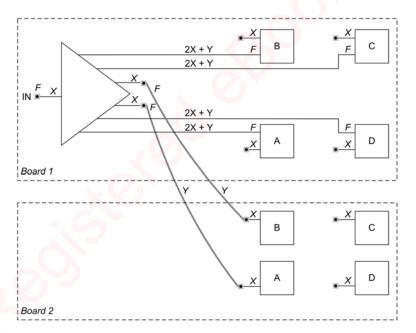

|     | 5.3. On-board clock resources 123                        |

|     | 5.3.1. Matching clock delays on and off board 124        |

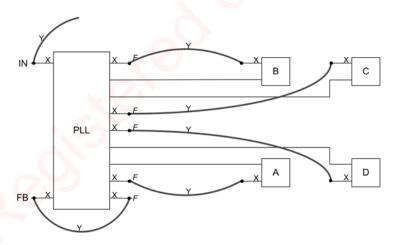

|     | 5.3.2. Phase-locked loops (PLL) 125                      |

|     | 5.3.3. System clock generation                           |

|     | 5.4. Clock control and configuration                     |

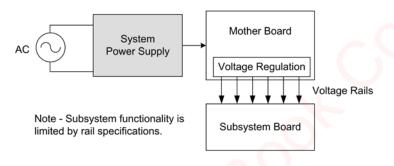

|     | 5.5. On-board Voltage Domains                            |

|     | 5.6. Power supply and distribution                       |

|     | 5.6.1. Board-level power distribution                    |

|     | 5.6.2. Power distribution physical design considerations |

|     | 5.7. System reliability management                       |

|     | 5.7.1. Power supply monitoring                           |

|     | 5.7.2. Temperature monitoring and management             |

|     | 5.7.3. FPGA cooling                                      |

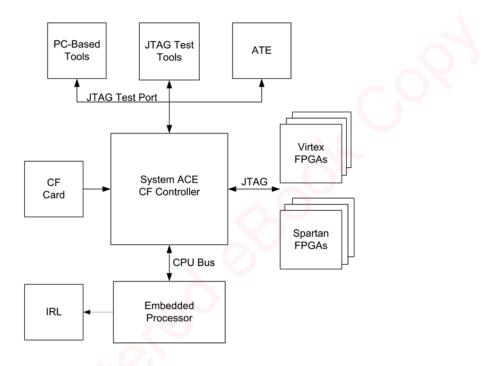

|     | 5.8. FPGA configuration                                  |

|     | 5.9. Signal integrity                                    |

|     | 5.10. Global start-up and reset                          |

|     | 5.11. Robustness                                         |

|     | 5.12. Adopting a standard in-house platform              |

| CHA | APTER 6 Which platform? (2) ready-made                   |

|     | 6.1. What do you need the board to do?                   |

|     | 6.2. Choosing the board(s) to meet your goals            |

|     | 6.3. Flexibility: modularity                             |

|     | 6.4. Flexibility: interconnect                           |

|     | 6.5. What is the ideal interconnect topology? 150        |

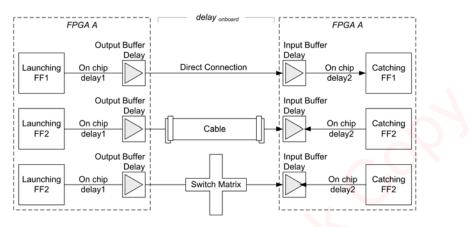

|     | 6.6. Speed: the effect of interconnect delay 153         |

|     | 6.6.1. How important is interconnect flight time?        |

|     | 6.7. Speed: quality of design and layout                 |

|     | 6.8. On-board support for signal multiplexing 158        |

|     | 6.9. Cost and robustness                                 |

|     | 6.9.1. Supply of FPGAs governs delivery of boards        |

|     | 6.10. Capacity                                           |

| 6.11. Sur | mmary                                                       |     |

|-----------|-------------------------------------------------------------|-----|

| CHAPTER 7 | Getting the design ready for the prototype                  |     |

| 7.1. Why  | "get the design ready to prototype?"                        |     |

|           | 7.1.1. RTL modifications for prototyping                    |     |

| 7.2. Adaj | pting the design's top level                                |     |

|           | 7.2.1. Handling the IO pads                                 |     |

|           | 7.2.2. Handling top-level chip support elements             |     |

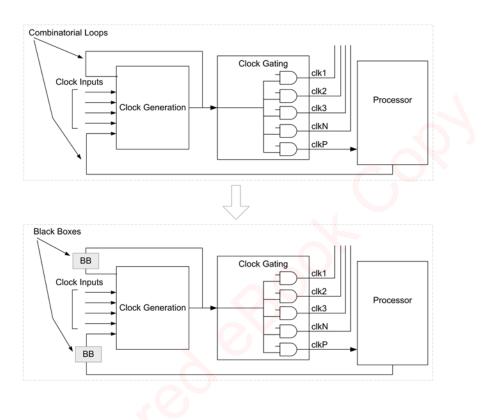

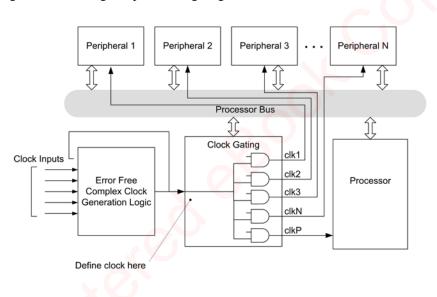

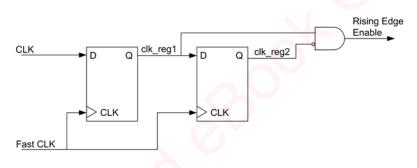

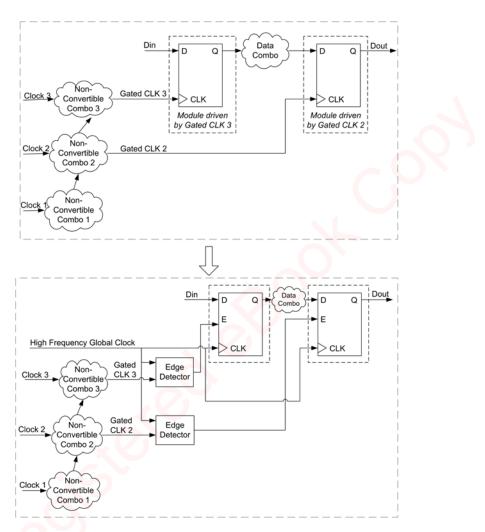

| 7.3. Cloc | k gating                                                    |     |

|           | 7.3.1. Problems of clock gating in FPGA                     |     |

|           | 7.3.2. Converting gated clocks                              | 172 |

| 7.4. Auto | omatic gated-clock conversion                               |     |

|           | 7.4.1. Handling non-convertible gating logic                |     |

|           | 7.4.2. Clock gating summary                                 |     |

| 7.5. Sele | cting a subset of the design for prototyping                |     |

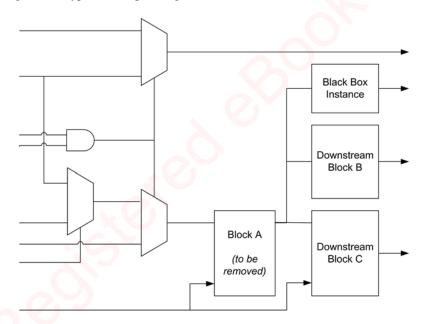

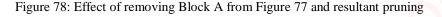

|           | 7.5.1. SoC block removal and its effect                     |     |

|           | 7.5.2. SoC element tie-off with stubs                       |     |

|           | 7.5.3. Minimizing and localizing RTL changes                |     |

|           | 7.5.4. SoC element replacement with equivalent RTL          |     |

|           | 7.5.5. SoC element replacement by inference                 |     |

|           | 7.5.6. SoC element replacement by instantiation             |     |

|           | 7.5.7. Controlling inference using directives               |     |

| 7.6. Hand | dling RAMs                                                  |     |

| 7.7. Hand | dling instantiated SoC RAM in FPGA                          |     |

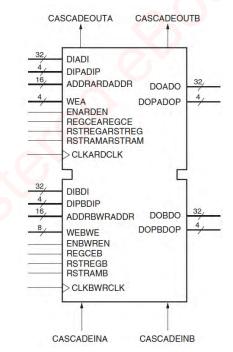

|           | 7.7.1. Note: RAMs in Virtex <sup>®</sup> -6 FPGAs           |     |

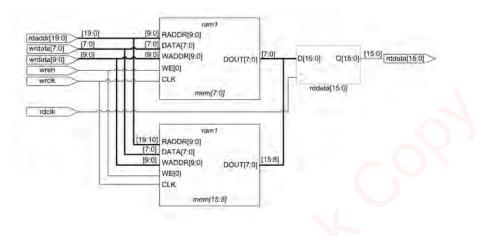

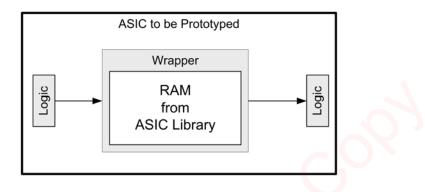

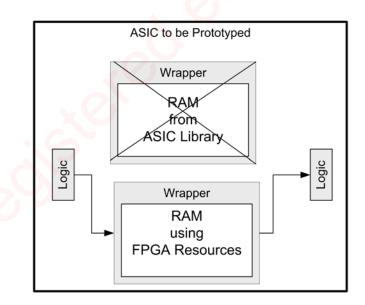

|           | 7.7.2. Using memory wrappers                                |     |

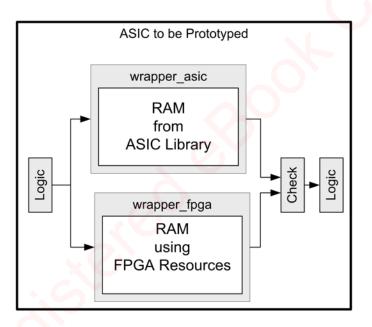

|           | 7.7.3. Advanced self-checking wrappers                      |     |

| 7.8. Impl | lementing more complex RAMs                                 |     |

|           | 7.8.1. Example: implementing multiport RAMs                 |     |

|           | 7.8.2. Example: bit-enabled RAMs                            |     |

|           | 7.8.3. NOTE: using BlockRAM as ROMs                         |     |

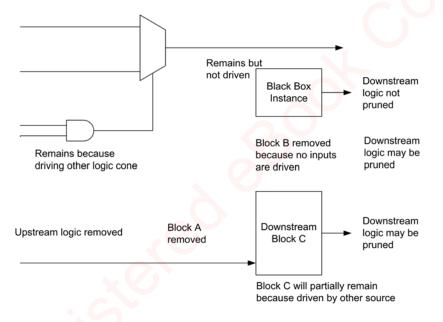

| 7.9. Desi | gn implementation: synthesis                                |     |

|           | 7.9.1. Note: using existing constraints for the SoC design. |     |

|           | 7.9.2. Tuning constraints                                   |     |

| 7.10. Pro | totyping power-saving features                              |     |

| 7.11. Des | sign implementation: place & route                          |     |

| 7.12. Revis | ion control during prototyping                           |     |

|-------------|----------------------------------------------------------|-----|

| 7.13. Sumn  | nary                                                     |     |

| CHAPTER 8   | Partitioning and reconnecting                            | 221 |

| 8.1. Do we  | always need to partition across FPGAs?                   |     |

| 8           | .1.1. Do we always need EDA partitioning tools?          |     |

| 8.2. Genera | l partitioning overview                                  |     |

| 8           | .2.1. Recommended approach to partitioning               |     |

| 8           | .2.2. Describing board resources to the partitioner      |     |

|             | .2.3. Estimate area of each sub-block                    |     |

| 8           | .2.4. Assign SoC top-level IO                            |     |

| 8           | .2.5. Assign highly connected blocks                     |     |

| 8           | .2.6. Assign largest blocks                              |     |

| 8           | .2.7. Assign remaining blocks                            |     |

| 8           | .2.8. Replicate blocks to save IO                        |     |

| 8           | .2.9. Multiplex excessive FPGA interconnect              |     |

| 8           | .2.10. Assign traces                                     |     |

|             | .2.11. Iterate partitioning to improve speed and fit     |     |

|             | ated partitioning                                        |     |

|             | ving prototype performance                               |     |

| 8           | .4.1. Time budgeting at sequential boundaries            |     |

| 8           | .4.2. Time budgeting at combinatorial boundaries         |     |

| 8.5. Design | synchronization across multiple FPGAs                    |     |

|             | .5.1. Multi-FPGA clock synchronization                   |     |

|             | .5.2. Multi-FPGA reset synchronization                   |     |

|             | .5.3. Multi FPGA start-up synchronization                |     |

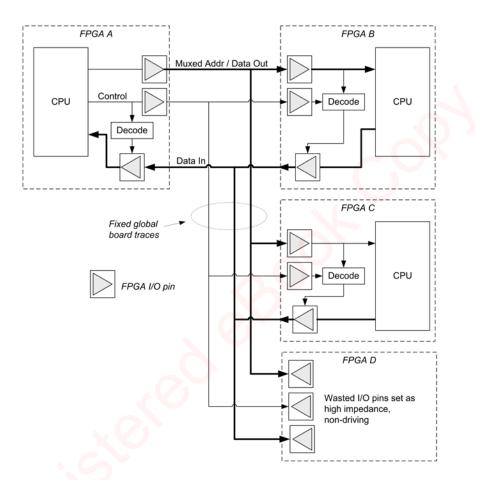

|             | bout multiplexing                                        |     |

|             | .6.1. What do we need for inter-FPGA multiplexing?       |     |

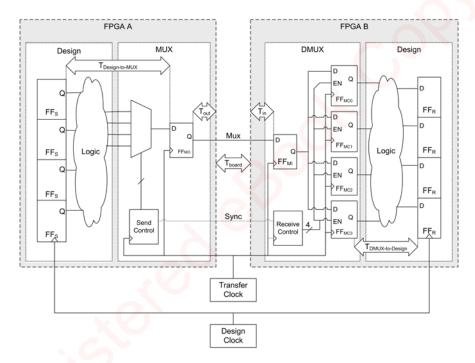

|             | lexing schemes                                           |     |

|             | .7.1. Schemes based on multiplexer                       |     |

|             | .7.2. Note: qualification criteria for multiplexing nets |     |

|             | .7.3. Schemes based on shift-registers                   |     |

|             | .7.4. Worked example of multiplexing                     |     |

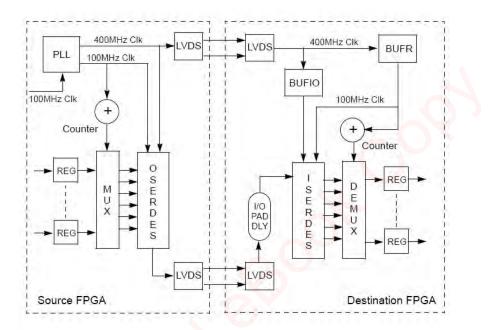

|             | .7.5. Scheme based on LVDS and IOSERDES                  |     |

|             | .7.6. Which multiplexing scheme is best for our design?  |     |

| 8.8. Timing | g constraints for multiplexing schemes                   |     |

| 8.9. Partiti      | ioning and reconnection: summary                         | 266 |

|-------------------|----------------------------------------------------------|-----|

| CHAPTER 9         | Design-for-Prototyping                                   | 267 |

| 9.1. What         | is Design-for-Prototyping?                               |     |

|                   | 9.1.1. What's good for FPGA is usually good for SoC      |     |

|                   | dural guidelines                                         |     |

|                   | 9.2.1. Integrate RTL team and prototypers                | 269 |

|                   | 9.2.2. Define list of deliverables for prototyping team  | 270 |

|                   | 9.2.3. Prototypers work with software team               | 272 |

| 9.3. Integr       | ate the prototype with the verification plan             | 272 |

|                   | 9.3.2. Documentation well and use revision control       | 274 |

|                   | 9.3.3. Adopt company-wide standard for hardware          | 274 |

|                   | 9.3.4. Include Design-for-Prototyping in RTL standards   | 274 |

| 9.4. Desig        | n guidelines                                             | 275 |

|                   | 9.4.1. Follow modular design principles                  | 277 |

|                   | 9.4.2. Pre-empt RTL changes with 'define and macros      | 278 |

|                   | 9.4.3. Avoid latches                                     | 279 |

|                   | 9.4.4. Avoid long combinatorial paths                    | 279 |

|                   | 9.4.5. Avoid combinatorial loops                         | 280 |

|                   | 9.4.6. Provide facility to override FFs with constants   | 280 |

| 9.5. Guide        | elines for isolating target specificity                  | 281 |

|                   | 9.5.1. Write pure RTL code                               | 281 |

|                   | 9.5.2. Make source changes as low-impact as possible     | 281 |

|                   | 9.5.3. Maintain memory compatibility                     |     |

|                   | 9.5.4. Isolation of RAM and other macros                 |     |

|                   | 9.5.5. Use only IP that has an FPGA version or test chip |     |

|                   | ing and architectural guidelines                         |     |

|                   | 9.6.1. Keep clock logic in its own top-level block       |     |

|                   | 9.6.2. Simplify clock networks for FPGA                  |     |

|                   | 9.6.3. Design synchronously                              |     |

|                   | 9.6.4. Synchronize resets                                |     |

|                   | 9.6.5. Synchronize block boundaries                      |     |

|                   | 9.6.6. Think how the design might run if clocked slowly  |     |

|                   | 9.6.7. Enable bottom-up design flows                     |     |

| 9.7. Summ         | nary                                                     |     |

| <b>CHAPTER 10</b> | IP and high-speed interfaces                             | 289 |

| 10.1. IP and prototyping                                 |     |

|----------------------------------------------------------|-----|

| 10.2. IP in many forms                                   |     |

| 10.2.1. IP as RTL source code                            |     |

| 10.2.2. What if the RTL is not available?                |     |

| 10.2.3. IP as encrypted source code                      |     |

| 10.2.4. Encrypted FPGA netlists                          |     |

| 10.2.5. Encrypted FPGA bitstreams                        | 293 |

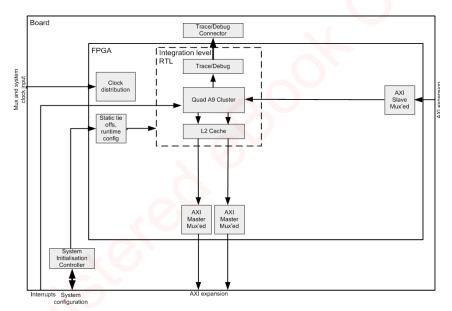

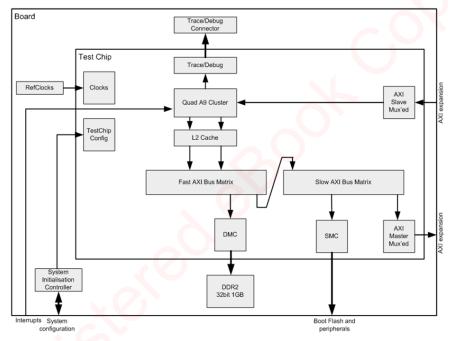

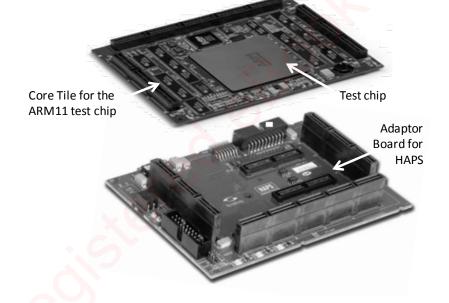

| 10.2.6. Test chips                                       |     |

| 10.2.7. Extra FPGA pins needed to link to test chips     |     |

| 10.3. Soft IP                                            |     |

| 10.3.1. Replacing instantiated soft IP                   |     |

| 10.3.2. Replacing inferred soft IP                       |     |

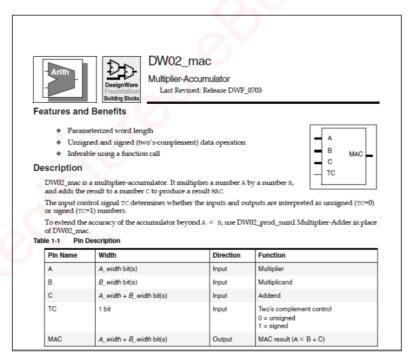

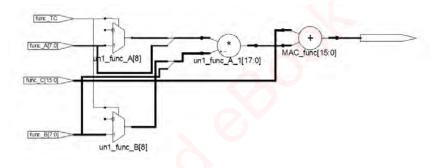

| 10.3.3. Replacing synthetic soft IP                      | 302 |

| 10.3.4. Other FPGA replacements for SoC soft IP          |     |

| 10.4. Peripheral IP                                      |     |

| 10.4.1. Use mode 1: prototype the IP itself              |     |

| 10.4.2. Use mode 2: prototype the IP as part of an SoC   | 306 |

| 10.4.3. Use mode 3: prototype IP for software validation |     |

| 10.5. Use of external hard IP during prototyping         |     |

| 10.6. Replacing IP or omitted structures with FPGA IP    |     |

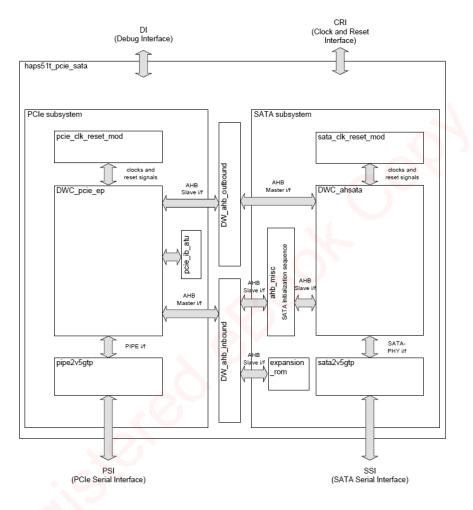

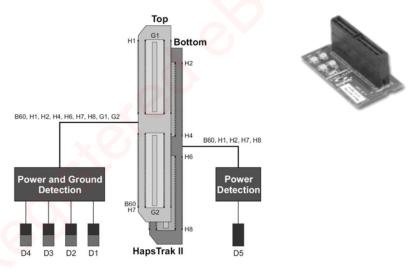

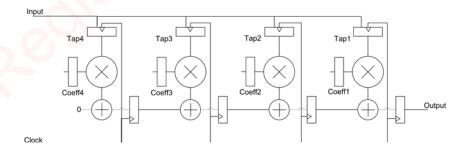

| 10.6.1. External peripheral IP example: PCIe and SATA    |     |

| 10.6.2. Note: speed issues, min-speed                    |     |

| 10.7. Summary                                            |     |

| CHAPTER 11 Bring up and debug: the prototype in the lab  |     |

| 11.1. Bring-up and debug-two separate steps?             |     |

| 11.2. Starting point: a fault-free board                 |     |

| 11.3. Running test designs                               |     |

| 11.3.1. Filter test design for multiple FPGAs            |     |

| 11.3.2. Building a library of bring-up test designs      |     |

| 11.4. Ready to go on board?                              |     |

| 11.4.1. Reuse the SoC verification environment           |     |

| 11.4.2. Common FPGA implementation issues                |     |

| 11.4.3. Timing violations                                |     |

| 11.4.4. Improper inter-FPGA connectivity                 | 325 |

| 11.4.5. Improper connectivity to the outside world       |     |

| 11.4.6. Incorrect FPGA IO pad configuration                                                                                                                                                                                                                                                                                                                                              | 328                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 11.5. Introducing the design onto the board                                                                                                                                                                                                                                                                                                                                              | 331                                                                                                     |

| 11.5.1. Note: incorrect startup state for multiple FPGAs                                                                                                                                                                                                                                                                                                                                 | 332                                                                                                     |

| 11.6. Debugging on-board issues                                                                                                                                                                                                                                                                                                                                                          | 333                                                                                                     |

| 11.6.1. Sources of faults                                                                                                                                                                                                                                                                                                                                                                | 333                                                                                                     |

| 11.6.2. Logical design issues                                                                                                                                                                                                                                                                                                                                                            | 334                                                                                                     |

| 11.6.3. Logic debug visibility                                                                                                                                                                                                                                                                                                                                                           | 335                                                                                                     |

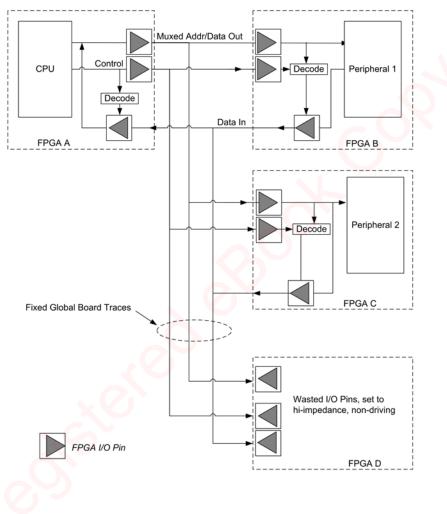

| 11.6.4. Bus-based design access and instrumentation                                                                                                                                                                                                                                                                                                                                      | 336                                                                                                     |

| 11.6.5. Benefits of a bus-based access system                                                                                                                                                                                                                                                                                                                                            | 339                                                                                                     |

| 11.6.6. Custom debug using an embedded CPU                                                                                                                                                                                                                                                                                                                                               | 341                                                                                                     |

| 11.7. Note: use different techniques during debug                                                                                                                                                                                                                                                                                                                                        | 342                                                                                                     |

| 11.8. Other general tips for debug                                                                                                                                                                                                                                                                                                                                                       | 343                                                                                                     |

| 11.9. Quick turn-around after fixing bugs                                                                                                                                                                                                                                                                                                                                                | 346                                                                                                     |

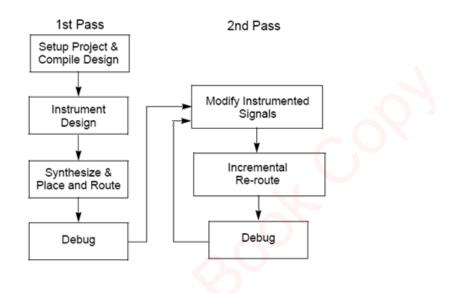

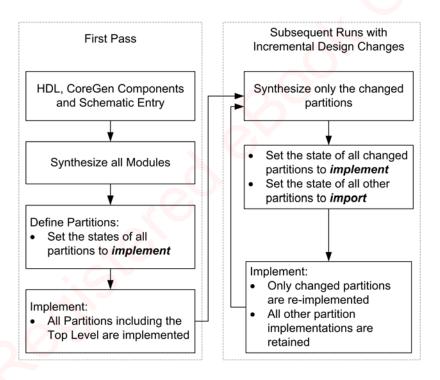

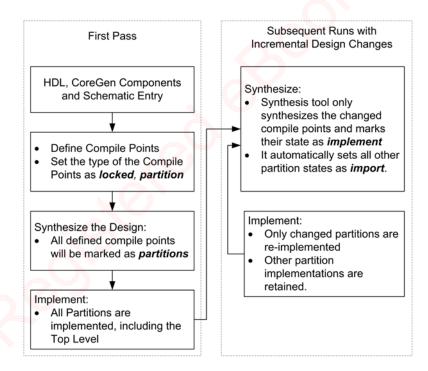

| 11.9.1. Incremental synthesis flow                                                                                                                                                                                                                                                                                                                                                       | 347                                                                                                     |

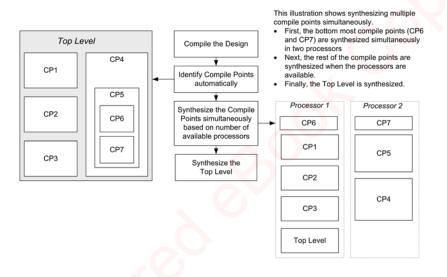

| 11.9.2. Automation and parallel synthesis                                                                                                                                                                                                                                                                                                                                                | 349                                                                                                     |

| 11.9.3. Incremental place & route flow                                                                                                                                                                                                                                                                                                                                                   | 350                                                                                                     |

| 11.9.4. Combined incremental synthesis and P&R flow                                                                                                                                                                                                                                                                                                                                      | 351                                                                                                     |

| 11.10. A bring-up and debug checklist                                                                                                                                                                                                                                                                                                                                                    | 352                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                         |

| 11.11. Summary                                                                                                                                                                                                                                                                                                                                                                           | 353                                                                                                     |

| 11.11. Summary         CHAPTER 12       Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                              |                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                          | 355                                                                                                     |

| CHAPTER 12 Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                                                           | <b> 355</b><br>355                                                                                      |

| CHAPTER 12       Breaking out of the lab: the prototype in the field         12.1. The uses and benefits of a portable prototype                                                                                                                                                                                                                                                         | <b> 355</b><br>355<br>357                                                                               |

| CHAPTER 12       Breaking out of the lab: the prototype in the field         12.1. The uses and benefits of a portable prototype                                                                                                                                                                                                                                                         | <b> 355</b><br>355<br>357<br>358                                                                        |

| CHAPTER 12       Breaking out of the lab: the prototype in the field         12.1. The uses and benefits of a portable prototype       12.2. Planning for portability         12.2.1. Main board physical stiffness                                                                                                                                                                      | <b> 355</b><br>355<br>357<br>358<br>358                                                                 |

| CHAPTER 12       Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                                                     | <b> 355</b><br>355<br>357<br>358<br>358<br>358                                                          |

| CHAPTER 12       Breaking out of the lab: the prototype in the field         12.1. The uses and benefits of a portable prototype                                                                                                                                                                                                                                                         | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359                                                   |

| CHAPTER 12       Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                                                     | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359                                            |

| CHAPTER 12       Breaking out of the lab: the prototype in the field         12.1. The uses and benefits of a portable prototype                                                                                                                                                                                                                                                         | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359<br>359<br>360                              |

| CHAPTER 12 Breaking out of the lab: the prototype in the field<br>12.1. The uses and benefits of a portable prototype<br>12.2. Planning for portability<br>12.2.1. Main board physical stiffness<br>12.2.2. Daughter board mounting<br>12.2.3. Board mounting holes<br>12.2.4. Main board connectors<br>12.2.5. Enclosure<br>12.2.6. Cooling                                             | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359<br>360<br>361                              |

| CHAPTER 12 Breaking out of the lab: the prototype in the field<br>12.1. The uses and benefits of a portable prototype<br>12.2. Planning for portability<br>12.2.1. Main board physical stiffness<br>12.2.2. Daughter board mounting<br>12.2.3. Board mounting holes<br>12.2.4. Main board connectors<br>12.2.5. Enclosure<br>12.2.6. Cooling<br>12.2.7. Look and feel                    | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359<br>360<br>361<br>362                       |

| CHAPTER 12 Breaking out of the lab: the prototype in the field<br>12.1. The uses and benefits of a portable prototype<br>12.2. Planning for portability<br>12.2.1. Main board physical stiffness<br>12.2.2. Daughter board mounting<br>12.2.3. Board mounting holes<br>12.2.4. Main board connectors<br>12.2.5. Enclosure<br>12.2.6. Cooling<br>12.2.7. Look and feel<br>12.2.8. Summary | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359<br>359<br>360<br>361<br>362<br><b> 363</b> |

| CHAPTER 12       Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                                                     | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>359<br>360<br>361<br>362<br><b> 363</b>        |

| CHAPTER 12       Breaking out of the lab: the prototype in the field                                                                                                                                                                                                                                                                                                                     | <b> 355</b><br>355<br>357<br>358<br>358<br>358<br>359<br>360<br>361<br>362<br><b> 363</b><br>363<br>364 |

| 13.4.1. Interfaces for co-simulation                   | 366 |

|--------------------------------------------------------|-----|

| 13.4.2. Interfaces for transaction-based verification  | 368 |

| 13.4.3. TLMs and transactors                           | 369 |

| 13.4.4. SCE-MI                                         | 369 |

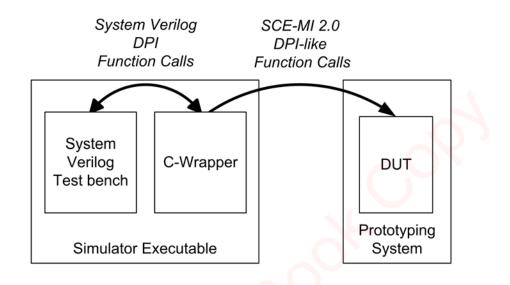

| 13.4.5. SCE-MI 2.0 implementation example              | 371 |

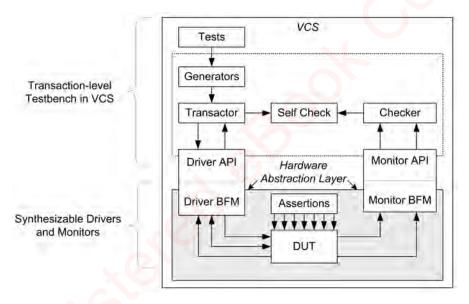

| 13.4.6. VMM HAL                                        | 373 |

| 13.4.7. Physical interfaces for co-verification        | 375 |

| 13.5. Comparing verification interface technologies    | 375 |

| 13.6. Use models – more detail                         | 377 |

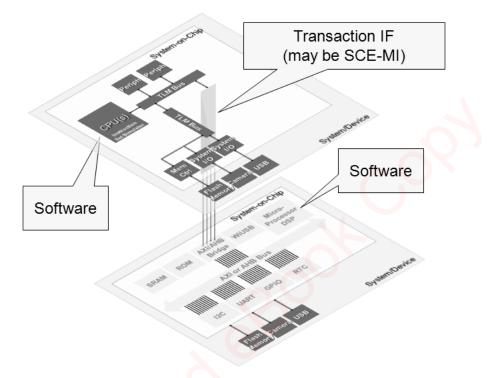

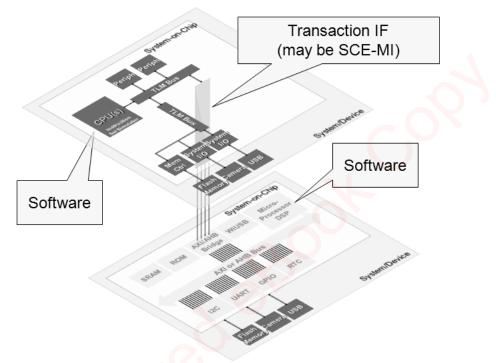

| 13.6.1. Virtual platform re-using existing RTL         | 377 |

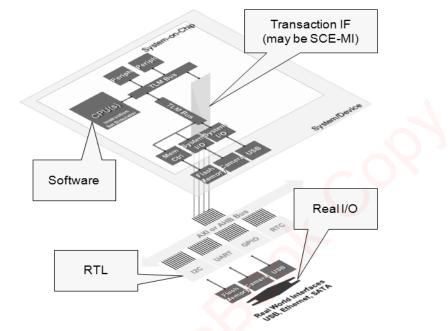

| 13.7. Virtual platform for software                    | 378 |

| 13.7.1. Virtual platform as a testbench                | 379 |

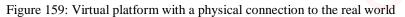

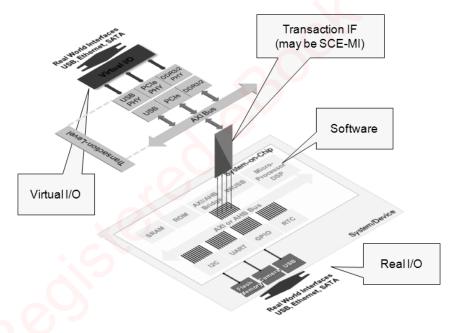

| 13.7.2. Virtual and physical IO (system IO)            | 380 |

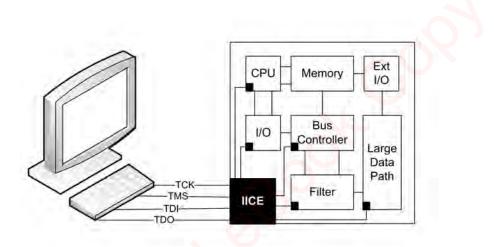

| 13.7.3. Virtual ICE                                    | 381 |

| 13.8. System partitioning                              | 383 |

| 13.9. Case study: USB OTG                              | 384 |

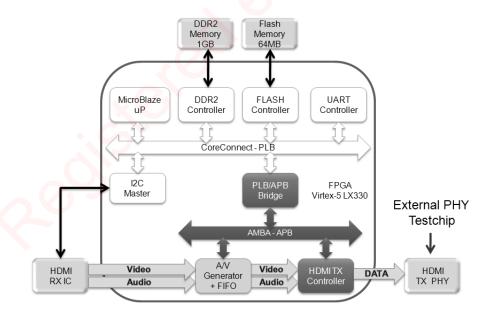

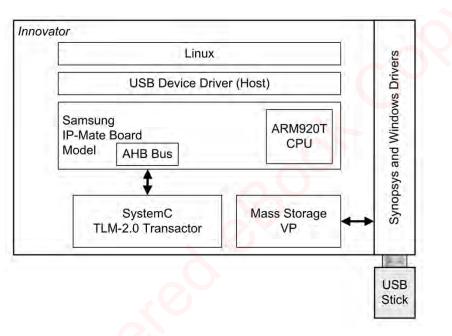

| 13.9.1. USB OTG System overview                        | 384 |

| 13.9.2. Integration use models                         | 385 |

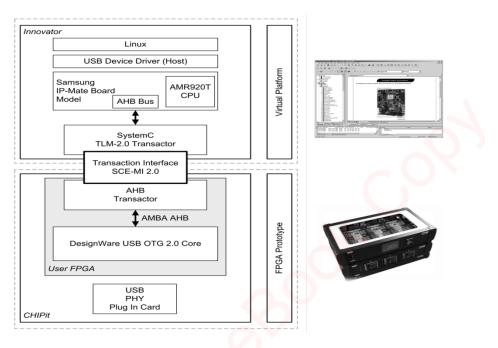

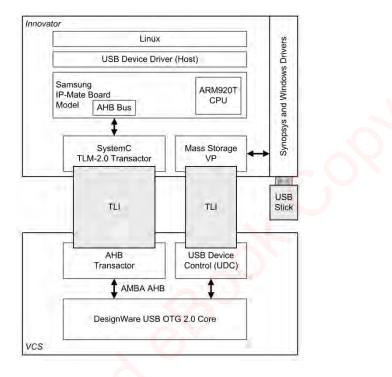

| 13.9.3. Innovator and VCS                              | 385 |

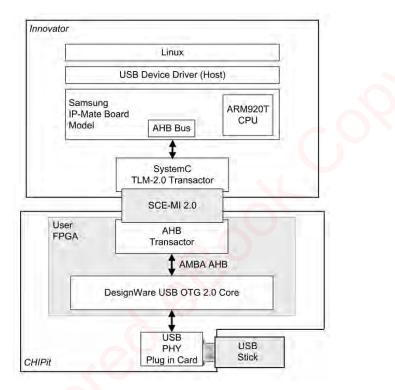

| 13.9.4. Innovator and CHIPit or HAPS                   | 386 |

| 13.9.5. Virtual platform                               | 387 |

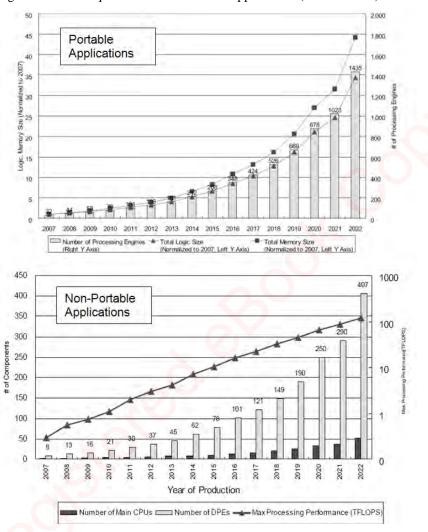

| CHAPTER 14 The future of prototyping                   | 391 |

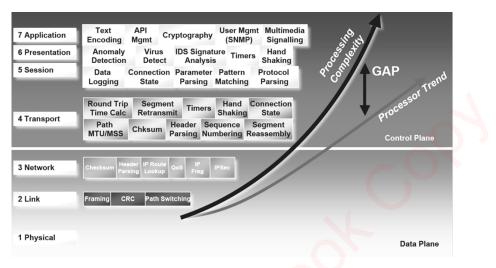

| 14.1. If prediction were easy                          | 391 |

| 14.2. Application specificity                          | 391 |

| 14.3. Prototyping future: mobile wireless and consumer | 392 |

| 14.4. Prototyping future: networking                   | 394 |

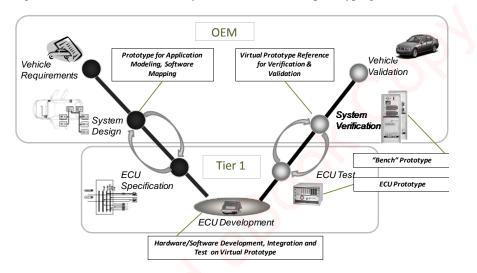

| 14.5. Prototyping future: automotive                   | 397 |

| 14.6. Summary: software-driven hardware development    | 400 |

| 14.7. Future semiconductor trends                      | 401 |

| 14.8. The FPGA's future as a prototyping platform      | 402 |

| 14.9. Summary                                          | 403 |

| CHAPTER 15 Conclusions                                 | 405 |

| 15.1. The FPMM approach to FPGA-based prototyping      | 405 |

| 15.2. SoCs are larger than FPGAs                       | 406 |

| 15.3. SoCs are faster than FPGAs                       | 407 |

| 15.4. SoCs designs are FPGA-hostile                      |     |

|----------------------------------------------------------|-----|

| 15.5. Design-for-Prototyping beats the three laws        |     |

| 15.6. So, what did we learn?                             |     |

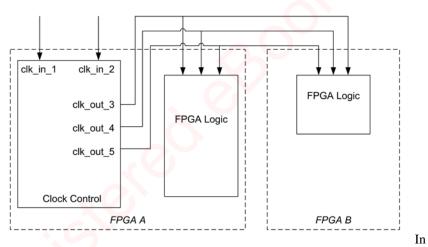

| APPENDIX A: Worked Example: Texas Instruments            | 411 |

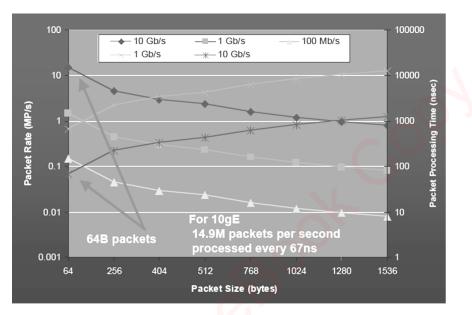

| A1. Design background: packet processing sub-system      |     |

| A2. Why does Texas Instruments do prototyping?           |     |

| A3. Testing the design using an FPGA-based prototype     |     |

| A4. Implementation details                               |     |

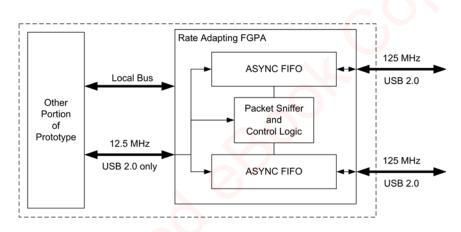

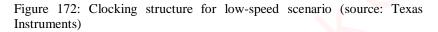

| A5. High-speed scenario                                  |     |

| A6. Low-speed scenario                                   |     |

| A7. Interesting challenges                               |     |

| A8. Summary of results                                   |     |

| APPENDIX B: Economics of making prototype boards         |     |

| B1. Prototyping hardware: should we make or buy?         |     |

| B2. Cost: what is the total cost of a prototyping board? |     |

| B3. Direct cost: personnel                               |     |

| B4. Direct cost: equipment and expertise                 |     |

| B5. Direct cost: material and components                 |     |

| B6. Direct cost: yield and wastage                       |     |

| B7. Direct cost: support and documentation               |     |

| B8. Business cost: time                                  |     |

| B9. Business cost: risk                                  |     |

| B10. Business cost: opportunity                          |     |

| B11. CCS worked example results                          |     |

| B12. Summary                                             |     |

| References and Bibliography                              |     |

| Acknowledgements                                         |     |

| Figure Sources                                           |     |

| Glossary of key terms                                    |     |

| Index                                                    |     |

| About the authors                                        |     |

|                                                          |     |

| About Synopsys Press                                     |     |

Table of Contents

### CHAPTER 1 INTRODUCTION: THE CHALLENGE OF SYSTEM VERIFICATION

This chapter will establish some definitions and outline the challenges we are trying to overcome with FPGA-based prototyping. We will explore the complexity of SoCbased systems and the challenges in their verification. We will also compare and contrast FPGA-based prototyping with other prototyping methods including systemlevel virtual modeling. After this chapter we will be ready to dive deeper into the ways that FPGA-based Prototyping has benefited some real projects and give some guidance on what is possible with FPGA-based prototyping technology.

#### **1.1. Moore was right!**

Since Gordon E. Moore described the trend of how many transistors can be placed inexpensively on an integrated circuit, electronic design enabled by semiconductor design has grown at a hard-to-imagine pace. The trend of transistors doubling every two years has already continued for more than half a century and is not expected to stop for a while despite repeated predictions that it would end soon.

A detailed review of the major trends driving chip design later in this chapter will make it clear why prototyping has grown in adoption, and is even considered mandatory in many companies. To further understand this trend, typical project dynamics and their effort distributions need to be understood.

#### 1.1.1. SoC: A definition . . . for this book at least

Let's start with a definition. For the purposes of this book, we define system on chip (SoC) as a device which is designed and fabricated for a specific purpose, for exclusive use by a specific owner. Some might think of SoC as a particular form of an ASIC (application specific integrated circuit) and they would be correct, but for the purposes of this book, we will refer only to SoCs. We will stick to the definition that an SoC always includes at least one CPU and runs embedded software. In comparison, an ASIC does not necessarily include a CPU and to that extent, SoCs can be considered to be a superset of ASICs.

We do not mean to imply that those who are creating an ASIC, ASSP (application-specific silicon product) or silicon produced by COT (customer's own tooling) or by third-party foundries should read another book. Technologies are not mutually unique for FPGA-based prototyping purposes and in fact, many FPGA-based prototyping projects are of an ASSP or even just pieces of IP that may be used in many different SoC designs.

As far as FPGA-based prototyping is concerned, if it works for SoC then it will work for any of the above device types. The reason for this book's focus on SoC is that the greatest value of FPGA-based prototyping is in its unique ability to provide a fast and accurate model of the SoC in order to allow validation of the software.

#### 1.2. The economics of SoC design

SoC designs are all around us. We can find them in all the new headline-grabbing consumer electronics products as well as in the most obscure corners of pure research projects in places like CERN, and in the guidance systems of interstellar probes.

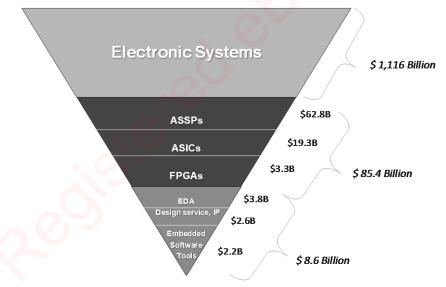

Figure 1: The relationship of IC design to the electronics market

For consumer products in particular, there is a seemingly insatiable hunger for maximum intelligence and functionalities in devices such as smart phones, cameras or portable media players. To meet these requirements a typical SoC design will

include several microprocessors, one or more digital signal processors and some different interfaces such as Bluetooth<sup>TM</sup> or WLAN, high resolution graphics and so on. That all adds up to a lot of software.

Considering the IC development and manufacture as a whole, it appears in Figure 1 as an inverted triangle. The figures shown are for 2009, and we see that chip development was a market of about \$85.4 billion and was enabled by a \$8.6 billion market for EDA tools, design services, IP and embedded software tools. Supported by this semiconductor design and manufacture is a huge \$1.116 billion market for electronic systems, which contain for example all the consumer gadgets, wireless devices and electronics we crave as end consumers.

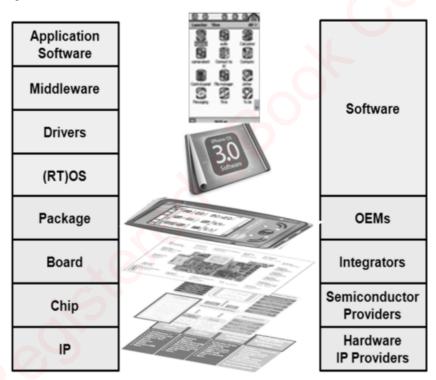

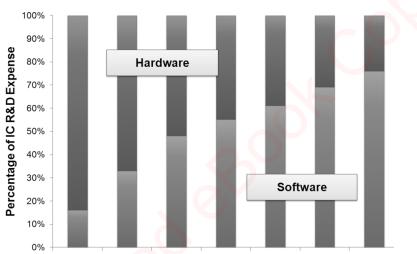

Figure 2: Hardware-software teardown of a consumer device

EDA tools, which include various types of prototyping for different stages within a design, are recently focusing to specifically enabling the design chain from IP providers, semiconductor providers, integrators and OEMs. Prototyping plays a key role in those interactions as early prototypes enable communication of requirements from customers to suppliers and early software development and verification for customers from suppliers.

To understand the impact that prototyping in its many forms can achieve, let's consider a typical complex SoC design. Figure 2 shows the tear down of a typical smartphone. The end user experience is largely influenced by the applications with which they are presented. Good old hardware, analog and antenna design is obviously still important but the user only really notices them when they go wrong! User applications are enabled by a software stack of middleware, operating system and drivers; all of which are specifically design to make the software as independent of the hardware as possible.

For example, application developers do not have direct access to the device's hardware memory, timing or other low-level hardware aspects. The stack of software is matched by a stack of hardware elements. The end device uses several boards, comprised of several peripherals and chips, which contain various blocks, either reused as IP or specifically developed by chip providers to differentiate their hardware.

The dependencies of hardware and software result in an intricate relationship between different company types. IP providers sell to semiconductor providers, who sell to integrators who sell to OEMs, all of whom are enabling software developers. Enablement of these interactions has arguably become the biggest problem to be addressed by tool vendors today.

The main challenges for this enablement have become today:

- (a) The enablement of software development at the earliest possible time.

- (b) Validation of hardware / software in the context of the target system.

- (c) Design and reuse of the basic building blocks for chips

- processors

- accelerators

- peripherals

- interconnect fabrics (e.g., ARM AMBA® interconnect)

- (d) Architecture design of the chips assembled from the basic building blocks.

#### **1.2.1.** Case study: a typical SoC development project

Considering the bottom three layers of the hardware stack in Figure 2, let's analyze a specific chip development project and the potential impact of prototyping. The chosen example is a wireless headset design by a large semiconductor company, performed in a mainstream 65nm technology. The chip is targeted for a high volume, fast moving market and has an expected production run of 27 months with an average volume of 1.5 million units per month and average selling price of

\$5.50. Things go well during development and only one metal mask spin is required allowing six months of customer and field evaluations after first silicon is available. In total the development cost for the project is estimated as \$31,650,000 based on a development cost model described in an International Business Systems study with scaling factors for mainstream applications.

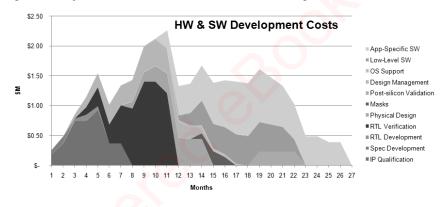

Let's now consider Figure 3, which illustrates how chip development cost is spread over the typical 12-month hardware design cycle, from complete specification to final verified RTL, ready for layout. Indeed, RTL verification consumes the majority of the effort and is the critical element in determining the project length of 12 months. Another portion of the design with significant impact is the overall design management accompanying the actual development of code. Physical design is finished about 15 months into the project (i.e., three months after RTL is verified) and then masks are prepared by month 17. The post silicon validation ramps up with engineering samples available in month 19 and takes several months.

Figure 3: Project effort for a 65nm wireless headset design

As Figure 3 further illustrates, software development ramps up in this project when RTL is largely verified and stable. It is split here between OS support and porting, low-level software development and high-level application software development. All the software development effort here is still the responsibility of the chip provider, rather than third-party providers. Overall, software development consumes 40% of the total cost for this design and extends the project schedule to a total of 27 months.

When amortizing development and production cost onto expected sales, this project reaches break even after about 34 months, i.e., seven months after product launch but almost three years after starting product development. The challenge in this example is that we have to predict nearly three years in advance what is going to sell in high-volumes in order to specify our chip. How can this almost intolerable situation be made easier? The answer is to "start software sooner."

Using the calculator for return on investment (ROI) developed by the Global Semiconductor Association (GSA), it can be calculated that if software development and validation started seven months earlier in our example project, production could have started three months earlier and subsequently the time to break even would have been reduced by five months. In addition a \$50 million revenue gain could have been expected over the production volume due to extra first-to-market design-wins for the chip.

This is exactly what prototyping in its many forms can achieve. The earlier start to software development and validation provided by prototyping means that its impact on ROI can be very significant.

For a deeper understanding of requirements and benefits of prototyping, let's look at the different types of prototyping available today from virtual to FPGA-based.

#### **1.3.** Virtual platforms: prototyping without hardware

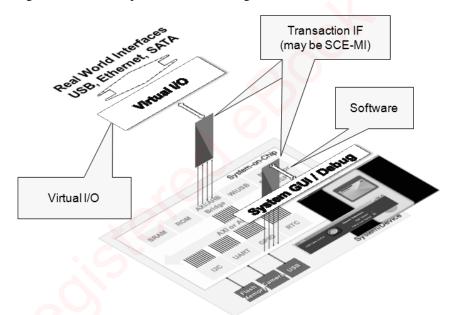

There are various forms of prototyping which we can employ in our projects. Available earliest in a project are virtual prototypes. They represent fully functional but loosely-timed software models of SoCs, boards, virtualized IOs and user interfaces, all running on a host-based simulation. Virtual prototypes can execute unmodified production software code on processor instruction set simulators and they run close to real-time. Being fully host-based virtual prototypes they can also offer good system visibility and control, which is especially useful for debug on multicore CPUs. Virtual prototypes can also have virtual user interfaces, allowing real-time interaction with us slow humans. The screenshot excerpts shown in Figure 4 are from a virtual prototype of an OMAP design running on the Synopsys Innovator tool. Here we see not only recognizable simulation windows but also the representation of key controls on the board and input from a virtual camera, in this case linked to a webcam on the host PC running the simulation, all done without hardware. We shall come back to Innovator in chapter 13 when we discuss the linking of an FPGA-based prototype with a virtual simulation.

While virtual prototypes offer very high speed (multiple tens of MIPS) when using loosely-timed models they do not offer the timing accuracy preferred by hardware design teams. More timing-accurate software models can be added to a virtual prototype but then their simulation speed will degrade to the single-digit MIPS range or even lower depending on the mix of cycle-accurate versus loosely-timed models.

However, virtual prototypes are available earliest in the flow, assuming models are available, so they are perfect for early software debugging. Virtual prototypes provide almost complete insight into the behavior of the system and they are also easy to replicate for multiple users.

Figure 4: Pre-Silicon virtual prototype of OMAP design

Finally, because they are created before the RTL, virtual prototypes allow codevelopment of hardware architecture along with early software. For example, extra or different CPUs might be added if the virtual prototype shows that there is not enough processing bandwidth for the product's concurrent applications.

#### 1.3.1. SDK: a very common prototyping environment

Related to virtual prototypes are so-called software development kits, or SDKs, of which a very common example is the SDK for developing applications for the Apple iPhone<sup>®</sup>. This SDK was downloaded more than 100,000 times in the first couple of days of its availability and so we can consider this a very widely available prototyping platform. Although simple in comparison, SDKs offer many of the advantages of full virtual prototypes, however, their accuracy is often more limited because they may not represent the actual registers as accurately as virtual prototypes.

Their aim is to have "just enough accuracy" in order to fool the application into thinking that it is running on the final platform. SDKs allow programming and interfacing over a higher-level application programming interface (API) into the platform. The developed software is usually compiled for the host machine on

which the SDK executes and then requires re-compilation to the actual target processor after programmers have verified functionality on the SDK.

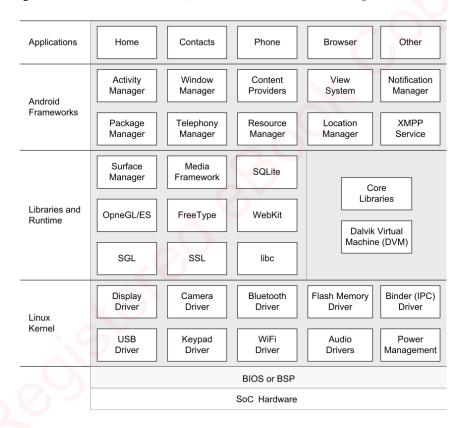

Figure 5 shows a screenshot of an Android<sup>TM</sup> SDK. Programming of applications is done in high-level languages like C using higher-level operating system APIs. The programming is done completely independent of the actual target hardware, so when actually targeting the final device, recompilation is necessary. User interfaces of the target device – as shown in Figure 5, can be modeled so that the end-user environment can be experienced virtually.

Figure 5: Android<sup>™</sup> SDK screenshot showing GUI emulation

#### **1.3.2. FPGA:** prototyping in silicon . . . but pre-silicon

Available later in the design flow, but still well before real silicon, an FPGA-based prototype also serves as a vehicle for software development and validation. FPGA-based prototypes are fully functional hardware representations of SoCs, boards and IOs. Because they implement the same RTL code as the SoC and run at almost realtime speed with all external interfaces and stimulus connected, they are very accurate. They offer higher system visibility and control than the actual silicon will provide when available but do not match the debug and control capabilities of

virtual platforms, or any other simulator, so they are not the first platforms we would choose on which to debug all of our RTL.

The key advantage of FPGA-based prototypes is their ability to run at high speed, yielding tens of MIPS per modeled CPU, while maintaining RTL accuracy. They are typically available later in the design flow than virtual prototypes because RTL needs to be available and relatively mature. Due to the complexity and effort of mapping the RTL to FPGA-based prototypes, it is not really feasible to use them before RTL verification has stabilized. For the same reason, FPGA-based prototypes are not intended for use as hardware/software co-development platforms because at this point in the SoC design flow, the hardware (i.e., the RTL) is pretty much fixed and partially verified. Design teams will be very hesitant to change the hardware architecture by the time the FPGA-based prototype is running, unless some major architectural bottlenecks have been discovered.

Finally, once stable and available, the cost of replication and delivery for FPGAbased prototypes is higher than for software-based virtual platforms, however still considerably cheaper than emulators, which we shall discuss next.

#### **1.3.3. Emulators: prototyping or verification?**

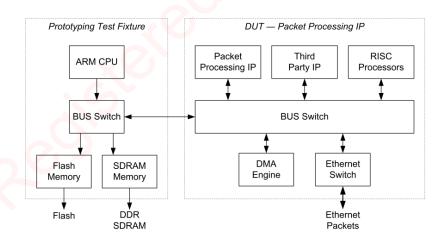

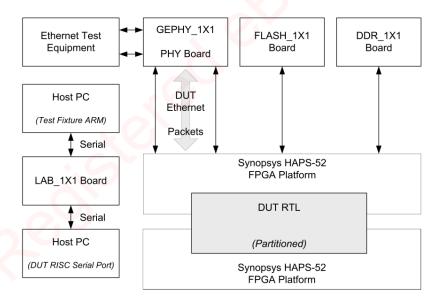

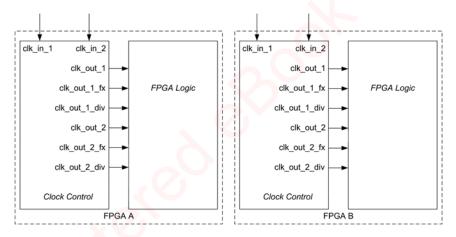

Emulation provides another hardware-based alternative to enable software development but differs from FPGA-based prototyping in that it aims at lower performance but with more automation. Emulators have more automated mapping of RTL into the hardware together with faster compile times, but the execution speed will be lower and typically drop to below the single-MIPS level. The cost of emulation is also often seen as a deterrent to replicating it easily for software development despite the fact that emulators are popular with software engineers because of their ease of use.