# **Enhanced Serial Peripheral Interface (eSPI)**

**Interface Specification (for Client Platforms)**

May 2012

Revision 0.6

Document Number: 327432-001EN

Intel hereby grants you a fully-paid, non-exclusive, non-transferable, worldwide, limited license (without the right to sublicense), under its copyrights to view, download, and reproduce the Enhanced Serial Peripheral Interface (eSPI) Specification ("Specification"). You are not granted any other rights or licenses, by implication, estoppel, or otherwise, and you may not create any derivative works of the Specification.

The Specification is provided "as is," and Intel makes no representations or warranties, express or implied, including warranties of merchantability, fitness for a particular purpose, non-infringement, or title. Intel is not liable for any direct, indirect, special, incidental, or consequential damages arising out of any use of the Specification, or its performance or implementation.

Intel retains ownership of all of its intellectual property rights in the Specification and retains the right to make changes to the Specification at any time. No license is granted to use Intel's name, trademarks, or patents.

If you provide feedback or suggestions on the Specification, you grant Intel a perpetual, non-terminable, fully-paid, non-exclusive, worldwide license, with the right to sublicense, under all applicable intellectual property rights to use the feedback and suggestions, without any notice, consent, or accounting. You represent and warrant that you own, or have sufficient rights from the owner of, the feedback and suggestions, and the intellectual property rights in them, to grant the above license.

This agreement is governed by Delaware law, without reference to choice of law principles. Any disputes relating to this agreement must be resolved in the federal or state courts in Delaware and you consent, and will not object, to the exclusive personal jurisdiction of the courts in Delaware.

This agreement is the entire agreement of the parties regarding the Specification and supersedes all prior agreements or representations.

This agreement is hosted at the following location: <a href="http://downloadcenter.intel.com/Detail\_Desc.aspx?agr=Y&DwnldID=21353">http://downloadcenter.intel.com/Detail\_Desc.aspx?agr=Y&DwnldID=21353</a>

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

Except for a limited copyright license to copy this specification for internal use only, no license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

Intel Corporation and the authors of this specification disclaim all liability, including liability for infringements of proprietary rights, relating to implementation of information in this document and the specification. Intel Corporation and the authors of this specification also do not warrant or represent that such implementation(s) will not infringe such rights.

Implementations developed using the information provided in this specification may infringe the patent rights of various parties including the parties involved in the development of this specification. Except as expressly granted hereunder, no license, express or implied, by estoppel or otherwise, to any intellectual property rights (including without limitation rights under any party's patents) is granted.

All suggestions or feedback related to this specification become the property of Intel Corporation upon submission.

Intel may make changes to the specifications, product descriptions, and plans at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document is an intermediate draft for comment only and is subject to change without notice. Do not finalize a design based on this document.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright 2012, Intel Corporation. All rights reserved.

# **Contents**

| 1 | Glossary                                                                                             |                                        | . 7                                                            |

|---|------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------|

| 2 |                                                                                                      | ion                                    |                                                                |

|   | 2.1 R                                                                                                | equirements1                           | LC                                                             |

| 3 | 3.1 S<br>3.2 A                                                                                       | ure Overview                           | 12<br>15                                                       |

| 4 | 4.1 B<br>4.2 C<br>4.3 Ti<br>4.4 R<br>4<br>4.5 A<br>4.6 G<br>4.7 G<br>4.8 N                           | asic Protocol                          | 21<br>23<br>27<br>28<br>28<br>31<br>33<br>35                   |

| 5 | 5.1 C<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | on Layer                               | 42<br>43<br>45<br>46<br>46<br>46<br>47<br>49<br>53<br>58<br>70 |

| 6 | 6.1 S                                                                                                | ingle I/O, Dual I/O and Quad I/O Modes | 71                                                             |

| 7 | 7.1 S                                                                                                | gisters                                | 75                                                             |

| 8 | Operatino                                                                                            | g Specification 8                      | 36                                                             |

|                | 8.1<br>8.2 | Electrical Specification                                                    |      |

|----------------|------------|-----------------------------------------------------------------------------|------|

| 9              | Syston     | n Architecture                                                              | ۵۸   |

| 9              | •          |                                                                             |      |

|                | 9.1        | Interrupts                                                                  |      |

|                | 9.2        | Error Detection and Handling                                                |      |

|                |            | 9.2.1 Slave Fatal Error Response                                            |      |

|                |            | 9.2.2 Slave Non-Fatal Error Response                                        |      |

|                |            | 9.2.3 Slave No Response                                                     |      |

|                |            | 9.2.4 Master Error Handling                                                 |      |

|                | 9.3        | Reset                                                                       |      |

|                | 9.4        | Power Management Event (PME)                                                |      |

|                | 9.5        | Power Sequencing & Initialization                                           |      |

|                |            | 9.5.1 Exit from G3                                                          | . 93 |

|                |            |                                                                             |      |

| <b>Figures</b> |            |                                                                             |      |

|                | Figure     | 1: EC/BMC/SIO Communication over LPC                                        | 9    |

|                | Figure     | 2: EC/BMC/SIO Communication over eSPI                                       | 9    |

|                | Figure     | 3: Single Master-Single Slave with eSPI Reset# from Slave to Master         | .12  |

|                | Figure     | 4: Single Master-Single Slave with eSPI Reset# from Master to Slave         | . 12 |

|                | Figure     | 5: Single Master-Multiple Slaves with Two eSPI Reset#                       | . 13 |

|                |            | 6: Single Master-Single Slave (Multiple Channels)                           |      |

|                |            | 7: Single Master-Multiple Slaves                                            |      |

|                |            | 8: EC/BMC/SIO Communication Over eSPI Channels                              |      |

|                |            | 9: eSPI Pin List                                                            |      |

|                |            | 10: Basic eSPI Protocol                                                     |      |

|                |            | 11: Slave Triggered Transaction (Single Master-Slave)                       |      |

|                |            | 12: Slave Triggered Transaction (Multiple Slave)                            |      |

|                |            | 13: Command Field                                                           |      |

|                |            | 14: Turn-Around Time Example (TAR = 4 clocks)                               |      |

|                |            | 15: Response Field                                                          |      |

|                |            | 16: Slave's Status Register Definition                                      |      |

|                |            | 18: Flow Diagram for a Back-to-back Slave to Master Peripheral Posted Write |      |

|                |            | 19: Flow Diagram for a Slave to Master Peripheral Posted Write passes Non-  |      |

|                |            | stedsted                                                                    | 22   |

|                | Figure     | 20: GET_STATUS Command                                                      | 33   |

|                |            | 21: GET_STATUS Command (with Response Modifier)                             |      |

|                |            | 22: GET_CONFIGURATION Command                                               |      |

|                |            | 23: SET CONFIGURATION Command                                               |      |

|                |            | 24: Connected Master Initiated Non-Posted Transaction                       |      |

|                |            | 25: Deferred Master Initiated Non-Posted Transaction                        |      |

|                |            | 26: Master Initiated Short Non-Posted Transaction                           |      |

|                |            | 27: Slave Initiated Non-Posted Transaction                                  |      |

|                |            | 28: Master Initiated Posted Transaction                                     |      |

|                |            | 29: Master Initiated Short Posted Transaction                               |      |

|                |            | 30: Slave Initiated Posted Transaction                                      |      |

|                | Figure     | 31: General eSPI Packet Format                                              | . 42 |

|                | Figure     | 32: Peripheral Memory or I/O Write Packet Format                            | 47   |

|                | Figure     | 33: Short Peripheral Memory or Short I/O Write Packet Format (Master        |      |

4

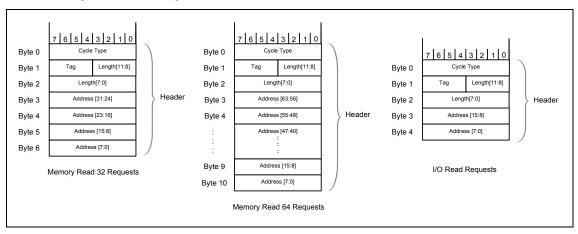

| Figure 34: Peripheral Memory or I/O Read Packet Format                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

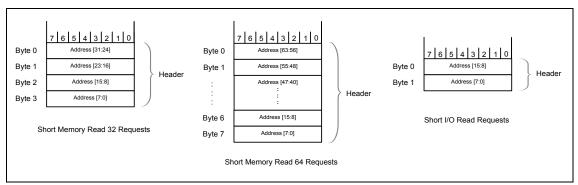

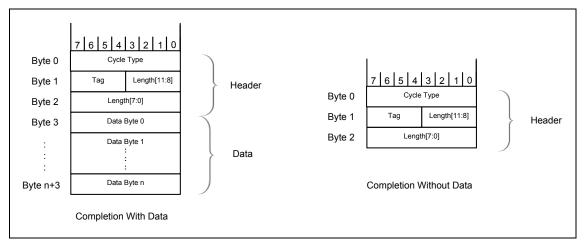

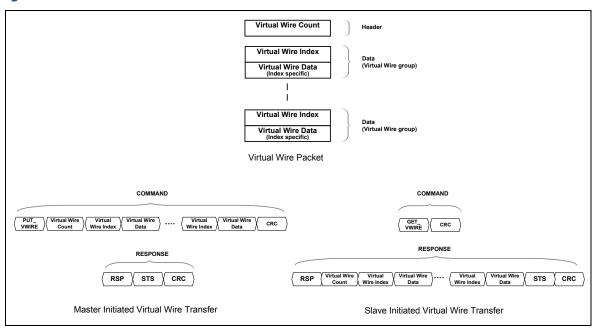

| Figure 36: Peripheral Memory or I/O Completion With and Without Data Packet Format49 Figure 37: Virtual Wire Packet Format                                                                                                                                                                                                                                                                                                                              |

| Table 1: Table of Glossary7Table 2: Command Opcode Encodings24Table 3: Response Field Encodings28Table 4: Status Field Encodings30Table 5: Cycle Types43Table 6: Virtual Wire Index Definition53Table 7: System Event Virtual Wires for Index=255Table 8: System Event Virtual Wires for Index=356Table 9: System Event Virtual Wires for Index=457Table 10: System Event Virtual Wires for Index=558Table 11: System Event Virtual Wires for Index=659 |

Table 12: Register Attribute Description75Table 13: Register Default Values Encoding Description75Table 14: Slave Registers76Table 15: Electrical Specification86Table 16: AC Timing Specification87

**Tables**

# **Revision History**

| Document<br>Number | Revision<br>Number | Description                     | Revision Date |

|--------------------|--------------------|---------------------------------|---------------|

| 31288              | 0.4                | • Initial release.              | February 2012 |

| 31312              | 0.45               | Updated legal disclaimer.       | February 2012 |

| 327432-001EN       | 0.6                | • Updated with review feedback. | May 2012      |

§ §

# 1 Glossary

**Table 1: Table of Glossary**

| Term | Definition |

|------|------------|

| TBD  | TBD        |

|      |            |

|      |            |

§ §

## 2 Introduction

This specification describes the architecture details of the Enhanced Serial Peripheral Interface (eSPI) bus interface. The devices that can be supported over this interface includes but not necessary limited to Embedded Controller (EC), Baseboard Management Controller (BMC), Super-I/O (SIO) and Port-80 debug card.

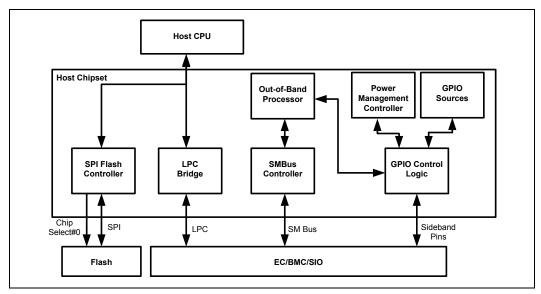

Prior to this specification, Embedded Controller (EC), Baseboard Management Controller (BMC) and Super I/O (SIO) are connected to the chipset through the Low Pin Count (LPC) bus. Low Pin Count (LPC) bus is a legacy bus developed as the replacement for Industry Standard Architecture (ISA) bus.

The specification generally refers to EC/BMC/SIO as the LPC device for the purpose of illustrating the eSPI bus capabilities and the comparison to LPC bus. However, EC/SIO is applicable for client platforms whereas BMC is generally associated with server platforms.

Here are some LPC bus limitations which led to the development of eSPI:

- LPC consists of 7 required pins and 6 optional pins that makes up to a total of 13 pins to implement.

- Present implementations of the LPC include a fabrication process cost burden as it is based on 3.3V I/O signaling technology.

- The frequency of the bus clock is fixed at 33 MHz. The fix LPC bandwidth of 133 Mbps is deemed insufficient to cater for the demands of new devices. Connecting these devices to high speed interfaces such as PCI Express and USB3 is prohibitive from cost perspective.

- There exist a significant number of sideband signals used for communication between chipset and EC, BMC and SIO that amounts to significant pin cost.

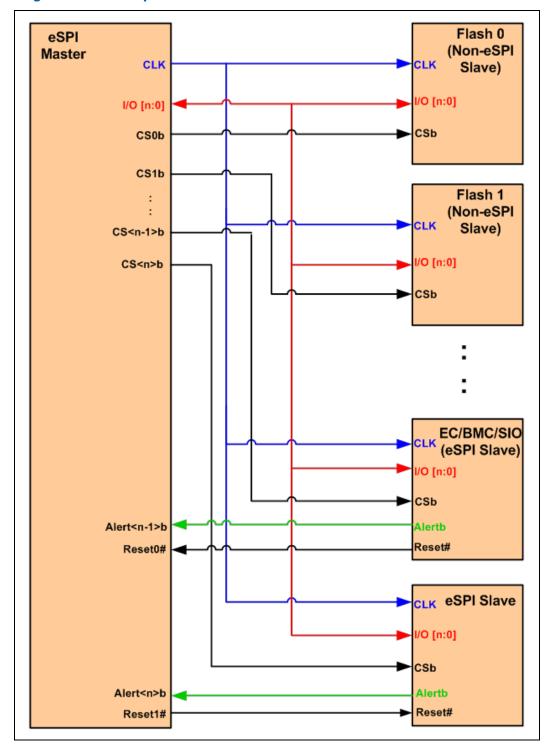

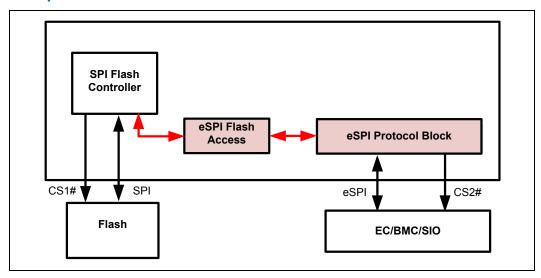

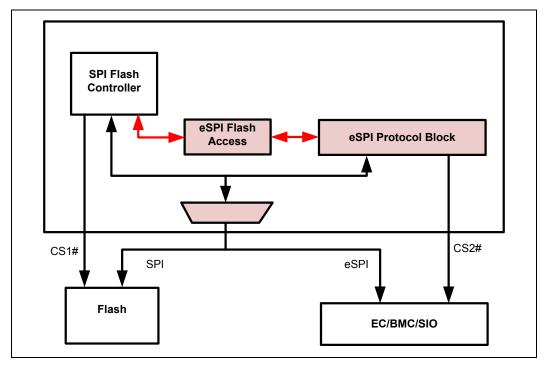

The diagram below shows how a EC/BMC/SIO is connected to the LPC bus.

Figure 1: EC/BMC/SIO Communication over LPC

The eSPI specification provides a path for migrating LPC devices over to the new eSPI interface. eSPI reuses the timing and electrical specification of Serial Peripheral Interface (SPI) but with different protocol to meet a set of different requirements.

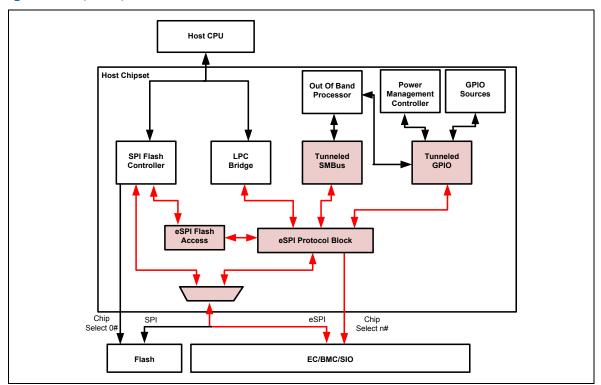

The diagram below shows how a EC/BMC/SIO can be connected to the eSPI bus.

Figure 2: EC/BMC/SIO Communication over eSPI

Sideband pin communications between chipset and these devices will be converted to in-band messages through the eSPI interface as part of the effort to reduce the component pin count and provide a migration path towards elimination of high-voltage 3.3V I/O pins.

Out-Of-Band (OOB) messaging between Out-Of-Band Processor in the chipset and Embedded Controller (EC) or Baseboard Management Controller (BMC) is also tunneled through the new eSPI interface as in-band messages, thus replacing the SMBus interface for this purpose.

Run-time flash sharing between chipset and slave devices will be supported over this new interface. The slave devices would be able to access the corresponding Flash partition through the Flash Access channel.

Depending on applications, eSPI bus may be active in all the S0-S5 system states. To lower the system power, the eSPI bus frequency and data pins may be a function of the system state.

#### 2.1 Requirements

eSPI is defined to meet the following requirements:

- **Low Power:** The interface may be active in all S0-S5 system states. The power consumed when the bus is operating in S3-S5 system states must be very low to meet the power requirements of these low power system states. When the interface is not transmitting or receiving, it should consume a negligible amount of power (at system level).

- **Pin Count Reduction:** Moving LPC devices over to the eSPI interface facilitates the removal of LPC pins in the longer term. On top of that messaging through sideband pins needed for communication between the chipset and slave devices (such as EC, BMC and SIO) is converted to in-band messages, resulting in further pin count reduction.

- **Medium Bandwidth:** The bus bandwidth needs to be higher than that of the Low Pin Count (LPC) bus.

- LPC Replacement: Supports all the capabilities needed to replace the parallel LPC interface. However, 8237 DMA and Firmware Hub (FWH) are not supported over this interface.

- **Sideband Pins as In-Band Messaging**: Facilitates the removal of sideband pins for communication between chipset and slave devices by converting this communication into in-band messages sent over the eSPI bus.

- Real Time Flash Sharing: Supports flash sharing based on partition-able memory mapping. Allows real-time operational access by chipset and slave devices.

- Chipset and Slave Devices SMBus Replacement: Supports tunneling of all SMBus communication between chipset and slave devices over the new interface as in-band messages.

#### Introduction

- **Scalable bandwidth:** Allows the bandwidth to be scaled based on application needs to optimize power versus performance. This could be done through frequency scaling or varying the number of active data pins.

- Low Voltage I/O Buffer: eSPI uses the same I/O buffer as Serial Peripheral Interface (SPI). The I/O buffer will support only 1.8V mode of operation for the eSPI bus.

§ §

## 3 Architecture Overview

#### 3.1 System Topology

The Enhanced Serial Peripheral Interface (eSPI) operates in master/slave mode of operation where the eSPI master dictates the flow of command and data between itself and the eSPI slaves by controlling the Chip Select# pins for each of the eSPI slaves. At any one time, only one of the Chip Select# pins can be asserted allowing transactions to flow between the eSPI master and the corresponding eSPI slave associated with the Chip Select# pin. The eSPI master is the only component that is allowed to drive Chip Select# when eSPI Reset# is de-asserted.

For an eSPI bus, there is only one eSPI master and one or more eSPI slaves.

In Single Master-Single Slave configuration, a single eSPI master will be connected to a single eSPI slave. In one configuration, the eSPI slave could be the device that generates the eSPI Reset# such as EC or BMC. In this case, the eSPI Reset# is driven from eSPI slave to eSPI master. In other configuration, the eSPI Reset# could be generated by the eSPI master and thus, it is driven from eSPI master to eSPI slave.

Figure 3: Single Master-Single Slave with eSPI Reset# from Slave to Master

Figure 4: Single Master-Single Slave with eSPI Reset# from Master to Slave

Figure 5: Single Master-Multiple Slaves with Two eSPI Reset#

Multiple SPI and eSPI slaves could be connected to the same eSPI bus interface in a multi-drop Single Master-Multiple Slaves configuration. The number of devices that can be supported over a single eSPI bus interface is limited by bus loading and signals trace length.

In this configuration, the clock and data pins are shared by multiple SPI and eSPI slaves. Each of the slaves has its dedicated Chip Select# and Alert# pins.

In an eSPI bus configuration with multiple slaves present, the eSPI master may support 2 eSPI Reset# pins, one from eSPI slave such as EC or BMC to eSPI master and another one from eSPI master to eSPI slaves. In this case, the master's eSPI interface will only be reset if all the slaves' eSPI interfaces are reset.

SPI slaves such as Flash and TPM are allowed to share the same set of clock and data pins with eSPI slaves. These non-eSPI slaves are selected using the dedicated Chip Select# pins and they communicate with the eSPI master through SPI specific protocols ran over the eSPI bus.

14

### **3.2** Architecture Descriptions

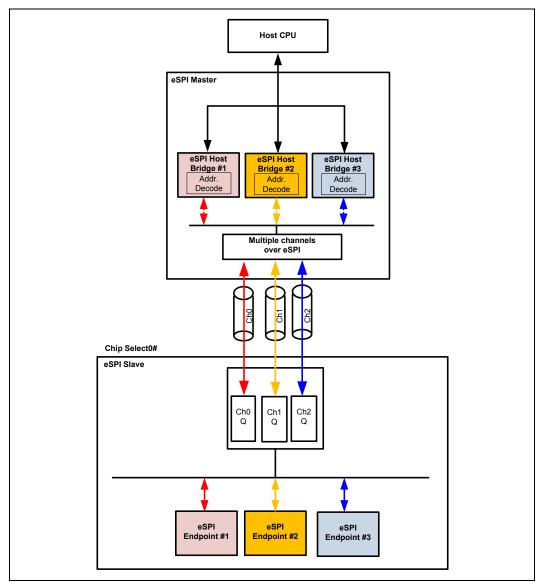

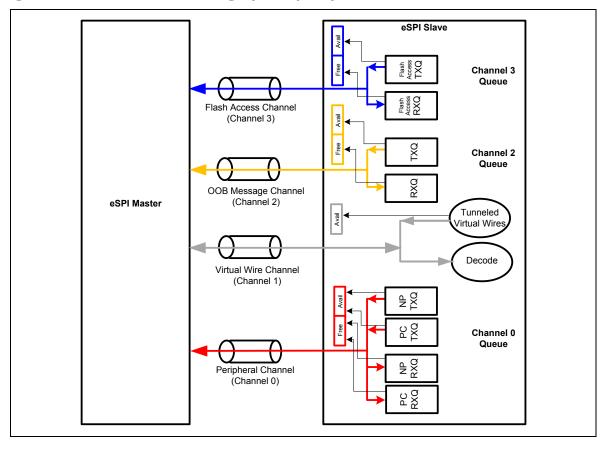

In a Single Master-Single Slave configuration as shown in the diagram below, there could be multiple eSPI host bridges within a single eSPI master and there could be multiple eSPI endpoints within a single eSPI slave.

**Figure 6: Single Master-Single Slave (Multiple Channels)**

When Chip Select# corresponding to the eSPI slave is asserted, command and data transfer happens between the eSPI master and eSPI slave, which could be a result of the eSPI host bridge and eSPI endpoint communications.

Each of the eSPI host bridges communicates with its corresponding eSPI endpoint through dedicated channel.

The use of channels allows multiple independent flows of command and data to be transferred over the same bus between the eSPI master and eSPI slave with no ordering requirement.

Resources such as flow control, command and data queues are dedicated for each of the channels to provide independent command and data flows.

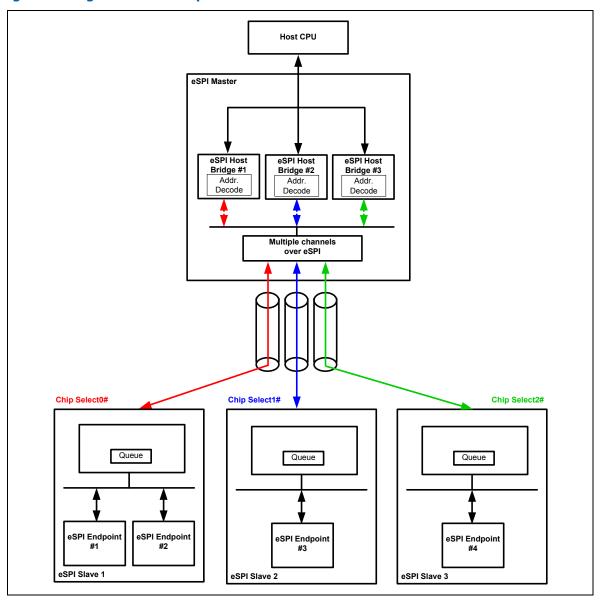

In Single Master-Multiple Slaves configuration shown in the diagram below, multiple discrete eSPI slaves can be dropped onto the eSPI bus. Each of the eSPI slaves should have a dedicated Chip Select# pin. On the master side, there are eSPI host bridges corresponding to each of the discrete slaves respectively, each driving the Chip Select# pin of the corresponding discrete slave.

At any one time, only one of the Chip Select# pins can be asserted. Command and data transfer can then happen between the eSPI host bridge and the corresponding eSPI slave.

16

**Figure 7: Single Master-Multiple Slaves**

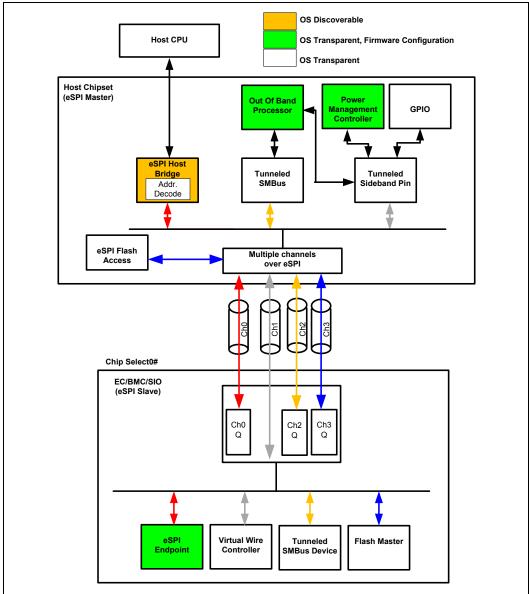

The next diagram shows one of the ways the specification can be used to support EC/BMC/SIO communication over the eSPI interface.

Figure 8: EC/BMC/SIO Communication Over eSPI Channels

In this example, the eSPI host bridge and the corresponding eSPI endpoint communicate through Channel 0. The Sideband Pins are tunneled as in-band messages through Channel 1. SMBus OOB messages are tunneled through Channel 2. Flash access transactions are accomplished through Channel 3. The transactions for different channels flowing between the eSPI master and EC/BMC/SIO share the same Chip Select# pin, and the same set of data and clock pins.

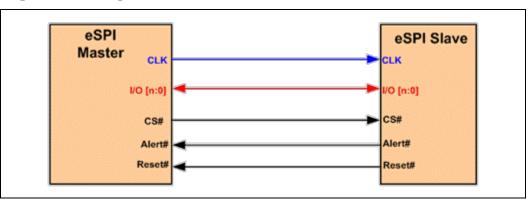

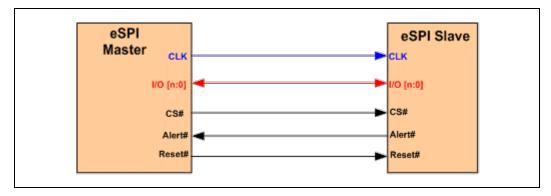

#### 3.3 Pin Descriptions

eSPI uses the existing SPI I/O buffer. The electrical specification for this new interface is the same as SPI.

eSPI Reset# is typically driven from eSPI master to eSPI slaves. The exception is when eSPI Reset# is generated by eSPI slave such as EC or BMC, which drives the eSPI Reset# to the eSPI master. eSPI Reset# is the reset to the eSPI interface on both sides.

eSPI master and eSPI slaves must tri-state the interface pins when their respective eSPI Reset# is asserted. These pins include Chip Select#, Serial Clock, I/O[n:0] and Alert# pins which have weak pull-up enabled during the reset. Weak pull-up should be implemented either as an integral part of the eSPI master buffer or on the board. eSPI slaves must not implement the weak pull-up.

Refer to Section 8.1 - Electrical Specification for the value of the weak pull-up resistor.

After eSPI Reset# is deasserted on the eSPI master, the eSPI master begins driving Chip Select# and Serial Clock pins to their idle state appropriately. The weak pull-up on the Chip Select# and Serial Clock are allowed to be disabled after the eSPI Reset# deassertion. However, I/O[n:0] and Alert# pins continue to have the weak pull-up enabled for the proper operation of the eSPI bus.

Figure 9: eSPI Pin List

| Pin Name     | Direction                                                                | Clock        | Description                                                                                                                                                                                                                                   |

|--------------|--------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| eSPI Reset#  | Master to<br>Slave <sup>1</sup><br>or<br>Slave to<br>Master <sup>2</sup> | Asynchronous | Reset#: Reset the eSPI interface for both master and slaves.  Note:  1. eSPI Reset# is typically driven from eSPI master to eSPI slaves.  2. eSPI Reset# is generated by eSPI slave such as EC or BMC, driven from eSPI slave to eSPI master. |

| Chip Select# | Master to<br>Slave                                                       | Asynchronous | Chip Select#: Driving Chip Select# low selects a particular eSPI slave for the transaction.  Each of the eSPI slaves is connected to a dedicated Chip Select# pin.                                                                            |

| Serial Clock | Master to<br>Slave                                                       | -            | <b>Clock:</b> This pin provides the reference timing for all the serial input and output operations.                                                                                                                                          |

| I/O [n:0]    | Bi-directional                                                           | Serial Clock | I/O: These are bi-directional input/output pins used to transfer data between master and slaves.  The value of 'n' may be 0, 1 or 3 depending on the I/O mode.                                                                                |

#### Architecture Overview

| Pin Name | Direction          | Clock        | Description                                                                                                                                          |

|----------|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                    |              | In Single I/O mode (n=0), I/O[0] is the eSPI master output/eSPI slave input (MOSI) whereas I/O[1] is the eSPI master input/eSPI slave output (MISO). |

| Alert#   | Slave to<br>Master | Asynchronous | Alert#: This pin is used by eSPI slave to request service from eSPI master.                                                                          |

|          |                    |              | Alert# is an open-drain output from the slave.                                                                                                       |

|          |                    |              | This pin is optional for Single Master-Single Slave configuration where I/O[1] can be used to signal the Alert event.                                |

§ §

## 4 Bus Protocol

The details of the Enhanced Serial Peripheral Interface (eSPI) protocol are described in this section. The electrical of eSPI bus is similar to SPI bus with deviations specifically called out in this specification.

The Serial Clock must be low when the Chip Select# is de-asserted and eSPI Reset# is de-asserted. The data is launched on the falling edge of the clock from master and sampled on the rising edge of the clock by slave. The data is launched on the falling edge of the clock from slave. The master could implement a more flexible sampling scheme since it controls the clock.

All transactions on eSPI must be in multiple of 8-bits (one Byte).

#### 4.1 Basic Protocol

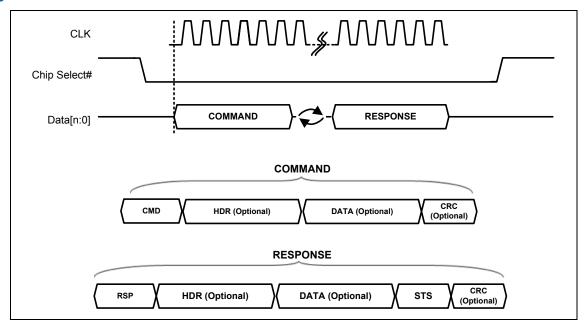

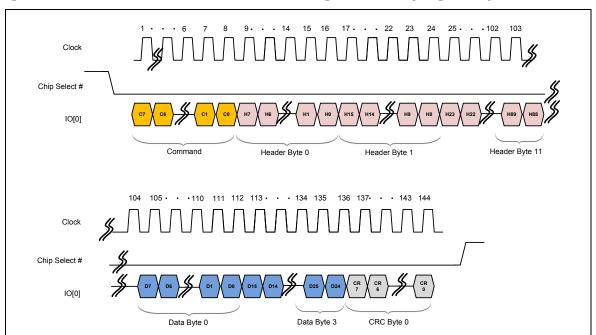

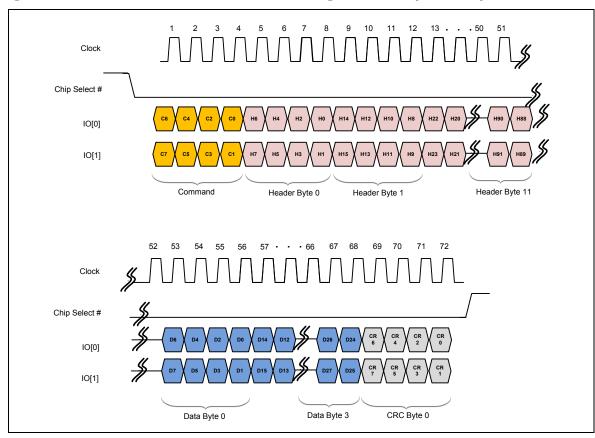

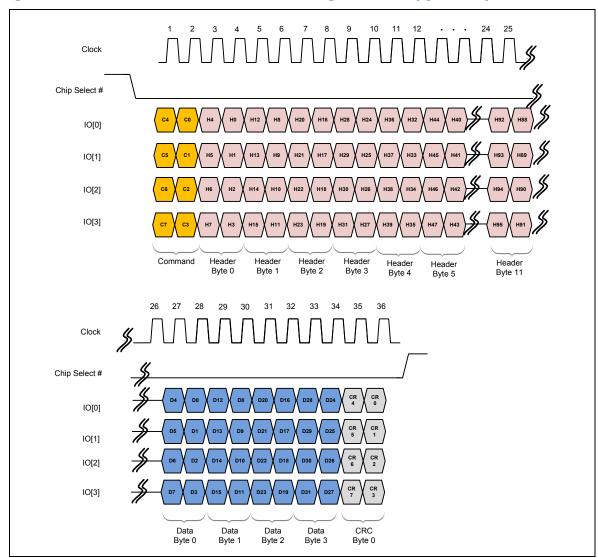

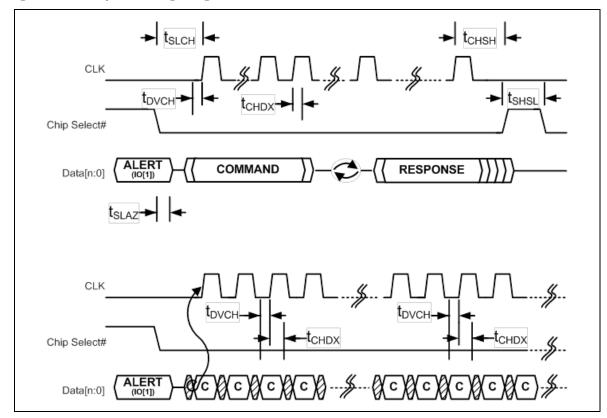

Figure 10: Basic eSPI Protocol

eSPI transaction consists of a Command phase driven by master, a Turn-Around (TAR) phase, and a Response phase driven by the slave. The Command phase consists of a CMD, an optional header (HDR), optional DATA and an optional CRC. The Response phase consists of a RSP, an optional header (HDR), optional data, Status and an optional CRC. When CRC support is disabled, the CRC bytes are not transmitted on the bus.

A transaction could be initiated by the master through the assertion of Chip Select#, start the clock and drive the command onto the data bus. The clock remains toggling until the complete response phase has been received from the slaves.

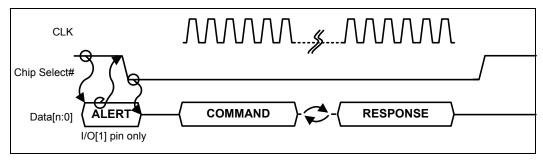

Figure 11: Slave Triggered Transaction (Single Master-Slave)

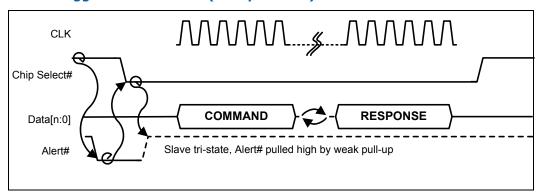

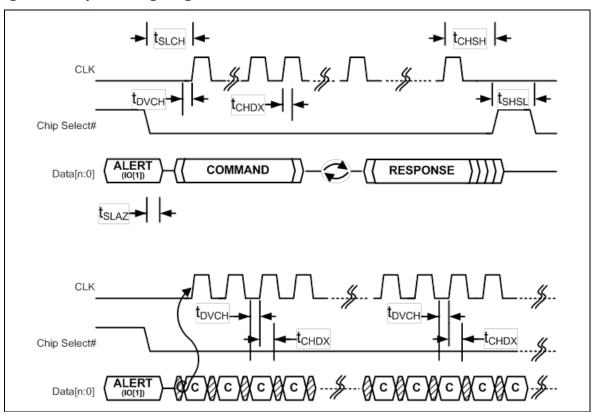

A transaction could be initiated by the slave by first signaling an Alert event to the master. The Alert event could be signaled through two ways. In the Single Master-Single Slave configuration, the I/O[1] pin could be used by the slave to indicate an Alert event. In the Single Master-Multiple Slaves configuration, a dedicated Alert# pin is required.

The Alert event can only be signaled by the slave when the Chip Select# is high. The pin, either I/O[1] or Alert# is toggled from tri-state to pulled low by the slave when it decides to request for service. The slave then holds the state of the pin until the Chip Select# is asserted by the master. Once the Chip Select# is asserted, the eSPI slave must release the ownership of the pin by tri-stating the pin and the pin will be pulled high by the weak pull-up. The master then continues to issue command to figure out the cause of the Alert event from the device and then service the request.

**Figure 12: Slave Triggered Transaction (Multiple Slave)**

The specification does not prevent the use of a dedicated Alert# pin for the Single Master-Single Slave configuration.

In the boundary case where the Alert event assertion aligns with Chip Select# assertion, the slave still tri-state the pin after sampling the corresponding Chip Select# assertion. The status is returned during the response phase and the master is then aware of the need to service the slave's outstanding requests.

The Alert event signaled on the pin is asynchronous to the Serial Clock.

The eSPI master and eSPI slaves must support both types of Alert mechanism. The method to determine which Alert mechanism to use for each of the eSPI slaves is implementation specific.

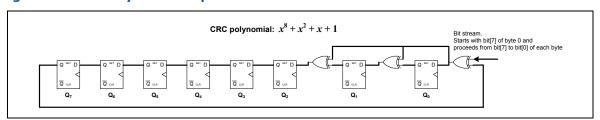

eSPI is defined to use packet-based split transaction protocol. On the transmit side, the packets are formed in the Transaction Layer based on the transaction to be sent. The Link Layer extends the packet with CRC when CRC support is enabled.

Similarly on the receive side, the CRC is checked at the receiving Link Layer when CRC support is enabled. Once the packet passes the CRC check, the packet is sent to Transaction Layer where it is decoded and acted upon.

#### 4.2 Command Phase

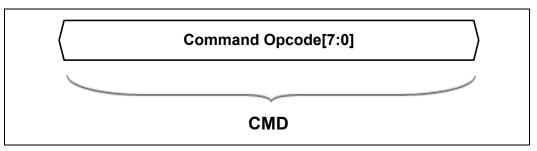

The Command phase is used by the eSPI master to initiate a transaction to the slave or in response to an Alert event by the slave. It consists of a CMD, an optional header (HDR), optional DATA and an optional CRC.

The CMD field consists of Command Opcode.

Figure 13: Command Field

The Command Opcode is used to indicate channel specific commands and to communicate link management events.

Channels specific commands communicated over the bus include Command Put and Command Get for the respective channels.

Link management events include GET\_STATUS, GET\_CONFIGURATION and SET\_CONFIGURATION.

The Command Opcode is 8-bits wide.

If the slave receives a Command Opcode on a packet which is not supported, the slave must not respond to the transaction. The transaction will be terminated with the default response (NO\_RESPONSE) on the bus.

**Table 2: Command Opcode Encodings**

| CMD Opcode              | Encoding[7:0]                                    | Description                                                                                                                              |  |  |  |

|-------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| eSPI Peripheral Channel |                                                  |                                                                                                                                          |  |  |  |

| PUT_PC 00000000         |                                                  | Put a posted or completion header and optional data.                                                                                     |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_PC unless the slave has indicated that it is free to take the Posted or Completion packet.            |  |  |  |

| PUT_NP                  | 00000010                                         | Put a non-posted header and optional data.                                                                                               |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_NP unless the slave has indicated that it is free to take the Non-Posted packet.                      |  |  |  |

| GET_PC                  | 00000001                                         | Get a posted or completion header and optional data.                                                                                     |  |  |  |

|                         |                                                  | Note: It is illegal to issue a GET_PC unless the slave has indicated that it has a Posted or Completion packet available                 |  |  |  |

| GET_NP                  | 00000011                                         | Get a non-posted header and optional data.                                                                                               |  |  |  |

|                         |                                                  | Note: It is illegal to issue a GET_NP unless the slave has indicated that it has a Non-Posted packet available.                          |  |  |  |

| PUT_IORD_SHORT          | 010000C <sub>1</sub> C <sub>0</sub> <sup>1</sup> | Put a short (1-4 bytes) non-posted I/O Read packet.                                                                                      |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_IORD_SHORT unless the slave has indicated that it is free to take the Non-Posted packet.              |  |  |  |

| PUT_IOWR_SHORT          | 010001C <sub>1</sub> C <sub>0</sub> <sup>1</sup> | Put a short (1-4 bytes) non-posted I/O Write packet.                                                                                     |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_IOWR_SHORT unless the slave has indicated that it is free to take the Non-Posted packet.              |  |  |  |

| PUT_MEMRD32_SHORT       | 010010C <sub>1</sub> C <sub>0</sub> <sup>1</sup> | Put a short (1-4 bytes) non-posted Memory Read 32 packet.                                                                                |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_MEMRD32_SHORT unless the slave has indicated that it is free to take the Non-Posted packet.           |  |  |  |

| PUT_MEMWR32_SHORT       | 010011C <sub>1</sub> C <sub>0</sub> <sup>1</sup> | Put a short (1-4 bytes) posted Memory Write 32 packet.                                                                                   |  |  |  |

|                         |                                                  | Note: It is illegal to issue a PUT_MEMWR32_SHORT unless the slave has indicated that it is free to take the Posted or Completion packet. |  |  |  |

| Virtual Wire Channel    |                                                  |                                                                                                                                          |  |  |  |

| CMD Opcode           | Encoding[7:0] | Description                                                                                                                             |

|----------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PUT_VWIRE            | 00000100      | Put a Tunneled virtual wire packet.                                                                                                     |

| GET_VWIRE            | 00000101      | Get a Tunneled virtual wire packet.                                                                                                     |

| OOB Message Channe   | el            |                                                                                                                                         |

| PUT_OOB              | 00000110      | Put an OOB (Tunneled SMBus) message.                                                                                                    |

|                      |               | Note: It is illegal to issue a PUT_OOB unless the slave has indicated that it is free to take the OOB message.                          |

| GET_OOB              | 00000111      | Get an OOB (Tunneled SMBus) message.                                                                                                    |

|                      |               | Note: It is illegal to issue a GET_OOB unless the slave has indicated that it has an OOB message available to send.                     |

| Flash Access Channel |               |                                                                                                                                         |

| PUT_FLASH_C          | 00001000      | Put a Flash Access completion.                                                                                                          |

|                      |               | Used in Master Attached Flash Sharing mode for the master to return a flash access completion to the slave.                             |

|                      |               | Note: It is illegal to issue a PUT_FLASH_C unless the slave has indicated that it is free to take the Flash Access completion.          |

| GET_FLASH_NP         | 00001001      | Get a non-posted Flash Access request.                                                                                                  |

|                      |               | Used in Master Attached Flash Sharing mode for the slave to issue a flash access request to the master.                                 |

|                      |               | It is illegal to issue a GET_FLASH_NP unless the slave has indicated that it has a non-posted Flash Access request available to send.   |

| PUT_FLASH_NP         | 00001010      | Put a non-posted Flash Access request.                                                                                                  |

|                      |               | Used in Slave Attached Flash Sharing mode for the master to issue a flash access request to the slave.                                  |

|                      |               | Note: It is illegal to issue a PUT_FLASH_NP unless the slave has indicated that it is free to take the non-posted Flash Access request. |

| GET_FLASH_C          | 00001011      | Get a Flash Access completion.                                                                                                          |

|                      |               | Used in Slave Attached Flash Sharing mode for the slave to return a flash access completion to the master.                              |

|                      |               | Note: It is illegal to issue a GET_FLASH_C unless the slave has indicated that it has a Flash Access completion available to send.      |

| CMD Opcode                       | Encoding[7:0] | Description                                                                                                                                                  |  |  |  |

|----------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Channel Independent <sup>2</sup> |               |                                                                                                                                                              |  |  |  |

| GET_STATUS                       | 00100101      | Command initiated by the master to read the status register of the slave.                                                                                    |  |  |  |

| SET_CONFIGURATION                | 00100010      | Command to set the capabilities of the slave as part of the initialization. This is typically done after the master discovers the capabilities of the slave. |  |  |  |

| GET_CONFIGURATION                | 00100001      | Command to discover the capabilities of the slave as part of the initialization.                                                                             |  |  |  |

#### Note:

1. The opcode encoding  $C_1C_0$  indicates the length of the request. The address together with the length must not cross the DWord boundary.

| Encoding[1:0] C <sub>1</sub> C <sub>0</sub> | Request Length |

|---------------------------------------------|----------------|

| 00                                          | 1 byte         |

| 01                                          | 2 bytes        |

| 10                                          | 3 bytes        |

| 11                                          | 4 bytes        |

2. Channel independent commands are enabled by default upon eSPI Reset# deassertion.

#### 4.3 Turn-Around (TAR)

After the last bit of the Command Phase has been sent out on the data lines, the data lines enter the Turn-Around window. The eSPI master is required to drive all the data lines to logic '1' for the first clock of the Turn-Around window and tri-state the data lines thereafter. The number of clocks for the Turn-Around window is specified by the Operating Turn-Around Time Value field in the General Capabilities and Configurations register. This is to provide sufficient time for the slave to sample the command and prepare the response.

The eSPI slave must drive the Response phase on the bus immediately upon the expiry of the Turn-Around time as shown in the next diagram.

During the Turn-Around window, the data lines will be pulled high by the weak pullup.

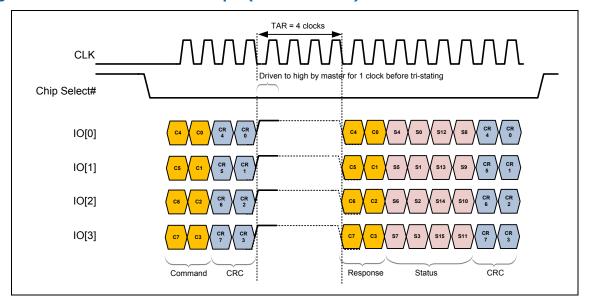

Figure 14: Turn-Around Time Example (TAR = 4 clocks)

The Turn-Around time can be queried from the individual eSPI slaves during initialization through the GET\_CONFIGURATION command. The Turn-Around time could be different between different slaves. The eSPI master could choose to use a common Turn-Around value for all slaves or choose to optimize the performance by using different Turn-Around values for each of the slaves.

Prior to initialization, a fixed  $t_{\rm INIT-TAR}$  eSPI clocks is used as the initial Turn-Around time. All the eSPI master and slaves must support the initial Turn-Around time coming out of reset. During initialization, eSPI master could change the Turn-Around time to be used for the slave through the SET\_CONFIGURATION command for each of the slaves. The Turn-Around time set by the eSPI master must be within the supported range advertised by the slaves. The new Turn-Around time will be effective at the deassertion edge of the Chip Select#.

#### 4.4 Response Phase

The Response phase is driven by the eSPI slave in response to command initiated by an eSPI master. It consists of a RSP opcode, an optional header (HDR), optional data, STATUS and an optional CRC.

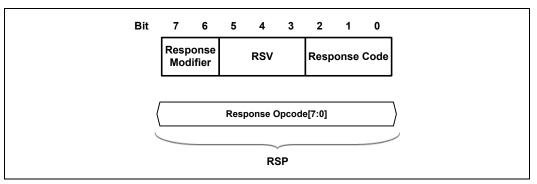

The RSP opcode is a 8-bit field consists of a Response Code and a Response Modifier.

Figure 15: Response Field

#### 4.4.1 Response

The Response Code indicates whether the request is successful, deferred or contains errors.

The Response Modifier is a 2-bit field defined for the GET\_STATUS with an ACCEPT response only. For all other responses, it must always have the value of "00".

The Response Modifier field indicates whether a peripheral (channel 0) completion, a virtual wire (channel 1) packet or a flash access (channel 3) completion is appended to the GET\_STATUS response phase.

The Reserved (RSV) field of the RSP opcode must be driven to all 0's when the slave drives the response phase. It is reserved for future use by the specification. For the purpose of backward compatibility, the Reserved (RSV) field must be ignored by the master.

NO\_RESPONSE is the default when the response phase is not driven by any slave. The eSPI master may terminate the transaction by deasserting Chip Select# at any point when this is detected.

**Table 3: Response Field Encodings**

| RESPONSE | Encoding   |       |       | Description                       |

|----------|------------|-------|-------|-----------------------------------|

|          | [7:6]      | [5:3] | [2:0] |                                   |

| ACCEPT   | $R_1R_0^1$ | RSV   | 000   | Command was successfully received |

| RESPONSE        | Encoding |     |     | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |          |     |     | If the command was a PUT_NP, a response of ACCEPT means that the non-posted transaction is being completed as a "connected" transaction.                                                                                                                                                                                                                                     |

| DEFER           | 00       | RSV | 001 | Only valid in response to a PUT_NP. A non-<br>posted command was successfully received, and<br>completing the non-posted transaction is<br>deferred to a future split completion.                                                                                                                                                                                            |

| NON_FATAL_ERROR | 00       | RSV | 010 | The received command had an error with non-<br>fatal severity. The error does not affect the<br>ability to process the received command.                                                                                                                                                                                                                                     |

| FATAL_ERROR     | 00       | RSV | 011 | The received command had a fatal error that prevented the transaction layer packet from being successfully processed. Fatal errors include malformed transactions, Put without Free, Get without Avail and etc.                                                                                                                                                              |

| NO_RESPONSE     | 11       | 111 | 111 | The response encoding of all 1's is defined as no response. It is the default response to the GET_CONFIGURATION when no slave is present as a result of the weak pull-up on the data lines. It is also the default response when fatal CRC error is detected on the command packet, or when command opcode is not supported and the slave must not drive the response phase. |

#### Note:

1. The response encoding  $R_1R_0$  is always "00" except for the GET\_STATUS with an ACCEPT response which has the following definition:

| Encoding[7:6]<br>R <sub>1</sub> R <sub>0</sub> | Description                                        |  |  |

|------------------------------------------------|----------------------------------------------------|--|--|

| 00                                             | No append.                                         |  |  |

| 01                                             | A Peripheral (channel 0) completion is appended.   |  |  |

| 10                                             | A Virtual Wire (channel 1) packet is appended.     |  |  |

| 11                                             | A Flash Access (channel 3) completion is appended. |  |  |

#### 4.4.2 **Status**

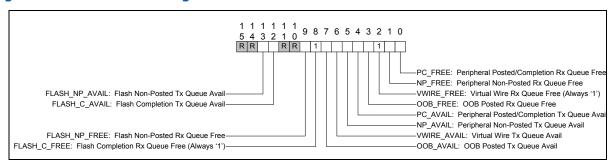

The Status field serves to provide information such as new pending requests from the slave and queue free information.

Refer to Section 5.3 - Slave Buffer Management for additional details about setting and clearing of the eSPI Status register bits.

**Figure 16: Slave's Status Register Definition**

**Table 4: Status Field Encodings**

| STATUS                      | Bits<br>Position | Description                                                                                                                                          |  |  |  |

|-----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Slave's Rx queues Free      |                  |                                                                                                                                                      |  |  |  |

| PC_FREE                     | 0                | When '1', indicates the slave is free to accept at least one channel 0 peripheral posted or completion header and data up to maximum payload size.   |  |  |  |

| NP_FREE                     | 1                | When `1', indicates the slave is free to accept at least one channel 0 peripheral non-posted header and 1 DW of Data (if applicable).                |  |  |  |

| VWIRE_FREE                  | 2                | This bit must be always a `1'. Tunneling of channel 1 virtual wires is not flow controlled.                                                          |  |  |  |

| OOB_FREE                    | 3                | When `1', indicates the slave is free to accept at least one channel 2 OOB (tunneled SMBus) message with data up to maximum payload size.            |  |  |  |

| Slave's Tx queues Available |                  |                                                                                                                                                      |  |  |  |

| PC_AVAIL                    | 4                | When '1', indicates the slave has a channel 0 peripheral posted or completion header and optional data up to maximum payload size available to send. |  |  |  |

| NP_AVAIL                    | 5                | When `1', indicates the slave has a channel 0 peripheral non-posted header available to send.                                                        |  |  |  |

| VWIRE_AVAIL                 | 6                | When '1', indicates the slave has a channel 1 tunneled virtual wire available to send.                                                               |  |  |  |

| OOB_AVAIL                   | 7                | When `1', indicates the slave has a channel 2 OOB (tunneled SMBus) message with data up to maximum payload size available to send.                   |  |  |  |

| Slave's Rx queues Free      |                  |                                                                                                                                                      |  |  |  |

| STATUS                      | Bits<br>Position | Description                                                                                                                                                                                                                                                     |  |  |

|-----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FLASH_C_FREE                | 8                | When '1', indicates the slave is free to accept at least one channel 3 Flash Access completion header and data up to maximum payload size.  This bit must be always a '1'. The slave must be able to accept the completion for the non-posted request it sends. |  |  |

| FLASH_NP_FREE               | 9                | When '1', indicates the slave is free to accept at least one channel 3 Flash Access non-posted header and data up to maximum payload size.                                                                                                                      |  |  |

| Reserved                    | 11:10            | Reserved.                                                                                                                                                                                                                                                       |  |  |

| Slave's Tx queues Available |                  |                                                                                                                                                                                                                                                                 |  |  |

| FLASH_C_AVAIL               | 12               | When '1', indicates the slave has a channel 3 Flash Access completion header and data up to maximum payload size available to send.                                                                                                                             |  |  |

| FLASH_NP_AVAIL 13           |                  | When '1', indicates the slave has a channel 3 Flash Access non-posted header and data up to maximum payload size available to send.                                                                                                                             |  |  |

| Reserved                    | 15:14            | Reserved.                                                                                                                                                                                                                                                       |  |  |

#### 4.5 Alert Phase

Alert phase is signaled by the slave to request for service. In response to an Alert, the master can issue a GET\_STATUS command to the corresponding slave to query for the cause of the Alert event.

The master then reacts accordingly to service the slave.

A slave could generate an Alert event due to any of the following reasons:

- There is a new request from slave. This could be a Posted, Non-Posted, deferred Completion, Virtual Wire messages, OOB messages or Flash Access requests.

- A slave buffer space has become free since the last status update was returned as not free.

Each of the cause that triggers the Alert event has the corresponding bit in the STATUS register. When the state of the STATUS register is different from the STATUS returned during the previous Response phase, the slave will generate a new Alert event. The difference in the STATUS register indicates a new event has occurred that requires the service from the master.

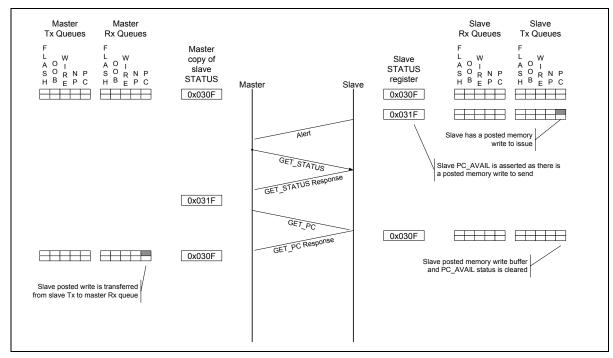

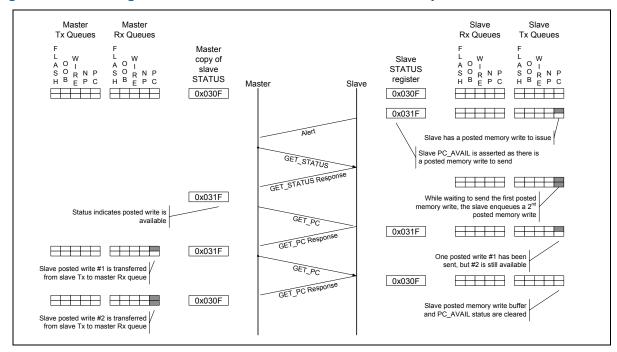

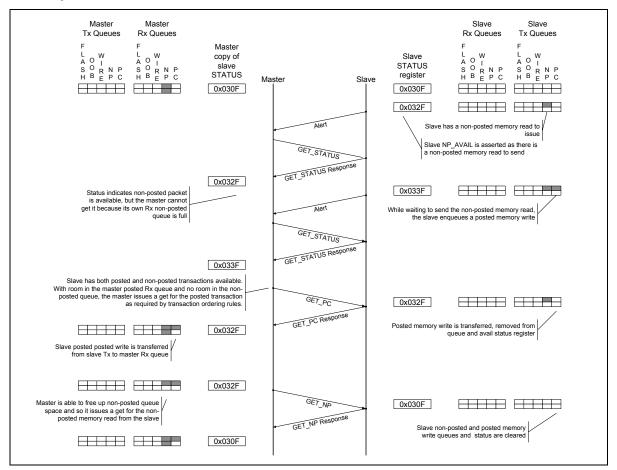

Following figures illustrate examples of the flow and the tracking of the slave's STATUS register on both sides of the bus.

Figure 17: Flow Diagram for a Slave to Master Peripheral Posted Write

Figure 18: Flow Diagram for a Back-to-back Slave to Master Peripheral Posted Write

Figure 19: Flow Diagram for a Slave to Master Peripheral Posted Write passes Nonposted

#### 4.6 Get Status Command

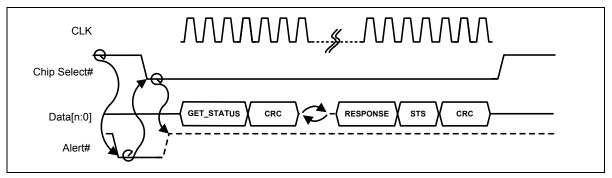

#### Figure 20: GET\_STATUS Command

GET\_STATUS is a channel independent command which is used to query the content of the Status register. The state of the Status register will be returned in the Response phase.

This command is typically used in response to the Alert event from the eSPI slave, to determine the cause of the Alert event and subsequently service the slave.

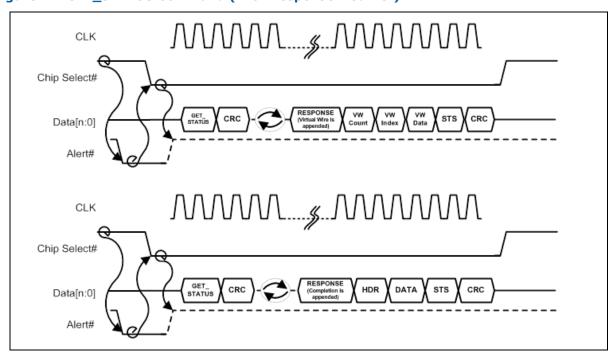

The response phase of the GET\_STATUS allows a peripheral (channel 0) completion, a virtual wire (channel 1) packet or a flash access (channel 3) completion to be appended and sent together with the response. Only one is allowed to be appended to the GET\_STATUS response as indicated by the Response Modifier field.

The eSPI master must always be ready to accept the peripheral (channel 0) completion, the virtual wire (channel 1) packet or the flash access (channel 3) completion. For the completion, it requires the eSPI master to pre-allocate the completion buffer appropriately when the non-posted transaction is initiated to the slave.

Refer to Section 4.4.2 for additional details of the Status register.

Figure 21: GET\_STATUS Command (with Response Modifier)

# 4.7 Get Configuration and Set Configuration Command

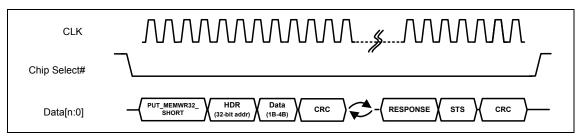

SET\_CONFIGURATION and GET\_CONFIGURATION commands are channel independent commands that are used to access the Channel Capability and Configuration registers on the eSPI slave side. Only DWord accesses are supported. Since there is no byte enables, software is required to perform a Read-Modify-Write access if modifying less than a full DWord.

SET\_CONFIGURATION and GET\_CONFIGURATION commands can never be deferred and must be completed within the same cycle.

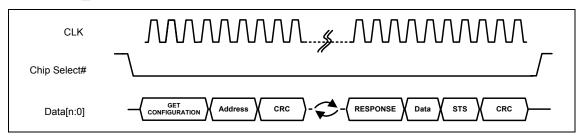

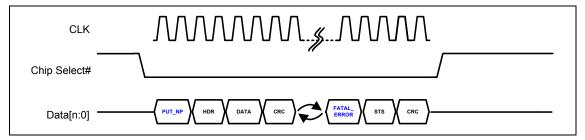

Figure 22: GET\_CONFIGURATION Command

GET\_CONFIGURATION command is used to read the Channel Capability and Configuration registers on the eSPI slaves. The GET\_CONFIGURATION command phase consists of an 8-bit Command Opcode, 16-bit address and an optional 8-bit CRC. The response phase includes the 8-bit Response, 1 DW of Data, 16-bit Status and an optional 8-bit CRC.

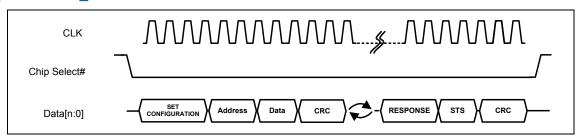

Figure 23: SET\_CONFIGURATION Command

SET\_CONFIGURATION command is used to write the Channel Capability and Configuration registers on the eSPI slaves. The SET\_CONFIGURATION command phase consists of an 8-bit Command Opcode, 16-bit address, 1 DW of Data and an optional 8-bit CRC. The response phase includes the 8-bit Response, 16-bit Status and an optional 8-bit CRC.

The eSPI slave contains addressable register space up to 4KB. The access is addressed at DWord boundary and only the lower 12-bits of the 16-bit address are used with address bit[1:0] hard-wired to always "00". The 4 MSB address bits must be driven to all zeros by eSPI master. eSPI slaves should ignore the 4 MSB address bits.

**Note:** Implementation Note: Upon coming out of eSPI Reset#, eSPI master can initiate a GET\_CONFIGURATION cycle to a particular eSPI slave to determine if the eSPI slave is present. If the eSPI slave is not present, the eSPI data lines remain pulled-up after the Turn-Around time. eSPI master can use this behavior to deduce that the eSPI slave is not present on the bus.

If the eSPI slave is present, the eSPI slave must drive the response phase upon the expiry of the Turn-Around time.

#### 4.8 Non-Posted Transaction

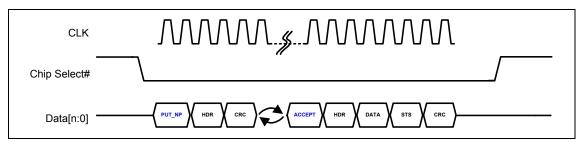

eSPI master initiated non-posted transaction can be terminated as connected or deferred completion.

The eSPI master initiated non-posted transaction is terminated as a connected completion when the data and all the information needed to generate the response are immediately available.

The valid responses for non-posted transactions terminated as connected include ACCEPT, FATAL ERROR and NON-FATAL ERROR.

**Figure 24: Connected Master Initiated Non-Posted Transaction**

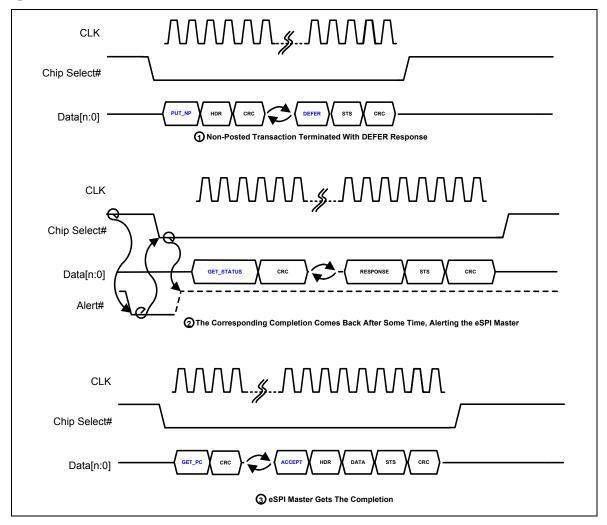

If the eSPI master initiated non-posted completion requires data or additional information which is not available immediately, the non-posted request is terminated with a "DEFER" response. The deferred completion can be returned some period of time in the future when the data or information is eventually available. The bus can be used for other transactions prior to the defer completion being returned, as long as the ordering rule is maintained.

When the deferred completion is returned, the valid responses include ACCEPT, FATAL ERROR and NON-FATAL ERROR.

The eSPI slave can complete the non-posted command with multiple split completions. If one of the split completions has an unsuccessful completion status, the remaining split completions will not be returned.

Figure 25: Deferred Master Initiated Non-Posted Transaction

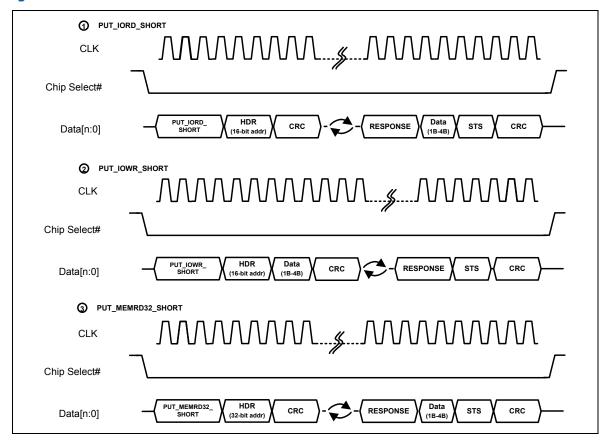

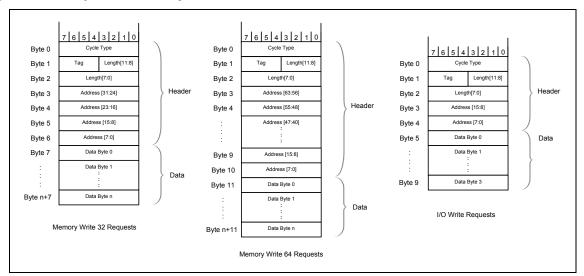

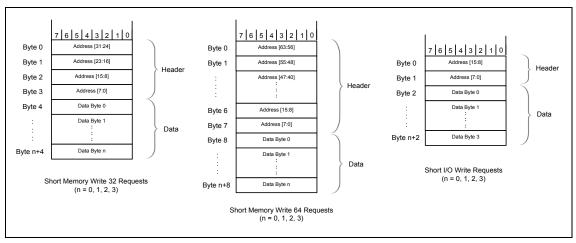

eSPI supports short non-posted transactions from master to slave for requests of length 1-4 bytes that have less overhead and are thus more efficient. The unique opcode indicates the type of non-posted transaction and the request length. The header contains the address only and the number of address bytes for the transaction is implied by the opcode. The short non-posted transaction does not have the Tag field. The Tag field is implied as all 0's which will be returned by the slave in the completion header.

The short non-posted transactions can be terminated as connected or deferred completion. However, for optimized performance of short transaction, the slave should complete the transaction as connected where it can.

**Figure 26: Master Initiated Short Non-Posted Transaction**

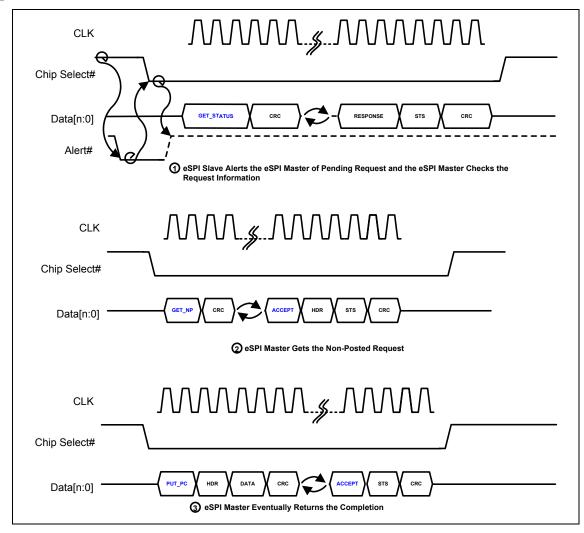

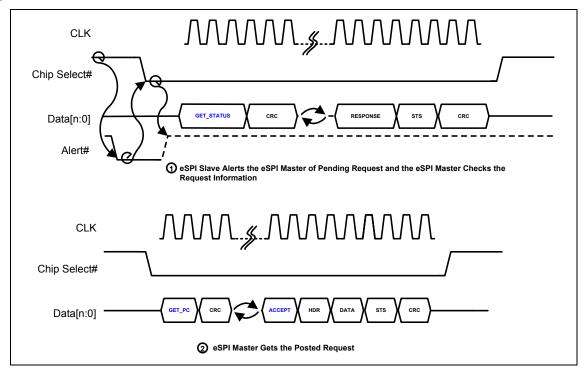

The eSPI slave can generate an Alert when there is a pending non-posted transaction. In response to that, the eSPI master would issue a GET\_STATUS command to check for the pending request information.

The eSPI master would then generate a GET\_NP command to fetch the non-posted transaction. Once the completion data and the information needed to return the response is available, the eSPI master would return the split completion back to the eSPI slave.

Completions to a non-posted request initiated by the eSPI slave are always split.

**Figure 27: Slave Initiated Non-Posted Transaction**

### 4.9 Posted Transaction

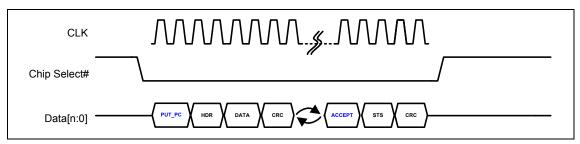

The valid responses for posted transactions initiated by eSPI master are ACCEPT, FATAL ERROR and NON-FATAL ERROR. DEFER response for posted transaction is invalid.

**Figure 28: Master Initiated Posted Transaction**

eSPI supports short posted transactions from master to slave for requests of length 1-4 bytes that have less overhead and are thus more efficient. The unique opcode indicates the short posted transaction and the request length. The header contains the address only and the number of address bytes for the transaction is implied by the opcode.

**Figure 29: Master Initiated Short Posted Transaction**

The eSPI slave can generate an Alert when there is a pending posted transaction. In response to that, the eSPI master would issue a GET\_STATUS command to check for the pending request information.

The eSPI master would then generate a GET\_PC command to get the posted transaction.

**Figure 30: Slave Initiated Posted Transaction**

# 5 Transaction Layer

# **5.1** Cycle Types and Packet Format

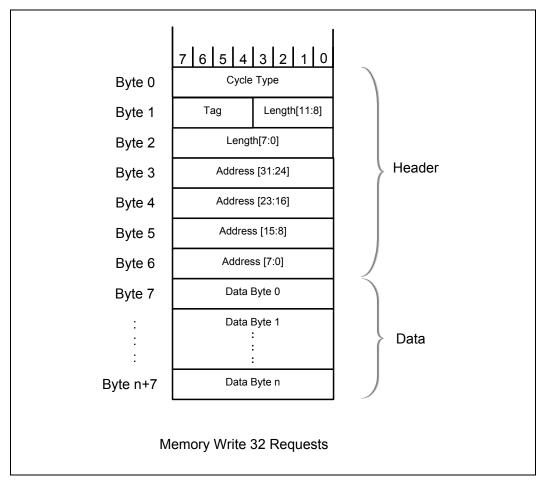

The following diagram shows a general Enhanced Serial Peripheral Interface (eSPI) packet format. The description of the respective fields within the packet is described in the subsequent sections.

Figure 31: General eSPI Packet Format

# **5.1.1** Cycle Types

The summary of cycle types supported over the eSPI interface is shown in the table below. The Least-Significant-Bit (LSB) of the encodings distinguishes between a cycle with data and a cycle without data.

The direction of cycle type supported is specified in the table as "Up" or "Down". "Up" refers to the direction from eSPI slave to eSPI master and "Down" refers to the direction from eSPI master to eSPI slave.

**Table 5: Cycle Types**

| Cycle Type                               | Encodings <sup>3</sup><br>[7:0] | Direction | Command<br>Type | Channel<br>Type               | Description                                                                                                                                  |

|------------------------------------------|---------------------------------|-----------|-----------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| eSPI Periphe                             | ral Channel                     |           |                 |                               |                                                                                                                                              |

| Memory<br>Read 32                        | 00000000                        | Up/Down   | Non-Posted      | eSPI<br>Peripheral<br>Channel | 32 bit addressing Memory Read<br>Request.<br>LPC Memory Read and LPC Bus<br>Master Memory Read requests<br>are mapped to this cycle type.    |

| Memory<br>Read 64                        | 00000010                        | Up/Down   | Non-Posted      | eSPI<br>Peripheral<br>Channel | 64 bit addressing Memory Read<br>Request.<br>LPC Memory Read and LPC Bus<br>Master Memory Read requests<br>are mapped to this cycle type.    |

| Memory<br>Write 32                       | 00000001                        | Up/Down   | Posted          | eSPI<br>Peripheral<br>Channel | 32 bit addressing Memory Write<br>Request.<br>LPC Memory Write and LPC Bus<br>Master Memory Write requests<br>are mapped to this cycle type. |

| Memory<br>Write 64                       | 00000011                        | Up/Down   | Posted          | eSPI<br>Peripheral<br>Channel | 64 bit addressing Memory Write<br>Request.<br>LPC Memory Write and LPC Bus<br>Master Memory Write requests<br>are mapped to this cycle type. |

| I/O Read                                 | 00000100                        | Down      | Non-Posted      | eSPI<br>Peripheral<br>Channel | I/O Read Request.  LPC I/O Read is mapped to this cycle type.                                                                                |

| I/O Write                                | 00000101                        | Down      | Non-Posted      | eSPI<br>Peripheral<br>Channel | I/O Write Request. LPC I/O Write is mapped to this cycle type.                                                                               |

| Successful<br>Completion<br>Without Data | 00000110                        | Up/Down   | Completion      | eSPI<br>Peripheral<br>Channel | Successful Completion Without Data. Corresponds to I/O Write, Flash                                                                          |

|                                          |                                 | Down      |                 | Flash<br>Access<br>Channel    | Write or Flash Erase.                                                                                                                        |

| Cycle Type                                 | Encodings <sup>3</sup> [7:0]                        | Direction | Command<br>Type | Channel<br>Type               | Description                                                                                         |  |

|--------------------------------------------|-----------------------------------------------------|-----------|-----------------|-------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Successful<br>Completion<br>With Data      | 00001P <sub>1</sub> P <sub>0</sub> <sup>1</sup> 1   | Up/Down   | Completion      | eSPI<br>Peripheral<br>Channel | Successful Completion With Data. Corresponds to Memory Read,                                        |  |

|                                            |                                                     | Down      |                 | Flash<br>Access<br>Channel    | I/O Read or Flash Read.                                                                             |  |

| Unsuccessful<br>Completion<br>Without Data | 00001P <sub>1</sub> P <sub>0</sub> <sup>1,2</sup> 0 | Up/Down   | Completion      | eSPI<br>Peripheral<br>Channel | Unsuccessful Completion Without Data. Corresponds to Memory, I/O or                                 |  |

|                                            |                                                     | Down      |                 | Flash<br>Access<br>Channel    | Flash accesses.                                                                                     |  |

| OOB Message                                | OOB Message Channel                                 |           |                 |                               |                                                                                                     |  |

| OOB<br>(Tunneled<br>SMBus)<br>Message      | 00100001                                            | Up/Down   | Posted          | OOB<br>Message<br>Channel     | SMBus Out-Of-Band Message.<br>SMBus packet tunneling.                                               |  |

| Flash Access                               | Flash Access Channel <sup>4</sup>                   |           |                 |                               |                                                                                                     |  |

| Flash Read                                 | 00000000                                            | Up/Down   | Non-Posted      | Flash<br>Access<br>Channel    | Read from Flash.                                                                                    |  |

| Flash Write                                | 0000001                                             | Up/Down   | Non-Posted      | Flash<br>Access<br>Channel    | Write to Flash.                                                                                     |  |

| Flash Erase                                | 00000010                                            | Up/Down   | Non-Posted      | Flash<br>Access<br>Channel    | Flash Erase instruction. Erase part or the whole partition owned by the corresponding flash master. |  |

#### Note:

1. The encoding  $P_1P_0$  has the following definition:

| Encoding P <sub>1</sub> P <sub>0</sub> | Description                                                     |

|----------------------------------------|-----------------------------------------------------------------|

| 00                                     | Indicates the middle completion of a split completion sequence. |

| 01                                     | Indicates the first completion of a split completion sequence   |

| 10                                     | Indicates the last completion of a split completion sequence.   |

| 11                                     | Indicates the only completion for a split transaction.          |

2. For Unsuccessful Completion without Data,  $P_1$  must be always a '1' as this is always the last or the only completion.

- 3. The combination of command opcode and cycle type encoding must be unique. There is no requirement that cycle type encodings must be unique across command opcodes.

- 4. Refer to Section 5.2.4 for detail operation of the Flash Access channel.

#### 5.1.2 Tag

The Tag field is allowed to be non-unique for multiple outstanding non-posted requests on the same Channel that require completion.

Refer to Section 5.4 - Transaction Ordering Rule for more details about Tag and its association with the ordering of completions.

For posted requests which do not require completion, the usage of Tag field is implementation specific and beyond the scope of the specification.

#### **5.1.3** Length

The length field indicates the request size or data payload specified in Bytes. The length field is 1-based. A value of all zeros indicates 4 KB of length.

For memory read, I/O read and Flash Read, the length field specifies the data payload size requested.

For memory write, I/O write, Flash write, OOB message with data and Completion with Data, the length field specifies the actual amount of data returned in the packet.

For Completion without Data or Un-Successful Completion, the length field must be driven to zeros by initiator. The receiver must ignore the length field.

I/O read and I/O write must not be more than 4 Bytes in length. eSPI slave must respond with Fatal Error if the request length exceeds 4 Bytes.

For Memory Write, Flash Write, OOB message with data and Completion, data payloads size should not exceed the Maximum Payload Size of the respective channels.

Read requests size initiated by eSPI slave on eSPI Peripheral Channel and Flash Access Channel should not exceed the Maximum Read Request Size set by the eSPI master in the Channel Capability and Configuration register for the respective channels.

Memory read and Flash read requests may be completed with one or multiple split completions.

A completion that does not cross 64B read completion boundary must be completed as a single transaction.

If the completion crosses 64B read completion boundary, the completion must be returned in multiple split completions, with each completion aligns to the 64B naturally

aligned address boundary except for the first completion which aligns to the starting address of the request.

For successful completion with data and unsuccessful completion without data, the additional cycle type encoding indicates whether the completion is the first, middle or the last completion for a split completion sequence, or whether it is the only completion that completes the split transaction.

#### 5.1.4 Address

The eSPI memory transactions support both 32 bits and 64 bits addressing formats. For I/O cycles, only 16-bits address is used.

#### 5.1.5 Data

The valid data field always starts at Byte 0, regardless of the address alignment. There is no byte enables associated with data. It is the responsibility of the requester to break the requests which are targeting non-contiguous locations into separate requests.

#### 5.2 Channels

A channel provides a means to allow multiple independent flows of traffic to share the same physical bus.

Each set of the put\_\*/get\_\*/\*\_avail/\*\_free associates with the command and response of a corresponding channel.

Each of the channels has its dedicated resources such as queue and flow control. There is no ordering requirement between traffics from different channels.

The number and types of channels supported by a particular eSPI slave is discovered through the GET\_CONFIGURATION command issued by the eSPI master to the eSPI slave during initialization.

The assignment of the channel type to the channel number is fixed. The eSPI slave can only advertise which of the channels are supported.

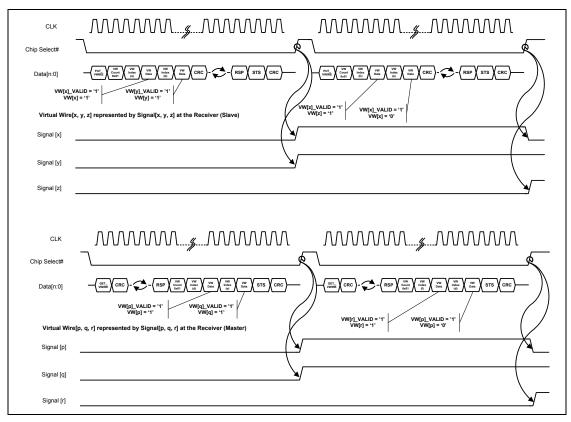

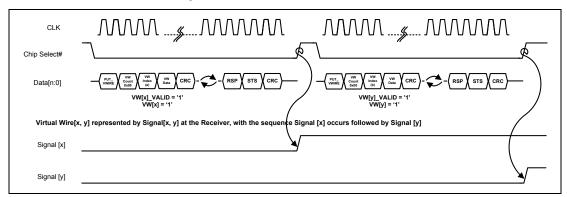

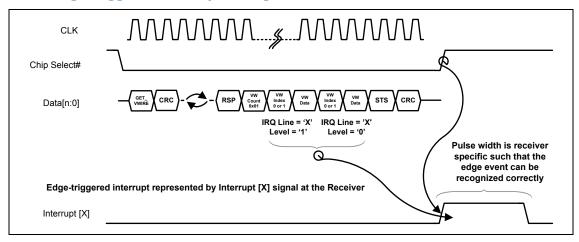

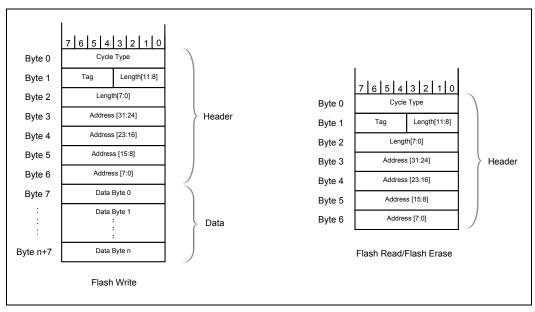

eSPI Peripheral transactions always use Channel 0. The PUT\_PC/ PUT\_NP/ GET\_PC/ GET\_NP/ PC\_FREE/ NP\_FREE/ PC\_AVAIL/ NP\_AVAIL commands and status fields are used for Channel 0 access.