# Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics

Paul E. Dodd, Senior Member, IEEE, and Lloyd W. Massengill, Senior Member, IEEE

*Abstract*—Physical mechanisms responsible for nondestructive single-event effects in digital microelectronics are reviewed, concentrating on silicon MOS devices and integrated circuits. A brief historical overview of single-event effects in space and terrestrial systems is given, and upset mechanisms in dynamic random access memories, static random access memories, and combinational logic are detailed. Techniques for mitigating single-event upset are described, as well as methods for predicting device and circuit single-event response using computer simulations. The impact of technology trends on single-event susceptibility and future areas of concern are explored.

*Index Terms*—Charge collection, heavy ion irradiation, radiation effects, radiation hardening, single-event effects, single-event upset, soft errors, terrestrial cosmic rays.

## I. INTRODUCTION

**S** INGLE-EVENT effects (SEE) in microelectronics are caused when highly energetic particles present in the natural space environment (e.g., protons, neutrons, alpha particles, or other heavy ions) strike sensitive regions of a microelectronic circuit. Depending on several factors, the particle strike may cause no observable effect, a transient disruption of circuit operation, a change of logic state, or even permanent damage to the device or integrated circuit (IC).

In this paper, we will examine the basic physical mechanisms causing SEE in digital microelectronics for spaceborne applications. Reflecting their relative importance in the commercial marketplace, we will concentrate on silicon MOS devices and digital ICs. Our focus is limited to nondestructive SEEs; destructive SEEs are covered elsewhere in this issue. We begin with a brief historical overview of the discovery of single-event upset (SEU) in space and terrestrial systems. We will then discuss the mechanisms and characteristics of nondestructive SEE in detail, with particular emphasis on SEU in dynamic random access memories (DRAM) and static random access memories (SRAM) and single-event transients (SET) in logic. We discuss various techniques that have been used to mitigate SEU at the device, circuit, and system levels. Next, we review modeling and simulation methods that have proved useful for gaining physical

P. E. Dodd is with Sandia National Laboratories, Albuquerque, NM 87185 USA (e-mail: pedodd@sandia.gov).

L. W. Massengill is with the Department of Electrical Engineering and Computer Science, Vanderbilt University, Nashville, TN 37235 USA (e-mail: lloyd.massengill@vanderbilt.edu).

Digital Object Identifier 10.1109/TNS.2003.813129

insight and predicting SEE in microelectronics. Finally, we conclude with a look into technology trends that may affect future device susceptibility to SEE and areas of emerging concern, including upsets in terrestrial microelectronics.

### II. SEE: A BRIEF HISTORY

Oddly enough, the first paper to ever deal with the issue of SEU was not a paper on the use of electronics in the space environment, but a paper assessing scaling trends in terrestrial microelectronics [1]. In this paper, the authors forecast the eventual occurrence of SEU in microelectronics due to terrestrial cosmic rays and further predicted that the minimum volume of semiconductor devices would be limited to about 10  $\mu$ m on a side due to these upsets! In fact, the authors wrote in 1962 that "already at the present time the essential part of semiconductor devices, the active region, is close to the minimum size possible" [1]. The first confirmed report of cosmic-ray-induced upsets in space was presented at the NSREC in 1975 by Binder et al. [2]. In this paper, four upsets in 17 years of satellite operation were observed in bipolar J–K flip–flops operating in a communications satellite. The authors used scanning electron microscope (SEM) exposures to determine the sensitive transistors and, using a diffusion model, calculated a predicted upset rate within a factor of two of the observed rate. Perhaps because the numbers of errors observed was so small, it was a few years before the importance of SEU was fully recognized, with significant numbers of SEU-related papers not appearing at the NSREC until 1978-1979.

The occurrence of soft errors in terrestrial microelectronics manifested itself shortly after the first observations of SEU in space [3]. This watershed paper from authors at Intel found a significant error rate in DRAMs as integration density increased to 16 and 64K, spurring a flurry of terrestrial SEU-related work in the late 1970s [4]. The primary cause of soft errors at the ground level was quickly diagnosed as alpha-particle contaminants in packaging materials [3]. For example, according to Ziegler, the Intel problem was traced to a new LSI ceramic packaging plant that had just been built downstream from the tailings of an abandoned uranium mine [5]. Radioactive contaminants in the water used by the factory were contaminating the ceramic packages they manufactured. By using low-activity materials for IC fabrication and on-chip shielding coatings [5], [6], the terrestrial soft error problem essentially disappeared for several years and has only recently become a serious concern again, as will be discussed in detail in Section VIII.

In the late 1970s, evidence continued to mount that cosmic-ray-induced upsets were indeed responsible for errors observed in satellite memory subsystems, and the first models

Manuscript received February 26, 2003. Sandia National Laboratories is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the U.S. Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

for predicting system error rates were formulated [7]. By this time satellite memory systems had increased in size, and on-orbit error rates of one per day could not be ignored as a fluke. In combination with the reports of soft errors in terrestrial systems, the evidence was compelling that an important new radiation effect had arrived.

Although the first papers attributed memory upsets to direct ionization by heavy ions such as those in the iron group [2], [7], by 1979 two groups reported at the NSREC on errors caused by proton and neutron indirect ionization effects [8], [9] (explained in Section III). This was a very important discovery because of the much higher abundance of protons relative to heavy ions in the natural space environment. In addition, it meant that not only would SEE be caused by galactic cosmic rays, but also by solar event protons and protons trapped in the Earth's radiation belts. In fact, proton-induced SEE often dominate the singleevent response of commercial parts operating in low earth orbits. The paper by Guenzer et al. [9] was the first to use the term "single-event upset," and this term was immediately adopted by the community to describe upsets caused by both direct and indirect ionization. The year 1979 also brought the first report of single-event latchup (SEL), an important discovery given the potentially destructive nature of the failure mode [10].

In the early 1980s, research on SEU continued to increase, and by 1980, single-event phenomena had become a dedicated session of the NSREC. Methods for hardening ICs to SEU were widely developed and used throughout this decade [11], [12]. At the same time, research into the fundamental mechanisms behind SEEs was paying dividends in increased scientific understanding of the problem. Much of the single-event research of the 1980s focused on errors observed in latched circuitry, such as DRAMs, SRAMs, nonvolatile memories, latches, and registers. An understanding of this phenomenon, and its mitigation for reliable data storage, proved critical to successful military and space deployments of that decade. The flurry of work to address the extremely significant problem of soft errors in memories shaped the early single-event research landscape, especially within the NSRE conference community.

There were, however, a few studies in the 1980s addressing another emerging and potentially troubling single-event issue: errors due to single events in combinational or imbedded core logic. In 1984, May and his coauthors from Intel were awarded "Best Paper" at the International Reliability Physics Symposium for a very revealing single-event experiment on an Intel microprocessor under dynamic operation [13]. Using an experimental technique of dynamic fault imaging, May demonstrated the temporal progression of a single-event disturbance from a local perturbation to a massive fault condition encompassing most of the microprocessor circuitry. Other studies of combinational logic appeared in the late 1980s (e.g., [14]–[16]), but were often overshadowed by the volume of work addressing memory upset.

The 1990s saw two major developments that continued to increase the importance of SEEs. One was the dramatic decrease in the number of manufacturers offering radiation-hardened (or more particularly to our purposes here, SEU-hardened) digital ICs. This (among other factors) led to the increased usage of commercial electronics in spacecraft systems. While many system designers embraced the use of modern commercial ICs because of the increased functionality and performance they provide, their relative sensitivity to SEE presented significant challenges to maintaining system reliability. The second development was the continued advance in fabrication technologies toward smaller IC feature sizes and the higher speeds and more complex circuitry that scaling enables. These advances typically increase sensitivity to SEE, even to the point of terrestrial errors in a benign desktop environment, and may also lead to new failure mechanisms. Absent new mechanisms, Ronen *et al.* have shown that simple scaling rules predict an increase in soft error susceptibility of about 40% per technology generation node [17].

These two developments of the past decade have led to an interesting convergence of mission from two historically disparate communities within the integrated circuit field: space and military vendors driven toward commercial (nonradiation-hardened) circuits and commercial vendors driven toward a very real concern about SEE in the everyday consumer environment.

In the late 1990s, a renewed interest in SEE in combinational (or core) logic emerged. This resurgence was fueled by several factors including: 1) a perception that the memory soft error situation was controllable with advanced technologies (e.g., SOI, <sup>10</sup>B-free materials, reduced-emission packaging) and the effectiveness of error detection and correction (EDAC) techniques [18], [19]; 2) a growing concern, based on extrapolated empirical and theoretical data, that technology scaling could lead to an inversion between the relative significance of memory-generated and core-logic-generated faults on observed soft error rates [20]–[22]; and 3) observations that clock speeds were driving up core-logic error rates [23], [24].

As we enter the 21st century, increasing sensitivity to SEU is expected to continue, both in memories and core logic. Upsets in terrestrial electronics are a serious reliability concern for commercial manufacturers. In fact, single-event vulnerability has become a mainstream product reliability metric for all facets of the integrated circuit industry, as outlined by the SEMATECH National Industry Association Roadmap [25]. A recent all-day tutorial at the International Reliability Physics Symposium was devoted entirely to soft errors in commercial semiconductor technologies [26] and in 2003 this topic became a regular technical session of that conference. At the same time, the feasibility of traditional SEU-hardening techniques is becoming questionable, especially in a paradigm where we see fewer dedicated rad-hard foundries to implement them. Circuit designs that are inherently radiation resistant [known as hardening by design (HBD)] are receiving considerable attention [27], [28]. Another current subject of interest is charge collection and SEU in silicon-on-insulator (SOI) and SiGe bipolar technologies [29], [30]. As these become mainstream fabrication technologies, their radiation response is of interest to spacecraft designers ready to insert the latest technologies into their systems.

## **III. PHYSICAL ORIGINS OF SEU**

## A. Charge Deposition

There are two primary methods by which ionizing radiation releases charge in a semiconductor device: direct ionization by the incident particle itself and ionization by secondary particles created by nuclear reactions between the incident particle and the struck device. Both mechanisms can lead to integrated circuit malfunction.

1) Direct Ionization: When an energetic charged particle passes through a semiconductor material it frees electron-hole pairs along its path as it loses energy. When all of its energy is lost, the particle comes to rest in the semiconductor, having traveled a total path length referred to as the particle's range. We frequently use the term linear energy transfer (LET) to describe the energy loss per unit path length of a particle as it passes through a material. LET has units of MeV/cm<sup>2</sup>/mg, because the energy loss per unit path length (in MeV/cm) is normalized by the density of the target material (in  $mg/cm^3$ ), so that LET may be quoted roughly independent of the target. We can easily relate the LET of a particle to its charge deposition per unit path length. In silicon, an LET of 97 MeV-cm<sup>2</sup>/mg corresponds to a charge deposition of 1 pC/ $\mu$ m. This conversion factor of about 100 is handy to keep in mind to convert between LET and charge deposition.

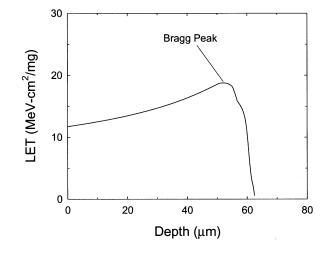

A curve of particular interest for understanding the interaction of a given energetic particle with matter is the LET of the particle versus depth as it travels through the target material. Fig. 1 shows such a curve for a 210-MeV chlorine ion traveling through silicon. Such curves are readily obtained using computer codes derived from the work of Ziegler *et al.* (e.g., the TRIM and SRIM family of codes, [31]). This figure shows the basic characteristics of ion-induced charge deposition as a function of depth. The peak in charge deposition is referred to as the *Bragg peak* and in general occurs as the particle reaches an energy near 1 MeV/nucleon. A useful rule of thumb is that the maximum LET (in MeV-cm<sup>2</sup>/mg) of an ion is roughly equal to its atomic number Z. A more rigorous discussion of the Bragg curve and the Bragg peak is found in [32].

Direct ionization is the primary charge deposition mechanism for upsets caused by heavy ions, where we define a heavy ion as any ion with atomic number greater than or equal to two (i.e., particles other than protons, electrons, neutrons, or pions). Lighter particles such as protons do not usually produce enough charge by direct ionization to cause upsets in memory circuits, but recent research has suggested that as devices become ever more susceptible, upsets in digital ICs due to direct ionization by protons may occur [33], [34].

2) Indirect Ionization: Although direct ionization by light particles does not usually produce enough charge to cause upsets, this does not mean that we can ignore these particles. Protons and neutrons can both produce significant upset rates due to indirect mechanisms. As a high-energy proton or neutron enters the semiconductor lattice it may undergo an inelastic collision with a target nucleus. Any one of several nuclear reactions may occur; examples for protons and neutrons can be found in [35] and [36]. Possible reactions include: 1) elastic collisions that produce Si recoils; 2) the emission of alpha or gamma particles and the recoil of a daughter nucleus (e.g., Si emits alpha-particle and a recoiling Mg nucleus); and 3) spallation reactions, in which the target nucleus is broken into two fragments (e.g., Si breaks into C and O ions), each of which can recoil. Any of these reaction products can now deposit energy along their paths by

Fig. 1. Linear energy transfer (LET) versus depth curve for 210-MeV chlorine ions in silicon.

direct ionization. Because these particles are much heavier than the original proton or neutron, they deposit higher charge densities as they travel and therefore may be capable of causing an SEU.

Inelastic collision products typically have fairly low energies and do not travel far from the particle impact site. They also tend to be forward-scattered in the direction of the original particle; this has consequences for the SEU sensitivity as a function of the angle of incidence [37], [38]. Once a nuclear reaction has occurred, the charge deposition by secondary charged particles is the same as from a directly ionizing heavy ion strike.

## B. Charge Collection

The basic properties of charge collection following a particle strike have been studied using a variety of experimental and theoretical methods. Broadbeam charge collection spectroscopy measurements have been used to determine SEU-sensitive volumes in SRAMs [39]-[41], and ion microbeams and lasers have been used with high-speed sampling oscilloscopes to measure charge-collection transients in Si devices [42]–[44]. Ion microbeams and lasers have also been used to map integrated charge collection as a function of position in ICs [45], [46] and more recently as a function of both time and position [47]. The physics of charge collection have also been studied in detail through the use of two-dimensional (2-D) and three-dimensional (3-D) numerical simulation [48], [49]. It is beyond the scope of this paper to comprehensively review the massive literature on charge collection; we seek to cover the main highlights and recent developments only.

1) Basic Physics of Charge Transport: When a particle strikes a microelectronic device, the most sensitive regions are usually reverse-biased p/n junctions. The high field present in a reverse-biased junction depletion region can very efficiently collect the particle-induced charge through drift processes, leading to a transient current at the junction contact. Strikes near a depletion region can also result in significant transient currents as carriers diffuse into the vicinity of the depletion region field where they can be efficiently collected. Even for

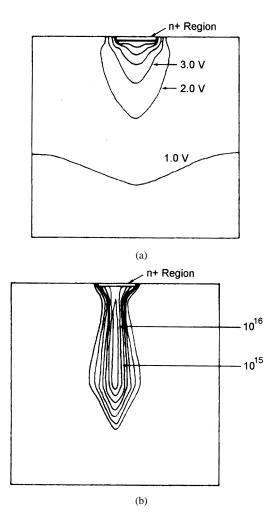

Fig. 2. Illustration of funneling in an  $n^+/p$  silicon junction following an ion strike: (a) electrostatic potential and (b) electron concentration. Note that contours of electrostatic potential are distorted along the path of the ion [51].

direct strikes, diffusion plays a role as carriers generated beyond the depletion region can diffuse back toward the junction.

Shortly following the discovery of SEU, researchers at IBM used numerical device simulators to compute the response of reverse-biased p/n junctions to alpha-particle strikes [48], [50]. An important insight gained from these early charge-collection simulations was the existence of a transient disturbance in the junction electrostatic potential, which was termed the "field funnel." Charge generated along the particle track can locally collapse the junction electric field due to the highly conductive nature of the charge track and separation of charge by the depletion region field, as shown in Fig. 2 [51]. This funneling effect can increase charge collection at the struck node by extending the junction electric field away from the junction and deep into the substrate, such that charge deposited some distance from the junction can be collected through the efficient drift process.

The funnel effect has been investigated in further detail by later researchers [52], [53], with the analytical models for funneling developed by McLean and Oldham [52] being an important early contribution to understanding several characteristics of funneling. Later research studied the influence of epitaxial substrates on the transient charge-collection characteristics [54]–[56]. Several important additional insights have been gained from these studies, and the reader is referred to [54]–[57] for comprehensive discussions of funneling.

While in some cases important to charge collection in isolated p/n junctions with constant applied bias, the role of the funnel is less significant in the case of static circuits such as SRAMs, where reverse-biased transistor junctions are connected to active external circuitry. In this scenario, the applied voltage at the struck junction is not constant, and in fact very often the struck node may switch from being reverse-biased to zero-biased. This loss of bias at the struck node tends to lessen the importance of drift collection (and hence the funnel) as the transient proceeds [58]. In such cases, funneling may play a role in the early-time response of the circuit by helping to initially flip the node voltage, but it is late-time collection by diffusion that ensures the bit stays flipped (see Section IV for further details about the upset process in SRAM circuits).

2) Charge-Collection Mechanisms in Submicron Devices: The charge-collection response of a single p/n junction is generally presumed to accurately depict the response of the sensitive junction of a transistor, typically a reverse-biased drain region. Studies have indicated that a new charge-collection mechanism may exist for submicron MOS transistors that requires considering the entire transistor [59]. Termed the alpha-particle source-drain penetration effect (ALPEN), this charge-collection mechanism results from a disturbance in the channel potential that the authors referred to as a funneling effect. The effect is triggered by a particle strike that passes through both the source and the drain at near-grazing incidence. Immediately following the strike, the electrostatic potential in the channel region is perturbed, leading to a significant (but short-lived) source-drain conduction current that mimics the "on" state of the transistor. This mechanism was revealed by 3-D alpha-particle simulations and has been experimentally verified. The experiments indicate that source charge injection due to this mechanism increases rapidly for effective gate lengths below about 0.5  $\mu$ m. Later work predicted the same direct channel conduction mechanism can occur in 0.3- $\mu$ m gate length MOSFETs even for normal incidence strikes and can lead to charge multiplication [60]. This mechanism may forebode a serious vulnerability to SEU for deep submicron MOSFETs.

A somewhat similar, but distinct mechanism exists when electrons or holes released by a particle strike are confined to a well or body region in which a transistor is located. For example, for an n-channel MOS transistor located in a p-well, electrons induced by a particle strike can be collected at either the drain/well junction or the well/substrate junction. However, as illustrated in Fig. 3, holes left in the well raise the well potential and lower the source/well potential barrier, and the source injects electrons into the channel [61]-[63]. These electrons can be collected at the drain, where they add to the original particle-induced current and can cause an increased SEU sensitivity. Because the electrons are injected over the source/well barrier, this is referred to as a bipolar transistor effect, where the source acts as the emitter, the channel as the base region, and the drain as the collector. Reducing the channel length effectively decreases the base width, and the effect becomes more pronounced [63].

Fig. 3. Electron concentration contours inside an n-channel MOS transistor following a heavy ion strike [63]. Bipolar effect is evidenced by the contours emanating from the source, showing that the source is injecting electrons into the p-well, where they may be collected at the substrate or at the drain.

3) Charge Collection in Silicon-on-Insulator Devices: Charge collection mechanisms in SOI devices are covered in detail elsewhere in this issue, but essentially the same bipolar effect discussed above occurs in SOI devices [64], [65]. Following a particle strike to the body of an n-channel SOI transistor, electrons can be collected at the source and drain electrodes. Holes can only escape through the body tie contact, if there is one, or slowly through recombination if there are no body ties. Residual holes left in the body raise the body potential and trigger the lateral parasitic bipolar transistor inherent to the SOI transistor. This bipolar current considerably lowers the SEU hardness of SOI. In some cases, bipolar amplification in concert with impact ionization can lead to snapback, a sustained high-current condition similar to latchup [29]. Even in devices with body ties, the bipolar effect results in significant charge amplification, especially for ion strikes far from the body ties [66]–[67].

### IV. SEU IN MEMORY CIRCUITS

#### A. SEU Mechanisms in DRAMs

DRAM technology refers to the broad class of information storage devices, usually one-transistor designs, which passively store packets of charge to represent binary information. The key to DRAM upset is that the information storage is passive (no active regeneration path), and any (no matter how small) disturbance of the stored information by a particle strike is persistent until corrected by external circuitry [19]. There is no inherent refreshing of this charge packet (e.g., charge resupply through a load device) and no active regenerative feedback as one observes in latches and SRAM cells. What is so often referred to as a bit flip, the transition from one stable binary state to the other, is not required in DRAMs for an SEU to occur. A degradation of the stored signal to a level outside the noise margin of the supporting circuitry is sufficient to lead to erroneous interpretation and a resultant error.

There are two key parameters related to DRAM upsets: the noise margin associated with a bit signal and a critical time window (because of the dynamic operation of the circuit, the vulnerability to upset is not constant with time). The noise margin is closely linked with the concept of critical charge,

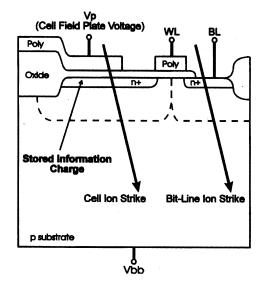

Fig. 4. One-transistor DRAM cell physical layout, illustrating ion strikes to the storage cell and bit-line.

$Q_{\rm crit}$ .  $Q_{\rm crit}$  is usually defined as the minimum amount of charge collected at a sensitive node necessary to cause a circuit upset. This definition is somewhat limited and is not totally appropriate in all circuit cases [68]. For example,  $Q_{\rm crit}$  may not be a circuit constant, but can vary with the timing of the strike relative to the dynamics of the circuit. The temporal characteristics of the ion strike in relation to the dynamic clocking of the cell are also important.

The most prevalent soft error source in DRAM arrays is single-event charge collection within each binary cell. These cell errors, as first described by May and Woods [3], are caused by a single-event strike in or near either the storage capacitor or the source of the access transistor, as illustrated in Fig. 4. Such a strike directly affects the stored charge and the information integrity by the collection of the ion-induced charge. A cell upset due to charge collection is usually observed as a  $1 \rightarrow 0$ transition; the collected charge relaxes a stored charge state [3]. This upset mechanism has been the primary concern and focus of study since the early investigations of SEU in DRAMs.

In the late 1980s, Takeda *et al.* reported the ALPEN sourcedrain penetration effect discussed in Section III [59]. While the normal effect of an ion strike is to deplete charge from a DRAM cell storage capacitance, the ALPEN mechanism causes the opposite result: the shunting of charge onto the storage node. Thus,  $0 \rightarrow 1$  transitions can also be introduced by ion strikes. A similar phenomenon has been found to occur between adjacent trench storage capacitors in trench-type DRAMs [69].

Upsets can also occur in DRAMs due to bit-line strikes. When the bit lines are in a floating voltage state (e.g., during a read cycle), DRAMs are sensitive to the collection of charge into diffusion regions that are electrically connected to the bit access lines [70]. This collection could arise from any of the access-transistor drains along the bit-line length or from a direct strike to the differential sense amplifier [71]. The bit-line SEU mechanism is the reduction of the sensing signal due to a charge imbalance introduced on the precharged bit lines, either prior to or during the sensing operation. Bit-line strikes are only possible during the floating precharge and sensing stages of operation, and therefore temporal characteristics of the strike in relation to the clocking signals are critical. Because the duty cycle of these stages to the overall cycle time increases with increasing overall clock frequency, the bit-line soft error rate is inversely proportional to DRAM cycle time [71]. In contrast, cell upsets are independent of the DRAM cycle time. Bit-line errors also show a strong inverse correlation with the signal charge [71]. As chip densities and speeds grow, bit-line errors are expected to be increasingly important.

In 1988, Rajeevakumar *et al.* observed a new failure mode in DRAMs due to a synergistic effect of bit-line and storage cell charge collection [72]. Both processes individually resulted in less charge collection than  $Q_{\rm crit}$ , but the combined effect during a read operation caused an error. This effect, termed the combined cell-bit line (CCB) failure mode, was shown to dominate both the cell and bit-line error components at very low cycle times.

Another very important factor in determining the SEU susceptibility of DRAMs is the storage cell technology [19]. Many different physical storage structures are used in DRAM manufacture, ranging from various stacked capacitor designs to buried trench capacitors. These different physical structures have been shown to have a dramatic effect on the observed soft error rate [73].

#### B. SEU Mechanisms in SRAMs

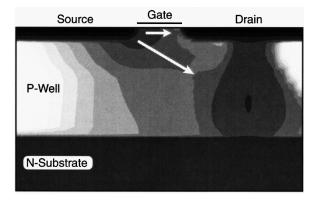

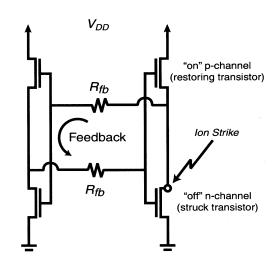

The upset process in SRAMs is quite different from DRAMs, due to the active feedback in the cross-coupled inverter pair that forms a typical SRAM memory cell as shown in Fig. 5. When an energetic particle strikes a sensitive location in a SRAM (typically the reverse-biased drain junction of a transistor biased in the "off" state [63], [74], for example the "off" n-channel transistor shown in Fig. 5), charge collected by the junction results in a transient current in the struck transistor. As this current flows through the struck transistor, the restoring transistor ("on" p-channel transistor in Fig. 5) sources current in an attempt to balance the particle-induced current. Unfortunately, the restoring transistor has a finite amount of current drive, and equally importantly, a finite channel conductance. Current flow through the restoring transistor therefore induces a voltage drop at its drain. This voltage transient in response to the single-event current transient is actually the mechanism that can cause upset in SRAM cells. The voltage transient is essentially similar to a write pulse and can cause the wrong memory state to be locked into the memory cell.

In SRAM cells, there are four possible sensitive strike locations, namely the four transistor drains interior to the SRAM circuit. An important consideration for charge collection is whether the junction is located inside a well or in the substrate [63], [74], because the well-substrate junction provides a potential barrier that prevents charge deposited deep within the substrate from diffusing back to the struck drain junction. For example, in the familiar outside-the-well "off" strike, because the struck drain is not located in a well, charge deposited deep in the substrate can diffuse back to the drain junction. This is the most sensitive strike location for most technologies [74].

Fig. 5. Competition between the feedback process and the recovery process governs the SEU response of SRAM cells.

Fig. 6. SRAM struck drain voltage transients for ion strikes with LET well below, just below, and just above the SEU threshold. Even the ion strike with LET well below the actual SEU threshold is sufficiently ionizing to momentarily flip the struck node voltage.

Inside-the-well strikes are particularly interesting because of shunt and bipolar effects that can occur in multilayer structures [61]. For the inside-the-well "off" strike, the initial drift current pulls down the struck node potential, initiating the upset process. As the transient proceeds, holes deposited in the p-well are collected at the p-well ties, raising the well potential and leading to injection of electrons by the source [61], [62], [75]. This initiates the inside-the-well bipolar effect discussed in Section III and illustrated in Fig. 3. Electrons collected by the substrate do not contribute to upset because the substrate is attached to  $V_{DD}$ . However, electrons collected by the n-drain constitute a bipolar current in the same direction as the initial photocurrent and do contribute to the upset process [63]. For small geometries, the inside-the-well "off" strike can become an important mechanism.

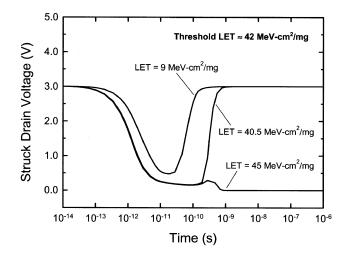

Interestingly, incident particles far below the upset threshold are often sufficiently ionizing to induce a momentary voltage "flip" at the struck node of an SRAM. For example, Fig. 6 shows drain voltage transients in an SRAM for a particle strike with LET well below the upset threshold, just below the upset threshold, and just above the upset threshold. Even the particle with LET well below the upset threshold causes a significant voltage transient on SET at the struck drain. Whether an observable SEU occurs depends on which happens faster: the feedback of the voltage transient through the opposite inverter, or recovery of the struck node voltage as the single-event current dies out [58], [76], [77]. Note that drift (including funneling effects) is responsible for the rapid initial flip of the cell, while long-term charge collection by diffusion prolongs the recovery process; both mechanisms are critical to the upset process.

The recovery time of an SRAM cell to a particle strike depends on many factors, such as the particle LET, the strike location, etc. From a technology standpoint, the recovery time depends on the restoring transistor current drive and minority carrier lifetimes in the substrate [76], [77]. The cell feedback time is simply the time required for the disturbed node voltage to feed back through the cross-coupled inverters and latch the struck device in its disturbed state. This time is related to the cell write time and in its simplest form can be thought of as the RC delay in the inverter pair. This RC time constant is thus a critical parameter for determining SEU sensitivity in SRAMs-the smaller the RC delay, the faster the cell can respond to voltage transients (including write pulses) and the more susceptible the SRAM is to SEU. Obviously, this has implications for the sensitivity of future, higher speed technologies, as discussed in Section VIII.

#### C. Single-Event Multiple Bit Upset

Single-event multiple-bit upsets (MBUs) occur when a single particle strike causes more than one error in an IC. For example, diffusion of charge to closely spaced junctions can upset more than one bit in both SRAM and DRAM cells [56], [78]. For a particle striking an IC at a grazing angle of incidence, the charge track may intersect several sensitive regions and cause multiple upsets [79]. The effects of MBU are typically alleviated by a combination of error-correcting codes that work on a word-by-word basis (see Section VI) and layout rules that prevent physically adjacent bits from belonging to the same word of memory. Still, single-word multiple-bit upsets (SMUs) can occur and pose a substantial threat to system integrity [80]. MBUs have been observed in on-orbit spacecraft data [81], [82]. As advanced technologies pack ever more bits into small areas, MBU may become more prevalent.

## D. Functional Interrupts

Single-event functional interrupts (SEFIs) are a complex failure mode whereby an ion strike triggers an IC test mode, a reset mode, or some other mode that causes the IC to temporarily lose functionality [83]. As devices become increasingly complex, they may be more likely to exhibit SEFIs. For example, synchronous DRAMs are very complicated ICs that incorporate built-in self-test (BIST) modes and self-repairing boot sequences that remap nonfunctional bits in the memory with redundant bits on the chip. An ion strike to a SDRAM with such circuits may initiate a BIST mode, cause a chip reset to occur, or throw the IC into an idle state [84]. These events can have serious consequences on system operation, sometimes requiring device reset to clear the condition [85].

## V. SEE MECHANISMS IN LOGIC

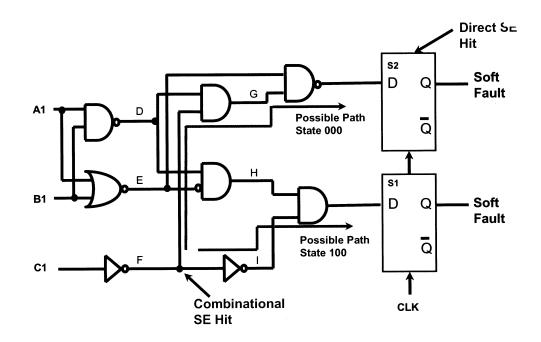

The quantification of SEU effects in combinational logic circuits (e.g., core logic of a microprocessor or microcontroller) is quite different than in memories. Whether or not an erroneous data signal caused by a single-event ion strike is captured by a storage element (latch or register) depends on the existence of active paths from the struck node to latches, the arrival time of the erroneous signal at the latches, and the erroneous pulse time profile at the latch input. Even if the erroneous signal is captured (stored) by one or more latches, there is still no guarantee that it will propagate to the output. The erroneous information may be blocked by superseding logic during the following clock cycles—i.e., the corrupted latch may become a "don't care" member of a subsequent state of the logic. In core logic, the concepts of "faults" and "errors" are distinct from memory circuits and require precise definition.

# A. Combinational Soft Faults

In a logic circuit, charge collection due to a single-event strike on a particular node will generate a low-to-high or high-to-low voltage transition or a transient noise pulse. If this pulse is larger than the input noise margin of a subsequent gate, it will compete with the legitimate digital pulses propagating through the circuit. The ability of the noise pulse to propagate depends not only on its magnitude, but also on the active logic paths from the node existing at that instant in time. An example of this is shown in Fig. 7 [86].

In Fig. 7, a single-event strike generates a voltage transition on node F of this circuit. The possible propagation of this pulse to a latch (storage) element depends on several factors. First, the active combinational paths at that instant in time. Two such distinct paths (one for an input vector of 000 and one for an input vector of 100) are shown by the arrows in Fig. 7. The active combinational paths depend on the dynamic state of the logic as determined by the particular code vectors executed with time (the present "state" of the logic). Second, assuming that an active path exists for the propagation of the noise pulse, the pulse will be shaped and phase delayed as it propagates through the intervening gates en route to a latch. Third, the temporal characteristics of the noise pulse as it arrives at a latch are important. The pulse must arrive within the setup and hold (S/H) time of the latch element to be captured (to be stored by the latch element). The clocking characteristics of the latch and the previous state of the latch contribute to this mechanism. If all three of the above conditions are properly met, then the SE-generated noise pulse will be captured by the latch as erroneous information-we define this as the generation of a soft fault (SF).

SFs may also be generated by direct single-event strikes to the latch nodes, where the latch information is corrupted via a bit flip. This effect is analogous to SEUs in memory circuits and can be modeled in a similar way [6].

Fig. 7. Example of a SET impulse propagating through a combinational logic system, taking various paths as a function of the system state, and creating a latch soft fault [151].

## B. Observable Error Events

Once an SF has been identified, or a soft fault probability has been calculated, information is known about the vulnerability of a circuit to single events and/or critical paths which may contribute a weak link for single-event tolerance. However, actual upset metrics which map to the observable operation of a particular circuit on orbit or in a beam experiment are not delivered by knowledge of SFs. Internal SFs may not be observable at the interface pins of a circuit (or the I/O ports of a subcircuit). For example, the particular latch affected by the soft fault may be part of a "don't care" state of the finite state machine; the change of state has no effect on subsequent operation of the circuit. Or, the erroneous latch data may be part of a data register that is scrubbed in a subsequent clock cycle. Thus, no observable error actually occurs.

However, if the soft fault eventually propagates to one or more of the I/O ports of the circuit, then an externally observed error exists; we define this and only this event as an *error event*. It is clear that one soft fault may cause erroneous information at many I/O ports and that this erroneous information may appear during many clock cycles.

#### VI. MITIGATION OF SEU

SEU mitigation techniques can be roughly classified into three distinct categories. System-level techniques deal with SEU at the system architecture level. Circuit-level techniques rely on changes in the circuit design to reduce SEU sensitivity. Technology- or device-level hardening requires fundamental changes to the underlying fabrication technology used to manufacture ICs. In this section, we will briefly present all three levels of hardening techniques. A review of several hardening techniques is also found in [87].

## A. Technology Hardening

The most fundamental method for hardening against SEU is to reduce charge collection at sensitive nodes. This can be accomplished in DRAMs and SRAMs by introducing extra doping layers to limit substrate charge collection [88]. In advanced SRAMs, triple-well [89] and even quadruple-well [90] structures have been proposed to decrease SEU sensitivity. In this case, all strikes are basically "inside-the-well" strikes. Retrograde wells and buried layers can also be used to provide an internal electric field that opposes collection of charge deposited in the substrate [91], [92]. Even the simple use of an epitaxial substrate instead of a bulk substrate affords some level of reduced charge collection [56].

Another effective technique for reducing charge collection in silicon devices is the use of SOI substrates [65]. In this case, the collection volume is reduced by the fact that the active device is fabricated in a thin silicon layer that is dielectrically isolated from the substrate. In a typical thin-film SOI device, the source and drain penetrate all the way to the buried isolation oxide (BOX). This substantially reduces the SEU-sensitive area because the reverse-biased drain junction area is limited to the depletion region between the drain and the body of the transistor. Charge deposited in the silicon substrate underneath the BOX cannot be collected at the drain due to the dielectric isolation, although recent research indicates that capacitive coupling across the BOX can lead to unexpected charge collection in SOI structures [93], [94]. Unfortunately, as briefly mentioned in Section III, charge deposited in the body region (for example, by a particle strike to the gate region) can trigger a bipolar mechanism that limits the SEU hardness of SOI circuits [64], [65]. Body ties are sometimes used commercially to reduce floating-body effects under dc operation, and careful attention to body tie design is crucial to maintaining good SEU performance [64], [95], [96]. Even in body-tied SOI designs, manufacturers

have found it necessary to incorporate other hardening methods for applications where very high upset thresholds are desired [93], [97], [98]. Fully depleted SOI transistors exhibit reduced floating-body effects and in some (but not all) cases have shown excellent SEU performance [99].

#### B. Circuit- and System-Level Hardening

Because of the invasive nature of device-level hardening (i.e., the requirement for fundamental changes in the manufacturing process), methods to improved single-event tolerance at the circuit level have been a frequent topic of research.

Given an understanding of the upset mechanism in SRAMs, we can immediately understand a typical technique used to harden SRAMs against SEU. We have discussed (Section IV) how the SEU process in an SRAM is essentially a race condition between the feedback and recovery processes. To harden an SRAM, we need to either slow the feedback process or decrease the recovery time. The feedback process can be slowed by adding either resistance or capacitance to the feedback loop [11]. Cross-coupled feedback resistors ( $R_{fb}$  in Fig. 5) are the classical method of increasing the cell feedback time by increasing the RC delay in the feedback loop. This technique is very effective, as illustrated in Fig. 8. This figure shows the measured SEU cross section (area of the chip sensitive to SEU) as a function of LET for a microprocessor before and after hardening by resistive decoupling [100]. The predicted upset rate in a geosynchronous orbit for the unhardened microprocessor is about once a day, while in the resistively hardened part it is about once per century.

Unfortunately, because the SEU process in SRAMs looks just like the write process, this same RC delay directly impacts the write pulse width of the SRAM. Thus, the effectiveness of resistive hardening does not come without a price. In addition to the speed penalty incurred by adding feedback resistors, increased process complexity results from adding feedback resistors. These resistors are typically implemented in the cell layout as lightly doped polysilicon regions. Because the resistivity of polysilicon is very sensitive to the doping concentration and numerous other factors, it is very difficult to control the resistor value [101]. To add to this problem, polysilicon resistivity has a negative temperature dependence. This leads to a temperature dependence of both the write speed and the SEU response and makes it challenging to optimize a resistively hardened technology so that it will operate within specifications across a wide temperature range.

Other decoupling techniques have been proposed that place resistors, diodes, or transistors in different locations within the feedback path [102]–[106], usually for the purpose of reducing the impact of the resistors on timing parameters or increasing manufacturability. For the most part, these techniques have not been widely used (if at all) and have their own associated tradeoffs. Capacitors have been successfully used as a feedback element in SOI SRAMs [65], [97], [98] and very recently as a means to improve the soft-error performance of deep-submicron CMOS SRAMs for terrestrial applications [107]. While adding capacitance still degrades timing parameters, one advantage is reduced temperature-dependence compared to resistive hardening.

LET (MeV-cm<sup>2</sup>/mg)

100

150

200

Commercial Part

10<sup>-2</sup>

10

10

10-5

10<sup>-6</sup>

10

10

0

50

Cross Section (cm<sup>2</sup>;

showing the effectiveness of resistive hardening for mitigating SEU [100].

Another important technique for hardening circuits, especially in a manner portable across any commercial fabrication process, is sometimes referred to as HBD [108]. Several design-hardened SRAM and latch circuits have been proposed and fabricated [109]-[114]. These memory cells typically rely on redundant circuit elements (usually 12-16 transistors per memory cell as opposed to six in a standard unhardened cell) to protect against SEU. Because of the large number of transistors per cell, these designs consume more area (and consequently more power) than six transistor cells. Other latch/memory cell designs employ spatial and/or temporal redundancy relative to the localized single-event charge deposition in a way that does not require a  $2 \times$  increase in transistor count [115], but sacrifice performance in other ways (usually speed). While these cells can be appropriate for protecting critical data paths, they have not usually been suitable for very highly integrated circuits. Still, as the gap widens between state-of-the-art commercial fabrication processes and radiation-hardened processes, HBD techniques are becoming increasingly attractive. These circuit-hardening approaches are likely to be very important for future high-performance radiation-hardened ICs.

Mitigation of SEEs in combinational (or core) logic can involve redundant data paths (as described above) or the enhancement of data paths with proper choices of circuit types. An example is the elimination of all dynamic logic [116]. Because of its passive and highly charge-sensitive mode of operation, dynamic logic is highly vulnerable to SEEs, both space and terrestrial. Another method includes the choice of data path latches to include static or keeper-based designs [117].

System-level hardening approaches include the use of error detection and correction (EDAC) circuitry to monitor and correct memory errors as they occur [118]–[120]. This approach requires that extra bits of information be stored with the data to reconstruct the original data in the event of an upset. System overhead can be nonnegligible, but this is sometimes the only method available if relatively susceptible parts must be used. Another important technique is triple-modular redundancy (TMR), which can be implemented at the circuit, system board, or module level. Cruder methods such as watchdog timers,

250

592

lockstep operation, majority voting, etc., are commonly used to detect control system errors [121]. While simple in concept, overhead can again be significant, but in many cases this is the only option available to the spacecraft engineer.

## VII. MODELING SINGLE-EVENT MECHANISMS

From the earliest history of numerical device modeling, the radiation effects community has recognized the value of computational modeling for providing insight into the effects of ionizing radiation on microelectronic devices. In fact, pioneering work on one-dimensional drift-diffusion numerical modeling was presented at the NSREC as early as 1967 [122], [123], winning the Best Paper award for that year [122]. This early work focused on transient radiation response, as SEU would not be observed experimentally until several years later [2]. The development and use of numerical models for radiation effects has proceeded on many levels: the interaction of ionizing particles with matter, physical device simulators that predict the response of devices to incident radiation, circuit simulators that model circuit response to a single event, and codes that predict the error rate that will be observed for a specific part flying in particular orbit. In this paper, we will only review the models that most directly pertain to the actual upset process itself, namely device and circuit models that predict the response of devices and circuits to the ion track. Models for predicting error rates are covered elsewhere in this issue.

## A. Physics-Based Device Models

The most commonly used formalism for device simulation is that of drift-diffusion models. In a drift-diffusion model, the semiconductor device equations are derived from the Boltzmann transport equation using numerous approximations. The equations to be solved are the Poisson equation and the current continuity equations, together with the constitutive relationships for current density (the actual drift-diffusion equations [124]). These equations are discretized and solved on a mesh using finite-difference or finite-element techniques [125]. Drift-diffusion models are highly evolved, and relatively speaking, not terribly computationally intensive, except in the case of 3-D models. Because of the assumptions they are based on, however, they are ill suited to treat many effects becoming important in small-geometry devices, such as velocity overshoot, carrier heating, and quasiballistic transport [124]. Nevertheless, due to their computational efficiency, they remain the workhorse simulation tool, even for deep submicron devices.

The next step up the device-simulation hierarchy is hydrodynamic and energy balance codes. Based on fewer assumptions, these codes begin to treat nonlocal effects, but are correspondingly more computer-intensive, based on five or six equations of state rather than the three of the drift-diffusion method [124].

The top rung of the device simulation ladder is Monte Carlo simulation, which makes the fewest assumptions and approximations [124]. Rather than being based on approximations to complicated macroscopic equations, Monte Carlo methods describe carrier transport on a fundamental, microscopic scale using classical equations of motion (e.g., Newton's first law). The motion of individual carriers is followed as they drift in fields and interact with scattering centers until statistical significance is achieved. Few assumptions are involved other than transport is described using classical physics. The penalty is very high computational intensity as the trajectories of many thousands of particles must be tracked to attain meaningful statistics.

## B. Multidimensional Device Simulations

One of the many challenges of device simulation of radiation effects is the need for advanced 3-D modeling tools. The inherently 3-D nature of an ion passing through a microelectronic device is difficult to address with the 2-D simulation programs that are routinely used in the semiconductor industry for device analysis. The development of full 3-D tools has been fairly recent, however, and much insight has been gained in the past through the use of 2-D programs [48], [50], [61], [74], [76], [77], [126]–[133].

In a 2-D rectangular simulation, all quantities are assumed to be extruded into the third dimension, and hence *either* the correct generated charge density *or* the correct total charge can be simulated, not both. Scaling schemes have been proposed that adjust the Auger recombination rate in an attempt to correct for geometry effects [129]. Another method is to use *quasi*-3-D versions of the popular PISCES-II code, based on cylindrical symmetry and coordinate transformations [134]. Many charge collection and SEU studies have been performed using these modified 2-D codes [53], [135]–[138]. Unfortunately, there are few devices that exhibit circular symmetry, although through clever use of geometrical approximations, cylindrically symmetric simulations have proven revealing and surprisingly accurate in some cases [78]. Full 3-D device codes are necessary to model the effects of angled ion strikes [62], [139].

Fully 3-D device simulators were first reported in the literature in the early 1980s [140], and some of the early work on 3-D device simulation was motivated by alpha-particle reliability issues [141], [142]. An early comparison of 2-D and 3-D charge-collection simulations showed that while the transient responses were qualitatively similar, significant quantitative differences existed, both in the magnitude of the current response and the time scale over which collection was observed [143]. The implication of these results is that while 2-D simulations may provide basic insight, 3-D simulation is necessary if truly predictive results are to be obtained. Throughout the 1980s, companies developed internal 3-D device simulators, but most of these were proprietary and optimized for supercomputers. Only in the 1990s did numerical techniques and microprocessor speeds improve sufficiently to bring such tools to the desktop workstation. In the last several years fully 3-D device simulators have become commercially available [144]–[147]. Optimized for high-end workstations, a fairly large 3-D simulation can generally be performed in a few hours.

#### C. Circuit Simulations

In the previous sections, we discussed physics-based device models that simulate the charge collection in a device following an ion strike. Stepping up in a hierarchical view, these models can be incorporated into macro-models of the devices interconnected in a subcircuit. The macro view of the circuit will relate the collection of charge in individual device junctions to changes in the circuit currents and voltages.

A common circuit model for the charge collection at a junction due to direct funneling or diffusion is a double-exponential, time-dependent current pulse [148]. Typical parameters of this pulse are a rise time on the order of tens of picoseconds and a fall time on the order of 200 to 300 ps [68]. The actual magnitude and time profile of the current model depend on material parameters, the ion species, the ion energy, device dimensions, and the hit location relative to the junction. If the time profile of the collection current is not important to the circuit response to the hit, then analytical current models such as these usually adequately describe the induced current pulse. If, however, the time profile is critical to the circuit response, more accurate models for the current pulse are necessary, such as those from a device simulation.

Historically, it has become common practice to use the total charge delivered by the current waveform as a single descriptor of the particle strike's impact on the affected circuit node. This can be an extremely dangerous simplification, since it assumes the time profile of the charge delivery to a sensitive node is unimportant to its response [58]. From this simplification comes the concept of critical charge,  $Q_{\rm crit}$ .  $Q_{\rm crit}$  is a property of the particular circuit (not the ion or environment) and is defined as the minimum charge delivered by the transient current waveform that causes that circuit to be upset. Of course,  $Q_{\rm crit}$  tells nothing about the time profile of the delivery of that charge. Critical charge is commonly used as a figure of merit in the comparison of circuit design types and technologies. The quantity describes the relative vulnerability of a circuit to single events without the complications of ion species, ion energies, LET, or type of charge collection.

The importance (or lack thereof) of the precise time profile of SE current models depends entirely on the dominant high-frequency pole associated with the circuit's hit node, given by the open-circuit time constant (total node capacitance and equivalent ac resistance) seen by the current source. That is, the hit node acts as a low-pass filter, integrating the charge delivered to the node by the SE current pulse. If the response of the circuit at the collecting node is much slower than the characteristic time constant of the SE pulse, then the pulse is effectively integrated by the nodal capacitance and only the total charge delivered by the pulse is important to the circuit response. If, however, the time constant at the node is much shorter than the time constant of the SE pulse, then the circuit responds to the delivered charge faster than the pulse can deliver it, so the pulse shape is critically important to the circuit response. These concepts are essential to the accurate modeling of SEUs at the circuit level, since they define the boundary between valid modeling using only the collected charge and modeling requiring a more accurate description of the time profile of the charge collection.

Deterministic circuit simulation of both memory elements and logic circuitry has been effectively performed in the circuit domain using industry standard analysis codes such as Berkeley SPICE, Synopsys HSPICE, Orcad PSPICE, Cadence Spectre, and others. Using these techniques, hardened memory designs have been explored and the propagation of SETs in core logic has been studied. However, as circuits grow exponentially in density and complexity, comprehensive circuit simulation is impractical. Over the past decade, other methods to track radiation vulnerability at the circuit level have emerged, primarily in the realm of core logic.

In the mid 1990s, Baze and Buchner performed a series of circuit simulations and laser experiments on combinational logic to extract general properties of single-event propagation [23], [149]. They concluded that: 1) the soft error rate is independent of the frequency in latch circuits when the setup and hold time is much less than clock period; 2) the soft error rate increases linearly with the operating clock frequency in the combinational circuits; and 3) soft errors in latch circuits dominate in present day technologies, but the errors in the combinational circuits will dominate in future technologies.

In 1997, Massengill *et al.* [150] presented a probabilistic description of single-event fault generation, propagation, and logic error events using a high-level VHDL circuit description. This method was demonstrated in simulation code at NSREC in 2000 [151]. Seifert *et al.* [24], [117] have presented an analytical description of core logic soft error vulnerability based on the "window of vulnerability" of in-data-path static and dynamic latch elements, the synchronous clock, and other deterministic elements.

#### D. Mixed Device/Circuit Simulations

It should be obvious from the preceding sections that the tight coupling of device and circuit response to incident particle strikes significantly complicates SEU modeling. In SRAMs, for example, device modeling of the struck transistor with typical constant boundary conditions (or even including passive, lumped elements) will never result in an upset being observed in the simulation-by construction the device will always return to its prestrike state. The best that can be done in this situation is to study the charge-collection characteristics of the struck device and compare the collected charge to some critical charge to upset. However, the usefulness of this approach is extremely limited for SRAMs, since the charge-collection characteristics are greatly influenced by external loading and the feedback mechanism in latches [58]. Nevertheless, unloaded device simulation has been useful for studying the basic physical properties of charge collection, and for studying DRAMs, where loading effects are not as prevalent and critical charge is well defined by noise margins [19].

As discussed in the previous section, for studying the upset process itself in SRAMs, circuit simulation has been a useful tool. One strength of this approach is the large scale of the circuit in question that can be modeled; another is its computational efficiency. A drawback is the accuracy of the transient current used as the input stimulus. For example, if the current is based on device simulations of a struck, unloaded device [152], then the circuit simulation inherits the inaccuracy of the improperly loaded device simulation. Still, circuit simulations have provided considerable insight into SEU in memories and have resulted in improvements to hardening techniques for a variety of circuits [12], [87], [103], [153], [154].

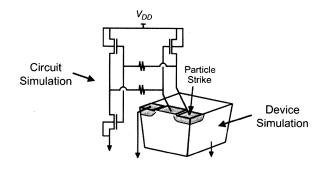

Recently, the simultaneous solution of device and circuit equations has been increasingly used. This technique, known as mixed-mode or mixed-level simulation, was developed by Rollins at USC/Aerospace in the late 1980s [155]. The term "mixed-level" is probably less confusing and more descriptive than "mixed-mode." In a mixed-level simulation of SEU, the struck device is modeled in the "device domain" (i.e., using multi-dimensional device simulation), while the rest of the memory cell is represented by SPICE-like compact circuit models, as illustrated in Fig. 9 [58]. The two domains are tied together by the boundary conditions at contacts, and the solution to both sets of equations is rolled into one matrix solution [155], [156]. The advantage is that only the struck device is modeled in multiple dimensions, while the rest of the circuit consists of computationally efficient SPICE models. This decreases simulation times and greatly increases the complexity of the external circuitry that can be modeled. Mixed-level capability has been incorporated into most of the commercially-available 3-D device codes [144]-[147]. These codes were first used to study SEU in CMOS SRAMs in 1991 [157] and since then have received a great deal of continued use for this purpose [49].

## E. Recent Enhancements

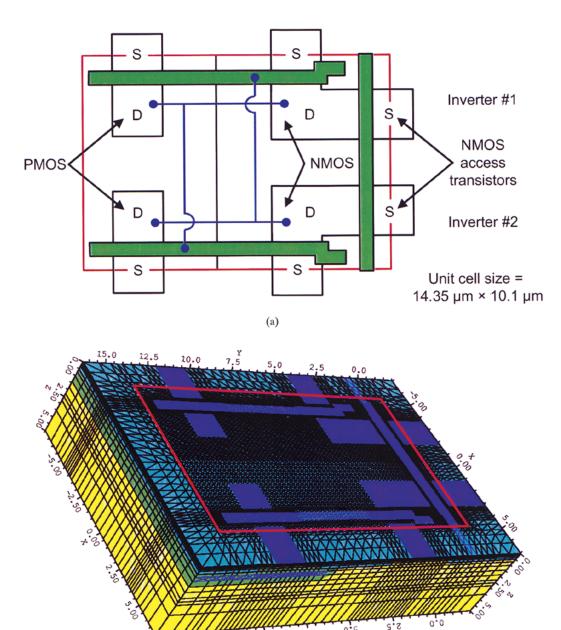

A drawback of the mixed-level method is that coupling effects between adjacent transistors have been shown to exist at the device level using 2-D simulations [129]. These effects cannot be taken into account when only the struck device is modeled at the device level. To address this difficulty, it is necessary to simulate the entire SRAM cell in the 3-D device domain [158]. An illustration of the technique is shown in Fig. 10 [93]. Fig. 10(a) shows a top-down view of the SRAM cell layout, while Fig. 10(b) shows the actual computational mesh used for simulations. When compared to the results of standard mixed-level simulations, it has been found that in cases where no coupling effects between transistors exist, mixed-level simulations are adequate to reproduce the full SRAM cell results. For some strike locations, however, coupling effects between adjacent transistors are observed [158], [159]. Mixed-level simulations are incapable of predicting such effects. As interdevice spacing decreases with increasing integration levels, coupling effects can be expected to become more important, and simulating the entire SRAM cell in the device domain may become routinely necessary [158].

Standard single-point (i.e., one ion strike location) 3-D mixed-level simulations are known to predict upset thresholds in very good agreement with measured thresholds [63]. In these simulations, the most sensitive strike location is assumed based on past experience. However, error rates in ICs are dependent not only on the threshold LET, but also on the sensitive area, which cannot be obtained from a single-point simulation. Researchers have generated simplified step-function cross-section curves from theoretical and simulation results by making assumptions about the sensitive area [160], [161]. Charge-collection contours in an SOI transistor have also been calculated using 2-D simulations [162]. Using a customized version of a commercial 3-D device simulator running on a large parallel computer, researchers have recently demonstrated the ability

Fig. 9. Mixed-mode simulation structure for SRAM cells. Iillustration is of an n-channel "off" drain strike [58].

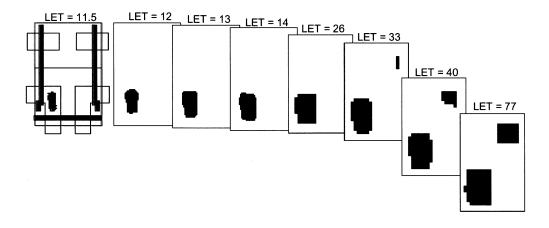

to directly compute the upset cross section of an SRAM [93]. These simulations were based on full-cell simulations, but separate simulations were performed for ion strikes incident every 0.5  $\mu$ m throughout an SRAM unit cell. One set of simulations gave a map of the SEU-sensitive area of the SRAM unit cell for a given ion and energy. By repeating the simulations for several ion/energy combinations, the authors generated the evolution of the sensitive area as a function of ion LET, as shown in Fig. 11. Combining the information in the individual upset maps, the full upset cross-section curve was predicted and found to be in excellent agreement with experimental results [93]. The simulated cross section curve was based on nearly 7000 individual soft error simulations and took about 3 months to perform on 30 nodes of a parallel computer. Continued advances in computational power may make such simulations more feasible in the future.

Techniques like mixed-level simulation are useful for in-depth studies of SEU in specific small-scale circuits and for given ion strikes. A system designer, however, is more likely to be interested in the total error rate for a large circuit containing many transistors and operating in some particular environment of interest. Because this is a very difficult problem, requiring detailed environmental models, the probability that a given ion strike causes an SEU is usually treated using analytical methods such as the rectangular parallelepiped (RPP) model. Typical methods of solution are covered elsewhere in this issue. Two groups have recently reported on large-scale SEU simulation systems that are aimed at predicting system error rates using a more first-principles basis of the interaction of ions with devices [163]–[165].

## **VIII.** FUTURE TRENDS

One of the biggest concerns for SEU is how technology trends will impact device susceptibility in the future. In this section, we discuss key technology drivers, how technology trends may affect hardening strategies, and the phenomenon of SEEs in ground-based and aircraft microelectronics, a topic of growing concern as devices become more susceptible to SEU.

#### A. Technology Drivers Impacting SEEs

Key technology parameters that influence SEU sensitivity include gate length, gate and drain area, and power supply voltage. If all parameters are taken into account, the overall trend is a general increase in SEU susceptibility with each

Fig. 10. (a) Layout of 256K six-transistor SRAM unit cell (D = drain and S = source). Red box indicates the boundaries of the unit cell, green regions are the gate polysilicon lines, and blue lines show the interconnections within the unit cell. (b) View of 3-D unit cell as laid out in device simulator. Mesh size is approximately 100 000 points [93].

(b)

0.01

12.5

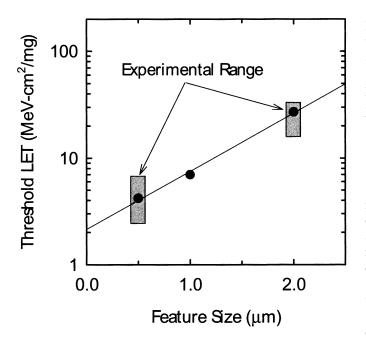

technology generation. This trend is shown in Fig. 12, which is a plot of the simulated and experimentally measured SEU threshold for SRAMs without feedback resistors in three recent Sandia CMOS technologies [63]. A factor that is at least as important as the fundamental changes to the physics is simply the reduction in total capacitance as technologies shrink. Remember that the feedback time for the SRAM cell is to first order related to the RC delay in the inverter pair. As device areas shrink, the gate and drain capacitance shrinks, making the device faster but consequently much more susceptible to SEU. SEU is therefore a grave concern for scaled technologies.

Another area that is becoming increasingly important is the propagation of SETs in digital logic circuits. The problem here is that as circuit speeds rise, the probability that a momentary glitch will be clocked as valid data and propagated through the logic path increases. For example, in Fig. 6 we saw that even a particle well below the upset threshold can cause a momentary flip in the state of an SRAM cell. Consider the case where this memory cell is actually a latch circuit in a microprocessor. In the example of Fig. 6, if this latch value is read 10 ps after an ion strike and the value is clocked down the line, it matters little that the struck latch eventually returns to its original state, because the corrupt value has already been passed on to the next stage of the circuit. These types of errors are likely to become a pervasive problem as clock speeds continue to increase and will be difficult to protect against, especially in commercial mi-

Fig. 11. Evolution of the soft-error sensitive area (black regions) of a 256K SRAM unit cell without feedback resistors as a function of increasing ion LET. Note increasing sensitive area of reverse-biased NMOS drain. At an LET of 33 MeV- $cm^2/mg$ , the reverse-biased PMOS drain also becomes SEU-susceptible.

Fig. 12. Overall SEU threshold LET technology trend for three generations of Sandia CMOS SRAMs without feedback resistors [63]. Points are the results of 3-D mixed-level simulations, and shaded regions are the measured range.

croprocessors where speed is paramount. It has been predicted that for circuits built in technologies below  $0.35 \,\mu$ m, propagated SETs will be a primary SE failure mode [115]. Temporal sampling circuit approaches have been developed that prevent the propagation of SETs and also provide the equivalent of triple spatial redundancy [115].

## **B.** Hardening Design Strategies

A considerable concern for SRAMs requiring SEU hardness in the future is whether traditional resistive hardening techniques will remain a viable option. The resistive decoupling technique is fundamentally incompatible with high speed because it relies on slowing the cell down so that it cannot respond quickly to SEU voltage transients. This tends to mean that the write performance of hardened SRAM cells has to be kept at a nearly constant level to maintain a constant level of SEU hardness. Also, because a smaller, faster SRAM cell has lower capacitance, the feedback resistance required to harden the cell has to be raised to compensate. Such large resistors are very difficult to controllably manufacture and show a significant temperature dependence [101]. Because of this problem and stagnant performance levels, it is likely that for applications requiring a high level of SEU hardness, devices below about 0.5- $\mu$ m will utilize other hardening techniques, such as SOI, active feedback elements, or circuit hardening.

## C. Terrestrial and High-Altitude SEEs

Much of this review has concentrated on the natural space radiation environment and its effect on microelectronics. A radiation environment also exists in the Earth's atmosphere and, although less harsh than the space environment, it can also give rise to SEE. The terrestrial radiation environment is covered elsewhere in this issue and will not be described here; in this section, we briefly discuss the interaction of this environment with microelectronics in aircraft systems and at ground level.

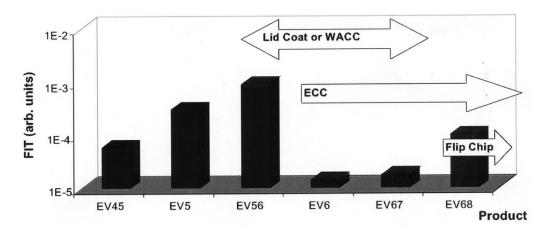

As discussed in Section II, SEU in terrestrial electronics was discovered in the late 1970s and was recognized as a significant reliability concern. However, after considerable early activity, the terrestrial soft error problem was effectively alleviated by using low-activity materials and on-chip shielding coatings [5], [6]. Occasionally, changes in suppliers or procedures have caused semiconductor manufacturers temporary but considerable headaches due to raised radioactive contaminant levels in materials such as nitric and phosphoric acid [5], [166]. The march toward higher integration densities has made soft-error concerns a continual design consideration for advanced DRAM and SRAM development in the last decade. A particular area of recent concern is flip-chip packaging technologies that place a source of alpha particles (Pb-Sn solder bumps) right on the die itself, where they cannot be shielded by coating layers [167]. Elimination of materials rich in <sup>10</sup>B, such as BPSG dielectric layers, has been shown to reduce the thermal neutron soft error rate (SER) by several orders of magnitude [168], [169].

Even in the absence of on-chip sources of radiation, recent studies have conclusively proved that terrestrial cosmic rays (primarily neutrons) are a significant source of soft errors in both DRAMs and SRAMs [170]–[172]. Upsets have been observed both at ground level and in aircraft and have been con-

vincingly correlated to the altitude and latitude variation of the neutron flux [173], [170], [172]. Lage *et al.* have shown that even without alpha particles, a baseline of cosmic-ray upsets still exists for high-density SRAMs [171]. O'Gorman has shown that neutron upsets disappear for DRAMs placed 200 m underground in a salt mine, while they increase dramatically for systems operated above 10 000 feet in Leadville, CO [170]. In addition to SEU observed in memories used in large computer systems and aircraft, upsets have been observed in SRAMs used in implantable medical devices such as cardiac defibrillators [174].

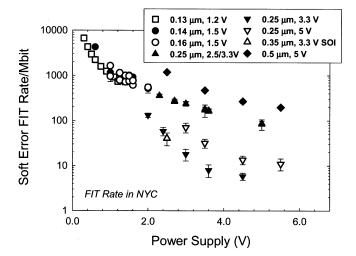

Fig. 13 shows the measured cosmic-ray neutron SER versus power supply voltage in several generations of SRAMs from a variety of vendors [175]. Terrestrial soft error failure rate specifications are usually given in terms of FIT rates, where FIT = Failure in Time = 1 error in  $10^9$  device hours. In this figure, SER is reported in FIT/Mb of memory to allow comparison between memories of different sizes. For reference, an uncorrected SER of 1000/Mb would lead to one error every three weeks in a system with 256 MB of memory. From this figure, it is clear that low-voltage SRAMs exhibit unacceptably high SER without error correction and that different IC technologies can have SER varying by two orders of magnitude at a given voltage.

Destructive SEEs can also occur in ground-based systems. For example, neutron-induced single-event burnout has caused destructive failures in large-area high-voltage power diodes used for railroad applications in Europe [176]. It has recently been experimentally demonstrated that significant neutron-induced latchup rates can occur in high-density SRAMs at ground level [175].

Revelations such as these have significant implications for manufacturers of commercial memory chips and computer systems, because systems cannot realistically be shielded against incident neutrons. Meeting specified failure rates is expected to be a significant challenge for commercial semiconductor manufacturers. A typical specification is to maintain a FIT rate less than 1000 [171]. A complicating factor is that since FIT rates are often specified *per device*, meeting a constant FIT rate specification actually requires reducing the error rate *per bit* as the number of bits per device is increased.

It has been suggested that because manufacturers of commercial microelectronics for terrestrial applications have had to deal with alpha-particle-induced upsets from packaging materials, commercial parts will by design remain hard to at least the alpha-particle threshold [177]. Indeed, there is historical evidence supporting this view as data from more than ten years of microprocessor evolution show a constant upset threshold just above the threshold for alpha particle upset [177]. However, it is also known that many manufacturers have specific soft-error driven design rules for placement of devices relative to on-chip solder bumps and/or use hardened circuit designs for I/O circuitry that must be in the vicinity of such on-chip alpha sources [178]. This clearly implies that many devices being manufactured are in fact already below the alpha-particle threshold for upset.

Many of the techniques traditionally used in the radiation effects community to SEU-harden devices are of such a nature that they are unlikely to be adopted by commercial manufacturers. They tend to consume more power, reduce manufacturability,