#### Analog Circuit Design Series Volume 3

## **Designing High-Performance Amplifiers**

### **D. Feucht** Innovatia Laboratories

Published by SciTech Publishing, Inc. 911 Paverstone Drive, Suite B Raleigh, NC 27615 (919) 847-2434, fax (919) 847-2568 scitechpublishing.com

Copyright © 2010 by Dennis Feucht. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United Stated Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600, or on the web at copyright.com. Requests to the Publisher for permission should be addressed to the Publisher, SciTech Publishing, Inc., 911 Paverstone Drive, Suite B, Raleigh, NC 27615, (919) 847-2434, fax (919) 847-2568, or email editor@scitechpub.com.

The publisher and the author make no representations or warranties with respect to the accuracy or completeness of the contents of this work and specifically disclaim all warranties, including without limitation warranties of fitness for a particular purpose.

Editor: Dudley R. Kay Production Manager: Robert Lawless Typesetting: SNP Best-set Typesetter Ltd., Hong Kong Cover Design: Aaron Lawhon Printer: Docusource

This book is available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information and quotes, please contact the publisher.

Printed in the United States of America

10 9 8 7 6 5 4 3

#### ISBN: 9781891121845 Series ISBN: 9781891121876

Library of Congress Cataloging-in-Publication Data Feucht, Dennis. Designing high-performance amplifiers / D. Feucht. p. cm. – (Analog circuit design series ; v. 3) Includes bibliographical references and index. ISBN 978-1-891121-84-5 (pbk. : alk. paper) – ISBN 978-1-891121-87-6 (series) 1. Amplifiers (Electronics)–Design and construction. 2. Electronic circuit design. I. Title. TK7871.2.F478 2010 621.3815'35–dc22 2009028290

#### Copyrighted Materials Copyright © 2010 SciTech Publishing Retrieved from www.knovel.com

## Preface

Solid-state electronics has been a familiar technology for almost a half century, yet some circuit ideas, like the transresistance method of finding amplifier gain or identifying resonances above an amplifier's bandwidth that cause spurious oscillations, are so simple and intuitively appealing that it is a wonder they are not better understood in the industry. I was blessed to have encountered them in my earlier days at Tektronix but have not found them in engineering textbooks. My motivation in writing this book, which began in the late 1980s and saw its first publication in the form of a single volume published by Academic Press in 1990, has been to reduce the concepts of analog electronics as I know them to their simplest, most obvious form, which can be easily remembered and applied, even quantitatively, with minimal effort.

The behavior of most circuits is determined most easily by computer simulation. What circuit simulators do not provide is knowledge of what to compute. The creative aspect of circuit design and analysis must be performed by the circuit designer, and this aspect of design is emphasized here. Two kinds of reasoning seem to be most closely related to creative circuit intuition:

- 1. Geometric reasoning: A kind of visual or graphic reasoning that applies to the topology (component interconnection) of circuit diagrams and to graphs such as reactance plots.

- 2. Causal reasoning: The kind of reasoning that most appeals to our sense of understanding of mechanisms and sequences of events. When we can trace a chain of causes for circuit behavior, we feel we understand how the circuit works.

These two kinds of reasoning combine when we try to understand a circuit by causally thinking our way through the circuit diagram. These insights, obtained

by *inspection*, lie at the root of the quest. The sought result is the ability to write down accurate circuit equations by inspection. Circuits can often be analyzed multiple ways. The emphasis of this book is on development of an intuition into how circuits work with a perspective that can be applied more generally to circuits of the same class.

The previous two volumes of this Analog Circuit Design series, Designing Amplifier Circuits and Designing Dynamic Circuit Response, provide the needed concepts for the investigation of fast and precise, or *Designing high-performance*, amplifiers as covered in this third volume. Much of the technology appearing here has been derived from the tradition of excellence in engineering found at Tektronix in the development of oscilloscopes and other electronic test and measurement instruments. It begins by considering the parameters of merit by which amplifier performance can be assessed and then the optimization of stage gain in a multistage amplifier of limited stage bandwidth. The method of characterizing amplifier performance in the complex-frequency or s-domain is continued, along with an intuitive method for determining poles of circuits without grinding through too much algebra. Bandwidth extension techniques using inductors is next, including a little-known method originating at Tektronix, applied notably to oscilloscope products by Carl Battjes, Bob Ross, and John Addis, known as *T-coil* peaking – another marvelous performance enhancer that has yet to become widely known. Some circuits deserve special attention, such as the source follower and shunt-feedback amplifier.

After concentrating on speed, the topics turn toward the other dimension of high performance, that of precision. Noise and distortion are topics as are the circuits of precision, operational amplifiers (op-amps), and instrumentation amplifiers. The bipolar junction transistor (BJT) differential pair is given more detailed treatment, as is thermal distortion, a topic that must be considered when setting the static operating point (or *bias*) of amplifier circuits. The often used complementary emitter-follower as a power driver output stage is given particularly detailed analysis and simplification so that the various oddities in its response have a simple explanation.

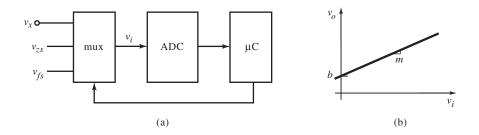

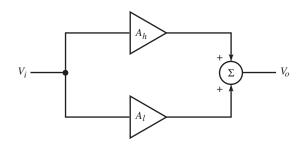

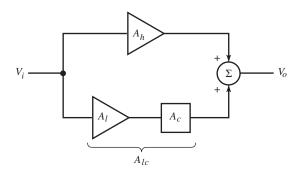

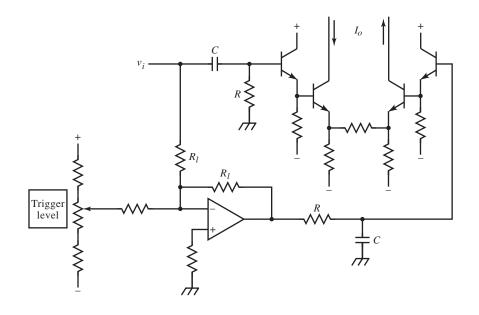

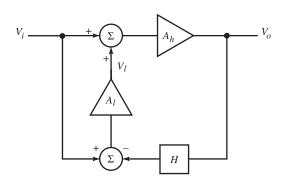

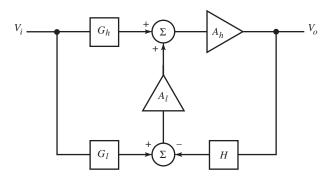

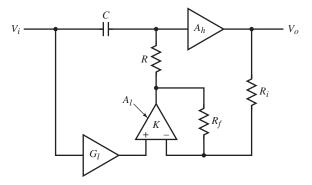

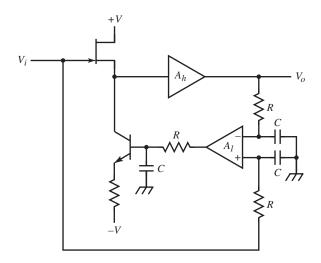

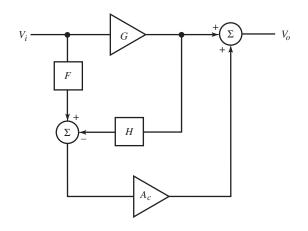

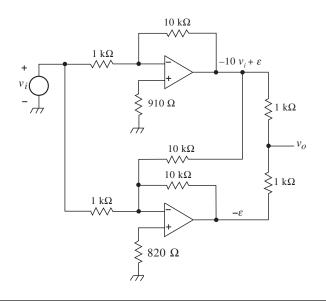

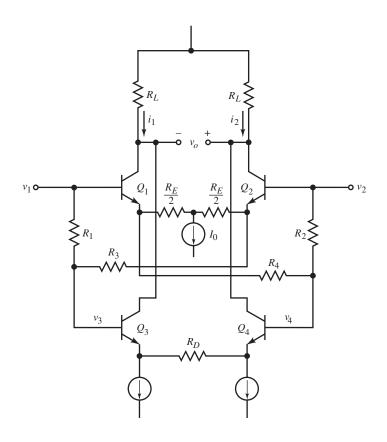

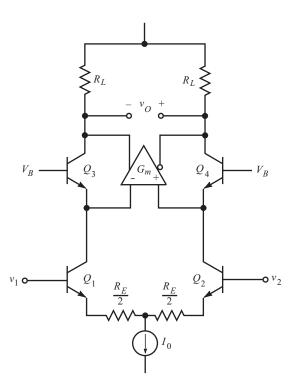

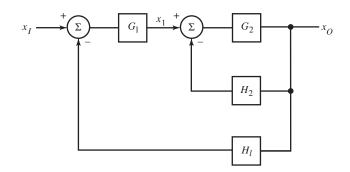

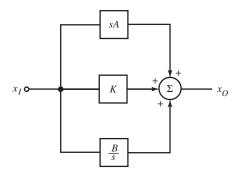

After this, speed and precision are combined to produce the highest in amplifier performance, deserving of a full chapter. It starts with well-known currentinput and current-feedback amplifiers and then covers another lesser-known topic: composite amplifiers. These have multiple paths to the output and are introduced first in block diagram form and then with some wonderful circuits, many originating at Tektronix. At center stage of these methods are feedforward amplifiers and Barrie Gilbert's translinear circuits, a conceptual breakthrough during the 1960s. Translinear circuits are simplified by reducing what historically was exponential math to ratios of sums and differences, and hopefully more engineers will venture into their use, for they are "powerful." Buffers receive special treatment, and a variety of other nifty circuits are also presented. Multipliers and programmable-gain amplifiers (PGAs) end this volume.

Much of what is in this book must be credited in part to others from whom I picked up essential ideas about circuits at Tektronix, mainly in the 1970s. I am particularly indebted to Bruce Hofer, a founder of Audio Precision Inc.; Carl Battjes, who founded and taught the Tek Amplifier Frequency and Transient Response (AFTR) course; Laudie Doubrava, who investigated power supply topics; and Art Metz, for his clever contributions to a number of designs, some extending from the seminal work on translinear circuits by Barrie Gilbert, also at Tek at the same time. Then there is Jim Woo, who, like Battjes, was another oscilloscope vertical amplifier designer; Ian Getreu and Bob Nordstrom, from whom I learned transistors; and Mike Freiling, an artificial intelligence researcher in Tektronix Laboratories whose work in knowledge representation of physical systems influenced my broader understanding of electronics.

In addition, in no particular order, are Fred Beckett, Lee Jalovec, Wayne Kelsoe, Cal Diller, Marv LaVoie, Keith Lofstrom, Peter Staric, Erik Margan, Tim Sauerwein, George Ermini, Jim Geddes, Carl Hollingsworth, Chuck Barrows, Dick Hung, Carl Matson, Don Hall, Phil Crosby, Keith Ericson, John Taggart, John Zeigler, Mike Cranford, Allan Plunkett, Neldon Wagner, and Paul Magerl. These and others I have failed to name have contributed personally to my knowledge as an engineer and indirectly to this book. Most of all, I am indebted to the creator of our universe, who made electronics possible. Any errors or weaknesses in this book, however, are my own.

#### Copyrighted Materials Copyright © 2010 SciTech Publishing Retrieved from www.knovel.com

## Contents

| Chapter 1 Wideband Amplification 1                    |

|-------------------------------------------------------|

| Multiple-Stage Response Characteristics1              |

| Amplifier Stage Gain Optimization                     |

| Pole Determination by Circuit Inspection10            |

| Inductive Peaking                                     |

| Bootstrap Speed-Up Circuit                            |

| Source-Follower Compensation                          |

| Emitter Compensation                                  |

| Cascode Compensation of the Common-Base Stage         |

| Compensation Network Synthesis                        |

| Differential-Amplifier Compensation                   |

| Shunt-Feedback Amplifier Design                       |

| Shunt-Feedback Cascode & Darlington Amplifiers        |

| Closure                                               |

| Chapter 2 Precision Amplification                     |

| Causes of Degradation in Precision                    |

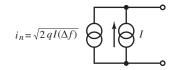

| Intrinsic Noise                                       |

| Extrinsic Noise: Radiation & Crosstalk                |

| Extrinsic Noise: Conductive Interference              |

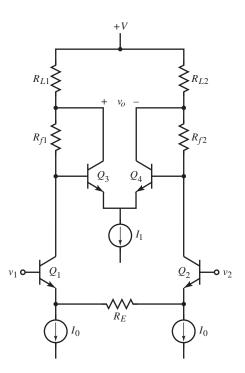

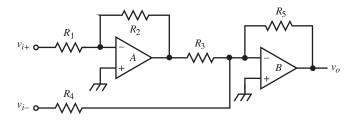

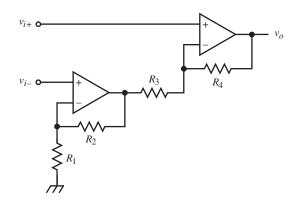

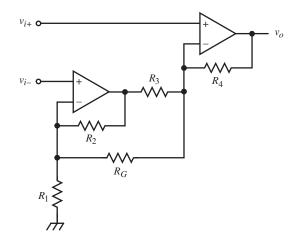

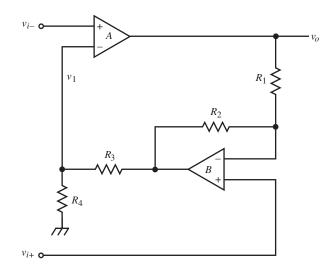

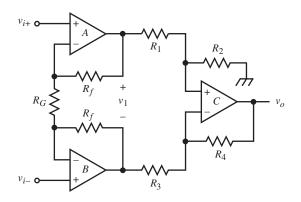

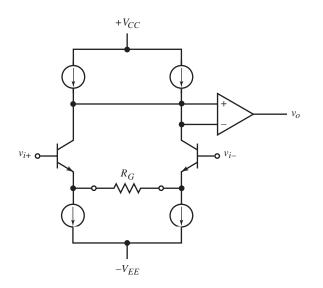

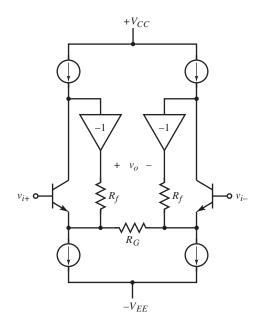

| Differential Amplifiers                               |

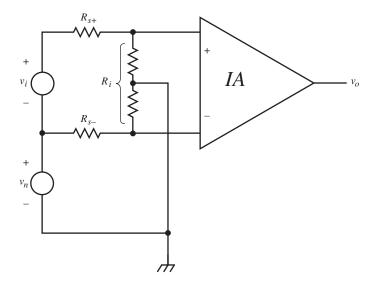

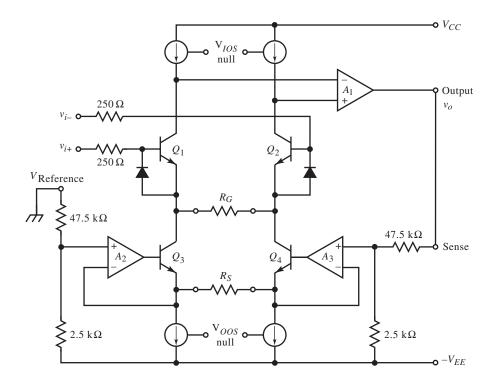

| Instrumentation Amplifiers                            |

| Low-Level Amplification and Component Characteristics |

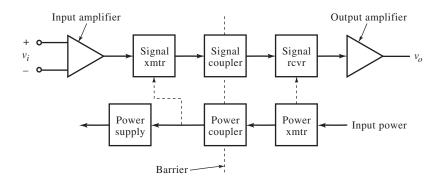

| Isolation Amplifiers                                  |

| Autocalibration                                       |

| Distortion                                                      | 6 |

|-----------------------------------------------------------------|---|

| Transconductance Linearity of BJT Diff-Amp                      | 2 |

| BJT and FET Diff-Amp Temperature Characteristics                | 7 |

| Thermal Distortion                                              | 7 |

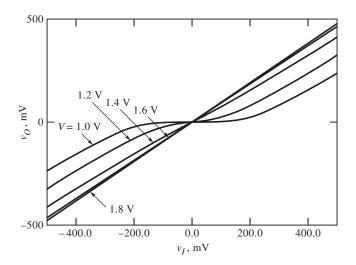

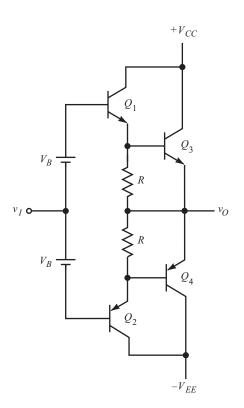

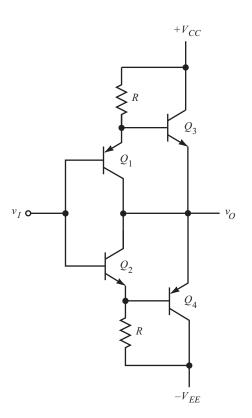

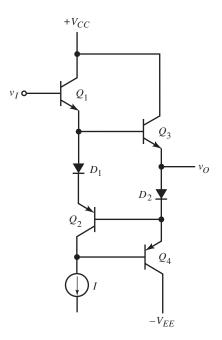

| Complementary Emitter-Follower Output Amplifier                 | 0 |

| Buffer Amplifier Design                                         | 3 |

| Chapter 3 High-Performance Amplification                        | 9 |

| Current-Input & Current-Feedback Amplifiers19                   | 9 |

| Split-Path, Low-Frequency Feedback and Feedbeside Amplifiers209 | 9 |

| Feedforward and Linearized Differential Cascode Amplifiers      | 1 |

| α-Compensated Gain Cells                                        | 8 |

| $f_T$ Multipliers                                               | 2 |

| High-Performance Buffer Amplifiers                              | 7 |

| Unipolar Voltage-Translating Amplifiers245                      |   |

| Bootstrapped Input Stages                                       | 9 |

| Composite-Feedback & Large-Signal Dynamic Compensation25        |   |

| The Gilbert Gain Cell and Multiplier25'                         |   |

| Programmable-Gain Amplifiers                                    | 9 |

| References                                                      | 5 |

| Index                                                           | 9 |

#### Copyrighted Materials Copyright © 2010 SciTech Publishing Retrieved from www.knovel.com

# **1** Wideband Amplification

Some amplifiers are performance limited mainly by speed. Oscilloscope vertical amplifiers, pulse and function generator output amplifiers, and video and nuclear signal-processing amplifiers are often speed limited. Fast amplifiers are usually open-loop, limited-gain stages, such as those analyzed at low frequency in *Designing Amplifier Circuits*, with one or two transistors per stage. New techniques have increased the speed of operational amplifer (op-amp) circuits, but the fastest amplifiers consist of limited-gain stages. For the fastest speed, these amplifiers are integrated to reduce parasitic reactances. Examined first is the strategy of amplifier design before analyzing various bandwidth extension techniques.

#### **MULTIPLE-STAGE RESPONSE CHARACTERISTICS**

The speed of an amplifier can be expressed by its response to a step input. For a single-pole amplifier with pole  $p = 1/\tau$ , the response to a unit step input can be characterized by its risetime. A single-pole amplifier has a transfer function of the form

$$A(s) = K \cdot \frac{1}{s/p+1}$$

with pole at -p. The pole is also at the bandwidth

$$\omega_{bw} = p$$

From the risetime formula, the single-pole risetime is

$$t_r = \tau \cdot \ln(9) \cong 2.2 \cdot \tau = \frac{2.2}{p} \cong \frac{0.35}{f_{bw}}$$

The unit step response is

$$v_{step}(t) = K \cdot \left(1 - e^{-pt}\right)$$

These equations assume a linear amplifier (or that small-signal analysis is valid). Large-signal amplifier behavior occurs when a waveform reaches the limit of its linear range. What often results is waveform slewing, in which waveform change is rate limited and characterized by its *slew rate*. The maximum slew rate of a waveform is determined by its maximum instantaneous slope and amplitude. The *full-power bandwidth*  $f_{BW}$  of an amplifier is related to the maximum slew rate of a sinusoid that spans the dynamic range of the amplifier. Differentiating the sinusoid and solving for the maximum value,

maximum slew rate =

$$\frac{d}{dt} (V_m \cdot \sin \omega_{BW} t) \Big|_{\max} = \omega_{BW} \cdot V_m$$

The sinusoid changes over its full range in the slewing time:

$$t_{slew} = \frac{2V_m}{\omega_{BW}V_m} \cong \frac{0.32}{f_{BW}}$$

When  $f_{bw} = f_{BW}$ ,  $t_{slew}$  is nearly the same as the risetime given above. A more general comparison of large- and small-signal risetime follows by finding the time it takes to slew from 10% to 90% of the final value. This time is

slewing

$$t_r = \frac{(0.8) \cdot 2 \cdot V_m}{\omega_{BW} \cdot V_m} \cong \frac{0.26}{f_{BW}}$$

When an amplifier operates with some slewing, the bandwidth lies between  $f_{BW}$  and  $f_{bw}$  where always  $f_{BW} < f_{bw}$ .

Another quantity that characterizes speed is time delay  $t_d$ , defined as the time that the response to a unit step input takes to reach half of its final value. It is found by setting  $v_{step}$  to 0.5 and solving for t:

$$t_d = \tau \cdot \ln\left(2\right) = \frac{\ln 2}{p} \cong \frac{0.69}{p} \cong \frac{0.11}{f_{bw}}$$

Delay time is useful for measuring the propagation delay of linear logic circuits, such as logic gates.

Fast amplifiers usually consist of several cascaded gain stages. An amplifier with *n* single-pole stages with poles at -p has a transfer function of the form

$$A(s) = K \cdot \frac{1}{\left(s/p+1\right)^n}$$

The unit step response of A(s) is

*n*-stage

$$v_{step} = \mathscr{L}^{-1}\left\{A\left(s\right) \cdot \frac{1}{s}\right\} = Kp^{n}\left(1 - e^{-pt}\sum_{k=0}^{n-1} \frac{t^{k}}{k!}\right)$$

Calculation of the risetime from this equation can be difficult. A simpler alternative is to derive expressions for bandwidth. The bandwidth of a single-pole amplifier is the pole frequency, or

$$\omega_{bw} = p$$

The magnitude at bandwidth of a single-pole stage with static gain of *K* is found by setting  $\omega$  to *p*:

$$||A(jp)|| = K \cdot \frac{1}{\sqrt{(\omega/p)^2 + 1}}|_{\omega = p} = K \cdot \frac{1}{\sqrt{2}}$$

An n-stage amplifier with single-pole stages has a transfer function of the form

*n*-stage

$$A(s) = K \cdot \frac{1}{(s/p+1)^n}$$

When the magnitude of  $A(j\omega)$  has rolled off to that of a single-pole stage, as in ||A(jp)||, this is the *n*-stage bandwidth:

$$\|A(j\omega)\| = K \cdot \frac{1}{\left[\left(\omega/p\right)^2 + 1\right]^{n/2}} = K \cdot \frac{1}{\sqrt{2}}$$

Solving for  $\omega = \omega_{bw}$ , and expressing it as a fraction of *p* by defining the *bandwidth shrinkage* or *bandwidth reduction factor*, *S*, then

$$S(n) = \frac{\omega_{bw}}{p} = \sqrt{2^{1/n} - 1}$$

Fast amplifiers usually have stages with quadratic pole factors in their transfer functions. The same kind of derivation of S(n) assumes an *n*-stage amplifier transfer function of the form

$$A(s) = K \cdot \frac{1}{\left(s^2 \tau_n^2 + 2\zeta \tau_n s + 1\right)^n}$$

Setting the magnitude of A(s) to that of a single-pole amplifier at bandwidth results in the expression

$$\|A(j\omega)\| = K \cdot \left(\frac{1}{\left(1 - \tau_n^2 \omega^2\right)^2 + \left(2\zeta \tau_n \omega\right)^2}\right)^{n/2} = K \cdot \frac{1}{\sqrt{2}}$$

The pole factor of A(s) does not contain p, and the bandwidth is related to the single-pole stage by  $\omega_n$ . (See *Designing Dynamic Circuit Response*, "Optimization of Time-Domain and Frequency-Domain Response" for derivation of bandwidth.) Solving for  $\omega$  in terms of  $\omega_n$ , the result is

$$S(n) = \frac{\omega_{bw}}{\omega_{n}} = \left(1 - 2\zeta^{2} + \sqrt{4\zeta^{4} + 4\zeta^{2} + 2^{1/n}}\right)^{1/2}$$

For *n* critically damped stages,

$$S(n) = \sqrt{2^{1/2n} - 1}, \quad \zeta = 1$$

A one-stage critically damped amplifier has S = 0.64, whereas for four stages *S* is about 0.3. For maximally flat envelope delay (MFED) stages ( $\zeta = \sqrt{3}/2$ ), with n = 1,  $S \cong 0.786$ ; with n = 4,  $S \cong 0.4$ . When the number of stages increases to 10,  $S \cong 0.25$ . For MFED response, *n* stages have the approximate *S* of

$$S_{\rm MFED} \cong \frac{0.786}{\sqrt{n}}$$

With these developments, we return to consider the risetime of multistage amplifiers. The transfer-function magnitude for a general amplifier of n poles is of the form

$$\|A(j\omega)\| = \frac{K}{\left[1 + \omega^2 \sum_{i} (1/p_i^2) + \omega^4 \sum_{i} \sum_{j} (1/p_i^2 p_j^2) + \cdots\right]^{1/2}} \cong \frac{K}{\left(1 + \omega^2 \sum_{i} \tau_i^2\right)^{1/2}}$$

where  $1/p_i = \tau_i$ . The higher-order terms in  $\omega$  are negligible for widely separated poles at much higher frequencies. The sum of time constants in the  $\omega^2$  term can be regarded as an equivalent single-pole time constant of

$$au \cong \sqrt{\sum_i au_i^2}$$

From  $t_n$ , an approximate risetime is therefore

$$t_r \cong 2.2\tau = 2.2\sqrt{\sum_i \tau_i^2} = \sqrt{\sum_i (2.2\tau_i)^2} = \sqrt{\sum_i t_{ri}^2}$$

In other words, the approximate risetime of a multistage amplifier is the square root of the sum of the squares of the risetimes of the individual stages. For *n* identical stages, risetime degrades by approximately  $\sqrt{n}$  that of a single stage.

#### **Example: Oscilloscope Risetime**

A 100 MHz oscilloscope has a probe with a 2 ns risetime. The total risetime is found by first calculating the risetime of the oscilloscope. Applying the  $t_r$  equation,

$$t_r \cong \frac{0.35}{10^8 \text{ Hz}} = 3.5 \text{ ns}$$

Then the total risetime is approximately

$$t_r \cong \sqrt{(3.5 \,\mathrm{ns})^2 + (2 \,\mathrm{ns})^2} = 4 \,\mathrm{ns}$$

An accompanying approximation to bandwidth can also be made since  $\tau$  is an equivalent single-pole time constant. From single-pole bandwidth,

$$\omega_{bw} \cong \frac{1}{\tau} = \sqrt{\sum_{i} \frac{1}{p_i^2}}$$

For *n* repeated poles, bandwidth, like risetime, degrades by approximately  $\sqrt{n}$ .

#### **AMPLIFIER STAGE GAIN OPTIMIZATION**

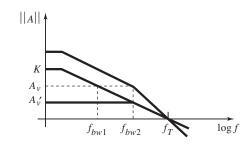

As the number of amplifier stages increases, bandwidth decreases. For a fastamplifier design strategy, therefore, the number of stages should be minimized. However, most amplifier designs also require a given overall gain. Reducing the stage count demands increased gain per stage. Amplifier stages have a gainbandwidth product,  $f_T$ , affected mainly by the active device. An increase of stage gain decreases stage bandwidth. An optimum stage gain,  $A_1(s)$ , that maximizes amplifier bandwidth,  $\omega_{bw}$ , for a given amplifier gain, A(s), is derived by first noting that

$\omega_{bw} = S \cdot \omega_1$

where  $\omega_1$  is the single-stage bandwidth. Then the gain-bandwidth product of the amplifier is expressed in relation to its stages as

$$A^{1/n} \cdot \boldsymbol{\omega}_{bw} = A_1(S \cdot \boldsymbol{\omega}_1)$$

assuming the *n*-stages have the same gain,

$$A_1 = A^{1/n}$$

Solving for  $\omega_{bw}$  yields

$$\boldsymbol{\omega}_{bw} = A_1 \cdot A^{-1/n} \cdot S(n) \cdot \boldsymbol{\omega}_1$$

The optimum number of stages is found by differentiating  $\omega_{bw}$  with respect to *n* to maximize bandwidth:

$$\frac{d}{dn}\omega_{bw} = A_{1} \cdot \omega_{1} \cdot \frac{d}{dn} \left[ S(n) \cdot A^{-1/n} \right]$$

For single-pole stages, S is substituted. S can be expressed differently by noting that

$$2^{1/n} = e^{\ln(2)/n} = \sum_{k=0}^{\infty} \frac{\left(\ln 2/n\right)^k}{k!} \cong 1 + \frac{\ln 2}{n}$$

Then

$$S(n) \cong \left(\frac{\ln 2}{n}\right)^{1/2} = \sqrt{\ln 2} \cdot n^{-1/2}$$

Substituting for S in the derivative above, the right side becomes

$$A_{1} \cdot \boldsymbol{\omega}_{1} \cdot \frac{d}{dn} \left( A^{-1/n} \cdot \sqrt{\ln 2} \cdot n^{-1/2} \right)$$

$$= A_{1} \cdot \boldsymbol{\omega}_{1} \sqrt{\ln 2} \cdot \left( A^{-1/n} \cdot \left( -\frac{1}{2} \right) \cdot n^{-3/2} + A^{-1/n} \cdot n^{-1/2} \cdot \frac{1}{n^{2}} \cdot \ln A \right)$$

To find the optimum number of stages  $n_{opt}$ , set the derivative to zero and solve. Then

$$n_{obt} = 2 \cdot \ln A$$

The optimum stage gain is

optimum

$$A_1 = A^{1/n_{opt}} = A^{1/2 \ln A} = e^{1/2} = \sqrt{e} \approx 1.65$$

This is not a large voltage or current gain. In practice, the optimum gain is somewhat larger than this value, usually around 2 to 3, due to bandwidth loss from interstage coupling.

Multistage amplifier frequency-response magnitude approaches a gaussian function as the number of stages increase. This gaussian response is quickly approached in practice by a few stages. It is derived by first rewriting  $||A(j\omega)||$  in terms of  $\omega_{bw}$  from S. Given  $p = \omega_{bw}/S$ , then

$$||A(j\omega)|| = \frac{K}{[(\omega/\omega_{bw})^2(2^{1/n}-1)+1]^{n/2}}$$

Next, as  $n \to \infty$  in  $2^{1/n}$ , and using the first two terms of the exponential series expansion,

$$2^{1/n} - 1 \rightarrow \frac{\ln 2}{n}, \quad n \rightarrow \infty$$

Substituting this into  $||A(j\omega)||$ , then

$$\|A(j\omega)\| \cong \frac{K}{\left[1 + (\omega/\omega_1)^2 (\ln 2/n)\right]^{n/2}} = \frac{K}{\left[1 + (2/n)(\omega/\omega_1)^2 (\ln 2/2)\right]^{n/2}}$$

$||A(j\omega)||$  is of the exponential form,

$$e^x = \lim_{x \to \infty} \left( 1 - \frac{x}{n} \right)^{-n}$$

So as  $n \to \infty$ ,

$$\|A(j\omega)\| = K \cdot e^{-(\ln 2/2) \cdot \left(\frac{\omega}{\omega_1}\right)^2}, \quad n \to \infty$$

This  $e^{x^2}$  form of ||A|| is the gaussian response function.

The maximum achievable bandwidth of an amplifier with a gaussian response is derived based on the unity-power-gain frequency  $f_{MAX}$ . If ||A|| is a power gain, then it can be expressed in decibel scaling as

$$\|A(j\omega)\|_{dB} = 10 \cdot \log K - 10 \cdot \left(\frac{\ln 2}{2}\right) \cdot \left(\log e\right) \cdot \left(\frac{f}{f_1}\right)^2 = \|A(0)\|_{dB} - c \cdot \left(\frac{f}{f_1}\right)^2$$

where c reduces to

$$c = 5 \cdot \log 2 \cong 1.51$$

The maximum bandwidth is achieved when ||A|| passes through  $f_{MAX}$  at unity power gain (0 dB). From  $||A(j\omega)||_{db}$ ,

$$||A(0)||_{dB} - c \cdot \left(\frac{f_{MAX}}{f_1}\right)^2 = 0$$

Solving for *c* and substituting it into  $||A(j\omega)||_{db}$ ,

$$||A||_{\mathrm{dB}} = ||A(0)||_{\mathrm{dB}} \cdot \left(1 - \frac{f^2}{f_{MAX}^2}\right)$$

The bandwidth is the frequency at which  $||A||_{dB}$  has rolled off by -3 dB:

$$\|A\|_{\mathrm{dB}} - \|A(0)\|_{\mathrm{dB}} = -3 = \|A(0)\|_{\mathrm{dB}} \cdot \left(-\frac{f^2}{f_{MAX}^2}\right)$$

The solution of this equation for f is the power-gain bandwidth  $f_{bw}$  and is

$$f_{bw} = f_{MAX} \cdot \sqrt{\frac{3}{\left\|A\left(0\right)\right\|_{\mathrm{dB}}}}$$

#### **Example: Oscilloscope Vertical Amplifier**

A wideband analog oscilloscope has a vertical deflection sensitivity of 2 V/cm at the cathode-ray tube (CRT) and a deflection plate termination resistance of 350  $\Omega$ . The input sensitivity is 50 mV/div into 100  $\Omega$  from the source when terminated by the 50  $\Omega$  scope input. The power gain is

$$||A(0)||_{dB} = 10 \cdot \log \left(\frac{(2 V/div)^2/350 \Omega}{(50 mV/div)^2/100 \Omega}\right) \approx 26.6 dB$$

The  $f_{MAX}$  is 2 GHz. The maximum  $f_{bw}$  is

$$f_{bw} = 2 \,\mathrm{GHz} \cdot \sqrt{\frac{3 \,\mathrm{dB}}{26.6 \,\mathrm{dB}}} = 672 \,\mathrm{MHz}$$

The actual bandwidth of the amplifier (without the CRT) is 550 MHz. The use of maximum bandwidth as a performance index can be taken as the ratio of actual to maximum theoretical bandwidth, or

$$\frac{550\,\mathrm{MHz}}{672\,\mathrm{MHz}} \cong 82\%$$

That is, 82% of the maximum achievable bandwidth is realized in the vertical amplifier, within 18% of the theoretical limit.

#### POLE DETERMINATION BY CIRCUIT INSPECTION

Circuit complexity increases as the number of reactive elements increases and makes derivation of the transfer function more difficult. At some complexity threshold (which varies among engineers), the urge to simulate the circuit by computer overwhelms the desire to achieve an intuitive understanding of it. Even for complexity that requires simulation, it is necessary to know what to simulate. Until circuit design is computerized, the choice of numeric values of circuit elements must be based on estimation techniques and qualitative reasoning.

Most circuits can be decomposed into *modules* with well-defined interfaces. Intrastage behavior is relatively free of interaction with other noncoupled stages. Interaction among modules can be considered apart from interaction within modules. The dynamic behavior of each circuit module can thus be determined individually, reducing the complexity of analysis.

A technique described by Cochrun and Grabel (1973) and streamlined by Rosenstark (1986) makes estimation of pole locations in active RC circuits simpler than solving the circuit for the transfer function. The degree of the characteristic equation (the transfer function denominator set to zero) equals the number of poles and the number of reactive circuit elements. Each capacitor in an RC circuit is associated with a pole. The characteristic equation in a normalized transfer function can be written as

$$D(s) = a_n s^n + a_{n-1} s^{n-1} + \dots + a_1 s + 1 = 0$$

The technique allows determination of the  $a_n$  from inspection of the circuit. The coefficients, in terms of circuit elements, are found as follows. The equation for  $a_1$  is

$$a_1 = \sum_{i=1}^n R_i (\text{open}) \cdot C_i = \sum \tau_i (\text{open})$$

$a_1$  is calculated as a procedure as follows

#### a<sub>1</sub> Procedure

- 1. Order the *C* by numbering them.

- 2. For each *C*, beginning with  $C_1$ , find the equivalent resistance across its terminals with all other *C* open. This is  $R_i$  (open). Multiply  $R_i$  (open) by  $C_i$  for  $\tau_i$  (open).

- 3. Sum the  $\tau_i$  (open) to obtain  $a_1$ .

This procedure is expedited by writing the time constants in the first column of a table beginning with  $\tau_1$  (open) in the top row and  $\tau_n$  (open) in the bottom row.

Next, for a multi-capacitor circuit,  $a_2$  is needed and is

$$a_2 = \sum_{i=1}^{n-1} \sum_{j=i+1}^n R_i(\text{open}) \cdot C_i \cdot R_j(C_i \text{ shorted}) \cdot C_j = \sum_{i=1}^{n-1} \sum_{j=i+1}^n \tau_i(\text{open}) \cdot \tau_j(C_i \text{ shorted})$$

The procedure for  $a_2$  continues the table by filling in the second column and then using the  $\tau_i$  (open) from the first column. All *C* not shorted are open when *R* is being found.

#### a<sub>2</sub> Procedure

- 1. For each  $C_i$ , do the following:

- a. Short  $C_i$ . For each C after  $C_i$  (in the order they were numbered in the  $a_1$  procedure), find the terminal R for  $C(C_j)$ . Multiply this  $R_j(C_i$  shorted) by  $C_i$  for  $\tau_i(C_i$  shorted).

- b. Multiply the  $\tau_i(C_i \text{ shorted})$  by  $\tau_i$  (open).

- 2. Add the time-constant products from step 1b to obtain  $a_2$ .

Each entry in the first column of the table from the  $a_1$  procedure will have n - i entries in the second column for each  $C_{j}$ .

For  $a_3$ , three summations are made, extending the  $a_2$  procedure. For the third column, two capacitors are shorted at a time (indices *i* and *j*), and *k* is indexed:

$$a_3 = \sum_{i=1}^{n-2} \sum_{j=i+1}^{n-1} \sum_{k=j+1}^{n} R_i(\text{open}) \cdot C_i \cdot R_j(C_i \text{ shorted}) \cdot C_j \cdot R_k(C_i, C_j \text{ shorted}) \cdot C_k$$

A way to keep the indexing straight is to base the entire procedure around the time-constant table. This *Rosenstark table* for three capacitances is sketched below.

|       | <b>a</b> 1     | a <sub>2</sub>           | <b>a</b> <sub>3</sub>                             |

|-------|----------------|--------------------------|---------------------------------------------------|

| 0     | r (opop)       | $	au_2$ ( $C_1$ shorted) | $	au_3$ (C <sub>1</sub> , C <sub>2</sub> shorted) |

| $C_1$ | $	au_1$ (open) | $	au_3$ ( $C_1$ shorted) |                                                   |

| $C_2$ | $	au_2$ (open) | $	au_3$ ( $C_2$ shorted) |                                                   |

| $C_3$ | $	au_3$ (open) |                          |                                                   |

The column numbering is for the *i* index. The procedure amounts to filling in the table and then, for  $a_1$ , summing the  $\tau_i$  in column 1; for  $a_2$ , summing the products of  $\tau$  in column 2 with  $\tau$  from column 1; for  $a_3$ , summing the products of  $\tau$  in column 3 with  $\tau$  from columns 2 and 1. The summation always involves the  $\tau$  of a column multiplied by the  $\tau$  of the columns to the left. When a  $\tau$  is found, the capacitors indexed in the columns to the left are shorted.

Active devices can change the resistance at a capacitor, for example, due to the Miller effect, and must be taken into account when finding equivalent resistances.

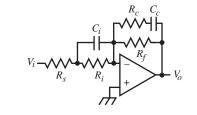

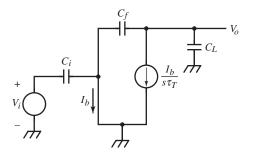

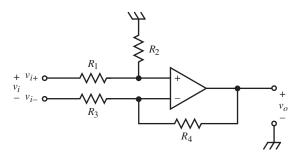

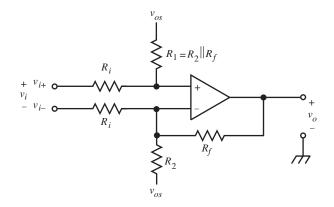

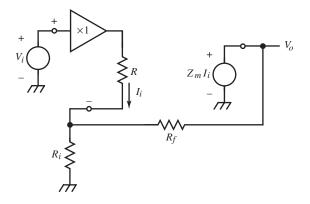

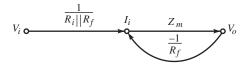

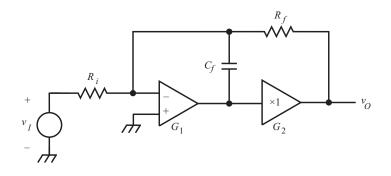

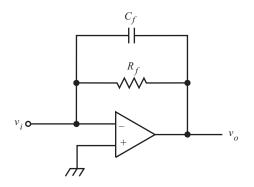

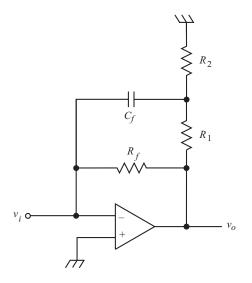

#### Example: Op-Amp Circuit Poles from the Cochrun-Grabel Method

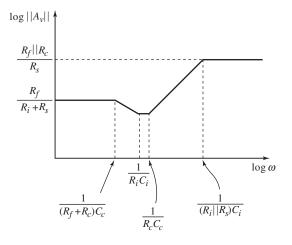

| 4 —       | $R_{f}$                | $(sR_cC_c+1)(sR_iC_j+1)$                                                                                 |

|-----------|------------------------|----------------------------------------------------------------------------------------------------------|

| $A_v = -$ | $\overline{R_i + R_s}$ | $\overline{\left(s\left[R_{i}\ R_{s}\right]C_{i}+1\right)\left(s\left[R_{f}+R_{c}\right]C_{c}+1\right)}$ |

This op-amp circuit, with transfer function as shown, can be analyzed using the Cochrun-Grabel method. The Rosenstark table is given below.

|                | a <sub>1</sub>                  | <b>a</b> <sub>2</sub>   |

|----------------|---------------------------------|-------------------------|

| Ci             | $(R_i \parallel R_s) \cdot C_i$ | $(R_c + R_f) \cdot C_c$ |

| C <sub>c</sub> | $(R_c + R_f) \cdot C_c$         |                         |

The ordering of capacitors, as shown in the table, is  $C_i$ ,  $C_c$ . This ordering is arbitrary. The  $a_1$  column is filled in, beginning at the  $C_i$  row, by finding the open-circuit resistance across the terminals of  $C_i$ . An active device (i.e., the op-amp) requires first a determination of its effect on resistance. The  $V_{-}$  input is a virtual ground for the ideal op-amp. Knowing this, the  $C_i$  terminals have across them  $R_i || R_s$  because  $V_i$  has zero resistance. The time constant for the first entry,  $C_i$  row,  $a_1$  column, is complete. For the  $C_c$  row,  $a_1$  column, examine  $C_f$ .  $R_c$  is in series with the  $C_c$  terminal and goes to ground. From the other terminal, we determined that the  $V_o$  node has a resistance of  $R_f$ to  $R_c$ . Thus, the total resistance across  $C_c$  is  $R_c + R_f$ . The second entry is complete.

Now, begin with the  $a_2$  column. Short  $C_i$  (from the first column) and determine resistance across  $C_c$ . Again this is  $R_c + R_f$ . The table is complete. The  $a_n$  are now found from the table. The sum of the first column is

$$a_1 = (R_i \| R_s) \cdot C_i + (R_c + R_f) \cdot C_c$$

Then  $a_2$  is found from the second column by multiplying its entries by the first column and adding them. Since there is only one, no addition is needed here, and

$$a_2 = (R_c + R_f) \cdot C_c \cdot (R_i || R_s) \cdot C_i$$

The characteristic equation is

$$a_2s^2 + a_1s + 1 = 0$$

This quadratic equation is easily solved by noting that the  $a_1$  terms are the  $a_2$  factors, and the poles are therefore

$$p_1 = \frac{-1}{(R_i || R_s) \cdot C_i}, \quad p_2 = \frac{-1}{(R_c + R_f) \cdot C_c}$$

This result agrees with the reactance chart method, as shown below.

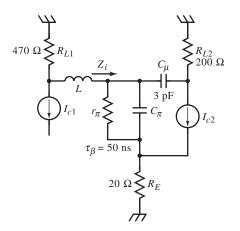

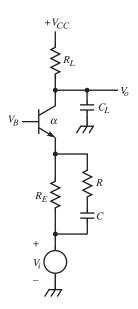

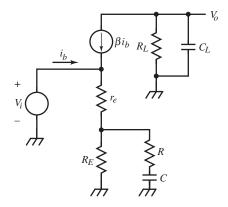

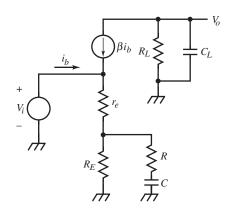

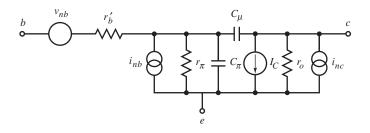

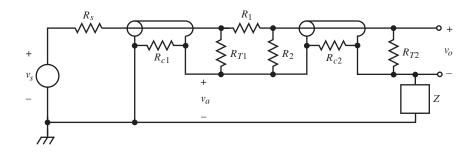

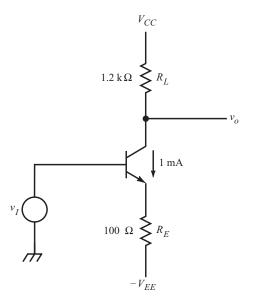

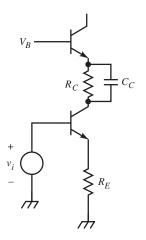

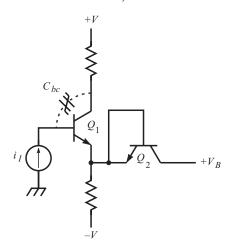

#### Example: BJT Amplifier Poles from the Cochrun-Grabel Method

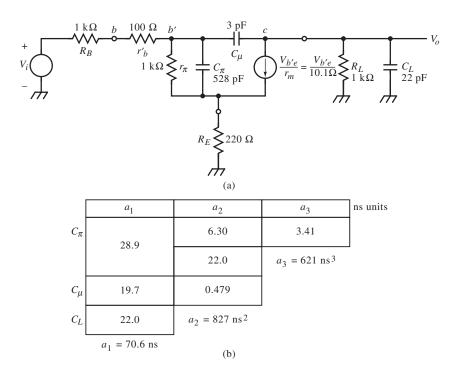

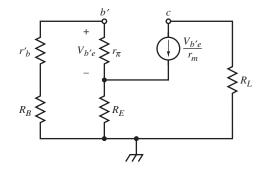

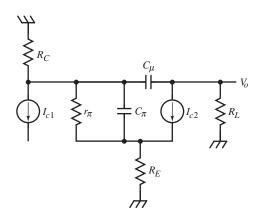

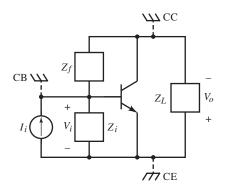

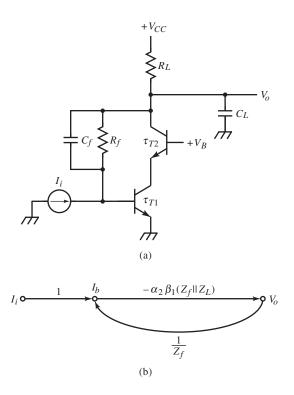

The poles of the BJT amplifier of (a) are found by the Cochrun-Grabel method using the Rosenstark table in (b) to obtain the characteristic equation. The third-degree equation can be solved by computer or approximated by a lowerdegree equation that retains an approximation of the dominant poles.

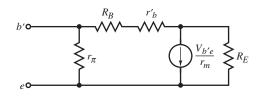

Begin with R of  $C_{\pi}$  in the first column. With all the other Cs open, the resistance is found by the following steps. First, the equivalent circuit is Nortonized.

Then the substitution theorem is applied and two branches are combined.

The resistance is

$$R_{\pi} = r_{\pi} \left\| \frac{(R_E + R_B + r_b')}{(1 + R_E/r_m)} \right\|$$

This has the form of Miller's theorem, in which  $K = R_E / r_m$ .  $R_{\pi} = 54.8 \Omega$ , and the resulting time constant is 28.9 ns.

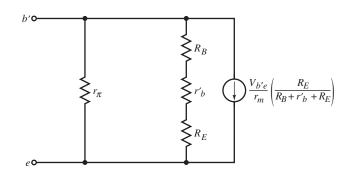

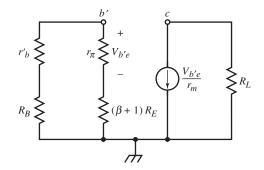

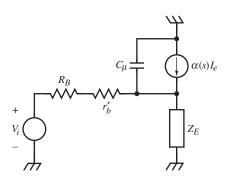

For  $C_{\mu}$ , the equivalent circuit is shown below.

Applying the  $\beta$  transform to  $R_E$  results in the equivalent circuit:

The resistance at the b' node to ground is

$$R_{b'} = (r_b' + R_B) \| (\beta + 1) \cdot (r_e + R_E)$$

The collector current source is controlled by  $V_{b'e}$ . From the base loop,

$$V_{b'e} = V_{b'} \cdot \left(\frac{r_{\pi}}{r_{\pi} + (\beta + 1) \cdot R_E}\right) = V_{b'} \cdot \left(\frac{r_e}{r_e + R_E}\right)$$

At the collector,

$$V_c = -R_L \cdot \frac{V_{b'e}}{r_m} = -\alpha \cdot \frac{R_L}{r_e + R_E} \cdot V_{b'} = -K \cdot V_{b'}$$

Current injected into the b' node causes the voltage across b'c to change by  $1 + V_c / V_{b'} = 1 + K$ . This Miller effect causes the voltage across the injecting current source to be larger by 1 + K times. This makes the effective resistance 1 + K times larger also.

Next, change the Norton circuit of the collector loop to a Thevenin source as shown below using the collector equation.

The voltage across  $R_{b'}$  is now  $(1 + K) V_{b'}$ , making  $R_{b'}$  appear (1 + K) times larger. This Miller resistance is in series with  $R_L$ . Thus, the resistance sought is

$$R_{\mu} = R_{b'} \cdot (1+K) + R_L = (r_b' + R_B) \| (\beta + 1) \cdot (r_e + R_E) \cdot \left[ 1 + \alpha \cdot \frac{r_e}{r_e + R_E} \right] + R_L$$

Substituting circuit values gives  $R_{\mu} = 6.57 \text{ k}\Omega$  and  $\tau = 19.7 \text{ ns}$ .

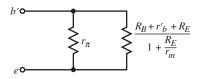

The time constant for  $a_1$  due to  $C_L$  is  $R_L \cdot C_L = 22.0$  ns. For the  $a_2$  column, the first capacitance  $C_{\pi}$  is shorted, and R across b'c is again determined. With  $C_{\pi}$  shorted,  $V_{b'e} = 0$ , and the transistor current source is nulled. This simplifies the resistance to

$$R_{\mu}(C_{\mu} \text{ shorted}) = (r_b' + R_B) \|R_E + R_L$$

which is 1.18 k $\Omega$ . The time constant is 6.30 ns. Next,  $C_{\pi}$  remains shorted as we find the resistance across  $C_L$ . It is  $R_L$ , and  $\tau = 22.0$  ns. The last entry in the  $a_2$

column is found by shorting  $C_{\mu}$  and finding the resistance across  $C_L$ . The collector current source is now across the *b'e* branch, and the substitution theorem reduces it to  $r_m$ . Applying  $r_m || r_{\pi} = r_e$ ,

$$R_L(C_\mu \text{ shorted}) = R_L \| (r_e + R_E) \| (r_b' + R_B)$$

This resistance is 160  $\Omega$  and  $\tau = 0.479$  ns.

The final entry, for  $a_3$ , is the resistance across  $C_L$  with  $C_{\pi}$  and  $C_{\mu}$  shorted.

$$R_L(C_{\pi}, C_{\mu} \text{ shorted}) = (r_b' + R_B) \|R_E\|R_L$$

This value is 155  $\Omega$  and  $\tau = 3.41$  ns. The table is complete.

Next, find the  $a_n$  as follows:

$$a_{1} = (28.9 + 19.7 + 22.0) \text{ ns} = 70.6 \text{ ns}$$

$$a_{2} = [(6.30)(28.9) + (22.0)(28.9) + (0.479)(19.7)] \text{ ns}^{2} = 827 \text{ ns}^{2}$$

$$a_{3} = (3.41)(6.30)(28.9) \text{ ns}^{3} = 621 \text{ ns}^{3}$$

The characteristic equation is therefore

$$(621 \text{ ns}^3) \cdot s^3 + (827 \text{ ns}^2) \cdot s^2 + (70.6 \text{ ns}) \cdot s + 1 = 0$$

This equation was solved by computer, producing real roots at

-2.83 MHz, -11.6 MHz, -198 MHz

A SPICE simulation shows a damped response due to the dominant real pole with magnitude roll-off of -3 dB at 2.7 MHz. The two slowest poles combine to yield an approximation bandwidth of 2.75 MHz.

If a computer is not used to solve the characteristic equation for the poles, some approximations can be made by ignoring higher-degree terms. By dropping the  $s^3$  term, two poles are found at 2.85 MHz and 10.7 MHz. By dropping the quadratic term also, the single pole is at 2.25 MHz, a 16% error. This error is acceptable for many pole estimates and leads to a simplified version of the Cochrun-Grabel approach; instead of building a table, build only the first

column. That is, sum the open-circuit time constants for each capacitor and invert it for the radian pole frequency. The hard work is in finding  $R_{\pi}$  and  $R_{\mu}$ , but we have done that already, and the equations for them can be used for BJT analysis (and, for field-effect transistors, with the BJT-to-FET transform) generally.

The  $f_T$  specified by transistor manufacturers is defined as the frequency at which  $\beta$  is one with the collector dynamically (ac) shorted to the emitter. Then  $C_{\mu}$  shunts  $C_{\pi}$ . This implies that

mfg

$$f_T = \frac{1}{2\pi\tau_T}$$

,  $\tau_T = r_\pi \cdot (C_\pi + C_\mu) \cong r_\pi \cdot C_\pi$

The manufacturer's  $f_T$  for the transistor in the previous example is 300 MHz and  $\beta_o = 99$ . For the single-pole BJT model (see *Designing Dynamic Circuit Response*, "Derivation of BJT High-Frequency Model")  $f_T$  is defined with  $C_{\mu} = 0$  to make the resulting theory simpler. This should cause no problem if the manufacturer's  $f_T$  and  $C_{\mu}$  (given as  $C_{ob}$ ) values are used to compute  $f_{\beta}$  and  $f_T$  as defined here. In most cases,  $f_T$  is close enough already. In this example, the error is 0.6%.

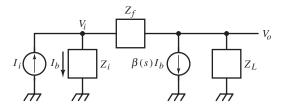

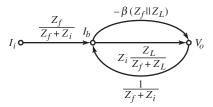

The Cochrun-Grabel method produces only poles. One technique for determining zeros begins by first writing the nodal equations of the circuit. A flow graph is especially helpful here. Those transmittances that lead from input to output are examined for evidence of zeros.

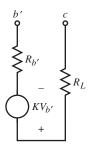

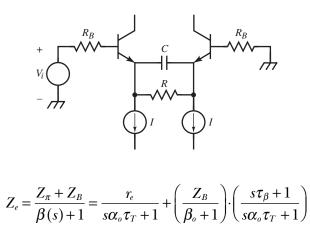

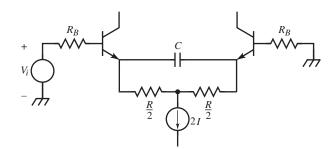

Pole estimation is often applied to interstage coupling, to the pole formed by the load resistance of a common-emitter (CE) or common-base (CB) stage and the following CE stage input.

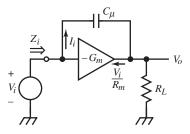

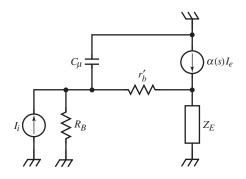

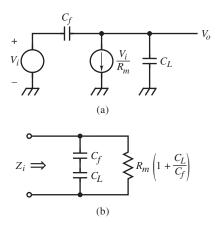

The input impedance of the loading BJT stage  $Z_i$  has branches through  $C_{\mu}$  and  $Z_{\pi}$ .

Consider first the branch involving  $C_{\mu}$ . The circuit is idealized above to eliminate the effect of the  $Z_{\pi}$  path. The BJT is represented by a transconductance amplifier. Its output current, representing collector current, is shown flowing into the amplifier with value  $G_m \cdot V_i = V_i/R_m$ . The input current to the amplifier flows into  $C_{\mu}$  and is

$$I_{i} = \frac{V_{i} - V_{o}}{1/sC_{\mu}} = sC_{\mu} \cdot (V_{i} - V_{o}) = \frac{V_{o}}{R_{L}} + \frac{V_{i}}{R_{m}}$$

Solving this Kirchhoff's current law (KCL) equation for  $V_o$ , substituting it into the first expression for  $I_i$ , and solving for  $V_i/I_i$ ,

$$Z_{i\mu} = \frac{1}{s[1 + (R_L/R_m)] \cdot C_{\mu}} + \frac{R_L}{[1 + (R_L/R_m)]} = \frac{1}{s(K_v + 1) \cdot C_{\mu}} + \frac{R_L}{K_v + 1}$$

Besides the Miller capacitance,  $R_L$  is reduced by  $K_v + 1$ . For large voltage gain, this branch presents a nearly capacitive impedance.

The impedance through  $Z_{\pi}$  is

$$Z_{i\pi} = (\beta_o + 1) \cdot (r_e + R_E) \cdot \frac{s\alpha_o \cdot \tau_T \cdot (R_E/(r_e + R_E)) + 1}{s\tau_\beta + 1}$$

For  $R_E >> r_e$  and  $\alpha_o \cong 1$ ,  $Z_{i\pi}$  is the hf  $Z_b(R_E)$ . If the series-peaking  $\omega_n \ll \omega_T$ , we can ignore the zero in  $Z_{i\pi}$ . The result is a shunt RC with  $R_i$  shunting

$\tau_{\beta}/R_i \cong \tau_T/R_E$ .  $R_i$  is large and usually presents negligible shunting. Consequently,  $Z_{i\pi}$  reduces to  $\tau_T/R_E$ . It shunts  $Z_{i\pi}$  so that

$$Z_i = Z_{i\mu} \| Z_{i\pi}$$

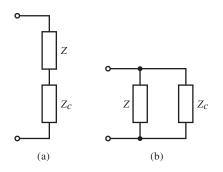

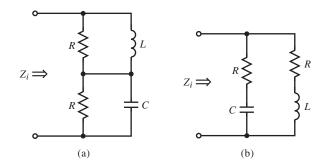

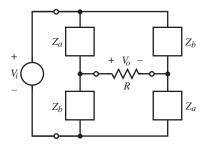

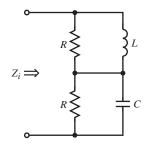

When the branches are combined,  $Z_i$  as shown below results.

$$Z_{i} \Longrightarrow \qquad \overbrace{(K_{\nu}+1) C_{\mu}}^{R_{L}} \overbrace{(K_{\nu}+1) C_{\mu}}^{R_{E}}$$

This simplifies, under these assumptions, to the following circuit.

Unless the transistor is very slow (large  $\tau_T$ ) or  $R_E$  is small (not much larger than  $r_e$  or less), the only significant capacitance is the Miller capacitance. Therefore,

$$Z_i \cong \frac{1}{s(K_v+1) \cdot C_{\mu}}, \quad R_E \gg r_e, \quad \beta_o \gg 1, \quad f \ll f_T, \quad \frac{R_L}{K_v+1} \cong 0$$

Another assumption of this equation is that the capacitance loading  $R_L$  from the stage following it is negligible. If not, shunt capacitance across  $R_L$  further reduces the impedance in series with  $C_{\mu}$ , making this a better approximation.

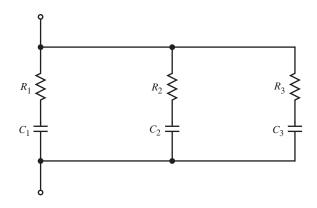

A more exacting estimate is based on  $Z_i$  of the previous (more exact) network above. Let the elements be designated more generally as  $R_1$  in series with  $C_1$ shunting  $R_2$  in series with  $C_2$ . Then,

$$Z_{i} = \frac{(sR_{1}C_{1}+1)\cdot(sR_{2}C_{2}+1)}{[s(C_{1}+C_{2})]\cdot[s(R_{1}+R_{2})\cdot(C_{1}||C_{2})+1]}$$

When element values are substituted, the zeros are at frequencies of  $1/\tau_T$  and  $1/R_L \cdot C_\mu$ ; the poles are at the origin, and  $1/(R_1 + R_2) \cdot (C_1 \| C_2)$  (where  $\|$  is a math operator, not a topological designator). The capacitance  $C_1 + C_2$  dominates  $Z_i$  until  $1/R_L \cdot C_\mu$ . The second pole causes  $Z_i$  to appear capacitive out to  $f_T$ .

#### **INDUCTIVE PEAKING**

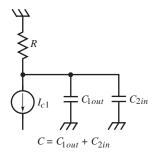

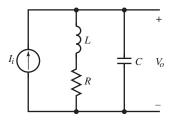

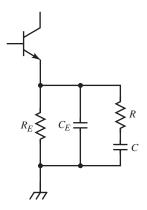

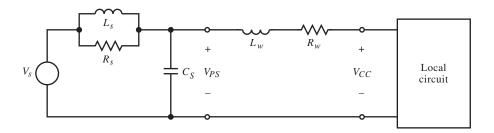

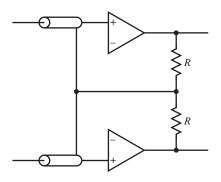

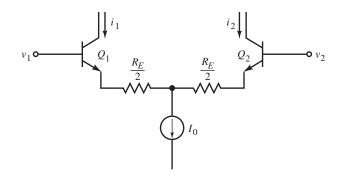

Interstage coupling often degrades bandwidth due to parasitic reactances. For example, collector output capacitance shunts the input base capacitance of the next stage in the circuit shown below.

The load resistor *R* is shunted by  $C = C_{1out} + C_{2in}$ . An unwanted pole is created at  $1/R \cdot C$ .

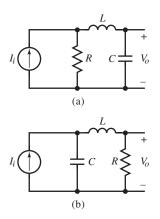

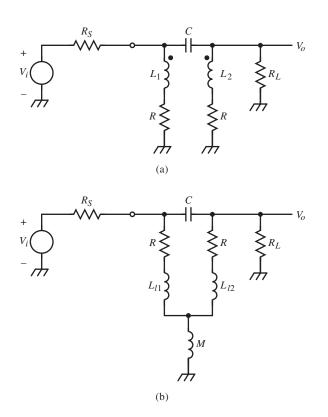

The addition of an inductor can extend the bandwidth by creating a series or parallel resonant circuit with a peak in the frequency or transient responses – hence the technique name of *inductive peaking*. Below are some *series peaking* circuits.

The transfer function is not changed by exchanging R and C. In both cases, L is in series with C. The transfer function for series peaking has a quadratic pole factor,

$$\frac{V_o}{I_i} = R \cdot \frac{1}{s^2 L C + s R C + 1}$$

This has a familiar quadratic-pole response. The basic parameters are

$$\omega_n = \frac{1}{\sqrt{a}} = \frac{1}{\sqrt{LC}} = \frac{2\zeta}{RC}; \quad \zeta = \frac{b}{2\sqrt{a}} = \frac{R}{2Z_n}, \quad Z_n = \sqrt{\frac{L}{C}}$$

Usually, *R* is chosen to set the gain, and *C* is parasitic. This leaves *L* as the design parameter. For a desired  $\zeta$ ,

$$L = \frac{R^2 \cdot C}{4 \cdot \zeta^2}$$

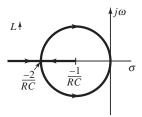

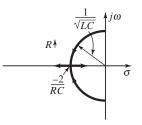

Because L is in a (the  $s^2$  coefficient) only, the poles move with increasing L as shown below.

It is worth noting that if R were varied instead, the pole locus would be as shown below.

And for increasing *C*, the direction of the root locus is vertical downward, splitting along the real axis.

When the poles become complex as *L* increases, pole radius  $\omega_n$  shrinks and  $\zeta$  decreases. The most desirable pole locations for a wideband amplifier are in a range slightly off the real axis, near the critically damped pole location -2/RC. Here,  $\omega_n$  is maximum and  $\zeta$  is in a range that gives a desired response.

For variation in R,  $\omega_n$  remains constant as  $\zeta$  changes proportionally. Variation in C causes the most trouble. While  $\zeta$  varies with the square root of C,  $\omega_n$  varies inversely. Consequently, with C usually parasitic, control over its range of values is least, and though response peaking (in time or frequency) is not so much affected by  $\Delta C$ , the risetime and bandwidth are. Causes for C, such as transistor process parameters and circuit-board layout, are significant in control of pole radius.

How much improvement in bandwidth can series peaking offer? To determine this, compare bandwidth improvement with the uncompensated RC circuit by expanding the meaning of the bandwidth reduction factor S to include bandwidth extension. Both definitions of S are useful here and are separately denoted as

$$S_n \equiv \frac{\omega_{bw}}{\omega_n}, \quad S_p \equiv \frac{\omega_{bw}}{p} = \frac{\omega_{bw}}{(1/RC)}$$

$S_n$  compares bandwidth with respect to pole radius;  $S_p$  compares it with the uncompensated *RC* circuit.

In the time domain,  $t_r \cdot \omega_n$  has been used to express relative risetime. Comparison against the risetime of the *RC* circuit also is a measure of improvement. The risetime improvement factor is

$$\frac{t_r}{t_r(RC)} \cong \frac{t_r}{2.2 \cdot RC}$$

All of these performance indicators are combined with those already derived in *Dynamic Response Compensation*, "Optimization . . .", in the following series-peaking summary table.

| ζ     | L                | <i>Ю</i> <sub>n</sub> | $\frac{\omega_{\scriptscriptstyle bw}}{\omega_{\scriptscriptstyle n}}$ | $rac{\omega_{\scriptscriptstyle bw}}{ ho}$ | <b>М</b> <sub>р</sub> ,% | $t_r \cdot \omega_n$ | $\frac{t_r}{2.2 \cdot RC}$ |                          |

|-------|------------------|-----------------------|------------------------------------------------------------------------|---------------------------------------------|--------------------------|----------------------|----------------------------|--------------------------|

| 1.00  | $\frac{R^2C}{4}$ | 2/RC                  | 0.644                                                                  | 1.288                                       | 0                        | 3.36                 | 0.765                      | critical damping         |

| 0.866 | $\frac{R^2C}{3}$ | 1.73/RC               | 0.786                                                                  | 1.361                                       | 0.433                    | 2.73                 | 0.717                      | MFED                     |

| 0.707 | $\frac{R^2C}{2}$ | 1.41/RC               | 1.000                                                                  | 1.414                                       | 4.32                     | 2.15                 | 0.692                      | maximally flat amplitude |

| 0.500 | $R^2C$           | 1/RC                  | 1.272                                                                  | 1.272                                       | 16.3                     | 1.64                 | 0.746                      | $\phi = 60^{\circ}$      |

For  $\zeta = 0.5$ , the poles are at a 60° angle and  $\alpha = 1/RC$ , the same as the singlepole case. From the root-locus plots above, at critical damping, both poles are at -2/RC and have twice the pole radius of a single-pole RC circuit. As L varies,

$$\left(\frac{\boldsymbol{\omega}_{bw}}{p}\right) = \left(\frac{\boldsymbol{\omega}_{bw}}{\boldsymbol{\omega}_n}\right) \cdot (2 \cdot \zeta) \Longrightarrow S_p = 2 \cdot \zeta \cdot S_n$$

By adding *L* for series peaking, the critically damped ( $\zeta = 1$ ) bandwidth increases by 29% and the risetime by 31%. This is a significant improvement caused by the addition of one component, but greater improvement is possible.

**Example: Series Peaking**

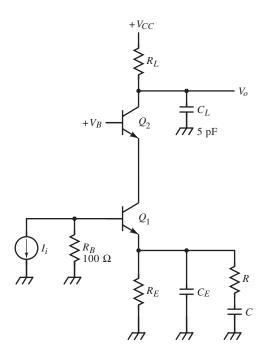

The amplifier stage output is loaded by the input impedance of a CE stage. The CE transistor has  $\tau_T = 500$  ps and  $\beta_o \approx 100$ . The collector capacitance to ground of the first BJT is negligible. A MFED response is desired.

The first step is to find the input impedance  $Z_i$  of the loading stage. The poles involved in inductive peaking will be in the hf region of the CE BJT stage. The emitter branch hf capacitance is 500 ps/20  $\Omega$  or 25 pF.  $Z_{\pi}$  in series with it is negligible. The voltage gain is about

$$\frac{R_{L2}}{R_E} = 10$$

and the Miller collector capacitance is  $11 \cdot (3 \text{ pF}) = 33 \text{ pF}$ . Because  $R_E$  is so small,  $\tau_T / R_E$  is significant. The collector output resistance, taking into account the Miller effect, is less than 20  $\Omega$ . The capacitance in series with *L* is thus

$$C_i \cong 25 \,\mathrm{pF} + 33 \,\mathrm{pF} = 58 \,\mathrm{pF}$$

The uncompensated bandwidth is

$$f_{bw}(\text{uncomp}) = \frac{1}{2\pi \cdot RC} \cong \frac{1}{2\pi \cdot (470\,\Omega) \cdot (58\,\text{pF})} = 5.8\,\text{MHz}$$

And risetime is

$$t_r \cong 2.2 \cdot RC = 60 \text{ ns}$$

or  $t_r \cong \frac{0.35}{f_{bw}} = 60 \text{ ns}$

From the inductive peaking table, for MFED response,

$$L = \frac{R^2 \cdot C}{3} \cong \frac{(470\,\Omega)^2 \cdot (58\,\mathrm{pF})}{3} = 4.3\,\mathrm{\mu H}$$

The value of  $R = R_L$  assumes negligible series resistance in  $Z_i$ . Each path in  $Z_i$  has about 20  $\Omega$ .  $Z_i$  becomes resistive at  $1/R_L \cdot C_\mu$  or 265 MHz. This is about 50 times larger than  $f_{bw}$  (uncomp), and the assumption that  $Z_i$  is purely capacitive over the frequency range of interest is valid.

The compensated bandwidth (from the table) is 1.36 times higher, or 7.9 MHz, and the risetime is 43 ns. The series resonance is at  $f_n = 10$  MHz.

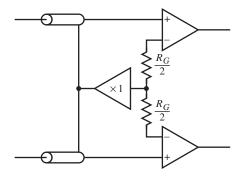

An alternative to series peaking is *shunt peaking*, as shown below. The addition of *L* in series with *R* places it in parallel with *C* and creates a parallel resonance. For a step of input current, most of it charges *C* at first because current does not change instantaneously in an inductor. Consequently, *C* charges faster and response speed increases.

The transfer function of the shunt peaking circuit is

$$\frac{V_o}{I_i} = R \cdot \frac{s(L/R) + 1}{s^2 LC + sRC + 1}$$

The addition of a zero over series peaking improves response speed but also peaks the response more. To compare shunt with series peaking, we need formulas for the performance parameters of a two-pole, one-zero circuit. We now digress to derive them generally and then apply them to shunt peaking.

The two-pole, one-zero transfer function can be generally expressed in terms of  $\tau_n = 1/\omega_n$  and *Q* as

$$\frac{V_o}{I_i} = R \cdot \frac{sQ\tau_n + 1}{s^2\tau_n^2 + (\tau_n/Q)s + 1}$$

In narrow-band amplifier terminology,

$$Q \equiv \frac{1}{2\zeta}$$

This quantity quantifies the amount of peaking and occurs frequently in resonant-circuit equations. The time constant of the zero of  $V_0/I_i$  is

$$\tau_z = Q \cdot \tau_n \Longrightarrow Q = \left(\frac{\tau_z}{\tau_n}\right)$$

Bandwidth is found in the usual way by setting the magnitude of  $V_o/I_i$  to  $1/\sqrt{2}$ . The general result is

$$\omega_{bw} = \omega_n \sqrt{1 - \frac{1}{2Q^2} + 2Q^2} + \sqrt{\left(1 - \frac{1}{2Q^2} + 2Q^2\right)^2 + 1}$$

The overshoot,  $M_p$ , is expressed in  $\zeta$  as

$$M_{p} = \frac{1}{2\zeta} \cdot \exp\left[\frac{-\zeta}{\sqrt{1-\zeta^{2}}} \cdot \left(\frac{3\pi}{2} - \cos^{-1}\zeta - \tan^{-1}\left\{\frac{\sqrt{1-\zeta^{2}}}{\zeta}\right\} + \sin^{-1}(-\zeta)\right)\right]$$

where  $3\pi/2 = 270^{\circ}$ .

The unit-step response for  $\zeta < 1$  is

$$v_{step}(t) = 1 - \frac{1}{2\zeta\sqrt{1-\zeta^2}} \cdot e^{-\zeta w_n t} \sin\left(\omega_n t \sqrt{1-\zeta^2} + \cos^{-1}\zeta + \tan^{-1}\left\{\frac{\sqrt{1-\zeta^2}}{\zeta}\right\}\right)$$

The 10% and 90% times are found by numerical computer solution for shunt peaking as  $t_r \cdot \omega_n$ . This is a convenient representation since  $\omega_n t$  is the independent variable.

For  $\zeta = 1$ , the poles are repeated, and the step response is

$$v_{step} = \left[ \left( \frac{p}{z} - 1 \right) \cdot p \cdot t - 1 \right] \cdot e^{-p \cdot t} + 1, \quad \zeta = 1$$

This function also has no closed-form solution and is numerically solved by computer.

We now apply these general results to shunt peaking and  $V_o/I_i$ , where the zero is

$$z = \frac{1}{\tau_z} = \frac{1}{L/R} = 2 \cdot \zeta \cdot \omega_n$$

and the repeated poles have a frequency of

$$2p = \frac{2}{RC} = \omega_n$$

It then follows that, when  $\zeta = 1$ ,

$$\frac{p}{z} = \frac{1}{2}$$

and  $v_{step}$  reduces to that for shunt peaking:

$$v_{step} = \left(-\frac{1}{2} \cdot \boldsymbol{\omega}_n \cdot t - 1\right) \cdot e^{-\boldsymbol{\omega}_n t} + 1$$

The values of  $t_r \cdot \omega_n$  are numerically computed from this equation.

A table similar to that for series peaking can now be constructed for shunt peaking.

| ζ     | Q     | $\frac{\omega_{bw}}{\omega_n}$ | $\frac{\omega_{\scriptscriptstyle bw}}{\rho}$ | <b>M</b> <sub>p</sub> ,% | $t_r \omega_n$ | $\frac{t_r}{2.2 \cdot RC}$ | φ   |

|-------|-------|--------------------------------|-----------------------------------------------|--------------------------|----------------|----------------------------|-----|

| 1.00  | 0.500 | 0.786                          | 1.572                                         | 0                        | 3.071          | 0.699                      | 0°  |

| 0.866 | 0.577 | 1.086                          | 1.881                                         | 0.620                    | 2.319          | 0.609                      | 30° |

| 0.707 | 0.707 | 1.554                          | 2.198                                         | 6.70                     | 1.559          | 0.502                      | 45° |

| 0.500 | 1.000 | 2.279                          | 2.279                                         | 29.8                     | 0.940          | 0.428                      | 60° |

Shunt peaking is faster than series peaking for the same pole parameters but is less damped in response. It achieves an 88% increase in bandwidth over the *RC* circuit and 39% decrease in risetime for a MFED pole response. Comparing the shunt and series peaking tables directly can be misleading, however. A pole angle of, say, 30° is *not* an MFED response for shunt peaking because of the zero. The values of  $\zeta$  for MFED and maximally flat amplitude (MFA) responses must be derived as in *Designing Dynamic Circuit Response*, "Graphical Representation . . .". For an MFED response,  $\zeta = 0.881$ , and for MFA,  $\zeta \cong 0.777$ . These values are somewhat higher than those without the zero.

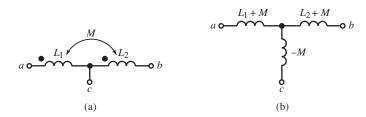

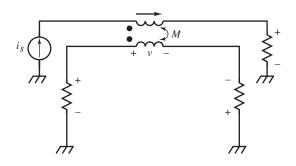

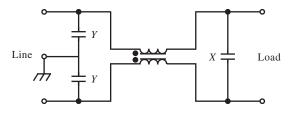

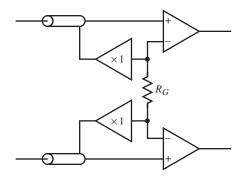

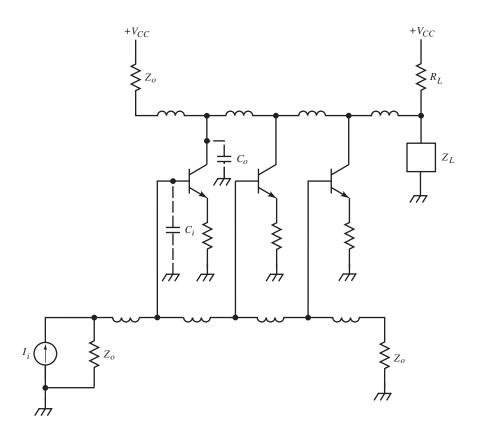

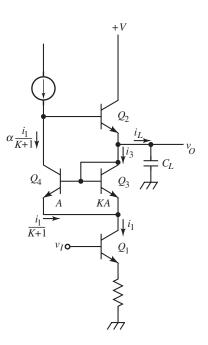

Greater speed improvement can be achieved by using a *T-coil* (a). This is a transformer with controlled coupling and a common connection at *c*. An equivalent circuit is shown in (b) where the polarity of coupling determines the

polarity of the mutual inductance -M to terminal c. With the coupling as shown,

$$L = L_{ab} = (L_1 + M) + (L_2 + M) = L_1 + L_2 + 2M$$

The addition of -M in the equivalent circuit produces the correct self-inductances:

$$L_{ac} = (L_1 + M) - M = L_1, L_{bc} = (L_2 + M) - M = L_2$$

If terminals *a* and *b* are shorted, the inductance from *a* or *b* to *c* is

$$L_{ab,c} = (L_1 + M) \| (L_2 + M) - M$$

Let the mutual inductance be signed. Then the coupling coefficient is always positive and is

$$k = \left| \frac{M}{\sqrt{L_1 \cdot L_2}} \right|$$

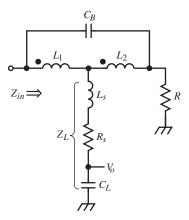

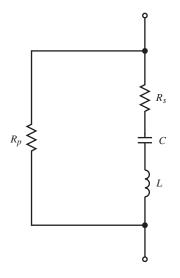

The use of the T-coil for bandwidth extension has resulted in the general form of the *bridged T-coil circuit*, shown below.

The coil is terminated in *R*, but the load is connected to the centertap. A general load,

$$Z_L = sL_s + R_s + \frac{1}{sC_L}$$

(or series RLC) is similar to the input impedance of BJT stages. The equivalent circuit is shown below.

At 0 Hz, the input impedance of the T-coil is *R*. Because of the bridging capacitor  $C_B$ , at high frequencies it is also *R*. For a given  $Z_L$  and by proper choice of  $L_1$ ,  $L_2$ , *M*, and  $C_B$ ,  $Z_{in} = R$  and is independent of frequency. For this circuit behavior, the resulting design equations are

$$L_{1} = \frac{C_{L}}{4} \cdot \left(1 + \frac{1}{4\zeta^{2}}\right) \cdot (R + R_{s})^{2} - RR_{s}C_{L} - L_{s}$$

$$L_{2} = \frac{C_{L}}{4} \cdot \left(1 + \frac{1}{4\zeta^{2}}\right) \cdot (R + R_{s})^{2} - L_{s}$$

$$M = \frac{C_{L}}{4} \cdot \left(R^{2} - R_{s}^{2} - \frac{1}{4\zeta^{2}}(R + R_{s})^{2}\right) + L_{s}$$

$$C_B = \frac{C_L}{16\zeta^2} \cdot \left(1 + \frac{R_s}{R}\right)^2$$

In addition to these design equations, the equivalent inductor element values are

$$L_1 + M = \frac{RC_L}{2} \cdot (R - R_s) - L_s$$

$$L_2 + M = \frac{RC_L}{2} \cdot (R - R_s) - L_s$$

$$L = R^2 C_L - 2L_s$$

The transfer function has two poles at

$$p_{1,2} = -\frac{4\zeta^2}{RC_L} \pm j \frac{4\zeta}{RC_L} \cdot \sqrt{\zeta^2 - 1}$$

The form of transfer function is the same as for series peaking but with twice the speed improvement! For MFED response,  $\omega_{bw}/p = 2.72$ , nearly three times better than the original *RC* circuit. The greatest improvement is 2.83 for an MFA response.

For  $Z_L = 1/sC_L$ , the transfer function for the load is

$$\frac{V_o}{I_i} = R \cdot \frac{1}{\frac{1}{4} \cdot \left(\frac{1-k}{1+k}\right) \cdot R^2 C_L^2 s^2 + \frac{1}{2} \cdot R C_L s + 1}$$

$$C_B = \frac{1}{4} \cdot \left(\frac{1-k}{1+k}\right) \cdot C_L, \quad L = R^2 C_L, \quad L_1 = L_2 = \frac{L}{2 \cdot (k+1)}$$

As *k* increases, the pole angle decreases for complex poles. With perfect coupling, k = 1, and the  $s^2$  term is zero, leaving a single-pole response but with twice the bandwidth of a simple *RC* circuit. This is a simpler, lower-performance T-coil

circuit with no bridging capacitance and with  $L_1 = 4 \cdot L_2$ . MFED response is achieved when k = 1/2, a relatively loose coupling not hard to implement. Then  $C_B = C_L/12$ ,  $L_1 = 3 \cdot L_2$ , and  $L = R^2 \cdot C_L$ . A balanced T-coil ( $L_1 = L_2$ ) that meets the above conditions has no coupling between the coils,  $C_B = C_L/4$ , and the pole angle is 60°.  $L_1 > L_2$  is necessary to meet these conditions with a capacitive load.

The basic theory of T-coils, including the full derivation of the above equations (and others), was originally worked out at Tektronix by Robert I. Ross and Carl Battjes (1982), inventor of T-coil compensation. Subsequently, Peter Starič and Erik Margan presented the derivation in *Wideband Amplifiers* (2006).

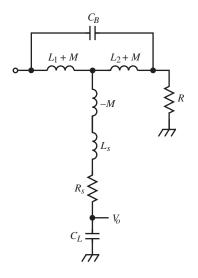

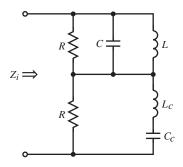

Even greater bandwidth improvement is possible by taking advantage of the constant-resistance input of the T-coil circuit. Series peaking can be cascaded in front of the T-coil, as shown below.

The input and output capacitances of the uncompensated circuit are separated and become part of different peaking circuits. Because the interstage coupling satisfies the requirement for series peaking, the bandwidth improvement of each circuit remains unchanged. Thus the total improvement is the product of the individual improvement factors.

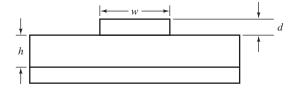

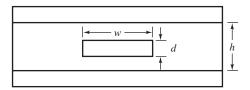

Amplifiers with bandwidths under 100 MHz usually have had T-coils constructed as tapped cylindrical coils wound on a plastic bobbin. The magnetic path is through air and plastic. For higher frequencies, a common T-coil is made of a bifilar-wound loop of magnet wire. The two wires are twisted together and then formed into a loop, or circuit-board traces can be spiraled on opposite sides of the board and connected at the center via plated-through holes. Two traces can be run next to each other to form coupled inductors. For very-high-speed circuits, integrated circuit (IC) bonding wires have even been used to form T-coils.

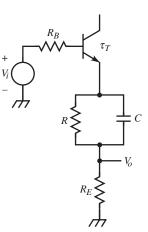

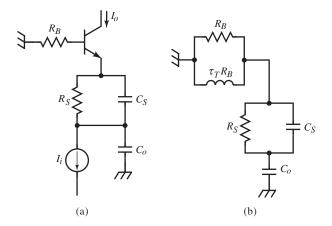

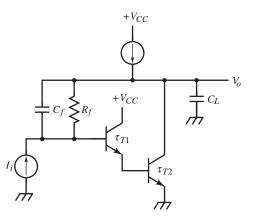

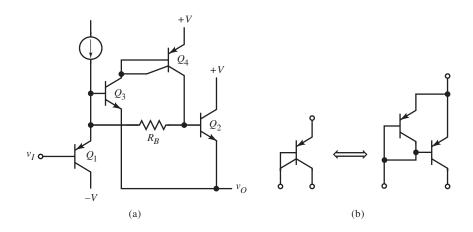

An inductive peaking circuit used in ICs, sometimes referred to as "emitter peaking," realizes a shunt inductance by the high-frequency gyration of a BJT base resistor. The emitter appears inductive. (See *Designing Dynamic Circuit Response*, "High-Frequency Impedance Transformations.") The adjustment of  $R_B$  adjusts the emitter inductance  $R_B \cdot \tau_T$ .

# **Example: T-Coil Compensation**

The circuit of the previous example is T-coil compensated. The T-coil formulas are applied directly. The loading is  $C_L = 58$  pF, and  $R_s = L_s = 0$ . Also,  $R = R_L = 470 \ \Omega$ . For MFED response,  $\zeta = 0.866$ . The results are

$$L_1 = L_2 = 4.3 \,\mu\text{H}, \quad M = 2.1 \,\mu\text{H}, \quad C_B = 4.8 \,\text{pF}$$

From the equation for k, the coupling of the inductors is k = 0.5. This is loose coupling and is easily implemented. The bandwidth has improved to 15.8 MHz and risetime to approximately 22 ns.

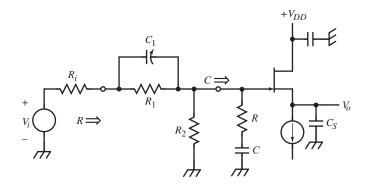

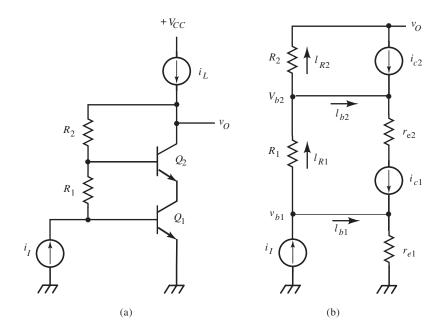

## **BOOTSTRAP SPEED-UP CIRCUIT**

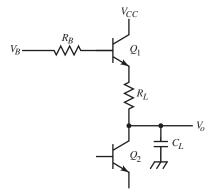

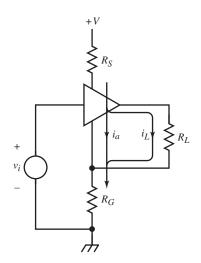

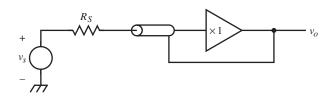

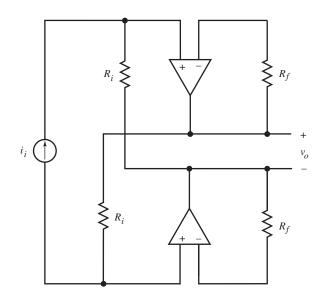

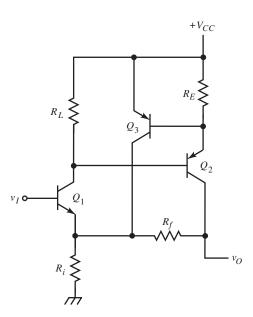

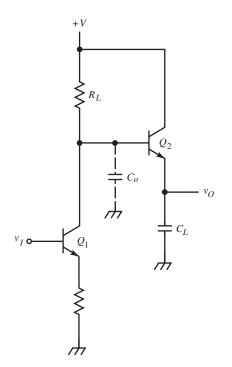

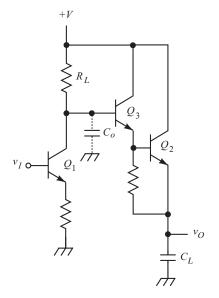

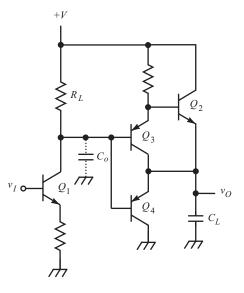

How can the speed of an amplifier be increased without increasing its power dissipation? Amplifier bandwidth can be extended by a simple technique that requires no inductors or complicated adjustments. In its simpler form, a collector- or drain-loaded transistor amplifier, as shown below, has a single-load resistor,  $R_L$ , followed by a buffer amplifier, usually an emitter- or source-follower.

The buffer stage keeps the output from directly loading  $R_L$  by providing current gain and approximately a ×1 voltage gain. This two-stage cascaded amplifier is typical in high-speed circuit design as a place to start before increasing amplifier "speed" (bandwidth).

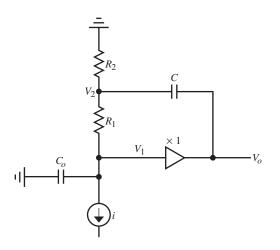

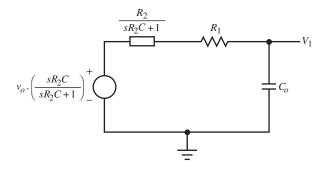

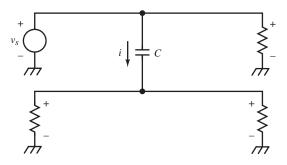

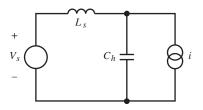

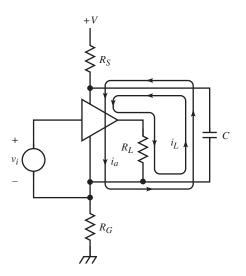

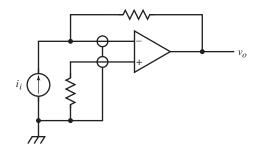

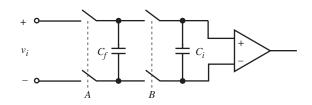

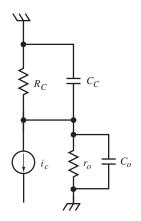

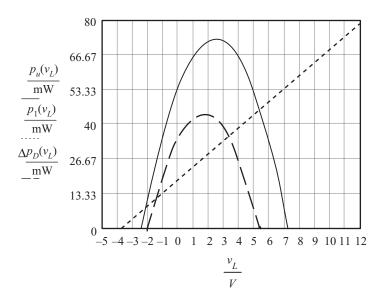

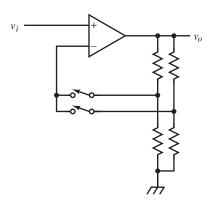

What mainly can limit speed is the capacitance,  $C_o$ , at the collector node of the first stage. It forms a time constant with  $R_L$  that slows the dynamic response. To increase speed, it is possible to introduce various inductive peaking techniques. However, for IC and some discrete design, inductors are problematic. A speed-up technique that uses capacitance instead is the *bootstrap speed-up circuit*, shown below, where  $Q_1$  has been replaced by a current source, *i*, and the  $Q_2$  stage by an ideal ×1 buffer amplifier.  $R_L$  has been split into  $R_1$  and  $R_2$ , and a bootstrap capacitor, *C*, added between the output and the split- $R_L$  node.

The idea behind this circuit is that if the voltage at the top of  $R_1$  can track the voltage at the bottom of  $R_1$ , the voltage change across  $R_1$  will be zero. Then none of *i* will be diverted into the load resistance. With all of *i* flowing into  $C_o$ , it charges faster and the circuit response is quicker. In effect, *C bootstraps* the voltage across  $R_1$  to accomplish this, and the buffer amplifier output has the needed current drive to provide  $R_2$  current.

To analyze the dynamic response of this circuit, the s-domain (pole-zero) expressions need to be derived. The full analysis takes some algebraic effort. To provide further insight into the circuit and guidance for checking the full result later, a simpler analysis omits  $C_o$ . By setting  $C_o = 0$ , the output-node voltage is

$$v_1 = i \cdot \left( R_1 + R_2 \| \frac{1}{sC} \right) + v_o \cdot \left( \frac{R_2}{R_2 + 1/sC} \right); \quad v_o = v_1$$

After some algebraic simplification, this becomes

$$v_1 = i \cdot \left( R_1 + \frac{R_2}{sR_2C + 1} \right) + v_o \cdot \left( \frac{sR_2C}{sR_2C + 1} \right)$$

Then the first-stage amplifier gain, a transresistance (current in, voltage out), is

$$\frac{v_o}{i} = \frac{R_1 + \frac{R_2}{sR_2C + 1}}{1 - \frac{sR_2C}{sR_2C + 1}} = (R_1 + R_2) \cdot (s[R_1 || R_2] \cdot C + 1)$$

From this result,  $R_L = R_1 + R_2$  is the static gain, followed by a zero at  $z = -1/(R_1 || R_2) \cdot C$ . The absence of a pole is due to bootstrapping. The pole formed by  $R_2$  and *C* is cancelled by the ×1 buffer gain. If its gain were a value of *K* other than one, a finite pole factor would appear at  $s \cdot (K-1) \cdot R_2 \cdot C + 1$ .

Now, include  $C_o$  in the analysis such that  $C_o \neq 0$ . Then the circuit can be modeled as shown below. The input current source is omitted but attaches to the output node, at  $v_1$ . The two-loop circuit reduces to a single loop by Thevenizing  $v_o$ , C, and  $R_2$ , as shown in the second circuit. Then superposition of the two sources,  $v_o$  and i, results in the following two equations:

$$v_{1} = v_{o} \cdot \left(\frac{sR_{2}C}{sR_{2}C+1}\right) \cdot \left(\frac{sR_{2}C+1}{s^{2}(R_{1}R_{2}CC_{o}) + s[(R_{1}+R_{2}) \cdot C_{o} + R_{2}C]+1}\right), \quad i = 0$$

$$v_{1} = i \cdot \left(\frac{1}{sC_{o}} \|(R_{1}+R_{2}\|1/sC)\right)$$

$$= i \cdot (R_{1}+R_{2}) \cdot \frac{s(R_{1}\|R_{2})C+1}{s^{2}R_{1}R_{2}CC_{o} + s[(R_{1}+R_{2})C_{o} + R_{2}C]+1}, \quad v_{o} = 0$$

The first equation simplifies quickly to

$$v_1 = v_o \cdot \left( \frac{sR_2C}{s^2(R_1R_2CC_o) + s[(R_1 + R_2) \cdot C_o + R_2C] + 1} \right), \quad i = 0$$

Applying the buffer condition,  $v_o = v_1$ , and by superposition,

$$\frac{v_o}{i} = (R_1 + R_2) \cdot \frac{s(R_1 \| R_2)C + 1}{s^2 R_1 R_2 C C_o + s(R_1 + R_2)C_o + 1}$$

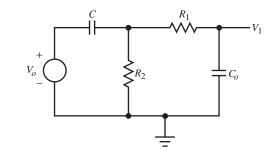

The bootstrap capacitor, *C*, provides for the additional zero. Without it (*C* = 0), the uncompensated circuit pole remains at  $-1/(R_1 + R_2) \cdot C_o$ , as in the uncompensated amplifier. The design question is now one of determining the optimal value of *C* and the split between  $R_1$  and  $R_2$ .

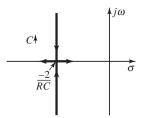

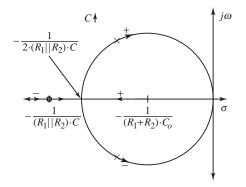

The contour (not root-locus) plot of the poles of this circuit is shown below. C appears only in the quadratic term, leading to a locus that varies with increasing C as shown.

The conjugate poles are marked with their polarities to show that the positive pole originates at the center of the pole-pair circle,  $-1/(R_1 + R_2) \cdot C_o$  (the pole location of the uncompensated amplifier), and the negative pole at  $-\infty$ . The contour plot itself begins at the frequency of the zero,  $-1/(R_1||R_2) \cdot C$ , and at the circle center. As *C* increases, the poles move toward each other and meet at  $-1/2(R_1||R_2) \cdot C$  before splitting off the real axis and eventually terminating at

the origin for excessively large (infinite, shorted) *C*. For equal poles on the real axis,

$$2(R_1 || R_2) \cdot C = \frac{1}{2} \cdot (R_1 + R_2) \cdot C_o$$

from which the design constraints are obtained:  $R_1 = R_2$  and  $C = C_0$ .

Optimal amplifier response usually has the poles off the real axis for a compromise between time- and frequency-domain response performance. For poles alone, the MFED angle is 30°. The relevant formulas are as follows. The damping factor is

$$\zeta = \frac{b}{2 \cdot \sqrt{a}} = \frac{1}{2} \cdot \sqrt{\frac{(R_1 + R_2) \cdot C_o}{(R_1 \parallel R_2) \cdot C}}$$

where the pole angle is

$$\phi = \cos^{-1} \zeta$$

The pole radius is

$$\omega_n = \frac{1}{\sqrt{a}} = \frac{1}{\sqrt{R_1 R_2 C C_o}}$$

Then for a pole angle of  $\phi = 30^\circ$ ,  $\zeta = \cos(30^\circ) = \sqrt{3}/2$  and

$$\frac{(R_1 + R_2) \cdot C_o}{(R_1 \| R_2) \cdot C} = 3$$

Given  $R_1$ ,  $R_2$ , and an estimate for  $C_o$ ,

$$C = \frac{\left(R_1 + R_2\right) \cdot C_o}{3 \cdot \left(R_1 \| R_2\right)}$$

For  $R_1 = R_2$ , then

$$C = \frac{4}{3} \cdot C_o$$

$C_o$  is an undesirable parasitic circuit element, is typically small, and takes on a small range of possible values. Because of its only approximate value, *C* might need to be adjustable to tune the pole angle for optimal response.

Because of its small size, C is also small, approximately the value of  $C_o$ . Consequently, small-variable-C methods might need to be applied. One simple discrete-circuit approach is to use what used to be called a "gimmick." Twist a length of insulated wire, strip and solder-coat one pair of ends as C terminals, then snip the length of the pair for optimal C. Varnish or glue C to retain its geometry and its C value. This works for relatively slow high-speed circuits. Better methods can also be applied. If approximate dynamic behavior is adequate, or by using a response trim elsewhere, no adjustment is needed. In this case, a circuit-board or IC capacitance, though approximate, can be sufficient.

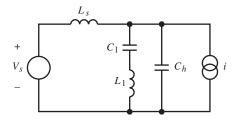

### SOURCE-FOLLOWER COMPENSATION

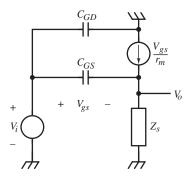

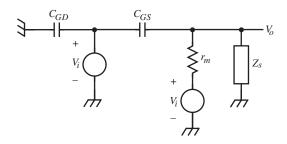

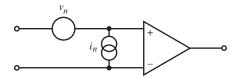

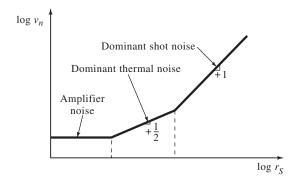

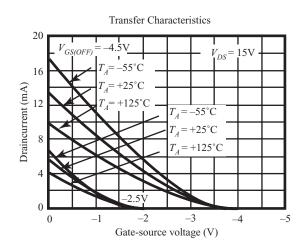

Common-source (CS) stages are often used at the input of instrument amplifiers to minimize resistive loading. Unlike their BJT counterpart (the CC), FET  $C_{GS}$ is typically much smaller than  $C_{\pi}$  of BJTs. Consequently, the  $Z_{\pi}$  term of  $Z_{b}$ (described in *Designing Dynamic Circuit Response*, "High-Frequency Impedance Transformations") cannot be ignored as it usually can for the BJT. Applying the transformation for FETs and including the effect of  $C_{GD}$ ,

$$Z_g = \left[\frac{1}{sC_{GS}} + Z_S \cdot \left(\frac{s\tau_T + 1}{s\tau_T}\right)\right] \left\|\frac{1}{sC_{GD}}\right\|$$

where  $\tau_T = r_m \cdot C_{GS}$ . The equivalent circuit is shown below.

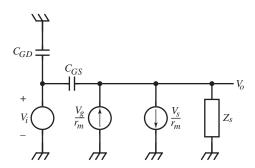

It is transformed by applying the substitution theorem to the circuit shown below.

Then Norton-to-Thevenin conversion of the current source results in the following circuit.

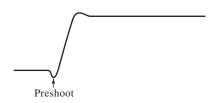

For a capacitive load of  $C_s$ ,  $V_i$  drives a capacitive divider that causes an input voltage step to immediately rise to a fraction of the step amplitude,

$$\frac{C_{GS}}{C_{GS} + C_S}$$

and then continues to rise exponentially, due to  $r_m$ , to the input step value. The transfer function of the above circuit is

$$\frac{V_o}{V_i} = \frac{sr_m C_{GS} + 1}{sr_m (C_{GS} + C_S) + 1} = \frac{s\tau_T + 1}{s(\tau_T + r_m C_S) + 1}$$

The pole is less than the zero, resulting in the response of a phase-lag circuit. The initial response step is p/z with a time constant of  $r_m \cdot (C_{GS} + C_S)$ . The

response can be compensated by adding a phase-lead circuit at another stage in the amplifier.

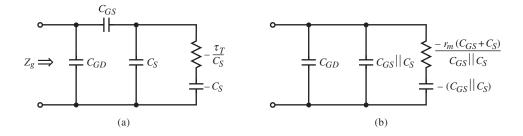

A second anomaly of the CS is its input impedance. From  $Z_g$ , the gyrating factor can be expressed in topological form as

$$Z_s \cdot \left(\frac{s\tau_T + 1}{s\tau_T}\right) = Z_s \cdot \frac{1}{1 - 1/(s\tau_T + 1)}$$

Substituting  $Z_s = 1/sC_s$ ,  $Z_g$  reduces to

$$Z_g = \frac{1}{sC_{GD}} \left\| \left( \frac{1}{sC_{GS}} + \frac{1}{sC_S} \right\| \left( -\frac{\tau_T}{C_S} - \frac{1}{sC_S} \right) \right)$$

A more useful form is

$$Z_{g} = \frac{1}{sC_{GD}} \left\| \left( \frac{s(C_{GS} + C_{S})\tau_{T} + C_{GS}}{s^{2}C_{GS}C_{S}\tau_{T}} \right) \right.$$

$$= \frac{1}{sC_{GD}} \left\| \left( \frac{1}{s(C_{GS} \| C_{S})} \right) \right\| \left( -r_{m} \cdot \frac{C_{GS} + C_{S}}{C_{GS} \| C_{S}} - \frac{1}{s(C_{GS} \| C_{S})} \right) \right\|$$

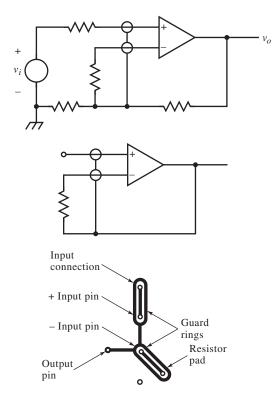

This equivalent hf gate impedance is shown below and is compensated by the method used to compensate the CC, that of shunting the gate with a series RC, which produces a purely capacitive input. (Keep in mind that  $\parallel$  is a mathematical operator, not a topological descriptor.) The values of the compensating elements are derived from the expression for  $Z_{gr}$ .

A source follower is usually used to prevent loading of a high-impedance source. If the source impedance is resistive, then it forms an uncompensated voltage divider with  $Z_g$ . This can be compensated by introducing a shunt *RC* in series with the input.

It forms a compensated divider with  $Z_{g}$  resulting in a resistive input.

The last CS problem to be considered is distortion due to large-signal effects. When a large-amplitude square-wave is applied to the compensated CS,  $C_{GS}$  and  $r_m$  both change significantly between levels. If  $C_1$  is adjusted for compensation of the positive transition, then for the negative transition,  $r_m$  and  $C_{GS}$  increase causing  $\tau_T$  to increase. An increase of  $C_{GS}$  increases the step fraction, causing negative overshoot or undershoot. The transfer function is also affected. Both pole and zero decrease, but with significant  $C_S$ , the pole decreases less. Consequently, p/z decreases, causing the compensator to overcorrect and produce undershoot. FETs with large  $C_{GS}$  have reduced undershoot, and if they also have a large  $\tau_T$ , undershoot error diminishes more quickly. Similarly, FETs with large pinch-off voltages have less  $r_m$  variation with  $V_{GS}$ .

### Example: CD Input Buffer Compensation

A source-follower FET has a transconductance of 50 mS ( $r_m = 200 \Omega$ ),  $C_{GS} = 6 \text{ pF}$  and  $C_{GD} = 2 \text{ pF}$ . Maufacturer data sheets give FET capacitances as

$$C_{iss} = C_{GS} + C_{GD}, C_{rss} = C_{GD}$$

With a load capacitance of  $C_s = 10$  pF, a series *RC* shunting the gate compensates the FET input. To calculate their values,  $\tau_T$  is needed:

$$\tau_T = r_m \cdot C_{GS} = 1.25 \,\mathrm{ns}$$

Then, from the above circuit diagram,

$$R = r_m \cdot \left(\frac{C_{GS} + C_S}{C_{GS} \| C_S}\right) = 853 \,\Omega \Longrightarrow 820 \,\Omega,$$

$$C = C_{GS} \| C_S = 3.75 \,\mathrm{pF} \Longrightarrow 3.9 \,\mathrm{pF}$$

The input now is a shunt *RC*, where  $C_g = C + C_{GD} = 5.9$  pF and  $R_2 = 1$  M $\Omega$ . To compensate this pole, a shunt *RC* is placed in series with the input (as in the figure above). In applications in which the input comes from a probe or passive attenuator, the compensating *RC* is in the probe body so that the probe itself contains the top part of the voltage divider. For a 10 M $\Omega$  input,

$$R_1 = 9 \operatorname{M\Omega}, \quad C_1 = \frac{R_2 C_g}{R_1} = \frac{C_g}{9} = 0.66 \operatorname{pF}$$

For such large  $R_1$ ,  $C_1$  is an extremely small capacitance. The  $R_1$  resistor probably has more parasitic shunt capacitance than the value  $C_1$ . As a consequence, practical values of capacitors make it infeasible to try to compensate the input divider. That is why, for example, oscilloscope vertical inputs are marked with labelings such as 1 M $\Omega$ , 22 pF.

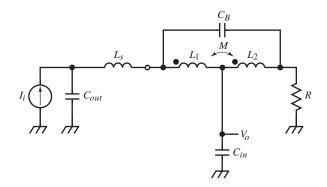

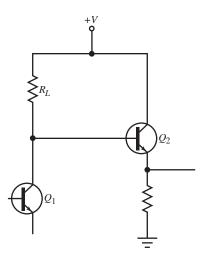

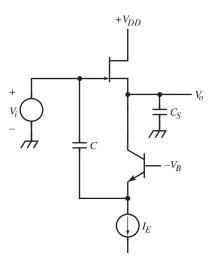

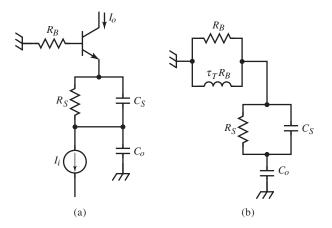

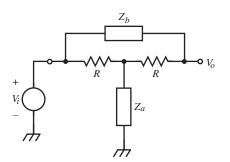

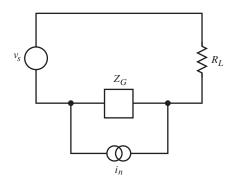

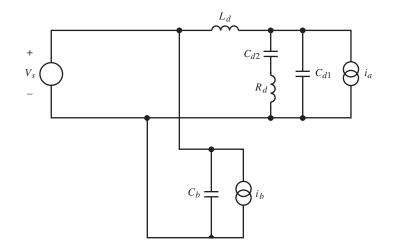

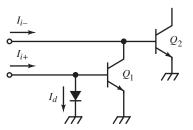

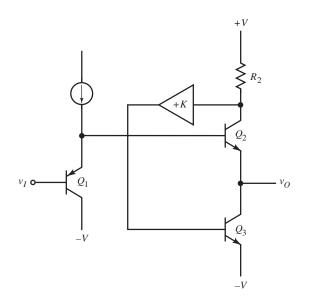

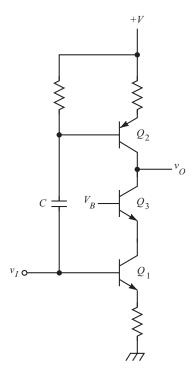

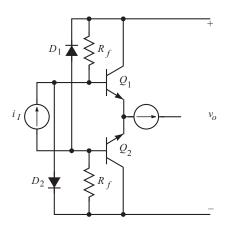

The following circuit takes an alternative approach to common-drain (CD) compensation. It has two paths: the main path through the FET and a compensation path through the CB BJT. The FET path transfer function is given by  $V_o/V_i$ , whereas for the compensation path, *C* forms a divider with  $Z_{\pi}/(\beta + 1)$ . The BJT-path voltage gain is

BJT

$$\frac{V_o}{V_i} = \alpha_0 \cdot \frac{sr_{mFET} \cdot C}{[sr_{mFET} \cdot (C_{GS} + C_S) + 1][sr_e \cdot (C_{\pi} + C) + 1]}$$

The paths add to produce the total transfer function. Both paths share the pole with time constant

$$r_{m\text{FET}} \cdot (C_{GS} + C_S) + \tau_{T\text{FET}} + r_{m\text{FET}}C_S$$

Then if the BJT time constant

$$r_e \cdot (C_{\pi} + C) = \tau_{TB|T} + r_e \cdot C$$

is much smaller than that for the FET path, its pole can be ignored and the transfer functions of the paths added:

$$\frac{V_o}{V_i} \cong \frac{s(\tau_{T\text{FET}} + \alpha_o r_{m\text{FET}}C) + 1}{s(\tau_{T\text{FET}} + r_{m\text{FET}}C_S) + 1}, \quad \tau_{T\text{BJT}} + r_e C \to 0$$

For flat response, the time constants are equated and

$$\alpha_o \cdot C = C_s \Longrightarrow C \cong C_s, \quad \alpha_o \cong 1$$

For step inputs with fast edges, the voltage differentiation of C can cause currents that exceed  $I_E$  and drive the BJT into cutoff.

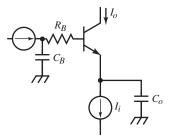

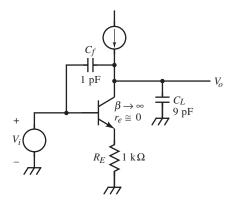

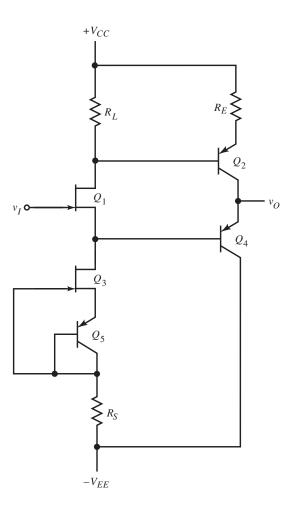

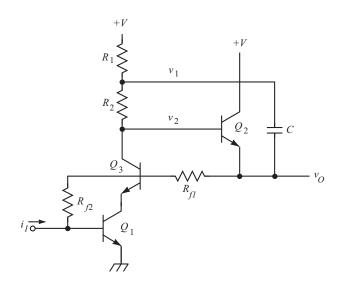

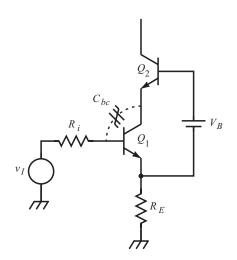

# **EMITTER COMPENSATION**

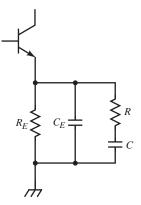

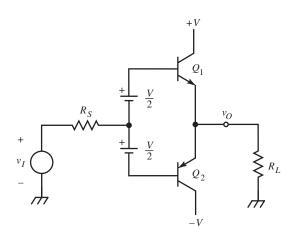

An impedance in series with the emitter (or source) of CB and CE (or CG and CS) amplifiers creates series feedback (see *Designing Amplifier Circuits*, "Noninverting Feedback Amplifier Examples") and can improve speed. Compensation networks can be connected to the emitter node that correct for speed limitations at the collector. The figure shows a CB stage with capacitive output loading.

A series *RC* is placed in parallel with  $R_E$  to provide correction. In the lf region (or for  $\tau_T \rightarrow \infty$ ), the transfer function is

$$\frac{V_o}{V_i} = \alpha \cdot \frac{R_L}{r_e + R_E} \cdot \frac{s(R_E + R) \cdot C + 1}{(sR_LC_L + 1) \cdot [s(R + r_e ||R_E)C + 1]}$$

For compensated response, the zero cancels the collector pole at frequency  $1/R_L \cdot C_L$ , leaving a much higher-frequency pole. For a flat frequency response, the compensating elements must have the values

$$R = R_L - R_E, \quad C = C_L$$

and for bandwidth extension,

$$(R + r_e || R_E) \cdot C \ll R_L \cdot C_L$$

For  $r_e \ll R$  and  $R_E$ , then  $R \ll R_L$ .

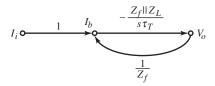

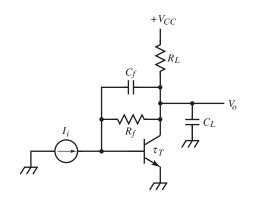

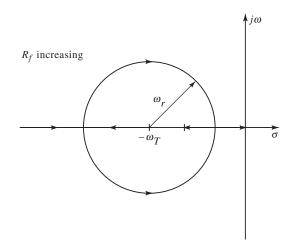

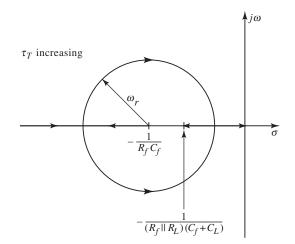

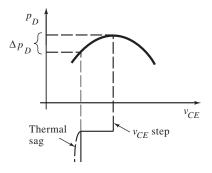

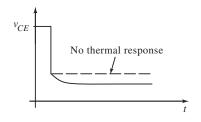

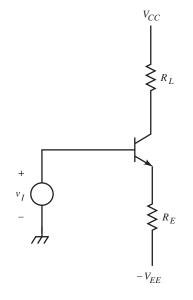

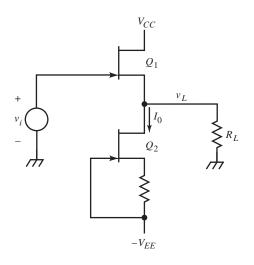

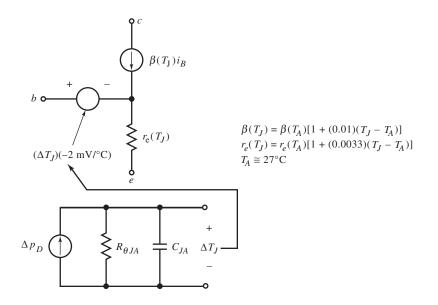

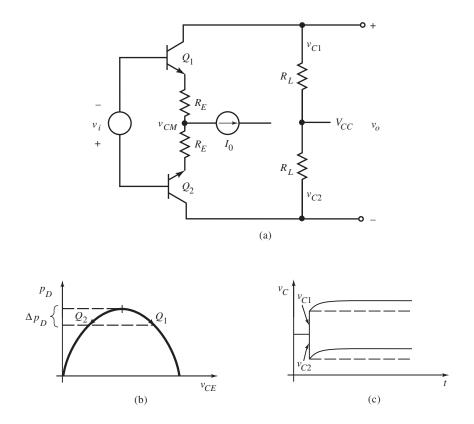

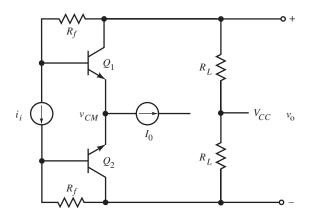

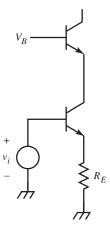

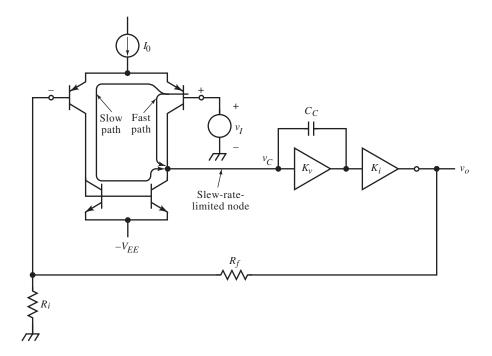

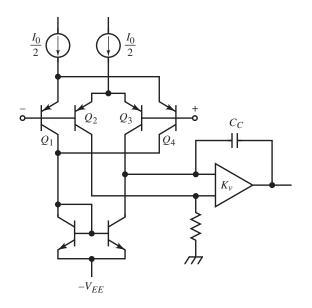

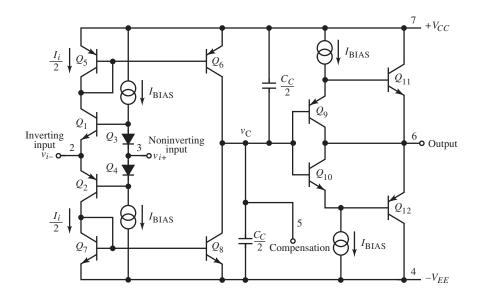

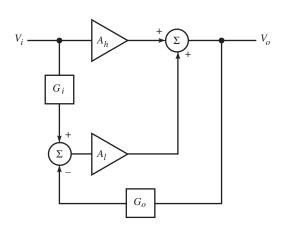

Compensation of CE (or CS) amplifiers is similar. In the circuit shown above, a similar network is connected to the emitter, resulting in a negative  $V_o/V_i$ . In both cases, transistor reactances have been ignored, and the resulting equations are useful for amplifiers for which the output pole is below  $f_\beta$ .