# Compact 0.3-to-1.125 GHz self-biased phase-locked loop for system-on-chip clock generation in 0.18 µm CMOS

Zhao Zhang, Liyuan Liu, Peng Feng, Jian Liu\*, and Nanjian Wu\*

State Key Laboratory for Superlattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, P. R. China \*E-mail: liujian@semi.ac.cn; nanjjan@red.semi.ac.cn

Received September 28, 2015; revised December 3, 2015; accepted December 20, 2015; published online March 7, 2016

In this paper, we propose a compact ring-oscillator-based self-biased phase-locked loop (SBPLL) for system-on-chip (SoC) clock generation. It adopts the proposed triple-well NMOS source degeneration voltage-to-current (*V–I*) converter instead of the operational amplifier (OPAMP) based *V–I* converter and a proposed simple start-up circuit with a negligible area to save power and area. The SBPLL is implemented in the 0.18  $\mu$ m CMOS process, and it occupies 0.048 mm<sup>2</sup> active core. The measurement results show the SBPLL can generate output frequency in a wide range from 300 MHz to 1.125 GHz with a constant loop bandwidth that is around 5 MHz and a relatively low jitter performance that is less than 4.9 mUI over the entire covered frequency range. From –20 to 70 °C the rms jitter variation and loop bandwidth variation at 1.125 GHz are 0.2 ps and 350 kHz, respectively. The rms jitter performance variation of all covered frequency points is less than 10% in the supply range from 1.5 to 1.7 V. Such SBPLL shows robustness over environmental variation. The maximum power consumption is 5.6 mW with 1.6 V supply at an output frequency of 1.125 GHz. © 2016 The Japan Society of Applied Physics

# 1. Introduction

The phase-locked loop (PLL) is the critical building block that is widely used in many system-on-chip (SoC) systems. There are several design challenges in the design of such PLLs. First, the PLL should cover a wide frequency range to meet different frequency requirements of building blocks such as a universe serial bus (USB) interface, low-voltage differential signal (LVDS), and dynamic random-access memory (DRAM). Secondly, the jitter should be relatively low to meet tightly timing constraint in some high speed building blocks. Thirdly, because of the need for the implementation of multiple PLLs in some SoC systems, low power and area efficiency are necessary. Last but not least, insensitivity to environmental variation is also required.

There are mainly two kinds of PLLs: the LC-oscillatorbased PLL (LC-PLL)<sup>1-6)</sup> and the ring-oscillator-based PLL (RPLL).<sup>7-13)</sup> The LC-PLLs show superior phase-noise performance at the cost of large area. LC oscillators need a multiple-switched-capacitors array<sup>14–16)</sup> and auto-frequency calibration (AFC)<sup>17-19)</sup> techniques to expand the tuning range, which raise the design complexity of the PLL. The RPLL is more attractive than the LC-PLL for SoC applications because it has the advantages of small area and large tuning range, but the phase noise is much worse than that of the LC-PLL, and may greatly degrade the jitter performance. To improve the jitter performance, several techniques were presented in prior works. The sub-sampling PLL (SSPLL)<sup>20)</sup> can increase the phase detector gain and thus suppress the in-band phase noise and jitter. However, it has a relatively narrow capture range and high spur level. The sub-harmonically injection-locked PLL (SILPLL)<sup>21)</sup> was proposed to suppress the either the in-band or the out-band phase noise, but complicated calibration is need to adjust the injection timing and to avoid the issue of losing locking. In addition, the spur level is also relatively high.

An alternative way of designing PLLs that meet the SoC requirement is to adopt the self-biased PLL (SBPLL).<sup>22–25)</sup> The loop bandwidth to reference frequency ratio can be kept relatively constant with the help of matched passive components regardless of the output frequency, and process,

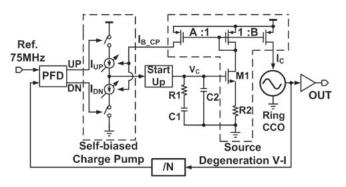

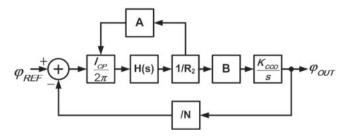

Fig. 1. Block diagram of proposed SBPLL.

voltage, and temperature (PVT) variations. Having such advantages, a wide loop bandwidth can be set to suppress the phase noise of the ring oscillator and thus achieve low jitter performance without the issue of stability due to the PVT variation. However, the SBPLL has a complex structure<sup>22,23)</sup> that leads to large area or high power consumption. Although the SBPLL was much simplified,<sup>24,25)</sup> but more than one operational amplifier (OPAMP) is needed, leading to high power consumptions and the occupation of a large area.

We propose a compact ring oscillator based SBPLL. It adopts a triple-well NMOS source degeneration voltage-tocurrent (*V–I*) converter instead of the operational amplifier (OPAMP)-based *V–I* converter and a simple start-up circuit with a negligible area to save power and area. The SBPLL can operate with a constant loop bandwidth in a wide range of output frequency and shows relatively low jitter. It occupies an active area of only 0.048 mm<sup>2</sup> in an inexpensive 0.18 µm CMOS process, which is a good choice for the clock generation of a low-cost SoC application.

## 2. Architecture of proposed SBPLL

## 2.1 Overall architecture

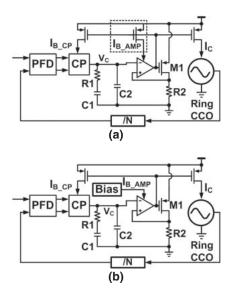

Figure 1 shows the block diagram of the proposed SBPLL. It consists of a phase/frequency detector (PFD), self-biased charge pump, start-up circuit, loop filter (LPF), source degeneration V-I converter, ring current-controlled oscillator

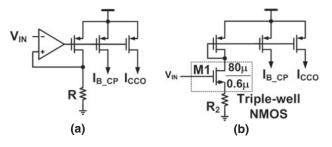

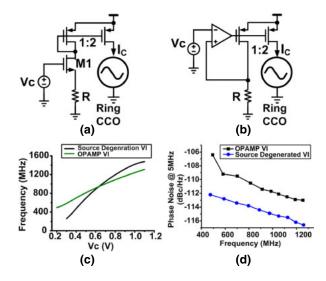

**Fig. 2.** Schematic of (a) OPAMP based *V*–*I* converter and (b) proposed triple-well NMOS source degeneration *V*–*I* converter.

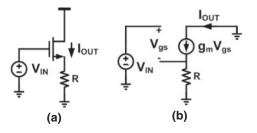

**Fig. 3.** (a) Simplified schematic of source degeneration *V*–*I* converter and (b) its small signal model.

(RCCO), frequency divider and output buffer. The proposed triple-well NMOS source degeneration V-I converter replaces the OPAMP based V-I converter to save power and area. The detailed performance comparison in detail between the two kinds of V-I converter is presented in Sect. 3. The proposed simple start-up circuit with a negligible area ensures a robust start-up operation of the SBPLL. Thus the SBPLL can robustly generate a wide range of output frequency with relatively low jitter. As shown in Fig. 1, the CP current is set proportional to the control current of the RCCO to keep the loop bandwidth to reference frequency ratio relatively constant. In order to suppress the phase noise contributed from RCCO, the reference clock is set to be a relatively high frequency of 75 MHz so that the loop bandwidth can be set to be as large as 5 MHz. The frequency divider and PFD are implemented with truly single-phase clock logic (TSPC) to lower the power consumption while maintaining high operation speed.

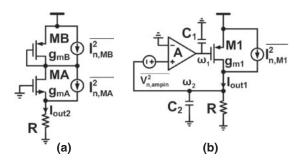

The proposed SBPLL adopts the proposed triple-well NMOS source degenerated *V*–*I* converter instead of the OPAMP-based *V*–*I* converter,<sup>24)</sup> as shown in Fig. 2. The source degenerated *V*–*I* converter consists of only four MOS transistors and one degeneration resistor  $R_2$ , which is much simpler than the OPAMP-based *V*–*I* converter. Therefore, the power consumption and area of the proposed SBPLL can be reduced. Figure 3 shows a simplified schematic of the source degenerated *V*–*I* converter and its small signal model. The transfer function of such a *V*–*I* converter can be written as

$$G_{\rm m} = \frac{I_{\rm out}}{V_{\rm in}} = \frac{g_{\rm m}}{1 + g_{\rm m}R},\tag{1}$$

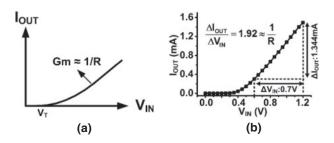

where  $g_m$  is the transconductance of the NMOS transistor. As  $V_{in}$  increases,  $g_m$  also rises, and  $G_m$  tends to be 1/R, as shown in Fig. 4(a). In order to increase the linearity of  $G_m$ , a large width/length ratio and low threshold voltage  $V_T$  are needed for NMOS to achieve larger  $g_m$  under the same input voltage

**Fig. 4.** (a) Theoretical transfer curve and (b) simulated transfer curve of the source degeneration *V*–*I* converter.

Fig. 5. Linear model of proposed SBPLL.

$V_{\rm in}$ . In our design, the source and body terminals of the triplewell NMOS transistor M1 shown in Fig. 2(b) are connected together to avoid the body effect. In addition, the triple-well NMOS has better noise isolation performance, compared with the normal NMOS. The channel width and length of M1 are chosen to be 80 and 0.6 µm. The long channel can reduce the  $V_{\rm T}$  by means of the reverse short-channel effect.<sup>26)</sup> The simulation result shows that M1 has  $V_{\rm T}$  of about 300 mV, which is a relatively low value in the 0.18 µm process. The simulated transfer curve of the proposed source degeneration V-I converter in this SBPLL is shown in Fig. 4(b). The source degeneration resistor used in the V-I converter is 450  $\Omega$ . As shown in Fig. 4(b), the simulation result can matches well with the theoretical analysis result shown in Fig. 4(a).

Figure 5 shows the linear model of proposed SBPLL, where  $K_{CCO}$  is the gain of the RCCO and  $I_{CP}$  is the current of the CP. As shown in Figs. 1 and 5, the ratio of  $I_{CP}$  to the control current of RCCO is *A*. By analyzing the linear model shown in Fig. 2, the loop bandwidth of the SBPLL can be expressed as

$$\omega_{\rm BW} \approx \frac{A}{2\pi} \times \frac{R_1}{R_2} \times \omega_{\rm REF},$$

(2)

where  $R_1$  and  $R_2$  are shown in Fig. 1, and  $\omega_{\text{REF}}$  is the angular frequency of the reference clock. Equation (2) indicates that the loop bandwidth to reference clock frequency ratio can not only be kept constant regardless of the divider ratio N but also is not sensitively to the PVT variation because such a ratio is proportional to the ratio between two matched resistors,  $R_1$  and  $R_2$ .

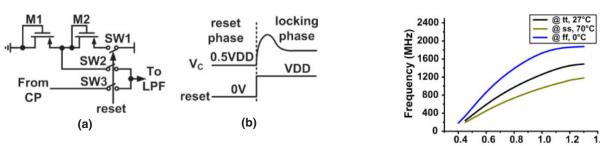

In SBPLL, it is necessary to implement the start-up circuit. Figure 6(a) shows the proposed simple start-up circuit, it consists of only two PMOS transistors, two switches, and one inverter, which occupy an area of only  $15 \times 14 \,\mu m^2$ , a negligible area. The operation process of SBPLL with the proposed start-up circuit is presented in Fig. 6(b). The operation process mainly includes two phase: the reset phase

**Fig. 6.** (a) Schematic of proposed start-up circuit. (b) Operation process of SBPLL.

Fig. 8. (Color online) Simulated CCO frequency tuning curve.

V<sub>c</sub> (V)

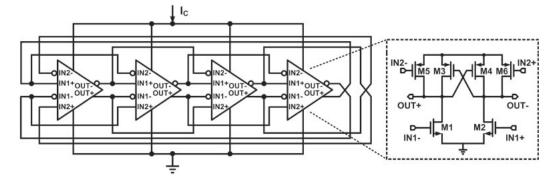

Fig. 7. Schematic of Ring CCO and its delay cell.

and the tracking/locking phase. In the reset phase, the SW1 and SW2 are open and SW3 is closed, the SBPLL loop is open and the control voltage  $V_{\rm C}$  of the LPF is set to be half the supply voltage  $V_{\rm DD}/2$  to make the oscillator and the charge pump start to work. In the tracking and locking phase, the reset signal goes high first, then SW2 turns off and SW3 turns on to close the loop and the PLL starts to lock to the desired frequency. By turning SW1 off, the start-up circuit is turned off not only to save power but also to avoid any effect on the PLL frequency tracking and locking. In summary, the SBPLL can start up and lock to the desired frequency correctly and robustly by following above the process.

The reset signal in the start-up circuit can be connected to the global reset signal in the SoC systems, which shows good compatibility to the SoC application.

#### 2.2 Ring CCO

Figure 7 shows the schematic of the RCCO and its delay cell. This CCO is implemented with a four-stage dual-delay path loop<sup>27,28)</sup> to achieve higher operation frequency and wide tuning range. The dual-delay path includes both the normal paths and the negative skew paths. The negative skew paths are achieved by adding the secondary differential input signals IN2+ and IN2- to every delay cell. The PMOS M3 and M4 are adopted as the regenerative cross-coupled transistors to achieve fast switching and rail-to-rail output and thus reduce the phase noise of RCCO.

Figure 8 shows the post-layout simulated frequency tuning range of the RCCO at different PVT corner. The RCCO and source degeneration V-I converter are connected together to simulate the frequency tuning range by sweeping the control voltage  $V_{\rm C}$  shown in Fig. 1. Figure 8 indicates that the design target frequency range from 0.3 to 1.125 GHz can be achieved at different PVT corners.

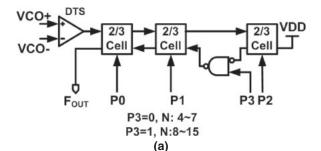

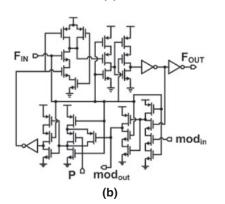

2.3 Multi-modules frequency divider, PFD and CP Figures 9(a) and 9(b) show the frequency divider and its cell, respectively. It is implemented with the three-stage multimodules frequency divider (MMD) with extended logic to extend the division ratio from 4 to 15. The differential to single-end converter (DTS) is adopted to convert the CCO differential output to the CMOS rail-to-rail single-ended signal. Although the MMD with a current-mode logic (CML) structure<sup>29)</sup> can achieve a very high operation speed, it has the drawbacks of high power consumption and large area occupation. Thus in this design, we adopt the TSPC MMD<sup>6</sup>) to meet the high-operation-speed requirement with low power and small area. The area is only 0.0013 mm<sup>2</sup> and its simulated power at 1.5 GHz operation frequency is only 0.45 mW.

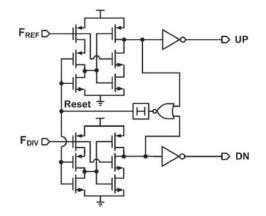

Figure 10 shows the schematic of PFD. Because of the relatively high reference frequency in this SBPLL, the TSPC structure is also adopted in the PFD.<sup>30)</sup> Moreover, compared with the classic static PFD, the delay of the reset path can be shorter than that in the TSPC PFD because it has fewer logic gates, which means the phase noise contributed by the PFD and CP can be reduced. In this design, the reset delay is set at about 300 ps. The CP<sup>8)</sup> is adopted to achieve fast switching speed and good current matching performance.

# 3. Performance comparison between the source degeneration *V*–*I* converter and the OPAMP based *V*–*I* converter in the SBPLL

In this section, the performance comparison between source degeneration V-I converter and the OPAMP based converter in the SBPLL is presented below.

#### 3.1 Noise and power comparison

First we compare the theoretical noise and power performance between the two V-I converter. Because the SBPLL phase

Fig. 9. Schematic of TSPC MMD and its cell.

Fig. 10. Schematic of TSPC PFD.

noise contributed from the V-I converter shows bandpass character and the SBPLL loop bandwidth is designed to be relatively high, we only consider the impact of the thermal noise and ignore the influence of the low frequency flicker noise. The output current noise of the source degeneration V-Iconverter shown in Fig. 11(a) can be expressed as

$$\overline{I_{n,out2}^2} = \frac{4KT\gamma_N g_{mA}}{\left(1 + g_{mA}R\right)^2} + 4KT\gamma g_{mB},$$

(3)

where  $g_{mA}$  and  $g_{mB}$  are the transconductances of MA and MB shown in Fig. 11(a) and  $\gamma_N$  is the thermal noise parameter of NMOS.

Figure 11(b) shows the small signal noise model of the OPAMP-based V-I converter. The current noise power of the output current  $I_{out1}$  can be expressed as

$$\overline{I_{n,out1}^2} = \frac{V_{n,amp}^2}{R^2} + \frac{4KT\gamma_P g_{m1}}{(1 + Ag_{m1}R)^2},$$

(4)

where  $V_{n,amp}$  is the equivalent input noise of the OPAMP,  $g_{m1}$  is the transconductance of the M1, A is the gain of the OPAMP and  $\gamma_P$  is the thermal noise parameter of PMOS. The

**Fig. 11.** Schematic of the (a) OPAMP-based V-I and (b) source degeneration V-I for noise calculation.

Fig. 12. Schematic of the folded-cascode OPAMP.

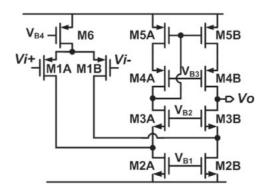

second item of Eq. (4) can be ignored owing to the high gain of the OPAMP. The typical folded-cascode OPAMP shown in Fig. 12 is adopted in such a V-I converter. The equivalent input noise power can be written as

$$\overline{V_{n,amp}^2} = 2\left(\frac{4KT\gamma}{g_{m1}} + \frac{4KT\gamma g_{m2}}{g_{m1}^2} + \frac{4KT\gamma Pg_{m5}}{g_{m1}^2}\right).$$

(5)

And Eq. (4) can be rewritten as

$$\overline{q_{n,\text{out1}}^2} = \frac{2}{R^2} \left( \frac{4KT\gamma_N}{g_{\text{m1}}} + \frac{4KT\gamma_N g_{\text{m3}}}{g_{\text{m1}}^2} + \frac{4KT\gamma_P g_{\text{m5}}}{g_{\text{m1}}^2} \right), \quad (6)$$

where  $g_{m1}$ ,  $g_{m3}$ , and  $g_{m5}$  are the transconductances of M1A(B), M3A(B), and M5A(B) shown in Fig. 12, respectively. Equations (3) and (6) indicate that the OPAMP based *V*–*I* converter has more noise source than the source degeneration one. To achieve the same amount of noise,  $g_{m1}$  must be higher than  $g_{mA}$ , and thus more power consumption of the OPAMP is needed.

Figures 13(a) and 13(b) show the schematic for simulating the tuning curve and the phase noise of the CCO with the two kinds of *V*–*I* converter, respectively. The CCOs in Figs. 13(a) and 13(b) are same and the details are shown in Fig. 7. Figure 13(c) shows that the CCO with both two *V*–*I* converters can achieve a similar linear tuning range. Figure 13(d) shows that the CCO with the source degenerated *V*–*I* converter has phase noise at least 3 dB lower than that of the CCO with the OPAMP converter. The OPAMP in this simulation consumes 0.36 mW with a 1.6 V supply, which is not a negligible value especially when the SBPLL generates low-frequency clock.

Thus both the theoretical and the simulation results show that the source degeneration V-I converter can achieve better noise performance than the OPAMP-based converter with less power consumption and smaller area.

**Fig. 13.** (Color online) Schematics for simulation comparison of the (a) source degeneration V-I converter and (b) the OPAMP-based V-I converter, and the simulation result of (c) the tuning curve and (d) phase noise performance.

**Fig. 14.** Solutions to generate the bias current for OPAMP (a) with the V-I converter itself and (b) with an additional bias generation circuit.

#### 3.2 Stability comparison

We analyze the stability of SBPLLs based on the OPAMP based *V*–*I* converter and source degeneration *V*–*I* converter, respectively. The OPAMP-based *V*–*I* converter has two poles,  $\omega_1$  and  $\omega_2$ , as shown in Fig. 11(b). If the SBPLL adopts the *V*–*I* converter, the two poles must be much higher than the loop bandwidth to maintain the stability of the PLL. Therefore, more power consumption is needed.

The OPAMP in the *V–I* converter requires a bias circuit. There are two possible solutions to generate the bias circuit. The first solution is to bias the OPAMP by the *V–I* converter itself,<sup>24)</sup> as shown in Fig. 14(a) and the second solution is to use a bias current generation circuit, as shown in Fig. 14(b). In the first solution, if the SBPLL generates a low-frequency clock, the bias current of the OPAMP in the *V–I* converter becomes lower and may cause a stability problem owing to the decrease of the two poles in the *V–I* converter. The second solution can avoid the problem in the first one, but the

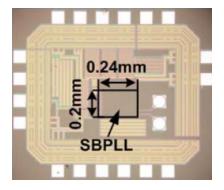

Fig. 15. (Color online) Chip micrograph.

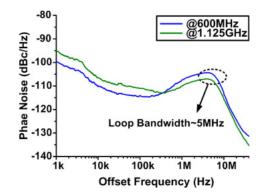

**Fig. 16.** (Color online) Phase noise at 1.125 GHz and 600 MHz, respectively.

additional bias generation circuit occupies more area and the bias current for the OPAMP should also be set high enough to make the PLL stable regardless of the PVT variation. Thus such a solution is also not efficient in terms of power and area.

In the source degeneration V-I converter, there is no high impendence node and thus there is no pole that can degrade the stability of the SBPLL. In addition, no bias circuit is needed for such a V-I converter. Therefore, the SBPLL implemented with such a V-I converter is easier to stabilize and more PVT variation tolerable with lower power consumption, compared with the SBPLL that adopts the OPAMP based one.

In summary, as the noise, power and stability comparisons show, it is an effective way to replace the OPAMP based V-I converter with the proposed source degeneration V-Iconverter to make the SBPLL more power and area efficient without the penalty of noise, stability and PVT tolerance.

#### 4. Implementation and measurement results

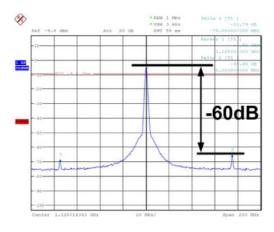

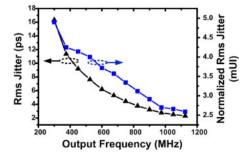

The chip micrograph is shown in Fig. 15. It is implemented with the 0.18  $\mu$ m process and occupies active area of only 0.048 mm<sup>2</sup> with 1.6 V supply voltage. Measurement shows that the SBPLL can generate a clock with the frequency range from 300 MHz to 1.125 GHz. Figure 16 shows the measured phase noise of 10 MHz offset frequency is -113 and -115 dBc/Hz at clock frequency of 600 MHz and 1.125 GHz, respectively. The loop bandwidth is around 5 MHz at the two frequency points. Figure 17 shows the reference spur level is -60 dB at 1.125 GHz clock frequency. The rms jitter integrated from 1 kHz to 40 MHz over all

Fig. 17. (Color online) Frequency spectrum at 1.125 GHz.

**Fig. 18.** (Color online) Integrated rms jitter over the entire covered frequency range.

Fig. 19. Loop bandwidth over the entire frequency range.

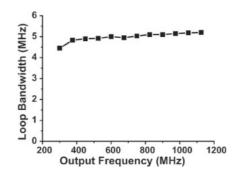

covered frequency range is presented in Fig. 18. The worst rms jitter is 4.9 mUI at 300 MHz, which indicates a relatively low jitter performance. The worse jitter performance at a lower clock frequency is mainly due to the smaller swing of CCO output at lower output frequency.

Figure 19 presents the loop bandwidth versus output frequency. It indicates that the loop bandwidth  $f_{BW}$  is around 5 MHz regardless of the output frequency. The maximum variation of the  $f_{BW}$  is only about 750 kHz or 15% over all covered frequency range. The variation of  $f_{BW}$  is mainly caused by the nonlinearity of the *V*–*I* converter, the gain of CCO and the channel length modulation effect of MOS in the current mirrors of the CP.

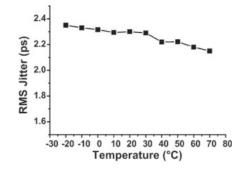

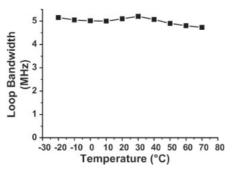

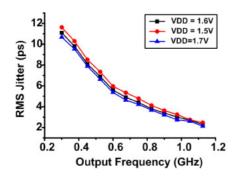

Figures 20 and 21 show the rms jitter and loop bandwidth over a temperature range from -20 to 70 °C at 1.125 GHz output. It indicates the rms jitter variation is 0.2 ps and the  $f_{BW}$  variation is 350 kHz over a wide temperature range. Figure 22 shows the rms jitter performance at supply voltage

**Fig. 20.** Rms jitter performance at carrier frequency 1.125 GHz over temperature range from -20 to  $70 \,^{\circ}\text{C}$ .

**Fig. 21.** Loop bandwidth at carrier frequency of 1.125 GHz over temperature range from -20 to 70 °C.

**Fig. 22.** (Color online) RMS jitter performance at different supply voltages.

of 1.5, 1.6, and 1.7 V, respectively. The rms jitter variation is less than 10% with a supply range from 1.5 to 1.7 V. In summary the SBPLL shows good tolerance of environment variation.

The performance summary of the SBPLL is listed in Table I, in which the figure of merit (FOM) is calculated by Eq. (3).<sup>31)</sup>

FOM =

$$10 \log \left[ \left( \frac{\sigma}{1 \text{ s}} \right)^2 \times \left( \frac{\text{Power}}{1 \text{ mW}} \right) \right]$$

(7)

where the  $\sigma$  is the rms jitter of the PLL. Compared with the SBPLL,<sup>24)</sup> the measurement results show that the proposed SBPLL has lower jitter and better FOM, which shows better noise performance and lower power of the proposed source degeneration *V*–*I* converter than the OPAMP-based one.<sup>24)</sup> Although the SBPLL<sup>24)</sup> shows the smallest area and lowest power to date, it is mainly due to the advanced process. If the proposed SBPLL is implemented in an advanced nanometer CMOS process, power and area can be further reduced.

Table I. Performance summary and comparison.

|                  | This work                      | Ref. 24             | Ref. 23           | Ref. 9              | Ref. 32             | Ref. 10             |

|------------------|--------------------------------|---------------------|-------------------|---------------------|---------------------|---------------------|

| Output frequency | 0.3-1.125 GHz                  | 1.5 GHz             | 240 MHz           | 3.1 GHz             | 2 GHz               | 1.21 GHz            |

| Phase noise      | -115 dBc/Hz@10 MHz             | NA                  | -102 dBc/Hz@1 MHz | NA                  | -105 dBc/Hz@1 MHz   | -119.6dBc@1MHz      |

| RMS jitter       | 2.3 ps                         | 5.8 ps              | NA                | 1.01 ps             | 2.77 ps             | 0.57 ps             |

| Reference spur   | -60 dB                         | NA                  | -60 dB            | NA                  | -50 dB              | -55 dB              |

| Power            | 5.6 mW                         | 1.2 mW              | 8.46 mW           | 27.5 mW             | 32 mW               | 51.6 mW             |

| Supply voltage   | 1.6 V                          | 1 V                 | 1.8 V             | 1.2 V               | 1.2 V               | 1.2 V               |

| FOM              | -225.3 dB                      | -223.9 dB           | NA                | -225.5 dB           | -216 dB             | -227.7 dB           |

| Area             | $0.048\mathrm{mm}^2$           | $0.02\mathrm{mm^2}$ | $0.078  mm^2$     | $0.32\mathrm{mm^2}$ | $0.13  \text{mm}^2$ | $0.12  \text{mm}^2$ |

| Temperature      | $-20$ to $70 ^{\circ}\text{C}$ | NA                  | NA                | NA                  | NA                  | NA                  |

| Technology       | 0.18 µm                        | 90 nm               | 0.18 µm           | 65 nm               | 65 nm               | 65 nm               |

Compared with the other prior works shown in Table I, the proposed SBPLL shows lower power and small area with comparable FOM.

#### 5. Conclusions

A compact 0.3-to-1.125 GHz SBPLL is proposed and implemented in inexpensive 0.18 µm CMOS process. The proposed triple-well NMOS source degeneration V-I converter is adopted in the SBPLL to save power and area. A simple start-up circuit is proposed to achieve robust start-up operation while occupies negligible area. The measured loop bandwidth can be kept at around 5 MHz with the variation of only 15%. The rms jitter integrated from 1 kHz to 40 MHz at a carrier frequency of 1.125 GHz is 2.3 ps and normalized rms jitter over the entire frequency range is less than 4.9 mUI. The variation in the rms jitter and loop bandwidth at 1.125 GHz is 0.2 ps and 350 kHz in the temperature range from -20 to 70 °C, respectively. The rms jitter performance variation of all the covered frequency points is less than 10% in the supply range from 1.5 to 1.7 V. The SBPLL shows good robustness to environmental variation. The maximum power is 5.6 mW at 1.125 GHz with 1.6 V supply and the FOM of  $-225.3 \, dB$ . Measurement shows that the proposed SBPLL has smaller area and lower power with comparable FOM than those of the prior works.

#### Acknowledgments

This work is financially supported by National Natural Science Foundation of China under Grant Nos. 61306027, 61331003, and 61474108 and Beijing Nature Science Foundation under Grant No. 4152051.

- 3) X. Liu, P. Feng, L. Liu, and N. Wu, Jpn. J. Appl. Phys. 53, 04EE18 (2014).

- 4) W. Lou, Z. Geng, P. Feng, and N. Wu, J. Semicond. 32, 065004 (2011).

- X. Gao, L. Tee, W. Wu, K.-S. Lee, A. A. Paramanandam, A. Jha, N. Liu, E. Chan, and L. Lin, IEEE int. Solid-State Circuit Conf. Dig. Tech. Pap., 2015, p. 166.

- B. M. Helal, C.-M. Hsu, K. Johnson, and M. H. Perrott, IEEE J. Solid-State Circuits 44, 1391 (2009).

- X. Kuang and N. Wu, IEEE Int. Solid-State Circuit Conf. Dig. Tech. Pap., 2006, p. 741.

- X. Shi, K. Imfeld, S. Tanner, M. Ansorge, and P.-A. Farine, IEEE European Solid-State Circuit Conf. Dig. Tech. Pap., 2006, p. 174.

- A. Sai, Y. Kobayashi, S. Saigusa, O. Watanabe, and T. Itakura, IEEE Int. Solid-State Circuit Conf. Dig. Tech. Pap., 2012, p. 248.

- A. Sai, T. Yamaji, and T. Itakura, IEEE Int. Solid-State Circuit Conf. Dig. Tech. Pap., 2011, p. 98.

- 11) J. Yishu, Z. Yumei, J. Jianhua, and W. Bin, J. Semicond. 31, 095002 (2010).

- 12) S.-Y. Kao and S.-I. Liu, IEEE Trans. VLSI Syst. 19, 592 (2011).

- 13) I.-T. Lee, Y.-T. Tsai, and S.-I. Liu, IEEE J. Solid-State Circuits 47, 2693 (2012).

- 14) J. Luo, L. Zhang, L. Zhang, Y. Wang, and Z. Yu, IEEE Int. Symp. Circuits and Systems, 2015, p. 2840.

- 15) S. S. Broussev, L. A. Lehtonen, and N. T. Tchamov, IEEE Microwave Wireless Components Lett. 17, 274 (2007).

- 16) L. Lu, J. Chen, L. Yuan, H. Min, and Z. Tang, IEEE Trans. Microwave Theory Tech. 57, 928 (2009).

- 17) L. Lu, Z. Gong, Y. Liao, H. Min, and Z. Tang, IEEE Int. Solid-State Circuit Conf. Dig. Tech. Pap., 2009, p. 396.

- 18) J. Shin and H. Shin, IEEE Trans. Circuits Syst. I 57, 1573 (2010).

- 19) J. Shin and H. Shin, IEEE J. Solid-State Circuits 47, 665 (2012).

- 20) K. Sogo, A. Toya, and T. Kikkawa, IEEE Euro. Solid-State Circuit Conf. Dig. Tech. Pap., 2012, p. 253.

- 21) C.-L. Wei, T.-K. Kuan, and S.-I. Liu, IEEE Trans. Circuits Syst. II 62, 548 (2015).

- 22) J. G. Maneatis, J. Kim, I. McClatchie, J. Maxey, and M. Shankaradas, IEEE J. Solid-State Circuits 38, 1795 (2003).

- 23) X. Meng, L. Huang, L. Chen, and F. Lin, IEEE Int. Symp. Radio-Frequency Integration Technology, 2011, p. 193.

- 24) W. Jung, H. Choi, C. Jeong, K. Kim, W. Kim, H. Jeon, G. Koo, J. Kim, J. Seo, M. Ko, and J. Kim, IEEE Int. Solid-State Circuit Conf. Dig. Tech. Pap., 2007, p. 310.

- 25) J. Liu, S. Jeon, T.-K. Jang, D. Kim, J. Kim, J. Park, and H. Park, Proc. IEEE Asian Solid-State Circuits Conf., 2011, p. 337.

- 26) T.-H. Kim, H. Eom, J. Keane, and C. Kim, Proc. IEEE Int. Symp. Low Power Electronics and Design, 2006, p. 127.

- 27) Y. A. Eken and J. P. Uyemura, IEEE J. Solid-State Circuits 39, 230 (2004).

- 28) J.-M. Kim, S. Kim, I.-Y. Lee, S.-K. Han, and S.-G. Lee, IEEE Trans. Circuits Syst. II 60, 71 (2013).

- 29) C. S. Vaucher, I. Ferencic, M. Locher, S. Sedvallson, U. Voegeli, and Z. Wang, IEEE J. Solid-State Circuits 35, 1039 (2000).

- 30) A. Homayoun and B. Razavi, IEEE Trans. Circuits Syst. I 60, 529 (2013).

- X. Gao, E. A. M. Klumperink, P. F. J. Geraedts, and B. Nauta, IEEE Trans. Circuits Syst. II 56, 117 (2009).

S. Lee, T. Kamimura, S. Yonezawa, A. Shirane, S. Ikeda, H. Ito, N.

- Ishihara, and K. Masu, IEEE Microwave Wireless Components Lett. 23, 96 (2013).

B. Shen, G. Unruh, M. Lugthart, G.-H. Lee, and M. Chambers, IEEE Symp. VLSI Circuits Dig. Tech. Pap., 2013, p. 192.

S.-Y. Yang, W.-Z. Chen, and T.-Y. Lu, IEEE J. Solid-State Circuits 45, 578 (2010).