# Verification Academy

# Advanced UVM Using the Register Layer

Tom Fitzpatrick

Verification Evangelist

# **UVM Register Use Models**

#### Stimulus Generation

- Firmware-level abstraction of stimulus:

- i.e. Set this bit in this register rather than write x to address y

- Stimulus reuse

- If the bus agent changes, the stimulus still works

#### Configuration

- Register model reflects hardware programmable registers

- Set up desired configuration in register model then dump to DUT

- Randomization with configuration constraints

#### Analysis 'Mirror'

- Current state of the register model matches the DUT hardware

- Useful for scoreboards and functional coverage monitors

# **UVM Register Class Access API**

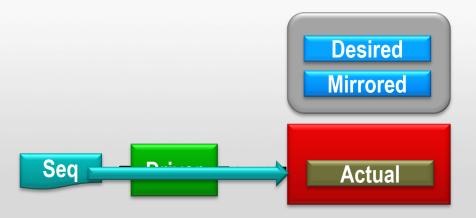

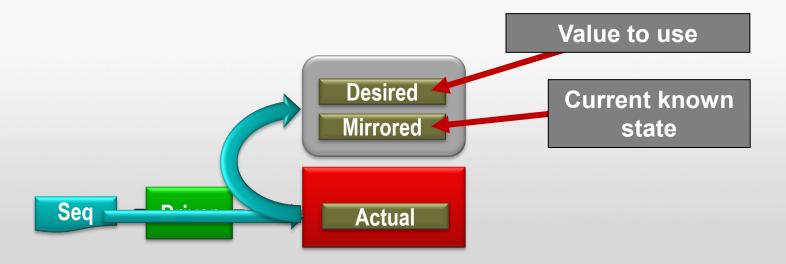

- The register model has two register variables:

- **Desired value:** For when a field has been updated, but not the hardware

- Mirrored value: Containing the latest known value

- reg.read() and reg.write()

- Access the hardware register and update the register database

- Front door access uses bus agent takes time and may create side effects

- Back door access is instant (via VPI) and does not cause side effects

- Not used for individual fields

- reg.peek() and reg.poke()

- For back door accesses, register model updated with result

- Can be used for individual fields

- reg.set() and reg.get()

- Access the desired value directly

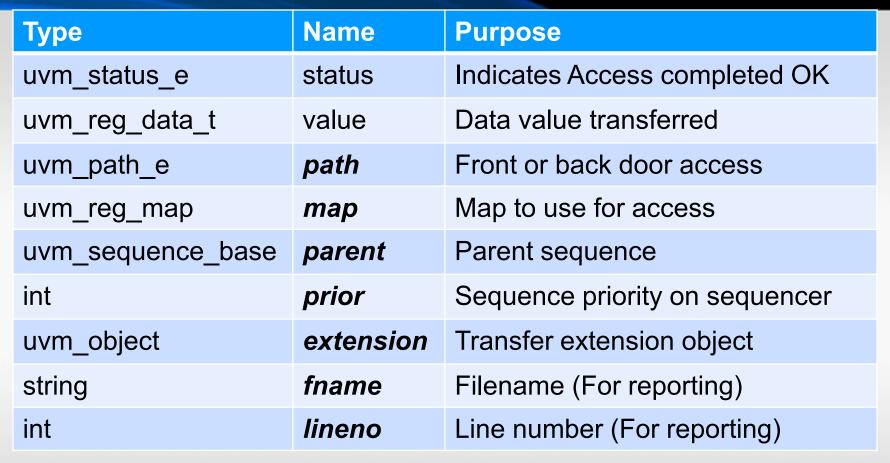

# Register Access Method Fields

- Good news most of these fields have defaults!

- A typical register access only needs a few of these:

```

spi_rm.ctrl.write(status, wdata, .parent(this));

```

```

spi_rm.ctrl.write(status, wdata, UVM_FRONTDOOR, .parent(this));

spi_rm.ctrl.read (status, rdata, UVM_FRONTDOOR, .parent(this));

```

```

spi_rm.ctrl.write(status, wdata, UVM_FRONTDOOR, .parent(this));

spi_rm.ctrl.read (status, rdata, UVM_FRONTDOOR, .parent(this));

```

- Desired and Mirrored values updated at end of transaction

- Based on transaction contents and field access mode

```

write_reg(model.ctrl, status, wdata, UVM_FRONTDOOR);

read_reg (model.ctrl, status, rdata, UVM_FRONTDOOR);

```

- Desired and Mirrored values updated at end of transaction

- Based on transaction contents and field access mode

```

write_reg(model.ctrl, status, wdata, UVM_FRONTDOOR);

read_reg (model.ctrl, status, rdata, UVM_FRONTDOOR);

```

- Desired and Mirrored values updated at end of transaction

- Based on transaction contents and field access mode

- Can access individual fields

- Only if hardware supports it

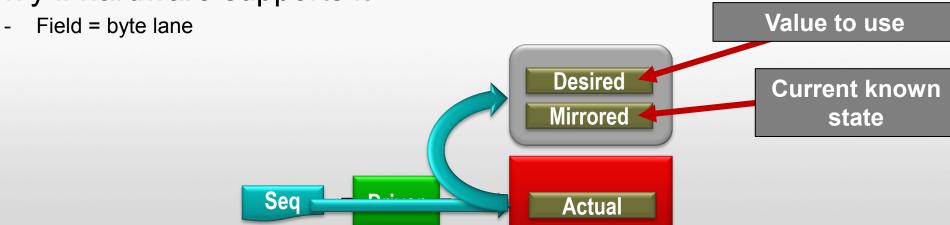

#### **Back-Door Access Modes**

```

write_reg(model.ctrl, status, wdata, UVM_BACKDOOR);

read_reg (model.ctrl, status, rdata, UVM_BACKDOOR);

```

- must be specified explicitly

- Desired and Mirrored values updated at end of transaction

- Based on transaction contents and field access mode

Can only access full register via back door

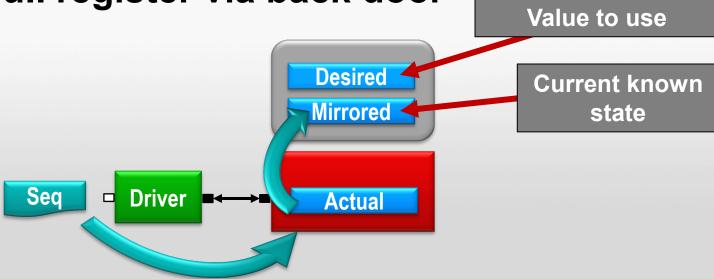

### **Back-Door Access Modes**

```

poke_reg (model.ctrl, status, wdata);

peek reg (model.ctrl, status, rdata);

```

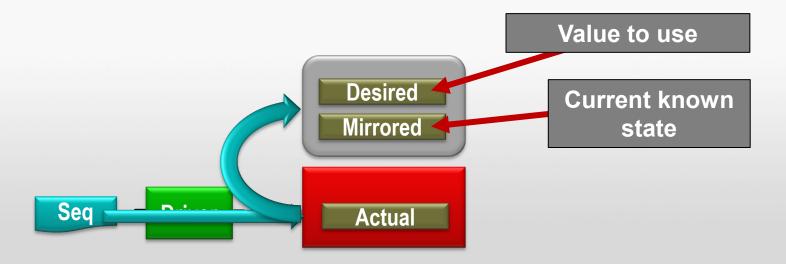

- Desired and Mirrored values updated directly at end of transaction

- Poke sets the actual register value

- Peek samples the actual value, which is written to model

Peek/Poke work on fields

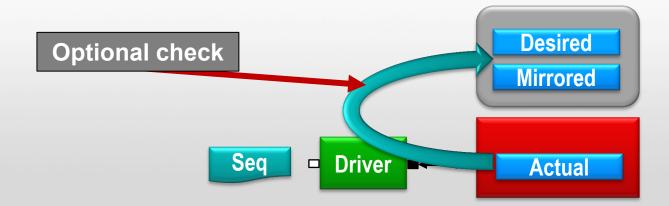

Pesired

Current known state

Seq

Driver

Actual

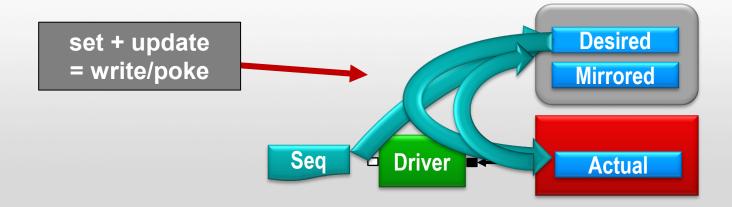

#### **Direct Access Modes**

- Consume no time on the bus

- Access the Desired Value directly

- Use update() method to update actual value

- Via frontdoor: update\_reg(model.ctrl, status, UVM\_FRONTDOOR);

- Or backdoor: update\_reg(model.ctrl, status, UVM\_BACKDOOR);

#### **Mirror Method**

- Read register and update/check mirror value

- via frontdoor

```

mirror_reg(model.ctrl, status, UVM_CHECK, UVM_FRONTDOOR);

```

or backdoor

```

mirror reg(model.ctrl, status, UVM CHECK, UVM BACKDOOR);

```

Can be called on field, reg or block

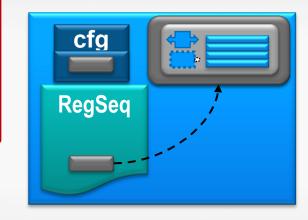

# Register Sequence Base Class

**Default item type**

# Register Sequence Base Class

```

class blk R test seq

extends uvm reg sequence;

`uvm object utils(blk R test seq)

Set correct type

reg block B

model; 🔫

function new(string name = "blk R test seq");

super.new(name);

endfunction: new

virtual task body();

uvm status e status;

uvm reg data t data, rd data;

write reg(model.R, status, data);

read reg (model.R, status, rd data);

endtask

endclass

```

Provides

convenience

methods for

reading/writing

registers and

memories

## Register Stimulus: Base Class

```

class spi bus base seq extends uvm reg sequence;

`uvm object utils(spi bus base seq)

spi rm model

// SPI env config object (contains register model handle)

spi env config m cfg;

// Properties used by the register access methods:

rand uvm reg data t data; // For passing data

task body;

m cfg = uvm config db #(spi_env_config)::get(null, get_full_name(),

"spi env config", m cfg)

model = m cfg.spi rm;

endtask: body

endclass: spi bus base seq

```

Base sequence contains variables common to all register sequences

Register model passed in via config\_db Can also be set directly

# Register Stimulus: Building on the Base

endclass: div load seq

```

class div load seq extends spi bus base seq:

Extends base sequence

`uvm object utils(div load seq)

// Interesting divisor values:

constraint div values {data[15:0] inside {16'h0, 16'h1, 16'h2,

16'h4, 16'h8, 16'h10,

16'h20, 16'h40, 16'h80};}

task body;

super.body;

Randomizes data value with

// Randomize the local data value

specific constraint

assert(this.randomize())

// Write to the divider register

Write data to divider

write reg (model.divider reg, status, data);

register

assert(status == UVM IS OK);

endtask: bodv

```

# Register Sequence: TX Data Load

```

class data load seq extends spi_bus_base_seq:

`uvm object utils(data load seq)

uvm_reg data_regs[]; // Array of registers

task body;

super.body;

// Set up the data register handle array

data regs = '{spi_rm.rxtx0_reg, spi_rm.rxtx1_reg,

spi_rm.rxtx2_reg, spi_rm.rxtx3_reg);

// Randomize order

data regs.shuffle() 🗲

foreach(data regs[i]) begin

assert(data regs[i].randomize());

update_reg(data_regs[i], status, UVM_FRONTDOOR);

end

endtask: body

endclass: data load seq

```

**Extends base sequence**

Get an array of register handles

Randomize the array index order

Foreach reg in the array

Randomize the content

**Update the register**

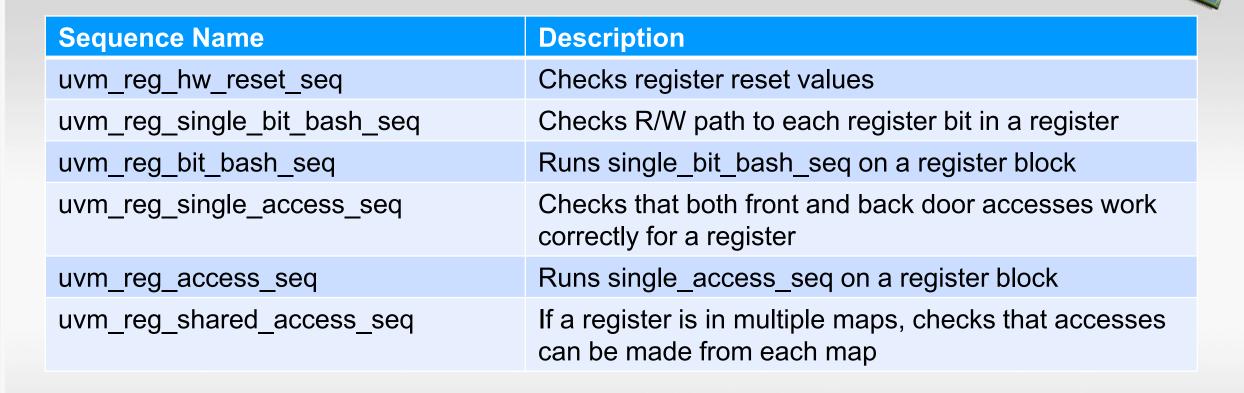

# **Built-In Sequences**

- Sequences are easy to run

- Low overhead to use

- Useful for initial sanity checks on bus connectivity

- Access modes are respected

- e.g. Read only registers are not bit bashed

- Read only memories are not tested

- Memories, Registers or Fields can be opted out of a test

- e.g. Clock enable bit

- Mechanism is to use the uvm\_config\_db to set an attribute for the register

# Register Built-In Sequences

# **UVM Register Summary**

- Register model follows hardware structure

- Fields, Registers, Blocks, Maps

- Internal access get(), set() etc.

- Sets up desired value

- External access Front and Backdoor

- Access layered via model

- Generic sequences adapted to target bus sequences

- Sequence reuse straight-forward

- Use the convenience API

- Extend uvm\_reg\_sequence

- write\_reg()/read\_reg() vs. write()/read()

- Don't have to worry about .parent() argument

# Verification Academy

# Advanced UVM Using the Register Layer

Tom Fitzpatrick

Verification Evangelist