# Symposium on VLSI Circuits Short Course 2

# Migrating Analog/Mixed-Signal (AMS) Designs to FinFET

Alvin L.S. Loke alvin.loke@ieee.org

Qualcomm Technologies, Inc.

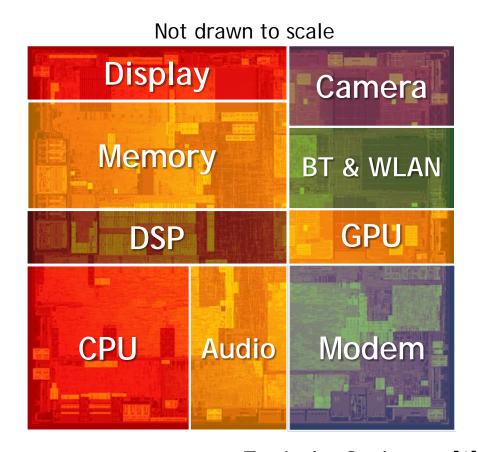

# Migrating Mobile SoC to 14nm FinFET

#### Snapdragon™ 820

Qualcomm Technologies' first 14nm product

#### AMS content

- PLLs & DLLs

- Wireline I/Os

- Data converters

- Bandgap references

- Thermal sensors

- Regulators

- ESD protection

Terzioglu, Qualcomm [1]

#### **Outline**

- MOSFET, Fully-Depleted & FinFET Basics

- Technology Considerations

- Analog/Mixed-Signal Design Considerations

- Conclusion

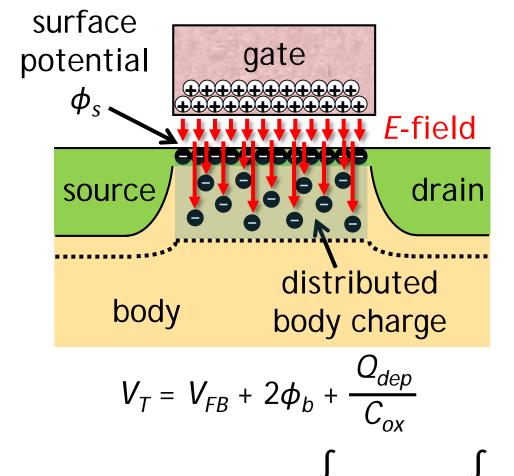

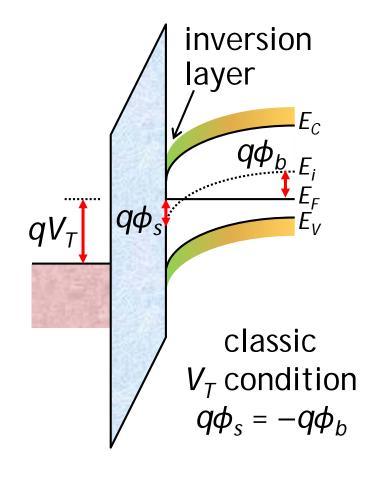

#### **Basic MOSFET Operation**

- Gate/body charge  $\rightarrow$  *E*-field  $\rightarrow$  energy band bending

- $V_{GS}$  modulates surface conductivity to induce S/D short

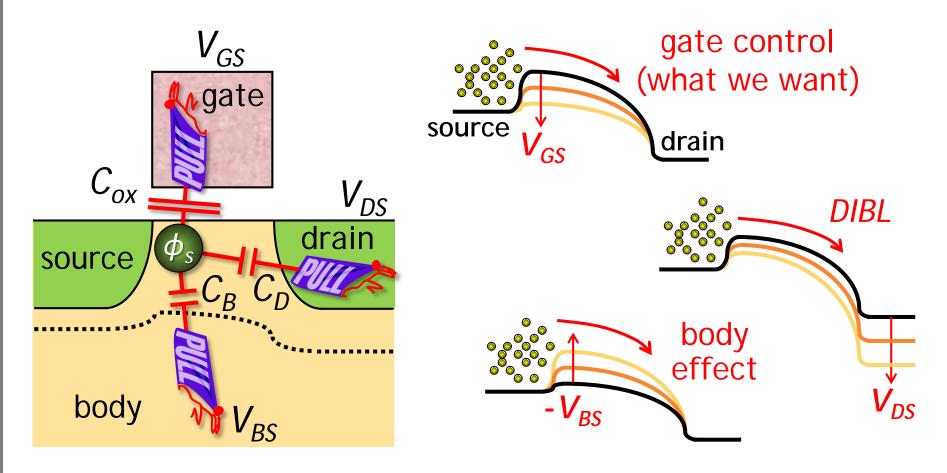

# Subthreshold Fight for Body Charge

- Capacitor divider dictates source-barrier  $\phi_s \& I_D$

- $C_B$ ,  $C_D << C_{ox}$   $\rightarrow$  weak body effect, weak DIBL, high  $I_{on}/I_{off}$

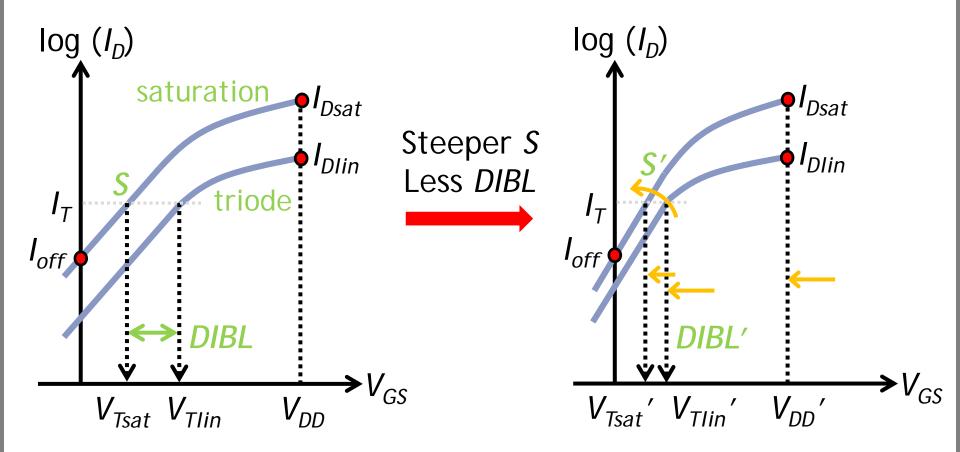

# Less Drain/Body Coupling, Lower Supply

- Steeper subthreshold swing S (ideally 60mV/decade @ 300K)

- Lower  $V_{DD}$ , lower power for same  $I_{off} \& I_{Dsat}$

- Fully-depleted finFET enables steeper S & less DIBL

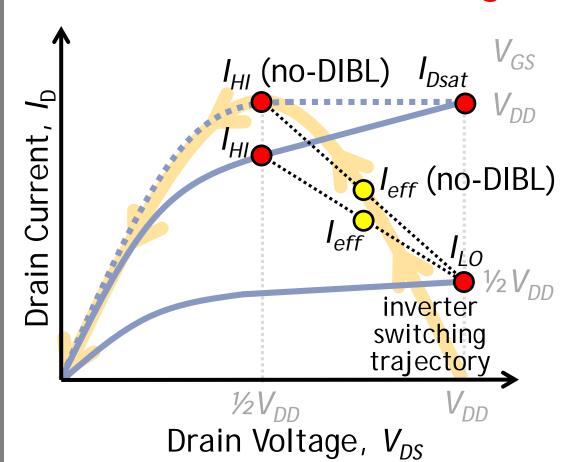

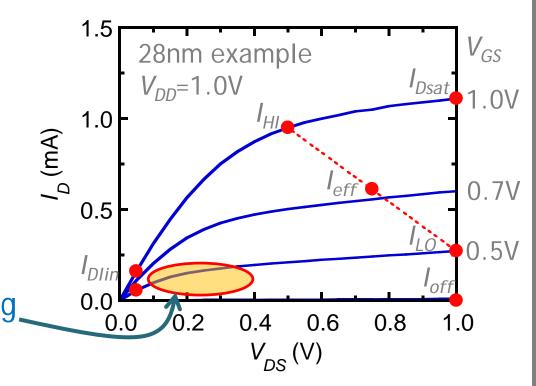

# Less DIBL -> Stronger FET for Digital

$$I_{eff} = \frac{I_{LO} + I_{HI}}{2}$$

$$I_{LO} @ V_{GS} = \frac{1}{2}V_{DD}, V_{DS} = V_{DD}$$

$$I_{HI} @ V_{GS} = V_{DD}, V_{DS} = \frac{1}{2}V_{DD}$$

*I<sub>eff</sub>* is better than *I<sub>Dsat</sub>* for estimating inverter *CV/I* switching delay

Less DIBL  $\rightarrow$  higher  $I_{eff} \& r_{out}$  for same  $I_{Dsat}$

Na et al., IBM [2] Wei et al., Stanford [3]

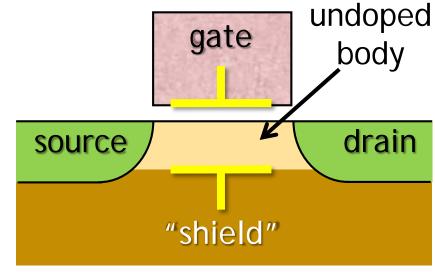

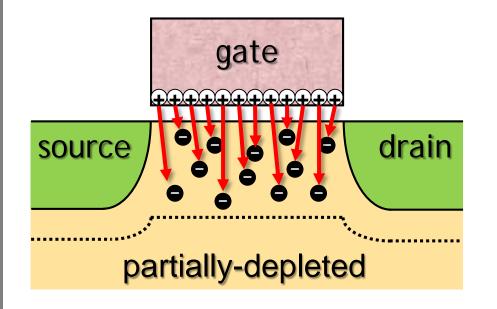

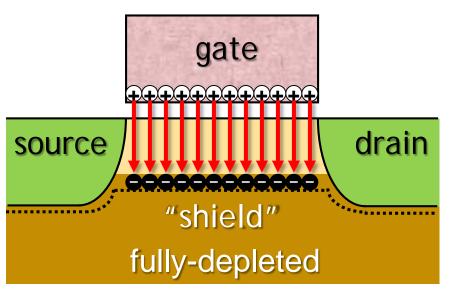

## Concept of Fully-Depleted

- Dopants *not* fundamental to field-effect action, just provide mirror charge to set up *E*-field to induce surface inversion

- Remove body dopants & insert heavily-doped conductive "shield" beneath undoped body to provide mirror charge (extreme retrograded-well)

- Body becomes fully-depleted as it has no charge to offer

- Implementations

- Planar on bulk

- Planar on SOI (FD-SOI)

- 3-D (e.g., finFET) on bulk

- 3-D on SOI

Yan et al., Bell Labs [4] Fujita et al., Fujitsu [5] Cheng et al., IBM [6]

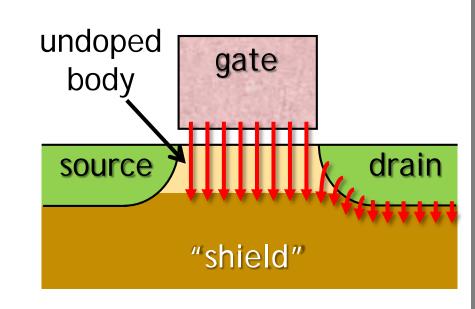

# **Fully-Depleted Considerations**

- Shield must be near drain to pull drain E-fields away from source barrier → less DIBL

- No dopant scattering in body → higher channel mobility

- Less  $\Delta V_{GS}$  to transition from flatband to inversion, so must adjust gate work function  $\Phi_M$  (¼-gap vs. band-edge)

- In practice, still need some body dopants to counterdope S/D diffusion & adjust  $V_T$

- Classic  $V_T$  condition no longer makes sense since  $\phi_p = 0$

Skotnicki, STMicroelectronics [7] Chang *et al.*, UC Berkeley [8]

# **Fully-Depleted Eliminates RDF**

- Body dopants vary in number but also in location

- Variation in length of *E*-field lines integrates to variation in band-bending or  $V_T$

- In fully-depleted, *E*-field lines have much tighter length distribution which eliminates  $V_T$  variation due to RDF

- But  $V_T$  becomes very sensitive to geometric variation

Asenov, U Glasgow [9]

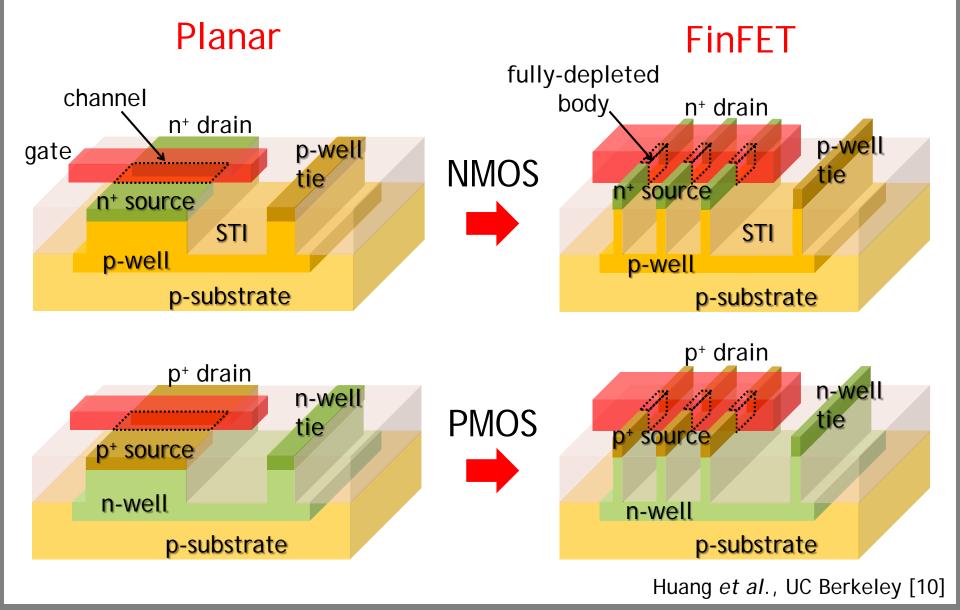

# Migrating to Fully-Depleted FinFET

#### **Outline**

- MOSFET, Fully-Depleted & FinFET Basics

- Technology Considerations

- Mechanical Stressors

- High-K/Metal-Gate

- Middle-Of-Line

- Multiple Patterning

- Analog/Mixed-Signal Design Considerations

- Conclusion

## Journey to FinFETs

- 16/14nm employs many new technology elements introduced across multiple earlier nodes

- Each element adds new design complexity

| Technology<br>Element             | Foundry<br>Debut                  | Reason<br>Required                                          |

|-----------------------------------|-----------------------------------|-------------------------------------------------------------|

| Mechanical stressors              | 90nm                              | Mobility boost for more FET drive & higher $I_{on}/I_{off}$ |

| HKMG replacement gate integration | 28nm (HK-first)<br>20nm (HK-last) | Higher $C_{ox}$ for more FET drive & channel control        |

| Middle-of-line                    | 20nm                              | Contact FET diffusion & gate with tighter CPP               |

| Multiple-patterning               | 20nm                              | Sub-80nm pitch lithography without EUV                      |

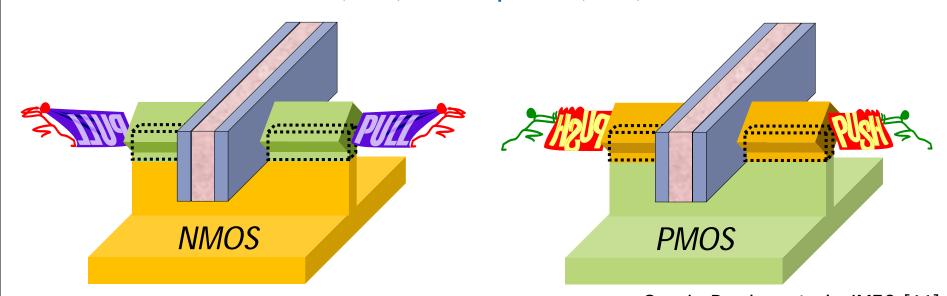

#### **Mechanical Stressors**

- Carrier mobility depends on lattice strain (Si is piezoresistive)

- Grow stressors to induce channel strain along L

- Tensile for NMOS, compressive for PMOS

- Techniques: STI fill, S/D epitaxy, gate stress memorization

- Anisotropic mobility & stress response

- L vs. W direction, (100) fin top vs. (110) fin sidewall

Garcia Bardon *et al.*, IMEC [11] Liu *et al.*, Globalfoundries [12]

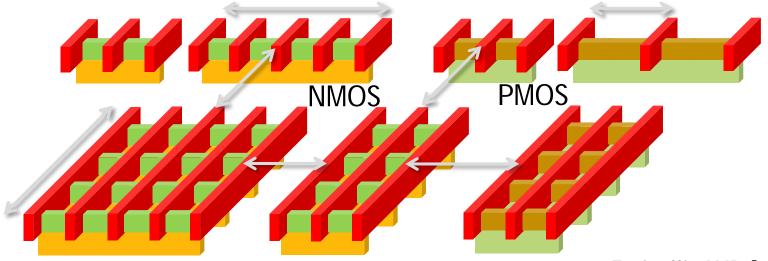

## **Stress-Related Layout Effects**

- Stressors are stronger in 16/14nm for more FET drive,

so layout effects can be more severe → schematic/layout ∆

- Stress build-up in longer active,  $I_D$ /fin not constant vs. # fins

- NMOS/PMOS stress mutually weaken each other

- Interaction with stress of surrounding isolation

Faricelli, AMD [13] Lee *et al.*, Samsung [14] Sato *et al.*, IBM [15]

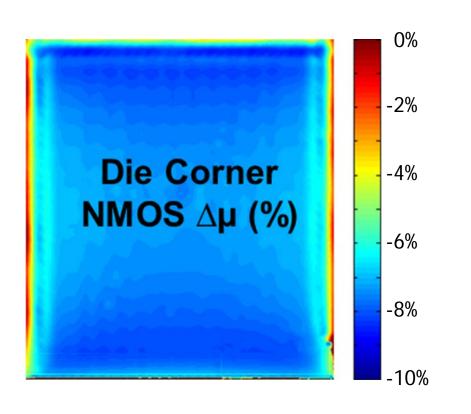

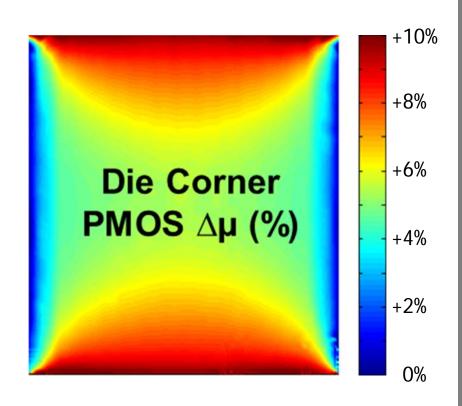

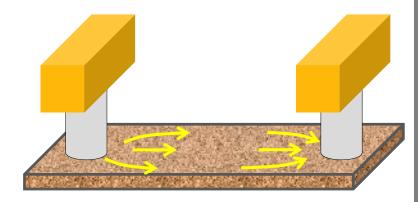

# **Electrical Chip-Package Interaction**

- FET mobility sensitive to stress from die attach to package

- Package stress can impact long-range device matching (e.g., I/O impedance, bias references, data converters)

Terzioglu, Qualcomm [1]

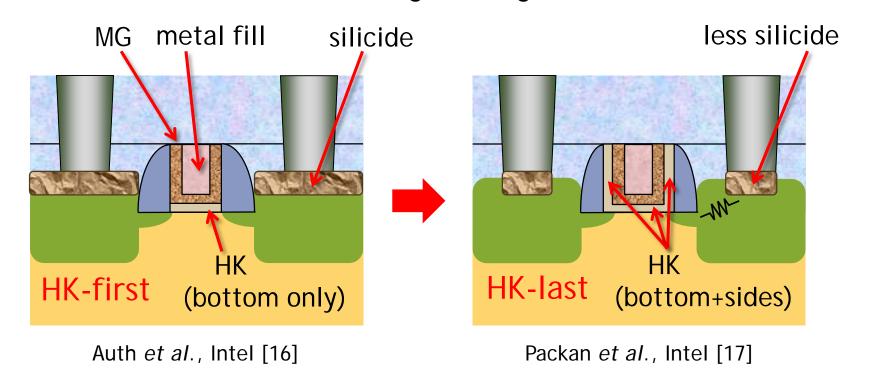

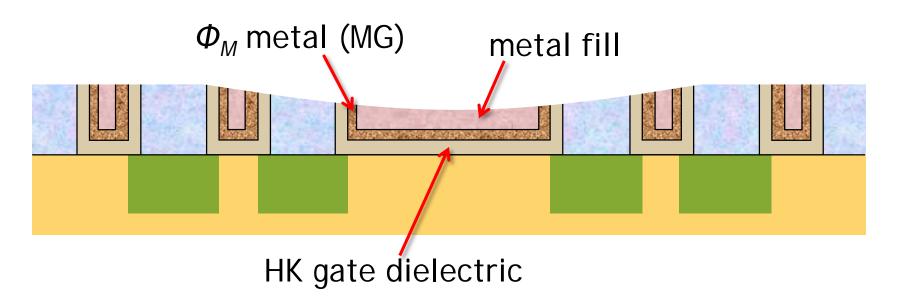

# High-K/Metal-Gate (HKMG)

- Higher  $C_{ox}$  without  $I_{gate}$  & poly depletion, but finicky interface

- Replace gate after S/D anneal for stable  $V_T = f(\Phi_M)$

- Gate = (ALD MG stack to set  $\Phi_M$ ) + (metal fill to reduce  $R_G$ )

- Variation in MG grain orientation  $\rightarrow V_T$  variation

- HK-first → HK-last for better gate edge control

## **Gate Density Induced Mismatch**

- Thin MG layer that sets gate  $\Phi_{M}$  is very resistive

- Gate charge spills into metal fill

→ gate Φ<sub>M</sub> is modulated by gate height & also gate L

- $V_T$  varies from gate CMP dishing/erosion  $\rightarrow$  matching concern

- Some gate types exposed to multiple CMP → more variation

Yang et al., Qualcomm [18]

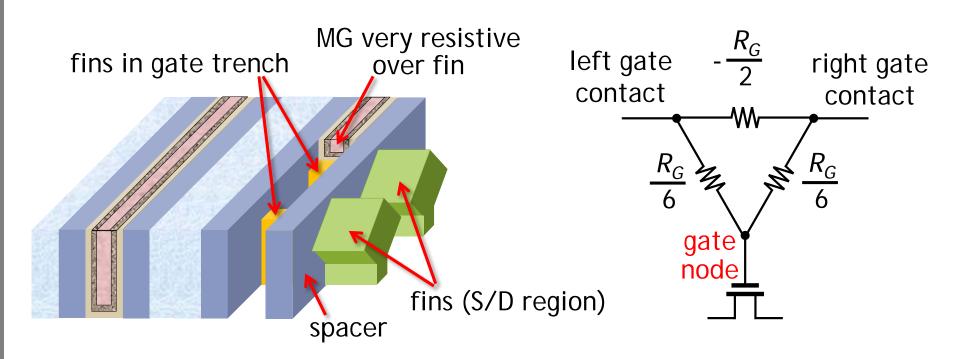

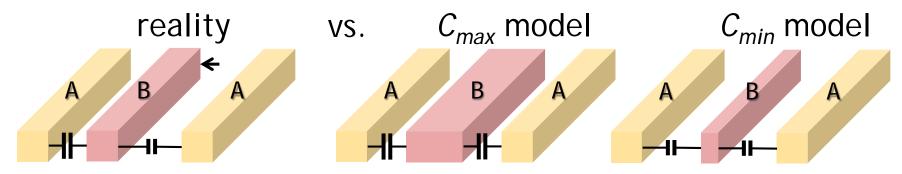

# Gate Resistance Very Significant

- $\Phi_M$  metal very resistive, little conductive metal fill for short L

- Δ model approximation

- Accounts for distributed RC, reality way more complicated

- $R_G/3$  for 1-side gate contact,  $R_G/12$  for 2-side contact

- R<sub>G</sub> for daisy chain connection

Wu & Chan, HKUST [19]

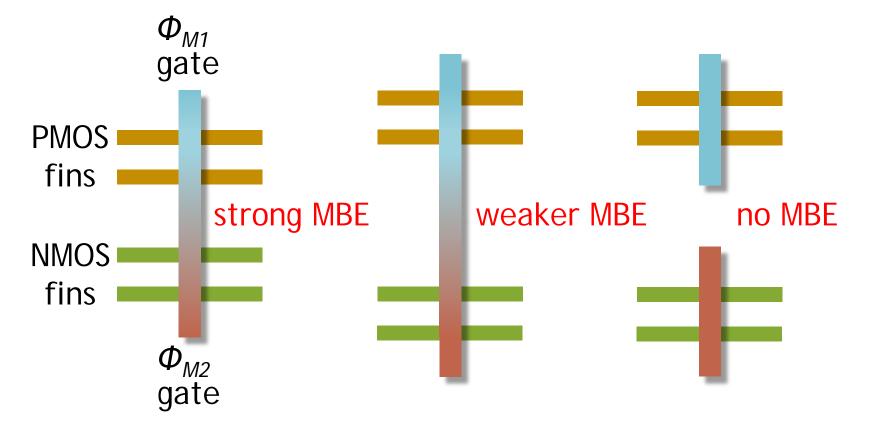

# Metal-gate Boundary Effect (MBE)

- $V_T$  affected when near interface between two  $\Phi_M$  metals

- 2 hypotheses:  $\Phi_M$  metal interdiffusion, etch-related footing

- Eliminate effect using only one  $\Phi_M$  in each gate  $\rightarrow$  area bloat

Yamaguchi et al., Toshiba [20]

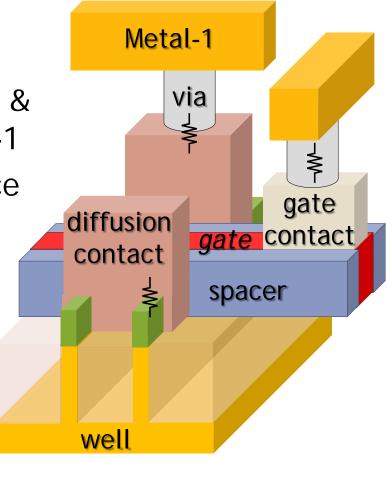

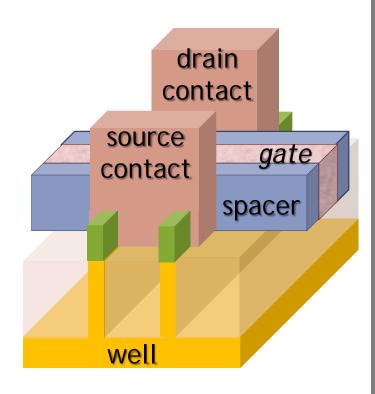

# Complex Middle-Of-Line (MOL)

Difficult to land diffusion & gate contacts on tight CPP using only one contact mask

Need separate contacts to diffusion & to gate, also insert via under Metal-1

• BEOL, MOL &  $R_{ext}$  parasitic resistance

are significant

Standard cell resistance channel intrinsic channel FET parasitic

Terzioglu, Qualcomm [1] Rashed *et al.*, Globalfoundries [21]

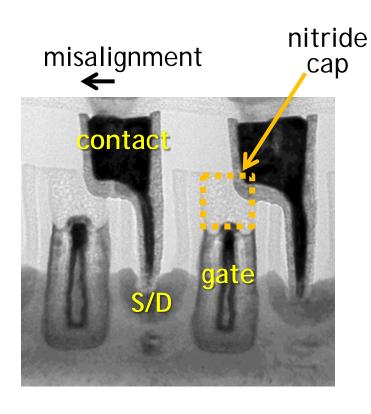

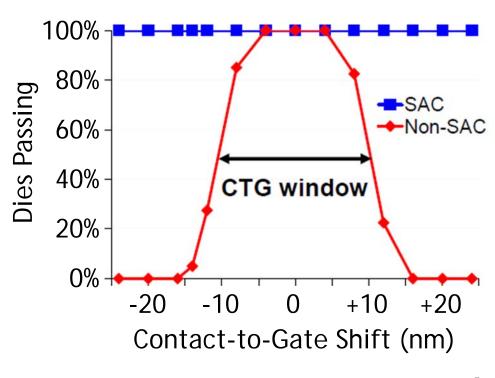

# Self-Aligned Contact (SAC)

- Allows misaligned contact to land on gate without short

- Etch gate partially after replacement gate CMP, then deposit insulator on top of gate → protects gate during contact etch

- $R_G$  increases & has more variation from partial (recess) etch

Auth *et al.*, Intel [22]

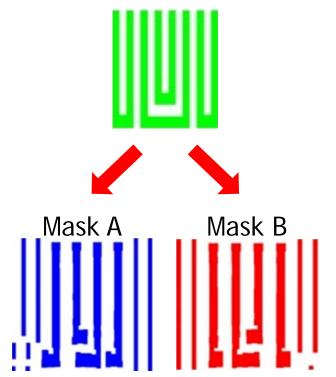

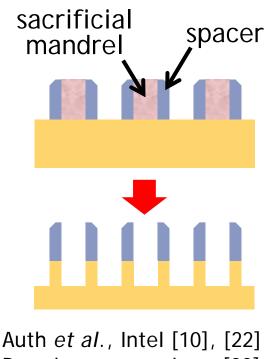

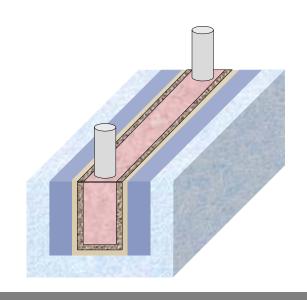

# Multiple-Patterning Lithography

- Needed for sub-80nm pitch, EUV not ready for HVM

- 1. Pitch-split mask decomposition (coloring) → complex DRC

- 2. Cut masks to reduce line-end-to-end spacing

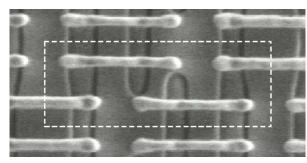

- 3. Spacer-based self-aligned double patterning (SADP) for fins

Dorsch, www.semi.org [23]

#### **Outline**

- MOSFET, Fully-Depleted & FinFET Basics

- Technology Considerations

- Analog/Mixed-Signal Design Considerations

- General Principles

- FETs

- Passives

- Conclusion

## Designing with FinFET

- More drive current for given footprint

- Quantized channel width (challenge for logic & SRAM, OK for analog)

- Better  $r_{out}$  (less DIBL) but shorter  $L_{max}$

- Essentially no body effect

- Mismatch variation depends on fin width/ height/shape, HK grains, gate density, stress, less on RDF

- Lower  $C_j$  but higher  $C_{gd}$  &  $C_{gs}$  coupling

- Higher  $R_s$  &  $R_d$  spreading resistance

- Less junction area efficiency to wells (higher diode series  $R_D$ , latch-up)

- No native (zero-V<sub>T</sub>) NMOS

Auth et al., Intel [22] Sheu, TSMC [24]

# Porting AMS Circuits to FinFET

- For most part can be done with expected node-to-node tweak

- Usual caveats in bleeding-edge nodes

- Technology & design concurrently developed for faster time-to-market

- Models are speculative → expect late updates

& late inclusion of new effects

- Stay vigilant on Si/model updates that can break design

- Choose logic-centric circuits/architectures (fab's priority), desensitize to or calibrate out model uncertainty

- Minimize churn with some upfront layout bloat to avoid constructs made for logic area reduction, e.g.,

- Single gate with more than one  $\Phi_M$  metal

- Devices with no active edge dummies

Bair, AMD [25]

# FET Modeling for Analog vs. Digital

- SoC technology/modeling driven by logic & SRAM

- Device targeting & model correlation at few I-V & C-V points for limited V<sub>DD</sub> values

typical analog biasing  $V_{GS} = V_T$  to  $V_T + 0.2V$

- Analog also needs accurate slope modeling  $(g_{m'}, g_{ds})$  which gets some attention but not priority

- Corner models (e.g., SS, FF) don't necessarily correlate to analog corners

Feng *et al.*, Globalfoundries [26] McAndrew *et al.*, Freescale [27]

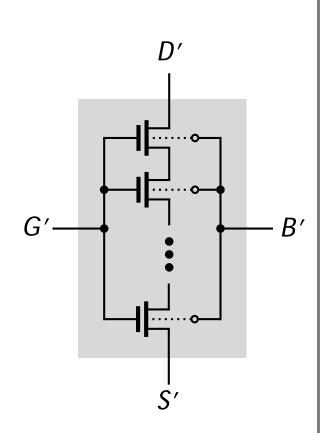

## **Composite FET**

- Need high  $r_{out}$  for accurate AC *V-to-I* conversion  $\rightarrow$  long *L*

- L<sub>max</sub> limited by gate litho/etch loading & HKMG integration

- Composite FET stack with shorted gate is now commonplace in current mirrors, op amps, data converters, etc.

- Only top FET in saturation, all other FETs in triode for source degeneration

- Not a cascode

- Insignificant body effect

- Intermediate parasitic  $C_{gd}$ ,  $C_{gs}$  &  $C_j$

- Designers mainly interested in composite FET characteristics

- Co-development with EDA vendors

## Don't Trust Simulator $V_T$ - Many Still Do

- Tough to stack >3 devices in saturation with low  $V_{DD}$

- Can only operate devices in weak/ moderate (not strong) inversion

- Dangerous to design to "usual"  $V_T$  reported by simulator

- Can get wrong FET sizing to ensure  $(V_{GS}-V_T)>0$  vs. low offset (e.g., diff pair)

- Correct goal: burn enough  $I_D$  for  $g_m \& BW \rightarrow g_m/I_D$  method

- Fab typically measures  $V_T$  using constant-current method

- Simulators now conveniently report constant-current  $V_T$

- Best to treat  $V_T$  as reference point that anchors I-V

Loke *et al.*, AMD [28] Silveira *et al.*, U República [29]

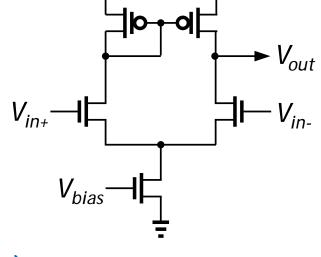

# Stronger Parasitic Coupling

- S/D trench contacts & gate form vertical plate capacitors

- Worse supply rejection in LDO regulators

- Kickback noise to analog biasing signals, e.g., DDR RX

- Adding capacitance increases area & wake-up time (concern for burst-mode operation, e.g., IoT)

# I/O Voltage Not Scaling With Core Supply

- Many I/Os still use 1.8V signaling despite core  $V_{DD}$  reduction

- Many peripheral ICs remain at lower cost nodes

- Backward compatibility is key constraint for some I/Os

- Increasingly tough to keep 1.8V thick-oxide devices

- Thick ALD gate oxide not easy for tighter fin pitch

- Voltage level shifters must deal with wider voltage gap

- Some standards no longer support legacy modes in favor of higher link rate & lower power (e.g., LPDDR5)

- Need ecosystem consensus

- Industry has migrated from 5.0V to 3.3V to 2.5V to 1.8V

- Obvious power & area benefit to migrate to say 1.2V

- 1.8V remains an industry-wide issue until next transition

Wei et al., Globalfoundries [30]

#### 16/14nm Passives

- Resistors

- Precision MOL thin film resistor (migration from poly)

- Metal-gate resistor

- Capacitors

- Metal-Oxide-Metal (MOM)

- Accumulation-mode varactor

- Metal-Insulator-Metal (MIM) extra cost, less common

- Inductors typically top BEOL layers

- PNP-BJT (analog diode) & ESD diodes

- Don't assume models capture all key effects even though we're the only customer

#### **Resistor Options**

- Precision MOL resistor (thin metal compound on STI/ILD)

- Difficult to build poly resistor ends in HK-last process

- Ends not well defined, current spreading near contacts

- Decouples resistor integration from FEOL

- Metal-gate resistor

- Available for free

- Not so well controlled

- $\rho_{sheet}$  depends on gate density, W,  $W_{max}$  limit

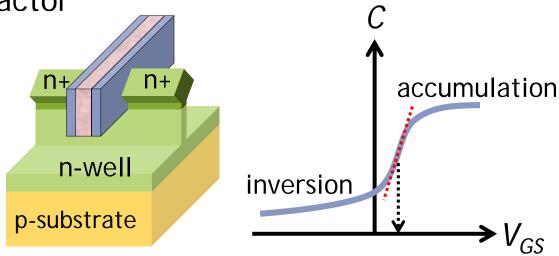

#### **Capacitor Options**

- Metal-Oxide-Metal (MOM)

- Rarely has scaling helped analog ©

- Be careful with non-physical BEOL overlay corner models

- Accumulation-mode varactor

- C-V transition may shift from  $\Phi_M$  tuning for fully-depleted

- Steeper transition for higher  $K_{VCO}$

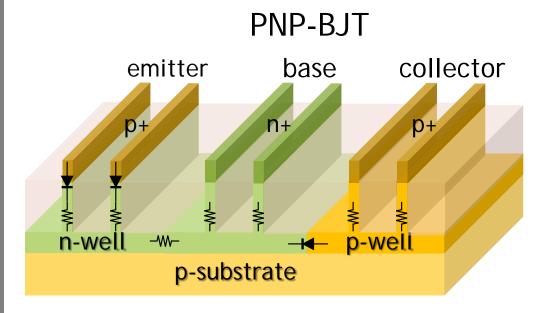

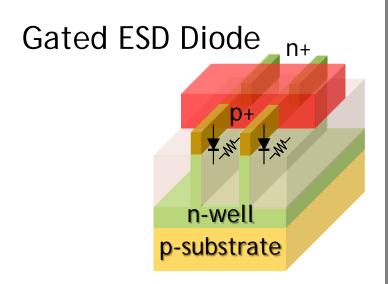

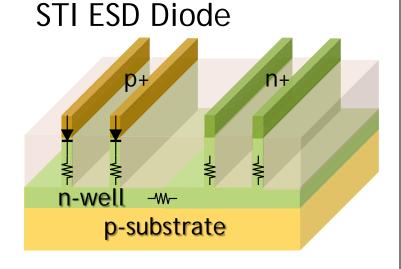

#### **PNP-BJT & ESD Diodes**

- Fin width << fin pitch</li>

→ higher R<sub>series</sub> than planar

- Hard to scale ESD area without reducing ESD HBM/CDM limits

- Maturity of ESD models often lags during technology development

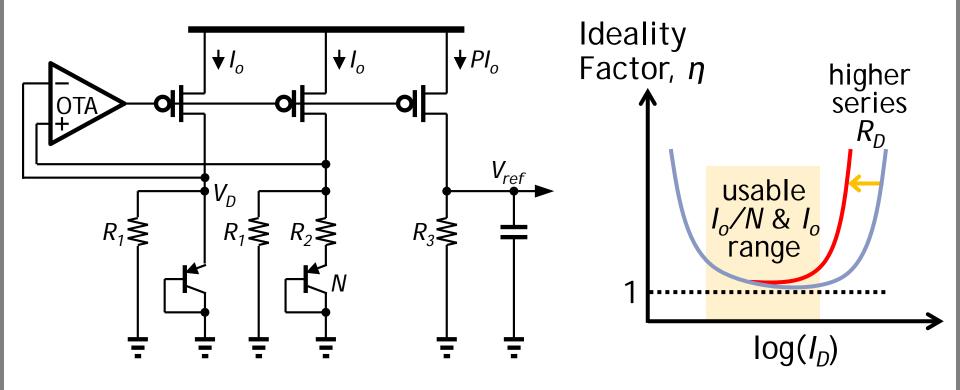

# Low-Voltage Bandgap Reference

$$V_{ref} = \frac{PR_3}{R_1} V_D + \frac{PR_3}{R_2} \frac{\eta kT}{q} \ln N$$

CTAT PTAT

- PTAT+CTAT using currents

- More  $R_D \rightarrow \text{smaller } N$

- Higher  $V_D \rightarrow$  headroom issue

Banba et al., Toshiba [31]

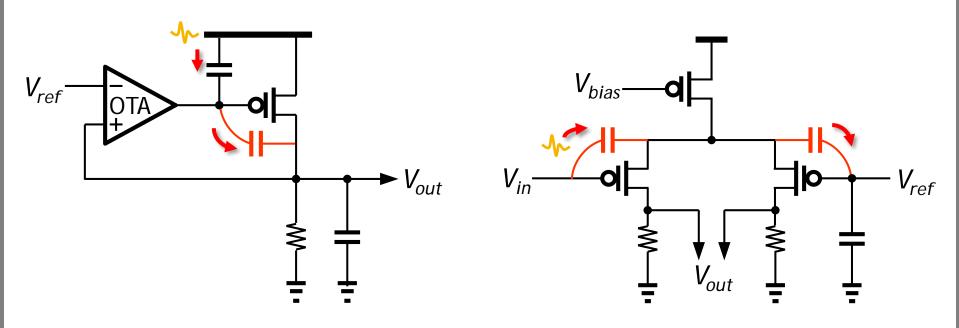

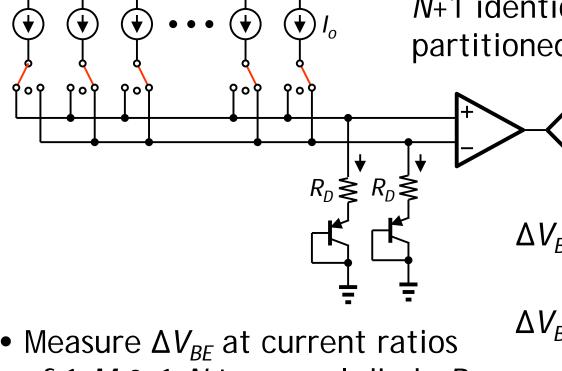

# Thermal Sensor with $R_D$ Cancellation

N+1 identical  $I_o$  current sources partitioned into 1, M & N sources

- Measure  $\Delta V_{BF}$  at current ratios of 1:M & 1:N to cancel diode  $R_D$

- Swap amp inputs to cancel diode mismatch

- Average out I<sub>o</sub> variation with **Dynamic Element Matching**

$$\Delta V_{BE,M} = \frac{\eta kT}{q} \ln M + (M-1) I_o R_D$$

$$\Delta V_{BE,N} = \frac{\eta kT}{q} \ln N + (N-1) I_o R_D$$

$$\frac{\eta kT}{q} = \frac{(N-1)\Delta V_{BE,M} - (M-1)\Delta V_{BE,N}}{(N-1)\ln M - (M-1)\ln N}$$

ON Semiconductor [32]

#### Conclusion

- 14nm mobile SoCs are already in production; no showstoppers to migrate AMS designs to finFET

- 16/14nm AMS design is about understanding all the precursor technologies that led to finFET as much as understanding finFET itself

- FinFET/HKMG/MOL parasitics & local layout effects have significantly increased AMS design effort

- Logic & SRAM will continue to drive CMOS scaling priorities into 10nm & 7nm, so expect AMS designs to continue adapting

#### References (1/3)

- [1] E. Terzioglu, "Design and technology co-optimization for mobile SoCs," in *Int. Conf. on IC Design & Technology*, Keynote, Leuven, Belgium, Jun. 2015.

- [2] M. Na et al., "The effective drive current in CMOS inverters," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, San Francisco, CA, Dec. 2002, pp. 121-124.

- [3] L. Wei et al., "Exploration of device design space to meet circuit speed targeting 22nm and beyond," in *Proc. Int. Conf. Solid State Devices and Materials*, Sep. 2009, pp. 808-809.

- [4] R.-H. Yan et al., "Scaling the Si MOSFET: From bulk to SOI to bulk," IEEE Trans. Electron Devices, vol. 39, no. 7, pp. 1704–1710, Jul. 1992.

- [5] K. Fujita *et al.*, "Advanced channel engineering achieving aggressive reduction of V<sub>T</sub> variation for ultralow power applications," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp. 32.3.1-32.3.4, Dec. 2011.

- [6] K. Cheng *et al.*, "Fully depleted extremely thin SOI technology fabricate by a novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain," in *IEEE Symp. VLSI Technology Tech. Dig.*, pp. 212-213, Jun.2009.

- [7] T. Skotnicki, "CMOS technologies- trends, scaling and issues," in *IEEE Int. Electron Devices Meeting Short Course*, Dec. 2010.

- [8] L. Chang et al., "Gate length scaling and threshold voltage control of double-gate MOSFETs," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, San Francisco, CA, Dec. 2000, pp. 719-722.

- [9] A. Asenov, "Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1- $\mu$ m MOSFET's with epitaxial and  $\delta$ -doped channels," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1718-1724, Aug. 1999.

- [10] X. Huang et al., "Sub-50nm finFET: PMOS," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Washington, DC, Dec. 1999, pp. 67-70.

- [11] M. Garcia Bardon et al., "Layout-induced stress effects in 14nm & 10nm finFETs and their impact on performance," in *IEEE Symp. VLSI Technology Tech. Dig.*, Kyoto, Japan, Jun. 2013, pp. 114-115.

#### References (2/3)

- [12] Y. Liu *et al.*, "NFET effective work function improvement via stress memorization technique in replacement metal gate technology," in *IEEE Symp. VLSI Technology Tech. Dig.*, Kyoto, Japan, Jun. 2013, pp. 198-199.

- [13] J. Faricelli, "Layout-dependent proximity effects in deep nanoscale CMOS," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Jose, CA, Sep. 2010, pp. 1-8.

- [14] C. Lee et al., "Layout-induced stress effects on the performance and variation of finFETs," in *IEEE Int. Conf. on Simulation of Semiconductor Processes and Devices*, Washington, DC, Sep. 2015, pp. 369-372.

- [15] F. Sato et al., "Process and local layout effect interaction on a high performance planar 20nm CMOS," in IEEE Symp. VLSI Technology Tech. Dig., Kyoto, Japan, Jun. 2013, pp. 116-117.

- [16] C. Auth et al., "45nm high-k + metal-gate strain-enhanced transistors," in *IEEE Symp. VLSI Technology Tech. Dig.*, Honolulu, HI, Jun. 2008, pp. 128-129.

- [17] P. Packan et al., "High performance 32nm logic technology featuring 2<sup>nd</sup> generation high-k + metal gate transistors," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Baltimore, MD, Dec. 2009, pp. 1-4.

- [18] S. Yang *et al.*, "High-performance mobile SoC design and technology co-optimization to mitigate high-K metal gate process variations," in *IEEE Symp. VLSI Technology Tech. Dig.*, Honolulu, HI, Jun. 2014 pp. 1-2.

- [19] W. Wu and M. Chan, "Gate resistance modeling of multifin MOS devices," *IEEE Electron Device Letters*, vol. 27, no. 1, pp. 68-70, Jan. 2006.

- [20] M. Yamaguchi et al., "New layout dependency in high-K/metal gate MOSFETs," in IEEE Electron Devices Meeting Tech. Dig., Washington, DC, Dec. 2011, pp. 579-582.

- [21] M. Rashed et al., "Innovations in special constructs for standard cell libraries in sub 28nm technologies," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, Washington, DC, Dec. 2013, pp. 248-251.

- [22] C. Auth *et al.*, "A 22nm high performance and low-power CMOS technology featuring fully-depleted trigate transistors, self-aligned contacts and high density MIM capacitors," in *IEEE Symp. VLSI Technology Tech. Dig.*, Honolulu, HI, pp. 131-132, Jun. 2012.

## References (3/3)

- [23] J. Dorsch, "Changes and challenges abound in multi-patterning lithography," *Semiconductor Manufacturing & Design Community*, www.semi.org/en/node/54491, Feb. 2015.

- [24] B. Sheu, "Circuit design using finFETs," in *IEEE Int. Solid-State Circuits Conf.*, Tutorial T4, San Francisco, CA, Feb. 2013.

- [25] L. Bair, "Process/product interactions in a concurrent design environment," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Jose, CA, Sep. 2007, pp. 779-782.

- [26] J. Feng et al., "Bridging design and manufacture of analog/mixed-signal circuits in advanced CMOS," in IEEE Symp. VLSI Technology Tech. Dig., Kyoto, Japan, Jun. 2011, pp. 226-227.

- [27] C. McAndrew *et al.*, "Corner models: inaccurate at best, and it only gets worst...," in *Proc. IEEE Custom Integrated Circuits Conf.*, San Jose, CA, Sept. 2013, pp. 1-4.

- [28] A. Loke *et al.*, "Constant-current threshold voltage extraction in HSPICE for nanoscale CMOS analog design," in *Synopsys Users Group (SNUG) Conf.*, San Jose, CA, Mar. 2010, pp. 1-19.

- [29] F. Silveira et al., "A  $g_m/I_D$  based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator OTA," *IEEE J. Solid-State Circuits*, vol. 31, no. 9, pp. 1314-1319, Sep. 1996.

- [30] A. Wei et al., "Challenges of analog and I/O scaling in 10nm SoC technology and beyond," in IEEE Electron Devices Meeting Tech. Dig., San Francisco, CA, Dec. 2014, pp. 462-465.

- [31] H. Banba *et al.*, "A CMOS bandgap reference circuit with sub-1-V operation," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 670-673, May 1999.

- [32] "ADT7461 ±1°C temperature monitor with series resistance cancellation," ON Semiconductor Publication No. ADT7461/D, Mar. 2014.

## Acknowledgments

- Esin Terzioglu

- Sam Yang

- Jihong Choi

- Albert Kumar

- Tin Tin Wee

- Ray Stephany

- Lixin Ge

- Bo Yu

- Zhiqin Chen

- Stanley S.C. Song

- Steven Dillen

- Stephen Knol

- Patrick Drennan

- Ken Rim

- Chidi Chidambaram

- Yanxiang Liu

- Jun Yuan

- Masoud Roham

- Reza Jalilizeinali

- Xiaohua Kong