# On-Chip Transformer Design and Application to RF and mm-Wave Front-Ends

John R. Long

RF/MMIC Group

University of Waterloo

jrlong@uwaterloo.ca

April 30, 2017

## **Outline**

- Introduction

- On-chip transformer types and circuit models

- Specifications

- Design for RF and mm-Wave circuit applications (LNA, PA, VCO)

- Summary

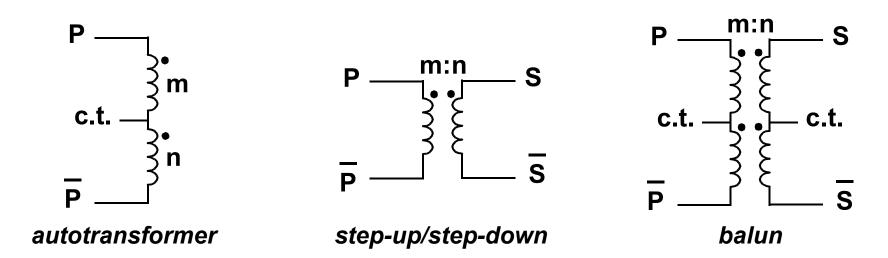

# **Transformer Types**

- Autotransformer: primary and secondary are <u>not</u> DC-isolated. Conductor losses and leakage inductance may be lower than a multi-winding transformer (optimal when m=n). Primary application is LC-oscillator tanks.

- Step-up/step-down transformer: Bias isolation between primary and secondary.

Applied to impedance matching, interstage (AC) coupling, feedback networks, filtering, etc. Can consist of more than two windings.

- Balun: center-tapped (c.t.) transformer used as a phase splitter/combiner.

Applications include: on- and off-chip interfacing, and interstage (AC) coupling.

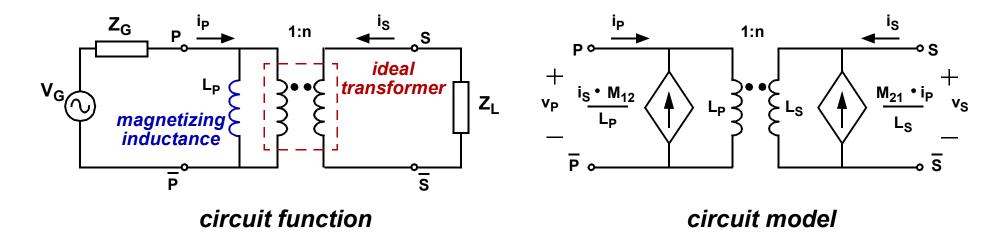

#### The "Perfect" Transformer

• When reactance of the magnetizing inductance  $(L_P)$  is much larger than the source impedance  $(Z_G)$  and the reflected load impedance  $(Z_I/n^2)$ :

$$v_S = n \cdot v_P$$

,  $i_S = i_P/n$ , and  $Z_S = n^2 \cdot Z_P$ .

Turns ratio,  $n = \frac{v_S}{v_P} = \frac{i_P}{i_S} = \sqrt{\frac{L_S}{L_P}}$ .

• For "perfect" (i.e., 100%) magnetic coupling:  $M_{21} = M_{12} = \sqrt{L_P L_S}$ .

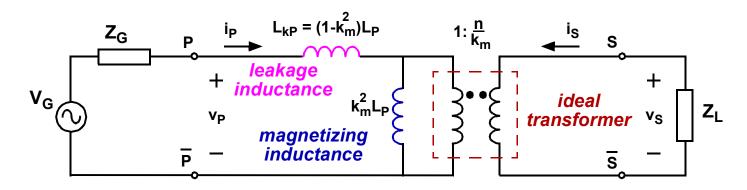

# **Transformer with Magnetic Leakage**

model for magnetic path including leakage

• Imperfect magnetic coupling between primary and secondary windings is called *leakage*, which is characterized by the coefficient of magnetic coupling,  $k_m$

$$k_m = \frac{M}{\sqrt{L_P L_S}}$$

, and  $0 < k_m < 1$ .

Leakage prevents signal at the primary input from reaching the secondary output as the frequency increases. Leakage is reduced by shrinking the gap between turns on the windings of an on-chip transformer.

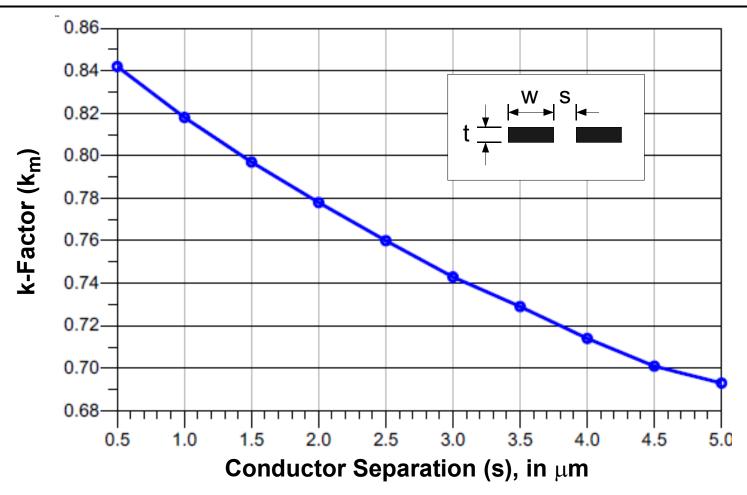

#### **Transformer k-Factor**

• k-factor approaches 0.9 for minimum spacing (s) between conductors. Ratio of conductor length and separation diminishes when scaling transformers to mm-wave frequency, which further reduces k-factor.

# Transformer L.F. Response

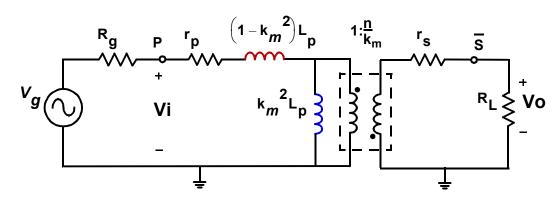

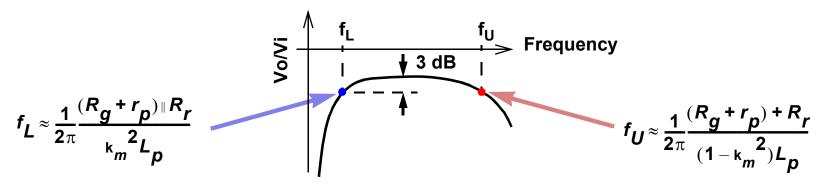

Low-frequency equivalent circuit with leakage k<sub>m</sub>

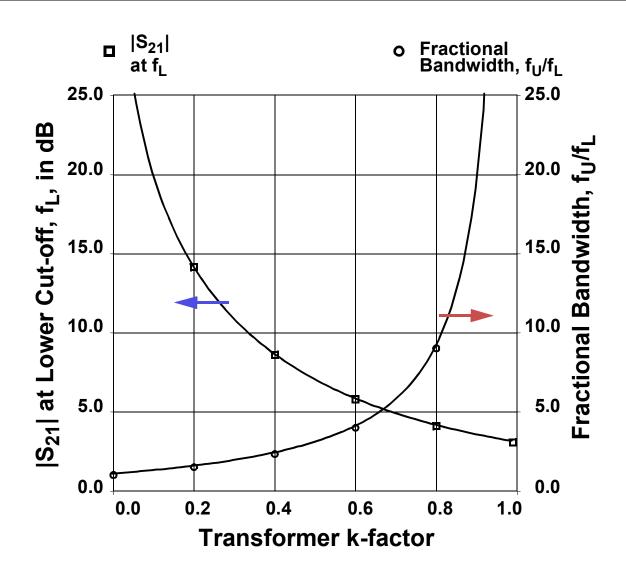

$$\frac{f_{U}}{f_{L}} = \frac{(1 + k_{m})}{(1 - k_{m})} \qquad f_{U}/f_{L} = 2, \text{ for km} = 0.33}$$

$$f_{U}/f_{L} = 9, \text{ for km} = 0.8$$

Rr = resistance reflected from secondary back to primary

# Transformer M.F. Response

Assuming capacitive parasitics are negligible and  $R = R_G + r_P = R_L + r_S$

Max. signal transmission in the passband is:

$$\left|S_{21}\right| = \frac{2v_0}{v_G} = \frac{k_m(R_L)}{R}$$

at

$$f_{pk} = \frac{R}{2\pi L_{p}\sqrt{1-k_{m}^{2}}}.$$

# Transformer H.F. Response

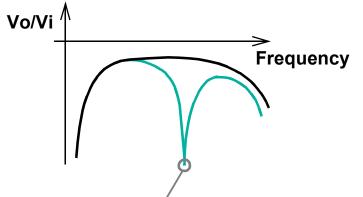

- For n > 0, (Co/n), L<sub>s</sub> and r<sub>s</sub> introduce a transmission zero.

- For n < 0, (Co/n) is an inductive reactance that decreases in magnitude with increasing frequency. No notch in response.

High-frequency equivalent circuit with leakage shifted to secondary

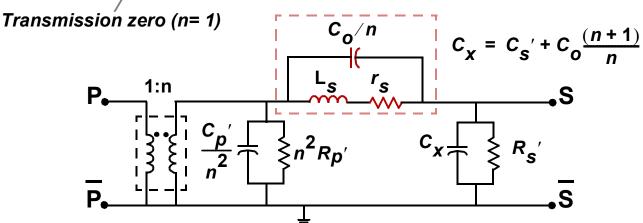

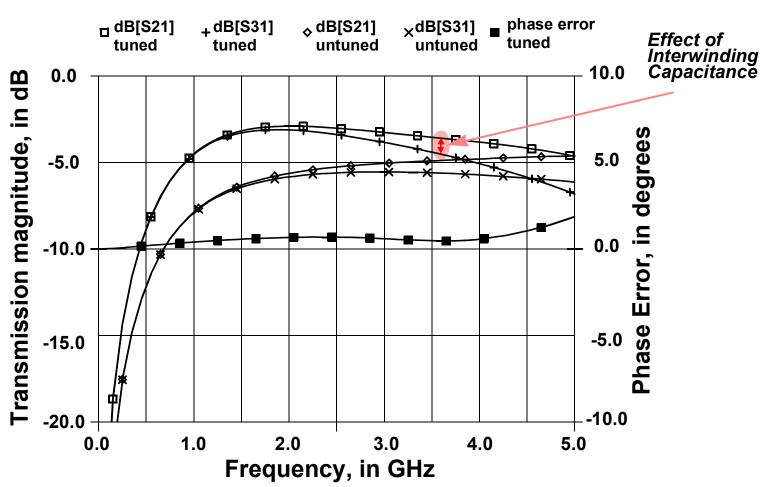

# Inverting vs. Non-Inverting

Frequency response in the inverting configuration (single-ended) is less constrained by effects of interwinding capacitance.

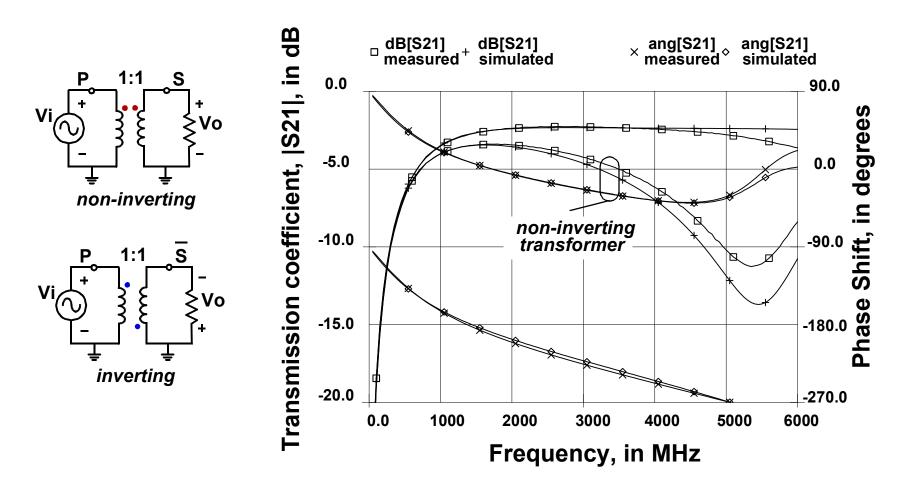

#### A 2-Wire Planar Transformer

Parasitic capacitance and substrate dissipation cannot be neglected at RF and mm-wave frequencies. Considering both capacitive and inductive couplings

$$v_4 = \frac{Z_4}{Z_3 + Z_4} \left( Z_3 C_{m\overline{dt}}^{dv_1} + L_{m\overline{dt}}^{di_1} \right)$$

, and

$$v_4 = L_{mdt} \frac{di_1}{dt}$$

for  $Z_3 = 0$  (i.e., magnetic coupling dominant).

# **Monolithic Transformer Layouts**

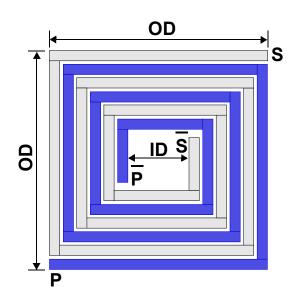

Interleaved (Frlan) winding

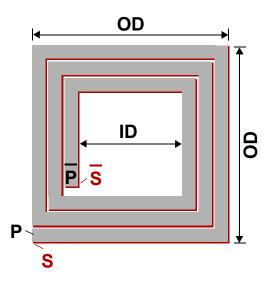

Stacked (Finlay) winding

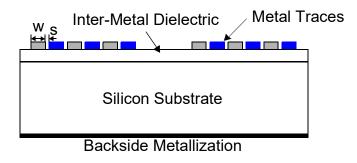

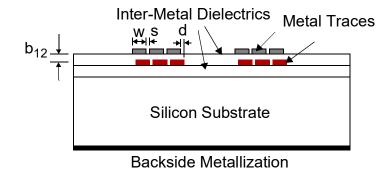

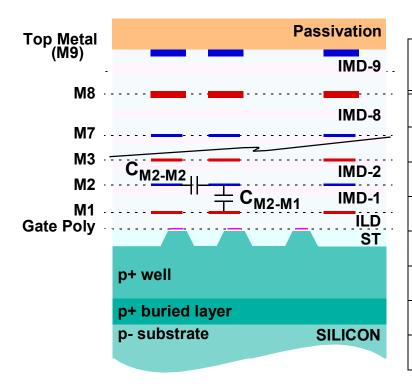

# **Example Submicron CMOS Backend**

| Layer | Thickness,<br>in μm |  |

|-------|---------------------|--|

| M9    | 0.9                 |  |

| M8    | 0.9                 |  |

| M7    | 0.3                 |  |

| M6    | 0.3                 |  |

| M5    | 0.3                 |  |

| M4    | 0.3                 |  |

| M3    | 0.3                 |  |

| M2    | 0.3                 |  |

| M1    | 0.2                 |  |

|       |                     |  |

| Layer       | Thickness,<br>in μm | Effective<br>Permittivity |

|-------------|---------------------|---------------------------|

| Passivation | 1.8                 | 5.75                      |

| IMD-9       | 1.6                 | 4.3                       |

| IMD-8       | 1.6                 | 4.3                       |

| IMD-2 to 7  | 0.6                 | 3.0                       |

| IMD-1       | 0.25                | 3.3                       |

| ILD         | 0.45                | 4.2                       |

| ST          | 0.35                | 3.9                       |

| Silicon     | 350                 | 11.7                      |

|             |                     |                           |

Example layers for a typical backend metal interconnect stack in deep submicron CMOS technology.

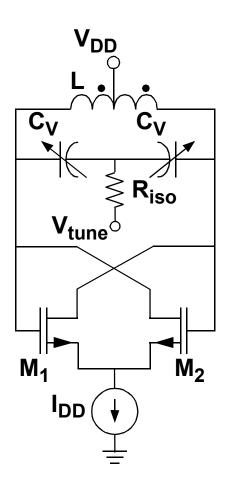

# **Cross-Coupled (Differential) LC-VCO**

Assuming a square-wave current driving the tank, phase noise in the 1/f² regime can be written as [13]

$$L_{DP}(\omega_{d}) = 10\log\left[\frac{kT(1+\gamma_{n})}{R_{T}[(4/\pi)I_{DD}Q_{T}(\omega_{d}/\omega_{o})]^{2}}\right],$$

where:

$Q_T = tank Q$

$R_T$  = tank resistance at resonance,  $\omega_o$

$\gamma_n$  = NMOS excess noise parameter

I<sub>DD</sub> = bias current

Amplitude of square-wave tank current is  $\mathbf{A_s} \approx (2/\pi)\mathbf{R_T}\mathbf{I_{DD}}$ . Increasing Q<sub>T</sub> reduces phase noise, but output swing also depends upon tank resistance at  $\omega_0$  and bias current.

Assuming: f<sub>o</sub>=2GHz, Q<sub>T</sub>=15 (L=5nH), γ<sub>n</sub>=2, L<sub>DP</sub>(20MHz)=-165dBc/Hz, I<sub>DD</sub>=6.8mA is required. Need to add margin for current source (i.e., noise, r<sub>out</sub>), PVT, etc.

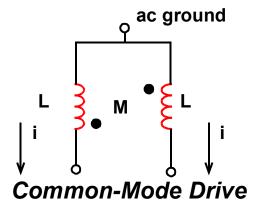

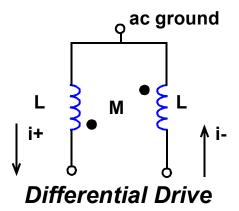

# k-Factor and Common-Mode Rejection

$$L_{to ground} = L(1 - k_m)$$

$$L_{diff} = 2L(1+k_m)$$

- Total inductance between terminals is 2x larger when driven differentially (i.e., 4L for k<sub>m</sub>=1) and smallest for a common-mode signal (i.e., 0 for k<sub>m</sub>=1).

- Common-mode rejection improves when tuned to resonate in differential mode, as common-mode components are "off-resonance" and shorted to ac ground.

- Substrate coupling to and from a symmetric inductor is reduced compared to 2 asymmetric inductor loads due to net cancellation at a distance from the coil.

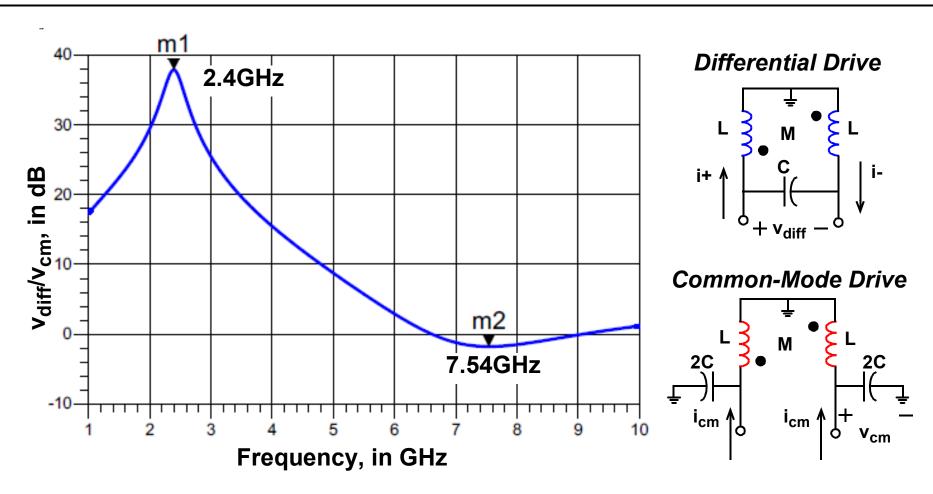

# Common-Mode Rejection of an LC Tank

In this example, a L=2nH inductor (k<sub>m</sub>=0.8) resonant in the differential mode has a CMRR of 38dB at 2.4GHz. The common-mode resonant peak is pushed out to 7.54GHz as lower inductance is seen for common-mode drive.

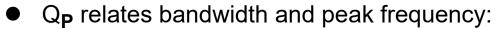

# **Quality Factor**

For the normalized quadratic bandpass function, Z(s)

$$\mathbf{Z}(\mathbf{s}) = \frac{\omega_{\mathbf{P}}\mathbf{s}}{\mathbf{s}^2 + \frac{\omega_{\mathbf{P}}\mathbf{s}}{\mathbf{Q}_{\mathbf{P}}} + \omega_{\mathbf{P}}^2}$$

$$\mathbf{Q}_{\mathbf{P}} = \frac{\omega_{\mathbf{P}}}{\Delta\omega} = \frac{-\omega_{\mathbf{P}}\partial\phi}{2} \frac{\partial\phi}{\partial\omega} \bigg|_{\omega = \omega_{\mathbf{P}}}.$$

- Another interpretation: [energy stored/energy dissipated] per cycle in the steadystate for sinusoidal excitation.

- Energy is dissipated as heat in the conductors and dielectric and is also radiated.

For a resonator:

$$\frac{1}{Q_{Total}} = \frac{1}{Q_{Conductor}} + \frac{1}{Q_{Dielectric}} + \frac{1}{Q_{Radiation}} \approx \frac{r}{\omega I} + \frac{g}{\omega c}.$$

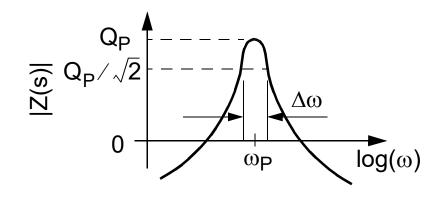

# Q-Factor vs. Conductor Spacing

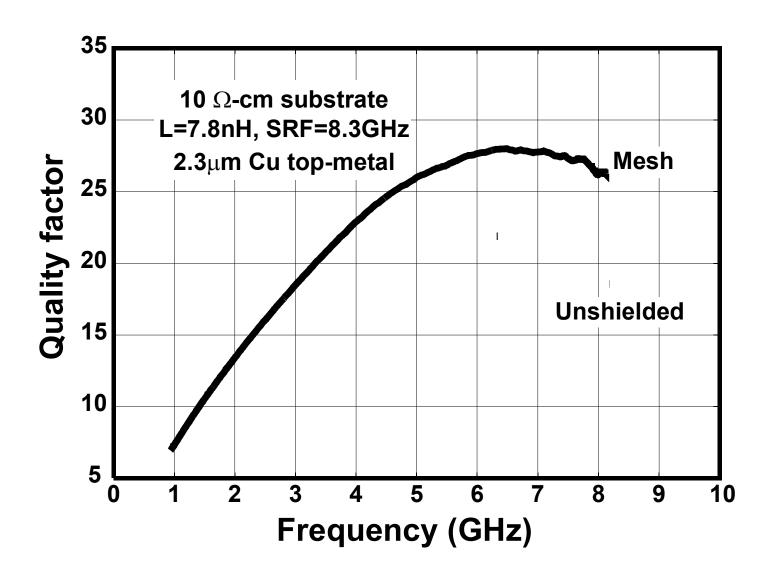

Single-ended Q for a 2-turn inductor with conductor spacing 0.5μm < s < 5.0μm.</li>

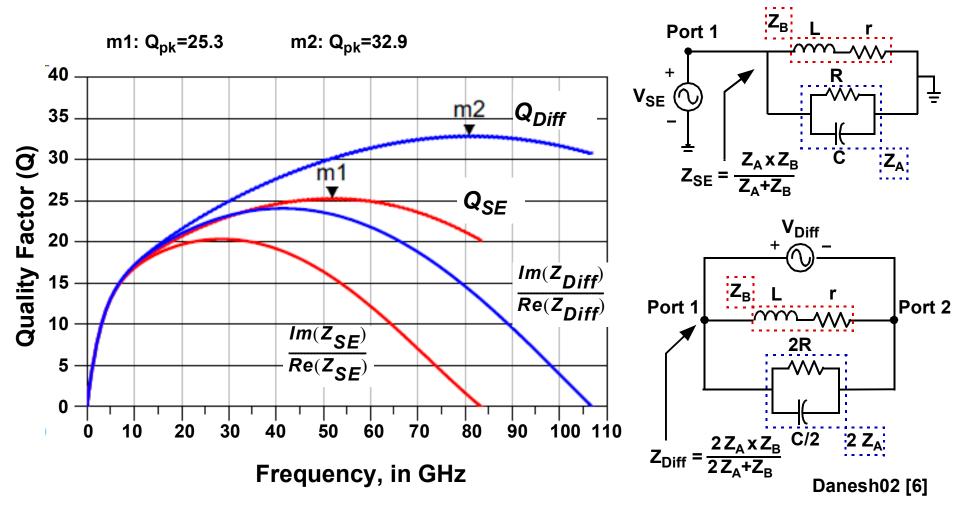

## **Q-Factor for Differential Drive**

Differential excitation gives higher Q-factor and a broader band across which the Q-factor is close to its peak.

# **Optimizing Tank Q-factor**

Q-factor and fractional tuning range for monolithic resonators in 65nm CMOS from simulation (C<sub>fixed</sub>=20fF).

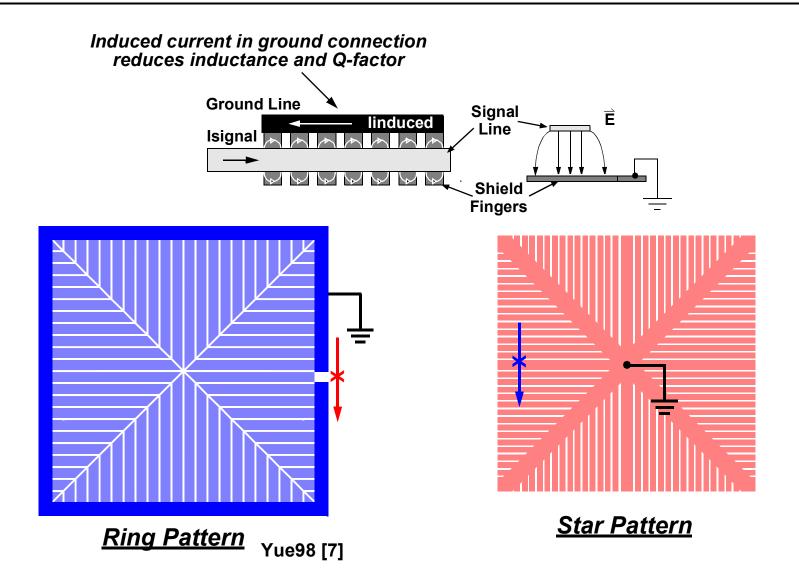

#### **Patterned Ground Shields**

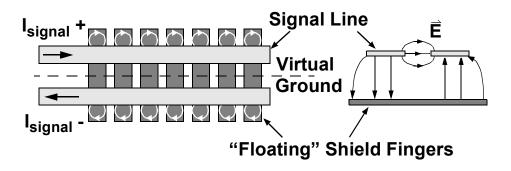

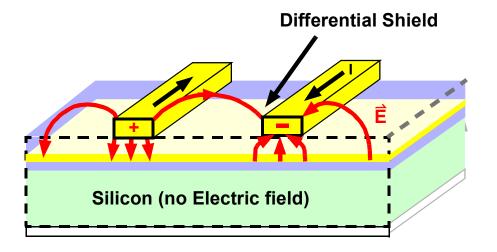

# **Differential Shielding**

Shielded Balanced Tx Line

top level

1μm

1μm

3<sup>rd</sup> level

**Shielded Symmetric Inductor**

Cheung03 [8] Cheung06 [9]

## **Differentially-Shielded Inductor**

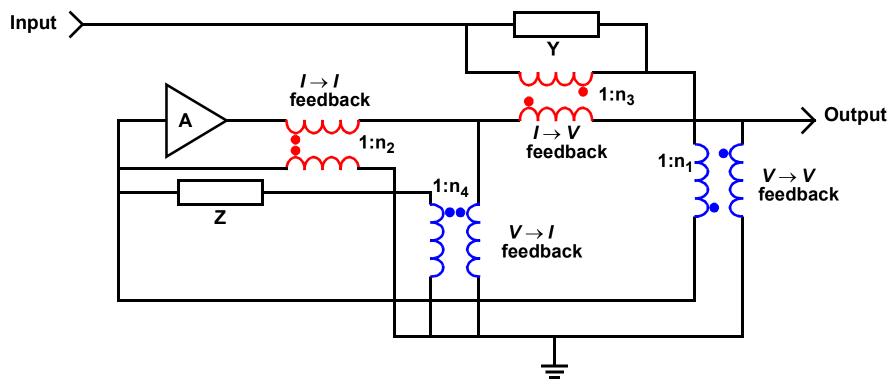

# **Transformers and RF Amplifiers**

Dual-loop amplifier with 4 feedback loops

Bandwidth of transformers with floating terminals (i.e., one terminal not at AC ground) is compromised by parasitics. V-V feedback is least affected by substrate parasitics (one terminal on each winding is grounded).

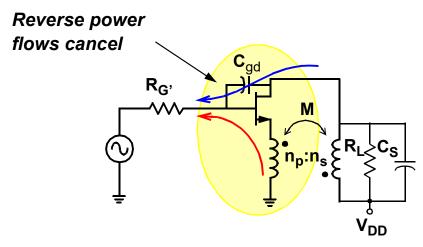

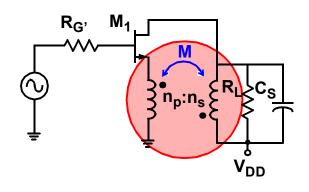

## **Transformer Neutralization**

- greater isolation simplifies matching and increases gain

- noiseless feedback stabilizes gain, reduces output impedance

- Neutralizing feedback increases gain and reverse isolation, promotes stability, and raises input and output impedances.

- Neutralization via a step-down transformer cancels signal flow through C<sub>qd</sub>,

$$\frac{C_{gs}}{C_{gd}} \approx \frac{n}{k} \Rightarrow \text{Neutralization condition}$$

.

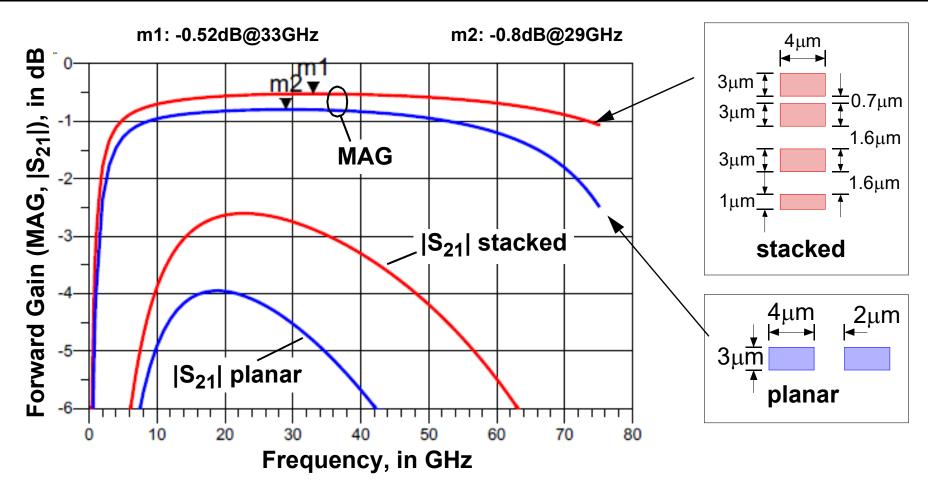

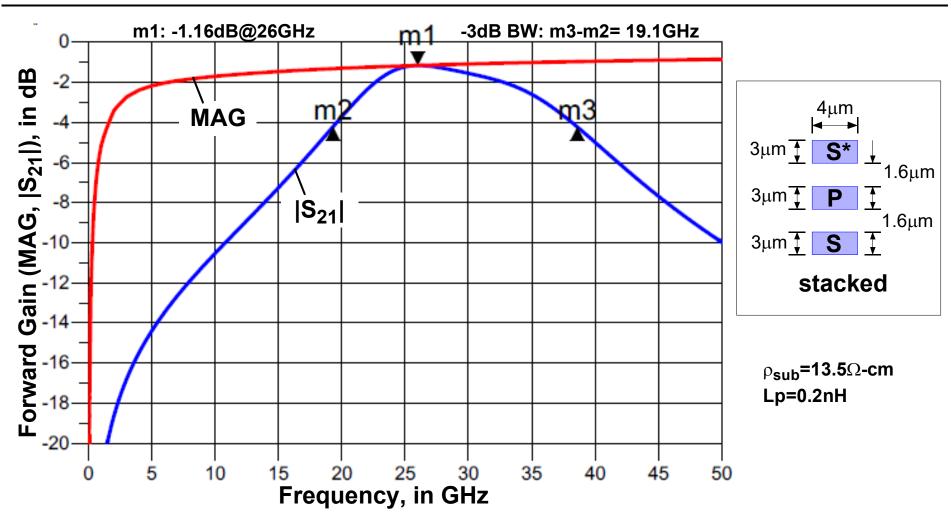

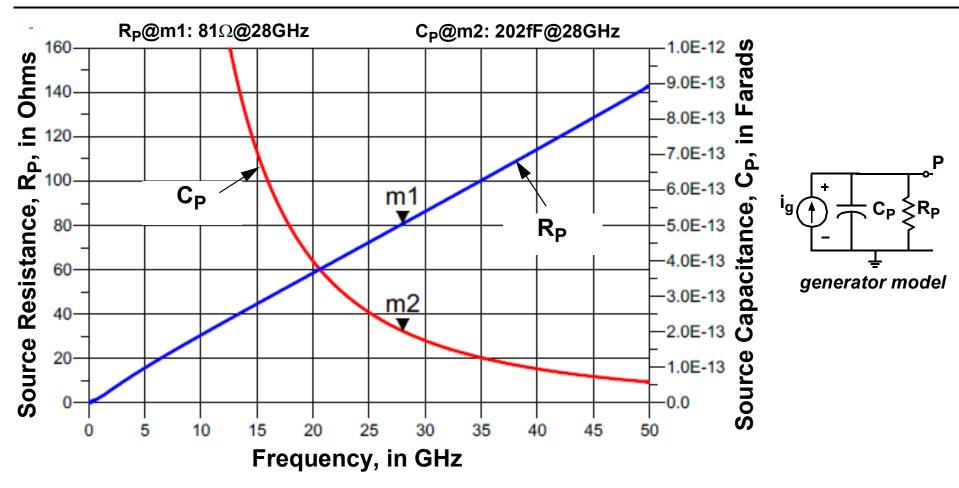

#### 1:1 Transformer MAG

• Maximum available gain (MAG) is realized for conjugate match at source and load ports at each frequency. Untuned (i.e.,  $S_{21}$ ) gain for  $50\Omega$  source/load is 2-3 dB lower than MAG. Note that tuning further reduces bandwidth.

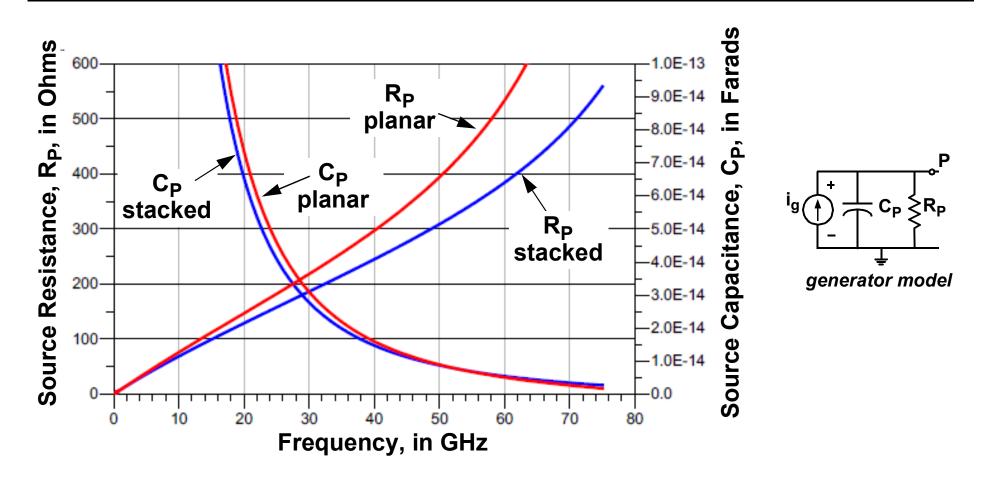

# 1:1 Tuning Impedances for MAG

Source impedances (parallel R-C equivalent, R<sub>P</sub>/C<sub>P</sub>) required to realize MAG vs. frequency are plotted above (load and source impedances are identical for a 1:1). Circuit loading at terminals must be included in R<sub>P</sub> and C<sub>P</sub>.

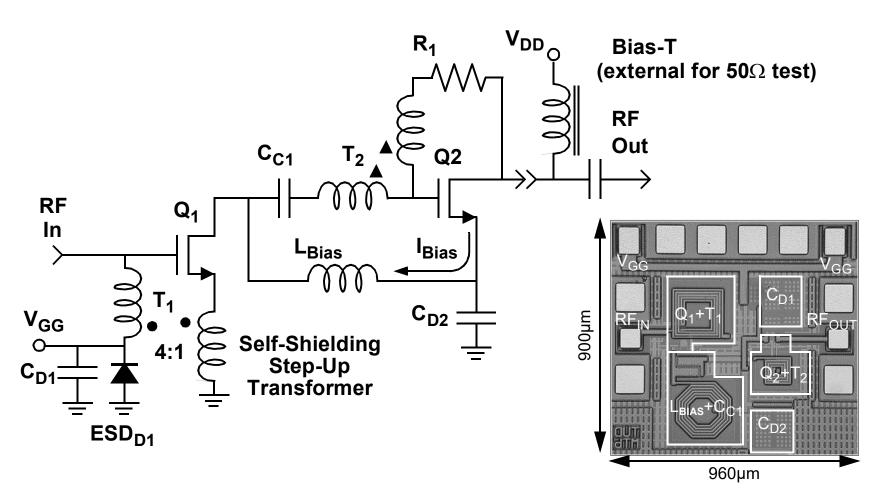

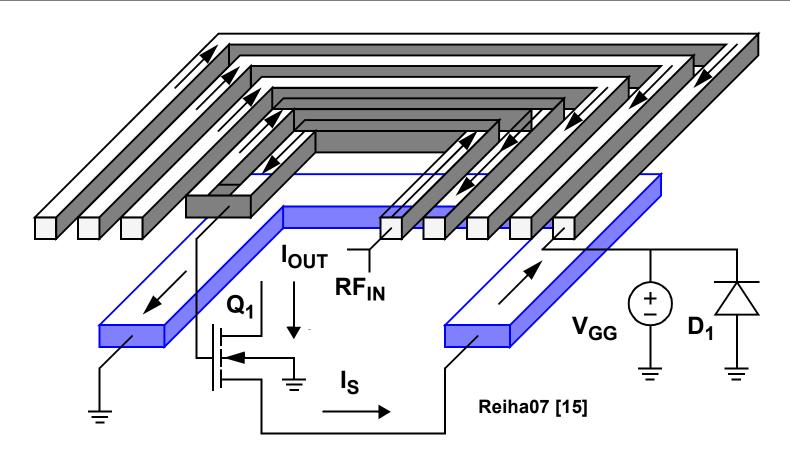

# Wideband Feedback Amplifier

2-stages: series/shunt feedback via self-shielding transformer sets input impedance;

transimpedance second stage lowers output impedance.

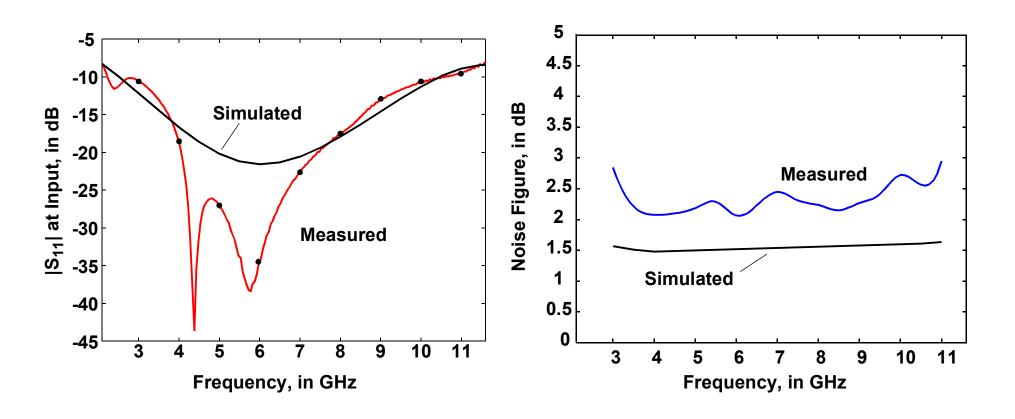

# **WB-LNA** Input Impedance and NF

Broadband gain of approx 15dB while drawing 7.5mA from 1.2V (0.13um CMOS).

Noise figure < 2.5dB and relatively flat across > 7GHz. Excellent input match across band (S<sub>11</sub> < -15dB).</li>

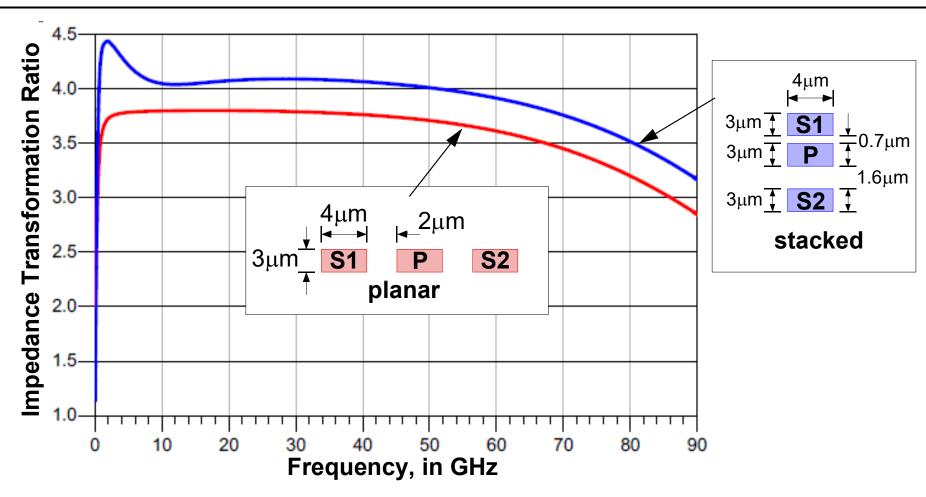

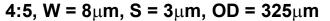

# **Step-Up Transformer Cutaway**

- Turns ratio is determined by the number of turns on each winding and k-factor.

- Stacked layout using separate wiring planes for primary and secondary simplifies implementation and saves chip area.

# 1:2 Step-Up Transformer

Impedance transformation ratio is 4x for a 1:2 transformer (ideally). Weaker coupling (lower k<sub>m</sub>) for the planar transformer results in an error (n<sup>2</sup>=3.75 vs. 4). Tighter coupling and lower substrate parasitics are advantages of the stacked layout.

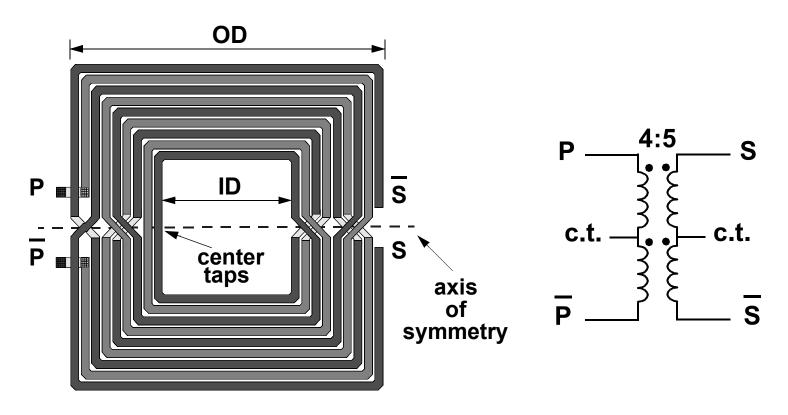

## **Transformer Balun**

Square symmetric 4:5 (Rabjohn) transformer

# **Balun Response**

Output magnitude and phase errors disappear when driven differentially.

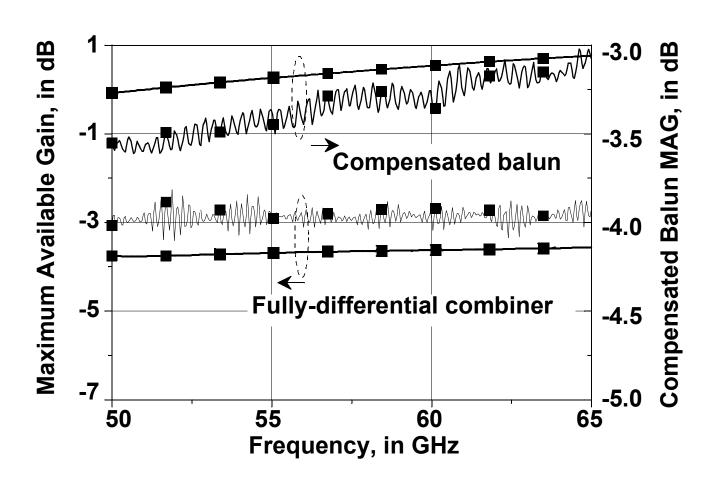

#### mm-Wave Balun

MAG and |S<sub>21</sub>| for a 3-conductor balun after conjugate match (i.e., v<sub>o-diff</sub>/v<sub>in</sub>). A fully-planar layout has ~0.5dB more attenuation in-band, and 2.4GHz less bandwidth.

# **Optimal Source Impedance**

Optimal source impedance decreases with decreasing frequency and magnetizing inductance. Tuning cap must be large enough to absorb circuit parasitics; can tune on primary, or secondary side (or both).

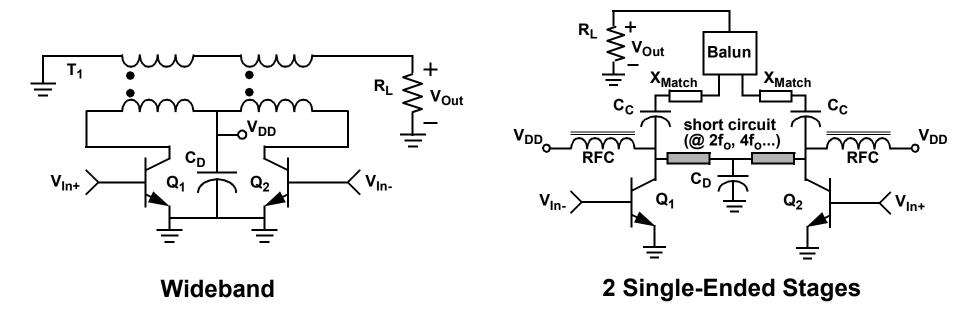

# **Push-Pull Amplifier**

- Push-pull topology shorts even harmonics via symmetry using a transformer balun.

Drain sees resistive load at fundamental and all odd-order harmonics.

- Coupling 2 single-ended amplifiers requires harmonic terminations (e.g., short-circuit at 2f<sub>o</sub>, 4f<sub>o</sub>, etc.) at each output and separate bias paths.

- Parasitics such as supply and ground path inductances have less effect on performance for push-pull and balanced amplifiers.

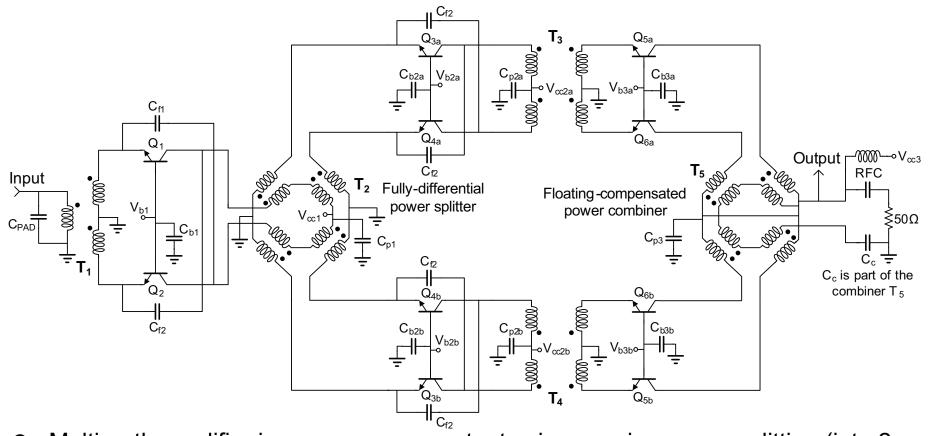

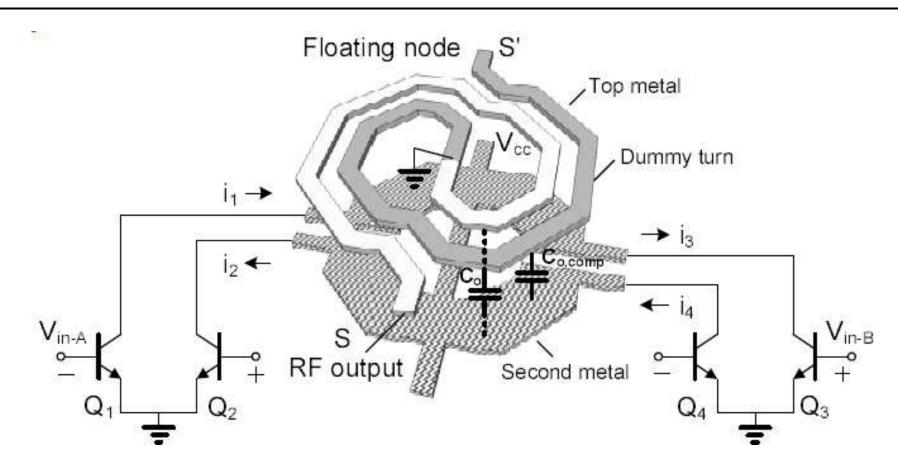

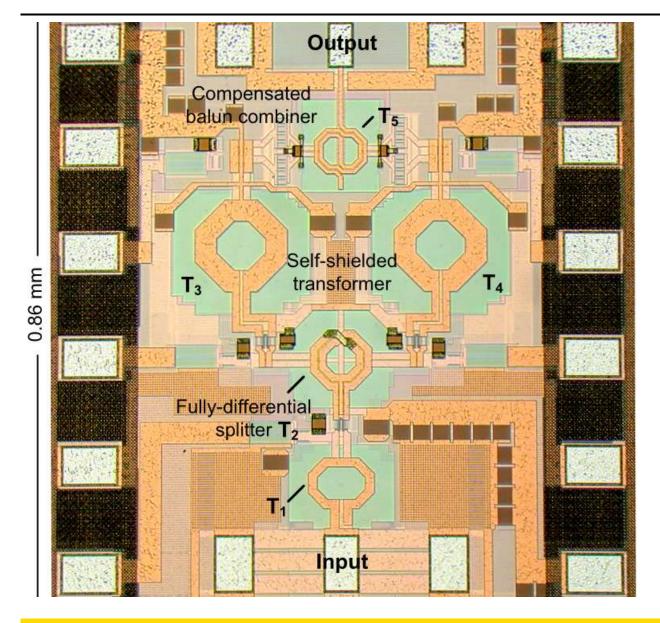

# Multi-Path mm-Wave Power Amplifier

- Multi-path amplifier increases power output using passive power splitting (into 2 paths) and power combining of multiple PA stages.

- Interstage gain realized using current-mode step-up transformers and impedance mismatch between active stages.

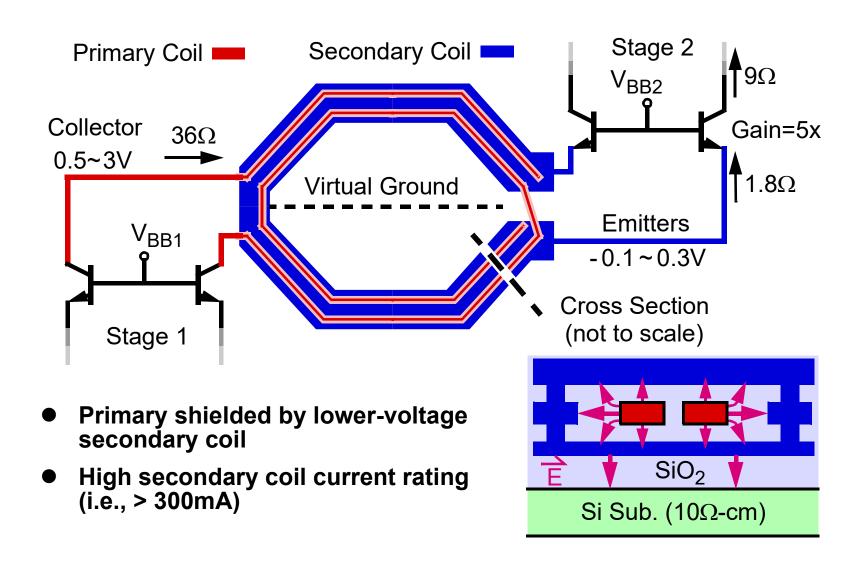

# **Self-Shielding Transformers**

#### **PA Power Combiner and Balun**

Back-to-back measurement of self-shielded power combiner and balun. Balun MAG

is 1.6dB, << 6dB increase in power from 4-way combining.</li>

# **Compensated Power Combiner**

Interwinding capacitance compensation mitigates amplitude and phase imbalances and maximizes efficiency when combining power from 4 transistors. Insertion loss at 60GHz is <1dB and chip area is <0.015mm<sup>2</sup>. Uniformity of impedances reflected from the load to the transistor outputs is better than 3%.

# **Dual-Path Power-Combining Amplifier**

3-stage 60GHz PA with integrated I/O baluns in 130-nm BiCMOS RF P<sub>out</sub>=200mW @ 1.8V

Maximum output power > 20dBm and peak-PAE above 20% at 61.5GHz

Small-signal gain > 20dB -3dB bandwidth > 10GHz

Reverse isolation > 51dB from 50-65GHz

0.25mm<sup>2</sup> active area 353mW quiescent @ 1.8V

# **Summary**

- Monolithic transformers are synthesized from transmission lines; they are not "lumped elements" but do behave that way over a limited frequency range.

Component parasitics must be captured to optimize RF circuit performance.

- Stacked metal windings offer wider bandwidth and higher k<sub>m</sub> than planar windings in some technologies. Metal thickness, intermetal dielectric thickness and metal height above substrate affects the performance of stacked vs. planar transformers.

- Interconnect performance at RF is not well-understood, modeled or captured in conventional CAD tools.

- Passive devices in Si-technology are not readily scalable, and further improvements in process technology and IC-CAD models of passive devices are needed for analog RF/MMIC applications.

#### References

- 1. J.R. Long, "Monolithic Transformers for Silicon RF IC Design" *IEEE Journal of Solid-State Circuits*, vol. 35, no. 9, Sept. 2000, pp. 1368-1382.

- 2. G.G. Rabjohn, Monolithic Microwave Transformers. M.Eng. thesis, Carleton University, 1991.

- 3. A. M. Niknejad and R. G. Meyer, "Analysis, Design, and Optimization of Spiral Inductors and Transformers for Si RF IC's", *IEEE Journal of Solid-State Circuits*, Vol. 33, No. 10, October 1998, pp. 1470-1481.

- 4. K.K. O, "Estimation Methods for Quality Factors of Inductors Fabricated in Silicon Integrated Circuit Process Technologies", *IEEE Journal of Solid-State Circuits*, vol. 33, no. 8, August 1998, pp. 1249-1252.

- 5. H. Hasegawa, M. Furukawa and H. Yanai, "Properties of Microstriplines on Si-SiO<sub>2</sub> System", *IEEE Transactions on Microwave Theory and Techniques*, Vol. 19, No. 11, November 1971, pp. 869-881.

- M. Danesh and J.R. Long, "Differentially Driven Symmetric Microstrip Inductors", IEEE Transactions on Microwave Theory and Techniques, vol. 50, no. 1, January 2002, pp. 332-341.

- 7. C. P. Yue and S. S. Wong, "On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC's", *IEEE Journal of Solid-State Circuits*, Vol. 33, No. 5, May 1998, pp. 743-752.

- 8. D. Cheung, J.R. Long, "Differentially shielded monolithic inductors," Proc. of the IEEE Custom Integrated Circuits Conference (CICC), 2003, p. 95-98.

- 9. Cheung, T.S.D.; Long, J.R.; "Shielded passive devices for silicon-based monolithic microwave and millimeter-wave integrated circuits," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 5, May 2006, pp. 1183 1200.

- 10. J.R. Long, Y. Zhao, W. Wu, M. Spirito, L. Vera and E. Gordon, "Passive Circuit Technologies for mm-Wave Wireless Systems on Silicon," *IEEE Transactions on Circuits and Systems I*, vol. 59, no. 8, Aug. 2012, pp. 1680-1693.

- 11. H.J. Finlay, U.K. patent application no. 8800115, 1985.

- 12. P. Andreani, B. Razavi and J.R. Long editors, Voltage-Controlled Oscillators, RFIC Virtual Journal Issue 1, IEEE, Dec. 2012, on-line via www.ieee.org.

- 13. P. Andreani and A. Fard, "More on the 1/f<sup>2</sup> phase noise performance of CMOS differential-pair LC-tank oscillators", *IEEE Journal of Solid-State Circuits*, vol. 41, no. 12, Dec. 2006, pp. 2703-2712.

- 14. P.I. Mak, D. Leenaerts, J.R. Long and H.C. Luong, editors, Low-Noise Amplifiers, RFIC Virtual Journal Issue 4, IEEE, April. 2014, on-line via www.ieee.org.

- 15. Reiha, M. T.; Long, J. R.; "A 1.2 V Reactive-Feedback 3.1–10.6 GHz Low-Noise Amplifier in 0.13um CMOS," IEEE Journal of Solid-State Circuits, Volume 42, Issue 5, May 2007 Page(s):1023 1033.

- 16. T.S.D. Cheung and J.R. Long, A 21-26-GHz SiGe bipolar power amplifier MMIC, IEEE Journal of Solid-State Circuits, vol. 40, no. 12, pp. 2583-2597, Dec. 2005.

- 17. Y. Zhao, J.R. Long, "A Wideband, Dual-Path, Millimeter-wave Power Amplifier with 20 dBm Output Power and PAE above 15% in 130 nm SiGe-BiCMOS," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 9, Sept. 2012.