# Gate Grounded NMOS 器件的 ESD 性能分析

朱科翰\*

## 摘要:

本文基于某  $0.18\mu\text{m}$ -CMOS 工艺制程的 1.8V NMOS 器件，从工艺的角度并用 TLP 测试系统对栅极接地的 NMOS (GGNMOS) ESD 器件进行比较分析。介绍了 SAB 和 ESD 注入对 GGNMOS 的性能影响。影响 GGNMOS ESD 性能的瓶颈是均匀开启性。在 GGNMOS 版图等其它特征参数最优的前提下，采用 SAB 能改善其均匀开启性，从而大大改进 ESD 性能。GGNMOS 的瞬态触发电压在 7V 左右，不会造成栅氧可靠性威胁，采用 PESD 并非必需。

## 1. 引言

MOS 管作为 ESD 防护器件广泛被业界采用，代工厂给设计公司提供的 ESD 版图设计规则文档中一般只有 MOS 管的规范。随着工艺的进步，MOS 管的特征尺寸缩小了、特征频率的增高了，但是使得器件 ESD 的抵抗能力减弱了。由此工艺工程师为提高 ESD 性能，推出了 SAB/SB(Salicide Block)，ESD 注入 (ESD implant) 供客户选择，但不是免费的。GGNMOS 作为 ESD 器件正向依靠寄生 NPN (漏极的 N+有源区-P 型衬底-源极的 N+有源区) BJT 泄放 ESD 电流；反向由 PN 二极管 (P 型衬底-N+有源区) 和栅源相接的 NMOS 二极管组成。在全芯片 ESD 网络中，当 ESD 事件来临时，GGNMOS 正向和反向都有可能导通，这由潜在的 ESD 路径决定，ESD 电流总会流向低阻路径。所以在设计时必需考虑 GGNMOS 的正向和反向 ESD 性能以绝对保证芯片的可靠性。通常 GGNMOS 作为二极管 ESD 性能很强大，但必需结合电源钳位器件 (Power Clamp) 一起使用，比如电源对输入发生正 ESD 应力。GGNMOS 作为 BJT 是一种击穿型 (Breakdown Device) 的工作机理[1, 2]，依靠漏极与衬底之间的雪崩击穿触发后形成低阻通路泄放 ESD 电流。然而多指 GGNMOS 器件通常不能如愿以偿的均匀开启，即 ESD 性能并不与器件的面积成正比。GGNMOS 的均匀开启性早有研究[3]，ESD 研究人员也提出了不增加额外工艺的前提下，改进 GGNMOS 均匀开启性的方法，比如采用 N-Well 电阻[4]，多米勒结构[5]。第 2 节介绍了工艺对 GGNMOS 的 ESD 性能影响。第 3 节以试验数据的形式直观的比较了 SAB 和 PESD 对 GGNMOS 的 ESD 性能影响。第 4 节分析了 GGNMOS 的非均匀导通性。所有的试验数据都是基于  $0.18\mu\text{m}$ -CMOS 工艺的 0.18V NMOS 器件测试而得。

## 2. 工艺对 NMOS 管 ESD 性能影响

### 2.1. ESD 注入

ESD implant 可以选择掺杂类型，常用的元素有硼 (Boron) 和砷 (Arsenic) 或磷 (Phosphorus)。

硼为受主杂质 P+，砷和磷为施主杂质 N+。某些代工厂只提供掺硼元素的 ESD implant，所以又称为 PESD。ESD implant 最早采用掺硼以降低 MOS 管的触发电压[6]。但先进工艺中的 LDD (LDD 减小 MOS 漏极端在沟道下的电场强度分布，以克服因热载流子效应所造成的 I-V 特性因长时间使用产生漂移的问题) 会产生尖端放电，使得 ESD 常发生在此尖端。采用掺砷的 ESD implant 可消除 LDD 结构，但会使得有源区的结的横向扩散比较严重，故 ESD 器件不能采用太短的沟道长度[7]。[8]在某 0.18μm-CMOS 工艺制程下采用硼和砷的 ESD implant 不仅大大提高了 MOS 器件的正向 ESD 性能，而且对反向二极管特性也有所提高。

## 2.2. 金属硅化物隔离

在先进半导体工艺中，金属硅化物扩散能降低 MOS 器件源漏极端的串联扩散电阻，提高 MOS 器件的工作速度，使 MOS 器件适用于高频应用。但低方块电阻使得 ESD 电流很容易从 PAD 传到 MOS 管的 LDD 结构从而 ESD 性能下降。为了从工艺的角度改进金属硅化物对 MOS 管 ESD 防护器件的性能影响，从而 SAB 应运而生。金属硅化物隔离层可提高有源区的电阻从而提高压舱电阻 (Ballasting Resistor) 使得多指 NMOS 器件在 ESD 事件下均匀开启。

## 3. SAB 与 PESD 对 GGNMOS 的影响

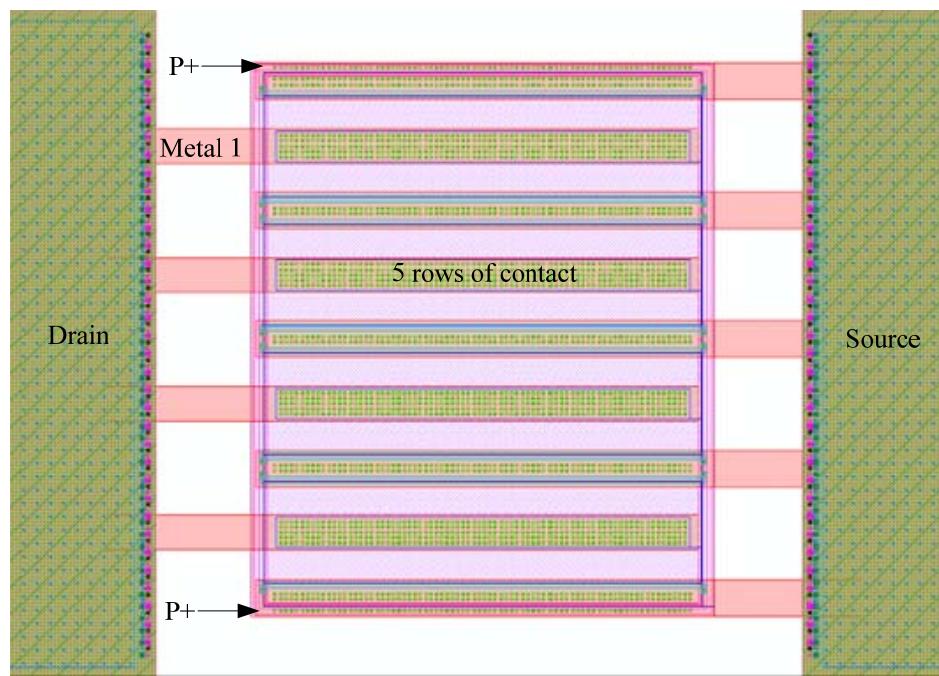

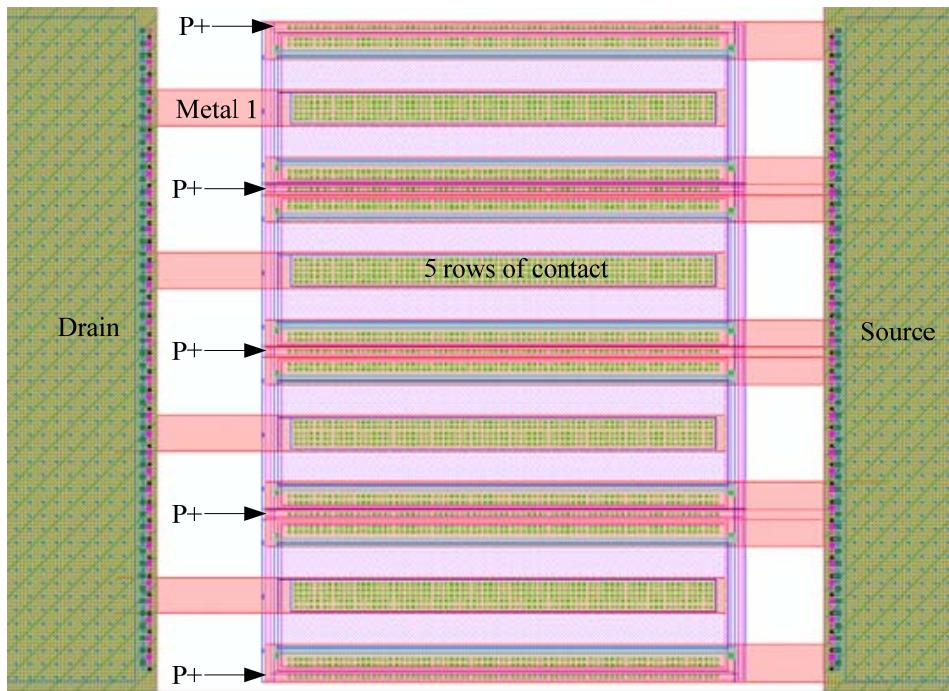

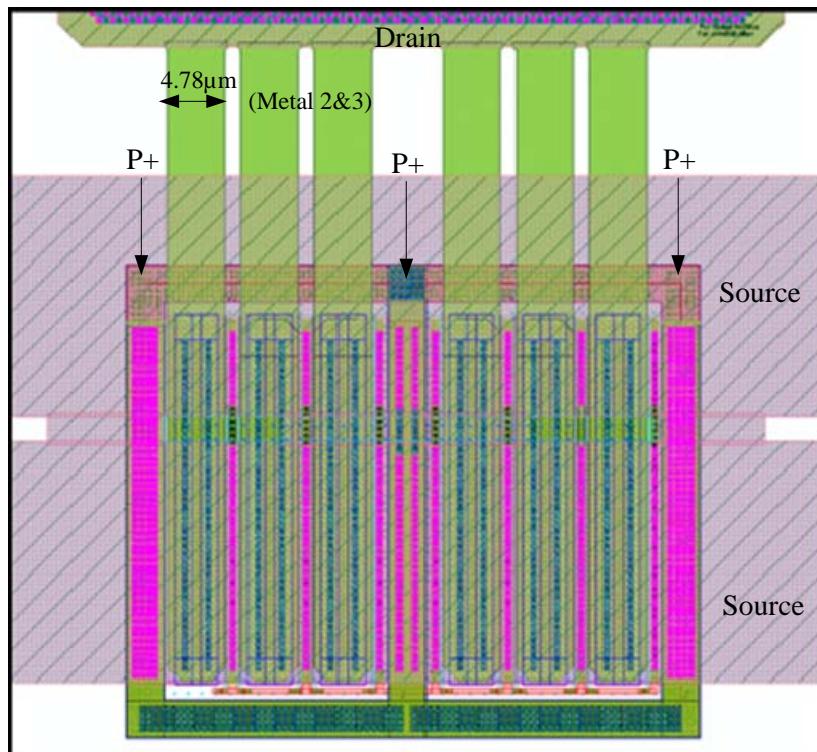

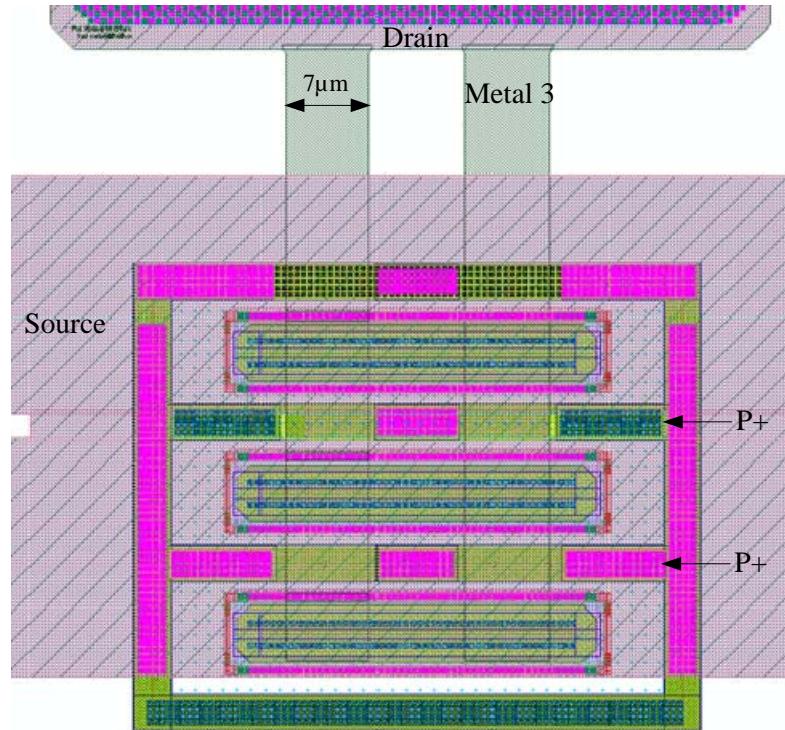

图 1 和图 2 分别为普通的 GGNMOS 和带均匀 P-tap 的 GGNMOS 器件。通常没有 P-tap 的 GGNMOS 结构中，中间的漏极比两边的漏极距离 P 衬底的距离远，电阻大，从而中间的漏极会较先开启。P-tap 的作用是使多叉指 MOS 管的每个叉指的漏极到 P 衬底的距离相等，从而保证个漏极均匀开启。但是 P-tap 使得漏极距离 P 衬底的距离减小，电阻减小，需要更大的雪崩电流才能使 GGNMOS 回跳 (Snapback)，从而意味着触发电压 (Vt1) 会变大。所以 P-tap 不一定有助于 GGNMOS 的 ESD 性能。

图 1. 8 叉指 GGNMOS 版图

图 2. 带 P-tap 的 8 叉指 GGNMOS 版图

表 1 为 5 个不同 GGNMOS 器件的 TLP 测试结果。5 个器件的关键版图尺寸相同：有源区宽度 (W) =40μm, 叉指数 (Finger) =8, 漏极端接触孔的排数=5, 漏端总金属宽度=12.96μm (仅有金属 1)。不同之处为是否有 SAB, PESD 和 P-tap。

表 1. GGNMOS 的 TLP 测试结果

| Device NO. | SAB | PESD | P-tap | Vt1/V | It1/mA | Vh/V | Ih/mA | Vt2/V | It2/A |

|------------|-----|------|-------|-------|--------|------|-------|-------|-------|

| 185        | N   | N    | N     | 6.55  | 2.36   | 4.78 | 60.6  | 9.95  | 2.32  |

| 186        | Y   | N    | N     | 6.57  | 2.53   | 5.14 | 53.7  | 20.64 | 4.56  |

| 187        | Y   | Y    | N     | 5.58  | -0.326 | 5.16 | 30.3  | 20.27 | 4.55  |

| 189        | N   | N    | Y     | 7.73  | 46.4   | 5.38 | 110   | 10.19 | 1.93  |

| 190        | Y   | Y    | Y     | 7.25  | 74.6   | 6.17 | 118   | 19.79 | 4.52  |

Note:

Width=40μm, #Fingers=8, #Rows of contact@Drain=5, Total metal width@Drain=12.96μm(metal 1 only).

从表 1 可知：

- SAB 可大大提高 It2 (从 2.32A 到 4.56A)。

- PESD 能降低其 Vt1 (从 6.55V 到 5.58V)。

- P-tap 使 Vt1 增大 (从 6.55V 到 7.73V)、It2 减小 (从 2.32A 到 1.93A)。

原因分别是：

- SAB 使得漏极的方块电阻值增大，从而 ESD 电流更加均匀分布，泄放能力提高。

- PESD 注入受主杂质在漏极 N+有源区下形成 P+，降低雪崩击穿。

- P-tap 减小了寄生 BJT 的基区到发射区的电阻 (Rbe) 值，从而需要更大的电流达到 BE

结的导通电压。P-tap 也会增大保持电压 ( $V_h$ )，从而  $It2$  减小，导致热击穿提前发生 (遵循能量守恒:  $P=IV$ )。

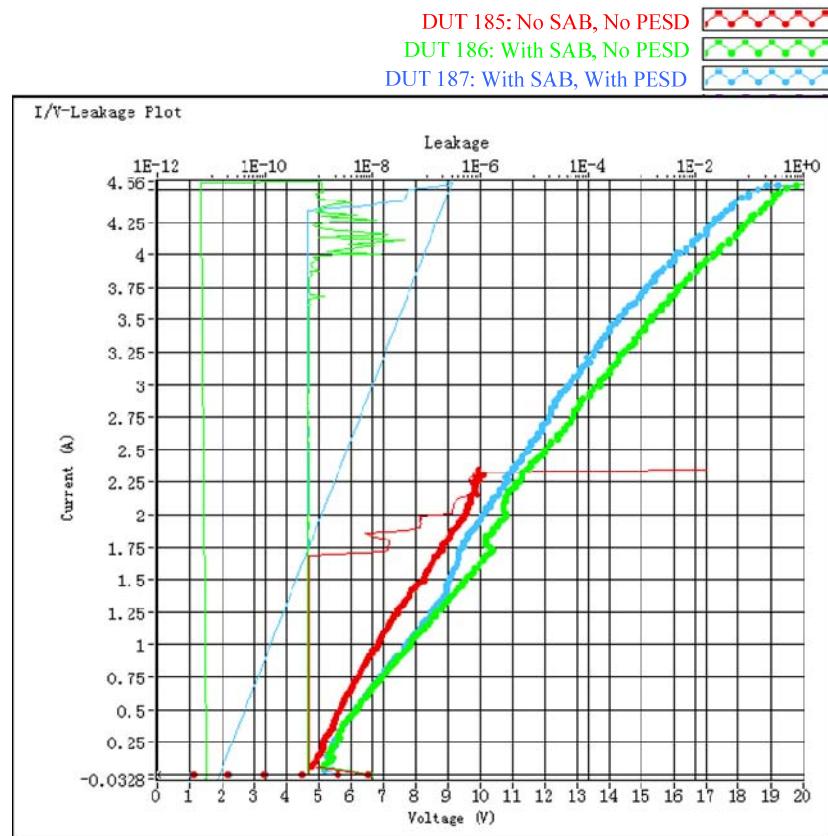

图 3 SAB 和 PESD 对 GGNMOS TLP I-V 曲线与漏电的影响

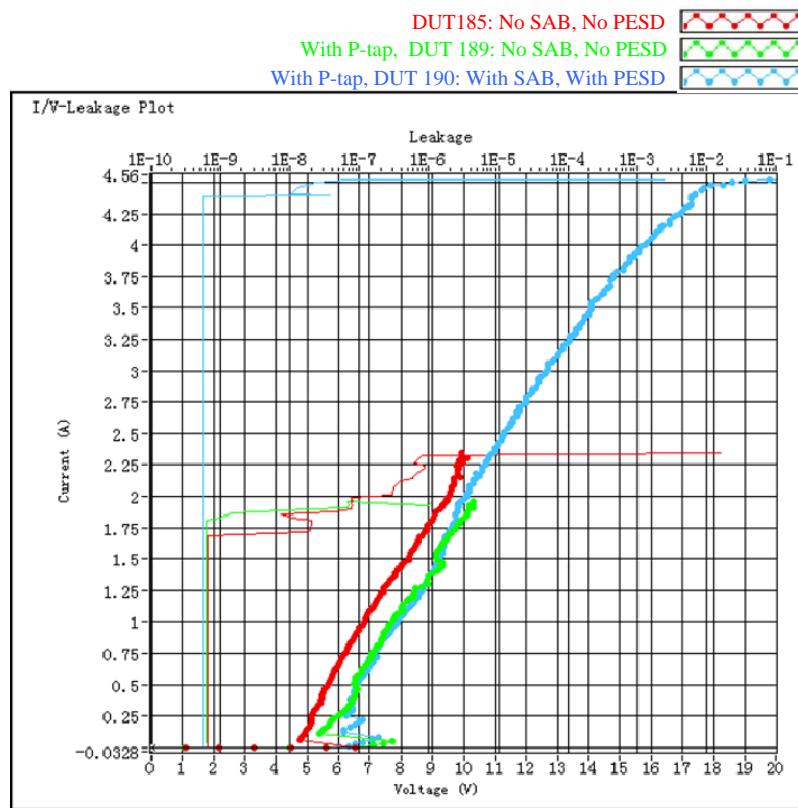

图 4. P-tap 和 SAB 与 PESD 对 GGNMOS TLP I-V 曲线与漏电的影响

图 3 和图 4 分别为 185 号、186 号、187 号 GGNMOS 和 185 号、189 号、190 号 GGNMOS 的 TLP I-V 曲线和漏电。

从图 3 和图 4 中的漏电可知：

- 常温下 GGNMOS 的漏电低于  $1\text{nA}$ 。

- 186 号 (With SAB) 和 187 号 (With SAB&PESD) 器件是金属熔断失效。

- 其它器件都是热击穿失效。

进一步可以推断：

- Metal 1 能承受 ESD 电流的能力为  $0.35\text{A}/\mu\text{m}$  ( $4.55\text{A}/12.96\mu\text{m}$ )。

- 带 P-tap 的 GGNMOS 的 ESD 能力低于普通的 GGNMOS (虽然 190 号器件的  $\text{It2}=4.52\text{A}$ ，但它的失效是由热击穿造成)。

## 4. 多叉指 GGNMOS 非均匀性导通分析

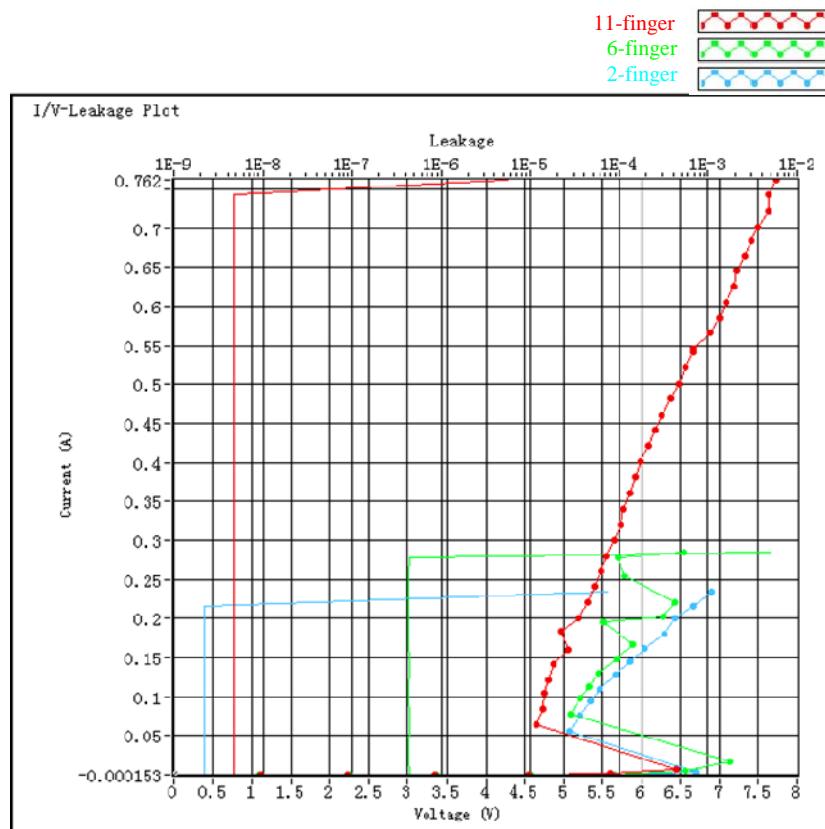

图 5 和图 6 分别为 11 叉指和 6 叉指的 GGNMOS 器件的版图。NMOS 的  $W=30\mu\text{m}$ ，漏端只有一排接触孔。11 叉指 GGNMOS 漏端的金属宽度共为  $39.8\mu\text{m}$ ，6 叉指 GGNMOS 漏端的金属宽度共为  $14\mu\text{m}$ 。都采用了 SAB 层。

图 6 为 11 叉指、6 叉指和 2 叉指的 TLP I-V 曲线和漏电，测试结果很不理想。

由图 6 可知：

- 漏电偏大，特别是 6 叉指 GGNMOS 的漏电高达  $0.4\mu\text{A}$ 。

- 用了 SAB， $\text{It2}$  却很低，GGNMOS 显然没有均匀开启，造成提前失效。

图 5. 11 叉指 GGNMOS 版图

图 5. 6 叉指 GGNMOS 版图

图 6. 不同叉指 GGNMOS 的 TLP I-V 曲线与漏电比较

本节中的测试器件的版图比第 3 节中测试器件的版图绘制得精细，但是其 ESD 性能让人大跌眼镜。GGNMOS 的 ESD 性能不与面积成正比，面积越大只会造成更加难以均匀开启。但

由于上面 GGNMOS 器件的漏端金属走线方法并不完全相同，所以没有绝对的可比性。

## 7. 总结

在 CMOS 工艺中，GGNMOS 是一种简单实用的 ESD 防护器件，但影响其 ESD 性能的瓶颈是均匀开启性。在 GGNMOS 版图等其它特征参数最优的前提下，采用 SAB 能改善其均匀开启性，从而大大改进 ESD 性能。0.18V NMOS 器件的栅氧直流击穿电压大约为 6V 左右，但瞬态击穿电压一般是 DC 击穿电压的两倍以上，GGNMOS 的  $V_{t1}$  在 7V 左右并不会造成栅氧可靠性威胁，所以采用 PESD 降低  $V_{t1}$  在成本上不合算，一般情况下也不需要。

## 8. 参考文献

1. Dabral, S. and T. Maloney, *Basic ESD and I/O Design*. 1998, Santa Clara, CA: John Wiley & Sons, Ltd.

2. Amerasekera, A. and C. Duvvury, *ESD in silicon integrated circuits – second edition*. 2002: John Wiley & Sons, Ltd.

3. Russ, C., et al. *Non-uniform triggering of gg-nMOS investigated by combined emission microscopy and transmission line pulsing*. *Electrical Overstress/Electrostatic Discharge Symposium Proceedings*, 1998.

4. Notermans, G. *On The Use Of N-well Resistors For Uniform Triggering Of ESD Protection Elements*. *Electrical Overstress/Electrostatic Discharge Symposium Proceedings*, 1997.

5. Trinh, S., et al. *Multi-finger turn-on circuits and design techniques for enhanced ESD performance and width scaling*. 2003. Bordeaux, France, France: Elsevier Ltd.

6. Hsue, C.-c. and J. Ko, *ESD Protection Improvement*. 1996, Hsinchu, TW: United States

7. Ker, M.D. *ESD (Electrostatic Discharge) Protection in CMOS Integrated Circuits*. Available from: <http://www.ics.ee.nctu.edu.tw/~mdker/ESD/index.html>.

8. Ming-Dou, K., C. Che-Hao, and L. Wen-Yu, *ESD implantations for on-chip ESD protection with layout consideration in 0.18um salicided CMOS technology*. *IEEE Transactions on Semiconductor Manufacturing* 2005. **18**(2): p. 328-337.