# Specification for I3C<sup>SM</sup>

## **Improved Inter Integrated Circuit**

Version 1.0 23 December 2016

MIPI Board Adopted 31 December 2016

**Public Release Edition**

Further technical changes to this document are expected as work continues in the Sensor Working Group.

#### NOTICE OF DISCLAIMER

The material contained herein is provided on an "AS IS" basis. To the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI Alliance Inc. ("MIPI") hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence. ALSO, THERE IS NO WARRANTY OR CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL.

IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. Any license to use this material is granted separately from this document. This material is protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI Alliance. MIPI, MIPI Alliance and the dotted rainbow arch and all related trademarks, service marks, tradenames, and other intellectual property are the exclusive property of MIPI Alliance Inc. and cannot be used without its express prior written permission. The use or implementation of this material may involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents, patent applications, or copyrights owned by one or more parties, whether or not members of MIPI. MIPI does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any IPR or claims of IPR as respects the contents of this material or otherwise.

Without limiting the generality of the disclaimers stated above, users of this material are further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the contents of this material; (b) does not monitor or enforce compliance with the contents of this material; and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance with MIPI specifications or related material.

Questions pertaining to this material, or the terms or conditions of its provision, should be addressed to:

MIPI Alliance, Inc. c/o IEEE-ISTO 445 Hoes Lane, Piscataway New Jersey 08854, United States Attn: Managing Director

## **Contents**

| C | ont  | ents               |                                                                  | iii  |

|---|------|--------------------|------------------------------------------------------------------|------|

| F | igur | es                 |                                                                  | vii  |

| T | able | es                 |                                                                  | X    |

| R | elea | se Histor          | у                                                                | xiii |

| 1 |      | Introduc           | tion                                                             | 1    |

|   | 1.1  |                    |                                                                  |      |

|   | 1.2  |                    | urpose                                                           |      |

|   | 1.3  | <b>I3C K</b>       | ey Features                                                      | 3    |

| 2 |      | Terminol           | ogy                                                              | 5    |

|   | 2.1  | Use of             | Special Terms                                                    | 5    |

|   | 2.2  | Defini             | tions                                                            | 5    |

|   | 2.3  | Abbre              | viations                                                         | 8    |

|   | 2.4  | Acron              | yms                                                              | 8    |

| 3 |      | Referenc           | es                                                               | 10   |

|   | 3.1  | Norma              | ative References                                                 | 10   |

|   | 3.2  | Inforn             | native References                                                | 10   |

| 4 |      | Technica           | l Overview (Informative)                                         | 11   |

| - | 4.1  |                    | undamental Principles                                            |      |

|   | 4.2  |                    | laster and Slave Devices                                         |      |

|   | 4.   | .2.1 I3C           | Master Device                                                    | 16   |

|   |      | 4.2.1.1            | I3C Master Device Roles                                          | 17   |

|   | 4.   |                    | Slave Device                                                     |      |

|   |      | 4.2.2.1            | I3C Slave Device Roles                                           | 19   |

| 5 |      | I3C Prote          | ocol                                                             | 20   |

|   | 5.1  | Single             | Data Rate (SDR) Mode                                             | 20   |

|   | 5.   | .1.1 Bus           | Configuration                                                    | 21   |

|   |      | 5.1.1.1            | I3C Device Characteristics                                       | 21   |

|   |      | 5.1.1.2            | I3C Characteristics Registers                                    |      |

|   |      | 5.1.1.2.1          | Bus Characteristics Register (BCR)                               |      |

|   |      | 5.1.1.2.2          | Device Characteristics Register (DCR)                            |      |

|   | _    | 5.1.1.2.3          | Legacy Virtual Register (LVR)                                    |      |

|   | 5.   |                    | Communication                                                    |      |

|   |      | 5.1.2.1<br>5.1.2.2 | Role of I3C Slave                                                |      |

|   |      | 5.1.2.2.1          | I3C Address Arbitration                                          |      |

|   |      | 5.1.2.2.2          | I3C Address Arbitration Optimization                             |      |

|   |      | 5.1.2.2.3          | Consequence of Master Starting a Frame with an I3C Slave Address |      |

|   |      | 5.1.2.2.4          | Address Header Following a Repeated START is Push-Pull           |      |

|   |      | 5.1.2.2.5          | I3C Slave Address Restrictions                                   |      |

|   |      | 5.1.2.3            | I3C SDR Data Words                                               |      |

|   |      | 5.1.2.3.1          | Transition from Address ACK to SDR Master Write Data             | 34   |

|   |      | 5.1.2.3.2          | Ninth Bit of SDR Master Written Data as Parity                   |      |

|   |      | 5.1.2.3.3          | Ninth Bit of SDR Slave Returned (Read) Data as End-of-Data       | 35   |

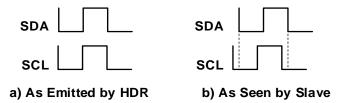

| 5.1.2.4          | Use of Clock Speed to Prevent Legacy I <sup>2</sup> C Devices From Seeing I3C Traffic | 36 |

|------------------|---------------------------------------------------------------------------------------|----|

| 5.1.2.4.1        | J J                                                                                   |    |

| 5.1.2.5          | Master Clock Stalling                                                                 | 37 |

| 5.1.2.5.1        | I3C/I <sup>2</sup> C Transfer, ACK/NACK Phase                                         | 38 |

| 5.1.2.5.2        | Write Data Transfer, Parity Bit                                                       | 39 |

| 5.1.2.5.3        | ·                                                                                     |    |

| 5.1.2.5.4        | , e                                                                                   |    |

| 5.1.3 Bus        | Conditions                                                                            |    |

| 5.1.3.1          | Open Drain Pull-Up and High-Keeper                                                    |    |

| 5.1.3.2          | Bus Free Condition                                                                    |    |

| 5.1.3.3          | Bus Available Condition                                                               |    |

| 5.1.3.4          | Bus Idle Condition                                                                    |    |

| 5.1.3.5          | Activity States                                                                       |    |

| <b>5.1.4</b> Bus | Initialization and Dynamic Address Assignment Mode                                    |    |

| 5.1.4.1          | Device Requirements for Dynamic Address Assignment                                    |    |

| 5.1.4.1.1        | Unique Identifiability                                                                | 46 |

| 5.1.4.2          | Bus Initialization Sequence with Dynamic Address Assignment                           | 46 |

| 5.1.4.3          | Provisional ID Collision Detection and Correction                                     |    |

| 5.1.5 Hot        | -Join Mechanism                                                                       | 50 |

| 5.1.5.1          | Failsafe Device Pads                                                                  |    |

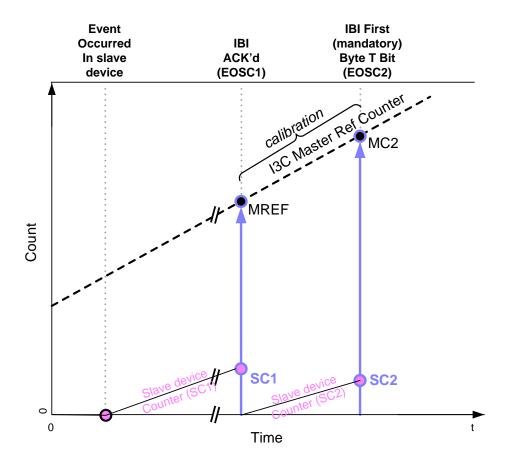

| 5.1.6 In-I       | Band Interrupt                                                                        | 52 |

| 5.1.6.1          | Priority Level                                                                        |    |

| 5.1.6.2          | I3C Slave Interrupt Request                                                           | 52 |

| 5.1.6.3          | I3C Secondary Master Requests to be Current Master                                    |    |

| 5.1.6.4          | I3C Main Master Initiating a Transaction                                              | 54 |

| 5.1.7 Seco       | ondary Master Functions                                                               | 55 |

| 5.1.7.1          | Hardware and Software Requirements                                                    | 55 |

| 5.1.7.2          | Bus Management Procedures                                                             | 55 |

| 5.1.7.3          | Reduced Functionality Secondary Masters                                               | 56 |

| 5.1.7.4          | In-Band Interrupt Handling                                                            | 56 |

| 5.1.7.5          | Hot-Join Management                                                                   | 56 |

| 5.1.8 Tim        | ing Control                                                                           | 57 |

| 5.1.8.1          | General Principles                                                                    | 57 |

| 5.1.8.2          | Synchronous Systems and Events                                                        | 58 |

| 5.1.8.3          | Asynchronous Systems and Events                                                       | 61 |

| 5.1.8.3.1        | Async Mode 0: Asynchronous Basic Mode                                                 | 66 |

| 5.1.8.3.2        | Async Mode 1: Asynchronous Advanced Mode                                              | 68 |

| 5.1.8.3.3        | Async Mode 2: Async High-Precision Low-Power Mode                                     | 70 |

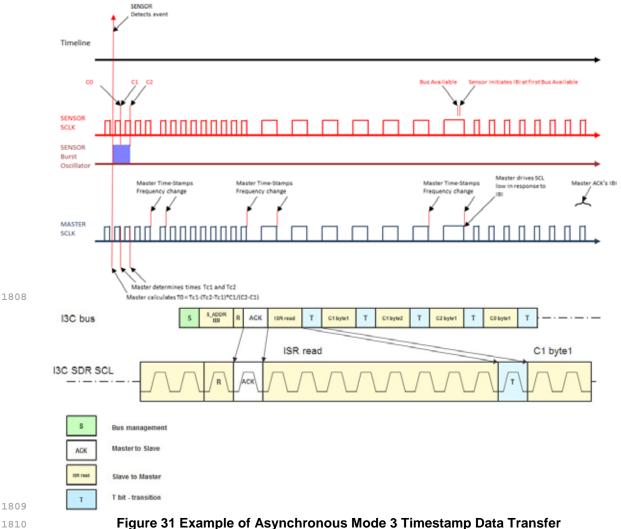

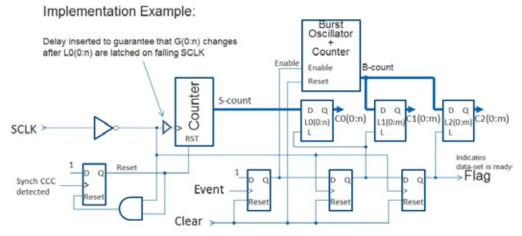

| 5.1.8.3.4        | Async Mode 3: Async High-Precision Triggereable Mode                                  | 73 |

| 5.1.9 Con        | nmon Command Codes (CCC)                                                              |    |

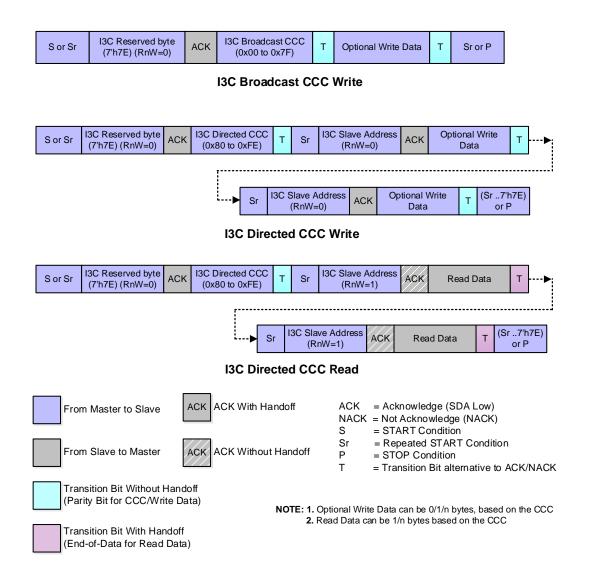

| 5.1.9.1          | CCC Command Format                                                                    | 76 |

| 5.1.9.2          | Broadcast CCCs vs Direct CCCs                                                         | 77 |

| 5.1.9.2.1        | End of a CCC Command                                                                  | 77 |

| 5.1.9.2.2        | Framing Model for Direct CCC Commands                                                 | 78 |

| 51023            | •                                                                                     | 79 |

| 5.1.9.3    | CCC Command Definitions                                         |     |

|------------|-----------------------------------------------------------------|-----|

| 5.1.9.3.1  | 1 Enable/Disable Slave Events Command (ENEC/DISEC)              | 84  |

| 5.1.9.3.2  | 2 Enter Activity State 0–3 (ENTAS0–ENTAS3)                      | 85  |

| 5.1.9.3.3  | Reset Dynamic Address Assignment (RSTDAA)                       | 85  |

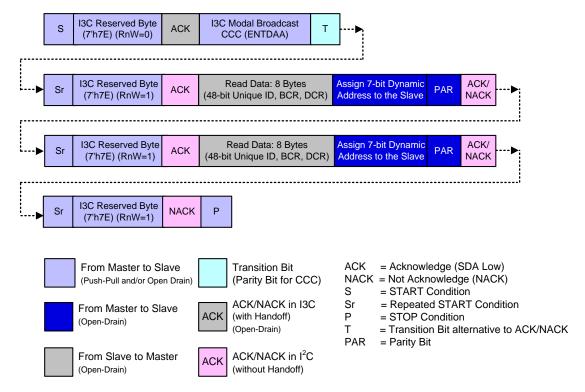

| 5.1.9.3.4  | 4 Enter Dynamic Address Assignment (ENTDAA)                     | 86  |

| 5.1.9.3.5  | 5 Set/Get Max Write Length (SETMWL/GETMWL)                      | 86  |

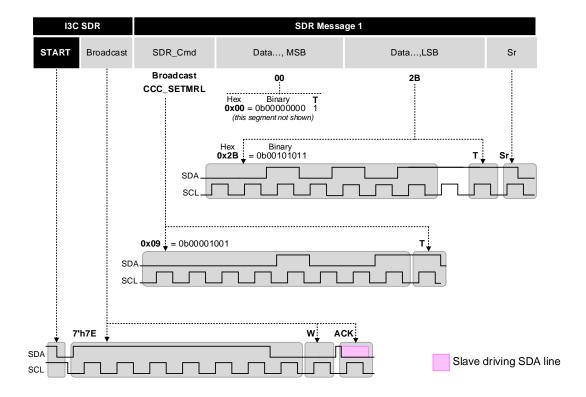

| 5.1.9.3.6  | Set/Get Max Read Length (SETMRL/GETMRL)                         | 87  |

| 5.1.9.3.7  | 7 Define List of Slaves (DEFSLVS)                               | 87  |

| 5.1.9.3.8  | 8 Enter Test Mode (ENTTM)                                       | 88  |

| 5.1.9.3.9  | Enter HDR Mode 0–7 (ENTHDR0–ENTHDR7)                            | 88  |

| 5.1.9.3.1  | 10 Set Dynamic Address from Static Address (SETDASA)            | 89  |

| 5.1.9.3.1  | 11 Set New Dynamic Address (SETNEWDA)                           | 90  |

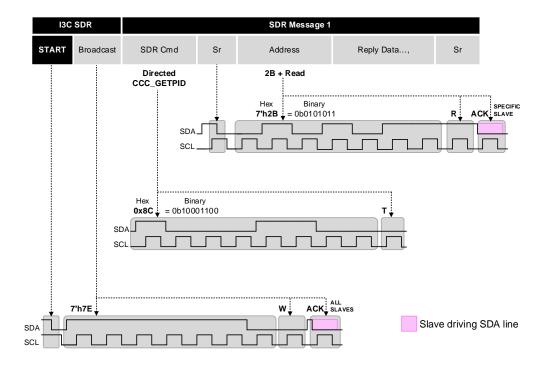

| 5.1.9.3.1  | 12 Get Provisional ID (GETPID)                                  | 90  |

| 5.1.9.3.1  | 13 Get Bus Characteristics Register (GETBCR)                    | 90  |

| 5.1.9.3.1  | 14 Get Device Characteristics Register (GETDCR)                 | 90  |

| 5.1.9.3.1  | 15 Get Device Status (GETSTATUS)                                | 91  |

| 5.1.9.3.1  | 16 Get Accept Mastership (GETACCMST)                            | 92  |

| 5.1.9.3.1  | 17 Set Bridge Targets (SETBRGTGT)                               | 93  |

| 5.1.9.3.1  | 18 Get Max Data Speed (GETMXDS)                                 | 93  |

| 5.1.9.3.1  | 19 Get HDR Capability (GETHDRCAP)                               | 95  |

| 5.1.9.3.2  | 20 Set Exchange Timing Information (SETXTIME)                   | 95  |

| 5.1.9.3.2  |                                                                 |     |

| 5.1.10 Err | or Detection and Recovery Methods for SDR                       | 98  |

| 5.1.10.1   | SDR Error Detection and Recovery Methods for I3C Slave Devices  | 98  |

| 5.1.10.1   | .1 Error Type S0                                                | 99  |

| 5.1.10.1   | .2 Error Type S1                                                | 99  |

| 5.1.10.1   | .3 Error Type S2                                                | 99  |

| 5.1.10.1   | .4 Error Type S3                                                | 99  |

| 5.1.10.1   | .5 Error Type S4                                                | 100 |

| 5.1.10.1   | .6 Error Type S5                                                | 100 |

| 5.1.10.1   | .7 Error Type S6 (Optional)                                     | 100 |

| 5.1.10.2   | SDR Error Detection and Recovery Methods for I3C Master Devices |     |

| 5.1.10.2   | .1 Error Type M0                                                | 101 |

| 5.1.10.2   | .2 Error Type M1 (Optional)                                     | 101 |

| 5.1.10.2   | .3 Error Type M2                                                | 101 |

| 5.1.10.2   |                                                                 |     |

|            | Data Rate (HDR) Modes                                           |     |

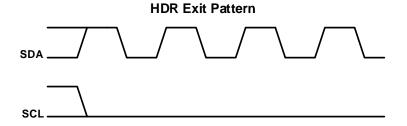

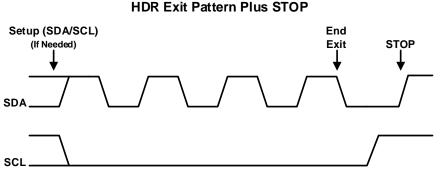

| 5.2.1 HD   | R Exit Pattern and HDR Restart Pattern                          |     |

| 5.2.1.1    | HDR Exit Pattern                                                |     |

| 5.2.1.2    | HDR Restart Pattern                                             |     |

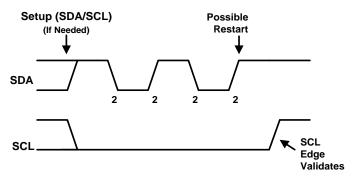

| 5.2.1.3    | HDR Exit Pattern Detector                                       |     |

| 5.2.1.4    | HDR Restart and Exit Pattern Detector                           |     |

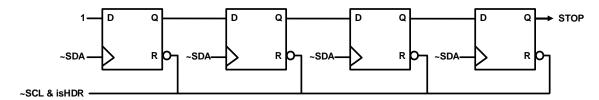

| 5.2.1.5    | Compatibility of HDR Pattern Detection and Ternary Modes        | 109 |

| 5.2.2 H        | DR Double Data Rate Mode (HDR-DDR)                           | 110 |

|----------------|--------------------------------------------------------------|-----|

| 5.2.2.1        | HDR-DDR Overview                                             | 113 |

| 5.2.2.2        | HDR-DDR Command Coding                                       | 117 |

| 5.2.2.3        | HDR-DDR Bus Turnaround                                       | 119 |

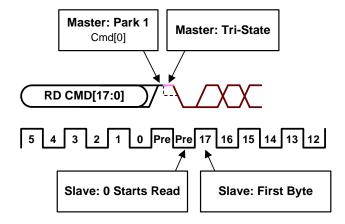

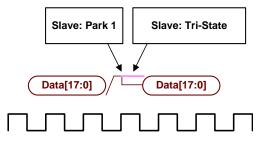

| 5.2.2.3        | 3.1 Command to Read Data from Slave                          | 119 |

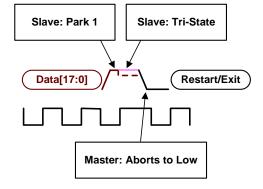

| 5.2.2.3        | 3.2 End of a Read Command Message                            | 120 |

| 5.2.2.3        | 3.3 Master Termination of a Read Command Message             | 120 |

| 5.2.2.4        | HDR-DDR Error Detection                                      | 121 |

| 5.2.2.5        | HDR-DDR CRC5 Algorithm                                       | 122 |

| 5.2.3 H        | DR Ternary Modes (HDR-TSP and HDR-TSL)                       | 123 |

| 5.2.3.1        | HDR Ternary Signaling and Coding Protocol                    | 123 |

| 5.2.3.1        | .1 Ternary Signaling                                         | 123 |

| 5.2.3.1        | .2 Ternary Coding Protocol                                   | 124 |

| 5.2.3.2        | HDR Ternary Command Coding                                   | 131 |

| 5.2.3.3        | HDR Ternary Bus Turnaround                                   | 133 |

| 5.2.3.4        | HDR Ternary Error Detection                                  | 134 |

| 6 I3C Ele      | ectrical Specifications                                      | 135 |

|                | I/O Characteristics                                          |     |

| <b>6.2</b> Tim | ing Specification                                            | 139 |

| Annex A        | I3C Communication Format Details                             | 159 |

| -              | CCC Transfers                                                |     |

|                | Private Write and Read Transfers                             |     |

|                | acy I <sup>2</sup> C Write and Read Transfers on the I3C Bus |     |

|                | namic Address and Enter HDR                                  |     |

| -              |                                                              |     |

| Annex B        | SDR Mode Error Type Origins                                  |     |

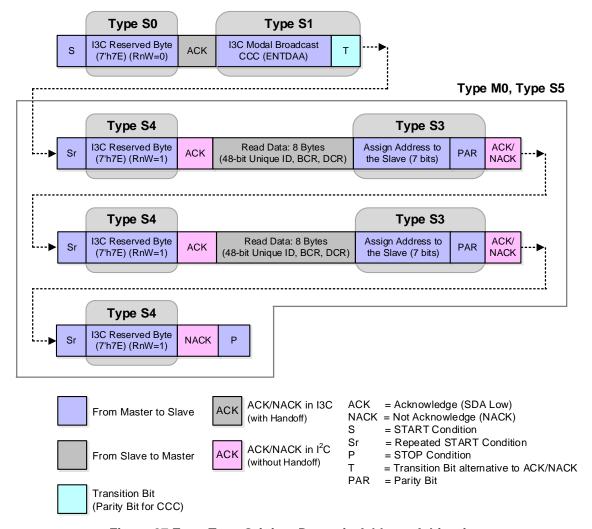

|                | or Types in I3C CCC Transfers                                |     |

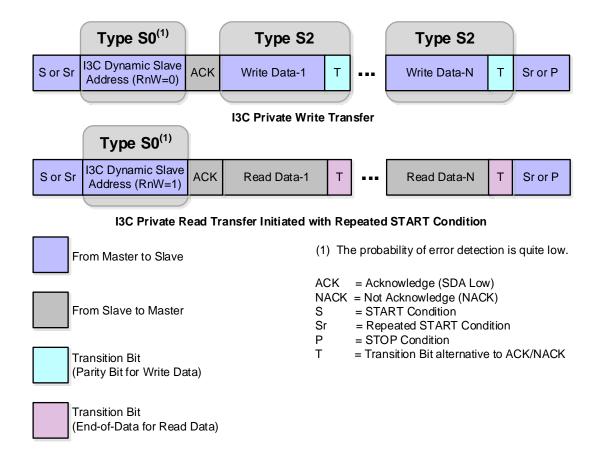

|                | or Types in I3C Private Read and Write Transfers             |     |

| B.3 Err        | or Types in Dynamic Address Arbitration                      |     |

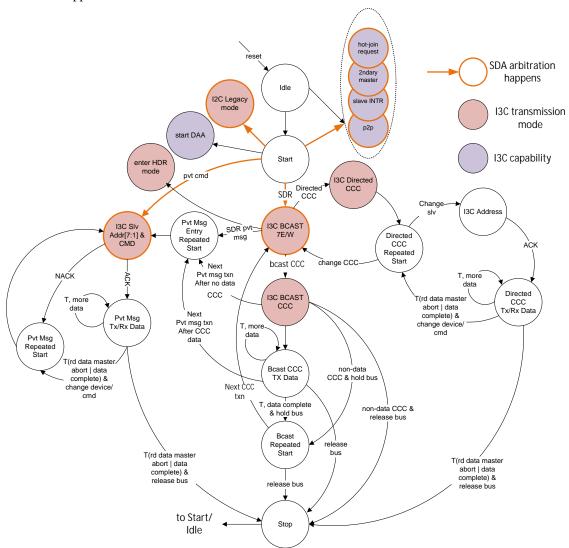

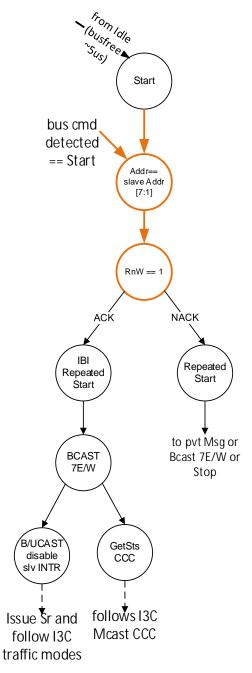

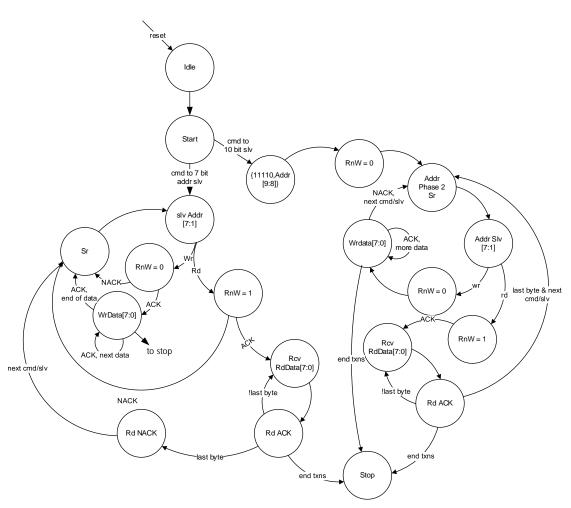

| Annex C        | I3C Master FSMs                                              | 169 |

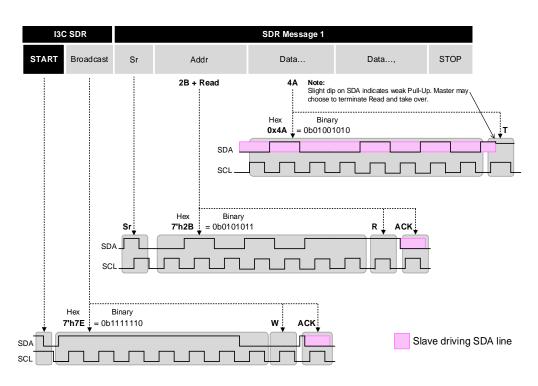

| Annex D        | Typical I3C Protocol Communications                          | 177 |

## **Figures**

| Figure 1 I3C System Diagram                                                  | 1  |

|------------------------------------------------------------------------------|----|

| Figure 2 Energy Consumption and Raw Data Rate: I3C vs. I <sup>2</sup> C      | 3  |

| Figure 3 Energy Consumption Comparison for I3C Data Modes                    | 4  |

| Figure 4 Example of Data Traffic on the I3C Bus                              | 12 |

| Figure 5 I3C Communication Flow.                                             | 13 |

| Figure 6 I3C Master Device Block Diagram                                     | 16 |

| Figure 7 I3C Slave Device Block Diagram                                      | 18 |

| Figure 8 I3C Bus with I <sup>2</sup> C Devices and I3C Devices               | 21 |

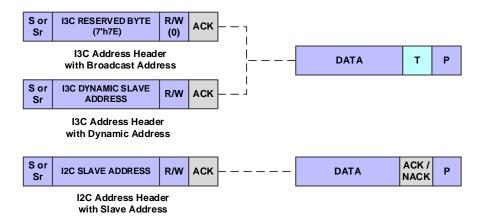

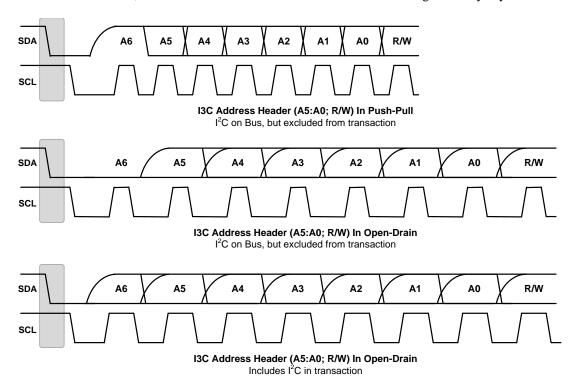

| Figure 9 Address Header Comparison                                           | 27 |

| Figure 10 Address Arbitration During Header                                  | 31 |

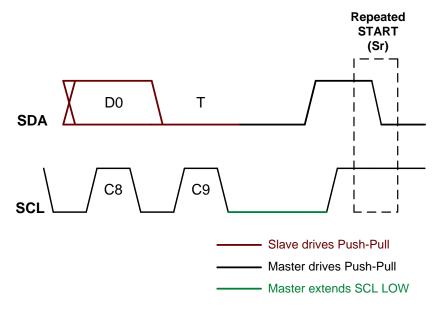

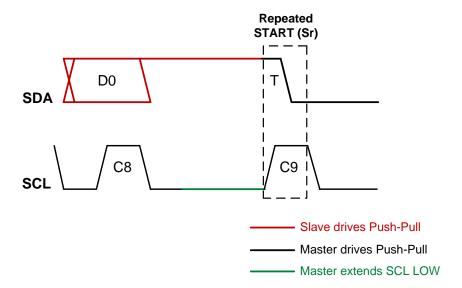

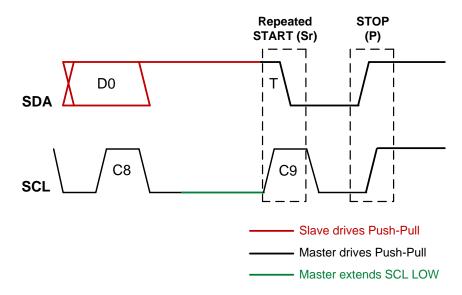

| Figure 11 Master Clock Stalling in ACK Phase                                 | 38 |

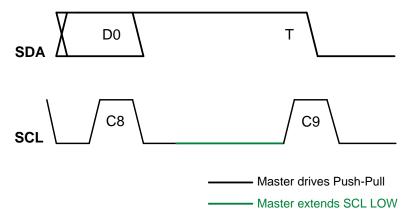

| Figure 12 Master Clock Stalling in Write Parity Bit                          | 39 |

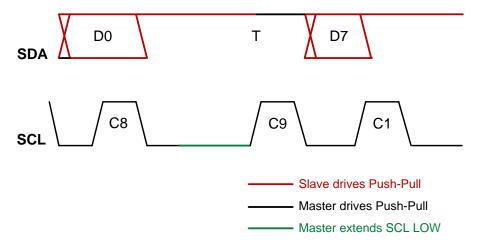

| Figure 13 Master Clock Stalling in T-Bit Before Next Read Data               | 39 |

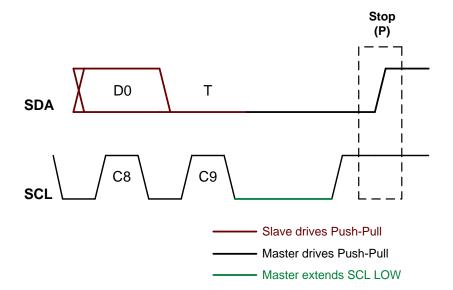

| Figure 14 Master Clock Stalling in T-Bit Before STOP                         | 40 |

| Figure 15 Master Clock Stalling in Low T-Bit Before Repeated Start           | 40 |

| Figure 16 Master Clock Stalling in High T-Bit Before Repeated START          | 41 |

| Figure 17 Master Clock Stalling in High T-Bit Before Repeated START and STOP | 41 |

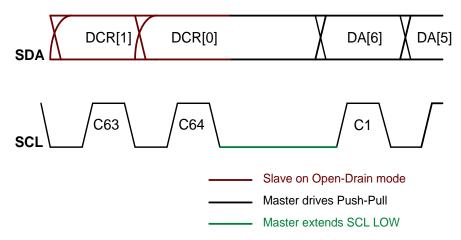

| Figure 18 Master Clock Stalling in Dynamic Address First Bit                 | 42 |

| Figure 19 Dynamic Address Assignment Transaction                             | 48 |

| Figure 20 IBI Sequence with Mandatory Data Byte                              | 52 |

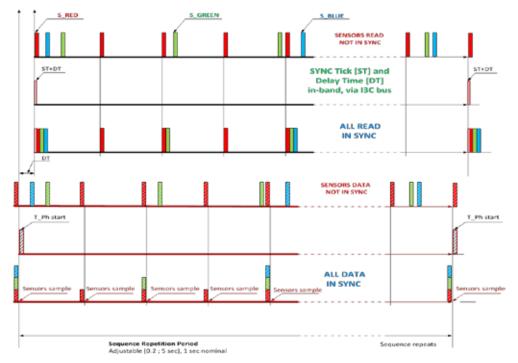

| Figure 21 Synchronization of Sampling Moments                                | 59 |

| Figure 22 Synchronization Procedure on a General-Purpose I3C Bus             | 60 |

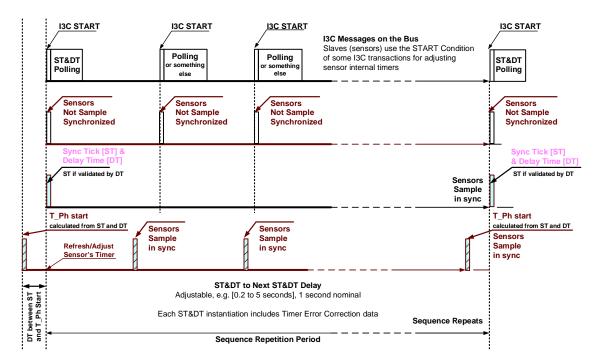

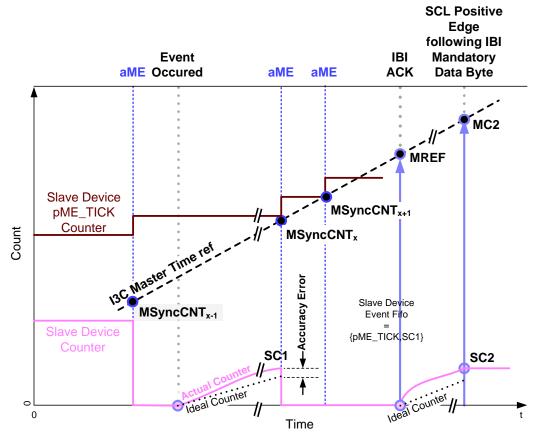

| Figure 23 Example Graph of Async Mode 0 Timestamp Interpolation              | 62 |

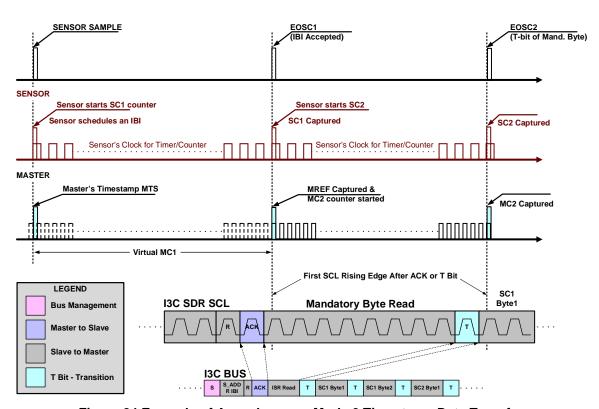

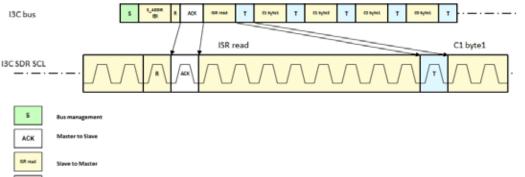

| Figure 24 Example of Asynchronous Mode 0 Timestamp Data Transfer             | 66 |

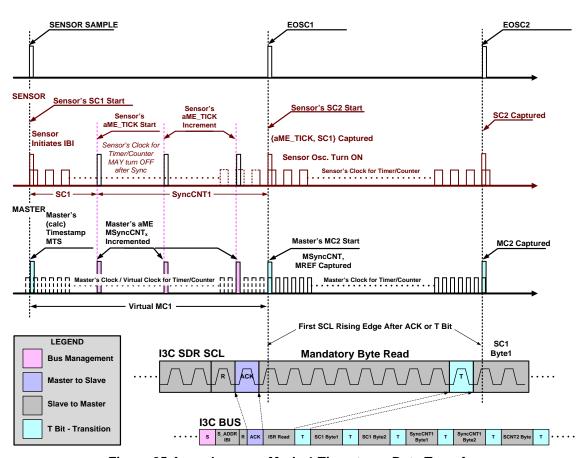

| Figure 25 Example of Asynchronous Mode 1 Timestamp Data Transfer             | 68 |

| Figure 26 Async Mode 1 Timestamp Interpolation                               | 69 |

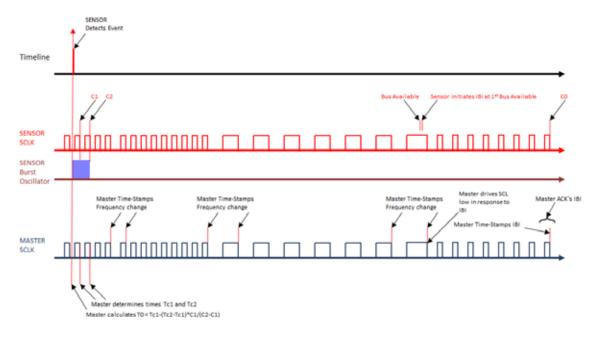

| Figure 27 Example of Asynchronous Mode 2 Timestamp Data Transfer             | 71 |

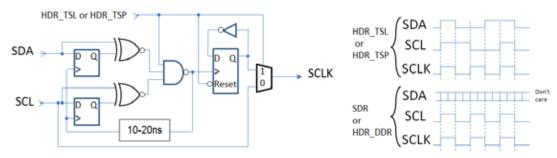

| Figure 28 Generating SCLK from SCL and SDA Implementation Example            | 71 |

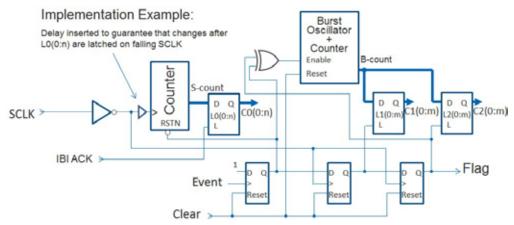

| Figure 29 Asynchronous Mode 2 Implementation Example                         | 72 |

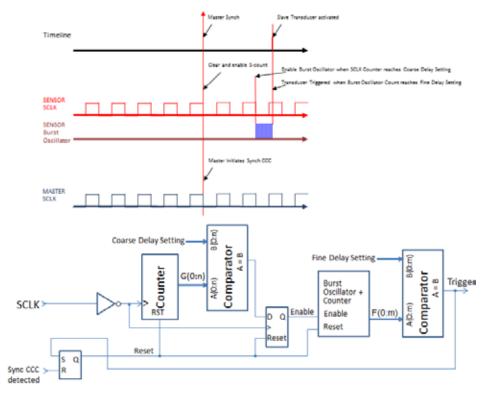

| Figure 30 Example of Asynchronous Mode 3 Triggering                          | 74 |

| Figure 31 Example of Asynchronous Mode 3 Timestamp Data Transfer             | 75 |

| Figure 32 Asynchronous Mode 3 Implementation Example                         | 75 |

| Figure 33 CCC General Frame Format                                           | 76 |

| Figure 34 Direct CCC Framing Model                                                 | 78  |

|------------------------------------------------------------------------------------|-----|

| Figure 35 Example Waveform for Error Type S0                                       | 99  |

| Figure 36 HDR Exit Pattern and Exit Plus STOP                                      | 104 |

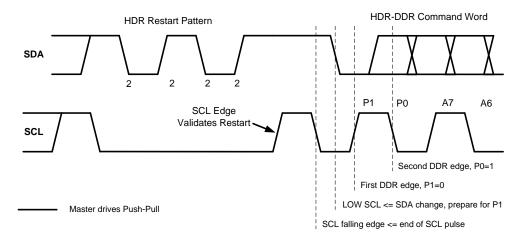

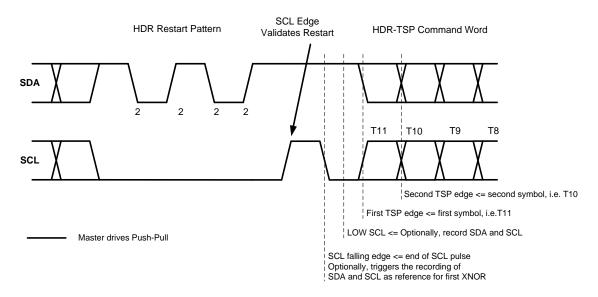

| Figure 37 HDR Restart with Next Edge                                               | 105 |

| Figure 38 Example HDR Exit Pattern Detector (Schematic)                            | 105 |

| Figure 39 Metastable Changes on SCL and SDA Do Not Break the Exit Pattern Detector | 106 |

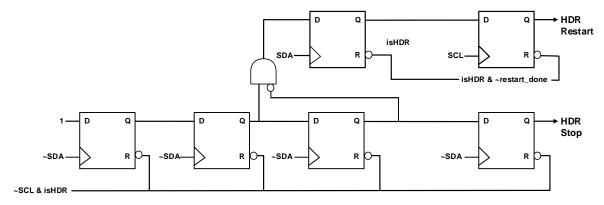

| Figure 40 Combined HDR Restart and Exit Pattern Detector (Schematic)               | 107 |

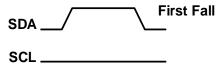

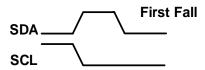

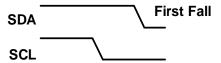

| Figure 41 SDA Moves Low to High                                                    | 109 |

| Figure 42 SDA and SCL Changing Metastable                                          | 109 |

| Figure 43 SCL Goes Low While SDA Already High                                      | 110 |

| Figure 44 HDR-DDR Format                                                           | 111 |

| Figure 45 DDR Preamble Bits State Diagram                                          | 113 |

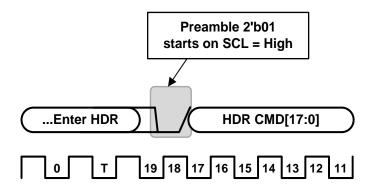

| Figure 46 Unused Bit Before Preamble of First HDR-DDR Command                      | 115 |

| Figure 47 Typical HDR-DDR Mode Frame                                               | 116 |

| Figure 48 HDR-DDR Command Code After ENTHDR0                                       | 118 |

| Figure 49 HDR-DDR Command Code After HDR Repeated Start Pattern                    | 118 |

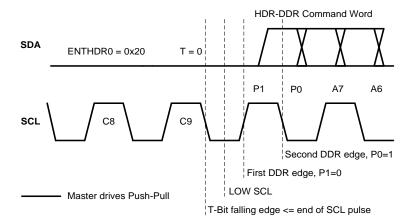

| Figure 50 Start of HDR-DDR.                                                        | 119 |

| Figure 51 Master Allows Normal Read.                                               | 120 |

| Figure 52 Master Terminates Read                                                   | 120 |

| Figure 53 Typical HDR Ternary Mode Frame                                           | 123 |

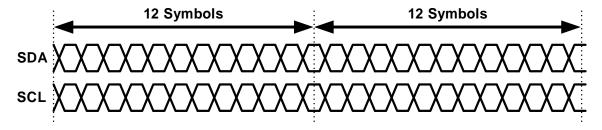

| Figure 54 Twelve Symbols Per Data Word                                             | 124 |

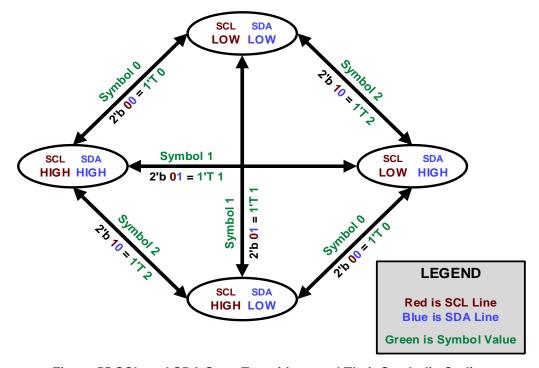

| Figure 55 SCL and SDA State Transitions and Their Symbolic Coding                  | 127 |

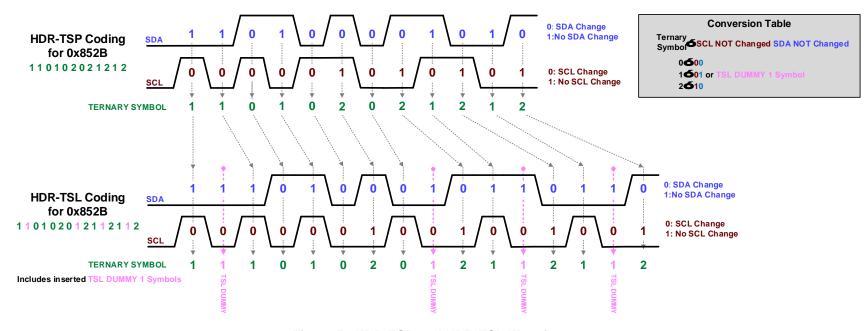

| Figure 56 HDR-TSP and HDR-TSL Waveforms                                            | 129 |

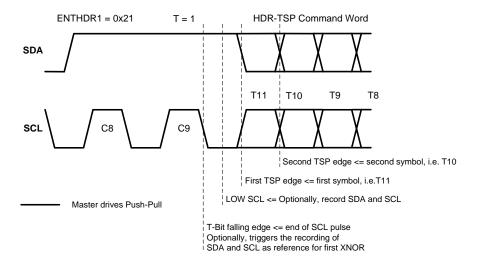

| Figure 57 HDR-TSP Command Code After ENTHDR1                                       | 131 |

| Figure 58 HDR-TSP Command Code After HDR Repeated Start Pattern                    | 132 |

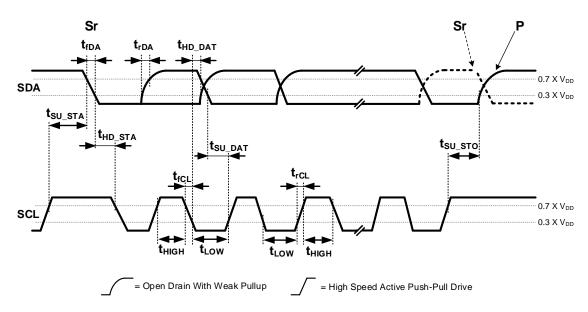

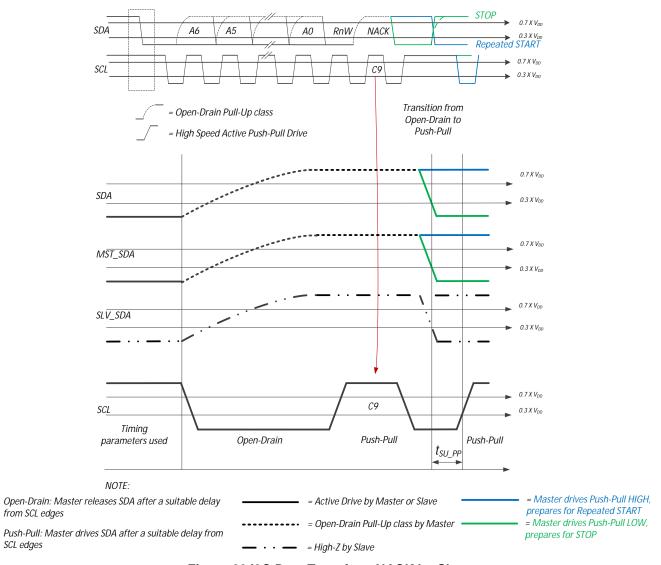

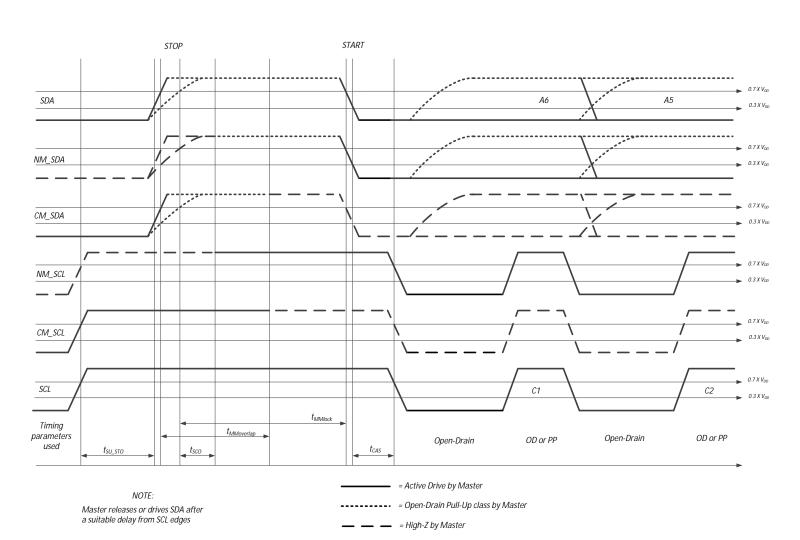

| Figure 59 I3C Legacy Mode Timing                                                   | 143 |

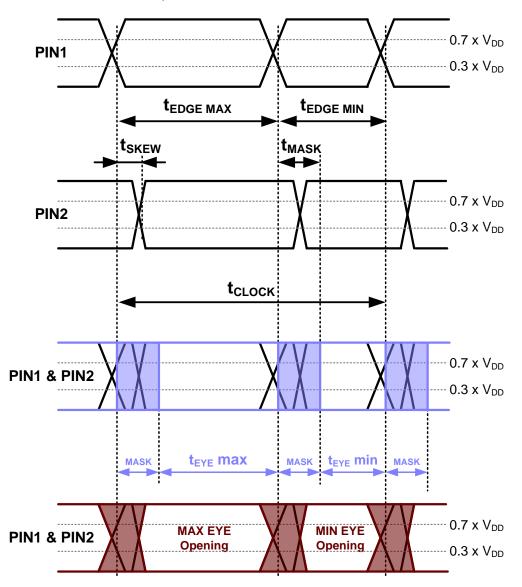

| Figure 60 tDIG_H and tDIG_L                                                        | 144 |

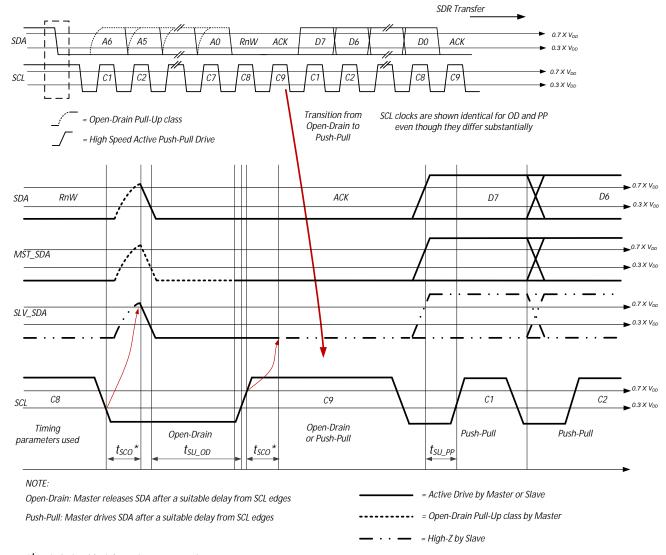

| Figure 61 I3C Data Transfer – ACK by Slave                                         | 145 |

| Figure 62 I3C Data Transfer – NACK by Slave                                        | 146 |

| Figure 63 I3C START Condition Timing                                               | 147 |

| Figure 64 I3C STOP Condition Timing.                                               | 147 |

| Figure 65 I3C Master Out Timing                                                    | 148 |

| Figure 66 I3C Slave Out Timing                                                     | 148 |

| Figure 67 Master SDR Timing                                                        | 149 |

| Figure 68 Master DDR Timing                                                        | 149 |

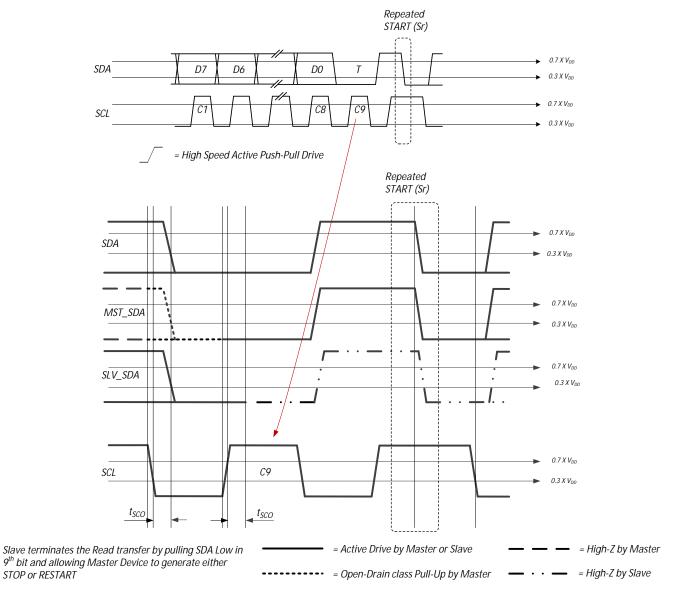

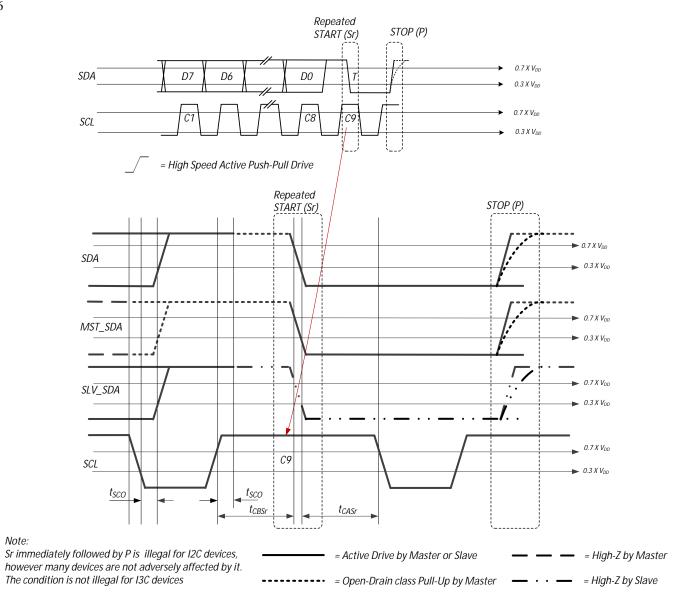

| Figure 69 T-Bit When Slave Ends Read and Master Generates STOP                              | 150 |

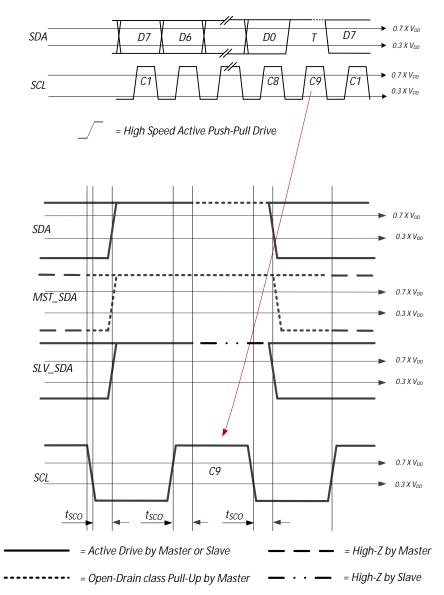

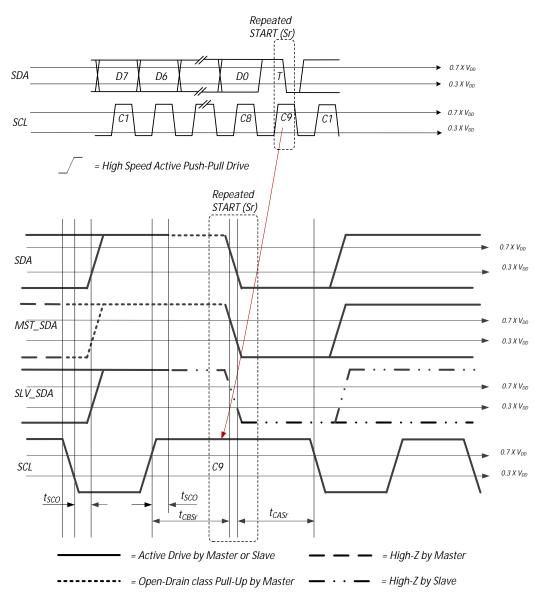

|---------------------------------------------------------------------------------------------|-----|

| Figure 70 T-Bit When Slave Ends Read and Master Generates Repeated START                    | 151 |

| Figure 71 T-Bit When Slave and Master Agree to Continue Read Message                        | 152 |

| Figure 72 T-Bit When Master Ends Read with Repeated START and STOP                          | 153 |

| Figure 73 T-Bit When Master Ends Read via Repeated START and Further Transfer               | 154 |

| Figure 74 Master to Master Bus Handoff                                                      | 155 |

| Figure 75 Ternary Protocol Timing                                                           | 156 |

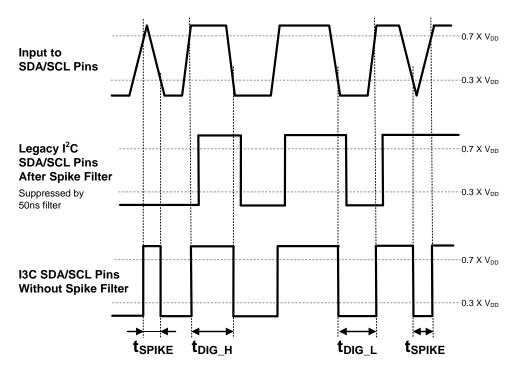

| Figure 76 I <sup>2</sup> C Spike Filter Behavior                                            | 157 |

| Figure 77 I3C CCC Transfers                                                                 | 159 |

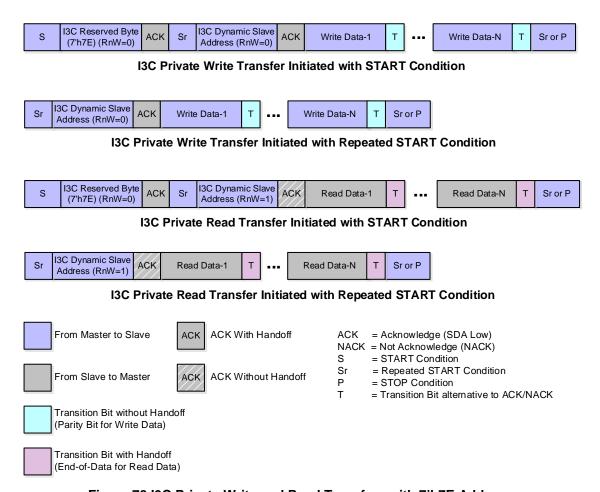

| Figure 78 I3C Private Write and Read Transfers with 7'h7E Address                           | 160 |

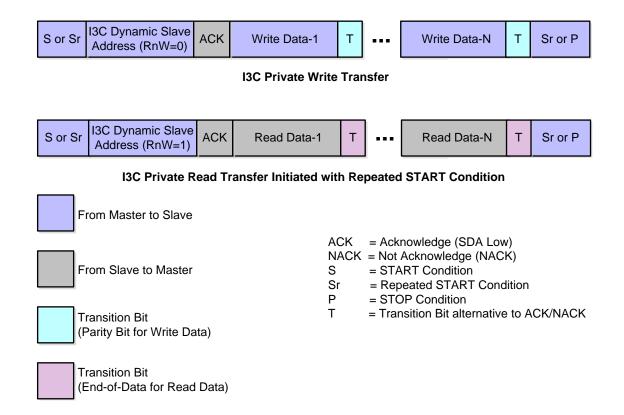

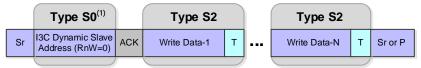

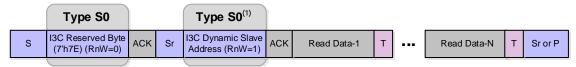

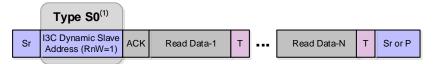

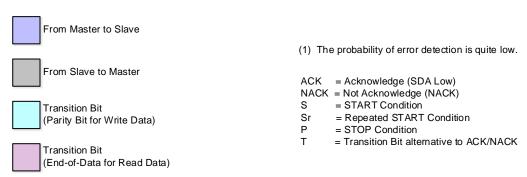

| Figure 79 I3C Private Write and Read Transfers without 7'h7E Address                        | 161 |

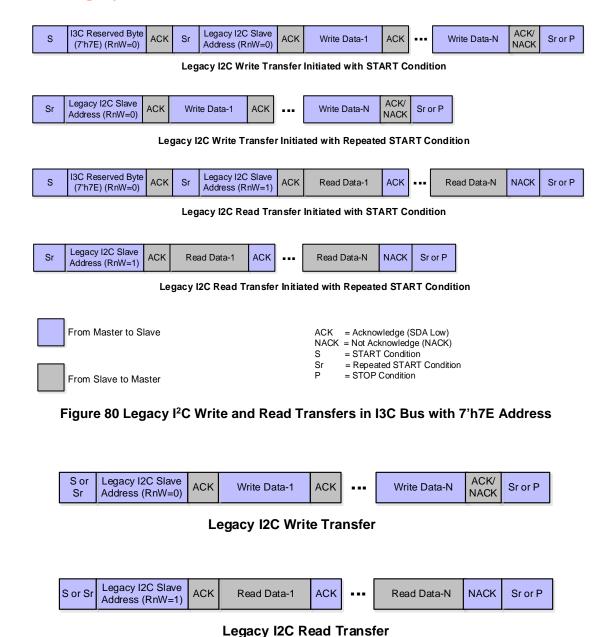

| Figure 80 Legacy I <sup>2</sup> C Write and Read Transfers in I3C Bus with 7'h7E Address    | 162 |

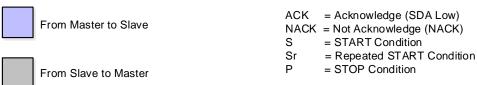

| Figure 81 Legacy I <sup>2</sup> C Write and Read Transfers in I3C Bus without 7'h7E Address | 162 |

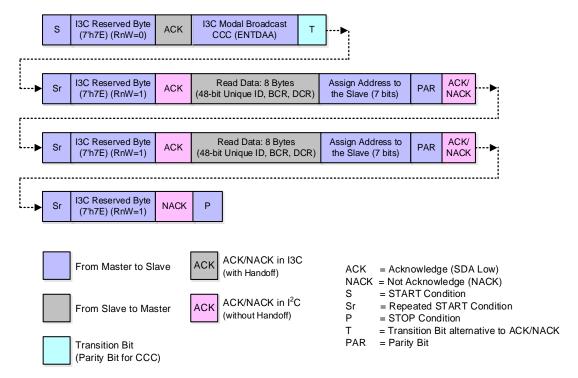

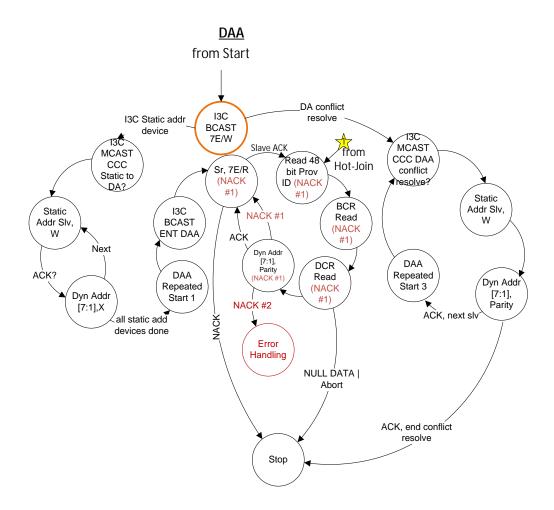

| Figure 82 Dynamic Address Allocation ENTDAA CCC Bus Modal                                   | 163 |

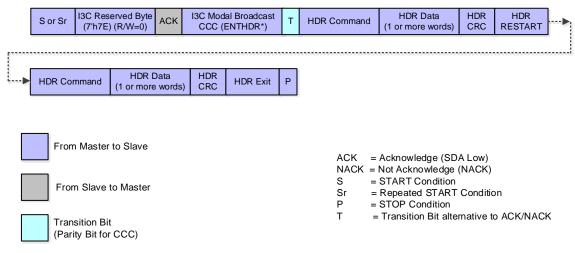

| Figure 83 Enter HDR Mode CCC Bus Modal                                                      | 163 |

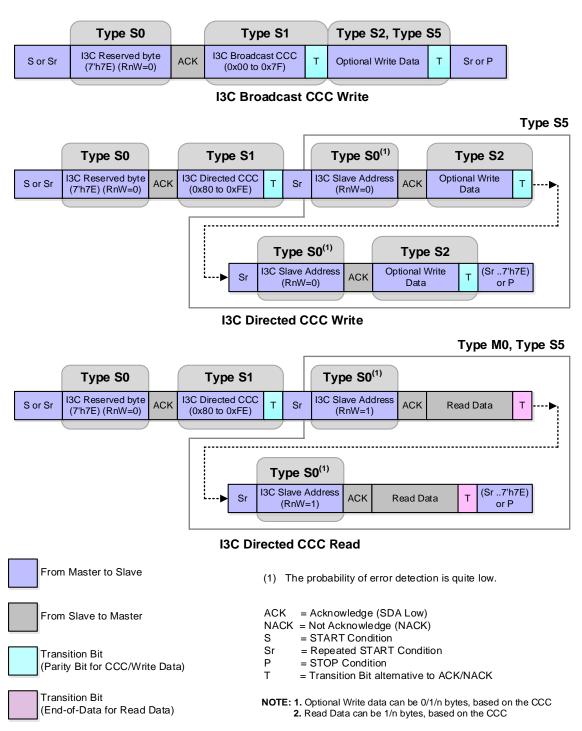

| Figure 84 Error Type Origins: I3C CCC Transfers                                             | 165 |

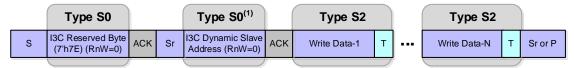

| Figure 85 Error Type Origins: I3C CCC Private Write & Read Transfers with 7'h7E Address     | 166 |

| Figure 86 Error Type Origins: I3C Private Read Transfers without 7'h7E Address              | 167 |

| Figure 87 Error Type Origins: Dynamic Address Arbitration                                   | 168 |

| Figure 88 I3C Main Master FSM                                                               | 169 |

| Figure 89 Slave Interrupt Request FSM                                                       | 170 |

| Figure 90 Dynamic Address Assignment FSM                                                    | 171 |

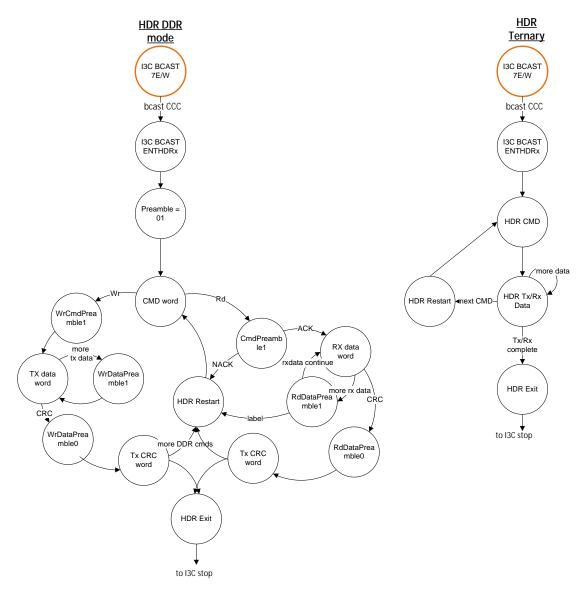

| Figure 91 Hot-Join FSM                                                                      | 172 |

| Figure 92 Secondary Master Request FSM                                                      | 173 |

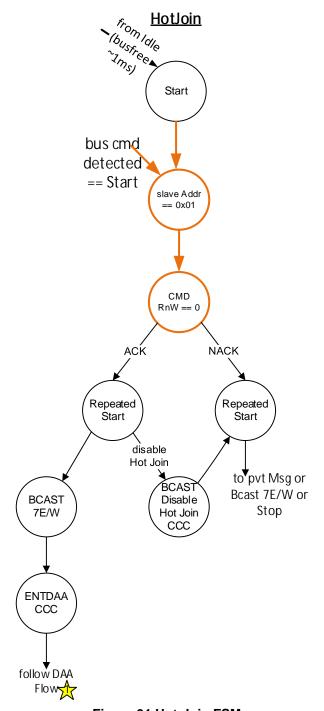

| Figure 93 Master Regaining Bus Ownership FSM                                                | 174 |

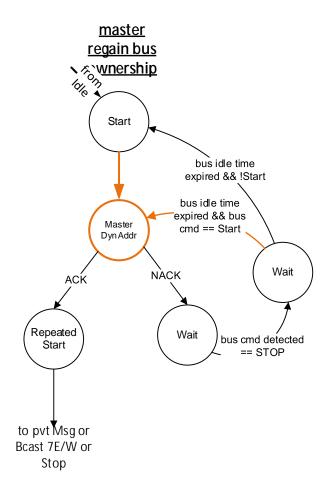

| Figure 94 HDR Ternary and HDR-DDR Mode FSMs                                                 | 175 |

| Figure 95 I2C Legacy Master FSM                                                             | 176 |

| Figure 96 Example Communication Using I3C Coding SDR                                        | 177 |

| Figure 97 Example Communication Using I3C Coding SDR with CCC Direct Addressing             | 178 |

| Figure 98 Example Communication Using I3C Coding SDR with CCC Broadcast                     | 179 |

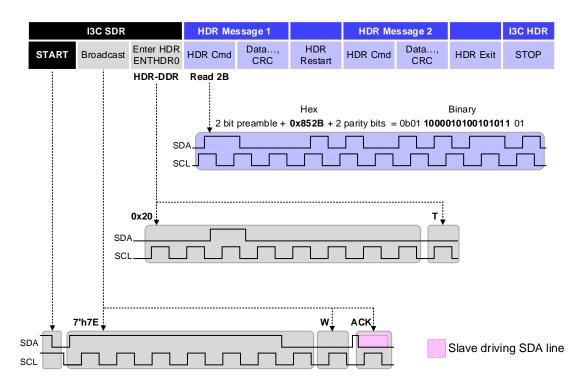

| Figure 99 Example Communication Using HDR-DDR Protocol                                      | 180 |

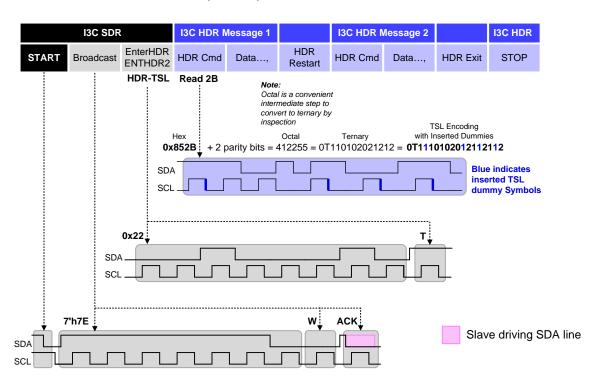

| Figure 100 Example Communication Using HDR-TSL Protocol                                     | 181 |

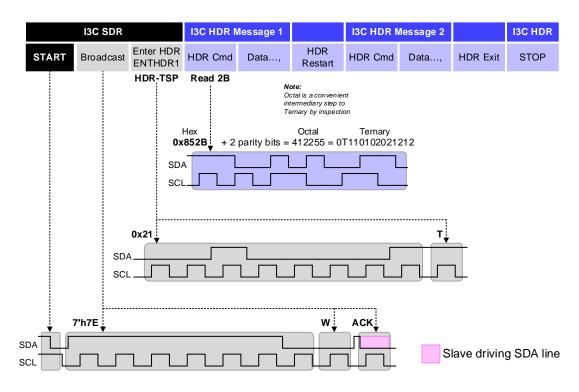

| Figure 101 Example Communication Using HDR-TSP Protocol                                     |     |

## 23-Dec-2016

## **Tables**

| Table 1 Sensor Classes Addressed by I3C                                            | 2  |

|------------------------------------------------------------------------------------|----|

| Table 2 Roles for I3C Compatible Devices                                           | 15 |

| Table 3 I3C Devices Roles vs Responsibilities                                      | 22 |

| Table 4 I <sup>2</sup> C Features Allowed in I3C Slaves                            | 23 |

| Table 5 Legacy I <sup>2</sup> C-Only Slave Categories and Characteristics          | 23 |

| Table 6 Bus Characteristics Register (BCR)                                         | 25 |

| Table 7 I3C Device Characteristics Register (DCR)                                  | 26 |

| Table 8 Legacy I <sup>2</sup> C Virtual Register (LVR)                             | 26 |

| Table 9 I3C Slave Address Restrictions                                             | 33 |

| Table 10 Available Options for Bus Operating Parameters, Per I3C Bus Configuration | 36 |

| Table 11 Master Clock Stall Times                                                  | 38 |

| Table 12 Activity States                                                           | 44 |

| Table 13 Asynchronous Timing Control Modes                                         | 65 |

| Table 14 CCC Frame Field Definitions                                               | 77 |

| Table 15 I3C Common Command Codes                                                  | 80 |

| Table 16 ENEC/DISEC Format 1: Direct                                               | 84 |

| Table 17 ENEC/DISEC Format 2: Broadcast                                            | 84 |

| Table 18 Enable Slave Events Command Byte Format                                   | 84 |

| Table 19 Disable Slave Events Command Byte Format                                  | 84 |

| Table 20 ENTASx Format 1: Direct                                                   | 85 |

| Table 21 ENTASx Format 2: Broadcast                                                | 85 |

| Table 22 Enter Activity State CCCs (ENTASx)                                        | 85 |

| Table 23 RSTDAA Format 1: Direct                                                   | 85 |

| Table 24 RSTDAA Format 2: Broadcast                                                | 85 |

| Table 25 ENTDAA Format                                                             | 86 |

| Table 26 Direct SETMWL/GETMWL Format                                               | 86 |

| Table 27 Broadcast SETMWL Format                                                   | 86 |

| Table 28 Direct SETMRL/GETMRL Format                                               | 87 |

| Table 29 Broadcast SETMRL Format                                                   | 87 |

| Table 30 DEFSLVS Format                                                            | 87 |

| Table 31 ENTTM Format                                                              | 88 |

| Table 32 ENTTM Test Mode Byte Values                                               | 88 |

| Table 33 Enter HDR Mode CCCs (ENTHDRx)                                             | 88 |

| Table 34 SETDASA Format 1: Primary                                    | 89  |

|-----------------------------------------------------------------------|-----|

| Table 35 SETDASA Format 2: Point-to-Point                             | 89  |

| Table 36 SETNEWDA Format                                              | 90  |

| Table 37 GETPID Format                                                | 90  |

| Table 38 GETBCR Format                                                | 90  |

| Table 39 GETDCR Format                                                | 90  |

| Table 40 GETSTATUS Format                                             | 91  |

| Table 41 GETSTATUS MSb-LSb Format                                     | 91  |

| Table 42 GETACCMST Format 1: Accepted                                 | 92  |

| Table 43 GETACCMST Format 2: Not Accepted                             | 92  |

| Table 44 GETACCMST Format 3: Incorrect Cancel                         | 92  |

| Table 45 SETBRGTGT Format                                             | 93  |

| Table 46 GETMXDS Format 1: Without Turnaround                         | 94  |

| Table 47 GETMXDS Format 2: With Turnaround                            | 94  |

| Table 48 maxWr Byte Format                                            | 94  |

| Table 49 maxRd Byte Format                                            | 94  |

| Table 50 maxRdTurn Format                                             | 94  |

| Table 51 GETHDRCAP Format                                             | 95  |

| Table 52 GETHDRCAP Byte Fields                                        | 95  |

| Table 53 SETXTIME Format 1: Broadcast                                 | 95  |

| Table 54 SETXTIME Format 2: Direct                                    | 95  |

| Table 55 SETXTIME Defining Byte Values                                | 96  |

| Table 56 GETXTIME Format                                              | 97  |

| Table 57 GETXTIME Supported Modes Byte Fields                         | 97  |

| Table 58 GETXTIME State Byte Fields                                   | 97  |

| Table 59 SDR Slave Error Types                                        | 98  |

| Table 60 SDR Master Error Types                                       | 100 |

| Table 61 HDR-DDR Preamble Values                                      | 112 |

| Table 62 HDR-DDR Word Format: Command, Data, Reserved                 | 114 |

| Table 63 HDR-DDR Word Formats                                         | 115 |

| Table 64 HDR-DDR Command Word Format                                  | 117 |

| Table 65 Read and Write Command Spaces for HDR-DDR Mode               | 117 |

| Table 66 Parity Bits                                                  | 125 |

| Table 67 Converting 3-bit Binary Triplet Value to Ternary Symbol Pair | 125 |

| Table 68 Converting Ternary Symbol Value to SCL and SDA Level Changes | 126 |

| Table 69 HDR Ternary Command Word Format                                                 | 131 |

|------------------------------------------------------------------------------------------|-----|

| Table 70 Read and Write Command Spaces for HDR Ternary Modes                             | 131 |

| Table 71 I3C I/O Stage Characteristics Common to Push-Pull Mode and Open Drain Mode      | 136 |

| Table 72 Legacy I <sup>2</sup> C Device Requirements When Operating on I3C               | 138 |

| Table 73 I3C Timing Requirements When Communicating With I <sup>2</sup> C Legacy Devices | 140 |

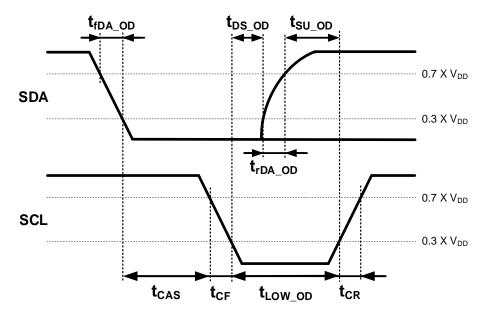

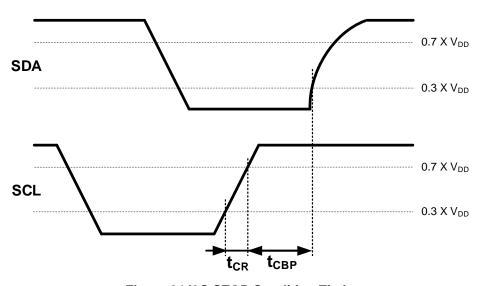

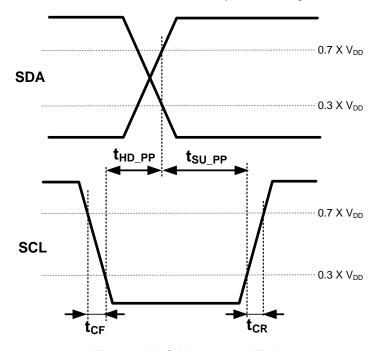

| Table 74 I3C Open Drain Timing Parameters                                                | 141 |

| Table 75 I3C Push-Pull Timing Parameters for SDR and HDR-DDR Modes                       | 142 |

| Table 76 I3C Push-Pull Timing Parameters for HDR-TSP and HDR-TSL Modes                   | 143 |

| Table 77 Timing and Drive for Start of New Frame: No Contention on A7                    | 158 |

| Table 78 Timing and Drive for Start of New Frame: With Contention on A7                  | 158 |

| Table 79 Timing and Drive for Continuation of Frame Using Repeated START                 | 158 |

## **Release History**

| Date       | Version | Description            |

|------------|---------|------------------------|

| 2016-12-31 | v1.0    | Board Adopted release. |

Specification for I3C Version 1.0 23-Dec-2016

This page intentionally left blank.

23-Dec-2016

### 1 Introduction

The proliferation of sensors in mobile wireless and mobile-influenced products has created significant design challenges. Because there are no consistent methods for interfacing physical sensors, Device and platform designers are faced with digital interface fragmentation that includes I<sup>2</sup>C, SPI, and UART among others.

- In addition to the main interface other signals may be needed, such as dedicated interrupts, chip select signals, and enable and sleep signals. This increases the required number of Host GPIOs, and that in turn drives up system cost with more Host package pins and more PCB layers.

- As time passes and the number of sensors increases, this situation is becoming increasingly difficult to support and manage.

- The MIPI I3C interface has been developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors.

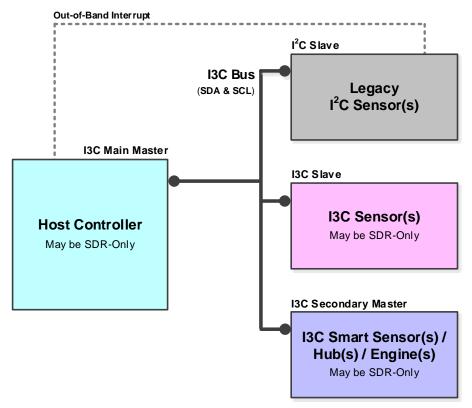

Figure 1 I3C System Diagram

Specification for I3C Version 1.0 23-Dec-2016

Example classes of sensor addressed by I3C are listed in *Table 1*.

#### Table 1 Sensor Classes Addressed by I3C

| Mechanical / Motion                                                                                                                                                                                        | Biometrics/Health                                                                                                                                                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Compass/Magnetometer</li> <li>Gyro</li> <li>Accelerometer</li> <li>Proximity</li> <li>Touch screen</li> <li>Grip</li> <li>Time of Flight (gestures)</li> <li>Audio/Ultrasonic (events)</li> </ul> | <ul> <li>Fingerprint</li> <li>Glucometer</li> <li>Heart rate</li> <li>Olfactory (e.g. breathalyzer)</li> <li>EKG</li> <li>GSR (galvanic skin response)</li> </ul> |  |  |

| Environmental Sensing                                                                                                                                                                                      | Other  NFC (Near Field Communication) Haptic feedback IR (smart TV remote) UV/RGB                                                                                 |  |  |

## 1.1 Scope

14

16 17

18

20

21

23

- The following topics are in scope for this Specification:

- I3C interface protocols and commands

- · Electrical specifications, such as timing and voltage levels

- · Support for specific classes of sensors and other Devices

- The following topics are out of scope for this Specification:

- · Mechanical, system, and implementation details within an I3C Device

- · ESD (Electrostatic Discharge) structures

- System power management

- · Use case specific data or format definitions besides Bus management command codes

### 1.2 I3C Purpose

- The I3C interface is intended to improve upon the features of the I<sup>2</sup>C interface [NXP01], preserving backward compatibility. This Specification defines a standard Multi-Drop interface between Host processors and peripheral sensors.

- Implementing the I3C Specification greatly increases the flexibility mobile terminal system designers have to support an ever-expanding sensor subsystem as efficiently and at as low a cost as possible.

29

31

32

33

34

35

36

37

38

39

40

41

42

43

45

46

47

48

49

50

#### 1.3 **I3C Key Features**

Two main concerns are paramount for the I3C interface: The use of as little energy as possible in transporting data and control, while reducing the number of physical pins used by the interface. 30

- Therefore, the I3C interface features:

- · Two wire serial interface up to 12.5 MHz using Push-Pull

- · Legacy I<sup>2</sup>C Device co-existence on the same Bus (with some limitations)

- Dynamic Addressing while supporting Static Addressing for Legacy I<sup>2</sup>C Devices

- · Legacy I<sup>2</sup>C messaging

- · I<sup>2</sup>C-like Single Data Rate messaging (SDR)

- · Optional High Data Rate messaging Modes (HDR)

- · Multi-Drop capability

- Multi-Master capability

- · In-Band Interrupt support

- · Hot-Join support

- · Synchronous Timing Support and Asynchronous Time Stamping

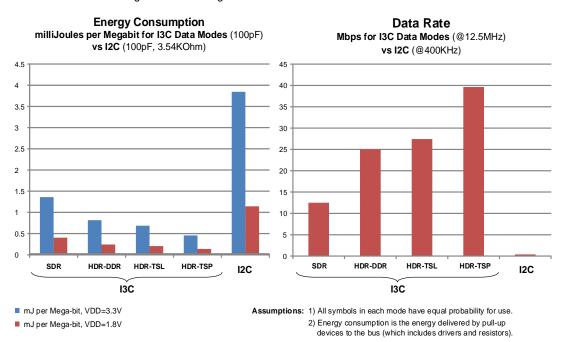

The I3C interface provides major efficiencies in Bus power while providing greater than 10x speed improvements over I<sup>2</sup>C. Figure 2 and Figure 3 show different Bus Mode options that provide tradeoffs for performance/power vs. target Device complexity.

The bar chart on the left shows energy consumption for a given amount of data for the different I3C modes, compared to I2C. The bar chart on the right shows the same comparison for data throughput. Both charts show a significant advantage for I3C.

Figure 2 Energy Consumption and Raw Data Rate: I3C vs. I2C

The bar chart in *Figure 2* shows energy consumption for a given amount of data for the different I3C Modes compared to I<sup>2</sup>C (units are milli-Joules per megabit) whereas on the right is data-throughput. Both show a significant advantage for I3C.

23-Dec-2016

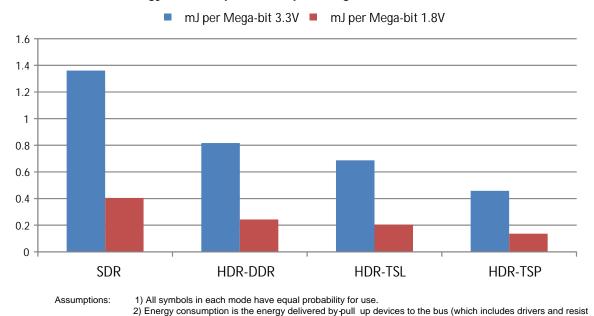

Figure 3 shows an expanded view of energy consumption for different I3C Modes.

## Energy Consumption: mJ per mega bit for I3C data modes

54

Figure 3 Energy Consumption Comparison for I3C Data Modes

23-Dec-2016

55

56

58

59

60

62

64

66

67

68

70 71

## 2 Terminology

## 2.1 Use of Special Terms

The MIPI Alliance has adopted Section 13.1 of the *IEEE Standards Style Manual*, which dictates use of the words "shall", "should", "may", and "can" in the development of documentation, as follows:

The word *shall* is used to indicate mandatory requirements strictly to be followed in order to conform to the Specification and from which no deviation is permitted (*shall* equals *is required to*).

The use of the word *must* is deprecated and shall not be used when stating mandatory requirements; *must* is used only to describe unavoidable situations.

The use of the word *will* is deprecated and shall not be used when stating mandatory requirements; *will* is only used in statements of fact.

The word *should* is used to indicate that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required; or that (in the negative form) a certain course of action is deprecated but not prohibited (*should* equals *is recommended that*).

The word *may* is used to indicate a course of action permissible within the limits of the Specification (*may* equals *is permitted to*).

The word *can* is used for statements of possibility and capability, whether material, physical, or causal (*can* equals *is able to*).

- All sections are normative, unless they are explicitly indicated to be informative.

- All quoted voltage and frequency values in the informative sections represent their typical values.

#### 2.2 Definitions

- 74 ACK: Short for "acknowledge". See also NACK.

- Address Arbitration: Process for determining arbitrated Addresses to resolve contention.

- Address: A set of bits designating a Device or the location of a register.

- 77 **Arbitrable:** Subject to decision by Arbitration.

- Arbitration: If two Devices start transmission at the same time, then Arbitration is required to determine

- 79 Bus control. Arbitration could also be required during a Slave transmission if a Master addresses multiple

- 80 Slaves.

- Bridge Device: Device on the I3C Bus that allows conversion from the native I3C Bus protocol to another

- protocol (such as SPI, UART etc.).

- **Broadcast:** A command intended for multiple Slave Devices, using the Broadcast Address 7'h7E.

- **Bus:** The physical and logical implementation of the SCL and SDA lines.

- Bus Available Condition: State on the I3C Bus where both the SCL line and the SDA line are High for at

- least t<sub>AVAL</sub> (see *Table 74*), and a Device is able to initiate a transaction on the Bus.

- Bus Free Condition: State on the I3C Bus after a STOP and before a START for at least t<sub>CAS</sub> (see *Table 74*).

- Bus Idle Condition: An extended duration of the Bus Free Condition that indicates that Devices may attempt

- 89 to Hot-Join the I3C Bus.

- 90 **Bus Turnaround:** When a transmitting Device sends a command, and then the receiving Device takes over

- 91 the I3C Bus in order to respond.

- 92 **Characteristics:** Quantification of a Device's available features and capabilities.

Specification for I3C Version 1.0

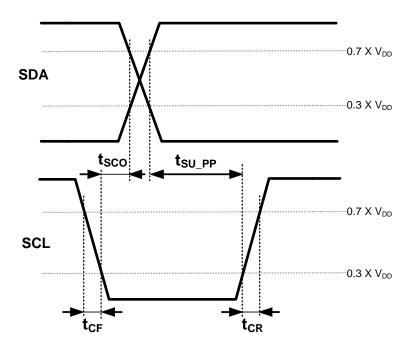

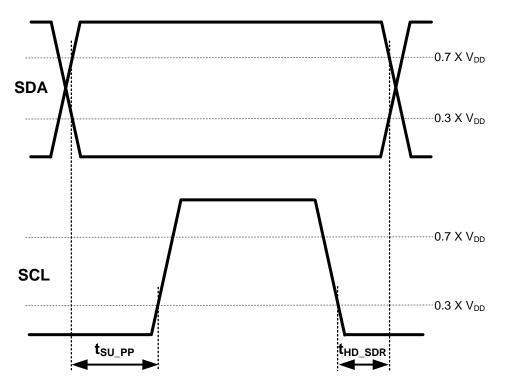

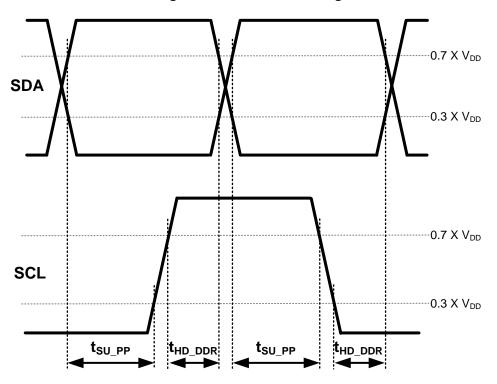

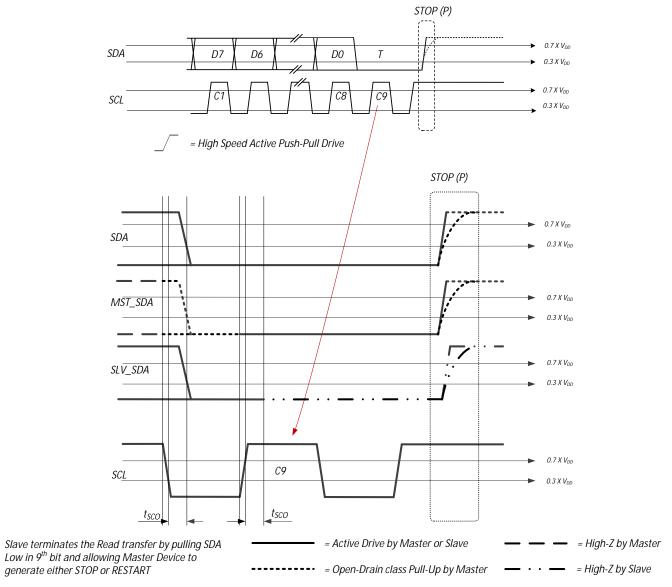

- 93 Clock to Data Turnaround Time: The time duration between reception of an SCL edge and the start of

- driving an SDA change. See t<sub>SCO</sub> in *Table 75*.

- 95 **CRC5:** Cyclic Redundancy Check with fifth-order polynomial length.

- 96 Current Master: The I3C Device that presently has Master control of the I3C Bus.

- 97 **Device:** A Master or Slave.

- **Device ID:** Defines a Device's characteristic or function within a sensor system.

- **Dynamic Address:** A Device Address that is assigned or allocated during initialization of the Bus. Usually

- occurs after power up.

- **Failsafe:** An I3C Device Bus pad is considered Failsafe if its leakage does not increase when it is unpowered.

- A pad may be unpowered because the Device is unpowered, because its IO rail is unpowered or clamped, or

- both. Failsafe only matters for some Hot-Join Devices.

- Frame: A Frame begins with a START, followed by the Address of the targeted Slave(s), Data, and finally a

- 105 STOP.

- **High:** Defines a signal level that is a logical "1".

- High Data Rate (HDR): High Data Rate Modes that achieve higher speed by transferring data on both clock

- 108 edges.

- High-Keeper: A weak Pull-Up type Device used when SDA, and sometimes SCL, is in High-Z with respect

- 110 to all Devices.

- Host: Hardware and software that provides the core functionality of a mobile device.

- Hot-Join: Slaves that join the Bus after it is already started, whether because they were not powered

- previously or because they were physically inserted into the Bus; the Hot-Join mechanism allows the Slave

- to notify the Master that it is ready to get a Dynamic Address.

- In-Band Interrupt (IBI): A method whereby a Slave Device emits its Address into the arbitrated Address

- header on the I3C Bus to notify the Master of an interrupt.

- I<sup>2</sup>C Device: A Master or Slave that meets the requirements of the I<sup>2</sup>C Specification [NXP01].

- **I3C Device:** A Master or Slave that meets the requirements of the I3C Specification.

- 119 **I3C Slave:** See Slave.

- Legacy I<sup>2</sup>C: I3C maintains the industry standard architecture of I<sup>2</sup>C and supports existing I<sup>2</sup>C Slave Devices.

- 121 I3C does not support I<sup>2</sup>C Bus Masters.

- Low: Defines a signal level that is a logical "0".

- Main Master: Master that has overall control of the I3C Bus. Including control and hand off to Secondary

- 124 Masters.

- Master: A reference to the I3C Bus Device that is controlling the Bus.

- Mastership: Control of the I3C Bus, in a Master role.

- Message: A packetized communication between Devices.

- Minimal Bus: An I3C Bus with one Master Device (potentially with reduced functionality), and one active

- Slave Device with a fixed and reserved Slave Address value of 7'h01. Additional Read-only Slave Devices

- may optionally also be present in a Minimal Bus, but there can be no additional Read-Write Slave Devices.

- MIPI Manufacturer ID: A two byte/16 bit unique identifier for a vendor of a MIPI compliant Device

- 132 [MIPI01].

- Mixed Fast Bus: I3C Bus topology with both I<sup>2</sup>C and I3C Devices present on the I3C Bus, where the I<sup>2</sup>C

- Devices have a true I<sup>2</sup>C 50 ns Spike Filter on the SCL line.

23-Dec-2016

Mixed Slow/Limited Bus: I3C Bus topology with both I<sup>2</sup>C and I3C Devices present on the I3C Bus, where

- the I<sup>2</sup>C Devices do not have a true I<sup>2</sup>C 50 ns Spike Filter on the SCL line.

- Mode: Distinguishes different data transfer methods used in I3C including Legacy I<sup>2</sup>C Mode, Single Data

- Rate Mode (SDR), High Data Rate Mode (HDR), Dual Data Rate Mode (HDR-DDR), Ternary Symbol

- Legacy Mode (HDR-TSL) and Ternary Symbol for Pure Bus Mode (HDR-TSP).

- Multi-Drop: A Bus that communicates through a process of Arbitration to determine which Device sends

- information at any point. The other Devices listen for data they are intended to receive.

- Multi-Master: Multiple Bus Masters present on the Bus. Used when multiple nodes on the Bus need to

- initiate a transfer.

- NACK: Short for "not acknowledge", which means No ACK was asserted. See also ACK.

- Offline Capable: An Offline Capable Device is able to disconnect from the physical I3C Bus and/or is able

- to ignore I3C traffic on the I3C Bus. A Device's Offline capability is one of the capabilities reflected in its

- Bus Characterization Register.

- Open Drain: High-Z with an active Pull-Down. Typically used in conjunction with a passive Pull-Up.

- Park: Logic level High set by the Master (or Slave on Read) before turning around the Bus to allow the other

- to drive to Logic level Low or not (will be held High by weak Pull-Up).

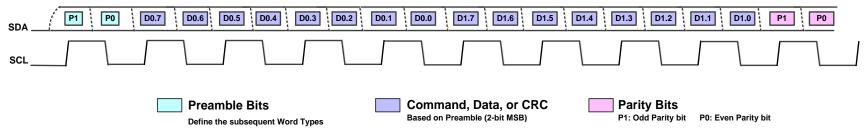

- Preamble: The bits preceding the data words in HDR-DDR.

- Pull-Down: Active mechanism used to pull the Bus to a logical Low state.

- Pull-Up: Mechanism used to pull the Bus to a logical High state. The mechanism may be either active or

- 154 passive.

- Pure Bus: A Bus topology with only I3C Devices present. No I<sup>2</sup>C Devices are permitted on a Pure Bus.

- Push-Pull: Active Pull-Down and active Pull-Up on output driver.

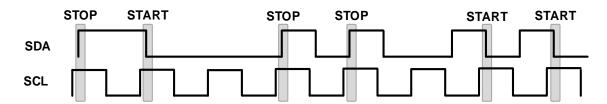

- Repeated START: Two or more instances of a START in a row without an intervening STOP. A Repeated

- START is used in circumstances where the Master wishes to continue communicating on the I3C Bus without

- having to first generate a STOP. In this Specification, a Repeated START is abbreviated as "Sr". This is

- equivalent to repeated START in I<sup>2</sup>C [NXP01].

- SDR-Only: An SDR-Only Device supports only SDR Mode, i.e. does not support HDR Mode.

- Secondary Master: A Secondary Master controls the I3C Bus only after receiving permission from the Main

- Master. Control of the Bus is temporary, and always ends with passing control back to the Main Master.

- Single Data Rate (SDR): Single Data Rate transfers data on only one edge of the clock.

- Slave: A Slave Device can only respond to either Common or individual commands from a Master. A Slave

- Device cannot generate a clock.

- Spike Filter: A filter that removes SCL (and SDA) spikes shorter than 50 ns in duration. See Input Filter (t<sub>SP</sub>

- parameter) in the I<sup>2</sup>C Specification [NXP01]. Also known as a glitch filter.

- Stall: The act of the I3C Master holding the SCL line Low under specific transitory conditions.

- START: START is the I3C Bus condition of a High to Low transition on the SDA line while the SCL line

- remains High. In this Specification, a START is abbreviated as "S".

- START Request: A method for a Slave to force the Master to issue a START on an idled I3C Bus.

- Static Address: A Device Address that is fixed and cannot be changed.

- STOP: STOP is the I3C Bus condition of a Low to High transition on the SDA line while the SCL line

- remains High. In this Specification, a STOP is abbreviated as "P".

- Symbol: In I3C Ternary Coding, a Symbol is an abstraction that can have any of three states. These states

- represent whether (for a given period on the I3C Bus) the SCL line changes state, the SDA line changes state,

- or both lines change state. If neither line changes state, then no Symbol is generated for that period.

Specification for I3C Version 1.0

23-Dec-2016

- **T-Bit:** Transition bit, an alternative to the ACK/NACK mechanism.

- Ternary Mode: I3C HDR-TSP (Ternary Symbol for Pure Bus) Mode or HDR-TSL (Ternary Symbol Legacy)

- 181 Mode.

- Timestamping: The act of determining and assigning the time at which an event occurred.

- Timing Control: Methods of exchanging and controlling system timing information, with the intent to

- synchronize and/or Timestamp I3C Bus Devices and events. See Section 5.1.8.

- Word: Transmission containing 16 payload bits and two parity bits.

- Word Types: Four Word Types are used: Command Word, User Data Word, CRC Word, and Reserved Word.

#### 2.3 Abbreviations

| cknowledge |

|------------|

|            |

- 188 e.g. For example (Latin: exempli gratia)

- i.e. That is (Latin: id est)

- High-Z An output driver that is set to high impedance mode (cannot source or sink current)

- 191 NACK Not Acknowledge

- 192 P STOP

- 193 PHY Physical Layer

- 194 S START

- 195 Sr Repeated START

- 196 T Transition Bit

### 2.4 Acronyms

- 197 BCR Bus Characteristics Register

- 198 BER Bit Error Rate

- 199 BMB Bus Management Block

- 200 CCC Common Command Code

- 201 CRC Cyclic Redundancy Check

- 202 DAR Dynamic Address Request

- 203 DCR Device Characteristics Register

- Double Data Rate

- 205 ESD Electro Static Discharge

- Finite State Machine

- 207 HDR High Data Rate

- HDR-DDR HDR Double Data Rate Mode

- 209 IBI In-Band Interrupt

- 210 ISTO Industry Standards and Technology Organization

- 211 LCR Legacy Characteristics Register

## 23-Dec-2016

| 212 | LSb   | Least Significant Bit                                     |

|-----|-------|-----------------------------------------------------------|

| 213 | Mbps  | Megabits per second                                       |

| 214 | MHz   | Mega Hertz                                                |

| 215 | MID   | MIPI Manufacturer Identification [MIPI01]                 |

| 216 | MSb   | Most Significant Bit                                      |

| 217 | NVMEM | Non-Volatile Memory                                       |

| 218 | OD    | Open Drain                                                |

| 219 | PICS  | Protocol Implementation Conformance Statement             |

| 220 | PUR   | Pull-Up Resistor                                          |

| 221 | SCL   | Serial Clock                                              |

| 222 | SDA   | Serial Data                                               |

| 223 | SDR   | Single Data Rate                                          |

| 224 | SPI   | Serial Peripheral Interface                               |

| 225 | SWG   | Sensors Interface Working Group, part of MIPI Alliance    |

| 226 | TSL   | Ternary Symbol Legacy                                     |

| 227 | TSP   | Ternary Symbol for Pure Bus (no I <sup>2</sup> C Devices) |

| 228 | UART  | Universal Asynchronous Receiver Transmitter               |

Specification for I3C Version 1.0 23-Dec-2016

## 3 References

## 3.1 Normative References

229 [MIPI01] MIPI Alliance, Inc., "MIPI Alliance Manufacturer ID Page", <a href="http://mid.mipi.org">http://mid.mipi.org</a>, July 24, 2015.

## 3.2 Informative References

| 231<br>232        | [NXP01] | UM10204, <i>I</i> <sup>2</sup> C Bus Specification and User Manual, Rev. 6 – 4, NXP Corporation, April 2014                                                                                                                                   |

|-------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 233<br>234<br>235 | [USB01] | <i>Universal Serial Bus 3.1 Specification</i> , Revision 1.0, <a href="http://www.usb.org/developers/docs/usb_31_072715.zip">http://www.usb.org/developers/docs/usb_31_072715.zip</a> , Hewlett-Packard Company <i>et al.</i> , July 26, 2013 |

23-Dec-2016

## 4 Technical Overview (Informative)

- This Section generally describes the I3C Bus, the I3C interface, and I3C Master and Slave Devices.

- I3C is a two-wire bidirectional serial Bus, optimized for multiple sensor Slave Devices and controlled by

- only one I3C Master Device at a time. I3C is backward compatible with many Legacy I<sup>2</sup>C Devices, but I3C

- Devices also support significantly higher speeds, new communication Modes, and new Device roles,

- including an ability to change Device Roles over time (i.e., the initial Master can cooperatively pass the

- Master role to another I3C Device on the Bus, if the second I3C Device supports that feature).

- I3C includes:

243

244

245

246

248

249

250

252

254

- · Support for many Legacy I<sup>2</sup>C Slave Devices and messages

- **I3C Single Data Rate (SDR) Mode:** New I3C enhanced version of the I<sup>2</sup>C protocol supporting private messages, and adding two kinds of standard built-in messages:

- Broadcast messages, which are sent to all I3C Slaves on the Bus

- · **Direct messages**, which are addressed to specific Slaves

- I3C High Data Rate (HDR) Modes: Additional optional Modes that add significant functionality:

- **Dual Data Rate (HDR-DDR) Mode:** Uses same signaling as SDR Mode (i.e. is not significantly different from the I<sup>2</sup>C protocol), but runs at about 2x the speed of SDR

- Ternary Symbol Legacy (HDR-TSL) Mode: Higher data rates plus Ternary coding, for Buses with a mix of I2C and I3C Devices. Significantly different from the I<sup>2</sup>C protocol

- Ternary Symbol Pure-bus (HDR-TSP) Mode: Higher data rates plus Ternary coding, for Buses with only I3C Devices. Significantly different from the I<sup>2</sup>C protocol

- Readers interested in a detailed, low-level introduction to the operation of the I3C Bus for each of the defined I3C Modes are encouraged to study and compare the example waveforms shown in informative *Annex D*.

Specification for I3C Version 1.0

23-Dec-2016

## 4.1 I3C Fundamental Principles

- I3C supports several communication formats, all sharing a two-wire interface.

- The two wires are designated SDA and SCL:

260

261

262

264

267

272

273

- · SDA (Serial Data) is a bidirectional data pin

- SCL (Serial Clock) can be either a clock pin or a Bi-directional data pin while in certain HDR Modes

- An I3C Bus supports the mixing of various Message types:

- 1. I<sup>2</sup>C-like SDR Messages, with SCL clock speeds up to 12.5MHz

- Broadcast and Direct Common Command Code (CCC) Messages that allow the Master to

communicate to all or one of the Slaves on the I3C Bus, respectively

- 3. HDR Mode Messages, which achieve higher data rates per equivalent clock cycle

- 4. I<sup>2</sup>C Messages to Legacy I<sup>2</sup>C Slaves

- 5. Slave-initiated START Request to the Master, for example to send an In-Band Interrupt or to request the Master role

- An example traffic pattern on the I3C Bus is shown in *Figure 4*.

Figure 4 Example of Data Traffic on the I3C Bus

23-Dec-2016

274

275

276

277

278

279

280

281

282

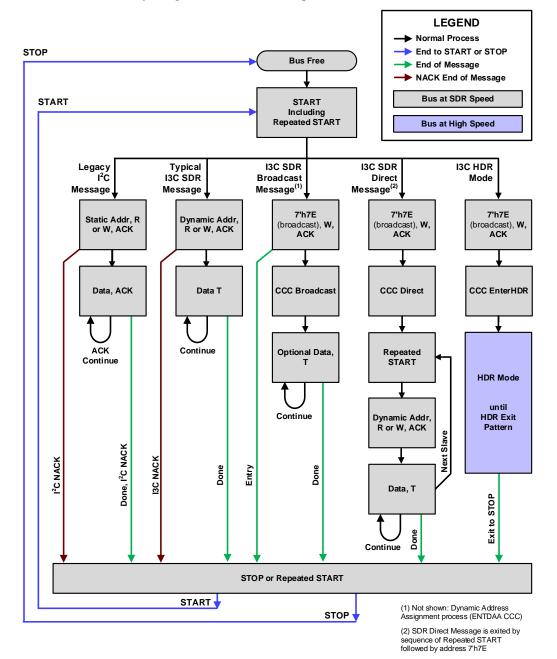

Figure 5 illustrates how I3C communication is initiated:

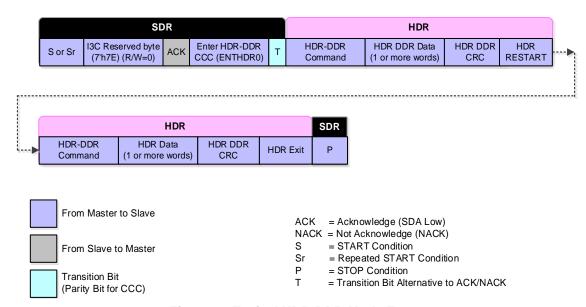

• All I3C communication occurs within a Frame. The Frame begins with a START, followed by one or more transfers, and a STOP.

- · For the HDR Modes:

- · First the dedicated Broadcast I3C Address (7'h7E) is issued to all Slaves on the I3C Bus.

- Then one of the EnterHDR CCCs is issued, indicating that the Master is entering an HDR Mode. Each HDR Mode has its own EnterHDR CCC.

- · This is followed by one or more HDR transfers.

- · HDR Mode is ended by using the HDR Exit Pattern protocol.

Figure 5 I3C Communication Flow

Specification for I3C Version 1.0

23-Dec-2016

- I3C is based on a Frame encapsulation approach. A Frame includes a Data Payload. The transfer protocol for the Data Payload is either SDR or HDR. One example of HDR is the ternary number symbol system specified in *Section 5.2*. Frames are bordered by I<sup>2</sup>C-like Bus management.

- The I3C Frame always includes at least the START, the Header, the Data, and the STOP.

- The Header following a START allows for Bus Arbitration. The Master uses the Header to address Slave

- Device(s). Slave Devices(s) may use the Header Arbitration for multiple purposes: for In-Band Interrupt, for

- Hot-Join, and for Secondary Master functionality.

- Common Command Codes (CCCs) are used to enter the High Data Rate (HDR) Modes. It is important to

- understand that I3C Bus activity for the HDR Message does not follow the Legacy I<sup>2</sup>C format. For example,

- the HDR-TSP payload is encoded using a ternary number symbol system where both the SDA line and the

- SCL line transfer data, with the clock embedded within the data transfer protocol.

- I3C allows only one Master to have control of the I3C Bus at a time. Mechanisms for handoff of the Master

- role from one Device to another Device are provided.

23-Dec-2016

300

301

302

303

304

305

306

307

309

310

311

312 313

314

315

316

317 318

319

#### 4.2 I3C Master and Slave Devices

A given I3C Bus always has one Master and one or more Slaves. This Section generally describes I3C Master Devices and I3C Slave Devices.

A given I3C Device can be designed to function either solely as an I3C Master, solely as an I3C Slave, or with both I3C Master and I3C Slave capabilities.

An I3C Device with both I3C Master and I3C Slave capabilities cannot function as both Master and Slave at the same time, instead it must be configured either as an I3C Slave Device or as an I3C Master Device. Such an I3C Device can be initially configured (initialized) on an I3C Bus either as the Master of that I3C Bus, or as a Slave on that I3C Bus. However for that I3C Bus to function properly, only one of the multiple I3C Devices on the Bus can be initially configured (initialized) as an I3C Master Device. That I3C Device will have the 'Main Master' Device Role, and will be the first I3C Device on the Bus to serve as Current Master; all other I3C Devices and Legacy I<sup>2</sup>C Devices on the I3C Bus will be initially configured (initialized) as Slaves.

I3C introduces the concept of Current Master, defined as the I3C Master Device on the I3C Bus that is functioning as Master (i.e., the one that is controlling the Bus) at the present time. Only one I3C Device on an I3C Bus can serve as Current Master at a time. However after initial Bus configuration the Current Master function can be cooperatively passed from the Current Master to any other I3C Device on the Bus with I3C Master Device capability, using provided I3C commands (CCCs).

I3C defines several Master and Slave Device Roles (see *Table 2* and *Table 3*) to reflect the functional capabilities of a given I3C Master or Slave Device. A given I3C Device must support at least one Device Role, and can be designed to support multiple Device Roles. Every I3C Device exposes the Device Roles it supports via its Bus Characteristics Register (BCR, see *Section 5.1.1.2.1*).

**Table 2 Roles for I3C Compatible Devices**

| Device<br>Type         | Device Role               | Description                                                   |  |  |  |

|------------------------|---------------------------|---------------------------------------------------------------|--|--|--|

| I3C                    | I3C Main Master           | Initially configures I3C Bus, has HDR support                 |  |  |  |

| Master <sup>1</sup>    | SDR-Only Main Master      | Master Initially configures I3C Bus, no HDR support           |  |  |  |

|                        | I3C Secondary Master      | Can Master but currently functioning as Slave                 |  |  |  |

|                        | SDR-Only Secondary Master | Can Master but currently functioning as Slave, no HDR support |  |  |  |

| I3C Slave <sup>2</sup> | I3C Slave                 | Ordinary I3C Slave, no Master capability                      |  |  |  |

|                        | I <sup>2</sup> C Slave    | No I3C Master or I3C Slave capabilities                       |  |  |  |

#### Note:

- Applies to Master-only Devices. In a Multi-Master context a Master Device may also implement functionality to join the Bus acting in a Slave role.

- Applies to Slave-only Devices. In a Multi-Master context a Slave Device may also implement functionality to join the Bus acting in a Master role.

#### 4.2.1 I3C Master Device

An I3C Bus requires there to be exactly one I3C Device at a time functioning as an I3C Master Device. In I3C terms, this I3C Master Device is the Current Master at that time. In typical applications, the Current Master is the I3C Device on the Bus that sends the majority of the I3C Commands (CCC), addressing either all Slaves (Broadcast CCCs) or specific individual Slaves (Directed CCCs). The Current Master is also the only Device on the I3C Bus allowed to send I<sup>2</sup>C Messages.

In addition to sending I3C Commands and I<sup>2</sup>C Messages, an I3C Master Device also:

- Generates the Bus clock when in SDR Mode and DDR Mode (there is no traditional clock in the Ternary Modes)

- Manages Pull-Up structures

325

327

328

329

330

331 332

333

335

- Manages the Dynamic Address Assignment procedure (including Hot-Join events) while acting as the Main Master

- Manages START Requests from I3C Slave Devices on the Bus along with Address Arbitration requests:

- · Generate In-Band Interrupts

- · For Hot-Join events

- To become Current Master

- Supports I<sup>2</sup>C Legacy Slave Devices

- Supports I3C SDR Mode

- In addition, an I3C Master Device can optionally support any combination of I3C's defined HDR Modes.

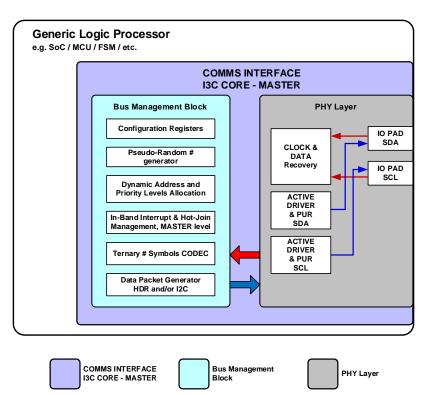

- Figure 6 is a block diagram of a typical generic I3C Master Device.

Figure 6 I3C Master Device Block Diagram

340

23-Dec-2016

344

345

346

348

351

352

353

354

355

356

357

359

#### 4.2.1.1 I3C Master Device Roles

All I3C Master Devices support one of the two Main Master Device Roles, and may also support one of the two Secondary Master Device Roles.

#### **Main Master Device Roles:**

- Main Master: The I3C Master Device on the I3C Bus that initially configures the I3C Bus and serves as the first Current Master. Only one I3C Device on a given I3C Bus can take the Main Master role, i.e. the role cannot be passed on to any other I3C Device on the I3C Bus. Supports both SDR Mode and HDR Mode.

- SDR-Only Main Master: A Main Master that only supports I3C's SDR Mode, i.e. does not support any of the HDR Modes.

#### **Secondary Master Device Roles:**

- I3C Secondary Master: Any I3C Device on the I3C Bus, other than the Current Master, with I3C Master Capability. There can be multiple Secondary Masters on an I3C Bus at the same time. By definition, a Secondary Master functions as an I3C Slave Device until and unless it eventually becomes Current Master. Supports both SDR Mode and HDR Mode.

- **SDR-Only Secondary Master:** A Secondary Master that only supports I3C's SDR Mode, i.e. does not support any of the HDR Modes.

- See also *Table 2* and *Table 3*.

#### Note:

Current Master is not formally defined as an I3C Device Role, and is not exposed in the I3C Device's

Bus Characteristics Register (BCR, see Section 5.1.1.2.1).

#### 4.2.2 I3C Slave Device

An I3C Bus supports up to 11 I3C Slave Devices, though the maximum number of Devices will depend on trace length, capacitive load per Device, and the types of Devices (I<sup>2</sup>C vs. I3C) present on the Bus, because

- these factors affect clock frequency requirements.

- An I3C Slave Device listens to I3C Bus for relevant I3C Commands (CCCs) sent by the Current Master, and

- responds accordingly. This includes all Broadcast Commands (CCC), and any Directed Commands (CCC)

- addressed specifically to that I3C Slave Device and supported by that I3C Slave Device.

- In addition to responding to I3C Commands, an I3C Slave Device always supports I3C SDR Mode.

- In addition, an I3C Slave Device can optionally:

- Request In-Band Interrupts

- Generate Hot-Join events

- · Request to become Current Master, if the I3C Slave Device also has I3C Master Device capability

- · Support any combination of I3C's defined HDR Modes

- While functioning as a Slave, an I3C Slave Device functions in one of the Slave Device Roles detailed in

- 375 Section 4.2.2.1.

370

371

372

373

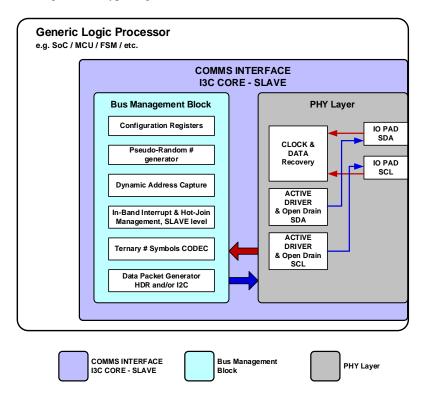

Figure 7 is a block diagram of a typical generic I3C Slave Device.

Figure 7 I3C Slave Device Block Diagram

23-Dec-2016

#### 4.2.2.1 I3C Slave Device Roles

- All I3C Slave Devices support one of the two I3C Slave Device Roles:

- **I3C Slave:** An ordinary I3C Slave Device without Master capability. Supports both SDR Mode and HDR Mode.

- SDR-Only I3C Slave: An I3C Slave without Master capability that only supports I3C's SDR Mode (i.e., does not support any of the HDR Modes).

- 384 **Note:**

- An additional Slave Device Role is defined for <sup>P</sup>C Slave, however this is not relevant for an I3C Slave Device.

- See also *Table 2* and *Table 3*.

## **I3C Protocol**

This Section specifies the communication protocols for all defined I3C Modes: 388

- · Single Data Rate (SDR) Mode: See Section 5.1

- · High Data Rate (HDR) Modes: See Section 5.2

- · HDR Ternary Symbol Pure-bus (HDR-TSP) Mode

- HDR Ternary Symbol Legacy-inclusive-bus (HDR-TSL) Mode

- · HDR Double Data Rate (HDR-DDR) Mode

It is important to note that the I3C Bus is always initialized and configured in SDR Mode, never in any of the HDR Modes. (The procedure for entering an HDR Mode from SDR Mode is detailed in Section 5.2.)

As a result, most of the essential basic I3C protocol specifications are found in *Section 5.1*, including:

| > | 0 | 7 |  |

|---|---|---|--|

| > | フ | / |  |

399

400

401

403

404

405

406

407

408

409

410

389

390

392

393

394 395

396

| Subject                                                | Section |

|--------------------------------------------------------|---------|

| Bus Configuration                                      | 5.1.1   |

| Bus Communication                                      | 5.1.2   |

| Bus Free Condition                                     | 5.1.3.2 |

| Bus Idle Condition                                     | 5.1.3.4 |

| Bus Initialization and Dynamic Address Assignment Mode | 5.1.4   |

| Hot-Join Mechanism                                     | 5.1.5   |

| In-Band Interrupt                                      | 5.1.6   |

| Secondary Master Functions                             | 5.1.7   |

| Timing Control                                         | 5.1.8   |

| Common Command Codes (CCC)                             | 5.1.9   |

#### 5.1 Single Data Rate (SDR) Mode

- This Section specifies the communication protocols for Single Data Rate (SDR) Mode. 398

- SDR Mode is the default Mode of the I3C Bus, and is primarily used for private messaging from the Current Master Device to Slave Devices. SDR Mode is also used to enter other Modes, sub-Modes, and states (as described in Section 5.1 and Section 5.2); and for built-in features such as Common Commands (CCCs), In-Band Interrupts, and transition from I<sup>2</sup>C to I3C by assignment of a Dynamic Address. 402

- I3C SDR Mode is significantly similar to the I<sup>2</sup>C protocol [NXP01] in terms of procedures and conditions, and as a result I3C Devices and many Legacy I<sup>2</sup>C Slave Devices (but not I<sup>2</sup>C Master Devices) can coexist on the same I3C Bus. However SDR Mode also includes numerous new features not present in I2C. For the procedures and conditions that I3C shares with I2C, SDR Mode closely follows the definitions in the I2C Specification. I<sup>2</sup>C traffic from an I3C Master to an I<sup>2</sup>C Slave will be properly ignored by all I3C Slaves, because the I3C protocol is designed to allow I<sup>2</sup>C traffic. I3C traffic from an I3C Master to an I3C Slave will not be seen by most Legacy I<sup>2</sup>C Slave Devices, because the I<sup>2</sup>C Spike Filter is opaque to I3C's higher clock speed.

**Public Release Edition**

#### 5.1.1 Bus Configuration

The I3C Bus can be configured as the link among several clients, in a flexible and efficient manner. At the system architecture level, eight roles are defined for I3C compatible Devices (see *Table 2*).

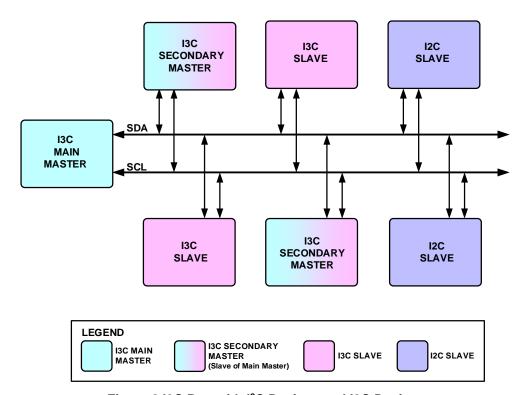

An example block diagram of I3C interconnections is shown in *Figure 8*. In this diagram the color blue indicates Devices with a Master role, the color pink indicates Devices with an I3C Slave role, and the color purple indicates Devices with an I<sup>2</sup>C Slave role. Note that I3C Secondary Master Devices are shaded from blue to pink, illustrating their ability to function in both Master and Slave roles (at different times).

Figure 8 I3C Bus with I2C Devices and I3C Devices

I3C compatible Devices may have diverse features, as appropriate for their function within the I3C Bus. Depending on the I3C Bus' system design, it may not be necessary for all features of a given Device to be enabled for any particular Bus instantiation. However, the enabled features of every I3C compatible Device shall be described in Characteristics Registers associated with the Device, as described in *Section 5.1.1.2*. The I3C Main Master shall obtain the Characteristics of any Legacy I<sup>2</sup>C Devices on the I3C Bus before power up (e.g. the fixed Address of each Legacy I<sup>2</sup>C Device present on the Bus).