# Verdi Basic Training & Technical Overview

Novas Software, Inc

Based on Verdi 5.4v6

# **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace

- nSchema & nState

- Break

- nWave

- Debugging with Verdi

# Verdi Background and Overview

Concepts and Technology

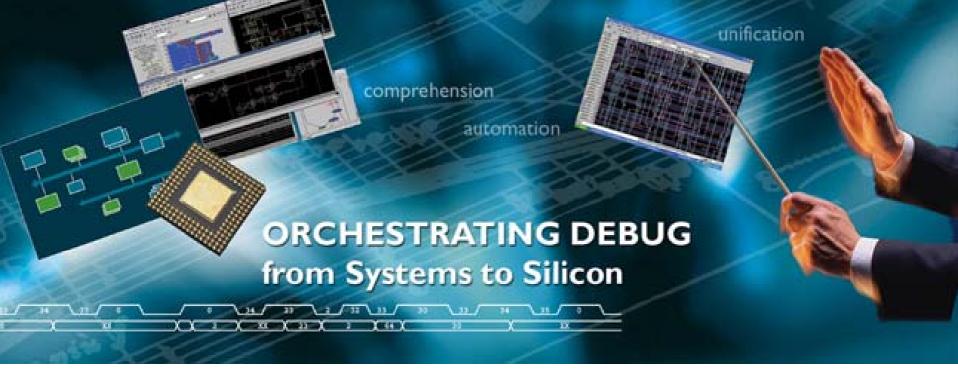

# Debug in the Design Flow

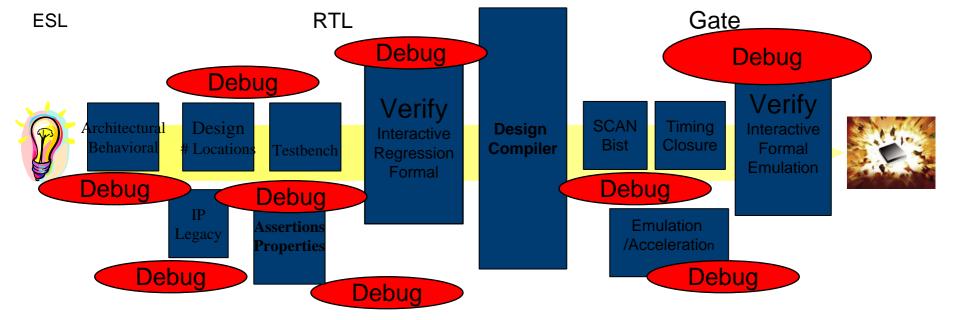

Do you know how much time your teams spend debugging?

What else could you be doing with that time?

Source: Novas Customer Survey, 161 Respondents

### The Barriers To Efficient Debug

- Complex Designs

- Increasing device size and complexity

- Barrier to required design understanding

- Complex Behavior

- Complex design cause and effect scenarios

- Increases conditions to be verified

- Complex multi-tool, multi-lingual, multi-team environments

- Compounds methodology complexity

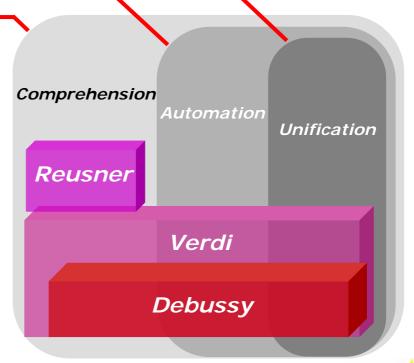

# Novas Solves the Tough Debug Issues

#### <u>Issues</u>

Complex Environments

Complex Behavior

Complex Designs

Knowledge sharing

Increasing automation

Powerful comprehension and debug

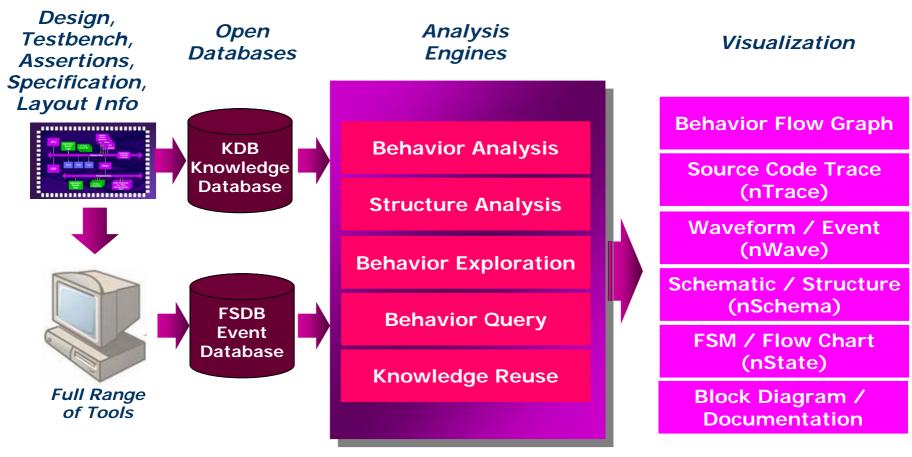

# Novas Technology

Comprehensive Debug System - More Than Simple Visualization

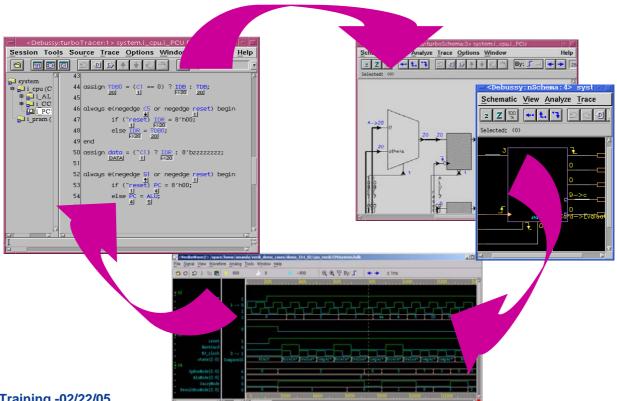

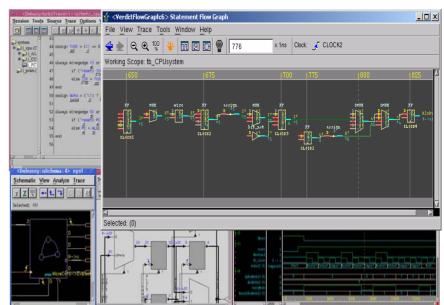

# Structural / Event Debug Process

Current process involves comparing events, code and structure across multiple windows to track possible issues

- Time consuming, error prone, complicated

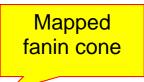

# Automating Debug Critical Productivity Enhancement

Utilizing behavior based debug to automate time consuming aspects of debug process

- Time and structure in single view

- Immediate visual of design behavior

- Automated cause / affect tracing

- Understand problem areas quickly

- Link back to regular views

- Bind problem to modelling issue

EDN Magazine Innovation Award 2002 Finalist

#### Benefits

- Captures design structure and behavior.

- Generates structural diagrams of RTL or gates.

- Verification results put in context of the design.

- Helps you understand unfamiliar or legacy code.

- Automates difficult debug operations.

- Maintains consistent view of the design through design and verification process.

- Dramatically cuts your debug time over traditional methods.

# **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

# Before you start...

- Environment Setup

- Verdi Setup File novas.rc

- Library Mapping

- Symbol Libraries

# **Environment Setup**

- Add binary to the search path.

- setenv NOVAS <Novas\_install\_dir>.

- set path=(\$NOVAS/bin \$path).

- Specify search path of license file.

- setenv NOVAS\_LICENSE\_FILE license\_file>

- setenv LM\_LICENSE\_FILE < license\_file>:\$LM\_LICENSE\_FILE

# Verdi Setup File – novas.rc

- The setup file for Verdi is called *novas.rc* and contains:

- Mapping information for pre-compiled designs.

- User preferences (set via Tools → Preferences).

- Reference to another novas.rc file (optional)

- Search sequence for novas.rc files:

- 1. -rcFile <filename> command line option (read/write pointer)

- 2. NOVAS\_RC environment variable (read/write pointer)

- 3. ./novas.rc

- 4. \$HOME/novas.rc

- 5. <verdi install>/etc/novas.rc

- Specify path for Verdi setup file

- setenv NOVASRC <path>/novas.rc

- Use -rcFile on the verdi command line to overwrite the environment variable.

# Logical Library Mapping Details - novas.rc

- Map a library logical name to a physical location in the novas.rc file.

- Mapping format (in novas.rc):

```

[Library]

logical name = physical location

pack = ../library/pack

Example:

[Library]

pack = ./work

vital = ./work

```

Necessary for VHDL or mixed language designs.

# Symbol Libraries

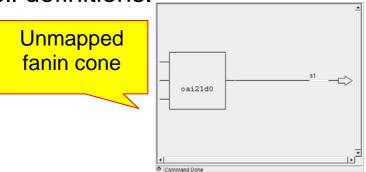

- Why are symbol libraries important?

- Without the symbol mappings for gate cells...

- Active fan-in cone, Fan-in cone and Fan-out cone schematics will NOT function properly.

- Schematics will show ONLY squares instead of logic cells.

- Symbol mappings differentiate logic gates from Sequential.

- Check the Novas web page, <a href="http://www.novas.com/">http://www.novas.com/</a> in the downloads section for a list of available libraries, Library Developer's Guide and cell definitions.

# Creating Symbol Libraries

- Automatic (recommend) If the .lib files of Synopsys are available

- Use the syn2SymDB utility to create symbol library target\_lib.lib++

- syn2SymDB -o target\_lib synopsys\_technology.lib

- Manual If the .lib files of Synopsys are not available

- You have special cells to create (ASIC/FPGA macro cells)

- Create a .map file using the Library Developer's Guide, then use the map2SymDB utility to create the symbol mappings library target\_lib.lib++

- map2SymDB -o target\_lib manual\_technology.map

# Specify Symbol Library and Paths

- Use common delimiters between libraries and paths.

- For NOVAS\_LIBS only specify the root of the <root>.lib++ directory name.

- setenv NOVAS\_LIBS "<LIB ROOT#1> <LIB ROOT#2> ..."

setenv NOVAS\_LIBPATHS "<Directory#1> <Directory#2> ..."

- Ex:

- setenv NOVAS\_LIBS "abc def etc" setenv NOVAS\_LIBPATHS "/home /home/on/the/range /etc"

- Where abc, def and etc represent libraries abc.lib++, def.lib++ and etc.lib++ and they can be found in the different paths listed.

- For the performance issue, set the same process libraries to NOVAS\_LIBS.

# Loading Your Design

- Pre-Compiling Design

- Pre-Compiling VHDL vhdlcom Utility

- Pre-Compiling Verilog vericom Utility

- Verdi Command Line Options

- Load Pre-Compiled Design from Command Line

- Load Design Files from Command Line

- Load Pre-Compiled Design from the GUI

- Load Design Files from the GUI

- Using Virtual Top

# Pre-Compiling a Design (KDB)

- Compile once, load many times.

- Saves load time and overall memory

- Necessary for mixed language or VHDL designs.

- Pre-compile VHDL source files using vhdlcom utility.

- Optional for Verilog language designs.

- Pre-compile Verilog source files using vericom utility.

- By default, a library called work.lib++ is created.

- Uses the novas.rc file logical mapping mechanism

# Pre-Compiling Verilog – vericom Utility

#### vericom [Verdi options] [<your verilog options>]

- Use vericom -h to get all command line options.

- Use vericom to replace verilog simulator commands to create the Verdi mirror database optimized for debug.

- MTI: vlog top.v –work /home/work –f other\_files.f

- NC: ncvlog top.v –WORK /home/work –FILE other\_files.f

- VCS: vcs top.v –f other\_files.f

- Verdi: vericom top.v –work /home/work –f other\_files.f.

# Pre-Compiling VHDL – vhdlcom Utility

#### vhdlcom [verdi options] [<your vhdl options>]

- Use vhdlcom -h to get all command line options.

- Verdi provides pre-compiled versions of STD, IEEE, SYNOPSYS, and NOVAS libraries which are located at: \$NOVAS/etc/kbd/vhdl/

- Use vhdlcom to replace vhdl simulator commands to create the mirror database.

- MTI: vcom -93 top.vhdl -work /home/work -f other\_files.f

- NC: ncvhdl –V93 top.vhdl –WORK /home/work –FILE other\_files.f

- Verdi: vhdlcom –93 top.vhdl –work /home/work –f other\_files.f

- The vhdlcom or vericom library is of the format work.lib++, pack.lib++, etc. Thus it never conflicts with simulators libraries.

# Verdi Command Line Options

#### verdi [general options]...

- Use verdi -h to get all command line options.

- -f <fileName> : specify a file that lists all source files

- -vhdl | verilog: specify language type for import design from source

- -vtop: loads Virtual top file

- -play commandHistoryFile: play command history file.

- -ssc licenseFile : specify the license file name.

- -ssr sessionFile : load session file (\*.ses).

- -ssf fastFile : load fast file (\*.fsdb).

- -sswr restoreFile(s): load waveform restore file(s) (\*.rc).

# Load Pre-Compiled Design From Command Line

#### verdi -lib compiled source> -top <top level>

- Reference pre-compiled source on the command line.

- verdi –lib abc –top system

- Where abc is the pre-compiled library, abc.lib++ that the design was pre-compiled into with vericom/vhdlcom.

- Where system is the top level module/architecture

# Load Design Files From Command Line

#### verdi [verdi options] [<your verilog options>]

- Reference source files on the command line (Verilog only).

- Verdi takes all the Verilog command line options.

verdi –f run.f

Where run.f is a file that contains the verilog source files and any command line switches.

verdi –ssv –v lib.v +libext+.v –ssy –y /src/abc –y /src/def top.v

Where –ssv and –ssy are needed only once for design modules specified with the –v and –y and top.v is the design file.

# Load Pre-Compiled Designs from the GUI

- Specify library mapping before importing design.

- Use File → Import Design...

or Import Design icon

to import your design.

- Select From Library tab.

- Lists all libraries in current directory or specified in map file.

- Supports mapping file to set a Virtual Top.

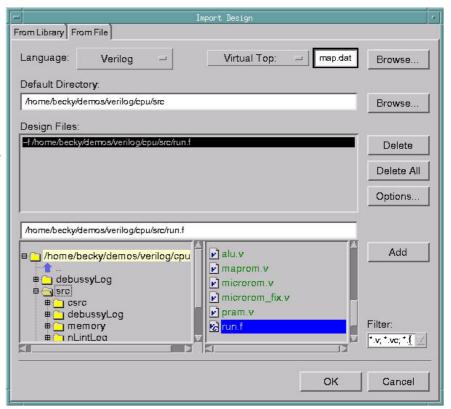

# Load Design Files from the GUI

- Use File → Import Design...

or Import Design icon

to import your design.

- Select From File tab.

- Specify language and run file or individual source files.

- Supports mapping file to set a Virtual Top.

Note: The imported design does not get saved as a library.

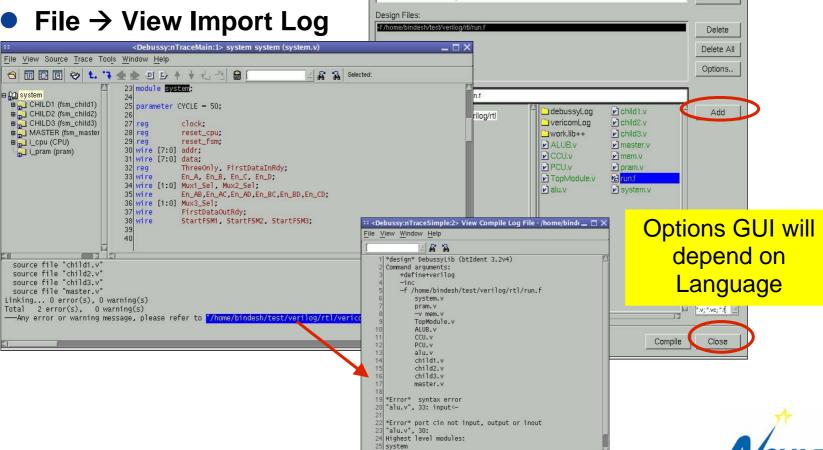

# Compile Design in GUI

Mapping...

Browse...

- File → Compile Design

Working Directory: /home/bindesh/test/verilog/rtl Library Name:

# **Using Virtual Top**

#### Scenario:

Design top doesn't match simulation top (i.e. don't wish to include the test bench, test bench code not available or only looking at a portion of a design)

#### Solution:

Create a file called map.dat that maps the top design module to the simulation hierarchy.

Format: <module name> = <full hierarchical path>

Example: *CPU* = *system.i\_cpu*

Add –vtop map.dat to the Verdi command line and a pseudo hierarchy will be created.

#### Why?

If a virtual top is not used, active annotation will not work and D&D to nWave will not work because hierarchical paths will not match.

# Loading Your Design – Summary

- At this time you should:

- Understand the Verdi environment setup

- Know how to pre-compile a design

- Know how to invoke Verdi

# **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

# nTrace - View and Debug Source Code

- Mouse Actions

- Overview

- Hierarchy Browser

- Source Code Browser

- Message Window

- Searching

- Find Scope

- Find Signal/Instance

- Find String

- Trace Drivers and Loads

- Bookmarks

- Source Code Editing

- Miscellaneous

- Lab

# Mouse Actions (all modules)

#### Left Mouse Button(LMB)

- Single-click to select design objects like signals, instances, groups, etc.

- Hold the Shift key and click the LMB to add object to selection list.

- Double-click(DC) to take action.

- Drag LMB through an area to select the objects enclosed.

- Drag LMB in schematics or waveforms will zoom in area.

#### Middle Mouse Button (MMB)

- Drag & Drop (D&D) across windows.

- Right Mouse Button(RMB)

- Context sensitive menu.

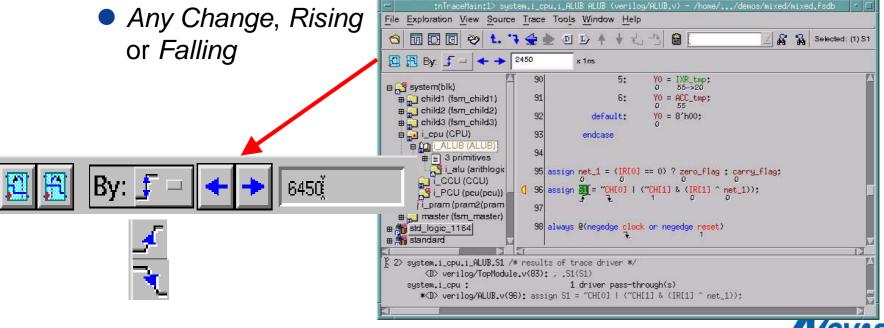

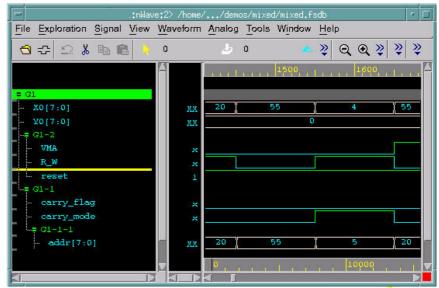

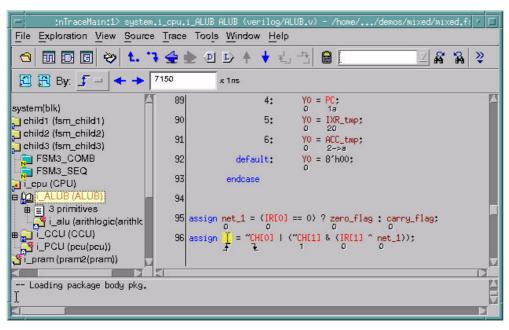

### nTrace Overview

- Displays source code and hierarchy

- Compiles the design

- Required for nSchema and nState

- Context sensitive tracing of drivers and loads

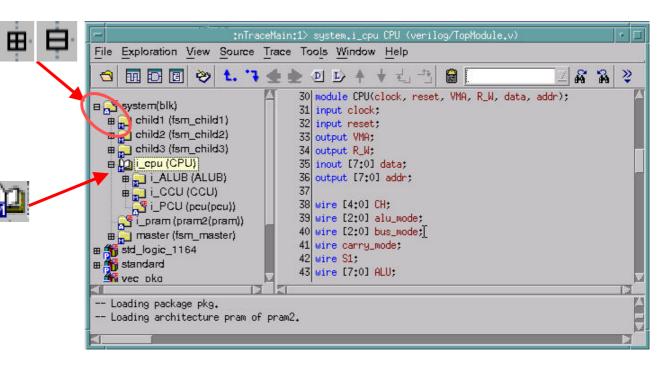

# nTrace - Overview

#### **Hierarchy Browser**

**Source Code Browser**

```

:nTraceMain:1> system.i_cpu.i_ALUB ALUB (verilog/ALUB.v) - /home/.../demos/mixed/mixed.fsdt

File Exploration View Source Trace Tools Window Help

□ □ □ □ ♥ t. '\ •

Selected: (1) IXR.

system(blk)

98 always @(negedge clock or negedge reset)

ighter in the contract of the

begin

child2 (fsm_child2)

(100)

if (!reset) IXR_tmp = 8'h00;

achild3 (fsm_child3)

(101

else IXR_tmp[= 1/8;

i_cpu (CPU)

102

end

ALUB (ALUB)

103

104 always @(negedge clock or negedge reset)

# 3 primitives

🥰 i_alu (arithlogic(arithlo

105

begin

if (!reset) ACC_tmp = 8'h00;

m 🔁 ĭ_ccu (ccu)

106

107

else ACC_tmp = ACC;

Fi_PCU (peu(peu))

108

end

🍠 i_pram (pram2(pram))

109

master (fsm_master)

110 always @(posedge T3 or negedge reset)

std_logic_1164

< 1> system.i_cpu.i_ALUB.IXR_tmp[7:0] /* results of trace driver */

*<D> verilog/ALUB.v(100): if (!reset) IXR_tmp = 8'h00;

*<B> verilog/ALUB.v(101); else IXR_tmp = IXR;

*system.i_cpu.i_ALUB :

2 driver(s)

*Total :

2 driver(s)

```

# nTrace - Hierarchy Browser

- Displays VHDL architectures and packages, Verilog modules, primitive instances, tasks and functions.

- Expand/Collapse design tree.

- Double click folder to change current scope.

- Open Folder icon indicates current scope.

Use File → Print to print out design tree.

#### nTrace - Source Code Browser

- Color-coded source code display.

- Double click

- Instance name to go to architecture or module definition.

- Module name or architecture type to return to calling instance.

- Architecture name to go to entity definition.

- Signal name to find the driver.

- vi compatible binding keys.

## nTrace - Message Window

- Log of debug session.

- Double click on line to go to that location in source code.

```

:nTraceMain:1> system.i_cpu.i_ALUB ALUB (verilog/ALUB.v)

Exploration View Source Trace Tools Window Help

systemiona

📜 child1 (fsm_chik 🖥

98 always @(negedge clock or negedge reset)

child2 (fsm_child

99

begin

child3 (fsm_chik

(100)

if (!reset) IXR_tmp = 8'h00;

i_cpu (CPU)

(101

else IXR_tmp = IXR;

a Log i_ALUB (ALU

102

end

# 3 primitive

103

🥂 i_alu (arith

104 always @(negedge clock or negedge reset)

< 2> system.i_cpu.i_ALUB.IXR_tmp[7:0] /* results of trace driver */

*<D> verilog/ALUB.v(100): if (!reset) IXR_tmp = 8"h00;

*<D> verilog/ALUB.v(101); else IXR_tmp = IXR;

*system.i_cpu.i_ALUB :

2 driver(s)

*Total :

2 driver(s)

```

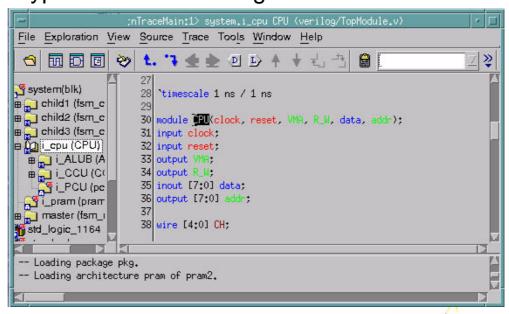

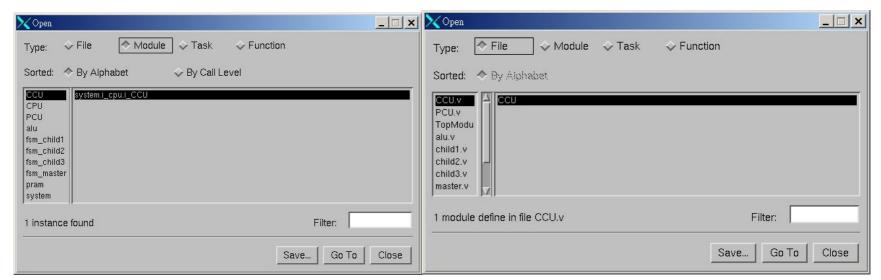

## nTrace - Find Scope

- Source -> Find Scope... is a fast way to directly open a Verilog module or VHDL architecture if the design tree is deep.

- Choose by type: File, Module, Task or Function.

- Enter search filter using wildcards.

Open by Module

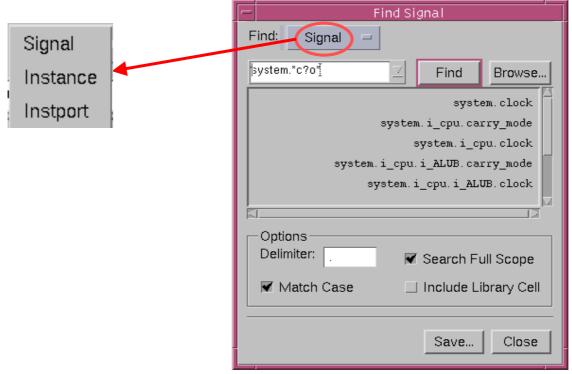

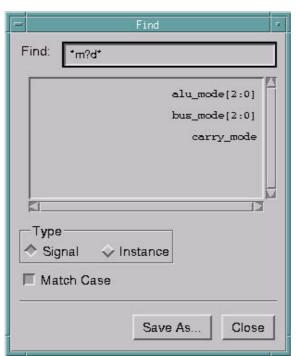

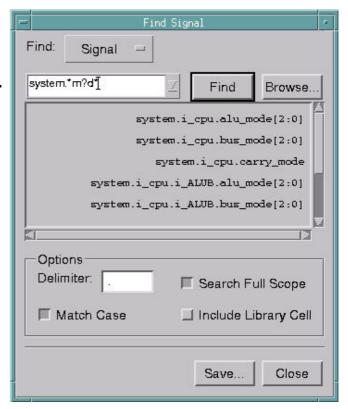

## nTrace - Find Signals and Instances

- Source -> Find Signal... is a fast way to find signals/instances/Instport in full design or selected scope.

- Supports wildcard characters and regular expressions.

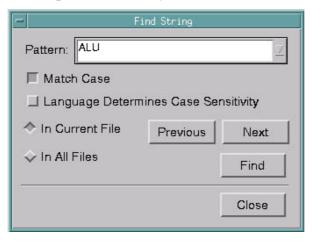

## nTrace - Find Strings

Source → Find String... quickly locates a string in current / all files.

- Find String on toolbar quickly locates a string in current scope.

- Enable/disable case matching under

Tools → Preferences, Source Code tab,

Miscellaneous tab.

Use Source → Go To command to jump to specified line or First Executable Line.

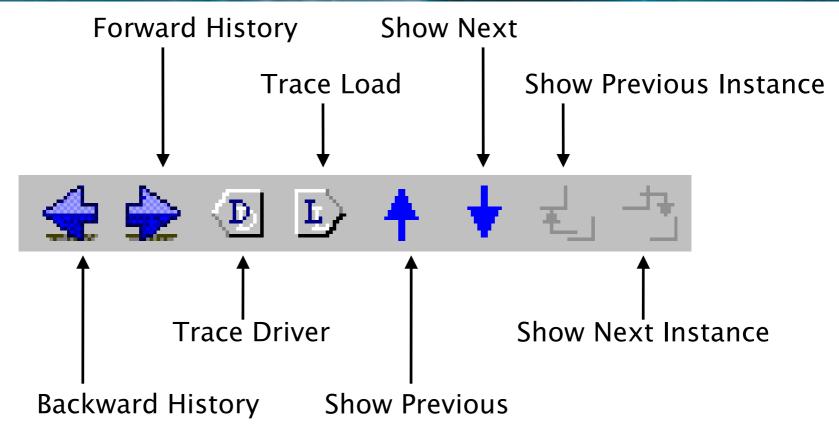

#### nTrace - Trace Drivers and Loads

- To quickly find all the drivers of a signal

- Double click a signal.

- Select signal and click on Trace Driver icon.

- Trace → Driver or Right Mouse Button menu.

- To quickly find all the *loads* of a signal

- Select signal and click on Trace Load icon.

- Trace → Load or Right Mouse Button menu.

- To quickly find all the drivers and loads of a signal

- Trace → Connectivity or Right Mouse Button menu.

- Dropping a signal in the source window will trace the connectivity of the signal.

- By default, tracing will cross hierarchical boundaries.

- Use Trace -> Trace Cross Hierarchy to keep within a hierarchy.

#### nTrace - Trace Driver/Load Tool Bar Icons

# nTrace – Search, View and Debug Source Code

- Searching

- Find Scope

- Source → Find Scope

- Find Signal/Instance

- Source → Find Signal

- Find String

- Source → Find String

- Bookmarks

- Source → Bookmark

- Multiple Source Code Windows

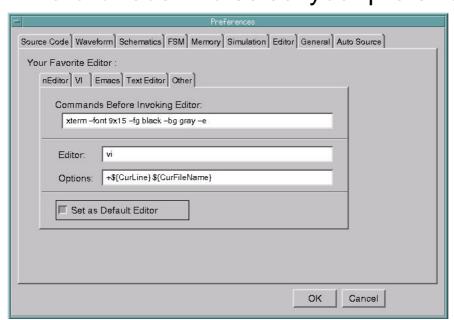

Editing Source Code

- Tools → Preferences... to select your preferred editor.

- Source → Edit Source File

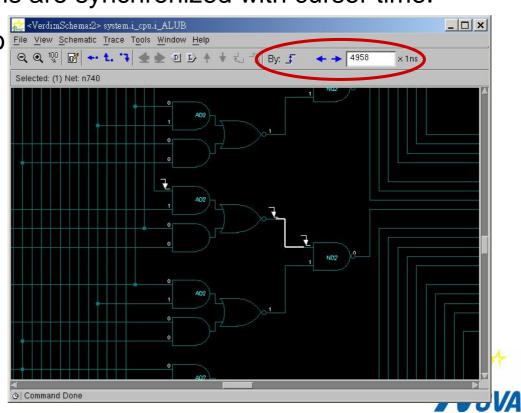

#### nTrace – Active Annotation

- Display simulation results on source.

- Source → Active Annotation in nTrace

- Signal values/transitions are synchronized with cursor time.

- Select signal(s) and go to next or previous transitions.

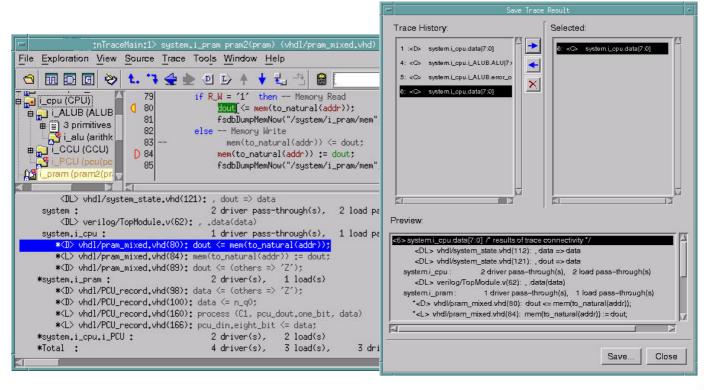

#### nTrace - Trace Results and Report

- Trace → Save Trace Result saves

Driver/Load/Connectivity in a file for future review.

- Record maximum 32 level trace results.

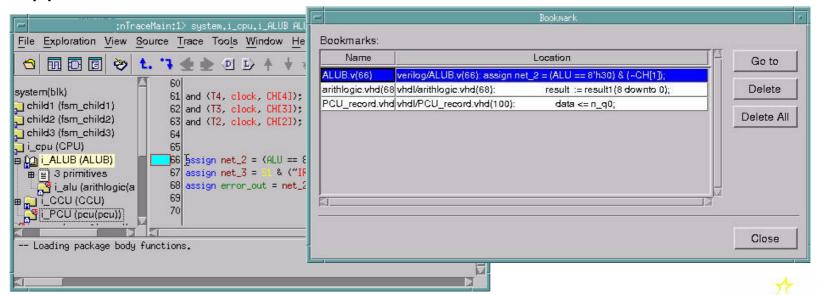

#### nTrace - Bookmarks

- Click on Bookmark icon on toolbar or use Ctrl-F2 to toggle a bookmark on/off at the current line.

- Use Source → Bookmark command to get list of current bookmarks.

- Supports unlimited bookmarks.

#### nTrace – Source Code Editing

Use Source → Edit Source File command or click icon your current module.

Use Tools -> Preferences... to select your preferred editor.

Use File -> Reload Design command to update the changes.

#### nTrace - Miscellaneous

Use Tools -> Preferences... to customize the appearance and fonts

of the hierarchy browser and source code browser.

Use Help -> Command Reference for additional information.

• Questions?

## Take 20 minutes to complete the nTrace LAB

## **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

## nSchema - View and Debug Designs Graphically

- Overview

- Invoke nSchema

- Resultant Schematics

- Display Source Code

- Traverse Hierarchy

- Searching Commands

- Display Options

- Schematic Window Types

- Full Hierarchical

- Browser

- Flatten

- View Detail RTL

- Clock/Reset Tree

- Miscellaneous

- Lab

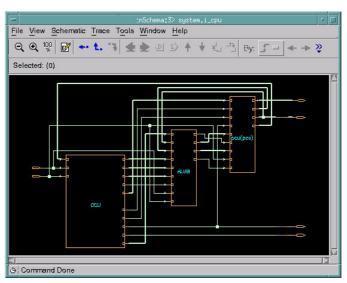

#### nSchema Overview

- Automatically generates schematic of design

- Gate Level, RTL, behavioral Level

- Hierarchical or flat

- Fan-in or fan-out cones

- Highlight logic between registers

#### Invoke nSchema

The "New Schematic" icon

- Select an instance in Hierarchy Browser and click on New Schematic icon.

- Drag & Drop an instance from the hierarchy browser or a Verilog module or VHDL architecture from the Source Code Browser to New Schematic icon.

- Execute Tools → New Schematic → Current Scope in nTrace.

#### nSchema - Resultant Schematics

- Storage elements need to be recognized for complete tracing ability.

- Gate level schematic displays cell level netlist.(Symbol libraries required)

- RTL logic diagram displays synthesized view.

- Signal type -- clock, reset, set, flip-flop / latch output or tri-state output

- Block type -- latch, flip-flop or combinational logic

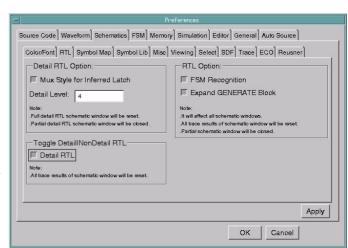

- Enable/Disable Detail RTL option under Tools → Preferences, Schematics tab, RTL tab.

- State machine recognition as symbolic or logical views.

- Enable/Disable FSM Recognition option under Tools → Preferences, Schematics tab, RTL tab.

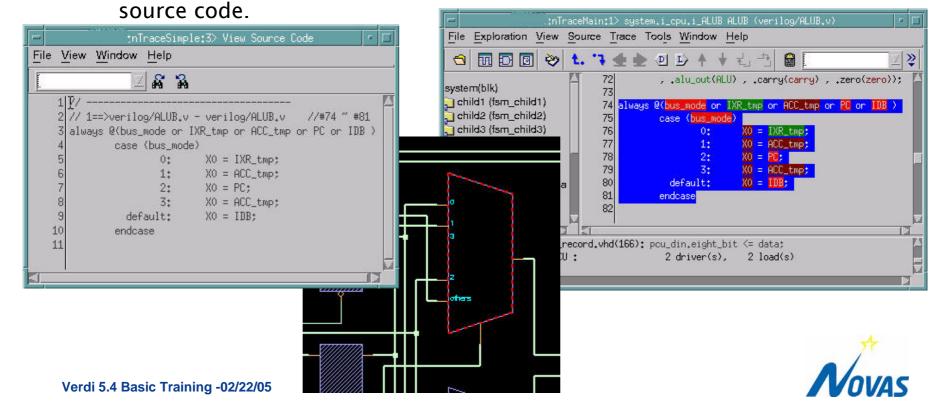

## nSchema - Display Source Code

- To quickly understand what RTL construct created a logic cell

- Double-click on the lowest level RTL to opens View Source Code box of the corresponding RTL code.

Drag & Drop a schematic object to nTrace displays the corresponding

## nSchema – Traverse Hierarchy

- Push Into a Module

- Double click on instance or instance port.

- Select an instance and click the Push View In icon

- Invoke right mouse button menu and select Push View In command.

- Pull down View → Push View In.

- Pop View Up

- Use the Pop View Up icon

- Double-click on a schematic port.

- Invoke right mouse button menu and select Pop View Up command.

- Pull down View → Pop View Up or View → Pop View Up from Port.

- Click the Last View icon to go to previous view.

## nSchema – Searching Commands

Schematic → Find Signal/Instance...

finds signals or instances in full design.

Schematic → Find In Current Scope...

finds signals or instances in current scope.

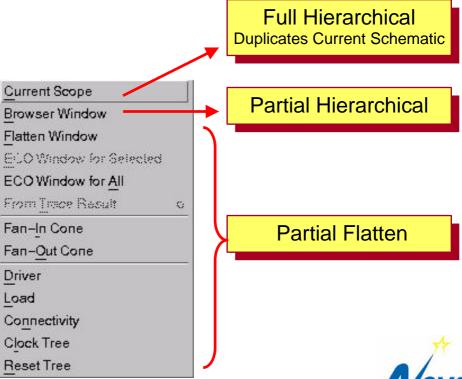

## nSchema – Schematic Window Types

- Full Hierarchical Window default type

- Partial Hierarchical Window

- Browser Window

- Partial Flatten Window

- Flatten Window

- Fan-In / Out Cones

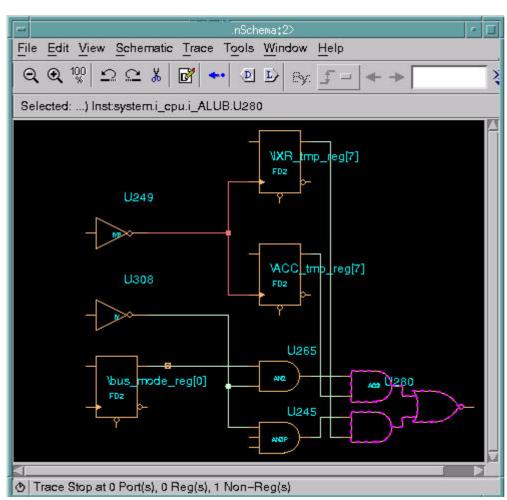

#### nSchema - Full Hierarchical Window

View, traverse and understand design hierarchy graphically.

Double click a symbol port to push into the lower level and highlight the

associated net.

Double click on a net to highlight all instances which connect to this net.

- Trace menu will highlight a variety of different objects in current window.

- Search commands

- Schematic → Signal/Instance/Instport...

- Schematic → In Current Scope...

#### nSchema – Active Annotation

- Display simulation results on source.

- Schematic → Active Annotation in nSchema

- Signal values/transitions are synchronized with cursor time.

- Select signal(s) and go to next or previous transitions.

- Any Change, Rising or Falling

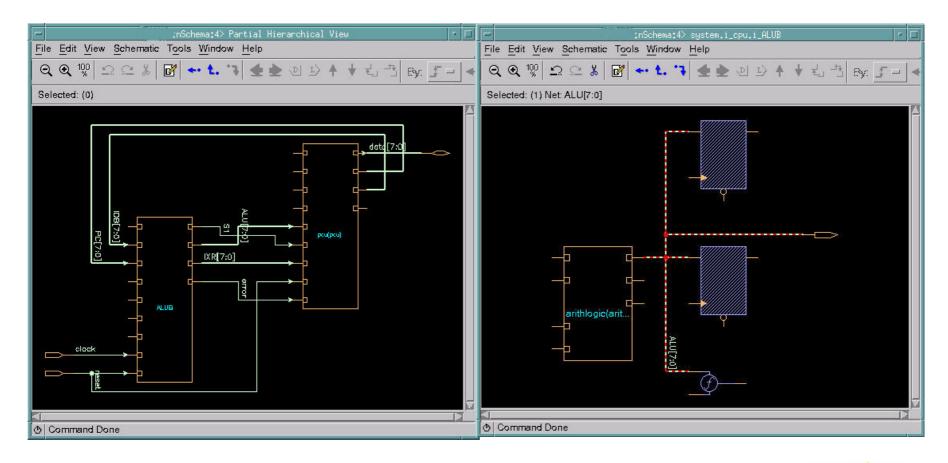

## nSchema – Create Partial Hierarchical Schematics

- Focus on a specified instance or net for debugging.

- Select net(s) or instance(s) while holding Shift key.

- Use Tools → New Schematic → Browser Window to generate partial schematic.

- Hierarchical schematic with only those instances connected to selected nets.

- Hierarchical schematic with only those nets connected to selected instances.

- Double click on symbol port to push into the lower level and highlight the associated net.

- Double click on I/O port to pop up one level.

- Add / delete objects.

- Undo / redo edits.

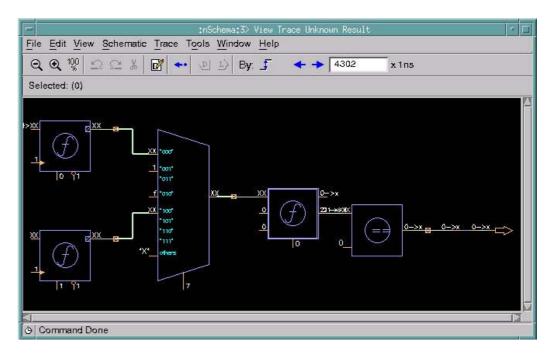

## nSchema – Browser Window Example

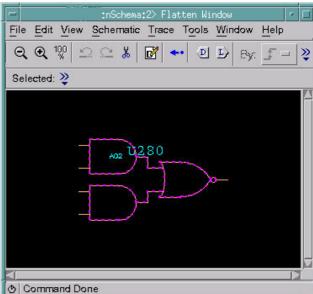

#### nSchema – Create Flattened Schematics

- Focus on a user specified area of the design.

- Select primitive.

- Use Tools → New Schematic → Flatten Window to generate flat schematic.

- Add logic by double clicking an instance pin or drag and drop from other windows.

- Select object and use <Delete> key or icon to remove object from schematic.

## nSchema – Flatten Window Example

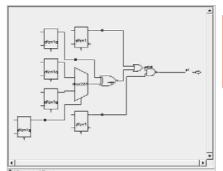

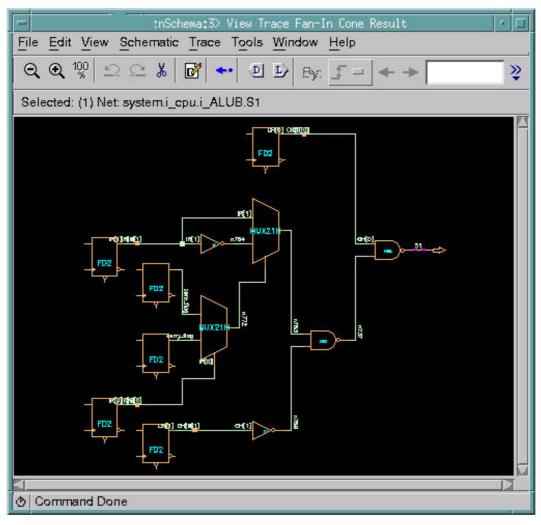

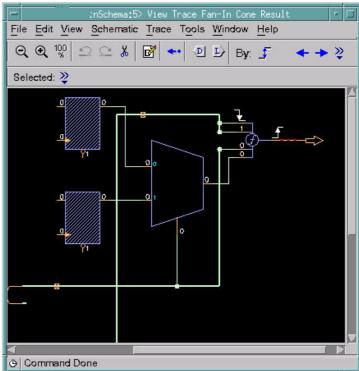

## nSchema – Create Flattened Schematics – Fan-in / Fan-out Cones

- Focus on all drivers or loads of selected object.

- Select object (net or primitive instance).

- Use Tools → New Schematic → Fan-In Cone / Fan-Out Cone to generate flat schematic.

- Add logic by double clicking an instance pin or drag and drop from other windows.

- Select object and use <Delete> key or from schematic.

icon to remove object

## nSchema – Fan-in Cone Example

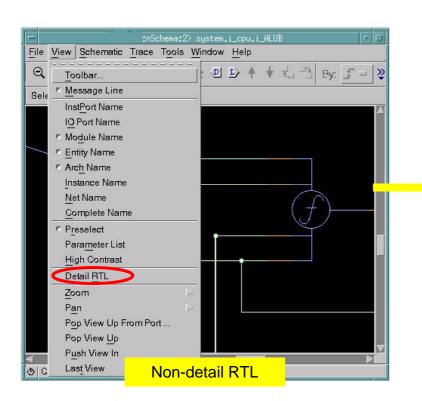

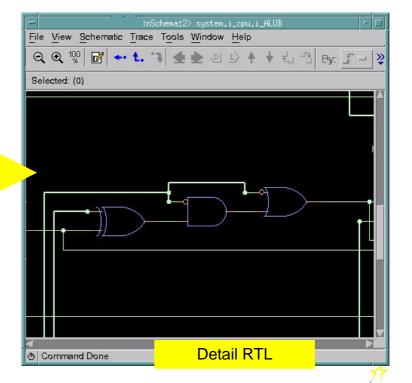

#### nSchema - View Detail RTL on a Window Basis

- New option: View → Detail RTL

- Effective in that window only

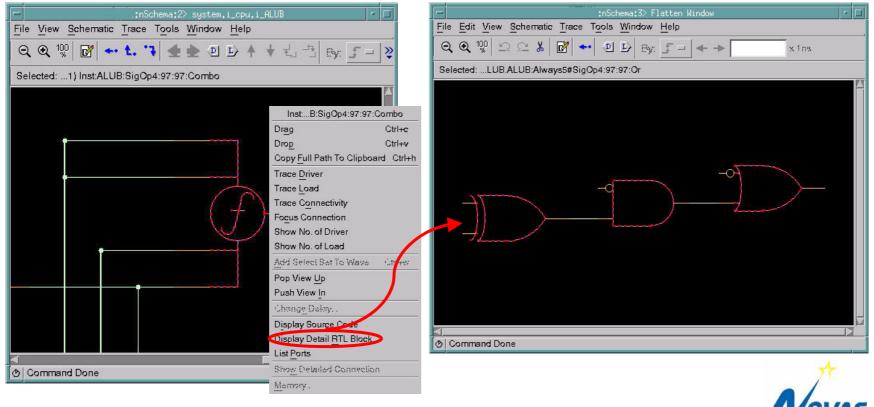

#### nSchema - View Detail RTL on Instance Basis

- On RTL Block, RMB → Display Detail RTL Block

- New window with details will pop up

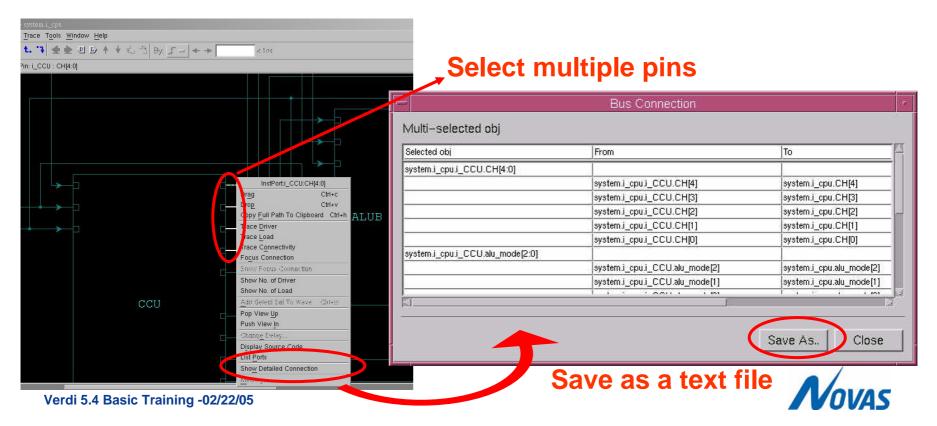

# nSchema — Show Detailed Connections for IO Pins

- Select one or more pins then invoke RMB -> Show Detail

Connection

- All detailed connection information will be shown and can be saved as text file.

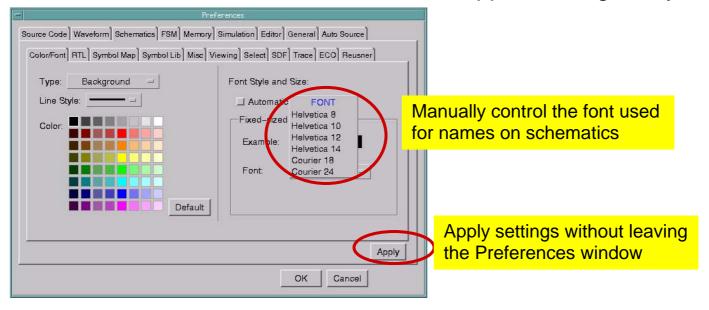

#### nSchema - Miscellaneous

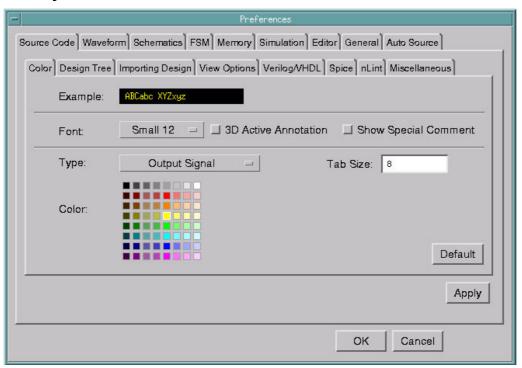

Use Tools → Preferences... to customize the appearance globally.

- Use File → Print to print multi-page schematics.

- Use Help -> Command Reference for additional information.

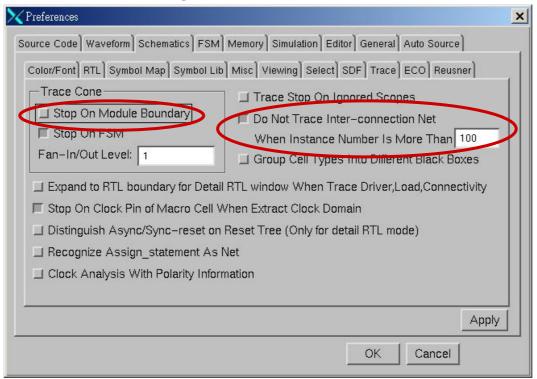

## nSchema – Miscellaneous (Count.)

- Use Tools → Options → Trace Cone Stop On Module Boundary or Tools → Preferences... → Trace tab to force Trace → Fan-In Cone / Fan-Out Cone to stop on module boundary.

- Set the constrain for tracing the inter-connection net.

# nSchema - Summary

- At this time you should

- Understand the nSchema functionality.

- Be able to open a schematic and relate the symbols back to the source code.

- Know how to locate signal(s) or instance(s) and generate different partial schematics.

- Be able to access and change the preferences.

# **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

# nState - View and Analyze State Machines

- Overview

- Invoke nState

- Display Options

- Partial FSM

- State Animation

- Analysis Report

- Interacting FSM Display

- Miscellaneous

- Lab

## nState Overview

- Display and analyze finite state machines.

- Show or hide conditions / actions on a state or a transition.

- Search by State Sequence.

- State Animation using current simulation results.

- Generate analysis reports using current simulation results.

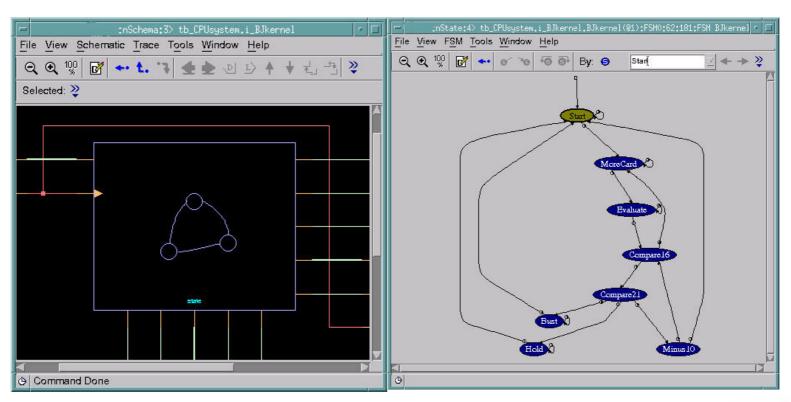

# Invoke nState

Double click on the state machine symbol in nSchema.

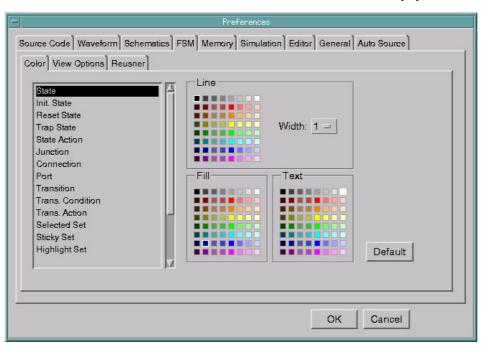

# nState - Display Options

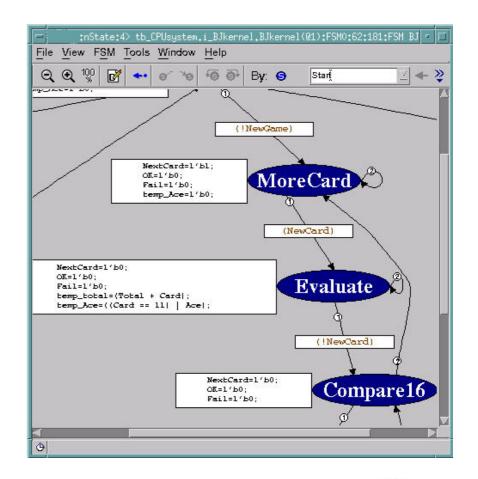

Use View -> State Action to display signal assignments for each state.

- Use View → Transition

Condition to display transition condition on the state diagram.

- Use View → Transition Action to display signal assignments for each transition.

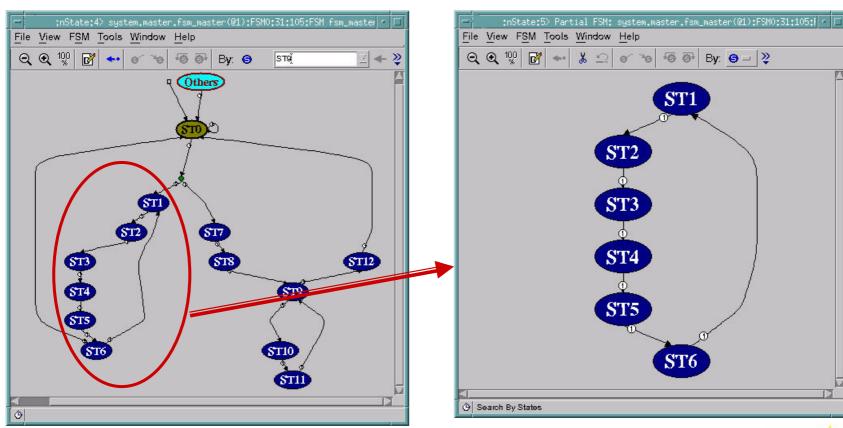

## nState - Partial FSM

Create partial FSM views to aid understanding

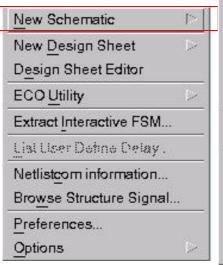

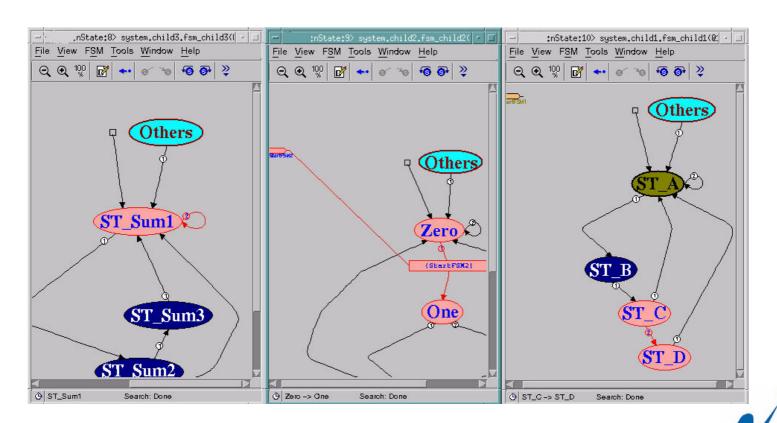

# nState - Interacting FSM Display

- Use Tools → Extract Interactive FSM... in nTrace or nSchema.

- Shows the interaction between multiple state machines.

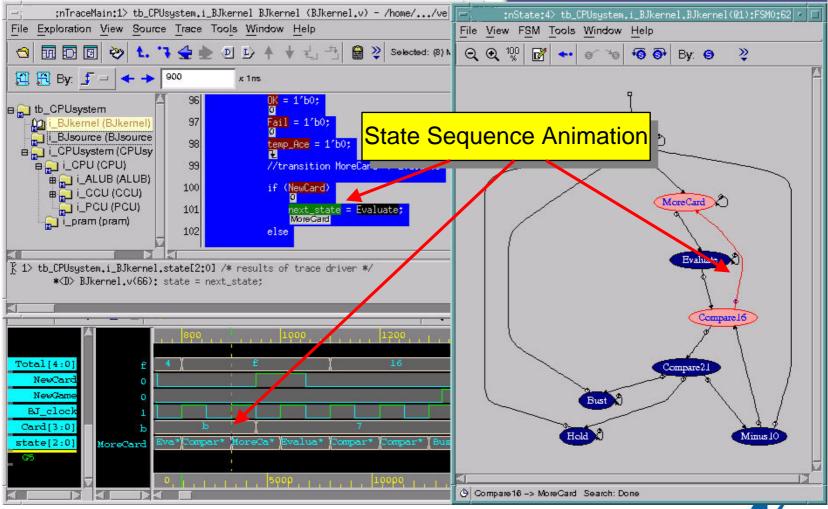

## nState - State Animation 1

- Load simulation results.

- Enable FSM → State Animation.

- Use Previous State / Next State tool bar icons to step through the states.

- Use FSM → Edit Search Sequence to create a sequence of states to search on.

## nState – State Animation 2

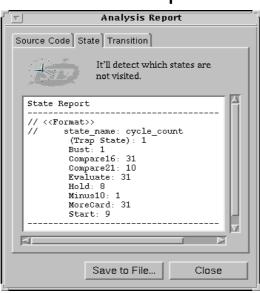

# nState - Analysis Report

- Use FSM → Analysis Report to display analysis report.

- Details of FSM interpretation.

- State coverage report.

- Transition coverage report.

- Save to File command provided.

```

Analysis Report

Source Code State Transition

It'll detect which transitions are

not visited.

Transition Report

(from state ->to state): cycle

(Bust ->Start): 1

(Compare16 ->Compare21): 10

(Compare16 ->MoreCard): 21

(Compare21 ->Bust): 1

(Compare21 ->Hold): 8

(Compare21 ->Minus10): 1

(Evaluate ->Compare16): 30

(Hold ->Start): 8

(Minus10 ->Compare16): 1

(Minus10 ->Start): 0

(MoreCard ->Evaluate): 31

(Start ->MoreCard): 9

= Warning !!! Untested Transition Dete

Save to File...

Close

```

## nState - Miscellaneous

Use Tools -> Preferences... to customize the appearance globally.

- Use File -> Print to print multi-page state diagrams.

- Use Help -> Command Reference for additional information.

## nState - Summary

- At this time you should

- Understand the nState functionality.

- Be able to open a FSM and enable different display options

- Know how to enable state animation and view analysis reports.

- Be able to access and change the preferences.

# nSchema - Wrap-up

• Questions?

Take 20 minutes to complete the nSchema and nState LAB

## **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

# nWave - View Design Behavior Using Waveforms

- Overview

- FSDB File

- Linking Overview

- System Tasks

- FSDB Utilities

- Invoke nWave

- Open Simulation Results

- Display and Organize Signals

- Adding Signals / Get Signals Form

- Group/Bus Operations

- Display Options and Preference

- Focus Debug Effort

- Search Value and Search Constraint

- Markers

- Zero Time Glitch and Event Sequence

- Logical Operations

- Complex Event

- Waveform Comparisons

- Analog v.s. Digital

- Aliasing

- Comments

- Save / Restore Signals

- Lab

## nWave Overview

- A complete waveform analysis environment.

- Supports FSDB format (through PLI) or VCD file format.

- Flexible signal group management.

- Fully integrated and synchronized with other verdi views.

- Interactive visual comparison of waveforms.

- Built-in logic analyzer and event searching.

- Capable of displaying analog waveforms.

# nWave - Fast Signal Database (FSDB) File

- Compact binary file format which contains the simulation signal data.

- Captured during simulation using PLI system tasks for both VHDL and VERILOG.

- Advantages:

- Smaller in size than VCD.

- Loads faster than VCD.

- Open file format so other vendor tools can dump data, Verisity, Vera, Ikos, etc.

# nWave - Brief Overview of Object File Linking

- In general, use LD\_LIBRARY\_PATH to point to pre-compiled PLI shared object files, but simulator and platform dependent.

- All pre-compiled PLI shared object files are found in the software release tree

- \$verdi\_HOME/share/PLI/<simulator>/<platform>

- Nearly all simulators supported, MTI, NC, VCS, etc.

- Standard PLI source files also available for further customization.

# nWave - System Tasks to Dump VHDL to FSDB File

- fsdbDumpfile Specify FSDB file name.

- fsdbDumpvars Dump the specified instances and nets.

- fsdbDumpvarsToFile Dump scope/depth from a designated file.

- fsdbDumpon Turn on FSDB dumping.

- fsdbDumpoff Turn off FSDB dumping.

- fsdbSwitchDumpFile Switch dumping to another FSDB file.

- fsdbAutoSwitchDumpfile Limit FSDB file size and switch dumping to new FSDB file automatically.

- fsdbDumpMem Dump the contents of specified memories.

**Note:** You must link your VHDL simulator before you can use the above system tasks. See Command Reference.

# nWave - System Tasks to Dump Verilog to FSDB File

- \$fsdbDumpvars Dump the specified instances and nets.

- \$fsdbDumpfile Specify FSDB file name.

- \$fsdbDumpon Turn on FSDB dumping.

- \$fsdbDumpoff Turn off FSDB dumping.

- \$fsdbSwitchDumpFile Switch dumping to another FSDB file.

- \$fsdbAutoSwitchDumpfile Limit FSDB file size and switch dumping to new FSDB file automatically.

- \$fsdbDumpflush Force to dump result to FSDB file.

- \$fsdbDumpMem Dump the contents of specified memories.

- \$fsdbDumpStrength Dump the strength of signals.

- \$fsdbDumpvarsToFile Dump scope/depth from a designated file.

**Note:** You must link your Verilog simulator before you can use the above system tasks. See Command Reference.

## nWave - FSDB Utilities

- vfast

- Command line conversion of VCD files.

- fsdbextract

- Extract signals, scopes, time periods from existing fsdb files without re-simulating.

- fsdbmerge

- Merge several fsdb files into one.

- fsdbreport

- Generates a report of value changes for specified signals.

Note: Use <utility> -h for a list of all options or see the Command Reference for more information.

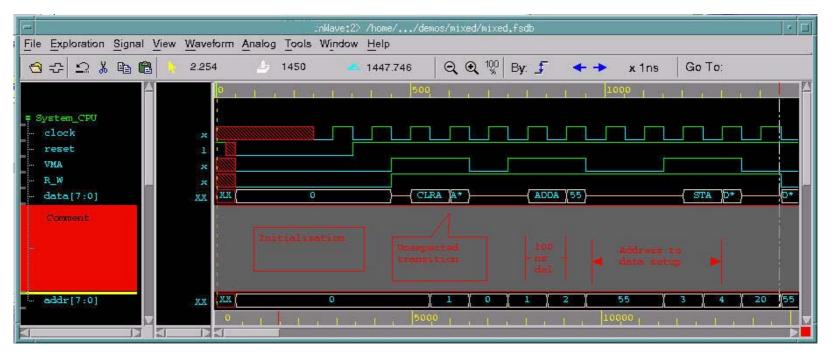

### nWave – Invoke nWave and Load FSDB File

To open *nWave* from *nTrace*, click on the **New Waveform** icon or Tools → New Waveform.

- Use File → Open or toolbar icon to open simulation results file.

- On the verdi command line use the option

- -ssf <filename>.fsdb

- Load VCD files generated by \$dumpvars.

- VCD files are automatically converted to FSDB at load time.

- Open several files in the same window.

- Use File → Set Active... to specify which file is active.

- Open several files in different *nWave* windows.

- Use Window → Change to Primary to specify which window is active.

# nWave - Adding Signals

- Recommended method:

- Drag & Drop signals/instances from other windows to nWave.

- All instance I/O.

- Selected signal(s).

- Signals in text region.

- Schematic hierarchical blocks or logic gates

- Other methods:

- Use Signal → Get Signals... or toolbar icon

- Select signals and use RMB Add Signal(s) to Wave in nTrace.

- Select objects and use RMB Add Select Set To Wave in nSchema.

- After executing a trace command in nSchema, use Trace → Add Result to Wave.

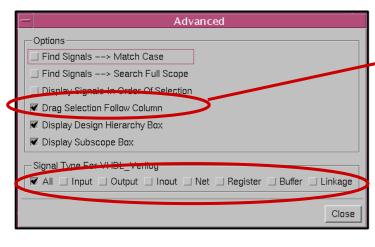

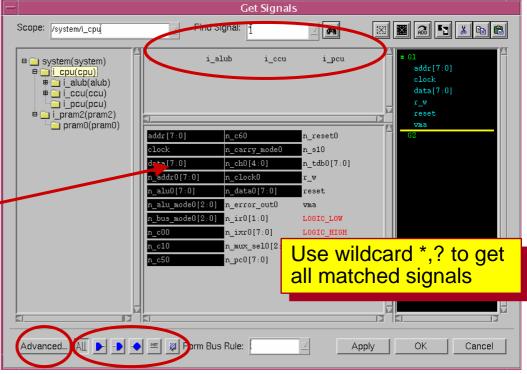

# nWave - Get Signals Form

Directly Form Bus based on user-defined rules.

Sub-block information of selected block in hierarchy browser

- Option to Find Signals in full scope.

- Option to display signals in order of selection not alphabetical.

- Signal type filter.

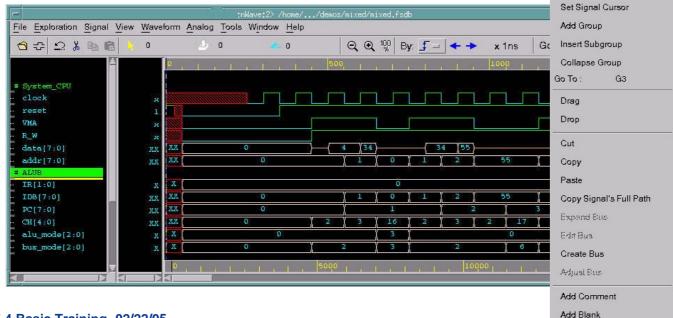

# nWave - Group Operations

- Use RMB menu in signal window to:

- Add Group

- Rename Group name

View → Go To Group... or RMB Go to Group <Select Group name> jumps to specified group.

Rename

Move

Expand / collapse group member by double clicking.

# nWave - Hierarchical Groups

- Invoke RMB → Insert Subgroup to create sub-groups of selected groups

- Each group/sub-group can be renamed with RMB → Rename

- Invoke View → Group Manager... to open the Group Manager form

Select a group in Group Manager form and click New Subgroup to add a new group under the selected group.

- Click the Move To button to move the selected group/signals in nWave into the selected group in the Group Manager

- Delete the selected group and subgroups

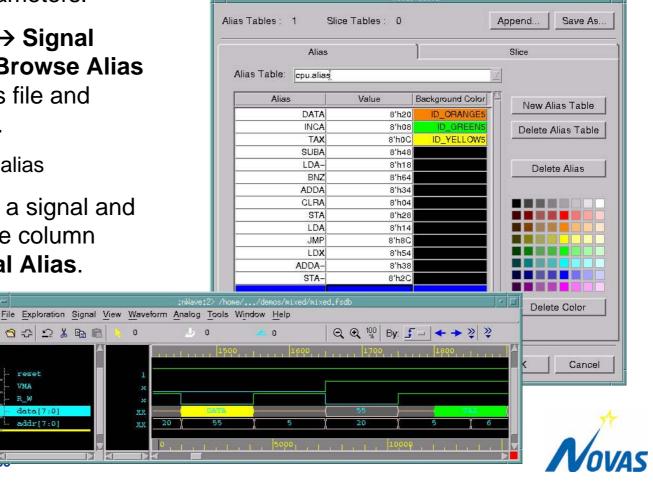

## nWave - Aliasing

Use -autoalias command line option for automatic mnemonic recognition for

'defines and parameters.

Use Waveform → Signal Value Radix → Browse Alias to create an alias file and apply to a signal.

- Apply color to alias

- Create a copy of a signal and use RMB in value column to Remove Local Alias.

白む □ % 畸 €

data[7:0] addr[7:0]

#### nWave - Add Comment

- Use Signal → Comment or RMB menu in signal window to insert a comment field at cursor position.

- Four comment box types provided: box, attached box, period and arrow period.

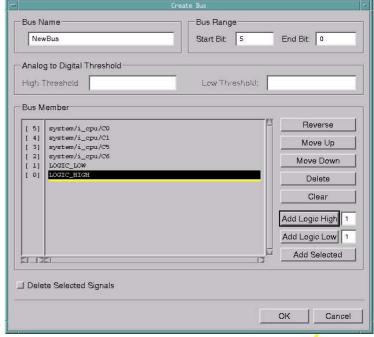

# nWave – Bus Operations

- Invoke Signal → Edit Bus or RMB menu in signal window to edit selected bus.

- Create bus from selected signals.

- Invoke Signal → Create Bus or RMB menu in signal window.

- Add Logic 0 or Logic 1 as place holders.

- Set radix and signal value notation.

- Waveform → Signal Value Radix → Binary, Octal, Hexadecimal, Decimal, ASCII, Alias

- Waveform → Signal Value Notation → Unsigned, Signed 2's Complement, Signed 1's Complement

- Expand / Collapse bus by double clicking.

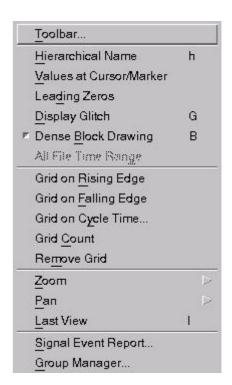

# nWave - Display Options

- View → Hierarchical Name to display hierarchy before signals

- View → Values at Cursor/Marker to display cursor and marker values simultaneously.

- View → Leading Zeros to display leading zeros

- View → Grid ... to display grid lines on rising/falling edges and a grid count.

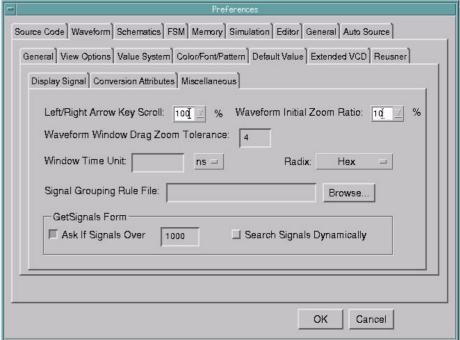

## nWave - Preferences

- Use Tools → Preferences... to customize waveform display.

(Settings saved in novas.rc)

- General: Display input/output signals in different colors, synchronize file browser, etc.

- View Options: Enable highlight signal, radix display, value and signal alignment.

- Value System: Change appearance based on values and strengths.

- Color / Font / Pattern: Change appearance of windows and signal types.

- Default Value: Change signal height and spacing. Change default time unit.

- Extended VCD: Change appearance based on values and strengths.

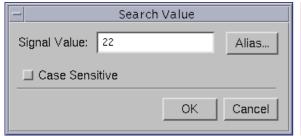

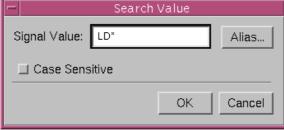

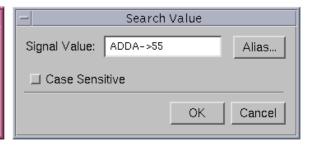

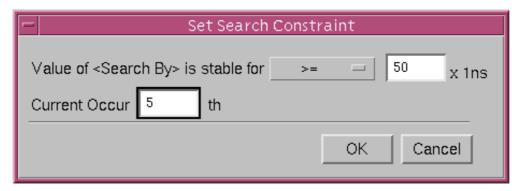

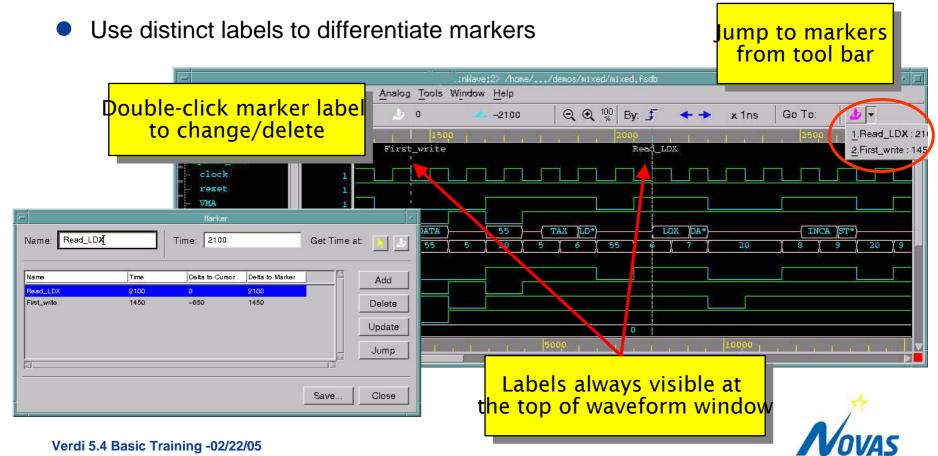

#### nWave - Search Value

- Use Waveform → Set Search Value... to search signal values.

- Search value accepts mnemonics, wild cards and transitions

Use Waveform → Set Search Constraint... to constrain search to a duration of time or nth occurrence of a condition.

- Use Waveform → Marker to name and place markers.

- Multiple markers supported.

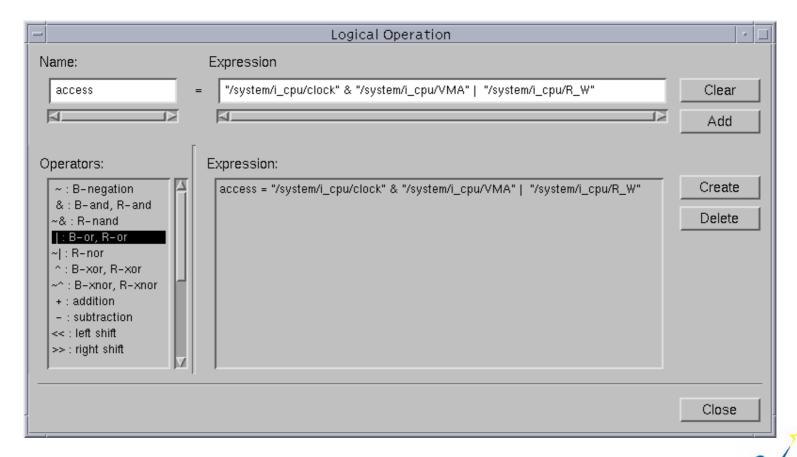

# nWave - Logical Operation

Use Signal → Logical Operation... to create a new signal from other signals.

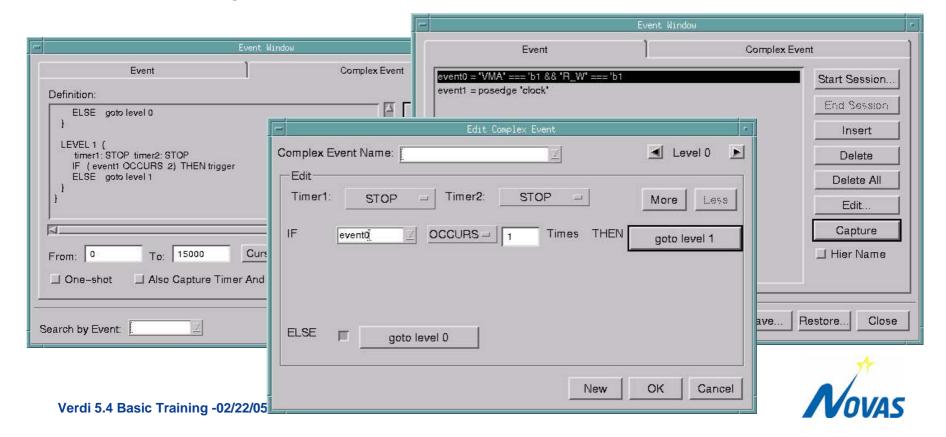

# nWave - Complex Event

- Use Signal → Event to define and name events.

- Events are signal value combinations or complex sequences of single events.

- Double clicking on Event Name or Expression will invoke edit mode.

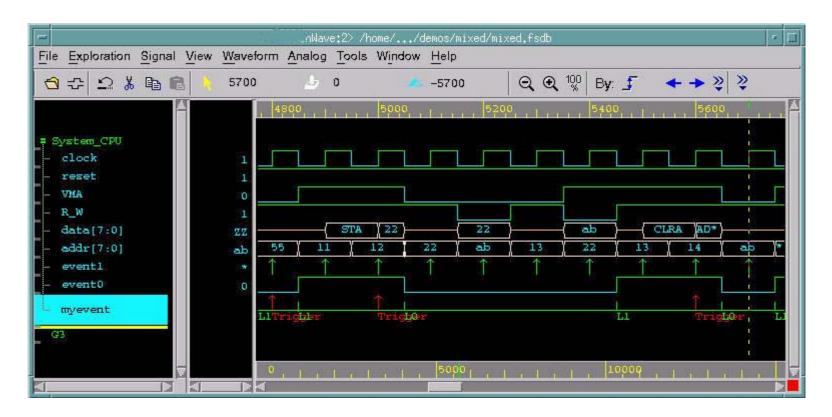

## nWave - Complex Event Waveform

Display captured event on waveform.

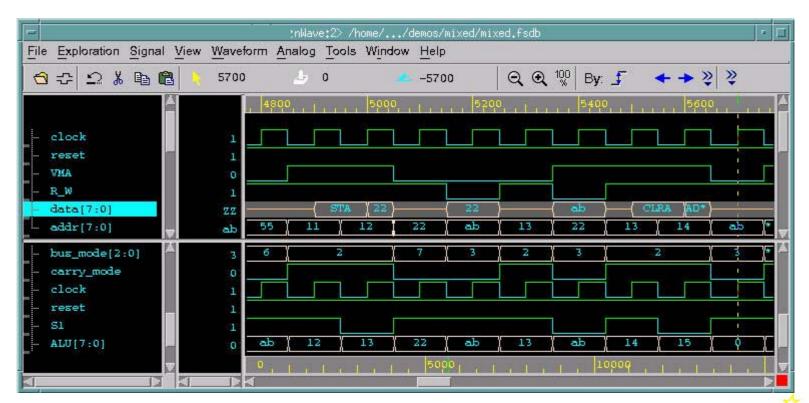

### nWave - Split Window

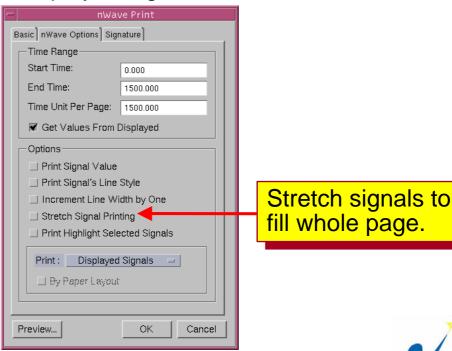

- Use Window → Horizontal Split to split window.

- Use Window → Stop Split to go back.

- File → Print... command to print out what you see in the window with a PostScript printer.

- Select to print to file or to printer.

- Support print selected signals or displayed signals.

### nWave – Save and Restore Signals

Select All

- Use File → Save Signals to save all waveform objects including:

- Signals

- Comments

- Color settings

- Markers and labels

- Logical operations

- Events

- Created Buses

- Restore the signals saved in a previous session

- In nWave, use File → Restore Signals

- On the command line, use –sswr <file>.rc

overwrite the loaded simulation results.

Note: If there is a file open in *nWave*, the **Restore Signals** command will not

/home/becky/demos/verilog/rtl Cursor Marker Marker □ /home/becky/demos/verilog/rtl Save Alias Table: By Alias Content -# Duglog User-defined Marker # C debussyLog □ nWaveLog Digital Logical Operations Signals # n verdiLoa Analog Logical Operations Signals ■ Events Created buses Digital to Analog Signals Analog to Digital Signals Renamed Signals Options Comments. Get Signals Form with Scope Hierarchies FSDB File Information Save Selected Group(s) only

RC Attribute Types

Window Lavout

Absolute Path

Cancel

### nWave - Additional Commands

- Logical Operations

- Signal → Logical Operation...

- Logic analyzer functions (Complex Events)

- Signal → Event

- Shift the time of selected signals.

- Waveform → Waveform Time → Shift Individual Signal Time...

- Create independently scrollable signal frames.

- Window → Horizontal Split

- Aliasing

- Waveform → Signal Value Radix → Browse Alias

### nWave - Summary

- At this time you should

- Understand the nWave functionality.

- Be able to open an FSDB file and add signals to the waveform display.

- Know how to create buses and search for a particular value.

- Be able to add markers, comments, aliases and logical operations.

- Know how to compare simulation results.

- Know how to view the analog waveform

- Be able to access and change the preferences.

• Questions?

## Take 20 minutes to complete the nWave LAB

### **Training Course**

- Verdi Background and Overview

- Loading Your Design

- nTrace View and Debug Source Code

- nSchema View and Debug Designs Graphically

- nState View and Analyze State Machines

- nWave View Simulation Results in Waveforms

- Debugging with Verdi

## Debugging With Verdi

- Alternate Ways to View Simulation Data

- Active Annotation

- State Annotation

- Complex Signal Browser

- Watch, Memory or MDA Windows

- Isolate Logic Relevant to a Specific Simulation Time

- Active Trace

- Trace X

- Post Process Simulation Data

- List X

- Save Debug Environment

- Lab

### **Active Annotation**

- Display simulation results on source or schematic.

- Source → Active Annotation in nTrace

- Schematic → Active Annotation in nSchema.

- Signal values / transitions are synchronized with cursor time.

### Active Annotation – Stepping through Time

- Select signal(s) in the source or schematic window and go to next or previous transitions

- The transition is selectable between: Any Change Falling

- In nTrace, search for the previous/next transition for all signals in the selected statement.

- The above commands will move the cursor time in all windows.

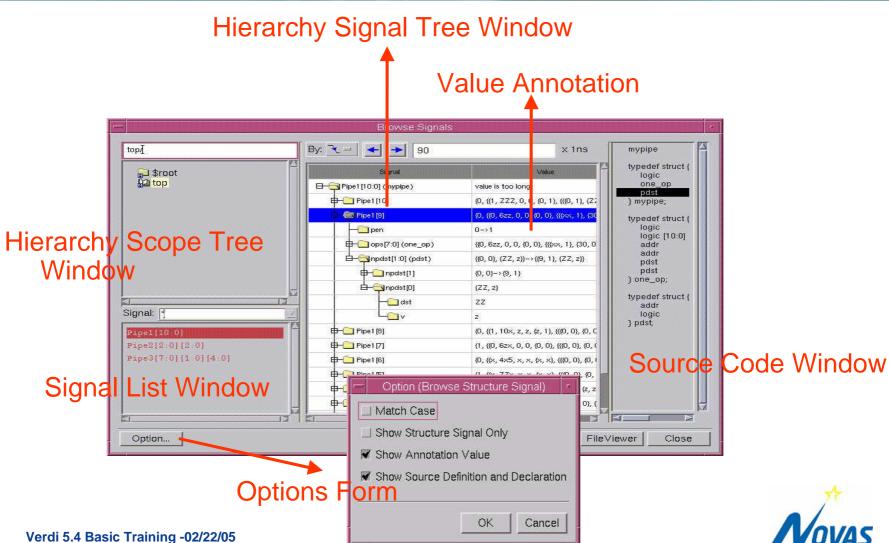

- Dedicated browser for visualizing complex signals

- What are complex signals?

- SystemVerilog struct

- MDAs

- VHDL record type signals

- Invoke the browser from nTrace, nSchema, or nWave

- Tools → Browse Structure Signal...

- RMB → Browse Structure Signal... (nTrace only)

- General

- Multiple Complex Signal Browser windows can be invoked.

- D&D is supported between Complex Signal Browser and other windows.

- Hierarchical Scope Window

- Same as nTrace but without package nodes

- Signal List Window

- Supports regular expression in search window

- Complex signals will be shown with Red color

- Signals are sorted alphabetically

- Two options Match Case and Show Structure Signal Only in Option form will be applied to this window.

- Hierarchical Signal Tree Window

- The signal tree will be built when selecting a signal in Signal List Window

- Settings for Source → Signal Value Radix and Source → Signal Value Notation in nTrace will be applied to this window.

- If an FSDB is loaded, the annotation value will be shown for all leaf nodes.

- The Value Annotation Window will be closed if Show Annotation Value option is turned off in the Option form.

- The annotated value will change according to current time point.

- Source Code Window

- Enabled/disabled with the Show Source Definition and Declaration option in the Option form.

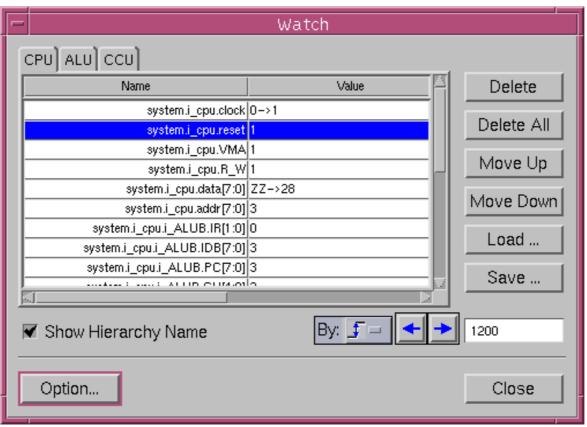

# Watch Signal

From nTrace, use Tools → Watch Signal to view the value of selected signals in a table.

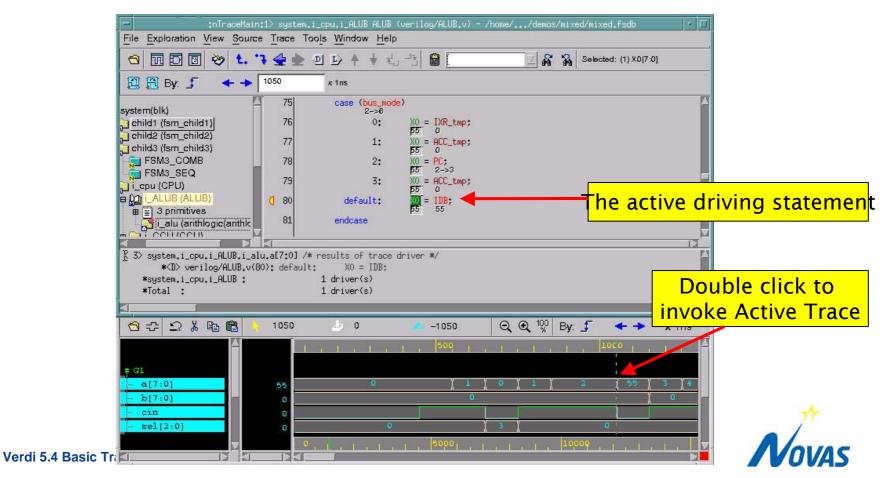

### Active Trace from Waveform

Double clicking on a signal transition in the waveform window will identify ONLY the active driving statements(s) in nTrace causing that transition.

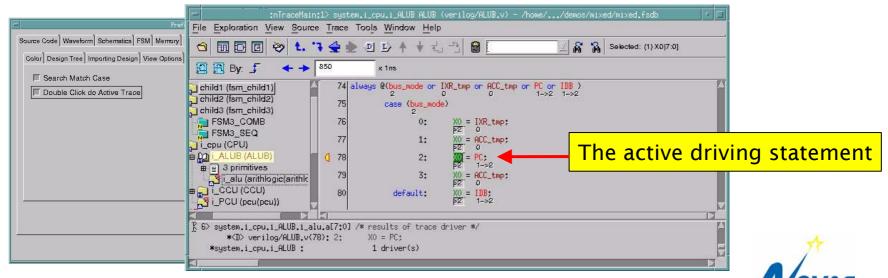

### Active Trace in Source

- Used to identify the active driver for the selected signal.

- Requires design and simulation results.

- Select signal in nTrace.

- Invoke RMB menu and select Active Trace.

- Ctrl-t also performs an Active Trace.

- Use Tools → Preferences, Source Code tab, Miscellaneous tab, to enable Double Click do Active Trace.

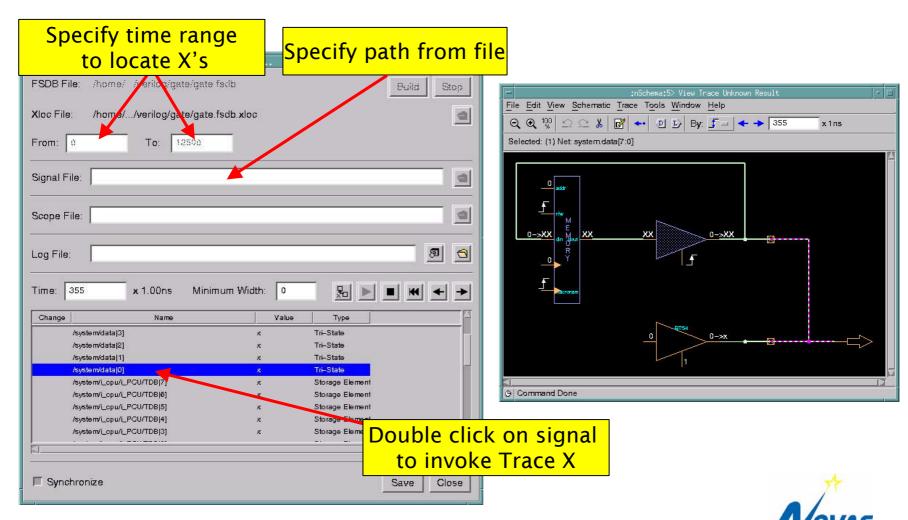

### Trace X

- Display logic cone relevant to the unknown.

- In nWave, select a signal.

- Place a cursor at the transition to X.

- Invoke Tools → Trace X.

- Generates a flattened schematic that shows the X propagation path back to first storage element or primary input.

- In resulting nSchema,

Trace → Trace X.

- Repeat as needed.

# List X

- Two common causes of X's:

- Timing violations

- Un-initialized storage elements

verdi can help to isolate storage elements and tri-state devices with unknowns.

- In nWave or nTrace, use Tools → List X.

- Build: parses fsdb file to find storage elements and tri-state devices which have value X.

- A batch build executable called xloc is supported.

- Play: to list storage elements and tri-state devices which have value X at selected time.

- Double click on a signal in the list or press Trace X icon to generate a flattened schematic (Trace X functionality).

## List X / Trace X Example

Verdi 5.4 Basic Training -02/22/05

#### Start Interactive Mode

- Confirm the PLI/FLI shared object files provided by verdi are linked with your simulator.

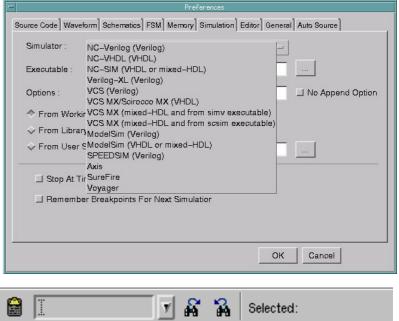

- Choose the simulator under Tools → Preferences → Simulation tab.

Interactive Toolbar

- Be sure to select stop at time 0.

- To enable interactive mode select

Tools → Interactive Mode.

- This adds a new toolbar and Simulation and Debug menu options to nTrace.

### Interactive Simulator Control

- Click the Run/Continue icon to start simulator.

- Click the Stop icon to stop simulator.

- Run the simulator to specified time by entering a value in the Time text field.

- Use Simulation → Reset to reset simulator.

- Use Simulation -> Finish to finish simulation.

- Use Simulation → Kill Simulator Process to kill the simulator process.

### Other Interactive Control Options

Execute Verilog or VHDL step by step.

- Enable Active Annotation for real time updates.

- Use Debug → Breakpoints to set and control breakpoints.

- Double click on the line number in source window to set/clear a breakpoint.

- Use Debug → Set Focus to focus on a scope(s).

If a focus is set, the source window will only step through the source code that is

in the focus modules.

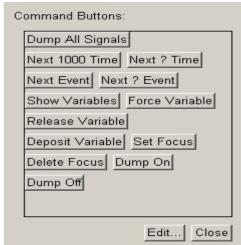

Use Debug → User-Defined Commands to bring up the user-defined commands window for frequently used commands.

### Save/Restore Debug Environment

- Save the debugging status to a session file

- In nTrace, File → Save Session...

- Information saved:

- Displayed waveforms and settings.

- All the windows, locations and content.

- Recover the previous debugging status from a session file.

- In nTrace, File → Restore Session...

- On the command line, use –ssr <file>.ses

## Summary

- At this time you should

- Be able to enable active annotation and debug a simulation problem with active trace.

- Apply the simulation result to nState

- Know how to load an SDF file, annotate values and calculate longest/shortest paths.

- Be able to use different techniques to isolate logic for active fanins, bus contention and X detection.

- Know how to save a debug session for future use.

• Questions?

Take 20 minutes to complete the Debug with Verdi LAB

## If you have problems...

- Contact support with the following information

- Complete description of the problem and what you were doing

- verdi or nLint version

- Platform and OS version

- Simulator and version (if simulation problem)

- Core stack (if applicable)

- verdiLog directory (at a minimum the verdi.cmd)

- Support contact:

- <name>

- <email>

- <phone>