# 集成电路可靠性评价技术

信息产业部电子第五研究所,电子元器件可靠性物理及其应用技术国家级重点实验室

孔学东 章晓文 恩云飞

摘要:对工艺过程进行评估的目的在于找出存在可靠性缺陷的地方,它是针对技术磨损的机理,通过对专门设计的测试结构进行封装级或圆片级可靠性测试,获取器件的可靠性模型参数和可靠性信息。超大规模集成电路主要的三个的失效机理分别是热载流子注入效应、金属化电迁移效应和氧化层的 TDDB 击穿。本文对这三种失效机理分别进行了介绍,对各自对应的可靠性模型进行了说明,强调了可靠性评价的重要性,给出了可靠性评价在工艺中的应用流程图。

## 1 引言

当今的微电子工艺技术发展迅速,在短短几年时间里特征线宽越来越小,金属化布线的宽度越来越细;与此同时 IC 的栅介质层厚度也是越来越薄,0.35 微米工艺的栅介质层厚度为 6 至 10nm,0.25 微米工艺的栅介质层厚度为 4 至 5nm,发展到 0.13 微米工艺时,栅介质层的厚度将仅为 2 至 3nm。这些情况会导致器件失效的可能性增加。因此,当集成电路的性能不断提升时,其可靠性水平必须得到保证。

电迁移现象是运动中的电子与金属原子相互交换动量的结果。因此铝原子在与电子流运动相同的方向迁移时,会在原有位置产生空洞。当空洞逐渐扩大到与金属导线相同的宽度时,就会使金属线断开,产生器件失效。 这种现象被称为电迁移(Electromigration,EM)失效。

栅氧化层质量直接关系到器件的电性能和可靠性,当有电荷注入时,会造成共价键断裂,产生缺陷,这些缺陷通过陷阱 (包括界面态)体现出来。介质击穿分为本征击穿和与缺陷相关的击穿,本征击穿的机理和材料性质有关,与缺陷相关的击穿与 Poly/Si/SiO<sub>2</sub> 两个界面的不平整有关。

器件特征尺寸减小到 1µm 以下时,沟道电场在

漏端形成强电场区,强电场使一部分沟道电子具有了一定的能量,当能量大于电子跃迁到氧化层的势垒高度时,发生电子到氧化层的跃迁,这部分电子称为热电子,跃迁到氧化层中的电子被氧化层陷阱俘获,会产生氧化层电荷和界面态,引起器件参数的退化,这种现象称为热载流子注入效应。

集成电路工艺的可靠性评价,就是利用微电子测试结构,通过加速试验获取基本的可靠性参数和可靠性信息,确认工艺线的可靠性水平。通过对测试结构进行封装级或圆片级的可靠性测试,找出存在可靠性缺陷的项目,确定技术磨损的机理,确保器件在整个产品寿命期间有良好的可靠性[1]。

# 2 可靠性模型

电迁移试验寿命采用 BLACK 方程来描述:

$$\tau \text{=} A J^{^{-n}} exp \Big( \frac{Ea}{kT} \Big) \qquad (1)$$

式中 Ea 为激活能,n 为电流密度因子,K 是波尔滋曼常数。

失效判据的选择是以金属条上的电阻值超过初始值的 5%至 20%时的时间为失效时间,将电迁移失效数据在威布尔坐标上描出累积失效分布,就可

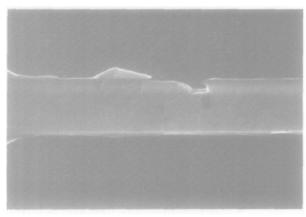

以推算工作应力条件下电迁移寿命。如厂家不能提供可靠性模型参数 Ea、n,则需要用样品进行提取。激活能 Ea 需要至少三组不同温度点的电迁移数据,而为了确定出电流密度因子的值,也至少需要三组不同的电流密度的电迁移数据,电流密度因子的值在激活能求出之后才能确定。激活能 Ea 的值与失效机制有关,当失效是由于晶粒扩散引起的,太约是0.6~0.7eV;当失效是由晶格扩散引起的,激活能的值大约是1.0~1.2eV之间。图1 是电迁移失效后的SEM图形。

图 1 电迁移失效的 SEM相

当器件尺寸进一步缩微时,导线延迟会上升。虽然缩短导线长度会降低延迟,但会使导线层增加,制造困难且成品率降低,必须更换电阻率更小的导线,这意味着更换金属材料的成份,目前在 0.13 微米工艺中使用的就是铜导线。

铜的电阻率约为  $1.7\mu\Omega$ -cm,而铝的电阻率约为  $2.7\mu\Omega$ -cm,故铜线的电阻率较铝的下降了 40%。另外,铜的熔点约是 1070%,高于铝的 660%,故铜可以承受较高的温度。因铜原子较铝原子不易移动,抗电迁移性能较好,且导电性能和散热也较铝好。

虽然铜线有很好的优点,但也有一些缺陷,这是由于铜在硅基板中扩散得非常快,故一定要有很好的阻挡层,以防止铜原子扩散出来。铜很容易在空气中氧化,且铜线不能采用一般的干法刻蚀,而需要使用所谓的大马士革方法(Dual Damascene)去刻蚀。

铜互连线(包括通孔互连线和沟槽互连线)的电

迁移和应力迁移特性,是现今互连线可靠性研究的 热点。铜比铝的电迁移寿命至少提高了一个数量级, 通孔和沟槽引线中的空洞形成是造成电迁移失效和 应力迁移失效的重要因素,通孔中空洞的形成与其 底部的 TaN 势垒层与铜界面的缺陷有关。在无空洞 的情形下,电迁移失效的位置主要发生在通孔的底 部,通孔抗电迁移的能力受铜互连后步工艺影响很 大,通过优化通孔结构和后步工艺可以大大改善电 迁移特性。研究表明,在淀积铜的过程中避免空洞的 形成是避免电迁移失效的重要因素[2]。一些可靠性 试验结果列举于表 1 中[3]:

表 1 铜互连线的可靠性评价

| 应力方式        | 结果                           |

|-------------|------------------------------|

| 电迁移         | 在目标时间内 0 失效发生                |

| 热疲劳         | 在-65℃至 150℃的 1000 次循环中 0 失效  |

| 应力迁移        | 在 1000 小时的温度应力作用后 0 失效, 应力温度 |

|             | 分别为 145、175、225、275℃         |

| 与时间有关的氧化层击穿 | 12.5V 和 150℃应力下 1000 小时 0 失效 |

| 封装应力        | 在-55℃至 150℃的 1000 次循环中 0 失效  |

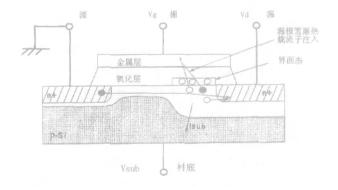

当器件的沟道长度逐渐变小时,由于电压不能够随比例下降,沟道中的电场强度会上升。以 NMOS 管为例,漏极是电场最强的地方。当沟道中的载流子进入漏极时,会获得高能量,通过碰撞离化作用产生电子空穴对。当载流子的能量超过 Si/SiO<sub>2</sub> 势垒高度时,会注入氧化层中形成陷阱电荷,或界面态,使器件的特性退化,如图 2 所示。

图 2 MOS 器件中热载流子注入示意图

在做热载流子寿命预计时,需要考虑如下的几个因素:决定最坏状况的偏压条件及器件特性退化机制,选择器件退化参数来测量器件的退化程度,选

用适当的加速模型来推算器件在正常工作条件下的寿命。

对 NMOSFET 器件而言, 推算寿命的加速模型有三种:第一种是衬底/漏极电流比率模型,第二种是基极电流模型,第三种是漏极电压加速模型。

三种加速寿命试验的模型方程如下所示:

衬底/漏极电流比率模型:

$$\tau = H \left(\frac{I_{_{D}}}{I_{_{sub}}}\right)^{n} \frac{1}{I_{_{D}}} \Delta G_{_{max}}^{^{1.5}} \cdot W \tag{1}$$

基极电流模型:

$$\tau = C(I_{\text{RUSE}}/W)^{-B}$$

(2)

漏极电压加速模型:

$$\tau = \tau_0 \exp(B/V_{\text{DUSE}}) \tag{3}$$

对 PMOSFET 器件而言,推算寿命的加速模型 有二种:第一种漏极电压加速模型,第二种是栅极电 流模型。

二种加速寿命试验的模型方程如下所示:

栅极电流模型:

$$\tau = C(I_{GUSE}/W)^{-B}$$

(4)

漏极电压加速模型:

$$\tau = \tau_0 \exp(B/V_{\text{D,USE}}) \tag{5}$$

式中 $\tau$  是热载流子退化寿命 $_{\tau}$ C $_{\tau_0}$ H 是比例常数 $_{\tau}$ n $_{\tau}$ B 是模型参数 $_{\tau}$ H 是比例常数 $_{\tau}$ AG 指的是参数退化量 $_{\tau}$ W 是沟道宽度。

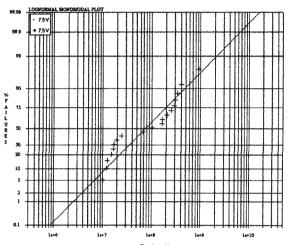

PMOSFET 的热载流子注入效应不显著,这是因为空穴的质量比电子的要大,碰撞离化的几率较低,热载流子注入效应不明显。图 3 是 7.5V 应力时漏极饱和电流失效概率分布图。

1μm 以下的 CMOS 器件中热载流子效应必然存在,工艺上虽然采用了 LDD 结构等方法提高了器件抗热载流子退化的能力,但热载流子效应仍然是影响亚微米和深亚微米集成电路可靠性的重要因素,热载流子效应的影响不是一开始就很严重,而是随时间逐渐引起器件参数的退化,主要退化参数有阈值电压 Vth、跨导 Gm、线性漏电流 Idlin 和饱和漏

电流 Idsat,因此在评价热载流子可靠性时就选择这几种参数来表征。

K-S distance: 18.9% (should be below 30.1%)

图 3 7.5V应力时的漏极饱和电流失效概率分布

栅氧化层 TDDB 特性的描述模型很多,对于恒定电压下的栅氧化层,电场与时间的关系有两种,即 1/E 模型或 E 模型。E 模型如下:

$$\tau = \tau_0 \exp(-\gamma \cdot \mathbf{E}_{ox}) \tag{6}$$

式中  $\tau$  是 TDDB 寿命,  $\tau_0$  是本征击穿时间,  $\gamma$  是模型参数, 单位是 cm/MV, Eox 是氧化层电场。

1/E 模型描述如下:

$$\tau = \tau_0 exp\left(\frac{G}{E}\right) \tag{7}$$

式中 $\tau$ 是 TDDB 寿命, $\tau_0$ 是本征击穿时间,G 是模型参数,单位是 MV/cm,Eox 是氧化层电场。在栅氧化层 TDDB 试验中的决定因素是氧化层电场 Eox,模型参数  $\gamma$  是由氧化层结构所决定的固有参数。对于恒定电压栅氧化层 TDDB,退化参数是氧化层漏电流 I。

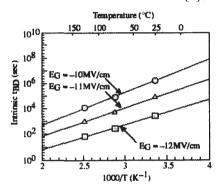

到目前为止,哪一种模型较正确还未有定论,不过 E 模型推算出的寿命比 1/E 模型推算出的要小,故工业界一般采用 E 模型。整合温度与电场的加速模型可得到下列 TDDB 加速模型:

$$\tau = C \cdot 10^{-\gamma E} \cdot \exp\left(-\frac{Ea}{KT}\right) \tag{8}$$

在 TDDB 加速模型中,有两个重要的加速因子需要事先被提取出来,即激活能 Ea 和模型参数  $\gamma$ 。一般 Ea 可在一个固定的电场下,测量两个以上的温度来得到。同理模型参数  $\tau$  可在一个固定的温度下,测量两个以上的电场值来得到。图 4 是 TDDB 试验过程中电场加速因子与温度的关系[4]。

图 4 电场加速因子与温度的关系

关于氧化层可靠性的评价,除了使用恒定电压以外,还可以使用斜坡电压的测量方法。根据击穿电场的分布,可以将氧化层缺陷分成三种类型,A模式、B模式和C模式。A模式的击穿电场小于1MV/cm,B模式的击穿电场介于2~6MV/cm,C模式的击穿电场通常大于8MV/cm。A、B模式是缺陷失效,C模式反映的则是本征击穿。

另外一种评估氧化层可靠性的方法是击穿电荷,而测量击穿电荷 Qbd 有两种方法,即恒定电流测量和指数斜坡电流测量。不同的测量方法会使击穿电荷 Qbd 的值不一样,故应当在同一条件下进行测量。

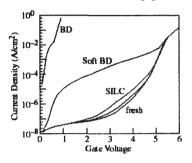

当氧化层越来越薄时,除了一般观察到的硬击穿(Hard Breakdown,HBD),外还有两种新的现象产生。一种是因应力导致的漏电流(Stress-Induced Leakage Current,SILC),另一种是软击穿(Soft Breakdown,SBD),如图 5 所示[4]。

软击穿又叫准击穿、预击穿等。器件发生软击穿时的漏电流比相同偏置条件下产生的 SILC 大 3-4 个数量级。软击穿的发生并不会导致栅氧化层的完全击穿,但是 MOS 电容发生软击穿后,漏电流会显著增大,而器件发生多次软击穿后,将可能引起整个

氧化层击穿,器件失效。因此,随着栅氧化层厚度降低,软击穿也将会作为一种新的氧化层失效机制而逐渐引起人们的注意,并且可能是标志未来的 MOS 器件栅氧化层可靠性的关键因素[4]。

图 5 超薄栅中的应力不同导致的漏电流不一样

## 3 小结

IC 产品的发展除了高性能以外,还要有高质量与高可靠性。当器件的尺寸持续缩小时,器件的可靠性显得越来越重要,因此对于引起器件失效的机制需要进行深入的研究,并发展出正确且适当的加速测试方法去预测寿命值。可靠性评价试验可以采用圆片级与封装级两种形式,是现代 VLSI 工艺线可靠性保证的重要环节,主要的应用在以下三个方面:

- (1) 主要失效机理的可靠性评价

- (2) 可靠性模型测试提取

- (3) 工艺可靠性监测 🚾

#### 参考文献

- 1. 恩云飞,章晓文."微电子工艺可靠性评价技术", 电子产品可靠性与环境试验,2000(3)。

- 2. 王阳元,康晋锋." 超深亚微米集成电路中的互连问题 低 K介质与 Qu 的互连集成技术",半导体学报 Vol (23), 2002(11), pp: 1121.

- 3. D. Edelstein, H. Rathore, C. Davis, et al. Comprehensive Reliability Evaluation of a 90 nm CMOS Technology with Ou/PECVD Low-K BEOL. I EEE I RPS 2004, pp: 316

- 4. 郑敦仁."元件可靠性",电子与材料,2003(8):49