# 华中科技大学 硕士学位论文 CMOS图像传感器中关键模拟电路的研究与设计 姓名: 刘旭 申请学位级别: 硕士 专业: 微电子学与固体电子学 指导教师: 邹雪城 20090525

#### 摘要

20世纪70年代以来,随着集成电路产业的快速进步,图像传感器开始出现并逐渐发展,而且它的广泛应用给人们的工作和生活带来了极大的便利与安全。在21世纪,CCD和CMOS两种图像传感器都得到了迅速的发展和更加广泛的应用。但是随着集成电路工艺的快速进步和集成度的日益提高,CMOS图像传感器由于与标准CMOS工艺兼容性好而逐渐占据并扩大优势,性能大大提高,应用更加广泛,成为了国内外学者的研究热点。

本文首先分析了CMOS图像传感器中光电探测器件即光电二极管的原理及特性,并从CMOS图像传感器的工作原理出发,进一步对CMOS图像传感器系统结构进行分析。同时,本文还以大量文献为基础,分别研究并分析了CMOS图像传感器系统中像素阵列与像素单元电路、模拟信号处理电路和模数转换电路等关键模块的不同实现方法,比较了每种方法的优缺点和电路性能。

其次,本文分别对像素单元电路、模拟信号处理电路、带隙基准源和模数转换模块中的斜坡发生器和比较器等关键模拟电路进行了设计;并针对CMOS图像传感器中传统的三管有源像素单元电路输出摆幅小的缺点,提出一种改进的像素单元电路,使信号输出摆幅增大了约0.7V,提高了图像传感器的动态范围。接着,针对模拟信号处理模块中传统相关双采样电路占用面积大和功耗较高的特点,本文采用一种改进的相关双采样电路大大降低了CMOS图像传感器的功耗。

最后,基于SMIC 0.35um 2P3M CMOS工艺,实现了CMOS图像传感器的关键模拟电路。整个CMOS图像传感器采用3.3V电源电压,在设计流程中使用Cadence公司的EDA软件进行电路性能仿真。通过对仿真结果进行分析,CMOS图像传感器的动态范围达到110dB,总功耗为113.3mW,符合预期的设计要求。

关键词: CMOS图像传感器,光电二极管,像素单元,模拟电路

#### **Abstract**

Since 1970s, as the integrated circuit industry advances fast, image sensors begin to emerge and gradually be developed, moreover, the wide use of image sensors bring great convenience and safety to people in their work and lives. In the 21st century, CCD and CMOS, the two kinds of image sensors, are both developed drastically and getting wider application. While as the process technology of integrated circuit advances fastly and the integration degree are improved increasingly, CMOS image sensor gradually takes up more advantages and exceeds because of its good compatibility to standard CMOS process technology. Thus, the performance of CMOS image sensor is greatly improved and its application range becomes wider and wider, so it becomes a hotspot of research among scholars all over the world.

Firstly, this paper analyses the basic theory and feature of photodiode, which is a kind of photon detector in CMOS image sensors, and further analyses the system frame of CMOS image sensors based on its operation theory. Also, this thesis is based on large amount of academic papers, probed and analysed the key analog blocks in CMOS image sensor system including pixel array and pixel cell block, analog signal processing block, and A/D conversion block as well as their different ways of implementation respectively, then compared the features and circuit performances of various realizations.

Secondly, this thesis respectively designed these key analog circuits including pixel cell circuit, analog signal processing circuit, bandgap reference circuit, ramp voltage generator and comparator in A/D conversion block. In order to overcome the disadvantages such as small output swing range of conventional 3 transistor-active pixel cell circuit in CMOS image sensors, this paper provides a improved pixel cell circuit which expends 0.7V to output swing range and thus improves the dynamic range of image sensor. Then, finding the features of large area and high power consumption in conventional CDS circuits of CMOS image sensor, this paper adopts an improved CDS circuit to lower the power consumption of CMOS image sensor.

Finally, based on SMIC 0.35um 2P3M process technology, the key analog circuits of CMOS image sensor are realized. The power supply of whole CMOS image sensor is 3.3V. In the design flow, the circuits are simulated in EDA software provided by Cadence Company. Through analyzing the simulation result, the dynamic range of CMOS image sensor is 110dB and total power consumption is 113.3mW, which meet the design

requirement of expectation.

**Keywords:** CMOS image sensor Photodiode Pixel cell Analog circuit

#### 独创性声明

本人声明所呈交的学位论文是我个人在导师的指导下进行的研究工作及取得的 研究成果。尽我所知,除文中已标明引用的内容外,本论文不包含任何其他人或集 体已经发表或撰写过的研究成果。对本文的研究做出贡献的个人和集体,均已在文 中以明确方式标明。本人完全意识到本声明的法律结果由本人承担。

学位论文作者签名:

年 月 日

## 学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定,即:学校有权保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。本人授权华中科技大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

保 密□,在 年解密后适用本授权书。

本论文属于

不保密□。

(请在以上方框内打"√")

学位论文作者签名:

指导教师签名:

年 月 日

年 月 日

#### 1 绪论

#### 1.1 课题研究背景及意义

CMOS 图象传感器是一种用半导体材料制作的可以将图象信号转换为电信号的固体摄象器件。最早的固态图像传感器是由 Westinghouse、IBM、Plessy和 Fairchild公司于 20 世纪 60 年代末开发的双极型和 MOS 型光电二极管阵列[1]。到了 70 年代,电荷耦合器件(CCD)被发明出来并且作为一种模拟存储器件很快成为了图像传感器的主流技术。尽管在 80 年代初期外国学者们发表了一些 MOS 图像传感器的研究成果,但是真正的 CMOS 图像传感器的研究工作是在 80 年代中期由 VLSI 视觉有限公司和 Jet Propulsion 实验室开始发起的。在 20 世纪 90 年代初期,CMOS 图像传感器一直采用无源像素传感器(PPS)技术[2]。当时的 CMOS 工艺的特征尺寸非常大,以至于在 PPS 的一个像素中只能容纳一个晶体管和三条金属互连线。当时的无源像素图像传感器的性能比 CCD 传感器差很多,它的应用只能限于低端的产品中[3]。现代 CMOS 有源像素图像传感器(APS)的研究工作是在 1968 年构想并在 90 年代早期开始的[4-5];研究人员们很快发现在每个像素单元中加入一个放大器可以极大地提高传感器的速度和信噪比(SNR),这样就克服了 PPS 的缺点。随着深亚微米 CMOS技术的出现和集成微透镜技术的发展,有源像素图像传感器成为了 CCD 图像传感器的一种替代选择。

CCD与CMOS传感器是当前被普遍采用的两种图像传感器,两者都是利用感光二极管(photodiode)进行光电转换,将图像转换为数字数据,而其主要差异是数字数据传送的方式不同<sup>[6]</sup>。

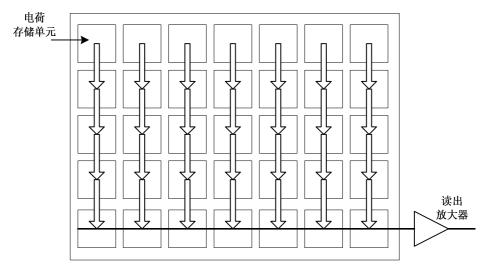

CCD 是由一组电荷存储器件即电容形成的移位寄存器,它工作的两个基本过程是电荷存储和电荷耦合<sup>[7]</sup>。在 CCD 图像传感器中,感受光照俘获光子的光敏单元构成光电传感器阵列积累电荷,光电荷沿着一排像素单元移向一个电荷敏感读出放大器,如图 1-1 所示。当最下面一行信息被读出后,它上面一行的电荷就移到该行,从而实现图像初始信号的传感与读出。

图 1-1 CCD 图像传感器中的读出结构

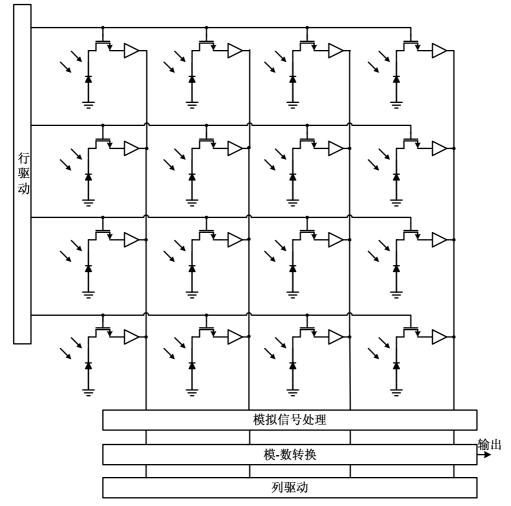

与 CCD 不同,在 CMOS 图像传感器中,像素单元上电荷产生的电压信号就像随机访问存储器(RAM)中一样利用行选择和列选择电路一次读出一行,如图 1-2 所示。CCD 和 CMOS 图像传感器由于读出结构不同,拥有各自不同的优缺点。CCD 传感器中电荷转移是无源的所以不会引入由于器件不对称产生的像素间噪声,即固定模式噪声(FPN);CMOS 传感器中含有有源器件所以会产生 FPN 噪声。CCD 传感器顺序读出信息的结构限制了它的读出速度,而且它需要高变化率高压时钟来满足电荷转移效率所以功耗很大;CMOS 传感器的随机读出结构保证了较高的读出速度和更低的功耗。

CCD 和 CMOS 图像传感器制造技术的不同也导致它们一些其它特性的不同。 CCD 图像传感器的制造是采用独特的为图像传感和电荷转移而优化的特殊工艺,同时,可控的制造工艺技术能够降低像素尺寸而不影响性能,但是缺点是使用这种特殊工艺不能实现整个图像系统芯片的片上集成。而 CMOS 图像传感器是由标准 CMOS 工艺制造,所以可以与模拟和数字处理电路和控制电路集成在同一块芯片中,这样就可以进一步降低系统功耗和芯片面积,而且还便于增加传感器的其它功能。

图 1-2 CMOS 图像传感器中的读出结构

在最近的十年间,由于无线和便携式电子快速发展,使得人们对微型化的、低功耗的和性价比高的图像传感器系统的需求持续上升。由于 CMOS 传感器的功耗比 CCD 传感器低三分之一到 100 倍<sup>[8]</sup>,所以导致在技术领域出现从基于电荷耦合器件 (CCD)的图像传感器到基于互补金属氧化物半导体 (CMOS)图像传感器的转移,因为 CMOS 图像传感器有潜在的片上集成低功耗信号处理电路和降低元器件和封装成本的优势。在 21 世纪,以 CMOS 图像传感器为核心的数码相机、微型和超微型摄象机可以广泛用于监控、保安、自动化、可视电话、可视门铃、图象采集等方面<sup>[9]</sup>,甚至应用到高端的医疗诊断系统<sup>[10]</sup>和生物医疗器械领域<sup>[11]</sup>。由于 CMOS 摄象系统存在功耗低、自动记时、随时存取、无损读取、抗光晕和耐辐射等优点, 所以 CMOS 图像传感器具有巨大和良好的市场发展前景。

在半导体技术快速进步、集成度成倍提高和工艺迅速发展的今天, CMOS 图像

传感器在高性能图像传感系统领域中的优势日益明显并逐渐超过 CCD 传感器成为研究的热点。为了使我国的集成电路产业得到长远的发展,芯片设计与研究开发水平不断提高,为了在 21 世纪我国更好的在全球数码摄像和移动通信等高科技领域发展,为了我国在图像传感器国际应用市场占有一席之地,必须重视高新图像传感技术的科研发展并加大该领域的投资,因此 CMOS 图像传感器的课题研究和 CMOS 图像传感器电路的优化设计具有非常重大的意义。本文主要针对 CMOS 图像传感器系统进行研究并对其中的关键模拟电路进行分析与设计。

#### 1.2 CMOS 图像传感器的国内外研究现状

CMOS 图像传感器由最开始的无源像素传感器(PPS)发展到有源像素传感器(APS),分辨率不断提高,从 256 像素到现在的千万像素。随着超大规模集成电路工艺水平的提高,CMOS 图像传感器采用的 CMOS 工艺尺寸从原来的几微米下降到 0.18 微米甚至更低;与提升图像传感器性能密切相关的彩色滤波器阵列技术、微透镜阵列制备技术、抑制噪声技术和深亚微米光刻技术等关键技术也逐渐发展起来并且不断有新的突破。在应用方面,微型化摄像机、数码相机、PDA 和保安监控设备的巨大市场需求也推动了高性能 CMOS 图像传感器的研发。CMOS 图像传感器使用的工艺在 1993 年还是 2um,到 1996 年已经发展到 0.25um<sup>[12]</sup>,目前 CMOS 传感器大都采用 0.35um 或 0.18um 的 CMOS 制造工艺,单元面积上的像素数已经可以达到或超过 CCD 器件的高分辨率水平。

在国外, CMOS 图像传感器的研究一直处于比较领先的地位:美国的哥伦比亚大学和喷气推进实验室(JPL)在1994年首次研制成功一种高性能的 CMOS 图像传感器,采用1.2um CMOS n 阱工艺,分辨率为128×128,像素尺寸为40um×40um,管芯尺寸为6.8mm×6.8mm,其动态范围达到72dB,固定模式噪声(FPN)小于0.15%饱和信号水平;美国工业界的Foveon公司和国家半导体公司于2000年又采用0.18微米工艺成功研制了一种分辨率高达一千六百万像素的CMOS 图像传感器,其像素尺寸是5um×5um,管芯尺寸为22mm×22mm<sup>[13]</sup>。在日本,东芝公司于1997年研制成功了640×480像素的光敏二极管型CMOS有源像素图像传感器,其像素尺寸是5.6um×5.6um,具有彩色滤色膜和微透镜阵列<sup>[14]</sup>;佳能公司在2000年也推出了像素更高的大尺寸CMOS 图像传感器。仅仅提高图像传感器的分辨率并不能成为CMOS图像传感器的发展趋势,2003年,Cho等人发表了一种分辨率为176×144的片上照

相机的研究,它在 1.5V 电源电压下的功耗仅为 550uW<sup>[15]</sup>。在 Cho 等人的研究中,首次在各模块设计层次上进行低功耗图像传感器的设计方法学考虑。2008 年,Alexander Fish 等人相继对 CMOS 图像传感器低功耗设计方法进行了研究,并对设计的各层次进行了优化<sup>[16]</sup>。最近几年,CMOS 图像传感器的性能不断提高,一些 CMOS 图像传感器的总体动态范围已经高达 120dB<sup>[17]</sup>甚至超过了 130dB<sup>[18]</sup>,像素随机噪声和暗电流分别可低于 4.8e $^{r}$ ms<sup>[19]</sup>和 15e $^{-}$ /s<sup>[20]</sup>,系统图像获取部分总噪声小于 1mV<sup>[21]</sup>。

现阶段国外对于 CMOS 图像传感器的研究主要向高速、低功耗、低噪声、大动态范围、高填充率和高精度并且带有数字接口的方向发展。

在国内,对 CMOS 图像传感器技术领域的研究还相对比较落后。国内一些大学和研究机构如天津大学、西安电子科技大学、中科院微电子研究中心等都对 CMOS 图像传感器的电路和芯片设计进行了分析研究;国内的一些公司如北京中星科技和格科微电子(上海)等也成功的开发了一些 CMOS 图像传感器产品。但是在总体上,国内大多数公司和厂商缺乏核心技术和品牌优势,CMOS 图像传感器的功耗、动态范围等性能参数与国外公司产品相比差距仍然比较大。

#### 1.3 后续章节安排

第二章主要介绍 CMOS 图像传感器的基础理论,第三章介绍 CMOS 图像传感器的系统结构,描述各个关键电路模块所实现的功能。第四章分别对 CMOS 图像传感器中的像素单元电路、模拟信号处理电路、带隙基准源电路和模数转换模块中的斜坡发生器和比较器电路进行分析研究与设计。最后,CMOS 图像传感器关键电路的总体仿真、结果分析和整体性能参数计算在第五章中进行,结论与展望写在本文的第六章。

#### 2 CMOS 图像传感器的基础理论

CMOS 图像传感器是通过光电二极管阵列把图像上一定范围的光信号转换成对应的一系列电压信号,然后进一步转换成一串数字信号输出。所以光电二极管作为光探测敏感元件是整个 CMOS 图像传感器系统中最重要和最基本的部分。而包含了一个光电二极管,几个晶体管和放大器的像素单元电路是 CMOS 图像传感器的核心。由一系列像素单元电路组成的图像传感器阵列可以实现初始光强信号到易探测的模拟电压信号的转变,然后进一步使电压信号顺利读出。以下就具体说明光电二极管的工作原理和模型的建立。

#### 2.1 光电二极管工作原理

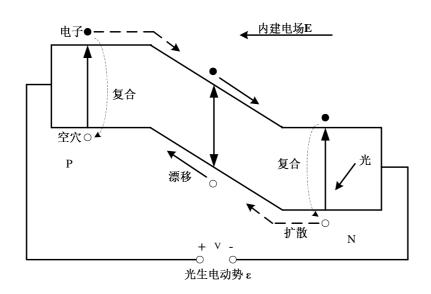

用一定波长的光照射半导体 p-n 结时,由于内建电场的作用,p-n 结内部产生电动势;如果将 p-n 结短接,则会出现光生电流。这种由内建电场引起的光电效应称为光生伏特效应。CMOS 图像传感器中光电二极管(Photodiode, PD)把光信号转换为电信号的功能就是由半导体 PN 结的光生伏特效应实现的。

图 2-1 光生伏特效应

如图 2-1 所示,当入射光作用在 PN 结时,如果光子的能量  $E_0$  大于或等于带隙  $E_g$ ,就会发生受激吸收,即价带的电子吸收光子的能量跃迁到导带形成光生电子-空穴对。由于光子的能量为

$$E_0 = hv = \frac{hc}{\lambda} \tag{2-1}$$

其中 h 表示普朗克常数, v 表示光的频率, c 为光速,  $\lambda$  为入射光波长; 又因为在可见光区红光的波长约为 700nm 最大, 所以由式 (2-1) 可得最小的光子能量  $E_0$  等于 1.8eV,大于半导体硅的禁带宽度 1.12eV,即整个可见光区的光子都可以激发半导体硅 p-n 结产生载流子。在光激发下多数载流子浓度一般改变很小,而少数载流子浓度却变化很大,因此主要分析光生少数载流子的运动 $[^{22}]$ 。

在空间电荷区,由于内建电场的作用,电子向 N 区运动,空穴向 P 区运动,形成漂移电流。在 p-n 结两边是没有电场的中性区,由于热运动,p-n 结两边的部分光生少数载流子通过扩散运动可能进入空间电荷区,然后在内建电场的作用下,光照产生的少数载流子各自向相反方向运动,从而在 p-n 结内部形成自 n 区向 p 区的光生电流  $I_r$ 。漂移电流分量和扩散电流分量的总和即为光生电流。

当与 P 区和 N 区连接的电路开路时,便在两端产生电动势  $\varepsilon$ ,这种效应称为光生伏特效应。当连接的外电路接通时,N 区过剩的电子通过外部电路流向 P 区。同样,P 区的空穴流向 N 区,便形成了光生电流。当入射光变化时,光生电流随之作线性变化,从而把光信号转换成电信号。

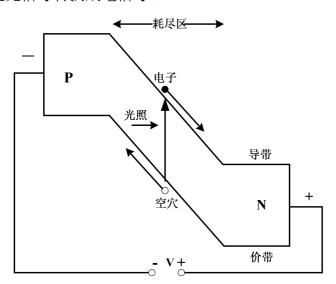

图 2-2 反向偏压下的 p-n 结光电二极管

由 PN 结构成的光电二极管是在反向偏置状态下工作,反向偏压下的能带如图 2-2 所示,当 p-n 结加反向偏压 V 时,反向偏压在势垒区产生的电场与内建电场方向一致,势垒区的电场增强,因而耗尽区的宽度也变大。施加适当反向偏压的目的是

增加耗尽区的宽度,减小 p-n 结两边中性区的宽度,从而减小光生电流中的扩散分量。由于载流子的扩散运动比漂移运动慢很多,所以减小光生电流中扩散分量的比例就可以显著提高响应速度。

#### 2.2 光电二极管模型的建立

在研究 CMOS 图像传感器的结构及电路之前清楚地了解光电二极管的特性是非常重要的,因此需要对光电二极管建立正确的模型。基于标准的 CMOS 工艺, CMOS 图像传感器所使用的光电二极管主要分为两层结构(n+-p 衬底, nwell-p 衬底), 三层结构(p+-n 阱-p 衬底)和多层结构。根据文献<sup>[23]</sup>采用待定系数的方法求解少数载流子的稳态连续性方程,建立了两层结构的模型,并推导得出光电流与入射光功率的关系。

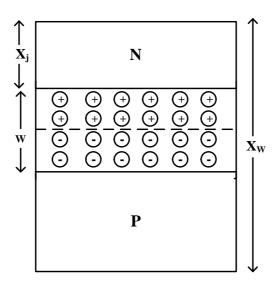

光电二极管的物理结构如图 2-3 所示,它可以表示 n+-psub。图中用符号表示了各层的厚度。

图 2-3 两层结构 n+ - Psub 光电二极管

光电二极管入射光通量Φ随入射深度的增加呈指数衰减的关系可表示为

$$\Phi(x) = \Phi_0 \cdot e^{-\alpha x} \tag{2-2}$$

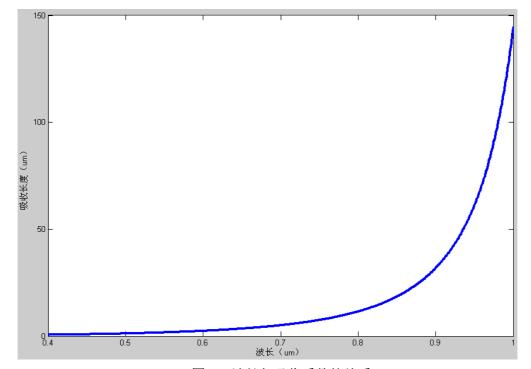

其中,x 表示光的入射深度, $\alpha$  表示光的吸收系数。 $\alpha$  与入射光的波长  $\lambda$  的关系 [24]可表示为

$$\alpha = \left(\frac{84.732}{\lambda} - 76.417\right)^2 cm^{-1} \tag{2-3}$$

λ表示波长, α是吸收长度的倒数。吸收长度定义为在某种特定波长的光的光通量衰减到初始值的 1/e 时所经历的距离。图 2-4 表示了波长与吸收系数的关系。

图 2-4 波长与吸收系数的关系

设Φ0是受光处的单位面积的光通量,可以表示为:

$$\Phi_0 = \frac{P_{opT} \cdot (1 - R)}{h\nu} \tag{2-4}$$

其中 Popt 表示单位面积的光功率, R 是光反射系数, h 为普朗克常数, v 表示入射光频率。n+-P 衬底光电二极管的物理结构如图 2-3 所示,分为 N 区、P 区和空间电荷区三个区域,每个区域都对电流有贡献。N 区和 P 区中的光生少数载流子通过扩散运动产生电流;在空间电荷区的内建电场作用下电子-空穴对通过漂移运动产生光电流。首先计算 N 区的电流密度, N 型半导体扩散方程为:

$$D_{P}\frac{\partial^{2} P_{n}}{\partial x^{2}} - \frac{P_{n} - P_{n0}}{\tau_{P}} + G(x) = 0$$

(2-5)

其中 Dp 是空穴扩散系数, τ p 为少子寿命, Pn<sub>0</sub>是少子平衡浓度, Pn 为光照后总的空穴浓度, G(x)为光生载流子的产生率。式(2-5)左边第一项表示单位时间单位体积内积累的电子-空穴对数,第二项是由于复合作用消失掉的电子-空穴对数,式(2-5)表示在光照恒定情况下,单位时间内产生的电子-空穴对数与复合的电子-空穴对数相等。光生载流子产生率

$$G(x) = -\frac{\partial \Phi(x)}{\partial x} = \alpha \Phi_0 \cdot e^{-\alpha x}$$

(2-6)

扩散方程边界条件是:

$$P_n(x_j) = P_{n0} \cdot e^{(-\frac{qV}{kT})}$$

(2-7)

$$qD_{p} \cdot \frac{\partial P_{n}(x)}{\partial x} \bigg|_{x=0} = -qS_{p}(P_{n}(0) - P_{n0})$$

(2-8)

其中 Sp 为表面空穴复合速率。式(2-5)的解为:

$$P_n(x) = P_{n0} + k_p e^{(-\alpha x)} + C_1 e^{(-x/Lp)} + C_2 e^{(x/Lp)}$$

(2-9)

其中 $k_p = \frac{\Phi_0 \cdot \alpha \cdot \tau_p}{1 - \alpha^2 L_p^2}$ ,  $L_p = \sqrt{D_p \cdot \tau_p}$ , 因此 N 区扩散电流密度为:

$$J_N = qD_p \cdot \frac{\partial P_n(x)}{\partial x} \bigg|_{x = x_i}$$

(2-10)

同样,根据P区扩散方程

$$D_n \frac{\partial^2 n_p}{\partial x^2} - \frac{n_p - n_{p0}}{\tau_n} + G(x) = 0$$

(2-11)

和方程边界条件:

$$n_p(x_j + w) = n_{p0} \cdot e^{(-\frac{qV}{kT})}$$

(2-12)

$$qD_n \frac{\partial n_p}{\partial x}\bigg|_{x=x_w} = qS_n(n_p(x_w) - n_{p0})$$

(2-13)

得到式(2-11)的解为:

$$n_p(x) = n_{p0} + k_n e^{(-\alpha x)} + C_3 e^{(-x/L_n)} + C_4 e^{(x/L_n)}$$

(2-14)

其中,  $k_n = \frac{\Phi_0 \cdot \alpha \cdot \tau_n}{1 - \alpha^2 L_n^2}$ ,  $L_n = \sqrt{\tau_n \cdot D_n}$ , 因此 P 区扩散电流密度为:

$$J_p = -qD_n \frac{\partial n_p(x)}{\partial x} \bigg|_{x = x_j + w}$$

(2-15)

再计算空间电荷区的电流密度,在空间电荷区,光生载流子的漂移电流密度为:

$$J_{drift} = q \int_{i}^{x+w} G(x) dx = q \Phi_0 \cdot e^{(-\alpha x_j)} \cdot (1 - e^{(-\alpha w)})$$

(2-16)

因此,得出总的光电流密度是:

$$J_{total} = J_N + J_P + J_{drif}t \tag{2-17}$$

本文比较关注的是光电流  $I_{ph}$  与光功率  $P_{OPT}$  的关系,首先计算  $J_N$  与光功率的关系,由式(2-9)和(2-10)得到:

$$J_{N} = qD_{p} \cdot \left( -\alpha \cdot k_{p} \cdot e^{-\alpha x} - \frac{1}{L_{p}} e^{-\frac{1}{L_{p}} x} + \frac{1}{L_{p}} e^{\frac{1}{L_{p}} x} \right) \Big|_{x = x_{i}}$$

(2-18)

把  $k_p = \frac{\Phi_0 \cdot \alpha \cdot \tau_p}{1 - \alpha^2 L_p^2}$ , 和式 (2-4) 代入式 (2-18) 中, 对于给定的光电二极管和一

定波长的入射光,得到电流密度  $J_N$ 与光功率  $P_{opT}$ 的关系:

$$J_N = A \cdot P_{opt} + D_1 \tag{2-19}$$

其中系数 A 和 D<sub>1</sub> 与光功率 P<sub>opT</sub> 无关, 同理得到:

$$J_P = B \cdot P_{opt} + D_2 \tag{2-20}$$

$$J_{drift} = C \cdot P_{opt} \tag{2-21}$$

综合式 (2-19), (2-20) 和 (2-21), 光电流密度可进一步表示为

$$J_{total} = (A + B + C) \cdot P_{opT} + D_1 + D_2 = K_0 \cdot P_{opT} + C_0$$

(2-22)

系数  $K_0$ 、 $C_0$  为与光功率  $P_{OPT}$  无关的常数。由此可知光电流与入射光功率成线性关系,所以在 CMOS 图像传感器中,通过含有光电二极管的像素单元就可以实现从图像和光强信号到电信号的光电线性变换。

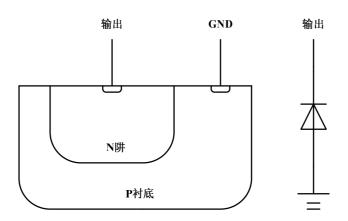

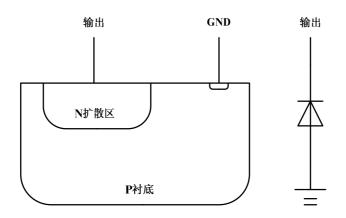

图 2-5 N 阱-P 衬底结型光电二极管

在实际应用中,关于 CMOS 图像传感器中光电二极管的类型,一般都采用 N 阱/P 衬底型的 PN 结光电二极管。两种常用的结型光电二极管如图 2-5 和图 2-6 所示。 N 扩散区—P 衬底型光电二极管在先进 CMOS 制造工艺中是浅结,这种浅结会降低

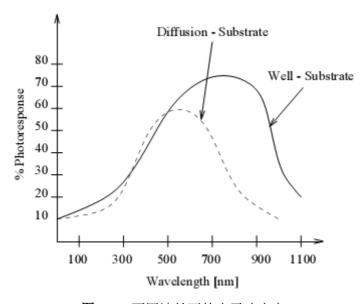

二极管的光子响应效率所以只能用于探测较短波长的光。N 阱—P 衬底型二极管有更宽的耗尽区,光子更易集中在阱上;而且这种二极管的结深比较大,在长光波段比 N 扩散区—P 衬底型二极管有更好的光子响应效率。光电二极管的典型特性如图 2-7 所示<sup>[7]</sup>。

图 2-6 扩散区-衬底结型光电二极管

图 2-7 不同波长下的光子响应率

#### 2.3 本章小结

本章详细阐述了 CMOS 图像传感器的核心器件光电二极管的基本原理,得出它在反偏状态下工作具有较高的效率。然后在对光电二极管建模的基础上,对其实现

光-电线性转换的特性进行了理论推导,得到了光电流与入射光之间的线性关系;之后又介绍了实际应用中适用于 CMOS 图像传感器的两种光电二极管类型。

#### 3 CMOS 图像传感器系统的研究与分析

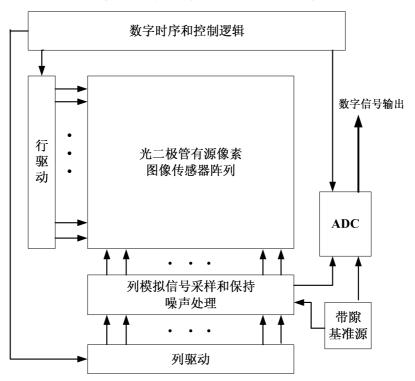

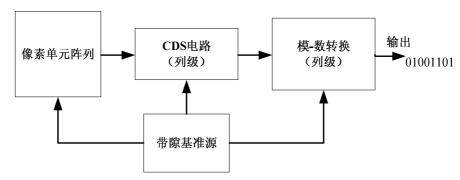

CMOS 图像传感器系统由光电二极管传感器阵列、模拟信号处理电路、带隙基准电路、地址译码和驱动电路、数字时序与逻辑控制电路和模-数转换电路等构成,如图 3-1 所示。其中关键电路包括像素单元电路模块,信号采样与保持模块,噪声降低处理模块和带隙电压产生模块。本章将对这些关键电路模块进行系统的研究分析。

图 3-1 CMOS 图像传感器系统结构框图

#### 3.1 本像素阵列与像素单元电路

CMOS 图像传感器的像素阵列是由 M 行×N 列的光电二极管(PD)阵列组成,即图像传感器阵列中包含 M×N 个像素单元,而每个像素单元中又包含一个光点二极管。CMOS 图像传感器阵列中的像素单元分为无源、有源和光栅型三种类型,其中最常用的像素单元是由三个晶体管和一个光电二极管所组成的有源像素单元(Active Pixel Sensor, APS)。这个光电二极管和这三个晶体管组成了的像素内部的读出电路,实现了把像素中的光信号转变为电信号并放大读出的功能。CMOS 有源像素传感器因为具有低电压、低功耗和片上集成功能等优点而被广泛的使用<sup>[25]</sup>。

CMOS 图像传感器每个像素单元中的光电探测器可以选择用 p-n 型、p-i-n 型或者光栅型光电二极管。像素阵列所消耗的功耗与阵列的规模大小(即分辨率大小)和其中的像素单元类型直接相关,一般是从几百 nW 到几百 mW。在设计中一般都采用 APS 像素单元,像素单元中的放大器的设计成为了决定 CMOS 图像传感器性能好坏的关键,大部分的放大器设计都采用了源极跟随的结构来实现,但是选择其它类型的放大器或者设计不同的有源像素单元电路有时也会大幅提高传感器某一方面的性能:文献<sup>[26]</sup>介绍了一种 shutter APS 像素单元,大大提高了图像传感器的动态范围;文献<sup>[27]</sup>提出了一种采用条件重置的像素单元电路,也增大了动态范围并降低了功耗。但是上述文献中提出的这两种像素单元占用了较大的面积,降低了 CMOS 图像传感器的填充率,芯片成本较高。为了平衡图像传感器在功耗、动态范围、填充率和面积等方面的性能,像素单元的设计需要更好的折衷。

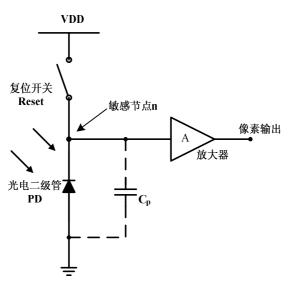

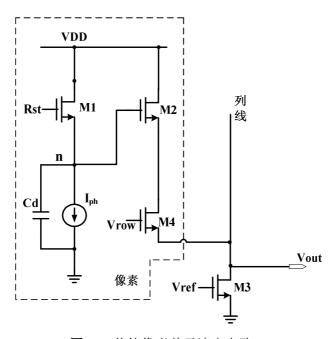

本文采用有源像素单元读出电路,如图 3-2 所示。

图 3-2 有源像素单元读出电路

一个复位开关控制着 3.3V 的电源 VDD 与光电二极管 PD 连接与否。当光照射 到像素单元中的光电二极管上,p-n 结上产生反向电流  $I_L$ ,根据本文第二章第二节对 光电流与光强关系的分析,可知光电流  $I_L$  与光照强度是成线性关系,其具体关系  $[^{28}]$  可表示为:

$$I_L = \frac{qA\eta\lambda P}{hc} \tag{3-1}$$

其中,q 为电子电荷,A 表示光电二极管的光敏面积,n 为光电转换效率, $\lambda$  是入射光波长,P 为入射光功率,h 为普朗克常数,c 为光速。像素单元电路的工作波

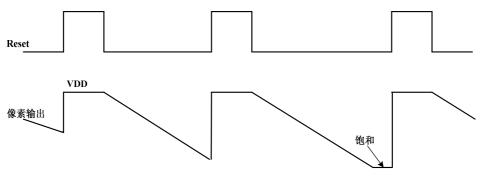

形示意图如图 3-3 所示。

图 3-3 像素单元工作波形示意图

当 reset 开关导通时,光电二极管 PD 反偏,由于光电二极管的两端存在寄生电容 Cp,电荷在电容 Cp 上积分,敏感节点 n 的电压为电源电压 3.3V。像素单元电路中敏感节点 n 与一个有源放大器连接,在输出端输出一个较高电平的复位电压信号。

当 reset 开关断开后,CMOS 图像传感器开始曝光,由于光电二极管 PD 受到光照产生反向的光电流,使敏感节点 n 处的电压逐渐下降,像素单元电路输出端的电压也逐渐跟随下降,输出端的波形示意图如上图 3-3 所示。由式(3-1)可知,对于每个特定的像素单元,光电流  $I_L$ 与光照强度成正比,又因为电容 Cp 上的电压变化与电荷变化具有以下关系

$$\Delta V = \frac{\Delta Q}{C_p} = \frac{I_L \cdot \Delta T \text{ int}}{C_p}$$

(3-2)

所以敏感节点 n 处的电压变化量  $\Delta V$  与该点的光强成正比,在特定的曝光时间  $T_{int}$  下,根据式(3-1)和(3-2),模块输出端电压的变化量就反应了该像素单元所感受到的光功率 P 的大小。进一步,通过 m 行 $\times n$  列的整个像素单元阵列,CMOS 图像传感器就可以探测到目标图像每一点的光强大小并输出相应的一系列模拟电压值,从而实现了线性光电转换功能。

但是,对于一个非理想的 NMOS 晶体管开关,由于阈值电压的存在使得敏感节点 n 处的最大电压 Vmax 不能达到电源电压 3.3V, Vmax 的值为 Vdd – Vth, 因此像素单元不能实现满摆幅的输出。同时,根据式(3-2),敏感节点 n 处的寄生电容 Cp 的大小决定着输出电压单位时间的变化量,即节点电容越小,信号感应越灵敏。这些能够影响 CMOS 图像传感器性能的因素在具体电路设计中应该重点关注和考虑。

像素单元模块中放大器的作用是防止输出端的负载对敏感节点 n 产生影响。放大器的输入电容会被计算到敏感节点 n 的总电容中,所以会影响到像素的灵敏度。

对于 APS 图像传感器,由于每个像素单元中都需要加入一个放大器,所以它会影响到像素阵列的总体面积和光敏面积与像素面积的比率,即填充率(Fill Factor)的大小。由于放大器的输入和输出电压大小都反应着光信号的强弱,所以在信号经过放大器的传输过程中不能允许有信号的损失,即放大器一般要采用单位增益放大器。同时,放大器上的噪声也直接影响着像素单元的性能。通过以上分析,像素单元中的放大器应该尽量满足小输入电容、无信号损失、大输入输出摆幅、面积小和低噪声的要求,在设计中要求特别注意。

#### 3.2 模拟信号处理电路模块

模拟信号处理电路主要是用来实现像素单元输出信号的采样与保持,得到准确反映光强大小的模拟电压(与光强呈线性关系)并降低固定模式噪声(Fixed Pattern Noise, FPN)的功能。该模块一般包括双关双采样(Correlated Double Sampling, CDS)电路和运算放大电路<sup>[29]</sup>。为了实现像素阵列信息的快速读出,大多数模拟信号处理电路模块都是采用列级的结构,即阵列中的每一列像素共同对应一个采样与保持电路和运算放大电路。对于列级模拟信号处理电路模块,被选择的一整行像素信息会同时被采样并输入到 CDS 电路中处理。由于模拟信号处理电路模块中一般采用相关双采样(CDS)的方法,所以对于一个 N 列的 CMOS 图像传感器阵列,其列线最底端需要连接由 2×M 个采样保持电容和 M 个用来降低信号噪声的放大器构成的电路模块。也有些模拟信号处理电路采用其它类型的多次采样技术进一步减小读出噪声 [30-32],还有些电路甚至不包括 CDS 电路和运算放大器,而是直接使用模拟可控增益放大器(VGA)来进行信号处理和进一步放大。

1/f 噪声、KTC 噪声和固定模式噪声(FPN)是 CMOS 图像传感器读出电路中最主要的噪声源,如果此类噪声发生在前级,那么噪声将经过放大器放大 A 倍传输到后级,对电路性能危害很大。所以为了提高输出信号的信噪比和动态范围,必须在前级将噪声消除<sup>[13]</sup>。CMOS 图像传感器系统中的模拟信号处理电路采用相关双采样技术(CDS)实现噪声抑制。

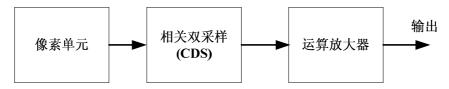

图 3-4 是 CMOS 图像传感器的前端设计和相关双取样电路的系统设计结构框图。

#### 图 3-4 前端系统设计结构框图

在图 3-4 中,前端设计和模拟信号处理电路系统主要由像素单元、相关双采样电路和运算放大器三个模块组成。像素单元电路完成光电线性转换功能,信号经过相关双采样模块存储在采样电容中,由于电容上的电压(或电荷)不能突变,即来自同一电路的噪声电压在时间上具有相关性,利用这种噪声电压在时间上的相关性在很短的时间内两次采样同一单元的信号,然后再通过运算放大器将两次采样信号相减,就可达到消除或减弱 1/f 噪声、KTC 噪声和固定模式噪声(FPN)的目的。

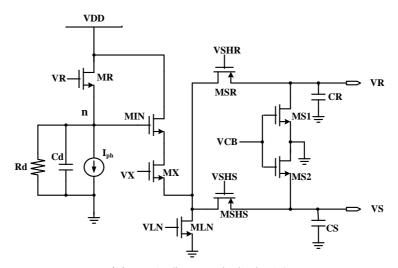

经典结构的相关双采样电路[29]如图 3-5 所示。

图 3-5 经典 CDS 电路原理图

在经典 CDS 电路中,光电二极管用电流源 Iph、电容 Cd 和电阻 Rd 来等效模拟,复位开关为 NMOS 晶体管 MR。NMOS 管 MLN 和 MIN 构成源极跟随放大器,PMOS 管 MSR 和 MSHS 是两个信号传输门,电容 CR 与 CS 构成两个采样电容,NMOS 管 MS1 和 MS2 用来给采样电容清零。

电路工作时序波形如图 3-6 所示, 电路工作原理如下:

图 3-6 CDS 电路工作时序波形

- (1) 采样复位信号 Vr: 时间 t 从 0 到 t0 过程中,复位开关管 MR 在复位信号 VR 控制作用下导通, n 点电位变为一高电平电压, VX 与 VLN 保持高电平; 在 t0 时刻图像传感器开始曝光, n 点电压通过源跟随器和传输门 MSR, 输出的第一个复位电压信号 Vr 被采样到电容 CR 上。

- (2) 采样积分信号 Vs: 从 t1 到 t2 过程中,两传输门断开,不进行信号采样,由于光电流 Iph 的作用使 n 点处的积分电压逐渐下降。在 t2 时刻,传输门 MSHS 导通,此时 n 点电压通过源跟随器和传输门,输出的第二个积分电压信号 Vs 被采样到电容 CS 上。

- (3) 实现 Vr-Vs: 在 t3 时刻,两个采样电容上的信号 Vr 和 Vs 分别输入到运算放大器的差分输入端,根据图 3-4 的相关双采样原理实现两信号相减。最后运放输出为纯光信号电压  $\Delta V$ ,大部分噪声被抑制。这样就实现了一个周期的光-电线性转换和噪声抑制功能。

#### 3.3 模一数转换(ADC)模块

模-数转换(ADC)模块是用来将模拟信号处理电路模块输出的与像素中光强成正比的电压信号转换成数字信号,实现图像信号的数字化输出。在 CMOS 图像传感器当中可以采用以下三种级别的 ADC: (1) 像素级 ADC,即阵列中的每个像素单元都要包含一个 ADC; (2) 列级 ADC,即每一列像素共用一个位于阵列底部的 ADC; (3) 芯片级 ADC,即整个传感器阵列只使用一个 ADC 电路。图 3-1 所示的 CMOS

图像传感器系统结构框图中采用的是芯片级的 ADC 电路。

早期的商业 CMOS 图像传感器通常使用一个单一的芯片级 ADC<sup>[33~34]</sup>。对于芯片级的 ADC 电路,因为只含有一个 ADC 模块,所以总体芯片的面积较小,功耗较低;然而,为了提高图像传感器的总体性能尤其是速度方面的性能,系统需要采用高速的 ADC 类型,如速度最快的 pipeline 型 ADC。但是,流水线 A/D 转换器各流水线级的余差放大器增大了流水线 A/D 转换器的功耗,而且硬件电路设计难度也较大,成本高。随着 CMOS 图像传感器像素阵列的不断扩大,芯片级 ADC 越来越难满足高性能的图像传感器的要求。

对于像素级的 ADC 电路,具有并行处理、高信噪比、对 A/D 转换器的速度要求最低等优点,但是每个像素中都包含一个 ADC 使得 CMOS 图像传感器像素单元占用了过大的面积,填充率大大降低,版图复杂。

最近几年,列级 ADC 开始变的常用起来<sup>[35~36]</sup>,因为采用折衷的列级 ADC 结构,既可以并行传输数据保持较高的速度,又不会占用太多的芯片面积,对 ADC 的速度要求也没有芯片级的高,而且不会降低像素的灵敏度和填充率。一般列级 ADC 可以采用单斜率结构模数转换器来实现,其中一种列级多斜坡的单斜率 ADC 可以实现更快的总体转换速度<sup>[37]</sup>。本设计选用较简单的 single-slope 型 ADC,其电路主要包括斜坡发生器和比较器两个关键模拟电路,具体的内容在第四章中论述。

#### 3.4 带隙基准源模块

带隙基准源模块是用来为芯片中的其它模块如模拟信号处理电路和ADC电路等产生一个稳定的模拟偏置电压,整个芯片共用一个带隙模块。由于 CMOS 图像传感器在大部分时间里都需要这个偏置电路保持工作状态,所以这个模块所消耗的功耗应该尽可能的小,但是如果带隙基准源模块的驱动能力不足又会引入新的噪声。实际上,在很多 CMOS 图像传感器中带隙基准源模块所消耗的功耗都非常小以至于可以忽略掉。

由于设计中电路其它模块的偏置参考电压都设定在 1.25V 左右, 所以设计采用 经典结构的带隙电压基准源电路, 具体的设计写在第四章。

#### 3.5 其它外围电路模块

CMOS 图像传感器系统中的其它外围电路模块包括选择与驱动电路,还有时钟

产生和数字控制模块。

与 CCD 传感器不同, CMOS 图像传感器的读出方式与存储器类似,是采用行地址译码和列地址译码来控制像素单元阵列读出图像信号。所有像素信号都是整行整行的读出到模拟信号处理电路模块中,然后在列驱动电路的控制下被处理放大并输出到 ADC 中。

在选择与驱动电路中,行选择和列选择电路一般采用模拟多路选择器、数字译码器或移位寄存器实现。对于一个M行 $\times N$ 列的图像传感器阵列,在系统采用列级采样与保持电路和列级的模-数转换电路情况下,行地址总线的宽度应该大于等于 $\log_2 M$ ,列多路选择器的地址线宽度则应该大于 $\log_2 N$ 。

CMOS 图像传感器中的时钟产生和数字控制模块是用来控制整个图像传感器系统的工作和运行。在图像传感器阵列的行列控制选择、相关双采样电路中的时序控制、ADC 电路中的时序、时钟和计数器的计数控制、以及把 M×N 个 8 位二进制数据通过多路选择器输入到存储器的过程中都需要时钟产生和数字控制模块的正常运行。把这个数字模块集成在图像传感器芯片中可以减少输入输出管脚的数量,减小芯片面积,实现 SOC 片上集成。数字模块部分采用硬件描述语言编写实现,性能良好正常工作的数字模块可以保证 CMOS 图像传感器中各个模块的时钟同步、ADC 的时序和像素阵列中数据的输出控制顺利进行,具有重要的意义。

#### 3.6 本章小结

本章首先介绍了 CMOS 图像传感器的系统结构,然后分别描述了各个子电路模块(像素阵列与像素单元电路、模拟信号处理电路、模-数转换电路、带隙基准源电路、选择与驱动电路和时钟产生与数字控制模块)实现的功能;同时,介绍了这些模块的不同实现方式对整个 CMOS 图像传感器性能参数的影响。

#### 4 CMOS 图像传感器的关键模拟电路设计

CMOS 图像传感器中的关键模拟电路如图 4-1 所示,四个主要模块共同实现图像信号的传感、处理与放大转换功能。

图 4-1 CMOS 图像传感器中的关键模拟电路模块

光信号进入像素单元,在像素单元电路模块中转化成大小与该束光强成正比的电压信号,接着,在前级电路中被引入噪声的电压信号被输出到 CDS 电路中,CDS 电路利用相关双采样原理大大降低电压信号中的噪声并且将信号毫无损失的处理放大。模数转换电路模块将电压信号转换成相应的一串 8 位二进制数字信号输出,这些8位的二进制数字大小就表示着不同像素中探测到的光强信号的强弱。一般 CMOS 图像传感器系统将这些数字信号存储到片上存储器中再进行进一步的数字图像处理。

下面各小节将分别介绍基于 SMIC 0.35um 2P3M 工艺的 CMOS 图像传感器各个关键模块模拟部分电路的设计。考虑到现阶段 CMOS 图像传感器大动态范围、低噪声和低功耗等方面的研究发展趋势,根据文献<sup>[13~21]</sup>,综合并且平衡考虑 CMOS 图像传感器的技术指标,本文设定如下预期的主要性能参数:

- (1) 分辨率 (像素总数): >1 万像素

- (2) 动态范围: >75dB

- (3) 功耗: <150mW

- (4) 输出电压摆幅: >1.2V

- (5) 总噪声: <1mV

- (6) 电源电压: 3.3V

- (7) 工艺: 0.35um CMOS

#### 4.1 像素单元电路设计

设计首先采用工艺较成熟的三管有源像素(APS)单元类型。传统的三管有源像素单元电路的基本结构如图 4-2 所示,图中虚线以内的部分为像素单元阵列中的一个像素单元,它包括一个复位管 M1,一个由 NMOS 管 M2 和 M3 组成的缓冲放大器(源极跟随器),一个行选通管 M4。

图 4-2 传统像素单元读出电路

M1~M4 均为 NMOS 晶体管。NMOS 管 M3 在其栅极偏置电压 Vref 作用下构成的电流源为整个一列像素所共用。RST 是复位信号,Vrow 为行选信号。Vout 输出端直接接到列线末端的采样与保持电路的输入端。

在像素单元电路的设计中,采用 CMOS 工艺中的 N+/P 衬底光电二极管作为光电探测器件,在图 4-2 的电路中用一个电流源 Iph 和电容 Cd 等效模拟。

根据 SMIC 提供的 0.35um 2P3M CMOS 工艺库中的参数, 先计算电容 Cd 的值, 取光电二极管的尺寸为 18um×18um, 则

$$C_{PD} = A_{PD} \cdot C_j = 18 \mu m \times 18 \mu m \times 1.01 \times 10^{-15} F / \mu m^2 \approx 0.33 pF$$

(4-1)

考虑到n点的寄生电容Cd的值会受到下一级放大器输入电容和复位管源极电容的影响,实际的Cd值应略大于光电二极管寄生电容 $C_{PD}$ ,所以取Cd=0.4pF来等效模拟。由式(3-1)知,光电流Iph的值与像素中入射光功率P和材料量子效率有关,

一般在 1pA~1uA, 在电路中取偏于中间值的 30nA 的电流源作为等效模型。

设计采用电流源作为负载的源极跟随器来增大驱动能力,减小外电路和列线上的容性和阻性负载对敏感节点 n 的影响。由于电流源是整列共用,电流不能太小否则驱动能力不足;另一方面考虑到传感器阵列中共需要 N 个电流源同时工作,电流太大会增加电路整体功耗,所以先取电流为 5uA。

由晶体管处于饱和工作状态下的电流方程

$$I = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{ref} - V_{th3})^2$$

(4-2)

可计算得出 M3 管的宽长比(W/L) 大小。

图 4-3 源极跟随器原理图

如上图 4-3 所示,对源极跟随器电路进行大信号分析,由于上下支路电流相等

$$\frac{1}{2}\mu_n C(\frac{W}{I})_3 (V_{ref} - V_{thn})^2 = \frac{1}{2}\mu_n C(\frac{W}{I})_2 (V_n - V_{out} - V_{thn})^2$$

(4-3)

可得到输出端电压

$$V_{out} = V_n - V_{thn} - \sqrt{\frac{K_3}{K_2}} (V_{ref} - V_{thn})$$

(4-4)

其中Kn表示管子的宽长比。又因为

$$V_n \approx V_{DD} - V_{thn} - \Delta V \tag{4-5}$$

$$\Delta V = \frac{\Delta Q}{C_d} = \frac{I_{ph} \cdot \Delta T_{\text{int}}}{C_d}$$

(4-6)

其中 $\Delta V$ 表示在曝光时间 $\Delta T$  int 内 n 点电压的变化量。由式(4-4)~(4-6),得

$$V_{out} = V_{DD} - 2V_{thn} - \frac{I_{ph} \cdot \Delta T_{int}}{C_d} - \sqrt{\frac{K_3}{K_2}} (V_{ref} - V_{thn})$$

(4-7)

所以输出电压最大值为

$$V_{out} = V_{DD} - 2V_{thn} \tag{4-8}$$

由式(4-8)知,像素单元电路的输出摆幅受到晶体管管 M1 和晶体管 M2 阈值电压的限制,当光强很大时,Iph 的值也很大,从第三章图 3-3 的像素单元工作波形示意图可以看出这种情况下像素输出很快就会饱和,造成图像传感器的动态范围降低,不能达到 CMOS 图像高性能的要求。

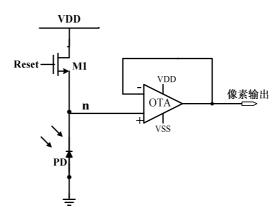

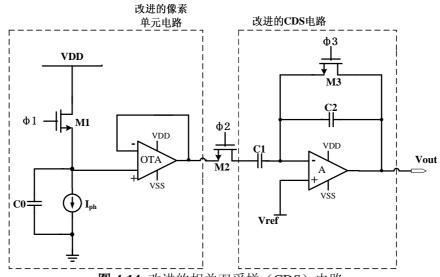

尽管传统像素单元中的源极跟随器可以提高读出速度和信噪比,但是源极跟随器也带来了诸如非线性度、灵敏度衰减和噪声等不理想特性<sup>[38~39]</sup>。因此,为了解决上述问题,改善 CMOS 图像传感器的动态范围和输出摆幅等性能,本文对像素单元电路进行优化设计,采用改进的像素单元电路,如图 4-4 所示。

图 4-4 改进的像素单元电路

在优化设计的像素单元电路中,仍然采用 NMOS 管复位开关,使用 NMOS 管主要是为了减小漏电流。在敏感节点 n 与外电路之间是一个单位增益缓冲放大器 (OTA)。此时的像素单元最大输出电压为

$$V_{out \max} = V_{n \max} \approx V_{DD} - V_{thn} \tag{4-9}$$

对比式 (4-9) 与式 (4-8),可知优化设计的像素单元电路使输出摆幅增大了  $V_{thn}$ ,约为 0.7V,电路性能得到改善,CMOS 图像传感器的动态范围提高。像素单元电路中单位缓冲放大器的设计如图 4-5 所示。

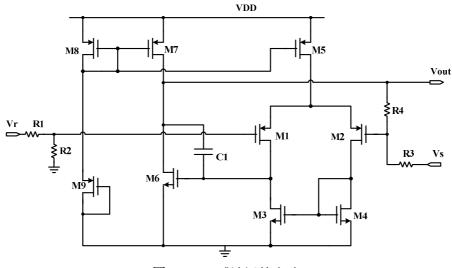

图 4-5 改进像素单元中的放大器

为了实现较高的增益,减小共模输入范围的最低限制,在放大器中对于输入管M1、M2 的尺寸设计要满足高跨导和低过驱动电压(V<sub>GS</sub>-V<sub>TH</sub>)。为了减小输入电容,设计中这些晶体管尽量采用最小沟长 0.35um。输出晶体管 M6、M7 要选取合适尺寸实现大的增益和大的输出摆幅。运放采用密勒补偿,补偿电容用 MOS 管电容(MOScap)来实现。

考虑到放大器输入信号的范围约为  $0\sim2.5V$ ,所以设计采用 PMOS 输入管 M1 和 M2。预设摆率 SR 为 10V/us,增益带宽为 10M,负载电容  $C_L$  为 3pF。根据文献  $[^{40]}$  的放大器经典设计过程,经过计算与仿真调试得到放大器具体参数如下表 4-1 所示。

| 符号 | 尺寸(um)    | 符号 | 尺寸 (um)   | 符号 | 尺寸 (um)   | 符号  | 值     |

|----|-----------|----|-----------|----|-----------|-----|-------|

| M1 | 2.45/0.35 | M4 | 0.5/0.5   | M7 | 16.8/0.35 | VDD | 3.3V  |

| M2 | 2.45/0.35 | M5 | 2.45/0.35 | M8 | 1/1       | C1  | 0.7pF |

| M3 | 0.5/0.5   | M6 | 6.3/0.35  | M9 | 1/32      |     |       |

表 4-1 放大器中尺寸和参数

运算放大器的增益为

$$A_V = A_{V1} \cdot A_{V2} \tag{4-10}$$

其中 Av1 和 Av2 分别是放大器第一级和第二级的增益。

$$A_{V1} = g_{m1} \cdot (r_{o1} / / r_{o3}) = \frac{74.0}{1.03 + 1.54} = 28.8$$

(4-11)

$$r_o = \frac{1}{g_{ds}} \tag{4-12}$$

$$A_{V2} = g_{m6} \cdot (r_o // r_{o7}) = \frac{743.3}{23.2 + 14.5} \approx 19.9$$

(4-13)

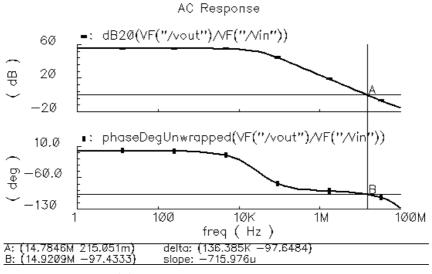

所以运算放大器总增益 Av≈573,与图 4-6 的仿真结果基本相同,运放的相位裕度为 82 度,增益带宽为 14.8M。

图 4-6 幅频特性和相频特性曲线

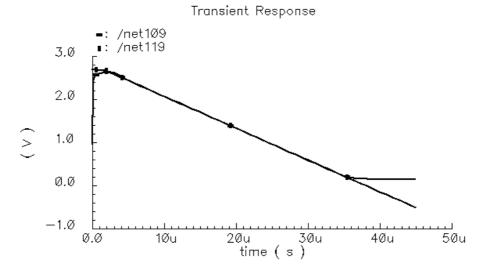

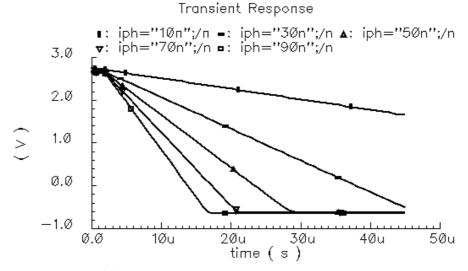

改进后的像素单元在光电流 Iph 为 30nA 时敏感节点 n 和输出端的输出波形如图 4-7 所示,从仿真波形图中可以看出改进像素单元电路的输出电压能够很好的跟随光电二极管敏感节点的光电转换电压,输出摆幅为 0.2~2.5V,性能明显优于传统像素单元电路。改进后的像素单元电路在不同光电流下的输出波形如图 4-8 所示,从图中可以看出,在 10us 的曝光时间内当光电流 Iph 高达 90nA 时,改进的像素单元输出仍然没有饱和,表示像素单元的最大非饱和信号与可探测到的最小信号(主要指像素暗电流,一般为 1fA)比例较高,即动态范围较大。

图 4-7 改进像素单元电路输出电压仿真波形

图 4-8 不同光强下改进像素单元的输出波形

#### 4.2 模拟信号处理电路的设计

在 CMOS 图像传感器的像素阵列中各个像素单元之间由于工艺和温度的偏差造成晶体管之间存在失配,不同像素单元的复位开关管之间阈值电压的偏差(在典型的 CMOS 工艺下有几十 mV 的偏差)会造成像素单元的输出在相同光照情况下存在固定偏差值,即固定模式噪声(FPN)。固定模式噪声将导致图像上出现条纹和斑点,严重影响图像质量。所以,在 CMOS 图像传感器中,需要在像素单元模块的输出端接入模拟信号处理电路来降低它的噪声。像素固定模式噪声一般在模拟信号处理电路中用相关双采样(CDS)技术进行消除。

#### 4.2.1 传统 CDS 电路设计

图 4-9 传统 CDS 电路设计

设计首先考虑用传统 CDS 电路实现信号采样保持和降低 FPN 噪声功能,电路如图 4-9 所示,两次采样信号 VR 和 VS 分别存储在电容 C1 和 C2 中。为了保证使采样与保持电路中的两个电容上的信号能够驱动具有较大负载的减法电路实现信号 VR 与 VS 相减,在 CDS 电路设计中,在采样与保持电路后面接入缓冲放大器来增强带负载能力。由于信号在采样与保持电路中的幅值并没有发生变化,即信号输入范围不变,所以单位增益缓冲放大器的设计仍然采用本章上一节介绍过的两级放大结构 OTA 实现。

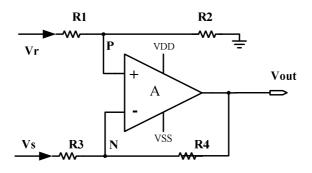

由于 VR 和 VS 是存储在电容上的两个大信号的直流信号,因此,不能使用一般的没有接入反馈的差分放大器来实现这两个信号相减,而应该用运算放大电路来实现。本文减法运算电路的设计如图 4-10 所示。

图 4-10 减法运算电路

为了节省设计时间,减法运算电路中的放大器采用前面提出过的共模输入范围较大的两级运放结构来实现。简化的电路结构如图 4-11 所示,从减法电路的结构上看,它是反相输入和同相输入结合的放大电路<sup>[41]</sup>。在理想运放的情况下有 Vp=Vn,由此可得下列方程式:

$$\frac{Vs - Vn}{R3} = \frac{Vn - Vout}{R4} \tag{4-14}$$

$$\frac{Vr - Vp}{R1} = \frac{Vp}{R2} \tag{4-15}$$

图 4-11 简化后的减法电路

由于 Vn=Vp, 由式 (4-14) 解出 Vn, 然后代入式 (4-15) 得

$$Vout = (\frac{R3 + V4}{R3})(\frac{R2}{R1 + R2})Vr - \frac{R4}{R3}Vs$$

(4-16)

设计中选取电阻 R1=R2=R3=R4=10K,则减法电路的输出电压为

$$V_{out} = Vr - Vs \tag{4-17}$$

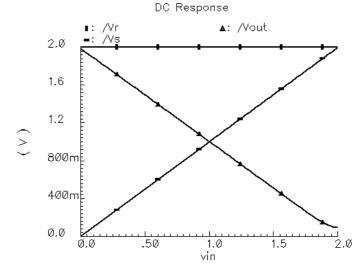

减法电路仿真波形如图 4-12 所示,图中,Vr 恒定为 2V,Vs 从 0V 线性上升到与 Vr 相等的电压值,可以看出减法电路的输出 Vout 波形具有较好的线性度。至此,设计实现了 CMOS 图像传感器的模拟信号处理电路中 CDS 电路去除 FPN 噪声的功能。在不同的光电流下传统 CDS 电路输出波形如图 4-13 所示。

图 4-12 减法电路输出波形

Transient Response

图 4-13 不同光强下传统 CDS 电路输出波形

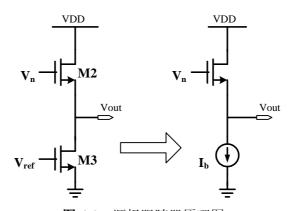

#### 4.2.2 改进的 CDS 电路设计

虽然传统的 CDS 电路能够较好的实现信号采样与去除 FPN 噪声的功能,但是考虑到传统的 CDS 电路中需要三个放大器,对于 CMOS 图像传感器中列级的模拟信号处理电路模块,总共需要 3×N 个放大器,所以传统的 CDS 电路占用了太多的面积和较大的功耗,而且在减法电路中使用的电阻在工艺制造中容易产生偏差,对运算

精度造成影响。

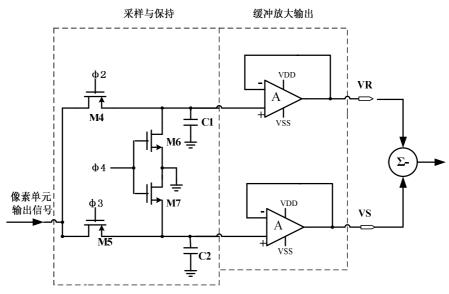

所以,为了尽可能的减少芯片面积,降低电路整体功耗,提高 CMOS 图像传感器性能,本文对模拟信号处理电路进行优化,采用改进设计的 CDS 电路,如下图 4-14 所示。

图 4-14 改进的相关双采样(CDS)电路

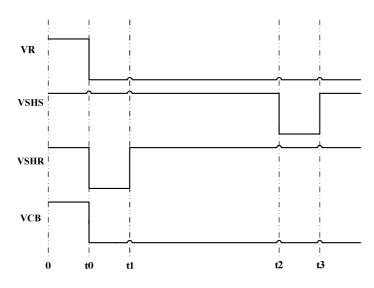

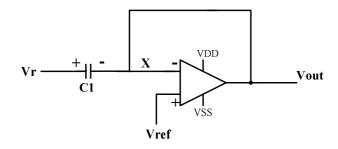

在改进的 CDS 电路中,使用由电容和放大器构成的开关电容电路代替了传统 CDS 电路中的采样保持电路和减法运算电路,工作原理如下:

首先数字控制信号 $\Phi$ 1 和 $\Phi$ 3 为高电平, $\Phi$ 2 为低电平。此时 M2 截止,没有信号进入 CDS 电路。因为此时 M3 导通,放大器两个输入端和一个输出端的电压值都为参考电压 Vref。接着 $\Phi$ 1 变为低电平, $\Phi$ 2 变为高电平, $\Phi$ 3 不变。此时复位信号 Vr 进入 CDS 电路采样到电容 C1 中,等效电路如图 4-15 所示。此时,

**图 4-15** Φ1=0, Φ2=1, Φ3=1 时 CDS 等效电路

$$V_{C1} = Vr - V_{ref} \tag{4-18}$$

$$V_{C2} = 0$$

(4-19)

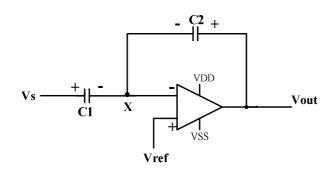

然后Φ2、Φ3 变为低电平,M2 管再次截止,没有信号进入 CDS 电路,像素单元开始曝光。经过一定曝光时间后,Φ2 变为高电平,M2 管导通,曝光后的积分电压信号 Vs 进入 CDS 电路,等效电路如图 4-16 所示。此时,

图 4-16 Ф1=0, Ф2=1, Ф3=0 时 CDS 等效电路

$$V_{C1} = V_S - V_{ref} \tag{4-20}$$

$$V_{C2} = V_{out} - V_{ref} \tag{4-21}$$

由电荷守恒定律,有

$$(V_{C1} - V_{C1}) \cdot C_1 = (V_{C2} - V_{C2}) \cdot C_2$$

(4-22)

将式(4-18)~(4-21)代入式(4-22)中,可得

$$V_{out} = V_{ref} + \frac{C_1}{C_2} (Vr - Vs)$$

$$(4-23)$$

在电路设计中,取 C2 为 2pF, C1 为 1pF。从式(4-23)中注意到输出电压中包含着 Vr-Vs 项,即包含反映像素中光强信息的电压分量,从而电路实现了采样与去除像素 FPN 噪声的功能。与传统 CDS 电路不同,改进的 CDS 电路只包含一个放大器,所以整个 CMOS 图像传感器列级模拟信号处理电路中可以减少 2N 个放大器,从结构上看,面积大大缩小,功耗也可以得到降低。

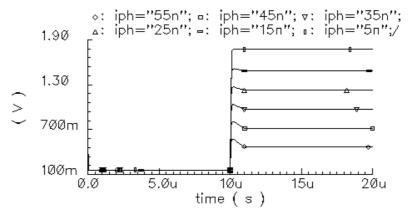

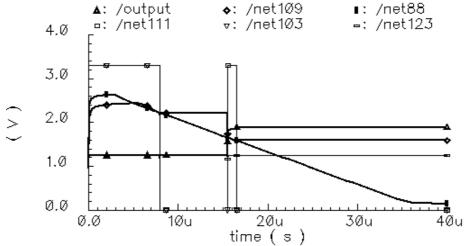

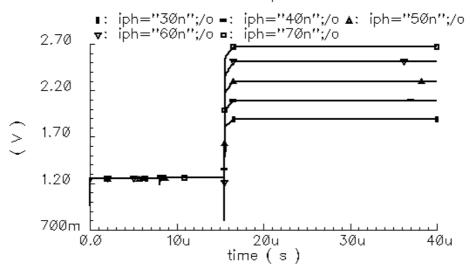

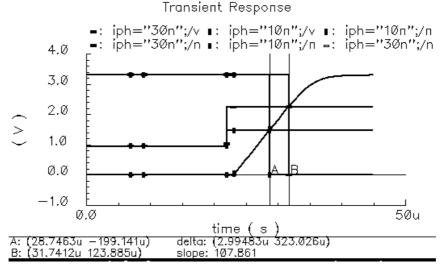

改进相关双采样电路的仿真输出波形如图 4-17 所示,从图中注意到曲线"output"的前后电压跳变增加量就是曲线"net109"表示的两次采样电压值之差。在不同的光电流下改进的 CDS 电路输出仿真波形如图 4-18 所示,从图中可以看出输出曲线之间的间隔基本相等,这也映证了输出信号电压与光电流成正比的关系。

图 4-17 改进的相关双采样电路仿真输出波形

#### Transient Response

图 4-18 在不同像素光电流下 CDS 电路输出波形

#### 4.3 带隙基准源的设计

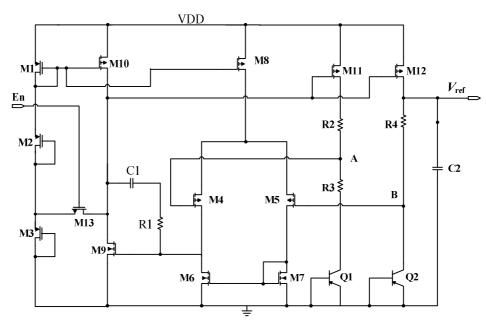

在 CMOS 图像传感器像素单元电路和模拟信号处理电路以及模-数转换电路中都需要一个稳定而且不受外界温度变化影响同时功耗较低的偏置电路,设计采用带隙基准源电路来实现一个电压恒定为 1.25V 的输出信号,以模块共用的方式为 CMOS 图像传感器中的其它电路模块提供偏置,其具体电路如图 4-19 所示。

图 4-19 带隙基准源电路

在带隙基准源电路中,当使能信号 En 拉高一次,控制 NMOS 管 M13 导通一个周期,带隙电路开始上电启动。PMOS 管 M1、M2 和 M3 组成内部偏置电路,这三个管子的长度尺寸设计为较大值可以减小漏源电流降低功耗。输出基准电压 Vout 计算如下:M11 和 M12 管的漏源电流相等,设为 I 。电路中部的两级结构放大器使 A 点和 B 点电位相等,即

$$V_{\text{eb2}} = V_{\text{R3}} + V_{\text{eb1}} = I \times R3 + V_{\text{eb1}}$$

(4-24)

$$V_{\rm eb1} = V_{\rm T} \ln \left( \frac{I}{I_{\rm S1}} \right) \tag{4-25}$$

$$V_{\text{eb2}} = V_{\text{T}} \ln \left( \frac{I}{I_{\text{S2}}} \right) \tag{4-26}$$

双极型晶体管 Q1 管为 24 个 PNP 管并联,Q2 为一个 PNP 管,所以  $I_{S1}=24I_{S}$ ,  $I_{S2}=I_{S}$  。 热电压 $V_{T}=\frac{kT}{q}=0.026$ V,它的温度系数是 $+0.087\,^{mV}\!/_{K}\,^{[42]}$ ,在 SMIC  $0.35\mu$ m 2P3M 标准 CMOS 工艺下,  $I_{S}=2.6\times10^{-17}A$  ,发射结 $V_{eb}$ 电压约为 0.8 V,温度系数是 $-1.413\,^{mV}\!/_{K}$  。 由式(4-24)~(4-26)解得

$$I \times R3 = V_{\rm T} \ln 24 \tag{4-27}$$

所以

$$V_{\text{ref}} = V_{\text{eb2}} + I \times R4 = V_{\text{eb2}} + V_{\text{T}} \frac{R4}{R3} \ln 24$$

(4-28)

令正负温度系数之和为0,则

$$\frac{\partial V_{\rm T}}{\partial T} \times \frac{R4}{R3} \ln 24 + \frac{\partial V_{\rm eb2}}{\partial T} = 0.087 \times \frac{R4}{R3} \ln 24 + (-1.413) = 0 \tag{4-29}$$

解得 $\frac{R4}{R3}$ =5.17。所以,代入式(4-28), $V_{\text{ref}}$ =0.026×5.17ln 24+0.83=1.257V,

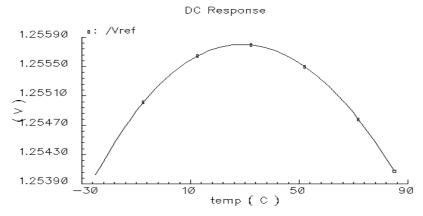

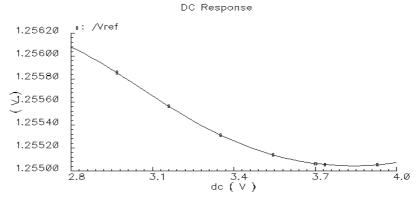

由此,电路的输出端得到了一个大小与温度和电源无关的稳定电压值,该模块消耗电流总共为 11.3uA。带隙基准源电路在温度为-25~75°C 范围内输出波形仿真结果如图 4-20 所示,电源电压变化时电路的输出电压仿真波形如图 4-21 所示,从图中可以看出,带隙基准源的输出电压精度分别达到 12.9 ppm/°C 和 16.7 ppm/V,电路性能良好,可以作为 CMOS 图像传感器中稳定的共用偏置电路模块。

图 4-20 带隙基准源电路输出电压温度扫描波形

图 4-21 带隙基准源电路输出随电源变化仿真波形

#### 4.4 模数转换电路的设计

CMOS 图像传感器有模拟输出和数字输出两种,由于输出信号为模拟电压的 CMOS 图像传感器芯片在应用时一般要与图像处理芯片、存储器芯片等共同实现和完成数字照相机等功能,产品成本较高,所以模拟输出的 CMOS 图像传感器没有得到广泛的应用;在 CMOS 图像传感器中集成一个模-数转换电路模块就可以实现图像信息的数字输出,从而解决了上述成本高、应用范围小的问题。虽然流水线型 ADC 和过采样型 ADC 都有较好的速度和精度特性,但是电路较复杂;低功耗 CMOS 图像传感器符合市场对便携式电子的要求并且是现阶段的研究发展趋势,所以为了减小 CMOS 图像传感器的功耗和面积,同时考虑到不能使模数转换时间太长,本文采用结构较简单的列级单斜 single-slope 型 ADC 来实现 CMOS 图像传感器的模数转换功能。

#### 4.4.1 模数转换电路系统结构

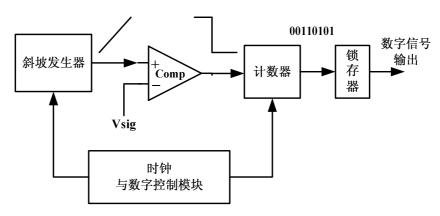

图 4-22 为 single-slope 型 ADC 整体框图。电路由斜坡发生器、比较器、计数器、锁存器和时钟与数字控制模块共同组成。其中,斜坡发生器采用芯片级,即所有列共用一个斜坡发生器;比较器和计数器则每一列对应一个。

图 4-22 模-数转换电路整体框图

整个列级模-数转换(ADC)电路的基本工作原理如下: 首先图像传感器前级电路输出的模拟电压信号 Vsig 进入比较器的反相输入端,然后时钟与数字控制模块开始工作,该模块控制斜坡发生器产生上升的斜坡电压 Vramp,同时控制计数器开始计时。当斜坡发生器输出到比较器正相输入端的斜坡电压 Vramp 与比较器反相输入端的模拟电压信号 Vsig 相等时,比较器的输出翻转,从而控制计数器停止计时。此

时计数器上的数字信号输出到锁存器中锁存,最后锁存器中的数字信号在 CMOS 图 像传感器外围电路中的数字部分电路模块的控制下输出到存储器中。

反映像素中光强信息的模拟电压值 Vsig 越大,计数器的计数时间就越长,输出的二进制数据对应的数值就越大;同样,从感受较弱光强的像素单元中输出的模拟电压值 Vsig 较小,比较器的输出电平则很快翻转,计数器的计数时间短,ADC 模块输出的数字信号对应的数值小。这样,AD 转换模块就完成了将模拟信号转化为数字信号的功能。斜坡发生器和比较器是模数转换模块中最重要的两个模拟子电路,斜坡信号的斜率稳定程度与比较器的分辨率决定了 ADC 的性能,所以本节以下两部分内容就针对这两个模拟电路模块分别进行具体分析和设计。

#### 4.4.2 斜坡产生电路设计

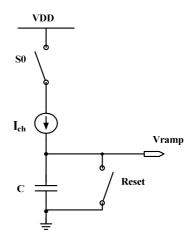

斜坡发生器的基本原理如图 4-23 所示,它由一个恒定电流源、一个充电电容和 2 个开关组成。开关 Reset 用来控制斜坡发生器的复位,开关闭合时将充电电容清零,同时斜坡发生器的输出端电压被下拉到初始电压 0V。

图 4-23 斜坡发生器工作原理图

当开关 Reset 完成电容清零并断开后,开关 SO 闭合,此时电流源开始向电容充电。电容上极板的输出电压与充电时间成正比,有

$$V_{ramp} = \frac{Q}{C} = \frac{I_{ch}}{C} \cdot T_{ramp} \tag{4-30}$$

其中,C 为电容, $I_{ch}$  表示充电电流大小, $I_{ramp}$  为斜坡发生器的充电时间。由式 (4-30) 可知斜坡发生器输出斜坡电压波形的斜率为充电电流大小  $I_{ch}$  与电容 C 取值 的比。所以,要保证得到斜率恒定的斜坡电压就必须采用输出电流不变的电流源。

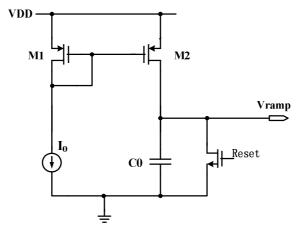

设计首先考虑使用一个简单的栅极电压为定值的 NMOS 管作为电流源,由于随着电压 Vramp 的上升,NMOS 管源极电压发生变化,电流大小改变。因此电路中的电流源不能用一个简单的 NMOS 管来实现。后来设计采用普通电流镜镜像一个一般的电流源为电容充电,电路如图 4-24 所示。在普通电流镜结构斜坡发生器电路中,由于充电时电容 C0 上不断积累电荷,输出端电压 Vramp 持续上升,晶体管 M2 漏极的电压也逐渐上升,虽然输出端电压变化对镜像电流的影响较小,但是逐渐微微变小的充电电流仍然使输出端斜坡电压波形的斜率发生了轻微的变化,这可能会导致模数转换出现微小的误差,影响到 CMOS 图像传感器的性能。为了较好的实现模数转换功能,需要斜率更加稳定的斜坡信号,因此,最后电路改进为采用共源共栅电流镜结构的斜坡发生器电路,具体的电路设计如图 4-25 所示。

图 4-24 普通电流镜结构斜坡发生器电路

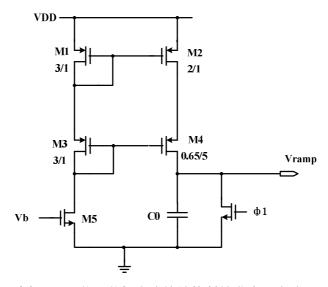

图 4-25 共源共栅电流镜结构斜坡发生器电路

这种形式的电流源因为具有很大的电路交流小信号输出电阻,使其底部晶体管免受输出端 Vramp 变化的影响,为斜坡发生器提供更加稳定的充电电流;共源共栅电流源的另一个优点是可以抑制沟道长度调制效应的影响。对于斜坡发生器,电流 Ich 和电容 CO 的值是设计中最重要的两个参数,因此需要根据斜坡发生器的性能选取合适的值。

考虑到 CMOS 图像传感器中前级电路输出的模拟信号电压为 1.25~2.5V, 所以为了尽量缩短模数转换时间,使每一个电压信号对应的 8 位二进制数之间有足够大的差,即有足够大的计数时间差,只需要将斜坡发生器的电压饱和值(信号摆幅)设定在 2.5V 就能满足较好的性能要求。由式(4-30)可推导得出

$$T_{\text{max}} = \frac{C_0 \cdot (V_{sat} - V_0)}{I_c} \tag{4-31}$$

其中, $V_{sat}$  是饱和电压值, $V_0$  是初始电压, $T_{max}$  是斜坡发生器从初始电压升到饱和电压所需要的时间。为了尽量降低功耗,取电流 Ic 为 2~3uA,在频率为 13MHz的时钟下,时钟周期为 77ns,所以 Tmax 取值在大于 256×0.077=19.7us 时模数转换电路有较好的性能。为了确定 C0 的值,保守计算取 Ic=3uA,Tmax 取 25us,代入上式得 C0=30pF,所以设计中取 C0 为 30pF。

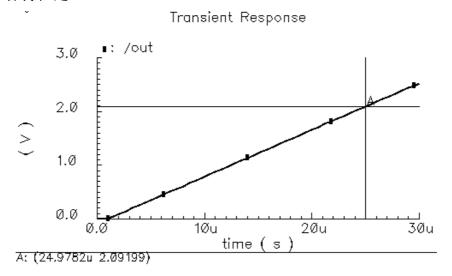

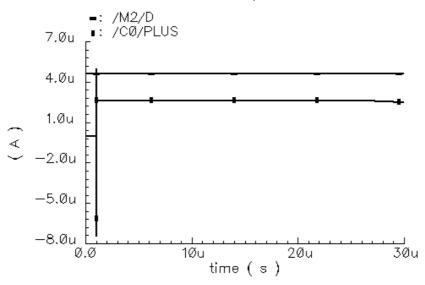

采用 SMIC 0.35 um 2P3M 标准 CMOS 工艺,在 Cadence Composer 环境下,使用 Spectre 仿真器对斜坡发生器进行了电路仿真。瞬态仿真波形如图 4-26 所示,可见斜坡发生器的输出波形斜率恒定。电路中的电流仿真如图 4-27 所示,从图中可以看出,斜坡发生器的两条支路电流相加为 7.2uA,充电支路电流小于 3uA,且电流大小在前 27us 保持恒定。

图 4-26 斜坡发生器输出仿真波形

Transient Response

图 4-27 斜坡发生器中的电流仿真

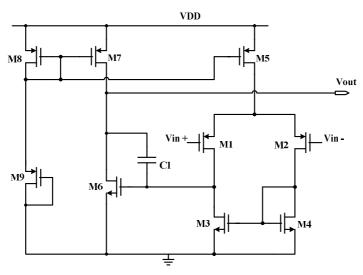

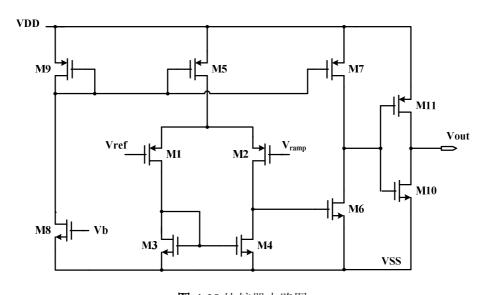

#### 4.4.3 比较器电路设计

CMOS 图像传感器模数转换电路中的比较器是用来比较反应像素光强信息的从CDS 电路输出的电压信号 Vsig 和斜坡发生器的输出信号 Vramp,比较器电路如图 4-28 所示。Vsig 作为参考信号加于运放的反相输入端,而斜坡信号 Vramp 则加于运放的同相输入端。

图 4-28 比较器电路图

比较器的具体设计尺寸如下表 4-2 所示。

表 4-2 比较器的设计尺寸

| 符号 | 尺寸(um) | 符号 | 尺寸 (um) | 符号 | 尺寸 (um) | 符号  | 值       |

|----|--------|----|---------|----|---------|-----|---------|

| M1 | 10/1   | M4 | 1/1     | M7 | 4/1     | M10 | 1/0.5   |

| M2 | 10/1   | M5 | 1/1     | M8 | 1/6.5   | M11 | 1.5/0.5 |

| M3 | 1/1    | M6 | 3/1     | M9 | 1/1     |     |         |

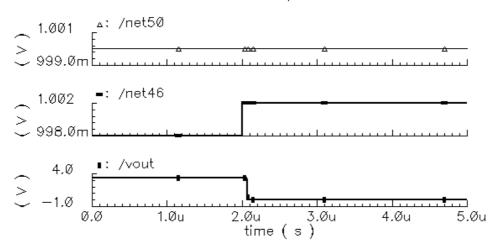

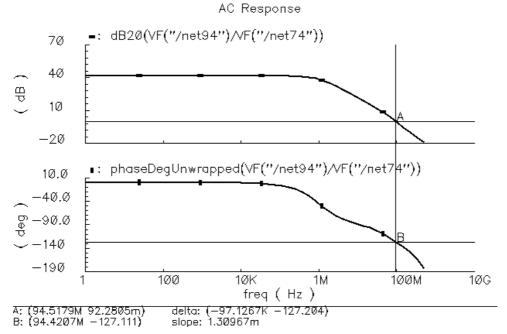

比较器电路的瞬态响应特性仿真如图 4-29 所示。图中,比较器反相输入端"net50"电压设为 1V,同相输入端"net46"的电压在 2us 处从 0.998V 跳变到 1.002V,此时比较器的输出"vout"仍然能够实现电平翻转,表现出较好的性能,从图中可以看出比较器的分辨率可以达到 4mV,延时约为 70ns。交流仿真结果如图 4-30 所示,从图中可以得到比较器低频增益为 42dB,相位裕度为 53 度,带宽(0 dB 带宽)为 100 MHz。

Transient Response

图 4-29 比较器瞬态响应特性仿真曲线

图 4-30 比较器交流特性仿真曲线

### 4.5 本章小结

本章详细介绍了 CMOS 图像传感器中关键模拟电路的设计过程。包含像素单元读出电路的设计,相关双采样(CDS)电路的设计,带隙基准源电路的设计和模数转换模块中斜坡发生器和比较器电路的设计,并给出了各个部分模块的性能参数和仿真结果。

### 5 仿真结果与性能参数计算

在完成 CMOS 图像传感器关键模拟电路设计之后,采用了 SMIC 0.35 μm 2P3M 标准 CMOS 工艺对设计进行了实现,然后对整个 CMOS 图像传感器系统模拟电路模块部分进行了仿真,给出了各个模块之间接口处和总体输出端的电压波形仿真结果;并进行了结果与性能参数计算。

### 5.1 仿真结果

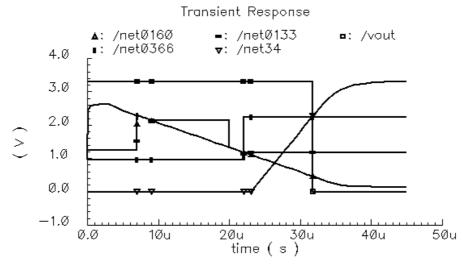

在 CMOS 图像传感器中,把设计好的一个像素单元电路、CDS 电路、带隙基准电路和模数转换电路中的斜坡产生电路与比较器电路共同连接起来进行总体仿真,像素单元中的 Iph 值为 30nA,在 8us 和 20us 处进行两次信号采样,仿真结果如图 5-1 所示。

图 5-1 总体电路瞬态仿真图

图中的曲线 "net0160" 呈现为一条从 2.5V 下降到 0.2V 且斜率固定的直线,这是像素单元电路的输出,这条曲线表示随着像素的曝光光电二极管寄生电容上的积分信号电压开始线性下降,符合式 (3-2) 的要求。曲线 "net0133" 和曲线 "net0366" 分别是模拟信号处理电路中信号采样处和 CDS 输出端的波形,从图中可见它在 8us 和 20us 处分别采用两次; "net0366" 最后的电压跳变上升后的值就是 CDS 电路去除噪声后输出的模拟电压值。曲线 "net34"为斜坡发生器输出波形,它在 CDS 电路实现电压信号采样与消除像素 FPN 噪声功能后开始工作升压。曲线 "vout" 为比较器

电路的输出,即 CMOS 图像传感器最后一个模拟电路模块的输出,在斜坡发生器输出电压(net34)Vramp 大于 CDS 电路输出电压(net0366)Vsig 时,输出电平从 3.3V 翻转到 0V,控制计数器停止计时。从图中可以看出计数时间为 31.8-23.1=8.7us,计数器最后输出的能够表示时钟周期个数的二进制数值就是 CMOS 图像传感器的数字电路部分最后要得到的数字信号。因此,仿真结果表明 CMOS 图像传感器的各个模拟电路模块较好的实现了其功能。

CMOS 图像传感器阵列中同一行的两个不同像素单元对应的光强不同时(光电流分别对应为 10nA 和 30nA),总体电路的输出仿真波形如图 5-2 所示。

图 5-2 不同像素对应的总体电路输出仿真波形

图中的结果表明不同列对应的两个比较器分别在 28.7 和 31.7us 处翻转,所以,在 13MHz 时钟下, CMOS 图像传感器数字电路模块中对应的数字计数器在这两个时刻的输出分别对应 74 个周期和 113 个周期,其数字输出值可分辨。

### 5.2 性能参数计算

CMOS 图像传感器的主要性能参数包括动态范围、功耗和传输速度等。由于本文对于 CMOS 图像传感器的设计仅限于模拟电路部分,不涉及数字与控制电路部分,所以不能得到传输速度等有关数字部分的性能参数。因此,本节分别从动态范围、灵敏度、功耗和噪声等几个方面来计算 CMOS 图像传感器的性能参数。

#### 5.2.1 动态范围

CMOS 图像传感器的动态范围 DR 定义为一个像素中产生的最大非饱和光电流 Imax 与能够探测到的最小光电流 Imin 之比。即

$$DR = 20\log_{10}\frac{I_{max}}{I_{min}} \tag{5-1}$$

CMOS 图像传感器的动态范围越大,那么它就能探测并转换更强光照下的图像信号。为了改善图像质量和更好的区分明暗像素,CMOS 图像传感器动态范围的增大变得非常重要。虽然在理论上最大非饱和光电流 Imax 由光电二极管节点寄生电容Cp 上的所容纳的最大电荷量决定,但在实际中 Imax 通常由像素单元中积分电压的最大值 Vmax 决定。所以有

$$I_{max} = \frac{C_p}{T_{\text{int}}} \cdot V_{\text{max}} - I_d$$

(5-2)

式中、Tint为曝光时间、La表示暗电流

$$I_d = I_s \cdot (e^{\frac{qV}{kT}} - 1) \tag{5-3}$$

其中,Is 为光电二极管反向饱和电流。像素中最小可测信号很难定义,一般认为最小可测信号为零输入时输入端噪声的标准差<sup>[43]</sup>,可假定 Imin 等于没有信号时输入相关噪声标准偏差,有

$$I_{\min} = \frac{1}{T_{\text{int}}} \cdot \sqrt{q \cdot I_d \cdot T_{\text{int}} + \sigma_r^2}$$

(5-4)

在设计中,像素单元电路的积分电压最大值 Vmax 为 2.5V,暗电流  $I_d$  为 1fA,量子噪声 $\sigma_r$ =20e<sup>-</sup>,积分时间  $T_{int}$  为 10us。结合式(5-1)~(5-4),计算求得图像传感器的动态范围 DR 是 110dB。可见,改进像素单元电路后的图像传感器与普通 CMOS 图像传感器(DR 值一般为 60~75dB)相比具有较大的动态范围。

#### 5.2.2 灵敏度

CMOS 图像传感器中一般用转换增益来反映灵敏度的大小。转换增益可表示为

$$Gn = \frac{\Delta V}{\Delta Q} = \frac{\Delta V}{I_{ph} \cdot \Delta T} \tag{5-5}$$

由图 4-7 中显示的像素单元输出波形可知,在光电流 Iph 为 30nA 时, Δ

T=35.0-5.5=29.5us,图中  $\Delta$  V=2. 5-0. 2=2. 3V,所以代入式(5-5)中计算得到 CMOS 图像传感器的转换增益 Gn 为 0. 42  $\mu$ V /  $e^-$  。

实际上,在 CMOS 图像传感器中,主要是光电二极管的寄生电容 Cp 决定着转换增益和灵敏度的大小,而电容 Cp 的值又是由光电二极管的制造工艺决定的。一般情况下节点电容 Cp 值越小,图像传感器的转换增益和灵敏度越高。所以现在 CMOS 图像传感器的发展趋势是把光电二极管的感光部分尺寸做得越来越小,以便提高图像传感器灵敏度这方面的性能。设计中,最初取光电二极管的尺寸为 18um×18um。为了获得更高的转换增益,可以把其尺寸取为 4um×4um,这样就可以使 CMOS 图像传感器的转换增益提高至少 20 倍。

#### 5.2.3 功耗

CMOS 图像传感器的功耗大小直接与传感器阵列规模大小有关,一般图像传感器阵列越大,所消耗的功耗就越多。同时,总体功耗大小也与电路实现采用的工艺和电源大小密切相关。表 5-1 中总结了 CMOS 图像传感器中各个模拟电路模块的功耗仿真大小。

| 模拟电路模块 | 总电流(uA) |

|--------|---------|

| 像素单元电路 | 132     |

| CDS 电路 | 136     |

| 斜坡发生器  | 7.2     |

| 比较器    | 22.3    |

| 带隙基准源  | 11.3    |

|        |         |

表 5-1 CMOS 图像传感器关键电路功耗列表

因为像素单元电路、CDS 电路和比较器是 N 列同时工作,而斜坡发生器和带隙 基准源是整个电路的共用模块,所以 CMOS 图像传感器模拟电路总功耗为

$$P = [N \times (132 + 136 + 22.3)\mu A + 7.2\mu A + 11.3\mu A] \times V_{DD}$$

(5-6)

由上式,对于一个列数 N 为 128 的分辨率过万的图像传感器,计算得出在电源电压  $\mathbf{V}_{DD}$  为 3. 3V 情况下的总功耗为 113. 3mW。

#### 5.2.4 噪声

CMOS 图像传感器中的主要噪声来源是像素单元电路中的热噪声和闪烁噪声。 以下分别分析和计算这部分噪声:因为等效的输入参考噪声主要由输入级器件决定, 所以可以通过计算改进像素单元中放大器输入级的噪声来确定总体噪声水平。

对于本文电路设计中要计算的噪声,即第四章图 4-5 的改进像素单元中的噪声, 其放大器的第二级对噪声基本上没有太大影响,可以忽略,所以只计算第一级的等效输入电压噪声。电路的等效输入电压噪声谱密度可近似地表示为:

$$e_{eq}^2 \approx 2e_{n1}^2 \left[1 + \left(\frac{g_{m3}}{g_{m1}}\right)^2 \left(\frac{e_{n3}^2}{e_{n1}^2}\right)\right]$$

(5-7)

又因为对于单个晶体管, 热噪声表示为

$$\overline{e_{ni}^2} = \frac{8kT}{3g_m} \tag{5-8}$$

闪烁噪声为

$$\overline{e_{ni}^2, f} = \frac{K_F}{C_{ox}WL} \cdot \frac{1}{f} \tag{5-9}$$

其中参数  $k=1.38\times10^{-23}$  J/K, $K_F$  为噪声常数,依据表 4-1 中晶体管的参数,结合式(5-7)~(5-9),计算得到像素单元电路的等效输入电压噪声为  $7.8\times10^{-14}$   $V^2/Hz$ ,所以像素中总的等效输出电压噪声为  $Av^2$  倍的  $e_{eq}^2$ ,即  $2.56\times10^{-8}$   $V^2/Hz$ ;由此进一步计算得出电路输出的均方根噪声(在 1Hz 时)为 0.16mV,符合小于 1mV 的预期设计要求。

CMOS 图像传感器的不同文献主要性能参数比较如表 5-2 所示。

| 年份   | 2001                    | 2004               | 2007    | 2009    |

|------|-------------------------|--------------------|---------|---------|

| 作者   | Pavan K.                | Suat Utku          | 林晓志[45] | 本文作者    |

|      | Hanumolu <sup>[7]</sup> | Ay <sup>[44]</sup> |         |         |

| 功耗   | -                       | 550mW              | -       | 113.3mW |

| 像素输出 | 2V                      | 1V                 | 1.5V    | 2.3V    |

| 摆幅   |                         |                    |         |         |

表 5-2 不同文献主要性能参数对比

| 动态范围 | 54dB  | 75dB  | 50dB | 110dB   |

|------|-------|-------|------|---------|

| 噪声   | 4mV   | -     | 1mV  | 0.16 mV |

| 工艺   | 0.4um | 0.5um | 0.35 | 0.35um  |

| 电源电压 | 3.3V  | 5V    | 3.3V | 3.3V    |

### 5.3 本章小结

本章首先给出了 CMOS 图像传感器模拟电路的总体仿真结果,并结合各个电路模块的功能对仿真结果进行了说明与分析。然后本章还对设计的 CMOS 图像传感器进行了动态范围、噪声和功耗等方面的性能参数计算,并与其它文献进行比较。

### 6 总结与展望

CMOS 图像传感器与 CCD 图像传感器相比,由于具有功耗低、数据读出速度快、生产成本低、与标准 CMOS 工艺兼容等特点,因此得到广泛的应用。CMOS 图像传感器中的关键模拟电路包括像素单元读出电路、相关双采样电路、带隙基准源电路和模数转换模块中的斜坡产生电路与比较器电路。

论文对 CMOS 图像传感器系统结构进行了详细的分析,阐述了 CMOS 图像传感器中核心器件光电二极管的光电转换原理并具体推导了光生电流与光强的关系; 然后得出了它们二者之间的线性关系,从而使图像传感的电路实现成为可能。最后采用 SMIC 0.35um 2P3M CMOS 工艺,设计了 CMOS 图像传感器中的关键模拟电路。本设计具有以下几个特点:

- 1) 具有较大信号输出摆幅:在传统像素单元电路的基础上进行改进,用单位增益缓冲放大器代替了传统的源极跟随器,增大了像素单元电路的输出信号摆幅,使其幅值增大了约0.7V。

- 2) 面积小:采用改进的相关双采样(CDS)电路代替传统的 CDS 电路,使模拟信号处理电路对应的每一列减少了两个放大器,从结构上大大降低了芯片面积和系统功耗;而且改进的模拟信号处理电路同样能够实现消除固定模式噪声和完成信号采样与保持的功能。

- 3) 功耗低:采用结构较为简单的单斜率 (single slope)型列级 ADC 的结构实现模数转换功能,每列只需要 29.5uA 的电流提供驱动;采用整行单元共用一个斜坡发生器的方式进一步减小了芯片面积,降低了系统总功耗。

- 4) 信号误差小: 采用稳定的带隙基准源作为 CMOS 图像传感器各模块的偏置电路, 其精度达到 12.9 ppm/°C,降低了像素间的输出误差,改善图像质量,并且使其不受外界温度变化的影响。

本设计基本满足了电路既定要求,但是还可以进一步的进行电路改进和性能优化。首先,对于模拟信号处理电路中的相关双采样(CDS)电路,可以继续改善其中放大器的性能,进一步提高增益减小失调电压,并设法降低放大器的输入级噪声。第二,虽然模数转换电路采用列级单斜率型 ADC,面积较小,设计简单,但是可以尝试采用精度更高速度更快的其它类型 ADC,由于把 ADC 模块从芯片级降为列级结构,不必太过担心它的总功耗和面积,所以有可能实现性能更好模-数转换功能。

第三,如果进一步进行数字电路的设计,完善 CMOS 图像传感器外围电路的驱动和行列选择电路以及 ADC 中数字部分和存储器或寄存器阵列的设计,则可以更好的分析 CMOS 图像传感器的传输速度和系统总功耗。第四,对 CMOS 图像传感器阵列中像素单元里的光电二极管进行物理层的研究与分析,从工艺和物理设计方面对 CMOS 图像传感器进行性能改进。以上这几个方面的考虑都很可能使 CMOS 图像传感器的性能进一步大幅提高,使 CMOS 传感器的性能优势更加明显于 CCD 传感器。

### 致 谢

在此论文完成之际,我首先要感谢我的导师邹雪城教授在我读研的两年期间给 予我的悉心指导和亲切关怀。他严肃的科学态度,严谨的治学精神和精益求精的工 作作风都深深地感染和激励着我。两年来,他不仅在学业上给我们以精心指导,同 时还在思想、生活上给我以无微不至的关怀,在此谨向邹老师致以诚挚的谢意和崇 高的敬意。

感谢张科峰副教授、刘政林副教授和雷鑑铭副教授,他们严谨的治学态度和谦 逊的为人是我今生学习的榜样。

感谢刘冬生老师在我攻读硕士学位两年来对我无微不至的关心和帮助,在刘老师的帮助下,我不但掌握了更多的专业知识,而且个人的综合能力也得到了极大的发展。感谢已毕业的谭波和余琼师兄,是他们引导我进入集成电路设计的美妙世界。感谢武汉集成电路工程设计研究中心的邹志革老师、陈晓飞老师、郑朝霞老师和余国义老。感谢杜芷君和龙爽同学,感谢师弟刘尧、黎明、蔡豪、李奉波和薛涵,师妹张丽;感谢工程师吕杰和夏玥;在两年的时光里,我们一起学习、共同进步,相互鼓励,相互支持,这些都是我记忆里的最美好时光。

感谢我的父母, 感谢你们一直无私的关心和支持我。

感谢其他很多可敬的师长、同学和朋友给了我无私的帮助,在这里请接受我诚 挚的谢意!

最后,我要特别感谢武汉集成电路工程设计研究中心,感谢它为我提供了一个学习和实践的平台,使我的理论水平和动手能力得以提高,没有它就不会有我今天的进步。

### 参考文献

- [1] G. Weckler. Operation of p-n junction photodetectors in a photon flux integrating mode. IEEE J. Solid-State Circuits, 1967, 2(3): 65~73.

- [2] [日]米本和也. CCD/CMOS 图像传感器基础与应用. 陈榕庭, 彭美桂 译. 北京: 科学出版社, 2006. 6~10

- [3] Abbas El Gamal, Helmy Eltoukhy. CMOS IMAGE SENSORS. IEEE CIRCULTS AND DEVICES MAGAZINE, 2005, 21(3):6~20

- [4] P. Noble. Self-scanned silicon image detector arrays. IEEE Trans. Electron Devices, 1968, 15(4): 202~209

- [5] E.R. Fossum. Active pixel sensors: Are CCD's dinosaurs?. In: Morley M.Blouke. Charge-Coupled Devices and Solid State Optical Sensors III. San Jose, CA,USA: SPIE, 1993. 30~39.

- [6] 刘磊. 图象感器种类比较与技术应用. 科技资讯, 2007, (18): 10

- [7] Pavan Kumar Hanumolu. Design of Low Noise, Low Power Linear CMOS Image Sensors:[Thesis for degree of Master]. WORCESTER POLYTECHNIC INSTITUTE, 2001.

- [8] S. Kempainen. CMOS image sensors: eclipsing CCDs in visual information. EDN 1997, 42 (21): 101~102.

- [9] 程开富. CMOS 图象传感器的原理及应用. 半导体情报, 2001, 38 (5): 5~6

- [10] Ho Yeung Chan, Jie Yuan. A Low-Distortion and Wide Dynamic Range CMOS Imager for Wireless Capsule Endoscopy. In: IEEE International Symposium on Circuits and Systems. Seattle: ISCAS, 2008. 2945~2948

- [11] H.Graf, C. Harendt, T. Engelhardt, et al. High dynamic range CMOS imager Technologies for Biomedical applications. IEEE J. of Solid-State Circuits, 2009, 44(1): 281~289

- [12] Hon-Sum.P.Wong. CMOS image sensors-recent advances and device scaling considerations. In: International Electron Devices Meeting. IEDM, 1997. 201~204.

- [13] 李晓磊. 有源像素 CMOS 图像传感器读出电路的研究: [硕士学位论文]. 湖南

- 大学图书馆. 2007.

- [14] 董守愚. CMOS 图象传感器. 安徽电子信息职业技术学院学报, 2006, 6(5):100~101

- [15] K. B. Cho, A. I. Krymski, E. R. Fossum. A 1.5-V 550-uW 176×144 Autonomous CMOS Active Pixel Image Sensor. IEEE Trans. On Electron Devices, Special Issue on Image Sensors, 2003, 50(1): 96~105

- [16] Alexander Fish, Orly Yadid-Pecht. Low-Power "Smart" CMOS Image Sensors. In: IEEE International Symposium on Circuits and Systems. ISCAS, 2008. 1408~1411

- [17] David Stoppa, Monica Vatteroni, Daniele Covi, et al. A 120-dB Dynamic Range CMOS Image Sensor With Programmable Power Responsivity. IEEE journal of solid-state circuits, 2007, 42(7):1555~1563

- [18] Xiuling Wang, Winnifred Wong, Richard Hornsey. A High Dynamic Range CMOS Image Sensor with Inpixel Light-to-Frequency Conversion. IEEE transactions on electron devices, 2006, 53(12): 2988~2992

- [19] Y. Nitta, Y. Muramatsu, K. Amano, et al. High-speed digital double sampling with analog CDS on column parallel ADC architecture for low-noise active pixel sensor. In: IEEE Solid-State Conference, Dig. Tech. Papers. San Francisco: ISSCC, 2006.2024~2031.

- [20] S. Yoshihara, Y. Nitta, M. Kikuchi, et al. A 1/1.8-inch 6.4 MPixel 60 frames/s CMOS image sensor with seamless mode change. IEEE Trans. Solid-State Circuits. 2006, 41(12):2998~3006

- [21] Arnaud Verdant, Patrick Villard, Antoine Dupret, et al. SystemC Validation of A Low Power Analog CMOS Image Sensor Architecture. In: IEEE Northeast Workshop on Circuits and Systems. Montreal: NEWCAS, 2007. 903~906

- [22] 刘恩科,朱秉升,罗晋生等. 半导体物理学(第 4 版). 北京: 国防工业出版社, 1997. 271~273

- [23] 刁静, 林祖伦. 用于 CMOS 图象传感器的光电二极管的模型. 传感技术学报, 2006, 19(3): 702~705

- [24] 刁静. 有源像素 CMOS 图像传感器的设计研究: [硕士学位论文]. 电子科技大

- 学图书馆. 2006.

- [25] B.S. Carlson. Comparison of modern CCD and CMOS image sensor technologies and systems for low resolution imaging. In: Sensors, Proceedings of IEEE. Orlando: IEEE, 2002. 171~176.

- [26] Alexander Fish, A. Belenky, O. Yadid-Pecht. Low power global shutter CMOS active pixel image sensor with ultra-high dynamic range. In: Proceedings of the 2004 11<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems. ICECS, 2004. 149~152

- [27] 朱青云, 卢洁成, 张小波等. 低功耗高动态范围 CMOS 图像传感器的设计. 半导体技术, 2008, 33(1): 19~21

- [28] 林聚承, 袁祥辉, 吕果林等. 采用新型读出电路的 CMOS 图像传感器研究. 光电工程, 2007, 34(5): 67~70.

- [29] 金湘亮,陈杰,仇玉林.一种低功耗低噪声相关双取样电路的研究. 电路与系统学报. 2003,8(3):23~26

- [30] A. M. Fowler, I. Gatley. Demonstration of an algorithm for read-noise reduction in infrared arrays. Astrophys. J. 1990, 353: L33~L34

- [31] S. Kawahito, N. Kawai, Y. Tadolsoro. A high-sensitivity oversampling digital signal detection technique for CMOS image sensors using non-destructive intermediate high-speed readout mode. In: Proc. IEEE Workshop CCD AIS. 2001. 24~27.

- [32] N. Kawai, S. Kawahito. A low-noise oversampling signal detection technique for CMOS image sensors. In: Proceedings of the 19<sup>th</sup> IEEE Instrum. and Meas. Technol. Conference. Anchorage, AK: IMTC, 2002. 256~268.

- [33] S.Smith, J.Hurwitz, M.Torrie, et al. A single-chip 306×244 pixel CMOS NTSC video camera. In: IEEE International Solid-State Circuits Conference, Dig. Tech. Papers. San Francisco: ISSCC, 1998. 170~171

- [34] M. Loinaz, K. Singh, A. Blanskby, et al. A 200 mW 3.3 V CMOS color camera IC producing 352×288 24b video at 30 Frames/s. IEEE J. of Solid-State Circuits, 1998, 33(12): 2092~2103.

- [35] T. Sugiki, S. Ohsawa, H. Miura, et al. A 60mW 10b CMOS Image Sensor with Column-to-Column FPN Reduction. In: IEEE international Solid-State Circuits Conference, Dig. Tech. Papers. ISSCC, 2000. 108~109.

- [36] M. Snoeij, A. Theuwissen, K. Makinwa, et al. Multiple-Ramp Column-Parallel ADC Architectures for CMOS Image Sensors. IEEE J. of Solid-State Circuits, 2007, 42(12): 2968~2977

- [37] M. Snoeij, P. Donegan, A.J.P. Theuwissen, et al. A CMOS Image Sensor with a Column-Level Multiple-Ramp Single-Slope ADC. In: IEEE international Solid-State Circuits Conference, Dig. Tec. Papers. ISSCC, 2007. 506~618

- [38] C. C. Hsieh, C. Y. Wu, F. W. Jih, et al. Focal-plane-arrays and CMOS readout techniques of infrared imaging systems. IEEE Trans. Circuits Syst. Video Technol., 1997, 7(4):594~605.

- [39] J. Zarnowski, M.Pace, M.Joyner. 1.5 FET per pixel standard CMOS active column sensor. In: Morley M. Blouke. Sensors, Cameras, and Systems for Scientific/Industrial Applications. San Jose, CA: SPIE, 1999. 186~196

- [40] Phillip E.Allen, Douglas R.Holberg. CMOS 模拟集成电路设计(第二版). 冯军, 李智群 译. 北京: 电子工业出版社, 2007. 218~224

- [41] 康华光,陈大钦。电子技术基础:模拟部分(第四版).北京:高等教育出版社,1999.330~333

- [42] [美]毕查德·拉扎维. 模拟 CMOS 集成电路设计. 陈贵灿,程军,张瑞智 译. 西安交通大学出版社. 2003. 309~321

- [43] 徐江涛,姚素英,赵毅强等.新型大动态范围 CMOS 图像传感器双采样像素阵列设计.传感技术学报,2003,(4):438~441

- [44] Suat Utku Ay. Design Issues and Performance of Large Format Scientific CMOS Image Sensors:[Thesis for Ph.D. degree]. University of Southern California, 2004.

- [45] 林晓志. CMOS 图像传感器中前级处理电路的研究: [硕士学位论文]. 天津大学图书馆, 2006.

## 附录 1 攻读硕士学位期间发表的主要论文和申请专利

[1] 邹雪城, 刘政林, 刘冬生, 余琼, 谭波, 惠雪梅, 李玲, 刘旭. 一种用于 EEPROM 的灵敏放大器及其构成的读电路. 国家发明专利, 申请号: 200810046620.3

## CMOS图像传感器中关键模拟电路的研究与设计

<u>刘旭</u> 华中科技大学 学位授予单位:

☐ 万万数据 WANFANG DATA 文献链接

本文链接: <a href="http://d.g.wanfangdata.com.cn/Thesis\_D086070.aspx">http://d.g.wanfangdata.com.cn/Thesis\_D086070.aspx</a>