### CURRENT EFFICIENT, LOW VOLTAGE,

# LOW DROPOUT REGULATORS

Gabriel Alfonso Rincón-Mora

## CURRENT EFFICIENT, LOW VOLTAGE, LOW DROP-OUT REGULATORS

## A THESIS Presented to the Academic Faculty by Gabriel Alfonso Rincon-Mora

In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Georgia Institute of Technology

November 1996

Copyright © 1996 by Gabriel Alfonso Rincon-Mora

## CURRENT EFFICIENT, LOW VOLTAGE, LOW DROP-OUT REGULATORS

| APPROVED:                  |   |

|----------------------------|---|

| Phillip E. Allen, Chairman |   |

| Richard Bass               |   |

| J. Alvin Connelly          |   |

| W. Marshall Leach          | _ |

| Date Approved by Chairman  |   |

For the hopes of

peaceful coexistence and universal brotherhood!

### **FOREWORD**

The research focuses on the realization of current efficient, low voltage, low dropout regulators. These characteristics are driven by portable and battery operated products requiring compactness and low power. The approach adopted is to develop circuit techniques that allow maximum use of current existing process technologies. As a result, future and more advanced technologies will have even greater benefits. The dissertation is organized to reflect the necessary sequence of events that lead up to the complete design of a system.

Chapter 1 introduces low drop-out regulators. Their definition and motivation for existence are addressed here. The alternative, or in some cases the supplement, type of regulator is compared to further elucidate the demand of low drop-out regulators in today's market. A typical circuit architecture is illustrated along with a description of the basic characteristics inherent to the system and required by the loading circuits. Lastly, the chapter concludes by identifying and defining the objective of the research.

Chapter 2 discusses the considerations necessary to successfully design the circuits. The loading requirements, which partially determine the frequency response of the control loop, are identified. Their implications on circuit limitations and challenges are illustrated. This is followed by a transient analysis describing the typical response of the system along with the difficulties imposed by low voltage and low quiescent current flow. Finally, the specific circuit implications and requirements of the major blocks of the system are discussed, i.e., the pass device, the error amplifier, and the reference circuit.

A literature survey of the different prevailing topologies for low drop-out regulators is illustrated in chapter 3. The circuit realization of each topology is discussed. The circuits highlighted are realized in relatively inexpensive technologies to constrain the research orientation to generalized circuit techniques and not towards manipulation of the processes. The main concepts are emphasized and evaluated for their appropriateness in a low voltage and low quiescent current atmosphere. Furthermore, circuit enhancement techniques are also studied to show the different ways that the system can be amended to yield improved performance on particular specification parameters.

Techniques that allow proper and practical realization of low drop-out regulators at low input voltages and low quiescent current flow are developed in chapter 4. The motivation and challenges are identified. The areas highlighted include current efficiency, current boosting, and load regulation enhancement. The advantages and the drawbacks of the circuits used to realize these concepts are discussed within the context of a low voltage environment.

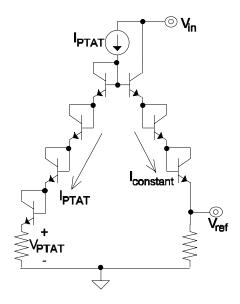

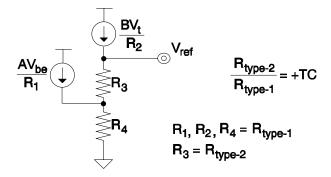

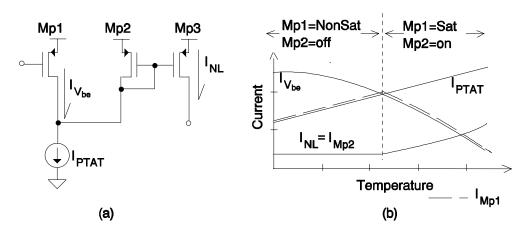

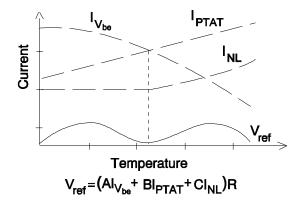

Chapter 5 shows the development of a low voltage and curvature corrected bandgap reference. The development starts at the conceptual roots of zener references and first order bandgaps and continues on to curvature corrected references. Respective output structures are discussed and evaluated for their propriety in the system at hand. The chapter then illustrates the different curvature correcting schemes and concludes with the most suitable for the system.

The concepts developed in chapters 4 and 5 are used to design the actual circuit blocks. These circuits are described and illustrated in chapter 6. They include the composite pass device, the gain stage of the amplifier, the buffer stage of the amplifier, and the curvature corrected bandgap reference. The pass device is developed to reap the

benefits of current boosting. The amplifier is designed to take advantage of the current efficiency and the load regulation enhancement concepts discussed in chapter 4. Lastly, the design of the reference reflects the concepts cultivated in chapter 5. The chapter ends with a discussion of the trimming requirements of the bandgap reference.

All the circuit blocks designed in chapter 6 are used to realize the system in chapter 7. Physical design issues are discussed within the context of existing process technologies, such as CMOS, bipolar, and biCMOS processes. This is followed by a discussion of appropriate protection circuitry. The chapter then continues to show the experimental results of the prototype circuit fabricated in MOSIS 2 µm CMOS technology with an added p-base layer. Finally, a summary of the performance specifications obtained as well as those targeted are discussed and illustrated in a table.

Chapter 8 brings forth the conclusions of the research as well as the implications thereof. The enabling techniques for low voltage and low quiescent current flow operation are summarized and discussed in perspective of the overall system. The direction of market demand in terms of technology and circuit requirements is also discussed. The chapter ends with a few concluding statements pertaining to the research as well as recommendations for future work in the area.

### **ACKNOWLEDGMENTS**

First of all, I would like to especially thank God for all that He has endowed upon me and the opportunities that He has presented to me. In the same token, I am extremely thankful for the encouragement and support of my parents, Gladys M. and Gilberto Rincon, and my brother, Gilberto Alexei Rincon-Mora.

My deepest appreciation goes to my advisor, Dr. Phillip E. Allen. His advice has been invaluable to my research as well as my career. I am also grateful for the support and advice that Mr. Nicolas Salamina has extended to me throughout my endeavors. I would like to thank, in alphabetical order, Dr. Bass, Dr. Casinovi, Dr. J.A. Connelly, and Dr. Leach for their advice and recommendations throughout my graduate program and for their service in my various examination committees. The technical and financial support of Texas Instruments Incorporated has been an invaluable asset in my program at Georgia Institute of Technology and a special thanks is extended. I am also thankful for the insightful comments offered by my fellow colleagues in the analog design group at Georgia Institute of Technology and the standard linear design group at Texas Instruments Incorporated. The technical exchange of ideas with Benjamin Blalock and Abdul Coban was especially helpful and therefore appreciated.

### TABLE OF CONTENTS

|                                                   | Page |

|---------------------------------------------------|------|

| Dedication                                        | iv   |

| Foreword                                          | v    |

| Acknowledgments                                   |      |

| List of Tables                                    |      |

| List of Figures                                   | xiv  |

| Summary                                           |      |

| CHAPTER I. INTRODUCTION                           | 1    |

| 1.1 Definition                                    | 1    |

| 1.2 Market Demand                                 | 2    |

| Current Efficiency, Low Voltage, and Low Drop-out | 2    |

| Alternative: Switching Regulators                 | 3    |

| 1.3 Characteristics                               | 5    |

| Block Level Description                           | 5    |

| Performance                                       |      |

| 1.4 Specifications                                | 7    |

| System                                            |      |

| Reference                                         |      |

| 1.5 Research Objective                            |      |

| 1.6 Summary                                       |      |

| CHAPTER II. SYSTEM DESIGN CONSIDERATIONS          | 17   |

| 2.1 AC Analysis                                   | 17   |

| Loading Conditions                                | 17   |

| Frequency Response                                |      |

| Design Challenge                                  | 21   |

| Worst-case Stability                              | 21   |

| Parasitic Pole Requirements                       | 22   |

| Maximum Load Regulation Performance               | 22   |

| 2.2 Transient Analysis                            | 23   |

| Typical Response                                  | 24   |

| Design Challenge                                  | 28   |

| 2.3 Pass Device Design Issues                     | 29   |

| 2.4 Amplifier Design Issues          | 30 |

|--------------------------------------|----|

| 2.5 Reference Design Issues          | 32 |

| 2.6 Summary                          |    |

| CHAPTER III. REGULATOR TOPOLOGIES    | 35 |

| 3.1 CMOS Topology                    | 35 |

| 3.2 Buffered Architecture            |    |

| 3.3 All-in-one Approach              |    |

| 3.4 System Enhancements              | 42 |

| Mixed-mode Technique                 |    |

| Multi-pass Device Approach           |    |

| Widely Adjustable Structure          |    |

| 3.5 Summary                          |    |

| CHAPTER IV. PERFORMANCE ENHANCEMENTS | 49 |

| 4.1 Current Efficiency               | 49 |

| Motivation                           |    |

| Challenge                            |    |

| Slew-Rate Dependent Boost            |    |

| Current Efficient Buffer             |    |

| Frequency Response                   |    |

| Transient Response                   |    |

| 4.2 Current Boosting                 |    |

| Motivation                           |    |

| Challenge                            | 60 |

| Composite Output Transistor          |    |

| Maximum Output Current               |    |

| Drop-out Voltage                     |    |

| Frequency Response                   |    |

|                                      | 66 |

| Challenge                            | 66 |

| Pole/Zero Pair Generation            | 67 |

| Circuit Realizations                 |    |

| Parallel Amplifier Structure         | 70 |

| Frequency Shaping Amplifier          |    |

|                                      | _  |

| 4.4 Summary                          | 75 |

| CHAPTER V. REFERENCE DEVELOPMENT     | 76 |

| 5.1 Topologies                       | 76 |

| Zener                    |                       | 76  |

|--------------------------|-----------------------|-----|

|                          | gap                   |     |

|                          | ted Bandgap           |     |

|                          |                       |     |

| V-mode and I-mo          | de                    | 80  |

|                          |                       |     |

| 5.3 Bandgap Curvature C  | orrection Techniques  | 83  |

| V <sub>be</sub> Loop     |                       | 84  |

| β Compensation _         |                       | 85  |

|                          | lation                |     |

|                          | endent Resistor Ratio |     |

|                          | on                    |     |

|                          |                       |     |

| CHAPTER VI. CIRCUIT      | DESIGN                | 93  |

| 6.1 Control Loon         |                       | 05  |

| Pass Daviga              |                       | 95  |

| Drop out I               | Handicap              | 90  |

|                          | паписар               |     |

|                          |                       |     |

|                          |                       |     |

|                          | e                     |     |

| _                        | <i></i>               |     |

|                          | nts                   |     |

|                          | Enhancement           |     |

|                          |                       |     |

|                          |                       |     |

| CHAPTER VII. SYSTEM      | I DESIGN              | 119 |

| 7 1 Block I evel Diagram |                       | 119 |

| 7.1 Block Level Blagfall | es                    | 120 |

|                          |                       |     |

| Overload Current         | Protection            | 125 |

| Reverse Battery P        | Protection            | 128 |

|                          | n Protection          |     |

|                          | nance                 |     |

|                          | <u></u>               |     |

CHAPTER VIII. CONCLUSIONS \_\_\_\_\_\_148

| 8.1 Obstacles                                      | 148 |

|----------------------------------------------------|-----|

| 8.2 Enabling Techniques                            | 150 |

| Current Efficiency                                 |     |

| Current Boosting                                   |     |

| Load Regulation Enhancement                        |     |

| Low Voltage Reference                              |     |

| 8.3 Direction of Market Demand                     |     |

| Technology                                         |     |

| LDO Implications                                   |     |

| 8.4 Conclusion and Recommendations                 |     |

| APPENDICES                                         | 158 |

| A. V <sub>be</sub> Temperature Dependence Analysis | 158 |

| B. IV-mode Bandgap Trimming Procedure              |     |

| C. Layout Plots                                    | 168 |

| REFERENCES                                         | 171 |

| Vita                                               | 175 |

### LIST OF TABLES

| Table |                                                                                                   | Page  |

|-------|---------------------------------------------------------------------------------------------------|-------|

| 1.1   | Summary of the objective specifications.                                                          | _ 16  |

| 3.1.  | Qualitative evaluation of regulator topologies.                                                   | _ 42  |

| 6.1.  | Comparison of pass element structures.                                                            | _ 97  |

| 7.1.  | Table of parameters affected by the current boosted pass device and the current efficient buffer. | _ 141 |

| 7.2.  | Performance summary.                                                                              | _ 147 |

| 8.1.  | Summary of original contributions.                                                                | 153   |

### **LIST OF FIGURES**

| Figu | re                                                                     | Page  |

|------|------------------------------------------------------------------------|-------|

| 1.1. | Generic low drop-out series linear regulator architecture.             | 6     |

| 1.2. | PSRR performance implications of high frequency operation.             | 14    |

| 2.1. | System model under loading conditions.                                 | 18    |

| 2.2. | LDO frequency response under loading conditions.                       | 20    |

| 2.3. | AC simulation results of an LDO under loading conditions.              |       |

| 21   |                                                                        |       |

| 2.4. | Typical LDO transient response to a load-current step.                 | 24    |

| 2.5. | Simplified LDO schematic for the purpose of transient analysis.        | 26    |

| 2.6. | Simulated LDO transient response of a circuit similar to that of Figur | e 2.5 |

| 28   |                                                                        |       |

| 2.7. | LDO buffered architecture.                                             | 31    |

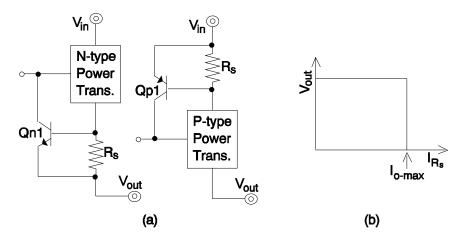

| 3.1. | CMOS low drop-out regulator topology.                                  | 36    |

| 3.2. | Buffered low drop-out regulator architecture.                          | 39    |

| 3.3. | All-in-one regulator approach.                                         | 40    |

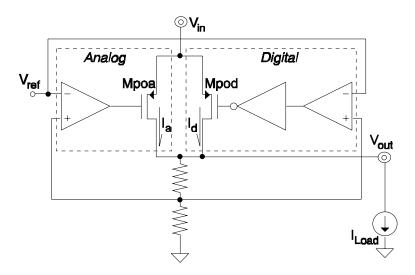

| 3.4. | Mixed-mode regulator.                                                  | 43    |

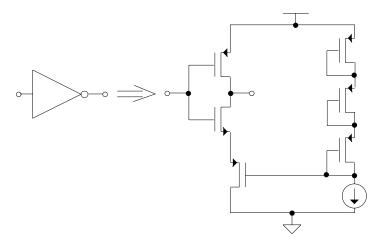

| 3.5. | Digital inverter for the mixed-mode regulator.                         | 44    |

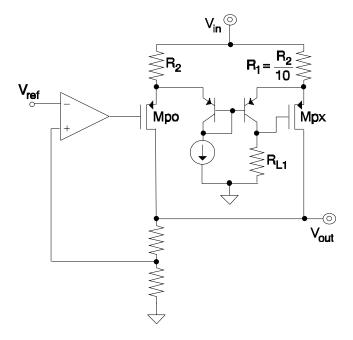

| 3.6. | Multi-path device regulator.                                           | 45    |

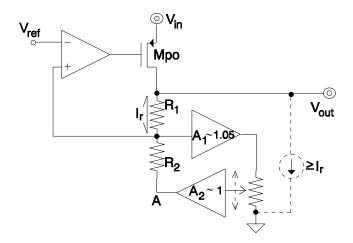

| 3.7. | Widely adjustable low drop-out regulator structure.                    | 47    |

| 4.1. | Slew-rate dependent boost circuit.                                     | 52    |

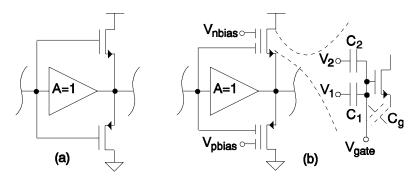

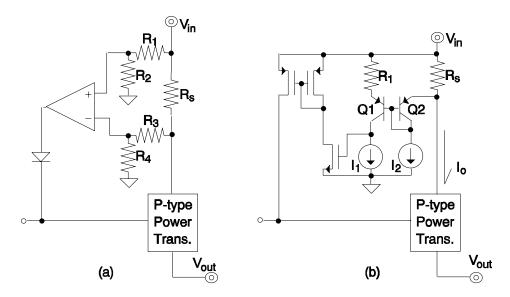

| 4.2. | Current efficient-transient boost LDO buffer stage.                    | 54    |

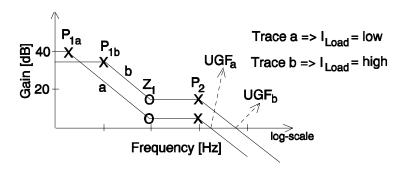

| 43   | System frequency response as a function of load-current                | 57    |

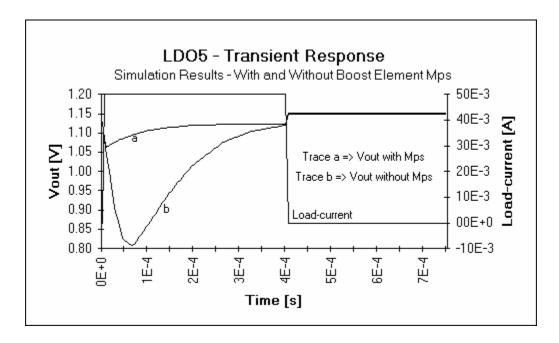

| 4.4.  | LDO output voltage variation with and without the boost element Mps in the current efficient buffer stage. | 59   |

|-------|------------------------------------------------------------------------------------------------------------|------|

| Figur | 'e                                                                                                         | Page |

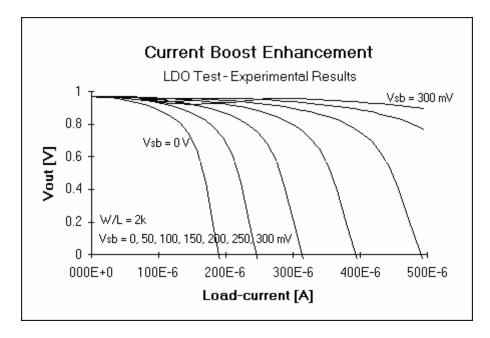

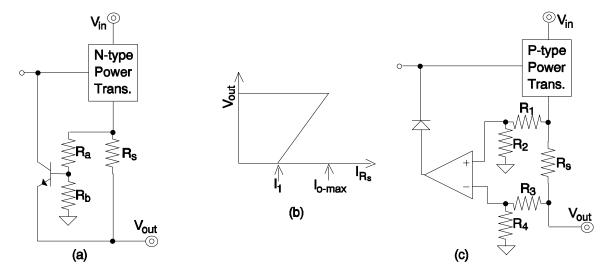

| 4.5.  | Maximum load-current performance of the current boost enhancement                                          | 62   |

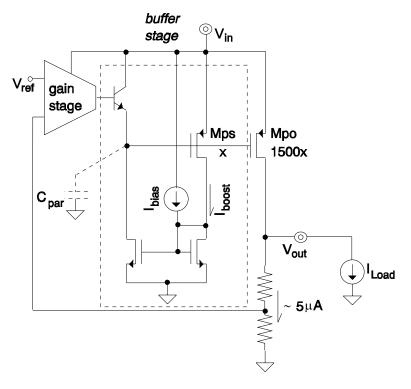

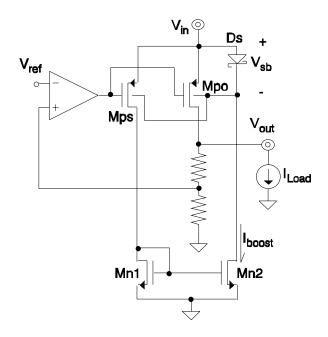

| 4.6.  | LDO with current boosting capabilities.                                                                    | 63   |

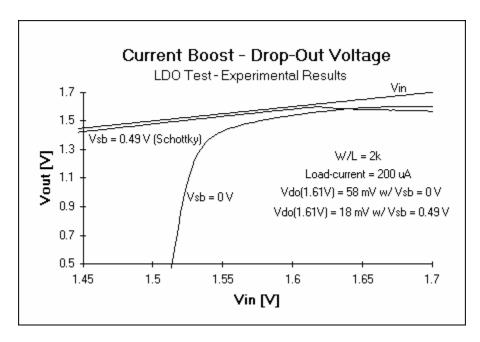

| 4.7.  | Drop-out voltage performance of the current boost topology.                                                | 64   |

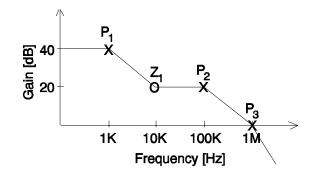

| 4.8.  | Linear regulator frequency response.                                                                       | 67   |

| 4.9.  | System's frequency response with an additional pole/zero pair.                                             | 68   |

| 4.10. | AC simulation of LDO with an additional pole/zero pair.                                                    | 69   |

| 4.11. | Parallel amplifier pole/zero pair realization.                                                             | 71   |

| 4.12. | Pole/zero pair generation by a feed-forward capacitor.                                                     | 72   |

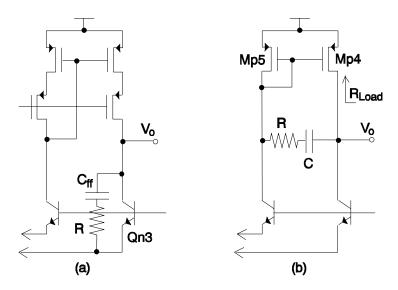

| 4.13. | Variations of the frequency shaping amplifier.                                                             | 74   |

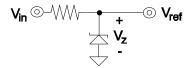

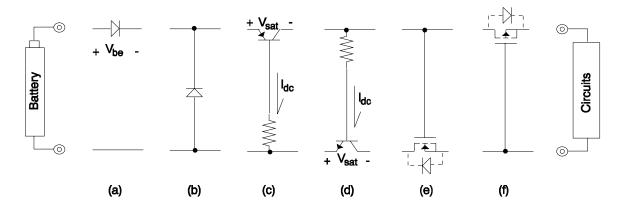

| 5.1.  | Zener diode reference.                                                                                     | 77   |

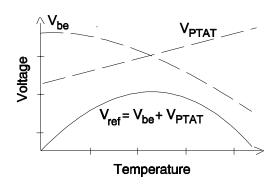

| 5.2.  | Temperature behavior of first order bandgaps.                                                              | 78   |

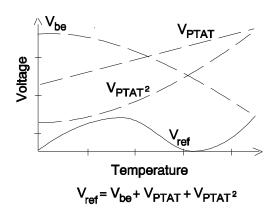

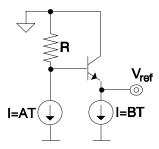

| 5.3.  | Squared PTAT curvature correction method for bandgaps.                                                     | 79   |

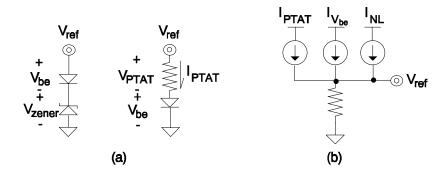

| 5.4.  | Output structures (a) voltage-mode and (b) current-mode.                                                   | 80   |

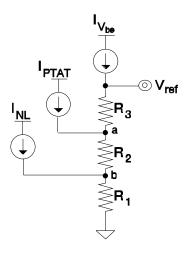

| 5.5.  | IV-mode output topology.                                                                                   | 83   |

| 5.6.  | V <sub>be</sub> loop curvature correction method.                                                          | 85   |

| 5.7.  | β curvature corrected bandgap.                                                                             | 86   |

| 5.8.  | Quasi-nonlinear term cancellation bandgap reference.                                                       | 87   |

| 5.9.  | Temperature dependent resistor ratio curvature correction.                                                 | 89   |

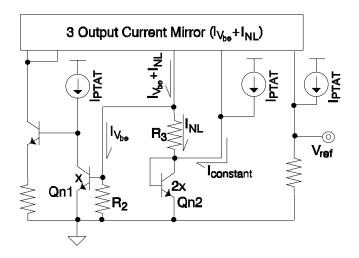

| 5.10. | Current subtraction method for generating I <sub>NL</sub> .                                                | 90   |

| 5.11. | Temperature dependence of the curvature corrected bandgap.                                                 | 91   |

| 6.1.  | Block level diagram of the system.                                                                         | 95   |

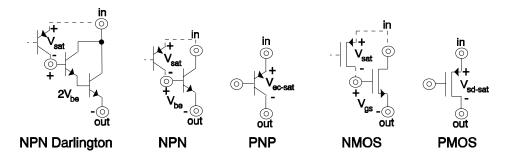

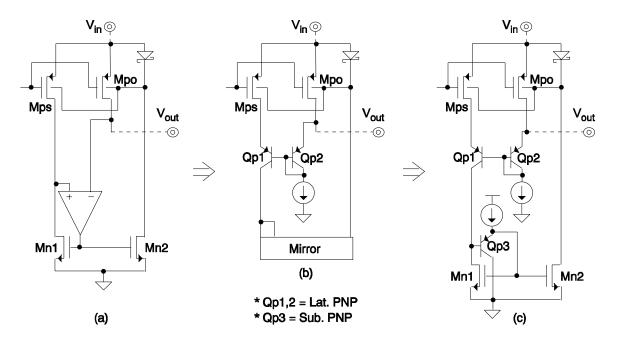

| 6.2.  | Pass element structures.                                                                                   | 96   |

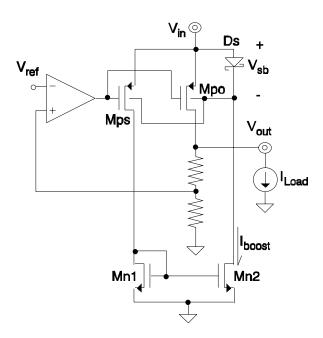

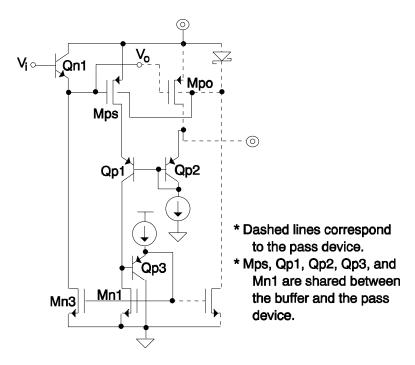

| 6.3.  | Composite PMOS pass device.                                                        | 98   |

|-------|------------------------------------------------------------------------------------|------|

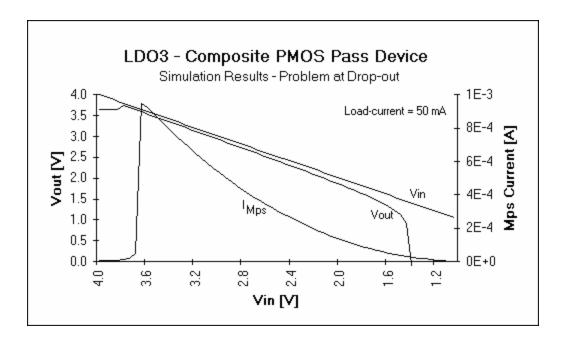

| 6.4.  | Simulation of current sensing problem at drop-out.                                 | 99   |

| Figur | e                                                                                  | Page |

| 6.5.  | Pass device design development for efficient current sensing.                      | 100  |

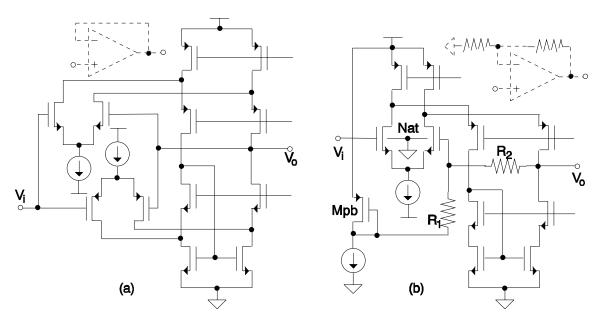

| 6.6.  | Non-inverting amplifier topologies.                                                | 102  |

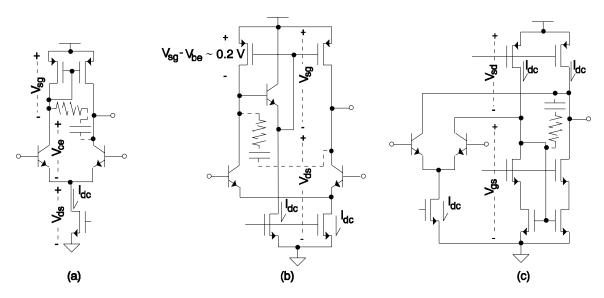

| 6.7.  | Feedback buffer structures.                                                        | 104  |

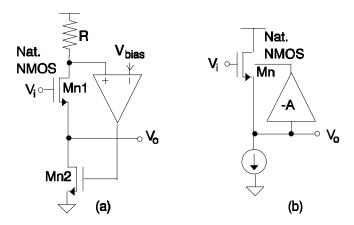

| 6.8.  | Current efficient buffer.                                                          | 105  |

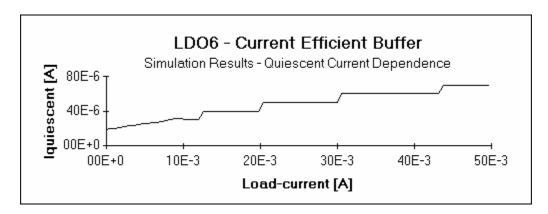

| 6.9.  | Quiescent current dependence of buffer on load-current.                            | 106  |

| 6.10. | Gain stage topologies.                                                             | 108  |

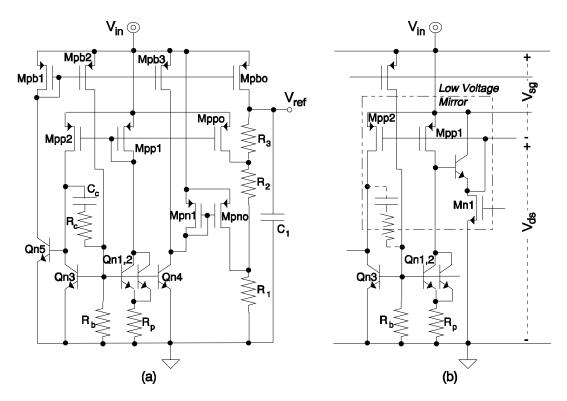

| 6.11. | Bandgap with current subtraction curvature correction.                             | 109  |

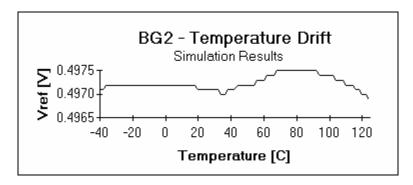

| 6.12. | Temperature drift performance of the bandgap reference.                            | 110  |

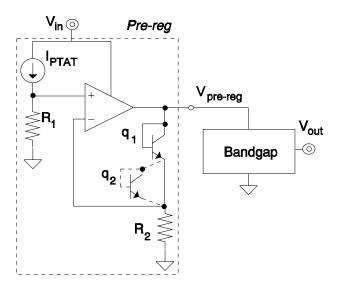

| 6.13. | Pre-regulated supply voltage realization.                                          | 112  |

| 6.14. | Low voltage curvature corrected bandgap.                                           | 114  |

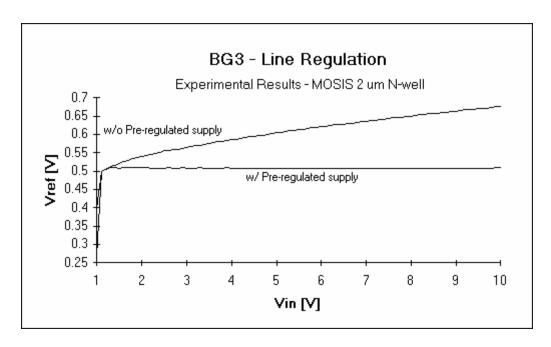

| 6.15. | Line regulation performance of the bandgap with and without the pre-<br>regulator. | 115  |

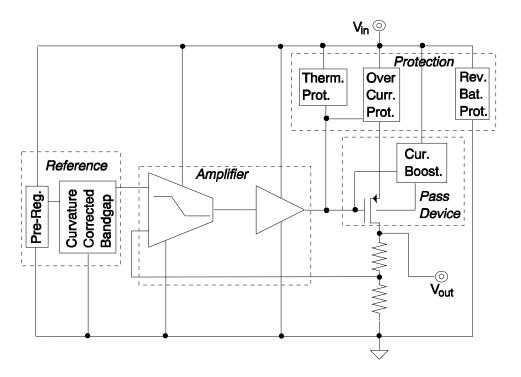

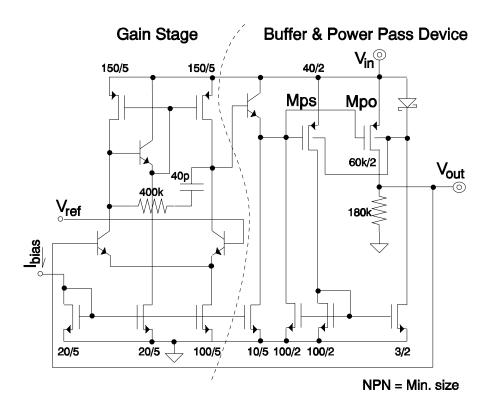

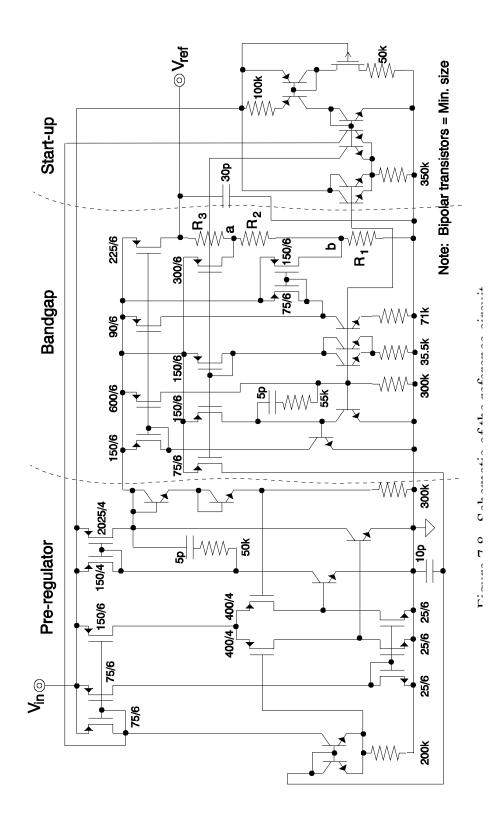

| 7.1.  | Complete system block level diagram.                                               | 120  |

| 7.2.  | Current limiting circuit protection.                                               | 125  |

| 7.3.  | Low voltage current limiting circuit protection.                                   | 126  |

| 7.4.  | Foldback current limiting circuit protection.                                      | 128  |

| 7.5.  | Reverse battery protection circuits.                                               | 129  |

| 7.6.  | Thermal shutdown protection circuit.                                               | 131  |

| 7.7.  | Schematic of the control loop circuit.                                             | 136  |

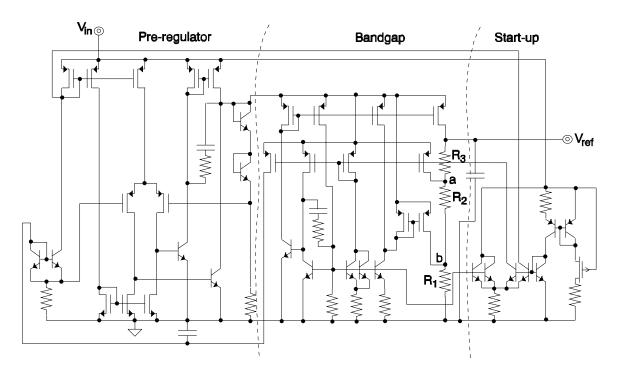

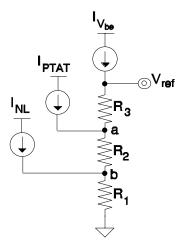

| 7.8.  | Schematic of the reference circuit.                                                | 137  |

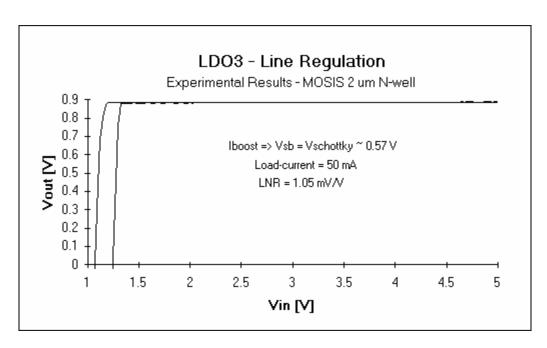

| 7.9.  | Line regulation performance of the control loop.                                   | 138  |

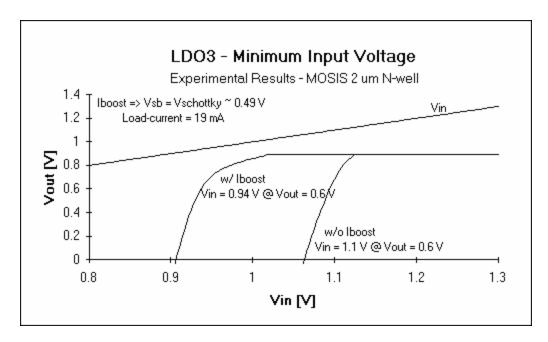

| 7.10. | Minimum input voltage of the control loop.                                         | 138  |

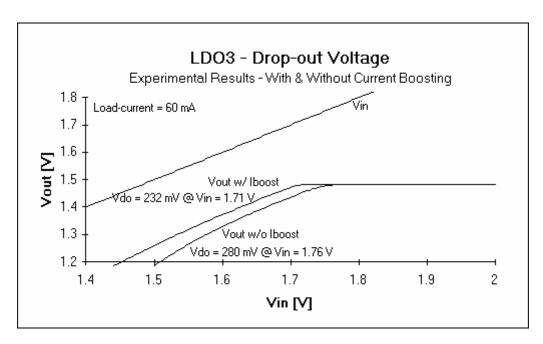

| 7.11. | Drop-out voltage performance.                                                                                                                    | _ 139 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|

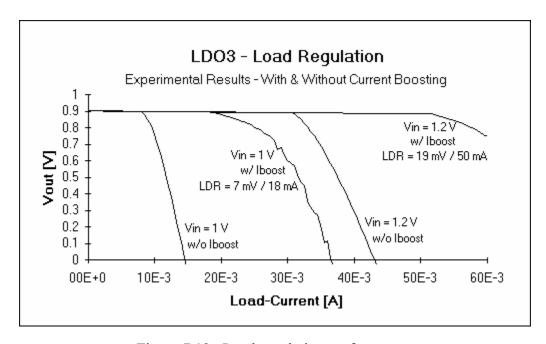

| 7.12. | Load regulation performance.                                                                                                                     | 139   |

| Figur | re                                                                                                                                               | Page  |

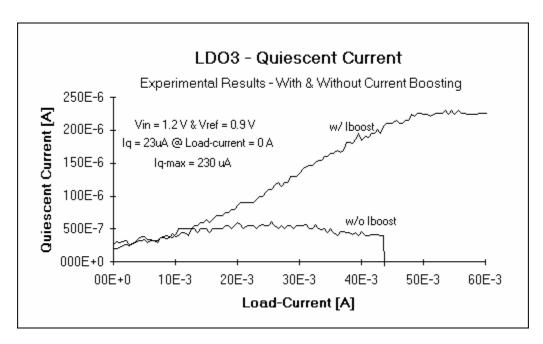

| 7.13. | Quiescent current flow of the control loop.                                                                                                      | 140   |

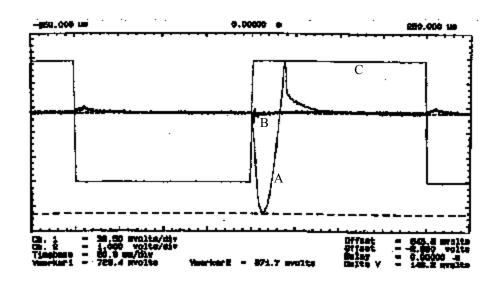

| 7.14. | Transient response to a full range load-current step (A) with and (B) without the aid of load dependent biasing in the current efficient buffer. | 140   |

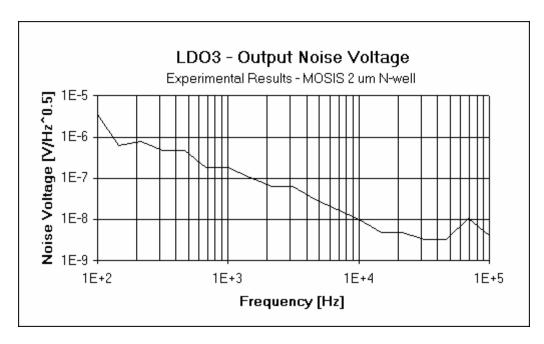

| 7.15. | Control loop output noise voltage performance.                                                                                                   | _ 141 |

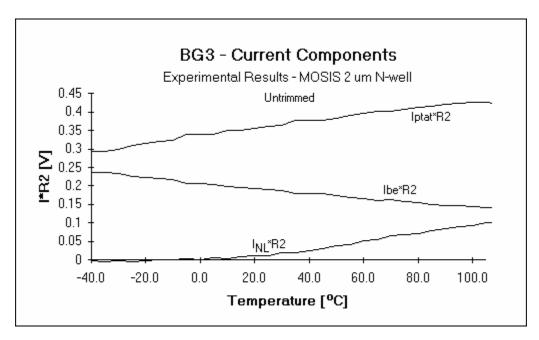

| 7.16. | Temperature dependent currents in the reference.                                                                                                 | 142   |

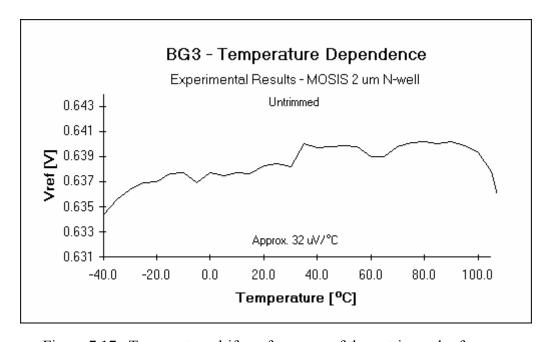

| 7.17. | Temperature drift performance of the untrimmed reference.                                                                                        |       |

| 142   |                                                                                                                                                  |       |

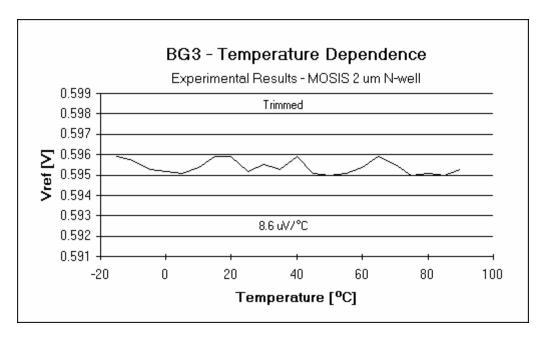

| 7.18. | Temperature drift performance of the trimmed reference.                                                                                          | _ 143 |

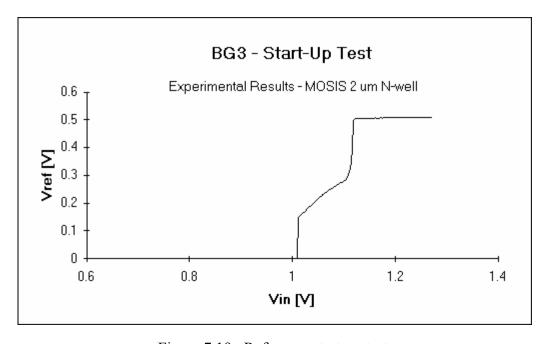

| 7.19. | Reference start-up test.                                                                                                                         | 143   |

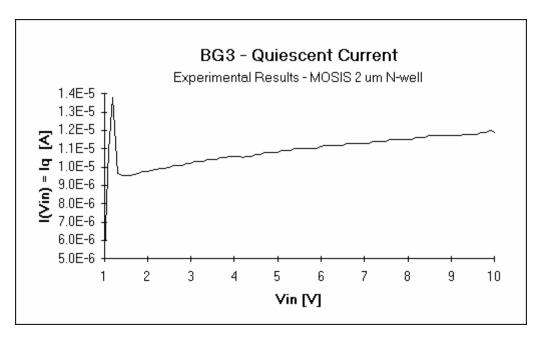

| 7.20. | Quiescent current flow of the reference.                                                                                                         | 144   |

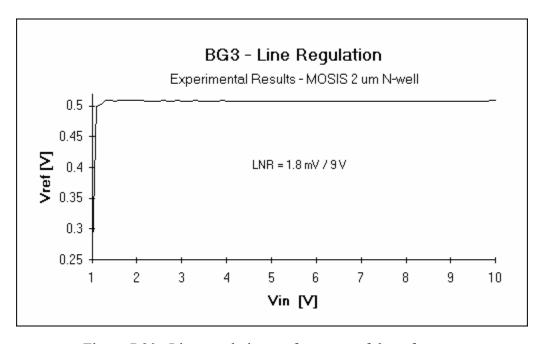

| 7.21. | Line regulation performance of the reference.                                                                                                    | 144   |

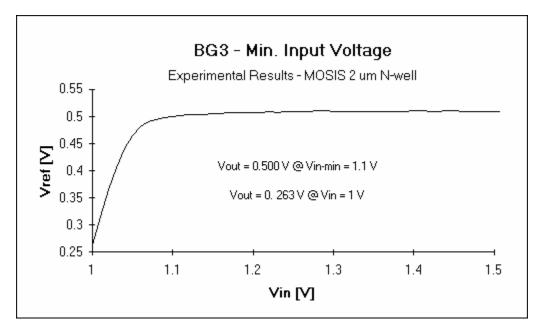

| 7.22. | Minimum input voltage of the reference.                                                                                                          | 145   |

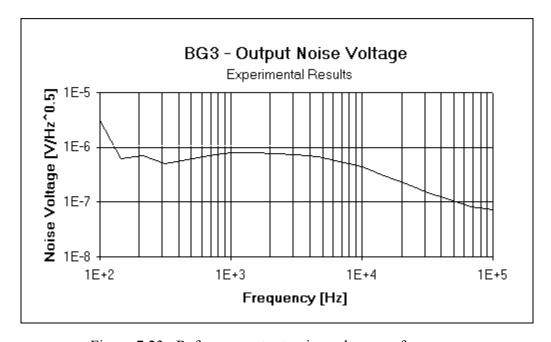

| 7.23. | Reference output noise voltage performance.                                                                                                      | 145   |

| B.1.  | IV-mode bandgap output structure.                                                                                                                | 162   |

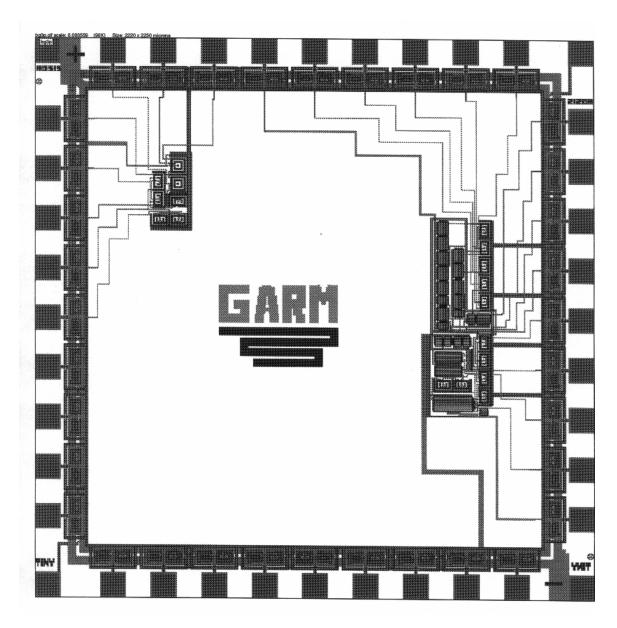

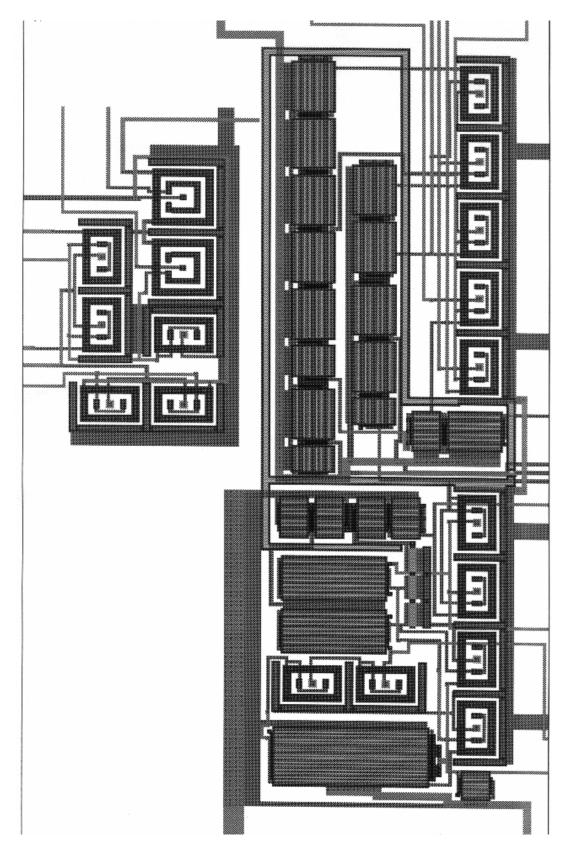

| C.1.  | Layout of the curvature corrected bandgap and associated start-up circuit                                                                        | 168   |

| C.2.  | Zoom-in plot of the start-up and reference (290 x 173 μm & 798 x 280 μm).                                                                        | _ 169 |

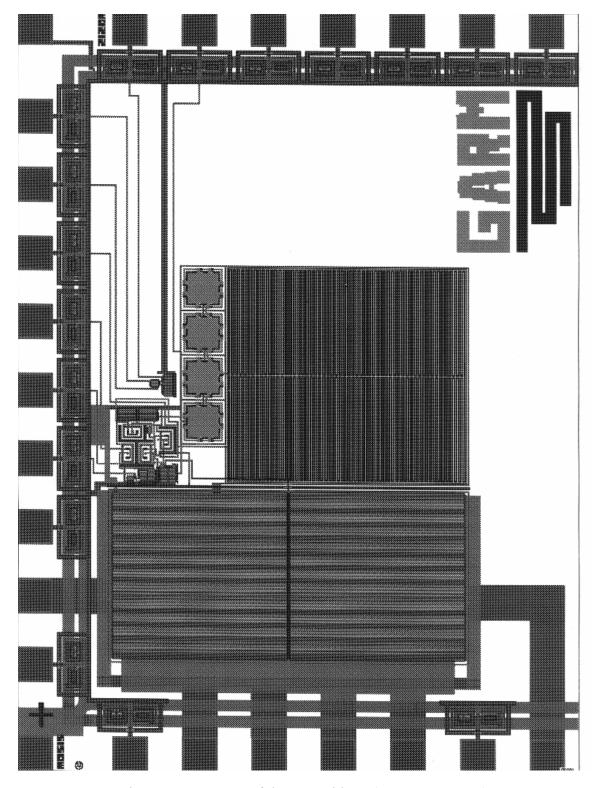

| C.3.  | Layout of the control loop (1103 x 1250 μm).                                                                                                     | 170   |

### **SUMMARY**

Regulators are an essential part of any electrically powered system, which includes the growing family of applications of portable battery operated products. Regulators are required to reduce the large voltage variations of battery cells to lower and more acceptable levels. Absence of these power supplies can prove to be catastrophic in most high frequency and high performance circuit designs. As a result, low drop-out regulators and other power supply circuits are always in high demand. In fact, the increasing drive towards total chip integration (single chip solutions) demands that power supply circuits be included in every chip. This is a consequence of the public demand for smaller and less expensive portable products.

In particular, the increasing demand for portable battery operated products has driven power supply design towards low voltage and low quiescent current flow, i.e., cellular phones, pagers, camera recorders, laptops, etc. The thrust is towards reducing the number of battery cells, required to decrease cost and size, while minimizing quiescent current flow to increase battery life. Current efficiency is particularly important because at low load-current conditions the life of the battery is adversely affected by low current efficiency, in other words, high quiescent current flow. At high load-currents, on the other hand, current efficiency is typically high because load-current is significantly larger than quiescent current. In this low voltage environment, a low drop-out regulator is the most appropriate form of linear regulators. However, the prevailing designs do not work at input voltages suitable for single, low voltage battery cells. This research develops techniques that enable practical circuit realizations of low

drop-out regulators at low input voltages and low quiescent current flow without sacrificing performance.

An intimate knowledge of the system reveals that the frequency stability requirements are dependent on load-current. As a result, a load dependent biasing buffer is designed to minimize current flow during low load-current conditions. Moreover, suitable biasing conditions result during transient load-current steps. This transient aid comes in the form of increased slew-rate current capabilities during conditions that warrant it. Another problem with low voltage in a CMOS environment is reduced gate drive for the power transistor. In other words, the output current capability per unit area of the power device under low voltage conditions is appreciably less than its higher voltage counterpart. However, gate drive can be effectively increased by reducing the threshold voltage. This is done by forward biasing the source to bulk junction of the power PMOS device and thus exploiting the bulk effect phenomenon. Yet another problem with low voltage is the realization of an accurate reference voltage. Typical bandgap references are restricted by input voltages greater than approximately 1.4 V (V<sub>sat</sub> above the bandgap voltage). A circuit topology suitable for low voltages and curvature compensation is developed.

The overall system is designed, simulated, and experimentally evaluated. The process technology utilized is MOSIS 2 µm CMOS with a p-base layer. However, most of the techniques can be adapted to almost any technology ranging from bipolar and vanilla CMOS to relatively inexpensive and full blown biCMOS processes. As a result, the resulting system can be designed and optimized for low cost. The physical layout implications of the circuit realization are discussed with emphasis on reliability and performance. The findings show that a successful low voltage design is achieved by implementing the techniques developed. Furthermore, the techniques also showed that

they are appropriate for maximizing performance of most linear regulator designs outside the realm of low voltage.

### **CHAPTER I**

### INTRODUCTION

The demand for low drop-out regulators has been driven by the portable electronics market as well as industrial and automotive applications. Most recently, the increasing demand for portable and battery operated products have forced these circuits to operate under lower voltage conditions. Furthermore, high current efficiency has also become necessary to maximize the lifetime of the battery. Battery life is determined by the total current drain composed of quiescent current and load-current. This chapter discusses the role and the characteristics of low drop-out regulators in today's market. The objective of the research is then identified and defined according to the demands that drive regulator design into the future.

### 1.1 Definition

A series low-drop-out regulator is a circuit that provides a well specified and stable dc voltage [1] whose input to output voltage difference is low [2]. The drop-out voltage is defined as the value of the input/output differential voltage where the control loop stops regulating. The term series comes from the fact that a power transistor (pass device) is connected in series between the input and the output terminals of the regulator [3]. The operation of the circuit is based on feeding back an amplified error signal to control the output current flow of the power transistor driving the load. This type of

regulator has two inherent characteristics: (1) the magnitude of the input voltage is greater than the respective output and (2) the output impedance is low to yield good performance [2]. Low drop-out (LDO) regulators can be categorized as either low power or high power. Low power LDOs are typically those with a maximum output current of less than 1 A, exhibited by most portable applications. On the other hand, high power LDOs can yield currents that are equal to or greater than 1 A to the output, which are commonly demanded by many automotive and industrial applications [4].

### 1.2 Market Demand

### Current Efficiency, Low Voltage, and Low Drop-out

As a result of high variations in battery voltage, regulators are demanded by virtually all battery operated applications. Furthermore, most designs find it necessary to include regulators and other power supply circuits as products achieve or approach total chip integration. Low drop-out regulator are appropriate for many circuit applications, namely, automotive, portable, industrial, and medical applications. In the automotive industry, the low drop-out voltage is necessary during cold-crank conditions where the battery voltage can drop below 6 V. The increasing demand, however, is readily apparent in mobile battery operated products, such as cellular phones, pagers, camera recorders, and laptops [5]. This portable electronics market requires low voltage and low quiescent current flow for increased battery efficiency and longevity [6]. As a result, high current efficiency is necessary to maximize battery life. Low voltage operation is also a consequence of the direction of process technology towards higher packing densities [7]. In particular, isolation barriers decrease as the component densities per unit area are increased thereby manifesting lower breakdown voltages [8, 9]. Minimization of drop-out voltages in a low voltage environment is also necessary to maximize dynamic

range. This is because the signal-to-noise ratio decreases as the power supply voltages decrease while noise typically remains constant [10, 11]. Consequently, low power and finer lithography drive regulators to operate at lower voltages, produce precise output voltages, and require low quiescent current flow [9]. By the year 2004, the power supply voltage is expected to be as low as 0.9 V in 0.14 µm technologies [9, 12]. Lastly, financial considerations also require that these circuits be fabricated in relatively simple processes, such as standard CMOS, bipolar, and stripped down biCMOS technologies [13].

### **Alternative: Switching Regulators**

The alternatives to low drop-out regulators are dc-dc converters, switching regulators. Switching regulators are essentially mixed-mode circuits that feed back an analog error signal and digitally gate it to provide bursts of current to the output. The circuit is inherently more complex and costly than LDO realizations [9]. Furthermore, switching regulators can provide a wide range of output voltages including values that are lower or greater than the input voltage depending on the circuit configuration, buck or boost. The circuit, for the most part, requires a controller with an oscillator, pass elements, an inductor, capacitors, and diodes. Some switched-capacitor implementations do not require an inductor [14, 15].

The worst-case response time of a dc-dc converter is dependent on the oscillating frequency of the controller (approximately 20 to 200 kHz [16]) and circuit delay. As a result, the corresponding response time is roughly between 6 and 8 µs, whereas the LDO typically requires between 1 and 2 µs [12]. Since the pass elements switch high currents through an inductor at the rate of the oscillator, the output voltage is inherently noisy. This is especially true for boost configurations where RF noise tends to be worse [17]. The high noise present is a consequence of the rectified inductor voltage behavior of the

output of these converters. Furthermore, start-stop clock operation (on/off sleep-mode transitions) further aggravates the noise content of the output voltage [12].

On the other hand, switching regulators benefit from having high power efficiency and the ability to generate larger output voltages than the input. They can yield efficiencies between 80 and 95 % [18]. The efficiency of the LDO counterpart is limited by the quiescent current flow and the input/output voltages, and is expressed as

Efficiency<sub>Power</sub> =

$$\frac{I_0 V_0}{\left[I_0 + I_q\right] V_i} \le \frac{V_0}{V_i}$$

, (1.1)

where  $I_o$  and  $V_o$  correspond to the output current and voltage,  $V_i$  is the input voltage, and  $I_q$  is the quiescent current or ground current. The main power issue in LDO design is battery life, in other words, the output current flow of the battery. When the load-current is low, which is the normal operating mode for many applications, the quiescent (ground) current becomes an intrinsic factor in determining the lifetime of the battery. Consequently, current efficiency is important during low load-current conditions. Power efficiency, on the other hand, becomes more pertinent during high load-current conditions where quiescent current is negligible relative to the output current.

If the maximum load-current is much greater than the ground current, then the maximum possible power efficiency is defined by the ratio of the output and the input voltages, as seen in equation (1.1). Power efficiency increases as the voltage difference between the input and the output decreases. Under these conditions, LDOs are better suited for many applications than switching regulators because of lower cost, complexity, and output noise. The choice becomes obscure, however, if the output current increases to the point where the LDO requires a heat sink [12]. A heat sink not only increases cost by requiring an additional component but it also means more real estate area overhead on

the board, which further increases cost. Applications that require high input/output voltage differentials with high output currents greatly benefit from the efficiency of dc-dc converters. Nevertheless, there are some cases where a high input/output voltage differential regulator is required to drive noise sensitive circuits. In these situations, a switching regulator is used to bring down the voltage and an LDO is cascaded to provide a low noise output [4, 18]. These conditions arise in mixed-mode designs where circuits that perform analog functions tend to be more sensitive to noise originated in the supply rails than the digital counterparts [17, 19]. Other applications require output voltages that are larger than the respective inputs. In these situations, dc-dc converters are necessarily used, be it in the form of a boost topology, a boosting switch capacitor implementation, or a charge pump structure. However, LDOs are still required in these applications to suppress noise generated by the switching pre-regulator. In summary, both LDOs and switching regulators have their place in today's market demand.

### 1.3 Characteristics

### **Block Level Description**

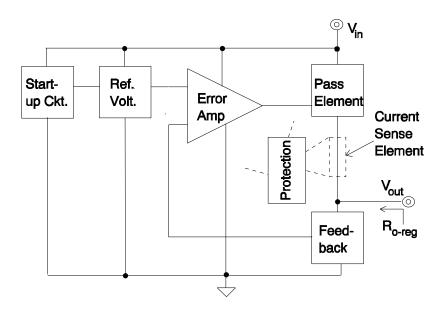

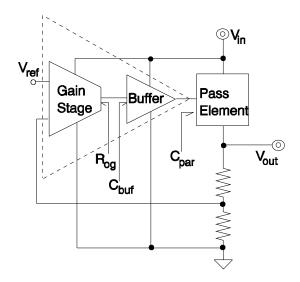

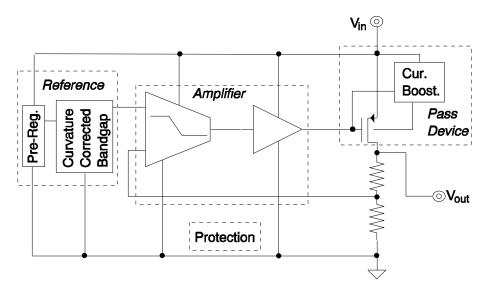

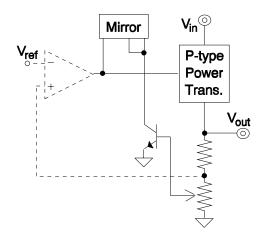

Figure 1.1 illustrates the block level diagram of a generic series low drop-out regulator. The circuit is composed of a reference and associated start-up circuit, protection circuit and associated current sense element, an error amplifier, a pass element, and a feedback network. The reference provides a stable dc bias voltage with limited current driving capabilities. This is usually a zener diode or a bandgap reference. The zener diode finds its applications in high voltage circuits (greater than approximately seven volts) with relaxed temperature variation requirements [1, 3]. The bandgap, on the other hand, is better suited for low voltage and high accuracy applications. The protection circuitry ensures that the LDO operates in safe stable conditions. Some of its

functions include over-current protection (typically a foldback current limiter [6]), thermal shutdown in case of self-heating (junction temperature increases beyond safety levels), and other similar functions. The error amplifier, the pass element, and the feedback network constitute the regulation loop. The temperature dependence of the reference and the amplifier's input offset voltage define the overall temperature coefficient of the regulator; hence, low drift references and low input offset voltage amplifiers are preferred [20, 21].

Figure 1.1. Generic low drop-out series linear regulator architecture.

### **Performance**

Overall noise performance is strongly dependent on the physical layout of the chip and the respective process technology. In particular, the noise present at the output of the LDO is composed of three components, namely, noise injected from the system through the substrate and the input voltage, noise generated by the reference circuit, and noise associated with the output trace (lead) inductance and resistance [4]. Switching

regulators can typically be used to provide power to LDOs and can be integrated in the same chip as the LDO thereby injecting noise through the substrate and the input voltage, i.e., cellular phones. In these cases, physical layout isolation techniques and high power supply rejection ratio are intrinsic circuit characteristics for good noise performance. Transient load-current changes also affect the noise content seen by the load. This results from the parasitic resistance and inductance of the trace (lead) from the LDO's output to the load. Therefore, physical proximity of the LDO to its load must be minimized to reduce the noise seen by the load [12].

Low drop-out regulators tend to necessitate large output capacitors that occupy large board areas. Furthermore, typical LDOs require that these capacitors have low electrical series resistance (ESR). Consequently, capacitors play an intrinsic role in the cost of the LDO. High power LDOs may require heat sinks further aggravating the cost issue. However, a system level design choice may circumvent the need for a heat sink by utilizing several smaller LDOs distributed throughout the board [4]. Finally, the emergence of finer lithography and the increasing demand for low power cause low voltage operation to be a necessary condition. Therefore, there are some circuit design techniques that are discouraged, which give rise to more complex and possibly more expensive circuits. Some of the discouraged techniques include unnecessary cascoding, emitter followers, and Darlington configurations [10].

### 1.4 Specifications

### **System**

The important aspects of the LDO can be summarized into three categories, namely, regulating performance, quiescent current flow, and operating voltages [22]. Some of the specifications that serve as metrics for the LDO include drop-out voltage,

line regulation, load regulation, tolerance over temperature, output voltage variation resulting from transient load-current steps, output capacitor and ESR range, quiescent current flow, maximum load-current, and input/output voltage range. The requirements of these performance characteristics often contradict each other giving rise to necessary compromises. The priority of the performance parameters is defined according to the particular application.

Drop-out voltage is the minimum input/output differential voltage where the circuit just ceases to regulate. This can be expressed in terms of switch "on" resistance,  $R_{on}$  [6],

$$V_{drop-out} = I_{Load} R_{on}. (1.2)$$

Typical drop-out voltages range from 0.1 to 1.5 V [4]. The output voltage variation arising from a specific change in input voltage is defined as line regulation. Similarly, load regulation is the change in output voltage for specific changes in load-current [2]. Load regulation is essentially the output resistance of the regulator ( $R_{o-reg}$ ),

$$R_{o-reg} = \frac{\Delta V_{LDR}}{\Delta I_o} = \frac{R_{o-pass}}{1 + A_{ol}\beta},$$

(1.3)

where  $\Delta V_{LDR}$  and  $\Delta I_{o}$  are the output voltage and the load-current changes,  $R_{o\text{-pass}}$  is the output resistance of the pass element,  $A_{ol}$  is the open-loop gain of the system, and  $\beta$  is the feedback factor [3]. Therefore, load regulation performance is improved as the dc open-loop gain is increased [12]. The temperature dependence of the output voltage is a function of the temperature drift of the reference and that of the input offset voltage of the error amplifier,

$$TC = \frac{1}{V_o} \cdot \frac{\partial V_o}{\partial Temp} \approx \frac{1}{V_o} \cdot \frac{\Delta V_{TC}}{\Delta Temp} = \frac{\left[\Delta V_{TC_{ref}} + \Delta V_{TC_{Vos}}\right] \frac{V_o}{V_{ref}}}{V_o \Delta Temp}, \quad (1.4)$$

where TC is the temperature coefficient,  $\Delta V_{TC}$  is the output voltage variation over the temperature range  $\Delta T_{emp}$ ,  $\Delta V_{TC_{ref}}$  and  $\Delta V_{TC_{vos}}$  are the voltage variations of the reference and input offset voltage of the error amplifier, and  $V_o$  /  $V_{ref}$  is the ratio of the nominal output and reference voltages. Transient output voltage variations resulting from sudden load-current changes are dominated by the closed-loop bandwidth of the system, output capacitor, and load-current. The worst-case situation occurs when the load-current suddenly steps from zero to its maximum specified value. The resulting output voltage variation is described as

$$\Delta V_{tr} \approx \frac{I_{Load-max}}{C_o + C_b} \Delta t + \Delta V_{esr},$$

(1.5)

where  $\Delta V_{tr}$  is the output voltage change,  $I_{Load-max}$  is the maximum specified load-current,  $C_o$  is the output capacitor,  $C_b$  refers to the bypass capacitors,  $\Delta V_{esr}$  is the voltage variation resulting from the electrical series resistance (ESR) of the output capacitor, and  $\Delta t$  is the time required for the LDO to respond (approximately equal to the reciprocal of the closed-loop bandwidth (BW<sub>cl</sub>) if internal slew-rate conditions are neglected). The voltage variation resulting from ESR results because of the momentary current (provided by  $C_o$ ) flowing through the ESR. This is reduced by the high frequency nature of the bypass capacitors (low ESR capacitors). In other words, the bypass capacitors ( $C_b$ ) help filter out the effects of the output capacitor ESR. Consequently, fast response times and low ESR values are necessary to yield low transient output voltage variations. Low

output voltage variations are desired to meet the overall accuracy requirements of the system, i.e., 150 - 300 mV [9]. Thus, the circuit as a whole benefits from the use of a high bandwidth amplifier in the feedback loop. A pivotal specification is the output capacitor and associated ESR range for which the LDO is stable. This can typically prove to be a difficult task if a wide range of values is to be allowed. The value of the load-current also affects the frequency response of the circuit. Lastly, long term stability and low external component count are also pertinent factors to keep in mind when designing LDOs.

The effects of line regulation, load regulation, temperature dependence, and transient output voltage variations can be summed up into one specification, accuracy. Accuracy refers to the total output voltage variation and can be described by the absolute minimum and maximum output voltages ( $V_{o-min}$  and  $V_{o-max}$ ), shown in the following equations:

$$V_{o-min} \le \Delta V_{LNR} + \Delta V_{LDR} + \Delta V_{TC} + \Delta V_{tr} + V_{reference} \left\langle \frac{V_o}{V_{ref}} \right\rangle \le V_{o-max}, (1.6)$$

$$V_{reference} = V_{ref} + \Delta V_{TC_{ref}} + \Delta V_{LNR_{ref}} \pm V_{os}, \qquad (1.7)$$

$$Accuracy_{system} = \left\langle \frac{V_{o-max} - V_{o-min}}{V_{o}} \right\rangle, \tag{1.8}$$

where  $\Delta V_{LNR}$ ,  $\Delta V_{LDR}$ ,  $\Delta V_{TC}$ ,  $\Delta V_{tr}$ ,  $\Delta V_{TCref}$ , and  $\Delta V_{LNRref}$  are voltage variations resulting from line regulation, load regulation, temperature dependence, worst-case transient load-current steps, reference circuit's temperature dependence, and reference circuit's line regulation respectively while  $V_{os}$  and  $V_{o}$  are the input offset voltage of the

error amplifier and the nominal output voltage of the regulator. In specifying accuracy, the effect of the transient load-current step and the reference circuit is sometimes excluded but they are included here for completeness. Low voltage operation often implies more stringent specifications in the form of overall accuracy. Typical implementations achieve roughly 1 to 2 % total variation resulting from load regulation, line regulation, and temperature dependence while leaving some headroom for transient output voltage variations [12].

### Reference

The specifications of the reference include line regulation, temperature dependence, quiescent current flow, and input voltage range. The effects of line regulation and temperature drift on system accuracy are shown in equations (1.6) - (1.7). Line regulation refers to the variation of the reference voltage arising from a unit change in input voltage. In the same token, the temperature coefficient of the reference  $(TC_{ref})$  refers to the variation in output voltage as a result of unit changes in temperature and can be expressed as

$$TC_{ref} = \frac{1}{V_{ref}} \cdot \frac{\partial V_{ref}}{\partial Temp} \approx \frac{1}{V_{ref}} \cdot \frac{\Delta V_{TC_{ref}}}{\Delta Temp},$$

(1.9)

where  $\Delta V_{TCref}$  is the reference voltage change resulting from a temperature variation equal to  $\Delta T$ emp and  $V_{ref}$  is the nominal reference voltage. The overall accuracy of references is determined by the combination of line regulation and temperature coefficient performance and is described as

$$Accuracy_{reference} = \frac{\Delta V_{TC_{ref}} + \Delta V_{LNR_{ref}}}{V_{ref}},$$

(1.10)

where  $\Delta V_{TCref}$  and  $\Delta V_{LNRref}$  are voltage variations resulting from temperature dependence and line regulation respectively. Load regulation is sometimes included in the accuracy of the reference but most appropriately specified for regulator structures.

### 1.5 Research Objective

The objective of this research is to enhance performance of low drop-out (LDO) regulators for battery powered electronics. This is targeted to fulfill the present commercial requirements as well as the projected demands of the future. Such an endeavor makes certain characteristics necessary, namely, low quiescent current flow for increased battery life, low voltage operation, and high output current. The techniques that are developed to overcome the aforementioned obstacles not only enhance the prevailing LDO circuit architecture but also push regulator design into the 21st century. This is done with existing standard technologies; thus, the designs take full advantage of all physical aspects of the process while maintaining fabrication costs to acceptable and competitive levels. Moreover, the new design techniques will be able to further exploit the benefits of more advanced technologies in the future.

The intrinsic issues in designing a current efficient (low quiescent current) and low drop-out linear regulator in a low voltage environment can be identified as stability, maximum output current, and regulating performance. Stability in a low quiescent current atmosphere is difficult to achieve because of the presence of potentially low frequency parasitic poles. These are easily circumvented by increasing bandwidth, which usually results at the expense of higher quiescent current flow. Maximum output current capabilities of regulators also becomes restricted under low voltage conditions. This results from the inherent reduction in gate drive for the pass element when input voltages

are decreased. Finally, low voltage circuits tend to limit the regulating performance of regulators because of problems with headroom. As input voltages decrease, the use of common circuit techniques that enhance performance becomes restrained, i.e., cascoding, Darlington configurations, and source [emitter] followers [10]. In a battery powered environment, the number of devices connected from the input voltage to ground must be kept low [10]. The ultimate limit is one diode drop plus one output saturation voltage,  $V_{be} [V_{gs}] + V_{ec-sat} [V_{sd-sat}]$ .

An input voltage range appropriate for single, low voltage battery cells is targeted (0.9 to 1.5 V). The circuit technology is MOSIS 2  $\mu m$  CMOS with an added p-base layer, a relatively inexpensive process. The minimum operating voltage possible for this technology is approximately between 1 and 1.1 V,  $V_{sg-pmos} + V_{ds-nmos}$ . For maximized battery life, the circuits must be current efficient and micro-power. The zero-load quiescent current goal is approximately 60 to 65  $\mu A$  including the reference and the regulating loop, 15 - 20  $\mu A$  for the reference and 40 - 45  $\mu A$  for the remainder. Since the thrust of the driving market demand lies in battery operated regulators, the output current range is defined to be between 50 and 100 mA for respective input voltages ranging from 1.2 to 1.5 V. The design criteria also focuses on minimizing transient output voltage variations resulting from fast load-current step transitions, less than 75 mV.

To further mitigate overall costs, standard tantalum capacitors are used for the output. These are among the least expensive with an electrical series resistance (ESR) range of up to approximately  $10~\Omega$  [23]. The target range of ESR is extended to zero to cater to applications where low ESR is necessary. Low values of ESR are demanded for high power supply rejection ratio (PSRR) performance at high frequencies and minimized transient output voltage variations. The PSRR performance of LDOs (generically illustrated in Figure 1.2) at high frequencies is approximated to be

$$PSRR = \frac{\Delta V_{supply}}{\Delta V_{o}} \cdot \frac{V_{o}}{V_{ref}} = \frac{\Delta V_{in}}{\Delta V_{o}} A_{v}(s) \approx \frac{R_{o-pass} + R_{esr}}{R_{esr}} A_{v}(s), \quad (1.11)$$

where  $\Delta V_{supply}$  is equivalent to  $\Delta V_{in}$  for regulators,  $A_v(s)$  is the open-loop gain from  $V_{ref}$  to  $V_o$ , and the terminology of Figure 1.2 is adopted. Consequently, PSRR at high frequencies, when  $A_v(s)$  approaches unity, greatly benefits from low ESR values. This is

Figure 1.2. PSRR performance implications of high frequency operation.

especially important when considering that  $R_{o\text{-pass}}$  for CMOS structures is relatively low because of short channel lengths, which result in poor early voltage performance. Power MOS transistors require shorter channel lengths to provide larger output currents. Power supply rejection ratio performance at high frequencies is important in designs that integrate a switching regulator on to the same chip as the LDO. This results in injection of systematic noise to the output at the frequency of the clock, typically between 100 and 500 kHz.

The typical specifications for low voltage LDOs ( $\geq 2.3$  V input voltage range) include drop-out voltages of 0.4 to 0.9 V at output currents of 40 mA and output voltage accuracy of 4 to 5 % [24, 25, 26]. The design target focuses on a drop-out voltage ranging from 0.2 to 0.3 V at a load-current of 50 to 100 mA (corresponding to an "on" resistance ( $R_{on}$ ) of 2 to 6  $\Omega$ ) with a total tolerance of roughly  $\pm$  3 to 5 %. Furthermore, the regulator's destination is the commercial market place with a temperature range of -10 to 90 °C, which includes customary temperature limits. Table 1.1 illustrates a summary of the objective performance parameters for this research.

### 1.6 Summary

This chapter has defined a low drop-out regulator (LDO) and discussed its standing in today's market. The characteristics that are most demanded by the growing number of applications were identified. This was followed by a discussion of switching regulators and their place alongside LDOs. The main building blocks of low drop-out regulators were described as well as some of their associated performance parameters. Moreover, the specifications that gauge these circuits were defined. Lastly, the research objective was identified and defined according to the growing requirements of current and future applications. Overall, this chapter forms the premise and establishes enough background to start analyzing the system under loading conditions and start considering the electrical implications of such an architecture.

Table 1.1 Summary of the objective specifications.

| Description                                                | Specification |

|------------------------------------------------------------|---------------|

| V <sub>in</sub>                                            | ≥ 1.2 V       |

| $I_{ m q}$                                                 | ≤ 65 μA       |

| I <sub>out-max</sub>                                       | ≥ 50 mA       |

| Accuracy                                                   | ± 3 to 5 %    |

| $V_{drop-out}$ @ $I_{Load} = 50 - 100 \text{ mA}$          | ≤ 0.3 V       |

| R <sub>on</sub>                                            | 2 to 6 Ω      |

| Transient $\Delta V_{o	ext{-for II.oad-Step}}$             | ≤ 75 mV       |

| Temperature                                                | -10 to 90 °C  |

| Output Capacitance                                         | 4.7 μF        |

| ESR                                                        | 0 to 10 Ω     |

| Technology: MOSIS 2 μm n-well CMOS with added p-base layer |               |

#### **CHAPTER II**

#### SYSTEM DESIGN CONSIDERATIONS

Proper design of a low drop-out (LDO) regulator involves intricate knowledge of the system and its load. The tasks of maximizing load regulation, maintaining stability, and minimizing transient output voltage variations prove to be challenging and often conflicting. This arises from the innate characteristics of the regulator architecture and its associated working environment. This chapter discusses the relevant analyses that describe the system. Lastly, some of the circuit design issues surrounding the major components of the low drop-out regulator are illustrated in terms of circuit theory and system requirements; these building blocks include the pass device, the amplifier, and the reference.

### 2.1 AC Analysis

## **Loading Conditions**

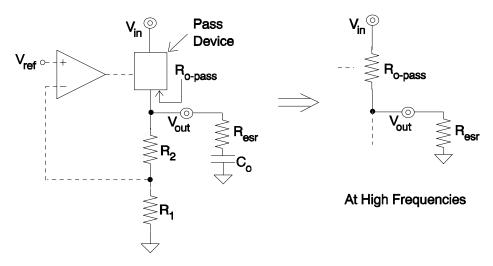

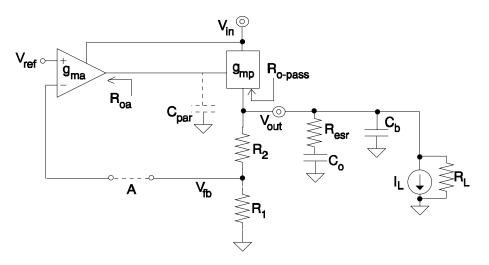

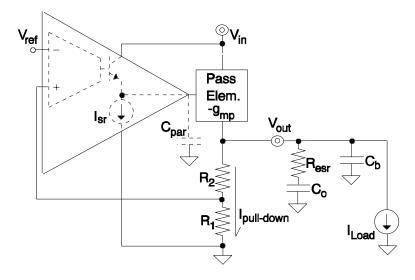

Figure 2.1 illustrates the intrinsic factors that determine the stability of the system, namely, an error amplifier, a pass element, feedback resistors, an output load-current and associated output impedance, an output capacitor and associated electrical series resistance (ESR), and bypass capacitors. It is assumed that there is no ac signal polarity inversion across the pass device, corresponding to n-type transistor implementations. The polarity of the error amplifier terminals would be reversed for p-

type devices, which introduce a polarity inversion (- $g_{mp}$  instead of  $g_{mp}$ ). The ESR of the bypass capacitors can typically be neglected because they are usually high frequency capacitors; in other words, they have low ESR values [23]. The pass device is modeled as a circuit element exhibiting a transconductance of  $g_{mp}$  and an output impedance of  $R_{o-pass}$ . The value of  $R_2$  is dependent on the desired value of the output voltage, i.e.,  $R_2$  is zero if  $V_{out}$  is desired to be equal to  $V_{ref}$ . The value of  $R_1$ , on the other hand, is designed to define the quiescent current flowing through resistors  $R_1$  and  $R_2$  ( $R_1 = V_{ref} / I_{R1}$ ), which is typically high to minimize quiescent current overhead.

Figure 2.1. System model under loading conditions.

## Frequency Response

For the purpose of analysis, the feedback loop can be broken at "A" in Figure 2.1. It is readily apparent that the system must be unity gain stable, considering  $V_{ref}$  and  $V_{fb}$  to be the input and the output voltages respectively. The open-loop gain can be described as

$$\frac{V_{fb}}{V_{ref}} = |A_v| = \frac{g_{ma} R_{oa} g_{mp} Z}{\left[1 + s R_{oa} C_{par}\right]} \cdot \frac{R_1}{\left[R_1 + R_2\right]},$$

(2.1)

where  $g_{ma}$  and  $g_{mp}$  refer to the transconductance of the amplifier and the pass element respectively,  $R_{oa}$  is the output resistance of the amplifier,  $C_{par}$  refers to the parasitic capacitance introduced by the pass element, and Z is the impedance seen at  $V_{out}$ ,

$$Z = R_{x} \left| \frac{1 + sR_{esr}C_{o}}{sC_{o}} \right| \left| \frac{1}{sC_{b}} \right| = \frac{R_{x} \left[ 1 + sR_{esr}C_{o} \right]}{s^{2}R_{x}R_{esr}C_{o}C_{b} + s\left[ R_{x} + R_{esr} \right]C_{o} + sR_{x}C_{b} + 1},$$

(2.2)

where  $C_o$  and  $R_{esr}$  are the capacitance and the ESR of the output capacitor,  $C_b$  represents the bypass capacitors, and  $R_x$  is the resistance seen from  $V_{out}$  back into the regulator defined as

$$R_x = R_{o-pass} || (R_1 + R_2),$$

(2.3)

where  $R_{o\text{-pass}}$  is the output resistance of the pass element. The output resistance of the load  $(R_L)$  is commonly neglected because its value is considerably larger than  $R_x$ . If  $C_o$  is assumed to be reasonably larger than  $C_b$  (typical condition), then Z approximates to

$$Z \approx \frac{R_{x}[1 + sR_{esr}C_{o}]}{[1 + s(R_{x} + R_{esr})C_{o}] \cdot [1 + s(R_{x}||R_{esr})C_{b}]}.$$

(2.4)

It can be observed from equations (2.1) - (2.4) that the overall transfer function of the system consists of three poles and one zero, a potentially unstable system. For the majority of the load-current range,  $R_x$  simplifies to  $R_{o-pass}$  since  $R_1 + R_2$  is greater in

magnitude (especially at high currents). The poles and the zero can thus be approximated to be the following:

$$P_1 \approx 1 / 2\pi R_{o-pass} C_o, \qquad (2.5)$$

$$P_2 \approx 1 / 2\pi R_{esr} C_b, \tag{2.6}$$

$$P_3 \approx 1 / 2\pi R_{oa} C_{par}, \qquad (2.7)$$

and

$$Z_1 \approx 1 / 2\pi R_{esr} C_o$$

. (2.8)

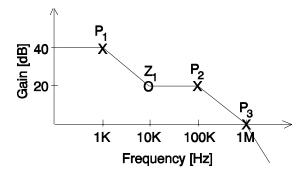

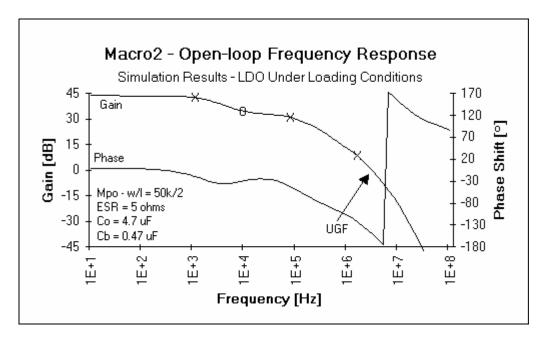

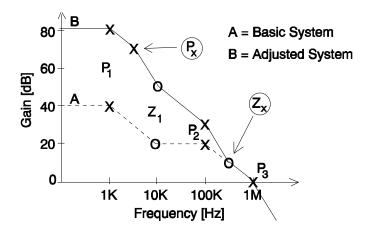

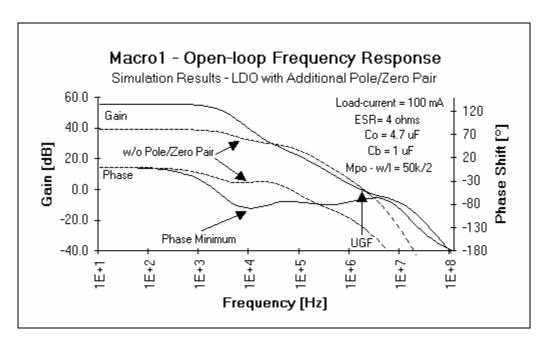

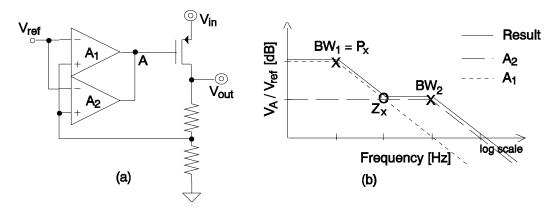

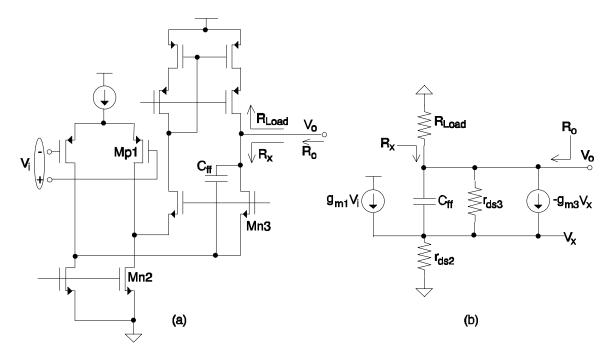

Figure 2.2 illustrates the typical frequency response of the system assuming that the output capacitor ( $C_0$ ) is larger than the bypass capacitors ( $C_b$ ). Figure 2.3 shows the simulation results of the circuit of Figure 2.1 using a macro-model for the amplifier, a PMOS device for the pass element, and a load-current of 70 mA. The simulation confirmed the overall behavior of the frequency response predicted by analysis with a dc open-loop gain of 43.6 dB, unity gain frequency of 3 MHz, and a phase margin of 29.5 °.

Figure 2.2. LDO frequency response under loading conditions.

Figure 2.3. AC simulation results of an LDO under loading conditions.

### **Design Challenge**

Worst-case Stability: The worst-case stability condition, given the set of elements shown in Figure 2.1, arises when the phase margin is at its lowest point, which occurs when the unity gain frequency is pushed out to higher frequencies where the parasitic poles reside. This happens when the load-current is at its peak value [23]. This is because the dominant pole  $(P_1)$  usually increases at a faster rate  $(R_{o\text{-pass}})$  decreases linearly with increasing current,  $1/\lambda I_o$  or  $V_a/I_o$  where  $\lambda$  is the channel length modulation parameter of MOS devices and  $V_a$  is the early voltage of bipolar transistors) than the gain of the system decreases  $(g_{mp}R_{o\text{-pass}})$  decreases with the square root of the increasing current for an MOS device or stays constant for a bipolar transistor). The type and value of the output capacitor determine the location of  $P_1$ ,  $P_2$ , and  $P_1$ . Therefore, the permissible range of values of ESR for a stable circuit is a function of load-current and circuit characteristics [5]. Simulations confirm the aforementioned tendencies.

**Parasitic Pole Requirements:** The parasitic poles of the system can be identified as  $P_3$  and the internal poles of the error amplifier. These poles are required to be at high frequencies, at least greater than the unity gain frequency (UGF). The phase margin for the case where only one parasitic pole was at the vicinity of the UGF is approximately 45°. Ensuring that  $P_3$  is at high frequencies is an especially difficult task to undertake in a low current environment. The pole is defined by the large parasitic capacitance ( $C_{par}$ ) resulting from a large pass device (necessary trait for reasonable output current capabilities) and the output resistance of the amplifier ( $R_{oa}$ ). The amplifier's output impedance is usually a function of the circuit topology and the bias current of its output stage. As a result, low quiescent current and frequency design issues have conflicting requirements that necessitate compromises.

<u>Maximum Load Regulation Performance</u>: Load regulation performance (output resistance of the regulator,  $R_0$ ) is a function of the open-loop gain  $(A_{ol})$  of the system and can be expressed as

$$R_o = \frac{\Delta V_{LDR}}{\Delta I_o} = \frac{R_{o-pass}}{1 + A_{ol}\beta},$$

(2.9)

where  $\Delta V_{LDR}$  is the output voltage variation arising from a load-current variation of  $\Delta I_{o}$ ,  $R_{o-pass}$  is the output resistance of the pass device, and  $\beta$  is the feedback factor. Consequently, the regulator yields better load regulation performance as the open-loop gain increases [12]. However, the gain is limited by the closed-loop bandwidth of the system, equivalent to the open-loop unity gain frequency (UGF). The minimum UGF is bounded by the response time required by the system during transient load-current variations, as discussed in the specifications section of chapter 1. Furthermore, the UGF is also bounded at the high frequency range by the parasitic poles of the system, i.e., the

internal poles of the amplifier and pole  $P_3$ . If these parasitic poles are assumed to be located at higher frequencies than 1 MHz, then the gain at 1.0 kHz has to be less than approximately 35 - 45 dB depending on the location of  $Z_1$  and  $P_2$ , as shown in Figures 2.2 and 2.3. In particular, the worst-case condition occurs when  $Z_1$  is at low frequencies and  $P_2$  is at high frequencies, which corresponds to the maximum value of ESR and the lowest bypass capacitance ( $C_b$ ). Moreover, the pass element's associated input capacitance (error amplifier's load capacitance) is significantly large. This places a ceiling on the value of the amplifier's output resistance ( $R_{oa}$ ). The pass element typically needs to be a large device to yield low drop-out voltages and high output current characteristics with limited voltage [current] drive in a low voltage and low power environment. Overall, load regulation is limited by the constrained open-loop gain of the system.

## 2.2 Transient Analysis

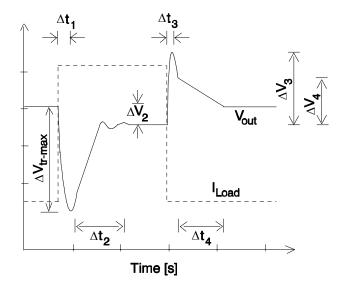

An important specification is the maximum allowable output voltage change for a full range transient load-current step. The application determines how low this value should be. For instance, a relatively relaxed specification for the peak output voltage variation can be tolerated if the regulator is used to provide power to digital circuits, which inherently have high noise margins [6]. However, this is not the case for many analog applications. Figure 2.4 shows the characteristic nature of the stimulus and the typical respective response for the typical system shown in Figure 2.1 [27].

## **Typical Response**

The worst-case time required for the loop to respond ( $\Delta t_1$ , which is ideally the reciprocal of the closed-loop bandwidth) is specified by the maximum permissible output voltage variation ( $\Delta V_{tr}$ ), which is a function of the output capacitor ( $C_0$ ), the electrical series resistance (ESR) of the output capacitor, the bypass capacitors ( $C_b$ ), and the maximum load-current ( $I_{Load-max}$ ),

$$\Delta V_{tr-max} \approx \frac{I_{Load-max}}{C_o + C_b} \Delta t_1 + \Delta V_{esr}$$

(2.10)

thus

$$\Delta t_1 \approx \frac{\left[C_o + C_b\right]}{I_{Load-max}} \left[\Delta V_{tr-max} - \Delta V_{esr}\right],$$

(2.11)

where  $\Delta V_{esr}$  is the voltage variation resulting from the presence of the ESR ( $R_{esr}$ ) of the output capacitor ( $\Delta V_{esr} \propto R_{esr}$ ). The effects of ESR are reduced by the bypass capacitors

Figure 2.4. Typical LDO transient response to a load-current step.

$(C_b)$ , which are typically high frequency thereby exhibiting low ESR values. In typical implementations the time  $\Delta t_1$  is not only a function of bandwidth but also defined by the internal slew-rate associated with the parasitic capacitance  $C_{par}$  of the pass element in Figure 2.1. The resulting time can be approximated to be

$$\Delta t_1 \approx \frac{1}{BW_{cl}} + t_{sr} = \frac{1}{BW_{cl}} + C_{par} \frac{\Delta V}{I_{sr}},$$

(2.12)

where  $BW_{cl}$  is the closed-loop bandwidth of the system,  $t_{sr}$  is the slew-rate time associated with  $C_{par}$ ,  $\Delta V$  is the voltage variation at  $C_{par}$ , and  $I_{sr}$  is the slew-rate limited current. For instance, if  $BW_{cl}$  is 500 kHz,  $C_{par}$  is 200 pF,  $\Delta V$  is 0.5 V,  $I_{sr}$  is 5  $\mu A$ ,  $C_{o}$  is 10  $\mu F$ ,  $R_{esr}$  is 0  $\Omega$ , and  $I_{Load-max}$  is 100 mA, then the maximum output voltage variation is approximately 220 mV (equations (2.10) and (2.11)). If the slew-rate current is large enough, the reciprocal of the closed-loop bandwidth predominantly defines  $\Delta t_{1}$ . This would be at the cost of quiescent current flow, in other words, battery life. Once the slew-rate condition is terminated, the output voltage recovers and settles to its final value,  $\Delta V_{2}$  below the ideal value,

$$\Delta V_2 \approx R_{o-reg} I_{Load-max},$$

(2.13)

where  $R_{o\text{-reg}}$  is the closed-loop output resistance of the regulator. This is essentially the effect of load regulation performance on the output. The settling time ( $\Delta t_2$ ) is dependent on the time required for the pass device to fully charge the load capacitors and the phase margin of the open-loop frequency response.

The slew-rate limitation is usually unidirectional in nature thereby creating the asymmetrical response of Figure 2.4. The slew-rate condition typically occurs when the

load-current steps from zero to full range. The direction for which this condition occurs is dependent on the configuration of the buffer and the output pass device. A typical topology is that of a class A buffer driving a PMOS pass element and associated parasitic capacitance (C<sub>par</sub>). An example of this is illustrated in the simplified schematic of Figure 2.5 where the pass device is assumed to be a p-type transistor. A class A stage yields high current in one direction and limited dc current in the other, i.e., emitter [source] follower biased with a dc current source. More complex topologies, however, could be implemented for the buffer to realize high symmetrical slew-rate currents. The portion of

Figure 2.5. Simplified LDO schematic for the purpose of transient analysis.

the time response that does not experience internal slew-rate is dominated by the capacitors, the electrical series resistance (ESR) of the output capacitor, the bandwidth of the system, and the low pull-down current capability of the LDO's output ( $I_{pull-down}$  in Figure 2.5). At first, the output voltage variation peaks at  $\Delta V_3$ , whose magnitude is defined by the voltage charged on the capacitors and the voltage generated across the ESR of the output capacitor. This results because the momentary current supplied by the

power device ( $I_{Load-max}$  until the circuit reacts to shut it off) flows to the output capacitor  $C_o$  and the bypass capacitors (the current is no longer flowing to the load). Consequently, the capacitors charge up and a temporary voltage drop is created across  $R_{esr}$ . This transient voltage can be approximtely described by

$$\Delta V_3 \approx \frac{I_{Load-max}}{C_o + C_b} \Delta t_3 + \Delta V_{esr} \approx \frac{I_{Load-max}}{C_o + C_b} \cdot \frac{1}{BW_{cl}} + \Delta V_{esr}, \qquad (2.14)$$

where the terminology of Figures 2.4 and 2.5 is adopted. When the output transistor is finally shut off (after  $\Delta t_3$ ) the variation settles down to  $\Delta V_4$ , the voltage charged on the capacitors ( $\Delta V_4 \approx \Delta V_3 - \Delta V_{esr}$ ). At this point, the output voltage takes time  $\Delta t_4$  to discharge to its final ideal value,

$$\Delta t_4 \approx \frac{C_o + C_b}{I_{\text{pull-down}}} \Delta V_4 = \frac{\left[C_o + C_b\right] R_1}{V_{\text{ref}}} \Delta V_4. \tag{2.15}$$

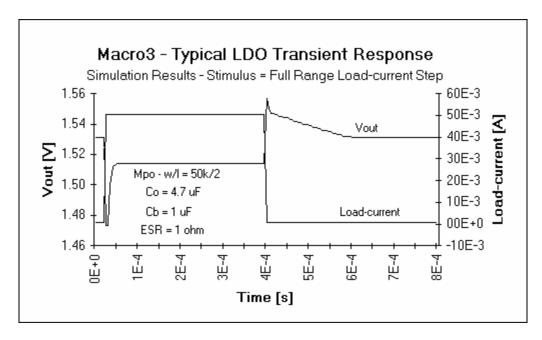

Figure 2.6 illustrates the simulation results of an LDO transient response analysis. The circuit utilized employs the basic topology shown in Figure 2.5 using a macro-model for the amplifier and a PMOS pass device. The addition of high frequency bypass capacitors (capacitors with low ESR) reduce the peaks of the transient response,  $\Delta V_{tr-max}$  and  $\Delta V_3$ . This results because the current supplied by the output capacitor ( $C_0$ ) during transient conditions is decreased as  $C_b$  is increased thereby exhibiting a lower voltage drop across  $R_{esr}$ . The remaining current is furnished by the bypass capacitors, which typically have negligible ESR voltage drops.

Figure 2.6. Simulated LDO transient response of a circuit similar to that of Figure 2.5.

# **Design Challenge**

The worst-case output voltage variation is a function of the bandwidth and the slew-rate limit of the circuit. However, bandwidth and slew-rate limit are highly dependent on quiescent current flow. As bandwidth is demanded to increase, the parasitic poles are required to increase accordingly thereby necessitating more current flow to decrease associated impedances. Consequently, the error amplifier's quiescent current must necessarily increase to yield faster response times. Moreover, increasing slew-rate performance requires an increase in bias current on the circuit driving the slew-rate limited node. This affects the design of the output stage of the amplifier. As a result, the overall minimum quiescent current flow is limited by the maximum allowable output voltage variation arising from full range load-current steps.

# 2.3 Pass Device Design Issues

Designing in a low voltage and low current environment provides difficult challenges that contradict performance and stability [23]. The first aspect that is affected is the series pass element of the low drop-out regulator. It must provide large amounts of current while displaying low drop-out characteristics. Drop-out voltage is governed by the on resistance of the pass transistor ( $V_{drop-out} = I_{Load}R_{on}$ ), which is inversely proportional to the physical size of the device. Drop-out voltage is further increased by series parasitic resistance inherent in the layout, such as the pass device's source [emitter] and drain [collector] contacts, metal traces, and diffusion links. As a result, the size of the transistor must be large under low voltage conditions, which translates to a large load capacitance for the error amplifier. A large device is further demanded because voltage drive is reduced as a result of decreased input voltages. This, in turn, causes the parasitic pole P<sub>3</sub> to move to lower frequencies effectively deteriorating phase margin and compromising the stability of the system. Moreover, the resulting increase in load capacitance for the feedback amplifier requires an increase in quiescent current flow. This is necessary to charge and discharge the capacitance quickly enough during slewrate conditions, as discussed in the transient analysis section. For the case of MOS pass devices, sub-threshold currents can become appreciably large as the aspect ratio is increased. In other words, the transistor can be difficult to shut off thereby creating problems at zero-load conditions. Finally, the physical design of the large device must also take into account line resistance and capacitance, current density per line, heat distribution, and parasitic devices inherent to the layout. Thermal symmetry as well as equal current density distribution must be maintained for reliability and best performance. Overall, the size of the pass device must be large for increased current capabilities but restrained by stability and slew-rate requirements in a low quiescent current flow and low voltage environment.

The problem of handling large output currents or reducing the "on" resistance of MOS pass devices is sometimes cost efficiently resolved by using a dc-dc converter in addition to the LDO. The purpose of the switching regulator is to bring down the voltage thereby reducing the operating voltages of the LDO. As a result, devices with lower breakdown voltages can be used. In other words, the MOS pass device can reduce its channel length without posing any threat to the reliability of the circuit. Thus, larger aspect ratios per unit area and higher output currents are achieved. The additional cost of the switching regulator is offset by the potential cost of increasing the size of the pass device, increased area overhead. The point where this technique becomes valuable is dependent on the process technology, the application, and the associated specifications.

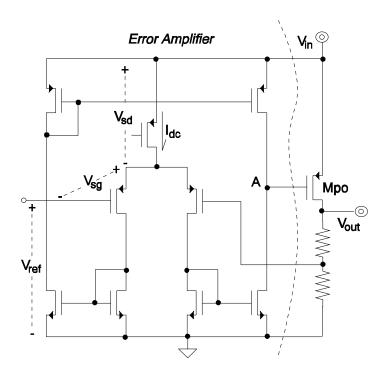

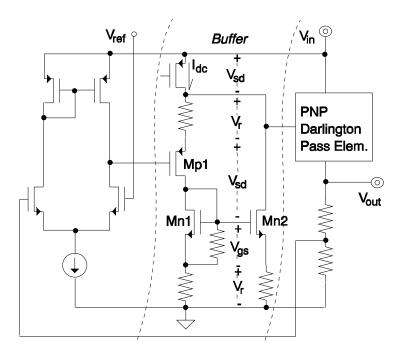

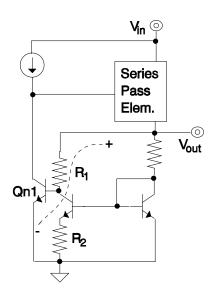

## 2.4 Amplifier Design Issues