■BCD technologies for 80 V -200 V and 700 V

F. Udrea Taiwan, January 2008 114

# **BCD** technology classification

### High Voltage BCD (HV BCD)

- : DMOS Voltage Capability from 500V/1200V

- : Medium Market Size

- : Medium Low complexity ( LSI)

#### Medium Voltage BCD

- : DMOS Voltage Capability from 80V/300V

- : Large arket Size

- : Medium complexity (LSI)

### High Power BCD (HP BCD)

- : DMOS Voltage Capability from 30V to 120V

- : Large Market Size

- : Medium Complexity (LSI)

### High Density BCD (HD BCD)

- : DMOS Voltage Capability from 5V to 80V

- : Small Market Size

- : Large Complexity (VLSI)

- : Follows the VLSI roadmap in terms of scaling (typically 3 generations behind)

### **BCD** technology classification

### □ HV and Medium Voltage BCD (medium-low complexity)

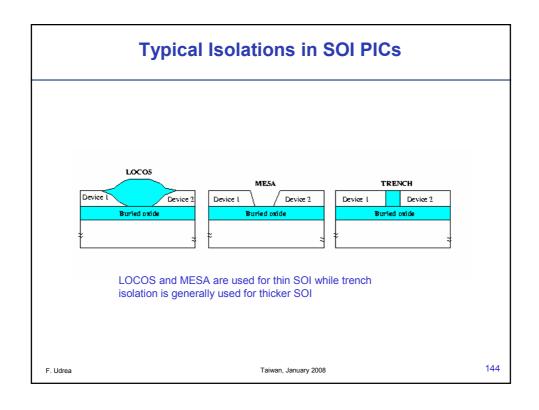

- From JI Resurf substrate to SOI + STI and DTI (Trench etch isolations)

- Single gate oxide

- DMOS Lateral Structure

- DMOS voltage capability from 80V/300V to 500V/1200V

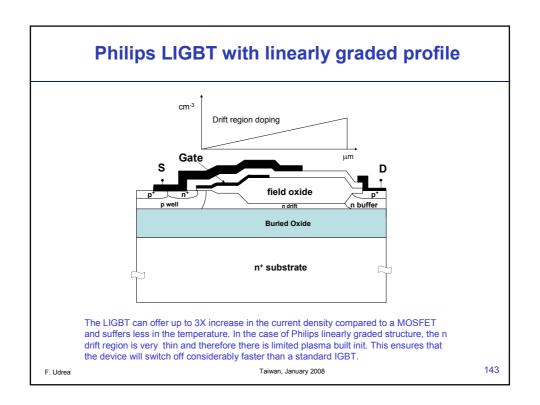

- \* Emerging LIGBT

#### ☐ HP BCD (high power, medium complexity)

- Conventional JI substrate, simple process architecture

- Single gate oxide

- DMOS Lateral(low voltage) and Vertical(high voltage)

- DMOS voltage capability from 30V to 120V

- \* Emerging Vertical and Lateral Superjunctions and LIGBTs

### ☐ HD BCD (high density, large complexity)

- CMOS like substrate and process architecture

- Dual gate oxide for CMOS and DMOS

- DMOS Lateral Structure

- DMOS voltage capability from 5V to 80V

- NVM compatibility

- RF capability

F. Udrea

- High degree of Modularity

Taiwan, January 2008

116

# 80 -200 V BCD Features for different generations

|                                      | BCD-SOI          | BCD-SOI<br>(ABCD 9) | BCD3s              | BCD4               | BCD5                      | BCD6                 | BCD8           | BCD9               |

|--------------------------------------|------------------|---------------------|--------------------|--------------------|---------------------------|----------------------|----------------|--------------------|

| Litho (um)                           | 1.0              | 0.13                | 1.0                | 0.8                | 0.6                       | 0.35                 | 0.18           | 0.13               |

| Dual Gate<br>Oxide                   | N                | Y                   | Y                  | N                  | Y                         | Y                    | Y              | Y                  |

| CMOS L-gate (um)                     | 1.0              | 0.13                | 1.0                | 0.8                | 0.6                       | 0.35                 | 0.18           | 0.13               |

| CMOS(V)                              | 5                | 1.2/3.3             | 5                  | 5                  | 5                         | 3.3/5                | 1.8/3.3        | 1.2/3.3            |

| DMOS Structure<br>(Lateral/Vertical) | L                | L                   | L&V                | L&V                | L                         | L                    | L              | L                  |

| Complementary<br>Power DMOS          | Y                | N                   | N                  | N                  | Υ                         | Y                    | Y              | Y                  |

| DMOS(V)                              | 12.0/170/20<br>0 | 100                 | 16/45<br>/65/80/90 | 30/45<br>/65/80/90 | 16/20/30/4<br>5<br>/65/90 | 5/12/20<br>/30/45/65 | 5/12/20/4<br>5 | 5/12/20            |

| NVM<br>Compatibility                 | -                | -                   | Y                  | -                  | Y                         | Y                    | Y              | Y                  |

| Metal Levels<br>(last one thick)     | 2-3              | 3                   | 2~3                | 2~3                | 2~3                       | 3~4~5                | 4~5~6          | 4~5~6              |

| Cu metal *(optional)                 | N                | Y                   | N                  | Y*(thick)          | Y*(thick)                 | Y*(thick)            | Y*(thick)      | Y*<br>(thin/thick) |

F. Udrea Taiwan, January 2008 Reference : ST roadmap 117

### **Gate Oxide Considerations**

### □ Double Poly - Dual Gate Oxide

- High Performance CMOS Logic

- Suitable for High bias DMOS gate voltage

- Process Complexity

### ☐ Single poly – Mono gate Oxide

- High Power DMOS and Low performance CMOS Logic

- Low cost Process

- Process Simplicity

F. Udrea Taiwan, January 2008

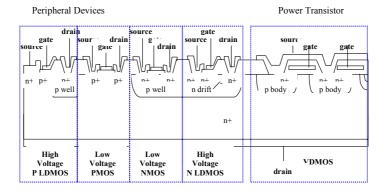

# BCD with a vertical power MOSFET and some LDD MOSFETs

118

A BCD type process employing a pure vertical high voltage device (Power MOSFET), CMOS cells and high voltage lateral devices

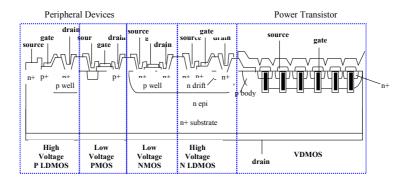

# **BCD** with a vertical power Trench MOSFET and some LDD MOSFETs

A BCD type process employing a pure high voltage vertical device (in the case a Trench Power MOSFET), CMOS cells and high voltage lateral transistors

F. Udrea Taiwan, January 2008 120

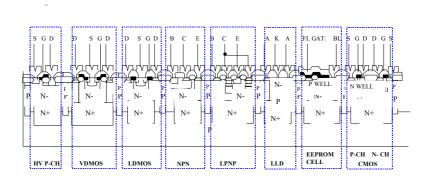

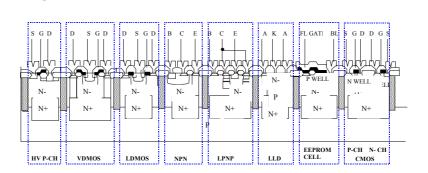

# Multipower BCD process BCD with quasi-vertical VDMOS, LDMOS, EEPROM and bipolar transistors

Cross-section of BCD-III process in bulk silicon featuring p+ isolations and n+ buried layers

# Multipower BCD process BCD with quasi-vertical VDMOS, LDMOS, EEPROM and bipolar transistors and trench isolation

Cross-section of Multipower BCD process in bulk silicon featuring trench isolations and n+ buried layers

F. Udrea Taiwan, January 2008 122

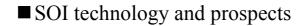

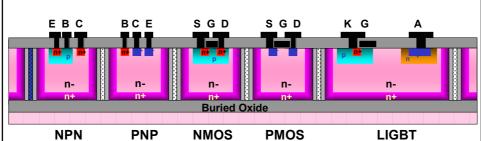

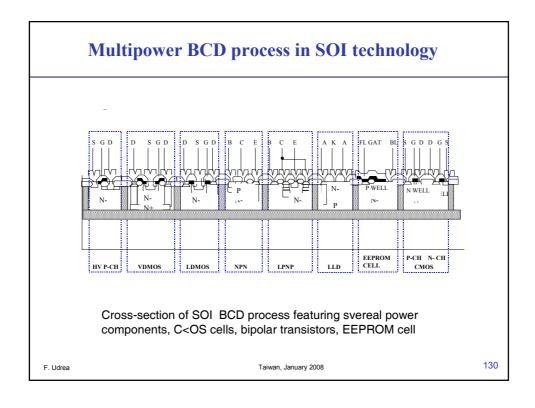

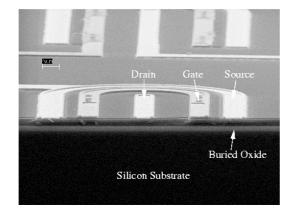

# Multipower BCD process in SOI technology

Cross-section of SOI BCD process featuring svereal power components, C<OS cells, bipolar transistors, EEPROM cell

F. Udrea Taiwan, January 2008

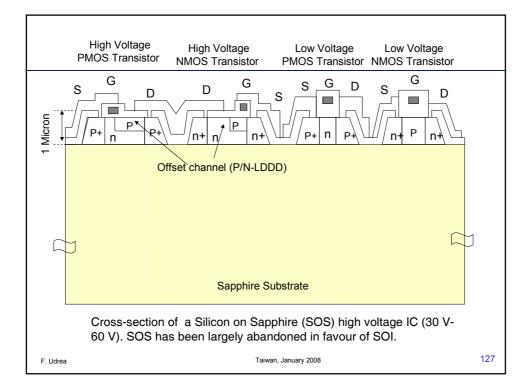

# The case for SOI in power ICs!

124

SOI = <u>Silicon On Insulator</u>

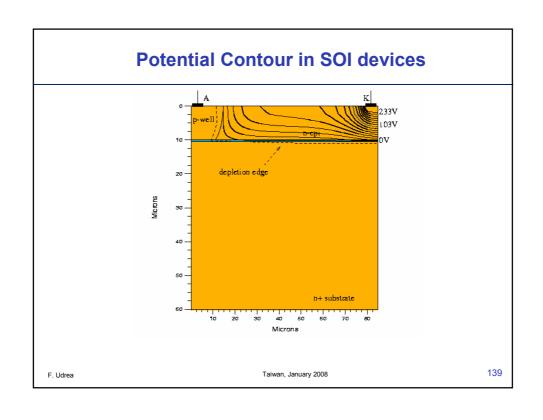

SOI: an active semiconductor layer that is separated from the passive semiconductor substrate through a buried insulating material

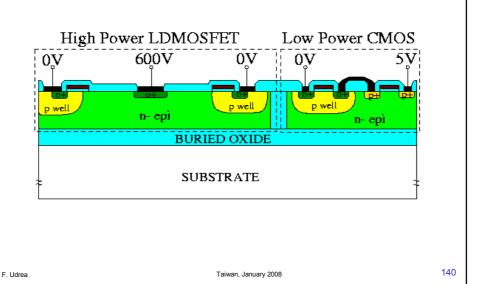

### **SOI** for Power ICs

- +

- vertical isolation is achieved via a buried insulated layer

- very low interference between adjacent devices

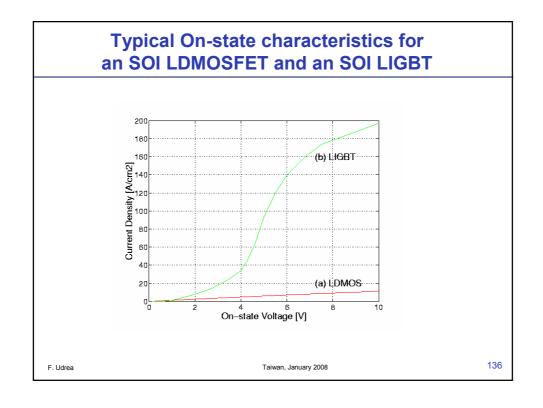

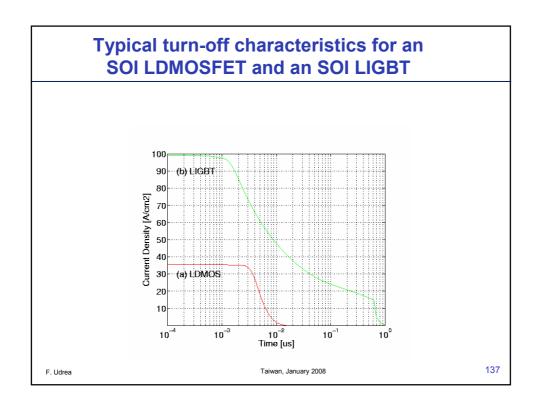

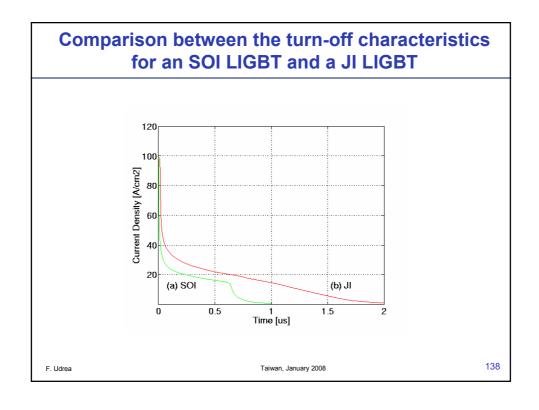

- high speed (for bipolar devices such as Diodes & LIGBT)

- low area consumption

- Fast reverse recovery for diodes

- Flexible to integrate a variety of high voltage devices (LIGBT, diodes, thyristors, high voltage BJT).

- Allows integration of more than one HV switch in the IC.

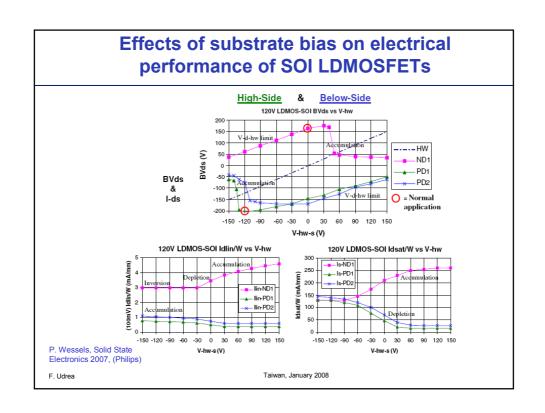

- Less affected by high side or bellow handle wafer operation

- No latch-up

- Substrate and BOX can form a back field plate that allows significant reduction in Ron

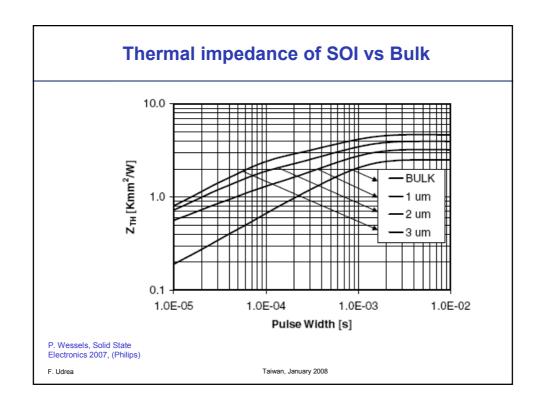

- self-heating

- the substrate is relatively expensive

- Breakdown limited by the BOX thickness

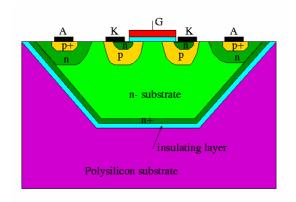

## An IGBT structure in the DI -tub technology

Cross-section of a Dielectric Isolation (DI) high voltage vertical IGBT (500 V) developed by Hitachi. The technology has been very successful but it is reaching its limit.

128 F. Udrea Taiwan, January 2008

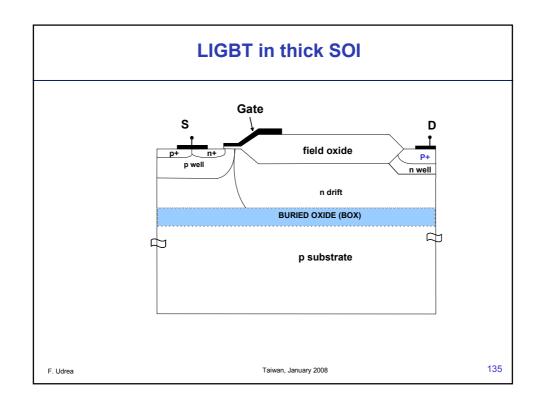

## An LIGBT structure in thick SOI technology

F. Udrea

Taiwan, January 2008

FAIRCHILD

129

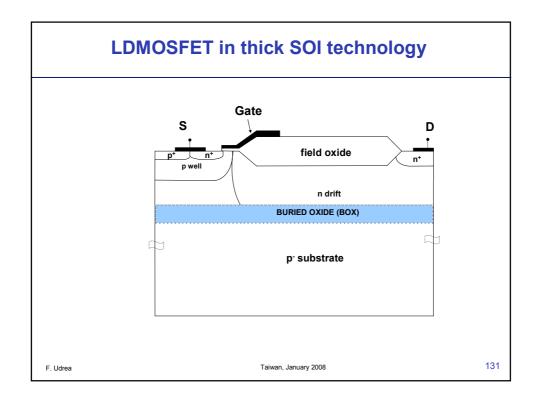

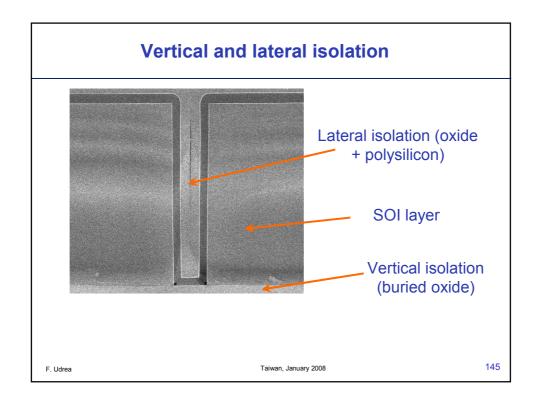

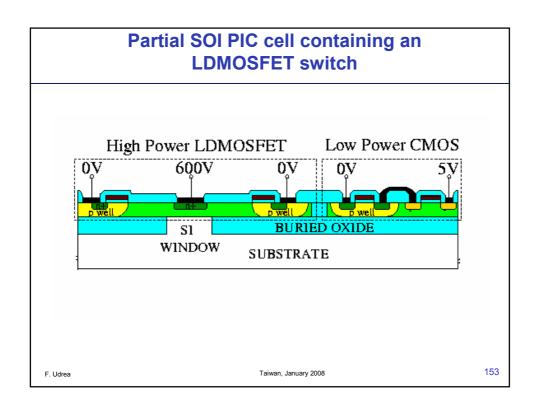

### **SOI HVIC cell containing an LDMOSFET switch**

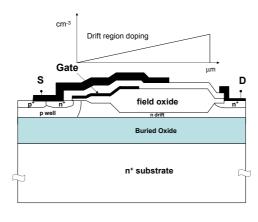

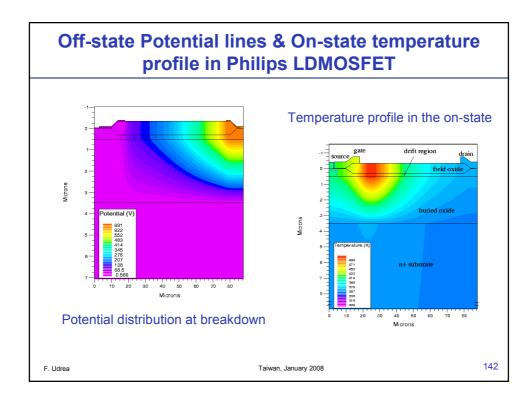

# Philips Ultra-thin SOI LDMOSFET with linearly doped drift region

### - The device features:

- (1) ultra thin SOI layer 0.3-0.5 microns

- (2) linearly graded doping profile with the concentration at the source ( $10^{15}$  cm<sup>-3</sup>) much lower than at the drain end ( $10^{16}$  cm<sup>-3</sup>).

- (3) The drift length for 600V is approx. 40 microns and the source extends above the field oxide (25 microns in the drift layer) to allow the formation of an accumulation layer which in the on-state helps to reduce the resistance of the drift layer. Further extension of the gate towards the drain may however degrade the breakdown capability.

# **SEM** photograph of a circular **LDMOSFET** fabricated at Southampton Microelectronics center

F. Udrea Taiwan, January 2008 146

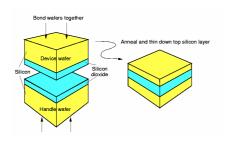

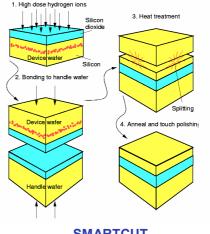

# **SOI technologies for Power ICs**

- Wafer bonding (bonding of two silicon wafers, one with a top oxide)

- SMARTCUT( uses implantation of He and wafer bonding)

## **SOI - Wafer bonding & SMARTCUT** (SOITEC)

Wafer bonding (bonding of tw0 silicon wafers, one with a top oxide)

**SMARTCUT**

F. Udrea

Taiwan, January 2008

148

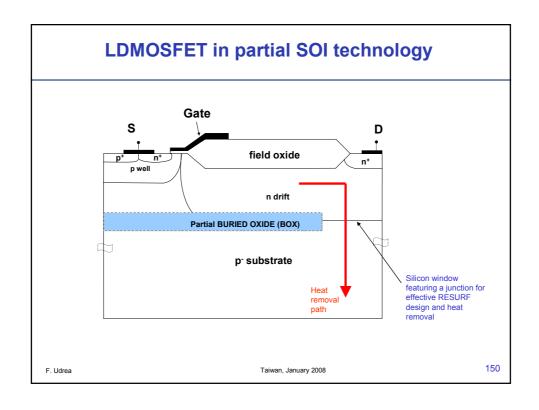

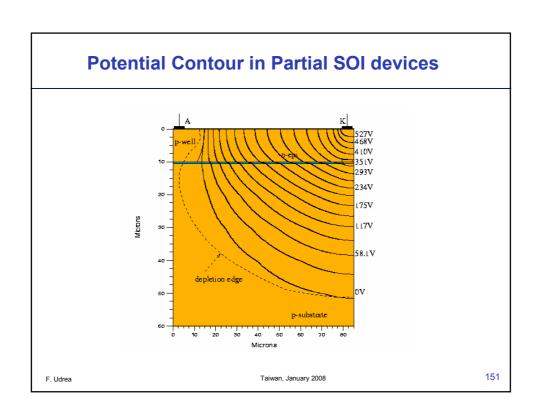

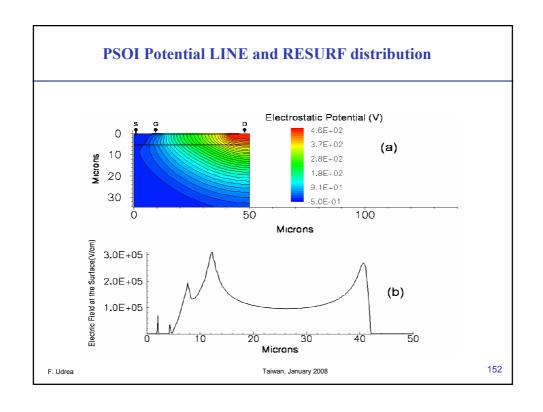

### Partial SOI power devices and ICs

- vertical isolation is achieved via buried insulated islands and reversebiased junctions

- high breakdown voltage (Resurf effect)

- low interference between adjacent devices

- high speed (for both unipolar and bipolar devices)

- reduced self-heating

- complex fabrication process

- very expensive

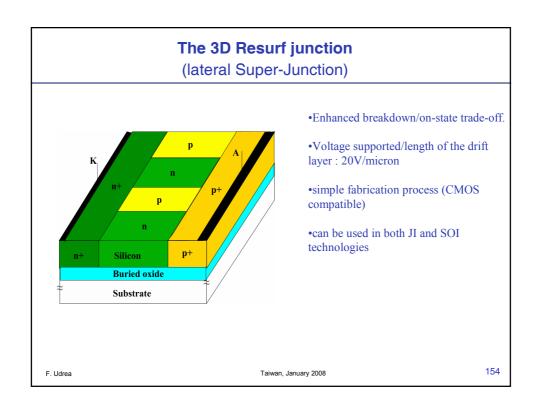

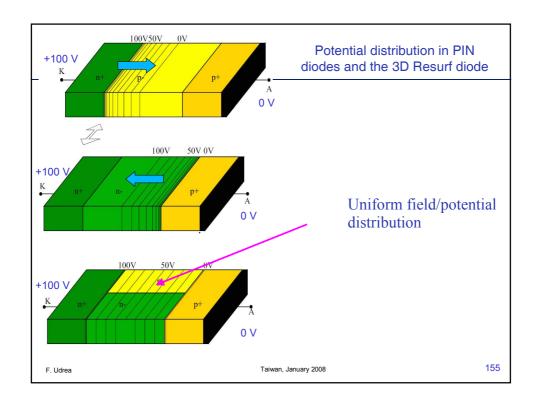

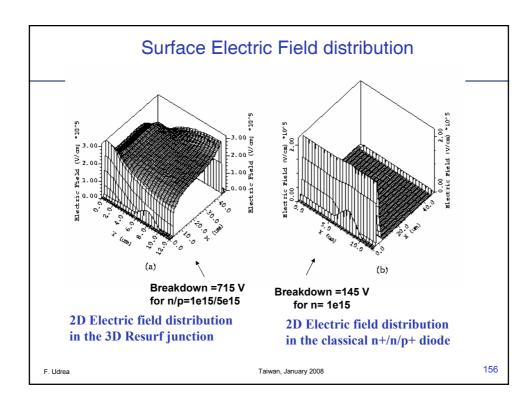

# Comparison of Breakdown voltage in the classical diodes and the ideal 3D Resurf (Super-junction) diode

|                         | Doping of drift layer | width of<br>drift layer | lenght of<br>drift layer | Breakdown<br>voltage |

|-------------------------|-----------------------|-------------------------|--------------------------|----------------------|

| Classical p+/n/n+ diode | n=1e15                | 12 μm                   | 40 μm                    | 145 V                |

| Classical p+/p/n+ diode | p=5e15                | 12 μm                   | 40 μm                    | 110 V                |

| 3D diode<br>p+/(n,p)/n+ | n=1e15<br>p=5e15      | n - 10 μm<br>p - 2 μm   | 40 μm                    | 780 V                |