# Design Compiler<sup>®</sup> Register Retiming Reference Manual

Version C-2009.06, June 2009

# **SYNOPSYS**<sup>®</sup>

# **Copyright Notice and Proprietary Information**

Copyright © 2009 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with the permission of Syn | psys, Inc., for the exclusive use of |  |

|---------------------------------------------------------|--------------------------------------|--|

|                                                         | its employees. This is copy number"  |  |

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, Design Compiler, DesignWare, Formality, HDL Analyst, HSIM, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Syndicated, Synplicity, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, the Synplicity logo, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, Galaxy Custom Designer, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance

ASIC Prototyping System, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (<sup>SM</sup>)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

# Contents

|    | What's New in This Release               | viii |

|----|------------------------------------------|------|

|    | About This Manual                        | viii |

|    | Customer Support                         | xi   |

| 1. | Introduction to Register Retiming        |      |

|    | Understanding Register Retiming          | 1-2  |

|    | A Register Retiming Example              | 1-2  |

|    | Design Flow Using Register Retiming      | 1-4  |

|    | Register Retiming Commands               | 1-4  |

|    | The optimize_registers Command           | 1-5  |

|    | The pipeline_design Command              | 1-5  |

|    | The balance_registers Command            | 1-6  |

| 2. | Register Retiming Concepts               |      |

|    | Basic Definitions and Concepts           | 2-2  |

|    | Flip-Flops and Registers                 | 2-2  |

|    | SEQGENs                                  | 2-3  |

|    | Control Nets                             | 2-4  |

|    | Register Classes                         | 2-5  |

|    | Forward Retiming                         | 2-6  |

|    | Backward Retiming                        | 2-7  |

|    | Asynchronous Control Inputs of Registers | 2-8  |

|    | Synchronous Control Inputs of Registers Translating Synchronous Input Pins to Equivalent SEQGEN Pins | 2-8<br>2-9 |

|----|------------------------------------------------------------------------------------------------------|------------|

|    | Transforming Synchronous Input Pins Through<br>Combinational Decomposition                           | 2-9        |

|    | Multiclass Retiming.                                                                                 | 2-12       |

|    | Pipeline and Nonpipeline Circuits                                                                    | 2-13       |

|    | Reset State Justification                                                                            | 2-14       |

| 3. | Writing HDL Code for Retiming                                                                        |            |

|    | Allowed Circuits                                                                                     | 3-2        |

|    | Writing HDL Code for Pipelines                                                                       | 3-2        |

|    | Calculating the Number of Pipeline Stages                                                            | 3-3        |

|    | Determining the Initial Location of the Registers                                                    | 3-4        |

|    | Using the DesignWare Pipeline Register Component                                                     | 3-4        |

|    | Writing HDL Code for Nonpipelines                                                                    | 3-5        |

| 4. | Performing Analysis and Elaboration for Retiming                                                     |            |

|    | Inferring Registers for Pipelines and Nonpipelines                                                   | 4-2        |

| 5. | Setting Attributes and Constraints for Retiming                                                      |            |

|    | Setting Timing Constraints                                                                           | 5-2        |

|    | Setting Timing Constraints for Pipelines                                                             | 5-2        |

|    | Setting Timing Constraints for Nonpipelines                                                          | 5-3        |

|    | Setting the Compile Command Option on SEQGEN Cells                                                   | 5-3        |

|    | Netlist Modifications to Avoid                                                                       | 5-3        |

|    | Test-Related Modifications.                                                                          | 5-3        |

|    | Physical Design-Related Modifications                                                                | 5-4        |

| 6. | Retiming the Mapped Netlist                                                                          |            |

|    | Preventing Retiming                                                                                  | 6-2        |

|    | Doing Timing Analysis During Retiming                                                                | 6-3        |

|    | Setting Timing Constraints                                                                           | 6-4        |

|    | Selecting Transformation Options                                                                     | 6-5        |

|    | Recommended Transformation Options for Pipelines                                   | 6-6<br>6-6 |

|----|------------------------------------------------------------------------------------|------------|

|    | Retiming Designs With Multiple Clocks                                              | 6-7        |

|    | Settings That Influence Register Retiming Runtime                                  | 6-8        |

|    | Netlist Changes Performed by Register Retiming.                                    | 6-9        |

| 7. | Analyzing Retiming Results                                                         |            |

|    | Standard Output of the optimize_registers Command                                  | 7-2        |

|    | Checking for Design Features That Limit the Quality of Results                     | 7-2        |

|    | Output Before Registers Are Moved                                                  | 7-2        |

|    | Output After Registers Are Moved                                                   | 7-4        |

|    | Displaying the Sequence of Cells That Limits Delay Optimization                    | 7-5        |

| Ар | pendix A. Additional Information on the Register Retiming Commands                 |            |

|    | Setting Retiming Attributes on Individual Cells                                    | A-2        |

|    | Other Commands Related to Retiming                                                 | A-2        |

|    | Examples of dc_shell Register Retiming Scripts                                     | A-4        |

|    | Script for a Nonpipelined Design, Using the optimize_registers Command             | A-4        |

|    | Script for a Pipelined Design, Using the optimize_registers Command                | A-4        |

|    | Script for Pipelining a Combinational Design,<br>Using the pipeline_design Command | A-5        |

|    |                                                                                    |            |

| Ар | pendix B. Command Syntax and Variable Syntax                                       |            |

|    | The balance_registers Command                                                      | B-2        |

|    | The optimize_registers Command                                                     | B-3        |

|    | The pipeline_design Command                                                        | B-9        |

|    | The set_balance_registers Command                                                  | B-12       |

|    | The set_optimize_registers Command                                                 | B-12       |

|    | The set_register_type Command                                                      | B-16       |

|    | The set_transform_for_retiming Command                                             | B-16       |

|    |                                                                                    |            |

Index

# Preface

This preface includes the following sections:

- What's New in This Release

- About This Manual

- Customer Support

#### What's New in This Release

Information about new features, enhancements, and changes, along with known problems and limitations and resolved Synopsys Technical Action Requests (STARs), is available in the *Design Compiler Release Notes* in SolvNet.

To see the Design Compiler Release Notes,

1. Go to the release notes page on SolvNet located at the following address:

https://solvnet.synopsys.com/ReleaseNotes

If prompted, enter your user name and password. If you do not have a Synopsys user name and password, follow the instructions to register with SolvNet.

2. Select Design Compiler, then select a release in the list that appears at the bottom.

#### **About This Manual**

The *Design Compiler Register Retiming Reference Manual* describes the concepts of register retiming and shows you how to use this capability to retime circuits. Register retiming performs a sequential optimization that moves registers to optimize timing and area. It optimizes gate-level netlists to meet timing while trying to use as few registers as possible.

This manual supports version B-2008.09 of the Synopsys synthesis tools, whether they are running under the UNIX operating system or the Linux operating system. The main text of this manual describes UNIX operation.

#### **Audience**

This manual is intended for logic designers and engineers who use the Synopsys synthesis tools to design ASICs, ICs, and FPGAs. Knowledge of high level techniques, a hardware description language, such as VHDL or Verilog is required. A working knowledge of UNIX is assumed.

#### **Related Publications**

For additional information about Design Compiler, see Documentation on the Web, which is available through SolvNet at the following address:

https://solvnet.synopsys.com/DocsOnWeb

You might also want to refer to the documentation for the following related Synopsys products:

- Automated Chip Synthesis

- Design Budgeting

- Design Vision

- DesignWare components

- DFT Compiler

- PrimeTime

- Power Compiler

- HDL Compiler

Also see the following related documents:

- Using Tcl With Synopsys Tools

- Synthesis Master Index

#### Conventions

The following conventions are used in Synopsys documentation.

#### Table 1

| Convention     | Description                                                                                                                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Courier        | Indicates command syntax.                                                                                                                                                                                                                              |

| Courier italic | Indicates a user-defined value in Synopsys syntax,<br>such as <i>object_name</i> . (A user-defined value that is<br>not Synopsys syntax, such as a user-defined value<br>in a Verilog or VHDL statement, is indicated by<br>regular text font italic.) |

| Courier bold   | Indicates user input—text you type verbatim—in<br>Synopsys syntax and examples. (User input that is<br>not Synopsys syntax, such as a user name or<br>password you enter in a GUI, is indicated by regular<br>text font bold.)                         |

| []             | Denotes optional parameters, such as<br>pin1 [pin2 pinN]                                                                                                                                                                                               |

| I              | Indicates a choice among alternatives, such as<br>low   medium   high<br>(This example indicates that you can enter one of<br>three possible values for an option:<br>low, medium, or high.)                                                           |

| -              | Connects terms that are read as a single term by the system, such as set_annotated_delay                                                                                                                                                               |

| Control-c      | Indicates a keyboard combination, such as holding down the Control key and pressing c.                                                                                                                                                                 |

| ١              | Indicates a continuation of a command line.                                                                                                                                                                                                            |

| /              | Indicates levels of directory structure.                                                                                                                                                                                                               |

| Edit > Copy    | Indicates a path to a menu command, such as opening the Edit menu and choosing Copy.                                                                                                                                                                   |

#### **Customer Support**

Customer support is available through SolvNet online customer support and through contacting the Synopsys Technical Support Center.

#### Accessing SolvNet

SolvNet includes an electronic knowledge base of technical articles and answers to frequently asked questions about Synopsys tools. SolvNet also gives you access to a wide range of Synopsys online services including software downloads, documentation on the Web, and "Enter a Call to the Support Center."

To access SolvNet, go to the SolvNet Web page at the following address:

#### https://solvnet.synopsys.com

If prompted, enter your user name and password. If you do not have a Synopsys user name and password, follow the instructions to register with SolvNet.

If you need help using SolvNet, click HELP in the top-right menu bar or in the footer.

#### **Contacting the Synopsys Technical Support Center**

If you have problems, questions, or suggestions, you can contact the Synopsys Technical Support Center in the following ways:

- Open a call to your local support center from the Web by going to https://solvnet.synopsys.com (Synopsys user name and password required), and then clicking "Enter a Call to the Support Center."

- Send an e-mail message to your local support center.

- E-mail support\_center@synopsys.com from within North America.

- Find other local support center e-mail addresses at http://www.synopsys.com/Support/GlobalSupportCenters/Pages

- Telephone your local support center.

- Call (800) 245-8005 from within the continental United States.

- Call (650) 584-4200 from Canada.

- Find other local support center telephone numbers at http://www.synopsys.com/Support/GlobalSupportCenters/Pages

# 1

# Introduction to Register Retiming

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

This chapter contains the following sections:

- Understanding Register Retiming

- A Register Retiming Example

- Design Flow Using Register Retiming

- Register Retiming Commands

#### **Understanding Register Retiming**

Register retiming is a sequential optimization technique that moves registers through the combinational logic gates of a design to optimize timing and area. Other optimization techniques, such as those implemented in the compile\_ultra command or compile command, optimize the combinational logic by performing Boolean optimization and mapping to cells in the technology library. These techniques leave unchanged the location and number of any registers present in the design. Register retiming adds an opportunity for improving circuit timing.

When you describe circuits at the RT-level prior to logic synthesis, it is usually very difficult and time-consuming, if not impossible, to find the optimal register locations and code them into the HDL description. With register retiming, the locations of the flip-flops in a sequential design can be automatically adjusted to equalize as nearly as possible the delays of the stages. This capability is particularly useful when some stages of a design exceed the timing goal while other stages fall short. If no path exceeds the timing goal, register retiming can be used to reduce the number of flip-flops, where possible.

Purely combinational designs can also be retimed by introducing pipelining into the design. In this case, you first specify the desired number of pipeline stages and the preferred flip-flop from the target library. The appropriate number of registers are added at the outputs of the design. Then the registers are moved through the combinational logic to retime the design for optimal clock period and area.

Register retiming leaves the behavior of the circuit at the primary inputs and primary outputs unchanged (unless you choose special options that do not preserve the reset state of the design or add pipeline stages). Therefore you do not need to change any simulation test benches developed for the original RTL design.

Retiming does, however, change the location, contents, and names of registers in the design. A verification strategy that uses internal register inputs and outputs as reference points will no longer work. Retiming can also change the function of hierarchical cells inside a design and add clock, clear, set, and enable pins to the interfaces of the hierarchical cells.

## **A Register Retiming Example**

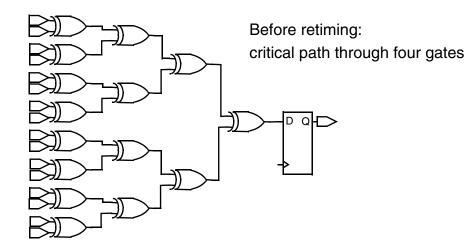

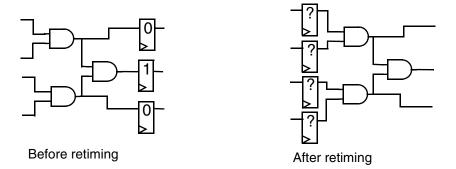

During retiming, registers are moved forward or backward through the combinational logic of a design. Figure 1-1 and Figure 1-2 illustrate an example of delay reduction through backward retiming of a register.

Figure 1-1 Circuit Before Retiming

Figure 1-2 Circuit After Retiming

In this example, before register retiming there are four levels of combinational logic and only one register at the endpoint of the critical path. After retiming, the register, which has been replaced by four registers, has been moved back through two levels of logic, and the critical path now consists of two stages. The critical path delay in each stage is less than the critical path delay in the initial single stage design. As in this example, delay reduction through retiming often leads to an increase in the number of registers in the design, but usually this increase is small.

## **Design Flow Using Register Retiming**

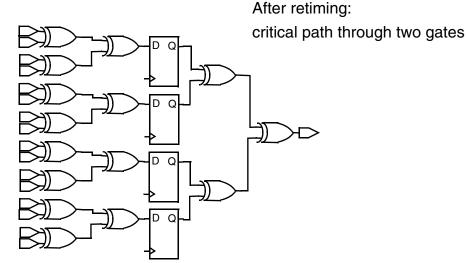

You optimize registers after you have compiled the design; that is, register retiming is performed on mapped netlists. Figure 1-3 shows the position at which register retiming is used in a typical design flow.

Figure 1-3 Design Flow With Register Retiming

As part of the register retiming functionality, an incremental compile is usually carried out automatically after retiming. Note, however, that there are three register retiming commands (see "Register Retiming Commands" on page 1-4), two of which include the incremental compile capability and one that does not. You can prevent the automatic incremental compile in the two commands by specifying the appropriate option.

#### **Register Retiming Commands**

Register retiming consists of three major retiming commands and a number of support commands for setting retiming-related attributes. The principal commands are

- optimize\_registers

- pipeline\_design

- balance\_registers

The optimize\_registers command offers the most convenient way to perform all retiming tasks for sequential designs. In general, this command optimizes both synchronous and asynchronous registers with respect to timing and area (minimum number of registers). An incremental compile is automatically done after the retiming, unless you specify otherwise. The command supports the retiming of level-sensitive latches and also includes analysis options.

The pipeline\_design command is used to pipeline purely combinational designs. After you specify the number of stages, the command inserts the registers into the design and then optimizes the registers with respect to timing and area by accessing the functions of the optimize\_registers command.

The balance\_registers command moves the existing registers of a sequential design to minimize the clock period. This command does not minimize the number of registers or retime asynchronous registers. Also, no incremental compile is carried out, and no analysis options are available.

Note:

Typically you apply these commands globally to a design. However, you can assign retiming attributes to individual cells. For more information, see "Setting Retiming Attributes on Individual Cells" on page A-2.

#### The optimize\_registers Command

The <code>optimize\_registers</code> command performs the following principal actions on a sequential design:

1. Minimizes the clock period

The registers are moved to ensure the smallest clock period for the retimed circuit.

2. Minimizes the register count

The minimum clock period determined in the first step is compared to a user-defined clock period target. If the minimum clock period is smaller than or equal to the target clock period, the target clock period is used and a register distribution is computed that accommodates the target clock period with the smallest number of registers possible. If the target clock period is smaller than the minimum clock period, the number of registers is minimized for the minimum clock period.

3. Executes an incremental optimization of the combinational logic

Because of the new distribution of registers, the loads for cells and the location of the critical paths change. An incremental logic optimization step identical to the compile -incremental command optimizes the combinational logic to reflect these changes.

#### The pipeline\_design Command

The pipeline\_design command performs the following principal actions on a purely combinational design:

1. Inserts registers at the outputs of a combinational design

The registers are first placed at the outputs of a design and then moved back through the combinational logic to create a staged, pipelined design.

2. Optimizes register retiming

The same principal actions as those of the  ${\tt optimize\_registers}$  command are performed.

## The balance\_registers Command

The  ${\tt balance\_registers}$  command performs the following principal actions on a sequential design:

1. Minimizes the clock period

The registers are moved to ensure the smallest clock period for the retimed circuit and to balance the pipeline stage delays.

2. Performs a sequential mapping after moving the registers

# **Register Retiming Concepts**

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

This chapter discusses fundamental register retiming concepts. A good understanding of these concepts will help you make the best use of the Design Compiler register retiming capabilities.

This chapter contains the following sections:

- Basic Definitions and Concepts

- Forward Retiming

- Backward Retiming

- Asynchronous Control Inputs of Registers

- Synchronous Control Inputs of Registers

- Multiclass Retiming

- Pipeline and Nonpipeline Circuits

- Reset State Justification

#### **Basic Definitions and Concepts**

To understand how register retiming works, you need first to understand certain basic definitions and concepts. In particular, you must understand what sequential generic elements (SEQGENs), control nets, and register classes are. These are important because during retiming, mapped registers are temporarily replaced by SEQGENs according to their classifications as determined by their control nets.

Note:

In this manual, the terms design, cell, leaf cell, hierarchical cell, combinational cell, and sequential cell are used in the same sense as in other Synopsys manuals.

#### **Flip-Flops and Registers**

Flip-flop, register, synchronous register, asynchronous register, and latch are familiar terms; however, with respect to register retiming as discussed in this manual, these terms have the following specialized usage:

- A *flip-flop* is an element of a technology library (target library) that has, unlike the combinational cells, a state and a distinguished clock input. Flip-flops can be edge triggered or level sensitive.

- A *register* is technically an instance of an edge-triggered flip-flop in the design. But for the purposes of this manual, since both edge-triggered flip-flops and level-sensitive latches can be retimed, the term register will refer to both types of sequential devices unless stated otherwise.

- A *synchronous register* is a register that can change its state only at the active edge of the clock signal.

- An *asynchronous register* is a register that, in addition to changing its state on a clock edge, can also change its state according to the control levels of asynchronous signals, which are independent of its clock signal.

- A *latch* is an instance of a level-sensitive flip-flop in the design. Register retiming supports designs with latches and retimes them instead of the registers if the -latch option is used.

The essential point here to understand is that flip-flops are technology library elements, while registers and latches are their design instances.

#### SEQGENs

A SEQGEN is a generic sequential element that is used by Synopsys tools to represent registers and latches in a design. SEQGENs are created during elaboration and are usually mapped to flip-flops during compilation. Because mapped flip-flops are temporarily replaced by SEQGENs during register retiming, it is important that you understand the basic functionality of these elements.

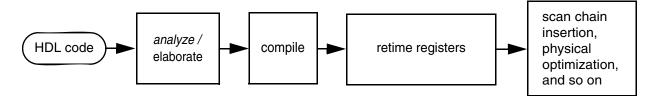

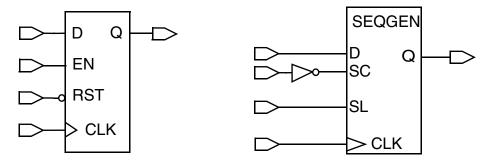

Figure 2-1 shows the pins that are used when the SEQGEN cell describes a synchronous or asynchronous register. (Additional pins occur when the SEQGEN is operated as a latch.)

Figure 2-1 Relevant Pins of the SEQGEN Cell

In register retiming, the operation of SEQGEN cells is as follows:

- The synchronous toggle pin (ST) has an inactive value of 0. Therefore, the SEQGEN cell will be retimed only if the ST pin is connected to a constant net with value 0.

- The clock (CLK) pin is always connected to the clock net of the design.

- The synchronous state changes occur at the rising edge of the clock signal.

- If set to 1, the synchronous load (SL) pin enables the next-state D input to become the next state. The SL pin should be tied to a constant 1 net when unused.

- The synchronous clear (SC) pin sets the state to 0 if active. This pin preempts the SL input and, to be inactive, must be tied to a constant 0 net.

- The synchronous set (SS) pin sets the state to 1 if active. This pin preempts the SL input and, to be inactive, must be tied to a constant 0 net.

- If both SC and SS are active, the constant set as an attribute on the particular SEQGEN instance becomes the new state.

- The asynchronous inputs AC and AS override all settings of the synchronous inputs; these pins change the state and output of a SEQGEN instance, independent of the clock input.

- The AC input sets the Q output to 0 if active; the AS input sets the Q output to 1 if active. Both inputs must be 0 to be inactive.

- The EN input replaces the CLK clock pin if the SEQGEN cell operates as a level-sensitive latch.

- The AD pin input replaces the D pin input if the SEQGEN cell operates as a level-sensitive latch.

#### **Control Nets**

A control net is a net connected to one of the SL, SC, SS, AC, or AS pins of a SEQGEN instance. The equivalence of control nets plays a crucial role in the movement of registers during retiming.

By definition, a set of control nets are equivalent if they meet either of the following conditions:

- All the nets can be reached from a common source, and between this common source and the SEQGEN instances, all the nets have an odd number of inverters or all the nets have an even number of inverters. (A net with no inverters is regarded as having an even number of inverters.)

- The control nets are constant and have the same constant values (0 or 1).

Thus, two nonconstant nets with a common source, one that includes an odd number of inverters and the other an even number of inverters, are not equivalent nets. Note that any number of buffers is allowed between the common source and the SEQGEN pin of an equivalent net.

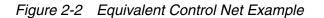

Figure 2-2 shows an example of equivalent and nonequivalent nets. Nets n1 and n3, which have even number of inverters (0 and 2), are equivalent, while net n2, which has an odd number of inverters (1), is not equivalent to either of them.

#### **Register Classes**

The SEQGEN instances are grouped into register classes according to their connections to control nets. Grouping is necessary because only registers belonging to the same group can be moved together across a combinational gate without violating the circuit logic.

Two SEQGEN instances belong to the same register class if the following conditions are fulfilled:

- Their SL pins are connected to equivalent control nets.

- Their SC and SS pins are connected to equivalent control nets. That is, a given control net can be connected to the corresponding SC or SS pins in the SEQGEN instances or to the SC pin of one SEQGEN instance and to the SS pin of the other.

- Their AC and AS pins are connected to equivalent control nets. The same conditions hold for the asynchronous pins as for the synchronous pins.

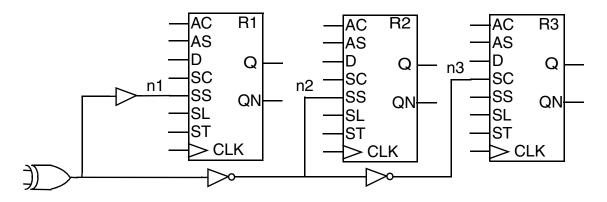

Figure 2-3 shows an example in which registers A and B belong to the same class.

Figure 2-3 Swapping of Control Net for Registers in the Same Class

In Figure 2-2 on page 2-5, if all pins not connected to nets n1, n2, and n3 are connected to their inactive constants, registers R1 and R3 belong to the same class, but register R2 belongs to a different class.

When registers belonging to the same class are moved, it is possible to swap their control nets as needed to accomplish the retiming. This swapping capability is true for both synchronous and asynchronous register pins.

#### **Forward Retiming**

To retime forward across a combinational cell, each net in the immediate fanin of the cell must be driven by the Q pin of a register, and all these registers must belong to the same class. After the forward retiming move, the registers in the fanout of the cell belong to the same class as those in the fanin before the move.

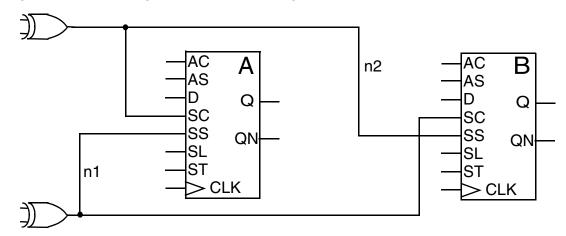

Figure 2-4 shows an example of retiming forward across the combinational cell g1.

Note:

In this and the following sections, the explicit control nets for registers are not drawn unless there is a special reason to do so. Register classes are denoted by class names (for example, C1 and C2).

Figure 2-4 Forward Retiming Example

Before the retiming move is executed, all the registers in the immediate fanin of the g1 cell belong to class C1. Notice that after the move the three registers have been replaced by two registers belonging to the same class C1. It is not possible to retime forward the next slice of registers in the fanin of the g1 cell because not all these registers belong to the same class. Also, after the first retiming, it is not possible to retime forward the class C1 register that drives one of the g2 cell inputs because only one input pin of the cell has a register driving it.

If during retiming the maximum number of forward retiming moves across a cell has been performed, the cell has reached its forward retiming boundary limit.

## **Backward Retiming**

Rules similar to the forward retiming rules govern backward retiming across a combinational cell is possible. All nets in the fanout of a combinational cell must fan out to the D pin of the registers, and all these registers must belong to the same class. After the backward retiming move, the registers in the fanin of the cell belong to the same class as those in the fanout before the move.

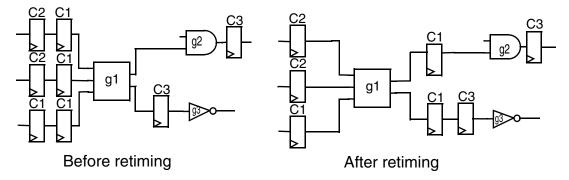

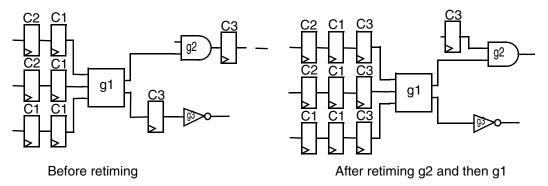

Figure 2-5 shows how the combinational cell g1 can be retimed backward *after* the cell g2 has been retimed backward. Note that two backward timing moves have been carried out.

Figure 2-5 Backward Retiming Example

If during retiming the maximum possible number of backward retiming moves across a cell has been performed, the cell has reached its backward retiming boundary limit.

## **Asynchronous Control Inputs of Registers**

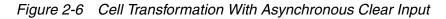

Before the registers of a circuit can be classified for retiming, all of them have to be represented by SEQGEN cells. For registers with typical asynchronous set or clear pins, this is a relatively straightforward and unambiguous procedure. In Figure 2-6, a register with an active-low asynchronous clear input is transformed into an equivalent SEQGEN instance. (All inputs of the SEQGEN not shown in the figure are connected to a constant net with their inactive value.)

## **Synchronous Control Inputs of Registers**

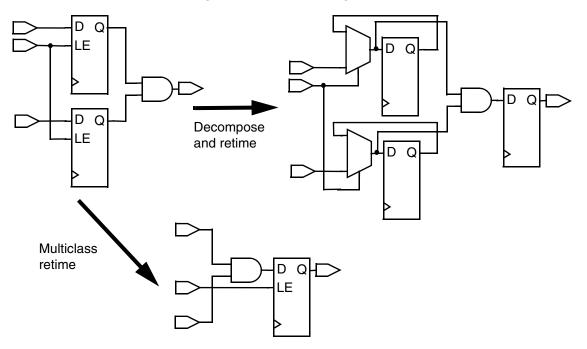

A register with typical synchronous control inputs can be represented with an equivalent SEQGEN instance in two ways:

- The synchronous control pins are directly translated to equivalent SEQGEN pins.

- The synchronous control nets are transformed through combinational decomposition of the register.

#### Translating Synchronous Input Pins to Equivalent SEQGEN Pins

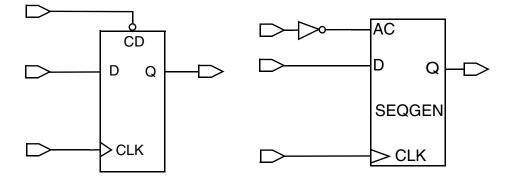

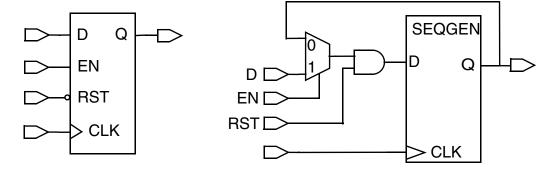

As with asynchronous pins, this method carries out a straightforward translation of the register pins to equivalent SEQGEN pins of the SEQGEN cell. Figure 2-7 shows an example of a register with an active-low synchronous reset signal and an active-high synchronous enable signal. That is, the RST pin has been translated to an active-low SC pin, and the EN pin has been translated to an active-high SL pin.

Note:

This method of transforming the original registers of a design leads to *multiclass* retiming because the resulting SEQGEN instances will probably not all belong to the same class.

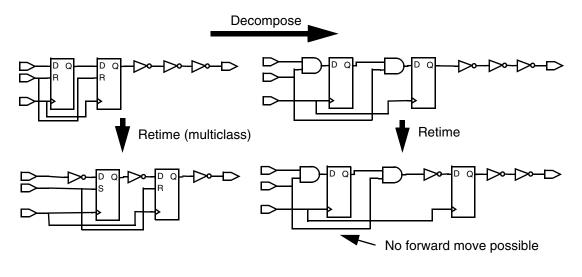

# Transforming Synchronous Input Pins Through Combinational Decomposition

Combinational decomposition transforms synchronous input pins by

- Using combinational cells to implement the synchronous functionality, and

- Connecting the output of the combinational cells to the D pin of a SEQGEN cell

Note:

Combinational decomposition can be applied to the synchronous pins of asynchronous registers.

Figure 2-8 shows the combinational decomposition of the register example of Figure 2-7.

Figure 2-8 Transformation by Decomposition Example

An advantage of combinational decomposition is that all purely synchronous registers belong to the same class after they are transformed to SEQGENs. Consequently, there are no limits to the number of forward or backward moves possible at multiple input or output gates due to registers belonging to different classes. Not using decomposition (multiclass retiming) can lead to register class conflicts, which ultimately limit the number of forward or backward retiming moves possible.

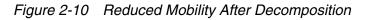

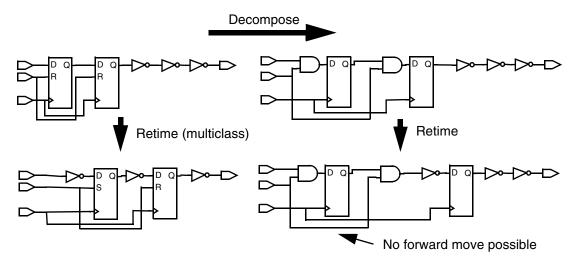

Figure 2-9 shows how registers with *different* enable control nets can be moved forward after decomposition. (To simplify the figure, the clock net is not drawn.) These registers could not be moved after multiclass retiming. Notice, however, that two D flip-flops remain with the fanouts belonging to synchronous combinational logic and cannot be forward retimed; the third flip-flop is free to move by forward retiming.

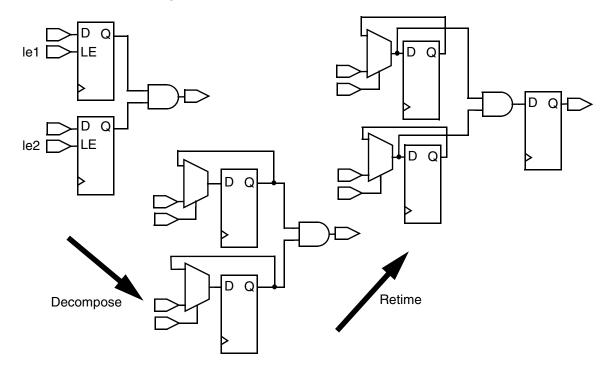

Figure 2-9 Forward Retiming of Decomposed Cells With Load Enable

Combinational decomposition can also limit the movability of registers. Figure 2-10 shows how decomposition applied to a sequence of two synchronous clear registers leaves the left register without the possibility of a forward move because the newly introduced AND gate does not have a register at its second port. (The right register is forward retimed through an inverter.) Alternatively, multiclass retiming allows both registers to move forward: The right register can be moved across two inverters and the left register across one buffer.

## **Multiclass Retiming**

Multiclass retiming can offer significant area savings compared with retiming after decomposition. A multiclass example is shown in Figure 2-11. The situation is similar to the example in Figure 2-9 except that the two load enable registers belong to the same class and therefore can be moved across the AND gate, leading to a single register. Using decomposition leads to a higher number of registers and additional cells after retiming.

Figure 2-11 Reduced Area Through Multiclass Retiming

## **Pipeline and Nonpipeline Circuits**

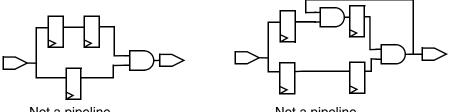

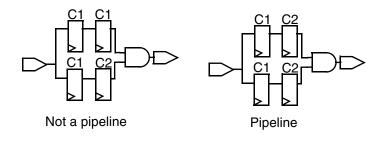

In deciding which retiming method (multiclass or decomposition) to apply to a design, it is useful to classify circuits or parts of circuits by their topology, as well as by the types, connections, and locations of registers within the design. Circuit topologies can be classified as pipeline or nonpipeline, as defined later in this section.

For pipeline circuits, multiclass retiming is recommended. For nonpipeline circuits, decomposition or a combination of decomposition and multiclass retiming works best.

#### **Defining Pipeline Circuits**

You can understand the concept of a pipelined circuit, including register indexes, slices, and stages, in the following way:

Circuit registers can be reached by different paths from the primary data inputs. (A primary data input is an input that does not drive any control pin of a register.) During the transversal of a path, cells are passed from their input pins to their output pins.

For a particular register, the number of other registers encountered along each path from the primary inputs to the given register can be counted. If this number is independent of the path chosen (that is, the same for every path to the register), each register can be assigned this number as a *register index* of the circuit. All registers in such a circuit that have the same index form a *slice*.

If all the registers in each slice belong to the same class and if there is the same number of registers on any path from a primary input to a primary output, the circuit is classified as a *pipeline*. All other circuits not satisfying this definition are defined as nonpipelines.

The largest index occurring for the registers in a pipeline plus one is the number of pipeline *stages*. For example, a pipeline with just one slice of registers has two stages.

Note:

This definition of pipeline does not require that registers be located at the primary outputs or primary inputs.

Figure 2-12 and Figure 2-13 show examples for pipeline circuits and nonpipeline circuits.

Figure 2-12 Nonpipeline Circuit Examples

Not a pipeline

Not a pipeline

Figure 2-13 Pipeline and Nonpipeline Circuit Examples

#### **Reset State Justification**

When you move the registers in a circuit, it is not sufficient to follow only the rules for retiming of a single gate. In addition, it is usually necessary to preserve an equivalent reset state.

The circuit state is defined by the values of all the registers in the circuit at a given point in time. A circuit and its retimed version have an equivalent state if they produce the same sequences of values at corresponding primary outputs for identical sequences of values at the corresponding primary inputs.

When power is switched on in a circuit, its state is unknown. Depending on the type of circuit, you might need to have an external reset or set input to reset the registers to a known value. This step ensures that the circuit has reproducible behavior after the input becomes active for the first time.

If a circuit is designed this way, by default register retiming ensures that the reset state of the retimed circuit is equivalent to that of the original circuit, and that the behavior is identical when a finite number of clock cycles has passed after the activation of the reset. If all registers are properly reset, output sequences should match immediately.

However, a typical case where the first few output values might not match is that of a pipelined data path where the registers do not have any set or clear connections. The maximum duration of the mismatch is the number of stages of the pipeline multiplied by the clock period.

The computation of the equivalent reset state is called *justification*. Justification for registers that have been moved forward across combinational gates is always possible and does not require significant amounts of CPU time. Justification for registers moved backward across combinational gates can be more complicated. Figure 2-14 shows an example of the difficulty with backward justification.

Figure 2-14 Impossible Backward Justification Example

The numbers inside the register symbols are the given reset values. When the registers are moved to the post-retiming positions, it is not possible to find an equivalent state for the circuit. Register retiming handles this case by finding a position for the registers where an equivalent state is found that is as close to the optimal position as possible.

Backward justification also can cost more CPU time than forward justification. If the circuit to be retimed has a reset but does not need to have an equivalent reset state after retiming, there is a method available that does not perform justification. This method can be applied to pipelined data paths, but it is not suitable for controllers.

You can use the -justification\_effort option of the optimize\_registers or set\_optimize\_registers command to specify the justification effort level during backward justification. The option can take one of the following values: low, high, or medium. For more information, see Appendix B, "Command Syntax and Variable Syntax."

# Writing HDL Code for Retiming

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

Successful register retiming very much depends on a compatible HDL description of the original design. In particular, certain design limitations must be observed, including ones specific to pipelined designs.

This chapter contains the following sections:

- Allowed Circuits

- Writing HDL Code for Pipelines

- Writing HDL Code for Nonpipelines

#### **Allowed Circuits**

For the retiming <code>optimize\_registers</code> command to work successfully, the circuit HDL description must conform to certain rules. Therefore you should check the original HDL code and constraints against the following rules:

- If the -latch option is used, registers are treated as fixed and only level-sensitive latches are retimed. (By default only edge-triggered registers are moved.)

- The clock distribution network can contain only buffer, inverter, and clock-gating cells. Note that clock-gating cells should be unate at their clock input pin, contain only one output, and have no more than one clock signal at their inputs. (Avoid using nonunate cells, such as XORs and XNORs, in clock networks.)

- The design can contain only master-slave or standard edge-triggered registers.

- Combinational feedback loops are not allowed.

The balance\_registers and pipeline\_designs commands have additional restrictions. See Appendix B, "Command Syntax and Variable Syntax," for more information on these commands.

Timing exceptions such as false paths, multicycle paths, and maximum delay constraints are supported only in a limited way by retiming. Sequential cells named explicitly as startpoints or endpoints of these exceptions will not be moved. The quality of results for designs with timing exceptions might be negatively affected. Therefore, it is better to avoid having the timing exceptions of a design retimed.

When retiming latches with the <code>optimize\_registers</code> command, latches must be driven by a symmetric, two-phase clock system. This system can be created by using two clock ports, one for each phase, or by using the clock signal directly for one phase and inverting this signal for the other phase.

## Writing HDL Code for Pipelines

This section describes how to write HDL code in the following sections:

- Calculating the Number of Pipeline Stages

- Determining the Initial Location of the Registers

- Using DesignWare Pipeline Register Component

#### **Calculating the Number of Pipeline Stages**

There are three cases to consider when you are setting the number of pipeline stages for your design. In two of the cases, you use formulas provided in this section to compute an approximate number. Note that the actual number of stages needed is often one less or one greater than this estimated number. (If the formulas yield a fractional result, you should round the number up to the next integer value.) In the third case, the number of stages is given, so no calculation is required.

The formulas that follow use these parameters with the following definitions:

- N is the number of pipeline stages in the design. It is one more than the number of registers on any path from the primary inputs to the primary outputs.

- $T_c$  is the clock period of the design *after* retiming.

- T<sub>s</sub> is the setup time of a typical flip-flop used for pipelining. Select a flip-flop with the same capabilities (load enable, reset) as needed for the final pipelined design.

- $T_q$  is the clock-to-Q delay of the typical flip-flop. (Use the same selection criteria as for the setup time.)

- T<sub>d</sub> is the maximum delay from inputs to outputs of the compiled combinational design *before* pipelining, including input and output delays. To obtain a value for this number, perform a separate compile before adding the pipeline stages.

The target clock period cannot be less than the sum of setup time and clock-to-Q delay for the flip-flop, that is,  $T_s + T_q < T_c$ . Furthermore,  $T_d > T_c$  is assumed. Otherwise, no pipeline registers are needed.

In the first case, the objective is to minimize the number of pipeline stages, N, when the clock period,  $T_c$ , is given. The combinational design should be compiled with tight timing constraints to achieve the smallest possible delay. If the outputs are not registered, the number of stages needed can be estimated as follows:

$$N = \frac{T_d - T_s - T_q}{T_c - T_s - T_q}$$

On the other hand, if the outputs are registered, the following estimate can be used:

$$N = \frac{T_{d} + T_{c} - T_{s} - 2T_{q}}{T_{c} - T_{s} - T_{q}}$$

In the second case, the objective is to minimize the overall area of the design when the clock period  $T_c$  is given. In this case, the combinational design should be compiled with an area constraint of 0 and no timing constraints. The resulting number for  $T_d$  can then be used in the same formulas as in the first case to obtain an estimate of the number of stages needed.

In the third case, the objective is to minimize the clock period when the number of stages, N, is given. Therefore nothing has to be calculated in this case. The design should be compiled with tight timing constraints, as in the first case. The retiming should then be performed with a very small target clock period that cannot be achieved (for example,  $T_s$ ). Based on the negative slack values you obtain, you can find the minimum clock period possible for the design.

#### **Determining the Initial Location of the Registers**

The initial location you specify for the registers influences the movability of the registers and the CPU time needed for retiming.

If none of the registers in the pipeline is connected to any synchronous or asynchronous set or clear signal or if you plan to use the don't-care state attribute for all registers, it is usually convenient to place the registers at the primary outputs. This is easy to code, and no CPU time-consuming backward justification is necessary. Even if you choose decomposition during retiming, only the forward movability through AND gates is limited, and this is irrelevant because the registers will not be moved forward during retiming.

In all other cases (that is, when there is a set or clear functionality for some of the registers and the equivalent reset state is important), you should register the primary inputs of the design. However, it is important that you not register the clock, set, clear, or load enable inputs, while registering all other inputs. Otherwise, the forward movability of the registers is limited. Placing the registers at the inputs ensures short justification times.

#### Using the DesignWare Pipeline Register Component

To infer pipeline registers in RTL is to use the DesignWare pipeline register component. The DesignWare library provides the *DW\_pl\_reg* pipeline register component, which makes it easy to pipeline the arbitrary logic of arithmetic structures using register retiming.

When you instantiate the *DW\_pl\_reg* component in your RTL, you specify the parameters to control the width, enable/reset, and the number of stages of the pipeline register component.

For more information on how to use the DesignWare pipeline register component, see the *DW\_pl\_reg DesignWare Building Block IP Datasheet*.

#### Writing HDL Code for Nonpipelines

No special restrictions or recommendations can be made for nonpipelined designs because the register locations relative to primary inputs and outputs are difficult to change in a way that still provides the required functionality. Often a complex hierarchical design contains parts that can be considered as pipelined, although the rest of the design is not. You can apply the previous guidelines to the pipelined parts of a nonpipelined design.

# 4

## Performing Analysis and Elaboration for Retiming

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

The chapter includes the following section:

• Inferring Registers for Pipelines and Nonpipelines

Note:

If any of the variables discussed in this chapter are to be set to nondefault values, they should be set before the analyze, elaborate, read, read\_verilog, or read\_vhdl commands for the HDL code are issued.

#### **Inferring Registers for Pipelines and Nonpipelines**

For pipelines, the only HDL variable that should be set differently from its default value is  $hdlin_ff_always_sync_set_reset$ . This variable controls whether the synchronous clear (SC) and synchronous set (SS) pins of the SEQGEN cells in the elaborated netlist are used instead of combinational cells to create set and clear. Set the variable as follows:

#### dc\_shell> set hdlin\_ff\_always\_sync\_set\_reset true

To enable multiclass retiming in pipelines, move the registers with their synchronous clear and set. Because all registers in one slice are in the same class, no moves are limited.

For nonpipelines, keep the HDL variable set at its default value as follows:

#### dc\_shell> **set hdlin\_ff\_always\_sync\_set\_reset false**

For nonpipelines, setting this variable to true can create registers belonging to too many different classes, which in turn limits the movability of registers and consequently the delay reduction.

### Setting Attributes and Constraints for Retiming

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

This chapter shows you how to set constraints before issuing the  $compile\_ultra$  command or compile command. It also discusses which of the steps often associated with compilation in the design flow should be deferred until after register retiming.

This chapter includes the following sections:

- Setting Timing Constraints

- Setting the Compile Command Option on SEQGEN Cells

- Netlist Modifications to Avoid

#### **Setting Timing Constraints**

For any type of design, you should set the input and output delays to realistic values by using the commands set\_input\_delay and set\_output\_delay. (For information on how to use these commands, see the appropriate man page.) How you set timing constraints depends on whether the design is pipelined or nonpipelined.

Note:

Be careful to choose the correct clock and clock edge when you set specific input and output delays.

#### **Setting Timing Constraints for Pipelines**

How you set timing constraints for pipelines depends on whether the registers are located at the primary inputs and outputs of the design or are already distributed throughout the design.

If the registers are still located at the primary inputs and outputs, the delay of the combinational circuit is usually larger than the clock period with registers at inputs and outputs. To avoid unnecessarily long processing time, set the clock period to a value greater than the target clock period for the retimed design. If the combinational delay,  $T_d$ , has already been determined as part of the computation of the number of stages, N, for a given final clock period,  $T_c$ , the combinational delay can be used as the target clock period for the initial compilation.

Otherwise, if the number of stages, N, the final clock period,  $T_c$ , the setup time,  $T_s$ , the clock-to-Q delay,  $T_q$ , and the output delay,  $T_o$ , or the input delay,  $T_i$ , are known, a target clock period, T, for the initial compilation can be computed as follows:

If the registers are located at the primary outputs,

$T = N * (T_c - T_q - T_s) + T_q + 2T_s - T_o$ If the registers are located at the primary inputs,

$T = N * (T_c - T_q - T_s) + 2T_q + T_s - T_i$

If the registers are already approximately in their final positions after you have retimed the clock period, the first compile clock period should be the same as the target clock period after retiming.

#### **Setting Timing Constraints for Nonpipelines**

For nonpipelines, the clock period for the first compile should be the same as the target clock period after retiming.

#### Setting the Compile Command Option on SEQGEN Cells

During compile, Design Compiler performs a step known as sequential mapping. This step maps the generic SEQGEN cells of the elaborated netlist to cells from the technology library. However, depending on the flip-flops available in the technology library and the optimizations that can be performed by sequential mapping, information about control nets can be lost in the process.

For example, if no synchronous set flip-flop is available, a SEQGEN cell whose synchronous set pin is connected to a nonconstant net might be mapped to a simple D flip-flop with an OR gate feeding its D pin. Another possibility is that the synchronous clear and the next state input might be swapped by sequential mapping, greatly increasing the number of classes and reducing the number of possible forward moves.

If you want to perform multiclass retiming, you need to restrict the sequential mapping to map the SEQGEN to the technology library cell that exactly matches the functionality of the SEQGEN cell. You can achieve this by using the <code>-exact\_map</code> option of the <code>compile\_ultra</code> command.

#### **Netlist Modifications to Avoid**

Certain design modifications and optimizations are often performed together with the first compilation. Some of them can still be performed before register retiming, but others must be deferred until the retiming has been performed. You should note carefully the following guidelines.

#### **Test-Related Modifications**

Test-ready compile by using the -scan option can be performed before register retiming. Test flip-flops and feedback loops are again inserted after retiming. You must perform retiming before scan-chain insertion; the presence of scan chains makes moving the registers impossible.

In some libraries, there are no scan equivalents for load-enable registers. Therefore, test-ready compile before retiming introduces feedback loops around the registers that retiming cannot remove. In this case, use the following commands:

```

#no scan option initially

compile_ultra

optimize_registers -no_compile

compile -incr -scan

....

```

#### **Physical Design-Related Modifications**

Avoid creating a clock tree before retiming. Register retiming can retime designs with clock trees consisting of inverters, buffers, and any clock-gating cell that is unate at its clock input pin. However, the tree is no longer balanced after retiming.

Defer other physical design-related optimization options until after retiming because register locations and the delays change significantly during retiming.

Using multibit flip-flops to realize registers is possible. However, if no  $dont\_touch$  attribute is put on these flip-flops before retiming, they are split up into single-bit registers and moved individually.

### **Retiming the Mapped Netlist**

In this document, the term "register" refers to both edge-triggered registers and level-sensitive latches unless stated otherwise. Both types of sequential cells can now be retimed. However, the pipeline\_design and balance\_register commands can be applied to only edge-triggered registers in the current release.

After the preparation and initial compilation, you can retime your design by using the <code>optimize\_registers</code> or <code>pipeline\_design</code> command. However, before using either of these retiming commands, you must set or reset certain constraints and attributes. This chapter discusses the steps you take to use the <code>optimize\_registers</code> command.

This chapter contains the following sections:

- Preventing Retiming

- Doing Timing Analysis During Retiming

- Setting Timing Constraints

- Selecting Transformation Options

- Retiming Designs With Multiple Clocks

- Settings That Influence Register Retiming Runtime

- Netlist Changes Performed by Register Retiming

#### **Preventing Retiming**

Sometimes it is best to avoid retiming some of the registers in a design. For example, registers driving primary outputs that have to stay in place because of a particular design style should not be retimed. In this case, you should set the dont\_retime attribute on these output registers.

Another example of not moving certain registers occurs when you want to keep the controller registers of a design in place while allowing the data-path registers to move. Keeping the controller registers in place lets you easily identify these registers and relate them to the original HDL code. In this case, you can set the dont\_retime attribute on the registers in the controller or on the controller cell itself (if it is a hierarchical cell).

The dont\_retime attribute prevents a register from moving during retiming but allows sequential mapping to map the register to a different flip-flop.

Use the set\_dont\_retime command to control the designs or cells that can be retimed. When set to true (the default), the command sets the dont\_retime attribute on specific cells and designs in the current design so that sequential cells are not moved during retiming optimizations. For example,

```

set_dont_retime [get_cells {z1_reg z2_reg}] true

```

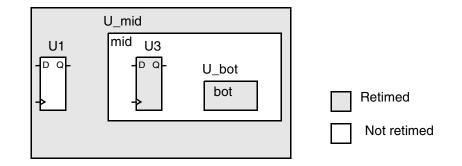

Setting the dont\_retime attribute on a hierarchical cell implies that the attribute is set on all sequential cells below it that do not have the dont\_retime attribute set to false. A leaf-level cell that has the dont\_retime attribute is not retimed if it is a sequential cell. When the dont\_retime attribute is set on a design, all sequential cells that do not have the dont\_retime attribute set to false are not retimed. For example, consider the following sequence of commands:

```

set_dont_retime [get_cells U1]

set_dont_retime [get_designs mid] true

set_dont_retime [get_cells U_mid/U3] false

set_dont_retime [get_cells U_mid/U_bot]false

optimize_registers

```

Figure 6-1 shows that cells U1 and design mid are not retimed.

#### Figure 6-1

Note:

The set\_dont\_retime command overrides the set\_transform\_for\_retiming command. That is, if the value of the dont\_retime attribute is true, setting the transform\_for\_retiming attribute to decompose or multiclass will not make a register retimable. A movable register cannot be moved across a register with the dont\_retime or the dont\_touch attribute.

#### **Doing Timing Analysis During Retiming**

When the registers are moved during retiming, their final location is unknown. Therefore the influence of the registers on the delay of the final circuit cannot be taken into account for each individual register. Instead, the combinational delay between registers is optimized. To set a realistic goal for the combinational delay, you must correct the target clock period by subtracting all the delay components related to the registers.

Because each register can have a different delay, you must find a representative delay value for all registers. You do this by selecting one flip-flop, called the preferred flip-flop, from the technology library. You select this flip-flop from the flip-flops instantiated in the design and similar ones available in the library. The selection criteria you should use, in the order of importance, are as follows:

- 1. Smallest setup time. The setup time is available directly from the library information.

- 2. Smallest average clock-to-Q delay. The average clock-to-Q delay is obtained by computing the average load of all nets in the design. This load is then driven by the flip-flop, and the resulting clock-to-Q delay is computed.

- 3. Smallest average load of all input pins. The average load of all input pins of the flip-flop is computed from the library information.

If there is a tie between several flip-flops after these criteria are applied, further selection criteria (not described here) are used. For more information on how to determine the selection of the preferred flip-flop, see Appendix A, "Additional Information on the Register Retiming Commands."

After you select the preferred flip-flop, a clock correction is computed. The clock correction is determined from the following three factors:

- Setup time

- Median clock-to-Q delay of the design

An instance of the preferred flip-flop is used to drive each net of the design. For each of these configurations, the clock-to-Q delay is computed. The median of all these values is taken as the clock-to-Q delay for the clock correction. Using the median value instead of the arithmetic average helps reduce the influence of a few extreme values on the outcome.

• Clock uncertainty

This quantity is set by the user when determining the clock for the design.

The sum of these three values is the clock correction. The clock correction is subtracted from the target clock period, and the resulting number is used as the target value for the combinational delay during the register moving phases. If the number is less than 0, a warning is issued, and 0 is used instead.

When retiming latches with different clock ports for the two clock phases, the difference in the clock source latency of the two clock ports is also added to the clock correction.

You can prevent the clock correction, if necessary. For information on how to circumvent the computation of the clock correction, see Appendix A, "Additional Information on the Register Retiming Commands."

During incremental compilation phase of the <code>optimize\_registers</code> command, exact timing, including register delays, is used for the design.

#### **Setting Timing Constraints**

Setting accurate input and output delays for all primary inputs and primary outputs is very important. If the correct values have already been set for the compilation of the design, no change is necessary. Otherwise, you should set the values before using the <code>optimize\_registers</code> command.

Input and output delays are set relative to clocks created for the design. If a port has an input or output delay set relative to a particular clock, the cells in the fanin or fanout of this port will be part of the network for this particular clock, if it is retimed. See "Retiming Designs With Multiple Clocks" on page 6-7.

For Design Compiler register retiming, the tool assumes that the input delay at each primary input is at least as large as the median clock-to-Q delay used for the clock correction. If the input delay is less, a warning is issued and the median clock-to-Q delay is used.

Similarly, for register retiming, the tool assumes that the output delay at each primary output is at least as large as the setup time used for the clock correction. If the output delay is less, a warning is issued and the setup time of the preferred flip-flop is used.

The clock period has to be set for the external clock port, using the create\_clock command. The value of the clock period might be different from the one used during initial compilation, especially if the design is a pipeline whose registers are still concentrated at the outputs. The clock period value is used by the register moving phases and the incremental compilation phase of the optimize\_registers command. For more information on how to set different constraints for the two phases, see Appendix A, "Additional Information on the Register Retiming Commands."

#### **Selecting Transformation Options**

The <code>optimize\_registers</code> command lets you specify how the mapped registers are transformed to SEQGEN cells. There is a transformation option for synchronous registers and another for asynchronous registers. (Recall that a synchronous register does not have any asynchronous input pins and an asynchronous register has at least one asynchronous input pin.)

The transformation option for synchronous registers is

#### -sync\_transform multiclass | decompose| dont\_retime

The multiclass value specifies that the synchronous clear, set, and enable functionality is moved with the synchronous sequential cells (if they are moved during retiming). The decompose value specifies that any synchronous sequential cell is decomposed (transformed into an instance of a D flip-flop or latch and additional combinational logic to create the necessary synchronous functionality). The dont\_retime value specifies that these registers are not to be moved. The default value for this option is multiclass.

The transformation option for asynchronous registers is

-async\_transform multiclass | decompose | dont\_retime

The multiclass value specifies that the asynchronous clear and set as well as any synchronous clear, set, and enable functionality are moved with the asynchronous sequential cells (if they are moved during retiming). The decompose value specifies that any asynchronous sequential cell is decomposed. The dont\_retime value specifies that these registers are not to be moved. The default value for this option is multiclass.

Registers that are already SEQGEN instances are not affected by these settings. Their set, clear, and enable connections are controlled by HDL Compiler options, as described earlier in Chapter 3, "Writing HDL Code for Retiming."

#### **Recommended Transformation Options for Pipelines**

For pipelined designs, the recommended transformation options for the optimize\_registers command are as follows:

optimize\_registers -sync\_trans multiclass -async\_trans multiclass

Because there are no class conflicts preventing registers in pipelines from being moved across combinational cells, using multiclass retiming for all types of registers is best. These settings give the best timing results with the smallest possible register count and area.

Note:

As described in Appendix A, individual attribute settings on cells or their parent cells override these option settings.

#### **Recommended Transformation Options for Nonpipelines**

For nonpipelined designs, the recommended transformation options for the optimize\_registers command are as follows:

optimize\_registers -sync\_trans decompose -async\_trans decompose

In most cases, decomposing all synchronous functionality ensures that no unnecessary class conflicts occur to limit the movability of the registers. The solution with the smallest possible delay or target delay should be found. An exception to this result can occur when the forward movability of registers is limited because of additional AND gates or OR gates as shown in Figure 6-2 on page 6-7. In this situation, setting the individual retiming attributes might help.

Note:

As described in Appendix A, individual attribute settings on cells or their parent cells override these option settings.

#### **Retiming Designs With Multiple Clocks**

If the registers of the design are triggered by multiple different clocks or by both the rising and the falling edge of the same clocks, the retiming can be performed on only one clock at a time. The <code>optimize\_registers</code> command offers you two ways to achieve this retiming, namely, by using the <code>-clock</code> option or not using this option.

With the -clock option you can specify that the registers for a single clock are retimed during one invocation of the <code>optimize\_registers</code> command. By default only the registers triggered by the rising edge of the clock are retimed. If you want to retime the registers triggered by the falling edge of the clock, you have to use the -edge option with the value *fall*.

If the -clock option is not used, registers for all clocks are retimed during the first (register moving) phase of retiming. The retiming is performed one clock at a time. Clocks with a larger clock period are retimed before clocks with a smaller clock period. If two clocks have the same clock period, the clock with the larger number of registers is retimed first. For each single clock, the registers triggered by the rising edge are retimed before those triggered by the falling edge. Note that this default order might not yield the best possible results. Also, retiming all clocks in the first phase means that there is no incremental optimization of the combinational logic when different clocks are retimed. Therefore it is recommended that you determine the best order for retiming clocks yourself and apply that order by using multiple runs of optimize\_registers with the -clock option.

When retiming latches, a two-phase clock system is being retimed. This means that the rising and falling edges of a clock or two or more different clocks have to be retimed together. If you specify a clock using the -clock option while using the -latch option, the  $optimize_registers$  command retimes all the clocks and edges that need to be retimed with this clock. Note that even though the -clock option take only one argument, the command finds the other clock of the two-phase clock system.

#### **Settings That Influence Register Retiming Runtime**

In larger designs, using the <code>optimize\_registers</code> command can result in increased CPU runtime. The following option settings can reduce the runtime while exploring the potential delay improvement resulting from register retiming. Note, however, that for the final optimization, you might not want to use some or any of the options.

-min\_period\_only

If this option is set, register count minimization is not performed. The registers are only moved to the locations that result in the smallest possible combinational delay between registers.

-justification\_effort low | medium | high

Specifies the effort level to be used during backward justification of registers. Specifying a low effort ensures that justification terminates quickly; however, the quality of results (QoR) can be poor. A medium effort might provide better QoR but result in a larger runtime. A high effort could give provide the best QoR without considering runtime. The default is medium.

-no\_compile

This argument omits the default incremental logic synthesis step normally performed after computation of the optimal sequential cell locations. If you specify this option, no design rule fixing is performed. Generic sequential cells might remain in the design.

When you use this option, you can choose a logic compilation script adapted to your design instead of relying on the default used internally by <code>optimize\_registers</code>. It is important to perform logic synthesis after sequential cell retiming to obtain the best possible timing results.

If the runtime of the <code>optimize\_registers</code> command is too long, you can use all these settings at one time and then successively switch them off again to see when the runtime increases greatly.

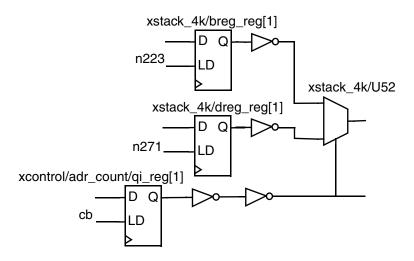

#### **Netlist Changes Performed by Register Retiming**