# **SystemVerilog in Simulation**

**Product Version 9.2**

**July 2010**

Copyright 1995-2010 Cadence Design Systems, Inc. All rights reserved.

Printed in the United States of America.

Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

1. The publication may be used solely for personal, informational, and noncommercial purposes;

2. The publication may not be modified in any way;

3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Patents:** Cadence products described in this document are protected by U.S. Patents 5,095,454, 5,418,931, 5,606,698, 6,487,704, 7,039,887, 7,055,116, 5,838,949, 6,263,301, 6,163,763, 6,301,578

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

**Licensed Copyrights:** This software includes, in binary form, a software package called CUDD V.2.4.1 1995–2004, Regents of the University of Colorado. All rights reserved. Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met: Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution. Neither the name of the University of Colorado nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission. THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# Contents

---

## 1

|                                                          |   |

|----------------------------------------------------------|---|

| <u>Introduction to SystemVerilog in Simulation</u> ..... | 7 |

| <u>Additional Documentation</u> .....                    | 7 |

| <u>Additional Examples</u> .....                         | 8 |

## 2

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| <u>Preparing SystemVerilog Designs for Simulation</u> .....                         | 9  |

| <u>Using Options for Compiling, Elaborating, and Simulating SystemVerilog</u> ..... | 9  |

| <u>Compilation Options (ncvlog and irun)</u> .....                                  | 9  |

| <u>Elaboration Options (ncelab and irun)</u> .....                                  | 9  |

| <u>Simulation Options (ncsim and irun)</u> .....                                    | 10 |

| <u>Using the Multi-Step Invocation Method</u> .....                                 | 15 |

| <u>Using the irun Utility</u> .....                                                 | 16 |

| <u>Compiling a Design with Packages</u> .....                                       | 16 |

| <u>Compiling Packages with irun</u> .....                                           | 17 |

| <u>Compiling Packages with ncvlog</u> .....                                         | 20 |

| <u>Compiling Source Files into Compilation Units</u> .....                          | 20 |

## 3

|                                                                                                 |    |

|-------------------------------------------------------------------------------------------------|----|

| <u>Accessing SystemVerilog Design Objects with SimVision</u> ..                                 | 23 |

| <u>Accessing SystemVerilog Objects in the Design Browser</u> .....                              | 23 |

| <u>Selecting SystemVerilog Objects with the Design Browser and Design Search Sidebars</u><br>24 |    |

| <u>Viewing Compilation Units in the Design Browser</u> .....                                    | 25 |

| <u>Viewing Parameterized Classes and Class Specializations in the Design Browser</u> ..         | 26 |

| <u>Expanding and Collapsing SystemVerilog Aggregate Signals in the Design Browser</u>           | 26 |

| <u>Sorting the Elements of a Queue, or Dynamic or Associative Array</u> .....                   | 27 |

| <u>Viewing SystemVerilog Objects in the Schematic Tracer</u> .....                              | 29 |

| <u>Accessing Classes in the SystemVerilog Class Browser</u> .....                               | 29 |

| <u>Opening the Class Browser</u> .....                                                          | 30 |

## SystemVerilog in Simulation

---

|                                                                |    |

|----------------------------------------------------------------|----|

| <u>Using the Class Browser with the Design Browser</u>         | 32 |

| <u>Using the Class Browser with the Source Browser</u>         | 34 |

| <u>Viewing SystemVerilog Objects in the Waveform Window</u>    | 35 |

| <u>Adjusting the Minimum Height of an Array</u>                | 36 |

| <u>Viewing Associative Arrays in the Waveform Window</u>       | 37 |

| <u>Following SystemVerilog Signals in the Source Browser</u>   | 39 |

| <u>Preparing Your Design for the Constraints Debugger</u>      | 40 |

| <u>Opening the Constraints Debugger</u>                        | 41 |

| <u>Constraint Debugger Overview</u>                            | 42 |

| <u>Displaying Variable Values as Inputs to Constraints</u>     | 45 |

| <u>Displaying Constraints and Variables</u>                    | 45 |

| <u>Enabling and Disabling Random Variables</u>                 | 45 |

| <u>Enabling and Disabling Constraints</u>                      | 45 |

| <u>Creating a Constraint</u>                                   | 46 |

| <u>Running the Current Randomize Call Again</u>                | 47 |

| <u>Handling Overconstraints</u>                                | 47 |

| <u>Viewing Dynamic Objects with the SimVision Data Browser</u> | 47 |

| <u>Setting Up the Data Browser</u>                             | 47 |

| <u>Preparing Your Design for the Data Browser</u>              | 48 |

| <u>Opening Data Browser Windows</u>                            | 49 |

| <u>Expanding and Collapsing a Dynamic Object</u>               | 51 |

| <u>Refreshing the Data Browser Contents</u>                    | 51 |

| <u>Setting Breakpoints on Dynamic Objects</u>                  | 52 |

| <u>Displaying Dynamic Objects for the Full Design</u>          | 52 |

| <u>Sending Dynamic Objects to the Design Browser</u>           | 52 |

| <u>Viewing Dynamic Objects in the Source Browser</u>           | 53 |

| <u>Sending Dynamic Objects to a New Data Browser Window</u>    | 53 |

| <u>Setting the Debug Scope in the Data Browser</u>             | 53 |

| <u>Copying a Dynamic Object</u>                                | 53 |

## 4

|                                                        |    |

|--------------------------------------------------------|----|

| <u>Accessing SystemVerilog Design Objects with Tcl</u> | 55 |

| <u>Debugging Compilation Units with Tcl</u>            | 55 |

| <u>Accessing Compilation Units with Tcl</u>            | 55 |

| <u>Examples</u>                                        | 56 |

# SystemVerilog in Simulation

---

|                                                                             |     |

|-----------------------------------------------------------------------------|-----|

| <u>Debugging Classes with Tcl</u> .....                                     | 58  |

| <u>Limitations on Tcl Commands for Parameterized Classes</u> .....          | 59  |

| <u>Tcl Syntax for Class Object Names</u> .....                              | 59  |

| <u>Tcl Syntax for Parameterized Class Names</u> .....                       | 60  |

| <u>Accessing Class Objects with Tcl</u> .....                               | 61  |

| <u>Determining the Class Instance Handle from Tcl</u> .....                 | 64  |

| <u>Listing Class Instance Handles with Tcl</u> .....                        | 65  |

| <u>Determining the Value of a Class Member with Tcl</u> .....               | 66  |

| <u>Traversing the Class Hierarchy with Tcl</u> .....                        | 68  |

| <u>Setting Object Breakpoints within Classes with Tcl</u> .....             | 74  |

| <u>Setting Line Breakpoints within Classes with Tcl</u> .....               | 76  |

| <u>Using the heap Command with Classes</u> .....                            | 79  |

| <u>Generating Heap Usage Reports</u> .....                                  | 83  |

| <u>Debugging Constraints with Tcl</u> .....                                 | 86  |

| <u>Stopping on Calls to randomize() with Tcl</u> .....                      | 86  |

| <u>Enabling Random Variables and Constraints with Tcl</u> .....             | 87  |

| <u>Adding a New Constraint from Tcl</u> .....                               | 88  |

| <u>Executing randomize() Calls with Tcl</u> .....                           | 88  |

| <u>Debugging Semaphores with Tcl</u> .....                                  | 91  |

| <u>Describing a Semaphore</u> .....                                         | 91  |

| <u>Determining the Value of a Semaphore Variable</u> .....                  | 92  |

| <u>Debugging Arrays, Structures, and Queues with Tcl</u> .....              | 92  |

| <u>Limitations on Tcl Commands for Arrays, Structures, and Queues</u> ..... | 92  |

| <u>Tcl Syntax for Packed Structures</u> .....                               | 93  |

| <u>Selecting Members of Structures</u> .....                                | 93  |

| <u>Selecting Members of Packed Arrays with Tcl</u> .....                    | 94  |

| <u>Describing Objects with Tcl</u> .....                                    | 94  |

| <u>Setting Breakpoints on Arrays and Queues with Tcl</u> .....              | 97  |

| <u>Displaying the Values of Arrays and Queues</u> .....                     | 99  |

| <u>Debugging Strings with Tcl</u> .....                                     | 100 |

| <u>Debugging Clocking Blocks with Tcl</u> .....                             | 102 |

| <u>Debugging Program Blocks with Tcl</u> .....                              | 103 |

| <u>Debugging Interfaces with Tcl</u> .....                                  | 104 |

| <u>Debugging Packages with Tcl</u> .....                                    | 106 |

| <u>Package Names in Tcl</u> .....                                           | 107 |

| <u>Using the Tcl scope Command with Packages</u> .....                      | 107 |

## SystemVerilog in Simulation

---

|                                                              |     |

|--------------------------------------------------------------|-----|

| <u>Describing Packages with Tcl Commands</u> .....           | 109 |

| <u>Probing Packages with Tcl Commands</u> .....              | 109 |

| <u>Analyzing Package Items with Tcl</u> .....                | 109 |

| <u>Using an Extended Value Change Dump (EVCD) File</u> ..... | 110 |

| <u>SystemVerilog and EVCD</u> .....                          | 110 |

| <u>Debugging DPI Exported Functions and Tasks</u> .....      | 111 |

| <u>Managing Breakpoints</u> .....                            | 111 |

| <u>Interactive Debugging</u> .....                           | 111 |

| <u>Limitations on DPI Debugging</u> .....                    | 112 |

| <u>Index</u> .....                                           | 115 |

---

# Introduction to SystemVerilog in Simulation

---

SystemVerilog is a set of extensions to the existing IEEE Verilog-2001 standard. These extensions provide new capabilities for modeling hardware at the RTL and system level, along with powerful new features for verifying model functionality. These SystemVerilog extensions also require extensions to the simulator tools, so that you can view and debug these constructs during simulation.

The simulator provides the following support for SystemVerilog:

- The *ncvlog*, *ncelab*, *ncsim*, and *irun* utilities provide options for compiling, elaborating, and simulating SystemVerilog constructs, such as compilation units, bind files, assertions, and random variables.

- The Cadence® Simulation Analysis Environment (SimVision) provides graphical tools especially for SystemVerilog objects, such as classes. SimVision also lets you access SystemVerilog objects in its standard windows, such as the Schematic Tracer and Source Browser.

**Note:** Support for dynamic objects is limited in this release.

- The simulator's Tcl interface provides support for SystemVerilog constructs, including compilation units, classes, and constraints. In particular, the `describe`, `value`, `scope`, and `stop` commands have been extended to support SystemVerilog constructs.

## Additional Documentation

- *SystemVerilog Reference*—For information about using the SystemVerilog constructs that are supported in the current release.

- *SimVision User Guide*—For information about using SimVision

- *Verilog Simulation User Guide*—For information about simulating Verilog designs

- *irun User Guide*—For information about using the irun utility

## Additional Examples

- *SystemVerilog Engineering Notebook*—Describes examples of various SystemVerilog constructs. You can download the examples and run them using the simulator.

- *SystemVerilog DPI Engineering Notebook*—Describes examples of SystemVerilog DPI. You can download the examples and run them using the simulator.

- *Examples Reference Guide*—Lists the examples located within your installation.

---

# Preparing SystemVerilog Designs for Simulation

---

Before you can simulate a design, you must compile and elaborate it for debugging. The Incisive compiler and elaborator, and *irun*, provide command options specifically for SystemVerilog designs.

## Using Options for Compiling, Elaborating, and Simulating SystemVerilog

The following options are available in *ncvlog*, *ncelab*, *ncsim*, and *irun* to support SystemVerilog.

### Compilation Options (ncvlog and irun)

`-sv`

Enables SystemVerilog constructs. You do not need to use this option with *irun*, if your SystemVerilog source files have the `.sv` extension.

### Elaboration Options (ncelab and irun)

`-extbind file`

Specifies a file containing `bind` directives that bind SystemVerilog assertion properties to design units.

`-noassert`

Disables PSL and SystemVerilog assertions.

`-svperf arg`

Disables checking for unique and/or priority violations.

`-dpi_void_task`

Starting with IUS 8.1, C and SystemC functions that correspond to an imported or exported task are required to return an `int` value. For backward compatibility, you can use the `-dpi_void_task` option with `ncelab` on existing DPI designs. Designs will not be affected by this new requirement, and will behave as they did prior to IUS 8.1.

## Simulation Options (ncsim and irun)

`-randwarn`

Enables warning messages for all failed `randomize()` calls. See [“Controlling Constraint Warnings from the Command Line”](#) on page 10 for more information.

`-nowarn SVRND`

Disables constraint warnings for all failed `randomize()` calls. See [“Controlling Constraint Warnings from the Command Line”](#) on page 10 for more information.

`-sv_lib`

`-sv_root`

`-svrnc`

Controls the behavior of the solver, which evaluates constraints during simulation.

See [“Using the -svrnc Option to Control the Solver”](#) on page 11 for information about `-svrnc` arguments.

`-svseed {n | random}`

Defines a default seed value for randomized testing. See [“Setting an RNG Default Seed from the Command Line”](#) on page 14 for more information.

## Controlling Constraint Warnings from the Command Line

By default, IUS displays warning messages at the following times:

- The first time an instance of `randomize()` is about to return a failure status, 0

- When a variable is over-constrained

- When a `solve...before` constraint is causing a loop conflict

- When a constraint conflicts with another constraint, and is causing the solver to fail

To disable these warning messages, use the `-nowarn SVRND` option with `ncsim` or `irun`.

To enable warning messages for all failed `randomize()` calls, use the `-RANDWARN` option.

Related topics:

- [“Using the `-svrnc` Option to Control the Solver”](#) on page 11

- [“Setting an RNG Default Seed from the Command Line”](#) on page 14

- [“Debugging Constraints with Tcl”](#) on page 86

- [“Random Constraints”](#) in the *SystemVerilog Reference*

## Using the `-svrnc` Option to Control the Solver

The `ncsim -svrnc` option controls the behavior of the solver, which evaluates constraints during simulation. It has the following arguments:

`sat_solver`

Specifies that the simulator use the SAT solver instead of the BDD solver.

`randc_max_iter=n`

In SystemVerilog, `randc` variable values are generated before the constraints are solved—with the `randc` variable values held constant. If the solver cannot find a solution for the constraints, it generates another set of `randc` variable values and tries the constraint again. The solver repeats this process until one of the following conditions is met:

- ❑ A solution is found.

- ❑ The solver reaches the maximum number of iterations, specified by `n`.

- ❑ The solver reaches the maximum number of unique values for all of the `randc` variables (default for `n`).

`fatal`

Terminates the simulation with a warning message that a `randomize()` call has failed. You might also receive warning messages that provide additional information about the cause of the failure.

For example:

- ❑ If `solve...before` constraints have a loop, the warning message identifies the specific constraints that are involved. To disable this warning, use the `-nowarn RNDSVB` command-line option.

- ❑ If a constraint can never be solved, the `RNDOVC` warning is given. For example, a constraint that contains `"a != a"` causes this warning.

- ❑ If one or more constraints cannot be solved, the `RNDOCS` warning identifies these constraints and the variables that cause the over-constrained condition.

`rng_old`

Currently, the LRM requires you to use the same default seed for each instance of a module, interface, program instance, and package. However, by default in the Cadence implementation, each initialization random number generator (RNG) is seeded with a value that is a function of both the default seed and of the hierarchical path of the instance. To use the LRM implementation, use the `-svrnc rng_old` option.

`gc_mem_limit=n`

Specifies the memory size at which randomization garbage collection starts. When the *ncsim* virtual memory footprint reaches this limit, garbage collection starts. At this time, the garbage collector identifies the least-accessed randomize call site and reclaims its allocated internal memory. If *ncsim* encounters a randomize call site whose memory has been reclaimed, it builds new data structures as needed.

The value of *n* is in megabytes, and the default value is 2000.

`gc_item_limit=n`

Specifies the minimum number of Verilog randomization calls required before starting garbage collection.

For example, when set to 5, garbage collection is not done when there are five or fewer randomize call sites in the code. When set to 0, garbage collection is based on the actual *ncsim* virtual memory footprint.

You can use this option to reduce resource contention between garbage collection and subsequent allocation of new memory.

The value of *n* is an integer, and the default is 5.

gc\_diff\_limit=*n*

When the difference between the total number of randomize calls and the number of times a randomize call has been accessed is less than this number, garbage collection is not done.

For example, the following sets *n* to 5 (10 is the default):

```

% irun -sv -svrnc gc_diff_limit=5 test.v

```

If there are 100 randomize calls in the code, the garbage collector will not reclaim memory for randomize calls that have been accessed more than 96 times.

For example, if you don't specify *n*, *ncsim* uses the default of 10:

```

% irun -sv -svrnc gc_diff_limit test.v

```

If there are 90 randomize calls in the code, the garbage collector will not reclaim memory for randomize calls that have been accessed more than 81 times.

real

Provides simple real number randomization support to match the Specman-AMS capability, for example:

```

module top;

integer success, x1;

class class1;

rand int i1, i2;

rand real r1, r2, r3;

constraint c1 { 0.0 < r1; r1 < 10.0; }

constraint c2 { 17 < r2; r2 < 213; }

constraint c3 { 1 < i1; i1 < i2; i2 < 17021; }

constraint c4 { r3 inside { [1.01:1.117] }; }

endclass

class1 p1 = new;

initial begin

for (x1 = 0; x1 < 100; x1 = x1 + 1) begin

p1.i1 = x1;

p1.i2 = x1 +1;

p1.r1 = 1.0 * x1;

p1.r2 = 1.1 * x1;

success = p1.randomize();

$display("i1 %d i2 %d r1 %e r2 %e r3 %e\n",p1.i1,p1.i2,p1.r1,p1.r2,p1.r3);

// Check the random values

if (success != 1) $display("Error0, success != 1");

if ( 0.0 >= p1.r1 || p1.r1 >= 10.0 ) $display("failed 0 < r1 < 10");

if ( 17 >= p1.r2 || p1.r2 >= 213 ) $display("failed 17 < r2 < 213");

if ( 1 >= p1.i1 || p1.i1 >= p1.i2 || p1.i2 >= 17021 )

$display("failed 1.1 < i1 < i2 < 17021");

if ( 1.01 >= p1.r3 || p1.r3 >= 1.117 )

$display("failed r3 inside [1.01,1.117]");

end

end

```

## Setting an RNG Default Seed from the Command Line

In the current release, you can define the default seed by using the `-svseed` simulation-time option. This option is an easy way to seed the RNGs everywhere in the design without making explicit calls to the built-in `srandom()` method. With this option, you can run simulations with new random number streams without recompiling and re-elaborating the design.

You can use the `-svseed` option with `ncsim` or `irun`. You provide either a 32-bit integer or the `random` keyword as an argument to the option. If you specify `random`, the simulator sets the value of the seed to a random number obtained from the current time of day and the current UNIX process ID. This algorithm ensures that multiple simulation runs submitted simultaneously have different seeds.

Calls to `srandom()` override the effect of the `-svseed` command-line option for all subsequent randomization within the thread or object. If `srandom()` is called at the beginning of the thread, the RNG for the thread is not affected by the command-line option. Similarly, if a call to an object's built-in `srandom()` method is made before the object is randomized, the RNG for the object is not affected by the command-line option.

## Using the Multi-Step Invocation Method

With the multi-step method, you compile, elaborate, and run the simulator in separate steps, as follows:

**1. Invoke *ncvlog* to compile the source files.**

When the design contains SystemVerilog, use the `-sv` option to enable the SystemVerilog constructs implemented in this release.

To make source line numbers available in SimVision for debugging, use the `-linedebug` option.

**2. Invoke *ncelab* to elaborate the design and generate a simulation snapshot.**

Use the `-access +rwc` option to make internal signals visible, so that you can trace the connectivity of the signals in your design.

**3. Invoke *ncsim* to simulate the snapshot.**

If you will be debugging the design, specify either the `-tcl` or `-gui` option:

- ❑ The `-tcl` option invokes the simulator in interactive mode and stops at time 0, so that you can enter Tcl commands.

- ❑ The `-gui` option invokes the simulator with SimVision. The simulator loads the design hierarchy into SimVision and stops at time 0, so that you can begin debugging with the SimVision tools.

For example, to compile and elaborate a design:

```

% ncvlog -sv -linedebug test.sv top.sv

% ncelab -access +rwc top

```

To simulate the design for debugging with Tcl:

```

% ncsim -tcl worklib.test:top

```

To simulate the design for debugging with SimVision:

```

% ncsim -gui worklib.test:top

```

See the *Incisive Simulator Tcl Command Reference* for information about all of the command-line options available for *ncvlog*, *ncelab*, and *ncsim*.

## Using the *irun* Utility

Cadence recommends that you use the *irun* utility to compile, elaborate, and simulate any design. The *irun* utility accepts files written in different simulation languages, such as Verilog, SystemVerilog, VHDL, Verilog AMS, VHDL AMS, and Specman e, as well as files written in general programming languages such as C and C++. Based on the file extension, it uses the appropriate compiler to compile the files. After the input files have been compiled, *irun* invokes *ncelab* to elaborate the design, and *ncsim* to run the simulator.

The *irun* utility accepts the same command-line options as *ncvlog*, *ncelab*, and *ncsim*, all on the same command line. For example, to compile, elaborate, and simulate a SystemVerilog design with *irun* for debugging in interactive mode, use the following command:

```

% irun -tcl top.v test.sv

```

The *irun* utility recognizes the `.v` file as a Verilog source file, and the `.sv` files as SystemVerilog files, so no `-sv` option is required to compile the SystemVerilog files. The `-tcl` option invokes the simulator in interactive mode and stops at time 0, so that you can enter Tcl commands.

For example, to compile, elaborate, and simulate the design with *irun* for debugging with SimVision:

```

% irun -gui -linedebug -access +rwc top.v test.sv

```

The source files are compiled with the `-linedebug` option so that source line numbers are displayed in SimVision. The *irun* utility then invokes *ncelab* to elaborate the design. The `-access` option is passed to the elaborator to provide read, write, and connectivity access to simulation objects. After the elaborator has generated a simulation snapshot, the `-gui` option is passed to *ncsim*, and the simulator is invoked with SimVision.

If you want to compile a `.v` file that contains SystemVerilog constructs, use the `-sv` option with *irun*. For example:

```

% irun -tcl -sv test.v

% irun -gui -sv -linedebug -access rwc test.v

```

See the *irun User Guide* for details on simulating with *irun*.

## Compiling a Design with Packages

Packages create order dependencies between the package and any design unit that uses the package. Packages, and the items they contain, must be defined before they can be used. That is, a package declaration must appear in a description before it can be imported.

Packages that depend on other packages in the same source file must also appear in the correct order.

Because packages must be compiled before the design units that use them, the design units that use the package must be recompiled whenever the package changes.

There are no compilation dependencies between packages and modules. <<Please explain>>

The default view name for a package is `verilog_package`. For example:

```

worklib.pack:verilog_package

```

Related topics:

- [“Accessing SystemVerilog Objects in the Design Browser” on page 23](#)

- [“Debugging Packages with Tcl” on page 106](#)

- [“Packages” in the \*SystemVerilog Reference\*](#)

## Compiling Packages with `irun`

When you use the `irun` utility, you can specify package design units in any of the following ways:

- On the command line

- In design source files

- In a library directory

- In a library file

### Specifying Packages on the Command Line

Source files that you specify on the command line typically contain the top-level modules of the design. Any source files that contain global packages must appear before source files that use the packages. If packages also have dependencies, the packages dependent on other packages must follow the packages that they depend on. For this reason, Cadence recommends that you place source files first on the command line.

For example, a design file, `repeater_dut.sv`, uses packages defined in the `repeater_pkg.v` package file. If both files reside in the current working directory, you compile them with the following command:

```

irun repeater_pkg.sv repeater_dut.sv

```

By specifying `repeater_pkg.sv` first, you ensure that the package is compiled before the design units that use the package.

### Including Packages in Design Source Files

You can use the ``include` directive to include packages in design source files. You must ``include` the package source file before you import the package or use a package item reference name.

In the following example, `repeater_pkg.sv` contains package item declarations. The design file, `repeater_dut.sv`, includes `repeater_pkg.sv` and imports the package. After that, all modules in `repeater_dut.sv` can refer to the package items.

```

// File: repeater_dut.sv

`include "repeater_pkg.sv"

import repeater_pkg::*;

module repeater_dut (input clock, input reset, cdn_idt_if.master tx_if,

cdn_idt_if.slave rx_if);

...

endmodule

// File: repeater_pkg.sv

package repeater_pkg;

...

endpackage

```

The ``include` directive ensures that the parser compiles the package design units before compiling the design units that use them. The package is compiled only once.

A single top-level design source file might contain multiple design units. If a design unit depends on another design unit, it must appear after that design unit in the source file.

### Specifying Packages in a Library Directory

A library directory can contain any number of source files, where each file describes a single design unit. Files in a library directory are named according to the following convention:

`design_unit_name.libext_suffix`

The `design_unit_name` is the name of the module, package, or other type of design unit. The `libext_suffix` is the extension for the files in the library directory.

Package source files delivered in a library directory must be compiled before the design units that use them. You can compile the package source files by including them on the command

line. You specify the file extension of the library files with the `-libext` option, and the path to the library directory with the `-y` option.

In the following example, the `-y` option specifies the relative path to the library directory. The `-libext` option specifies that all library files in that directory have the `.sv` extension:

```

irun -libext .sv -y ../../cdn_idt/sv idt_repeater.sv

```

The files in a library directory are compiled only if the definitions they contain are instantiated by other instances.

You can also `include package source files in any source file in the library directory that uses the package. This technique ensures that packages are always compiled before the design units that import them.

For example, assume that module `m` is in a library directory (`lib/m.v`), and module `m` imports package `p` (`lib/p.v`).

```

// File: lib/m.v                                // File: lib/p.v

`include "p.v"                                `ifndef p

import p::*;                                `define p

module m;                                package p;

...                                ...

endmodule                                endpackage

endif

```

**Note:** SystemVerilog package names are in a different name space than other design unit types, so a module and a package can have the same name. However, a package and a module cannot have the same name in a library directory, because the files will have the same name. For example, if you have a module `m` and a package `m`, and if the libext is `.v`, both files are called `m.v`, which is not allowed.

## Specifying Packages in a Library File

A library file is a single source file that contains many design units. Design units present in the file are compiled only if they are referenced by the design.

Packages delivered in a library file must always be the first design units encountered in the file, before any other modules in the library file. All packages in the library file are compiled as soon as *irun* starts searching the library file for a design unit. The packages are compiled once, so packages in a library file are always compiled, even if they are not used in the design. Compilation errors due to non-legal Verilog code in unused packages can be reported.

Design units in a library file can also use global packages that have been provided as top-level units on the command line.

## Compiling Packages with *ncvlog*

Package design units must be compiled before design units that use the packages. You can compile packages with *ncvlog* in any of the following ways:

- By compiling all package source files before compiling the designs that use the packages. You can compile all packages with one *ncvlog* command. For example:

```

ncvlog repeater_pkg.sv package2.sv package3.sv

```

- By placing package source files on the *ncvlog* command line before the source files that contain the design units that use the packages. For example:

```

ncvlog repeater_pkg.sv repeater_dut.sv

```

- By using the `include directive to include the package source files in the design files that use the packages, as described in [“Including Packages in Design Source Files”](#) on page 18.

Packages create a compilation dependency on their importing design units. Specifying the same package twice on the *ncvlog* command line generates an error, because it causes the design units compiled with the previous version of the package to be out-of-date. The *-update* option can also require the recompilation of out-of-date design units that use modified packages.

A package name does not need to appear on the *ncelab* command line, because packages are elaborated as a consequence of being dependent units of the importing modules. Regardless of how many *import* clauses exist for the same package, a single instance is created for that package in the design. That instance is shared by all importing design units.

## Compiling Source Files into Compilation Units

A *compilation unit* is an implicitly-named scope composed of all source files compiled at the same time. If any of the source files use the `include directive, those files are included in the compilation unit.

Compilation units are identified by the *\$unit\_#* designator, where *#* is a unique number assigned to the compilation unit. You can refer to the current compilation with the *\$unit* scope resolution operator.

For example, suppose you have the following source files, *top.sv* and *test.sv*:

```

// top.sv

// External declarations

integer a;

reg che;

wire [2:0] chetan;

```

## SystemVerilog in Simulation

### Preparing SystemVerilog Designs for Simulation

---

```

module unit;

integer a;

reg che;

reg clk = 0;

always

#2 clk = ~clk;

always @clk

i = a;

initial

begin

#0 a = 0;

#5 a = 5;

#5 a = 2;

#5 a = 6;

#5 a = 9;

#5 a = 1;

#10 $finish;

end

endmodule

integer i, j;

struct packed { bit A, B; } mem [0:1][0:1];

task t;

endtask

// test.sv

module test;

integer a;

reg clk = 0;

always

#2 clk = ~clk;

always @clk

i = a;

initial

begin

#0 a = 0;

#5 a = 5;

#5 a = 2;

#5 a = 6;

#5 a = 9;

#5 a = 1;

#10 $finish;

end

endmodule

```

The compiler creates a compilation unit that contains `a`, `che`, `chetan`, `i`, `j`, and `mem[0:1] [0:1]` when you compile the design, as follows:

```

irun test.sv top.sv

```

When you compile each source file separately, the compiler creates a separate compilation unit for each file. In this case, the declarations in each compilation-unit scope are accessible within only its corresponding file. For example:

```

irun test.sv

irun top.sv

```

The declarations in `test.sv` will not be accessible from `top.sv`. In other words, the references in `top.sv` to `a`, `che`, `chetan`, `i`, `j`, and `mem[0:1] [0:1]` will result in an error.

Related topics:

- [“Viewing Compilation Units in the Design Browser”](#) on page 25

- [“Debugging Compilation Units with Tcl”](#) on page 55

- [“Compilation Units”](#) in the *SystemVerilog Reference*

- For an example that you can download and run, refer to the example in “Disabling DPI Tasks and Functions” in the [SystemVerilog DPI Engineering Notebook](#).

---

## Accessing SystemVerilog Design Objects with SimVision

---

The SimVision Design Browser, Schematic Tracer, Source Browser, and Waveform windows support SystemVerilog constructs. In addition, the SystemVerilog Class Browser sidebar is available in the Design Browser and Source Browser windows to help you navigate a SystemVerilog class hierarchy.

Refer to [Chapter 2, “Preparing SystemVerilog Designs for Simulation,”](#) for information about how to simulate a SystemVerilog design for debugging with SimVision.

### Accessing SystemVerilog Objects in the Design Browser

The Design Browser gives you access to the objects in your design, as follows:

- The Design Browser and Design Search sidebars help you locate signals and variables within the design hierarchy.

- The signal list displays the signals and variables that you select in the Design Browser and Design Search sidebars, including the values of these objects at the current simulation time. Aggregate signals, such as structures and arrays, are displayed in the scope in which they occur.

Related topics:

- [Chapter 6, Monitoring Signal Values,](#) in the *SimVision User Guide*.

## Selecting SystemVerilog Objects with the Design Browser and Design Search Sidebars

To open the sidebars:

Click the *Design Browser* tab. Use the Design Browser sidebar to navigate the hierarchy of your design, including SystemVerilog modules, packages, compilation units, interfaces, modports, program blocks, and classes.

Click the *Design Search* tab. Use the Design Search sidebar to search the entire design, without regard to hierarchy.

The sidebars use the following icons to represent SystemVerilog constructs.

**Table 3-1 SystemVerilog Icons**

SystemVerilog interface

SystemVerilog modport

SystemVerilog program block

SystemVerilog class

SystemVerilog class specialization

SystemVerilog package

SystemVerilog structures and unions

Related topics:

- [Chapter 5, Accessing Design Objects](#), in the *SimVision User Guide*.

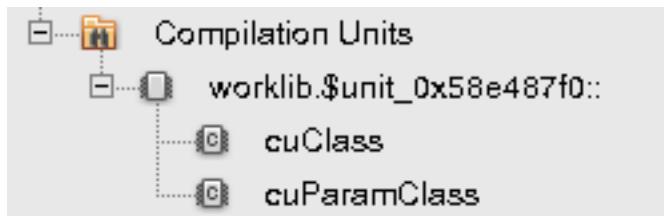

## Viewing Compilation Units in the Design Browser

The Design Browser displays compilation units in a folder labeled *Compilation Units* in the Design Browser sidebar. Each compilation unit has a name that begins with the string `$unit_`, followed by a unique number assigned to it when it is created.

To expand the list of compilation units:

1. Click the + button next to the *Compilation Units* folder to see the list of compilation units in the design.

2. Click the + button next to a `$unit_` name, if there is one, to see any scopes declared within that compilation unit's scope.

3. Click on a scope to display the objects defined within that scope in the signal list on the right side of the window.

If an object is included in several compilation units, it shows up in the signal list for each `$unit_` in which it occurs.

**Note:** If you select a particular compilation unit, any signals (non-scope objects) declared within that compilation unit scope are also displayed in the signal list.

To collapse the list of compilation units:

- Click the - button next to the scope, compilation unit, or folder.

Related topics:

- [“Compiling Source Files into Compilation Units” on page 20](#)

- [“Debugging Compilation Units with Tcl” on page 55](#)

- [“Compilation Units” in the \*SystemVerilog Reference\*](#)

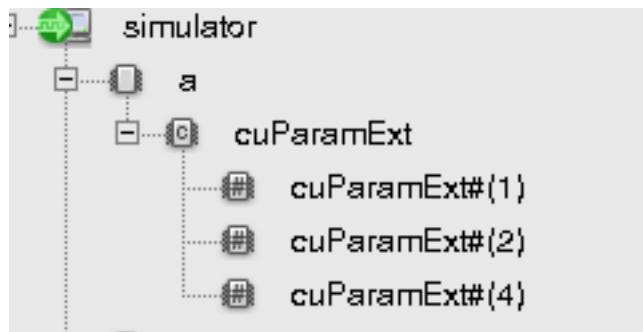

## Viewing Parameterized Classes and Class Specializations in the Design Browser

Parameterized classes can be instantiated with new parameter values. The combination of the generic class and its actual parameter values is called a *class specialization* or *variant*. The Design Browser displays parameterized class definitions in the scope list. If you click the + button next to a parameterized class name, you will see the specializations for that class. Each specialization is followed by `#(p_value)`, where *p\_value* denotes the new parameter value. For example:

```

// In file a.v

class cuClass;

...

endclass

class cuParamClass #(int count = 1) extends cuClass;

endclass

module a;

class cuParamExt #(int size = 1) extends cuParamClass #(4);

endclass

cuParamExt #(2) arraysize2; // Sets size to 2

cuParamExt #(4) arraysize4; // Sets size to 4

cuParamExt #() arrayone; // Sets size to default, which is 1

...

endmodule

```

The Design Browser shows the parameterized class called `cuParamExt` and its three specializations:

## Expanding and Collapsing SystemVerilog Aggregate Signals in the Design Browser

In the Design Browser, when you view aggregate signals, such as SystemVerilog structures and arrays, you might want to see all of its individual elements, or only the name of the object. The Design Browser provides several ways to expand and collapse aggregates.

**Note:** Queues, and dynamic and associative arrays can be expanded only when *Watch Live Data*, , is enabled.

Related topics:

- [“Expanding and Collapsing Aggregates,”](#) in the *SimVision User Guide*

- [“Splitting a Signal,”](#) in the *SimVision User Guide*

- [“Creating a Scrollable Region,”](#) in the *SimVision User Guide*

## Sorting the Elements of a Queue, or Dynamic or Associative Array

The Design Browser lets you sort the elements of a queue, or a dynamic or associative array (QDA) in either index-0-first or reverse index order.

Next to the name of a QDA, the Design Browser displays an arrow that indicates the order in which the elements of the queue or array are sorted. An up-arrow, , indicates first-to-last index order; a down-arrow, , indicates reverse order.

To change the order of elements:

- Click the arrow to change the order in which elements are sorted.

- Choose *Edit – Expand Signal – View End* or *View Top*.

- Right-click the + or - next to the object and choose *View End* or *View Top*.

For example, [Figure 3-1](#) on page 28 shows a queue in first-to-last order. The array indexes are absolute—0, 1, and so on. [Figure 3-2](#) on page 28 shows a queue displayed in reverse order. The index of the last element is referred to by the dollar sign (\$), and all other elements are referred to by their relative indexes, such as \$-1, \$-2, and so on.

**Figure 3-1 Queue Displayed in First-to-Last Order**

| Name                                                                                         | Value (as recorded) |

|----------------------------------------------------------------------------------------------|---------------------|

|  a          | 11 elements         |

|  a[0]       | 'd 0                |

|  a[1]       | 'd 1                |

|  a[2]       | 'd 2                |

|  a[3]       | 'd 3                |

|  a[4]       | 'd 4                |

|  a[5]       | 'd 5                |

|  a[6]       | 'd 6                |

|  a[7]       | 'd 7                |

|  a[8]       | 'd 8                |

|  a[9]       | 'd 9                |

|  a[10]      | 'd 10               |

|  clk        | 1                   |

|  enable    | 'd 1                |

|  myglobal | 'd 0                |

**Figure 3-2 Queue Displayed in Reverse Order**

| Name                                                                                         | Value (as recorded) |

|----------------------------------------------------------------------------------------------|---------------------|

|  a        | 11 elements         |

|  a[0]     | 'd 00               |

|  a[1]     | 'd 9                |

|  a[2]     | 'd 0                |

|  a[3]     | 'd 1                |

|  a[4]     | 'd 6                |

|  a[5]     | 'd 5                |

|  a[6]     | 'd 4                |

|  a[7]     | 'd 3                |

|  a[8]     | 'd 2                |

|  a[9]     | 'd 1                |

|  a[10]    | 'd 0                |

|  clk      | 1                   |

|  enable   | 'd 1                |

|  myglobal | 'd 0                |

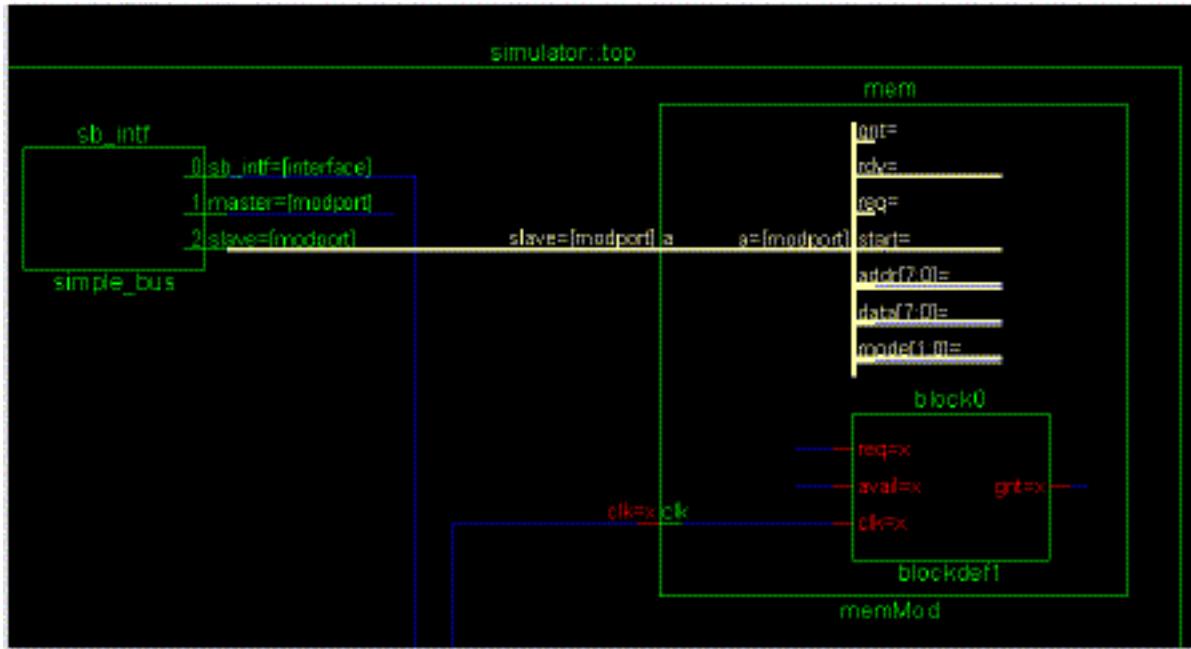

## Viewing SystemVerilog Objects in the Schematic Tracer

In the Schematic Tracer, interfaces and modports are displayed as wires labeled with the interface or `modport` name on the outer connection of the block that instantiates it. Inside the block, the wire fans out to show the ports defined in the interface or `modport`.

For example, [Figure 3-3](#) on page 29 shows a `modport` named `slave` that is instantiated in the `mem` module. It appears as a wire going into the module, and its ports are displayed within the module.

**Figure 3-3** Displaying a SystemVerilog Modport in the Schematic Tracer

Related topics:

- [Chapter 14, “Viewing a Design Schematic,”](#) in the *SimVision User Guide*

## Accessing Classes in the SystemVerilog Class Browser

You can navigate and debug a SystemVerilog class hierarchy by using the SystemVerilog Class Browser. The Class Browser is a sidebar on the Design Browser and Source Browser windows.

SimVision creates a dynamic scope for each class object. Within the dynamic scope, you can see values associated with an instance of a class object, and set instance-specific line

breakpoints in methods, or set breakpoints on value changes to local data members. When a class object no longer has any references to it, the scope is removed, and you cannot access its local data members.

The SystemVerilog Class Browser sidebar lets you browse the class hierarchy in your design. The sidebar is present in the Design Browser and Source Browser windows. The sidebar itself behaves the same in both windows, but it interacts with each window in a slightly different way:

- In the Design Browser, you use the sidebar to select the class objects you want to monitor.

- In the Source Browser, you use the sidebar to locate class definitions in the source code.

Related topics:

- [“Debugging Classes with Tcl” on page 58](#)

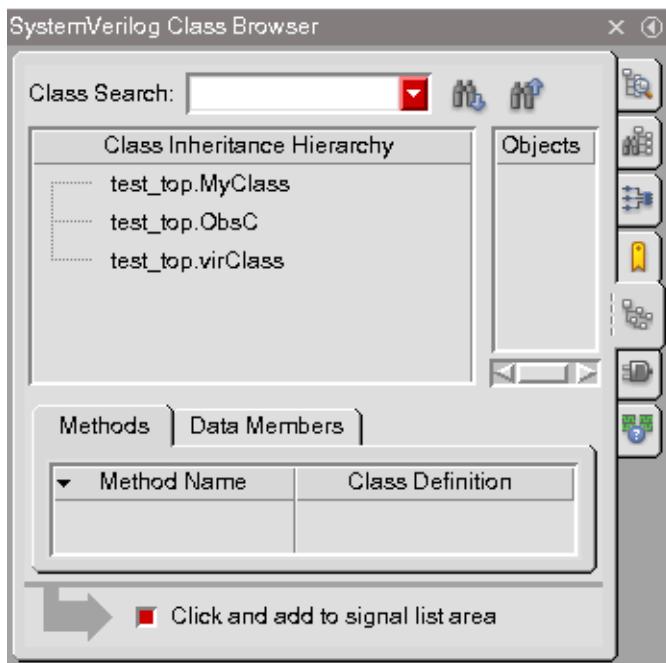

## Opening the Class Browser

To open the SystemVerilog Class Browser:

Click the *Class Hierarchy* tab in a Source Browser or Design Browser window.

*Tip*

If the sidebar is not visible, enable the *Sidebar* option in the *View* menu, then click the *Class Hierarchy* tab.

The class hierarchy is displayed in the upper region of the sidebar, as shown in [Figure 3-4](#) on page 31.

**Figure 3-4 Loading Data into the Class Hierarchy Browser**

The browser displays the class hierarchy as a tree, with subclasses indented below their parent classes. Initially, the tree is collapsed, showing only the top-level classes. The browser also displays any class specialization types, with each specialization shown separately.

To expand and collapse the hierarchy:

- Click the + and - buttons next to a class name. If these buttons do not appear next to a class name, the class has no subclasses.

After the hierarchy is loaded, the *Load* button changes to a *Class Search* field. If the class hierarchy is large, you can use this field to locate a class definition.

To search for a class definition:

- Enter a search string in the *Class Search* field, and click *Search Up*, , or *Search Down*, , to find the next or previous occurrence of the string within the hierarchy. The search function does not find occurrences of the string in subclasses that are collapsed.

The string can include any of the following special characters:

- \* Match any number of characters

- ? Match a single character

When you select a class, its class instances are listed in the *Objects* column on the right. The name displayed in the *Objects* column is the instance handle for the selected class object. If the column is empty, no instances of that class exist at the current simulation time.

The tabbed area at the bottom of the sidebar displays the methods and data members for the selected class. You can sort these tables by any column heading in ascending or descending order.

To sort the Methods and Data Members tables:

- Open the *Methods* or *Data Members* tab to display the information you want to sort.

- Click the column heading to choose the way you want to sort the information—*Method Name* or *Class Definition* in the Methods tab; *Member Name*, *Type*, or *Class Definition* for the Data Members tab.

- An arrowhead in the selected column indicates the sorting order— for ascending order;  for descending order. Click the arrowhead to reverse the order.

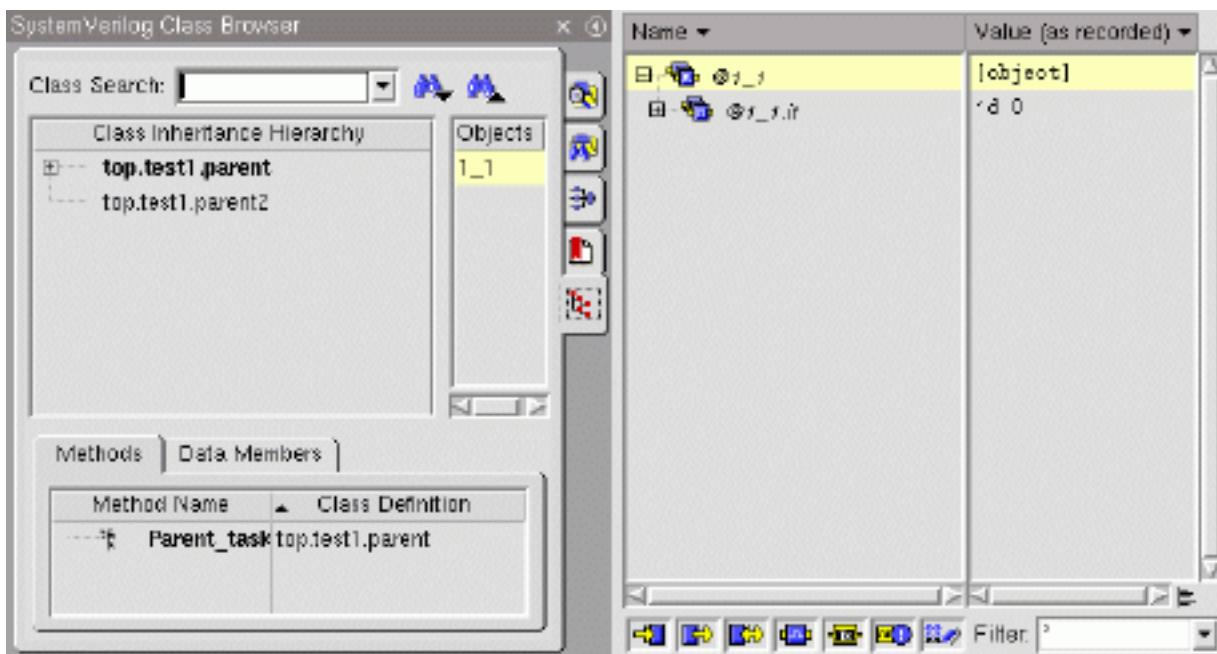

## Using the Class Browser with the Design Browser

In the Design Browser, use the sidebar to select the class objects you want to monitor, as follows:

- Select a class from the hierarchy tree, and it is added to the Design Browser signal list. Expand the class, and you can see the variables declared within the class. Because they are not instances, these variables have no value, as shown in [Figure 3-5](#) on page 33.

- Select a class instance from the *Objects* column, and the class object is added to the signal list. You can expand that object to display its local variables. Variables of class objects have a value, as shown in [Figure 3-6](#) on page 33.

- Select objects in the Methods and Data Members tables, and they are added to the signal list. The variables added to the signal list in this way have no values, because they are associated with the class definition, not the class instance.

## SystemVerilog in Simulation

### Accessing SystemVerilog Design Objects with SimVision

**Figure 3-5 Adding a Class Definition to the Signal List**

**Figure 3-6 Adding a Class Instance to the Signal List**

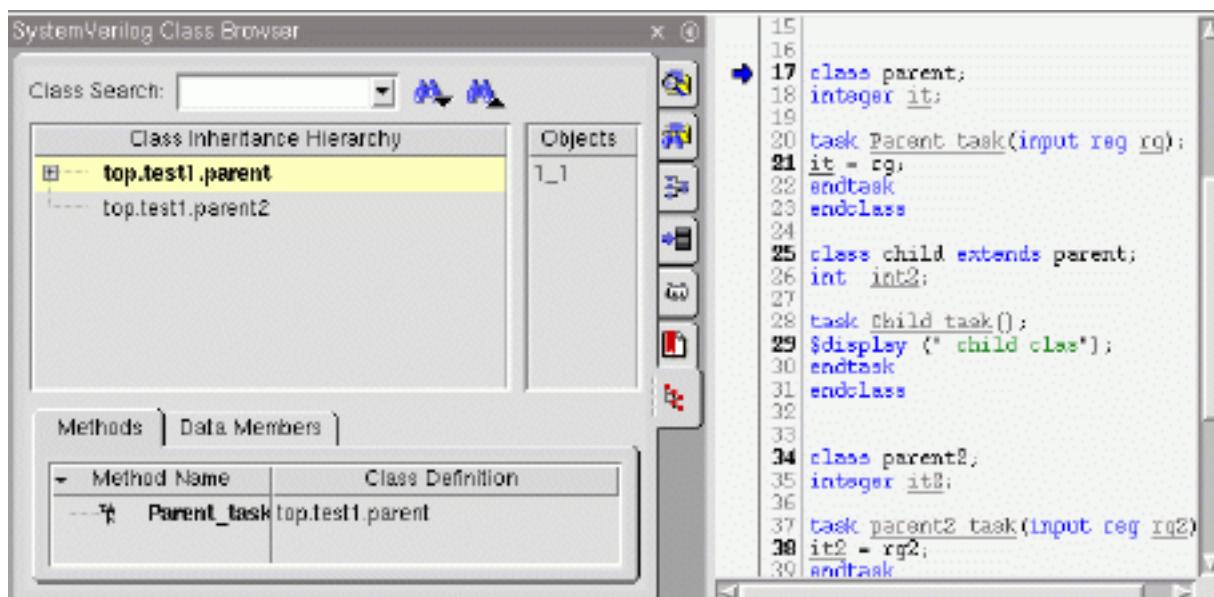

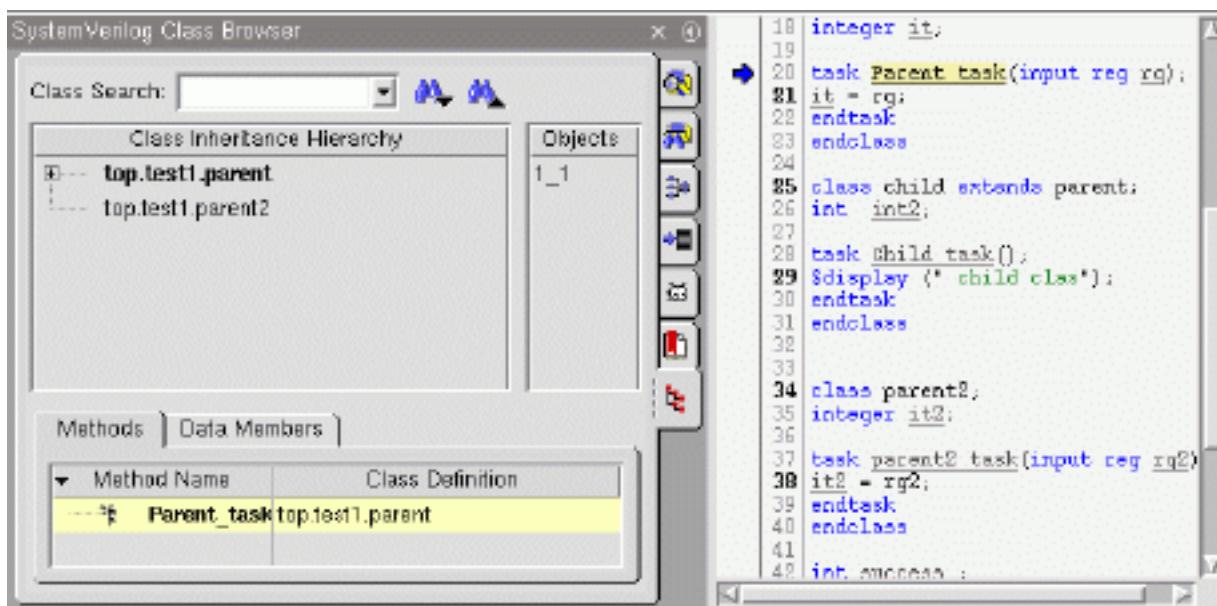

## Using the Class Browser with the Source Browser

In the Source Browser, you use the sidebar to locate class definitions in the source code, as follows:

- Select a class.

The Source Browser scrolls to the location in the source file where the class is defined, as shown in [Figure 3-7](#) on page 34.

- Select a method or data member.

The Source Browser scrolls to the location in the source file where the method or data member is defined, as shown in [Figure 3-8](#) on page 35.

**Figure 3-7 Locating a Class Definition in the Source Browser**

**Figure 3-8 Locating a Method Definition in the Source Browser**

## Viewing SystemVerilog Objects in the Waveform Window

**Note:** In this release, you cannot probe queues and dynamic arrays, so you cannot view them in the Waveform window.

When you view packed structures, packed arrays, and associative arrays in the Waveform window, you can display the entire object as a single waveform, or expand the object to see its logic elements or bits.

The Waveform window provides several ways to expand and collapse aggregates.

Related topics:

- [“Expanding and Collapsing Signals.”](#) in the *SimVision User Guide*

- [“Splitting a Signal.”](#) in the *SimVision User Guide*

- [“Creating a Scrollable Region.”](#) in the *SimVision User Guide*

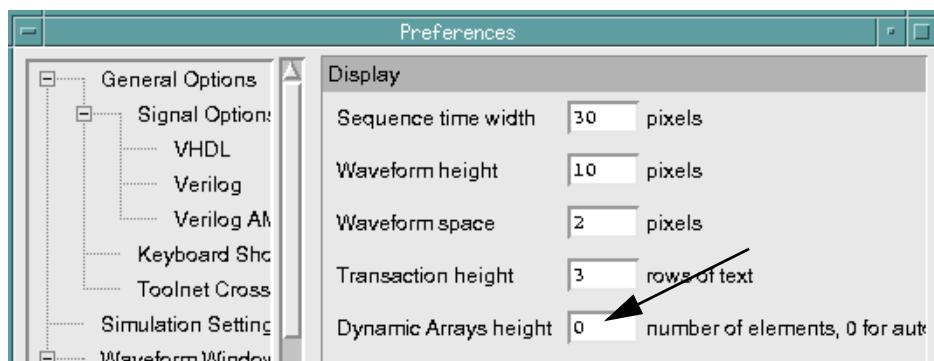

## Adjusting the Minimum Height of an Array

When an array is added to the Waveform window, it is displayed in a collapsed state—in that it displays only the minimum height. Click on + to expand the array, or use the red sizer to adjust the vertical height, as shown in the following figure:

To adjust the minimum height of dynamic arrays:

1. Go to *Edit – Preferences*.

2. Under the *Waveform window* heading, select *Display*.

3. Enter a new value for the *Dynamic Arrays height # number of elements*.

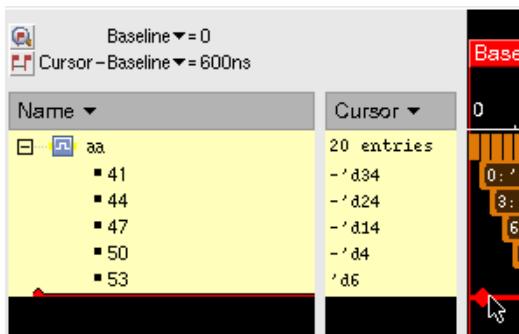

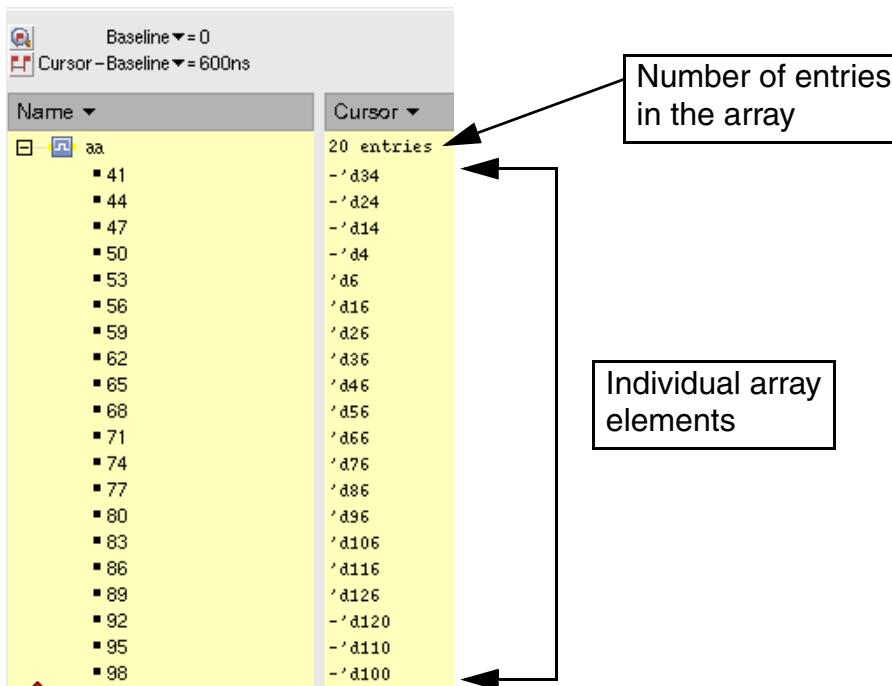

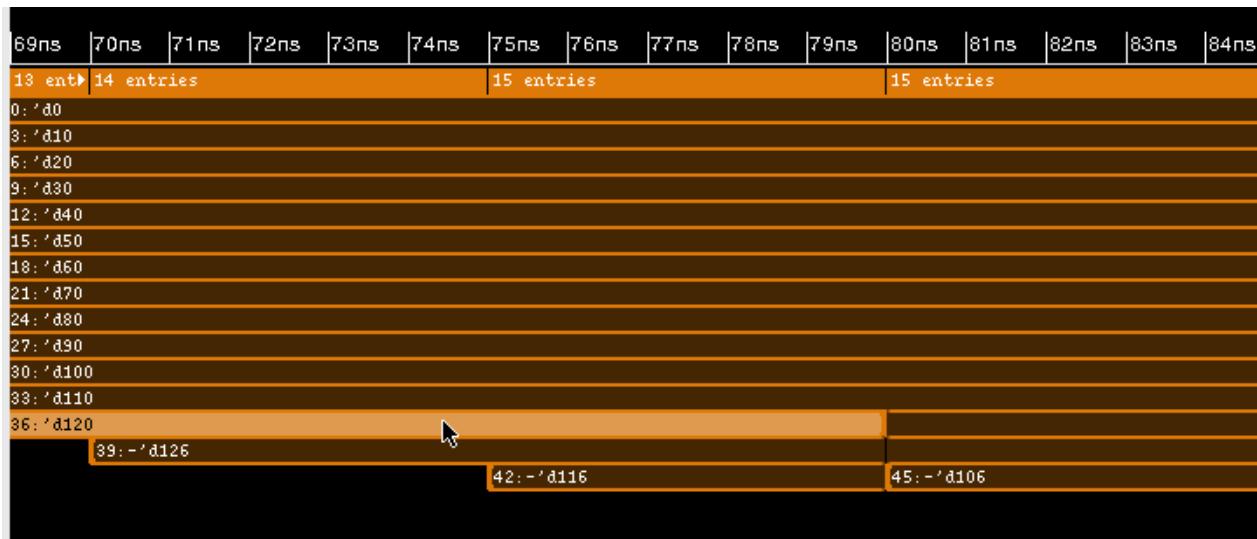

## Viewing Associative Arrays in the Waveform Window

When you expand an associative array in the Waveform window, the top row displays the number of entries in the array, and subsequent rows display the individual array elements. The order of the individual array elements is determined by the type of the index. For example, numerical indexes are in numerical order, and strings are in lexicographical order—lesser to greater. When an entry is created or deleted, the remaining entries shift up or down as needed.

## SystemVerilog in Simulation

### Accessing SystemVerilog Design Objects with SimVision

When the value of an entry changes, a transition is displayed on the corresponding row. In the following example, array `aa` has 14 entries at 70 ns. New entries, such as 42 created at 75 ns, are shown with a rounded left edge. Deleted entries, such as 36 at 80 ns, are shown with a rounded right edge.

If you move your mouse over a segment of an expanded associative array, all of the segments that correspond to that array element are highlighted, and the key and value of that segment are displayed in the status bar.

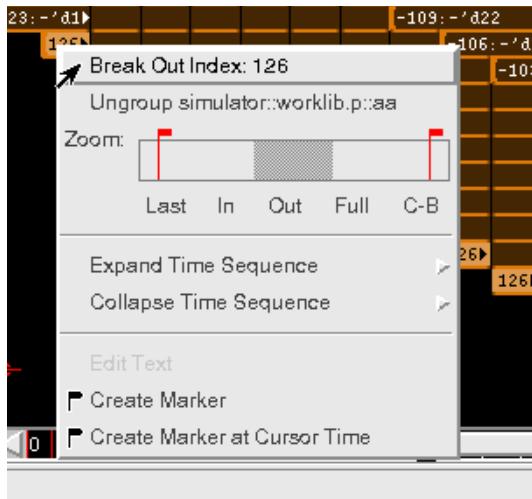

### Breaking Out Separate Waveform Traces

You cannot select an individual entry of an associative array. You can, however, break out a separate waveform trace for an array entry. To open a separate waveform trace for an

associative array entry, right click and hold on a segment, and choose *Break out Index: XXX*, where XXX displays the entry's key.

You can select and manipulate a broken-out waveform as for any other waveform. You can expand the element, search for edges on the element, and plot the element in analog form.

You can also use *Edit – Ungroup* to break out each entry of an array that exists at the time indicated by the cursor.

## Following SystemVerilog Signals in the Source Browser

When you select a SystemVerilog signal or variable in the Source Browser, you can right-click to pop up a menu of functions that you can perform on the object.

The *Follow Signal* option lets you look at the source code in other scopes where the signal appears. If your design contains SystemVerilog implicit port connections, the Source Browser displays the port connections as written—that is, with the `.*` notation.

The *Follow Signal* pop-up menu choice cannot follow these signals. However, the Schematic Tracer and the Trace Signals sidebar display them as if they were explicitly defined.

## Working with the Constraints Debugger

In SystemVerilog, constraints are used to restrict the values that can be assigned to random variables. Related constraints are often defined together in a class. When a class instance is randomized at run time, the solver within the simulator processes all of the constraints, and chooses values for the `rand` or `randc` variables that satisfy the constraints enabled at the time.

The constraint debugger offers the following features:

- Consolidated constraint viewing and manipulation

Constraints for a class instance are not always defined in one part of the source code, in the case of packages or extended classes. The constraint debugger lists all of the constraints for a class instance in one window, making it easier to view, enable, disable, and add constraints for a particular class instance.

- Overconstraint analysis

When values cannot be generated to satisfy all of the constraints, you can use the Constraint Debugger to view constraints and add local constraints that modify the constraint environment.

## Preparing Your Design for the Constraints Debugger

To make the values of random variables visible in SimVision and the Constraint Debugger, you must enable read and write access, as follows:

- Use the `-access +rw` option on the `ncelab` or `irun` command line.

The simulation must be stopped during the randomization of an instance (a `randomize()` stop). Otherwise, the Constraints Debugger will either be empty, or not reflect the true state of the system.

In the event of a `randomize` failure during simulation, SimVision automatically brings up the Constraints debugger and creates a breakpoint by issuing the `stop -randomize` simulator command. The breakpoint is created if all of the following conditions are met:

- The simulator is in interactive mode (`ncsim` run with `-tcl` or `-gui`)

- The simulator encounters a `randomize` call

- There is no `randomize` breakpoint already set

The breakpoint shows in the normal text and graphical interfaces; for example:

```

ncsim> stop -show

Randomize           Enabled           Randomize stop on failure

```

This breakpoint can be disabled as for any other breakpoint, by using `stop -enable`, `-disable`, or `-delete`, or the Simvision equivalents.

Refer to [“Stopping on Calls to randomize\(\) with Tcl”](#) on page 86 for more information about creating or operating on breakpoints on calls to `randomize()`.

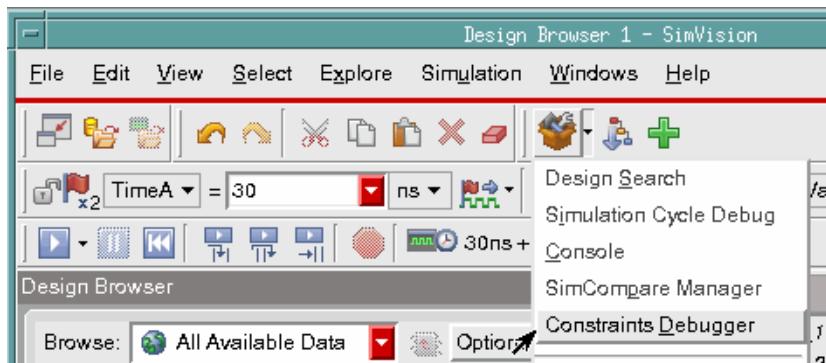

## Opening the Constraints Debugger

You can open the Constraints debugger from the menu bar or toolbox of any SimVision window, as follows:

- Choose *Constraints Debugger* from the *Windows – Tools* menu bar of any SimVision window, or from the toolbox of any SimVision window, as shown in the following figure.

**Note:** If you are not stopped during the randomization of an instance by a `randomize()` stop, the constraint window will either be empty, or will not reflect the true state of the system. Click on the button to run the simulation until the next stopping point.

Refer to [“Stopping on Calls to randomize\(\) with Tcl”](#) on page 86 for more information about creating or operating on breakpoints on calls to `randomize()`.

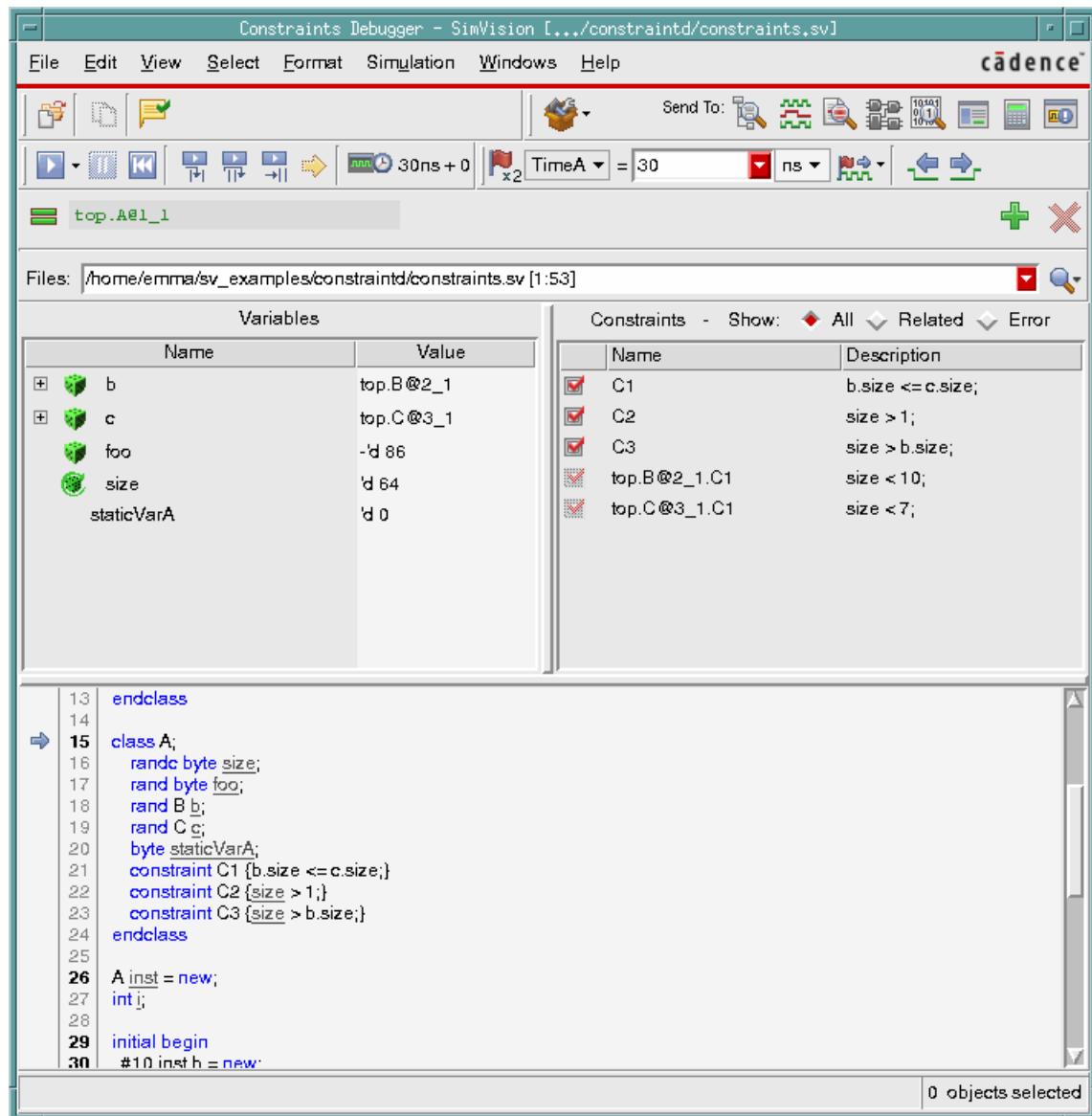

## Constraint Debugger Overview

**Figure 3-9 Constraint Window**

## Random Variables

The left side of the Constraint window lists all of the variables for the class instance being randomized, including state variables. It shows the following information:

- *Name*—Variable name

- **Value**—Value as the result of the most recent run of the solver

You can expand aggregate members, such as queues, to view its member values.

**Note:** To view variable values as inputs to constraints, see [“Displaying Variable Values as Inputs to Constraints” on page 45](#).

## Constraints

The right side of the window lists all of the constraints in the design, as follows:

- **Name**—Constraint name

- **Description**—First line of the constraint definition from the source file

**Note:** By default, the constraint window displays all of the constraints in the design. Refer to [“Displaying Constraints and Variables” on page 45](#) for information about how to control which constraints are displayed.

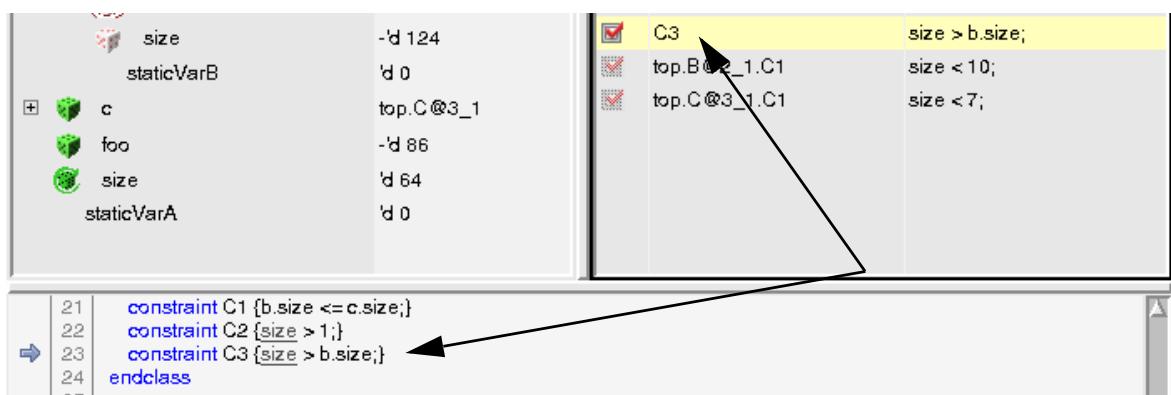

## Source Code Viewer

The bottom portion of the window shows the source code. When you select a variable or constraint, the source view region points to that particular variable or constraint definition.

## Icons for Constraints and Random Variables

Table 3-2 on page 44 describes the icons for variables and constraints.

**Table 3-2 Icons for Constraints and Random Variables**

|                                                                                     |                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Enabled <code>rand</code> variable                                                                                                                                                                                                    |

|    | Enabled <code>randc</code> variable                                                                                                                                                                                                   |

|    | Disabled <code>rand</code> or <code>randc</code> variable                                                                                                                                                                             |

|                                                                                     | A random variable that has been disabled is treated as a state variable. It is not randomized by the <code>randomize()</code> method, and random values are not assigned to it during a <code>randomize()</code> call.                |

|    | Indicates that the <code>rand</code> variable is enabled, but is not local to this <code>randomize()</code> instance, so it cannot be enabled or disabled within the Constraint Debugger                                              |

|    | Indicates that the <code>randc</code> variable is enabled, but is not local to this <code>randomize()</code> instance; therefore, it cannot be enabled/disabled within the Constraint Debugger.                                       |

|  | Enabled constraint                                                                                                                                                                                                                    |

|  | Indicates that the constraint either <ul style="list-style-type: none"><li>■ Is not local to this <code>randomize()</code> instance, and cannot be enabled or disabled</li><li>■ Was created within the constraint debugger</li></ul> |

|  | Constraint is disabled                                                                                                                                                                                                                |

|                                                                                     | Constraints that are disabled are not considered by the <code>randomize()</code> method.                                                                                                                                              |

## Displaying Variable Values as Inputs to Constraints

Use the  value annotation button to update the source code so that it displays the current variable values as inputs to the constraints.

```

1 module top;

2 class B;

3     rand byte size;

4     randc byte bar;

5     byte staticVarB;

6     constraint C1 {size < 10;}

7 endclass

8

```

## Displaying Constraints and Variables

By default, the constraint window displays all of the constraints in the design. Use the following radio buttons to control which constraints are displayed:

- All—Displays all of the constraints related to the class instance.

- Related—When a variable is selected on the left side of the Constraint Debugger, this button hides all constraints that are not related to that variable.

- Error—Displays the constraints that the solver thinks are involved in an overconstraint.

## Enabling and Disabling Random Variables

Each random variable has a button that you can toggle to enable or disable that variable through the `rand_mode()` method.

### Notes

- If a random variable is static, the `rand_mode()` setting affects all instances of the variables of the base class.

- Individual array elements cannot be enabled or disabled.

## Enabling and Disabling Constraints

Each constraint has a button that you can toggle to enable or disable a constraint through the `constraint_mode()` method.

**Notes:**

- If a constraint is static, the `constraint_mode()` setting affects the constraint in all instances of the class for which it is declared.

- The constraint debugger supports inline constraints, but these constraints cannot be enabled or disabled.

## Creating a Constraint

To add a constraint:

1. Click on the  button.

If you want to add a variable to the constraint, select the variable to add from the left pane, then click on the  button.

This creates a new constraint entry and assigns a default constraint name.

2. Optionally, you can edit the constraint expression of a simple constraint.

A simple constraint contains:

- Simple variables (unsigned integers or variables). If they are variables, they must be random variables declared in the class of the current `randomize()` call; they cannot use hierarchical references.

- One of the following operators: `==`, `!=`, `>`, `>=`, `<`, or `<=`

For example:

```

constraint int1==200

```

3. Hit the Return key to add the new constraint, or the Esc key to remove the constraint.

The window is updated to reflect the new state of the class instance.

**Notes:**

- If you enter an invalid constraint expression, the simulator issues an error message but does not remove the constraint, so that you can edit the constraint expression.

- To remove the constraint, click the  button. The  button disables ALL locally created constraints. Locally created constraints cannot be re-enabled.

- The constraint is persistent, in that it remains in effect even after you complete the `randomize()` debugging session.

## Running the Current Randomize Call Again

Use the  button when you want to execute the current `randomize()` call again. The simulator uses the currently enabled constraints and variables, and the current state variable values. The  button runs only a single call to randomize—it does not continue running the simulation.

## Handling Overconstraints

If some constraints are overly restrictive, in that some random values cannot be satisfied, the solver issues an overconstrained message and aborts the randomization attempt.

To debug the overconstraint, you can either disable one or more constraints (see [“Enabling and Disabling Constraints”](#) on page 45) or add a simple constraint (see [“Creating a Constraint”](#) on page 46), then re-run the randomize call (see [“Running the Current Randomize Call Again”](#) on page 47).

## Viewing Dynamic Objects with the SimVision Data Browser

The SystemVerilog Data Browser lets you view SystemVerilog dynamic objects, such as classes, queues, and dynamic arrays. The Data Browser displays dynamic objects hierarchically, based on their location in the design. This merged hierarchical view is particularly useful in designs that are based on OVM, where the structure of the verification hierarchy is represented through the use of class-based dynamic objects.

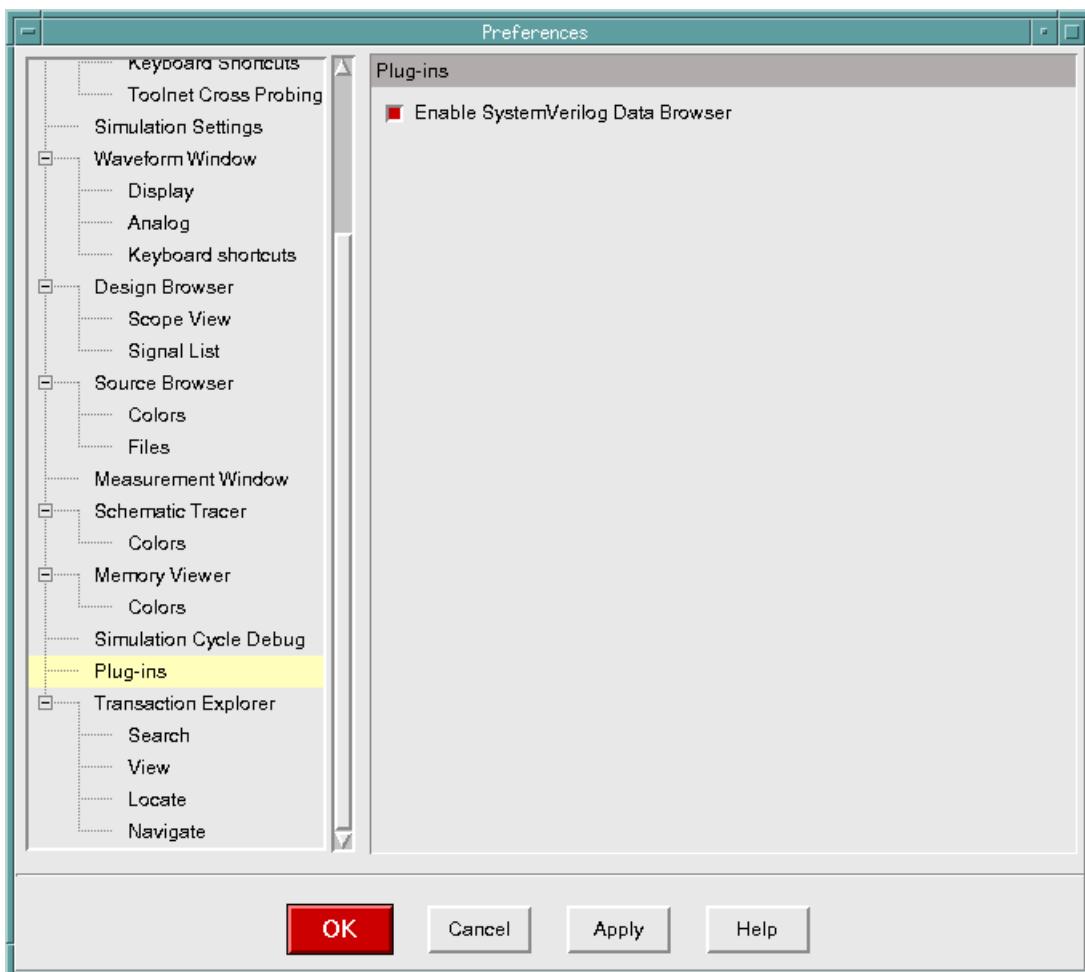

## Setting Up the Data Browser

To make the Data Browser available in the SimVision session:

1. Choose *Edit – Preferences* from the Design Browser.

## SystemVerilog in Simulation

### Accessing SystemVerilog Design Objects with SimVision

2. Under *Plug-ins*, choose *Enable SystemVerilog Data Browser*.

## Preparing Your Design for the Data Browser

You must enable line debugging and read access to make the values of dynamic objects visible in SimVision and the Data Browser.

To enable line debugging:

- Use the `-linedebug` option on the `ncvlog` or `irun` command line.

To enable read access:

- Use the `-access r` option on the `ncelab` or `irun` command line.

## Opening Data Browser Windows

As for other SimVision windows, you can open any number of Data Browser windows, and the first one you open is the target, or default Data Browser window. You can make any Data Browser the target by enabling the *Target* button, , in the lower left corner of the window.

To open a Data Browser window:

- Choose *Windows – New – SystemVerilog Data Browser* from the menu in any SimVision window. The Data Browser opens and displays information about all dynamic objects in the design.

- Click *Data Browser*, , in the Source Browser toolbar. If you have selected a class object in the Source Browser or the Class Browser sidebar, the Data Browser opens and displays information about that class object. If no class object is selected, but the debug scope is within a class object, the Data Browser displays information about that class object. Otherwise, the Data Browser displays information about all dynamic objects in the design.

The *Data Browser* button sends selected objects to the target window. To send objects to a new window, disable the *Target* button in the target Data Browser window.

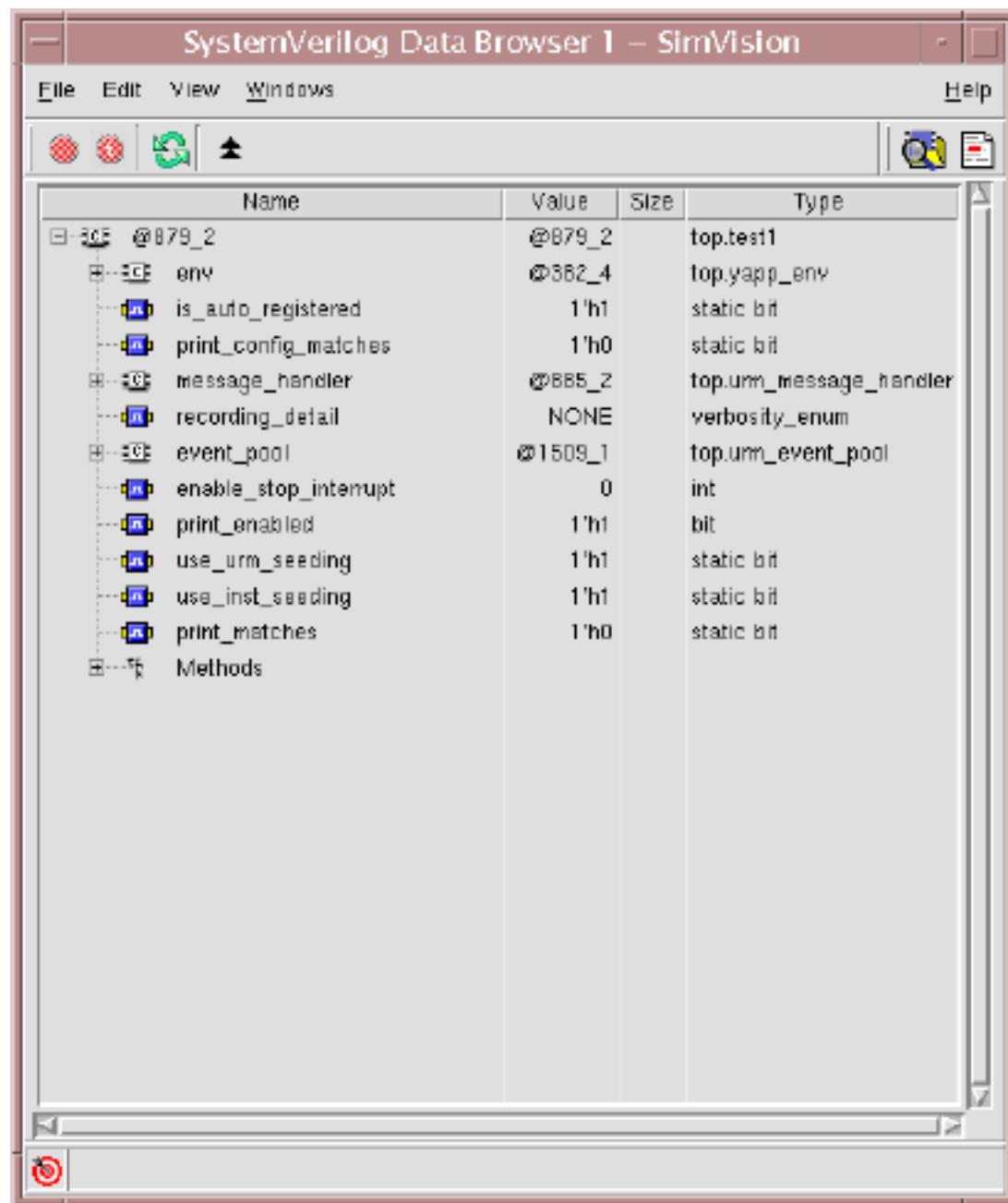

Figure 3-10 on page 50 shows a Data Browser window that contains a class object.

## SystemVerilog in Simulation

### Accessing SystemVerilog Design Objects with SimVision

**Figure 3-10 Data Browser Window**

For each object, the Data Browser displays the following information:

- **Name**—Either the path to a SystemVerilog dynamic object or a class handle.

**Note:** Class constraints are not displayed in the Data Browser.

- *Value*—The class instance handle or the value of each data member or array element at the current simulation time.

- *Size*—The size of queues and arrays; otherwise blank.

- *Type*—The class object type. For class data members, this column includes additional information, such as whether the variable was randomized or protected.

The information in the table is similar to what the `describe` command returns.

To issue a `describe` command from the Data Browser:

- Right-click an object in the Data Browser and choose *Describe* from the pop-up menu. The output from the `describe` command is displayed in the *simulator* tab of the Console window.

## Expanding and Collapsing a Dynamic Object

Non-null class objects, queues, and arrays can reference other SystemVerilog dynamic objects, which can then be expanded in the Data Browser. The hierarchy for a queue or array contains its elements. The hierarchy for a class object contains its data members, functions, and tasks. Tasks and functions are listed under a pseudo-hierarchy, labeled *Methods*.

To expand or collapse an object:

- Click the + or - button next to the object name.

- Right-click the object and choose *Expand All* or *Collapse All* from the pop-up menu.

- Select the object and choose *View – Expand All* or *View – Collapse All* from the Data Browser menu.

## Refreshing the Data Browser Contents

The contents of Data Browser windows are automatically updated whenever the simulator goes into an idle state, such as at a breakpoint. You can explicitly refresh the windows at any time. For example, you might want to refresh the windows

- When you perform a simulation reset or other operation that does not trigger an automatic refresh.

- When the design is large. The contents of the Data Browser window might be cut short when the data exceeds the limit for the number of lines kept in the Console window. By default, the limit is 5000 lines. You can increase this limit by going to the General Options

tab of the Preference window and increasing the *Maximum number of lines kept in console*.

- When spurious output from the Console window appears in the Data Browser. Sometimes, messages from the Console are inadvertently written to the Data Browser. A refresh removes these messages.

To refresh the Data Browser contents:

- Click *Refresh*, .

## Setting Breakpoints on Dynamic Objects

To set a breakpoint on a dynamic object:

- Select an object and click  to set a breakpoint on a task or function of a class. The breakpoint is triggered on any instance of that class.

- Select an object and click  to set a breakpoint on a task or function of a specific class instance.

## Displaying Dynamic Objects for the Full Design

To display dynamic objects for the full design:

- Click .

This button is useful when you are viewing a single class object and want to add dynamic objects for the full design, or when you have expanded a hierarchy by many levels and want to quickly return to the top.

## Sending Dynamic Objects to the Design Browser

To send dynamic objects to the Design Browser:

- Select the object and click *Send to Design Browser*, .

- Right-click the object and choose *Send to Design Browser* from the pop-up menu.

The Design Browser adds the object and its containing class to the signal list, if they are not already there, and selects the object.

## Viewing Dynamic Objects in the Source Browser

To view a dynamic object definition in the Source Browser

- Select the object and click *Send to Source Browser*, .

- Right-click the object and choose *Send to Source Browser* from the pop-up menu.

To view a class handle declaration in the Source Browser

- Right-click the object and choose *Send to Source Browser (handle declaration)* from the pop-up menu.

## Sending Dynamic Objects to a New Data Browser Window

To send an object to a new Data Browser window:

- Right-click and choose *Send to new Data Browser* from the pop-up menu.

This technique is useful when you have isolated a dynamic object that you want to observe.

## Setting the Debug Scope in the Data Browser

To set the simulator debug scope:

- Right-click a scope or class object and choose *Set Debug Scope* from the pop-up menu.

## Copying a Dynamic Object

To copy a dynamic object

- Right-click the object and choose *Copy* from the pop-up menu.

- Select the object and choose *Edit – Copy* from the Data Browser menu.

You can paste the object into another SimVision window, or paste the full path of the object as text into a text-based window, such as an xterm window.

**SystemVerilog in Simulation**

Accessing SystemVerilog Design Objects with SimVision

---

---