# Analog Integrated Circuits

## Chapman & Hall Solid State Science and Engineering Series Michael N. Kozicki, Series Editor

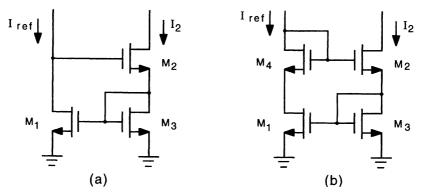

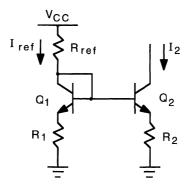

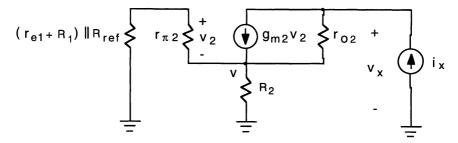

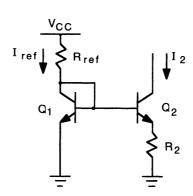

Arizona State University

Analog Integrated Circuits, by Edwin W. Greeneich

Handbook of Experimental Methods for Process Improvement, by David Drain

Statistical Methods for Industrial Process Control, by David Drain

#### JOIN US ON THE INTERNET WWW: http://www.thomson.com EMAIL: findit@kiosk.thomson.com

thomson.com is the on-line portal for the products, services and resources available from International Thomson Publishing (ITP). This Internet kinds gives users immediate access to more than 34 ITP publishers and over 20,000 products. Through thomson.com Internet users can search catalogs, examine subject-specific resource centers and subscribe to electronic discussion lists. You can purchase ITP products from your local bookseller, or directly through thomson.com.

Visit Chapman & Hall's Internet Resource Center for information on our new publications, links to useful sites on the World Wide Web and the opportunity to join our e-mail mailing list. Point your browser to: http://www.chaphall.com/chaphall.html or http://www.chaphall.com/chaphall/for Electrical Engineering

A service of INT

# Analog Integrated Circuits

## Edwin W. Greeneich

Associate Professor Department of Electrical Engineering Arizona State University

Cover design: Trudi Gershenov Cover photo: @ 1997 PhotoDisc, Inc. Copyright © 1997 by Chapman & Hall

For more information, contact:

Chapman & Hall 115 Fifth Avenue

New York, NY 10003

Thomas Nelson Australia 102 Dodds Street

South Melbourne, 3205 Victoria, Australia

International Thomson Editores

Campos Eliseos 385, Piso 7 Col. Polanco

11560 Mexico D. F. Mexico

International Thomson Publishing Asia

221 Henderson Road #05-10

Henderson Building

Singapore 0315

All rights reserved. No part of this book covered by the copyright hereon may be reproduced or used in any form or by any means—graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems — without the written permission of the publisher.

Japan

Chapman & Hall

2-6 Boundary Row London SE1 8HN England

Postfach 100 263 D-69442 Weinheim

Germany

Chapman & Hall GmbH

1-2-1 Hirakawacho-cho

Chiyoda-ku, 102 Tokyo

International Thomson Publishing - Japan

Hirakawacho-cho Kyowa Building, 3F

2 3 4 5 6 7 8 9 10 XXX 01 00 99 98 97

#### Library of Congress Cataloging-in-Publication Data

Greeneich, Edwin W., 1941-

Analog integrated circuits / Edwin W. Greeneich.

p. cm. Includes index.

ISBN 0-412-08521-6 (alk. paper)

. Title. 1. Linear integrated circuits.

TK7874.G715 1996

621.3815--dc20 96-26747

To order this or any other Chapman & Hall book, please contact International Thomson Publishing, **7625 Empire Drive, Florence, KY 41042.** Phone: (606) 525-6600 or 1-800-842-3636.

Fax: (606) 525-7778. e-mail: order@chaphall.com.

For a complete listing of Chapman & Hall's titles, send your request to Chapman & Hall, Dept. BC, 115 Fifth Avenue, New York, NY 10003.

# **CONTENTS**

|    |       |                                                              | Page |

|----|-------|--------------------------------------------------------------|------|

| Pr | eface |                                                              | ix   |

| 1  | Mod   | dels for Integrated-Circuit Devices                          | 1    |

|    | 1.1   | Bipolar Junction Transistor                                  | 1    |

|    |       | Ebers-Moll Static Model                                      | 2    |

|    |       | Ebers-Moll Dynamic Model                                     | 9    |

|    |       | Base-Width Modulation                                        | 10   |

|    |       | Small-Signal Models of Bipolar Junction Transistors          | 14   |

|    |       | Parasitic Elements in Integrated-Circuit Bipolar Transistors | 17   |

|    |       | Transistor Cutoff Frequency                                  | 18   |

|    | 1.2   | Junction Diode                                               | 22   |

|    | 1.3   | Junction Field-Effect Transistor                             | 23   |

|    |       | Device Characteristics                                       | 24   |

|    |       | Large-Signal Model                                           | 28   |

|    |       | Large-Signal Dynamic Model of the JFET                       | 30   |

|    |       | Small-Signal Model of the JFET                               | 31   |

|    |       | Parasitic Elements in Integrated-Circuit JFETs               | 32   |

|    |       | Transistor Cutoff Frequency                                  | 33   |

|    | 1.4   | Metal-Oxide-Semiconductor Field-Effect Transistor            | 35   |

|    |       | Device Characteristics                                       | 35   |

|    |       | MOSFET Capacitance                                           | 40   |

|    |       | Small-Signal Model of the MOSFET                             | 42   |

|    |       | Transistor Cutoff Frequency                                  | 43   |

|    |       | Problems                                                     | 44   |

|    |       | References                                                   | 47   |

| 2  | Ana   | log Integrated-Circuit Blocks                                | 49   |

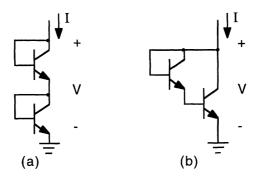

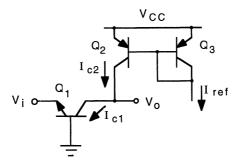

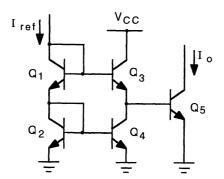

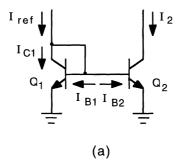

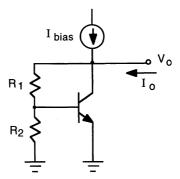

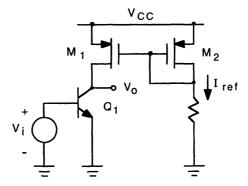

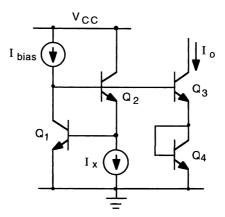

|    | 2.1   | Current Sources                                              | 50   |

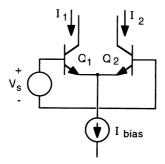

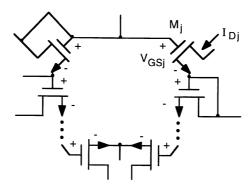

|    |       | Basic Current Mirror                                         | 50   |

|    |       | Base-Current Compensated Current Mirror                      | 54   |

|    |       | Cascode Current Source                                       | 55   |

vi Contents

|   |     | Wilson Current Source                              | 58  |

|---|-----|----------------------------------------------------|-----|

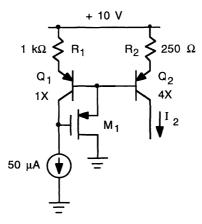

|   |     | Resistor-Ratioed Current Source                    | 61  |

|   |     | Widlar Current Source                              | 64  |

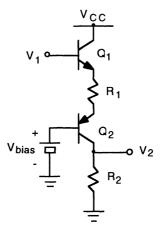

|   | 2.2 | DC Level-Shift Stages                              | 65  |

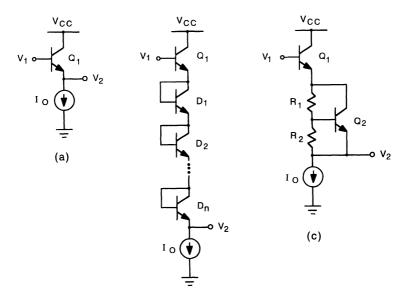

|   |     | V <sub>BE</sub> Voltage Shift Stages               | 65  |

|   |     | Cascade Emitter Follower Level-Shift Stage         | 67  |

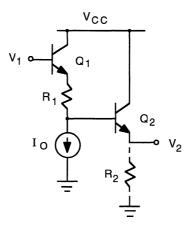

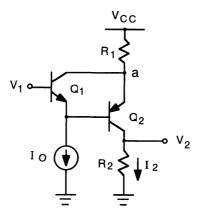

|   |     | Composite npn-pnp Level-Shift Stage                | 67  |

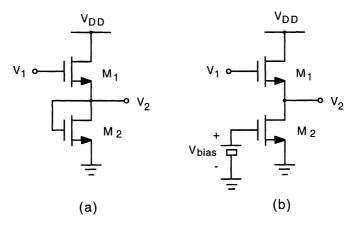

|   |     | MOS Level-Shift Stages                             | 68  |

|   | 2.3 | Single-Transistor Gain Stages                      | 69  |

|   |     | Common-Emitter Gain Stages                         | 70  |

|   |     | Common-Emitter Gain Stage with Resistive Load      | 72  |

|   |     | Common-Emitter Gain Stage with Active Load         | 74  |

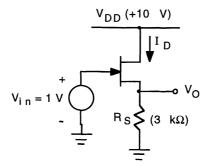

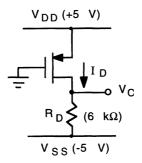

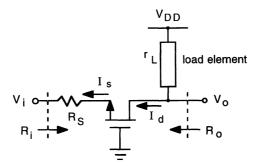

|   |     | Common-Source Gain Stage with Resistive Load       | 77  |

|   |     | Common-Source Gain Stage with Active Load          | 80  |

|   |     | Common-Collector (Emitter Follower) Gain Stage     | 82  |

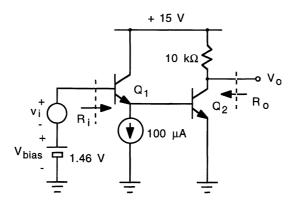

|   |     | Emitter Follower Stage with Active Load            | 87  |

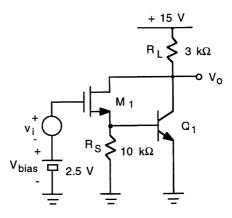

|   |     | Common-Drain (Source Follower) Gain Stage          | 87  |

|   |     | Source Follower with Active Load                   | 89  |

|   |     | Common-Base Gain Stages                            | 89  |

|   |     | Common-Base Gain Stage with Resistive Load         | 92  |

|   |     | Common-Base Stage with Active Load                 | 95  |

|   |     | Common-Gate Gain Stage                             | 96  |

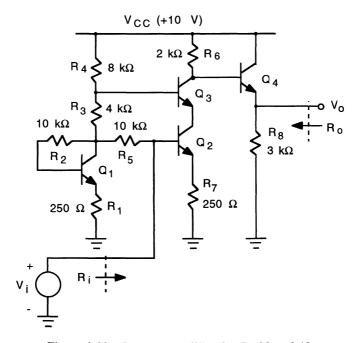

|   | 2.4 | Two-Transistor Gain Stages                         | 97  |

|   |     | Cascode Configuration                              | 97  |

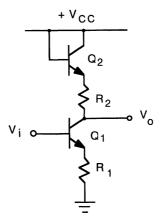

|   |     | Cascade Configuration                              | 100 |

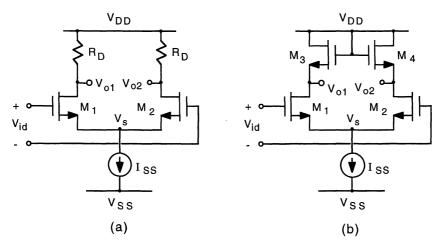

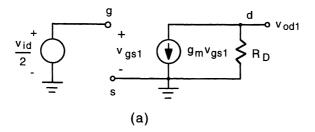

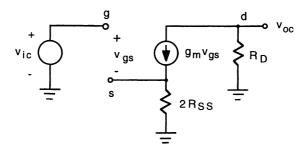

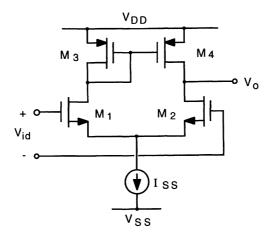

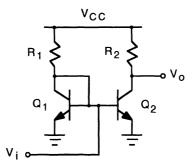

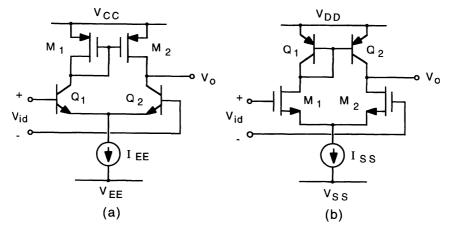

|   |     | Differential-Pair Configuration                    | 110 |

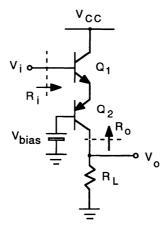

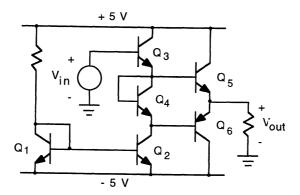

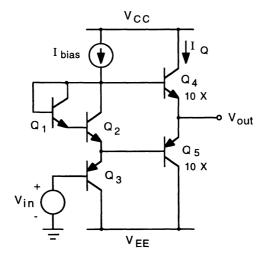

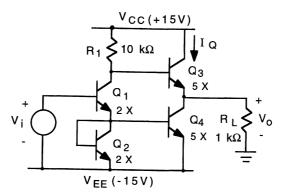

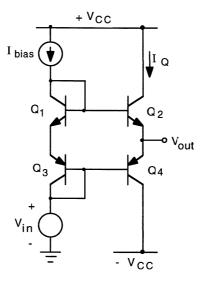

|   | 2.5 | Output Stages                                      | 132 |

|   |     | Emitter Follower and Source Follower Output Stages | 133 |

|   |     | Complementary Output Stages                        | 136 |

|   |     | Problems                                           | 142 |

|   |     | References                                         | 156 |

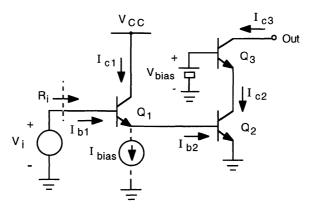

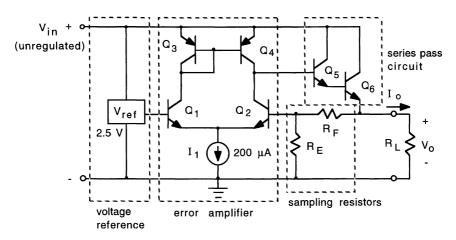

| 3 | Ope | rational Amplifiers                                | 157 |

|   | 3.1 | Voltage-Feedback Amplifiers                        | 157 |

|   |     | Single-Stage Op-Amp                                | 159 |

|   |     | Two-Stage Op-Amp                                   | 162 |

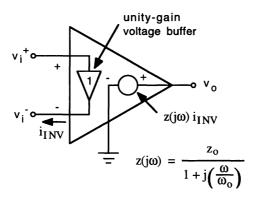

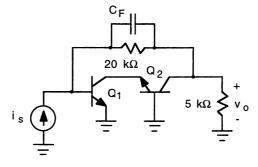

|   | 3.2 | Current-Feedback Amplifiers                        | 172 |

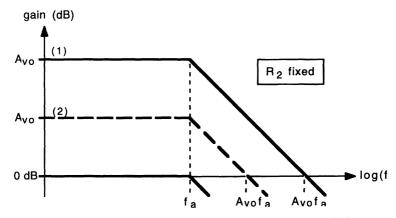

|   |     | Transimpedance                                     | 176 |

|   |     | Slew Rate                                          | 177 |

|   | 3.3 | Current-Differencing Amplifers                     | 178 |

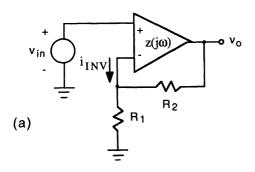

|   |     | Inverting Amplifier                                | 181 |

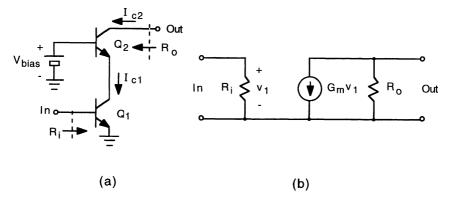

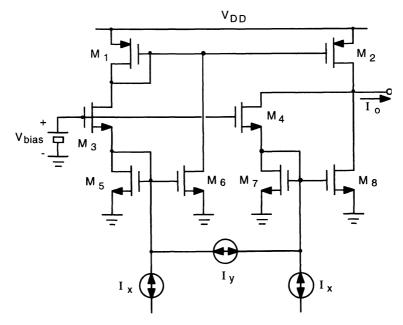

|   | 3.4 | Transconductance Amplifiers                        | 183 |

|   |      | Contents                                          | vii |

|---|------|---------------------------------------------------|-----|

|   |      | Linearization                                     | 186 |

|   |      | Applications                                      | 188 |

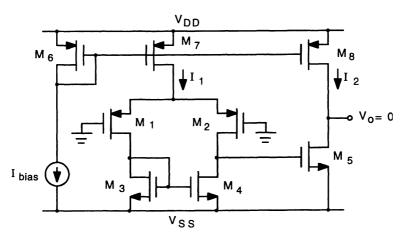

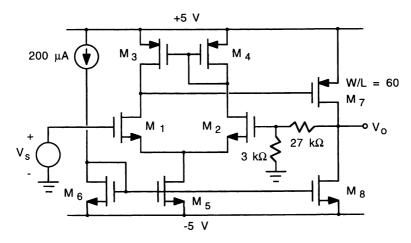

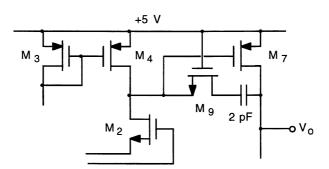

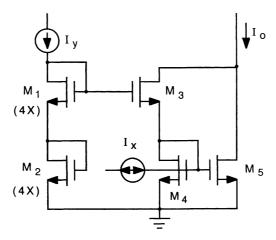

|   |      | CMOS Transconductance Amplifier                   | 191 |

|   |      | Problems                                          | 194 |

|   |      | References                                        | 201 |

| 4 | Feed | lback and Compensation of Feedback Amplifiers     | 203 |

|   | 4.1  | Basic Feedback Concepts                           | 203 |

|   |      | Gain Stabilization                                | 204 |

|   |      | Reduction in Distortion                           | 205 |

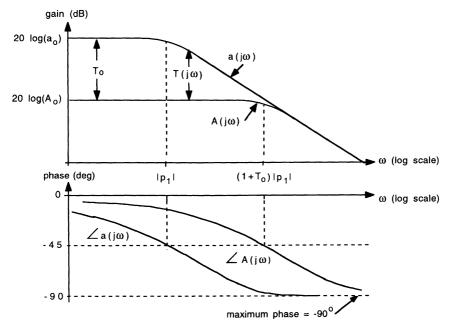

|   |      | Increased Bandwidth                               | 206 |

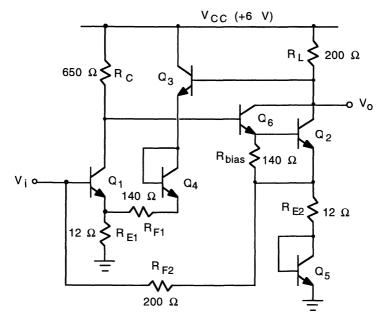

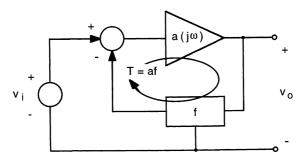

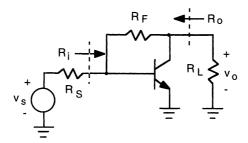

|   | 4.2  | Feedback Circuit Example                          | 208 |

|   |      | Input Resistance                                  | 211 |

|   |      | Output Resistance                                 | 212 |

|   | 4.3  | Feedback Configurations                           | 213 |

|   |      | Series Voltage                                    | 215 |

|   |      | Shunt Voltage                                     | 223 |

|   |      | Series Current                                    | 230 |

|   |      | Shunt Current                                     | 239 |

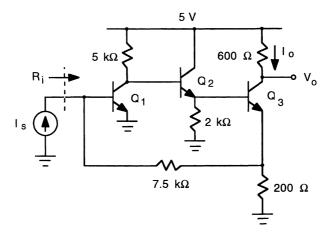

|   | 4.4  | Dual-Loop Feedback                                | 244 |

|   |      | Series Current-Shunt Voltage                      | 247 |

|   |      | Series Voltage-Shunt Current                      | 258 |

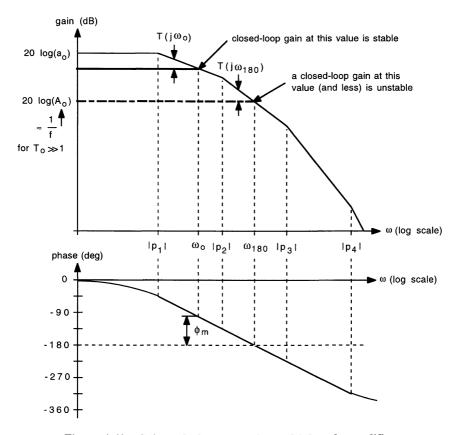

|   | 4.5  | Stability of Feedback Amplifiers                  | 264 |

|   |      | Gain and Phase Relationship                       | 264 |

|   | 4.6  | Compensation of Feedback Amplifiers               | 270 |

|   |      | Compensation Methods                              | 271 |

|   |      | Problems                                          | 284 |

|   |      | References                                        | 294 |

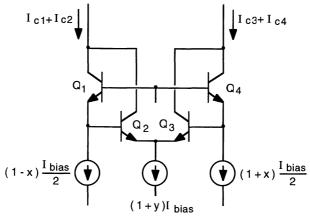

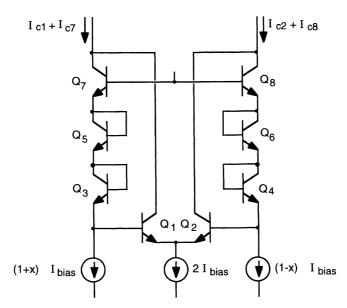

| 5 | Tra  | nslinear Circuits                                 | 295 |

|   | 5.1  | Translinear Circuit Classes                       | 295 |

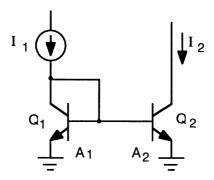

|   |      | Transconductance Linear with Current              | 295 |

|   |      | Transconductance Linear with Voltage              | 302 |

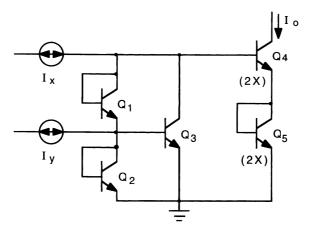

|   | 5.2  | Analog Functions with Translinear Circuits        | 305 |

|   |      | Vector Magnitude                                  | 305 |

|   |      | Two-Quadrant Squarer                              | 306 |

|   |      | Absolute Value                                    | 308 |

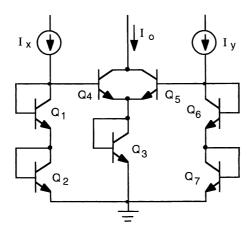

|   |      | Analog Multipliers                                | 309 |

|   | 5.3  | Trigonometric Functions with Translinear Circuits | 322 |

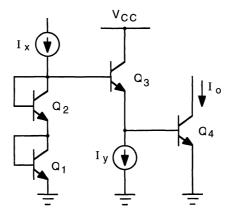

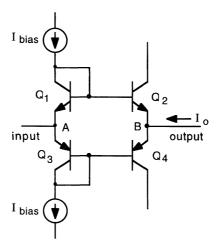

|   | 5.4  | Gilbert Gain Cell                                 | 327 |

|   |      | Problems                                          | 328 |

|   |      | References                                        | 335 |

|   | Ind  | ex                                                | 337 |

## **PREFACE**

Analog Integrated Circuits deals with the design and analysis of modern analog circuits using integrated bipolar and field-effect transistor technologies. This book is suitable as a text for a one-semester course for senior level or first-year graduate students as well as a reference work for practicing engineers. Advanced students will also find the text useful in that some of the material presented here is not covered in many first courses on analog circuits. Included in this is an extensive coverage of feedback amplifiers, current-mode circuits, and translinear circuits. Suitable background would be fundamental courses in electronic circuits and semiconductor devices.

This book contains numerous examples, many of which include commercial analog circuits. End-of-chapter problems are given, many illustrating practical circuits.

Chapter 1 discuses the models commonly used to represent devices used in modern analog integrated circuits. Presented are models for bipolar junction transistors, junction diodes, junction field-effect transistors, and metal-oxide-semiconductor field-effect transistors. Both large-signal and small-signal models are developed as well as their implementation in the SPICE circuit-simulation program.

The basic building blocks used in a large variety of analog circuits are analyzed in Chapter 2; these consist of current sources, dc level-shift stages, single-transistor gain stages, two-transistor gain stages, and output stages. Both bipolar and field-effect transistor implementations are presented.

Chapter 3 deals with operational amplifier circuits. The four basic op-amp circuits are analyzed: (1) voltage-feedback amplifiers, (2) current-feedback amplifiers, (3) current-differencing amplifiers, and (4) transconductance amplifiers. Selected applications are also presented.

In Chapter 4 feedback amplifiers are discussed. A detailed analysis procedure for various feedback configurations is developed and numerous examples of feedback circuits are presented. Stability considerations and methods for compensation of feedback amplifiers are also discussed.

x Preface

Chapter 5 deals with translinear circuits; these are circuits that exploit the linear relationship between the transconductance of a transistor and either its current or voltage. Applications of translinear circuits include implementation of analog functions and generation of trigonometric functions. These circuits find use in communications, signal processing, and control systems.

## Chapter 1

# Models for Integrated-Circuit Devices

In the analysis, design and simulation of integrated circuits, models are used to represent the electrical behavior of the devices in the circuit. Consequently, the accuracy to which the actual circuit performance is predicted depends directly on the suitability and accuracy of the models used to represent the devices. It is important that the circuit designer understand the limitations and range of applicability of the device models and the approximations used in their derivation.

In this chapter we discuss the models commonly used to represent devices in analog integrated circuits: bipolar junction transistors, junction diodes, junction field-effect transistors, and metal-oxide-semiconductor field-effect transistors. Included will be models as implemented in the circuit simulation program SPICE.

### 1.1 Bipolar Junction Transistor

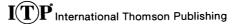

A bipolar junction transistor (BJT) is formed with two pn junctions in close proximity to each other. Shown in Fig. 1-1 is a cross-sectional view of a typical silicon bipolar transistor structure used in modern integrated circuits. Depicted is an npn transistor comprised of a heavily doped  $(N^+)$  emitter region, a lighter-doped  $(N^-)$  collector region, and an intervening (P) base region. Electrical contact to the base region is provided by the  $P^+$  polysilicon layer, and the  $P^+$  contact enhancement region (which reduces series parasitic base resistance), and contact to the collector region is made through the  $N^+$  buried layer (which reduces the series parasitic collector resistance), the  $N^-$  layer, and the  $N^+$  contact enhancement region. Isolation from other devices in the circuit is provided by the insulating silicon dioxide (SiO<sub>2</sub>) layer (which completely surrounds the device laterally) and by the p-type substrate (which forms a pn junction—normally reverse biased—between the collector region and the substrate).

Figure 1-1 Cross-sectional view of an npn bipolar integrated-circuit transistor.

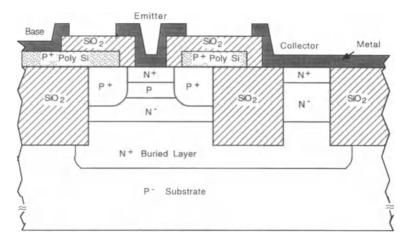

The active portion (also termed the intrinsic portion) of the transistor is the vertical  $N^+/P/N^-$  layer structure shown beneath the emitter metallization. A one-dimensional representation of this intrinsic device portion is shown in Fig. 1-2(a). Under normal operation, the emitter-base junction is forward biased and the collector-base junction is reverse biased. In this configuration, carriers (electrons for an *npn* transistor) are injected into the base by virtue of the forward bias on the emitter junction. These carriers move by a combination of drift and diffusion through the base to the collector junction, where, due to the reverse bias on this junction, are swept into the collector region, giving rise to a current in the collector. This current, originating in the emitter, is thus controlled predominantly by the emitter-base junction bias and accounts for this structure being an active (transistor) device.

Figure 1-2(b) shows the circuit symbol for an npn transistor and the sign convention for voltages and currents. Under normal operation (in which the device is operating in the forward-active region),  $V_{\rm be}$  is positive,  $V_{\rm bc}$  is negative, and currents flow in the directions depicted in the figure. A one-dimensional representation of the intrinsic portion of a pnp transistor is shown in Fig. 1-2(c) and its circuit symbol is illustrated in Fig. 1-2(d). For a pnp transistor operating in the forward-active region,  $V_{\rm be}$  is negative,  $V_{\rm bc}$  is positive, and currents flow in the directions depicted.

#### Ebers-Moll Static Model

A relatively simple, but yet adequate for many cases, large-signal model for the bipolar transistor is the Ebers-Moll model [1]. It describes the transistor

Figure 1-2 (a) One-dimensional representation of the intrinsic portion of an npn transistor structure; (b) *npn* transistor symbol and sign convention; (c) *pnp* transistor structure; (d) *pnp* transistor symbol and sign convention.

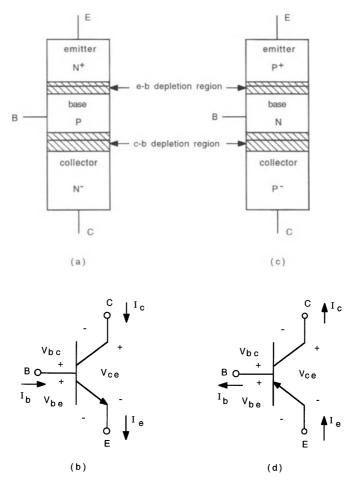

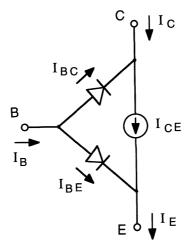

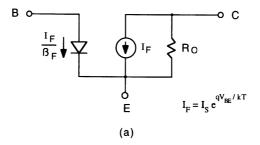

currents in terms of the two pn junction currents and their respective junction voltages and is illustrated in Fig. 1-3. The emitter-base and collector-base junction currents are given by

$$I_{\rm EF} = I_{\rm ES} \left( e^{qV_{\rm BE}/kT} - 1 \right) \tag{1-1}$$

$$I_{\rm CR} = I_{\rm CS} (e^{qV_{\rm BC}/kT} - 1)$$

(1-2)

where  $I_{\rm ES}$  and  $I_{\rm CS}$  are the reverse saturation currents of the emitter-base and collector-base junctions, respectively and kT/q is the thermal voltage.

#### 4 Chapter 1 - Models for Integrated-Circuit Devices

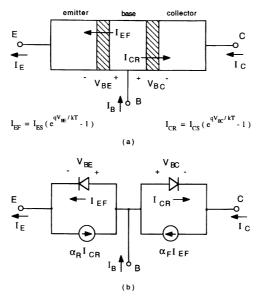

Figure 1-3 (a) Emitter and collector junction currents used in the Ebers-Moll model of the bipolar transistor. (b) Common-base Ebers-Moll static model of an *npn* transistor.

The total collector current  $(I_C)$  is comprised of the collector junction current  $(I_{CR})$  and the fraction of the emitter junction current  $(I_{EF})$  reaching the collector. This current arises from the carriers injected from the emitter into the base and their subsequent transport through the base to the collector. This fraction is denoted  $\alpha_F$  and represents the ratio of the collector to emitter current when the transistor is operating in the normal (forward-active) mode of operation; that is, with the emitter-base junction forward biased and the collector-base junction reverse biased. Typical values for  $\alpha_F$  in modern integrated-circuit transistors are 0.98–0.995. With reference to the circuit model shown in Fig. 1-3(b), the terminal collector current is

$$I_C = \alpha_F I_{\rm EF} - I_{\rm CR} \tag{1-3}$$

Likewise, the total emitter current  $(I_E)$  is comprised of the emitter junction current  $(I_{EF})$  and the fraction  $\alpha_R$  of the collector junction current reaching the emitter.  $\alpha_R$  represents the ratio of the emitter to collector current when the transistor is operating in the inverse (reverse-active) mode of operation (collector-base junction forward biased and emitter-base junction reverse biased). Owing primarily to the large difference in the impurity doping concentrations in the emitter and collector regions of the transistor,  $\alpha_R$  is

smaller than  $\alpha_F$ , with typical values ranging from 0.5 to 0.9. From Fig. 1-3(b),

$$I_E = I_{EF} - \alpha_R I_{CR} \tag{1-4}$$

Applying Kirchoff's current law for the base current  $(I_B = I_E - I_C)$  gives

$$I_B = (1 - \alpha_F)I_{EF} + (1 - \alpha_R)I_{CR}$$

(1-5)

It can be shown from reciprocity conditions applied to the emitter and collector junctions [2] that

$$\alpha_F I_{ES} = \alpha_R I_{CS} = I_S \tag{1-6}$$

where  $I_S$  the saturation current of the BJT and is given as

$$I_S = \frac{qD_B n_i^2 A_E}{Q_B} \tag{1-7}$$

$D_B$  is the diffusion constant for minority carriers in the base (electrons for an npn, holes for a pnp),  $n_i$  is the intrinsic carrier concentration of the semiconductor,  $A_E$  is the area of the emitter-base junction, and  $Q_B$  is the number of majority carrier charges per unit area in the base (holes for an npn, electrons for a pnp). Typical values for  $I_S$  in an integrated-circuit transistor range from about  $10^{-17}$  A for a small-geometry, low-current device to  $10^{-15}$  A for a large device such as might be used in the output stage where large currents are required.

Using Eq. (1-6) in Eqs. (1-3) and (1-4) gives for the Ebers-Moll equations:

$$I_C = I_S(e^{qV_{BE}/kT} - 1) - \frac{I_S}{\alpha_R}(e^{qV_{BC}/kT} - 1)$$

(1-8)

$$I_E = \frac{I_S}{\alpha_F} (e^{qV_{\text{BE}}/kT} - 1) - I_S (e^{qV_{\text{BC}}/kT} - 1)$$

(1-9)

These equations describe the large-signal behavior of the bipolar transistor and, as such, there is no restriction on either the magnitude or polarity of the junction voltages. They can thus be used to describe transistor operation in four regions of operation:

(i) Forward-active. Here, the emitter-base junction is forward biased ( $V_{\rm BE}$  positive for an npn, negative for a pnp) and the collector-base junction is reverse biased ( $V_{\rm BC}$  negative for an npn, positive for a pnp). If the reverse bias on the collector junction is at least several kT/q in magnitude, then the  $exp(qV_{\rm BC}/kT)$  terms in Eqs. (1-8) and (1-9) are much smaller than -1 and can be neglected. This gives for forward-active region:

$$I_C = I_S(e^{qV_{\text{BE}}/kT} - 1) + \frac{I_S}{\alpha_R}$$

(1-10)

$$I_E = \frac{I_S}{\alpha_E} (e^{qV_{\text{BE}}/kT} - 1) + I_S$$

(1-11)

Equation (1-11) can be used in Eq. (1-10) to express the collector current in terms of the emitter current:

$$I_C = \alpha_F I_F + I_{CO} \tag{1-12}$$

where

$$I_{CO} = \frac{I_S(1 - \alpha_F \alpha_R)}{\alpha_R} \tag{1-13}$$

$I_{\rm CO}$  is the collector current obtained with the emitter open circuited ( $I_E=0$ ). At room temperature (27°C),  $I_{\rm CO}$  is small (typically in the range of  $10^{-13}$  A– $10^{-10}$  A) and can usually be neglected. However, for silicon,  $I_{\rm CO}$  doubles for about every 8°C increase in temperature and so may not be negligible at high temperatures.

Normally in the forward-active mode the base-emitter bias is at least several kT/q in value so that  $\exp(qV_{\rm BE}/kT)$  is  $\gg 1$ . Neglecting the -1 and  $I_S$  terms in Eqs. (1-10) and (1-11) gives

$$I_C \approx I_S e^{qV_{\text{BE}}/kT} \tag{1-14}$$

and

$$I_E \approx \frac{I_S}{\alpha_E} e^{qV_{\text{BE}}/kT} \tag{1-15}$$

as commonly used expressions for the collector and emitter currents.

(ii) Reverse-active. In this region, the emitter-base junction is reverse biased and the collector-base junction is forward biased, which results in carriers being injected from the collector region (which now acts like and emitter) into the base where they transport through the base and are collected by the reverse bias on the emitter (which now acts like a collector). The transistor is operating in an inverse mode and the directions of the emitter and collector currents are now reversed from that depicted in Fig. 1-2.

For  $|V_{BE}| \ll -kT/q$ ,  $|V_{BE}| \gg kT/q$ , and neglecting the reverse bias leakage current, we have from Eqs. (1-8) and (1-9)

$$I_C \approx -\frac{I_S}{\alpha_R} e^{qV_{BC}/kT} \tag{1-16}$$

$$I_E \approx -I_S e^{qV_{BC}/kT} \tag{1-17}$$

(iii) Saturation. Here, both junctions are forward biased and hence both are injecting carriers into the base. Each junction acts both as an emitter and collector, and the net behavior can be described by a superposition of forward-active and reverse-active modes.

$$I_{BE} = \frac{I_S}{\beta_F} (e^{qV_{BE}/kT} - 1), \ I_{BC} = \frac{I_S}{\beta_R} (e^{qV_{BC}/kT} - 1), \ I_{CE} = I_S \frac{I_S}{\beta_F} (e^{qV_{BE}/kT} - e^{qV_{BC}/kT}),$$

Figure 1-4 Common-emitter Ebers-Moll static model of an npn transistor.

For  $|V_{\rm BE}| \gg kT/q$  and  $|V_{\rm BC}| \gg kT/q$ , again neglecting the reverse leakage current,

$$I_C \approx I_S e^{qV_{\rm BE}/kT} - \frac{I_S}{\alpha_B} e^{qV_{\rm BC}/kT} \tag{1-18}$$

$$I_E \approx \frac{I_S}{\alpha_F} e^{qV_{\rm BE}/kT} - I_S e^{qV_{\rm BC}/kT} \tag{1-19}$$

$I_C$  and  $I_E$  may both be positive or negative, depending on which junction injects more heavily. The base current is always positive (flowing into the base for an npn transistor and flowing out of the base for a pnp transistor) because it is supplying carriers to the base for injection back into the emitter and collector regions due to the forward bias on each junction.

(iv) Cutoff. In this region, both junctions are reverse biased and the only currents that flow are those which comprise the small reverse leakage currents of the two junctions. For For  $|V_{\rm BE}| \ll -kT/q$  and  $|V_{\rm BC}| \ll -kT/q$ ,

$$I_C \approx -I_S(1-1/\alpha_R) \tag{1-20}$$

$$I_E \approx -I_S(1/\alpha_F - 1) \tag{1-21}$$

A common-emitter configuration of the Ebers-Moll model is shown in Fig. 1-4. This form is used in many circuit simulation programs (e.g., SPICE [3])

to model the large-signal static characteristics of bipolar junction transistors. From the model, the terminal currents are

$$I_C = I_S(e^{qV_{BE}/kT} - 1) - I_S\left(1 + \frac{1}{\beta_R}\right)(e^{qV_{BC}/kT} - 1)$$

(1-22)

$$I_E = I_S \left( 1 + \frac{1}{\beta_F} \right) (e^{qV_{BE}/kT} - 1) - I_S (e^{qV_{BC}/kT} - 1)$$

(1-23)

$$I_{B} = \frac{I_{S}}{\beta_{F}} \left( e^{qV_{BE}/kT} - 1 \right) + \frac{I_{S}}{\beta_{R}} \left( e^{qV_{BC}/kT} - 1 \right)$$

(1-24)

$\beta_F$  is the forward common-emitter current gain,  $I_C/I_B$  at  $V_{BC} = 0$ , and is related to the forward common-base current gain  $\alpha_F$  as

$$\beta_F = \frac{\alpha_F}{1 - \alpha_F} \tag{1-25}$$

$\beta_R$  is the reverse common-emitter current gain,  $-I_E/I_B$  at  $V_{\rm BE}=0$  and is related to the reverse common-base current gain  $\alpha_R$  as

$$\beta_R = \frac{\alpha_R}{1 - \alpha_R} \tag{1-26}$$

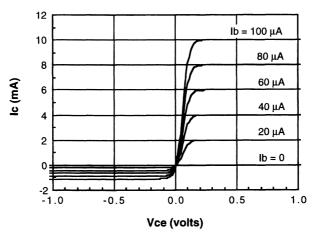

Figure 1-5 shows simulated  $I_C$ – $V_{CE}$  characteristics of an npn transistor using Eqs. (1-22) and (1-24), illustrating the behavior in the four regions of operation. Note that in the saturation region,  $V_{CE}$  is small. A bipolar transistor operating in this region is often modeled by assuming a constant voltage,  $V_{CE}$  (sat), typically 0.1–0.2 V in value, to represent the saturation condition.

Figure 1-5 Simulated common-emitter output characteristics for an *npn* transistor at 27°C. Device parameters are  $I_S = 2 \times 10^{-16} \, \text{A}$ ,  $\beta_F = 100$ , and  $\beta_R = 10$ .

Figure 1-6 Common-emitter Ebers-Moll large-signal model of an npn transistor.

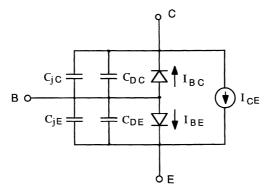

#### Ebers-Moll Dynamic Model

Charge storage in the bipolar transistor is modeled by adding capacitances to the equivalent circuit. These capacitances model the charges associated with the junction depletion regions and the neutral regions of the device. Figure 1-6 shows the large-signal common-emitter Ebers-Moll model with these capacitances added.  $C_{\rm jE}$  and  $C_{\rm jC}$  represent the space-charge capacitances of the emitter-base junction and collector-base junction depletion regions, respectively. They vary in accordance with the bias voltage applied to the junction and can be adequately modeled for reverse and small forward bias as

$$C_{jE}(V_{BE}) = \frac{C_{jE}(0)}{(1 - V_{BE}/\Phi_E)^{m_E}}$$

(1-27)

$$C_{\rm jC}(V_{\rm BC}) = \frac{C_{\rm jC}(0)}{(1 - V_{\rm BC}/\phi_{\rm c})^{m_{\rm c}}}$$

(1-28)

$C_{\rm jE}(0)$  and  $C_{\rm jC}(0)$  are the values of the emitter-base and collector-base junction capacitances at zero bias ( $V_{\rm BE}=0$  or  $V_{\rm BC}=0$ ),  $\phi_E$  and  $\phi_C$  are the emitter-base and collector-base junction barrier potentials, and  $m_E$  and  $m_C$  are the emitter-base and collector-base junction gradient factors. For a uniformly doped step junction, m is  $\frac{1}{2}$ , whereas for a linearly graded junction, m is  $\frac{1}{3}$ . In practice, actual junctions will have a value for m between these values, the specific value dependent on the particular impurity dopant concentration profile. It is common to choose either  $\frac{1}{2}$  or  $\frac{1}{3}$  to represent a given junction, the choice being made based on whether the junction doping profile appears closer to a step grade or to a linear grade. In SPICE [4], if the Ebers–Moll model is used, the value for m is fixed at  $\frac{1}{3}$ .

Equations (1-27) and (1-28) are written for an npn transistor, where  $V_{BE}$  and  $V_{BC}$  are negative for reverse bias. For a pnp transistor, use  $V_{EB}$  and  $V_{CB}$  in Eqs. (1-27) and (1-28), respectively.

To prevent infinite values for the junction capacitances at forward voltages equal to the junction barrier potentials, SPICE limits the forward bias for which Eqs. (1-27) and (1-28) are used to  $F_C \phi_E$  and  $F_C \phi_C$ , where  $F_C$  is a factor between 0 and 1 (SPICE default = 0.5). For forward biases larger than these values, the junction capacitances are modeled by a linear extrapolation:

$$C_{jE}(V_{BE}) = \frac{C_{jE}(0)}{(1 - F_C)^{1 + m_E}} \left( 1 - F_C(1 + m_E) + \frac{m_E V_{BE}}{\Phi_E} \right) \text{ for } V_{BE} \ge F_C \Phi_E \quad (1-29)$$

$$C_{\rm jC}(V_{\rm BC}) = \frac{C_{\rm jC}(0)}{(1 - F_{\rm C})^{1 + m_{\rm C}}} \left( 1 - F_{\rm C}(1 + m_{\rm C}) + \frac{m_{\rm C}V_{\rm BC}}{\Phi_{\rm C}} \right) \text{ for } V_{\rm BC} \ge F_{\rm C}\Phi_{\rm C} \quad (1-30)$$

Charge storage due to the mobile carriers injected into the neutral regions of the transistor are modeled by the diffusion capacitances  $C_{\rm DE}$  and  $C_{\rm DC}$ .  $C_{\rm DE}$  represents the capacitance associated with injection at the emitter junction and  $C_{\rm DC}$  represents the capacitance associated with injection at the collector junction. They are given as

$$C_{\rm DE}(V_{\rm BE}) = \tau_F \frac{qI_{\rm S}}{kT} e^{qV_{\rm BE}/kT} \tag{1-31}$$

$$C_{\rm DC}(V_{\rm BC}) = \tau_R \frac{qI_S}{kT} e^{qV_{\rm BC}/kT} \tag{1-32}$$

where  $\tau_F$  is the forward transit time across the neutral base region from emitter to collector, and  $\tau_R$  is the reverse transit time across the neutral base region from collector to emitter. Under reverse bias, the diffusion capacitance is small compared to the junction capacitance and is usually neglected.

#### Base-Width Modulation

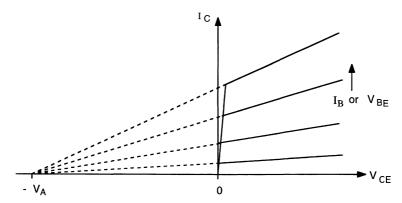

As depicted in Fig. 1-5 the Ebers-Moll model gives a constant collector current with respect to  $V_{\rm CE}$  for a transistor operating in the forward-active or reverse-active regions. In practice, the collector current is seen to increase with increasing collector-emitter voltage, as illustrated in Fig. 1-7 for forward-active bias. This increase in collector current is a result of a change in the neutral base width with collector junction bias. An increase in the reverse bias on the collector junction increases the width of the collector-base depletion region, which, in turn, causes the width of the neutral base region to decrease. The effect of this base-width modulation on the collector current (called the

Figure 1-7 Common-emitter output characteristics illustrating the effects of basewidth modulation (Early effect) on output conductance.

Early effect [5]) can be seen from Eqs. (1-7) and (1-14), which combine to give

$$I_C = \frac{qD_B n_i^2 A_E}{Q_B} e^{qV_{\text{BE}}/kT} \tag{1-33}$$

for the collector current in the forward-active region. Recall that  $Q_B$  is the number of majority carrier charges per unit area in the base and is equal to the volume density of this charge times the width of the neutral base region. A reduction in base-width reduces  $Q_B$  and thereby increases  $I_C$ .

For modeling purposes, a linear fit to the output characteristics is often made. The extrapolated curves then intersect the negative  $V_{\rm CE}$  axis at a point which is defined as the Early voltage,  $V_A$ , as shown in Fig. 1-7. Using this parameter, the slope of the collector current-voltage characteristics is given by

$$\frac{\partial I_C}{\partial V_{CE}} = \frac{I_C(0)}{V_A} \tag{1-34}$$

where  $I_C(0)$  is the value of the collector current at  $V_{CE} = 0$ , given by Eq. (1-14). It should be remarked that a similar effect occurs for a transistor operated in the reverse-active mode. Here, the base width is modulated by the reverse bias on the emitter-base junction, and the increase in current with collector voltage is characterized by the reverse *Early voltage*,  $V_B$ . The corresponding model parameters in SPICE for the forward Early voltage and the reverse Early voltage are VAF and VAR, respectively.

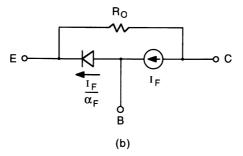

Equation (1-34) defines the output conductance which can be incorporated into the large-signal model for the forward-active region, shown in Fig. 1-8 for both common-emitter and common-base configurations. In Fig. 1-8,

$$R_O = \frac{V_A}{I_C(0)} = \frac{V_A}{I_S e^{qV_{BE}/kT}}$$

(1-35)

Figure 1-8 (a) Large-signal static common-emitter model for forward-active region; (b) common-base model.

The collector current is

$$I_C = I_F + \frac{V_{CE}}{R_O} = I_S e^{qV_{BE}/kT} \left( 1 + \frac{V_{CE}}{V_A} \right)$$

(1-36)

**EXAMPLE.** Figure 1-9(a) shows a simple common-emitter amplifier circuit, driven by a current of 5  $\mu$ A. Determine the collector current  $I_C$  and the output voltage  $V_o$ . The transistor parameters are  $I_S = 5 \times 10^{-16}$  A,  $\beta_F = 100$ , and  $V_A = 50$  V. From Eq. (1-36) and the model depicted in Fig. 1-8(a),

$$I_C = \beta_F I_B (1 + V_{CE}/V_A)$$

where from the circuit

$$V_{\rm CE} = V_o = V_{\rm CC} - I_C R_C$$

which combined with the previous equation gives

$$I_C = \frac{\beta_F I_B (1 + V_{CC}/V_A)}{1 + \beta_F I_B R_C/V_A} = \frac{(100) (5 \times 10^{-6}) (1 + 15/50)}{1 + (100) (5 \times 10^{-6}) (10 \times 10^{3})/50} = 591 \,\mu\text{A}$$

Figure 1-9 Example common-emitter amplifier circuit: (a) current driven; (b) voltage driven.

and

$$V_o = 15 - (0.591 \,\mathrm{mA}) (10 \,\mathrm{k}\Omega) = 9.09 \,\mathrm{V}$$

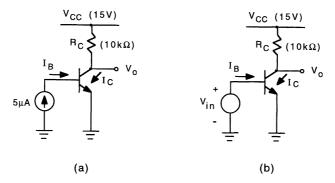

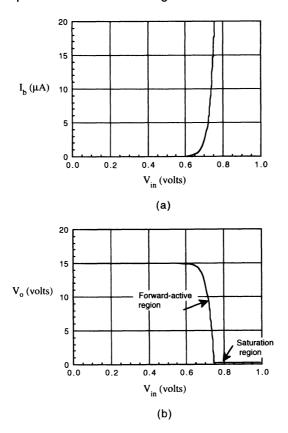

Figure 1-9(b) shows the same amplifier circuit driven by a voltage source. Determine and sketch (a)  $I_B$  as a function of the input,  $V_{\rm in}$ , for  $V_{\rm in}$  ranging from 0 to 1 V and (b)  $V_o$  as a function of  $V_{\rm in}$ . Take room temperature, kT/q = 26 mV. Here,  $V_{\rm BE} = V_{\rm in}$ , so

$$I_B = \frac{I_S}{6\pi} e^{qV_{in}/kT} = \frac{5 \times 10^{-16}}{100} e^{V_{in}/0.026} = 5 \times 10^{-18} e^{V_{in}/0.026} A$$

This result is plotted in Fig. 1-10(a). Note the steep increase in base current with base-emitter voltage for  $V_{\rm BE}$  beyond about 0.7 V. This is, of course, due to the exponential current-voltage characteristic. As an approximation to the circuit model, the base-emitter voltage is often taken to be constant for a transistor operating in the active region. For a silicon bipolar transistor operating at room temperature this voltage, denoted  $V_{\rm BE}$  (on), is typically in the range of 0.7-0.8 V.

For the voltage drive (b),

$$I_C = I_S e^{qV_{\rm in}/kT} \left( 1 + \frac{V_o}{V_A} \right)$$

which combined with  $V_o = V_{CC} - I_C R_C$  gives

$$V_o = \frac{15 - (5 \times 10^{-16}) (10 \times 10^3) e^{V_{\rm in}/0.026}}{1 + (5 \times 10^{-16}) (10 \times 10^3) e^{V_{\rm in}/0.026}/50} = \frac{15 - (5 \times 10^{-12}) e^{V_{\rm in}/0.026}}{1 + (1 \times 10^{-13}) e^{V_{\rm in}/0.026}}$$

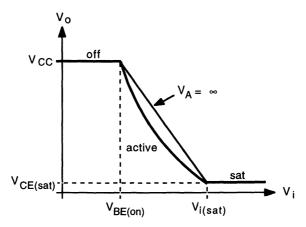

This result is plotted in Fig. 1-10(b) for the portion of the curve labeled "forward-active region." At  $V_{\rm in}$  equal to approximately 0.75 V the transistor enters the saturation region (both emitter and collector junctions are forward-biased)

Figure 1-10 (a) Base current and (b) output voltage as a function of  $V_{\rm in}$  for example common-emitter amplifier circuit.

and the collector-to-emitter voltage,  $V_{CE}$  (and hence  $V_o$  in this example), saturates at a small value, typically 0.1-0.2 V, as illustrated in the figure. Also note that for  $V_{\rm in}$  less than about 0.6 V the output remains high (at  $V_{\rm CC}$ ), even though the transistor is still operating in the forward-active region. This is because the collector current at these base-emitter voltages is small such that  $I_C R_C \ll V_{CC}$ .

### Small-Signal Models of Bipolar Junction Transistors

In some applications, the magnitudes of the signals in a circuit are small compared to the bias voltages and currents. In these situations, linear circuit models for the device may be used to determine the circuit response to these small signals. The advantage of doing this is that now a linear circuit is to be analyzed instead of a nonlinear circuit.

Figure 1-11 (a) Decomposition of transistor currents and voltages into dc and small-signal components. (b) Common-emitter small-signal equivalent circuit model.

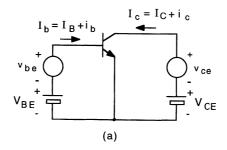

Figure 1-11(a) illustrates the decomposition of transistor currents and voltages into dc (quiescent) and small-signal components. Base drive to the transistor consists of the dc bias voltage  $V_{\rm BE}$  connected in series with the signal voltage  $v_{\rm be}$ , giving a total base-emitter voltage  $V_{\rm be} = V_{\rm BE} + v_{\rm be}$  and a corresponding total base current  $I_b = I_B + i_b$ . The convention followed here is to represent dc quantities by uppercase symbols and subscripts, and small-signal quantities by lowercase symbols and subscripts and total quantities by uppercase symbols and lowercase subscripts.

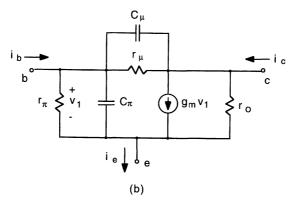

A common-emitter small-signal equivalent circuit model for a bipolar transistor operating in the forward-active region is shown in Fig. 1-11(b). Its parameters are determined as follows:

Using Eq. (1-36),

$$g_m = \frac{dI_c}{dV_{be}}\Big|_{V_{be} = 0} = \frac{qI_s}{kT} e^{qV_{BE}/kT} \left(1 + \frac{V_{CE}}{V_A}\right) = \frac{qI_C}{kT}$$

(1-37)

$g_m$  the transconductance and its value is seen to depend linearly on the collector dc bias current.

Figure 1-8(a) and Eq. (1-37) can be used to determine the variation in base current with base-emitter voltage.

$$g_{\pi} = \frac{dI_b}{dV_{be}}\Big|_{v_b = 0} = \frac{d(I_F/\beta_F)}{dV_{be}} \approx \frac{1}{\beta_F} \frac{dI_c}{dV_{be}} = \frac{g_m}{\beta_F}$$

(1-38)

The approximation here is that  $\beta_F$  remains constant for small-signal variations in  $V_{be}$ , which is generally true. Hence, the small-signal base resistance is

$$r_{\pi} = \frac{1}{g_{\pi}} = \frac{\beta_F}{g_m} \tag{1-39}$$

The small-signal output resistance  $r_o$  results from the variation in collector current with collector bias voltage (Early effect). Using Eq. (1-36),

$$\frac{1}{r_o} = g_o = \frac{dI_c}{dV_{ce}} \bigg|_{V_{ce} = 0} = \frac{I_S e^{qV_{BE}/kT}}{V_A} = \frac{I_C}{V_A}$$

(1-40)

$r_{\mu}$  models the variation in base current with collector bias voltage:

$$\frac{1}{r_{\mu}} = g_{\mu} = \frac{dI_b}{dV_{ce}} \bigg|_{v_{ce} = 0} = \frac{d(I_F/\beta_F)}{dV_{ce}} \approx \frac{1}{\beta_F} \frac{dI_c}{dV_{ce}} = \frac{1}{\beta_F r_o}$$

(1-41)

$r_{\mu}$  is typically a very large resistance and in most cases is neglected in the small-signal model.

The capacitance  $C_{\pi}$  is the diffusion capacitance  $C_{\text{DE}}$  in parallel with the emitter-base junction capacitance  $C_{\text{iE}}$ :

$$C_{\pi} = \tau_F \frac{qI_S}{kT} e^{qV_{BE}/kT} + C_{jE}(V_{BE}) = g_m \tau_F + C_{jE}(V_{BE})$$

(1-42)

With a reverse-biased base-collector junction, the diffusion capacitance  $C_{\rm DC}$  is negligibly small, so the capacitance  $C_{\mu}$ , is just the base-collector junction capacitance

$$C_{\mu} = C_{\rm iC}(V_{\rm BC}) \tag{1-43}$$

Generally, the diffusion capacitance is much larger than the junction space-charge capacitance so that  $C_{\pi}$  is usually much larger than  $C_{\mu}$ .

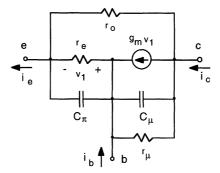

An alternate form of the common-emitter small-signal model is the common-base configuration illustrated in Fig. 1-12. Here, the input is applied to the emitter and the output is taken at the collector. In application to a circuit in which a transistor is connected in a common-base configuration, this form of the model is often more convenient to analyze. Either form of the model is valid, however, and may be used irrespective of the particular circuit

Figure 1-12 Common-base small-signal equivalent circuit model.

configuration. With reference to Fig. 1-11, the small-signal emitter current is

$$i_e = \left(\frac{1}{r_{\pi}} + g_m\right) v_1 + \frac{v_{ce}}{r_o} + sC_{\pi} v_1 \tag{1-44}$$

From Fig. 1-12,

$$i_e = \frac{v_1}{r_e} + \frac{v_{ce}}{r_0} + sC_{\pi}v_1 \tag{1-45}$$

Equating Eqs. (1-44) and (1-45) gives the value of the small-signal emitter resistance

$$r_e = \frac{1}{g_m + \frac{1}{r_{\pi}}} = \frac{1}{g_m (1 + 1/\beta_F)} = \frac{\alpha_F}{g_m}$$

(1-46)

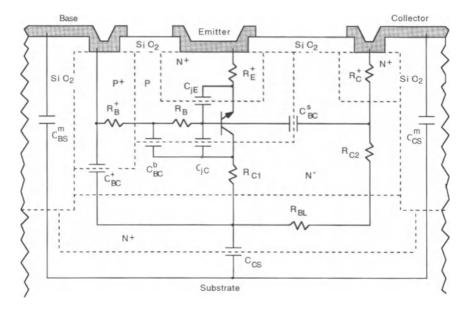

#### Parasitic Elements in Integrated-Circuit Bipolar Transistors

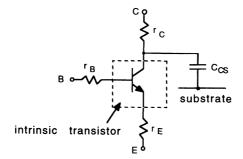

The fabrication process for integrated circuit transistors introduces other circuit elements (parasitics) in addition to those associated with the intrinsic portion of the device. Figure 1-13 illustrates the origin of these parasitic elements for an *npn* transistor. Table 1-1 identifies each element.

A simplified model which combines the principal parasitic elements affecting circuit performance is illustrated in Fig. 1-14. With reference to Fig. 1-13,  $r_E = R_E^+$ ,  $r_B = R_B^+ + R_B$ ,  $r_C = R_{C1} + R_{BL} + R_{C2} + R_C^+$ . In addition,  $C_{BC}^+$  and  $C_{BC}^b$  can be combined with  $C_{jC}$ . Typical values for the parasitic resistances in an integrated circuit BJT range from a few ohms for  $r_E$  to a few hundred ohms for  $r_B$  and  $r_C$ . The ohmic emitter resistance  $r_E$  is often neglected;  $r_B$  and  $r_C$  can be

Figure 1-13 Principal parasitic circuit elements associated with an integrated-circuit BJT.

Figure 1-14 Simplified equivalent circuit which retains the principal parasitic elements.

neglected if they are small in relation to the other resistances in the base circuit and collector circuit, respectively.

### Transistor Cutoff Frequency

A useful figure-of-merit to characterize the frequency performance of a bipolar transistor is the cutoff frequency,  $f_T$ , which is defined as the frequency at which the common-emitter small-signal short-circuit current gain is equal to unity. A

| Table 1-1 | Parasitic | Elements | for an | Integrated-Circuit I | 3JT |

|-----------|-----------|----------|--------|----------------------|-----|

|-----------|-----------|----------|--------|----------------------|-----|

| Element                                                          | Description                                                             |

|------------------------------------------------------------------|-------------------------------------------------------------------------|

| $R_B$                                                            | Ohmic base resistance of the active transistor                          |

| $R_B^{+}$                                                        | Resistance of the extrinsic base region                                 |

| $R_{C1}$                                                         | Ohmic collector resistance of the active transistor                     |

| $R_{ m BL}$                                                      | Lateral resistance of the buried layer                                  |

| $egin{aligned} R_{C2} \ R_C^+ \ R_E^+ \ C_{ m BC} \end{aligned}$ | Vertical resistance of the extrinsic collector region                   |

| $R_C^+$                                                          | Resistance of the collector contact region                              |

| $R_E^{+}$                                                        | Ohmic emitter resistance of the active transistor                       |

| $C_{ m BC}^b$                                                    | Bottom wall junction capacitance of the extrinsic base-collector region |

| $C_{\mathrm{BC}}^{s}$                                            | Side-wall junction capacitance of the extrinsic base-collector region   |

| $C_{\mathrm{BC}}^{+}$                                            | Junction capacitance of the base contact and extrinsic collector region |

| $C_{\mathrm{BC}}^{m}$                                            | Base metallization-substrate capacitance                                |

| $C_{\mathrm{CS}}$                                                | Buried layer-substrate capacitance                                      |

| $C_{\mathrm{CS}}^{m}$                                            | Collector metallization-substrate capacitance                           |

| $C_{jC}$                                                         | Collector-base junction capacitance of the active transistor            |

| $C_{\rm jE}$                                                     | Emitter-base junction capacitance of the active transistor              |

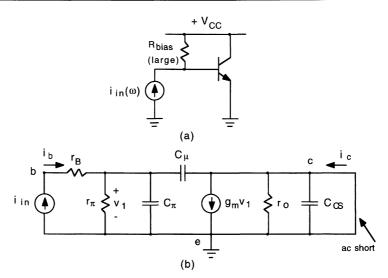

Figure 1-15 (a) Circuit for determining the common-emitter cutoff frequency  $f_T$ . (b) Small-signal equivalent circuit, neglecting  $r_E$ ,  $r_C$ ,  $r_\mu$ , and  $R_{bias}$ .

circuit used to determine this cutoff frequency is shown in Fig. 1-15(a) and the corresponding small-signal equivalent circuit is shown in Fig. 1-15(b). From Fig. 1-15(b), the small-signal current gain [denoted  $\beta(j\omega)$ ] is found to be

$$\frac{i_c}{i_b}(j\omega) = \beta(j\omega) = \frac{g_m r_\pi (1 - j\omega C_\mu / g_m)}{1 + j\omega r_\pi (C_\pi + C_\mu)}$$

(1-47)

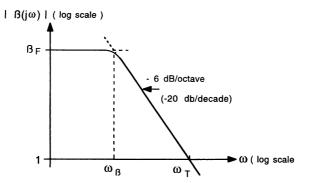

Figure 1-16 Magnitude of the small-signal short-circuit current gain versus frequency.

At low frequencies,  $\beta(j\omega) \rightarrow g_m r_\pi = \beta_F$ . Because  $C_\pi$  is usually much larger than  $C_\mu$ , the second term in the numerator of Eq. (1-47) (which represents the feedforward current in  $C_\mu$ ,) is small and can be neglected. Thus,

$$\beta(j\omega) \approx \frac{\beta_F}{1 + j\omega r_{\pi}(C_{\pi} + C_{\mu})}$$

(1-48)

The variation in the magnitude of the small-signal current gain with frequency is illustrated in Fig. 1-16. The corner frequency  $\omega_{\beta}$  is the frequency at which  $|\beta(j\omega)|$  is down by 3 dB  $(1\sqrt{2})$  from the low-frequency value  $\beta_F$ . From Eq. (1-48),

$$\omega_{\beta} = \frac{1}{\beta_F} \frac{g_m}{C_m + C_m} \tag{1-49}$$

At high frequencies, where  $\beta(j\omega)$  approaches unity, the 1 in the denominator of Eq. (1-48) can be neglected and

$$\beta (j\omega) \approx \frac{g_m}{j\omega (C_{\pi} + C_{\mu})}$$

(1-50)

which has unity magnitude at

$$\omega = \omega_T = \frac{g_m}{C_x + C_u} = \beta_F \omega_\beta \tag{1-51}$$

and the cutoff frequency is

$$f_T = \frac{1}{2\pi} \frac{g_m}{C_{\pi} + C_{\mu}} \tag{1-52}$$

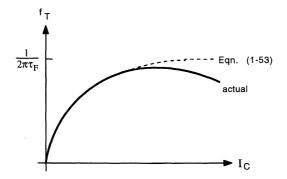

Figure 1-17 Variation in  $f_T$  with collector current.

Using Eqs. (1-37) and (1-42),

$$f_T = \frac{1}{2\pi} \left[ \frac{1}{\frac{kT}{qI_C} (C_{jE} + C_{jC}) + \tau_F} \right]$$

(1-53)

The cutoff frequency is seen to increase with collector current at low currents due to the increased charge and discharge rates of  $C_{\rm jE}$  and  $C_{\rm \mu}$ . At high currents,  $f_T$  is dominated by the base transit time  $\tau_F$  and according to Eq. (1-53) approaches a constant value  $1/2\pi\tau_F$ . In practice, the neutral base width of a bipolar transistor widens at high currents (Kirk effect [6]), causing an increase in  $\tau_F$  with current and a subsequent fall-off in  $f_T$  at high currents. This behavior is illustrated in Fig. 1-17.

**EXAMPLE.** A bipolar transistor has a cutoff frequency of 4 GHz, measured at a collector current of 1 mA. It is used in an amplifier circuit at 500  $\mu$ A. Determine (a) the elements of the common-emitter small-signal equivalent circuit of Fig. 1-11(b) and (b) the transistor cutoff frequency. The transistor has the following parameters:  $\beta_F = 150$ ,  $V_A = 100$  V,  $C_{\rm jE} = 0.2$  pF and  $C_{\rm jC} = 0.1$  pF. Take room temperature kT/q = 26 mV.

Unknown is the forward transit time  $\tau_F$ . Using Eq. (1-53) for the known value of  $f_T$  at  $I_C = 1$  mA,

$$\tau_F = \frac{1}{2\pi f_T} - \frac{kT}{qI_C} (C_{jE} + C_{jC})$$

yielding

$$\tau_F = \frac{1}{(2\pi)(4 \times 10^9)} - \frac{26 \text{ mV}}{1 \text{ mA}} (0.2 + 0.1) \times 10^{-12} \text{ F} = 32 \text{ ps}$$

(a) From Eq. (1-37) the transconductance at  $I_C = 500 \,\mu\text{A}$  is

$$g_m = \frac{qI_C}{kT} = \frac{0.5 \,\text{mA/V}}{0.026 \,\text{V}} = 19.2 \,\text{mA/V}$$

The small-signal base resistance from Eq. (1-39) is

$$r_{\pi} = \frac{\beta_F}{g_m} = \frac{150}{19.2 \,\mathrm{mA/V}} = 7.81 \,\mathrm{k}\Omega$$

The output resistance from Eq. (1-40) is

$$r_o = \frac{V_A}{I_C} = \frac{100 \text{ V}}{0.5 \text{ mA}} = 200 \text{ k}\Omega$$

and from Eq. (1-41), the collector-base resistance is

$$r_{\mu} = \beta_F r_o = (150) (200 \,\mathrm{k}\Omega) = 30 \,\mathrm{M}\Omega$$

From Eq. (1-42), the small-signal base-emitter capacitance is

$$C_{\pi} = g_m \tau_F + C_{jE} = (19.2 \times 10^{-3} \text{ A/V}) (32 \times 10^{12} \text{ s}) + 0.2 \times 10^{-12} \text{ F}$$

=  $8.14 \times 10^{-13} \text{ F} = 0.814 \text{ pF}$

and, finally, from Eq. (1-42), the small-signal collector-base capacitance is

$$C_{\rm u} = C_{\rm iC} = 0.1 \, \rm pF$$

(b) The new cutoff frequency from Eq. (1-52) is

$$f_T = \frac{g_m}{2\pi (C_{\pi} + C_{\mu})} = \frac{19.2 \,\text{mA/V}}{(2\pi) (0.814 + 0.1) \,\text{pF}} = 3.34 \,\text{GHz}$$

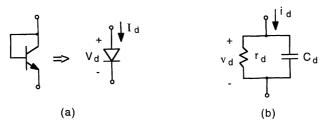

#### 1.2 Junction Diode

Any of the pn junctions that comprise the bipolar transistor structure may be used as an integrated-circuit junction diode: the base-emitter junction, the base-collector junction, and the collector-substrate junction all produce viable diodes, each with differing characteristics [7]. The most common diode structure for analog integrated circuits is produced by connecting the base and collector terminals of an npn transistor, as illustrated in Fig. 1-18(a). There are good reasons for fabricating diodes in this form: With the base and collector shorted,  $V_{\rm BC} = 0$ ; from Eq. (1-8), we have for the diode

$$I_D = I_S(e^{qV_D/kT} - 1) (1-54)$$

Figure 1-18 (a) Integrated-circuit junction diode formed from an npn transistor. (b) Small-signal equivalent circuit.

The diodes are fabricated concurrently with the npn transistors, and thus they both have identical reverse saturation currents  $(I_S)$ , except as scaled by their respective emitter areas [see Eq. (1-7)]. Hence, for example, if an equal-area diode and bipolar transistor are connected in a circuit in which  $V_D$  and  $V_{BE}$  are equal, then the diode current and the collector current of the transistor will be the same (neglecting transistor base current and Early effect). This behavior (as we shall see later) can be quite useful in analog circuits.

The small-signal equivalent circuit of the junction diode is shown in Fig. 1-18(b). Directly from the small-signal bipolar transistor model (Fig. 1-12) we have

$$r_d = r_e || r_o \approx \frac{1}{g_m} \tag{1-55}$$

and

$$C_d = C_{\pi} \tag{1-56}$$

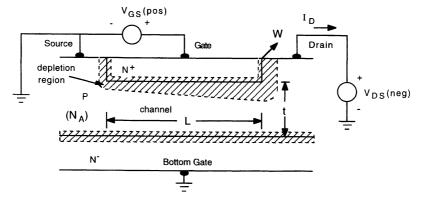

#### 1.3 Junction Field-Effect Transistor

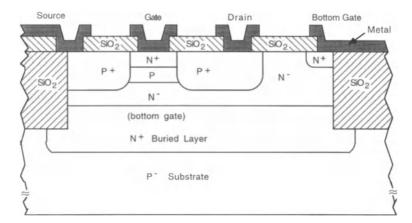

A junction field-effect transistor (JFET) is a device whose operation results from the modulation of a conducting channel by a voltage applied to a gate control electrode. Unlike the bipolar transistor where current transport involves both majority and minority carriers, current transport in the JFET is by majority carriers only; hence, it is termed a unipolar device. Shown in Fig. 1-19 is a cross-sectional view of an integrated-circuit p-channel junction field-effect transistor. The active region of the device consists of the thin p-type layer bounded on top and bottom by n-type regions, forming two pn junctions between the gate (top and bottom) and the channel (P region). The two heavily doped  $P^+$  regions provide ohmic contacts to the source and drain ends of the conducting channel.

Figure 1-19 Cross-sectional view of an integrated-circuit p-channel junction field-effect transistor.

#### **Device Characteristics**

Figure 1-20 illustrates the active region of the p-channel JFET with normal biases applied. The thickness of the depletion region surrounding the gate-channel pn junction is determined by the voltage across the junction, in this case being a function of the gate-source bias ( $V_{\rm GS}$ ) and the drain-source bias ( $V_{\rm DS}$ ).  $V_{\rm GS}$  is normally positive and  $V_{\rm DS}$  is negative, resulting in a reverse-biased gate junction. This produces essentially zero gate current—just a small reverse-bias junction leakage current. The undepleted portion of the p-type layer provides

Figure 1-20 Active region of a p-channel JFET with normal biases applied. The reverse bias on the gate-channel junction is largest at the drain end of the channel and smallest at the source end, resulting in a variation in the thickness of the conducting channel region.

the conducting channel, whose thickness (and hence its conductance) is controlled by both  $V_{GS}$  and  $V_{DS}$ . Drain current  $I_D$  flows out of the drain terminal.

With reference to Fig. 1-20, several operating points are worthy of note: As  $V_{\rm GS}$  is increased, the thickness of the depletion layer increases, narrowing the conducting channel. At a sufficiently large value of  $V_{\rm DS}$  the depletion layer will extend completely through the channel to the bottom-gate pn junction. Because  $V_{\rm DS}$  is negative, the reverse voltage across the gate-channel junction is smallest at the source end of the channel and is largest at the drain end of the channel. Thus, if the channel is depleted at the source end, then the entire channel region will be depleted (pinched off) and no conduction will occur. The transistor will be turned off. For the p-channel device depicted in Fig. 1-20, this occurs at a gate-source voltage of

$$V_{\rm GS} = \frac{qN_A t^2}{2\varepsilon_c} - \phi_i = V_P \tag{1-57}$$

where  $N_A$  is the doping concentration of the p-type channel (assumed constant), t is the thickness of the P layer,  $\varepsilon_s$  is the dielectric permittivity of the semiconductor, and  $\phi_i$  is the barrier potential of the gate-channel junction. Also assumed in this calculation is that the doping concentration of the  $N^+$  gate region is much greater than that of the P-channel, so that the depletion layer at the top gate appears mostly on the p-side of the junction. In addition, with the P-channel doping concentration larger than the  $N^-$  bottom gate, the depletion layer thickness on the p-side of bottom gate junction is negligibly small. This voltage [Eq. (1-57)] is denoted the pinch-off voltage  $V_P$ , and represents the gate-source voltage at which the device is cut off. When  $V_{DS} = V_{GS} - V_P$ , the depletion region of the top gate extends through the channel to the bottom gate just at the drain end of the channel, resulting in the channel being pinched off at that point. This voltage is denoted the saturation voltage

$$V_{Dsat} = V_{GS} - V_P \tag{1-58}$$

For  $V_{\rm DS}$  less than  $V_{\rm Dsat}$  the drain current in the JFET is controlled by both  $V_{\rm GS}$  and  $V_{\rm DS}$ ; for  $V_{\rm DS}$  greater than  $V_{\rm DS}({\rm sat})$ , the drain current is relatively independent of  $V_{\rm DS}$  and depends mainly on  $V_{\rm GS}$ . To keep the gate-channel junction reverse biased, the maximum gate-source voltage is zero and thus the maximum drain current occurs for  $V_{\rm GS}=0$ . At  $V_{\rm DS}=V_{\rm Dsat}$ , this maximum current is denoted  $I_{\rm DSS}$  and for a uniformly doped channel region is given by

$$I_{DSS} = G_0 \left[ V_P - \frac{2}{3} \frac{(V_P + \phi_i)^{3/2} - \phi_i^{3/2}}{(V_P - \phi_i)^{1/2}} \right]$$

(1-59)

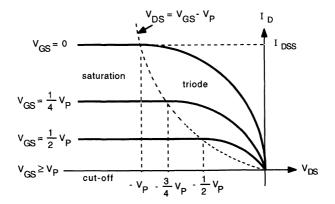

Figure 1-21 Idealized I-V characteristics of a p-channel JFET.

where

$$G_0 = \frac{q\mu_p N_A tW}{L} \tag{1-60}$$

and represents the conductance of the complete undepleted channel.

Figure 1-21 shows the idealized I - V characteristics of a p-channel JFET, illustrating the three regions of operation: cutoff, saturation, and triode. For a detailed analysis of the JFET, the reader is referred to one of the many references in the literature, such as Refs. 2 and 8. A simple quadratic model [9] has been found to adequately describe the characteristics of JFET devices, independent of their particular doping profile.

In the triode region, the drain current is approximated by

$$I_{D} = I_{DSS} \left[ 2 \left( 1 - \frac{V_{GS}}{V_{P}} \right) \left( - \frac{V_{DS}}{V_{P}} \right) - \left( - \frac{V_{DS}}{V_{P}} \right)^{2} \right]$$

(1-61)

for  $V_{\rm DS} > V_{\rm GS} - V_{\rm P}$ .

In the saturation region, the drain current is approximated by

$$I_D = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_P} \right)^2 \tag{1-62}$$

for  $V_{\rm DS} \leq V_{\rm GS} - V_{\rm P}$ .

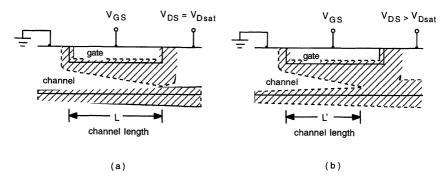

Actual JFET devices operated in the saturation region do not show a constant drain current – drain voltage characteristic, as depicted in Fig. 1-21, but rather  $I_D$  is seen to increase with increasing  $V_{\rm DS}$ . This behavior is brought about by a decrease in the effective channel length resulting from the increased gate-drain depletion region for  $|V_{\rm DS}| > |V_{\rm Dsat}|$ . This channel-length modulation with

Figure 1-22 Illustration of channel length modulation in a JFET. (a) At  $V_{\rm DS} = V_{D\rm sat}$ , the channel is pinched off just at the drain end of the channel. (b) For  $V_{\rm DS} > V_{D\rm sat}$ , the channel pinch-off point moves back toward the source, resulting in an effective channel length L' that is less than the geometrical channel length L.

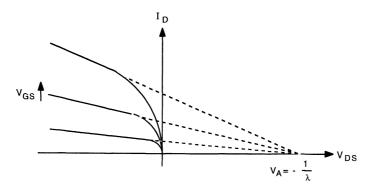

drain voltage is illustrated in Fig. 1-22 and is analogous to the base-width modulation (Early effect) in a bipolar transistor. Figure 1-23 illustrates the actual characteristics for a p-channel JFET. The slope in the drain current characteristics are characterized by the Early effect voltage  $V_A$ , and for operation in the saturation region, the drain current is approximated by

$$I_D = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_P} \right)^2 \left( 1 - \frac{V_{\rm DS}}{V_A} \right)$$

(1-63)

For FET devices, it is common practice to use the channel-length modulation parameter  $\lambda$  in place of the Early voltage. For a p-channel JFET,  $\lambda = -1/V_A$ ,

Figure 1-23 Actual characteristics of a p-channel JFET illustrating the effects of channel-length modulation. The finite slope in the drain current is characterized by the Early voltage  $V_A$ .

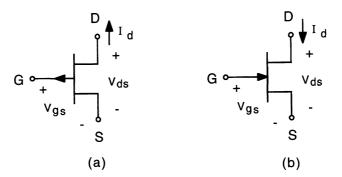

Figure 1-24 Circuit symbols and sign conventions for (a) p-channel and (b) n-channel JFET.

and the drain current characteristics in the saturation region are thus expressed as

$$I_D = I_{\rm DSS} \left( 1 - \frac{V_{\rm GS}}{V_P} \right)^2 (1 + \lambda V_{\rm DS})$$

(1-64)

Figure 1-24 shows the circuit symbols and sign conventions for p-channel and n-channel JFETs. For an n-channel JFET, the pinch-off voltage is negative and the parameter  $\lambda$  is positive; in normal operation, the gate-source voltage is negative, the drain-source voltage is positive, and current flows into the drain terminal. Thus, Eqs. (1-61) and (1-64) may be used to model the n-channel characteristics provided  $V_{\rm DS} < V_{\rm GS} - V_P$  for operation in the triode region and  $V_{\rm DS} \ge V_{\rm GS} - V_P$  for operation in the saturation region.

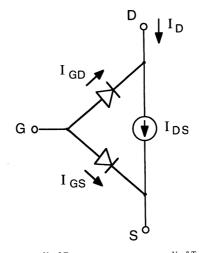

# Large-Signal Model

The large-signal static model of an *n*-channel JFET is shown in Fig. 1-25. With negative gate voltage, the gate-source and gate-drain pn junctions are reverse biased, resulting in negligible gate current and  $I_D \approx I_{DS}$ . In the SPICE simulation program, the large-signal static drain current is modeled as

$$I_{DS} = \begin{cases} 0 & \text{for } V_{GS} - V_{TO} < 0\\ \beta V_{DS} [2(V_{GS} - V_{TO}) - V_{DS}] (1 + \lambda V_{DS}) & \text{for } V_{GS} - V_{TO} > V_{DS} > 0\\ \beta (V_{GS} - V_{TO})^{2} (1 + \lambda V_{DS}) & \text{for } V_{DS} \ge V_{GS} - V_{TO} > 0 \end{cases}$$

(1-65)

where  $V_{T0}$  (threshold parameter) =  $V_P$  and is taken as negative for both p- and n-channel JFETs. The parameter  $\beta$  is given as

$$\beta = \frac{I_{\rm DSS}}{V_P^2} \tag{1-66}$$

$$\begin{split} I_{GD} &= I_{S} \left( e^{q v_{GD}/kT} - 1 \right), \quad I_{GS} = I_{S} \left( e^{q v_{GS}/kT} - 1 \right) \\ I_{DS} &= \begin{cases} 0 & \text{for } V_{GS} \leq V_{P} \\ I_{DSS} \left[ 2 \left( 1 - V_{GS}/V_{P} \right) \left( - V_{DS}/V_{P} \right) - \left( V_{DS}/V_{P} \right)^{2} \right] \right) & \text{for } V_{GS} - V_{P} > V_{DS} > 0 \\ I_{DSS} \left( 1 - V_{GS}/V_{P} \right)^{2} \left( 1 + \lambda V_{DS} \right) & \text{for } V_{DS} \geq V_{GS} - V_{P} \end{split}$$

Figure 1-25 Large-signal static model of an *n*-channel JFET.

It may be readily shown that the two forms given in Eqs. (1-64) and (1-65) for operation in the saturation region are equivalent. The SPICE model adds the channel-length modulation term  $(1 + \lambda V_{DS})$  to the characteristic for operation in the triode region to avoid a discontinuity in the drain current at  $V_{DS} = V_{GS} - V_{TO}$ . In practice, of course, there is no channel-length modulation in this region; the error, however, is small.

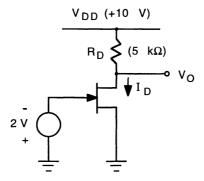

**EXAMPLE.** Figure 1-26 shows a simple common-source JFET circuit. Determine the drain current  $I_D$  and the output voltage  $V_O$ . The transistor parameters are  $V_P = -5 \text{ V}$ ,  $I_{DSS} = 1.5 \text{ mA}$ , and  $\lambda = 0.03 \text{ V}^{-1}$ .

Not known is the operating region of the device.  $V_{\rm GS} = -2 \, {\rm V} > V_P$ , so the JFET is not turned off. It is, therefore, operating in either the triode or saturation region. We will assume initially that it is in saturation and see if the results are consistent with that assumption.

From Eq. (1-64)

$$I_D = I_{DSS} (1 - V_{GS}/V_P)^2 (1 + \lambda V_O)$$

where from the circuit

$$V_O = V_{\rm DD} - I_D R_D$$

Figure 1-26 Example common-source JFET circuit.

yielding

$$I_D = I_{DSS} (1 - V_{GS}/V_P)^2 [1 + \lambda (V_{DD} - I_D R_D)]$$

Solving for  $I_D$  gives

$$I_D = \frac{I_{\text{DSS}} (1 - V_{\text{GS}} / V_P)^2 (1 + \lambda V_{\text{DD}})}{1 + \lambda I_{\text{DSS}} R_D (1 - V_{\text{GS}} / V_P)^2} = \frac{(1.5) (1 - 2/5)^2 [1 + (0.03) (10)]}{1 + (0.03) (1.5) (5) (1 - 2/5)^2} = 0.649 \,\text{mA}$$

and

$$V_0 = 10 - (0.649)(5) = 6.75 \text{ V}$$

Here,  $V_{\rm DS} = V_{\it O} = 6.75 \, {\rm V} > V_{\rm GS} - V_{\it P} = 3 \, {\rm V}$ , so the device is operating in the saturation region.

**EXERCISE.** Determine the value for  $R_D$  in the previous example for which the JFET just enters the triode region. (Ans. 11.9 k $\Omega$ )

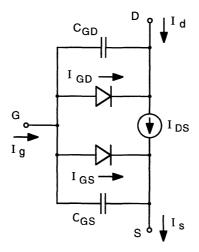

# Large-Signal Dynamic Model of the JFET

Charge storage in the JFET is modeled by the space-charge capacitances associated with the gate junction. With the gate junction reverse biased, the diffusion capacitance is negligibly small and can be neglected. Figure 1-27 shows the large-signal dynamic model of an n-channel JFET. The capacitances  $C_{\rm GS}$  and  $C_{\rm GD}$  are the capacitances associated with the gate-source and gate-drain junctions and are modeled as

$$C_{\rm GS}(V_{\rm GS}) = \frac{C_{\rm GS}(0)}{(1 - V_{\rm GS}/\Phi_i)^m}$$

(1-67)

$$C_{\rm GD}(V_{\rm GD}) = \frac{C_{\rm GD}(0)}{(1 - V_{\rm GD}/\phi_i)^m}$$

(1-68)

Figure 1-27 Large-signal dynamic model of an n-channel JFET.

where  $C_{\rm GS}(0)$  and  $C_{\rm GD}(0)$  are the zero-bias values of the gate-source and gate-drain junction capacitances, respectively, and m is the junction grading coefficient. In SPICE, m is set to 0.5 and cannot be changed.

For a p-channel JFET model, reverse the two diodes and the current source, reverse the directions of the terminal currents in Fig. 1-27, and change the signs in the denominators of Eqs. (1-67) and (1-68) from minus to plus.

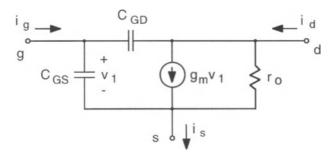

# Small-Signal Model of the JFET

Figure 1-28 shows the small-signal equivalent circuit for a JFET operating either in the triode or saturation region. The transconductance is found from Eqs. (1-61) and (1-64):

$$g_{m} = \frac{dI_{d}}{dV_{gs}} \bigg|_{V_{gs} = 0} = \begin{cases} \frac{2I_{DSS}}{V_{P}^{2}} V_{DS} & \text{for } V_{DS} < V_{GS} - V_{P} \\ -\frac{2I_{DSS}}{V_{P}} \left(1 - \frac{V_{GS}}{V_{P}}\right) (1 + \lambda V_{DS}) & \text{for } V_{DS} \ge V_{GS} - V_{P} \end{cases}$$

(1-69)

The small-signal output resistance is determined using Eqs. (1-61) and (1-64):

$$\frac{1}{r_o} = g_o = \frac{dI_d}{dV_{ds}} \bigg|_{v_{ds} = 0} = \begin{cases}

\frac{2I_{DSS}}{V_P} \left( \frac{V_{GS}}{V_P} - \frac{V_{DS}}{V_P} - 1 \right) & \text{for } V_{DS} < V_{GS} - V_P \\

\lambda I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2 & \text{for } V_{DS} \ge V_{GS} - V_P

\end{cases}$$

(1-70)

Figure 1-28 Small-signal equivalent circuit model for a JFET.

If  $\lambda V_{\rm DS} \ll 1$ , the output resistance in saturation may be approximated as

$$r_o \approx \frac{1}{\lambda I_D}$$

(1-71)

The values of  $C_{\rm GS}$  and  $C_{\rm GD}$  are determined from Eqs. (1-67) and (1-68), evaluated at the dc operating point.

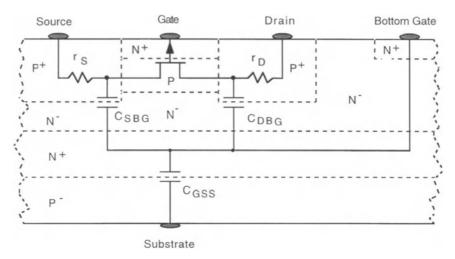

## Parasitic Elements in Integrated-Circuit JFETs

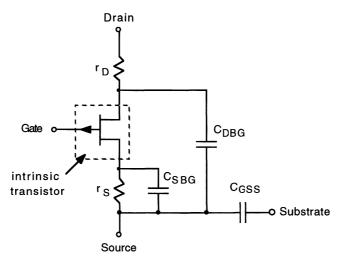

The principal parasitic elements associated with integrated-circuit junction field-effect transistors are the ohmic resistances of the source and drain contact regions, denoted  $r_S$  and  $r_D$ , respectively, and the junction capacitances associated with the bottom gate. Figure 1-29 illustrates the origin of these parasitic

Figure 1-29 Principal parasitic circuit elements associated with an integrated-circuit JEFT.

Figure 1-30 Adding parasitic circuit elements to the JFET.

elements for a p-channel JFET:  $C_{\rm SBG}$  is the capacitance between the source and bottom gate,  $C_{\rm DBG}$  is the capacitance between the drain and bottom gate, and  $C_{\rm GSS}$  is the capacitance between the bottom gate and substrate.

In practice, only the top gate is driven, which gives the highest frequency response [10]. The bottom gate can either be connected to a separate dc bias voltage or connected directly to the source terminal; for the latter, the JFET including the parasitic elements can be represented as shown in Fig. 1-30.

# Transistor Cutoff Frequency

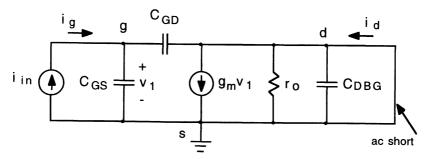

The unity-gain cutoff frequency  $f_T$  for a JFET is calculated in a fashion similar to that for the bipolar transistor. The small-signal equivalent circuit for this analysis is given as shown in Fig. 1-31, from which the current gain is found to be

$$\frac{i_d}{i_g}(j\omega) = \frac{g_m - j\omega C_{GD}}{j\omega (C_{GS} + C_{GD})} \approx \frac{g_m}{j\omega (C_{GS} + C_{GD})}$$

(1-72)

where in the last term the feed-forward current in  $C_{\rm GD}$  has been neglected in relation to  $g_m$ . From Eq. (1-72), the unity-gain frequency is found to be

$$f_T = \frac{g_m}{2\pi (C_{GS} + C_{GD})}$$

(1-73)

**EXAMPLE.** Determine the cutoff frequency for an *n*-channel JFET operating at  $I_D = 1 \text{ mA}$  and  $V_{DS} = 5 \text{ V}$ . The device parameters are  $I_{DSS} = 1.5 \text{ mA}$ ,  $V_P = -3 \text{ V}$ ,

Figure 1-31 Small-signal circuit for determining cutoff frequency  $f_T$  of the JFET. The parasitic source and drain resistances,  $r_S$  and  $r_D$ , are normally small compared to  $1/g_m$  and are neglected here.

$\lambda = 0.02 \, \text{V}^{-1}$ ,  $C_{GS}(0) = 0.25 \, \text{pF}$ , and  $C_{GD}(0) = 0.1 \, \text{pF}$ . For this device,  $\phi_i = 0.8 \, \text{V}$  and  $m = \frac{1}{3}$ .

From Eq. (1-64), the gate-source voltage, assuming operation in the saturation region, is

$$V_{\text{GS}} = V_P \left( 1 - \sqrt{\frac{I_D}{I_{\text{DSS}} (1 + \lambda V_{\text{DS}})}} \right) = -3 \left( 1 - \sqrt{\frac{1}{1.5 (1 + 0.02 \times 5)}} \right) = -0.665 \text{ V}$$

Here,  $V_{DS} = 5 \text{ V} > V_{GS} - V_P = 2.34 \text{ V}$ , so the JFET is in saturation. From Eq. (1-69), the transconductance is

$$g_m = -\frac{2I_{\text{DSS}}}{V_P} \left( 1 - \frac{V_{\text{GS}}}{V_P} \right) = -\frac{(2)(1.5 \text{ mA})}{-3 \text{ V}} \left( 1 - \frac{0.665}{3} \right)^{1/3} = 0.778 \text{ mA/V}$$

From Eq. (1-67), the gate-source capacitance at  $V_{\rm GS} = -0.665\,{\rm V}$  is

$$C_{\text{GS}} = \frac{C_{\text{GS}}(0)}{(1 - V_{\text{GS}}/\phi_i)^m} = \frac{0.25 \,\text{pF}}{(1 + 0.665/0.8)^{1/3}} = 0.204 \,\text{pF}$$

The gate-drain voltage is

$$V_{GD} = V_{GS} - V_{DS} = -0.665 \text{ V} - 5 \text{ V} = -5.665 \text{ V}$$

Using Eq. (1-68), the gate-drain capacitance is

$$C_{\rm GD} = \frac{C_{\rm GD}(0)}{(1 - V_{\rm GD}/\phi_i)^m} = \frac{0.1 \,\mathrm{pF}}{(1 + 5.665/0.8)^{1/3}} = 0.0498 \,\mathrm{pF}$$

The cutoff frequency from Eq. (1-73) is

$$f_T = \frac{g_m}{2\pi (C_{GS} + C_{GD})} = \frac{0.778 \times 10^{-3}}{(2) (\pi) (0.204 + 0.0498) \times 10^{-3}} = 488 \,\text{MHz}$$

Figure 1-32 Cross-sectional view of an n-channel MOS integrated-circuit transistor.

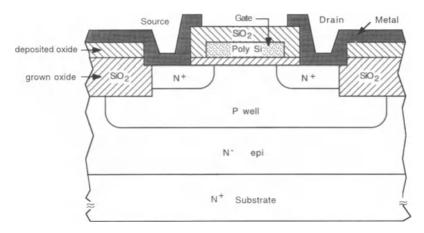

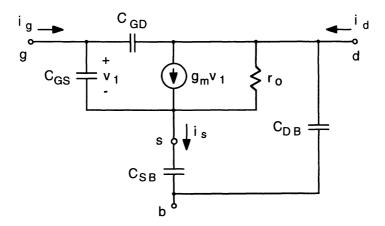

## 1.4 Metal-Oxide-Semiconductor Field-Effect Transistor

In the metal-oxide-semiconductor field-effect transistor (MOSFET), the gate control electrode is physically separated from the conducting channel by a thin insulating dielectric layer. The voltage applied to the gate electrode modulates the concentration of mobile carriers in the channel and hence its conductance. Like the JFET, the MOSFET is also a unipolar device. Shown in Fig. 1-32 is a cross-sectional view of an integrated-circuit n-channel MOS transistor. This structure, as with most modern MOSFETs, utilizes a polysilicon layer as the gate electrode in place of a metal layer; they are still referred to as metal-oxide-semiconductor (MOS) transistors, however. A thin (typically 30 - 80 nm thick) silicon dioxide layer separates the gate from the channel region, which extends laterally between the  $N^+$  source and drain contact regions.

#### **Device Characteristics**

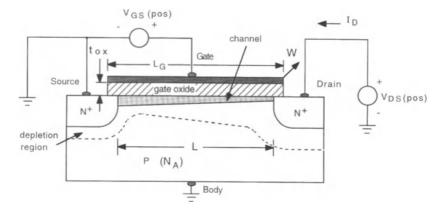

Figure 1-33 illustrates the active region of the n-channel MOSFET with normal biases applied. With zero voltage applied to the gate, there is no conducting channel between the  $N^+$  source and drain regions;\* the device acts like two back-to-back pn junctions and only a small reverse-leakage current flows from

<sup>\*</sup> There is a class of MOSFET devices in which a conducting channel exists even in the absence of an applied gate voltage. These are called depletion-mode devices and a negative gate voltage (positive for *p*-channel devices) is required to turn them off.

Figure 1-33 Active region of an *n*-channel MOSFET with normal bias applied.

source to drain. The gate-oxide-semiconductor sandwich acts like a parallel-plate capacitor; with a positive gate voltage  $V_{\rm GS}$  applied to the structure, negative charge is induced in the top surface region of the semiconductor beneath the gate oxide. If the gate voltage is large enough, this induced electron concentration will exceed the background hole concentration of the p-type semiconductor, creating an n-type region (inversion layer) at the surface, and there is now a complete n-type conducting channel between source and drain. The gate voltage required to create the inversion layer is termed the threshold voltage  $V_{\rm TH}$ ; for  $V_{\rm GS}$  less than  $V_{\rm TH}$ , no conducting channel exists and the device is turned off.

In normal practice, the semiconductor body (substrate) is connected to the source. In some applications, however, the body is connected to separate bias voltage. This bias changes the semiconductor channel potential and hence the charge that is induced by the gate. The effect on the threshold voltage is related to the body-source voltage  $V_{\rm BS}$  and is modeled as

$$V_{\rm TH} = V_{TO} + \gamma \left( \sqrt{2\phi_P - V_{\rm BS}} - \sqrt{2\phi_P} \right) \tag{1-74}$$

where  $V_{\text{T0}}$  is the threshold voltage for  $V_{\text{BS}} = 0$ . The parameter  $\gamma$  is given as

$$\gamma = \frac{\sqrt{2\varepsilon_s q N_A}}{C'_{\text{OX}}} \tag{1-75}$$

$C'_{OX}$  is the capacitance per unit area of the gate-oxide region, given by

$$C_{\rm ox}' = \frac{\varepsilon_{\rm ox}}{t_{\rm ox}} \tag{1-76}$$

where  $\varepsilon_{OX}$  is the dielectric permittivity of the oxide and  $t_{OX}$  is its thickness.  $\phi_P$  is the Fermi potential of the semiconductor, given by

$$\phi_P = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \tag{1-77}$$

With  $V_{\rm GS} > V_{\rm TH}$ , a conducting channel exists and the drain current  $I_D$  increases with increasing drain voltage  $V_{\rm DS}$ . As  $V_{\rm DS}$  is increased, the potential in the channel increases, being largest at the drain end of the channel. When  $V_{\rm DS} = V_{\rm GS} - V_{\rm TH}$ , the voltage across the gate oxide at the drain ( $V_{\rm GD} = V_{\rm GS} - V_{\rm DS}$ ) is no longer large enough to create the n-type inversion layer and the channel is pinched off at that point. This value of drain voltage, denoted  $V_{\rm Dsat}$ , is given by

$$V_{D\text{sat}} = V_{GS} - V_{TH} \tag{1-78}$$

and the corresponding drain current, denoted  $I_{Dsat}$ , is given by

$$V_{Dsat} = \frac{\mu_n C'_{OX} W}{2L} (V_{GS} - V_{TH})^2$$

(1-79)

where  $\mu_n$  is the electron mobility in the channel, and W and L are the channel width and length dimensions, respectively (as illustrated in Fig. 1-33).

For values of  $V_{\rm DS}$  less than  $V_{D\rm sat}$ , the drain current is well approximated by

$$I_{D=} \frac{\mu_n C'_{OX} W}{L} \left( V_{GS} - V_{TH} - \frac{1}{2} V_{DS} \right) V_{DS}$$

(1-80)

for  $V_{\rm DS} < V_{\rm GS} - V_{\rm TH}$  and describes operation in the triode region [11]. Note that the drain current is proportional to the channel width – channel length ratio W/L; this is analogous to the variation in collector current with emitter area  $A_E$  in a bipolar transistor.

For  $V_{\rm DS}$  larger than  $V_{D\rm sat}$ , the device is operating in the saturation region and the current is given by

$$I_D = \frac{\mu_n C'_{OX} W}{2L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(1-81)

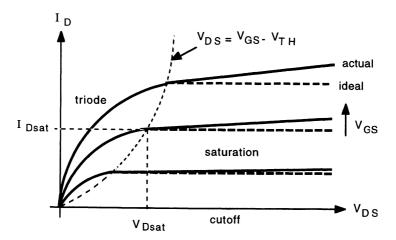

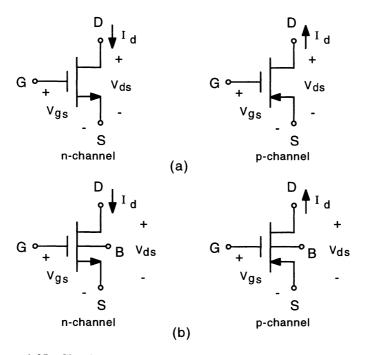

for  $V_{\rm DS} \ge V_{\rm GS} - V_{\rm TH}$ . In Eq. (1-81) we have included the channel-length modulation parameter  $\lambda$ , which models the narrowing of the inversion channel length as  $V_{\rm DS}$  is increased beyond  $V_{\rm DSat}$ . Figure 1-34 illustrates the  $I\!-\!V$  characteristics for an n-channel MOSFET. In a p-channel MOSFET,  $V_{\rm TH}$  is negative (positive for a depletion-mode device),  $V_{\rm GS}$  and  $V_{\rm DS}$  are negative, and current flows out of the drain. Figure 1-35 illustrates the circuit symbols and sign conventions for n-channel and p-channel MOSFETs.

Figure 1-34 I-V characteristics of an n-channel MOSFET. Actual devices show a finite output conductance in the saturation region, characterized by the channel-length modulation parameter  $\lambda$ .

Figure 1-35 Circuit symbols and sign conventions for n-channel and p-channel MOS transistors. (a) Normal symbols for body connected to source. (b) Symbols for separate body connection.

In the SPICE simulation program, the drain current is modeled as

$$I_{D} = \begin{cases} KP \frac{W}{L - 2X_{jl}} \left( V_{GS} - V_{TH} - \frac{1}{2} V_{DS} \right) V_{DS} (1 + \lambda V_{DS}) & \text{for } V_{GS} - V_{TH} > V_{DS} > 0 \\ \frac{KP}{2} \frac{W}{L - 2X_{jl}} (V_{GS} - V_{TH})^{2} (1 + \lambda V_{DS}) & \text{for } V_{DS} \ge V_{GS} - V_{TH} > 0 \end{cases}$$

(1-82)

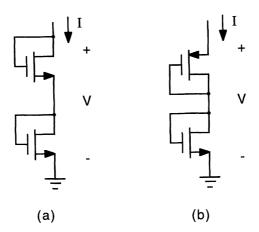

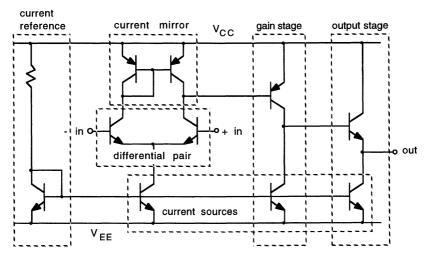

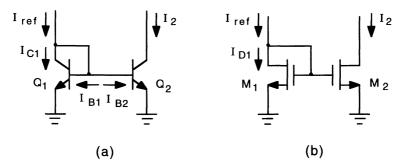

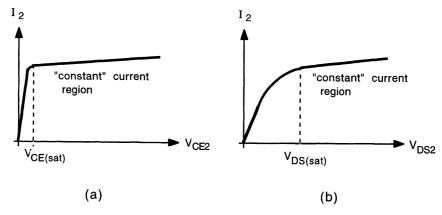

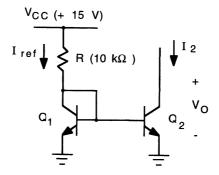

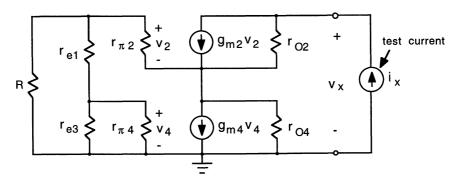

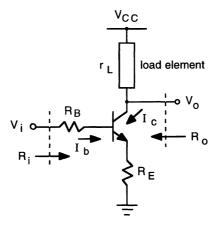

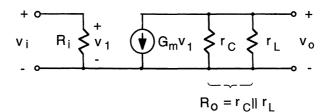

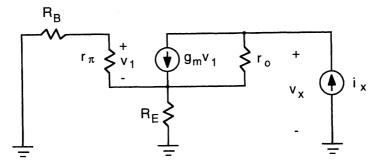

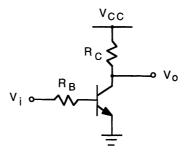

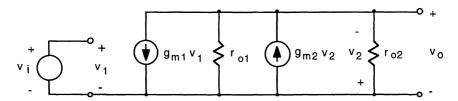

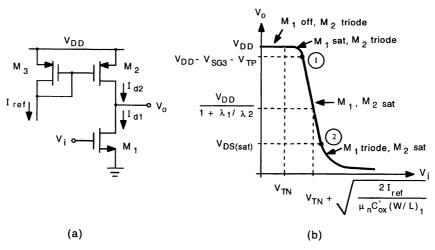

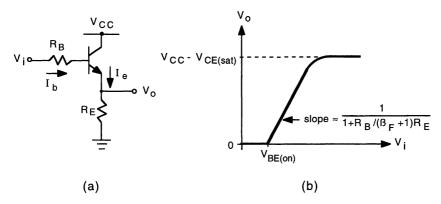

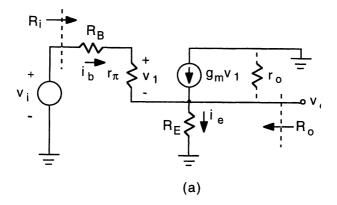

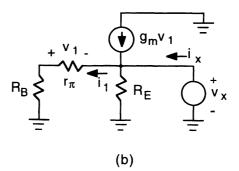

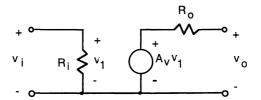

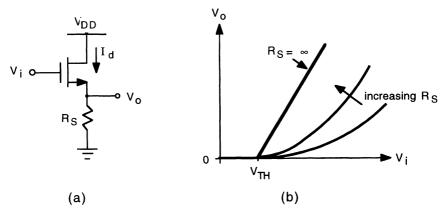

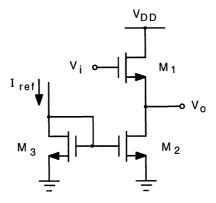

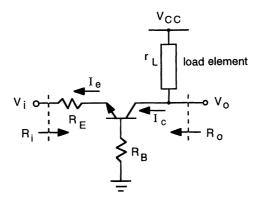

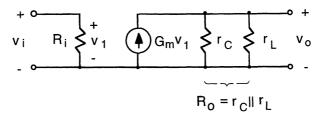

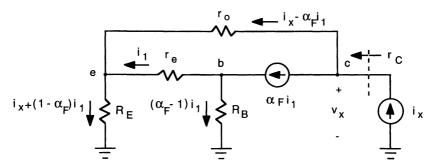

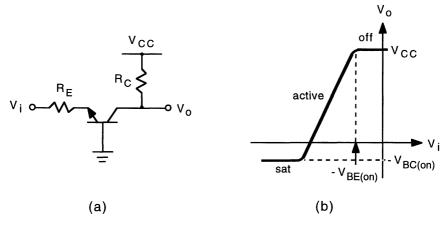

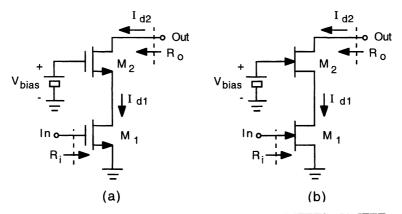

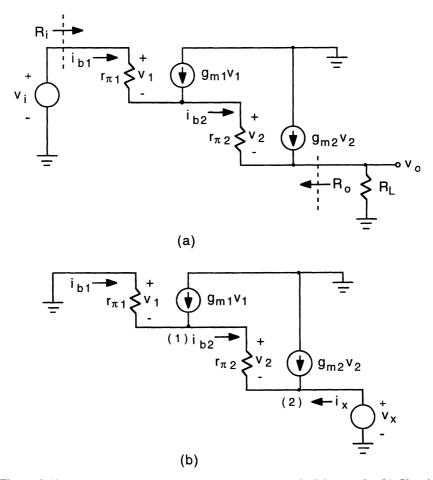

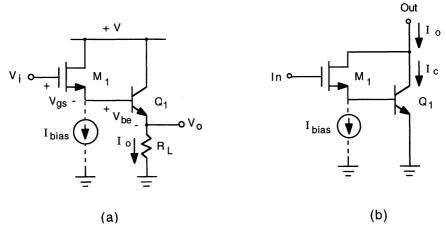

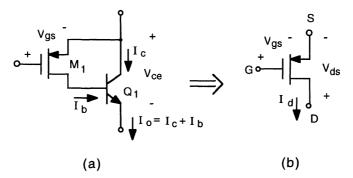

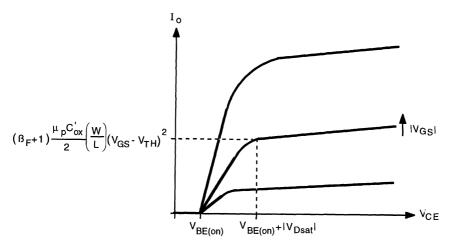

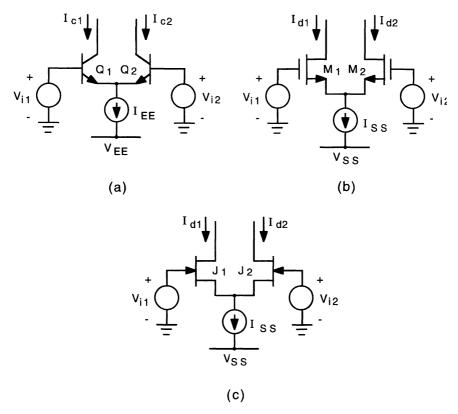

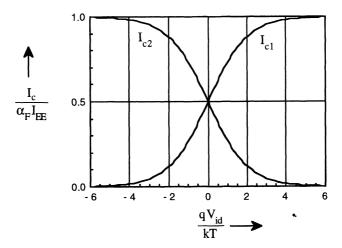

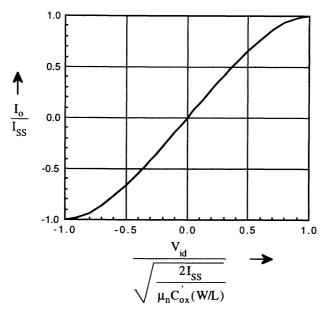

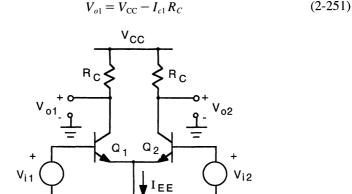

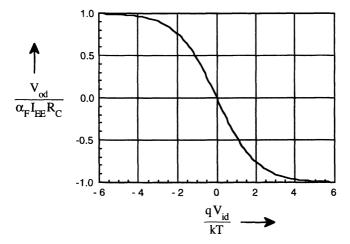

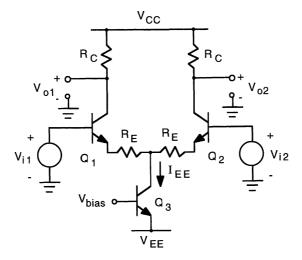

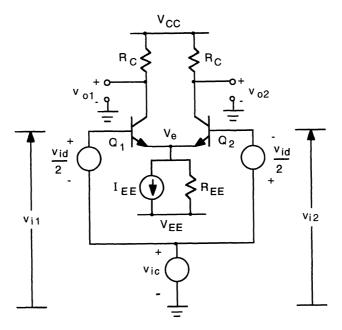

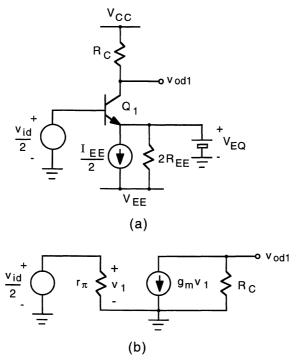

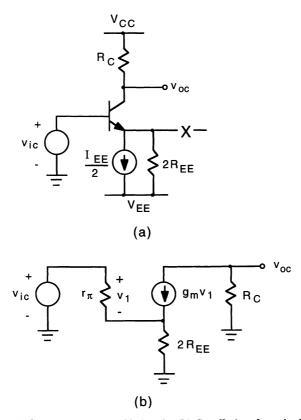

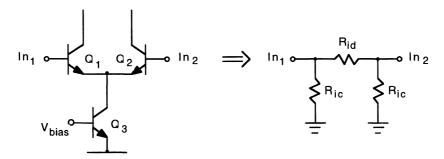

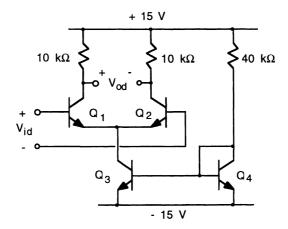

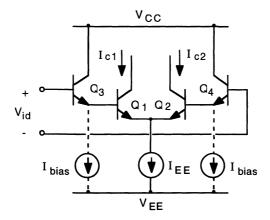

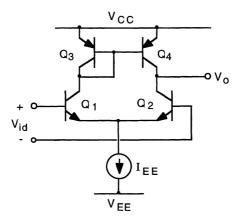

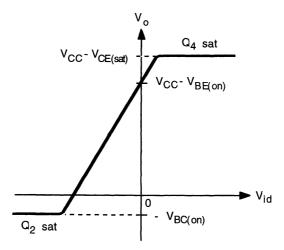

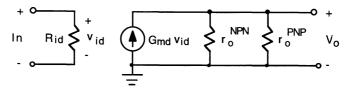

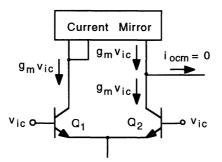

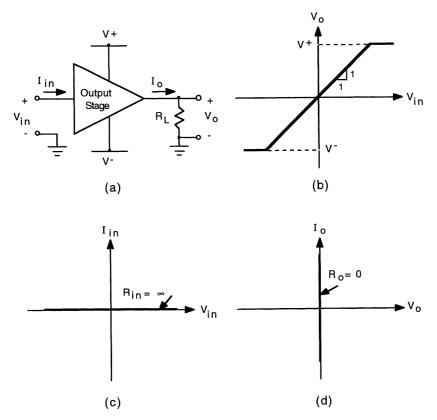

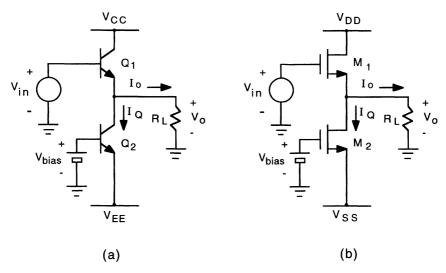

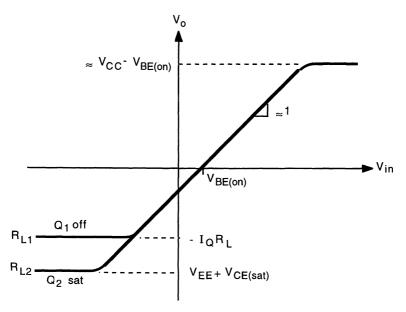

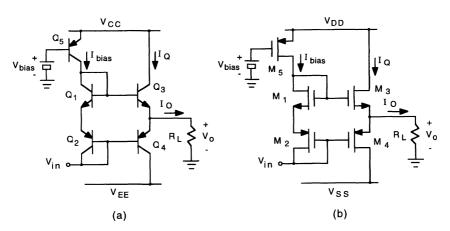

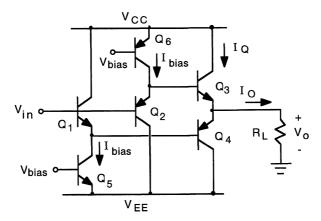

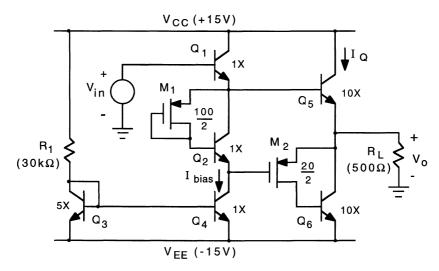

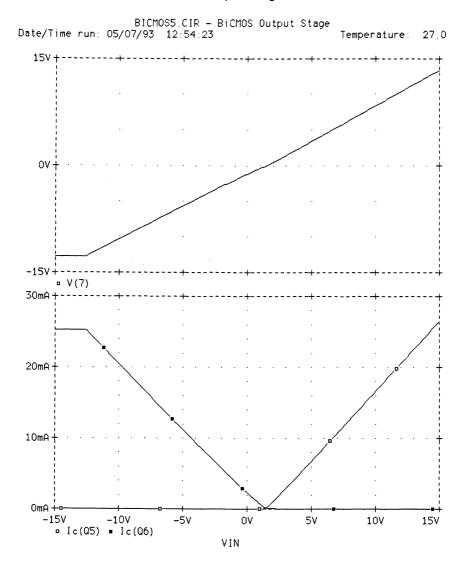

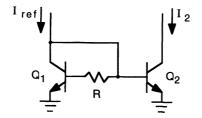

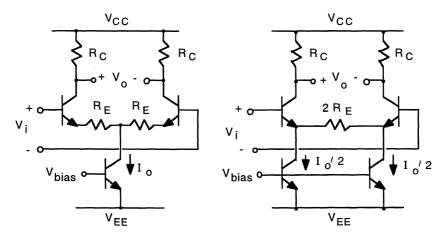

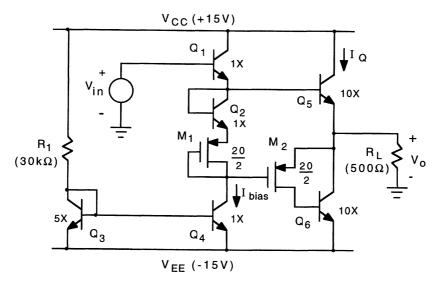

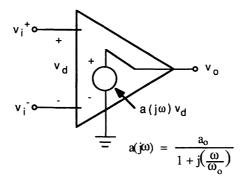

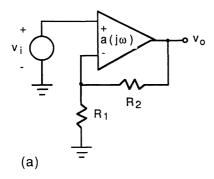

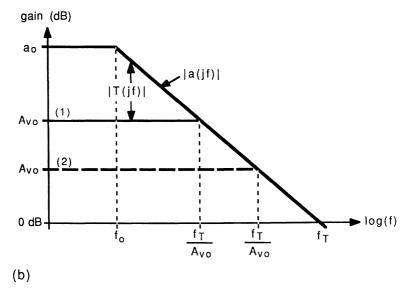

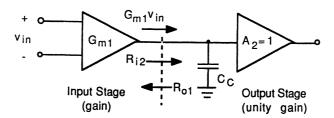

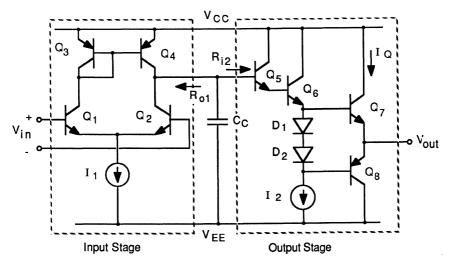

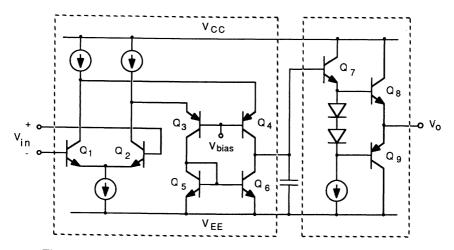

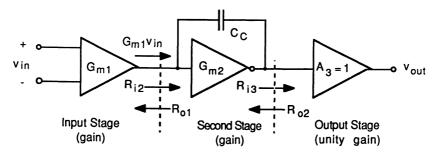

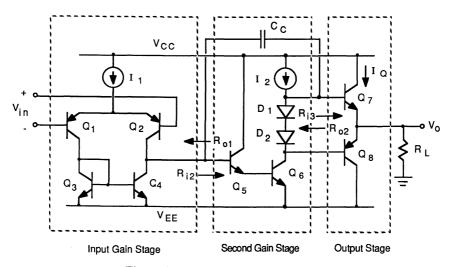

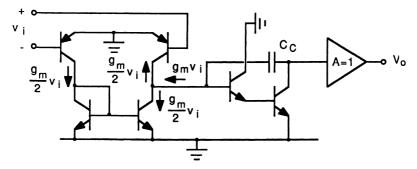

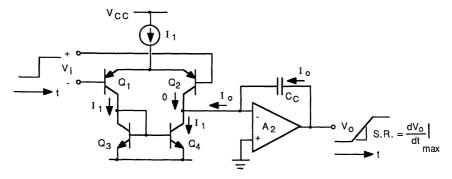

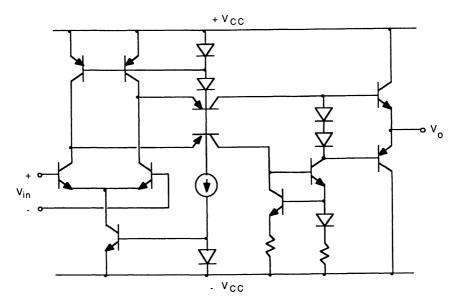

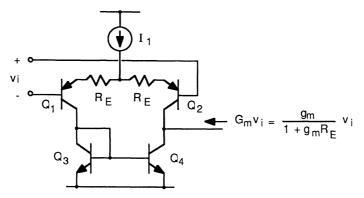

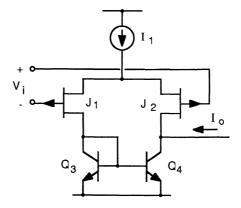

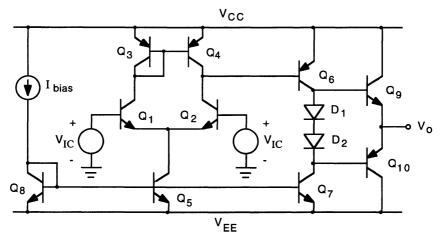

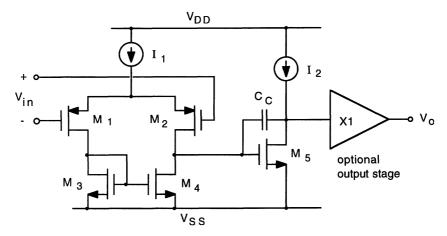

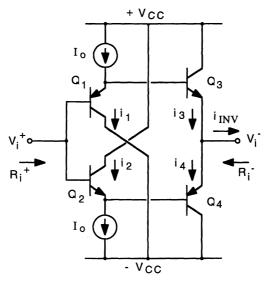

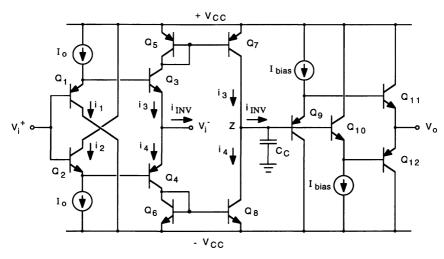

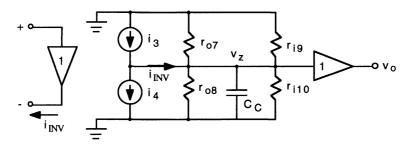

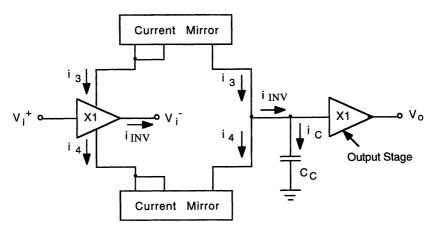

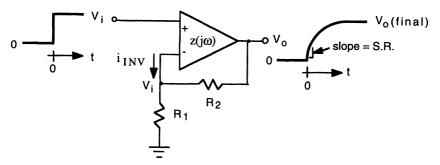

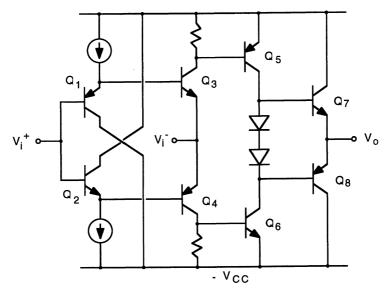

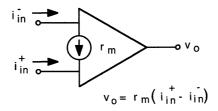

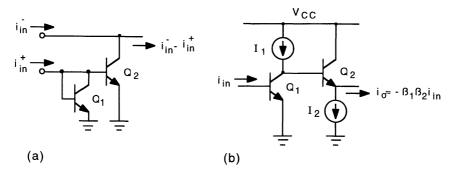

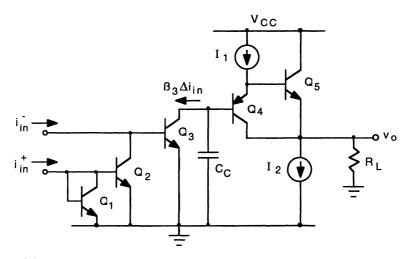

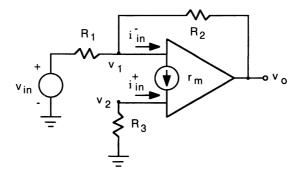

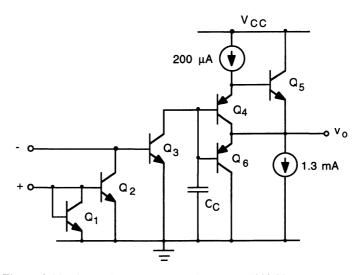

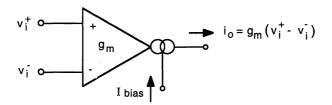

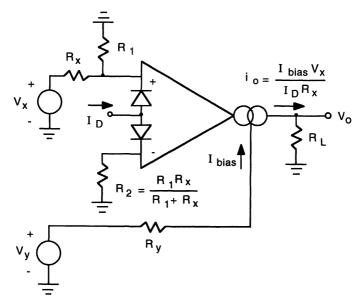

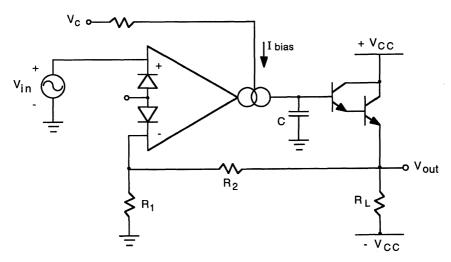

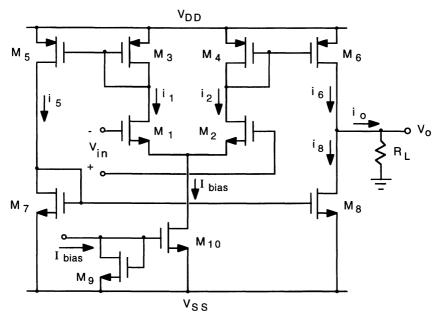

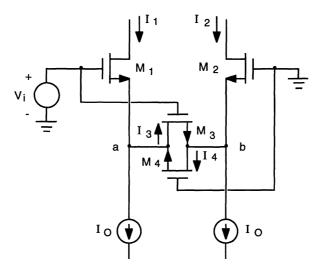

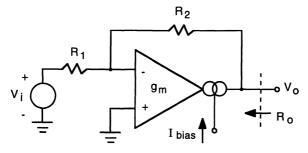

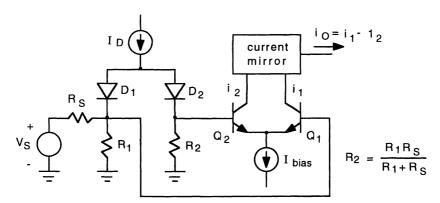

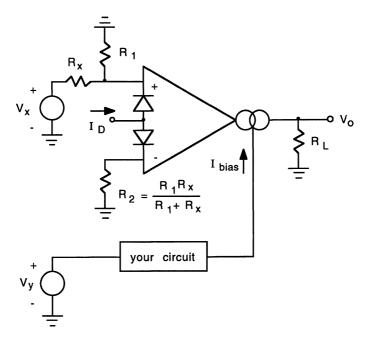

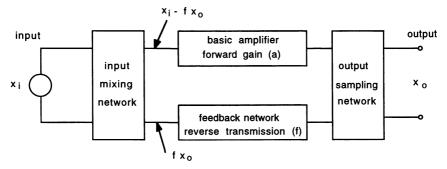

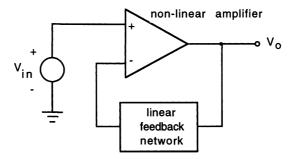

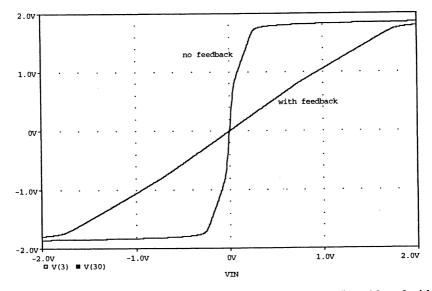

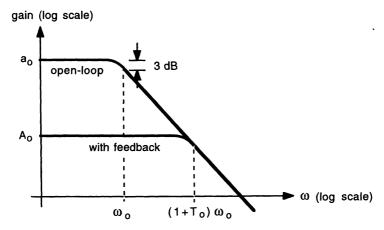

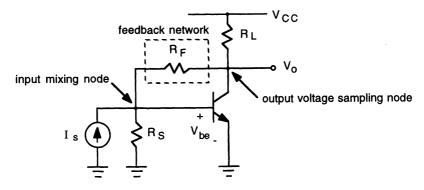

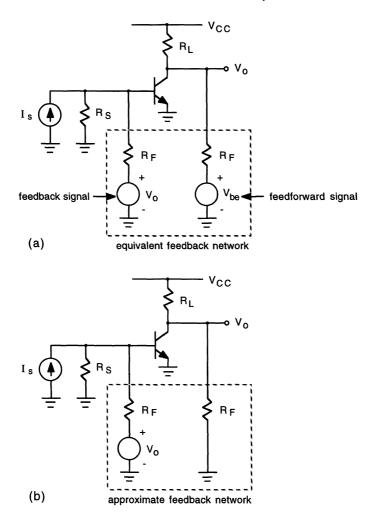

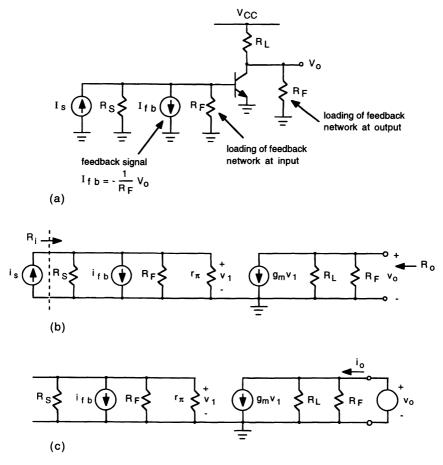

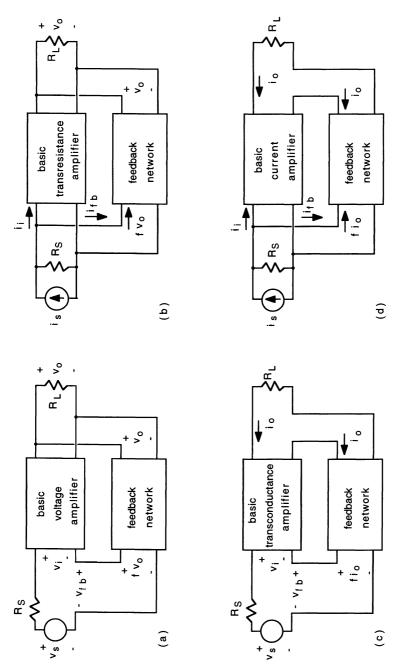

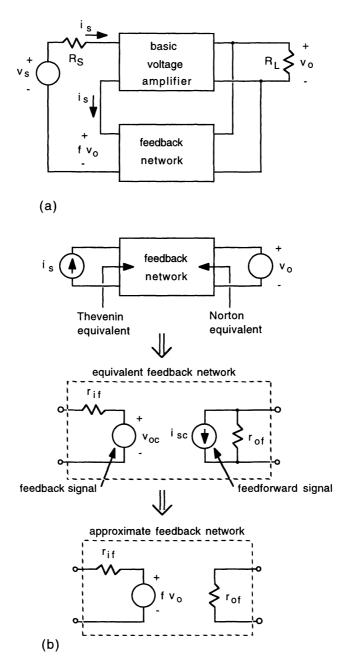

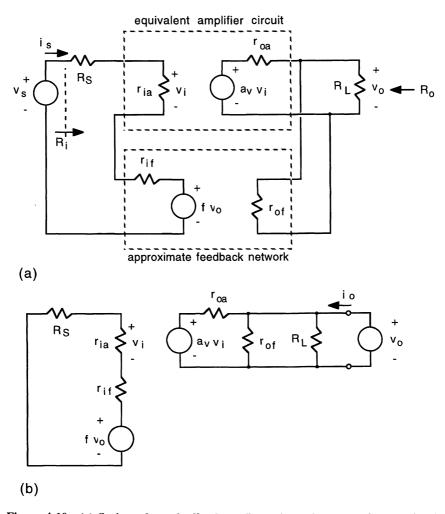

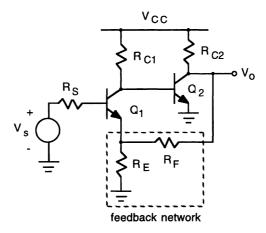

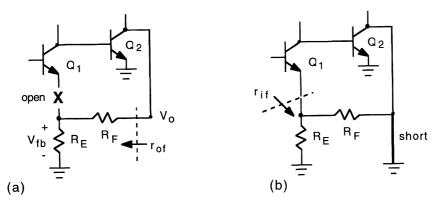

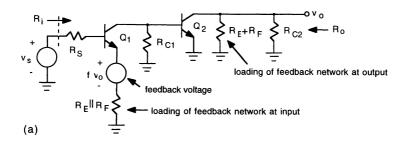

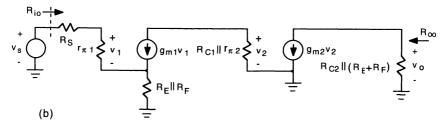

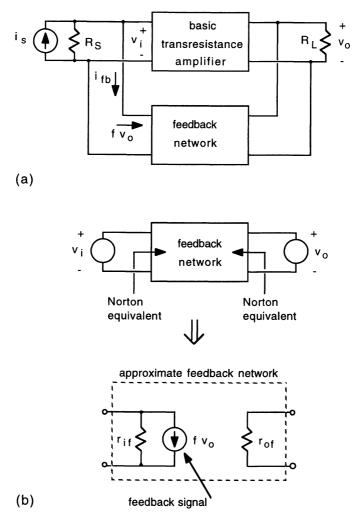

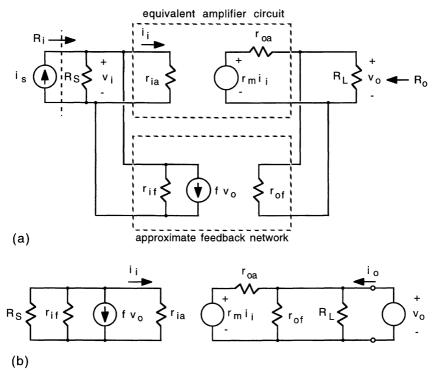

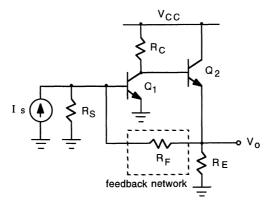

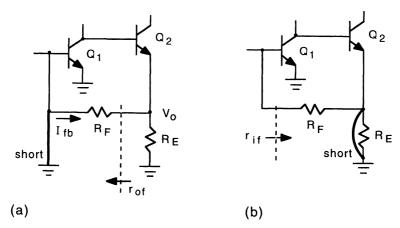

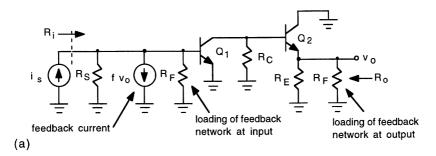

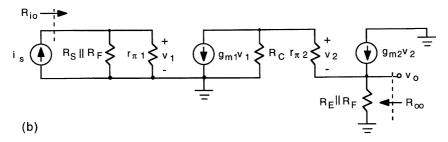

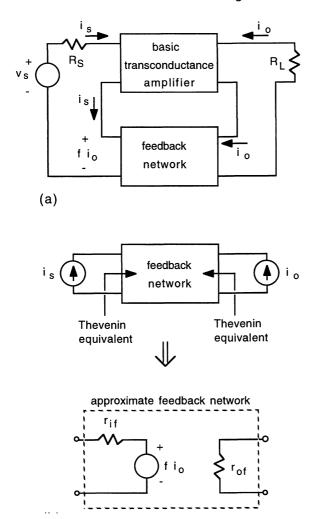

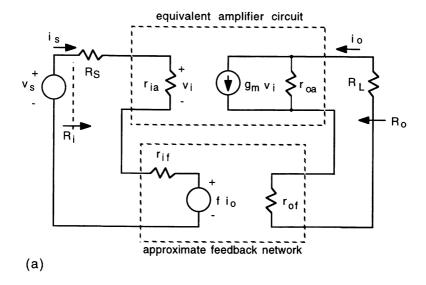

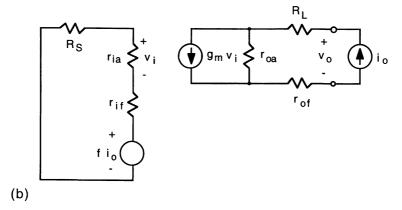

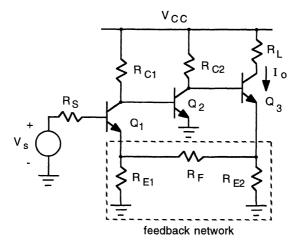

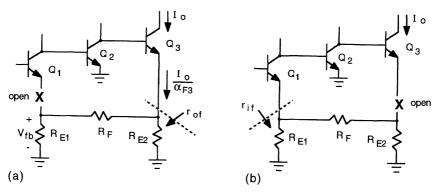

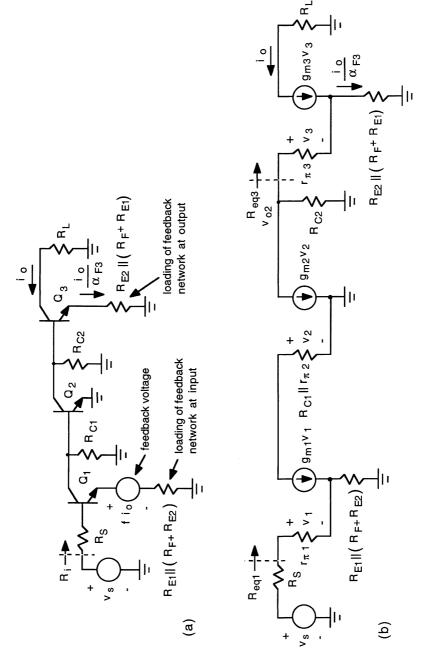

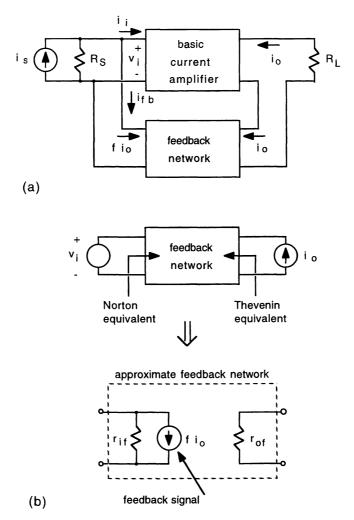

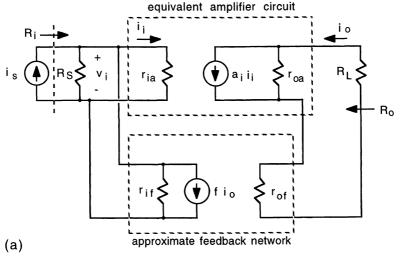

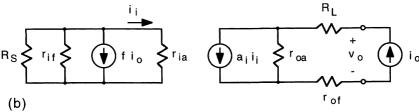

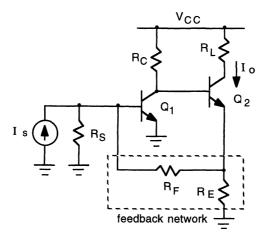

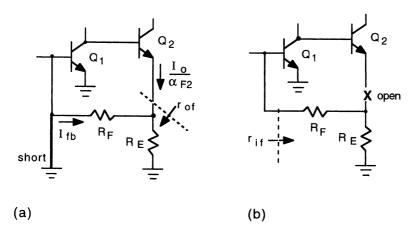

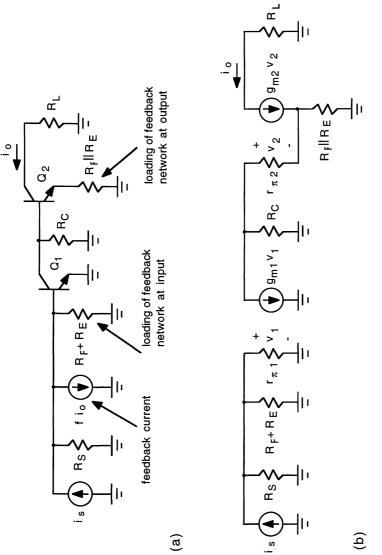

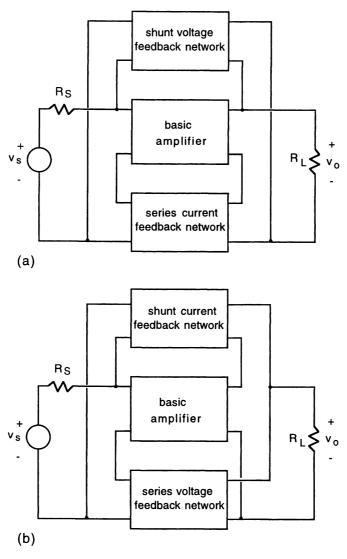

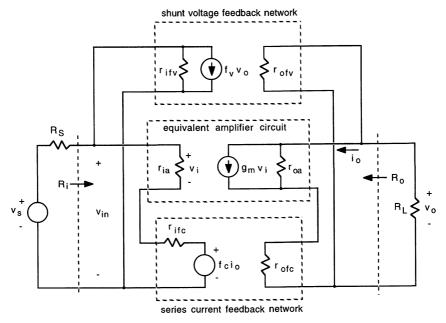

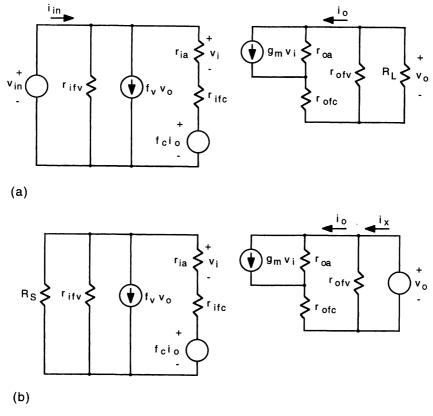

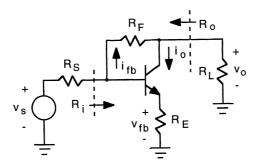

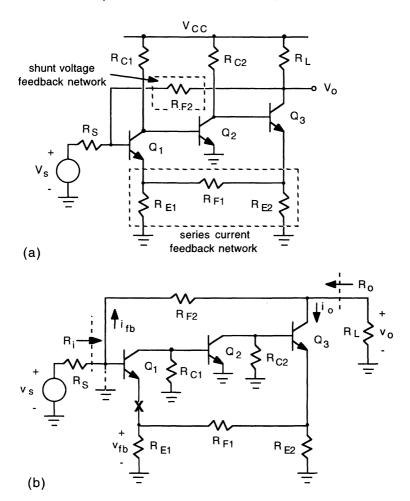

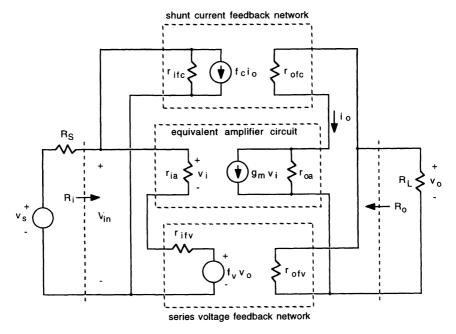

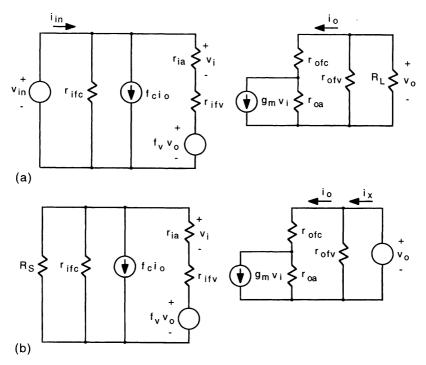

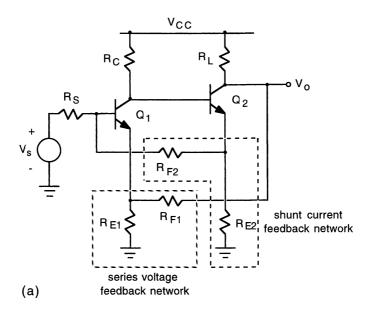

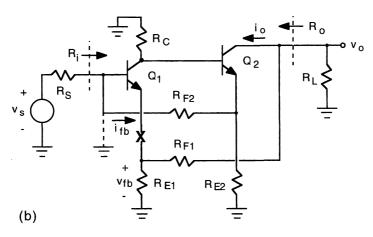

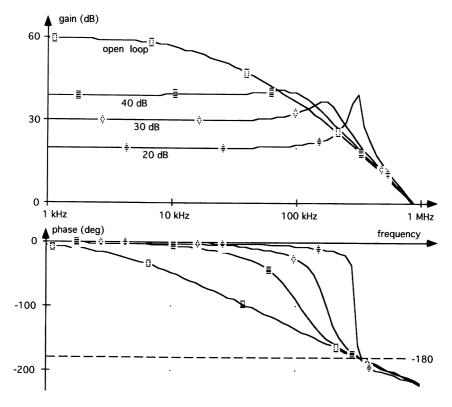

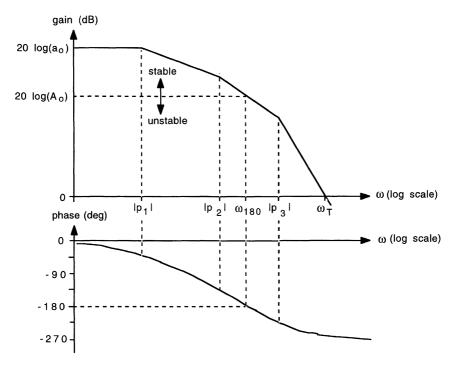

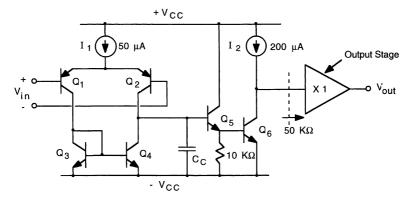

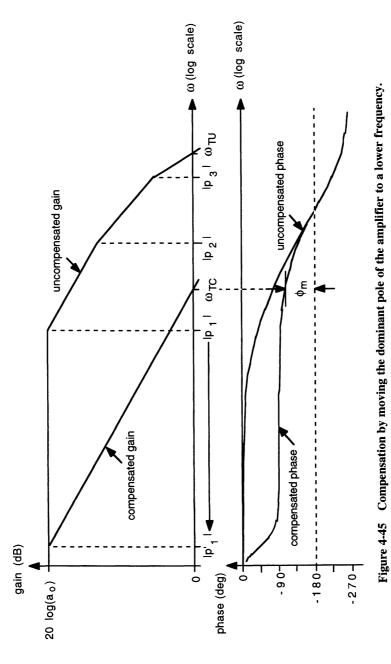

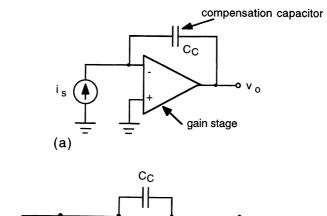

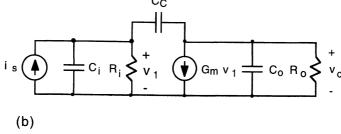

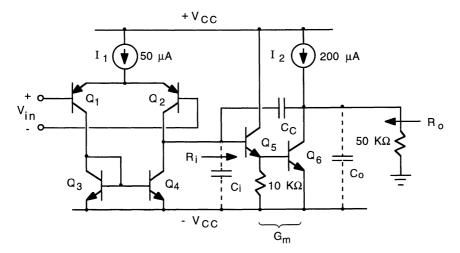

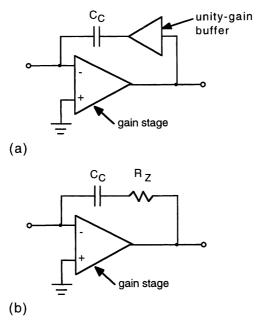

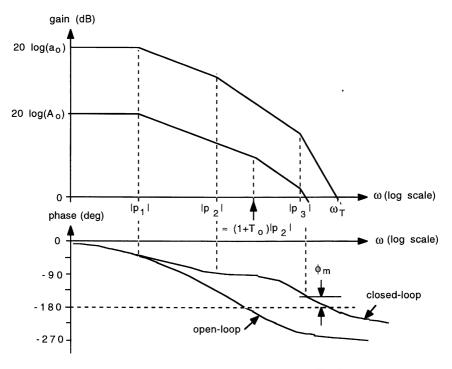

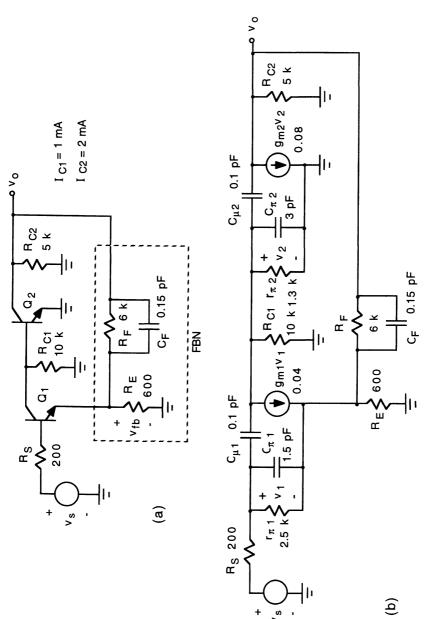

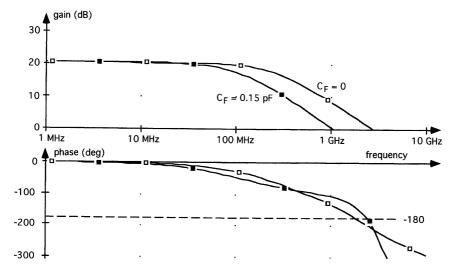

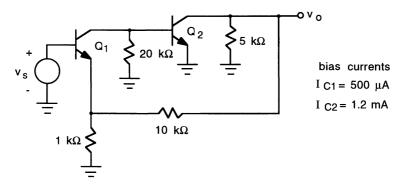

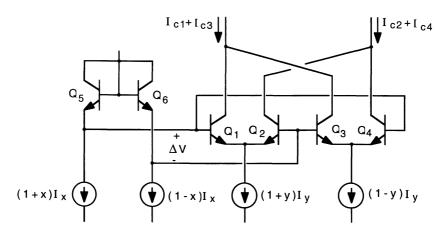

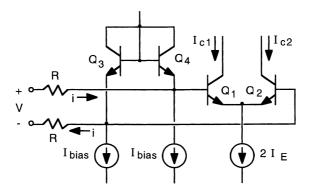

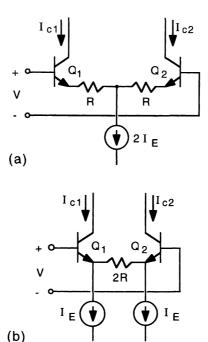

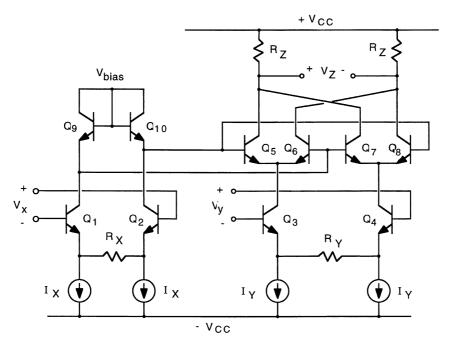

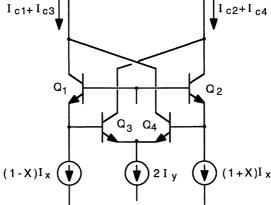

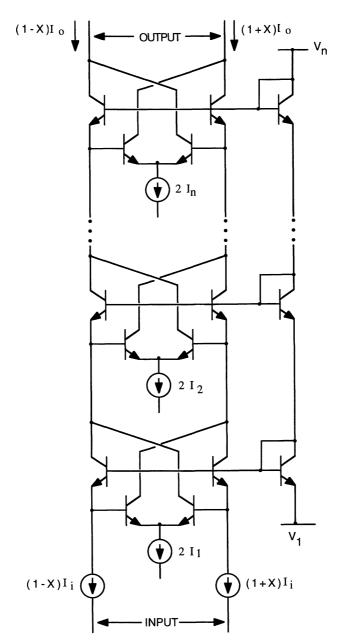

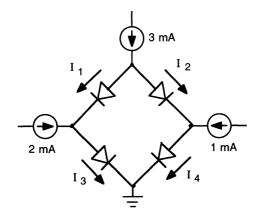

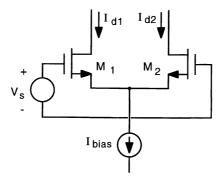

KP is the transconductance parameter and is equal to  $\mu_n C'_{OX}$ .  $X_{jl}$  is the distance by which the gate electrode overlaps the source and drain regions  $(2X_{jl} = L_G - L)$  in Fig. 1-33), and L is the gate length (labeled  $L_G$  in Fig. 1-33). The threshold voltage  $V_{TH}$  is modeled after Eq. (1-74) using the zero-bias threshold voltage parameter  $V_{TO}$  and the body-effect parameter  $\gamma$ . Alternately, in place of  $\gamma$ , the channel mobility  $\mu_n$  ( $\mu_p$  for the p-channel), oxide thickness  $t_{OX}$ , and channel doping concentration  $N_A$  ( $N_D$  for the p-channel) may be used as model parameters.