# Electronic Circuit and System Simulation Methods

Lawrence T. Pillage

Ronald A. Rohrer

Chandramouli Visweswariah

### Library of Congress Cataloging-in-Publication Data

Pillage, Lawrence.

Electronic circuit and system simulation methods / Lawrence Pillage, Ronald A. Rohrer, Chandramouli Visweswariah.

p. cm.

Includes index.

ISBN 0-07-050169-6

1. Linear integrated circuits—Computer simulation. 2. SPICE (Computer file) I. Rohrer, Ronald A. II. Visweswariah, Chandramouli. III. Title.

TK7874.P52 1994 621.3815'01'1353—dc20

94-24429

CIP

Copyright © 1995 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1234567890 DOC/DOC 90987654

ISBN 0-07-050169-6

The sponsoring editor for this book was Stephen S. Chapman.

Printed and bound by R. R. Donnelley & Sons Company.

Information contained in this work has been obtained by McGraw-Hill, Inc., from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein, and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

### Other McGraw-Hill Books of Interest

### **Handbooks**

CHEN • Computer Engineering Handbook

COOMBS • Printed Circuits Handbook

COOMBS • Electronic Instruments Handbook, Second Edition

DI GIACOMO • Digital Bus Handbook

FINK AND CHRISTIANSEN • Electronics Engineers' Handbook

HARPER • Electronic Packaging and Interconnection Handbook

JURAN AND GRYNA • Juran's Quality Control Handbook

RORABAUGH • Digital Filter Designer's Handbook

TUMA • Engineering Mathematics Handbook

WAYNANT • Electro-Optics Handbook

WILLIAMS AND TAYLOR • Electronic Filter Design Handbook

### Other

ANTOGNETTI • Power Integrated Circuits

BEST • Phase-Locked Loops, Second Edition

BUCHANAN • CMOS/TTL Digital Systems Design

BUCHANAN • BiCMOS/CMOS Systems Design

BYERS • Printed Circuit Board Design with Microcomputers

DAUGHERTY • Analog to Digital Conversion

**ELLIOTT** • Integrated Circuits Fabrication Technology

HECHT • The Laser Guidebook

KIELKOWSKI • Inside SPICE

LICARI • Multichip Module Design

MASSOBRIO AND ANTOGNETTI • Semiconductor Device Modeling with SPICE, Second Edition

SZE • VLSI Technology

TABAK • Advanced Microprocessors, Second Edition

TSUI • LSI/VLSI Testability Design

WATERS • Active Filter Design

WOBSCHALL • Circuit Design for Electronic Instrumentation

WALKER • Optical Engineering Fundamentals

### Table of Contents

| Preface | ••••••                                                             | ix |

|---------|--------------------------------------------------------------------|----|

| Chapte  | r 1 Introduction to Circuit Simulation                             | 1  |

| 1.1     | Traditional Circuit Simulation                                     | 1  |

| 1.2     | Linear, Time-Invariant Circuits                                    | 2  |

| 1.3     | Nodal Analysis                                                     | 4  |

| 1.4     | Nodal Admittance Equation Stamps                                   | 6  |

| 1.5     | Nonlinear (dc) Circuit Analysis                                    | 11 |

| 1.6     | Small Signal (ac) Analysis                                         | 17 |

| 1.7     | Linear Transient Analysis                                          | 18 |

| 1.8     | Nonlinear Transient Analysis                                       | 24 |

| 1.9     | Summary                                                            | 24 |

| 1.10    | References                                                         | 26 |

| Chapte  | r 2 Linear dc Nodal Analysis                                       | 27 |

| 2.1     | Voltage-Controlled Current Sources                                 | 27 |

| 2.2     | Independent Voltage Sources                                        | 31 |

| 2.3     | (Conventional) Nodal Analysis                                      | 34 |

| 2.4     | Controlled Sources in General                                      | 36 |

| 2.5     | Operational Amplifiers                                             |    |

| 2.6     | When Do Nodal Equations Fail?                                      | 42 |

| 2.7     | DC Solution of Circuits with Energy Storage: C-cutsets and L-loops | 43 |

| 2.8     | Summary                                                            | 44 |

| 2.9     | References                                                         | 45 |

| Chapte  | er 3 Solution of Linear Equations                                  | 47 |

| 3.1     | Gaussian Elimination                                               | 47 |

| 3.2     | LU Factorization                                                   | 50 |

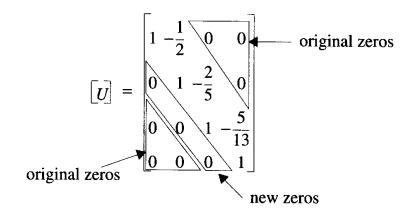

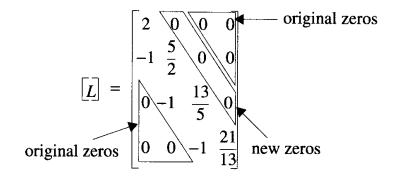

| 3.3     | How LU Factorization Works                                         | 54 |

| 3.4     | Pivot Conditioning                                                 |    |

| 3.5     | Iterative Refinement                                               |    |

|              | 3.6                                    | Sensitivity Analysis                                                                                                                                                                                                                                            | 67                                     |

|--------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|              | 3.7                                    | Summary                                                                                                                                                                                                                                                         | 74                                     |

|              | 3.8                                    | References                                                                                                                                                                                                                                                      | 74                                     |

| Ch           | antei                                  | 4 Linear Transient Analysis I                                                                                                                                                                                                                                   | 75                                     |

| <b>O</b> 1.  | 4.1                                    | The One-Step Integration Approximations                                                                                                                                                                                                                         | /3                                     |

|              | 4.2                                    | Forward Euler Approximation                                                                                                                                                                                                                                     | 80                                     |

|              | 4.3                                    | Backward Euler Approximation                                                                                                                                                                                                                                    | 81                                     |

|              | 4.4                                    | Trapezoidal Approximation                                                                                                                                                                                                                                       | 82                                     |

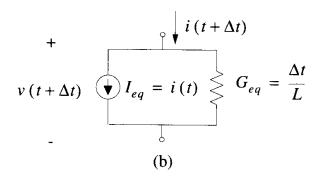

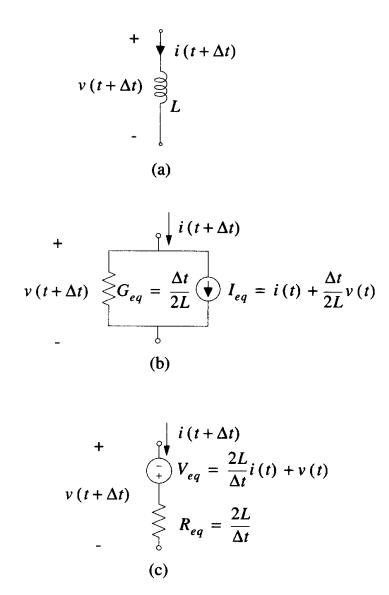

|              | 4.5                                    | Companion Models for Inductors                                                                                                                                                                                                                                  | 82                                     |

|              | 4.6                                    | Preliminary Comments on Accuracy                                                                                                                                                                                                                                | 86                                     |

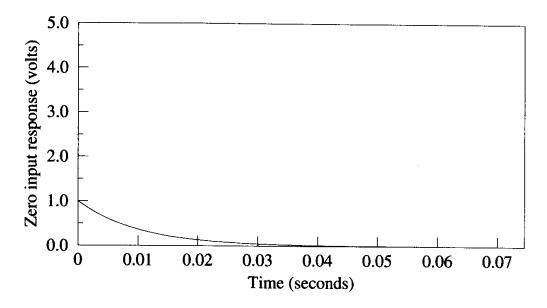

|              | 4.7                                    | The Exact Solution of a Simple Series RC Circuit                                                                                                                                                                                                                | 87                                     |

|              | 4.8                                    | Comparison of One-Step Integration Approximations with the Exact                                                                                                                                                                                                |                                        |

|              |                                        | Solution                                                                                                                                                                                                                                                        | 95                                     |

|              | 4.9                                    | Accuracy of One-Step Approximations                                                                                                                                                                                                                             | 100                                    |

|              | 4.10                                   | Stability of One-Step Integration Approximation                                                                                                                                                                                                                 | 105                                    |

|              | 4.11                                   | LTE Estimation via Divided Difference Approximations                                                                                                                                                                                                            | 109                                    |

|              | 4.12                                   | Inductance                                                                                                                                                                                                                                                      | 113                                    |

|              | 4.13                                   | Summary                                                                                                                                                                                                                                                         | 113                                    |

|              | 4.14                                   | References                                                                                                                                                                                                                                                      | 113                                    |

|              | h 4                                    | r 5 Linear Transient Analysis II                                                                                                                                                                                                                                | 115                                    |

| C            | _                                      | r 5 Lillear Transfellt Analysis 11                                                                                                                                                                                                                              | 115                                    |

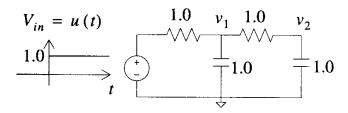

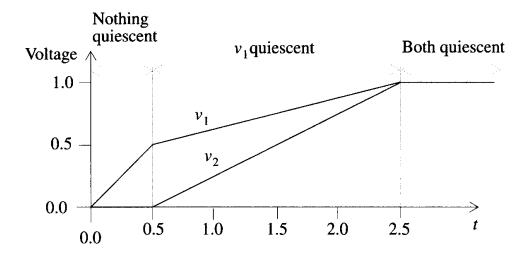

|              | 5.1                                    | Multiple Energy Storage Elements                                                                                                                                                                                                                                | 125                                    |

|              | 5.2                                    | Step and Ramp Inputs                                                                                                                                                                                                                                            | 128                                    |

|              | 5.3                                    | One-Step Integration Approximations                                                                                                                                                                                                                             | 134                                    |

|              | 5.4                                    | Stability                                                                                                                                                                                                                                                       | 130                                    |

|              | 5.5                                    | Limitations of One-Step Integration Models                                                                                                                                                                                                                      | 1 <i>37</i><br>1 <i>4</i> 0            |

|              | 5.6                                    | References                                                                                                                                                                                                                                                      | 140                                    |

| $\mathbf{C}$ | hante                                  | er 6 Frequency Domain Analysis and Moment-                                                                                                                                                                                                                      |                                        |

| _            |                                        |                                                                                                                                                                                                                                                                 | 1/1                                    |

|              |                                        | Matching Methods                                                                                                                                                                                                                                                | 141                                    |

|              | 6.1                                    | Matching Methods                                                                                                                                                                                                                                                | 141                                    |

|              | 6.1<br>6.2                             | Small Signal ac Analysis                                                                                                                                                                                                                                        | 141                                    |

|              | 6.2                                    | Small Signal ac Analysis                                                                                                                                                                                                                                        | 141<br>145                             |

|              | 6.2<br>6.3                             | Small Signal ac Analysis  Pole/Zero Analysis  Laplace Transform of the State Equations                                                                                                                                                                          | 141<br>145<br>147                      |

|              | 6.2<br>6.3<br>6.4                      | Small Signal ac Analysis                                                                                                                                                                                                                                        | 141<br>145<br>147<br>149<br>152        |

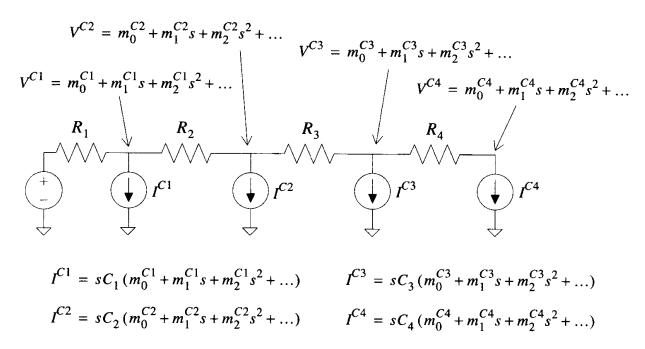

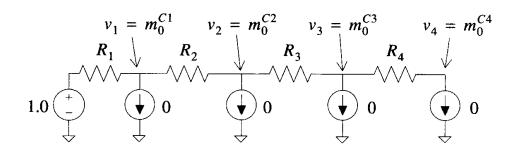

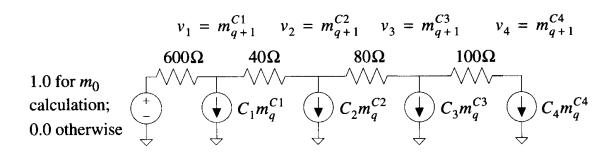

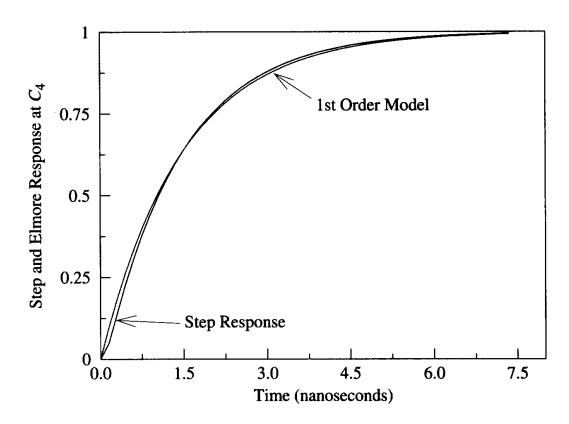

|              | 6.2<br>6.3<br>6.4<br>6.5               | Small Signal ac Analysis                                                                                                                                                                                                                                        | 141<br>145<br>147<br>149<br>152        |

|              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6        | Small Signal ac Analysis  Pole/Zero Analysis  Laplace Transform of the State Equations  Moments of the Impulse Response and Linear Delay Estimation  The Elmore Delay and RC Trees  Moments of the Impulse Response  Efficiently Computing Moments for RC Trees | 141<br>145<br>147<br>149<br>153<br>156 |

|              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Small Signal ac Analysis  Pole/Zero Analysis  Laplace Transform of the State Equations  Moments of the Impulse Response and Linear Delay Estimation  The Elmore Delay and RC Trees  Moments of the Impulse Response  Efficiently Computing Moments for RC Trees | 141<br>145<br>147<br>152<br>153        |

|              | 6.2<br>6.3<br>6.4<br>6.5<br>6.6        | Small Signal ac Analysis                                                                                                                                                                                                                                        | 141145147152153156                     |

| 6.11         | Generalized Moment Matching                                         | 169 |

|--------------|---------------------------------------------------------------------|-----|

| 6.12         | Practical (Numerical) Considerations                                |     |

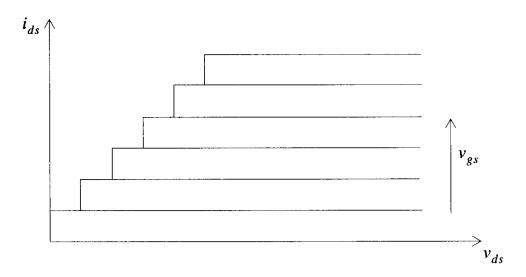

| 6.13         | Sensitivity Analysis                                                |     |

| 6.14         | Conclusions                                                         |     |

| 6.15         | References                                                          |     |

| Chanta       | r 7 Sparsa Matrices and Same of Their                               |     |

| Chapte       | r 7 Sparse Matrices and Some of Their Implications                  | 180 |

| 77 1         | -                                                                   |     |

| 7.1          | Introduction                                                        |     |

| 7.2          | Sparse Nodal Admittance Matrices                                    |     |

| 7.3          | Ordering of Sparse Matrices                                         |     |

| 7.4          | Suboptimal Ordering                                                 |     |

| 7.5          | Numerical Conditioning and Partial Pivoting                         |     |

| 7.6          | Sparse Tableau Analysis                                             |     |

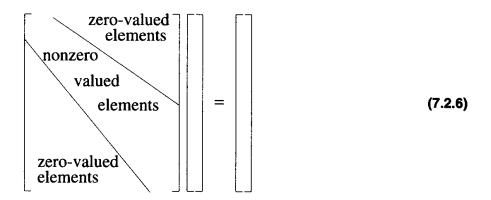

| 7.7          | Qualitative Attributes of the Sparse Tableau                        |     |

| 7.8          | Relation of the Sparse Tableau to Other Solution Schemes            |     |

| 7.9          | The Original Sparse Tableau Approach                                |     |

| 7.10         | Some Sparse Tableau Modeling Considerations                         |     |

| 7.11         | References                                                          | 214 |

| Chapte       | r 8 Circuit Partitioning and Large Change                           |     |

| onupte       | Sensitivity                                                         | 217 |

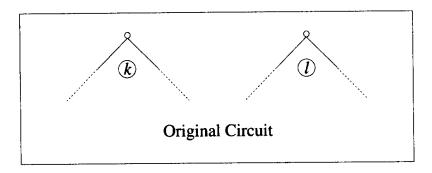

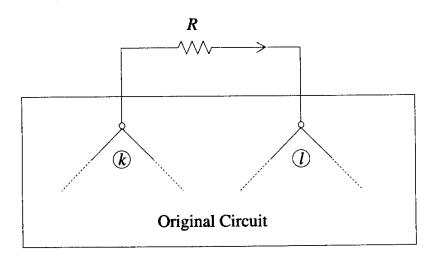

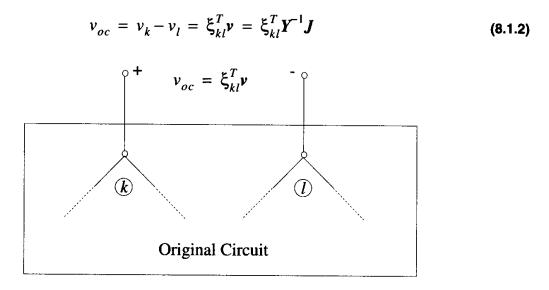

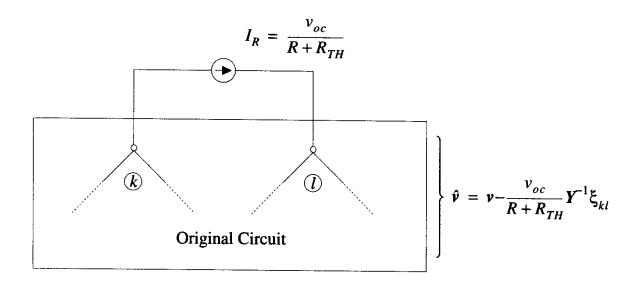

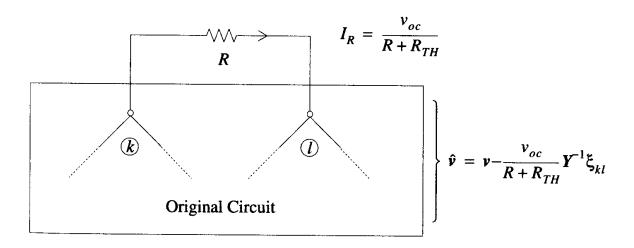

| 8.1          | Adding a Resistance Between Two Nodes                               |     |

| 8.2          | Node Tearing                                                        |     |

| 8.3          | Multiple Voltage Source Additions                                   |     |

| 8.4          | References                                                          |     |

| Chanta       | w O. Imamamantal Canaitivity                                        | 220 |

| _            | r 9 Incremental Sensitivity                                         |     |

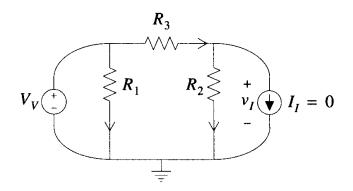

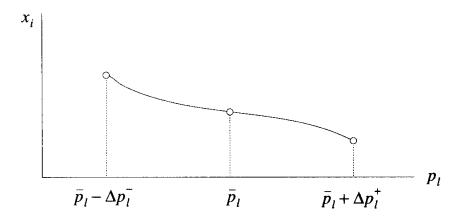

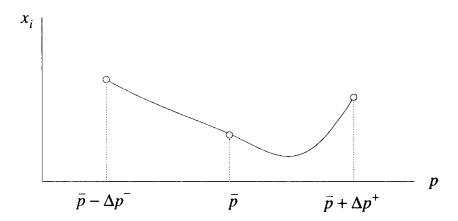

| 9.1          | Direct Circuit Sensitivities                                        |     |

| 9.2          | Matrix Interpretation of Direct Sensitivity                         |     |

| 9.3          | Controlled Sources and Nonlinear Elements                           |     |

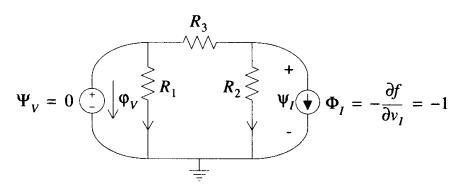

| 9.4          | Adjoint Sensitivity Analysis                                        |     |

| 9.5          | The Adjoint Sensitivity Relation                                    |     |

| 9.6          | Simple Reciprocal (R, G, V, I) Linear dc Circuits                   |     |

| 9.7          | Sensitivities with Respect to Dependent Source Values               | 259 |

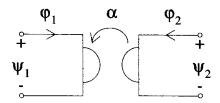

| 9.8          | Adjoint Circuit Representation of Some Other Multi-Terminal Circuit | 044 |

| 0.0          | Elements                                                            |     |

| 9.9          | The Sparse Tableau Interpretation of Adjoint Sensitivity            |     |

| 9.10         | Some Possible Applications of Adjoint Sensitivity                   |     |

| 9.11<br>9.12 | Time and Frequency Domain Sensitivity Analysis                      |     |

| 7.1 <i>2</i> | References                                                          | 283 |

| 10.1       | SPICE                                           | 285 |

|------------|-------------------------------------------------|-----|

| 10.2       | Nonlinear de Analysis                           | 287 |

| 10.3       | Newton-Raphson Iteration                        | 288 |

| 10.4       | Damped Newton-Raphson Iteration                 | 291 |

| 10.5       | Multi-Dimensional Newton-Raphson Iteration      | 295 |

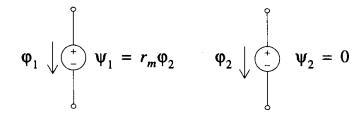

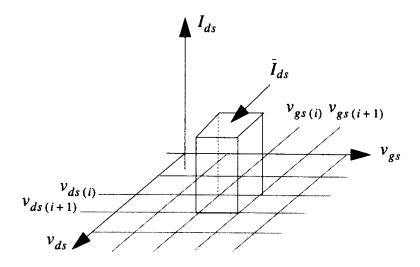

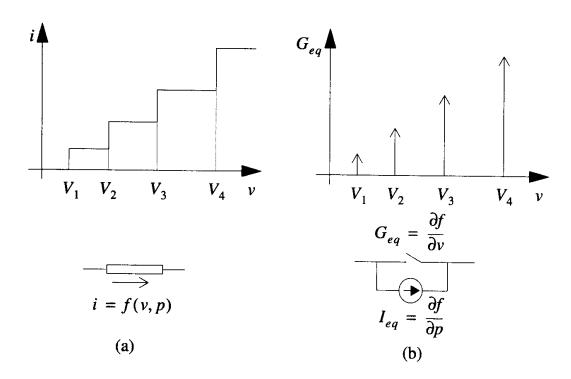

| 10.6       | Multi-Terminal Elements                         | 297 |

| 10.7       | Nonlinear Transient Analysis                    | 306 |

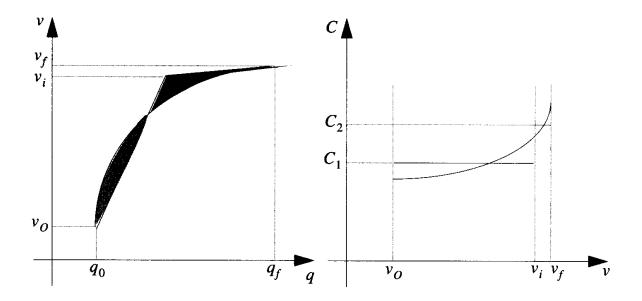

| 10.8       | Nonlinear Energy Storage Elements               | 308 |

| 10.0       | The Rottom Line                                 | 313 |

| 10.10      | References                                      | 314 |

|            |                                                 |     |

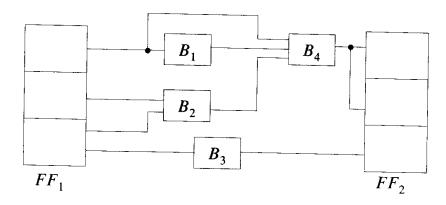

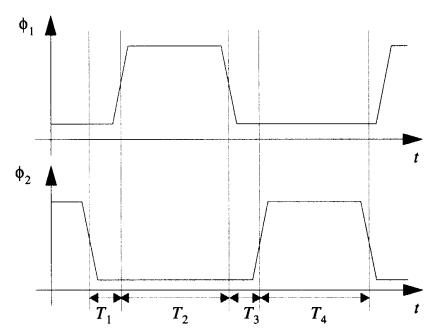

| hapter     | 11 Timing Simulation                            |     |

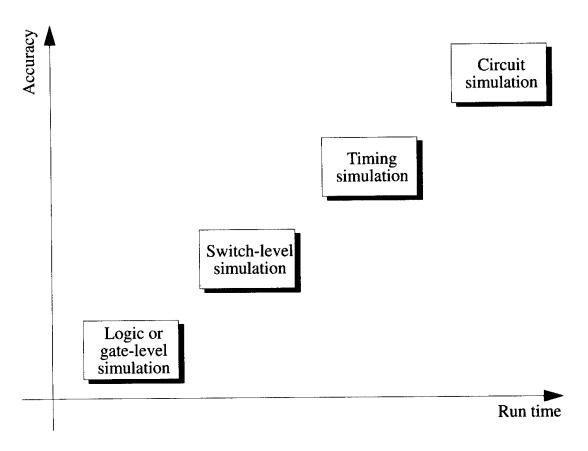

| 11.1       | The Quest for Other Methods of Simulation       | 313 |

| 11.2       | Static vs. Dynamic Simulation                   | 316 |

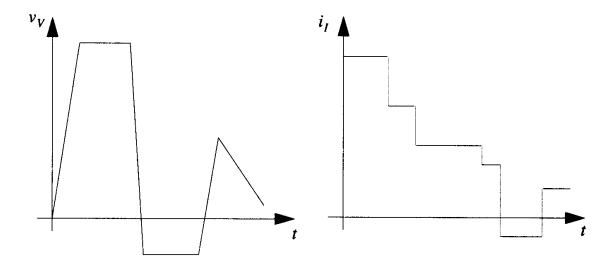

| 11.3       | Dynamic Simulation                              | 317 |

| 11.4       | Motivation for Timing Simulation                | 322 |

| 11.5       | The MOS Timing Simulator (MOTIS)                | 325 |

| 11.6       | ELogic and SAMSON                               | 328 |

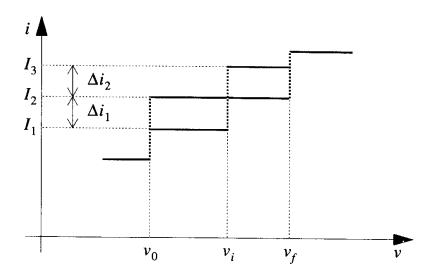

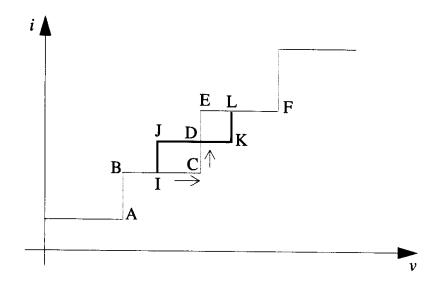

| 11.7       | Piecewise Approximate Timing Simulation         | 332 |

| 11.8       | Relaxation Methods in Circuit Simulation        | 349 |

| 11.9       | Conclusions                                     | 356 |

| 11.10      | References                                      | 356 |

| nnend      | ix A Tree/Link Analysis                         | 361 |

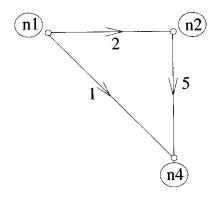

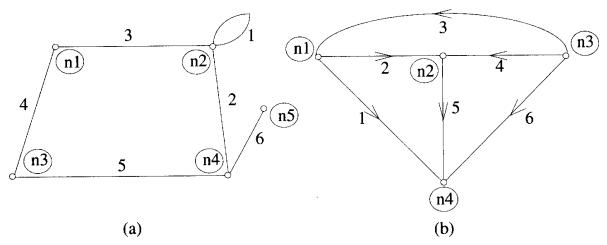

| A.1        | Graphs                                          | 361 |

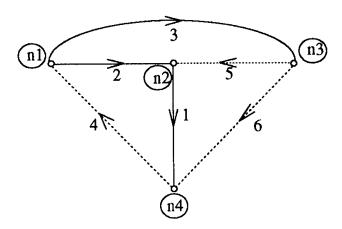

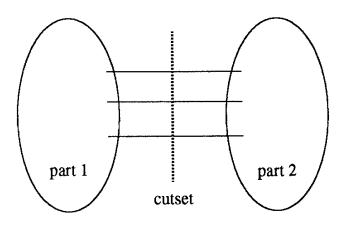

| A.1<br>A.2 | Fundamental Loops and Cutsets                   | 363 |

| A.3        | The Incidence Matrix                            | 366 |

| A.4        | Sparse Tableau and Reduced Tableau Analysis     | 368 |

| A.5        | Loop and Cutset Matrices                        | 369 |

| A.6        | Circuit Equations in Terms of Loops and Cutsets | 371 |

| A.7        | Tree Selection Procedure                        | 376 |

| A.8        | References                                      | 383 |

|            |                                                 |     |

### Preface

The field of circuit simulation has seen some exciting developments ever since the advent of integrated circuits. Modern integrated circuits continually challenge circuit simulation algorithms and implementations with the verification problems they pose. What makes circuit simulation unique is its multi-disciplinary nature. It is an intertwined set of concepts borrowed and adapted from mathematics, circuit theory, graph theory, physics, device modeling, electrical engineering, and software development. Although there is much active research in the subject, this book attempts to clearly explain some of the fundamentals of circuit simulation, on which most modern techniques are based. Some of the more recent advances are covered in the book, too.

This book evolved from our teaching and research activities over the years. We are indebted to all those who invented the concepts and techniques described in the book and to those who wrote earlier books on the subject.

This book would not have been possible without the collaboration, cooperation, and help of many colleagues, students, and friends. While it is not possible to mention all of them, we would particularly like to thank our spouses Leah Pillage, Casey Jones, and Patricia Buchanan for their constant support and encouragement; Catherine Rapinett for typing early drafts of the manuscript; all of the graduate students from the simulation courses at Carnegie Mellon University and the University of Texas at Austin for their critique of the notes; and David Ling, Ellen Yoffa, and Bill Joyner at the IBM T. J. Watson Research Center for their support and encouragement. We also thank Steve Chapman and Jim Halston at McGraw Hill for an outstanding job.

L.T.P., R.A.R., and C.V.

Electronic Circuit and System Simulation Methods

|  |  |  | * |

|--|--|--|---|

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

## Chapter 1 Introduction to Circuit Simulation

The simulation techniques introduced in the 1950s to analyze circuits with tens of transistors are substantially the same as those used today to analyze circuits with tens of thousands of transistors. With the availability of powerful computers and the advent of workstations, circuit simulators can run much faster today than they did then. But these programs are often called upon to verify the potential performance of the next generation of workstations and parallel processors, and with each new generation of computers the underlying circuitry becomes ever more complex. Due to this increasing complexity, circuit simulation as a pre-manufacturing design verification strategy is barely keeping up with the demands that are being placed upon it. And in many areas of application it has even fallen behind, being supplemented by less precise switch- and logic-level simulation. But such reduced-precision simulation strategies may only work reliably when design styles are restricted. In the fierce competition for faster and smaller circuits, more often than not, presumed restrictions on design styles are bent or broken. In the final analysis then, only circuit simulation is trusted -- sometimes more so than it should be -- to verify the essential electrical-system behavior. As a result, huge computing resources are assigned to the circuit simulation task, which is often the bottleneck in the design process.

This chapter provides an overview of circuit simulation techniques. In particular, it is an introduction to some of the algorithms and methodologies used in the industry standard circuit simulator SPICE [Nagel71, Nagel75]. The techniques introduced in this chapter will be covered in greater detail in the chapters that follow. In addition, alternatives to SPICE and various nontraditional simulation techniques will be introduced in subsequent chapters.

### 1.1 Traditional Circuit Simulation

Before introducing circuit simulation techniques it may be helpful to first discuss some of the capabilities of a simulator such as SPICE. Most general purpose circuit simulation programs provide the following capabilities:

- Linear dc analysis to evaluate the dc currents and dc voltages for a lumped, linear, time-invariant circuit.

- Nonlinear dc analysis to obtain the quiescent operating point of a circuit which contains nonlinear elements, such as transistors.

- Linear ac analysis to obtain the frequency response of a lumped, linear, time invariant circuit.

- Small signal ac analysis to obtain the frequency domain response of a circuit by replacing nonlinear elements with their linearized equivalents computed from the quiescent operating point.

- Linear transient analysis to determine the time domain response of a circuit to various input waveforms starting with the initial conditions obtained from the linear dc analysis.

- Large signal transient analysis to obtain the time domain response of a circuit which

contains nonlinear elements, such as transistors. The time domain responses are

determined by considering the various input waveforms starting with the initial conditions obtained from the nonlinear dc analysis.

In addition to the modes listed above, circuit simulators provide a variety of other functions, such as pole/zero analysis and noise analysis. There are also special purpose simulation programs for thermal analysis, switched capacitor circuit analysis, and so on. By far the most common way in which the above modes are used is a nonlinear dc analysis to establish the quiescent point at the start of the simulation, followed by a large signal transient analysis. The analyses listed above, which form the core for most general purpose circuit simulators, also share a common analysis core in that they all rely on the linear dc analysis algorithm. Therefore, to consider how a circuit simulator provides these capabilities we start with the foundations of linear dc analysis.

### 1.2 Linear, Time-Invariant Circuits

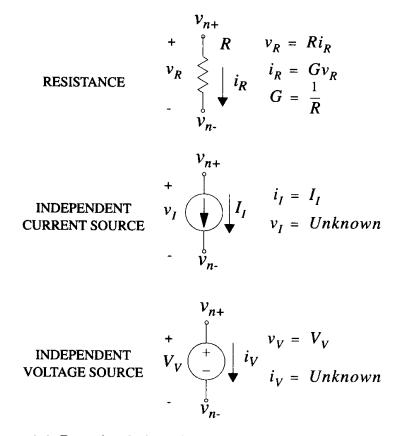

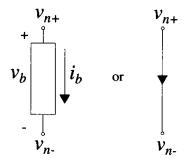

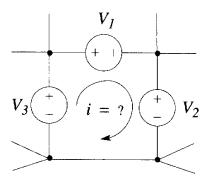

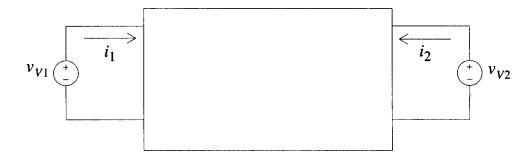

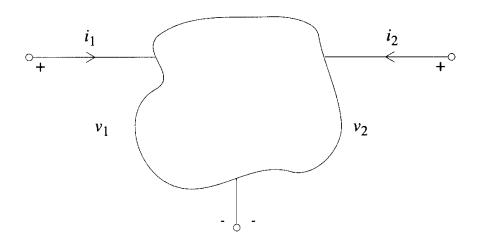

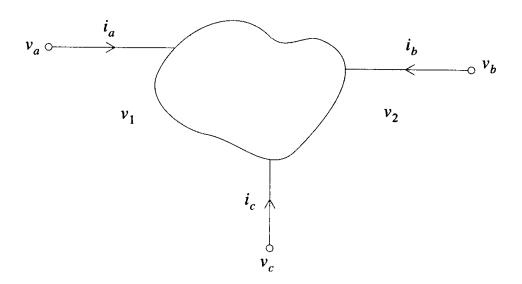

Consider a simple linear time-invariant circuit comprised of the most basic two-terminal elements: resistors, ideal independent current and voltage sources. The branch relations for these circuit elements are shown in Figure 1.1. The current-voltage relationships for any of these elements can be abstracted in terms of a generic two-terminal element or a topological branch as shown in Figure 1.2. In order to treat all types of branches in a consistent and systematic manner, we use associated reference directions.

Associated Reference Directions: The positive (+) reference for the branch voltage  $(v_b)$  is at the tail of the branch current  $(i_b)$  reference arrow, and the negative (-) reference for the branch voltage is at the head of the branch current reference arrow.

Figure 1.1 Branch relations for some two-terminal circuit elements.

Figure 1.2 Generic two-terminal element and a topological branch.

The (positive referenced) branch voltage drop is in the same direction as the (positive referenced) branch current. Using the associated reference directions, we can compute instantaneous branch power as follows:

- $p_b = v_b i_b > 0$  implies power is being delivered to the element from the rest of the circuit.

- $P_b = v_b i_b < 0$  implies power is being delivered to the rest of the circuit from the element.

Using the topological branch model in Figure 1.2 and the associated reference direction conventions, Kirchhoff's Laws of Interconnection are easily defined:

Kirchhoff's Voltage Law (KVL): Every circuit node has a unique voltage (with respect to the ground or datum node, which is 0 volts by convention). The voltage (drop) across a branch,  $v_b$ , is equal to the difference between the (positive and negative referenced) voltages of the nodes on which it is incident.

$$v_b = v_{n+} - v_{n-} ag{1.2.1}$$

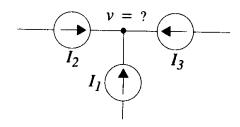

Kirchhoff's Current Law (KCL): The (algebraic) sum of all of the currents flowing out of (or into) any circuit node is zero.

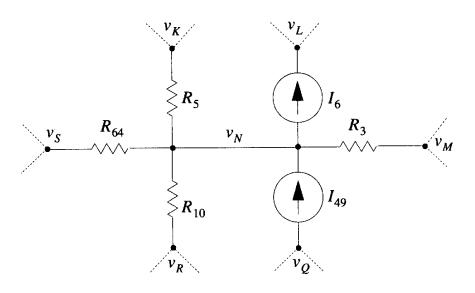

An example of the application of KCL at a node is shown in Figure 1.3. The branch relations along with the KCL expression for node N result in the following equation in terms of the node voltage variables:

$$\frac{v_N - v_M}{R_3} + \frac{v_N - v_K}{R_5} + \frac{v_N - v_R}{R_{10}} + \frac{v_N - v_S}{R_{64}} + I_6 - I_{49} = 0$$

(1.2.2)

Figure 1.3 KCL at the  $N^{th}$  node.

### 1.3 Nodal Analysis

Consider a b branch, (n+1) node circuit (in the rest of this book, we will consider (n+1) node circuits so that the number of non-datum nodes will always be n). Writing a

KCL equation in terms of node voltages, as described above, for every non-datum node, leads to n nodal equations in terms of n non-datum node voltages. The *datum* node is also called the *ground* or *reference* node, and usually is taken to be at a potential of zero volts. We can write programs to formulate and then solve such sets of equations in general.

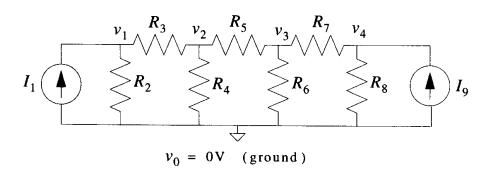

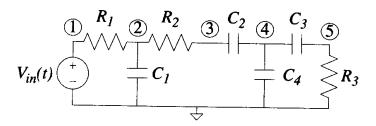

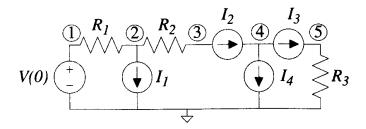

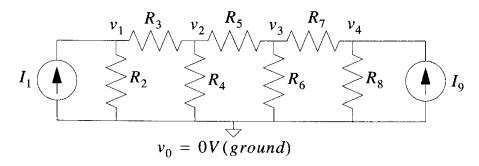

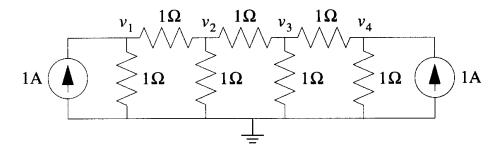

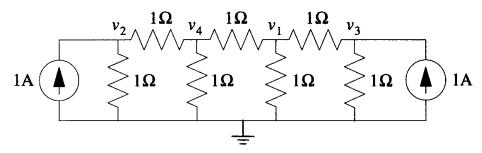

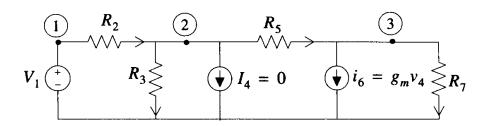

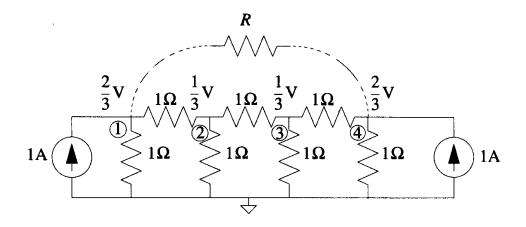

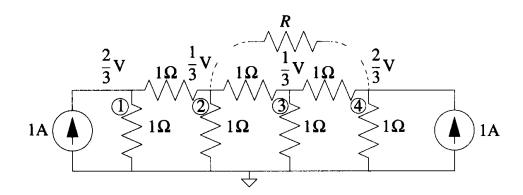

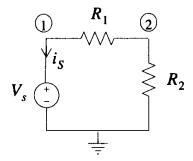

For example, consider the analysis of the dc circuit shown in Figure 1.4. This circuit has four nodes not counting the ground node; therefore, n=4. Consider for now that all of the resistances are  $1\Omega$  and the two current sources have values of 1A. By inspection we can write the KCL expression for the n non-datum nodes resulting in the following set of nodal equations:

$$\frac{v_1 - v_0}{R_2} + \frac{v_1 - v_2}{R_3} - I_1 = 0 \qquad \Rightarrow \qquad 2v_1 - v_2 = 1$$

$$\frac{v_2 - v_1}{R_3} + \frac{v_2 - v_0}{R_4} + \frac{v_2 - v_3}{R_5} = 0 \qquad \Rightarrow \qquad -v_1 + 3v_2 - v_3 = 0$$

$$\frac{v_3 - v_2}{R_5} + \frac{v_3 - v_0}{R_6} + \frac{v_3 - v_4}{R_7} = 0 \qquad \Rightarrow \qquad -v_2 + 3v_3 - v_4 = 0$$

$$(1.3.1)$$

$$\frac{v_4 - v_3}{R_7} + \frac{v_4 - v_0}{R_8} - I_9 = 0 \qquad \rightarrow \qquad -v_3 + 2v_4 = 1$$

Figure 1.4 Resistor ladder circuit example.

$$Yv = J ag{1.3.2}$$

where Y is the  $n \times n$  nodal admittance matrix, J is the  $n \times 1$  vector of current source inputs and v is the  $n \times 1$  vector of node voltages which are being sought. Writing the set of nodal equations by applying KCL at each node is not, however, the most efficient means of formulation for a software program.

### 1.4 Nodal Admittance Equation Stamps

In general, the circuit being analyzed is described for a circuit simulation program in terms of a netlist file. Even computer-aided engineering (CAE) tools which include schematic capture will first convert the graphical representation into a netlist description. Figure 1.5 is a simple netlist format (similar to the SPICE language) which describes the circuit shown in Figure 1.4.

| Branch type/<br>name | From node | To node | Value |

|----------------------|-----------|---------|-------|

| I1                   | 0         | 1       | 1.0   |

| R2                   | 1         | 0       | 1.0   |

| R3                   | 1         | 2       | 1.0   |

| R4                   | 2         | 0       | 1.0   |

| R5                   | 2         | 3       | 1.0   |

| R6                   | 3         | 0       | 1.0   |

| R7                   | 3         | 4       | 1.0   |

| <b>R</b> 8           | 4         | 0       | 1.0   |

| 19                   | 0         | 4       | 1.0   |

Figure 1.5 A netlist representation of the circuit shown in Figure 1.4.

For the nodal admittance (matrix) equations, the elements in the netlist contribute terms in a procedural manner. Branches 2 through 8, the resistors, contribute terms to the  $\boldsymbol{Y}$  matrix while branches 1 and 9, the independent current sources, contribute to the  $\boldsymbol{J}$  vector.

From the input list these contributions can be characterized on a branch-by-branch basis in terms of matrix stamps (sometimes called element stencils or just stencils). To explain how stamps work, we will assume that the circuit nodes are consecutively numbered. Of course this is not the case in general, however, unique alphanumeric node names in the user-specified netlist are easily mapped into consecutively numbered nodes internal to the circuit simulator.

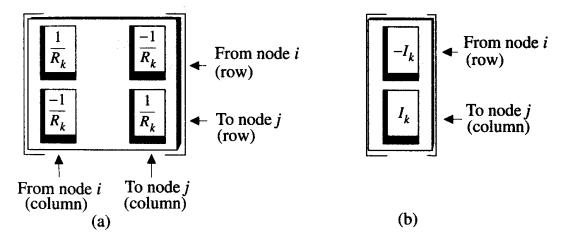

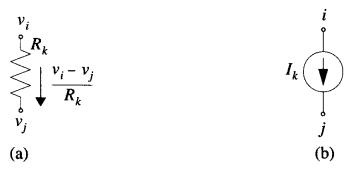

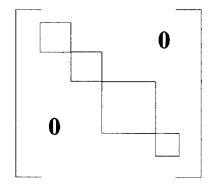

The resistor matrix-stamp is shown in Figure 1.6(a). For a resistor of value  $R_k$  from node i to node j as shown in Figure 1.7(a), a positive conductance value  $(1/R_k)$  is added to matrix locations (i, i) and (j, j) while a negative value  $(-1/R_k)$  is added to matrix locations (i, j) and (j, i). The stamp for independent current sources is shown in Figure 1.6(b). For a current source branch of value  $I_k$  directed from node i to node j, as shown in Figure 1.7(b) a negative current source value is added to the  $i^{th}$  entry of the J vector and a positive value is added to the  $j^{th}$  entry. We postpone the treatment of the independent voltage source stamp until Chapter 2 where we discuss Modified Nodal Analysis.

Figure 1.6 Element stamps: (a) For a resistor of value  $R_k$  connected from node i to node j; (b) For an independent current source of value  $I_k$  connected from node i to node j.

Figure 1.7 (a) A resistor connected from node i to node j, and (b) a current source connected from node i to node j.

We can obtain the overall set of nodal admittance equations by stamping in the branch contributions on an element-by-element basis. To understand the stamp concept, note that the current entering node i and leaving node j due to  $I_k$  adds two terms to the J vector. For example, the first line of the netlist in Figure 1.5 is stamped into the nodal matrix equations as follows:

Note that this section builds up the equations the way a computer program would. The intermediate forms of the equations (1.4.1), (1.4.4), and (1.4.5) are not mathematically valid equations, but the final set of equations (1.4.6) and (1.4.7) are complete. For resistors (see Figure 1.7(a)), the current is expressed in terms of the node voltages on the left hand side. For example, the current *leaving* node i due to resistor  $R_k$  is

$$\frac{1}{R_k} (v_i - v_j) {(1.4.2)}$$

and the current leaving node j through resistor  $R_k$  is

$$\frac{1}{R_k} \left( v_j - v_i \right) \tag{1.4.3}$$

Therefore, stamping in the second element  $(R_2)$  from the netlist in Figure 1.5 results in

Similarly, after stamping the third element  $(R_3)$  from the netlist the partial matrix equations are

Finally, after stamping in all of the elements from the netlist we have the following set of nodal equations:

$$\begin{bmatrix} (\frac{1}{R_2} + \frac{1}{R_4} + \frac{1}{R_6} + \frac{1}{R_8}) & -\frac{1}{R_2} & -\frac{1}{R_4} & -\frac{1}{R_6} & -\frac{1}{R_8} \\ -\frac{1}{R_2} & \frac{1}{R_2} + \frac{1}{R_3} & -\frac{1}{R_3} & 0 & 0 \\ -\frac{1}{R_4} & -\frac{1}{R_3} & \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} & -\frac{1}{R_5} & 0 \\ -\frac{1}{R_6} & 0 & -\frac{1}{R_5} & (\frac{1}{R_5} + \frac{1}{R_6} + \frac{1}{R_7}) - \frac{1}{R_7} \\ -\frac{1}{R_8} & 0 & 0 & -\frac{1}{R_7} & \frac{1}{R_7} + \frac{1}{R_8} \end{bmatrix} \begin{bmatrix} v_0 \\ v_1 \\ v_2 \\ v_3 \\ v_4 \end{bmatrix} = \begin{bmatrix} -I_1 - I_9 \\ I_1 \\ 0 \\ 0 \\ I_9 \end{bmatrix}$$

(1.4.6)

We need not -- and usually do not -- bother to build the zeroth (ground node) row and corresponding column, but here it does show the symmetry of the nodal formulation. What we have here is the *indefinite* (or "floating") admittance formulation: each row and each column sums algebraically to zero, indicating that we do not have an independent set of equations. We can pick any node to be the reference and obtain the definite admittance formulation by crossing out its row and the corresponding column. In this case the zero row and column correspond to the designated ground node, and can be omitted:

$$\begin{bmatrix} (\frac{1}{R_2} + \frac{1}{R_3}) & -\frac{1}{R_3} & 0 & 0 \\ -\frac{1}{R_3} & (\frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5}) & -\frac{1}{R_5} & 0 \\ 0 & -\frac{1}{R_5} & (\frac{1}{R_5} + \frac{1}{R_6} + \frac{1}{R_7}) & -\frac{1}{R_7} \\ 0 & 0 & -\frac{1}{R_7} & (\frac{1}{R_7} + \frac{1}{R_8}) \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ v_3 \\ v_4 \end{bmatrix} = \begin{bmatrix} I_1 \\ 0 \\ 0 \\ I_9 \end{bmatrix}$$

(1.4.7)

Because all rows and columns sum algebraically to zero, we can reconstruct the indefinite admittance formulation from the definite in case we want to change reference nodes. The indefinite admittance formulation will be useful to us later when we consider multi-terminal elements. For now, we should note that the two-terminal element stamps are indefinite. They can be made definite, of course, by eliminating any matrix entries that correspond to the ground node's row or column.

The final step for dc Nodal Analysis is to solve the matrix equations in (1.4.7) to obtain the dc node voltages. Constructing the inverse of Y and multiplying it by J is one way of obtaining the vector of node voltages. However, there are more efficient means of solving circuit equations (more on this later in Chapter 3 and Chapter 7). In fact, most simulators use a direct method for solving sets of linear simultaneous equations to obtain the node voltages. Gaussian Elimination or LU factorization are the most often applied algorithms for generalized circuit simulation. In this book we will often use the matrix inverse notation to indicate solution of a set of simultaneous equations, like

$$v = Y^{-1}J \tag{1.4.8}$$

In almost all such instances, a practical implementation would use Gaussian Elimination or LU factorization in the interests of efficiency. Thus any references to obtaining the inverse of a matrix can be assumed to mean factoring the equations with either of these direct methods. Further, the equations of large circuits produce sparse matrices, i.e., matrices with very few non-zero entries. The sparsity of such matrices is exploited to obtain the solution on a computer with reasonable memory and runtime requirements. The matrix in (1.4.7) is somewhat sparse since the percentage of non-zeros is only 62.5 percent. For large circuits, however, the matrices can be extremely sparse with less than 1 percent of the entries being non-zero. The special handling of *sparse matrices* will be covered in detail in Chapter 7 where it is shown that one of the reasons that we do not attempt to invert large sparse matrices is that the sparsity gets destroyed.

The importance of the linear solution cannot be overstated since the following sections will demonstrate that nonlinear dc and time domain transient circuit analysis are based upon successive applications of a linear circuit solver.

### 1.5 Nonlinear (dc) Circuit Analysis

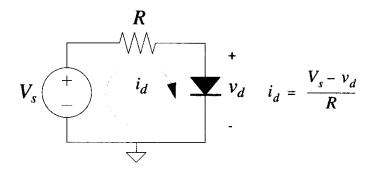

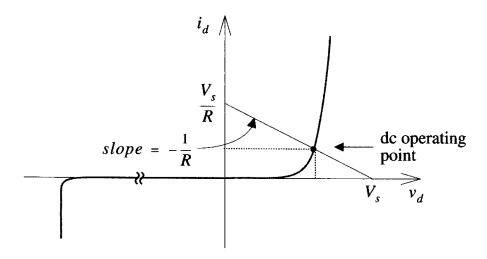

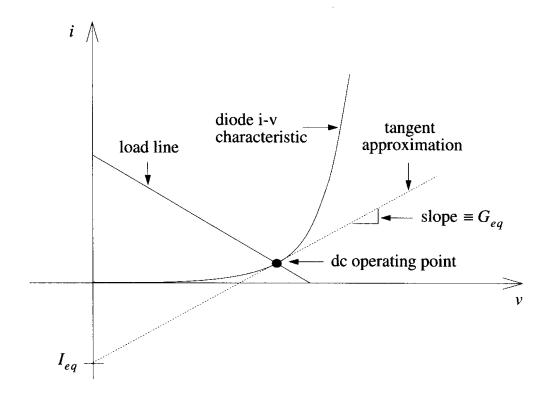

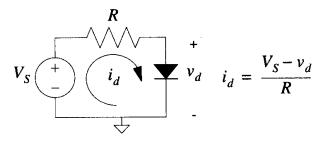

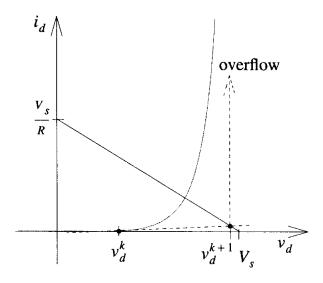

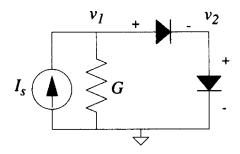

Consider the problem of determining the dc bias point for the simple diode circuit shown in Figure 1.8. This single loop circuit can be most easily described in terms of a loop equation for the current  $i_d$ . Suppose that the diode in Figure 1.8 is characterized in the i-v plane by the curve shown in Figure 1.9. Classically, we can obtain the dc operating point by means of the (Thevenin equivalent) load line also shown in this figure. The load line represents the voltage source and series resistor, and its intersection with the i-v curve for the diode is the dc operating point for this circuit.

Figure 1.8 Simple diode circuit.

Figure 1.9 Diode i-v curve and graphical solution of dc operating point.

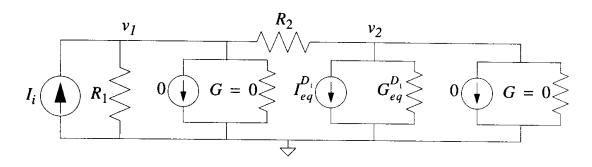

Computationally, we solve for this dc operating point iteratively. To describe how this circuit would be analyzed in a circuit simulator we will first convert the Thevenin equivalent in Figure 1.8 to the Norton equivalent shown in Figure 1.10 in order to simplify this discussion. The single KCL equation at the non-datum node, hence, the nodal equation is

$$\frac{v_d}{R} + i_d = \frac{V_s}{R}$$

$$\downarrow V_s$$

$$\downarrow R$$

$$\downarrow V_d$$

$$\downarrow i_d = \frac{V_s - v_d}{R}$$

Figure 1.10 Diode circuit with a Norton equivalent source.

For completeness, however, we must also include the branch relation equation for the diode. The nonlinear expression for the diode's current could be the following:

$$i_d = I_{SAT} \left[ exp\left(\frac{qv_d}{\eta kT}\right) - 1 \right]$$

(1.5.2)

where  $I_{SAT}$  is the reverse saturation current, q is the charge on an electron,  $\eta$  is the non-ideality factor, k is Boltzmann's constant, and T is the absolute temperature in degrees Kelvin. Equation (1.5.2) describes a curve in the first quadrant of the  $i_d$ - $v_d$  plane similar to the one in Figure 1.9. Combining (1.5.1) and (1.5.2) we can express the nodal equation in terms of the node voltage variable exclusively, as

$$\frac{v_d}{R} + I_{SAT} \left[ exp\left(\frac{qv_d}{\eta kT}\right) - 1 \right] = \frac{V_s}{R}$$

(1.5.3)

Equation (1.5.3) represents a nodal equation in terms of a single node voltage. The only difference between it and other nodal equations considered thus far is that the equation is a nonlinear function  $f(v_d)$ :

$$f(v_d) = \frac{V_s}{R} - (\frac{v}{R} + I_{SAT} \left[ exp(\frac{qv_d}{\eta kT}) - 1 \right]) = 0$$

(1.5.4)

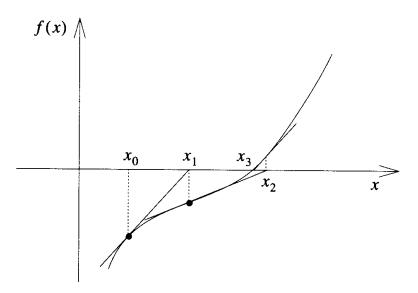

To solve (1.5.4) using Newton-Raphson [Ralston78] we would start with some initial guess  $v_d = V_{init}$  and attempt to evaluate the node voltage as follows:

Start:

n = 0

Guess:

$v_n = V_{init}$

Linearize:

$f(v_n + \Delta v_n) \approx f(v_n) + f'(v_n) \Delta v_n = 0$  (Taylor expansion)

$$\Delta v_n = -\frac{f(v_n)}{f'(v_n)}$$

where  $f'(v_n) = \frac{df}{dv}\Big|_{v=v_n}$

Increment:

$$v_{n+1} = v_n + \Delta v_n$$

Test:

Is

$$|f(v_{n+1})| \le \varepsilon$$

?

If yes, we have converged to the required solution; if no, then return to the linearization step.

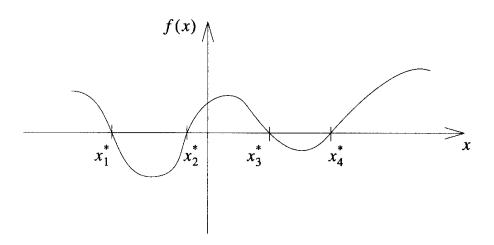

Newton-Raphson iteration will converge provided that:

- 1. The first derivative of f(v), f'(v), is continuous (which presents certain restrictions on the device models).

- 2. The initial guess is "sufficiently close" to the final solution (SPICE uses the *node-set* concept to allow the user to force this situation).

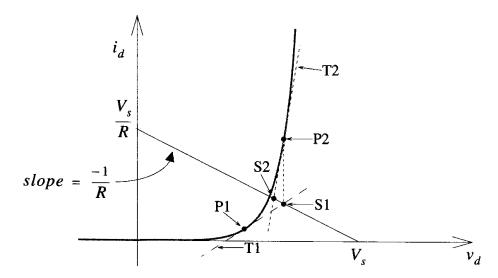

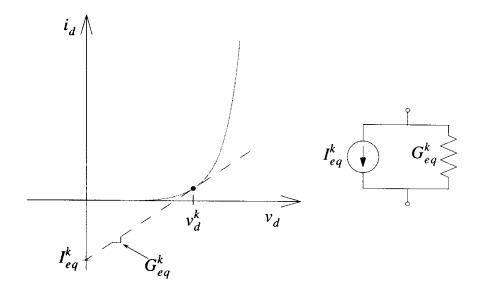

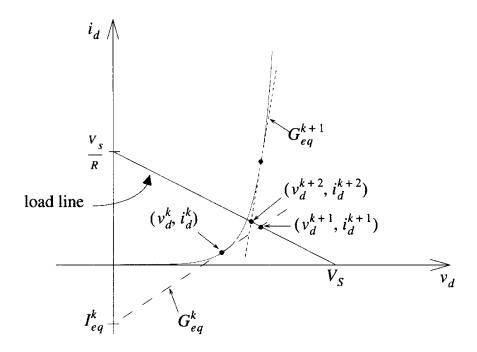

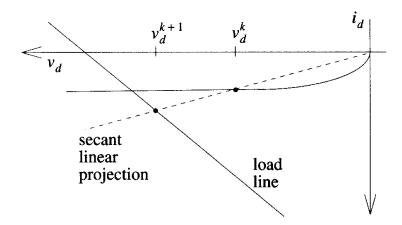

The Newton-Raphson steps outlined above can also be explained graphically for the simple circuit in Figure 1.10. For example, consider the linear load line and the diode curve in Figure 1.11. Starting with an initial guess P1, a tangent T1 is extended from this presumed operating point. At the intersection of T1 and the load line, solution S1 is obtained. This tangent projection represents the Newton-Raphson linearization step while the solution represents the solve step. If S1 is not within  $\mathcal{E}$  (the error tolerance) of the actual operating point, a new guess, P2, is obtained from this first solution. The next solution attempt is then the intersection of tangent T2 with the load line. These iterations are repeated until a solution is found to be acceptably close to the exact operating point. (Since the exact solution is not known, convergence is assumed when successive solutions are within  $\mathcal{E}$  of each other.)

Figure 1.11 Iteration to obtain dc operating point.

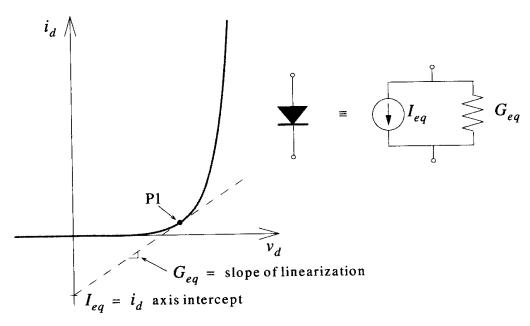

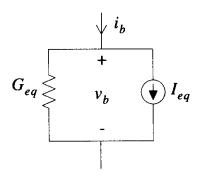

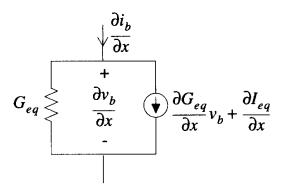

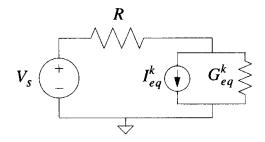

The linearization about a presumed operating point can be depicted as replacing the diode by a linear Norton equivalent circuit at each iteration. The relation between the tangent linearization and a linear Norton equivalent circuit is shown in Figure 1.12. The iteration procedure amounts to successive solutions of linear(ized) dc circuits with each nonlinear device being replaced by its tangent-determined Norton equivalent circuit.

Figure 1.12 The companion model which represents the linearized approximation (tangent) about the presumed operating point.

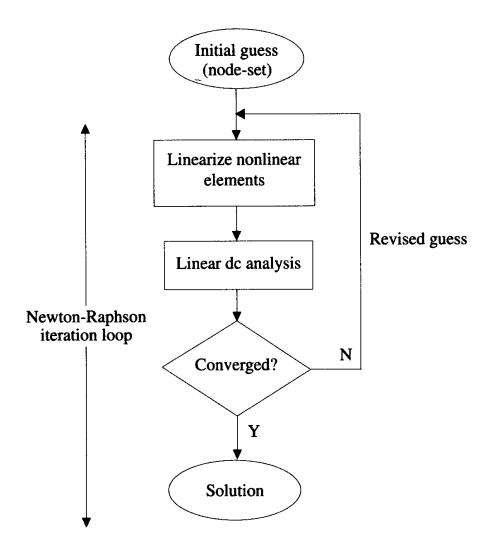

In general, this nonlinear iteration procedure is attempted with multiple nonlinear elements, all being linearized simultaneously. The overall procedure is as follows:

1. Initialize: Guess circuit voltages and/or currents.

2. Linearize: Obtain linearized Norton equivalents for all nonlinear elements about their presumed operating points.

3. Solve: Formulate (nodal) equations that characterize the linearized circuit, and solve them for the new presumed operating points.

4. Convergence: Return to Step 1 using the new presumed operating points as the "guesses" unless the change from the last iteration has been acceptably small. If the changes are small, then the iteration terminates successfully. If the number of iterations has exceeded a pre-determined number of iterations, then the solu-

tion procedure has failed.

Since multiple elements are linearized simultaneously, each element which should "see" a nonlinear load line will actually "see" a moving linear load line from one iteration to the next. Mathematically, this is multi-dimensional Newton-Raphson iteration which will be covered in more detail in Chapter 10. Assuming that such iterations are feasible,

we can extend our dc analysis of linear circuits to solve dc nonlinear circuits by adding to it *model routines* that provide linearized equivalent circuits as functions of their presumed node voltages. Note that such nonlinear elements contribute a stamp both to the Y matrix and to the J vector.

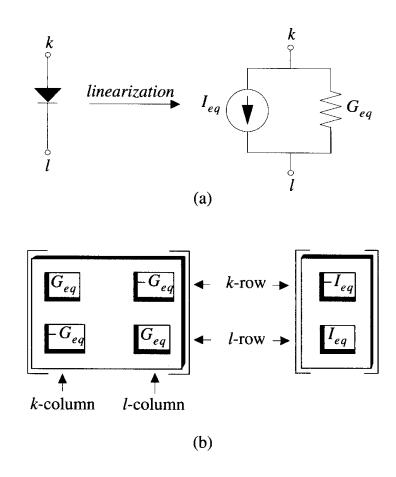

For example, we showed that each nonlinear iteration corresponded to a tangent approximation of the curve. In terms of (1.5.2) the linearized model in Figure 1.13(a) is

Figure 1.13 Stamp for linearized diode model.

obtained by evaluating the tangent (partial derivative of (1.5.2)) at the voltage operating point (the last nonlinear iteration value). Note that the figure shows the direction of  $I_{eq}$ , which is to be treated algebraically.  $I_{eq}$  may be negative, as shown in the figure. This linearization will be covered in more detail in Chapter 10, however, we note here that the resulting linear Norton equivalent circuit has a Y matrix and J vector stamp as shown in Figure 1.13(b). Therefore the heart of the nonlinear analysis routine is the repeated stamping and linear circuit solving as summarized by the flowchart in Figure 1.14.

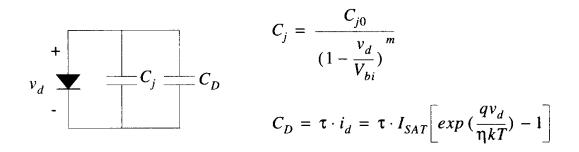

We should also point out that the dc diode equation (1.5.2) does not include the capacitance effects associated with a diode junction. Capacitance is, of course, excluded from consideration simply because we are performing a dc analysis. In a dc analysis, there is no concept of time. The assumption is that time is allowed to go to infinity so that all tran-

Figure 1.14 Flowchart for nonlinear dc analysis. Convergence is reached when approximately the same answer is obtained twice in a row. The rate and fact of convergence are affected by the initial guess.

sients in the circuit die out, and our only interest is in computing the final "steady state" values of the circuit. Therefore, capacitors are made into open circuits and inductors into short circuits for the purposes of a dc analysis. However, if this dc analysis is a precursor to a nonlinear transient analysis or an ac analysis, the energy storage elements are reintroduced once the dc solution has been obtained. In this case, the diffusion and depletion capacitances associated with the diode are evaluated at the computed operating point and introduced into the circuit for the transient or ac analysis.

### 1.6 Small Signal (ac) Analysis

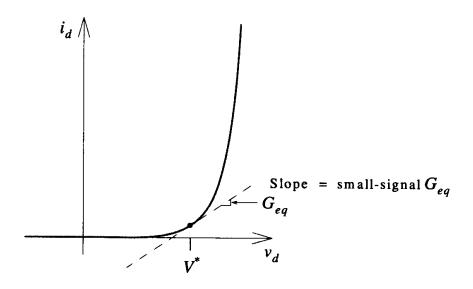

Due to the way in which the nonlinear (Newton-Raphson) iterations are performed, the final Newton-Raphson linearization step produces a portion of the small signal equivalent circuit model used for ac analysis. For example, the small signal model for the diode in Figure 1.8, biased at a voltage  $V^*$ , is the tangent about the operating point (the last Newton-Raphson iteration) as shown in Figure 1.15. Of course this is not the complete small

Figure 1.15 Small signal diode model at the dc bias point.

signal model since the curve in Figure 1.15 represents the dc characteristics of the diode as shown in equation (1.5.2). The model does not account for the small signal capacitance effects. The small signal capacitances (both the diffusion and depletion capacitance) are simply obtained by evaluating them at the dc operating point,  $V^*$ .

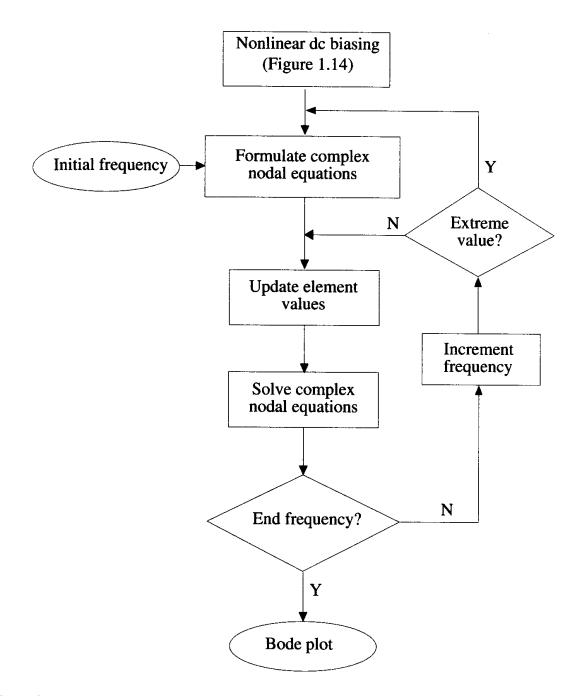

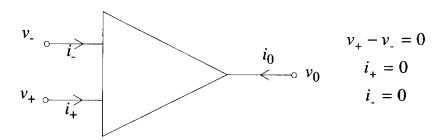

For small signal ac analysis the energy storage elements (constituting the linearized small signal capacitances and inductances) are modeled in the frequency domain, as shown in Figure 1.16. With these branch relations in terms of complex admittances, we can extend linear dc analysis to linear ac analysis simply by using complex valued voltages and currents (phasors) and stamping the complex admittances into the Y matrix. The stamps are identical to those for linear resistors in every way except that the admittances are now complex values. Therefore, we must extend the linear simultaneous equation solver to handle complex values. The analysis steps for an ac analysis are summarized in Figure 1.17.

Figure 1.16 Complex admittances for capacitors and inductors during ac analysis.

It is important to note that we must exercise caution when performing an ac analysis at the frequency extremes. Specifically, as  $\omega \to 0$  the capacitors become open circuits and the inductors become shorts. Conversely, as  $\omega \to \infty$  the inductors become open circuits and the capacitors become shorts. Nodal Analysis, which handles only admittance branch relations, may not cope well with these frequency extremes. Even values close to the extremes may cause the Y matrix entries to become excessively large or small, thus causing numerical problems due to the finite precision and range of number representation in a computer. We will discuss ways to overcome such problems later. Figure 1.17 assumes that reformulation of the nodal equations will solve the problem of extreme values. SPICE is set up to handle the extreme case of  $\omega \to \infty$  only under the assumption that the frequency specified will never be sufficiently close to infinity to cause trouble. However, the limit  $\omega = 0$  is a more difficult problem since this is a practical frequency (dc) and the inductor admittance becomes infinite.

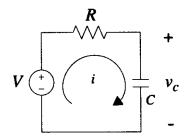

### 1.7 Linear Transient Analysis

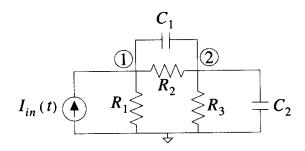

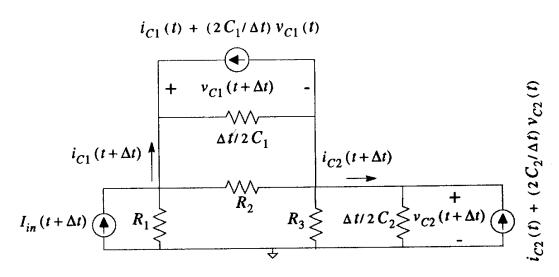

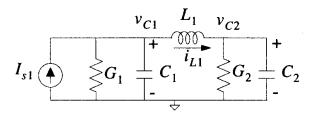

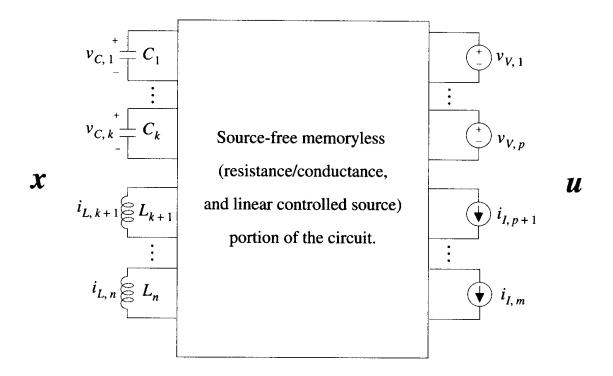

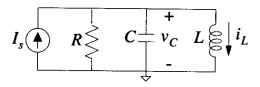

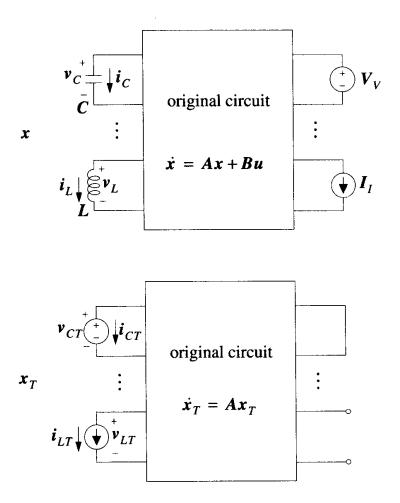

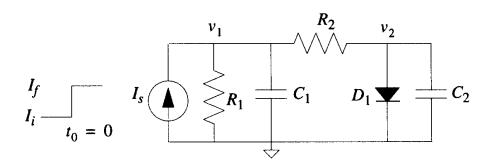

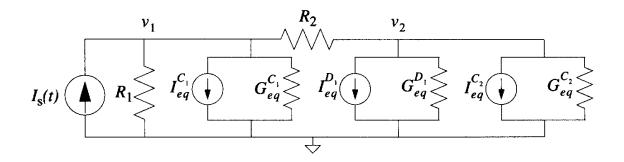

In contrast to small signal ac analysis, linear transient analysis is applied to evaluate the large signal behavior of a linear circuit as a function of time, t. For example, consider the lumped, linear (C is a constant and not a function of the voltage v), time-invariant capacitance shown in Figure 1.19. Suppose that we have a circuit with two such capacitors and a large signal time-varying current source as shown in Figure 1.18. The nodal equations for this circuit are:

$$\frac{v_1}{R_1} + \frac{v_1 - v_2}{R_2} + C_1 \cdot \frac{d}{dt} (v_1 - v_2) = I_{in}(t)$$

$$\frac{v_2}{R_3} + \frac{v_2 - v_1}{R_2} + C_1 \cdot \frac{d}{dt} (v_2 - v_1) + C_2 \cdot \frac{dv_2}{dt} = 0$$

(1.7.1)

Figure 1.17 Small signal ac analysis. As the frequency is incremented it must be checked to ensure that the frequency is not at some extremal point that will cause ill-conditioning.

Notice that the equations in (1.7.1) form a set of first order linear differential equations. Suppose that we know the solution of the circuit in Figure 1.18 at time t, and we seek to find the solution at some subsequent time  $t + \Delta t$ . First we replace the differential equation in Figure 1.19 with an equivalent integral equation:

Figure 1.18 An RC circuit with a large signal time-varying current source.

$$v = C \downarrow i \qquad i = C \frac{dv}{dt}$$

Figure 1.19 Lumped, linear, time-invariant capacitor.

$$\int_{t}^{(t+\Delta t)} \frac{dv}{d\tau} \cdot d\tau = \frac{1}{C} \int_{t}^{(t+\Delta t)} i(\tau) d\tau$$

(1.7.2)

Integrating over the time interval of interest results in

$$v(t + \Delta t) - v(t) = \frac{1}{C} \int_{t}^{(t + \Delta t)} i(\tau) d\tau$$

(1.7.3)

or

$$v(t + \Delta t) = v(t) + \frac{1}{C} \int_{t}^{(t + \Delta t)} i(\tau) d\tau$$

(1.7.4)

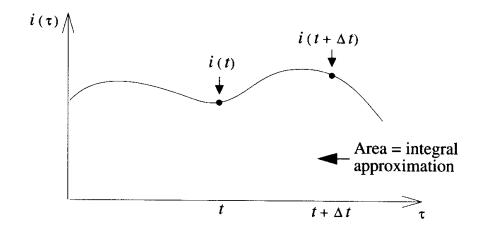

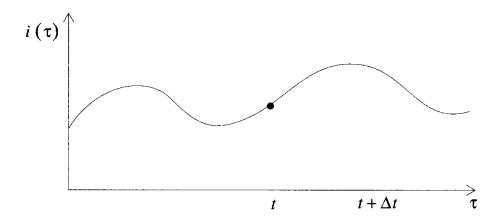

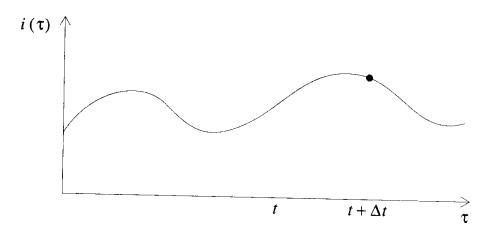

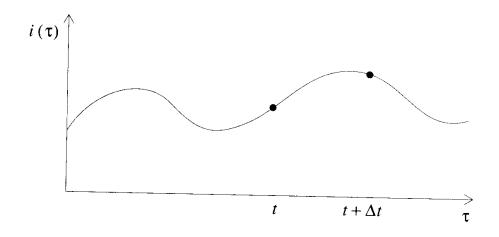

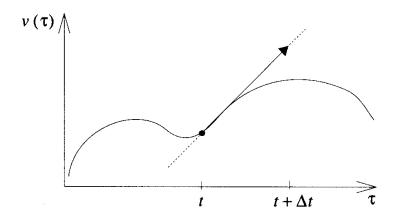

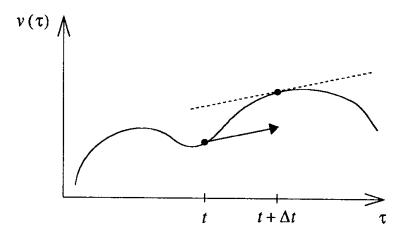

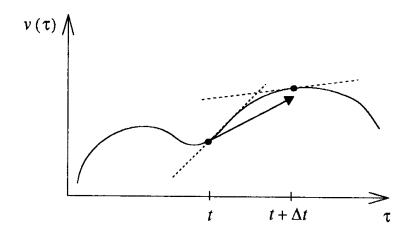

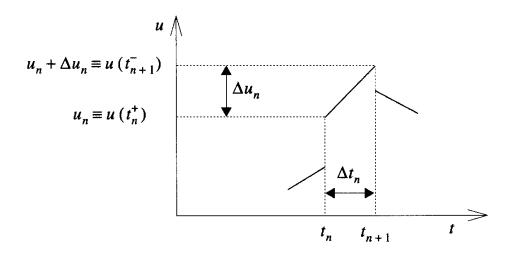

From (1.7.4) we see that the voltage at some future time  $t + \Delta t$  depends upon the voltage at time t and the current which flows through the capacitor for the time interval  $(t, t + \Delta t)$ . We do not know the value of i(t) for this complete interval, but only at the endpoints where its (approximate) values are computed. Therefore, we can approximate the integral of i(t) in equation (1.7.4) by means of the trapezoidal approximation shown in Figure 1.20. The integral from t to  $t + \Delta t$  is approximated by the shaded area, therefore,

$$\int_{t}^{(t+\Delta t)} i(\tau) d\tau \approx \frac{\Delta t}{2} [i(t) + i(t+\Delta t)]$$

(1.7.5)

$$v(t + \Delta t) \approx v(t) + \frac{\Delta t}{2C} [i(t) + i(t + \Delta t)]$$

(1.7.6)

Figure 1.20 The trapezoidal approximation for the integral of the capacitor current.

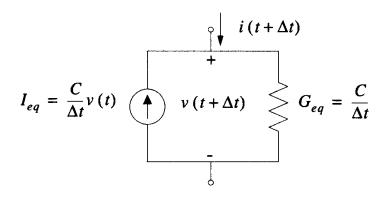

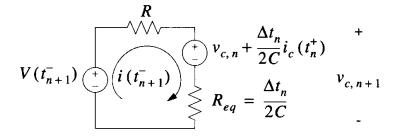

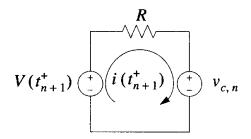

We do not know  $v(t + \Delta t)$  or  $i(t + \Delta t)$  since we are attempting to compute them in the circuit solution at time  $t + \Delta t$ . Hence this is an *implicit* formula. It would be explicit if we had an expression for  $v(t + \Delta t)$  or  $i(t + \Delta t)$  entirely in terms of known quantities. Equation (1.7.6) has two unknowns in one equation, however, this is not a problem because it too has a simple circuit interpretation. A *companion model* for the capacitance voltage approximation in equation (1.7.6) is shown in Figure 1.21.

$$i(t + \Delta t) \qquad V_{eq} = v(t) + \frac{\Delta t}{2C}i(t) \qquad R_{eq} = \frac{\Delta t}{2C}$$

$$+ \qquad v(t + \Delta t) \qquad - \qquad i(t + \Delta t)$$

Figure 1.21 Capacitance companion model for trapezoidal integration approximation.

Notice that the unknown voltage,  $v(t + \Delta t)$ , appears across the Thevenin companion model which consists of a known voltage source value and a resistor which is a function of  $\Delta t$ . Therefore we can perform numerical integration on our differential equations in (1.7.1) by solving a linear circuit with resistors which are functions of the numerical time step.

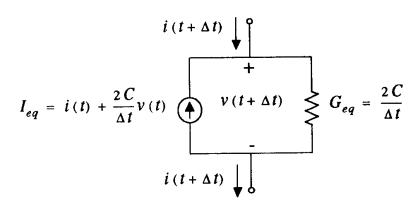

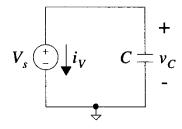

Since we have considered only Nodal Analysis so far, we transform the Thevenin equivalent in Figure 1.21 into its Norton equivalent in Figure 1.22. (This is the approach used by SPICE with the trapezoidal integration option. We will discuss alternative integration schemes in subsequent chapters.) We note that the Norton equivalent capacitance companion model in Figure 1.22 degenerates gracefully to an open circuit for dc analysis,

$\Delta t \to \infty$ . But for very small time steps,  $\Delta t \to 0$ , elements of the Norton equivalent capacitance model may become excessively large. This is the origin of the SPICE error message: "...Time Step Too Small." In such situations the Thevenin equivalent companion model derived originally is preferable. We should recognize, however, that the Thevenin equivalent capacitance companion model may present problems for dc analysis,  $\Delta t \to \infty$ . Hence the Thevenin and Norton representations of the trapezoidal companion model have their relative advantages and disadvantages.

Figure 1.22 Norton equivalent circuit for capacitance trapezoidal model.

Using the Norton equivalent models in Figure 1.22 for the capacitors in Figure 1.18, the linear "dc" equivalent circuit in Figure 1.23 is solved to approximate the node voltages at time  $t + \Delta t$ . Then, time is moved ahead again and the solution procedure is repeated, until the required time of simulation has passed.

Figure 1.23 The RC equivalent circuit for a trapezoidal integration approximation.

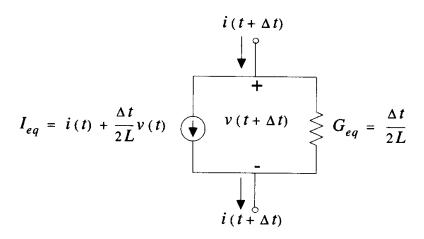

Inductance is the dual of capacitance, so we need not repeat in detail the steps above. Figure 1.24 includes the differential equation and the corresponding trapezoidal approximation for an inductor. The trapezoidal integration approximation provides directly the Norton equivalent companion model form in Figure 1.25.

$$v = L \frac{di}{dt}$$

$$i(t + \Delta t) \approx i(t) + \frac{\Delta t}{2L} [v(t) + v(t + \Delta t)]$$

Figure 1.24 Trapezoidal integration approximation equation for an inductor.

SPICE does not use the Norton companion model for inductors; to facilitate dc analysis, it uses the Thevenin equivalent circuit inductance companion model shown in Figure 1.26. To handle the voltage source in this companion model SPICE resorts to Modified Nodal Analysis (MNA), which will be discussed in the next chapter.

Figure 1.25 Norton equivalent companion model for an inductor.

$$V_{eq} = v(t) + \frac{2L}{\Delta t}i(t) \qquad R_{eq} = \frac{2L}{\Delta t}$$

$$+ \qquad v(t + \Delta t) \qquad i(t + \Delta t)$$

Figure 1.26 Thevenin equivalent companion model for an inductor.

We can implement linear transient analysis for RLC circuits using the companion models shown above as follows:

- 1. Start with a known set of capacitance voltages and inductance currents at a specified time (the initial conditions are either user-specified or obtained from a dc bias computation);

- 2. Increment time by a prescribed amount  $\Delta t$  and invoke the appropriate companion models;  $\Delta t$  is selected based on stability, accuracy, and efficiency considerations and can be different at different times.

- 3. Perform a "dc type" analysis;

- 4. Return to step (1) with the results and appropriately modify the companion model values until the specified end time is attained.

In this section, we have not discussed how best to choose the time step  $\Delta t$ . This, along with other numerical integration details, will be covered extensively in Chapter 4.

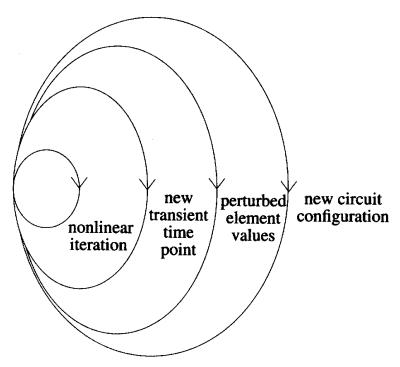

### 1.8 Nonlinear Transient Analysis

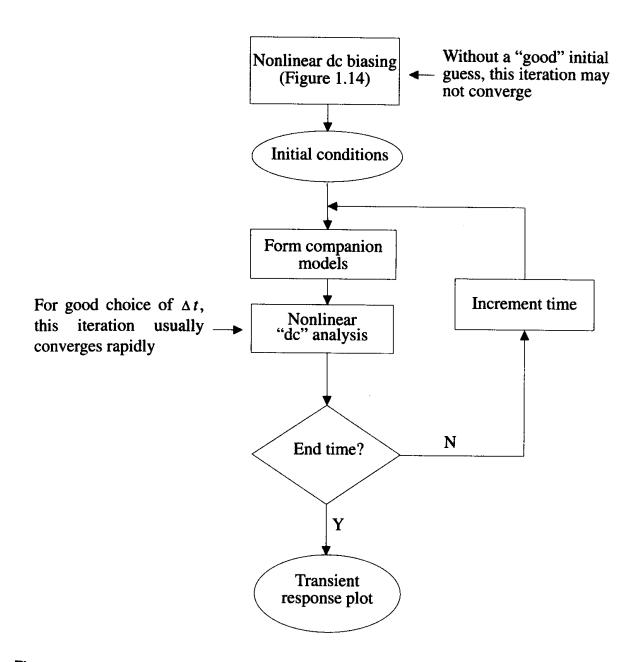

Finally, we consider what may be the most often applied circuit simulation analysis; namely, nonlinear transient analysis. This analysis is used to determine the large signal time domain behavior of circuits containing nonlinear elements. There are many subtleties involved, however, so we will delay the introduction of nonlinear transient analysis until later chapters. For now we will present a superficial flowchart (Figure 1.27) for nonline transient analysis to once again emphasize that linear dc analysis is a critical component of everything we seek to do. At each time step, companion models are used to obtain a nonlinear circuit which is solved iteratively by techniques described in Section 1.5.

### 1.9 Summary

The critical observation to be made is that linear circuit solution lies at the core -- the deepest inner loop -- of all of the above modes of analysis. Our linear circuit solution routine(s) must be robust, reliable, and as efficient as possible. To this end we discuss in more detail the traditional Modified Nodal Analysis approach to linear circuit solution in the next chapter. In later chapters we will discuss some alternatives to the traditional methods along with their advantages and disadvantages.

Figure 1.27 Nonlinear transient analysis. Both nonlinear dc analysis stages may require significant iteration -- especially the one for determining the dc operating point.

# 1.10 References

[Nagel71] L. W. Nagel and R. A. Rohrer. Computer Analysis of Nonlinear Circuits, Excluding Radiation (CANCER). *IEEE Journal of Solid State Circuits*, vol. SC-6, pp. 162-182, August 1971.

[Nagel75] L. W. Nagel. SPICE2, A Computer Program to Simulate Semiconductor Circuits. Technical Report ERL-M520, UC-Berkeley, May 1975.

[Ralston78] A. Ralston and P. Rabinowitz. A First Course in Numerical Analysis. McGraw-Hill, 1978.

# Chapter 2 Linear dc Nodal Analysis

As we have seen in Chapter 1, Nodal Analysis is well suited to the formulation of equations for circuits containing only resistances (or conductances) and ideal independent current sources. In our preliminary discussion of dc, ac, transient, and nonlinear analyses, we studiously avoided voltage sources and dependent sources of any kind. In this chapter we will consider the extension of the nodal equations to handle independent voltage sources and various linear controlled sources. With these extensions, Nodal Analysis will provide the means for performing analysis in general on a wide range of electronic circuits.

# 2.1 Voltage-Controlled Current Sources

Of independent voltage sources and the four kinds of controlled sources, voltage-controlled current sources are the ones that most naturally fit into the nodal equation formulation. We will first discuss these controlled sources, and then generalize our discussion to the other elements listed above.

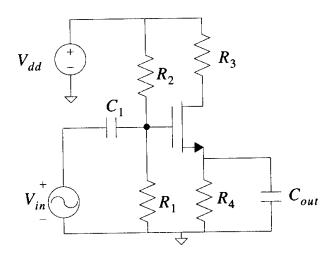

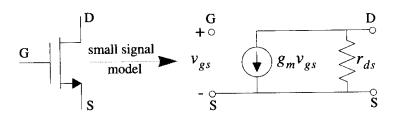

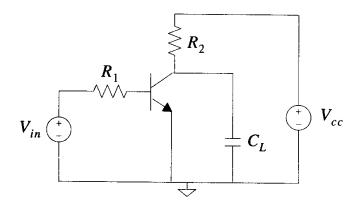

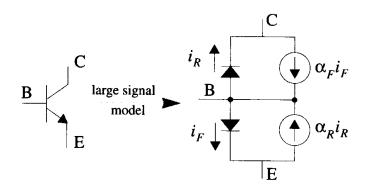

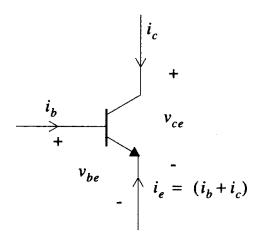

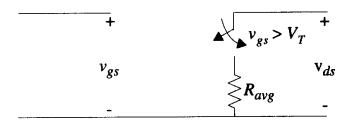

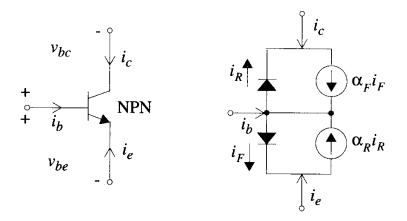

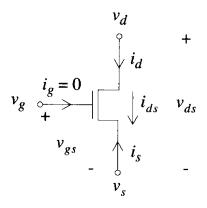

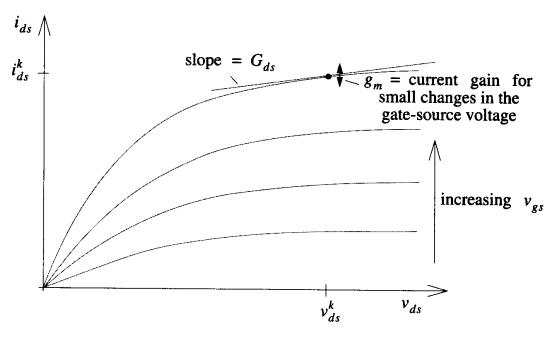

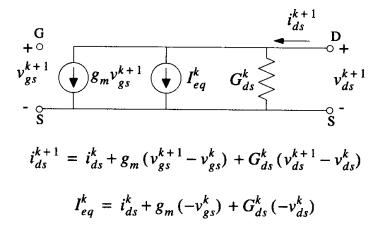

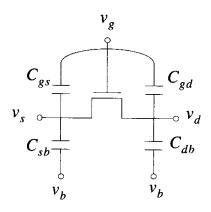

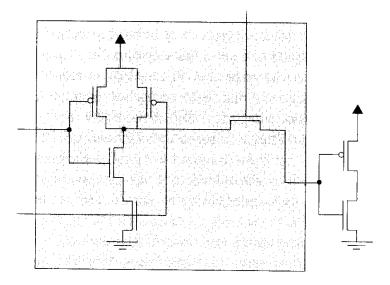

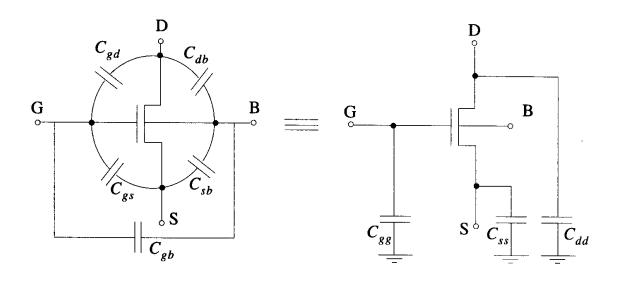

Linear controlled sources are not elements which you will find in electronic circuits explicitly. They are, however, important elements for modeling the behavior of various linear and nonlinear circuit components. For example, consider the N-MOSFET amplifier circuit shown in Figure 2.1. To analyze the frequency response of this amplifier we use a small signal model for the MOSFET and perform an ac analysis on the complete linear(ized) circuit. A small signal model for a MOSFET, such as the one shown in Figure 2.2, contains a linear voltage-controlled current source. That is, under the small signal assumption, the circuit behaves linearly such that small signal voltages applied to the gate of the MOSFET (for example, a 10 mV-peak sine wave in Figure 2.1) produce an amplified drain-to-source current sine wave. The small signal current gain is the transconductance,  $g_m$ , which will be considered in more detail in Chapter 10. For now we will consider the incorporation of such a model into our Nodal Analysis equations.

The voltage-controlled current source from Figure 2.2 is a *natural* for Nodal Analysis. For generality we model any voltage-controlled current source as a four-terminal element, such as the one shown in Figure 2.3. Note that the controlling branch in the figure is a

Figure 2.1 MOSFET amplifier circuit.

Figure 2.2 Low frequency small signal N-MOSFET model.

$$v_{kl} \underbrace{\downarrow}_{-\downarrow l} V_{kl} = 0 \qquad \underbrace{\downarrow}_{pq} p_{pq} = g_m v_{kl}$$

Figure 2.3 Voltage-controlled current source.

zero-valued current source. This source is merely an open circuit and does not affect the operation of the circuit. It acts as an *ideal voltmeter* that helps us measure the controlling voltage in a convenient way. In a circuit, the controlling branch of a voltage-controlled current source may be anything: a resistor, a diode, a capacitor, and so on. Rather than formulate equations differently in each of these cases, we add a zero-valued current source and then build equations in a canonical fashion. Thus, representing a voltage-controlling

branch by a zero-valued current source leads to notational and computational convenience. Moreover, in Chapter 9 it will be shown that this "ideal voltmeter" facilitates the calculation of the circuit sensitivities.

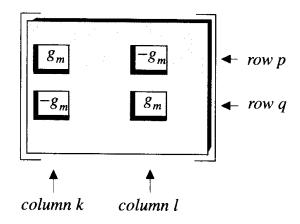

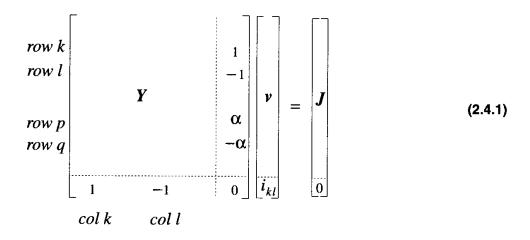

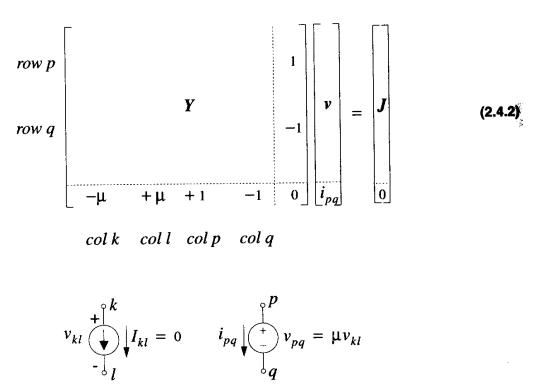

The voltage-controlled current source in Figure 2.3 contributes the stamp shown in Figure 2.4 to the Y matrix.

Figure 2.4 Stamp for a voltage-controlled current source.

Notice that this stamp contributes conductance terms to the Y matrix much like those for linear resistors. The distinction here is that the conductance terms do not appear symmetrically about the diagonal of the matrix. For example, the current out of node p, hence the expression appearing in row p of the matrix, is

$$i_{pq} = g_m v_{kl} \Rightarrow i_{pq} = g_m (v_k - v_l)$$

(2.1.1)

From (2.1.1) it is apparent that for row p of the matrix, which sums the current flowing out of row p, the conductance terms appear as a positive value in column k and a negative value in column l. Similarly, conductance terms appear with exactly the opposite signs for the entries in columns k and l for row q, since  $i_{pq}$  is flowing into this node. Note that we could show it formally, but we recognize that the zero-valued current source that represents the controlling branch contributes nothing to the J vector. In other words, we recognize that the zero-valued current source is not even required, but included only for our notational convenience.

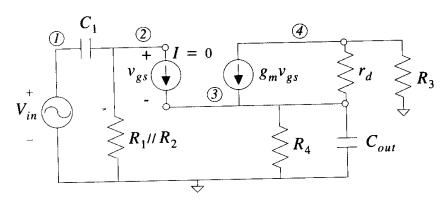

To clarify the use of this controlled-source matrix stamp we will replace the MOSFET in Figure 2.1 with the small signal model in Figure 2.2 and construct the complete set of nodal equations. The complete small signal circuit model is shown in Figure 2.5. Note that for this small signal transistor model we have applied the low-frequency assumption. That is, we do not consider the effects in the small signal model due to the parasitic MOSFET capacitances. Of course, if the frequency of the input sine wave were high enough, these capacitance effects would have to be considered.

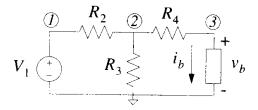

The stamping of all of the elements in Figure 2.5 leads to the following set of nodal equations:

$$\begin{bmatrix} 1 & 0 & 0 & 0 \\ -j\omega C_1 & (j\omega C_1 + G_1 + G_2) & 0 & 0 \\ 0 & -g_m & (G_4 + g_m + g_d + j\omega C_{out}) & -g_d \\ 0 & g_m & (-g_d - g_m) & (g_d + G_3) \end{bmatrix} \begin{bmatrix} V_1(j\omega) \\ V_2(j\omega) \\ V_3(j\omega) \\ V_4(j\omega) \end{bmatrix} = \begin{bmatrix} V_{in}(j\omega) \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(2.1.2)

Figure 2.5 Small signal equivalent circuit for the MOSFET amplifier.

Note that the resistors in Figure 2.5 have been expressed in conductance form in (2.1.2). The voltages are expressed as complex voltages due to the complex admittances of the capacitors. As was shown in Chapter 1, capacitor stamps are identical in form to linear conductance stamps, except that the admittance is  $j\omega C$  instead of simply G.

Although we haven't discussed voltage source stamps yet, equation (2.1.2) includes an independent voltage source. Since one end of the voltage source in Figure 2.5 is connected to ground, we can trivially include it with an equation  $V_1 = V_{in}$ , just as we have done in row one of (2.1.2). However, non-grounded, or floating voltage sources are not as easily handled. In the section which follows we seek a more generalized approach for stamping voltage sources using the *Modified Nodal Analysis* (MNA) method. Once we can handle voltage source stamps, we will return to the other three types of linear controlled sources since all of them depend upon the ability to handle voltage source elements.

# 2.2 Independent Voltage Sources

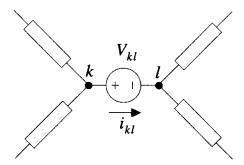

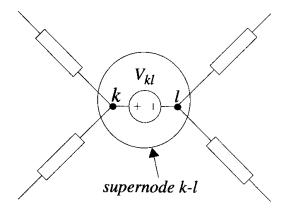

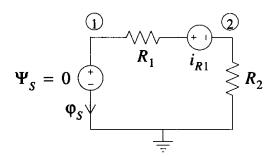

Since they do not have an admittance description form, it might appear that independent voltage sources complicate Nodal Analysis, but when properly handled they actually simplify it. Suppose that we have a floating voltage source connected between non-datum nodes k and l in a circuit, as shown in Figure 2.6. (The more common situation of a grounded voltage source can be easily obtained as a simpler special case of this treatment.)

Figure 2.6 A floating voltage source between nodes k and l.

The voltage,  $V_{kl}$ , between nodes k and l is known, so we cannot declare both node voltages,  $v_k$  and  $v_l$ , to be independent variables. To resolve this problem we introduce the voltage source current,  $i_{kl}$ , as a new independent variable and add the voltage constraint,

$$v_k - v_l = V_{kl} \tag{2.2.1}$$

as a new equation. Now we have one more equation and one more unknown in addition to those for conventional Nodal Analysis. Thus, for an (n+1) node (including datum) circuit with one floating voltage source  $V_{kl}$  from node k to node l, we have the following set of Modified Nodal Analysis (MNA) equations:

The y terms and the I terms represent the Y matrix and J vector entries without inclusion of the floating voltage source. In other words, (2.2.2) is equivalent to having the following stamp for a voltage source,

where the dashed lines indicate the augmentation of the original matrix Y and vector J which represent the conventional nodal admittance equations.

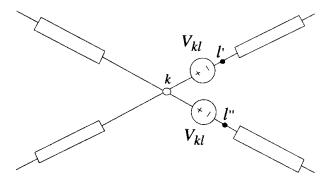

So long as they do not form loops, several independent voltage sources can be treated similarly, each having a simple set of stamps and adding a new row and column to the MNA equations. A loop of independent voltage sources is illegal and non-physical (more on this topic in Section 2.6) so we do not have to worry about such a situation. Note, however, that there is a zero on the diagonal in the (n+1, n+1) place for equations (2.2.2) and (2.2.3). Some simultaneous equation solution schemes may expect to be able to divide

the entries in a row by the corresponding diagonal element. Modified Nodal Analysis (MNA) [Ho75] overcomes this problem by exchanging row k with row n, which results in a +1 in the (k, k) location and a +1 in the (n+1, n+1) location:

$$col \ 1 \ col \ k \ col \ 1 \ col \ n$$

$$col \ n+1$$

$$row \ 1 \ \begin{bmatrix} y_{11} & \dots & y_{1k} & \dots & y_{1l} & \dots & y_{1n} & 0 \\ \vdots & \vdots & & \vdots & & & \\ 0 & \dots & 1 & \dots & -1 & \dots & 0 & 0 \\ \vdots & & & \vdots & & & \vdots \\ row \ l \ & y_{l1} & \dots & y_{lk} & \dots & y_{ll} & \dots & y_{ln} & -1 \\ \vdots & & & & \vdots & & & \vdots \\ row \ n \ & y_{n1} & \dots & y_{nk} & \dots & y_{nl} & \dots & y_{nn} & 0 \\ y_{k1} & \dots & y_{kk} & \dots & y_{kl} & \dots & y_{kn} & 1 \end{bmatrix} \begin{bmatrix} v_{I} \\ \vdots \\ v_{k} \\ \vdots \\ v_{l} \\ \vdots \\ v_{n} \\ \vdots \\ v_{n} \\ \vdots \\ I_{n} \\ \vdots \\ I_{n} \\ I_{k} \end{bmatrix}$$

$$(2.2.4)$$

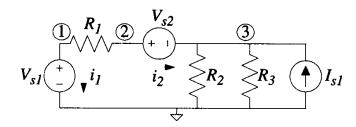

As an example of how the nodal equations appear when there are voltage sources, consider the simple circuit in Figure 2.7. Since there are three non-datum nodes and two volt-

Figure 2.7 Circuit example with a floating voltage source.

age sources, the MNA equations are characterized by the following  $5 \times 5$  Y matrix and  $5 \times 1$  J vector:

$$\begin{bmatrix} G_1 & -G_1 & 0 & 1 & 0 \\ -G_1 & G_1 & 0 & 0 & 1 \\ 0 & 0 & (G_2 + G_3) & 0 & -1 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & -1 & 0 & 0 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ v_3 \\ i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ I_{s1} \\ V_{s1} \\ V_{s2} \end{bmatrix}$$

(2.2.5)

Of course, we could swap rows 1 and 2 with rows 4 and 5, respectively, in order to ensure that there is a nonzero term for each diagonal entry. Next, we will show that it is easier, however, just to eliminate the *excess* rows and columns.

# 2.3 (Conventional) Nodal Analysis