# 國立成功大學電機工程學系博士論文

高速低耗能逐漸趨近式類比至數位轉換器 之設計

Design of High-Speed Energy-Efficient

Successive-Approximation

Analog-to-Digital Converters

研究生: 劉純成 Student: Chun-Cheng Liu

指導教授: 張順志 Advisor: Soon-Jyh Chang

Department of Electrical Engineering National Cheng Kung University Tainan, Taiwan, R.O.C. Dissertation for Doctor of Philosophy June 2010

中華民國 九十九年六月

# 國立成功大學電機工程學系博士論文

高速低耗能逐漸趨近式類比至數位轉換器之設 計

研究生:劉純成

本論文業經審查及口試合格特此證明論文考試委員

强激志 新五烈 参泰政

鹅菇烷 到道道 沙原家

指導教授: 延光表

系主任:陳建富

. 中華民國 九十九年六月九日

### Design of High-Speed Energy-Efficient Successive-Approximation Analog-to-Digital Converters

by Chun-Cheng Liu

A dissertation submitted to the graduate division in partial fulfillment of the requirement for the degree of Doctor of Philosophy

at

National Cheng Kung University

Tainan, Taiwan, Republic of China

June, 2010

Approved by:

| Soon-Jyh Chang Meng-Lieh Shen Vai- has La   |

|---------------------------------------------|

|                                             |

| Ter Membro - Hav Chiarthory Ching-yuan yang |

| Chin-Lij Wei Som Shua-Chin Wang             |

| 144 (1501.                                  |

| Soon-Jyh Chang                              |

| Chairman:                                   |

| Tians - Fuh Chan                            |

# 高速低耗能逐漸趨近式類比至數位轉換器 之設計

學生: 劉純成 指導教授: 張順志

國立成功大學電機工程研究所

#### 摘 要

本論文提出三個應用於逐漸趨近式類比至數位轉換器的電路設計技術,並且透過實際的晶片下線和量測驗證,證實所提出之電路設計技術可以有效提升電路的操作速度以及降低每次轉換所消耗的能量。所提出的電路設計技術以及晶片實作成果簡述如下:

第一個技術為單調式的電容切換機制,其比傳統架構的切換方式節省約81.3%的切換能量以及50%的取樣電容。在0.13 微米互補式金氧半電晶體製程下,我們利用此技術來實現一個10 位元,每秒5 千萬次取樣的逐漸趨近式類比至數位轉換器。此類比至數位轉換器在1.2 伏特的電壓下,其功率消耗為0.92 毫瓦,有效位元為8.48 bits,等效的FOM僅為52 fJ/conversion-step。然而,單調式的電容切換機制會導致比較器輸入端訊號共模電壓的改變,使得比較器的動態偏移嚴重影響電路的效能。為了改善這個問題,我們提出一個改良版的比較器電路,可以有效控制比較器的動態偏移量。此外,在電路內部改採用非同步操作方式以避免使用數倍於取樣速度的高頻時脈訊號,降低系統整合的複雜度。同樣在0.13 微米互補式金氧半電晶體製程下,我們實現另一個10 位元,每秒5 千萬次取樣的逐漸趨近式類比至數位轉換器。在1.2 伏

特的電壓下,其功率消耗為 0.826 毫瓦,有效位元提升為 9.18 bits,等效的 FOM 僅為 29 fJ/conversion-step。

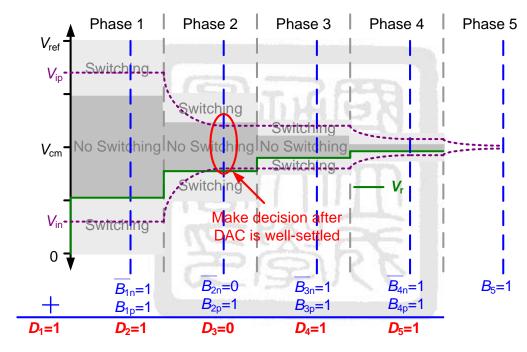

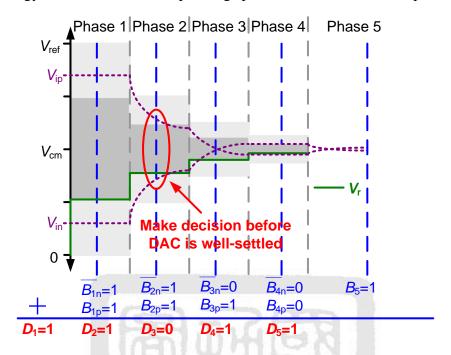

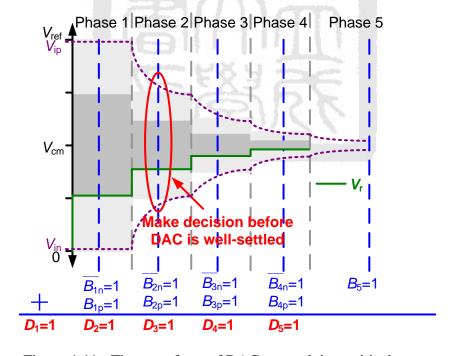

第二個技術為二進制的錯誤補償機制。高速操作的逐漸趨近式類比至數位轉換器,由於每個位元週期的時間非常短,常常在 DAC 電壓還沒穩定的時候就必須要做下一次的比較,DAC 電壓穩定的問題嚴重影響電路的效能,也限制了電路的操作速度。我們提出了一個二進制的錯誤補償機制,在電路中插入額外的補償位元來做錯誤校正,因此比較器可以在 DAC 還沒穩定的時候先做比較,以提升電路操作速度。在65 奈米互補式金氧半電晶體製程下,我們利用此技術來實現一個 10 位元,取樣速度可以達到每秒 1 億次的逐漸趨近式類比至數位轉換器。在 1.2 伏特的電壓下,其功率消耗為 1.13 毫瓦,有效位元為 9.51 bits,等效的 FOM 僅為 15.5 fJ/conversion-step。

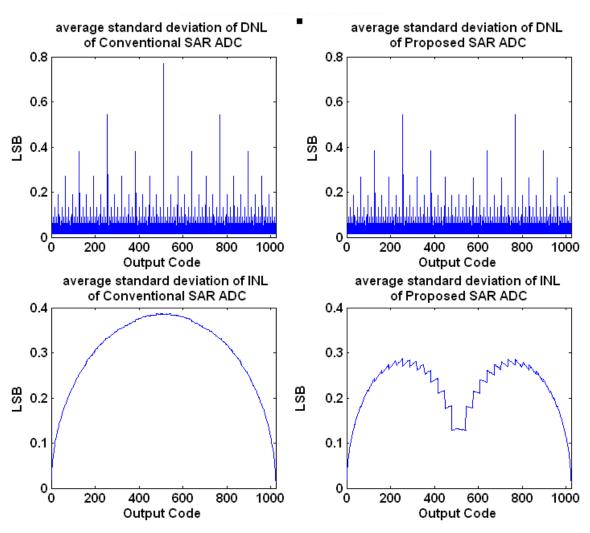

第三個技術則是利用一個輔助預測電路,來避免不必要的電容切換,此技術可以 省下 40-45%的電容切換能量消耗。配合第一個技術,電容切換的能量消耗可以比傳 統方法減少約 90%左右。除此之外,這個技術還能改善電路的靜態以及動態效能。在 0.18 微米互補式金氧半電晶體製程下,我們利用此技巧來實現一個 10 位元,每秒 1 千萬次取樣的逐漸趨近式類比至數位轉換器。在 1 伏特的電壓下,其功率消耗僅為 98 微瓦,有效位元為接近理想的 9.83 bits,等效的 FOM 僅為 11 fJ/conversion-step。

# Design of High-Speed Energy-Efficient Successive-Approximation Analog-to-Digital Converters

Student: Chun-Cheng Liu Advisor: Soon-Jyh Chang

Department of Electrical Engineering National Cheng Kung University Tainan, Taiwan, R.O.C.

#### **Abstract**

This dissertation proposes three circuit design techniques for successive-approximation register (SAR) analog-to-digital converters (ADCs). According to the measurement results of the proof-of-concept prototypes, the proposed techniques are able to improve the operating speed and achieve excellent energy efficiency. The proposed techniques and chip measurement results are sketched as follows:

The first technique is a monotonic capacitor switching procedure. Compared to converters that use the conventional procedure, the average switching energy and total sampling capacitance are reduced by about 81.3% and 50%, respectively. A 10-bit, 50-MS/s SAR ADC with the proposed monotonic capacitor switching procedure is implemented in a 0.13- $\mu$ m 1P8M CMOS technology. The prototype ADC consumes 0.92 mW from a 1.2-V supply, and the effective number of bit (ENOB) is 8.48 bits. The resulting figure of merit (FOM) is 52 fJ/conversion-step. However, the signal-dependent offset caused by the variation of the input common-mode voltage degrades the linearity of ADC. We proposed an improved comparator design to avoid the linearity degradation. Besides, to avoid a clock signal with frequency higher than sampling rate, we used an

asynchronous control circuit to internally generate the necessary control signals. The revised prototype is also implemented in a 0.13- $\mu$ m 1P8M CMOS technology. It consumes 0.826 mW from a 1.2-V supply and achieves an ENOB of 9.18 bits. The resultant FOM is 29 fJ/conversion-step.

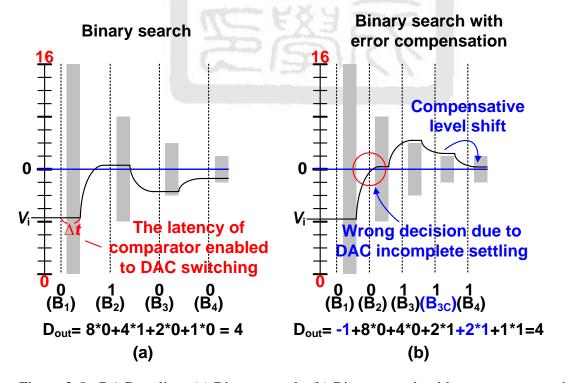

The second technique is a binary-scaled error compensation method. In a medium-to-high resolution case, the DAC settling issue limits the operating speed of a SAR ADC, because it is not easy for the capacitive DAC to stabilize in a short time interval. We insert extra binary-scaled compensation bits to compensate for the DAC settling error. Accordingly, the comparator can perform comparison before the DAC is completely settled, resulting in improved operating speed. A 10-bit, 100-MS/s SAR ADC using the binary-scaled error compensation method is implemented in a 65-nm 1P6M CMOS technology. The prototype consumes 1.13 mW from a 1.2-V supply and achieves an ENOB of 9.51 bits. The resultant FOM is 15.5 fJ/conversion-step.

The third technique is a predictive capacitor switching method that uses a predictive circuit to avoid unnecessary switching in a DAC network. This method saves  $40\sim45\%$  switching energy. Combined with the first technique, the average switching energy is reduced by about 90% than the conventional one. In addition, this technique improves static and dynamic performance of a SAR ADC. A 10-bit, 10-MS/s SAR ADC using this method is implemented in a  $0.18-\mu m$  1P6M CMOS technology. The prototype consumes 98  $\mu W$  from a 1-V supply and achieves an excellent ENOB of 9.83 bits. The resultant FOM is only 11 fJ/conversion-step.

#### 誌謝

四年的博士班生涯即將告一個段落,回首過去這一路上的點點滴滴,心中的感觸 真的是難以用筆墨來形容。雖然大部分的時間都是在忙碌中度過,但這段期間的學習 及成長,不論是解決問題的能力或者待人處事,各方面都有長足的進步,如今終於順 利取得博士學位,對於這一路上所有幫助過我及關心我的人,我有說不盡的感謝。

首先,先向我的指導教授張順志博士致上由衷的謝意。從大學專題開始到博士班一共六年半的時間,不但提供了我良好的研究環境及學習資源,更不厭其煩的在研究上細心指導,培養我專業客觀的研究精神與獨立思考的能力,並教導我做人處事之道,讓我在學業和待人處事上皆獲益匪淺。老師那工作認真、遇事不推拖的態度更是我學習的楷模。也感謝老師在生活上的關心與照顧,於此獻上最真摯的謝意。

接著,感謝口試委員<u>劉濱達博士、郭泰豪博士、王朝欽博士、許孟烈</u>博士、<u>李泰</u>成博士、<u>洪浩喬</u>博士、<u>楊清淵</u>博士以及<u>魏嘉玲</u>博士,於百忙中撥冗細審,並惠賜寶貴的意見,使本論文更臻完善。

另外,要特別感謝林英儒學長協助我論文的撰寫及編修,讓我論文投稿的過程格外的順利。也感謝所有的實驗室夥伴們,謝謝歐信宏、丁信文、林英儒、林進富、陳仁禮、趙安生、鄭乃禎、林城伍、劉彥廷、丁振國、陳卓凡等學長,還有黃冠穎、趙宜任、羅世明、黃宏裕、呂政家等同學,以及陳鵬宇、孔德潔、李婉菁、黃素鈴、黃意婷、蘇品岱、鐘明良、連昱彰、許雅婷、邵姿菁、李彥龍、黃俊博、黃詩雄、楊孟法、蔡肇芳、褚嶸興、陳柏穎、謝明學、王南元、郭建良等學弟妹,謝謝你們在這段期間不論是在研究上,或者生活上諸多的幫助。在實驗室裡的諸多歡笑,還有每次晶片下線前一起熬夜看日出的日子,都是我值的珍藏的美好回憶。

也謝謝從91級到102級,所有曾一起頂著中午的大太陽在光復籃球場練球的<u>系籃</u> 夥伴們,我永遠記得與你們一同在球場上揮灑汗水的日子,不但讓我忘卻了研究上的 壓力,也讓我有充沛的體力來面對這如此繁忙的研究生活,謝謝你們。

此外,特別感謝<u>朱芳葦</u>小姐在我博士班這段期間對我的關懷、支持與鼓勵。謝謝你一直持續關心我的健康,照料我的日常生活,包容我的缺點,體諒我的忙碌,沒有你在背後默默的為我付出與犧牲,我難以在如此短的時間內完成我的博士論文,在此致上我對你最誠摯的感謝。

最後我要感謝我的父母及家人對我的關心及照顧。感謝父親<u>劉藤旺</u>先生與母親<u>黃</u> 實玉女士,從小對我的悉心培育,提供我理想的求學環境,給予我完全的支持。同時 也感謝二姐<u>劉娟伶</u>,在生活上諸多的協助。謝謝你們為我的付出,讓我無後顧之憂的 追求我的理想,我才能夠順利的完成學業。今後我將更努力的充實自己並發揮所長, 以不負大家對我的期望。

最後,謹以此論文,獻給所有曾幫助過我和關心我的人,希望你們能和我共同分享這份榮耀與喜悅!謝謝你們!

劉純成 謹誌於 國立成功大學電機系 SSCAS 實驗室 民國九十九年七月十五日

### **Table of Contents**

| Abstract                                                        | III |

|-----------------------------------------------------------------|-----|

| Table of Contents                                               | VII |

| List of Tables                                                  | IX  |

| List of Figures                                                 | X   |

| Chapter 1 Introduction                                          | 1   |

| 1.1 MOTIVATION                                                  | 1   |

| 1.2 Organization of the dissertation                            | 5   |

| Chapter 2 Monotonic Capacitor Switching Procedure for SAR ADC   | 6   |

| 2.1 Proposed Monotonic Capacitor Switching Procedure            | 7   |

| 2.1.1Conventional SAR ADC                                       | 7   |

| 2.1.2Proposed SAR ADC                                           | 8   |

| 2.1.3Analysis of Switching Energy in DAC Network                | 11  |

| 2.2 A 0.92mW 10-BIT 50-MS/s SAR ADC                             | 15  |

| 2.2.1 Sample and Hold Circuit                                   | 15  |

| 2.2.2Comparator Design                                          | 17  |

| 2.2.3SAR Control Logic                                          | 18  |

| 2.2.4Capacitor Array                                            | 20  |

| 2.2.5Measurement Results                                        | 21  |

| 2.3 A 10-BIT 50-MS/S SAR ADC WITH AN IMPROVED COMPARATOR DESIGN |     |

| 2.3.1S/H circuit                                                | 25  |

| 2.3.2Dynamic Comparator with a Current Source                   | 26  |

| 2.3.3SAR Control Logic                                          | 28  |

| 2.3.4Unit Capacitor                                             | 29  |

| 2.3.5Measurement Results                                        | 30  |

| 2.4 A 6-BIT 220-MS/S TIME-INTERLEAVING SAR ADC                  | 37  |

| 2.4.1Architecture                                               | 37  |

| 2.4.2Comparator Design                                          | 39  |

| 2.4.3SAR Control Logic                                          | 39  |

| 2.4.4Unit Capacitor                                             | 40  |

| 2.4.5Layout and Floorplan                                       | 41  |

| 2.4.6Measurement Results                                        | 42  |

| 2.5 SUMMARY                                                     | 46  |

| Chapter 3 Binary-Scaled Error Compensation Method for High-Speed SAR AI    | )C 47 |

|----------------------------------------------------------------------------|-------|

| 3.1 Introduction                                                           | 47    |

| 3.2 THE PROPOSED BINARY-SCALED ERROR COMPENSATION METHOD                   | 48    |

| 3.2.1Conventional Binary Search                                            | 48    |

| 3.2.2Non-binary Search                                                     | 50    |

| 3.2.3Proposed Binary Search with Error Compensation                        | 51    |

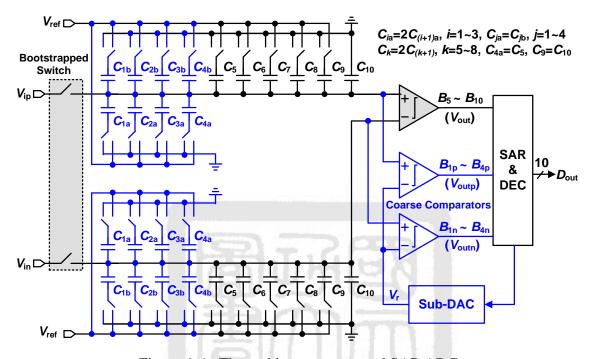

| 3.3 A 10-BIT 100-MS/S 1.13MW SAR ADC WITH BINARY-SCALED ERROR COMPENSATION | 53    |

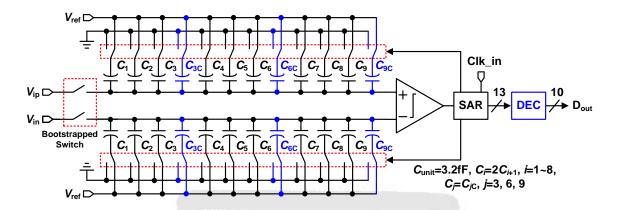

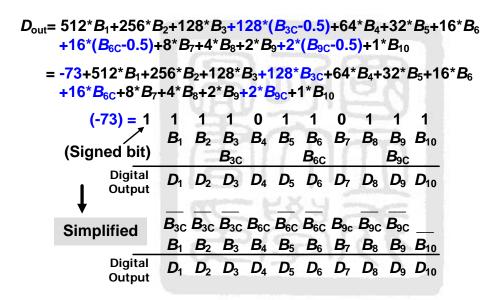

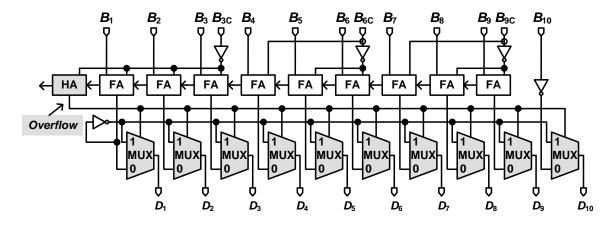

| 3.3.1Architecture                                                          | 53    |

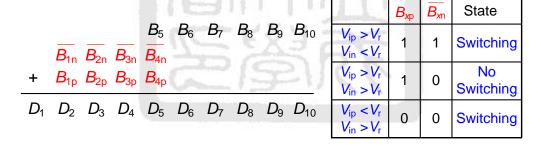

| 3.3.2Digital Error Correction Logic                                        | 54    |

| 3.3.3Measurement Results                                                   | 56    |

| 3.4 SUMMARY                                                                | 61    |

| Chapter 4 Predictive Capacitor Switching Procedure for SAR ADC             | 62    |

| 4.1 Introduction                                                           | 62    |

| 4.2 SPLITTING MONOTONIC CAPACITOR SWITCHING PROCEDURE                      | 63    |

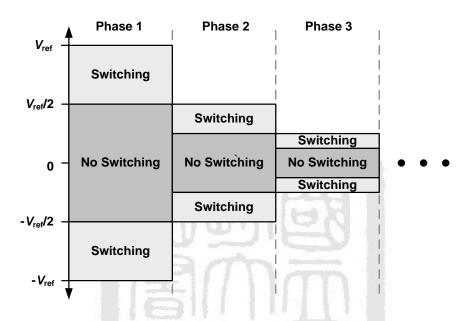

| 4.3 Predictive Capacitor Switching Procedure                               | 65    |

| 4.4 A 1-V 11 FJ/CONVERSION-STEP 10-BIT 10-MS/S ASYNCHRONOUS SAR ADC        | 68    |

| 4.4.1Architecture                                                          | 68    |

| 4.4.2Discussion on DAC Settling                                            |       |

| 4.4.3Matlab Simulation Result                                              |       |

| 4.4.4Measurement Results                                                   | 75    |

| 4.5 SUMMARY                                                                | 81    |

| Chapter 5 Conclusions and Future Work                                      |       |

| 5.1 CONCLUSIONS                                                            | 82    |

| 5.2 FUTURE WORK                                                            | 84    |

| Reference                                                                  | 85    |

| Publication List                                                           | 89    |

| Biography                                                                  | 91    |

## **List of Tables**

| <b>Table 2-1</b> | Comparison of Switching Procedures                 |    |  |

|------------------|----------------------------------------------------|----|--|

| Table 2-2        | Summary of ADC Performance                         | 24 |  |

| Table 2-3        | Comparison to State-of-the-Art Works               | 24 |  |

| Table 2-4        | Summary of ADC Performance                         | 34 |  |

| Table 2-5        | Specification Summary at Different Supply Voltages | 35 |  |

| Table 2-6        | Comparison to State-of-the-Art Works               | 36 |  |

| Table 2-7        | Summary of ADC Performance                         | 45 |  |

| Table 2-8        | Comparison to the Other Works                      | 45 |  |

| Table 3-1        | Summary of ADC Performance                         | 59 |  |

| Table 4-1        | Power Consumption of Each Parts                    | 70 |  |

| Table 4-2        | Settling Times with Different Methods              | 73 |  |

| Table 4-3        | Summary of ADC Performance                         | 78 |  |

| Table 4-4        | Comparison to State-of-the-Art Works               | 80 |  |

# **List of Figures**

| Figure 2-1  | A conventional 10-bit SAR ADC7                                                                 |

|-------------|------------------------------------------------------------------------------------------------|

| Figure 2-2  | The proposed SAR ADC architecture 8                                                            |

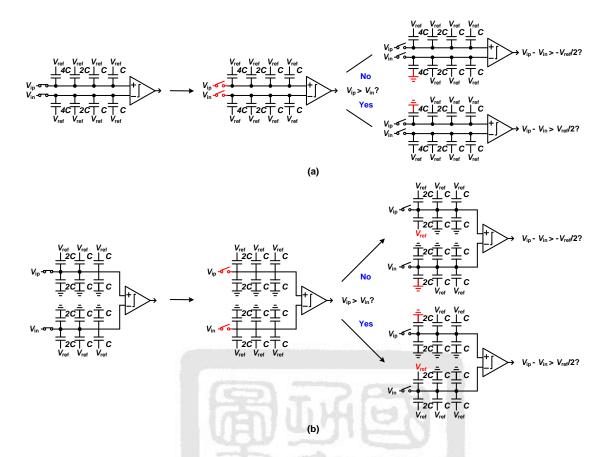

| Figure 2-3  | Flow chart of the proposed SAR ADC9                                                            |

| O           | (a) Waveform of conventional switching procedure. (b) Waveform of onotonic switching procedure |

| Figure 2-5  | A 3-bit capacitor array with conventional switching method11                                   |

| Ü           | (a) Conventional switching procedure. (b) Proposed switching procedure.                        |

|             |                                                                                                |

|             | Switching energy versus output code in a 10-bit ADC                                            |

| Figure 2-8  | Bootstrapped switch                                                                            |

| Figure 2-9  | The schematic of a latch-based dynamic comparator 17                                           |

| Figure 2-10 | Internal clock generator: (a) Schematic. (b) Timing diagram 18                                 |

|             | DAC control bgic                                                                               |

| Figure 2-12 | The layout floorplan of the capacitor array20                                                  |

| Figure 2-13 |                                                                                                |

| Figure 2-14 | Measured DNL and INL                                                                           |

| Figure 2-15 | Measured FFT spectrum at 50 MS/s with a 20-MHz input frequency 22                              |

| Figure 2-16 | Measured SFDR and SNDR versus input frequency at 50 MS/s 23                                    |

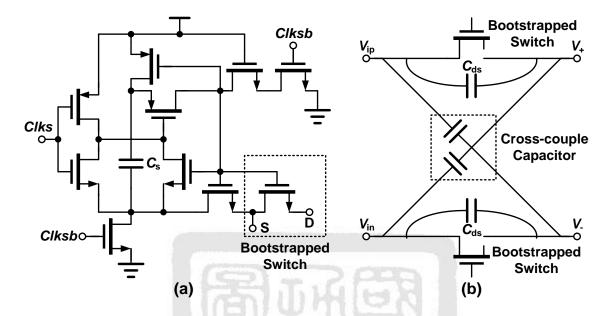

| Figure 2-17 | (a) Bootstrapped switch. (b) Cross-coupled capacitors                                          |

| Figure 2-18 | Dynamic comparator with a current source                                                       |

| Figure 2-19 | Asynchronous control logic: (a) Schematic. (b) Timing diagram 28                               |

| Figure 2-20 | (a) Sandwich capacitor. (b) Multi-layer sandwich capacitor 29                                  |

| Figure 2.21 | Die micrograph and the zoomed view                                                             |

| Figure 2-22 | Measured DNL and INL                                                                           |

| Figure 2-23 | Measured FFT spectrum at 50 MS/s with a 10-MHz input frequency 32                              |

| Figure 2-24 | Measured performance versus input frequency at 1.2 V and 50 MS/s 32                            |

| Figure 2-25 | Measured dynamic performance versus sampling frequency                                         |

| Figure 2-26 Measured performance versus input frequency at 0.6 V and 10 MS/s 35             |

|---------------------------------------------------------------------------------------------|

| Figure 2-27 Timing diagram of the time-interleaving SAR ADC38                               |

| Figure 2-28 Architecture of a 6-bit single channel SAR ADC                                  |

| Figure 2-29 Schematic of the comparator                                                     |

| Figure 2-30 The SAR logic implementation                                                    |

| Figure 2-31. Unit capacitor structure: (a) sandwich capacitor (b) finger sandwich capacitor |

| Figure 2-32 Layout of the implemented SAR ADC                                               |

| Figure 2-33 Floor plan of ADC core                                                          |

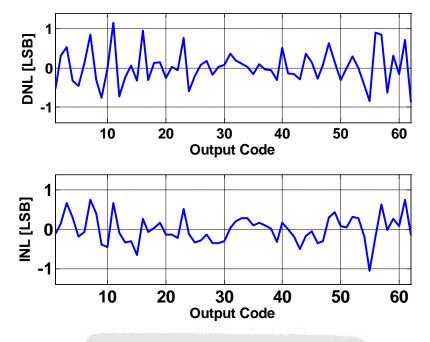

| Figure 2-34 Measured INL and DNL                                                            |

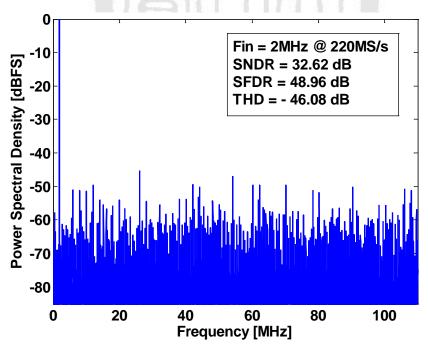

| Figure 2-35 Measured FFT spectrum at 220 MS/s with a 2-MHz input frequency 43               |

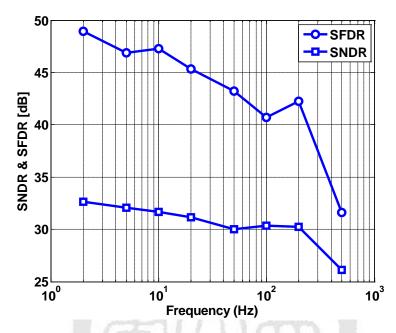

| Figure 2-36 Measured performance versus input frequency at 1.8 V and 220 MS/s.44            |

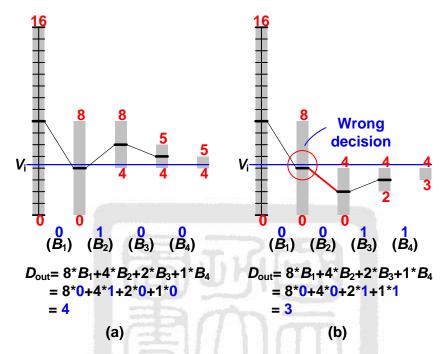

| Figure 3-1 Conventional binary search: (a) Correct conversion. (b) Wrong conversion         |

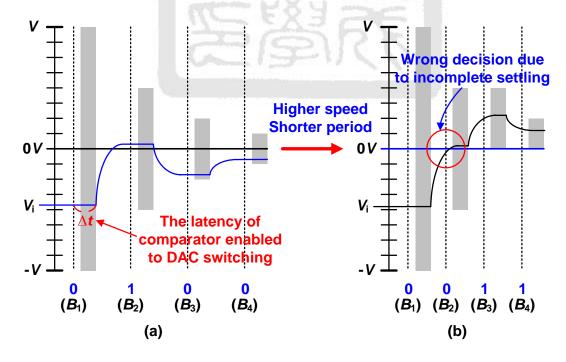

| Figure 3-2 DAC settling: (a) Longer period. (b) Shorter period                              |

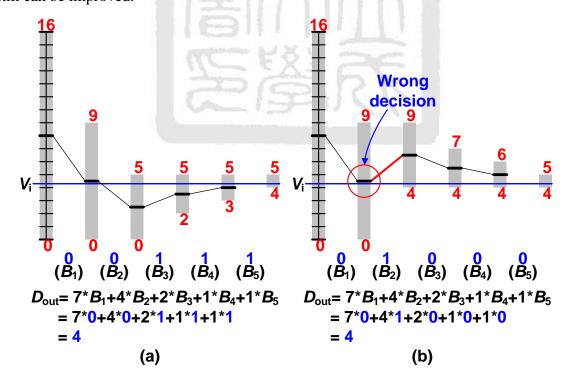

| Figure 3-3 Non-binary search: (a) Correct conversion. (b) Conversion with wrong decision    |

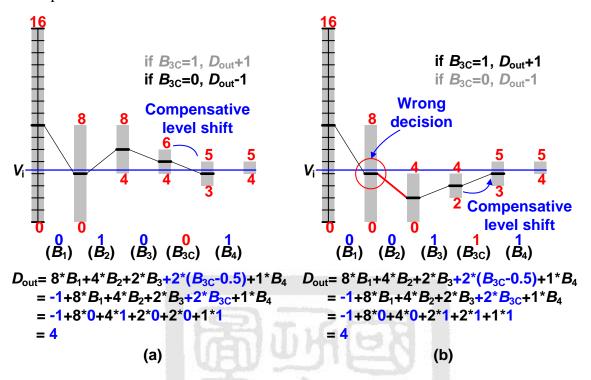

| Figure 3-4 Binary search with error compensation: (a) Correct conversion (b)                |

| Conversion with wrong decision 52                                                           |

| Figure 3-5 DAC settling: (a) Binary search. (b) Binary search with error compensation       |

| Figure 3-6 Block diagram of a 10-bit SAR ADC with binary-scaled error                       |

| compensation 53                                                                             |

| Figure 3-7 Digital error correction logic                                                   |

| Figure 3-8 Implementation of digital error correction logic                                 |

| Figure 3-9 Chip micrograph and zoomed view                                                  |

| Figure 3-10 Measured INL and DNL performance                                                |

| Figure 3-11 Measured FFT spectrum at 100 MS/s with a 9.9-MHz input frequency.               |

| Figure 3-12 Measured dynamic performance versus input frequency at 100 MS/s. 58             |

| ${\bf Figure~3-13~~Measured~dynamic~performance~versus~sampling~frequency}$                                                 | 59         |

|-----------------------------------------------------------------------------------------------------------------------------|------------|

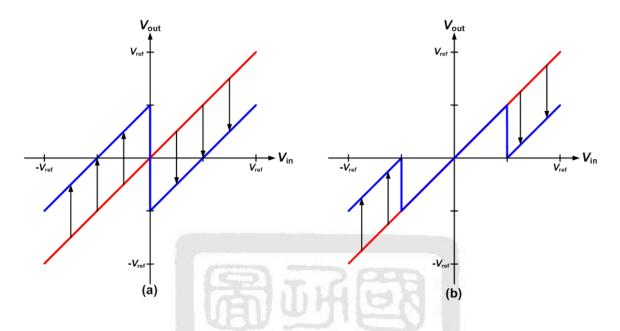

| Figure 4-1 Switching examples: (a) Monotonic switching method. (b) Splitting monotonic switching method.                    | 64         |

| Figure 4-2 (a) Waveform of monotonic switching procedure. (b) Waveform of splitting monotonic switching procedure.          | 64         |

| Figure 4-3 The approximations of conventional and proposed methods                                                          | 65         |

| Figure 4-4 The graph of proposed switching procedure.                                                                       | 66         |

| Figure 4-5 Transfer curves in the first bit cycle: (a) Conventional 1-bit/cycle SAR ADC. (b)Proposed 1.5-bit/cycle SAR ADC. | 67         |

| Figure 4-6 The architecture proposed SAR ADC.                                                                               | 68         |

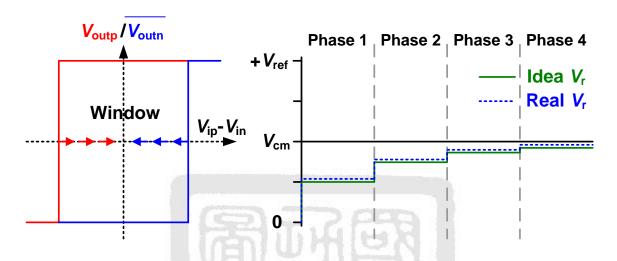

| Figure 4-7 Variable window function                                                                                         | 69         |

| Figure 4-8 Digital error correction logic.                                                                                  | <b>7</b> 0 |

| Figure 4-9 The waveform of the DAC network with sufficient settling time                                                    | <b>7</b> 1 |

| Figure 4-10 The waveform of DAC network without sufficient settling time                                                    | 72         |

| Figure 4-11 The waveform of DAC network in a critical case                                                                  | 72         |

| Figure 4-12 The standard deviation of INL and DNL                                                                           | 74         |

| Figure 4-13 Die micrograph and the zoomed view.                                                                             | 75         |

| Figure 4-14 Measured DNL and INL.                                                                                           | 75         |

| Figure 4-15 Measured FFT spectrum at 10 MS/s with a 4.98-MHz input frequency.                                               |            |

| Figure 4-16 Measured dynamic performance versus input frequency at 1 V and 10 MS/s.                                         | ı          |

| Figure 4-17 Measured dynamic performance versus sampling frequency                                                          | 77         |

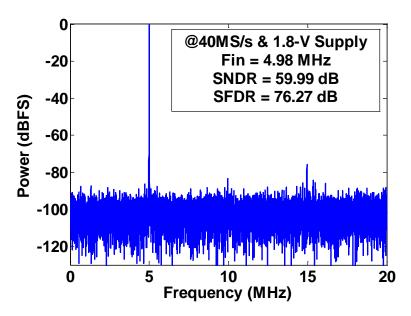

| Figure 4-18 Measured FFT spectrum at 40 MS/s with a 4.98-MHz input frequency                                                |            |

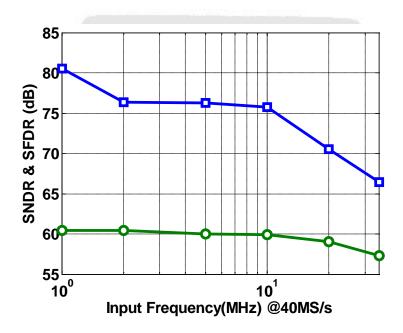

| Figure 4-19 Measured performance versus input frequency at 1.8 V and 40 MS/s                                                |            |

# Chapter 1 Introduction

#### 1.1 Motivation

Conventionally, successive-approximation register (SAR) analog-to-digital converters (ADCs) are extensively used in low-power and low-speed (below several MS/s) applications. For medium- to high-speed applications, the flash ADC and pipelined ADC have been the popular architectures. In recent years, with the feature sizes of CMOS devices scaled down, the increasing speed of devices has enabled the SAR ADCs to achieve several tens of MS/s to low GS/s sampling rates with 5- to 12-bit resolutions [1-15]. Additionally, SAR ADCs have the features of low power and low cost that makes it more appealing than the other architectures for some portable systems or low-power-demand applications. Many recent researches have been involved in this ADC. The main techniques of SAR ADCs in recent published papers can be categorized as follows:

#### (1)Passive charge sharing SAR ADC

The passive charge sharing SAR ADC [1-2] works completely in charge domain instead of voltage domain. During the SAR algorithm, charge is added or subtracted to the sampling capacitor until the result converges to zero. The ADC uses tracking capacitors to pre-track the input signals in all clock period except the sampling phase. Therefore, it has a sufficient time interval to track the input and no settling problems occur.

#### (2) Non-binary SAR ADC

To reduce the power consumption, a SAR ADC usually uses a capacitive DAC to generate the reference voltage instead of a resistive DAC. However, the capacitive DAC has a longer settling time which is proportional to the resolution. Therefore, a capacitive-DAC-based SAR ADC has limited operation speed. The non-binary SAR ADC [3-5] uses a non-binary-scaled capacitor sizes (e.g., 1 1.85 1.85<sup>2</sup> 1.85<sup>3</sup> 1.85<sup>4</sup>...). More decision levels are generated than the conventional design. There are several digital codes for every input voltage. Hence, a certain range of DAC settling error does not affect the conversion result. The conversion rate of the ADC was improved.

#### (3) Time-interleaving SAR ADC

The sampling rate of a single SAR ADC is not as fast as the flash ADC or pipelined ADC. The time-interleaving SAR ADC [5-12] was proposed to improve the sampling rate. However, the time-interleaving SAR ADC has a channel mismatch problem. For medium-to high-resolution applications, the interleaved ADC must use digital calibration or post processing [5] to overcome the channel mismatch and some non-ideal effects to achieve sufficient performance. The time-interleaving SAR ADC increases the sampling rate, but on-chip digital calibration circuit usually occupies large area and results in large power consumption. Therefore, developing a low-cost high-efficiency digital calibration

technique is one of the hottest topics of SAR ADCs.

#### (4) Asynchronous SAR ADC

Conventional SAR ADCs only convert one bit in each bit cycle. For an N-bit SAR ADC, it needs N+1 clock cycles to complete one conversion (one clock cycle is used to sample the input signal). An extra PLL circuit is needed to provide the high frequency clock that increases the design and hardware overhead. The asynchronous SAR ADC [11] internally generates the necessary control signal. The sampling rate is equal to the clock rate. Therefore, an asynchronous SAR ADC does not need any extra PLL circuit.

#### (5)Reduce the switching energy in DAC network

In SAR ADCs, the primary sources of power dissipation are the digital control circuit, comparator, and capacitive reference DAC network. Digital power consumption becomes lower with the advancement of technology. Technology scaling also improves the speed of digital circuits. On the other hand, the power consumption of the comparator and capacitor network is limited by mismatch and noise. Recently, several energy-efficient switching methods have been proposed to lower the switching energy of the capacitor network. The split capacitor method [12] reduces switching energy by 37%, and the energy-saving method [16] reduces energy consumption by 56%.

There are some other techniques, like multi-bit/step [8], pipelined-SAR [13], etc., are also presented to improve the sampling rate or reduce the power consumption of the SAR ADC. The SAR architecture become feasible alternatives to flash ADCs and pipelined ADCs in nanometer scaled CMOS processes.

Except the above techniques, we proposed and demonstrated several circuit techniques to improve the operating speed and achieve excellent energy efficiency. The proposed monotonic switching procedure leads to both lower switching energy and smaller total

capacitance. It also simplifies the digital logic control circuit that reduces the power consumption and improves the operating speed. The proposed method is suited for high-speed, low-power and low-cost design. However, the signal-dependent offset caused by the variation of the input common-mode voltage degrades the linearity of ADC. Therefore, we proposed a biased comparator to reduce the dynamic offset. The improved comparator design mitigates the linearity degradation. In addition, a splitting monotonic switching procedure is also proposed to avoid the input common-mode voltage variation. Hence, the signal-dependent offset has no influence on the ADC linearity.

A binary-scaled error compensation method is proposed to overcome the DAC settling issue in the high-speed SAR ADC. Similar to the non-binary search technique, the binary-scaled error compensation method is capable of enhancing the sampling rate, and results in fewer design and hardware overhead compared to the non-binary search technique.

We proposed an improved switching scheme which uses a predictive circuit to avoid unnecessary switching in DAC network. This method reduces the power consumption and improves linearity of ADC without degrading the operation speed.

#### 1.2 Organization of the dissertation

This dissertation presents the design and implementation of several circuit design techniques for SAR ADCs. The remainder of the dissertation is organized as follows:

Chapter 2 discusses and analyzes the conventional switching procedure and the proposed monotonic capacitor switching procedure. Chapter 3 introduces the proposed binary-scaled error compensation method. In Chapter 4, we will introduce a splitting monotonic switching method and a predictive capacitor switching procedure which uses a predictive circuit to reduce unnecessary switching in DAC network. Finally, generalized conclusions are presented in Chapter 5, and future works of this research are summarized

for further exploration.

### Chapter 2

# Monotonic Capacitor Switching Procedure for SAR ADC

Recently, several energy-efficient switching methods [12] [16] have been proposed to lower the switching energy of the capacitor network for the SAR ADC. Although these methods reduce the switching energy, they make the SAR control logic more complicated due to the increased number of capacitors and switches, yielding higher digital power consumption. In Section 2.1, we proposed a monotonic switching procedure that reduces power consumption by 81.3% in the DAC network without splitting or adding any capacitors and switches. The total capacitance in the DAC capacitor network is reduced by 50%. In Section 2.2, a SAR ADC with proposed monotonic switching procedure is introduced. The work demonstrates the effectiveness of the switching procedure. However, the signal-dependent offset caused by the variation of the input common-mode voltage degrades the ADC linearity. Section 2.3 presents an improved comparator design to avoid the linearity degradation, and the implementation of the revised prototype is also presented. Section 2.4 introduces the implementation of a 6-bit time-interleaving SAR ADC using the proposed switching scheme.

#### 2.1 Proposed Monotonic Capacitor Switching Procedure

#### 2.1.1 Conventional SAR ADC

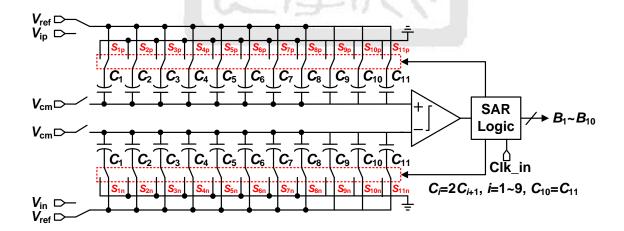

To achieve medium-to-high resolutions, a fully differential architecture suppresses the substrate and supply noise and has good common-mode noise rejection. SAR ADCs usually use a binary-weighted capacitor array rather than a C-2C capacitor array for better linearity. Figure 2-1 shows a conventional 10-bit fully differential SAR ADC. The fundamental building blocks are the comparator, sample-and-hold (S/H) circuit, capacitor network, and successive approximation registers. In the charge-redistribution based architecture, the capacitor network serves both as a S/H circuit and a reference DAC capacitor array. Therefore, this architecture does not require a monolithic S/H circuit. The main function of the capacitor network is D/A conversion. The input voltage is subtracted from the output voltage of the D/A converter, which is realized by properly controlling the switches of the capacitor network. The comparator connects to the outputs of capacitor arrays. The result of the comparison will send to SAR control logic.

Figure 2-1 A conventional 10-bit SAR ADC.

Since this ADC is fully differential, the operation of the two sides is complementary. For simplicity, only the positive-side (upper-side) operation of the ADC is described below. At the sampling phase, the bottom plates of the capacitors are charged to  $V_{\rm ip}$ , and the top plates are reset to the common-mode voltage  $V_{\rm cm}$ . Next, the largest capacitor  $C_1$  is switched to  $V_{\rm ref}$  and the other capacitors are switched to ground. The comparator then performs the first comparison. If  $V_{\rm ip}$  is higher than  $V_{\rm in}$ , the most significant bit (MSB)  $B_1$  is 1. Otherwise,  $B_1$  is 0, and the largest capacitor is reconnected to ground. Then, the second largest capacitor  $C_2$  is switched to  $V_{\rm ref}$ . The comparator does the comparison again. The ADC repeats this procedure until the least significant bit (LSB) is decided. Although the trial-and-error search procedure is simple and intuitive, it is not an energy efficient switching scheme, especially when unsuccessful trials occur.

#### 2.1.2 Proposed SAR ADC

Figure 2-2 The proposed SAR ADC architecture.

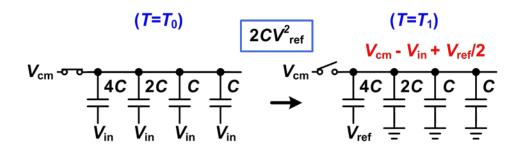

Figure 2-2 shows the proposed SAR ADC. The proposed ADC samples the input signal on the top plates via bootstrapped switches, which increases the settling speed and input bandwidth. At the same time, the bottom plates of the capacitors are reset to  $V_{\rm ref}$ . Next, after the ADC turns off the bootstrapped switches, the comparator directly performs the first comparison without switching any capacitor. According to the comparator output, the

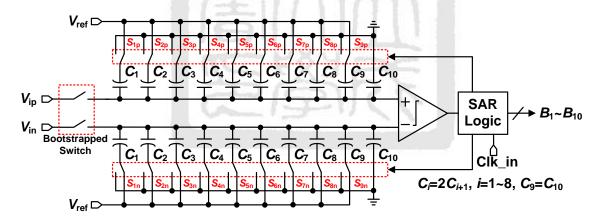

largest capacitor  $C_1$  on the higher voltage potential side is switched to ground and the other one (on the lower side) remains unchanged. The ADC repeats the procedure until the LSB is decided. For each bit cycle, there is only one capacitor switched, which reduces both charge transfer in the capacitive DAC network and the transitions of the control circuit and switch buffer, resulting in smaller power dissipation. The proposed switching procedure can be either upward or downward. For fast reference settling, i.e., discharging through n-type transistors, downward switching was selected in this ADC. The flow chart of the proposed successive-approximation procedure is shown in Figure 2-3.

Figure 2-3 Flow chart of the proposed SAR ADC.

The proposed switching sequence does not require upward transition. At the same transistor size, the on-resistance of a NMOS switch is only about 1/3 that of a PMOS one. Having no upward transition speeds up the DAC settling. In addition, since sampling is

done on the top plate [17], the comparator can perform the first comparison without any capacitor switching, leading to a faster algorithm. For an n-bit ADC, the number of unit capacitors in a capacitor array is  $2^{n-1}$ , only half that of the conventional one.

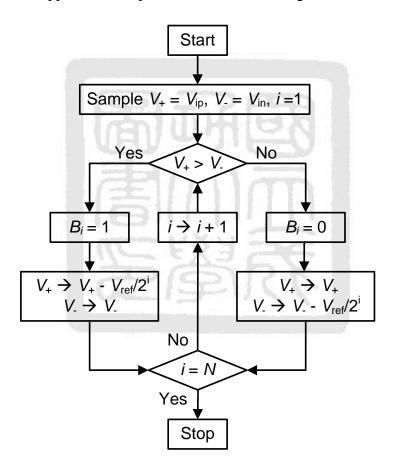

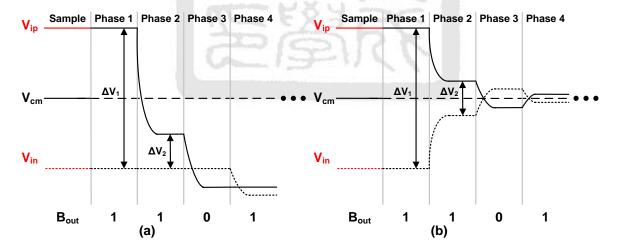

One of the major differences between the proposed method and the conventional one is that the common-mode voltage of the reference DAC gradually decreases from half  $V_{\text{ref}}$  to ground as shown in Figure 2-4.

Figure 2-4 (a) Waveform of conventional switching procedure. (b) Waveform of proposed monotonic switching procedure.

#### 2.1.3 Analysis of Switching Energy in DAC Network

Figure 2-5 A 3-bit capacitor array with conventional switching method.

It is instructive to calculate the total energy drawn from  $V_{\rm ref}$  when switching the capacitor array. For alleviating the computation, a 3-bit capacitor array is taken as an example (Figure 2-5). If the capacitor array settles in the time interval  $T_0 \sim T_1$ , the total energy drawn from  $V_{\rm ref}$  is:

$$E_{T_0 \to T_1} = \int_{T_0}^{T_1} I_{\text{ref}}(t) V_{\text{ref}} dt = V_{\text{ref}} \int_{T_0}^{T_1} I_{\text{ref}}(t) dt$$

(2-1)

Since  $I_{\text{ref}}(t) = -dQ_{\text{C}}/dt$  and  $Q_{\text{C}}(T) = 4CV_{\text{X}}[T]$ , equation (2-1) simplifies to:

$$E_{T_0 \to T_1} = -V_{\text{ref}} \int_{T_0}^{T_1} \frac{dQ_{\text{C}}}{dt} dt = -V_{\text{ref}} \int_{Q_{\text{C}}(T_0)}^{Q_{\text{C}}(T_1)} dQ_{\text{C}} = -V_{\text{ref}} (Q_{\text{C}}(T_1) - Q_{\text{C}}(T_0))$$

$$= -V_{\text{ref}} (4C)(V_{\text{X}}[T_1] - V_{\text{X}}[T_0])$$

(2-2)

Since  $V_X[T_0] = \Delta V_C[T_0], V_X[T_1] = \Delta V_C[T_1],$

and

$$\Delta V_{\rm C}[T_0] = V_{\rm cm} - V_{\rm in}, \ \Delta V_{\rm C}[T_1] = (V_{\rm cm} - V_{\rm in} + \frac{1}{2}V_{\rm ref}) - V_{\rm ref}$$

.

Then, equation (2-2) is:

$$E_{T_0 \to T_1} = 2CV_{\text{ref}}^2 \tag{2-3}$$

Figure 2-6 (a) Conventional switching procedure. (b) Proposed switching procedure.

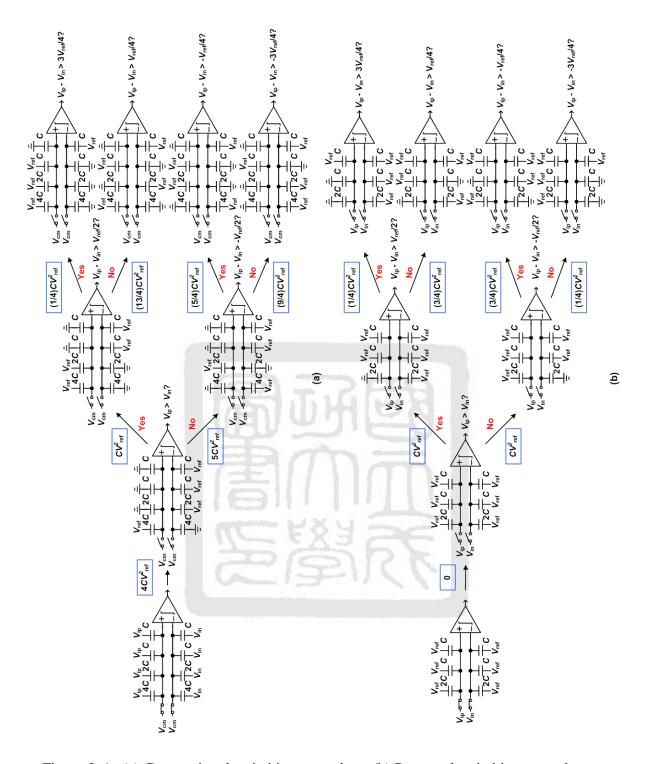

Figure 2-6 shows 3-bit examples of the conventional and proposed switching methods. The conventional switching method is based on a trial-and-error search procedure. Figure 2-6(a) shows all possible conversions. The quantitative energy consumption of each switching phase is also shown in the figure. The conventional switching sequence is efficient when all the attempts are successful, as in the upper cases. However, the switching sequence consumes a lot of energy when attempts are unsuccessful, as in the lower cases. Figure 2-6(b) shows all possible switching cases of the proposed method. After the sampling switches turn off, the comparator directly performs the first comparison without switching any capacitor. Therefore, the proposed switching sequence consumes no energy before the first comparison. In contrast, the conventional sequence consumes  $4CV_{\rm ref}^2$  before the first comparison. The subsequent switching sequence of the proposed method is also more efficient than that of the conventional one.

For an *n*-bit conventional SAR ADC, if each digital output code is equiprobable, the average switching energy can be derived as:

$$E_{\text{avg,conv}} = \sum_{i=1}^{n} 2^{n+1-2i} (2^{i} - 1) C V_{\text{ref}}^{2}$$

(2-4)

The average switching energy for an *n*-bit SAR ADC using the proposed switching procedure can be derived as:

$$E_{\text{avg,mono}} = \sum_{i=1}^{n-1} (2^{n-2-i}) CV_{\text{ref}}^2$$

(2-5)

For a 10-bit case, the conventional switching procedure consumes  $1365.3\,CV_{\rm ref}^2$  while the proposed switching procedure consumes only  $255.5\,CV_{\rm ref}^2$ . The proposed technique thus requires 81.3% less switching energy than that of the conventional one. Split capacitor [12] and energy-saving [16] switching methods provide only 37% and 56% reductions, respectively.

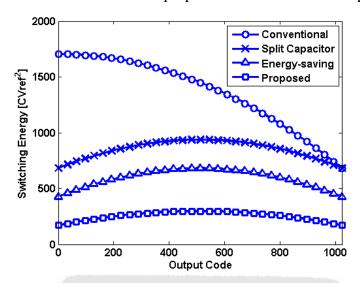

Figure 2-7 shows a comparison of switching energy for the four methods versus the digital output code in a 10-bit ADC. The proposed method has the best power efficiency.

Figure 2-7 Switching energy versus output code in a 10-bit ADC.

Table 2-1 Comparison of Switching Procedures

| Switching<br>Procedure                    | Conventional   | Split Capacitor | Energy-saving  | Proposed         |

|-------------------------------------------|----------------|-----------------|----------------|------------------|

| Normalized<br>Switching Power             | 古              | 0.63            | 0.44           | 0.19             |

| No. of Switches                           | 4 <i>N</i> +10 | 8 <i>N</i> +6   | 8 <i>N</i> +2  | 4 <i>N</i>       |

| No. of Capacitors                         | 2N+2           | 4N              | 4N-2           | 2 <i>N</i>       |

| No. of Unit Capacitors in Capacitor Array | 2 <sup>N</sup> | 2 <sup>N</sup>  | 2 <sup>N</sup> | 2 <sup>N-1</sup> |

Table 2-1 summarizes the features of the four methods. The proposed architecture not only has the lowest switching power consumption but also the fewest switches and unit capacitors, which simplifies digital control logic. Therefore, the proposed ADC is very hardware efficient as well.

#### 2.2 A 0.92mW 10-bit 50-MS/s SAR ADC

This section presents the design of a 10-bit 50-MS/s SAR ADC with the proposed monotonic switching procedure [18]. The schematic of the proposed SAR ADC is as shown in Fig 2-2. The fundamental building blocks of the proposed ADC are a S/H circuit, a dynamic comparator, SAR control logic, and a capacitor network. The design considerations of the building blocks are described in the following sub-sections.

#### 2.2.1 Sample and Hold Circuit

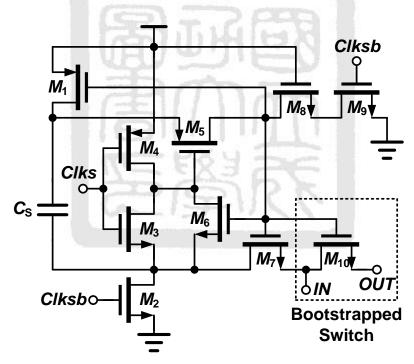

The proposed SAR ADC samples the input signal via the bootstrapped switches at the top plates of capacitors. An NMOS transistor used as a switch has a non-zero on-resistance, which can roughly be approximated as [19]:

$$R_{ON} = \frac{1}{\mu_n C_{ox}(\frac{W}{L})(V_G - V_T - \frac{V_S + V_D}{2})}.$$

(2-6)

This means that the on-resistance is signal dependent. When applying such a switch in a switched capacitor network, this non-linearity will result in harmonic distortion. A known solution for this problem is bootstrapping, which increases the overdrive voltage without special processing steps or compromising on reliability. The bootstrapped switch [20] shown in Figure 2-8 performs the S/H function. With the bootstrapped switch, the gate-source voltage of the sampling transistor is fixed at the supply voltage ( $V_{\rm DD}$ ), which makes the on-resistance a small constant value and thus improves the switch linearity. Although the absolute voltage applied to the gate may exceed  $V_{\rm DD}$  for a positive input signal, none of the terminal-to-terminal device voltages exceeds  $V_{\rm DD}$ .

The bootstrapped circuit operates with a single phase clock (Clks) that turns the switch  $M_{10}$  on and off. During the off phase, Clks is low. Devices  $M_8$  and  $M_9$  discharge the gate of

$M_{10}$  to ground. At the same time,  $V_{DD}$  is applied across capacitor  $C_S$  by  $M_2$  and  $M_1$ . This capacitor will act as the battery across the gate and source during the on phase.  $M_5$  and  $M_7$  isolate the switch from  $C_S$  while it is charging. When Clks goes high,  $M_3$  pulls down the gate of  $M_5$ , allowing charges from the capacitor  $C_S$  to flow onto the gate of  $M_7$  and  $M_{10}$ . This turns on both  $M_7$  and  $M_{10}$ .  $M_7$  enables the gate of  $M_{10}$  to track the input voltage (IN) with a shift of  $V_{DD}$ , keeping the gate-source voltage constant regardless of the input signal.

In this design, the value of  $C_S$  is 400 fF, where the capacitor is a Metal-Insulator-Metal (MIM) capacitor. Because the switch  $(M_{10})$ ,  $V_{GS}$  is independent of the signal. Rail-to-rail signals can be used. The switch linearity is also improved, and signal-dependent charge injection is reduced. The result obtains fast settling and large input bandwidth.

Figure 2-8 Bootstrapped switch.

#### 2.2.2 Comparator Design

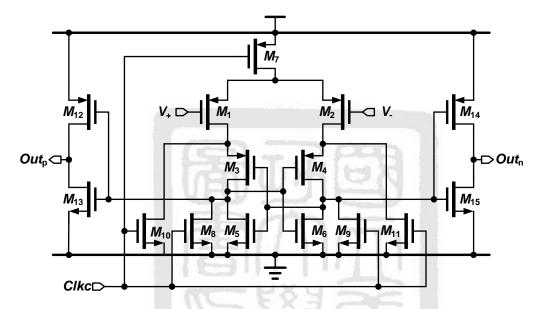

A high-speed, low-power and accurate CMOS comparator is crucial for the SAR ADC. To satisfy the above considerations, a latched differential input comparator [1] is chosen. Figure 2-9 shows the schematic of the comparator without static power consumption. In order to work properly in a common-voltage range from  $V_{\text{ref}}/2$  to ground, the comparator utilizes a p-type input pair.

Figure 2-9 The schematic of a latch-based dynamic comparator.

The operation principle is described as follow: When Clkc is high, the comparator is in pre-charge phase. The comparator outputs  $Out_p$  and  $Out_n$  are reset to high. When Clkc goes to low, the comparator is in comparison phase. The differential pair,  $M_1$  and  $M_2$ , compares the differential input voltages  $V_+$  and  $V_-$ . Then, the latch regeneration forces one output to high and the other to low according the comparison result. When the comparator is in steady-state, there is no dc current flowing from  $V_{DD}$  to ground. Therefore, it is suitable for low power applications.

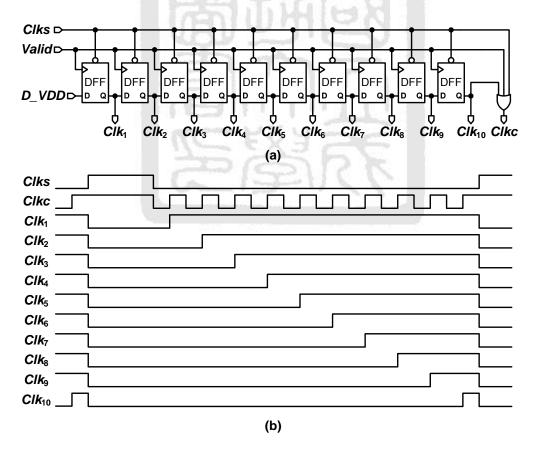

#### 2.2.3 SAR Control Logic

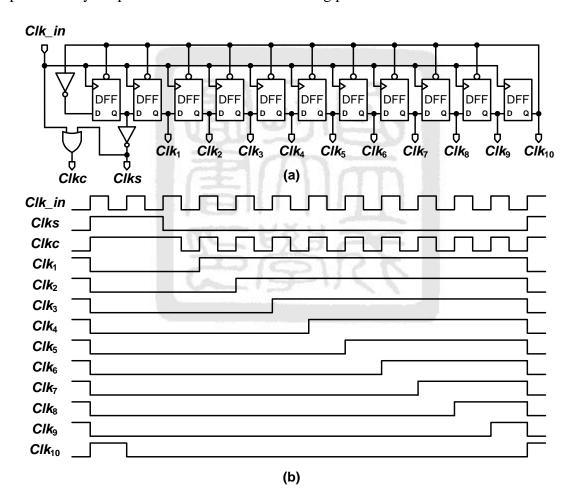

Figure 2-10 shows the schematic of the internal clock generator and its timing diagram. Clks is used to sample the input signal. We use two clock cycles as the sampling phase to ensure the sampling bandwidth is larger than the Nyquist frequency. Therefore, the SAR ADC needs 12 clock cycles to complete one conversion. At 50 MS/s sampling rate, it needs a global 600-MHz clock. Clkc is the control signal of the comparator.  $Clk_1$  to  $Clk_{10}$  sample the digital output codes of the comparator and serve as control signals for the capacitor arrays to perform the monotonic switching procedure.

Figure 2-10 Internal clock generator: (a) Schematic. (b) Timing diagram.

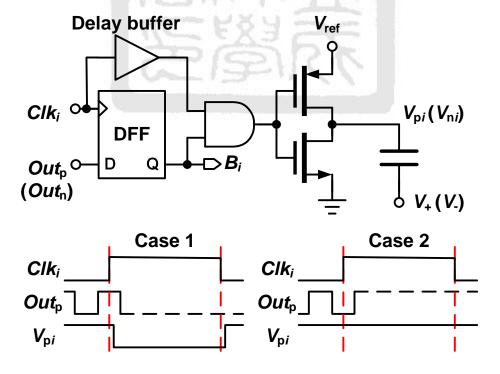

Figure 2-11 shows the schematic and timing diagram of the DAC control logic. At the rising edge of  $Clk_i$ , a static flip-flop samples the comparator output. If the output is high,

the relevant capacitor is switched from  $V_{\rm ref}$  to ground. If the output is low, the relevant capacitor is kept connected to  $V_{\rm ref}$ . At the falling edge of  $Clk_i$ , all capacitors are reconnected to  $V_{\rm ref}$ . The delay buffer guarantees that  $Clk_i$  triggers the AND gate after the output of the static flip-flop arrived. This timing arrangement avoids unnecessary transitions. This work uses an inverter as a switch buffer. The conventional architecture in Figure 2-1 samples both the input signal and reference voltages on the bottom plates. If the input swing is nearly rail-to-rail, transmission gates are needed to sample input signal. This work uses bootstrapped switches to sample input signal onto top plates of the capacitors and uses inverter buffers to switch between positive and negative voltages. Hence, compared to the conventional architecture, no transmission gates are used, which enables high-speed and low-power operation.

To prevent unnecessary energy consumption and to keep the RC value the same, the sizes of the first six switch buffers are scaled down according to the driven capacitances and the buffers of the last three capacitors are unit size ones.

Figure 2-11 DAC control logic.

#### 2.2.4 Capacitor Array

This prototype used MIM capacitors to construct the capacitor array. For device matching, a unit capacitor of 10 fF is used. The binary capacitor array of the 10-bit SAR ADC uses 2<sup>9</sup> unit capacitors. Therefore, the total sampling capacitance is 5.12 pF in each terminal.

Due to the small unit capacitance, the routing parasitic capacitance has a considerable influence on the matching of capacitances. The capacitors were placed in an intuitive way to simplify the layout routing. Figure 2-12 shows the layout floorplan of the capacitor array.

Figure 2-12 The layout floorplan of the capacitor array.

#### 2.2.5 Measurement Results

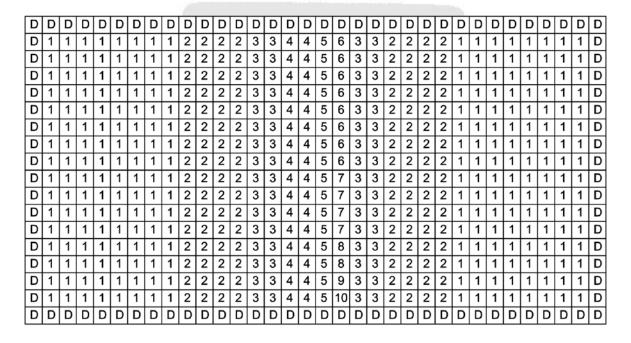

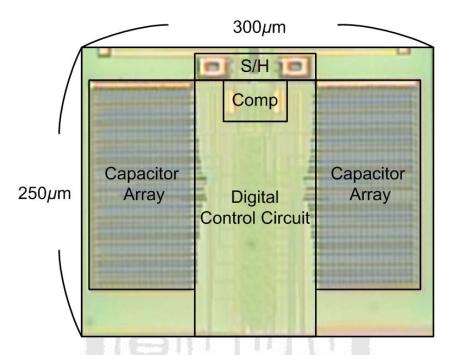

The prototype is fabricated in TSMC 0.13- $\mu$ m 1P8M triple well CMOS technology. The micrograph is shown in Figure 2-13. The active core area is 0.075 mm<sup>2</sup> (250  $\mu$ m × 300  $\mu$ m).

Figure 2-13 Micrograph of the prototype ADC.

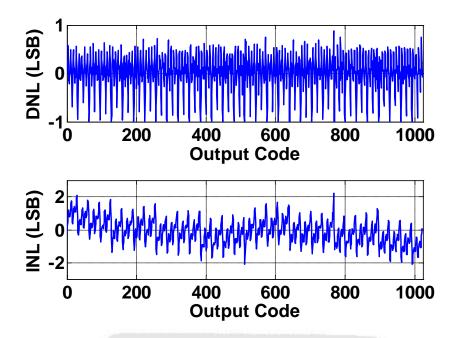

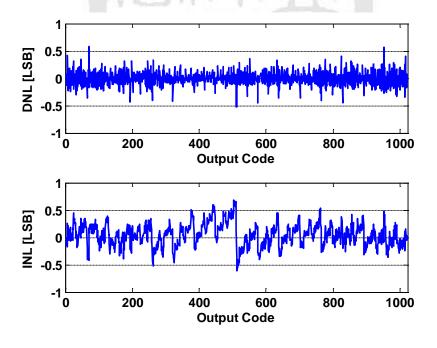

The dynamic specifications, including SNDR and SFDR were analyzed by fast Fourier transform (FFT). The specifications of the static linearity, including integral nonlinearity (INL) and differential nonlinearity (DNL), were measured based on the code density testing method [21]. At 1.2-V supply and 50-MS/s sampling rate, the measured DNL and INL are shown in Figure 2-14. The measured peak DNL and INL are +0.88/-1.00 LSB and +2.20/-2.09 LSB, respectively. Large DNL peaks appear periodically every 32 digital codes, which possibly come from the underestimated comparator dynamic offset. The signal-dependent dynamic offset caused by the variation of the input common-mode voltage degraded ADC linearity.

Figure 2-14 Measured DNL and INL.

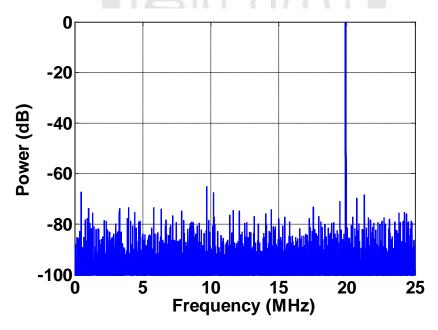

Figure 2-15 shows the measured FFT spectrum with an input frequency close to 20 MHz at 1.2-V supply and 50-MS/s sampling rate. The measured SNDR and SFDR are 52.18 dB and 63.91 dB, respectively.

Figure 2-15 Measured FFT spectrum at 50 MS/s with a 20-MHz input frequency.

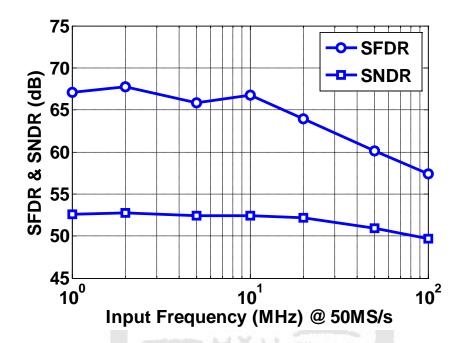

Figure 2-16 plots the measured SNDR, SFDR values versus the input frequency at 50 MS/s. At a 2-MHz input frequency, the measured SNDR and SFDR are 52.8 dB and 67.7 dB, respectively. The resultant ENOB is 8.48 bits. When the input frequency is up to 50 MHz, the measured SNDR and SFDR were 50.9 dB and 60.1 dB, respectively. The effective resolution bandwidth (ERBW) is higher than 100 MHz.

Figure 2-16 Measured SFDR and SNDR versus input frequency at 50 MS/s.

The power dissipation consumed by analog circuits including the comparator, T/H circuit and capacitor network is 0.39 mW. The digital power consumption is 0.53 mW. The total power consumption of the ADC is 0.92 mW. The measured results of the proposed ADC are summarized in Table 2-2. A comparison with state-of-the-art ADCs is listed in Table 2-3. To compare the proposed ADC to other works with different sampling rates and resolutions, the well-known figure-of-merit (FOM) equation [6] is used.

$$FOM = \frac{Power}{2^{ENOB} \times \min\{2 \times ERBW, f_s\}}$$

(2-7)

The resultant FOM of the prototype ADC is 52 fJ/conversion-step. The result shows our work is comparable to those excellent designs with similar speed and resolution.

Table 2-2 Summary of ADC Performance

| Specification (Unit)            | Experimental Result |         |       |

|---------------------------------|---------------------|---------|-------|

| Supply Voltage (V)              | 1.2                 |         |       |

| Input CM Voltage (V)            | 0.6                 |         |       |

| Input Range (V <sub>p-p</sub> ) | 2                   |         |       |

| Sampling Capacitance (pF)       | 5.12                |         |       |

| Sampling Rate (MS/s)            | 50                  |         |       |

| Active Area (mm²)               | 0.075               |         |       |

| DNL (LSB)                       | +0.88 / -1.00       |         |       |

| INL (LSB)                       | +2.20 / -2.09       |         |       |

| ENOB (bits)                     | 8.48                |         |       |

| ERBW (MHz)                      | 100                 |         |       |

|                                 | Analog              | Digital | Total |

| Power (mW)                      | 0.39                | 0.53    | 0.92  |

| FOM (fJ/Convstep)               | 52                  |         |       |

Table 2-3 Comparison to State-of-the-Art Works

| Specifications       | /SSCC'07<br>[1] | /SSCC'08<br>[2] | /SSCC'10<br>[13] | ISSCC'10<br>[14] | <i>VLSI</i> *08<br>[22] | This Work       |

|----------------------|-----------------|-----------------|------------------|------------------|-------------------------|-----------------|

| Architecture         | SAR             | SAR             | SAR              | SAR              | Pipelined               | SAR             |

| Technology           | 90 nm           | 90 nm           | 65 nm            | 65 nm            | 90 nm                   | 0.13 <i>μ</i> m |

| Supply Voltage (V)   | 1(              | J15             | 1.1              | 1.2              | 1.2                     | 1.2             |

| Sampling Rate (MS/s) | 50              | 40              | 40               | 50               | 50                      | 50              |

| Resolution (bits)    | 9               | 9               | 10               | 10               | 9.4                     | 10              |

| ENOB (bits)          | 7.8             | 8.56            | 8.9              | 9.16             | 7.91                    | 8.48            |

| Power (mW)           | 0.7             | 0.82            | 1.21             | 0.82             | 1.44                    | 0.92            |

| FOM (fJ/Convstep)    | 65              | 54              | 65               | 30               | 119                     | 52              |

| Active Area (mm²)    | 0.08            | 0.09            | 0.06             | 0.039            | 0.123                   | 0.075           |

# 2.3 A 10-bit 50-MS/s SAR ADC with an Improved Comparator Design

The experimental results in Section 2.2 demonstrate the power and hardware efficiency and also the high-speed potential of the proposed SAR ADC. However, the signal-dependent offset caused by the variation of the input common-mode voltage degraded ADC linearity. The synchronous control logic needs a high-frequency global clock that results in extra design and hardware overhead. Based on the design in Section 2.2, an improved comparator was proposed to avoid the linearity degradation [23]. An asynchronous SAR control logic is proposed to avoid the requirement of a high frequency clock. Besides, the S/H circuit and capacitor network are redesigned to enhance the performance of the ADC. The design considerations of those building blocks are described in the following sub-sections.

## 2.3.1 S/H circuit

The bootstrapped switch shown in Figure 2-17(a) performs the S/H function. With the bootstrapped switch, the gate-source voltage of the sampling transistor is fixed at the supply voltage ( $V_{\rm DD}$ ), which makes the on-resistance a small constant value and thus improves the switch linearity. When the bootstrapped switch is off, the input signals couple to the sampling capacitors through the  $C_{\rm ds}$  (around 5fF) which is composed of the drain-source capacitor of the sampling transistor and the routing parasitic capacitance. The coupling effect degrades the high frequency performance because  $C_{\rm ds}$  induces unequal charges in the comparison cycles, which results in a dynamic offset. Therefore, two cross-coupled metal-oxide-metal (MOM) capacitors (around 5fF) are used to neutralize the effect (see Figure 2-17(b)). The two cross-coupled capacitors reduce the coupling effect to

less than 1/2 LSB (2.5fF) in the 10-bit case under processing variation. To achieve higher precision, dummy switches and dummy routing are alternative solutions to reduce the coupling effect.

Figure 2-17 (a) Bootstrapped switch. (b) Cross-coupled capacitors.

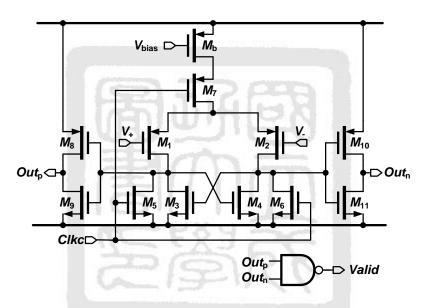

## 2.3.2 Dynamic Comparator with a Current Source

Figure 2-18 shows a schematic of the comparator. During the conversion phase, the input voltages of the comparator approach ground. For the proper function within the input common-mode voltage range from half  $V_{\text{ref}}$  to ground, the comparator uses a p-type input pair. Because a dynamic comparator does not consume static current, it is suitable for energy efficient design.

When Clkc is high, the comparator outputs  $Out_p$  and  $Out_n$  are reset to high. When Clkc goes to low, the differential pair,  $M_1$  and  $M_2$ , compares the two input voltages. Then, the latch regeneration forces one output to high and the other to low according the comparison result. Consequently, the Valid signal is pulled to high to enable the asynchronous control clock. The offset voltage of this comparator can be expressed as [24]:

$$V_{os} = \Delta V_{TH1,2} + \frac{(V_{GS} - V_{TH})_{1,2}}{2} \left(\frac{\Delta S_{1,2}}{S_{1,2}} + \frac{\Delta R}{R}\right)$$

(2-8)

where  $\Delta V_{\text{TH}1,2}$  is the threshold voltage offset of the differential pair  $M_1$  and  $M_2$ ,  $(V_{\text{GS}}-V_{\text{TH}})_{1,2}$  is the effective voltage of the input pair,  $\Delta S_{1,2}$  is the physical dimension mismatch between  $M_1$  and  $M_2$ , and  $\Delta R$  is the loading resistance mismatch induced by  $M_3-M_6$ . The first term is a static offset which does not affect the performance of a SAR ADC. However, the second term is a signal-dependent dynamic offset. The effective voltage of the input pair varies with the input common-mode voltage. The dynamic offset degraded the performance of the work in Section 2.2.

Figure 2-18 Dynamic comparator with a current source.

There are several possible approaches to improve the dynamic offset. The comparator size can be enlarged, which results in larger power consumption. The effective voltage of the input pair can be reduced, but this decreases the comparison speed. The error tolerant non-binary search algorithm [3] is also a feasible method. A simple and reliable way is to cascode a biased MOS ( $M_b$ ) at the top of the switch MOS ( $M_7$ ), as shown in Figure 2-18. Because  $M_b$  is in the saturation region, the change of its drain-source voltage has only a slight influence on the drain current. Hence,  $M_b$  keeps the effective voltage of the input

pair near a constant value when common-mode voltage changes. The dynamic offset thus has a minor influence on the conversion linearity.

## 2.3.3 SAR Control Logic

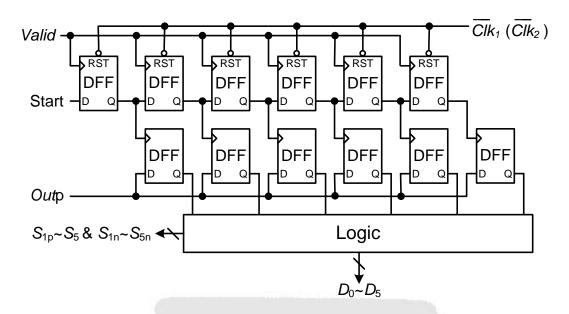

To avoid a high frequency clock generator, an asynchronous control circuit is used to internally generate the necessary clock signals. Figure 2-19 shows a schematic and a timing diagram of the asynchronous control logic. The dynamic comparator generates the *Valid* signal. *Clks* is the control signal of the sampling switches which turns on these switches at high potential and turns off the switches at low potential. The sampling phase is about 20% of the whole clock period. *Clkc* is the control signal of the dynamic comparator.  $Clk_1$  to  $Clk_{10}$  sample the comparator output and trigger the control logic.

Figure 2-19 Asynchronous control logic: (a) Schematic. (b) Timing diagram.

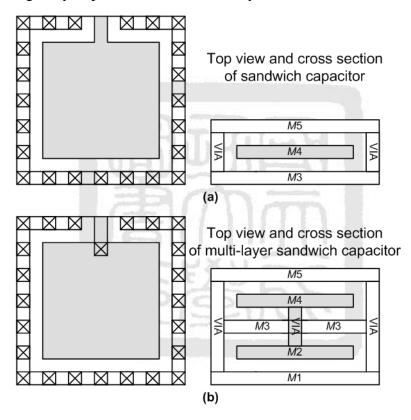

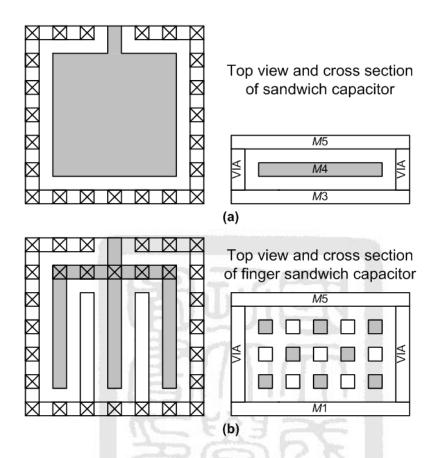

## 2.3.4 Unit Capacitor

The first prototype used MIM capacitors while this revised work uses MOM capacitors to construct the capacitor array. Figure 2-20(a) shows a sandwich capacitor [8], where the gray part is the top plate. The bottom plate encloses the top plate to minimize the parasitic capacitance. The capacitor consists of only three metals, yielding a small capacitance per unit area. For a SAR ADC, capacitors occupy most of the area. Therefore, increasing the unit capacitance greatly improves the area efficiency.

Figure 2-20 (a) Sandwich capacitor. (b) Multi-layer sandwich capacitor.

Figure 2-20(b) shows a multi-layer sandwich capacitor which doubles the effective capacitor area. The capacitance of a unit multi-layer sandwich capacitor (3.3  $\mu$ m × 3.3  $\mu$ m) is about 4.8 fF while that of a sandwich capacitor of the same size is only 2.4 fF. Therefore, the multi-layer sandwich capacitor is much more hardware efficient. The binary capacitor array of the proposed 10-bit SAR ADC uses  $2^9$  unit capacitors. Therefore, the total

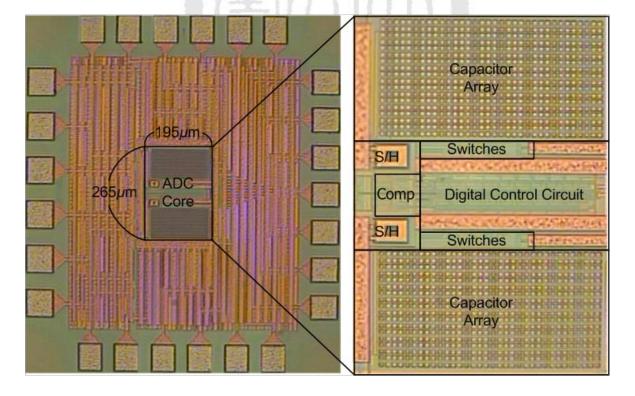

sampling capacitance of one capacitor network is 2.5 pF. The two capacitor networks occupy a total active area of 195  $\mu$ m × 195  $\mu$ m, about 72% of the whole ADC.

### 2.3.5 Measurement Results

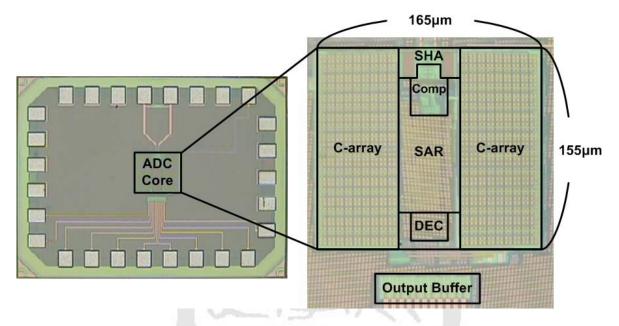

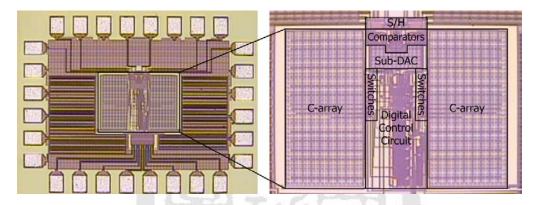

The prototype ADC was fabricated in TSMC 0.13- $\mu$ m 1P8M triple well CMOS technology. The full micrograph and the zoomed-in view of the core are shown in Figure 2-21. The total area of the chip is  $0.93 \text{ mm} \times 1.03 \text{ mm}$ , with the ADC core taking up only  $195 \mu$ m  $\times 265 \mu$ m. The switches for capacitors are placed close to the capacitor arrays. In this improved work, the logic control circuit has been optimized for power consumption and area, and the layout of the digital logic circuit is more compact. Therefore, the core area is smaller than that of the first prototype. An on-chip 100- $\Omega$  resistor is placed between the differential input ports to match the 50- $\Omega$  resistance of the signal cable. The measurement results of the prototype are presented below.

Figure 2.21 Die micrograph and the zoomed view.

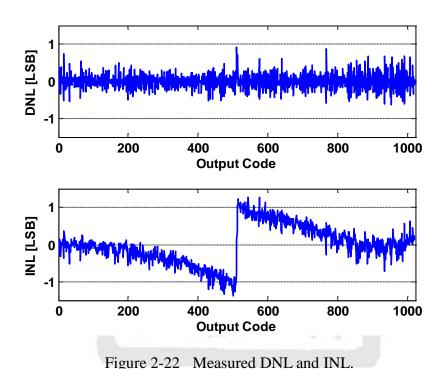

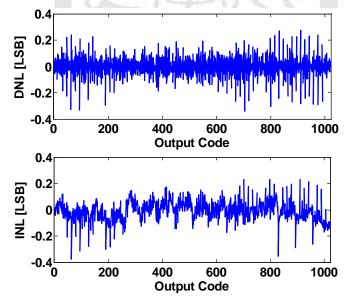

At a 1.2-V supply and a 50-MS/s sampling rate, the measured DNL and INL are shown in Figure 2-22. The peak DNL and INL are +0.91/-0.63 LSB and +1.27/-1.36 LSB, respectively. The figure shows that the INL has a jump at the middle of output codes. Since each test chip has this characteristic, the parasitic capacitance induced by the layout routing might be responsible for this inference. The MSB capacitance is around one LSB larger than the expected value. The performance of the ADC is mainly limited by this deterministic capacitor mismatch.

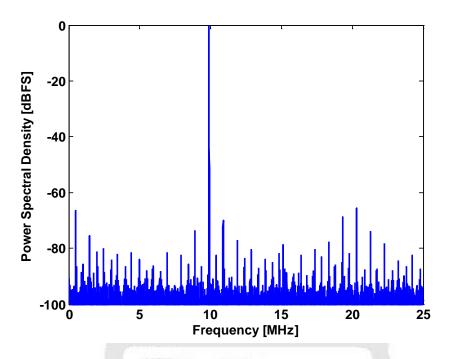

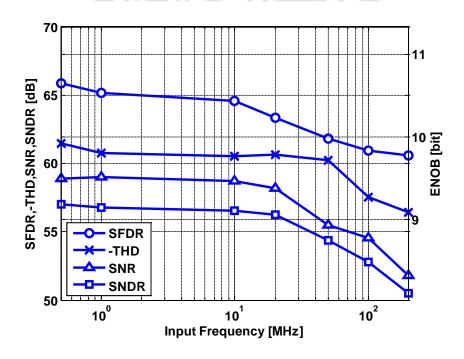

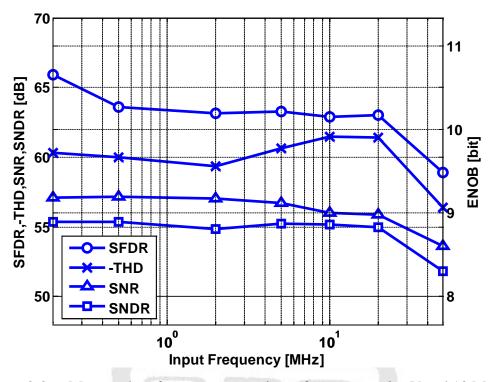

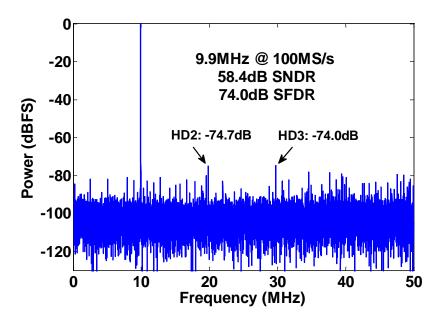

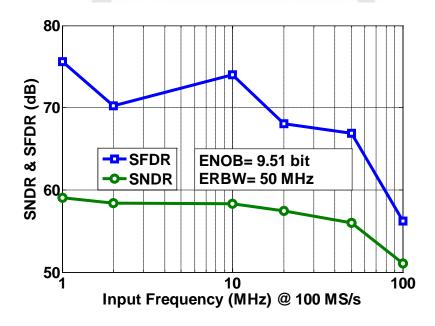

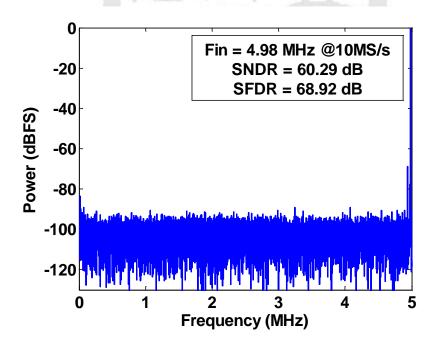

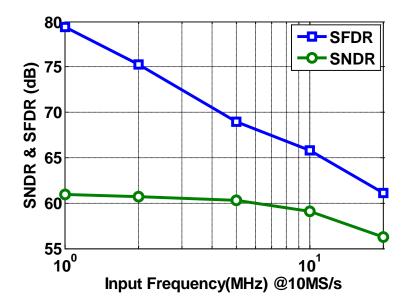

Figure 2-23 shows the measured FFT spectrum with an input frequency of close to 10 MHz at a 1.2-V supply and a 50-MS/s sampling rate. The measured SNDR and SFDR are 56.5 dB and 64.6 dB, respectively. Figure 2-24 plots the measured SNDR, SNR, SFDR, THD, and ENOB values versus the input frequency at 50 MS/s. At low input frequency, the measured SNDR and SFDR are 57.0 dB and 65.9 dB, respectively. The resultant ENOB is 9.18 bits. When the input frequency was increased to 50 MHz, the measured SNDR and SFDR were 54.4 dB and 61.8 dB, respectively. The ERBW is higher than 50 MHz.

Figure 2-23 Measured FFT spectrum at 50 MS/s with a 10-MHz input frequency.

Figure 2-24 Measured performance versus input frequency at 1.2 V and 50 MS/s.

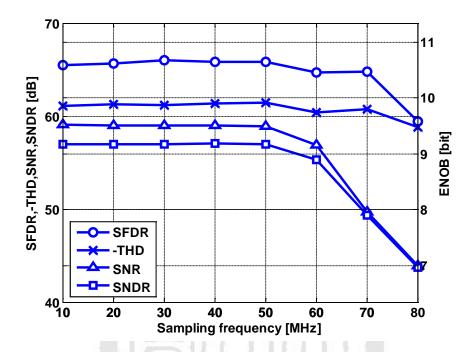

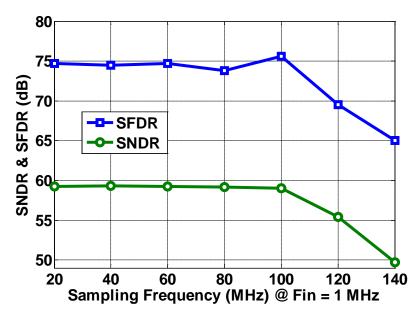

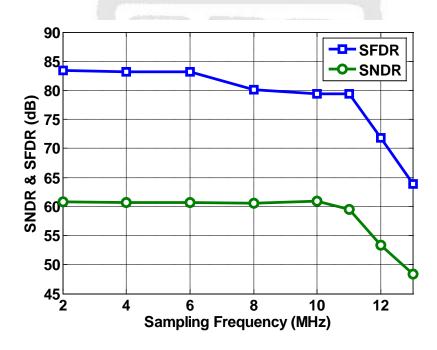

Figure 2-25 shows the measured performance versus the sampling frequency with a 0.5-MHz sinusoidal stimulus. When the sampling rate was 60 MS/s, the ENOB was still close to 9 bits. Further increasing the sampling rate rapidly degraded the performance because the conversion time was insufficient.

Figure 2-25 Measured dynamic performance versus sampling frequency.

At a 1.2-V supply, the analog part, including the S/H circuit and comparator, consumes 0.276 mW, and the digital control logic draws 0.42 mW. The ideal power consumption of the reference voltage  $V_{\text{ref}}$  is

$$P(V_{\text{ref}}) = \frac{E_{\text{avg},n-\text{bit}}}{T} = f \cdot \sum_{i=1}^{n-1} (2^{n-2-i}) C V_{\text{ref}}^{2}$$

(2-9)

At a 1-V reference voltage, a 50-MS/s sampling rate, and a 4.8-fF unit capacitance, the expected power consumption is 0.062 mW. The measured value was 0.13 mW because the switch buffers consume dynamic current during transitions. The parasitic capacitors at the bottom plates and the drains of the switch MOS transistors also increase power consumption. Excluding the output buffers, the total power consumption of the active circuit is 0.826 mW. A summary of the ADC is listed in Table 2-4.

Table 2-4 Summary of ADC Performance

| Experimental Result   |  |  |

|-----------------------|--|--|

| 1.2                   |  |  |

| 0.6                   |  |  |

| 2                     |  |  |

| 2.5                   |  |  |

| 50                    |  |  |

| 0.052                 |  |  |

| +0.91 / -0.63         |  |  |

| +1.27 / -1.36         |  |  |

| 57.0 / 65.9 (0.5 MHz) |  |  |

| 56.5 / 64.6 (10 MHz)  |  |  |

| 54.4 / 61.8 (50 MHz)  |  |  |

| 9.18 (0.5MHz)         |  |  |

| 50                    |  |  |

| 0.826                 |  |  |

|                       |  |  |

Because the ADC has no transmission gates or preamplifiers, it can operate at low supply voltage conditions. At 40 MS/s and a 1-V supply, the low frequency ENOB is 9.15 bits and the ERBW is around 50 MHz. At 20 MS/s and a 0.8-V supply, the low frequency ENOB is 9.19 bits and the ERBW is around 20 MHz. When the sampling rate and supply voltage were decreased to 10 MS/s and 0.6 V, respectively, the low frequency ENOB and ERBW were 8.91 bits and 20 MHz. Figure 2-26 plots the performance versus input frequency at 0.6 V. Table 2-5 shows a performance summary for various supply voltages. The excellent low-voltage performance demonstrates that the proposed ADC is a feasible alternative to switched-operational-amplifier pipelined ADCs [25].

Figure 2-26 Measured performance versus input frequency at 0.6 V and 10 MS/s.

Table 2-5 Specification Summary at Different Supply Voltages

| ************************************** |                     |       |       |       |

|----------------------------------------|---------------------|-------|-------|-------|

| Specification (Unit)                   | Experimental Result |       |       |       |

| Supply Voltage (V)                     | 1.2                 | 1.0   | 0.8   | 0.6   |

| Input CM Voltage (V)                   | 0.6                 | 0.4   | 0.3   | 0.2   |

| Input Range (V <sub>p-p</sub> )        | 2                   | 1.6   | 1.2   | 0.8   |

| Sampling Rate (MS/s)                   | 50                  | 40    | 20    | 10    |

| ERBW (MHz)                             | 50                  | 50    | 20    | 20    |

| ENOB (bits)                            | 9.18                | 9.15  | 9.19  | 8.91  |

| Power (mW)                             | 0.826               | 0.496 | 0.154 | 0.046 |

| FOM (fJ/Convstep)                      | 29                  | 22    | 13    | 9.6   |

The FOM of the proposed ADC is 29 fJ/conversion-step at 50 MS/s and a 1.2-V supply. The FOM is 9.6 fJ/conversion-step when the sampling rate and supply voltage are 10 MS/s and 0.6 V, respectively. Table 2-6 compares the proposed ADC with other state-of-the-art ADCs. Although the proposed ADC was fabricated in older technology, it still has the lowest FOM and smallest active area compared to those ADCs with similar sampling rates and resolutions.

Table 2-6 Comparison to State-of-the-Art Works

| 0 10 11              | ISSCC'07 | ISSCC'08 | ISSCC '10 | First           |                 |  |

|----------------------|----------|----------|-----------|-----------------|-----------------|--|

| Specifications       | [1]      | [2]      | [13]      | Prototype       | This Work       |  |

| Architecture         | SAR      | SAR      | SAR       | SAR             | SAR             |  |

| Technology           | 90 nm    | 90 nm    | 65 nm     | 0.13 <i>μ</i> m | 0.13 <i>µ</i> m |  |

| Supply Voltage (V)   | / 1      | -1       | 1.1       | 1.2             | 1.2             |  |

| Sampling Rate (MS/s) | 50       | 40       | 40        | 50              | 50              |  |

| Resolution (bits)    | 9        | 9        | 10        | 10              | 10              |  |

| ENOB (bits)          | 7.8      | 8.56     | 8.9       | 8.48            | 9.18            |  |

| Power (mW)           | 0.7      | 0.82     | 1.21      | 0.92            | 0.826           |  |

| FOM (fJ/Convstep)    | 65       | 54       | 65        | 52              | 29              |  |

| Active Area (mm²)    | 0.08     | 0.09     | 0.06      | 0.075           | 0.052           |  |

## 2.4 A 6-bit 220-MS/s Time-Interleaving SAR ADC

In digital data processing fields like hard disk drives and some local-area networks, a high sampling speed ADC is required in these applications where a 6-bit resolution is sufficient. This section shows a 6-bit asynchronous time-interleaved SAR ADC [26]. The sampling rate was enhanced by time-interleaving two slices. We use the time-interleaved architecture to avoid high frequency clock which will double the sampling rate. There are power and area overheads as the number of parallel converters increases. Therefore, a single ADC should be optimized for high speed, low power and small silicon area. This work was fabricated in a 0.18- $\mu$ m 1P5M digital CMOS process. The ADC achieves a peak SNDR of 32.62 dB, while only occupies an active area of 240  $\mu$ m × 130  $\mu$ m and power consumption of 6.8 mW.

#### 2.4.1 Architecture

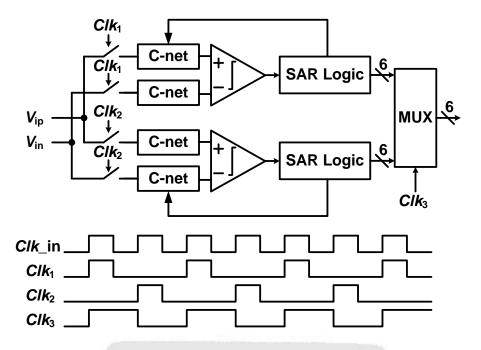

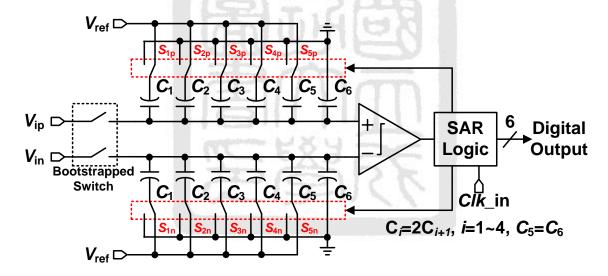

Figure 2-27 shows a time-interleaving SAR ADC architecture composed of two sub-ADCs with the proposed monotonic switching procedure. Each sub-ADC needs two clock cycles to convert analog signal into digital signal. It takes half a clock cycle to sample and the remaining time is for successive approaching. The SAR logic block provides all the control signals which ensure the switches and the comparator working correctly, and provides control signals for the D/A converter capacitor network to implement the proposed switching sequence. It also generates the digital output code. The multiplexer is adopted to synchronize clock and two sub-ADCs' output data.

Figure 2-28 shows the schematic of the proposed SAR ADC. The fundamental building blocks of the SAR ADC are the comparator, S/H circuit, capacitor network, and successive approximation registers.

Figure 2-27 Timing diagram of the time-interleaving SAR ADC.

Figure 2-28 Architecture of a 6-bit single channel SAR ADC.

## 2.4.2 Comparator Design

Figure 2-29 shows the schematic of the comparator. When Clkc is high, the comparator outputs  $Out_p$  and  $Out_n$  are reset to high. When Clkc goes low, the differential pair  $M_1$  and  $M_2$  compares the voltage difference of  $V_+$  and  $V_-$ . Because of latch regeneration,  $Out_p$  and  $Out_n$  go to high or low according by the input voltage. Then the Valid signal is pulled to high to enable the asynchronous clock. In order to reduce the channel mismatch of two sub-ADCs, the offset voltages of each comparator are designed to be less than 1/6 LSB. The layout is carefully done by using the common-centroid technique. In addition, when the comparator is in steady-state, there is no dc current flowing from  $V_{DD}$  to ground. Therefore, it is suitable for low power application.

$Out_{p} \longrightarrow V_{a}$   $Out_{p} \longrightarrow Valid$   $Out_{p} \longrightarrow Valid$

Figure 2-29 Schematic of the comparator.

## 2.4.3 SAR Control Logic

Figure 2-30 shows the SAR controller which samples the digital output codes from the comparator and provides control signals for the DAC capacitor network to implement the

monotonic switching sequence.

Figure 2-30 The SAR logic implementation.

## 2.4.4 Unit Capacitor

As process scales, the accuracy of interconnect metal patterns improve, making it possible to realize highly matched, very small value capacitors using interconnect metals. In this ADC, the capacitor is a low-cost MOM finger sandwich capacitor available in any standard digital CMOS process instead of a higher quality MIM capacitor.

Figure 2-31(b) shows the structure of the proposed finger-sandwich capacitor, which combines finger capacitor and sandwich capacitor [8]. The unit capacitor is composed of metal 1 to metal 5. The gray part is the top plate, which is almost encaged by the bottom plate that minimizes the parasitic capacitor.

The capacitance of a unit finger-sandwich capacitor ( $5\mu$ m ×  $5\mu$ m) is 10 fF while that of a sandwich capacitor as shown in Figure 2-31(a) with the same size is only 2.8 fF. Therefore, the proposed finger sandwich capacitor is very hardware efficient. The binary

capacitor array of the proposed 6-bit ADC needs 32 unit capacitors, and the total input capacitance of the capacitor network is 320 fF. A single capacitor array occupies only 100  $\mu$ m × 50  $\mu$ m which is about 16.7% of the layout core area.

Figure 2-31. Unit capacitor structure: (a) sandwich capacitor (b) finger sandwich capacitor.

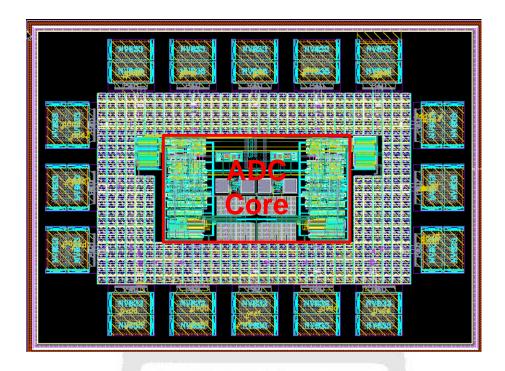

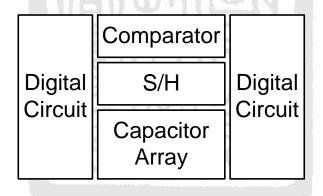

## 2.4.5 Layout and Floorplan

The layout of the SAR ADC and the floorplan of ADC core are shown in Figure 2-32 and Figure 2-33, respectively. To achieve high-speed operation and reduce power consumption, it is crucial to minimize layout parasitic, which requires the layout to be as compact as possible. The chip occupies  $0.57 \text{ mm} \times 0.41 \text{ mm}$  and the ADC core (the major circuit without pad and output buffer) only occupies an active area of  $240 \mu\text{m} \times 130 \mu\text{m}$ .

Figure 2-32 Layout of the implemented SAR ADC.

Figure 2-33 Floor plan of ADC core.

## 2.4.6 Measurement Results

The proposed ADC is fabricated in TSMC 0.18- $\mu m$  1P5M digital CMOS technology with MOM capacitors. At 1.8-V supply and 220-MS/s sampling rate, the measured DNL and INL are shown in Figure 2-34. The measured peak DNL and INL are +1.15/-0.88 LSB and +0.75/-1.05 LSB, respectively.

Figure 2-34 Measured INL and DNL.

Figure 2-35 shows the measured FFT spectrum with an input frequency of 2 MHz at a 1.8-V supply and a 220-MS/s sampling rate. The measured SNDR and SFDR are 32.62 dB and 48.96 dB, respectively. The ENOB is 5.13 bits.

Figure 2-35 Measured FFT spectrum at 220 MS/s with a 2-MHz input frequency.

Figure 2-36 plots the measured SNDR, SFDR values versus the input frequency at 220 MS/s. At 200-MHz input signal frequency, the peak SNDR and peak SFDR are 30.25 dB and 42.56 dB, respectively. The resultant ENOB is 4.73 bits. The ERBW is higher than 200MHz.

Figure 2-36 Measured performance versus input frequency at 1.8 V and 220 MS/s.

The power dissipation consumed by analog circuits including the comparator, T/H circuit and capacitor network is 0.84 mW. The digital power consumption (clock generator and successive approximation register logic) is 5.96 mW. The total power dissipation of this ADC is 6.8 mW. The performance of this ADC is summarized in Table 2-7.

Table 2-8 summarizes the comparison with the other ADCs with sampling rates in excess of 100 MS/s and resolutions of 8-bit or less. The result shows that our work is more power efficient than the previous publications. This ADC is fabricated in a digital process without MIM capacitor, and the core area of the ADC is pretty small. The fabrication cost is reduced obviously. In addition, this work requires no digital post-processing or post-calibration between two sub-ADC channels.

Table 2-7 Summary of ADC Performance

| Experimental Result     |                                                                                                         |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| 6                       |                                                                                                         |  |  |

|                         |                                                                                                         |  |  |

| 220                     |                                                                                                         |  |  |

|                         |                                                                                                         |  |  |

| 32.62 / 48.96 (2 MHz)   |                                                                                                         |  |  |

|                         |                                                                                                         |  |  |

| 30.25 / 42.56 (200 MHz) |                                                                                                         |  |  |

| +1.15 / -0.88           |                                                                                                         |  |  |

| +0.75 / -1.05           |                                                                                                         |  |  |

| 0.88                    |                                                                                                         |  |  |

| 200                     |                                                                                                         |  |  |

| Analog                  | 0.84                                                                                                    |  |  |

| Digital                 | 5.96                                                                                                    |  |  |

| Total                   | 6.8                                                                                                     |  |  |

| 240 × 130               |                                                                                                         |  |  |

| 570 × 410               |                                                                                                         |  |  |

|                         | 1.8 220 2 32.62 / 48.90 31.17 / 45.34 30.25 / 42.56 +1.15 / +0.75 / 0.88 200 Analog Digital Total 240 × |  |  |

Table 2-8 Comparison to the Other Works

| Specifications                  | JSCC'07 [7]     | JSCC'07 [12] | ISSCC '04 [27]  | This Work       |

|---------------------------------|-----------------|--------------|-----------------|-----------------|

| Technology                      | 0.18 <i>μ</i> m | 65 nm        | 0.18 <i>µ</i> m | 0.18 <i>μ</i> m |

| Supply Voltage (V)              | 1.8             | 1.2          | 1.8             | 1.8             |

| Resolution (bits)               | 5               | 5            | 8               | 6               |

| Convertion Rate (MS/s)          | 500             | 500          | 150             | 220             |

| Input Range (V <sub>p-p</sub> ) | 0.8             | 0.8          | 1.6             | 2               |

| Power (mW)                      | 7.47            | 5.93         | 71              | 6.8             |

| SNDR (dB)                       | 20.2            | 27.8         | 45.4            | 32.62           |

| SFDR (dB)                       | 24              | 36           | 52.5            | 48.96           |

| ENOB (bits)                     | 3.06            | 4.04         | 7.25            | 5.13            |

| FOM (pJ/Convstep)               | 1.8             | 0.75         | 2.5             | 0.88            |

| Core Area (mm²)                 | 0.5             | 0.91         | 1.8             | 0.031           |

## 2.5 Summary

In this chapter, an efficient capacitor switching procedure for SAR ADCs was presented. The proposed switching procedure leads to both lower switching energy and smaller total capacitance. It also simplifies the digital logic control circuit. The switching method also improves the settling speed of the DAC capacitor network. Three works are designed to demonstrate power and hardware efficiency of the proposed method.

In work I, the prototype ADC demonstrated the effectiveness of the monotonic switching scheme. However, the signal-dependent offset caused by the variation of the input common-mode voltage degraded ADC linearity. In work II, the revised prototype of work I, a biased comparator was proposed to reduce the dynamic offset induced by input common-mode voltage variation. The improved comparator design avoids the linearity degradation. In addition, an asynchronous control circuit is used to internally generate the necessary clock signals to avoid a high frequency clock generator. Moreover, a hardware-efficient multi-layer sandwich capacitor implemented with normal metal layers was proposed to reduce the area of the capacitor network. In work III, the prototype using asynchronous processing and time interleaved technique achieves excellent power efficiency. In addition, a hardware-efficient finger sandwich capacitor was proposed to construct the capacitor network.

The experiment results of the three works demonstrate the power and hardware efficiency and also the high-speed potential of the proposed SAR ADC.

## Chapter 3

## Binary-Scaled Error Compensation Method for High-Speed SAR ADC

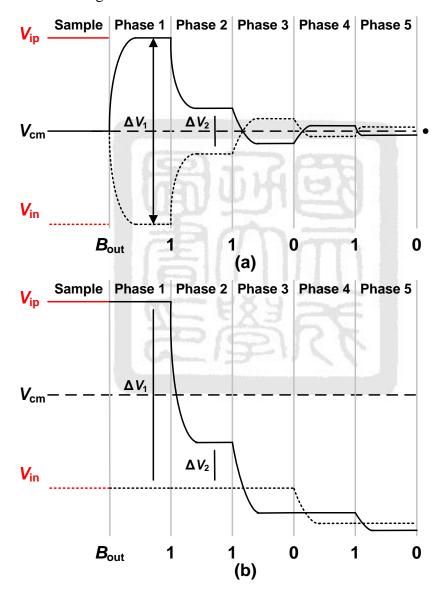

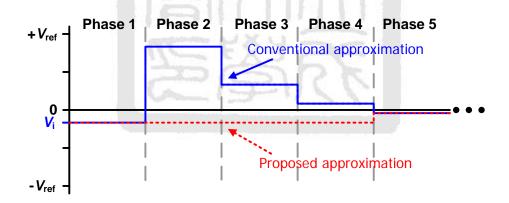

## 3.1 Introduction