# DESIGN OF HIGH PERFORMANCE FREQUENCY SYNTHESIZERS IN COMMUNICATION SYSTEMS

A Dissertation

by

SUNG TAE MOON

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2005

Major Subject: Electrical Engineering

UMI Number: 3172056

### UMI Microform 3172056

Copyright 2005 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

# DESIGN OF HIGH PERFORMANCE FREQUENCY SYNTHESIZERS $\qquad \qquad \text{IN COMMUNICATION SYSTEMS}$

A Dissertation

by

SUNG TAE MOON

Submitted to Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Approved as to style and content by: |                                   |

|--------------------------------------|-----------------------------------|

| Edgar Sánchez-Sinencio               | José Silva-Martinez               |

| (Chair of Committee)                 | (Member)                          |

| Aydin Ilker Karsilayan               | Laszlo Kish                       |

| (Member)                             | (Member)                          |

| Eva M. Sevick-Muraca<br>(Member)     | Chanan Singh (Head of Department) |

$\mathrm{May}\ 2005$

Major Subject: Electrical Engineering

#### ABSTRACT

Design of High Performance Frequency Synthesizers in Communication Systems. (May 2005) Sung Tae Moon, B.S., Seoul National University Chair of Advisory Committee: Dr. Edgar Sánchez-Sinencio

Frequency synthesizer is a key building block of fully-integrated wireless communication systems. Design of a frequency synthesizer requires the understanding of not only the circuit-level but also of the transceiver system-level considerations. This dissertation presents a full cycle of the synthesizer design procedure starting from the interpretation of standards to the testing and measurement results.

A new methodology of interpreting communication standards into low level circuit specifications is developed to clarify how the requirements are calculated. A detailed procedure to determine important design variables is presented incorporating the fundamental theory and non-ideal effects such as phase noise and reference spurs. The design procedure can be easily adopted for different applications.

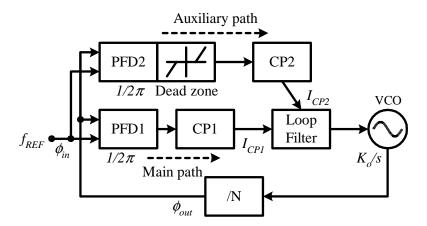

A BiCMOS frequency synthesizer compliant for both wireless local area network (WLAN) 802.11a and 802.11b standards is presented as a design example. The two standards are carefully studied according to the proposed standard interpretation method. In order to satisfy stringent requirements due to the multi-standard architecture, an improved adaptive dual-loop phase-locked loop (PLL) architecture is proposed. The proposed improvements include a new loop filter topology with an active capacitance multiplier and a tunable dead zone circuit. These improvements are crucial for monolithic integration of the synthesizer with no off-chip components.

The proposed architecture extends the operation limit of conventional integer-

N type synthesizers by providing better reference spur rejection and settling time performance while making it more suitable for monolithic integration. It opens a new possibility of using an integer-N architecture for various other communication standards, while maintaining the benefit of the integer-N architecture; an optimal performance in area and power consumption.

To my beloved wife Sung Hwa and son Hahnseok

#### ACKNOWLEDGMENTS

I would like to acknowledge the contribution of many people who helped me throughout my education in Texas A&M.

I would like to express my sincere gratitude to my advisor, Dr. Edgar Sánchez-Sinencio, who has been a constant source of encouragement and support. He provided me with the time, space, and all the resources, and I am really thankful for that. I also would like to thank Dr. José Silva-Martinez for the valuable suggestions and constructive criticisms. My sincere thanks to Dr. Aydin Ilker Karsilayan for the valuable remarks and support. I also want to thank Dr. Laszlo Kish for serving on my committee and providing suggestions. My special thanks to Dr. Eva M. Sevick-Muraca with whom I had the privilege to work in her group.

By being part of Analog and Mixed-Signal Group (AMSC), I benefited from the company of many smart and wonderful friends. I would like to thank my good friend Ari Yakov "Saint" Valero-Lopez, for his selfless help and support during my hard times. I also want to thank the members of Bluetooth and Chameleon projects; Alberto Valdes, Ari Valero, Bo Xia, Ahmed Mohieldin, Ahmed Emira, Chunyu Xin and Wenjun Sheng. I learned a great deal during our projects, and the experience we shared was most valuable and exciting. I also want to thank my friends Antonio, Benoit, Fikret, Daehyun, Jinseok, Myungjae, Jinnki, Yunyoung, Hunhee, Juhwan, Sanghoon, Sangwook, Artur, David, Felipe, Chinmaya, Fan, Sualp, Faisal, Feyza, Jinwoo, Faramarz, and Tianwei for their friendship and help.

Ella Gallagher deserves special thanks. She always goes far out of her way to help students. I am grateful to her for having helped me any time I asked.

I would like to express my gratitude to Jaehong Hahn for his brotherly love and invaluable help and encouragements. I cannot thank him enough for all the opportunities he provided me.

My deepest gratitude to my beloved wife Sung Hwa who has always been by my side. I would also like to thank my son Hahnseok for giving me so much joy and happiness. Their unconditional support and love have been the source of strength I needed to go though all the challenges. They are my greatest treasure and the reason for my life.

I find myself in great debt to my parents and my sister, for their love and kindness.

I have no words to thank them for their sacrifice supporting me for so long. For that

I will always be grateful.

# TABLE OF CONTENTS

| CHAPTER |                                            | Page           |

|---------|--------------------------------------------|----------------|

| I       | INTRODUCTION                               | 1              |

|         | A. Background and Motivation               |                |

| II      | INTERPRETING STANDARDS INTO SPECIFICATIONS | 4              |

|         | A. Introduction                            |                |

| III     | FREQUENCY SYNTHESIZER: A PRIMER            | 20             |

|         | A. Introduction                            | 23<br>24<br>25 |

|         | 1. Charge Pump PLL                         | 27<br>30<br>33 |

|         | D. Non-ideal Effects                       | 42<br>42       |

|         | E. Recent FS Design Techniques Progress    | 52             |

|         | F. Conclusion                              | 55<br>55       |

| CHAPTER |                                                  | Page  |

|---------|--------------------------------------------------|-------|

| IV      | VOLTAGE CONTROLLED OSCILLATOR DESIGN             | . 57  |

|         | A. Introduction                                  | . 57  |

|         | B. Specifications Study                          |       |

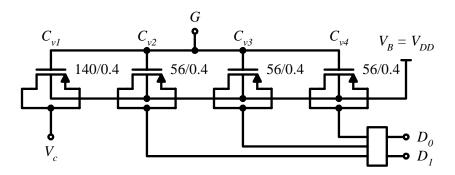

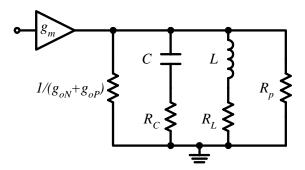

|         | C. Circuit Topology                              |       |

|         | D. Design Trade-offs                             |       |

|         | 1. Power-Noise Trade-off                         |       |

|         | 2. Inductance-Noise Trade-off                    |       |

|         | 3. Inductance-Tuning Range Trade-off             |       |

|         | E. Bluetooth CMOS VCO Design Details             |       |

|         | 1. Bias Current                                  |       |

|         | 2. Inductor in Standard CMOS Process             |       |

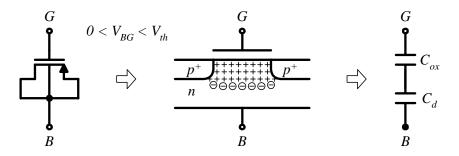

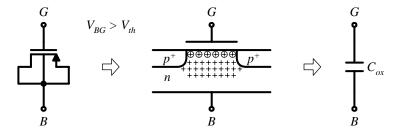

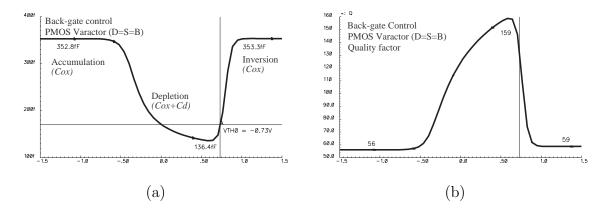

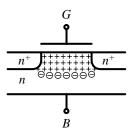

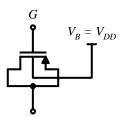

|         | 3. CMOS Varactor                                 |       |

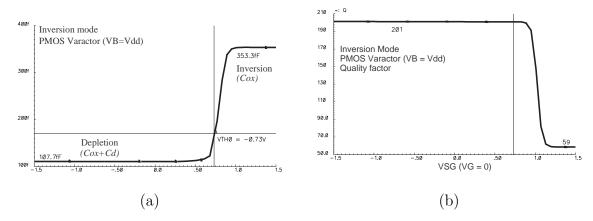

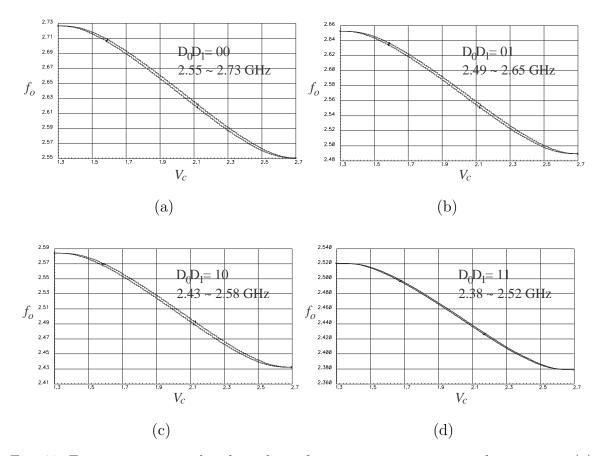

|         | 4. Discrete-Tunable Varactor Array               |       |

|         | 5. CMOS Transistor Drivers                       |       |

|         | 6. Layout                                        |       |

|         | 7. Simulation Results                            |       |

|         | 8. Testing and Measurement                       |       |

|         | F. Multi-Standard BiCMOS VCO Design Details      |       |

|         | 1. Bias Current                                  |       |

|         | 2. Inductor in Analog BiCMOS Process             |       |

|         | 3. BiCMOS Varactor                               |       |

|         | 4. Bipolar Transistor Driver                     |       |

|         | 5. Layout                                        |       |

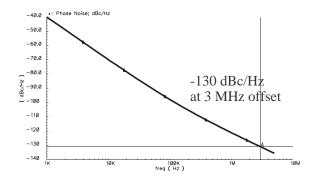

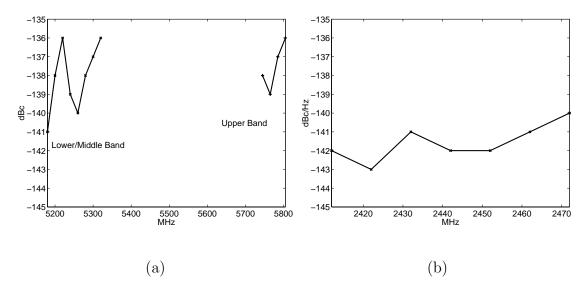

|         | 6. Testing and Measurement                       |       |

|         | o. Testing and Weastrement                       | . 101 |

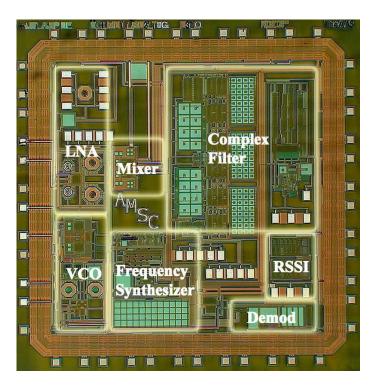

| V       | MULTI-STANDARD FREQUENCY SYNTHESIZER             | . 102 |

|         | A. Introduction                                  | . 102 |

|         | B. Specification Study                           | . 103 |

|         | C. System Architecture                           | . 107 |

|         | D. Circuit Description                           | . 109 |

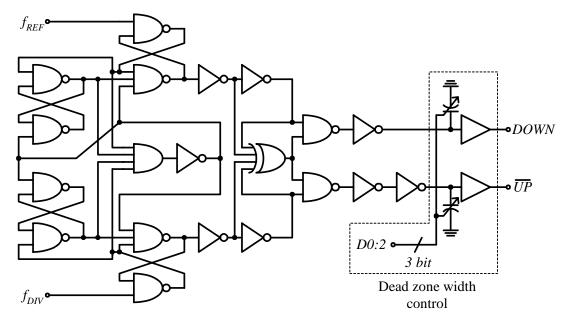

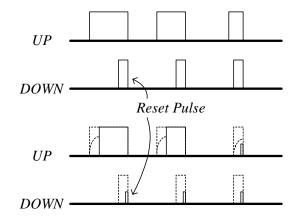

|         | 1. Phase Frequency Detector with Dead Zone Width |       |

|         | Control                                          | . 109 |

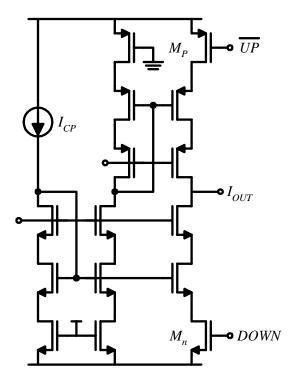

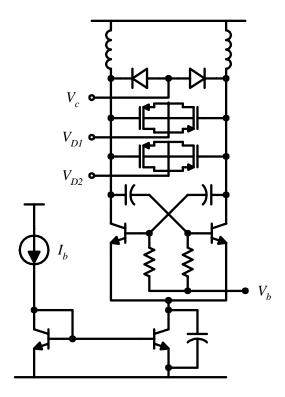

|         | 2. Charge Pump                                   | . 112 |

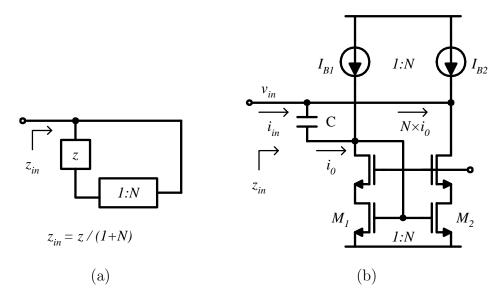

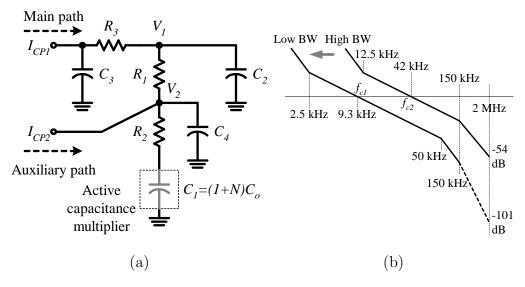

|         | 3. Capacitance Multiplier                        | . 113 |

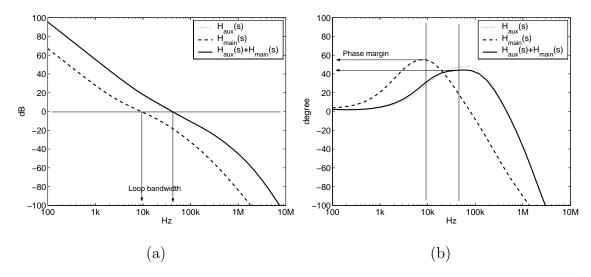

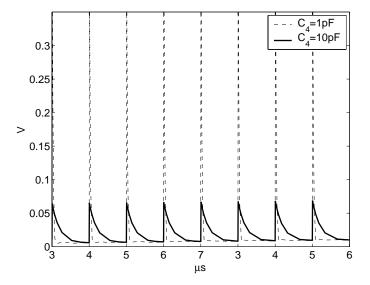

|         | 4. Loop Filter                                   | . 114 |

|         | 5. VCO                                           | . 120 |

|         | 6. Prescaler                                     | . 121 |

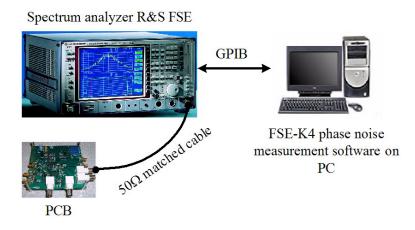

|         | E. Testing and Measurement                       | . 122 |

| CHAPTER     | F                                                                            | age |

|-------------|------------------------------------------------------------------------------|-----|

|             | <ol> <li>Printed Circuit Board (PCB) Design</li> <li>Testing Setup</li></ol> | 125 |

| VI          | CONCLUSIONS                                                                  | 132 |

| REFERENC    | CES                                                                          | 134 |

| APPENDIX    | X A                                                                          | 144 |

| APPENDIX    | ХВ                                                                           | 148 |

| $VIT\Delta$ |                                                                              | 151 |

# LIST OF TABLES

| TABLE |                                                                  | Page |

|-------|------------------------------------------------------------------|------|

| Ι     | Short range wireless communications standards                    | 6    |

| II    | Tuning range requirements under process variations (unit:MHz) $$ | 10   |

| III   | Settling time requirements                                       | 12   |

| IV    | Spectral purity requirements                                     | 18   |

| V     | Summary of specification mapping                                 | 19   |

| VI    | The effect of pseudo-damping factor in third order system        | 36   |

| VII   | Summary of PLL design trade-offs                                 | 40   |

| VIII  | VCO specifications                                               | 58   |

| IX    | Ring oscillator applications                                     | 60   |

| X     | VCO design procedure                                             | 68   |

| XI    | Spiral inductor parameters for Bluetooth VCO                     | 72   |

| XII   | Spiral inductor parameters for multi-standard VCO                | 95   |

| XIII  | Wireless LAN 802.11a and 802.11b Standards                       | 104  |

| XIV   | PLL design parameters                                            | 120  |

| XV    | Measurement results summary                                      | 131  |

# LIST OF FIGURES

| FIGUR | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

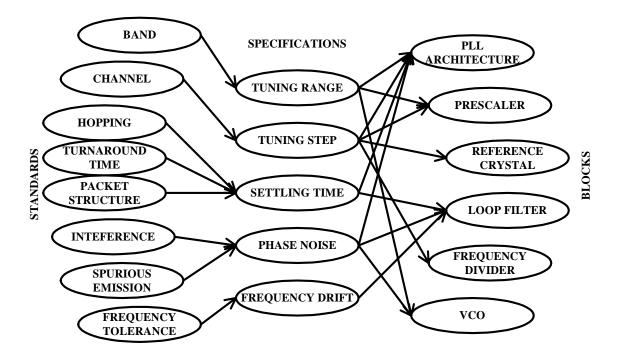

| 1     | From standards to specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5    |

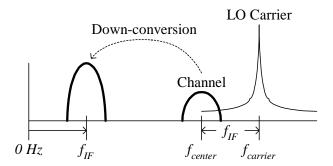

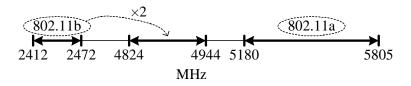

| 2     | Channel center frequency and carrier frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7    |

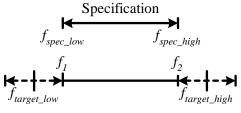

| 3     | Determining tuning range specification under process variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8    |

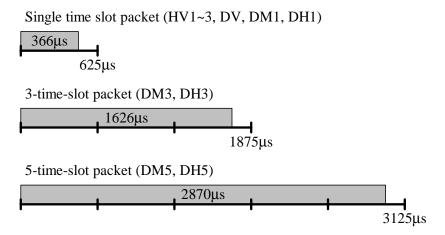

| 4     | Bluetooth packet length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11   |

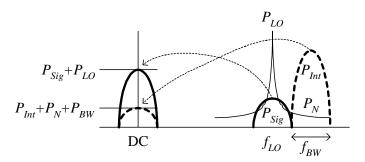

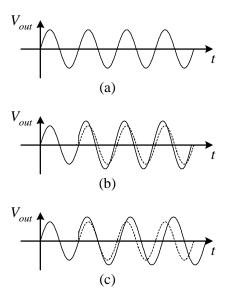

| 5     | The effect of phase noise and interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13   |

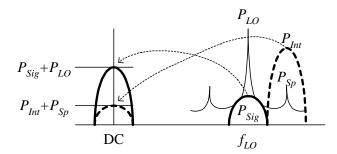

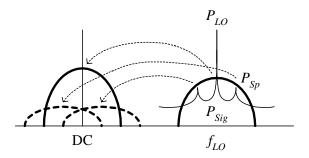

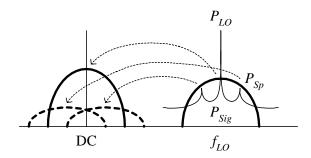

| 6     | The effect of reference spur and interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14   |

| 7     | The effect of reference spur in 802.11b system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15   |

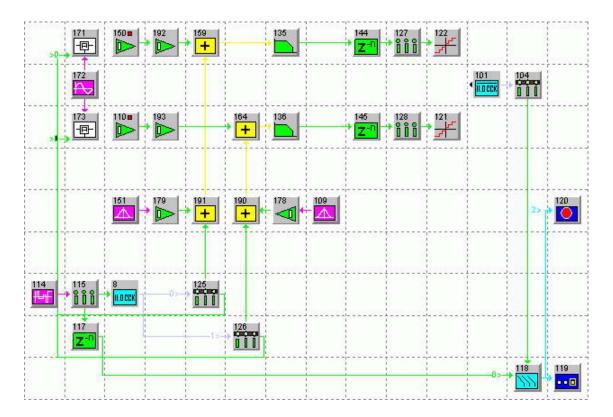

| 8     | Block diagram of System<br>View<br>$^{\rm TM}$ setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16   |

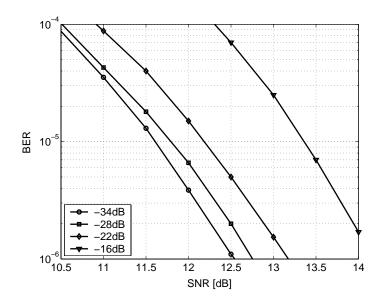

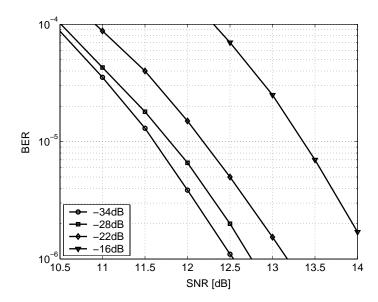

| 9     | The effect of reference spur at 2 MHz in 802.11b system $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18   |

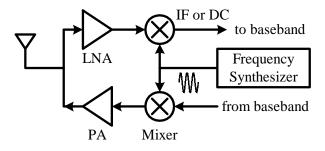

| 10    | The role of a frequency synthesizer in a communication transceiver $% \left( 1\right) =\left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right$ | 20   |

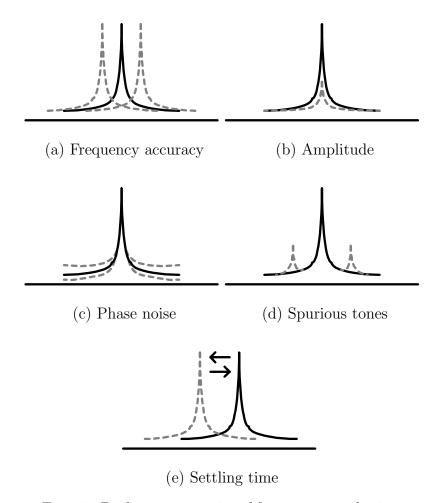

| 11    | Performance merits of frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21   |

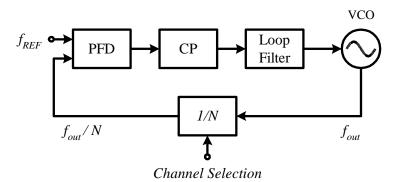

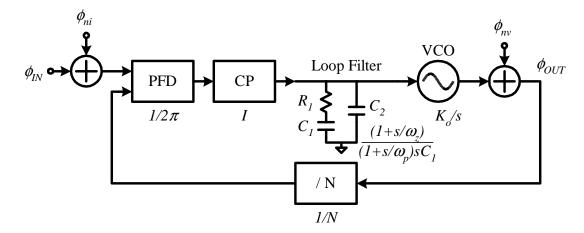

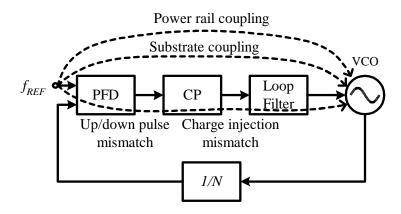

| 12    | Integer-N architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23   |

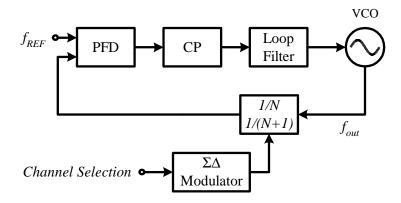

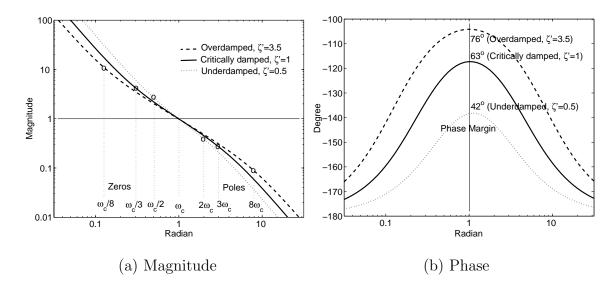

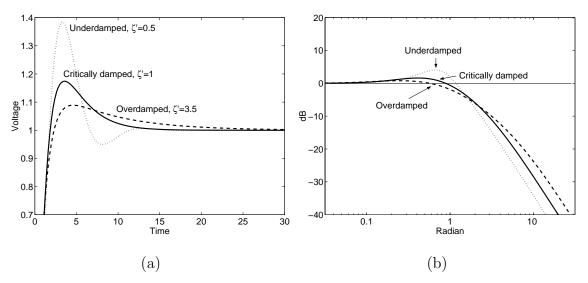

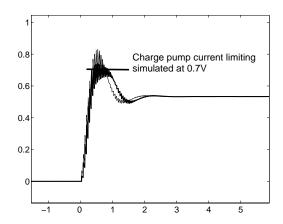

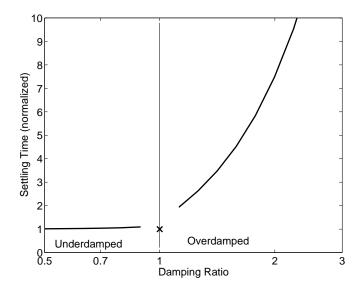

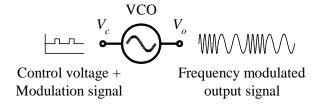

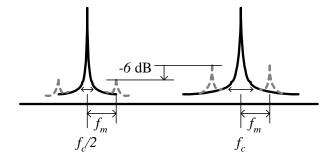

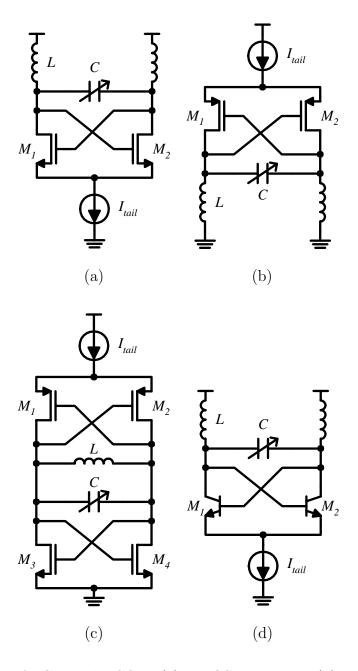

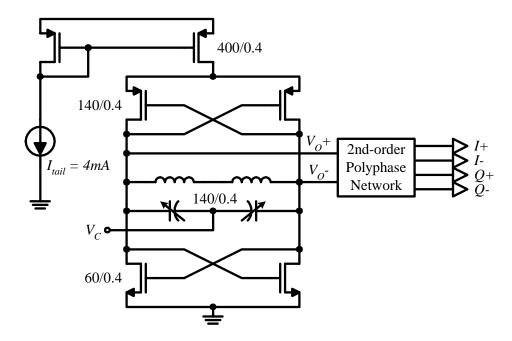

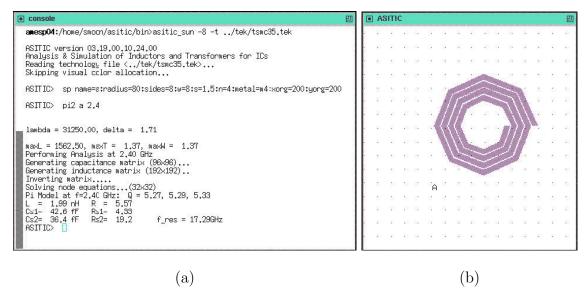

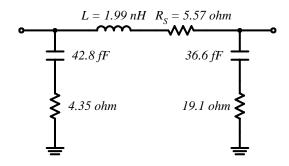

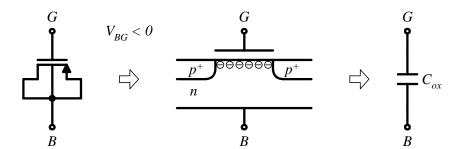

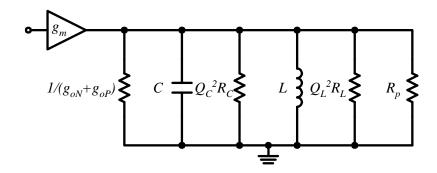

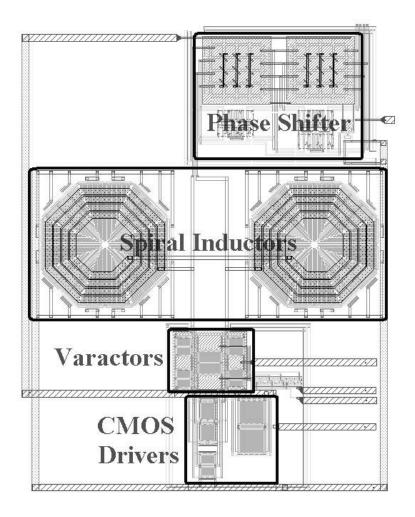

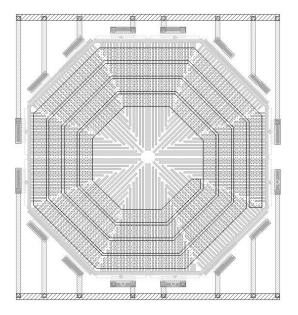

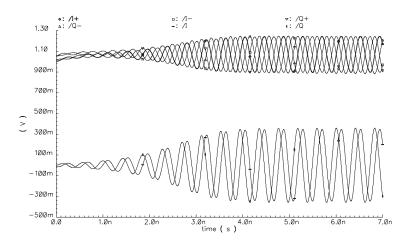

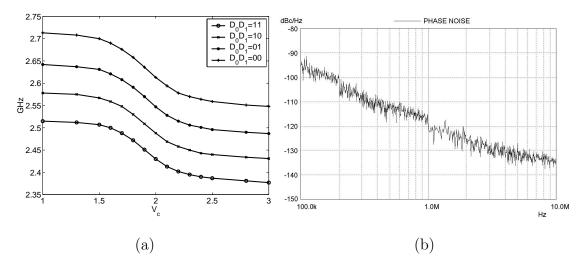

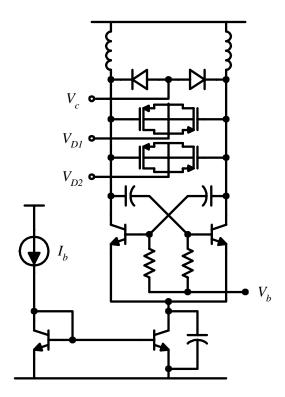

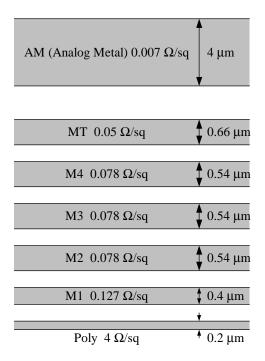

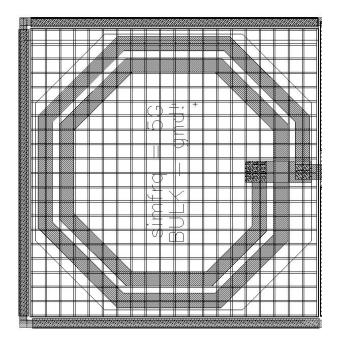

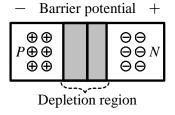

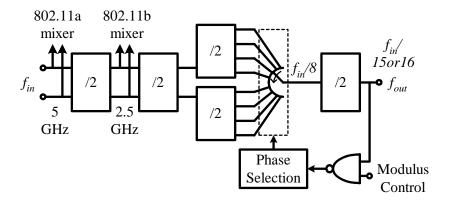

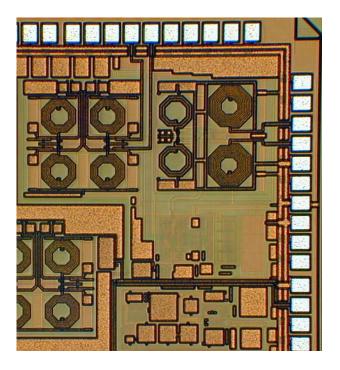

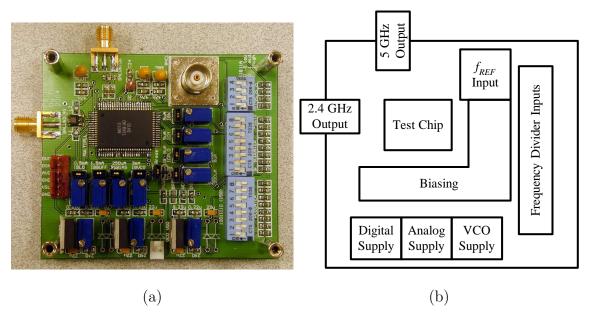

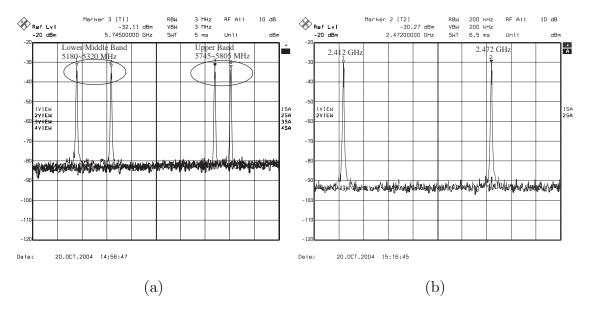

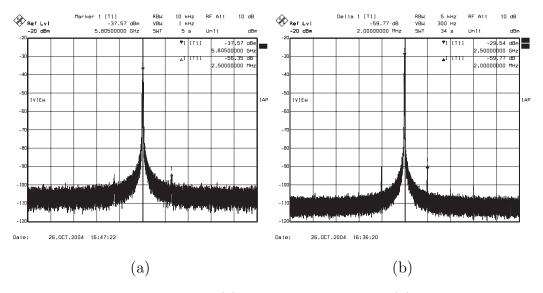

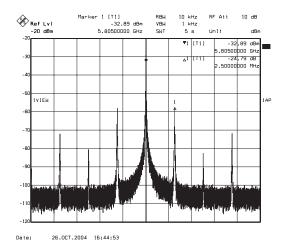

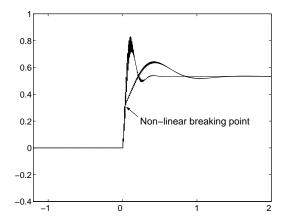

| 13    | Fractional-N architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25   |