# 第三章 CMOS 反相器

# 第一节 对逻辑门的基本要求

# (1) 鲁棒性(用静态或稳态行为来表示)

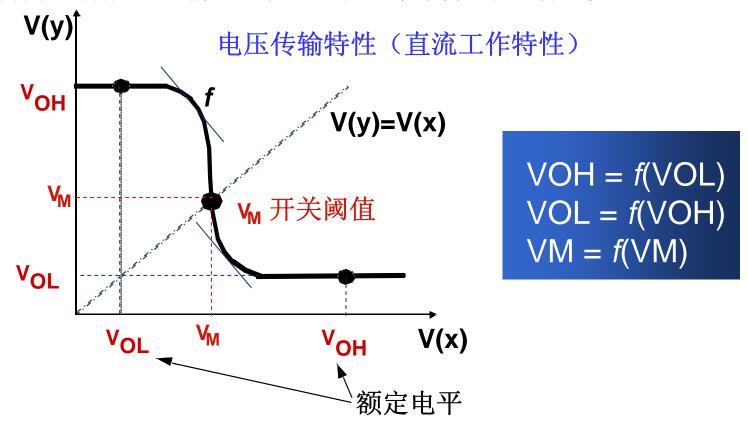

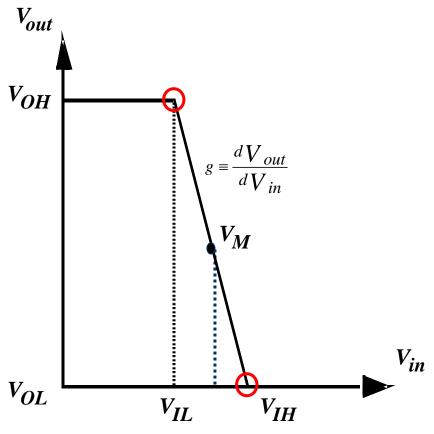

静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

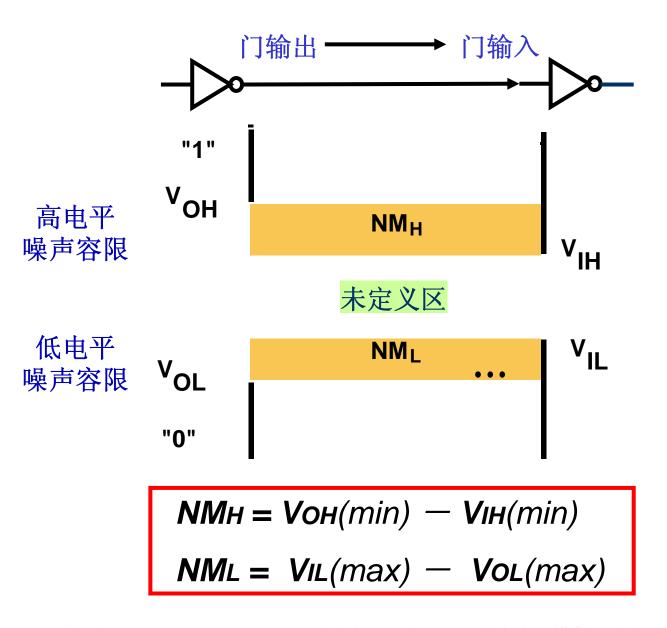

- (2) 噪声容限: 芯片内外噪声会使电路响应偏离设计期望值 一个门对于噪声的敏感程度由噪声容限表示

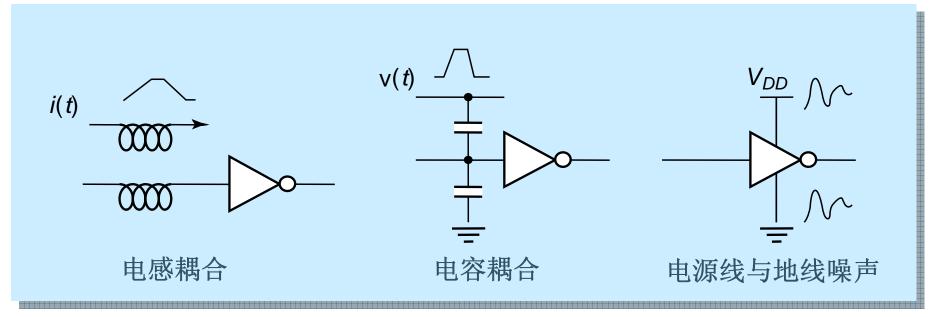

- 噪声来源: (1) 串扰 (2) 电源与地线噪声 (3) 失调 (4) 片外干扰 数字集成电路中的噪声

应当区分: (1)固定噪声源 (2)比例噪声源

浮空节点比由低阻抗电压源驱动的节点更易受干扰

设计时将所要求的总的噪声容限分配给所预见到的各个噪声源

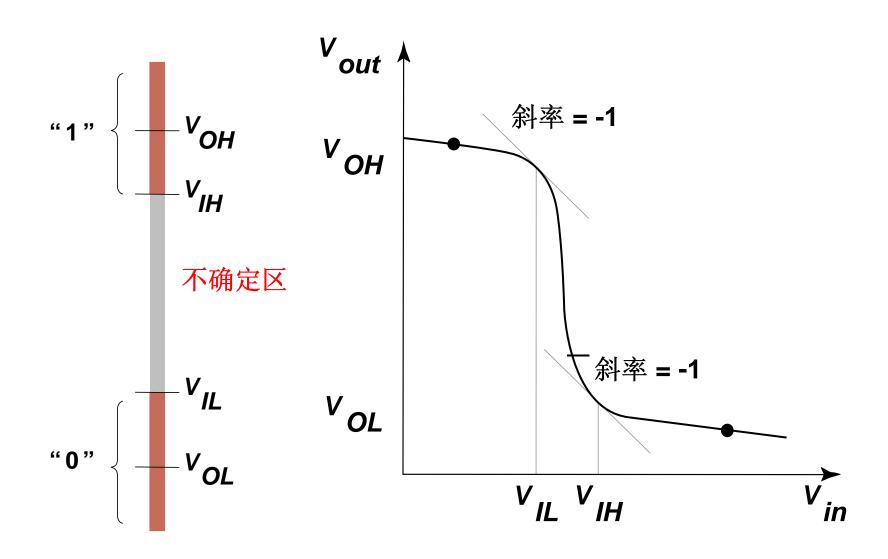

# 输入低电平 VIL 与输入高电平 VIH

# 噪声容限定义

噪声容限 (Noise Margin)

容许噪声的限度

抗噪声能力 (Noise Immunity)

抑止噪声的能力

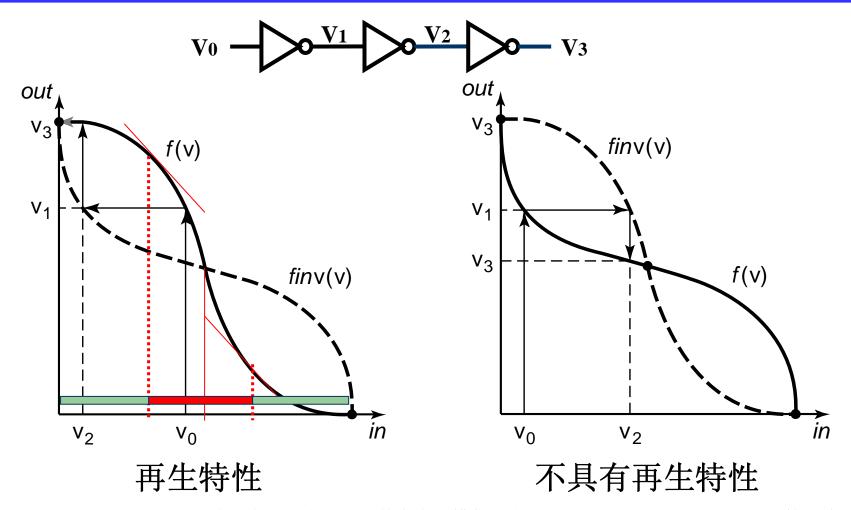

(3) "再生"特性:逻辑门的"再生"特性能使被干扰的信号恢复到名义的逻辑电平。

逻辑门具有"再生"特性的条件:合法区增益小于1,过渡区增益大于1

# 再生特性使被干扰的信号恢复到名义的逻辑电平

# (4) 逻辑门的"单向性":

输出电平的变化不应出现在任何一个输入上。 但实际上输出与输入之间总有寄生反馈(如密勒效应)

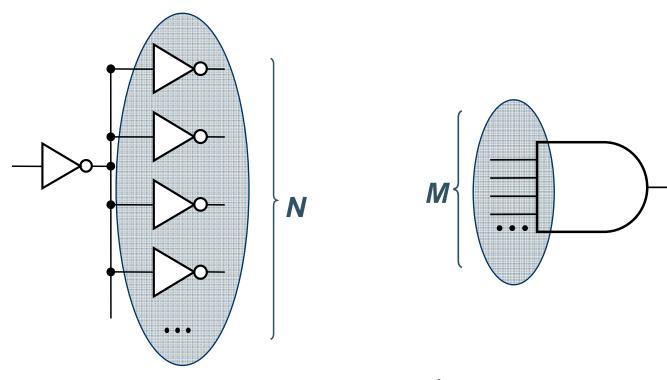

# (5) 逻辑门的扇出 (Fan-out) 和 逻辑门的扇入 (Fan-in)

扇出 (Fan-out) 扇入 (Fan-in)

扇出(Fan-out) N

扇入(Fan-in) M

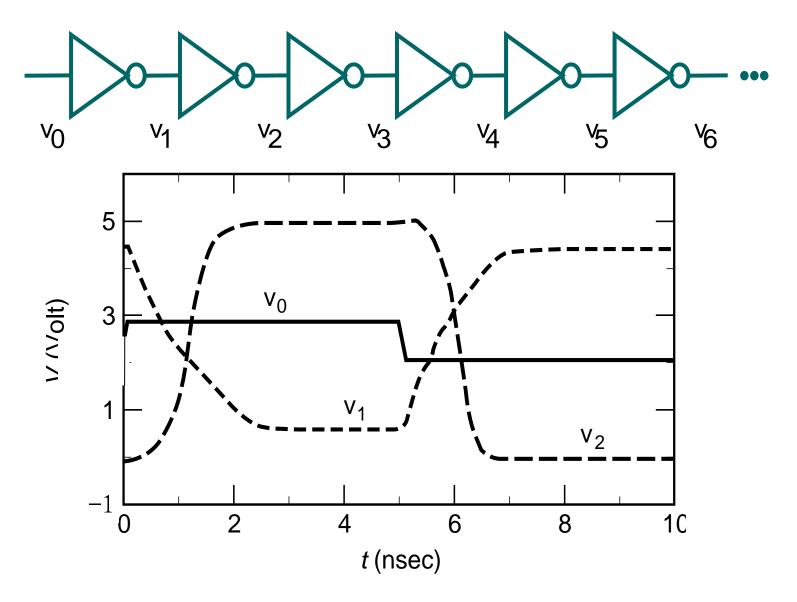

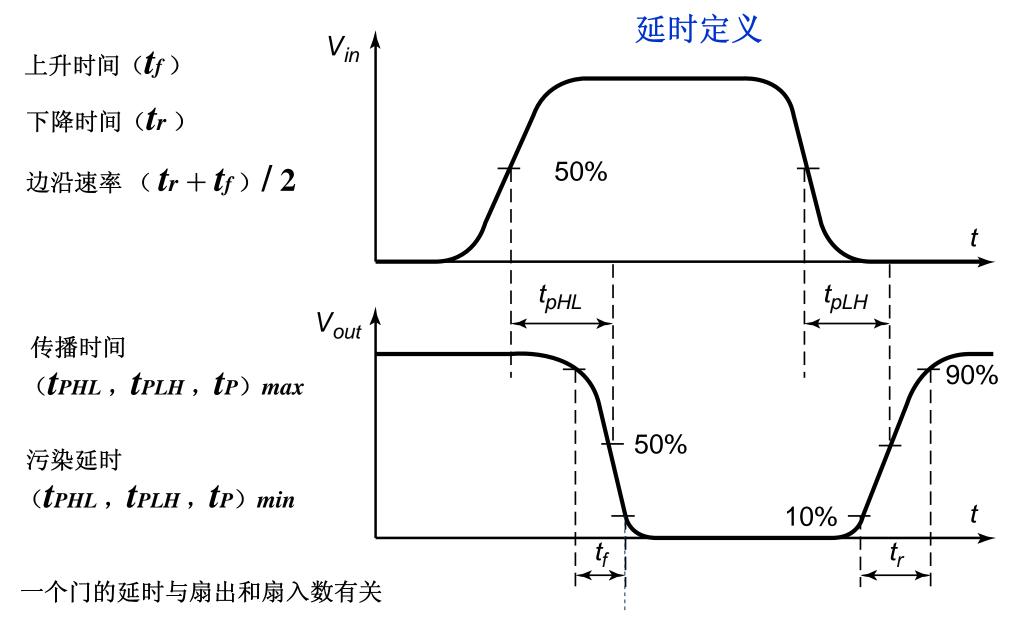

# (6) 动态性能(由动态或瞬态响应来决定)

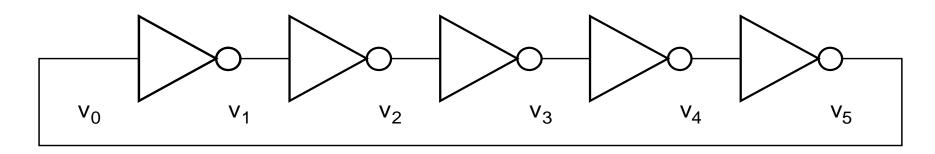

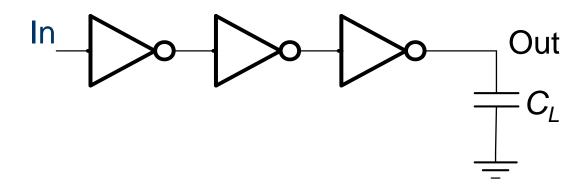

# 利用环振荡器测量门延时

环振由奇数级反相器形成环路,一般至少需五级反相器

$$T=2$$

X  $t_p$  X N  $(2Nt_p >> t_f + t_r$  时成立)

实际电路的最高工作频率比环振测得的低 50-100 倍

- (7) 逻辑门的面积与复杂性(将影响集成度与速度)

- (8) 逻辑门的功耗和能耗

### 功耗

瞬时功耗:

$$p(t) = v(t)i(t) = V_{supply}i(t)$$

峰值功耗:

$$P_{peak} = V_{supply} i_{peak}$$

平均功耗:

$$P_{ave} = \frac{1}{T} \int_{t}^{t+T} p(t) dt = \frac{V_{supply}}{T} \int_{t}^{t+T} i_{supply}(t) dt$$

# 功率延时积 (综合考虑传播延时与功耗的指标):

功率延时积(PDP) = E = 每操作消耗的能量 =  $P_{av} \times t_p$

# 能量延时积 (综合考虑传播延时与能耗的指标):

能量延时积( $\mathrm{EDP}$ ) = 门的品质(度量)因子=  $E \times t_p$

### 功耗来源及对设计的影响

### CMOS电路中功耗的来源:

动态功耗 (翻转功耗一充放电电容功耗)

短路功耗 (翻转功耗-电源与地直通功耗)

漏电功耗 (泄漏电流功耗)

静态功耗 (维持功耗、偏置电流功耗)

### 功耗对设计的影响:

功耗影响电路可行性、性能、可靠性、成本。

功耗影响设计封装、冷却、电源线尺寸、电源容量、集成度

峰值功耗 (确定电源线尺寸)

平均功耗 (确定冷却、对电池要求)

每单位面积功耗(研究工艺特征尺寸缩小时功耗变化的趋势以及芯片的热耗与温升) 功耗延时积(器件优值,确定每翻转消耗的能量。忽略漏电流时,PDP 与性能及 *VTH* 无关) 能量延时积(同类电路的 EDP 几近常数,设计时可在性能和能量之间进行 Trade-offs)

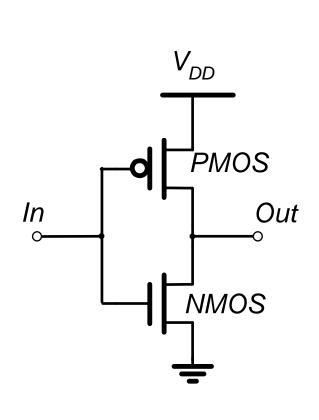

# 第二节 CMOS 反相器

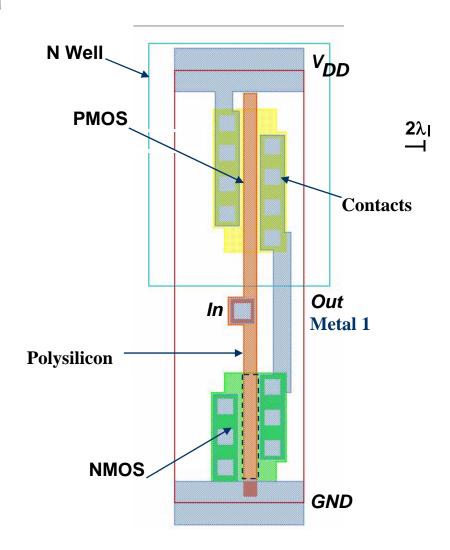

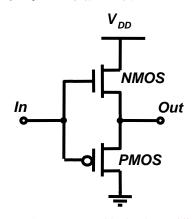

# (一) CMOS 反相器及其版图

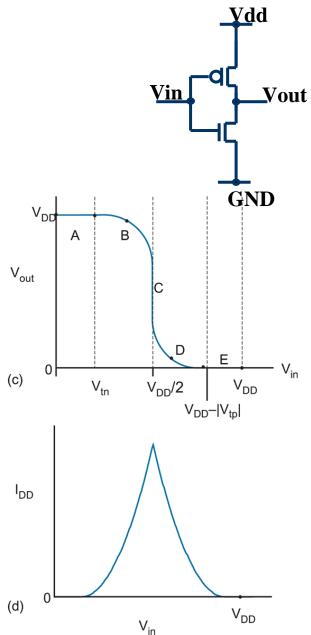

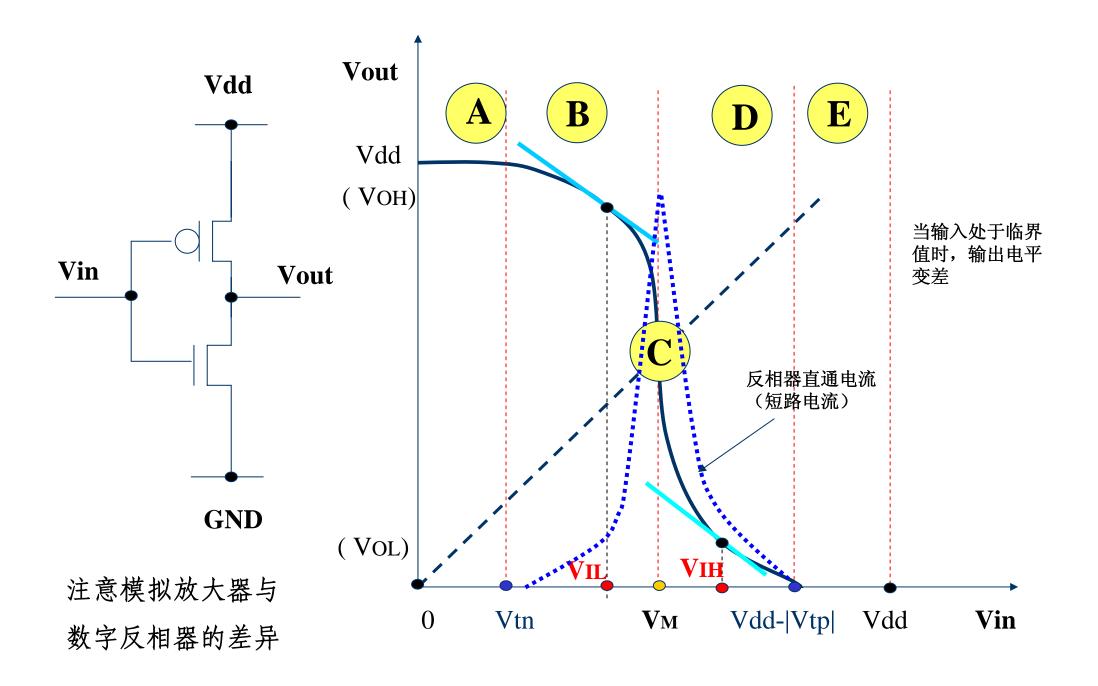

# (二) CMOS 反相器的传输特性

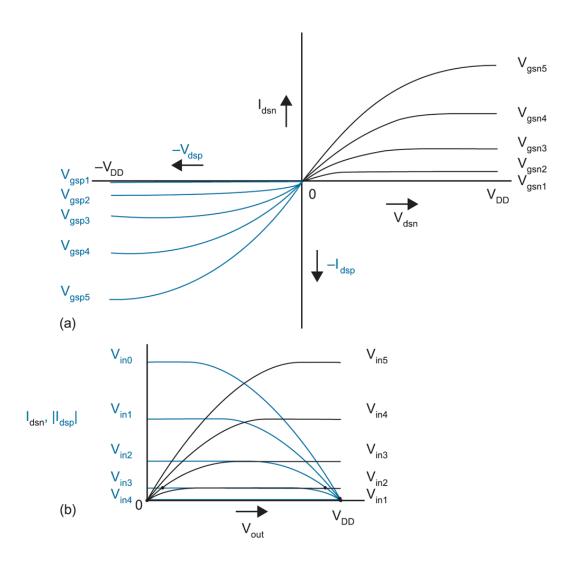

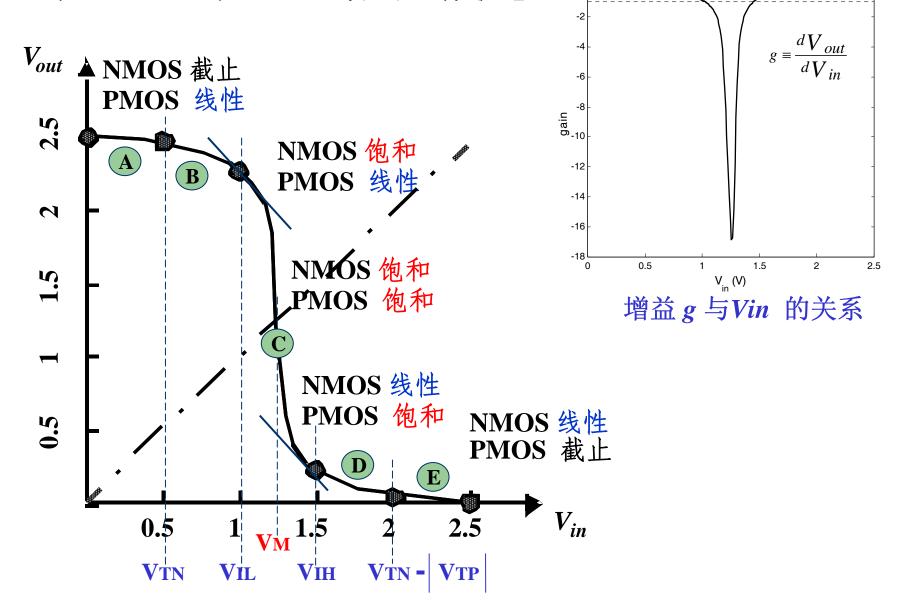

### 反相器中 NMOS 与 PMOS 管的工作状态

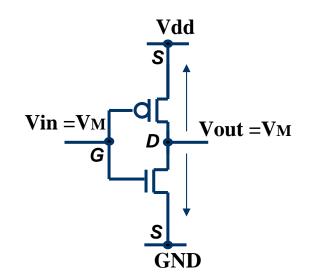

# 确定 Vm 的方法

在翻转区PMOS和NMOS器件同时处于(速度)饱和状态, 使这两个器件的电流相同:

$$k_n V_{DSATn} \left( V_M - V_{Tn} - \frac{V_{DSATn}}{2} \right) + k_p V_{DSATp} \left( V_M - V_{DD} - V_{Tp} - \frac{V_{DSATp}}{2} \right) \ = \ 0$$

# 求解 $V_M$ 得到:

Vout =VM

$$V_{M} = \frac{\left(V_{Tn} + \frac{V_{DSATn}}{2}\right) + r\left(V_{DD} + V_{Tp} + \frac{V_{DSATp}}{2}\right)}{1 + r}$$

其中:

$$r = \frac{k_p V_{DSATp}}{k_n V_{DSATn}} = \frac{\upsilon_{satp} W_p}{\upsilon_{satn} W_n}$$

注意: 这不同于长沟器件

对于长沟器件:

$$V_{M} = \frac{V_{Tn} + \sqrt{\frac{-k_{p}}{k_{n}}} (V_{DD} + V_{Tp})}{1 + \sqrt{\frac{-k_{p}}{k_{n}}}}$$

# 确定VIH和VIL的简化方法

增益

$$g = \frac{dV_{out}}{dV_{in}}$$

$$g = -\frac{1}{I_D(V_M)} \frac{k_n V_{DSATn} + k_p V_{DSATp}}{\lambda_n - \lambda_p}$$

$$\approx \frac{-(1+r)}{(V_M - V_{Tn} - V_{DSATn}/2)(\lambda_n - \lambda_p)}$$

$$\lambda_n = \lambda_p$$

为沟长调制系数

$$V_{IH} = V_M - \frac{V_M}{g} \qquad V_{IL} = V_M + \frac{V_{DD} - V_M}{g}$$

$$NM_H = V_{DD} - V_{IH} \qquad NM_L = V_{IL}$$

### **Exercise**

# (1) 研究以下两种器件情形时的反相器传输特性

长沟器件(非速度饱和)

短沟器件(速度饱和)

| 区域 | Vin | Vout | nMOS状态 | pMOS状态 |

|----|-----|------|--------|--------|

| Α  |     |      |        |        |

| В  |     |      |        |        |

| С  |     |      |        |        |

| D  |     |      |        |        |

| Е  |     |      |        |        |

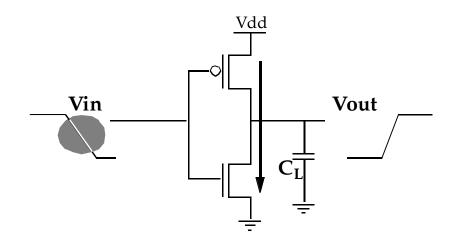

### (2) 可否设计如下图所示的反相器?

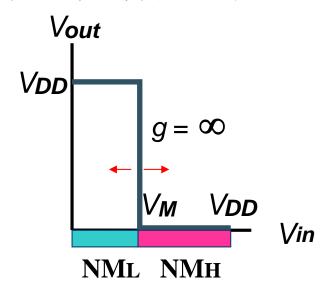

# (三) 噪声容限

### 静态噪声容限:

无限长时间所能容许的最大噪声电平 动态噪声容限

与噪声持续时间有关的容许的最大噪声电平

# Vin Vout VOH NMH VIH Transition Region NML VOL

### 反相器的 静态噪声容限:

- (1) 与P管和N管的阈值电压有关

- (2) 需权衡"噪声容限"和反相器速度

- (3) 常表示为与电源电压之间的比值

理想情况下的噪声容限估算 (改变 Vm 值可改变 NML 与 NMH)

# (四) 影响传输特性的因素

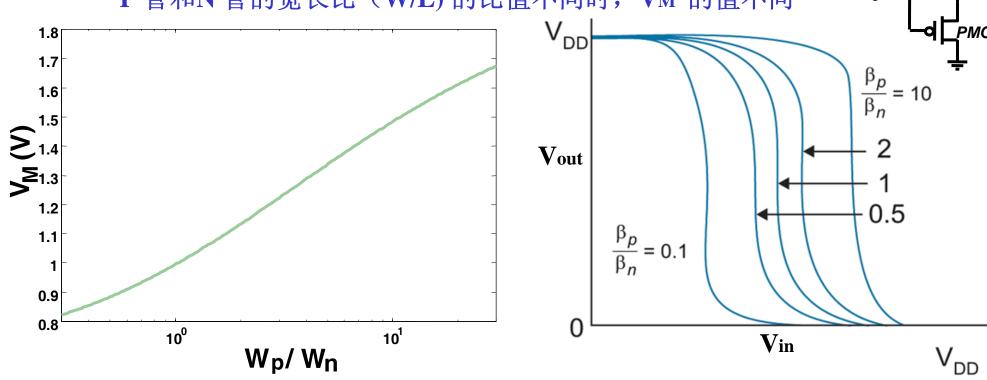

(1) P 管和N 管的宽长比(W/L比值)

P 管和N 管的宽长比 (W/L) 的比值不同时, VM 的值不同

增加 P 管的宽度使 V<sub>M</sub> 移向 V<sub>dd</sub>,增加 N 管的宽度使 V<sub>M</sub> 移向 GND

但 VM 值对于器件尺寸较不敏感

$$k = k \frac{W}{L} = \mu C_{ox} \frac{W}{L}$$

工业设计中使 P 管的尺寸为 N 管的 2 倍可以节省面积,

器件的二次效应(例如沟长调制和速度饱和)使这一比例更为合理。

$V_{DD}$

NMOS

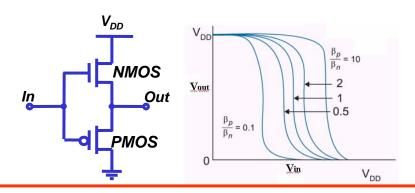

# 不对称 (Skewed) 反相器 ( $kp \neq kn$ )

增加 P 管的宽度使 Vm 移向 Vdd 增加 N 管的宽度使 Vm 移向 GND

kp/kn > 1 时,称为 HI-Skewed 反相器(输入从高到低时易于使反相器翻转)

kp/kn < 1 时,称为 LO-Skewed 反相器(输入从低到高时易于使反相器翻转)

kp/kn = 1 时,称为标准(对称)反相器

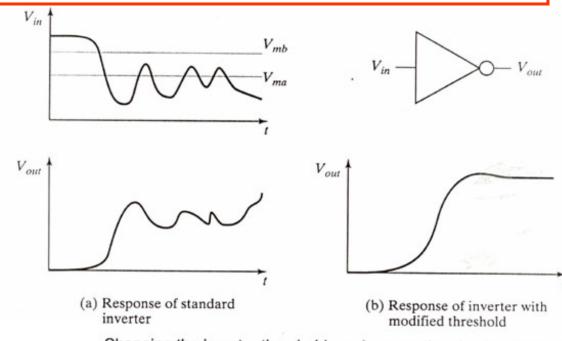

### 不对称(Skewed)反相器的应用

改变 VM 有时可以改善电路的可靠性 (改变翻转阈值消除输入抖动的影响)

利用不对称性可组成电荷分布放大器 (使不对称性有利于电荷快速放电)

Changing the inverter threshold can improve the circuit reliability.

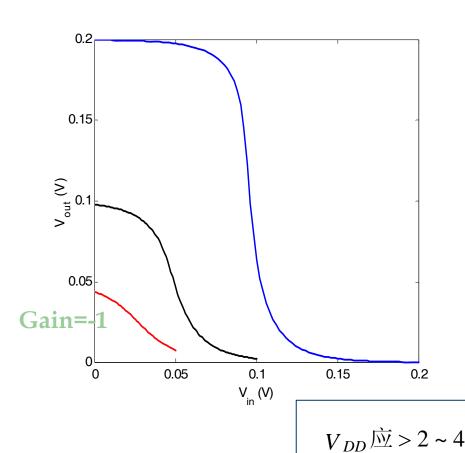

### (2) 电源电压

降低电源电压,使VTC 特性改善。

但过低的电源电压(<0.1V时)使VTC 明显变差

降低电源电压将增加延时。

电源电压较低时, VTC 对器件参数的变化较为敏感

降低电源电压虽降低系统内部噪声(如串扰),但外部噪声并不能得到改善。

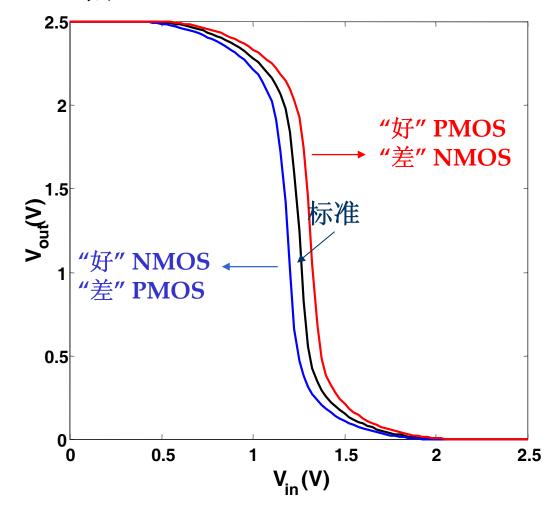

### (3) 工艺偏差

### "好"的 MOS 管是指:

沟道较短、较宽 栅氧较薄、器件阈值较低

(4) 环境: 例如温度

温度上升时, $V_{tn} \downarrow$ , $|V_{tp}| \downarrow$ ,传输特性发生变化。

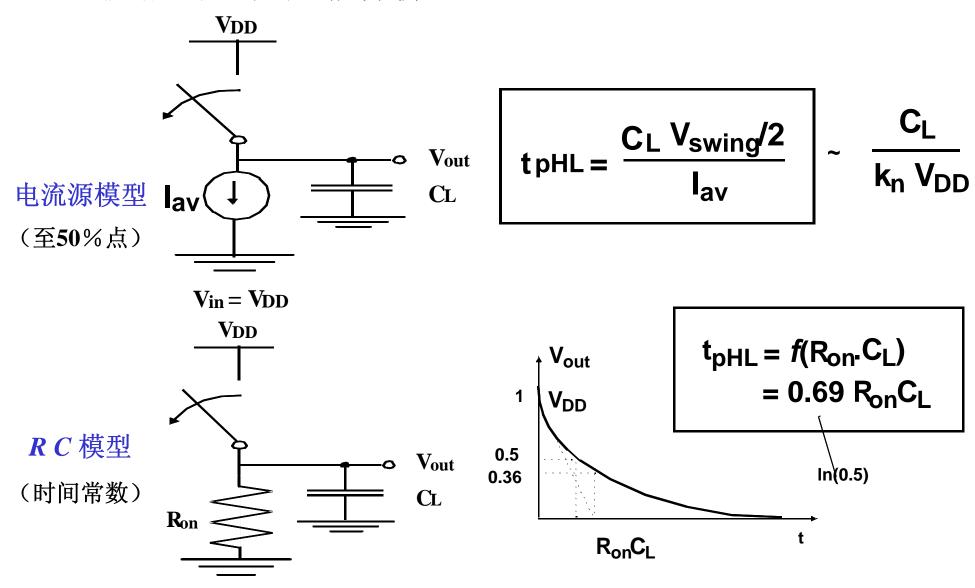

# (五) 反相器延时

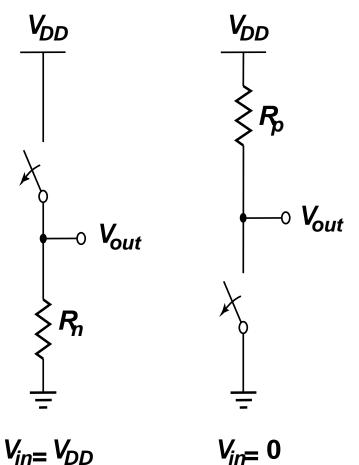

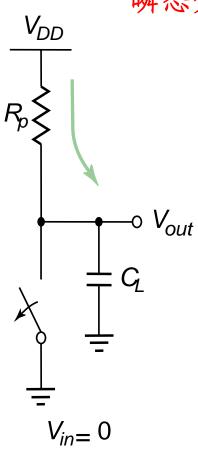

# (1) 反相器延时的一阶分析

$V_{in} = V_{DD}$

### 直流分析

$$V_{OL} = 0$$

$$V_{OH} = V_{DD}$$

$$V_{M} = f(R_{n}, R_{p})$$

### 瞬态分析

$$V_{in} = V_{DD}$$

### (b) 高至低过渡

$$t_{pHL} = f(R_{on}.C_L)$$

= 0.69  $R_{on}C_L$

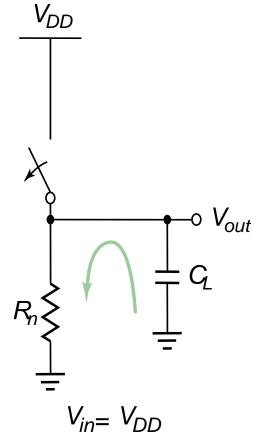

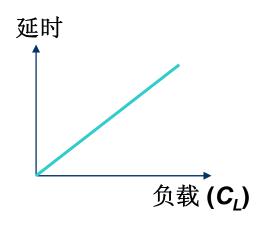

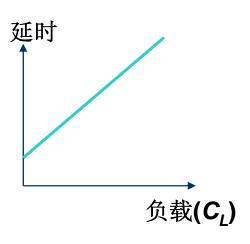

### (2) 影响反相器延时的因素

1. 瞬态响应取决于器件的输出电阻、寄生(栅漏、漏体)电容、连线电容和负载电容

反相器寄生电容

(栅漏)密勒电容

# 瞬态响应

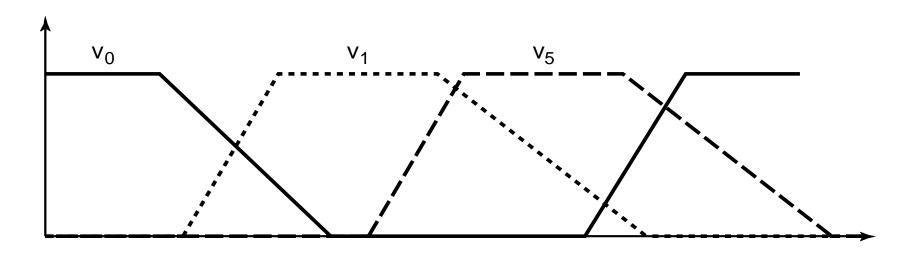

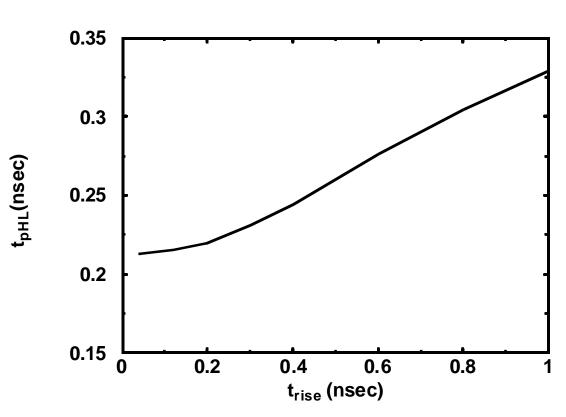

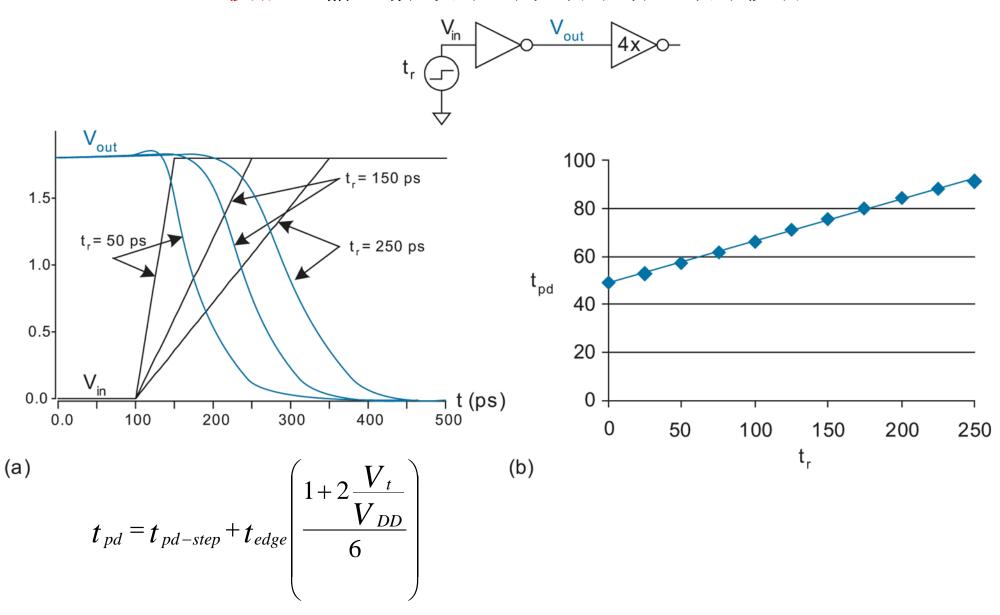

### 2. 反相器延时与输入信号的斜率有关

## 输入信号的上升时间对延时的影响

由于驱动门有限的驱动能力,被驱动门的输入信号上升时间不为零。

门延时与输入信号的上升时间有关:

$$t_{pHL} = \sqrt{t_{pHL(step)}^2 + (t_r/2)^2}$$

反相器链中, 第 i 级反相器的延时:

$$t_p^i = t_{step}^i + \eta t_{step}^{i-1}$$

### SPICE模拟:输入信号的上升时间对延时的影响

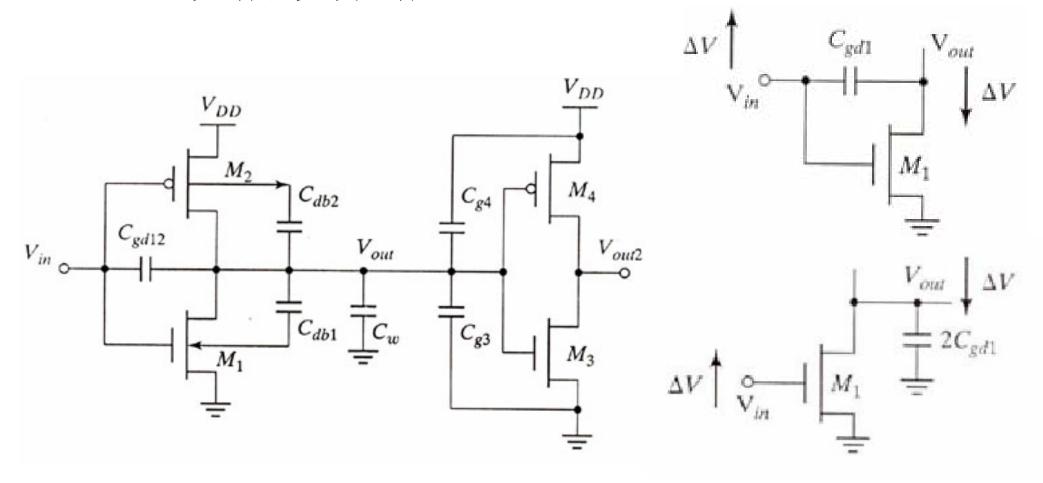

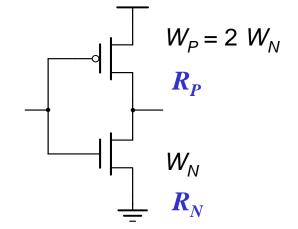

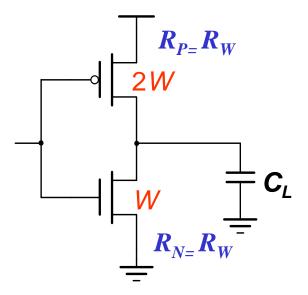

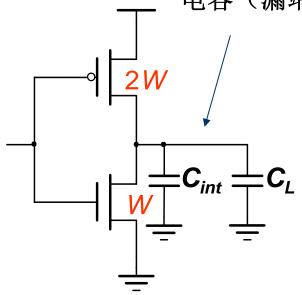

### (3) 对称反相器的延时

• 假设  $\mu_n = 2\mu_p$

- 设对称反相器  $W_P = 2W_N = 2W$ ,此时:

- 上拉电流与下拉电流相等

- PMOS 管和 NMOS 管的电阻大致相同:  $R_N = R_P = R_W$

- •上升延时( $t_{pLH}$ )和下降延时( $t_{pHL}$ )大致相同

- 上升延时与下降延时 (不考虑漏端扩散电容 Cintrinsic 时):

$$t_{pLH} = (\ln 2) R_P C_L = (\ln 2) R_W C_L = 0.69 R_W C_L$$

$$t_{pHL} = (\ln 2) R_N C_L = (\ln 2) R_W C_L = 0.69 R_W C_L$$

### $C_{int} = 0$ 时:

延时=

$$t_p = k R_W C_L$$

### C<sub>int</sub>为反相器本征 电容(漏端电容)

### $C_{int}$ 不为零时:

延时 =

$$kR_W(C_{int} + C_L)$$

$$= k R_W C_{int} + k R_W C_L$$

$$= k R_W C_{int} (1 + C_L / C_{int})$$

# 第三节 优化反相器的速度

$$tpHL = \frac{C_L V_{swing}/2}{I_{av}} \sim \frac{C_L}{k_n V_{DD}}$$

优化反相器速度的措施:

(1) 使电容(自载电容、连线电容、负载电容) 较小:

漏端扩散区的面积应尽可能小

- 输入电容要考虑: (1) Cgs 随栅压而变化

- (2) 密勒效应

- (3) 自举电路

- (2) 使晶体管的等效导通电阻(输出电阻)较小: 加大晶体管的尺寸(驱动能力)

但这同时加大了它的源漏电容(自载电容)和输入电容(驱动它的上一级的负载电容)

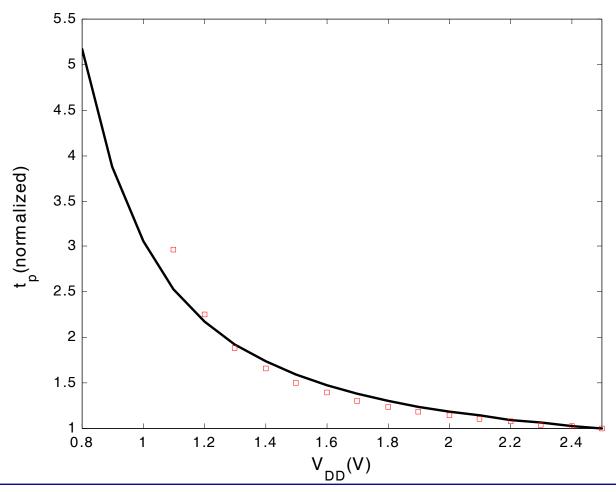

### (3) 提高电源电压

提高电源电压可以降低延时即可用功耗换取性能。

$$R_{eq} = \frac{3}{4} \frac{V_{DD}}{I_{DSA}} \left( 1 - \frac{5}{6} \lambda V_{DD} \right)$$

$$R_{eq} = \frac{3}{4} \frac{V_{DD}}{I_{DSA}} \left( 1 - \frac{7}{9} \lambda V_{DD} \right)$$

但超过一定程度后改善有限  $V_{DD} >> V_{TH} + \frac{1}{2} V_{DSAT}$  时, 延时事实上与 **VDD** 无关。

电压过高会引起可靠性问题 (氧化层 击穿、热电子等)

$$t_{pHL} = 0.69 \frac{3}{4} \frac{C_L V_{DD}}{I_{DSATn}} = 0.52 \frac{C_L V_{DD}}{(W/L)_n k'_n V_{DSATn} (V_{DD} - V_{Tn} - V_{DSATn}/2)}$$

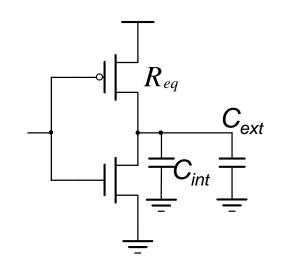

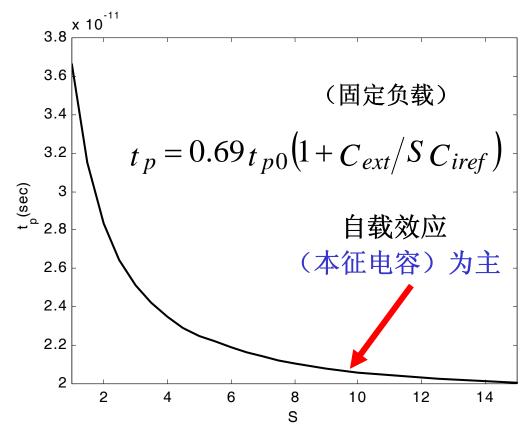

# Case Study 1: 单个反相器驱动固定负载( $C_{ext}$ )时的延时

假设参照反相器的本征电容为  $C_{iref}$  , 其晶体管的等效电阻为  $R_{ref}$

若一个反相器的晶体管尺寸(宽度)为参照反相器晶体管尺寸的 S 倍,则该反相器的本征电容( $C_{int}$ )及晶体管等效电阻( $R_{eq}$ )分别为::

$$C_{\rm int} = S C_{iref}$$

$R_{eq} = R_{ref}/S$

于是,单个反相器驱动固定负载( $C_{ext}$ )的(平均)延时可表示为:

$$t_{p} = 0.69 R_{eq} (C_{int} + C_{ext}) = 0.69 R_{eq} C_{int} (1 + C_{ext}/C_{int}) =$$

$$= 0.69 (R_{ref}/S) (SC_{iref}) (1 + C_{ext}/SC_{iref}) =$$

$$= 0.69 R_{ref} C_{iref} (1 + \frac{C_{ext}}{SC_{iref}}) = t_{p0} (1 + C_{ext}/SC_{iref})$$

其中:  $t_{p0} = 0.69 R_{ref} C_{iref} = 0.69 R_{eq} C_{int}$  为反相器的本征延时。

可见: 反相器的本征延时与它的尺寸加大多少倍无关。

反相器的本征延时  $t_{p0}$  与门的尺寸加大无关,而仅与工艺及版图有关。(尺寸加大时,晶体管等效电阻减小但本征电容加大)

无负载时,增加门的尺寸不能减少延时。

有负载时, S 很大时将使反相器延时趋于本征延时, 因此继续加大尺寸将对延时不会有什么改善, 而只会显著增加面积。

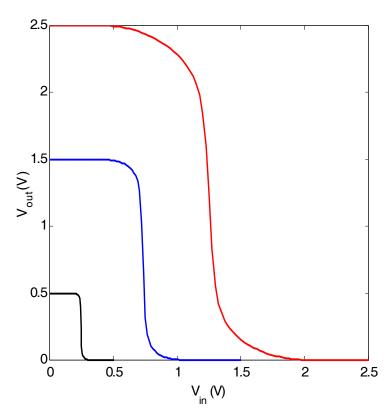

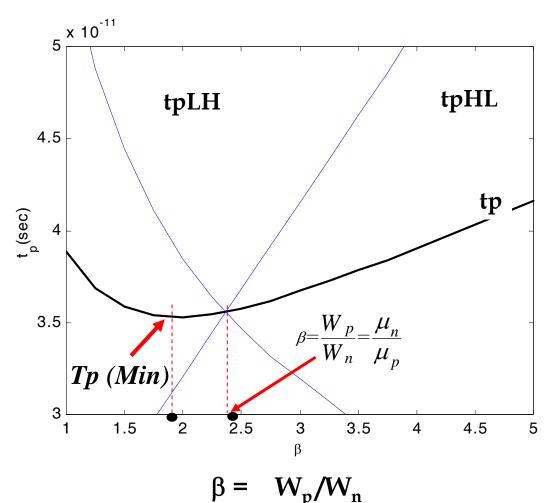

# NMOS 和 PMOS 尺寸比值 $\beta = W_p/W_n$ 对反相器平均延时的影响 (即当 PMOS 器件的尺寸为 NMOS 器件尺寸的 $\beta$ 倍时)

对称设计的反相器( $\beta = \frac{W_p}{W_n} = \frac{\mu_n}{\mu_p}$ )不一定能得到最小的平均延时 $t_p$

当对称性和噪声容限不是主要考虑时,可以通过适当减小 PMOS 尺寸来减小平均延时

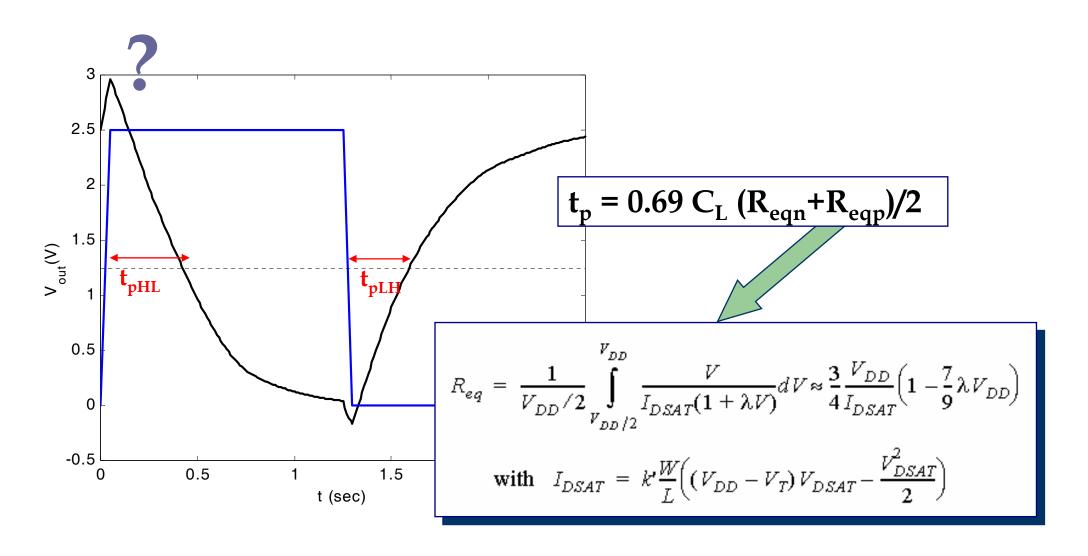

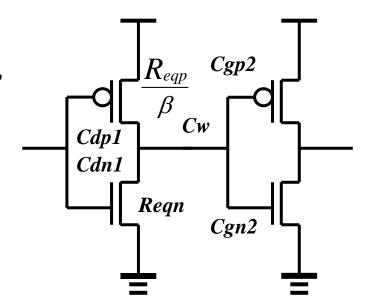

## Case Study 2: 单个反相器驱动同样的反相器时(驱动级)的延时

假设:

反相器 NMOS管 的等效电阻为  $R_{eqn}$ ,

与 NMOS 管尺寸相同的 PMOS 管的等效电阻为  $R_{eqp}$ ,

则有:

$$r = \frac{R_{eqp}}{R_{eqn}} = \frac{\mu_n}{\mu_p}$$

当单个反相器驱动同样的反相器时(即两个相同的 反相器串联时),第一个反相器的负载电容为:

$$C_L = (C_{dp1} + C_{dn1}) + (C_{gp2} + C_{gn2}) + C_W$$

若 P 管的尺寸为 N管尺寸的  $\beta$  倍,则 P 管的等效电阻为:  $\frac{K_{eq}}{\beta}$  第一个反相器(驱动级)的 平均 延时为:

$$t_{p} = \frac{0.69}{2} \left( (1 + \beta) (C_{dn1} + C_{gn2}) + C_{W} \right) \left( R_{eqn} + \frac{R_{eqp}}{\beta} \right)$$

对第一个反相器(驱动级)的平均延时,即:

$$t_p = \frac{0.69}{2} ((1+\beta)(C_{dn1} + C_{gn2}) + C_W) \left( R_{eqn} + \frac{R_{eqp}}{\beta} \right)$$

求导,得到第一个反相器(驱动级)的平均延时最小时最优值  $\beta$  为:

$$\beta_{opt} = \sqrt{r \left( 1 + \frac{C_W}{C_{dn1} + C_{gn2}} \right)}$$

$C_W << C_{dn1} + C_{gn2}$  时,  $\beta_{opt} = \sqrt{r}$

即第一个反相器(驱动级)的平均延时最小时,

驱动门 PMOS 管与 NMOS 管的尺寸比应为  $\sqrt{r}$

$$r = \frac{R_{eqp}}{R_{eqn}} = \frac{\mu_n}{\mu_p}$$

r 为具有相同尺寸的 PMOS 管 和 NMOS管 的等效电阻之比。

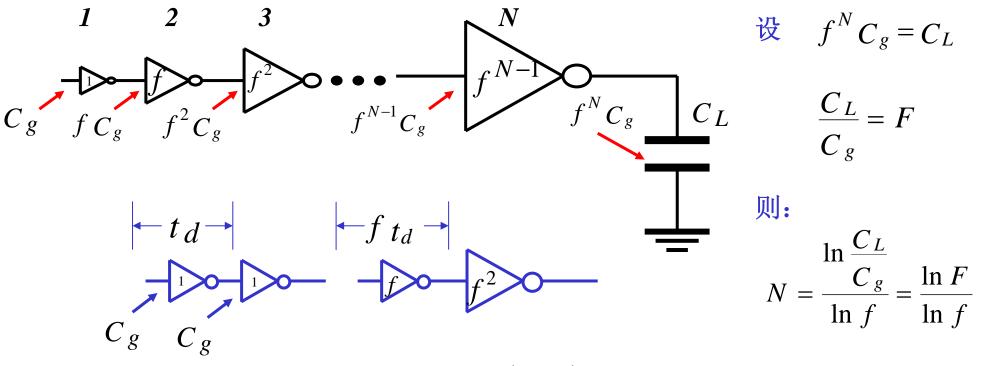

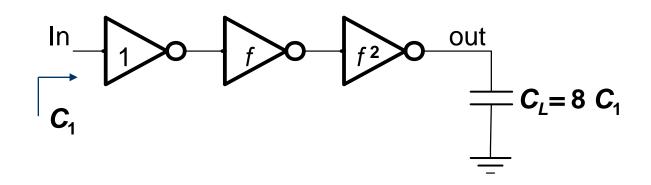

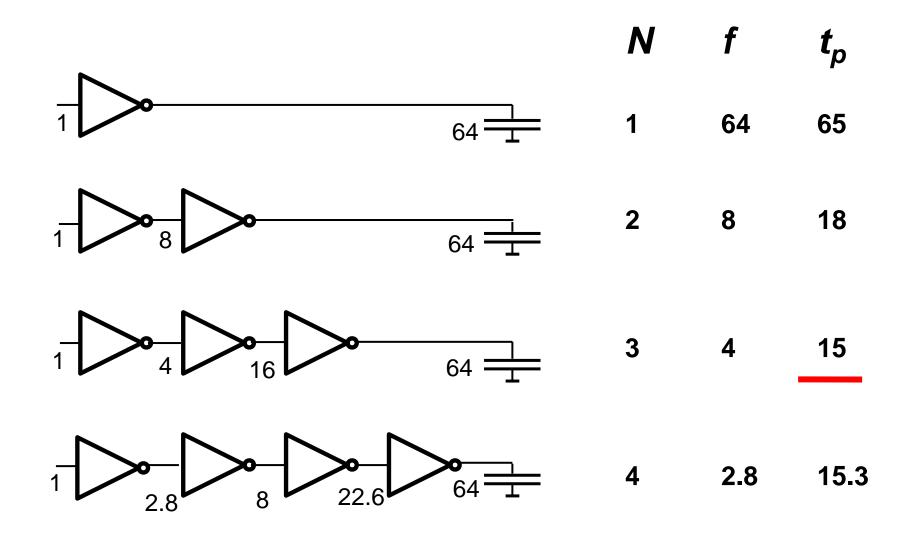

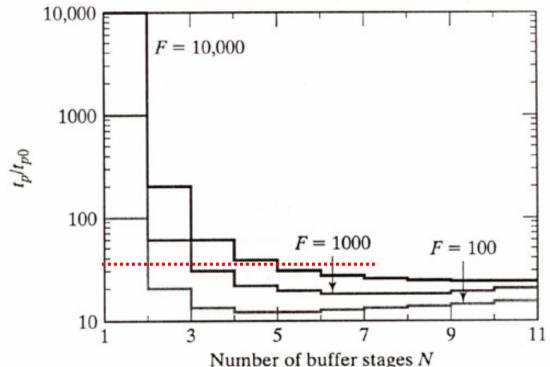

# Case Study 3: 反相器链的尺寸优化

#### 如 C<sub>L</sub> 固定:

- 需要多少反相器级能使延时最小?

- 如何确定每级反相器的尺寸?

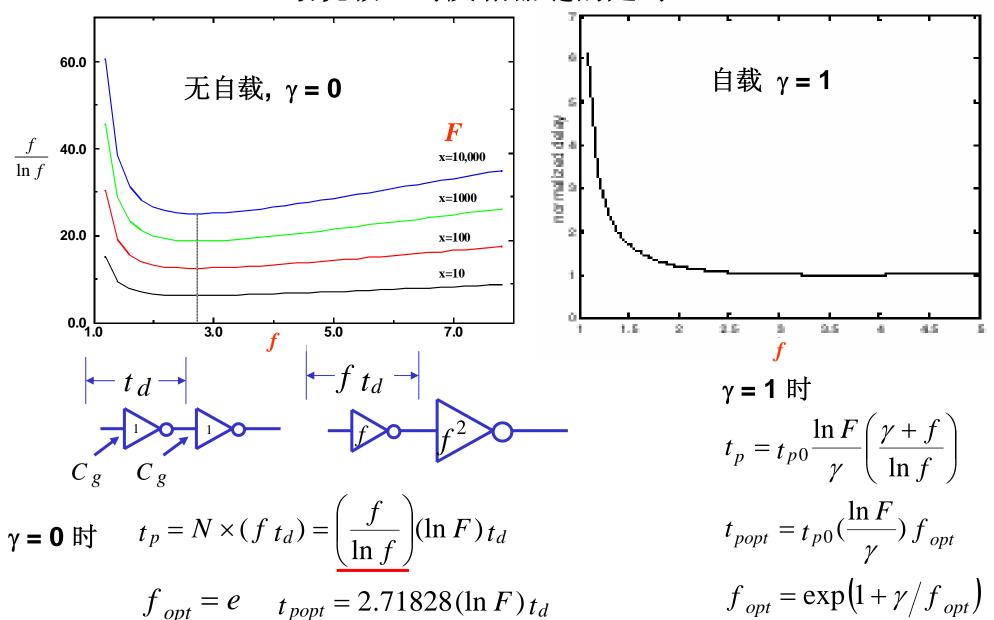

## (1) 漏端扩散电容 = 0 时优化反相器链的级比

$$t$$

总延迟 =  $N \times (f t_d) = \left(\frac{\ln F}{\ln f}\right) f t_d$

令

$$\frac{\partial t_{\text{总延迟}}}{\partial f} = \ln(F) t_d \frac{\ln f - f \bullet \frac{1}{f}}{\left(\ln f\right)^2} = 0$$

得:  $f = e = 2.71828\cdots$  时 可使总延迟最小

## (2) 漏端扩散电容 ≠0 时优化反相器链的级比

每一级反相器的延时均具有如下形式:

$$t_p = 0.69 R_{eq} (C_{int} + C_L) = 0.69 R_{eq} C_{int} (1 + C_L/C_{int}) =$$

$$= 0.69 R_{eq} C_{int} \left( 1 + \frac{C_L/C_{gin}}{C_{int}/C_{gin}} \right) = 0.69 R_{eq} C_{int} \left( 1 + \frac{f}{\gamma} \right)$$

其中:

$C_{gin}$  为反相器输入栅电容,  $f = C_L/C_{gin}$  为等效扇出,  $\gamma = C_{int}/C_{gin}$   $(\gamma \approx 1)$

假设: 反相器晶体管尺寸(宽度)为参照反相器晶体管尺寸的S倍,

则该反相器与参照反相器本征电容  $C_{iref}$  和晶体管等效电阻  $R_{ref}$  间的关系为:

$$C_{\rm int} = S C_{iref}$$

$R_{eq} = R_{ref}/S$

而  $t_{p0} = 0.69 R_{eq} C_{int} = 0.69 R_{ref} C_{ref}$  为本征延时

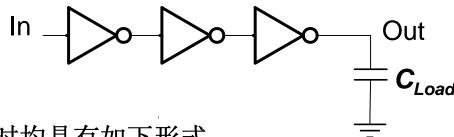

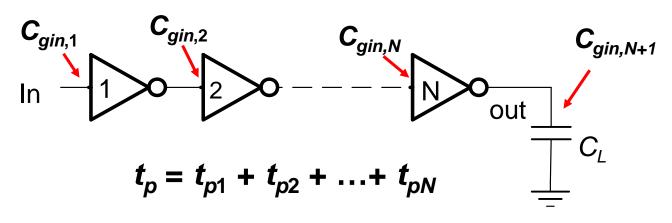

#### 反相器链的级数 N 固定时的最优尺寸比

$$t_{pj} \sim R_{unit} C_{unit} \left( 1 + \frac{f_j}{\gamma} \right)$$

$$= R_{unit} C_{unit} \left( 1 + \frac{C_{gin, j+1}}{\gamma C_{gin, j}} \right)$$

$$t_p = \sum_{j=1}^{N} t_{p,j} = t_{p0} \sum_{j=1}^{N} \left( 1 + \frac{C_{gin,j+1}}{\gamma C_{gin,j}} \right), \qquad C_{gin,N+1} = C_L$$

延时方程含 N-1 未知数,  $C_{gin,2}-C_{gin,N}$  , 求这 N-1 个偏导数并令它们为 0 ,可求得反相器链<mark>延时最小</mark>时的条件:  $C_{gin,i+1}/C_{gin,i}=C_{gin,i}/C_{gin,i-1}$

(1) 每级具有相同的等效扇出  $f = C_L = C_{gin,N}$

$$f = \frac{C_L}{C_{gin,N}} = \frac{C_{gin,N}}{C_{gin,N-1}} = \bullet \bullet \bullet = \frac{C_{gin,2}}{C_{gin,1}} = \sqrt[N]{\frac{C_L}{C_{gin,1}}} = \sqrt[N]{\frac{C_L}{C_L}} = \sqrt[N]{\frac{C_L}{C_$$

(2) 每级尺寸是它相邻两个反相器尺寸的几何平均数

$$C_{gin,j} = \sqrt{C_{gin,j-1}}C_{gin,j+1}$$

$(C_{out}/C_{in})$

$$t_p = t_{p0} \left( 1 + \sqrt[N]{F} / \gamma \right)$$

(4) 反相器链最小总延时:

$$t_p = N t_P = N t_{p0} \left( 1 + \sqrt[N]{F} / \gamma \right) \qquad F = \frac{C_L}{C_{gin}},$$

#### 举例:

级数 N=3 时的最优尺寸比

$$C_L/C_1 = 8$$

$N = 3$

$$f = \sqrt[3]{8} = 2$$

| F      | Unbuffered | Two Stage | Inverter Chain |

|--------|------------|-----------|----------------|

| 10     | 11         | 8.3       | 8.3            |

| 100    | 101        | 22        | 16.5           |

| 1000   | 1001       | 65        | 24.8           |

| 10,000 | 10,001     | 102       | 33.1           |

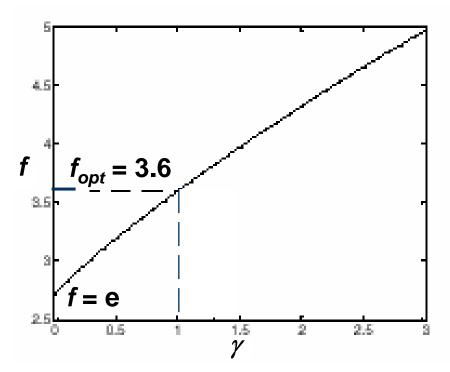

## 最优级比 与 最优级数

由于每级等效扇出相同均为 f , 因此:  $f^N = F = C_L / C_{gin,1}$

$$f^N = F = C_L / C_{gin,1}$$

每级等效扇出相同均为  $f = \sqrt[N]{F}$

或反相器链的级数为  $N = \frac{\ln F}{\ln f}$

反相器的总延时为:

$$t_{p} = Nt_{p0} \left( 1 + \sqrt[N]{F} / \gamma \right) = t_{p0} \frac{\ln F}{\gamma} \left( \frac{\gamma + f}{\ln f} \right)$$

最优级比:

$$f_{opt} = \exp(1 + \gamma / f_{opt})$$

(超越方程)

For

$$\gamma = 0$$

,

$f_{opt} = e$ ,  $N = \ln F$

For

$$\gamma = 1$$

,  $f_{opt} = 3.6$

一般取 f = 4

γ由工艺决定

## 最优级比时反相器链的延时

# 驱动缓冲器(反相器)设计

#### 有时采用最小尺寸或相同尺寸的管子并不影响反相器链的总的延时

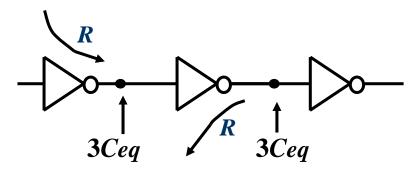

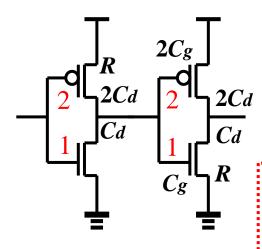

$$Wp = 2Wn$$

$$Ceq = Cg + Cd$$

t反相器对  $^{\infty}t_f + t_r = R \cdot 3C_{eq} + R \cdot 3C_{eq} = 6RC_{eq}$

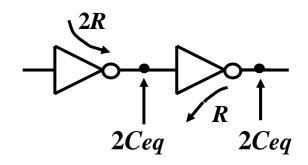

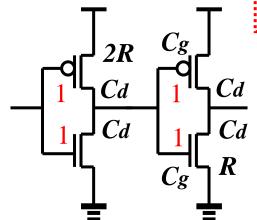

$$Wp = Wn$$

$$Ceq = Cg + Cd$$

$$= \frac{1}{2C} = 6RC$$

$$t_{\text{反相器对}} \propto t_f + t_r = 2R \cdot 2C_{eq} + R \cdot 2C_{eq} = 6RC_{eq}$$

# 第四节 反相器中的功耗

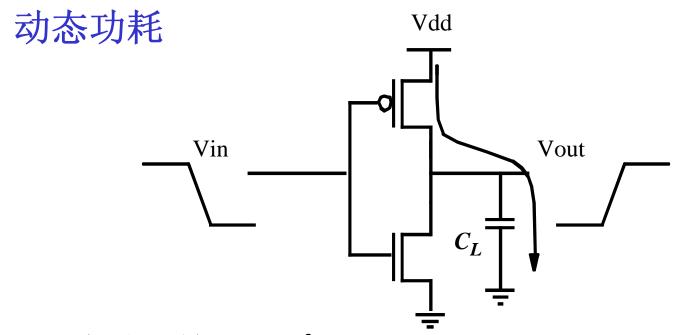

# 动态功耗

充放电电容

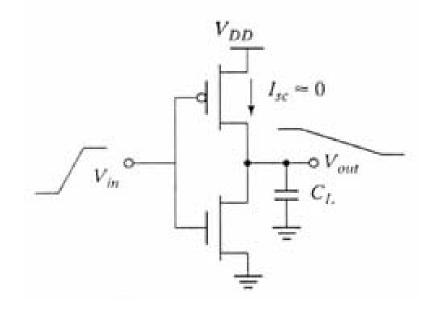

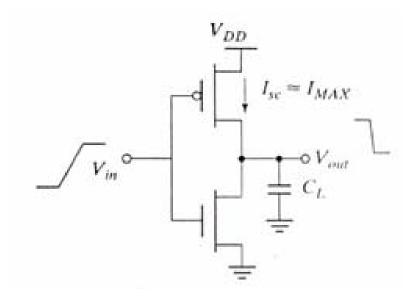

# 短路电流

切换时在电源和地线之间的直通短路电流通路

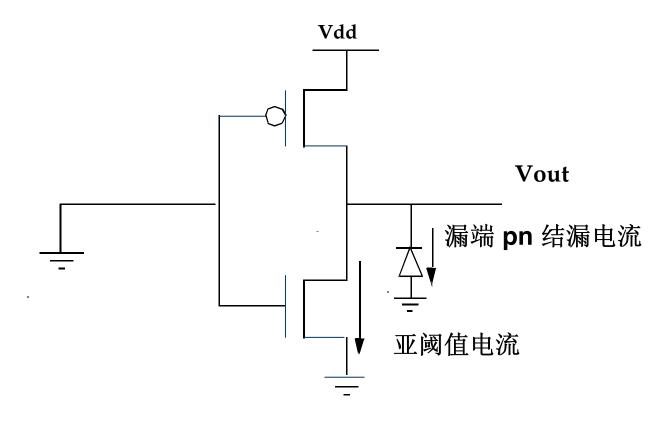

# 漏电

二极管与晶体管漏电

# 静态电流

维持电流、偏置电流

能量/每次翻转 =  $C_L V_{DD}^2$

功率= (能量/每次翻转)  $\times f = C_L V_{DD}^2 f$

- 动态(翻转)的功耗和能量: 与驱动器件的电阻无关

- lacktriangle 为减小功耗需要减小  $C_L$  ,  $V_{DD}$  和 f

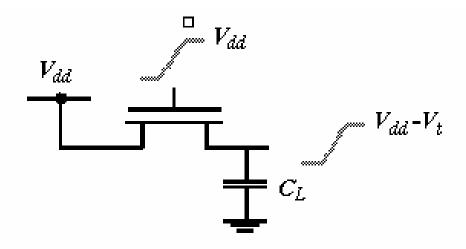

# 减少电压摆幅(Voltage Swing)以降低动态功耗

$$\mathbf{E_{0 \to 1}} = \mathbf{C_L} \bullet \mathbf{V_{dd}} \bullet (\mathbf{V_{dd}} - \mathbf{V_t})$$

例:在存储器中,降低在存储器位线上的电压摆幅

# 节点的翻转活动性与功耗

一个CMOS门在 N个时钟周期中的翻转能量为:

$$\mathbf{E}_{\mathbf{N}} = \mathbf{C}_{\mathbf{L}} \cdot \mathbf{V}_{\mathbf{d}\mathbf{d}}^{2} \cdot \mathbf{n}(\mathbf{N})$$

$E_{M}$  N个时钟周期中总的翻转能量

n(V): N个时钟周期中 0  $\rightarrow$  1 的翻转次数

平均功耗

$$P_{avg} = \lim_{N \to \infty} \frac{E_N}{N} \bullet f_{clk} = \left(\lim_{N \to \infty} \frac{n(N)}{N}\right) \bullet C_L \bullet V_{dd}^2 \bullet f_{clk}$$

翻转活动性(概率)

$$\alpha_{0\rightarrow 1} = \lim_{N\rightarrow \infty} \frac{\mathbf{n}(N)}{N}$$

$$P_{avg} = \alpha_{0 \to 1} \cdot C_{L} \cdot V_{dd}^{2} \cdot f_{clk}$$

等效电容:

$$^{lpha}\mathbf{0}

ightarrow \mathbf{1}^{ullet}\,^{\mathbf{C}}_{\mathbf{L}}$$

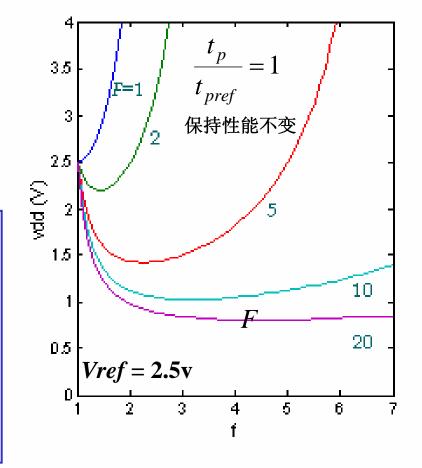

优化器件尺寸以降低电路能量 (考虑单位反相器扇出为 f 时的情形)

- 目的: 使整个电路在满足延时要求的情况下消耗的能量最小,即:

- tp ≤ tpref (tpref 为参考电路即 f =1 及 V<sub>DD</sub> = V<sub>ref</sub> 时的延时)

- 求出满足延时要求但能量最小时的最优设计参数: f 与  $V_{DD}$

电路延时

$$t_{p} = t_{p0} \left( \left( 1 + \frac{f}{\gamma} \right) + \left( 1 + \frac{F/f}{\gamma} \right) \right) = t_{p0} \left( 2 + \frac{f}{\gamma} + \frac{F}{f\gamma} \right) \quad (\gamma = 1 \text{ fb}) \quad t_{p0} \left( 2 + f + \frac{F}{f} \right)$$

参考电路延时

$$t_{pref} = t_{p0ref} \left( 2 + \frac{f}{\gamma} + \frac{F}{f\gamma} \right) \quad \stackrel{\textbf{(f=1 lb)}}{=} t_{p0ref} \left( 2 + \frac{1}{\gamma} + \frac{F}{\gamma} \right) \quad \stackrel{\textbf{(\gamma=1 lb)}}{=} t_{p0ref} \left( 3 + F \right)$$

$$t_{p0} \propto \frac{V_{DD}}{V_{DD} - V_{TE}}$$

$t_{p0ref} \propto \frac{V_{ref}}{V_{ref} - V_{TE}}$   $V_{TE} = V_T + \frac{V_{DSAT}}{2}$

$$t_{pHL} = 0.69 \frac{3}{4} \frac{C_L V_{DD}}{I_{DSATn}} = 0.52 \frac{C_L V_{DD}}{(W/L)_n k'_n V_{DSATn} (V_{DD} - V_{Tn} - V_{DSATn}/2)}$$

假设反相器的本征输出电容等于栅电容 (γ=1)

$$\frac{t_{p}}{t_{pref}} = \frac{t_{p0}}{t_{p0ref}} \frac{\left(2 + f + \frac{F}{f}\right)}{(3 + F)} =$$

$$= \frac{V_{DD}}{V_{ref}} \frac{V_{ref} - V_{TE}}{V_{DD} - V_{TE}} \frac{\left(2 + f + \frac{F}{f}\right)}{(3 + F)}$$

$$= 1$$

即要求:  $tp \le t$ pref

#### 由图可见:

达到最优尺寸系数  $f = \sqrt{F}$  之前,

加大 f ,可以在保持性能不变时降低电源电压或在电源电压不变时提高性能。

达到最优尺寸系数时,进一步加大尺寸只会加大自载影响而使性能降低。

$$t_{p} = t_{p0} \left( 2 + f + \frac{F}{f} \right) \quad (\gamma = 1)$$

$$t_{pref} = t_{p0ref} \left( 3 + F \right)$$

$$V_{DD} = f(f)$$

## ❖ 发生一次翻转的能量

电路能量

$$E = V_{DD}^2 C_{g1} [(1+\gamma)(1+f)+F] =$$

$$= V_{DD}^2 C_{g1} [2+2f+F] \qquad (\gamma = 1 \text{ bt})$$

参考电路能量  $E_{ref} = V_{ref}^2 C_{g1} [4+F]$  (f=1 时)

$$\frac{E}{E_{ref}} = \left(\frac{V_{DD}}{V_{ref}}\right)^2 \left(\frac{2+2f+F}{4+F}\right)$$

( Eref 为参考电路即 f=1 及  $V_{DD}=V_{ref}$  时的能量)

- ▶ 通过改变器件尺寸并同时降低电源电压 是降低能耗的有效办法。

- ➤ 在 f 的最优值之外进一步加大器件尺寸将 使能量显著增加。

- ▶ 当 VDD 接近 VTE 时,增加尺寸只允许降低很少的电压,因而只能达到很少的能量降低。

- > 能量最小时的最优尺寸系数小于使性能最好时的最优尺寸

$E/E_{ee}$ =f(f) nomalized energy ರ 20 9 F=20 时, fopt (能量) = 3.53 (性能) = 4.47

2008年秋

## 在限定最大传播延时情况下优化反相器链使总面积最小

给出最大允许的传播延迟时间  $t_{p,\max}$ ,确定反相器链的级数 N 和所需要的级比,使反相器链的总面积最小。假设最小反相器的面积为  $A_{\min}$ 。

$$N\left(1+\frac{f}{\gamma}\right) = N\left(1+\frac{F^{\frac{1}{N}}}{\gamma}\right) = \frac{\ln(F)}{\ln(f)}\left(1+\frac{F^{\frac{1}{N}}}{\gamma}\right) \le \frac{t_{p,\text{max}}}{t_{p0}} \qquad f^{N} = F$$

反相器链的总面积:  $A_{driver} = (1 + f + f^2 + ... + f^{N-1})A_{min} = \frac{f^N - 1}{f - 1}A_{min} = \frac{F - 1}{f - 1}A_{min}$

选择较大的 f 值(因而较小的 N 值)时可显著减小面积。

对于给定的F 和延时的最大值  $t_{p,\text{max}}/t_{p0}$ ,由图中合适的曲线可找出达到最小面积时的级数N

#### 驱动器消耗的额外能量:

$$E_{driver} = \left(1 + f + f^{2} + \dots + f^{N-1}\right)\left(1 + \gamma\right)C_{i}V_{DD}^{2}$$

$$= \left(\frac{F - 1}{f - 1}\right)\left(1 + \gamma\right)C_{i}V_{DD}^{2} \approx \frac{2C_{L}}{f - 1}V_{DD}^{2} \qquad (\gamma = 1)$$

当 f = 3.6 时,这一额外的能量占到未缓冲时能量( $C_L V_{DD}^2$ )的80%。加大 f 有助于减小这一额外的能量开销。

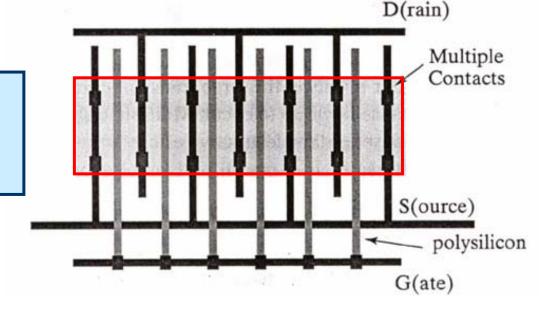

驱动器宽晶体管(f 较大时)的版图设计: 采用"指状"结构可缩短晶体管多晶栅长度

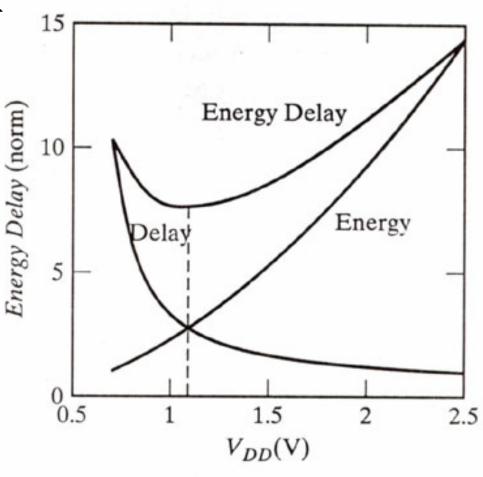

# 能量延时积(EDP)与电源电压的关系

#### 提高电源电压能减少延时,但会增加功耗。

设 NMOS 和 PMOS 管具有相同的阈值电压 和饱和电压,则反相器传播延时可简化为:

$$t_p = \frac{\alpha C_L V_{DD}}{V_{DD} - V_{TE}}$$

式中:

在一次翻转中的能量为 $\frac{1}{2}C_LV_{DD}^2$ , 于是:

$$EDP = \frac{\alpha C_L^2 V_{DD}^3}{2(V_{DD} - V_{TE})}$$

EDP 达最小值时的 VDD 值为

$$V_{DDopt} = \frac{3}{2}V_{TE}$$

对阈值在 0.5V 范围的亚微米工艺,最优电源电压为 1V左右

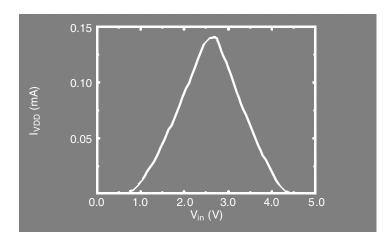

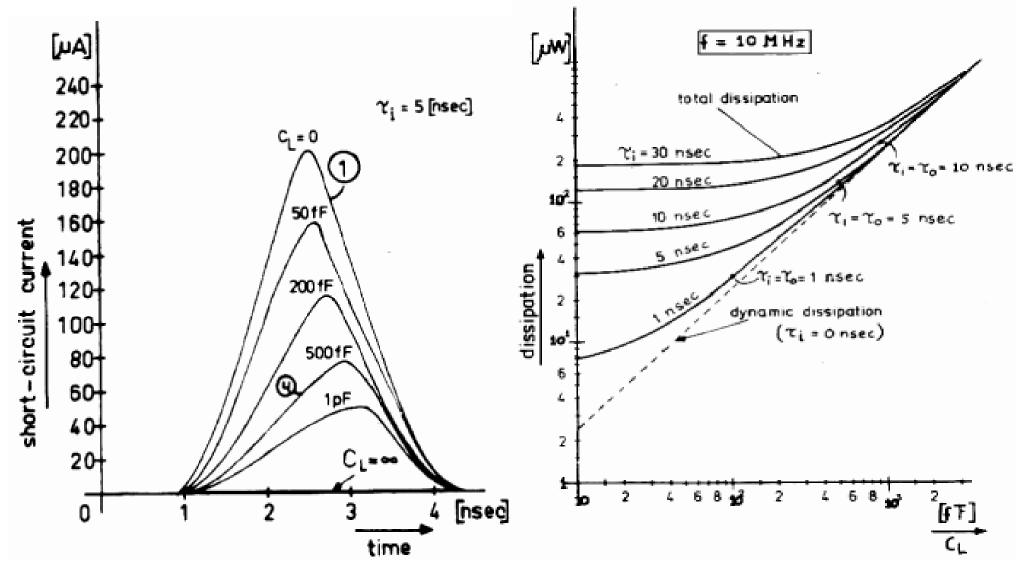

# 短路电流功耗

每翻转周期(上升+下降)的能量:

$$E_{dp} = V_{DD} \frac{I_{peak} t_{sc}}{2} + V_{DD} \frac{I_{peak} t_{sc}}{2}$$

$$= V_{DD} I_{peak} t_{sc}$$

#### 平均功耗:

$$P_{dp} = V_{DD} I_{peak} t_{sc} f = C_{sc} V_{DD}^2 f$$

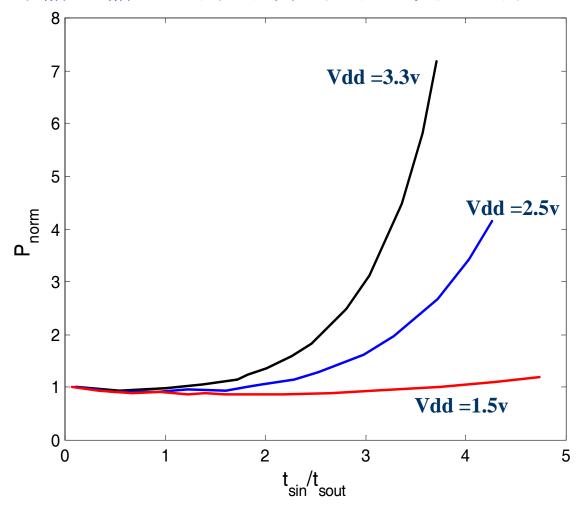

短路电流功耗与翻转的活动性成正比降低电源电压可以减小短路电流 短路电流功耗可以用  $C_{sc}$ 来模拟

# 峰值短路电流

- (1) 取决于器件的饱和电流,因此与器件的尺寸有关。

- (2) 降低电源电压可以减小短路电路

- (3) 与输入输出的斜率之比有关:

输出上升/下降时间大于 输入的上升/下降时间时, 短路电流较小

输出上升/下降时间小于 输入的上升/下降时间时 短路电流较大

输出上升/下降时间比输入的上升/下降时间长时可使短路电流较小,但将降低速度并在负载门中引起短路电流。

# 短路电流功耗(归一至零输入上升时间时的功耗)与输入输出上升/下降时间比率及电源电压的关系

使输入和输出上升/下降时间相等可以使短路电流功耗小于总功耗的 10% 如果  $V_{DD} < V_{Tn} + V_{Tp}$  则可以消除短路电流功耗

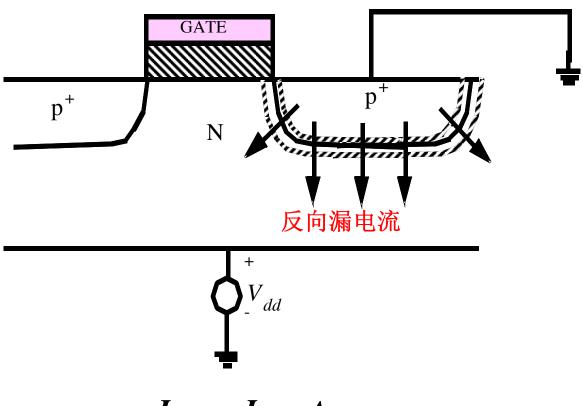

# 静态功耗 (漏电流功耗)

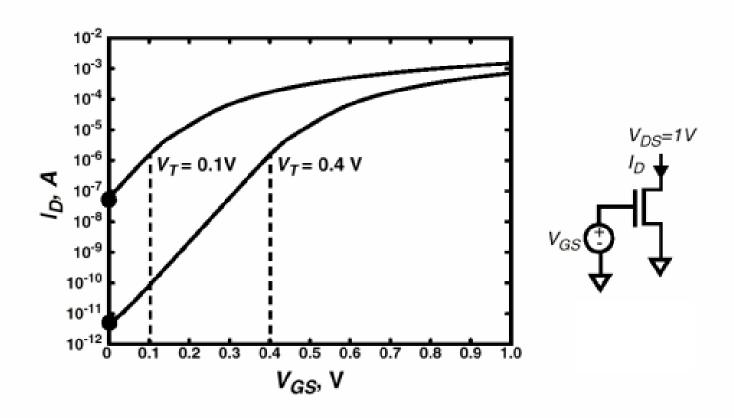

漏电电流与温度有关亚阈值电流是漏电的主要来源

# PN 结(二极管)反向偏置电流

$$I_{DL} = J_S \times A$$

$Js = 10 \sim 100 \text{ pA/}\mu\text{m}^2$ ( 25 °C、 0.25  $\mu$ m CMOS 的 Js 每 9°C 翻一倍! )

# 亚阈值电流与 VGS及VT的关系

亚阈值电流是漏电的主要来源它是低功耗电路设计中的难题

# 设计的综合考虑

#### CMOS 反相器

#### 总功耗

$$P_{tot} = \underline{P_{dyn} + P_{dp}} + P_{stat} = (C_L V_{DD}^2 + V_{DD} I_{peak} t_s) \underline{f_{0 \to 1}} + V_{DD} I_{leak}$$

功耗延时积(PDP),或每操作的能耗:衡量切换一个门所需的能量

$$PDP = P_{av} t_p$$

能量延时积(EDP): 同时考虑性能和能耗的衡量

$$EDP = PDP \times t_p = P_{av} t_p^2 = \frac{C_L V_{DD}^2}{2} t_p$$

# CMOS 反相器 小结

(一) 电压摆幅接近电源电压, 噪声容限大。

#### (二) 为无比逻辑

逻辑门的 (1) 静态输出摆幅 及(2) 正确翻转不取决于上拉和下拉器件的强度(晶体管的尺寸)

#### (三)传输特性:

对长沟器件当

$$k_n = k_p$$

,  $V_{tn} = |V_{tp}|$  时,  $V_M = V_{INV} = V_{DD}/2$  对短沟器件当  $k_n = k_p$  ,  $V_{tn} = |V_{tp}|$  ,  $V_{DSATn} = |V_{DASATp}|$  时, $V_M = V_{INV} = V_{DD}/2$

$$k = k \frac{W}{L} = \mu C_{ox} \frac{W}{L}$$

(四)噪声容限大。当反相器的阈值在电压摆幅的中点时,高与低电平的噪声余量相同,此时的噪声容限最大,接近 VDD/2。

- (五)输入阻抗大,输出阻抗可设计得较小 (导通电阻与器件尺寸及器件端电压有关,典型值为  $k\Omega$ )

- (六)传播延时主要由充放电负载电容 CL 所需时间决定。 延时的一阶近似为:  $R_{am}+R_{am}$

$t_p = 0.69 C_L \frac{R_{eqn} + R_{eqp}}{2}$

当延时主要受扇出负载和导线电容影响时,加大晶体管尺寸有助于提高性能。

#### (七) 功耗低:

- 1. 理想上无静态功耗(无直流通路),但实际上有漏电流功耗(PN 结漏电流,亚阈值电流)。随工艺尺寸缩小,漏电功耗所占比例将显著加大。

- 2. 由负载电容充放电引起 动态功耗 (与充放电的频率有关)

- 3. 由切换过程中的直流通路造成 短路功耗。它可以通过改善信号斜率来加以限制。