# 硬件描述语言 Verilog

(第四版)

Donald E. Thomas, Philip R.Moorby 著 刘明业 蒋敬旗 刁岚松 等译

清华大学出版社 KLUW ER ACADEM IC PUBLISHERS

## (京)新登字 158号

#### 内容简介

Thomas 和 Moorby 合写的《硬件描述语言 Verilog》已经成为 Verilog 标准的参考书。

这次修改的入门辅导部分通过示例讲述了该语言。这些示例表现了几种重要的描述风格,包括:结构模型、用于逻辑综合的组合电路和时序电路的行为模型、FSM 数据通道模型以及周期精确的描述。 行为综合是新添加的一章,讲述了怎样使用这些方式来实现周期精确的描述。

对那些有兴趣描述、模拟和综合数字系统的工程师和学生来说,《硬件描述语言 Verilog》(第四版)是一本很有价值的参考书。

本书是为大学课程编写的。描述风格的介绍顺序符合典型的入门课程的要求(结构的、可综合的、 FSM 数据通道的、周期精确的)。本书有一个像学习手册一样的附录。为了有助于体系结构课程的教学,书中还给出了一个简单流水线处理器的模型。

#### 光 盘 介 绍

本书附带一张光盘。其中包含 Veriwell<sup>TM</sup> Verilog 模拟器、Synplicity Synplify FPGA 综合软件、纯文本的和 PDF 格式的书中示例以及 PDF 格式的讲义。综合工具的使用是有时间限制的,可以根据提示去获取永久性使用权。模拟器和综合工具可在多个平台上使用。

#### The Verilog Hardware Description Language (Fourth Edition)

Donald E Thomas, Philip R . Moorby

Copyright 1998 by Kluwer Academic Publishers

All Rights Reserved.

本书中文简体字版由 Kluwer Academic Publishers 出版公司授权清华大学出版社独家出版、发行。未经出版者书面许可,不得以任何方式复制或抄袭本书的任何部分。

本书封面贴有清华大学出版社激光防伪标签,无标签者不得销售。

北京市版权局著作权合同登记号: 图字 01-2001-1569 号

书 名: 硬件描述语言 Verilog (第四版)

作 者: Donald E. Thomas, Philip R. Moorby 著 刘明业 蒋敬旗 刁岚松 等译

出版者: 清华大学出版社(北京清华大学学研大厦,邮编 100084)

http:// www.tup.tsinghua.edu.cn

印刷者: 清华大学印刷厂

发行者: 新华书店总店北京发行所

开 本: 787×960 1/16 印张: 20 字数: 411 千字

版 次: 2001年8月第1版 2001年8月第1次印刷

书 号: ISBN 7-900635-36-X

印 数: 0001~6000

定 价: 36.00元

## 译者序

数字集成电路在过去近 30 年的时间里得到迅速发展, EDA 技术在设计过程中起着至关重要的作用。硬件描述语言(HDL)采用形式化的方法,可以直观准确地描述数字电路,应用于模拟验证、设计综合等设计过程中。在众多的硬件描述语言中, Verilog 逐渐发展成为标准的硬件描述语言,是当前 HDL 设计方法学的基础。

硬件描述语言 Verilog 是本书的作者之一——Philip R .Moorby 于 1983 年在英格兰阿克顿市的 Gateway Design Automation 硬件描述语言公司设计出来的,用于从开关级到算法级的多个抽象设计层次的数字设计的建模。该语言提供了一整套功能强大的基元集,包括逻辑门和用户定义的基元;并提供了丰富的结构,这些结构不仅用于硬件的并发行为的建模,而且用于硬件的时序特性和结构的建模。也可以通过编程语言接口(PLI)对该语言进行扩展。Verilog 语言从诞生起就与生产实际紧密结合在一起,具有结构清晰、文法简明、功能强大、高速模拟和多库支持等优点,并获得许多工具的支持,深受用户的喜爱。据报道,全世界近 90% 的半导体公司都使用硬件描述语言 Verilog。 Verilog 实际上是 IC 行业标准,特别是在 1995 年 12 月被 IEEE 接纳为正式标准后,它成为一种很有竞争力的硬件描述语言。

在国内,国家技术监督局于 1998 年正式将硬件描述语言 Verilog 列入国家标准制定项目。本书是 Verilog 的经典著作,由 Verilog 的发明人撰写。本书的翻译工作是配合制订国家标准《集成电路/ 计算机硬件描述语言 Verilog》(国家标准编号为 GB/ T18349-2001,2001年 10月1日实施)来进行的。在国家标准制订和本书的翻译过程中,得到国内众多专家的帮助和指导,译者在此向北京华大集成电路设计中心王正华研究员,清华大学薛宏熙教授,中科院计算所林宗楷研究员,北京华虹集成电路设计中心李云岗研究员,中科院半导体所薄建国研究员,北京微电子技术研究所王隆望研究员,林守勋研究员,北京理工大学韩月秋教授及陈禾博士表示衷心的感谢。

参加本书翻译的有: 蒋敬旗(译前言、第 1、3、4、5、9、10 章), 刁岚松(译第 2 章及附录), 李杰(合译第 4 章), 李春(合译第 5 章), 王娟(译第 6 章), 吕秀锋(译第 7、8 章)。

全书由刘明业、蒋敬旗和刁岚松统校。

我们在翻译过程中力求翻译准确,但限于译者的水平,一定存在错误和不足之处,恳请读者批评指正。

**译 者** 2001年5月

## 前言

Verilog 语言是一种在广泛的抽象层次设定说明数字系统的硬件描述语言。这种语言支持早期的行为级抽象设计概念,以及后期结构级抽象设计的实现。它包括层次式结构,从而允许设计人员控制描述的复杂度。

Verilog 最初于 1983 年至 1984 年之间的冬季被设计为一种专用的验证/模拟工具。后来,基于这种语言又开发了其他几种专用分析工具,包括故障模拟器和时序分析器。最近 Verilog 也为逻辑综合工具和行为综合工具提供了输入规范。 Verilog 语言有助于提供这些工具的一致性。现在,这种语言已标准化为 IEEE # 1364-1995 标准,并且广泛用于多种工具。本书介绍 Verilog 语言,为该语言的初学者和高级用户提供素材。

有时很难将该语言和模拟工具分离开,原因是该语言的动态特性是由模拟器的工作方式确定的。而且,将它和综合工具分离开也是困难的,因为它的语义是由综合工具所允许的输入规范以及所产生的实现来限定的。我们尽可能避开专用模拟器和专用综合器的细节而集中考虑设计的规范。但是,书中包含的内容足以写出可以工作的可执行模型。

本书采用辅导的方法来介绍 Verilog 语言。首先我们从辅导入门开始,通过举例介绍 Verilog 语言的主要特点和进行系统描述的一般方式。接着详细介绍该语言结构,给出大量的示例,使读者通过这些示例可以更容易地学习和复习。最后,在附录中给出 Verilog 语言的形式化描述。总之,我们的方法是通过研讨举例和做练习题来提供一种学习方式。

我们还给出一些练习题供阅读时思考,并建议读者尽可能早地借助 Verilog 模拟器来试试这些练习题。如果你有自己的设计,也可以进行彻底检验。书中所举的例题以电子信号的形式存储在密封的 CD 上。另外,还可参阅 http://www.ece.cmu.edu/~thomas。CD 上还包括一个模拟器和一个逻辑综合工具,模拟器所处理的描述规模有限,综合工具给出一个时间不很长的综合演示。

本书的大部分内容假定读者具备初步的逻辑设计和软件编程知识。因此,本书适合于进行集成电路设计的工程师、研究生及电子或计算机工程专业的学生。辅导入门中的内容适于作为逻辑设计的入门课程。它首先介绍结构化组合电路,接着介绍更复杂的可综合的组合电路和时序电路,最后介绍周期准确的系统规范。附录中嵌入辅导入门的内容,给出所讨论的一般错误及辅导入门中要解决的练习题。本书也适合作为高层次逻辑设计、集成电路设计、计算机体系结构及计算机辅助设计(CAD)课程的参考教材。本书为设计课程介绍了覆盖该语言的全部内容,为 CAD 课程介绍了模拟器是怎样工作的。

本书共有十章和七个附录。第1章是 Verilog 语言的辅导入门。第2章和第3章讨论该语言的行为建模方式。第4章为逻辑级建模。第5章包括定时驱动模拟和事件驱动模拟的高级课题。第6章和第7章介绍语言在综合中的应用。第8章和第9章讲述更高级的课题:用户自定义的基元和开关级建模。第10章推荐两个可以用作大学教学使用的Verilog 工程。附录 A 为初学者介绍了辅导入门的内容, 附录的其他部分是出现在语言手册中更枯燥的问题, 读者可根据自己的需要选择阅读。

祝愿您在设计大型系统时获得乐趣。

您永远的朋友

Donald E . Thomas, Philip R . Moorby

. .

# 致 谢

作者向维护和促进 Verilog 标准的 Open Verilog International (http://www.ovi.org) 以及对该语言的不断开发做出贡献的 CAD 工具开发人员和系统设计人员表示感谢。特别是,感谢 Leigh Brady 帮助审阅了初稿,感谢 Elliot Mednick 帮助组织了随书所附 CD 中的内容。

作者也感谢 JoAnn Paul 的帮助及对入门介绍和 CD 内容提出的建议, 感谢 John Langworthy 帮助收集附录 A 中的辅导材料, 感谢 Tom Martin 帮助整理了第 10 章中的练习题, 感谢 H. Fatih Ugurdag 提供了例 7.4。我们也感谢使用本书并提供反馈信息的工程师、教师和学生。最后, 感谢 Margaret Hanley 设计了封面和版式。

IEEE 通过了 Verilog 硬件描述语言标准(IEEE # 1364-1995), 感谢他们认可了附录 G 中语法的形式化规范。标准的副本可以从 http:// standard ieee .org 获得。

# 目 录

| 第1章  | Verilog i | 吾言入门辅导              | 1  |

|------|-----------|---------------------|----|

| 1 .1 | 开始        |                     | 1  |

|      | 1 1 1     | 结构描述                | 1  |

|      | 1 .1 2    | 模拟 binaryToESeg 驱动源 | 3  |

|      | 1 1 3     | 为模块建立端口             | 5  |

|      | 1 1 4     | 为模块建立测试台            | 6  |

| 1 .2 | 组合电       | 路的行为建模              | 9  |

|      | 1 2 .1    | 过程模型                | 9  |

|      | 1 2 2     | 综合组合电路的规则           | 11 |

| 1.3  | 时钟时       | 序电路的行为建模            | 11 |

|      | 1 3 1     | 建立有限状态机模型           | 12 |

|      | 1 3 2     | 综合时序系统的规则           | 15 |

|      | 1 3 3     | 非阻塞赋值(" <= ")       | 15 |

| 1.4  | 模块的。      | 层次                  | 17 |

|      | 1 4 1     | 计数器                 | 17 |

|      | 1 4 2     | 系统时钟                | 18 |

|      | 1 4 3     | 将整个电路结合在一起          | 19 |

|      | 1 4 4     | 将行为模块和结构模块连接在一起     | 22 |

| 1 .5 | 有限状态      | 态机和数据通道             | 23 |

|      | 1 5 .1    | 简单计算示例              | 24 |

|      | 1 5 2     | 系统的数据通道             | 24 |

|      | 1 5 3     | 数据通道功能模块的细节         | 25 |

|      | 1 5 4     | 用连线将数据通道连在一起        | 27 |

|      | 1 5 5     | FSM 说明              | 28 |

| 1 .6 | 周期精       | 确的行为描述              | 32 |

|      | 1 6 1     | 规范方法                | 33 |

|      | 1 6 2     | 几点注释                | 35 |

| 1 .7 | 赋值语       | 句的总结                | 35 |

| 1 .8 | 小结…       |                     | 37 |

| 1 .9  | 练习      |                       | 37 |

|-------|---------|-----------------------|----|

| 第 2 章 | 行为建模    | ₹                     | 39 |

| 2 .1  | 进程模     | 型<br>                 | 39 |

| 2.2   | If-Then | ı-Else                | 40 |

|       | 2 2 1   | else 如何与 if 语句配对      | 44 |

|       | 2 2 2   | 条件操作符                 | 45 |

| 2.3   | 循环语     | 句                     | 46 |

|       | 2 3 1   | 四种基本循环语句              | 46 |

|       | 2 3 2   | 循环的异常退出               | 49 |

| 2.4   | 多分支     | 语句                    | 50 |

|       | 2 4 1   | If-Else-If            | 50 |

|       | 2 4 2   | Case                  | 50 |

|       | 2 4 3   | Case 和 If-Else-If 的比较 | 53 |

|       | 2 4 4   | Casez 和 Casex         | 53 |

| 2.5   | 函数和     | 任务                    | 54 |

|       | 2 5 .1  | 任务                    | 56 |

|       | 2 5 2   | 函数                    | 59 |

|       | 2 5 3   | 结构视域                  | 61 |

| 2 .6  | 作用域     | 规则和层次名                | 63 |

|       | 2 6 1   | 作用域规则                 | 64 |

|       | 2 6 2   | 层次名                   | 66 |

| 2 .7  | 小结…     |                       | 66 |

| 2 .8  | 练习      |                       | 67 |

| 第3章   | 并发进程    | Ē                     | 69 |

| 3 .1  | 并发进     | 程                     | 69 |

| 3.2   | 事件      |                       | 70 |

|       | 3 2 1   | 事件控制语句                | 71 |

|       | 3 2 2   | 有名事件                  | 72 |

| 3 .3  | 等待语     | 句                     | 75 |

|       | 3 3 1   | 一个完整的生产者和消费者握手示例      | 76 |

|       | 3 3 2   | Wait 语句和 While 语句的对比  | 79 |

|       | 3 3 3   | Wait 语句和事件控制语句的比较     | 80 |

|    | 3.4   | 并发进   | 程示例            | 80  |

|----|-------|-------|----------------|-----|

|    | 3 .5  | 简单流   | 水线处理器          | 86  |

|    |       | 3 5 1 | 基本处理器          | 86  |

|    |       | 3 5 2 | 流水线之间的同步       | 88  |

|    | 3 .6  | 有名块   | 的终止            | 89  |

|    | 3 .7  | 赋值语   | 句内部控制和定时事件     | 91  |

|    | 3 .8  | 过程持:  | 续赋值            | 94  |

|    | 3.9   | 顺序模   | 块和并行模块         | 95  |

|    | 3 .10 | 练习    |                | 98  |

| 第4 | 1章    | 逻辑级建  | ■模             | 100 |

|    | 4 .1  | 引言    |                | 100 |

|    | 4 .2  | 逻辑门   | 与线网            | 101 |

|    |       | 4 2 1 | 用基元逻辑门建模       | 101 |

|    |       | 4 2 2 | 四级逻辑值          | 104 |

|    |       | 4 2 3 | 线网             | 105 |

|    |       | 4 2 4 | 模块例示与端口规范      | 108 |

|    |       | 4 2 5 | 有关逻辑级的一个示例     | 109 |

|    | 4 .3  | 示例数   | 组              | 115 |

|    | 4 .4  | 持续赋   | 值              | 118 |

|    |       | 4 4 1 | 组合电路的行为建模      | 119 |

|    |       | 4 4 2 | 线网与持续赋值语句声明    | 120 |

|    | 4 .5  | 参数化   | 定义             | 123 |

|    | 4 .6  | 行为级   | 结构级的混合示例       | 127 |

|    | 4 .7  | 逻辑延   | 迟建模            | 131 |

|    |       | 4 7 1 | 门级建模示例         | 131 |

|    |       | 4 7 2 | 门和线网延迟         | 133 |

|    |       | 4 7 3 | 时间单位的规定        | 135 |

|    |       | 4 7 4 | 最小延迟、典型延迟和最大延迟 | 136 |

|    | 4 .8  | 模块中   | 的延迟路径          | 137 |

|    | 4 .9  | 小结    |                | 139 |

|    | 4 .10 | 练习    |                | 139 |

| 第5章                  | 高级时序                                                                                                                                                        | 142                                                                              |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 5 .1                 | Verilog 时序模型                                                                                                                                                | 142                                                                              |

| 5 .2                 | 模拟器的基本模型                                                                                                                                                    | 145                                                                              |

|                      | 5 2 1 门级模拟                                                                                                                                                  | 145                                                                              |

|                      | 5 2 2 更通用的模型                                                                                                                                                | 146                                                                              |

|                      | 5 2 3 行为级模型的调度                                                                                                                                              | 148                                                                              |

| 5 .3                 | 模拟算法的不确定行为                                                                                                                                                  | 150                                                                              |

|                      | 5 3 1 临近不确定区                                                                                                                                                | 150                                                                              |

|                      | 5 3 2 Verilog 是一种并发语言                                                                                                                                       | 152                                                                              |

| 5 .4                 | 非阻塞过程赋值语句                                                                                                                                                   | 155                                                                              |

|                      | 5 4 1 阻塞和非阻塞赋值的比较                                                                                                                                           | 155                                                                              |

|                      | 5 4 2 非阻塞赋值的一般用法                                                                                                                                            | 156                                                                              |

|                      | 5 4 3 事件驱动调度算法的扩展                                                                                                                                           | 157                                                                              |

|                      | 5 4 4 非阻塞赋值的举例分析                                                                                                                                            | 159                                                                              |

| 5 .5                 | 小结                                                                                                                                                          | 162                                                                              |

| 5 .6                 | 练习题                                                                                                                                                         | 162                                                                              |

|                      |                                                                                                                                                             |                                                                                  |

|                      |                                                                                                                                                             |                                                                                  |

| 第6章                  | 逻辑综合                                                                                                                                                        | 167                                                                              |

| 第 <b>6</b> 章<br>6.1  |                                                                                                                                                             | 167<br>167                                                                       |

|                      |                                                                                                                                                             |                                                                                  |

|                      |                                                                                                                                                             | 167<br>167                                                                       |

|                      | 综合概述                                                                                                                                                        | 167<br>167<br>168                                                                |

| 6 .1                 | 综合概述                                                                                                                                                        | 167<br>167<br>168<br>168                                                         |

| 6 .1                 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明                                                                                                                              | 167<br>167<br>168<br>168<br>170                                                  |

| 6 .1                 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句                                                                                                  | 167<br>167<br>168<br>168<br>170<br>171                                           |

| 6 .1                 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础                                                                                         | 167<br>167<br>168<br>168<br>170<br>171                                           |

| 6 .1                 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器                                                                     | 167<br>168<br>168<br>170<br>171<br>172<br>174                                    |

| 6 .1                 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构                                            | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175                             |

| 6 .1<br>6 .2<br>6 .3 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构                                            | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175<br>176                      |

| 6 .1<br>6 .2<br>6 .3 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构 时序元件的推断                                    | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175<br>176                      |

| 6 .1<br>6 .2<br>6 .3 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构 时序元件的推断 6 4 1 锁存器的推断 6 4 2 触发器的推断 6 4 3 小结 | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175<br>176<br>176<br>178        |

| 6 .1<br>6 .2<br>6 .3 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构 时序元件的推断 6 4 1 锁存器的推断 6 4 2 触发器的推断          | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175<br>176<br>176<br>178        |

| 6 .1<br>6 .2<br>6 .3 | 综合概述 6 1 1 寄存器传输级系统 6 1 2 限制声明 使用门和持续赋值的组合逻辑 用来说明组合逻辑的过程语句 6 3 1 基础 6 3 2 复杂形式——推断出的锁存器 6 3 3 说明无关项 6 3 4 过程循环结构 时序元件的推断 6 4 1 锁存器的推断 6 4 2 触发器的推断 6 4 3 小结 | 167<br>168<br>168<br>170<br>171<br>172<br>174<br>175<br>176<br>176<br>178<br>180 |

|     |      | 6 6 2 FSM 说明的另一种方式     | 184 |

|-----|------|------------------------|-----|

|     | 6 .7 | 逻辑综合的总结                | 185 |

|     | 6 .8 | 习题                     | 186 |

|     |      |                        |     |

| 第 7 | 7章   | 行为综合                   | 188 |

|     | 7 .1 | 行为综合的介绍                | 188 |

|     | 7 .2 | 周期精确的说明                | 189 |

|     |      | 7 2 1 always 块的输入和输出   | 189 |

|     |      | 7 2 2 always 块的输入和输出关系 | 190 |

|     |      | 7 2 3 复位功能说明           | 193 |

|     | 7 .3 | 米利/摩尔机的说明              | 194 |

|     |      | 7 3 1 复杂控制的说明          | 195 |

|     |      | 7 3 2 数据与控制路径的折中       | 196 |

|     | 7.4  | 小结                     | 199 |

|     |      |                        |     |

| 第 8 | 3章   | 用户定义的基元                | 200 |

|     | 8 .1 | 组合基元                   | 200 |

|     |      | 8 1 1 用户定义基元的基本特征      | 200 |

|     |      | 8 1 2 组合逻辑电路的描述        | 202 |

|     | 8 .2 | 时序基元                   | 203 |

|     |      | 8 2 1 电平敏感的基元          | 204 |

|     |      | 8 2 2 边沿敏感的基元          | 205 |

|     | 8 .3 | 速记表示法                  | 207 |

|     | 8 .4 | 电平敏感与边沿敏感混合的基元         | 208 |

|     | 8 .5 | 小结                     | 210 |

|     | 8 .6 | 练习                     | 210 |

|     |      |                        |     |

| 第9  | ) 章  | 开关级建模                  | 212 |

|     | 9 .1 | 动态 MOS 移位寄存器示例         | 212 |

|     | 9 .2 | 开关级建模                  | 216 |

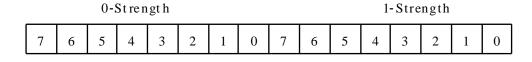

|     |      | 9 2 1 强度建模             | 216 |

|     |      | 9 2 2 强度的定义            | 218 |

|     |      | 9 2 3 使用强度的示例          | 220 |

|     |      | 9 2 4 电阻型 MOS 门        | 221 |

| 9.3    | 二义性强度                      | 223 |

|--------|----------------------------|-----|

|        | 9 3 1 二义性强度的说明             | 223 |

|        | 9 3 2 基本计算                 | 224 |

| 9 .4   | miniSim 示例                 | 228 |

|        | 9 4 1 概述                   | 228 |

|        | 9 4 2 miniSim 的源码          | 229 |

|        | 9 4 3 模拟结果                 | 239 |

| 9 .5   | 小结                         | 241 |

| 9 .6   | 练习                         | 241 |

| 第 10 章 | 工程项目                       | 243 |

| 10 .1  | 建立功耗模型                     | 243 |

|        | 10 1 1 对功耗进行建模             | 243 |

|        | 10 1 2 需要做什么               | 243 |

|        | 10 1 3 步骤                  | 244 |

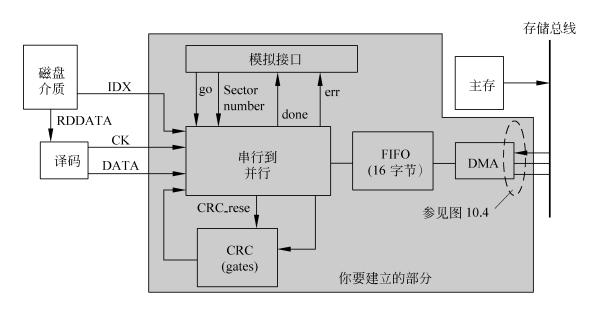

| 10 2   | 软盘控制器                      | 245 |

|        | 10 2 1 介绍                  | 245 |

|        | 10 2 2 磁盘格式                | 245 |

|        | 10 2 3 功能描述                | 247 |

|        | 10 2 4 真实设备                | 248 |

|        | 10 2 5 你一直想知道的有关 CRC 的各种情况 | 249 |

|        | 10 2 6 起支持作用的 Verilog 模块   | 249 |

| 附录A    | 学习指南                       | 251 |

| A .1   | 结构描述                       | 251 |

| A .2   | 测试台模块                      | 259 |

| A .3   | 使用 always 的组合电路            | 259 |

| A 4    | 时序电路                       | 262 |

| A .5   | 层次化描述                      | 264 |

| A .6   | 有限状态机和数据通道                 | 264 |

| A .7   | 周期精确描述                     | 265 |

| 附录 B   | 词法                         | 266 |

| B .1   | 空白符和注释                     | 266 |

| В .2   | 操作符                                           |      |

|--------|-----------------------------------------------|------|

| В .3   | 数字                                            | 266  |

| В 4    | 字符串                                           |      |

| В 5    | 标识符、系统名和关键字                                   | 268  |

|        |                                               |      |

| 附录 C V | /erilog 操作符                                   | 270  |

| C .1   | 操作符表                                          | 270  |

| C .2   | 操作符优先级                                        | 272  |

| C .3   | 操作符真值表                                        | 273  |

| C .4   | 表达式的位数                                        | 273  |

|        |                                               |      |

|        | /erilog 门类型                                   |      |

| D .1   | 逻辑门                                           |      |

| D .2   | BUF和NOT门                                      |      |

| D .3   | BUFIF和 NOTIF门                                 |      |

| D .4   | MOS 门                                         | 277  |

| D .5   | 双向门                                           | 278  |

| D .6   | CMOS 门                                        |      |

| D .7   | Pullup 和 Pulldown门                            | 278  |

| 附录 E 音 | 寄存器、存储器、整数和时间                                 | 2.79 |

| E.1    | 寄存器                                           |      |

| E 2    | 存储器                                           |      |

| E 3    | 整数和时间                                         |      |

| 2 0    | ± ∞ 14 · 31 3 · · · · · · · · · · · · · · · · | 200  |

| 附录 F 系 | 系统任务和函数                                       | 282  |

| F .1   | Display 和 Write 任务                            | 282  |

| F .2   | 持续监视                                          | 283  |

| F .3   | 选通监视                                          | 283  |

| F .4   | 文件输出                                          | 283  |

| F .5   | 模拟时间                                          | 284  |

| F .6   | 停止和完成                                         |      |

| F .7   | 随机函数                                          |      |

| F .8   | 从磁盘文件读数据                                      | 285  |

| 附录 | G    | 形式化语法定义2       | 286 |

|----|------|----------------|-----|

|    | G .1 | 形式化语法规范指南 2    | 286 |

|    | G 2  | 2 源文本 2        | 290 |

|    | G 3  | s 声明 2         | 291 |

|    | G 4  | 基元示例 2         | 293 |

|    | G 5  | 5 模块例示 2       | 294 |

|    | G &  | 5 UDP的声明和例示 2  | 295 |

|    |      | 7 行为语句 2       | _   |

|    | G 8  | S Specify 部分 2 | 298 |

|    | G S  | 表达式 3          | 301 |

|    | G .1 | 0 通用说明 3       | 304 |

. .

# 第1章 Verilog语言入门辅导

数字系统是非常复杂的。从最基本的层次来看,如果我们把一个系统看作逻辑门或传输晶体管的集合,它们可能由数以百万计的元件组成。从更抽象的层次来看,这些元件可以组成一些功能部件,如高速缓存、浮点部件、信号处理器或实时控制器等。硬件描述语言已经发展起来,用来辅助设计具有大量元件、从电路级到逻辑抽象级诸多层次的系统。

数字系统的设计过程是先建立逻辑系统设计的概念、最终实现必须满足的一组约束以及建立系统的一组基本元件。设计是一个先用手工做或者先用自动综合、然后再根据给出的约束进行测试的迭代过程。一个设计一般可划分为许多更小的部分(根据众所周知的分治工程方法),而各部分可以再划分,直到整个设计用已知的基本元件说明为止。

Verilog 语言为数字系统设计人员提供了一种在广泛的抽象层次上描述数字系统的方式,同时,在这些层次上为计算机辅助设计工具在工程设计中进行辅助设计提供了方法。该语言支持早期的行为结构设计的概念,以及其后层次化结构设计的实现。在设计过程中,进行逻辑结构设计部分时可以将行为结构和层次化结构混合起来。为确认正确性可以将描述进行模拟,也有一些用于自动设计的综合工具。Verilog 语言为设计者进行大型复杂的数字系统设计提供了途径。本章概括介绍了 Verilog 语言的基本特点。

## 1.1 开始

Verilog 语言将一个数字系统描述为一组模块。每个模块与其他模块及其本身的描述内容都有一个接口。一个模块代表一个逻辑单元,可以通过规定其内部逻辑结构来进行描述——例如描述实际的逻辑门,或者通过用像程序一样的方式来描述它的行为——在这种情况下主要考虑模块所完成的功能而不是其逻辑实现。然后将这些模块互连起来,使它们能够互相通信。

## 1.1.1 结构描述

首先介绍初级逻辑设计过程中的一个基本逻辑电路:一个二进制七段显示驱动源,如例 1.1 所示。显示驱动源具有一个 4 位二进制输入,驱动七个段显示数字 0 至 9 及十六进制数 A 到 F。本例中所示的只是驱动 E 段的逻辑。

例 1 .1 二进制七段显示驱动源(仅仅 E 段)

```

module binaryToESeg;

wire eSeg, p1, p2, p3, p4;

reg A, B, C, D;

nand #1

g1 (p1, C, ~ D),

g2 (p2, A, B),

g3 (p3, ~ B, ~ D),

g4 (p4, A, C),

g5 (eSeg, p1, p2, p3, p4);

endmodule

```

例 1.1 中也给出了这个电路的 Verilog 描述。描述表示的是一个模块的基本定义,模块名为 **binaryToESeg**。每个模块定义包括关键字 module, 紧随其后的模块名, 以及最后的 endmodule 语句。描述中的第二行规定在这个模块的子模块间传送逻辑值的 wire 的名称。第三行说明保持逻辑值的存储单元名称。这些寄存器是触发器电路元件的一个抽象。

第 5 行及随后的第 6 行到第 10 行示例化(instantiate)了 5 个与非门,每个与非门有一个单位时间的延迟。与非门是语言中的一个预定义逻辑门类型,其他类型包括 AND、OR 及 XOR,后边会有详细介绍。这个语句规定电路中的 5 个门,称作 g1 到 g5。"#1"表示每个门都有一个单位时间的延迟。最后,括号内的符号表示连接这些门的连线和寄存器。括号内的第一个符号是门的输出,其他符号是输入。NOT 的运算符("~")用来规定连接到输入端逻辑值的补码。为进一步说明逻辑图和与之等效的 Verilog 描述之间的一致性,原理图中包括连线、寄存器及示例名称。

尽管这个示例简单,但它列举出 Verilog 语言的几个要点。首先是模块定义与模块例示的概念。使用模块语句,如上例所示,一旦规定了所有的内部细节就定义了一个模块。而后这个模块可以在设计中多次使用(例示)。每个例示称为模块的一个示例,可以分别命名和连接。基元门,如与非门,是语言提供的预定义逻辑基元。第 4 章内有更详细的介绍。

各种逻辑门是由线网(net)连接起来的。线网是语言中两个基本数据类型中的一个(寄存器是另外一种数据类型),用来模拟像门这样的结构化实体间的连接。连线(wire)是 net 的一种类型,其他类型包括 wired-AND 连接、wired-OR 连接及 trireg 连接。不同的 net 类型分别在第 4 章和第 9 章中有更详细的描述。

我们知道多个逻辑门以层次化方式可以构成更大的模块。在本例中,用与非门来构造 binaryToESeg 模块。如果这个 binaryToESeg 模块有输入输出端口,通过将它例示成另一个模块就可以作为更大模块中的一部分,依此类推。通过将设计划分为更小更有意

义的部分(即子模块),利用层次化描述可以控制设计的复杂度。在例示子模块时,必须知道各子模块的接口,而子模块复杂的实现细节在其他地方描述,因此不用出现在当前模块的描述中。

最后,应当指出 A、B、C、D 命名为寄存器显得不规则。读者可能会认为它们应当是模块 binaryToESeg 的输入端,而 eSeg 值应当是一个输出端,最终它们会变成输入端和输出端。但是现在我们仍保持这些寄存器定义,并且它们会在下一节的模拟中发挥作用。

参考: 门基元 4 2 .1, net 规范 4 2 .3。

## 1.1.2 模拟 binaryToESeg 驱动源

例 1.2 给出了一个更完整的 **binaryToESeg** 模块定义,称作 **binaryToESegSim**。这个示例包括为 NAND 门示例提供激励的语句,以及监视其输出端变化的语句。尽管没有给出所有可能的输入组合,但给出的这些输入组合将解释怎样提供输入激励。

#### 例 1 2 用于模拟的 binary ToE Seg 驱动源

```

module binaryToESegSim;

eSeg, p1, p2, p3, p4;

wire

A, B, C, D;

reg

nand #1

g1 (p1, C, \sim D),

g2 (p2, A, B),

g3 (p3, \sim B, \sim D),

g4 (p4, A, C),

g5 (eSeg, p1, p2, p3, p4);

initial

// two slashes introduce a single line comment

begin

$ monitor ($ time,,,

A = \% b B = \% b C = \% b D = \% b, eSeg = \% b,

A, B, C, D, eSeg);

// waveform for simulating the binaryToESeg driver

#10 A = 0; B = 0; C = 0; D = 0;

#10D = 1;

#10 C = 1; D = 0;

# 10 $ finish:

end

endmodu le

```

数字系统的模拟器是一个程序,它执行例 1 .2 中的 initial 语句(以及我们随后将要看到的 always 语句),并从门和寄存器的输出端将变化的值传播到其他的门和模块的输入端。模拟器的特点还表现在它能保持时间轨迹,使变化的值在将来某一特定时间显示出来而不是立即显示。这些未来的改变值一般存储在按时间排序的事件表中。当模拟器在没有语句可执行或没有值可传播时,就从事件表中找出按时间排序的下一个事件,将时间更新为下一个事件的时间,并执行这个事件。该事件在未来时间可能产生事件也可能不产生事件。模拟循环一直进行,直至不再有模拟的事件或者用户通过其他手段中止模拟。

例 1 .2 与例 1 .1 不同,它包含驱动模拟的 initial 语句。模拟器通过执行 initial 语句进行模拟的初始化。关键词 begin 和 end 将一些单个语句括起来,它们是初始化语句的一部分。本例的模拟结果如图 1 .1 所示。

图 1.1 例 1.2 的模拟结果

initial 中的第一个语句是一个模拟命令,当任何一个值改变时,监视(和打印)一组值。先打印时间(\$ time 请求打印当前时间),然后打印引证串(quoted string),用 A、B、C、D 的值代替% b(b 代表二进制)串中的打印控制。在 \$ time 和引证串之间有几个附加的逗号。需要用一个附加逗号来把 \$ time 和引证串分开;其他每个附加逗号引进一个附加空间。当发出监视命令时,监视命令就打印设计中的当前值,随后只要有一个值发生变化将会自动打印出来(但是,当只有 \$ time 改变时就不打印)。如图 1 .1 所示,开始打印为 X,意思是未知,行中的第一个值是时间。初始语句通过调度将来要发生的 4 个事件来连续工作。语句

```

#10A = 0; B = 0; C = 0; D = 0;

```

规定寄存器 A、B、C、D 从当前时间起分别加载 10 个单位时间的 0。本行的执行结果是模拟器将初始语句的执行挂起 10 个单位时间。模拟器检查到在当前(0)时间没有其他动作时,转移到按时间排序的事件表中的下一个事件,重新激活初始语句。在时间为 10 时,初始语句从它挂起的地方重新激活并执行下一个语句。模拟器检查到下一个# 10 时继续执行下一行。此时初始语句挂起,等待下一个单位时间。

但是在当前时间(时间 10),传播(A、B、C、D 的)变化值。通过传播,将每个基元门连

接到任何一个改变了的值上。而后这些门可以在将来变化时调度它们的输出。由于本例中门的时间延迟规定为1,它们的输出变化在未来(在时刻11)传播一个单位时间。因此,模拟器调度这些值在将来显示一个单位时间。

如上所述,初始语句继续执行直到在下一行中找到延迟;下一行规定了在时刻 20, D 将加载为 1。初始块被挂起并且在时刻 20 被激活。模拟器及时查找下一个事件,发现有 4 个与非门(g1 到 g4)在时刻 11 需要改变它们的输出值,并将它们的值传播到最后的与非门 g5。

有意思的是,门 g1 到 g4 在同一时刻更新各自的输出值。在相同的"模拟时间"时刻 11 都更新各自的值。然而,模拟器仅能更新 1 个,而更新的顺序是任意的——我们不能假定哪一个先更新。

在线 p1, p2, p3, p4 上传播这 4 个新值的结果是门 g5 将在时刻 12 改变它的输出值。由于在当前时刻(11)没有其他事件,下一个事件在下一个时刻(即时刻 12)从事件表中取出来。在时刻 12, eSeg 的变化不会引起其他门的求值,因为它没有连接到其他门上。

模拟继续进行,直到初始语句执行了完成命令为止。需要特别说明的是,在时刻 20, D 被设置为 1。这在两个单位时间之后会引起 eSeg 的改变。在时刻 30, D 被设置为 0, C 被设置为 1, eSeg 将其输出值改变 2 个单位时间。在时刻 40, \$ finish command 停止模拟。

图 1.1 中的模拟器输出值例举了模拟器中一个二进制位具有的 4 个值中的 3 个: 1(真),0(假)和 x(未知)。第 4 个值 z 用来模拟三态门的高阻输出。注意: 模拟开始时, net 和 register 的值都是 x。

现在我们看看本节示例中 A、B、C、D 为什么被定义为寄存器。由于只有'外部的'与非门输入端,在模拟期间我们需要一种方式来设置和保持各输入端的值。因为连线不能保持值——它们仅能从输出端将值传送到输入端——寄存器机制就用来保持输入端的值。

我们已经注意到 Verilog 语言中使用了两种主要的数据类型:线网和寄存器。基元门用来将数值驱动到线网上;初始语句(及我们在后面将要看到的 always 语句)用来给寄存器赋值。

最后,我们应该注意到模拟时间是由"单位时间"来描述的。Verilog 描述是用如上所示特定的时间延迟写出的。编译指令 timescale 用来将单位和精确度(四舍五入)连接到这些数据上。本书中的示例不规定实际的时间单位。

参考:逻辑值422;编译程序指令473

辅导: 见附录 A 1 中的辅导问题

## 1.13 为模块建立端口

前面的例 binary To ESeg 既没有输入也没有输出——一种相当有局限性的情况,在

开发模块层次中是没有用的。本例将扩展定义模块的概念,使模块具有端口。

#### 例 1 3 给模块加上端口

```

module binaryToESeg (eSeg, A, B, C, D);

output eSeg;

input A, B, C, D;

nand #1

g1 (p1, C, ~ D),

g2 (p2, A, B),

g3 (p3, ~ B, ~ D),

g4 (p4, A, C),

g5 (eSeg, p1, p2, p3, p4);

endmodule

```

第一行是模块定义语句,模块端口显示在括号内。模块内这些端口必须说明为inputs,outputs或双向的inouts。注意输出端口不一定要出现在第一位,通常基本的与非门就是这种情况。在第二行,说明 eSeg 是一个输出端口。在第三行,说明 4 个输入端口名称为 A、B、C、D。与例 1.2 相比, A、B、C、D 现在是连接输入端口和门的连线。binary ToESeg 模块的逻辑图如示例右边所示。注意逻辑图中所示模块内部的端口名称,它们仅在模块内部已知。

模块可以例示成其他模块。模块定义中的端口表在模块的内部工作和外部应用之间建立起联系,即有一个输出和 4 个输入。模块内其他连接(即连线 p1)不可以连到端口的外面。外部不知道模块的内部结构——模块的内部结构可以用或非门来实现。因此,模块一旦被定义后就是一个黑盒子,可以被多次例示和连接到设计中。但是由于每次例示时不用干涉模块的内部细节,所以我们可以控制设计的描述复杂度。

最后我们注意到例 1.3 中不再说明 eSeg, p1, p2, p3, p4 是连线(在前面例 1.2 中, 我们任意选定将它们说明为连线)。由于门只能驱动线网,在默认情况下,它们的名称被隐式地说明为连线。

## 1.1.4 为模块建立测试台

本书中一般都给出了说明 Verilog 语言专有特性的单个模块。但是,在写出 Verilog 描述时,通常采用测试台的方法来组织描述。这种思想来源于工程师的工作台,把要设计的系统连接到一个测试生成器上,测试生成器在被控制的时间间隔内提供输入并监视输出。在 Verilog 中,定义模块时尽可能给出 testBench 的名称。在这个模块内部还有两个模块,一个表示要设计的系统,另一个表示测试生成器和监视器,如图 1.2 所示。

#### 图 1.2 测试台模块的概貌

这种方法清晰地把设计的描述和测试设计描述的方法区分开来。待设计的系统如模块右边所示,可以通过其端口来进行模拟和监视;然后设计可采用其他 CAD 工具来综合。需要指出的是被模拟和被综合的描述是相同的。此外,所有测试功能都密封在模块的右边。如果在设计的模块内包含测试设计的行为,那么在综合时需要删除这个行为——这是一个容易产生错误的过程。例 1 2 的 binaryToESegSim 模块显示的是一个将设计的描述(与非门例示)和测试行为(初始语句)结合在一起的模块,例 1 4 显示的是用测试台的方法重新写出的描述。

模块 testBench 例示了两个模块:设计模块 binaryToESeg 和测试模块 testbToESeg。在例示模块时,如第 4 行和第 5 行所示,给出了名称。第 4 行说明所例示的模块是 binaryToESeg,名称为 d。第 5 行用名称 t 例示 test bToESeg。系统有什么功能(它是一个二进制七段译码器)以及它有哪些端口现在是很清楚的。此外,怎样来测试系统(在测试模块中给出)也是清楚的。测试台方法将这些信息分开,使描述变得清晰,更易于使用像逻辑综合这样的设计工具。这两个模块的连接如图 1 .3 所示。

#### 图 1 3 设计模块和测试模块的互连

在将模块连接在一起的时间为 0 的时候需要说明连线。本例中在第 2 行说明的连线 w1 至 w5 规定了互连。我们可以看到模块 test\_bToESeg 中的寄存器 A 连接到模块的一个输出上。在模块 testBench 中,这个端口连接到线 w2 上,也连到模块 binaryToESeg 的端口 A 上。在模块 binaryToESeg 中,该端口连到门 g2 和 g4 上。因此寄存器 A 驱动

g2 和 g4 的输入。模拟 testBench 模块与模拟例 1 2 中 binary ToESegSim 模块会产生相同的结果。

## 例 1.4 采用测试台方式进行描述

```

module testBench;

w1, w2, w3, w4, w5;

wire

binary ToESeg

d (w1, w2, w3, w4, w5);

test_bToESeg

t = (w1, w2, w3, w4, w5);

endmodule

module binaryToESeg (eSeg, A, B, C, D);

A, B, C, D;

input

output

eSeg;

nand #1

g1 (p1, C, \sim D),

g2 (p2, A, B),

g3 (p3, \sim B, \sim D),

g4 (p4, A, C),

g5 (eSeg, p1, p2, p3, p4);

endmodule

module test. bToESeg (eSeg, A, B, C, D);

input

eSeg;

output

A, B, C, D;

A, B, C, D;

reg

initial

# two slashes introduce a single line comment

begin

$ monitor ($ time,,

A = \% b B = \% b C = \% b D = \% b, eSeg = \% b,

A, B, C, D, eSeg);

// waveform for simulating the nand flip flop

#10 A = 0; B = 0; C = 0; D = 0;

#10D = 1;

#10 C = 1; D = 0;

# 10 $ finish;

```

end

endmodule

在模块 test. bToESeg 中, 说明 A, B, C, D 是寄存器。必须这样说明, 原因是在初始块中它们要被赋值。在初始块和 always 块中的赋值必须是寄存器。

你也许会认为模块 test. bToESeg 中的寄存器 A 和模块 binaryToESeg 中的输入线 网 A 是相同的,原因是名称相同。然而在 Verilog 中,每个模块有它自己的名称作用域; 在这个示例中的每个模块仅在它所说明的模块内是可知的。因此,两个 A 是不同的实体 名,尽管在本例中,连线 w2 将它们连接在一起使它们在电学上相同。

参考:综合6,名称空间2.6

辅导: 见附录 A 2 中的辅导问题

## 12 组合电路的行为建模

我们对 Verilog 语言的观察迄今主要集中在它描述结构的能力上——模块定义、模块示例及其互连。对它在行为上描述模块功能的语言能力观察不够。

一个模块的行为模型是这个模块怎样工作的抽象。模块的输出在描述时与它的输入相关,但是不用结构化的逻辑门来费力地描述模块是怎样实现的。

行为模型在设计过程的初期很有用。在设计初期,设计人员更关心的是模拟这个系统的预期行为以便了解系统总的性能特性,而不用考虑最终实现。随后,采用具有最终实现的准确细节的结构化模型,再重新模拟以便说明功能和时序的正确性。设计过程中的要点在于选定模块的具体实现结构之前,采用行为描述方法来描述和模拟一个模块通常是很有用的。采用这种方法,设计人员可以在工作之前集中精力开发出正确的设计(即能够与系统的其他部分一起正确地工作并具有预期的行为)。然后可以将这个行为模型作为综合几个结构化的实现方案的起点。

行为模型以类似于编程语言的方式来进行描述。正如我们后面将要看到的那样,我们可以在很多抽象层次模拟系统的行为。对于大型系统,我们可以描述要实现的算法。事实上,算法可以是一个对于 C 这样的编程语言的直接转换。在较低的抽象层次,我们可以描述电路的寄存器传输级行为,说明各个系统的寄存器传输的时钟沿和先决条件。在更低的层次,我们可以描述逻辑门或触发器的行为。在各种情况下,我们都使用Verilog 语言的行为建模结构来说明模块的功能而不用直接说明它的实现。

## 1 2 1 过程模型

例 1.5 介绍了组合逻辑建模的行为方法。模块的功能是根据过程语句来描述的,而没有用门例示。这里介绍的 always 语句是行为建模的基础。always 语句本质上是一个

"while (TRUE)"语句,包含一个或多个反复执行的过程语句。这些过程语句的执行很像执行一个软件程序:用" = "赋值改变寄存器的值,并执行循环和条件表达式。注意:在always 语句中,所有使用" = "的赋值都用于说明为寄存器的实体。前面出现过的初始语句也是如此。

### 例 1 5 binary To E Seg 行为模型

```

module binary To ESeg - Behavioral (eSeg, A, B, C, D);

output

eSeg;

input

A,B,C,D;

eSeg;

reg

always @ (A or B or C or D) begin

eSeg = 1;

if (\sim A\&D)

eSeg = 0;

if (\sim A\&B\&\sim C)

eSeg = 0;

if (\sim B\& \sim C\&D)

eSeg = 0;

end

endmodule

```

这个示例给出二进制七段显示驱动源的行为模型。端口说明与前面相同。我们也说明了一个寄存器 eSeg。这是我们将在 always 语句中进行赋值的寄存器,它也将作为纯组合电路的输出。这个 always 语句由事件控制" @ "语句开始。语句:

```

@(A or B or C or D) begin ... end

```

说明模拟器应暂停这个 always 块的执行,直到其中的一个命名实体发生变化。因此,提取出 A,B,C 和 D 中各个数值。当任何一个(或多个)命名实体发生变化时,那么将执行下一条语句——这些语句包含在 begin . . .end 块内。

当发生一个变化并继续执行时,赋值语句和条件语句很像编程语言那样执行。这种情况下,各语句描述了输出(eSeg)是如何根据输入计算出来的。将这些语句与卡诺图比较,可以看出输出被设置为 1,如果函数的一个零值在输入端上,那么输出设回为 0。当begin ... end 块结束时,always 块重新开始,等待 A,B,C 或 D 的变化。此时,模拟器将eSeg 的最终值传送给与之相连的设计的其他各个部分。

这个示例中有两个特征要注意。第一,它所描述的行为功能与前面示例相同,但它没有提到具体的门级实现;这个模型是行为级的。

第二,eSeg 被声明为一个寄存器可能会使你觉得它不是一个组合电路。但是,当仅仅从外部来看它的端口时,考虑一下这个模块的行为,会很快得出结论:任何一个输入上有任何变化,输出将会只根据模块输入重新计算并驱动输出。这是组合电路的基本特征。从模块外部来看,显然,这具有组合电路的行为。

参考: always 2 .1; if 2 .2

### 122 综合组合电路的规则

综合工具可以读取电路的行为描述并能够自动设计出该电路的门级结构。因此,例 1.5 给出输入规范,综合工具可以产生例 1.3 中规定的设计;也可以是其他实现方法。

并不是任何行为语句序列都适用于组合电路的综合。为了使用综合工具,必须十分仔细地写出描述。这里仅概括总结出综合组合电路的规则,更详细的介绍见第 6 章。确定你要综合的电路是组合电路:

· 检查所有组合函数的所有输入是否都包含在控制事件的敏感表(用" or "分开的名称表)内,如果其中的一个输入改变了,那么重新计算输出。

这种要求来源于纯组合电路的定义。组合电路的输出是当前输入的一个函数;如果一个输入改变了,输出应当重新计算。

· 检查是否不执行 begin . . .end 循环就不对组合输出(本例中的 eSeg)赋一个数值。 也就是,在执行每个 begin . . .end 循环中输出至少被赋值一次。在例 1 .5 中,第 7 行 (eSeg=1;)对 eSeg 赋一个数值,满足要求。

为理解这个要求,考虑一下如果执行 begin ...end 循环而不对输出赋值这种情况。在此情况下,电路需要记住以前的值。因此,输出就成为当前输入和以前输出的函数相与。这是时序电路的基本特征。这种电路的综合需要有锁存器来实现描述的时序特性。在设计组合电路时,这是不正确的。

遵循这两条规则有助于你写出既可用于模拟也可用于综合的组合电路的行为描述。

参考: 综合 6

辅导: 见附录 A 3 中的辅导问题

## 13 时钟时序电路的行为建模

行为模型也可以用于描述有限状态机。图 1.4 展示了一个具有三种状态的机器的状态转换图,它有一个输入和一个输出。用两个名称为 Q1 和 Q0 的触发器为这些状态进行编码。复位状态的编码是两个触发器均为 0。图中也给出了使用 D 触发器和逻辑门的一种实现方法。

图 1.5 显示出一个传统的有限状态机。该图实际上说明几个状态寄存器。它们的输

出是机器的当前状态。它们的输入是寄存器在时钟沿过后将要加载的下一个状态。下一个状态是当前状态和输入的组合函数。输出是当前状态和(在某些系统中的)输入的组合函数。这个传统的结构出现在 Verilog 描述中。下一个状态和输出的组合函数将在行为上被描述在一个单独的 always 块中,并遵循前一节中的规则。状态寄存器将被描述在分开的 always 块中并遵循不同的规则。

图 1.4 状态转换图

#### 图 1 5 有限状态机标准模型

## 131 建立有限状态机模型

图 1.4 中机器的行为描述在例 1.6 中。我们把输出命名为 out,输入命名为 in,并且为时钟和复位提供端口。机器的当前状态命名为 currentState。定义

reg [1:0] currentState, nextState;

表示 currentState 和 nextState 是二位向量。方括号("[]")的结构说明了每个寄存器的位数范围,第一个数字是最高位,第二个数字是最低位。out 也被说明为寄存器。它和 nextState 在执行下一个状态和输出函数的组合 always 块内被赋值。本例中我们已经在描述寄存器 nextState 和 currentState 时介绍了术语向量(vector)。寄存器(如 out)和一位的线网被认为是标量的(scalar)。

例 1.6 可综合的有限状态机

```

module fsm(out,in,clock,reset);

output

out;

input

in, clock, reset;

reg

out;

currentState, nextState;

reg [1:0]

always @ (in or currentState) begin

# the combinational portion

out = ~ currentState[1] & currentState[0];

nextState = 0;

if (currentState = 0)

if (in) nextState = 1;

if (currentState = 1)

if (in) nextState = 3;

if (currentState = = 3) begin

if (in) nextState = 3;

else nextState = 1;

end

end

always @ (posedge clock or negedge reset) begin // the sequential portion

if (~reset)

currentState <= 0;</pre>

else

currentState <= nextState;</pre>

end

endmodule

```

第一个 always 块描述输出和下一个状态逻辑的组合行为。敏感表表示当 in 或 currentState 上出现一个变化时,就执行 begin ... end 语句。 begin ... end 中的各个语句规定了组合输出 nextState 和 out 的新值。out 被规定为

```

out = ~currentState[1] & currentState[0];

```

它表示 currentState 的第一位的补码 ("~")同 currentState 的第零位相与。结构 "currentState[1]"称为向量的一个位选(bit-select)——整个向量中仅有一位在运算中使用。NextState 在随后的 if 语句中计算。考虑第三种情况。

end

这表明如果 currentState 等于 3(即二位二进制的 11,相应于状态转换图 1.4 中左下边的状态),那么 nextState 的新值取决于 in 的值。如果 in 为 True,则 nextState 为 3(即二位二进制的 11)。否则 nextState 为二位二进制的 01。其他的 always 语句规定其他状态的 nextState 是如何进行计算的。

第一个 always 块规定了一个组合电路,重新检查 1.2.2 节中给出的组合规则是很有用的。首先,这个组合函数只有输入 in 和 currentState。这可以通过 always 块中赋值语句和条件表达式的右边来进行检查。没有其他命名的实体出现,所有这些一定是输入。作为组合电路,以 or 分开的事件表一定包含 in 和 currentState。其次,组合输出 out 和 nextState 一定要说明为寄存器并在 always 块的每一次执行中都被赋值。它们在 always 块中前两行语句中被赋值,不管它们随后是否被重写。

第二个 always 块规定有限状态机的时序部分。我们已经看到过程 1 赋值" = "用在 initial 语句和 always 语句中。这个 always 块引入非阻塞赋值" <= "—— 一种可描述为并发赋值的赋值语句——使用在具有边沿规范(即 posedge 或 negedge)的 initial 语句和 always 语句中。到目前为止,只认为" = "和" <= "是相同的;以后我们将解释区别。

always 块中的敏感表等待两个事件中有一个事件要出现:或者是一个时钟上升沿,或者是一个 reset 的下降沿。一个信号的上升沿就是它从 0 变为 1,下降沿就是从 1 变为 0。当其中一个事件或两个事件都出现时,就执行 begin ... end 块。假设 reset 上出现一个下降沿。当 begin ... end 块开始执行时, reset 将为 0,因此 currentState 也将被设置为 0。只要 reset 保持 0,即使 clock 出现上升沿, currentState 的结果也只设置为 0。这是一个异步复位信号的动作,它忽略了触发器上的时钟。

现在考虑 reset 为 1 并且 clock 上出现上升沿的情况; begin ... end 循环被执行,但此时执行 else 子句。赋值

currentState <= nextState;</pre>

将 nextState 的值送给 currentState。这些语句建立了一个两位寄存器的边沿触发的行为模型,两位寄存器由 D 型触发器组成。

现在,我们可以理解整个有限状态机模型是如何工作的。假设我们处于状态 0 (currentState 为 0), reset 为 1(无效), clock 为 0, in 为 1。给定了这些值,那么两个组合输出是: out 是 0, nextState 是 1。当 clock 的上升沿出现时,第二个 always 块将执行并且把 nextState 的值赋给 currentState,再等待 clock 的下一个上升沿或 reset 的下一个下降沿。由于 currentState 刚变为 1,第一个 alway 块将执行并且计算 out 和 nextState 的新值。out 将变为 1,如果 in 仍为 1, nextState 将变为 3。如果 in 变为 0,第一个 always 块

将再一次执行,重新计算 out 和 nextState,而与时钟沿无关; nextState 将变为 0, out 将变为 0。

参考: @3 2; if 2 2; bit-select E 1,2 2

## 132 综合时序系统的规则

除了 1.2.2 节中列出的组合电路规则外,还有时序系统的规则。例 1.6 中的时序部分是第二个 always 块。这些规则是:

· always 块的敏感表仅包括时钟沿、复位和预置条件。

只有这些输入可以引起一个状态改变。例如,如果我们正在描述一个 D 触发器,D 上的一个变化不会改变触发器 D 的状态,所以 D 输入不包括在敏感表内。

- · 在 always 块内,首先规定复位和预置条件。如果规定一个复位的下降沿,那么 if 语句应当是" if (~ reset)..."。如果等待的是复位的上升沿,则 if 语句应当是" if (reset)..."。

- · 在 begin . . .end 块内没有规定时钟的条件。最后面的 else 中的赋值语句是由综合工具来假定为下一个状态。

- · 在顺序 always 块中进行赋值的任何寄存器将采用在综合结果电路中的触发器来实现。因此,你不可能在描述时序逻辑的同一个 always 块中描述纯组合逻辑。你可以写出一个组合表达式,但是表达式的结果将在时钟沿处计算并存入寄存器中,这样的一个示例见例 1.7。

- · 当规定边沿敏感的电路行为时,前面的非阻塞赋值(" <= ")是特别的赋值操作符。 " <= "表示规定在敏感表中的边沿上出现的整个系统的所有转换将并发地出现。尽管采用常规的" = "描述能正确地综合,但都不能够正确地模拟。因为模拟和综合通常是很重要的,所以使用" <= "。

尽管这些规则看起来好像是很'随意的(picky)",但对于综合工具推导出被综合的电路中需要触发器,进而推导出它是如何连接的,这是很必要的。

最后,注意一下 fsm 模块。名称 clock 和 reset 的使用对于综合工具没有特别的含义。我们在示例中使用这些名称是为了清晰,它们在模型中可以被任意命名。通过使用例 1.6 中所示的规范形式,综合工具可以推导出需要一个触发器,并知道有哪条线连接到它的 D、clock 和 reset 输入上。

## 133 非阻塞赋值(" <= ")

非阻塞赋值用来使赋值语句同步,所以它们仿佛是同时——并发地出现的。如模块 fsm 中所示的边沿使用非阻塞赋值。当规定的边沿出现时,新值就并发地存储在正在等待信号边沿的所有的赋值中。与通常的赋值("=")相比,等待信号边沿的所有赋值的右

边被首先计算,然后左边再被赋值(更新)。将这看作为所有的赋值都是并发出现的——在同一时刻——不依赖于描述中任何阻塞语句。实际上,在大型数字系统中,所有触发器是由相同的时钟边沿控制的,非阻塞赋值模拟了这个行为。

考虑例 1.6 中 fsm 模块的另一种表示方法,如例 1.7 所示。此时 Verilog 几乎是直接根据图 1.4 中的逻辑图进行描述的。我们将当前状态触发器模型化为分开命名的寄存器 cS0 和 cS1,并且我们在第二个 always 块——时序块中包含了下一个状态等式。模块fsm 和 fsmNB 应综合出相同的硬件。

再考虑第二个 always 块是怎样进行工作的。该模块等待一个 clock 的上升沿或 reset 的一个下降沿,如果 reset 上出现一个下降沿,那么 cS0 和 cS1 被设置为 0。如果时钟上出现一个上升沿,则计算两个" <= "赋值的右边,然后对左边寄存器进行赋值。从而计算出" Q0 & in "( Q0 和 in 的与)和" Q1 | in "( Q1 和 in 的或),然后将结果分别赋给 cS1 和 cS0。

检查描述时,应当考虑下述两条语句

```

cS1 \le in \& cS0;

cS0 \le in | cS1;

```

是同时(即并发)出现的。将右边当作是两个触发器的输入,并且 cS0 和 cS1 中的变化在时钟边沿出现时才会出现。应当认识到它们是并发出现的。第一行中左边的 cS1 不是用在第二行右边的 cS1 的值,右边的 cS0 和 cS1 是时钟边沿出现之前的值。左边的 cS0 和 cS1 是时钟边沿出现之后的值。这些语句可以用时钟边沿出现之后 cS0 和 cS1 的相同结果数值的任意顺序写出。

#### 例 1.7 说明非阻塞赋值

```

module fsmNB (out, in, clock, reset);

output out;

input in, clock, reset;

reg out, cS1, cS0;

always @ (cS1 or cS0)  // the combinational portion

out = \sim cS1 & cS0;

always @ (posedge clock or negedge reset) begin  // the sequential portion

if (\sim reset) begin

cS1 <= 0;

cS0 <= 0;

end

```

```

else begin  cS1 <= in \& cS0; \\ cS0 <= in \mid cS1; \\ end \\ end \\ endmodule

```

这个示例说明用非阻塞赋值规定的功能。在一个完整的设计中,许多不同的模块会有很多 always 语句等待相同信号的相同边沿。非阻塞赋值功能强大的特点在于所有的右边表达式是在左边寄存器更新之前来被计算出来的。因此,你不必担心用 cS1 的哪个值来计算 cS0。使用" <= "使你明白使用的是在时钟边沿出现之前的那个值。

辅导: 见附录 A 4 中的辅导问题

## 1.4 模块的层次

现在建立一个更大的设计示例:包括更多个不同的部件,如图 1.6 所示。本节将详述每一个模块以及它们之间的互连。该例由一个 board 模块组成,它包括一个 clock 模块 (m555),一个 4 位计数器(m16)及 1.2 节中的 binaryToESeg。

图 1.6 计数器

## 1.4.1 计数器

我们首先观察例 1.8 中所示的计数器模块定义。计数器有 2 个端口: 一个加 1 计数器的时钟和 4 位计数器数值 ctr。该例声明内部寄存器 ctr 和它的输出端口是 4 位向量。计数器采用一个 always 块来进行行为建模。该模块等待时钟上升沿。当上升沿出现时,ctr 加 1,模块等待下一个时钟上升沿。由于新的计数器数值产生在信号的边沿上, 因此使用了非阻塞赋值操作符(" <= ")。

例18 四位计数器

```

module m16 (ctr, clock);

output [3:0] tr;

reg [3:0] ctr;

input clock;

always @ (posedge clock)

ctr <= ctr + 1;

endmodule

```

### 1.4.2 系统时钟

计数器需要一个时钟来驱动它。例 1 9 抽象地定义一个称作 m555 的 555 "定时器 芯片,并给出了模拟描述所产生的波形。

#### 例19 计数器的时钟

```

module m555 (clock);

output clock;

reg clock;

initial

# 5 clock = 1;

always

# 50 clock = ~ clock;

endmodule

```

m555 模块有一个内部寄存器(clock),它也是模块的输出。在模拟开始时,输出值是x,如该例时序图中灰色区域所示。clock 在 5 个单位时间过后被初始化为 1。m555 用一个 always 语句来进行行为建模,该 always 语句说明 clock 在 50 个单位时间后取其补值。由于一个 always 语句本质上是一个"while (TRUE)"循环,第一个 50 个单位时间过后,在另一个 50 个单位时间内调度执行 always 语句并改变它的值;即,这时时间为 100。由于 clock 每隔 50 个单位时间将改变它的数值,因此我们建立一个周期为 100 个单位时间的时钟。

我们可以用实际时间单位来规定时钟周期。时标编译指令用来规定延迟操作符(#)的时间单位,并且时间计算的精度是四舍五入的。如果编译指令

`timescale 1ns/ 100ps

在模块定义之前被设置,那么该模块中所有延迟操作符和随后的任何模块将以纳秒为单

位,任何时间的计算在内部将对最接近 100ps 进行四舍五入。

参考: 时标 4.7.3

## 1.4.3 将整个电路结合在一起

现在我们已经定义在本系统中要用到的基本模块,剩下要做的是将它们结合在一起完成图 1.6 所示的设计。例 1.10 通过定义另一个模块(称作 board)将例 1.3、例 1.8 和例 1.9 中的模块定义结合在一起,而模块 board 例示这些模块并将它们互连在一起,如图 1.7 所示。

#### 例 1.10 计数器的顶层模块

```

module board;

[3:0]

count;

wire

clock, eSeg;

wire

m16

(count, clock);

counter

m555

clockGen

(clock);

(eSeg,count[3],count[2],count[1],count[0]);

binary ToESeg

disp

initial

monitor ( $ time, , , count = mode M d , eSeg = mode M d , count, eSeg);

endmodule

```

图 1.7 带有互连的计数器示例

在 board 模块定义中的大多数语句在前面已经描述过,但还有几个细节需要指出来, 计数器模块说明给出两个端口 ctr 和 clock。

module m16(ctr, clock);

ctr 是一个 4 位输出, 而 clock 是一个 1 位输入。例 1.10 中计数器的输出与

binary ToE Seg 模块相连,但是,该模块定义具有5个1位端口。

module binaryToESeg(eSeg,A,B,C,D);

在 board 模块中,我们定义一个四位线网 count 连接到 m16 上,当我们将它连到 binary ToE Seg 上时,我们需要分别连接每一位(A 到 D)。我们用连线类型的 count 的位选(bit-select)来做这个工作,为每个连接规定合适的位,位选允许在被声明为向量的寄存器或连线内指定一位。因此,在模块 board 中 binary ToE Seg 的连接变成

```

binaryToESeg disp (eSeg, count[3], count[2], count[1], count[0]);

```

这将 count[3]连到 A, count[2]连到 B, count[1]连到 C, count[0]连到 D。

作为一种选择方案,如例 1.11 所示,当与 m16 模块连接时,我们可以声明四个标量线,然后将它们连在一起。这里,我们定义标量线 w3, w2, w1, w0,并将它们连到 binary ToE Seg 的端口 A,B,C,D 上。然而,模块 m16 期待一个 4 位向量连接到它的 ctr 端口。并置操作符' $\{...,...\}$ "允许将几个线合并在一起形成一个多位线。这里 w3, w2, w1, w0 结合(并置)在一起,在与 m16 连接时作为一个 4 位实体。

#### 例 1 .11 顶层模块的一种方案

module board With Concatenation;

如果将例 1 3、例 1 8、例 1 9 和例 1 .10 中的模块定义一起编译,可以形成一个可被模拟的完整描述。尽管这样做很有意义,但是什么也不会发生!因为 ctr 没有被初始化,它是未知的(x)。当它在 clock 上升沿被加 1 时,对于一个未知数,加 1 的结果仍然是未知的。为使这个模拟模型能够工作,ctr 需要初始化。将语句

```

initial ctr = 1;

```

插入到模块 m16 中将会解决这个问题。将这些组合在一起的示例(包括 ctr 的初始化)模拟 802 个单位时间,模拟轨迹如图 1.8 所示。

起初,在时刻 0,系统中所有的值都是未知的,然后使所有初始块和 always 块能够运 · 20 ·

行;它们以任意顺序开始运行。m555 中的初始语句开始时分别延迟 # 5 和 # 50。m16 中的 always 开始时等待 clock 的上升沿。binary To E Seg 中的门基元等待改变它们的输入。board 和 m16 中的初始语句也可以运行。我们可以看到 m16 首先执行将 ctr 设置为 1。然后,board 中的初始语句运行,执行 \$ monitor statement 并打印图中的第一行(如果 ctr 初始化执行 \$ monitor statement,那么 count 打印 x)。

假定 ctr(count)在时刻 0 设置为 1,2 个单位时间后 eSeg 将值改变为 0(当显示 ctr 为 1 时,eSeg 为 0)。在时刻 5,clock 从 x 变为 1。在 Verilog 中,这翻译为一个上升沿,它将 ctr(count)变为 2。2 个单位时间后,在时刻 7,eSeg 改变为 1,因为在显示 ctr 为 2 时 eSeg 为 1。在时刻 50,clock 改变为 0。但在我们的模拟中没有显示出来,因为我们没有监视 clock 的变化。在时刻 100,clock 变为 1,建立一个 clock 上升沿并使 ctr(count)加 1。ctr 变为 3 并且 eSeg 在 2 个单位时间后相应改变。模拟继续执行,如图 1.8 所示。

```

0 \text{ count} = 1, \text{eSeg} = x

2 \text{ count} = 1, \text{eSeg} = 0

5 \text{ count} = 2 \text{ , eSeg} = 0

7 \text{ count} = 2, \text{eSeg} = 1

100 \text{ count} = 3, \text{ eSeg} = 1

102 \text{ count} = 3, \text{ eSeg} = 0

200 \text{ count} = 4, \text{ eSeg} = 0

300 \text{ count} = 5, \text{ eSeg} = 0

400 \text{ count} = 6, \text{ eSeg} = 0

402 \text{ count} = 6, \text{ eSeg} = 1

500 \text{ count} = 7, \text{ eSeg} = 1

502 \text{ count} = 7, \text{ eSeg} = 0

600 \text{ count} = 8, \text{ eSeg} = 0

602 \text{ count} = 8, \text{ eSeg} = 1

700 \text{ count} = 9, \text{ eSeg} = 1

702 \text{ count} = 9, \text{ eSeg} = 0

800 \text{ count} = 10, \text{eSeg} = 0

802 \text{ count} = 10, \text{eSeg} = 1

```

图 1 8 例 1 3、例 1 8、例 1 9 和例 1 .10 的模拟轨迹

我们注意到初始语句对于模拟例 1.8 是必要的, 但是在综合时都是不必要的。实际上, 逻辑综合忽略了初始块。

参考: 模块例示 4 .2 .4; always 2 .1; \$ display F .1

## 1.4.4 将行为模块和结构模块连接在一起

现在把分别在几个示例中定义的模块连接在一起。其中一些模块在结构上只采用门级基元来定义。一些模块在行为上是采用 always 块来定义的。这是语言功能强大的一个方面,因为它允许我们在一个详细的层次(即结构化模型)上建立系统的一部分模型,而系统的其他部分建立在不很详细的层次(行为模型)上。在设计工程的开始,系统中大部分是建立在行为级上,然后一部分被细化为结构模型。而最终的模拟结果与进行准确的时序模拟及功能模拟的门级定义的模块相同。因此,Verilog 有助于完成整个设计过程,允许设计从行为级到结构级进行转换。

例 1.10 及其各子模块局部地显示行为元件和结构元件是怎样连接在一起的。在本例中,例 1.3 的结构模块 binary ToE Seg 与例 1.8 的行为模块 m16 连接在一起。m16 中的寄存器 ctr 声明为一个输出。ctr 的任何变化从模块端口进行传播,最终传到门的输入端。因此,我们看到行为模型中规定的寄存器可以驱动门基元的输入端。在分开的模块中不需要这样做。

我们将如例 1.12 所示的两个模块的功能组合在一起。这样,在一个模块内我们既有结构元件也有行为元件。无论在什么时候 ctr 被更新后,门 g1 至 g4 将重新计算它们的输出,因为它们的输入连接在 ctr 上。因此,一个 always 块的"输出"——由 always 块赋值的寄存器的值——可以用作门级基元的输入。

同样,门级基元的输出可以作为 always 块的'输入",如例 1.13 所示。这里我们将原来的结构模块 binary To ESeg 改变成产生 mixed Up ESeg Driver。变化是,与其他 NAND 门的输出 NAND 在一起的最终的 NAND 门在行为上是采用一个 always 块来描述的。这个 always 块等待 p1, p2, p3 或 p4 上的任何一个变化。当有一个变化出现时,行为语句计算它们的 NAND 并将它存储在寄存器 eSeg 中,这个值是模块的组合输出。因此,门基元的输出可以驱动行为模块的输入端——行为表达式右边的值。

#### 例 1 .12 驱动结构的行为

```

module counterToESeg (eSeg, clock);

output eSeg;

reg [3:0] ctr;

input clock;

initial

ctr = 0;

always @ (posedge clock)

```

```

ctr <= ctr + 1;

nand #1

g1 (p1, ctr[1], \sim ctr[0]),

g2 (p2, ctr[3], ctr[2]),

g3 (p3, \sim ctr[2], \sim ctr[0]),

g4 (p4, ctr[3], ctr[1]),

g5 (eSeg, p1, p2, p3, p4);

endmodu le

例 1 .13 驱动行为的结构

module mixedUpESegDriver (eSeg, A, B, C, D);

output

eSeg;

eSeg;

reg

input

A, B, C, D;

nand #1

g1 (p1, C, D),

g2 (p2, A, \sim B),

g3 (p3, \sim B, \sim D),

g4 (p4, A, C);

```

endmodule

这些示例用来说明 Verilog 语言中两个主要数据类型: 寄存器和线网, 并说明它们是如何在一起工作的。门基元将它们的输出驱动到线网(即上述示例中的连线)上。门输入既可以是其他的线网, 也可以是寄存器。行为模型, 即 always 块, 改变寄存器的值作为它们的执行结果。它们的输入既可以是其他寄存器, 也可以是由门基元驱动的线网。

参考: 过程赋值 2 .1; 连续赋值 4 .4; 时序模型 5 .1

辅导: 见附录 A 5 中的辅导问题

always @ (p1 or p2 or p3 or p4)

$eSeg = \sim (p1 \& p2 \& p3 \& p4);$

## 15 有限状态机和数据通道

上述已经使用 Verilog 语言来规定组合逻辑和有限状态机。现在我们开始说明寄存器传输级系统。我们将使用一种规范方法,称为有限状态机和数据通道或 FSM-D。我们

的系统将由两部分构成:一个可以做计算并将结果存入寄存器的数据通道,一个控制数据通道的有限状态机。

### 151 简单计算示例

我们先做一个简单计算并说明怎样用 Verilog 语言规定逻辑硬件。以类 C 的语法计算如下所示:

```

for (x = 0, i = 0; i <= 10; i = i + 1)

x = x + y;

if (x < 0)

y = 0;

else x = 0;

```

计算一开始将 x 和 i 清为 0, 然后, 当 i 小于或等于 10 时, x 被赋值为 x 和 y 的和, 并将 i 加 1。当退出循环时, 如果 x 小于 0, y 被赋值为 0, 否则, x 被赋值为 0。用这个示例来说明建立更大系统的方法。

我们假定这些是8位计算,因此系统中所有寄存器都是8位的。

### 152 系统的数据通道

用硬件实现这个计算有很多方法,我们只集中考虑一种方法。这个系统的数据通道必须用寄存器表示 x, i 和 y。需要能够将 i 加 1,将 x 和 y 相加,并能清除 i, x, y。也需要能够将 i 和 10 比较,将 x 和 0 比较。图 1 9 显示出能够执行这些寄存器传输的一个数据通道。

图中每个方框的名称建议用它的功能来命名。名称上有横线的是控制信号,它们是低电平有效。在标为 register i 的块上,我们看到它的输出(从底部产生)连接回到加法器的输入端,而加法器其他输入端连接到 1 上。加法器的输出(从底部产生)连接到 register i 的输入端。假定寄存器存储一个值,而加法器是个组合电路, register i 的输入将总是比 register i 的当前值大 1。寄存器也有两个控制输入端: iLoad 和 iClear。当其中一个输入端有效时,规定的功能将出现在下一个时钟沿上。如果我们发出 iLoad 信号,那么下一个时钟沿之后 register i 将加载并存储它的输入值,同时将 i 加 1。另一方面, iClear 将 0 存入 register i。比较模块也是组合电路,并产生指定的布尔结果。

计算中给出的寄存器传输是 x = 0, i = 0, y = 0, i = i + 1, x = x + y。从上面数据通道是如何工作的描述中,我们可以看出,计算中所有的寄存器传输可以在这个数据通道上执行。此外,所有在 FSM 中需要分叉的条件值也在数据通道中产生。

#### 图 1.9 有限状态机和数据通道

左边所示的 FSM 通过一系列导致计算发生的状态来进行排序。 FSM 的输出是 yLoad、yClear、xLoad、xClear、iLoad 和 iClear。它的输入是 x < 0 和 i <= 10。一个主时钟 驱动 FSM 中的状态寄存器及数据通道寄存器。一个 reset 信号也连在上面。

## 153 数据通道功能模块的细节

数据通道由三个基本模块组成:寄存器、加法器和比较器。寄存器模块定义如例1.14所示。首先在 always 块中,我们注意到它与我们在时序电路看到的描述十分相似。寄存器是上升沿触发的,但没有异步复位。为了与数据通道定义的寄存器模块保持一致,它有两个控制点:clear 和 load。当这两个控制点有效时,将导致寄存器执行必要的功能。如果 clear 输入有效,在 clock 边沿它会装入 0。如果 load 有效,它会在 clock 边沿将输入 in 装入到寄存器 out 中。如果这两个信号都有效,那么寄存器将执行清除功能。

#### 例 1 .14 寄存器模块

module register (out, in, clear, load, clock);

always @ (posedge clock)

这个示例介绍一个新语句:参数语句。参数定义一个名称具有一个数值;在这种情况下,width的值是 8。这个名称在模块内是已知的,并可以用在任何语句中。这里我们看到它被用来为输出端寄存器 out 和输入端 in 定义向量的最左位编号。假定 width 定义为8,最左边位数是 7(即 8 - 1),out 和 in 的位宽都是 8(即位 7 至 0)。参数的意义在于默认值可以在例示时被覆盖(override)。也就是说,这个模块定义可用来例示不同位宽的寄存

加法器模块显示在例 1 .15 中。它被参数化为 8 位的默认位宽。但是,它也使用了新的行为结构:持续赋值语句。该赋值语句允许我们描述组合逻辑功能而不管它实际的结构化实现——也就是,这里没有带连线和端口连接的示例门。在电路模拟过程中,无论何时,只要逻辑表达式的一个值发生变化,就得计算等号右边逻辑表达式的结果,这个结果驱动输出 sum。持续赋值语句的另外一个形式是,它允许我们写出一个布尔表达式,但是需采用 Verilog 语言中更大的行为运算符集合。本例的赋值语句给出生成'加法器'功能的一种方式。输出 sum 被输入 a 和 b 的和赋值, a 和 b 用运算符'+'连接。在第 4 章会进一步讨论赋值语句。

#### 例 1 .15 加法器模块

器, 随后我们会看到。

```

module adder (sum, a, b);

parameter Width = 8;

input [Width - 1:0] a, b;

output [Width - 1:0] sum;

assign sum = a + b;

endmodule

```

例 1.16 给出了 compareLT 和 compareLEQ 模块,又一次用到持续赋值语句。在 compareLT 模块中, a 和 b 比较,如果 a 比 b 小,那么 out 设置为真,否则设置为假。在计算中用来将 i 和 10 进行比较的模块 compareLEQ,与这个模块类似,只是用'<="运算符代替'<"运算符。这两个模块的宽度都被参数化了。不要被第二个赋值语句,即

```

assign out = a \le b;

```

搞混。

这不是用非阻塞块赋值语句将 b 赋给 a, 然后再用阻塞块赋值语句将 a 赋给 out。在一个语句中仅允许一个赋值。因此,通过它们在语句中的位置, 我们可以知道第一个是一个赋值, 而第二个是一个小于或等于的比较。

### 例 1 .16 CompareLT 和 CompareLEQ 模块

```

module compareLT (out, a, b);

// compares a < b

Width = 8;

parameter

[Width - 1:0]

input

a, b;

output

out:

assignout = a < b;

endmodu le

module compareLEQ(out, a, b);

/\!/ compares a \leq b

Width = 8;

parameter

input

[width - 1:0] a,b;

output

out;

as sign out = a \le b;

endmodule

```

模块 adder、compareLEQ 和 compareLT 可以用前面 1 .2 节中讨论过的 always 块的组合电路形式描述出来。这几个示例中用过的这两种形式是相等的。当用简单语句描述组合函数时,一般采用持续赋值的方法。而更复杂的组合函数,包括具有无关项规范的组合函数,一般采用组合的 always 语句更易于描述。

参考: 持续赋值 4 4

## 154 用连线将数据通道连在一起

现在建立一个模块来例示所有必需的 FSM 和数据通道模块,并用连线将这些模块连在一起。这个模块,如例 1 .17 所示,首先说明了把数据通道模块连在一起的几个 8 位连线,后面是把控制线连接到 FSM 的几个 1 位连线。在连线定义的后面,模块例示规定图 1 .9 所示的互连。

#### 例 1 .17 将 FSM 和数据通道结合在一起

```

module sillyComputation (yIn, y, x, ck, reset);

parameter Width = 8;

input ck, reset;

input [Width - 1:0] yIn;

```

```

output

[Width - 1:0] y, x;

wire

[Width - 1:0] i, addiOut, addxOut;

wire

yLoad, yClear, xLoad, xClear, iLoad, iClear;

register

# (Width)

I

(i, addiOut, iClear, iLoad, ck),

(y, yIn, yClear, yLoad, ck),

Y

X

(x, addxOut, xClear, xLoad, ck);

adder

# (Width)

addI

(addiOut, 1, i),

(addxOut, y, x);

addX

compareLT

cmpX

(xLT0, x, 0);

# (Width)

compareLEQ

# (Width)

cmpI

(iLEQ10, i, 10);

fsm

ct1

(xLT0, iLEQ10, yLoad, yClear, xLoad, xClear, iLoad, iClear, ck, reset);

endmodule

```

注意这个模块也定义了一个 Width 参数,在连线定义中用到它,模块例示中也用到它。考虑一下例 1.17 中寄存器 I 的模块例示。

```

register # (Width) I (i, addiOut, iClear, iLoad, ck),

```

这一行中第二项," # (Width)",是新出现的。这个值在模块例示中用它的参数来代替。因此,通过将模块 sillyComputation 中的参数 Width 改为,比如说 23,那么数据通道的所有模块例示将是 23 位宽。参数化模块允许我们在更多的地方可以重复使用类属模块定义,这使描述变得更容易。如果在模块例示语句中没有规定 # (Width),那么采用在模块register 中规定的默认值 8。

## 1.5.5 FSM 说明

既然已经规定了数据通道,那么就需要有限状态机来激活(evoke)寄存器的顺序传输,必须满足原计算规定的条件。首先介绍这个系统的状态转换图,然后描述出实现它的fsm 模块。

图 1.10 给出了状态转换图和规定的计算。用"…"标出的状态表示在我们所关心部分之前和之后的计算。每个状态表示在该状态期间将是有效值的 FSM 输出;所有其他信号都将是无效值。箭头指向后继状态;箭头旁边的条件表达式表示状态转换的条件。这个图表示的是一个莫尔(Moove)机,其中输出仅是当前状态的函数。最后,为了讨论方便,状态用  $A \subseteq F$ 表示。

#### 图 1.10 状态转换图

沿着计算和状态转换图,我们看到第一个动作是清除状态 A 中的两个状态寄存器 x 和 i。这意味着当机器在状态 A 时, x Clear 和 i Clear 信号为有效值(低电平)。注意寄存器 i 和 x 直到时钟上升沿过后才变为 0, 并且状态为 B。然后状态 B 发出 x 和 i 的装入信号。图 1 9 中的数据通道显示出实际上要装入的值分别是 x+y 和 i+1。因此,状态 B 执行循环体和循环更新。系统从状态 B 进入没有 FSM 输出信号的状态 C。但是,从状态 C 起,有 3 个可能的后继状态,取决于我们或者正处在循环中(回到状态 B),或者退出循环并进入条件语句的 then 部分(状态 D),或者退出循环进入条件语句的 else 部分(状态 E)。D 或 E 的下一个状态是状态 F,进行其他计算。

理解为什么系统的实现中需要状态 C 是很重要的。到底状态 C 的条件转换能不能从装入 x 和 i 的状态 B 中产生出来?回答是否定的。图 1 .11 中的时序图说明状态 A、B 和 C 之间的转换。在系统处在状态 B 期间,有限状态机的有效输出是 xLoad 和 iLoad,意思是寄存器 x 和 i 能够从它们的输入端加载。但是它们直到下一个时钟沿——将有限状态机转换到状态 C 的同一个时钟沿——才能加载。因此,i(执行循环的判断条件)和 x (执行 if-then-else 的判断条件)的值直到系统处在状态 C 时对于比较判断才是有用的。在时序图中,可以看到由于 i 小于等于 10, C 的下一个状态是 B。

应注意到在系统的实现中,在进入循环之前不检查 for 循环的退出条件。但是,假定进入循环之前我们刚清除 i,检查它小于或等于 10 是不必要的。而且,对于不同的数据通道,状态 C 可能是不必要的。例如,将 i、x 和各自的未来值的比较可以根据寄存器的输入值来进行。否则,进行比较的常数可能会改变。当然,这些任凭设计者自行处理。

现在考虑例 1.18 所示系统中有限状态机的 Verilog 模型。机器的输入是两个条件, x < 0 和 i <= 10。在 fsm 模块内部,分别称作 LT 和 LEQ。模块 fsm 也有一个 reset 输入和一个时钟(ck)输入。模块的输出是寄存器(yLoad, yClear, xLoad, xClear, iLoad, iClear)上的控制点。就像前面的 fsm 示例一样,有两个 always 模块:一个用于时序状态

#### 图 1.11 状态 A、B、C的时序图

改变,而另一个用来实现下一个状态和输出组合逻辑。所有组合逻辑的输出都说明为寄存器。

状态机将只执行状态转换图中所示的状态,尽管在其他计算中还有许多状态。因此,状态寄存器(cState)的宽度选定为 3 位。此外,复位状态显示为状态 0,尽管在整个系统中它可能是其他某个状态。选定一个很简单的状态赋值,状态 A 编码为 0,B 编码为 1,等等。

第一个 always 块与前面的状态机示例很相似。如果 reset 是有效值,那么就进入复位状态;否则,在时钟上升沿,组合值 nState 在时钟上升沿装入 cState。

第二个 always 块执行下一个状态和输出组合逻辑。该组合逻辑的输入是当前状态 (cState)和 fsm 的输入(LT 和 LEQ)。Always 块的主体根据 cState 的值来安排。一个 case 语句,实际上是一个多路分支,用来规定当给定 cState 的每个可能值时所要发生的动作。括号内表达式的值,与列在每行上的值进行比较。执行具有匹配值的那一行。

在 case 关键字后面的行规定一个数值,并跟着一个冒号。数字 3 b000 是 Verilog 语言对一个 3 位数的表示,此处以二进制规定 000, b 表示二进制——其他选择包括: h 表示十六进制, d 表示十进制。

如果当前状态变为状态 A, 我们的编码 cState 的值是 0。结果, 当这个改变发生时, always 块将会执行,并且执行  $3\ b000$ : 右边的语句。这个语句说明除了 iClear 和 xClear 外所有的输出都是无效的(1), 而下一个状态是  $3\ b001$ (即状态 B)。如果当前状态是 B, 那么执行第二个 case 项 $(3\ b001)$ ,将 iLoad 和 xLoad 设置为有效值, 而其他信号设置为无效值。状态 B 的下一个状态是 C, 编码为  $3\ b010$ 。状态 C 给出了一个更复杂的后继状态

计算:3 个 if 语句规定状态 C 可能的后继状态以及每个状态选择的条件。

最后一个 case 项规定默认情况,这个语句在 cState 的值不能与其他项目匹配时才执行。为了能够模拟,如果到达了一个非法状态,可能需要一个 \$ display 语句来打印出一个错误警告。 \$ display 在模拟期间在屏幕上打印一条信息,动作非常像编程语言中的打印语句。这会显示信息" Oops, unknown state: % b",用 cState 的二进制表示代替 % b。

为了使这个 always 块具有可综合的组合功能,默认情况是需要的。考虑一下,如果我们没有默认语句,一旦 cState 的值是个规定值以外的其他值,那会发生什么情况。在此情况下,case 语句会执行,但是没有规定的动作执行。因此,不会赋值给输出。这就违反了组合逻辑综合规则,该规则声明 always 块的每个可能路径必须对每个组合输出进行赋值。因此,尽管模拟中调试一个描述时具有默认项是任选的,但是对于综合组合电路的always 块而言,默认项是必需的。当然,如果已经规定了所有已知值情况或者在 case 语句之前 cState 已经赋值,对于综合来说就不需要一个默认项。

在我们的描述中,几个 always 块正在等待 cState、x 和 i 的改变。这些块包括 fsm 的组合 always 块、加法器模块及比较模块。由于 cState、x 和 i 的改变,这些 always 块现在可以执行。模拟器将以任意顺序执行它们。实际上,模拟器可以对其中一些块执行多次。(考虑这样一种情况:fsm 的组合 always 块首先执行。然后执行比较模块以后,它必须再执行一次)。最后,将会为比较器的输出产生新值。fsm 模块中 LT 和 LEQ 的改变将引起组合 always 块的执行,为 nState 产生一个新值。在下一个时钟上升沿,这个值将装入cState 并进入另一个状态。

#### 例 **1.18** 用于数据通道的 FSM

```

module fsm (LT, LEQ, yLoad, yClear, xLoad, xClear, iLoad, iClear, ck, reset);

input LT, LEQ, ck, reset;

output yLoad, yClear, xLoad, xClear, iLoad, iClear;

reg yLoad, yClear, xLoad, xClear, iLoad, iClear;

reg [2:0] cState, nState;

always @ (posedge ck or negedge reset)

if (~reset)

cState <= 0;

else cState <= nState;

```

```

always @ (cState or LT or LEQ)

case (cState)

3 b000 : egin

// state A

yLoad = 1; yClear = 1; xLoad = 1; xClear = 0;

iLoad = 1; iClear = 0; nState = 3 b001;

end

3 b001 : begin

// state B

yLoad = 1; yClear = 1; xLoad = 0; xClear = 1;

iLoad = 0; iClear = 1; nState = 3 b010;

end

3 b010 : begin

// state C

yLoad = 1; yClear = 1; xLoad = 1; xClear = 1;

iLoad = 1; iClear = 1;

if (LEQ) nState = 3 b001;

if (\sim LEQ & LT) nState = 3 b011;

if (\sim LEQ \& \sim LT) nState = 3 b100;

end

// state D

3 b011 : begin

yLoad = 1; yClear = 0; xLoad = 1; xClear = 1;

iLoad = 1; iClear = 1; nState = 3 b101;

end

3 b100 : begin

// state E

yLoad = 1; yClear = 1; xLoad = 1; xClear = 0;

iLoad = 1; iClear = 1; nState = 3 b101;

end

// required to satisfy combinational synthesis rules

default : begin

yLoad = 1; yClear = 1; xLoad = 1; xClear = 1;

iLoad = 1; iClear = 1; nState = 3 b000;

$ display (Oops, unknown state: %b, cState);

end

endcase

endmodule

参考: case 2.4; 数字表示 B.3

```

# 16 周期精确的行为描述

辅导:见附录 A 6 中的辅导问题

由于我们已经学习了这个辅导, Verilog 描述抽象层次的概念增加了。我们再上升到

一个更高的层次:周期精确 (cycle accurate),有时称为调度行为(scheduled behavior)。在这个层次,我们用一个时钟周期一个时钟周期的方式来描述系统,规定每个状态中将要发生的行为。使用术语 cycle accurate 的原因是系统中的值只有在系统状态改变的时候——在一个时钟沿处——才规定是有效的。可以用模拟结果描述,或者通过用行为综合工具可以综合结果描述,产生 1.5 节中所述的 FSM-D 描述风格。

### 1.6.1 规范方法

调度行为用 always 块来规定,用"@(posedge clock);"语句将规范分成时钟周期或状态。例 1.19 例示一个 1.5 节中简单计算的预定行为描述。模块的端口是寄存器 x、y 和 clock。寄存器 i 是一个循环计数器,仅在模块内部使用。

在讨论周期精确的特性之前,先解释 always 块和块内用到的新语句——while 语句。while 语句与编程语言中用到的 while 语句类似。这个语句计算 while 条件 (" i <= 10 ")。如果条件为真,则进入循环执行循环体,此时我们将 y 和 x 相加并将 i 加 1。然后我们继续计算 while 条件并执行循环体,只要条件仍然为真。如果条件为假,则不执行循环体。在本例中,假定第一次计算 while 条件时 i 小于或等于 10,则进入循环(但是,当第一次计算时如果 while 条件为假,则不执行循环体并且控制传送到 while 后面的下一条语句)。因此,只有当条件为真时 while 语句的循环体才会执行。

采用这种描述风格,一个"@(posedge clock);"语句后面跟随着行为语句,然后是另一个"@(posedge clock);"语句。我们将这个"@(posedge clock);"语句称作时钟事件。在两个时钟事件之间的语句构成一个状态。时钟事件语句不需要成对出现;如果在一个循环体内仅有一个时钟事件语句,那么循环在一个状态内执行,下一个时钟事件实际上是它自身。

#### 例 1 .19 采用预定行为方法的描述

```

module simple Tutorial (clock, y, x);

input

clock;

output

[7:0]

x, y;

[7:0]

reg

x, y, i;

always begin

@ (posedge clock) x \ll 0;

i = 0;

state A

while (i \le 10) begin

@ (posedge clock);

x \ll x \ll y;

state B

i = i + 1;

```

在例 1.19 中,考虑状态 C、最后一个时钟事件和跟随其后的语句,如图 1.12 所示。跟随在时钟事件后面的语句是一个 if-else 语句。假定 always 连续循环,下一个时钟事件在 always 块的顶部,开始执行状态 A。因此,这些语句给出一个状态的规范。在这个状态,y 或 x 赋值为 0,取决于 x 是否小于 0。与描述相对应的状态显示在图的右边。采用米利机(Mealy)概念(输出是输入和当前状态的函数),表明如果 x 小于 0,那么我们将沿着上边的弧到状态 A 并将寄存器装入 0(使用非阻塞赋值),而下边的弧给出相反的条件(当 x 设置为 0 时)。在模拟中,当等待在 if 语句之前的时钟事件时,则执行状态 C。

```

@ (posedge clock);  if \ (x < 0) \\ y <= 0; \\ else \ x <= 0;  图 1 .12 状态 C

```

整个状态转换图如图 1.13 所示。状态 A 将 x 和 i 初始化为 0,并进入循环。状态 B 是循环体,状态 C 是 if-else,如上面描述所示。状态 B 是具有特殊意义的,因为它给出两种可能的后继状态。状态的开始是循环体中的时钟事件语句。但是,下一个时钟事件可以是执行循环体并处在循环体内的语句(即同一个语句),也可以是执行循环体并退到while 语句后面的那一个语句。这解释了状态 B 的两个可能的后继状态。

图 1.13 周期精确行为的状态转换图

### 1.6.2 几点注释

关于这个示例和调度行为或周期精确的描述风格,有几点注释。

当需要一个周期一个周期地规定系统的行为,但又不太关心设计的实际数据通道时,使用这种描述风格。我们已经规定简单计算以及产生新值的那些状态。但是没有任意规定数据通道;这留给后面的设计阶段来作。

在这个规范中混合使用阻塞赋值(" = ")和非阻塞赋值(" <= ")。寄存器 x 和 y 使用非阻塞赋值,而寄存器 x 和 y 在 always 块的外面说明。这有效地将寄存器的加载同步到规定的时钟沿上。对于只使用在一个 always 块内的寄存器,例如寄存器 i,这是不必要的。请记住当你使用非阻塞赋值语句进行赋值时,这个数值直到时钟沿过后才可以被寄存器的名称所引用,也就是,在描述的下一行是不可用的!而且,对于一个状态内的任何一个寄存器只进行一次无条件的非阻塞赋值。但是,可以使用阻塞赋值来计算中间值和仅使用在 always 块内的数值。当然,这些数值在描述的下一行是立即可用的。在本例中,使用在循环结束比较判定中的 i 是在循环中计算的那个 i,因为我们使用了一个阻塞赋值。

最后,实现简单计算的两种方法的状态转换图(如图 1 .10 和图 1 .13 所示)是不同的。 这是有意这样做的,并不是哪种规范风格有什么局限性。

参考: 周期精确 7.2

辅导: 见附录 A 7 中的辅导问题

## 1.7 赋值语句的总结

当开发数字系统的 Verilog 模型时,一个重要特点是抓住新值(输出)是在什么时间如何产生的。这个辅导给出产生新值的四种不同方法:门基元,持续赋值,过程赋值("=")和非阻塞赋值("<=")。在 Verilog 语言中,这四种方法分成两大类。这两大类在时间上产生输出的方式不同。因此,我们将它们称为时序模型。这些模型是门级时序模型和过程时序模型。

门基元(例如例 1.3)和持续赋值(例如例 1.15)例示了门级时序模型。当写出一个简单的 AND 表达式时,我们既可以写成

and (a,b,c);

#### 又可以写成

assign a = b & c;

这两个语句是等价的; 两者都执行 b 和 c 的按位与运算, 并将结果赋给 a。认识这些语句

的方式是无论什么时候只要任何一个输入(b 或 c)发生变化,都要重新计算输出 a 的值。此外,在这两个语句中, a 是一个线网。

过程时序模型使用 initial 块和 always 块中的过程语句来产生新值。正规的过程赋值(" = ")如例 1.5 中所示,非阻塞过程赋值(" <= ")如例 1.7 中所示。always 块:

```

always @ (posedge clock)

Q <= D;</pre>

```

有两个输入(clock 和 D)和一个输出 Q。与门级时序模型相对应,过程赋值对它的所有输入不敏感;只在特定的时刻对特定的输入敏感。这里, always 块只对时钟上升沿的变化敏感。当时钟上升沿出现时, Q 被 D 的值更新。但是, 如果 always 块的输入端另一个输入 D 改变了, Q 的值不更新。过程模型只对它们显式等待的输入敏感。此外, 所有过程赋值语句的左侧都是寄存器。

只有当控制被传送到过程赋值语句的时候才将值装入寄存器或存储器。控制以顺序方式传送给过程赋值语句,从一条语句到另一条语句。在这种方式下,过程赋值功能与一般的软件编程语言的赋值语句相似。但是,控制流可能被事件(@)语句(及我们在后面将要看到的 wait 语句和 # 延迟语句)所中断,并且只有当事件发生时才被重新激活。

过程赋值"="和"<="当左边更新时,还能进一步分类。正如 1 .3 .3 节所讨论的那样,"="立即更新它左边的值,所以新值可以使用在下一条过程语句中。相反,"<="只有当整个设计中等待同一个边沿的所有"<="语句的右边计算完毕后才更新它左边的值。因此,左边的新值在下一条过程语句中是不能使用的。这就导致了下面的异常描述:

问题是什么值赋给了 r? 答案是 75。虽然第三条语句把 n 的值改为 3,但是这个左侧的值并不立即更新。实际上 always 块不停下来(即阻塞)更新 n; 而是继续执行(非阻塞),使用时钟变化之前的 n 值。最终,n 会被更新为 3,但只有在所有其他非阻塞赋值的右侧计算完毕之后才更新。最好不要写出像上面这样一个不好的模型; 它们很难阅读。而且,它们也不能被综合工具接受,所以它们的使用受到限制。只有描述边沿敏感系统中的并发传输时,才使用非阻塞赋值。

本质上讲,这两种时序模型与 Verilog 语言的两种基本数据类型(线网和寄存器)有紧密联系。持续赋值和基元门只能驱动线网,而过程赋值只能用于寄存器(和存储器)。

参考: 过程赋值 2.1; 连续赋值 4.4; 时序模型 5.1

## 18 小结

这个简介例示了 Verilog 语言的基本性能,这些重要的性能是:

- · 能够将设计划分为模块,而模块可进一步划分直到设计可以用基本的逻辑单元来规定。结构的模块化使设计人员可以通过有名的大型工程设计的分治方法来控制设计的复杂度。

- · 能够根据设计的抽象行为或者根据实际逻辑结构来描述设计。行为描述使得早期的设计活动能够集中在功能上。当行为确定后,它就变成了设计几种可以选择的结构化实现的规范,这可以通过使用综合工具来完成。

- · 能够使并发系统同步。系统的并发部分共享数据,必须互相同步,以便在并行部件间正确地传递信息。我们例示了系统是如何对信号边沿(即一个时钟)进行同步的。

本章辅导的主要目的是对 Verilog 语言进行一个快速介绍。因此,许多细节都省略了。目的是使读者对 Verilog 语言有一个感性认识,方法是给出并描述一些示例,例示语言的主要特点和应用。后面几章的目的是深度覆盖语言,仍然采用面向示例的方法来介绍该语言。我们在本章和全书其他章节中的目标并不是仅仅像一个正规文法规范那样来介绍 Verilog 语言。但是,由于意识到我们给出的示例并不能说明所有的语言文法,所以将要开始介绍语言的一些形式化文法规范。这个文法规范对第一次接触 Verilog 的读者来说可能没用。但是,这对于将本书当作参考书的读者和进行设计描述的读者来说是极其珍贵;附录 G 中有完整的形式化文法规范。

书中的其他部分深度例示了 Verilog 语言的文法和语义。

## 19 练习

更多的练习见附录 A。

- 1 .1 用持续赋值语句重新描述例 1 .4 中的 eSeg 模块。

- 1.2 写出一个两位全加器(包括 carry-in 和 carry-out 端口)的三种不同的描述,其中一个描述使用门级模型,另一个使用持续赋值语句,第三个使用组合的 always。

- 1.3 改变例 1.9 中的时钟发生器 m555, 使得时钟周期保持不变, 但低脉冲宽度是 40, 高脉冲宽度是 60。

- 1.4 写出一个二相位时钟发生器,相位二被相位一偏移 1/4 周期。

- 1.5 保持相同的输出时序,用门基元代替例 1.9 中时钟发生器 m555 中的初始语句和 always 语句。

1.6 写出一个串行加法器的描述,模块定义是:

```

module serialAdder(clock,a,b,sum,start);

input clock,a,b,start;

output sum;

...

endmodule

```

- A.各个二进制位以低阶优先的顺序进入模块。进入低阶二进制位的进位假定为 0。在时钟下降沿之前所有输入都是有效的。a 和 b 是要进行相加的两个二进制位, sum 是结果。如果 start 是 1, 那么这两个二进制位是第一个要相加的字的二进制位。就在时钟下降沿之后, sum 正好在时钟沿之前基于 a 和 b(和前面二进制位的进位)的新值来更新。

- B. 建立一个测试模块验证串行加法器的正确性。

- 1.7 设有一个 Verilog 模块,除了寄存器、输入和输出的说明外,模块是完整的。假定 a, b,c 是 8 位的'元件",而其余的是 1 位的,请注意必须加到输入输出表中。不要加任何其他赋值——只有输入、输出和寄存器的说明。

# 第2章 行为建模

现在开始更深入地讨论数字系统行为建模的结构。它们分为两组。第一组是主要部分,它们类似于编程语言中的语句,如 if-then-else, loops 等。第二组是对数字硬件并行特征进行建模的语句,下一章将讨论它们。

## 2.1 进程模型

行为模型的本质是进程。一个进程可以被看作一个独立的运行单元,它可能十分简单,只涉及一个循环动作,也可能非常复杂,像一个软件程序。它可以作为一个时序状态机,一个微代码控制器,一个寄存器异步清零器,或者一个组合电路。关键在于我们将数字系统的行为看作单独的,但相互通信的进程的集合。它们真正的实现与描述的上下文(正处理的层次)以及实现的时空约束有关。

描述进程的基本 Verilog 语句是 always 结构:

always. construct

#### = **always** statement

always 结构反复执行其中语句,永远不退出或者终止执行。一个行为模型可以包含一个或多个 always 语句。(一个不包含 always 语句的模块纯粹是一个层次结构的描述,即子模块示例和它们的互连。)

initial 结构类似于 always 语句, 不过它只执行一次。

initial - construct

#### = **initial** statement

initial 结构提供一种在实际描述开始模拟之前初始化输入波形和模拟变量的方式。一旦 initial 结构中的语句执行完毕,它不会重复再执行;并且它不再活跃。

这种语言中有很多种类型的语句。它们中的一些在前面的示例中已经出现过,比如 "if", "while"和过程赋值语句 ("out = ~currentState[1] & currentState[0];")。这些语句和大多数其他类型的语句将会在下两章见到。

当在一个 always 或 initial 块中使用这些语句为系统建模时,必须清楚这些语句的执行模型。这些语句按照描述中的顺序执行。使用阻塞赋值符号(" = ")的赋值语句立即生效,并且下一条语句就可以使用写到符号" = "左侧的值。当执行一个事件语句(" @ ")、延

迟语句("#")或者其表达式的值为 FALSE 的等待语句(后面将会见到)时, always 或 initial 语句的执行将被挂起,直到出现下面的某种情况:发生一个事件,经过延迟中的时间单元数,或者等待语句的表达式的值变为真。那时,将继续执行 always 或 initial 中的语句。

即使一个 always 或 initial 块中的语句顺序执行, 其他 always 或 initial 块中的语句也可能与当前进程中的语句交叉执行。当一个 always 或 initial 块在等待(用@, # 或 wait 表示)继续执行时, 其他 always 或 initial 块、门基元和持续赋值语句可以执行。结果, 建立了并发和交叉行为的模型。

与门基元和持续赋值语句不同,行为模型不会因为某个输入发生变化而执行。确切地说,仅当正在等待的上述三个条件之一发生时,它们才会执行。行为模型与 5 .1 节中讨论的过程时序模型一致。

模拟开始时,执行所有的 initial 和 always 语句,直到它们因为一个事件、延迟或等待而被挂起。在这里,initial 或 always 中设置的寄存器值可能激活一个门的输入,或者模拟时间前进到下一个事件,这些都可能唤醒一个或多个挂起的进程。当某一特定时刻有多个进程要执行时,它们执行的顺序是不确定的。一定要注意确保按合适的顺序为寄存器和连线赋值。

总之, initial 和 always 语句是描述并发性的基本结构。运用这些语句时, 我们应该注意交叉执行的并发活动进程。虽然可以把行为描述混合写入 always 和 initial 语句, 但是, 更合适的做法是在 always 语句中描述硬件的行为, 在 initial 语句中描述模拟的初始化工作。

参考: 对照持续赋值 4 4 节; 对照门级建模 4 .1 节; 交叉 5 .3 节; 过程时序模型 5 .1 节

## 2 2 If-Then-Else

顺序行为描述中的条件语句用于改变控制流程。if 语句和它的变化形式是条件语句的常见形式。例 2.1 是一个除法模块的行为模型,它表现出几个新特征,包括两种 if 语句,有 else 子句的和没有 else 子句的。

该 divide 模块根据两个输入(dvInput 和 ddInput)决定输出 quotient,它使用重复移位减的算法。首先,定义四个文本宏。定义一个宏的名字并且为它赋一个常量文本值,编译器就能够接受它。这个名字就可以用在描述中;编译时,这个文本值将被替换。通常的形式是:

'define A alpha

不管何时编译这个描述,所有出现"`A"的地方都将被 alpha 所替代。注意所有的宏左侧都要求有左单引号("`")。例 2.1 给出了一种通过宏将常数的值送入描述的方式。

### 例2.1 除法模块

```

'define DvLen 15

'define DdLen 31

'define QLen 15

'define HiDdMin 16

module divide (ddInput, dvInput, quotient, go, done);

ddInput, dvInput;

[`DdLen:0]

input

[`QLen:0]

output

quotient;

input

go;

output

done;

[`DdLen: 0]

dividend;

reg

[`QLen:0]

quotient;

reg

reg

['DvLen:0]

divisor;

done, negDivisor, negDividend;

reg

always begin

done = 0;

wait (go);

divisor = dvInput;

dividend = ddInput;

quotient = 0;

if (divisor) begin

negDivisor = divisor[DvLen];

if (negDivisor)

divisor = - divisor;

negDividend = dividend[`DdLen];

if (negDividend)

dividend = - dividend;

repeat ('DvLen + 1) begin

quotient = quotient << 1;

dividend = dividend << 1;

dividend[`DdLen:`HiDdMin] =

dividend[`DdLen:`HiDdMin] - divisor;

if (! dividend[DdLen]) quotient = quotient + 1;

else

```

除法从对输出 done 清零并等待 go 变为 TRUE 开始。这两个信号是握手信号,它们允许 divide 模块与其他模块通信、同步。 done 表示除法模块已经完成了除法运算,并且将结果保存在 quotient 中。既然开始时没有计算出商值, done 被设置为 FALSE(或 0)。然后,等待输入 go 变为 1(或 TRUE),它意味着输入 dvInput 和 ddInput 有效。当 go 变为 TRUE 时, dvInput 和 ddInput 和 ddInput 被分别赋值给 divisor 和 dividend。

等待语句等待外部条件变为 TRUE。当它执行(即等待)时,如果圆括号中的条件为 TRUE,就继续执行。然而,如果条件为 FALSE, always 块停止执行并等待条件变为 TRUE。执行将从 wait 语句之后的语句继续开始。wait 语句将在 3 3 节继续讨论。

第一个 if 语句的示例是测试这个语句中的除数是否为零:

```

if (divisor)

begin

// ...statements

end

```

该例展示 if 语句的基本形式。if 后跟圆括号括起来的表达式;零值表达式记为 FALSE,任何其他非零值记为 TRUE。与不确定值(x)或高阻抗值(z)相比较可能产生一个不确定的或高阻抗的结果。这样一个结果被解释为 FALSE。在这个示例中,要测试 divisor。如果它不为零,就继续下面正常的除法运算。if 语句后的 begin-end 块表示所有 被包含其中的语句被看作与这个 if 语句相对应的 then 语句部分。

更形式化的说明是:

继续分析这个除法算法。它继续计算每个输入的绝对值并且保存它们的符号。需要特别说明的是,语句

首先把除数的第 DvLen 位(即第 15 位)的值赋值给 negDivisor。如果这位是 1, 意味着该二进制补码表达式的值为负, 所以执行 then 语句部分, divisor 取反, 使它的值变为正值。注意, 既然这个 if 语句没有 begin-end 块, then 语句就是 if 语句后面的第一条语句(直到分号为止)。

这个语句也说明一个位选操作。位选操作指定向量中的某一位参与运算。也可以说明位的范围,通过冒号分隔的位号表达式来说明被选择的位的范围。这叫作域选操作。 位选或域选操作以如下所示的表达式形式表示。

在这个形式化语法中, primary 是表达式的一种定义。primary 的第一个定义是位选择,第二个定义是域选择。位选择和域选择的索引号可以是正数,也可以是负数。

初始化中判定了最终的算术符号之后, repeat 语句将把 begin-end 块中的语句执行 16 次。每次, quotient 和 dividend 都要左移一位, 用操作符 << 表示。接着, dividend 的高位部分减去 divisor。如果结果为正, quotient 加 1; 如果结果为负(最高位为 1), 执行 if 条件语句的 else 部分, 把 divisor 加回到 dividend 的高位部分。

更准确地说,如果符号位为 1,那么结果为负。这个非零值(即符号位)将被 if 语句解释为 TRUE。然而,操作符!对值取补,结果 if 表达式的值为 FALSE。这样,如果 dividend 为负,将执行 else 部分。

最后,如果操作数的符号不同,则将 quotient 取反。计算出 quotient 之后, done 被赋值为 1,通知别的模块已经可以读取这个输出值了。

本示例展示了将要讨论的这种语言的一些其他方面。

向量线网和寄存器都遵循算术的模  $2^n$  规则,这里 n 是向量的位数。实际上,这种语言把数字看作无符号量。如果用 \$ display 或 \$ monitor 语句打印这种值,它们将被解释为无符号值。然而,这并不能妨碍我们书写那些采用二进制补码表示法的硬件描述,算术的模  $2^n$  规则仍然有效。事实上,该语言中提供的取反能正确地实现操作。

常用于条件表达式中的关系操作符被列在附录 B 中。它们包括 > (大于), > = (大

于 于), ==(等于)和!=(不等于)。在出现了不确定和高阻抗值的情况下,比较操作的结果被模拟器看作 FALSE。然而,可以使用 case 等于操作符(===)和不等于操作符(!==)来说明每个不确定和高阻抗位将参与比较。也就是说,四值逻辑比较操作要比较每一位.包括不确定位和高阻抗位。

因此,如果执行下面这条语句,

```

if (4 \text{ b}110z = = = 4 \text{ b}110z)

then. statement;

```

将执行 if 语句的 then 部分。然而,如果执行语句

```

if (4 b110z = 4 b110z)

then. statement;

```

将不会执行 if 语句的 then 部分。

条件表达式比上面出现的这些独立表达式更复杂。逻辑表达式可以用下例中所示的 & & (与), ||(或)和!(非)等逻辑操作符来连接:

```

if ((a > b) & ((c > = d) | (e = = f)))

then statement

```

本例中, then 语句仅当 a 大于 b, 并且或者 c 大于等于 d, 或者 e 等于 f 时才会执行。 参考: 位选择, 域选择 E .1; \$ display F .1; \$ monitor F .2; Verilog 操作符 C

## 2.2.1 else 如何与 if 语句配对

例 2 1 也例示出与 if 语句配对的 else 子句的用法。else 子句是可选项,如果它存在,它与最近的不完整的 if 语句配对。形式化说明如下:

从这个示例中可以找到下面的语句:

这里,如果减去 divisor 以后, dividend 是一个正数, quotient 的最低位就设为 1。否·44·

则,把 divisor 加回到 dividend 的高位部分。

正像大多数的过程语言一样,在涉及多个 if 语句的地方,要注意说明 else 子句。看下面的示例:

```

if (expressionA)

if (expressionB)

a = a + b;

else

q = r + s;

```

该示例中有两个嵌套的 if 语句和一个 else 语句。通常,语言把 else 与最近的 if 语句配对。上例中,如果 expressionA 和 expressionB 都为 TRUE,就为 a 赋新值。如果 expressionA 为 TRUE并且 expressionB 为 FALSE,则为 q 赋新值。即 else 与第二个 if 语句配对。

下面是另一种描述,它将产生不同的结果:

```

if (expressionA) begin if (expressionB) a = a + b; end else q = r + s;

```

这个示例中,第一个 if 语句中的 begin-end 块使 else 与第一个 if 语句配对,而不是第二个。当对 else 与谁配对感到迷惑时,可以使用 begin-end,使结构更清晰。

## 222 条件操作符

如果要从两个值中选一个来赋值,可以用条件操作符(?:)。例如,例 2.1 中判断 quotient 最终符号的语句可以写成如下的等价形式:

```

quotient = (negDivisor != negDividend) ?-quotient : quotient;

```

该操作符这样工作:首先,计算圆括号中的条件表达式。如果它的值为 TRUE(或非零),则语句右侧的值就是紧跟在问号后面的值。如果它的值为 FALSE,则是紧跟在冒号后面的值。其结果是两个值中的一个赋给 quotient。本例中,如果符号不等,则 quotient 取反。否则,quotient 保持原值不变。例 2 1 中描述了使用二进制补码系统的硬件,它具有这个事实,即 Verilog 的取反操作实现了二进制补码取反操作。

条件操作符的一般形式是:

```

expression

```

```

= expression ?expression : expression

```

如果第一个 expression 为真,则条件操作的值是第二个 expression; 否则,它的值是第三个 expression。这个操作符是右结合的。

if-then-else 与条件操作符之间有个重要的区别。作为一个操作符,条件操作符可以出现在一个表达式中,这个表达式或者是过程赋值语句的一部分,或者是持续赋值语句的一部分。if-then-else 结构是语句,它只能出现在 initial 或 always 语句体中,或一个任务或函数中。因此,if-then-else 只能用在行为建模中,然而,条件操作符既能用在行为级建模中,又能用在门级结构建模中。

参考: if-then-else 2 .2; 与多分支语句比较 2 .4

## 23 循环语句

重复的顺序行为用循环语句来描述。有四种循环语句,包括 repeat, for, while 和 forever 循环。

### 231 四种基本循环语句

例 2 2 是从例 2 1 摘录的,它例示了怎样使用 repeat 循环。这种形式的循环只在关键字 repeat 后面的圆括号中给出一个循环数。

#### 例 2 2 例 2 1 的摘录

在循环开始执行前,已经确定了循环数表达式的值。然后,循环执行给定的次数。循环数表达式只在循环开始处计算一次值,所以,不可能通过改变循环数变量的值来达到退

出循环执行的目的。disable 语句可以用来提前退出循环,后面将讨论它。

repeat 语句的一般形式是:

这里,必须指定一个寄存器来保存循环数。 for 循环在函数中与 C 语言的 for 循环很相似。从本质上说,这个 for 循环把 i 初始化为 16,并且,当 i 不为 0 时,都要先执行语句,然后 i 减 1。

for 循环语句的一般形式是:

需要特别说明的是,第一条赋值语句在循环开始时执行一次。在循环体执行之前要计算 expression 的值,判断是否停留在循环中。当 expression 为真时,执行循环。循环体执行之后,下一次循环结束条件检查之前,再执行第二条赋值语句。statement 是循环体。for 循环和 repeat 循环之间的区别是: repeat 只是一种指定固定循环次数的方式。for 循环要灵活得多,它赋予了访问和更新循环变量的能力,从而控制循环结束条件。

正像 C 语言中一样,上面的 for 语句可以写成如下的 while 语句的形式:

```

i = 16;

while (i)

begin

.. // 移位减语句

i = i - 1;

end

while 语句的一般形式:

```

计算 expression 的值,如果为真,执行语句。再次计算 while 表达式。结果,当 expression 为真时,我们进入循环,并在循环中重复执行。

while 表达式必须在循环内部更新,本例中是"i=i-1"。 while 语句不能用于等待它所属的 always 语句外部所产生的值的变化,正如下例所示。

这里, while 语句表达式依赖于 inputA 的值, while 语句是空语句。上面的 while 语句在 inputA 的值变为 TRUE 之前不执行任何操作,接着执行 while 语句之后的其他语句。然而,既然在等待一个外部值的变化,正确的方式是使用 wait 语句。进一步的讨论请看 3 3 节的 wait 语句。

#### 例 2 3 抽象的微处理器

module microprocessor;

```

always

begin

powerOnInitializations;

forever

begin

fetchAndExecuteInstructions;

end

end

end

end

endmodule

```

最后, forever 循环语句将一直循环执行。使用它的一个示例是微处理器的抽象描

述。这里我们可以发现特定的初始化工作仅发生在 power-on 时刻。其后,一直在 forever 循环中读取和执行指令。可以使用 disable 语句退出 forever 循环,这将在下一节 讨论。如果退出了 forever 循环,那么 always 语句将开始执行 power-on 的初始化工作,并且再次开始 forever 循环。

forever 循环语句的一般形式:

```

loop- statement

= forever statement

...

```

参考: disable 2 3,3 .6; 等待 3 .3; 与等待比较 3 .3 .2; 内部赋值循环 3 .7

### 232 循环的异常退出

通常,循环语句会有一个"正常"的出口,比如,循环次数达到了循环计数器所指定的次数或者 while 表达式不再为 TRUE。然而,使用 disable 语句可以退出任何循环。disable 语句能终止任何有名 begin-end 块的执行;从紧接这个块的下一条语句继续执行。begin-end 块可以将块名放在 begin 关键字后面的冒号之后。C 编程语句有 break 和 continue 语句,例 2.4 展示了类似的用法。

#### 例 2.4 终止和继续循环

```

begin: break for \ (i=0;i < n\,;i=i+1) begin: continue if \ (a==0) disable \ continue; \ /\!\!/ \ proceed \ with \ i=i+1 .. \ /\!\!/ \ other \ statements if \ (a==b) disable \ break; \ /\!\!/ \ exit \ for \ loop .. \ /\!\!/ \ other \ statements end end

```

例 2 4 列出了两个命名块: break 和 continue。C 语言中的 continue 语句跳过循环体的剩余部分,更新循环条件并再次执行循环。break 语句彻底退出循环,不进行循环条件的更新,也不判断循环结束条件是否满足。本例中的 disable 语句具有相似的功能。具体说来, disable continue 语句终止名为 continue 的 begin-end 块的执行,并且进行 for 循环条件的更新。disable break 语句终止包含 for 循环的块的执行。执行将从下一条语句继续。

disable 语句的一般形式如下:

statement

= disable statement

disable statement

= **disable** task. identifier; **disable** block. identifier;

参考: 终止有名块 3.6; 任务 2.5

## 2.4 多分支语句

多分支语句接受一个或多个动作的说明,每个动作基于特定的条件。 Verilog 提供两种分支语句: if-else-if 和 case。

#### 2 4 1 If-Else-If

if-else-if 只使用 if-else-if 语句说明多分支动作。它是多路选择的最一般的方式,它可以在 if 条件表达式中检查不同的表达式。试看例 2 5 中简单计算机的描述。本例让我们想起早期的 Mark-1 计算机(某些细节不同),这里是它的简单模型。其中采用了一个精确周期风格的描述,它将读取指令和执行指令分别在两个不同的时钟周期完成。

本例使用 if-else-if 语句说明计算机的指令译码。指令寄存器的第 15 到第 13 位 (ir[15:13])与 8 种可能组合中的 7 种相比较。由匹配项决定执行哪一条指令。

参考: if-then-else 2 2; 条件操作符 2 2 2

### 2 4 2 Case

当 if 条件可以用一个共同的基本表达式来表示时, 可以使用 case 语句表达多分支结构。例 2.6 中,通过用 case 语句进行指令译码重写了 Mark-1 的描述。

case 表达式按照描述中的顺序进行计算。本例中,指令寄存器的第 15 到第 13 三位 (控制表达式)与 7 个 case 表达式中的每一个进行比较,位数必须一致。如果第一个表达式与控制表达式相匹配,则执行它后面的冒号后的语句。接着执行 case 语句后面的语句。这里进行的是四值逻辑比较。因此,一个两位的 case 条件可以出现十六种不同的值。

例 2 5 用 if-else-if 实现的 Mark-1 处理器

module mark1;

```

reg [15:0]

m[0:8191]; # 8192 x 16 位存储器

// 13 位程序计数器

reg [12:0]

pc;

∥ 13 位累加器

reg [12:0]

acc;

// 16 位指令寄存器

reg [15:0]

ir;

∥ 时钟信号

ck;

reg

always

begin

@ (posedge ck)

ir = m [pc];

∥ 取指令

@ (posedge ck)

if (ir[15:13] == 3 b000) // 开始译码

// 执行

pc = m [ir [12:0]];

else if (ir[15:13] = 3 b001)

pc = pc + m [ir [12:0]];

else if (ir[15:13] = 3 b010)

acc = -m [ir [12:0]];

else if (ir[15:13] = 3 b011)

m [ir [12:0]] = acc;

else if ((ir[15:13] = 3 b101) \parallel (ir[15:13] = 3 b100))

acc = acc - m [ir [12:0]];

else if (ir[15:13] = 3 b110)

if (acc < 0) pc = pc + 1;

// 累加程序计数器

pc = pc + 1;

end

endmodule

case 语句的一般形式:

statement

= case_statement

| ...

case - statement

= case ( expression ) case - item { case - item } endcase

```

case - item

· 51 ·

```

= expression { ,expression} : statement- or- null | default [:] statement- or- null

```

### 例 2.6 用 case 语句实现的 Mark-1 处理器

```

module mark1Case;

∥ 8192 x 16 位存储器

reg [15:0]

m[0:8191];

// 13 位程序计数器

reg [12:0]

pc;

∥ 13 位累加器

reg [12:0]

acc;

∥ 16 位指令寄存器

reg [15:0]

ir;

∥ 时钟信号

reg

ck:

always

begin

@ (posedge ck)

ir = m [pc];

@ (posedge ck)

case (ir [15:13])

3 b000 :

pc = m [ir [12:0]];

3 b001:

pc = pc + m [ir [12:0]];

3 b010 :

acc = -m [ir [12:0]];

3 b011 :

m [ir [12:0]] = acc;

3 b100,

3 b101 :

acc = acc - m [ir [12:0]];

3 b110 :

if (acc < 0) pc = pc + 1;

endcase

pc = pc + 1;

end

```

可以在 case 表达式的位置使用 default 关键字来说明默认情况。当有默认语句时,如果没有其他 case 表达式匹配控制表达式,将执行默认语句。默认语句可以列在 case 语句的任意位置。

本例也例示了怎样说明同一个动作属于几个 case 项的情形。case 表达式之间的逗号说明任何一个比较如果为真,都将执行后面的语句。在 Mark-1 的示例中,如果选定的三位值为 4 或 5,累加器将被减去一个值。

最后,注意控制表达式和 case 表达式不必是常数。

参考: casez, casex 2 4 4; 与 if-else-if 比较 2 4 3; 条件操作符 2 2 2; 寄存器说明

endmodule

### 2 A 3 Case 和 If-Else-If 的比较

在上述的 Mark-1 例中, case 和 if-else-if 都可能使用。该例中使用 case 会更加简洁, 更加易读。进一步说, 既然所有的表达式都要和相同的控制表达式相比较, case 语句更加合适。然而, 这些结构之间有两个主要区别。

- · if-else-if 结构中的条件表达式更具有一般性。任意一种形式的表达式都可以用在 if-else-if 中,然而在 case 语句中,所有的 case 表达式都与控制表达式具有相同的形式。