# 第一章 互连设计的重要性

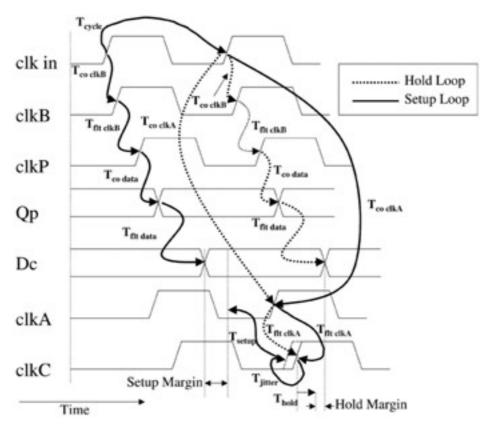

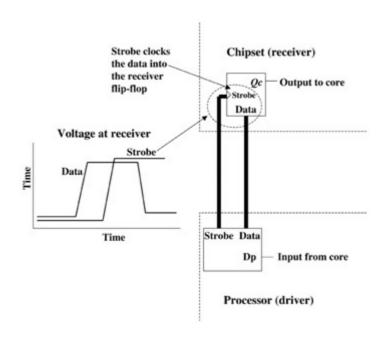

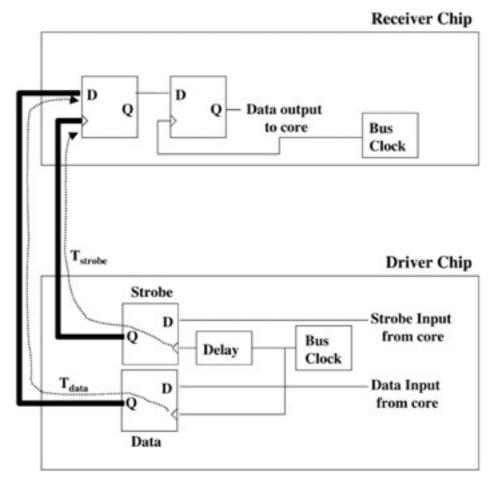

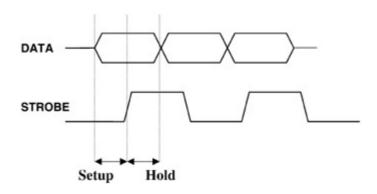

光速已经太慢了,当前大规模生产的普通数字电路要求时序控制达到皮秒的范围。光从人的鼻子传输到耳朵所需要的时间大概为 100ps (在 100ps 的时间里,光将传输 1.2 英寸)。这样级别的时序控制不但要维持在硅芯片里,而且还必须在级别更大的系统板上实现,比如一个计算机的主板。在这些系统中,将器件互连的导体不应再被看作一根简单的导线,而是呈现了高频效应的传输线。如果这些传输线没有被合理的设计,他们将在不经意间毁灭系统时序。有些数字设计(并非全部)的复杂程度已经达到甚至超过了模拟电路设计。数字技术经历了令人瞩目的空前发展。确实,在技术公司的市场部存在着这样的信条:如果让市场来告诉你公众需要什么,那已经太迟了!

本书将要解决由于数字电路的迅速发展而而带来的技术瓶颈。这要求现代数字电路设计者们掌握以前不需要的知识,而很多人却没有。相关知识的缺乏导致了大量的错误信息在工程师中流行起来,高速设计的概念经常成为了谬论,由于知识的缺乏,这些谬论一直没有得到解决。事实上,许多相同的概念已经在电子工程的其他学科被用了几十年。例如射频设计和微波设计。问题是阐述相关主题的参考书都太抽象而不能立即的被电子工程师接受,又或者工程师们太注重实际而没有足够多的理论知识来完全理解相应的主题。本书将直接针对数字设计领域,以一种让工程师或学生能够理解的方式来讲解一些必要的概念,以使他们能理解并解决目前及将来的问题。值得注意的是,本书所讲的内容已经被成功的运用到了现代设计当中。

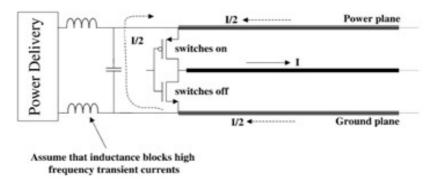

# 1.1 基础知识

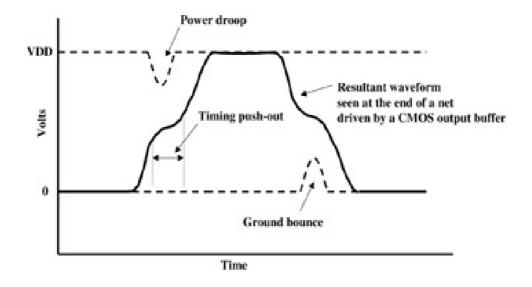

读者应该知道,数字设计的基本思想是进行信号通讯,这些信号以0s或1s来表达并传递信息。典型的数字电路是发送或接受一系列的梯形电压波(如图1.1所示)来进行通讯,这里,高电平代表1,低电平代表0,数字电路之间用来传输信号的路径被称作互连。互连是从发送信号的芯片到接收信号芯片间的完整的电子路径,它包括芯片封装、连接器,插座及许多其他的结构。一组互连被称作总线。数字信号接受设备用来区别高电压和低电压的区域被称为阈值区。 在这区域里面,接收器有可能识别信号为高,也有可能识别为低。 在硅芯片中,实际的开关电压因温度、供应电压,硅芯片的生产过程及其他的变量的变化而变化。从系统设计者的观点来看,通常每一个接收芯片都有其识别信号状态为高或低的电压阈值,即Vih 和 Vil。当信号电压值位于Vih上方或Vil下方时,其状态在所有的情况下都可以被接收芯片正确的识别。 因此,为了确保信号完整性,设计者必须保证系统在所有的情况下,状态为高时的电压值不低于 Vih,低时不高于Vil。

为了最大化数字系统的运作速度,通过状态不确定区的开关时间必须被减到最少。 这意谓着数字信号的上升和下降时间得尽可能地快。尽管在理想情况下,无限快的边沿速率应该被使用,但实际存在的很多问题限制了这种可能。实际上,我们很可能遭遇几百皮秒的边沿速率。通过傅立叶分析,读者可以验证边沿速率越快,那么更高的频率成分将在信号的频谱中被发现。对于这个难于理解的问题可以这样理解,每根导线都存在电容,电感和与频率

图1.1、数字信号波形

相关的电阻。当频率足够高是,这些东西都是不可忽略的。因此导线不再是一根简单的导线,在波形从驱动芯片传播到接收芯片的过程中,其上面分布的寄生参数将产生延迟,其瞬间阻抗变化会引起信号波形失真、干扰等,并使系统失灵。导线现在成为了一种被耦合到其周围所有事物的元素,其中包括电源和地结构及其他的迹线。信号并不被完全地包含在其自身的导线中,而是一个围绕着导线周围的所有的局部电磁场的组合体。在一条互连中的信号将影响其他的互连中的信号,同时也被它们所影响。此外,在高频时,复杂的相互作用将发生在相同互联的不同部分,例如封装,连接器,过孔,和拐角处。 所有的这些高速效应容易产生奇特的,失真了的波形,这的确会让设计者以一个完全不同的观点来对待高速逻辑信号。在保证合适的信号以适当的时间通过Vil和Vih的简单工作中,互连附近的每个结构的物理和电子属性都扮演着一个重要的角色。 这些事物也决定了系统将会辐射多少能量到外部空间中,这又会导致了政府决定是否系统遵从相应的辐射要求。我们将会在较后的章节中看到如何解释所有的这些事物。

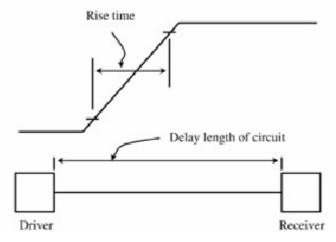

当一个导体必须被看作一系列的分布的电容和电感时候,它就被认为是一条传输线。一般来说,当被考虑的电路尺寸接近信号中所关心的最高频率的波长时,应该按照传输线来对待。在数字世界中,因为边沿速率几乎完全决定了信号中的最大的频率成分,因此人们能像图1.2所显示的那样用信号的上升和下降时间来对比电路尺寸,这样可以替代地决定电路是否按照传输线来处理。在典型的线路板上,信号大致按照光速的一般来传播(精确的公式将会是在较后的章节中),因此500ps的边沿相当于在信号在线路上传播 3 in. 长度的时间。通常认为,任何超过相当于1/10 边沿时间的走线都必须被看作传输线。

图 1.2: 上升时间和线路长度。

高速设计中最困难的方面之一是各种影响数字设计结果的变量相互作用和依赖这个事实。其中一些变数是可控的,而另一些则迫使设计者任其自由变化。高速设计的难点其中一个方面就是表现在如何处理这些变量,而无论他们是否可控。通常,设计者可以忽略或假定一些变量的值来简化设计,但这也可能导致无法从未知的失败中找到起因。随着设计周期的限制,过去的简化过程正快速地从现代设计者的程序中减少。这本书也将讨论如何合并大量的变量,不然的话,很多问题将很难处理。没有一种方法能够操作大量的变数,无论设计者对系统的理解有多么深刻,最后设计还是要求助于臆测。处理所有变数的最后步骤通常是最困难的部分,并且这一部分通常容易被设计者忽略。一个设计者在无法处理大量变数情况下将会最终改为得到一些"要点问题",而且希望它们近似地表现为所有已知情况。有时这种方法是不可避免的,这可能是一种危险的假设游戏。 当然,一定的假设总是在设计中存在,但是系统设计者的目标应该将不确定性减到最少。

# 过去和将来

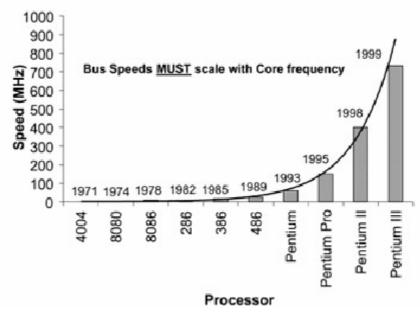

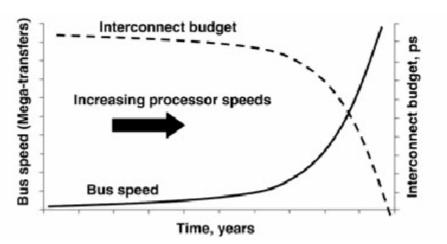

支登摩尔, 英特尔公司的合伙创办人, 曾经预测计算机的性能每18个月会翻一番。历史验证了这个有洞察力的预言。显然, 计算机的性能几乎每1.5年便增加一倍, 同时它们的价格却在减少。有关测量处理器性能的方法是内在的时钟频率。图1.3展示了过去各个时期的许多处理器与其内部的时钟频率。从现在的角度看, 即使图中最快的处理器或许也不能满足人们的需求。重点是计算机的速度正随着核心频率呈指数地增加, 如图1.4所示, 负责吞吐信息到处理器的总线的数据率越快, 那么将导致互连的时序预算按指数减少。减少时序裕量意味着应该适当地考虑一些可能导致数字波形时序不确定性的现象, 这对于信号能够正确到达接收芯片甚至更重要。这有两个无法避免的障碍会使数字系统设计非常困难。第一个障碍是数字设计中必须考虑的变量的绝对数量正在增加。随着频率的增加, 那些在低速设计中可以被忽略的新的影响开始变得重要。一般而言, 设计的复杂度随着变量的增加按照指数增加。第二个障碍是在过去的设计中可能被忽略的新效应必须以非常高的精度去建模。这些新模型在本质上经常是三维的, 或要求专门的模拟技术, 而这些技术往往又超出了数字设计者的知识范畴。对于围绕处理器的子系统来说, 这些障碍也许具有更深远的意义, 因为他们相对来说更慢一些, 但又不得不满足处理器不断增长的需求。

图 1.3: 莫尔定律。

图 1.4: 随着系统频率的增加互连的时间裕量减少。

所有的这些导致了目前的情况:新的问题有待解决。能解决这些问题的工程师将会决定未来。这一本书将会使读者具备必要的实际经验来理解现代高速数字设计的内容,同时也会使读者具有足够的理论来看清本书以外的世界,解决作者目前还没有遇到的问题。谨此。

# 第二章 理想传输线原理

在当今的高速数字系统设计中,已经必须把 PCB 或多片模块(MCM)的走线当作传输线来处理。我们再也不能如同处理低速设计一般,视互连为集总电容或简单的延迟线。这是因为与传输线相关的时序问题在总的时序裕量中占有越来越大的比例。我们要对 PCB 的结构给予极大的关注,这样才能使传输线的电气特性得以控制并可预测。本章将介绍用于数字系统中的典型的基本传输线结构和理想情况下的基本传输线理论。本章介绍的内容将提供充分理解随后章节所需的必要知识基础。

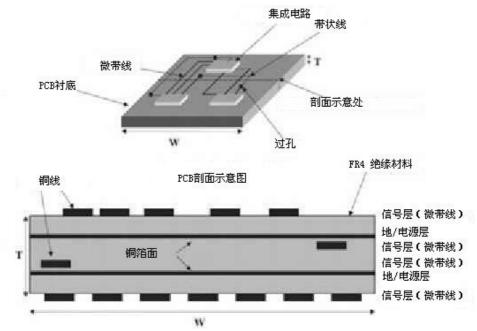

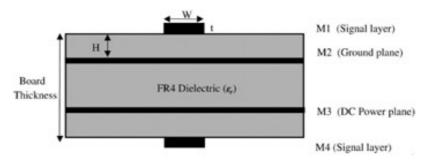

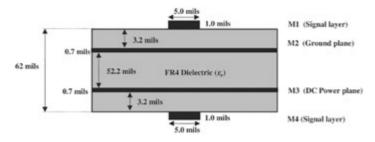

### 2.1 PCB 或 MCM 中的传输线结构

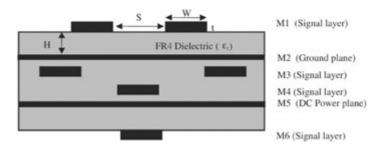

典型 PCB 或 MCM 中所见到的传输线结构是由嵌入或临近电介质或绝缘材料,并且具有一个或多个参考平面的导线构成。典型 PCB 中的金属是铜,而电介质是一种叫 FR4 的玻璃纤维。数字设计中最常见的两种传输线类型是微带线和带状线。微带线通常指 PCB 外层的走线,并且只有一个参考平面。微带线有两种类型:埋式或非埋式。埋式(有时又称作潜入式)微带线就是将一根传输线简单地嵌入电介质中,但其依然只有一个参考平面。带状线是指介于两个参考平面之间的内层走线。图 2.1 所示为 PCB 上不同元件之间的内层走线(带状线)和外层走线(微带线)。标识处的剖面图显示了传输线与地/电源层的相对关系。在本书中,传输线通常会用剖面图的方式来表示。这在对以后计算和直观化不同传输线的描述参数很有用。

图 2.1 典型 PCB 设计的传输线

如图2.1所示的多层PCB能提供多种带状线和微带线结构。要求进行导体层和绝缘层的控制(即叠层)以使传输线的电气特性可以预测。高速系统中,传输线电气特性的控制是极重要的。本章定义的基本电气特性称为传输线参数。

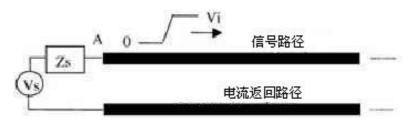

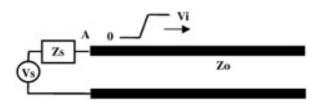

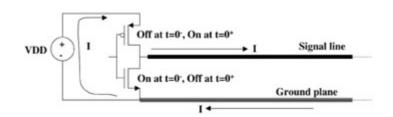

# 2.2 波形传播

在高频中,当数字信号的边沿速度(上升或下降时间)比在PCB走线上传送的电信号的传播延迟来得小时,信号将受到传输线效应的极大影响。电信号在传输线的传送方式就如水流过一根长的方形管子一样。这就是所谓的电波传播。就如水是以波的形式流过管子,电信号会以波的形式沿传输线传送。另外,就如水在一定时间里流过管子一定长度,电信号也将在一定时间里沿着传输线传送一定长度。进一步打个简单的比方,传输线上的电压比作水在管子中的高度,而电流比作水的流量。图2.2所示为表示传输线的常见方

式。上面的线是信号路径,而下面的线是电流的返回路径。电压V<sub>s</sub>是从节点A输入的初始电压,而V<sub>s</sub>和Z<sub>s</sub>是通常被定义为信号源或者激励的输出缓冲器的戴维南等效描述。

图2.2 描述数字信号在传输线上传播的典型方法

### 2.3 传输线参数

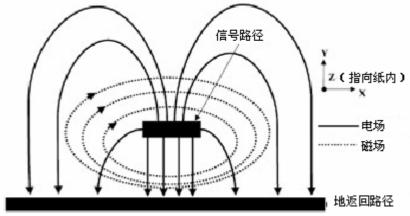

为了分析高速数字系统的传输线效应,必须定义传输线的电气特性。定义传输线基本电气特性的是它的特性阻抗和它的传播速度。特性阻抗类似于水管的宽度,而传播速度类似于水流过管子的速度。为了定义和导出这些术语就有必要分析传输线的基本特性。如图2.2所示,沿着传输线传送的信号将会在信号路径和回流路径(通常被称为地回路或地,甚至参考平面是电源层)之间产生一个电压差。当信号到达传输线上任意点Z时,位于信号路径上的导线将存在一个Vi代特的电势,而地回路导线上存在0V的电势。这个电压差在信号和地回路导线之间建立一个电场。而且,安培定律表明任何给定封闭路径所包围磁场的线积分等于此路径所包围的电流。用简单术语来说就是,如果一个电流流过导体,它将形成一个环绕导体的磁场。因此可以确定,如果一个输出缓冲器向传输线注入一个电压Vi、电流Ii的信号,那么它将分别感应出一个电场和一个磁场。然而,应该明白的是直到时间z/v为止,线上任意点Z的电压Vi和电流Ii,都将会是零,v是信号沿着传输线的传送速度,而z是到源端的距离。注意,这个分析暗示信号不仅仅在传输线的信号导线上传播;当然,它会以电磁场的形式在信号导体和参考平面之间传播。

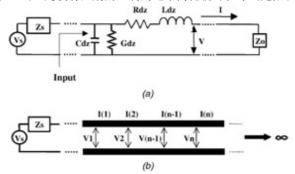

既然建立了传输线的基本电磁特性,它就有可能为线的一段构造一个简单电路模型。图 2.3所示为微带状传输线的一个截面和线上电流相关的电磁场模型。如果假定在Z方向(指向纸内)没有电场或磁场的分量传播,电场和磁场将是正交的。这就是所谓的横向电磁场模型(TEM)。传输线在通常情况下将会处于TEM模型中传送,而且它甚至在相对高频还是适当的近似值。这就允许我们分析沿着Z方向传播的导线的微分段(或片)传输线。图 2.3 所示的二个分量是长度dz的无限小或微分段(片)传输线的电磁场。因为在电场和磁场中都储存了能量,所以我们的电路模型要包括与这个能量储存有关的电路元件。传输线的一个微分段的磁场可用一个串联电感Ldz来代表,L是单位长度电感。一个长度为dz的信号路径和地回路之间的电场可用并联电容Cdz来代表,C为单位长度电容。理想模型应该是由无限多个这种小部分成批级联而成。这个模型足够描述无损传输线的一个区段(例如,一条无阻的传输线)。

图 2.3: 微带线的截面描述了假定电信号沿线进入纸内传播的电磁场

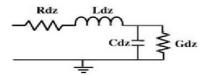

然而,因为PCB板使用的金属不是无限传导的并且绝缘材料也不是无限阻尼的,所以损耗结构必须以一个串联电阻Rdz和一个接地的并联电阻Gdz的形式加入到模型中,电导单位为西门子(1/ohm)。图2.4所示为传输线微分段的等效电路模型。串联电阻Rdz代表导体有限传导率引起的损耗;并联电阻Gdz代表分隔导体和地层的电介质的有限电阻引起的损耗;串联电感Ldz代表磁场;而电容Cdz代表导体与地层之间的电场。在本书剩余部分,这些部分之一被称为RLCG单元。

图2.4 长度为dz的传输线微分段的等效电路模型(RLCG模型)

#### 2.3.1. 特性阻抗

传输线的特性阻抗Zo定义为线上任意点的电压波和电流波的比率,即V/I =Zo。图2.5所示为一条传输线的二种表示法。图2.5a所示为用上述RLCG单元建模的长度为dz传输线的微分段,并且用一个阻抗为Zo的器件终结。RLCG单元的特性阻抗被定义为电压V和电流I的比率,如图2.5a所示。假定负载Zo完全等于RLCG单元的特性阻抗,图2.5a所示可以用图 2.5b 所示的无限长传输线表示。图2.5a中的终端Zo简单表示了组成整个传输线模型的无限个阻抗为Zo的附加RLCG片段。因为终接装置处电压/电流比率Zo将会与RLCG片段的相同,则从电压源看过去,图2.5a和b是没有区别的。利用这个简化就可以导出无限长传输线的特性阻抗。

图2.5 导出传输线特征阻抗的方法: a) 微分片段; b) 无限长传输线

为了导出传输线的特征阻抗必须分析图2. 5a。假定线的特征阻抗等于终端阻抗Zo,求解图2. 5a的等效 电路的输入阻抗得到等式2. 1。为了简单起见,微分长度dz用一小段长度 $\Delta$ z替代。推导如下: 假定,

$$jwL(\Delta z) + R(\Delta z) = Z\Delta z$$

(线长  $\Delta z$ 的串联阻抗)

$iwC(\Delta z) + G(\Delta z) = Y\Delta z$ (线长  $\Delta z$ 的并联阻抗)

则有,

$$\begin{split} Z(\text{input}) &= Z_o = \frac{(Z_o + Z \, \Delta z)(1/Y \, \Delta z)}{Z_o + Z \, \Delta z + 1/Y \, \Delta z} \qquad \big( \, \text{假定负载阻抗等于特征阻抗} \big) \\ Z_o \left( Z \, \Delta z + Z_o + \frac{1}{Y \, \Delta z} \right) &= (Z_o + Z \, \Delta z) \frac{1}{Y \, \Delta z} \\ &\Rightarrow Z_o Z \, \Delta z + Z_o^2 + \frac{Z_o}{Y \, \Delta z} = \frac{Z_o}{Y \, \Delta z} + \frac{Z \, \Delta z}{Y \, \Delta z} \\ &\Rightarrow Z_o (Z \, \Delta z + Z_o) &= \frac{Z}{Y} \\ &\Rightarrow Z_o Y (Z \, \Delta z + Z_o) = Z \\ &\Rightarrow \lim_{\Delta z \to 0} [Z] &= Z_o^2 Y \end{split}$$

因此,

$$Z_o = \sqrt{\frac{Z}{Y}} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(2.1)

其中,R 为每单位长度欧姆,L 为每单位长度亨利,G 为每单位长度西门子,C 为每单位长度法拉,而 w 为 每秒弧度。因为 R 和 G 都比其他项要小得多,通常特征阻抗近似为 $Z_o = \sqrt{L/C}$  是足够的。仅在甚高频或有极 大损耗线时,阻抗的 R 和 G 分量才变得重要(有损传输线包含在第四章)。有损耗的线也将导出复杂的特征 阻抗(如含有虚部分量)。不过为了数字设计的目的,只有特征阻抗的幅值才是重要的。

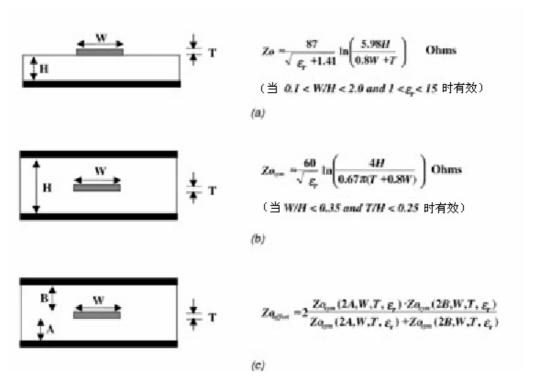

为了得到最大的精确度,需要使用众多商业可用的二维电磁场求解器之一去计算设计目的的PCB走线阻抗。求解器将提供单位长度的阻抗、传播速度、L和C分量。这就足够了,因为R和G通常对阻抗影响极微。如果没有场求解器时,图2.6所示的公式将提供典型传输线阻抗值的有效近似,它是走线的几何结构和介电系数( $\mathcal{E}_x$ )的函数。更精确的特征阻抗公式如附录A所示。

图2.6 典型传输线的特性阻抗近似: (a) 微带线; (b) 对称带状线; (c) 偏移带状线。

#### 2.3.2 传播速度、传播时间和传播距离

传输线上的电信号的速度传播将由周围介质决定。传播延迟通常用米每秒来度量,它是传播速度的倒数。传输线的传播延迟按周围介质系数的平方根的比例增加。传输线的时间延迟仅指信号传播过整个线长所用的时间总量。以下等式表示了介电系数、传播速度、传播延迟和时间延迟之间的关系:

$$v = \frac{c}{\sqrt{\varepsilon_r}} \tag{2.2}$$

$$\mathbf{PD} = \frac{1}{v} = \frac{\sqrt{\varepsilon_r}}{c} \tag{2.3}$$

$$TD = \frac{x\sqrt{\varepsilon_r}}{c}$$

(2.4)

其中,

v = 传播速度,单位 m/s

c = 真空光速 (3 × 10 $^{8}$  m/s)

ε<sub>r</sub> = 电介质常数

PD = 传播延迟,单位 s/m

TD = 信号在传输线上传播长度 x 的时间延迟

x = 传输线长度,单位 m

时间延迟也可以由传输线的等效电路模型求出:

$$TD = \sqrt{LC} \tag{2.5}$$

其中L是线长的总串联电感,而C是线长的总并联电容。

必需注意等式 (2.2) 到 (2.4) 是假设没有磁性材料存在的,即  $\mu_r = 1$ ,这是由于在公式中不考虑磁性材料。

传输线的延迟取决于绝缘材料的介电系数、线长和传输线剖面几何结构。剖面几何结构决定了电场是完整地抑制在板内还是散射到空中。由于典型的 PCB 板是用介电系数近似为 4.4 的 FR4 制造的,而空气的介电系数是 1.0,最后得到的有效介电系数是两者加权平均。电场在 FR4 的数量和在空气的数量决定了有效值。当电场完全被包围在板内时(例如带状线)其有效介电系数将大一些,因而信号将比外层走线传播慢一些。当信号走在板子的外层时(例如微带线),电场散射到绝缘材料和空气中,具有较低的介电系数;因而信号将会比内层的传播更快。

微带线的有效介电系数计算如下:

$$\varepsilon_{\epsilon} = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left( 1 + \frac{12H}{W} \right)^{-1/2} + F - 0.217(\varepsilon_r - 1) \frac{T}{\sqrt{WH}}$$

(2.6)

$$F = \begin{cases} 0.02(\varepsilon_r - 1) \left(1 - \frac{W}{H}\right)^2 & \text{for } \frac{W}{H} < 1\\ 0 & \text{for } \frac{W}{H} > 1 \end{cases}$$

(2.7)

其中  $\varepsilon$  r是板材的介电系数,H是导线到地层的高度,W是导线宽度,而T是导线厚度。

# 2.3.3 SPICE 仿真等效电路模型

在 2.3 节中我们介绍了由无限数量 RLCG 片段串联而成的传输线等效分布电路模型。因为用无限个单元建模传输线是不实用的,所以在仿真中足够数量的单元是基于最小上升或下降时间来决定的。仿真数字系统时,当所选的值满足最短 RLCG 片段的时间延迟( $TD=\sqrt{LC}$ )不大于最小的系统上升或下降时间的十分之一时,通常就足够了。上升或下降时间定义为信号在最小量和最大量之间转换的时间量。典型的上升时间是指最大幅值由 10%达到 90%之间的时间。例如,如果信号从 0V 转换到 1V,那么上升时间是指电压从 0.1V 达到 0.9V 的时间。

# 经验法则:选择足够数量的 RLCG 片段

当使用一个分布 RLCG 模型建模传输线时, RLCG 片段的数量由下式确定:

segments

$$\geq 10 \left( \frac{x}{T_r v} \right)$$

其中x是传输线的长度, v是传输线的传播速度, 而 Tv是上升(下降)时间。模型中的每

个参数应该与片段数量成比例。例如,如果知道每米的参数,则用于单个片段的最大值为:

$$C_{\text{segment}} = \frac{(x)(C/\text{meter})}{\text{segments}}$$

$$L_{\text{segment}} = \frac{(x)L/\text{meter}}{\text{segments}}$$

$$R_{\text{segment}} = \frac{(x)R/\text{meter}}{\text{segments}}$$

$$G_{\text{segment}} = \frac{(x)G/\text{meter}}{\text{segments}}$$

$$TD_{\text{segment}} = \sqrt{L_{\text{segment}}C_{\text{segment}}} \leq \frac{T_r}{10}$$

#### 例子 2.1: 创建传输线模型。

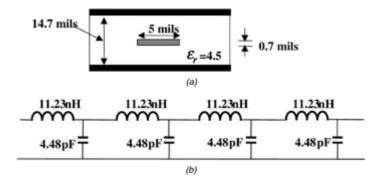

创建一条剖面如图 2.7a 所示的长 5 英寸无损耗 50  $\Omega$  传输线的等效电路模型。假定驱动器的最小上升时间 2.5ns,介电系数为 4.5。

图 2.7 创建传输线模型: (a) 剖面图; (b) 等效电路。

解法: 首先计算传输线的电感和电容。因为没有求解器可用, 所以要用以上所述的等式。

$$Z_o \approx \frac{60}{\sqrt{\varepsilon_r}} \ln \frac{4H}{0.67\pi(T+0.8W)} = \frac{60}{\sqrt{\varepsilon_r}} \ln \frac{4(14.7)}{0.67\pi[0.7+0.8(5)]} = 50 \ \Omega$$

$$TD = \frac{x\sqrt{\varepsilon_r}}{c} = 5 \text{ in.} (0.0254 \text{ m/in.}) \frac{\sqrt{4.5}}{3 \times 10^8 \text{ m/s}} = 898 \text{ ps}$$

$$v = \frac{c}{\sqrt{\varepsilon_r}} = \frac{3 \times 10^8 \text{ m/s}}{\sqrt{4.5}} = 1.41 \times 10^8 \text{ m/s}$$

如果传输线是微带线,计算速度的过程是一样的,但是有效介电系数要用等式(2.6)来计算。 因为 $Z_o = \sqrt{L/C}$ 和 $TD = \sqrt{LC}$ ,我们有两个等式和两个未知数。求解 L 和 C。

$$L_{\text{total}} = (\text{TD})(Z_o) = (898 \times 10^{-12})(50 \ \Omega) = 44.9 \text{ nH}$$

$$C_{\text{total}} = \frac{\text{TD}}{Z_o} = \frac{898 \times 10^{-12} \text{ s}}{50 \ \Omega} = 17.9 \text{ pF}$$

以上L和C值是5英寸线的总电感和总电容。

segments

$$\ge 10 \left( \frac{X}{T_r v} \right) = 10 \left[ \frac{5 \text{ in.} (0.0254 \text{ m/in.})}{2.5 \text{ ns} (1.41 \times 10^8 \text{ m/s})} \right] = 3.6$$

因为3.6不是约整数,所以我们在模型中使用4个片段。

$$C_{\text{segment}} = \frac{C_{\text{total}}}{\text{segments}} = \frac{17.9 \text{ pF}}{4} = 4.48 \text{ pF}$$

$$L_{\text{segment}} = \frac{L_{\text{total}}}{\text{segments}} = \frac{44.9 \text{ nH}}{4} = 11.23 \text{ nH}$$

最后无损耗传输线等效电路如图 2.7b 所示。仔细检查以确认满足经验法则。

$$TD_{segment} = \sqrt{L_{segment}C_{segment}} = \sqrt{(4.48 \text{ pF})(11.23 \text{ nH})} = 0.224 \text{ ns} \le \frac{T_r}{10}$$

#### 2.4 发射初始波和传输线反射

激励电路特性和传输线特性极大地影响了从一个装置传送到另一个装置信号的完整性。其次,理解信号如何发射进入传输线和它在接收器端看起来如何是很重要的,虽然很多参数会影响接收器端信号的完整性。本节中我们将描述最基本的性能。

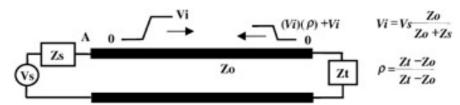

#### 2.4.1 初始波

当驱动器发射一个信号进入传输线时,信号的幅值取决于电压、缓冲器的内阻和传输线的阻抗。驱动器端看到的初始电压决定于内阻和线阻抗的分压。图2.8描述了一个初始波被发射进入传输线。初始电压*Vi*将沿着传输线传播直到它到达终端。*Vi*的幅值决定于内阻和线阻抗之间的分压:

$$V_i = V_s \frac{Z_o}{Z_o + Z_s} \tag{2.8}$$

图2.8 发射一个波进入一条长传输线

如果传输线末端终接的阻抗正好和线的特征阻抗匹配时,幅值为1/2的信号端接到地,这样电压1/2将保持直到信号源再次转变。这种情况下电压1/2是直流稳态值。否则,如果传输线的末端出现的阻抗不同于传输线特征阻抗,信号的一部分端接到地,而信号的剩余部分将沿着传输线向源头端反射回去。反射系数决定了反射回去的信号数量,它被定义为给定节点上的反射电压和入射电压的比值。在本文中,节点定义为传输线上的阻抗不连续点。阻抗的不连续可以是一段不同特征阻抗的传输线、一个终端电阻或芯片上缓冲器的输入阻抗。反射系数计算如下:

$$\rho = \frac{V_{\text{reflected}}}{V_{\text{incident}}} = \frac{Z_t - Z_o}{Z_t + Z_o}$$

(2.9)

其中Zo为传输线特征阻抗,而Zt是不连续的阻抗。等式假定信号沿着特征阻抗为Zo的传输线行进并遇到不连续阻抗Zt。注意:如果Zo等于Zt则反射为零,意味着没有反射。Zo等于Zt的情况称为终端匹配。

如图 2.9 所示, 当入射波达到终端 Zt 时,信号的一部分 Viρ被反射回到源头端,并与入射波叠加在线上产生一个总的幅值 Viρ+Vi。反射的分量将会传播回源头端,并可能产生另一次离开源头的反射。这个反射和逆反射过程将继续,直到传输线达到稳定状态。

图 2.9 入射信号被不匹配负载反射

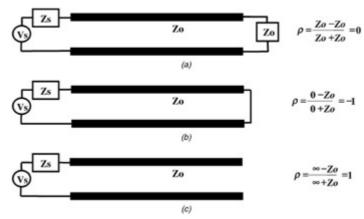

图 2.10 描述了反射系数的特殊例子。当传输线终接了一个正好等于特征阻抗的值时,将没有不连续,而信号将不反射地终接到地。当负载开路和短路时反射是 100%,不过反射信号分别是正的和负的。

图 2.10 特殊情形的反射系数: (a) 终接 Zo; (b) 短路; (c) 开路。

#### 2.4.2 多次反射

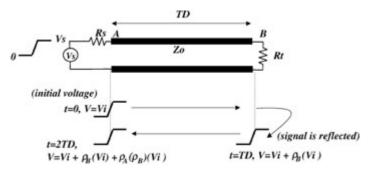

如上所述,当信号在线终端处的阻抗不连续点被反射时,信号的一部分将反射回源头。当反射信号到 达源头时,若源头端阻抗不等于传输线阻抗就将产生二次反射。接着,若传输线的两端都存在阻抗不连续, 信号将在驱动线路和接收线路之间来回反射。信号的反射将最后达到直流稳态。

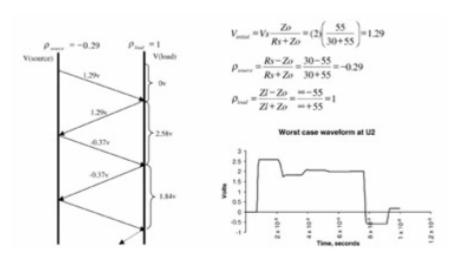

如图2.11所示为几个TD的时间区间的一个例子(TD为从源到负载的传输线的时间延迟)。当信号源转变为Vs,传输线上的初始电压Vi决定于分压式Vi=VsZo/(Zo+ Rs)。当t=TD时,初始电压Vi达到了负载Rt。 此时产生幅值为  $\rho_{\scriptscriptstyle R}V_i$  的反射分量,它和初始电压叠加在负载处产生总电压 $V_i+\rho_{\scriptscriptstyle B}V_i$ (其中  $\rho_{\scriptscriptstyle B}$  是负载

端的反射系数)。波的反射分量( $ho_{\it B} V_i$ )然后传播回到源端,并在 ${\it t}={\it 2}{\it T}{\it D}$ 时产生一个由 $ho_{\it A}

ho_{\it B} V_i$  决定的

离开源端的反射( $ho_A$  是源端的反射系数)。此时源端的电压将是先前的电压(m Vi)加上来自反射的入射

瞬态电压( $\rho_B V_i$ )再加上反射波( $\rho_A \rho_B V_i$ )。反射和逆反射将持续到线上电压趋近稳态直流值。如读者所见,若终端不匹配,反射要一段长的时间才能稳定下来,并会有一些重要的时序影响。

图2.11 传输线反射的例子

明显手工计算多次反射是相当繁重的。一种推算信号反射效应的更简单方法就是使用网格图。

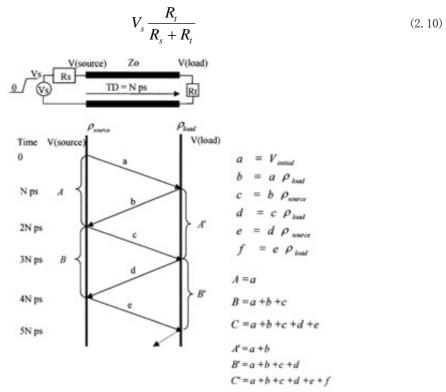

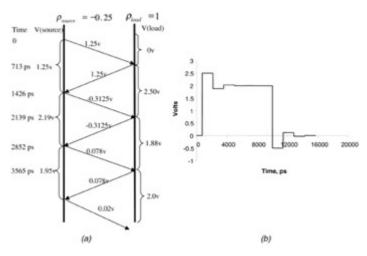

#### 网格图和过载/欠载传输线

网格图(有时称为反弹图)是用于解决带线性负载传输线上多次反射的方法。图2.12所示为网格图实例。左右两侧的垂直线分别代表了传输线的源头端和负载端。垂直线之间的斜线代表了信号在源头和负载之间来回反弹。图从上到下表示时间的增加。注意:时间的增量等于传输线的时间延迟。图中垂直线的顶部标识了反射系数,反射系数表示了传输线和负载之间的反射(从线看进负载)以及源端的反射系数。小写字母表示沿着传输线传播的反射信号的幅值,大写字母表示源端看到的电压,而带逗号的大写字母代表负载端看到的电压。例如,参照图2.12,线的近端将保持A伏的电压,且持续时间为2N皮秒,其中N是传输线的时间延迟(TD)。电压A就是初始电压 Vintial,它将不变直到负载端的反射到达源端。电压A'就是电压a加

上反射电压b。电压B是初始电压a、负载端的发射信号b和源头端的反射信号c的总和。如果传输线开路,线上的反射最终使电压稳定为源端电压Vs。然而,如果传输线终接电阻Rt,稳态电压如下计算:

图2.12 用于计算传输线多次反射的网格图

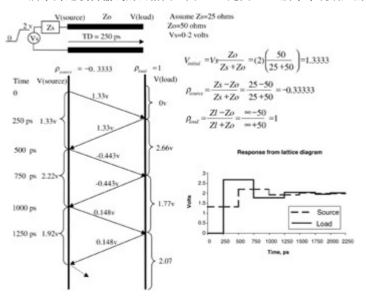

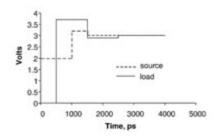

#### 例子2.2: 欠载传输线的多次反射。

如上所述,当驱动器发射信号进入传输线时,传输线上呈现的初始电压决定于驱动器阻抗 Zs 和线阻抗 Zo 之间的分压。如图 2.13 所示,这个值为 0.8V。初始信号 0.8V 将沿着传输线传播直到到达负载。此特殊情况下,负载开路因而反射系数为 1。接着,整个信号被反射回源头端,并和入射信号 0.8V 叠加。则在 t=TD (本例中为 250ps)时,负载端的信号为 0.8+0.8V(或 1.6V)。0.8V 反射信号将沿着传输线向源头端传播。当信号到达源头,信号的部分将反射回负载端。反射信号的幅值决定于传输线阻抗 Zo 和源头端阻抗 Zs 之间的反射系数。本例中反射回负载端的值为 0.8V\*0.2,即 0.16V。反射信号将与传输线上已有的信号叠加,总的幅值为 1.76V,带着 0.16V 的反射部分移向负载端。这个过程将重复直到电压达到 2V 的稳态值。

#### 图 2.13 例子 2.2: 用于计算欠载传输线多次反射的网格图

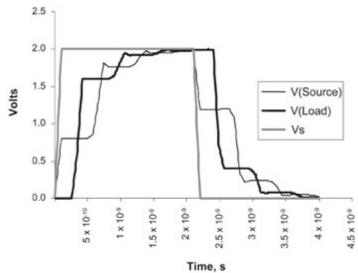

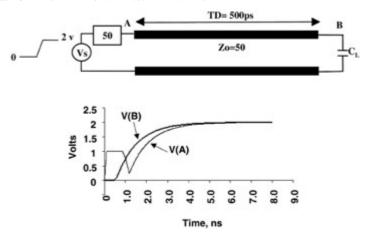

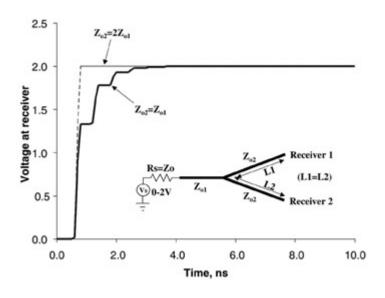

网格图的响应如图 2.13 右下角所示。响应的计算机仿真如图 2.14 所示。注意:尽管电压源的空载输出是方波,反射依然引起波形在接收端呈现"阶梯步幅"。这种效应发生在源头端阻抗 Zs 比传输线阻抗 Zo 大的时候,并被称为欠载传输线。

图 2.14 例子 2.2 的传输线系统仿真,其中传输线阻抗小于源头端阻抗(欠载传输线)

#### 例子 2.3:过载传输线的多次反射。

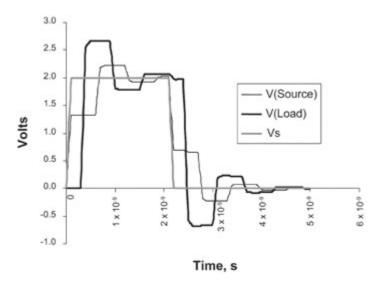

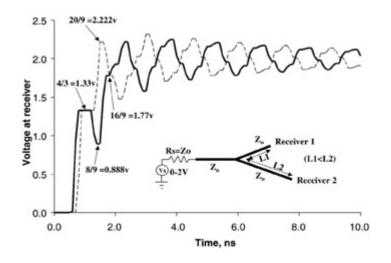

当传输线阻抗大于源头端阻抗时,看进源头端的反射系数将为负数,这将产生"振铃"效应。此所谓过载传输线。如图 2.15 所示为过载传输线的网格图。图 2.16 是图 2.15 所示系统响应的 SPICE 仿真。

图 2.15 例子 2.3: 用于计算过载传输线多次反射的网格图。

(2.11)

图 2.16 例子 2.3 所述传输线的仿真, 其中传输线阻抗大于源头端阻抗(过载传输线)。

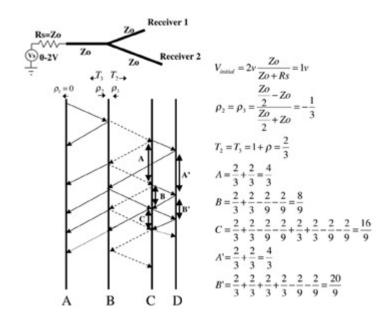

接着,考虑如图 2.17 所示的传输线结构。此结构由两个传输线片段串联组成。第一部分,长度为 X,特征阻抗为 Zo1 欧姆。第二部分,长度也为 X,阻抗为 Zo2 欧姆。最后,结构终接 Rt。当信号遇到 Zo1/ Zo2 阻抗结点时,部分信号将被反射(决定于反射系数),而部分信号将被传送(决定于传输系数):

图 2.17 多阻抗传输线系统的网格图。

$T_3 = 1 + \rho_3$

$k = i\rho_1 + hT_2$

图 2.17 也描述了网格图是如何用于解释一个具有多于一个特征阻抗的传输线系统的多次反射。注意,在本例中传输线是等长的,这简化了问题,因为每段的反射是同相的。例如,参照图 2.17 并注意,反射 e 直接叠加到反射 f。当两条传输线不等长时,一段的反射将与另一段的反射不同相,这彻底使图复杂化了。一旦图 2.17 所示系统的点变得复杂,使用如 SPICE 的仿真器来求解系统更可取。

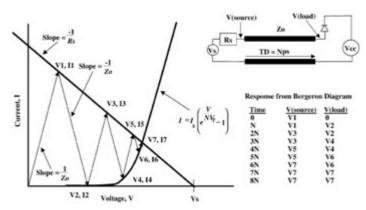

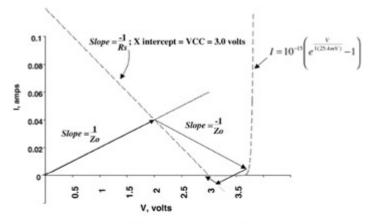

#### Bergeron图和非线性负载反射

Bergeron 图是另一种用于解答传输线多次反射的方法。系统中存在非线性负载和源的时候,Bergeron 图用来替代网格图。需要 Bergeron 图的好例子就是,当传输线终接一个钳位二极管以防止过度的信号过冲或静电放电引起的破坏。此外,输出缓冲器很少完美地呈现线性 I-V 特性;因而如果知道缓冲器的 I-V 特性,Bergeron 图将给出反射更准确的表达。

参照图2.18。为作Bergeron图,绘制负载和源端的I-V特性曲线。源端I-V特性曲线有负的斜率-1/Rs,因为电流偏离原点并且和X轴的交点在Vs。然后,由传输线的初始状态(如,V=0, I=0)开始,作一条斜率1/Zo的直线。此线与源端I-V特性曲线的交点给出了头端t=0时传输线上的初始电压和电流。你可以把这作为负载图。从与源端直线的交点作一条斜率-1/Zo的直线,并延伸到负载特性曲线。与负载线的交点定义了t=TD时负载端的电压和电流,其中TD是传输线的时间延迟。交替使用的斜率1/Zo和-1/Zo重复这个过程,直到传输线矢量到达负载线与源端线的交点。传输线矢量与负载及源头I-V曲线的交点给出了稳态的电压和电流值。图2.19是计算一个类似系统响应的例子,其中Vs=3V,TD=500ps,Zo=50  $\Omega$ ,Rs=25  $\Omega$ ,且二极管如等式所示工作。

图 2.18 用于计算非线性负载多次反射的 Bergeron 图

Response from Bergeron Diagram

图 2.19 用于计算带二极管终端传输线多次反射的 Bergeron 图

记住: 当源头或负载任何一个呈现非线性I-V特性曲线时,使用Bergeron图计算传输线的反射。

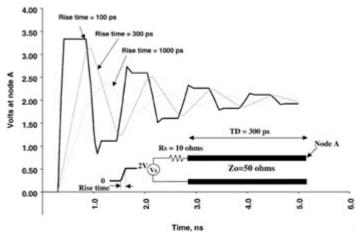

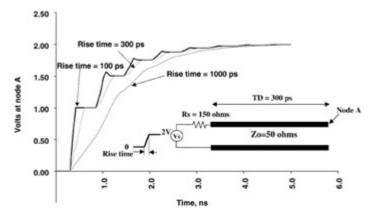

#### 2.4.3 上升时间队反射的影响

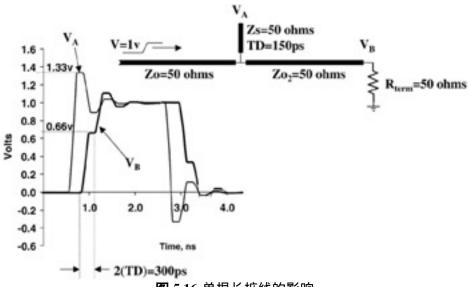

当上升时间变得小于传输线延迟(TD)的两倍时,上升时间开始对波的形状存在重要的影响。图 2.20 和 2.21 分别显示了欠载和过载传输线上边沿速度产生的影响。留心当上升时间超过传播延迟两倍时波的形

状变化有多大。当边沿速度超过两倍线延迟时,来自源头的反射在一个状态到另一状态转换(如,高-低或低-高转换)完成之前到达。

图 2.20 慢边际速度的影响(过载)

图 2.21 慢边际速度的影响(欠载)

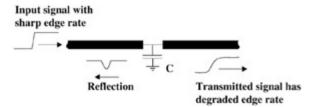

# 2.4.4 电抗性负载的反射

在实时系统中少有负载是纯电阻的例子。例如,CMOS 门的输入是趋向容性的。另外,芯片封装的接头线和引线框完全是电感性的。这使得有必要理解这些电抗性元件如何影响系统中的反射。本节介绍电容和电感对反射的影响。这些知识将作为以后章节更多细节地探讨电容性和电感性寄生效应的基础。

## 容性负载的反射

当传输线终接一个电抗性元件(如电容)时,驱动端和负载端的波形将有一个与典型传输线响应完全不同的形状。实质上,电容是时间相关负载,当信号到达电容时开始看起来是短路,而当电容完全充电之后看起来是开路。让我们考虑 t=TD 和 t=t1 时的反射系数。当 t=TD 时,信号已经沿着传输线传播并到达容性负载,电容还没有充电并看起来是短路。如本章先前所述,短路电路的反射系数为-1。这意味着幅值 V 的初始波形将被反射离开负载(幅值-V)形成初始电压 0V。电容开始以决定于 $\tau$  的速度充电, $\tau$  是 RC 电路的时间常数,其中 C 是终端电容,R 是传输线的特征阻抗。一旦电容充电完全,反射系数将为 1,因为电容类似于开路。开始于 t=TD 的电容电压如下式:

$$V_{\text{capacitor}} = 2V_i(1 - e^{-(t-\text{TD})/\tau}), \qquad t > \text{TD}$$

(2.12)

$$\tau = CZ_o \tag{2.13}$$

图 2.22 所示为容性负载传输线的响应仿真。负载电容 10pF,线长 3.5 英寸(TD=500ps),驱动器和传输线阻抗都是  $50\,\Omega$ 。注意源端(节点 A)波形的形状,它在 1ns(2TD)时向 0 下降又上升,此时来自负载的反射到达源头端。它向零下降,因为电容初始反射系数为-1,所以反射回源头端的电压是 Vi+(-Vi),

其中 Vi 是射入传输线的初始电压。然后电容充电到稳态值 2V。

图 2.22 终接电容性负载的传输线。

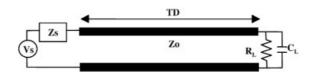

如果传输线终接并联的电阻和电容,如图 2.23 所示,则电容电压决定于:

$$V_{\text{capacitor}} = 2V_i \frac{R_L}{R_L + Z_o} (1 - e^{-(t - \text{TD})/\tau_1}), \quad t > \text{TD}$$

(2. 14)

而时间常数决定于CL以及RL和Zo的并联:

$$\tau_1 = \frac{C_L Z_o R_L}{R_L + Z_o} \tag{2.15}$$

图 2.23 终接并联电容性和电阻性负载的传输线。

#### 电感性负载的反射

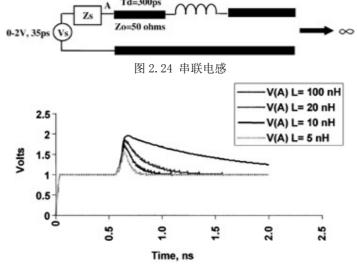

当一个串联电感出现在传输线的电气路径时,如图 2.24 所示,它也成了一个时间相关的负载。开始 t=0,电感就像开路。如果开始使用的是阶梯电压,则几乎没有电流流过电感。这使得反射系数为 1。如果 电感足够大,信号的幅值将加倍。最后,电感将以决定于 LR 电路时间常数  $\tau$  (其值为 L/Zo) 的速度释放 它的能量。图 2.25 所示为四种不同值的串联电感(如图 2.24 示)的反射。注意,反射的幅值和衰减时间 随电感值增加而增加。

图 2.25 对于不同电感值在节点 A (图 2.24) 看到的反射

#### 2.4.5 消除反射的终接方案

如后续章节阐述,传输线上的反射会对数字系统性能有重要的负面影响。为了最小化反射的负面影响,必须发展控制它们的方法。基本上有三种方法减低这些反射的负面影响。第一种方法就是降低系统的频率以使传输线上的反射将在另一个信号驱动到线上之前达到稳态。然而通常这是不可能的,对于高速系统因为它要求降低工作频率,会产生低速系统。第二种方法是缩短 PCB 走线长度以使反射在更短时间内达到稳态。通常这是不实用的,因为通常这样做涉及使用更多层面的 PCB 板,这大大增加了成本。另外,在一些情况下缩短走线在物理上是不可能的。当总线频率增加到一个周期内反射不能达到稳态时,前两种方法通常就有限了。第三种方法就是给传输线两端终接一个等于特征阻抗的阻抗,并消除反射。

当传输线源端设计成匹配于传输线特征阻抗时,总线被认为是源端终接的。此时,因为反射系数为 0,任何由于在线远端存在的阻抗不连续(如开路)所产生的反射将在其达到源端时被消除。当终端电阻放在传输线远端时,总线认为是并联的或负载终接的。多次反射将在负载处消除,因为负载处的反射系数为 0。有多种方式实现这些终接方法。每种方法都有各自的优点和缺点。以下部分概述了几种方法。

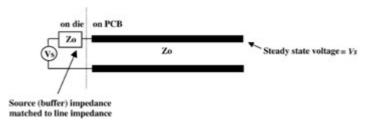

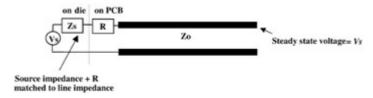

#### 片上源端终接

片上源端终接要求输出缓冲器的 I-V 曲线在工作范围内非常线性,并输出一个阻抗与传输线阻抗非常接近的 I-V 曲线。理论上,这是最佳的方案,因为它不要求任何额外的元件而导致增加成本和浪费板空间。然而,有许多变量能彻底地影响缓冲器的输出阻抗,所以难以达到缓冲器阻抗和传输线阻抗之间的良好匹配。影响缓冲器阻抗的变量是硅制作过程中的偏差、电压、温度、功率输出因数和同步开关噪声。这些偏差使得很难保证缓冲器阻抗与传输线阻抗匹配。图 2. 26 描述了这种终接方法。

图 2.26 片上源端终接

# 串联源端终接

串联源端终接要求加一个电阻与输出缓冲器串联。图 2.27 所示为串联源端终接。此类终接法要求缓冲器阻抗和电阻值的总和等于传输线的特征阻抗。通常设计输出缓冲器 I-V 曲线产生一个极低阻抗,以至于从源端看进去的阻抗的大部分都包含在电阻中,这样可以取得到最好的效果。因为能选择精密电阻,加工引起的片上阻抗偏差和晶元环境变化引起的片上源端终接困难能最小化。阻抗的总偏差将会很小,因为电阻(并非输出缓冲器本身)包含大部分的阻抗。这种方法的缺点是电阻增加了板的成本并且占用有效的板面积。

图 2.27 串联源端终接

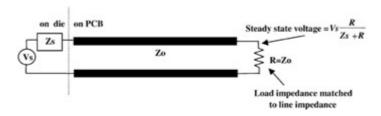

### 带电阻负载的负载终接

因为使用了精密电阻,负载或带电阻负载的并联终接消除了缓冲器阻抗相关的未知变量。反射在负载端消除,并可使用低阻抗输出缓冲器。缺点是大部分的直流电流被分流到地,这加大了功率输出和发热问题。稳态电压也由源端电阻和负载电阻之间分压来确定,这引起更强大缓冲器的需求。在现代计算机里,功率输出是一个难以解决的问题。例如,便携式电脑需要非常有效的功率输出系统,因为它们要求电池使用持续很长一段时间。随着功耗增加,成本也增加,因为更多精巧的冷却装置必须引进以消散过多的热量。图 2. 28 描述了这种终接方案。

图 2.28 带电阻负载的负载终接

#### 交流负载终接

交流负载终接在传输线的负载末端使用串联的电容和电阻以消除反射。电阻R应等于传输线的特征阻抗,而电容  $\alpha$  应选择负载端的RC时间常数近似等于一个或两个上升时间。对于具体设计,建议执行仿真以选择最优电容。这种终接方案的前提是电容初始状态为短路,且在上升或下降沿的持续时间内通过电阻R传输线以它的特征阻抗终接。电容然后充电并将达到源头端稳态电压Vs。这种方法的优点是在负载端上反射被消除,并且不产生直流功耗。缺点是电容性负载将减缓负载端的上升或下降时间而增加信号延迟。此外,附加电阻和电容占用板子空间并增加成本。图2.29描述了这种终接方案。

图 2.29 交流负载终接

#### 常见的终接问题

总线设计中遇到的常见阻碍之一是由PCB生产偏差引起的传输线特征阻抗变化较大。PCB偏差影响全部的终接方法,然而它对源头端终接会有更大的影响。一般地,例如低成本PCB板通常在加工后会与目标阻抗有差不多 $\pm$ 15%变化。这意味着如果工程师规定PCB板的传输线阻抗为65 $\Omega$ ,则厂家将保证阻抗在55.25 $\Omega$  (65 $\Omega$ -15%) 和74.75 $\Omega$  (65 $\Omega$ +15%)之间。最后,串扰将引入额外的阻抗变量。串扰感应变量的影响取决于走线之间的间隔、绝缘系数和横截面几何结构。串扰将在第三章充分讨论。

对于短的传输线,当最小数字脉冲宽度长于传输线的时间延迟(TD)时,源终端是合乎要求的,因为它消除了驱动器电流部分并联接地的要求。对于长的传输线,当数字脉冲宽度小于传输线延迟时间(TD)时,负载终端是较好的。后面例子是任意给定时间内多信号沿传输线传输(被称为流水线模式)。因为负载端的反射将反射回源头端,并干扰沿线传播的信号,反射必须在负载端消除。

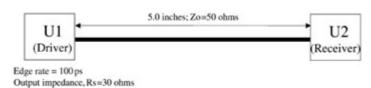

#### 2.5 附例

#### 2.5.1 问题

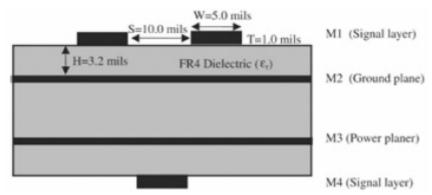

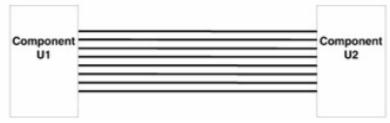

假定两个元件U1和U2需要通过一条高速数字总线彼此通信。元件安装在如图2.30层叠的标准四层主板上。元件U1驱动缓冲器的阻抗为30 $\Omega$ ,边沿速度100ps,摆幅为0~2V。PCB上走线要求为50 $\Omega$ 和5英寸长。板子的相对绝缘系数( $\varepsilon$ r)是4.0,假定传输线是理想的导体,且接收器电容足够小到可以忽略。图2.31描述了电路的拓扑结构。

图 2.30 标准四层主板的叠层

图 2.31 实例电路的拓扑结构

#### 2.5.2 目的

- 1、确定正确的如图 2.30 所示 PCB 垂直截面几何结构而得到 50 Ω 的阻抗。

- 2、计算信号从驱动器 U1 传输到接收器 U2 的时间。

- 3、确定当系统被 U1 驱动时 U2 处的波形。

- 4、建立系统的等效电路。

#### 2.5.3 计算 PCB 的垂直截面几何结构

因为如图2.30所示的叠层的信号线是微带线,垂直截面几何结构可以由图2.6所示的等式确定。事实上,有些微带线参考电源层而非地层将不会引起混淆。为了传输线设计目的,直流电源层将作为交流地层,并在传输线设计中被作为地层处理。这种近似的结果将在后续章节分析。图2.6显示走线阻抗是H, W, t, 和 $\varepsilon_T$  的函数(见图2.30)。

$$Z_{o_{\text{microstrip}}} = \frac{87}{\sqrt{\varepsilon_r + 1.41}} \ln \frac{5.98H}{0.8W + t}$$

标准 PCB 板的微带线层的金属厚度通常为 1.0mil。因为要求的阻抗、绝缘系数  $\varepsilon_r$ 和厚度都知道,只剩下一个等式和两个未知量。接着选择 H 或 W 中任何一个值。典型 PCB 生产商通常提供 5mil 的最小线宽。因小的线宽将使用较少的板子有效空间,这允许 PCB 在物理上变得更小并花费更少,所以选择 5mil 的最小线宽。把已知的  $\varepsilon_r$ 、W、t 和 Zo 值代入到上述等式,并求解 H:

$$50 = \frac{87}{\sqrt{4.0 + 1.41}} \ln \frac{5.98H}{0.8(5.0) + 1.0}$$

$$\frac{50\sqrt{5.41}}{87} = \ln \frac{5.98H}{5.0}$$

$$e^{1.337} = 1.196H$$

# H = 3.2 mils

图 2.32 描述了 PCB 的合成叠层。

图 2.32 50ohm 传输线的合成 PCB 叠层

注意内层金属和绝缘层的厚度。内部金属层只有 0.7mil 厚而不是 1.0mil 厚。这是因为外层通常会镀锡以防止外层铜线暴露在空气中氧化。内部走线是没有电镀的。因为工业要求典型的 PCB 板厚度为 62mils,增加电源层和地层之间的绝缘层厚度以得到想要的板厚度。

## 2.5.4 计算传播延迟

为了计算信号从 U1 传播到 U2 的时间,有必要确定信号沿所设计传输线行进的传播速度。因传输线是 微带线,有效绝缘系数必须用于计算传播速度。有效绝缘系数用等式(2.6)和(2.7)计算:

$$\varepsilon_{\epsilon} = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \left(1 + \frac{12H}{W}\right)^{-1/2} + F - 0.217(\varepsilon_r - 1) \frac{t}{\sqrt{WH}}$$

因 W/H=5/3.2>1.0, 而 F=0。因此,

$$\varepsilon_e = \frac{4.0+1}{2} + \frac{4.0-1}{2} \left[ 1 + \frac{12(3.2)}{5.0} \right]^{-1/2} + 0 - 0.217(4.0-1) \frac{1.0}{\sqrt{5.0(3.2)}} = 2.84$$

传播速度用等式(2.2)确定:

$$v = \frac{c}{\sqrt{\varepsilon_r}} = \frac{3.0 \times 10^8 \text{ m/s}}{\sqrt{2.84}} = 1.78 \times 10^8 \text{ m/s}$$

用等式(2.4)计算信号沿连接 U1 和 U2 的 5 英寸传输线的时间延迟:

TD =

$$\frac{\text{length}\sqrt{\varepsilon_r}}{c} = \frac{5.0 \text{ in.}}{1.78 \text{ m/s}} \left(\frac{0.0254 \text{ m}}{1.0 \text{ in.}}\right) = 713 \text{ ps}$$

#### 2.5.5 确定接收器端看到的波形形状

计算接收器端看到的波形形状的最简单方法是用网格图(图 2.33)。必须注意的是也可以用 Bergeron 图,然而因在接收器端没有诸如二极管的非线性器件,网格图是优选的分析方法。参考 2.4 节。

图 2.33 确定接收器端的波形形状: (a) 网格图; (b) U1 驱动时 U2 端的波形。

$$\begin{split} V_{\text{initial}} &= V_{\text{in}} \frac{Z_{o_{\text{PCB}}}}{Z_{o_{\text{PCB}}} + R_s} = 2.0 \left( \frac{50}{50 + 30} \right) = 1.25 \text{ V} \\ \rho_{\text{source}} &= \frac{R_s - Z_{o_{\text{PCB}}}}{R_s + Z_{o_{\text{PCB}}}} = \frac{30 - 50}{30 + 50} = -0.25 \\ \rho_{\text{load}} &= \frac{R_{\text{load}} - Z_{o_{\text{PCB}}}}{R_{\text{load}} + Z_{o_{\text{PCB}}}} = \frac{\infty - 50}{\infty + 50} = 1.0 \end{split}$$

其中Rs是U1的缓冲器阻抗,fload是在U2端看到的开路电路(假定缓冲器的输入电容很小,如2~3pF)。

#### 2.5.6 建立等效电路

为建立此例的等效电路模型,有必要确定要求的 LC 片段数量。这使用 2. 3. 3 节提出的拇指规则。这样方便地变换先前的速度计算为英寸/皮秒的单元:

velocity (in./ps) =

$$\frac{5.0 \text{ in.}}{713 \text{ ps}} = 0.0070 \text{ in./ps}$$

segments  $\geq 10 \left( \frac{\text{length}}{T_c v} \right) = 10 \left[ \frac{5 \text{ in.}}{(100 \text{ ps})(0.0070 \text{ in./ps})} \right] = 71.4$

因此,最少要求72段以建立准确的传输线模型。

现在使用等式 (2.1) 和 (2.5) 计算单位英寸的等效电感和电容。因这个是无损耗的特殊例子(例如,假定为理想导体),等式 (2.1) 简化为  $Zo=\sqrt{L/C}$  。单位英寸的延迟是 TD=713 ps/5. 0 in=142. 6 ps/in= $\sqrt{LC}$  ,其中 L 和 C 是单位英寸的。

求解带 L 和 C 的 TD 和 Zo 可以计算每单位英寸的等效 L 和 C。

$$C = \frac{\text{TD}}{Z_o} = \frac{\sqrt{LC}}{\sqrt{L/C}} = \frac{142.6 \text{ ps}}{50} = 2.85 \text{ pF}$$

$$L = (\text{TD})(Z_o) = \sqrt{LC}\sqrt{\frac{L}{C}} = 7.130 \text{ nH}$$

参考 2.3.3 节提出的拇指规则, 计算每段的 L 和 C:

$$\begin{split} C_{\text{segment}} &= \frac{(\text{length})(C/\text{in.})}{\text{segment}} = \frac{5.0 \text{ in.} (2.85 \text{ pF/in.})}{72} = 0.198 \text{ pF/segment} \\ L_{\text{segment}} &= \frac{(\text{length})(L/\text{in.})}{segment} = \frac{5.0 \text{ in.} (7.13 \text{ nH/in.})}{72} = 0.495 \text{ nH/segment} \end{split}$$

为再次检验计算的结果,可以计算每段的阻抗和延迟:

$$\label{eq:delay/segment} \begin{split} \text{delay/segment} &= \frac{713 \text{ ps}}{72} = 9.9 \text{ ps} \approx \sqrt{(0.198 \text{ pF})(0.495 \text{ nH})} = 9.9 \text{ ps} \\ \text{impedance/segment} &= \sqrt{\frac{0.495 \text{ nH}}{0.198 \text{ pF}}} = 50 \ \Omega \end{split}$$

传输线的等效电路由 72 段 LC 片段组成。U1 的驱动缓冲器描述为一个简单电压源和一个串联电阻。传输线末端开路近似为一个很大的电阻(图 2.34)。

图 2.34 最终等效电路

# 第三章 串 扰

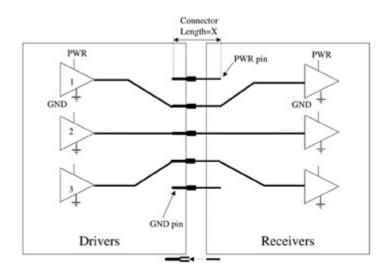

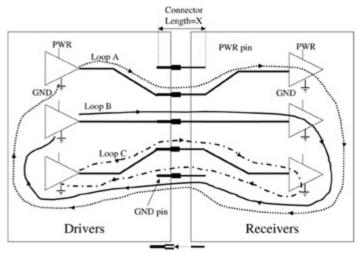

串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着:芯片内部、PCB 板、接插件、芯片封装,以及通信电缆中,都可能出现。而且,随着技术的发展,消费者对产品的要求越来越倾向于小而快,在这种情况下,就必须更加注意数字电路系统中的串扰现象。为了避免和减小这些串扰,学习串扰的原理和如何在设计中避免这些现象的发生就显得相当重要。

在多导线系统中,过多的传输线间的耦合或者说串扰,将有两个不利的影响。首先,串扰会改变总线中单根传输线的性能,比如传输线特征阻抗和传输速度等,而这些将会对系统时序和信号完整性问题产生一定的影响;再者,串扰会将噪声感应耦合到其他的传输线上,这将进一步降低信号完整性,导致噪声裕量变小。串扰对系统性能的危害程度在很大程度上取决于数据模式、线间距以及开关速度等方面。在这章里,我们将详细介绍串扰产生的原理,提供建模的方法,以及对串扰在系统性能中的各方面影响进行详细得阐述。

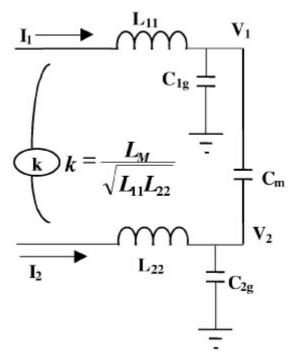

# 3.1. 互感和互容

互感是引起串扰的两个重要因素之一, 互感系数  $L_m$ 标志了一根驱动传输线通过磁场对另外一根传输线产生感应电流的程度。从本质上来说, 如果"受害 (Victim)线"和驱动线(侵略线)的距离足够接近, 以至于侵略线产生的磁场将受害线包围其中, 则在受侵略的传输线上将会产生感应电流, 而这个通过磁场耦合产生的电流在电路模型中就通过互感参数来表征。

互感  $L_m$  的作用下,将根据驱动线上的电流变化率而在受害线上引起一定的噪声,噪声电压的大小与电流变换率成正比,通常可以由下式计算:

$$V_{\text{noise},L_m} = L_m \frac{dI_{\text{driver}}}{dt}$$

由于感应噪声正比于信号的变化率, 互感在高速数字电路的应用中显得尤为重要。

互容是引起串扰的另外一个重要因素,互容是两导体间简单的电场耦合,这种耦合在电路模型中以互容的形式表现出来。 互容 $C_m$ 将产生一个与侵略线上电压变换率成正比的噪声电流到受害线:

$$I_{\text{noise},C_m} = C_m \frac{dV_{\text{driver}}}{dt}$$

同样可以看到: 感应噪声也是正比于信号的变化率,因此互容在高速数字应用中也是非常重要的。

应该指出的是: 用来解释噪声耦合机理的公式 3.1 和 3.2 仅仅是一种简单的近似,对于串扰的具体计算公式会在后面的章节中给出。

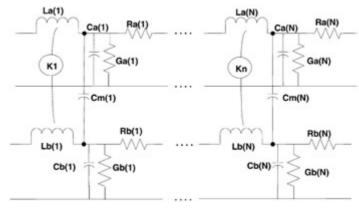

# 3.2. 电感和电容矩阵

在一个系统中,如果传输线之间发生了严重的耦合,那么像第二章提出的使用电容和电感组成的简单传输线模型就不再适合分析传输线的电气特征,在这种多导线系统中,我们必须考虑互感和互容来全面评估传输线的电气性能。等式 3.3 和 3.4 描述了反映寄生耦合效应影响传输线系统性能的典型方法。电感矩阵和电容矩阵被通称为传输线矩阵。场仿真器(见3.3 节)通常用来计算传输线系统中的电感和电容矩阵,下面例子就是一个场仿真器给出的用于 N 条导线系统中的典型报告。

$$\text{Inductance matrix} = \begin{bmatrix} L_{11} & L_{12} & \cdots & L_{1N} \\ L_{21} & L_{22} & & & \\ \vdots & & \ddots & & \\ L_{N1} & & & L_{NN} \end{bmatrix}$$

这里, $L_{NN}$ 表示线 N 的自感, $L_{MN}$ 表示线 M 和 N 之间的互感。

Capacitance matrix =

$$\begin{bmatrix} C_{11} & C_{12} & \cdots & C_{1N} \\ C_{21} & C_{22} & & & \\ \vdots & & \ddots & & \\ C_{N1} & & & C_{NN} \end{bmatrix}$$

在这里, $C_{NN}$ 是指传输线 N 上的寄生电容。它包括导线 N 自身的对地电容及和其它传输线的互容之和。 $C_{NN}$ 就是传输线 N 和传输线 M 之间的互容。

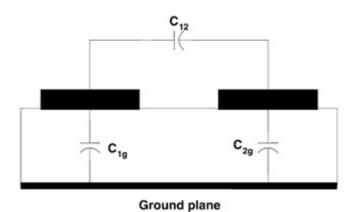

## 例 3.1:两根传输线之间的矩阵

图 3.1 的电容矩阵为:

capacitance matrix =

$$\begin{bmatrix} C_{11} & C_{12} \\ C_{21} & C_{22} \end{bmatrix}$$

在这里,  $C_{11}$ , 即传输线 1 自身的电容, 它的数值等于传输线 1 对地电容值( $C_{1g}$ )和对传输线 2 的互容值( $C_{12}$ )之和。

$$^{(3.\,6)}\ C_{11} = C_{1g} + C_{12}$$

图 3.1: 理解寄生矩阵的两导线简单系统示意图

另外,图 3.1 所示系统的感性矩阵为

inductance matrix =

$$\begin{bmatrix} L_{11} & L_{12} \\ L_{21} & L_{22} \end{bmatrix}$$

这里,  $L_{11}$ 为传输线 1 的自感系数, $L_{12}$ 是传输线 1 和 2 的互感系数。需要注意的是和电容值 $C_{11}$  不一样, $L_{11}$ 并不是自感系数和互感系数之和。

# 3.3. 场仿真器

场仿真器被用来模拟多导线系统中传输线之间的电磁干扰作用,并且可以通过它计算出传输线的特征阻抗,传输速度和所有自身的和相互之间寄生的参数。它的输出结果为代表导体有效感性和容性参数的典型矩阵。这些矩阵是所有等效电路模型的基础,并且可以用来计算传输线特征阻抗,传输速度和串扰。场仿真器可以被分为两类:两维的(或者说静电的),和三维的(或者说全波的)。大部分两维仿真器得到的电感和电容矩阵是以导体长度为变量的函数表达式,它通常适用于互连分析和建模。两维(静电)仿真器的优点就是使用简单,通常可以通过非常短的时间来完成计算。它们的缺点是仿真仅仅和简单的几何尺寸有关,它们是基于对电场的静态计算来进行仿真,而没有考虑到随频率变化的参数所带来的影响,比如内在的电感和趋肤效应引起的电阻等。但由于互连的结构通常比较简单,而且可以通过别的方法来计算与频域的电阻和电感变化效应,上述缺点并不是很大的问题。

另外,在市场上也存在许多三维(全波)仿真器。他们的优点是可以仿真复杂的三维空间,他们可以预测和频率相关的损耗以及内在的一些感应,散射和其他的一些电磁场现象,包括辐射等等。这种仿真器本质上是以麦克思韦等式为基础来解决所有的三维问题。而它的缺点就是非常难于使用,而且仿真时间的花费将以小时或者天数来计算。而且,全波仿真的输出是以 S 参数来表示,这对于数字电路应用中的互连级仿真并不是非常有用。所以,从本书的目的出发,我们将把重点放在两维的静电仿真分析。

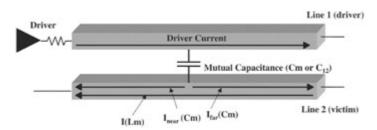

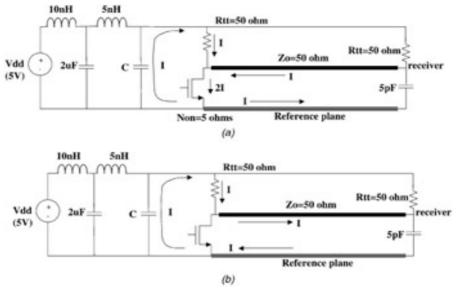

# 3.4. 串扰引起的噪声

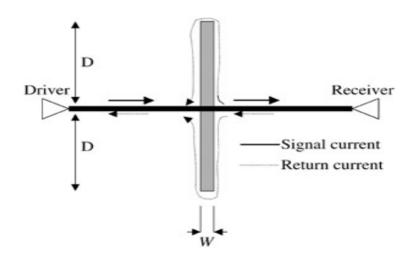

前面 3.1 节已经阐述过了,串扰是由于临近两导体之间的互容和互感所引起的。因而在临近传输线上引起的感应噪声的大小和他们之间的互感和互容大小都有关系。例如,如果一信号进入传输线 1 (如图 3.2),由于互感  $L_{i}$ 和 互容  $C_{i}$ 的作用,将在传输线 2 上产生一电流,为了

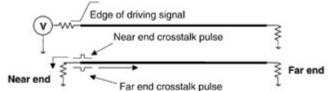

方便起见,我们定义了两个概念:近端串扰和远端串扰。近端串扰是指在受侵害线上靠近侵害线的驱动端的串扰(有时候也将这个串扰称为后向串扰)。将受侵害线上靠近侵害线接受端方向的串扰称为远端串扰(有时候也称为前向串扰)。由互容引起的电流分别向受侵害线的

图 3.2: 互容互感引起的串扰电流示意图

两个方向流动,而由互感引起的电流从受侵害线的远端流向近端,这是因为互感产生的电流总是与侵害线中的电流相反。所以,从受侵害线近端到远端的串扰电流由很多部分组成(见图 3.2)。

(3.8)

$$I_{\text{near}} = I(L_m) + I_{\text{near}}(C_m)$$

(3.9)

$$I_{\text{far}} = I_{\text{far}}(C_m) - I(L_m)$$

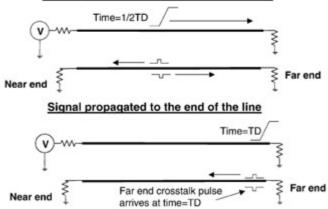

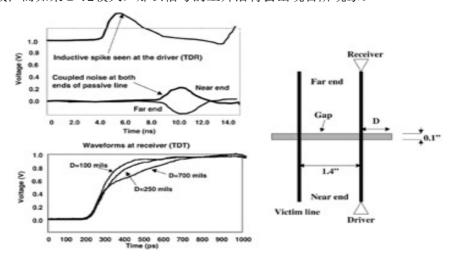

受侵害线上近端和远端串扰噪声的波形可以从图 3.3 看出, 当一个数字脉冲进入传输线,它的上升沿和下降沿将不断地在受侵害线上感应出噪声,在这里的讨论中,我们假设信号上升沿或者下降沿的变化速度非常快,远远小于传输线延迟。则根据前面的描述,一部分串扰噪声将传向近端,另一部分将传向远端,也就是我们所定义的近端串扰脉冲和远端串扰脉冲。如图 3.3,远端串扰脉冲将和侵害线上的信号同步流向终端,而近端串扰脉冲将起始于侵害线上信号变化沿出现时刻,并流向近端。这样,当驱动线上的信号变化沿在时间 t=TD (这里 TD 是信号在传输线上的延迟时间)到达传输线远端时,如果远端存在匹配,那么,侵害信号和远端串扰将在远端被匹配消除。同时,侵害信号的变化沿在被终端匹配消除前产生的最后一部分近端串扰信号将在 t=2TD 时才到达近端,这是因为,这部分信号又要经过整条传输线才能被传回近端。所以,对于一对被终端匹配好的传输线来说,近端串扰起始于 t=0 并且持2TD 的时间,或者说两倍于传输线的电气长度。相反,受侵害线远端接收到的远端串扰起始于 TD,持续时间为数字信号的上升或者下降时间。

# Signal injected into the beginning of the line

#### Signal propagated to the middle of the line

图 3.3: 串扰噪声示意图

串扰噪声的大小和形状很大程度上取决于耦合的大小与端接的情况。图 3.4 给出的等式和插图详细地描述了一条安静的受侵害线上由于串扰而得到的最大电压的状况。这里假设了受侵害线上存在多种端接策略,驱动线上也使用了端接来消除反射,使问题简化。这些等式主要是用来估计串扰的幅度,并使读者了解特殊的端接策略对噪声幅度的影响。当图 3.4 中所示的拓扑结构变得更加复杂时,则必须采用类似 SPICE 的工具来进行仿真。

图 3.4: 各种匹配情况下的串扰反射示意图

图 3.4 中假设了信号在传输线上的传输时间为两倍上升时间:

(3.10) TD =

$$X\sqrt{LC}$$

在这里,X是指传输线长度,L和C是指单位长度传输线本身的电感和电容,注意:如果

$T_r > 2X \sqrt{LC}$  (例如,边沿变化率大于两倍的传输线延迟),近端串扰将不能到达其

最大振幅,为了正确计算 $T_r > 2X\sqrt{LC}$  时的串扰电压,近端串扰只须乘以  $2X\sqrt{LC}$  / $T_r$ 即可,而远端串扰不会因为长度变化而改变。需要注意的是:当上升时间小于传输线时延时(长线情况),近端串扰的最大幅值和信号上升时间没有什么关系,而当上升时间大于传输线时延的时候(短线情况),近端串扰的大小和信号上升时间有一定关系。因为这个原因,定义长传输线的标准为传输线的电气时延必须大于信号的 1/2 上升时间(或下降时间),这时可以得到,近端串扰的幅度与线长无关(即前向串扰的饱和),而远端串扰则总是取决于上升时间和线长。

应该指出的是图 3.4 中的公式假设了受侵害线上的终端电阻与传输线完全匹配,消除了不完全匹配的影响。为了重现这些影响,可以使用第二章中提到的反射概念来分析。例如,假设图 3.4 中第一种情况的终端匹配电阻 R 并不等于受侵害线的传输线阻抗(为了简单起见,在这里假设了侵害线的匹配完全),此种情况下,近端和远端串扰值就必须加上各自的串扰反射电压。所以,在不完全匹配系统中,串扰信号的计算公式为:

(3.11)

$$V_x = V_{\text{crosstalk}} \left( 1 + \frac{R - Z_o}{R + Z_o} \right)$$

在这里, $V_x$  为不完全匹配情况下调整后的近端或远端串扰值,R就是终端匹配电阻, $Z_o$  为传输线特性阻抗, $V_{\text{crosstalk}}$  是通过公式 3. 4 计算出来的串扰值。

#### 要点

如果信号的上升或者下降时间小于传输线延迟,那么近端串扰最大幅值与上升时间无关。 如果信号的上升或下降时间长于传输线延迟,那么近端串扰的大小与上升时间有关。 远端串扰在任何情况下都和信号的上升或者下降时间有关。

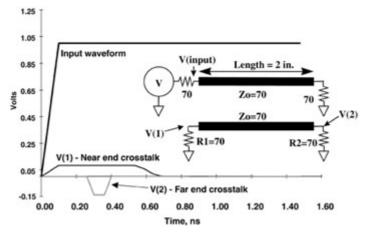

#### 例 3.2 计算一终端匹配系统的串扰噪声

如图 3.5 所示的两条传输线系统,在这里 $Z_o \approx 70$  Ω,终端匹配电阻为70 Ω,V(input) = 1.0 V, $T_r = 100$  ps,X = 2 in。计算近端和远端串扰的大小,下面假设了系统的电容与电感矩阵。

$$L/\text{in.} = \begin{bmatrix} 9.869 \text{ nH} & 2.103 \text{ nH} \\ 2.103 \text{ nH} & 9.869 \text{ nH} \end{bmatrix}$$

$$C/\text{in.} = \begin{bmatrix} 2.051 \text{ pF} & 0.239 \text{ pF} \\ 0.239 \text{ pF} & 2.051 \text{ pF} \end{bmatrix}$$

图 3.5 近端和远端串扰脉冲大小

解答:

$$\begin{split} V(1) &= \frac{V(\text{input})}{4} \left( \frac{L_{12}}{L_{11}} + \frac{C_{12}}{C_{11}} \right) = \frac{1}{4} \left( \frac{2.103 \text{ nH}}{9.869 \text{ nH}} + \frac{0.239 \text{ pF}}{2.051 \text{ pF}} \right) = 0.082 \text{ V} \\ V(2) &= -\frac{V(\text{input})(X\sqrt{LC})}{2T_r} \left( \frac{L_{12}}{L_{11}} - \frac{C_{12}}{C_{11}} \right) \\ &= \frac{1[2\sqrt{(9.869 \text{ nH})(2.051 \text{ pF})}]}{2(100 \text{ ps})} \left( \frac{2.103 \text{ nH}}{9.869 \text{ nH}} - \frac{0.239 \text{ pF}}{2.051 \text{ pF}} \right) = -0.137 \text{ V} \end{split}$$

图 3.5 同时给出了上例中系统的仿真结果,我们可以看到,实际的近端和远端串扰与图 3.4 的计算结果相吻合。

# 例 3.3: 计算一不完全匹配系统的串扰大小

同样取 3.2 中的两传输线系统为例,假设R=45 和R=100  $\Omega$ ,那么近端串扰和远端串扰电压分别为多少?

解答:

$$\begin{split} Z_o &= \sqrt{\frac{L_{11}}{C_{11}}} = \sqrt{\frac{9.869 \text{ nH}}{2.051 \text{ pF}}} = 69.4 \ \Omega \\ V(1) &= V_{\text{crosstalk}} \left(1 + \frac{R - Z_o}{R + Z_o}\right) = 0.082 \left(1 + \frac{45 - 69.4}{45 + 69.4}\right) = 0.0645 \ \text{V} \\ V(2) &= V_{\text{crosstalk}} \left(1 + \frac{R - Z_o}{R + Z_o}\right) = -0.137 \left(1 + \frac{100 - 69.4}{100 + 69.4}\right) = -0.162 \ \text{V} \end{split}$$

# 3.5. 使用等效电路模型仿真串扰

使用等效电路来进行串扰模拟是最为普遍的串扰分析方法,图 3.6 描述了将两条耦合传输线按照 SPICE 模型分为 N 段的等效电路模型,此处的 N 为建立一个传输线所必需的段落数,只有这样建立的电路模型才能表征连续的传输线特性,而不是一些集总的电感、电容和电阻的特性。就像在第二章中所提及的,传输线模型中的分段数量 N 与仿真时考虑的最快边沿速率有关。一般来说,有个比较好的经验法则是:每段线的传输延迟最好小于等于 1/10 的上升时间(第二章中有详细的描述)。

图 3.6:两耦合传输线的等效模型

在典型的SPICE类型的仿真器中,使用一个耦合因素K来代表互感系数:

(3. 12)

$$K = \frac{L_{12}}{\sqrt{L_{11}L_{22}}}$$

这里 $L_{12}$  是指传输线 1 和 2 之间的互感系数,而 $L_{11}$  和  $L_{22}$  指的是两传输线各自的电感。

#### 例 3.4: 建立一个耦合传输线模型

假设一对长度为 5 英寸,上升时间为 100ps 的耦合传输线被仿真,在下列电感和电容矩阵条件下,计算特征阻抗,总的传输延迟,电感耦合因子,被要求的段数,每段的最大延迟和每段最大的 L, R, C, G, Cm 和 K 值。

Capacitance matrix (per unit inch) =

$$\begin{bmatrix} 2 \text{ pF} & 0.1 \text{ pF} \\ 0.1 \text{ pF} & 2 \text{ pF} \end{bmatrix}$$

Inductance matrix (per unit inch) =

$$\begin{bmatrix} 9 \text{ nH} & 0.7 \text{ nH} \\ 0.7 \text{ nH} & 9 \text{ nH} \end{bmatrix}$$

解答: 传输线特性阻抗为:

$$Z_o = \sqrt{\frac{L_{11}}{C_{11}}} = \sqrt{\frac{9 \text{ nH}}{2 \text{ pF}}} = 67.09$$

总共传输延时为:

TD =

$$\sqrt{L_{11}C_{11}}$$

=  $\sqrt{(9 \text{ nH})(2 \text{ pF})}$  = 134 ps/in.  $\rightarrow$  ×5 in. = 670 ps

耦合感应系数:

$$K = \frac{L_{12}}{\sqrt{L_{11}L_{22}}} = \frac{0.7 \text{ nH}}{9 \text{ nH}} = 0.078$$

最少分段数为:

$$N = \text{segments} = 10 \frac{X}{vT_r} = 10 \frac{(5 \text{ in.})(134 \text{ ps/in.})}{100 \text{ ps}} = 67$$

长度为 5 英寸的传输线最少需要被分为 67 段,这样建立的模型通过仿真,才能反映传输线的特性。由于电容和电感矩阵中的参数使用英寸作为单位,那么L, C, 和  $C_{\mathbb{H}}$ 的值必须乘以  $\frac{5}{67}$ (英寸/段)。所以L(N)=0.67 nH,  $C_{\mathbb{H}}(N)=C_{11}-C_{12}=0.1425$  pF, 和  $C_{\mathbb{H}}(N)=0.0075$  pF。由于感应耦合因子没有单位(使用等式 3. 12 进行计算,所有单位都抵消掉),没有必要将它除以段数,所以此时K(N)=0.078。

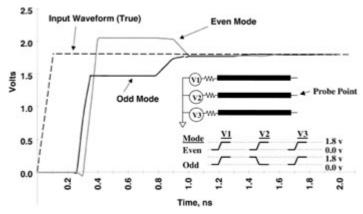

# 3.6. 串扰引起的飞行时间和信号完整性的变化

在线间串扰耦合比较严重的总线系统中,传输线的有效特征阻抗和传输延迟将随着开关方式的改变而改变。电场和磁场之间的相互影响取决于数据状态的变化,数据状态的不同也会造成传输线等效的电感和电容等参数发生变化,可能增大也可能减小。由于传输线参数随数据传输模式的变化而改变,而且这些参数对于精确的时序设计和信号完整性分析来说非常的重要,所以我们在高密度的高速系统设计中就必须要考虑这些因素。在本节里面,我们将解释一下串扰会带来怎样的阻抗和传输速度的变化,以及它们对时序和信号完整性的影响。另外,我们还将介绍一种简单的信号完整性分析方法,使用这种方法能准确地对计算机总线中多条传输线进行建模。

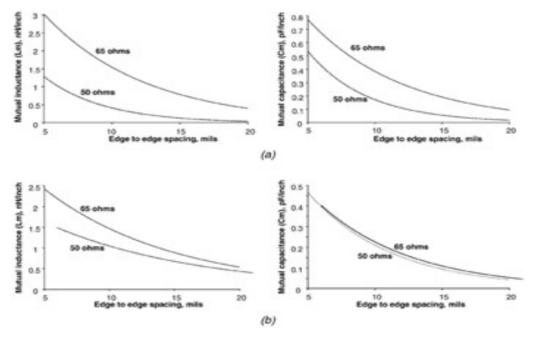

## 3.6.1. 开关状态对传输线性能的影响

当多根传输线相互之间靠得很近的时候,传输线之间的电场和磁场将以各种特殊的方式 互相作用,传输线上的信号状态决定了这种特殊方式。这种相互作用的重要性在于能改变传 输线等效的特性阻抗和传输速率。特别是当很多非常靠近的传输线同时开关时,这种现象尤 为严重,它能使总线出现阻抗和延迟过于依赖数据模式的现象,从而影响总线的性能。因此, 在系统设计中必须考虑到这些方面的影响。

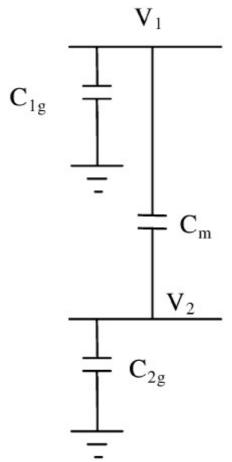

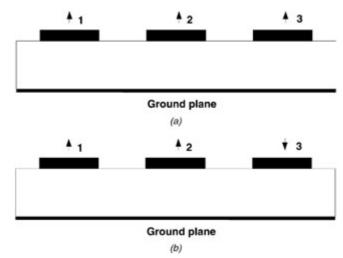

#### 差模:

当两根耦合的传输线相互之间的驱动信号幅值相同但相位相差 180 度的时候,就是一个差模传输的模型。此情况下,传输线的等效电容因为互容的加倍而增加,但是等效电感因为互感的减小而变小。为了得出两相邻的传输线在差模传输模式下,传输线特征阻抗和传输速率的变化情况,我们可以参考图 3.7。

图 3.7: 差模和共模情况下用于推导阻抗和速度变化的等效电路图

在差模传输中,线上电流  $I_1$  和  $I_2$ 大小相同,极性相反。首先,让我们先来考虑互感的影响。如图 3.8 所示,假设  $I_{11} = I_{22} = I_0$ ,通过公式 3.1 计算出由于电感耦合产生的电压,代入基尔霍夫电压准则,得到下面的结果:

(3. 13)

$$V_{1} = L_{0} \frac{dI_{1}}{dt} + L_{m} \frac{dI_{2}}{dt}$$

$$V_{2} = L_{0} \frac{dI_{2}}{dt} + L_{m} \frac{dI_{1}}{dt}$$

$$I_{1} \longrightarrow V_{1} \longrightarrow V_{1}$$

$$k = \frac{L_{M}}{\sqrt{L_{11}L_{22}}}$$

$$L_{22} \longrightarrow V_{2} \longrightarrow V_{2}$$

图 3.8: 推导差模等效电感的简化电路模型

由于差模情况下的信号极性总是相反,可以将 $I_1 = -I_2$  与  $I_1 = -I_2$  带入 3. 13 和 3. 14。

得到以下等式:

(3. 15)

$$V_1 = L_0 \frac{dI_1}{dt} + L_m \frac{d(-I_1)}{dt} = (L_0 - L_m) \frac{dI_1}{dt}$$

(3. 16)

$$V_2 = L_0 \frac{dI_2}{dt} + L_m \frac{d(-I_2)}{dt} = (L_0 - L_m) \frac{dI_2}{dt}$$

这样,在以差模形式进行传输的一对耦合传输线中,从线1上观察到的等效电感为:

(3. 17)

$$L_{odd} = L_{11} - L_m = L_{11} - L_{12}$$

图 3.9: 推导差模等效电容的等效电路图

同样,互容的影响也可以被推导,参考图 3.9,假设 $C_{1g}=C_{2g}=C_0$ ,在点 $V_1$ 与 $V_2$ 处运用基尔霍夫电流法则,得

(3. 18)

$$I_1 = C_0 \frac{dV_1}{dt} + C_m \frac{d(V_1 - V_2)}{dt} = (C_0 + C_m) \frac{dV_1}{dt} - C_m \frac{dV_2}{dt}$$

(3. 19)

$$I_2 = C_0 \frac{dV_2}{dt} + C_m \frac{d(V_2 - V_1)}{dt} = (C_0 + C_m) \frac{dV_2}{dt} - C_m \frac{dV_1}{dt}$$

对于差模情况,可以将 $I_1 = -I_2$ ,和 $V_1 = -V_2$ ,代入上式得:

(3.20)

$$I_1 = C_0 \frac{dV_1}{dt} + C_m \frac{d(V_1 - (-V_1))}{dt} = (C_{1g} + 2C_m) \frac{dV_1}{dt}$$

(3. 21)

$$I_2 = C_0 \frac{dV_2}{dt} + C_m \frac{d(V_2 - (-V_2))}{dt} = (C_{2g} + 2C_m) \frac{dV_2}{dt}$$

所以, 在以差模形式传输的一对耦合传输线中, 从线 1 上观察到的等效电容为:

(3.22)

$$C_{\text{odd}} = C_{1g} + 2C_m = C_{11} + C_m$$

因此,可以得到以差模形式进行传输的一对耦合线的等效阻抗与等效传输线速度为:

$$Z_{\rm odd} = \sqrt{\frac{L_{\rm odd}}{C_{\rm odd}}} = \sqrt{\frac{L_{11} - L_{12}}{C_{11} + C_{12}}}$$

(3. 24)

$$TD_{odd} = \sqrt{L_{odd}C_{odd}} = \sqrt{(L_{11} - L_{12})(C_{11} + C_{12})}$$

#### 共模

当两条耦合传输线上驱动信号的幅度与相位都相同时,称为共模传输模式。此时,传输线的等效电容将随着互容的减少而减少,同时等效电感却因为互感的增加而增加。为了得出 共模传输对两相邻传输线的特性阻抗和传输速率的影响,请参考图 3.7。

在共模传输中,电流 $I_1$  和 $I_2$ 大小相同且同向传输。首先,让我们先考虑对互感的影响,再次参考图 3.8,用于差模开关的分析方法同样可以用来决定共模情形下的有效电容和电感。对于共模传输,将 $I_1 = I_2$  和  $I_1 = I_3$  和  $I_2 = I_4$  和  $I_3 = I_4$  和 3.14 中得到:

$$V_1 = L_0 \frac{dI_1}{dt} + L_m \frac{d(I_1)}{dt} = (L_0 + L_m) \frac{dI_1}{dt}$$

$$V_2 = L_0 \frac{dI_2}{dt} + L_m \frac{d(I_2)}{dt} = (L_0 + L_m) \frac{dI_2}{dt}$$

所以, 在一对以共模形式传输的耦合传输线中, 传输线 1 上呈现的等效电感为:

$$^{(3.27)}$$

$L_{\text{even}} = L_{11} + L_m$

同样可以推导出互容带来的影响,再次参考图 3.9,对于共模传输来说,将  $I_1 = I_2$  和  $I_1 = I_2$  带入等式 3.18 与 3.19 中得:

(3.28)

$$I_1 = C_0 \frac{dV_1}{dt} + C_m \frac{d(V_1 - V_1)}{dt} = (C_0) \frac{dV_1}{dt}$$

$$I_2 = C_0 \frac{dV_2}{dt} + C_m \frac{d(V_2 - V_2)}{dt} = (C_0) \frac{dV_2}{dt}$$

所以一对耦合共模传输线中线1上呈现的等效电容为:

$$(3.30)$$

$C_{\text{even}} = C_0 = C_{11} - C_m$

那么,就可以计算出耦合双线系统的共模传输特性:

(3.31)

$$Z_{\text{even}} = \sqrt{\frac{L_{\text{even}}}{C_{\text{even}}}} = \sqrt{\frac{L_{11} + L_{12}}{C_{11} - C_{12}}}$$

(3.32)

$$TD_{even} = \sqrt{L_{even}C_{even}} = \sqrt{(L_{11} + L_{12})(C_{11} - C_{12})}$$

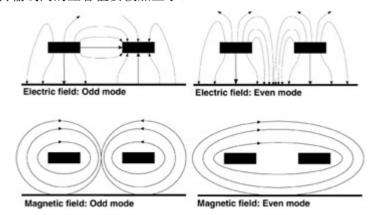

图 3.10 描述了在简单的两传输线系统中,差模和共模情况下的电磁场分布。正如第二章中解释的,磁力线和电力线总是正交的(TEM 模型)。注意在共模传输情况下,两导体上的电势相同,所以两传输线之间没有电压差,这就是说线间没有电容的影响存在,这样就很容易记住,在共模情况下,要从传输线的电容中减去互容值。而在差模情况下,由于两导体之间一直存在电位差,所以,两传输线之间电容的影响就一定存在,这样也很容易记住,在差模情况下,传输线间的互容值要被加上了。

图 3.10: 两简单耦合传输线系统中共模和差模情况下的电磁场分布

图 3.11 表明了差模与共模带来的阻抗和传播速率的变化是如何影响信号传输的。虽然在这个例子中只有三根传输线,但是仿真结果给出了计算机总线中处于其他线之间的信号线受到的串扰的影响。该图显示了串扰将会给信号完整性和速度(假设为微带线)带来严重的影响,并且这种影响将随开关模式变化的变化。由于信号完整性直接依赖于源端和传输线的阻抗,所以耦合程度和开关模式将在很大程度上影响系统性能,这些影响归根到底是由线的等效特征阻抗变化引起的。而且,如果传输线为微带线,传输速率也会改变,从而影响了传输线(特别是长传输线)时序的正确性。由于串扰的主要影响来自于与之相邻的传输线的影响,所以在实际仿真中使用三根传输线来进行分析已基本能正确的反映串扰对系统性能的影响。

图 3.11: 开关模式对三导线系统的影响

大家会注意到一个非常有趣的现象,在差模或者共模传输中,传输线的互感的增减正好和互容相反。这些能在图 3.10 的场示意图中被清楚地看见。例如,在差模传输中,由于导体间存在电位差,互容的影响必须被加上,而另一方面,因为两条导线中的电流总是按相反

方向流动,由于磁场在每条线上耦合出来的电流总是彼此相反,这样就抵消掉了互感的影响。 所以,在计算差模特性时,互感必须被减去,互容必须被加上。

共模和差模的这些传输特性计算是基于一种假设的前提下,即信号仅仅以 TEM 模式 (横向电磁)进行传播,也就是说:电场和磁场在任何时候都彼此正交。TEM 模式假设的条件下,在介质均匀的系统中(即电磁场处于同一介质中), L与C的积保持不变。所以,在处于同类介质的多导体系统中,比如带状线阵列,如果L由于互感而增加,那么C必定由于互容而减少,以保证LC乘积不变。因而,处在同一介质中的带状线或者埋式微带线的传输速度将不会随着不同的开关模式而变化。当然,它的等效阻抗仍然会改变。

在非均匀系统中(指电磁场分布在不同的电介质材料中),比如微带线阵列,在不同的传输模式中,LC 值就不能保持常数,这是因为传输信号的电磁场分布在空气与板子的介质中。在微带线系统中,系统的等效介电常数为空气和板上介质的介电常数的加权平均值,因为场的模式随着不同的传输模式而改变,有效介电常数将根据包含在板上介质材料和空气中的场密度的改变而改变,这样LC 乘积在非均匀系统中是可变的。然而对于一种给定的模式,LC 积将保持常数。所以,微带线的传输速度和阻抗都会因为传输模式和信号变化而改变。

#### 要点

差模传输线阻抗一般比单根传输线的低 共模传输线阻抗一般比单根传输线的高 在带状线种,串扰不改变传输速度 在微带线种,串扰会改变传输速度

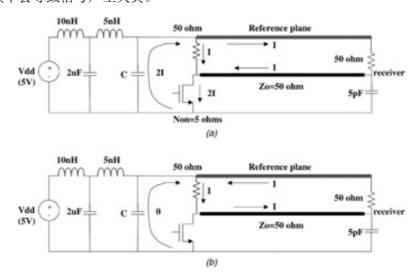

# 3.6.2. 使用单导线等效模型来仿真多导线系统

在差模或共模情况下,如果我们计算出了传输线对的等效阻抗和传输速度,我们就可以将这些参数代入到单根传输线模型中,用单线模型来建模两条耦合导线。这种技术可以被扩展到多传输线系统中,用来决定串扰引起的阻抗和延迟的变化。这样设计者就可以在布局以前估计出由串扰所带来的最坏影响,此举将大大提高前端设计的效率,因为这与等效电路模型仿真相比大大减少了计算量,也可以使我们在设计的前端就可以充分考虑到串扰引起的阻抗和速度的变化。

为了在多导线系统中利用这一技术,我们必须先引入一种方法,可以通过仿真一条导线来代替多导线的仿真。这个方法能够很快地估算出由于其他几条传输线引起的串扰导致受害线阻抗和速率的变化情况。首先,要确定给定传输线在特定开关模式下的等效电容和等效电感。这可以通过观察多导线系统中的对线,然后计算出差模或共模情况下的等效电容和电感值来完成。由对线计算出的值可以组合为最终的等效值。为了达到这个目的,将互容和互感值与给定传输线的总电容和电感或加或减:当信号线与给定传输线同相开关时,将两条线间的互容从给定传输线的总电容中减去,同时互感被相应地加上;相反,当信号线与给定传输线反相开关时,将两条传输线间的互容加到总电容中,同时互感被相应地减去。此时,就可以将这些等效电容和电感代入到单根传输线的等效模型(SLME)中来计算等效特性阻抗和传输速率。举个例子,如图 3.12,我们假设图中三导线系统以相同的相位传输所有数据。

**图 3.12:** 两种开关模式,(a) 三传输线为同相位信号,(b) 1 与 2 同相位, 3 与 1, 2 相差 180 度的相位

如果我们的主要任务是用一根单线来快速等效多导线系统(如图 3.12a),传输线 2 为目标线,那么线 2 上每单位长度的等效阻抗和传输延时可以计算如下:

(3.33)

$$Z_{2,\text{eff}} = \sqrt{\frac{L_{22} + L_{12} + L_{23}}{C_{22} - C_{12} - C_{23}}}$$

(3. 34)

$$TD_{2,eff} = \sqrt{(L_{22} + L_{12} + L_{23})(C_{22} - C_{12} - C_{23})}$$

## 例 3.5: 模型的阻抗和延时。

假设三导线系统中传输线 1 上的开关信号与 2 的同相, 而 3 的与它们有 180 度的相位差。如图 3.12b 所示(传输线 2 仍为受侵害线)。

导线 2 和 1 的共模电容= $C_{22}$  -  $C_{12}$

导线 2 和 3 的差模电容= $C_{22} + C_{23}$

导线 2 的等效电容= $C_{22}$  -  $C_{12}$  +  $C_{23}$

导线 2 和 1 的共模电感= $L_{22} + L_{12}$

导线 2 和 3 的差模电感= $L_{22}$  -  $L_{23}$

导线 2 的等效电感= $L_{22} + L_{12} - L_{23}$

对于这个多导线系统而言, 其等效单线模型中的传输线参数为:

$$Z_{2,\text{eff}} = \sqrt{\frac{L_{22} + L_{12} - L_{23}}{C_{22} - C_{12} + C_{23}}}$$

$$TD_{2,eff} = \sqrt{(L_{22} + L_{12} - L_{23})(C_{22} - C_{12} + C_{23})}$$

值得注意的是,在总线的缓冲器阻抗和传输线间距正在进行选择的设计阶段,这种简化技术还是非常有用的。但是必须提醒读者,此技术一般使用在信号按照相同的方向传播时,当信号间的传播方向不同时,如果要考虑串扰的影响,就必须建立等效电路模型和使用电路仿真器。

还有一点应该注意, SLEM 方法仅仅是一种近似, 其用处是在布线前的设计中, 能很快

缩小解决方案的范围。最后的仿真还是必须使用完全的耦合模型来进行。与完全的耦合仿真和测量相比较: 当走线间距和介质厚度的比例大于 1 时, SLEM 模型可以得到比较精确的近似,如果比例小于 1,建议不使用 SLEM 模型。当然,在一般地进行两条传输线的耦合分析时,这种方法还是比较精确的。

## 要点

SLEM 方法主要使用在前端设计中,以快速获取串扰的影响。SLEM 很有用是因为其计算速度快。而最后的设计还是需要进行完全仿真。

共模(所有位同相)和差模(目标位反相)将产生最坏的阻抗和速度变化。

当传输线之间的距离与介质高度(参考平面到传输线距离)之比小于 1 的时候,SLEM 将失效。

# 3.7. 串扰引起参数变化的趋势

在前面 3.6 节中已经阐述过,由串扰引起的阻抗变化取决于互感和互容的幅度大小。而这些相互耦合的寄生参数又在很大程度上与迹线的截面几何尺寸有关,因此阻抗的变化也就和传输线截面的尺寸有很大关系。在恒定的介电常数下,低阻抗传输线上因为串扰引起的阻抗变化比高阻抗线上的来得小一些,这是因为低阻抗传输线和参考平面的耦合比较大(存在更大电容,参考第二章)。如果传输线与参考平面的耦合加强,那么它和相邻线之间的耦合将减弱。低阻抗传输线通常通过增加传输线的线宽和减少介质的厚度实现。然而,这些选择都有负面效果。线宽太大将占用更大的布线空间,介质太薄将大大地提高成本(太薄的介质往往容易使信号与参考平面短路,因此成品率比较低)。

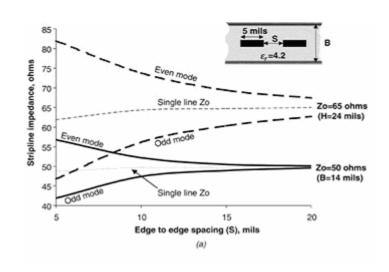

图 3.13a 和 b 表现了共模和差模情况下阻抗随传输线之间距离变化的情况。注意:不管 差模还是共模,他们的阻抗值变化趋势都是靠近一固定阻抗值的渐近线。目标线的阻抗计算

图 3.13 耦合阻抗随线间距的变化趋势: a. 典型的带状线 b. 典型的微带线

没有考虑邻近传输线的影响 (65 和 50Ω)。此阻抗值计算方法就是板厂提供的测试方法 (他们通常通过测试点测量孤立的单根传输线)。注意,在距离非常小时,信号线的阻抗值是小于目标值的(65 和 50Ω)。这是因为邻近传输线的存在提高了信号线本身的容性参数,即使线上没有信号通过,其传输线的有效阻抗值也会变低。而在邻近传输线都有信号通过时,将会产生完全的共模和差模阻抗,所以在设计高密度电路板的时候,这些影响都是必须要考虑到的。

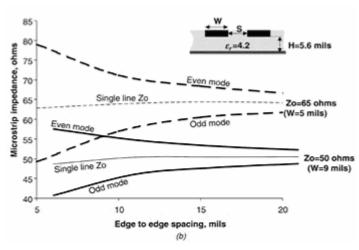

在图 3.14a 和 b 中,选用了与现实接近的 50 和 60 Ω的传输线(工业中常用得阻抗值),通过改变传输线的尺寸得到了寄生参数变化曲线。注意,高阻抗传输线阻抗值的变化比低阻抗传输线阻抗值的变化要大很多,这是因为高阻抗传输线与参考平面的距离要远大于线间距。图 3.14 给出了产生的耦合寄生参数随迹线截面的变化示意图。我们可以注意到相互的耦合寄生参数随着线距的变小而呈指数衰减。同时也应该看到,较低阻抗传输线的相互间的耦合寄生参数也相对较小些。读者应该了解:这些曲线是对简单的两条耦合传输线计算的结果,如果遇到的是更多的传输线耦合情况,将会带来更大的变化。

图 3.14: 3.14a 显示带状线中互感互容的变化, 3.14b 为微带线中互感互容的变化

#### 要点

在给定的介电常数下,串扰对低阻抗传输线产生的阻抗改变较小。 即使周围的传输线没有信号变化,传输线的阻抗也会受到一定的影响。 互感互容参数随着传输线间距的变化而呈指数衰减

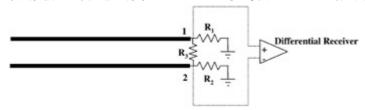

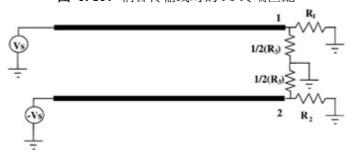

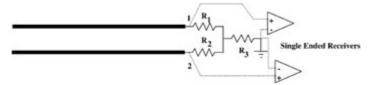

# 3.8. 共模与差模传输线的匹配

剩下来还没有讨论过的问题就是如何匹配一对耦合传输线。在通常的大多数设计时,经常需要谨慎地将所有线间的耦合减至最小。但是在某些设计中,这却没有必要,或者两条传输线之间的高度耦合还会给我们带来益处。一种情况就是计算机的系统时钟以差分形式传送的时候,两条传输线之间存在很大的耦合是有益的。一对差分线包含两条紧密耦合的传输线,它们以差分形式传输,接受电路由差分或者单端缓冲器构成。差分接受器的输入端通常包含一对差分触发器,并在两个信号交点处,即两信号之间的幅度差值为零的时候触发。差分线对信号传输有益主要是因为他比单根传输线具备更好的信号完整性,对噪声有更强的免疫力,以及能大大降低电磁辐射(EMI)。

## 3.8.1. Pi 型匹配网络

一种在差模和共模情况下都能很好匹配一对耦合传输线并防止反射的办法是使用Pi型网络。这个特殊的匹配方案对差分接受器非常有用。参照图 3.15,电阻 R, R, 和 R。必须进行合适地选择以匹配共模和差模时的传输。首先,我们考虑共模情况,当  $K = V_2 = V_6$ 时,由于点 1 和点 2 处的电压差总是相等,故两点间没有电流流过。所以,R 与 R 必须等于共模阻抗值。而R数值的决定,必须考虑到差模传输。由于 R 和 R 在差模情况下总是数值相等,极性相反(R = R = R ),R 可以分为两串联电阻,每个值等于 $\frac{1}{2}$  R 在差模传输过程中,两串联电阻中间变成一个虚拟的交流(ac)地。参考图 3.16,它给出了差模情

图 3.15: 耦合传输线对的 Pi 终端匹配

图 3.16: 差模形式下的等效 Pi 终端匹配

况下的等效终结模型。为了理解为什么电阻  $R_3$  的中点在差模形式下会成为AC地,我们可以

$$^{(3.35)}$$

$R_1 = R_2 = Z_{\text{even}}$

(3.36)

$$R_3 = \frac{2(Z_{\text{even}})(Z_{\text{odd}})}{Z_{\text{even}} - Z_{\text{odd}}}$$

但是必须注意的是,如果一对传输线只处在一种模式(比如差分时钟线)下,那么中间的电阻&就没有必要使用了。

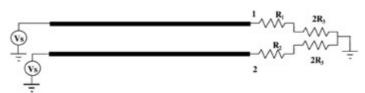

# 3.8.2. T 型匹配网络

另外一个能够同时解决共模和差模匹配的方法是使用 T 型电阻网络。如图 3.17 所示,

图 3.17: 耦合传输线对的 T 型终端匹配

图 3.18: 共模情况下耦合传输线对的等效 T 型终端匹配

这种匹配方式在单端接收器接收差分信号线时很有用。首先,让我们先考虑对差模的匹配,由于图中 1 点和 2 点处的电压大小相等,极性相反,我们可以认为与R 相连的中心点为ac 地。这样意味着我们可以通过R 与 R来对差模进行匹配。所以,R 与R的值必须相等并等于差分阻抗。下面,让我们来考虑共模传输情况,通过图 3.18 可以看出,这里将R 等效为两个阻值为 2R 的并联。由于在共模情况下,点 1、2 之间没有电流流过,那么R 或者R 与 2R 的串联阻值必须与传输线的共模阻抗相等。所以R, R, 和 R 在这个匹配网络中的阻值如下:

$$^{(3.\,37)}\ R_1 = R_2 = Z_{\text{odd}}$$

$$(3.38)$$

$R_3 = \frac{1}{2}(Z_{\text{even}} - Z_{\text{odd}})$

# 3.9. 如何减小串扰

既然串扰在很多设计中都会出现,而且它会破坏系统的性能,本节就总结了一些减少串 扰的一般规则,可能会对设计者们有一定的帮助。但是必须注意的事,所有的措施都会对印

图 3.19: 尺寸对串扰的影响

刷电路板的布通率上带来一定的麻烦。由于很多电路板实际上需要满足预先设计的尺寸要求 (比如,某些主板设计就可能需要符合标准的 ATX 底板规格),那么就不可避免得会产生一 定程度的串扰。下面的规则将可以帮助你有效地减少串扰。参照图 3.19。

- 1. 将两条传输线之间的距离 S 增大到规则允许的最大情况。

- 2. 在设计目标阻抗时,应该尽量使导体靠近地平面(例如,最小化H)。使得传输线可以紧密地与地平面进行耦合,这样可以减少对临近信号线的干扰。

- 3. 对于要求严格的网络在系统设计允许时可以使用差分线技术,比如系统时钟信号

- 4. 如果相邻层的传输线有较严重的耦合存在(如层 $M_3$ 和 $M_4$ )时,走线时应彼此正交。

- 5. 如果有可能,信号线应该设计成带状线或埋式微带线,以消除传输速度的变化。

- 6. 最小化信号间平行走线的长度。

- 7. 妥善布局, 防止布线时出现拥挤。

- 8. 尽量使用上升边沿慢的器件,但是使用此方法要非常小心,否则容易产生负面影响。

# 3.10. 附例

这个例子是基于第二章的附加例子,所不同的是在高速总线例子中增加了串扰的影响。串扰的存在经常大大限制了系统性能的发挥,因此,理解本章提出的概念是非常重要的。

## 3.10.1.问题提出

假设两个器件, $U_1$ 和 $U_2$ 需要通过一条 8 位宽的高速数据总线进行通讯。器件被安装在一块标准的四层主板上,该板叠层设置如图 3. 20 所示。驱动缓冲器的输出阻抗为  $30\Omega$ ,其开关幅度从 0V 到 2V。印刷电路板上(PCB)的信号线要求 5 英寸长,线中心到中心的间距为 15 mils,阻抗  $50\Omega$ (忽略串扰影响)。板上介质的相对介电参数( $\varepsilon_r$ )为 4.0,传输线假设为一个完美的导体,并且接收器上的寄生电容小到可以被忽略。图 3.21 描述了电路的拓扑结构。

图 3.20 此例中涉及的 PCB 板的截面图

图 3.21 电路的拓扑结构

传输线参数如下:

互感=0.54nH/in.

互容=0.079pF/in.

自感=7.13nH/in. (来自第二章的例子)

自容=2.85pF/in. (来自第二章的例子)

## 3.10.2. 目标

- 1. 决定传输线上由于串扰引起的最大的阻抗变化

- 2. 决定由于串扰引起的最大的速度变化

- 3. 假设器件 $U_2$ 上的输入缓冲在 1. 0V 时进行开关,决定是否缓冲器会因为串扰的影响而错误触发

## 3.10.3. 决定由串扰引起的最大的阻抗和速度漂移

按照 3. 6. 2 节的讨论,耦合系统中传输线的等效阻抗与邻近线上信号的开关模式有关。为了决定由于串扰引起的最差情况的阻抗漂移,我们必须选择总线中将经受到串扰最大的信号线来进行分析,而位于总线中间的线通常是最好的选择。就像本章早些时候所提及的,仅仅与之最近的线将对串扰的影响负主要责任,因此,可以用前面例子中使用的程序来计算串扰引起的阻抗变化。另外,产生最大串扰影响的模式通常是共模或差模中的一种。在共模传输模式中,总线上信号的相位总是相等的,在差模传输时,目标线的相位总是与总线上其他的信号线相位相差 180 度。

首先,让我们来计算共模传输模式(所有的信号位同相)时的影响。假设图 3.22 中的线 2表示了 8 位总线中间的一条导线。

Ground plane

图 3.22: 共模开关模式

导线 2 和 1 之间的共模电容= $C_{22}$ - $C_{12}$

导线 2 和 3 之间地共模电容= $C_{22}$  -  $C_{23}$

导线 2 的等效电容= $C_{22}$ - $C_{12}$ - $C_{23}$

导线 2 和 1 之间的共模电感= $L_{22} + L_{13}$

导线 2 和 3 之间的共模电感=  $L_{22} + L_{23}$

导线 2 的等效电感= $L_{22} + L_{12} + L_{23}$

$= 148.6 \, pF / in$ .

所以有:

$$\begin{split} Z_{2,common} &= \sqrt{\frac{L_{22} + L_{12} + L_{23}}{C_{22} - C_{12} - C_{23}}} \\ &= \sqrt{\frac{7.13nH + 0.54nH + 0.54nH}{2.35pF - 0.079pF - 0.079pF}} = 55.26\Omega \\ TD_{2,common} &= \sqrt{(L_{22} + L_{12} + L_{23})(C_{22} - C_{12} - C_{23})} \\ &= \sqrt{(7.13nH + 0.54nH + 0.54nH)(2.85pF - 0.079pF - 0.079pF)} \end{split}$$

现在,让我再来估计一下差模传输时的影响。假设图 3.23 中的线 2表示 8 位总线中间的线 2。

图 2.23 差分开关模式

导线 2 和 1 之间的差模电容= $C_{22}+C_{12}$

导线 2 和 3 之间的差模电容= $C_{22}$ + $C_{23}$

导线 2 的等效电容= $C_{22}+C_{12}+C_{23}$

导线 2 和 1 之间的差模电感= $L_{22}$  - $L_{12}$

导线 2 和 3 之间的差模电感= $L_{22}-L_{23}$

导线 2 的等效电感= $L_{22}-L_{12}-L_{23}$

所以有,

$$\begin{split} Z_{2,differential} &= \sqrt{\frac{L_{22} - L_{12} - L_{23}}{C_{22} + C_{12} + C_{23}}} \\ &= \sqrt{\frac{7.13nH - 0.54nH - 0.54nH}{2.85\,pF + 0.079\,pF + 0.079\,pF}} = 44.8\Omega \end{split}$$

$$\begin{split} TD_{2,differential} &= \sqrt{(L_{22} - L_{12} - L_{23})(C_{22} + C_{12} + C_{23})} \\ &= \sqrt{(7.13nH - 0.54nH - 0.54nH)(2.85pF + 0.079pF + 0.079pF)} \\ &= 135ps/in. \end{split}$$

因此可得由串扰引起的速度和阻抗的变化为:

$$44.8\Omega < Z_0 < 55.26\Omega$$

$135 \, ps / in. < TD < 148.6 \, ps / in.$

# 3.10.4 确认串批是否会引起误触发

当信号存在严重的信号完整性问题时,将发生误触发。当信号达到阈值时,接收器将被触发。典型的 CMOS 缓冲器的触发电平为  $\frac{1}{2}V_{cc}$ 。如果信号振荡到接收器的阈值电平以下,这种信号完整性问题可能会引起误触发。当这种情况发生在数字系统中时,可能会引起大量的问题,轻则暂时数据失效,重则系统崩溃(特别是当选通信号或系统时钟被误触发时)。为了确定是否串扰将引起一个错误的信号这个问题,我们必须评估信号完整性。有很多方法可以实现这种评估。最简单的方法就是用简单的反弹(例如网格)图,比如第二章的例子中用来决定信号波形的方法,不过我们也不需要完全的反弹图,因为到达接收端的第二次反射将产生最大幅度的振荡,因此我们只需要第二次反射时接收端上呈现的信号电压幅值,而且,当驱动端阻抗低于传输线的特征阻抗时,最大的振荡才发生(见第 2 章)。所以,当总线中的耦合线彼此之间同相传输(比如共模)时,最大的振荡发生了。前面已经计算出共模阻抗高于  $55.2\Omega$ 。用反弹图计算出的信号完整性问题如图 3.24 所示:

图 3.24 最终波形计算图

从图中可见,信号将向下振荡到 1.84V 的位置,因为这个缓冲器的阈值电压被定义在 1.0V, 信号的下冲不会达到这个值, 信号完整性问题不会引起接收器的误触发。

# 第四章 非理想互连的问题

现代的技术已经朝着更高的速度和更小的封装发展,这是一种不可改变的趋势。随之而来,在以前的数字设计过程中经常被认为微不足道或可以忽略的影响现在常常成为主要的设计焦点。在这些现代设计中必须被考虑的新变量中,非理想效应就是其中的一个方面,比如频域衰耗、阻抗不连续和蛇行线影响等等。这些高频的效应通常是很难模拟的,很多大学都正在不断地研究中。所以,随着系统速度的突飞猛进,工程师们不仅要处理技术上的难点,还必须应对大量的可变因素。在这一章里我们要解决许多由于非理想互连所带来的问题,它们都必须在现代设计中被考虑。这一章的焦点是过去的设计中被极大忽略,而现在却成为关键的高速时的传输特性问题。这里提出的许多模型中也存在许多缺点,就像过去简单模型中的缺点一样,这些需要在将来被修订。随着一些模型的调整,读者应该一直明白这里有许多假设和近似被建立。

#### 4.1. 传输线损耗

随着技术的进步,数字系统正朝着更小、更快的方向发展,器件封装和传输线的几何尺寸都在缩小。而更小的尺寸和更高的频率会加剧传输线上的电阻损耗。因此,如何建模传输线上的电阻损耗变得越来越重要。电阻损耗的结果是减小了信号的幅度,从而降低了数字系统的性能,比如会影响噪声门限和减慢边沿速率,这最终都将会影响到时序裕量。在以前,由于系统工作在比较低的频率下,我们可以忽略 PCB 和封装上的这种损耗,然而,现在就不同了,系统要求对损耗进行更严格的分析,因为它们的存在,常常是导致数据互连性能恶化的首要原因。

#### 4.1.1. 导体的直流损耗

正如第二章中所提到的,在传输线模型中有电阻性成分。这个电阻性成分存在的原因是由于在 PCB 上用于制造传输线的导体并不是完美的导体。微带线和带状线上的损耗能被分成两个部分: DC (直流)和 AC (交流)损耗。当传输线的截面尺寸小,线很长,并且带多负载(也被称为多分支)时应该特别关注直流损耗。例如,因为信号衰减,长距离的通讯铜线必须每隔几英里就加上中继器来接收和重发数据。另外,在设计多处理器计算机系统时,也会面临电阻损耗的问题,这将损害逻辑门限,并降低噪声裕量。

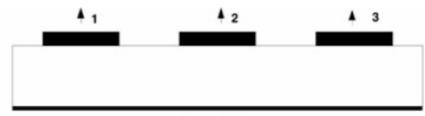

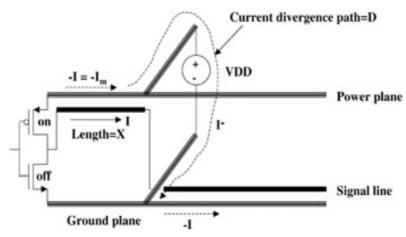

直流损耗主要由两个因素决定:导体的电阻率和电流流过的总面积。图 4.1 显示在直流(0Hz)时微带线中的电流分布。电流流过导体的整个横截面,电阻性衰耗能用下面等式得到:

$$R = \frac{\rho L}{A} = \frac{\rho L}{Wt} \quad \text{ohms}$$

这里 R 是线路上的总电阻, $\rho$  是导体材料的电阻率,单位为欧姆米(电导率的倒数),L 是线的长度,W 为线宽,t 是导体厚度,A 为导体的横截面积。在传统设计中,地回流路径上的损耗在 dc 时通常可以被忽略,因为它的横截面与信号线的相比要大的多。

图 4.1: 直流时微带线中的电流密度图。直流时,电流流过完全的横截面,这里,A=Wt

## 4.1.2. 介质上的直流损耗

因为被用在 PCB 上的介质材料不是完美的介质体,在信号导线和参考平面之间的介质材料上有电阻存在,因而也有直流损耗。然而,对于传统基板来说,直流下的介质损耗通常非常的小以致可以忽略不计。与频率相关的介质损耗将在 4.1.4 节中被讨论。

## 4.1.3. 趋肤效应

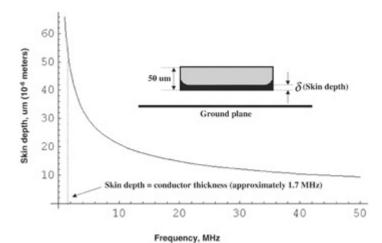

对低频的系统进行仿真时,仅仅考虑直流损耗就足够了,但是随着频率增加,随着数字信号频谱的变化而带来的各种其它现象开始起主要作用。这些与频率相关的变量中,最重要的就是"趋肤效应",之所以这样命名,是因为在高频时,导体上的电流将趋于集中在导体外围或"皮肤"上。

## 频域电阻和电感

趋肤效应主要是表现为电阻和电感变化。在低频时,电阻和电感呈现直流值,但是随着频率的增加,传输线横截面上的电流分布变得不均匀并向导体的外部移动。电流分布的改变使电阻随着频率的平方根成比例增长,同时总电感渐渐回落到一个常值,即外部电感。

为了理解这种现象是如何发生的,我们可以假设一个信号在微带线上传输。图 2.3 中的横截面积显示了高频信号在信号线和参考平面之间的传输形式为随时间变化的电场和磁场,他们不是完全在导体内部。当这些场与信号线导体或地平面导体交叉时,他们将穿过金属同时信号将衰减。衰减的幅度取决于金属的电阻率(或电导率)和信号的频谱分量。穿透金属的厚度为趋肤深度,用符号  $\delta$  来标识。如果金属是完美的导体,电磁场将不能进入金属所以趋肤深度将是 0。如果金属只是有限传导的,那么一部分进入金属的电磁波将被衰减,在趋肤深度处它的衰减幅度为表面初始值的  $\delta$  倍。(如果读者对趋肤深度的导数感兴趣,任何标准的电磁课本对此都有足够的解释。)这将限制信号以致总电流的 63%将在趋肤深度里流动,同时进入导体内部电流密度按指数下降。当然,导体的物理尺寸将调整这个电流分布。趋肤深度  $\delta$ 将用下面的公式来计算:

$$\delta = \sqrt{\frac{2\rho}{\omega\mu}} = \sqrt{\frac{\rho}{\pi F \mu}} \qquad \text{meters}$$

这里的  $\rho$  是金属的电阻率(电导率的倒数),w是角频率( $2\pi P$ ), $\mu$  是自由空间的穿透能力(单位为亨利每米)[Johnk, 1998]。(在使用了铁或镍等磁性金属的罕见环境里,应该用相应的渗透率来代替。但是这种情况极少发生。)我们已经看到,随着频率的增加,电流将被限制在一个更小的区域内,这将使电阻增加,就如直流电阻计算公式  $4.1~\mathrm{ff}$  质显示的那样。

这种现象也会引起电感随频率的变化而变化。导体总电感是由电流产生的磁通量来决定的。部分 磁通量是由导线自身的电流产生的。因为在高频时,电流主要被限制在趋肤深度以内,电流很难传播 到导体中间。因此,内部电感(因为由导体内部电流产生而得名)将被忽略,总电感下降。外部电感 是假设了所有的电流都在导体外围流动时计算得到的值。总电感是由外部电感和内部电感之和。在大 多数高速数字系统中,信号的频谱成分足够高以至于可以近似忽略频率相关的电感。所以,对于本书 的其他部分,仅仅考虑外部电感。

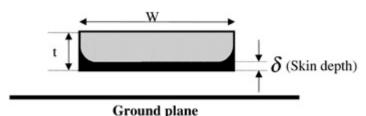

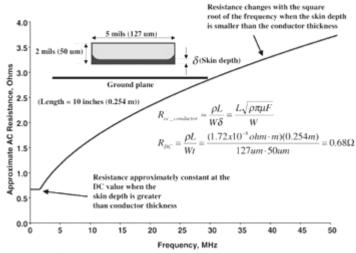

## 微带线中导体的频域损耗

通过扩展等式 4.1 中的直流电阻的计算公式,可以近似得到传输线导体上频域的电阻值。在本书中,和频率相关的电阻有时被称为交流(AC)电阻。在低频时,因为趋肤深度大于导体厚度,因此交流电阻和直流电阻是相等的。随着频率的逐渐增加,当趋肤深度小于导体厚度时,交流电阻将大于直流电阻。图 4.2 描述了高频时微带线上的电流分布情况。注意这时电流集中分布在传输线的底部边缘。这是因为信号线和地平面之间的电场把电荷拉向底部边缘。同时还可以看到导体的边缘的电流分布成曲线向上翘起,其原因在于边缘的区域,大部分的场仍然沿着导体的厚度(图 4.2 中的 t 参数)集中分布。电流流过的横截面积随着频率的增高越来越小。(见等式 4.2)

图 4.2: 微带线上的电流分布。63%的电流因为趋肤效应而集中在黑色阴影部分。

导体的损耗可以用直流电阻和趋肤效应的计算公式来估算,其中导体厚度用趋肤深度来代替。

(4. 3a)

$$R_{\text{ac signal}} \approx \frac{\rho}{W\delta} = \frac{\sqrt{\rho\pi\mu F}}{W}$$

$\Omega/\text{m}$

注意这个估算只是当趋肤深度比导体厚度小的时候才有效。而且,等式 4.3 也只是一个近似,因为它假定了所有的电流分布在趋肤深度区域内,引用这个等式的目的只是为了更好的解释这个现象。在本章的后面,会提出更多的精确方法来计算交流损耗。注意当用等式 4.2 所表达的趋肤深度直接代入到直流电阻计算等式时,交流电阻直接和频率 F 及电阻率  $\rho$  的平方根成正比。注在意等式 4.3 中,长度因子由于交流电阻单位变为每单位长度电阻而被去掉。

图 4.3 是一段铜导体的趋肤深度与频率的关系曲线。注意在 1.7MHz以下,趋肤深度大于导体厚度。对于给定的铜导体的横截面,图 4.4 给出了电阻作为频率函数的曲线。注意曲线的开始部分为常数,其值等于直流电阻值,这一曲线段是针对趋肤深度大于导体厚度的频率区域。当趋肤深度小于导体厚度后,曲线开始随频率的平方根变化。尽管图 4.4 中的曲线不是基于实际模型的,但它对于帮助读者理解趋肤效应的基本行为还是很适合的。使用类似SPICE的仿真器可以同时仿真传输线交流和直流电阻,如果让仿真的结果和实际测量的值相符合,一个很好的方法就是合并Rac 和 Rac为一个总的电阻:

(4.3b)

$$R_{

m total} pprox \sqrt{R_{

m ac}^2 + R_{

m dc}^2}$$

图 4.3: 趋肤深度随频率的变化曲线

图 4.4: 交流电阻随频率的变化曲线

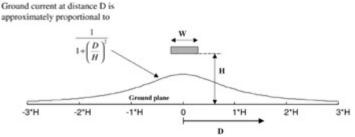

然而导体中的趋肤效应电阻只是总的交流电阻的一部分。等式 4.3a 中没有包括的部分是参考平面上的信号回流电阻。回路电流在信号线下方的参考平面上流动,大部分集中在趋肤深度以内,并向与迹线垂直的方向展开,但是电流的大部分集中在信号导体的正下方。微带传输线所参考的地平面上近似的电流密度分布如下所示[Johnson and Graham, 1993]:

(4.4)

$$I(D) \approx \frac{I_o}{\pi H} \frac{1}{1 + (D/H)^2}$$

图 4.5: 地平面上的电流分布

这里的  $I_o$ 是总信号电流,D为离开线的距离(如图 4.5 所示),H是离地平面的高度。图 4.5 是这种电流密度分布的图形化表示。

地平面上有效电阻的近似计算可以用上面曾用过的计算信号导体交流电阻的方法来得到。首先,因为 63%的电流被限制在趋肤深度  $\delta$  内,那么可以近似地认为地平面上的电流完全在趋肤深度内,正如信号导线的交流电阻近似计算一样。其次,等式 4.5

(4.5)

$$\int_{-3H}^{3H} \frac{I_o}{\pi H} \frac{1}{1 + (D/H)^2} = \frac{2I_o}{\pi} \tan^{-1}(3) \approx 0.795I_o$$

$$= 79.5\% \text{ of the total current}$$

显示 79. 5%的电流集中在离导体中心 $\pm 3H$  (总共 6H  $\mathcal{B}$   $\mathcal{B}$ )的范围内。这样,地回流路径电阻可以近似认为由横截面积为 $A_{ground} = \delta \times 6H$ 的导体产生的。将这种近似结果代入等式 4.1 中得:

(4.6)

$$R_{\text{ac ground}} \approx \frac{\rho}{A_{\text{ground}}} = \frac{\rho}{6\delta H} = \frac{\rho}{6H} \sqrt{\frac{\pi \mu F}{\rho}}$$

$$= \frac{\sqrt{\rho \pi \mu F}}{6H} \qquad \Omega/\text{m}$$

总交流电阻为导体和地平面的交流电阻之和:

(4.7)

$$R_{\text{ac microstrip}} = R_{\text{ac signal}} + R_{\text{ac ground}}$$

(4.8)  $\approx \frac{\sqrt{\rho\pi\mu F}}{W} + \frac{\sqrt{\rho\pi\mu F}}{6H} = \sqrt{\rho\pi\mu F} \left(\frac{1}{W} + \frac{1}{6H}\right) \quad \Omega/m$

等式 4.8 被认为是一阶近似。而表面的粗糙程度也会增加 10%到 50%的电阻(参考下面"导体表面粗糙程度的影响"),当然,等式 4.8 的计算方法对于大多数情况能提供足够的精度。

可以通过保角映射(conformal mapping)原理得到更精确的微带线上交流电阻的计算公式。

(4.9)

$$R_{\text{signal}} = [\text{loss ratio}] \left(\frac{1}{\pi} + \frac{1}{\pi^2} \ln \frac{4\pi W}{t}\right) \frac{\sqrt{\pi \mu F \rho}}{W}$$

$$\text{Loss ratio} = \begin{cases} 0.94 + 0.132 \frac{W}{H} - 0.0062 \left(\frac{W}{H}\right)^2 & \text{for } 0.5 < \frac{W}{H} < 10 \\ 1 & \text{for } 0.5 \ge \frac{W}{H} \end{cases}$$

$$R_{\text{ground}} = \frac{W/H}{W/H + 5.8 + 0.03(H/W)} \frac{\sqrt{\pi \mu F \rho}}{W} & \text{for } 0.1 < \frac{W}{H} < 10$$

$$R_{\text{ac microstrip}} = R_{\text{signal}} + R_{\text{ground}} \qquad \Omega/m$$

等式组 4.9 由保角映射技术得到,与实际结果非常吻合[Collins, 1992]。这些公式明显比 4.8 复杂得多,但是可以得到更精确的结果。等式 4.8 得到的结果比 4.9 的要大。通常,由 4.8 式得到的较大的结果被用来近似由表面粗糙带来的额外电阻。

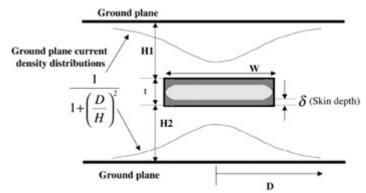

## 带状线中导体的频域损耗

在带状传输线里,高频信号电流集中在导体的上下边缘。电流密度取决与地平面的接近程度。如果带状线距其两个参考地平面的距离相等,就象图 4.6 那样,其上下部分将分布相等的电流。在非平衡传输线中,上下边缘的电流分布取决于导体和地平面的各自距离(图 4.6 中的H1 和H2)。在带状线中每个回流平面的电流密度分布可以用类似 4.4 的等式来确定,其唯一的差别在于参数 *I* 的大小不同

图 4.6: 带状线中的电流密度分布

,明显地,它是带状线距各个参考平面距离的函数。这样带状线的电阻可以通过导体上下两部分电阻的并联得到。带状线的上下电阻可用等式 4.8 或者 4.9 得到,只要代入适当的 H 值即可。这两个电阻必须并联来得到带状线的总电阻[见等式 4.10]。

带状线交流电阻的较好的近似为:

(4. 10)

$$R_{\text{ac stripline}} = \frac{(R_{(H1)\text{ac microstrip}})(R_{(H2)\text{ac microstrip}})}{R_{(H1)\text{ac microstrip}} + R_{(H2)\text{ac microstrip}}} \Omega/m$$

这里的微带线电阻值由等式 4.8 或者 4.9 得来,高度取值为 H1 或 H2。参考图 4.6 得到相关尺寸。

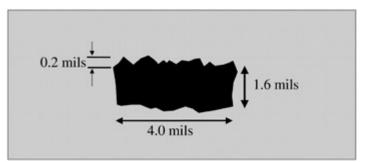

#### 导体表面粗糙程度的影响

前面提到,信号处于高频时,由于电流向导体表面移动而使串联电阻增加。然而前面提到的关于损耗的公式都基于金属表面完全光滑的假设,但事实上,金属表面都是粗糙的,当平均的表面粗糙度和趋肤深度相当时,材料的有效电阻值将明显地增加。实际研究发现高频信号在表面非常粗糙的线上传播时,损耗比公式计算出的理想情况大 10-50%。因为粗糙情况的随机性,不可能精确的预计趋肤效应损耗。然而,通过观察粗糙程度相对于趋肤深度的大小,很容易决定表面粗糙程度是否成为主导因素。图 4.7 是一个典型 PCB 上的带状线在显微镜下观察到的的横截面图。注意,在这个例子中,导体上部的表面粗糙程度大约为 0.2 mil  $(5~\mu\text{m})$ 。

图 4.7: 典型PCB上带状线的横截面图,显示了其表面粗糙度

导体的粗糙程度通常被描叙为齿状结构,表面变化的幅度称为齿尺寸。例如,图 4.7 中的齿尺寸为 5 μm。根据 PCB 厂商的调查表明典型的 FR4 板平均齿尺寸为 4-7 μm。暴露在蚀刻工艺流程中的导体表面将有明显较小的齿尺寸。因此,具有最大齿尺寸的齿结构通常在与参考平面相邻的导体面上。从图 4.7 可以看出,导体下表面(导体的蚀刻面)有明显小的齿尺寸。现有工艺技术可以明显的减少参考平面相邻表面的粗糙程度,但是因为这需要大量的制造工序所以价格更贵。

当齿尺寸大到于趋肤深度相当时,表面粗糙度开始影响理想交流电阻等式的计算精度。例如,当频率到达 200MHz 时,铜趋肤深度将近似等于典型 PCB 表面的粗糙度。在这个频率上的频谱分量将不断地背离理想公式。为了测量表面粗糙程度的大小,要么象图 4.7 展示的那样做横截面测量,要么问 PCB 制造商相应的粗糙度规范。如果需要考虑导体表面粗糙程度,那么交流电阻就必须要测量。

## 各种金属的频域属性

表面电阻(R<sub>s</sub>)经常被用作描叙给定材料交流电阻的参数。表面电阻可以简化为等式 4.3 到 4.9 计算得到的交流电阻除以频率的平方根。因此,交流电阻可用下面的式子表示:

$$(4.11) R_{ac} = R_s \sqrt{F}$$

为了区分材料性质的类别,表面电阻常常作为一个长宽相等(L/W=1)的半无限平面来计算。也可以假定所有的电流都在趋肤深度内,用 4.3 式子来计算电阻值。近似值由式 4.12b表示:

$$R_s = \begin{cases} \frac{\rho}{\delta} = \frac{L}{W} \sqrt{\rho \pi \mu} & \text{ohms} \cdot \sqrt{\text{seconds}} \\ \sqrt{\rho \pi \mu} & \text{ohms} \cdot \sqrt{s}/\text{square} \quad (L = W) \end{cases}$$

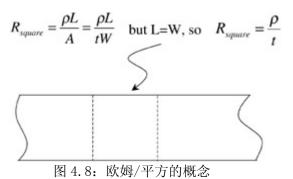

对于面积有限的导体,交流电阻可以通过 R。(单位为欧姆每平方)乘以长度和频率的平方根再除以宽度来得到。 R。 的单位为欧姆每平方,注意术语"每平方"简单可认为是任何单位的平方(长等于宽),因为对于给定厚度的印制板走线,其一个几何正方形电阻和正方形的单位无关。这样,通过计算多少平方符合测试区域,然后将平方数乘以 R。,再乘以频率的平方根即可简单地估计表面交流电阻的值。每平方直流电阻的概念在图 4.8 中说明。记住,在互连仿真中,计算导体和地回流路径的电阻是很重要的。表 4.1 显示了典型的几种材料趋肤效应的属性。

| 表 4.1: 典型材料的频率相关属性                |                       |                    |                                               |

|-----------------------------------|-----------------------|--------------------|-----------------------------------------------|

| 金属                                | 电阻率(Ω · m)            | 趋肤深度(m)            | 表面电阻率, $R_s$ ( $\Omega$ • $\sqrt{s}$ /square) |

| Copper (300K)                     | $1.72 \times 10^{-8}$ | $0.066 F^{^{1/2}}$ | $2.61 \times 10^{-7}$                         |

| Copper (77K)                      | $5.55 \times 10^{-9}$ | $0.037F^{1/2}$     | 1.5 × 10 <sup>-7</sup>                        |

| Brass                             | $6.36 \times 10^{-8}$ | $0.127F^{1/2}$     | 5. 01 × 10 <sup>-7</sup>                      |

| Silver                            | $1.62 \times 10^{-8}$ | $0.0642 F^{1/2}$   | $2.52 \times 10^{-7}$                         |

| Aluminum                          | $2.68 \times 10^{-8}$ | $0.0826 F^{1/2}$   | $3.26 \times 10^{-7}$                         |

| 数据来源: <u>Ramo et al. [1994]</u> . |                       |                    |                                               |

## 信号交流损耗的影响

有两种典型的人需要经常面对交流损耗的问题:一种人是数字设计者,另外一种人是微波设计者。微波设计者通常只是对频域仿真中的交流电阻感兴趣,这是比较容易实现的,因为大多数模拟器,象 HSPICE,都有与频率相关的电阻,它能随着频率的平方根变化(见 4.11 等式),并且可以用在图 2.4 中由 LRC 片组成的等效电路中。

然而,数字工程师会遇到更加困难的问题。近似方波的数字信号有很宽的波段,这意味它们包含了许多频谱成分。这是一个重要概念,可以通过下式来理解[Selby, 1973]:

(4.13)

$$f(x) = \frac{2}{\pi} \sum_{n=1,3,5,\dots} \frac{1}{n} \sin 2\pi n F x$$

这是占空比为 1: 1 的周期方波的傅立叶展开,这里 F 指频率,X 指时间。例如一个频率为  $100 \, \text{MHz}$  的方波将是无数个频率为奇数倍基频(例如  $100 \, \text{MHz}$ ,  $300 \, \text{MHz}$ ,  $500 \, \text{MHz}$  等等)的正弦波的叠加。这些频谱成分被称为谐波,n=1 是一次谐波,n=3 是三次谐波,如此类推。趋肤效应使每个谐波随频率增加而呈现更多的衰减。当然实际信号并不像等式 4.13 中假设的那样,它不是占空比正好为 1:1 的方波,并且没有无限快的上升时间,所以其还还有额外的频谱成分。显然,读者可以验证,当方波没有 50% 的有效时间时,偶次谐波将出现,这在第十章将重点讲述。

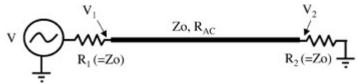

由于数字信号被定义在时域而交流电阻被频域参数定义,所以在时域仿真中很难正确地考虑与频率相关的损耗。幸运的是,目前许多仿真工具在这一方面已经做得很好,只要用户插入正确的交流表面电阻 R<sub>s</sub>,仿真器就能得出比较精确的结果。而交流电阻通常用向量网络分析仪(VNA)来测量。在频域中,交流电阻通常用衰减因子 a 来表征。 a 是传输线上随频率变化的信号幅度衰减的测量值。在

图 4.9: 等式(4.14a)到(4.14c)的参考图

类似于图 4.9 中描叙的匹配系统中,很容易用等式 4.14a—c 计算单一频率下的衰减因子,它是基于信号在接收端的分压,交流电阻包含在分母里面。如果终端阻抗和源端阻抗和传输线的特征阻抗不匹配,4.14c 等式中电压相比的方法就不合适,其原因在于反射将干扰测量。由于传输线的特征阻抗通常与 VNA 的内部电阻不匹配,就必须采用相应的技术来消除反射的影响。测量交流损耗的技术将在 11章中作具体描述。

$$V_{1} = V \frac{R_{\rm ac} + R_{2}}{R_{1} + R_{\rm ac} + R_{2}}$$

$$V_{2} = V \frac{R_{2}}{R_{1} + R_{2} + R_{ac}}$$

$$V_{3} = V \frac{R_{2}}{R_{1} + R_{2} + R_{ac}}$$

$$\alpha = \frac{V_{2}}{V_{1}} = \frac{R_{2}}{R_{ac} + R_{2}}.$$

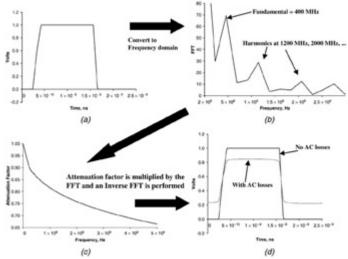

为了阐明频率相关的损耗对时域信号的影响,请参考图 4.10 所示, 4.10a 是一个代表数字信号的理想梯形波。图 4.10b 是这个数字信号的傅氏变换,显示了信号包含的频谱。图 4.10c 是一条 10 英寸长的微带线衰减随频率的变化图。图 4.10d 是当衰减曲线与傅氏变换后的曲线相乘后再做反傅氏变换得到的曲线。注意波形被圆滑了,边缘也变得平坦了一些,信号幅度也被衰减。这种影响的发生是由于信号的高频分量被显著衰减,这使尖锐的边沿消失且边沿下降。

图 4.10: 频率相关的损耗对于时域信号的影响: (a) 理想数字信号(400 MHz 周期, 脉冲宽度 = 1.25 ns, 周期 = 2.5 ns); (b) 经过傅立叶变换后得到的频率成分; (c) 频率相关的衰减; (d) 频率相关的衰减对信号时域的影响

每个仿真器都会有各自处理交流电阻的方法。所有的都需要用户输入表面电阻(R<sub>s</sub>)和传输线的横截面尺寸参数或是电容和电感矩阵(见第二章),后两个通常只要输入其中的任一项。

#### 4.1.4. 频域的介质损耗

在大多数设计中,导体损耗起决定作用,而介质损耗可以被忽略。但是,随着频率的增加,这种假设就不再是正确了。因而,理解介质频域损耗的基本机制就变得很重要。

当时变的电场加到一种材料上时,材料中任何本质上存在极性的分子将倾向于朝着施加电场的反方向排列,这被称作电极化。由实验测量得到的介质损耗的经典模型包含分子粒子的振荡系统,它会根据应用的电场做出随频率变化的衰减机制[johnk,1988]。介质损耗中的任何频率变化都是由这种机制引起的。

当考虑介质损耗时,材料的介电常数计算就变得复杂了:

$$(4.15) \qquad \varepsilon = \varepsilon' - i\varepsilon''$$

这里虚部表示损耗,实部表示介电常数的典型值。由于等式 4.15 的虚部代表损耗,那么它可以很方便地认为是有损介质的有效电导率(电阻率的倒数)。

因此,正如电磁书中所说, $1/\rho = 2\pi F \varepsilon$  "为损耗机制的等效形式,这里的  $\rho$  为介质材料的等效电阻率,F 为频率。然而,和金属的损耗不同,介质损耗通常不是用电阻率来表现的。表现介质损耗特性的典型方法是利用损耗正切参数[Johnk, 1988]:

$$\tan|\delta_d| = \frac{1}{2\rho\pi F\varepsilon} = \frac{\varepsilon''}{\varepsilon'}$$

这里的  $\rho$  为介质电阻率。在大多数实际应用中,仿真器用等式 4.16 中的损耗正切来作为输入。然而,如果设计者想通过 2.3.3 节中给出的RLC段来建立传输线的等效电路,那么必须建立 $\tan | \delta_d|$ 和并联电阻G之间的关系。这个关系可以表示如下[Collins, 1992]:

(4.17)

$$G = \frac{\varepsilon''}{\varepsilon'} (2\pi F C_{11}) \qquad \text{siemans}$$

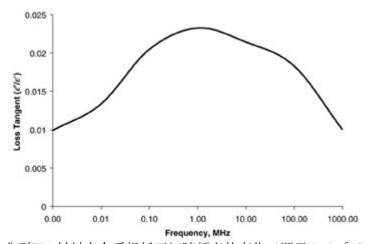

这里的 $G_1$  是单位长度上的自耦电容,F为频率。损耗正切将随着频率和材料属性变化而变化。图 4.11 展示了典型的FR4 板材的损耗正切和频率变化的关系。

图 4.11: 典型FR4 材料中介质损耗正切随频率的变化(源于Mumby[1988].)

# 例 4. 1 计算损耗

参考图 4.6 中的带状线横截面

1. 假设W=5 mils, H=H=1 0 mils, t=0.63 mil,  $\varepsilon_r=4.0$ , 计算表面电阻 (Rs)

- 2. 确定电阻如何随着频率变化

- 3. 计算在 400MHz 下由于介质损耗引起的并联电阻

- 4. 计算在 400MHz 下由于导体损耗引起的串联电阻

解答: 等式 4.9、4.10、4.11 常被用作计算传输线的表面电阻率。开始时,传输线上部和下部的电阻都被假定用微带线等式来计算。接着等式 4.10 被用作确定带状线电阻,为了得到电阻率,需要除以频率的平方根。

$$\frac{W}{H} = \frac{5}{10} = 0.5$$

$$\begin{split} R_{\text{signal}} &= 1.0 \left( \frac{1}{\pi} + \frac{1}{\pi^2} \ln \frac{4\pi(5)}{0.63} \right) \frac{\sqrt{(\pi \cdot 12.56 \times 10^{-7})1.72 \times 10^{-8}(F)}}{(0.005 \text{ in.})(0.0254 \text{ m/in.})} \\ &= 0.00172 \sqrt{F} \qquad \Omega / \text{m} \\ R_{\text{ground}} &= \left( \frac{1}{0.5 + 5.8 + 0.03 \cdot 0.5} \right) \frac{\sqrt{(\pi \cdot 12.56 \times 10^{-7})1.72 \times 10^{-8}(F)}}{(0.005 \text{ in.})(0.0254 \text{ m/in.})} \\ &= 0.0003 \sqrt{F} \qquad \Omega / \text{m} \\ R_{(H1)\text{ac microstrip}} &= R_{\text{signal}} + R_{\text{ground}} = (0.00172 + 0.0003) \sqrt{F} \\ &= 0.0020 \sqrt{F} \qquad \Omega / \text{m} \\ R_{(H2)\text{ac microstrip}} &= R_{(H1)\text{ac microstrip}} \\ R_{\text{ac stripline}} &= \frac{(R_{(H1)\text{ac microstrip}})(R_{(H2)\text{ac microstrip}})}{R_{(H1)\text{ac microstrip}} + R_{(H2)\text{ac microstrip}}} \\ &= \frac{R_{(H1)\text{ac microstrip}}}{2} = 0.0010 \sqrt{F} \qquad \Omega / \text{m} \\ R_{s} &= 0.0010 \frac{\Omega}{\text{m} \cdot \sqrt{\text{Hz}}} \end{split}$$

为了确定电阻是如何随频率而变化的,我们必须确定趋肤深度小于导体厚度时的频率。为了得到 这个结果,我们用导体厚度代替趋肤深度并代入到等式 4.2 中,得到频率。

$$0.63 \text{ mil} \frac{25.4 \times 10^{-6} \text{ m}}{\text{mil}} = \sqrt{\frac{1.72 \times 10^{-8} \Omega \cdot \text{m}}{\pi [12.56 \times 10^{-7} (H/m)]F}} \Rightarrow F = 17 \text{ MHz}$$

低于 17MHz 时,导体的电阻近似等于直流电阻[等式 4.1]:

$$R_{\rm dc} = \frac{1.72 \times 10^{-8} \ \Omega \cdot \text{m}}{5 \ \text{mil} \frac{25.4 \times 10^{-6} \ \text{m}}{\text{mil}} \left(0.63 \frac{25.4 \times 10^{-6} \ \text{m}}{\text{mil}}\right)} = 8.5 \ \Omega/\text{m}$$

在 17MHz 以上, 电阻将随频率的平方根变化

$$R_{\rm ac} = (0.0010)\sqrt{F} \qquad \Omega/\mathrm{m}$$

所以,频率为 400MHZ 时的电阻为:

$$R_{ac}(400 \text{ MHz}) = 0.0010\sqrt{400 \times 10^6} = 20.2 \Omega/m$$

为了计算 G(信号导体和地平面之间的并联电阻),导线的自电容可以用 2.3 节中的等式得到

TD =

$$\frac{\sqrt{\varepsilon_r}}{c}$$

=  $\frac{\sqrt{4}}{3 \times 10^8 \text{ m/s}}$  = 6.67 ns/m

$Z_o = \frac{60}{\sqrt{4.0}} \ln \frac{4(10 + 10 + 0.63)}{0.67\pi[0.63 + 0.8(5)]}$  = 64  $\Omega$

$C = \frac{\text{TD}}{Z_o} = \frac{\sqrt{LC}}{\sqrt{L/C}} = \frac{6.67 \times 10^{-9}}{64} 104 \text{ pF/m}.$

由于介质的有限可传导性产生的等效电阻可以用等式 4.17 来计算,400MHz 时的损耗正切可以在图 4.11 中得到

$$G = \frac{\varepsilon''}{\varepsilon'} (2\pi F C_{11}) = 0.013(2\pi)(400 \text{ MHz})(104 \text{ pF})$$

$$= 0.0034 \text{ m}/\Omega \Rightarrow \frac{1}{G} = 294 \text{ }\Omega/\text{m}$$

可以看出由于介质损耗引起的并联电阻几乎是导体串联电阻的 15 倍。

# 4.2. 介电常数的变化

PCB基材的介电常数  $\epsilon$ ,直接影响着信号间高速互联的传输线特性。与  $\epsilon$ ,有关的特性有传播速度,特征阻抗和串扰。对于给定的材料,  $\epsilon$ ,并非是常数而是随着频率、温度、湿度在变化。另外,对于一些复合型的材料,介质属性还和其组成成分的比例有很大关系[Mumby, 1988]。

在商业应用中,大多数PCB的基板使用的是一种叫做FR4 的复合物,它由环氧玻璃树脂构成。这种复合物的特点为厚度范围变化大并且玻璃和树脂的组成成分比例也可相应改变。因此,每个不同FR4 的层压样板的介质属性都不尽相同,而大多数制造商仅提供在某一频率下的  $\varepsilon$ -,值。为了确保数字设计的健壮性,需要在所有生产和环境容许的条件下得到足够的性能裕量,所以,考虑介质常数的变化是很重要的。

等式 4.18 可以作为 FR4 复合物介质常数计算的一阶近似:

$$(4.18) \qquad \varepsilon_r = \varepsilon_{\rm rsn} V_{\rm rsn} + \varepsilon_{\rm gls} V_{\rm gls}$$

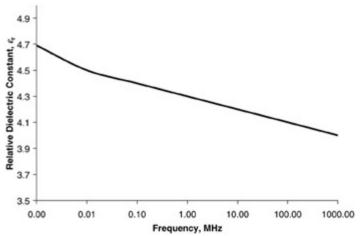

这里的  $\varepsilon_{rsn}$  和  $\varepsilon_{gls}$  分别是环氧树脂和有机玻璃的介质常数, $V_{rsn}$  和  $V_{gls}$  是他们的各自所占的分量。玻璃和树脂的相应组成比例在每一个实际样品中都是有差别的。PCB板的不同层有可能用不同成分比例的FR4 材料生产,因此,相同的PCB的不同层间的介电常数可能存在相对大的变化。实际测量结果也表明FR4 的介电常数随频率和树脂成分的不同而变化。针对树脂成分占到 0.724 的FR4 材料,图4.12 给出了其介电常数随频率变化的曲线图。

图 4.12: 典型的FR4 中介电常数随频率的变化曲线(源自 Mumby [1988].)

通过频率和树脂成分来估算 FR4 的相对介电常数的等式为:

(4. 19)

$$\varepsilon_r(V_{rsn}, F) = 6.32 - [2.17 + 0.168 \log_{10} F(kHz)]V_{rsn}$$

上面这个等式对大多数的 FR4 板材都适用, 在 1kHz 到 1GHz 范围内, 计算精度与实验测量的结果 只相差几个百分点。由于这个只是个经验公式, 当遇到 1GHz 以上的频率就应该小心使用了 [Mumby, 1988]。根据试验测量的结果表明,在 1kHz 到 1GHz 频率范围内玻璃纤维的含量变化没有引起 介电常数的变化,因此上面等式中只是频率和材料中树脂成分的函数。

PCB 制造商应该能够提供树脂成分所占比例。当然,如果没有得到这个信息,它可以这样估算:

$$V_{\rm rsn} \approx 1 - \frac{H_{\rm gls}}{H}$$

这里的Has是玻璃纤维的总厚度,H是介质层的总厚度。当PCB在制造时,介质层是通过堆叠许多 层的玻璃纤维并用环氧树脂粘接起来,继而达到所希望的厚度。制造商会提供玻璃纤维的材料类型和 厚度,还有所用的层数,这些将产生出。总的叠层厚度也可以通过横截面积测量或直接从制造商那里 获得得到。

#### 4.3. 蛇形线

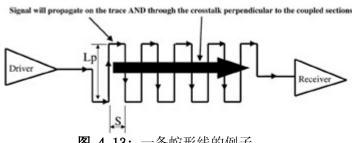

当布局工程师在布线时,通常不可能在每一个网络节点上都用一条直线连接。板的长宽比、时序 要求和实际的状态限制下,要求将线布成图 4.13 所示的蛇形线。特别是当数字系统的设计规范要求板 上所有的线等长,而板的布线空间等条件有限时,将大量使用到蛇形线。蛇行线经常是通过增加数据 信号延迟,保持和时钟信号之间的相对时序,从而满足时序上"保持时间"的要求。

图 4.13: 一条蛇形线的例子

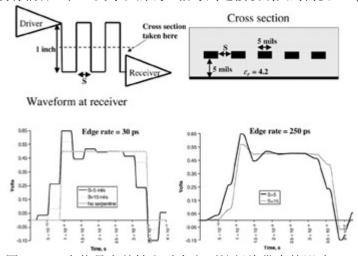

蛇行线对信号的传播延时和信号完整性都会产生影响。这些影响主要是由传输线平行部分(图 4.13 中的L<sub>p</sub>)的自耦合引起的。为了理解这一点,可以想象信号沿着传输线传播,如果传输线蛇形线的并行部分有足够的间距,从而去除了串扰的影响,那么在接收端看到的波形就好像它在一条直线上传播得到的结果一样。然而,如果平行部分有很大的串扰存在,信号的一部分将通过互感和互容沿着垂直于蛇形线方向的路径传播,如图 4.13 所示。结果,一部分信号将提前到达,这将影响信号完整性和传输延迟。图 4.14 显示了 5 英寸长直线和 5 英寸长 5mi1宽 15mi1间距的蛇行线之间的差别。需要注意的是,随着平行部分间距(图 4.13 和 4.14 中的S)的增加,波形就越来越接近理想直线的情况。这些仿真是在介电常数为 4.2 的埋式微带线上进行的,它的传输时延大概为 174ps/in(见第二章)。所以,如果在平行线之间没有耦合,在 5 英寸长的线上信号到达接收端大约需要 870ps。然

图 4.14: 在信号完整性和时序方面蛇行线带来的影响

而,如图 4.14 所示,在蛇行线上传播的一部分信号比理想的 870ps要早到达接收端。这些较早到达的部分是信号通过平行段时。由于之间的互容和互感而产生的耦合干扰信号。注意:由于耦合程度的不同,波形中台阶部分幅度的大小也会显著变化,但是持续时间不变。台阶的持续时间正比于耦合部分(*L<sub>o</sub>*)的物理长度,电压幅度取决于平行部分的间距。

需要注意的是,即使蛇行线对信号完整性的影响不会直接带来时序问题(比方说,台阶出现在阈值区域以外),但是它会带来其他的问题,比如 ISI(这将在 4.4 节讨论)。

## 规则:蛇形线

下面的设计规范将帮助我们把蛇形线对信号完整性和时序的影响尽可能降低到最小。

- 使平行部分(S)的最小间隔至少达到 3H 到 4H,这里的 H 指信号导体到参考地平面的高度。这将减少平行部分的耦合。

- 尽可能减少蛇形区域的长度(L<sub>o</sub>),这将减少总的耦合幅度

- 蛇线对嵌入式微带线和带状线带来更少的影响

- 对于时钟信号线不要进行蛇形走线

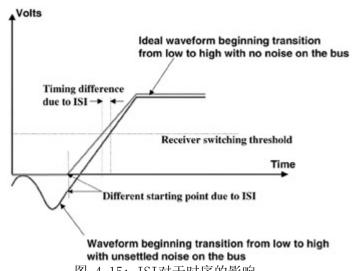

#### 4.4. 码间干扰

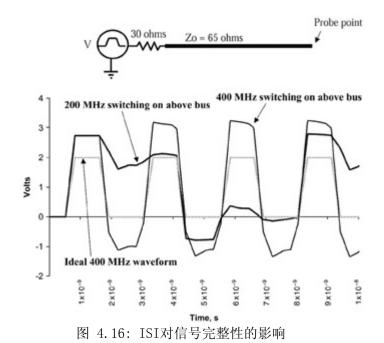

当信号沿着传输线传播时,由于反射、串扰和其他源产生的噪声没能完全稳定,线上新传输的信号将受到影响,降低了时序裕量和信号完整性,这种情况被称作码间干扰(ISI)噪声。ISI 在任何高速设计中都要的重点考虑的因素,尤其是当时钟周期小于两倍的传输线延迟的时候。正因为它对性能有极大的影响,所以在系统设计时必须要仔细分析 ISI。图 4.15 是 ISI 如何影响时序的一个图例。注意看理想波形和总线上原有噪声还没有稳定时便进行新的信号传输而得到的信号波形之间的时序差别,这些差别可以达到几百皮秒,足以消耗掉高速设计中所有时序裕量。

图 4.15: ISI对于时序的影响

为了得到 ISI 的完整影响,用长的伪随机码流进行仿真是很重要的,同时每次选取不同的仿真时间。数据码流的选择也要很合适,要能体现所有最激烈的系统谐振情况,也允许部分噪声稍微提前于下次传输之前稳定。当然,为了捕捉大多数的时序影响情况,应该在最快的总线周期下以单周期的位模式执行仿真,接着是 2 倍、3 倍的最快总线时钟。比如,如果总线的最快频率为 400MHz,一个位的脉冲周期为 1.25ns。数据模式就应该以 2.5 和 3.75 为脉冲周期重复。可以使用下面提供的数据流模式在最快的总线速率下仿真。

- **•** 010101010101010

- 001100110011001

- 000111000111000

这些模式的飞行时间或飞行时间偏移的最大差别可以看成是 ISI 影响的一阶近似(数字系统设计中的飞行时间的定义参见第九章)。这种分析可以用这种仿真方法来实现,就是先运行长伪随机码流模式的仿真,然后选取其中任一小段时间来观察结果。这里必须强调的是,如果要得到 ISI 较为精确的影响结果,就必须要使用足够长的伪随机码流来做仿真评估。

ISI 也能很强烈地影响信号完整性。图 4.16 显示了当系统内存在显著反射时,不同的位模式对信号波形的影响。研究不同的位模式对确定系统的健壮性是非常重要的。比方说,如果信号在振铃发生的同时切换,那么这个振铃可能恰好在某个开关频率下被屏蔽而在另外一个频率则不会,正如图 4.16 中表现的那样。图 4.16 只是证明码流如何影响信号完整性的一个非常简单的例子,现实中的总线技术,特别是那些带多个负载的情况将存在非常复杂的 ISI 依赖关系,如果没有考虑到这些情况将很可能会破坏这个设计。在第九章中我们将描叙在设计过程中正确考虑 ISI 的方法。

# 大拇指规则: ISI

下面的规则可以帮助减少 ISI 的影响:

- 通过避免阻抗的不连续和最小化分支线长度和减少大寄生参数(例如来自封装、插座、连接头的)来减少反射。

- 保持内部连接线尽可能短

- 避免紧耦合的蛇行走线

- 避免存在在总线传输的可能同时发生的信号完整性问题(例如振铃、横杆、过冲)的走线。

- 最小化串扰影响

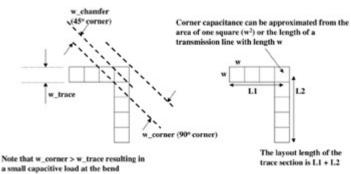

#### 4.5. 90 度拐角的影响

事实上每个 PCB 设计者都将在部分甚至全部走线中用到拐角。因此,如何评估传输线的拐角对仿真来说是非常重要的。当考虑如何建模一个拐角时,每一个细节的考虑都将给模型的建立带来不必要的复杂度。通过实际测量发现,将其当成一个简单的电容模型对于大多数系统来说都是合适的。当然,读者应该知道这种模型存在一定的局限性,有时需要修正。

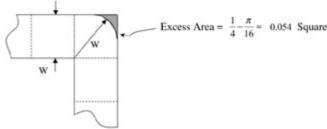

90° 拐角的经验模型为图 4.17 中传输线上过剩电容的一角。这意味着这个拐角的电容值等于相同宽度传输线的电容值。这个电容应该加在被仿真传输线存在拐角的地方,对于典型的 50-65 欧姆传输线的线宽来说,90° 拐角带来的多余电容可近似估计为:

$$(4.21) C_{90^{\circ} \text{ bend}} \approx C_{11} w$$

图 4.17: 由 90 度拐角产生的过剩电容

这里的 $G_1$  是线上的自身的电容,w是线宽。虽然通常这个电容是非常小的,但线宽如果很宽并且 拐角的数量过多时也会产生问题。如果小量的过剩电容也需要在考虑范围之内,那么,简单的圆角能 在拐角处保持线的宽度不变,这样能在本质上消除这种影响。但是对于很多布线工具来说,圆角会引 起一些问题。另一个方法就是斜 45° 走线,通过用 45° 线来代替直角,这种最简单的方法完全避免了 90° 拐角,45° 拐角的过剩电容明显比 90° 拐角的小得多,在大多数应用中可以被忽略。

读者可能会注意到等式 4.21 中方形所带来的过多电容并不是图 4.18 中的过多区域带来的,实际测量并不用图 4.18 中的小区域电容,而更喜欢用方块电容,这其中的原因也不是很清楚。

图 4.18: 拐角的过多区域。过多区域带来的电容远小于正方形方块区域的电容

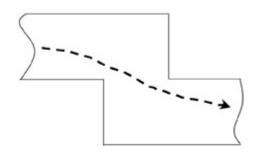

在这节里有一些经验推测的影响是没有价值的。传输线上流动的某些部分的电流将按照这样一种方式(图 4.19)流动,这种流动方式使它们偏离基于布线长度计算出来的传输延时。在图 4.19 中所示,虚线是可能按照这种方式流动的电流,由于电流直接从两个角直线流出,所以将比预想的提早到达。这种影响可以在实验室的环境中看到,我们只需要有心里有这样一个认识,对于那些带有许多拐角的两条或更多的走线,如果必须要保持相同延时,那我们应该加以注意。

图 4.19: 一些电流成分贴着拐角前进,导致信号提早到达目的地

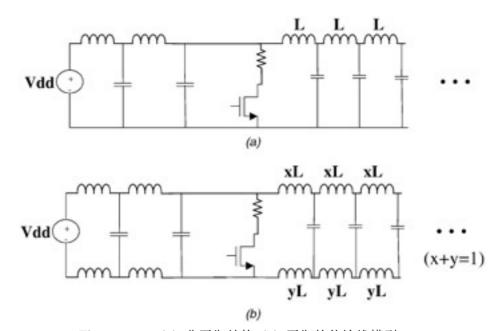

## 4.5. 拓扑的影响

讲到现在,我们已经谈到了两个元件间进行互连的很多问题。然而,实际情况下不是总是只有两个器件的互连,通常一个驱动电路需要连接两个或更多的接收电路,这种情况下内部连接的拓扑结构就会极大地影响系统性能。例如,图 4.20 是一个驱动电路连接两个接收电路的例子。主干线的特征阻抗是和每个分支的特征阻抗相等的。当信号传播到连接点时,连接点的等效特征阻抗变为 $Z_{\alpha}/2$ ,结果是波形一步步渐进式的达到最后稳定值。这些反射现象可以用图 2.17 中的网格图来计算。

图 4.20: 平衡的 T 拓扑产生的信号完整性问题

当分支的阻抗是干线的两倍时,节点处看到的有效阻抗和干线一致,结果是反射就不再产生,结果可以参见图 4.20 的波形。当结构不平衡时,有一种情况就是一个分支比另一个长,由于反射到达节点的时间不同,信号完整性将变坏。图 4.21 的波形就反映了这种情况。其信号完整性可以用网格图来计算,但是过程相当复杂,所以通常都用计算机来代替。图 4.22 就是一个网格图,计算了图 4.21 中

图 4.21: 不平衡的T结构信号完整新问题.

图 4.22: 不平衡T结构的网格图

开始几次反射的情况。参考上图,垂直线 A 和 B 代表驱动电路和节点之间的电气路径,B 和 C 代表节点和接收电路 1 的路径,B 和 D 代表节点和接收电路 2 的路径。当拓扑中有更多的分支后,对于分支之间长度差异也更加敏感。进一步说,负载的任何分支差别都会引起相似的电路不稳定。

从这里我们可以学到些什么呢?答案就是"对称"。当我们需要考虑一个拓补结构的时候,最关键的地方就是对称。要确保从任何一个方向看过去电路都要对称,这就要求拓扑每个分支的长度和负载都相同。接下来应该考虑的是尽量使拓扑结构中连接点的阻抗不连续降低到最小,当然,这在一些设计中往往是不可能的。

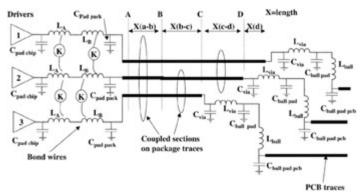

# 第四章 连接器、封装和过孔

前面讨论了很多内容,基本上涉及了有关 PCB 板的绝大部分相关的知识。第二章探讨了传输线的基本原理,第三章探讨了串扰,在第四章里我们阐述了许多在现代设计中必须关注的非理想互连的问题。对于信号从驱动端引脚到接收端引脚的电气路径的相关问题,我们已经做了一些探究,然而对于硅芯片,即处于封装内部的 IC 来说,其信号传输通常要通过过孔和连接器来进行,对这样的情况我们该如何处理?在本章中,我们将通过对封装、过孔和连接器的研究,阐述其原理,从而指导大家在设计的时候对整个电气路径进行完整地分析,即从驱动端内部 IC 芯片的焊盘到接受器 IC 芯片的焊盘。

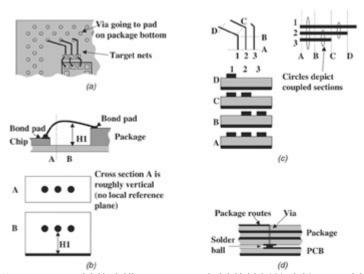

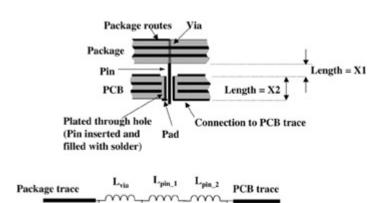

# 5.1. 过孔

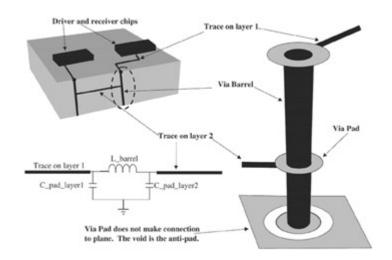

为了让 PCB 的各层之间或者元器件和走线之间实现电气连接,需要在 PCB 板上钻一些具有导电特性的小孔,这就被称为过孔。它包括筒状孔壁 (Barrel)、焊盘(pad)和反焊盘(anti-pad)。过孔的筒状孔壁是为了保证 PCB 各层之间的电气连接而对钻孔进行填充的导电材料;焊盘的作用把孔壁和元件或者走线相连;反焊盘就是指过孔焊盘和周围不需要进行连接的金属之间的间隔。最普通的过孔类型是通孔,之所以把它称为通孔,是因为它穿过 PCB 板上的所有层,孔中间填入焊料,任何一个层都可以通过焊盘进行必要的电气连接。此外,还有些特殊类型的过孔,比如盲孔、埋孔和微型孔等等,这些主要应用于多芯片模组(MCMs)和其它先进的 PCB 中。图 5.1 描述了一个典型的通孔和它的等效电路,可以注意到:过孔的焊盘和筒状孔壁在第一层和第二层连接了外部走线,而第三层没有连接。盲孔和埋孔的结构和通孔有一些区别,但因为通孔是目前为止在工业中应用最普遍,所以我们这里主要讨论通孔的情况。

图 5.1: 一个通孔的等效电路

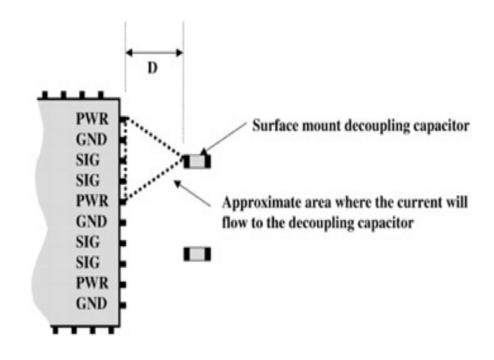

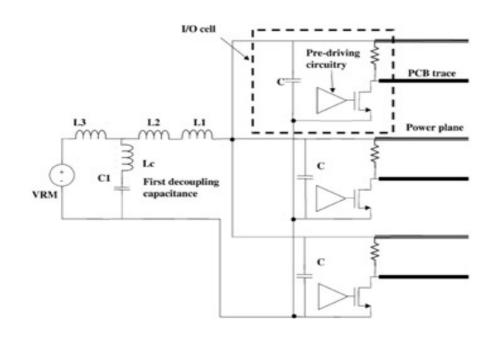

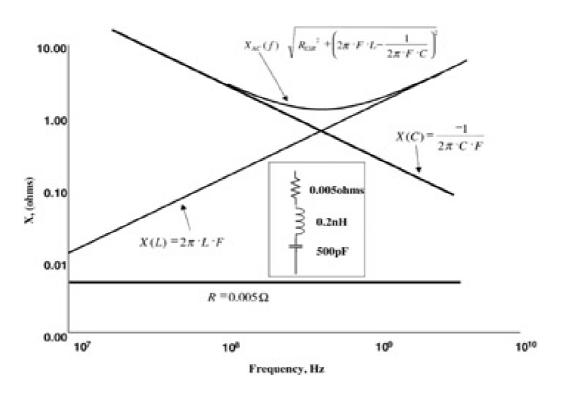

从上图可以看到,过孔的模型是一个简单的 型网络。电容代表过孔焊盘在第一层和第二层的电容。串联电感代表过筒状孔壁的特性。由于过孔的结构很小,它们就可以建立为集总元件的模型。当然,当过孔的延迟大于十分之一的信号上生时间时,这种假设将不再成立。过孔的电容效应对于信号的主要影响就是延缓信号的边沿速率,特别是需要通过几个过孔的时候,这样的效应更加明显。过孔对信号边沿的影响大小,可以通过检测信号从容性负载上传输后的劣化(degradation)程度来估算,具体可以参见本章公式 5.21 中的描述。此外,如果几个连续的过孔放置的距离很近,将会降低传输线的特征阻抗,这个问题会在 5.3.3 部分做详细解释。过孔焊盘的近似容值为:[Johnson and Graham, 1993]

1

$$C_{\text{via}} \approx \frac{1.41\varepsilon_r D_1 T}{D_2 - D_1}$$

picofarads

上式中, $D_2$ 是过孔反焊盘的直径, $D_1$ 是过孔焊盘的直径,T 是 PCB 的厚度, T 是相对介电常数。 典型的一个通孔的总电容大概是  $D_1$  0.3 pF。应当注意是,对于图  $D_2$  1 中所描述的过孔模型,这里假设了每个焊盘的电容占过孔总等效电容的一半。

对于数字电路设计者来说,过孔的电感通常比电容更重要。过孔会对系统增加一定量的串联电感,从而降低信号完整性,使去耦电容的效果减弱。过孔的电感特性可以用图 5.1 所示模型中的串联电感来表征,近似计算为:[Johnson and Graham, 1993]

(5.2)

$$L \approx 5.08h \left[ \ln \left( \frac{4h}{d} \right) + 1 \right]$$

nanohenries

式中, h 是过孔长度, d 是筒状孔壁的直径。

# 5.2. 连接器

连接器是用作 PCB 板之间相互连接的器件。随着信号速率的提高,连接器的设计也变的愈加困难。关于高速连接器设计的一个很好的例子就是计算机系统中插槽 1(slot 1)的设计,它就是用来连接 Pentium 处理器和主板的连接器。另外,一个更加先进的例子是 RIMM(Rambus Inline Memory Module)连接器,RIMM的工作速率达到了800兆每秒。

因为连接器的几何结构通常是很复杂的,如果不借助于两维或者是三维空间的场解析器或者是测试,想精确计算其等效的寄生参数几乎是不可能的。当然,在设计中通过调用一阶近似的模型,我们也能从中学习到连接器的基本效应,并理解它是如何影响系统的性能。

在这一部分中,我们将通过对基本问题的分析得出一些特性规律,对于设计和建模高速连接器来说是非常重要的。我们探讨的主题主要可以分为:连接器的串扰、串联寄生因素以及电流回路电感等。图 5.2 所示的是一个概念性的模型,用来演示连接器对于信号完整性的若干不利影响。

图 5.2: PCB 连接器的一个实例

## 5.2.1. 串联电感

连接器最基本的影响是给电路增加了一定的串联电感,我们可以利用计算简单直线电感的公式来对这个串联电感值进行一阶估算。下面两个公式分别是圆形和矩形导线的串联电感近似计算表达式:[Poon, 1995]

(5.3)

$$L \approx \frac{\mu_0}{2\pi} l \left[ \ln \left( \frac{2l}{r} \right) - \frac{3}{4} \right]$$

nanohenries for  $r \ll 1$

(5.4)

$$L \approx \frac{\mu_0}{2\pi} l \left[ \ln \left( \frac{4l}{p} \right) + \frac{1}{2} \right]$$

nanohenries

式中, $\mu_0$  是自由空间的磁导率,I 是导线长度,I 是导线半径(圆形导线),I 是导线周长(矩形导线)。应该注意的是,长度是寄生串联电感的主要原因;如果导线截面的尺寸和其长度相比要小得多的话,则导体的形状对于寄生电感影响并不显著。

# 5.2.2. 并联(shunt)电容

虽然并联互容也是连接器设计中需要考虑的一个比较重要的因素,但是在初期的连接器性能评估中通常可以忽略。这个电容对于系统主要的影响是能降低系统的边沿速率。需要注意的是,这个外加的电容有时也能被利用来降低连接器处的阻抗不连续,它能降低引脚的有效阻抗。因此,在做仿真分析的时候必须仔细、严谨,以保证设计的合理性。通过使用比较宽的焊盘,或者加一个小薄片,或者加宽连接器的引脚等方法都可以增大这个额外电容。但要提醒的是,如果没有两维或者三维的工具模拟或者进行实验室测量,要想评估这个电容的影响是非常困难的。

## 5.2.3. 连接器串扰

串扰对于连接器性能的影响也很大。通常情况下,互感比互容的影响更大,因此,在一阶的近似中,互容的影响通常可以忽略。如果需要更加精确的模拟,二维和三维的仿真器或者通过测试,可以比较精确得反应连接器之间的相互耦合寄生效应。

连接器的两个引脚之间产生的互感可以用如下的表达式近似计算[Poon, 1995]:

(5.5a)

$$L_{M} \approx \frac{\mu_{0}}{2\pi} l \left[ \ln \left( \frac{l}{s} + \sqrt{1 + \left( \frac{l}{s} \right)^{2}} \right) - \sqrt{1 + \left( \frac{s}{l} \right)^{2}} + \frac{s}{l} \right] \quad \text{nanohenries}$$

(5.5b)

$$L_{M} \approx \frac{\mu_{0}}{2\pi} l \left[ \ln \left( \frac{2l}{s} \right) - 1 \right] \quad \text{nanohenries} \quad \text{for} \quad s \ll l$$

式中, $\mu_0$  是自由空间的磁导率,/ 是长度,s 是导体之间的中心距。可以注意到,连接器之间的 互感和导体的横截面及形状基本无关。

## 5.2.4.连接器引脚之间感性耦合场的效应

观察图 5.2 中的连接器,从本质上讲,连接器的那些引脚形成了一个耦合电感网络。由于这种研究问题的方便,我们考察三个驱动源,一个电源引脚,一个接地引脚。目标是驱动 2 的走线。在引脚 2 上总的感应电压是由于其本身以及引脚 1 和引脚 3 的电流变化引起的:

$$v_2 = L_{22}\dot{I}_2 + L_{21}\dot{I}_1 + L_{23}\dot{I}_3$$

式中, $I_n$ 代表  $dI_n/dt$ 。假设每个缓冲器的电流和边沿速率是相同的,可以构建单线的等效模型来做简化分析(相关部分参见 3.6.2 节):

(5.7)

$$v_2 = \begin{cases} (L_{22} + L_{21} + L_{23})\hat{I} & \text{(all bits switching in phase)} \\ (L_{22} - L_{21} - L_{23})\hat{I} & \text{(bit 2 switching out of phase with bits 1 and 3)} \end{cases}$$

(5.8)

$$v_2 = \begin{cases} (L_{22} + L_{21} + L_{23})\hat{I} & \text{(all bits switching in phase)} \\ (L_{22} - L_{21} - L_{23})\hat{I} & \text{(bit 2 switching out of phase with bits 1 and 3)} \end{cases}$$

从公式(5.6)到(5.8)表明了多位同时开关的信号在通过连接器的时候,将如何产生感性噪声,从而导致一系列取决于数据流模式的信号完整性问题。而电源和地引脚上感应噪声的影响常常被忽略。

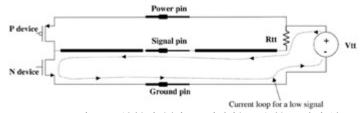

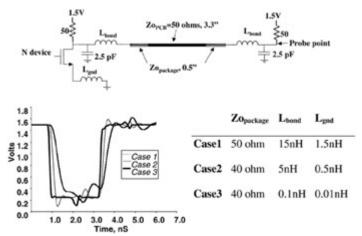

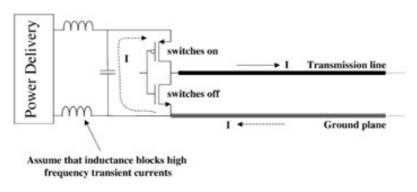

考虑图 5.3 所示电路。这是标准的 GTL+总线结构。当开关输出为低电平的时候,N 型管打开,P型管关闭;而输出高电平时,N关闭,P打开,就是在这样相反的开关过程中实现信号的高

Figure 5.3: 驱动器开关输出低电平时连接器上的回路电流

速转换。我们现在考虑当总线被 N 型管拉到低电平时,电流会发生什么变化。电流从  $V_{tt}$  引出,流经传输线,信号引脚,通过 N 型器件,接着流经地层,接地引脚,最后回到  $V_{tt}$  源。这个过程就是图 5.3 中描述的电流回路路径。由于瞬变电流将流经接地引脚,那就将给系统引入一定的感性噪声  $L_{gnd}i$ ,因此,在分析中也需要考虑地回路上存在的电感。这种影响在几个缓冲器共享同一个接地引脚的情况下尤其显著,如图 5.4 所示。在这种特殊的情况下,由于三倍大的电流将流经同一个接地引脚,因而被引入系统的噪声为  $3L_{gnd}i$ 。当瞬变电流流经电源引脚时,也会产生相同的效应。所以在总线设计中,我们要注意了解其特殊的电流回路情况,这样才能在设计连接器的时候正确地考虑瞬变电流流经电源和地引脚所产生的效应。GTL 和 CMOS 总线设计中的不同的电流回路情况以及它们对于信号的影响将在第六章中详细探讨。总而言之,对于电流回路的理解是必需的,掌握了这个理论之后才能实现连接器的优化设计。

Figure 5.4: 拥有几个驱动器的连接器的回路电流。

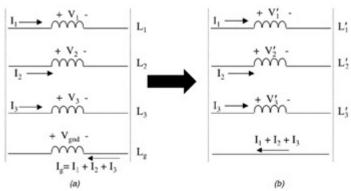

如图 5.3 和图 5.4 所示,我们暂时假设回路电流将全部流经同一个接地引脚。参考图 5.5,可以得出电感在回流路径的影响。图 5.5a 表示三个信号引脚感性耦合到一个地回路引脚上。注意,通过三根信号传输线的所有电流都必须通过这个唯一的地引脚回流。图 5.5b 显示了地回路引脚的影响,已经对代表信号路径的感应器模型做了修正,计入了感性地回路的效应。图 5.5a 所示系统的响应情况可以通过如下一系列的公式来描述:

(5.9)

$$V_{2} = L_{22}\dot{I}_{2} + L_{21}\dot{I}_{1} + L_{23}\dot{I}_{3} + L_{2g}\dot{I}_{g}$$

$$V_{gnd} = L_{gg}\dot{I}_{g} + L_{g1}\dot{I}_{1} + L_{g2}\dot{I}_{2} + L_{g3}\dot{I}_{3}$$

$$\dot{I}_{g} = -(\dot{I}_{1} + \dot{I}_{2} + \dot{I}_{3})$$

$$V'_{2} = V_{2} - V_{gnd}$$

$$V'_{2} = \dot{I}_{1}(L_{21} - L_{2g} - L_{g1} + L_{gg}) + \dot{I}_{2}(L_{22} - L_{2g} - L_{g2} + L_{gg})$$

$$+ \dot{I}_{3}(L_{23} - L_{2r} - L_{g3} + L_{gr})$$

$V_2$  是给定的简化模型中的电压。公式(5.9)的结果还可以很容易扩展到包含 N 个导体且共用同一个信号地回路的系统:

(5.10)

$$L'_{ij} = L_{ij} - L_{ig} - L_{gj} + L_{gg}$$

图 5.5b 中所示的电压  $V_2'$  可以用下式表示:

(5.11)

$$V_2' = L_{22}'\dot{I}_2 + L_{21}'\dot{I}_1 + L_{23}'\dot{I}_3$$

注意:回路的等效电感可以简单地通过信号引脚电感,加上地回路电感,减去互感来计算。

Figure 5.5: 回路电感合并到信号导体中: (a)三个信号感性耦合到同一个接地回路引脚上; (b) 地回路引脚的影响。

应当注意到上面的公式应用仅仅对互耦的一系列引脚有效。总的回路电感将随着到相应的信号引脚之间的距离增大而增加,在回路很长或者总回路电感远大于  $L_{gg}$  等不同假设条件的情况下要分别独立建模。总的回路电感是引脚的本身电感和地回路上的电感之和。电流回路所包含的区域越大则电感就越大。比如在图 5.4 中,回路 A 的总电感最大,回路 C 的总电感最小。

由于接地引脚流出的电流最终一定会流回到电源,而电源将把这个电流提供给驱动器,因此无论信号的回流是通过电源还是地,都必须同时保证电源和地的低电感,从而将感性噪声尽可能降低。一个常用的方法就是增加电源和地引脚的数目,这样就能降低回路的电感,在上面的公式中,这样做能有效地减少  $L_{gg}$ 。此外,还有一个经常用最佳的设计方案是把电源引脚和接地引脚相邻放置,因为电流方向相反,这样就可以利用它们之间的互感效应进一步减少总电感。

## 5.2.5. EMI(电磁干扰)

一个比较差的连接器设计会带来的另外一个不利影响就是增加了 EMI 辐射,关于 EMI 的问题将会在第 10 章中详细阐述。如图 5.4 所示的大面积电流环路,通过第 10 章的分析可以得出,电磁辐射能量的大小正比于回路的面积。由于连接器增加了地回路和信号回路的电感,因而同样会产生同步开关噪声的问题,这部分将在第 6 章中详细讨论。

#### 5.2.6. 连接器设计的准则

基于前面的分析,我们可以得到一些基本的连接器设计准则。最显而易见的一点就是最小化连接器引脚的物理长度来减少总的串联电感;其次要尽量保证电源、地引脚的数目和信号引脚数目的比例达到最大,这样可以降低电源和地引脚的电感效应;放置电源引脚和接地引脚的原则也是使电流环路最小,继而可以减少连接器处的电磁辐射;每个信号引脚都需要尽可能靠近电源引脚或者地引脚放置。

应当注意的是,如果相当一部分比例的信号是以差分形式通过连接器,那么,刚才列举的几条设计准则就需要相应得调整。例如,对于主要针对差分信号设计的连接器或者封装来说,电源和接地引脚的数目将远少于相近的单端系统。而且有时差分信号可能是大量成组布线的,中间不需要电源和接地引脚进行隔离。

通过上面的讨论,我们可以得到如下几点结论:

由于信号引脚和电流回路引脚的互耦能够减少总电感,那么最理想的方法就是直接让每个信号引脚和电流回路引脚紧密耦合(通过相邻位置靠近放置的方式实现)。总线的类型和结构将决定是否每个信号引脚都应当同时和电源、地引脚耦合,还是只需和接地或者电源引脚的

其中一个进行耦合。第 6 章中我们会讨论到如何判断信号回路电流在哪里流动。如果回路电流正在流经地平面层,那么信号引脚就应当和接地引脚进行互耦;如果回路电流正在流经电源层,则信号引脚就应当和电源引脚进行互耦;如果回路电流正在同时流经接地和电源层,那么如果可能的话,每个信号引脚都应当同时和电源及地引脚进行耦合。

- 2. 电源和接地引脚应当相邻放置以尽量减小电源和地回路上的电感。

- 3. 在连接器设计中,通常比较理想的方案把电源引脚数和信号引脚数的比值以及接地引脚数和信号引脚数的比值均设计为大于等于 1,这样可以把总的回路电感降到最低。而在差分系统中这点可能不是主要的影响因素。

- 4. 通常使用尽可能短的连接器以降低电感效应和阻抗不连续性。

- 5. 有时也可以通过增大连接器的引脚电容来降低阻抗,减小阻抗的不连续性。实现的方法可以是加宽连接器的引脚或者在 PCB 上加一些铜箔片。

- 6. 连接器电容将延缓信号的边沿速率。

#### 大拇指规则:连接器设计

- 保证连接器引脚的长度最短。

- 将电源和接地引脚数对信号引脚数目的比设计为最大。如果可能的话,这些比例的最小值应该是 1。

- 每个信号引脚应当尽可能的靠近电流回路引脚。

- 电源引脚应当靠近接地引脚。

.

## 例 5.1: 选择连接器引脚模式

图 5.6 描述了一个 8 位连接器的几种引脚分布方案。为了让这个例子起到更好的说明作用,我们假设回路电流将等量地通过电源和接地引脚返回。对于方案(a),由于电源引脚和接地引脚距离

Figure 5.6: 假设回路电流通过电源和接地引脚返回的 8 位连接器的几种引脚分布方案: (a) 差的; (b) 改进的; (c) 二次改进的; (d) 最佳的. G,接地引脚; P, 电源引脚; S,信号引脚。

信号很远,所以它的性能是最差的。这种引脚分布方案中,八个信号引脚中的电流都必须通过同一个电源和接地引脚回流,回路距离很大,这将使得电源和地回路产生最大的感性噪声。而且,由于电源引脚和接地引脚距离信号引脚很远,大面积的回路加剧了 EMI 和串联电感。最后一点,由于所有的信号引脚相邻放置,引脚之间的串扰噪声很显著,这将恶化信号的完整性。这种引脚分布方式的唯一优点就是将连接器物理尺寸做的很小,同时降低了生产的成本。

方案(b)在方案(a)的基础上做了改进,将电源和接地引脚靠近了信号引脚。而且,电源和接地引脚数目增多也能降低回路的电感和保证较好的电源分配。由于信号对之间有电源和接地引脚的屏蔽,信号引脚之间的串扰也降低了。然而,在信号引脚对中的两个信号之间的串扰还是非常高的,因此,这种方案是针对 4 位差分总线的理想方案。可以注意到:连接器尺寸已经比方案(a)增加了30%。

方案(c)做了进一步的改进。可以看到电源引脚和接地引脚把所有的信号引脚都间隔开了,这样就尽可能减小了通过电源和接地引脚的回路电感。此外,中间的电源、地引脚能起到屏蔽作用,很大程度上减少了信号引脚之间的串扰。然而,大家也注意到,和方案(a)相比连接器的尺寸已经增大了70%。

如果仅仅从性能的角度上看,方案(d)则是最佳的选择(前提是假设回流等量通过电源和地引脚返回)。电源引脚和接地引脚包围着每一个信号引脚。同时,电源和接地引脚总是彼此相邻放置而且电源/接地引脚数对信号引脚数之比为 9:8。这些措施大大降低了电源和接地引脚的回路电感,并为信号引脚之间提供了更好的屏蔽,把 EMI 的影响降低到最小。方案(d)的最明显缺点就是它的尺寸达到了方案(a)的 2.6 倍。

这个例子表明对于连接器设计来说,要想性能越好,就需要越大的物理尺寸,这也势必会影响 到成本。所以设计者必须很小心谨慎,尽量在性能要求和这些实际约束中取得平衡。

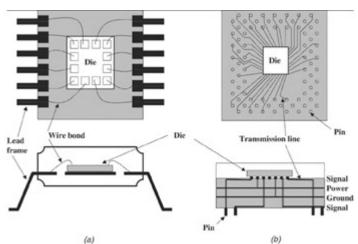

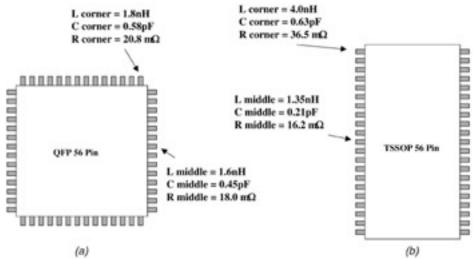

#### 5.3. 芯片封装

芯片封装对于 IC 来说就是一个外包装。它可以为芯片电路和系统之间的互连提供必需的机械、热、电气连接等方面的功能,芯片封装的种类有很多种,它随着系统和电路结构的不同而相应变化。不同的芯片封装类型还在不断的推陈出新,因此,我们不可能讨论到现有的所有芯片封装类型。在本节中,我们将集中精力讨论几乎所有的芯片封装都存在的共同的问题,以及适合于任何封装形式的建模方案。芯片封装的设计需要针对总线的类型进行优化,这里我们将对封装设计中某些能影响性能的基本属性进行探究,既包含点对点总线(比如 PC 上的 AGP----advanced graphics port),也包括多负载总线(比如 PC 上不至连接一个处理器的 GTL 前端总线)。

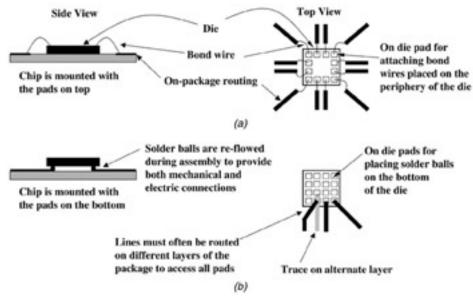

#### 5.3.1.封装的大致分类

从物理属性上,芯片的封装主要可以分为三部分:晶元(die)和封装基板的连接,封装基板上的电气连接以及芯片封装和系统 PCB 的连接。

#### 晶元和封装基板的连接

图 5.7 描述了晶元连接到封装基板两种最常见的方法。当然,还存在很多别的技术,但是这两种是到目前为止最具普遍性的。首先我们讨论通过打金线(wire bond,也称绑定线)实现晶元和封装互连的方式,这是应用最广泛的一种技术。金线是一根很细的导线,通常要求直径只有 1mil,而相比较而言,我们的头发直径大概是 3mil。打金线的方式最主要的影响是增加了串联电感。金线的

长度通常从 50mil 到 500mil 不等,因为金线并不很长,在建模的时候通常可以把它看成是一个分立的电感元件。有好几种方法可以获取一根金线的等效电感。前面给出的公式 5.3 可以用作电感的快速近似计算,不过精确的电感计算还需要考虑到金线的弧形结构以及相临近的地平面的影响。如果

图 5.7: 晶元封装的常见方法: (a) 打金线; (b)倒装

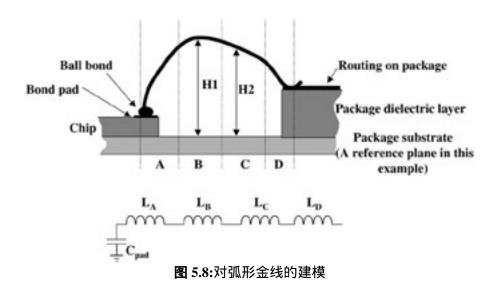

附近不存在地或者电源层,公式(5.3)就能做一个很好的近似。但如果金线平面层正上方通过,就必须要考虑到金线的弧度以及距离地或者电源层的高度。图 5.8 描述了处理这种情况时的一种最好的方法。在这个特殊的例子中,把金线分割为 4 段。对于第一段 A,可以粗略认为金线是垂直于参考平面层,因此参考层对其电感的影响最小,电感值可以使用公式(5.3)来计算。B 段部分可以粗略认为是平行于参考层并且近似高度为  $H_1$ ,这样就可以利用存在参考层情况下的直导线的电感计算公式计算其电感  $L_B$  [Johnson and Graham, 1993]:

(5.12)

$$L = l(5.08 \times 10^{-9}) \ln \frac{4h}{d}$$

nanohenries

式中 I 是长度,基本单位是英寸,h 是距离参考层的高度,d 是金丝直径。 $L_C$  段的计算和 B 部分一样,只是距离参考层的高度为  $H_2$ 。 $L_D$  则仍然使用公式(5.3)来计算,因为它也是基本上垂直于参考层。为了提高准确性,我们通常不通过上述的公式而是使用一个两维的仿真器来进行电感计算。如果使用一个三维的仿真器,则能提供更加精确的计算结果,但是由于封装中的每根金线都可能有不同的弧度,不值得我们花那么大的精力。事实表明,要想很准确地评估封装系统中每根金线的物理特性是不可能的,即便是通过三维仿真器得到一些更加精确的电感值,也不一定是完全可信的。

金线也同时还会产生大量的串扰,根据数据位模式的不同,产生电磁感应的大小也不同,另外还引起地回流路径的问题,这些可以通过公式(5.6)到(5.11)来分析。如果金线没有参考平面,就可以使用公式(5.5)估算两根金线之间的互感。否则,就需要用到下面的公式来估算存在参考层的金线间的互感影响[Johnson and Graham, 1993]:

(5.13)

$$L_M = L \frac{1}{1 + (s/h)^2}$$

nanohenries

式中 L 是两根金丝的自感,s 是金线的中心距,h 是距离参考层的高度。当然,为了获得最精确的结果,必须使用场仿真器来分析。而且,金线也会产生 rail collapse 和同步开关噪声等问题,这将在第 6 章中讨论。

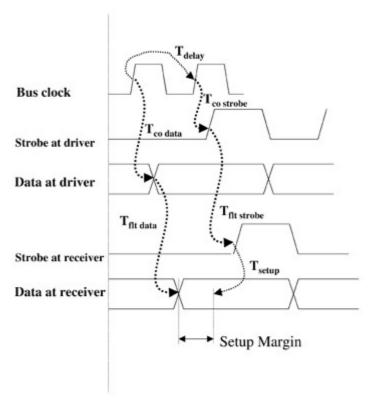

虽然使用打金线的互连方式导致了较大的电感,降低了信号完整性,但是它也有一些优点:成本低,结构简单,可以调整金线焊盘的位置以及基板上的走线。而且,由于芯片的背部直接放置在封装基板上,使得芯片能够与封装进行最大面积的接触,这非常有利于芯片的散热。另外,使用打金线的封装方式时,I/O 的数目受到晶元周长的限制,所以只要增大晶元的面积就可以容纳更多的I/O 数目。