# Power-Efficient Computer Architectures

Recent Advances

Magnus Själander Margaret Martonosi Stefanos Kaxiras

Synthesis Lectures

Computer Architecture

# Power-Efficient Computer Architectures

Recent Advances

# Synthesis Lectures on Computer Architecture

### Editor

Margaret Martonosi, Princeton University

### Founding Editor Emeritus

Mark D. Hill, University of Wisconsin, Madison

Synthesis Lectures on Computer Architecture publishes 50- to 100-page publications on topics pertaining to the science and art of designing, analyzing, selecting and interconnecting hardware components to create computers that meet functional, performance and cost goals. The scope will largely follow the purview of premier computer architecture conferences, such as ISCA, HPCA, MICRO, and ASPLOS.

### Power-Efficient Computer Architectures: Recent Advances

Magnus Själander, Margaret Martonosi, and Stefanos Kaxiras 2014

### FPGA-Accelerated Simulation of Computer Systems

Hari Angepat, Derek Chiou, Eric S. Chung, and James C. Hoe 2014

### A Primer on Hardware Prefetching

Babak Falsafi and Thomas F. Wenisch 2014

### On-Chip Photonic Interconnects: A Computer Architect's Perspective

Christopher J. Nitta, Matthew K. Farrens, and Venkatesh Akella 2013

### Optimization and Mathematical Modeling in Computer Architecture

Tony Nowatzki, Michael Ferris, Karthikeyan Sankaralingam, Cristian Estan, Nilay Vaish, and David Wood

### Security Basics for Computer Architects

Ruby B. Lee 2013

### The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines, Second edition

Luiz André Barroso, Jimmy Clidaras, and Urs Hölzle 2013

### Shared-Memory Synchronization

Michael L. Scott 2013

### Resilient Architecture Design for Voltage Variation

Vijay Janapa Reddi and Meeta Sharma Gupta

### Multithreading Architecture

Mario Nemirovsky and Dean M. Tullsen 2013

### Performance Analysis and Tuning for General Purpose Graphics Processing Units (GPGPU)

Hyesoon Kim, Richard Vuduc, Sara Baghsorkhi, Jee Choi, and Wen-mei Hwu 2012

### Automatic Parallelization: An Overview of Fundamental Compiler Techniques Samuel P. Midkiff

2012

### Phase Change Memory: From Devices to Systems

Moinuddin K. Qureshi, Sudhanva Gurumurthi, and Bipin Rajendran 2011

### Multi-Core Cache Hierarchies

Rajeev Balasubramonian, Norman P. Jouppi, and Naveen Muralimanohar 2011

### A Primer on Memory Consistency and Cache Coherence

Daniel J. Sorin, Mark D. Hill, and David A. Wood 2011

### Dynamic Binary Modification: Tools, Techniques, and Applications

Kim Hazelwood 2011

### Quantum Computing for Computer Architects, Second Edition

Tzvetan S. Metodi, Arvin I. Faruque, and Frederic T. Chong 2011

### High Performance Datacenter Networks: Architectures, Algorithms, and Opportunities

Dennis Abts and John Kim

2011

### Processor Microarchitecture: An Implementation Perspective

Antonio González, Fernando Latorre, and Grigorios Magklis

### Transactional Memory, 2nd edition

Tim Harris, James Larus, and Ravi Rajwar 2010

### Computer Architecture Performance Evaluation Methods

Lieven Eeckhout

2010

### Introduction to Reconfigurable Supercomputing

Marco Lanzagorta, Stephen Bique, and Robert Rosenberg 2009

### On-Chip Networks

Natalie Enright Jerger and Li-Shiuan Peh 2009

### The Memory System: You Can't Avoid It, You Can't Ignore It, You Can't Fake It

Bruce Jacob 2009

### Fault Tolerant Computer Architecture

Daniel J. Sorin 2009

### The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines

Luiz André Barroso and Urs Hölzle

### Computer Architecture Techniques for Power-Efficiency

Stefanos Kaxiras and Margaret Martonosi

### Chip Multiprocessor Architecture: Techniques to Improve Throughput and Latency

Kunle Olukotun, Lance Hammond, and James Laudon 2007

### Transactional Memory

James R. Larus and Ravi Rajwar 2006

Quantum Computing for Computer Architects Tzvetan S. Metodi and Frederic T. Chong 2006

### Copyright © 2015 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

Power-Efficient Computer Architectures: Recent Advances Magnus Själander, Margaret Martonosi, and Stefanos Kaxiras

www.morganclaypool.com

ISBN: 9781627056458 paperback ISBN: 9781627056465 ebook

DOI 10.2200/S00611ED1V01Y201411CAC030

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE

Lecture #30

Series Editor: Margaret Martonosi, Princeton University

Founding Editor Emeritus: Mark D. Hill, University of Wisconsin, Madison

Series ISSN

Print 1935-3235 Electronic 1935-3243

# Power-Efficient Computer Architectures

Recent Advances

Magnus Själander Uppsala University

Margaret Martonosi Princeton University

Stefanos Kaxiras Uppsala University

SYNTHESIS LECTURES ON COMPUTER ARCHITECTURE #30

### **ABSTRACT**

As Moore's Law and Dennard scaling trends have slowed, the challenges of building high-performance computer architectures while maintaining acceptable power efficiency levels have heightened. Over the past ten years, architecture techniques for power efficiency have shifted from primarily focusing on module-level efficiencies, toward more holistic design styles based on parallelism and heterogeneity. This work highlights and synthesizes recent techniques and trends in power-efficient computer architecture.

### **KEYWORDS**

power, architecture, parallelism, heterogeneity

# **Contents**

| 1 | Intr | oduction 1                                                                        |

|---|------|-----------------------------------------------------------------------------------|

|   | 1.1  | From the Beginning                                                                |

|   | 1.2  | The End of Dennard Scaling and the Switch to Multicores                           |

|   | 1.3  | Dark Silicon, the Utilization Wall, and the Rise of the Heterogeneous Parallelism |

|   | 1.4  | Other Issues and Future Directions                                                |

|   | 1.5  | About the Book                                                                    |

|   | 1.3  | 1.5.1 Differences from the Prior Synthesis Lecture [103]                          |

|   |      | 1.5.2 Target Audience                                                             |

| 2 | Volt | age and Frequency Management                                                      |

|   | 2.1  | Technology Background and Trends                                                  |

|   |      | 2.1.1 Relation of $V$ and $f$                                                     |

|   |      | 2.1.2 Technology Solutions                                                        |

|   |      | 2.1.3 DVFS Latency                                                                |

|   |      | 2.1.4 DVFS Granularity                                                            |

|   | 2.2  | Models of Frequency vs. Performance and Power                                     |

|   |      | 2.2.1 Analytical Models                                                           |

|   |      | 2.2.2 Correlation-based Power Models                                              |

|   |      | 2.2.3 A Combined Power and Performance Model                                      |

|   | 2.3  | OS-Managed DVFS Techniques                                                        |

|   |      | 2.3.1 Discovering and Exploiting Deadlines                                        |

|   |      | 2.3.2 Linux DVFS Governors                                                        |

|   | 2.4  | Parallelism and Criticality                                                       |

|   |      | 2.4.1 Thread- and Task-Level Criticality: Static Scheduling                       |

|   |      | 2.4.2 Thread- and Task-Level Criticality: Dynamic Scheduling                      |

|   |      | 2.4.3 Criticality                                                                 |

|   | 2.5  | Chapter Summary                                                                   |

| 3 | Hete | erogeneity and Specialization                                                     |

|   | 3.1  | Dark Silicon                                                                      |

|   |     | 3.1.1 Dark Silicon Analysis and Models                             | 32 |

|---|-----|--------------------------------------------------------------------|----|

|   |     | 3.1.2 Designing for Dark Silicon: Brief Examples                   | 32 |

|   |     | 3.1.3 The Sentiments Against Dark Silicon                          | 33 |

|   | 3.2 | Heterogeneity in On-Chip CPUs                                      | 34 |

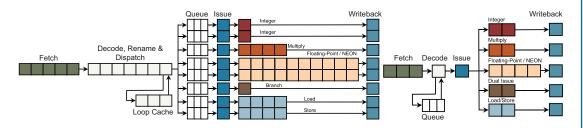

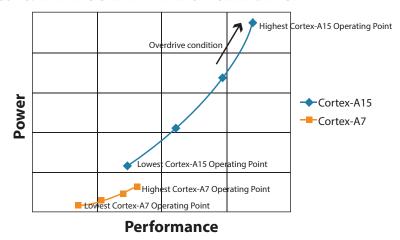

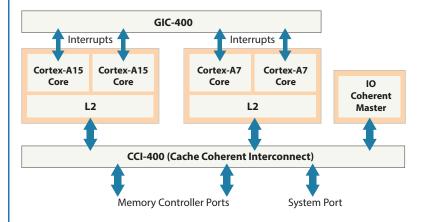

|   |     | 3.2.1 Current Industry Approaches                                  | 34 |

|   |     | 3.2.2 Research and Future Trends                                   | 37 |

|   | 3.3 | Single-ISA Configurable Heterogeneity                              | 37 |

|   | 3.4 | Mixing GPUs and CPUs                                               | 39 |

|   |     | 3.4.1 CPU-GPU Pairs: The Power-Performance Rationale               | 39 |

|   |     | 3.4.2 Industry Examples                                            | 39 |

|   |     | 3.4.3 Selected Research Examples                                   | 40 |

|   | 3.5 | Accelerators                                                       | 40 |

|   |     | 3.5.1 Background                                                   |    |

|   |     | 3.5.2 Selected Research                                            |    |

|   |     | 3.5.3 Industry Examples                                            |    |

|   | 3.6 | Reliability vs. Energy Tradeoffs                                   | 42 |

|   | 3.7 | Chapter Summary                                                    | 43 |

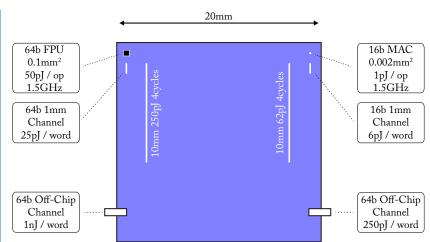

| 4 | Con | nmunication and Memory Systems                                     | 45 |

|   | 4.1 | The Energy Cost of Data Motion:                                    |    |

|   |     | A Holistic View                                                    | 45 |

|   | 4.2 | Power Awareness in On-Chip Interconnect: Techniques and Trends     | 46 |

|   |     | 4.2.1 Background and Industry State                                | 46 |

|   |     | 4.2.2 Power Efficiency of Interconnect Links                       |    |

|   |     | 4.2.3 Exploiting Emerging Technologies to Improve Power Efficiency | 48 |

|   | 4.3 | Power Awareness in Data Storage: Caches and Scratchpads            |    |

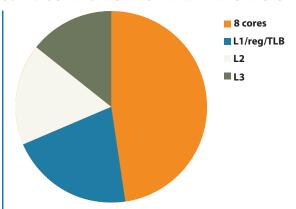

|   |     | 4.3.1 Cache Hierarchies and Power Efficiency                       |    |

|   |     | 4.3.2 Cache Associativity and its Implication on Power             |    |

|   |     | 4.3.3 Cache Resizing and Static Power                              |    |

|   |     | 4.3.4 Cache Coherence                                              |    |

|   |     | 4.3.5 The Power Implications of Scratchpad Memories                |    |

|   | 4.4 | Chapter Summary                                                    | 57 |

| 5 | Con | clusions                                                           | 59 |

|   | 5.1 | Future Trends: Technology Challenges and Drivers                   | 59 |

|   | 5.2 | Future Trends: Emerging Applications and Domains                   | 60 |

|   | 5.3 | Final Summary                                                      | 60 |

| Bibliography         | 61 |

|----------------------|----|

| Authors' Biographies | 83 |

### Introduction

### 1.1 FROM THE BEGINNING...

Managing the power dissipation of current computer systems is a Grand Challenge problem. Power affects computer systems at all scales: from the computational capacity of our large-scale data centers [18], to the processing performance of our high-end servers [25], and the battery life and performance of our mobile devices [45, 152, 207].

To today's computer architects, the emergence of power as a grand challenge [91] may seem like a relatively recent issue, but the reality is that the very earliest computer systems faced vexing power challenges. For example, the ENIAC computer first became operational in 1946, and its initial press release [191] included this alarming text<sup>1</sup> about its kilowatts of power dissipation:

The ENIAC consumes 150 kilowatts. This power is supplied by a three-phase, regulated, 240-volt, 60-cycle power line. The power consumption may be broken up as follows; 80 kilowatts for heating the tubes 45 kilowatts for generating d.c. voltages, 20 kilowatts for driving the ventilator blower and 5 kilowatts for the auxiliary card machines.

Over the decades that have followed, computer systems benefited from technology refinements that improved circuit performance, cost, and power. Gordon Moore's predictions of technology scaling linked integration levels (transistors per chip) to production cost [138]. For many years, these cost-driven integration improvements also translated quite naturally into performance improvements.

Nearly concurrently, Dennard articulated a scaling principle that would lower supply voltages as transistors became smaller [42]. It is Dennard scaling that enables the transistor increases predicted by Moore's Law to be parlayed into performance improvements and power savings.

Despite the benefits of Dennard Scaling, the power dissipation of integrated systems has spiked before. Most notably, some of the high-performance bipolar ECL processors of the late 1980s and early 1990s dissipated over 100 W [100]. While these designs were impressive and offered then unmatched performance, the costs and challenges of designing and packaging such chips [99] are considered to have played a major role in the adoption of CMOS technology for high-performance designs. The challenge for us today is that we have reached a similarly difficult operating point regarding CMOS power dissipation, but without any viable alternative technology available to turn to next.

<sup>&</sup>lt;sup>1</sup>The text's punctuation is as in the original.

### 2 1. INTRODUCTION

**Table 1.1:** Dennard scaling rules [42]

| Device or Circuit Parameter      | Scaling Factor   |

|----------------------------------|------------------|

| Device dimension $T_{ox}$ , L, W | 1/k              |

| Doping concentration Na          | k                |

| Voltage V                        | 1/k              |

| Current I                        | 1/k              |

| Capacitance eA/t                 | 1/k              |

| Delay time per circuit VC/I      | 1/k              |

| Power dissipation per circuit VI | 1/k <sup>2</sup> |

| Power density VI/A               | 1                |

In addition to technology trends, our industry is also driven by application trends that further drive the need for power-efficient computing systems. Compared to 30 years ago, much more of today's computing market (phones, laptops, tablets, games) is at least moderately mobile, and therefore designed with battery life as an important characteristic. In years past, mobile technology would simply "trickle down" from the server world, as old designs are shrunk in new processes. Now the mobile domain is a distinct target with great need for nimble, adaptive power/performance tradeoffs [70]. At the other extreme—the server and enterprise end of the spectrum—power also matters more than ever. Data centers co-locate thousands of high-end servers, and are often limited by their ability to offer sufficient power and cooling to sustain their desired execution throughput [19].

Thus, both technology and application drivers have placed us at a point where power-efficient computation is both vital to future computer systems' viability, and also increasingly difficult to achieve. The following sections elaborate on this.

### 1.2 THE END OF DENNARD SCALING AND THE SWITCH TO MULTICORES

The power problem as we have faced it over the past decade is largely due to two effects. First, it is primarily a consequence of the end of the Dennard scaling rules (Table 1.1) that parlayed Moore's Law into performance and power benefits for more than three decades. Dennard scaling rests on several key shifts that can be made when transitioning to a smaller feature size. For example, smaller transistors can switch quickly at lower supply voltages, resulting in more power efficient circuits and keeping the power density constant. But supply voltages cannot drop forever. A breakdown of Dennard scaling occurred when voltages dropped low enough to make static power consumption a major issue. Second, even if Dennard scaling had continued on-track, our propensity for faster clock rates and larger die sizes meant that each generation's power dissipation was scaling up faster than Dennard effects were able to hold it in check.

In particular, a key advantage of CMOS technology for many years was its lack of static power dissipation. That is, the complementary p- and n-networks in CMOS gates (theoretically) do not allow any path from supply voltage to ground, consuming power only when switching (dynamic power and some glitch power). Static power consumption was therefore safely ignored at the architectural level. However, when technology scaling broke the 100 nm barrier, transistors showed their analog nature: they are never truly off, and this allows sub-threshold leakage currents to flow. Worse, sub-threshold leakage currents are exponential to threshold voltage reductions. In Dennard scaling, the major mechanism to improve power efficiency is the reduction of the supply voltage, which assumes a reduction of the threshold voltage (since the difference of the two voltages dictates transistor switching speed). The rise of static power brought a complete stop to the power benefits architects took for granted for many technology generations. One-time reductions of static power consumption are possible but the trends remain the same with scaling. For example, current technologies employ multi-gate transistors also known as FinFETs. In these transistors, a fin between the drain and source is "wrapped" by silicon in a non-planar fashion to enable the gate to better encompass the channel, which reduces leakage. As one particular example, Intel switched to 3D or tri-gate transistors in their 22 nm technology [24]. While this change provided a step reduction in leakage going from 32 nm to 22 nm, further reductions will be limited in subsequent scalings.

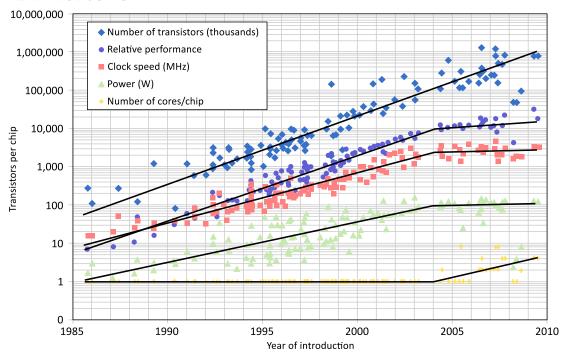

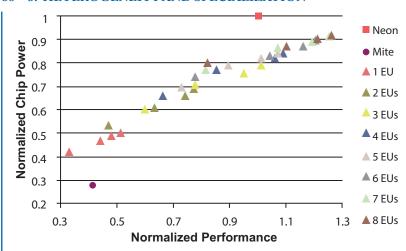

In the 1980s and early 1990s (the heyday of Moore's Law scaling), architects primarily improved performance by exploiting instruction-level parallelism (ILP)—parallelism found in the dynamic instruction stream during execution of a program. To discover and exploit this parallelism, significant hardware resources were thrown at the problem. Sophisticated techniques such as out-of-order execution, branch prediction and speculative execution, register renaming, memory dependence prediction, among others, were developed for this purpose. These approaches can be highly complex and do not scale well. This results in diminishing performance returns (number of instructions executed in parallel) for increasing hardware investments. Dynamic power scales even worse, deteriorating the power efficiency of such approaches. In fact, as illustrated in Figure 1.1, power dissipation scales as performance raised to the 1.73 power for the typical ILP core: a Pentium 4 is about six times the performance of an i486 at 23 times the power [71]!

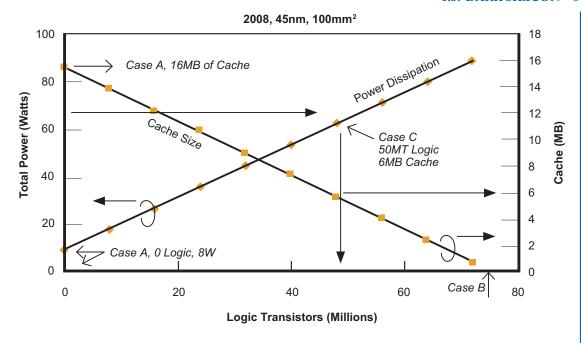

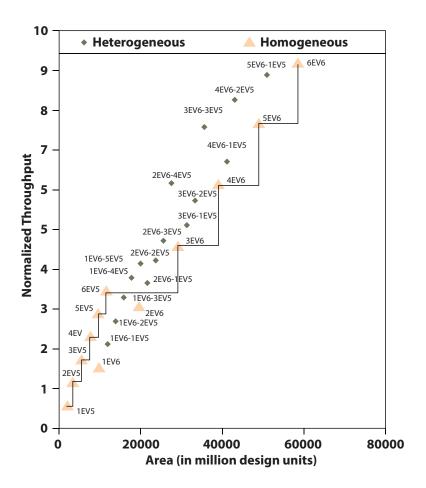

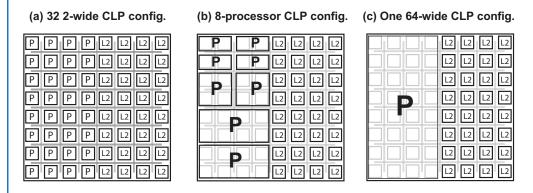

The shift to multicore architectures started in 2004 as a reaction to this looming problem of increased power consumption and power density. Effectively, we abandoned frequency scaling (which resulted in significant increases in both dynamic and static power consumption) in favor of laying down more cores on the same chip. This dramatic shift to chip multiprocessors (CMPs) in the past decade is a response to the power wall and the end of Dennard scaling. In particular, Borkar et al. [26] walks through an example for 45 nm technology that is still instructive. For a 45 nm chip with 150M transistors, Figure 1.2 shows a range of possible options for implementing the processor. To abide by the total limit of 150M transistors, one can use more logic transistors (x-axis) in opposition with fewer cache transistors. The resulting power dissipation is shown on the left y-axis, and the resulting cache capacity is shown on the right y-axis. As one increases

### 4 1. INTRODUCTION

**Figure 1.1:** Moore's Law and corollaries. Data shows scaling trends, with clear shifts in trend lines at roughly 2004 [37].

the number of transistors devoted to logic, the power dissipation increases (because caches are "cool" from a power standpoint). Pollack's rule [154] argues that microprocessor performance scales roughly as the square root of its complexity, where the logic transistor count is often used as a proxy to quantify complexity.

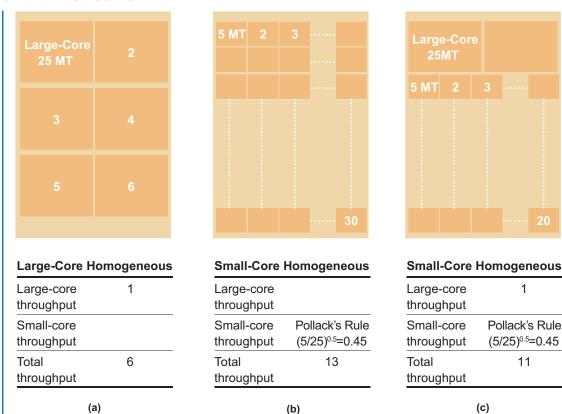

From these rules of thumb, multiple parallel cores essentially always beat monolithic single cores on power-normalized performance. For example, Figure 1.3 shows three approaches that use parallel cores to enhance throughput while maintaining the same power envelope [26]. Case A (far left of Figure 1.2) harnesses 6-way parallelism at a fairly coarse-grain, and is out-performed by Case B (far right), which is more aggressively parallel, when enough thread/task level parallelism exist in the workload. Case C represents heterogeneous parallelism, in which two large cores are mixed with several small ones, to good effect. An even more heterogeneous approach would be to include some specialized accelerators, which use very few transistors or chip area, but have large performance and power benefits when applicable.

Overall, these examples and rules of thumb begin to explain the direction that industry has taken: a quick and aggressive adoption of medium-scale, on-chip parallelism. Parallelism helps with the impending power wall, by offering a path to high performance that does not rely on

Figure 1.2: A range of implementation options trading off processor area devoted to cache, and resulting power tradeoffs [26].

high clock rates and high supply voltages. Parallelism—particularly heterogeneous parallelism also helps with the so-called "utilization wall" [186] and the "Dark Silicon" problem [54], as discussed next.

### DARK SILICON, THE UTILIZATION WALL, AND THE 1.3 RISE OF THE HETEROGENEOUS PARALLELISM

Our inability to scale a single core to further exploit ILP in a power efficient manner turned computer architecture toward exploring alternative kinds of parallelism (task/thread parallelism, data parallelism). Multicore and manycore architectures are designed for explicit parallelism, and recalling Figures 1.2 and 1.3, they offer greater performance-per-watt than large monolithic approaches. Unfortunately, even homogeneous CMPs will not be sufficient to solve the power problem for more than a few more generations [137]. This road is also faced with the same problems as with the single core architecture: we are unable to efficiently extract sufficient speedup from parallel programs (Amdahl's Law [7]).

Furthermore, some postulate a near future in which the number of dynamically active transistors on a die may be greatly constrained, forming the "utilization wall" [186]. The concept of the utilization wall is that power envelopes may lead to scenarios in which few (perhaps 20% or less)

### 6 1. INTRODUCTION

Figure 1.3: Enhancing throughput while maintaining power envelope [26].

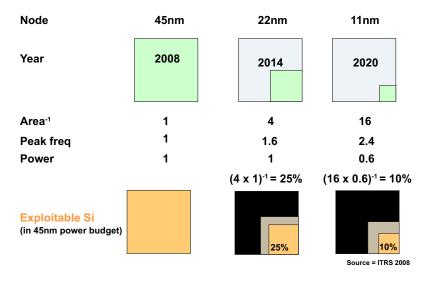

of a chip's transistors can be "on" at a time. The argument for this possible future is exemplified in Figure 1.4. If transistor density increases in line with Moore's Law, a 45 nm chip will shrink to one-quarter the size at 22 nm in 2014, and one-sixteenth at 11 nm in 2020. Using the ITRS roadmap [91] for scaling, the smaller chips would be more efficient, drawing the same power at 22 nm even though the peak frequency increases by a factor of 1.6, and 40% less at 11 nm with 2.4 peak clock speed. But, if we maintain the same chip area, we can pack four times the number of transistors at 22 nm and 16 times at 11 nm. For the same initial power budget this means that only 25% of the transistors can be powered-up in 22 nm, and 10% in 11 nm. These results are also supported in recent academic studies [54].

The answer to the challenge of the utilization wall is the rise of heterogeneous architectures where some general-purpose cores are augmented by other cores of different microarchitectures or even specialized accelerators that offer outstanding performance-per-watt by being very lean hardware designs for a particular computational purpose. The approach of heterogeneous paral-

Figure 1.4: A depiction of Dark Silicon trends as seen by ARM [2, 143].

lelism with specialized accelerators is well-suited for "Dark Silicon" scenarios. A large number of accelerators can be built on the same chip to be woken up only when needed. These heterogeneous architectures are fast becoming the dominant paradigm after multicore.

In fact, we do not need to speculate about future heterogeneity, as heterogeneous parallel computing is here today. If we examine the product lines from the major chip manufacturers we see that they now have separate multicore x86 architectures targeted at high performance (2-12 cores, 100W, 100 GFLOPs) and low power (1-2 cores, 10W, 10 GFLOPs), and are integrating data-parallel graphics cores onto their CPU devices with distinct programming and memory models [28]. In the embedded world, there are a range of cores at different performance/efficiency points (1–8 cores, 2W, 10 GMIPS) with a range of programmable graphics cores [133]. NVIDIA, Samsung, and Qualcomm all sell heterogeneous ARM/GPU processors with many fixed-function accelerator blocks for the smart phone market [12, 144, 159], and there are multiple start-ups with 64–100 core devices [183] for networking and telecom. This present-day processor heterogeneity forces system and software designers to address the difficult optimization challenge of choosing the right processor (both at design time and runtime) for their product's power and performance requirements.

Beyond simply considering heterogeneity in the types of instruction-programmable cores on-chip, the field is also increasingly considering approaches involving specialized accelerators that may not be instruction-programmable, and that are tuned to particular application kernels of interest. Specialized accelerators are a particularly natural response to the Dark Silicon scenario in which we may have many more transistors than what we can power up at once. With these "dormant" transistors we could build a plethora of specialized accelerators that cost little either

### 8 1. INTRODUCTION

in terms of "active" area or power when not in use. The expectations of generality—all transistors must be useful to all applications—shift considerably in a Dark Silicon world, and what once might have been viewed as "niche" accelerators become a viable method for achieving performance goals under dramatic power constraints.

### 1.4 OTHER ISSUES AND FUTURE DIRECTIONS

Overall, computer systems have reached an intriguing inflection point. For architects, power has been *a* fundamental design constraint for well over a decade now, with the initial reaction being fairly localized, per-module efforts to improve power efficiency. These efforts have been the equivalent of turning lights off in unused rooms of one's house—very sensible, but insufficient in leverage to dramatically change the overall power-performance design landscape. The second wave in power-aware computing has been the recent and seismic shift toward on-chip parallelism.

Software and Programmability Issues: In many ways, the hardware industry's shift toward parallelism has occurred much faster than the abilities of the software and systems designers to react. We know how to build CMPs, and we must build them to keep Moore's Law rolling along. But we do not yet know how to program them efficiently—both in terms of software development time and in terms of getting the best power-performance outcomes from them. Furthermore, the shift toward on-chip accelerators offers even greater programmability challenges. Finally, there are a host of programmability concerns that emanate from the basic goal of elevating power to a first-class design constraint alongside performance. For example, from a power perspective, information on the relative criticality of different communication or computation operations may be very useful, but current programming models offer few abstractions or constructs to help programmers manage this.

**Reliability Tradeoffs:** Until now, power-performance tradeoffs have been viewed by architects as a two-dimensional optimization landscape. There is emerging research, however, on the possibilities of *three-dimensional* optimization scenarios in which power, performance, and *reliability* are traded off against each other. Such tradeoffs are already frequently considered at the device and circuit level, but in ways that enable the architecture and software levels to be shielded from their effects; abstraction layers give the impression of perfect reliability even when device or circuit tricks are being employed [52].

Intuitively, there seem to be rich opportunities for raising the abstraction layer at which reliability, energy, and performance are traded off, in order to enable architects to exploit them as well. For example, operating with smaller supply voltage noise margins (by lowering supply voltage) may offer high leverage on power savings, at the expense of possible calculation or storage errors. Likewise, reducing or eliminating parity/checksum protection on memory or interconnect also seems to offer some intuitive power/reliability tradeoff possibility. The key research questions in this space, however, focus on whether the power/performance benefits achievable through some approaches are large enough to be appealing given the serious impact of relaxing reliability guarantees to software.

Beyond the Processor Core: Much of the "first wave" of power optimizations focused on the CPU itself, because the most serious thermal and power density concerns were experienced there. And even more specifically, most optimizations were focused on the CPU's processor cores and cache memories. As we look, however, to future power issues and ideas, there is a growing need to look beyond the processor core. Data communications and on-chip interconnect will play an increasingly important role in power dissipation, especially since the adoption of parallelism has led to much higher levels of data motion and inter-processor communication in many cases. One also needs to consider the energy issues related to the memory hierarchy as well. Chapter 4 covers these topics in this book, but considerable future work in this area is likely to be forthcoming.

#### ABOUT THE BOOK 1.5

To conclude this introduction, we include here some further explanations about the book that may be helpful to readers in finding relevant material and in comparing with contents from a prior Synthesis Lecture by Kaxiras and Martonosi [103].

#### DIFFERENCES FROM THE PRIOR SYNTHESIS LECTURE [103] 1.5.1

We view the two books as largely complementary. The first book offered extensive details on the sorts of local, per-module power optimizations that comprised the industry's "first wave" response to the power challenge. In this current book, we take a more holistic view. As a result, both the structure and content of the book have changed dramatically.

There are three core chapters, which synthesize highlights of power-efficient computer architecture techniques. Chapter 2 covers voltage and frequency scaling issues, with a particular emphasis on trends and techniques that have emerged in the years since the first edition of the book. Chapter 3 covers techniques related to specialization and heterogeneity that have emerged with greater prominence in the five years since Dark Silicon began to emerge. Chapter 4 covers the power implications of data motion and storage, again with a particular emphasis on more recent techniques and trends. Finally, Chapter 5 concludes the book.

We note that while the power dissipation of main memory has emerged as an important problem, we feel that this topic is too broad to be covered well as part of this book. Thus, this book does not cover main memory issues in earnest, and we hope that another synthesis lecture will take on this topic in detail.

Finally, a note on power modeling approaches. These were covered in the first book [103]. While new tools and modeling environments have been created in the years since then (e.g., [76, 122, 127]), these tools employ fairly similar basic philosophies and approaches as previous generations of tools. Thus due to space and scope constraints we have chosen not to cover them further here.

### 10 1. INTRODUCTION

### 1.5.2 TARGET AUDIENCE

This book is written for researchers who have taken a basic course in computer architecture, and are interested in becoming somewhat fluent in the power implications of architectural choices. We envision it being particularly useful for a new graduate student who may be familiar with the basics of computer design and architectural simulations, but perhaps has been less exposed to power issues. In addition, systems researchers from related fields (e.g., operating systems, compilers, parallel programming, and others) may find the book useful for understanding some of the architectural viewpoints and issues interposed between the technology challenges emerging "from below" and the applications trends "from above."

## Voltage and Frequency Management

Issues addressing dynamic power have predominated the power-aware architecture landscape. Amongst these dynamic power techniques, most methods focus on dynamic voltage and frequency scaling (DVFS). The intuition behind many of these approaches [82, 92, 93, 164, 197, 200, 201] is that if the processor and memory operate largely asynchronously from each other, then the processor can be dialed down to much lower clock frequencies during memory-bound regions, with considerable energy savings but no significant performance loss. A good overview of early DVFS techniques is given by S. Kaxiras and M. Martonosi [103]. This chapter discusses the motivation for these techniques, DVFS technology trends, DVFS power and performance models, and OS managed DVFS. Also discussed, is the concept of criticality in parallel applications and its applicability for controlling DVFS.

### 2.1 TECHNOLOGY BACKGROUND AND TRENDS

The basic dynamic power equation:  $P = CV^2Af$  clearly shows the significant leverage possible by adjusting voltage (V) and frequency (f) [32, 78]. If we can reduce voltage by some small factor, we can reduce power by the square of that factor. Reducing supply voltage, however, might possibly reduce the performance of systems as well. Reducing supply voltage often slows transistors such that reducing the clock frequency is also required.

The benefit of DVFS is that within a given system, scaling supply voltage down offers the potential of a cubic reduction in power dissipation. The downside is that it may also degrade performance. If the program runs at lower power dissipation levels, but for longer durations, then the benefit in terms of total energy will not be cubic. It is interesting to note that while voltage/frequency scaling improves the energy delay product (EDP) (because the reduction in power outpaces the reduction in performance), it can do no better than break even on the energy delay-squared product (ED<sup>2</sup>P) metric—assuming performance is proportional to frequency.

However, there is the opportunity for more benefit when the relationship between performance and frequency (f) is *non-linear*. This happens when there is *slack* in the execution, which cushions the effect of frequency scaling. This is the main premise of the DVFS approaches that we discuss in this chapter.

### 12 2. VOLTAGE AND FREQUENCY MANAGEMENT

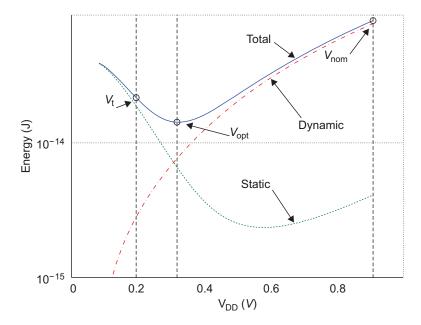

### **2.1.1** RELATION OF V AND f

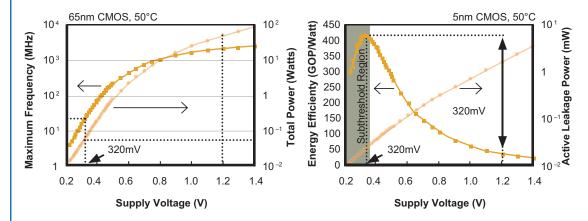

Figure 2.1 shows the relation between supply voltage, frequency, leakage, and energy efficiency. The darker curve in the left graph of Figure 2.1 illustrates how the maximum operational frequency depends on the supply voltage, while the lighter curve illustrates how the total power depends on the same. The darker curve in the right graph of Figure 2.1 illustrates how the energy efficiency changes with the supply voltage. The greatest energy efficiency is achieved just above the subthreshold voltage at which point the leakage power is much lower than if the supply voltage is raised, as shown by the lighter curve.

Figure 2.1: Showing the dependency between (left graph) maximum frequency and supply voltage and (right graph) leakage and energy efficiency and supply voltage [26].

The frequency (f) at which a circuit can operate is proportional to the difference in supply voltage (V) and subthreshold voltage  $(V_{th})$  as given by  $f \propto \frac{(V - V_{th})}{V}$ . To maintain the same maximum operating frequency any scaling of the supply voltage requires an equal scaling of the subthreshold voltage. But since subthreshold leakage increases exponentially with the reduction in subthreshold voltage, static power has become an increasing concern for submicron technologies.

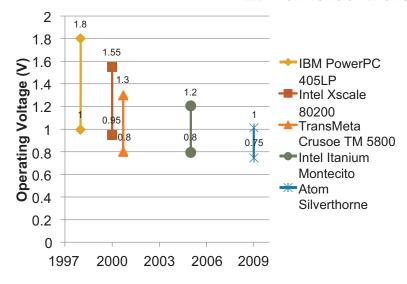

The increase of subthreshold and gate leakage in submicron technologies, the two major contributors to static power, has led to a stagnation in the scaling of the subthreshold voltage. Over the years, this led to the shrinking of the supply-voltage range for which dynamic scaling can be performed. The maximum operational voltage has continued to shrink while the minimum operational voltage has remained roughly the same for the past decade, which is illustrated in Figure 2.2.

While for many technology generations, the voltage and frequency range enabled us to successfully reduce energy by adapting to current performance requirements of the system, the end of Dennard scaling reduces the opportunity for using DVFS in contemporary systems.

Figure 2.2: Shrinking V range [192]. IBM PowerPC 405LP: 1.0V-1.8V, TransMeta Crusoe TM 5800: 0.8V-1.3V, Intel XScale 80200: 0.95V-1.55V, Intel Itanium Montecito: 1.2V-0.8V, Intel Atom Silverthorne: 1.0V-0.75V.

#### 2.1.2 **TECHNOLOGY SOLUTIONS**

The increase in leakage currents, and thus static power, is the fundamental cause for the DFVS problems we are facing in future technologies. Thus, solutions aimed to combat leakage at the technology or other levels are of particular interest here.

The issue with increasing leakage currents comes from the challenge of controlling the conducting channel between the drain and source of a transistor. When the channel length is of the same order of magnitude as the source and drain depletion regions, which it is for submicron technologies, a number of physical properties affect the capability to turn the channel off. These physical properties have been termed short-channel effects [147].

There are several ways to mitigate these effects:

- To counteract short-channel effects the gate oxide thickness can be reduced. This provides better control of the channel without increasing the subthreshold voltage.

- Thinner gate oxides increase the chance for gate leakage currents where electrons tunnel through the oxide. To reduce gate leakage currents new materials with High-i<sup>0</sup> dielectric structures are used instead of the more conventional silicon dioxide.

- Multi- $V_{th}$  designs where performance-critical parts are implemented using low- $V_{th}$  transistors that are fast but leaky, and less critical parts are implemented using high- $V_{th}$  transistors that are slower but much less leaky.

### 14 2. VOLTAGE AND FREQUENCY MANAGEMENT

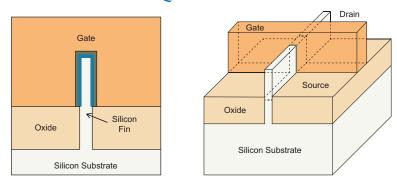

Figure 2.3: Intel's 22 nm FinFET tri-gate transistors [24].

Figure 2.4: Intel's 22 nm FinFET characteristics [24].

• Another option is to construct three-dimensional gates where the channel is surrounded on three sides by the gate, so-called FinFET [75] transistors. For example, Intel's 3D Tri-Gate transistors in 22 nm depicted in Figure 2.3 form conducting channels on three sides of a vertical fin structure, which provides "fully depleted" operation. The "fully depleted" characteristics of such transistors provide a steep sub-threshold slope that can be used to lower leakage. The steep sub-threshold slope (Figure 2.4, left graph) enables the use of a lower threshold voltage, in turn enabling the transistors to operate at lower voltage (100–200mV) to reduce power and/or improve switching speed (Figure 2.4, left graph). Compared to a planar FET, a FinFET transistor can operate faster at the same operating voltage (Figure 2.4, middle graph), or at lower operating voltage at the same speed (Figure 2.4, right graph).

Figure 2.5: Voltage stepping vs. frequency stepping latencies [150].

#### 2.1.3 **DVFS LATENCY**

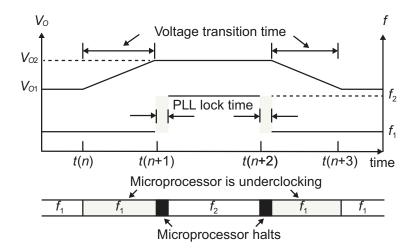

Some of the implementation characteristics for DVFS can have significant influence on the strategies an architect might choose, and the likely payoffs they might offer. For example, what is the delay required to engage a new setting of (V, f)? (And, can the processor continue to execute during the transition from one (V, f) pair to another?) If the delay is very short, then simple reactive techniques may offer high payoff. If the delay is quite long, however, then techniques based on more intelligent or offline analysis might make more sense.

Typically, DVFS transition latencies are in the order of tens of microseconds [150]. This limits the timeframe for DVFS techniques to that of operating system (OS) task-switching, at best. The reason for such a high transition latency is the latency of voltage stepping by the off-chip voltage regulator (VR). Typical off-chip voltage regulators constructed of discrete components (board-level inductors and capacitors) operate at a switching frequency of less than 5 MHz and have relatively slow voltage adjustment capabilities [110] (see Figure 2.5). Frequency stepping is faster, accounting for only 7.6% of the delay overhead, depending on the frequency steps and the response time of the PLL [150].

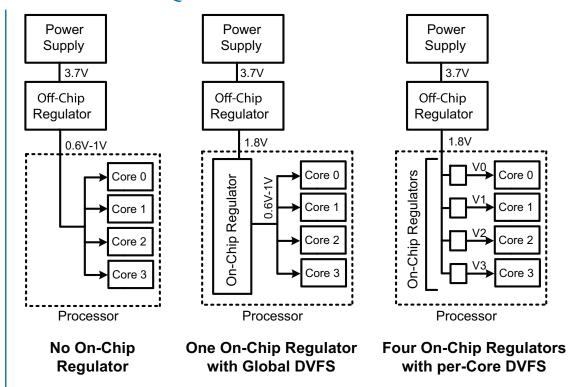

A solution to the voltage-stepping latency problem is to use *on-chip* voltage regulators operating at much higher switching frequencies (see Figure 2.6). This solution is first explored at the architectural level in the work of Kim et al. [110]. The downside of using on-chip voltage regulators is that conversion efficiency drops, leading to increased energy losses [110]. However, the benefits from fine-grain (V, f) control outweigh the negatives [110]. Intel's Haswell processor family has a fully integrated on-chip voltage regulator [88].

### 16 2. VOLTAGE AND FREQUENCY MANAGEMENT

Figure 2.6: On-chip voltage regulators [105].

### 2.1.4 DVFS GRANULARITY

The bulk of the DVFS research has focused on cases in which the entire processor core operates at the same (V, f) setting but is asynchronous to the "outside" world, such as caches. In such scenarios, the main goal of DVFS is to capitalize on cases in which the processor's workload is heavily memory-bound. In these cases, the processor is often stalled, waiting on memory, so reducing its supply voltage and clock frequency will reduce power and energy without having significant impact on performance.

Some of the early architectural work on DVFS focused on opportunities within multiple-clock-domain (MCD) processors [168, 169, 181, 198, 199]. The rationale for MCD processors is that as feature sizes get smaller, it becomes more difficult and expensive to distribute a global clock signal with low skew throughout the whole processor die.

The multi-core paradigm, is a natural MCD design [44]. Cores can be scaled more aggressively than memories, resulting in multiple voltage and clock domains with asynchronous communication between them. One example of this aggressive scaling is *core boosting* where the supply voltage of a core is temporarily increased if power and temperature envelops are not breached in

order to boost the performance of individual cores. The power budget cannot sustain permanent core boosting of all the cores at the same time and a boosted core can result in reduced power budgets for the remaining cores that have to operate at a lower frequency. Both Intel [86] and AMD [3] implement core boosting in their latest processor architectures.

Another related question regards whether continuous settings of (V, f) pairs are possible, or whether these values can only be changed in fixed, discrete steps. If only discrete step-wise adjustments of (V, f) are possible, then the optimization space becomes difficult to navigate because it is "non-convex." As a result, simple online techniques might have difficulty finding global optima, and more complicated or offline analysis becomes warranted. Industry has now settled in a discrete and small number of DVFS states.

### 2.2 MODELS OF FREQUENCY VS. PERFORMANCE AND **POWER**

A naive approach for estimating the impact of frequency scaling in performance is to assume that the execution time of an application is inversely proportional to the processor's frequency. This, however, is a very pessimistic estimation of the penalty implied by frequency scaling. The processor communicates with the memory in an asynchronous way, i.e., accessing the main memory is not affected by the processor's frequency. Therefore, changing the core's frequency only affects the parts of the application that do not exhibit any accesses to the main memory. In other words, memory-bound programs can be scaled down in frequency with only minor impact on their performance. This effect has been exploited empirically in a number of approaches [82, 92, 93, 164, 197, 200, 201]. Recently, analytical models quantify the relationship of performance to f scaling, giving a better insight for such techniques. As with other DVFS techniques applied at the OS level the key enabler is slack [103]—in this case, the slack that results from waiting for memory (memory slack). We present these models here, for the insight they offer on DVFS behavior.

#### 2.2.1 ANALYTICAL MODELS

Karkhanis and Smith introduced a first-order *interval-based* analytical model for superscalar processors [102]. Eyerman and Eeckhout together with Karkhanis and Smith later refined this model and proposed practical approaches for the on-line collection of its parameters [57]. The interval model estimates performance as a function of various event counts, such as cache misses, branch mispredictions, etc., and the instruction-level parallelism (ILP) that is inherent to an application. Apart from predicting raw performance numbers, an equally important contribution of the interval model is to serve as a framework for understanding how the so-called "miss events" affect the performance of a processor. In this direction, three different groups, working independently (Keramidas et al. [106], Eyerman and Eeckhout [56], and Rountree et al. [160]) extended the basic interval model to describe how frequency scaling affects the execution time of a program.

### 18 2. VOLTAGE AND FREQUENCY MANAGEMENT

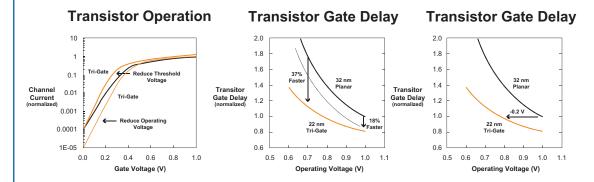

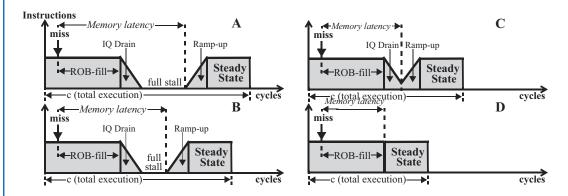

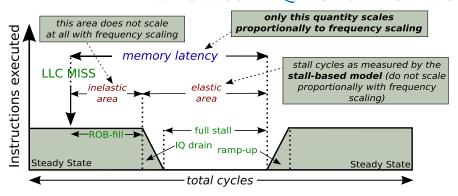

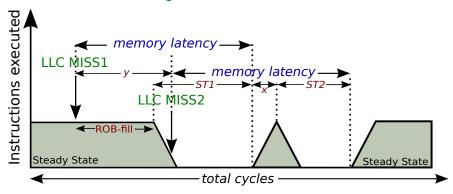

The model introduced by Karkhanis and Smith breaks the execution of a program into intervals. During "steady state" intervals, the execution rate in instructions-per-cycle (IPC) of the processor is only limited by the processor's width and the program's dependencies within an instruction window (for sufficiently large instruction windows). Steady state intervals are interrupted by "miss-intervals," which introduce stalls cycles to the processor. A miss-interval starts with a miss-event (off-chip load accesses in our case), and lasts until the pipeline reaches again a steady state (a period related to the memory latency). The realization that underlies all DVFS models is that *core frequency scaling in these models is equivalent to changing the memory latency in cycles*. This is depicted in the diagram of Figure 2.7.

Figure 2.7: Performance scaling with f. Memory latency, measured in cycles, shrinks as we scale f lower, eliminating the stalls caused by the miss [106].

Scaling down frequency does not always result in a proportional slowdown in the processor's performance. This is due to the asynchronous way that a processor core communicates with the remaining system and main memory. Processor core operations that do not incur an L1 cache miss have a fixed latency in terms of cycles because every core component and the L1 cache operate under the same clock signal. Thus, in a program with few L1 misses, scaling the clock frequency does not change the total number of cycles required for the program to execute. Of course, the duration of the cycle (cycle period) is affected in an inverse proportional way, thus the execution time is also inversely proportional to frequency. However, latencies to components outside the core and the L1 cache scale proportional to the difference between the core and the components' clock frequencies. This effect is particularly tangible for off-chip accesses (e.g., to main memory) as they operate at a relatively low frequency and have long latencies.

Figure 2.8 shows in more detail what happens upon an access that misses in the last level cache (LLC). When the miss occurs, the processor continues to issue instructions at a steady-state rate, since there are still instructions that do not depend on the pending miss. This area is called *ROB-fill* (reorder buffer fill), and corresponds to the number of cycles required until the pending miss reaches the head of the reorder buffer. At this point, no more instructions can be

Figure 2.8: Interval model for f scaling [106].

committed, thus no more new instructions can enter the instruction window. The processor now has a limited pool of instructions to choose from for issuing to the execution units—a pool that gradually shrinks as instructions execute. This results in the IQ (instruction queue) drain area of the graph: the processor has fewer and fewer candidate instructions to pick from, thus the issue rate starts dropping. At some point, all of the remaining instructions will depend on the pending LLC miss, and the processor stalls waiting for the miss to be resolved (full-stall area). When the miss is finally resolved, pending instructions can execute, new instructions can enter the instruction window and, thus, the issue rate ramps-up to the stead-state rate again.

Examining Figure 2.8, and keeping in mind that time is measured in processor core cycles, the models identify how different regions are affected by frequency scaling. Individual regions of the miss-interval are affected by frequency scaling in different ways. Regarding the ROB-fill area, the number of cycles that it takes until the reorder buffer fills up *does not depend on frequency*. All of the operations that occur during this period are core operations, synchronized at the same clock, and changing the clock-period does not affect the number of cycles these operations take. IQ drain, full-stall and ramp-up intervals, on the other hand, scale with frequency in a way that the total memory latency (measured in processor cycles) will scale proportionally to frequency.

There are two models that can be constructed based on these observations, a simple model called *stall-based*, which is practical for on-line implementations, and a more elaborate, more accurate *leading-loads* model, which, however, is less practical given the current event-counter support in commercial processors. Both are explained below.

### Stall-based Model

The simplest model assumes that the time it takes to fill the ROB is negligible and therefore the bulk of the memory latency is elastic to frequency scaling. This corresponds to the case of an isolated LLC-miss. When multiple LLC-misses overlap (Figure 2.9), the issue rate begins to rise after the first miss has been serviced but drops again when the second miss reaches the ROB

### 20 2. VOLTAGE AND FREQUENCY MANAGEMENT

Figure 2.9: Interval model for multiple overlapping misses [106].

head. When the data of the second miss arrive from the main memory, the issue rate rises until it reaches the steady-state rate. In Figure 2.9, although the second miss occurs y cycles after the occurrence of the first miss the second miss reaches the ROB head x cycles (where  $x \ll y$ ) after the first miss has been serviced. As a result, two separate stall intervals appear: ST1 and ST2.

The stall-based model assumes that either stalls are generated by an isolated miss or the sum of stalls generated by overlapping misses (e.g., ST1 and ST2) are both approximately equal to the memory latency (in cycles). Because memory latency is proportional to core frequency, these quantities are approximately proportional to frequency as well. Consequently, the total number of stall cycles is approximately proportional to frequency, while the total number of non-stall cycles (steady state) is independent of frequency (measured in cycles).

The advantage of this model is that only in-core information (number of stall cycles) is used to predict performance under various frequencies. However, the model assumes that ROB-fill is negligible, which is a source of errors especially in applications characterized by little dependence between instructions and thus large ROB-fill time.

### **Leading Loads Model**

While the stall-based model assumes that the number of stall cycles is approximately equivalent to the memory latency for both isolated and overlapping misses, the "leading loads" model recognizes that there is an inelastic area in the miss-intervals (the ROB-fill time) that does not scale with frequency (in cycles). While this is not modeled or measured directly, its implications, especially with respect to overlapping misses, are captured in the model: stall cycles of only the first miss of a group of overlapping misses or the stall cycles of an isolated miss are taken into account.

Leading load models require an accurate accounting of *the number of groups of overlapping misses*. Support for measuring these at run-time is not readily available in contemporary processors but has been proposed by Eyerman and Eeckhout [56].

There are several assumptions underlying these models, for example, the conditions that stall the processor [56], and the effect of store misses [106]. Perhaps one of the most important simplifications is that the access latency of the main memory is considered constant, even though in reality it may vary considerably. This assumption is addressed in the work of Miftakhutdinov et al. [134] where the authors show improvement in accuracy by adopting a more elaborate memory latency model.

### CORRELATION-BASED POWER MODELS

Power models can be split in two broad categories: highly parameterized models that try to estimate power consumption of non-existent hardware (CACTI [119], WATTCH [27], Mc-PAT [127]) and models that characterize a specific hardware. This subsection briefly discusses the second approach.

The standard method for building a model to characterize the power behavior of a specific system is to train a correlation model [39, 64, 65]. Different benchmarks (or microbenchmarks) are used to stress different parts of the system (caches, ALU, out-of-order engine, etc.) and performance counters are programmed to measure different statistics such as caches misses, branch mispredictions, and integer/floating point instructions. At the same time, power consumption is measured for each of the benchmarks of the training set, and curve-fitting techniques are used to derive the relationship between the performance-counter statistics measured and the power observed for each benchmark. The mathematical representation of the above is to express power as a linear function of all the statistics that are believed to correlate strongly with power consumption,

$$Power = \sum_{k=0}^{i} \frac{param_k \times event_k}{time}$$

(2.1)

Power and values for the performance counter events are used to derive the parameters param<sub>k</sub> that best fit the observed measurements. Notice that this model is tightly connected with a specific (V, f) pair, the one that the benchmarks were run at while creating the correlation model. Recently, Spiliopoulos et al. [177] proposed an extension to this approach to create a unified power model that estimates power consumption not only for the voltage and frequency that were used during the training of the correlation model, but for any frequency of interest. Their model acknowledges that, since power consumption is given by the formula  $P = P_{static} + P_{static}$  $afCV^2 = P_{static} + fC_{eff}V^2$ , and  $C_{eff}$  is the only non-deterministic part of the equation, the correlation formula can now be constructed for  $C_{eff}$

$$C_{eff} = \sum_{k=0}^{i} \frac{param_k \times event_k}{cycles}$$

(2.2)

The parameters are derived in a similar way, but the model is now decoupled from specific voltage and frequency values—the accounting of V and f is done once using the generic equation

### 22 2. VOLTAGE AND FREQUENCY MANAGEMENT

$P = P_{static} + f C_{eff} V^2$ . The most important aspect of this approach is that, by using the analytical DVFS models presented in the previous subsection, statistics can be collected in a base frequency and estimated for a target frequency, therefore power can be estimated not only for the base but also for the target frequency.

### 2.2.3 A COMBINED POWER AND PERFORMANCE MODEL

Throughout this chapter, it is clear that abstract models play a significant role toward understanding the efficiency of DVFS. It is also important to realize that DVFS is something that should be explored not statically for each program, since the impact of (V, f) scaling into performance and energy dissipation can vary significantly within the same program, depending on the behavior of the different phases. Spiliopoulos et al. built a tool that takes all this into account and analyzes the behavior of different phases in terms of energy dissipation and execution time for any frequency of interest [178]. This tool, called PowerSleuth, combines three basic components:

- The first component is a phase-detection library called ScarPhase [167]. ScarPhase is an online phase detection tool that is capable of detecting phases at a very low overhead (2%) concurrently with the execution of the application.

- The second component is an approximation of the stall-based model discussed earlier in this chapter. The "approximation" is due to the fact that contemporary processors do not provide the necessary information for applying the model as it is, hence certain approximations have to be taken in order to predict the impact of frequency scaling in the execution time of an application.

- The final component is a model to correlate the power consumption to various performance events in a real processor, similarly to other works [39, 64, 65].

PowerSleuth can capture the runtime variation of an application over different phases, as well as estimate how execution time and energy are impacted by frequency scaling.

### 2.3 OS-MANAGED DVFS TECHNIQUES

Architectural techniques for dynamic voltage and frequency scaling first appeared in the literature pertaining to the system (or operating system) level. Commercial implementations controlled at this level are also the most common form of DVFS (e.g., Intel's Enhanced SpeedStep® [85] and AMD's PowerNow!<sup>TM</sup> [4]).

Weiser et al. first published on this type of DVFS [193]. They observed that *idle time represents energy waste*. To understand why this is, consider the case of a processor finishing up all its tasks well within the time of a scheduling quantum. The remaining time until the end of the quantum is *idle time*. Typically, an idle loop is running in this time, but let us assume that the processor can be stopped and enter a sleep mode during this time. One could surmise that a prof-

itable policy would be to go as fast as possible, finish up all the work and then enter the sleep mode for the idle time and expend little or no energy. But that is not so.

### 2.3.1 DISCOVERING AND EXPLOITING DEADLINES

Whereas the DVFS techniques of Weiser et al. are based on the idle time as seen by the operating system (OS) (e.g., the idle loop), Flautner, Reinhardt, and Mudge look into a more general problem of how to reduce frequency and voltage without missing deadlines [59]. Their technique targets general purpose systems that run interactive workloads.

What do "deadlines" mean in this context? In the area of real-time systems, the notion of a deadline is well defined. Hard real-time systems have fixed, known deadlines that have to be respected at all times. Since most real-time systems are embedded systems with a well-understood workload, they can be designed (scheduled) to operate at an optimal frequency and voltage, consuming minimum energy while meeting all deadlines. An example would be a mobile handset running voice codecs. If the real-time workload is not mixed with non-real-time applications, then DVFS controlled by an on-line policy is probably not necessary—scheduling can be determined off-line.

Flautner et al. consider an entirely different class of machines. In general-purpose machines running an operating system such as Linux, program deadlines have more to do with user perception than with some strict formulation. Thus, the goal in their work is to discover "deadlines" in irregular and multiprogrammed workloads that ensure the quality of interactive performance.

The approach to derive deadlines is by examining communication patterns from within the OS kernel. Application interaction with the OS kernel reveals the so-called execution episodes corresponding to different communication patterns. This enables the classification of tasks into interactive, periodic producer, and periodic consumer. Depending on the classification of each task, deadlines are established for their execution episodes. In particular, the execution episodes of interactive tasks are assigned deadlines corresponding to the user-perception threshold, which is in the range of 50-100 ms. Periodic producer and consumer tasks are assigned deadlines corresponding to their periodicity. All this happens within the kernel without requiring modification of the applications.

# LINUX DVFS GOVERNORS

DVFS is handled in the Linux kernel by the so-called *cpufreq* component. Cpufreq is modular, in the sense that it separates the low-level operations for setting voltage and frequency and the higher-level operations of selecting the frequency to run at. The low-level operation are handled by the *cpufreq driver*, which is responsible of setting up the voltage and frequency tables, exposing this information to the higher levels, and controlling voltage and frequency according to the commands that it receives from the higher levels of the software stack. On the other hand, the frequency governors are responsible for selecting the frequency to run at depending on the workload executing on the system. Essentially, a single cpufreq driver is enough for a specific system, but

# 24 2. VOLTAGE AND FREQUENCY MANAGEMENT

various different *frequency governors* can co-exist in the system, and the user can easily switch between them at runtime depending on the power and performance profile that better suit the current use-case. Here we briefly discuss the standard governors that come with every Linux distribution:

- **Performance:** The simplest possible governor, runs always at maximum frequency.

- **Powersave:** The complete opposite of the *performance governor*, runs always at minimum frequency. This governor minimizes the power consumption but may severely prolong the execution time of certain applications.

- Ondemand: The default governor used in many systems, tries to set frequency based on the CPU utilization. Frequency is reduced in steps when utilization drops below some certain low-threshold, and it is restored back to the maximum value if CPU utilization rises above the high-threshold. Notice that CPU-utilization is expressed at a system-level, which means that a CPU that is waiting for some cache misses to be serviced by the main-memory still appears to be fully utilized to the OS.

- **Conservative:** Very similar to the *ondemand* governor, with the difference that this governor is much more conservative to increase the frequency when an increase in the CPU-utilization is detected.

- **Interactive:** This is also a utilization-based governor, but it does not use any threshold to rise and drop the frequency. Instead, the governor uses the observed CPU-utilization to determine what fraction of the maximum frequency should the frequency be.

# **Green Governors**

Based on the analytical performance-model and the power-correlation model presented earlier in this chapter, Spiliopoulos et al. proposed a class of frequency governors that intelligently select the voltage and frequency setting that optimizes an energy efficiency metric [177]. Being based on models that estimate performance and power as a function of frequency, these governors can be tuned for various different policies, i.e., for optimizing different power efficiency metrics. The authors demonstrate two different policies, optimizing energy delay product (EDP), and also a variation of this policy that minimizes EDP to the extent possible, without harming performance by more than 10% compared to the execution of the application at maximum frequency. However, any policy that involves some tradeoff between power and performance can be created by using the two models presented in the previous subsections.

Green Governors are implemented as Linux kernel modules, in a similar way as the standard frequency scaling governors that come with all the popular Linux distributions. Given the performance and power models presented in previous subsections, the idea is really simple. The kernel profiles the workloads running on the system for a short period of time, typically a few tens of milliseconds, and gathers the information required by the models. The models determine

what the performance and the power consumption of the workload would have been in any other possible frequency, and based on the policy used, the optimal frequency for the interval that just executed is estimated. Assuming the next interval has a similar behavior with the previous one, the best frequency estimated for the previous interval is the frequency that the upcoming interval will execute at.

### 2.4 PARALLELISM AND CRITICALITY

As chip multiprocessors (CMPs) have become the predominant general-purpose, highperformance microprocessor platform, it becomes important to consider how DVFS management can be applied to them most effectively. One major design decision concerns whether to apply DVFS at the chip level or at the per-core level. As with other MCD designs, per-core DVFS is considered more expensive; it requires more than one power/clock domain per chip, and synchronizer circuits are required to avoid metastability between domains. On the other hand, multiple clock domains may be employed anyway for circuit design or reliability reasons, in addition to voltage and frequency control.

Early research has explored the benefits of per-core versus per-chip DVFS for CMPs. For example, on a four-core CMP in which DVFS was being employed to avoid thermal emergencies (rather than simply to save power), a per-core approach had 2.5× better throughput than a perchip approach [44]. This is because the per-chip approach must scale down the entire chip's (V, f) when even a single core is close to overheat. With per-core control, only the core with a hot spot must scale (V, f) downward; other cores can maintain high speed unless they themselves encounter thermal problems.

The discussion so far in this chapter centered on the DVFS behavior of a core running a single-threaded program. When considering one single-threaded application in isolation, one need only consider the possible asynchrony between compute and memory.

While a multicore processor can be used to run independent programs for throughput, its promise for single-program performance lies in thread-level parallelism. Managing power in a multicore when running parallel (multi-threaded) programs is currently a highly active area of research. Many research groups are tackling the problem, considering both symmetric architectures, which replicate the same core and asymmetric architectures that feature a variety of cores with different power/performance characteristics [117]. Independent DVFS for each core [8], a mixture of chip-wide DVFS and core allocation [123], or work-steering strategies at the program level in heterogeneous architectures [117, 139] are considered. In this scenario, reducing the clock frequency of one thread may impact other dependent threads that are waiting for a result to be produced. Thus, when considering DVFS for parallel applications, some notion of critical path analysis may be helpful.

# 26 2. VOLTAGE AND FREQUENCY MANAGEMENT

Figure 2.10: An application and its static schedule [136].

**Figure 2.11:** Various static schedules that result from distributing the global slack and scaling (V, f) [136].

# 2.4.1 THREAD- AND TASK-LEVEL CRITICALITY: STATIC SCHEDULING

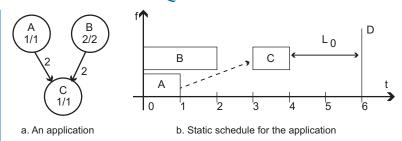

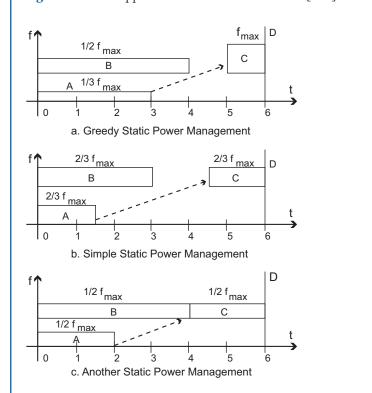

Mishra et al. performed some of the early work (2003) on power management of multithreaded workloads [136]. They examined the case of distributed real-time systems where a set of real-time tasks with precedence constraints and deadlines is statically scheduled to execute. Their starting point is a static schedule generated by any list scheduling algorithm, such as for example the one

given in Figure 2.10. In this example three tasks, A, B, and C, run for the specified amount of time (at a given f). The communication between A and C (with a cost of two time units) is indicated with a dotted line in the schedule. A global deadline D is set at time 6.

Prior to their work, simple static algorithms distribute the global slack ( $L_0$  in Figure 2.10) proportionally to the tasks and by scaling (V, f) obtain energy savings respecting at the same time the precedence constraints, the communication, and the deadlines. Scheduling results of three static algorithms are shown in Figure 2.11. The authors argue that these static approaches are not optimal for parallel and distributed systems when parallelism varies in an application. Thus their proposal is based on the intuition that more energy savings can be obtained by distributing proportionally more slack to sections with higher degree of parallelism. The effect is to further reduce the idle periods in the system. Although their approach is static and relies on a statically scheduled real-time task graph, it saw the seeds for later work. The authors keenly observe:

"Due to synchronization of tasks and parallelism of an application, gaps may exist in the middle of a static schedule. After distributing global static slack, gaps in the middle of the schedule can be further explored. Finding an optimal usage of such gaps seems to be a non-trivial problem. One simple scheme is to stretch tasks adjacent to the gap when such stretching does not affect the application timing constraints."

Subsequent work in this area addresses exactly this observation: how to detect "gaps" in execution and exploit them for energy savings. The key is to detect load imbalance between threads and slow down non-critical threads to achieve energy savings. However, it has proven more fruitful to detect critical threads that cannot be slowed down (on account of their direct impact on the total program execution) than to try to assess which threads are non-critical.

### 2.4.2 THREAD- AND TASK-LEVEL CRITICALITY: DYNAMIC **SCHEDULING**

The first attempt to exploit "gaps" in execution of parallel programs is the proposal for *Thrifty* Barriers by Li, Martinez, and Huang [124]. The gaps in question are experienced by threads that arrive early at a barrier. At this point a thread can select to set its core in a sleep mode. However, because entering the sleep mode involves significant latency, and exiting the sleep mode late can impact performance (as it can delay crossing the barrier for all threads) it is important to be able to gauge the size of the "gaps" before sleep decisions are made. To solve this problem Li, Martinez, and Huang use prediction. The size of the gaps cannot be accurately correlated to the executing threads, since it is unpredictable how the barrier load imbalance is distributed between the threads. However, they found that the interval between successive invocations of the same barrier is quite stable and therefore predictable. Thus, in their proposal, each thread arriving at a barrier has a prediction of the inter-barrier interval and can gauge its own compute time. The difference between the two is the predicted gap for this particular thread's execution. This enables threads to decide whether to set their core to sleep or not while waiting for the end of the barrier.

# 28 2. VOLTAGE AND FREQUENCY MANAGEMENT

If a thread decides to enter a sleep mode it must also wake up in a timely manner so as to not penalize the whole execution. A thread sets an alarm (according to its predicted gap), which is also guarded by a safety net in case the prediction is widely off. The safety net is provided by the coherence mechanisms and concerns the flag that is typically used in barriers to signify the crossing of the barrier by the last thread. This flag's address is monitored by the cache controller of the thread's sleeping core, and in case an external coherence invalidation is detected for this address the core is immediately woken up.

Whereas Li, Martinez, and Huang aimed at detecting and predicting the gaps in execution, Cai et al. first turned the attention to *thread criticality* [30]. They proposed a technique to dynamically detect critical threads in a parallel region. As a critical thread they simply define the thread with the longest completion time in the parallel region. To find a solution Cai et al. constrain the problem. They detect imbalance in parallel loop iterations. For this reason, the approach is not appropriate for dynamic scheduling of irregular code but rather tuned to static scheduling as offered, for example, in OpenMP.

The approach is simple: a *meeting point* is established (by the programmer or compiler, or conceivably by the hardware itself) such that each thread regularly visits this point. For example, a meeting point can be the back edge of a parallel loop. The number of times that each thread passes the meeting point corresponds to the amount of "work" the thread executes. A thread running behind others in terms of the number of times it passes the meeting point, means it is critical (i.e., has the potential of delaying the whole execution as it does not progress as fast as the others on its assigned work). The slack between a slow thread and other threads can be estimated by the difference in the times they pass the meeting point.

Knowing the relative rate at which threads go through their assigned work permits slowing-down the fast threads (since the total execution time is bounded by the slowest) to gain in energy or alternatively speeding up the slow (critical) thread to gain in performance. In both cases the DVFS decisions are taken locally by each core running a thread. This, however, assumes global knowledge at every core. The authors propose that each core periodically broadcasts to all other cores, the number of times it passed a meeting point. Once this global knowledge is established then distributed decisions can be made. Each core attempts to match the rate of the slowest core by proportionally adjusting its frequency.

# 2.4.3 CRITICALITY

While the work of Cai et al. focused specifically on parallel loop iterations and monitored each core's relative progress, the general problem of how to assess thread criticality in arbitrary code remained unsolved. A first solution came by turning to prediction. Bhattacharjee and Martonosi [22] proposed to predict—rather than to try to accurately track—thread criticality.

Their goal is to construct predictors out of readily available run-time information from hardware performance counters. To this end they examined which metrics correlate best with thread criticality. Instruction rate (number of instructions executed in a specific period of time)

proved to be successful only in some applications, but failed to correlate with criticality in others. However, cache hierarchy events such as misses proved to be much better indicators of criticality across a wide range of applications. A thread that misses in its L1 more than its peers is very likely to be the bottleneck in the computation. The inclusion of L2 misses further improves accuracy for the cases where the L1 misses alone do not provide enough. Establishing a strong correlation between memory system events and criticality, Bhattacharjee and Martonosi are able to construct simple and effective predictors out of information readily available in processors. Similar to other works, once the critical thread is identified, it can be sped up for performance, or the non-critical threads slowed down for energy savings.