# Analog Design at 65 nm

Bob Lefferts, Navraj Nandra Mixed-Signal IP SNUG Israel 2007

#### •CONFIDENTIAL INFORMATION

•The following material is being disclosed to you pursuant to a non-disclosure agreement between you or your employer and Synopsys. Information disclosed in this presentation may be used only as permitted under such an agreement.

#### •LEGAL NOTICE

Information contained in this presentation reflects Synopsys plans as of the date of this presentation. Such plans are subject to completion and are subject to change. Products may be offered and purchased only pursuant to an authorized quote and purchase order. Synopsys is not obligated to develop the software with the features and functionality discussed in the materials.

## Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

## Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

## Analog Versus Digital @ 65 nm

- Digital design

- Significant density increase

- Small, high speed, leaky devices

- With lots of variation in timing.....

- Effort focused on lower power techniques, SI effects, DFM

- Analog design

- Increase in gate & off-state leakage

- Decreased output impedance (poorer current sources)

- Increased "Sources of Variation"

- Mixed signal design: using thin gate vs. thick gate circuits

- Most analog designs use more than one gate oxide (core + I/O)

- Analog device sizes set by precision, not minimum dimensions

- "Same old" thick gate devices for slow speed analog circuits

- It is still possible to build high precision circuits

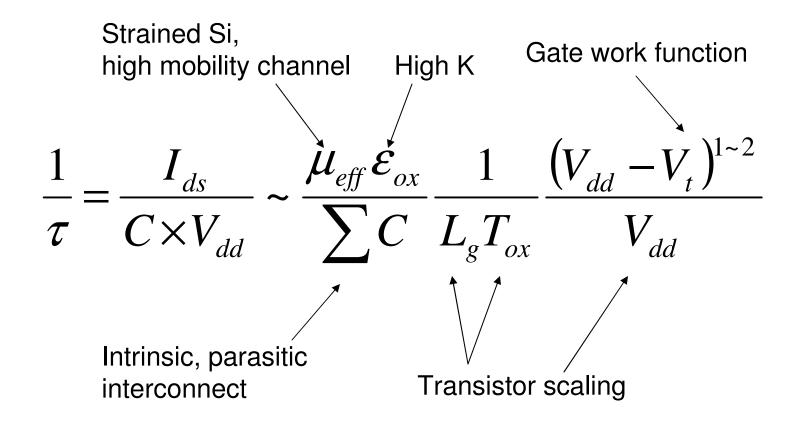

### **Key Trends In Transistor Scaling**

Bottom-line: technology scaling hurts analog Scaling effects not understood & modeled hurts SoC

# **Analog vs Digital Partitioning**

- Move as much as possible into the digital domain

- Digitally controlled PLL

- PVT insensitive loop filter, loop dynamics

- Digital control of simple analog function

- Digital access into analog domain analog test bus

- You need visibility into analog circuits to be able to verify device matching

- Use analog circuits (feedback) to remove normal variation

- Examples:

- PLL

- Duty cycle correction

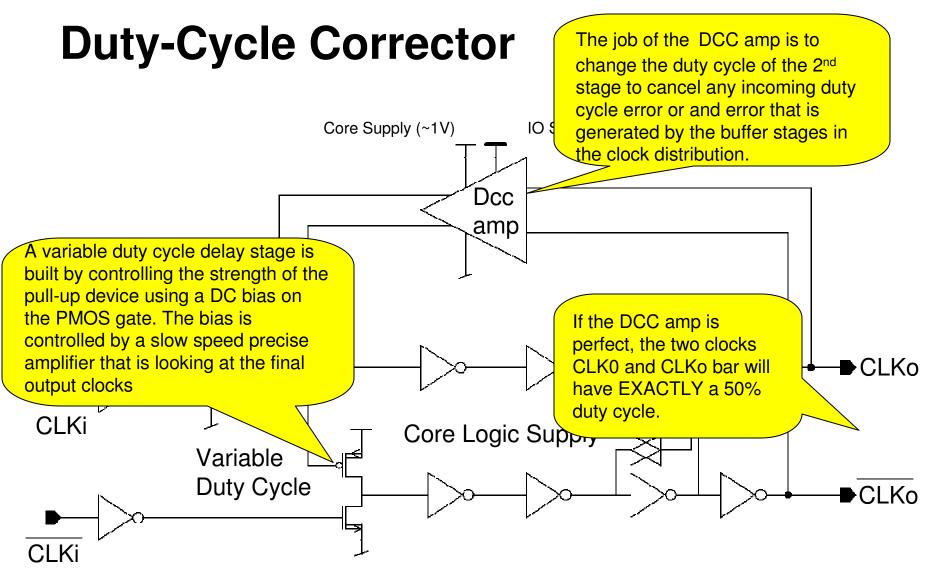

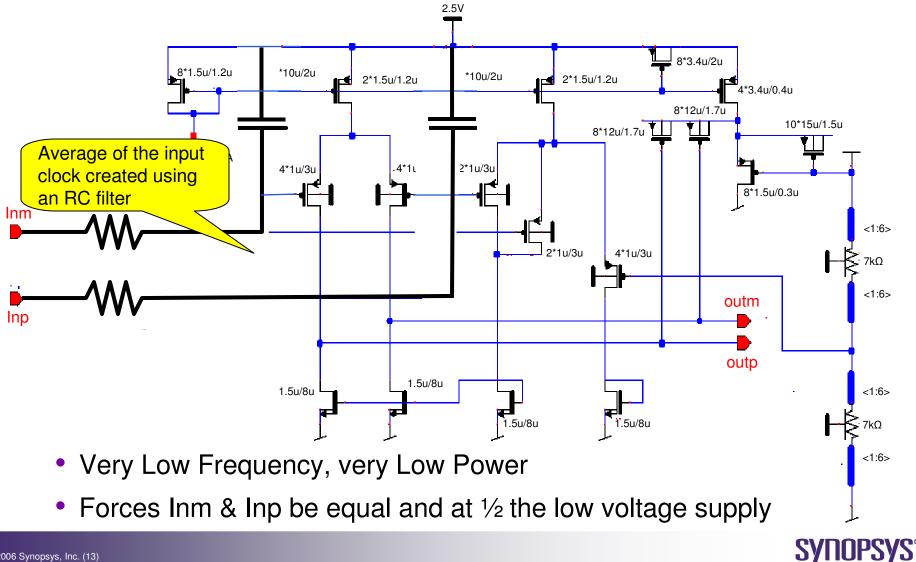

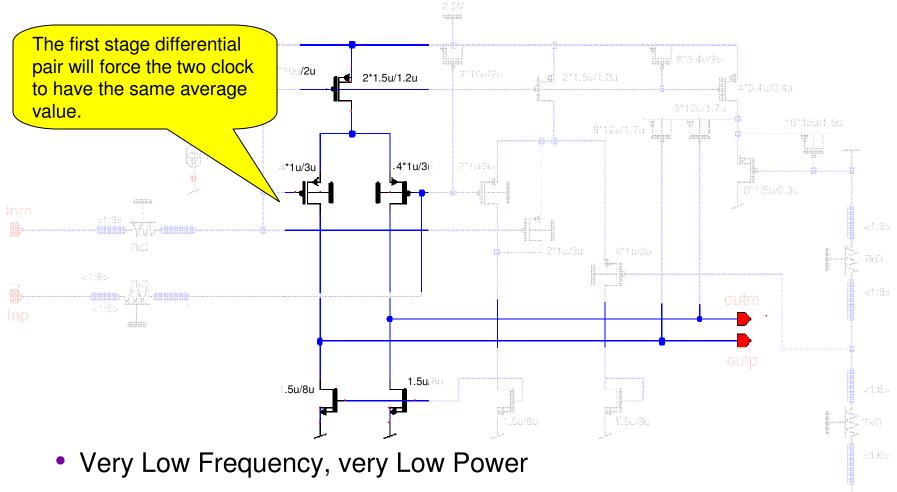

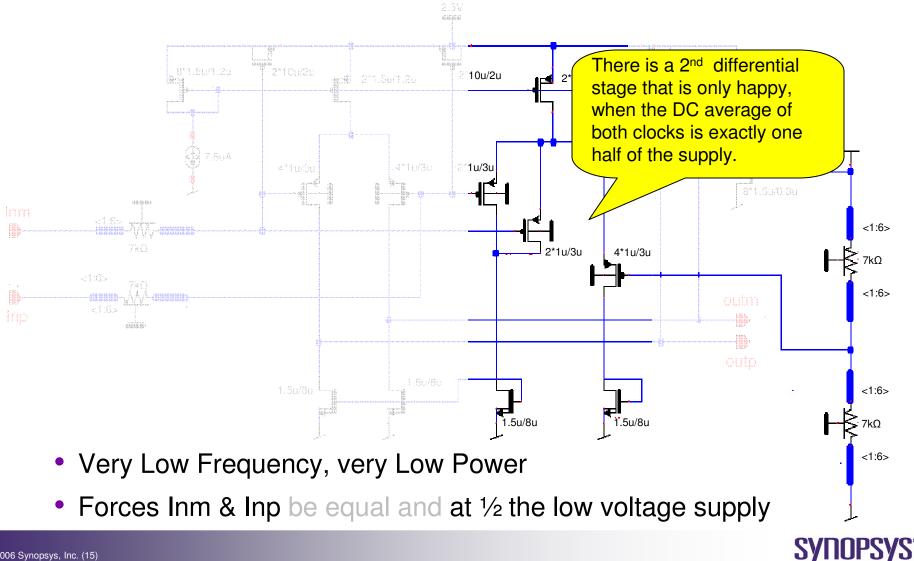

- Mixed Signal Design Example : DCC

## Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

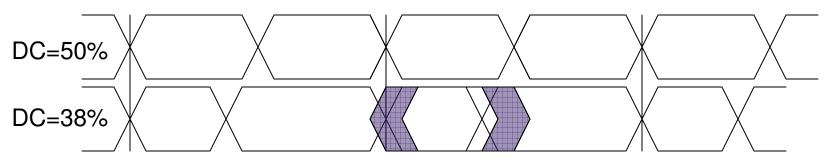

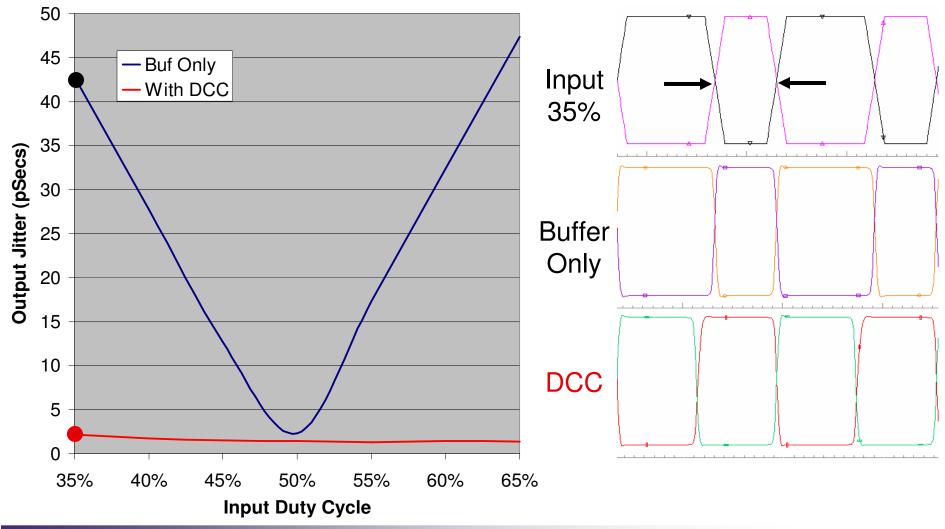

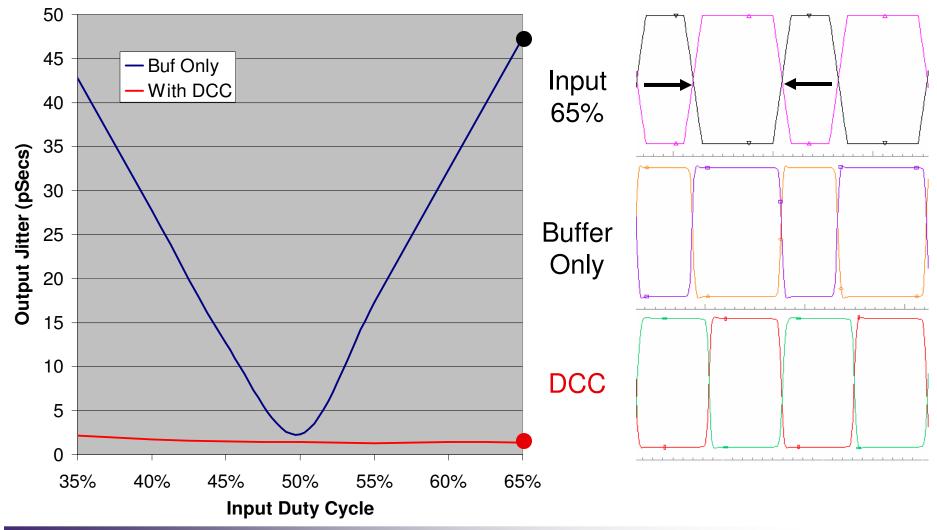

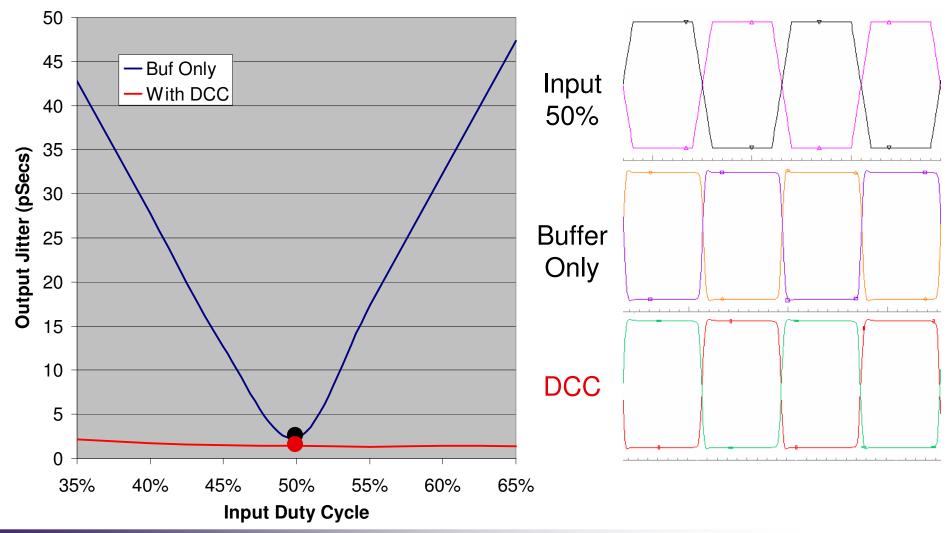

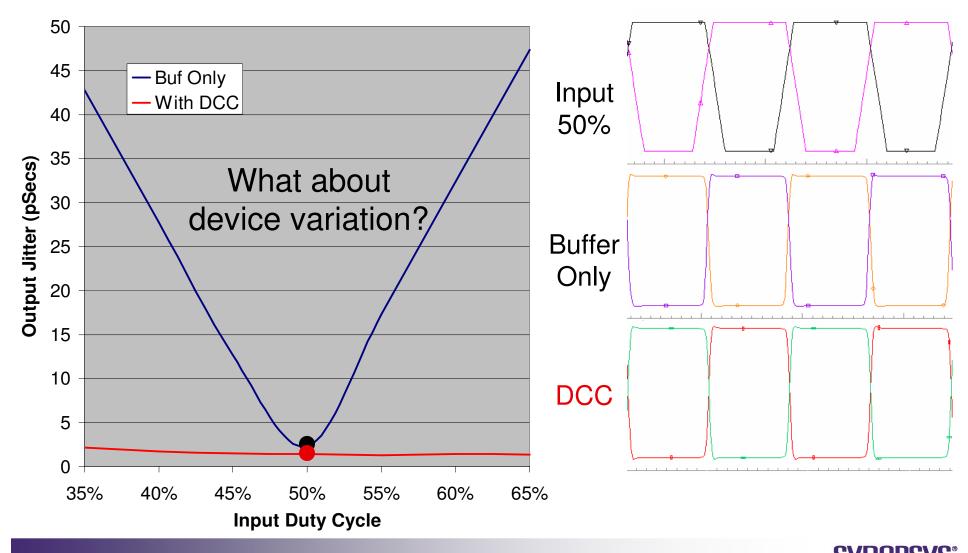

## **Duty Cycle Correction : Clocks**

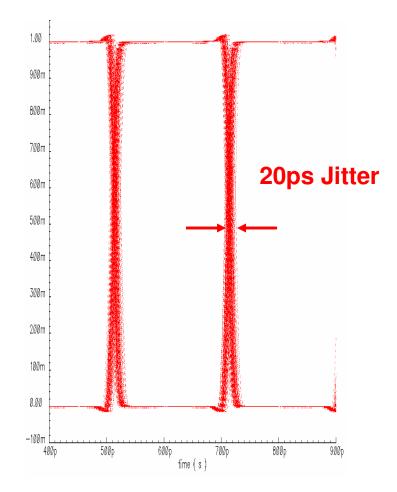

- Many systems use DDR (Double Data Rate) techniques where data transitions on BOTH edges of the clock

- PLL's can remove variation in period (frequency) but Duty Cycle variations show up as jitter with DDR

- Clock sources do not naturally produce exactly a 50% duty cycle

- PMOS pulls up, NMOS pulls down

- Difficult to "Dead Recon"

- Duty Cycle Correction

- Actively force 50% duty cycle independent of the source clk

Add a variation to cancel another variation...

Predictable Success

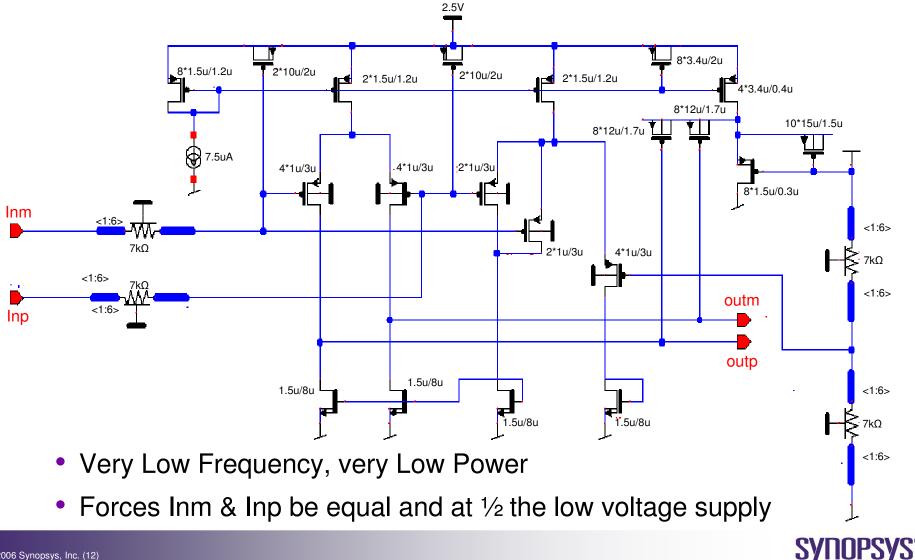

© 2006 Synopsys, Inc. (13)

Predictable Success

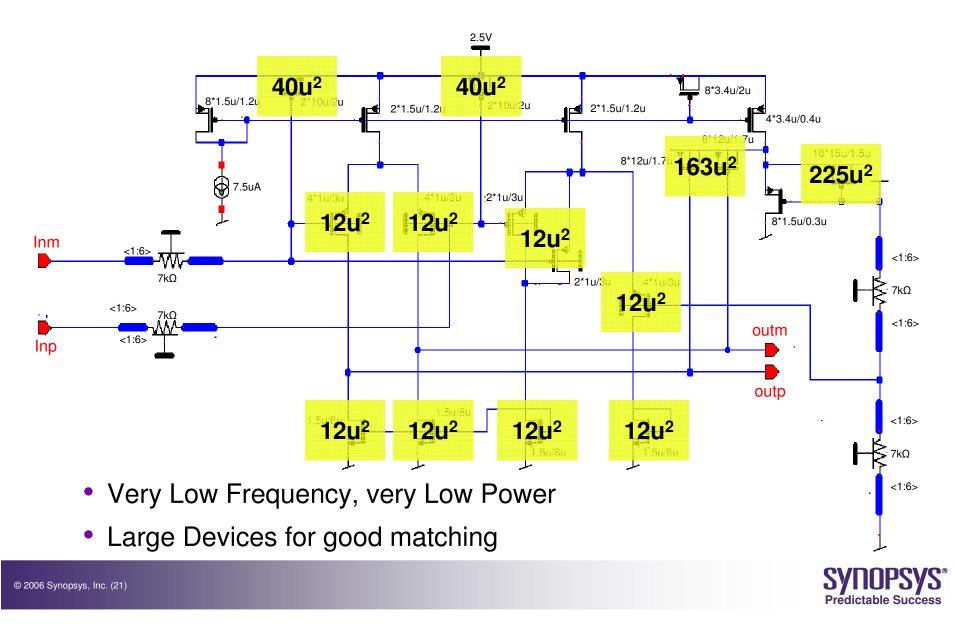

• Forces Inm & Inp be equal and at 1/2 the low voltage supply

Predictable Success

Syllupsys Predictable Success

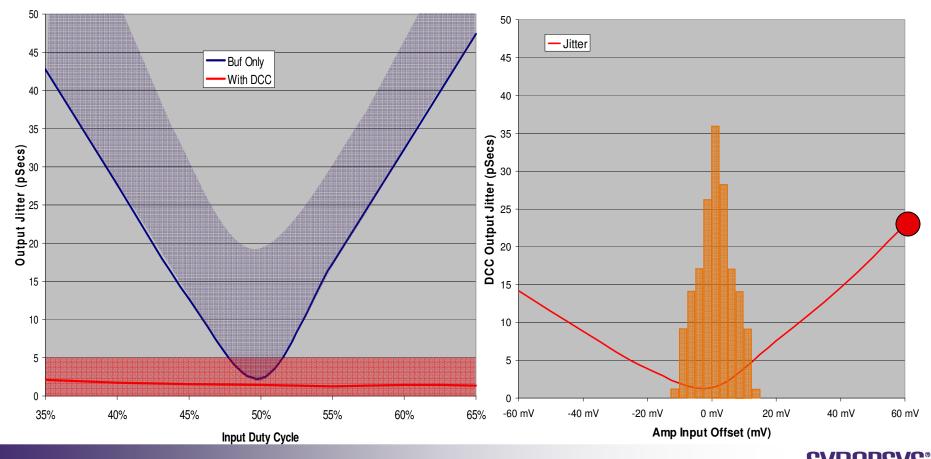

#### Variation due to device miss-match

- Buffer chain rise and fall times are dependent on the relative strengths of NMOS & PMOS.

- Variation in devices due to their small size causes variation in the output of a buffer chain

- 3σ Idsat miss-match

$$\frac{\sim 3\%}{\sqrt{L \cdot W}}$$

- 0.5 X 0.065 device → 16%

- Variation in the Op Amp changes the performance of the analog correction

## Analog Functionality Depends on Device Matching

- Monte Carlo Simulations are mandatory in analog design

- Systematic Offsets can Kill an Analog Circuit

Predictable Success

© 2006 Synopsys, Inc. (22)

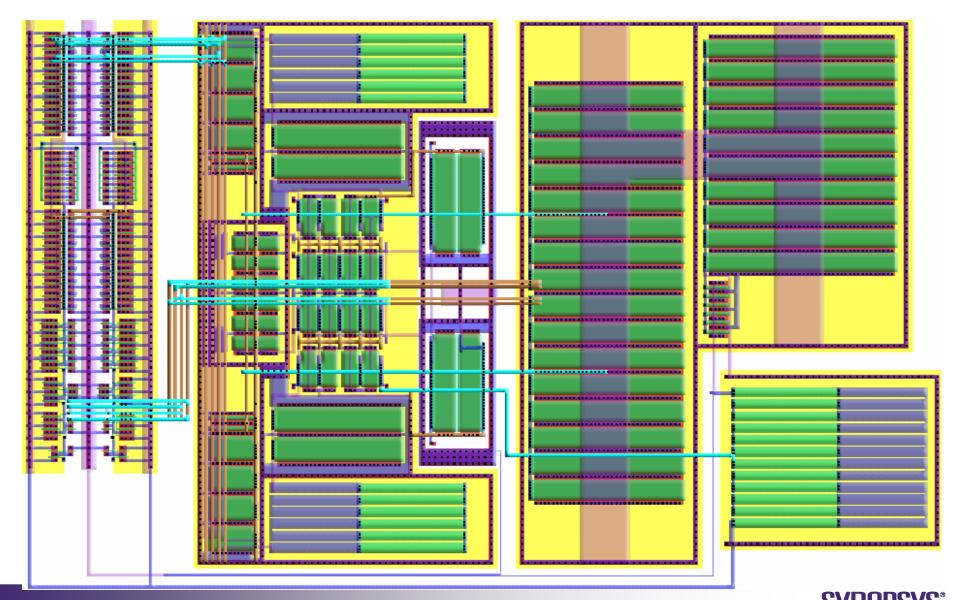

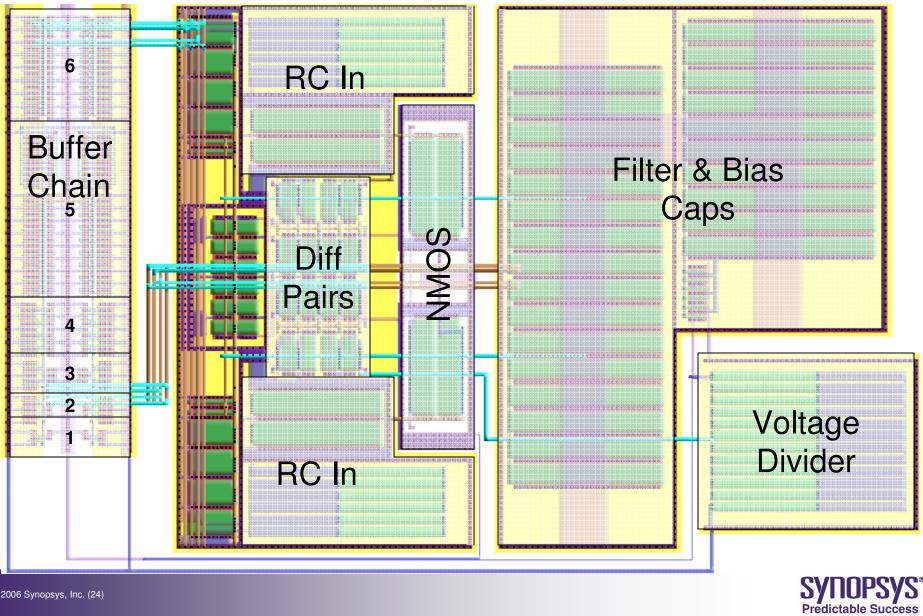

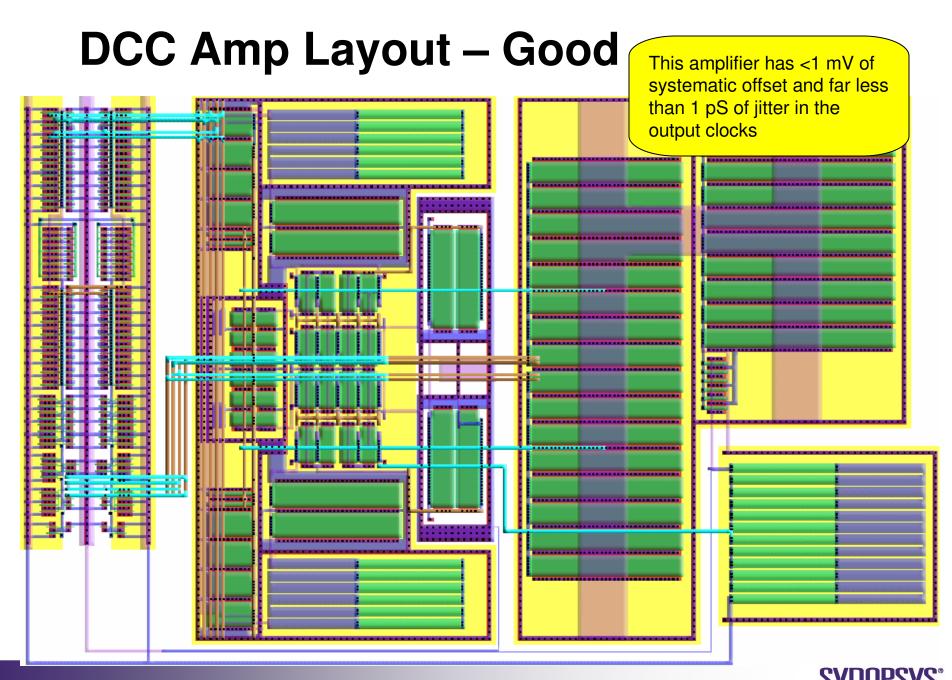

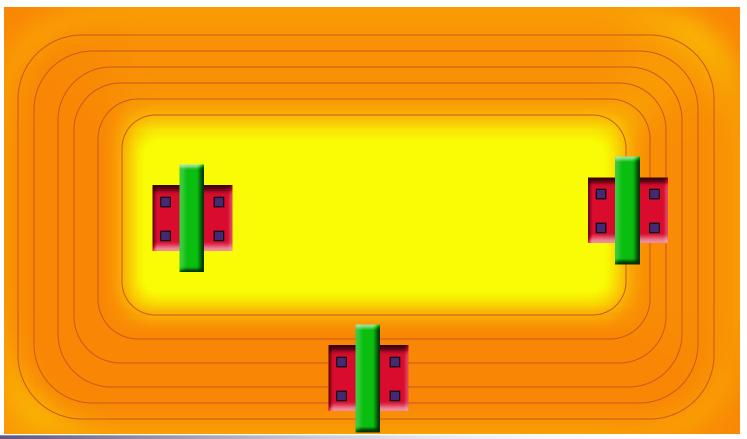

#### DCC Amp Layout @ 65nm

SYNOPSYS Predictable Success

## **DCC Amp Layout**

© 2006 Synopsys, Inc. (24)

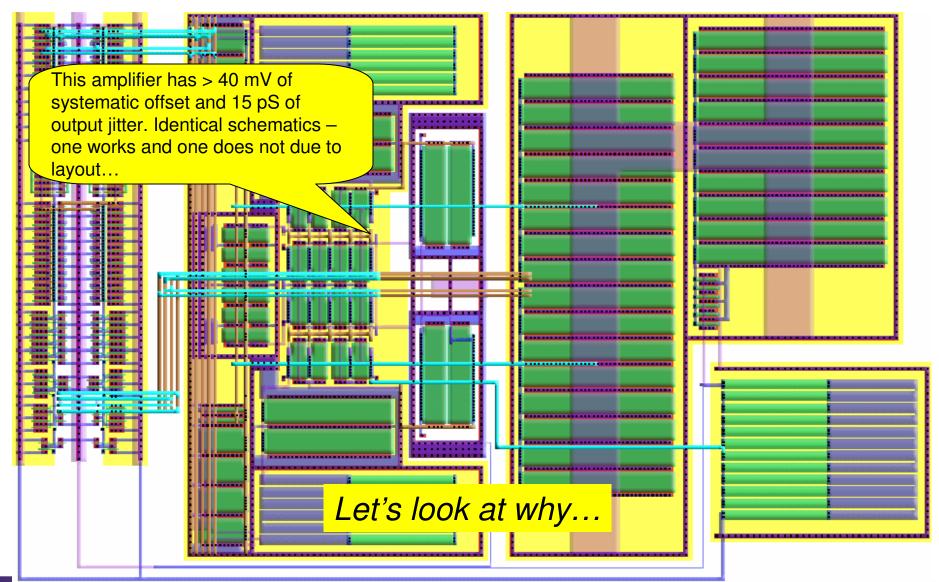

© 2006 Synopsys, Inc. (25)

SYNOPSYS Predictable Success

## **DCC Amp Layout – BUSTED!**

SYNOPSYS® Predictable Success

## Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

## **Killer Sources of Variation**

- Variation due to device size is well understood...

- Monte Carlo simulations of Vt & Idsat miss-match

- Systematic Variation based on <u>Physical Changes</u> to the device

- STI Stress

- Well Proximity

- Contact Stress

- OPC/PSM Variations

- Time Dependent Variation

- NBTI

- HCI

We are operating in a regime well beyond what would have been described as already broken 10 yrs ago!

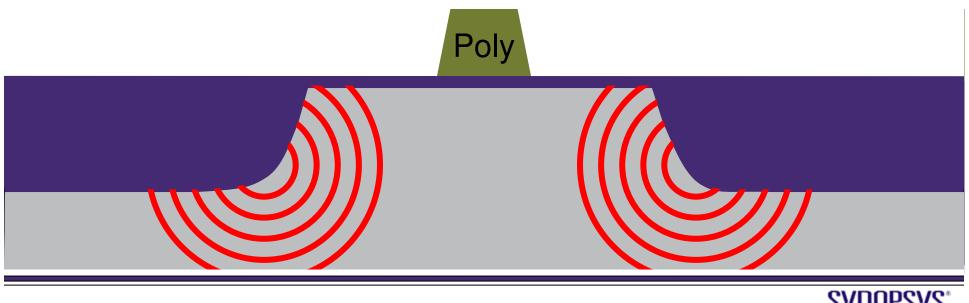

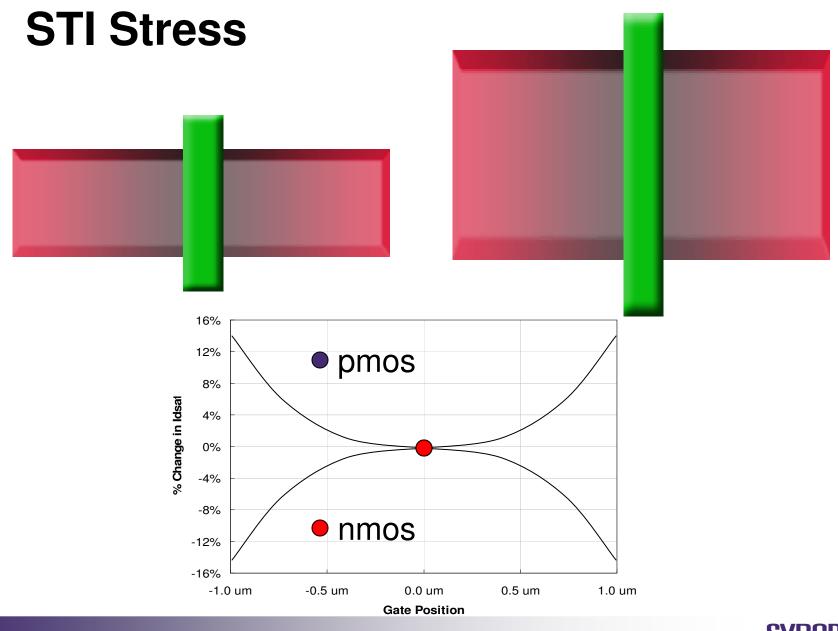

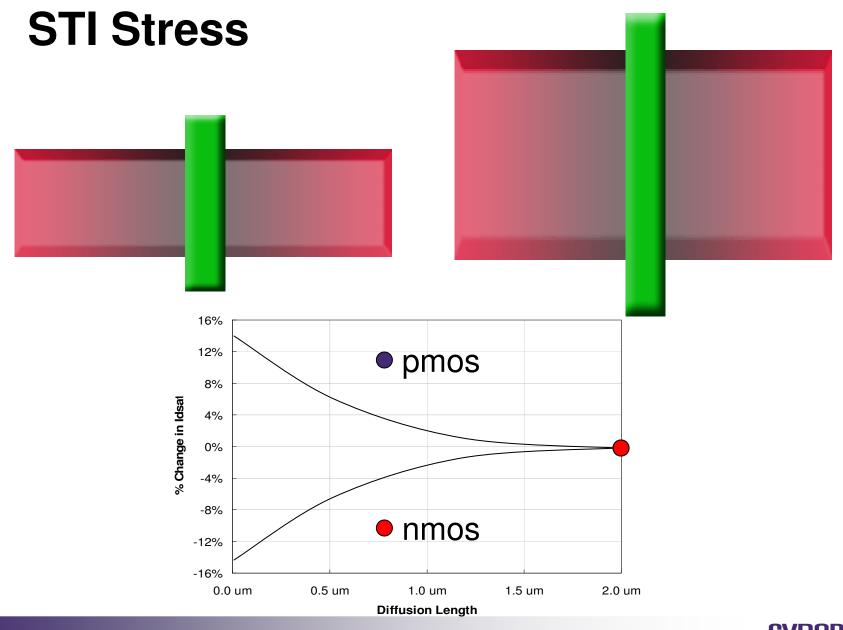

# Stress due to Shallow Trench Isolation (Modulates Mobility)

SYNOPSYS Predictable Success

© 2006 Synopsys, Inc. (30)

SYNOPSYS<sup>®</sup> Predictable Success

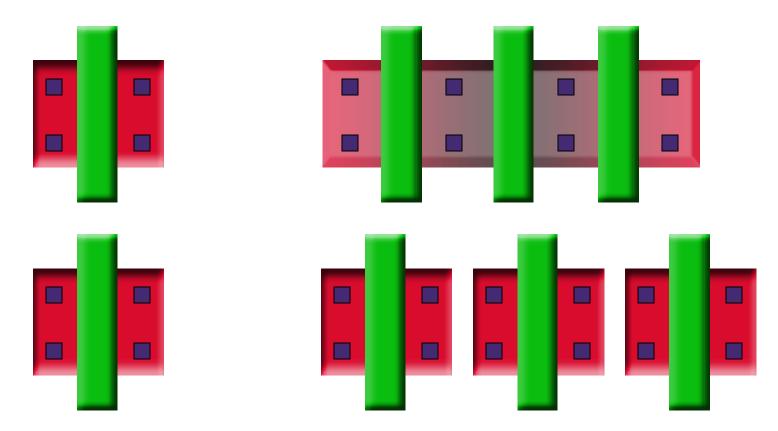

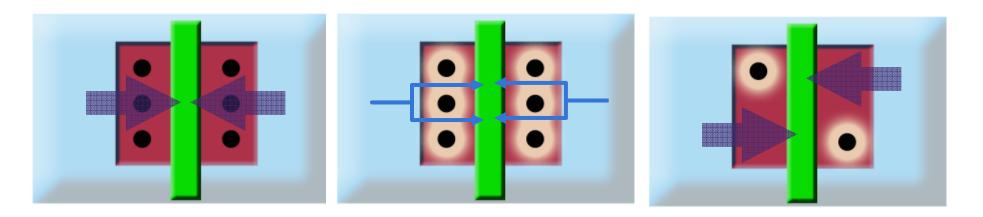

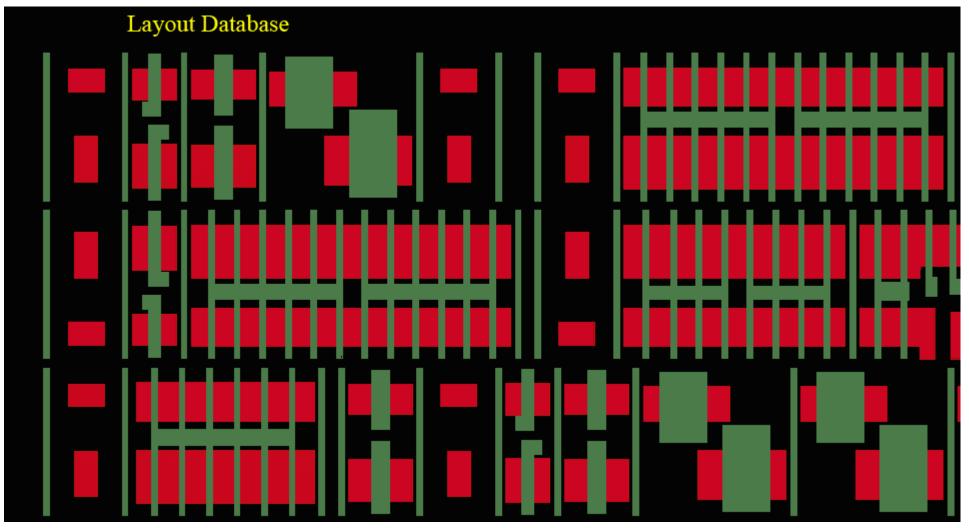

#### **Device Matching and Current Scaling**

- Every Poly Leg of a multi-fingered device becomes a separate SPICE model to account for placement inside the diffusion

- Current scaling errors of up to 60mV & 25% are possible due to STI

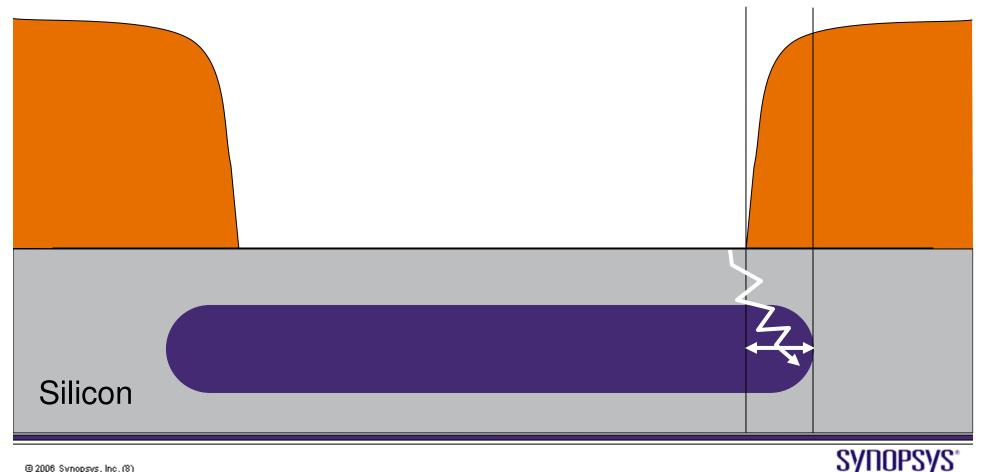

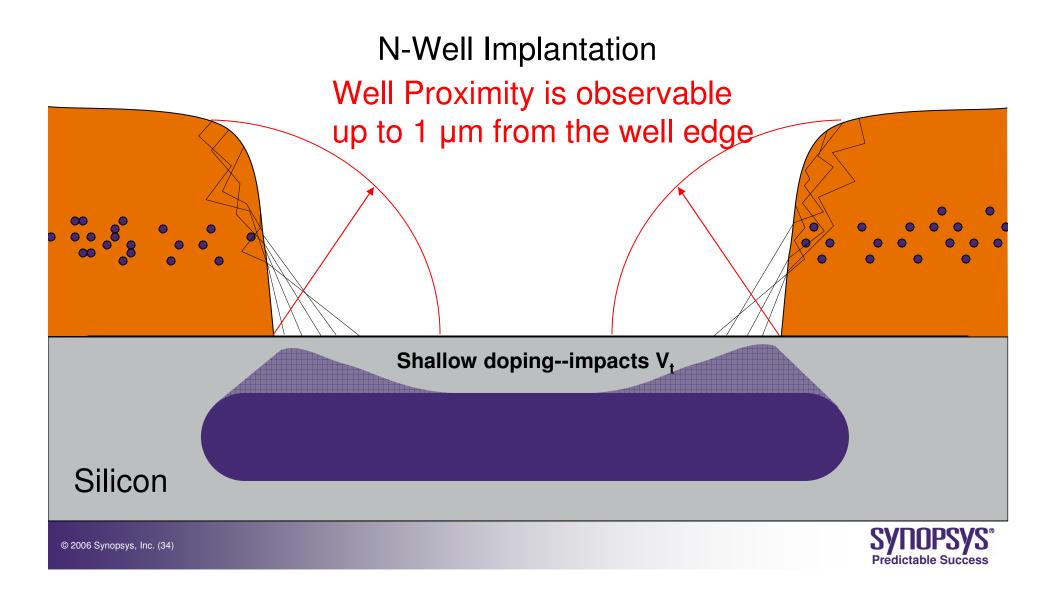

#### Ion Implantation : High Energy Well Implants **Miss-Match due to Well Proximity**

**N-Well Implantation**

Predictable Success

#### Ion Implantation: High Energy Well Implants Miss-Match due to <u>Well Proximity</u>

## **Well Proximity**

- 100 mV Threshold shift based on placement in a well

- Occurs for both N-Well and P-Well implants

#### **Contact Stress**

- If STI stress can change mobility lets feature it

- Add stress layers to increase device performance

- Different stress for N & P Channel

- But contacts cut the stress layer & reduce the improvement

- Device "On Current" becomes a function of contact density

# 65nm : Poly OPC/PSM Masks

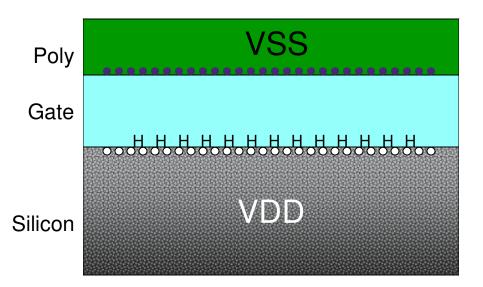

#### **Time Dependent Variation: NBTI**

- PMOS devices that are "ON" have large gate field and high hole surface density

- This causes a <u>molecular</u> <u>change</u> in the gate oxide!

- Hydrogen disassociates from the interface and diffuses away CHANGING the threshold Voltage

- If the voltage is removed, the hydrogen diffuses back!

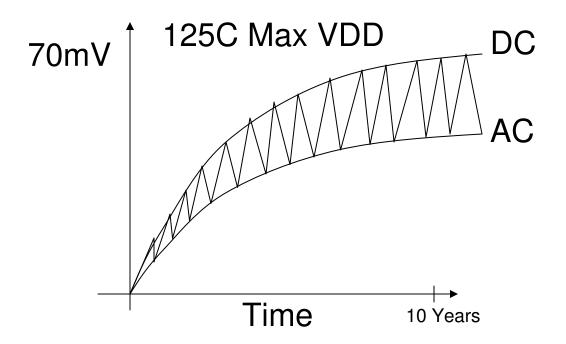

#### **Threshold Voltage vs. Time**

- NBTI has dramatic impact when matched PMOS devices do not have the same gate bias

- This shows up more in power-down modes than in normal operation

- NBTI can be simulated using Verilog-A if you are clever

- Commercially available simulation capability will be released soon

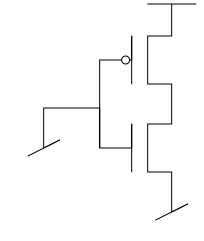

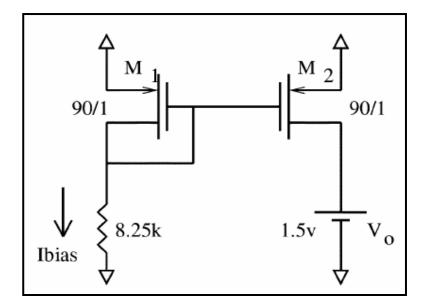

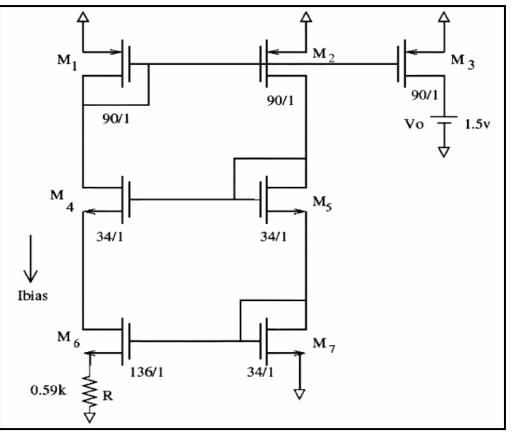

#### **NBTI Impact on Current Mirror (1)**

- Simple mirror

- Used where high output resistance not needed

- As M1 and M2 undergo identical gate stress voltage, delta Vt will vary identically for both of them. The output current follows the bias current for the range considered

- The variation in gate-to-source voltage for transistors M1 and M2 causes a further increase in stress voltages, which therefore must be taken into account for lifetime prediction

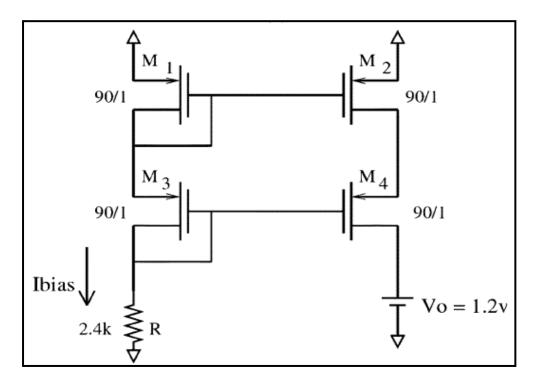

## **NBTI Impact on Current Mirror (2)**

- Cascode current mirror

- Higher output impedance

#### **NBTI Impact on Current Mirror (3)**

- Constant biasing (gm) circuit

- Applications where stable transconductances are required

- Positive feedback is always maintained to match all the gm's to the conductance of R

- Because of this reason, as long as R is constant, the bias currents are maintained at a constant value irrespective of PVT variations

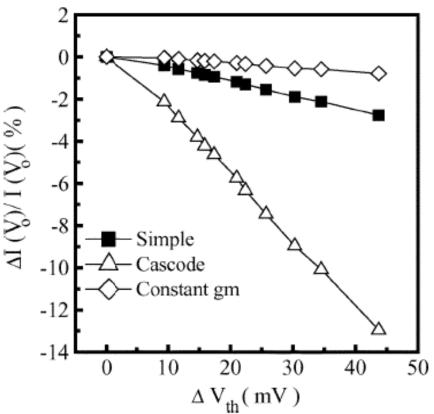

# Drift Current For Equal NBTI Induced $\Delta V_{th}$ Degradation

• Cascode current mirror shows the maximum drift (12.5%) in the output current for the same amount of NBTI-induced degradation

Constant biasing mirror shows the least degradation (1%)

• The highest degradation in the cascode current mirror because there are two diode connected transistors in series and hence the change in voltage across the biasing resistor is a result of change in the Vth's of M1, M3

• The least degradation observed in the constant gm biasing circuits a result of the positive feedback, which accounts for NBTI variation

"NBTI Degradation and Its Impact for Analog Circuit Reliability", Jha et al IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 52, NO. 12, DECEMBER 2005

## **Current Mirror Summary**

Therefore it is clear that for the same amount of variation due to NBTI, different current mirror configurations behave differently and hence must be chosen depending on the application

# Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

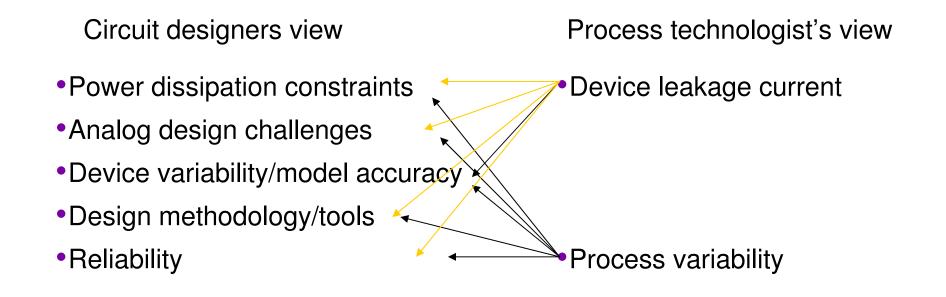

## **Trends: Fab/Design/EDA Cooperation**

At  $\leq$  65 nm fab engineers need to work together with designers and EDA vendor to address power dissipation and process variability concerns

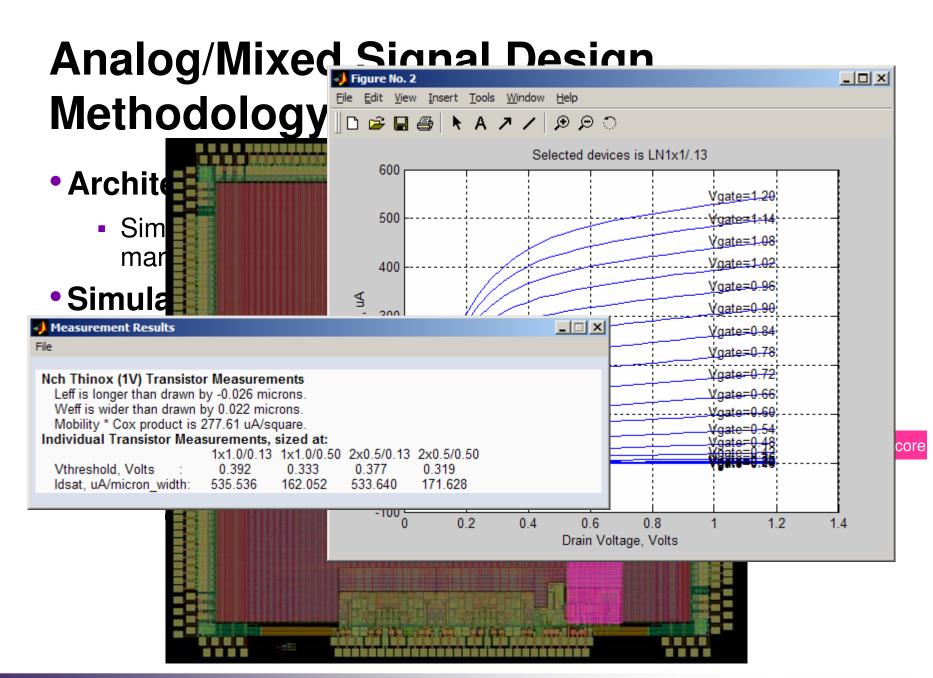

## Analog design trends @ 65 nm

- SPICE model complexity

- Layout re-use

- Dual oxide partitioning

- On-chip voltage regulators

- On-chip RF components

- Inductors Cost

- Special Processing

#### **Compact Device Models**

- BSIM continues to be used

- Modern models formulated as a function of surface potential, rather than threshold voltage, in the channel and s/d edges

- Compact models at 65 nm require:

- Scalability of sub-threshold currents and output resistance from short to long channels due to lateral doping nonuniformities

- Dependence

SYNOPSYS® Predictable Success

© 2006 Synopsys, Inc. (49)

## **Analog Test-Bus**

Visibility into critical analog circuits - methodology allows analog voltages and currents to be measured

12

2.75

© 2006 Synopsys, Inc. (50)

2.8

2.85

2.9

2.95

3

3.2 3.15 3.1 3.05 3 2.95 2.9 • 2.85 2.8 2.75 L 1.55 1.85 x 10<sup>9</sup> 1.6 1.65 1.7 1.75 1.8 ThinoxRingo,3xGateloaded-ring\_oscillator 1.2V\_lcc\_sleep\_mA-icc 74 72 70 68 66 64 62 60 └─ 1.55 1.85 x 10<sup>9</sup> 3.1 3.15 3.2 3.05 1.6 1.65 1.7 1.75 1.8 MPLLOscillatorBiasCurrent-mpll ThinoxRingo,3xGateloaded-ring\_oscillator **311013** Predictable Success

MPLLOscillatorBiasCurrent-mpll

# Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

#### **Example: Low Jitter PCI Express® PHY**

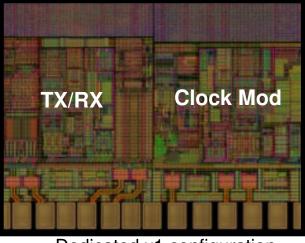

Dedicated x1 configuration

## High Performance PHY @ 65 nm...

- PSRR, Jitter

- Robustness

- Power

- Testability

- PVT invariance

# → Need *digital* CDR

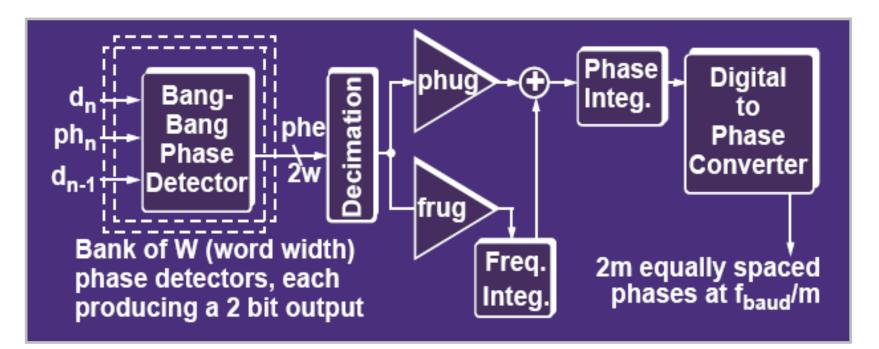

#### **Example PCIe PHY: Digital CDR**

"A Digital Clock and Data Recovery Architecture for Multi-Gigabit/s Binary Links", Jeff Sonntag and John Stonick Synopsys, Inc. CICC 2005

# **Advantages Of Digital CDR**

- PSRR, Jitter

- Digital components

- No PSRR

- Jitter controlled by design resolution

- Only analog component is DPC

- May include high b/w PLL, always tracking reference clock

- Tracking reference clock allows use of linear PFD and about 10 times the b/w of the CDR

- High b/w effective at correcting power supply injected errors and thermally generated jitter

# Advantages Of Digital CDR, cont.

#### Robustness

- False lock impossible

- Tolerance of low transition densities

- CDR is not integrating any noise when there are zero transitions as opposed to an analog CDR when you are always integrating → it is a perfect zero input!

- PVT invariance

- K<sub>DPC</sub> is not a function of PVT

- Analog CDR depends on

- K<sub>VCO</sub>, R, C

- Charge pump

- Current

- Up/down mismatch

- leakage

# Advantages Of Digital CDR, cont.

#### Power

- In order to achieve similar thermal jitter performance, the analog CDR would require much more power

- Testability

- Standard digital SCAN techniques

- Phase programmability can be used for margining purposes in vector-only ATE

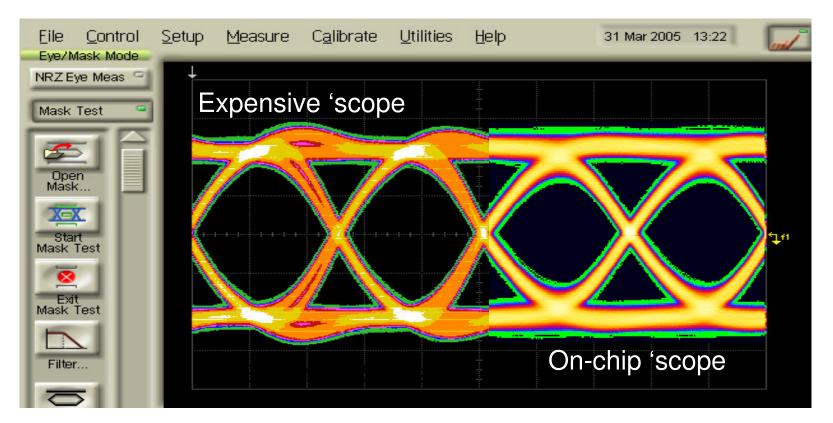

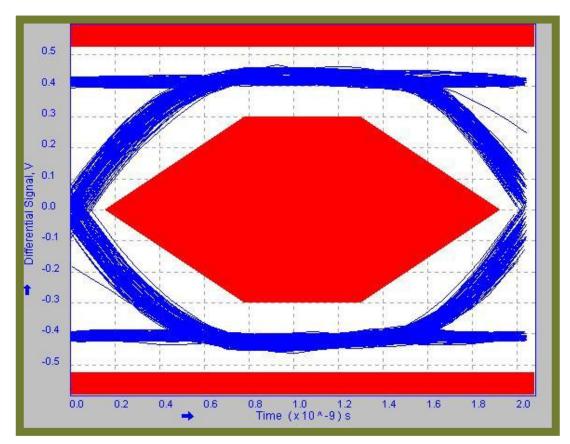

#### **Precision Is Possible**

- Example: On-chip, per RX, sampling scope

- Eye diagrams available through JTAG port

- Synchronous and asynchronous operation supported

- Measure channel pulse response, S21 insertion loss

- Directly measure cross-talk in connectors, layout

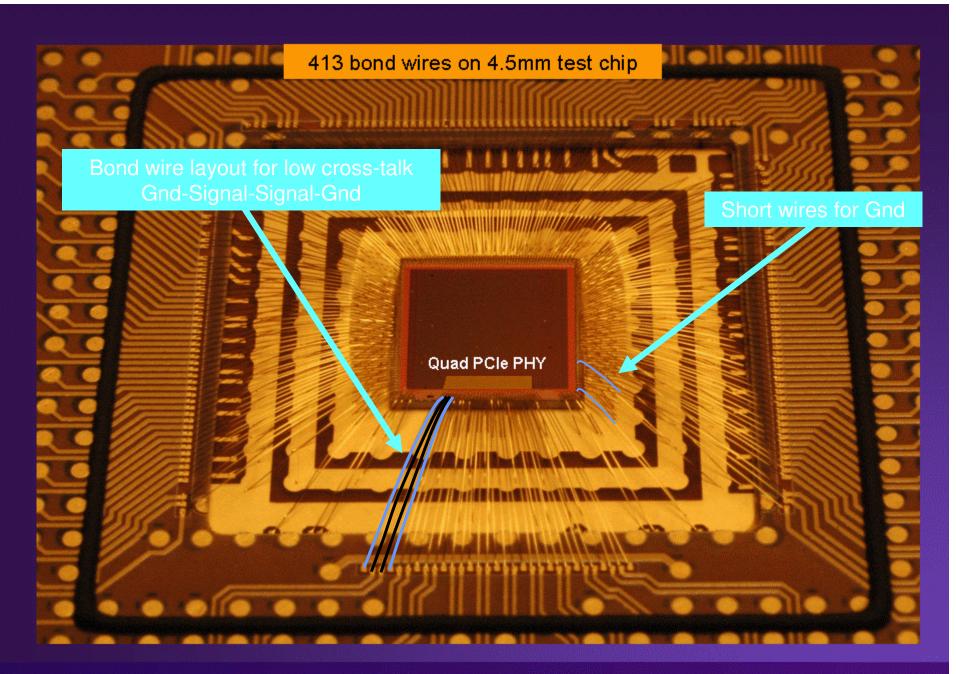

# **On-Chip Sampling Scope per Lane**

- Differences between external scope and internal diagnostics?

- External Scope sees TX + Channel (16" FR4 + cables)

- Internal scope sees TX + Channel + Bond Wires in the package

- Internal scope sees the high frequency filtering effects of the bond wires and the actual RX eye!

#### SYNOPSYS'

@ 2004 Synopsys, Inc. (5)

# Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

# USB 2.0 PHY "Yield By Design"

- Architecture optimizes parametric yields and minimize current consumption

- User controls many performance parameters to allow for various packages, systems and customization

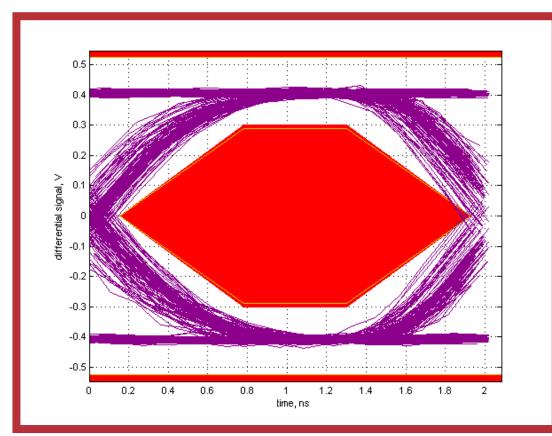

#### **USB 2.0 Compliance – Eye Diagram**

Supply de-coupling removed

- Noisy power supplies can affect jitter

- Power supply filtering (decoupling) recommended

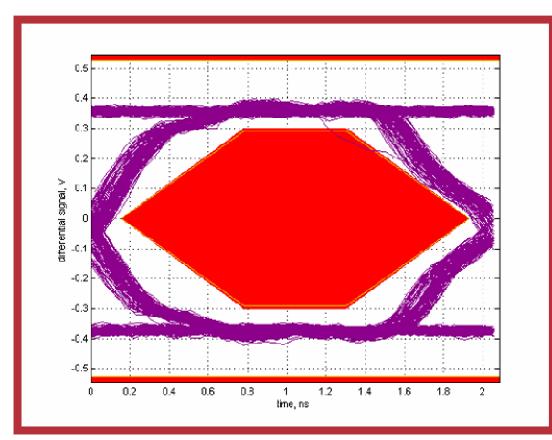

#### **USB 2.0 Compliance – Eye Diagram**

**Excess board parasitics introduced**

- Low HS DC levels

- Rise/fall shape not smooth

- High jitter

- Last bit transition violates

#### **USB 2.0 Compliance – Eye Diagram**

- HS DC levels

Rise/fall shape

Jitter

- ✓ Crossover voltage

# Outline

- Analog versus digital design in sub-wave length technologies

- Design partitioning (Mixed-signal design)

- Mixed-signal design example: a duty cycle corrector

- Killer sources of variation in analog design

- STI, WP, CS, OPC/PSM, NBTI, HCI

- Current mirror example

- Analog design trends @ 65 nm

- Low jitter PCI Express<sup>®</sup> PHY

- Yield by design USB 2.0 PHY

- Summary

# Summary

- High performance analog/mixed-signal circuits are possible in standard deep sub-micron CMOS technologies

- A thorough understanding of the deep-submicron process effects must be made in order to produce working, robust production worthy analog/mixedsignal designs

- This requires close co-operation between the fab. process engineers, circuit designers and EDA vendor

© 2006 Synopsys, Inc. (68)