# FUNCTIONAL VERIFICATION COVERAGE MEASUREMENT AND ANALYSIS

# FUNCTIONAL VERIFICATION COVERAGE MEASUREMENT AND ANALYSIS

by

**Andrew Piziali**

Verisity Design, Inc.

#### KLUWER ACADEMIC PUBLISHERS

NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW

eBook ISBN: 1-4020-8026-3 Print ISBN: 1-4020-8025-5

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://kluweronline.com

and Kluwer's eBookstore at: http://ebooks.kluweronline.com

# **Table of Contents**

| F            | oreword . |                                      | • •       | •     | •   | •   | •   | •    | •   | •   | • | • | ٠ | • | • | ix  |

|--------------|-----------|--------------------------------------|-----------|-------|-----|-----|-----|------|-----|-----|---|---|---|---|---|-----|

| P            | reface .  |                                      |           | •     | •   |     |     |      |     |     |   | • | • |   |   | xii |

| Introduction |           |                                      |           |       |     |     |     |      |     |     |   |   | • |   |   | 1   |

| 1.           | The Lar   | nguage of Co                         | verage    |       | •   |     | •   |      |     |     |   | • |   |   | ٠ | 5   |

| 2.           |           | nal Verificatio                      |           |       |     |     |     |      |     |     |   |   |   |   |   | 15  |

|              | 2.1. Des  | sign Intent Dia                      | agram     |       |     |     |     |      |     |     |   |   |   |   |   | 16  |

|              | 2.2. Fun  | nctional Verific                     | cation    |       |     |     |     |      |     |     |   |   |   |   |   | 17  |

|              | 2.3. Tes  | sting versus Venctional Verification | erificati | on    |     |     |     |      |     |     |   |   |   |   |   | 19  |

|              | 2.4. Fur  | nctional Verifi                      | cation l  | Proc  | ess |     |     |      |     |     |   |   |   |   |   | 19  |

|              | 2.4.1.    |                                      |           |       |     |     |     |      |     |     |   |   |   |   |   | 20  |

|              | 2.4.2.    |                                      |           |       |     |     |     |      |     |     |   |   |   |   |   | 26  |

|              | 2.4.3.    |                                      | g-up .    | •     | •   |     | •   | •    |     | •   |   | • | • | • |   | 27  |

|              | 2.4.4.    | Device Regi                          |           |       |     |     |     |      |     |     |   |   |   |   |   | 28  |

|              | 2.5. Sur  | nmary                                |           | •     | •   | •   | •   | •    | •   | •   | • | ٠ | • | • | • | 30  |

| 3.           | Measuri   | ng Verificatio                       | on Cov    | era   | ge  |     |     |      |     |     |   |   |   |   |   | 31  |

|              | 3.1. Cov  | verage Metrics                       |           |       |     |     |     |      |     |     |   |   |   |   |   | 31  |

|              | 3.1.1.    | Implicit Met                         | rics .    |       |     |     |     |      |     |     |   |   |   |   |   | 32  |

|              | 3.1.2.    | Explicit Met                         | rics .    |       |     |     |     |      |     |     |   |   |   |   |   | 33  |

|              | 3.1.3.    | Specification                        | n Metri   | cs    |     |     |     |      |     |     |   |   |   |   |   | 33  |

|              | 3.1.4.    | Implementat                          | ion Me    | etric | S   |     |     |      |     |     |   |   |   |   |   | 34  |

|              | 3.2. Cov  | verage Spaces                        |           |       |     |     |     |      |     |     |   |   |   |   |   | 34  |

|              | 3.2.1.    | Implicit Imp                         |           |       |     |     |     |      |     |     |   |   |   |   |   | 35  |

|              | 3.2.2.    | Implicit Spe                         | cificati  | on (  | Cov | era | ge  | Spa  | ace |     |   |   |   |   |   | 35  |

|              | 3.2.3.    | Explicit Imp                         | lement    | atio  | n C | ov  | era | ge ( | Spa | ice |   |   |   |   |   | 36  |

|              | 3.2.4.    | Explicit Spe                         | cificati  | on (  | Cov | era | ge  | Spa  | ace |     |   |   |   |   |   | 37  |

|              | 3.3. Sun  | nmary                                |           | •     | •   |     | •   | •    | •   |     | • | • | • | • | • | 38  |

| 4.           | Function  | nal Coverage                         |           |       |     |     |     |      |     |     |   |   |   |   | • | 39  |

|              | 4.1. Cov  | verage Modeli                        | ng .      |       |     |     |     |      |     |     |   |   |   |   |   | 39  |

|              | 4.2. Cov  | verage Model                         | Examp     | le    |     |     |     |      |     |     |   |   |   |   |   | 40  |

|              |           | -Level Design                        |           |       |     |     |     |      |     |     |   |   |   |   |   | 44  |

|           | 4.3.1   | Attribute Identification                |   |   |   |   |   | 45  |

|-----------|---------|-----------------------------------------|---|---|---|---|---|-----|

|           | 4.3.2   | Attribute Relationships                 |   |   |   |   |   | 50  |

|           | 4.4. D  | etailed Design                          |   |   |   |   |   | 61  |

|           | 4.4.1   | What to Sample                          |   |   |   |   |   | 62  |

|           | 4.4.2   | Where to Sample                         |   |   |   |   |   | 65  |

|           |         | When to Sample and Correlate Attributes |   |   |   |   |   | 66  |

|           | 4.5. N  | Iodel Implementation                    |   |   |   |   |   | 67  |

|           | 4.6. R  | elated Functional Coverage              |   |   |   |   |   | 75  |

|           | 4.6.1   |                                         |   |   |   |   |   | 75  |

|           | 4.6.2   | Temporal Coverage                       |   |   |   |   |   | 76  |

|           | 4.6.3   | Static Verification Coverage            |   |   |   |   |   | 77  |

|           | 4.7. S  | ummary                                  |   |   |   |   |   | 78  |

|           |         |                                         |   |   |   |   |   |     |

| <b>5.</b> | Code    | Coverage                                |   |   |   |   |   | 79  |

|           | 5.1. In | stance and Module Coverage              | • |   |   | • | • | 79  |

|           | 5.2. C  | ode Coverage Metrics                    | • | ٠ | • | ٠ | ٠ | 80  |

|           | 5.2.1.  |                                         |   |   |   |   |   | 80  |

|           | 5.2.2.  | $\mathcal{C}$                           |   |   |   |   |   | 81  |

|           | 5.2.3.  |                                         |   |   |   |   |   | 82  |

|           |         | Condition Coverage                      |   |   |   |   |   | 84  |

|           |         | Event Coverage                          |   |   |   |   |   | 84  |

|           | 5.2.6.  |                                         |   |   |   |   |   | 85  |

|           | 5.2.7.  |                                         |   |   |   |   |   | 85  |

|           | 5.2.8.  | $\mathcal{C}$                           |   |   |   |   |   | 88  |

|           |         | se Model                                |   |   |   |   |   | 89  |

|           | 5.3.1   |                                         |   |   |   |   |   | 89  |

|           | 5.3.2   | Record Metrics                          | • |   | • |   |   | 90  |

|           | 5.3.3   |                                         |   |   |   |   |   | 90  |

|           | 5.4. S  | ammary                                  | • | • | • | • | • | 95  |

| 6.        | Assert  | ion Coverage                            |   |   |   |   |   | 97  |

| ••        | 6.1. W  | That Are Assertions?                    | • | • |   | • | · | 97  |

|           | 6.2. N  | leasuring Assertion Coverage            |   |   |   |   |   | 102 |

|           | 6.3. O  | pen Verification Library Coverage       |   |   |   |   |   | 103 |

|           | 6.4. S  | atic Assertion Coverage                 |   |   |   |   |   | 104 |

|           | 6.5. A  | nalyzing Assertion Coverage             |   |   |   |   |   | 104 |

|           |         | Checker Assertions                      |   |   |   |   |   | 105 |

|           |         | Coverage Assertions                     |   |   |   |   |   | 106 |

|           |         | ımmary                                  |   |   |   |   |   |     |

| 7.  | Cov    | erage-Driven Verific               |            |     |      |      |      |    |    |    |   |   |   |   | 109 |

|-----|--------|------------------------------------|------------|-----|------|------|------|----|----|----|---|---|---|---|-----|

|     | 7.1.   | Objections to Covera               | age-Driv   | en  | Vei  | ific | cati | on |    |    |   |   |   |   | 110 |

|     | 7.2.   | Stimulus Generation                |            |     |      |      |      |    |    |    |   |   |   |   | 112 |

|     | 7.2    | 1. Generation Con                  | nstraints  |     |      |      |      |    |    |    |   |   |   |   | 113 |

|     | –      | <ol><li>Coverage-Direct</li></ol>  |            |     |      |      |      |    |    |    |   |   |   |   | 115 |

|     | 7.3.   | Response Checking                  |            |     |      |      |      |    |    |    |   |   |   |   | 120 |

|     | 7.4.   | Coverage Measurem                  | ent .      |     |      |      |      |    |    |    |   |   |   |   | 122 |

|     | 7.4    | <ol> <li>Functional Cov</li> </ol> | erage      |     |      |      |      |    |    |    |   |   |   |   | 123 |

|     | 7.4    | <ol><li>Code Coverage</li></ol>    |            |     |      |      | •    |    |    |    |   |   |   |   | 124 |

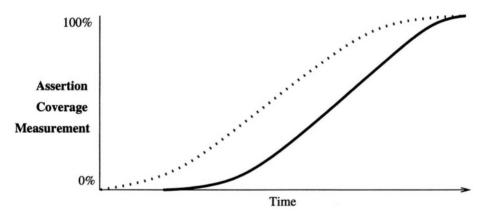

|     |        | 3. Assertion Cove                  |            |     |      |      |      |    |    |    |   |   |   |   | 126 |

|     | 7.4    | 4. Maximizing Ve                   | rification | n E | ffic | ien  | сy   |    |    |    |   |   |   |   | 127 |

|     | 7.5.   | Coverage Analysis .                |            |     |      |      |      |    |    |    |   |   |   |   | 129 |

|     |        | 1. Generation Fee                  | dback      |     |      |      |      |    |    |    |   |   |   |   | 129 |

|     | 7.5    | <ol><li>Coverage Mode</li></ol>    | el Feedb   | ack |      |      |      |    |    |    |   |   |   |   | 130 |

|     | 7.5    | 3. Hole Analysis                   |            |     |      |      |      |    |    |    |   |   |   |   | 131 |

|     | 7.6.   | Summary                            |            |     | •    |      |      | •  | •  | •  |   | • | • | • | 136 |

| Q   | Imn    | oving Coverage Fid                 | elity W    | ith | н    | hr   | id I | Mα | de | le |   |   |   |   | 139 |

| 0.  | 8.1.   | Sample Hybrid Cove                 |            |     |      |      |      |    |    |    |   |   |   |   | 140 |

|     | 8.2.   | Coverage Overlap .                 |            |     |      |      |      |    |    |    |   |   |   |   | 147 |

|     | 8.3.   | Static Verification C              |            |     |      |      |      |    |    |    |   |   |   |   | 149 |

|     | 8.4.   | Summary                            |            |     |      |      |      |    |    |    |   |   |   |   | 150 |

|     | 0.4.   | Summary                            | • •        | •   | •    | •    | •    | •  | •  | •  | • | • | • | • | 130 |

| Aŗ  | pendix | A: e Language BNI                  | ₹          |     | •    |      |      |    |    |    | • |   |   |   | 151 |

| Inc | dex .  |                                    |            |     |      |      |      |    |    |    |   |   |   |   | 193 |

# **Foreword**

As the complexity of today's ASIC and SoC designs continues to increase, the challenge of verifying these designs intensifies at an even greater rate. Advances in this discipline have resulted in many sophisticated tools and approaches that aid engineers in verifying complex designs. However, the age-old question of *when is the verification job done*, remains one of the most difficult questions to answer. And, the process of measuring verification progress is poorly understood.

For example, consider automatic random stimulus generators, model-based test generators, or even general-purpose constraint solvers used by high-level verification languages (such as *e*). At issue is knowing which portions of a design are repeatedly exercised from the generated stimulus — and which portions of the design are not touched at all. Or, more fundamentally, exactly what functionality has been exercised using these techniques. Historically, answering these questions (particularly for automatically generated stimulus) has been problematic. This challenge has led to the development of various coverage metrics to aid in measuring progress, ranging from *code coverage* (used to identify unexercised lines of code) to contemporary *functional coverage* (used to identify unexercised functionality). Yet, even with the development of various forms of coverage and new tools that support coverage measurement, the use of these metrics within the verification flow tends to be ad-hoc, which is predominately due to the lack of well-defined, coverage-driven verification methodologies.

Prior to introducing a coverage-driven verification methodology, *Functional Verification Coverage Measurement and Analysis* establishes a sound foundation for its readers by reviewing an excellent and comprehensive list of terms that is common to the language of coverage. Building on this knowledge, the author details various forms of measuring progress that have historically been applicable to a traditional verification flow, as well as new forms applicable to a contemporary verification flow.

Functional Verification Coverage Measurement and Analysis is the first book to introduce a useful taxonomy for coverage metric classification. Using this taxonomy, the reader clearly understands the process of creating an effective coverage model. Ultimately, this book presents a coverage-driven verification methodology that integrates multiple forms of coverage and strategies to help answer the question when is the verification job done.

Andrew Piziali has created a wonderfully comprehensive textbook on the language, principles, and methods pertaining to the important area of *Functional Verification Coverage Measurement and Analysis*. This book should be a key reference in every engineer's library.

Harry Foster Chief Methodologist Jasper Design Automation, Inc. Andy and I disagree on many fronts: on the role of governments, on which verification language is best, on gun control, on who to work for, on the best place to live and on the value of tightly integrated tools. But, we wholeheartedly agree on the value of coverage and the use of coverage as a primary director of a functional verification process.

Yesterday, I was staring at a map of the Tokyo train and subway system. It was filled with unfamiliar symbols and names — yet eerily similar to maps of other subway systems I am more familiar with. Without a list of places I wished to see, I could wander for days throughout the city, never sure that I was visiting the most interesting sites and unable to appreciate the significance of the sites that I was haphazardly visiting. I was thus armed with a guide book and recommendations from past visitors. By constantly checking the names of the stations against the stations on my intended route, I made sure I was always traveling in the correct direction, using the shortest path. I was able to make the most of my short stay.

Your next verification project is similar: it feels familiar — yet it is filled with new features and strange interactions. A verification plan is necessary to identify those features and interactions that are the most important. The next step, using coverage to measure your progress toward that plan, is just as crucial. Without it, you may be spending your effort in redundant activities. You may also not realize that a feature or interaction you thought was verified was, in fact, left completely unexercised. A verification plan and coverage metrics are essential tools in ensuring that you make the most of your verification resources.

This book helps transform the art of verification planning and coverage measurement into a process. I am sure it will become an important part of the canons of functional verification.

Janick Bergeron Scientist Synopsys Tokyo, April 2004

# **Preface**

Functional verification is consuming an ever increasing share of the effort required to design digital logic devices. At the same time, the cost of bug escapes<sup>1</sup> and crippled feature sets is also rising as missed market windows and escalating mask set costs take their toll. Bug escapes have a number of causes but one of the most common is uncertainty in knowing when verification is complete. This book addresses that problem.

There are several good books<sup>2</sup> on the subject of functional verification.<sup>4</sup> However, the specific topic of measuring verification progress and determining when verification is done remains poorly understood. The purpose of this book is to illuminate this subject. The book is organized as follows.

The introduction chapter is an overview of the general verification problem and the methods employed to solve it.

Chapter 1," The Language of Design Verification," defines the terminology I use throughout the book, highlighting the nuances of similar terms.

Chapter 2, "Functional Verification," defines functional verification, distinguishes it from test and elaborates the functional verification process.

Chapter 3, "Measuring Verification Coverage," introduces the basics of coverage measurement and analysis: coverage metrics and coverage spaces.

<sup>&</sup>lt;sup>1</sup> Logic design bugs undetected in pre-silicon verification.

<sup>&</sup>lt;sup>2</sup> Writing Testbenches, Second Edition, Janick Bergeron, Kluwer Academic Publishers, 2003

<sup>&</sup>lt;sup>3</sup> Assertion-Based Design, Harry D. Foster, Adam C. Krolnik, David J. Lacey, Kluwer Academic Publishers, 2003

<sup>&</sup>lt;sup>4</sup> "Design verification" and "functional verification" are used interchangeably throughout this book.

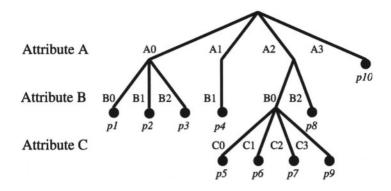

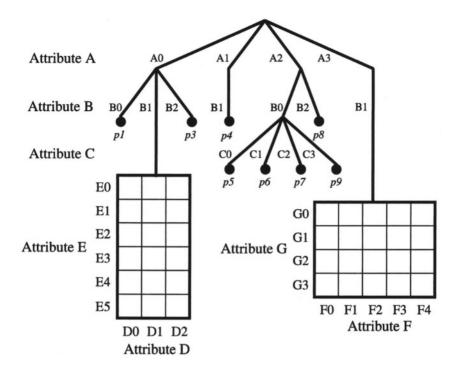

Chapter 4, "Functional Coverage," delves into coverage derived from specifications and the steps required to model the design intent derived from the specifications. Two specific kinds of functional coverage are also investigated: temporal coverage and finite state machine (FSM) coverage.

Chapter 5, "Code Coverage," explains coverage derived from the device implementation, the RTL. It addresses the various structural and syntactic RTL metrics and how to interpret reported data.

Chapter 6, "Assertion Coverage," first answers the question of "Why would I want to measure coverage of assertions?" and then goes on to describe how to do so.

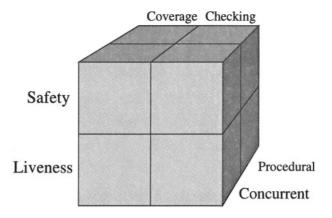

Chapter 7, "Coverage-Driven Verification," integrates all of the previous chapters to present a methodology for minimizing verification risk and maximizing the rate at which design bugs are exposed. In this chapter, I explain stimulus generation, response checking and coverage measurement using an autonomous verification environment. The interpretation and analysis of coverage measurements and strategies for reaching functional closure — i.e. 100% coverage — are explained.

Chapter 8, "Improving Coverage Fidelity with Hybrid Models," introduces the concept of coverage model fidelity and the role it plays in the coverage process. It suggests a means of improving coverage fidelity by integrating coverage measurements from functional, code and assertion coverage into a heterogeneous coverage model.

#### The Audience

There are two audiences to which this book addressed. The first is the student of electrical engineering, majoring in digital logic design and verification. The second is the practicing design verification — or hardware design — engineer.

When I was a student in electrical engineering (1979), no courses in design verification were offered. There were two reasons for this. The first was that academia was generally unaware of the magnitude of the verification challenge faced by logic designers of the most complex designs: mainframes and supercomputers. Second, no textbooks were available on the subject. Both of these reasons have now been dispensed with so this book may be used in an advanced design verification course.

The practicing design verification and design engineer will find this book useful for becoming familiar with coverage measurement and analysis.

It will also serve as a reference for those developing and deploying coverage models.

#### **Prerequisites**

The reader is expected to have a basic understanding of digital logic design, logic simulation and computer programming.

#### Acknowledgements

I want to thank my wife Debbie and son Vincent for the solitude they offered me from our limited family time. My technical reviewers Mark Strickland, Shmuel Ur, Mike Kantrowitz, Cristian Amitroaie, Mike Pedneau, Frank Armbruster, Marshall Martin, Avi Ziv Harry Foster, Janick Bergeron, Shlomi Uziel, Yoav Hollander, Ziv Binyamini and Jon Shiell provided invaluable guidance and feedback from a variety of perspectives I lack. Larry Lapides kept my pride in writing ability in check with grammar and editing corrections. My mentors Tom Kenville and Vern Johnson pointed me in the direction of "diagnostics development," later known as design verification. The Unix text processing tool suite groff and its siblings — the -ms macros, gtbl, geqn and gpic — allowed me to write this book using my familiar Vim text editor and decouple typesetting from the composition process, as it should be. Lastly, one of the most fertile environments for innovation, in which my first concepts of coverage measurement were conceived, was enriched by Convex Computer colleagues Russ Donnan and Adam Krolnik.

"Preface" xv

## Introduction

What is functional verification? I introduce a formal definition for functional verification in the next chapter, "The Language of Design Verification," and explore it in depth in chapter 2, "Functional Verification." For now, let's just consider it the means by which we discover functional logic errors in a representation of the design, whether it be a behavioral model, a register transfer level (RTL) model, a gate level model or a switch level model. I am going to refer to any such representation as "the device" or "the device-under-verification" (DUV). Functional verification is not timing verification or any other back-end validation process.

Logic errors (bugs) are discrepancies between the intended behavior of the device and its observed behavior. These errors are introduced by the designer because of an ambiguous specification, misinterpretation of the specification or a typographical error during model coding. The errors vary in abstraction level depending upon the cause of the error and the model level in which they were introduced. For example, an error caused by a specification misinterpretation and introduced into a behavioral model may be algorithmic in nature while an error caused by a typo in the RTL may topological. How do we expose the variety of bugs in the design? By verifying it! The device may be verified using static, dynamic or hybrid methods. Each class is described in the following sections.

#### Static Methods

The static verification methods are model checking, theorem proving and equivalence checking.

Model checking demonstrates that user-defined properties are never violated for all possible sequences of inputs.

Theorem proving demonstrates that a theorem is proved — or cannot be proved — with the assistance of a proof engine.

Equivalence checking, as its name implies, compares two models against one another to determine whether or not they are logically equivalent. The models are not necessarily at the same abstraction level: one may be RTL while the other is gate level. Logical equivalence means two circuits implement the same Boolean logic function, ignoring latches and registers.

There are two kinds of equivalence checking: combinational and sequential. Combinational equivalence checking uses a priori structural information found between latches. Sequential equivalence checking detects and uses structural similarities during state exploration in order to determine logical equivalence across latch boundaries.

Lastly, I should mention that Boolean satisfiability (SAT) solvers are being employed more frequently for model checking, theorem proving and equivalence checking. These solvers find solutions to Boolean formulae used in these static verification techniques.

#### **Dynamic Methods**

A dynamic verification method is characterized by simulating the device in order to stimulate it, comparing its response to the applied stimuli against an expected response and recording coverage metrics. By "simulating the device," I mean that an executable software model — written in a hardware description language — is executed along with a verification environment. The verification environment presents to the device an abstraction of its operational environment, although it usually exaggerates stimuli parameters in order to stress the device. The verification environment also records verification progress using a variety of coverage measurements discussed in this book.

### **Static versus Dynamic Trade-offs**

The trade-off between static and dynamic method is between capacity and completeness. All static verification methods are hampered by capacity constraints that limit their application to small functional blocks of a device At the same time, static methods yield a complete, comprehensive verification of the proven property. Together, this leads to the application of static methods to small, complex logic units such as arbiters and bus controllers.

<sup>&</sup>lt;sup>1</sup> C.A.J. van Eijk, "Sequential Equivalence Checking Based on Structural Similarities," IEEE Trans. CAD of ICS, July 2000.

Dynamic methods, on the other hand, suffer essentially no capacity limitations. The simulation rate may slow dramatically running a full model of the device, but it will not fail. However, dynamic methods cannot yield a complete verification solution because they do not perform a proof.

There are many functional requirements whose search spaces are beyond the ability to simulate in a lifetime. This is because exhaustively exercising even a modest size a device may require an exorbitant number of simulation vectors. If a device has N inputs and M flip-flops,  $(2^N)^M$  stimulus vectors may be required<sup>2</sup> to fully exercise it. A modest size device may have 10 inputs and 100 flip-flops (just over three 32-bit registers). This device would require  $(2^{10})^{100}$ , or  $2^{1,000}$  vectors to fully exercise. If we were to simulate this device at 1,000 vectors per second, it would take 339,540,588,380, 062,907,492,466,172,668,391,072,376,037,725,725,208,993,588,689,808, 600, 264, 389, 893, 757, 743, 339, 953, 988, 988, 382, 771, 724, 040, 525, 133, 303,203,524,078,771,892,395,266,266,335,942,544,299,458,056,845,215,567. 848,460,205,301,551,551,163,124,606,262,994,092,425,972,759,467,835, 103,001,336,336,717,048,865,167,147,297,613,428,902,897,465,679,093, 821,821, 978, 784, 398, 755, 534, 655, 038, 141, 450, 059, 156, 501 years<sup>3</sup> to exhaustively exercise. Functional requirements that must be exhaustively verified should be proved through formal methods.

#### **Hybrid Methods**

Hybrid methods, also known as semi-formal methods, combine static and dynamic techniques in order to overcome the capacity constraints imposed by static methods alone while addressing the inherent completeness limitations of dynamic methods. This is illustrated with two examples.

Suppose we postulate a rare, cycle distant<sup>4</sup> device state to be explored by simulating forward from that state. The validity of this device state may be proven using a bounded model checker. The full set of device properties may be proven for this state. If a property is violated, the model checker will provide a counter example from which we may deduce a corrective

<sup>&</sup>lt;sup>2</sup> I say "may be required" because it depends upon the complexity of the device. If the device simply latches its N inputs into  $\frac{M}{N}$ -deep FIFOs, it would only require  $\frac{M}{N}$  vectors to exhaustively exercise.

<sup>&</sup>lt;sup>3</sup> Approximately  $3.4 \times 10^{308}$  years.

<sup>&</sup>lt;sup>4</sup> "Distant" in the sense that it is many, many cycles from the reset state of the device, perhaps too many cycles to reach in practice.

modification to the state. Once the state is fully specified, the device may be placed in the state using the simulator's broadside load capability. Simulation may then *start* from this point, as if we had simulated to it from reset.

The reverse application of static and dynamic methods may also be employed. Perhaps we discovered an unforeseen or rare device state while running an interactive simulation and we are concerned that a device requirement, captured as a property, may be violated. At the simulation cycle of interest, the state of the device and its inputs are captured and specified as the initial search state to a model checker. The model checker is then directed to prove the property of concern. If the property is violated, any simulation sequence that reached this state is a counter-example.

#### **Summary**

4

In this introduction, I surveyed the most common means of functionally verifying a design: static methods, dynamic methods and hybrid methods. In the next chapter, The Language of Coverage, I methodically define the terminology used throughout the remainder of the book.

# 1. The Language of Coverage

Stripped of all of its details, design verification is a communication problem. Ambiguities lead to misinterpretations which lead to design errors. In order to clearly convey the subject of coverage measurement and analysis to you, the reader, we must communicate using a common language. In this chapter, I define the terminology used throughout the rest of the book. It should be referenced whenever an unfamiliar word or phrase is encountered.

You will find references to the high-level verification language e in this glossary. I use e to illustrate the implementation of coverage models in this book. The e language syntax may be referenced in appendix A. You may find the complete language definition in the "e Language Reference Manual," available at the IEEE 1647 web site, http://www.ieee1647.org/.

assertion An expression stating a safety (invariant) or

liveness (eventuality) property.

passed or failed. Assertion coverage is the sub-

ject of chapter 6.

assertion coverage

density

The number of assertions evaluated per

simulation cycle.

attribute In the context of the device, a parameter or

characteristic of an input or output on an interface. In the context of a coverage model, a parameter or dimension of the model. Attributes and their application is discussed in chapter 4,

"Functional Coverage."

branch coverage A record of executed, alternate control flow

paths, such as those through an if-then-else statement or case statement. Branch coverage is

the subject of section 5.2.3.

checker coverage The fraction of verification environment

checkers executed and passed or failed.

code coverage A set of metrics at the behavioral or RTL

abstraction level which define the extent to which the design has been exercised. Code

coverage is the subject of chapter 5.

code coverage density

The number of code coverage metrics executed

or evaluated per simulation cycle. A metric may be a line, statement, branch, condition, event, bit

toggle, FSM state visited or FSM arc traversed.

condition coverage A record of Boolean expressions and

subexpressions executed, usually in the RTL. Also known as *expression coverage*. Condition

coverage is discussed in section 5.2.4.

coverage A measure of verification completeness.

coverage analysis The process of reviewing and analyzing

coverage measurements. Coverage analysis is

discussed in section 7.5.

coverage closure Reaching a defined coverage goal.

coverage database A repository of recorded coverage observations.

For code coverage, counts of observed metrics such as statements and expressions may be recorded. For functional coverage, counts of

observed coverage points are recorded.

simulation cycle. See also functional coverage density, code coverage density and assertion

coverage density.

coverage goal That fraction of the aggregate coverage which

must be achieved for a specified design stage, such as unit level integration, cluster integration

and functional design freeze.

coverage group A related set of attributes, grouped together for

implementation purposes at a common correlation time. In the context of the e language, a struct member defining a set of items

for which data is recorded.

coverage item The implementation level parallel to an attribute.

In the context of the e language, a coverage

group member defining an attribute.

coverage measurement The process of recording points within a

coverage space.

recorded, which defines a dimension of a coverage space. The role of coverage metrics is the subject of chapter 3, "Measuring Verification

Coverage."

> composed of attributes and their relationships. Coverage model design is discussed in chapter 4,

"Functional Coverage."

coverage point A point within a multi-dimensional coverage

model, defined by the values of its attributes.

coverage report

A summary of the state of verification progress — as measured by coverage — capturing all facets of coverage at multiple abstraction levels.

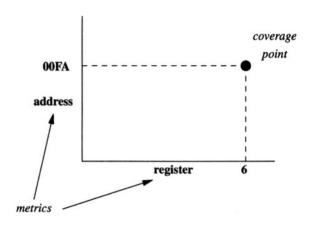

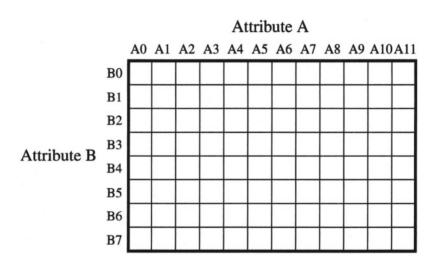

coverage space

A multi-dimension region defined by the attributes of the coverage space and their values. Usually synonymous with "coverage model." The following diagram illustrates a coverage space.

The coverage space is discussed in section 3.2.

cross coverage

A coverage model whose space is defined by the full permutation of all values of all attributes. More precisely known as multi-dimensional matrix coverage. Cross coverage is discussed in section 4.3.2, "Attribute Relationships."

data coverage

Coverage measurements in the data domain of the device behavior.

device

Device to be verified. Sometimes referred to as the device-under-verification (DUV).

DUT

Acronym for "device under test;" i.e. the device to be tested. This is distinguished from DUV (device under verification) in that a DUV is verified while a DUT is tested.

DUV

Acronym for "device under verification;" i.e. the device to be verified. This is distinguished from DUT (device under test) in that a DUT is tested while a DUV is verified.

e

A high-level verification language (HLVL) invented by Yoav Hollander and promoted by Verisity Design. The BNF of the *e* language is in appendix A. The "*e* Language Reference Manual" may be referenced from http://www.ieee1647.org/.

event

Something which defines a moment in time such as a statement executing or a value changing. In the context of the *e* language, a struct member defining a moment in time. An *e* event is either explicitly *emitted* using the *emit* action or implicitly *emitted* when its associated temporal expression succeeds.

explicit coverage

Coverage whose attributes are explicitly chosen by the engineer rather than being a characteristic of the measurement interface.

expression coverage

A record of Boolean expressions and subexpressions executed, usually in the RTL. Also known as *condition coverage*. Expression coverage is discussed in section 5.2.4, "Condition Coverage."

fill

To fill a coverage space means to reach the coverage goal of each point within that space.

Coverage whose metrics are derived from a functional coverage

functional or design specification. Functional

coverage is the subject of chapter 4.

functional coverage

density

The number of functional coverage points traversed per simulation cycle. Coverage density is discussed in section 7.4.4.

"Maximizing Verification Efficiency."

For a single coverage model, the fraction of the grade

coverage space it defines which has been observed. Regions of the coverage space or individual points may be unequally weighted. For a set of coverage models, a weighted

average of the grade of each model.

Observing a defined coverage point during a hit

simulation

HLVI. High-level verification language.

> programming language endowed with semantics specific to design verification such as data generation, temporal evaluation and coverage

measurement

hole A defined coverage point which has not yet been

observed in a simulation or a set of such points

sharing a common attribute or semantic.

Coverage whose attributes are implied by implicit coverage

characteristics of the measurement interface

rather than explicitly chosen by the engineer.

Coverage measured at the primary inputs of a input coverage

device.

internal coverage Coverage measured on an internal interface of a

device

line coverage The fraction of RTL source lines executed by one

or more simulations. Line coverage is discussed

in section 5.2.1, "Line Coverage."

merge coverage To coalesce the coverage databases from a

number of simulations.

model An abstraction or approximation of a logic

design or its behavior.

output coverage Coverage measured at the primary outputs of a

device.

during one or more simulations. Path coverage is discussed in section 5.2.3, "Branch Coverage."

sample To record the value of an attribute.

sampling event A point in time at which the value of an attribute

is sampled. Sampling time is discussed in

section 4.3.1, "Attribute Identification."

sequential coverage A composition of data and temporal coverage

wherein specific data patterns applied in specific

sequences are recorded.

statement coverage The fraction of all language statements —

behavioral, RTL or verification environment — executed during one or more simulations. See section 5.2.2 for an example of statement

coverage.

temporal Related to the time domain behavior of a device

or its verification environment.

temporal coverage

Measurements in the time domain of the behavior of the device

test

The verb "test" means executing a series of trials on the device to determine whether or not its behavior conforms with its specifications. The noun "test" refers to either a trial on the device or to the stimulus applied during a specific trial. If referring to stimulus, it may also perform response checking against expected results.

toggle coverage

A coverage model in which the change in value of a binary attribute is recorded. Toggle coverage is discussed in section 5.2.6.

verification

The process of demonstrating the intent of a design is preserved in its implementation.

verification interface

An abstraction level at which a verification process is performed. If dynamic verification (simulation) is used, this is a common interface at which stimuli are applied, behavioral response is checked and coverage is measured.

verify

Demonstrate the intent of a design is preserved in its implementation.

weight

A scaling factor applied to an attribute when calculating cumulative coverage of a single coverage model or applied to a coverage model when totaling cumulative coverage of all coverage models.

weighted average

The sum of the products of fractional coverage times weight, divided by the sum of their weights.

I.e. weighted average =

$$\frac{\sum_{i=1}^{N} coverage_i * weight_i}{\sum_{i=1}^{N} weight_i},$$

where  $coverage_i$  is a particular coverage measurement,  $weight_i$  is the weight of the measurement and N is the number of coverage models.

## 2. Functional Verification

In this chapter, I define functional verification, distinguish verification from testing and outline the functional verification process.

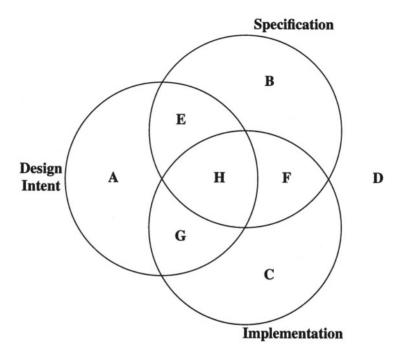

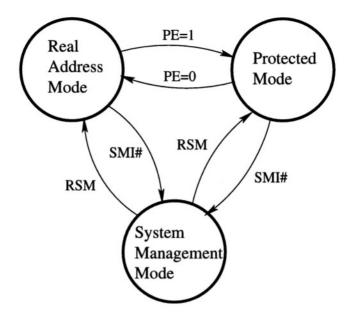

What is functional verification? A definition which has served me well for many years is the following: *Functional verification is demonstrating the intent of a design is preserved in its implementation.* In order to thoroughly understand functional verification, we need to understand this definition. The following diagram<sup>1</sup> is useful for explaining the definition.

<sup>&</sup>lt;sup>1</sup>Tony Wilcox, personal whiteboard discussion, 2001.

# 2.1. Design Intent Diagram

Figure 2-1 Design Intent Diagram

The diagram is composed of three overlapping circles, labeled "Design Intent," "Specification" and "Implementation." All areas in the diagram represent device behavior. The space defined by the union of all of the regions (A through G) represents the potential behavioral space of a device. The region outside the three circles, D, represents unintended, unspecified and unimplemented behavior. The first circle, "Design Intent" ( $A \cup E \cup G \cup H$ ), represents the intended behavior of the device, as conceived in the mind's eye(s) of the designer(s). The second circle, "Specification" ( $B \cup E \cup F \cup H$ ), bounds the intent captured by the device functional specification. The third circle, "Implementation" ( $C \cup F \cup G \cup H$ ), captures the design intent implemented in the RTL.

<sup>&</sup>lt;sup>2</sup> The conventional set operators are used.  $\cup$  for set union,  $\cap$  for set intersection,  $\subseteq$  for subset,  $\subset$  for proper subset and – for set exclusion.

If the three circles were coincident, i.e. region H defined all three circles, all intended device behavior would be specified and captured in the device implementation, but no more. However, in reality, this is rarely the case. Let's examine the remaining regions to understand why this is so.

Region E is design intent captured in the specification but absent from the implementation. Region F is unintended behavior which is nonetheless specified and implemented (!). Region G is implemented, intended behavior which was not captured in the specification.

Region **EH** ( $\mathbf{E} \cup \mathbf{H}$ ) represents design intent successfully captured by the specification but only partially implemented. The remaining part of the specification space, **BF** ( $\mathbf{B} \cup \mathbf{F}$ ), is unintended yet specified behavior. This is usually results from gratuitous embellishment or feature creep.

Region **FH** ( $F \cup H$ ) represents specified behavior successfully captured in the implementation. The remaining part of the implementation space, **CG** ( $C \cup G$ ), is unspecified yet implemented behavior. This could also be due to gratuitous embellishment or feature creep. Region **GH** ( $G \cup H$ ) represents intended and implemented behavior.

There are four remaining regions to examine. The first,  $AE (A \cup E)$ , is unimplemented yet intended behavior. The second,  $AG (A \cup G)$ , is unspecified yet intended behavior. The third,  $BE (B \cup E)$ , is specified yet unimplemented behavior. The fourth,  $CF (C \cup F)$ , is unintended yet implemented behavior.

The objective of functional verification is to bring the device behavior represented by each of the three circles — design intent, specification and implementation — into coincidence. To do so, we need to understand the meaning of design intent, where it comes from and how it is transformed in the context of functional verification.

# 2.2. Functional Verification

A digital logic design begins in the mind's eye of the system architect(s). This is the original intent of the design, its intended behavior. From the mind, it goes through many iterations of stepwise refinement until the layout file is ready for delivery to the foundry. Functional verification is an application of information theory, supplying the redundancy and error-correcting codes required to preserve information integrity through the design cycle. The redundancy is captured in natural (human) language

specifications.

However, there are two problems with this explanation. First of all, this "original intent" is incomplete and its genesis is at a high abstraction level. The concept for a product usually begins with a marketing requirements document delivered to engineering. An engineering system architect invents a product solution for these requirements, refining the abstract requirements document into a functional specification. The design team derives a design specification from the functional specification as they specify a particular microarchitectural implementation of the functionality.

The second problem with the explanation is that, unlike traditional applications of information theory, where the message should be preserved as it is transmitted through the communication channel, it is intentionally refined and becomes less abstract with each transformation through the design process. Another way to look at the design process is that the message is incrementally refined, clarified and injected into the communication channel at each stage of design. Next, let's distinguish implementation from intent

In this context, the implementation is the RTL (Verilog, SystemVerilog or VHDL) realization of the design. It differs from intent in that it is not written in a natural language but in a rigorous machine readable language. This removes both ambiguity and redundancy, allowing a logic compiler to translate the code into a gate description, usually preserving the semantics of the RTL. Finally, what is meant by "demonstrate" when we write "demonstrate the intent of a design is preserved in its implementation?"

Verification, by its very nature, is a comparative process. This was not apparent to a director of engineering I once worked for. When I insisted his design team update the design specification for the device my team was verifying, he replied: "Andy, the ISP is the specification!" (ISP was a late eighties hardware design language.) That makes one's job as a verification engineer quite easy, doesn't it? By definition, that design was correct as written because the intent — captured in an ISP "specification" — and implementation were claimed to be one and the same. The reality was the system architect and designers held the design intent in their minds but were unwilling to reveal it in an up-to-date specification for use by the verification team.

The intent of a design is demonstrated to have been preserved through static and dynamic methods. We are concerned with dynamic methods in this book, executing the device in simulation in order to observe and compare its behavior against expected behavior. Now, let's look at the difference

# 2.3. Testing versus Verification

Many engineers mistakenly use the terms "test" and "verification" interchangeably. However, testing is but one way to verify a design, and a less rigorous and quantitative approach at that. Why is that?

Writing for "Integrated System Design" in 2000, Gary Smith wrote: "The difference between 'test' and 'verification' is often overlooked ... You test the device ... to insure that the implementation works. ... Verification ... checks to see if the hardware or software meets the requirements of the original specification." There are subtle, but important, differences between the two.

Testing is the application of a series of tests to the DUT<sup>4</sup> to determine if its behavior, for each test, conforms with its specifications. It is a sampling process to assess whether or not the device works. A sampling process? Yes. It is a sampling process because not all aspects of the device are exercised. A subset of the totality of possible behaviors is put to the test.

A test also refers to the stimulus applied to the device for a particular simulation and may perform response checking against expected behavior. Usually, the only quantitative measure of progress when testing is the number of tests written and the number of tests passed although, in some instances, coverage may also be measured. Hence, it is difficult to answer the question "Have I explored the full design space?"

Verification encompasses a broad spectrum of approaches to discovering functional device flaws. In this book, we are concerned with those approaches which employ coverage to measure verification progress. Let us examine an effective verification process.

# 2.4. Functional Verification Process

The functional verification process begins with writing a verification plan, followed by implementing the verification environment, device bringup and device regression. Each of these steps is discussed in the following

<sup>&</sup>lt;sup>3</sup>Gary Smith, "The Dream," "Integrated System Design," December 2000

<sup>&</sup>lt;sup>4</sup>See definitions of test, verify, DUT and DUV in chapter 1, "The Language of Coverage."

#### 2.4.1. Functional Verification Plan

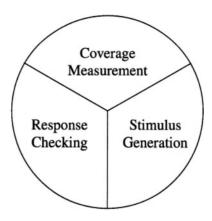

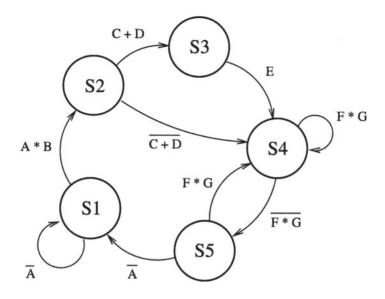

The verification plan defines what must be verified and how it will be verified. It describes the scope of the verification problem for the device and serves as the functional specification for the verification environment. Dynamic verification (i.e. simulation-based) is composed of three aspects, as illustrated below in figure 2-2.

Figure 2-2 Functional Verification Aspects

This leads to one of three orthogonal partitions of the verification plan: first, by verification aspect. The scope of the verification problem is defined by the coverage section of the verification plan. The stimulus generation section defines the machinery required to generate the stimuli required by the coverage section. The response checking section describes the mechanisms to be used to compare the response of the device to the expected, specified response.

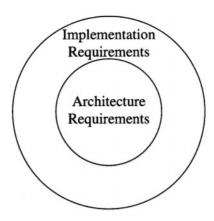

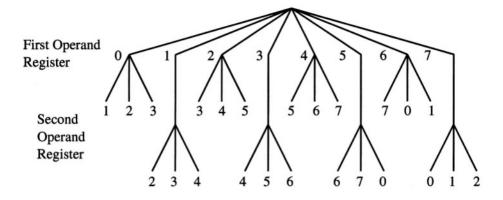

The second partitioning of the verification plan is between verification requirements derived from the device functional specification and those derived from its design specification. These are sometimes called architecture and implementation verification, as illustrated below in figure 2-3.

Figure 2-3 Functional Verification Requirements Sources

Architecture verification concerns itself with exposing device behaviors which deviate from its functional behavioral requirements. For example, if an add instruction is supposed to set the overflow flag when the addition results in a carry out in the sum, this is an architectural requirement. Implementation verification is responsible for detecting deviations from microarchitectural requirements specified by the design specification. An example of an implementation requirement is that a read-after-write register dependency in an instruction pair must cause the second instruction to read from the register bypass rather than the register file.

The third partitioning of the verification plan is between *what* must be verified and *how* it is to be verified. The former draws its requirements from the device functional and design specifications while the latter captures the top-level and detailed design of the verification environment itself. What must be verified is captured in the functional, code and assertion coverage requirements of the coverage measurement section of the verification plan. How the device is to be verified is captured in the top- and detailed-design section of each of the three aspects of the verification plan: coverage measurement, stimulus generation and response checking.

In the following three sections, we examine each of the verification

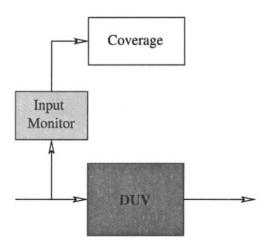

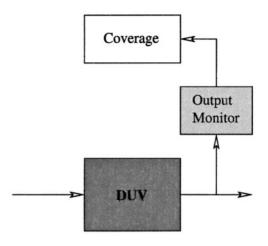

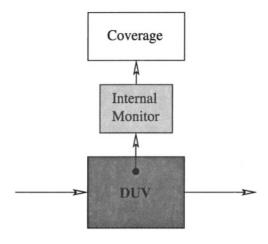

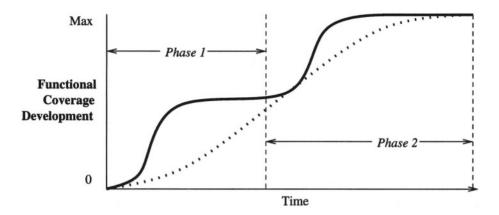

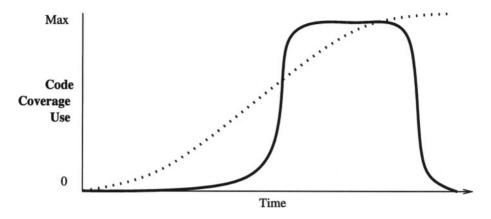

#### 2.4.1.1. Coverage Measurement

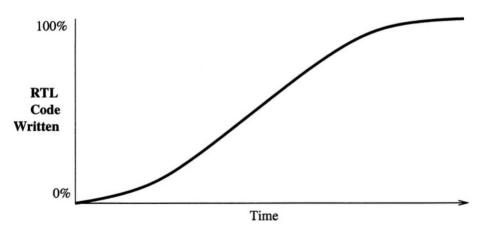

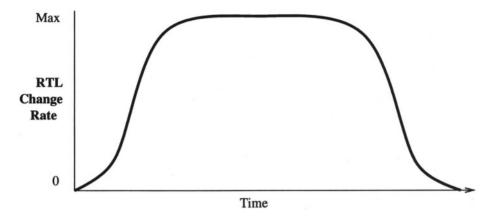

The coverage measurement section of the verification plan — sometimes referred to as the coverage plan — should describe the extent of the verification problem and how it is partitioned, as discussed above. It should delegate responsibility for measuring verification progress among the kinds of coverage and their compositions: functional, code, assertion and hybrid. <sup>5</sup> The functional coverage section of the coverage plan should include the top-level and detailed design of each of the coverage models. The code coverage section should specify metrics to be employed, coverage goals and gating events for deploying code coverage. For example, you should be nearing full functional coverage and have stable RTL before turning on code coverage measurement. The responsibility of assertion coverage in your verification flow should also be discussed.

Next, we need to consider how stimulus will be generated to achieve full coverage.

#### 2.4.1.2. Stimulus Generation

The stimulus required to fully exercise the device — that is, to cause it to exhibit all possible behaviors — is the responsibility of the stimulus generation aspect of the verification environment. Historically, a hand-written file of binary vectors, one vector (line) per cycle, served as simulation stimulus. In time, symbolic representations of vectors such as assembly language instructions were introduced, along with procedural calls to vector generation routines. Later, vector generators were developed, beginning with random test program generators (RTPG)<sup>6</sup> and evolving through model-based test generators (MBTG)<sup>7</sup> to the general purpose constraint solvers of current high-

<sup>&</sup>lt;sup>5</sup> These coverage techniques are described in chapters 4, 5 and 6: "Functional Coverage,", "Code Coverage" and "Assertion Coverage." The application of these coverage techniques is explained in chapter 7, "Coverage-Driven Verification" while their composition is the subject of chapter 8, "Improving Coverage Fidelity With Hybrid Models."

<sup>&</sup>lt;sup>6</sup> Reference the seminal paper "Verification of the IBM RISC System/6000 by a Dynamic Biased Pseudo-Random Test Program Generator" by A. Aharon, A. Ba-David, B. Dorfman, E. Gofman, M. Leibowitz, V. Schwartzburd, IBM Systems Journal, Vol. 30, No. 4, 1991.

<sup>&</sup>lt;sup>7</sup> See "Model-Based Test Generation for Processor Design Verification" by Y.

level verification languages (HLVL).8

In this book, I illustrate verification environment implementations using the HLVL *e*. As such, the stimulus generation aspect is composed of generation constraints and sequences. Generation constraints are statically declared rules governing data generation. Sequences define a mechanism for sending coordinated data streams or applying coordinated actions to the device.

Generation constraints are divided into two sets according to their source: the functional specification of the device and the verification plan. The first set of constraints are referred to as functional constraints because they restrict the generated stimuli to valid stimuli. The second set of constraints are known as verification constraints because they further restrict the generated stimuli to the subset useful for verification. Let's briefly examine each constraint set.

Although there are circumstances in which we may want to apply invalid stimulus to the device, such as verifying error detection logic, in general only valid stimuli are useful. Valid stimuli are bounded by both data and temporal rules. For example, if we are generating instructions which have an opcode field, its functional constraint is derived from the specification of the opcode field. This specification should be referenced by the stimulus section of the verification plan. If we are generating packet requests whose protocol requires a one cycle delay between grant and the assertion of valid, the verification plan should reference this temporal requirement.

In addition to functional constraints, verification constraints are required to prune the space of all valid stimuli to those which exercise the device boundary conditions. What are boundary conditions? Depending upon the abstraction level — specification or implementation — a boundary condition is either a particular situation described by a specification or a condition for which specific logic has been created. For example, if the specification says that when a subtract instruction immediately follows an add instruction and both reference the same operand, the ADDSUB performance monitoring flag is set, this condition is a boundary condition. Functional and verification constraints are discussed further in the context of coverage-driven verification in chapter 7.

Lichtenstein, Y. Malka and A. Aharon, Innovative Applications of Artificial Intelligence, AAAI Press, 1994.

<sup>&</sup>lt;sup>8</sup> Reference U.S. patent 6,219,809, "System and Method for Applying Flexible Constraints," Amos Noy (Verisity Ltd.), April 17, 2001

Having designed the machinery required to generate the stimulus required to reach 100% coverage, how do we know that the device is behaving properly during each of the simulations? This is the subject of the next section of this chapter, response checking.

### 2.4.1.3. Response Checking

The response checking section of the verification plan is responsible for describing how the behavior of the device will be demonstrated to conform with its specifications. There are two general strategies employed: a reference model or distributed data and temporal checks.

The reference model approach requires an implementation of the device at an abstraction level suitable for functional verification. The abstraction level is apparent in each of the device specifications: the functional specification and the design specification. The functional specification typically describes device behavior from a black box perspective. The design specification addresses implementation structure, key signals and timing details such as pipelining. As such, a reference model should only be used for architecture verification, not implementation verification. If used for implementation verification, such a model would result in a second implementation of the device at nearly the same abstraction level as the device itself. This would entail substantial implementation and maintenance costs because the model would have to continually track design specification changes, which are often quite frequent.

A consideration for choosing to use a reference model is that the reference model must itself be verified. Will this verification entail its own, recursive process? Although any device error reported by a verification environment must be narrowed down to either an error in the DUV or an error in the verification environment, the effort required to verify a complex reference model may be comparable to verifying the device itself.

Another consideration when using a reference model is that it inherently exhibits implementation artifacts. An implementation artifact is an unspecified behavior of the model resulting from implementation choices. This unspecified behavior must not be compared against the device behavior because it is not a requirement.

<sup>&</sup>lt;sup>9</sup> Why aren't black box and white box verification called opaque and transparent box verification? After all, black box verification means observing device behavior from its primary I/Os alone. White box verification means observing internal signals and structures.

In the context of response checking using a reference model, the *exe-cutable specification* is often cited. *Executable specification* is really an oxymoron because a specification should only define device requirements at some abstraction level. An executable model, on the other hand, must be defined to a sufficient level of detail to be run by a computing system. The implementation choices made by the model developer invariably manifest themselves as behavioral artifacts not required by the device specification. In other words, the device requirements and model artifacts are indistinguishable from one another.

The second response checking strategy, distributed checks, uses data and temporal monitors to capture device behavior. This behavior is then compared against expected behavior. One approach used for distributed checking is the scoreboard.

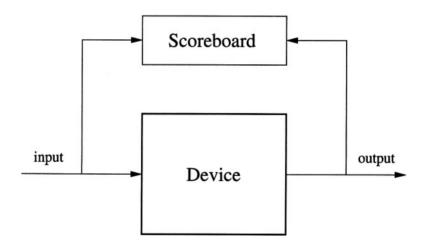

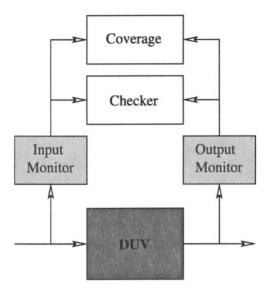

A scoreboard is a data structure used to store either expected results or data input to the device. Consider the device and scoreboard illustrated below in figure 2-4.

Figure 2-4 Scoreboard

The device captures input on the left, transforms it, and writes output on the right. Consider the case where packets are processed by the device. If expected results are stored in the scoreboard, each packet is transformed per the device specification before being written to the scoreboard. Each time a packet is output by the device, it is compared with the transformed packet in the scoreboard and that packet is removed from the scoreboard.

If input data is stored in the scoreboard, each packet read by the device is also written to the scoreboard. Each time a packet is output by the device, the associated input packet is read from the scoreboard, transformed according to the specification, and compared with the output packet.

Reference models and distributed checks are often employed at the same time in a heterogeneous fashion. For example, an architectural reference model may be used for processor instruction set architecture (ISA) checking but distributed checks used for bus protocol checking.

Once the verification plan is written, it must be implemented. We address implementing the verification environment in the next section.

### 2.4.2. Verification Environment Implementation

The verification plan is written (at least the first draft) and now it is time to turn to use it as a design specification. It will serve as the functional specification for the verification environment. Each of the aspects of the verification environment — coverage, stimulus and checking — are defined in the verification plan. The architecture of each should be partly dictated by reuse.

For the same reasons reusable design IP has become critical for bringing chips to market on time, reusable verification IP has also become important. This has two consequences. First, acquire verification components rather than build them whenever possible. Commercial verification components are available for a variety of common hardware interfaces. You may also find pre-built verification components within your organization. Second, write reusable verification components whenever you build a verification environment.

When e is used to implement verification IP, the e Reuse Methodology  $(eRM)^{10}$  should be followed. "The e Reuse Methodology Developer Manual ... is all about maximizing reusability of verification code written in e. eRM ensures reusability by delivering the best known methods for designing, coding, and packaging e code as reusable components."

The first application of the verification environment is getting the DUV to take its first few baby steps. This is known as "bring-up," the subject of

<sup>10</sup> http://www.verisity.com/.

<sup>&</sup>quot;e Reuse Methodology Developer Manual," Verisity Design, © 2002-2004.

## 2.4.3. Device Bring-up

The purpose of bring-up is to shake out the blatant, show-stopper bugs that prevent the device from even running. Although the designer usually checks out the basic functionality during RTL development, invariably the first time the verification engineer gets their hands on the block, all hell breaks loose. In order to ease the transition from the incubation period, where the designer is writing code, to hatching, the verification engineer prepares a small set of simulations (also known as *sims*) to demonstrate basic functionality.

These simulations exercise an extremely narrow path through the behavioral space of the device. Each must be quite restricted in order to make it easy to diagnose a failure. Almost anything may fail when the device is first simulated. The process of bringing up a device is composed of making an assumption, demonstrating that the assumption is true and then using the demonstrated assumption to making a more complex assumption.

For example, the first bring-up sim for a processor would simply assert and de-assert the reset pin. If an instruction is fetched from the reset vector of the address space, the first step of functionality is demonstrated. For a packet processing device, the first sim may inject one packet and make sure the packet is routed and reaches egress successfully. If the packet is output, transformed as (or if) required, the simulation passes.

If we are using an autonomous verification environment,  $^{13}$  rather than directed tests, how do we run such basic simulations? In an aspect-oriented HLVL like e, a constraint file is loaded on top of the environment. This constraint file restricts the generated input to a directed sequence of stimuli. In the case of the processor example above, the constraint file might look like this:

<sup>&</sup>lt;sup>12</sup> The DV engineer's motto is "If it has not been verified, it doesn't work."

<sup>&</sup>lt;sup>13</sup> An *autonomous verification environment* is self-directed and composed of stimulus generation, response checking and coverage measurement aspects. It is normally implemented using an HLVL because of its inherent verification semantics.

Reset is active low and the field reset\_sig is written to the processor reset pin. reset\_sig is constrained to the value one (de-asserted) between cycles zero to three. It is constrained to zero (asserted) for two cycles, starting on cycle four. For all cycles beyond cycle five, it is again constrained to one. Finally, sim\_length (the number of simulation cycles to run) is constrained to seven.

After the device is able to process basic requests, the restrictions imposed on the verification environment are incrementally loosened. The variety of stimuli are broadened in both the data domain and the time domain. The data domain refers to the spectrum and permutation of data values that may be driven into the device. The time domain refers to the scope of temporal behavior exhibited on the device inputs by the verification environment.

Once the device can run any set of simulations which deliver full coverage, we need to be prepared to repeatedly run new sims as changes are made to the device up until it is frozen for tape-out. This is the subject of the next section: regression.

### 2.4.4. Device Regression

Curiously, the name given to re-running a full (or partial) set of simulations in order to find out if its behavior has regressed — i.e. deviated from its specification — is *regression*. <sup>14</sup> The subject of device regression is interesting because, with the advent of HLVLs, controversy has developed over its purpose and how to achieve its goals. First, I examine the purpose of running regressions. Then, I review the classical regression and explain how it differs from a regression performed using an autonomous verification environment.

<sup>&</sup>lt;sup>14</sup> A French national I once worked for, just learning colloquial English, always referred to re-running simulations as "non-regression."

Finally, a recommended regression flow is discussed.

The dictionary definition of regress is "to return to a previous, usually worse or less developed state." Hence, the purpose of running regressions is to detect the (re-)introduction of bugs that lead the device to a "less developed state." Some bugs have the characteristic that they are easily reintroduced into the design. They need to be caught as soon as they are inserted. There are two approaches to detecting re-injected bugs: classical regression and autonomous regression.

The classical regression is performed using a test suite incrementally constructed over a period of time. The test suite is composed of directed tests specified by a test plan. Each test verifies a particular feature or function of the device. The selection criteria for adding a test to the regression test suite include that it:

- verifies fundamental behavior

- exercises a lot of the design in very few cycles

- has exposed one or more bugs in the past

Contrasted against the classical regression is the autonomous regression. An autonomous regression is performed by an autonomous verification environment, characterized by generation, checking and coverage aspects. Hundreds to thousands of copies of this environment are dispatched to a regression ranch each evening, <sup>15</sup> each differing from the next only in its initial random generation seed. I use the term "symmetrical simulation" to refer to a simulation whose inputs are identical to another simulation, with the exception of its random generation seed. Each regression contributes to the coverage goals of the design: functional, code and assertion. The bugs that have been found to date have been exposed by simulating until the coverage goals are achieved. The associated checkers ensure that device misbehavior does not go undetected.

Autonomous regression is preferred over classical regression because it makes use of a self-contained verification environment, dispatches symmetri-

$<sup>^{15}</sup>$  In Texas we have *simulation ranches*. In other parts, you might call them *simulation farms*.

<sup>&</sup>lt;sup>16</sup> See chapter 7, "Coverage-Driven Verification."

## 2.5. Summary

In this chapter I defined functional verification, explained the difference between verification and test and outlined the functional verification process. The process is composed of writing a verification, implementing it, bringing up the DUV and running regressions.

The verification plan must define the scope of the verification problem — using functional, code and assertion coverage — and specify how the problem will be solved in the stimulus generation and response checking aspects.

The verification environment is implemented using pre-built verification components wherever possible. When new components are required, they should be implemented as reusable verification IP, according to eRM guidelines when e is the implementation language.

Device bring-up is used to get the device simulating and expose any gross errors. An iterative cycle of "make an assumption, validate the assumption" is followed, incrementally increasing the complexity of the applied stimuli until the device is ready for full regression.

The purpose of regression is to detect the reintroduction of bugs into the design. Regression methodology has progressed from running a directed regression test suite to dispatching symmetrical autonomous simulations. The autonomous simulations are coverage-driven by the functional, code and assertion coverage goals of the verification plan.

# 3. Measuring Verification Coverage

In order to measure verification progress, we measure verification coverage because verification coverage defines the extent of the verification problem. In order to measure anything however, we need metrics. In this chapter I define coverage metrics and a useful taxonomy for their classification. Using this taxonomy, I introduce the notion of a coverage space and define four orthogonal spaces into which various kinds of coverage may be classified.

## 3.1. Coverage Metrics

A coverage metric is a parameter of the verification environment or device useful for assessing verification progress in some dimension. We may classify a coverage metric according its kind and its source. By kind, I mean whether or not a metric is implied from the verification interface<sup>1</sup> or is explicitly defined. Hence, a metric kind is either implicit or explicit.

The second classification is the source of a metric, which has a strong bearing on what verification progress we may infer from its value. I will consider two sources, each at a different abstraction level: implementation and specification. An implementation metric is one taken from the device implementation, for example the RTL. A specification metric is a metric extracted from one of the device specifications: the functional or design specification.

These two classifications of coverage metrics define four metrics, as illustrated in table 3-1 below.

<sup>&</sup>lt;sup>1</sup> See chapter 1, "The Language of Coverage," for the definition of "Verification interface."

#### Metric Kind

|               |                | Implicit                   | Explicit                   |  |

|---------------|----------------|----------------------------|----------------------------|--|

| Metric Source | Specification  | Implicit<br>Specification  | Explicit<br>Specification  |  |

| Metric        | Implementation | Implicit<br>Implementation | Explicit<br>Implementation |  |

**Table 3-1** Coverage Metric Taxonomy

The following four sections explore in greater detail these coverage metric classifications. The first two describe metric kinds while the second two describe metric sources.

## **3.1.1.** Implicit Metrics

An implicit coverage metric is inherent in the representation of the abstraction level from which the metric is taken. For example, at the RTL abstraction level, hardware description language structures may be implicit metrics. A Verilog statement is an implicit metric because statements are a base element of the Verilog language. The subexpressions of a VHDL Boolean expression in an "if statement may be implicit metrics. The same metrics may be applied to the verification environment, independent of its implementation language.

Another abstraction level from which implicit metrics may derived is the device specification. The implicit metrics of a natural language specification include chapter, paragraph, sentence, table and figure.

### 3.1.2. Explicit Metrics

An explicit coverage metric is invented, defined or selected by the engineer. It is usually selected from a natural language specification but it could also be chosen from an implementation. Explicit metrics are typically used as components for modeling device behavior.

Examples of explicit metrics from the CPU application domain are:

- opcode

- register

- address

- · addressing mode

- execution mode

Examples from an ethernet application are:

- preamble

- start frame

- source address

- destination address

- length

- CRC

The next two sections describe the two sources of coverage metrics: the device specifications and its implementation.

## 3.1.3. Specification Metrics

A specification coverage metric is a metric derived from one of the device specifications: the functional specification or the design specification. Since these specifications record the intended behavior of the device, the metrics extracted from them are parameters or attributes of that behavior. In effect, these metrics quantify the device behavior, translating its description from a somewhat ambiguous natural language abstraction to a precise specification.

Some examples of specification metrics are:

- instruction opcode

- · packet header

- processing latency

- processing throughput

## **3.1.4.** Implementation Metrics

An implementation coverage metric is a metric derived from the implementation of the device. The device implementation is distinguished from its specification in that the implementation is much less abstract, less ambiguous and machine readable. Recall that the design specification describes the microarchitecture of the device. However, it still leaves many design choices to the designer writing the RTL. Metrics derived from the implementation are design choices which are not present in its specification because they are an implementation choice.

These are a few examples of implementation metrics:

- · one-hot mux select value

- finite state machine state

- pipeline latency

- pipeline throughput

- bandwidth

Having introduced the four types of coverage metrics, let's turn our attention to the coverage spaces which are defined from these metrics.

## 3.2. Coverage Spaces

What do we mean by a "coverage space?" As defined in chapter 1, "The Language of Coverage," a coverage space is a multi-dimensional region defined by its attributes and their values. A coverage space is often referred to as a coverage model because it captures the behavior of the device at some abstraction level.<sup>2</sup> The kind and source of coverage metric, each having two

<sup>&</sup>lt;sup>2</sup> Simone Santini eloquently defined an abstraction in the May 2003 issue of "Computer" magazine: "An abstraction ignores the details that distinguish specific instances and considers only those that unify them as a class."

values, define four types of coverage spaces: implicit implementation, implicit specification, explicit implementation and explicit specification. Each of these coverage spaces is discussed in the following sections.

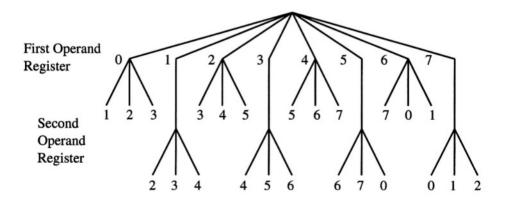

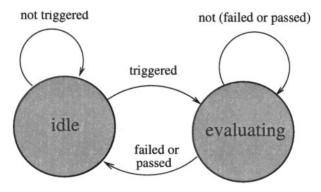

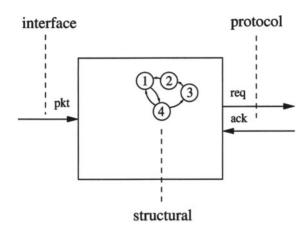

## 3.2.1. Implicit Implementation Coverage Space