# 西安电子科技大学

# 硕士学位论文

无滤波器立体声音频D类功率放大器专用集成电路的设计与实现

姓名: 牟在鑫

申请学位级别:硕士

专业: 电路与系统

指导教师: 王松林

20071201

## 摘要

本论文的设计工作来源于西安电子科技大学科研项目"高效低 THD 音频 D 类功率放大器的研究与设计",主要对 D 类功率放大器的工作原理及性能进行理论研究并设计实现。

论文首先分析了各种音频功率放大器的工作原理以及各自的性能特点,重点阐述了 D 类音频功率放大器的工作原理和脉宽调制方案,并在此基础上设计了一款大功率输出、低功耗、无需输出滤波器的立体声音频 D 类功率放大器 XPD7026。

该芯片采用一种新颖的脉宽调制方案,通过对 PWM 调制信号进行半波整形并利用全桥输出级降低了 D 类功率放大器对输出滤波器的依赖。文中重点阐述了 D 类功率放大器的关键子模块设计,如振荡器、前置运算放大器、积分器、PWM 比较器以及基准源。特别是文中提出了一种新颖的可以作为片内电源的带隙电压基准,从而降低了 D 类功率放大器的静态功耗,提高了 D 类功率放大器的效率。另外,通过引入电荷泵驱动模块使得输出级可以全部采用 NMOS 晶体管作为开关管,大大节省了芯片面积。

整体电路基于某公司 0.6μm BCD 工艺设计,使用 Cadence 等 EDA 软件完成整体电路的前仿真验证。仿真结果表明,电路功能和性能指标均已达到设计要求。

关键词: 音频功率放大器 D 类功放 脉宽调制 全桥输出 免滤波器

#### **Abstract**

The paper is based on the research project "The Theoretical Reach on and Design of High efficiency Low THD Audio Class-D Power Amplifier (PA)" and deals mainly with the design implementation and theoretical study of operating principle of Class-D PA.

On the basis of the analysis of operating principles and performance characteristics of various audio PAs, and emphatic description of PWM and operating principle of class-D audio PAs, the design of a class-D stereo audio PA XPD7026, with high power output, low power dissipation and free output filter, is presented in this paper.

XPD7026 adopts a novel PWM strategy, which reduces the dependence of class-D PA on output filter by half-wave rectifying PWM signals and taking advantage of full-bridge output. The design of key sub-blocks in class-D, such as OSC, pre-amplifier, integrator and voltage reference is described in detail .Also, a novel band-gap voltage reference as internal voltage supply, which reduces the power dissipation and enhance the efficiency of class-D PA is proposed in this paper. In addition, by introducing a charge pump driver module, the output stage can adopt only NMOS as switch transistors, which saves layout area substantially.

The whole circuit is designed on the basis of the  $0.6\mu m$  BCD process. The simulation and verification are completed by EDA tools such as Cadence etc. According to the simulation results, the function and performance of the whole circuit can meet all the requirements.

Keyword: Audio Power Amplifier Class-D Pulse Width Modulation

Full Bridge Output Mono Filter-free

# 西安电子科技大学

# 学位论文独创性声明

秉承学校严谨的学风和优良的科学道德,本人声明所呈交的论文是我个人在导师指导下进行的研究工作及取得的研究成果。尽我所知,除了文中特别加以标注和致谢中所罗列的内容以外,论文中不包含其他人已经发表或撰写过的研究成果;也不包含为获得西安电子科技大学或其它教育机构的学位或证书而使用过的材料。与我一同工作的同志对本研究所做的任何贡献均已在论文中做了明确的说明并表示了谢意。

申请学位论文与资料若有不实之处,本人承担一切的法律责任。

本人签名:

日期 2008 1.7

# 西安电子科技大学

# 关于论文使用授权的说明

本人完全了解西安电子科技大学有关保留和使用学位论文的规定,即:研究 生在校攻读学位期间论文工作的知识产权单位属于西安电子科技大学。学校有权 保留送交论文的复印件,允许查阅和借阅论文;学校可以公布论文的全部或部分 内容,可以允许采用影印、缩印或其它复制手段保存论文。同时本人保证,毕业 后结合学位论文研究课题再撰写的文章一律署名单位为西安电子科技大学。

本人签名: 444

日期 2008.1.7

导师签名: 3 花柱

日期 2001/10

# 第一章 绪论

本论文的目的是设计一款无需滤波器、输出功率为6W的音频D类功率放大器芯片,通过采用一些先进的电路结构,在输出功率、效率和非线性之间进行折衷,以获得失真度小、输出功率大、转换速率快、输出电压摆幅大的性能指标。所设计的音频D类功率放大器主要应用对象是便携式电子、通信、计算机产品以及汽车音响。

### 1.1 论文选题意义与音频功放的发展趋势

随着便携式电子、通信和计算机产品技术的不断发展,功率放大器的性能对产品的质量有着越来越重要的影响,特别是功率放大器的功耗将直接决定以电池为供电主体的便携式电子产品的使用周期<sup>[1]</sup>。而线性功放(A、B、AB、C类)虽然具有较好的线性度和THD性能,但它们的功耗均较大,且散热量大,严重制约了其在便携式电子产品上的应用。在国外,早在1958年就提出了D类功放,随着各项关键技术的成熟,近些年逐渐流行起来。其与线性功放最大的区别在于,可以提供高效率和大功率输出<sup>[2]</sup>。

低失真、大功率、高效率是对功率放大器提出的普遍要求。D类功率放大器工作于开关状态,理论效率可达100%,实际的运用也可达80%以上。其功率器件的耗散功率小,产生热量少,可以大大减小散热器的尺寸,连续输出功率很容易达到数百瓦,而对于便携式应用通常可以去掉散热器。D类功放的功率MOS器件设计有自保护电路,而且不会引入非线性失真。但由于D类功放采用PWM调制方式,为了提高音质,降低失真,必须提高调制频率,但是在较高频率下,会产生一定的问题。同时,D类功率放大器对器件的要求较高,不利于降低成本<sup>[3]</sup>。但是,音频D类功率放大器具有高效、节能、数字化、体积小、重量轻的特点,因此,音频D类功率放大器取代模拟音频放大器是必然的发展趋势。

目前,国际上几家著名的模拟IC设计公司早在20世纪末就推出了自己的音频D 类功率放大器系列产品和评估套件,如德州仪器(TI)的TPA系列,美国国家半导体公司(National Semiconductor)的LM46、47系列以及美信(MAXIM)的MAX97系列。这些D类功放产品,在芯片效率、输出功率、信噪比以及芯片面积等特性上有较出色的表现。国内有几家公司正在研究开发音频D类功率放大器,但大多采用的是国外"评估件"、专用IC,开发成本高,如:成都天奥集团投资45万人民币在 其博士后工作站研究音频D类功率放大器,但目前仍处在研究中小功率阶段。因此,国内便携式设备所应用的音频D类功放市场大部分被国外公司所垄断。

## 1.2 论文的主要工作及章节安排

本论文的设计工作是西安电子科技大学电路 CAD 所的科研项目"高效低 THD 音频 D 类功率放大器的研究与设计",在研究了各种音频功率放大器及其效率、失真系数的基础上,设计了一款无滤波器立体声音频 D 类功率放大器专用集成电路芯片 XPD7026。

论文中详细介绍和分析了该芯片的调制方式、拓扑结构、工作原理及各模块晶体管级电路。该芯片基于国外某公司的 0.6µm BCD 工艺,采用 Cadence 仿真平台对所设计的电路进行了仿真验证。仿真结果表明该芯片具有较好的性能,符合设计要求,可以满足市场应用的需要,具有较高的经济价值。

论文共分为六章。第一章是绪论;第二章介绍了音响的基本知识、音频功放的分类及 D 类功放的基本工作原理;第三章介绍了 D 类功放的三个关键设计技术,即利用负反馈改善 D 类功放的性能,噪声整形技术,EMI 改善技术;第四章主要介绍 XPD7026 的系统设计及高压 BCD 工艺;第五章详细介绍了 XPD7026 中关键模块的功能定义、电路实现及仿真结果;第六章是芯片整体功能仿真;最后是结束语。

# 第二章 音频功率放大器的基本工作原理

功率放大电路主要实现信号电压和电流的放大,以便送到执行机构中去完成 某种任务,如使扬声器发声、继电器动作或仪表指示等。

功率放大器是一种十分常用的电子电路,广泛应用于家庭影院、音响系统、 立体声唱机、乐器系统、车载娱乐系统、手机、掌上电脑以及 LCD 监视器、LCD 投影仪等电子系统。本论文的研究主要涉及音频功率放大器的设计。

### 2.1 音响的相关知识简介

### 一、声音的基本特性[4]

音量:它与声波的物理量"振幅"有关,声波的振幅大,人耳就感觉声音响, 音量大,反之,则声音轻,音量小,音量的大小是人耳听觉的主观感觉。

音调:是人耳对声音调子高低的主观感觉,声调的高低与声音的物理量"频率"有关,其对应人耳的听觉范围为:20Hz~20KHz称之为可听声,低于20Hz称为次声,高于20KHz称为超声,人耳对3KHz~4KHz的声音最敏感。

音色:又叫音品或音质,它是由声音的波形决定的,电子管功放的偶次谐波 多,奇次谐波少,声音柔美,甜润,晶体管功放奇次谐波多,偶次谐波少,声音冷艳,清丽。

#### 二、音响的结构及参数

音响由前置放大器和功率放大器构成。前置放大器承担控制任务为主,对各种声音源信号进行选择和处理,对微弱信号放大到0.5V~1V,进行各种音质控制,以美化音色。功率放大器,承担放大任务,是将前置放大器输出的音频信号进行功率放大,以推动扬声器发声。功率放大器有电压放大和电流放大之分,对其要求是输出的声音宏亮而不失真。

## 三、放大器技术指标[5]

1.额定功率: 音频放大器输出失真度小于某一数值(r<1%)的最大功率称为额定功率,表达式:  $P_0=U_0^2/R_L$ , $U_0$ 为负载两端的最大不失真电压, $R_L$ 为额定负载阻抗。

测量条件:可以利用信号发生器输出频率为1KHz,电压 $U_i$ =20mV正弦信号。功率放大器的输出端接额定负载电阻 $R_L$ (代替扬声器),输入端接 $U_i$ ,逐渐增大输入电压 $U_i$ ,直到 $U_0$ 的波形刚好不出现谐波失真(r<1%),此时对应的输出电压

为最大输出电压。测量后应迅速减小Ui以免损坏功率放大器。

2.频率响应: 放大器的电压增益相对于中音频f。(1KHz)的电压增益下降3dB时所对应的低音频率f<sub>L</sub>和高音频率f<sub>H</sub>称为放大器的频率响应。

测量条件:调节音量控制器使输出电压约为最大输出电压的50%,输入端接音调控制器,使信号发生器的输出频率f从20Hz~20KHz(保持U<sub>I</sub>=20mV不变)测出负载电阻上对应的输出电压U<sub>O</sub>。

- 3.输入灵敏度: 使音响放大器输出额定功率时所需的输入电压(有效值)称为灵敏度。

- 4.噪声电压: 使输入为零时,输出负载R<sub>1</sub>上的电压称为噪声电压U<sub>0</sub>。

测量条件: 使输入端对地短路, 音量电位器调至最大值, 用示波器观察输出负载R<sub>L</sub>的电压波形, 用交流电压表测量其有效值。

### 2.2 功率放大器的分类

功率放大器<sup>[6][7]</sup>按照信号导通角,可分为 A、B、C 和 AB 类四类。因为它们通常工作在线性放大区,所以也叫做线性放大器。

长期以来,高品质音频放大器的工作类别,只限于 A 类和 AB 类。其原因在于过去只有电子管这样的器件,B 类电子管放大器产生的失真使它们甚至在公共广播中使用时都难于被人们所接受,因此 B 类功放的使用并不是很常见。所有自称为高保真的放大器均工作于推挽式的 A 类。

随着半导体器件的出现和发展,放大器的设计得到了更多的自由。就放大器的类别而言,已不限于 A 类和 AB 类,而出现了更多类别的放大器。就目前来说用于音频功率放大器的工作类别,A 类、AB 类和 B 类这三类放大器仍覆盖着半导体放大器的绝大多数。

#### 一、A类放大器

A 类(甲类) 放大器,是指电流在整个周期内连续地流过所有输出器件的一种放大器。因为其避免了器件开关所产生的非线性,只要偏置和动态范围控制得当,仅从失真的角度来看,可认为它是一种良好的线性放大器。

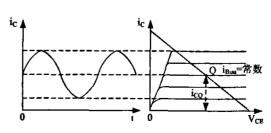

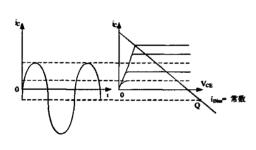

A 类放大器的典型工作状态如图 2.1 所示。右边为晶体管输出特性,固定偏置所形成的直流工作点在 Q 点,此时 ic>0。当输入音频信号幅度未超出线性范围,集电极工作状态处于截止区和饱和区之内,

图 2.1 A 类放大器典型的工作方式

集电极电流为完整的全周期导通的正弦波,此时导通角为 180 度(导通角是以最 小值至最大值之间占全周期的部分来计算,全周期导通时为 180 度)。这种放大 状态失真度较小, 只受器件特性曲线的影响, 若器件线性好则失真最小, 但是, 当无交流输入时,有约一半幅度(Q点)的直流电流,其损耗为 Ico×Vnn, 故效率 是最低的,低于 50%, 所以这种 A 类功率放大仅用于很小功率的收音机、助听器 中, 也有用干高级的 Hi-Fi 功放中[7]。

### 二、B类放大器

B 类 (乙类) 放大器, 是指器件导通时 间为50%的一种工作状态。

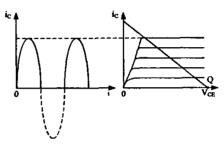

从 A 类放大器可以看出, 静态电流是造 成管耗的主要因素, 也是 A 类放大器效率低 的原因。B 类放大的典型工作状态如图 2.2 所示。

图 2.2 B 类放大器典型的工作方式

B 类放大器是把静态工作点偏置为图 2.2 中的 O 点,处于截止点上,此时 ic=0,使信号等于零时电源输出的功率也等于 零(或者很小)。当输入信号增大时电源供给的功率也随之增加,这样电源供给功 率及管耗都随着输出功率的大小而变化,效率超过 50%,理想情况下最高可达 78.5%, 从这一点可以看出, B 类放大器 改变了A类放大器效率低的状况。

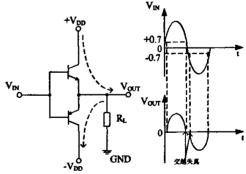

但是当有信号输入时,输出功率管 只有半个周期导通,集电极输出半个正 弦波,这种状态的失真度就很大了,所 以一般 B 类放大器都做成双管推挽式结 构,每管工作半个周期构成完整的正弦 波以减小失真。但是由于没有直流偏置, B 类放大器必定会出现交越失真, 即输 入信号低于管子的阈值电压时 (对于锗 (a)推挽输出 B 类放大器 (b)交越失真示意图 硅工艺的 NPN 管其阈值电压约为 0.7V, PNP 管的阈值电压约为 0.8V), 两个管 子  $Q_1$ 、 $Q_2$  同时截止,如图 2.3 所示。

图 2.3 B 类放大器拓扑结构 与交越失真示意图

#### 三、AB类放大器

AB 类 (甲乙类) 放大器,实际上是 A 类和 B 类的结合。每个功率管的导通 时间在50%~100%之间,依赖于偏置电流的大小和输出电平。

AB 类放大器是在 B 类设计基础上,增加偏置电流,使放大器进入 AB 类,这 也是克服B类放大器交越失真的一种方法。

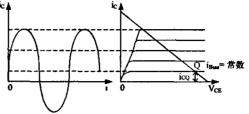

AB 类放大器的典型工作状态如图 2.4 所示。AB 类放大器是把静态工作点偏

置为 Q 点,有半个周期以上 ic>0。 AB 类放大器,在输入低于某一电平时,两个输出功率管皆导通,其状态工作于 A 类; 当电平增高时,一个功率管将完全截止,而另一个功率管将提供更多的电流。这样在 AB 类工作

图 2.4 AB 类放大器典型的工作方式

状态开始时,失真将会突然上升,其线性劣于 A 类或 B 类。由于两个输出功率管均少量正向导通偏置,故其效率低于 B 类,一般不能高于 60%~70%,不过在某些应用领域可以认为它是对 A 类的补充,且当面向低负载阻抗时可以继续较好的工作。通常 AB 类放大器也作为 BUFFER 电路使用,来提高系统的带载能力。

图 2.5 C 类放大器典型的工作方式

频功放,多用于高频功放作为倍频或用于射频放大[1]。

### 四、C类放大器

C 类(丙类)放大器,是指器件导通时间小于50%的工作类别。

C 类放大的典型工作状态如图 2.5 所示。C 类放大器是把静态工作点 Q 偏置在截止点之下,当有信号输入时,只有超过偏置点稍许,管子才导通,效率更高,但是由于失真过大,很难用于音

## 2.3 D 类放大器的工作原理

D 类放大器又称为数字放大器<sup>[8]</sup>,多采用 PWM 方式,功率管工作于开关状态,无信号时无电流信号,而导通时没有直流损耗。

事实上 D 类放大器由于关断时器件尚有微小漏电流,而导通时,器件并没有完全短路,尚有一定管子压降,故存在较少的直流损耗,效率不能达到 100%,实际在 80%~90%,是实用放大器中效率最高的。

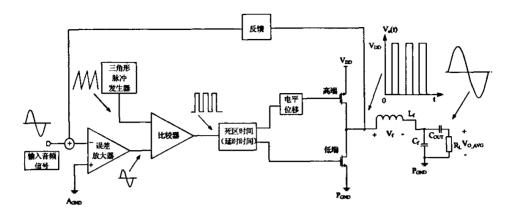

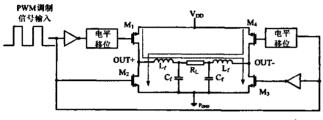

现代 D 类放大器使用多种调制器拓扑结构,而最基本的拓扑包括了脉宽调制 (PWM) 以及三角波振荡器<sup>[9]</sup>。图 2.6 给出了一个基于 PWM 的半桥式 D 类放大器简化框图。

图 2.6 D 类放大器典型的工作方式

由图 2.6 可知,基本 D 类功放包括一个脉宽调制器,两个输出 MOSFET 和一个用于恢复被放大的音频信号的外部低通滤波器  $(L_F \ n \ C_F)$ 。其中两个 N 沟道的

MOSFET 用作电流导向开关,将其输出节点交替连接至 V<sub>DD</sub> 和地。由于输出晶体中的一种,所以 D 以为大器的最级,所以 D 类放大器的方法。 为 D 类放大器的开关

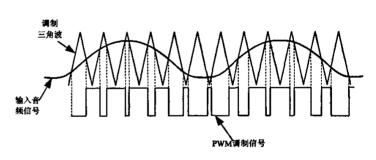

图 2.7 D 类放大器典型的 PWM 调制波形

频率(f<sub>SW</sub>)通常在 250KHz 至 1.5MHz 之间。音频输入信号对输出方波进行脉宽调制,即音频信号与内部振荡器产生的三角波进行比较,可得到 PWM 信号。这种调制方式通常被称作"自然采样",其中三角波振荡器作为采样时钟。方波的占空比与输入信号电平成正比。没有输入信号时,输出波形的占空比为 50%。图 2.7 显示了不同输入信号电平下所产生的 PWM 输出波形。

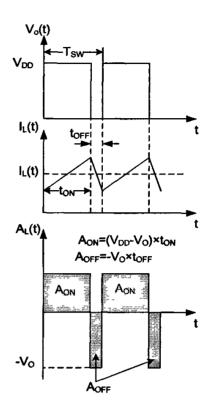

为了从 PWM 波形中提取出放大后的音频信号,需将 D 类放大器的输出送入一个低通滤波器。图 2.6 中的 LC 低通滤波器作为无源积分滤波器(假设滤波器的截止频率比输出级的开关频率至少低一个数量级),它的输出等于方波的平均值。此外,低通滤波器可防止在阻性负载上消耗高频开关能量。假设滤波后的输出电压( $V_{O\_AVG}$ )和电流( $I_{AVG}$ )在单个开关周期内保持恒定。这种假设较为准确,因为  $f_{SW}$  比音频输入信号的最高频率要高得多。因此,占空比与滤波后的输出电压之间的关系,可以通过对电感电压和电流进行简单的时间域分析得到 $^{[10]}$ 。

流经电感的瞬时电流为:

$$I_L(t) = \frac{1}{L} \int V_L(t) dt$$

(2-1)

其中, V<sub>L</sub>(t)是图 2.6 中 LC 滤波器电感的瞬时电压,由于流入负载的平均电流(I<sub>AVG</sub>)在单个开关周期内可以看作恒定(f<sub>SW</sub> 远大于信号频率),所以开关周期(T<sub>SW</sub>)开始时的电感电流必定与开关周期结束时的电感电流相同,如图 2.8 所示。

根据数学计算,在单个周期内电感电流 与电感电压满足下式:

$$\frac{1}{I_L} \int_{0}^{T_{SW}} V_L(t) dt = I_L(T_{SW}) - I_L(0) = 0 \qquad (2-2)$$

式(2-2)表明,电感电压在一个开关周期内的积分必定为 0。利用等式(2-2)并观察图 2.8 给出的 A<sub>L</sub>(t)波形,可以看出,各区域面积(A<sub>ON</sub>和 A<sub>OFF</sub>)的绝对值只有彼此相等,等式(2-2)才成立。基于这一信息,可以利用开关波形的占空比来表示滤波后的输出电压,即有:

图 2.8 基本 D 类功放半桥输出中的电 感电压电流波形

$$A_{ON} = |A_{OFF}| \tag{2-3}$$

$$A_{ON} = (V_{DD} - V_O) \times t_{ON} \tag{2-4}$$

$$|A_{OFF}| = V_O \times t_{OFF} \tag{2-5}$$

将等式(2-4)和(2-5)带入(2-3)式,可得:

$$(V_{DD}-V_O)\times t_{ON}=V_O\times t_{OFF} \tag{2-6}$$

最后,得到 Vo 的表达式:

$$V_O = V_{DD} \times \frac{t_{ON}}{t_{ON} + t_{OFF}} = V_{DD} \times D \tag{2-7}$$

其中 D 为输出开关波形的占空比。

由式(2-7)可知,输出方波的占空比直接反映了输入音频信号的幅值,所以可以实现音频功率放大的目的。从这一点来看,D类功放的工作原理与BUCK型DC-DC很类似[11][12]。

### 2.4 D 类放大器的调制方式

由2.3节可知,D类功率放大的输出级相当于两个放大器反相连接,实际上构成推挽状态,起到开关作用去控制与电源串联的负载回路(R<sub>L</sub>),低通滤波器LPF可以滤去脉冲波的高频部分,得到基波成分,所以D类功率放大器的输出级实际上成为数/模(D/A)转换电路,重新将脉冲波还原成为正弦波。

图2.7表示了如何将正弦波变为脉冲波,使得脉冲波的宽度受正弦波幅度调制,通常PWM比较器输出的方波称为"PWM信号",即"脉宽调制"信号。本节从数学推导的角度来证明PWM调制的可行性<sup>[13]</sup>。

D类放大器按其调制方式可分为AD类和BD类,下面通过进行傅里叶分析<sup>[14]</sup>, 阐明AD类和BD类的特点。

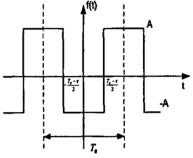

#### 一、AD类调制

首先来分析AD类对称调制的傅里叶变换。 对于图2.9所示的对称调制波根据:

$$T_0 = \frac{2\pi}{\omega} \tag{2-8}$$

$$\tau = \frac{T_0}{2} (1 + m \sin \theta) = \frac{\pi}{6} (1 + m \sin \theta) \quad (2-9)$$

图 2.9 AD 类的调制波形

其表达式为:

$$f(t) = \begin{cases} -A & \left( -\frac{T_0 - \tau}{2} + nT_0 < t \le \frac{T_0 - \tau}{2} + nT_0 \right) \\ A & \left( \frac{T_0 - \tau}{2} + nT_0 < t \le \frac{T_0 + \tau}{2} + nT_0 \right) \end{cases}$$

(2-10)

则其傅里叶级数为:

$$F(t) = \begin{cases} mA\sin\theta - \sum_{n=1,3,5,...} \frac{4A}{n\pi} \sin\frac{n\pi}{2} \cdot \sum_{a=...-2,0,2,4,...} j_a \left[ \frac{n\pi m}{2} \right] \cos(n\omega t + a\theta) \text{ (n : odd number)} \\ mA\sin\theta - \sum_{n=2,4,6,...} \frac{4A}{n\pi} \cos\frac{n\pi}{2} \cdot \sum_{a=...-3,-1,1,3,...} j_a \left[ \frac{n\pi m}{2} \right] \sin(n\omega t + a\theta) \text{ (n : even number)} \end{cases}$$

(2-11)

其中ja是a阶贝塞尔函数。

分析式(2-11)可以得到:调制后的PWM信号中含有音频基波分量,其幅度和脉冲幅度A、调制度m成正比。改变脉冲的幅度和调制度,都可以对音频信号进行放大。由此可以得到如下结论:

1.调制后的PWM信号中含有音频信号基波以及载波的高次谐波。

- 2.调制后的PWM信号中含有载波谐波和音频谐波的组合频率。

- 3.载波和音频的高次谐波落入音频基带(0~20KHz)中,形成固有失真。通过分析可知,采样频率越高,固有失真越小。

4.在对称调制中,载波的偶次谐波抵消。载波的奇次谐波和音频的奇次谐波的 组合频率抵消;载波的偶次谐波和音频的偶次谐波相互抵消。

通过以上的傅里叶分析,可以得知,提高采样频率,可以大大降低音频基带的固有失真。这也是D类功放的调制频率至少为200KHz的理论基础。当然,对于AD类调制,增加调制频率可以改善D类功放的失真,但是随着调制频率的增加,开关管的损耗也在增大,因此,需要在失真与

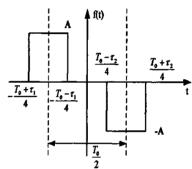

### 二、BD类调制

功耗这两方面进行折衷考虑。

BD类对称调制的波形如图2.10所示,其表达式为(2-15)。

$$T_0 = \frac{2\pi}{\alpha} \tag{2-12}$$

$$\tau_1 = T_0 m \sin \theta = \frac{2\pi}{\omega} m \sin \theta \tag{2-13}$$

图 2.10 BD 类的调制波形

$$\tau_2 = -T_0 m \sin \theta = -\frac{2\pi}{\omega} m \sin \theta \tag{2-14}$$

$$f(t) = \begin{cases} -A & \left(\frac{T_0 - \tau_2}{4} + nT_0 < t \le \frac{T_0 + \tau_2}{4} + nT_0\right) \\ A & \left(-\frac{T_0 + \tau_1}{4} + nT_0 < t \le \frac{T_0 - \tau_1}{4} + nT_0\right) \end{cases}$$

(2-15)

其傅里叶级数为:

$$F(t) = mA\sin\theta + \sum_{n=1}^{\infty} \frac{2A}{n\pi} \cos\frac{n\pi}{2} \cdot \sum_{n=-\infty}^{+\infty} \left\{ \left[ 1 + (-1)^{n+1} \right] j_n \left[ \frac{mn\pi}{2} \right] \sin(n\omega t + a\theta) \right\}$$

(2-16)

由此可得到如下结论:

- 1.当采用BD类调制方案时,音频信号有效的采样频率加倍,而开关损耗没有改变,因此BD类调制提供了理论上开关频率减半的可能性。

- 2.在BD类调制中,载波和它的谐波在调制信号中都不存在,且互调部分的幅度随着音频信号线性减少,剩余部分中没有高频成分。

- 3.在BD类调制中,PWM输出终端包括了峰峰值幅度为A的高电平共模成分。 而在AD类调制中的高电平幅度仅为A/2。

# 第三章 D 类功率放大器关键设计技术

上一章介绍了各种音频功率放大器的分类及各自的工作原理。这一章将针对本论文所设计的音频 D 类功放实现电路来详细说明 D 类功放的关键设计技术,包括噪声整形,无需滤波器调制技术,EMI 改善技术。

### 3.1 利用负反馈来改善 D 类功放的性能

由第二章 2.3 节的分析可知, PWM 调制结构的 D 类功放, 其增益是与电源电压成正比的, 而对于线性功放, 其增益与电源电压没有直接关系, 因此线性功放要比 D 类功放有更好的电源抑制比 (PSRR)。而 PSRR 性能的好坏直接影响音频功率放大器的音质, 因此许多 D 类功放采用 PWM 输出至器件输入的负反馈环路 (见图 2.6)。闭环方案不仅可以改善器件的线性度, 而且使器件具备电源抑制能力。在闭环拓扑中, 因为会检测输出波形并将其反馈至放大器的输入端, 所以能够在输出端检测到电源的偏离情况, 并通过控制环路对输出进行校正。但闭环设计的优势是以可能出现稳定性问题为代价的, 这也是所有反馈系统共同面临的问题。因此, 必须精心设计控制环路并进行补偿, 确保在任何工作条件下其都能够保持稳定。

#### 一、失真和噪音的产生

音频 D 类功率放大器最主要的性能指标之一是 THD+N,这一指标是指 D 类功率放大器输出音频信号相对原输入信号所产生的失真以及噪声的大小。D 类功率放大器在以下情况会产生失真和噪声。

- 1.开关管不必要的特征,例如导通阻抗、有限的开关速度以及寄生晶体二极管;

- 2.由于限定的输出阻抗和通过直流供电的能量的反作用而引起电源电压的波动:

- 3.开关管驱动信号上的时间误差,如死区时间、开通关断时间、上升下降时间等:

- 4.从调制器到输出开关级,由于调制逻辑的分辨率限制和时间抖动而导致 PWM 信号中的非线性,以及调制三角波的非线性;

- 5.输出滤波器(LPF)的非线性。

综上所述,对于 D 类功放所产生的噪声,其主要来自于数字逻辑,即 PWM 调制逻辑;而 D 类功放所产生的失真不仅与调制逻辑有关而且与输出级的开关管

也有很大的关系。一般来讲,开关管栅极驱动信号的时间误差是导致非线性的主要原因。特别是死区时间严重影响了 D 类功放的线性度。通常,几十纳秒的死区时间很容易产生 1%以上的 THD (总谐波失真)。

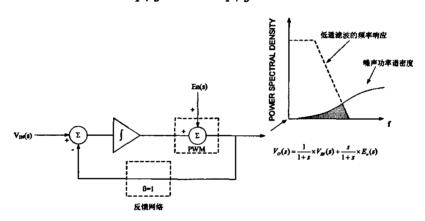

### 二、利用负反馈技术进行噪声整形[15]

典型的 D 类放大器采用具有噪声整形功能的反馈环路,可极大地降低由脉宽调制器、输出级以及电源电压偏离的非线性所引入的带内噪声。这种拓扑结构与用在∑-△调制器中的噪声整形类似。图 3.1 给出了一个 1 阶噪声整形器的简化框图。通常,反馈环路包含一个电阻分压网络,出于简便起见,图 3.1 的反馈比例为 1。由于理想积分器的增益与频率成反比,图中积分器的传递函数也被简化为 1/s。同时假定 PWM 模块具有单位增益,并且在控制环路中具有零相位偏移,即不考虑稳定性问题。使用基本的控制模块分析方法,可得到以下输出表达式:

$$V_O(s) = \frac{1}{1+s} \times V_{IN}(s) + \frac{s}{1+s} \times E_n(s)$$

(3-1)

图 3.1 1 阶噪声整形原理图

由等式(3-1)可知,噪声项 En(s)与一个高通滤波器函数(噪声传递函数)相乘,而输入项  $V_{IN}(s)$ 与一个低通滤波器函数(信号传递函数)相乘。噪声传递函数的高通滤波器对 D 类放大器的噪声进行整形。如果输出滤波器的截止频率选取得当,大部分噪声会被推至带外(图 3.1)。

本设计中采用 2 阶噪声整形,以获得良好的线性度和电源电压抑制特性。这 将在第四章进行说明。

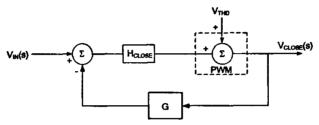

# 三、利用负反馈技术改善 D 类功放的 THD 性能[16]

根据前面的分析,功放的总谐波失真系数 THD (Total Harmonic Distortion) 是 衡量音频 D 类功放性能的主要参数之一。根据图 2.6,假设 D 类功放开环工作,则有:

$$V_{OUT}(s) = H_{OPEN}(s) \cdot V_{IN} + V_{THD}$$

(3-2)

其中, $V_{IN}$  为放大器输入音频信号, $H_{OPEN}(s)$  为放大器的开环增益, $V_{THD}$  为功放产生的谐波失真函数。则 D 类功放总的谐波失真系数为:

$$THD_{OPEN} = \frac{\sqrt{\sum_{n=2}^{\infty} (V_{THD})^2}}{H_{OPEN}V_{IN}}$$

(3-3)

对于 D 类功放的闭环系统,可用图 3.2 表示,得:

图 3.2 D 类功放闭环等效模型

$$V_{OUT\_CLOSE}(s) = \frac{H_{CLOSE} \cdot V_{IN}}{1 + H_{CLOSE} \cdot G} + \frac{V_{THD}}{1 + H_{CLOSE} \cdot G}$$

(3-4)

其中,H<sub>CLOSE</sub>为闭环模型的传递函数,G为反馈网络的反馈系数。 为了得到相同的放大倍数设计使得:

$$H_{OPEN}(s) = \frac{H_{CLOSE}}{1 + H_{CLOSE} \cdot G}$$

(3-5)

因此式(3-4)变为:

$$V_{OUT\_CLOSE}(s) = H_{OPEN}V_{IN} + \frac{V_{THD}}{1 + H_{CISCE} \cdot G}$$

(3-6)

总的谐波失真系数变为:

$$THD_{CLOSE} = \frac{\sqrt{\sum_{n=2}^{\infty} (V_{THD})^2}}{H_{OPEN} \cdot V_{IN} \cdot (1 + H_{CLOSE} \cdot G)}$$

(3-7)

比较式(3-3)与式(3-7)可以看出,闭环控制的 D 类功放的失真系数比开环时减小了  $(1+H_{CLOSE}\times G)$  倍,从而达到了改善 D 类功放 THD 性能的目的。

此外,若在图 3.2 的反馈设计中,采用求和积分器代替简单的加法器,则图 3.2 即为图 3.1 所示的闭环系统。因此从某种程度上说,D 类功放的失真可以认为是由环内噪声引起的。由此可知,本文介绍的噪声整形具有改善 D 类功放 THD 性能的功能。

若要获得更好的噪声整形效果和 THD 性能,可采用电压、电流双环反馈的方案,即电流反馈环为内环,电压反馈为外环,电压反馈环为电流反馈环提供参考信号。这种双环反馈方式可改善放大器带宽,增加放大器放大倍数的恒定性,获得良好的线性度,提高放大器效率[17][18]。

### 3.2 免除滤波器设计技术

### 一、D 类功放的输出级[19]

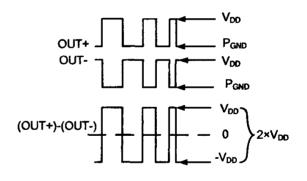

图 2.6 所示 D 类功放的输出级称之为"半桥"输出级。与之相对应的是"全桥"输出级,即 H 桥输出级。全桥电路使用两个半桥输出级,并以差分的方式驱动负载。这种负载连接方式通常称为桥接负载(BTL)。如图 3.3 所示,全桥结构是通过转换负载的导通路径来工作的。因此负载电流可以双向流动,无需负电源或隔直电容,而对于半桥输出级,传统 PWM 调制方案是必须要有隔直电容的。

图 3.3 D 类运放的 H 桥输出级

图 3.4 给出了基于 PWM 的 BTL型 D类放大器输出波形。在图 3.4 中,各输出波形彼此互补,从而在负载两端产生一个差分 PWM 信号。与半桥拓扑类似,输出端需要一个外部 LC 滤波器,用

以提取低频音频信号并防止在负载上耗散高频能量。

全桥式 D 类放大器除具有与 AB 类 BTL 放大器相同的优点外,还具有高效特性。BTL 放大器的 第一个优点是,采用单电源供电时输出端无需隔直电容。半桥式功放则不然,因为它的输出会在 VDD 与地之间摆动,输入空闲时输出占空比为 50%的方波。这意味着它的输出具有约 VDD/2 的直流偏移,这个直流偏移会在 D 类功

图 3.4 H 桥输出级的波形

放处于闲置状态时产生很大的功率损耗。全桥式放大器中,这个偏移会出现在负载的两侧,输出端的直流电流为零(如图 3.4 所示)。其具有的第二个优点是,在相同的电源电压下,输出信号摆幅是半桥式放大器的 2 倍。因为负载是差分驱动的,在相同电源电压下,理论上它可以提供的最大输出功率是半桥式放大器的 4 倍。

综合上述原因,本设计中选择全桥输出级为 D 类功放的输出级。其中 H 桥的 4 个开关管全部选择相同的 N 型 MOSFET。这是考虑到,首先,开关管选用 NMOS 可以减小输出级的芯片面积。其次,选用 NMOS 可以达到较好输出阻抗匹配目的,

降低输出级阻抗不匹配产生的失真。

### 二、免除滤波器的设计技术

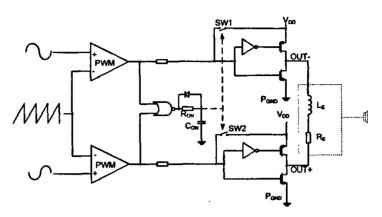

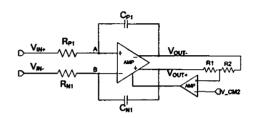

图 3.5 XPD7026 调制器简化框图

省掉或至少是最大限度的降低了对外部滤波器的要求。

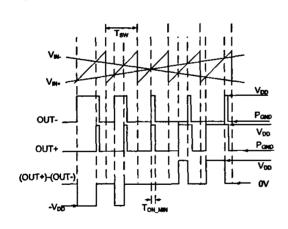

图 3.5 给出了 XPD7026 免滤波器调制方案的简化功能框图。与传统的 PWM型 BTL 放大器不同,每个半桥都有自己专用的 PWM 比较器,从而可以独立控制每个输出。调制器由差分音频信号和高频三角波驱动。当两个比较器输出均为低

图 3.6 免滤波器方案的输入输出波形

电平时,D类放大器的每个输出均为高。与此同时,或非门的输出变为高电平,但会因为 Ron和 Con组成的 RC 电路而产生一定的延迟。一旦或非门延时输出超出特定的门限,开关 SW1 和 SW2 随即闭合。这使得 OUT+和 OUT-变为低电平,并保持到下个采样周期的开始。这种设计使 得两个输出同时开通一段最短时间(ton\_min),这个时间由 Ron和 Con的值决定。

如图 3.6 所示,输入为零时,两个输出同相并具有 ton\_MIN 的脉冲宽度。随着音频信号的增加或减小,其中一个比较器会在另一个之前先翻转。这种工作特性外加最短时间导通电路的作用,将促使一个输出改变其脉冲宽度,另一个输出的脉冲宽度保持为 ton\_MIN。这意味着每个输出的平均值都包含输出音频信号的半波整流结果。对两路输出的平均值进行差值运算,便可得到完整的输出音频波形。

基于上述所述方案, XPD7026 的输出端在空闲时为同相信号, 所以负载两端没有差分电压, 从而最大限度地降低了静态功耗, 并且无需外部滤波。

## 3.3 EMI 改善技术

D 类功率放大器正常工作时处于非线性开关状态。开关电源由于快速变换而引起的电磁干扰 EMI(Electro Magnetic Interference)是 D 类放大器设计中应注意的又一个关键点<sup>[21]</sup>。

因长的非屏蔽扬声器连接线就象天线一样能发射电磁波。因此,重建滤波器可以起到防止幅射的重要作用。低截止频率的滤波器可以抑制 EMI,但是也损耗音频频谱的高端分量,而高截止频率会保持平坦的频率响应,却要付出增加 EMI 的代价。高阶滤波器可以满足这两种要求。在放大器内部,可以通过使输出级和滤波器之间的供电线和连接线尽可能短而降低 EMI。这些元件应该尽量与供电电源设计在同一块 PCB 上。由于降低了阻性损耗,短而宽的铜箔线也使得放大器的效率更高。但在多声道系统中,很难将大量的功率 MOSFET 靠近电源放置,为了防止串扰,XPD7026 在每端设计了一个低 ESR 的存储电容器。

在版图布局时,振荡器、PWM 比较器的版图设计需要特别注意,应尽量远离 其他模块电路。此外,为了防止来自其它系统模块的干扰在 PWM 信号中引入抖动, XPD7026 每一路运放均采用全差分结构。

另外,目前还有一种降低 EMI 的技术,即扩散频谱技术 (SSM)。扩频调制技术可以有效的展宽输出信号的频谱能量,而不是使频谱能量集中在开关频率及其各次谐波上,换句话说,输出频谱的总能量没有改变,只是重新分布在更宽的频带内,这样就降低了输出端的高频能量峰值,因此,将输出扬声器电缆辐射 EMI 的机会降至最少,虽然一些频谱噪声可能由扩频调制引入音频带宽内,这些噪声可以被反馈环路的噪声整形功能抑制掉。扩散频谱调制技术对于无滤波器 D 类功放的效率很重要,其可以减少输出端的高频能量损耗。

对于扩散频谱调制,可以利用伪随机序列产生振荡器充放电电流源的偏置电压,从而产生在一定范围内随机变化的调制频率,达到输出端频率扩散的目的。

# 第四章 XPD7026 的系统设计

前面已经介绍了有关 D 类功率放大器的相关原理,也提到本论文是在此理论研究的基础上设计了一款无滤波器立体声音频 D 类功率放大器专用芯片。本章将详细介绍 XPD7026 芯片的系统设计,包括系统性能参数设计、系统原理框图设计并重点讲述了 XPD7026 的反馈环路设计,最后介绍了 XPD7026 所采用的 BCD 工艺。

### 4.1 系统性能参数设计

根据前面的介绍,本设计采用全差分输入 PWM 控制模式。由于 XPD7026 是立体声 D 类功率放大器,所以其包含两路音频放大通路,分别称为左通路及右通路,左通路与右通路电路结构及设计参数是完全一样的。

一、芯片功能设计要求

XPD7026 是一款固定调制频率 PWM 控制模式的无需滤波器 D 类功放芯片。可应用于汽车音响、免提电话、LCD 监视器等电子设备。它具有以下一些功能。

- 1).无需输出滤波器;

- 2).输出功率可达 6W;

- 3).8Ω 负载下效率高达 85%;

- 4).10V 至 25V 单电源供电:

- 5).差分输入降低共模噪声;

- 6).引脚可控增益,减少元件数量:

- 7).较低工作静态电流(18mA):

- 8).具有短路、过流保护及过热保护功能:

- 芯片引脚功能设计如下。

Vpp (引脚 1): 该引脚为电路的输入电源。

PGND (引脚 2、18): 芯片的电源地。

C1N (引脚 3): 电荷泵飞电容的负端。

C1P (引脚 4): 电荷泵飞电容的正端。

VRFF 1 (引脚 5): 内部 6V 基准输出。

A<sub>GND</sub> (引脚 6): 模拟地。

INL-(引脚 7): 左声道音频信号反相输入端。

INL+(引脚 8): 左声道音频信号正相输入端。

INR-(引脚 9): 右声道音频信号反相输入端。

INR+(引脚 10): 右声道音频信号正相输入端。

SS (引脚 11): 软启动信号。

G1 (引脚 12): 增益选择输入端。

G2(引脚13):增益选择输入端。

OUTL-(引脚 14): 左声道音频输出负端。

OUTL+(引脚 15): 左声道音频输出正端。

OUTR-(引脚 16): 右声道音频输出负端。

OUTR+(引脚 17): 右声道音频输出正端。

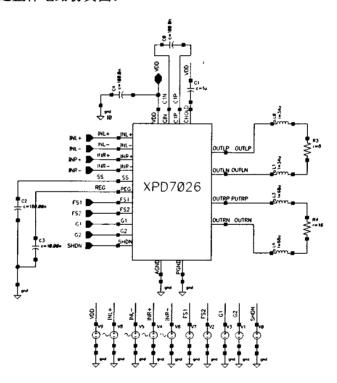

### 二、典型应用电路图

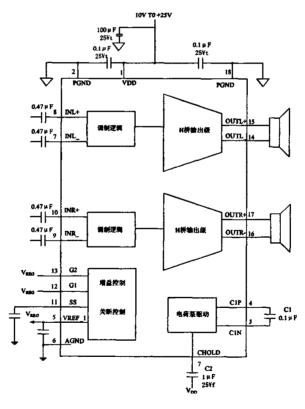

XPD7026 的典型应用电路如图 4.1 所示。

图 4.1 XPD7026 典型应用电路图

### 三、电特性指标

根据应用场合的要求以及工艺参数,参照国外新型芯片的参数指标,确定各电特性参数如下。

所设计的典型值的指标适用于  $V_{DD}$ =10V, $T_A$ =27℃。除特别说明外,最大/最小值均对应全温度范围( $T_I$ =-40℃~+105℃)。

表 4.1 电特性参数表

| 表 4.1 电符性参数表               |                                                |               |          |      |      |    |  |

|----------------------------|------------------------------------------------|---------------|----------|------|------|----|--|

| 符号                         | 参数说明                                           |               | 最小值      | 典型值  | 最大值  | 单位 |  |

| $\mathbf{V}_{\mathtt{DD}}$ | 对地的电压                                          |               | 10       |      | 25   | v  |  |

| I <sub>ss</sub>            | 静态电流的测量是在负载为无穷<br>大的条件下测得的,即 R <sub>L</sub> =∞ |               |          | 18   | 23   | mA |  |

| Turn_On Time               | C <sub>SS</sub> =180nF                         |               |          | 55   |      | mS |  |

| Output Offset Voltage      |                                                |               |          | ±6   | ± 30 | mV |  |

| Input Impedance            | A <sub>V</sub> =13dB                           |               | 35       | 58   | 80   | ΚΩ |  |

|                            | $A_V=16dB$                                     |               | 30       | 48   | 65   |    |  |

|                            | A <sub>V</sub> =19.1dB                         |               | 23       | 39   | 55   |    |  |

|                            | A <sub>V</sub> =22.1dB                         |               | 20       | 31   | 42   |    |  |

| Voltage Gain               | G1=L,G2=L                                      |               | 21.9     | 22.1 | 22.3 | dB |  |

|                            | G1=L,G2=H                                      |               | 18.9     | 19.1 | 19.3 |    |  |

|                            | G1=H,G2=L                                      |               | 12.8     | 13   | 13.2 |    |  |

|                            | G1=H,G2=H                                      |               | 15.9     | 16   | 16.3 |    |  |

| Gain Matching              | 两路前置运放增益的误差                                    |               |          | 0.5  |      | %  |  |

| PSRR                       | 200mVp-p                                       | Fripple=1kHz  |          | 76   |      | dB |  |

|                            |                                                | Fripple=20kHz |          | 60   |      |    |  |

| Output Power               | R <sub>L</sub> =16Ω                            |               | 5.5      | 8    |      | w  |  |

|                            | R <sub>L</sub> =8Ω                             |               |          | 6    |      |    |  |

| THD                        | $f_{IN}=1$ KHz, $R_L=8\Omega$ , Pout=4W        |               | <u> </u> | 0.09 |      | %  |  |

| Efficiency                 | Pout=5W, $f_{iN}$ =1KHz, $R_L$ =16 $\Omega$    |               |          | 85   |      | %  |  |

|                            | Pout=4W, $f_{IN}$ =1KHz, $R_L$ =8 $\Omega$     |               |          | 75   |      |    |  |

| Input Leakage<br>Current   |                                                |               |          | ± 1  |      | μΑ |  |

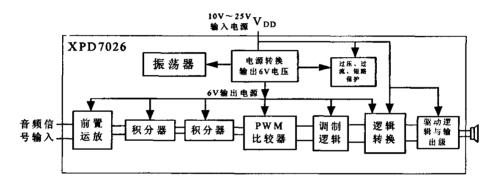

### 4.2 系统原理框图设计

#### 一、系统框图

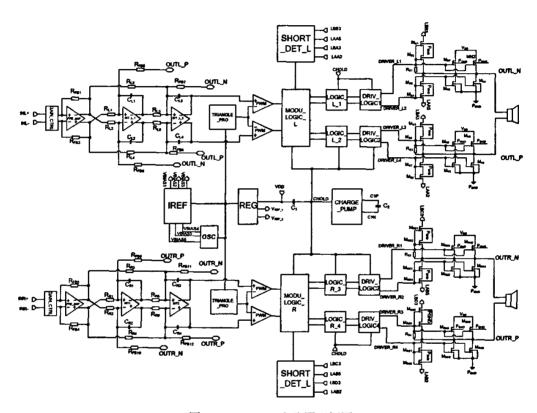

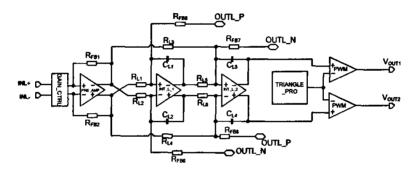

上一节介绍了系统的架构, 再结合电特性指标, 根据芯片需要完成的功能, 确定系统子模块框图如图 4.2 所示。电路大体上分为以下二十六个模块:

图 4.2 XPD7026 电路原理框图

基准模块 (REG): 该模块产生高压基准,用来作为内部电路的 6V 电源;电流基准模块 (IREF): 该模块产生系统的偏置电流;

振荡器模块(OSC)×2: 该模块产生用来对音频信号进行调制的三角波信号,送到 PWM 比较器。

电荷泵模块(CHARGE\_PUMP): 该模块产生 2 倍  $V_{DD}$  的电压,用以驱动 H 桥上半桥的 NMOS 开关管。

增益控制(GAIN\_CTRL)×2:该模块实际上为 2-4 编码器,产生编码信号用来控制前置运放的反馈电阻,实现音频信号的增益控制。

前置运算放大器(PRE\_AMP) ×2: 该模块实现音频信号的放大。

积分器(INTEGRATOR1/2) ×4: 该模块主要用来进行音频信号的噪声整形,

提高 THD+N 性能。

PWM 比较器×4: 该模块实现音频信号与调制三角波信号的比较,产生占空比随音频信号幅度变化的方波,送入调制逻辑。

调制逻辑(MODU\_LOGIC)×2: 该模块实现对已调制音频信号进行半波整形,以达到无需滤波器的目的。

驱动逻辑(DRIV LOGIC) ×4: 该模块产生驱动H桥开关管的驱动信号。

短路保护(SHOT\_DET)×2:该模块采样输出电流,当输出电流超过1A时强制关断开关管,实现芯片的过流、短路保护。

过温保护(OTP): 该模块实现芯片的过温保护, 当温度超过 150℃时, 功率 MOS 管被强制关断, 它有一个 30℃的迟滞量。

这二十六个模块是 XPD7026 芯片的主体电路,其中乘号表示模块电路功能完全相同或相似,对于关键模块详细的情况将在第五章中分别介绍。

#### 二、系统级功能描述

结合图 4.1 应用电路及图 4.2 的系统框图,从系统角度对 XPD7026 的工作情况进行描述。因为子模块内部具体工作情况将在下一章详细介绍,所以将不考虑各个子模块的内部工作原理,只介绍各个子模块的外部实现功能,从而清晰明了地介绍 XPD7026 的系统工作情况。

根据第三章已经知道,设计音频 D 类功放的实质就是产生占空比随音频信号幅度变化的方波信号,通过输出级解调还原出频率相同幅值放大的音频信号,从而实现音频信号的功率放大。XPD7026 采用固定的调制频率,并对输入音频信号进行半波整形配合 H 桥全桥输出级,实现了无需滤波器的 D 类功放的设计。D 类功放关键的设计技术主要有三点,即噪声整形技术、调制技术、反馈技术。这些技术涉及到 D 类功放的主要性能指标,如 THD+N、PSRR、线性度以及是否需要滤波器。XPD7026 的噪声整形技术采用二阶噪声整形可以获得较满意的 THD+N。

D 类功放的整体设计分为前端模拟及后端数字设计两大块。前端模拟设计部分主要包括:增益控制,前置放大,积分器,PWM 比较器模块。这主要实现了对输入音频信号进行预放大,噪声整形。后端数字设计部分主要实现对调制信号进行半波整形,驱动 H 桥输出级,实现无需滤波器的目的。

## 4.3 XPD7026 的反馈环路设计

第三章讲述了在 D 类功放中引入负反馈的必要性,本节详细介绍 XPD7026 的 反馈环路设计 $^{[22]}$ 。

PWM调制的增益是输出PWM信号幅度和输入三角波幅度之比,即:

$$G_{PWM} = \frac{V_P}{V_T} \tag{4-1}$$

其中  $V_P$  是 PWM 调制信号的幅值, $V_T$  是输入三角波的幅值。为了说明方便,将图 4.2 所示的系统框图简化为图 4.3 所示的单通道 D 类功放。

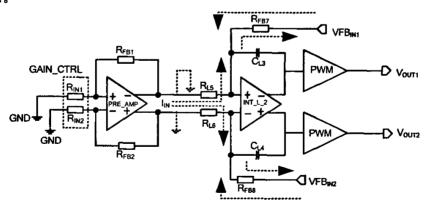

图4.3 单通道音频D类功放简化框图

对于图 4.3 计算其闭环增益为:

$$\frac{V_{OUT}}{V_{IN}} = \frac{R_{FB1}}{R_{IN1}} \cdot \frac{R_{FB7}}{R_{L5}} \tag{4-2}$$

其中电阻  $R_{FB1}$ 、 $R_{INI}$ 、 $R_{FB7}$ 、 $R_{L5}$  必须具有良好的线性度和匹配性,以获得良好的闭环性能。对于图 4.3 的反馈结构,将 PWM 比较器利用式(4-1)等效,如图 4.4 所示。

图4.4 单通道音频D类功放环路增益计算等效图

图 4.4 即为单通道 D 类功放环路增益计算的等效框图,由此可得:

$$V_{OUT} = \frac{V_{FBIN1,2}}{R_{FB7,8}} \cdot \frac{1}{s \cdot C_{L3,4}} \cdot G_{PWM} = \frac{V_{FBIN1,2}}{R_{FR7,8}} \cdot \frac{1}{s \cdot C_{L3,4}} \cdot \frac{V_P}{V_T}$$

(4-3)

则环路增益为:

$$H_{close}(s) = \frac{V_{OUT}}{V_{FRIVI_2}} = \frac{1}{R_{FR7.8} \cdot s \cdot C_{I3.4}} \cdot G_{PWM}$$

(4-4)

由式 (4-4)可得环路的单位增益带宽为:

$$f_{UGB} = \frac{G_{PWM}}{2\pi \cdot R_{FB7.8} \cdot C_{L3.4}} \tag{4-5}$$

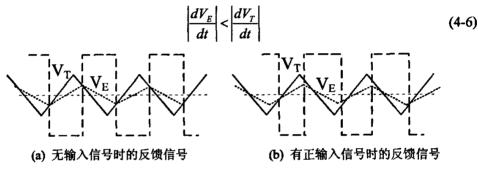

图4.5所示为放大器内部环路信号,V<sub>E</sub>为积分器的输出波形,V<sub>T</sub>为振荡器的输出波形。为了使这个音频功率放大器能够正常工作,振荡器三角波的幅度应该比积分器输出三角波的幅度大,更为准确的说是振荡器三角波的斜率应该比误差三角波的斜率大,否则就会出现发散的现象,即反馈不收敛而出现不稳定现象。

图4.5 单通道音频D类功放的内部反馈信号

由图 4.4 可知,输入积分器电容的电流为反馈电流  $I_{FB}$  和输入电流  $I_{IN}$  之和。输入信号为零的情况,如图 4.5(a)所示,反馈电流  $I_{FB}$  交替注入积分器电容里,积分器输出三角波的斜率为:

$$\left| \frac{dV_E}{dt} \right| = \frac{I_{FB}}{C} = \frac{V_{OUT}}{2R_{FB7.8} \cdot C_{L3.4}} \tag{4-7}$$

当有一个正输入信号电流注入这个环路时,积分器输出三角波的下降沿斜率变的更大,上升沿斜率变的更小,如图 4.5(b)所示,输出信号的占空比开始发生变化。

当输入信号电流 $I_{IN}$ 等于反馈信号电流 $I_{FB}$ 时,音频功率放大器的调制深度是 100%,误差三角波 $V_E$ 的下降沿斜率大约是没有输入信号时的两倍,整个环路收敛 和稳定的标准是:

$$2\left|\frac{dV_E}{dt}\right| < \left|\frac{dV_T}{dt}\right| \tag{4-8}$$

V<sub>c</sub>的最大斜率是:

$$2\left|\frac{dV_E}{dt}\right| = \frac{V_{OUT}}{R_{ER7.8} \cdot C_{I3.4}} \tag{4-9}$$

调制三角波的斜率为:

$$\left| \frac{dV_T}{dt} \right| = 2 \cdot V_T \cdot f_C \tag{4-10}$$

根据式(4-5)、式(4-8)~式(4-10)可以得到 D 类功放单位增益带宽与调制频率之间的关系为:

$$f_{UGB} < \frac{f_C}{\pi} \tag{4-11}$$

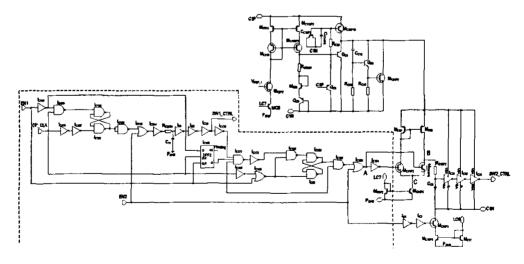

以上以单极点系统为例介绍了 XPD7026 的反馈环路设计,实际中 XPD7026 采用二阶环路反馈系统,因此在音频带宽内具有更高的增益,以及具有更好的 THD 性能和 PSRR 性能。图 4.6 即为 XPD7026 完整的反馈环路电路图。

图 4.6 XPD7026 完整的反馈环路电路图

根据图 4.6 所示的电路图, 计算其环路增益:

$$H_{close}(s) = \frac{V_{OUT}}{V_{FBIN}} = \frac{R_{FB7} + R_{FB5} \cdot R_{L5} \cdot C_{L1} \cdot s}{R_{FB5} \cdot R_{L5} \cdot R_{FB7} \cdot C_{L1} \cdot C_{L3} \cdot s^2} \cdot G_{PWM}$$

(4-12)

根据式(4-12)可知,系统环路中存在一个左半平面的零点:

$$\omega_z = \frac{R_{FB7}}{R_{FB5} \cdot R_{L5} \cdot C_{L1}} \tag{4-13}$$

因此只要合理设计 R<sub>FB7</sub>、R<sub>FB5</sub>、以及 R<sub>L5</sub> 的阻值,系统的环路相位裕度是可以 保证的。由于环路的反馈波形与上述的一阶系统相似,在此就不再赘述。

这样, XPD7026 不仅具有二阶噪声整形的环路特性, 而且比一阶系统具有更高的环路增益, 这为 XPD7026 获得较好的 THD 以及 PSRR 性能提供了理论基础。

## 4.4 工艺介绍

由前面的叙述可知 XPD7026 是功率芯片,那么自然就会想到高压,所以 XPD7026 采用了高压工艺设计,即国外某公司 0.6µm BCD 工艺。BCD 工艺是目前 国内较新的一种工艺,但国外已经使用地非常普遍了,BCD 工艺即 Bipolar、CMOS、 DMOS 器件可在同一个芯片中同时采用,它是一个比较完整的可以制作任何器件

的一种工艺。下面详细地介绍一下 BCD 工艺[8][9][10]。

BCD 工艺把 Bipolar 器件、CMOS 器件和 DMOS 器件同时制作在同一芯片上。了解 BCD 工艺的特点,需要先了解 Bipolar、CMOS 和 DMOS 这三种器件的特点,详见表 4.2。它综合了双极器件高跨导、强负载驱动能力和 CMOS 集成度高、低功耗的优点,使其互相取长补短,发挥各自的优点。更为重要的是,它集成了 DMOS 功率器件,DMOS 可以在开关模式下工作,功耗极低。不需要昂贵的封装和冷却系统就可以将大功率传递给负载。低功耗是 BCD 工艺的一个主要优点之一。整合过的 BCD 工艺制程,可大幅降低功率耗损,提高系统性能,节省电路的封装费用,并具有更好的可靠性。

| 器件类别    | 器件特点                  | 应用             |  |  |

|---------|-----------------------|----------------|--|--|

| Bipolar | 两种载流子都参加导电,驱动能力强,工作   | 模拟电路对性能要求较高的   |  |  |

|         | 频率高,集成度低              | 部分(高速、强驱动、高精度) |  |  |

| CMOS    |                       | 适合做逻辑处理,模块电路的  |  |  |

|         | 集成度高,功耗低,与数字工艺兼容      | 输入,也可做输出驱动     |  |  |

| DMOS    | 高压大电流驱动(器件结构决定漏端能承受   | 模拟电路和驱动,尤其是高压  |  |  |

|         | 高压,高集成度可在小面积内做超大 W/L) | 功率部分,不适合做逻辑处理  |  |  |

表 4.2 Bipolar、CMOS 和 DMOS 器件的特点

#### 一、BCD 工艺的基本要求

首先,BCD 工艺必须把双极器件、CMOS 器件和 DMOS 器件同时制作在同一芯片上,而且这三种器件在集成后应基本上能具有各自分立时所具有的良好性能。 其次,BCD 工艺制造出来的芯片应具有更好的综合性能。此外,相对于其中最复杂的工艺(如双阱、多层布线、多层多晶硅的 CMOS 工艺)不应增加太多的工艺步骤。

#### 二、BCD 工艺兼容性考虑

BCD工艺典型器件包括低压CMOS管、高压MOS管、各种击穿电压的LDMOS、垂直NPN管、垂直PNP管、横向PNP管、肖特基二极管、阱电阻、多晶电阻、金属电阻等,有些工艺甚至还集成了EEPROM、结型场效应管JFET等器件。由于集成了如此丰富的器件,这就给电路设计者带来极大的灵活性,可以根据应用的需要来选择最合适的器件,从而提高整个电路的性能。

由于BCD工艺中器件种类多,必须做到高压器件和低压器件的兼容;双极工艺和CMOS工艺的兼容,尤其是要选择合适的隔离技术;为控制制造成本,必须考虑光刻版的兼容性。考虑到器件各区的特殊要求,为减少工艺制造用的光刻版,应尽量使同种掺杂能兼容进行。因此,需要精确的工艺模拟和巧妙的工艺设计,有时必须在性能与集成兼容性上作折中选择。通常BCD采用双阱工艺,有的工艺

会采用三阱甚至四阱工艺来制作不同击穿电压的高压器件。

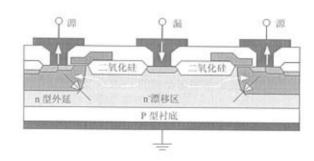

#### 三、DMOS 器件的结构、工作原理与特点

功率输出级DMOS管是此类电路的核心,往往占据整个芯片面积的1/2~2/3,它是整个集成电路的关键。DMOS与CMOS器件结构类似,也有源、漏、栅等电极,但是漏端击穿电压高。DMOS主要有两种类型,垂直双扩散金属氧化物半导体场效应管VDMOSFET(vertical double-diffused MOSFET)和横向双扩散金属氧化物半导体场效应管LDMOSFET(lateral double-diffused MOSFET)。

LDMOS由于更容易与CMOS工艺兼容而被广泛采用。LDMOS器件结构如图 4.7所示,LDMOS是一种双扩散结构的功率器件。这项技术是在相同的源/漏区域注入两次,一次注入浓度较大的砷(As),另一次注入浓度较小的硼(B)。注入之后再进行一个高温推进过程,由于硼扩散比砷快,所以在栅极边界下会沿着横向扩散更远(图中P阱),形成一个有浓度梯度的沟道,它的沟道长度由这两次横向扩散的距离之差决定。为了增加击穿电压,在源区和漏区之间有一个漂移区。LDMOS中的漂移区是该类器件设计的关键,漂移区的杂质浓度比较低,因此,当LDMOS 接高压时,漂移区由于是高阻,能够承受更高的电压。图4.7所示LDMOS的多晶扩展到漂移区的场氧上面,充当场极板,会弱化漂移区的表面电场,有利于提高击穿电压。场极板的作用大小与场极板的长度密切相关。要使场极板能充分发挥作用,一要设计好SiO2层的厚度,二要设计好场极板的长度。

图4.7 LDMOS结构图

DMOS器件是由成百上千单一结构的DMOS单元所组成的。这些单元的数目是根据一个芯片所需要的驱动能力所决定的,DMOS的性能直接决定了芯片的驱动能力和芯片面积。对于一个由多个基本单元结构组成的LDMOS器件,其中一个最主要的考察参数是导通电阻,用R<sub>ds(on)</sub>表示。导通电阻是指在器件工作时,从漏到源的电阻。对于 LDMOS器件应尽可能减小导通电阻,就是BCD工艺流程所追求的目标。当导通电阻很小时,器件就会提供一个很好的开关特性,因为漏源之间小的导通电阻,会有较大的输出电流,从而可以具有更强的驱动能力。DMOS的主要技术指标有:导通电阻、阈值电压、击穿电压等。

对LDMOS而言,外延层的厚度、掺杂浓度、漂移区的长度是其最重要的特性参数。可以通过增加漂移区的长度以提高击穿电压,但是这会增加芯片面积和导通电阻。高压DMOS器件耐压和导通电阻取决于外延层的浓度、厚度及漂移区长度的折衷选择。因为耐压和导通阻抗对于外延层的浓度和厚度的要求是矛盾的。高的击穿电压要求厚的轻掺杂外延层和长的漂移区,而低的导通电阻则要求薄的重掺杂外延层和短的漂移区,因此必须选择最佳外延参数和漂移区长度,以便在满足一定的源漏击穿电压的前提下,得到最小的导通电阻。另外,由于DMOS芯片面积大,对缺陷密度较敏感。

#### 四、BCD 工艺发展趋势

BCD工艺技术的发展不像标准CMOS工艺那样,一直遵循Moore定律向更小线宽、更快的速度方向发展。BCD工艺朝着三个方向分化发展:高压、高功率、高密度。

#### 1.高压 BCD

主要的电压范围是 500~700V,目前用来制造 LDMOS 的唯一方法为 RESURF 技术,原意为降低表面电场(reduced surface field)<sup>[9][10]</sup>,在 1979 年由 J.A.Appels 等人提出。它是利用轻掺杂的外延层制作器件,使表面电场分布更加平坦从而改善表面击穿的特性,使击穿发生在体内而非表面,从而提高器件的击穿电压。高压 BCD 主要的应用领域是电子照明(electronic lamp ballasts)和工业应用的功率控制。

#### 2. 高功率 BCD

主要的电压范围是40~90V,主要的应用为汽车电子。它的需求特点是大电流驱动能力、中等电压,而控制电路往往比较简单。因此主要发展趋势侧重于提高产品的鲁棒性(robustness),以保证在恶劣的环境下应用能够具备良好的性能和可靠性:另一个方面是降低成本。

#### 3.高密度 BCD

主要的电压范围是5~50V,一些汽车电子应用会到70V。在此应用领域,BCD 技术将集成越来越复杂的功能,今天,有的产品甚至集成了非挥发性存储器。许 多电路集成密度如此之高,以致于需要采用数字设计的方法(如集成微控制器) 来实现最佳驱动以提高性能。这代表了持续增长的市场需求,即将信号处理器和 功率激励部分同时集成在同一块芯片上。它不仅仅是缩小了系统体积和重量,更 带来了高可靠性,减少了各种电磁接口。由于有着非常广阔的市场应用前景,代 表了BCD工艺的主流方向,也是最大的应用领域。

最新的BCD工艺趋向于采用先进的CMOS工艺平台,根据不同的应用场合呈现模块化和多样性的特点。高密度BCD工艺发展的一个显著趋势是模块化的工艺开

发策略被普遍采用。所谓模块化,是指将一些可选用的器件做成标准模块,根据应用需要选用或省略该模块。模块化代表了BCD工艺发展的一个显著特征,采用模块化的开发方法,可以开发出多种不同类型的IC,在性能、功能和成本上达到最佳折中,从而方便地实现产品的多样化,快速满足持续增长的市场需求。自0.6µm线宽以下BCD工艺普遍采用双栅氧,薄栅氧实现低压CMOS,厚栅氧用于制造高压DMOS。此外,一种新型的大斜角注入工艺正被采用以减少热过程。

#### 五、BCD 工艺在 XPD7026 电路设计中的应用

在 XPD7026 具体电路设计中,主要利用 BCD 工艺中 DMOS 器件具有高击穿电压特性来设计高压向低压转换以及低压向高压转换的模块电路。图 4.8 所示为芯片内电源转换过程的示意图。由图 4.8 可知,芯片外部电源电压在芯片内进行了转换。芯片内大部分模块均处于低压工作状态,从而大大降低了系统的静态功耗。

图4.8 XPD7026片内电源电压分配示意图

另外,采用 DMOS 器件可以作为高电源电压运放的偏置电路和有源负载以适应过压、过流、短路保护模块的需要。

# 第五章 XPD7026 主要模块电路设计与仿真验证

前面详细介绍了 XPD7026 的设计原理及系统设计要求,根据芯片的系统结构设计,将 XPD7026 划分为二十六个模块。本章将针对所选取的工艺,对其中一些重要的子模块电路进行详细的分析、设计,并给出关键的仿真波形。

### 5.1 基准电路设计

#### 一、模块电路功能

该模块的主要功能是产生一个受电源电压、温度变化影响较小的基准电压 V<sub>REF</sub> 和基准电流 I<sub>REF</sub>。XPD7026 中电压基准电路的设计与传统基准的设计有所不同,因为该基准不仅可以输出一个 6V 的稳定电压,而且可以输出高达 20mA 的电流,因此该基准可以作为芯片的片内电源使用。这样不仅降低了芯片的成本,而且减小了芯片的面积,降低了系统的静态电流。

该基准采用传统的一阶温度补偿方案,下面详细介绍。

# 二、电路设计[23][24][26]

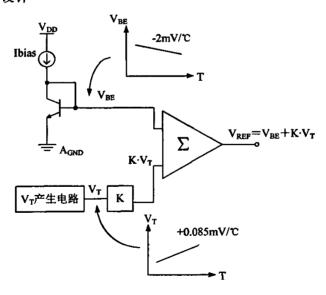

图 5.1 带隙基准原理示意图

带隙基准电路的基本思想是利用晶体管的发射结电压  $V_{BE}$  具有负温度系数,而热电压  $V_{T}$ =kT/q 具有正温度系数的特性,将两者结合可以获得零温度系数很小的基准电压。可以从图 5.1 得到输出基准电压表达式为:

$$V_{REF} = V_{BE} + KV_{T} = V_{g0} - C \cdot T + K \frac{kT}{q}$$

(5-1)

其中  $V_{g0}$  是半导体在绝对零度(0K)下的带隙电压,即禁带宽度。硅材料的  $V_{g0}$  为 1.25V,锗材料的值为 0.72V,该值是一个固定不变的电压量,C 是常数,T 是温度。若选择合适的 K 值使式(5-1)中的后两项抵消,则  $V_{REF}=V_{g0}$  就是与温度 几乎无关的电压量。

传统的高电源电压基准如图 5.2 所示,为典型的带隙基准结构,由三个 NPN 晶体管、两个 PMOS 晶体管和五个电阻组成。

图  $5.2 + M_{P1}$ 、 $M_{P2}$  为 LDMOS 管, $V_{DD}$  的大部 分压降均落在  $M_{P1}$ 、 $M_{P2}$ 上 ,因此该电路可以承受较高的电源电压。若忽略三极管的基极电流,则有:

$$I_1 = I_2 \tag{5-2}$$

$$V_{RE1} + I_1 R_1 = V_{RE2} (5-3)$$

X | I<sub>1</sub> | Q<sub>3</sub> | V<sub>0</sub> | Q<sub>3</sub> | V<sub>0</sub> | Q<sub>1</sub> | Q<sub>1</sub>

图 5.2 传统带隙基准电路图

且有:

$$V_{BE1} = V_T \ln(I_1 / I_{S1}) \tag{5-4}$$

$$V_{RE2} = V_T \ln(I_2 / I_{S2}) \tag{5-5}$$

$$V_{REF} = V_{RE2} + (I_1 + I_2)R_2 (5-6)$$

$$V_O = V_{RFF} (1 + R_4 / R_5) \tag{5-7}$$

由式(5-2)~式(5-7)可以得到:

$$V_O = (V_{BE2} + 2V_T \ln N \cdot \frac{R_2}{R_1})(1 + \frac{R_4}{R_5})$$

(5-8)

其中  $N=I_{S1}/I_{S2}$  为  $Q_{N1}$  和  $Q_{N2}$  的发射极面积之比。 $V_{BE2}$  的温度系数 $^{[27]}$  为  $-1.5 \text{mV/}^{\circ}\text{C}$ ,  $V_{T}$  的温度系数为 $+0.086 \text{mV/}^{\circ}\text{C}$ , 所以选择适当的 N 值和  $R_{2}/R_{1}$  的比值,就可以得到零温度系数的输出电压。另外,调节  $R_{4}$  和  $R_{5}$  的比值,可以得到期望的基准电压,且不会改变已调整好的零温度系数特性。

但实际中三极管  $Q_3$  的基极电流使得  $I_1$  并不完全等于  $I_2$ ,并且  $Q_1$ 、 $Q_2$  的基极电流流过电阻  $R_4$ ,使得基准输出存在较大的误差。虽然通过设定合适的  $R_3$  值可以补偿  $Q_1$ 、 $Q_2$  基极电流引起的误差,但  $Q_3$  基极电流引起的误差却无法补偿  $P_1$  以补偿  $P_2$  构成电流镜结构,其中二极管形式连接的  $P_2$  的集电极直接对电源  $P_3$  以为进行箝位,而  $P_3$  以为成的负反馈使得  $P_4$  点电位与  $P_4$  点电位相等,所以该电路的  $P_4$  好低,稳定性较差  $P_4$  。

基于上述缺点,传统高电源电压基准虽然可以输出较高的直流电压,但并不 能作为片内电源使用。

#### 三、电压基准电路设计

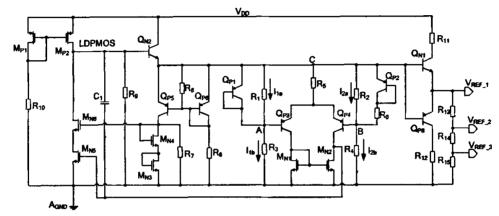

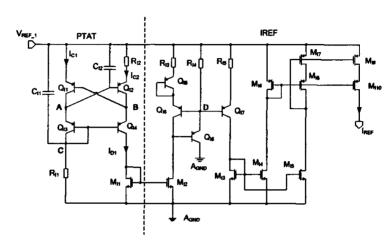

图 5.3 所示即为 XPD7026 所设计的高电源电压基准实际电路。该电路采用带隙原理,可实现高电压、大电流输出,可以作为芯片内部电源使用。下面分析该电路的具体工作情况。

由图 5.3 可知  $Q_{P1}$ 、 $Q_{P2}$ 、 $R_0$ ~ $R_4$  组成带隙基准的核心电路;  $Q_{P3}$ 、 $Q_{P4}$  以及  $M_{N1}$ 、 $M_{N2}$ 、 $R_5$  构成差分运算放大器, $M_{N5}$ 、 $M_{N6}$ 、 $M_{P2}$  为共源共栅放大电路, $Q_{N2}$  为射随器;  $Q_{N1}$ 、 $Q_{P8}$ 、 $R_{11}$  和  $R_{12}$  构成了推挽输出级以输出基准电压  $V_{REF\_1}$ 。

图 5.3 XPD7026 所设计的高压基准电路图

其中差分运放、共源共栅放大器以及  $Q_{N2}$  构成了一个负反馈环路,使得差分运放的输入端电压相等,即  $V_A=V_B$ ,且令  $R_1=R_2$ 、 $R_3=R_4$ ,可得:

$$I_{1a} = I_{2a} = \frac{V_{EB\_QP1}}{R_{1.2}} \tag{5-9}$$

$$I_{1b} = I_{2b} = \frac{V_{A,B}}{R_{3A}} \tag{5-10}$$

电阻 Ro两端的电压差为:

$$V_{EB\_QP1} - V_{EB\_QP2} = \Delta V_{EB} \tag{5-11}$$

流过电阻 Ro 的电流为:

$$I_{R0} = \frac{\Delta V_{EB}}{R_0} \tag{5-12}$$

由式(5-9)、 (5-12)可以计算出电流 I<sub>1b</sub>、 I<sub>2b</sub> 的大小, 即为:

$$I_{1b} = I_{2b} = \frac{V_{EB\_QP1}}{R_{12}} + \frac{\Delta V_{EB}}{R_0}$$

(5-13)

由式(5-10)可得到 A、B 两点的电压值:

$$V_{A} = V_{B} = R_{3,4} \left( \frac{V_{EB\_QPI}}{R_{1,2}} + \frac{\Delta V_{EB}}{R_{0}} \right)$$

(5-14)

这样即可得到基准电压:

$$V_{REF\_1} = V_{A,B} + V_{EB\ QP1} - V_{BE\ QN1}$$

(5-15)

设 V<sub>EB QPI</sub>≈V<sub>BE QNI</sub>, I<sub>C QPI</sub>= I<sub>C QP2</sub> 可得:

$$V_{REF\_1} = V_{A,B} = R_{3,4} \left( \frac{V_{EB\_QP1}}{R_{1,2}} + \frac{\Delta V_{EB}}{R_0} \right) = \frac{R_{3,4}}{R_{1,2}} \left( V_{EB\_QP1} + \frac{R_{1,2} \cdot V_T \cdot \ln N}{R_0} \right)$$

(5-16)

其中N为Om与On的发射极面积之比。

由式(5-16)可知通过选择合适的  $R_{1,2}$ 与  $R_0$ 的比值,即可得到典型的零温度系数电压(1.25V),而调节  $R_{3,4}$ 与  $R_{1,2}$  的比值即可得到需要的高压输出。

由于反馈环路中第二级运放采用 Cascode 输入级,因此图 5.3 中利用  $Q_{P5}$ 、  $Q_{P6}$ 、 $M_{N3}$ 、 $M_{N4}$  和  $R_6$ 、 $R_7$ 、 $R_8$  构成不随电源电压变化的直流偏置电路,为  $M_{N6}$  提供稳定的偏置,使  $M_{N5}$  一直处于饱和区,使得共源共栅放大器的增益稳定。电容 C1 为环路的密勒补偿电容。另外,设计中差分运放的电源电压直接采用基准电压,可以减小运放的电源噪声,从而提高反馈环路的稳定性[30]。

由于电路输出级为推挽输出,这样基准电路不仅可以提供足够大的驱动电流, 而且具有较小的输出阻抗,因此可以作为片内电源使用。

对于基准电路通常要考虑电路的启动问题。差分运放的两条支路允许零电流存在,即  $I_{1b}=I_{2b}=0$ ,因此  $I_{C\_QP1}=I_{C\_QP2}=0$ ,此时基准无法建立。这便需要启动电路来使基准摆脱零电流状态<sup>[25]</sup>。图 5.3 中自偏置电流源  $M_{P1}$ 、 $M_{P2}$  以及射随器  $Q_{N2}$  可以完成启动电路的功能。

在电路上电时, $M_{P1}$ 产生参考电流, $M_{P2}$ 管导通,从而  $Q_{N2}$ 的基极被拉至高电位, $Q_{N2}$ 得以导通,其射极电流注入基准核心电路,使得基准摆脱零电流状态,基准得以启动。当上电完成后, $M_{P2}$ 即作为共源共栅放大器的有源负载,且承受较高的电源电压。

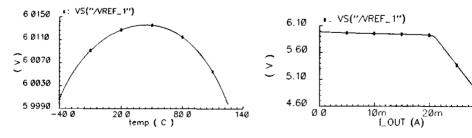

#### 四、电压基准的仿真结果

设计中取  $R_{1,2}$ =22k $\Omega$ ,  $R_{3,4}$ =106k $\Omega$ ,  $R_0$ =2.5k $\Omega$ , N=8 则可得到 6V 的输出电压。基于某公司 0.6 $\mu$ m BCD 工艺对电路进行了整体仿真,图 5.4 为基准温度特性的仿真结果。由图 5.4 可知,在-40 $^{\circ}$ C~125 $^{\circ}$ C之间基准输出变化了 13.2mV,温度系数为 13.3ppm/ $^{\circ}$ C。

图 5.4 基准输出的温度特性

图 5.5 基准输出随负载电流变化的仿真结果

30m

图 5.5 为基准输出随负载电流变化的仿真结果,由图 5.5 可知,所设计的基

准最大输出电流可达 20mA, 且在输出电流由零到 20mA 之间输出电压变化了 55mV, 电压变化率为 0.9%。

图 5.6 为基准输出随电源电压变化的仿真结果, 由图 5.6 可知, 基准输出在 电源电压由 8V~30V 之间变化了 72.3mV, 电压变化率为 0.3%。由此可见, 所设 计的基准电路在宽电源电压范围内可以保持较好的稳定性。

图 5.6 基准输出随电源电压变化的仿真结果

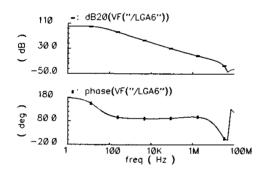

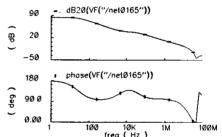

图 5.7 基准的 PSRR

图 5.7 为基准电源电压抑制的仿真结果,由图 5.7 可知,当频率为 1MHz 时, 基准的 PSRR 为 51dB, 可见所设计的基准具有良好的稳定性。

图 5.8 为基准启动仿真结果,由图 5.8 可知所设计的基准具有自启动功能,且启动 后可以保持很好的稳定性[31]。

## 五、电流基准电路设计

本设计中的电流基准具体电路如图 5.9 所示。

此模块采用带隙结构, 利用负温度系数 的 Ver 与具有一定加权系数的具有正温度系 数的  $\Delta V_{BE}$  相加得到零温度系数的基准电压,进而产生基准电流。

图 5.8 基准启动的仿真结果

三极管 Q<sub>11</sub> 和 Q<sub>12</sub> 构成反馈电路,发射极面积比为 1:8。三极管 Q<sub>13</sub> 和 Q<sub>14</sub> 发 射极面积相等且匹配,因此当 Q<sub>13</sub> 和 Q<sub>14</sub> 导通时, A、B 两点电压相等,从而两者 集电极电流相等,产生PTAT电流,其计算公式如下:

$$I_{C1} = I_{S1} \cdot e^{\frac{V_{REF_{-1}} - V_{B}}{V_{T}}}$$

(5-17)

$$I_{C2} = I_{S2} \cdot e^{\frac{V_{REF_1} - I_{D1} \cdot R_{I2} - V_A}{V_I}}$$

(5-18)

$$\frac{I_{C1}}{I_{C2}} = \frac{I_{S1}}{I_{S2}} \cdot e^{\frac{I_{D1} \cdot R_{I2} + V_A - V_B}{V_T}}$$

(5-19)

$$I_{C3} = I_{S3} \cdot e^{\frac{V_A - V_C}{V_T}} \tag{5-20}$$

$$I_{C4} = I_{S4} \cdot e^{\frac{\nu_B - \nu_C}{\nu_T}} \tag{5-21}$$

图 5.9 电流基准电路图

$$\frac{I_{C3}}{I_{C4}} = \frac{I_{S3}}{I_{S4}} \cdot e^{\frac{V_A - V_B}{V_T}}$$

(5-22)

由式(5-19)和式(5-22)得:

$$e^{\frac{V_A - V_B}{V_T}} = \frac{1}{2} e^{\frac{I_{D1} \cdot R_{I_2} + V_A - V_B}{V_T}}$$

(5-23)

$$V_T \ln 8 = I_{D1} \cdot R_{I2} \tag{5-24}$$

$$I_{D1} = \frac{V_T \ln 8}{R_{I2}} \tag{5-25}$$

因为  $V_T$  是正温度系数的电压值,所以流过  $Q_{14}$  的电流  $I_{D1}$  为 PTAT 电流。电阻  $R_{14}$  和三极管  $Q_{18}$  用于补偿三极管  $Q_{16}$  的基极电流  $[^{32}]$ ,使镜像更加准确。

由于 $V_D = V_{REF\_1} - I_{D1} \cdot R_{I3} - (V_{BES} + V_{BE6})$ ,可以通过设计合适的  $R_{I1}$  和  $R_{I2}$ ,使得  $I_{D1} \cdot R_{I3}$  的温度系数与  $V_{BE5,6}$  的温度系数抵消,这样可以得到正温度系数的  $V_D$ ,其与三极管  $Q_{I7}$  的 BE 结的负温度系数电压  $V_{BE}$  相抵消,在电阻  $R_{I5}$  上产生零温度系数的电压,进而产生零温度系数的电流。即有:

$$I_{REF} = \frac{1}{R_{I5}} (V_T \ln 8 \frac{R_{I3}}{R_{I2}} + V_{EB5})$$

(5-26)

由式(5-26)可知, IREF 即为零温度系数的电流。

## 六、电流基准模块仿真结果

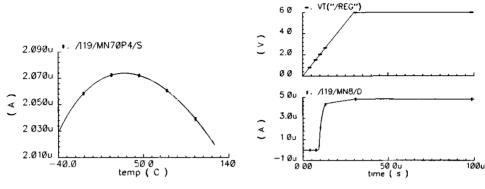

图 5.10 为基准电流随温度变化的仿真结果,由图 5.10 可知所设计的基准电流在全温度范围内变化了 49.1nA,满足设计要求。

图 5.10 基准电流随温度变化的仿真波形

图 5.11 启动信号仿真波形

图 5.11 为基准电流启动仿真结果,由图 5.11 可知所设计的基准具有自启动功能,且启动后可以保持很好的稳定性。

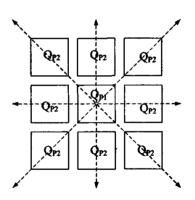

### 七、基准核心的版图设计

基准核心的版图设计对基准的精度有至关重要的影响<sup>[36]</sup>。为了保证 Q<sub>P1</sub>(Q<sub>I1</sub>)与 Q<sub>P2</sub>(Q<sub>I2</sub>)只有面积上的差别即减少扩散浓度等加工误差,在版图设计中将基准核心的 PNP 管排成 3×3 或 5×5 的阵列,且将它们的发射极放在同一基极扩散区内,采用共质心版图设计可以有效解决三极管不匹配的问题。对于电压基准电路中的 Q<sub>P1</sub>、Q<sub>P2</sub> 的版图设计如图 5.12 所示。对于电流基准电路中的 Q<sub>I1</sub>、Q<sub>I2</sub> 也有相同的版图结构。

图 5.12 基准核心 BJT 的版图设计

## 5.2 增益控制及前置运放的设计

#### 一、模块电路功能

增益控制完成的主要功能是根据输入引脚 G1、G2 的状态输出 4 位数字信号,控制前置运放的输入级,以实现前置运放的增益控制,也即实现了输出音量的控制。

前置运算放大器实现对输入音频信号的预放大处理,使得音频信号的幅值满足 PWM 比较的要求。

## 二、增益控制逻辑实际电路图

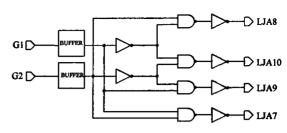

图 5.13 为实际设计电路的原理图,由此可见增益控制逻辑实际为 2-4 编码器的组合数字逻辑<sup>[33]</sup>。

考虑到 G1、G2 为片外引 脚信号,在增益控制逻辑中加 入BUFFER 电路可以防止 G1、

图 5.13 增益控制逻辑的实际电路

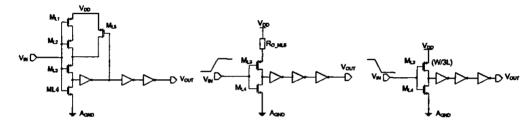

G2 的抖动引起增益控制逻辑的非正常翻转,即通过  $M_{L5}$  引入迟滞量。图 5.14(a) 为增益控制逻辑中 BUFFER 的实际电路图。下面对该电路进行详细的分析。

(a)实际电路

(b)输入由低向高翻转的等效电路 (c)输入由高向低翻转的等效电路 图 5.14 BUFFER 的实际电路图及其等效图

当输入信号由低向高跳变,则 BUFFER 电路等效为图 5.14(b)所示的电路。对此可以得到非门的翻转阈值为:

$$V_{T_{-1}} = \frac{V_{DD} - V_{THN} - V_{THP} - I_D \cdot R_{O_{-}ML5}}{1 + \sqrt{\frac{\beta_{ML4}}{\beta_{Ml3}}}} + V_{THN}$$

(5-27)

其中, $V_{THN}$ 、 $V_{THP}$ 分别为 NMOS 和 PMOS 管的阈值电压, $R_{O\_MLS}$  为  $M_{LS}$  工作在线性区的导通电阻, $I_D$  为电路的导通电流。  $\beta$  为 MOS 管的导电因子。

当输入信号由高向低跳变, 考虑到  $M_{L1}$ ~ $M_{L3}$  的宽长比相等,则 BUFFER 电路等效为图 5.14(c)所示的电路。对此可以得到非门的翻转阈值为:

$$V_{T_{2}} = \frac{V_{DD} - V_{THN} - V_{THP}}{1 + \sqrt{\frac{3 \cdot \beta_{ML4}}{\beta_{ML3}}}} + V_{THN}$$

(5-28)

则由式(5-27)和式(5-28)可以得到 BUFFER 电路的翻转阈值的迟滞量为:

$$\Delta V = V_{T-1} - V_{T-2} \tag{5-29}$$

三、增益控制逻辑具体电路分析

增益控制逻辑的真值表如表 5.1 所示。

| G1 G2 | LJA7 | LJA8 | LJA9 | LAJ10 |

|-------|------|------|------|-------|

| 00    | 0    | 0    | 0    | 1     |

| 0 1   | 0    | 1    | 0    | 0     |

| 10    | 0    | 0    | 1    | 0     |

| 1 1   | 1    | 0    | 0    | 0     |

| 10    | 0    | 0    | 0    | 0     |

表 5.1 增益控制逻辑的真值表

由增益控制逻辑的真值表可以看出其逻辑功能是实现 2-4 编码器的功能。输出 4 位数字信号控制前置运放的输入级,以实现前置运放的增益控制。 四、增益控制的原理

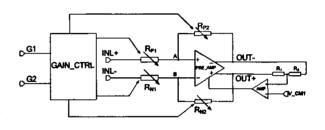

图 5.15 为整个增益控制的等效架构图。由等效架构图可知,增益控制的实质是增益控制逻辑输出相应的数字编码来改变前置运放的反馈电阻,从而实现输入音量的增益控制。

图 5.15 增益控制模块的等效架构图

前置运放为一个全差分运

放<sup>[34][35]</sup>,其接成负反馈形式。这样,如果运放的开环增益足够大,则A、B点即为虚地点,全差分运放的闭环增益为:

$$\frac{V_{OUT-}}{V_{INL+}} = -\frac{R_{P2}}{R_{P1}} \tag{5-30}$$

$$\frac{V_{OUT+}}{V_{INL-}} = -\frac{R_{N2}}{R_{N1}} \tag{5-31}$$

由式(5-30)、(5-31)可知,可以通过改变电阻比值  $\frac{R_{P2}}{R_{P1}}$ 、 $\frac{R_{N2}}{R_{N1}}$ 来改变前置运放的闭环增益。对于反馈电阻要求其具有较精确的匹配性,本设计中选择 POLY2 电阻。

前置运放的闭环增益与增益控制信号 G1、G2 的关系由表 5.2 给出。

11

| G1 G2 | GAIN(dB) | $\triangle$ (dB) |

|-------|----------|------------------|

| 0 0   | 9.5      | 2.7              |

| 0 1   | 6.8      | 2.7              |

|       | 4.1      | 2.4              |

1.7

表 5.2 前置运放的增益与增益控制信号 G1、G2 的关系

由表 5.2 可知前置运放闭环增益的调节步长约为 2.7dB, 满足设计要求。

## 五、前置运放的实际电路

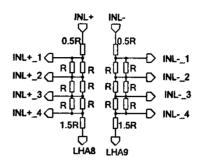

图 5.16 为前置运放的输入电阻分压网络实际电路。

图 5.16 前置运放的输入电阻分压网络

图 5.17 为前置运放的输入级实际电路。

图 5.17 前置运放的输入级电路

图 5.18 为前置运放的增益级、共模反馈、偏置部分的实际电路。

图 5.18 前置运放增益级、共模反馈、偏置的实际电路

## 六、前置运放具体电路分析

本设计中前置运放的输入级由 4 个相同的差分对构成,所不同的是 4 个差分对的外接反馈电阻比值不同,所以,只需用 2-4 编码器来选通所需的一个差分输入对,就可以实现增益控制。

前置运放的增益级为两级共源级组成,其增益为:

$$A_{V} = g_{m1} R_{OUT1} \cdot g_{m2} R_{OUT2}$$

(5-32)

其中 gml 和 Routl 分别为第一级运放的等效跨导和输出阻抗, gm2 和 Routl 分

别为第二级运放的等效跨导和输出阻抗。

全差分运放的输出必须要共模反馈来稳定其输出直流电平,如果前置运放的输出直流电平设置不合理,其输出的音频信号将产生严重的失真<sup>[37]</sup>。由共模反馈实际电路图 5.18 可知 R<sub>JA983</sub>、R<sub>JA782</sub>、R<sub>JA12P2</sub> 构成电阻分压网络,产生 3V 的比较基准电压(V<sub>REF\_1</sub> 为 6V 电压)。Q<sub>JA1</sub>~Q<sub>JA3</sub>,M<sub>JA56P2</sub>、M<sub>JA58P6</sub>、M<sub>JA64</sub> 以及 C<sub>JA1</sub>、C<sub>JA4</sub>、R<sub>JA382</sub>、R<sub>JA482</sub> 构成共模反馈电路。其中 C<sub>JA1</sub>、C<sub>JA4</sub>、R<sub>JA382</sub>、R<sub>JA482</sub> 将前置运放的输出电压平均值,即(V<sub>LHA8</sub>+V<sub>LHA9</sub>)/2。若前置运放的输出共模电压增大,则流过 Q<sub>JA2</sub> 的电流减小,从而 M<sub>JA56P2</sub> 的栅压减小。由于 M<sub>JA56P2</sub> 的栅压偏置输入级的电流源负载,所以第一级输出直流电平增大,导致输出级的直流电平降低。从而使得输出结点的共模电平等于 V CM1。

该共模反馈设计的优点是对前置运放的输入共模范围影响较小。另外,共模 反馈放大器的输出采用 Q<sub>JA3</sub> 的射级输出,可使该点处的极点很大,也即使得共模 反馈环路的单位增益带宽内只有一个极点,从而得到了 90 度的相位裕度<sup>[38]</sup>,保 证了共模反馈环路的稳定性。

## 七、前置运放的仿真结果

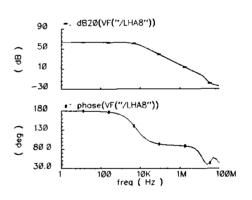

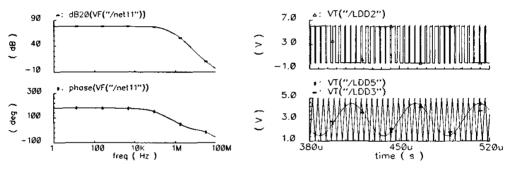

图 5.19 为前置运放开环的频率特性仿真结果,由此可知前置运放的低频增益为 65dB,开环相位裕度为 90 度。满足设计要求。

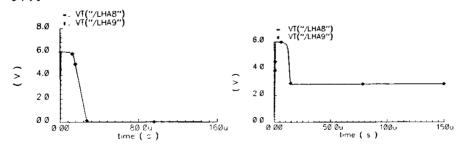

图 5.20 为前置运放输出电平的仿真结果,图 5.20(a)为没有共模反馈电路的输出仿真结果,图 5.20(b)为加上共模反馈电路的仿真结果,通过对比可以发现,共模反馈电路使得全差分运放的输出共模电平稳定在 3V (电源电压为6V)。

图 5.19 前置运放开环频率特性仿真结果

(a)无共模反馈全差分运放的输出电平 (b)有共模反馈全差分运放的输出电平 图 5.20 前置运放输出电平的仿真结果

## 5.3 积分器的设计

## 一、模块电路功能

积分器模块的功能是实现音频信号的积分运算,主要用于 D 类功率放大器的噪声整形。

## 二、积分器电路设计

#### 1、电路的等效架构

本设计中的积分器采用全差分运放, 其架构如图 5.21 所示。

由图 5.21 可知,积分器为全差分输出连续时间积分器。如果运放 AMP 的开环增益足够大,接成负反馈结构后,则 A、B点即为虚地点,则有下式成立:

图 5.21 积分器的等效架构图

$C_{P1} \frac{dV_{OUT^{-}}}{dt} = -\frac{V_{IN^{+}}}{R_{P1}}$  (5-33)

$$C_{N1} \frac{dV_{OUT+}}{dt} = -\frac{V_{IN-}}{R_{VI}}$$

(5-34)

由式(5-33)、(5-34)可得:

$$V_{OUT-} = -\frac{1}{C_{P1} \cdot R_{P1}} \int V_{IN+} dt$$

(5-35)

$$V_{OUT+} = -\frac{1}{C_{N1} \cdot R_{N1}} \int V_{IN-} dt$$

(5-36)

由式(5-35)、(5-36)可知此积分器为反相积分器。

积分器的频域分析也很重要,式(5-37)为积分器的传输函数:

$$H(s) = \frac{V_{OUT}}{V_{OU}} = -\frac{1}{R \cdot C \cdot s}$$

(5-37)

由式(5-37)可知,积分器可以作为低通滤波器来使用,并且其截止频率为:

$$f = \frac{1}{2\pi \cdot R \cdot C} \tag{5-38}$$

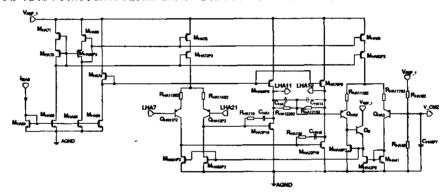

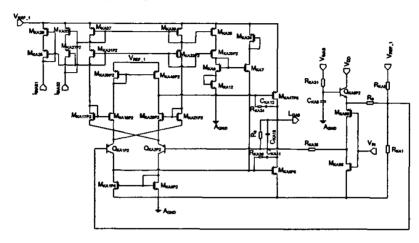

## 2、全差分运放的设计

图 5.22 为积分器的全差分运放的设计,该运放为两级共源级运放的级联形式。就半边电路而言,Q<sub>HA11P2</sub>、M<sub>HA51P2</sub>构成第一级共源级运放; M<sub>HA22P19</sub>、M<sub>HA79P6</sub>构成第二级共源级运放。其中 R<sub>HA129</sub>及 C<sub>HA15</sub>作为两级运放的米勒补偿,使得运放开环的相位裕度达到 90 度。

该差分运放的开环增益为:

$$A_{V} = g_{m1} R_{OUT1} g_{m2} R_{OUT2}$$

(5-39)

其中  $g_{m1}$  和  $R_{OUT1}$  分别为第一级运放的等效跨导和输出阻抗, $g_{m2}$  和  $R_{OUT2}$  分别为第二级运放的等效跨导和输出阻抗。考虑到运放的开环增益直接影响反馈放大器的增益误差,所以设计时要保证运放的开环增益为 60dB 以上。

由于所设计的积分器采用全差分运放结构,所以也设计了相应的共模反馈电路。图 5.22 的右半部分即为共模反馈电路。M<sub>HA48P2</sub> 输出共模反馈电压,为 M<sub>HA51P2</sub> 及 M<sub>HA50P2</sub> 提供偏置。电阻 R<sub>HA122S2</sub>、R<sub>HA121S2</sub> 及电容 C<sub>HA2</sub>、C<sub>HA14</sub> 构成共模输出的采样网络,其将采样值与基准电平 V\_CM2 作比较从而决定 M<sub>HA51P2</sub> 及 M<sub>HA50P2</sub> 的栅极电位。当输出共模电平(V<sub>LHA10</sub>+V<sub>LHA11</sub>)/2 小于 V\_CM2 时 Q<sub>HA2</sub> 的集电极电流将增大,导致 Q<sub>0</sub> 的基极电位升高,从而 M<sub>HA51P2</sub> 及 M<sub>HA50P2</sub> 的栅极电位升高,继而 M<sub>HA3P19</sub>、M<sub>HA22P19</sub> 的栅极电位降低,输出共模电平下降,直至输出共模电平等于 V CM2,反之亦然。

该共模反馈的优点同前置运放共模反馈,在此就不再赘述。

图 5.22 积分器的全差分运放电路

#### 三、积分器的仿真结果

图 5.23 为积分器电路的瞬态仿真结果。其中输入信号是共模电平为 3V,幅度为 10mV,频率 1KHz 的正弦信号。输出为共模电平为 3V,幅度为 100mV,频率为 1KHz 的余弦信号(见图 5.23 中的 L<sub>HA10</sub>与 L<sub>HA11</sub>)。幅度放大倍数为 10 倍(20dB),相位延迟为 90 度,实现了积分运算,且将共模输出电压稳定在 3V。

图 5.23 积分器的瞬态仿真结果

图 5.24 积分器的闭环频率特性仿真结果

图 5.24 为积分器闭环的频率特性曲线,由此可知,该积分器的截止频率为 30KHz 且对截止频率以内的所有信号可实现相位延迟 90 度,从而实现积分运算。

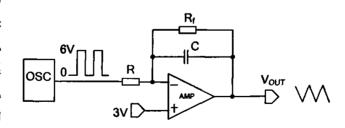

## 5.4 振荡器电路设计

## 一、模块电路功能

振荡器电路模块主要产生 D 类功放中 PWM 调制所使用的三角波信号,即载波信号。根据自然采样(双边采样)的要求,所产生的三角波是对称的。

产生三角波的方法主要有两种[39]:

- 1、利用张驰振荡器[40],直接使用电容上的电压信号;

- 2、先产生方波信号,对方波信号进行积分运算,得到三角波信号。

第一种方法要求电容的充、放电电流严格匹配,因为三角波的线性度直接决

图 5.25 三角波产生原理图

会使电路的设计过于复杂。而第二种方法可以很容易的得到所需要的占空比为50%的方波信号,因此可以简化电路的设计,从而得到线性度优良、摆幅较大的对称三角波信号。本设计采用第二种方法。图 5.25 即为三角波产生原理图。

## 二、方波振荡器电路设计

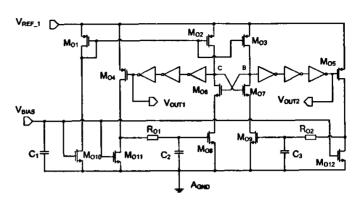

图 5.26 为方波 产生模块的电路。 由于电路启动时, $C_2$ 和  $C_3$  上的初始电压 为零, $M_{O8}$  和  $M_{O9}$  截止,C 和 B 点均被拉 至高电位,经非门反 相后使得  $M_{O4}$  和  $M_{O5}$ 导通,从而对  $C_2$  和  $C_3$  充电,

图 5.26 方波产生模块的电路图

$R_{01}$ 和  $C_2$ , $R_{02}$ 和  $C_3$ 构成的 RC 网络的时间常数决定。根据:

$$V_C(t) = V_{REF_{-1}}(1 - e^{-\frac{t}{\tau}})$$

(5-40)

其中  $\tau = R_{O1.02} \cdot C_{2.3}$ 。

$V_{C}$  为充电电容上的电压,其终值为  $V_{C}(t_{0})$ ,且  $V_{C}(t_{0}) < V_{REF\_1}$ 。由式(5-40)可解得电容 C2、C3 的充电时间为:

$$t_{charge} = -R_{O1,O2} \cdot C_{2,3} \cdot \ln(1 - \frac{V_C(t_0)}{V_{RFF-1}})$$

(5-41)

$R_{O1}$  的阻值为  $R_{O2}$  的两倍,所以  $C_2$  的充电时间为  $C_3$  的两倍, $M_{O9}$  先于  $M_{O8}$  导通。此时由于 C 点和 B 点为高电位, $M_{O6}$ 和  $M_{O7}$  导通,所以 B 点被  $M_{O9}$  拉至 低电位,同时关断  $M_{O6}$ 。由于 B 点变为低电位,经非门反相后关断  $M_{O5}$ ,从而停止对  $C_3$  充电,转而通过  $M_{O12}$  恒流对电容放电,放电电流  $I_{discharge}$  由偏置电路镜像而来。放电时间:

$$t_{discharge} = \frac{C_3 \cdot V_C}{I_{discharge}} \tag{5-42}$$

其中  $V_C$  为  $C_3$  放电前后的压差,且  $V_C \approx V_C(t_0) - V_{THN MO9}$ 。

当  $C_3$  上的电压低于  $M_{O9}$  的阈值时, $M_{O9}$  关断,B 点变为高电位,并使  $M_{O6}$  导通。由于  $C_2$  充电完成后始终没有放电,所以  $M_{O8}$  开始流过电流,将 C 点拉至低电位,关断  $M_{O7}$ 。由于 C 点和 B 点电位的改变,此时控制  $M_{O4}$  和  $M_{O5}$  对  $C_2$  放电,对  $C_3$  充电, $C_2$  的放电时间与  $C_3$  的放电时间相同。当  $C_2$  放电至  $M_{O8}$  的阈值电压时, $M_{O8}$  截止,C 点变为高电位,使  $M_{O7}$  导通,通过  $M_{O9}$  将 B 点拉至低电位。由此振荡器开始正常工作,对  $C_2$  和  $C_3$  交替充放电, $V_{OUT1}$  和  $V_{OUT2}$  输出反相的占空比为 50%的方波信号。

因为振荡器的电源电压直接对 C2、C3 充电, 且由于电容放电时间只与放电电

流有关,与电阻 Ro1 和 Ro2 的阻值无关,根据上述原理可以得到振荡器的周期为:

$$T = 2 \cdot t_{discharge} = 2 \cdot \frac{C_{2,3} \cdot V_C}{I_{discharge}}$$

(5-43)

#### 三、积分器的设计

图 5.27 为积分器的实际电路。

图 5.27 方波积分器的实际电路

$V_{IN}$  为振荡器模块产生的方波信号,经过二分频后用来控制  $M_{KA95}$  和  $M_{KA96}$  轮流导通从而产生送入积分器的方波信号。方波信号的高电位由输入的电压信号  $V_{BIAS}$  经过源随器  $Q_{KA5P2}$  后产生;积分器正端输入的直流电压信号由内部电源  $V_{REF\_1}$  经过电阻  $R_{KA1}$  和  $R_{KA5}$  分压产生,作为输出三角波的直流参考电平。 $I_{BIAS1}$  和  $I_{BIAS2}$  产生运放的偏置电流。

该积分器所采用的运放为高增益运放。采用该运放主要考虑到运放的开环增益直接影响到反馈放大器的增益误差。运放由两部分组成,下半部分为电流源作负载的共源级放大; 上半部分为电流源为负载的共栅级放大,M<sub>KA17P2</sub>和 M<sub>KA21P2</sub>通过改变 M<sub>KA16P2</sub>和 M<sub>KA20P2</sub>的栅极信号来增加电压放大倍数。上下两部分通过 M<sub>KA47P6</sub>和 M<sub>KA9P6</sub>双端转单端输出。R<sub>KA34</sub>,C<sub>KA12</sub>和 R<sub>KA36</sub>,M<sub>KA11</sub>分别为上下两端的米勒补偿,保证环路稳定。该运放真正的跨导级是 M<sub>KA16P2</sub>以及 M<sub>KA20P2</sub>,即运放的差模小信号是加在上述两个管子上,由此可得运放的开环增益约为:

$$A_{V} = g_{M_{KA16P2,KA20P2}} \cdot R_{o\_M_{KA47P6} \cdot KA9P6} \cdot (g_{M_{KA47P6}} \cdot R_{o\_M_{KA40P2}} + \frac{3}{2} g_{M_{KA9P6}} R_{o\_M_{KA1P4}})$$

(5-44)

式(5-44)是该运放的一个近似表达式,其中假设了  $M_{KA47P6}$  与  $M_{KA9P6}$  的小信号导通阻抗相等,因此,运放输出端的等效阻抗为  $\frac{R_{o\_MKA47P6,MKA9P6}}{2}$ 。这可以通过设计  $M_{KA47P6}$ 、 $M_{KA9P6}$  具有不同的栅长来实现。另外,由式(5-44)可知,该运放的开环增益约为普通二级运放的 2.5 倍,因此,可以获得更高的开环增益,从而保证

积分器的增益误差相对较小。

电容 CKAIS 即为积分器的积分电容, 电阻 R8 的作用有两点:

- 1).电阻 R<sub>8</sub> 可以引入直流反馈,从而稳定运放输入级的直流工作点。这是因为,如果没有电阻 R<sub>8</sub>,则运放的直流漂移会使输入级的管子进入线性区,从而在输出端产生严重的失真。但 R<sub>8</sub> 的引入会也产生积分误差问题,通常要求 R<sub>8</sub> 的阻值较高。

- 2).电阻 R<sub>8</sub> 的引入可以使输出三角波的直流电平稳定在 3V,而不随方波的初始相位的变化而改变。对此具体分析如下<sup>[41]</sup>:

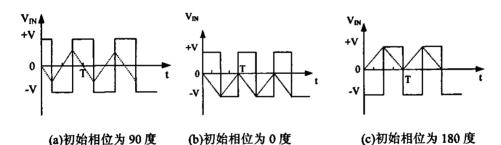

对于图 5.28(a)所示的方波信号,其幅度为±V,周期为 T,初始相位为 90 度,若方波右移或左移 T/4,则初始相位定义为 0 度和 180 度。若没有 R<sub>8</sub>,则对于初始相位为 90 度的方波输入,输出为关于横坐标对称,峰值为 VT/2R<sub>KA26</sub>C<sub>KA18</sub> 的 三角波;而方波初始相位为 0 度和 180 度时,输出三角波则位于横坐标之下(0~-VT/2R<sub>KA26</sub>C<sub>KA18</sub>)或之上(0~+VT/2R<sub>KA26</sub>C<sub>KA18</sub>),由此可知,三角波的直流分量与方波的初始相位有关,如图 5.28(b)及图 5.28(c)所示。

图 5.28 积分器输入方波初始电位与输出三角波的关系

对于图 5.25 所示的等效架构图,考虑到 R<sub>8</sub> 的影响时,对运算放大器反相端的结点应用基尔霍夫电流定律,得到关于输出 Vour 的微分方程:

$$\frac{dV_{OUT}}{dt} + \frac{1}{R_8 \cdot C_{K418}} \cdot V_{OUT} = \mp \frac{V_{IN}}{R_{K426} \cdot C_{K418}}$$

(5-45)

式中: 干号对应输入方波的正负半周期。出于计算的方便,时间 t 仅限于方 波的正负半周期内,于是解得:

$$V_{OUT}(t) = e^{-t/R_8 \cdot C_{KAIB}} \left( A \mp \frac{V_{IN} \cdot R_8}{R_{KA26}} e^{t/R_8 \cdot C_{KAIB}} \right)$$

(5-46)

式中: A 是待定常数,可利用稳态时三角波形的连续性确定并带入式(5-46) 得:

$$V_{OUT}(t) = \mp \frac{V_{IN} \cdot R_8}{R_{KA26}} \left(1 - \frac{2}{1 + e^{t/2R_8 \cdot C_{KAIS}}} e^{-t/R_8 \cdot C_{KAIS}}\right)$$

(5-47)

由(5-47)式可得三角波的最大、小值:

$$V_{OUT\_max,min}(t) = \pm \frac{V_{IN} \cdot R_8}{R_{KA26}} \left( \frac{1 - e^{-T/2R_8 \cdot C_{KA18}}}{1 + e^{-T/2R_8 \cdot C_{KA18}}} \right)$$

(5-48)

由式(5-47)、(5-48)可知,由于  $R_8$  的存在,输出达到稳态时,三角波的直流分量恒为零,不再与输入方波的初始相位有关。其与忽略  $R_8$  时理想三角波峰值  $V_{IN}T/4R_8C_{KAI8}$  的相对误差的绝对值在二阶近似下为:

$$\delta = \frac{T^2 / 8R_8^2 \cdot C_{KA18}^2}{2 - T / 2R_8 C_{KA18} + T^2 / 8R_8^2 \cdot C_{KA18}^2} \times 100\%$$

(5-49)

由此估算,时间  $R_8C_{KA18}=T$  时,  $\delta=7.7\%$  ,而  $R_8C_{KA18}=3T$  时  $\delta=0.75\%$  。因此只要满足  $R_8C_{KA18}\ge 3T$ ,即可认为输出的三角波形较为理想。

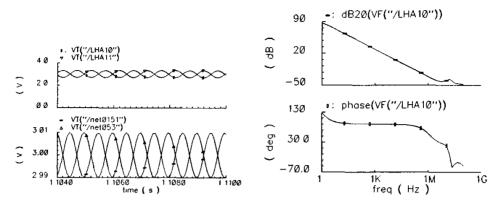

## 四、振荡器的仿真结果

图 5.29 为积分器运放开环增益仿真结果。由图可知,积分器运放开环增益为 103dB,带宽为 6.8MHz。

图 5.29 积分器运放的开环增益

图 5.30 积分器的环路频率特性

图 5.30 为积分器环路频率特性仿真结果。由图可知,积分器的环路相位裕度为 97度,满足稳定性要求。

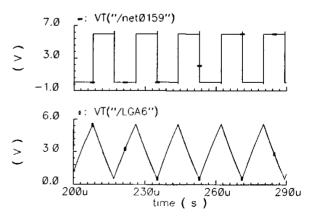

图 5.31 为振荡器输出方 波及三角波的仿真结果。由图 可知,振荡器输出频率为 200KHz 的方波信号,积分器输出 100KHz,振幅为 5V 的三角波信号,且中心电平为 3V,保证了三角波幅值大于音频信号的幅值,满足设计要求。

图 5.31 振荡器输出方波及三角波

## 5.5 PWM 比较器的电路设计

## 一、模块电路功能

PWM 比较器的功能是将三角波与积分器输出音频信号进行比较,输出可以 反映音频信号幅值的方波信号,送入调制逻辑,从而产生输出驱动信号。

## 二、电路设计

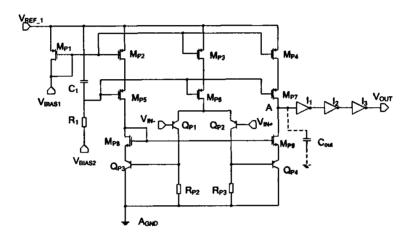

图 5.32 为 PWM 比较器模块的电路图。其中,M<sub>P3</sub>、M<sub>P6</sub>、Q<sub>P1</sub>、Q<sub>P2</sub> 、R<sub>P2</sub>、R<sub>P3</sub>构成第一级运放。Q<sub>P3</sub>、Q<sub>P4</sub>、M<sub>P2</sub>、M<sub>P4</sub>、M<sub>P5</sub>、M<sub>P7</sub>、M<sub>P8</sub>、M<sub>P9</sub>构成第二级运放。

图 5.32 PWM 比较器模块实际电路图

由于比较器的开环增益直接决定比较器的精度,所以本设计主要考虑到比较器所用运放具有较高的开环增益。对于运放增益,根据跨导等效原理,运放的开环增益为:

$$A_{v} = -Gm \cdot R_{OUT} \tag{5-50}$$

由此可知,若想增大比较器的开环增益,可以通过增大运放的输出电阻来实现。所以,本设计采用 Cascode 有源电流镜作为负载,且采用新颖的双端转单端结构使得比较器具有较高的带宽,从而使得比较器具有良好的小信号阶跃响应。在这里需要说明,第二级运放实际的跨导级是 Mpp, 即第一级运放输出的差模信号其实是加在了 Mpp 的栅源之间,从而比较器的开环增益为:

$$A_{V} = g_{Q_{P_{1},P_{2}}} \cdot R_{P_{2,3}} \cdot g_{M_{P_{9}}} \cdot (g_{M_{P_{7}}} \cdot R_{O_{M_{P_{7}}}} \cdot R_{O_{M_{P_{4}}}} \parallel g_{M_{P_{9}}} \cdot R_{O_{M_{P_{9}}}} \cdot R_{e_{Q_{P_{4}}}})$$

(5-51)

比较器输出端转换延迟的时常数可以近似认为  $\tau \approx R_{OUT} \cdot C_{OUT}$ ,由此可知  $\tau$  越大转换延迟越大,比较器速度越慢;  $\tau$  越小转换延迟越小,比较器速度越快。而  $\tau$  与  $R_{OUT}$  成正比,即  $R_{OUT}$  越大。因此,为了获得较高的开环增益势必需要增大  $R_{OUT}$ ,而  $\tau$  也会随之增大,使得比较器的转换速度降低。这反映了比较器速

度与精度的矛盾。为了解决时常数τ与输出电阻 Rout 之间的矛盾,设计时除了增大比较器的偏置电流外而且在比较器的输出端加入了三个非门驱动器。另外,转换延迟还与输出端的寄生电容 Cout 有直接关系。考虑到寄生电容 Cout 与晶体管的面积有关,所以设计时使得 Mpt、Mpp 的宽长比较小,从而达到减小 Cout 的目的。

对于比较器的分析,需要从静态特性和 动态特性两方面进行考虑。

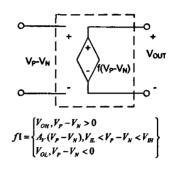

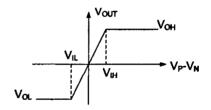

比较器的静态特性分析主要是利用压控电压源 (VCVS)来对比较器的静态特性进行建模。对于二进制比较器的一阶建模与通常的运放建模相似,图 5.33 即为有限增益比较器的一阶模型。图 5.34 为有限增益比较器

图 5.33 有限增益比较器的一阶等效模型

图 5.34 有限增益比较器的传输曲线

的传输曲线,根据图 5.34 可以得到比较器一阶模型的增益为:

$$A_{V} = \frac{V_{OH} - V_{OL}}{V_{HI} - V_{IL}} \tag{5-52}$$

其中, $V_{IH}$ 和  $V_{IL}$ 是输出分别达到上限和下限所需的输入电压差  $V_{P}$ - $V_{N}$ 。这种输入变化称为比较器的精度。由式(5-52)可知,比较器的增益是描述比较器工作的重要特性,因为它定义了输出能够在两个二进制状态之间改变所需的最小的输入变化量,即比较器的精度。

比较器的动态特性分析又分为小信号动态分析和大信号动态分析。对于小信号动态特性,其取决于比较器的频率响应。假设一个两级比较器的频率响应为:

$$A_{\nu}(s) = \frac{A_0}{(1 + \frac{s}{p_1})(1 + \frac{s}{p_2})}$$

(5-53)

其中  $P_1$ 、 $P_2$  为比较器两个互不相同的极点,而  $P_2$  为比较器的主极点。则其输出的时域响应为:

$$V_{out}(t) = V_{IN} \cdot A_0 \left[ 1 + \frac{p_2 e^{-tp_1}}{p_1 - p_2} - \frac{p_1 e^{-tp_2}}{p_1 - p_2} \right]$$

(5-54)

根据式(5-54)可知,若比较器的主极点越大则小信号传输时延越小。对于所设计的比较器,其主极点在输出端(A点),其极点大小约为:

$$p_A = \frac{1}{R_{OUT} \cdot C_{OUT}} \tag{5-55}$$

对于比较器大信号动态特性, 其取决于比较器的压摆率, 即:

$$S_R^{\pm} = \frac{I_{QUT}}{C_{QUT}} \tag{5-56}$$

式(5-54)~式(5-56)为减小比较器的传输延迟(减小 Com)提供了理论依据。

## 三、比较器的仿真结果

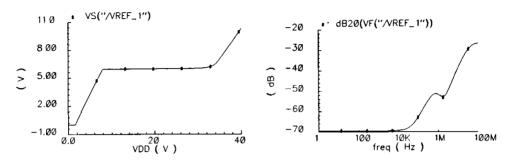

图 5.35 为比较器运放的开环频率特性的仿真结果,由图可知,运放的低频增益为 85dB,开环单位增益带宽为 5.8MHz。

图 5.35 比较器运放的开环频率特性

图 5.36 PWM 比较器的输出

图 5.36 为比较器输出的仿真结果,从图中可知, PWM 比较器的输出方波的 占空比反映了音频信号的幅值,满足设计要求。

## 5.6 驱动逻辑电路的设计

#### 一、模块电路功能

驱动逻辑电路主要处理前级调制逻辑输出信号,从而产生 H 桥半边电路控制信号,其主要设计要点是死区时间的控制。因为死区时间直接影响着 D 类功放的 THD 性能,所以死区时间的控制一定要精确。另外,设计驱动电路还要考虑到驱动能力的问题,因此本设计中采用源极输出来提高驱动电路的带载能力,减小驱动信号的转换延迟。

#### 二、电路设计

如图 5.37 为驱动逻辑的具体电路。电路可以看成数字逻辑电路和死区时间控制电路两部分。对于驱动逻辑输出端,考虑到加快其由低电平向高电平的翻转速度,引入了一个正反馈,这样可以降低驱动信号的误差时间,改善 D 类功放的

THD 性能。

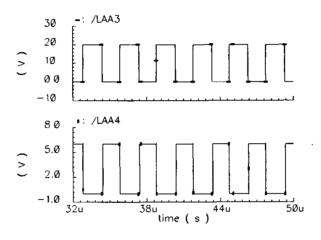

L<sub>AA3</sub> 与 L<sub>AA4</sub> 为 H 桥的驱动信号。L<sub>BB4</sub> 为电荷泵输出,其电压值为 2 倍的电源电压。

L<sub>BB8</sub>、L<sub>BB5</sub> 输入为反相方波信号。当 L<sub>BB8</sub> 为高电平时,经数字逻辑电路输出 L<sub>AA4</sub> 与反馈信号 L<sub>BB9</sub> 无关,直接为低电平;虽然此时 L<sub>BB5</sub> 为低电平,但需在 L<sub>BB8</sub> 产生的反馈信号控制共同作用下,经数字逻辑电路 L<sub>AA3</sub> 输出为高电平;由于 L<sub>AA3</sub> 上升沿比 L<sub>AA4</sub> 下降沿滞后,产生死区时间。同理,L<sub>BB8</sub> 为低电平 L<sub>BB5</sub> 为高电平时,输出 L<sub>AA4</sub> 为高电平,L<sub>AA3</sub> 为低电平,L<sub>AA4</sub> 上升沿滞后 L<sub>AA3</sub> 下降沿,产生死区时间。

图 5.37 驱动逻辑模块电路图

对于死区时间控制电路的分析如下。

当  $L_{BB8}$  为上升沿时,初始状态 P 管  $M_{D4}$  和 N 管  $M_{D8}$  都处于深线性区,A 点 ( $M_{D4}$  管漏端)为高, B 点( $M_{D8}$  管漏端)为低。由于经数字逻辑电路使得高压 管  $M_{D7}$  栅端控制信号也为上升沿, $M_{D7}$  管导通,因为其宽长比很大,且漏端电压 为高压、漏电流较小,所以  $M_{D7}$  进入饱和区,此时虽然 A 点电压下降,但 B 点电压可以在  $M_{D7}$  未进入线性区前维持在  $V_{C}$ - $V_{GS\_MD7}$ ,并对电容  $C_{D2}$  充电。 $M_{D8}$  管、 $M_{D4}$  管相继进入饱和区。根据宽长比设置可知  $M_{D8}$  管镜像电流为  $M_{D4}$  管镜像电流的两倍。当 A 点电压下降到使得  $M_{D7}$  管进入线性区时,电容开始放电,B 点电压 随 A 点电压一起下降,直到  $M_{D8}$  管进入线性区,A 点为低,电路处于稳定状态。当 B 点下降到非门  $I_{10}$  的翻转阈值时,电平翻转,从而使  $I_{AA3}$  翻转。

电容值大小对死区时间的影响。电容值越大,则由 $I=C\frac{dV}{dt}$ 知, $M_{D7}$ 管瞬时漏电流越大,即 B 点电压上升的峰值越小。这样, $M_{D7}$ 管两端电流相差更大,迫

使 A 点电压更快下降,使得  $M_{D7}$  管更早进入线性区。随后 B 点电压随 A 点一起下降,直到  $M_{D8}$  管进入线性区,A 点为低,电路处于稳定状态。

同理,当  $L_{BB8}$  为下降沿, $L_{BB5}$  为上升沿时。高压管  $M_{D10}$ 、P 管  $M_{D5}$ 、N 管  $M_{D11}$ 、电容  $C_{D6}$  构成死区时间控制电路。此时,电容值越大,死区时间越大。

驱动电路的输出级采用源极输出来提高驱动电路的带载能力,减小驱动信号的转换延迟。

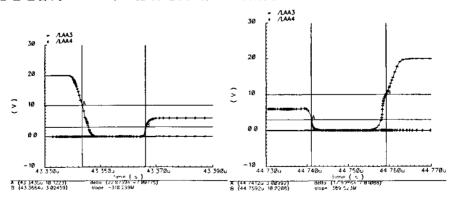

## 三、驱动逻辑的仿真结果

图 5.38 为驱动逻辑的仿真结果,由图可知  $L_{AA3}$  为驱动 H 桥上半桥的驱动信号,高电平达 20V;  $L_{AA4}$  为驱动 H 桥下半桥的驱动信号,高电平达 6V。它们的死区时间为 15 纳秒。

图 5.38 驱动逻辑模块的仿真结果

图 5.39 是充电电容为 150fF 时的驱动逻辑死区时间仿真结果,由图 5.39 可知 当充电电容为 150fF 时,驱动逻辑的死区时间为 20 纳秒。

图 5.39 死区时间为 20 纳秒的仿真结果

## 5.7 电荷泵电路的设计

#### 一、模块电路功能

电荷泵电路的主要功能是产生 2 倍  $V_{DD}$  的驱动电压,用来驱动 H 桥上半桥的 开关管。

## 二、设计原理

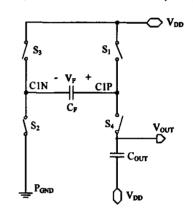

如图 5.40 所示 2 倍压电荷泵的典型拓扑结构 $^{[42]}$ 。其中  $C_F$  为电荷泵飞电容, $C_{OUT}$  为输出电容。下面分两个阶段进行具体分析:

阶段 1: 开关  $S_1$ 、 $S_2$  闭合, $S_3$ 、 $S_4$  断开,泵飞电容两端的电压为:

$$V_{F1} = V_{C1P} - V_{C1N} = V_{DD}$$

(5-57)

阶段 2: 开关  $S_3$ 、 $S_4$  闭合, $S_1$ 、 $S_2$  断开,泵飞电容两端的电压为:

$$V_{F2} = V_{C1P} - V_{C1N} = V_{OUT} - V_{DD}$$

(5-58)

根据电容两端的电压差不能突变,则式(5-57)与(5-58)相等,即:

$$V_{F1}=V_{F2}$$

(5-59)

因此得到:

$$V_{OUT} = 2V_{DD}$$

(5-60)

综上所述,即为电荷泵基本的工作原理。 究其根本是利用泵飞电容进行电源与输出负载 之间的电荷传递,其可以获得高于电源的 输出电压,因此可以利用电荷泵来驱动 H 桥上半桥的 NMOS 开关管。

## 三、电路设计

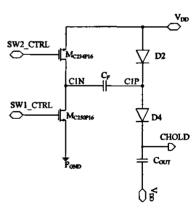

电荷泵的设计可以分为两个模块进行设计即驱动模块设计以及输出级的设计。图 5.41 即为所设计电荷泵电路的输出级。考虑到节省芯片的面积所以采用 NMOS 管 M<sub>C250P16</sub>、M<sub>C234P16</sub> 代替开关 S<sub>2</sub>、S<sub>3</sub>; 二极管 D2、D4 代替开关 S<sub>1</sub>、S<sub>4</sub>。

下面结合 SW1\_CTRL 和 SW2\_CTRL

图 5.40 典型电荷泵拓扑图

图 5.41 所设计电荷泵的输出级

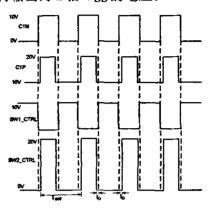

的波形来分析此电路。如图 5.42 所示,其中  $T_{SW}$  为开关控制频率的周期, $T_D$  为驱动信号的死区时间。

当 SW1\_CTRL 为高电平、SW2\_CTRL 为低电平时, 开关管 M<sub>C250P16</sub>, 二极管

D2 导通,此时 D4 由于反向偏置处于截止状态。泵飞电容 CF 充电。

当 SW2\_CTRL 为高电平、SW1\_CTRL 为低电平时,开关管  $M_{C234P16}$ ,二极管 D4 导通,此时 D2 由于反向偏置处于截止状态。泵飞电容  $C_F$  放电,将其存储的 能量传递给输出电容  $C_{CRT}$ ,从而获得输出为 2 倍  $V_{DD}$  的电压。

接下来的问题是如何获得图 5.42 所示的驱动电压,尤其是 SW2\_CTRL。这就引出了电荷泵驱动逻辑的设计。如图 5.43 所示即为 所设计的电荷泵驱动具体电路。

根据 C1P 端高电压为 2 倍的 V<sub>DD</sub>,所以设计时可以考虑利用 C1P 电压自举来产生 SW2\_CTRL 驱动。图中虚线内的数字逻辑采用 内部电源电压,即其逻辑高电平为 6V,其余部分的逻辑高电平为

图 5.42 电荷泵的输入输出波形

C1P。因此两部分逻辑连接需要高电平逻辑转换电路。M<sub>C88</sub>、M<sub>C89</sub>、M<sub>C41P2</sub>、M<sub>C43P2</sub>、M<sub>C13P4</sub>即完成了上述功能。当 A 点(或非门 I<sub>C153</sub>的输出)电压为低电平时,由于 M<sub>C13P4</sub>将 C 点拉至低电平,所以 M<sub>C41P2</sub>导通将 M<sub>C88</sub>的栅极拉低,M<sub>C88</sub>导通。此时,由于 M<sub>C43P2</sub> 截止,因此 B 点电压输出高电平。当 A 点电压为高电平时,M<sub>C41P2</sub>、M<sub>C89</sub>、M<sub>C88</sub> 截止,B 点输出低电平,因此完成了不同逻辑高电平之间的转换。

图 5.43 电荷泵驱动逻辑具体电路

高压管  $M_{C98P10}$  的栅端为近似 C1P 的电压,而  $M_{C98P10}$  接成了源随器结构,因此其输出电平基本接近 C1P。当 C1P 为高电平 2 倍  $V_{DD}$  时,B 点为低电平,因此

非门  $I_{C34}$  输出高电平为 C1P 的逻辑高电平。也就是说,SW2\_CTRL 的高电平即为 C1P 的高电平,这就为 SW2\_CTRL 自举创造了条件。对于阶段 1,SW1\_CTRL 为高电平,将 C1N 拉至地电位,C1P 为电源电压  $V_{DD}$ ,当 SW1\_CTRL 变为低电平时,由于开关管漏端的寄生电容,C1N 此时仍为地电位,SW2\_CTRL 为  $V_{DD}$  电压,因此足以开启开关管  $M_{C234P16}$ ,使得 C1N 电压为  $V_{DD}$ ,从而 C1P 为  $V_{DD}$ + $\Delta V$ ,SW2\_CTRL 亦为  $V_{DD}$ + $\Delta V$ ,这样经过若干振荡周期后,C1P 的高电平即可达到 2倍的电源电压,而 SW2\_CTRL 的高电平也可达到 2 倍的电源电压。上述,即为 SW2 CTRL 自举驱动的过程。

对于电荷泵驱动逻辑信号 SW1\_CTRL、SW2\_CTRL 之间的死区时间是必须 考虑的问题。通过设置合适的电阻  $R_{C32S2}$  和电容  $C_{11}$  即可得到所需的死区时间, 这里就不再赘述。

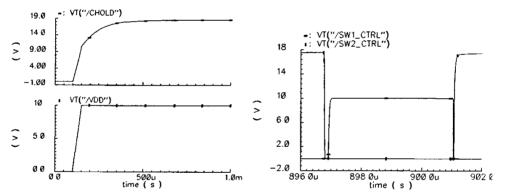

### 三、电荷泵的仿真结果

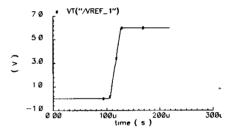

图 5.44 为电荷泵输出的仿真结果,电源电压  $V_{DD}$ 在 100 微秒~150 微秒的时间内从零上升至 10V。 由图 5.44 可知,电荷泵输出 CHOLD 在电源电压升至 10V后,输出 19V的驱动电压。满足了设计要求。

图 5.44 驱动逻辑模块的仿真结果

图 5.45 电荷泵驱动信号死区时间仿真结果

图 5.45 是电荷泵驱动信号死区时间的仿真结果。由图 5.45 可知,驱动信号的死区时间分别为 141 纳秒和 31 纳秒。满足设计要求。

# 第六章 芯片整体功能仿真

在前几章详细介绍了 XPD7026 的系统设计原理和具体子模块设计仿真结果。而研究设计一个芯片的目的不仅是要完成所有功能,更主要的就是在于实际应用,即实现芯片的电特性参数要求。由于元器件特性随着工艺步骤的变动会产生漂移,根据元器件参数漂移范围,存在慢模型、典型模型、快模型之分,所以在仿真中需要进行多种工艺参数、各种温度、不同电压的组合仿真。在本章中,给出了芯片整体电路的典型模型下部分 Cadence 仿真结果,包括主要的电特性参数和电路特性曲线。

## 6.1 芯片整体电路

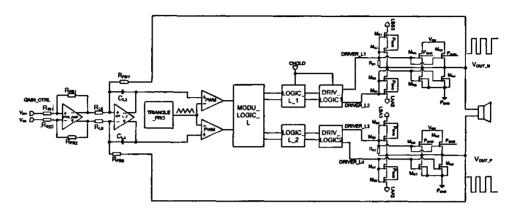

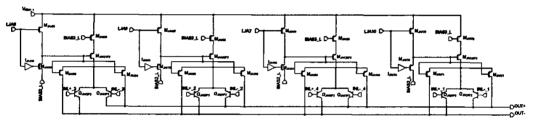

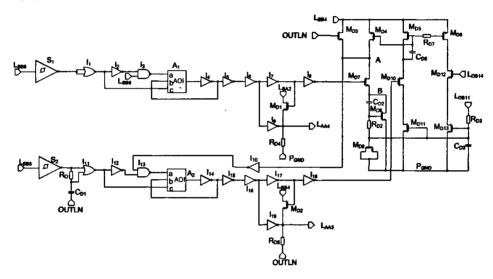

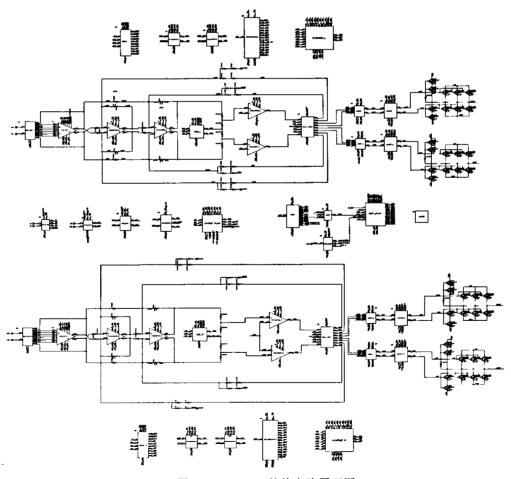

图 6.1 XPD7026 整体电路原理图

在第五章中讨论了 XPD7026 的主要子模块电路的设计、仿真,那么将前面的模块按照图 4.2 原理框图中的连接关系有机地组合,就得到了该芯片实际的整体电路框架图,如图 6.1 所示。带有 ESD 保护结构的是芯片外部引脚,其余均为内部连线,为不使电路连接复杂,使用对线标记的方法连接电路。

## 6.2 芯片整体电路仿真

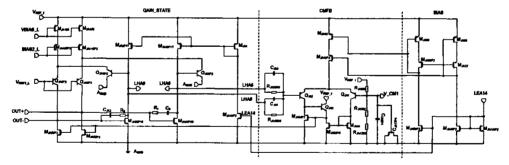

XPD7026 在具体电路设计过程中,采用的是国外某公司的 0.6μm BCD 工艺模型进行仿真。所以,对整体进行仿真时也采用该模型。另外,考虑到整体电路仿真要使用外围元件,还特别根据设计要求选择了相应的外围元件 Cadence 仿真模型。图 6.2 是整体电路仿真图。

图 6.2 整体电路仿真图

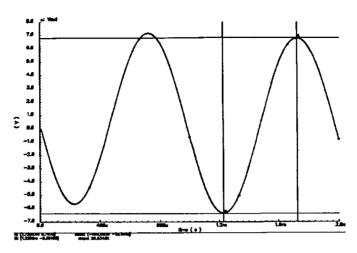

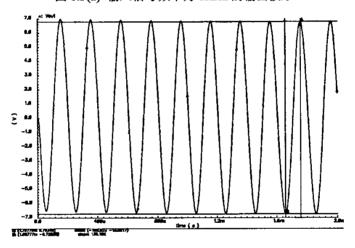

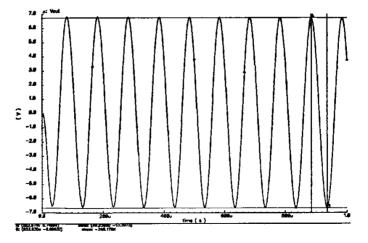

图 6.3 分别给出了图 6.2 电路的仿真结果。仿真条件: 输入信号幅度为 55mV, 频率为 1KHz,5KHz,10KHz,负载为 8 $\Omega$ ,电源电压为  $V_{DD}$ = 12V,温度为 27℃ 的输出波形。

图 6.3(a) 输入信号频率为 1KHz 的输出波形

图 6.3(b) 输入信号频率为 5KHz 的输出波形

图 6.3(c) 输入信号频率为 10KHz 的输出波形

由图 6.3 可知,输出音频信号的失真小于 0.09%,达到了设计要求。

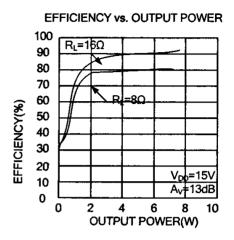

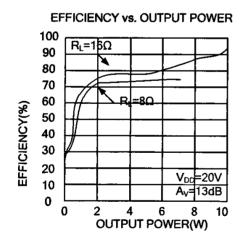

图 6.4 给出了电源电压为 15V,增益 13dB 条件下, D 类功率放大器输出功率与 其效率的关系曲线图。在典型输出功率 6W 的条件下其效率为 81%满足了设计要求。另外,由图 6.4 可知,当 D 类功放输出功率较小时,其效率相对较低,这是由于在输出功率较低时,芯片的静态电流与输出负载电流相当,静态电流引起的静态损耗占电源供给功率的比重增大造成的,因此 D 类功放适合大负载功率输出。

图 6.5 给出了电源电压为 20V,增益 13dB 条件下,D 类功率放大器输出功率与 其效率的关系曲线图。比较图 6.4 与图 6.5

图 6.4 电源电压为 15V、增益为 13dB 条件下输出功率与效率的关系

可知,D类功率放大器的效率在相同负载条件下是随电源电压升高而有所降低的。由此可知,对于D类功率放大器,降低其输出开关管的导通阻抗以及静态电流是至关重要的。因此,在所设计的D类功放中全部采用NMOSFET作为输出开关管。

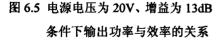

图 6.6 开关管导通阻抗随温度变化的关系曲线

图 6.6 给出了所设计 D 类功放输出开关管导通阻抗随温度变化的关系曲线。由图 6.6 可知在室温 27°C 时,开关管导通阻抗为 339mΩ。在 8Ω 负载、输出 6W 功率的典型情况下仅耗散 0.5W 的功率,满足了设计要求。另外,由图 6.6 可知,随着温度的升高,开关管导通阻抗会随之升高,这将引起 D 类功率放大器效率的下降。

## 结束语

D类音频功率放大器相对于其它功率放大器具有效率高,输出功率大等特点,特别适合于电池供电的便携式电子设备。但由于其属于非线性运放,增益直接与电源电压有关,所以其线性度和电源抑制的性能存在设计难点,成为 D 类音频功率放大器的设计瓶颈。

本论文的设计工作是来源于西安电子科技大学电路 CAD 研究所的科研项目 "高效低 THD 音频 D 类功率放大器的研究与设计"。在广泛调研和深入分析国内外此课题发展情况的基础上,本文从 D 类音频功率放大器基本原理入手,深入研究和分析了 D 类音频功率放大器的关键设计技术,基于研究的理论基础提出了无需输出滤波器的半波整流调制方案,并且设计出一款大功率、高效率、低 THD+N的 D 类音频功率放大器 XPD7026。整个电路基于 0.6 μm BCD 工艺设计,利用 Cadence 等 EDA 软件进行仿真验证。仿真结果表明,该设计电路较好的完成了无需输出滤波器、高效率设计要求。本论文主要成果有:

- 1.介绍了各种音频功率放大器的拓扑结构及各自的工作原理,并且比较了它们之间 THD+N、效率等性能参数的特点:

- 2. 着重阐述了 D 类音频功率放大器的工作原理及特点,重点介绍了 D 类音频功率放大器关键的设计技术,如利用负反馈改善 D 类音频功率放大器的线性度,减少失真;提出了一种免去输出级滤波器的调制方案并指出了 EMI 干扰的产生及如何降低 EMI 的方法;

- 3.系统介绍了芯片 XPD7026 的设计过程,包括芯片指标的制定、系统方案的选择、系统功能的电路实现及仿真验证;

- 4.针对 D 类音频功率放大器提出了一种用于高压芯片的带隙基准源设计,该带隙基准可输出 6V 的带隙电压,不仅具有良好的温度特性,而且可输出高达 20mA 的电流,完全可以作为片内电源使用,为降低 D 类音频功率放大器的静态功耗,提高整体效率创造了条件;

- 5.采用了积分器输出宽摆幅,高频率的三角波,比直接应用电容电压,可以 降低静态电流的消耗;

- 6. PWM 比较器的设计采用 NMOS 电流镜进行双端转单端变换,从而提高了 PWM 比较器的单位增益带宽:

- 7.精心设计输出驱动死区时间的控制电路,使得驱动死区时间控制精确,减小了失真。

8. 所设的 D 类音频功率放大器输出级全部采用 NMOS 开关管,从而不仅使得功放的输出阻抗的匹配性好,而且极大的降低了芯片的面积。

文中详细介绍该芯片目前已完成的设计和前仿真工作,由于无滤波器 D 类音频功率放大器的设计还处于一个新的发展阶段,而我们的技术力量并不是很成熟,所以设计工作还有不足之处需要进一步完善。

本文还需要改进的是可以考虑利用输出级自举电路完成 H 桥上半桥的驱动,这样可以进一步降低系统的静态电流而且可以通过采用扩频技术来进一步降低 D 类功放的 EMI。

## 致谢

值此论文完成之际, 谨向给予过我指导、关心和帮助的人们表示最衷心的感谢。

首先要向我的导师王松林教授致以最崇高的敬意。感谢王松林老师带我进入 模拟 IC 设计这一行,使我可以在自己喜欢的专业上充分发挥。在我攻读硕士学位 期间,王老师给了我非常大的帮助和教导,不仅在工作和学习中严格要求和谆谆 教诲,而且在生活上也给了我无微不至的关怀。王老师的谆谆教诲是我以后职业 生涯中永远的财富。

本论文的完成也凝聚着来新泉教授的心血,在此向来老师致以最由衷的谢意。 来新泉教授在模拟集成电路设计方面有着很深的造诣,来老师渊博的知识和严谨 的治学作风给我留下了很深的印象,让我学到了很多东西。来老师经常教导我们 要重视基础知识学习、重视个人能力培养,这将对我今后的学习、工作产生深远 的影响。

感谢西安电子科技大学电子工程学院代国定副教授,特别感谢代老师给予我 在工艺、模型知识方面的指导和帮助。

感谢西安电子科技大学机电工程学院王辉老师在科研工作和日常生活中给我 提供了大量的指导和帮助。在此,衷心地向王老师致以诚挚的敬意。

感谢一起工作过的师兄师姐:叶强、尤勇、刘心泽、王江燕、谢飞,他们对 我的学习工作给予了很多帮助,在此对他们的帮助致以衷心的感谢。

感谢实验室的诸位同学: 孙朝阳、巫炜、黄虎、洪益文、李磊、李琳、郭海朝、罗莉、吕亚兰等同学在学习和生活上所给予的帮助。和他们的探讨与交流,令我不断开阔视野,受益匪浅; 感谢师弟师妹,特别是井海霞、胡佳民、冯旭,他们为论文的完成做了较多的工作。另外,还要感谢舍友徐庆,感谢他在生活上给予我的帮助。

最后,我要深深感谢我的父母,在两年多的研究生学习生活中,他们的鼓励、 支持和无私的爱给我强大的精神支柱,他们博大无私的爱和深切的期望是我不断 进取的精神动力。

# 参考文献

- [1] 张绍高. 数字声频技术原理及应用[M].北京:国防工业出版社,2000,07. pp:2-68.

- [2] 周全才,李斌. 数字音频功率放大器的技术与现状[J]. 电子制作,2000,06. pp:11-12.

- [3] 张虔铭. 浅谈音频功放失真[J].视听世界,2002,11. pp: 23-25.

- [4] 王以真. 实用扩音技术[M].北京:国防工业出版社, 2004. pp:2-56.

- [5] 韩宪柱. 声音制作基础[M].北京:中国广播电视出版社,2001. pp:71-112.

- [6] 莫爱雄. 音色纯美的纯直流 Hi-Fi 大功率纯甲类功放 DIY[J].家庭电子,2005,03. pp:37-39.

- [7] 戴春风. 音响技术的新台阶一浅析数字功率放大器[J].实用影音技术,2004,08. pp:34-36.

- [8] 孟祥浩. D 类音频功率放大器的评估及应用[J].电子设计技术,2006,05. pp:80-88.

- [9] 雷张伟. D 类音频功率放大器设计[D]. 成都:电子科技大学图书馆,2001.

- [10]陈杰生.高效电压模同步升降压型 DC-DC 集成电路设计与实现[D]. 西安电子科技大学硕士论文集. 2006.

- [11]华伟.通信开关电源的五种 PWM 反馈控制模式研究[J].通信电源技术, 2001,6,02.pp:8-10.

- [12] Vorpérian V. Simplified analysis of PWM converters using model of PWM switch, Part I :continuous conduction mode[J]. IEEE Trans Aerospace Elect ron Syst, 1990, 25 (5).pp:490-494.

- [13]李伟东等.一种脉宽调制型功率放大器的研究及应用[J]. 微电子学,2007,04.pp: 584-587.

- [14]吴大正,王松林等. 信号与线性系统分析[M]. 北京: 高等教育出版社,2005. pp:101-160.

- [15] CHANG J S,GWEE B H,LON Y S,et al. A Novel Low-Power Low-Voltage Class D Amplifier with Feedback for Improving THD Power Efficiency and Gain Linearity[A].Proc-IEEE International Symposium On Circuits And System[C].2001, 1.pp:I-635-I-638.

- [16] J EONGJ H, SEONG H H, YI J H, et al. A Class D Switching Power Amplifier with High Efficiency and Wide Bandwidth by Dual Feedback Loops[C]. Digest of Technical Papers-IEEE International Conference On Consumer Electronics, 1995.

- pp:428-429.

- [17] CHANG J S, GWEE B H, LON Y S, et al. A Novel Low-Power Low-Voltage Class D Amplifier with Feed back for Improving THD Power Efficiency and Gain Linearity[J]. Proc-IEEE International Symposium On Circuits And System. 1999,14(1). pp:142-150.

- [18] SMITH KM, LAI Z R, SMEDLEY KM. A New PWM Controller with One-cycle Response [J]. IEEE Transaction On Power Electronics, 1999. pp:142-150.

- [19]M.T.Tan etal. Analysis and two proposed design methodologies for optimizing power efficiency of a Class D amp output stage[J]. IEEE Int Symp Circuits and Systems, 1998. pp:158-162.

- [20] 龚伟,周雒维. D 类音频功率放大器控制方式综述[J].重庆大学学报,2003,02.pp: 117-121.

- [21]BAI Tong yun,LU Xiao de. Design for Electromagnetic Compatibility[M]. BEIJING: Beijing University of Posts and Telecommunications Press, 2001.pp:63-168.

- [22]黄黎.D 类音频功率放大器的环路设计[J].中国集成电路,2007,08(99).pp.60-61.

- [23] Phillip E. Allen, Douglas R. Holberg. CMOS 模拟集成电路设计 (第二版) [M]. 北京: 电子工业出版社, 2005. pp:128-130.

- [24] Behzad Razavi. Design of Analog CMOS Integrated Circuits[M]. New York: MrGraw-Hill, 1996. pp:169-187.

- [25]R. Jacob Baker, Harry W. Li, David E. Boyce.著.陈中建等 译.CMOS 电路设计布局与仿真[M].北京: 机械工业出版社,2006.pp:353-370.

- [26] Brokaw A P. A simple three-terminal IC bandgap reference [J]. IEEE J. Solid-State Circuits, 1974,9 (6).pp: 388-393.

- [27]Razavi. B.著.陈贵灿等 译.模拟 CMOS 集成电路设计 [M].西安: 西安交通大学 出版社,2005.pp:310-327.

- [28]Brokaw A P.A simple tree-terminal IC bandgap reference[J]. IEEE Journal of Solid-state Circuit, 1974,9(6).pp:388-393.

- [29]Razavi. B.著.陈贵灿等 译.模拟 CMOS 集成电路设计 [M].西安: 西安交通大学 出版社,2005.pp:192-290.

- [30] Paul R. Gray, Paul R. Hurst, Stephen H. Lewis. 模拟集成电路的分析与设计(第四版)[M]. 北京: 高等教育出版社, 2003. pp:431-510.

- [31] Maloberti Piero, Maloberti Franco, Frocchi Carlo. Curvature-Compensated BiCMOS Bandgap with 1-V Supply Voltage[J]. IEEE Journal of Solid-state Circuit, 2001, July, 36(7). pp. 1076-1081.

- [32]孙肖子,张企民.模拟电子技术基础[M].西安: 西安电子科技大学出版社, 2001. pp:96-97.

- [33]杨颂华,冯毛官等.数字电子技术基础[M].西安: 西安电子科技大学出版社, 2001. pp:56-83.

- [34] E. Sackinger and W. Guggenbuhl. A Versatile Building Block: The CMOS Differential Difference Amplifier[J]. IEEE J. Solid-state Circuit. 1987, April, SC-22(2). pp:287-294.

- [35]朱正涌. 半导体集成电路[M]. 北京: 清华大学出版社(第一版), 2001. pp:216-327.

- [36]张家川,刘伯安.新型低电压能隙基准电压源[J].半导体技术,2006,31(8).pp:591-593.

- [37]ZHU Gao-feng WU Li-ming WANG Gui-tang. Key techniques of class D audio power amplifier[J]. TECHNICAL ACOUSTICS, 2006, 05(25),pp: 452-456.

- [38] 康华光,陈大钦.电子技术基础(模拟部分)[M].北京:高等教育出版社,1999.pp: 277-314.

- [39] Abidi A. Linearization of voltage controlled oscillators using switched capacitor feedback[J]. IEEE J Sol Sta Circ, 1987, 22(3). pp:494-496.

- [40] Abidi A A, Meyer R G. Noise in relaxation oscillators [J]. IEEE J Sol Sta Circ, 1993, 18(6). pp: 794-802.

- [41]ZHANG Jing-hua,LI Zhi-hua,XU Wei-dian.Effect of Shunt Resistance on the Output of Triangle-wave Generator[J]. Journal of Electric Power,2004,04(19).pp: 287-289.

- [42]Floyd M Gardner. Charge-Pump Phase-Lock Loops[J].IEEE Transactions on Communications, 1980, 28(11).pp:1849-1858.

# 在读期间研究成果

## 一、在读期间参加科研项目

- 1.参加西安电子科技大学电路 CAD 所科研项目"电源管理类系列集成电路设计",本人负责一款具有 LDO 模式的同步降压型芯片的设计与验证工作。该芯片采用 CSMC 0.5μm CMOS 工艺进行仿真。

- 2.参加西安电子科技大学电路 CAD 所科研项目 "无需滤波器、高效率音频功率放大器的研究与设计",本人完成无需滤波器、高效率 D 类音频功率放大器专用集成电路芯片 XPD7026 的设计与仿真验证,该芯片采用国外某公司的 0.6μm BCD 工艺。

- 3.参加西安电子科技大学电路 CAD 所科研项目"电源管理类系列集成电路设计",本人负责全功能线性锂离子电池充电器、USB 功率控制器、电源无缝转换以及热插拔模块的设计与仿真。该芯片基于 CSMC 0.5 μm CMOS 工艺进行设计。

- 4.参加西安电子科技大学电路 CAD 所科研项目"低 THD+N 的音频功率放大器关键技术理论研究与设计",参与完成音频功率放大器 XPD001 中的 32 位增益控制模块的设计与仿真报告撰写工作。

## 二、论文发表情况

- 1. 王松林, 牟在鑫, 来新泉, 代国定. 《一款基于复合运放的线性锂离子电池 充电器》被中文核心期刊《微电子学》录用。

- 2. 牟在鑫,王松林,来新泉.《一种 CMOS 混合电源供给方案》被专业科技期刊《电源技术学报》录用。

- 3. 来新泉,郭海朝,牟在鑫.《一种用于高压芯片的带隙基准源的设计》被中 文核心期刊《电子器件》录用。

#

现

作者: 牟在鑫

学位授予单位: 西安电子科技大学

#### 相似文献(10条)

1. 期刊论文 周生雷 内含可程控锁相环的立体声音频DAC芯片PCM1723及其应用 -国外电子元器件2001. ""(3)

PCM1723是BURR-BROWN公司推出的一种带有可程控锁相环的立体声音频D/A转换器,它具有软件静音、数字衰减及数字去加重等功能。其音频输出模 式具有立体声、单声道可选,可用于视音频解码器中。文中介绍了PCM1723的工作原理及其典型应用电路。

2. 期刊论文 贾懋珅. 鲍长春. JIA Mao-shen. BAO Chang-chun 一种符合ITU-T指标要求的嵌入式立体声语音频编码方 法 -电子学报2009, 37(10)

基于国际电信联盟标准化组织(ITU-T)编码标准G. 729. 1, 本文提出了一种嵌入式变速率立体声语音与音频编码方法. 本算法利用G. 729. 1和改进的调制 叠接变换(Modulated Lapped Transform, MLT)编码技术对输入信号的中值与边带信息进行分层编码, 形成具有嵌入式结构的码流. 编码器可处理宽带和超 宽带的立体声信号, 宽带立体声信号编码的最大码率为48kb/s, 超宽带立体声信号编码的最大速率为64kb/s. 实现结果表明, 本编码器的编码质量均达到了 ITU-T对G. EV-VBR立体声编码的指标要求,

3. 学位论文 吴永辉 立体声增强功能音频功放芯片的设计与试制 2007

本文设计了一个音频功率放大器芯片,主要应用于小体积便携式电子产品,对此本芯片主要有以下三个特点:首先设计了低功耗关断模式和开关噪 声抑制电路;具有高线性和高保真度的AB类放大器;另外,在系统中还设计了3D立体声增强功能。

低功耗模式有效时,系统所有模块均被关断,只有一些逻辑控制电路在工作,因功耗很小。系统中的电源旁路电路,在系统开启和关断时能够延缓 信号传输,当系统稳定后才有信号输出,故抑制了"咔嚓"声;便携式产品体积有限,立体声的两个扬声器不可能相距足够远,因而音效往往很差,本 文在深入分析了立体声原理、声音串扰及解决方法之后,设计了一种电路结构,此结构基于音频放大系统并集成于音频放大系统之内,能够增强3D立体 声的声场。另外,文中还优化设计了运算放大器、电流源、过温保护等模拟电路,使之性能更好、功耗更小。

本芯的整个设计流程都是在cadence工具下完成,在模块电路设计中,仿真与设计循环进行,并最终确定了系统的电路。对芯片系统进行整体仿真 ,模拟其功能和性能参数,都在可接受的范围之内。本论文还细致地设计了系统的版图,尤其是运算放大器和功率器件等决定芯片性能的关键模块。电 路和版图的设计都采用0.5 μm N阱CMOS工艺的器件模型和设计规则,并最终流片。封装为QFN24,具有面积小、散热性能好的特点。

对芯片进行详细测试的结果表明,过温关斯、3D立体声增强、单双端模式及低功耗关断模式功能正常。关断模式下功耗几乎为零,而芯片最大静态 功耗20mW,在5V电源电压、4Ω负载、频率为1KHz及1W输出功率时的THD+N为0.2%。各项性能指标均达到了设计的预期值。

4. 期刊论文 王辉. 马维华. WANG Hui. MA Wei-hua 蓝牙高级音频分发框架协议的研究与实现 -装备制造技术 2007, ""(4)

通过对蓝牙高级音频分发框架(A2DP)协议栈进行系统地分析,提出了一种基于消息机制的协议方案,在无A2DP框架的蓝牙1.1协议栈基础上实现了轻型 的A2DP应用框架,并且利用嵌入式蓝牙开发平台,实现了基本的点对点蓝牙立体声音频数据的传输,

5. 期刊论文 毛兴武. 李建文. Mao Xingwu. Li Jianwen 第三代Boomer (R) 音频立体声功率放大器的特点及应用 -电子 元器件应用2001, 3(11)

LM4867是第三代Boomer()音频立体声功放电路. 该电路含有立体声耳机功能并消除了输出耦合电容器. 当连接到5V电源时,这种双桥连接功率放大器对 4Ω和3Ω的负载分别提供2,1W和2,4W的功率,而THD+N小于1%,LM4867利用先进的新一代电路消除了卡塔声和喀呖声,

6. 期刊论文 裴跃波. 杨旭东 音频输入信号相位与电平差对调频立体声广播质量的影响 -广播与电视技术 2002, 29(8)

本文分析了在进行调频立体声广播过程中, 左右两路音频输入信号的电平与相位差过大, 对调频立体声播出质量的影响, 并结合实例加以探讨.

7. 期刊论文 靳文瑞. 靳文献. 靳文峰. JIN Wen-rui. JIN Wen-xian. JIN Wen-feng 16/20位立体声音频编解码器 PCM3002 - 国外电子元器件2005, ""(4)

PCM3002是TI公司推出的16/20位立体声音频编解码芯片. 文中简要分析了该芯片的性能特点和工作原理,给出了PCM3002的典型应用电路.

8. 学位论文 周蕙瑜 双通道立体声的虚拟重发技术研究 2006

我们周围环境的声音能帮助我们判断物体的方位和距离,以及环境的细节。为了使使用虚拟现实系统的用户能完全沉浸在虚拟环境中,虚拟系统必 须符合人类的可靠感知系统。虽然大多数虚拟系统重点在视觉方面,然而三维声音系统能使听者感知声源的位置及环境的变化,提高环境声学的声音交 互作用。因此,虚拟声定位技术是当前计算机、视听技术及虚拟现实技术研究的一个重要内容,也是声学仿真的音频输出技术的一个重要研究领域和当 前研究热点。

人类听觉生理学和心理学是研究虚拟声定位技术的基础,本论文回顾了心理声学相关听觉系统以及听觉特性,包括音频定位因素的影响和哈斯效应 , 掩蔽效应等因素对多音叠加的影响, 为本文奠定了研究基础。

接着描述了人类感知声音的过程,介绍了音频定位的依据,引入双耳听觉传输原理的核心部分——头部相关传输函数(HRTF)。然后简述了麻省理工 学院和CIPIC实验室测量HRTF的方法,通过声波的散射理论以及利用人头模型提出一种简化的理论计算对头部尺寸对声音定位的影响进行了理论分析,并 且利用心理学测试验证利用匹配数据库实现HRTF的个性化。根据心理学家对声音频谱定位特性的研究,分频段对HRTF进行增益改变以尽量减少虚拟声前 后声像混淆的发生。为了得到更真实自然的虚拟运动声源,研究了HRTF的空间插值以弥补空间测量HRTF数据不足的缺点。以上几点为音频定位系统奠定

在多媒体计算机虚拟声重发的实际应用中,要求对音频信号进行实时处理。文中探讨了多媒体计算机音频的实时处理方法,强调了数据处理模块的 运算速度要足够快。在本论文,针对项目环境的要求,提出了包括静止单声源的音频定位的生成方案;静止多声源的音频定位系统方案以及音频混音的 算法: 三维动态声源的音频定位的生成方案, 重点研究了音频信号处理过程的实时性。

最后,本论文通过利用CIPIC实验室测量的HRTF合成双通道虚拟声的音频定位仿真系统,对该仿真系统进行感知测试,验证了双通道虚拟声音频定位 系统实现方案的可行性,并总结出该音频仿真系统存在的问题以及改进方法。

9. 期刊论文 王玮 基于数字立体声光端机的数字光纤音频传输系统 -西部广播电视2003, ""(1) 文章简要介绍了数字光纤音频传输系统的基本结构、工作原理和主要特点.

10. 会议论文 朱觉 多声道数字立体声录音制作 2002

近年来, 数字技术在影视制作中的应用愈来愈普遍. 随着数字媒体传播方式的发展和人们对娱乐消费的需求, 数字音频制作正向多声道立体声迅速演变. 本文就多声道数字立体声录音制作(5.1声道)做一介绍.

本文链接: http://d.g.wanfangdata.com.cn/Thesis\_Y1246652.aspx

授权使用: 中南民族大学(znmzdx), 授权号: b72d0026-cab1-40f0-8e76-9e550008d78f

下载时间: 2010年12月23日