## **Understanding Jitter and Phase Noise**

A Circuits and Systems Perspective

Gain an intuitive understanding of jitter and phase noise with this authoritative guide. Leading researchers provide expert insights on a wide range of topics, from general theory and the effects of jitter on circuits and systems, to key statistical properties and numerical techniques. Using the tools provided in this book, you will learn how and when jitter and phase noise occur, their relationship with one another, how they can degrade circuit performance, and how to mitigate their effects – all in the context of the most recent research in the field. Examine the impact of jitter in key application areas, including digital circuits and systems, data converters, wirelines, and wireless systems, and learn how to simulate it using the accompanying Matlab code. Supported by additional examples and exercises online, this is a one-stop guide for graduate students and practicing engineers interested in improving the performance of modern electronic circuits and systems.

**Nicola Da Dalt** is Analog Engineering Manager for High-Speed Serial Interfaces at Intel Corporation, having previously worked at Telecom Italia and Infineon Technologies.

**Ali Sheikholeslami** is Professor in the Department of Electrical and Computer Engineering at the University of Toronto.

As we continue to push operating speeds in electronic systems, timing jitter has emerged as an increasingly important showstopper across a wide range of applications. Consequently, pushing the envelope requires a thorough understanding of jitter from its mathematical description, to its manifestation in circuits and its impact on systems. This book delivers the most comprehensive treatment of this subject to date and provides valuable content to jitter-plagued engineers at all levels of experience.

Boris Murmann, Stanford University

All components generate noise. They give rise to thermal and 1/f noise. All amplifiers and filters have Signal-to-Noise ratio as one of their most important specifications. In oscillators however, noise gives rise to jitter and phase noise. This is why this book is so important. It provides unique insight in the origins and the analysis of these specifications. Many applications are highlighted in the field of data converters, wireless and wireline systems, and a number of digital applications. Examples are the jitter in a CMOS inverter, in a LC oscillator, in a ring oscillator, etc. As a result this book is a necessity for all designers who have to know about noise and its performance limitations.

Willy Sansen, KU Leuven

Phase noise is the primary source of performance deterioration in all wireless/wireline communication systems – and yet, dedicated books have been conspicuously absent to date. We are therefore very fortunate that two real experts – Dr. Da Dalt and Professor Sheikholeslami – have finally decided to fill this gap, presenting us with what will become standard reading for anyone desirous to understand the peculiar and often elusive nature of phase noise.

Professor Pietro Andreani, Lund University

The rigorous mathematical description of jitter, its link to phase noise as well as its practical impact on different classes of circuits (e.g. digital, wireline, wireless, data converters) are all known as difficult and sometimes obscure topics even for experienced designers. This is the only book that I know which covers all of these subjects, providing at the same time both the intuitive understanding, the Matlab codes are particularly useful from this standpoint, and the appropriate mathematical rigour. The authors, that are two leading experts in the field, have also done a significant effort also in discussing the key findings available in both classical and more recent open literature, not just presenting their own work. I highly recommend this book.

Carlo Samori, Politecnico di Milano

This excellent reference provides a wealth of material to satisfy both engineers new to clocking and seasoned veterans that are experts in jitter and phase noise. The authors address all the important aspects of these critical topics and provide great insights for readers.

Samuel M Palermo, Texas A&M University

# Understanding Jitter and Phase Noise

A Circuits and Systems Perspective

NICOLA DA DALT Intel Corporation

ALI SHEIKHOLESLAMI University of Toronto

# **CAMBRIDGE**UNIVERSITY PRESS

University Printing House, Cambridge CB2 8BS, United Kingdom

One Liberty Plaza, 20th Floor, New York, NY 10006, USA

477 Williamstown Road, Port Melbourne, VIC 3207, Australia

314–321, 3rd Floor, Plot 3, Splendor Forum, Jasola District Centre, New Delhi – 110025, India

79 Anson Road, #06-04/06, Singapore 079906

Cambridge University Press is part of the University of Cambridge.

It furthers the University's mission by disseminating knowledge in the pursuit of education, learning, and research at the highest international levels of excellence.

www.cambridge.org

Information on this title: www.cambridge.org/9781107188570

DOI: 10.1017/9781316981238

© Cambridge University Press 2018

This publication is in copyright. Subject to statutory exception and to the provisions of relevant collective licensing agreements, no reproduction of any part may take place without the written permission of Cambridge University Press.

First published 2018

Printed in the United Kingdom by TJ International Ltd. Padstow Cornwall

A catalogue record for this publication is available from the British Library

Library of Congress Cataloging-in-Publication data

Names: Da Dalt, Nicola, 1969– author. | Sheikholeslami, Ali, 1966– author.

Title: Understanding jitter and phase noise: a circuits and systems perspective /

Nicola Da Dalt (Altera Corporation), Ali Sheikholeslami (University of Toronto).

$Description: Cambridge, United\ Kingdom\ ; New\ York, NY: Cambridge$

University Press, 2018.

Identifiers: LCCN 2017031090 ISBN 9781107188570 (hardback)

ISBN 1107188571 (hardback)

Subjects: LCSH: Electric circuits-Noise. | Electric noise. | Oscillators, Electric-Noise.

Classification: LCC TK454 .D3 2018 | DDC 621.382/24-dc23

LC record available at https://lccn.loc.gov/2017031090

ISBN 978-1-107-18857-0 Hardback

Cambridge University Press has no responsibility for the persistence or accuracy of URLs for external or third-party internet websites referred to in this publication, and does not guarantee that any content on such websites is, or will remain, accurate or appropriate.

To our parents, Giuliana and Guido Fatemeh and Hadi

# **Contents**

|   | Prefe | ace                    |                                                       | <i>page</i> xiii |

|---|-------|------------------------|-------------------------------------------------------|------------------|

|   | Ackn  | owledgi                | ments                                                 | XV               |

| 1 | Intro | Introduction to Jitter |                                                       |                  |

|   | 1.1   | What Is Clock Jitter?  |                                                       | 1                |

|   |       | 1.1.1                  | Period Jitter                                         | 2                |

|   |       | 1.1.2                  | Absolute Jitter                                       | 3                |

|   |       | 1.1.3                  | Intentional Jitter                                    | 4                |

|   | 1.2   | What I                 | Is Data Jitter?                                       | 5                |

|   |       | 1.2.1                  | Eye Diagram                                           | 5                |

|   |       | 1.2.2                  | Random Versus Deterministic Jitter                    | 7                |

|   | 1.3   | Jitter i               | n Measuring Time                                      | 8                |

|   | 1.4   | Jitter i               | n a Ring Oscillator                                   | 10               |

|   |       | 1.4.1                  | Jitter in Delay of a CMOS Inverter                    | 10               |

|   |       | 1.4.2                  | Modeling Jitter of the Ring Oscillator                | 12               |

|   | 1.5   | Jitter i               | n Electronic Systems                                  | 12               |

| 2 | Basi  | Basics of Jitter       |                                                       |                  |

|   | 2.1   | Genera                 | al Jitter Terminology and Definitions                 | 15               |

|   |       | 2.1.1                  | Absolute Jitter                                       | 17               |

|   |       | 2.1.2                  | Relative Jitter                                       | 18               |

|   |       | 2.1.3                  | Period Jitter                                         | 18               |

|   |       | 2.1.4                  | N-Period Jitter                                       | 20               |

|   |       | 2.1.5                  | Other Jitter Definitions                              | 21               |

|   |       | 2.1.6                  | Summary of Jitter Definitions and Their Relationships | 25               |

|   | 2.2   | Statist                | ics on Jitter                                         | 25               |

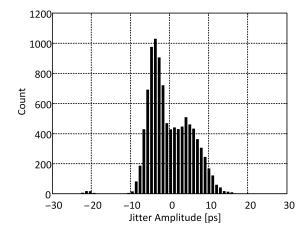

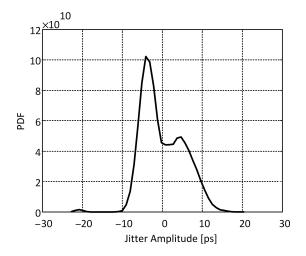

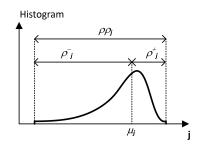

|   |       | 2.2.1                  | Histograms and Probability Density Functions          | 27               |

|   |       | 2.2.2                  | Jitter Mean                                           | 31               |

|   |       | 2.2.3                  | Jitter Median                                         | 31               |

|   |       | 2.2.4                  | Jitter Standard Deviation and Variance                | 32               |

|   |       | 2.2.5                  | Jitter Peak and Peak-Peak                             | 32               |

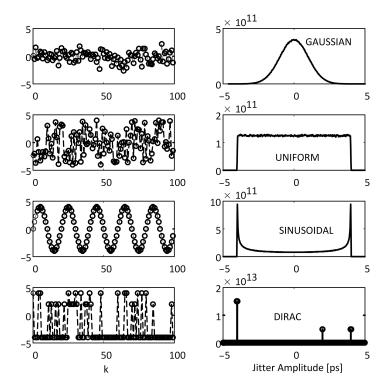

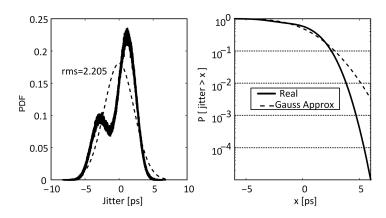

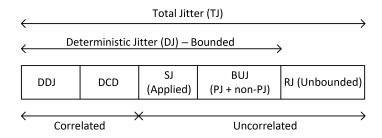

|   |       | 2.2.6                  | Taxonomy of Jitter Based on PDF                       | 35               |

|   |       | 2.2.7                  | Combination of Jitter Components                      | 37               |

|   |        | 2.2.8 Jitter Decomposition                                           | 39  |

|---|--------|----------------------------------------------------------------------|-----|

|   |        | 2.2.9 Total Jitter and Probability of Error                          | 40  |

| 3 | .litte | r and Phase Noise                                                    | 43  |

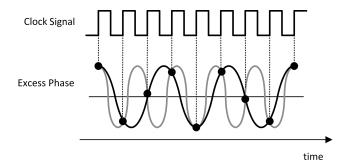

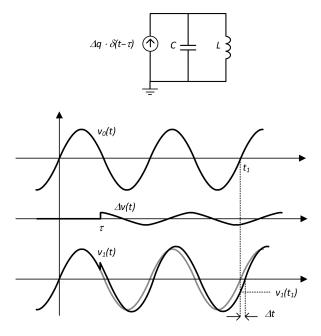

| • | 3.1    | Basic Relationship Between Jitter and Excess Phase                   | 43  |

|   | 0.12   | 3.1.1 Excess Phase and Absolute Jitter in the Time Domain            | 43  |

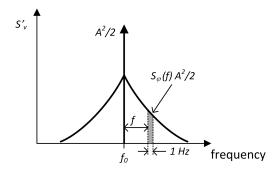

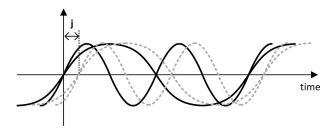

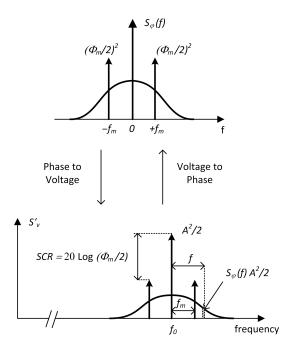

|   |        | 3.1.2 Excess Phase and Absolute Jitter in the Frequency Domain       | 45  |

|   |        | 3.1.3 Voltage to Excess Phase Transformations: Random Noise          | 46  |

|   |        | 3.1.4 Voltage to Excess Phase Transformations: Modulation            | 49  |

|   |        | 3.1.5 Definition of Phase Noise                                      | 51  |

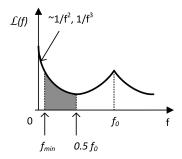

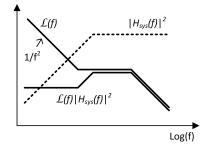

|   | 3.2    | From Phase Noise to Jitter                                           | 52  |

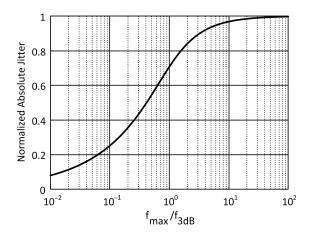

|   |        | 3.2.1 Absolute Jitter                                                | 52  |

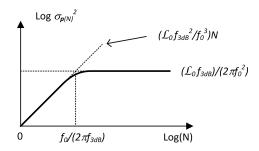

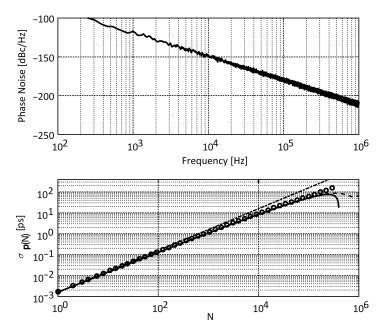

|   |        | 3.2.2 <i>N</i> -Period and Period Jitter                             | 59  |

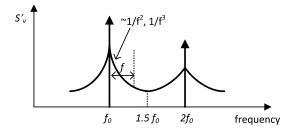

|   | 3.3    | Spectral Spurious Tones and Jitter                                   | 65  |

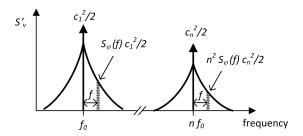

|   | 3.4    | Superposition of Different Spectral Components                       | 66  |

|   | 3.5    | Summary of Mathematical Relationships Between Jitter and Phase Noise | 68  |

| 4 | Jitte  | r and Phase Noise in Circuits                                        | 69  |

|   | 4.1    | Jitter in Basic Circuits                                             | 69  |

|   |        | 4.1.1 Noisy Current Charging a Capacitor                             | 69  |

|   |        | 4.1.2 Jitter of a CMOS Inverter                                      | 72  |

|   |        | 4.1.3 Jitter of a CMOS Differential Stage                            | 74  |

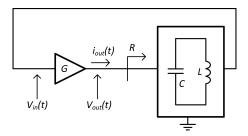

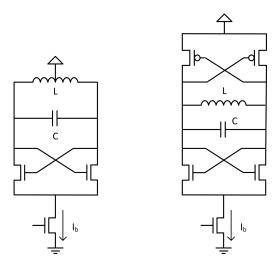

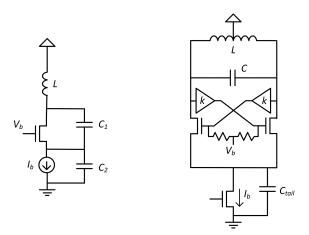

|   | 4.2    | Jitter in Oscillators                                                | 77  |

|   |        | 4.2.1 Ring Oscillators                                               | 77  |

|   |        | 4.2.2 Relaxation Oscillators                                         | 78  |

|   | 4.3    | Phase Noise in Oscillators                                           | 80  |

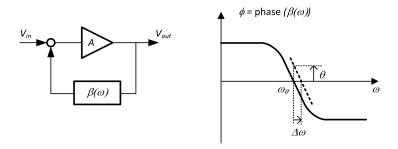

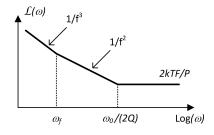

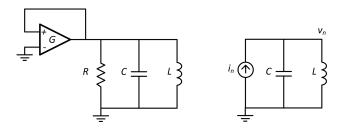

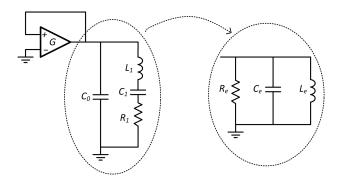

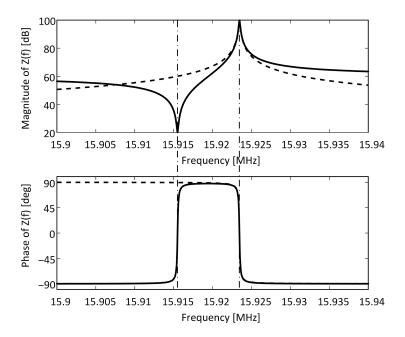

|   |        | 4.3.1 Leeson's Model                                                 | 80  |

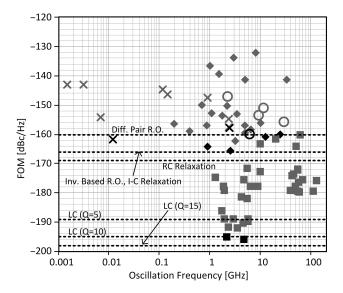

|   |        | 4.3.2 Oscillator Figure of Merit                                     | 83  |

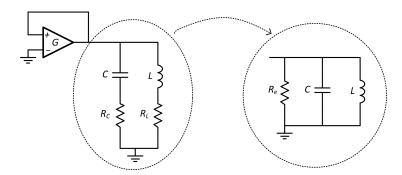

|   |        | 4.3.3 LC Oscillators                                                 | 84  |

|   |        | 4.3.4 Crystal and Other Oscillators                                  | 86  |

|   | 4.4    | Linear Time-Variant Analysis                                         | 90  |

|   |        | 4.4.1 The Impulse Sensitivity Function                               | 90  |

|   |        | 4.4.2 Application to Ring Oscillators                                | 93  |

|   |        | 4.4.3 The ISF of an LC Tank                                          | 94  |

|   |        | 4.4.4 A General Result on Leeson's Noise Factor <i>F</i> for LC      |     |

|   |        | Oscillators                                                          | 96  |

|   |        | 4.4.5 Application to Some Common LC Oscillator Topologies            | 98  |

|   | 4.5    | Comparison of Best Achievable FOM                                    | 101 |

|   | 4.6    | A Note on Flicker Noise                                              | 103 |

|   | 4.7    | Ideal Frequency Divider                                              | 104 |

|   | 4.8    | Ideal Frequency Multiplier                                           | 108 |

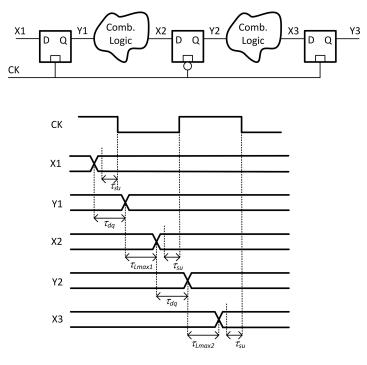

| 5 |        | ets of Jitter in Synchronous Digital Circuits                        | 111 |

|   | 5.1    | Edge-Triggered Synchronous Design                                    | 111 |

**Contents** ix

|   | 5.2  | Gated Clock, Divided Clock, Enabled Systems                    | 114 |  |  |

|---|------|----------------------------------------------------------------|-----|--|--|

|   | 5.3  | Multicycle Paths                                               | 116 |  |  |

|   | 5.4  | Latch-Based Synchronous Design                                 | 117 |  |  |

| 6 | Effe | ects of Jitter on Data Converters                              |     |  |  |

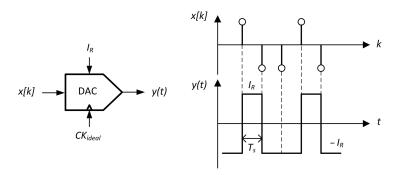

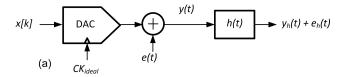

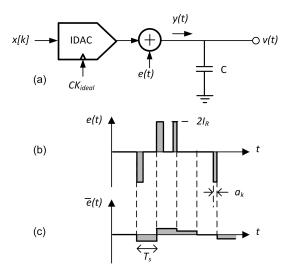

|   | 6.1  | Effects of Jitter on Current DACs                              | 121 |  |  |

|   |      | 6.1.1 Background                                               | 121 |  |  |

|   |      | 6.1.2 Non-Return-to-Zero (NRZ) IDAC                            | 121 |  |  |

|   |      | 6.1.3 NRZ IDAC Followed by a Linear Filter                     | 124 |  |  |

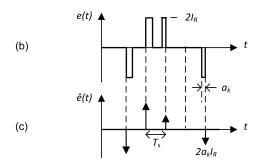

|   |      | 6.1.4 NRZ IDAC Followed by an Integrating Capacitor            | 126 |  |  |

|   |      | 6.1.5 Return-to-Zero IDAC                                      | 127 |  |  |

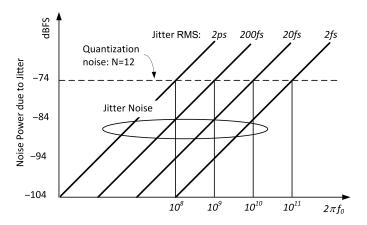

|   | 6.2  | Effects of Jitter on Nyquist Data Converters                   | 128 |  |  |

|   |      | 6.2.1 Background                                               | 128 |  |  |

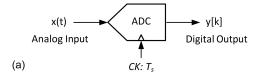

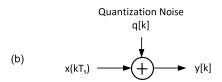

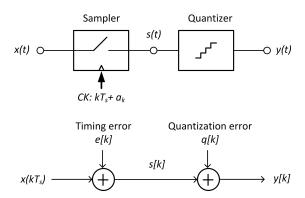

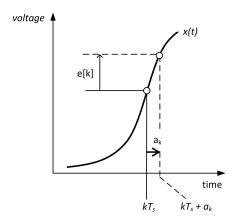

|   |      | 6.2.2 ADC Timing Error                                         | 129 |  |  |

|   |      | 6.2.3 Design Considerations                                    | 133 |  |  |

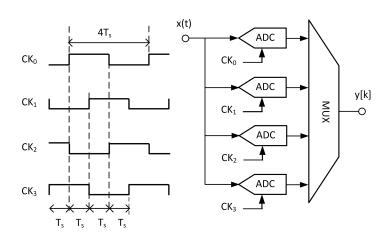

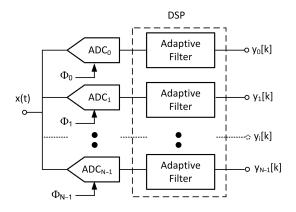

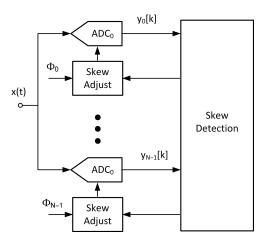

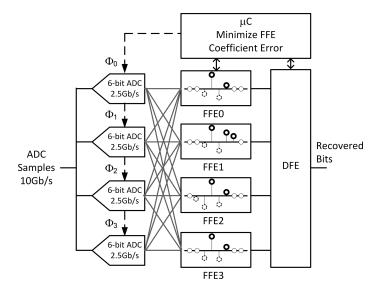

|   | 6.3  | Effects of Timing Skew in Time-Interleaved ADCs                | 133 |  |  |

|   |      | 6.3.1 Background                                               | 134 |  |  |

|   |      | 6.3.2 Effects of Timing Skew                                   | 134 |  |  |

|   |      | 6.3.3 Alternative Approach                                     | 136 |  |  |

|   |      | 6.3.4 Design Considerations                                    | 137 |  |  |

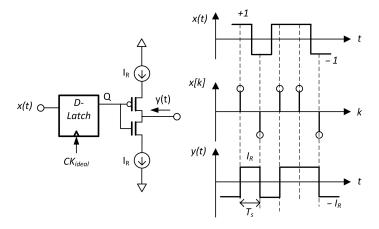

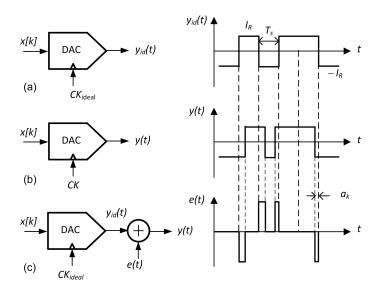

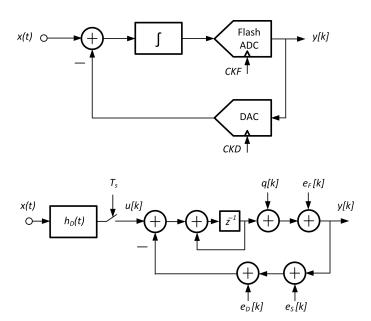

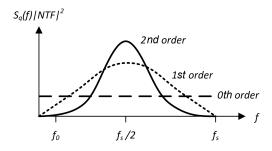

|   | 6.4  | Effects of Jitter on Continuous-Time $\Delta\Sigma$ Modulators | 139 |  |  |

|   |      | 6.4.1 Background                                               | 139 |  |  |

|   |      | 6.4.2 Effects of Flash ADC Timing Error on SNR                 | 141 |  |  |

|   |      | 6.4.3 Effects of DAC Timing Error on SNR                       | 141 |  |  |

| 7 | Effe | cts of Jitter in Wireline Applications                         | 143 |  |  |

|   | 7.1  | Basic Concepts in Wireline Signaling                           | 143 |  |  |

|   | 7.2  | Jitter in Analog CDR                                           | 145 |  |  |

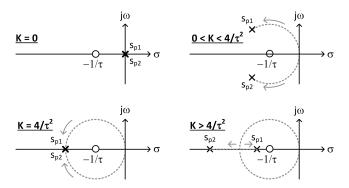

|   |      | 7.2.1 Linear Model of the CDR                                  | 145 |  |  |

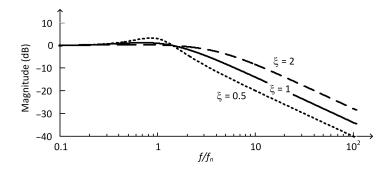

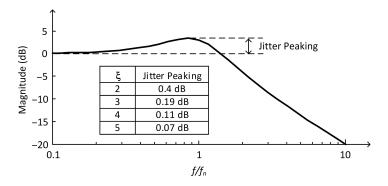

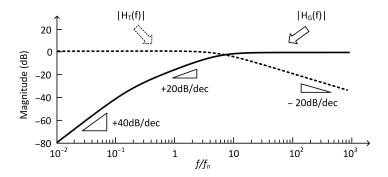

|   |      | 7.2.2 Jitter Transfer                                          | 146 |  |  |

|   |      | 7.2.3 Jitter Generation                                        | 150 |  |  |

|   |      | 7.2.4 Jitter Tolerance                                         | 151 |  |  |

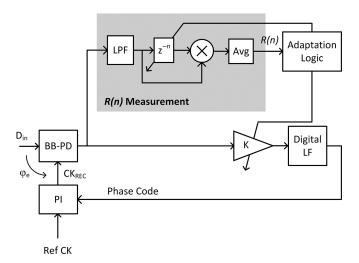

|   | 7.3  | Effect of Jitter on Bang-Bang CDR                              | 155 |  |  |

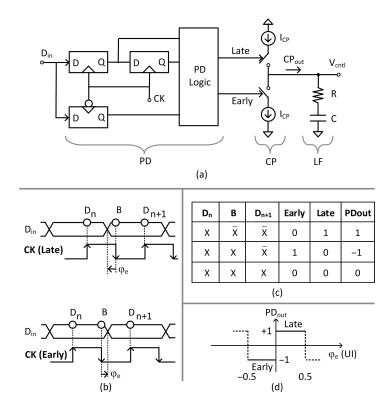

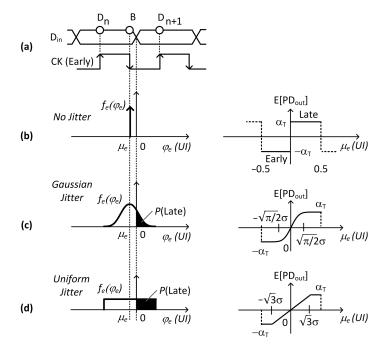

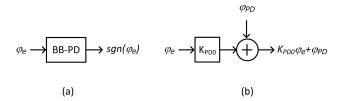

|   |      | 7.3.1 Background                                               | 155 |  |  |

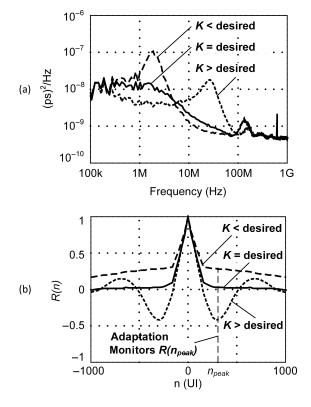

|   |      | 7.3.2 Effect of Jitter on BB-PD Gain                           | 157 |  |  |

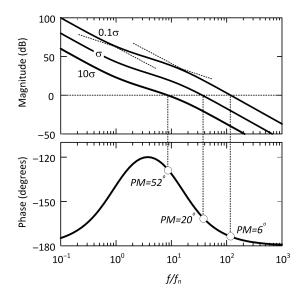

|   |      | 7.3.3 Added Jitter due to BB-PD                                | 158 |  |  |

|   |      | 7.3.4 Effect of Jitter on BB-CDR Stability                     | 159 |  |  |

|   | 7.4  | Jitter in the Received Eye                                     | 160 |  |  |

|   | 7.5  | Jitter Amplification by Passive Channels                       | 161 |  |  |

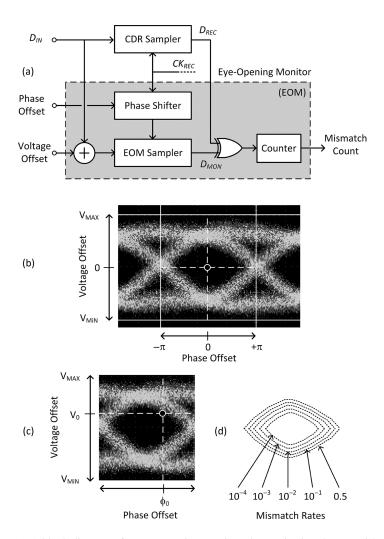

|   | 7.6  | Jitter Monitoring and Mitigation                               | 163 |  |  |

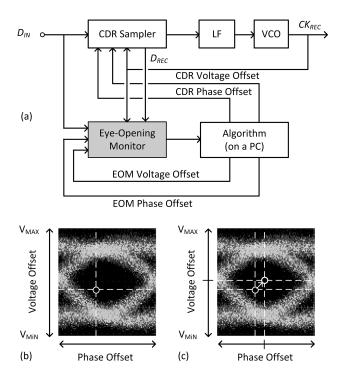

|   |      | 7.6.1 Eye-Opening Monitor                                      | 164 |  |  |

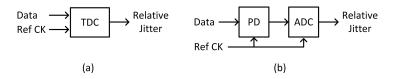

|   |      | 7.6.2 Relative Jitter Measurement                              | 166 |  |  |

|   |      | 7.6.3 Absolute Jitter Measurement                              | 168 |  |  |

|   | 7.7  | Intentional Jitter                                             | 171 |  |  |

|   |      |                                                                |     |  |  |

|            |       | 7.7.1     | Jitter Injection for Improved Linearity                           | 171        |

|------------|-------|-----------|-------------------------------------------------------------------|------------|

|            |       | 7.7.2     | Jitter Injection for Jitter Measurement                           | 172        |

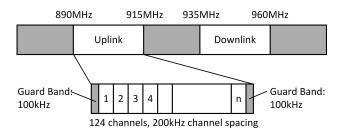

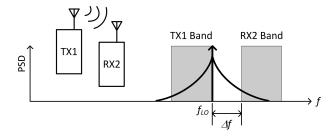

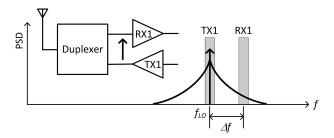

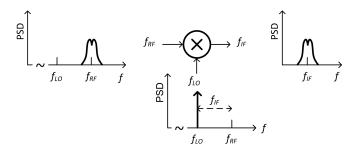

| 8          | Phas  | e Noise i | in Wireless Applications                                          | 174        |

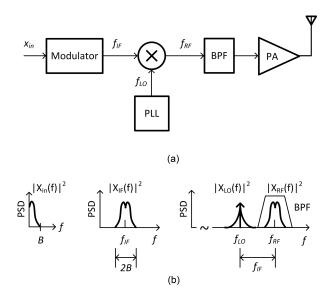

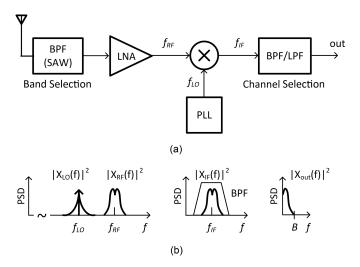

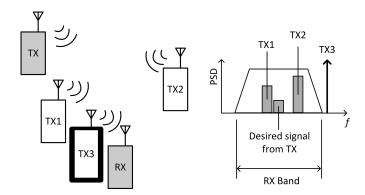

|            | 8.1   | Basics    | of Wireless Transceivers                                          | 174        |

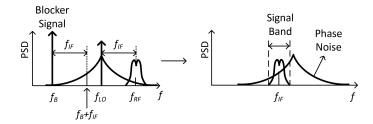

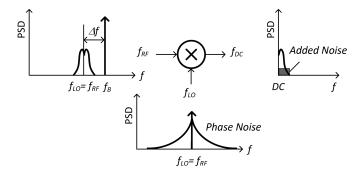

|            |       | 8.1.1     | Blockers in Wireless Receivers                                    | 175        |

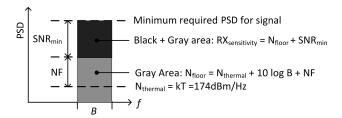

|            |       | 8.1.2     | Noise Figure                                                      | 176        |

|            |       | 8.1.3     | Receiver Sensitivity                                              | 176        |

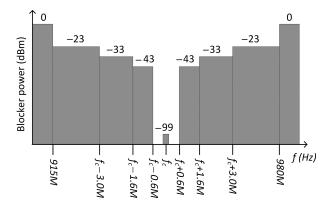

|            | 8.2   | Examp     | oles of Phase Noise Requirements for the Transmitter VCO          | 177        |

|            | 8.3   | Recipr    | ocal Mixing at the Receiver                                       | 179        |

| 9          | Adva  | nced Co   | ncepts on Jitter and Phase Noise                                  | 183        |

|            | 9.1   |           | eral Method to Convert Phase Noise to Jitter                      | 183        |

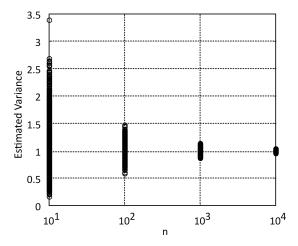

|            | 9.2   |           | ence Intervals of Statistical Parameters                          | 184        |

|            |       | 9.2.1     | Confidence Interval on the Jitter Mean                            | 186        |

|            |       | 9.2.2     | Confidence Interval on the Jitter Variance and Standard Deviation | 188        |

|            |       | 9.2.3     | Confidence Interval on the Jitter Peak and Peak-Peak Values       | 191        |

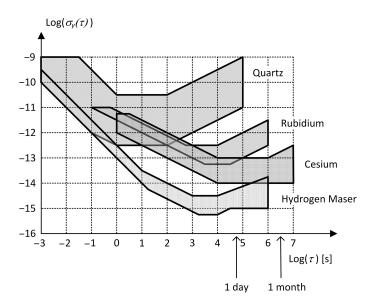

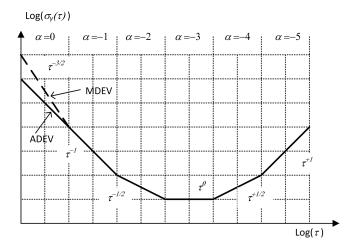

|            | 9.3   |           | ators for Frequency Stability                                     | 193        |

|            |       | 9.3.1     | Basic Concepts                                                    | 194        |

|            |       | 9.3.2     | Allan Deviation (ADEV)                                            | 195        |

|            |       | 9.3.3     | Relation Between Allan Deviation and Jitter                       | 195        |

|            |       | 9.3.4     | Relation Between Allan Deviation and Phase Noise                  | 197        |

|            |       | 9.3.5     | Modified Allan Deviation (MDEV) and Time Deviation (TDEV)         | 199        |

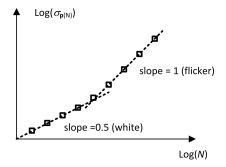

|            | 9.4   |           | erview of Flicker Noise                                           | 200        |

|            | 9.5   | Lorent    | ian Spectrum of Oscillator Phase Noise                            | 205        |

| 10         | Nume  | erical Me | ethods                                                            | 207        |

|            | 10.1  |           |                                                                   |            |

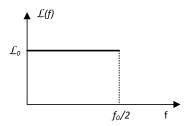

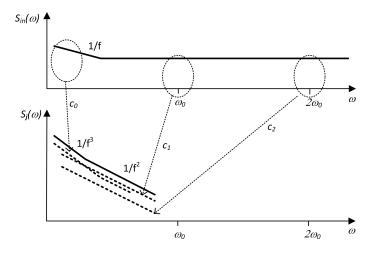

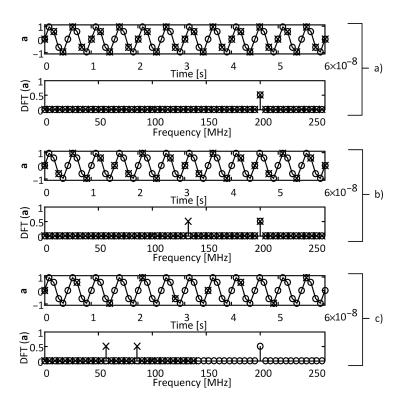

|            |       |           | Generation of Jitter Samples with Flat Phase Noise Profile        | 207<br>208 |

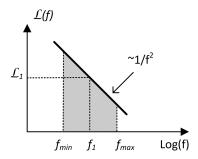

|            |       |           | Generation of Jitter Samples with Low-Pass, High-Pass, or         |            |

|            |       |           | Band-Pass Phase Noise Profiles                                    | 208        |

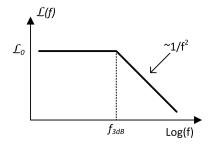

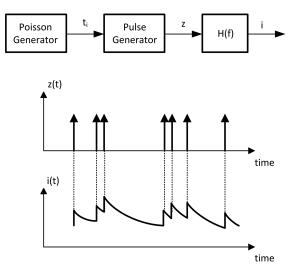

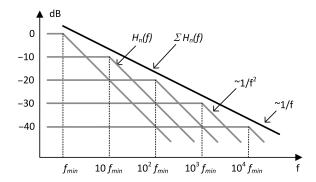

|            |       | 10.1.3    | Generation of Jitter Samples with $1/f^2$ Phase Noise Profile     | 208        |

|            |       |           | Generation of Jitter Samples with $1/f$ and $1/f^3$ Phase         |            |

|            |       |           | Noise Profiles                                                    | 209        |

|            |       | 10.1.5    | Generation of Jitter Samples with More Complex Phase Noise        |            |

|            |       |           | Profiles                                                          | 211        |

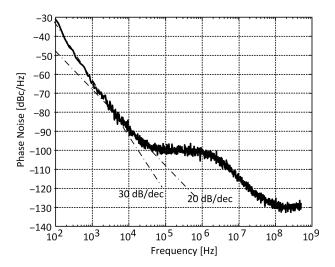

|            | 10.2  | Compi     | utation of Jitter from Vector of Time Instants                    | 211        |

|            | 10.3  | _         | utation of Phase Noise Plot from Jitter Samples                   | 214        |

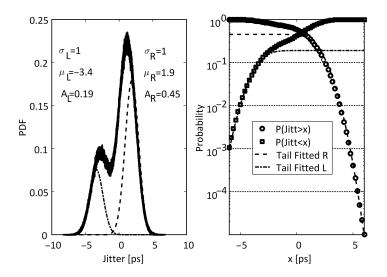

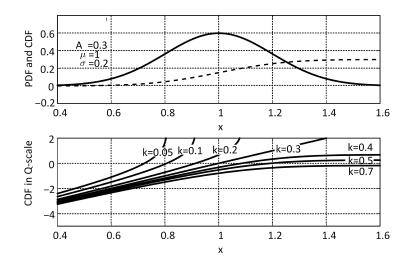

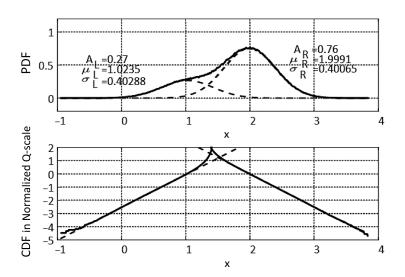

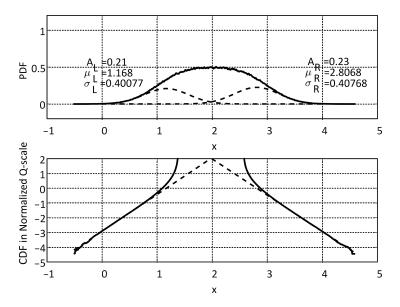

|            |       | -         | thms for Tail Fitting                                             | 214        |

| Appendix A | \ Rev | riew of R | Random Variables and Processes                                    | 220        |

|            | A.1   |           | m Variables                                                       | 220        |

|            |       | A.1.1     | Definition                                                        | 220        |

|            |       | A.1.2     | Distribution and Density Functions                                | 221        |

|            |       |           |                                                                   |            |

χi

|                | A.1.3     | Expectation                                            | 221 |

|----------------|-----------|--------------------------------------------------------|-----|

|                | A.1.4     | Mean, Variance, and Higher-Order Moments               | 222 |

|                | A.1.5     | Two Random Variables                                   | 223 |

|                | A.1.6     | Independent Random Variables                           | 223 |

|                | A.1.7     | Expectation of a Function of Two Random Variables      | 224 |

|                | A.1.8     | Correlation and Covariance                             | 224 |

| A.2            | Randon    | n Processes                                            | 225 |

|                | A.2.1     | Definition                                             | 225 |

|                | A.2.2     | Classification of Random Processes                     | 225 |

|                | A.2.3     | Mean, Autocorrelation, and Autocovariance              | 225 |

|                | A.2.4     | Stationary Processes                                   | 226 |

|                | A.2.5     | Wide-Sense Cyclostationary Processes                   | 227 |

|                | A.2.6     | Gaussian Processes                                     | 227 |

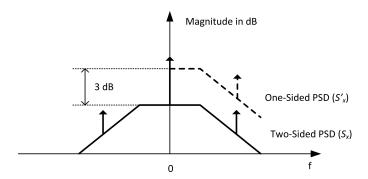

|                | A.2.7     | Power Spectral Density and the Wiener–Khinchin Theorem | 227 |

|                | A.2.8     | Engineering Definitions of the Power Spectral Density  | 228 |

|                | A.2.9     | The Physical Meaning of the Power Spectral Density     | 230 |

|                | A.2.10    | Random Processes and Linear Systems                    | 231 |

|                | A.2.11    | Ergodicity                                             | 232 |

| Appendix B Mat | tlab Code | e for Jitter Generation and Analysis                   | 233 |

| B.1            | Genera    | tion of Jitter                                         | 233 |

|                | B.1.1     | Flat Phase Noise Profile                               | 233 |

|                | B.1.2     | Low-Pass, High-Pass, or Band-Pass Phase Noise Profiles | 233 |

|                | B.1.3     | $1/f^2$ Phase Noise Profile                            | 234 |

|                | B.1.4     | 1/f Phase Noise Profiles                               | 234 |

|                | B.1.5     | $1/f^3$ Phase Noise Profiles                           | 235 |

|                | B.1.6     | More Complex Phase Noise Profiles                      | 236 |

| B.2            | Analysi   | is of Jitter                                           | 237 |

| B.3            | Tail Fit  | ting                                                   | 239 |

| Biblio         | ography   |                                                        | 242 |

| Index          |           |                                                        | 249 |

## **Preface**

This book provides a rigorous yet intuitive explanation of jitter and phase noise as they appear in electrical circuits and systems. The book is intended for graduate students and practicing engineers who wish to deepen their understanding of jitter and phase noise, and their properties, and wish to learn methods of simulating, monitoring, and mitigating jitter. It assumes basic knowledge of probability, random variables, and random processes, as taught typically at the third- or fourth-year undergraduate level, or at the graduate level, in electrical and computer engineering.

The book is organized as follows: Chapter 1 provides a qualitative overview of the book and its contents. Chapter 2 covers the basics of jitter, including formal definitions of various types of jitter and the key statistical concepts, starting from jitter mean and the standard deviation up to random and deterministic jitter. Phase noise will be first introduced in Chapter 3, and its relation to jitter and to the voltage spectrum of the clock signal will be extensively investigated. In particular, how to derive from phase noise the values of the several jitter types introduced previously will be explained. Chapter 4 is dedicated to the effects of jitter and phase noise in basic circuits and in basic building blocks such as oscillators, frequency dividers, and multipliers. Chapters 5 to 8 discuss the effects of jitter and phase noise in various circuit applications. Chapter 5 is dedicated to the effects of jitter on digital circuits, Chapter 6 to data converters, Chapter 7 to wireline, and Chapter 8 to wireless systems. More advanced topics on jitter are covered in Chapter 9, followed by numerical methods for jitter in Chapter 10. This chapter also explains how to generate jitter and phase noise, with various characteristics, for simulation purposes. The corresponding Matlab code for producing jitter is included in Appendix B.

As mentioned earlier, this book assumes the reader has a basic knowledge of random variables and random processes. However, to refresh the reader's memory of the definitions of some key terms, Appendix A simply lists these key terms along with their basic definitions.

#### Guidance for the Reader

The book does not require the reader to adhere strictly to the order in which the chapters appear, nor to read all of them. Its structure and the content of each chapter allow different paths to be followed, depending on the particular interests or learning objective of

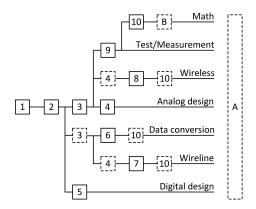

the reader. The graph below summarizes the possible paths, with the solid boxes indicating strongly recommended chapters and the dashed boxes the suggested additional readings.

While Chapters 1 and 2 form the fundamentals, and thus should be read before any other chapter, the remaining chapters are relatively independent from each other. Chapter 3 introduces the concept of phase noise and its relation to jitter. Even though this chapter constitutes, together with Chapter 8, a required path to the reader active in the wireless field, its contents are relevant to a number of other application fields, among them wireline and jitter testing. For this reason the authors suggest it should be included independently of the particular focus. Chapter 4 is an important reading for analog IC designers, while Chapter 5 addresses specifically the needs of custom digital designers. The latter chapter does not require knowledge of phase noise; thus Chapter 3 could be omitted. Both Chapters 4 and 5 can be skipped by readers interested exclusively in the system or mathematical aspects of jitter and phase noise. Chapters 6 and 7 can be read directly after the first three chapters by readers interested in data converters or wireline communication systems respectively. For the reader whose interest lies in the mathematical treatment of jitter and phase noise, the first three chapters plus Chapter 9 will provide a complete path. Finally, Chapter 10 and Appendix B are suggested reading for students or engineers who want to analyze the effect of jitter and phase noise on systems of any nature by means of transient simulation. The book uses a number of terms from probability and random processes. For ease of reference, we have included these key terms and their brief definitions in Appendix A.

# 1 Introduction to Jitter

Imagine a lunar eclipse is to occur later tonight at around 1:57 am when you are fast asleep. You decide to set your camera to capture the event, but being uncertain of the actual time, you would set the camera to start a few minutes before the nominal time and run it for a few minutes after 1:57 am. In this process, you have included a margin around the nominal time so as to minimize the risk of not capturing the event on your camera.

Imagine you have an important meeting at 8:00 am sharp, but you are uncertain about your watch being a bit too fast or too slow. Determined not to be late, you decide to arrive by 7:55 am according to your watch, just in case your watch is a bit slow. This is indeed a practical way to deal with uncertainty in time.

Imagine you have a ticket for the bullet train in Tokyo that leaves the train station at 1:12 pm sharp. You are at the station and on the right platform, and you take the train that leaves the station at 1:12 pm sharp. But a few minutes later, you notice that your watch is two minutes fast compared to the time being displayed on the train, and you realize that you are on the 1:10 pm train and you are moving towards a different destination.

Missing an event, being late or early, and getting on the wrong train are all consequences of timing uncertainties in our daily lives. In digital circuits, we deal with very similar situations when we try to time events by a clock that has its own timing uncertainty, called *jitter*, and in doing so we may miss an event, such as not capturing critical data, or cause bit errors, e.g., capturing the wrong data. Our goal, however, is to prevent such errors from occurring, or to minimize their probabilities. We do this first by carefully studying the nature of these uncertainties and modeling their characteristics.

This chapter provides a few concrete examples from electronic circuits and systems where timing uncertainties have a profound impact on the accuracy of their operation. Our goal here is to qualitatively introduce the concept of jitter and intuitively explain how it should be characterized and dealt with. A formal definition of jitter, its types, and its full characterization will be presented in Chapter 2.

## 1.1 What Is Clock Jitter?

This section provides an intuitive explanation of two fundamental jitter concepts: period jitter and absolute jitter.

#### 1.1.1 Period Jitter

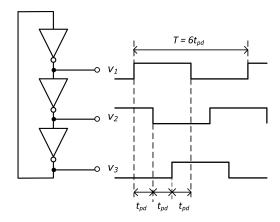

Most microprocessors ( $\mu P$ ) and digital signal processing (DSP) units work with clock signals to time the execution of instructions. A basic instruction such as a shift by one bit may take a single clock cycle, whereas addition and subtraction instructions may take three to four clock cycles, and more complex instructions, such as multiplication, may take tens of clock cycles to complete. In all these cases, the underlying assumption is that the clock is accurate; that is, the clock cycles are all identical in duration. In reality, however, the cycles of a clock are only identical with a finite (not infinite) accuracy. This is because the clock signals are generated using physical devices that inevitably have some uncertainty or randomness associated with them. For example, a clock may be generated by three identical CMOS inverters in a loop, as shown in Figure 1.1. If we assume  $t_{pd}$  is the propagation delay of each inverter in response to a transition at the input, then it takes  $3t_{pd}$  for a state "0" at node  $v_{out}$  to transition to state "1" and another  $3t_{pd}$  to transition back to "0". In total, it takes  $6t_{pd}$  for the clock to complete one cycle, and therefore we can write  $T_{nom} = 6t_{pd}$  where  $T_{nom}$  represents a nominal clock cycle. However, strictly speaking,  $t_{pd}$  is not constant, but rather a random variable that results in a different propagation delay every time the inverter is used. This randomness is inherent in any physical device that deals with the motion of electrons at temperatures above zero degrees Kelvin.

If we accept that  $t_{pd}$  is a random variable, then the clock period, which is the sum of six random variables, is also a random variable that deviates from its nominal (or expected) value. The good news is that these random variables may have tight distributions and, as such, may not adversely affect the circuit operations, especially at low clock frequencies where the period is much larger than the deviations. However, as we increase the clock frequency, the same absolute deviation in period may compromise circuit operation.

A typical clock frequency of 4GHz, for example, corresponds to a nominal period of 250ps, but this period may have a normal (Gaussian) distribution with a standard

Figure 1.1 A simple ring oscillator and its voltage waveforms.

deviation of  $\sigma=1$ ps. This implies that a clock cycle is close to 250ps but may deviate from this value with a probability that is a decreasing function of the deviation magnitude. For example, as we will see in Chapter 9 (Table 9.1), the probability of the period being smaller than 243ps is about  $10^{-12}$ . What does this mean for designs using this clock? A straightforward answer is that we must ensure that any task that is supposed to complete in one clock cycle must do so assuming the worst-case clock cycle, that is, 243ps (not the nominal 250ps). This will ensure that, with a high probability  $(1-10^{-12})$ , all the tasks are completed within one clock cycle even when one clock cycle is 7ps shorter than the nominal cycle. If we were to reduce the probability of failure (i.e., the probability of failing to meet the timing), we could simply design for a 242ps minimum cycle time while working with a nominal cycle time of 250ps. This reduces the probability of failure to  $6.22 \times 10^{-16}$ , which corresponds to one error in every 4.6 days (assuming 4GHz operation).

The concept we just described, i.e., the deviation of a clock cycle from its nominal value, is referred to as *clock period jitter*, or *period jitter* for short. A concept closely related to period jitter is *N-period jitter*, which is the deviation of a time interval consisting of N consecutive periods of the clock from the time interval of N nominal periods. We will formally define period jitter, N-period jitter, and other types of jitter for a clock signal in Chapter 2. Let us now provide an intuitive explanation for *absolute jitter*.

## 1.1.2 Absolute Jitter

Period jitter is only one method to characterize the timing uncertainties in a clock signal. This method is particularly useful in digital circuits where we are concerned with the time period we need to complete a task. In other applications, such as in clock and data recovery, where the clock edge is used to sample (capture) data, we are concerned with the instants of time, not with time durations! This is because sampling occurs at an instant of time, not over a period of time. In this case, it is the absolute time of the clock edge (at which sampling occurs) that matters, not the interval between the edges (i.e., the clock period). In these applications, it is important for the clock's edges to be precise; i.e., for them not to deviate from their ideal locations by certain amount. Let us elaborate on this further.

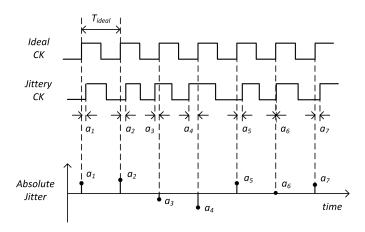

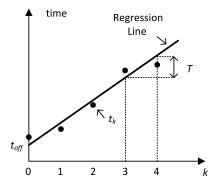

In an ideal clock, if we assume the first rising edge occurs at time t = 0, then the subsequent rising edges will occur at exactly t = kT, where k is a positive integer and T is the period of the ideal clock. In a non-ideal clock, the rising edges,  $t_k$ , will deviate from their ideal values kT. We refer to this deviation as the clock's *absolute jitter*, with the word *absolute* signifying the deviation in instants of time as opposed to deviations in intervals of time, as in period jitter.

The reader notes that absolute jitter and period jitter are closely connected concepts. Indeed, we will see in Chapter 2 how we can obtain one from the other.

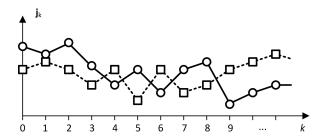

Figure 1.2 shows an example of a jittery clock signal (CK) along with an ideal clock signal ( $CK_{ideal}$ ). The absolute jitter can be abstracted from the clock signal and shown separately as a function of time. From this example, absolute jitter appears to be a

Figure 1.2 Ideal clock versus jittery clock waveforms.

discrete-time random signal. We will see later in Chapter 2 that, similar to any random signal, absolute jitter has a well-defined spectrum and, as such, may contain a continuous range of frequency components.

## 1.1.3 Intentional Jitter

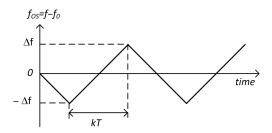

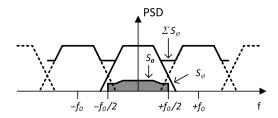

Jitter is not always an unwanted property of a clock signal. In some applications, such as in spread-spectrum clocking, we intentionally add carefully controlled jitter to a clean clock so as to shape its power spectral density.

It is well known that a clean clock, by virtue of being a periodic signal, has energy peaks at its fundamental frequency and its second- and higher-order harmonics. At clock frequencies in excess of 100MHz, some of the harmonics may have a wavelength that is of the same order of magnitude as the length of the wire carrying the clock signal between chips on the same board or between boards. If left unattenuated, the signal energy of these harmonics may radiate and cause electromagnetic interference (EMI) with neighboring electronic components (mostly the components on the same PCB). For this reason, it is desirable to limit the amount of radiation a clock signal can produce. This radiation level is directly related to the peaks in the clock signal power spectrum.

Spread-Spectrum Clocking is a technique that spreads the peak energy over a larger frequency band, thereby reducing the peak values and their associated EMI. This is accomplished by adding a controlled amount of jitter to the clock. The jitter profile is typically in the form of a frequency offset that goes up and down linearly with time. Figure 1.3 shows an example of a frequency offset which increases linearly over a certain period of time (kT) and then decreases over the same period (kT). This increase in clock frequency (assuming  $\Delta f \ll f_0$ ) is equivalent to a decrease in the period by a factor of  $2\Delta f/f_0$ .

**Figure 1.3** Frequency offset  $(f_{OS})$  as a function of time.

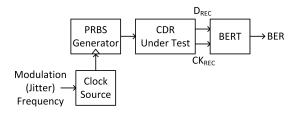

Another example of using intentional jitter is in characterizing clock and data recovery circuits for their robustness to jitter. In this application, we intentionally add jitter to the incoming data and observe the system's robustness (in terms of its bit error rate) as a function of jitter frequency. We discuss this example in further detail in Chapter 7.

## 1.2 What Is Data Jitter?

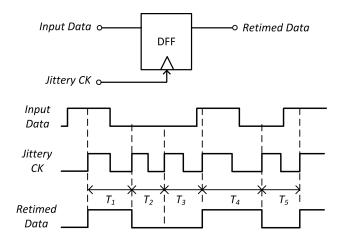

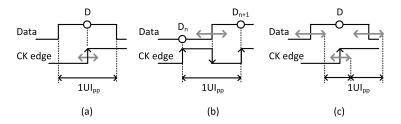

Consider a D flip-flop with data input D, clock input CK, and output Q, where D is captured and transferred to Q at the rising edge of the clock. As a result, Q is synchronized with the clock, and therefore the clock jitter directly affects the timing of the data at the output. In clock and data recovery applications, it is common to refer to the duration of one data bit as a unit interval or UI. An ideal clock results in a data stream that has a fixed UI, where each UI is exactly equal to the clock period. We refer to this data stream as *ideal* or *clean* (i.e., the data without jitter). A non-ideal clock results in a jittery data stream where each UI is slightly different from the nominal UI. This situation is shown in Figure 1.4, where jittery data is compared against an ideal data stream. Note that, due to the random nature of the data sequence, data transitions do not occur at every UI edge. As such, jitter is not observable from data when there is no transition. However, by overlaying several UIs of data on top of each other, in what is known as an eye diagram, we can observe the overall characteristics of data jitter.

## 1.2.1 Eye Diagram

In clock and data recovery applications, the clock samples a jittery data waveform at instants that are one clock period (T) apart. These instants usually correspond to the rising edges of a clean clock, i.e., a clock with little or no jitter. Since the act of sampling repeats itself every T, we are interested in seeing how the data waveform looks if we chop it into segments of length T and overlay all the segments on top of each other. The resulting composite waveform, which resembles an eye, is known as an eye diagram.

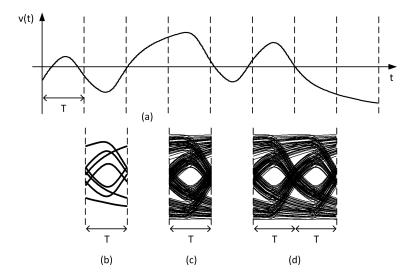

Figure 1.5 shows the process by which we generate an eye diagram. This is essentially the data waveform as a function of time modulo 1T. The eye diagram clearly shows the

Figure 1.4 Input data is retimed with a jittery clock.

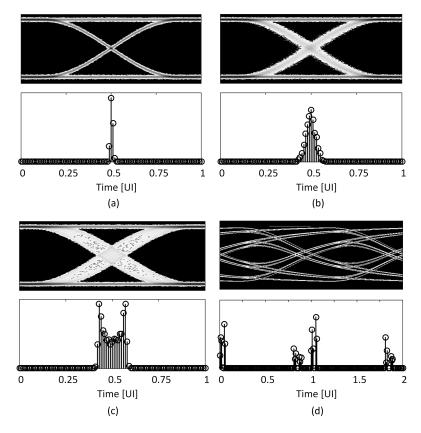

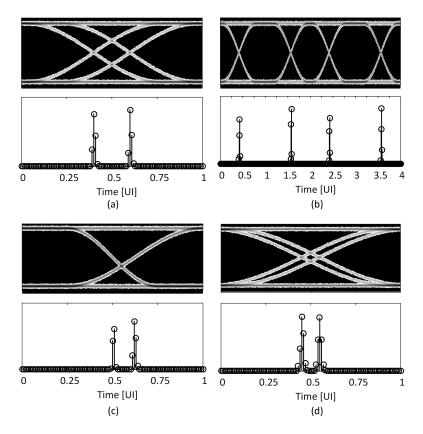

**Figure 1.5** (a) A sketch of a voltage waveform as a function of time, (b) an eye diagram with eight traces, (c) an eye diagram with 500 traces, (d) an eye diagram showing two eyes (corresponding to two periods).

time instants at which the data "0" and "1" are farthest apart. This is the instant at which the eye height (also known as vertical eye opening) is at a maximum, and this is the instant at which we strive to sample the data by the rising edge of the clock.

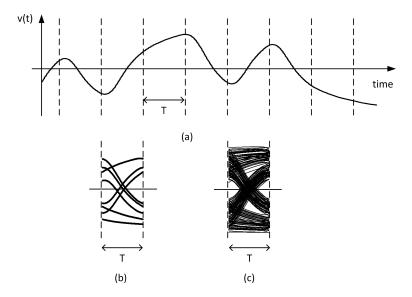

The eye diagram also reveals how jitter can accumulate over time so as to close the eye in the horizontal direction (see Figure 1.6). Accordingly, the horizontal eye opening is an indication of the timing margin left for error-free operation.

When the noise, interference, attenuation, and jitter are excessive in a design, the eye may be completely closed: there is then no instant at which the data "1" and "0" can be

**Figure 1.6** (a) A sketch of a voltage waveform as a function of time, (b) an eye diagram centered around the zero crossings (eight traces), (c) the same eye diagram using 500 traces.

consistently distinguished. These situations require equalization and jitter cleaning so as to open an otherwise closed eye for data detection.

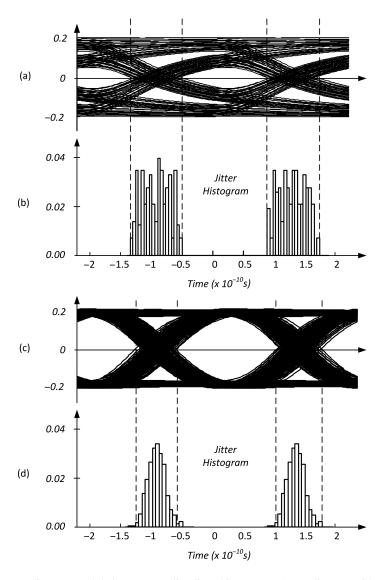

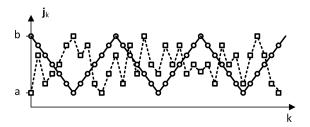

#### 1.2.2 Random Versus Deterministic Jitter

Jitter, in general, refers to any timing deviations from an ideal clock. These deviations may be random or deterministic depending on the underlying sources producing them. We have already provided several examples where random jitter is produced. Let us now consider an example that produces deterministic jitter. Consider a binary random sequence (produced using an ideal clock) that travels the length of a wire on a PCB. The wire acts as a low-pass filter and, as such, slows the data transitions, creating jitter. The jitter produced in this way is considered deterministic because one can predict the exact jitter if an accurate model of the wire is available. Note that this is in contrast with the random jitter produced by random movement of electrons, as we cannot predict the electron movement.

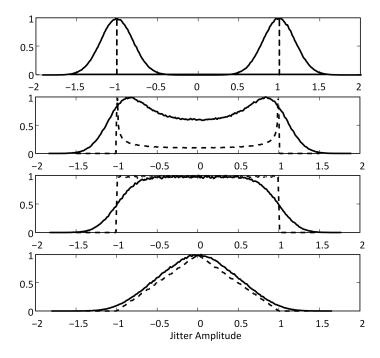

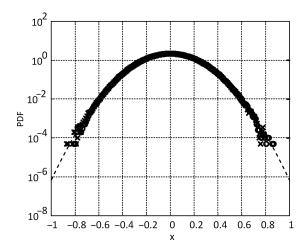

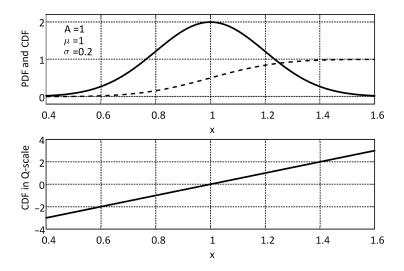

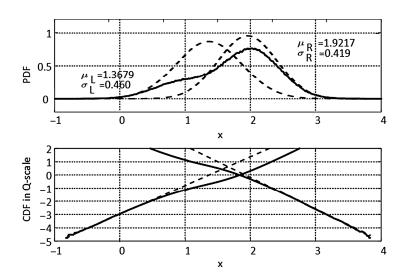

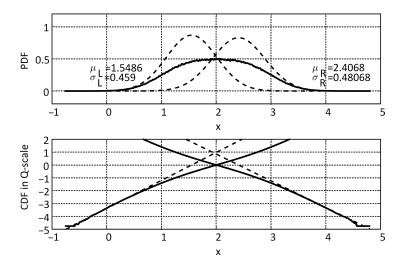

An easy way to characterize jitter is to look at its histogram or its probability density function (PDF). As shown in Figure 1.7, deterministic jitter is bounded (having a histogram with limited range) whereas random jitter is unbounded (having a Gaussian-like PDF). In most cases, several jitter sources are at work at the same time, producing composite jitter that includes both deterministic and random jitter. We will discuss this in depth in Chapters 2 and 7 and describe ways to decompose jitter into its components. Independent of the type of jitter, however, one can always characterize jitter, which is a discrete-time sequence, by its peak-to-peak or its root mean square (RMS) values.

**Figure 1.7** Eye diagrams and their corresponding jitter histograms (a) eye diagram with deterministic jitter only, (b) corresponding jitter histogram, (c) eye diagram with random jitter only, (d) corresponding jitter histogram.

## 1.3 Jitter in Measuring Time

We often measure time by observing the completion of a physical phenomenon or event. For example, in an hourglass (also known as a sandglass), shown in Figure 1.8, the event is the falling of sand from the top to the bottom compartment. The completion of this event marks one unit of time, which may be from a few minutes to a few hours depending on the hourglass design. Note that an hourglass has limited

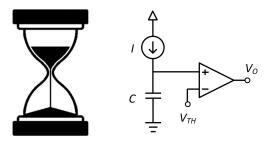

Figure 1.8 An hourglass behaves similarly to a current source charging a capacitor.

accuracy and limited resolution. The accuracy relates to the variation in time measurement as we repeat the same experiment. Depending on the size distribution of the grains of sand and their random arrangement, we will actually experience a slightly different time interval every time we use the hourglass. This variation (or uncertainty) is considered the jitter in the hourglass. The resolution relates to the minimum time interval (seconds or fractions of a second, for example) that could be measured using the hourglass.

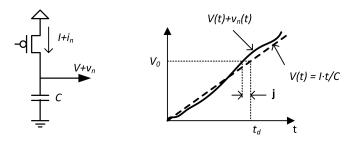

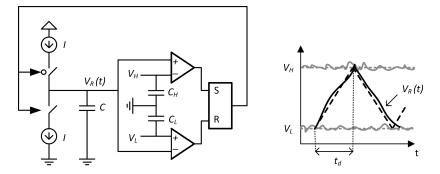

If we replace the grains of sand with electrons and the glass with a capacitor, then we have an electronic version of an hourglass that can measure time with much better accuracy and far better resolution. Figure 1.8 shows an ideal current source charging a capacitor. The event in this case is defined as the time it takes for the capacitor to charge from 0V (corresponding to an empty capacitor) to a threshold voltage,  $V_{TH}$  ( $V_{DD}/2$ , for example). If the current source is ideal, having an amplitude of  $I_0$ , this event takes  $CV_{TH}/I_0$  to complete. Accordingly, this advanced hourglass has several knobs to turn in order to adjust its resolution. For example, one could reduce the capacitance, increase the current, or lower the threshold voltage of the comparator. The accuracy, however is limited by the current noise that is inherent in the methods by which we implement a current source.

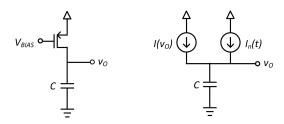

A very simple current source may be implemented using a PMOS transistor with its gate connected to ground, as shown in Figure 1.9. This current source differs from an ideal current source in two ways: first, the current it produces is not constant; it becomes smaller as the capacitor is charged from 0 to  $V_{TH}$ ; and second, the current includes noise such as thermal noise due to the random movements of electrons. The voltage dependency of the current slows down the process of charging the capacitor as there is simply less current. This deviation in time, however, can easily be absorbed by calibrating the time unit. The current noise, on the other hand, will result in different measurements of time as we repeat the experiment. To see this, let us model our practical current source as a constant current source in parallel with a noise current source, as shown in Figure 1.9. The current is now the sum of the nominal current,  $I_0$ , and the noise current. The additional noise current will cause the voltage across the capacitor to deviate from its ideal waveform, which is simply a ramp, and to arrive faster or slower at  $V_{TH}$ . This time deviation is a random process, which we call jitter, and is directly related to the characteristics of the noise current (itself a random process).

**Figure 1.9** A simple PMOS current source charging a capacitor.

## 1.4 Jitter in a Ring Oscillator

The circuits we use to generate clock signals are called *oscillators*. One common type of oscillator, called a *ring oscillator*, consists of three inverters in a closed loop (a ring), as shown in Figure 1.1. We analyze this ring oscillator to explain intuitively how jitter is generated. A more rigorous treatment of this topic will be presented later in Chapter 4, once we mathematically define jitter and its characteristics.

As mentioned earlier in this chapter, the ring oscillator of Figure 1.1 produces oscillations (in voltage) with an expected period of  $6t_{pd}$ , where  $t_{pd}$  is the expected value of the propagation delay through each of the three stages. Let us now explore the properties of the delay of a CMOS inverter.

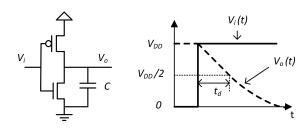

## 1.4.1 Jitter in Delay of a CMOS Inverter

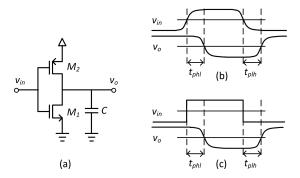

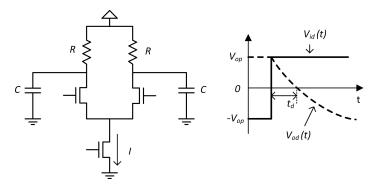

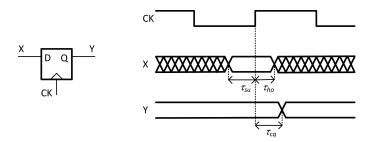

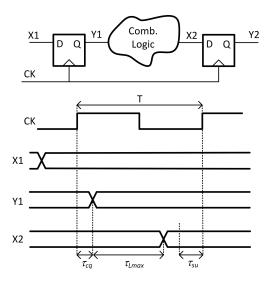

When the input of an inverter rises from 0 to VDD, its output falls from VDD to 0. The high-to-low delay of an inverter (denoted by  $t_{phl}$ ) is defined as the time elapsed between the input (at 50% of its swing) and the output (at 50% of its swing). The low-to-high delay of an inverter (denoted by  $t_{plh}$ ) is defined similarly, as shown in Figure 1.10. If we assume the input transitions from low to high and high to low occur instantaneously, then  $t_{phl}$  and  $t_{plh}$  simply correspond to the time it takes for the output to reach 50% of its full swing. With this simplifying assumption, during the low-to-high transition of the output, only the PMOS transistor is ON, while during the high-to-low transition of the output, only the NMOS transistor is ON. Accordingly, we have two equivalent circuits to calculate  $t_{phl}$  and  $t_{plh}$ , as shown in Figure 1.11. In both circuits, two current sources charge or discharge the load capacitor. Of the two current sources in parallel, one is assumed to be deterministic and controlled by the gate voltage. The other source provides a random current corresponding to the thermal movement of electrons.

The deterministic parts of  $t_{phl}$  and  $t_{plh}$  are simply  $C_L V_{TH}/I_0$ . We refer to these as the base delays of the inverter. The remaining parts are two random variables which are also functions of time. We refer to these as the excess delays, or jitter, of the inverter. Jitter is random for the following reasons: if we measure two identical inverters at the same time, they exhibit different noise currents and hence result in different measurements of the delays. They are also time-dependent because if we attempt to measure  $t_{phl}$  (for

**Figure 1.10** (a) A CMOS inverter, (b) propagation delays for non-ideal input, (c) propagation delays for ideal input.

Figure 1.11 (a) A CMOS inverter, (b) the inverter model for high input, (c) the inverter model for low input.

example) of the same inverter, but at two different times, we end up with two different numbers, again due to the noise current changing with time. For these reasons, we say jitter is a random process.

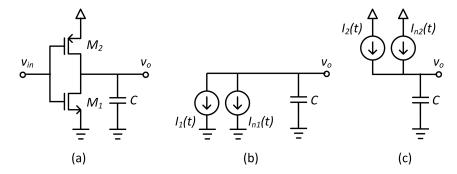

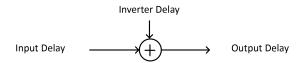

To summarize, we have intuitively explained that the delay of a CMOS inverter has two components: the base delay and the excess delay, or jitter. The base delay is a deterministic number whereas the jitter is a random process (i.e., a time-dependent random variable). Accordingly, we can build a simple model of an inverter, as shown in Figure 1.12, where the input and the output are simply the time delays of the input and output signals with respect to a reference. Note that although we arrived at this model assuming an ideal (jitter-less) input, this model is still valid if the input has its own jitter. Since we are only concerned with jitter (i.e., the random part of any delay), we simply assume that both the input and the output of this model are random processes, where the output random process is the sum of the input random process and the random process created by the noise current inside the inverter. If we consider the input to the inverter to be an ideal clock, then the corresponding input to this model will simply be zero. We will use this simple model in the next section to better understand the jitter produced in a ring oscillator.

Figure 1.12 A simple model of an inverter.

Figure 1.13 A simple model of a ring oscillator.

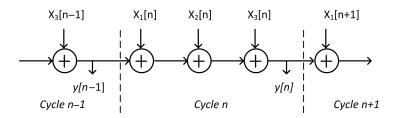

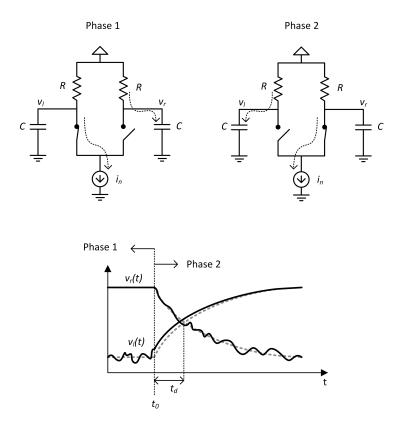

## 1.4.2 Modeling Jitter of the Ring Oscillator

Figure 1.13 shows a model to predict the absolute jitter of a three-stage ring oscillator. In this model,  $X_i[n]$  represents the total excess delay introduced by inverter i in the n-th cycle, where n is the discrete time index. Note that this is the sum of the high-to-low and low-to-high excess delays of inverter i. The output (absolute) jitter is also described by a random process identified as Y[n]. Let us now explore some characteristics of Y[n].

Given the model in Figure 1.13, one can clearly see that Y[n] is the sum of the excess delays in each of the three inverters, plus the excess delay that was accumulated over all the past cycles. In other words, we can write:  $Y[n] = Y[n-1] + X_1[n] + X_2[n] + X_3[n]$ . If we further assume all  $X_i[k]$  s are identical  $(X_i[k] = X \text{ for all } i \text{ and } k)$  and uncorrelated with each other, then Y[n] would be a *random walk* process, which keeps a running sum of successive trials of a discrete-time random variable (X). It is well known [1] that the variance of a random walk process increases linearly with the number of trials, n. Similarly, the absolute jitter variance of a ring oscillator output grows linearly with the number of cycles, unless controlled by other means such as a phase-locked loop.

We can resort to the same model (Figure 1.13) to gain insight into the period jitter produced by the ring oscillator. Since period jitter is essentially the excess delay produced in a single cycle, it would be equal to the sum of the three excess delays only, that is  $X_1[n] + X_2[n] + X_3[n]$ ; it does not account for the excess delays of previous cycles. As a result, the period jitter will have a finite variance, independent of the number of cycles.

## 1.5 Jitter in Electronic Systems

The timing uncertainty that manifests itself in charging a capacitor or in the delay of an inverter extends to all electronic systems, including digital circuits and systems, data converters, wireline, and wireless applications. However, the consequences or the

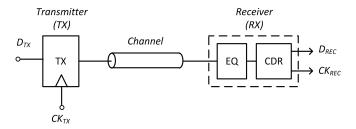

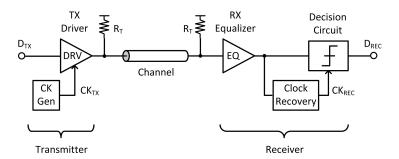

Figure 1.14 Block diagram of a wireline transceiver.

adverse effects of timing uncertainty are different among these applications. In digital systems, we are mostly concerned with completing an operation (e.g., multiplication) within a certain number of clock periods. In the presence of timing uncertainty, the time to completion will become uncertain. In a digital-to-analog converter, as we will see in Chapter 6, the timing uncertainty in the clock will result in voltage uncertainty at the analog output, compromising the accuracy of the analog voltage. We highlight the wireline application in this section to provide insight on how timing uncertainty can propagate through various blocks in a system and influence its performance.

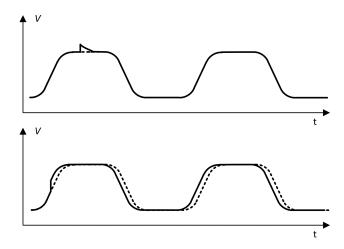

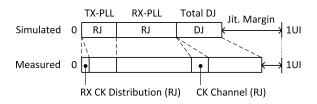

A wireline link, as shown in Figure 1.14, consists of a transmitter, a channel, and a receiver. The transmitter, in its simplest form, sends digital "1" and "0" data on the rising edge of the transmit clock ( $CK_{TX}$ ) to the channel. Since the transmit clock contains jitter, even when it is produced by a phase-locked loop, it will transfer this jitter to data edges. This is the first place in the link where the clock jitter is transferred directly to the data. Let us now follow the data through the channel and the receiver to see how this jitter is influenced by the channel and shaped by the receiver.

The channel is known to have a low-pass filter characteristic, caused mainly by the capacitive nature of the interconnect and the dielectric loss of the board. Equivalently, we can say that the channel has memory, i.e., the pulse corresponding to the previous bit (in a non-return-to-zero signaling) does not vanish immediately as we send the current bit, but partially interferes with the current and future bits. This interference, known as the inter-symbol interference (ISI), adds to the current bit level, and, as such, moves its zero crossings, creating jitter. This jitter is deterministic because it can be fully determined if the input data pattern and the channel response are both known. This is the second place in the link where jitter has been added to the data.

An equalizer (EQ) at the front end of the receiver is usually capable of reducing, or, in an ideal case, eliminating the deterministic jitter of the received data. However, the equalized data will still contain some random and some deterministic jitter. This equalized data is then fed to the Clock and Data Recovery (CDR) unit.

CDR is a simple feedback loop that controls the frequency and phase of an internal clock so as to minimize the phase error between the internal clock and the input data, producing the recovered clock. However, in this process, the recovered clock will inherit some of the input data jitter. In addition, other blocks in this control loop (such as a digital block that determines the phase difference between the input data and the recovered clock) will contribute additional jitter to the recovered clock.

The reader will appreciate that the jitter present in the recovered clock is influenced by the data jitter and by all the building blocks within the CDR. An immediate question that comes to mind is whether the recovered clock will have jitter characteristics similar to those of the data. Another question is whether the timing uncertainty in the recovered clock is reduced or increased compared to that of the data. To answer these questions, we need to characterize and quantify jitter. We will do this in Chapter 2.

## 2 Basics of Jitter

In the industry as well as in academia, the concept of jitter is sometimes treated using approximations, leading to misunderstandings and possibly to systems which are not optimally designed with respect to jitter performance. This chapter lays the foundation for a thorough and clear understanding of jitter in practice.

The chapter starts by providing four fundamental definitions of jitter: absolute jitter, relative jitter, period jitter and *N*-period jitter. It proceeds with an overview of other jitter definitions commonly found in literature. It will be shown that these additional definitions can be expressed in terms of the four fundamental jitter definitions.

A large part of the chapter handles the important topic of jitter statistics and the estimation of key parameters such as root mean square (RMS) and peak or peak-peak values. This will lead to the classification of jitter based on its distribution, and eventually to the introduction and explanation of the concepts of deterministic jitter, random jitter and total jitter.

## 2.1 General Jitter Terminology and Definitions

A variety of terms are commonly used to express the concept of jitter, and several different definitions can be found in the open literature, mostly dependent on the particular background of the author or on the specific application considered. A short and incomplete list of these terms includes period jitter, cycle jitter, cycle-to-cycle jitter, *N*-period jitter, accumulated jitter, adjacent jitter and long-term jitter. It is not uncommon to find the same term used with different meanings by different authors, leading to possible misunderstandings and confusion.

In this chapter jitter will be defined according to the way it can be measured, at least in principle. This will not result in jitter definitions that are different from the ones already found in the literature; rather, it will put the existing definitions in a clear and solid framework. These operative definitions of jitter turn out to be very intuitive, simple and of high practical value. Since the definition is connected to a measurement process, it is easier to relate it to a specific application. And, conversely, given a specific application, this approach makes it is easier to find the relevant jitter definition.

Generally speaking, jitter is the deviation of the time instant at which a given event occurs, relative to a reference time frame, which can be chosen arbitrarily. In the context of this book, the event we consider is the edge of a clock signal, or, more specifically,

the time when a signal crosses a given threshold. The choice of the reference time frame can essentially be made in two ways: either the edges of the clock under investigation are compared to the edges of another clock, or they can be compared to some previous edges of the same clock (self-referenced). The first approach leads to the definition of absolute and relative jitter, while the second leads to the definition of period jitter. These three definitions of jitter, plus a fourth one, *N*-period jitter, which is an extension of the concept of period jitter, constitute the main topic of the next sections. We believe that most of the jitter aspects in modern electronic systems can be covered and properly described using only these definitions.

To set the stage for the next sections, let us introduce a generic clock signal v(t) which will be used to clarify some initial concepts:

$$v(t) = A(t)\sin(\omega_0 t + \varphi(t)). \tag{2.1}$$

If we consider the quantity A(t) as constant (independent of time t) and  $\varphi(t)$  identical to zero, this signal is a perfect sinusoid with period  $T=2\pi/\omega_0$ . The signal crosses zero with positive slope at equidistant times kT, with k any integer. We can consider this to be an ideal clock, in the sense that its zero crossings define a very accurate, noise-free time frame. Needless to say, this kind of signal does not exist in nature. In real applications, both A(t) and  $\varphi(t)$  are nonzero and depend on time, thus changing the characteristics of the signal.

The quantity A(t) affects primarily the amplitude of the signal and is the origin of amplitude modulation, either intentionally, as in the case of AM data transmission, or unintentionally, in which case it is generally called amplitude noise or amplitude distortion. It is important to notice that, as long as A(t) is not zero, the zero crossing of the signal are not perturbed and still occur at kT, so that this signal can still be used as ideal clock. As this condition is met for all practical clock signals, we will consider A(t) to be constant, unless otherwise noted.

By contrast, the quantity  $\varphi(t)$  added to the ideal phase  $\omega_0 t$  in the argument of the sinusoid shifts the position of the zero crossings to deviate from the ideal instants kT, causing the phenomenon of jitter. The quantity  $\varphi$  is given different names in the literature: *excess phase*, *phase deviation*, *phase noise* or *phase jitter*. In order to avoid confusion, we will refer to it by the name *excess phase*. Note that the terms *phase noise* and *phase jitter* in particular might give rise to serious misunderstandings, as they are also used to describe different concepts (as will become clear in the next chapters), so they should be used with caution.

The signal shown in Equation 2.1 is just one particular case, in which the basic waveform is a sinusoid, but this is not the only possibility. Assume a generic waveform  $x(\omega_0 t)$  periodic in t with period  $T = 2\pi/\omega_0$  and with only one positive zero crossing per period. Such a waveform can be used to describe a generic clock signal as:

$$v(t) = A(t)x(\omega_0 t + \varphi(t)) \tag{2.2}$$

where the considerations above about A(t) and  $\varphi(t)$  can be exactly replicated.

In most of the practical applications in this book, the basic shape of the clock signal is rectangular. Although it is not common to talk about "phase" for a periodic rectangular

signal, this concept can profitably be used if we think of the rectangular clock as the result of passing the signal 2.1 through a zero crossing comparator, with output A if the input is positive, -A if negative and 0 if zero. This operation can be described with the help of the sgn function, so that the rectangular clock can be expressed as:

$$v(t) = A \operatorname{sgn}[\sin(\omega_0 t + \varphi(t))]. \tag{2.3}$$

With this in mind, all considerations about phase and excess phase for a sinusoidal signal can be transported to a rectangular signal.

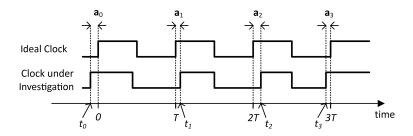

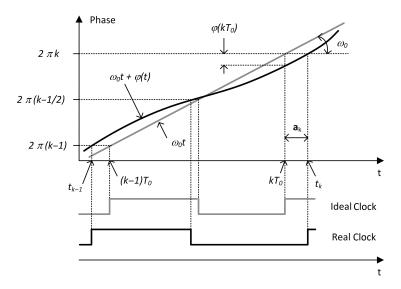

#### 2.1.1 Absolute Jitter

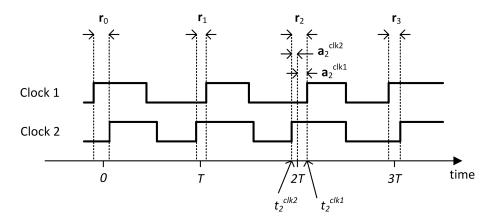

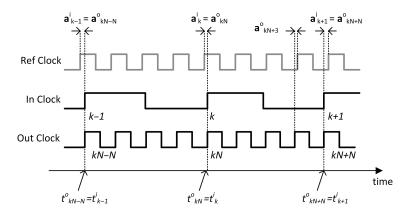

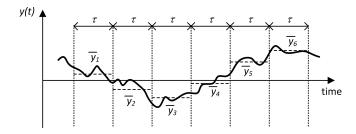

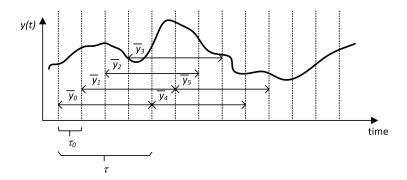

Assume the clock under investigation has a nominal period T. This means that the edges are affected by jitter, and each period of the clock is different, but the mean period is equal to T. One can think of comparing the position of each edge of the clock under investigation with the edges of another clock (called the *ideal clock* in the following) not affected by jitter and having exactly the same period T. The *absolute jitter* is defined as a discrete time random sequence  $\mathbf{a}$ , where the k-th element, denoted as  $\mathbf{a}_k$ , is the time displacement of the k-th rising edge  $t_k$  of the real clock with respect to the corresponding edge of the ideal clock. This concept is explained in Figure 2.1.

Since the ideal clock is not jittery, its edges are spaced exactly by T. If the time axis is chosen properly, the edges of the ideal clock occur at time kT, so that the definition of absolute jitter can be given as:

$$\mathbf{a}_k := t_k - kT. \tag{2.4}$$

Since both the clock under investigation and the ideal clock have the same period, it is always possible to choose the position of the ideal clock so that the mean value of the absolute jitter is zero. If for any reason the position of the ideal clock is such that the average value of the absolute jitter calculated with Equation 2.4 is equal to a certain offset value  $t_{OS} \neq 0$ , the absolute jitter can be redefined as:

$$\mathbf{a}_k := t_k - kT - t_{OS}. \tag{2.5}$$

In the rest of the book, we will assume, unless otherwise stated, that the time axis is chosen so that  $t_{OS} = 0$ .

Figure 2.1 Illustration of the definition of absolute jitter.

The name "absolute" is chosen because the edges are compared to the edges of an ideal clock, which defines the time scale in an absolute manner, independent of any particular implementation or further reference. The ideal clock defines the absolute time scale to which the clock under investigation is compared.

#### 2.1.2 Relative Jitter

In the previous section, the edges of the clock are compared to the edges of an ideal clock. However, one can think of comparing the edges of the clock under investigation (ck1) to the edges of another real, non-ideal clock (ck2), having the same average period T. This leads to the definition of *relative jitter* as a discrete-time random process  $\mathbf{r}$ , where the element  $\mathbf{r}_k$  is the time displacement of the k-th rising edge  $t_k^{ck1}$  of the clock under investigation with respect to the corresponding edge  $t_k^{ck2}$  of the reference clock (see Figure 2.2):

$$\mathbf{r}_k := t_k^{ck1} - t_k^{ck2}. (2.6)$$

It can easily be seen that the relative jitter can be expressed in terms of the absolute jitter of each of the two clocks considered. Indeed, adding and subtracting kT in the second term of Equation 2.6 and recalling Equation 2.4, the relative jitter can be rewritten as:

$$\mathbf{r}_k := \mathbf{a}_k^{ck1} - \mathbf{a}_k^{ck2}. \tag{2.7}$$

As in the case of absolute jitter, this definition assumes that the average value of the relative jitter is zero. If there is a fixed time offset between the edges of the two clocks, this offset must be subtracted, as is done for the absolute jitter in Equation 2.5.

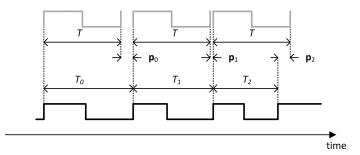

## 2.1.3 Period Jitter

The two jitter definitions above are based on comparing the edges of the clock under investigation to the edges of another clock. Alternatively, one can think of comparing

Figure 2.2 Illustration of the definition of relative jitter.

**Figure 2.3** Illustration of the definition of period jitter. Each period of the clock is compared to the nominal period (gray clock signals).

the position of one edge of the clock with respect to the position of the previous edge of the same clock. Operatively, this corresponds to feeding the clock to an oscilloscope, triggering on one edge of the clock and looking at how much the following edge moves around its average position.

This procedure leads to the definition of *period jitter* as a discrete time random process  $\mathbf{p}$ , where the element  $\mathbf{p}_k$  is the variation around its nominal value of the position of one clock edge with respect to the previous edge. It is clear that this is equivalent to considering the variation of the actual clock period with respect to the nominal period. Figure 2.3 illustrates the concept. Each period of the clock is compared to the nominal period (gray clock signals). Any deviation contributes to period jitter.

The k-th sample of the period jitter will be indicated as  $\mathbf{p}_k$  and can be mathematically defined as:

$$\mathbf{p}_k := (t_{k+1} - t_k) - T = T_k - T \tag{2.8}$$

where  $t_k$  and  $t_{k+1}$  are the time instants of two consecutive rising edges of the clock, T is the nominal clock period, and  $T_k$  is the actual clock period (see Figure 2.3).

By adding and subtracting (k + 1)T to the right hand side of Equation 2.8, the period jitter can be expressed in terms of absolute jitter as:

$$\mathbf{p}_k = \mathbf{a}_{k+1} - \mathbf{a}_k. \tag{2.9}$$

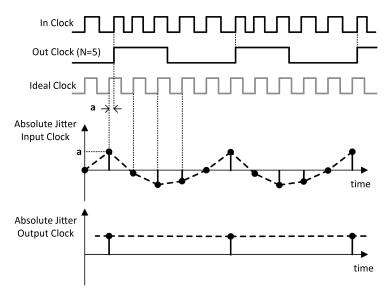

In many cases it is of interest to know the variation of one edge relative not to the edge immediately preceding it, but to the N-th previous one. Consider for instance an ideal (delay-free and noiseless) digital frequency divider by N. The flip-flops in the divider are triggered by the rising edges of the incoming clock. Since the divider is noiseless and introduces no delay, the edges of one period of the output clock are perfectly aligned with the edges of the input clock spaced N periods apart. Therefore the period jitter of the output clock is equal to the relative variation of two input clock edges spaced N periods apart. This leads to the definition of N-period jitter, which is the subject of the next section.

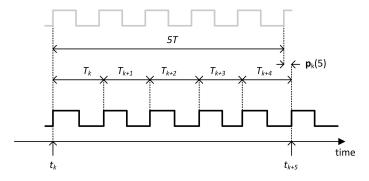

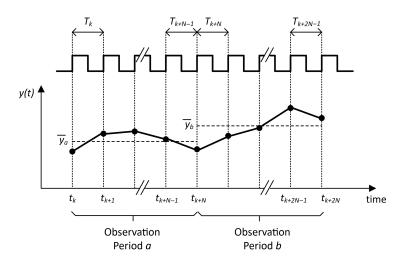

## 2.1.4 *N*-Period Jitter

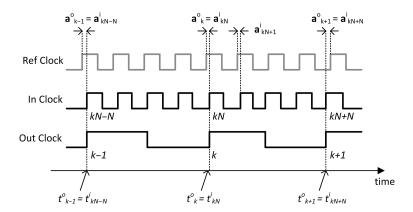

As mentioned in the previous section, it is possible to compare the position of one edge of the clock relative to the position of an arbitrary previous edge of the same clock. Operatively, this corresponds to connecting the clock to an oscilloscope, triggering on one edge of the clock and looking at how much the following edges move around their average position. This procedure leads to the definition of *N-period jitter* as the discrete time random process, denoted by  $\mathbf{p}(N)$ , where the element  $\mathbf{p}_k(N)$  is the variation around the nominal value of the position of one clock edge with respect to the *N*-th previous edge.

This concept is illustrated in Figure 2.4 for N = 5, where a clock with nominal period T is shown affected by jitter. The k-th sample of the N-period jitter  $\mathbf{p}_k(N)$  can then be expressed as the deviation of the time difference between the k-th and the k+N-th edges from the nominal value NT:

$$\mathbf{p}_k(N) := (t_{k+N} - t_k) - NT. \tag{2.10}$$

Considering that  $t_{k+N} - t_k$  is equal to the duration of the first N periods of the clock, the expression for the N-period jitter can also be written as:

$$\mathbf{p}_{k}(N) = \left(\sum_{i=k}^{i=k+N-1} T_{i}\right) - NT$$

(2.11)

where  $T_i$  is used to indicate the *i*-th period of the clock.

By adding and subtracting (k + N)T to the right side of Equation 2.10, the *N*-period jitter can be expressed in terms of absolute jitter as:

$$\mathbf{p}_k(N) = \mathbf{a}_{k+N} - \mathbf{a}_k. \tag{2.12}$$

Following from the definition above, it is clear that the value of N-period jitter for N = 1 corresponds to the period jitter defined in the previous section.

**Figure 2.4** Illustration of the definition of *N*-period jitter.

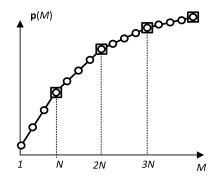

An important and easily derived relation exists between *N*-period jitter and period jitter. Equation 2.11 can indeed be written as:

$$\mathbf{p}_{k}(N) = \sum_{i=k}^{i=k+N-1} (T_{i} - T) = \sum_{i=k}^{i=k+N-1} \mathbf{p}_{i}$$

(2.13)

so that, recalling 2.8, the *N*-period jitter turns out to be equal to the sum of the period jitter over *N* consecutive periods. In the literature, the *N*-period jitter is also called *accumulated* jitter, since it originates from the accumulation of the jitter over consecutive periods. In this book, the term *N*-period jitter is preferred, but the two identify the same concept.

Before we proceed, one comment on notation: in a general context, the term N-period jitter refers to jitter over multiple periods, and N does not represent any particular number. When addressing a more specific case, though, N can be replaced by the actual number of periods being considered, or by the name of a variable or any other mathematical symbol representing it. One can thus speak of 5-period jitter, m-period jitter, or (k+1)-period jitter, with m and k representing integer numbers.

#### 2.1.5 Other Jitter Definitions

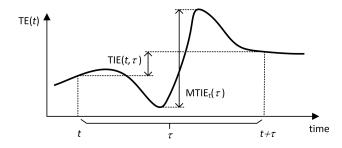

In addition to the jitter definitions given in the previous sections, the technical literature often presents the reader with others. Some of them, like the Time Error (TE) or the Time Interval Error (TIE), are well known, standardized, and used extensively in specific applications. Others are used in papers, technical reports, application notes, and don't always share the same meaning.

This section will give a brief overview of the most popular among those additional jitter definitions. This list is by no means exhaustive or complete.

#### Time Error (TE) and Time Interval Error (TIE)

In 1996 the Telecommunication Standardization Sector of the International Telecommunication Union (ITU-T), the agency of the United Nations which regulates the interoperability of geographical communication networks worldwide, released the Recommendation G.810 [2]. This Recommendation standardizes definitions and terminology for telecommunication networks, among them the Time Error (TE) and the Time Interval Error (TIE).

Given a generic clock signal of the form reported in Equation 2.2, the Recommendation defines a *time function*  $T(t) := \phi(t)/(2\pi f_0)$ , where  $\phi(t) := 2\pi f_0 t + \varphi(t)$  is the total phase of the clock signal under investigation and  $\varphi(t)$  is the excess phase. Similarly it defines a *reference time function*  $T_{ref}(t) := \phi_{ref}/(2\pi f_0)$  as the total phase of a reference clock signal divided by its radian frequency. Typically, an ideal clock with no excess phase (no jitter) is taken as reference signal, so that  $T_{ref}(t) = t$ .

After giving those definitions, the Recommendation defines the Time Error (TE) at time t as:

$$TE(t) := T(t) - T_{ref}(t).$$

(2.14)

Based on the relations above and on the jitter definitions given in the previous sections, it is easy to show (this is left as an exercise for the reader) that the Time Error at a time t corresponding to the k-th edge of the clock under investigation is nothing other than the absolute jitter at k:

$$TE(t) = \mathbf{a}_k. \tag{2.15}$$

The Recommendation finally introduces the Time Interval Error (TIE) as a measure of the accuracy in determining the duration of a time interval  $\tau$  when using the clock under investigation, as opposed to using the reference clock. It is defined as:

$$TIE(t,\tau) := [T(t+\tau) - T(t)] - [T_{ref}(t+\tau) - T_{ref}(t)].$$

(2.16)

From here it can be shown that  $TIE(t, \tau) = TE(t + \tau) - TE(t)$ . Assuming that the times t and  $t + \tau$  correspond to the k-th and k + N-th edges of the clock, respectively, using Equation 2.15 the Time Interval Error can be written as:

$$TIE(t,\tau) = \mathbf{a}_{k+N} - \mathbf{a}_k = \mathbf{p}_k(N). \tag{2.17}$$

It is thus revealed that the TIE over a time interval  $\tau$  is nothing other than the *N*-period jitter, with *N* equal to the number of clock periods contained in  $\tau$ .

A quantity connected to the TE and widely adopted by both the ITU-T and ANSI standardization bodies is the Maximum Time Interval Error, MTIE [3], defined as the maximum peak-to-peak value of TE(t) over a given interval  $\tau$ :

$$MTIE_{t}(\tau) := \max_{t \le t_{1} \le t + \tau} TE(t_{1}) - \min_{t \le t_{1} \le t + \tau} TE(t_{1}).$$

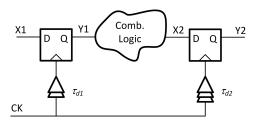

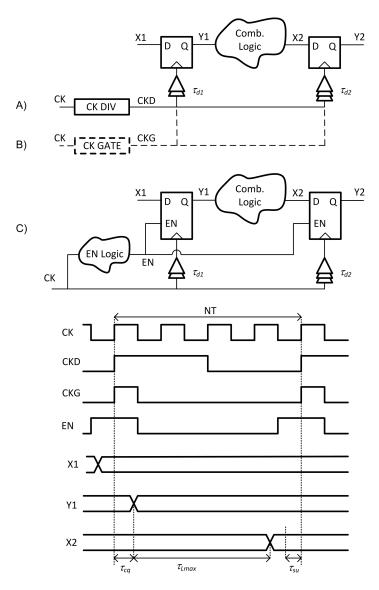

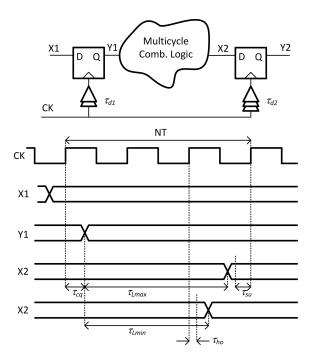

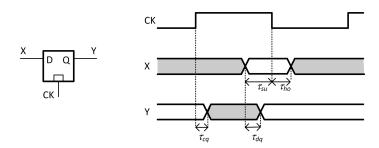

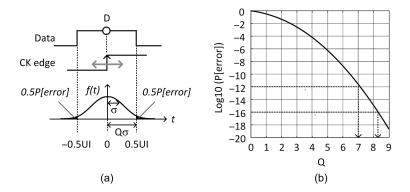

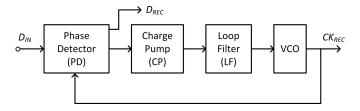

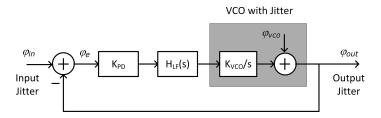

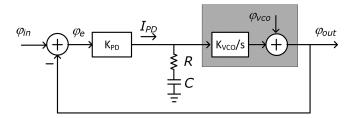

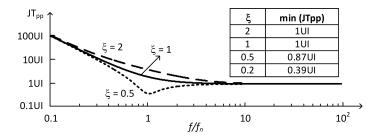

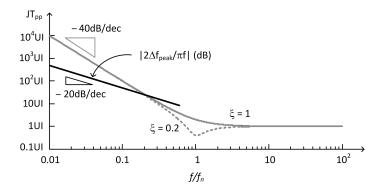

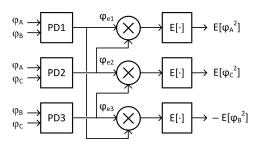

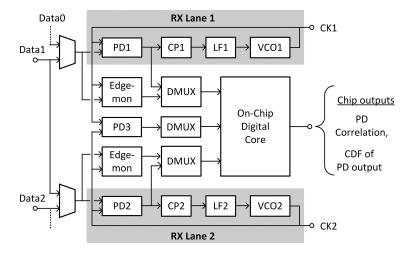

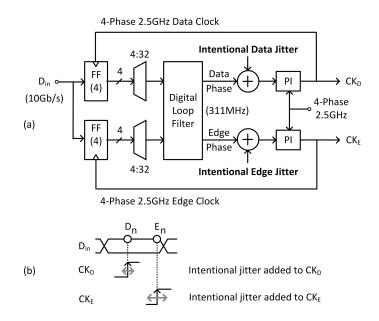

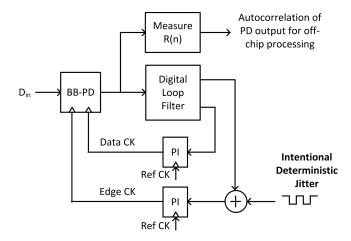

(2.18)