# RTL Coding Guidelines

DEC, 1999

Professional Service Group Synopsys, Inc. Asia Pacific Operations

Disclosure of information shared to other than those authorized, is strictly prohibited.

- A common set of problems facing everyone who is designing design-reuse ASICs:

- Time-to-market pressures demand rapid development

- Quality of results, in performance and area, are keys to market success

- Increasing chip complexity makes verification more difficult

- The development team has different levels and areas of expertise

- Design team members may have worked on similar designs in the past, but cannot reuse these designs because the design flow, tools, and guidelines have changed

- ☐ The "Design Reuse Coding Style" offers design team members a collection of coding rules and guidelines.

- □ A high quality HDL code is a prerequisite for a high quality product.

#### Presentation:

**HDL Coding Style Guidelines**

- **General HDL Code Structure**

- **Partitioning**

- **Implying Logic Structure**

- **Safe Coding & Avoiding Problems**

- **Source Code Readability**

- **Coding Style for Design Reuse**

- **Design for Testability**

- **Practices**

# HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

**HDL Coding Style Guidelines**

- General HDL Code Structure

- Partitioning

- □ Implying Logic Structure

- Safe Coding & Avoiding Problems

- Source Code Readability

- □ Coding Style for Design Reuse

- Design for Testability

- Practices

#### General HDL Code Structure: Checklist Items

- ☐ Standard File Headers (101)

- □ File Naming Conventions (102)

- Architecture Naming Conventions (103)

- Signal Naming Conventions (104)

- Use of Labels (105)

- Linking in Verilog (106)

- Clear & Meaningful Comments (107)

#### Standard File Headers (101)

- Make sure the code look familiar, no matter who writes the module.

- Make sure every file has a file header containing information on

- file name or module function, author, creation date, abstract or summary, modification history

- copyright, licensing agreement (if need)

```

// FILE: design.v

// AUTHOR: Brooke Tioga

// $Id$

Used by RCS!

// ABSTRACT: Description of the design object

// KEYWORDS: dsp, telecom, graphics

// MODIFICATION HISTORY:

// $Log$ ←

// Brooke

11/9/97 original

3/3/98

revised as follows...

Susie

// (C) Copyright 1997 Synopsys Inc. All rights reserved

```

#### Headers for Major Constructs (101)

```

// FUNCTION:

double trouble

// AUTHOR: Ornithal Shapiro

// $Id$

// ABSTRACT: to double throughput of filter

// MODIFICATION HISTORY:

// $Log$

Ornithal

12/9/97

original

4/4/98

Brooke

revised as follows...

This function performs the interpolation of data ...

```

- Use for each function and task

- Use for each major section of code

# File Naming Conventions (102)

**Enabling Productivity**

- A consistent approach to naming files greatly improves communication among designers.

- Create individual files for each module:

| Convention  | Object            | Example      |

|-------------|-------------------|--------------|

| design.v    | Module            | arbiter.v    |

| tb_design.v | Verilog Testbench | tb_arbiter.v |

Use module/function name as part of file name.

# Architecture Naming Conventions (103)

- While the term "architecture" is a VHDL construct, it is used to categorize VHDL modules based on their level of abstraction.

- Keep the same file names for all architectures, and manage the design data with different file directories for each architecture.

- □ Verilog reserved words (module, endmodule, wire, reg, always, begin, end, if, else, case, endcase, ...)

- must use lower case (Verilog requirement)

- Names (module names, function names, block names, wires, regs, integers, ...)

- use lower case

- Names (macro ...)

- use upper case

- Names (Clock Signal)

- w use clk1, clk2, or clk interface

- Use the same name for all clock signals that are driven from the same source.

- Names (Reset Signal)

- use rst for reset signal

- Names (active low signal)

- end the signal name with an underscore followed by a lowercase character

- example\_b, example\_n

- Names (multibit-buses)

- use a consistent ordering of bits

- for VHDL (y downto x) or (x to y)

- for Verilog [x:0] or [0:x]

- Names (meaningful)

- don't use ra for a RAM address, instead, use ram\_addr

- ☐ Check with your vendor for their name restrictions

- (e.g. case, length)

- Noun/verb paradigm

- spot\_run not run\_spot

- processor\_interrupt not interrupt\_processor

- ☐ For net names, use the same name throughout the hierarchy

- □ Consider dc\_shell commands when choosing names:

```

set_input_delay 7.0 find(pin, "xi_pci*")

```

- Use naming conventions to indicate type of signal:

- input, output, register output, etc.

- **Examples:**

| Admpico. |                              |  |

|----------|------------------------------|--|

| clk_*    | Clock signal                 |  |

| rst      | Reset signal                 |  |

| *_n      | Negative logic (active low)  |  |

| *_r      | Output of a register         |  |

| *_a      | Asynchronous signal          |  |

| *_#n     | Signal used in the "n" phase |  |

| *_nxt    | Data before being registered |  |

| *_z      | Three-state internal signal  |  |

| xi_*     | Primary chip input           |  |

| xo_*     | Primary chip output          |  |

| xz_*     | Primary chip three state     |  |

| xb_*     | Primary chip bidirectional   |  |

|          |                              |  |

### Use of Labels (105)

**Enabling Productivity**

- Labels improve readability & debugging

- ☐ If labels are not specified, arbitrary labels are generated internal to simulation/synthesis tools

- ☐ Labeled always@ facilitate repartitioning with the group command.

```

always@(posedge CLK)

begin: CHT2BIT

if (RESET == 1'b1)

QOUT <= 2'b00;

else

QOUT <= QOUT + 1'b1;

end</pre>

```

Use Labels at begin

dc\_shell\_script:

group -hdl\_block CHT2BIT

Use Labels on always@, & function constructs

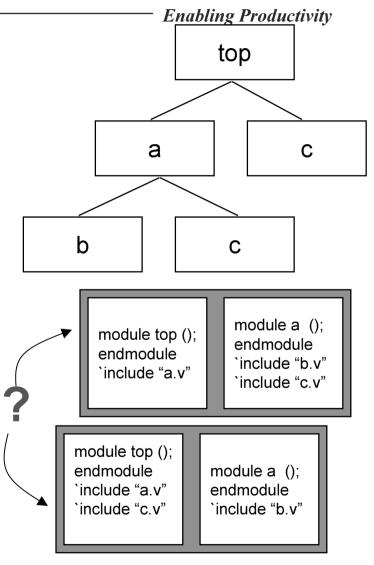

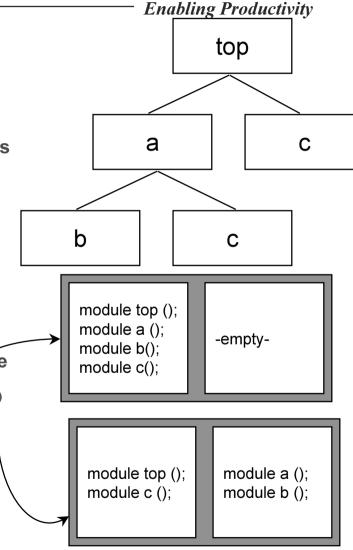

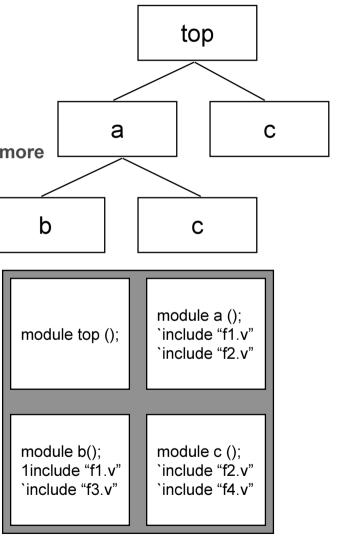

# Linking Modules (106): Avoid Modules linked with `include

- Avoid modules linked with 'include'

- □ Reasons:

- Locating the file

- ⇒ The included file has to reside in the same directory from which the tool(simulation or synthesis) is invoked, or a path to the file must be specified in the source code.

- Compilation

- ⇒ The included file may complicate the design partitioning and may result in greater effort when developing a bottomsup compile strategy.

#### Linking Modules (106): Avoid Multiple Modules in a Single File

- Avoid multiple modules in single file.

- Reasons:

- Locating the file

- ⇒ Determining which files contain which modules cannot be inferred using the file name conventions.

- Compilation

- ⇒ Performing incremental compiles in DC due to small changes become more complex and timing consuming.

- Revision Control (RCS)

- ⇒ Revision control and bug tracing become more complicated.

# Linking Functions (106): Avoid Multiple Functions in a Single File

- Avoid: Multiple functions in single file

- □ Reasons:

- Revision Control (RCS)

- ⇒ Revision control and bug tracing become more complicated.

# Clear Meaningful Comments (107)

- Improve readability, maintainability, ability to reuse, easy review, traceability

- ☐ Typical engineers response ...

- "I don't have the time to comment now"

- When complete do you go back & comment or do you move on to the next assignment?

# HDL for Synthesis Guidelines

**Enabling Productivity**

#### Presentation:

HDL for Synthesis Guidelines

- General HDL Code Structure

- **Partitioning**

- **Implying Logic Structure**

- Safe Coding & Avoiding Problems

- Source Code Readability

- **Coding Style for Design Reuse**

- **Design for Testability**

- **Practices**

- ☐ Partitioning is not just a functional issue. It can significantly affect the following process:

- Synthesis Quality-of-Result (QOR)

- Synthesis constraints

- Synthesis scripts

- Synthesis compile time

- Static timing analysis

- Floorplanning

- Layout

- □ Physical Implementation Issues

- Keep related combinational logic together

- Combine shareable resource

- Merge user-defined resources and driven logic

- Partition based on design goals

- □ Partitioning to Speed Up the Compile Process

- Eliminate glue logic

- Maintain a reasonable gate size

- Maintain a reasonable number of levels

- Isolate point-to-point exceptions in the same module

- □ Partitioning to Simplify Scripts and Constraint Files

- Register all outputs

- At chip-level create core logic, pad ring, and test hierarchy

- Commands that Manipulate Hierarchy

- If artificial and suboptimal barriers exist in critical combinational logic path, you can rearrange the hierarchy to eliminate the suboptimal interface.

- ⇒ DC command: group

- ⇒ DC command: ungroup

#### Partitioning: Checklist Items

**Enabling Productivity**

#### □ Physical Implementation Issues

- No snake paths in critical paths (201)

- Combine sharable resources (202)

- Merge User-Defined Resources with the logic they drive (203)

- Separate logic with different synthesis goals

- ⇒ area vs. speed sensitive (204)

- ⇒ random vs. structured (205)

- Separate Clock Generation Module (206)

- Separate Asynchronous Logic (207)

- Separate Finite State Machines (208)

#### Partitioning: Checklist Items

- Partitioning to Speed Up the Compile Process

- Eliminate glue logic (209)

- Reasonable design size (210)

- Reasonable hierarchy (211)

- Isolate Point-to-Point Exceptions (212)

- Partitioning to Simplify Scripts and Constraints Files

- Register the outputs (213)

- Chip-Level Partitioning (214)

- Commands that Manipulate Hierarchy

- Ungroup

- Group

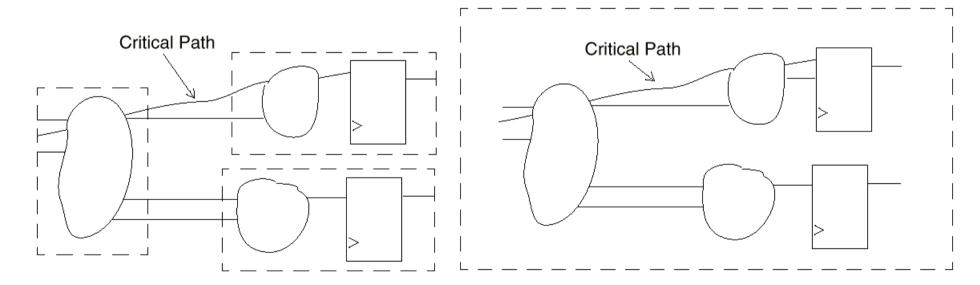

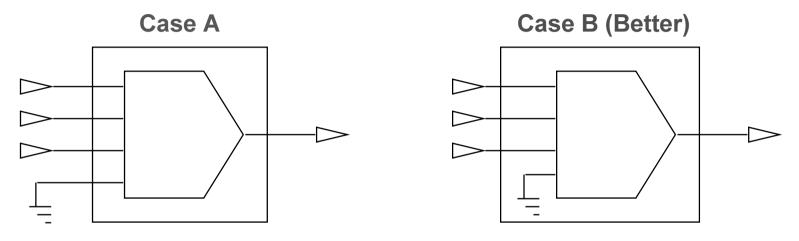

### Avoid Snake Paths (in critical path) (201)

- Enabling Productivity

- Design Compiler cannot move logic across hierarchical boundaries.

- Dividing related combinational logic into separate modules introduces artificial barriers restrict logic optimization

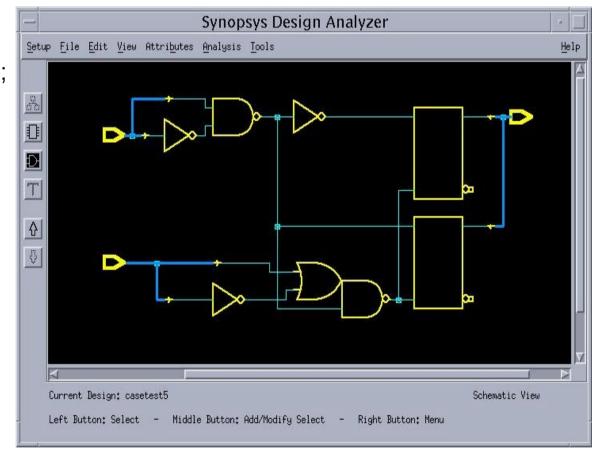

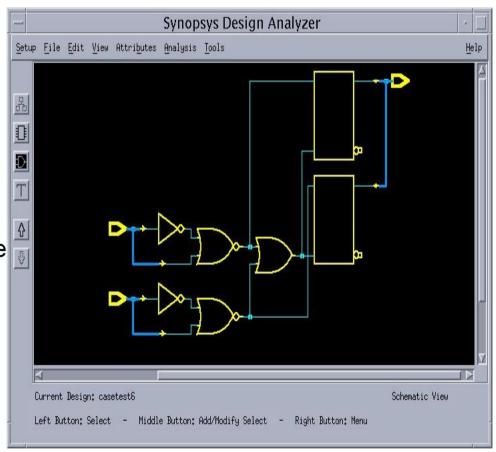

Poor Partitioning of Related Logic

Keep Related Logic in the Same Module

### Avoid Snake Paths (in critical path) (201)

- □ Snake Path combinational logic path distributed over multiple modules

- □ DC does not allow cross boundary optimization & requires time budgeting

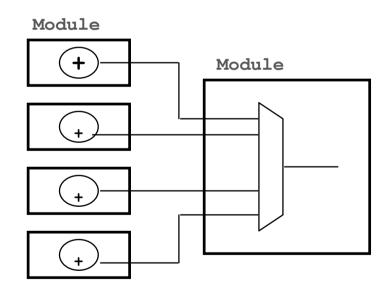

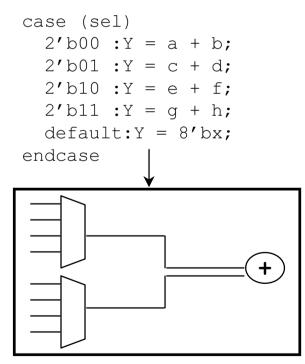

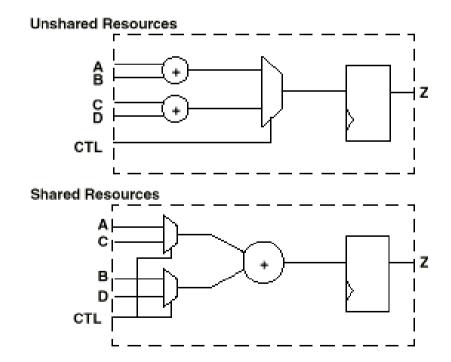

#### Combine Sharable Resources (202)

**Enabling Productivity**

- Resources (e.g. adders) can be shared if they are never used at the same time.

- □ For HDL Compiler to determine this, the resources MUST be in the same module and always@ block

#### **BAD**

(Cannot Share Across Modules)

#### GOOD

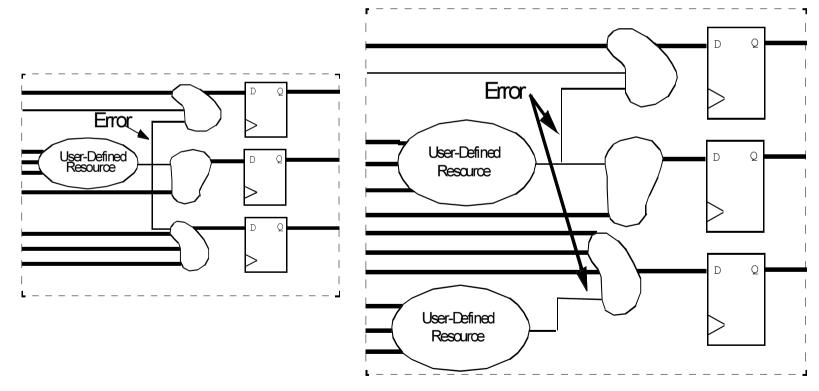

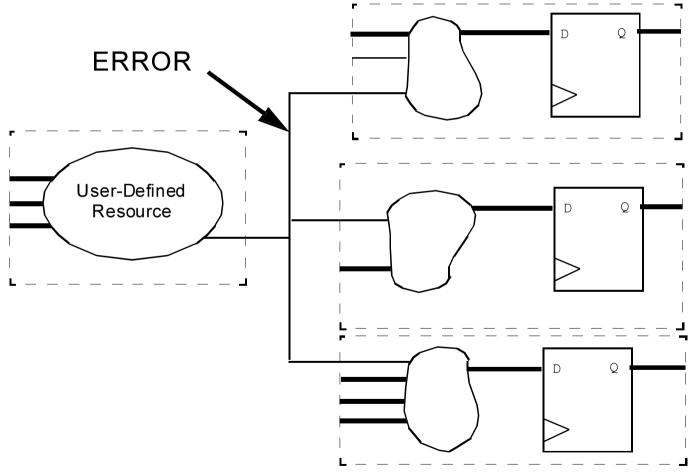

#### Merge User-Defined Resources with the Logic They Drive(203)

- ☐ A user defined resource is any logic that drives a large fanout.

- (e.g. mux-select for 100 muxes)

- ☐ You may want to replicate user defined resources to balance the load.

- (e.g. 10 mux-selects to drive 10 muxes)

#### Merge User-Defined Resources with the Logic They Drive(203)

**Enabling Productivity**

■ A poor partitioning might bring more synthesis and timing analysis problems.

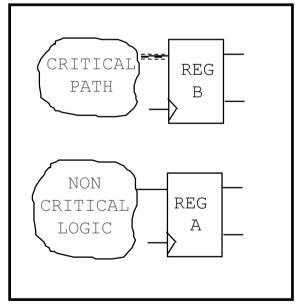

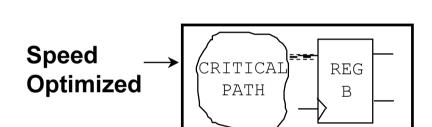

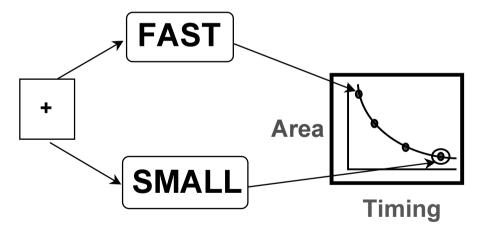

### Separate Area & Speed Logic (204)

**Enabling Productivity**

- Area and Speed Critical Logic are best optimized with different compile strategies

- Separate the logic so you can apply these strategies individually

set structure ???

**GOOD**

Might need to be flattened to make timing

Should not be flattened

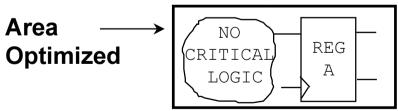

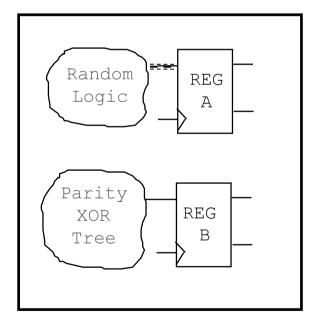

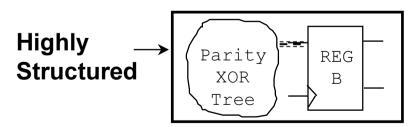

#### Separate Random & Structured Logic (205)

**Enabling Productivity**

- Random and Structured Logic are best optimized with different compile strategies.

- □ Separate logic so you can apply these strategies individually.

**BAD**

set structure ???

GOOD

Might need to be flattened to make timing

Should not be flattened

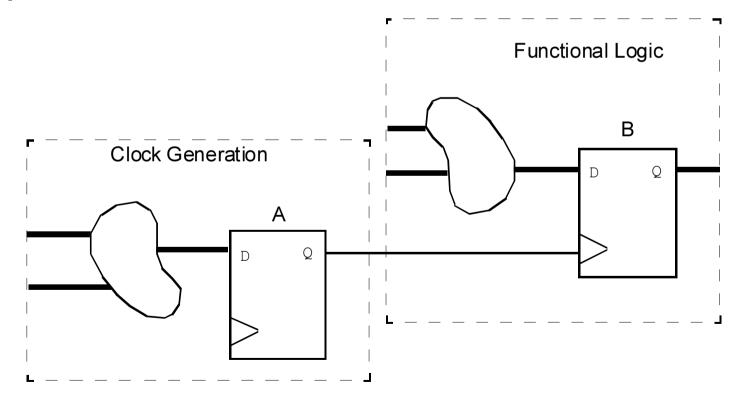

#### Separate Clock Generation Module (206)

- ☐ Clock generation logic is typically handcrafted and often requires special timing analysis.

- It is often recommended that clock generation logic be put into its own module.

### Separate Asynchronous Logic (207)

- Asynchronous logic is sometimes technology-dependent, and typically requires gate-level instantiation and a special synthesis methodology.

- Asynchronous logic typically requires special test considerations and verification strategies.

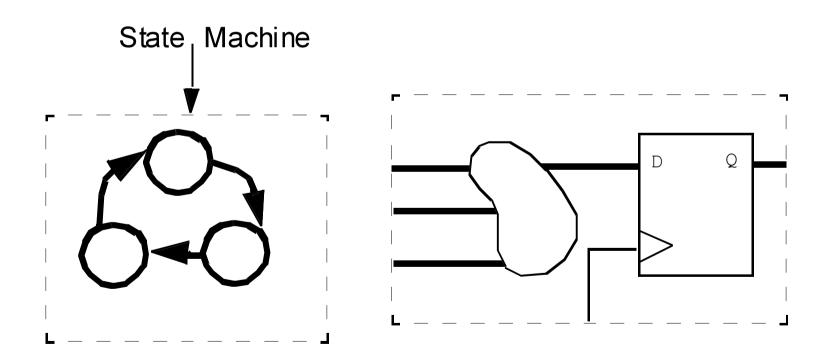

#### Separate Finite State Machines (208)

- ☐ A state machine may benefit from the state machine compiler or from a flattening optimization strategy.

- Modules that contain only state machines simplify the state extraction and optimization process.

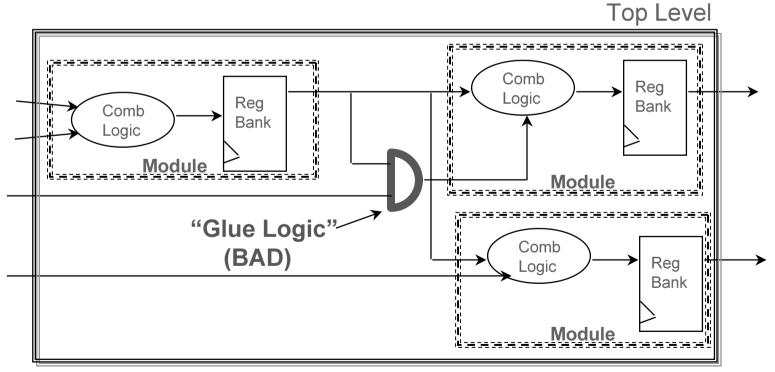

### Eliminate Glue Logic (209)

- ☐ Design should only contain gates at the leaf level of the hierarchy tree

- Reduces CPU time to compile small amounts of logic for glue.

- Synthesis compile scripts are simplified when glue logic is removed.

# Reasonable Design Size (210)

- Symptom: Too many lines of code in block

- □ Pitfalls:

- analyze / elaborate steps are slow

- code is difficult to read / inspect

- **□** Recommendation:

- blocks should contain only clock

- blocks should have few timing exceptions

- add a new level of hierarchy

#### Reasonable Hierarchy (211)

- ☐ Use a reasonable number of levels in the hierarchy

- □ Pitfalls:

- reduced readability

- longer compile times

- more error prone (more places for error)

- □ Recommend:

- Use 2-3 levels per major function block or algorithm,

- Use no more than 8 levels per design.

- A new level is introduced via DesignWare (can be eliminated by ungroup)

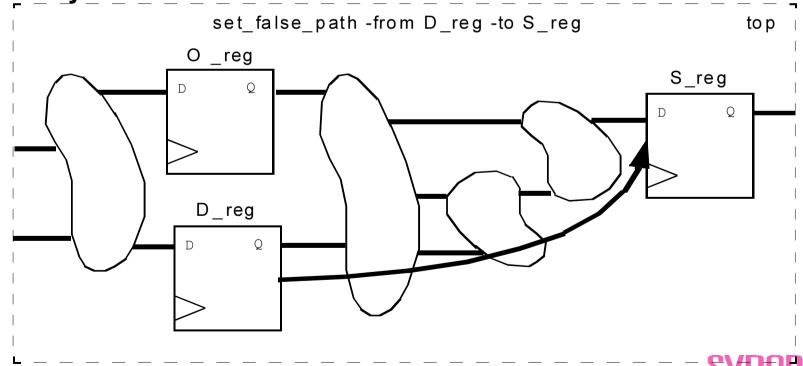

### Isolate Point-to-Point Exceptions (212)

- ☐ If a design contains point-to-point exceptions (false path/multiple cycles), keep those exceptions within a module.

- By containing the point-to-point exception within one module, execution-time in static timing analysis or synthesis is minimized.

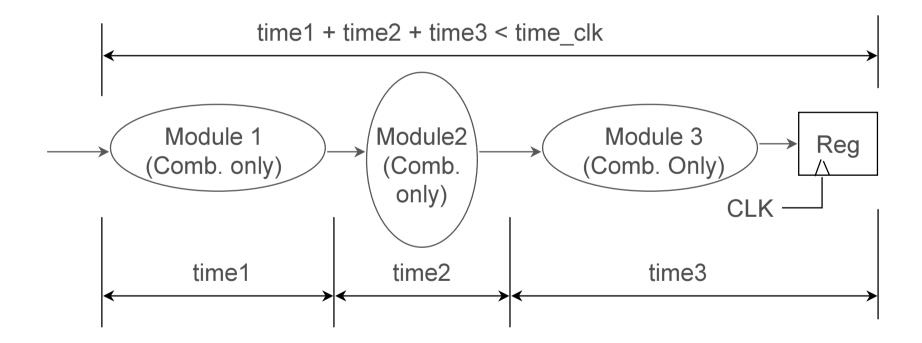

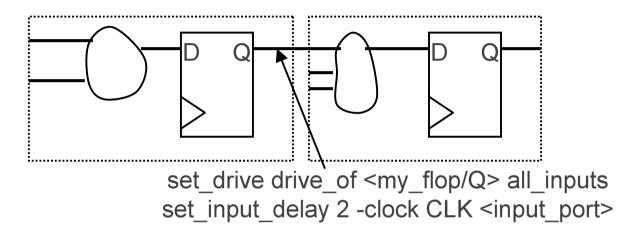

#### Register the Outputs (213)

**Enabling Productivity**

■ To simplify the constraints and scripts process, register all outputs of a block.

- ☐ The drive strength of the inputs is predictable.

- ☐ The input delays from the previous block are predictable.

- It speeds up simulation, since the process activate only once per clock cycle.

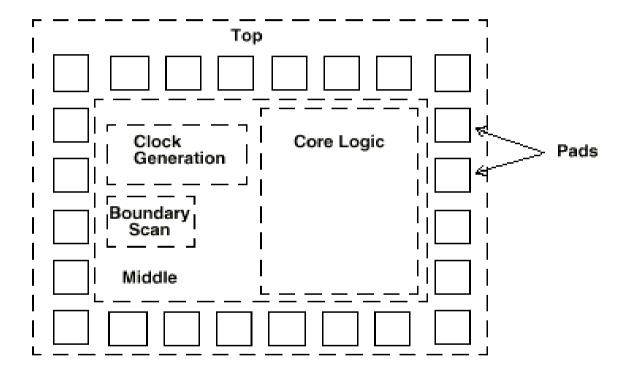

#### Chip-Level Partitioning (214)

**Enabling Productivity**

The partitioning recommendation for the top of an ASIC

□ The clock generation circuitry is isolated from the rest of the design, since typically it is handcrafted and carefully simulated.

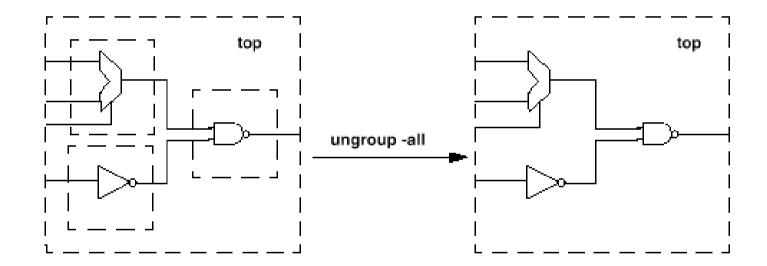

#### Ungrouping a Design Hierarchy

**Enabling Productivity**

■ The ungroup command collapses hierarchy.

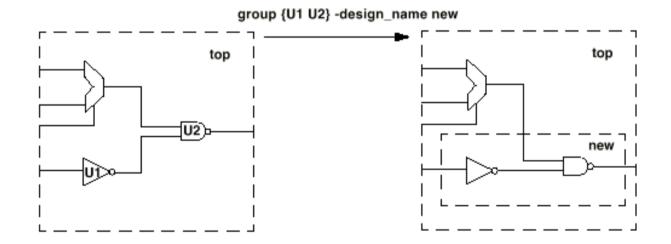

#### Group Cells into a Module

**Enabling Productivity**

The group command allows you to create new levels of hierarchy from the objects at this level.

#### Group Cells into a Module

**Enabling Productivity**

You can group individual HDL blocks with the hdl\_block option of the group command.

> Block label examples for Verilog source code // This is a named always block always @(A or B or C) begin: My Process end

group -hdl block My Process -design My Block

# HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

HDL for Synthesis Guidelines

- General HDL Code Structure

- Partitioning

- **Implying Logic Structure**

- Safe Coding & Avoiding Problems

- Source Code Readability

- □ Coding Style for Design Reuse

- Design for Testability

- Practices

#### Implying Logic Structure: Checklist Items

**Enabling Productivity**

**Unintentional latches (301)** If vs. Case statement (302) Code organization & optimization (303) Resource sharing (304) **Finite Statement Machines (305)** Don't care inference (306) Coding of repetitive structures (307) **Sharing Common Subexpression (308)** Avoid Redundant Logic and Subexpress. (309) **Inferring the Correct Register (310) Structure for Minimum Delay (311) Inferring Tri-State Drivers (312)**

**Enabling Productivity**

- Poor structure may never converge on the right results

- □ Poor structure usually means at least an increase in synthesis run times

- Designers imply lots of structure!

# You get what you write!

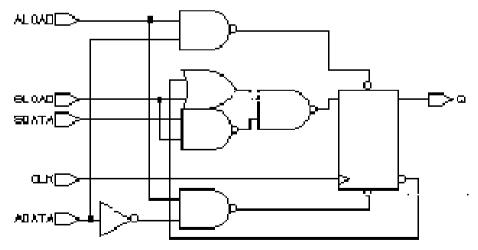

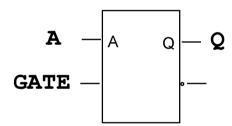

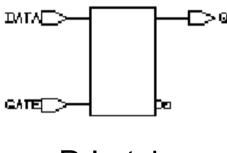

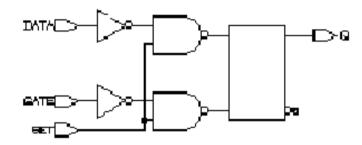

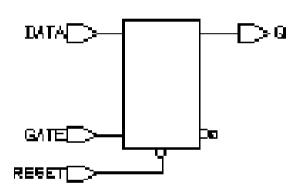

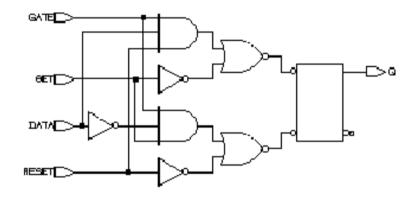

#### Unintentional Latches (301)

**Enabling Productivity**

An IF statement with outputs not fully specified synthesizes to a latch. Example:

```

module oops_latch ...

always @ (GATE or A)

begin

if (GATE == 1)

Q = A;

end

```

endmodule

□ hdlin\_check\_no\_latch = 'false' is default If set to "true" HDL Compiler will issue a warning if a latch is synthesized.

#### Unintentional Latches (301)

**Enabling Productivity**

A 'case' statement with paths that bypass reg assignment synthesizes to a latch. Example:

```

module oops latch (bus err, par err, sys err, irq err, err code);

input bus err, par err, sys err, irq err;

output [1:0] err code;

[1:0] err code;

req

always @ (bus err or par err or sys err or irq err)

begin

case ({bus err, par err, sys err, irq err})

4'b1000: err code = 0;

4'b0100: err code = 1;

comb

4'b0010: err code = 2;

err code[1]

4'b0001: err code = 3;

endcase:

bus err

end

par err

err code[0]

sys err

endmodule

irq err

comb

```

Assign a value under all conditions. Assign value to all variables. Use a 'default' clause. Use 'full\_case' directive.

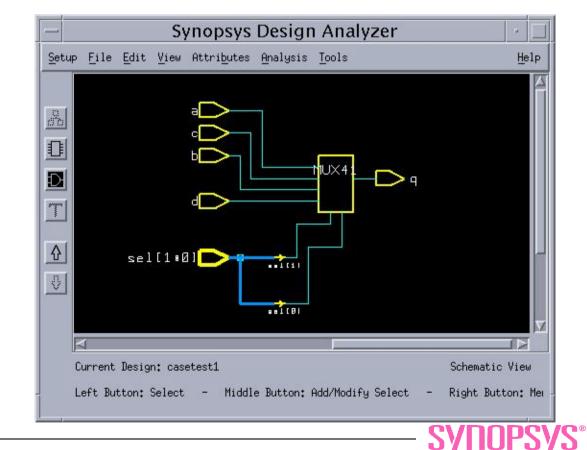

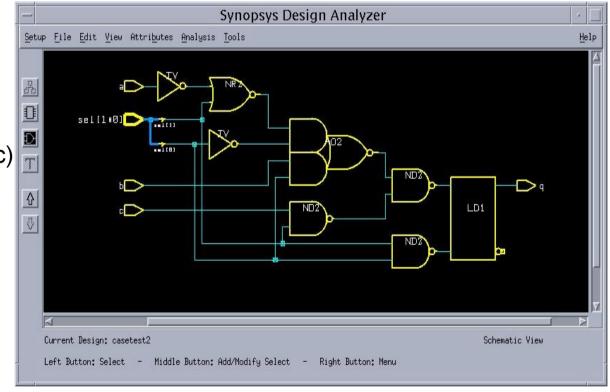

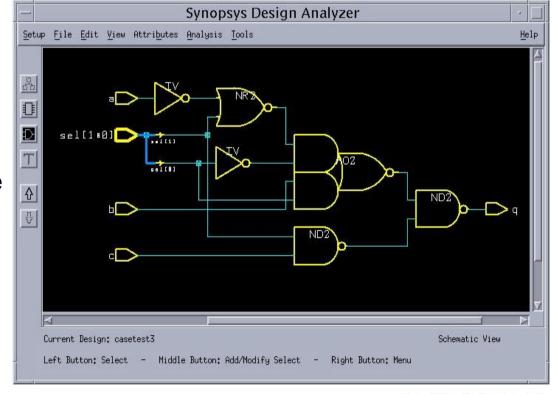

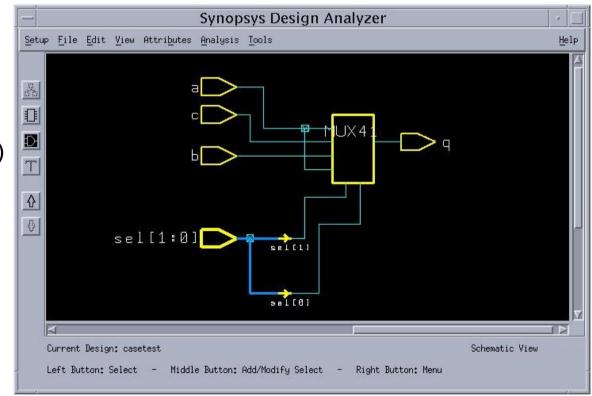

### If vs. Case Statements (302)

**Enabling Productivity**

#### Priority Encoder :

```

if (sel[0])

z = dat[0];

else if (sel[1])

z = dat[1];

else if (sel[2])

z = dat[2];

else

z = dat[3];

```

If HDL compiler cannot statically determine that branches are parallel, it synthesizes hardware that include a priority encode.

#### Simple "One Hot" Encoder:

```

case (1'b1) // synopsys parallel case

sel[0] : z = dat[0];

sel[1] : z = dat[1];

sel[2] : z = dat[2];

sel[3] : z = dat[3];

endcase;

```

Parallel case: no cases overlap

Is synopsys directive needed?

# Code Organization & Optimization (303)

**Enabling Productivity**

Organize code such that the latest arriving (design speed) or most frequent (simulation speed) event is evaluated first:

```

if (often)

....

else if (rare)

case (state)

often: ...

lessoften: ...

rare: ....

```

- ☐ This approach speeds up design speed since the latest arriving signal is further down the logic cone

- This approach speeds simulation since the first condition evaluated is usually true eliminating the need for further processing.

# Resource Sharing (304)

- □ Design Compiler can share resources like adders or multipliers.

- Resource sharing can only occur if the resource allocation do not violate the limitations of scope and restrictions.

**Enabling Productivity**

#### **Resource Sharing** =

**Resource Allocation**

+

Implementation Selection

#### Resource Allocation (304)

**Enabling Productivity**

☐ Resource Allocation is the process of determining the number of resources in your design.

```

// Depending upon adder_control,

// select correct inputs.

if (adder_control)

adder_output = busa + busb;

else

adder_output = busc + busd;

```

# Implementation Selection (304)

**Enabling Productivity**

☐ Implementation selection is the process of choosing the correct DesignWare architecture according to your constraints.

#### **Carry look-ahead**

Ripple Adder

### Limitations of Resource Sharing (304)

**Enabling Productivity**

■ Not all operations in your design can be shared. The following operators can be shared.

- □ Operations can be shared only if they lie in the same always block.

- Two operations can be shared only if no execution path exists from the start of the block to the end of the block that reaches both operations. (Control Flow Conflicts)

- Operations cannot be shared if doing so cause a combinational feedback loop. (Data Flow Conflicts)

#### Resource Sharing (304): Scope

**Enabling Productivity**

#### Allowed & Disallowed Sharing

|       | A1+B1 | C1+D1 | A2+B2 | C2+D2 |

|-------|-------|-------|-------|-------|

| A1+B1 | -     | yes   | no    | no    |

| C1+D1 | yes   | -     | no    | no    |

| A2+B2 | no    | no    | -     | yes   |

| C2+D2 | no    | no    | yes   | -     |

Only Operators in the same always@ block can be SHARED!

#### Resource Sharing (304): Control Flow Conflicts

**Enabling Productivity**

```

always @ (A or B or C or D or E or F or G

or H or I or J or OP)

begin: ADDER SELECT

Z1 = A + B;

case (OP)

2'b00 : Z2 = C + D;

2'b01 : Z2 = E + F;

2'b10 : Z2 = G + H;

Allowed & Disallowed Sharings

2'b11 : Z2 = I + J;

endcase;

C+D

E+F

A+B

G+H

I+J

end

A+B

no

no

no

no

C+D

no

yes

yes

yes

```

no

no

no

ves

ves

yes

Disable resource sharing only if logic is in CRITICAL PATH

E+F

G+H

I+J

ves

ves

ves

yes

ves

yes

#### Resource Sharing (304): Control Flow Conflicts

**Enabling Productivity**

- Operations in separate branches of a ?: (conditional)

construct cannot share the same hardware.

- ☐ Consider the following line of code where expressions\_n represents any expressions.

```

z = expression_1 ? expression_2 : expression_3;

```

HDL Compiler interprets this code as

```

temp_1 = expression_1;

temp_2 = expression_2;

temp_3 = expression_3;

z = temp_1 ? temp_2 : temp_3;

```

HDL Compiler evaluates both expression\_2 and expression\_3, regardless of the value of the conditional.

Therefore, operations in expression\_2 cannot share the same resource as operations expression\_3.

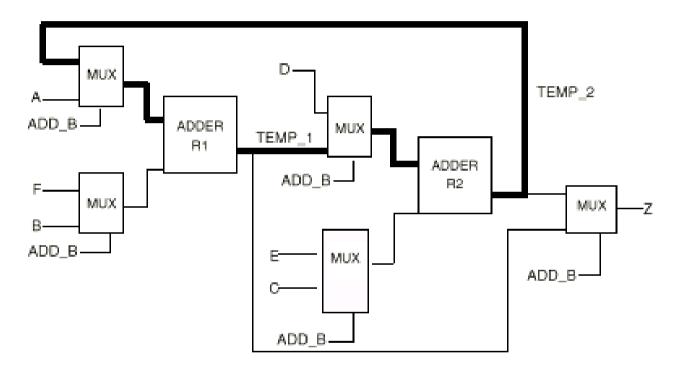

#### Resource Sharing (304): Data Flow Conflicts

**Enabling Productivity**

To understand how sharing can cause a feedback loop, consider the following example.

```

//Data Flow Conflict

always @(A or B or C or D or E or F or Z or ADD_B)

begin

if(ADD B) begin

TEMP_1 = A + B;

Z = TEMP 1 + C:

end

else begin

TEMP 2 = D + E;

Z = TEMP 2 + F;

end

end

```

When the A+B addition is shared with the TEMP 2+F addition on an adder call R1 and the D+E addition is shared with the TEMP 1+C addition on an adder called R2, a feedback loop results

#### Resource Sharing (304): Data Flow Conflicts

**Enabling Productivity**

#### ☐ Feedback Loop For the previous example.

HDL Compiler resource sharing mechanism does not allow combinational feedback paths to be created because most timing verifiers cannot handle them properly.

### Critical Path Considerations...(304)

**Enabling Productivity**

☐ To enable automatic sharing for all designs, set the dc\_shell variable as shown before you execute the compile command.

```

dc_shell> hlo_resource_allocation = constraint_driven

```

- ☐ The default value for this variable is *constraint\_driven*.

- ☐ To disable automatic sharing for uncompiled designs, and enable resource sharing only for selected designs, enter the following commands:

```

dc_shell> hlo_resource_allocation = none

dc_shell> current_design = MY_DESIGN

dc shell> set resource allocation constraint driven

```

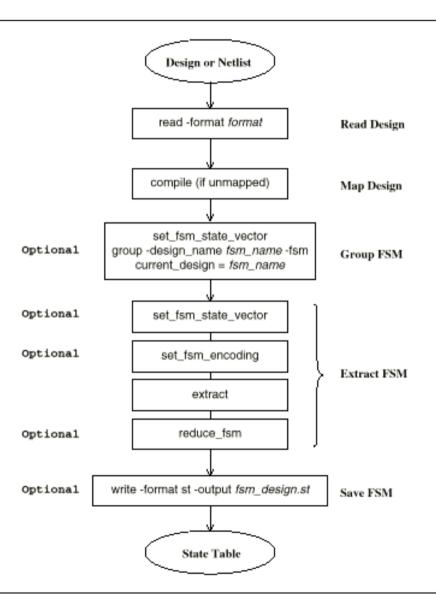

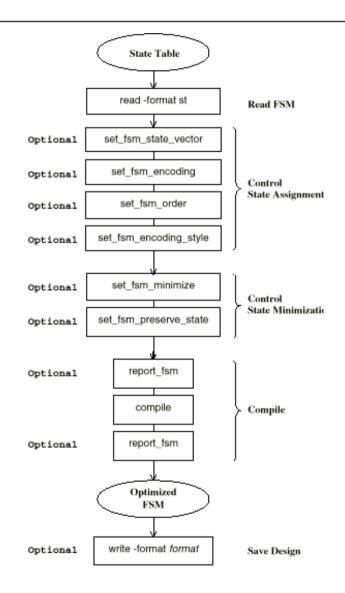

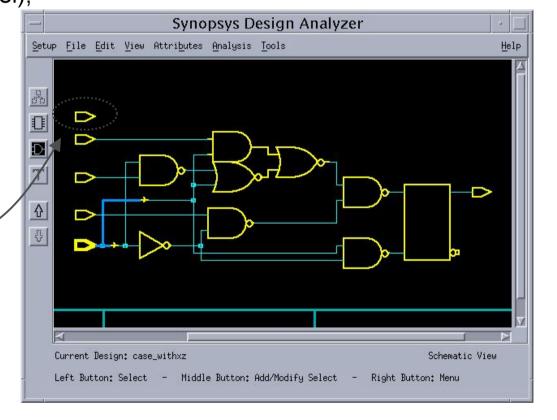

#### Finite State Machines (305): Extracting

### Finite State Machines (305): Compile

# Finite State Machines (305)

- □ Design Compiler uses logic and gate-level optimization techniques for synthesis.

- **☐** Two additional techniques are available for FSMs:

- State Minimization

removal of redundant states

- State Assignment encoding styles (e.g. binary, gray, one-hot)

- ☐ Technique: (1) read in design, (2) map to gates, and (3) extract FSM

# State Machine Extraction (305)

- Extract out the state machine when:

- Number of states is from 15-32

AND

- States and surrounding logic are random

AND

- Best state ordering and number of bits is unpredictable *AND*

- Constraints are a mix of timing and area

### State Machine Syntax (305)

**Enabling Productivity**

- Use Synopsys' directives and style if you wish to extract out a state machine.

- □ Synopsys Style:

- Separate state machine into two processes

- Create an enumerated type for the state vector

- Drive FSM with embedded Synopsys directives

- Read HDL Compiler for Verilog manual for detailed information

After FSM extraction and optimization, back-annotate states into HDL code - but do not routinely flow through the extraction process.

### FSM Verilog Example (305)

// This finite-state machine (Mealy type) reads 1 bit // per cycle and detects 3 or more consecutive 1s. module enum2 V(signal, clock, detect); input signal, clock; output detect: rea detect: // Declare the symbolic names for states parameter [1:0]//synopsys enum state info NO ONES =  $2^{\circ}h0$ , ONE ONE =  $2^{\circ}h1$ . TWO ONES =  $2^{\circ}h2$ . AT LEAST THREE ONES = 2'h3; // Declare current state and next state variables. reg [1:0] /\* synopsys enum state info \*/ cs; reg [1:0] /\* synopsys enum state info \*/ ns:

```

// synopsys state vector cs

always @ (cs or signal)

begin

detect = 0:// default values

if (signal == 0)

ns = NO ONES;

else

case (cs) // synopsys full case

NO ONES: ns = ONE ONE:

ONE ONE: ns = TWO ONES;

TWO ONES,

AT LEAST THREE ONES:

begin

ns =

AT LEAST THREE ONES;

detect = 1:

end

endcase

end

always @ (posedge clock) begin

cs = ns;

end

endmodule

```

#### Example Synopsys (Non Verilog) FSM Code

**Enabling Productivity**

```

# Soft drink machine -- Price is 15 cents

.desian

soft drink machine

# Inputs: clock and reset signals;

nickel, dime, and quarter input signals

inputnames clk reset nickel in dime in quarter in

# Outputs: nickel change, dime change, dispense drink

outputnames nickel out dime out dispense

# Clock signal name and type

.clock clk rising edge

# Asynchronous reset signal, type, and reset state

.asynchronous reset reset rising IDLE

# State table

100 IDLE

FIVE

000

010 IDLE

TEN

000

%%% OWE DIME IDLE

010

# Wait in current state until money is deposited

000 IDI F

IDI F

000

000 FIVE

FIVE

000

000 TEN

TEN

000

```

Refer to the Design Compiler Family Reference Manual 's appendix for more information regarding Synopys FSM Code

#### Don't Care Inference (306)

- You can greatly reduce circuit area with don't-cares in your design.

- Use x, z, ? in case items of the casex statement to infer don't-care conditions.

- Use z, ? In case items of the casez statement to infer don't-care conditions.

```

module decoder8 c(A, Z);

parameter N = 8:

parameter log2N = 3;

input [N-1:0] A;

output [log2N-1:0] Z;

req [log2N-1:0] Z:

always @(A) begin: encode

casex (A) // synopsys full case parallel case

8 00000001: Z = 3 000:

8 0000001x:Z=3 001:

8 000001xx : Z = 3 010:

8 00001xxx : Z = 3 011:

8 0001xxxx : Z = 3 100:

8 001xxxxx : Z = 3 101:

8 01xxxxxxx : Z = 3 110:

1xxxxxxx : Z = 3 111:

endcase

end

endmodule

```

#### Coding of Repetitive Structures (307)

```

module foo (j, k, l, z);

module foo (j, k, l, z);

input [7:0] j, k, 1;

input [3:0] j, k, 1;

output [7:0] z;

output [3:01 z;

req [7:0] z;

req [3:01 z;

integer i;

integer i;

always @(j or k or 1)

always @(j or k or l)

begin

begin

for (i=0; i <=7; i=i+1)

z[0] = (\dot{\eta}[0] + k[0]) ^ 1[0];

z[i] = (i[i] + k[i]) ^ 1[i];

z[1] = (j[1] + k[1]) ^ 1[1];

end

z[2] = (\dot{\eta}[2] + k[2]) ^ 1[2];

z[3] = (\dot{j}[3] + k[3]) ^ 1[3];

endmodule

z[4] = (\dot{7}[4] + k[4]) ^ 1[4];

z[5] = (j[5] + k[5]) ^ 1[5];

z[6] = (\dot{7}[6] + k[6]) ^ 1[6];

z[7] = (\dot{7}[7] + k[7]) ^ 1[7];

end

endmodule

```

# Sharing Common subexpressions (308)

**Enabling Productivity**

- ☐ Sharing common subexpressions might reduce the area of your circuit.

- You can manually force common subexpressions to be shared by declaring a temporary variable to store the subexpression, then use the temporary variable where you want to repeat the subexpressions.

// Simple Additions with a Common Subexpression

```

temp = a + b;

x = temp;

y = temp + c;

```

# Sharing Common subexpressions (308)

**Enabling Productivity**

■ You can let Design Compiler automatically determine whether sharing common subexpressions improves your circuit; however, there are some limitations that you should know.

// Unidentified Command Subexpression

$$Y = A + B + C$$

;

$$Z = D + A + B$$

The parser does not recognize A+B as a common subexpression, because the second equation as (D+A).

You can force the parser to recognize the common subexpression by rewriting the second assignment statements.

$$Z = A + B + D$$

;

or

$$Z = D + (A + B)$$

### Avoid Redundant Logic and subexpressions (309)

**Enabling Productivity**

#### Minimize redundant recalculation

```

// Bad - Will synthesize four adders

X = A + B + C;

Y = D + C + A:

// Better - Will only synthesize three adders

T = A + C;

X = T + B;

Y = T + D;

// Bad - Will synthesize 4 multipliers and 3 adders

Z = A*C + A*D + B*C + B*D;

// Better - Will synthesize 1 multiplier and 2

adders

Z = (A + B) * (C + D);

```

### Avoid Redundant Logic and subexpressions (309)

**Enabling Productivity**

Don't include statements in loops when their values don't change!

```

for (i=0; i<=7; i=i+1)

proc data = pci data;

for (i=0; i<=7; i=i+1)

begin

proc data = pci data;

begin

fifo(i) = cache(i-1);

fifo(i) = cache(i-1);

end

end

Better

if (flag)

proc data = pci data;

begin

if (flag)

proc_data = pci data;

begin

proc add = cache add;

proc add = cache add;

end

end

else

else

begin

begin

proc data = pci data;

proc add = int add;

proc add = int add;

end

end

```

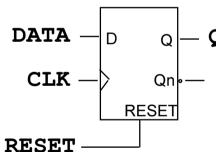

# Inferring the Correct Register - Synchronous Resets (310)

**Enabling Productivity**

☐ An attribute is needed to guide DC in inferring synchronous sets or resets in a design.

```

module dff sync reset (data, clk, s reset, q);

input data, clk, s reset;

output q;

reg

q;

// synopsys sync set reset "s reset"

DATA -

DATA O

always @ (posedge clk)

if (s reset)

CLK -

Qn

q = 1'b0;

S RESET

else

s reset

q = data;

```

endmodule

**Check Your Technology Library For Sync Set/Reset Cells**

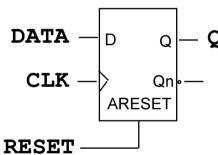

# Inferring the Correct Register - Asynchronous Resets (310)

**Enabling Productivity**

□ No attribute is needed to guide DC in inferring asynchronous sets or resets in a design. (Guidance is via coding style)

```

module dff_async_reset (data, clk, a_reset, q);

input data, clk, a_reset;

output q;

reg q;

always @ (posedge clk or posedge a_reset)

if (a_reset)

q = 1'b0;

else

q = data;

endmodule

a_reset

q = a_reset

a_reset

```

**Check Your Technology Library For Async. Set/Reset Cells**

# Check Inference Report

**Enabling Productivity**

#### ■ During Elaboration an Inference report is produced:

#### **Sample Inference Report:**

Inferred memory devices in process 'synchronizer\_reg' in routine m68k line 334 in file '/home/design/syn/try8/hdl/m68k.v'.

| <br>===                  | Register Name                                                   | Type   W                                    | /idth    | Bus                 | AR                            | AS                            | SF                            | R SS                                  | ST  <br>==                           |

|--------------------------|-----------------------------------------------------------------|---------------------------------------------|----------|---------------------|-------------------------------|-------------------------------|-------------------------------|---------------------------------------|--------------------------------------|

| <br> <br> <br> <br> <br> | asn_d_reg asn_s_reg ldsn_d_reg ldsn_s_reg mrwn_d_reg mrwn_s_reg | Flip-flop  <br>  Flip-flop  <br>  Flip-flop | 1  <br>1 | - İ<br>  - <u> </u> | N  <br>N  <br>N  <br>N  <br>N | N<br>  N<br>  N<br>  N<br>  N | N<br>  N<br>  N<br>  N<br>  N | Y  <br>  Y  <br>  Y  <br>  Y  <br>  Y | N  <br>N  <br>N  <br>N  <br>N  <br>N |

|                          | udsn_d_reg<br>udsn_s_reg<br>                                    | Flip-flop  <br>  Flip-flop                  | 1        | -  <br>  -          | N<br>N                        | N<br>  N                      | N<br>  N                      | Y  <br>  Y                            | N                                    |

# Environment Var's for FF Inference

**Enabling Productivity**

- hdlin\_ff\_always\_sync\_set\_reset = 'true'

- Each object in the reference design is interpreted as if sync\_set\_reset attribute/directive is present

- ☐ hdlin check no latch = 'true'

Used to generate a warning message during elaborate if a memory element is inferred in reference design.

**See Synthesis Reference Manual for Others**

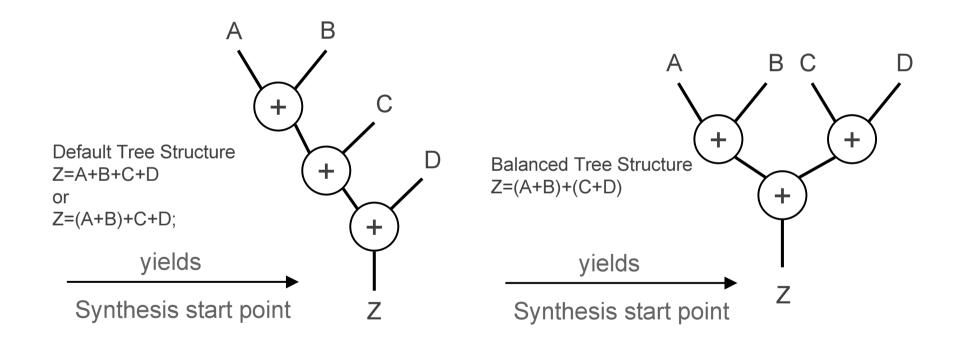

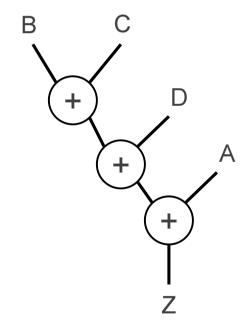

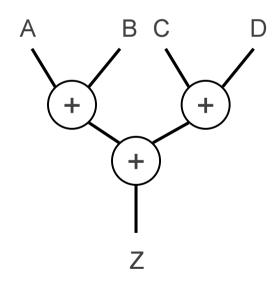

### Structure for Minimum Delay (311)

**Enabling Productivity**

■ You can define the synthesis structure starting point and possibly obtains better quality of results.

### Structure for Minimum Delay (311)

**Enabling Productivity**

#### □ Consider the signal arrival times.

// Expression Tree with Minimum Delay // Signal A arrives Last

$$Z = ((B+C) + D) + A;$$

// Expression Tree with Minimum Delay // Same Arrival Times for All Signals

$$Z = (A + B) + (C + D);$$

### Inferring Tri-State Drivers (312)

- ☐ Tri-state logic is synthesized on the output driver when the output signal is assigned "Z".

- ☐ It's important to know that each always block can generate only one Tri-state buffer as an output driver.

```

always @(from_table or enable)

begin: DRIVE_OUTPUT

if (enable)

to_bus = from_table;

else

to_bus = 8'bz;

end

```

```

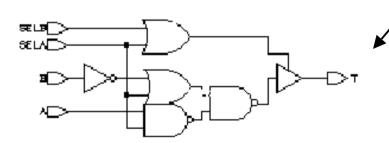

always @(SELA or SELB or A or B) begin:

T=1'bz;

if (SELA)

T = A;

if(SELB)

T = B;

end

```

# Inferring Tri-State Drivers - Multiple Tri-state Drive Inference (312)

```

module tristate_a (a, b, sela, selb, out1);

input a, b, sela, selb;

output out1;

reg out1;

always @(slea or a)

out1 = (sela) ? a : 1'bz;

always @(selb or b) begin

if (selb)

out1=b:

else

out1=1'bz;

end

endmodule

```

```

module tristate_a ( a, b, sela, selb, out1);

input a, b, sela, selb;

output out1;

wire out1;

assign out1= (sela) ? a : 1'bz;

assign out1= (selb) ? b : 1'bz;

endmodule

```

### HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

#### HDL for Synthesis Guidelines

- General HDL Code Structure

- Partitioning

- Implying Logic Structure

- Safe Coding & Avoiding Problems

- Source Code Readability

- Coding Style for Design Reuse

- Design for Testability

- Practices

### Safe Coding & Problems: Checklist Items

| One clock per module (401)                          |

|-----------------------------------------------------|

| Separate Sequential & Combination Processes (402)   |

| Proper sensitivity lists (403)                      |

| Blocking Statement vs. Non-blocking Statement (404) |

| Named association (405)                             |

| Instantiation of Sensitive or Asynch Circuits (406) |

| Avoid Continuous Signal Assignments (407)           |

| Reset Strategy Consistency and properly coded (408) |

| Instantiation of black-box (no timing) cells (409)  |

| Avoid Initialization (410)                          |

| Avoid Mixed-Edge Sensitivity (411)                  |

| Constant Propagation (412)                          |

### One Clock per Module (401)

- Synthesis was designed to optimize combinational logic clocked by a register driven from a single clock source

- Synthesis script development becomes much more complex with multiple clocks

- Asynchronous logic is often introduced as a result of logic with clock interfaces

- However .... it's sometimes unavoidable. If more than one clock in a module then:

- Estimate impact on testability

- Estimate impact on synthesis

- Estimate impact on mixed clocks timing analysis

### Separate Sequential & Combination Processes

(402)

```

module count (CLOCK, RESET, RESULT);

input CLOCK, RESET:

output RESULT;

reg RESULT, AND BITS, OR BITS, XOR BITS;

reg [2:0] COUNT:

always @(posedge CLOCK) begin: BAD EXAMPLE

if (RESET) begin

Code That Implies Extra

COUNT <= 0:

RESULT <= 0:

Unwanted Registers

end

else begin

COUNT <= COUNT + 1:

AND_BITS <= & COUNT; // AND BITS gets a Flip Flop

OR BITS <= | COUNT; // OR BITS gets Flip Flop

XOR BITS <= ^ COUNT; // XOR BITS get a Flip Flop

RESULT <= AND BITS & OR BITS & XOR BITS;

end

end // BAD EXAMPLE

endmodule

```

### Separate Sequential & Combination Processes

(402)

**Enabling Productivity**

```

module count (CLOCK, RESET, RESULT);

input CLOCK, RESET;

output RESULT:

reg RESULT, AND BITS, OR BITS, XOR BITS;

reg [2:0] COUNT;

always @(posedge CLOCK) begin : SEQ BLK

if (RESET) begin

COUNT <= 0:

Code Without Implying

RESULT <= 0:

end

Extra Registers

else begin

COUNT <= COUNT + 1;

RESULT <= AND BITS & OR BITS & XOR BITS;

end

end // SEQ BLK

always @(COUNT) begin : COMB BLK

AND BITS = & COUNT;

OR BITS = | COUNT;

XOR BITS = ^ COUNT:

end // COMB BLK

endmodule

```

- SYNOPSYS°

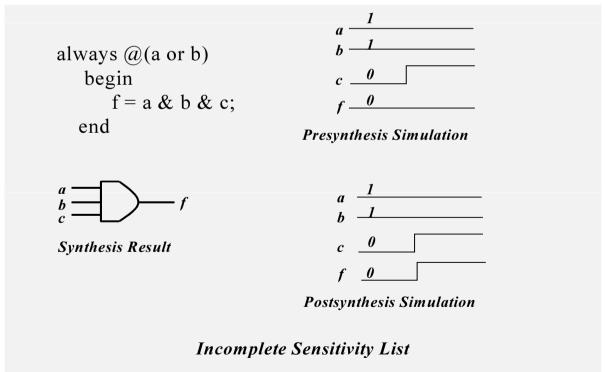

### Proper Sensitivity Lists (403)

- Pitfall: gate-level simulation mismatch

- **Symptoms:**

- Warnings during DC read/elaborate

- Inconsistent behavior with slight change in stimulus

- □ Blocking procedural assignments are more like S/W

- reg changes immediately

- Sensitive to dependence

- Sensitive to assignment order

- Simulation speed improvement

- Non-blocking procedural assignments are more like H/W

- reg changes scheduled

- Insensitive to dependence

- Insensitive to assignment order

**Enabling Productivity**

#### **Example of Blocking vs. Non-blocking**

```

always @(a or b or sel) begin : My_Mux

if ( sel == 1'b0)

out = a:

else

out = b:

end

```

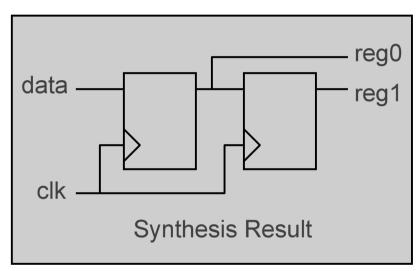

**Blocking Assignment**

```

always @(posedge CLK) begin:

Shift_reg

st1 reg <= data in;

st2 reg <= st1 reg;

out_reg <= st2_reg;

end

```

Non-blocking Assignment

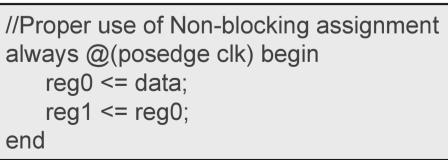

**Enabling Productivity**

Proper Use of Blocking and Non-blocking assignment in the sequential always block.

```

//Improper use of Blocking assignment

always @(posedge clk) begin

reg0 = data;

reg1 = reg0;

end

```

**Enabling Productivity**

- Improper use of blocking assignment might cause race condition.

- Potential Race

- The intention here is that **a** is shifted to **b** and **b** is shifted to **c** on the positive edge of the clock. However, since Verilog HDL does not specify the order where the always blocks are scheduled, the simulator may schedule that statement **b=a** before the statement c=b

//Potential Race always @(posedge clk) c=b: always @(posedge clk) b=a;

### Named Association (405)

**Enabling Productivity**

Instantiation port connection via order (implicit)

```

my_adder U1 (base, offset, eff);

- is not equivalent to -

my_adder U1 (base, eff, offset);

```

■ Instantiation port connection via name (explicit)

Recommend: Always use name based port association.

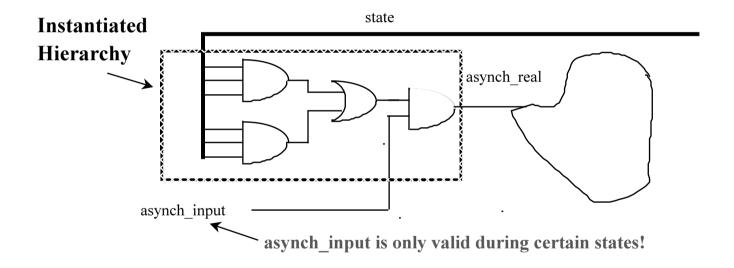

# Instantiation of Sensitive or Asynchronous Circuits (406) Enabling Productivity

☐ Asynchronous logic is difficult to describe in an HDL or to time accurately through static timing analysis.

INSTANTIATION and GATE SIMULATION is the correct methodology for asynchronous logic.

### Avoid Continuous Signal Assignment (407)

- □ Continuous assignment are executed in no defined order and synthesize to combinational logic.

- To facilitate the option to repartition in synthesis, and to improve code readability, you should place the logic in a combinational always block instead.

```

// Continuous Assignment Example -- Not Recommended assign sum = a_in ^ b_in ^ c_in; assign c_out = (a_in & b_in) | (b_in & c_in) | (a_in & c_in);

```

```

// Combinational process -- Recommended always @(a_in or b_in or c_in) begin: Full_Adder sum = a_in ^ b_in ^ c_in; c_out = (a_in & b_in) | (b_in & c_in) | (a_in & c_in); end // Full_Adder

```

**Enabling Productivity**

- Synchronous or asynchronous external reset ?

- What FF cells are available in the library ?

- Sync set/reset

- Async set/reset

- Which strategy does the ASIC vendor prefer ?

- What attributes should I set in source code?

- How can I audit proper inference of registers?

Plan a Reset Strategy & Then Use it Consistently

**Enabling Productivity**

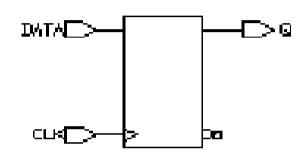

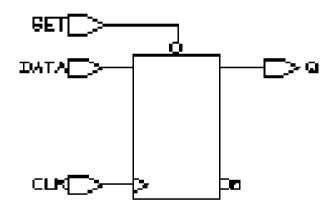

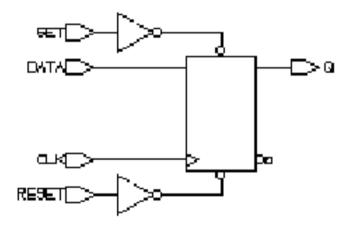

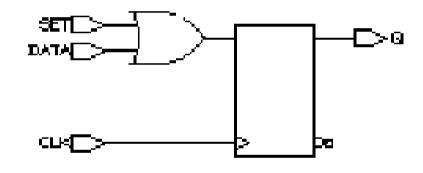

**☐** Example: Synchronous Reset

**Enabling Productivity**

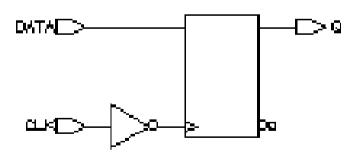

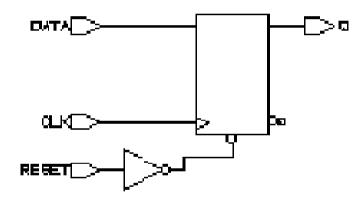

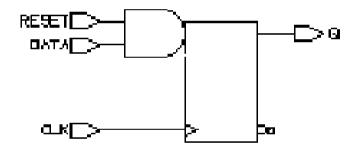

**☐** Example: Asynchronous Reset

```

always @ (posedge CLK or posedge RESET)

begin

if (RESET)

Q <= 1'b0;

else

Q <= DATA;

end</pre>

```

- Apply a consistent reset strategy, synchronous or asynchronous.

- Simplify Synthesis, DFT...efforts.

- ☐ Infer minimum area D flip-flop cells only when the designer is 100 percent certain that the circuit will self-initialize with no ambiguity.

- Make sure that the circuit will self-initialize.

- Simulate the gate level design before logic implementation.

### Instantiation of Black-Box Cells (409)

- □ Timing-Driven Synthesis Requires Timing to be Defined for all Components

- Static-Timing Analysis is also Dependent on Full Timing

- Synthesis Timing Models:

- Vendor Supplied (ie. LSI RAM Model)

- Designer Created with Library Compiler Constructs

- ⇒ No Special Library License Required (cell's don't have function statements thus cannot be inferred)

### Example Synthesis-Timing Model (409)

```

library (RAM_LIBRARY) {

cell(RAM_64x8) {

area: 0;

pin(WE) {

direction: input;

capacitance: 1;

bus (A) {

bus_type : BUS6 ;

direction: input;

capacitance: 1;

```

### Ex. Synthesis-Timing Model-cntd (409)

```

bus (D_IN) {

bus type: BUS8;

direction: input;

capacitance: 1;

bus (D_OUT) {

bus_type : BUS8 ;

direction: output;

pin(D_OUT[0]) {

timing () {

intrinsic_rise: 25.0;

intrinsic fall: 25.0;

related_pin: "A[5] A[4] A[3] A[2] A[1] A[0] D_IN[0] WE";}

```

### Avoid Initialization (410)

**Enabling Productivity**

□ Do not initialize; synthesis will ignore!

```

initial

begin

count = 0;

end

always @ (posedge CLK)

begin

count = count + 1;

end

```

What will synthesis produce?

### Avoid Mixed-Edge Sensitivity (411)

**Enabling Productivity**

```

always @ (posedge CLK or negedge CLK)

begin

if (CLK)

countA = countA + 1;

else if (!CLK)

countA = countA + 2;

end

always

begin

@ (posedge CLK);

countB = countB + 1;

@ (negedge CLK);

countB = countB + 2;

end

1.The

issue free

end

2. Mos

```

Mixing Clock Edges Example

- 1. The duty cycle of the clock becomes a critical issue in timing analysis, in addition to the clock frequency itself.

- 2. Most scan-based testing methodologies requires separate handling of positive and negative edge triggered flops.

### Constant Propagation -1 (412)

**Enabling Productivity**

- □ Tie-off pins on subdesigns at the lowest level and don't propagate as a primary port if not necessary

- ☐ This will help avoid:

- problems with constant propagation

- possible unconnected port issues

- netlist translation issues (VHDL, Verilog, EDIF, etc.)

DC can't eliminate redundant logic across boundaries when connected to ports

### HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

#### HDL for Synthesis Guidelines

- General HDL Code Structure

- Partitioning

- Implying Logic Structure

- Safe Coding & Avoiding Problems

- Source Code Readability

- Coding Style for Design Reuse

- Design for Testability

- Practices

# Readability: Checklist Items

- Meaningful embedded comments (501)

- ☐ Use of Loops & Arrays (502)

- Use of Constants (503)

- ☐ Reduction Operators (504)

- □ Proper use of 'define & parameter' (505)

### Meaningful Embedded Comments (501)

**Enabling Productivity**

- Improve readability, maintainability, ability to reuse, easy review, trace-ability to spec, etc.

- Typical engineers response ...

"I don't have the time to comment now"

■ When complete do you go back & comment or do you move on to the next assignment?

# Use of Arrays and Loops (502)

- Use Higher-Level Looping Constructs

- For Loop & While Loop

- ☐ For Verilog: use 'defines

- Use Arrays instead of group of bits (see example next)

### Example of Register Bank (502)

```

module RGBANK (CLK, WE, ADDR, DATA IN, DATA OUT);

input

CLK, WE;

input [1:0] ADDR:

input [7:0] DATA IN;

output [7:0] DATA OUT;

req

[7:0] DATA OUT;

reg [7:0] RG 0, RG 1, RG 2, RG 3;

always @ (ADDR or RG 0 or RG 1 or RG 2 or RG 3)

begin

DATA OUT = 0;

case (ADDR)

0: DATA OUT = RG 0;

1: DATA OUT = RG 1;

2: DATA OUT = RG 2;

3: DATA OUT = RG 3;

endcase;

end

always @ (posedge CLK)

begin

if (WE)

case (ADDR)

0: RG 0 = DATA IN;

1: RG 1 = DATA IN;

2: RG 2 = DATA IN;

3: RG 3 = DATA IN;

endcase;

end

endmodule // RGBANK

```

### Register Bank Using Arrays (502)

# Use of Constants (503)

**Enabling Productivity**

- Constants are a very simple way of improving Verilog source code readability and code quality by eliminating typographical errors.

- Sometimes, if the architecture changes, only the constants need to be updated.

// in a header file, declare all constants shared by more than // one module

- `define INTBUS\_WIDTH 16

- `define EXTBUS WIDTH 32

. . .

- 'define DEVICE ID 16'h0007

- `define REVISION\_ID 16'h0002

# Use of Constants (503)

# Use of Reduction Operators (504)

# Use of Reduction Operators (506)

**Enabling Productivity**

#### **□** Parity Logic:

```

EVEN_PARITY = ^DATA[7:0];

ODD_PARITY = ~^DATA[7:0];

```

-or-

### Proper Use of `defines & parameters (505)

- □ `define

- **☞ Text substitution**

- Typical uses include

- **⇒** constants

- ⇒ readability improvement

- parameter

- Represents constants

- Can be modified at compile time

- Modified via

- **⇒** defparam statement

- ⇒ module instance statement

- Typical uses include

- ⇒ delay specification

- ⇒ width of variables

### Proper Use of `defines & parameters (505)

**Enabling Productivity**

#### pc\_defines.v

```

`define SERIAL_CS 16'h1050

`define PARALLEL_CS 16'h23ff

`define FLOPPY_CS 16'h4b80

```

#### Do you have a preference?

#### io\_control.v

```

`include "pc_defines.v"

...

if (ADDR == `SERIAL_CS)

...

else if (ADDR == `PARALLEL_CS)

...

else if (ADDR == `FLOPPY_CS)

...

```

```

if (ADDR == 16'h1050)

...

else if (ADDR == 16'h23ff)

...

else if (ADDR == 16'h4b80)

...

```

### Proper Use of `defines & parameters (505)

```

module regbank (clk, data_in, data_out);

parameter size = 8, delay = 1;

input [size-1:0] data_in;

output [size-1:0] data_out;

reg [size-1:0] data_out;

always @ (posedge clk)

data_out = #delay data_in;

endmodule

```

```

module top;

reg clk;

reg [15:0] inA;

reg [3:0] inB;

wire [15:0] outA; // need delay of 3

wire [3:0] outB; // need delay of 2

regbank #(16, 3) U1 (clk, inA, outA);

regbank U2 (clk, inB, outB);

endmodule

```

```

module annotate;

defparam

top.U2.size = 4,

top.U2.delay = 2;

endmodule

```

# HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

#### HDL for Synthesis Guidelines

- General HDL Code Structure

- Partitioning

- Implying Logic Structure

- □ Safe Coding & Avoiding Problems

- Source Code Readability

- Coding Style for Design Reuse

- Design for Testability

- Practices

# Code Reuse: Checklist Items

- Don't Embed Synthesis scripts in source code (601)

- Maintain technology independence (602)

- Use GTECH for simple cell instantiation (603)

- Databook Quality Description (604)

- □ Parameterize modules (605)

# Code Reuse Principal

- Design reuse is the action of utilizing objects in the form of macros, subsystems, and systems in the development of new systems

- Design object with it's associated views (interface, functional spec, etc.) is intended for use in an "object oriented" way

- ☐ For example, an implementation of CCITT H.261 (Video Compression Std) should be implemented such that it can be reused in other systems with minimal effort

- □ Other examples: PCI bus, ADPCM, MPEG decoder, JPEG, etc.

# Levels of Code Reuse

- Reuse by the individual

- Commonly done, but limited

- For example: Counter, Mux, RAM Model, etc.

- □ Reuse within a group

- Short lifetime, but improved

- For example: Adaptive Equalizer

- □ Reuse by department/lab

- Reasonable lifetime, significant productivity benefits

- For example: MPEG Decoder

- Reuse across enterprise Highest level of reuse

- Significant competitive advantage

# Don't Embed Synthesis Scripts in Source Code(601)

**Enabling Productivity**

**Example of embedded dc shell script:**

```

// synopsys dc script begin

// set max area 2500.0

// set drive -rise 1 port b

// synopsys dc script end

```

Or hiding simulation constructs or other (e.g. FPGA) from synthesis compiler

```

-- translate off

initial

-- translate on

-- then set hdlin translate_off_skip_text = false

to have DC analyze and elaborate the module

```

# Maintain Technology Independence (602)

**Enabling Productivity**

#### ■ Use DesignWare components

- DesignWare components are pre-verified for synthesis and can save you time coding and testing your design.

- Using DesignWare components can also improve your quality of results.

# ☐ The DesignWare Library is extensive and is broken down into five families:

- Standard Family(adder, subtractor, multiplier, comparator, etc)

- ALU Family(barrel, shifter, incrementer/decrementer, etc)

- Advanced Math Family(advanced multiplier, vector add/subtract, etc)

- Sequential Family(FIFOs, Gray-Scale counters, stack, etc)

- Fault Tolerant Family(parity checker, CRC generator, etc)

- Refer to DesignWare Library documentation for detailed information.

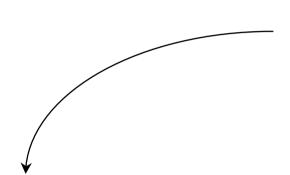

### Synthetic Parts: Using DesignWare (602)

**Enabling Productivity**

#### Through HDL inference

Reference Design Synthesis Binds to Synthetic Module

Synthesis Selects Proper Implementation Implementation

Optimized for Context

# Use GTECH for simple cell instantiation (603) Enabling Productivity

#### **□** When necessary to instantiate ... use GTECH!

- Provides technology independence

- **™** Typical GTECH cells (AND, NAND, OR, NOR, XOR, FA, HA, FF, LATCH, AOI, MUX, etc.)

- Use map\_only attribute to prevent DC from ungrouping or

- In dc\_shell:

```

set_map_only { find(reference "my_gtech_cell" }

```

# Using GTECH - verilog (603)

**Enabling Productivity**

```

`include "<SYNOPSYS_ROOT>/packages/gtech/src_ver/gtech_lib.v"

module top (...);

...

...

GTECH_AND2 U1 (.A(in1), .B(in2), .Z(out1));

GTECH_NAND2 U2 (in3, in4, out2);

...

endmodule

```

GTECH instantiation allows a technology independent HDL description.

# Databook Quality Description (604)

- Databook-like quality implies published quality documentation.

- It's worth spending the effort to produce databook-like comments and consider the following characteristics:

- Readable Documentation

- Traceability to Specification

- Block diagrams

- Functional specification

- Description of parameters and their use

- Interface signal descriptions

- Timing diagrams and requirements

- Verification strategy

- Synthesis constraints

# Databook Quality Description (604)

- **□** Continue...

- Useful Examples of How To Use the Module

- A complete Testbench for the Module

- Verification reports (what was tested)

- Technology used

### Parameterize Modules (605)

**Enabling Productivity**

■ The use of the parameter construct improve the ability to reuse this module because of the parameterization provided by the parameter statement.

```

module FIFO (CLK, WRITE_ENABLE, WRITE_SELECT, READ_SELECT, DATA_IN, DATA_OUT);

parameter SELECT_WIDTH = 3;

parameter DATA_WIDTH = 8;

parameter FIFO DEPTH = 8;

```

input CLK, WRITE\_ENABLE; input [SELECT\_WIDTH-1:0] READ\_SELECT, WRITE\_SELECT; input [DATA\_WIDTH-1:0] DATA\_IN;

You can change the parameter value in a module during instantiation or elaborating designs in synthesis.

module\_name #(parameter\_value,.....) instance\_name(port list) or elaborate design name -parameters parameter list

# HDL for Synthesis Guidelines

**Enabling Productivity**

#### Presentation:

#### HDL for Synthesis Guidelines

- General HDL Code Structure

- **Partitioning**

- Implying Logic Structure

- Safe Coding & Avoiding Problems

- Source Code Readability

- Coding Style for Design Reuse

- **Design for Testability**

- **Practices**

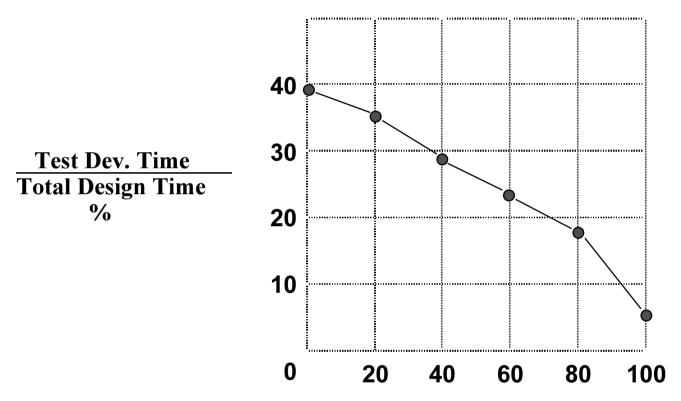

# Why Design for Test?

**Enabling Productivity**

Controllability & Observability as Percentage of Circuit

Source of Graph: "ASIC Testing Upgraded", by Marc Levitt, IEEE Spectrum, May 1992, pp26-29

# Use Synchronous Design Style

- Avoid One Shots

- Avoid Asynchronous State Machines

- Isolate Asynchronous Logic

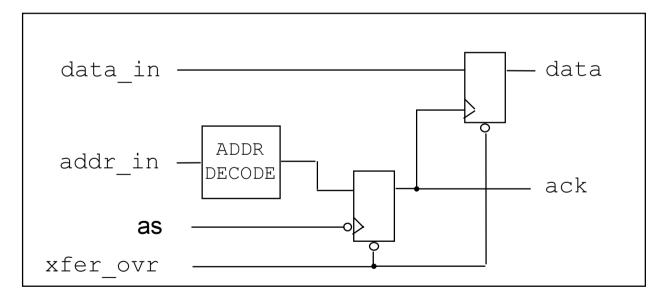

Fig. 1 Example Asynchronous Bus Interface

# Exercise: Make Asyn. Xface Testable

```

module bus xface (data in, addr in, as, xfer ovr, ack,data);

input [3:0] data in:

input [3:0] addr in;

input as, xfer ovr;

output [3:0] data;

output ack:

reg [3:0] data:

reg ack;

always @ (negedge as or negedge xfer over)

if(~xfer over)

ack \le 1'b0':

else

ack <= addr dec;

ADDR DECODE U1(addr in, addr dec);

always @ (posedge ack or negedge xfer over)

if(~xfer over)

data <= 4'b0000:

else

data <= data in:

endmodule

```

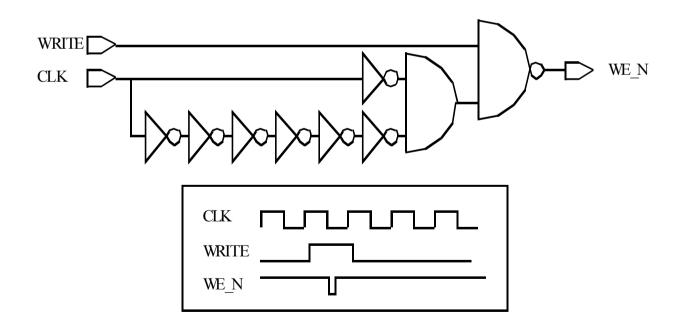

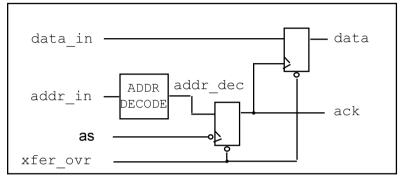

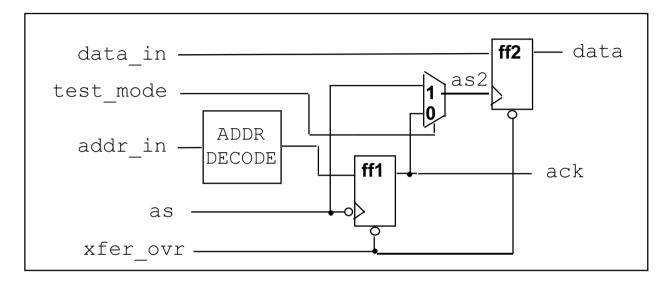

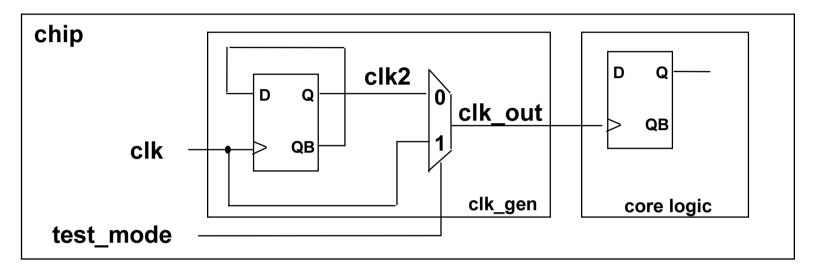

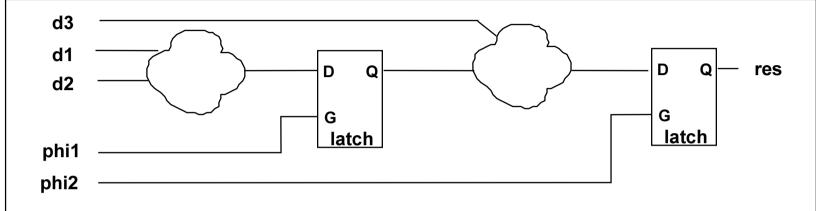

# Bypass Internally Created Clock

Fig 2. Testable "Asynchronous" Xface with Controlled Clock Ckt.

- Internal clock is not controllable: bypass it during test.

- Two phases of clock used: route scan chain ff1 to ff2 to prevent "shoot thru".

- Assume "as" is available at chip I/O and synchronous relative to other clocks during test.

### Verilog Code for Bypassed Asyn Ckt

```

module bus xface (data in, addr in, as, xfer ovr, ack,data,test mode);

input [3:0] data in;

input [3:0] addr in;

input as, xfer ovr; test mode;

output [3:0] data:

output ack;

reg addr dec:

reg [3:0] data;

reg ack;

wire as2:

assign as2 = test mode? as: ack;

always @ (negedge as or negedge xfer over)

if(~xfer over)

ack <= 1'b0:

else

ack <= addr dec;

ADDR DECODE U1(addr in, addr dec);

always @ (posedge a or negedge xfer over)

if(~xfer over)

data <= 4'b0000:

else

data <= data in;

endmodule

```

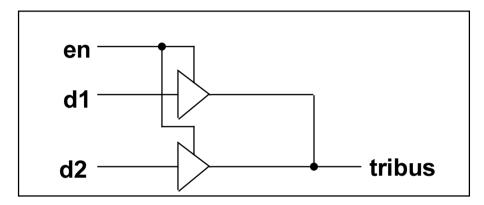

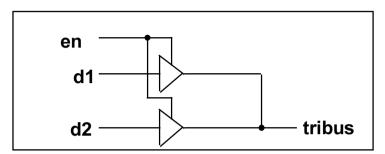

# Avoid Internal Three State Buses

**Enabling Productivity**

Fig. 3 Example Three-State Circuit

Rule: Cannot have multiple drivers active at the same time.

• Can potentially cause bus contention and a power sink, if the values driven by the drivers are different.

Rule: Must have at least one driver active at all times.

Cannot test enable signal, if disabling drivers causes bus to float.

# Exercise: Make 3 States Testable

```

module tri state (en,d1,d2,tribus);

input d1, d2;

input [1:0] en;

output tribus;

reg tribus;

always @(d1 or en)

if (en)

tribus = d1;

else

tribus = 1'bz;

always @(d2 or en)

if (en)

tribus = d2;

else

tribus = 1'bz

endmodule

```

# Use Pull-Ups & Muxed Enables

en2 +5v

en1 d1 Pull-up

d1 tribus

Fig. 4 Example Three-State w/ Pull-ups & Multiplexed Enables

• All tri-state controls are preferably fully decoded to ensure one active driver

### Verilog Code for Pull-ups & 3-States

**Enabling Productivity**

```

module tri state (en1, en2,d1,d2,tribus);

input d1, d2;

input en1,en2;

output tribus:

reg tribus;

always @(d1 or en1 or en2)

if (en1 & ~en2)

tribus = d2:

else

tribus = 1'bz;

always @(d2 or en1 or en2)

if (~en1 & en2)

tribus = d1;

else

tribus = 1'bz;

pullup (tribus); // not synthesizable

endmodule

```

• Pull-ups can ONLY be instantiated, not inferred in Verilog code.

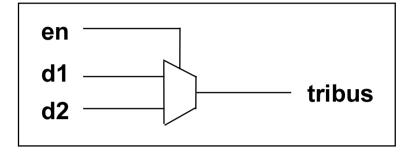

# Use Mux Instead of Three -State

Fig. 5 Example Multiplexed Bus

- Simpler to code.

- No possibility of bus contention

```

module mux_example (en,d1,d2,tribus);

input d1, d2;

input en;

output tribus;

reg tribus;

always @(d1 or d1 or en)

if (en)

tribus = d1;

else

tribus = d2;

endmodule

```

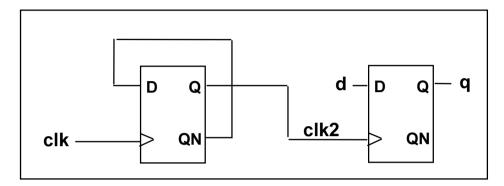

# Avoid Uncontrollable Clocks

**Enabling Productivity**

Fig. 6 Example Clock Divider Circuit

### Rule: All clocks must be controllable and accessible from top level ports.

- Chip tester would require multiple tester cycles per serial scan chain data item.

- Clock dividers inherently untestable, belong to asynchronous circuit category.

# Exercise: Make Clk2 Controllable

#### **Enabling Productivity**

module clk\_gen (d, clk, q);

input clk, d;

output q;

reg clk2;

always @ (posedge clk)

clk2 <= ~clk2;

always @ (posedge clk2)

q <= d;

endmodule

### Bypass Bad Clocks During Test

Fig. 7 Example Asynchronous Clock Generator Bypass

- Bypass circuitry added to source code by <u>designer</u>.

- During test: use chip level clock, during regular operation: use derived clock.

- TEST\_MODE signal is active high during test, and requires a dedicated port.

## Verilog Code for Clock Bypass Logic

**Enabling Productivity**

• General Rule: Isolate clock generation circuit into its own level of hierarchy.

```

module clk gen (d, clk, test mode, q,clk out);

input clk, d, test mode;

output q.clk out:

reg clk2,clk out;

always @ (posedge clk)

clk2 <= ~clk2:

always @ (posedge clk out)

a \le d:

always @ (test mode or clk or clk2)

if (test mode)

clk out = clk;

else

clk out = clk2;

endmodule

```

```

module chip (clk, test_mode, data_in, instr_in, data_out); input clk, test_mode; input [31:0] data_in; input[7:0] instr_in; output [15:0] data_out; wire [15:0] data_out; wire clk_inner; clk_gen_clk_gen_0(clk,test_mode,clk_inner); core_logic_core_logic_0(clk_inner, data_in, instr_in,data_out); endmodule

```

### Avoid Using Clocks as Data Inputs

**Enabling Productivity**

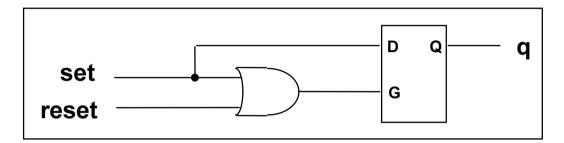

Fig. 8 Example Set - Reset Latch

#### Rule: DO NOT Use Clocks as Data Inputs.

- Race condition could exist between the enable and data of the latch.

- Even if race condition fixed it's very difficult to detect and correct such problems.

- Falls under category of asynchronous logic.

## Exercise: Make Clock Testable

```

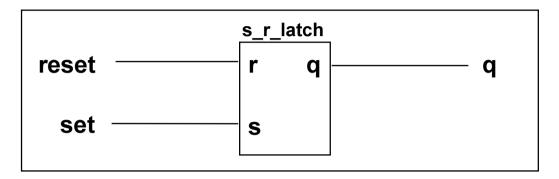

module s_r_latch(set, reset, q);

input set, reset;

output q

reg q;

always @ (set or reset)

if(set |reset)

q <= set;

endmodule

```

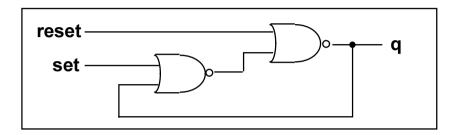

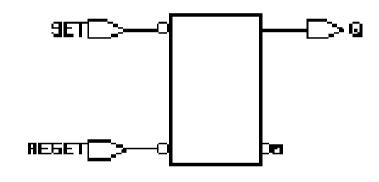

### Use a S-R Flip-flop

Fig. 9 Example S-R FF

```

module s_r_ff ( set, reset, clk, q);

input set, reset, clk;

output q;

reg q;

// synopsys sync_set_reset "set, reset"

always @ (posedge clk)

if (set)

q <= 1'b1;

else if (reset)

q <= 1'b0;

endmodule</pre>

```

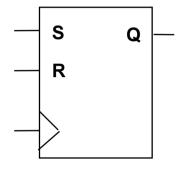

#### Uncontrollable Asynchronous Resets

**Enabling Productivity**

Fig. 10 Example Uncontrollable Reset During Test

Rule: All asynchronous reset / set signals should be controllable through a chip level port.

- The integrity of data scanned through the register during scan shifting must be upheld.

- Uncontrolled reset/set signals could overwrite/erase parts of the scan chain data

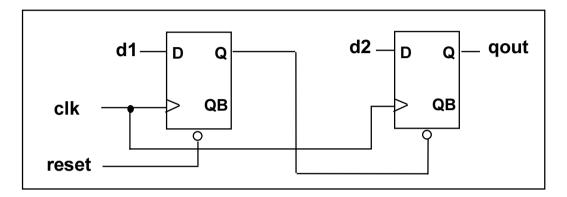

### Exercise: Fix Uncontrollable Reset

```

module asyn_reset (clk,d1,d2, reset,qout);

input d1, d2, clk, reset;

output qout;

reg ar;

always @ (posedge clk or negedge reset)

if (~reset)

ar <= 1'b0;

else

ar <= d1;

always @ (posedge clk or negedge ar)

if (~ar)

qout <= 1'b0;

else

qout <= d2;

endmodule

```

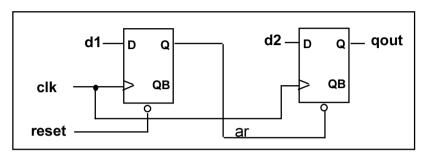

### Controlling Asynchronous Resets

Fig. 11 Example Test Override of Asynchronous Reset

- During scan shift operation, reset held inactive, scan data integrity upheld.

- During capture cycle of test, scan\_enable is low and thus asynchronous reset signal can be tested.

#### Vevilog Code to Control Asynch. Reset

**Enabling Productivity**

Internal reset signal "gated" within asynchronous reset description

```

module asyn reset (clk, d1, d2, reset, scan enable, gout);

input d1, d2, clk, reset, scan enable;

output gout;

reg ar;

always @ (posedge clk or negedge reset)

if (~reset)

ar <= 1'b0:

else

ar \le d1:

wire ar n = ar | scan enable;

always @ (posedge clk or negedge ar n)

if (~ar n)

qout \le 1'b0:

else

qout <= d2:

endmodule

```

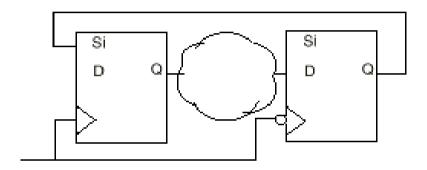

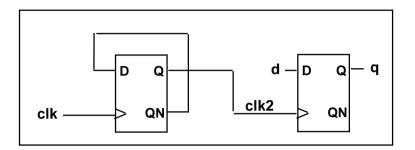

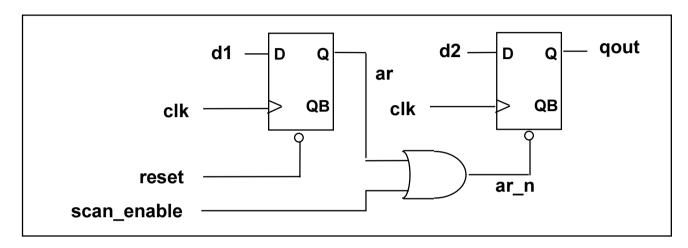

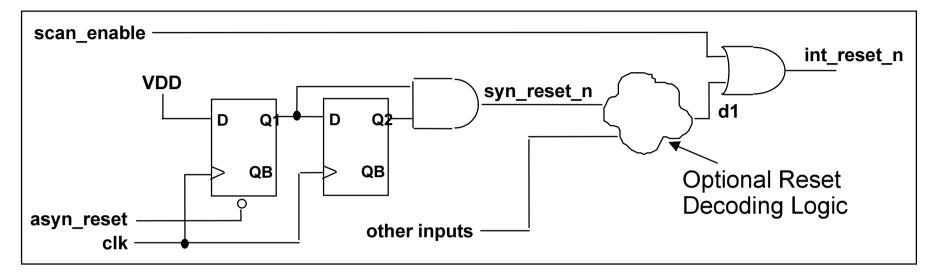

#### Testable Reset Synchronizer

Fig. 12 Example Testable Reset Synchronizer Circuit

- Extension of controlling asynchronous signals scheme.

- The synchronized reset signal,  $syn\_reset\_n$  can be combined with other inputs if necessary, then gated with  $scan\ enable$ .

- Don't forget to identify the scan enable port as part of your test circuitry.

### Verilog Code for Reset Synchronizer

```

Module syn_reset(clk,asyn_reset,scan_enable, int_reset_n);

input clk, asyn_reset, scan_enable;

output int_reset_n;

reg q1, q2;

always @ (posedge clk or negedge asyn_reset)

if (~asyn_reset)

q1 <= 1'b0;

else

q1 <= 1'b1;

....

always @ (posedge clk)

q2 <= q1;

wire int_reset_n = scan_enable | d1;

endmodule

```

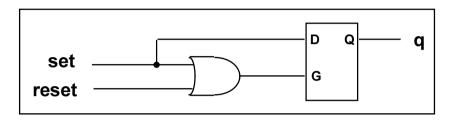

### Avoid Combinational Feedback Loops

**Enabling Productivity**

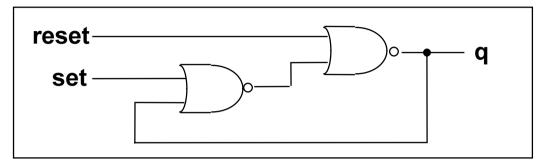

Fig. 13 Example S-R Latch

#### Rule: Do not have combinational feedback loops in design.

- Introduces states in the design which cannot be synchronously controlled.

- Faults within the logic of the combinational feedback loop may not be testable.

- · Asynchronous feedback loops cause problems with synthesis.

## Exercise: Make S-R Latch Testable

```

module s_r_latch ( set, reset, q);

input set, reset;

output q;

wire tmp;

nor (q, reset, tmp);

nor (tmp, set, q);

endmodule

```

# Model S-R Latch as a Leaf Cell

Fig.14 Example s\_r\_latch as a leaf cell

- If SR Latch is modelled as a leaf cell in the technology library, then internal feedback loop not visible to the test generation software.

- Should not be a problem IF a scannable equivalent of the cell exists in the library.

- Otherwise must treat latch as you treat other latches in your design (latches discussed in Test Schemes).

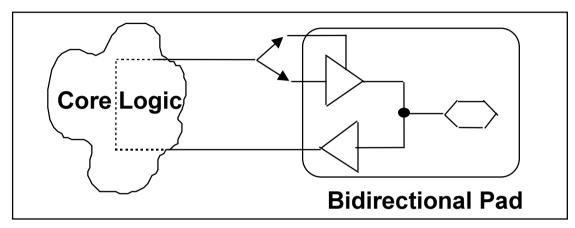

#### Bi-di Pads Introduce Feedback Loops

Fig. 15 Example of Feedback Loop w/Bi-Directional Pad

- Combinational feedback path might exist from the input driver thru the internal core logic to the enable or data pin of the output driver.

- Feedback is evident only when the pad is in "output mode".

- Feedback may or may not be detected by test design rule checker.

- Feedback loop might have to be explicitly broken. Best practice: eliminate loops altogether from design.

## Design for Test Rules Summary

- Use Synchronous design styles.

- Avoid Asynchronous designs

- Asynchronous: Isolate Asynchronous logic

- Avoid Three-State Drivers

- 3States: Cannot have more than one driver active at a time

- 3States: Must have at least one driver active at all times (or use a pullup)

- All clocks must be controllable and accessible from top level ports.

- Do NOT use clocks as data inputs.

- All asynchronous reset/set signals must be controllable thru top level port

- Do not have combinational feedback loops in the design.

- Latches in Flip-flop Based Designs

- Improving Control & Observability

- Techniques for Testing RAMs

### Latches in Flip-flop Based Designs

**Enabling Productivity**

Fig. 16 Example Latches in a Design

#### You can:

- Leave them as is let test tool deal with them.

- Replace them with a scannable equivalent (for example use a LSSD cell).

- Model them as black boxes, with the resultant loss of fault coverage

- Hold them transparent during test (watch out for combinational feedback loops!)

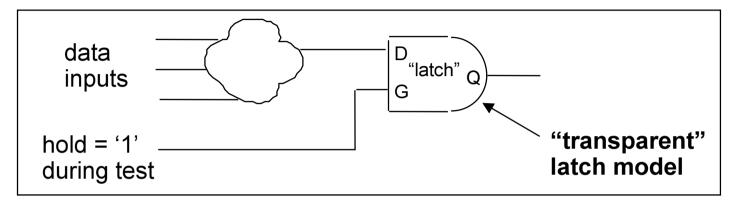

## Making Latches Transparent

Fig. 17 Example Transparent Model for a Latch

- Latch is modelled as a combinational circuit which represents a latch in active (pass thru) mode.

- Lose some fault coverage on enable pin of latch.

- Treat enable pin as data, do not "hook" it up to clock source.

- This treatment of latches is tool specific (ie. beyond Verilog coding style).

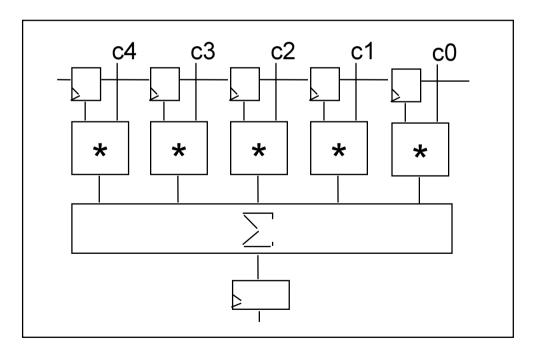

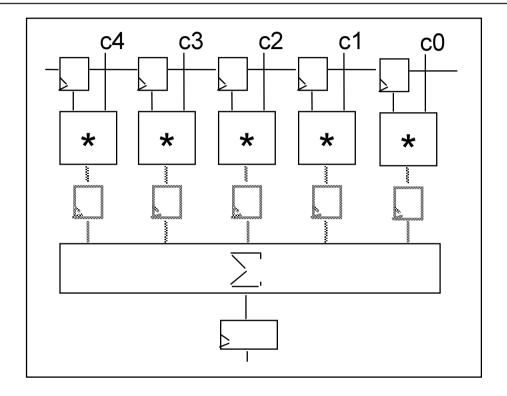

## Improving Control & Observability

- Given: Scan chains improve testability by providing access to internal registers.

- You can make a design more observable and/or controllable and thus better for test by adding flip-flops at crucial points.

Fig.18 Example "Difficult to Test" Circuit

### MAdding FF's to Improve Controllability

Fig.19 Example Design with Improved Testability

- Simplifies the timing constraints of the design (increases latency, decreases critical paths).

- Can test adder without adding primary input/outputs to the multipliers.

## Partitioning to Improve Testability

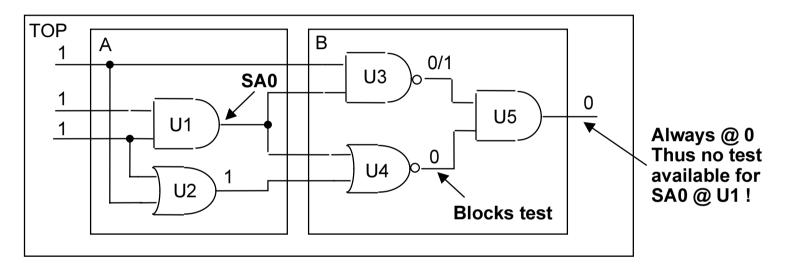

**Enabling Productivity**

Rule: Do not allow hierarchical boundaries in combinational paths.

Fig. 20 Testing for a Stuck-At-0 Fault with a Reconvergent Fanout Design

Reconvergent fanout: different paths from the same signal converge again at the same component downstream in the logic.

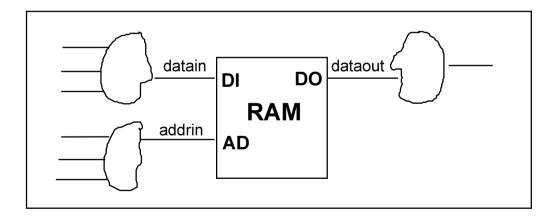

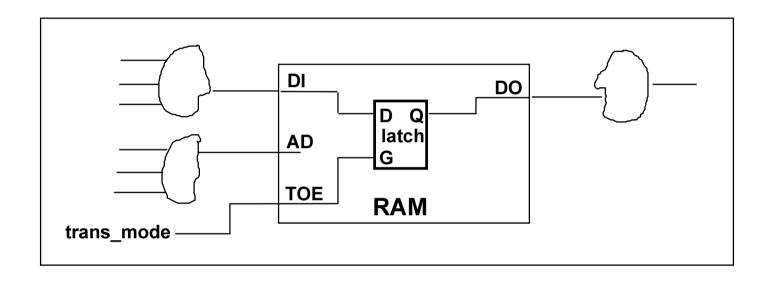

# Techniques for Testing RAMs

- Multiplexed I/O

- Register Bounding

- Transparent RAMs

- Built-In-Self-Test (BIST)

Fig.21 Example RAM with surrounding logic

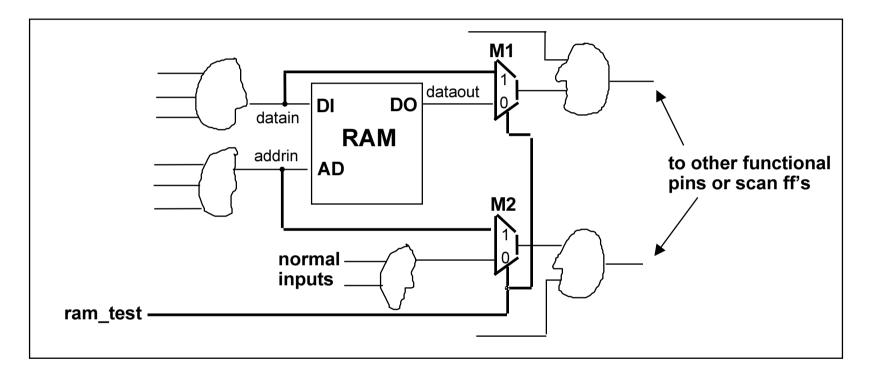

## Multiplexed I/O for RAMs

Fig.22 Example Multiplexed I/O Test Scheme applied

# Multiplexed I/O Test Scheme

- Increases the observability of the data input to the RAM.

- Increases the controllability of the data output by the RAM.

- Increases the observability of the address driving the RAM.

- If the RAM has a known state during test, then output mux is not needed.

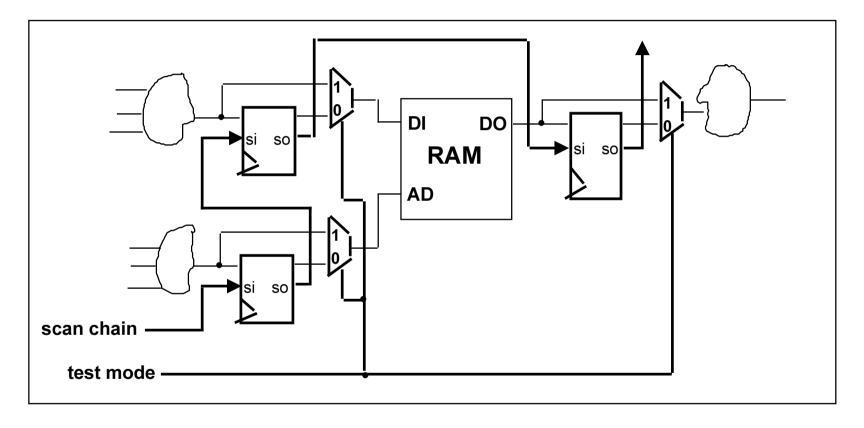

## Register Bounding for RAMs

Fig.23 Example Register Bounding Scheme applied to RAM

# Register Bounding Scheme

- In normal mode, the bounding registers are bypassed.

- The rest of the ASIC is isolated from the memory and can be tested independently.

- Bounding registers can be used to access & test RAM array.

- All memory arrays to be tested are usually connected into one scan chain.

- Not appropriate for memory arrays more than 1K words.

- Muxes only necessary if combo logic in between internal registers and RAM pins.

- RAM read/write control might need to be controlled by scan\_enable signal.

Fig.24 Example Transparent RAM

# Transparent RAM Scheme

- Treats the RAM array as if it consists of an array of latches.

- Meant to allow observability of data inputs at data output.

- Must have technology library support from vendor.

- Does not test address inputs or RAM array.

# Comparison of RAM Test Schemes

| Test Method          | Coverage & Ease                         | Implementation<br>Limitations          | Comments                        |

|----------------------|-----------------------------------------|----------------------------------------|---------------------------------|

| Multiplexed I/O      | Easiest<br>Tests Logic Only             | Adds mux delay to paths                |                                 |

| Register<br>Bounding | Tests Logic & RAM                       | Mux if combo logic;<br>Arrays<1K words |                                 |

| Transparent<br>Mode  | No Additional Muxes<br>Tests Logic Only | Additional Test Protocol               | Limited ASIC<br>Library Support |

| BIST                 | Tests RAM only<br>Comprehensive         | Additional real-estate                 | Limited by available S/W tools  |

**Table 1 Comparison of RAM Test Schemes**

# Recommended Test Schemes for RAMs

- If the address, datain, and dataout pins of the RAM are connected directly to internal registers with no combinational logic in between, then *use register bounding* (ie. make surrounding registers part of a scan chain).

- If combinational logic exists between internal registers and the address & data pins of the RAM, consider the following in the order given:

| Small / Medium Arrays | Large Arrays      |  |

|-----------------------|-------------------|--|

| Register Bounding     | BIST              |  |

| Multiplexed I/O       | Register Bounding |  |

| BIST                  | Multiplexed I/O   |  |

Table 2: Test Schemes For Combo Logic Surrounding RAM

# Test Scheme Summary

- Hold Latches in transparent mode.

- Add flip-flops to a design to increase controllability & observability

- Do not partition a combinational logic path across hierarchical boundaries.

- Use register bounding to test RAMs (as a first choice).

## Test Methodology Summary

- Test is a *design methodology*. It has it's own testability rules, created to insure that scan chains can be added to a design, with the ultimate goal of using an Automated Test Pattern Generator (ATPG) to create test patterns for the chip.

- Most problems associated with test can be avoided or anticipated and corrected up front, during the INITIAL synthesis of the source Verilog code to gates.

## HDL for Synthesis Guidelines

**Enabling Productivity**

#### **Presentation:**

#### HDL for Synthesis Guidelines

- General HDL Code Structure

- Partitioning

- Implying Logic Structure

- Safe Coding & Avoiding Problems

- Source Code Readability

- Coding Style for Design Reuse

- Design for Testability

- Practices

| _ | Enabling Productivity                                |

|---|------------------------------------------------------|

|   | Unsupported Verilog Language Constructs              |

|   | Limitations of Blocking and Non-blocking Assignments |

|   | Limitations of D Flip-Flop Inferences                |

|   | while Loops Limitations                              |

|   | forever Loops Limitations                            |

|   | Handling Comparisons to X and Z                      |

|   | Limitations of Using Delay Specification             |

|   | Limitations of Tri-State Inferences                  |

|   | Limitations of Arithmetic Operators                  |

|   | Limitations of casex and casez Statement             |

|   | Case Statement usage                                 |

|   | Register Inferring                                   |

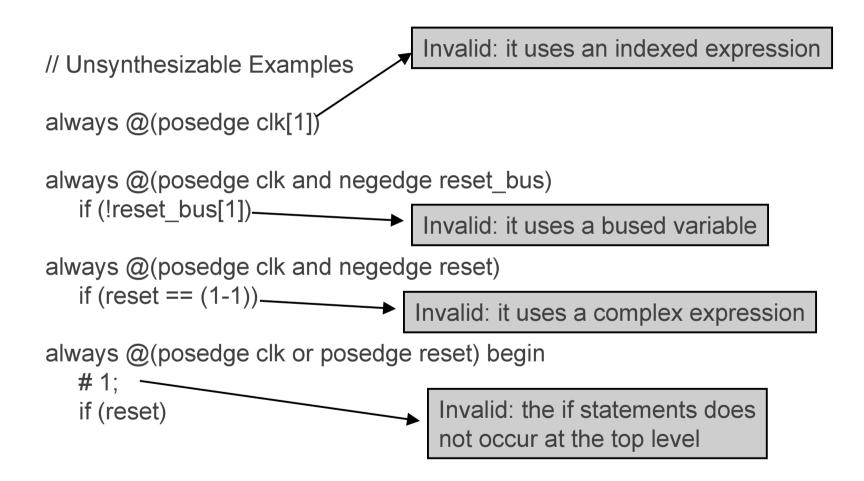

#### Unsupported Verilog Language Constructs

- Unsupported Definitions and Declarations

- time declaration

- event declaration

- triand, trior, tri1, tri0, and trireg net types

- Ranges and arrays for integers

- Unsupported operators

- Case equality and inequality operators (=== and !==)

- Division and modules operators for variables

- Unsupported gate-level constructs

- mos, pmos, cmos, rpmos, rcmos, pullup, pulldown, tranif0, tranif1, rtran, rtranif0, and rtranif1 gate types

#### Unsupported Verilog Language Constructs

**Enabling Productivity**

#### Unsupported Statements

- defparam statement

- initial statement

- repeat statement

- delay control

- event control

- wait statement

- fork statement

- deassign statement

- force statement

- release statement

- procedural continuous assignment

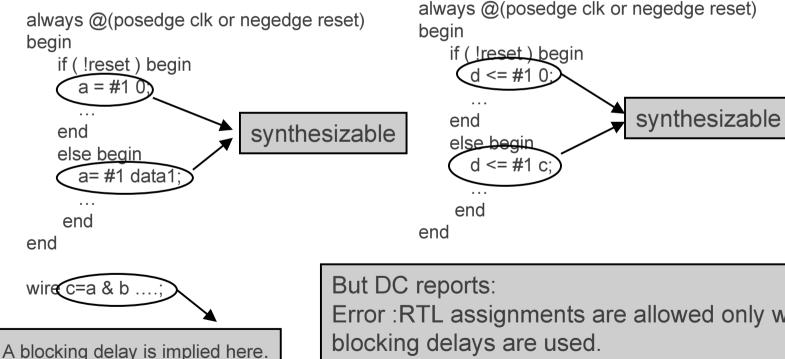

# Limitations of Blocking and Non-blocking Assignments

**Enabling Productivity**

■ A variable can follow only one assignment method and cannot be the target of both Blocking and Non-blocking assignments.

```

// Unsynthesizable Example

always @(posedge clk or negedge reset)

begin

if (!reset ) begin

a = 0;

b = 0;